Patents

Literature

206results about How to "Avoid electrical connection" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

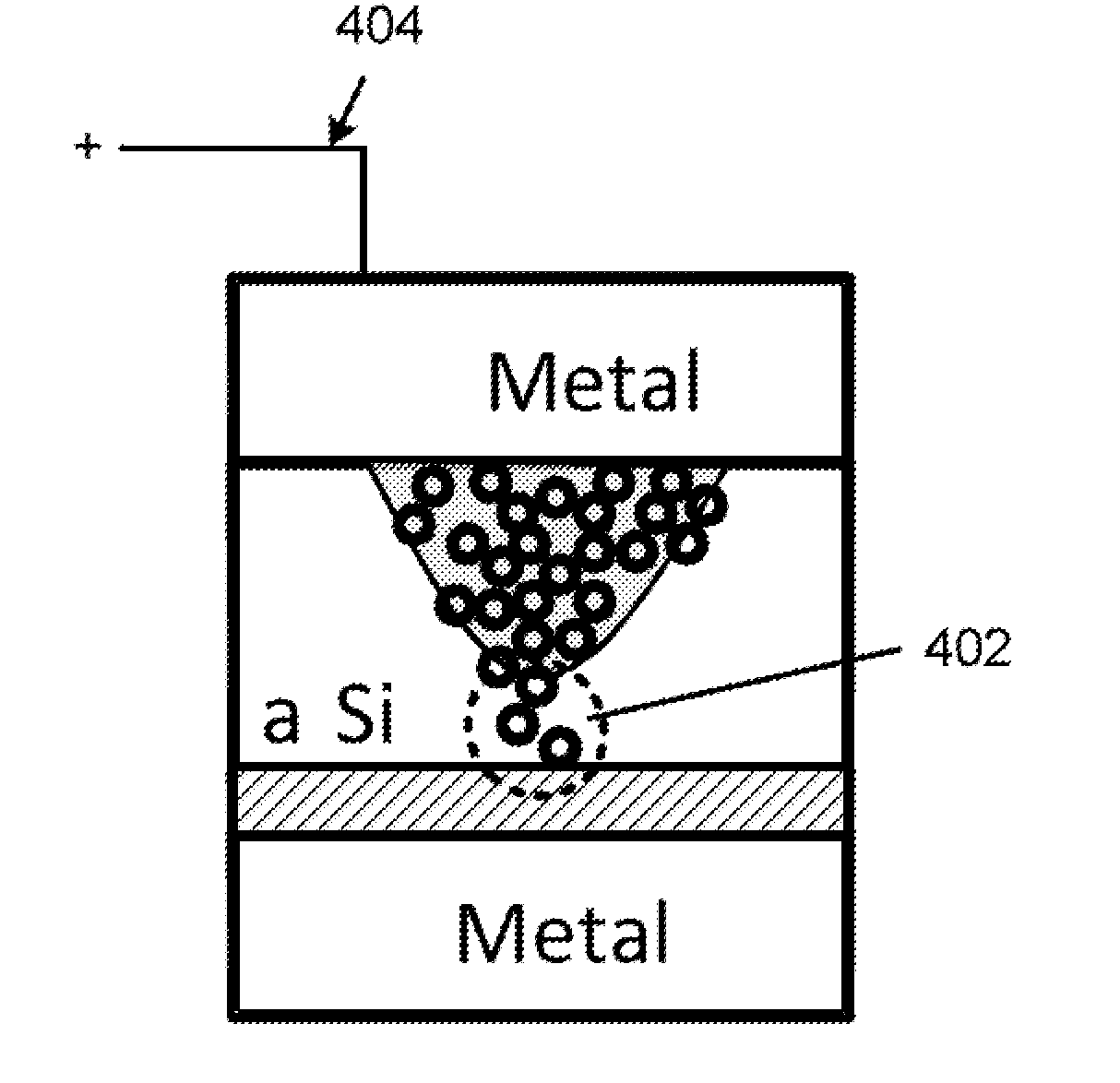

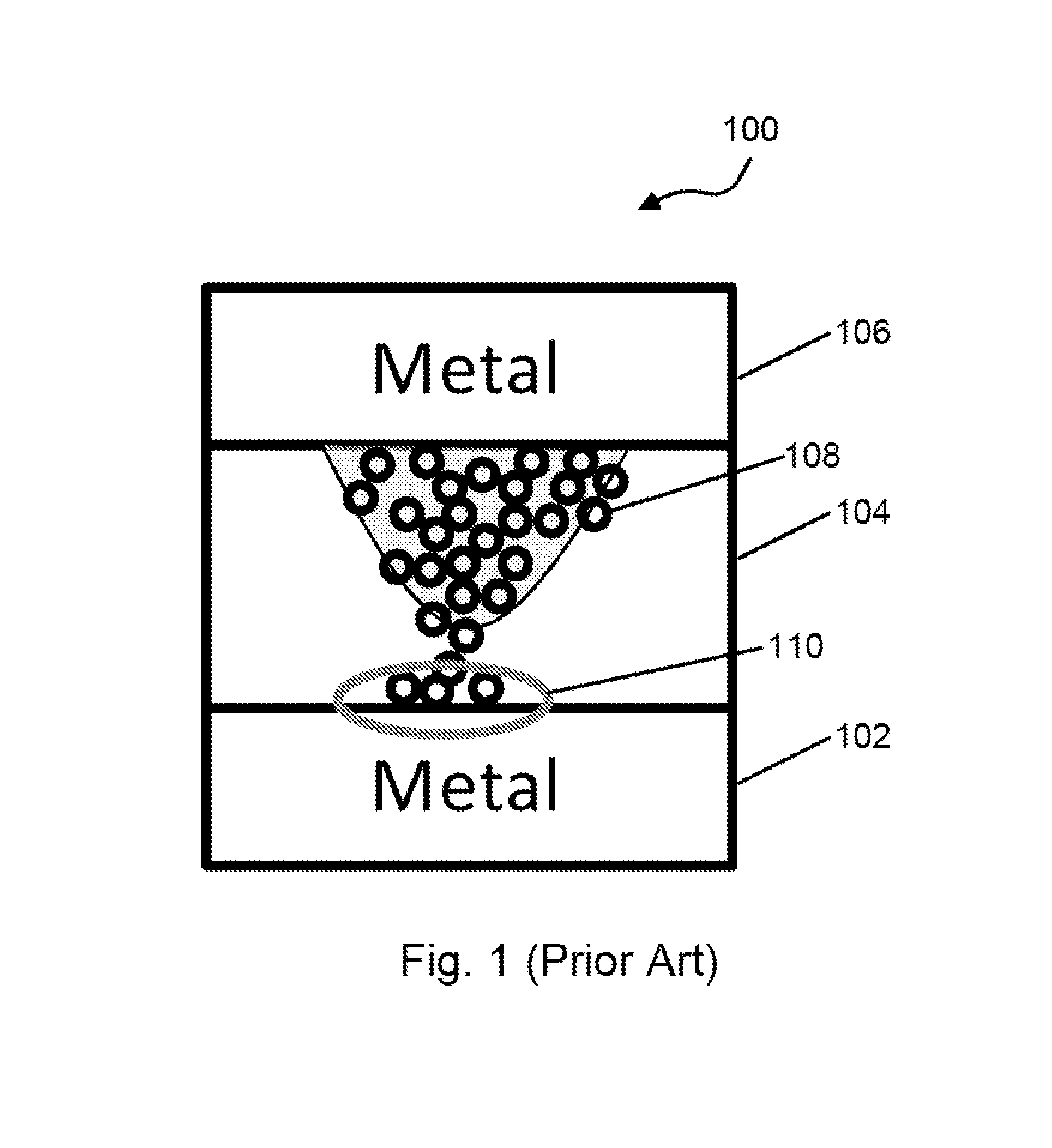

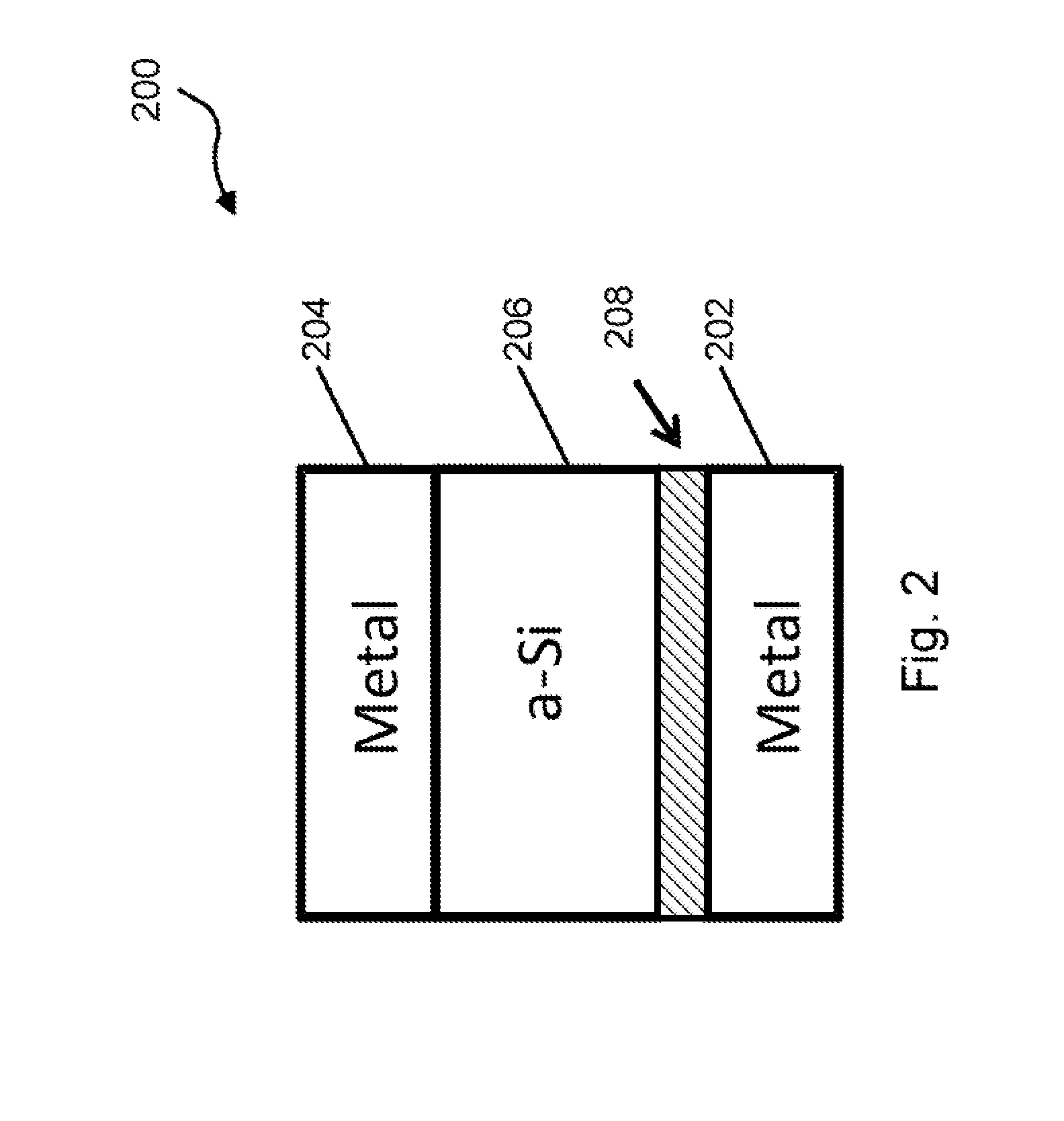

Device switching using layered device structure

ActiveUS20120043519A1Total current dropImproved switchingSolid-state devicesDigital storageElectricityElectrical resistance and conductance

A resistive switching device. The device includes a first electrode comprising a first metal material overlying the first dielectric material and a switching material comprising an amorphous silicon material. The device includes a second electrode comprising at least a second metal material. In a specific embodiment, the device includes a buffer material disposed between the first electrode and the switching material. The buffer material provides a blocking region between the switching material and the first electrode so that the blocking region is substantially free from metal particles from the second metal material when a first voltage is applied to the second electrode.

Owner:CROSSBAR INC

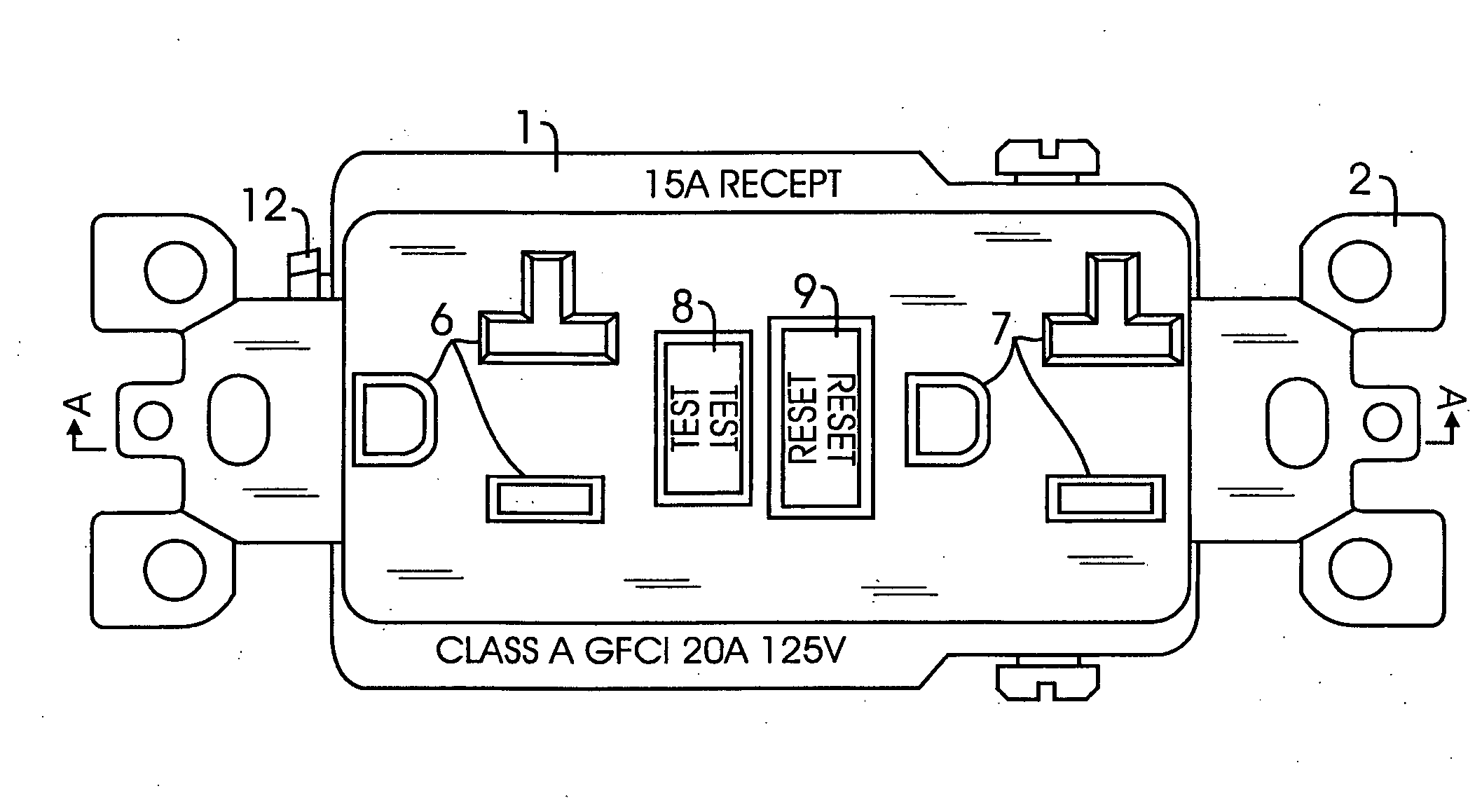

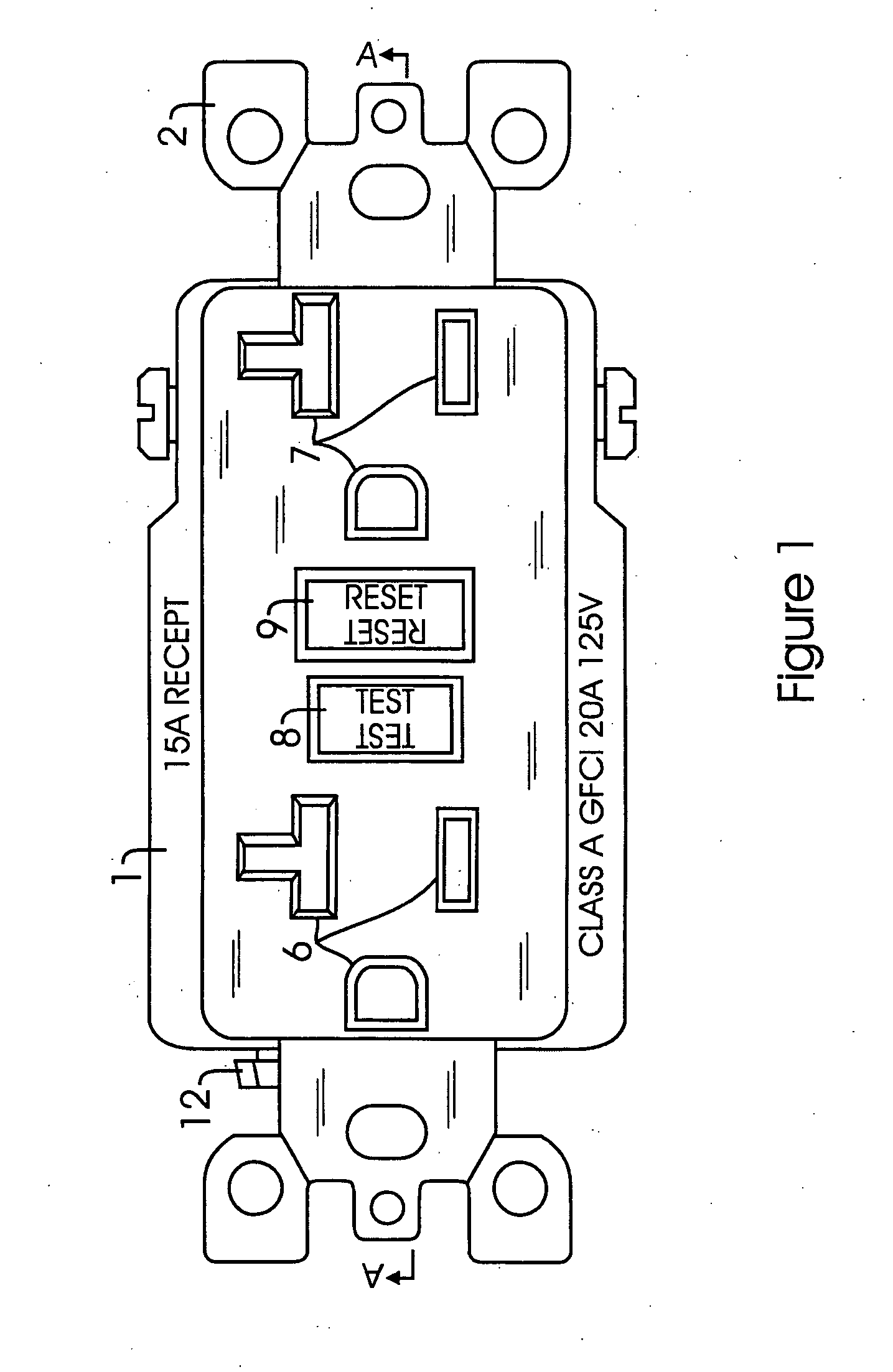

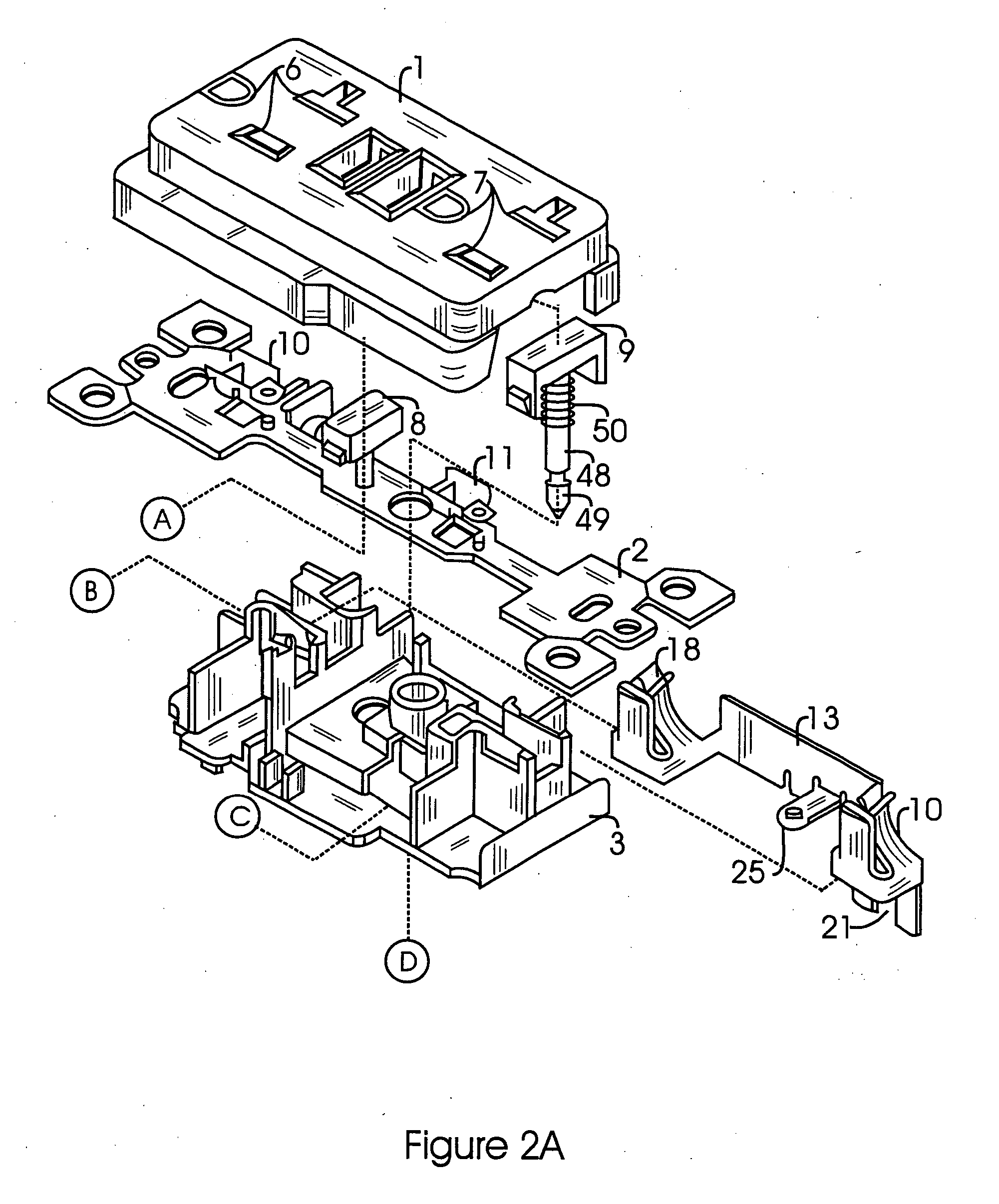

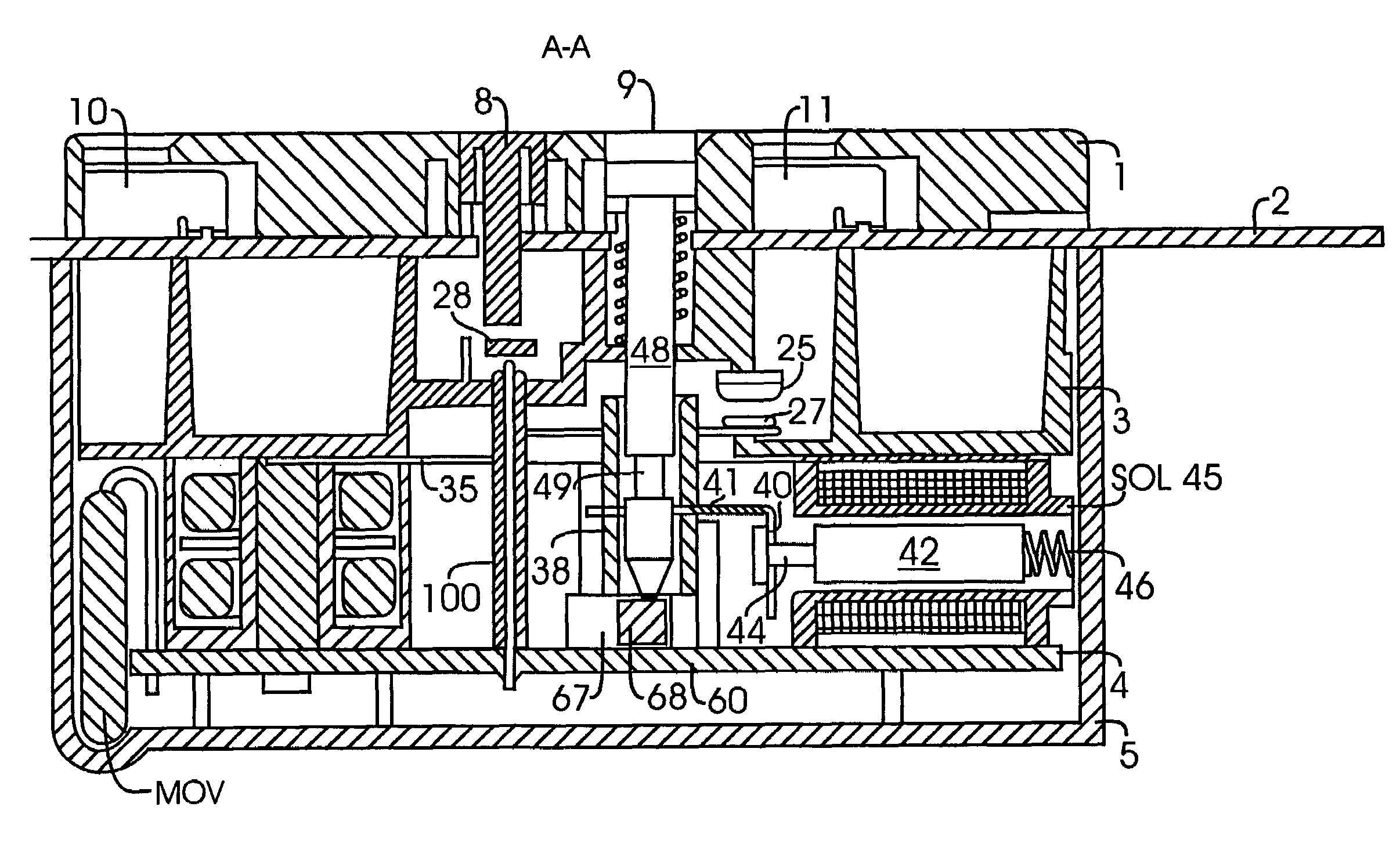

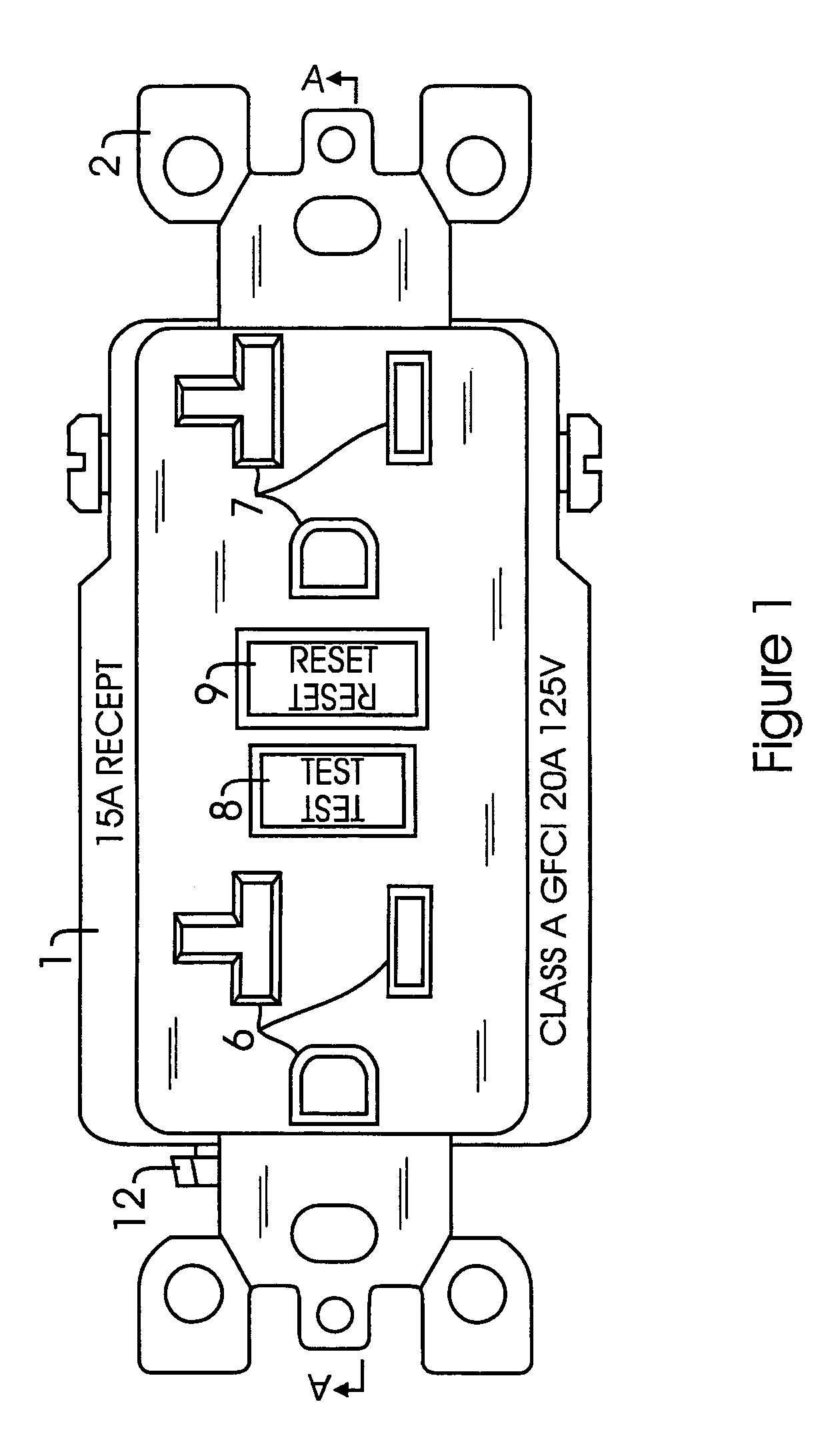

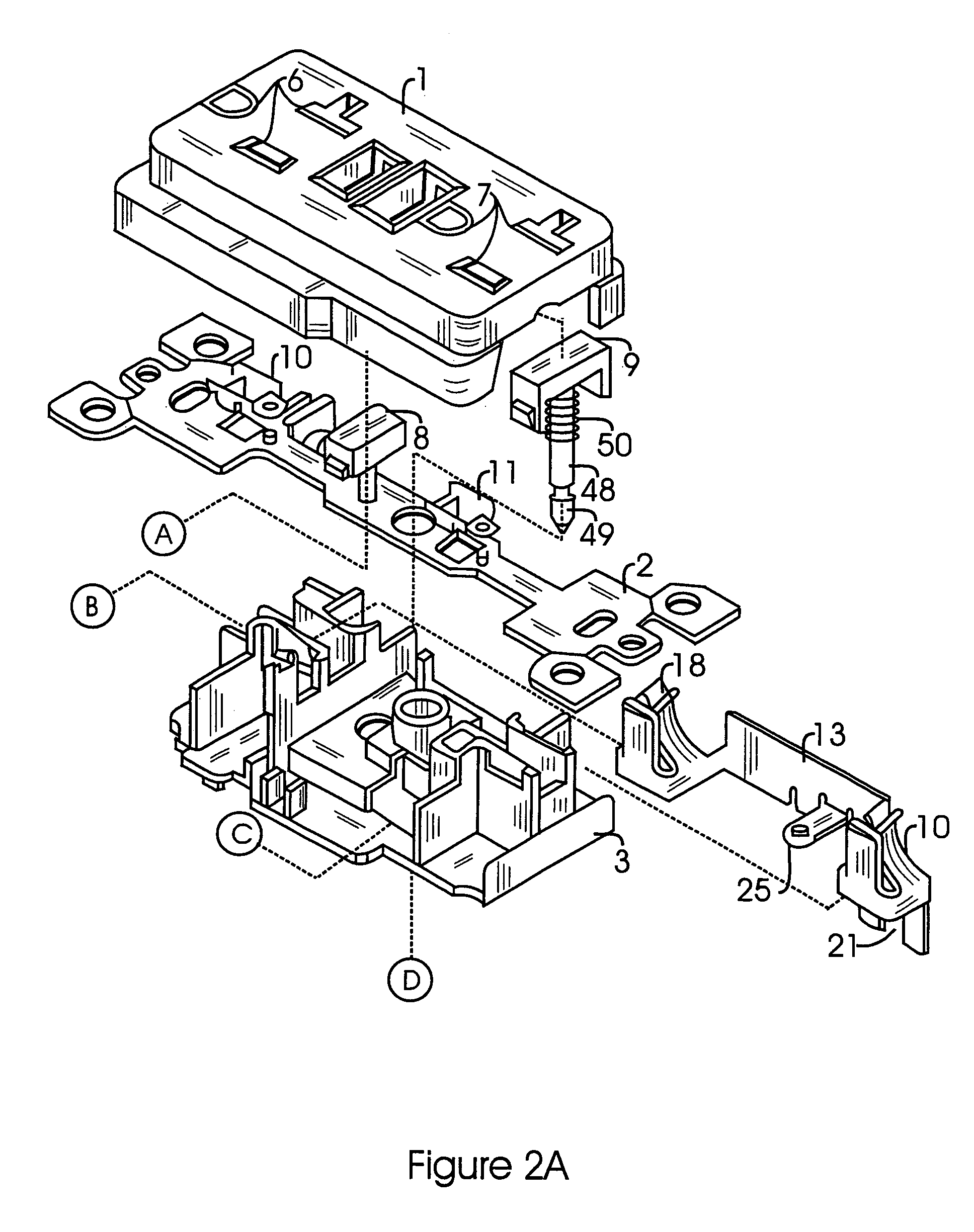

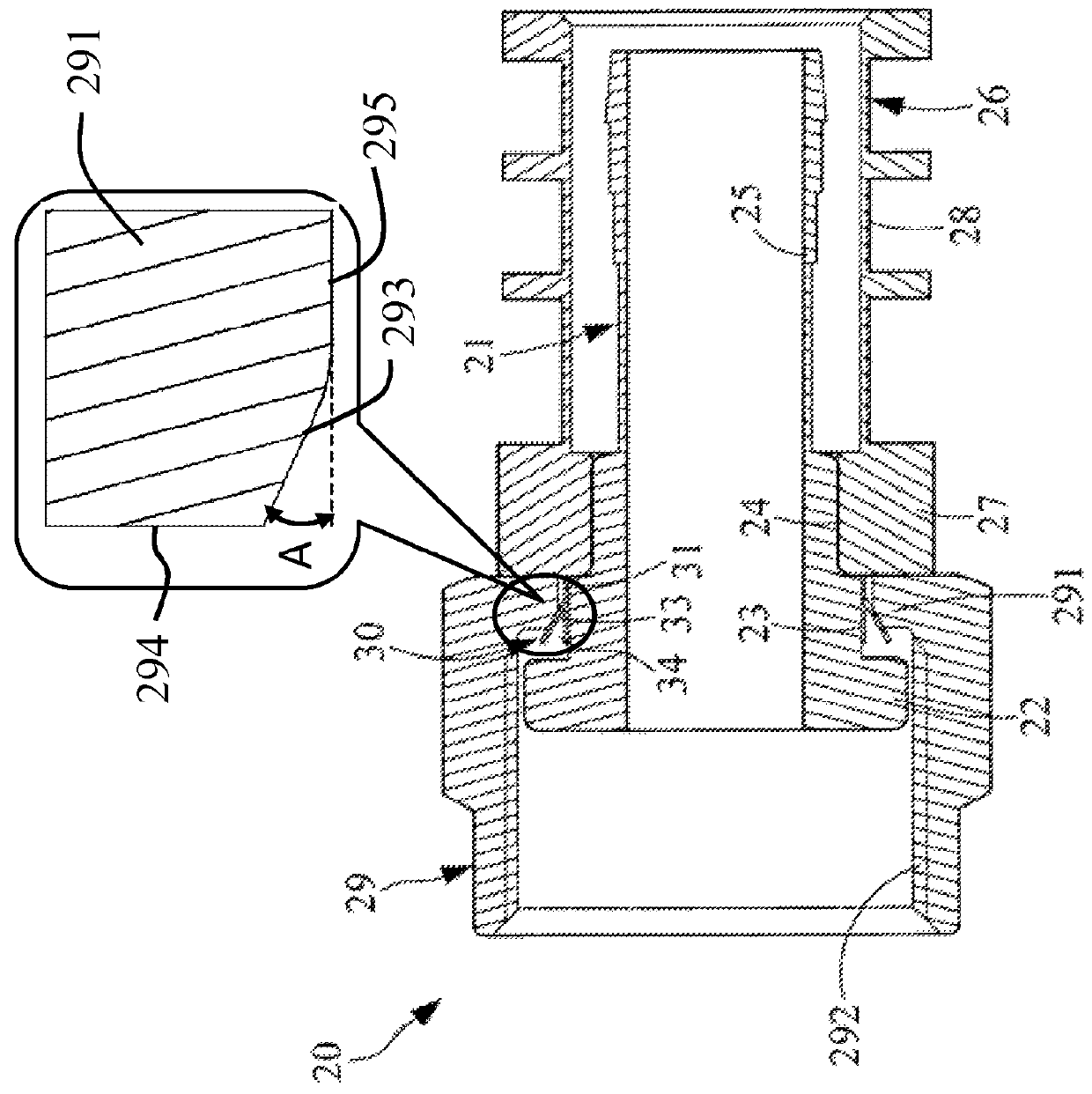

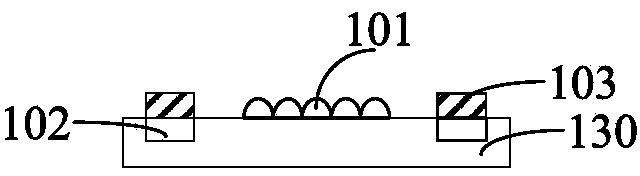

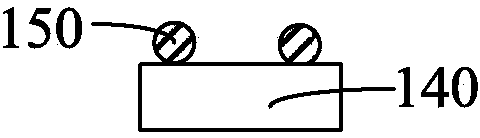

Ground-fault circuit interrupter with reverse wiring protection

InactiveUS20050264383A1Reduce functionPrevent movementTwo pole connectionsIncorrect coupling preventionGround and neutralElectricity

A circuit interrupting device having a reverse wiring protection function is disclosed. The circuit interrupting device includes a housing having a cover and a base, a mounting plate, and an electrical component mounting member, a pair of input hot and neutral conductors and a pair of output hot and neutral conductors, a differential transformer for detecting a leakage current, a disconnecting mechanism for connecting and disconnecting the output conductors to and from input conductors, and a mechanism for preventing reverse wiring, which includes a coil connected to the input hot and neutral conductors and a moveable piece that moves when the coil is energized. The input and output conductors are electrically connected only when the coil is energized by correctly connecting the power wires to the input conductors of the device. This device thus provides both leakage current protection and reverse wiring protection that protects against incorrect wiring during installation.

Owner:BINGHAM MCCUTCHEN +1

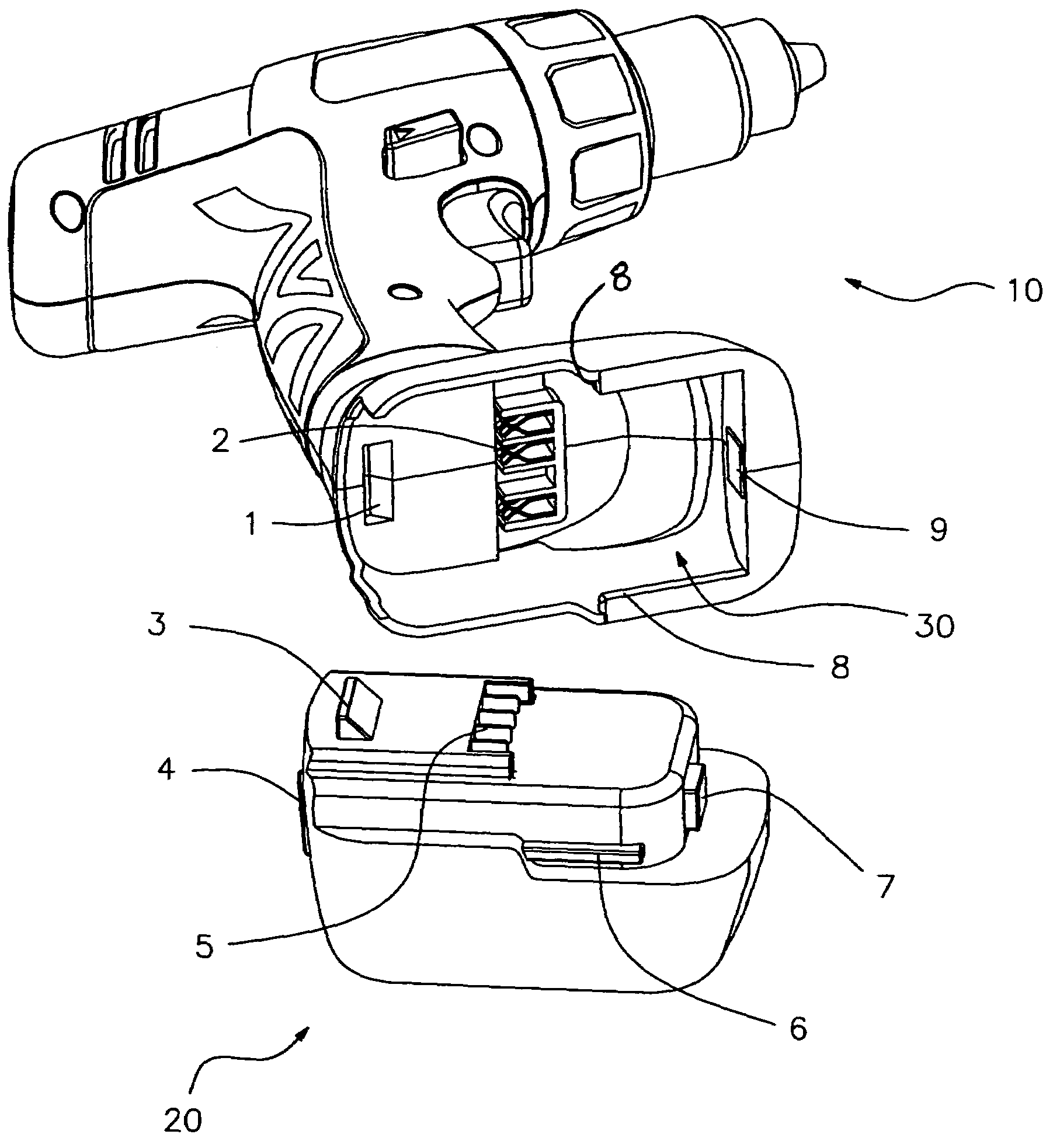

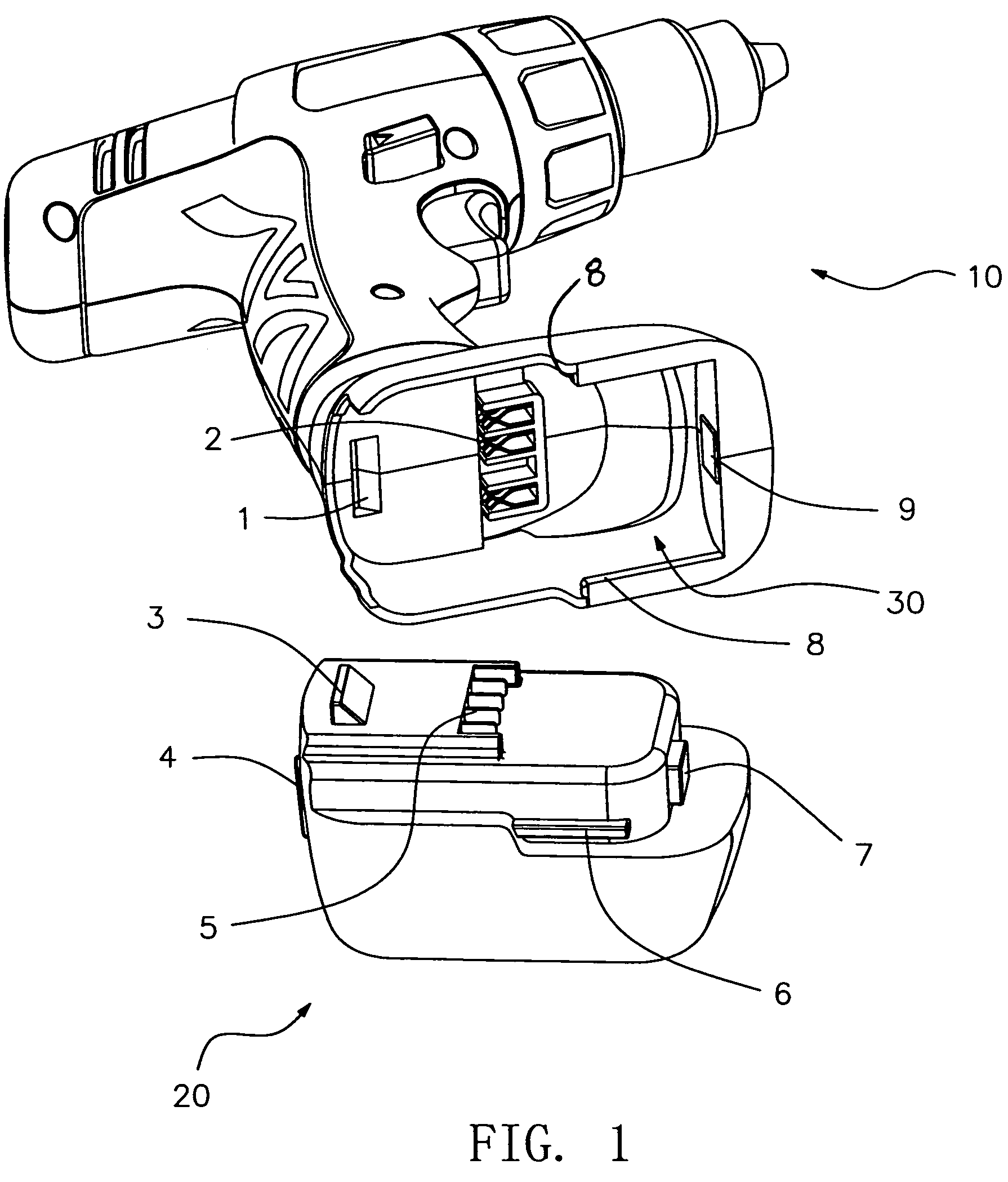

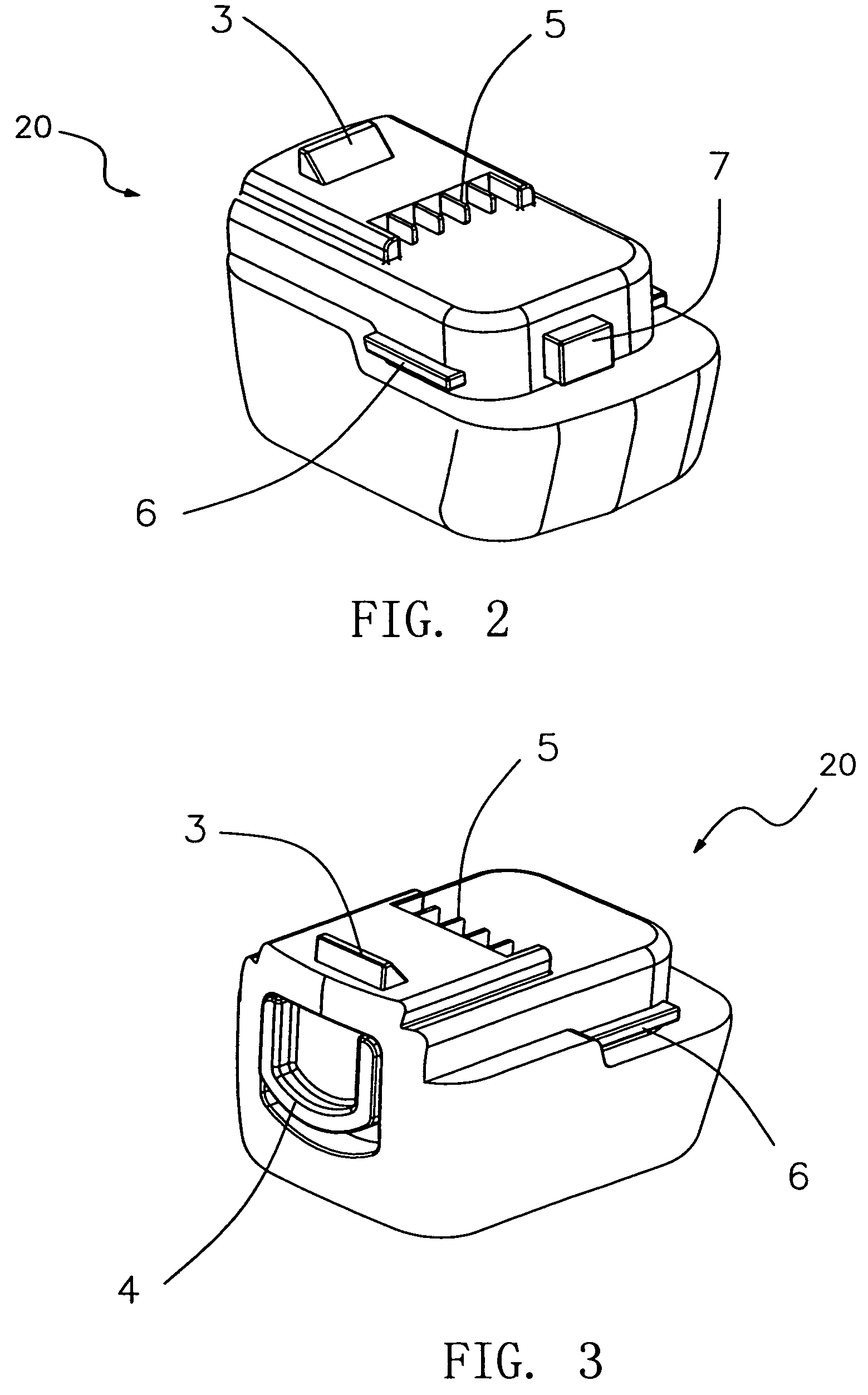

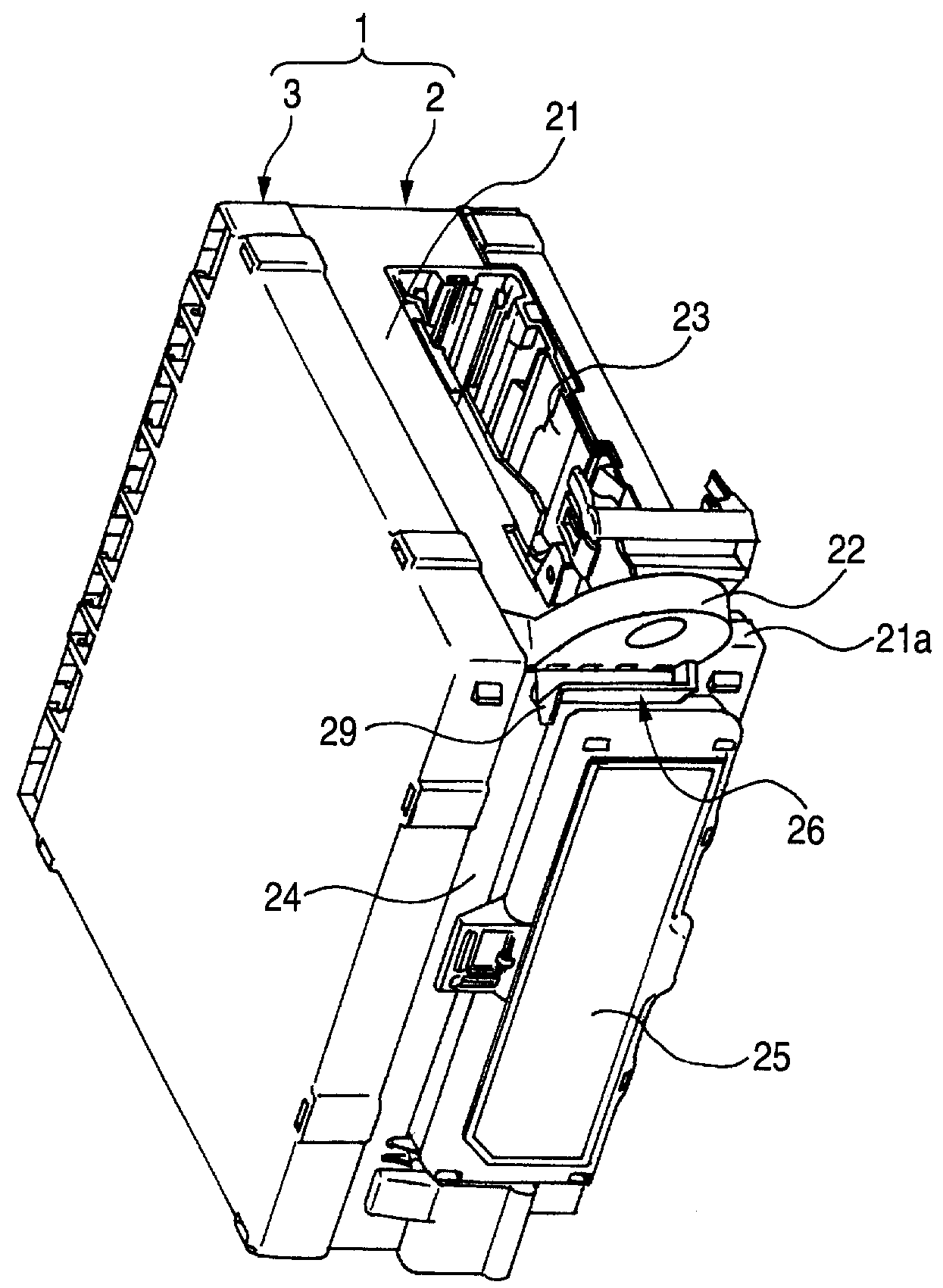

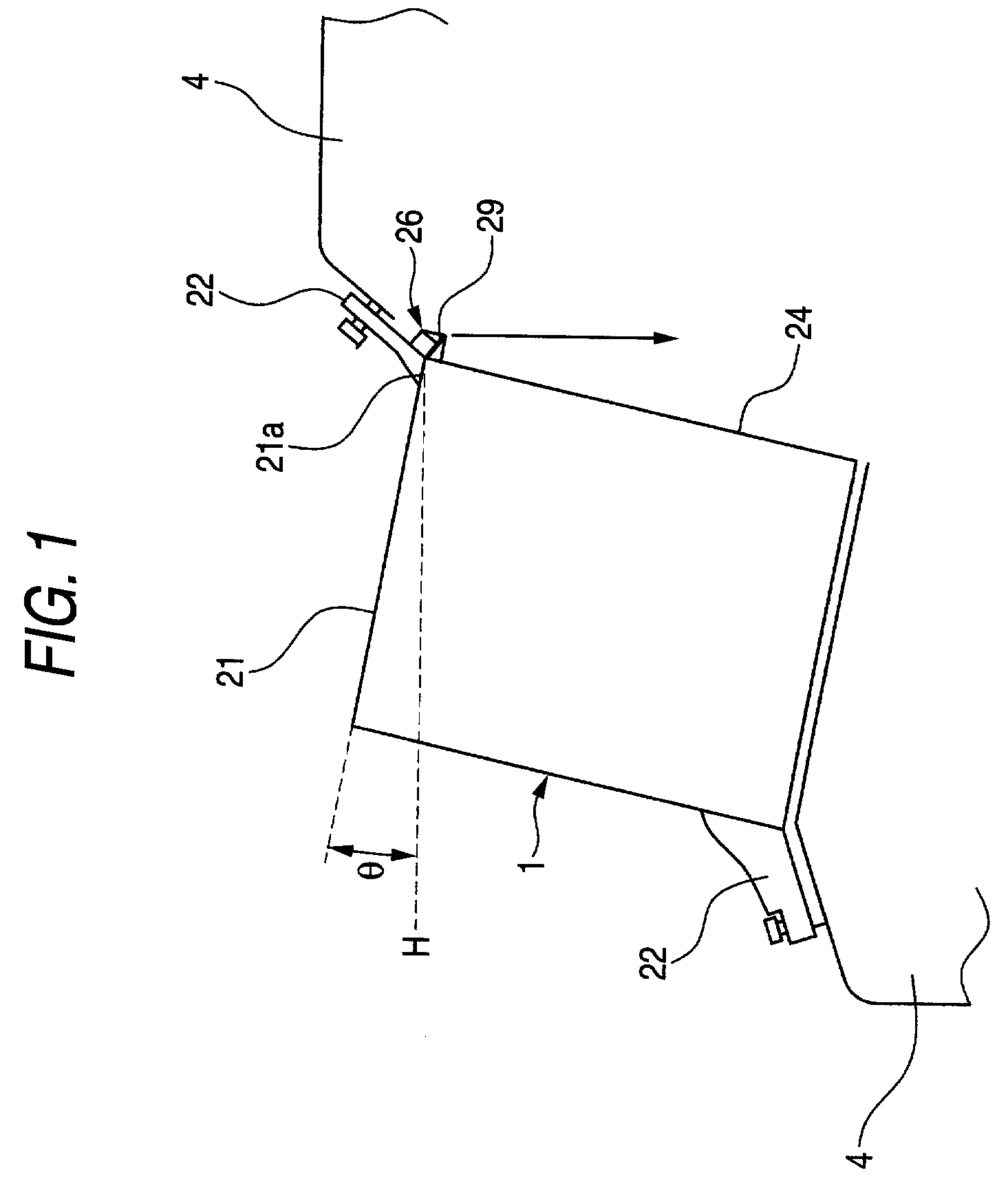

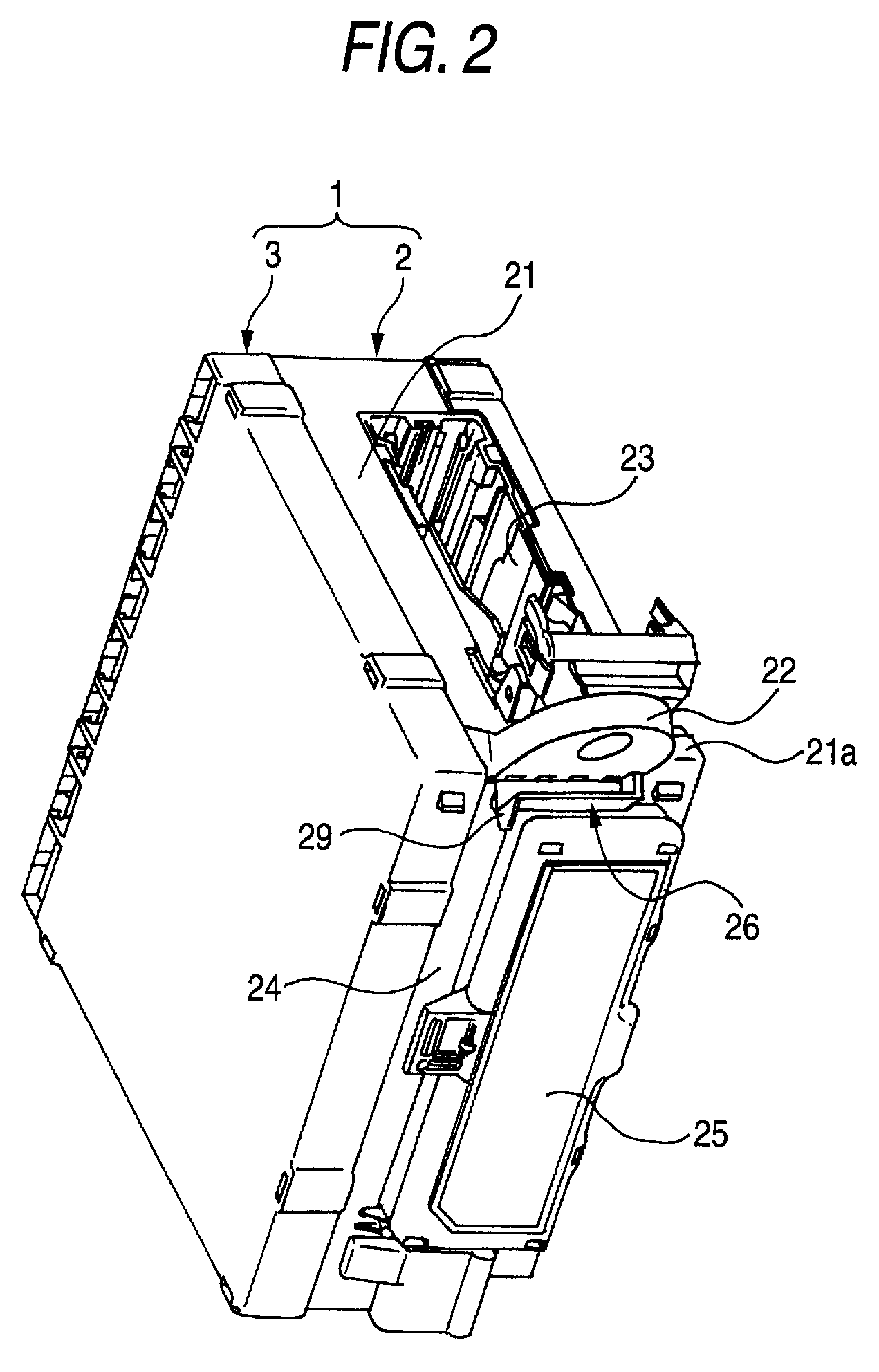

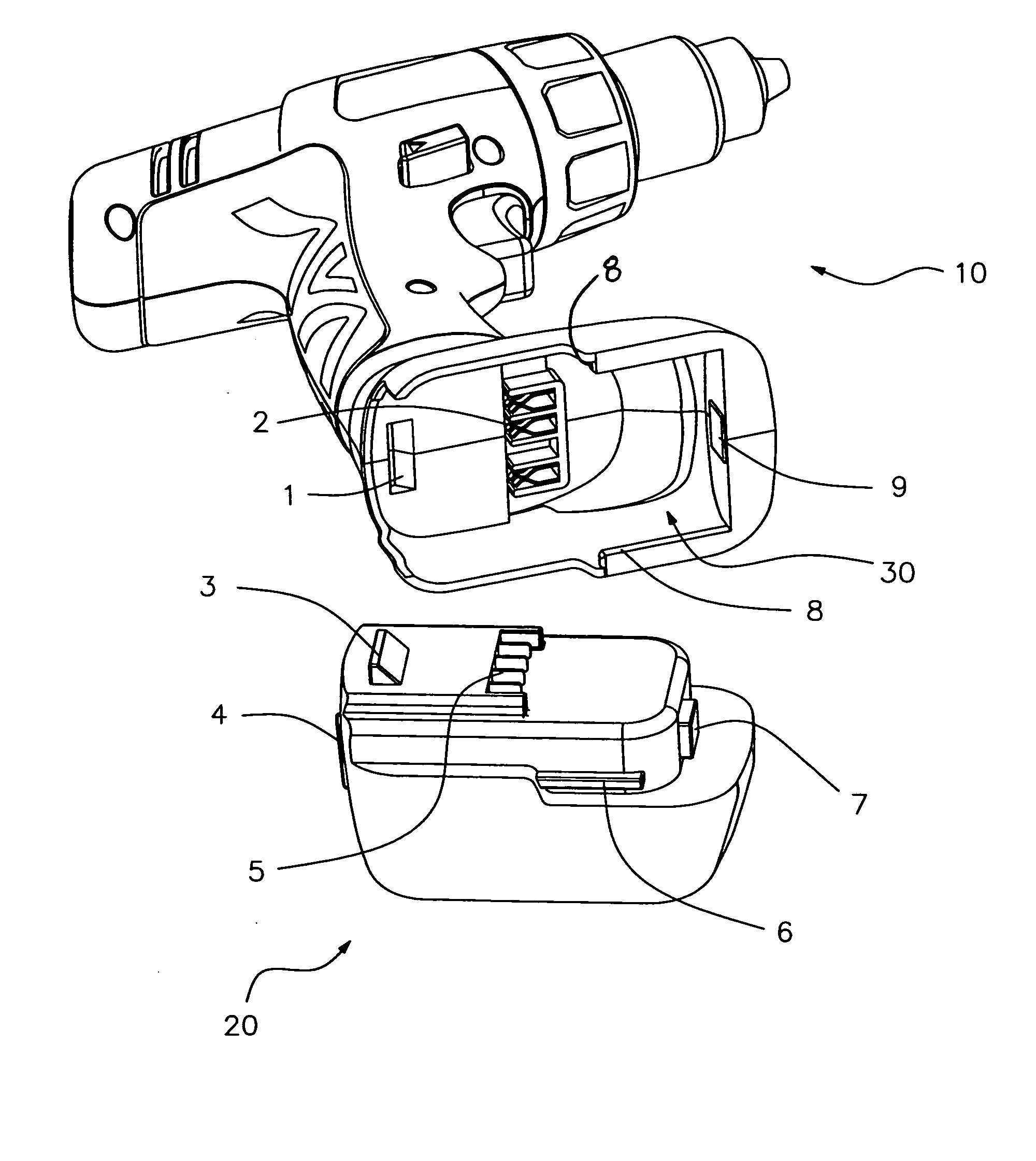

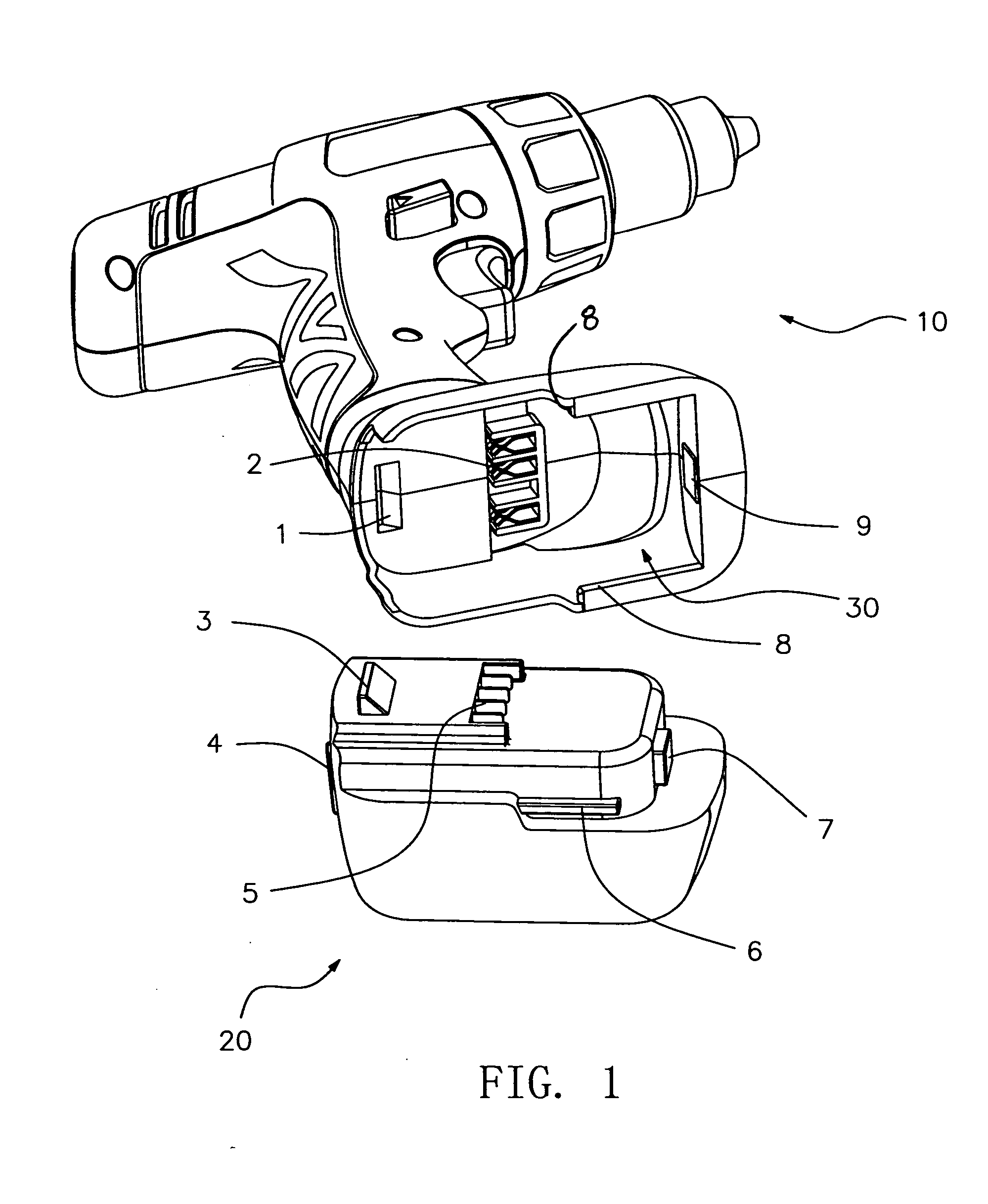

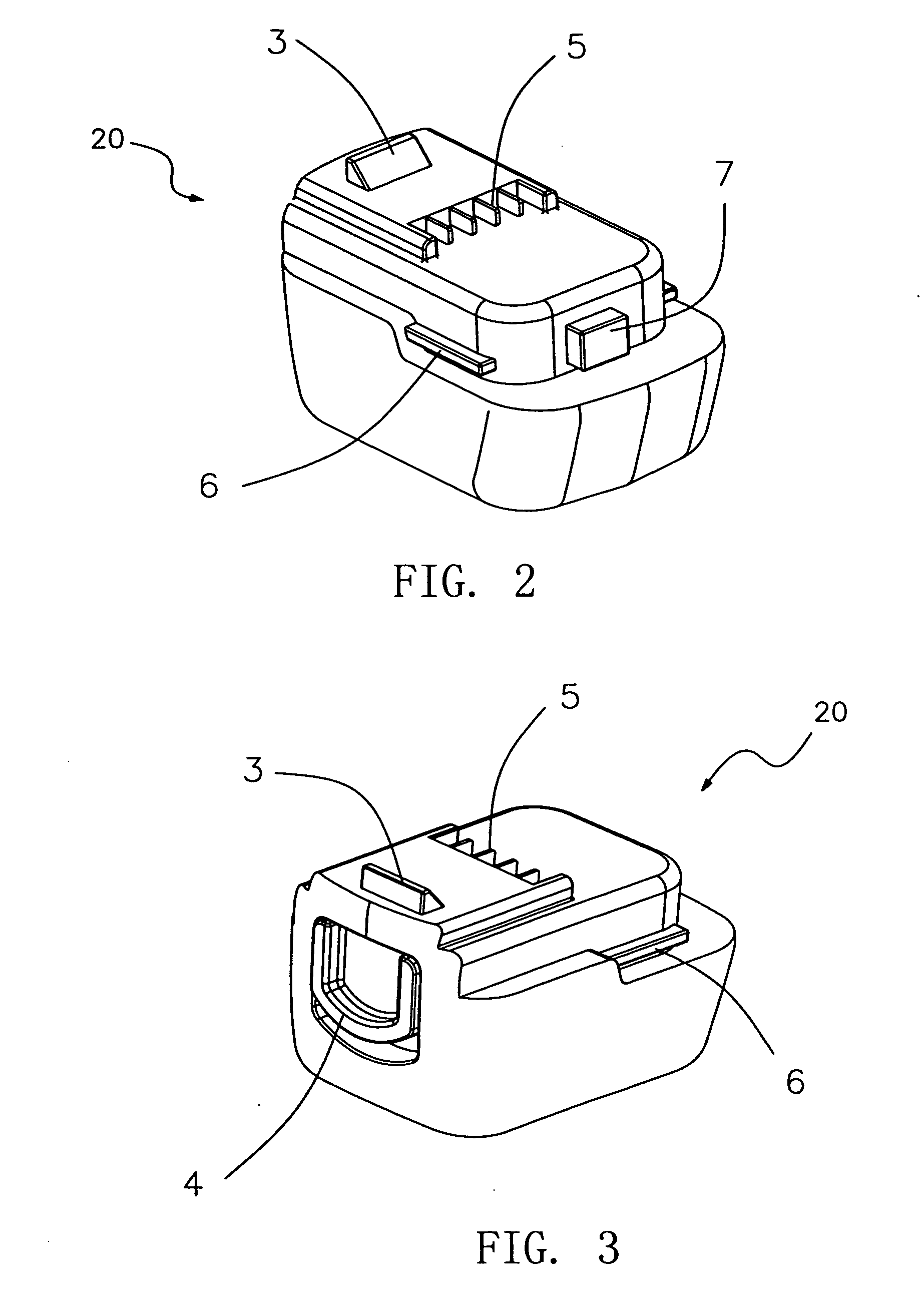

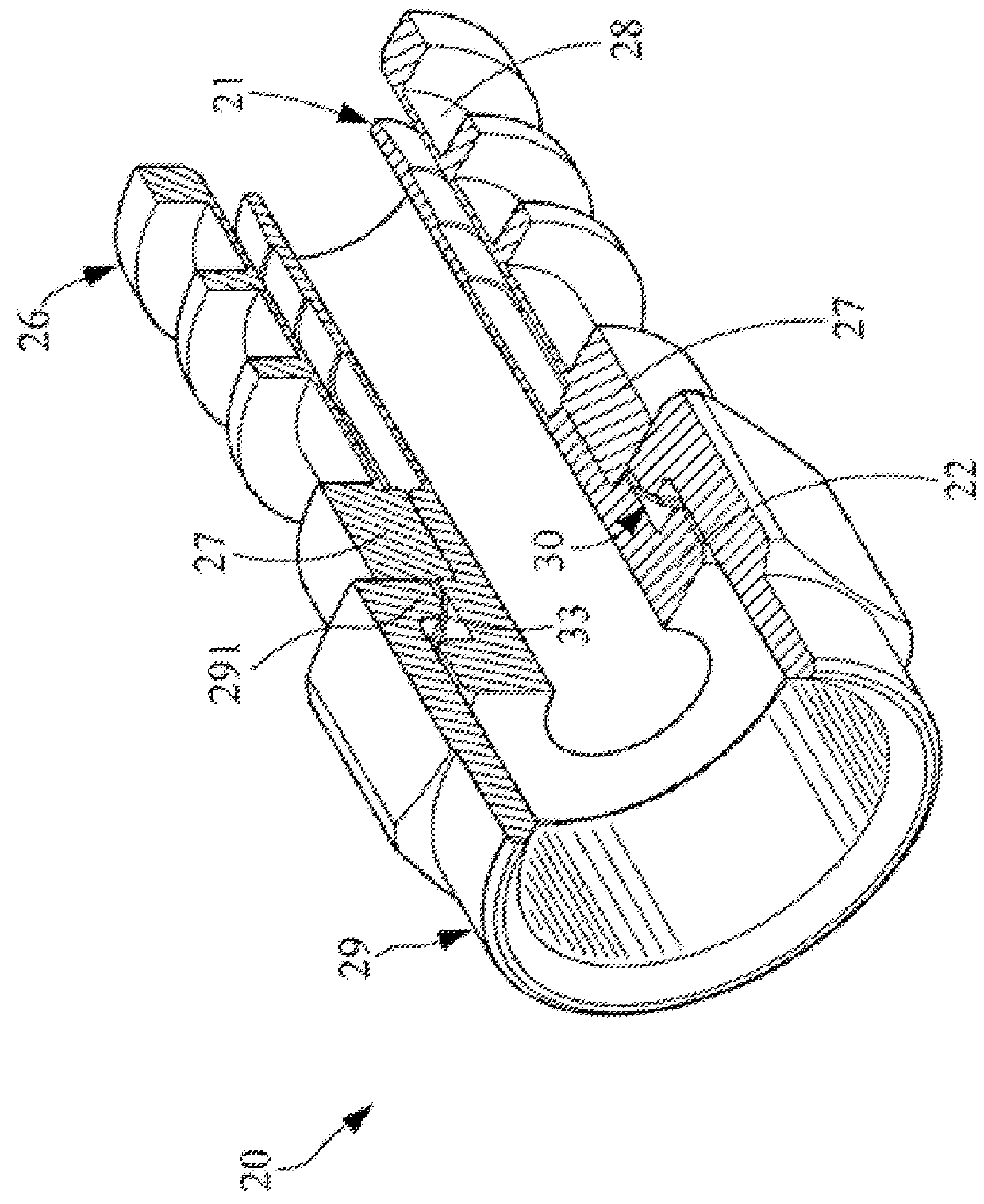

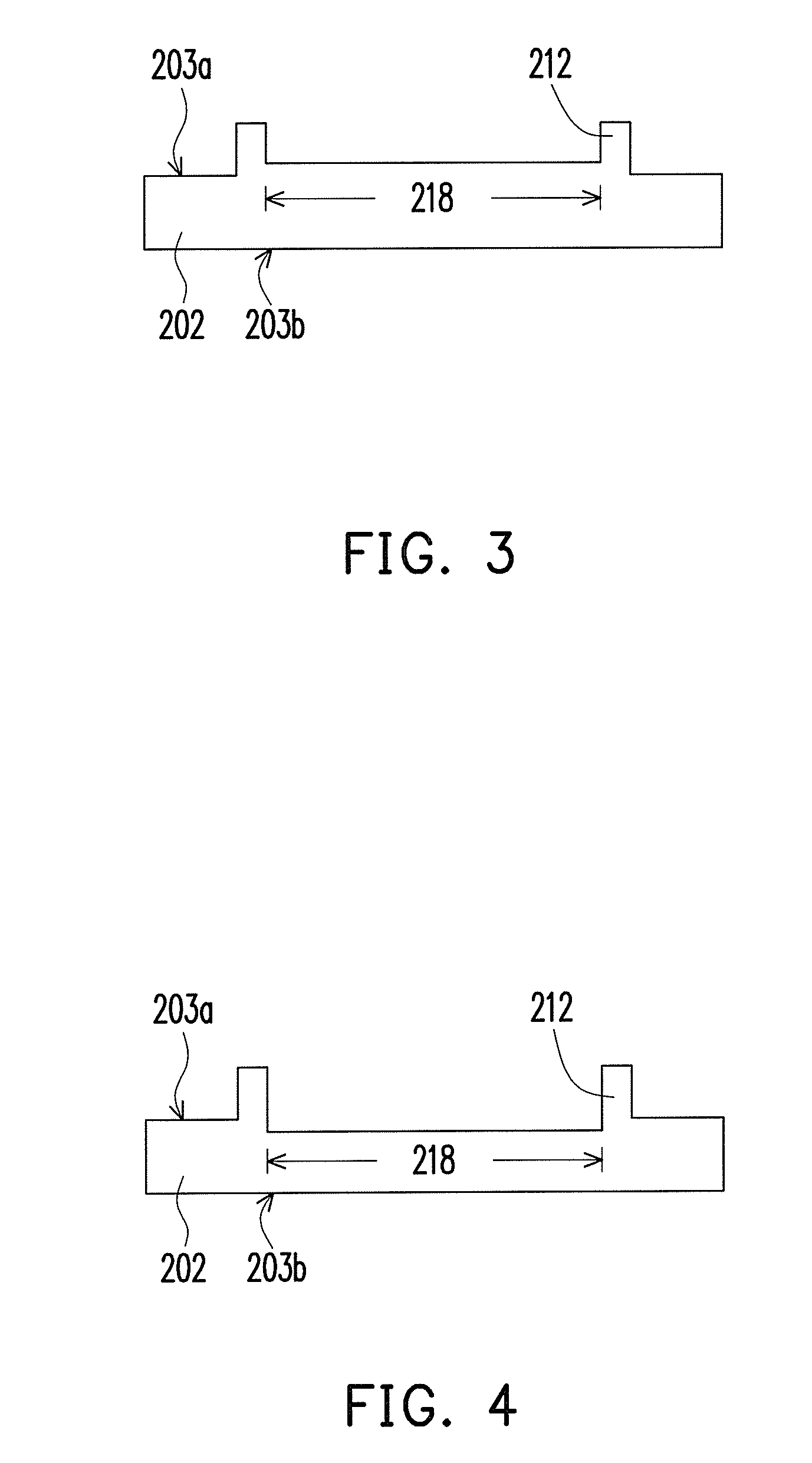

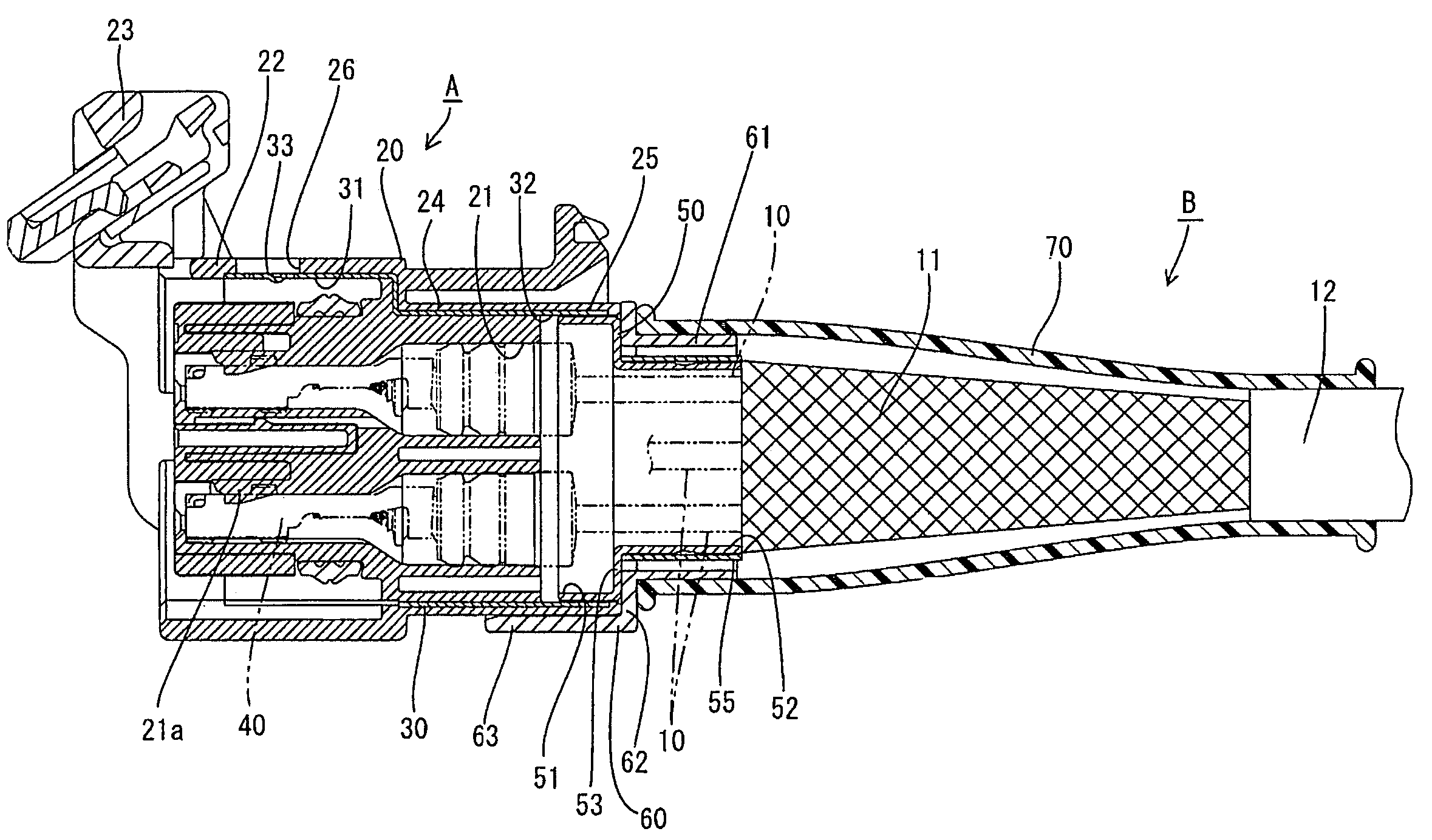

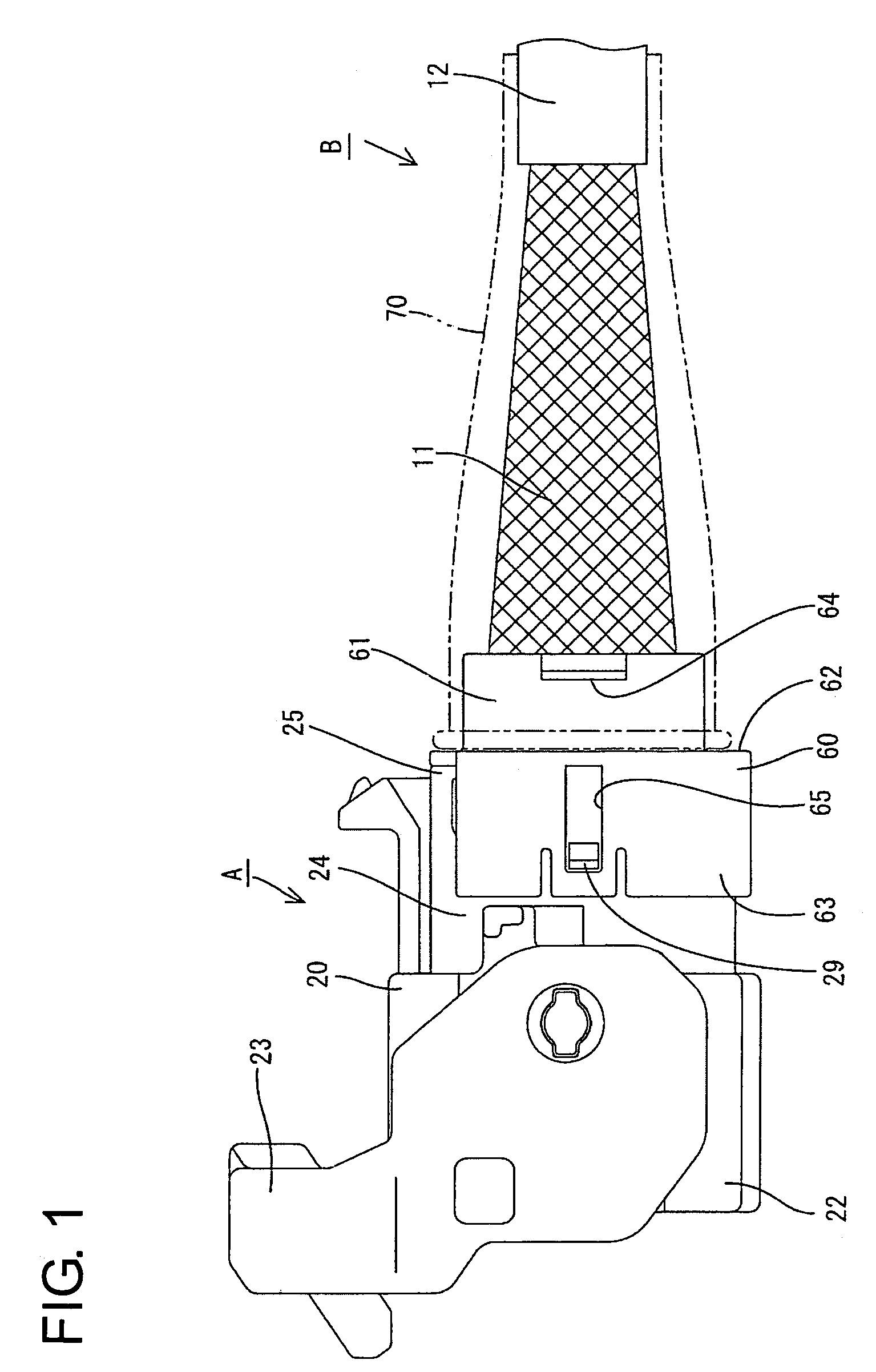

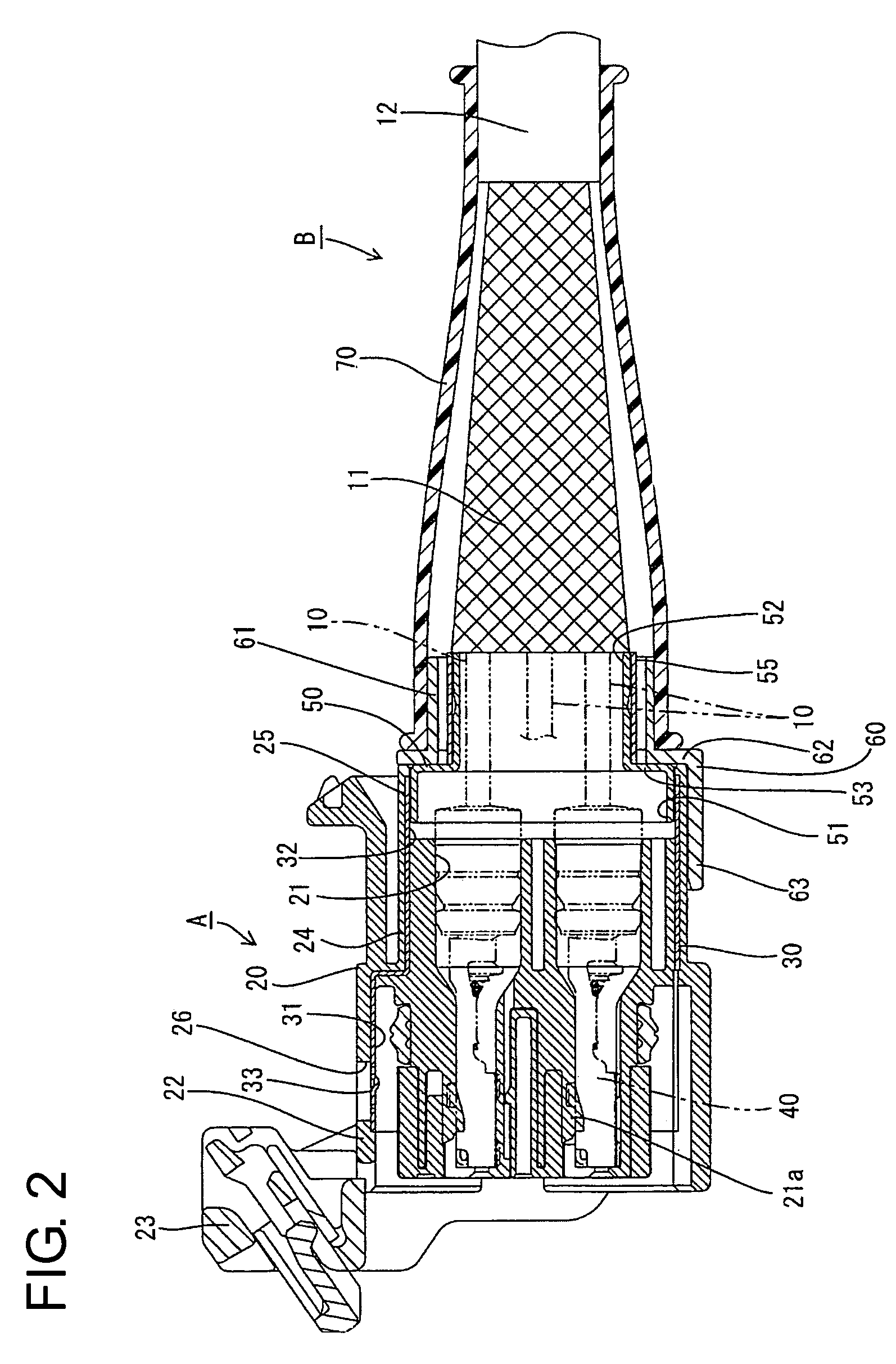

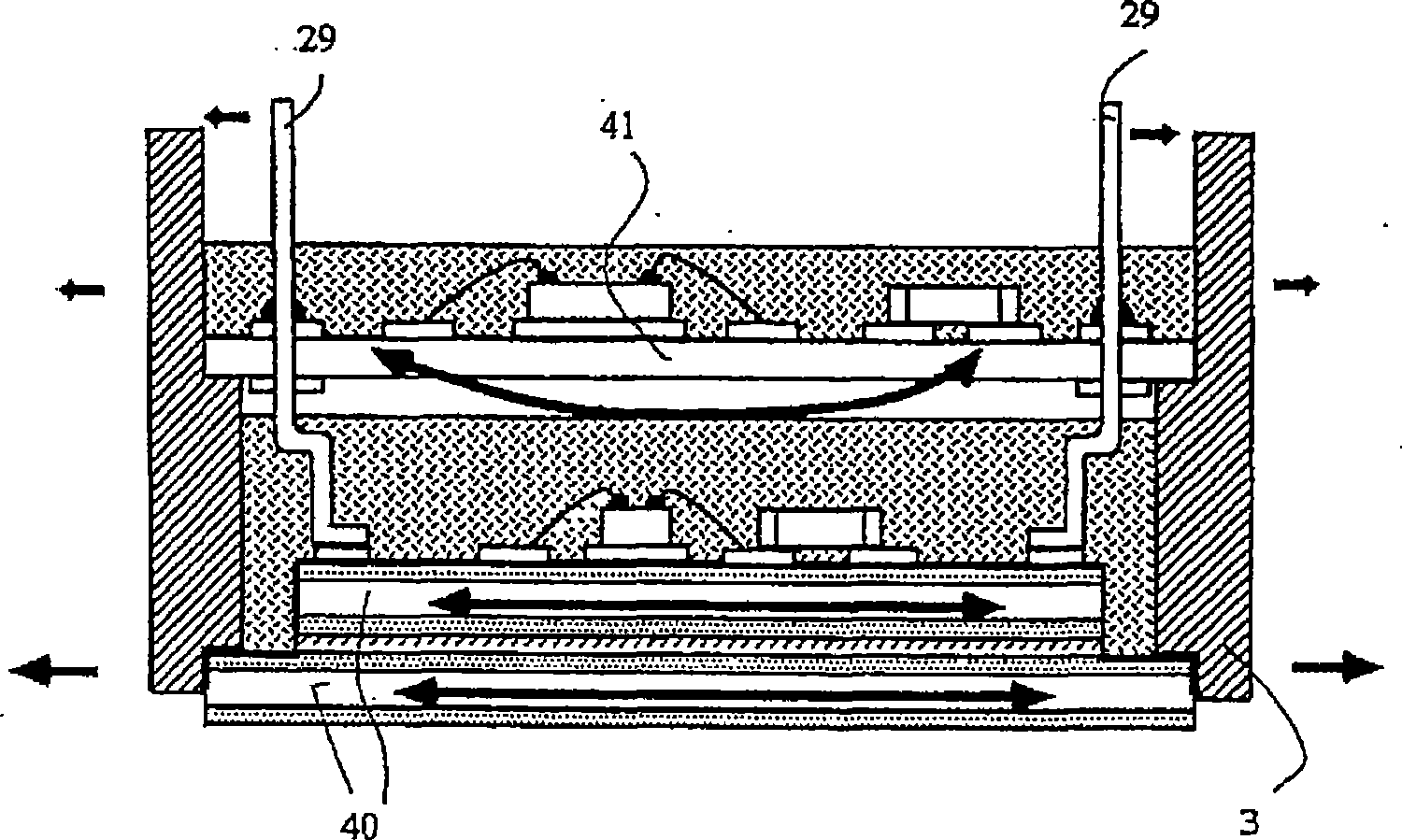

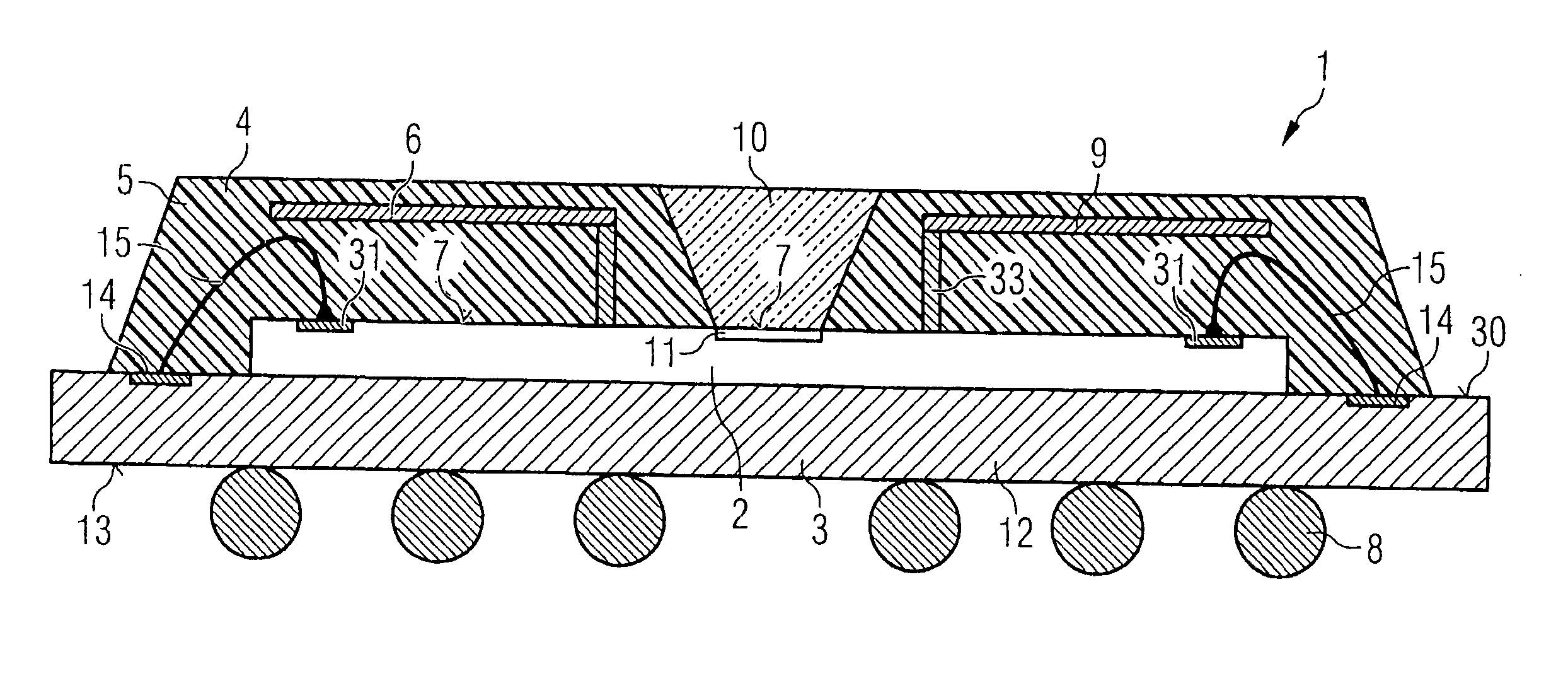

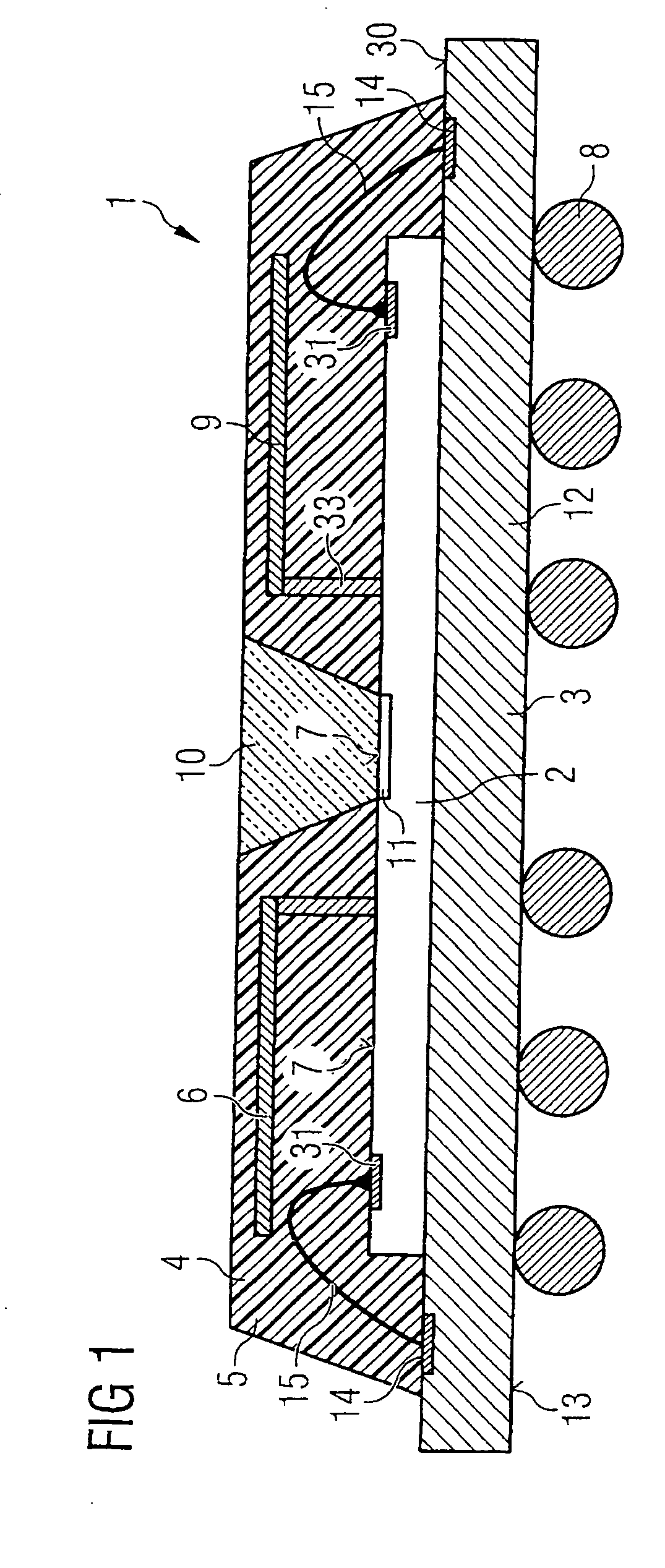

Power tool with battery power supply

InactiveUS7243734B2Durable and reliable attachment mechanismAvoid electrical connectionBatteries circuit arrangementsDrilling rodsElectricityElectrical battery

The present invention relates to a power tool with battery power supply comprising a main body and a detachable battery package which are connected with each other via a securing frame and a locking assembly. The securing frame includes a guiding device, an locking / unlocking button located on one of the main body and the battery package. An electrical connection is provided between a motor in the main body and the battery package, and includes a plurality of electrode connectors and corresponding electrode contact tabs. A mechanism for creating a non-mechanical force is located between the main body and the battery package for pushing the battery package out of the securing frame. With such a mechanism, when the battery package is required to be replaced by another one or detached for charging, it is merely necessary to press the unlocking button downward, and the battery package then automatically slides out of the securing frame via the effect of the force so as to facilitate detaching the battery package from the main body of the power tool.

Owner:NANJING CHERVON IND

Ground-fault circuit interrupter with reverse wiring protection

InactiveUS7009473B2Reduce functionPrevent movementTwo pole connectionsContact vibration/shock dampingElectricityTransformer

A circuit interrupting device having a reverse wiring protection function is disclosed. The circuit interrupting device includes a housing having a cover and a base, a mounting plate, and an electrical component mounting member, a pair of input hot and neutral conductors and a pair of output hot and neutral conductors, a differential transformer for detecting a leakage current, a disconnecting mechanism for connecting and disconnecting the output conductors to and from input conductors, and a mechanism for preventing reverse wiring, which includes a coil connected to the input hot and neutral conductors and a moveable piece that moves when the coil is energized. The input and output conductors are electrically connected only when the coil is energized by correctly connecting the power wires to the input conductors of the device. This device thus provides both leakage current protection and reverse wiring protection that protects against incorrect wiring during installation.

Owner:BINGHAM MCCUTCHEN +1

Electrical connection box

InactiveUS7671275B2Prevent short-circuitingWater can be preventedInorganic gasesTransformers/inductances coils/windings/connectionsElectrical connectionEngineering

An electrical connection box includes a box body. The box body has a top wall and a side wall. The top wall is inclined to a horizontal plane and has an edge portion arranged at a lower side in an inclination of the top wall. The side wall is connected to an edge portion of the top wall. A drainage channel is provided along the edge portion of the top wall. A drainage port is provided at an edge of the drainage channel. The drainage port is placed at a position spaced from the side wall.

Owner:YAZAKI CORP

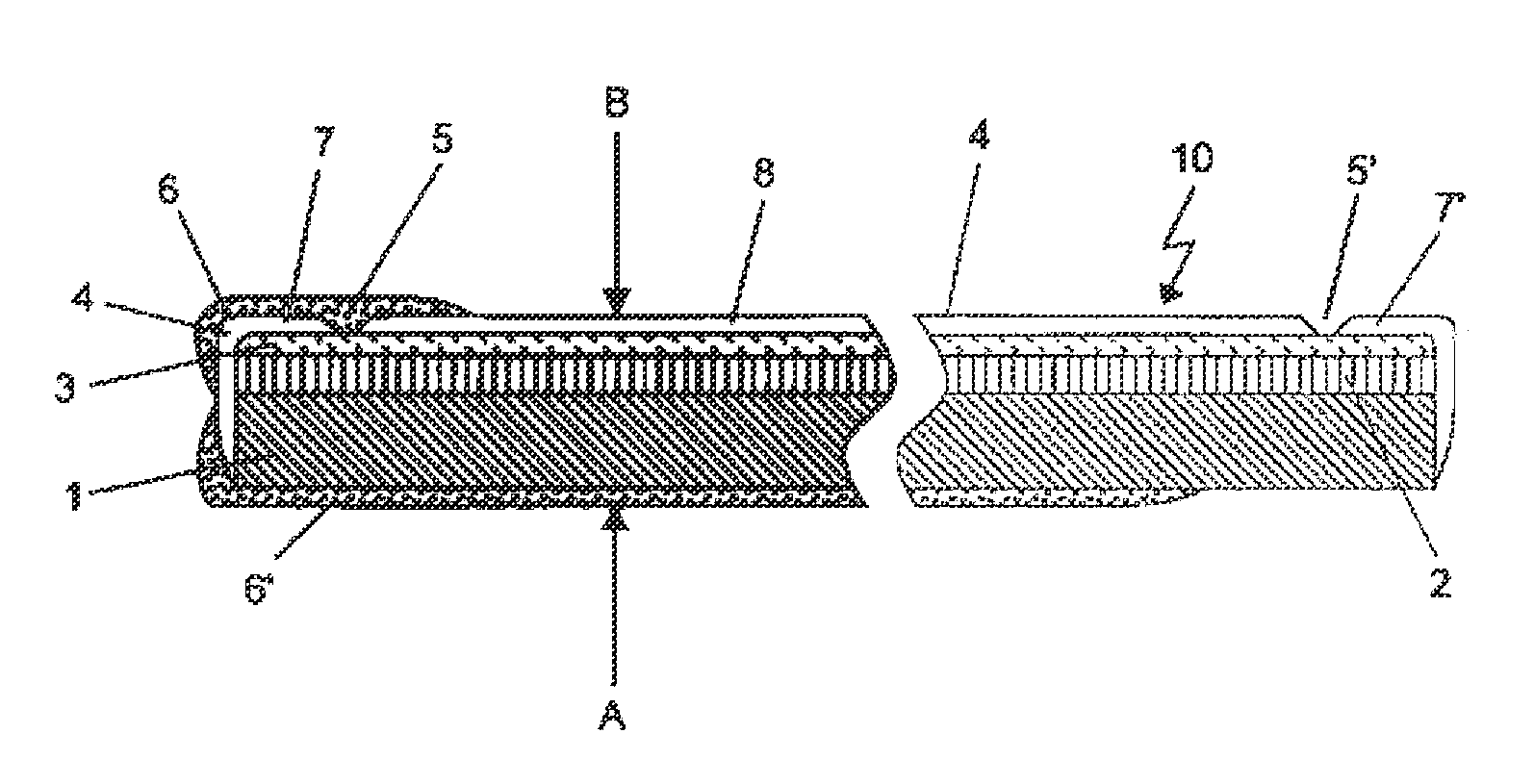

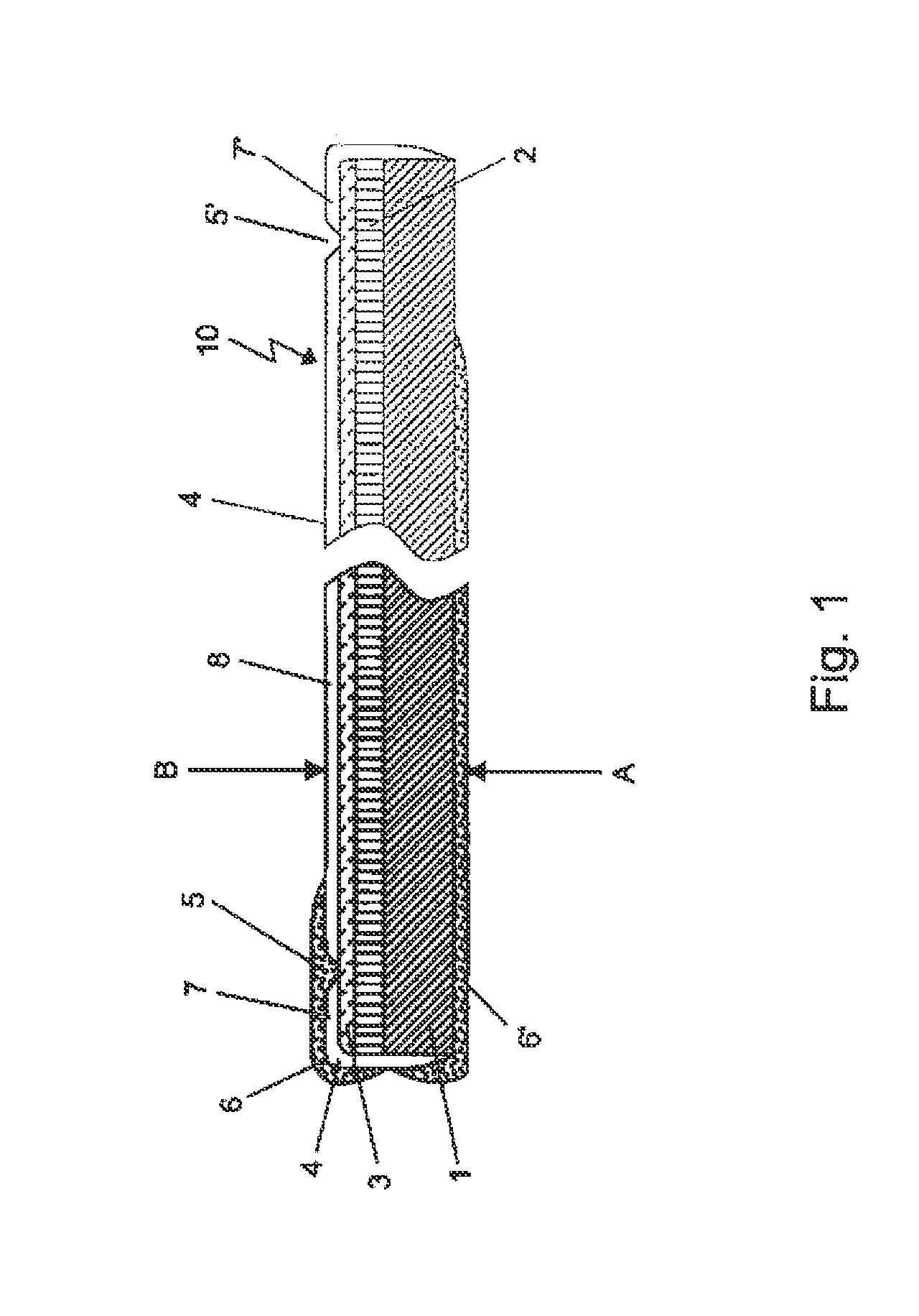

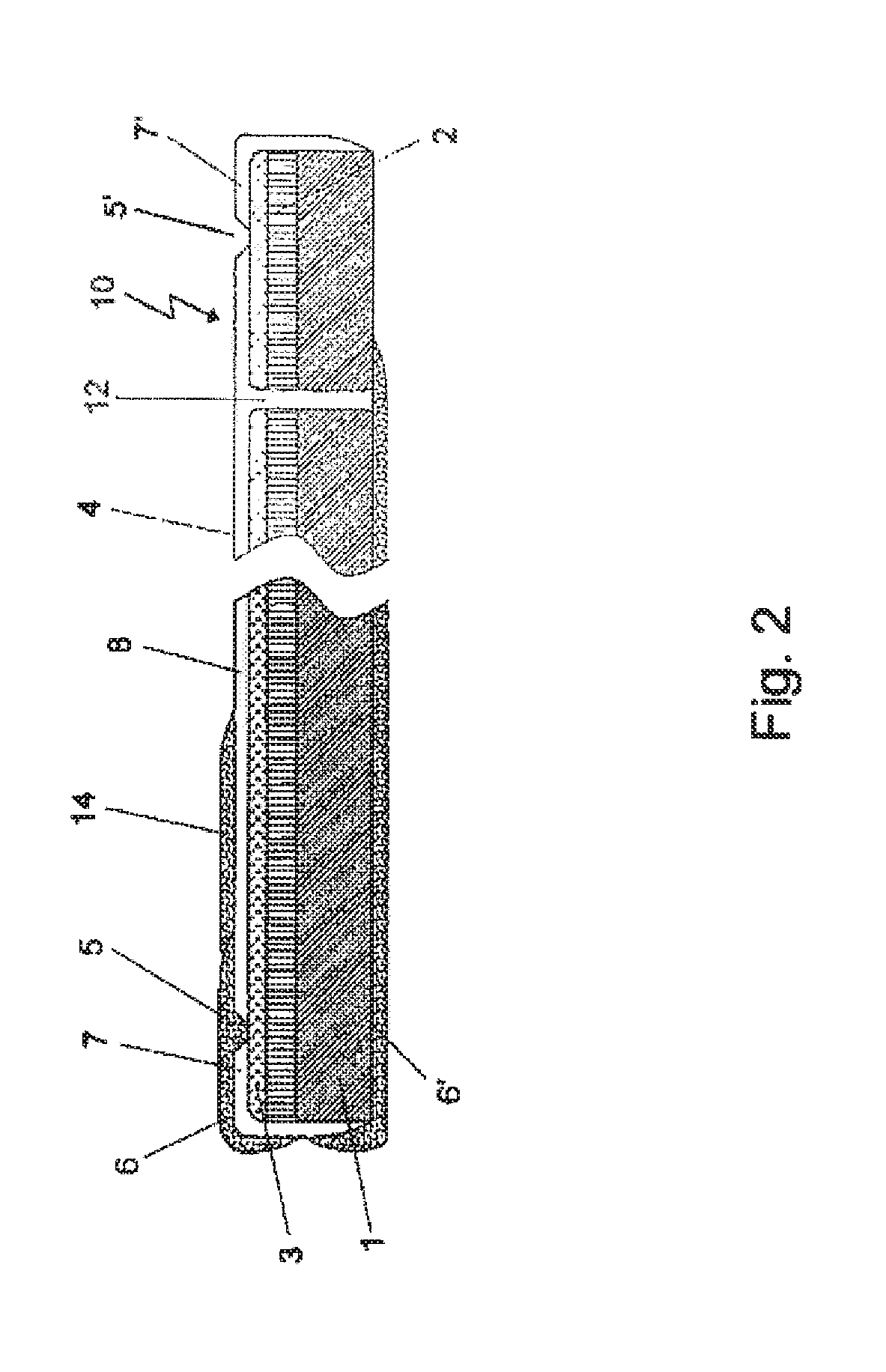

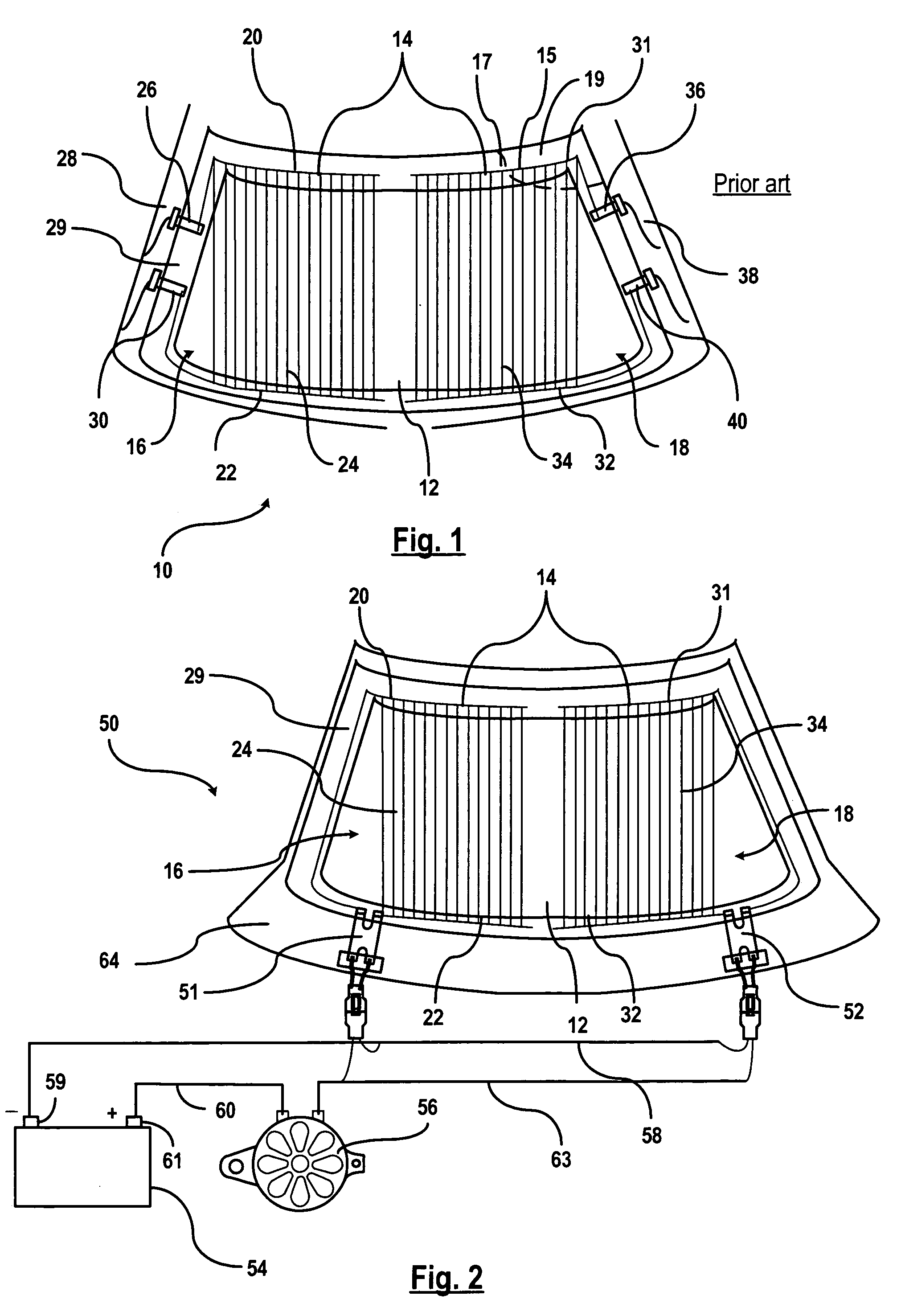

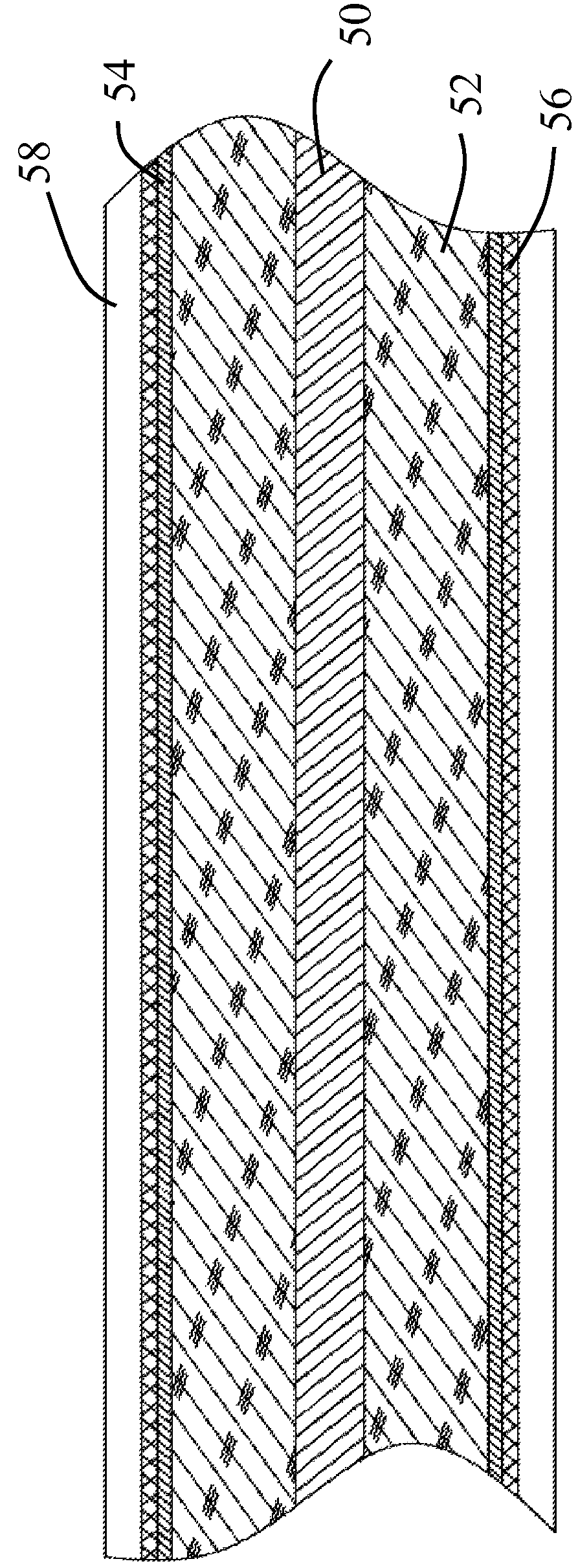

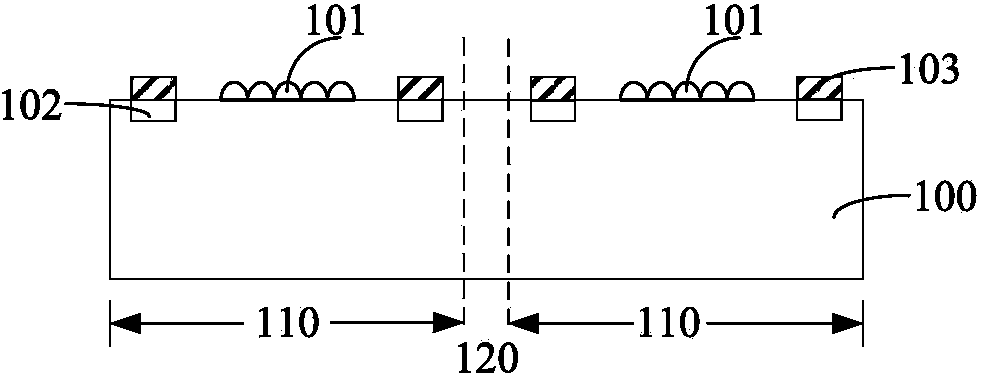

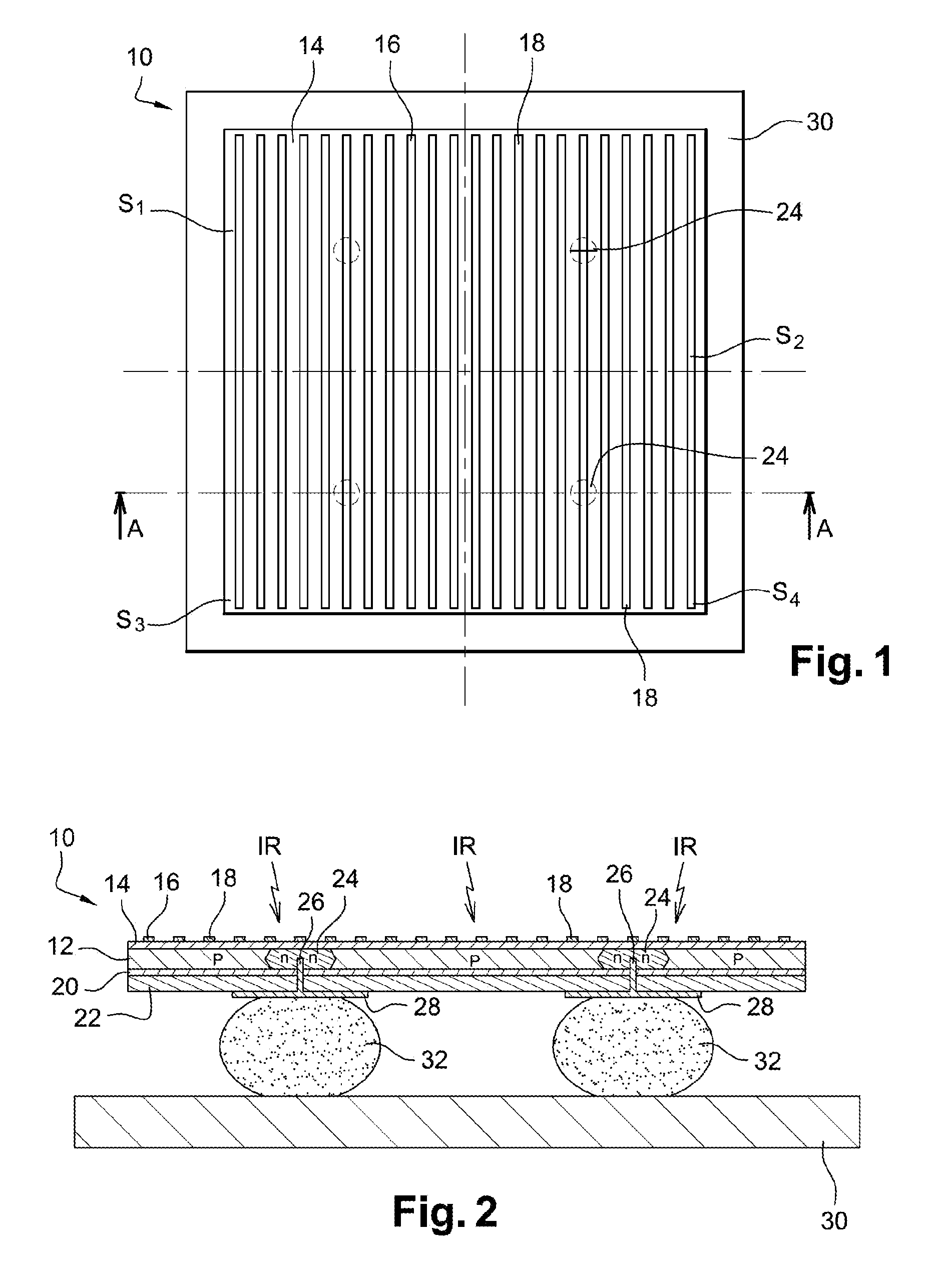

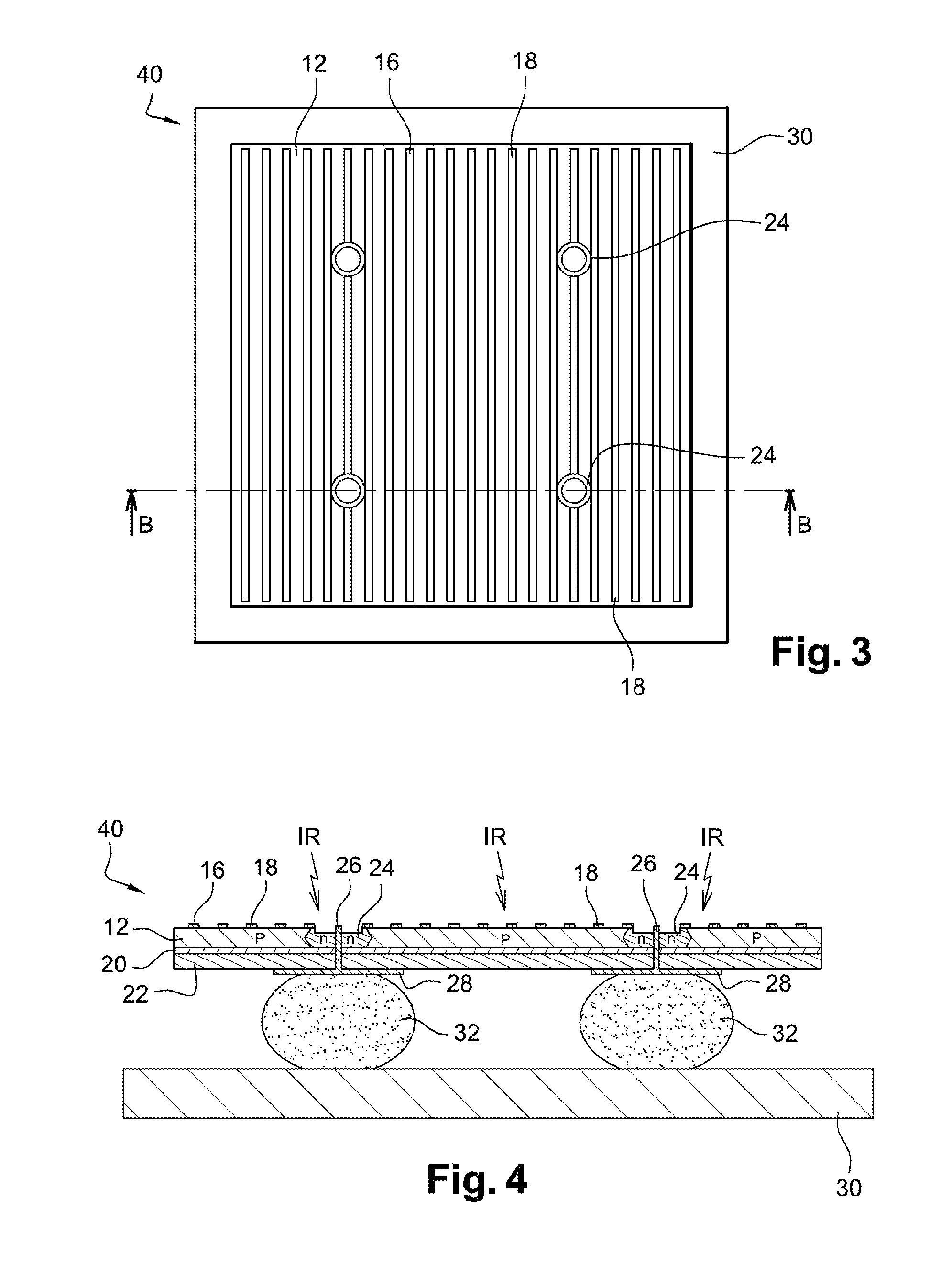

Thin film solar cell and photovoltaic string assembly

InactiveUS20110155209A1Avoid electrical connectionUndesirable electrical connectionSemiconductor/solid-state device testing/measurementPV power plantsEngineeringThin film solar cell

Owner:ODERSUN

Power tool with battery power supply

InactiveUS20060151189A1Durable and reliable attachment mechanismAvoid electrical connectionDrilling rodsConstructionsPower toolElectrical battery

The present invention relates to a power tool with battery power supply comprising a main body and a detachable battery package which are connected with each other via a securing frame and a locking assembly. The securing frame includes a guiding device, an locking / unlocking button located on one of the main body and the battery package. An electrical connection is provided between a motor in the main body and the battery package, and includes a plurality of electrode connectors and corresponding electrode contact tabs. A mechanism for creating a non-mechanical force is located between the main body and the battery package for pushing the battery package out of the securing frame. With such a mechanism, when the battery package is required to be replaced by another one or detached for charging, it is merely necessary to press the unlocking button downward, and the battery package then automatically slides out of the securing frame via the effect of the force so as to facilitate detaching the battery package from the main body of the power tool.

Owner:NANJING CHERVON IND

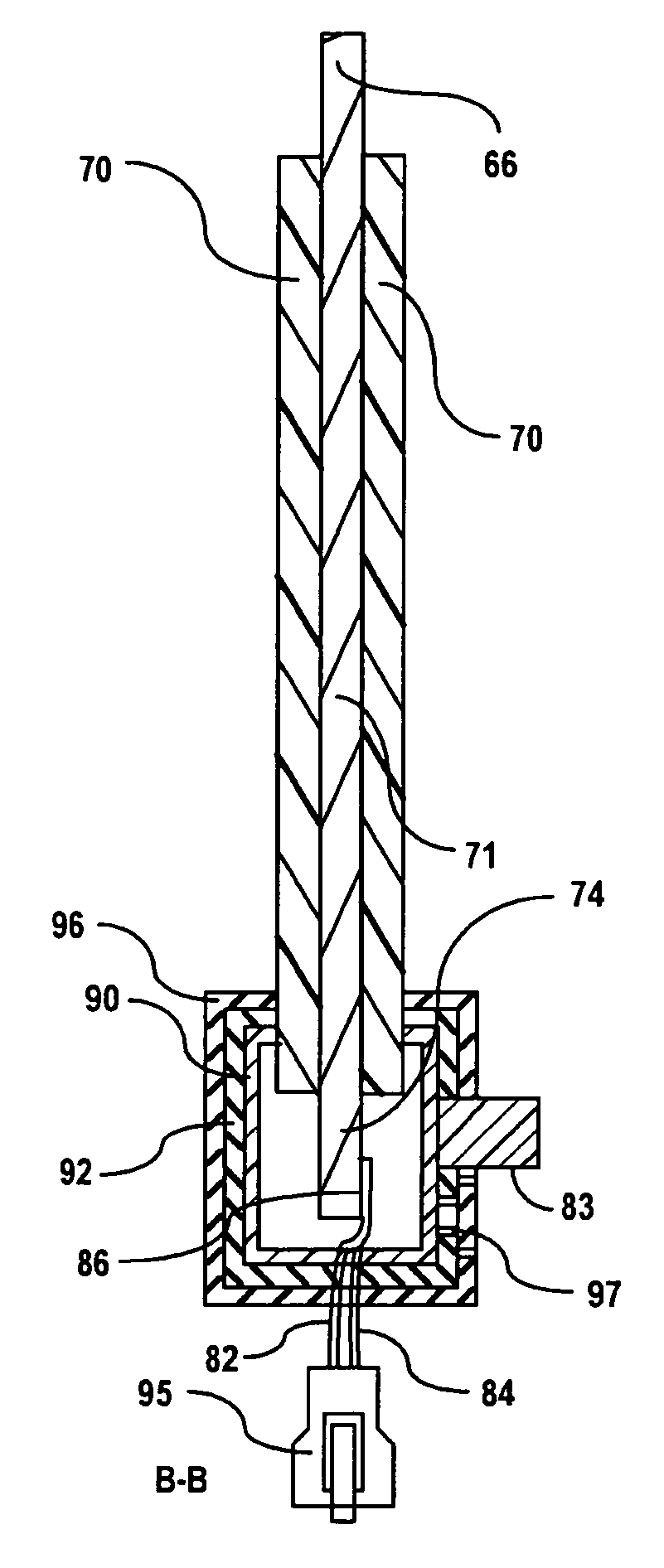

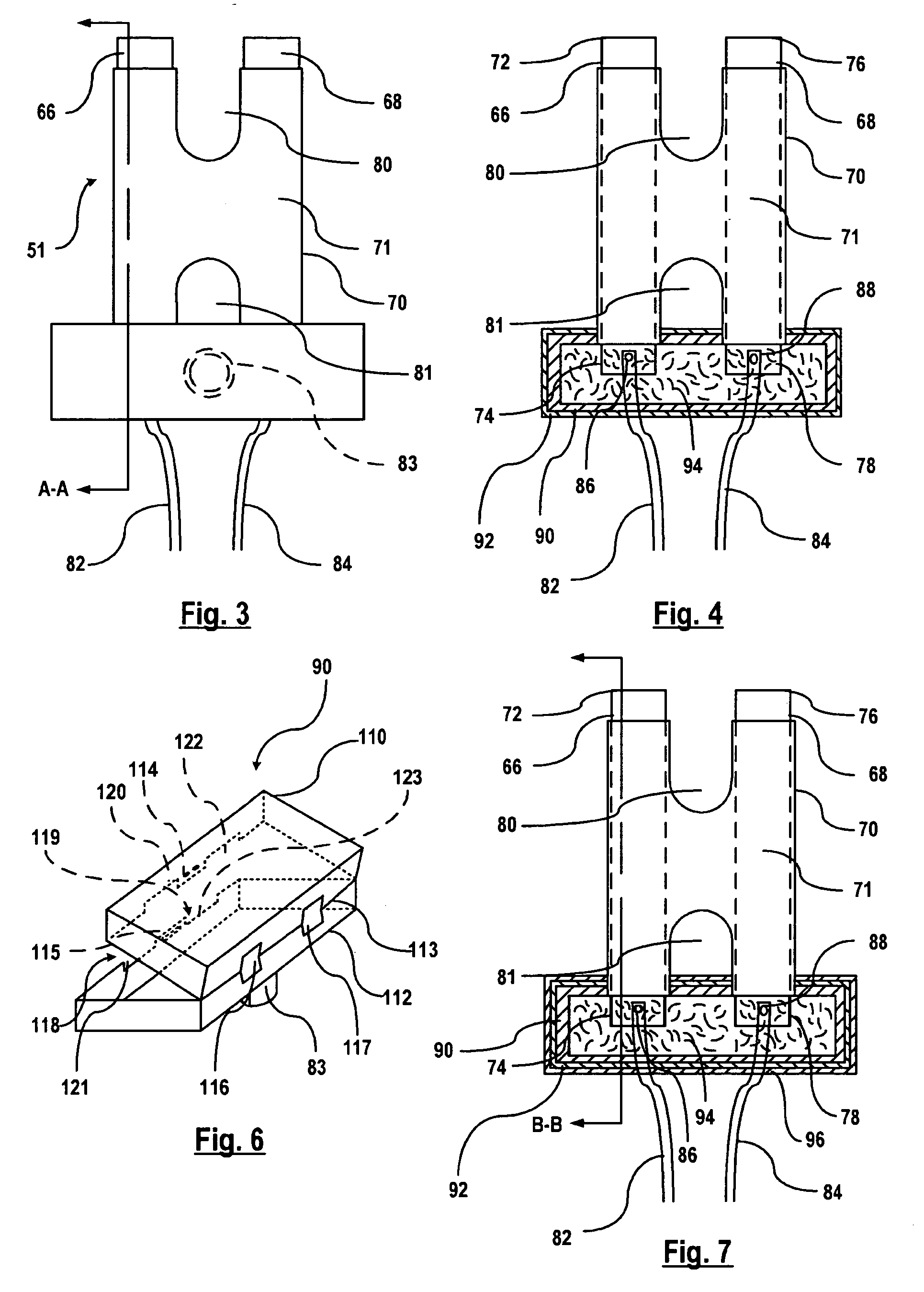

Electrical connection in glazing operations

InactiveUS7180031B1Avoid electrical connectionPreventing short circuitsEngagement/disengagement of coupling partsHeater elementsElectrical conductorElectrical connection

A power connection apparatus of a vehicle is provided that includes a pair of substantially flat electrical conductor strips each having a first end and a second end. The first ends are adapted to be electrically coupled to integrated heater conductors in an automobile glazing. A film forms a protective coating over an intermediate section of the pair of electrical conductor strips. The film insulates and maintains a spaced relationship between the pair of substantially flat electrical conductors. A pair of wires is electrically coupled to the second ends. A first protective overmold seal is formed over the second ends of the pair of substantially flat electrical conductor strips for sealing the electric coupling of the second ends of electrical conductor strips and the wires.

Owner:CARLEX GLASS AMERICA LLC +1

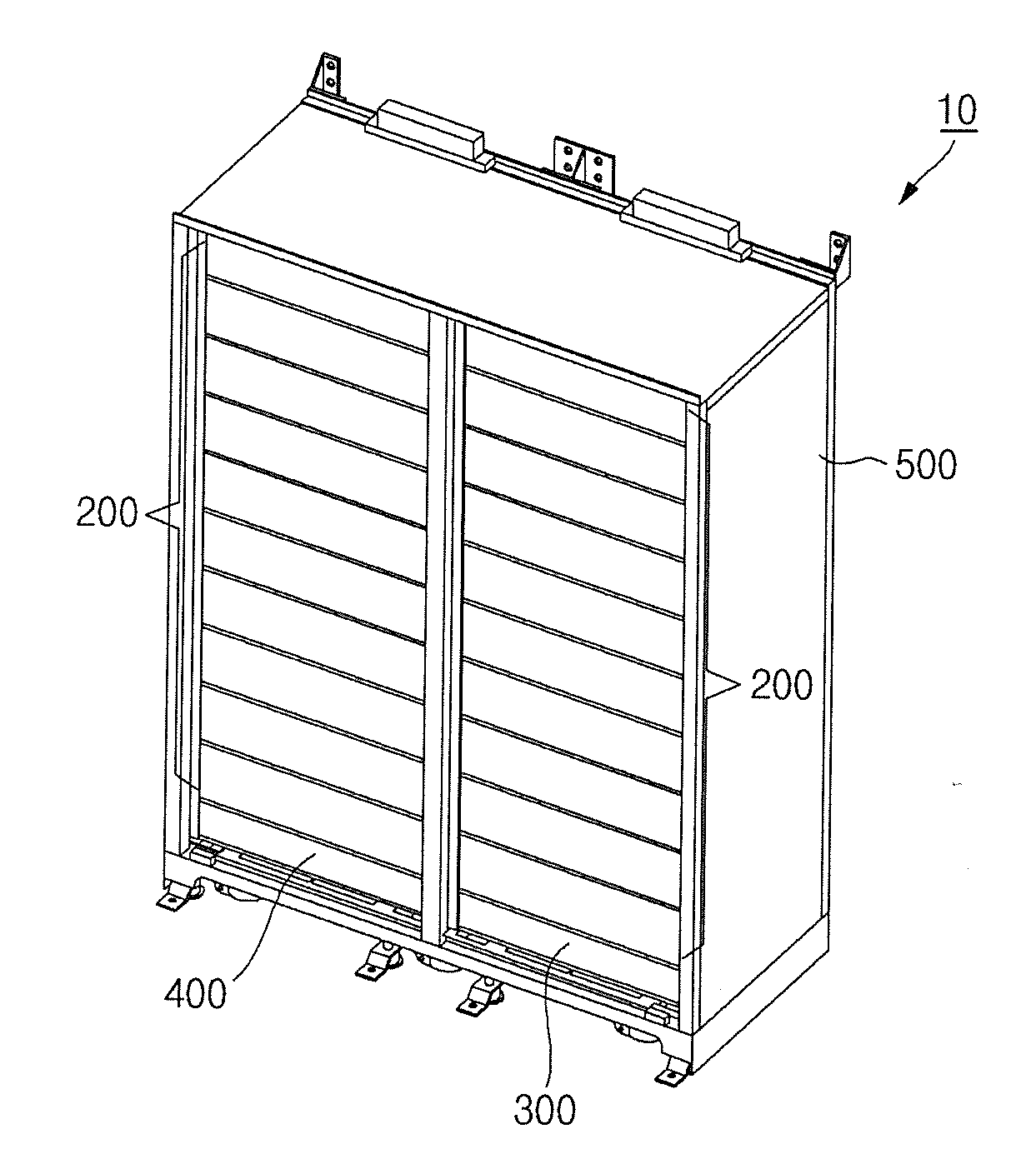

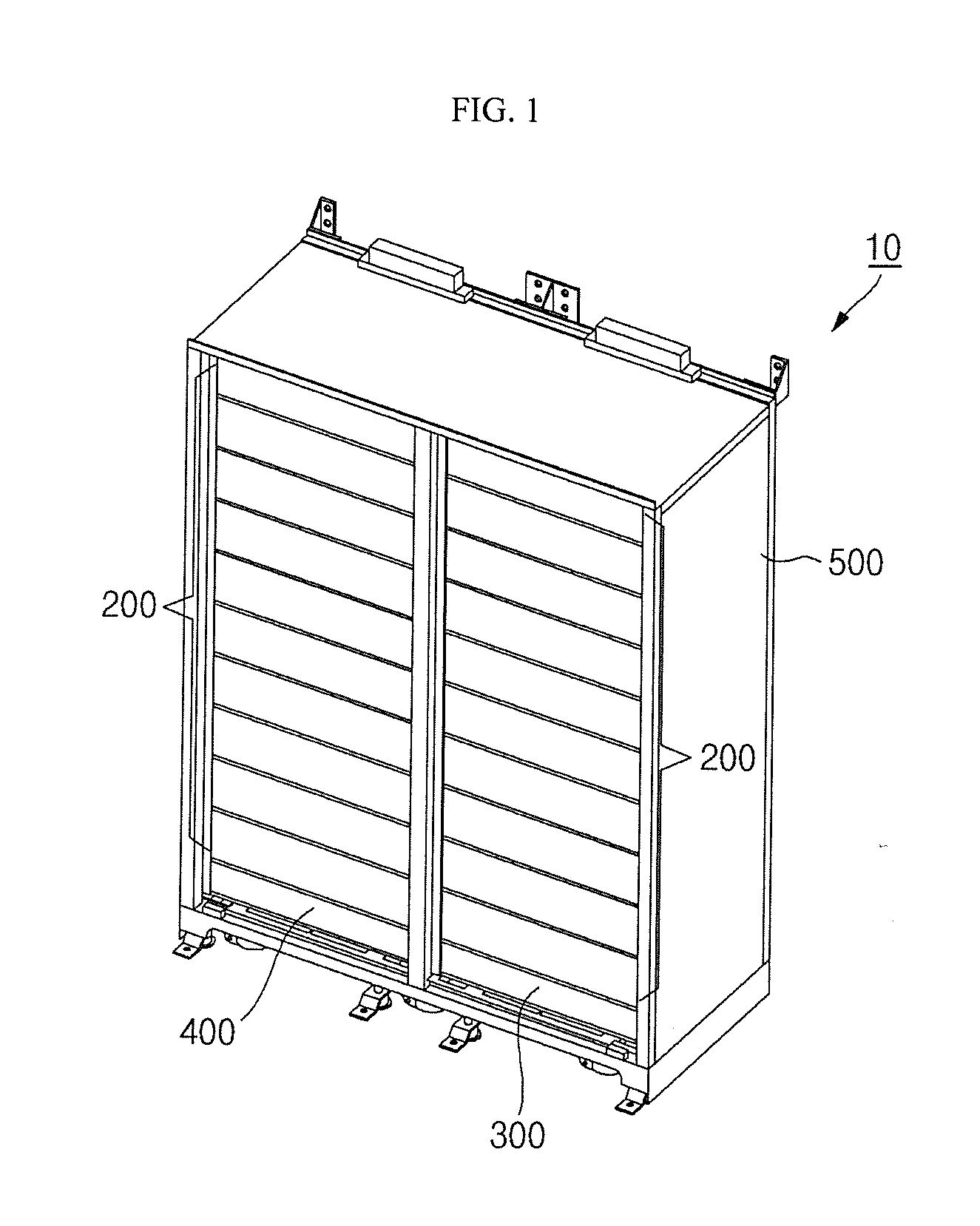

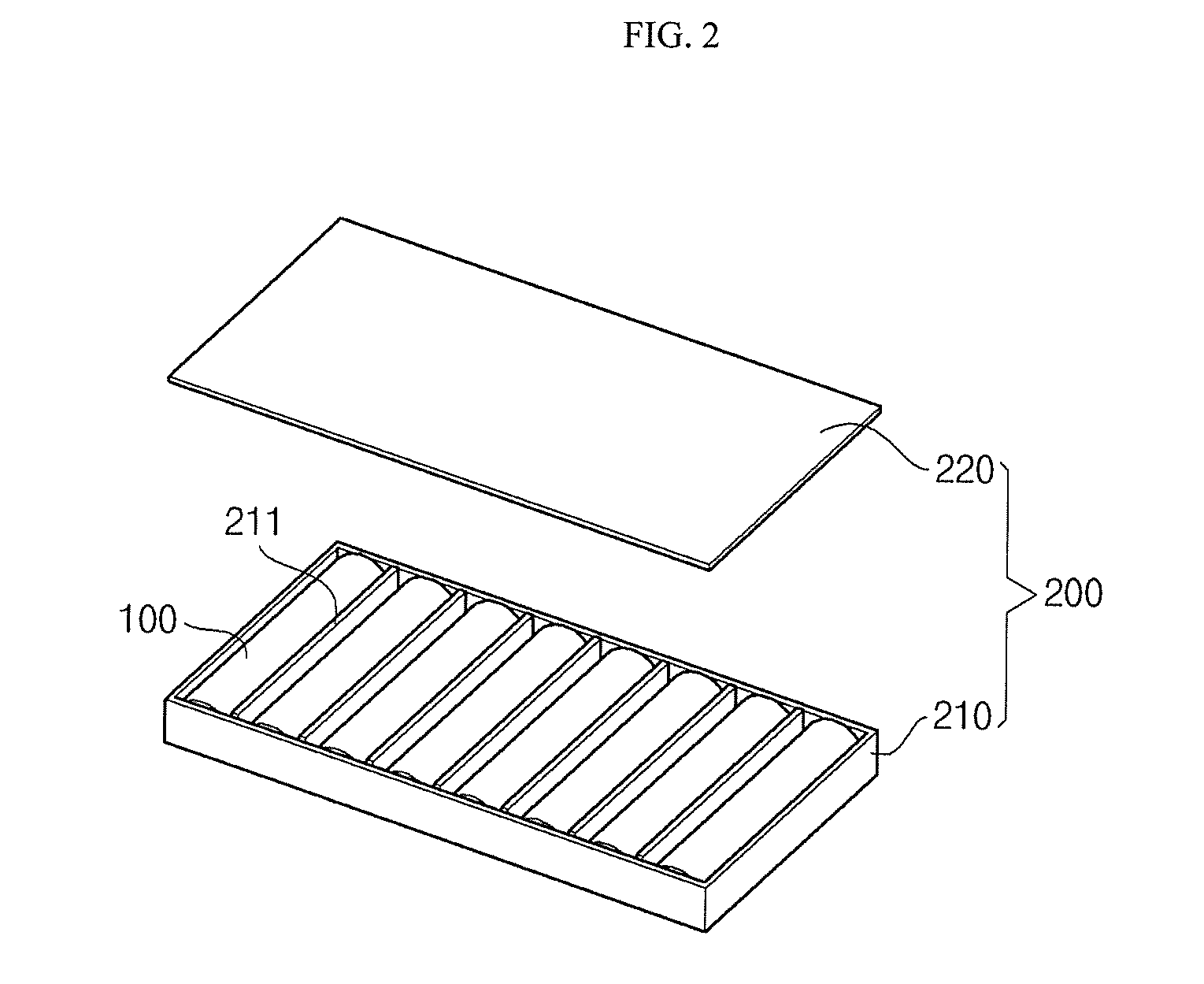

Energy storage system

ActiveUS20130065087A1Suppress and prevent vibrationAvoid electrical connectionCurrent conducting connectionsSecondary cellsElectricityEngineering

An energy storage system including a battery cell, a tray for receiving the battery cell, and a rack for receiving the tray. The rack includes a connector unit. The connector unit is configured to connect to the tray inserted into the rack and to vibrate together with the tray when the tray vibrates due to, for example, an earth quake or external impact applied to the rack, thereby preventing an electric connection between the tray and the connector unit from being broken.

Owner:SAMSUNG SDI CO LTD

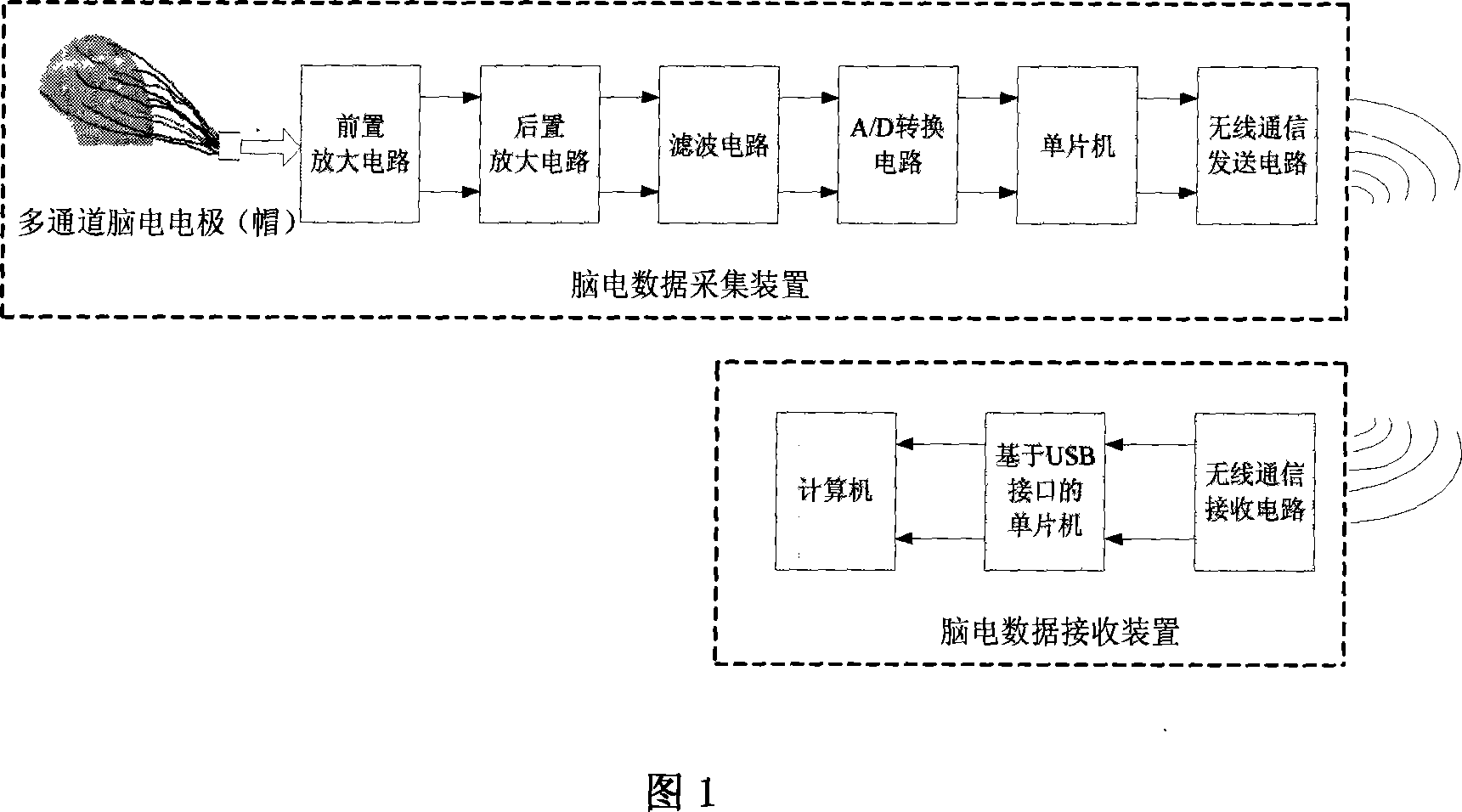

Portable wireless communication multichannel brain electric data collecting instrument

InactiveCN101032397AAvoid electrical connectionsEliminate the effects ofTransmission systemsDiagnostic recording/measuringComputer basedVIT signals

The portable radio multichannel electrocerebral data acquiring instrument consists of one electrocerebral data acquiring device and one electrocerebral data receiving device communicating mutually in radio communication mode. The electrocerebral data acquiring device includes multichannel electrocerebral electrodes, a pre-amplifier circuit, a post-amplifier circuit, a filter circuit, an A / D converter circuit, a monolithic computer and a radio communication sending circuit; and the electrocerebral data receiving device includes a radio communication receiver circuit, a monolithic computer based on USB interface and a computer. The electrocerebral signal is first amplified, filtered, A / D converted and sent, and then received and transmitted to the computer for real-time analysis and treatment. The present invention has no electric connection between the testee and the computer, and is flexible, safe and reliable.

Owner:SHANGHAI JIAO TONG UNIV

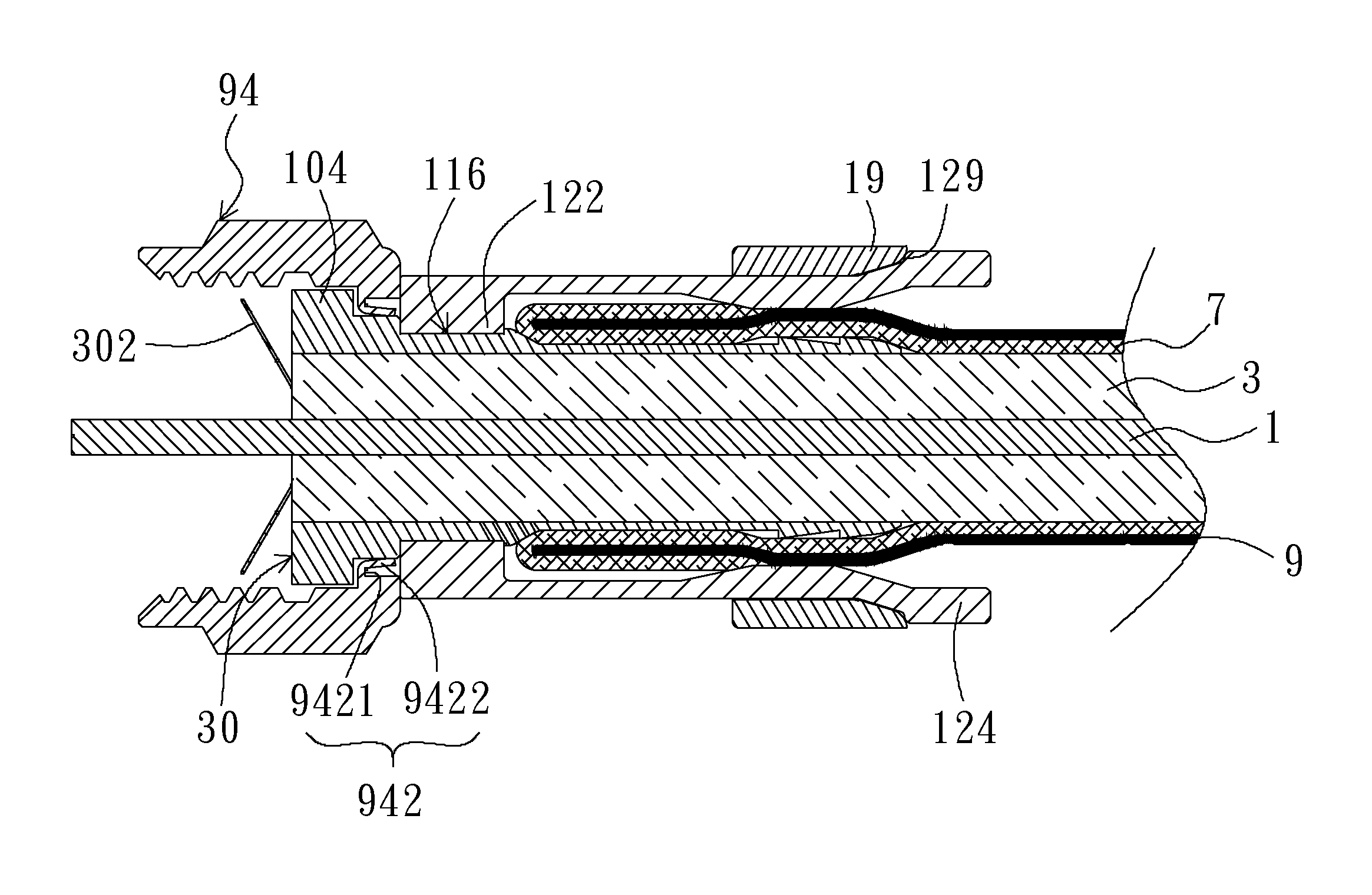

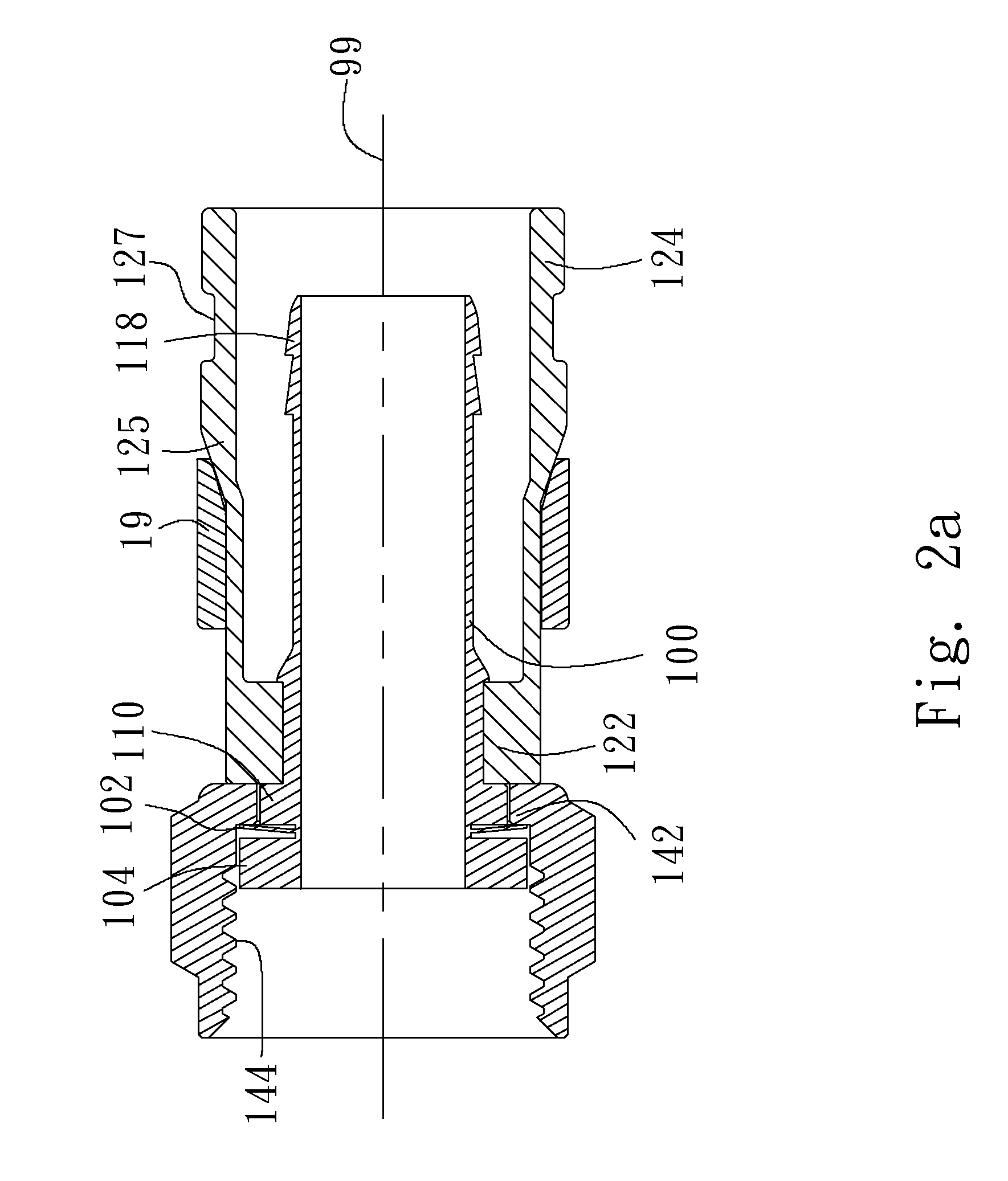

Coaxial cable connector

ActiveUS9343855B2Avoid electrical connectionEngagement/disengagement of coupling partsTwo-part coupling devicesCoaxial cableEngineering

A spring has a first resilient tab configured to be radially outward bent at a first angle when the spring is in an expanded position, wherein when a coaxial cable connector is tightly screwed with a threaded connector of an electronic device, an inner flange of a nut of the coaxial cable connector is configured to press the first resilient tab such that the spring is in a contracted position and the first resilient tab is radially between the inner flange and an inner sleeve of the coaxial cable connector, wherein the spring has a plate configured to be arranged between opposing surfaces of an outer flange of the inner sleeve and the inner flange, wherein the plate is integral with the first resilient tab.

Owner:EZCONN

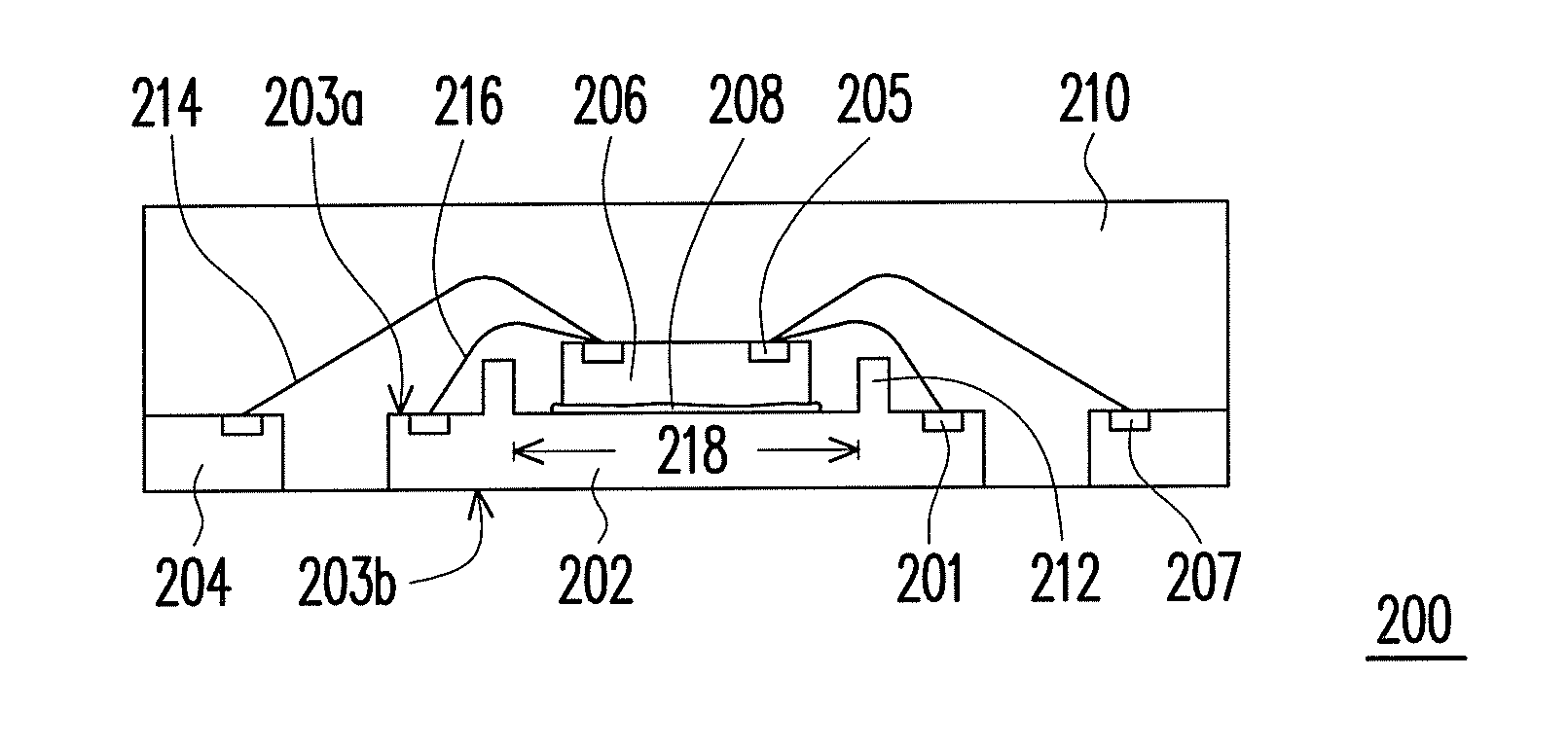

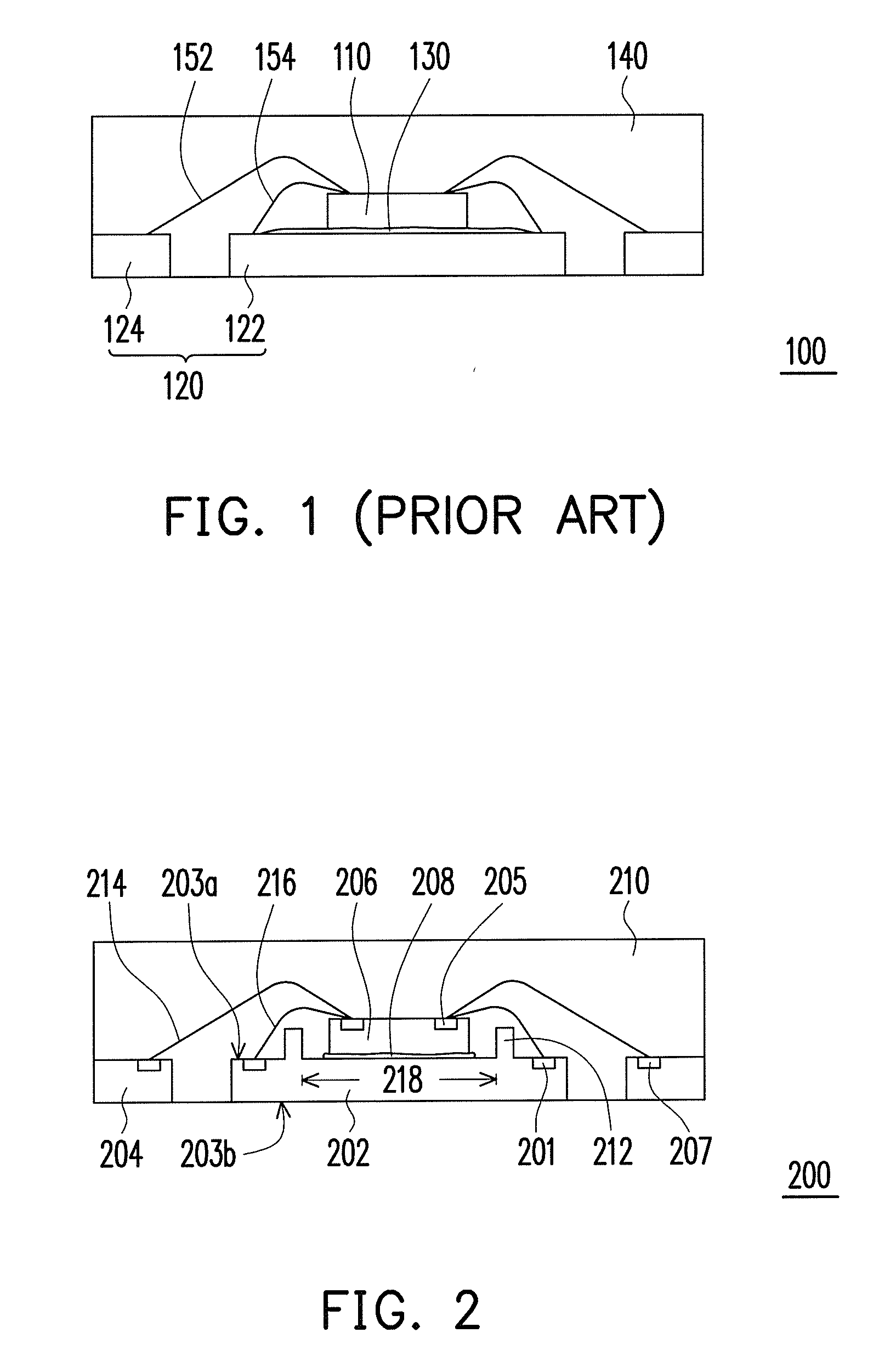

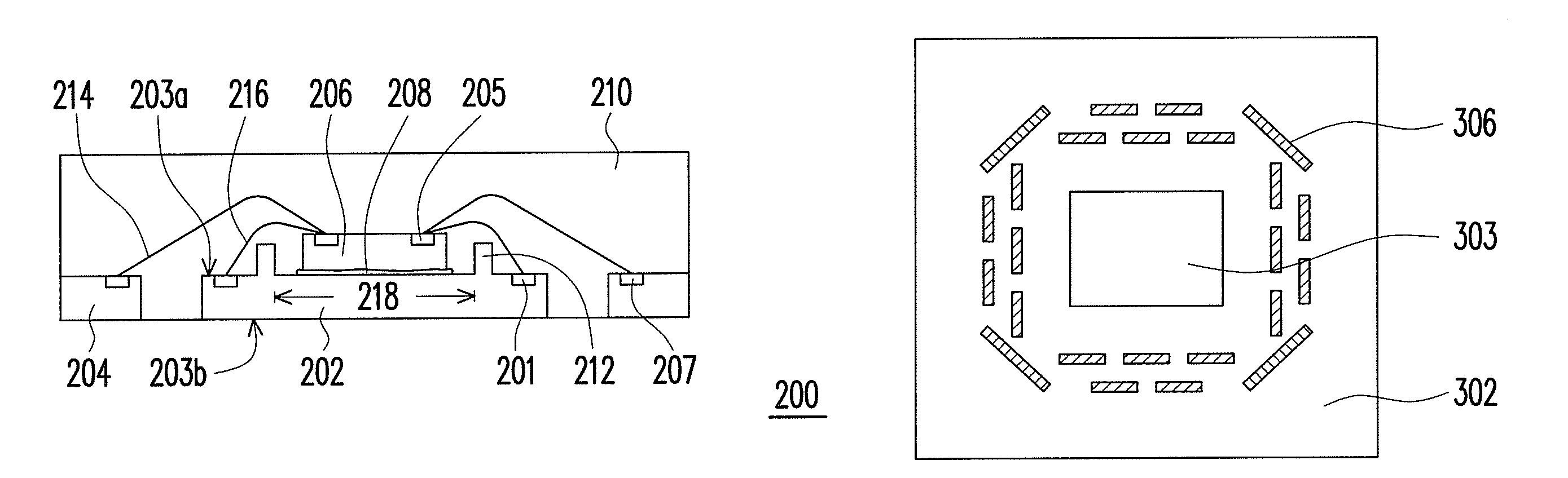

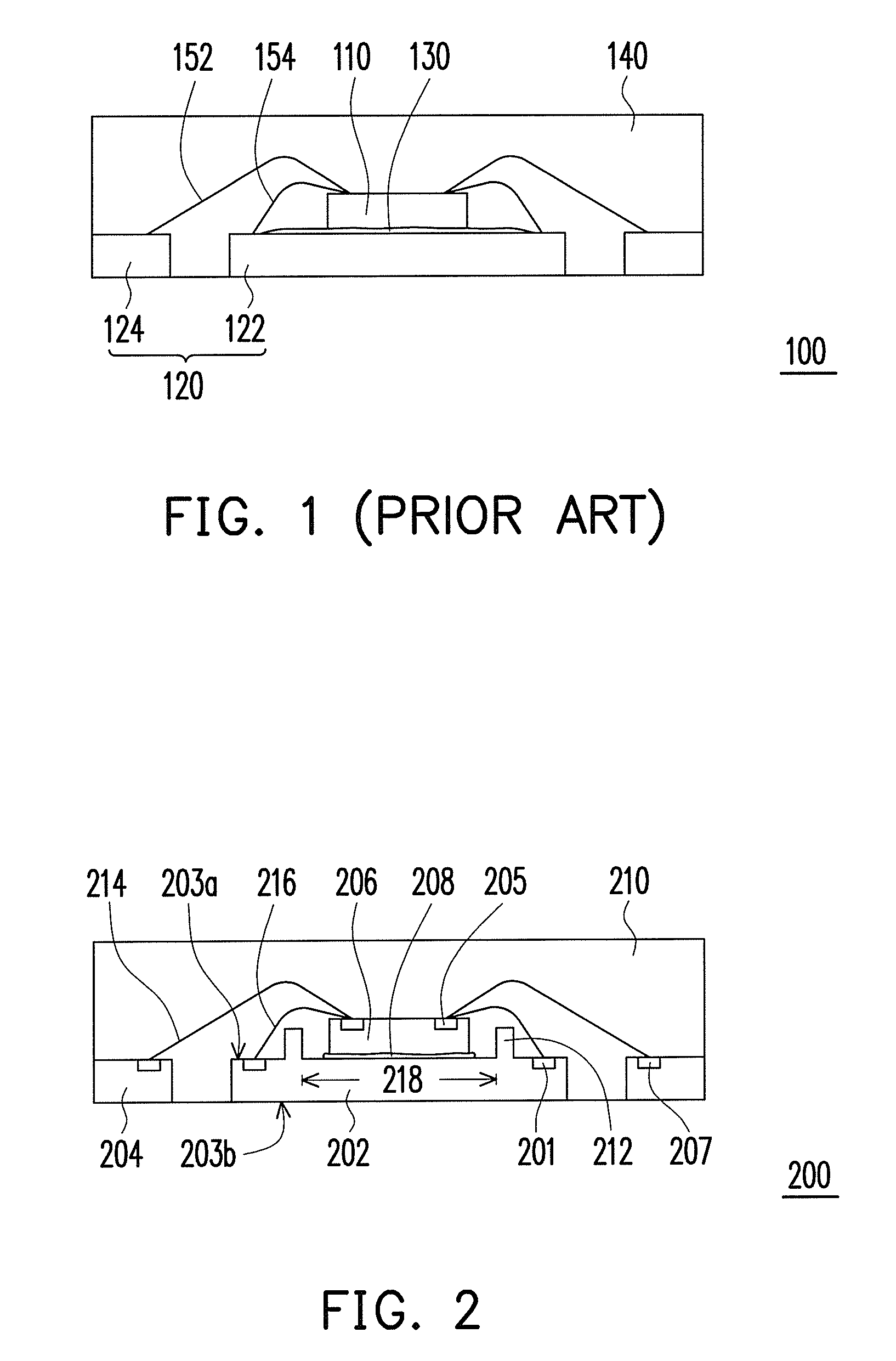

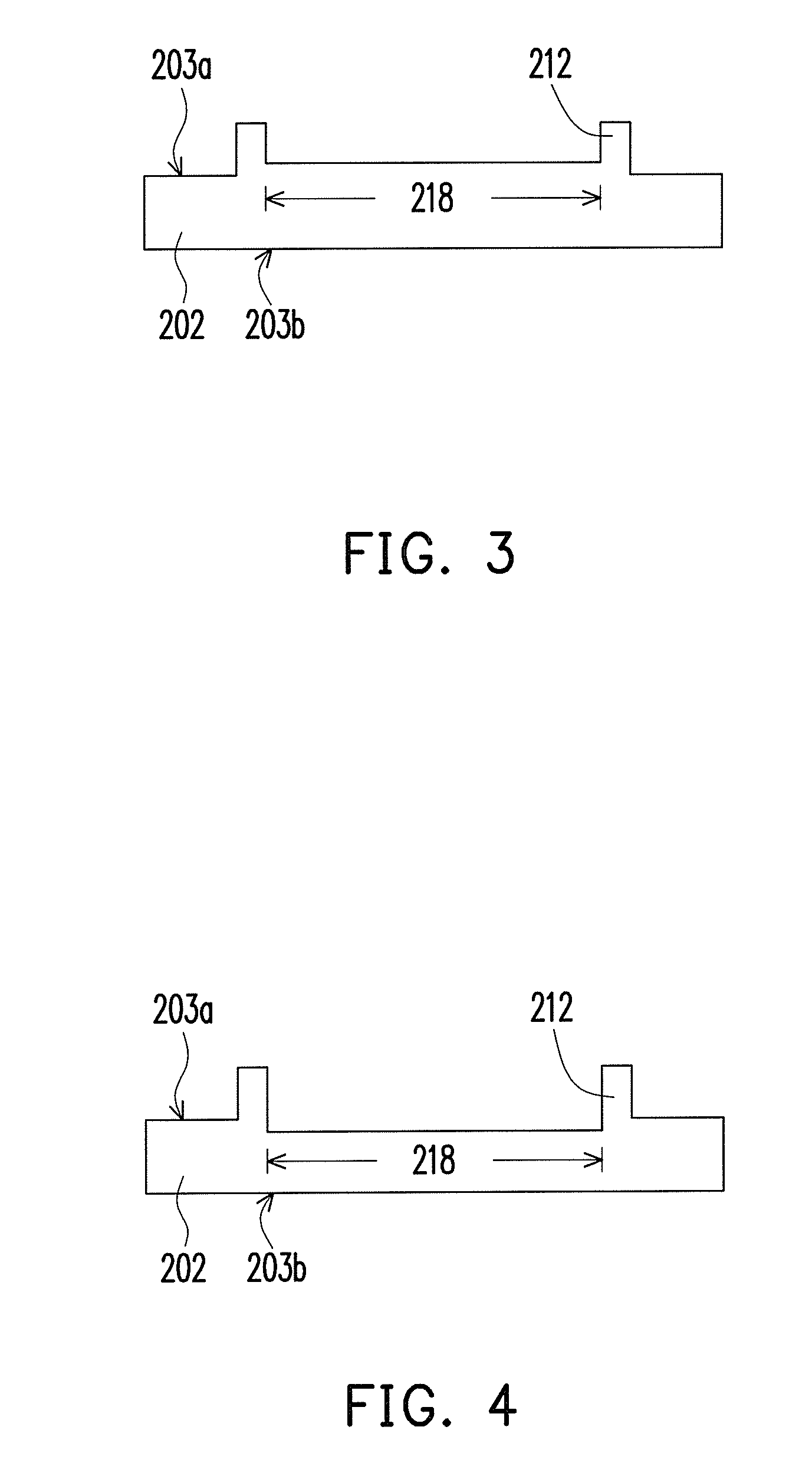

Chip package

InactiveUS20090224384A1Improve chip reliabilityImprove reliabilityElectrically conductive connectionsSemiconductor/solid-state device detailsAdhesiveElectrical and Electronics engineering

A chip package including a die pad, a plurality of leads, a chip, an adhesive, and a molding compound is provided. The die pad has a top surface and a bottom surface opposite to the top surface, wherein the die pad has a blocking portion disposed on the top surface, and the leads are disposed around the die pad. The chip is disposed on the top surface of the die pad surrounded by the blocking portion and is electrically connected to the leads. A top surface of the blocking portion is higher than the top surface of the die pad surrounded by the blocking portion. The adhesive is disposed between the chip and the die pad. The molding compound encapsulates the chip, a portion of the leads, and the die pad.

Owner:CHIPMOS TECH INC

Coaxial cable connector and threaded connector

ActiveUS9306324B2Reliable electrical connectionAvoid electrical connectionEngagement/disengagement of coupling partsTwo-part coupling devicesCoaxial cableMetal sheet

An coaxial cable connector is configured to engage with an outer thread of a threaded connector. The coaxial cable connector comprises an inner sleeve, an outer sleeve arranged around the inner sleeve and a nut arranged around the inner sleeve. The nut comprises a metal sheet integral with an inner flange of the nut, wherein the metal sheet is between the inner flange and a cylindrical surface of the inner sleeve. The metal sheet has a fixed side, close to an outer flange of the inner sleeve, fixed to the inner flange of the nut, and a free side, away from the outer flange of the inner sleeve, abutting against the cylindrical surface of the inner sleeve. An empty gap is between the metal sheet and the inner flange. When the nut comprises an inner thread engaging with the outer thread, the outer flange is configured to be between the inner flange and the threaded connector.

Owner:EZCONN

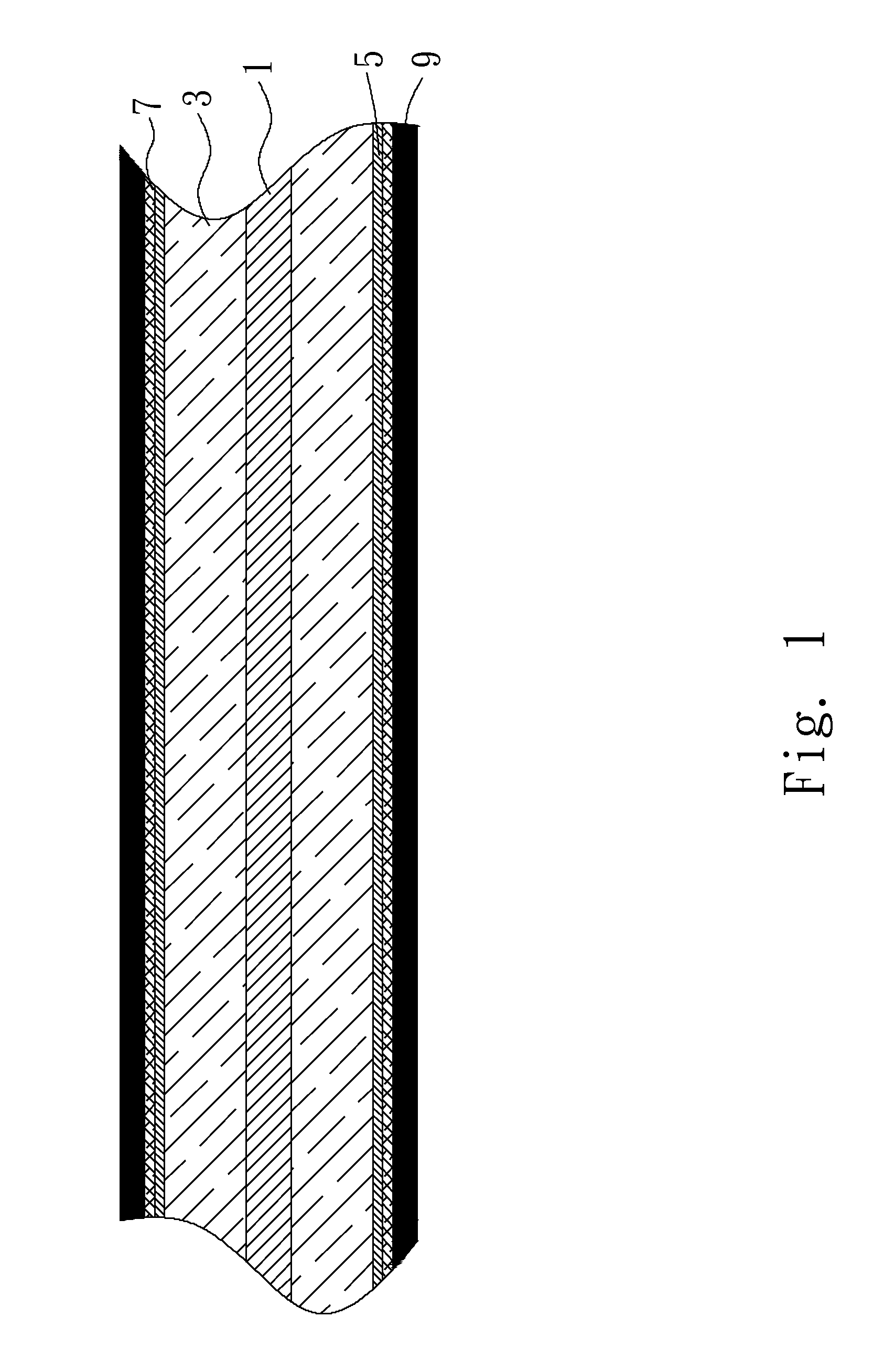

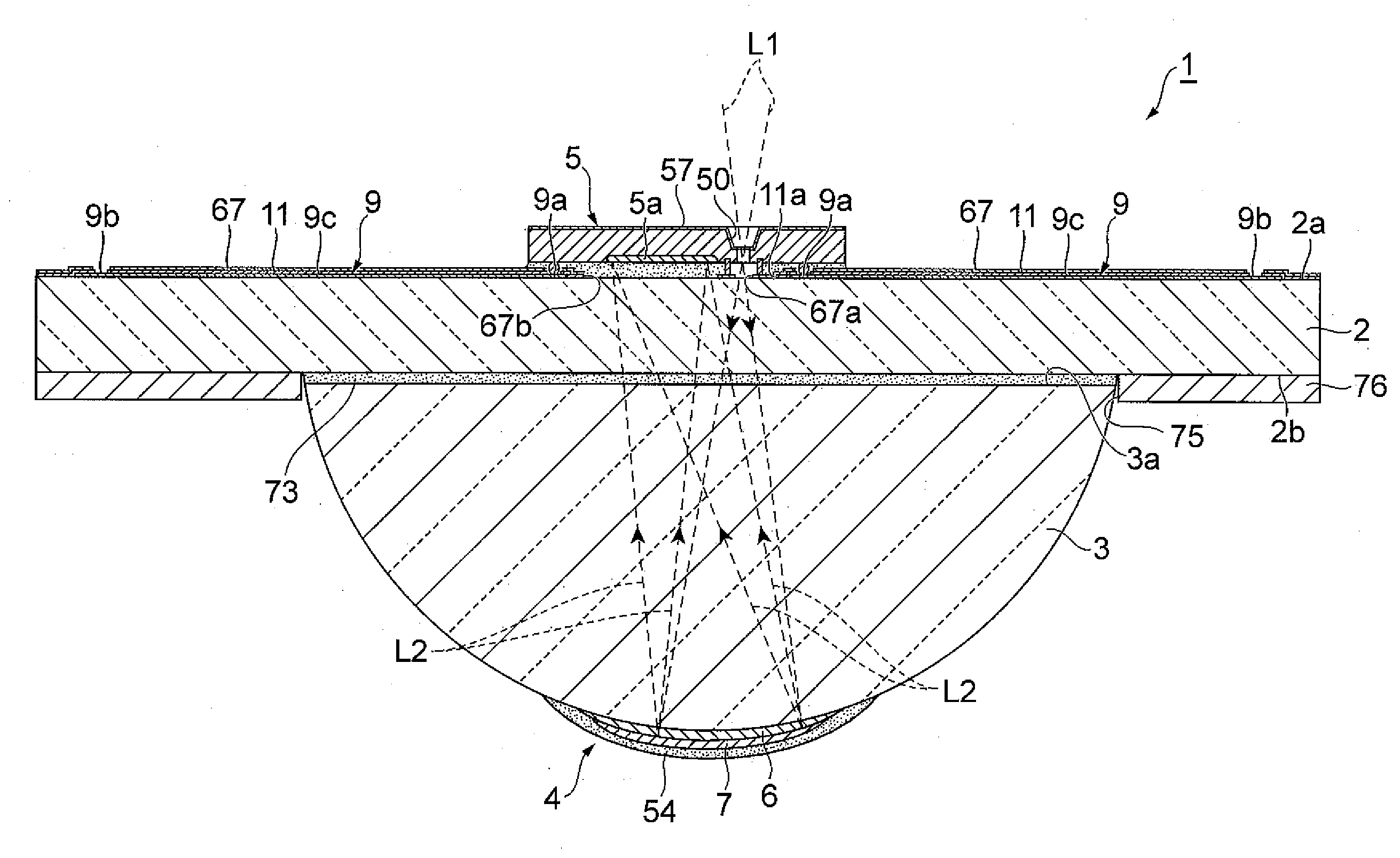

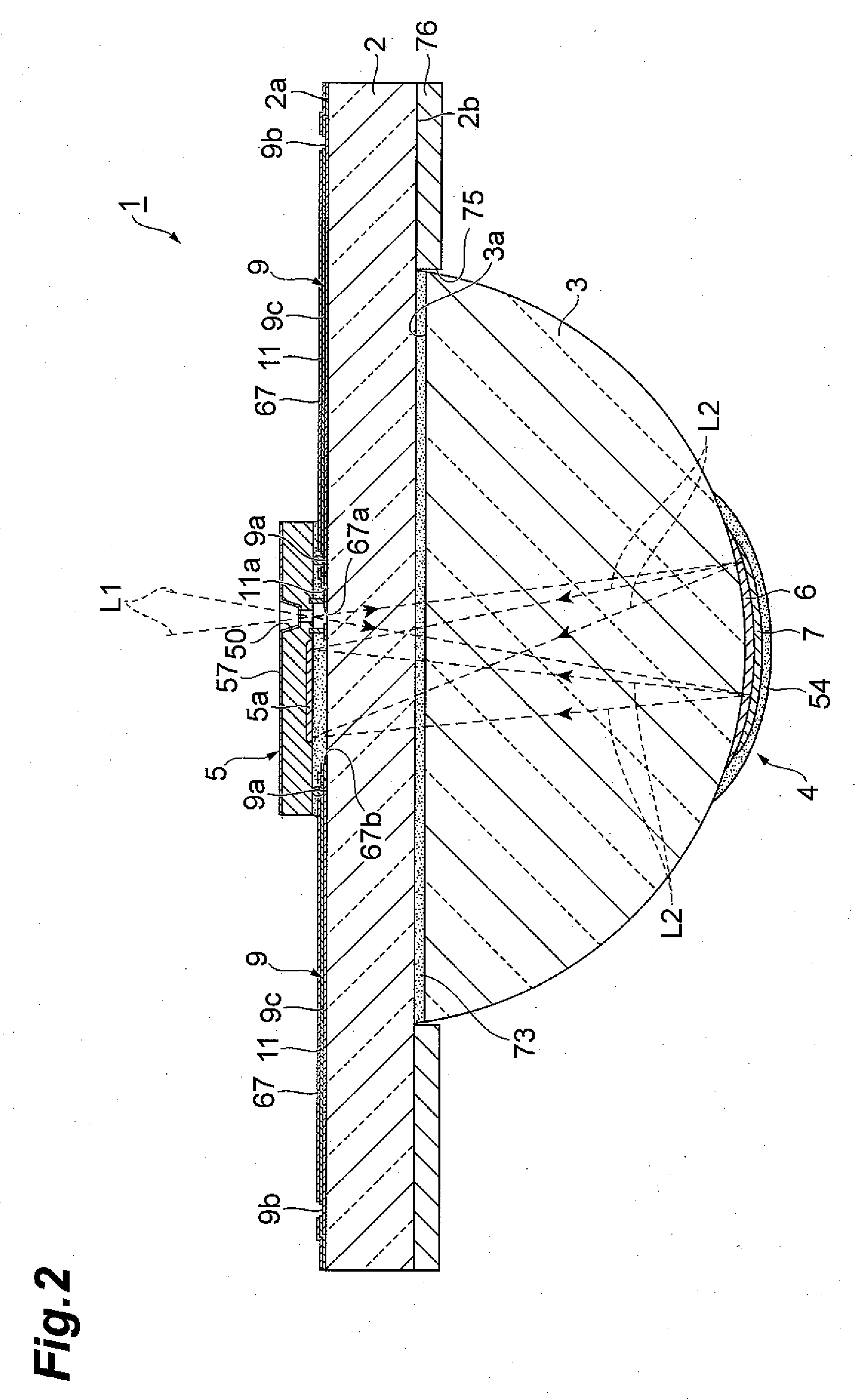

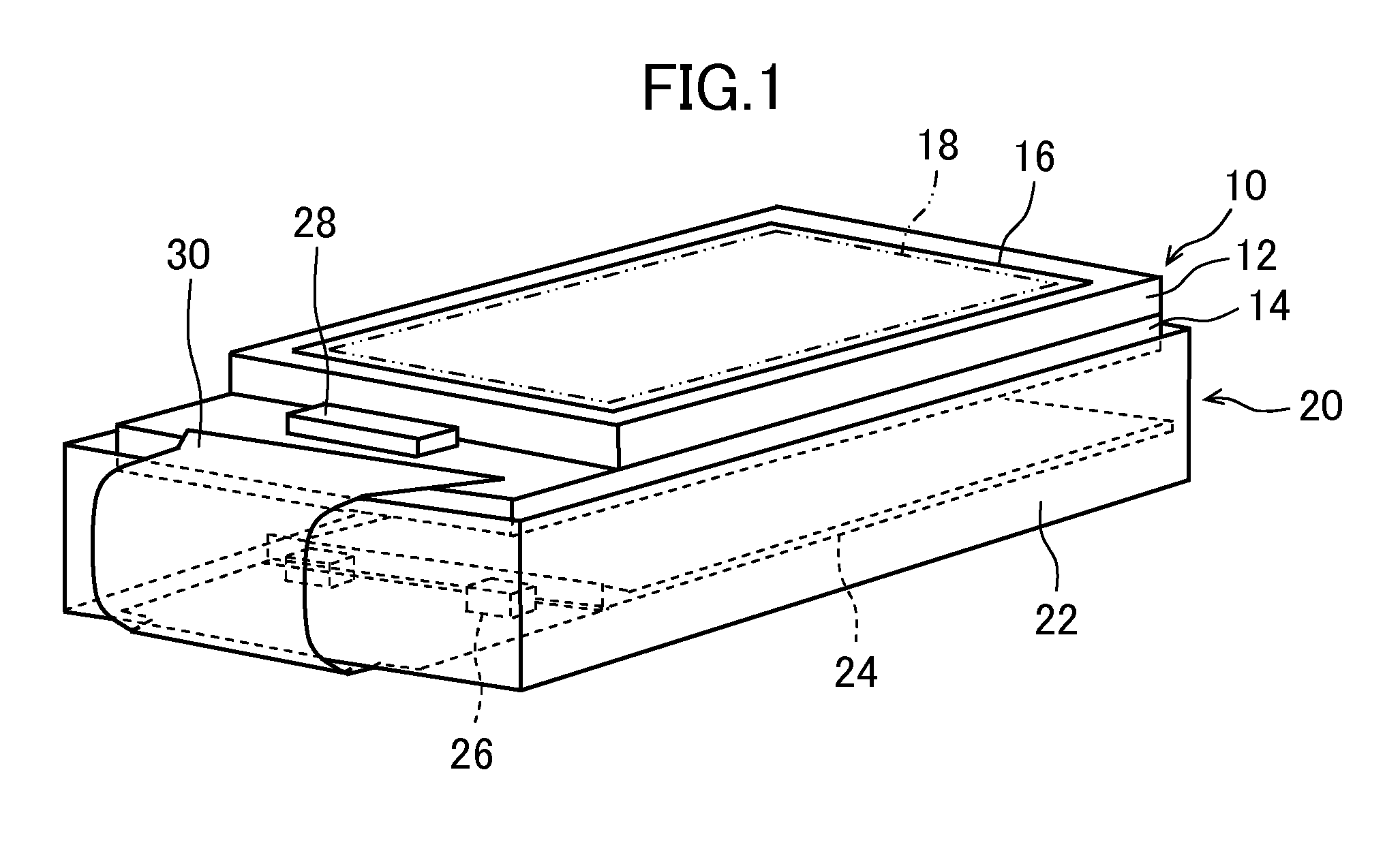

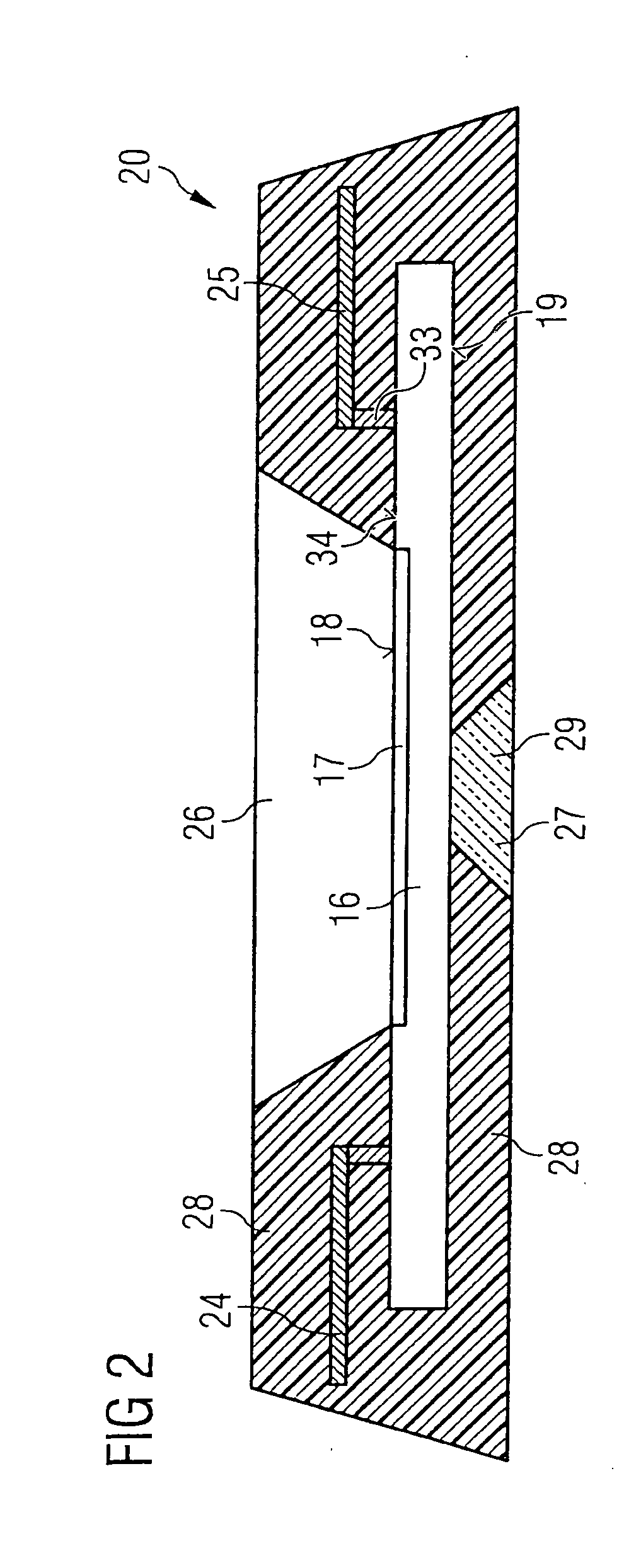

Method for manufacturing spectroscopy module, and spectroscopy module

InactiveUS20090290154A1Improve light absorption capacitySimple processRadiation pyrometrySpectrum investigationSpectroscopyOptoelectronics

In a spectroscopy module 1, a light detecting element 5 having a light passing hole 50 is used. Therefore, it is possible to prevent the relative positional relationship between the light passing hole 50 and a light detecting portion 5a of the light detecting element 5 from deviating. Moreover, the light detecting element 5 is electrically connected to a wiring 9 formed on a front plane 2a of a substrate 2 by face-down bonding, and a resin layer 79 is formed as an underfill resin between the substrate 2 and the light detecting element 5. Therefore, it is possible to improve the fixing strength between the substrate 2 and the light detecting element 5. Additionally, before the resin layer 79 is formed, a resin layer 78 is formed along a guide portion 77 that surrounds the passing hole 50. Thus, the resin layer 79 is prevented from penetrating into the light passing hole 50, which makes it possible to make a light be appropriately incident into the substrate 2.

Owner:HAMAMATSU PHOTONICS KK

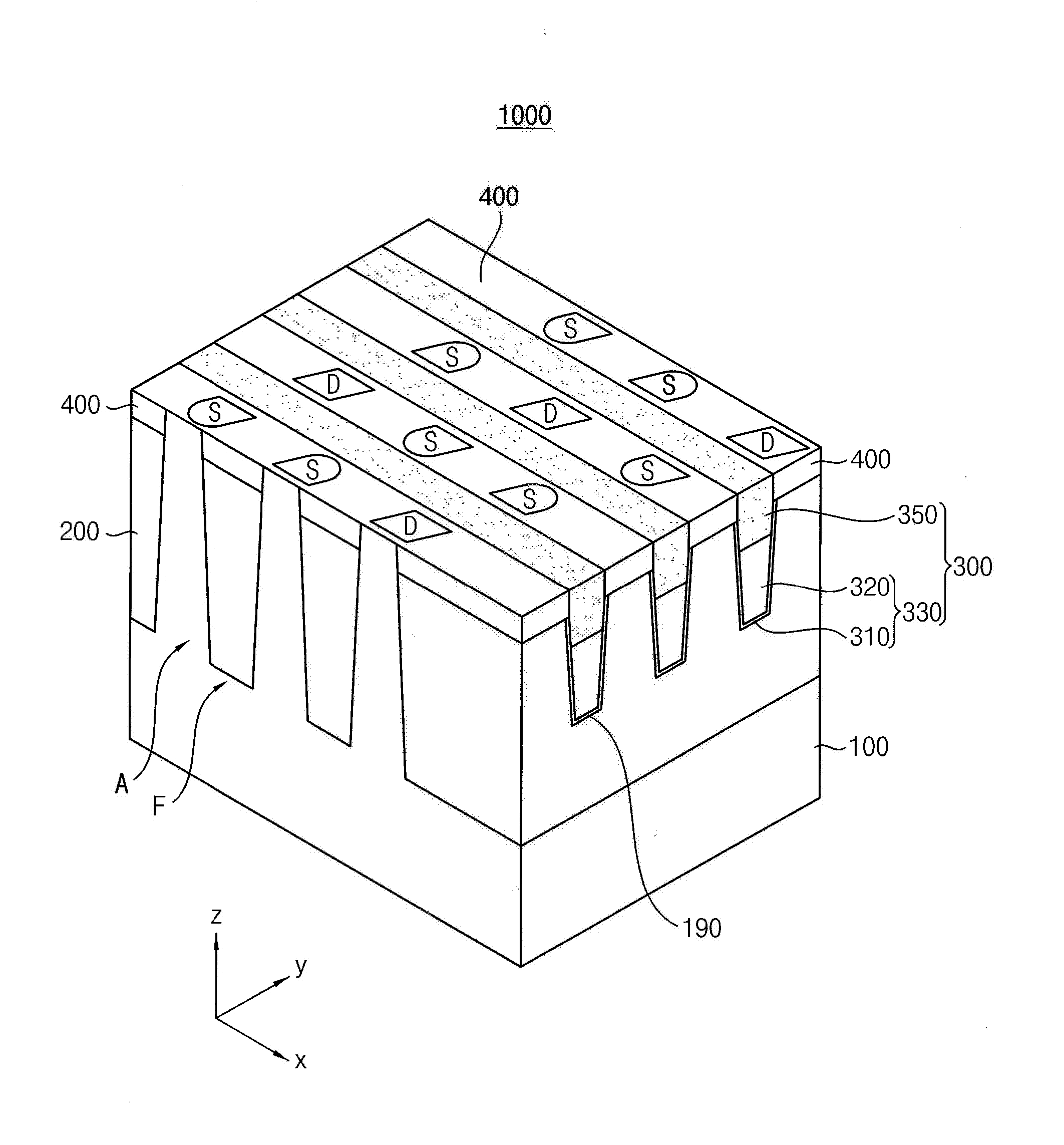

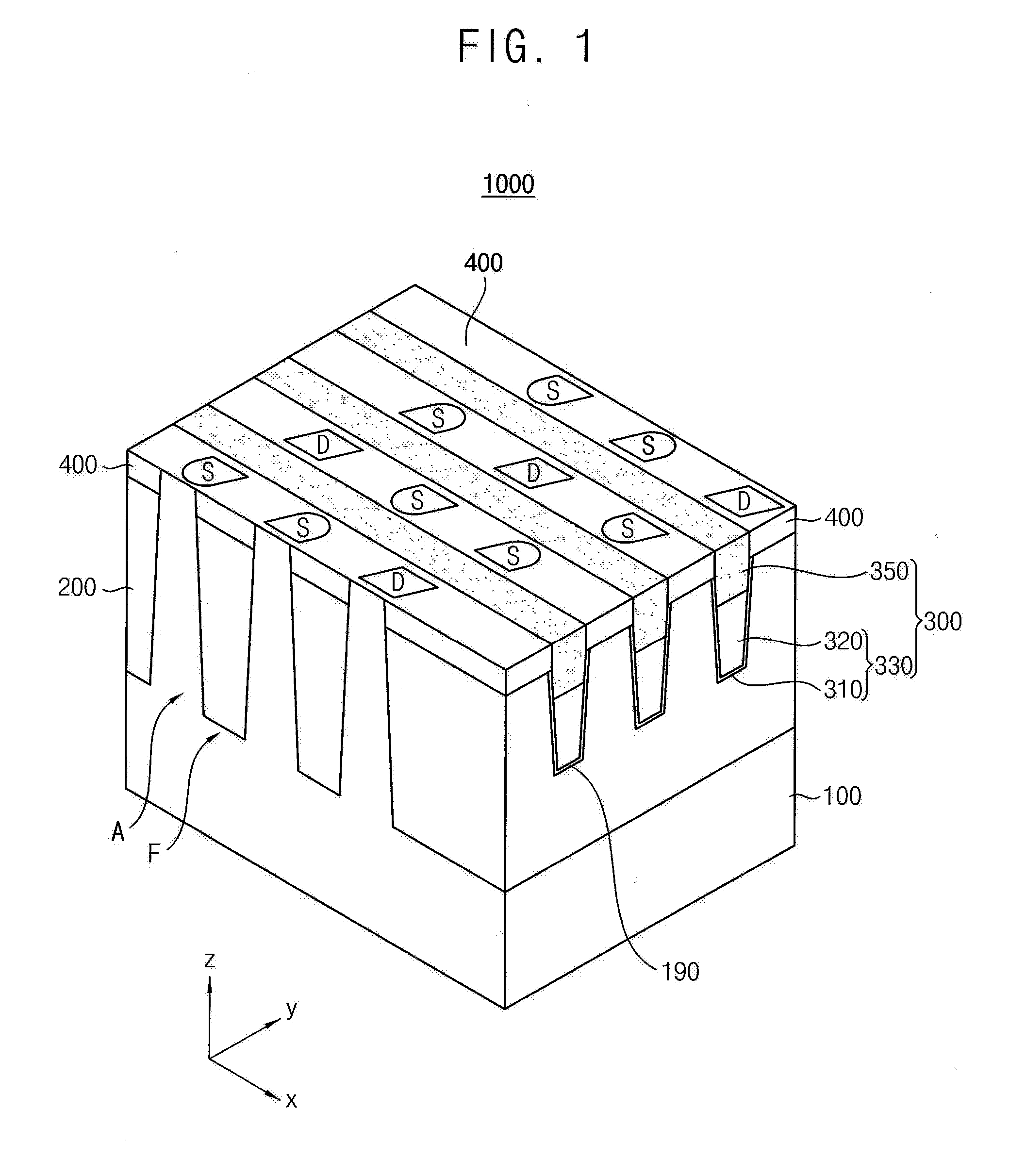

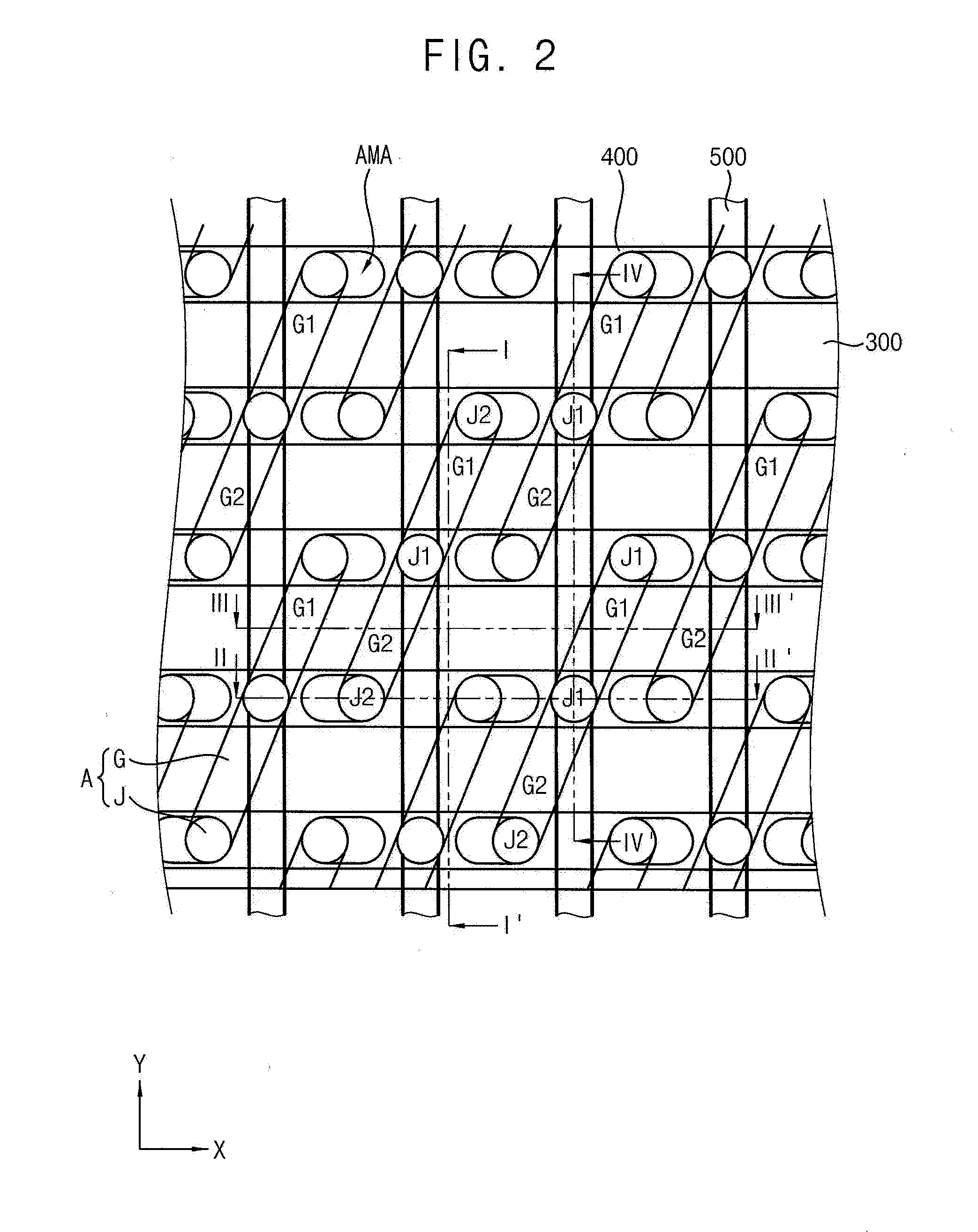

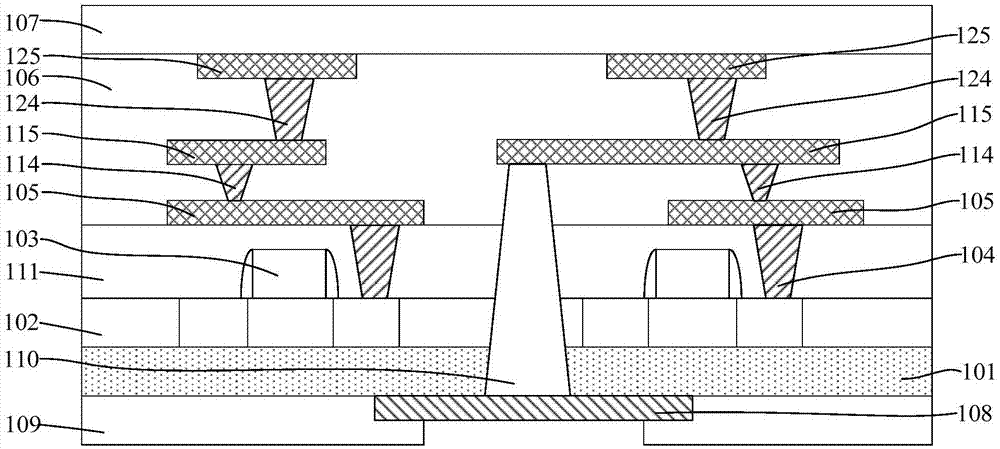

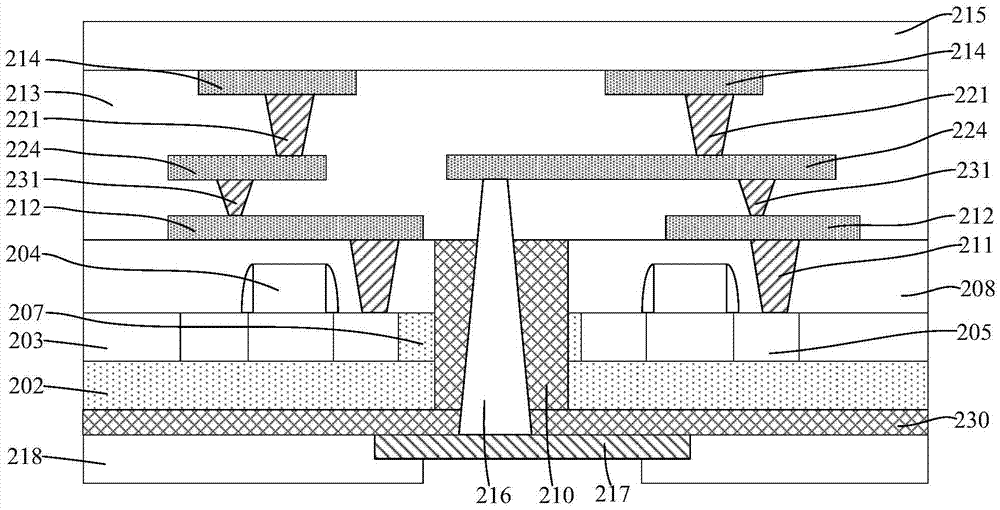

Semiconductor device and method of manufacturing the same

ActiveUS20160197084A1Improving operational reliabilityImprove stabilityTransistorSolid-state devicesDopantDevice material

A semiconductor device includes a substrate having an active region defined by a device isolation layer and at least a gate trench linearly extending in a first direction to cross the active region, the active region having a gate area at a bottom of the gate trench and a junction area at a surface of the substrate. The device further may include a first conductive line filling the gate trench and extending in the first direction, the first conductive line having a buried gate structure on the gate area of the active region. The device also may include a junction including implanted dopants at the junction area of the active region, and a junction separator on the device isolation layer and defining the junction. The junction separator may be formed of an insulative material and have an etch resistance greater than that of the device isolation layer.

Owner:SAMSUNG ELECTRONICS CO LTD

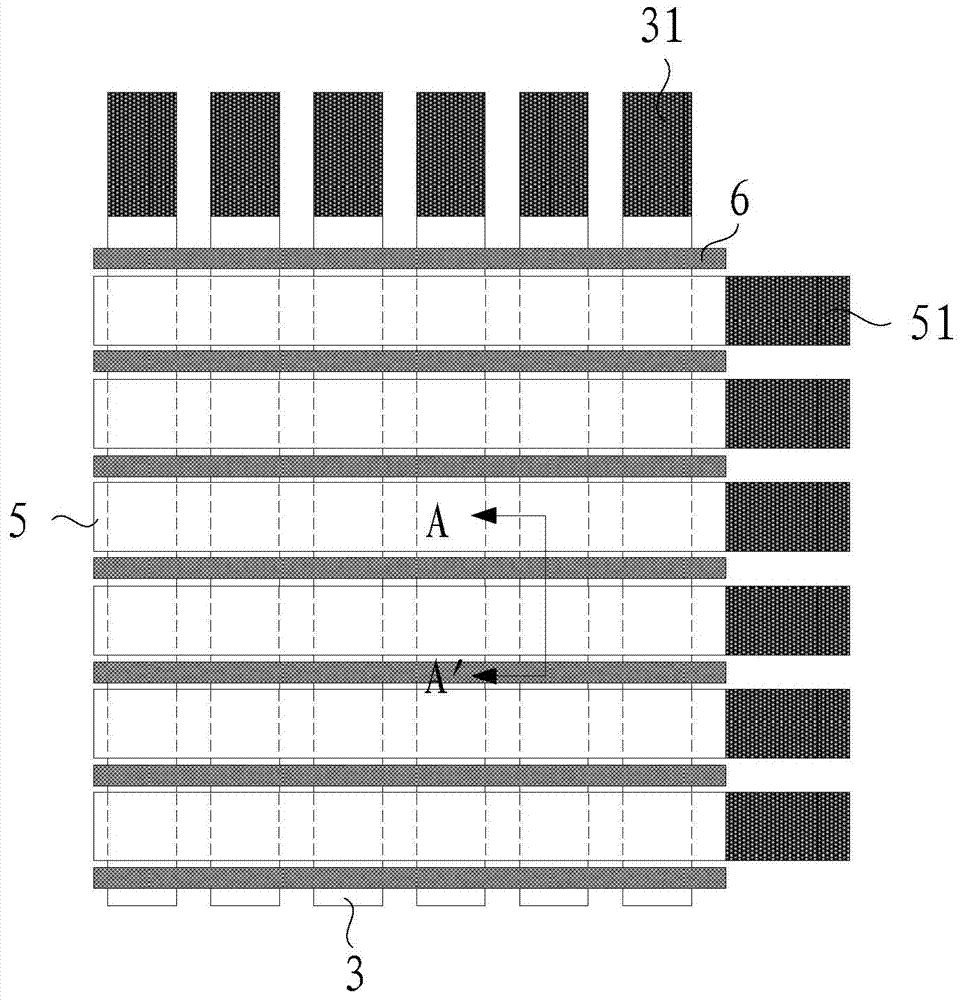

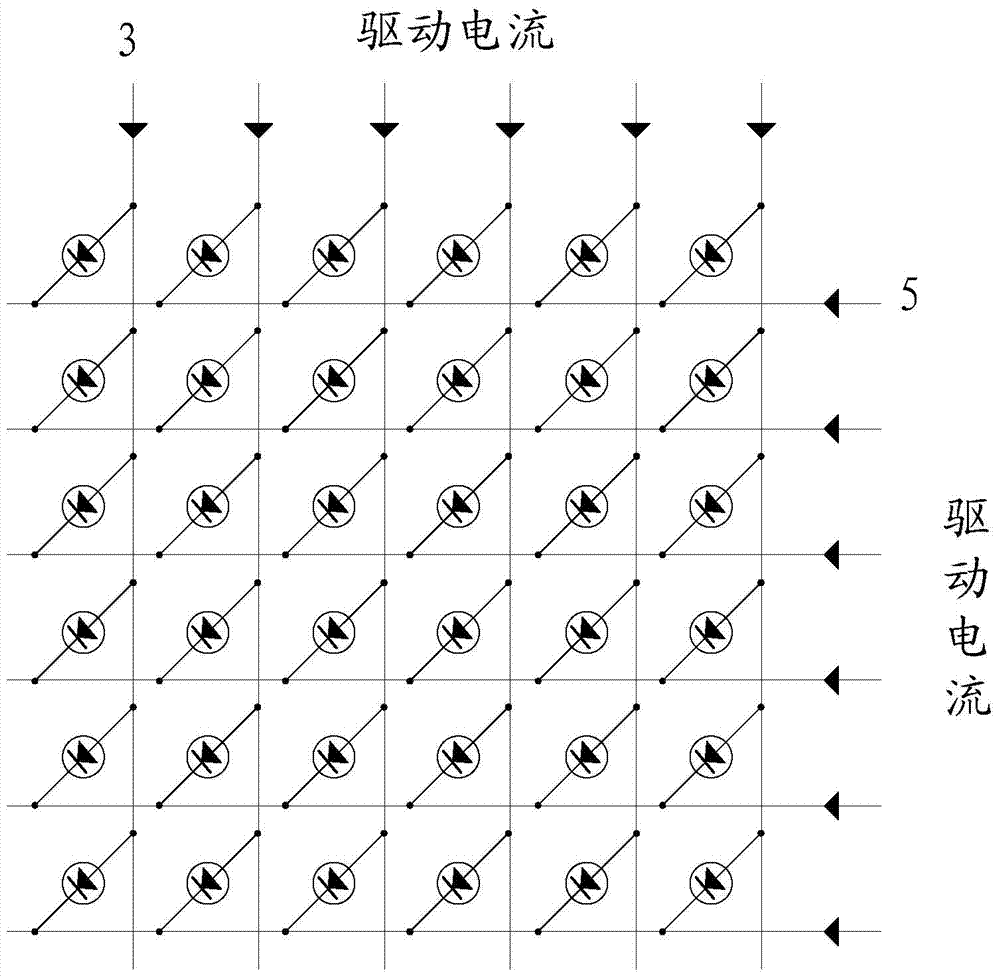

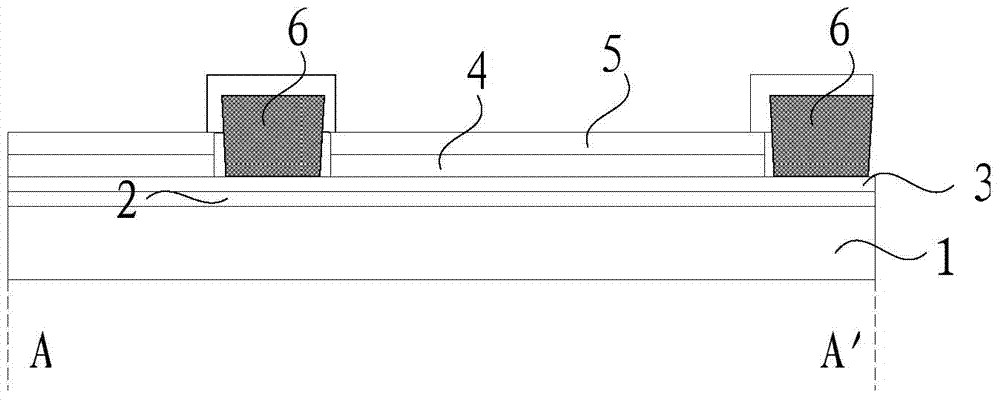

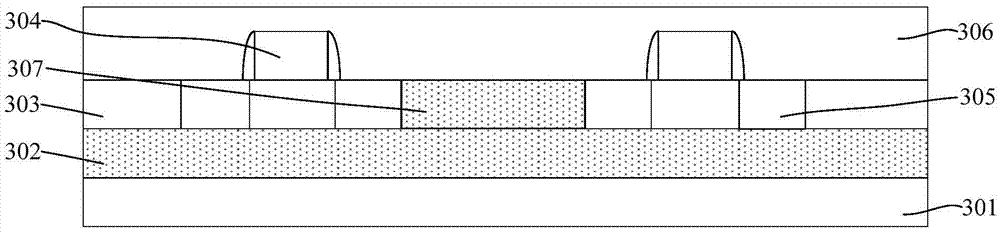

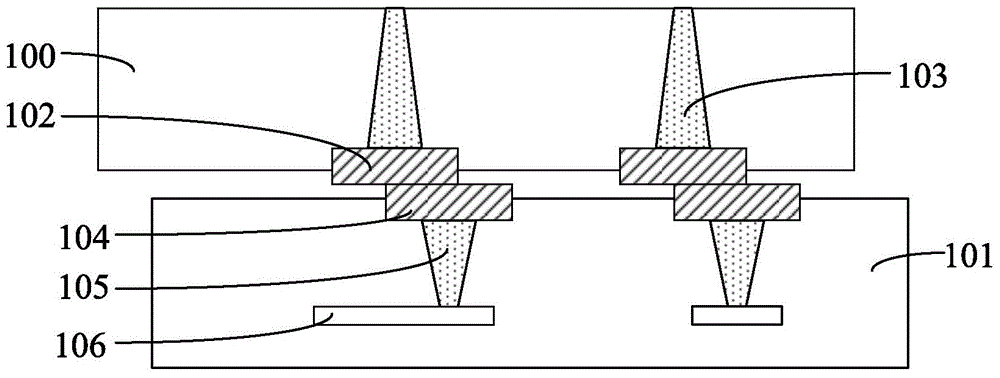

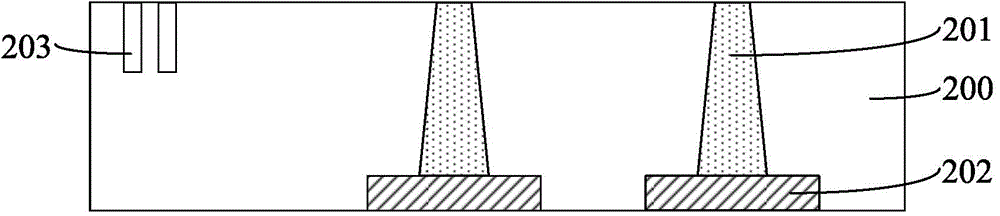

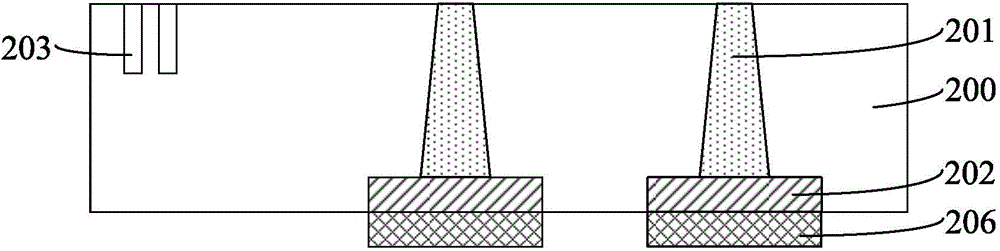

Isolating pillar, manufacturing method of isolating pillar, display panel and display device

ActiveCN104766933AAvoid electrical connectionSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceEngineering

The invention provides an isolating pillar, a manufacturing method of the isolating pillar, a display panel and a display device and relates to the field of display technologies. The problem that every two adjacent strip-shaped electrodes in a plurality of first strip-shaped electrodes formed by an existing isolating pillar are likely to be connected is solved. The isolating pillar comprises a first material pattern and a second material pattern located on the first material pattern. The first material pattern comprises an upper surface, a lower surface, a first isolating side face and a second isolating side face, wherein the upper surface is opposite to the lower surface, and the first isolating side face and the second isolating side face are opposite and are located between the upper surface and the lower surface. The second material pattern comprises an upper surface and a lower surface which are opposite to each other, the upper surface of the first material pattern makes direct contact with the lower surface of the second material pattern, and the projections, in the plane where the lower surface of the second material pattern is located, of the first isolating side face and the second isolating side face of the first material pattern are located among edges of the lower surface of the second material pattern. The isolating pillar is applied to the PMOLED display panel and a manufacturing method thereof.

Owner:BOE TECH GRP CO LTD

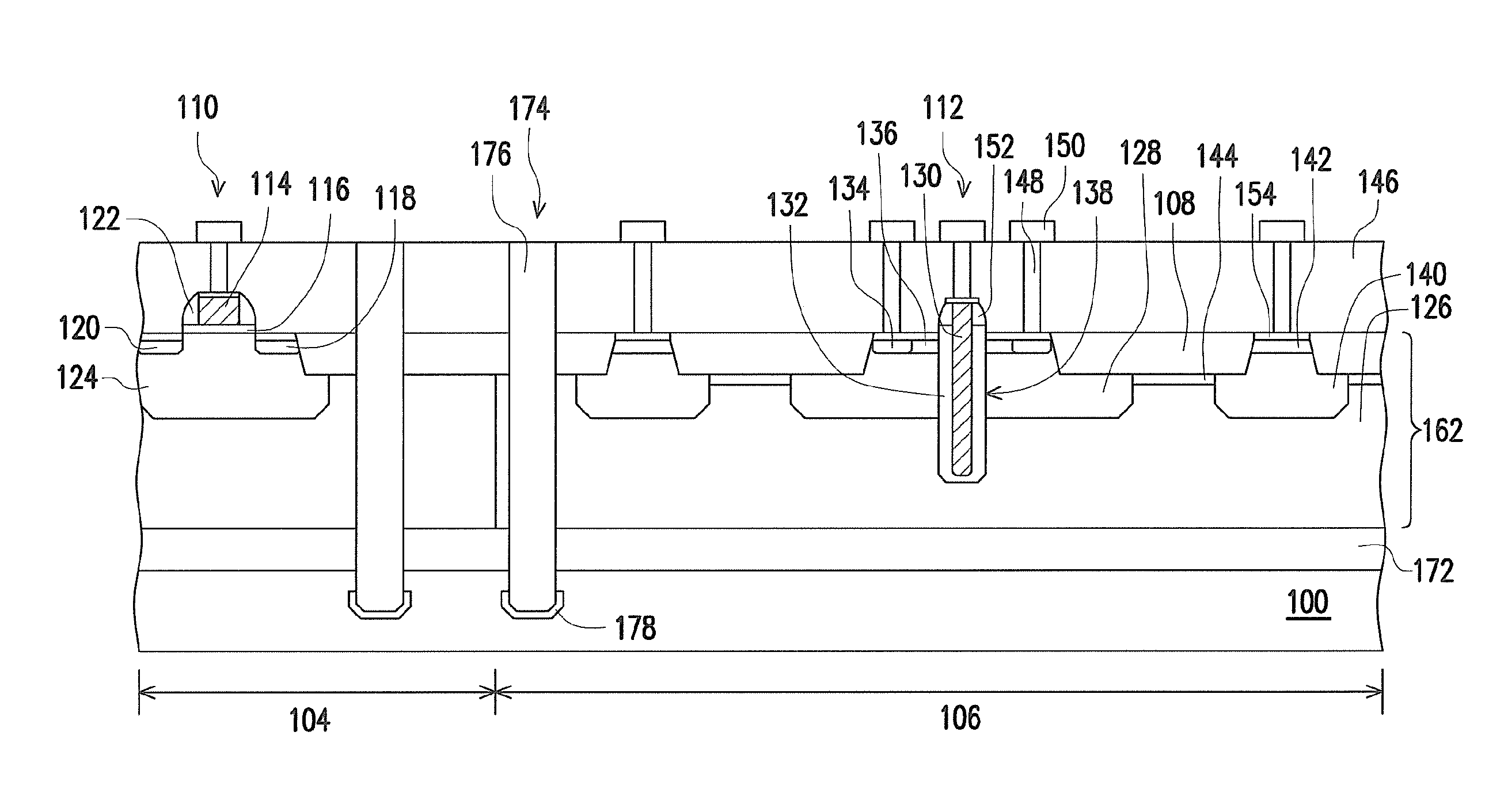

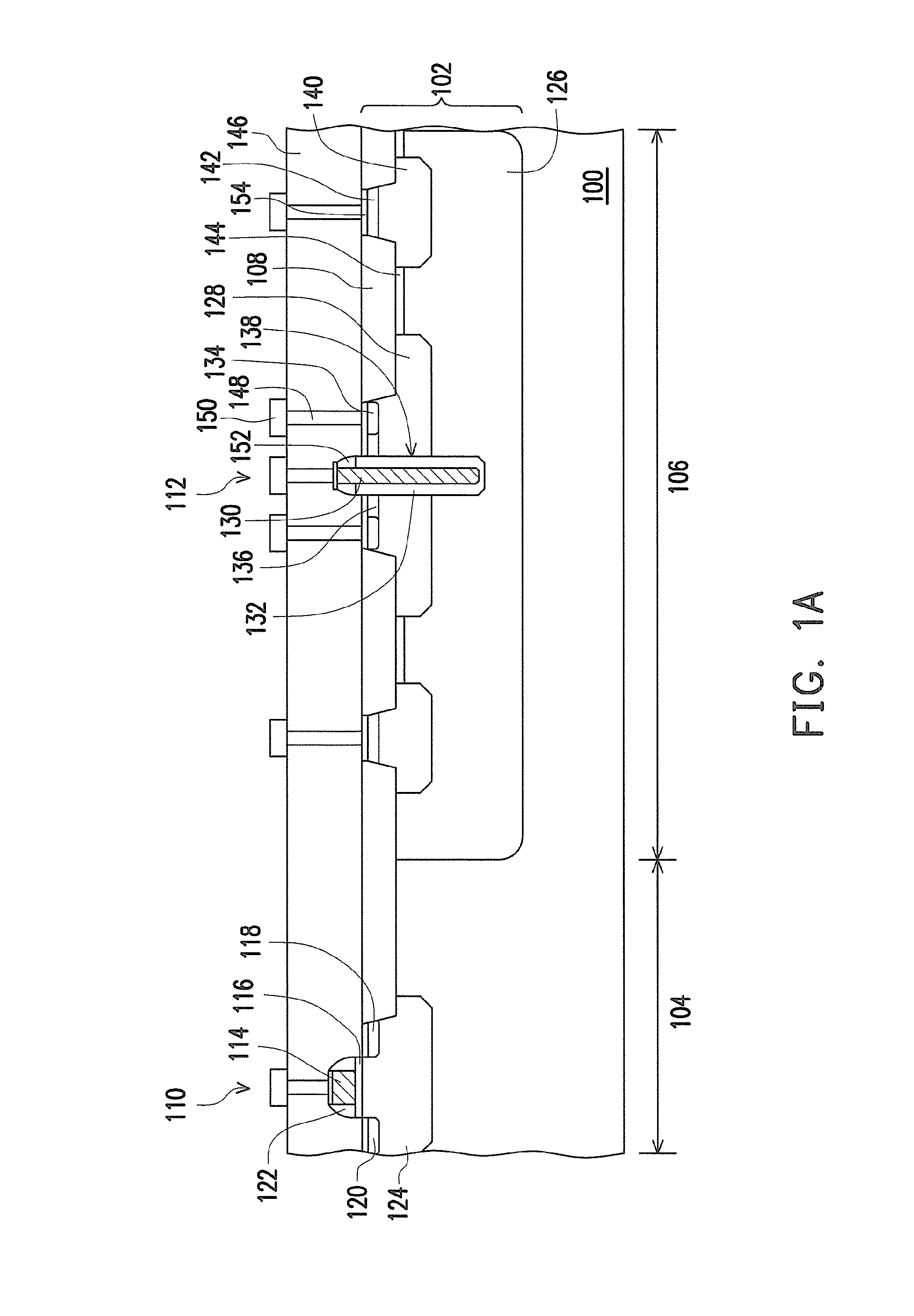

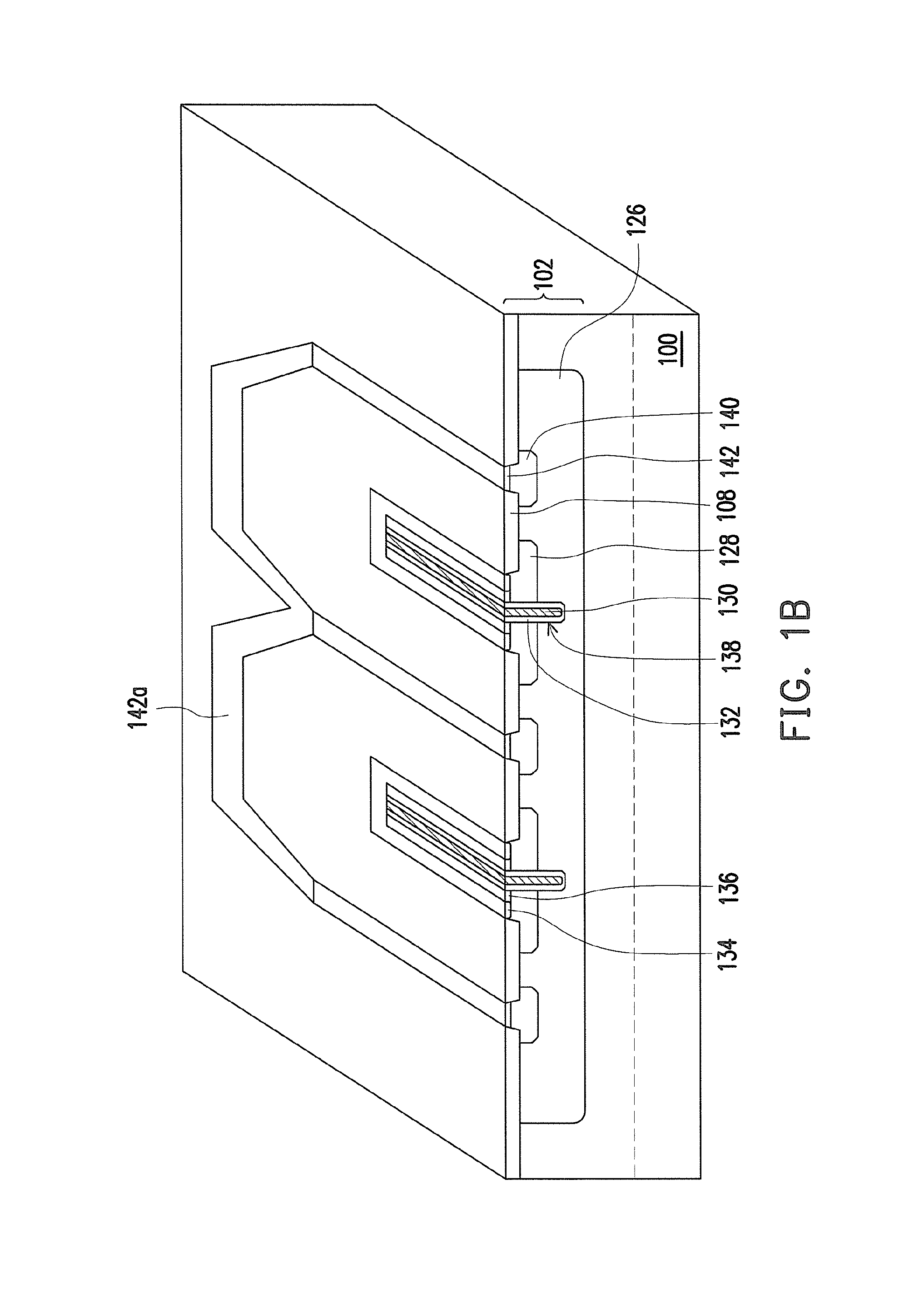

Trench lateral diffusion metal oxide semiconductor device and manufacturing method of the same

InactiveUS20160211348A1Improve device performanceAvoid electrical connectionTransistorSemiconductor/solid-state device manufacturingLDMOSSalicide

A trench lateral diffusion metal oxide semiconductor (LDMOS) device, disposed on a substrate, comprising: a transistor and an LDMOS transistor. The transistor has a gate. The LDMOS transistor has a trench gate, wherein the trench gate protrudes from a surface of the substrate. Electrical connection of the trench gate and a doping region due to a metal silicide may be prevented by protruding the trench gate from the surface of the substrate. And furthermore a step height difference between a gate and the trench gate may be decreased, and openings respectively exposing a top portion of the trench gate and a top portion of the gate may be formed without changing the manufacturing conditions.

Owner:MAXCHIP ELECTRONICS CORP

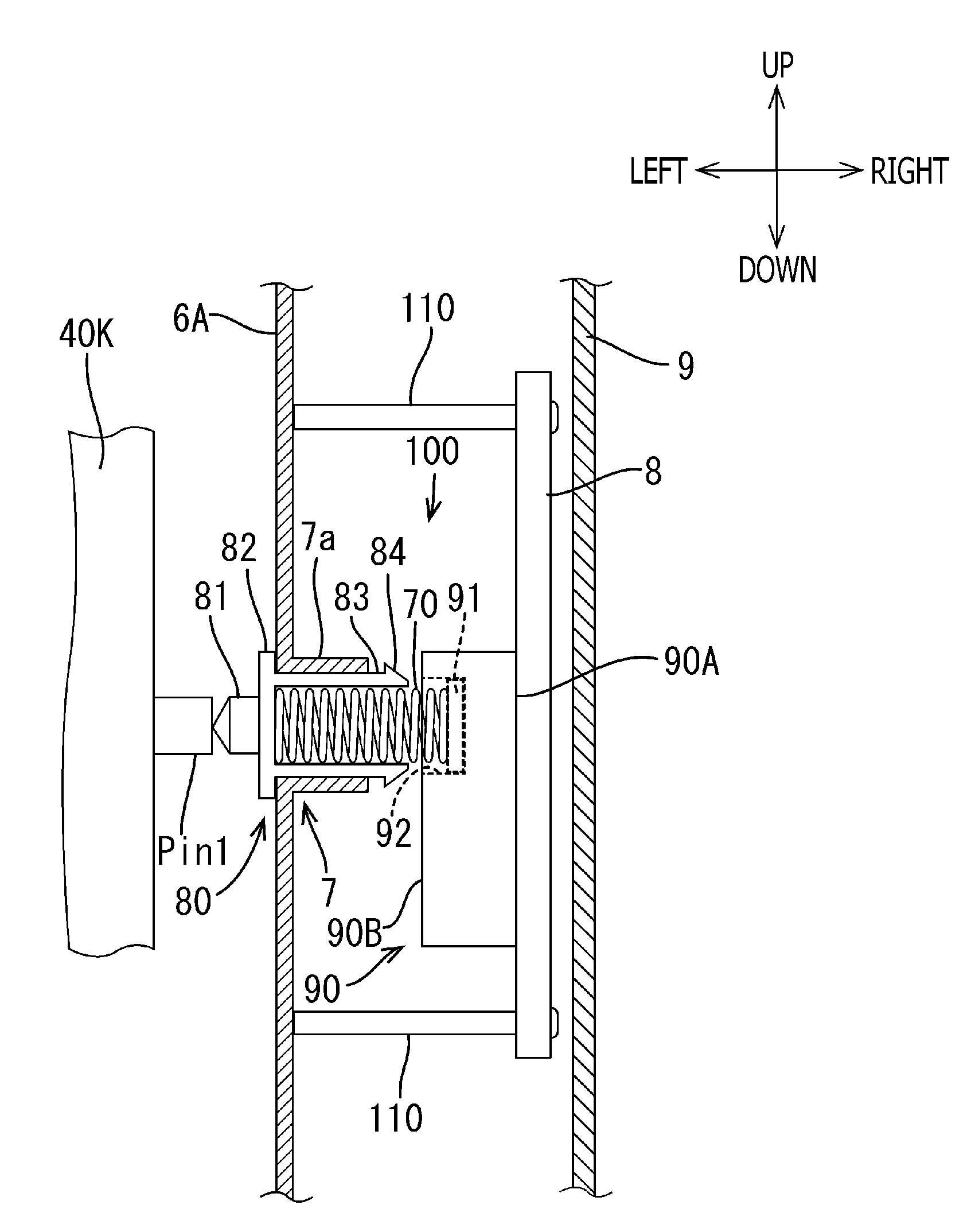

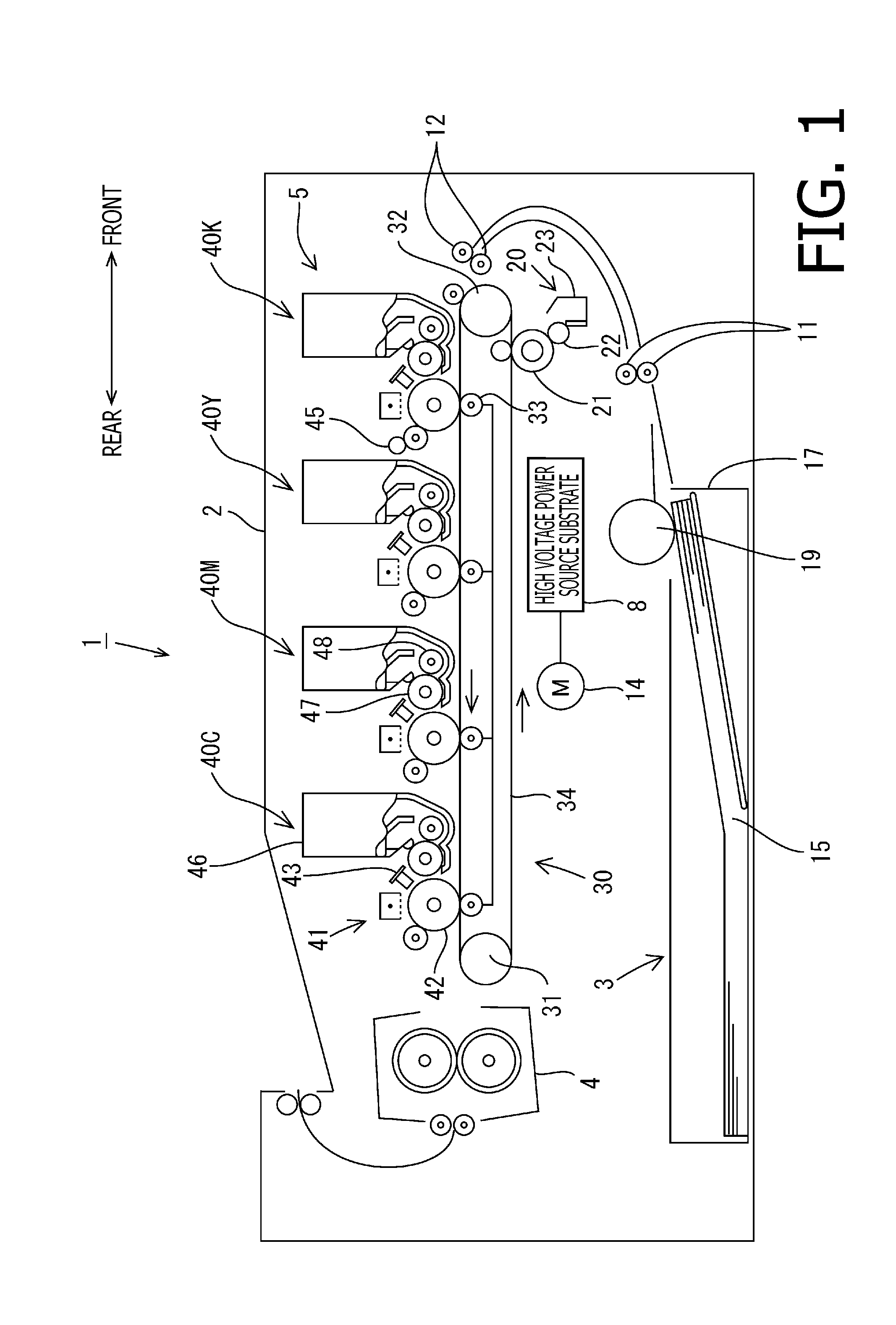

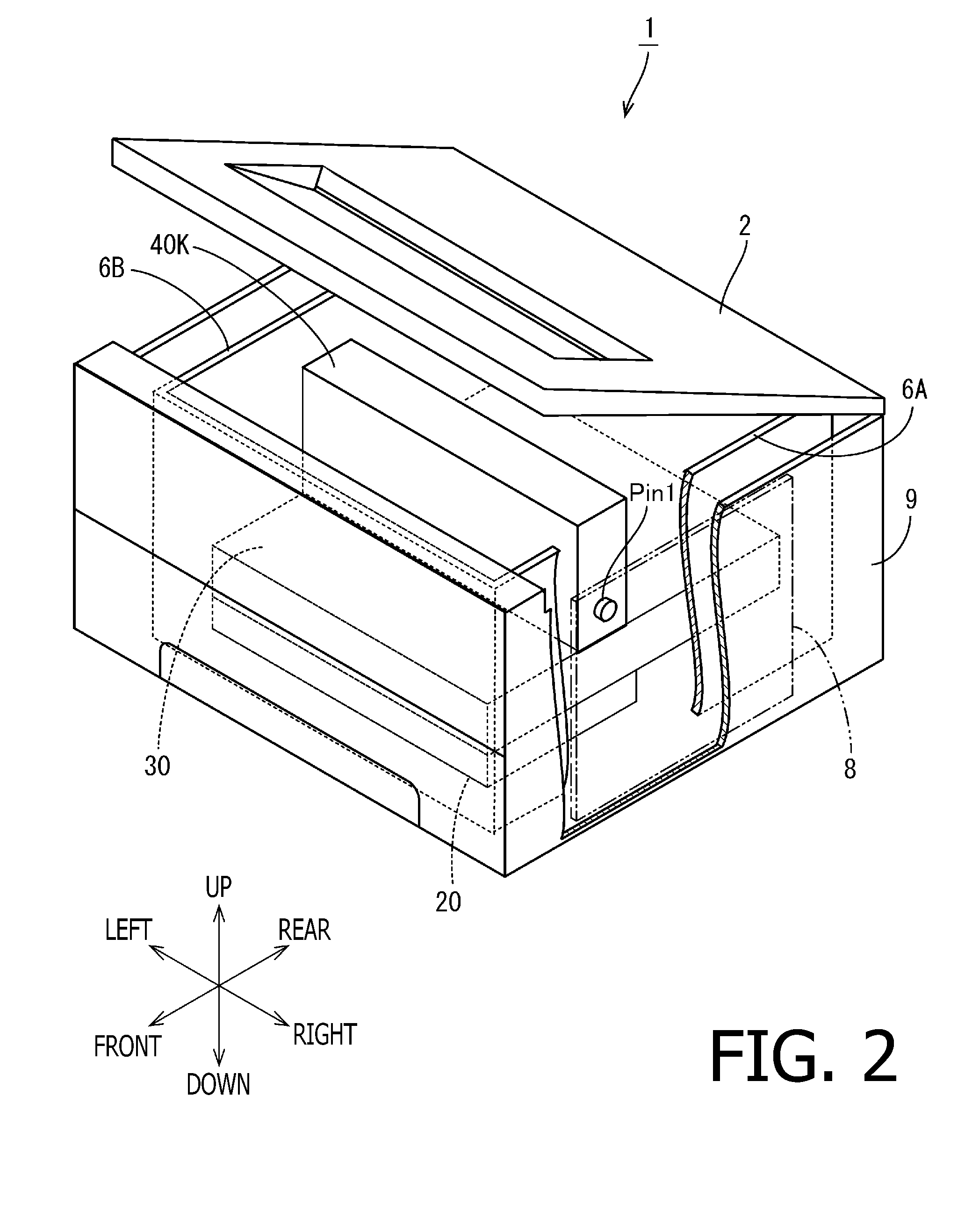

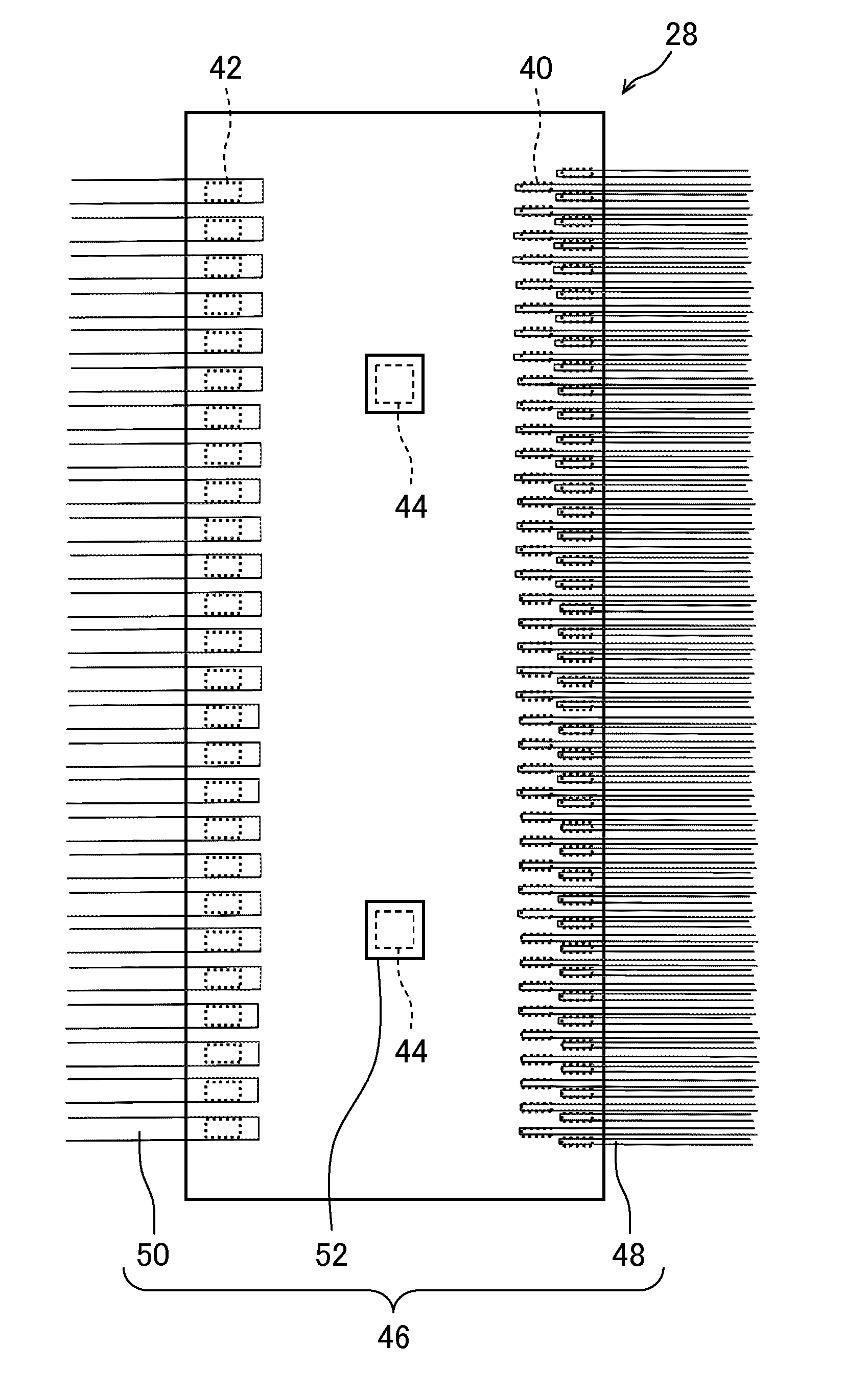

Image forming apparatus and manufacturing method for the same

ActiveUS20150037060A1Avoid electrical connectionAvoid failureLine/current collector detailsElectrographic process apparatusImage formationVoltage

An image forming apparatus, comprising: a frame body to which an attachment unit is detachably attachable, the attachment unit being configured to have an input electrode and to be used for image formation on a recording medium; a power source substrate configured to have an output electrode for outputting a voltage and to be attached to the frame body from an opposite side with respect to a side on which the attachment unit is attached; and a connection electrode configured to electrically connect the output electrode to the input electrode of the attachment unit, wherein the frame body comprises an insertion part into which the connection electrode is inserted from an opposite side with respect to a side on which the power source substrate is attached.

Owner:BROTHER KOGYO KK

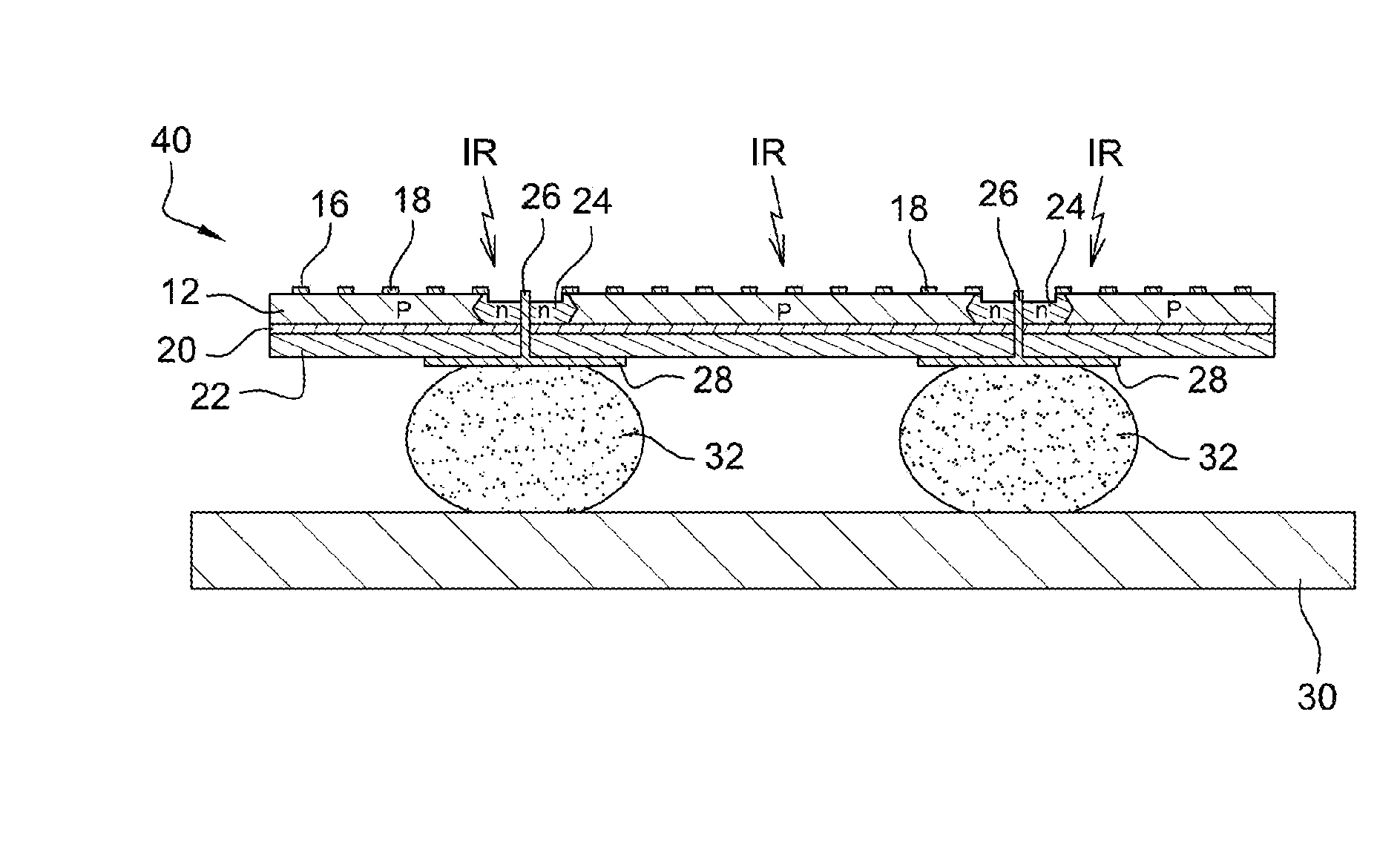

Image sensor module and forming method thereof

InactiveCN103956371AExcellent structural performanceReduce design difficultyRadiation controlled devicesImage sensorEngineering

The invention discloses an image sensor module and a forming method of the image sensor module. The image sensor module comprises a PCB substrate, a metal layer, an image sensing chip, a signal processing chip and welding protrusions. The PCB substrate is provided with a hole penetrating through the PCB substrate, the metal layer is arranged on the surface of the PCB substrate, the image sensing chip is inversely arranged above the PCB substrate, the image sensing chip is provided with an image induction area and a bonding pad surrounding the image induction area which is arranged above the hole, the bonding pad is electrically connected with the metal layer, the signal processing chip is inversely arranged above the PCB substrate, the signal processing chip is electrically connected with the metal layer, and the welding protrusions are arranged on the surface of the metal layer. The packaging performance of the image sensor module is improved, and the production cost of the image sensor module is reduced.

Owner:CHINA WAFER LEVEL CSP

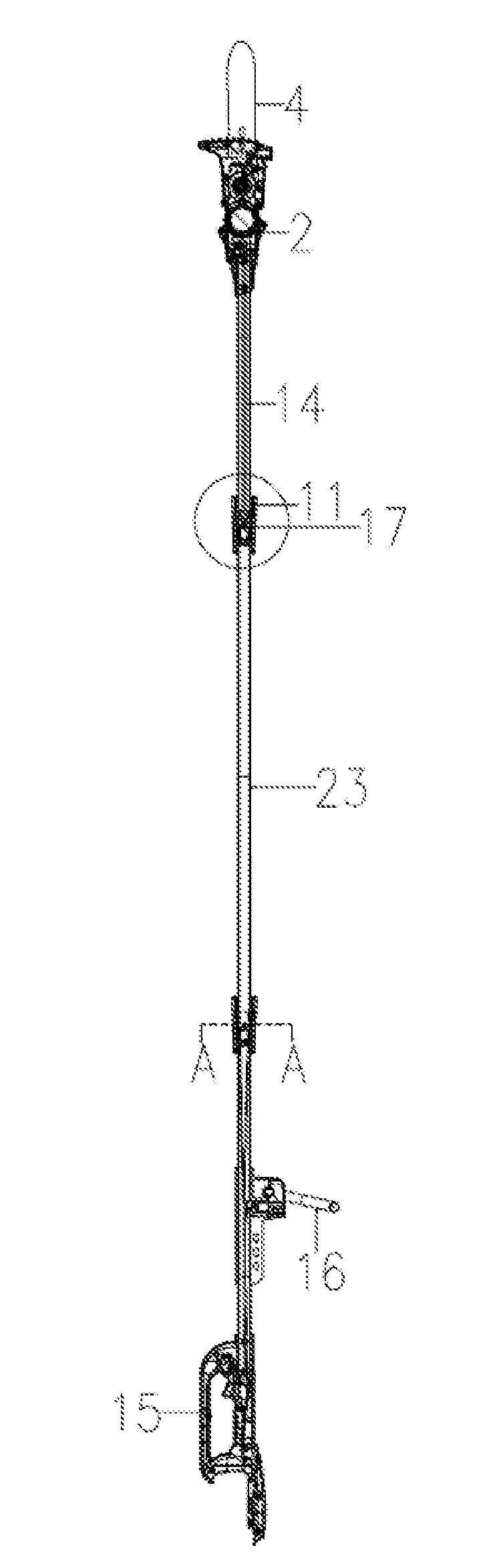

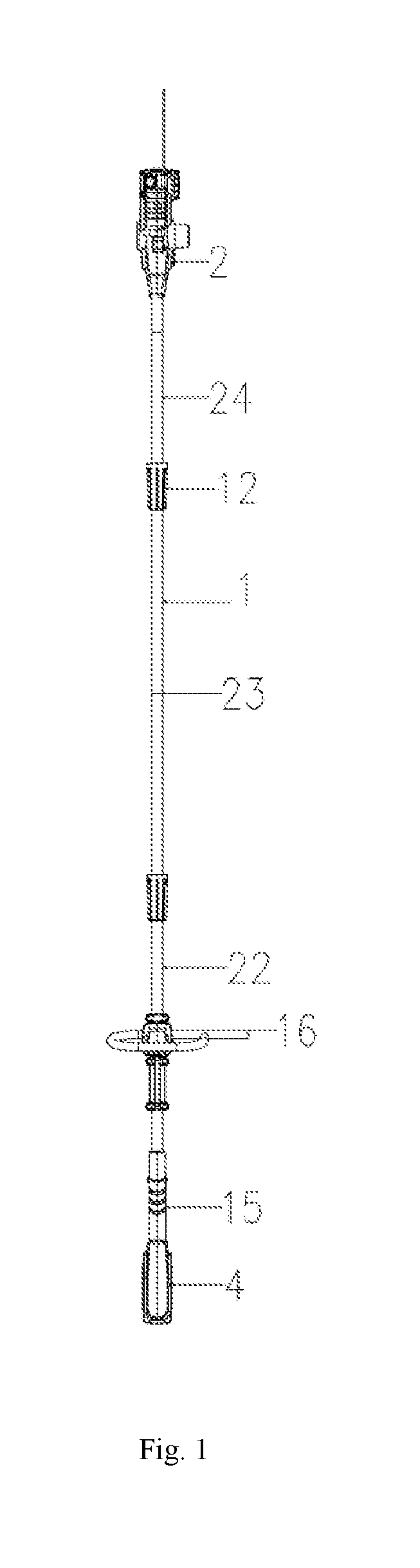

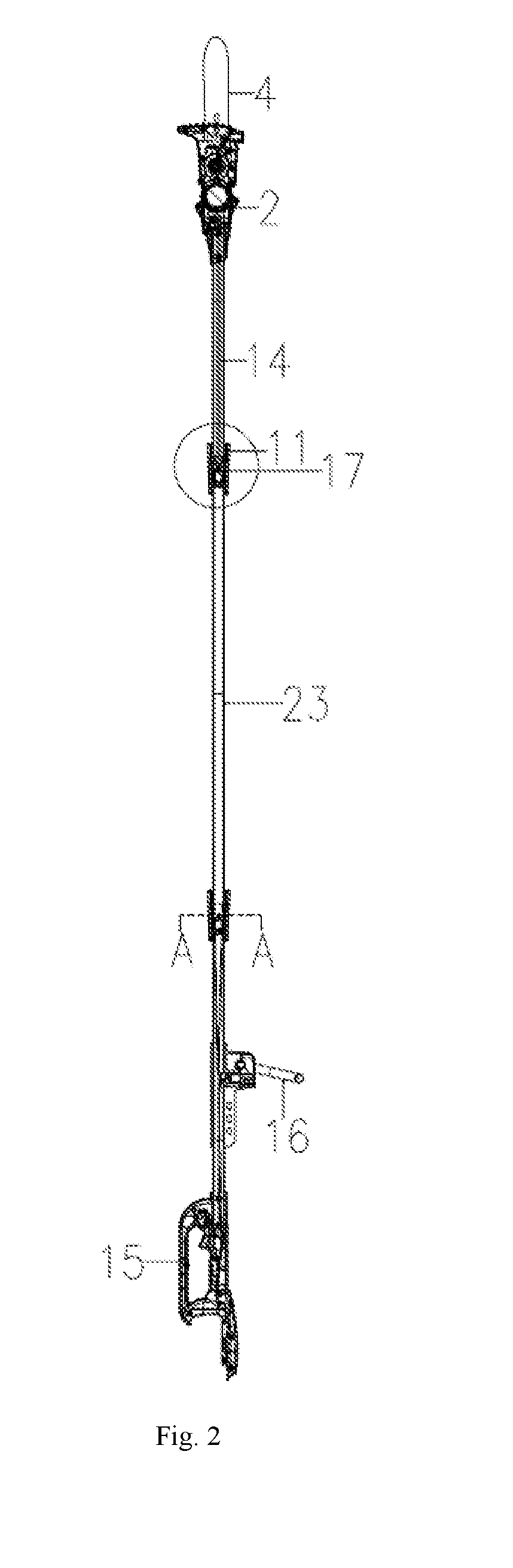

Extension Rod and Power Tool Having Extension Rod

ActiveUS20170079215A1Certain elasticityReduce swingCuttersMotor driven pruning sawsEngineeringPower tool

An extension rod for a power tool may include a plurality of rod portions, with a first connector and a second connector connecting two of the rod portions. The second connector has a sleeve and a primary fastener. The first connector has a guide rod sized for insertion into the sleeve. The first connector also has a secondary fastener engaging with the primary fastener. A first guide ring, a second guide ring, and a third guide ring are located between the guide rod and the sleeve. The first guide ring, the second guide ring, and the third guide ring each include respective conical faces. At least one of the first, second, and third guide rings defines a notch.

Owner:SUZHOU CLEVA ELECTRIC APPLIANCE CO LTD

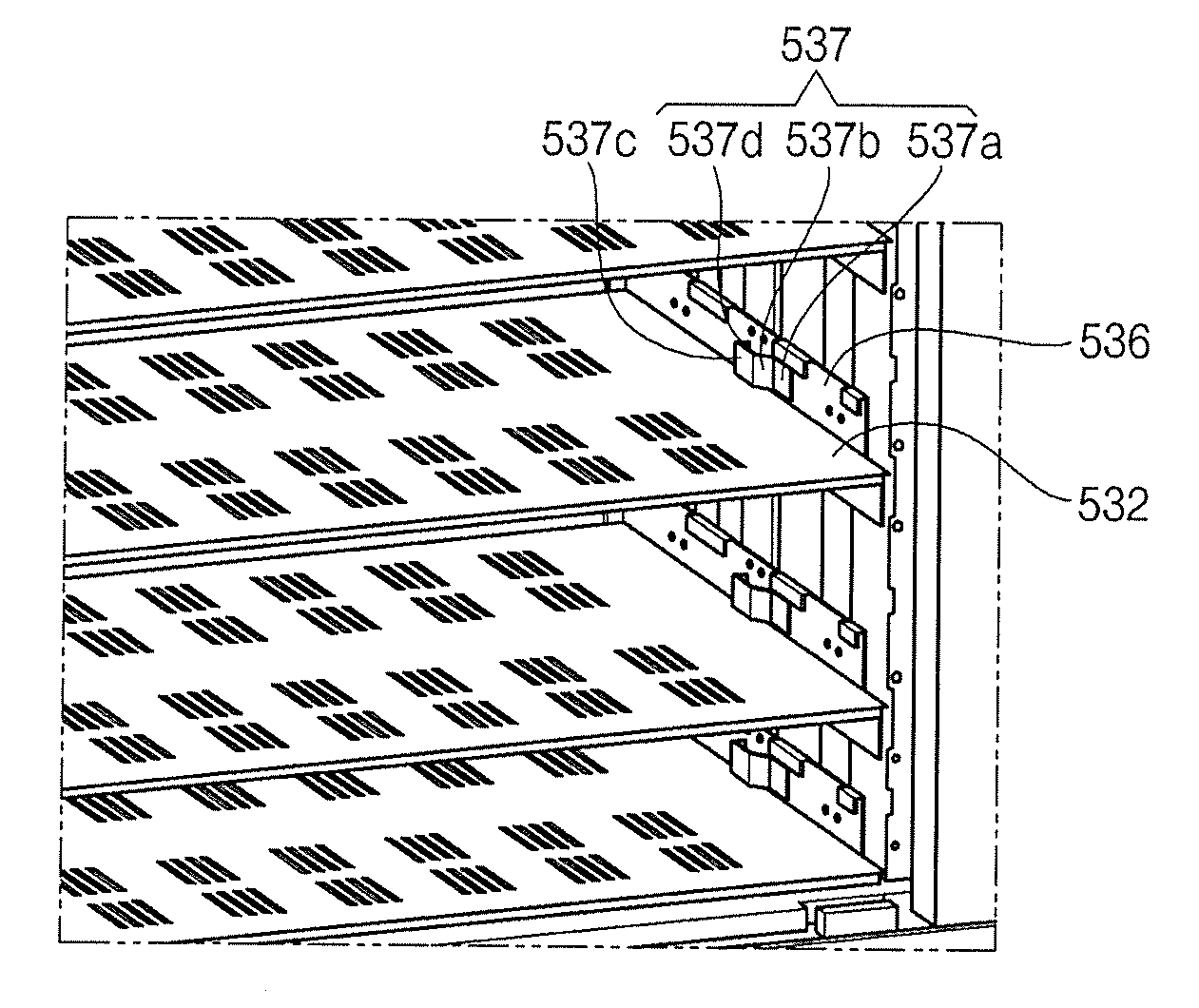

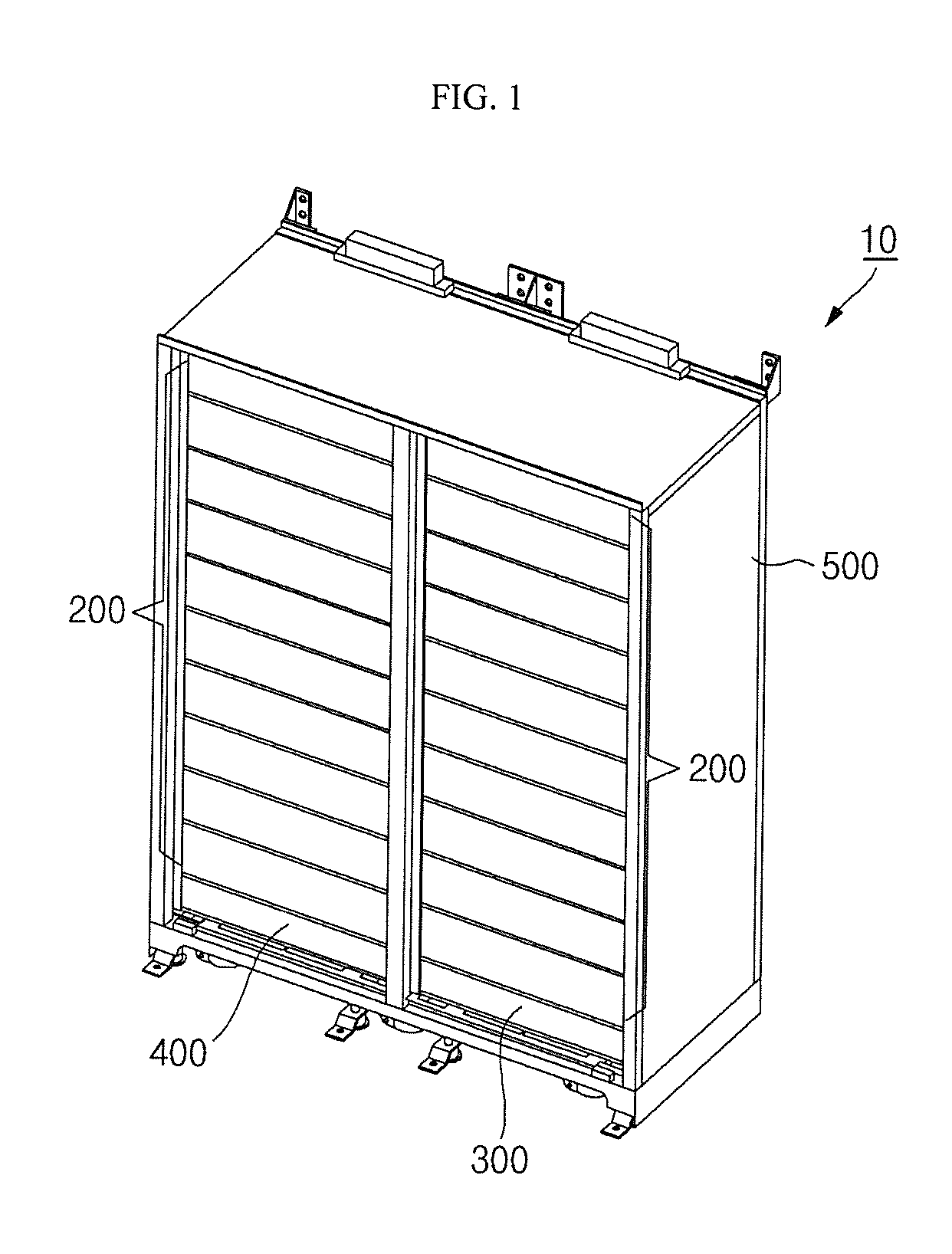

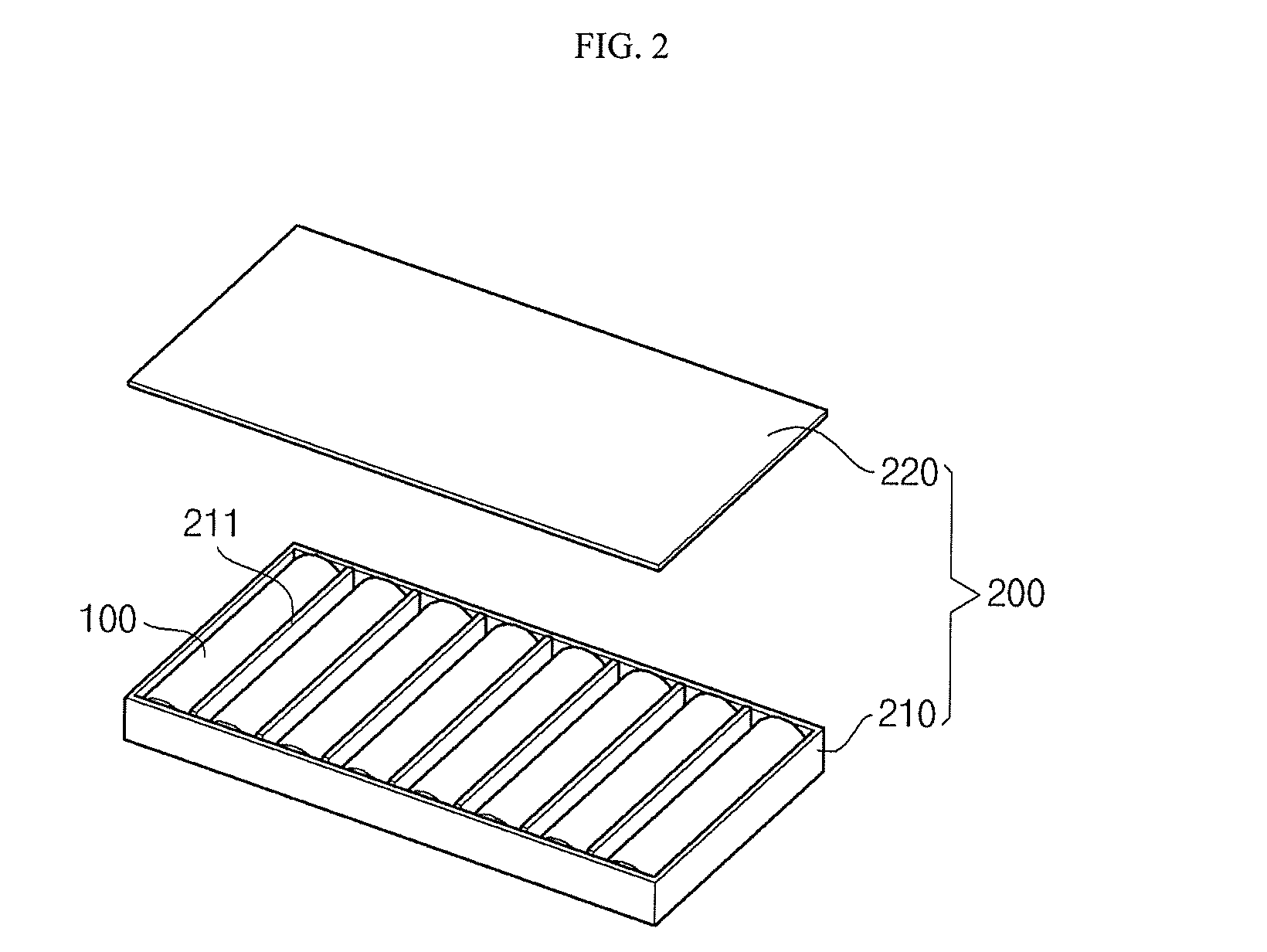

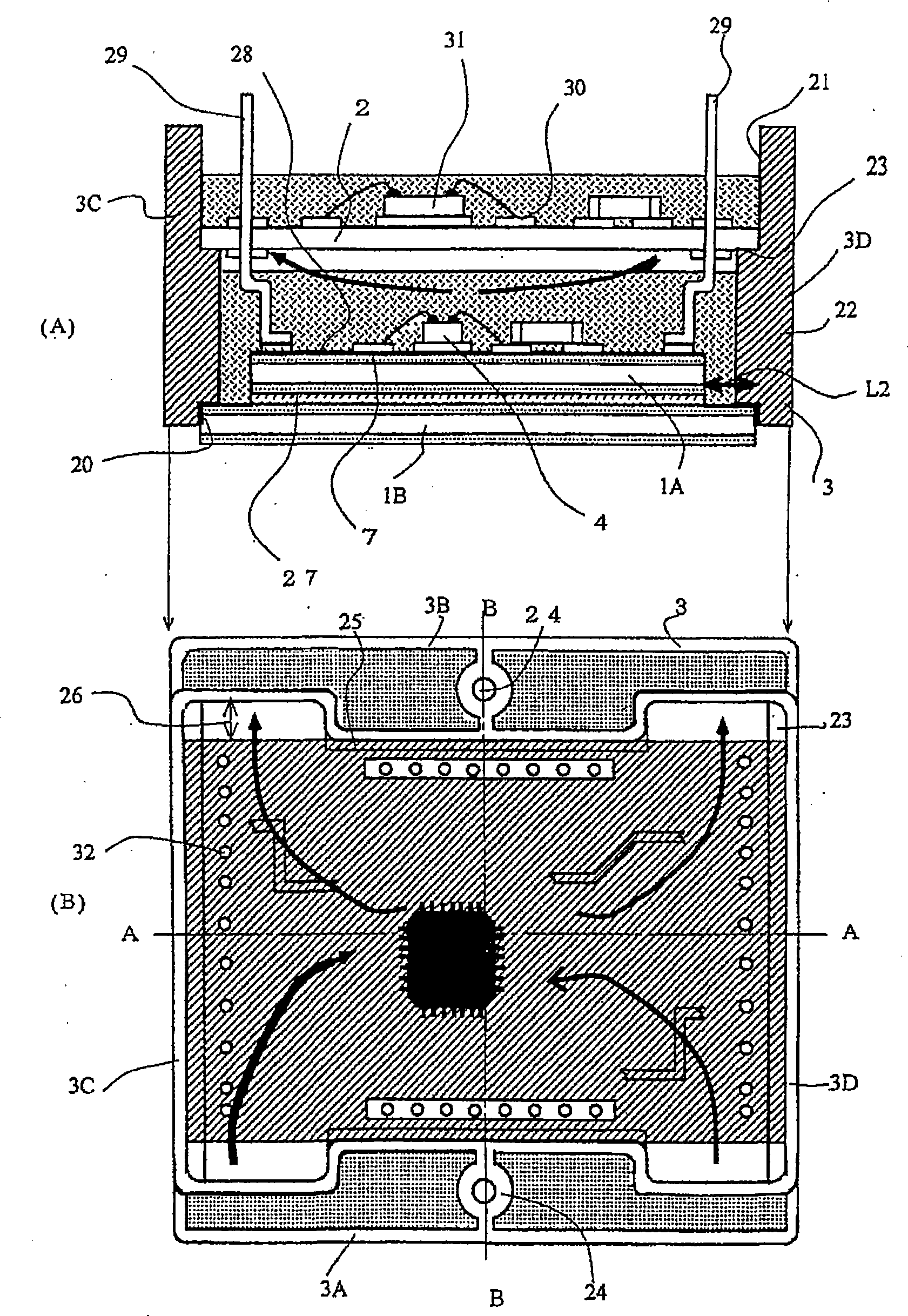

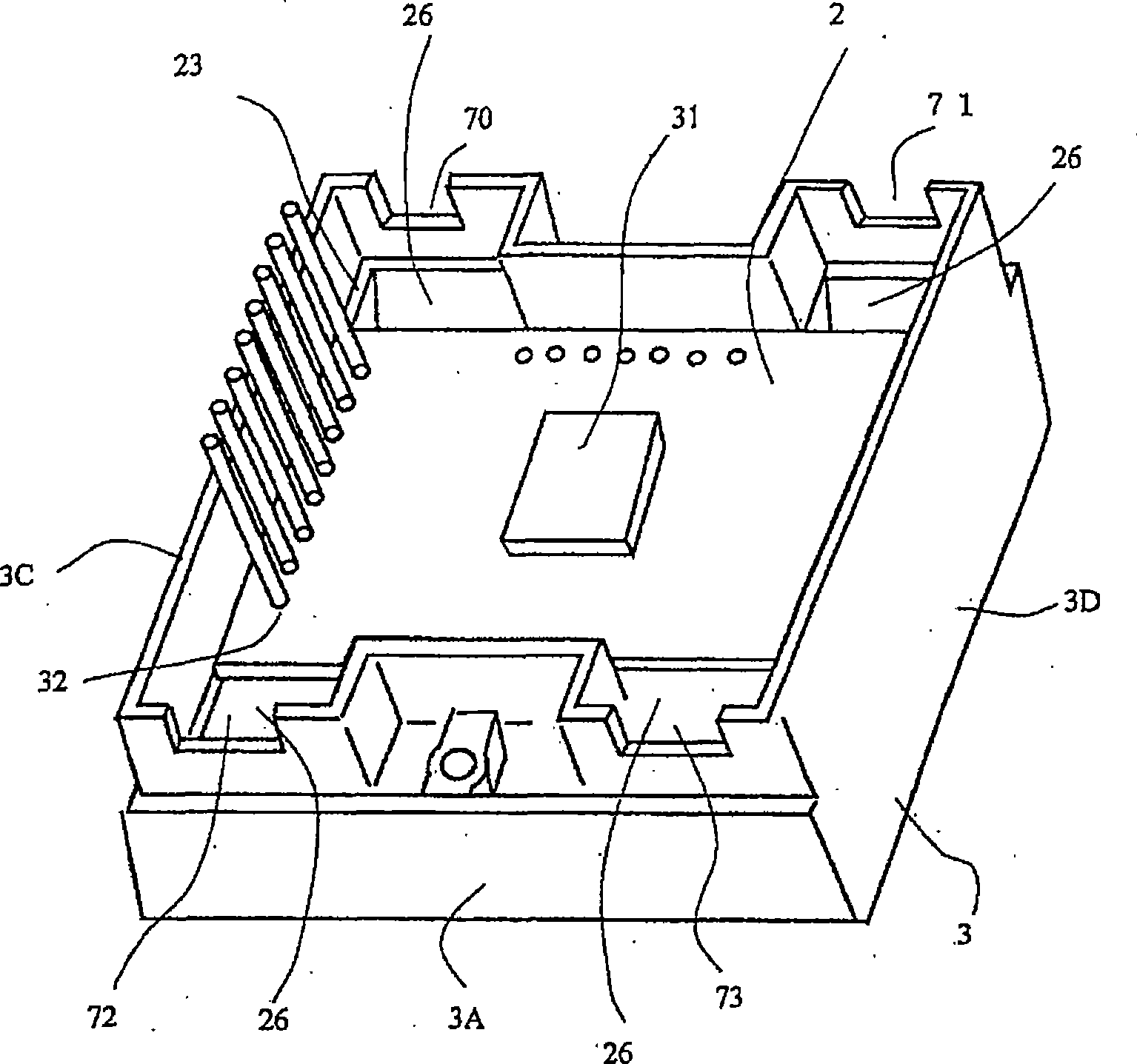

Energy storage system

ActiveUS8900737B2Suppress and prevent vibrationAvoid electrical connectionCurrent conducting connectionsSecondary cellsElectricityEngineering

An energy storage system including a battery cell, a tray for receiving the battery cell, and a rack for receiving the tray. The rack includes a connector unit. The connector unit is configured to connect to the tray inserted into the rack and to vibrate together with the tray when the tray vibrates due to, for example, an earth quake or external impact applied to the rack, thereby preventing an electric connection between the tray and the connector unit from being broken.

Owner:SAMSUNG SDI CO LTD

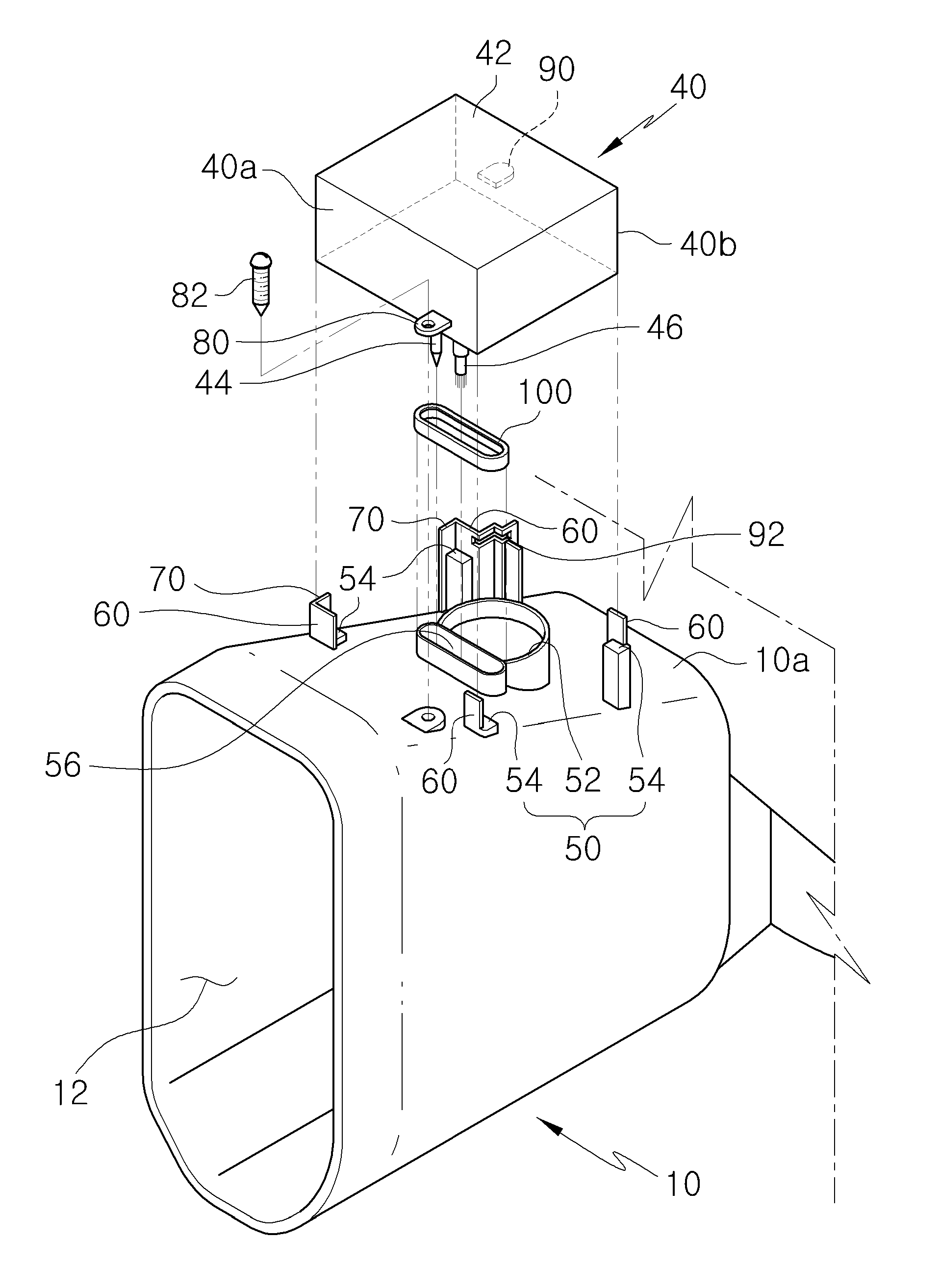

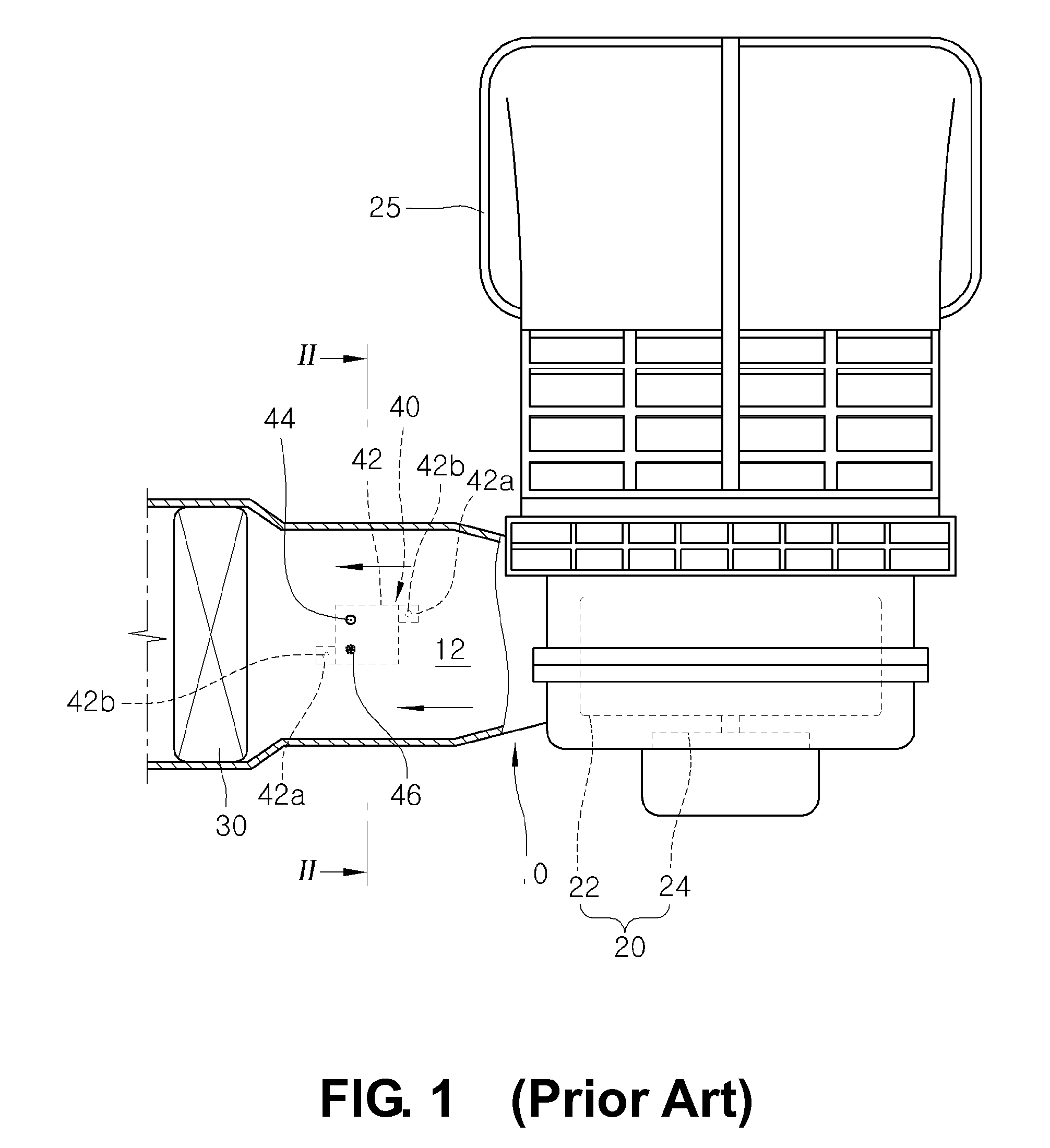

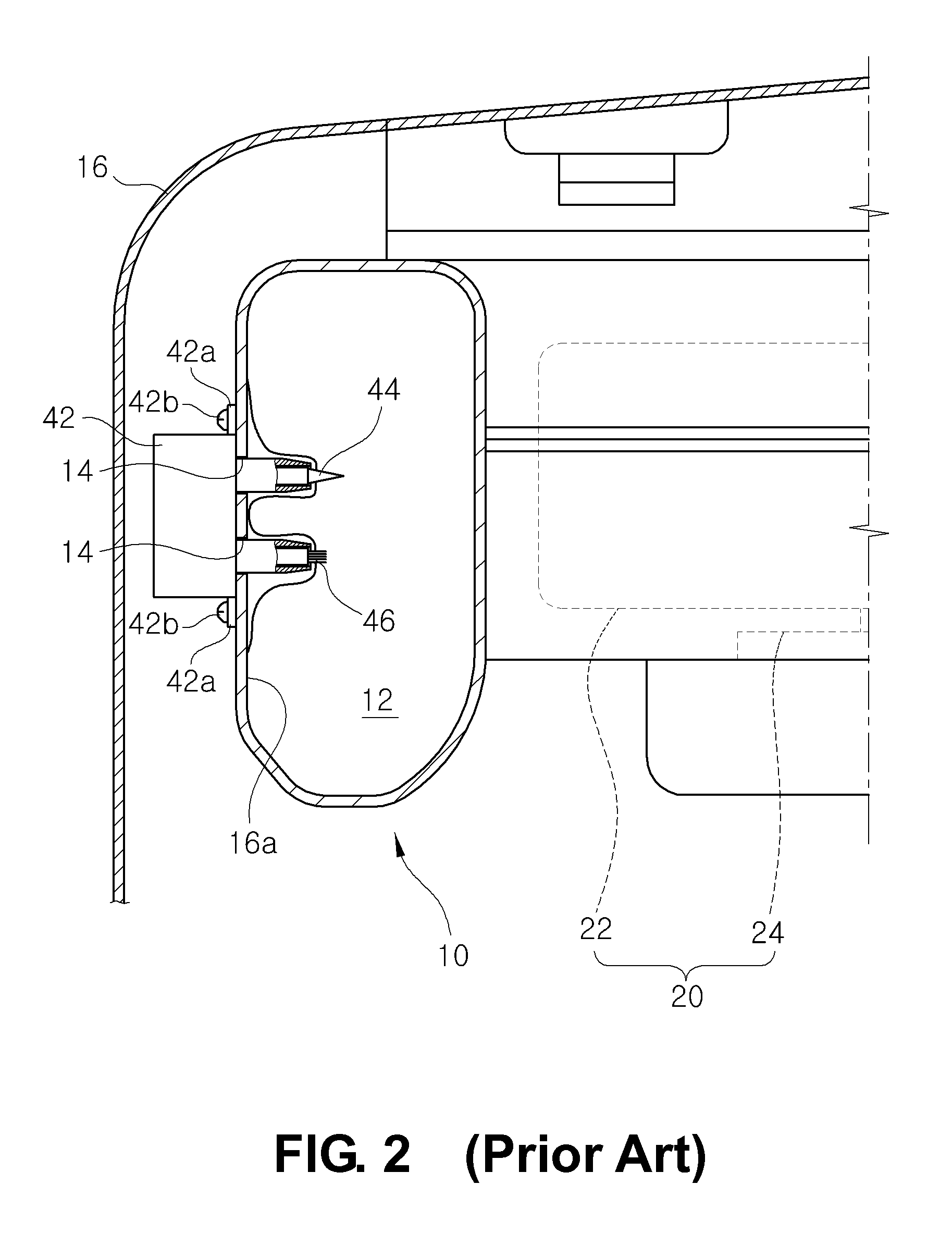

Ionizer mounting structure for a vehicle air conditioning system

ActiveUS7824477B2Simple and easy mannerEasy maintenanceAir-treating devicesElectrostatic separation housingElectrode insertionEngineering

The present invention relates to an ionizer mounting structure for a vehicle air conditioning system. The air conditioning system includes an air conditioning case having an internal passageway and an ionizer for generating negative ions and positive ions within the internal passageway. The air conditioning case has a discharge electrode insertion hole and the ionizer has a plurality of discharge electrodes extending into the internal passageway through the discharge electrode insertion hole. The ionizer mounting structure includes a mounting and demounting structure for allowing the ionizer to be mounted to the air conditioning case through sliding movement from a demounting position on a passenger room side to a mounting position above the air conditioning case and for allowing the ionizer to be demounted from the air conditioning case through sliding movement from the mounting position to the demounting position.

Owner:HANON SYST

Display device

InactiveUS20140029226A1Avoid skewAvoid it happening againElectrically conductive connectionsSolid-state devicesElectrical connectionDisplay device

An integrated circuit chip includes first and second electrode terminals electrically connected to an internal circuit, and a dummy bump arranged between the first and second electrode terminals on a back surface thereof. A wiring pattern includes first lines electrically connected to the first electrode terminals below the back surface of the integrated circuit chip and extend in the direction toward a display region outside the integrated circuit chip, and second lines electrically connected to the second electrode terminals below the back surface of the integrated circuit chip and extend in the direction opposite to the display region outside the integrated circuit chip. The dummy bump is configured to avoid at least one of the electrical connection between the dummy bump and all of the first lines and all of the second lines and the electrical connection between the dummy bump and the internal circuit.

Owner:JAPAN DISPLAY INC

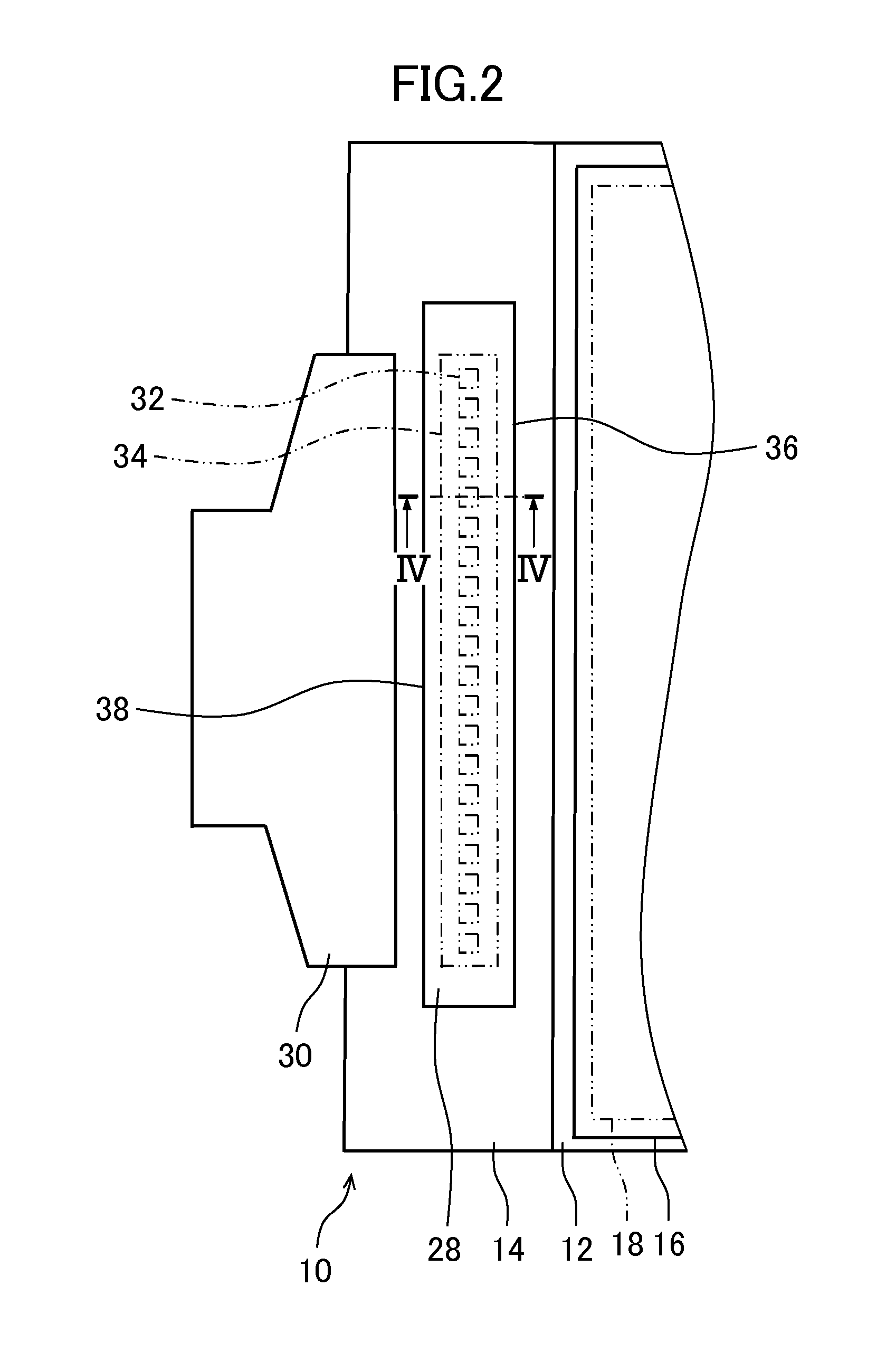

Photodetector with a plasmonic structure

InactiveUS20110156194A1Effectively electrically insulateAvoid electrical connectionSolid-state devicesSemiconductor devicesElectrical conductorPhotovoltaic detectors

This photodetector comprises a doped semiconductor layer; a reflective layer located underneath semiconductor layer; a metallic structure placed on semiconductor layer that forms, with semiconductor layer, a surface plasmon resonator, a plurality of semiconductor zones formed in semiconductor layer and oppositely doped to the doping of the semiconductor layer; and for each semiconductor zone, a conductor that passes through the photodetector from reflective layer to at least semiconductor zone and is electrically insulated from metallic structure, with semiconductor zone associated with corresponding conductor thus determining an elementary detection surface of the photodetector.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

Shielded connector with insert molded shielding shell and resin cover

InactiveUS7147513B2Few stepsEasy to transformLine/current collector detailsElectrically conductive connectionsElectric wireElectrical and Electronics engineering

A shielded connector (A) has a housing (20) for accommodating terminal fittings (40) connected with ends of wires (10). A metallic shielding shell (30) is provided in the housing (20), and a tubular connecting member (50) connects an end of the shield (11) and the shielding shell (30). Thus, the shielding shell (30) can be connected with grounding members of a mating housing when the housing (20) is connected with the mating housing. Thus, it is not necessary to connect the shield (11) with the grounding members in addition to a connecting operation of the housing (20).

Owner:SUMITOMO WIRING SYST LTD

Chip package with a dam structure on a die pad

InactiveUS7812432B2Improve chip reliabilityImprove reliabilityElectrically conductive connectionsSemiconductor/solid-state device detailsAdhesiveElectrical and Electronics engineering

Owner:CHIPMOS TECH INC

Semiconductor structure and formation method thereof

ActiveCN107039372AImprove structural performanceReduce internal temperatureSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureInterconnection

The invention provides a semiconductor structure and a formation method thereof. The semiconductor structure comprises a first opening which penetrates through a first dielectric layer and isolating structures which are arranged between adjacent transistor regions and an insulating material layer; a first thermal conducting layer which fully fills in the first opening, wherein the thermal conductivity of the first thermal conducting layer material is greater than that of the isolating structure material; zeroth conductive plugs which are arranged on the surface of a doped region and penetrate through the first dielectric layer; a zeroth conductive layer which is arranged on the first dielectric layer and electrically connected with the zeroth conductive plugs; a second dielectric layer which is arranged on the first dielectric layer and covers the zeroth conductive layer, wherein an interconnection structure electrically connected with the zeroth conductive layer is formed in the second dielectric layer; carrier wafers which are bonded with the surface of the second dielectric layer and the surface of a top conductive layer; a through hole which penetrates through the insulating material layer and is electrically connected with the interconnection structure; and an underlying conductive plug which fully fills in the through hole. The problem of the self-heating effect of the semiconductor structure can be improved and the electrical performance of the semiconductor structure can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Circuit module

InactiveCN101399260AEliminate deformationAvoid electrical connectionSemiconductor/solid-state device detailsSolid-state devicesElectrical and Electronics engineering

Owner:SANYO ELECTRIC CO LTD +1

Semiconductor structure and manufacture method thereof

ActiveCN105448862AReduce or even eliminate bond offset issuesReduce adverse effectsSemiconductor/solid-state device detailsSolid-state devicesHeat processingSurface tension

The present invention provides a semiconductor structure and a manufacture method thereof. The manufacture method of the semiconductor structure comprises: providing a first wafer and a second wafer, the first wafer being provided with a first metal layer, the second layer being provided with a second metal layer; forming a first material layer at the surface of the first wafer; forming a second material layer at the surface of the second wafer; performing alignment processing and bonding processing of the first wafer and the second wafer to align the first material layer with the second material layer and contact the surface of the first material layer with the surface of the second material layer; performing heat processing of the first material layer and the second material after the bonding processing to mutually fuse the first material layer and the second layer so that the alignment precision between the first metal layer and the second layer is improved. The surface tension generated by mutually fusing the first material layer and the second material layer is employed to get close the first material layer to the second material layer, so that the alignment precision between the first metal layer and the second layer is improved and the bonding offset is decreased.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Semiconductor component and sensor component for data transmission devices

InactiveUS20050104149A1Increase measurement throughputImprove throughputSemiconductor/solid-state device detailsSolid-state devicesWireless transmissionCoupling

The invention relates to a semiconductor component and a sensor component with data transmission devices, for wireless transmission the semiconductor component having a main coupling element and the sensor component having a sensor coupling element. The invention affords the possibility of multiple sensor applications without direct electrical contact between sensor component and semiconductor component, which may have a logic chip.

Owner:INFINEON TECH AG