Patents

Literature

445 results about "Step height" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Standard Step Height. On average, American architects have used a standard stair height of 7.5 inches. On stairs built inside, the average step length is 9 inches tall, while outside steps have an average length of 11 inches tall.

Circuit and method for adaptive incremental step-pulse programming in a flash memory device

Owner:SAMSUNG ELECTRONICS CO LTD

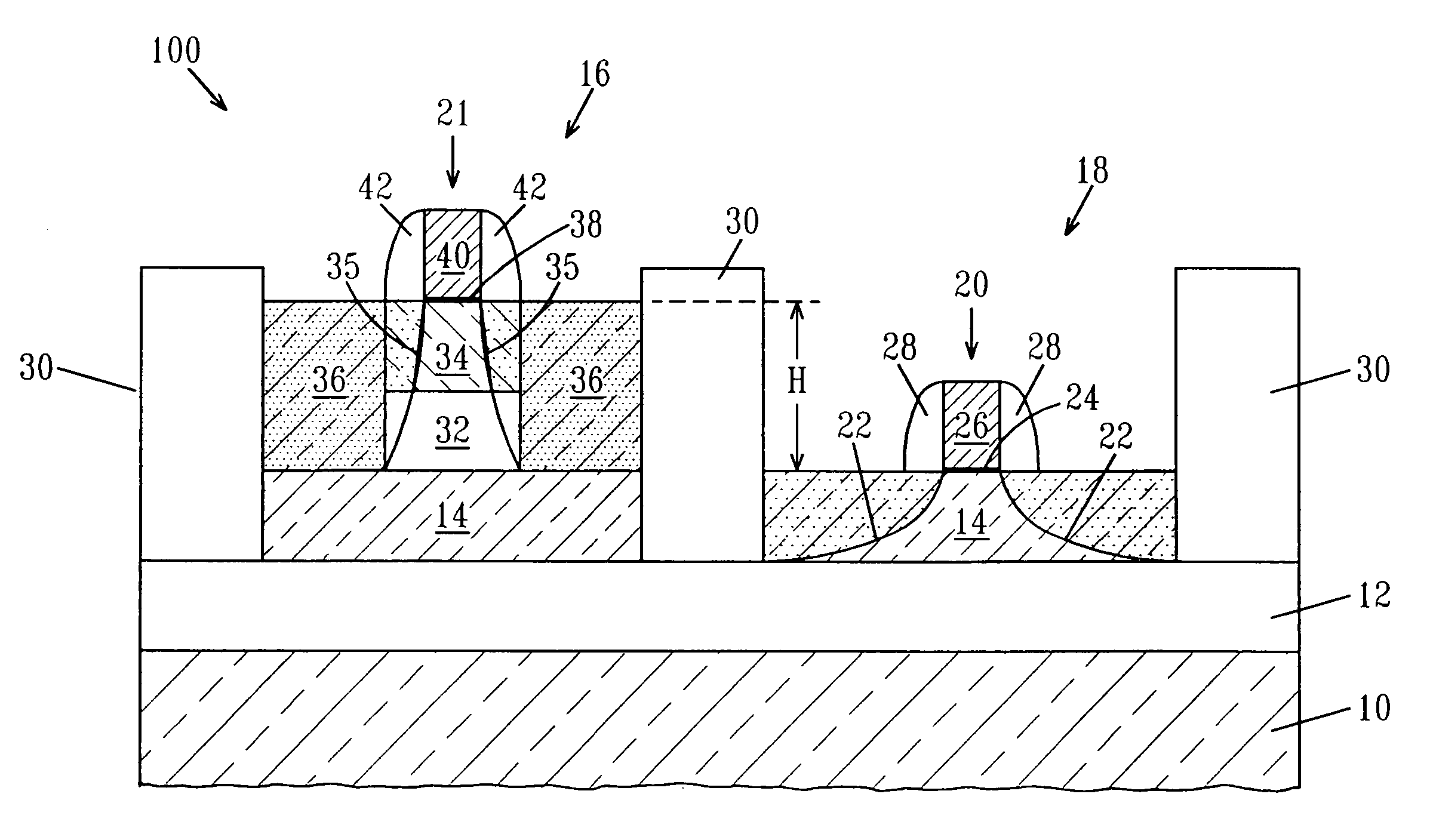

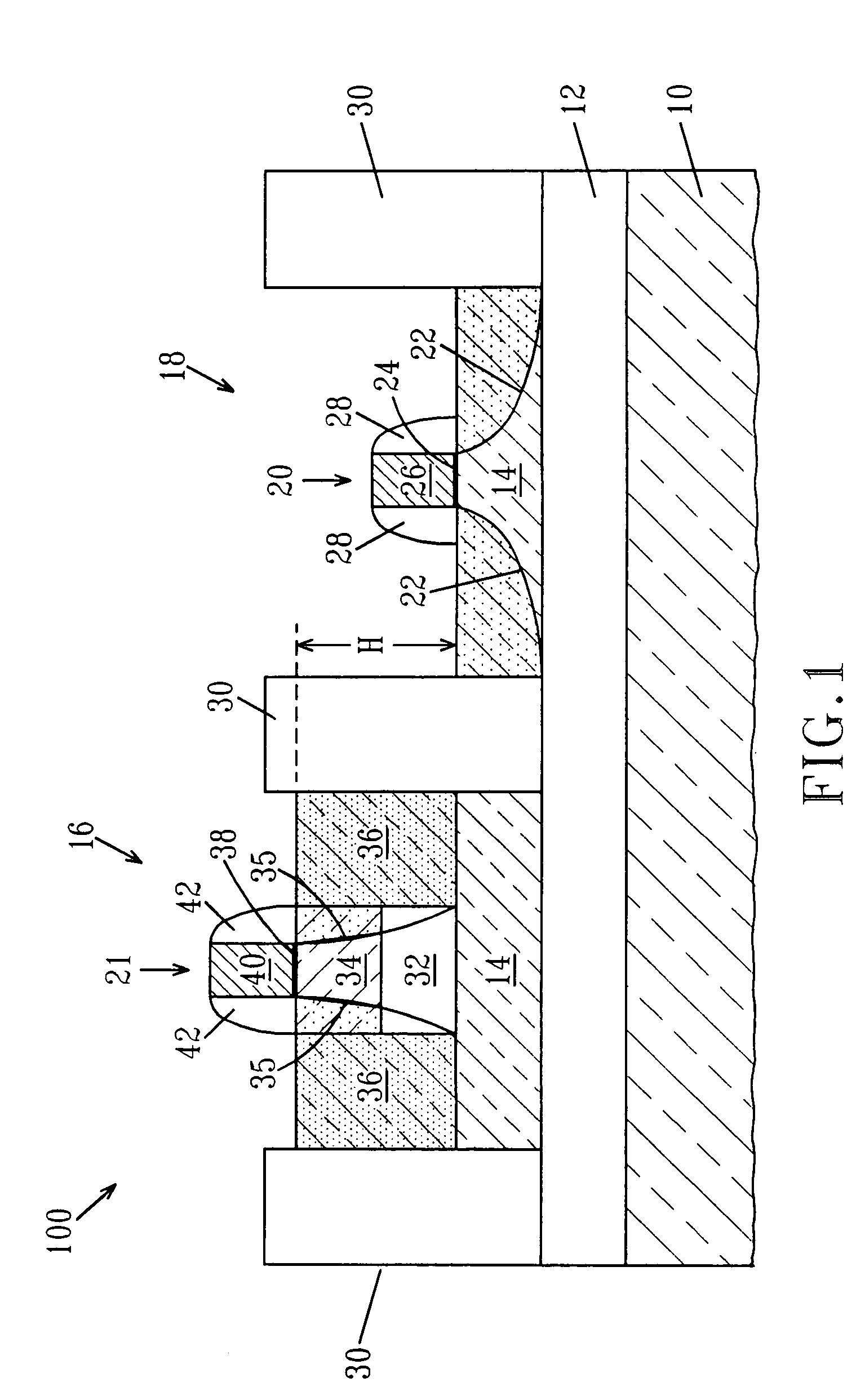

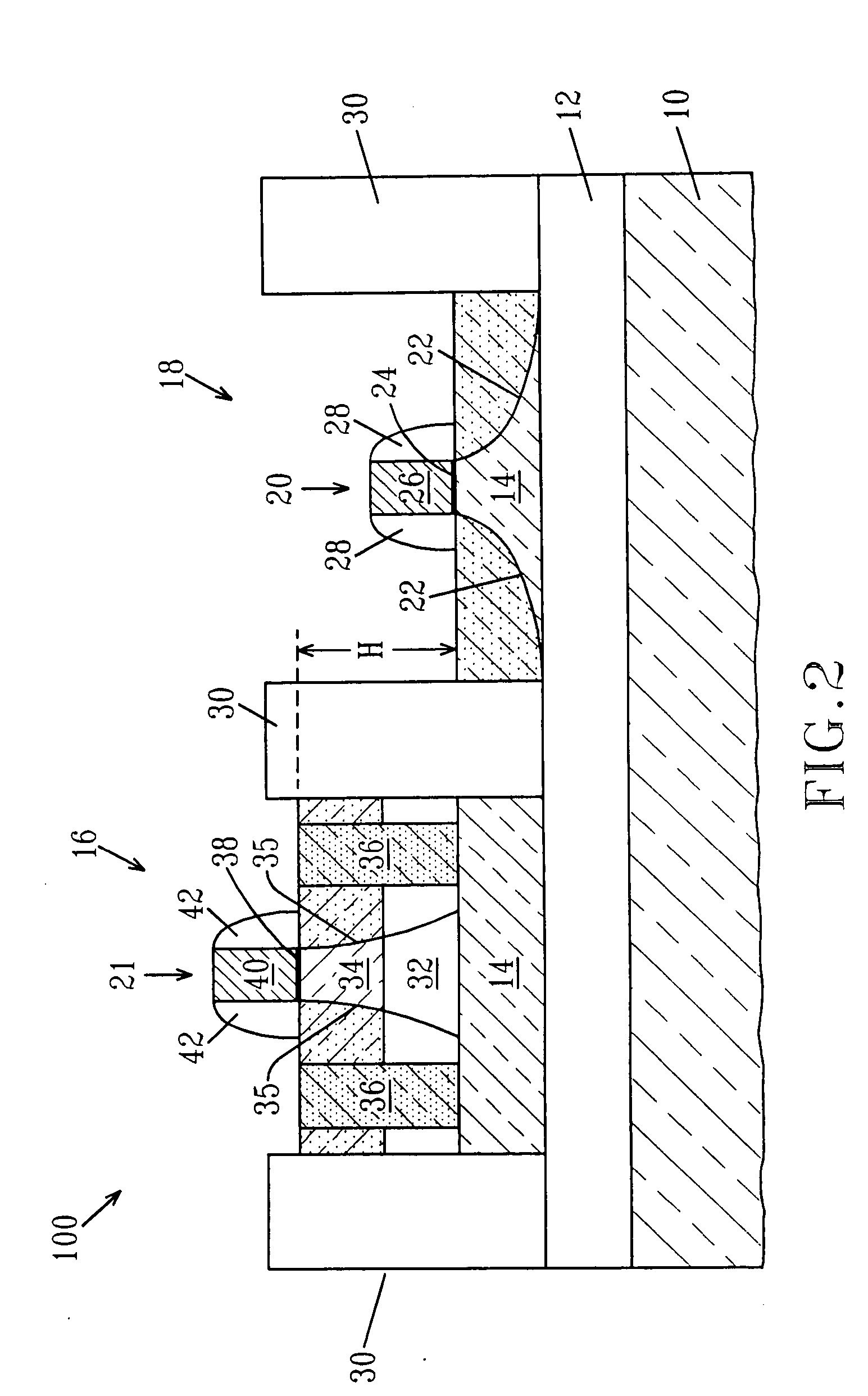

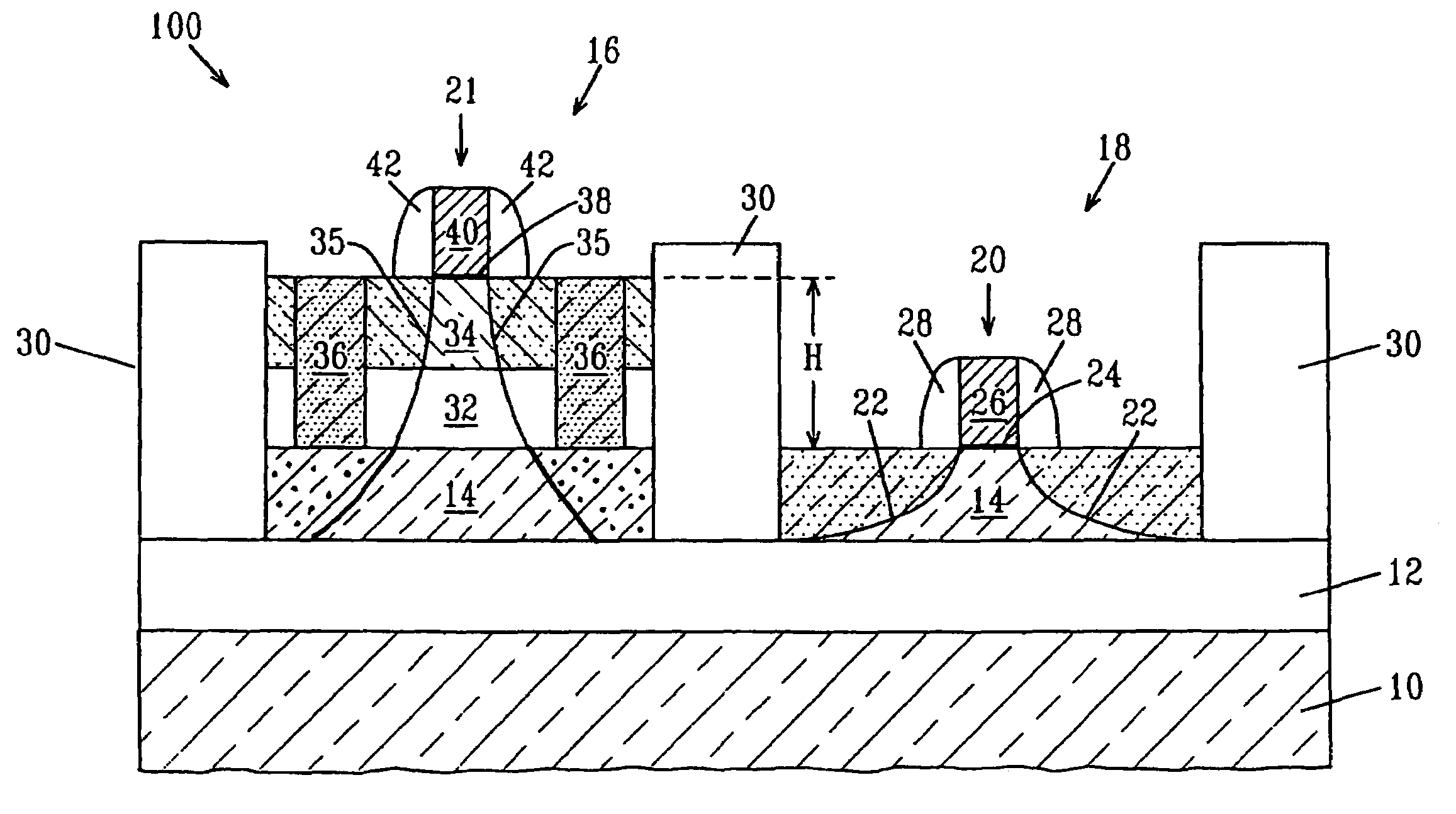

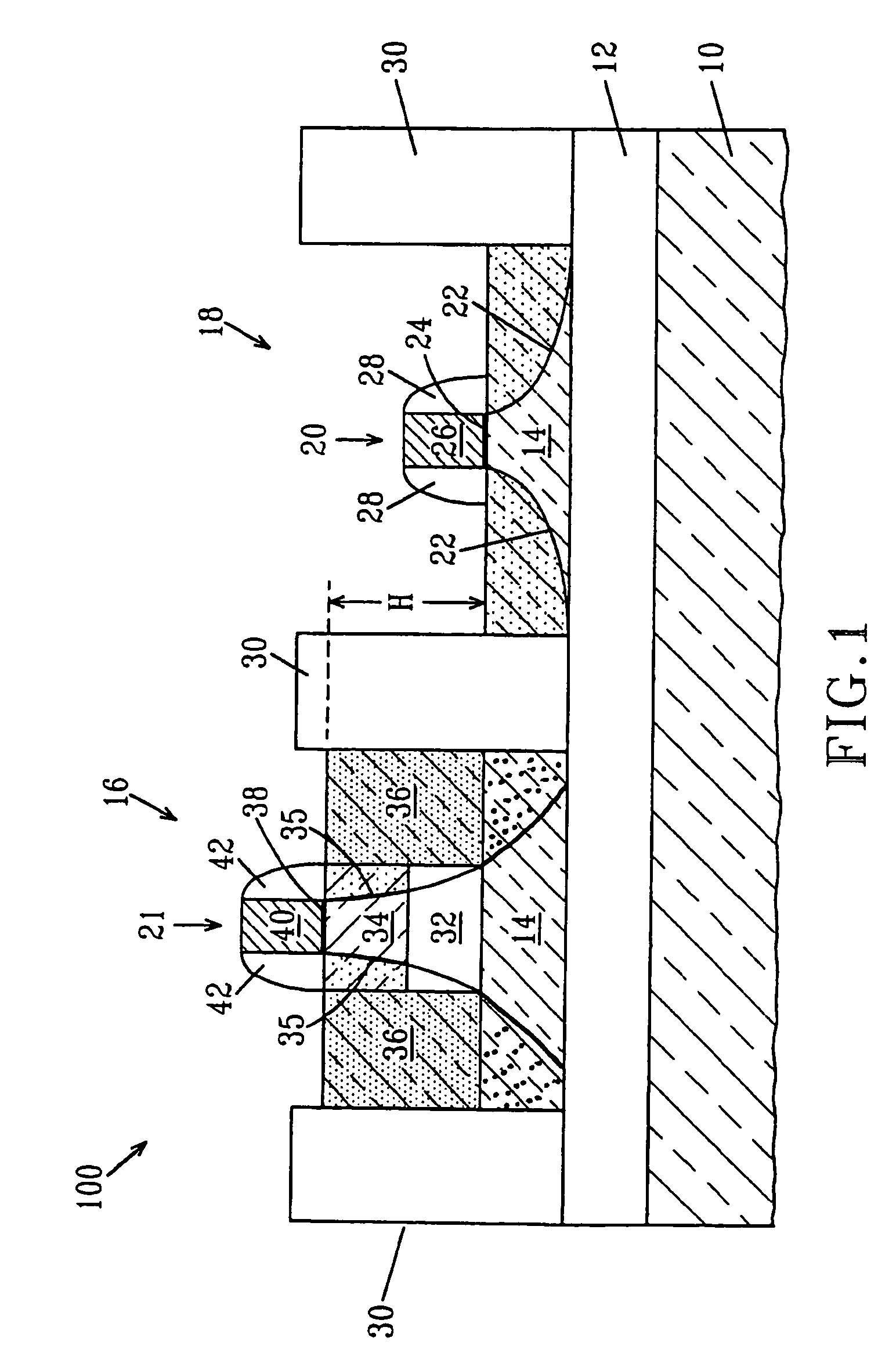

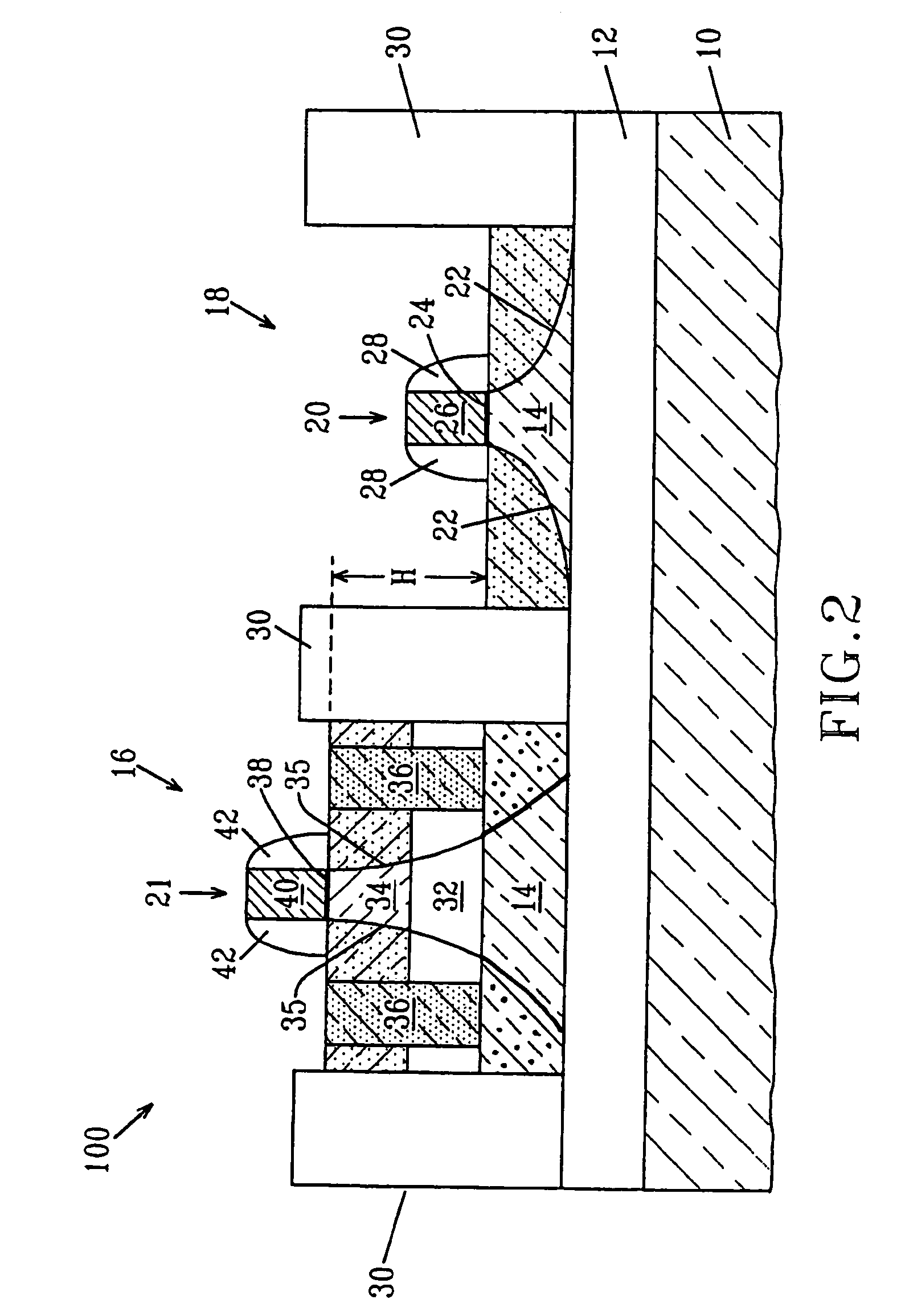

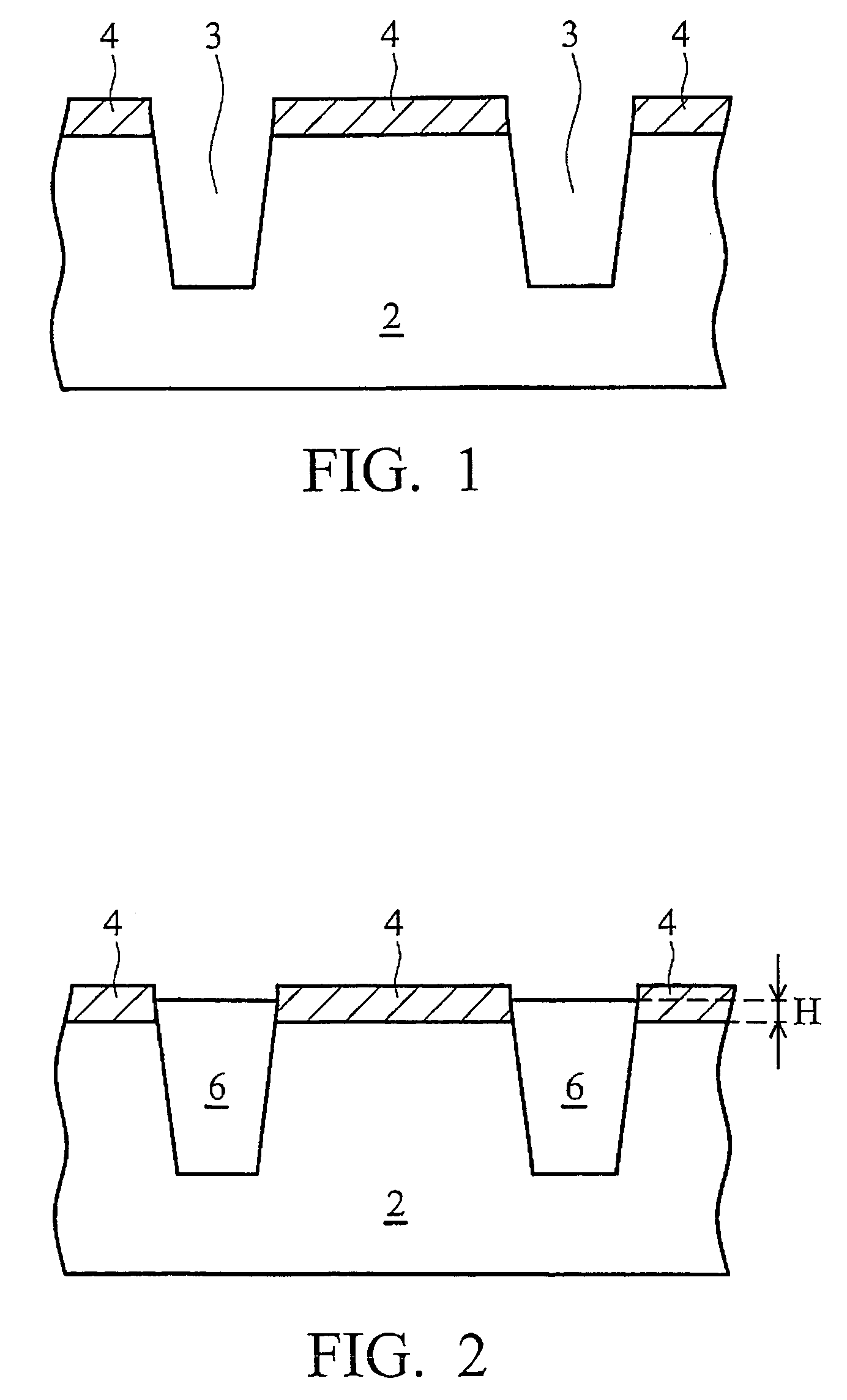

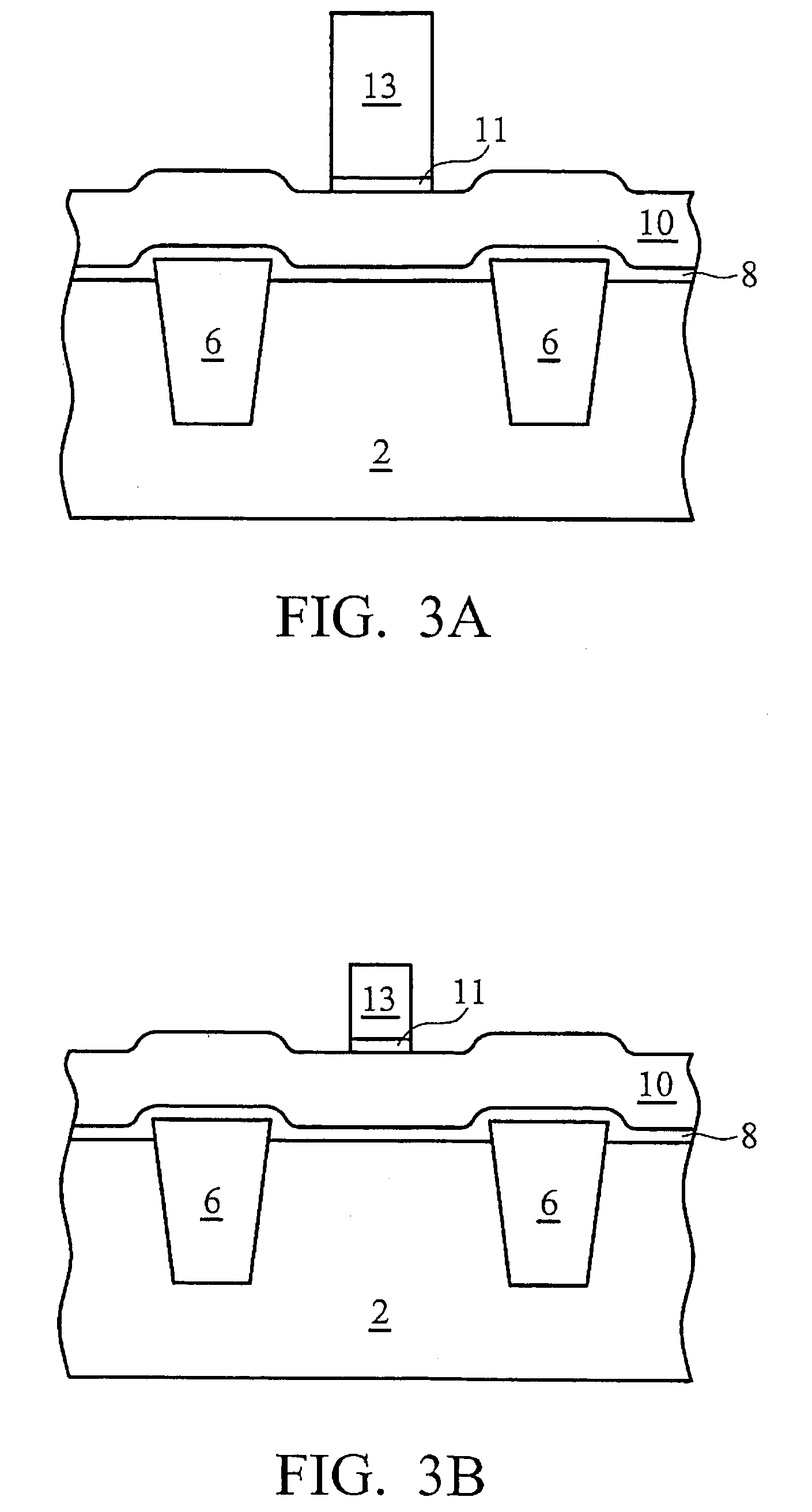

Double silicon-on-insulator (SOI) metal oxide semiconductor field effect transistor (MOSFET) structures

ActiveUS20050082531A1Reduce step heightWithout junction capacitanceTransistorSolid-state devicesMOSFETCapacitance

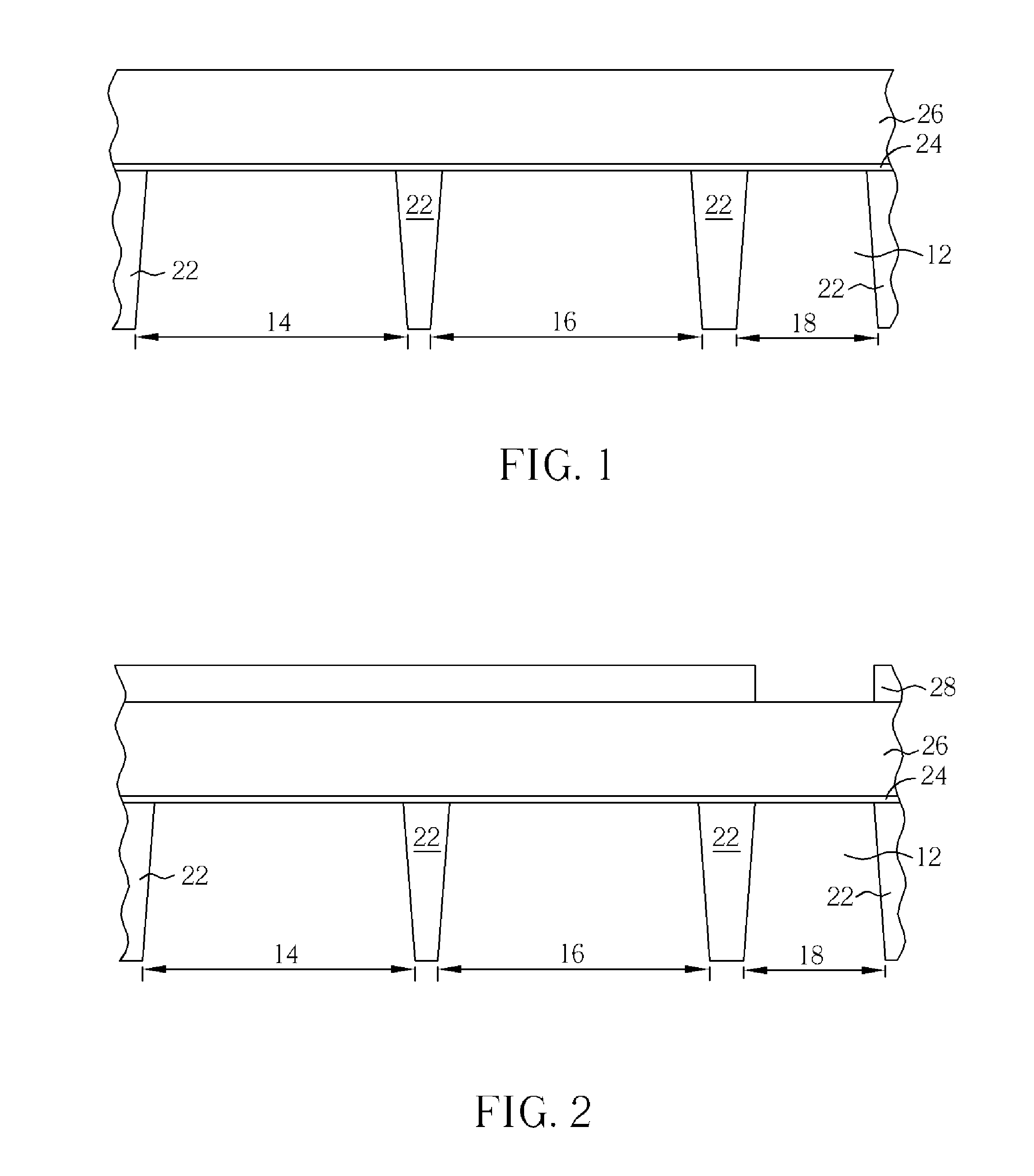

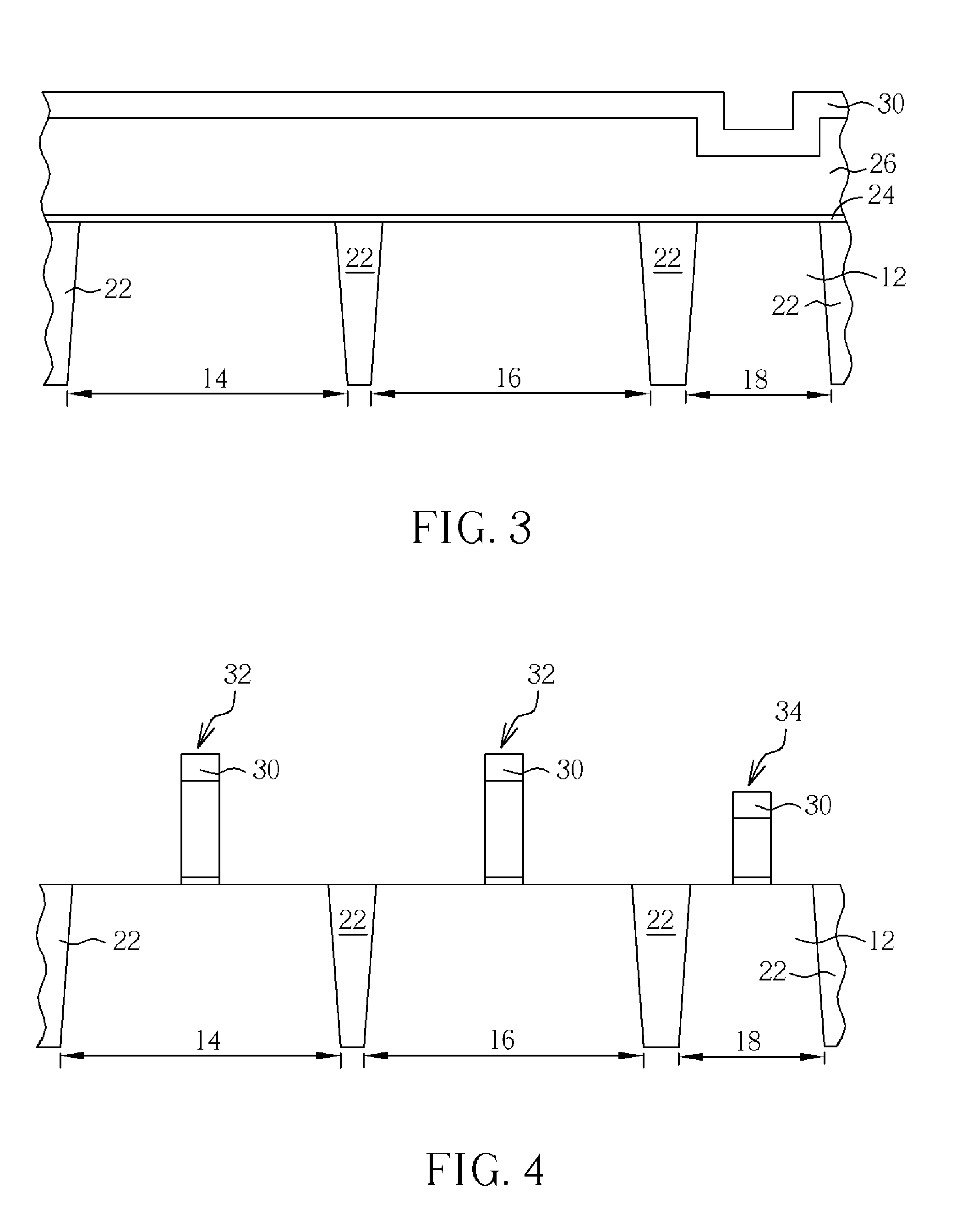

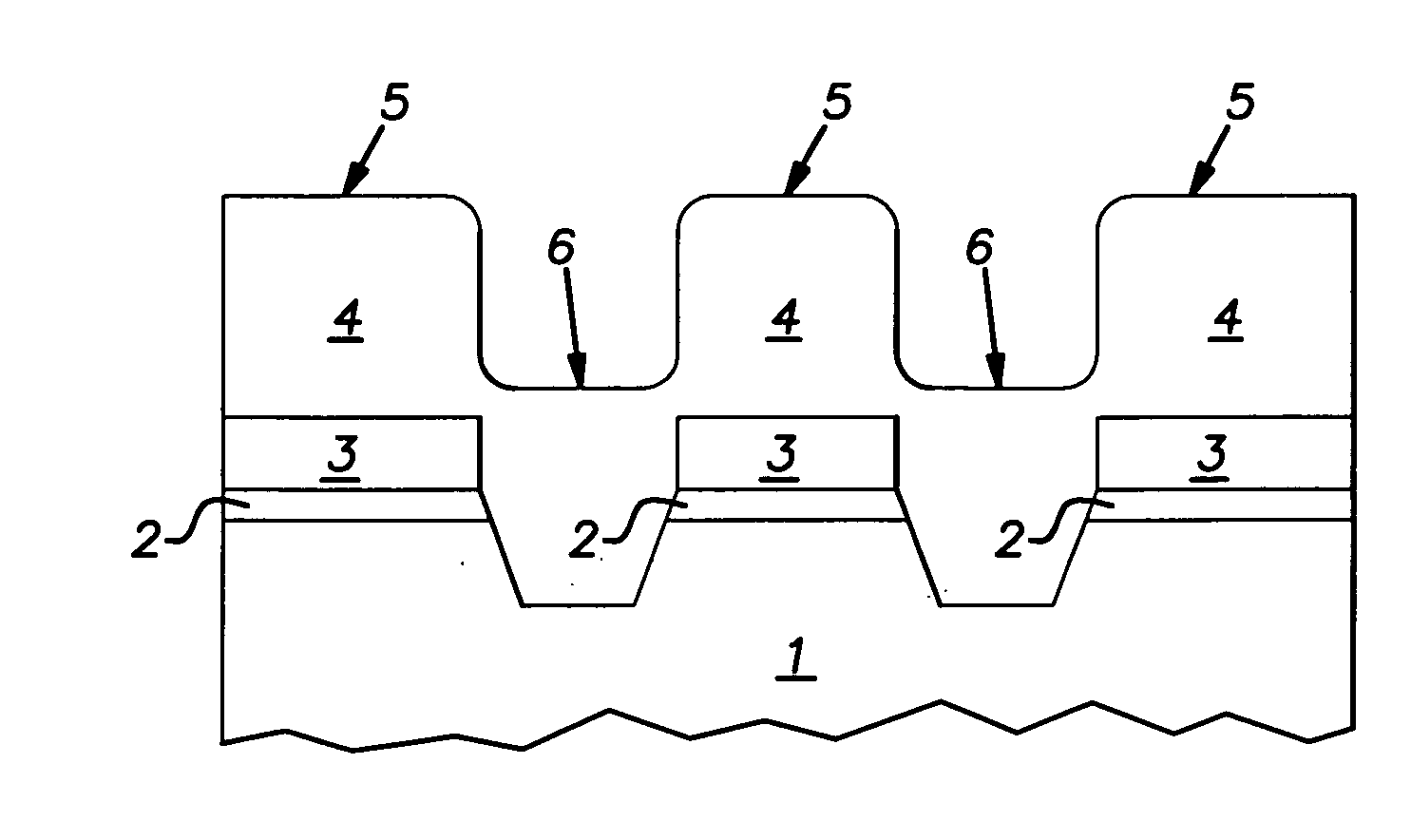

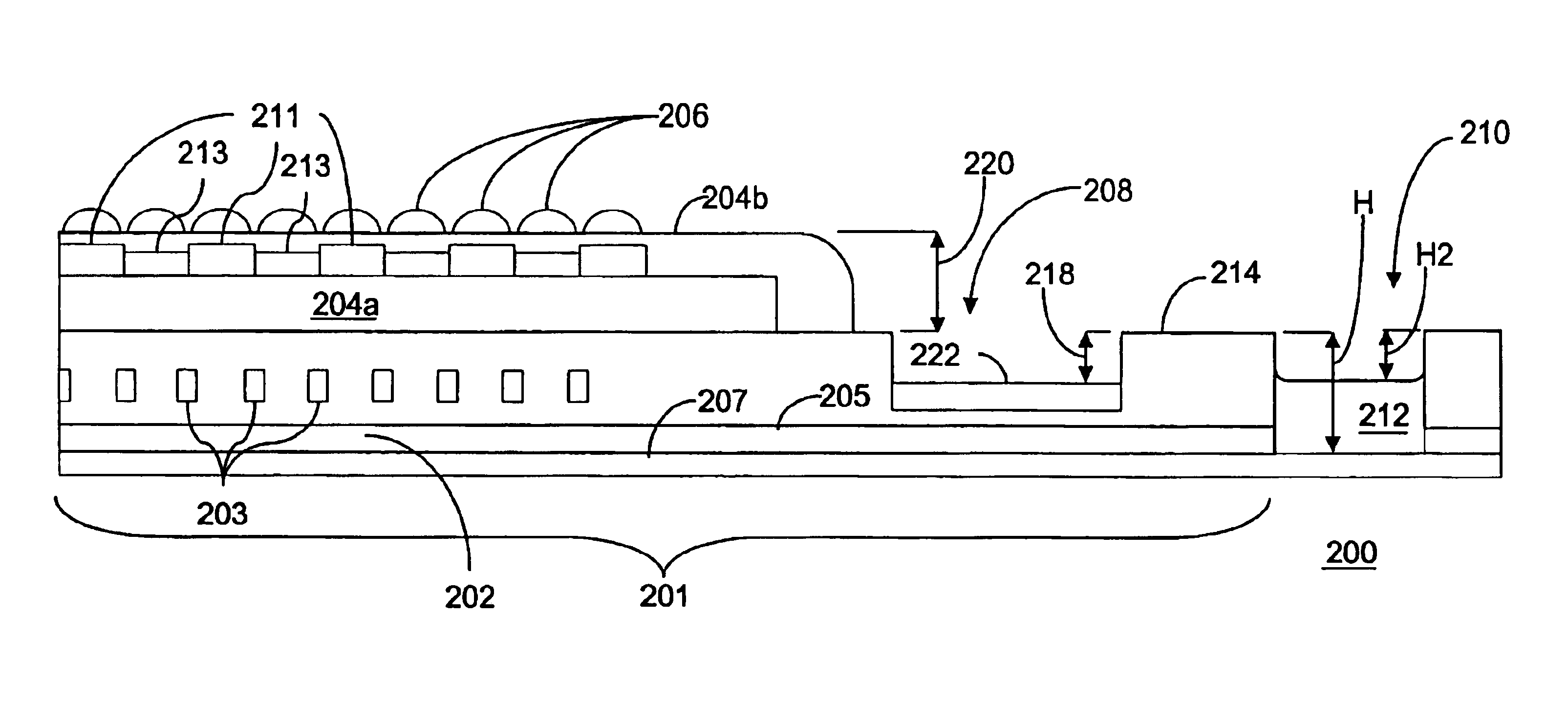

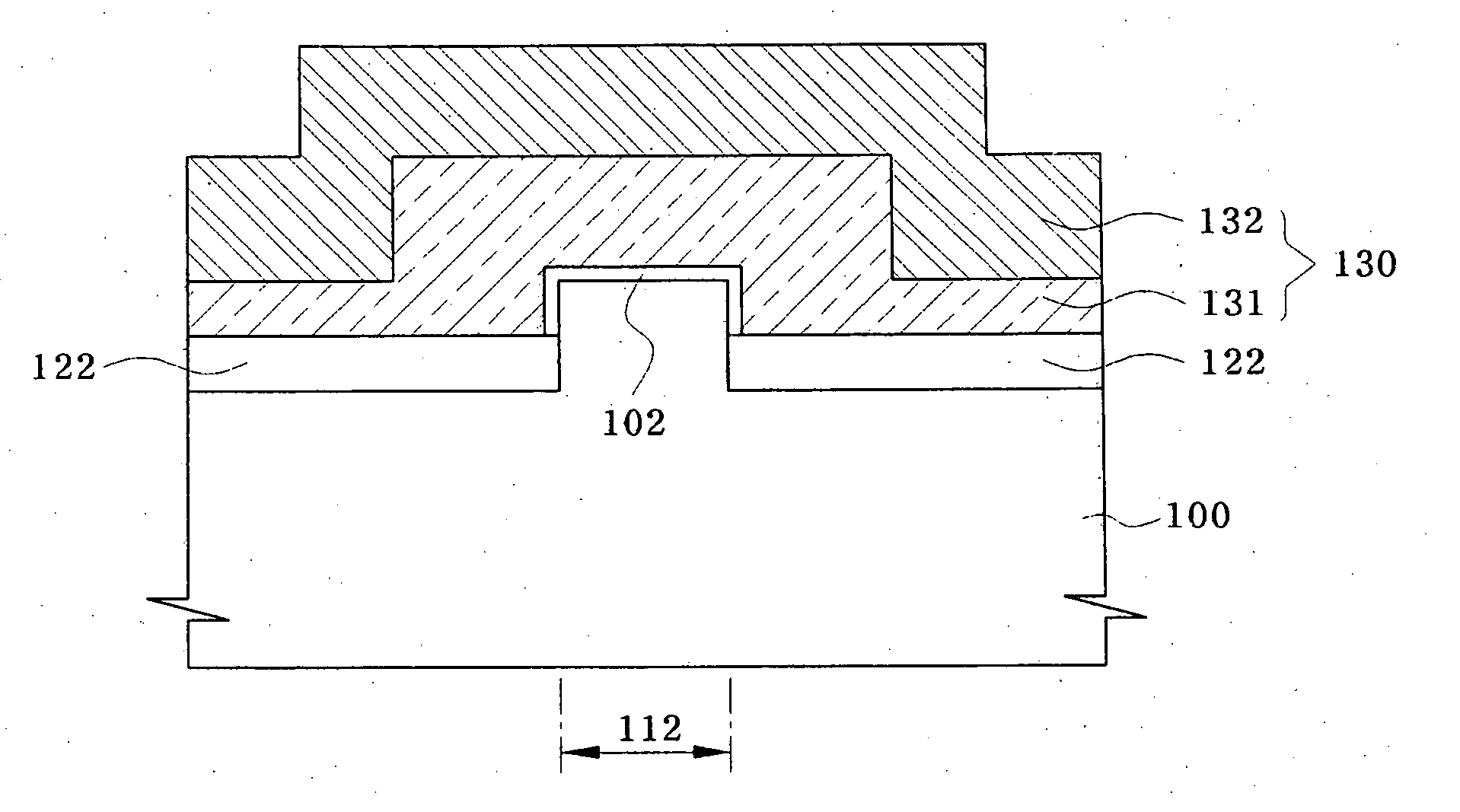

A SOI MOSFET structure having a reduced step height between the various semiconductor layers without adversely affecting the junction capacitance of the semiconductor device formed on the uppermost semiconductor layer as well as a method of fabricating the same are provided. The structure of the present invention includes an elevated device region having at least one semiconductor device located on a second semiconductor layer. The elevated device region further includes a source / drain junction that extends from the second semiconductor layer down to a first buried insulator layer that is located on an upper surface of the semiconductor substrate. The structure also includes a recessed device region having at least one semiconductor device located atop a first semiconductor layer which is located on an upper surface of the first buried insulator. An isolation region separates the elevated device region from the recessed device region.

Owner:GLOBALFOUNDRIES US INC

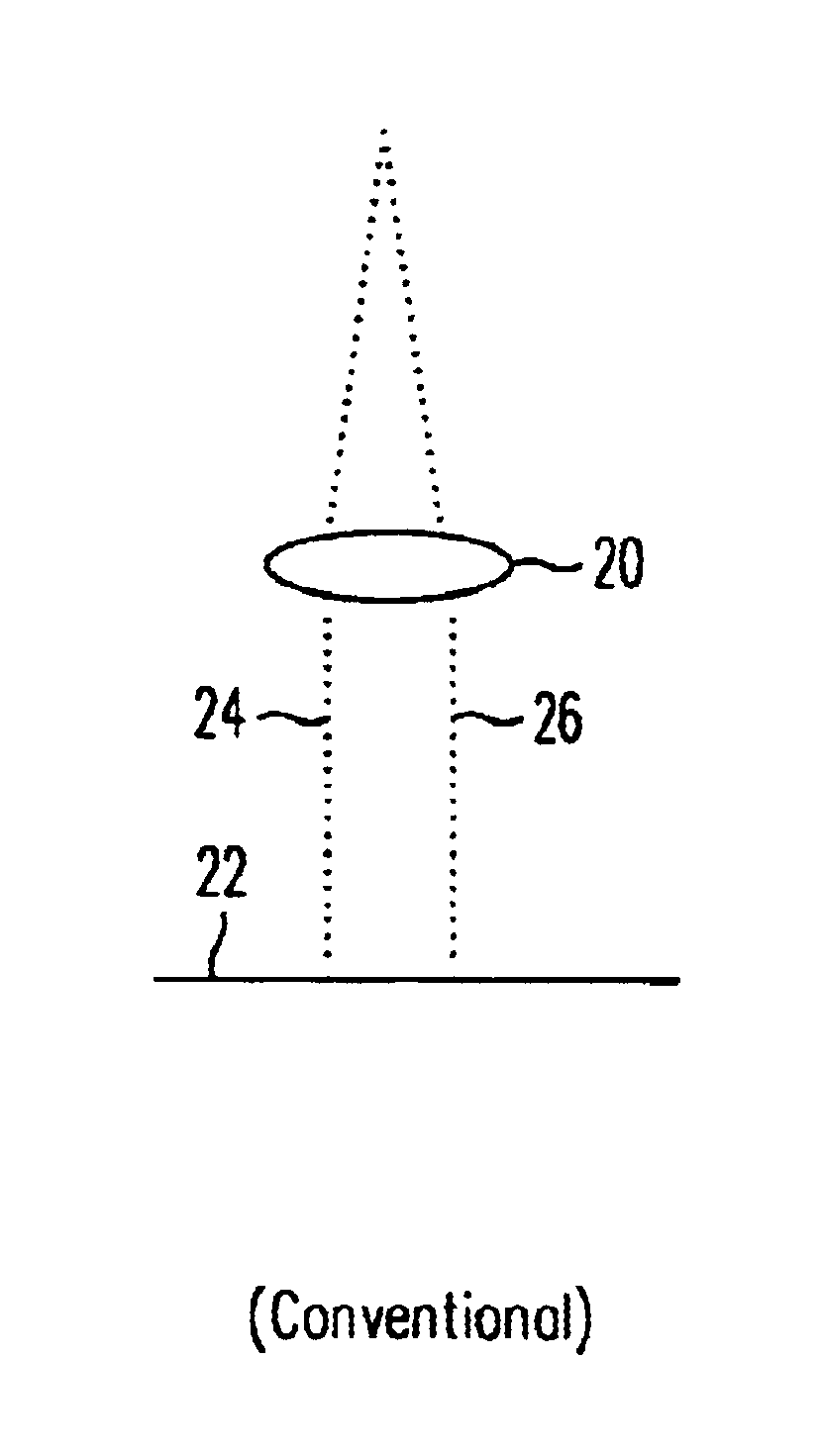

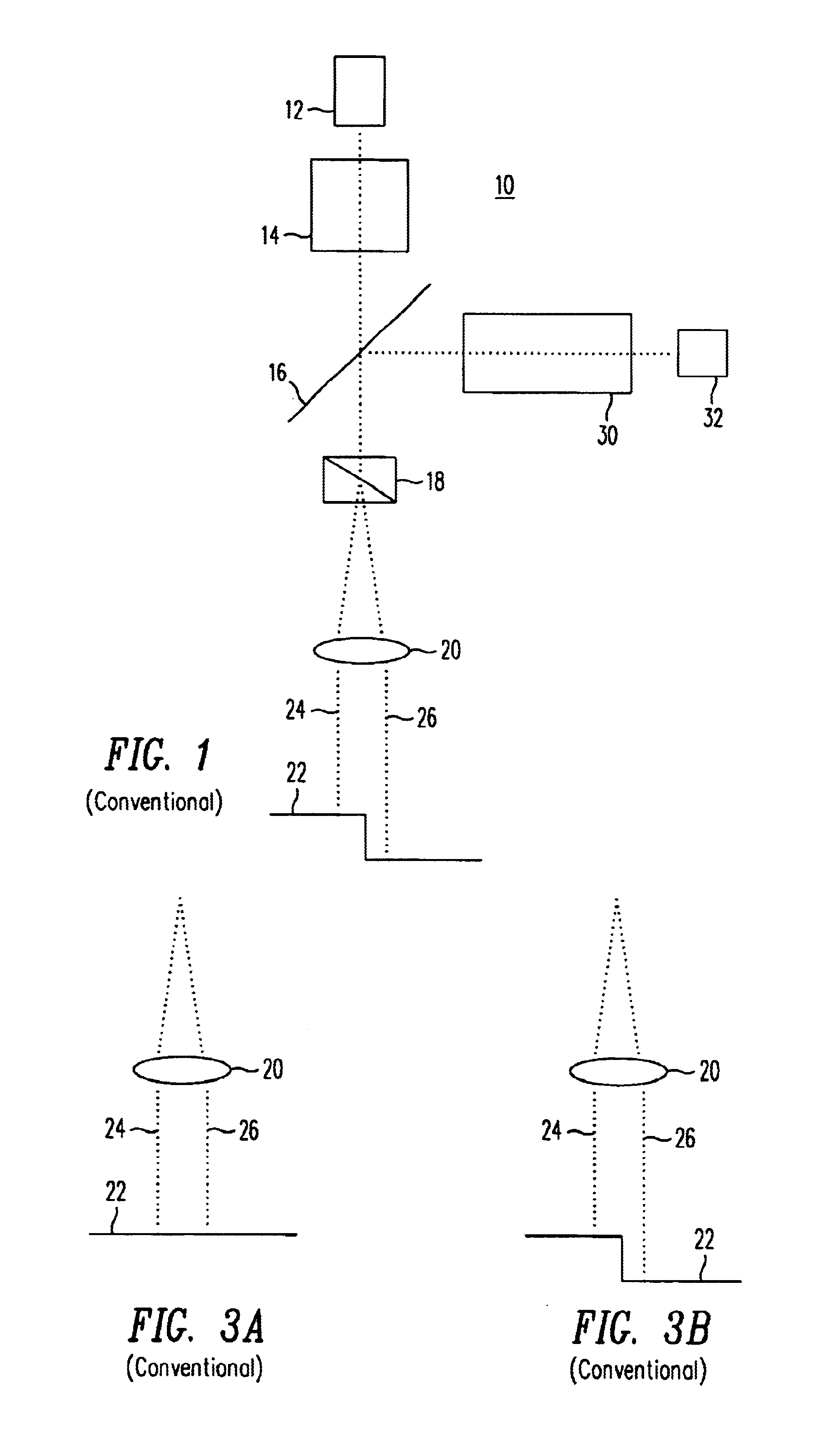

Optical metrology system with combined interferometer and ellipsometer

An interferometer and ellipsometer are combined in a metrology tool to measure the step height of a sample, which may include transparent layers. The metrology tool includes a shared light source that provides a light beam for an interferometer and a light beam for an ellipsometer, interferometer optics which direct the light beam for an interferometer to reflect off of a sample and ellipsometer optics which direct the light beam for an ellipsometer to reflect off a sample, and a detector element for receiving both the reflected light beam for an interferometer and the light beam for an ellipsometer. The light source may produce a single beam that is split into an interferometer and an ellipsometer beam with a beam splitter. In another embodiment, the interferometer and ellipsometer may share at least one of a polarizer, analyzer, or detector element.

Owner:NANOMETRICS

Metal gate transistor and polysilicon resistor and method for fabricating the same

A method for fabricating metal gate transistors and a polysilicon resistor is disclosed. First, a substrate having a transistor region and a resistor region is provided. A polysilicon layer is then formed on the substrate to cover the transistor region and the resistor region of the substrate. Next, a portion of the polysilicon layer disposed in the resistor is removed, and the remaining polysilicon layer is patterned to create a step height between the surface of the polysilicon layer disposed in the transistor region and the surface of the polysilicon layer disposed in the resistor region.

Owner:UNITED MICROELECTRONICS CORP

Composition for oxide CMP in CMOS device fabrication

InactiveUS20060216935A1Easy to polishSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingCMOSSilicon oxide

The present invention provides an oxide CMP slurry composition for use in planarizing silicon oxide-containing films via CMP during CMOS device fabrication, and a method of planarizing silicon oxide-containing films via CMP using the slurry composition. The oxide CMP slurry composition according to the invention includes: (i) proline, lysine and / or arginine; (ii) a pyrrolidone compound; and (iii) abrasive particles. Proline is presently most preferred for use in the invention. In the STI sub-process of the CMOS device fabrication process, the oxide CMP slurry composition according to the present invention acts to aggressively remove only the silicon dioxide overburden on the processed wafer that is in contact with a polishing pad, which results in the formation of a substantially planar, defect-free surface. The oxide CMP slurry composition according to the invention does not aggressively remove trench silicon dioxide thereby allowing for extended polishing beyond the end point without substantially increasing the minimum step height.

Owner:FERRO CORP

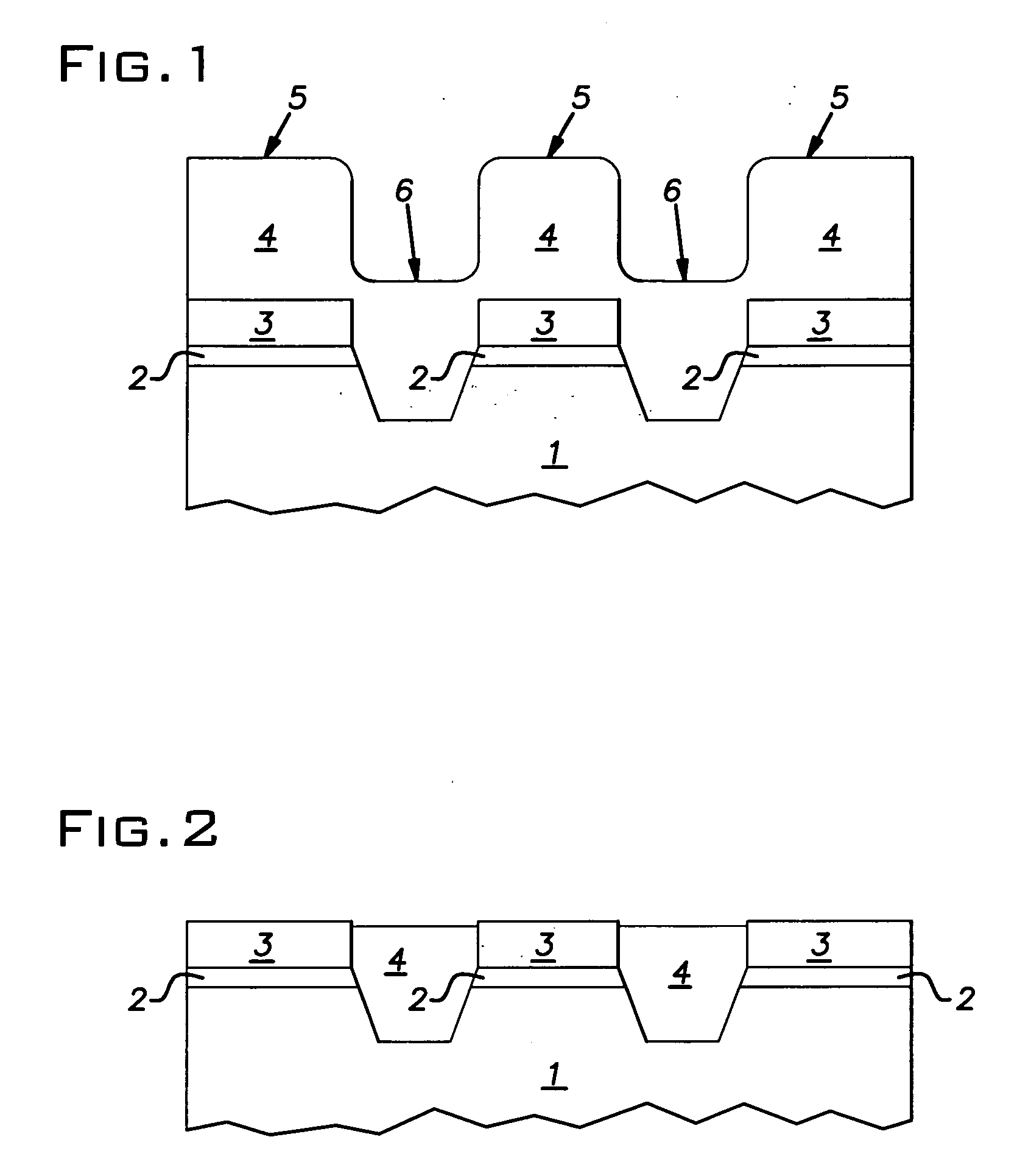

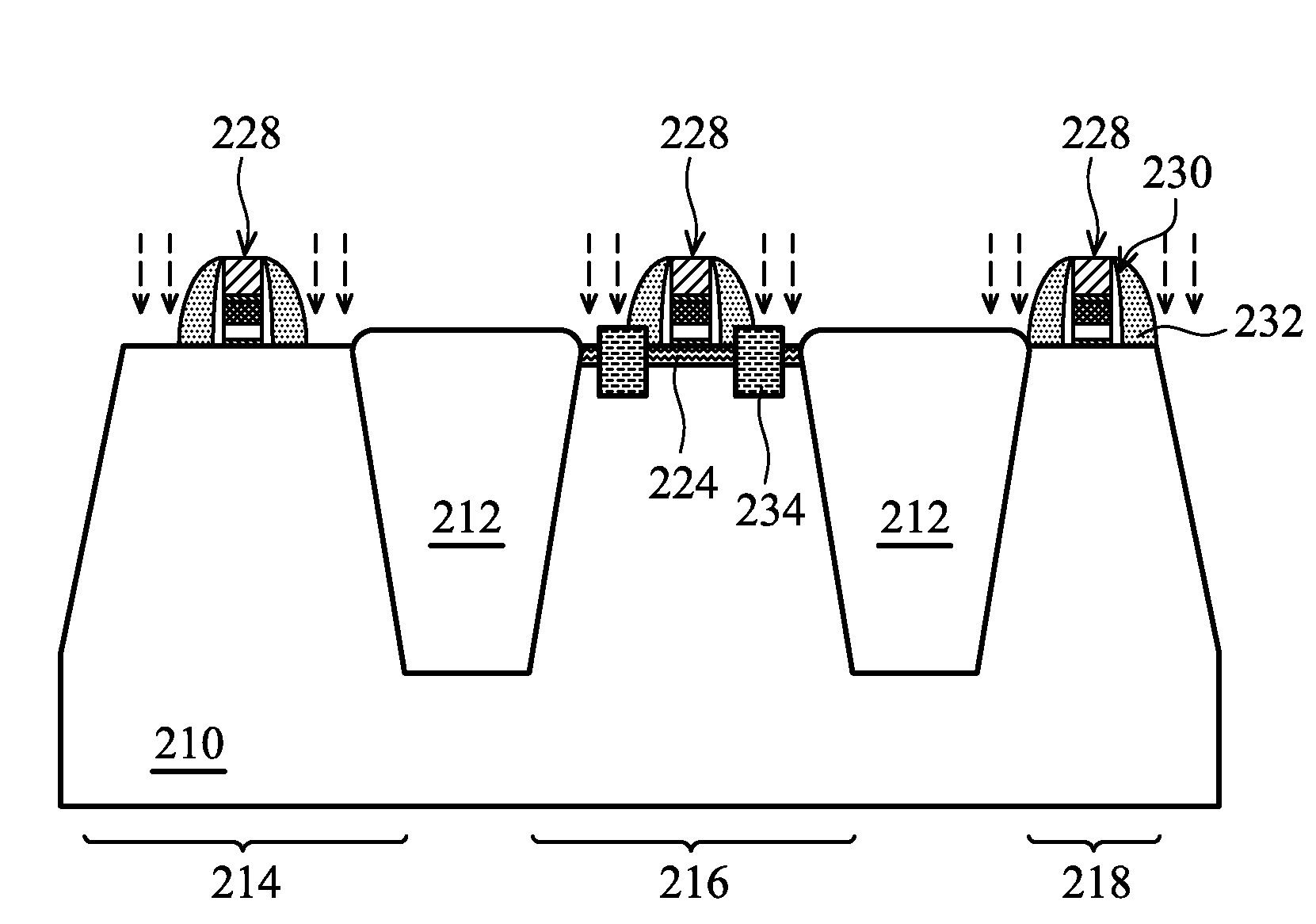

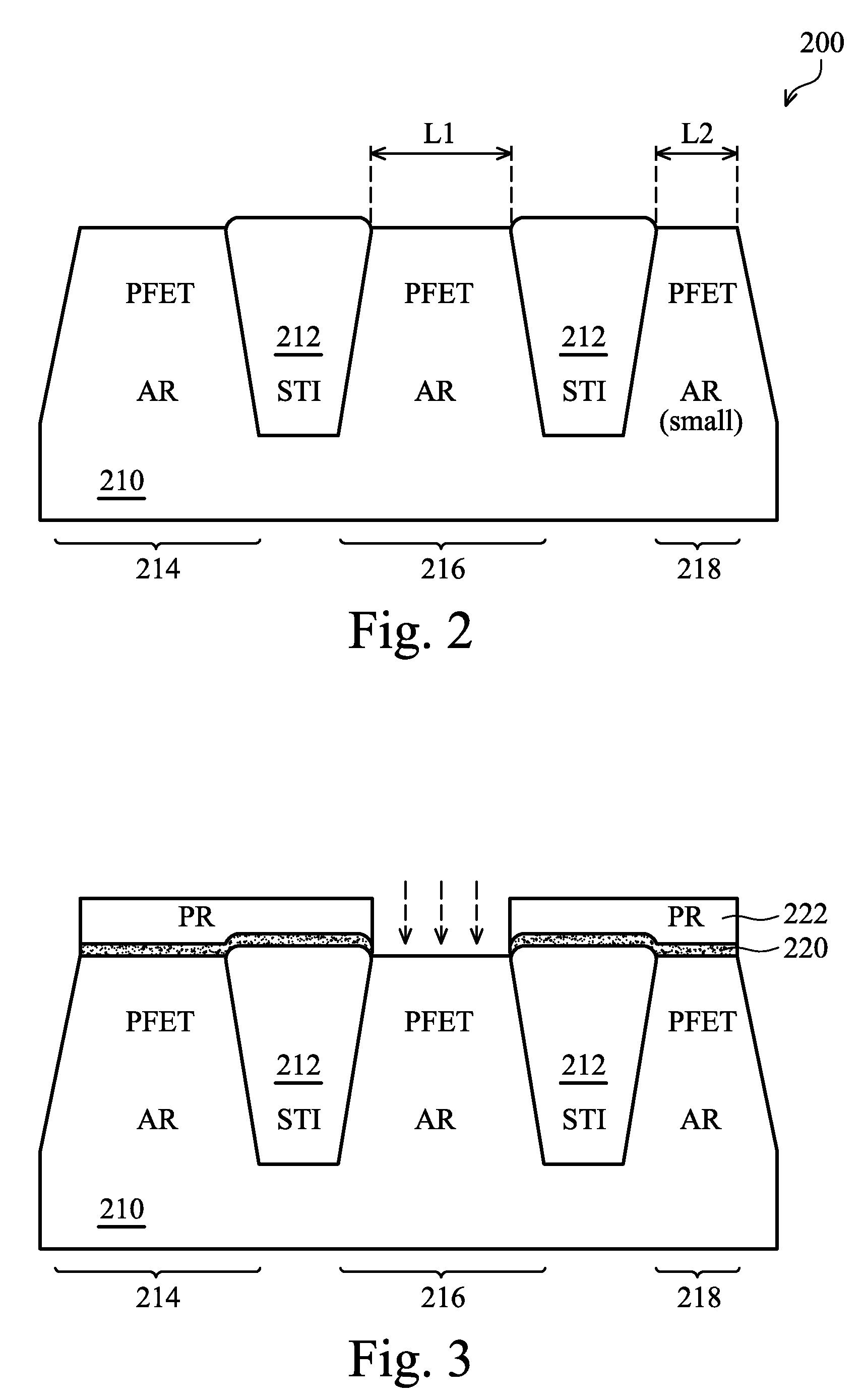

Balance step-height selective bi-channel structure on hkmg devices

The present disclosure provides a method including forming STI features in a silicon substrate, defining a first and a second active regions for a PFET and an NFET, respectively; forming a hard mask having an opening to expose the silicon substrate within the first active region; etching the silicon substrate through the opening to form a recess within the first active region; growing a SiGe layer in the recess such that a top surface of the SiGe layer within the first active region and a top surface of the silicon substrate within the second active region are substantially coplanar; forming metal gate material layers; patterning the metal gate material layers to form a metal gate stack on the SiGe layer within the first active region; and forming an eSiGe S / D stressor distributed in both the SiGe layer and the silicon substrate within the first active region.

Owner:TAIWAN SEMICON MFG CO LTD

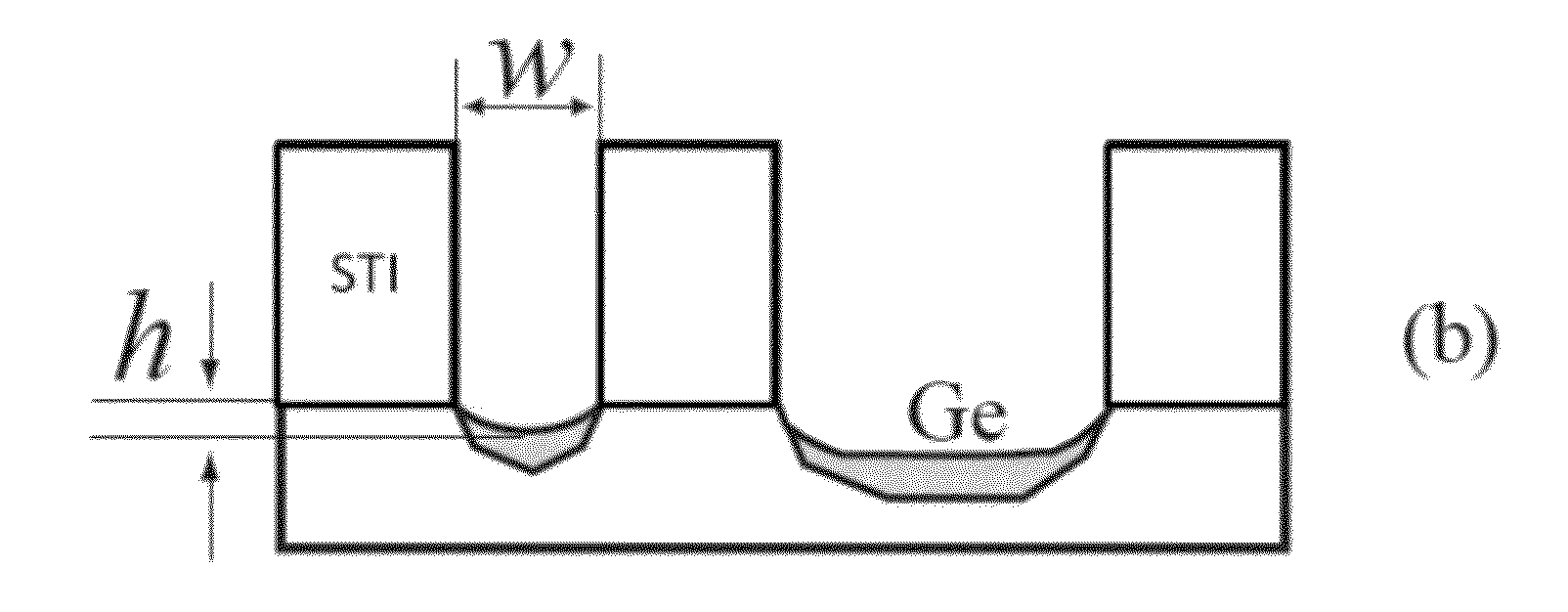

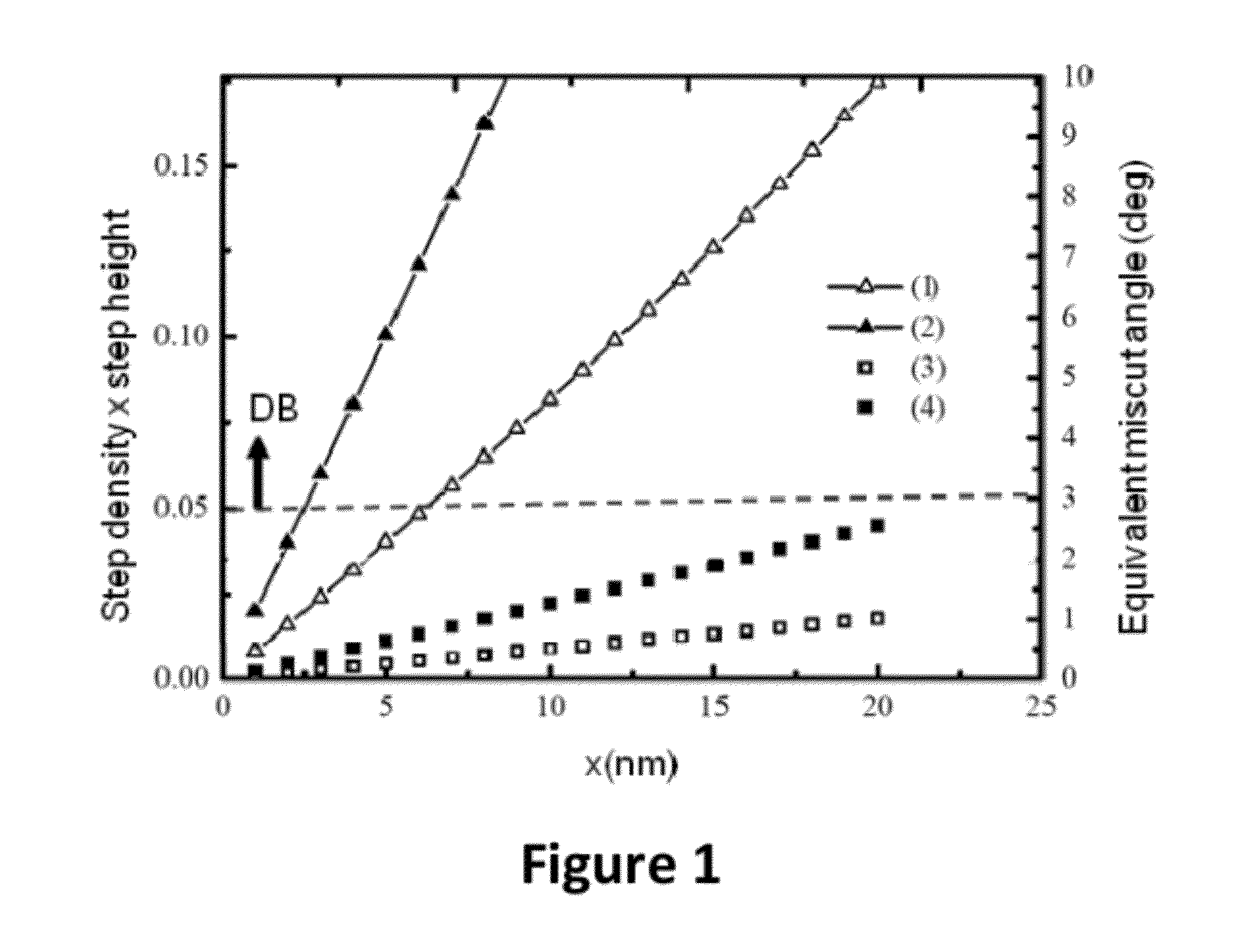

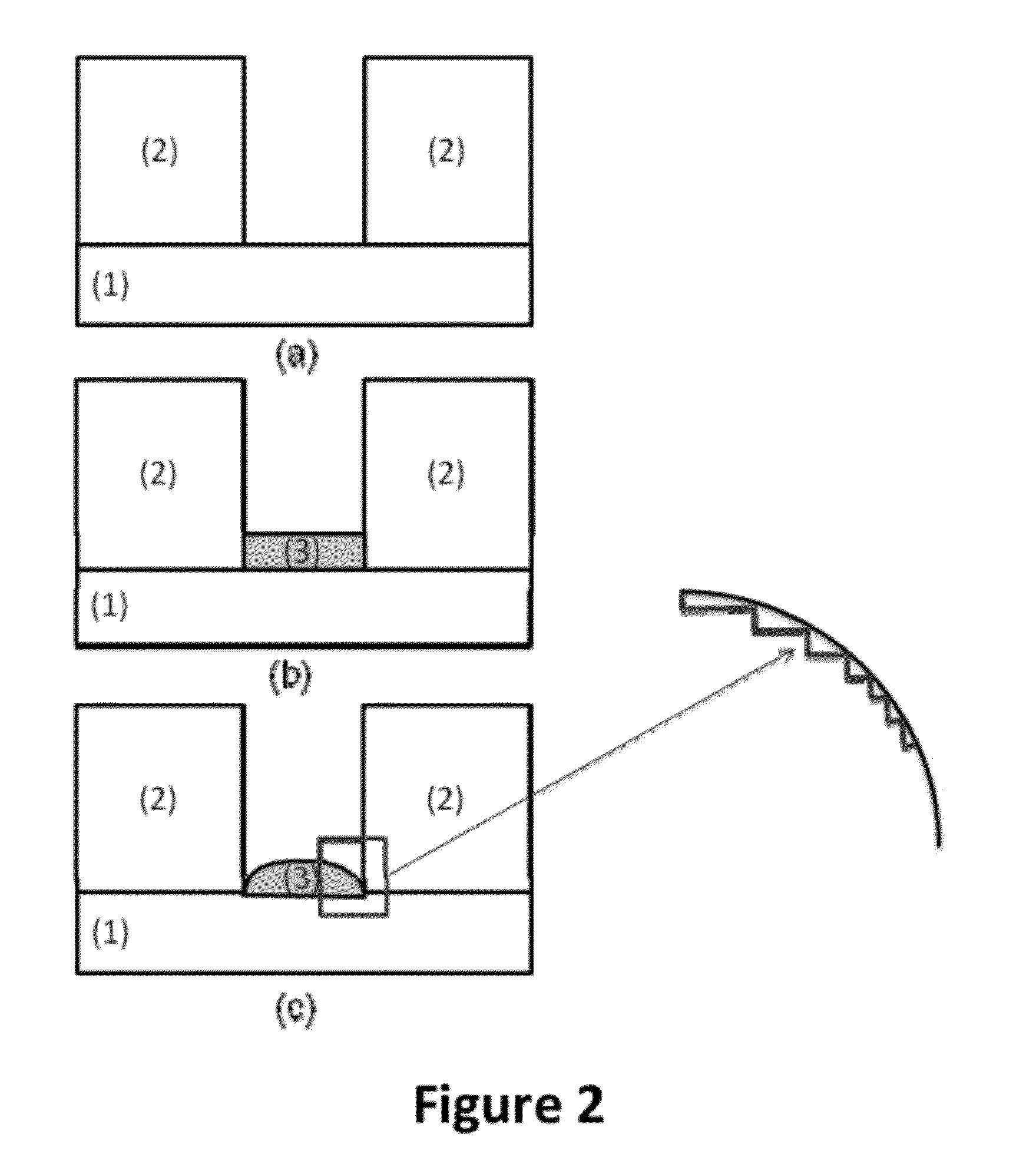

Antiphase Domain Boundary-Free III-V Compound Semiconductor Material on Semiconductor Substrate and Method for Manufacturing Thereof

ActiveUS20120032234A1Avoid formingSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsStep height

Methods of manufacturing a III-V compound semiconductor material, and the semiconductor material thus manufactured, are disclosed. In one embodiment, the method comprises providing a substrate comprising a first semiconductor material having a {001} orientation and an insulating layer overlaying the first semiconductor material. The insulating layer comprises a recessed region exposing an exposed region of the first semiconductor material. The method further comprises forming a buffer layer overlaying the exposed region that comprises a group IV semiconductor material. The method further comprises thermally annealing the substrate and the buffer layer, thereby roughening the buffer layer to create a rounded, double-stepped surface having a step density and a step height. A product of the step density and the step height is greater than or equal to 0.05 on the surface. The method further comprises at least partially filling the recessed region with a III-V compound semiconductor material overlaying the surface.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW) +1

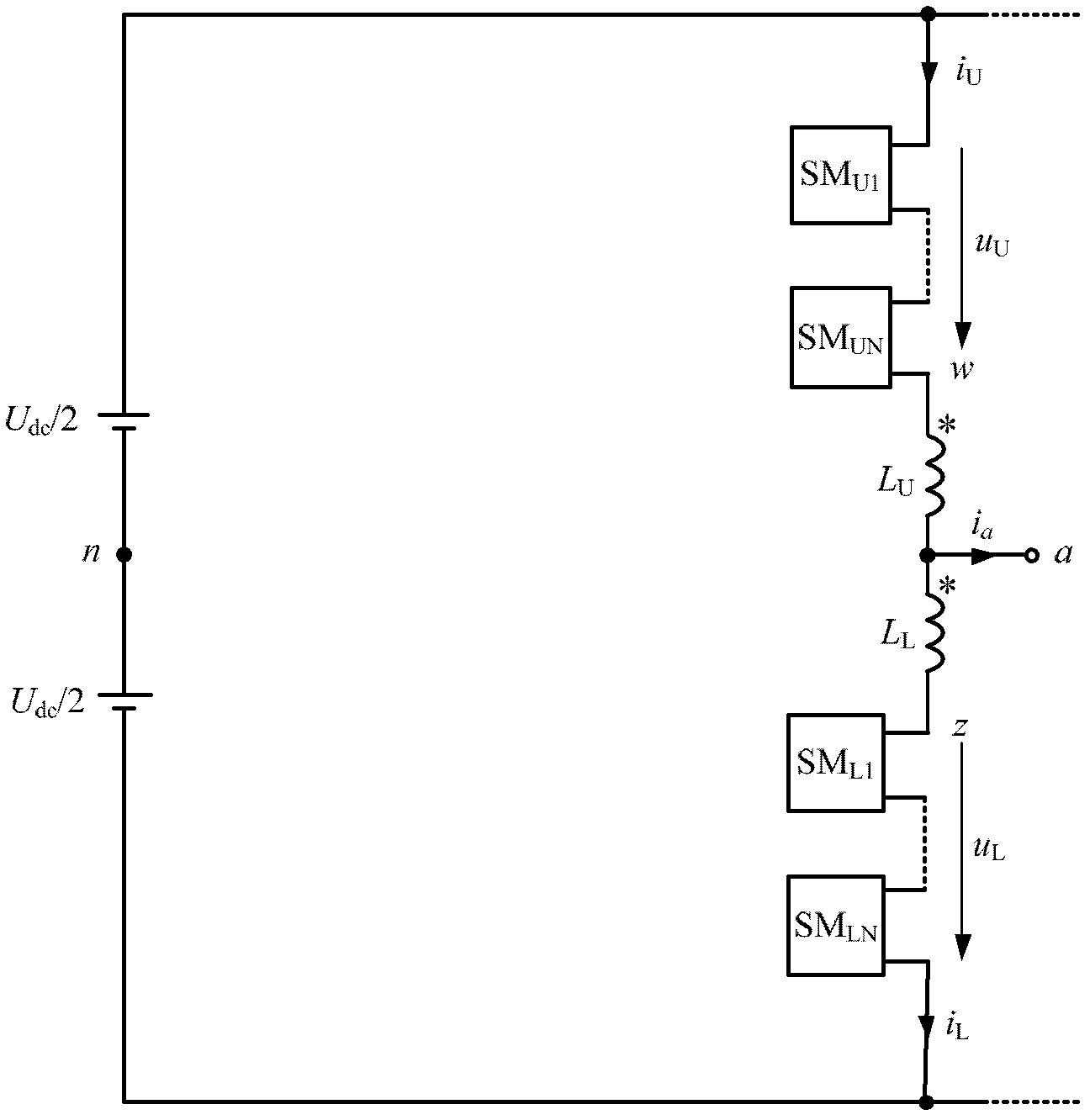

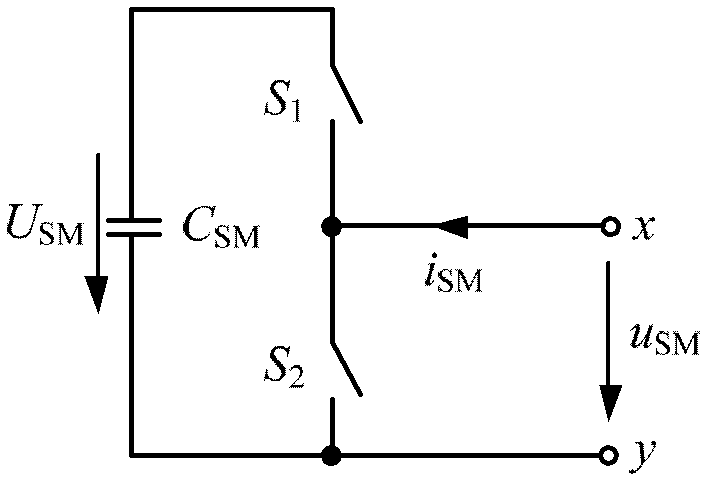

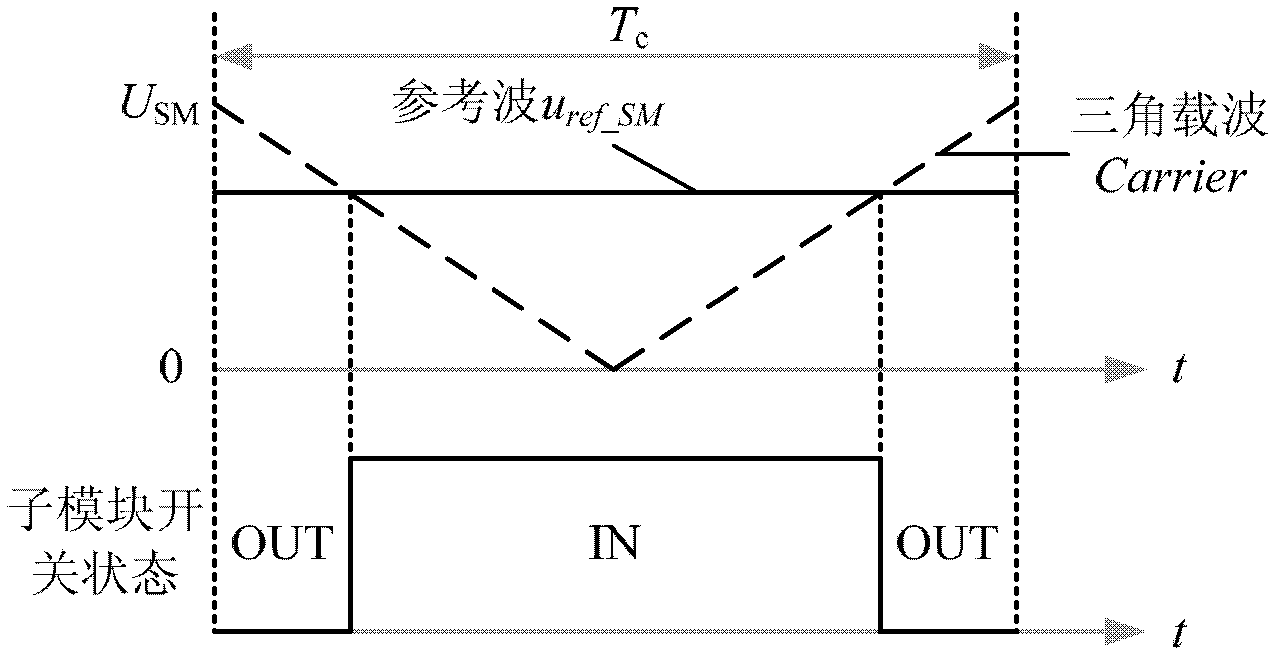

Modulation method of modular multilevel converter (MMC)

InactiveCN102195508AReduce harmonic contentEasy to implementAc-dc conversionCapacitanceCarrier signal

The invention provides a modulation method of a modular multilevel converter (MMC). The modulation method comprises the following steps: calculating a reference voltage of each submodule according to the reference voltage of each bridge arm, current direction of buffer inductance of each bridge arm and capacitive voltage of each submodule; and comparing the reference voltage of each submodule with the same triangular carrier so as to decide the on-off state in each submodule and realize pulse width modulation (PWM). The modulation method has the beneficial effects that output voltage of the MMC can generate 2N+1 (N is the number of the submodules of the upper bridge arm or the lower bridge arm in the MMC) electrical levels without carrier phase shifting (CPS), thus simplifying implementation procedures and saving software and hardware resources; the step height of a step wave of the output voltage is only 50% of that of each capacitive voltage, thus obviously reducing the harmonic content of the output voltage; the capacitive voltage on each submodule can be balanced without any capacitive voltage closed-loop controller; and meanwhile the average voltage on the buffer inductance of each bridge arm is zero without a direct current (DC) component and a low frequency component, thus reducing volume and weight of the inductance.

Owner:INST OF ELECTRICAL ENG CHINESE ACAD OF SCI

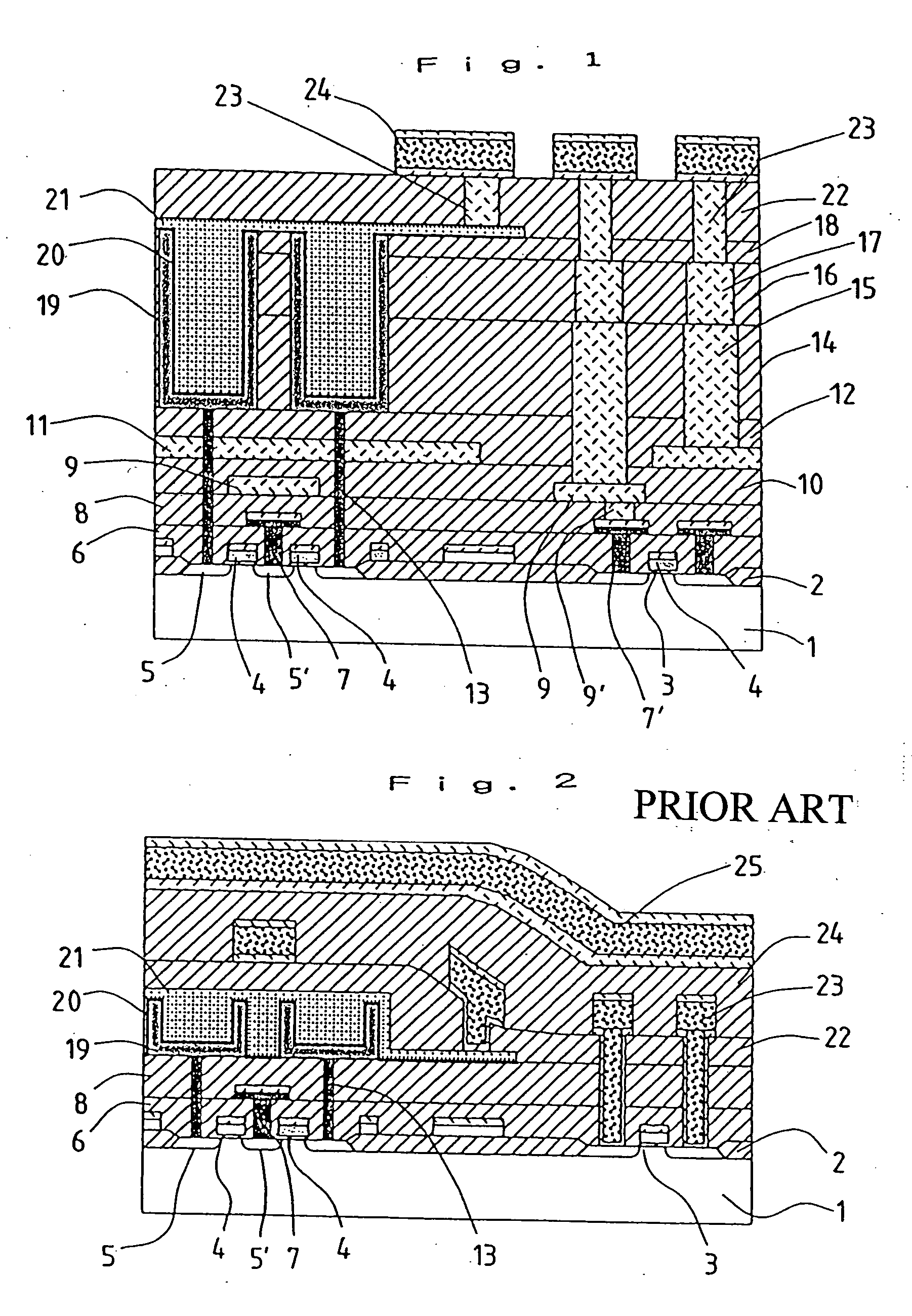

Method for fabricating dynamic random access memory cells

A method for fabricating DRAM cells according to the present invention includes the steps of: forming a trench within a semiconductor substrate using a stacked layer as a mask, said stacked layer composed of a silicon oxide film and a silicon nitride film formed in an active region of said semiconductor substrate; forming a first insulation layer on a bottom and sides of said trench; depositing a first conductive layer on whole surface of said semiconductor substrate including said trench; etching back said conductive layer to be recessed from a top surface of said semiconductor substrate and forming bit lines of said first conductive layer on said bottom of said trench in a direction of column; filling a second insulation layer in said trench; removing said stacked layer and a part of said second insulation layer to expose said semiconductor substrate in said active region and planarizing said semiconductor substrate simultaneously; forming a gate insulation layer on said semiconductor substrate;forming a gate structure of a second conductive layer on said gate insulation layer; forming a spacer of an insulation layer on said sides of said gate structure of said second conductive layer; forming source and drain regions on both sides of said gate structure of said second conductive layer;forming a third insulation layer on said semiconductor substrate; connecting said bit lines to a first one of said source and drain regions with a plug of a third conductive layer filled in a contact hole inside said third insulation layer and said second insulation layer; forming a storage node electrode connected to a second one of said source and drain regions; andforming a plate electrode overlying a dielectric layer disposed said storage node electrode.Accordingly, the present invention has the buried bit lines in the trench, making it easy to secure a process margin in the subsequent process, maintaining a constant width of the bit lines to lower the resistance thereof. Furthermore, the bit lines disposed under the word lines has an advantage over patterning the node contact due to the low step height, with enhanced capacitance of the capacitor.

Owner:HYUNDAI ELECTRONICS IND CO LTD

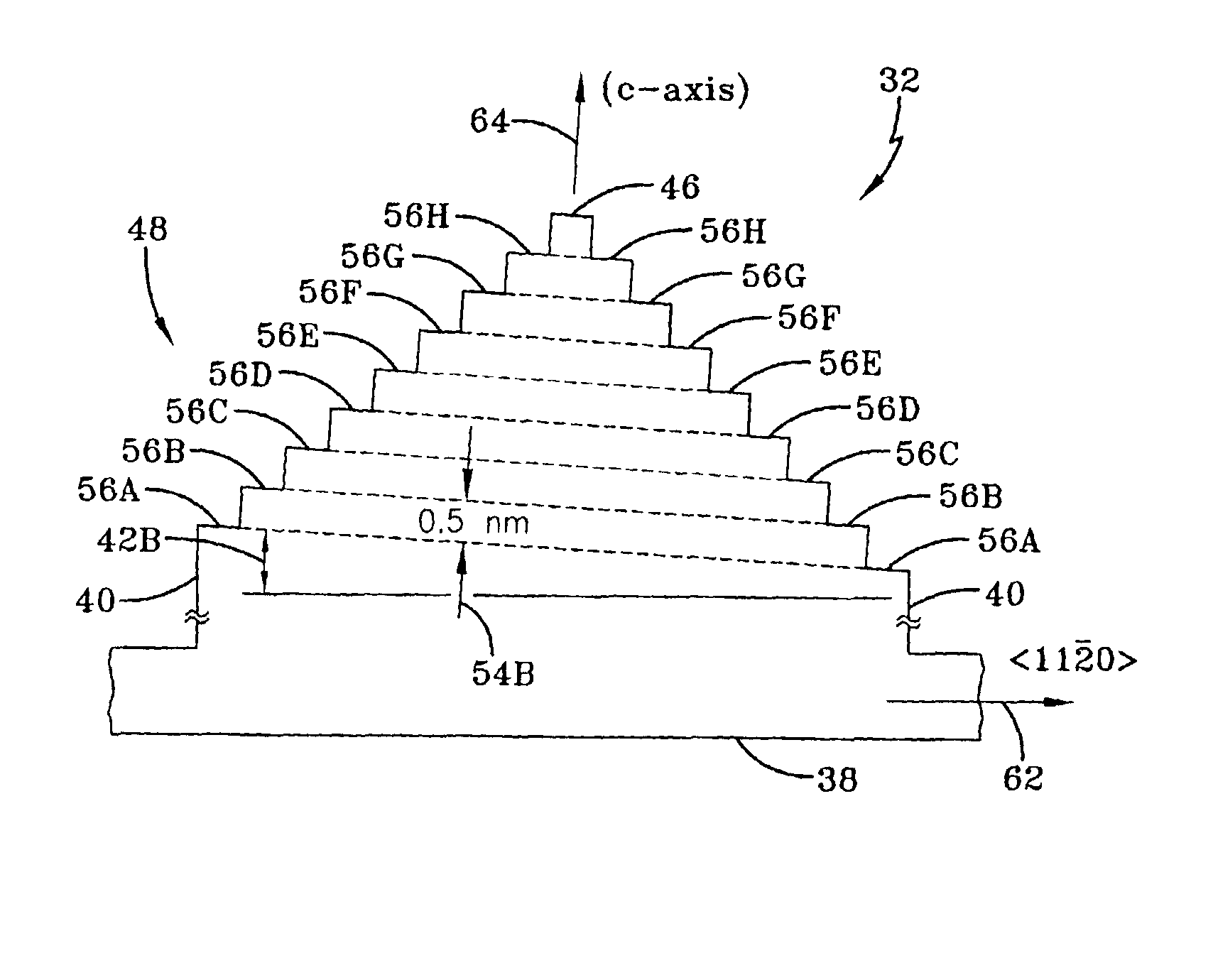

Method for the production of nanometer scale step height reference specimens

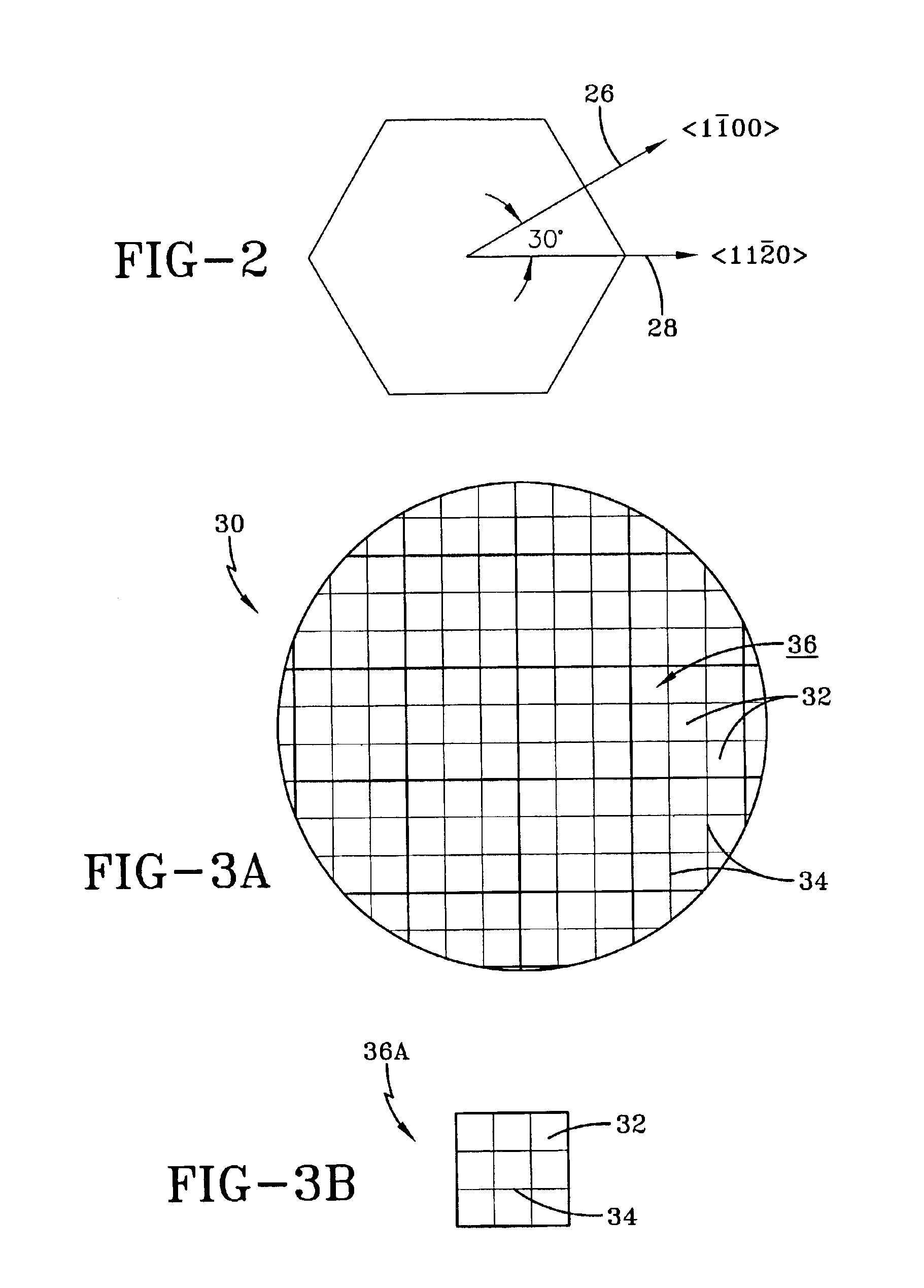

InactiveUS6869480B1Good precisionEliminate needPolycrystalline material growthAfter-treatment detailsReference sampleSingle crystal substrate

Methods are disclosed that provide for structures and techniques for the fabrication of ordered arrangements of crystallographically determined nanometer scale steps on single crystal substrates, particularly SiC. The ordered nanometer scale step structures are produced on the top surfaces of mesas by a combination of growth and etching processes. These structures, sometimes referred to herein as artifacts, are to enable step-height calibration, particularly suitable for scanning probe microscopes and profilometers, from less than one nanometer (nm) to greater than 10 nm, with substantially no atomic scale roughness of the plateaus on either side of each step.

Owner:NASA

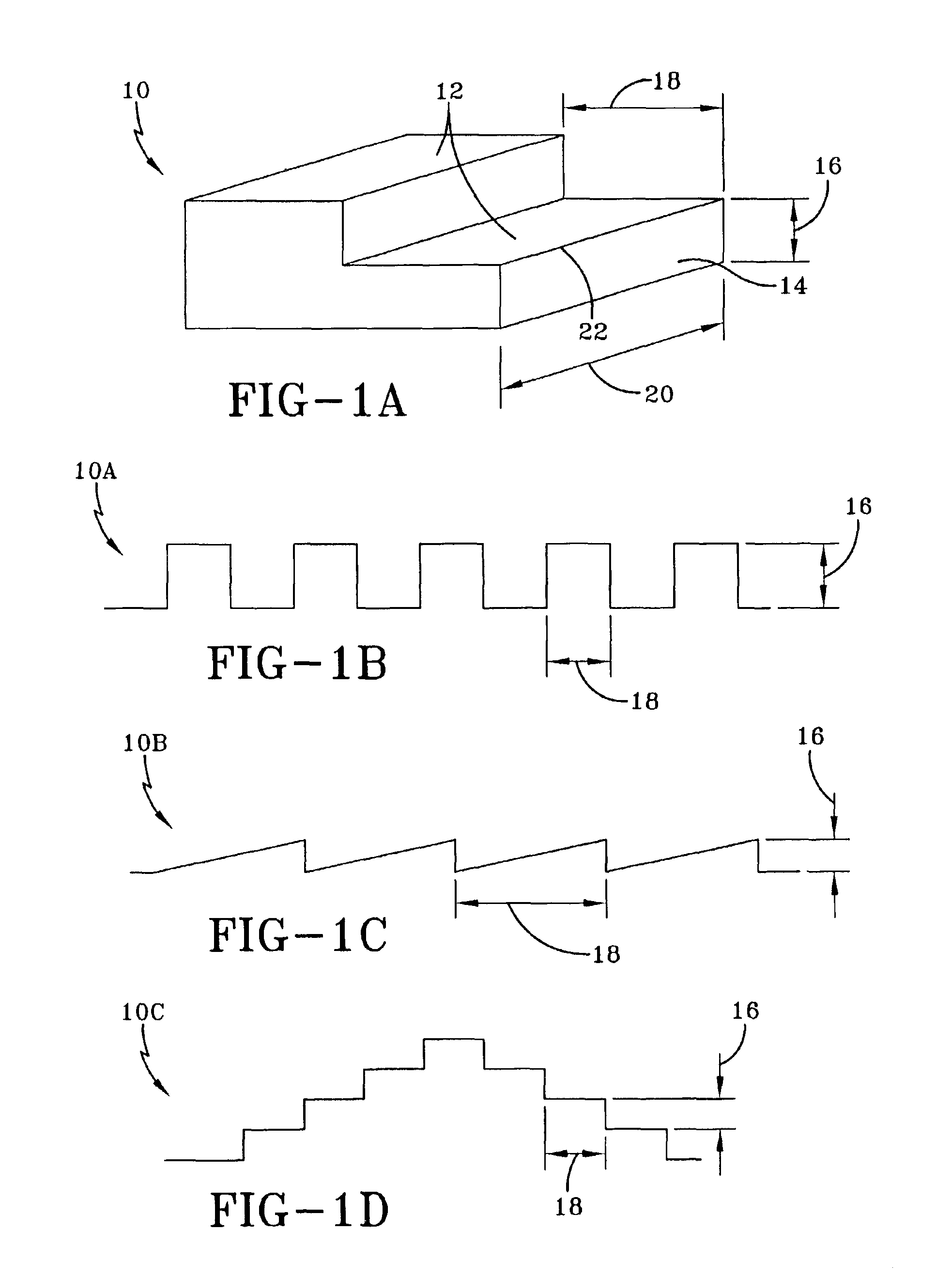

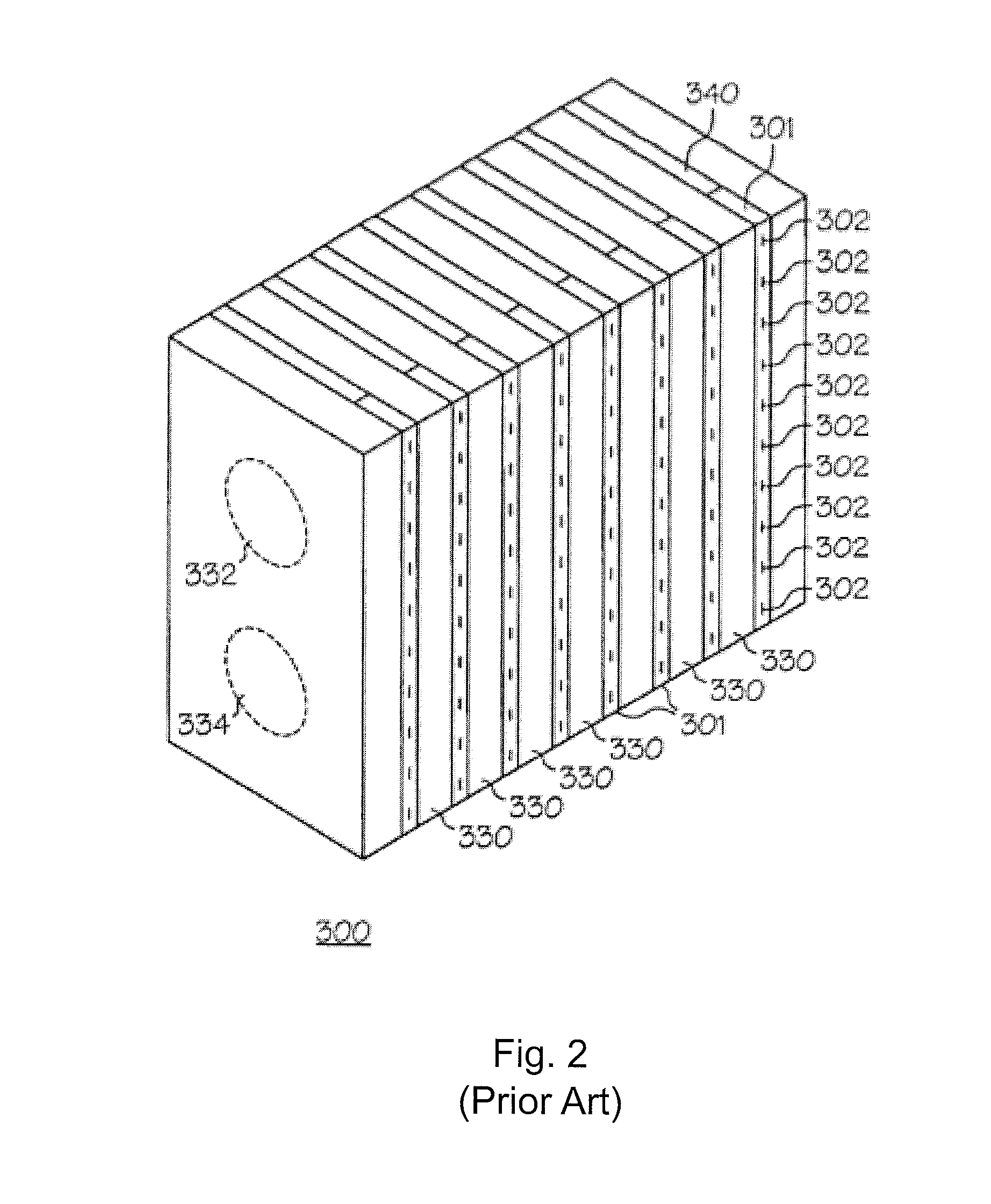

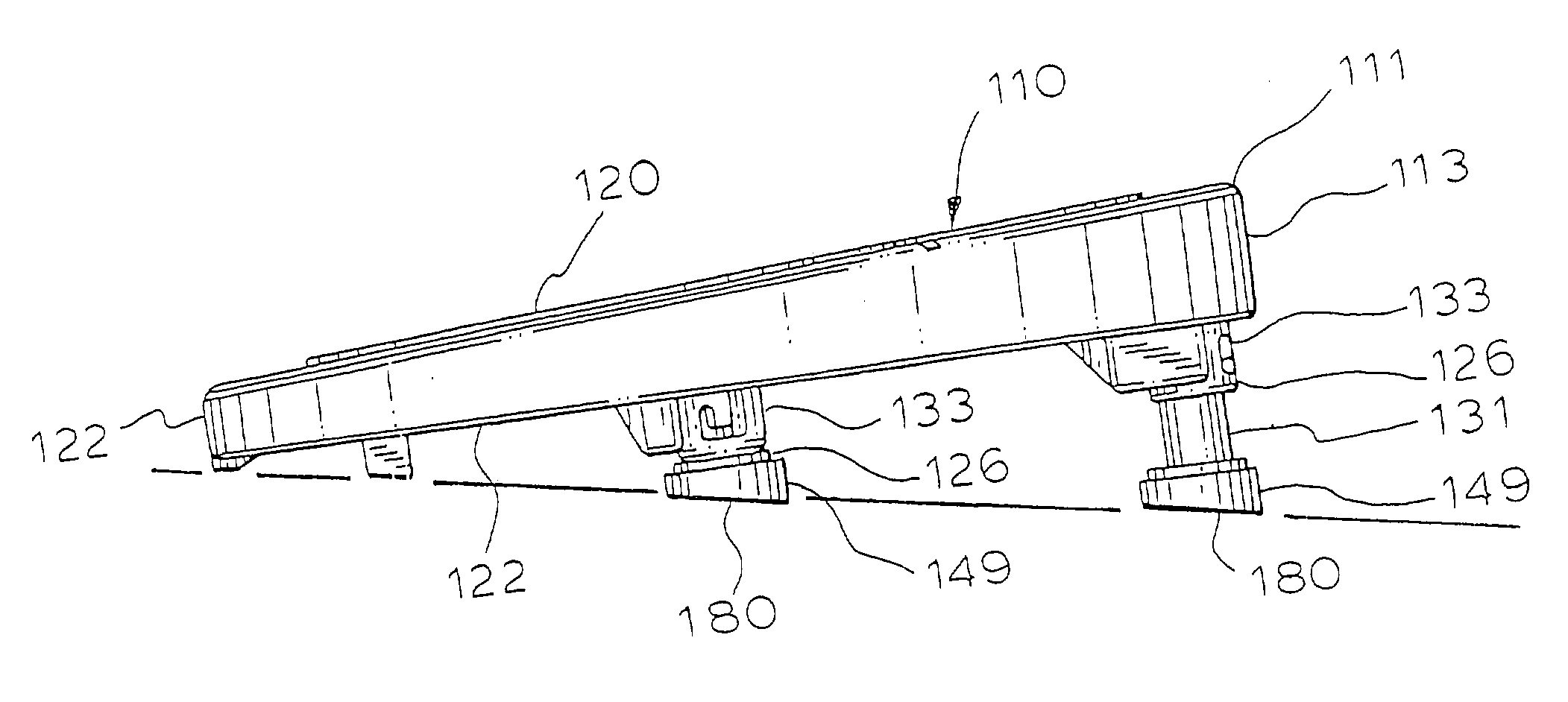

High-brightness spatial-multiplexed multi-emitter pump with tilted collimated beam

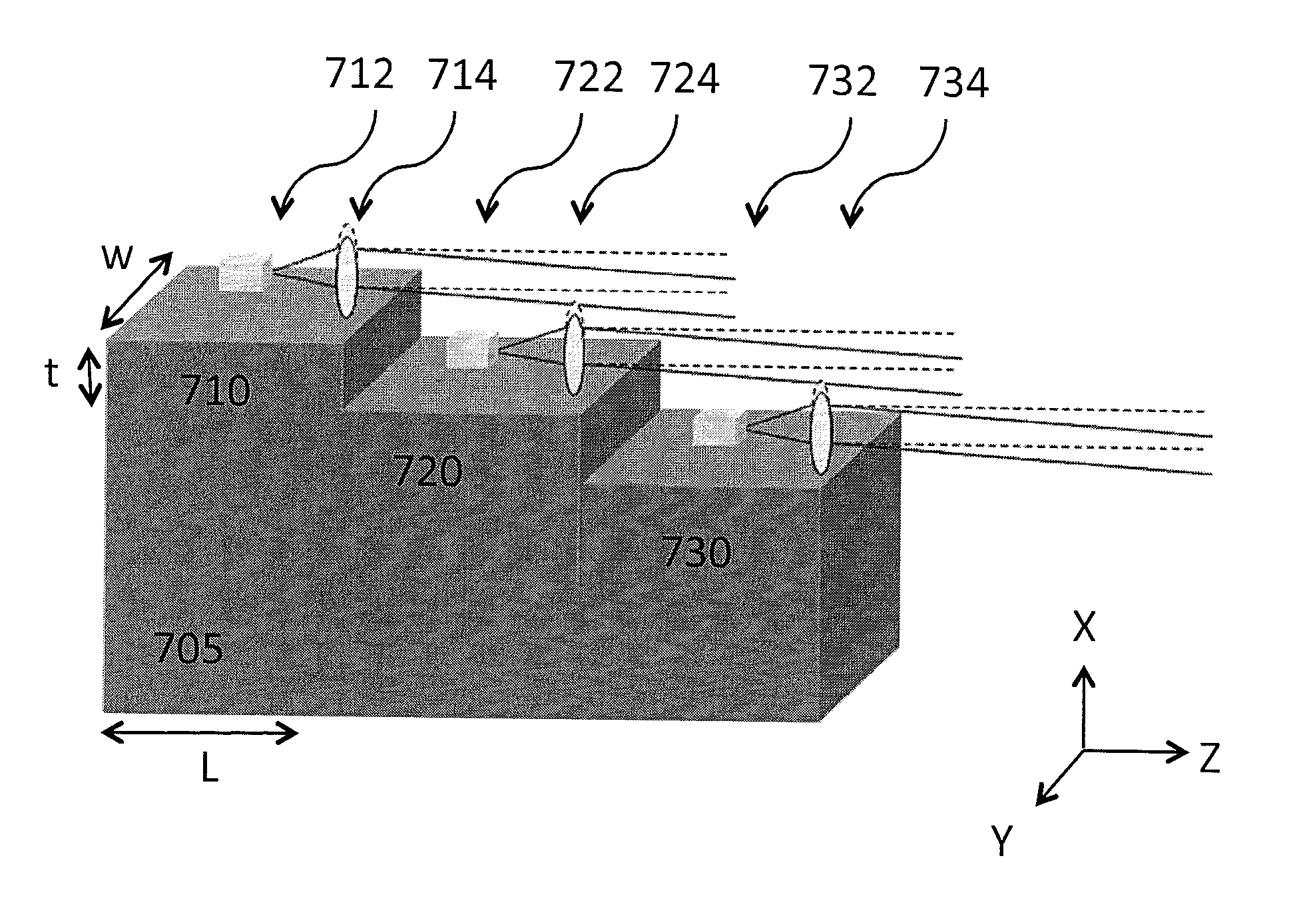

ActiveUS20130148684A1Coupling efficiency is highReduce feedbackLaser detailsSemiconductor laser optical deviceLight beamStep height

Multi-mode diode emitters are stacked in a staircase formation to provide a spatially-mulitplexed output. Improved coupling efficiency is achieved by providing tilted collimated output beams that determine an effective step height of the stepped structure. Since the effective step height is dependent on the tilt angle, a variable number of emitters can be used inside packages having a same physical step height, while still attaining high coupling efficiency.

Owner:LUMENTUM OPERATIONS LLC

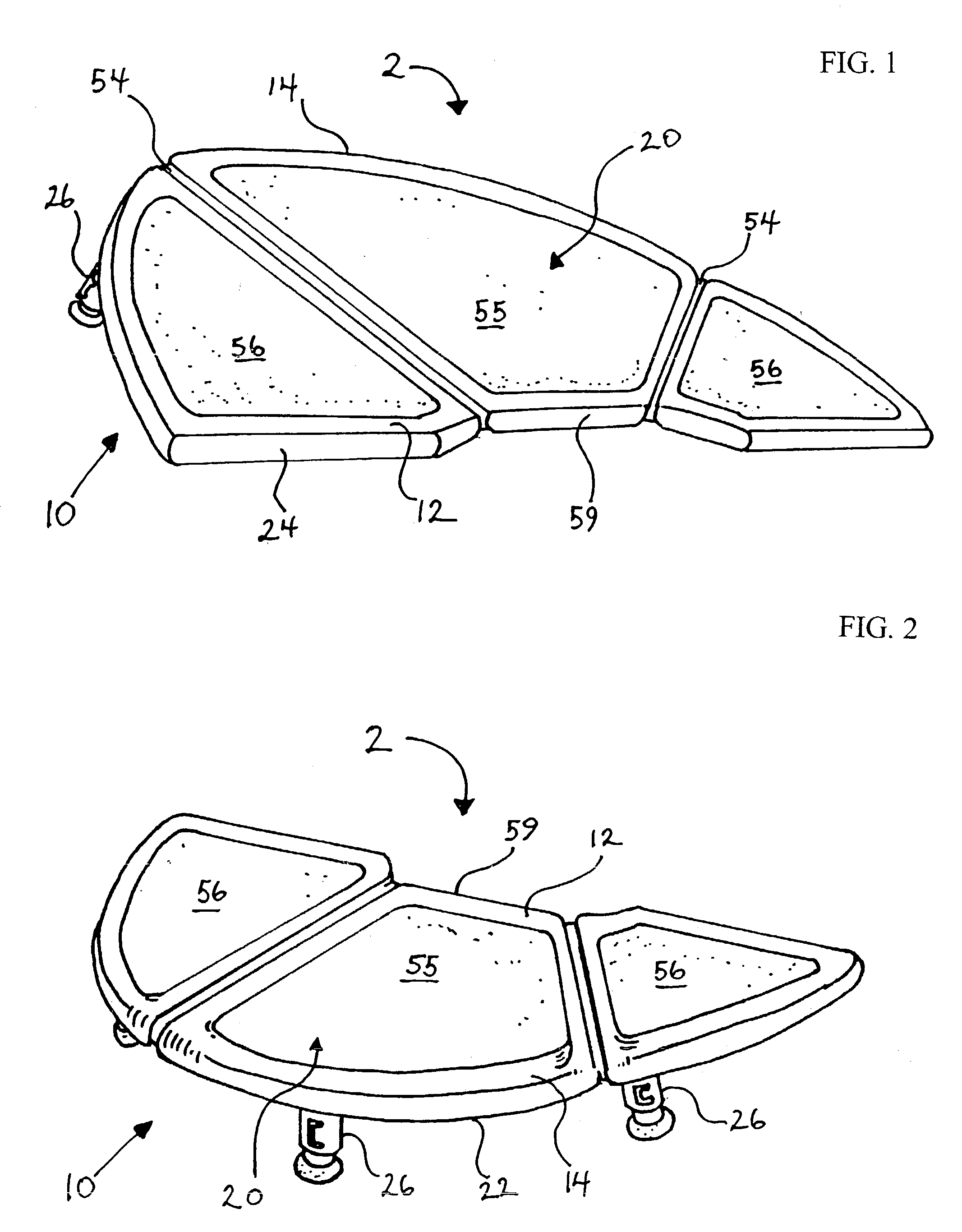

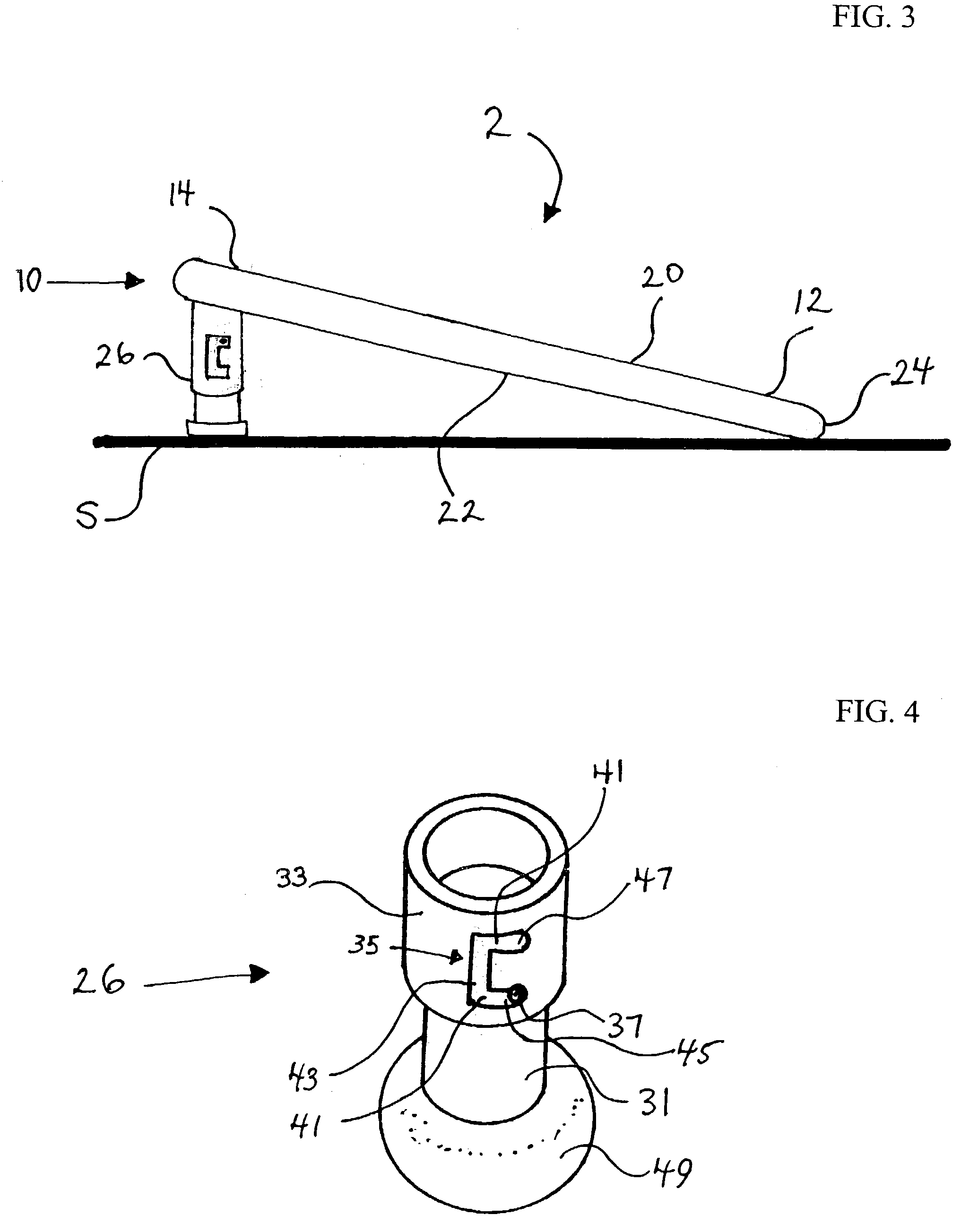

Aerobic ramp

InactiveUS6926643B1Easy to superviseRelieve pressureMovement coordination devicesCardiovascular exercising devicesEngineeringStep height

A step exercising system for an aerobic step workout is constructed as a portable inclined step ramp. The ramp is sloped towards a user such that the user can step up onto the ramp at various heights, thereby regulating the degree of intensity of the workout without having to suspend the workout to adjust the step height, as is the case when using a conventional aerobic step having a raised level platform.

Owner:GT MERCHANDISING & LICENSING +1

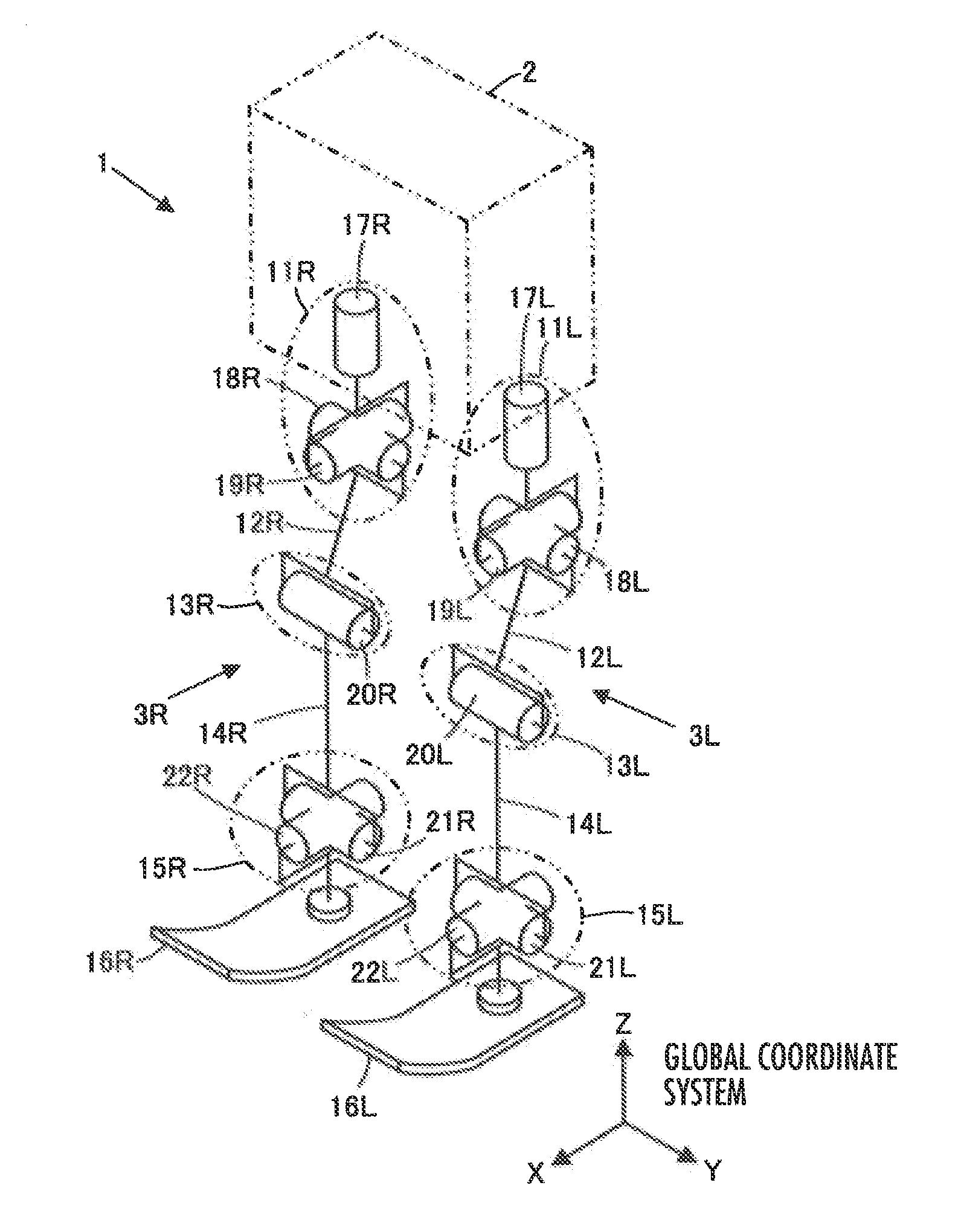

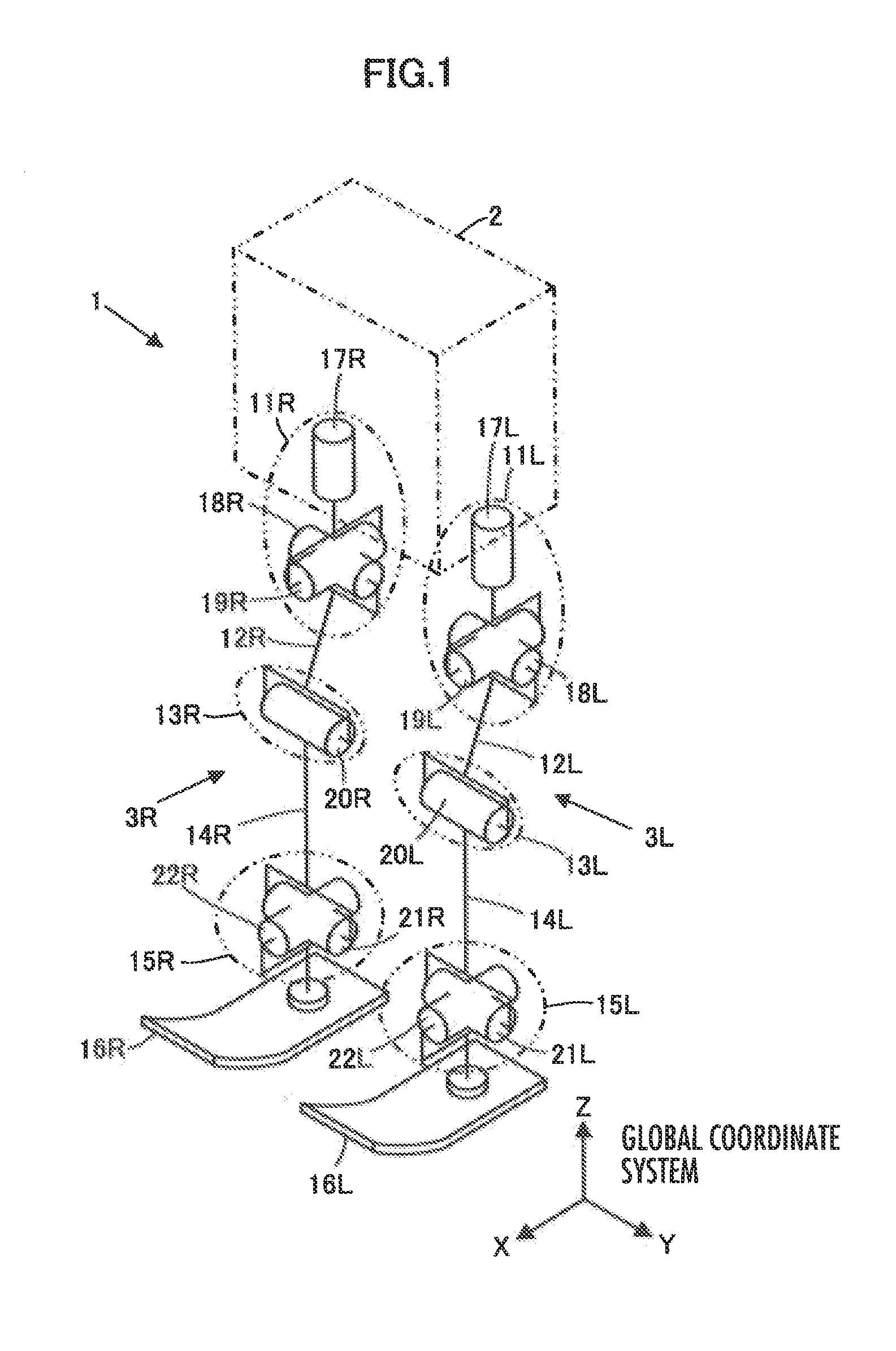

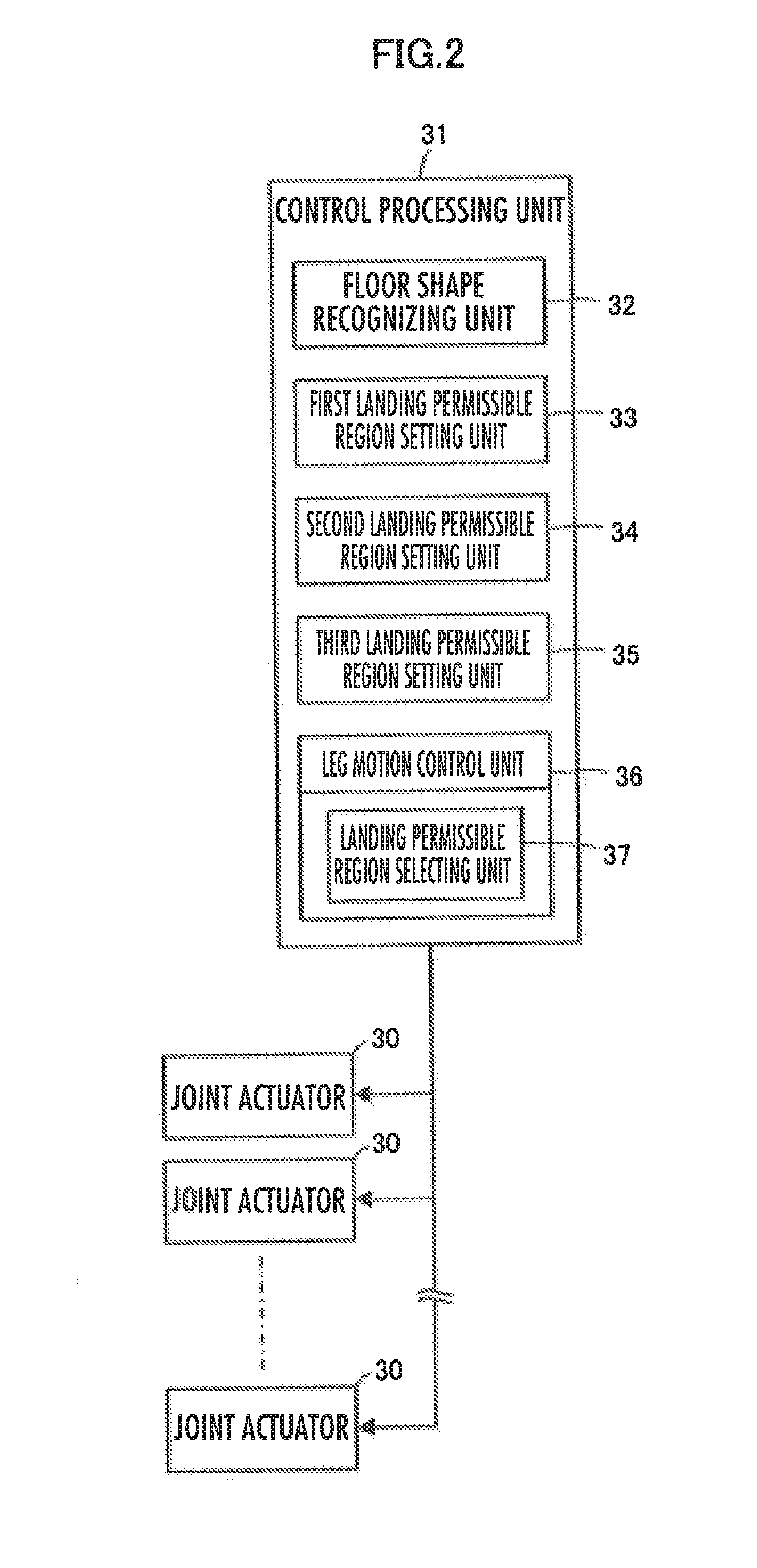

Control device for legged mobile robot

ActiveUS20150073592A1Increasing sizeIncreasing weightProgramme-controlled manipulatorRobotMobile robot controlEngineering

A setting unit 33 configured to set a first landing permissible region in order to ground a free leg side foot 16 within an upper tread surface or a lower tread surface of a step existing ahead of a legged mobile robot 1 in a traveling direction, and a setting unit 34 configured to set a second landing permissible region in order to ground the free leg side foot 16 on an edge of the upper tread surface or the lower tread surface are provided to switch landing permissible regions for movement control of the robot 1 according to a step height.

Owner:HONDA MOTOR CO LTD

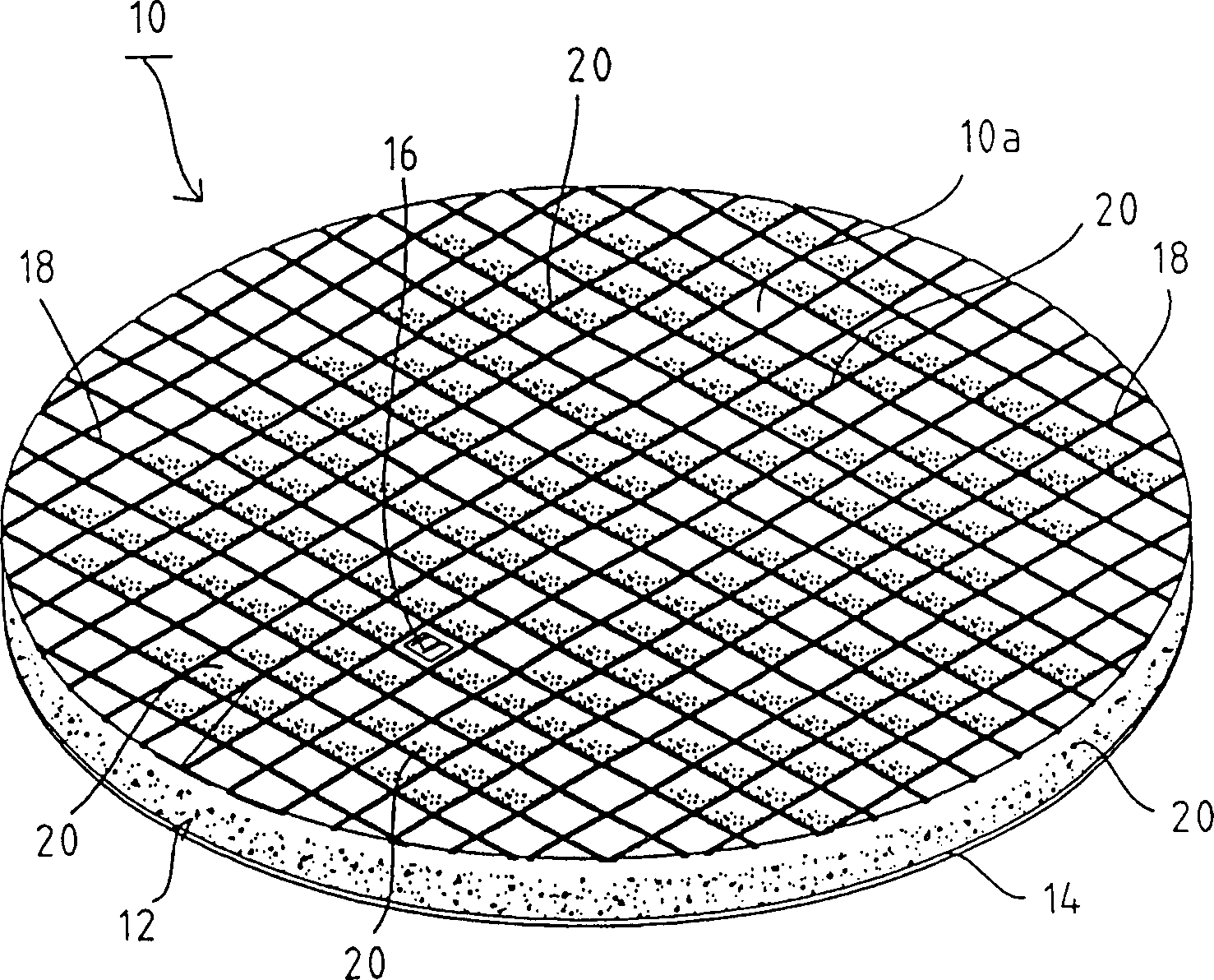

Polishing pad

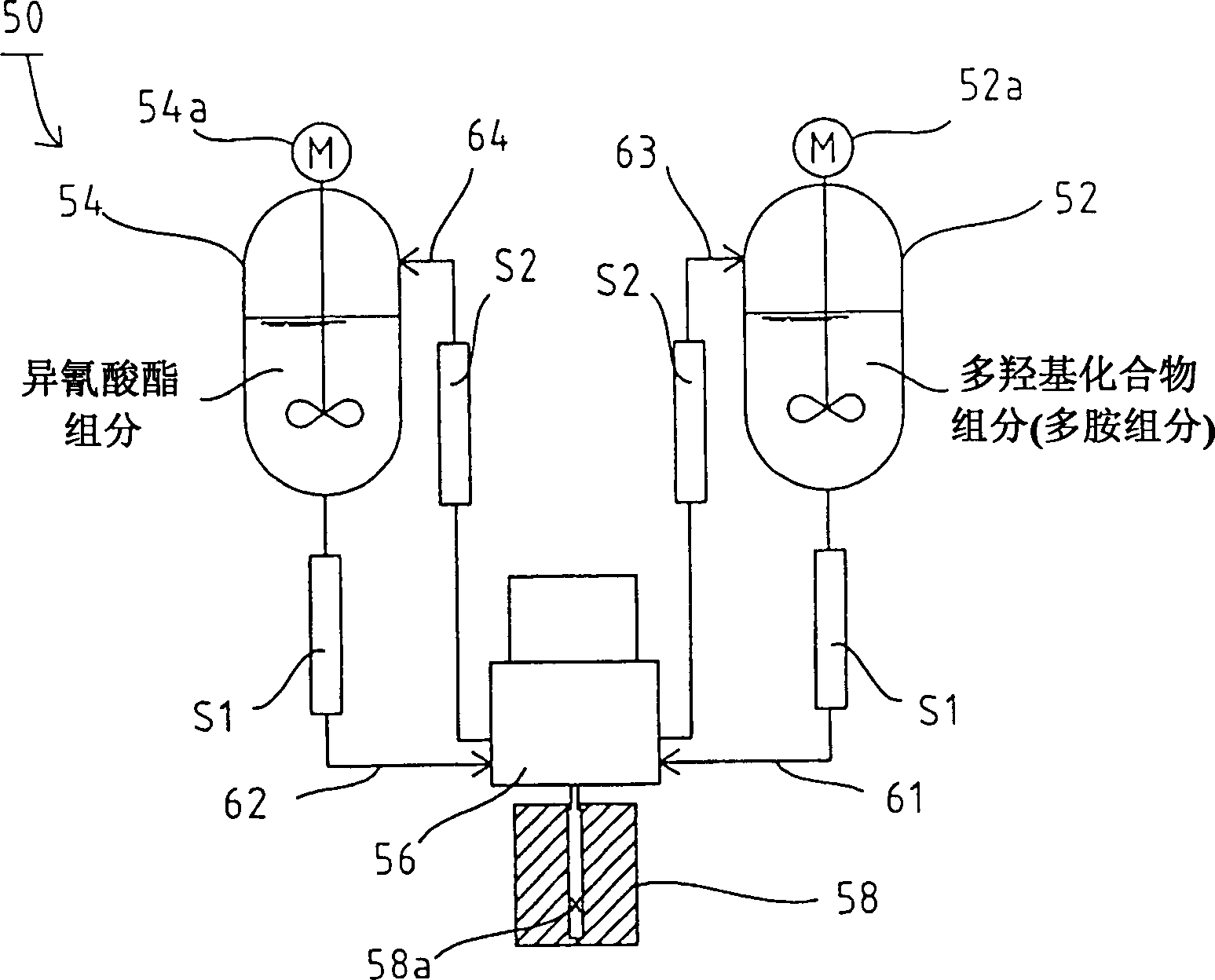

InactiveUS6705934B1Reduce global step heightDepression depressionOther chemical processesSemiconductor/solid-state device manufacturingSurface layerHardness

The present invention relates to a polishing pad which is characterized in that it is of micro rubber A-type hardness at least 80°, has closed cells of average cell diameter no more than 1000 mum, is of density in the range 0.4 to 1.1 and contains polyurethane and polymer produced from a vinyl compound. When planarizing local unevenness on a semiconductor substrate with the polishing pad relating to the present invention, the polishing rate is high, the global step height is low, dishing does not readily occur at the metallic interconnects, clogging and permanent set of the surface layer region do not readily occur and the polishing rate is stable.

Owner:TORAY IND INC

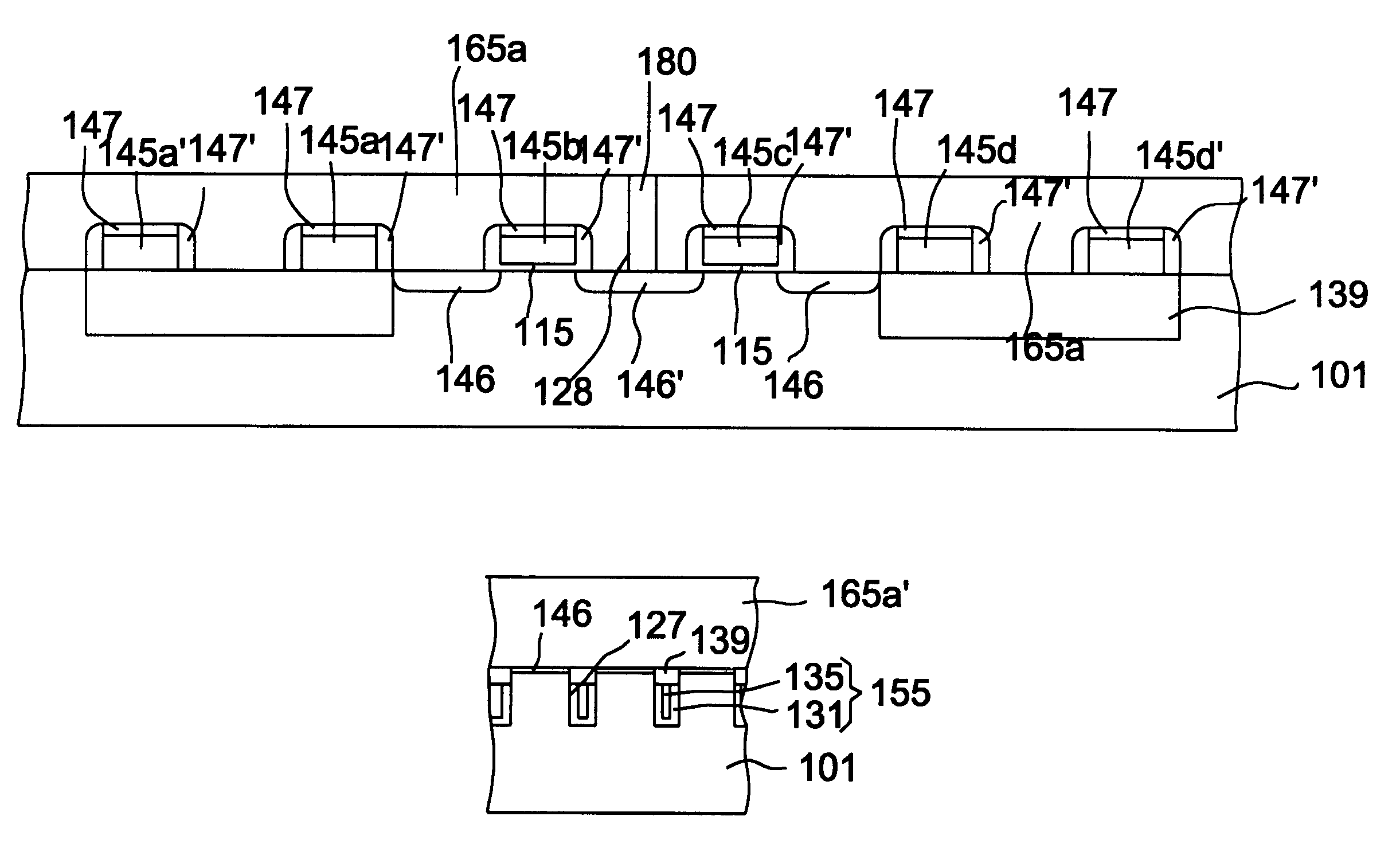

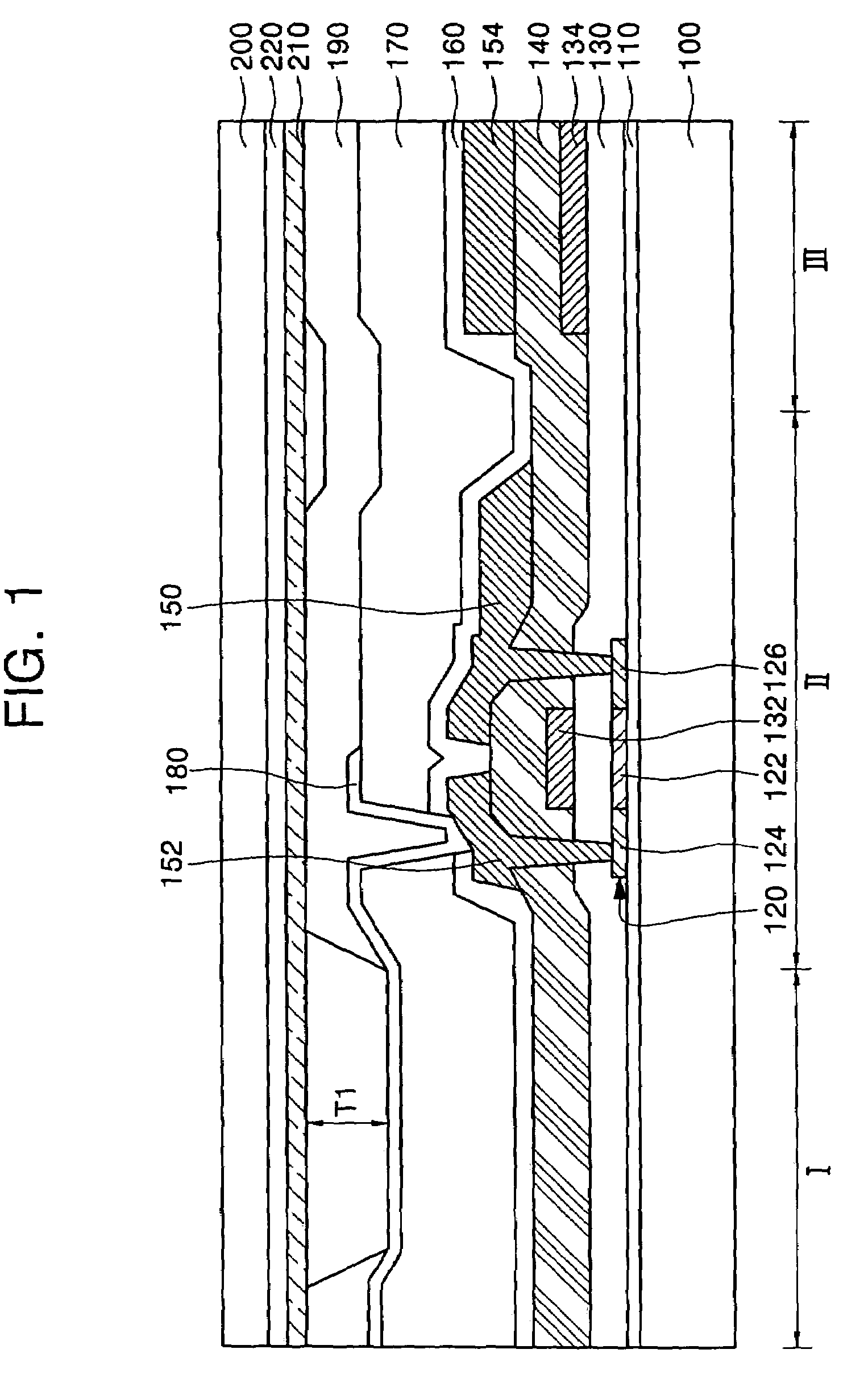

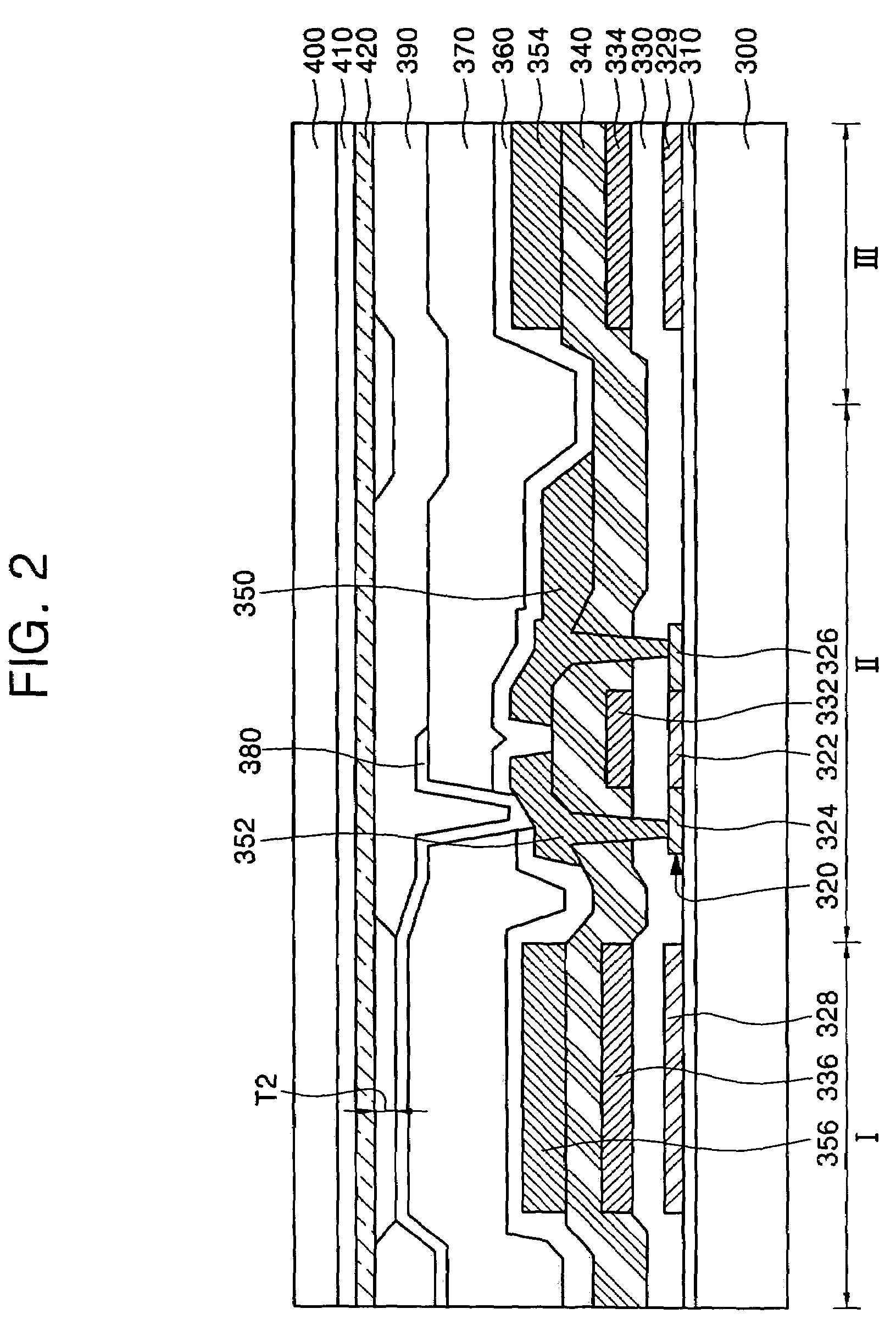

Double silicon-on-insulator (SOI) metal oxide semiconductor field effect transistor (MOSFET) structures

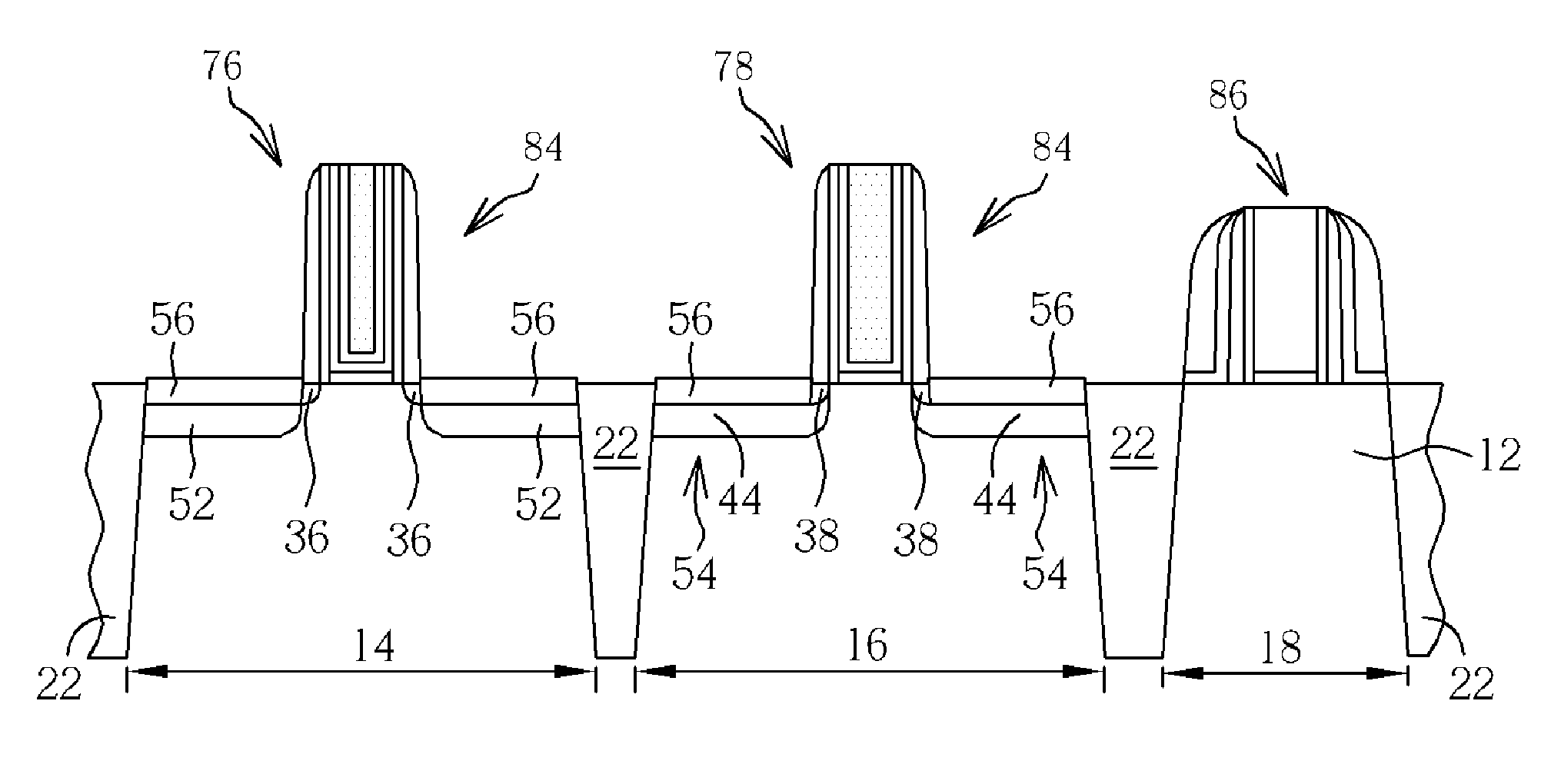

ActiveUS7034362B2Reduce step heightWithout junction capacitanceTransistorSolid-state devicesMOSFETCapacitance

A SOI MOSFET structure having a reduced step height between the various semiconductor layers without adversely affecting the junction capacitance of the semiconductor device formed on the uppermost semiconductor layer as well as a method of fabricating the same are provided. The structure of the present invention includes an elevated device region having at least one semiconductor device located on a second semiconductor layer. The elevated device region further includes a source / drain junction that extends from the second semiconductor layer down to a first buried insulator layer that is located on an upper surface of the semiconductor substrate. The structure also includes a recessed device region having at least one semiconductor device located atop a first semiconductor layer which is located on an upper surface of the first buried insulator. An isolation region separates the elevated device region from the recessed device region.

Owner:GLOBALFOUNDRIES U S INC

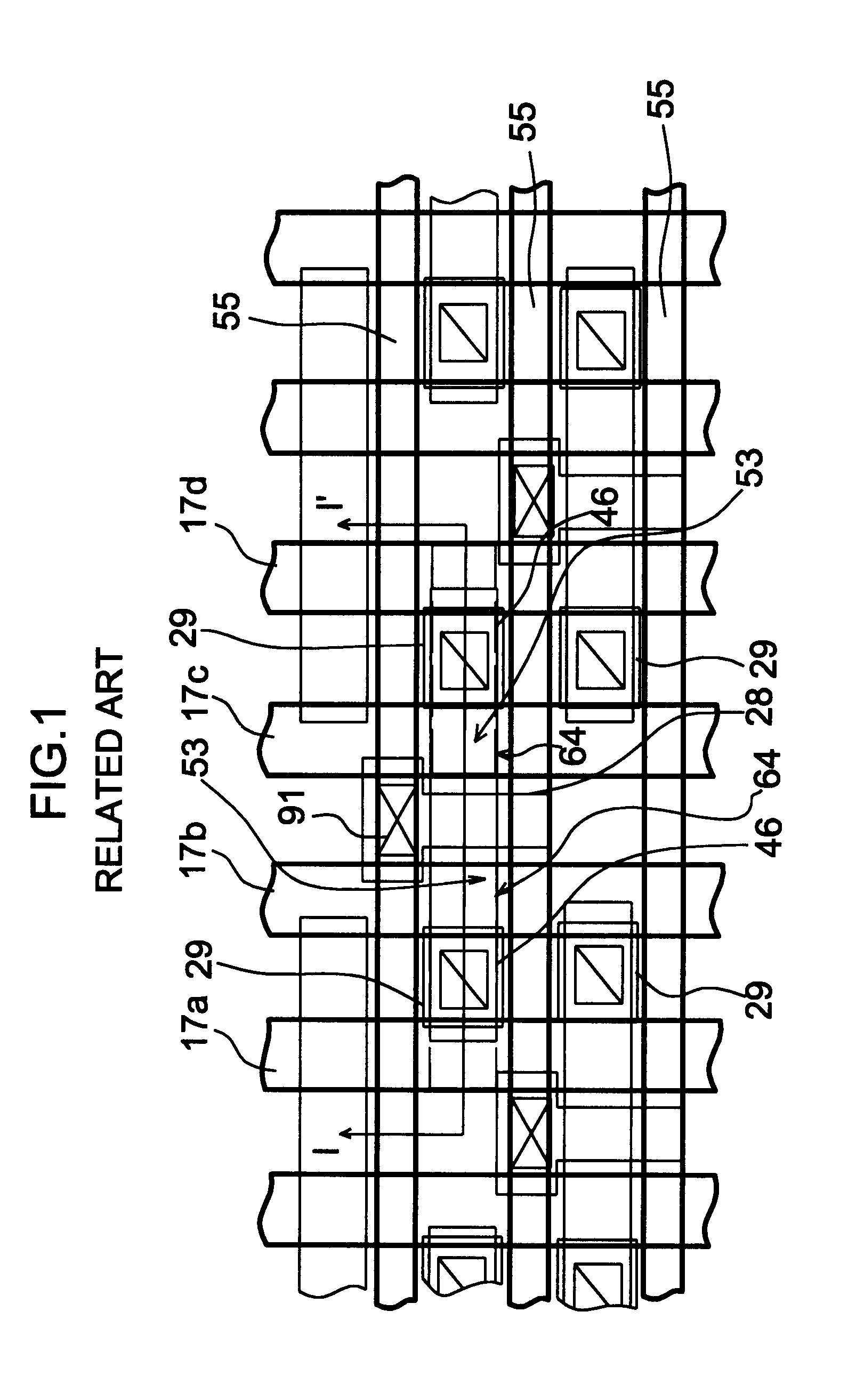

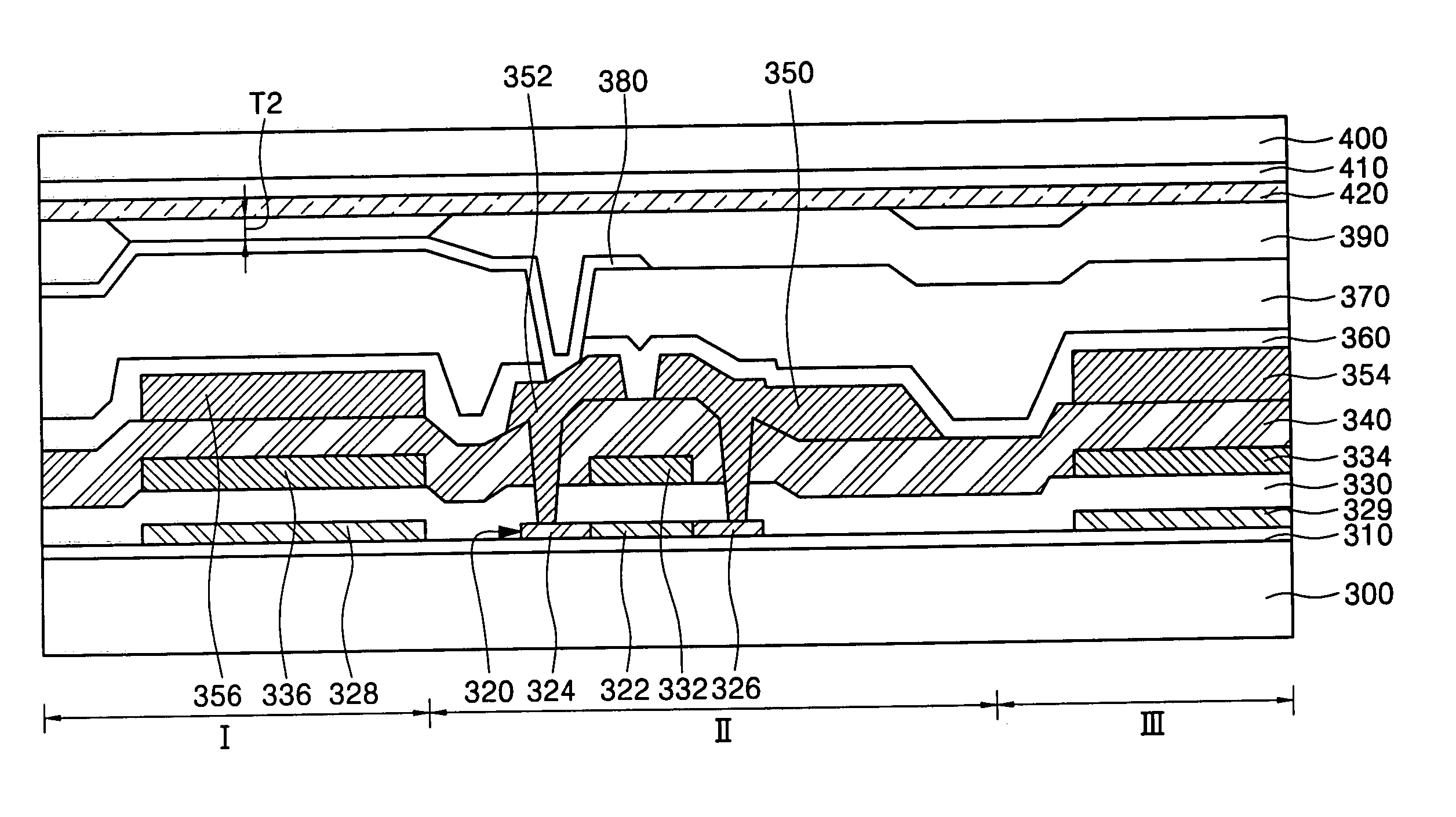

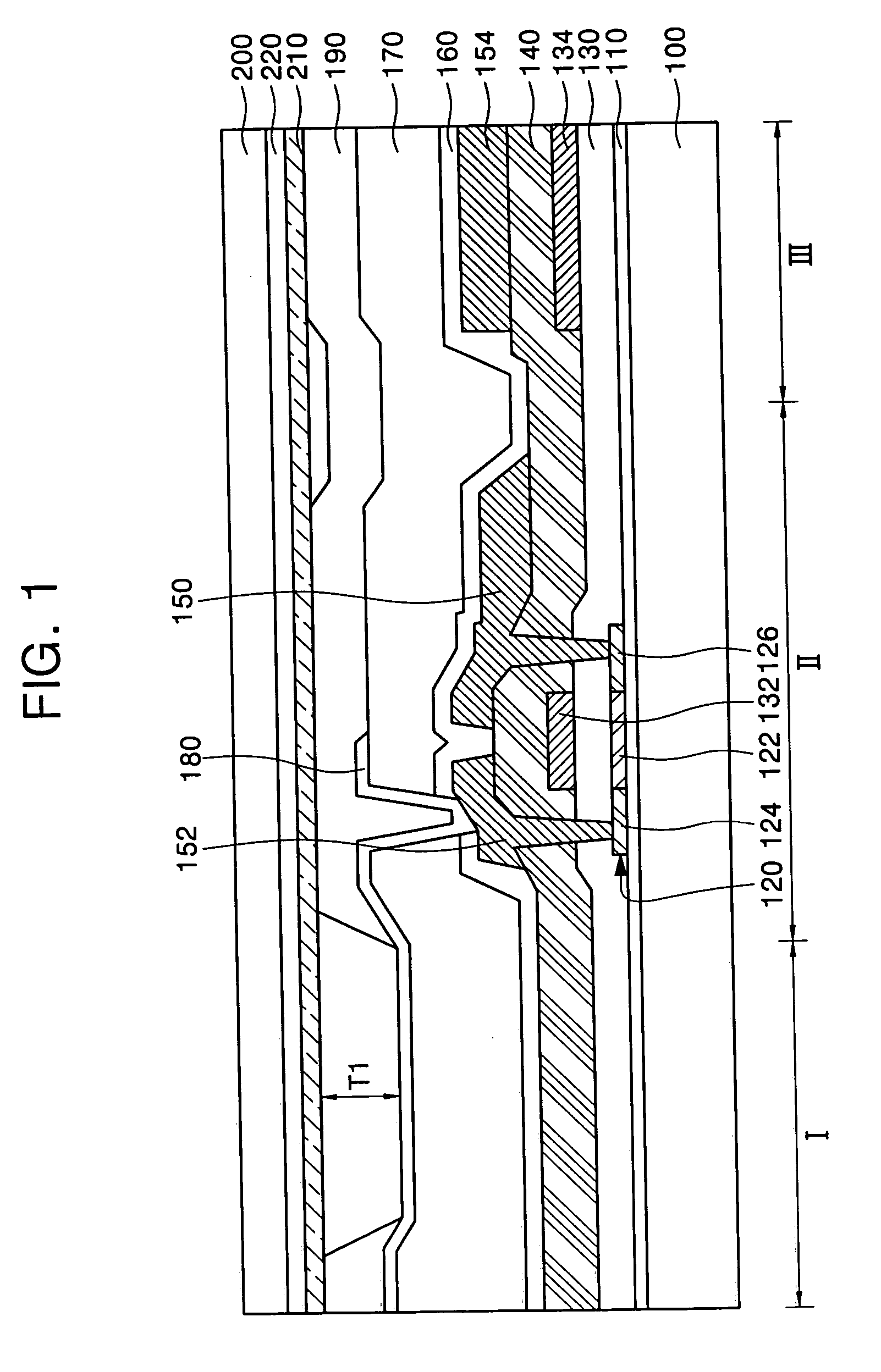

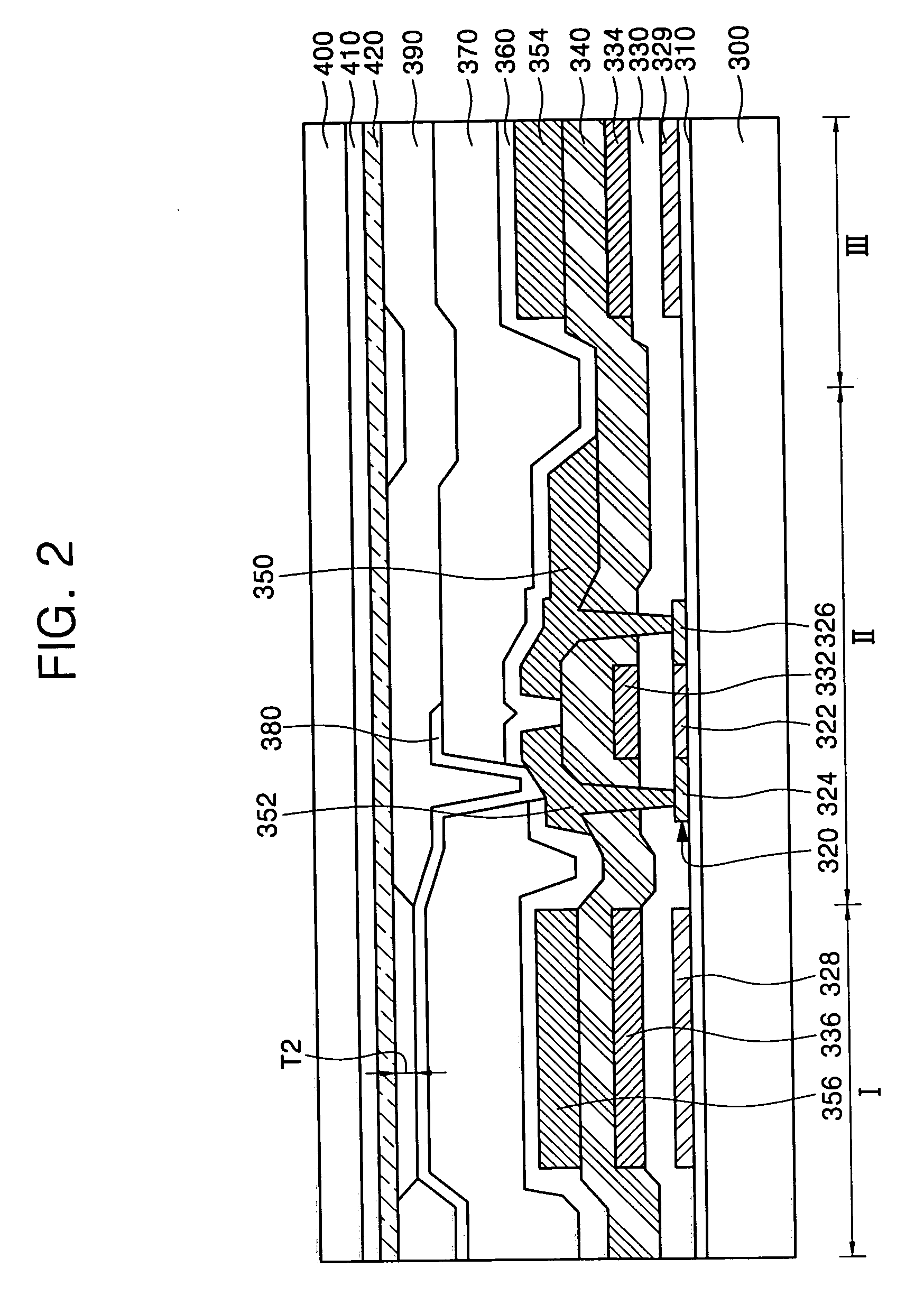

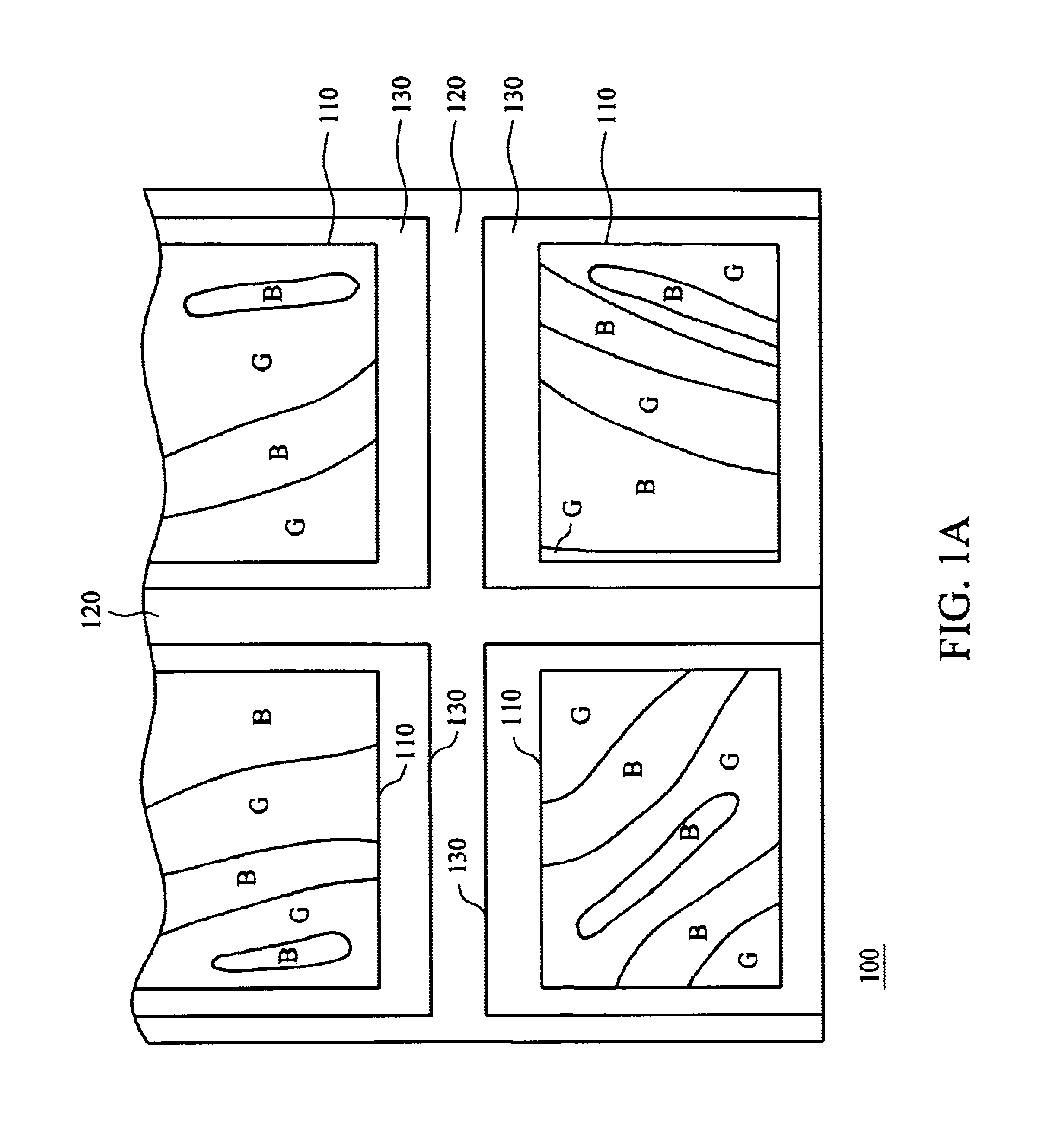

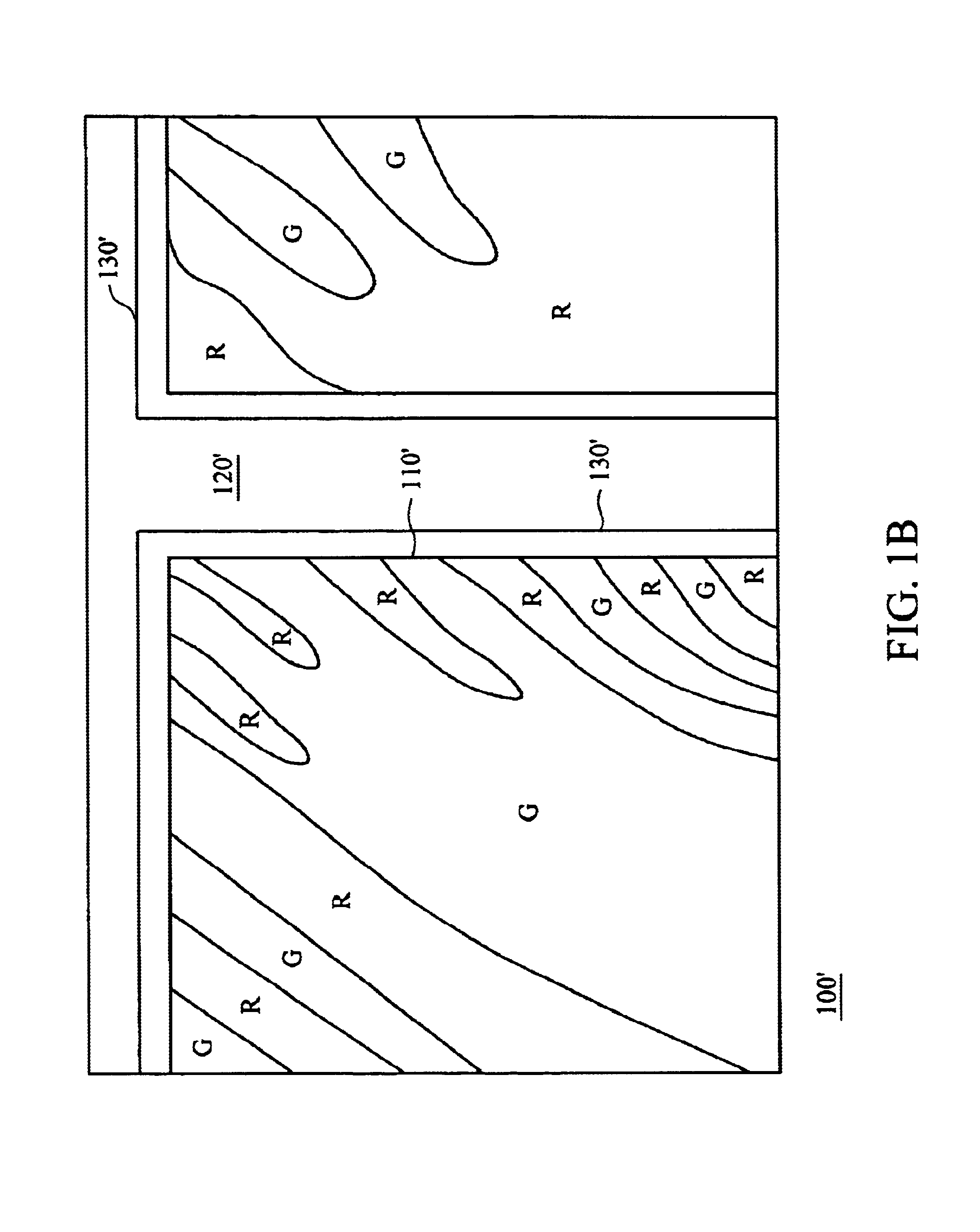

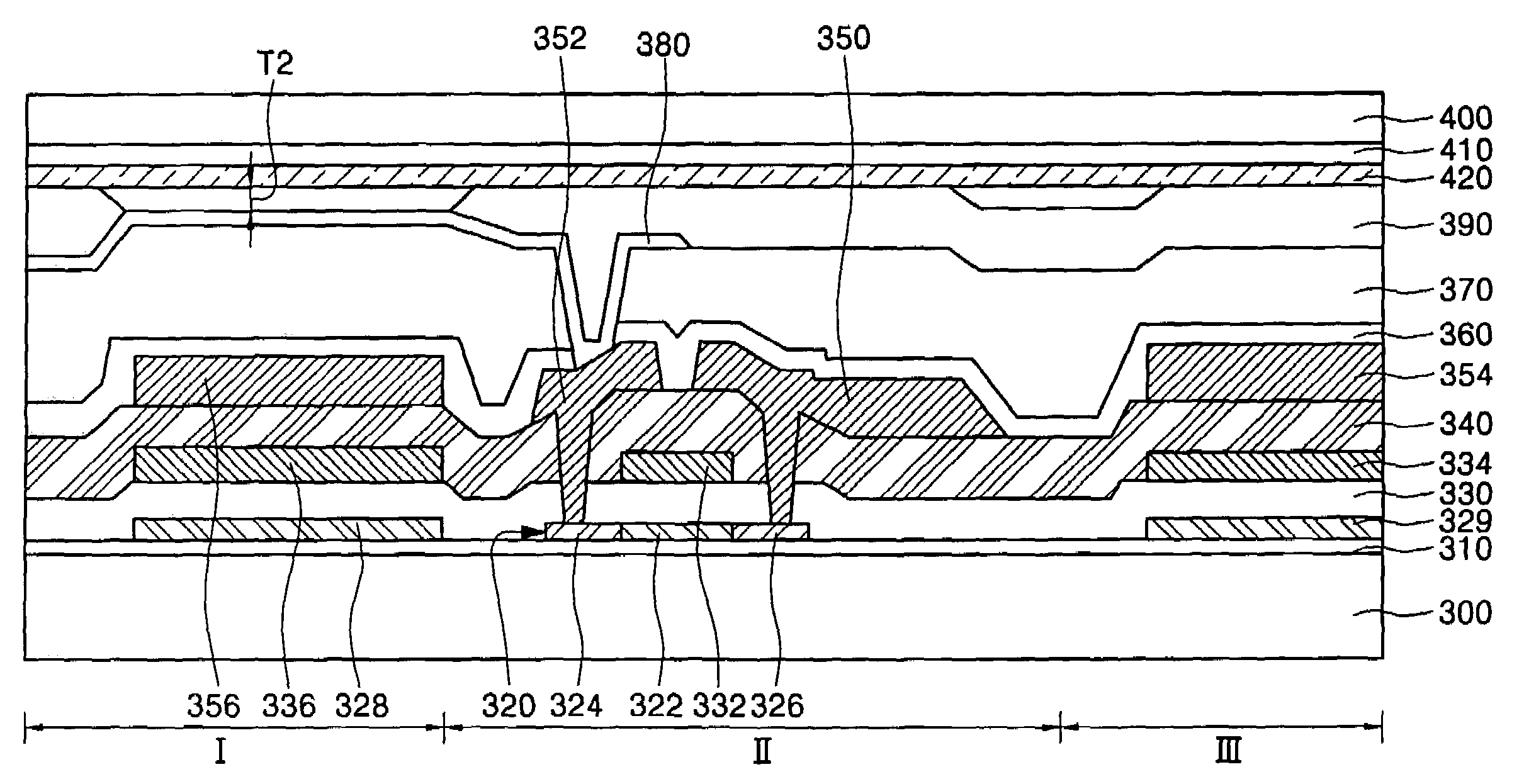

Organic light emitting display device and method of fabricating the same

ActiveUS20060124933A1Simple methodReduce gapElectroluminescent light sourcesSolid-state devicesOrganic layerDisplay device

An organic light emitting display device and a method of fabricating the same. A dummy pattern is formed in an emission region to increase the step height of the emission region by an electrode material while a thin film transistor is fabricated, so that a distance between a pixel electrode and a donor film is decreased during fabrication of an organic layer. This reduced distance reduces laser energy for transfer using laser-induced thermal imaging, thus improving life span and efficiency of the device. Further, the pixel electrode can extend into a thin film transistor region and a capacitor region, thus enhancing an aperture ratio.

Owner:SAMSUNG DISPLAY CO LTD

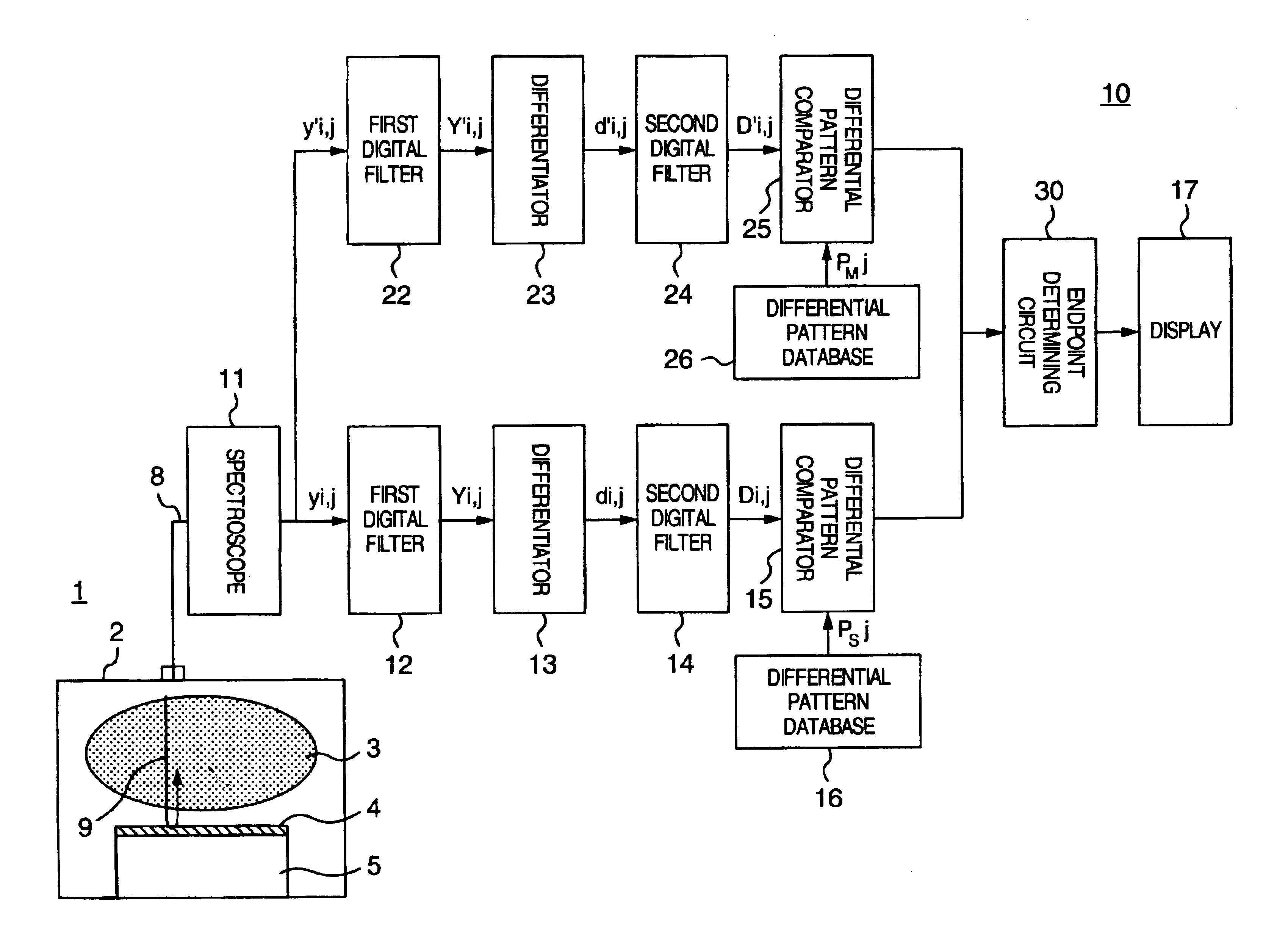

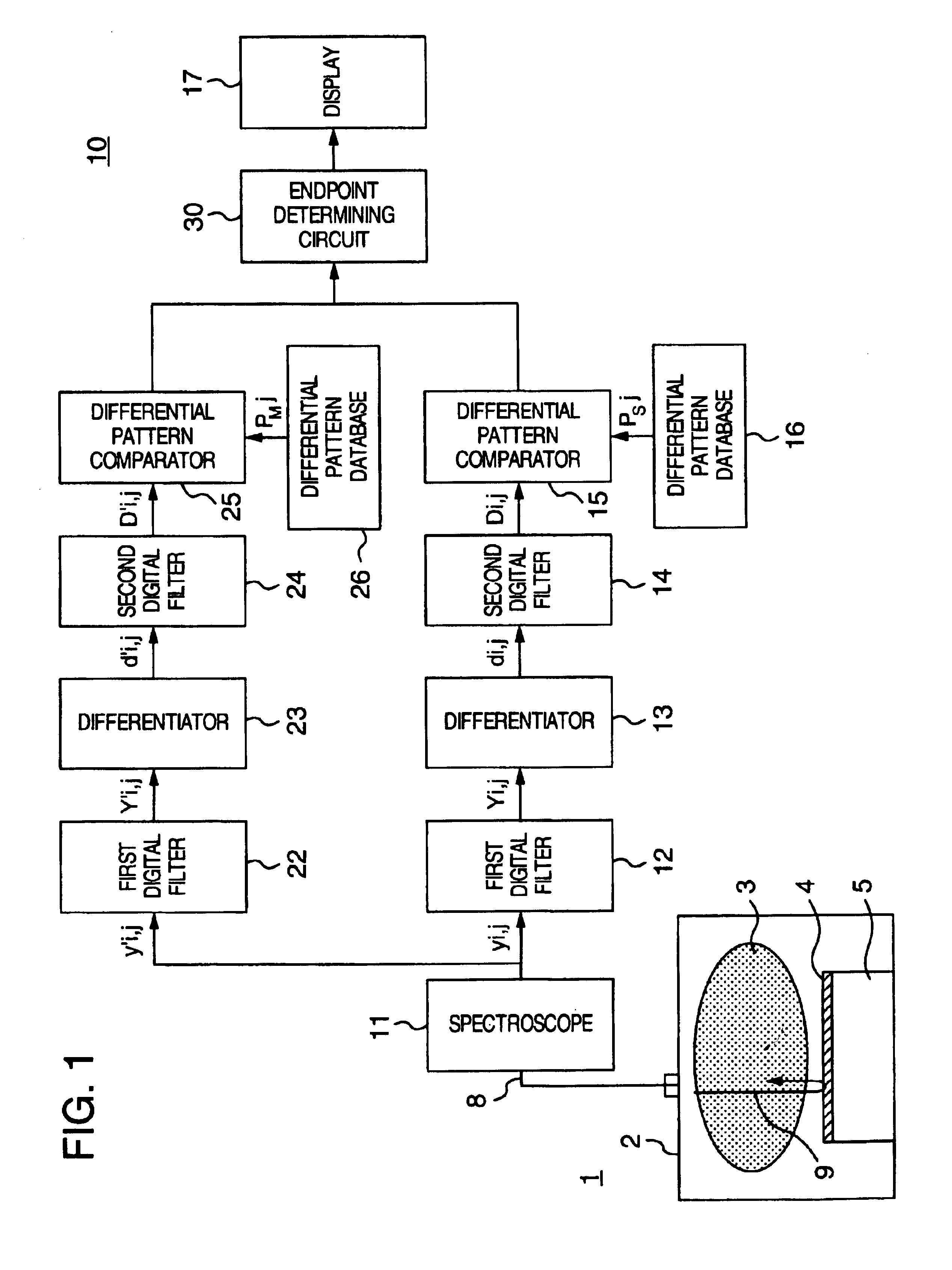

Method and apparatus for determining endpoint of semiconductor element fabricating process

InactiveUS6903826B2Improve accuracyAccurate measurementSemiconductor/solid-state device testing/measurementElectric discharge tubesComputational physicsStep height

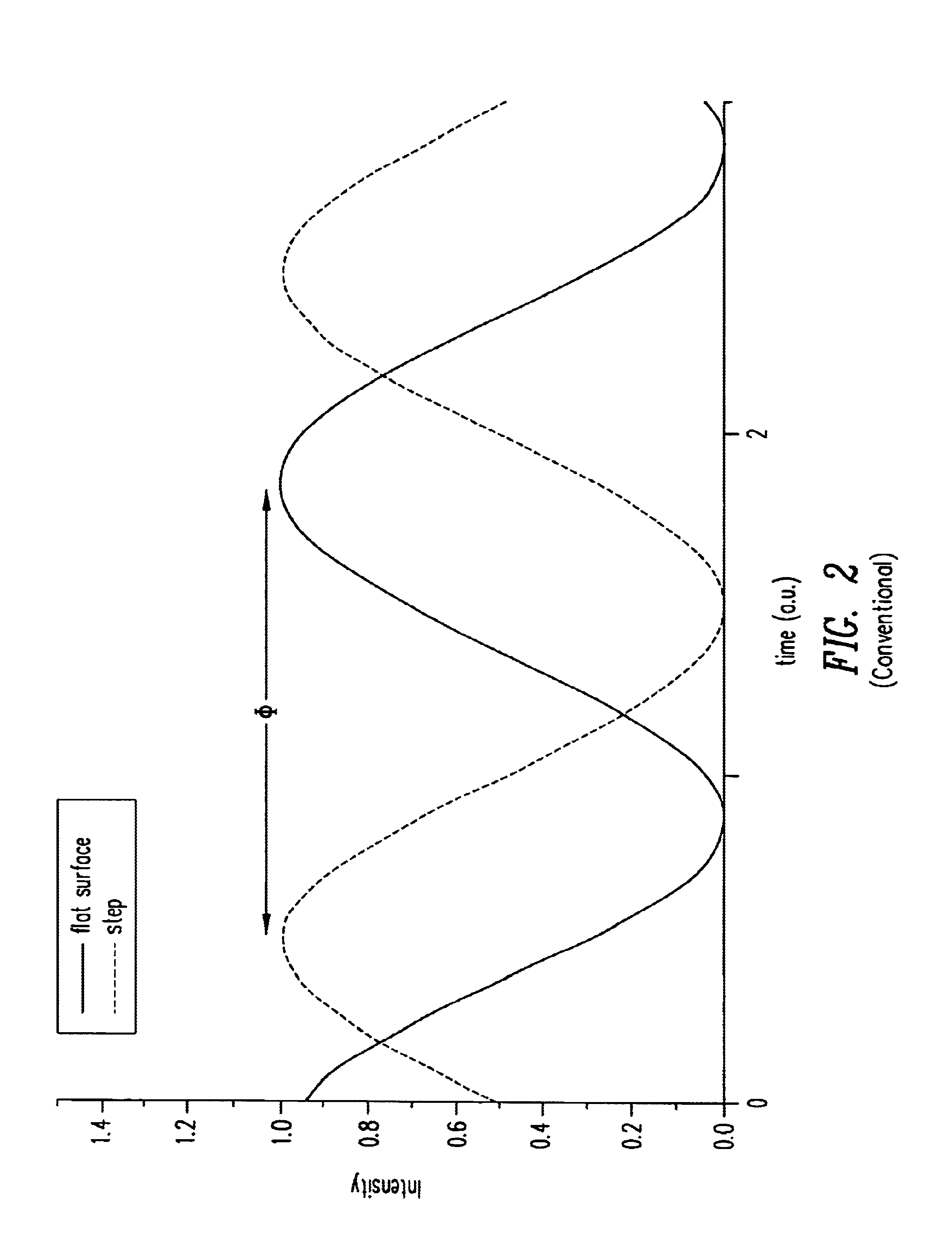

Standard patterns of differential values of interference light that correspond to a predetermined step height of the first material being processed and standard patterns of differential values of interference light that correspond to a predetermined remaining mask layer thickness of the material are set. These standard patterns use wavelengths as parameters. Then, the intensities of interference light of multiple wavelengths are measured for a second material that has the same structure as the first material. Actual patterns with wavelength as parameter are determined from differential values of the measured interference light intensities. Based on the standard patterns and the actual patterns of the differential values, the step height and the remaining mask layer thickness of the second material are determined.

Owner:HITACHI LTD

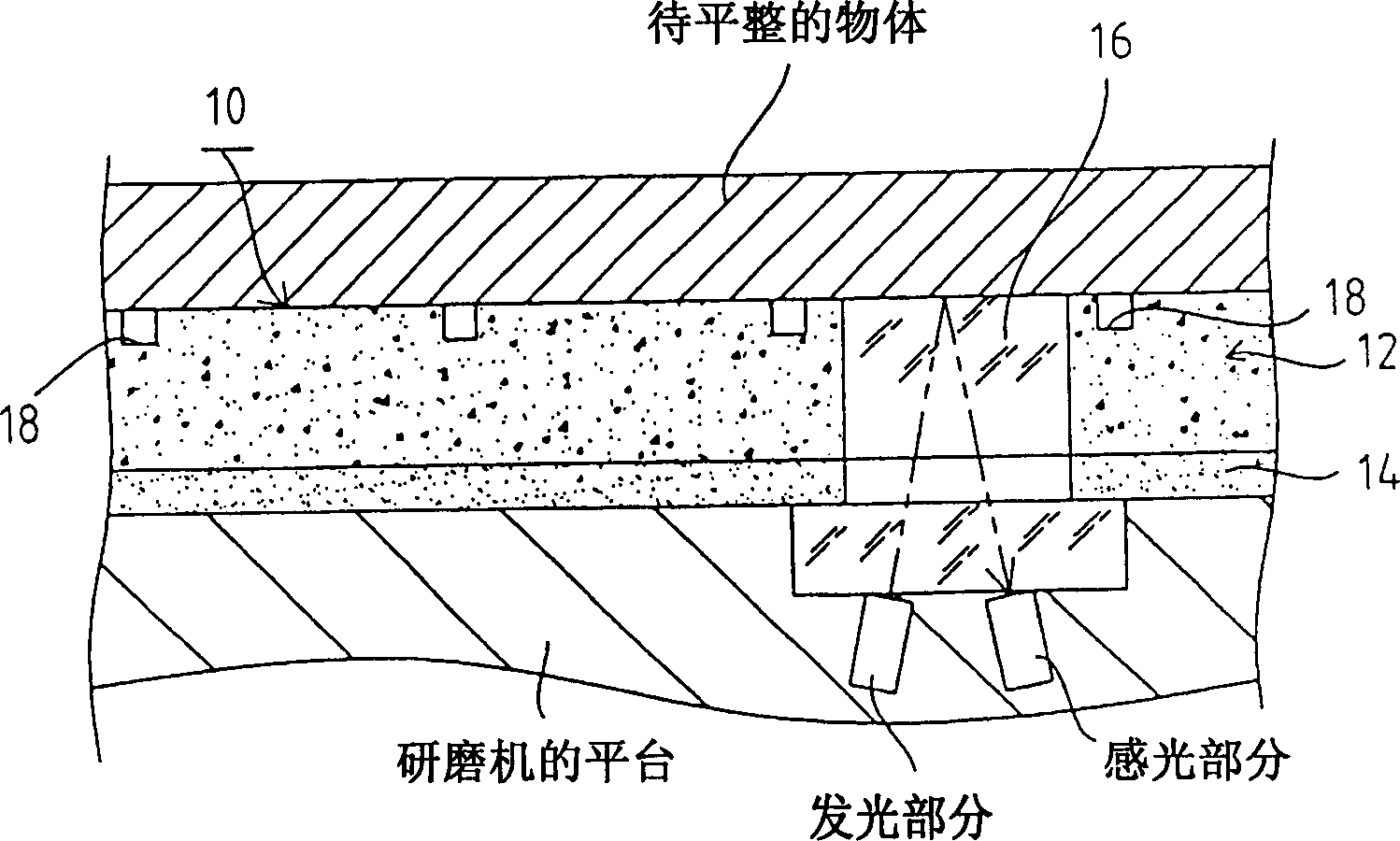

Grinding pad

InactiveCN1407606AGrinding fitSemiconductor/solid-state device manufacturingFlexible-parts wheelsSemiconductor materialsMetallurgy

Owner:ROGERS INOAC CORP

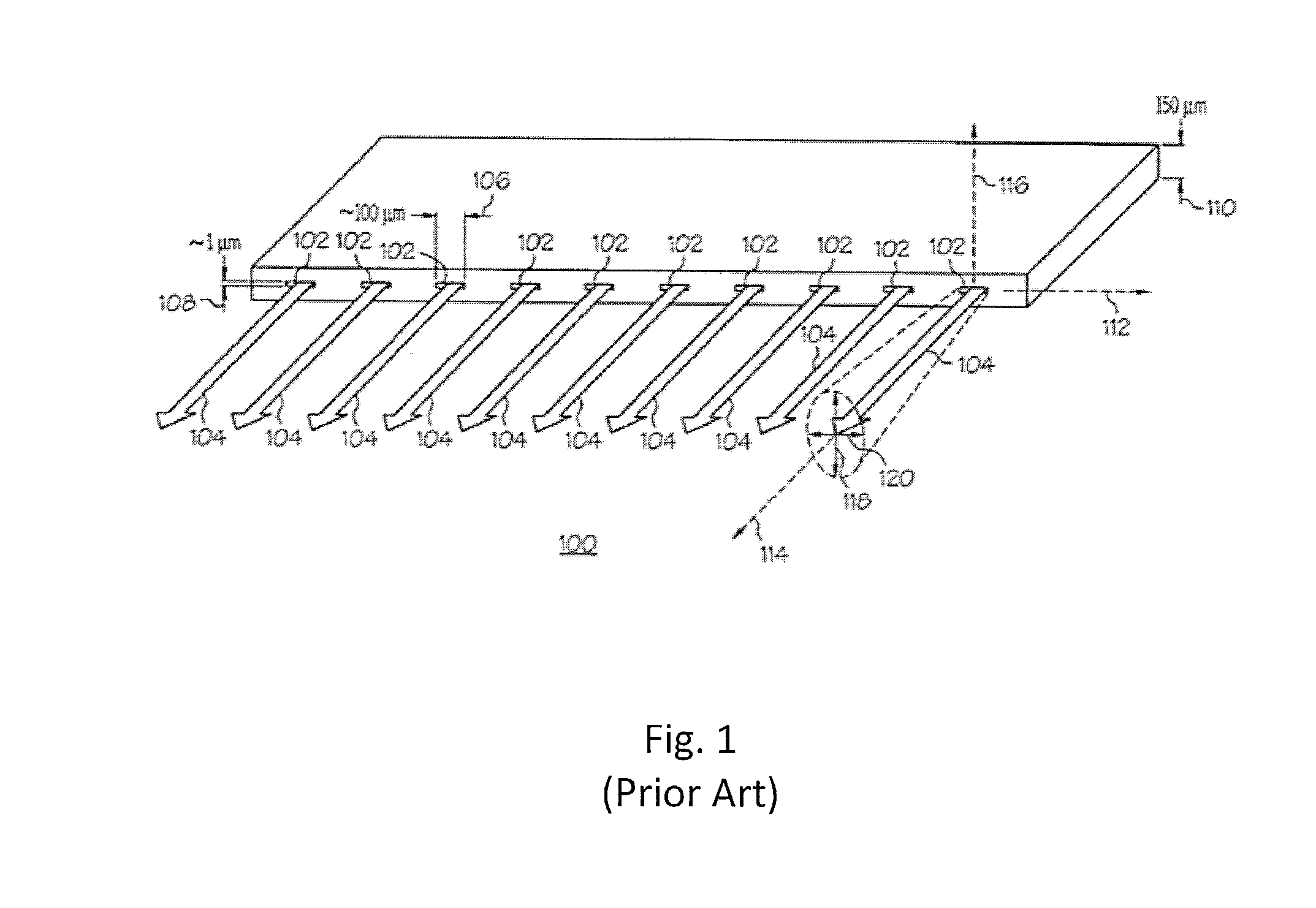

Image sensor fabrication method and structure

InactiveUS6964916B2Reduce step heightSolid-state devicesSemiconductor/solid-state device manufacturingResistStep height

A method for processing a semiconductor substrate includes providing a substrate having at least one filter region with a plurality of bond pads in it. Metal is deposited above the bond pads, to reduce the bond pad step height. A planarization layer is formed such that the deposited metal has a height near to a height of the planarization layer. At least one color resist layer is formed above the planarization layer.

Owner:TAIWAN SEMICON MFG CO LTD

Controlling system for gate formation of semiconductor devices

InactiveUS7588946B2Semiconductor/solid-state device testing/measurementSolid-state devicesControl systemEngineering

A method of controlling gate formation of semiconductor devices includes determining the correlation between the step heights of isolation structures and the over-etching time by measuring step heights of isolation structures, determining an over-etching time based on the step heights, and etching gates using the over-etching time. The method may include an after-etching-inspection to measure the gate profile and fine-tune the gate formation control. Within-wafer uniformity can also be improved by measuring the step height uniformity on a wafer and adjusting gate formation processes.

Owner:TAIWAN SEMICON MFG CO LTD

Organic light emitting display device and method of fabricating the same

ActiveUS7408192B2Simple methodReduce gapDischarge tube luminescnet screensElectroluminescent light sourcesOrganic layerDisplay device

An organic light emitting display device and a method of fabricating the same. A dummy pattern is formed in an emission region to increase the step height of the emission region by an electrode material while a thin film transistor is fabricated, so that a distance between a pixel electrode and a donor film is decreased during fabrication of an organic layer. This reduced distance reduces laser energy for transfer using laser-induced thermal imaging, thus improving life span and efficiency of the device. Further, the pixel electrode can extend into a thin film transistor region and a capacitor region, thus enhancing an aperture ratio.

Owner:SAMSUNG DISPLAY CO LTD

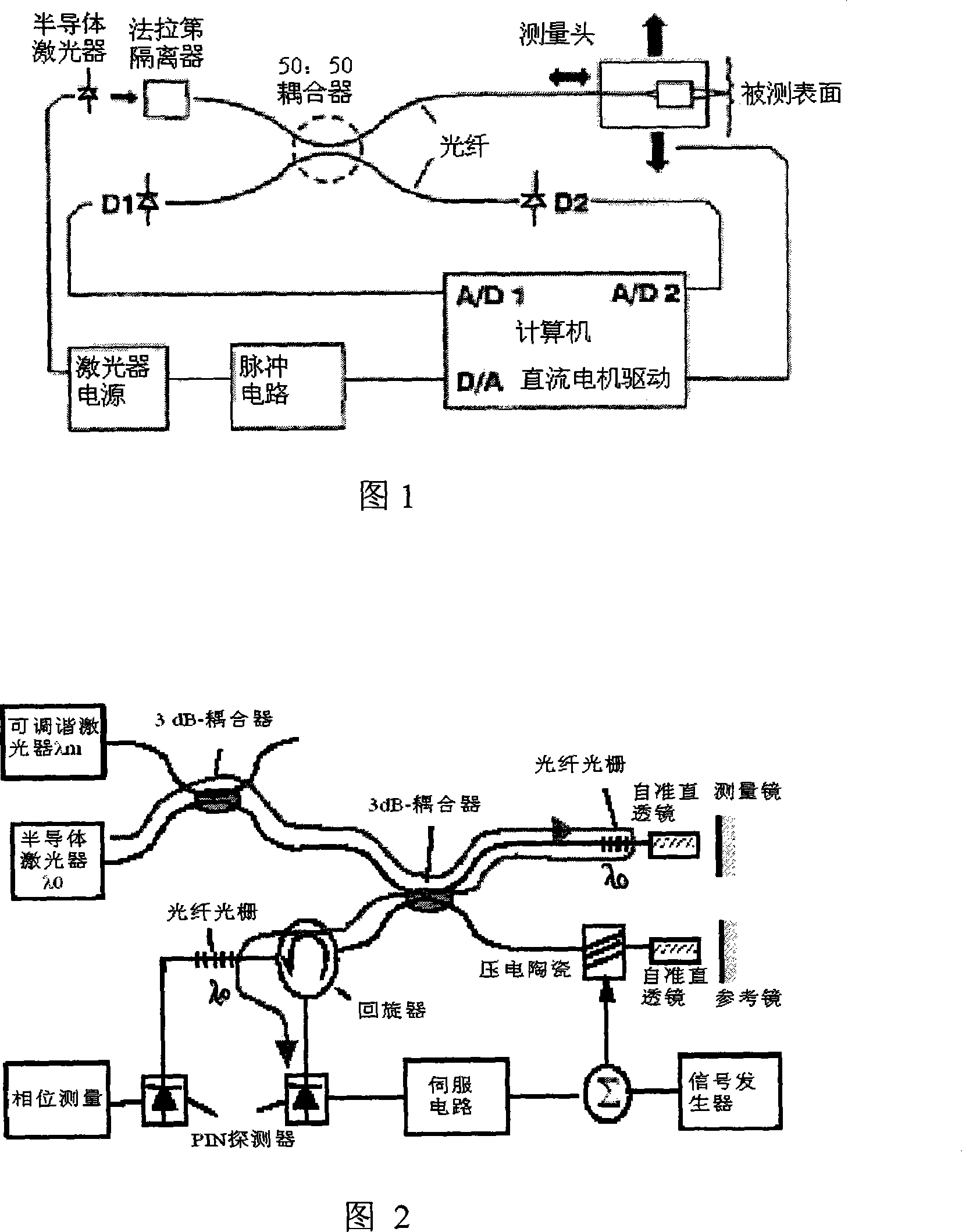

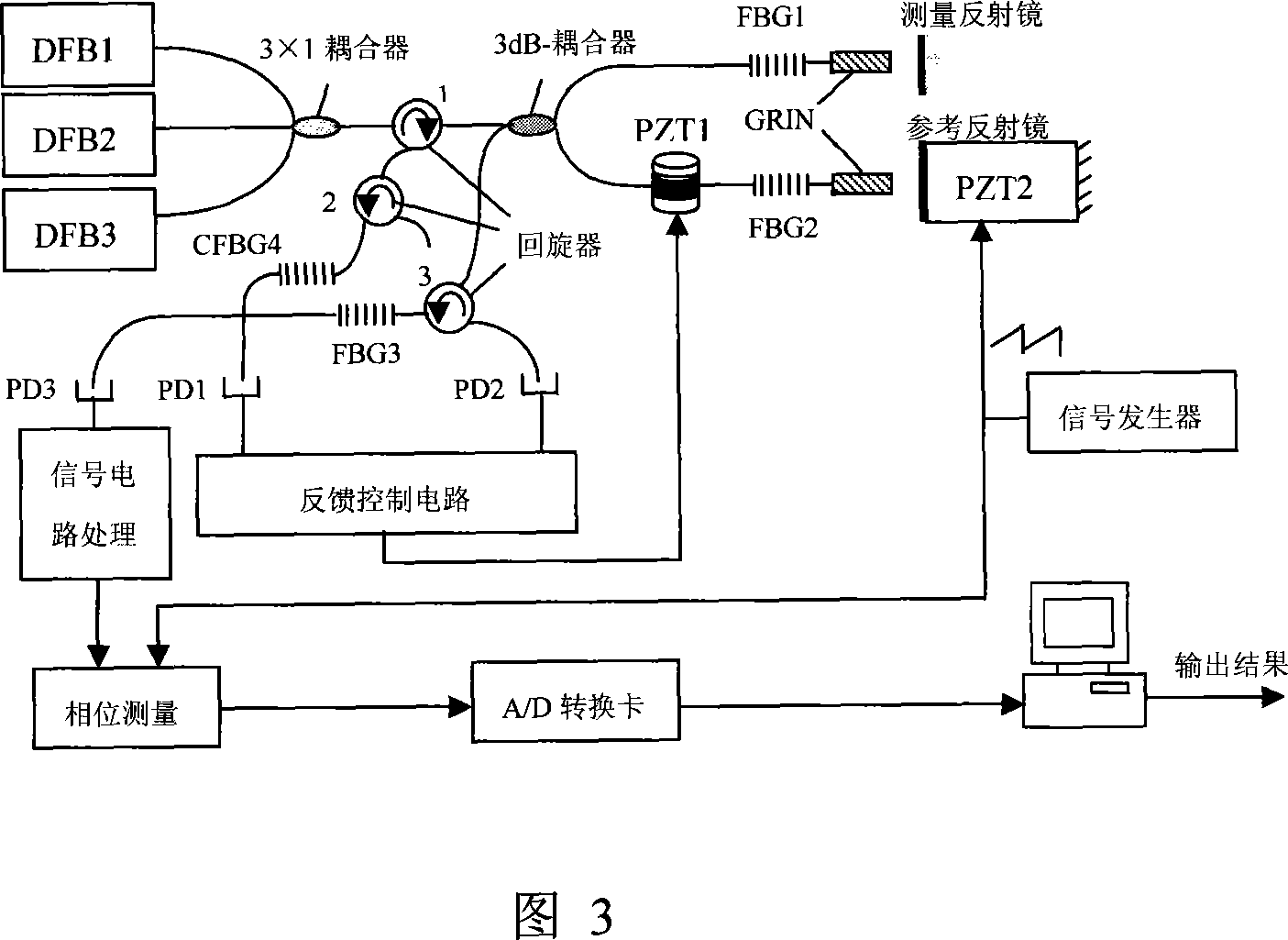

On-line measuring system using optical fiber grating synthetic wave for interfering step height

InactiveCN101126629AMeasurement stabilitySuitable for online measurementUsing optical meansConverting sensor output opticallyGratingMichelson interferometer

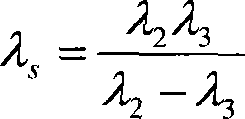

The utility model discloses an on-line measuring system for interference step height in composite wave from optical fiber raster. A composite optical fiber interferometer is built by making use of the Bragg wavelength reflective property in the optical fiber raster. The composite interferometer comprises two optical fiber Michelson interferometers with almost coincident light paths. A Michelson interferometer is used for measuring, and the other is used for stabilizing the system. The impact on the measuring system brought by the environmental interference is corrected through the feedback control compensation, so that the system is applicable to online measuring. Three lasers emit lights of slightly different wavelength but within 1550nm waveband. Because of the effects of the optical fiber raster reflecting Bragg wavelength and self-chirped optical fiber raster reflecting the specific spectrum, a wavelength acts on the stabilizing interferometer for stabilizing the measuring system, and the other two wavelengths act on the measuring interferometer to produce composite wave interference for actual measurement. Different composite wavelengths can be gained by regulating the two wavelengths acting on the measuring interferometer; and the measurement of different step heights can be carried out.

Owner:BEIJING JIAOTONG UNIV

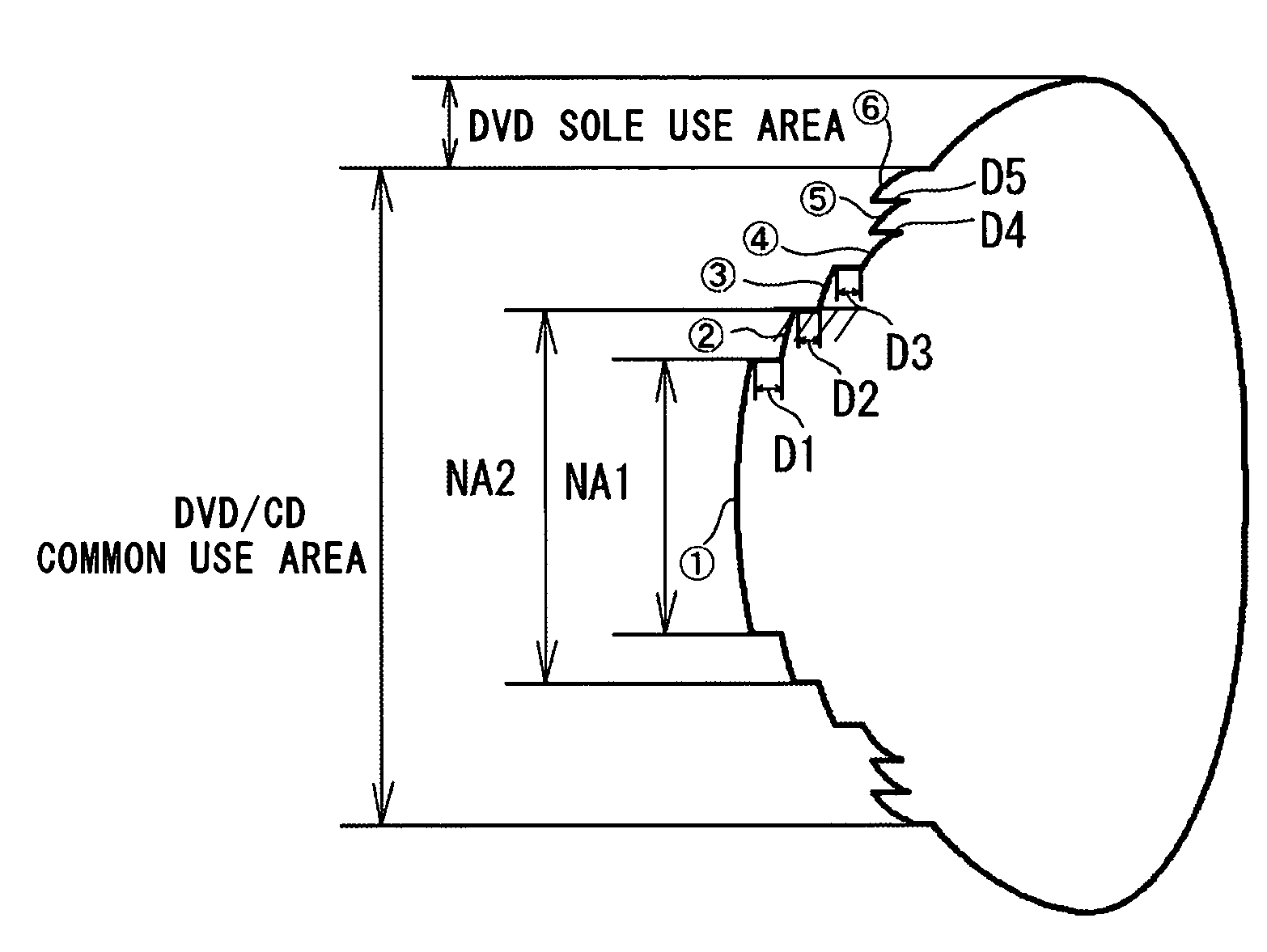

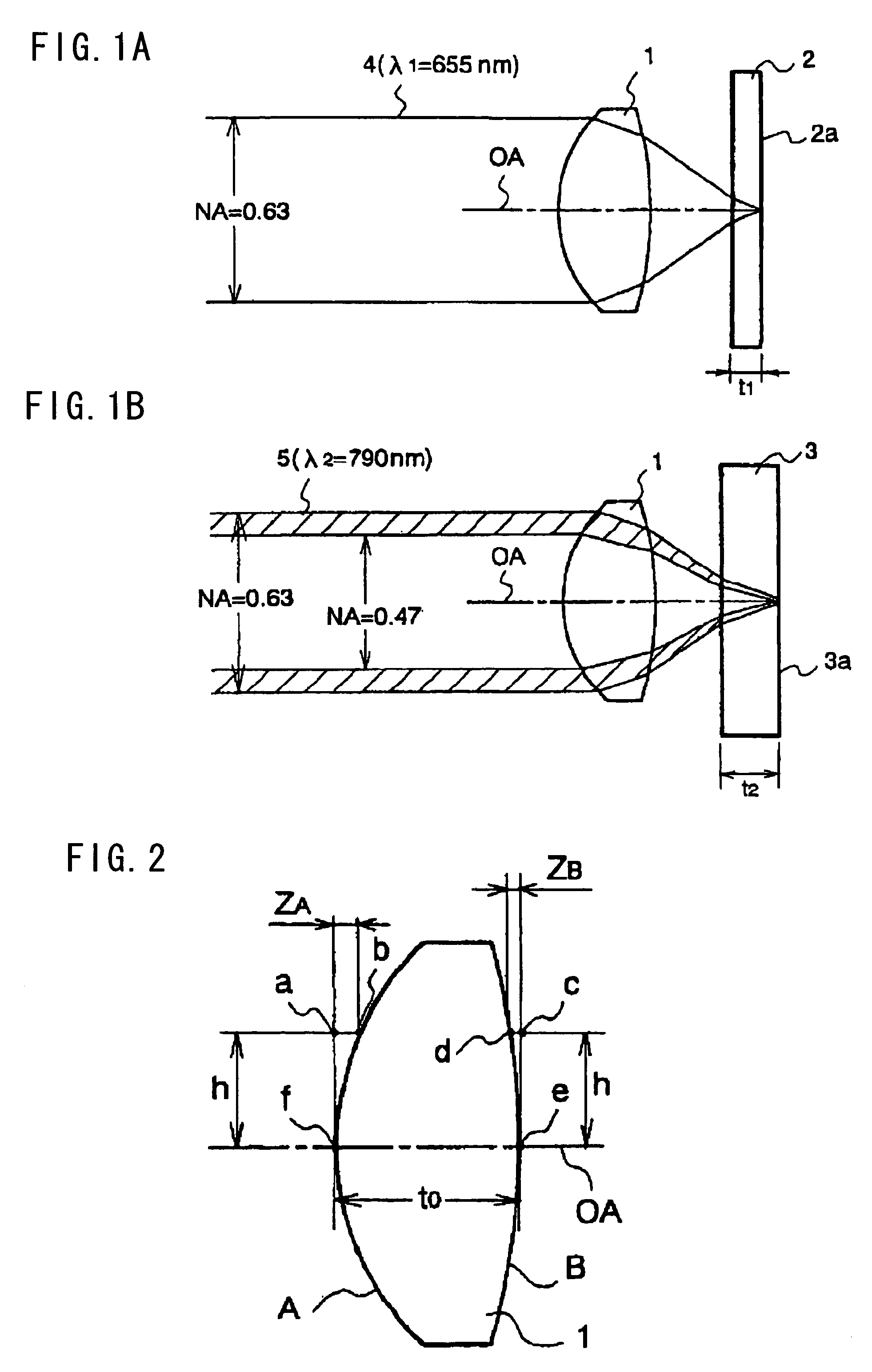

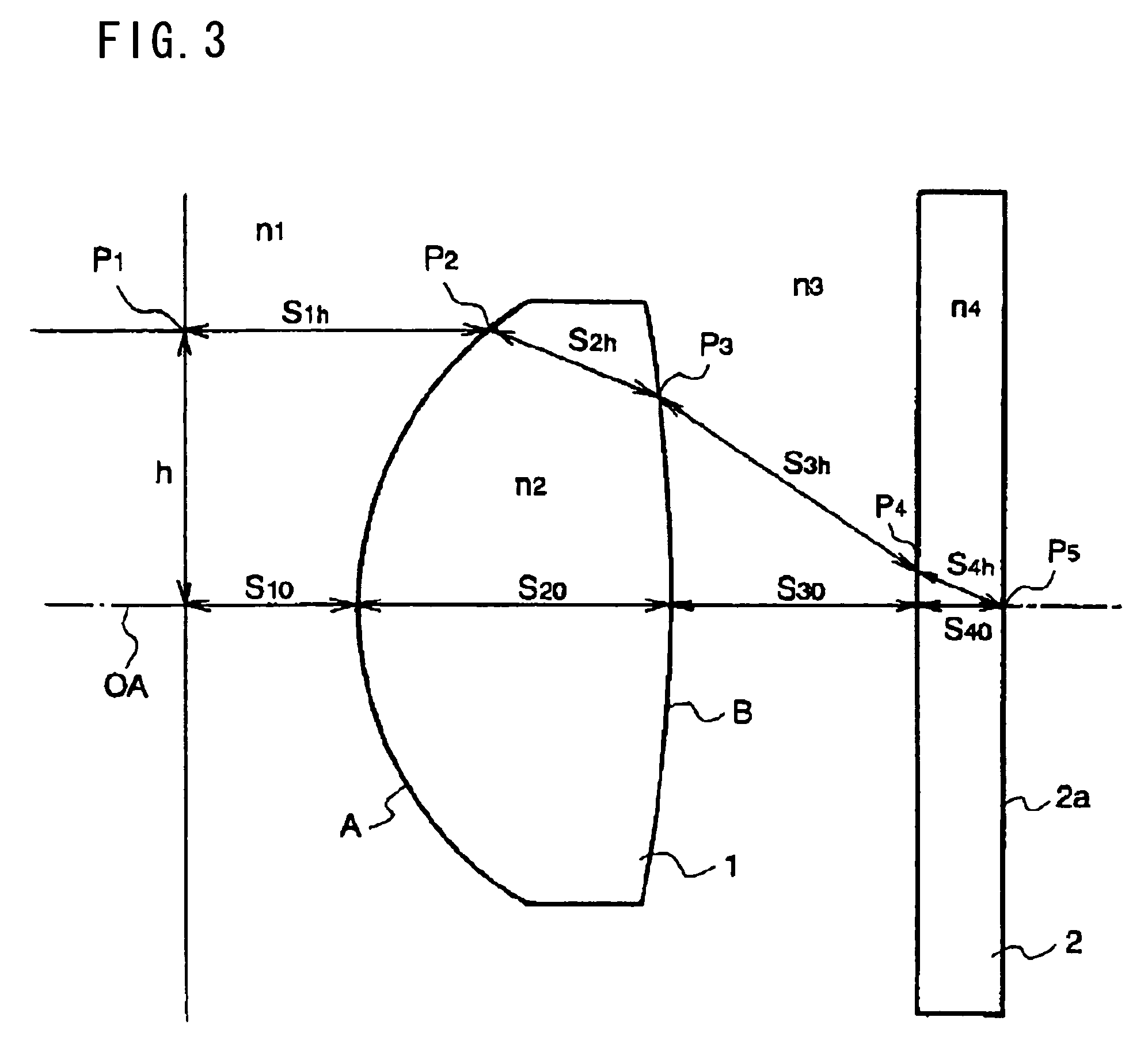

Multi-wavelength lens, and optical system, optical head and optical disc apparatus using the lens

InactiveUS7411743B2Improve light utilization efficiencyLow wavefront aberrationOptical beam sourcesRecord information storageOptical axisMonochromatic color

The multi-wavelength lens for condensing a plurality of kinds of monochromatic light by refraction is disclosed. The lens comprises a common use area for all monochromatic light on at least one lens surface, the area sectioned into a plurality of aspherical zones each of which having a different refractive power; and step portions, each of which formed between adjacent aspherical zones of the plurality of aspherical zones and having a step height Dj (j=1,2,3,4, and so on, in order of closeness to a lens optical axis) in a direction parallel to the lens optical axis. At least half of the step portions satisfy a following formula when a minimum value and a maximum value of Aij for each wavelength λi are MIN(Aij) and MAX(Aij), respectively:MAX(Aij) / MIN(Aij)<3where, Aij=absolute(Bij−mij),Bij=(absolute(Dj))*(ni−1) / λi−C, ni is a refractive index of a lens for a wavelength λi, mij is an integral number closest to Bij, and C is a corrective term.

Owner:MAXELL HLDG LTD

Touchscreen

ActiveUS20140152916A1Small cross-capacitanceChange in cross-capacitanceNon-linear opticsInput/output processes for data processingEngineeringStep height

A touchscreen of the present invention is covered by wiring patterns of a row-directional line and a column-directional line being upper and lower two layers. A step height that is produced by an upper electrode riding on a lower electrode when a floating electrode is provided at a region adjacent to the row-directional line and the column-directional line is suppressed.

Owner:MITSUBISHI ELECTRIC CORP

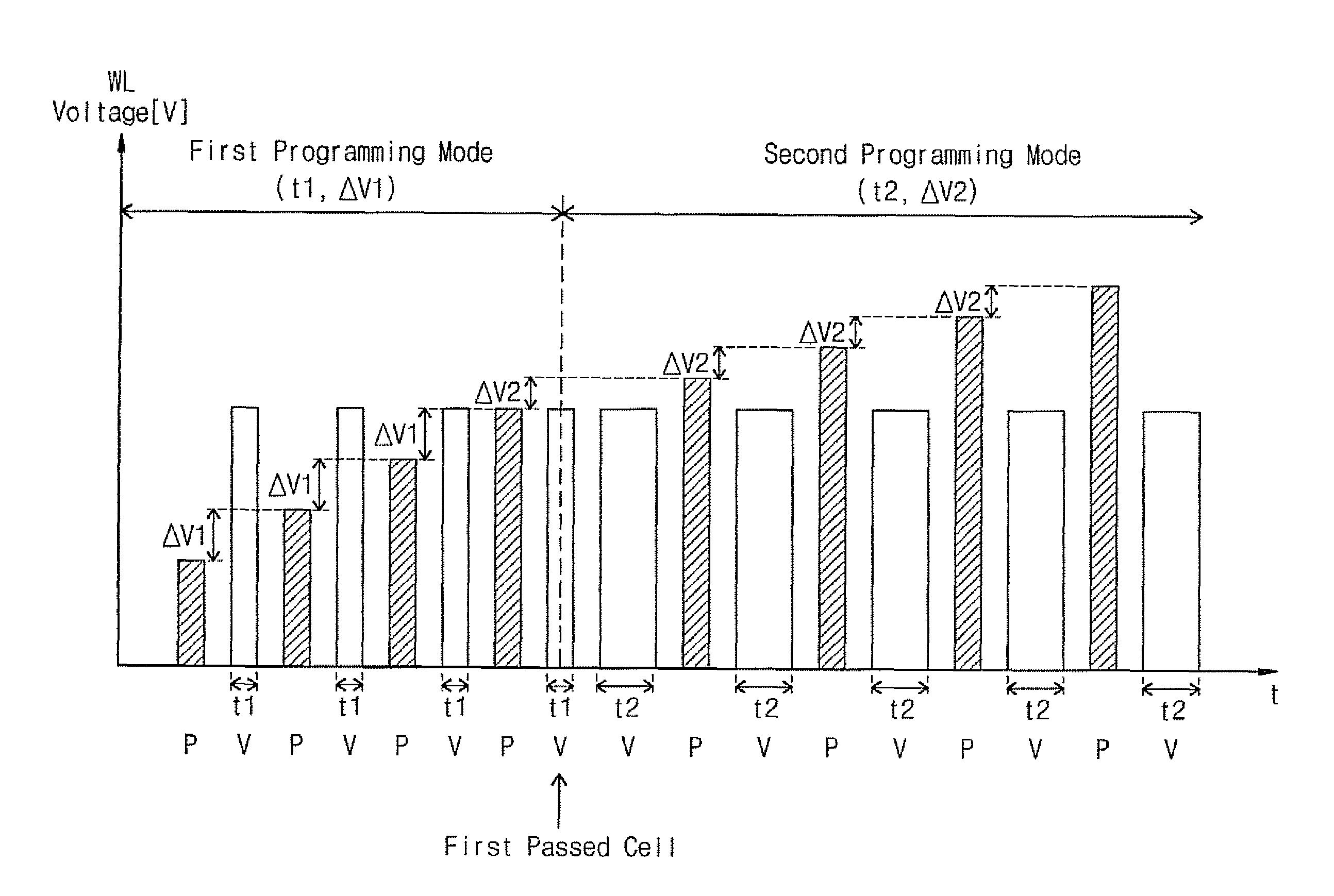

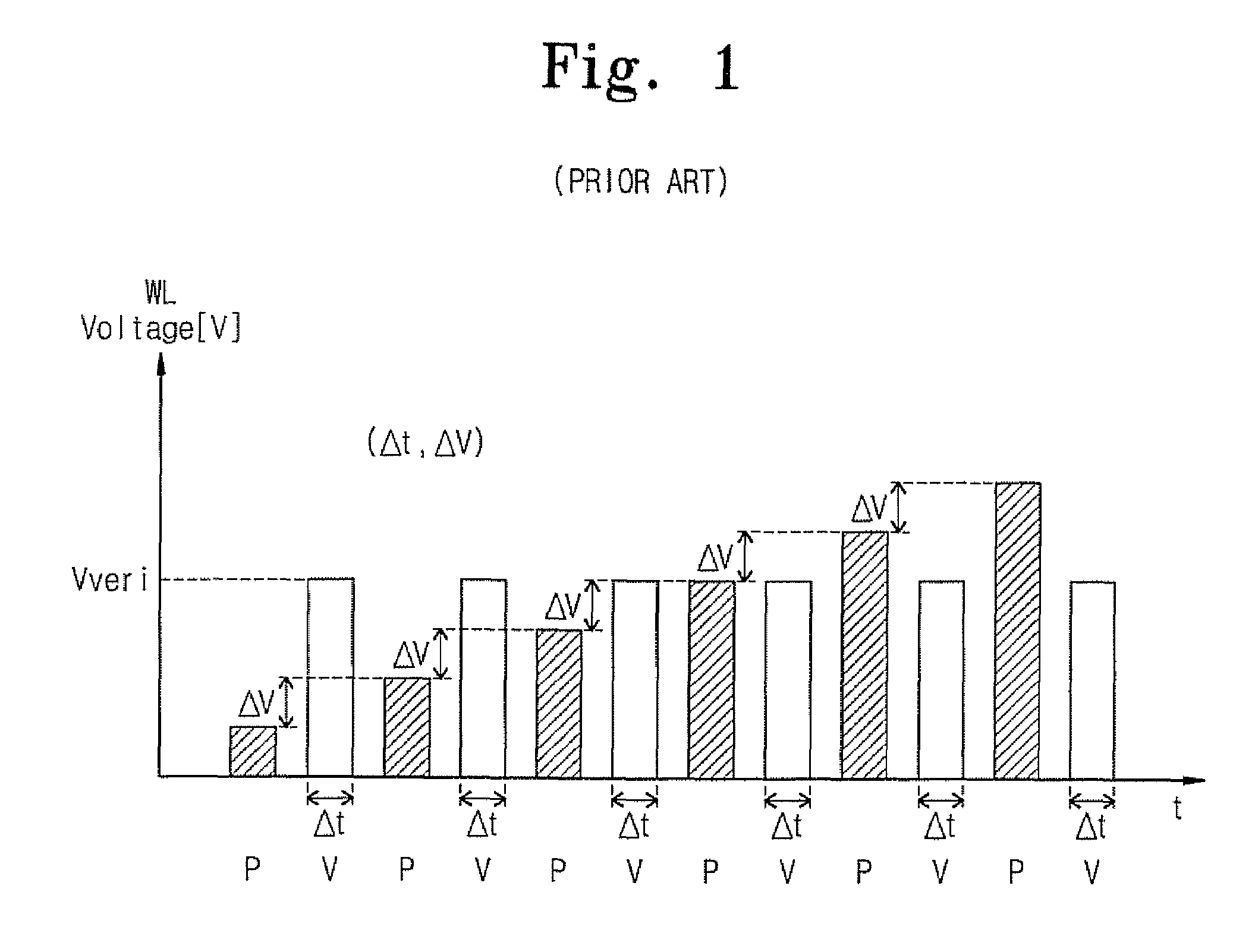

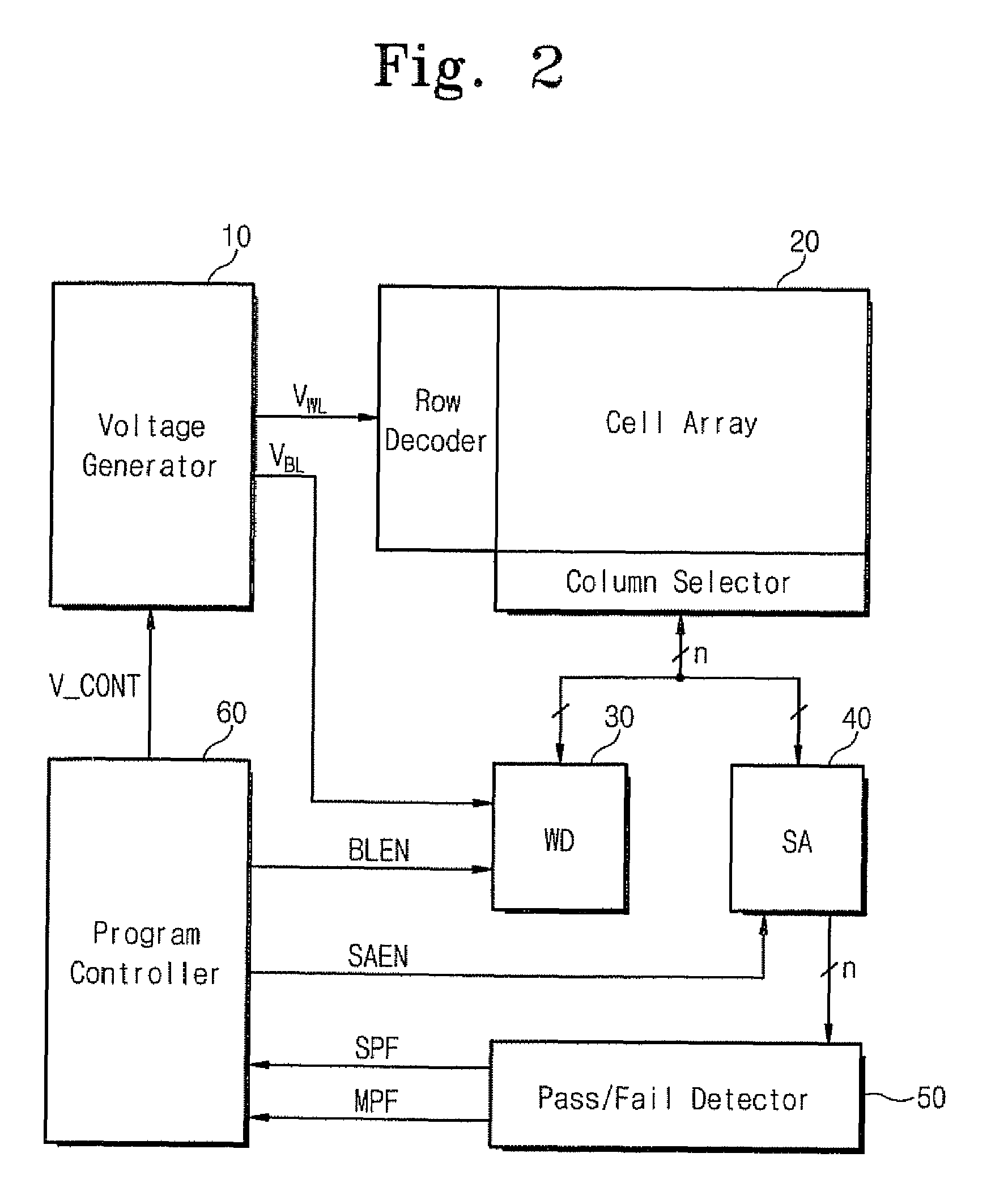

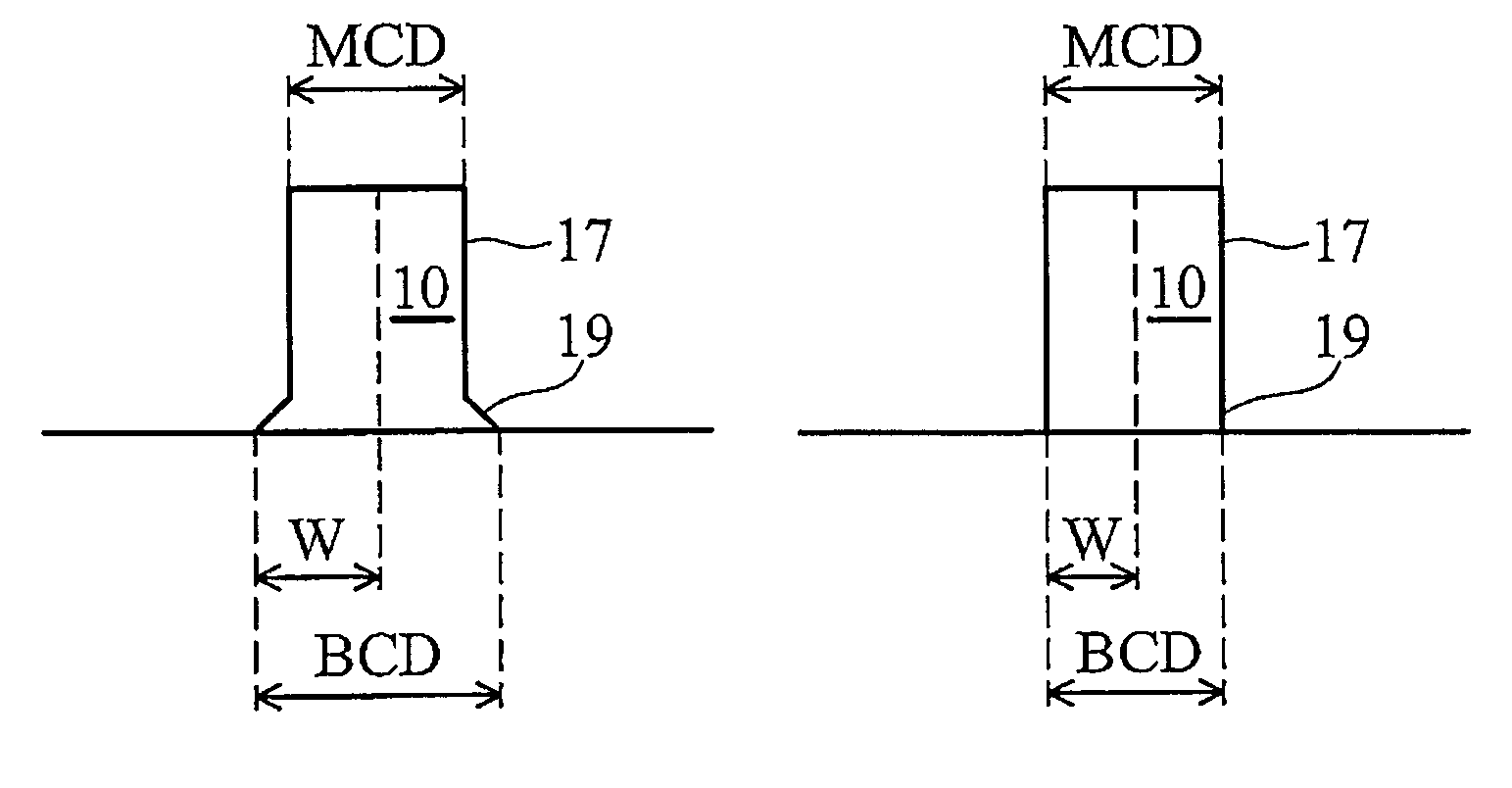

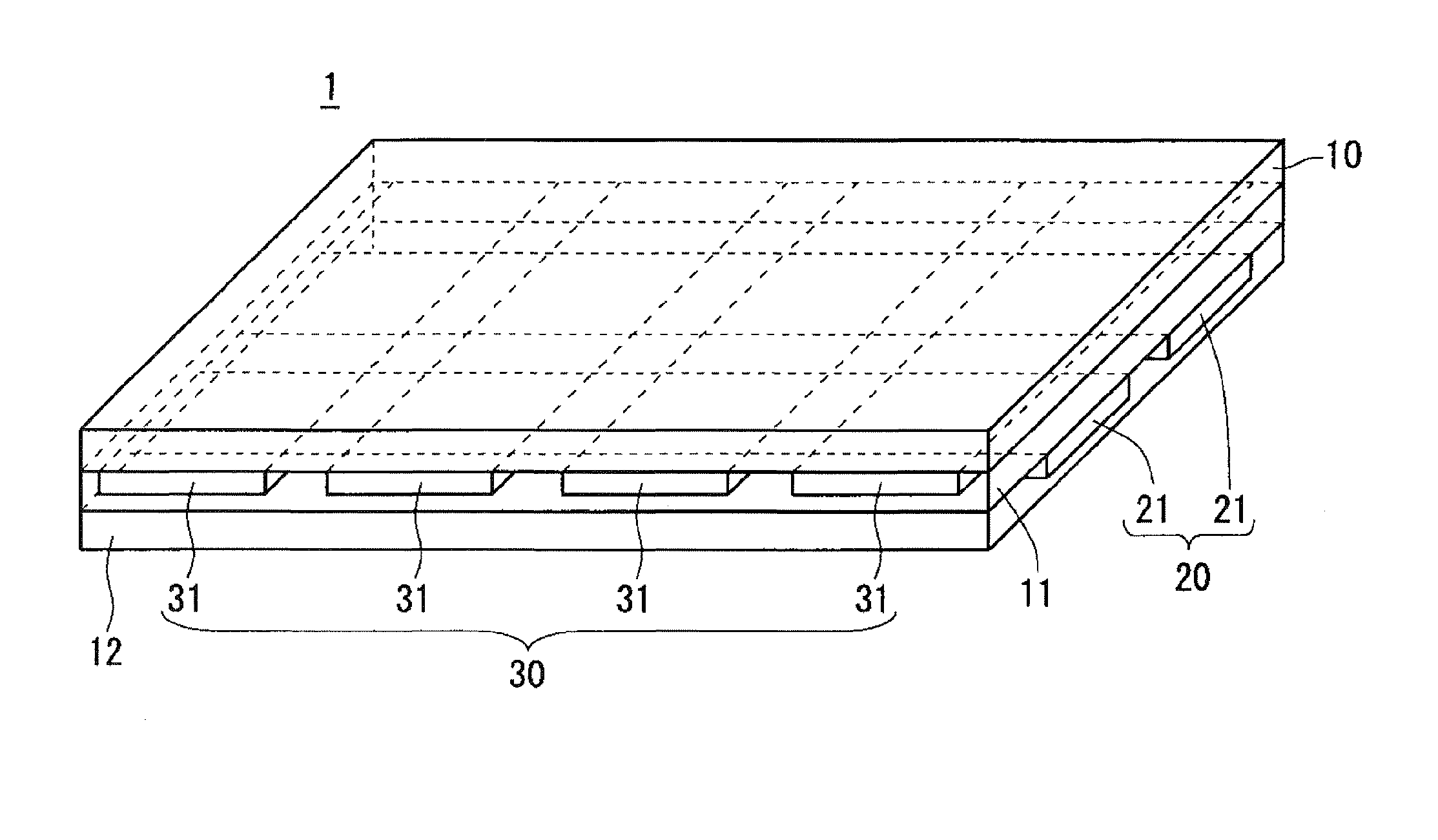

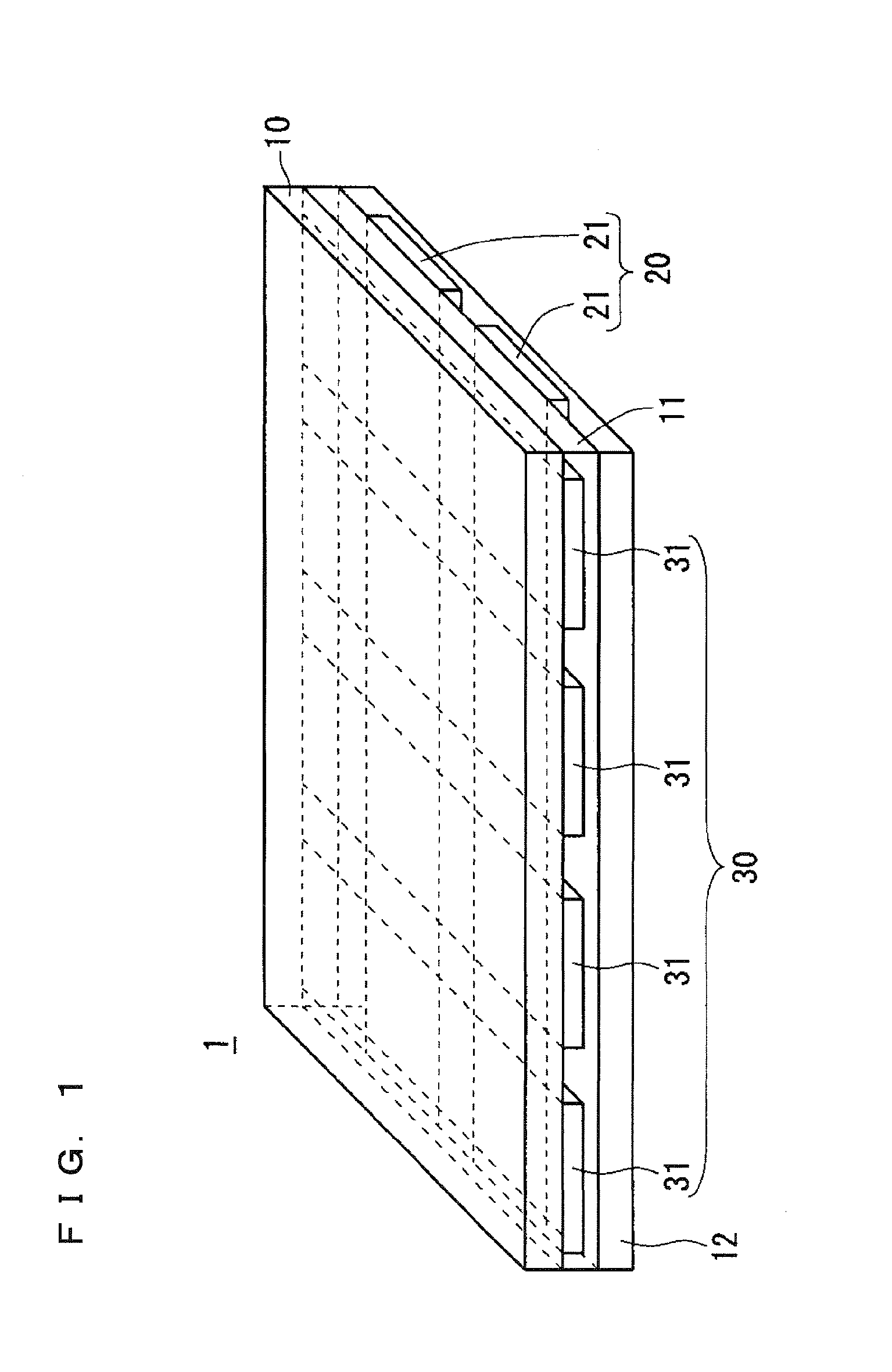

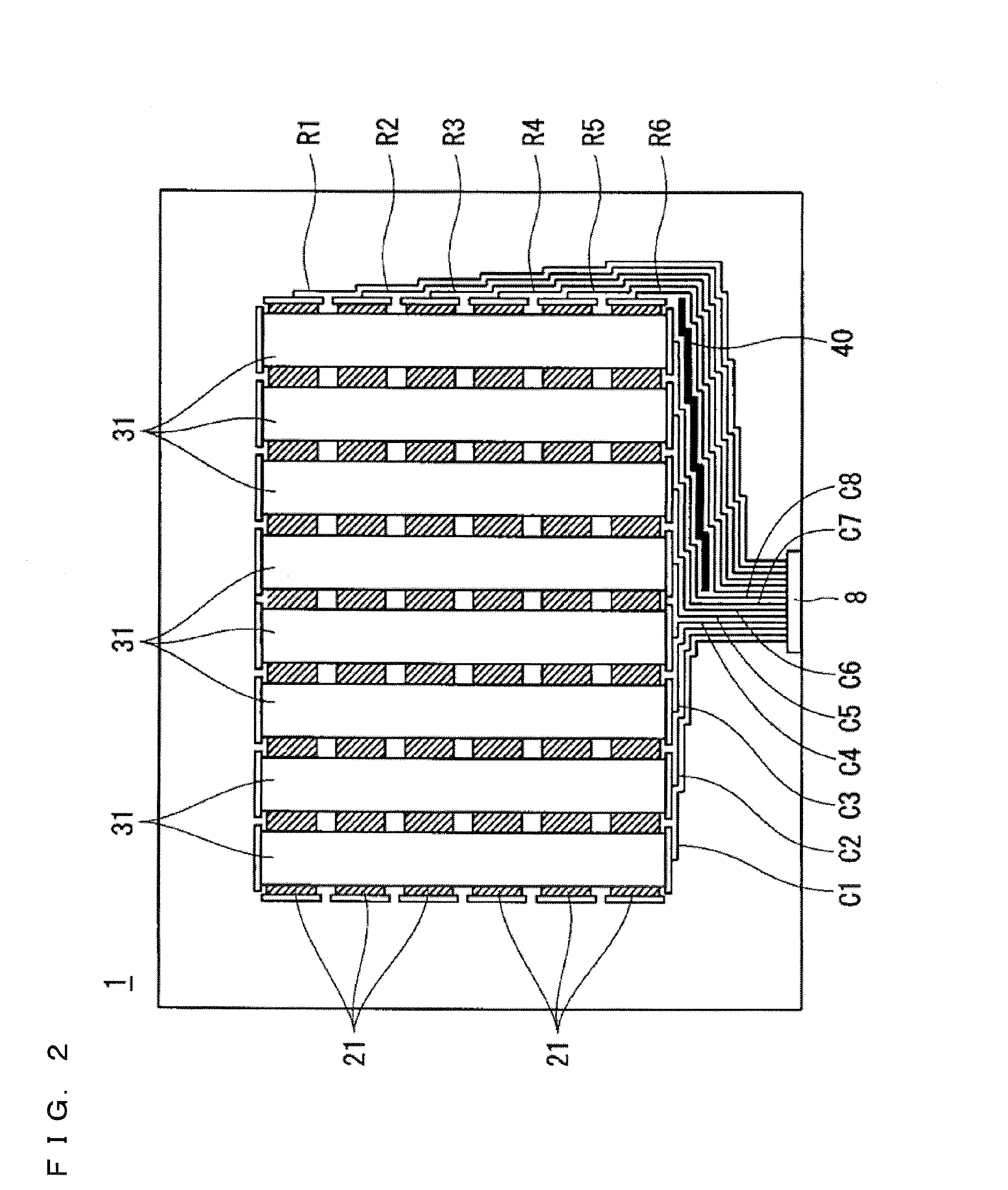

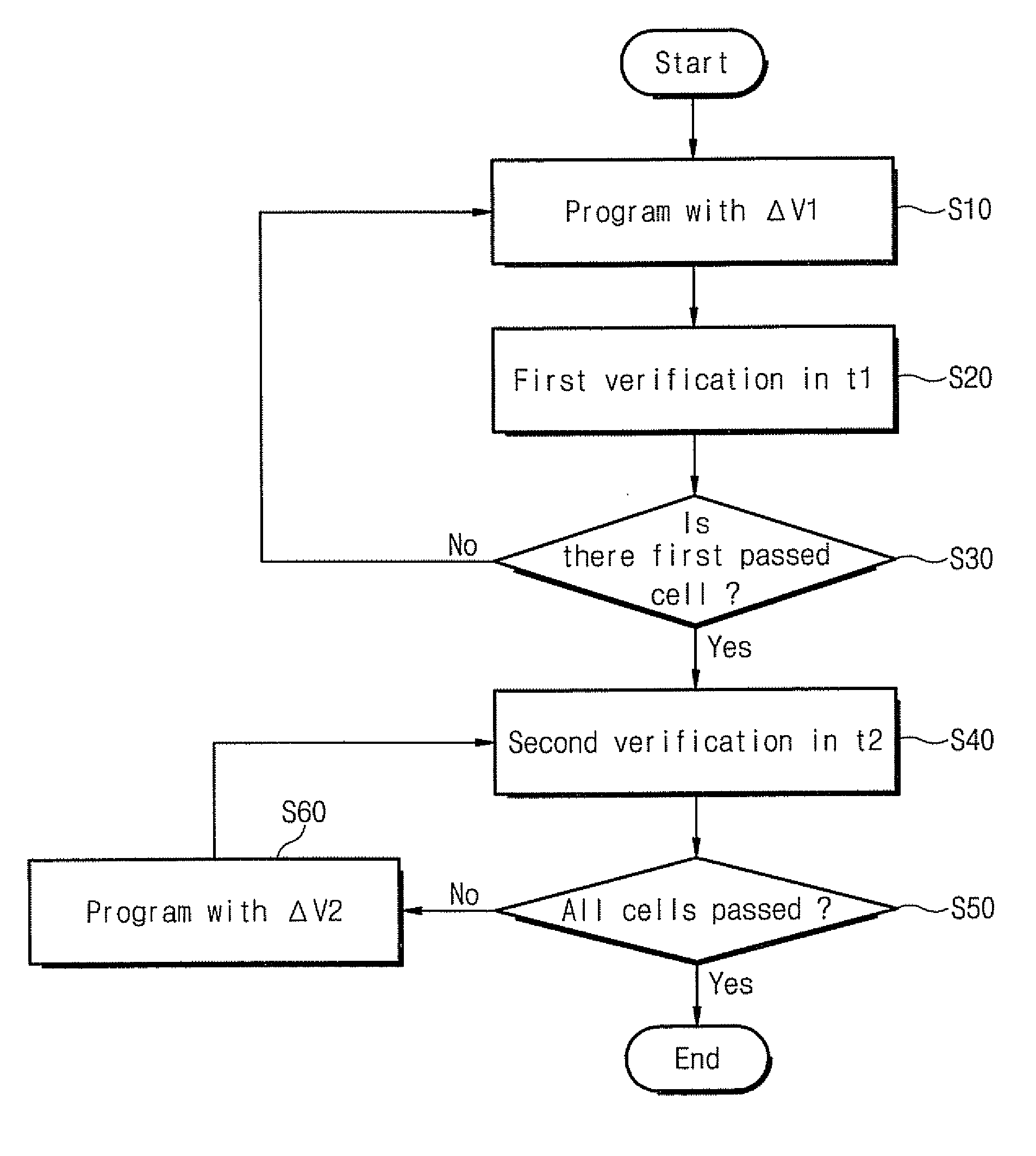

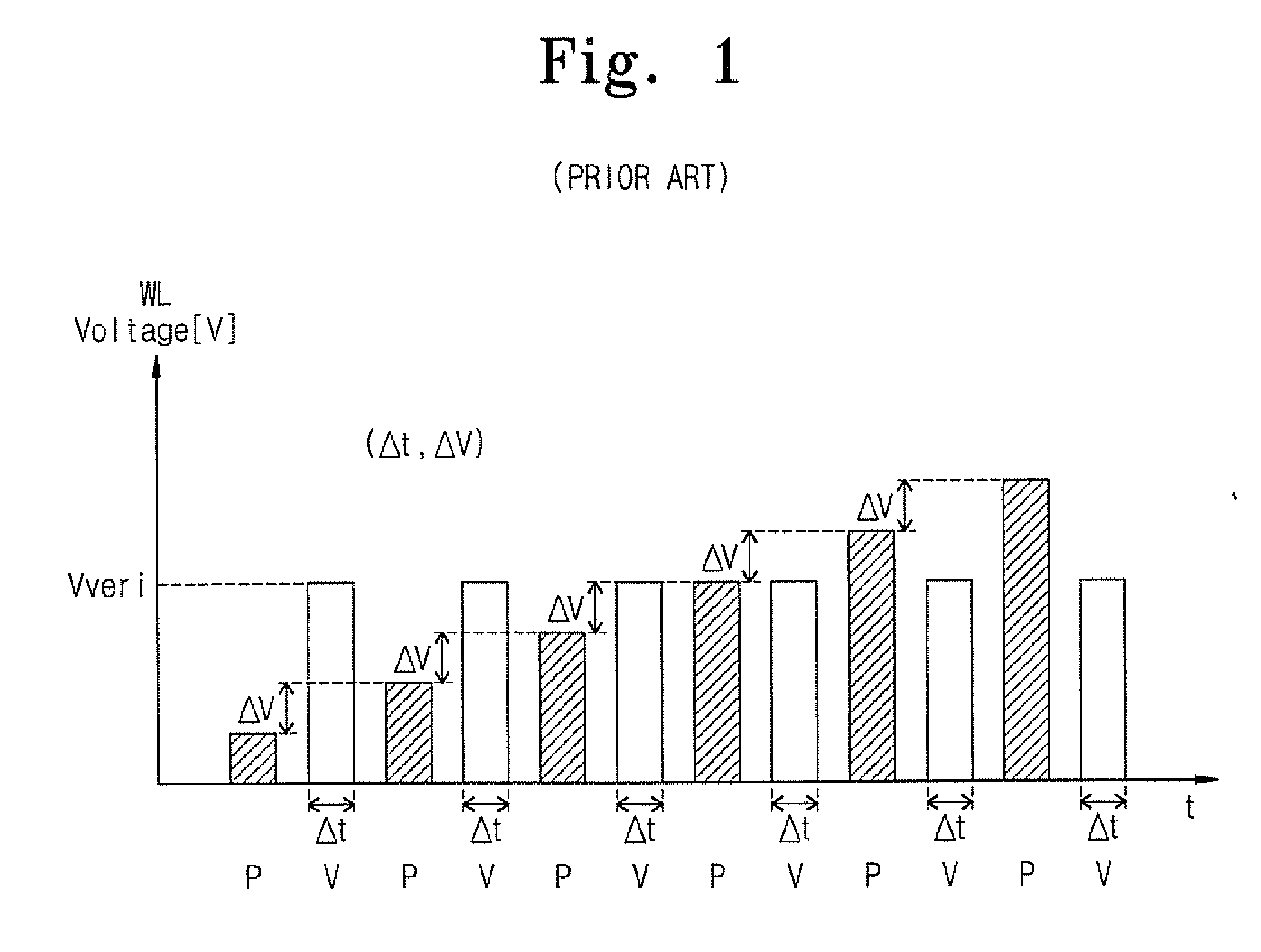

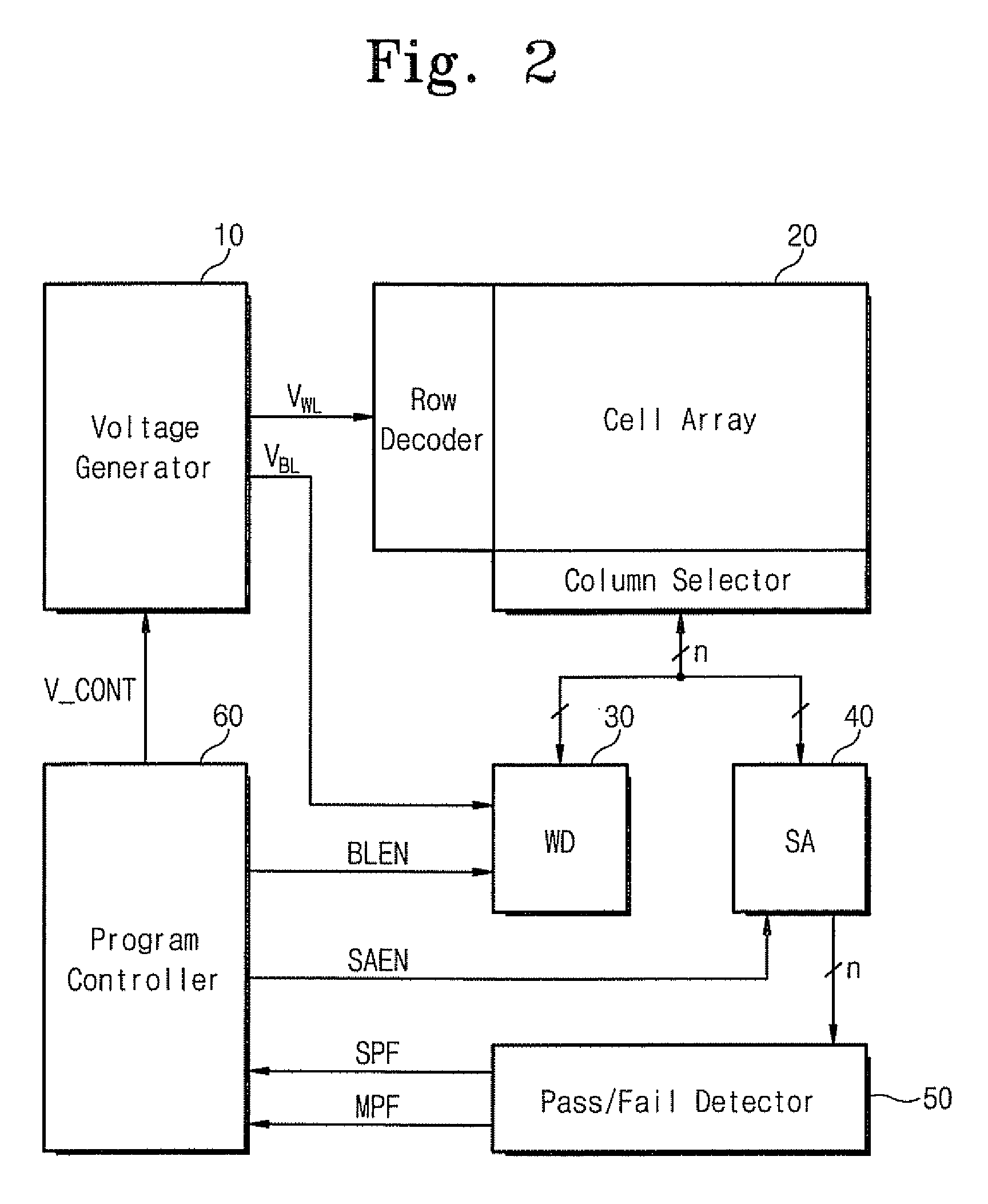

Circuit and Method for Adaptive Incremental Step-Pulse Programming in a Flash Memory Device

Nonvolatile memory devices support programming and verify operations that improve threshold-voltage distribution within programmed memory cells. This improvement is achieved by reducing a magnitude of the programming voltage steps and increasing a duration of the verify operations once at least one of the plurality of memory cells undergoing programming has been verified as a “passed” memory cell. The nonvolatile memory device includes an array of nonvolatile memory cells and a control circuit, which is electrically coupled to the array of nonvolatile memory cells. The control circuit is configured to perform a plurality of memory programming operations (P) by driving a selected word line in the array with a first stair step sequence of program voltages having first step height (e.g., ΔV1) and then, in response to verifying that at least one of the memory cells coupled to the selected word line is a passed memory cell, driving the selected word line with a second stair step sequence of program voltages having a second step height (e.g., ΔV2) lower than the first step height.

Owner:SAMSUNG ELECTRONICS CO LTD

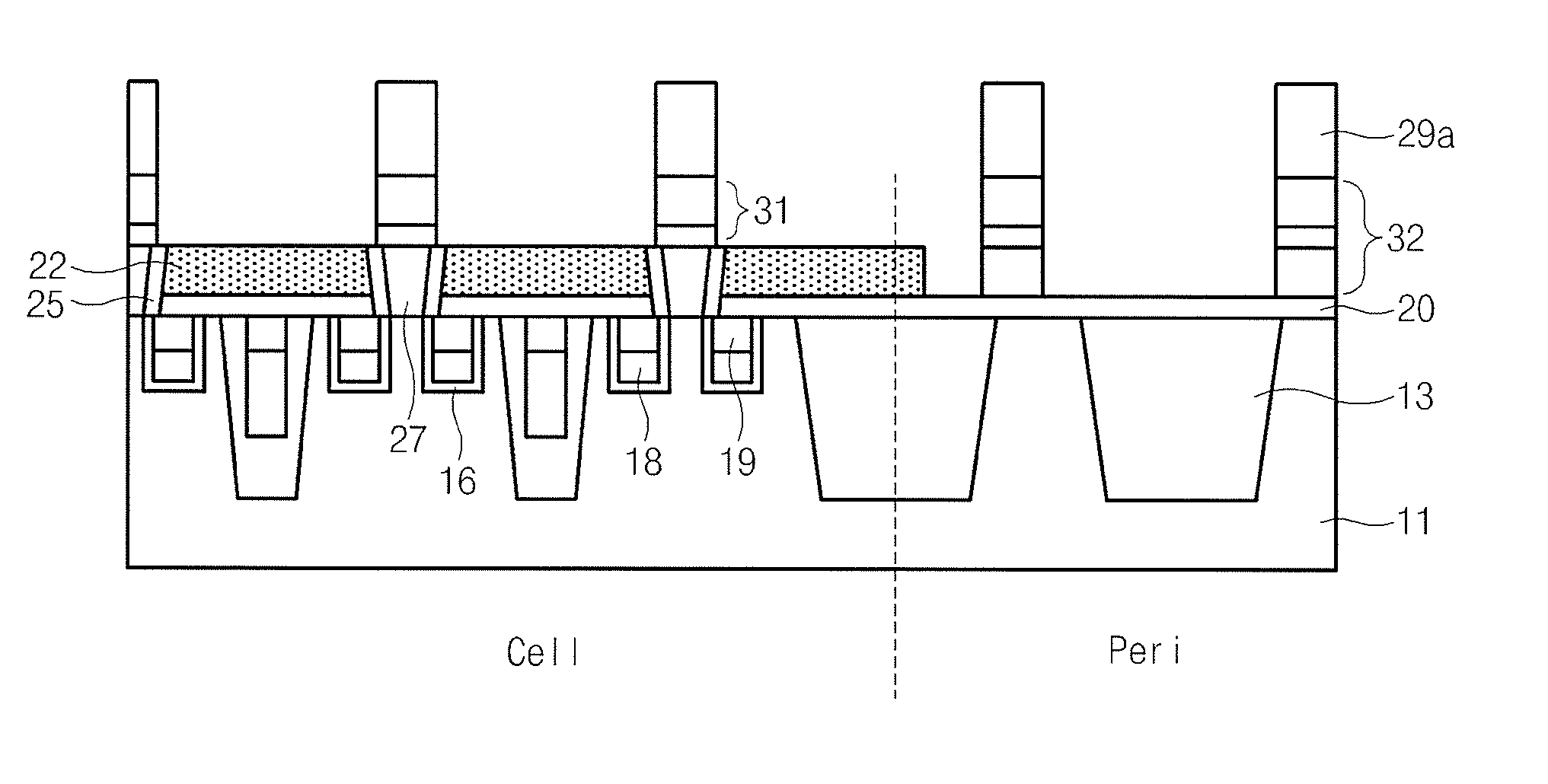

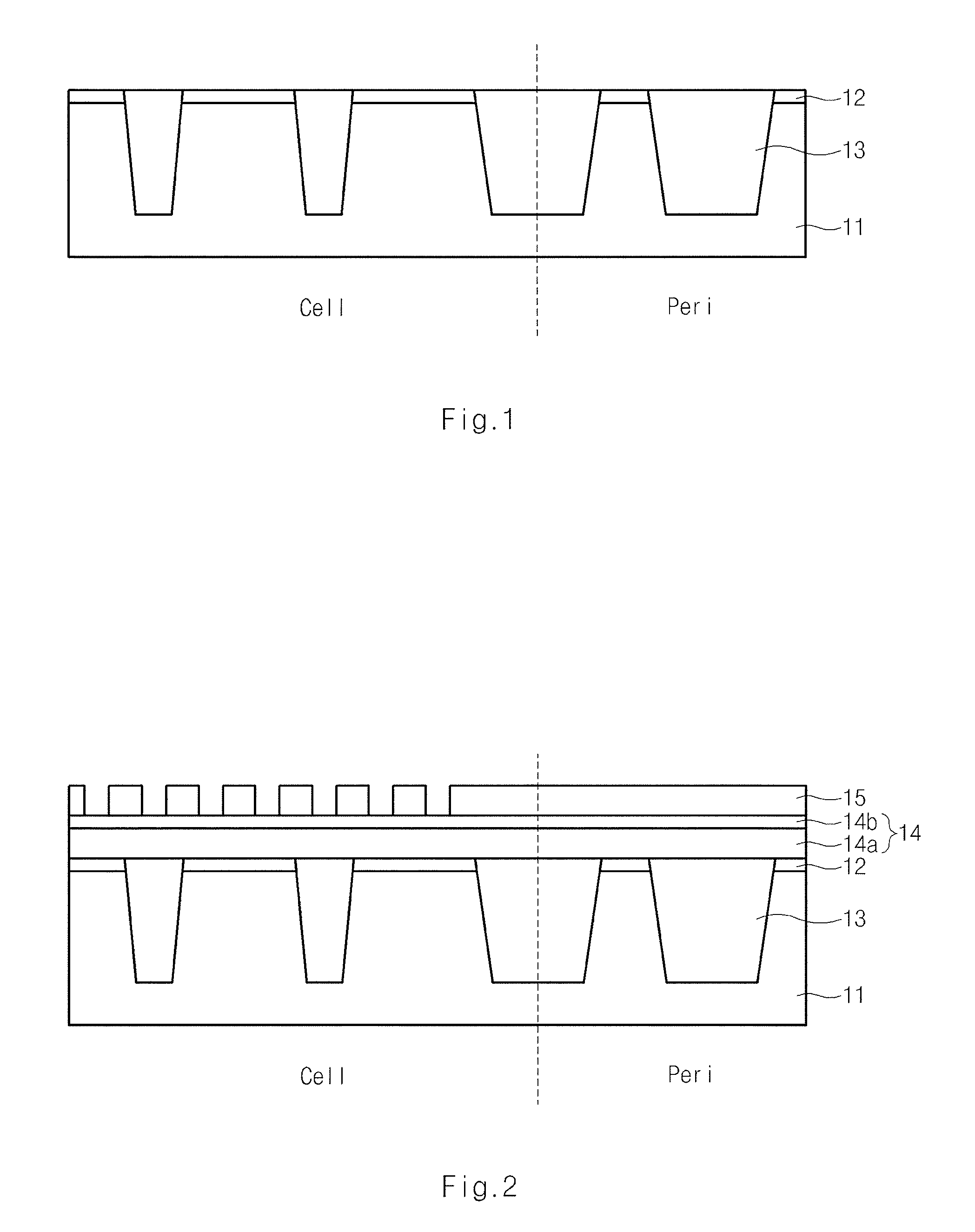

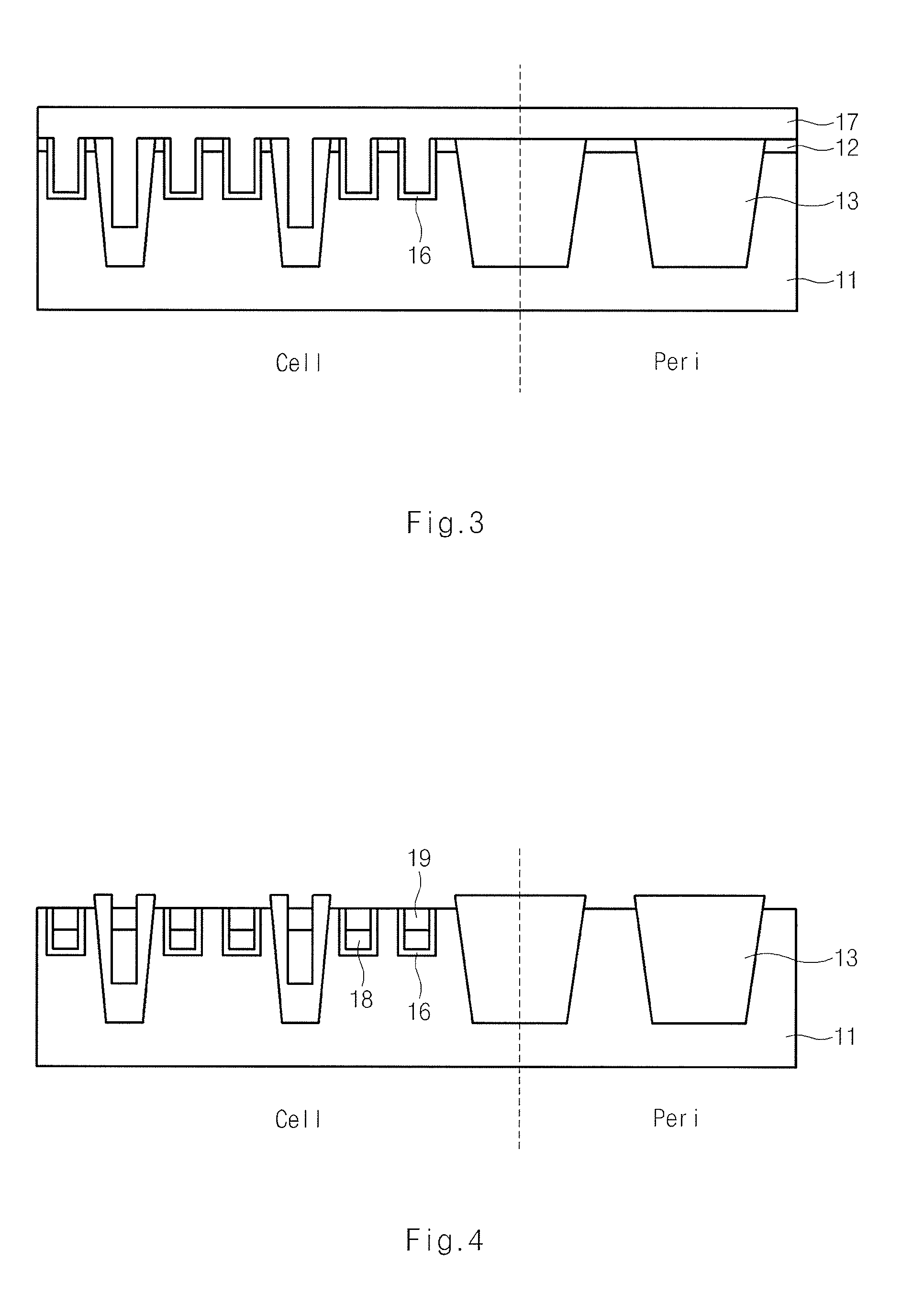

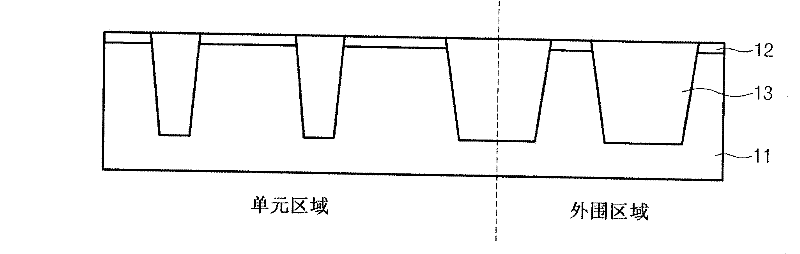

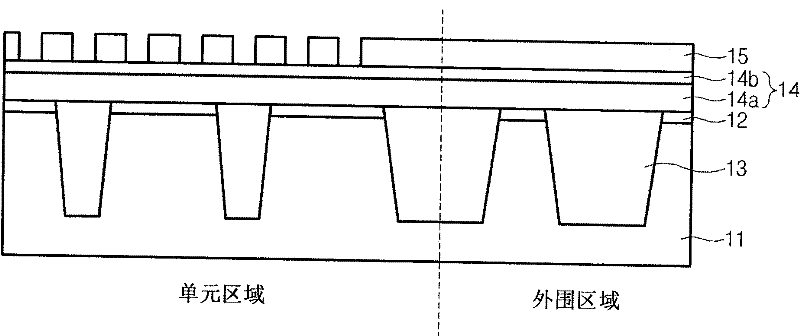

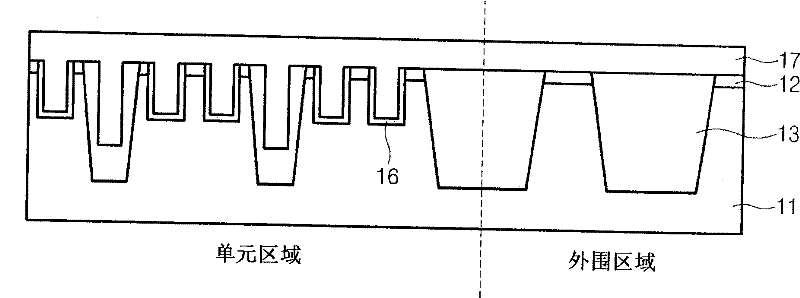

Method for manufacturing semiconductor device having buried gate

ActiveUS7915121B1Reduce in quantityAvoid problemsSolid-state devicesSemiconductor/solid-state device manufacturingBit lineCell region

A method for manufacturing a semiconductor device having a buried gate is provided. A gate conductive layer is first formed in the peri region before a bit line contact is formed in the cell region, so that a fabrication process is simplified and the problem caused by a step height between the cell region and the core / peri region is not encountered.

Owner:SK HYNIX INC

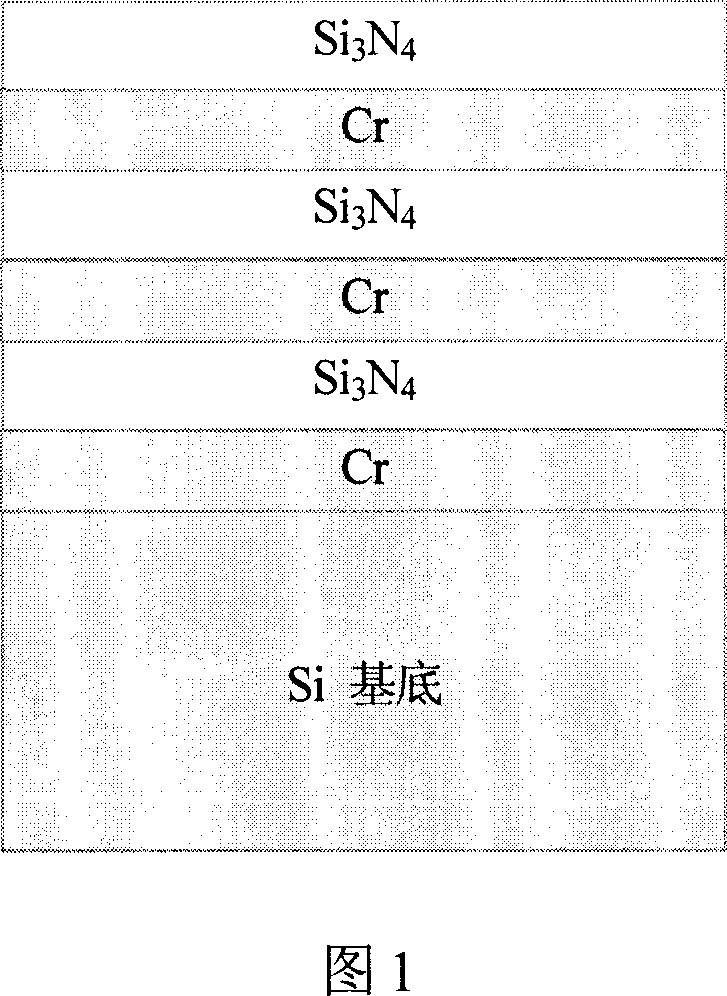

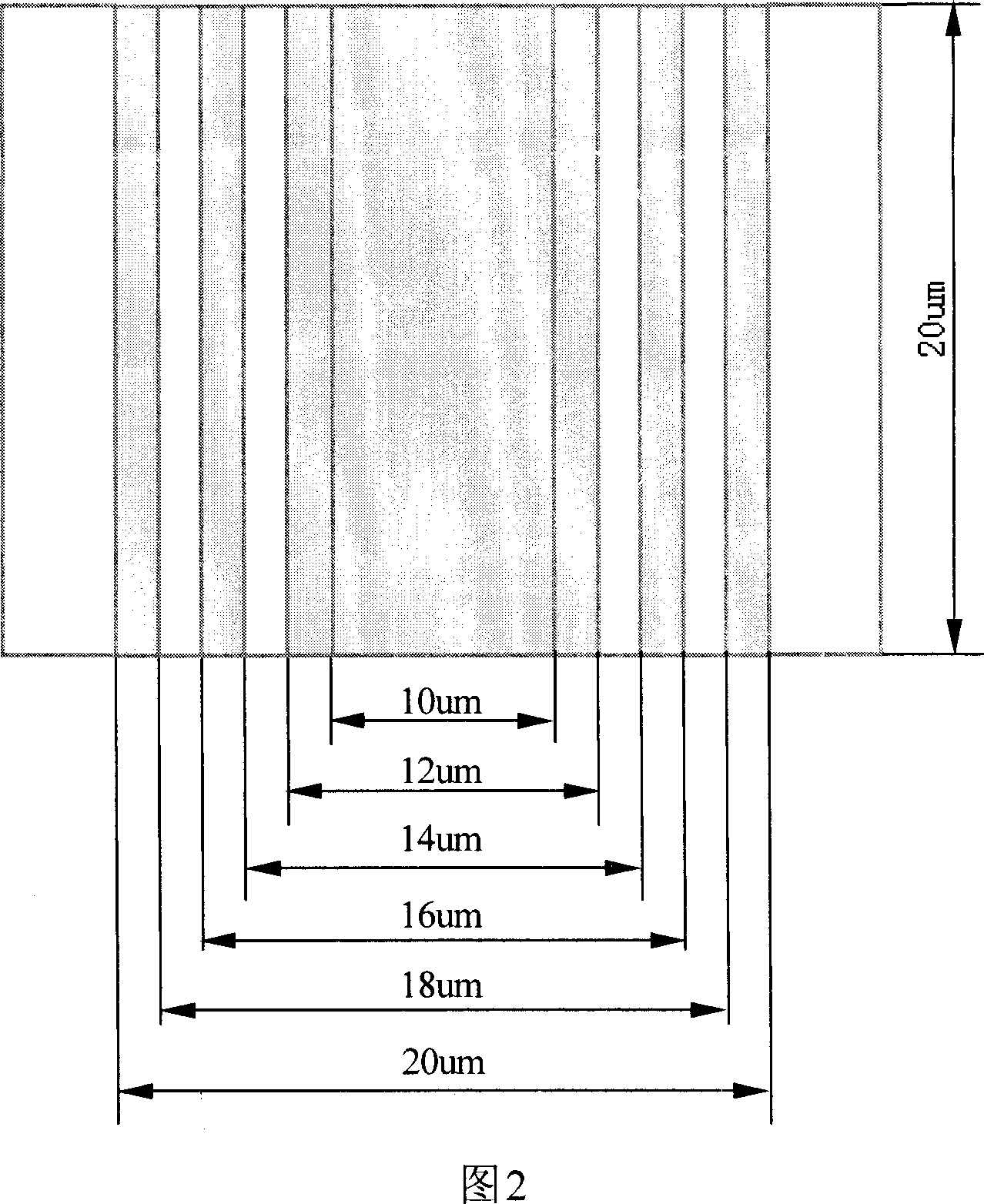

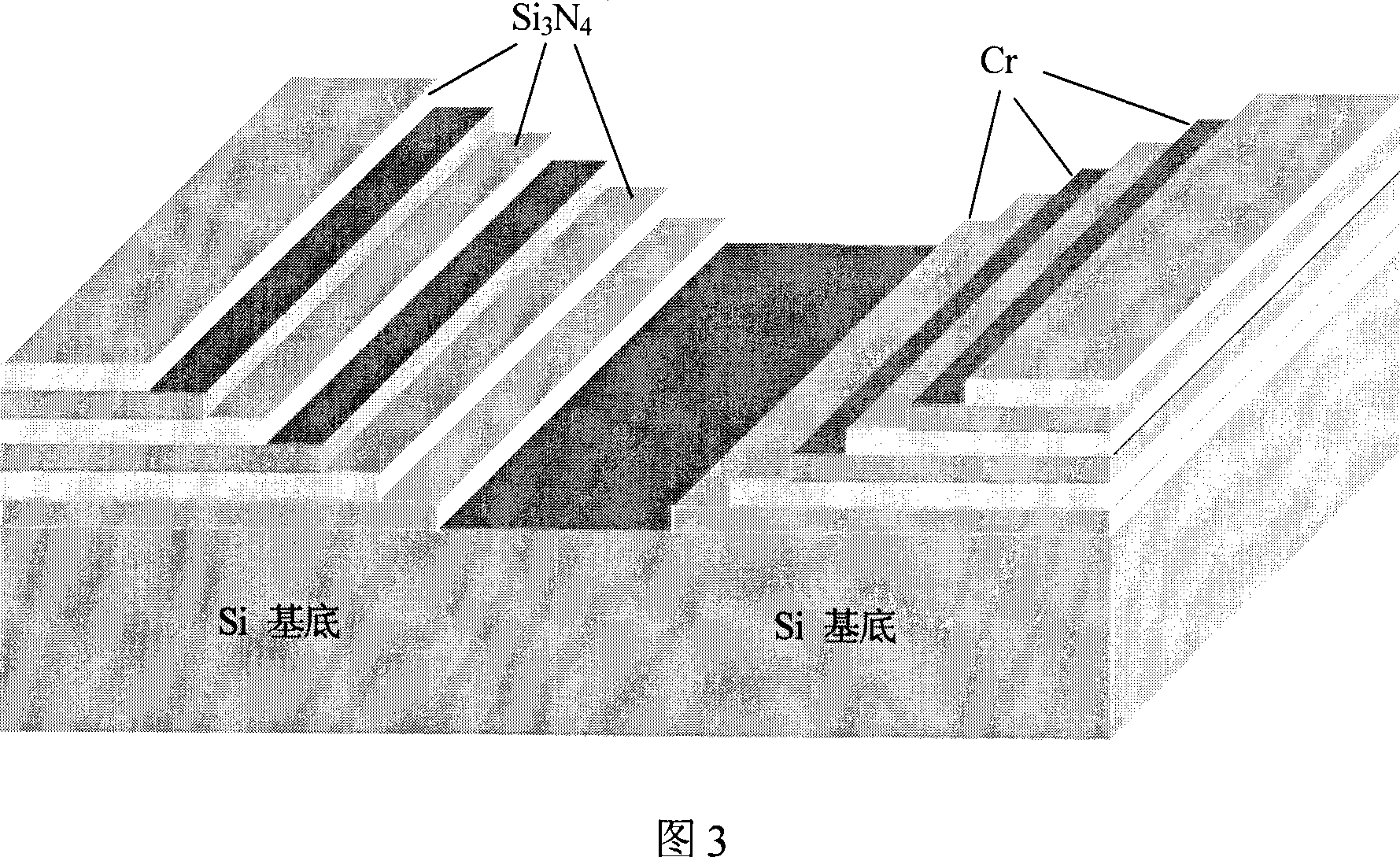

Nano multi-step height sample plate and its preparation

InactiveCN1920476AReduce manufacturing difficultyLow costSurface/boundary effectScanning probe techniquesHardnessElectron microscope

The invention relates to a nanometer multi-step height sample template and relative production / , wherein it transforms the thickness of film into the step height of said template, and controls its thickness to control the height of step, etches the step shape via dry and wet etching techniques to obtain the nanometer multi-step height sample template. Since the film preparation can realize Si3N4 film and Cr film at 10nm level, and the dry and wet etching techniques can etch multi-step shape, the invention can reduce the hardness of production, with low cost. The inventive product can be used to test and collect of scanning electric microscope, etc.

Owner:XI AN JIAOTONG UNIV

Method for manufacturing semiconductor device having buried gate

ActiveCN102097375AAvoid problems caused by high stepsReduce in quantitySolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceCell region

A method for manufacturing a semiconductor device having a buried gate is provided. A gate conductive layer is first formed in the peri region before a bit line contact is formed in the cell region, so that a fabrication process is simplified and the problem caused by a step height between the cell region and the core / peri region is not encountered.

Owner:SK HYNIX INC

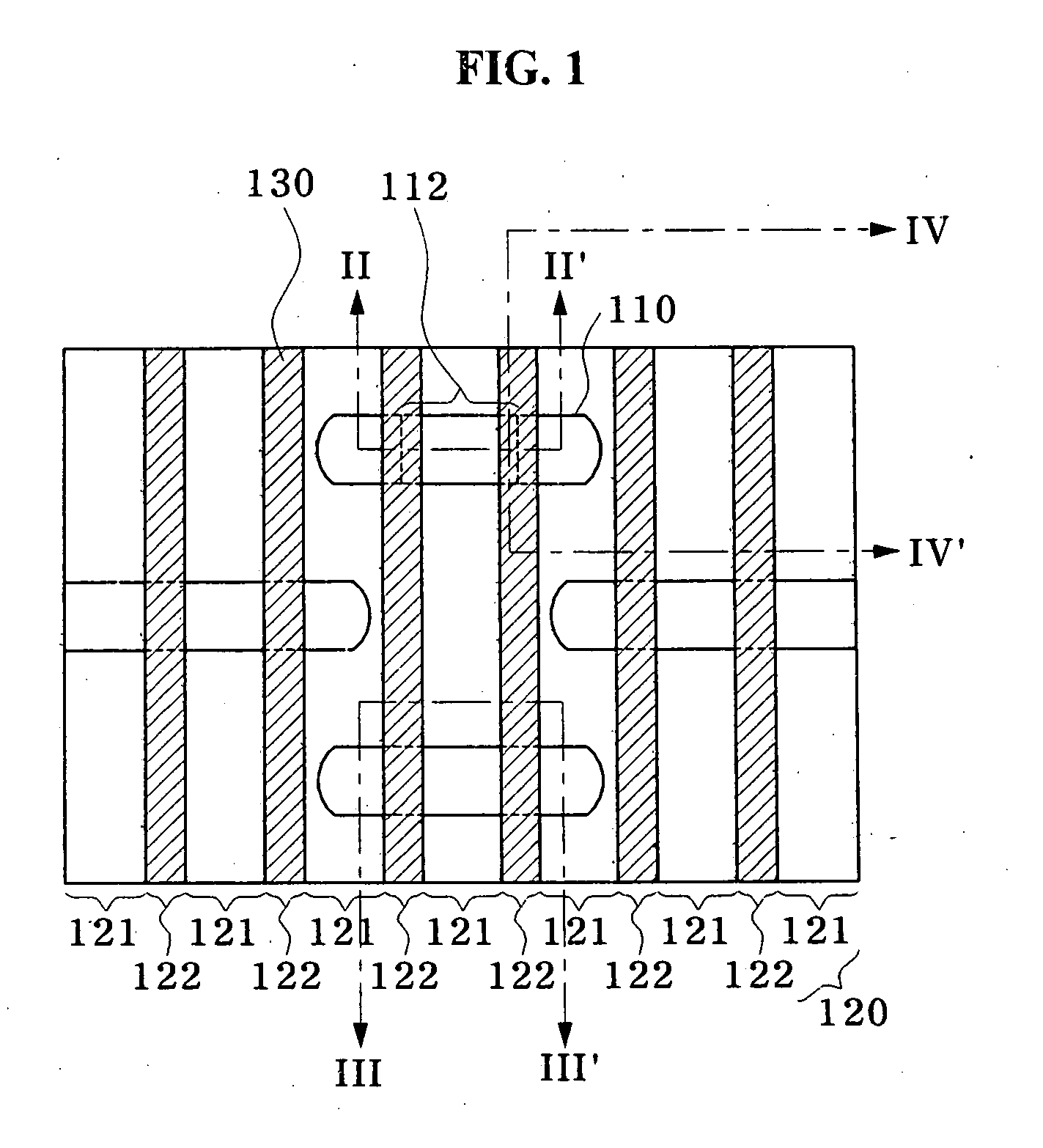

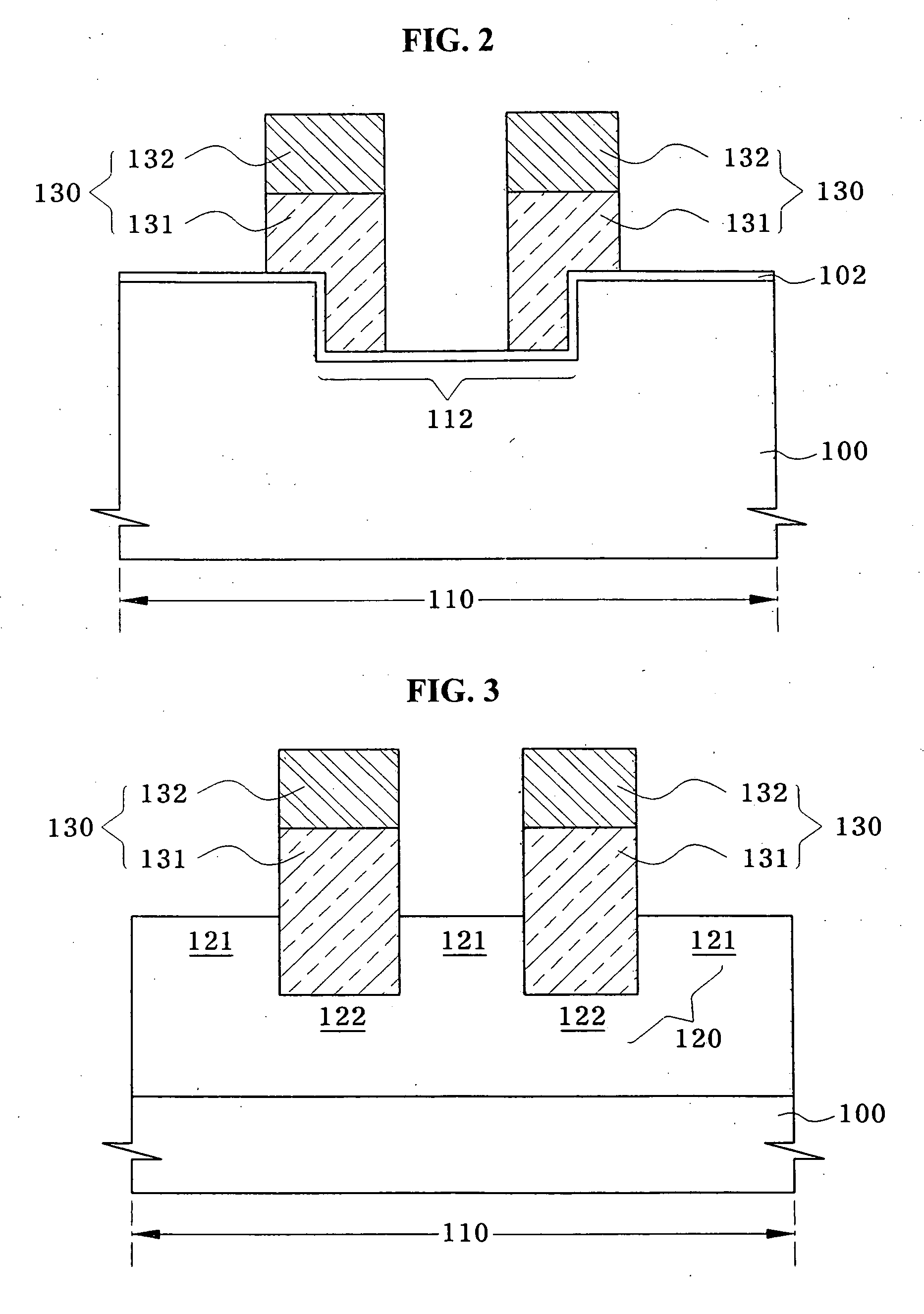

Transistor of semiconductor memory device and method for manufacturing the same

ActiveUS20070057312A1Improve operating characteristicsSufficient data retention timeTransistorSolid-state devicesInsulation layerIsolation layer

A transistor of a semiconductor memory device including a semiconductor substrate having a plurality of active regions and a device isolation region, a plurality of first and second trench device isolation layers, which are arranged alternately with each other on the device isolation region of the semiconductor substrate, the first trench device isolation layers having a first thickness corresponding to a relatively high step height, and the second trench device isolation layers having a second thickness corresponding to a relatively low step height, a recess region formed in each of the active regions by a predetermined depth to have a stepped profile at a boundary portion thereof, the recess region having a height higher than that of the second trench device isolation layers to have an upwardly protruded portion between adjacent two second trench device isolation layers, a gate insulation layer, and a plurality of gate stacks formed on the gate insulation layer to overlap with the stepped profile of the respective active regions and the protruded portion of the relevant recess region.

Owner:CONVERSANT INTPROP MANAGEMENT INC

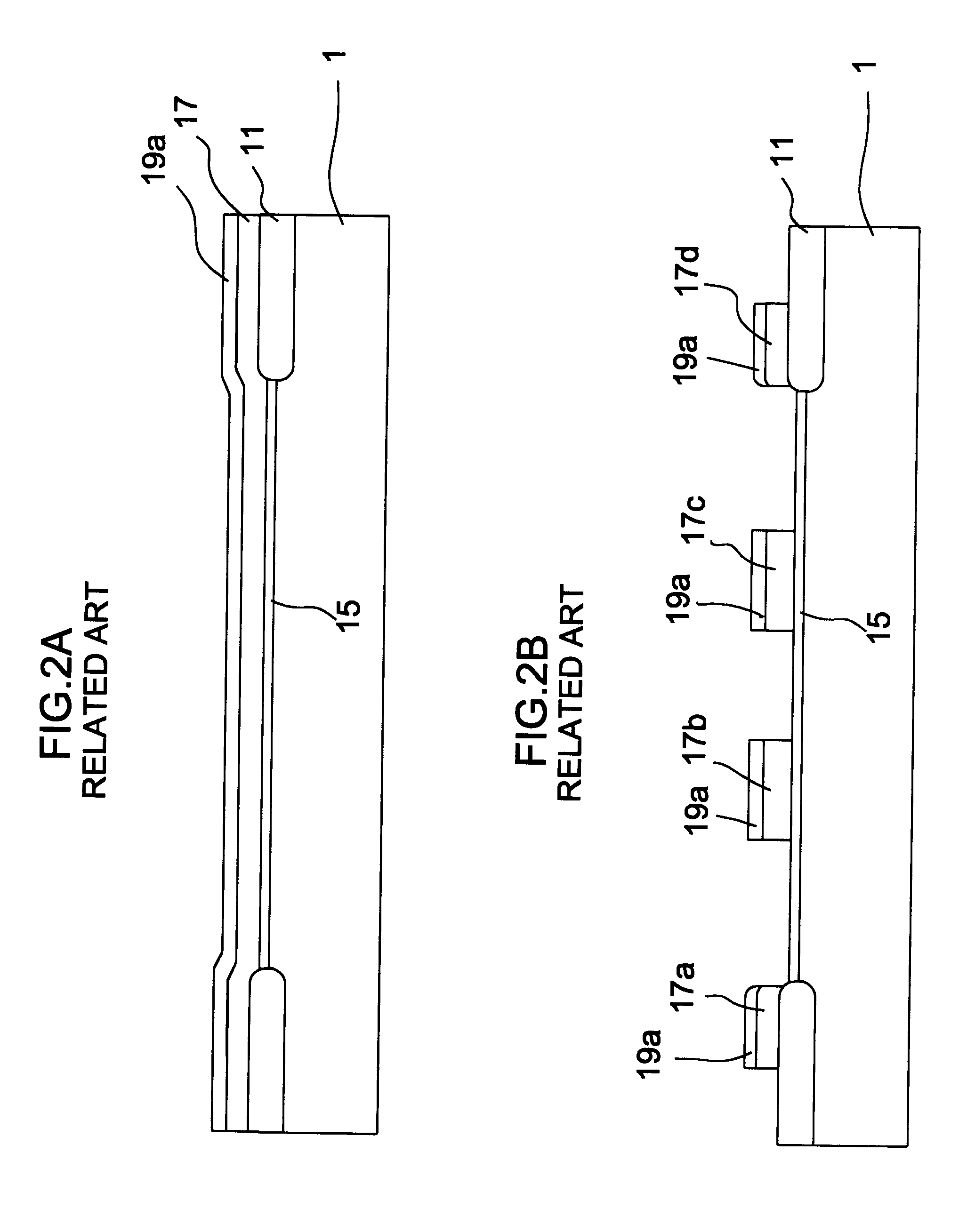

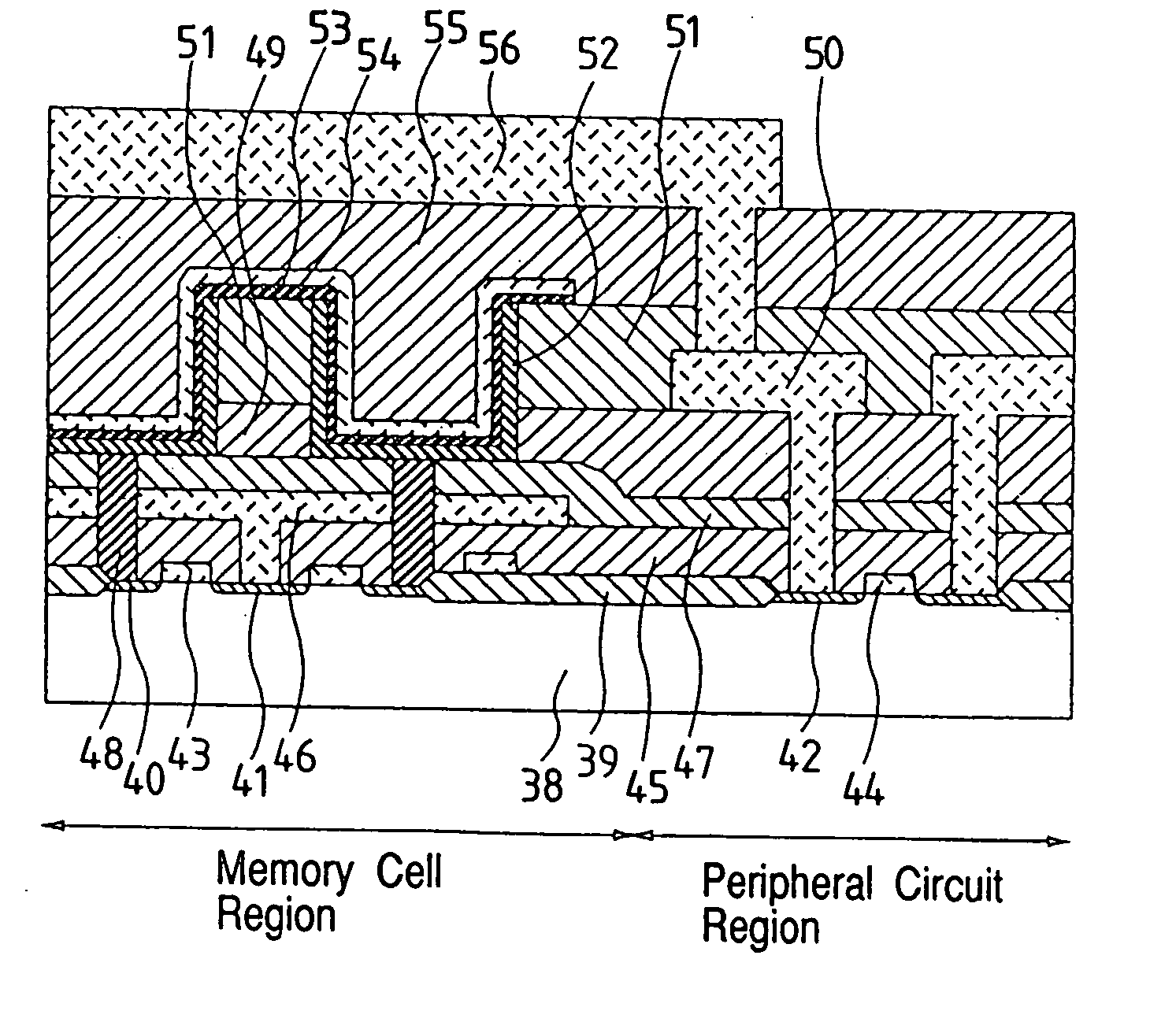

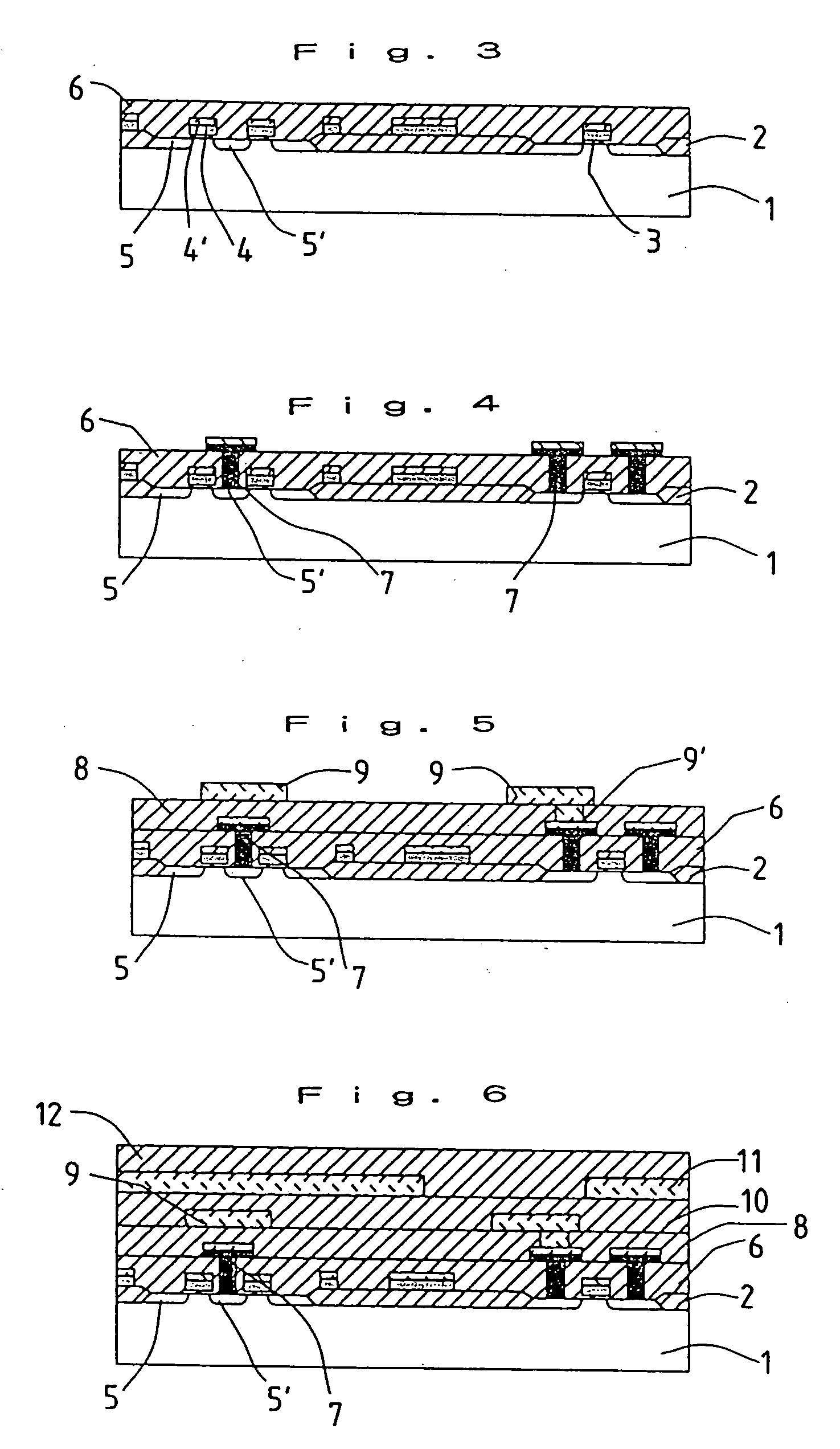

Semiconductor memory device and manufacturing method thereof

InactiveUS20050045933A1Large storage capacityWell formedTransistorSolid-state devicesEngineeringStep height

A capacitor consisting of a storage electrode (19), a capacitor dielectric film (20) and a plate electrode (21) is formed in a trench formed through dielectric films (6, 8, 10 and 12) stacked on a semiconductor substrate (1) and buried wiring layers (9 and 11) are formed under the capacitor. As the capacitor is formed not in the semiconductor substrate but over it, there is room in area in which the capacitor can be formed and the difficultly of forming wiring is reduced by using the wiring layers (9 and 11) for a global word line and a selector line. As the upper face of an dielectric film (32) which is in contact with the lower face of wiring (34) in a peripheral circuit area is extended into a memory cell area and is in contact with the side of the capacitor (33), step height between the peripheral circuit area and the memory cell area is remarkably reduced.

Owner:RENESAS ELECTRONICS CORP