Method for manufacturing semiconductor device having buried gate

A buried, gate conductive layer technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical solid-state devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] As required, detailed embodiments of the invention are disclosed herein. However, it is to be understood that the disclosed embodiments are merely examples of the invention, and that the invention can be embodied in various forms. Therefore, specific details disclosed herein are not to be interpreted as limiting, but merely as a basis for the claims and as a representative basis for teaching one skilled in the art to employ the present invention in virtually any suitable manner.

[0028] Reference will now be made in detail to the embodiments of the invention, examples of which are illustrated in the accompanying drawings. Wherever possible, the same reference numbers will be used throughout the drawings to refer to the same or like parts.

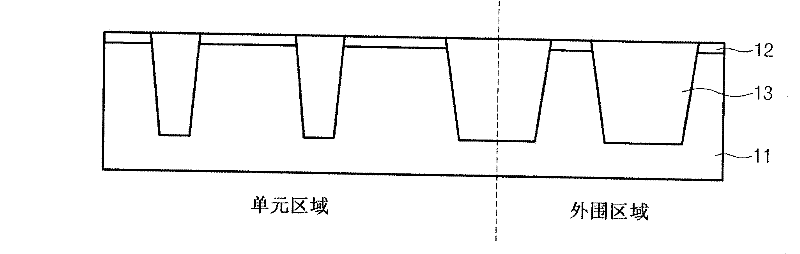

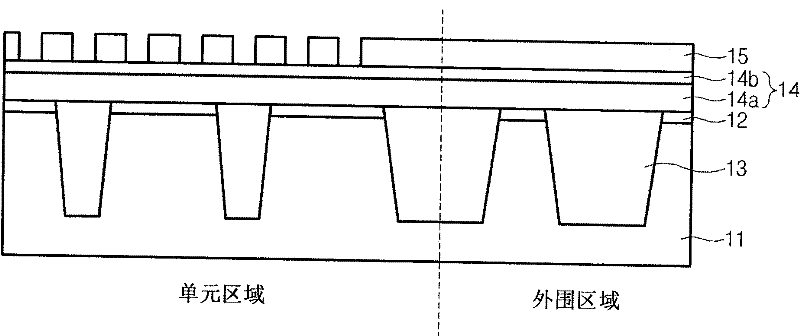

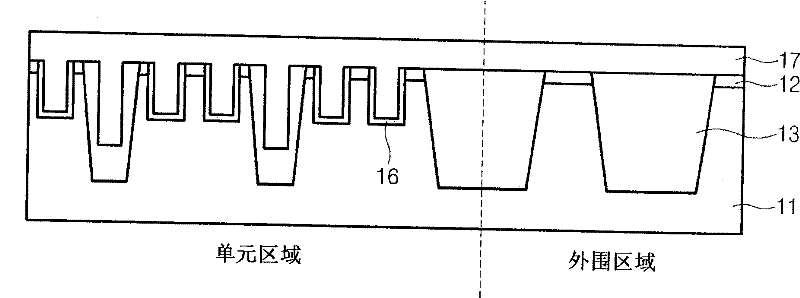

[0029] Figure 1 to Figure 11 is a cross-sectional view showing a semiconductor device including a buried gate according to an embodiment of the present invention.

[0030] refer to figure 1 , a pad oxide layer (not shown) and a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More