Patents

Literature

57results about How to "Reduce lateral spread" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

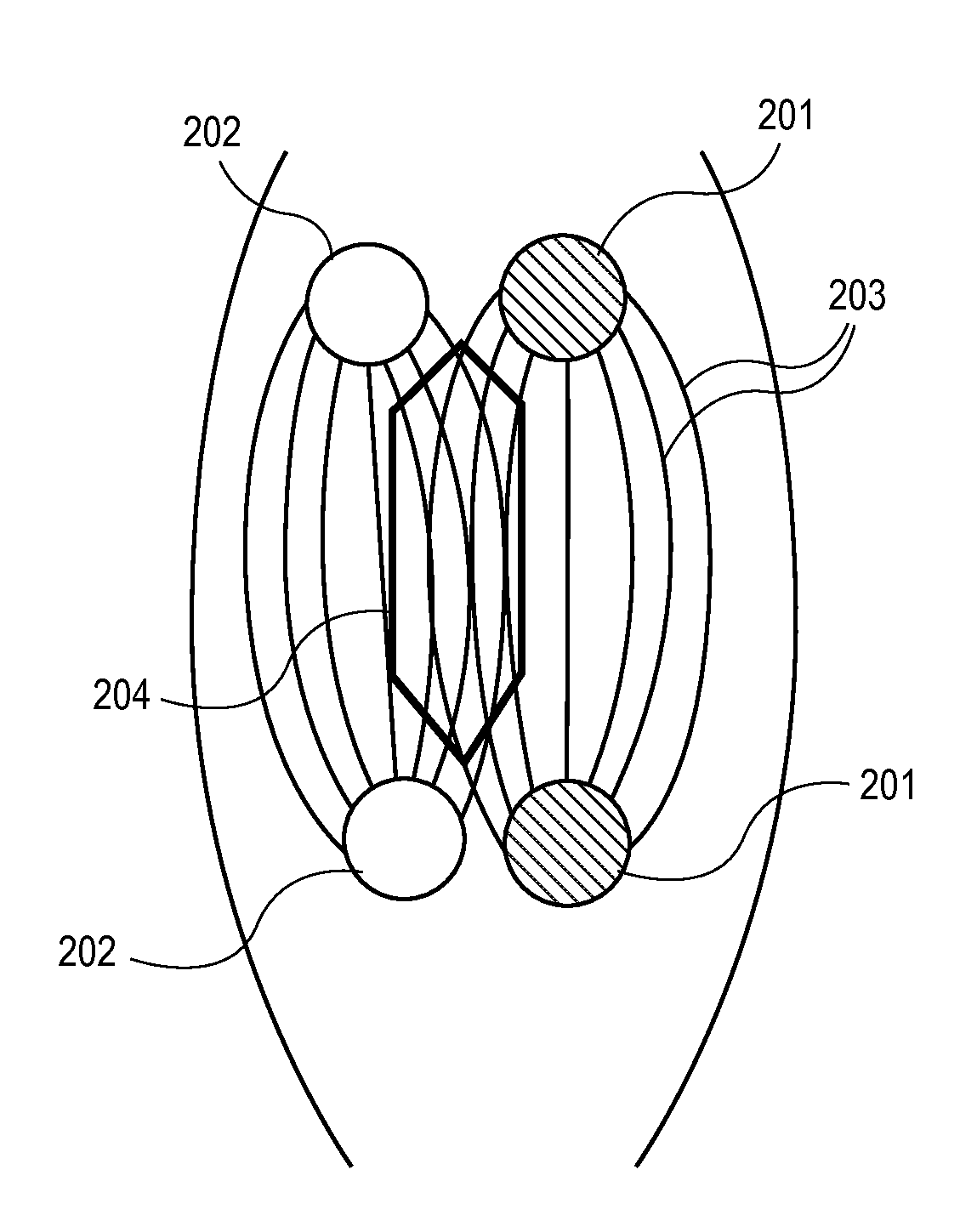

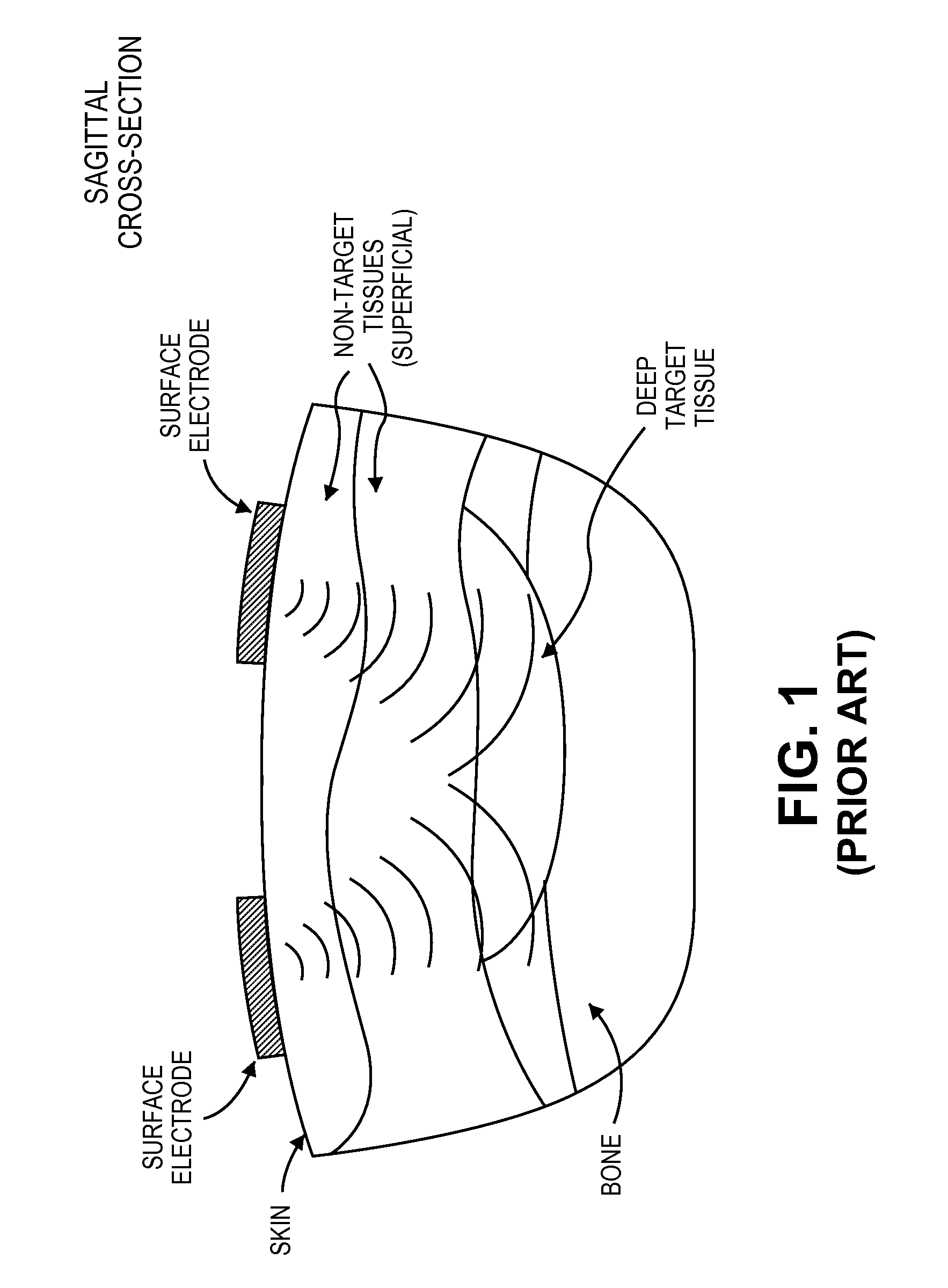

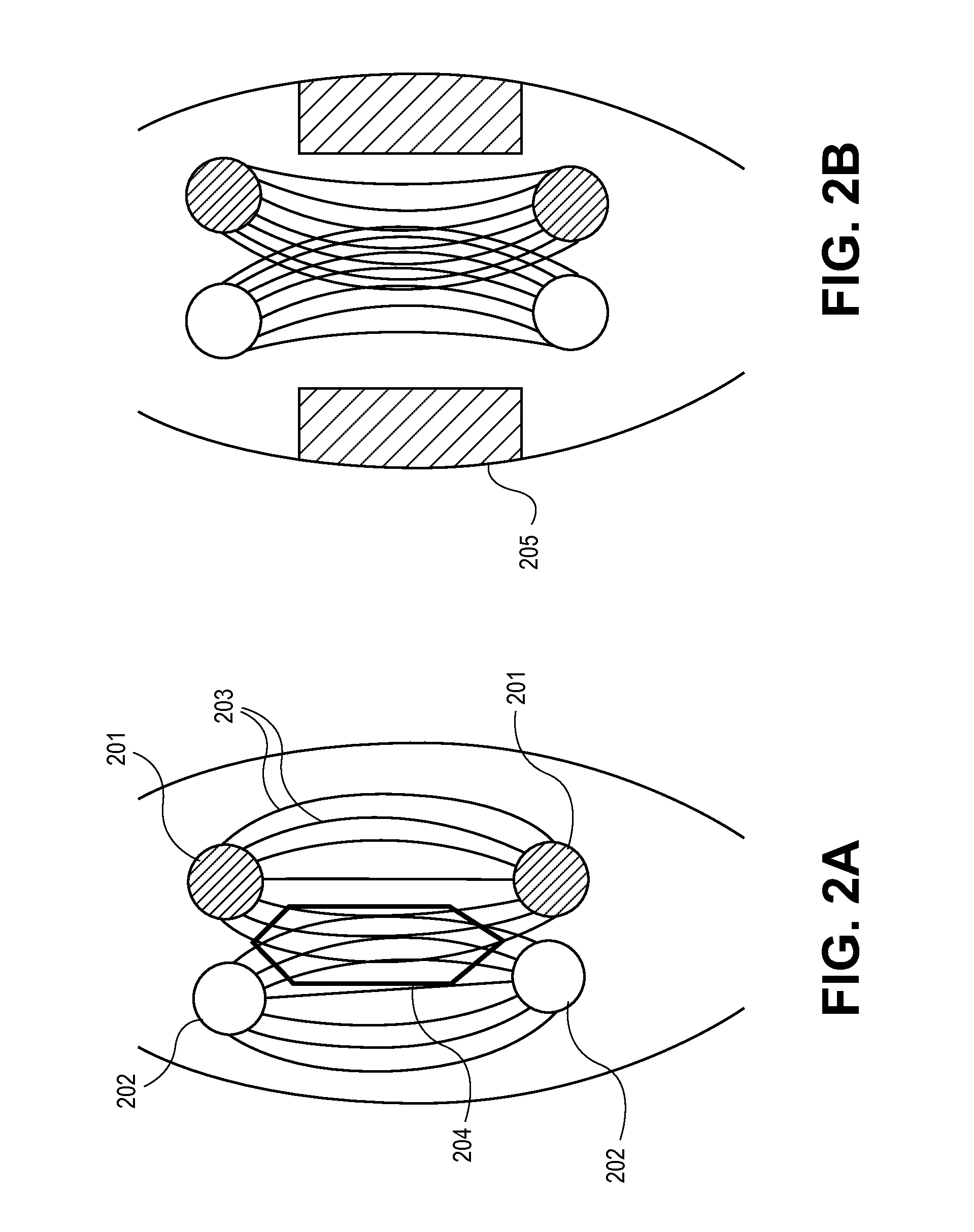

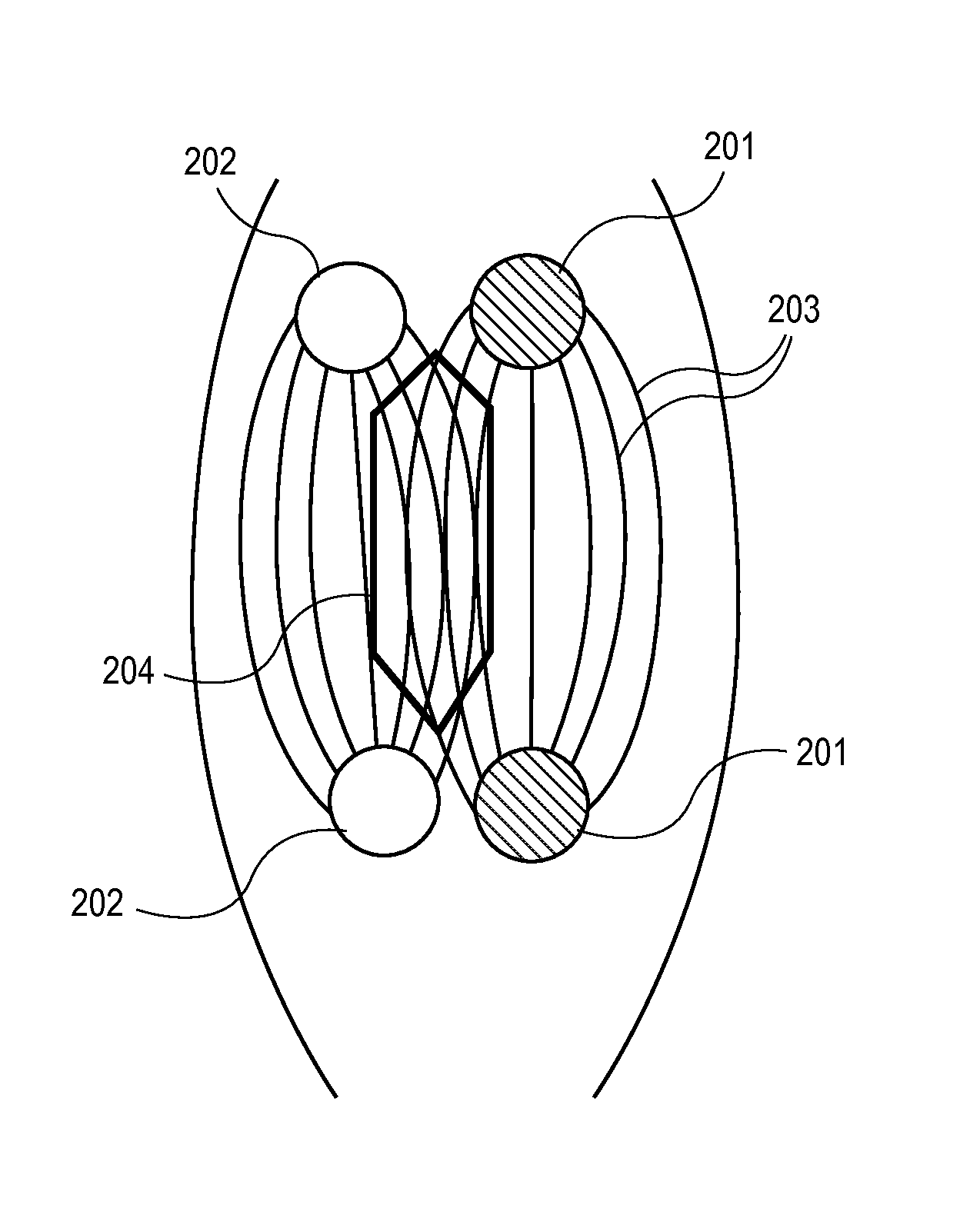

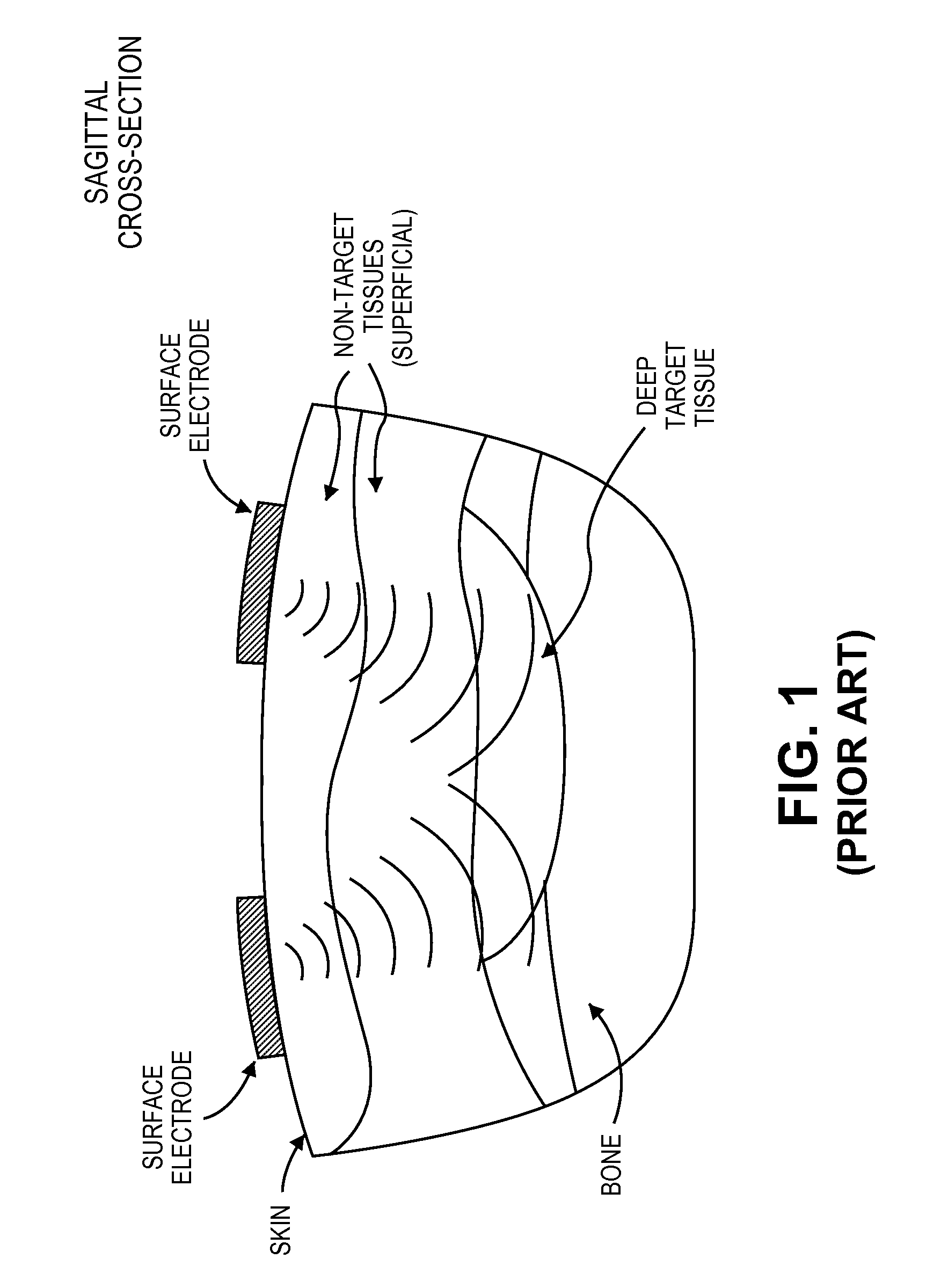

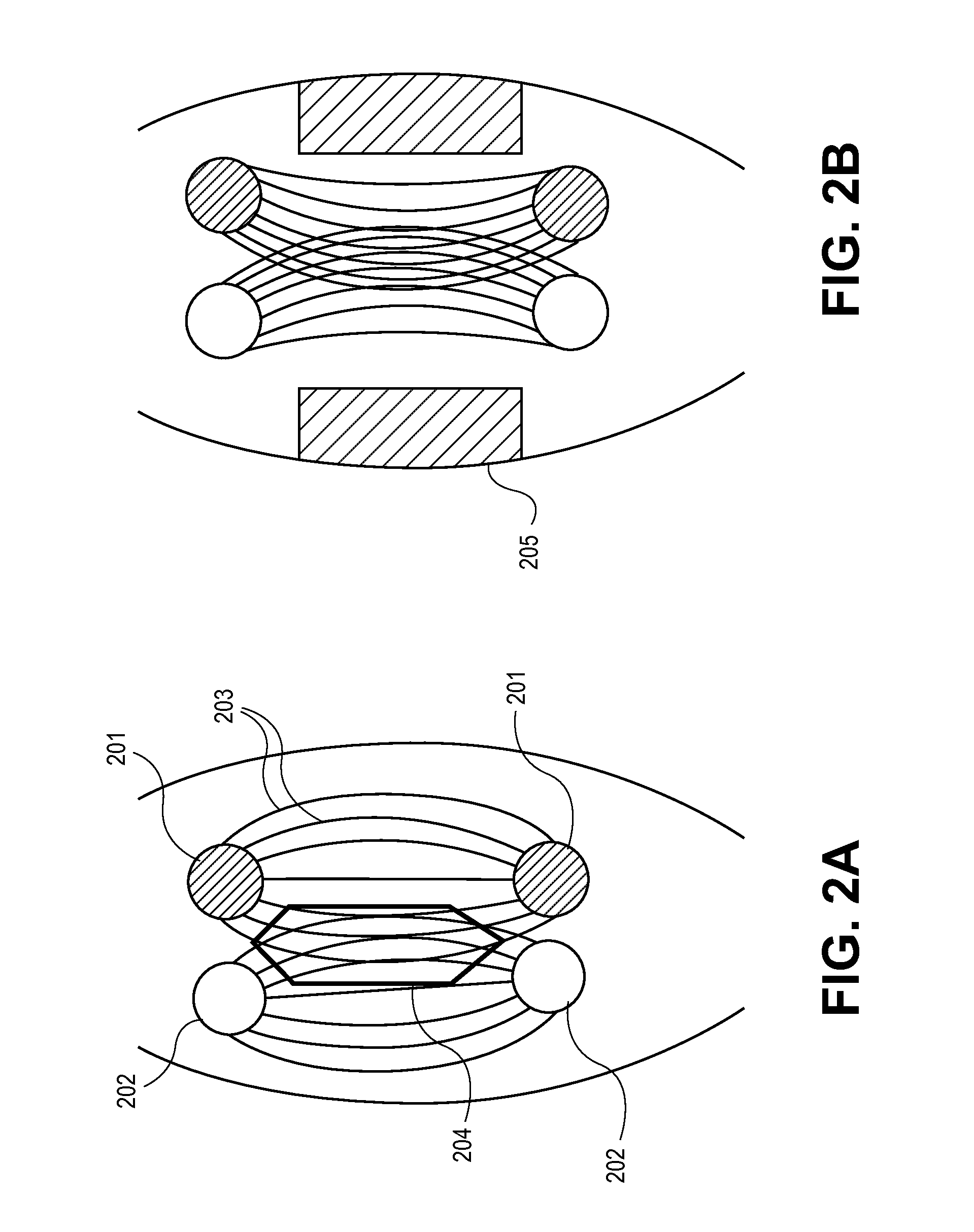

Synergistic Muscle Activation Device

ActiveUS20110112605A1Reduce amountUse energy savingElectrotherapyTherapeutic coolingAnesthesiaMuscle activation

Owner:SAGE PRODS

Synergistic muscle activation device

ActiveUS8588901B2Reduce amountUse energy savingInternal electrodesExternal electrodesAnesthesiaMuscle activation

Owner:SAGE PRODS

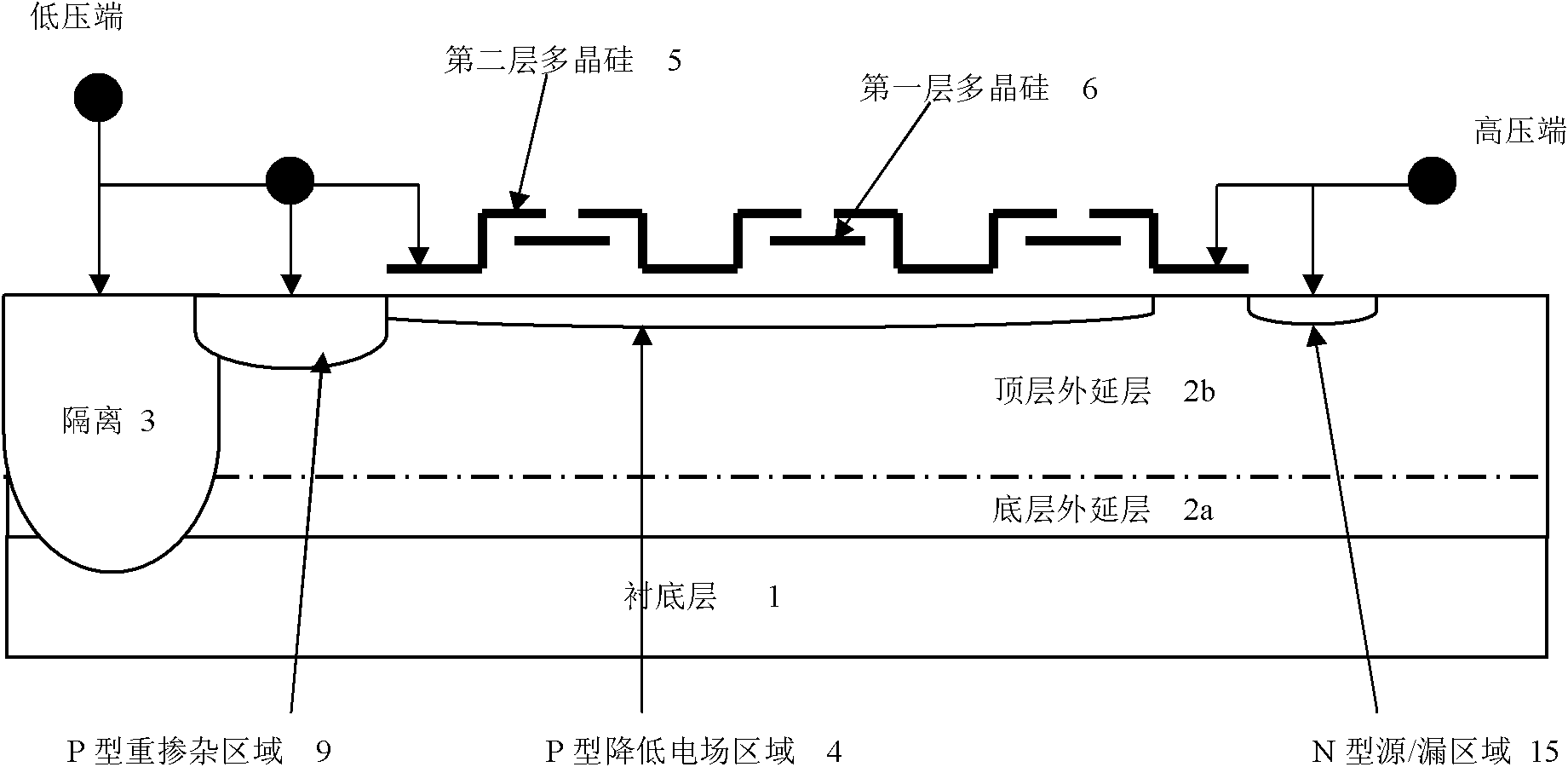

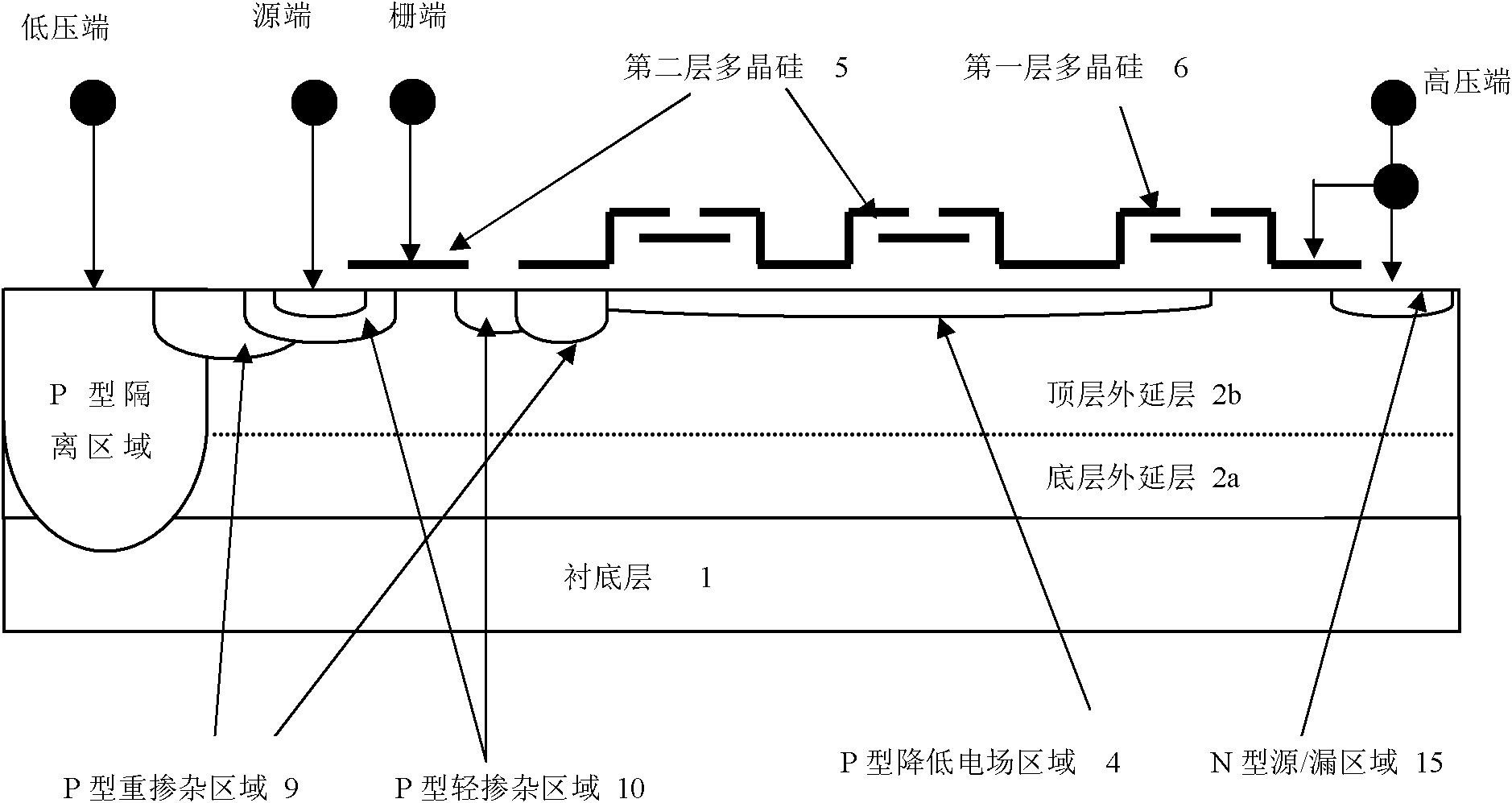

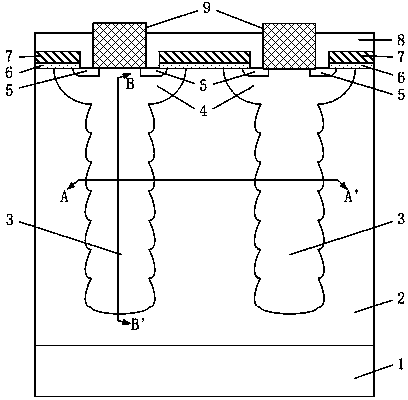

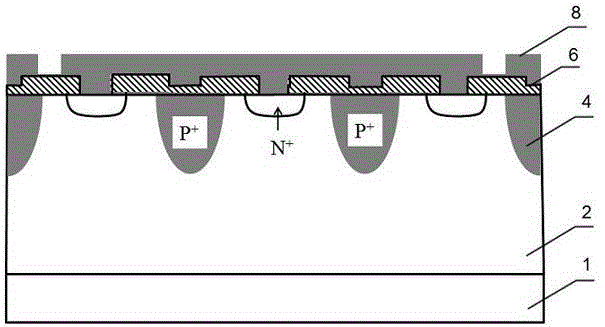

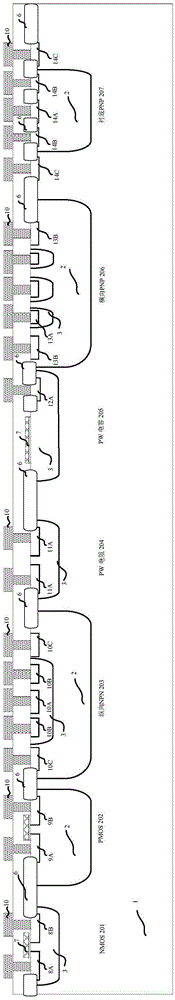

Method for producing high-voltage grid drive chip for directly driving power device

ActiveCN102130060AReduce lateral spreadHigh energySemiconductor/solid-state device manufacturingSemiconductor devicesCMOSLow voltage

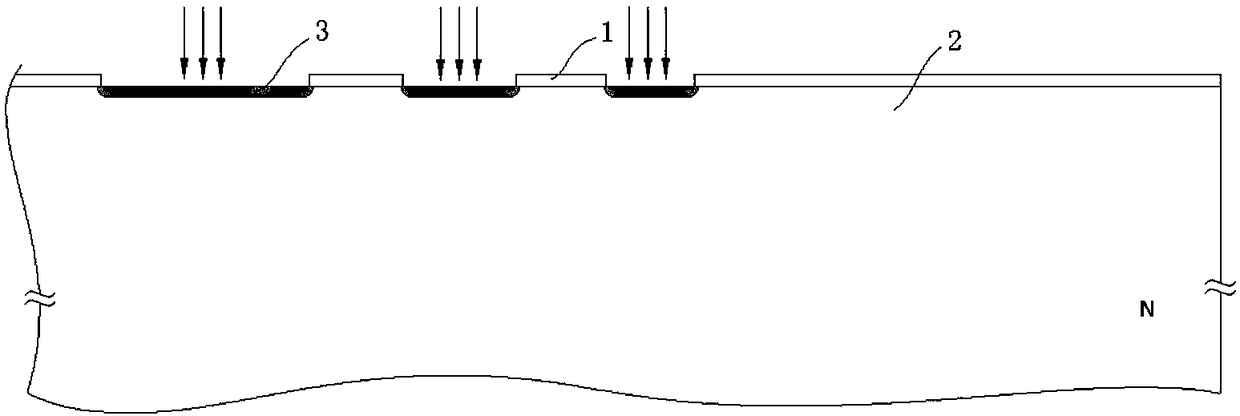

The invention discloses a method for producing a high-voltage grid drive chip for directly driving a power device. By adopting a high-voltage junction isolating process, a high-voltage side drive control module is isolated from a low-voltage side drive control module; on the basis of the PN junction isolation in the conventional CMOS (Complementary Metal-Oxide-Semiconductor Transistor) transistorprocess, a surface electric field reducing region is formed on the surface of a PN junction; a capacitive voltage divider is formed by using two layers of polysilicon; the distribution of an electricfield on the surface of the PN junction is effectively changed; the high-voltage isolation of a high-voltage transverse DMOS (Double-Diffused Metal Oxide Semiconductor) transistor is formed; and a high-voltage N type DMOS transistor is obtained by forming a P type lightly-doped region. Compared with the conventional transverse DMOS transistor, the voltage resistant requirement of over 700V can bemet by additionally arranging a P type surface electric field reducing region structure and a dual-layer polysilicon capacitor structure; and meanwhile, the production method has concise work procedures and lower cost; and a high-voltage grid drive circuit device for directly driving the power device can be formed by only needing 13 structure levels.

Owner:NINGBO SEMICON INT CORP

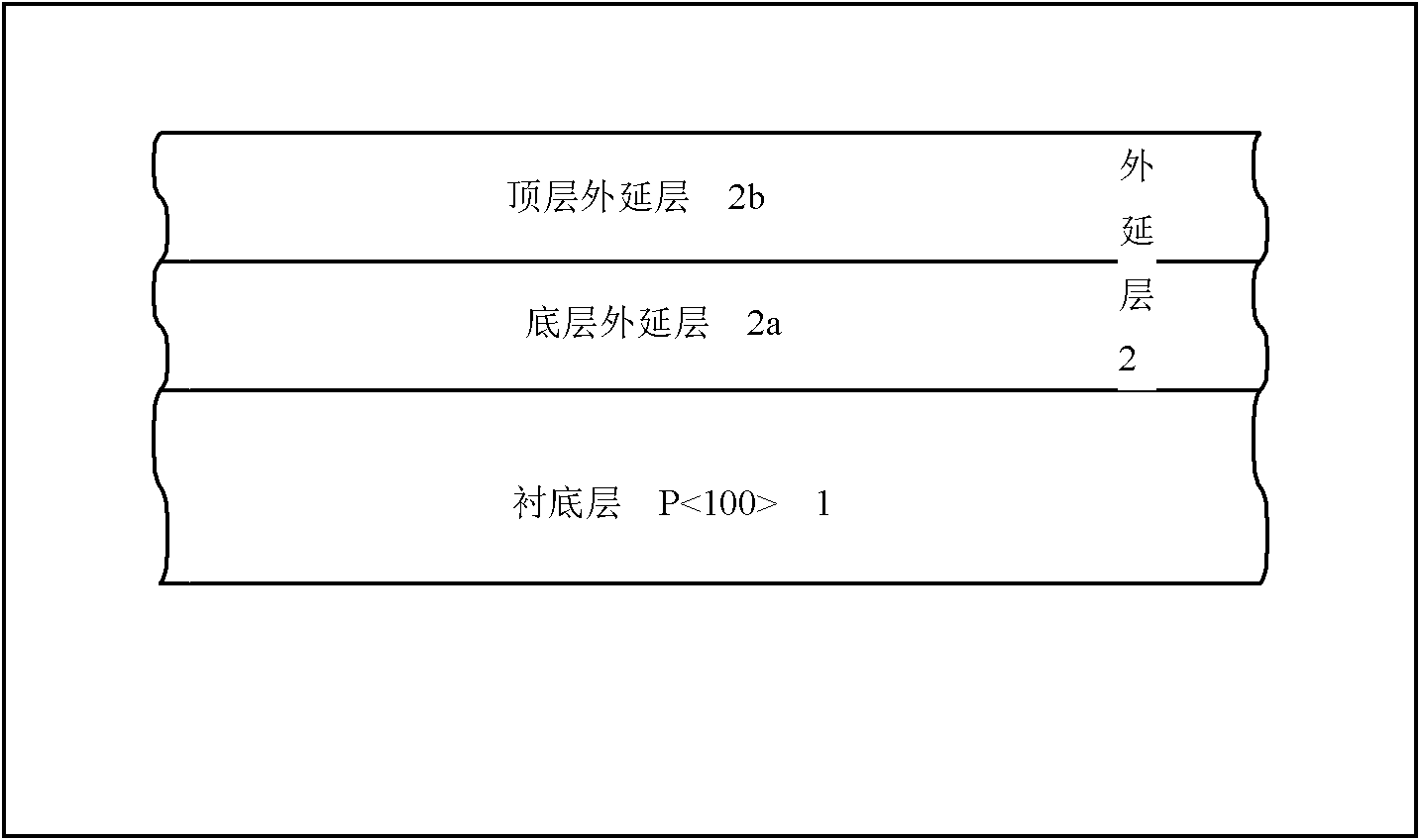

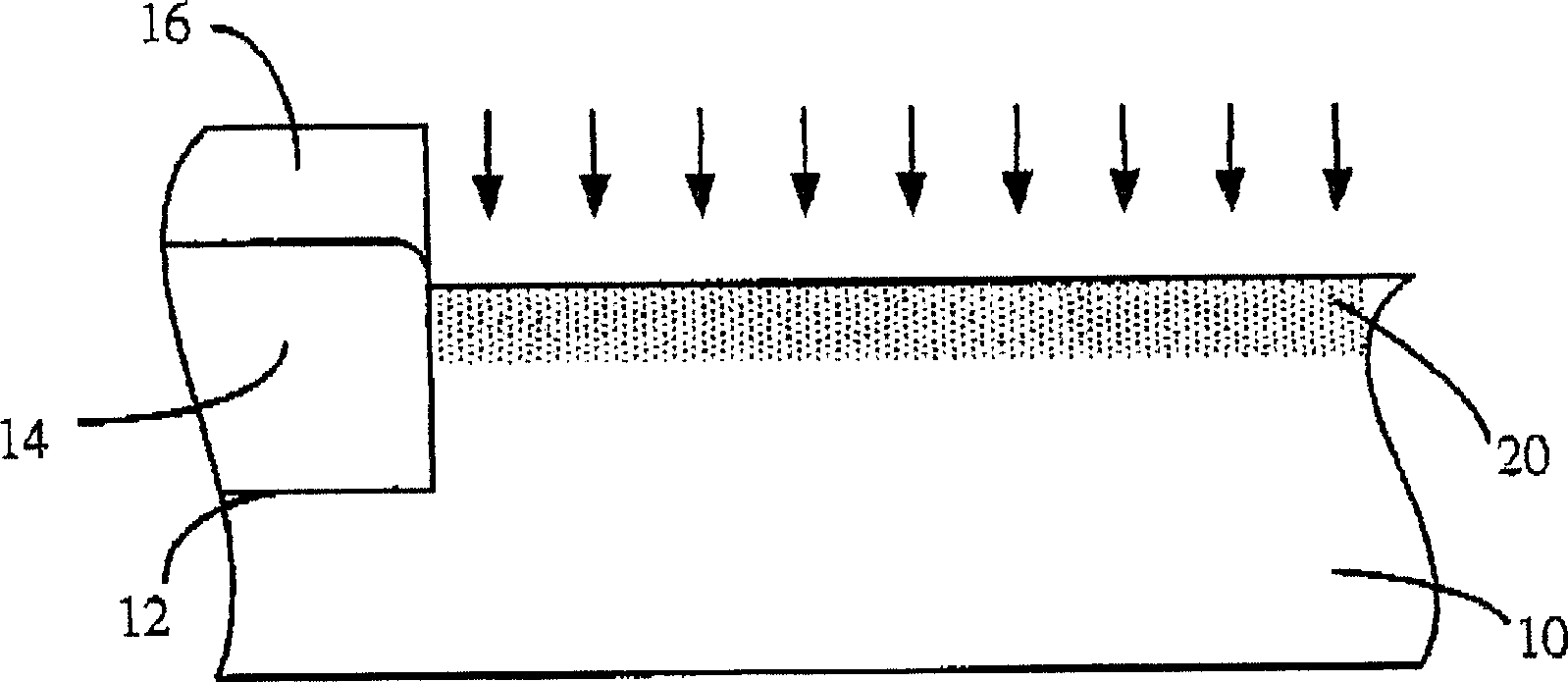

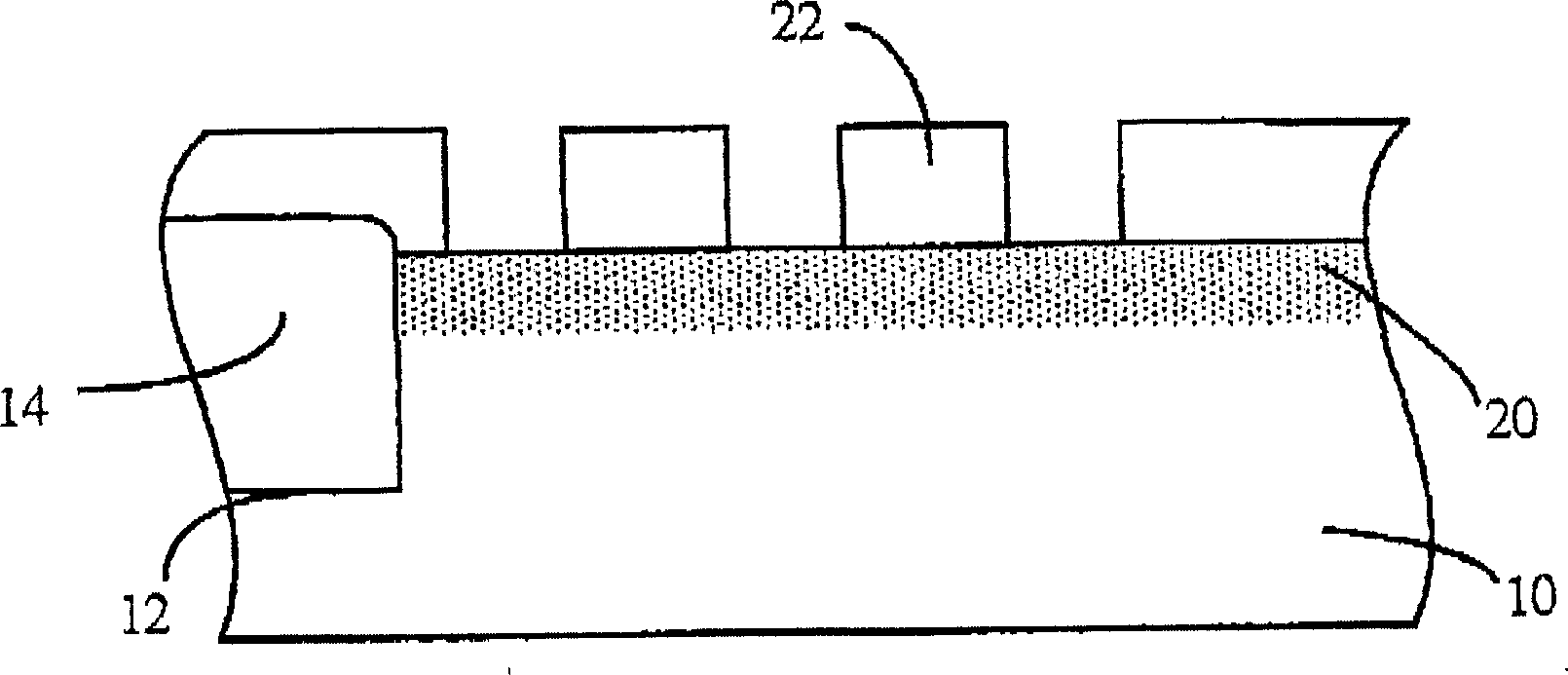

Method for manufacturing metal-oxide-semiconductor transistor

ActiveCN101179027AReduce lateral spreadReduced TED effectSemiconductor/solid-state device manufacturingEngineeringCo injection

The invention provides a method for manufacturing an MOS transistor. The method provides a substrate including a gate structure. Then a pre-non-crystallization technology is carried out and a non-crystallization region is formed in the substrate at two sides of the gate structure; the co-injection technology is carried out, and the impurity for co-injection is injected in the non-crystallization region. A first ion injection technology and a first quick-annealing technology are carried out in such a manner that a slight-doping drain electrode is formed. Finally, a separation wall is respectively formed at two sides of the gate structure in such a manner that a source cathode or a drain electrode is formed.

Owner:UNITED MICROELECTRONICS CORP

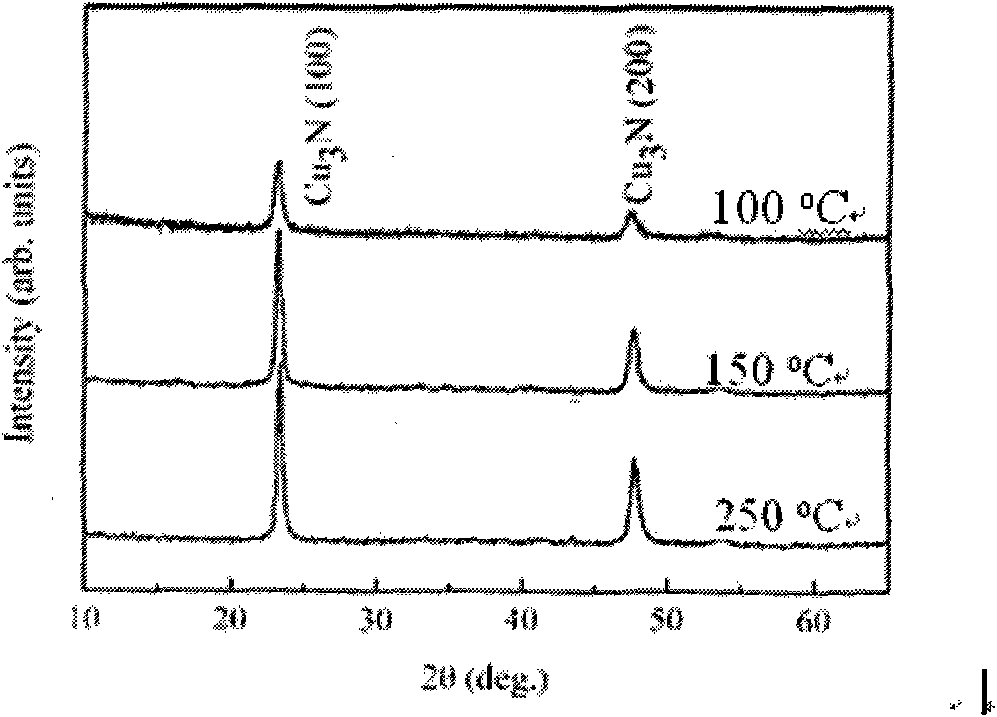

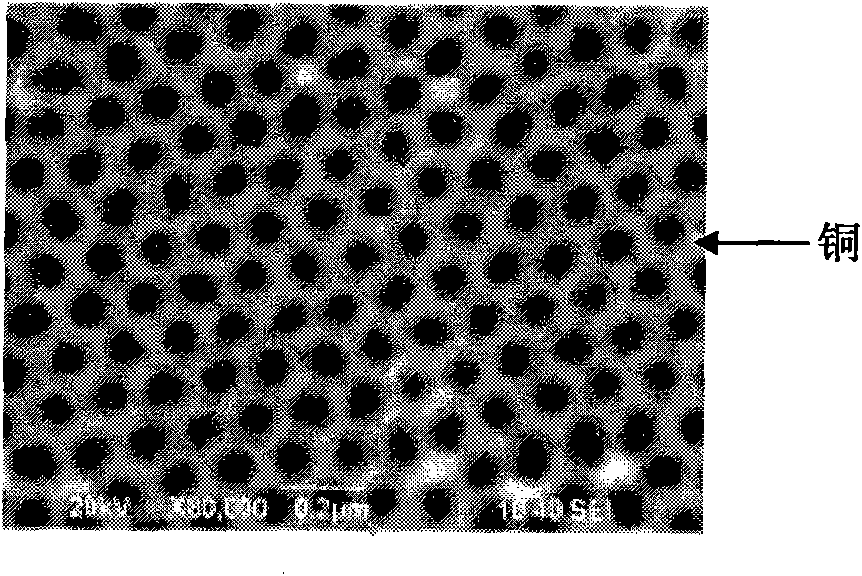

Method for preparing copper nitride film, copper nitride/copper and copper two-dimensional ordered array

ActiveCN101949006AChange structureChange feature sizeVacuum evaporation coatingSputtering coatingMicro nanoSemiconductor materials

The invention discloses a method for preparing a copper nitride film, a copper nitride / copper and copper two-dimensional ordered array, and belongs to the technical field of semiconductor material and micro-nano structure preparation. The method comprises the following steps of: preparing the copper nitride by adopting ion implantation synthesis, growing a layer of copper film on a silicon slice,a silicon dioxide slice, a ceramic slice or a metal substrate by adopting a sputtering method, and forming the copper nitride film by using nitrogen ion implantation; forming the copper nitride / copper two-dimensional array by adopting a prepared uniform ordered anodic aluminum oxide through-hole template as a mask and using nitrogen ion implantation; and corroding the copper nitride / copper two-dimensional array by using a wet corrosion process to obtain an elemental copper hole array. The ion implantation concentration and the ion implantation depth can be accurately controlled by adopting the ion implantation process, and the transverse diffusion is low. The structure of the two-dimensional array and the characteristic dimension of the array can be changed by selecting the proper aluminum oxide template.

Owner:CHANGZHOU UNIV

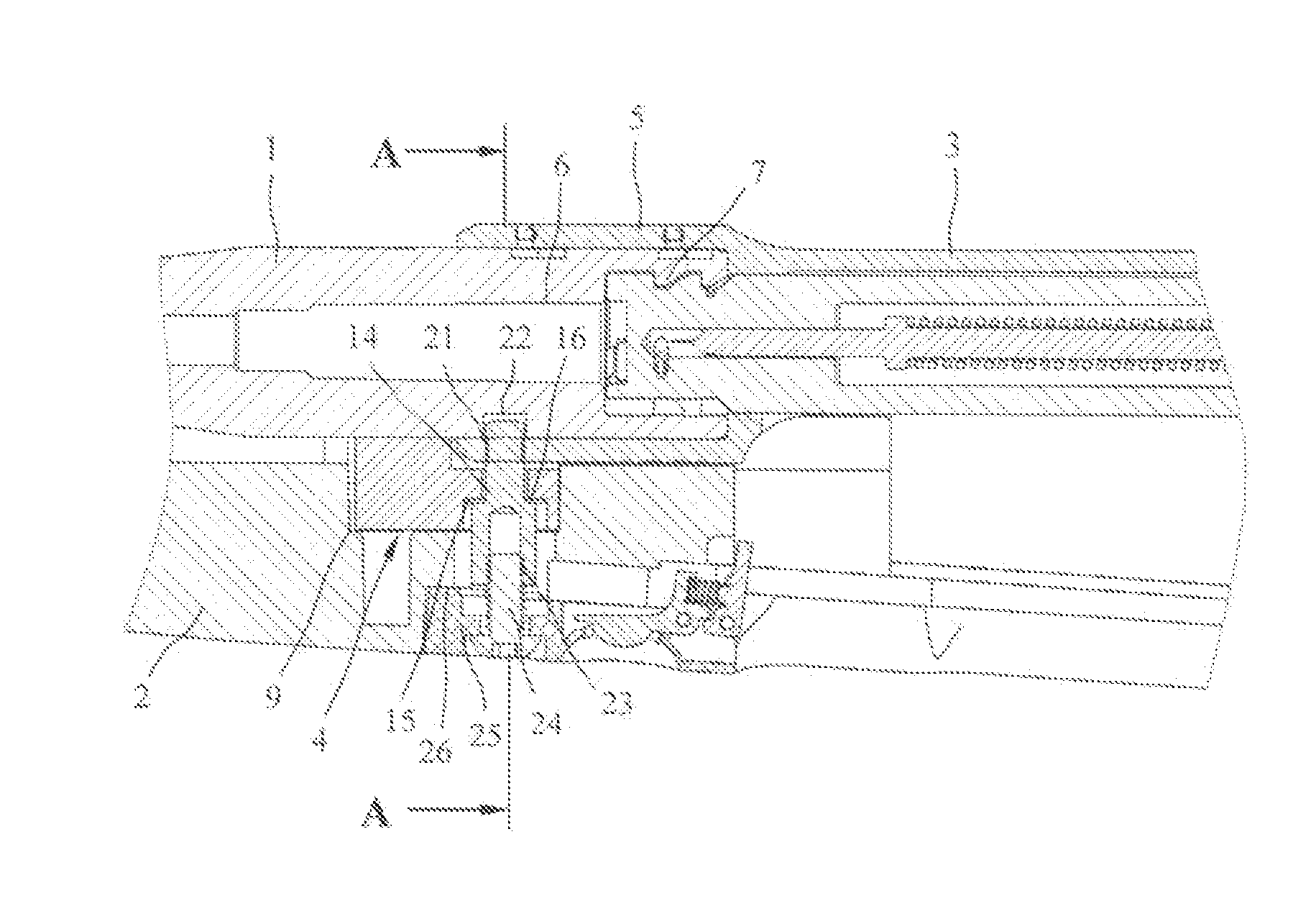

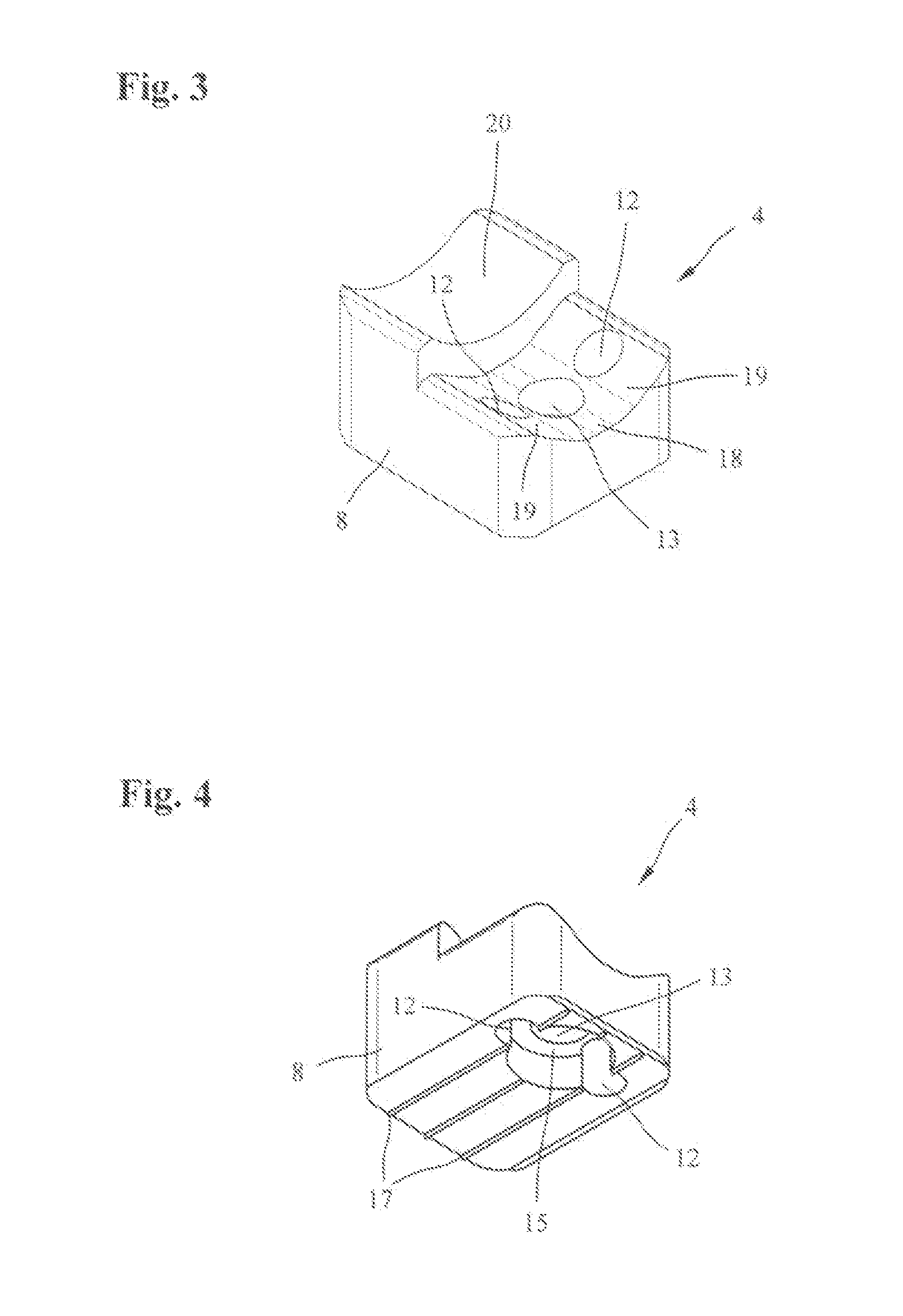

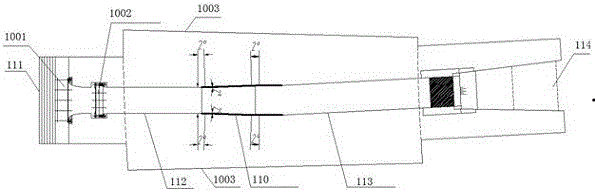

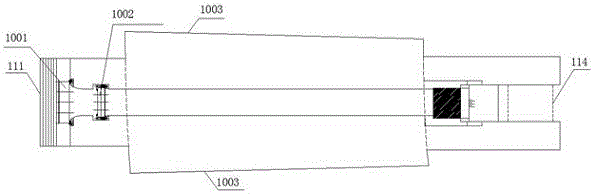

Rifle stock

A rifle stock with a support part which is attached in the rifle stock, and which includes, on its top side, a support area for the support of a receiver and / or of a barrel, and on its bottom side, a profiling for positive-fitting holding of the support part in the rifle stock. In order to make possible a bedding of the receiver and / or barrel that is not influenced by changes of the rifle stock, the support part is connected by an adhesive connection undetachably to the rifle stock.

Owner:L & O HUNTING GRP

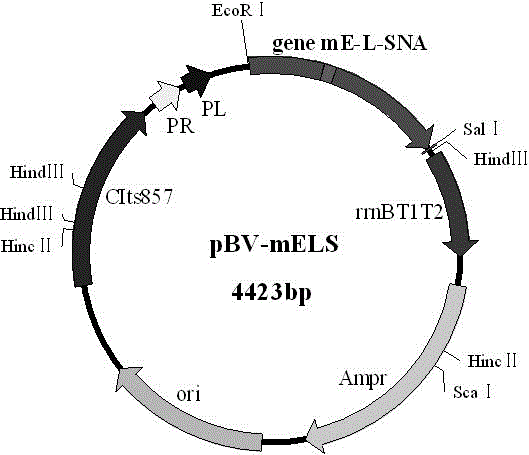

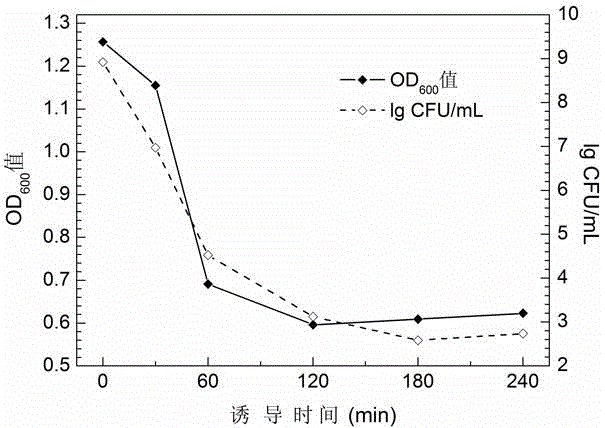

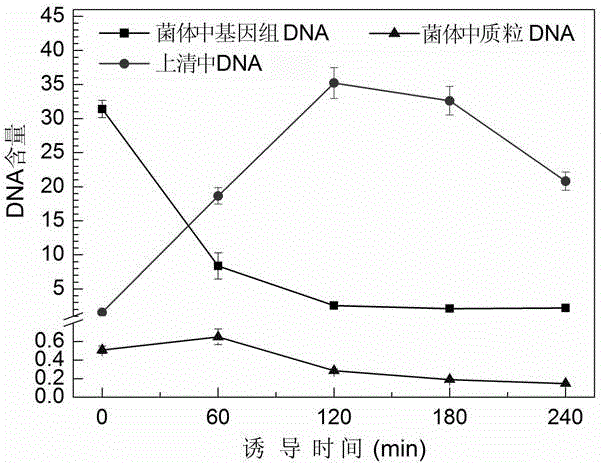

Efficient splitting tandem gene, efficient splitting plasmid and construction method and appliance

ActiveCN103146732AIncrease productionReduce lateral spreadBacteriaVector-based foreign material introductionEscherichia coliGenetic engineering

The invention relates to the field of genetic engineering, in particular to an efficient splitting tandem gene which is composed of a phage PhiX174 mutation splitting gene mE and a staphylococcus nuclease A gene SNA, an efficient splitting plasmid which contains the efficient splitting tandem gene and appliance of the efficient splitting plasmid in preparation of ghost, and a gene sequence is shown as a sequence 3 in a sequence list. A structured safe and efficient splitting plasmid pBV-mELS is capable of conducting induction when an Escherichia coli liquid OD600 value reaches more than 1.0. Splitting efficiency can be 99.99995%. Not only is limitation that a splitting gene E mediated fragmentation process relies on a growing state (OD600 is 0.4 to 0.6) of host bacteria broken through, output of the ghost is greatly improved, but also heritage materials left in the ghost is effectively eliminated, and side-direction spread of a perniciousness heredity element (an antibiotics resistance gene and a pathogenic determinant cluster gene) is reduced.

Owner:INST OF ANIMAL SCI & VETERINARY MEDICINE SHANDONG ACADEMY OF AGRI SCI

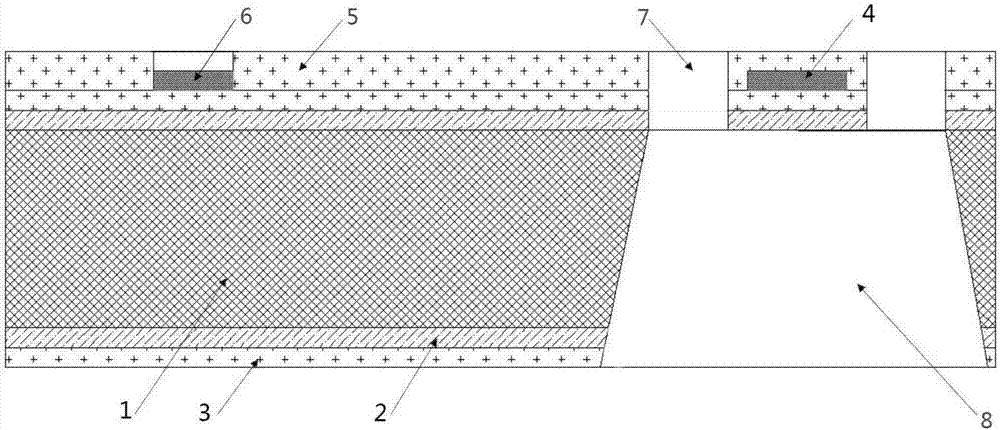

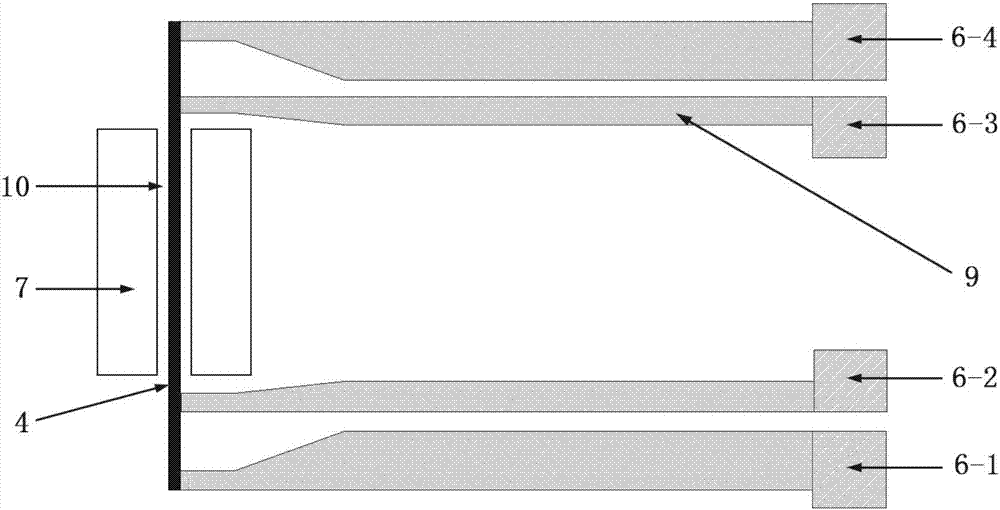

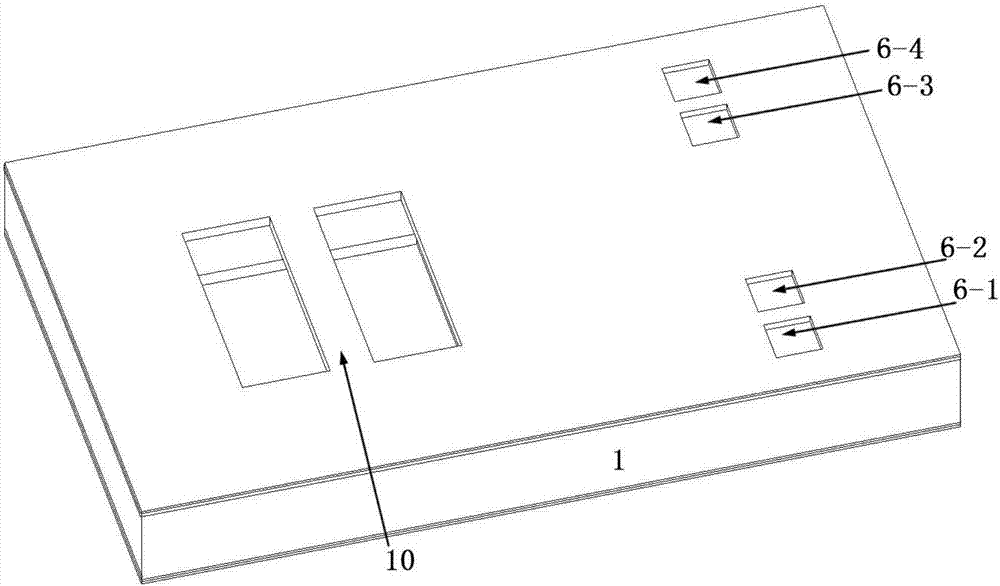

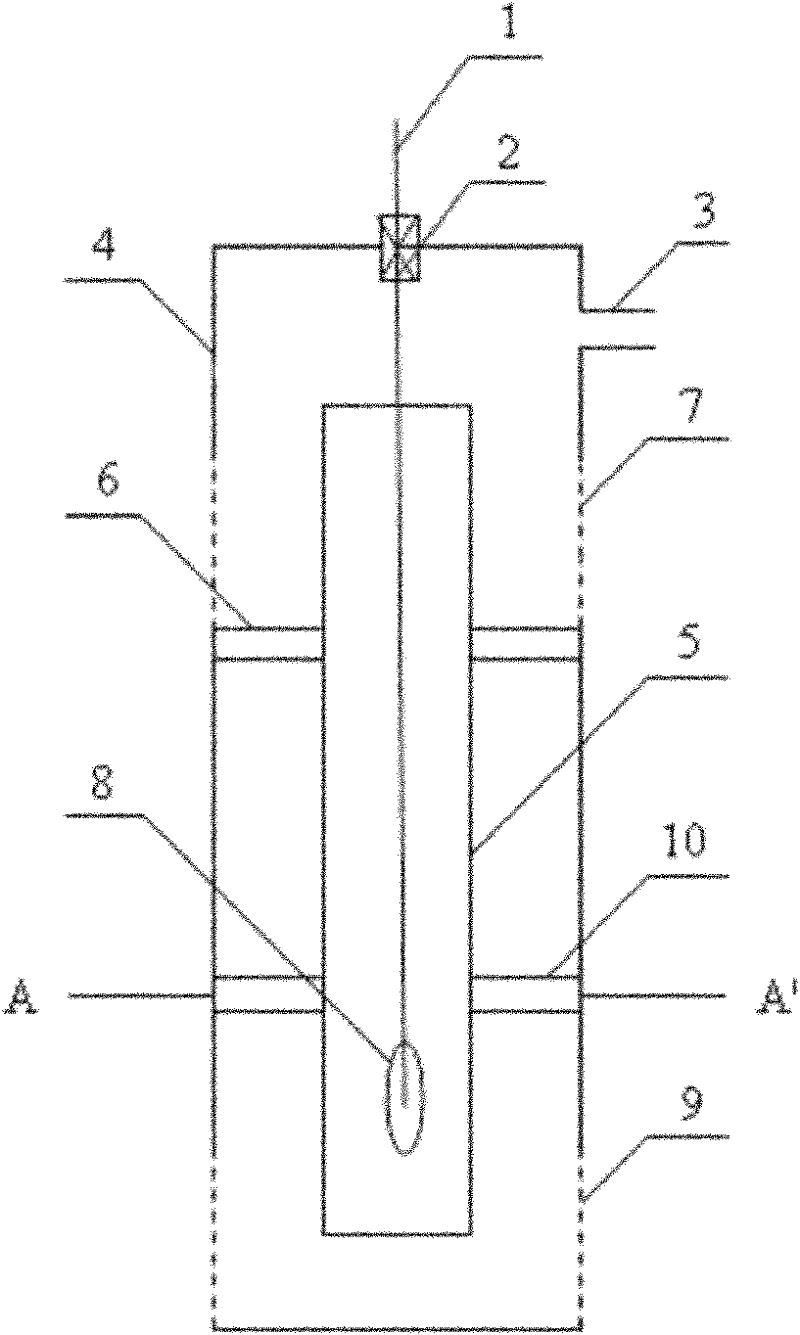

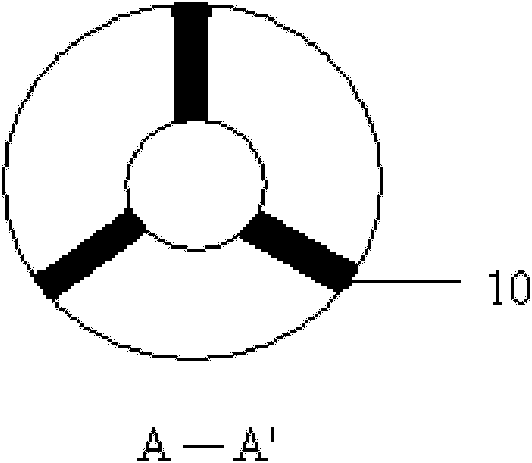

Support-beam-type MEMS (micro electromechanical systems) fluid thermal conductivity and thermal diffusion coefficient sensor and preparation and testing methods thereof

ActiveCN107037079AThe testing process is simpleReduce lateral spreadMaterial thermal conductivityMaterial heat developmentThermal diffusion coefficientEngineering

The invention discloses a support-beam-type MEMS (micro electromechanical systems) fluid thermal conductivity and thermal diffusion coefficient sensor and preparation and testing methods thereof; a heater is arranged at the center of the upper surface of a substrate, a pad is arranged beside the heater on the upper surface of the substrate and is connected to the heater, film of an insulating layer covers the heater, the pad and the substrate, the film of the insulating layer is provided with cavities on two sides of the heater, the bottom of the substrate is provided with a back cavity, and a support beam structure is formed. The heater also acts as a temperature sensor; the heater is of elongated strip structure and is connected to the pad through four leads; by using the back cavity, a fluid under test is used as a substrate of the sensor, thermal conductivity and thermal diffusion coefficient of the fluid under test can be measured directly, and the test process is simplified. The sensor provided herein is suitable for measuring the thermal conductivity and thermal diffusion coefficient of conductive and nonconductive trace liquids.

Owner:XI AN JIAOTONG UNIV

Improved aeration well for in-situ remediation of polluted underground water and remediation method

InactiveCN102219293AReduce lateral spreadSimple processWater/sewage treatment by oxidationPollutantIn situ remediation

The invention relates to an improved aeration well for in-situ remediation of polluted underground water and a remediation method. In the improved aeration well, an inner well tube is sleeved in an outer well tube; the inner well tube is fixed in the outer well tube by using an upper fixed bracket and a lower fixed bracket; an aeration head is arranged at the lower part of the inner well tube and is connected with an aeration pump through an aeration pipe; an exhaust hole is arranged at the upper part of the outer well tube and is connected with a contaminated gas monitor; an upper shock tube is arranged at the lower part of the exhaust hole at the upper part of the outer well tube; a top hole of the upper shock tube is lower than the inner well tube; a lower shock tube is arranged on the lower section of the outer well tube; a top hole of the lower shock tube is higher than the bottom end face of the inner well tube; and the bottom end face of the outer well tube is in contact with a base plate of an underground water layer. The invention has the advantage that the transverse diffusion of the pollutants is reduced by increasing the vertical flow of underwater. Compared with the traditional underground water aeration technology and extraction treatment technology, the remediation method has a simpler process, the improved aeration well can continuously operate by conventional maintenance, the remediation efficiency is improved and the remediation cost and the maintenance cost are reduced.

Owner:JILIN UNIV

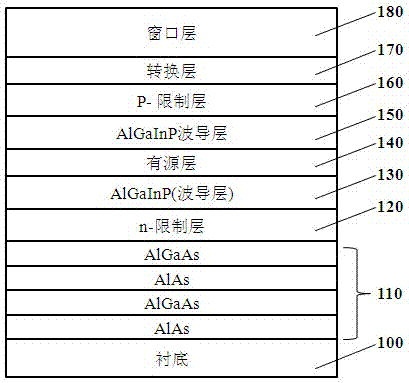

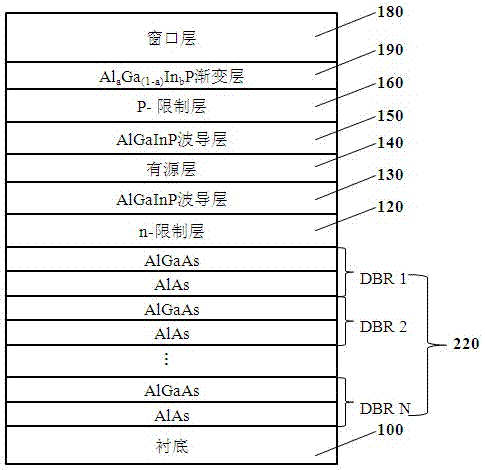

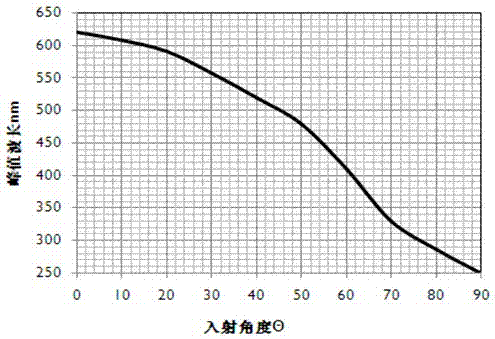

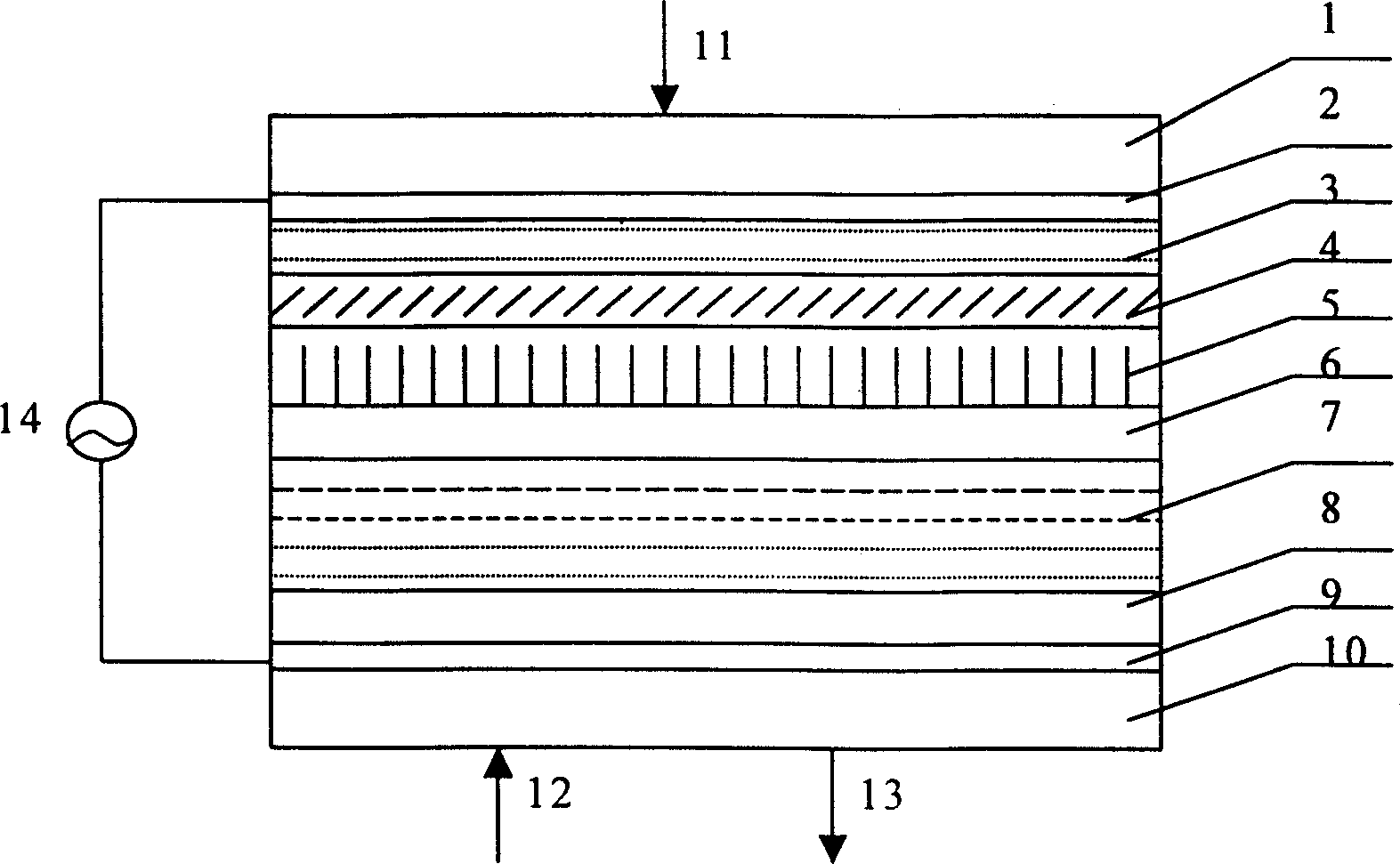

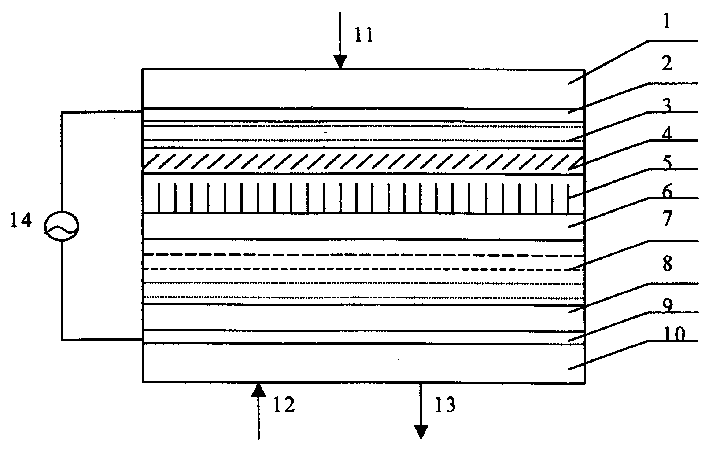

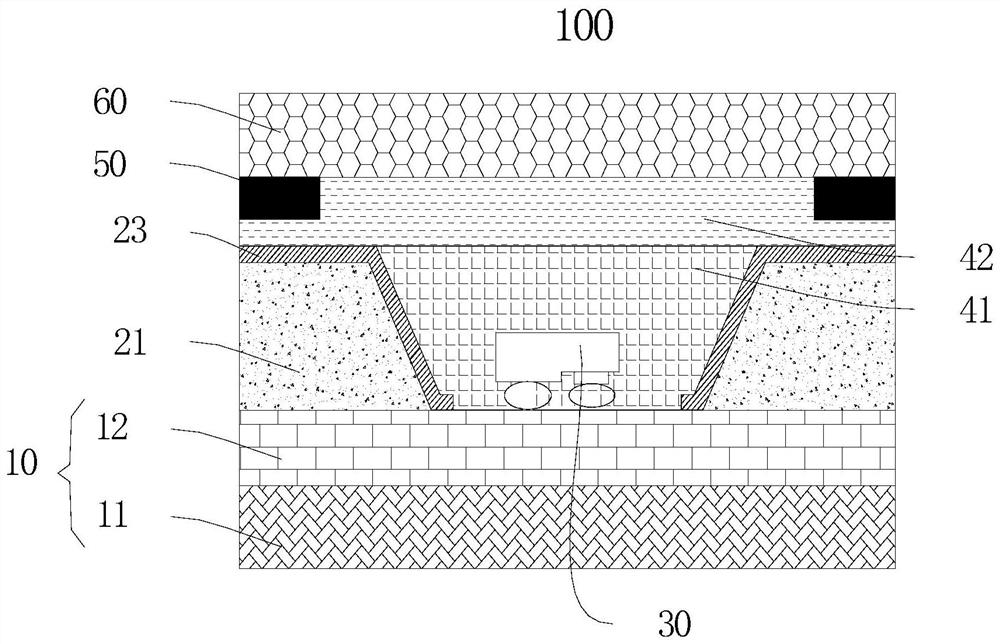

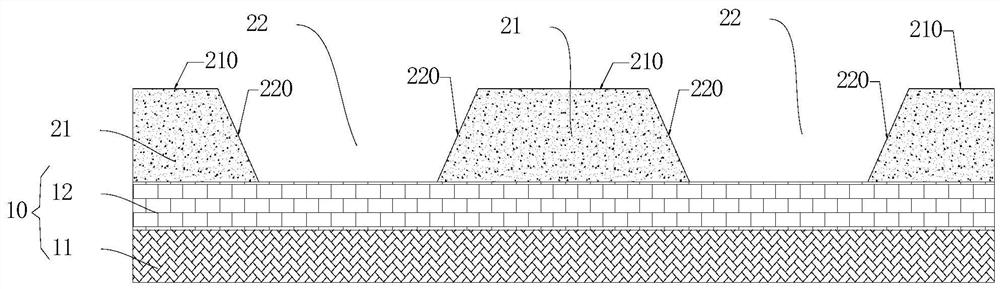

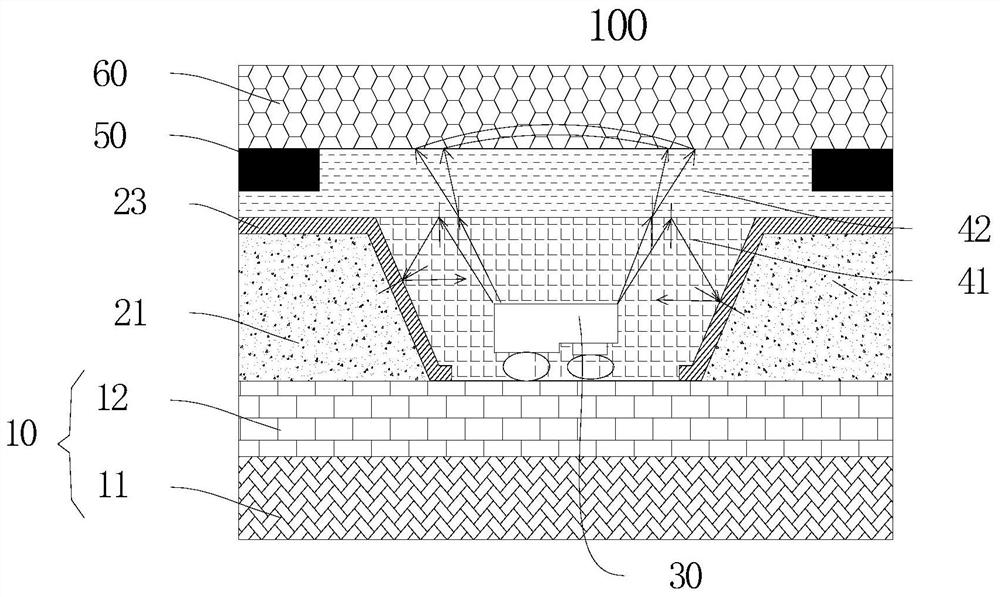

Light emitting diode

ActiveCN107492586AEffective reflectionReduce lateral spreadSemiconductor devicesWavelengthActive layer

The invention discloses a light emitting diode. By virtue of the light emitting diode, forward effective light output can be increased and / or the inclined incident light can be reflected with the maximum effect through a combined type DBR structure. According to one embodiment of the invention, the light emitting diode comprises a light emitting epitaxial lamination layer which has opposite first surface and second surface and comprises an N type limiting layer, an active layer and a P type limiting layer, wherein the first surface is a light output surface; the combined type DBR structure is arranged on the lower surface of the epitaxial lamination layer, wherein the structure is formed by a combination of N groups of DBR sub layers; and counting from the first pair of DBR sub layers adjacent to the active layer of the N groups of DBR sub layers, the central reflective wavelengths of the DBR sub layers in each layer are <lambda>, <lambda>+<lambda>0, <lambda>+2<lambda>0 until <lambda>+(N-1)*<lambda>0, wherein <lambda> is the light emitting wavelength of the active layer, the (N-1)*<lambda>0 is the maximum blue shift quantity generated by oblique incidence of the active layer, and <lambda>0 is greater than 0.

Owner:TIANJIN SANAN OPTOELECTRONICS

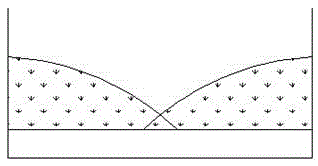

Super junction semiconductor device manufacturing method capable of improving avalanche capacity

ActiveCN103560086AImproved avalanche capabilityReduce the equivalent resistance R

<sub>B</sub>

resistance valueSemiconductor/solid-state device manufacturingSemiconductor devicesElectron avalancheHigh dosage

The invention relates to a super junction semiconductor device manufacturing method capable of improving the avalanche capacity. On-resistance is increased correspondingly due to transverse diffusion caused by the traditional high dosage concentration of a column P, and puncture voltage is reduced due to electric charge unbalance of the column P and a column N. According to the method, the epitaxy technology is utilized to form an N-type epitaxy layer; a P-type and N-type epitaxy layer is formed by injecting boron ions; the injection amount of the boron ions increases gradually, and the boron ions are pushed under the high temperature to form a P-type and N-type alternant epitaxy layer; a Pbody area is formed by injecting the boron ions; a polycrystalline silicon gate electrode is formed by etching polycrystalline silicon through the dry method; an N+ source area is formed by injecting arsenic ions; a layer of aluminum is deposited on the upper surface of a whole device, a source metal electrode is formed by etching the aluminum, and a drain electrode is formed on the back face through metallization. According to the super junction semiconductor device obtained through the method, the avalanche capacity of the super junction semiconductor device is improved, and at the same time, on-resistance is reduced.

Owner:XIAN LONTEN RENEWABLE ENERGY TECH +1

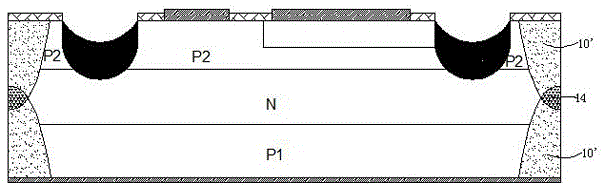

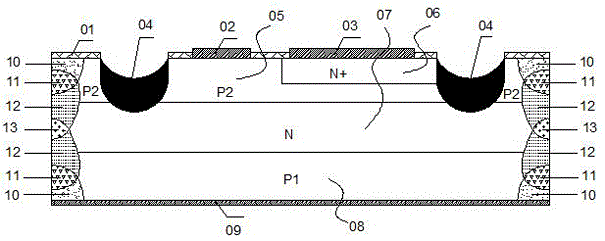

Thyristor chip with seven-layer p-n junction isolation structure and preparation method of thyristor chip

ActiveCN105633129AImprove completenessReduce areaSemiconductor/solid-state device manufacturingSemiconductor devicesSilicon-controlled rectifierEngineering

The invention discloses a thyristor chip with a seven-layer p-n junction isolation structure and a preparation method of the thyristor chip. The thyristor chip comprises an anode region P1, an N-type long base region, a short base region P2, an N<+>-type cathode region, a front oxidation film, a front gate metal electrode, a front cathode metal electrode, a back anode metal electrode, an annular passivation groove and an isolation ring of the seven-layer p-n junction isolation structure, wherein the isolation ring of the seven-layer p-n junction isolation structure comprises a boron impurity region, a boron-aluminum mixed impurity region, an aluminum impurity region, an aluminum-aluminum overlapping impurity region, an aluminum impurity region, the boron-aluminum mixed impurity region and the boron impurity region from top to bottom; and the isolation ring of the seven-layer p-n junction isolation structure is arranged between the front oxidation film and the back anode metal electrode along the vertical direction and surrounds the peripheries of the anode region P1, the N-type long base region and the short base region P2. The thyristor chip is short in diffusion time, low in production energy consumption, high in efficiency, high in silicon wafer integrity rate, little in transverse diffusion of the isolation region surface and small in isolation region width, and saves the area of the silicon wafer.

Owner:JIANGSU JIEJIE MICROELECTRONICS

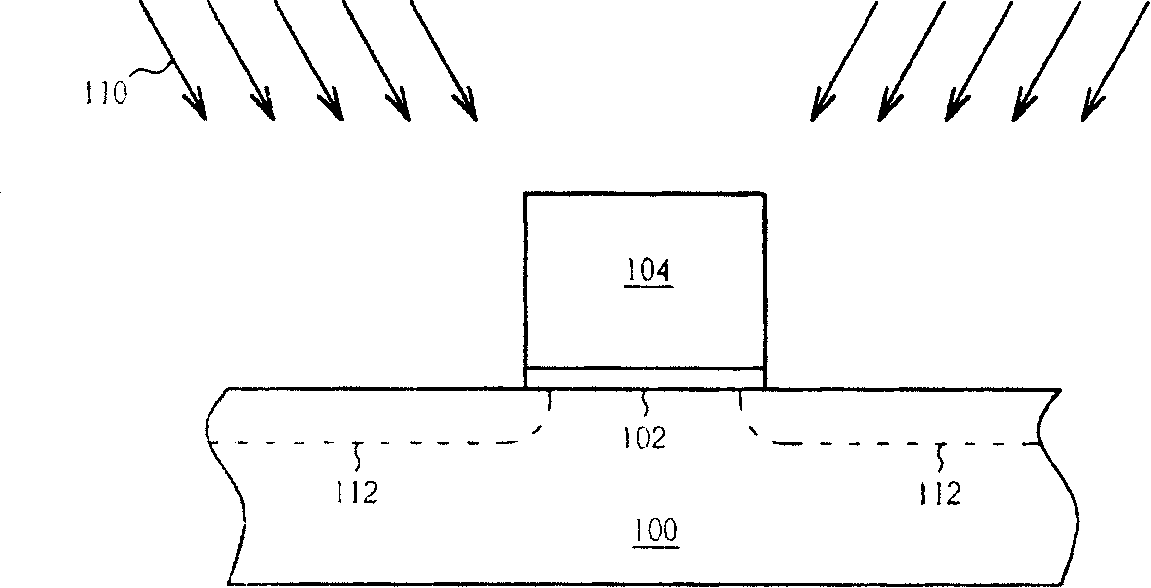

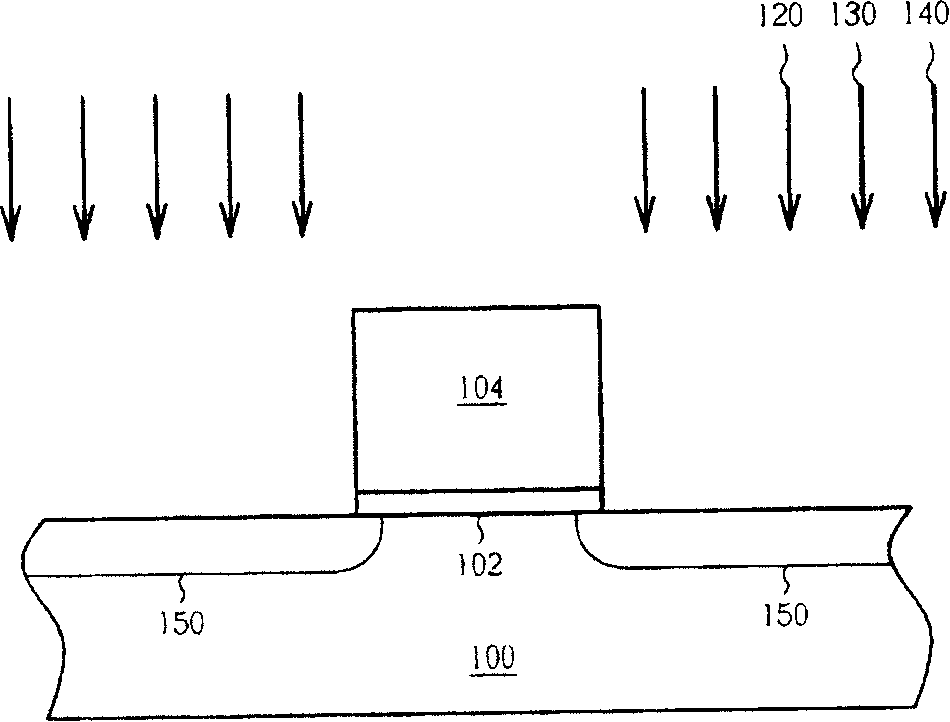

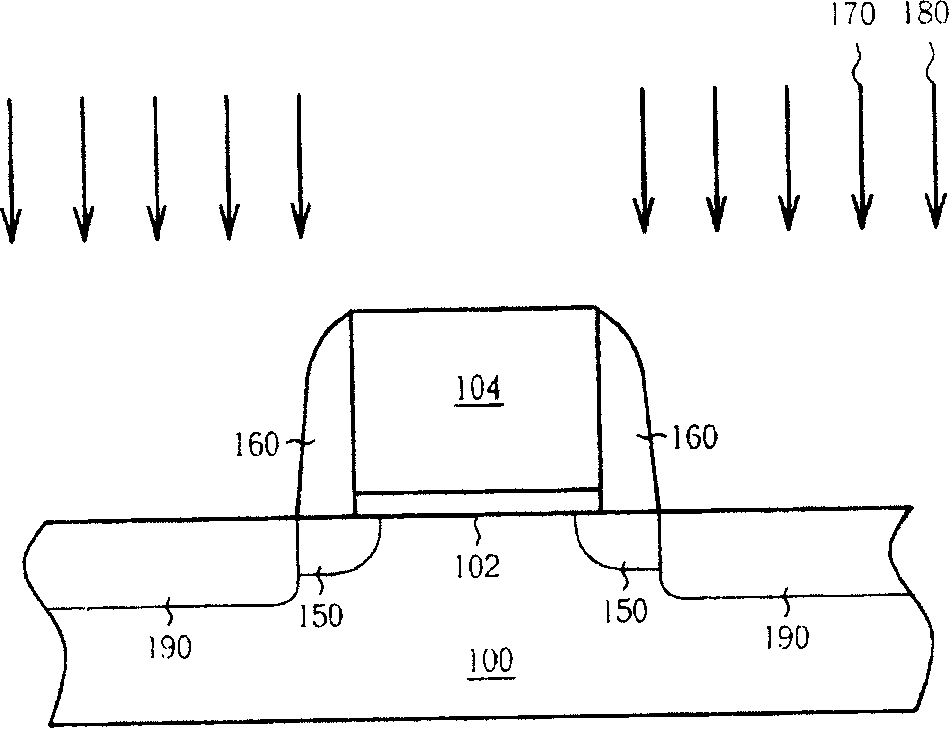

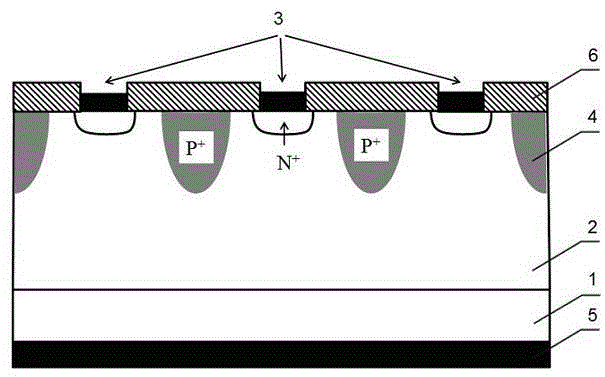

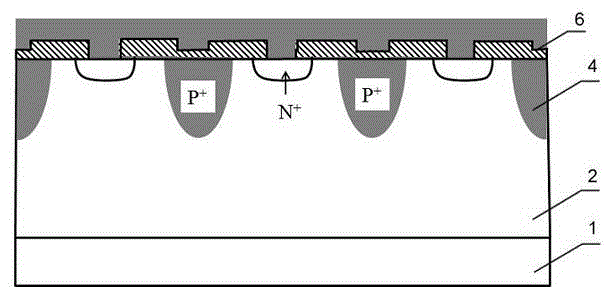

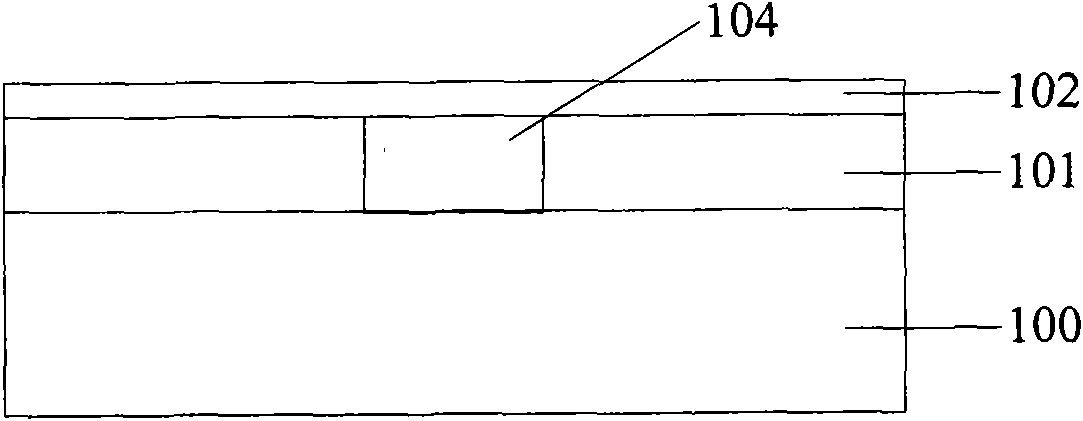

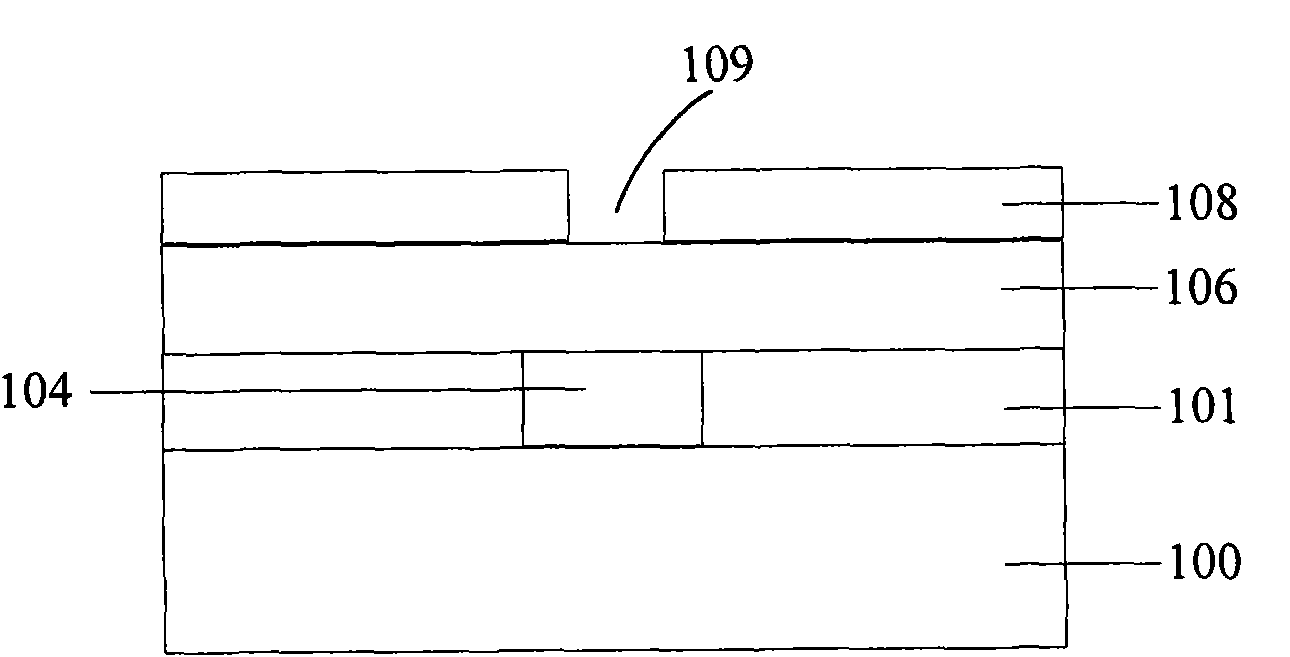

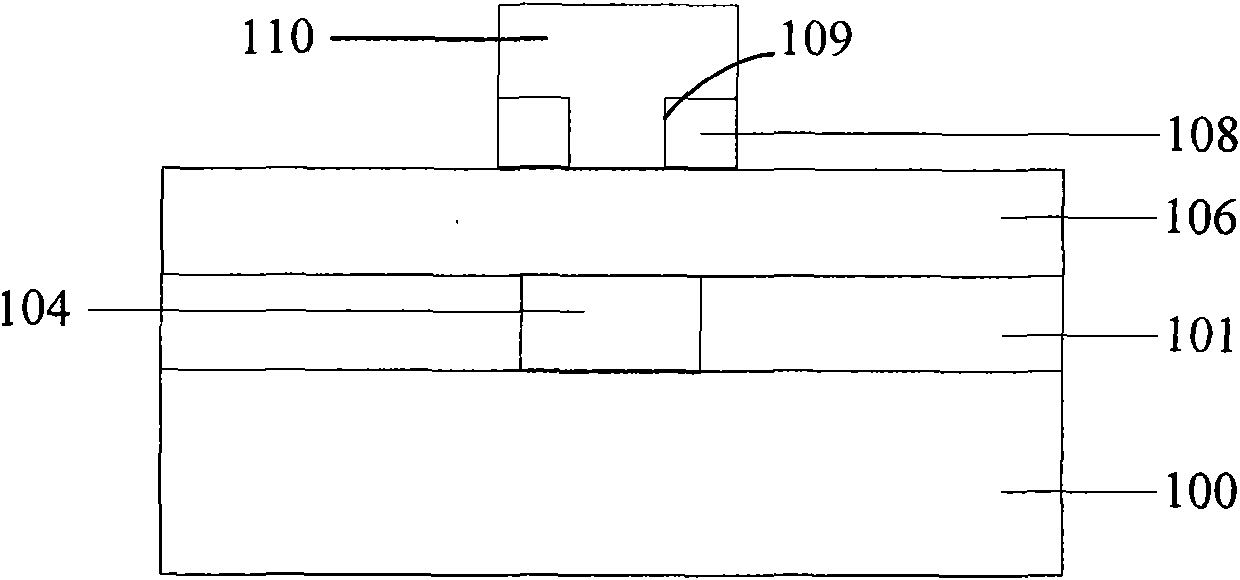

Structure of channel shielded Rom memory unit and producing method thereof

InactiveCN1472817AReduce lateral spreadImprove featuresSolid-state devicesSemiconductor/solid-state device manufacturingInternal memoryArray data structure

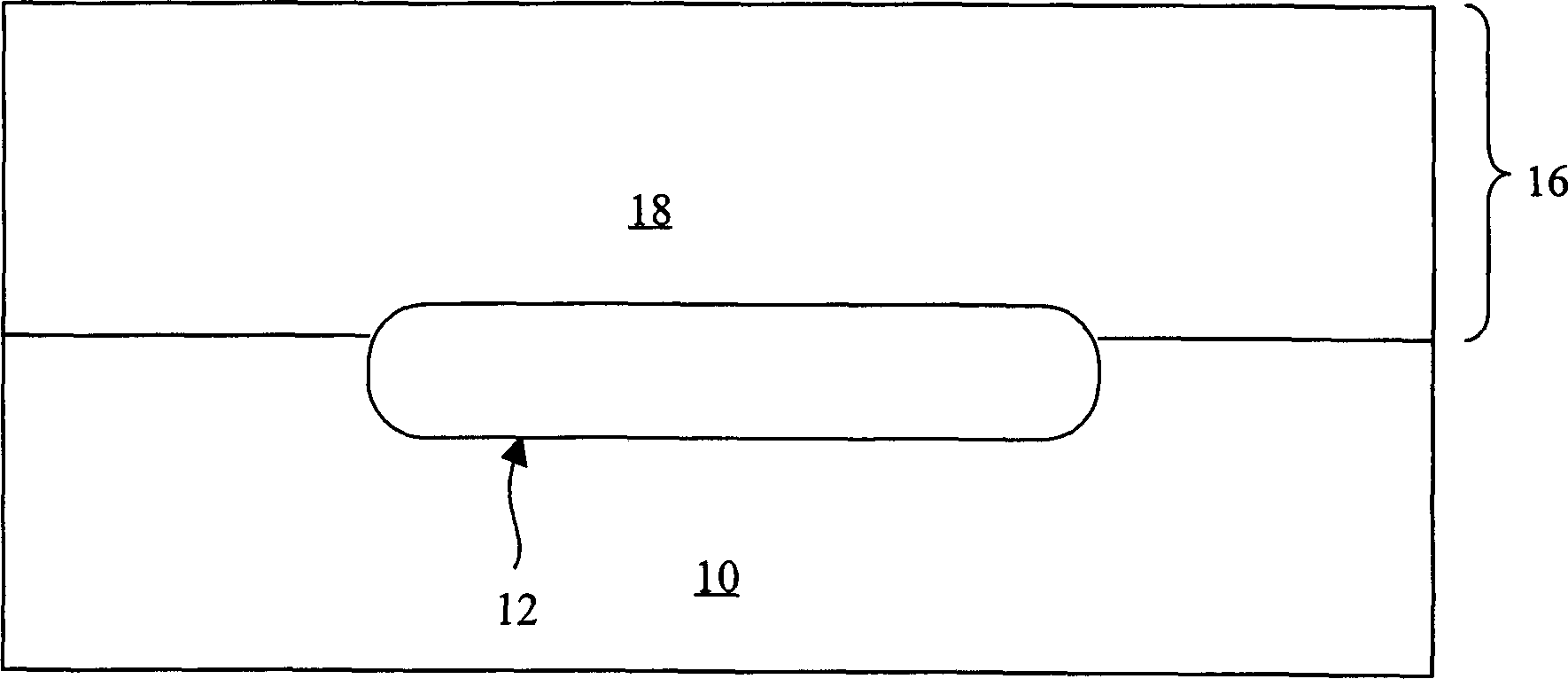

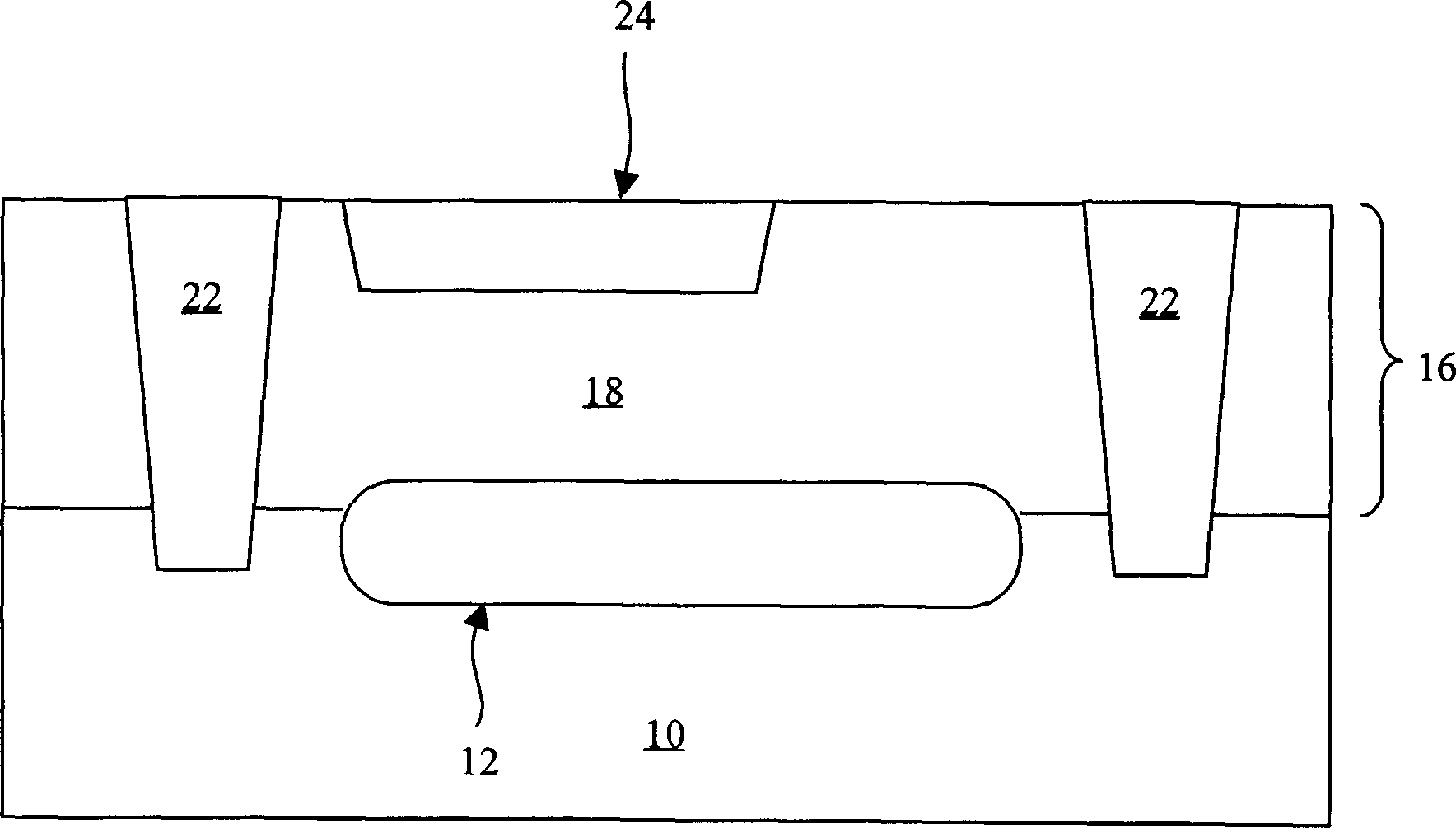

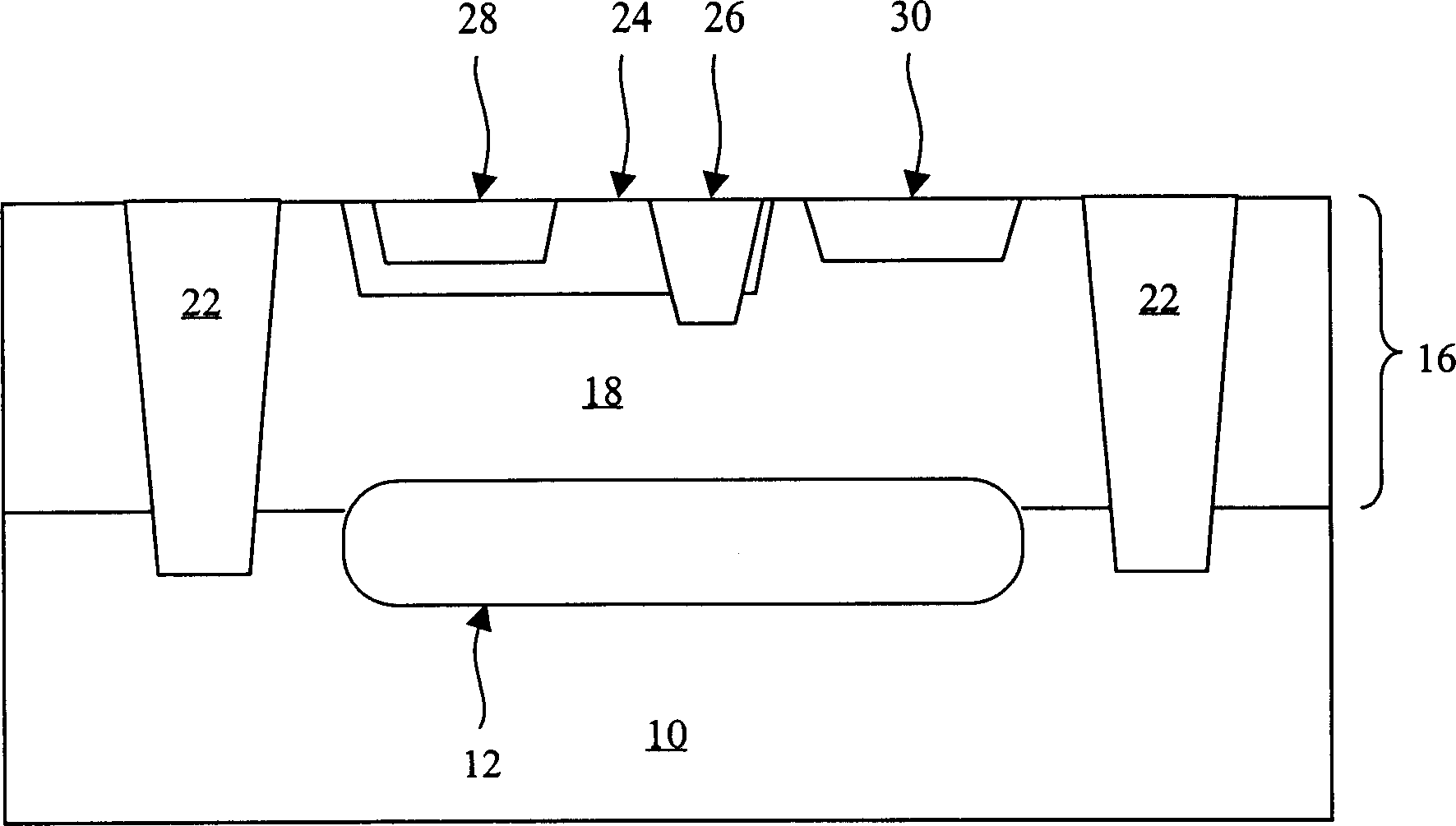

In the method, a shallow ditch is formed on surface of a silicon base material and to implant simultaneously buried ion and anti-punch through dopand in the silicon base material and array region of internal memory storage unit. The buried ion doping region is defined and multiditch is formed at array region of the storage unit. Then, a gate-oxide and a patternized polysilicon grid are formed at the silicon base material and furthermore multitransistor can be formed at peripheral circuit region of the silicon base material.

Owner:GRACE SEMICON MFG CORP

Surface grid-type static induction transistor

InactiveCN104810395AImprove transconductanceReduce parasitic capacitanceTransistorSemiconductor/solid-state device manufacturingParasitic capacitanceVoltage drop

The invention relates to a normally closed surface grid-type static induction transistor (SIT) of low power and a manufacturing method. The transistor is formed by parallelly connecting a drain electrode, a substrate of N+ low resistance monocrystal located on the drain electrode, an N- high resistance epitaxial layer located on the substrate of N+ low resistance monocrystal and multiple mutually parallelly-connected SIT units located in the N- high resistance epitaxial layer, wherein the active region uses the short channel design. The transistor is capable of enabling the impurity concentration of the device grid body to be high and enabling the impurity distribution to be more uniform under the corresponding technology support, reducing the own voltage drop of the grid body, increasing the sensitivity of the grid control, improving the device transconductance, reducing the grid source area, reducing the stray capacitance of the grid source, and increasing the SIT working frequency. Compared with the prior art, the short channel design is completely improved revolutionarily.

Owner:LANZHOU UNIVERSITY

Column shaped structure nano-silicon/non crystal silicon carbon composite photoconductive layer liquid crystal light valve and its preparation method

InactiveCN1493899AHigh-resolutionReduce lateral spreadNon-linear opticsCarbon compositesLiquid crystal light valve

A liquid crystal light valve with composite optical conducting nano Si / non-crystal SiC layer having cylindrical structure is sequentially composed of the first optical glass, the first transparent electric conductive film, optical conducting layer, light barrier layer, medium reflecting layer, the first and the second LC orientating layer, the second transparent electric conductive film and the second optical glass. It features that an anisotropic composite optical conducting nano Si / non-crystal SiC layer having cylindrical structure is plated on said first transparent electric conductive film. Its advantages are less transverse diffusion of current carriers, and high resolution of LC light valve.

Owner:ZHEJIANG UNIV

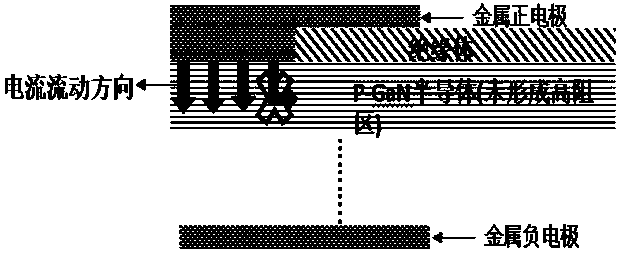

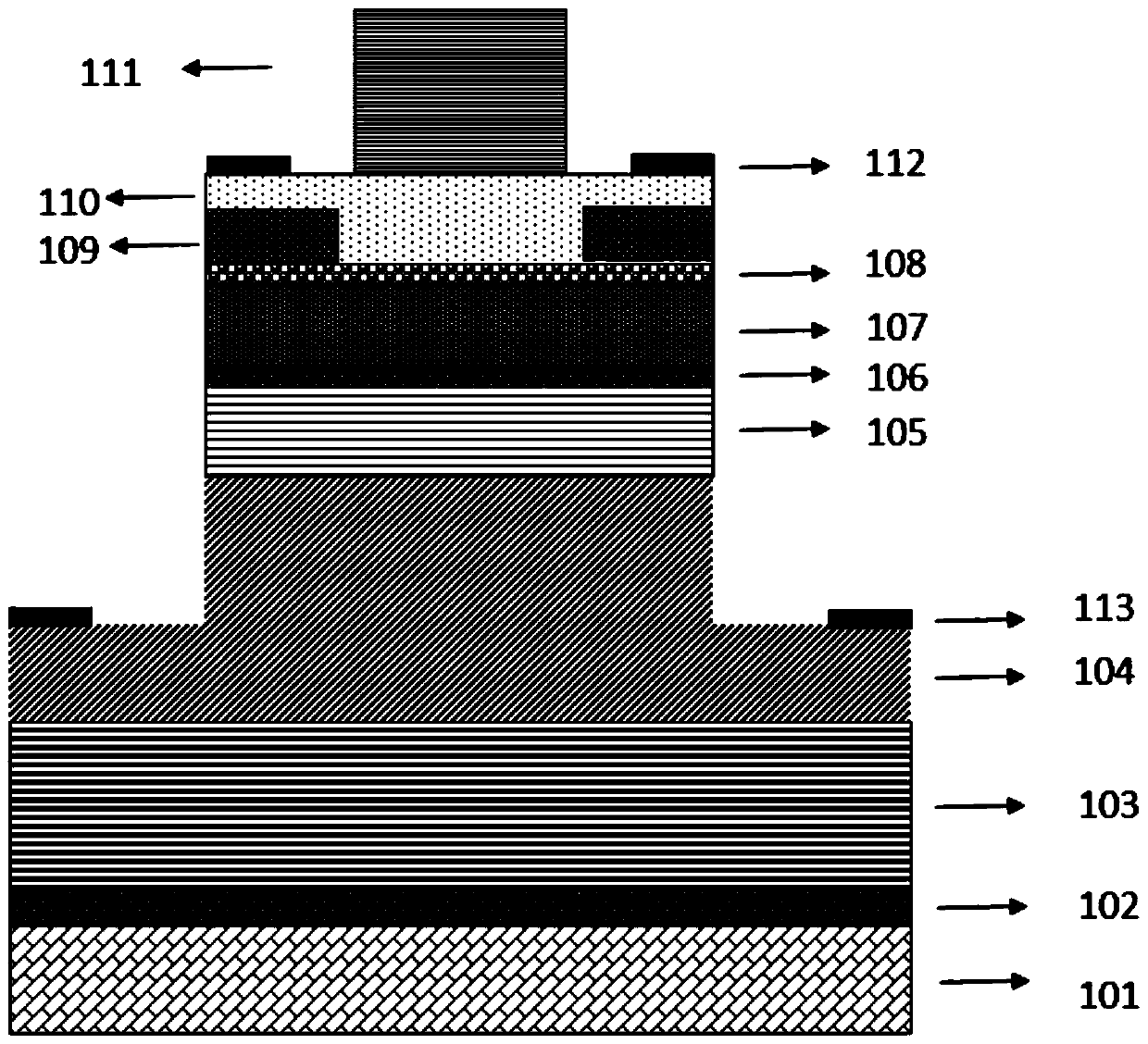

VCSEL device with high-dielectric-constant limiting hole and preparation method thereof

PendingCN110277732AUnexpected effectReduce lateral spreadLaser detailsSemiconductor lasersEngineeringNitride

The invention discloses a VCSEL device with a high-dielectric-constant current limiting hole and a preparation method thereof. An epitaxial structure of the device sequentially comprises a substrate, a buffer layer, a nitride epitaxial DBR and an N-type semiconductor transmission layer in the epitaxial growth direction. The N-type semiconductor transmission layer is divided into two parts, wehrein the lower layer completely covers the nitride epitaxy DBR. A multi-quantum well layer, a P-type current blocking layer and a P-type semiconductor transmission layer are sequentially arranged on the N-type semiconductor transmission layer; a P-type heavily-doped semiconductor transmission layer; and the outer side of the upper surface of the P-type heavily-doped semiconductor transmission layer is provided with an annular high-dielectric-constant insulating layer which is made of non-doped HfO2 or Ta2O5. Compared with a device with a tunneling junction, the device with the high-dielectric-constant current limiting hole has the advantages that the process time can be reduced by nearly 40%, the light-emitting threshold value can be reduced by about 0.5 mA, and the output power at the temperature of 80 mA is improved by 14.3% compared with that of a conventional device.

Owner:HEBEI UNIV OF TECH

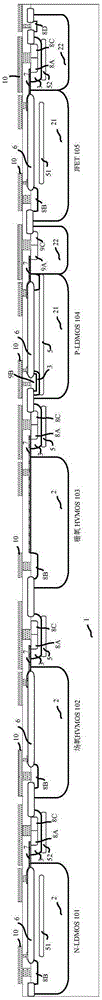

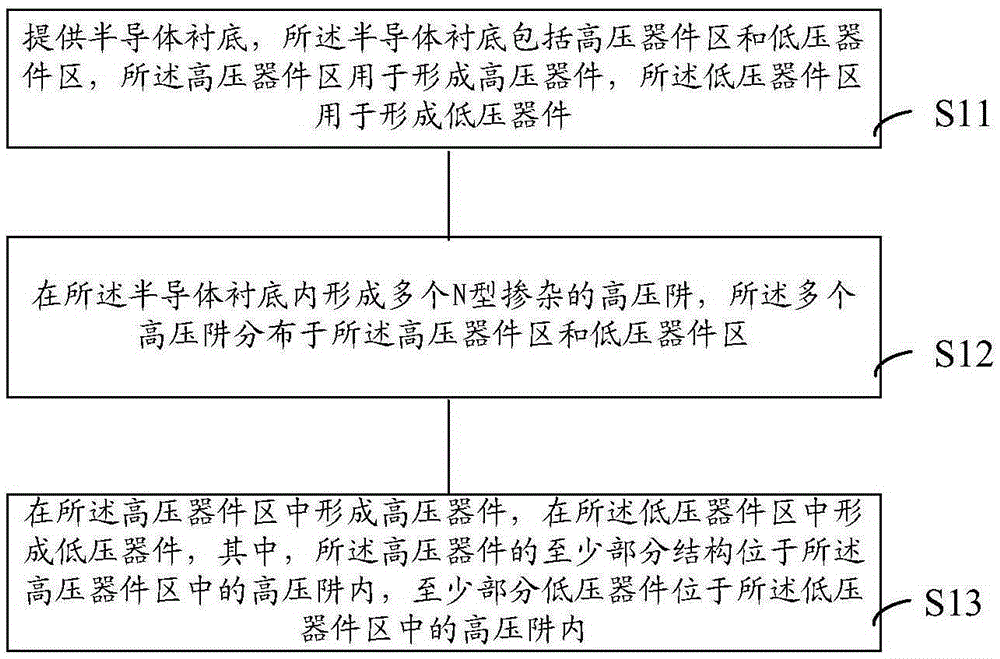

BCD device and manufacturing method thereof

ActiveCN105336736ASave forming stepsReduce the number of photolithographySolid-state devicesSemiconductor/solid-state device manufacturingCMOSLow voltage

The invention provides a BCD (Bipolar-CMOS-DMOS) device and a manufacturing method thereof. The BCD device comprises a semiconductor substrate and a plurality of N type doped high voltage wells, wherein the semiconductor substrate includes a high voltage device area and a low voltage device area; the high voltage device area is used for forming high voltage devices; the low voltage device area is used for forming low voltage devices; the plurality of N type doped high voltage wells are distributed in the high voltage device area and the low voltage device area; at least part of the component structures of the high voltage devices are formed in the high voltage wells of the high voltage device area; and at least part of the low voltage devices are formed in the high voltage wells of the low voltage device area. The BCD device and the manufacturing method thereof can reduce the frequency for the photoetching process, and can be conductive to cost reduction and efficiency improvement.

Owner:HANGZHOU SILAN MICROELECTRONICS

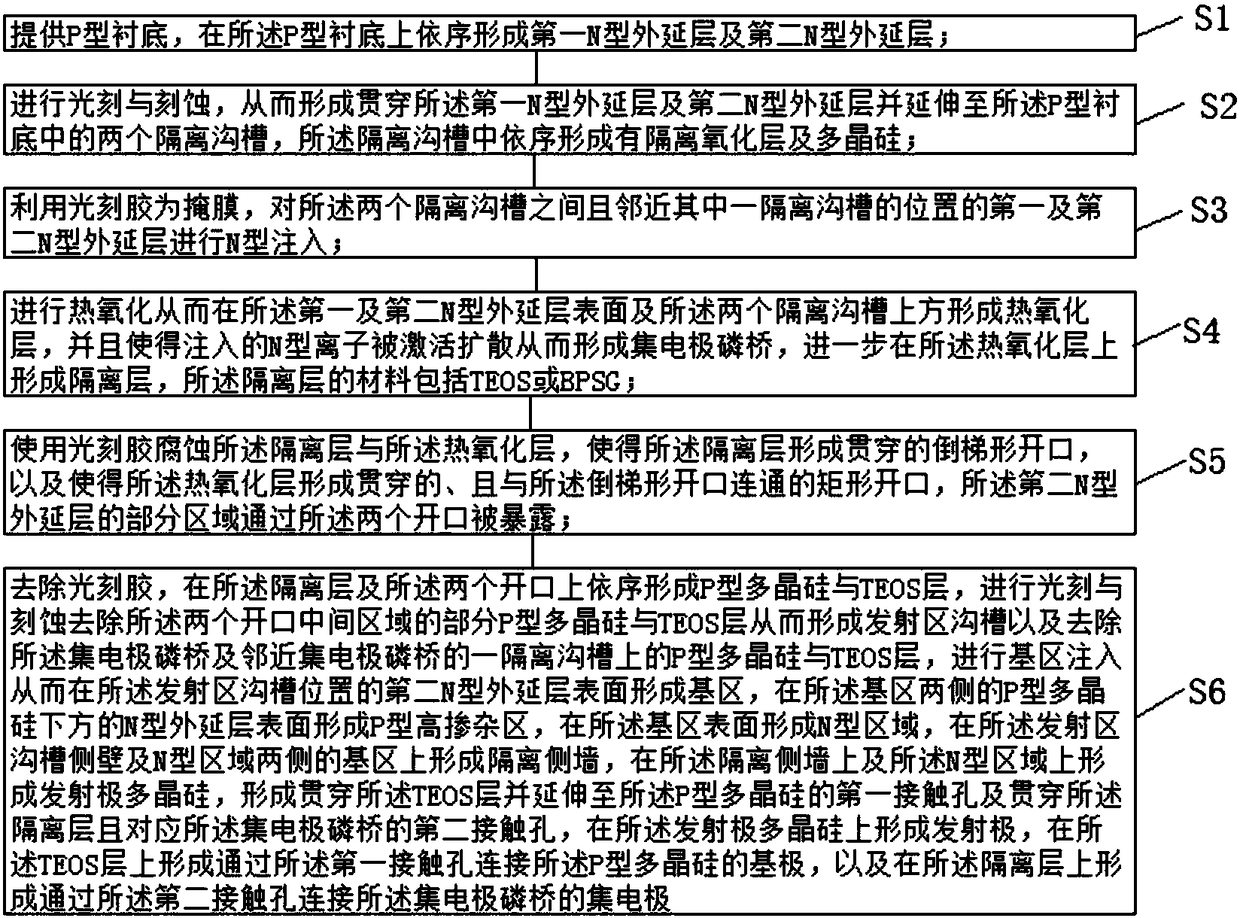

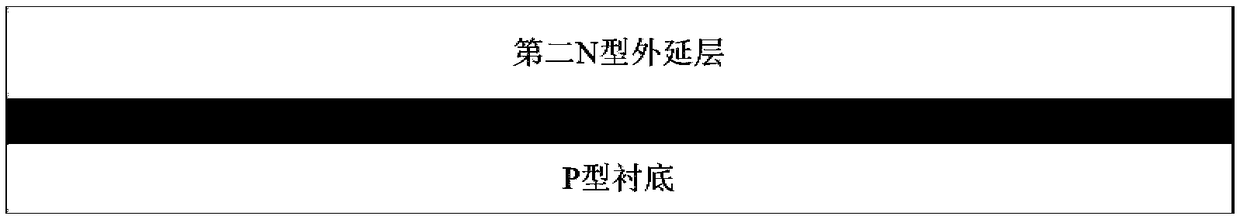

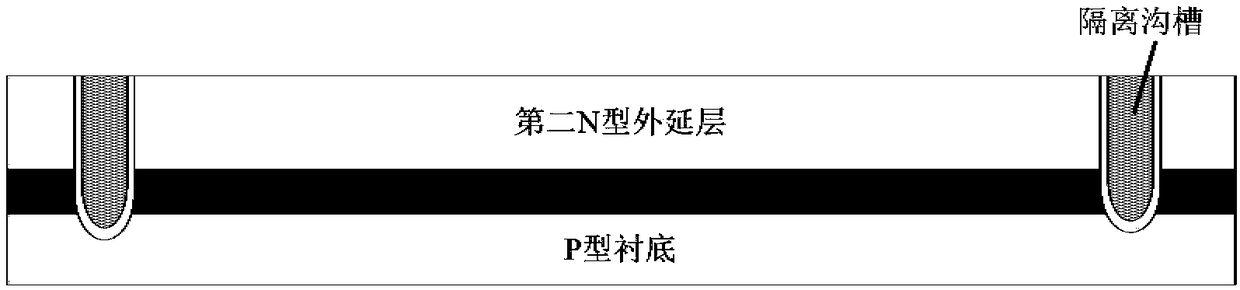

High-frequency triode and manufacturing method

InactiveCN108091568ALow costGood performance and reliabilityTransistorSemiconductor/solid-state device manufacturingEngineeringContact hole

The invention relates to a high-frequency triode and a manufacturing method. The high-frequency triode acquired through the manufacturing method comprises a P-type substrate, a first N-type epitaxiallayer and a second N-type epitaxial layer, two isolation grooves, a collector-electrode phosphorus bridge, a thermal oxide layer and an isolation layer, an inverted trapezoidal opening penetrating thethermal oxide layer, a rectangular opening which penetrates the isolation layer and is connected with the inverted trapezoidal opening, P-type polysilicon and a TEOS layer, an emitting electrode groove penetrating the P-type polysilicon and the TEOS layer, a base region, P-type highly-doped regions on two sides of the base region, an N-type region formed on the surface of the base region, an isolation side wall, emitting electrode polysilicon, a first contact hole, a second contact hole, an emitting electrode, a base electrode and a collector electrode. The first N-type epitaxial layer can bean N-type highly-doped epitaxial layer. The second N-type epitaxial layer is an N-type low-doped epitaxial layer. An isolation oxide layer and the polysilicon are sequentially formed in the isolationgrooves. The material of the isolation layer includes TEOS or BPSG.

Owner:SHENZHEN JINGTE INTELLIGENT MFG TECH CO LTD

Electro-optic modulator

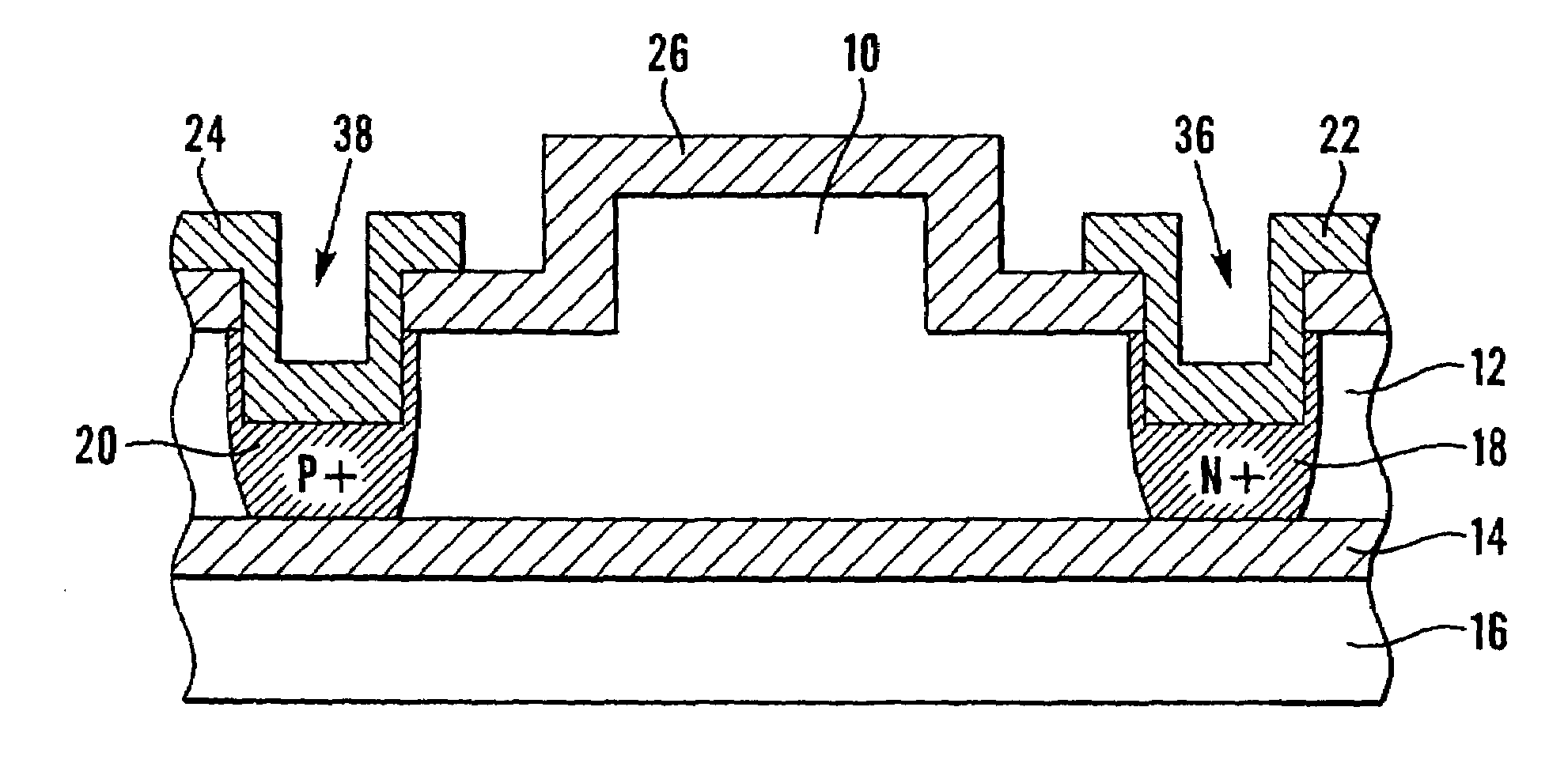

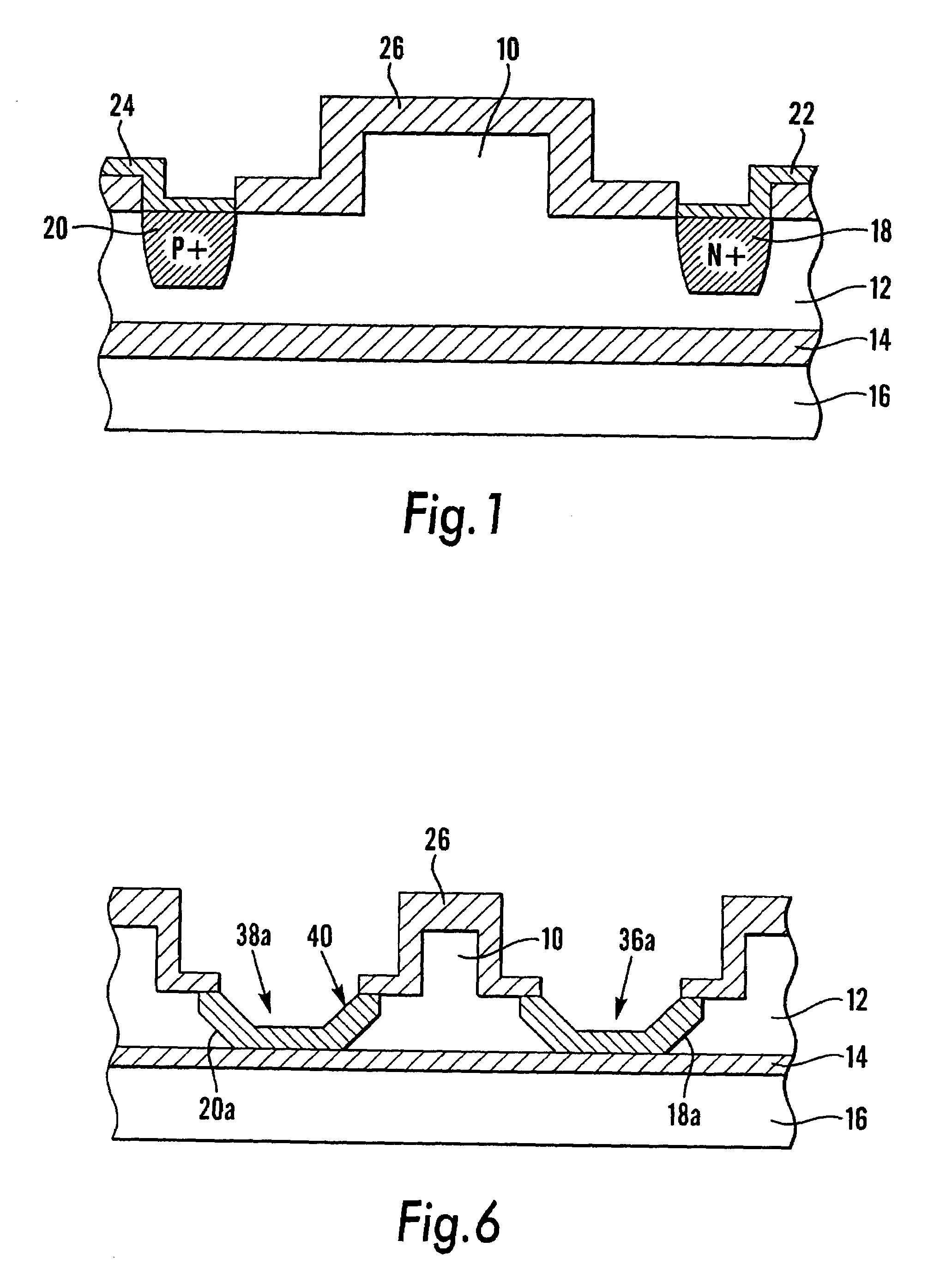

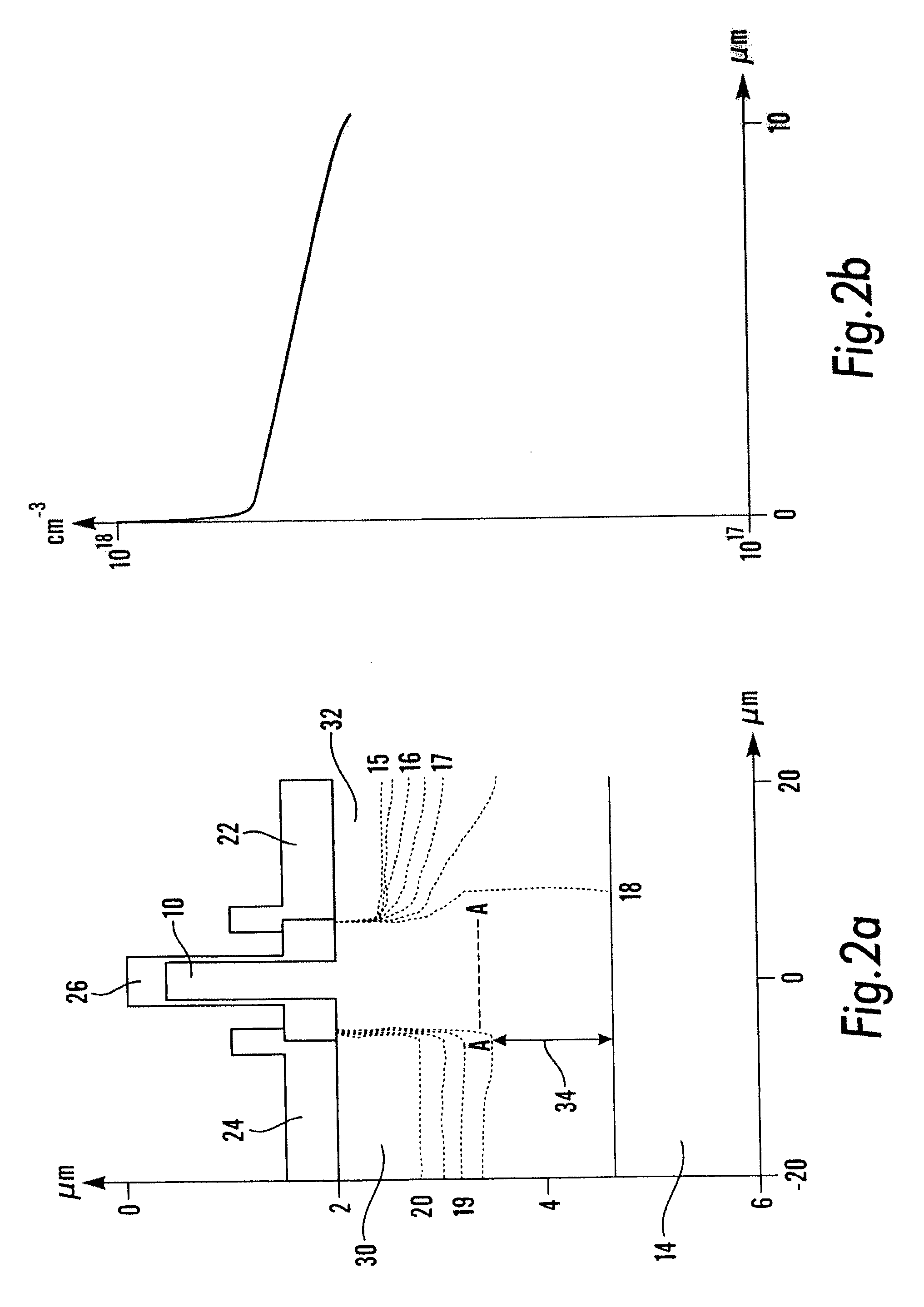

InactiveUS7684655B2Clearly definedEliminate the effects ofSolid-state devicesSemiconductor/solid-state device manufacturingDopantDiffusion

An electro-optic device includes a semiconducting layer in which is formed a waveguide, a modulator formed across the waveguide comprising a p-doped region to one side and an n-doped region to the other side of the waveguide, wherein at least one of the doped regions extends from the base of a recess formed in the semiconducting layer. In this way, the doped regions can extend further into the semiconducting layer and further hinder escape of charge carriers without the need to increase the diffusion distance of the dopant and incur an additional thermal burden on the device. In an SOI device, the doped region can extend to the insulating layer. Ideally, both the p and n-doped regions extend from the base of a recess, but this may be unnecessary in some designs. Insulating layers can be used to ensure that dopant extends from the base of the recess only, giving a more clearly defined doped region. The (or each) recess can have non-vertical sides, such as are formed by v-groove etches, A combination of a vertical sidewall at the base of the recess and a non-vertical sidewall at the opening could be used.

Owner:KOTURA

Novel shape deep hole with outlet water flow lateral diffusion reduction function

PendingCN106836154AReduced lateral spread angleAvoid shockBarrages/weirsHydro energy generationWater flowStructural engineering

The invention discloses a novel shape deep hole with an outlet water flow lateral diffusion reduction function and belongs to the technical field of drainage building design. The novel shape deep hole with the outlet water flow lateral diffusion reduction function comprises a deep hole body with an emergency valve, a maintenance valve and a transverse seam, the deep hole body comprises an inlet, a barrel and an outlet, both the two sides of the outlet are provided with abutment piers, both the inlet cross section and the outlet cross section of the deep hole body are rectangular, the inlet cross section vertical height is higher than the outlet cross section vertical height, the deviation of the vertical height is not more than 35%, and the transverse width of the inlet cross section is smaller than the transverse width of the outlet cross section. The novel shape deep hole with the outlet water flow lateral diffusion reduction function has a more reasonable shape and is suitable for the deep hole of which sizes of the inlet cross section and the outlet cross section are different, and meanwhile, the phenomenon of outlet water flow lateral diffusion is significantly reduced, water flow is prevented from lashing against the abutment piers, and the structure stability of the deep hole outlet abutment piers is protected effectively.

Owner:NANJING HYDRAULIC RES INST

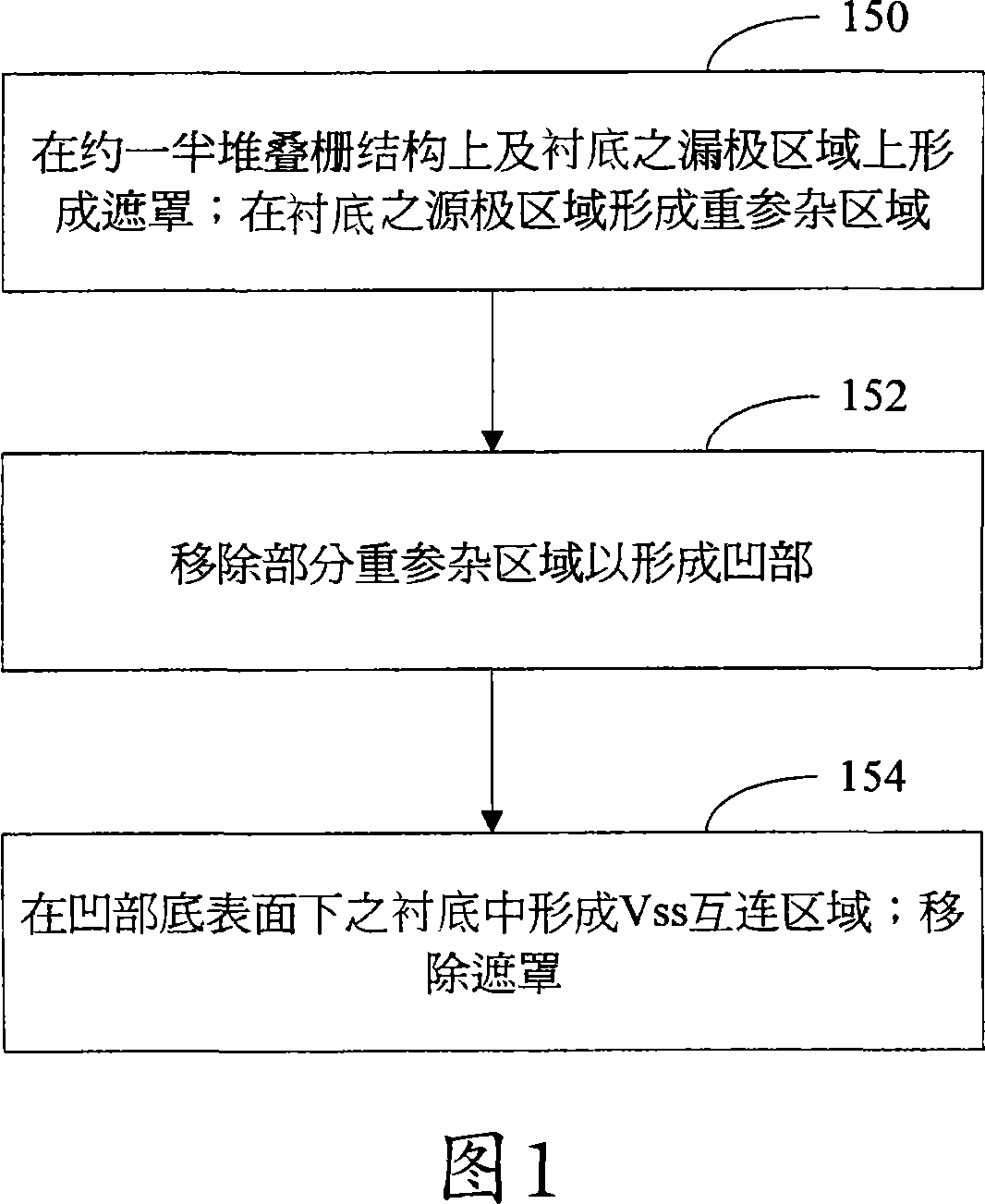

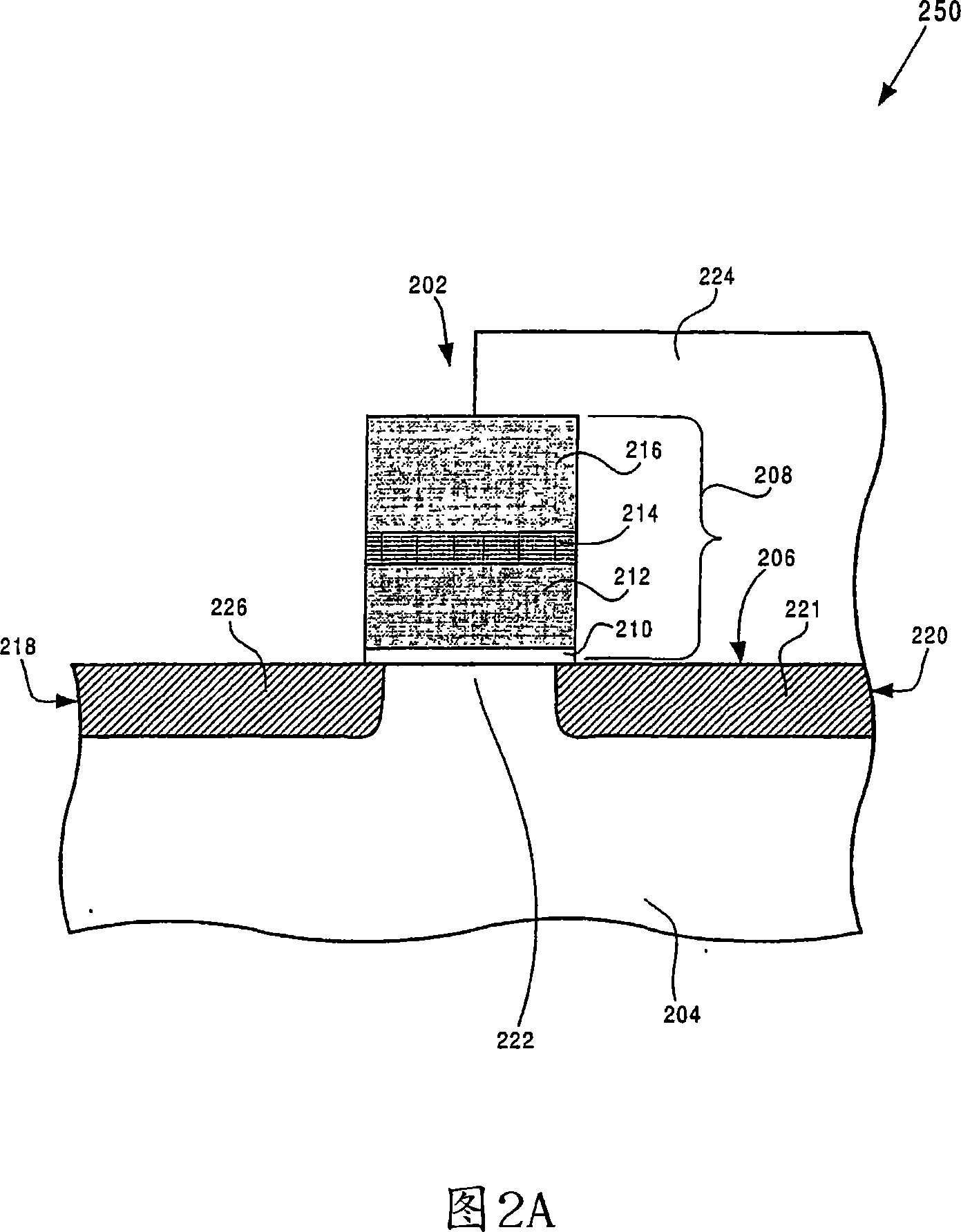

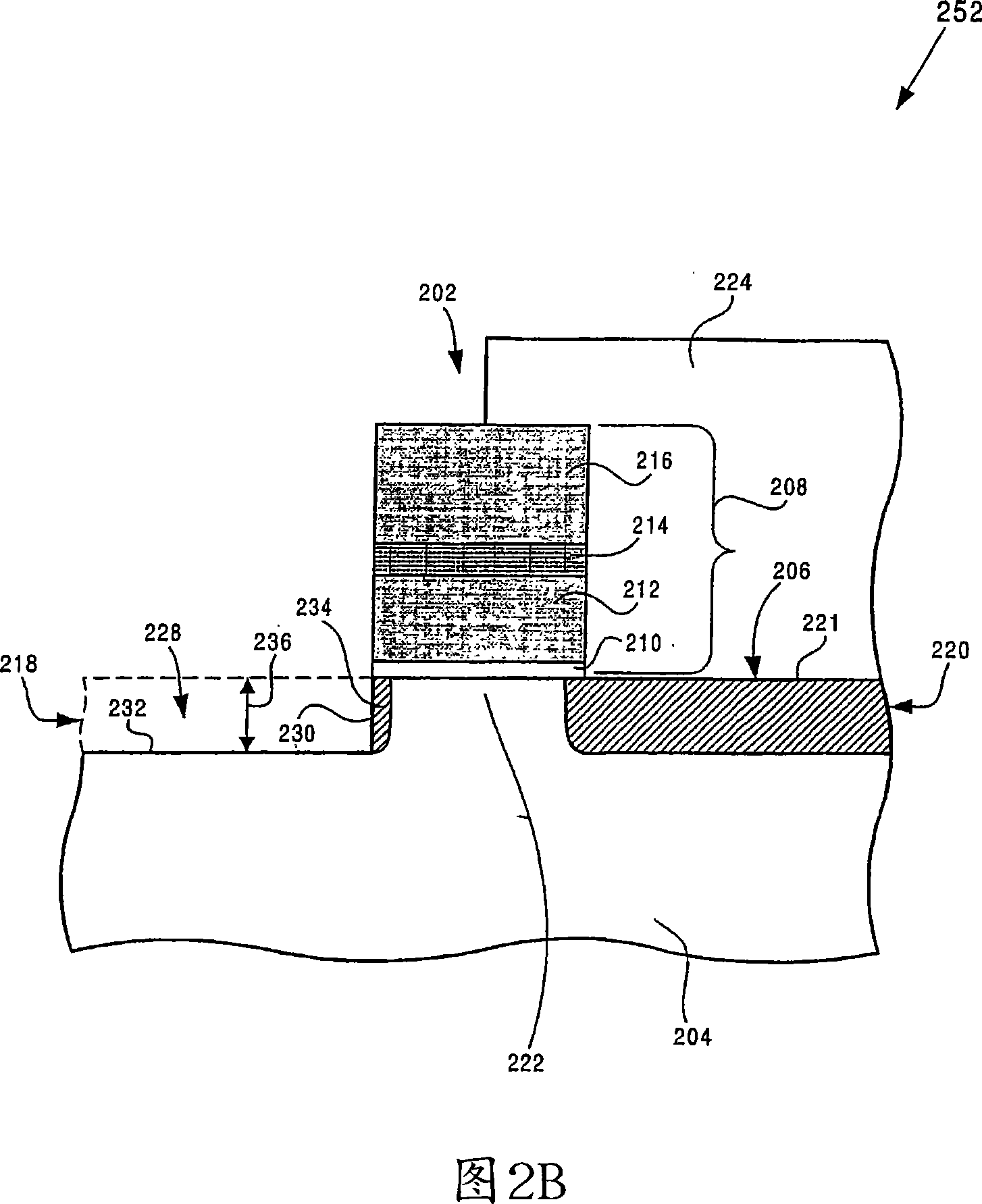

Structure and method for low Vss resistance and reduced dibl in a floating gate memory cell

ActiveCN1926671AReduce lateral spreadDrain Induced Energy Barrier ReductionSemiconductor/solid-state device manufacturingSemiconductor devicesLateral diffusionElectrical and Electronics engineering

According to one exemplary embodiment, a floating gate memory cell (202) comprises a stacked gate structure (208) situated on a substrate (204) and situated over a channel region (222) in the substrate (204). The floating gate memory cell (202) further comprises a recess (228) formed in the substrate (204) adjacent to the stacked gate structure (208), where the recess (228) has a sidewall (230), a bottom (232), and a depth (236). According to this exemplary embodiment, the floating gate memory cell (202) further comprises a source (234) situated adjacent to the sidewall (230) of the recess (228) and under the stacked gate structure (208). The floating gate memory cell (202) further comprises a Vss connection region (238) situated under the bottom (232) of the recess (228) and under the source (234), where the Vss connection region (238) is connected to the source (234). The Vss connection region (238) being situated under the bottom (232) of the recess (228) causes the source (234) to have a reduced lateral diffusion in the channel region (222).

Owner:INFINEON TECH LLC

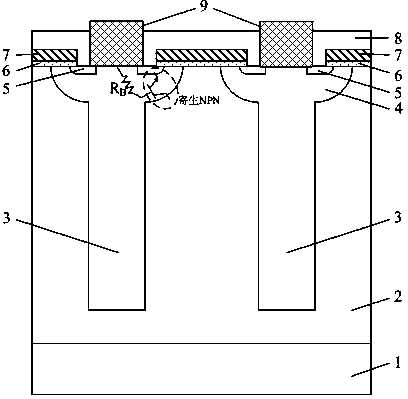

NPN transistor and fabricating method thereof

InactiveCN101866856AReduce lateral spreadReduced series resistanceTransistorSemiconductor/solid-state device manufacturingEngineeringContact position

The invention provides an NPN transistor and a fabricating method thereof, wherein the NPN transistor comprises a semiconductor substrate, an N-type buried layer region positioned in the semiconductor substrate, a collector electrode positioned in the N-type buried layer region, base electrodes positioned on the N-type buried layer region and the collector electrode, a second oxidization layer positioned on the surface of the base electrodes, an emitting electrode, shallow-doped metal contacts positioned in the base electrodes at two sides of the emitting electrode, side walls positioned at two sides of the emitting electrode and the second oxidization layer and deep-doped regions positioned in the emitting electrode and the base electrodes at two sides of the side walls, wherein the second oxidization layer is internally provided with a contact hole penetrating the thickness of the second oxidization layer; the emitting electrode is filled in the contact hole and cover the surface of the second oxidization layer around the contact hole; and the deep-doped regions are deeper than shallow-doped regions in the base electrodes. The invention can greatly reduce the series resistance, and can lower the influence of side and transient diffusion.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

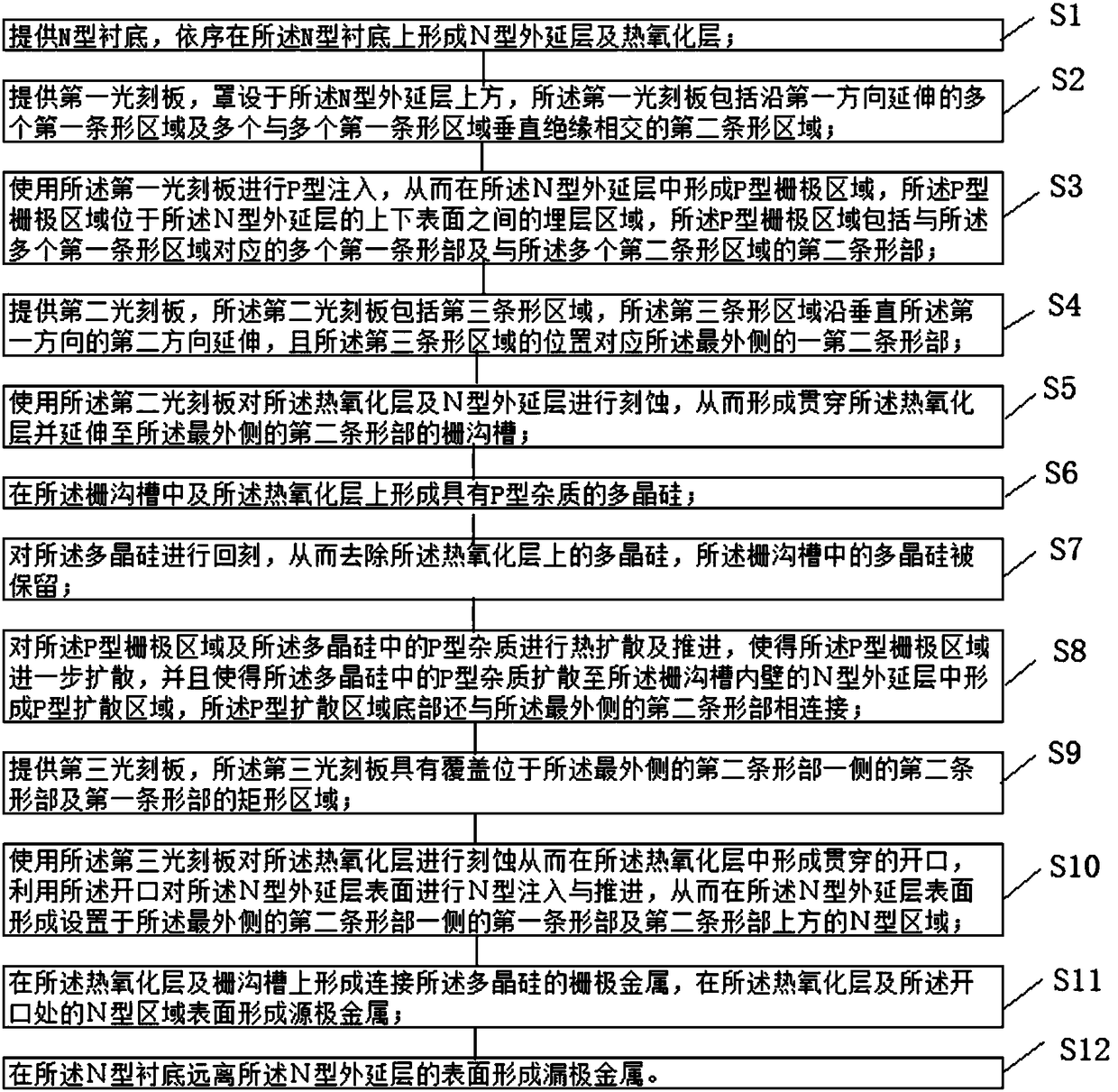

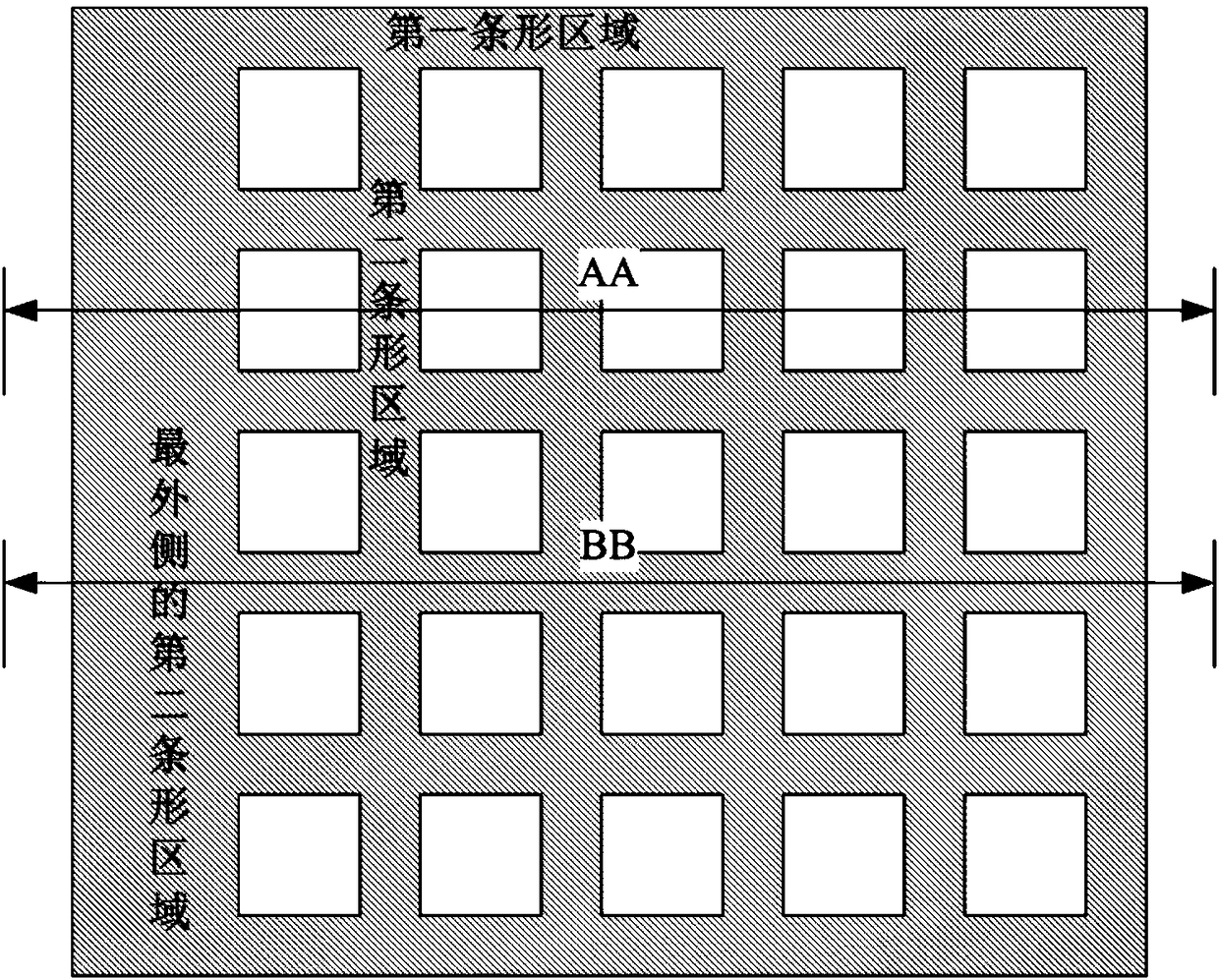

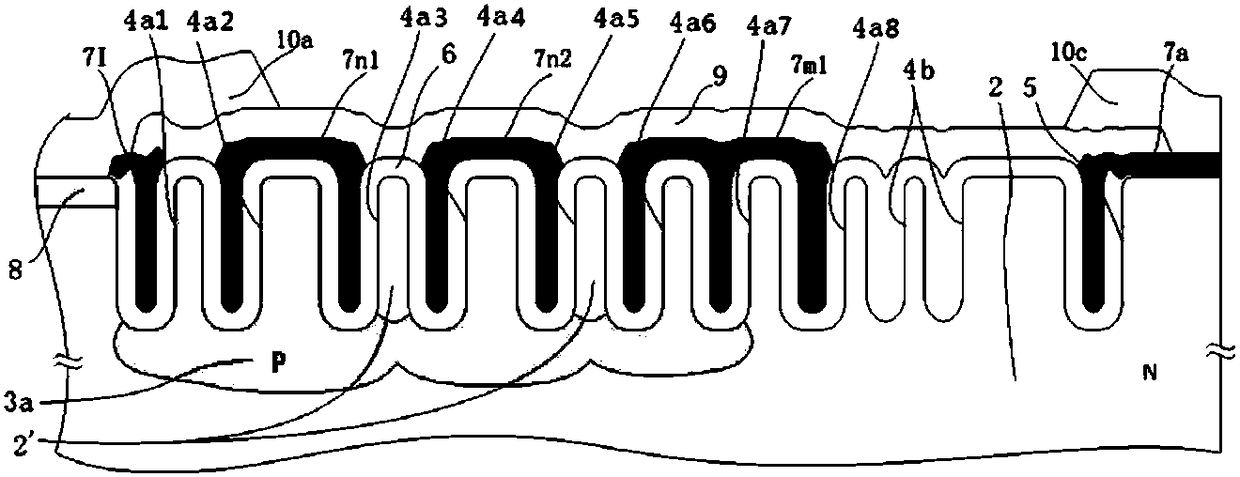

Junction field-effect transistor and manufacturing method thereof

InactiveCN108091575ALow propulsion temperatureShort advance timeSemiconductor/solid-state device manufacturingSemiconductor devicesPolycrystalline siliconOxide

The invention relates to a junction field-effect transistor and a manufacturing method thereof. The junction field-effect transistor obtained by the manufacturing method includes an N-type substrate,an N-type epitaxial layer, a buried P-type gate region formed in the N-type epitaxial layer, an oxide layer, a gate trench penetrating through the oxide layer and extending to the P-type gate region,a P-type diffusion region formed on the inner wall of the gate trench and connected to the P-type gate region, polysilicon formed in the gate trench, an N-type region formed on the surface of the N-type epitaxial layer, an opening penetrating through the oxide layer and corresponding to the N-type region, gate metal formed on the oxide layer and the gate trench and connected to the polysilicon, source metal, and drain metal. The P-type gate region includes a plurality of first parallel bar portions and a plurality of second bar portions perpendicularly intersecting with the first bar portions,the outermost second bar portion being in contact with the gate trench and the P-type diffusion region, and the first bar portion at one side of the outermost second bar portion and the second bar portion being located below the N-type region.

Owner:眉山国芯科技有限公司

Groove infield plate buried layer termination structure of semiconductor device and manufacturing method

ActiveCN108336016AHigh terminal efficiencyReduce lateral spreadSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A groove infield plate buried layer termination structure of a semiconductor device and a manufacturing method belongs to the field of the semiconductor device. The termination structure of the semiconductor device includes an air floating doping buried layer and a plurality of grooves, which are located in a semiconductor area of the semiconductor device. An n-shaped infield plate is formed in atleast one groove among the grooves, and an m-shaped infield plate is formed in at least one groove. The termination structure has good termination efficiency, and the voltage endurance can be easilyadjusted through the number of the grooves and the length of the air floating doping buried layer.

Owner:JILIN SINO MICROELECTRONICS CO LTD

Methdo for fabricating bipolar type longitudinal plane mode transistors

InactiveCN1797720AReduce areaSaturation pressure drop reductionSemiconductor/solid-state device manufacturingElectrical resistance and conductanceLongitudinal plane

The method includes steps: selecting a semiconductor substrate; forming non-intrinsic collector region in the semiconductor substrate; forming preparative layer of lower isolation layer of isolation transistor in the semiconductor substrate; forming intrinsic collector region on the non-intrinsic collector region; forming the lower isolation layer on the intrinsic collector region; on the intrinsic collector region, forming male contact to connect to non-intrinsic collector region; forming a upper isolation layer; forming following regions: intrinsic base region on the intrinsic collector region, and non-intrinsic base region on the intrinsic base region; forming emitter region on intrinsic base region and forming collector region on the male contact. Features are: using two isolation layers make area of transistor smaller; small block resistance on intrinsic base region; low saturation voltage of collector; obtaining dielectric film for protecting transistor through saving method.

Owner:SHANGHAI BEILING

Display panel and display device

PendingCN113838991AImprove luminous efficiencySuppress crosslightSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceRefractive index

The invention relates to a display panel and a display device. The display panel comprises a driving substrate, a reflection cup structure, a light emitting unit, a first packaging layer and a second packaging layer. The reflection cup structure comprises a plurality of comprising cavities arranged at intervals. The light-emitting unit is arranged in the comprising cavity. The first packaging layer and the second packaging layer are used for packaging the light-emitting unit. The reflection cup structure can form an important barrier for spacing the light-emitting units with different colors, and optical crosstalk and color crosstalk of the light-emitting units are inhibited. The refractive index of the first packaging layer is smaller than that of the second packaging layer, so that the emergent angle of light entering the second packaging layer from the first packaging layer through the contact interface of the first packaging layer and the second packaging layer is smaller than a critical angle, and the propart that the light is transversely transmitted to other structures to be absorbed is reduced; therefore, the light extraction efficiency of the display panel is improved.

Owner:CHENGDU VISTAR OPTEOLECTRONICS CO LTD

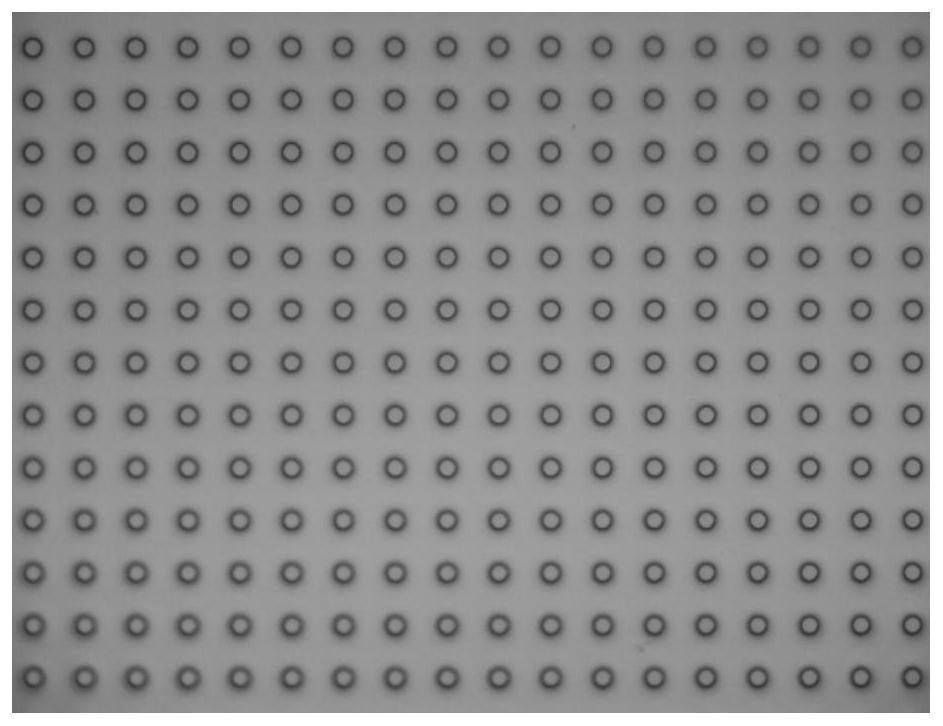

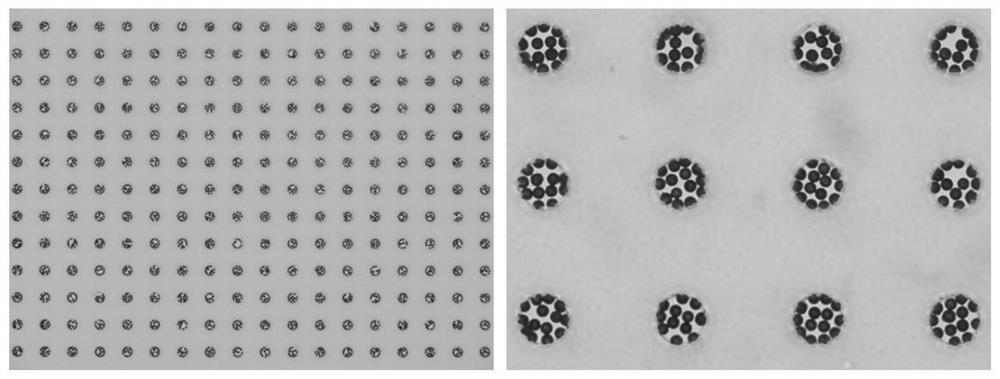

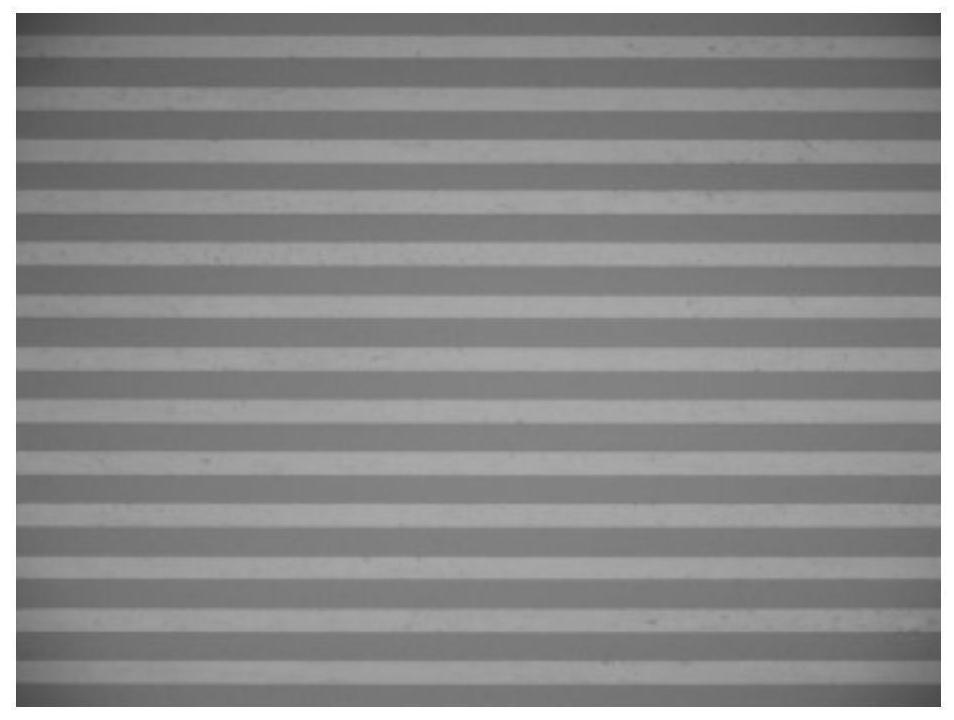

High-resolution spatial omics detection method for tissue sample

ActiveCN113604547AEasy to makeReduce instrument costMicrobiological testing/measurementICT adaptationTissue sampleMicrocarrier

The invention is applicable to a high-resolution spatial omics detection device, system and method for a tissue sample, and provides the high-resolution spatial omics detection device, system and method for the tissue sample, respectively comprising a slide with a micro-well reaction chamber array capable of accommodating a micro-carrier, a method for modifying nucleic acid molecule identifiers and a method for reducing cross contamination of omics information in the process of capturing spatial omics information of the tissue sample. By adopting the spatial omics detection method disclosed by the invention, the resolution ratio of spatial omics detection is remarkably improved, the detection cost is reduced, and meanwhile, the cross contamination of spatial omics information is fundamentally reduced.

Owner:JILIN UNIV

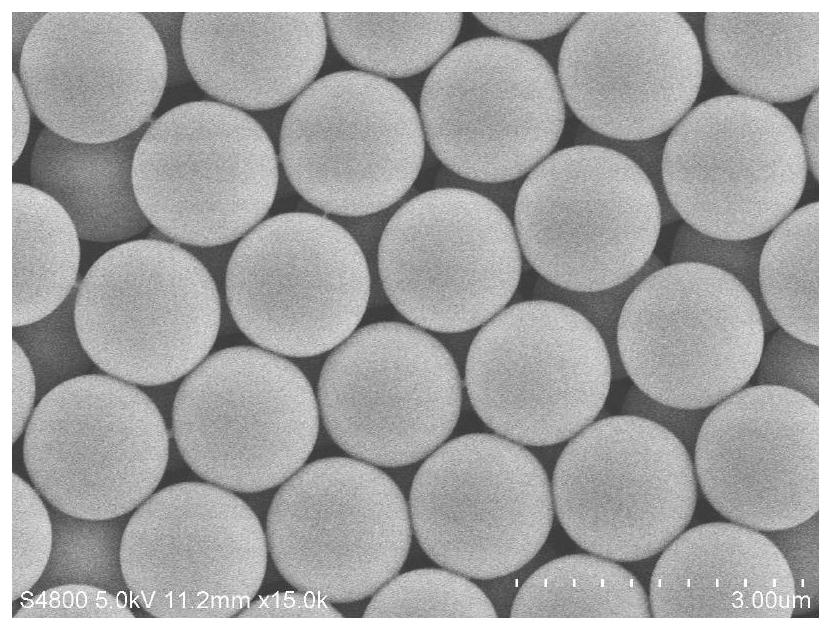

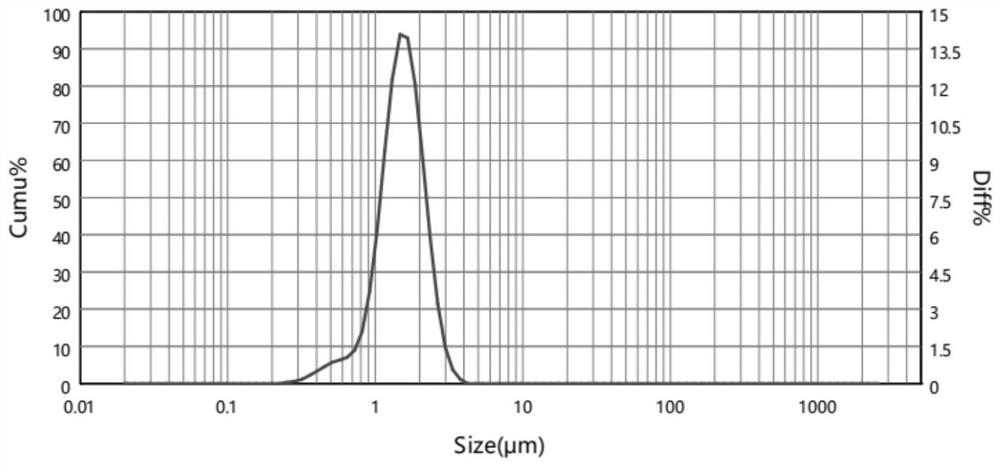

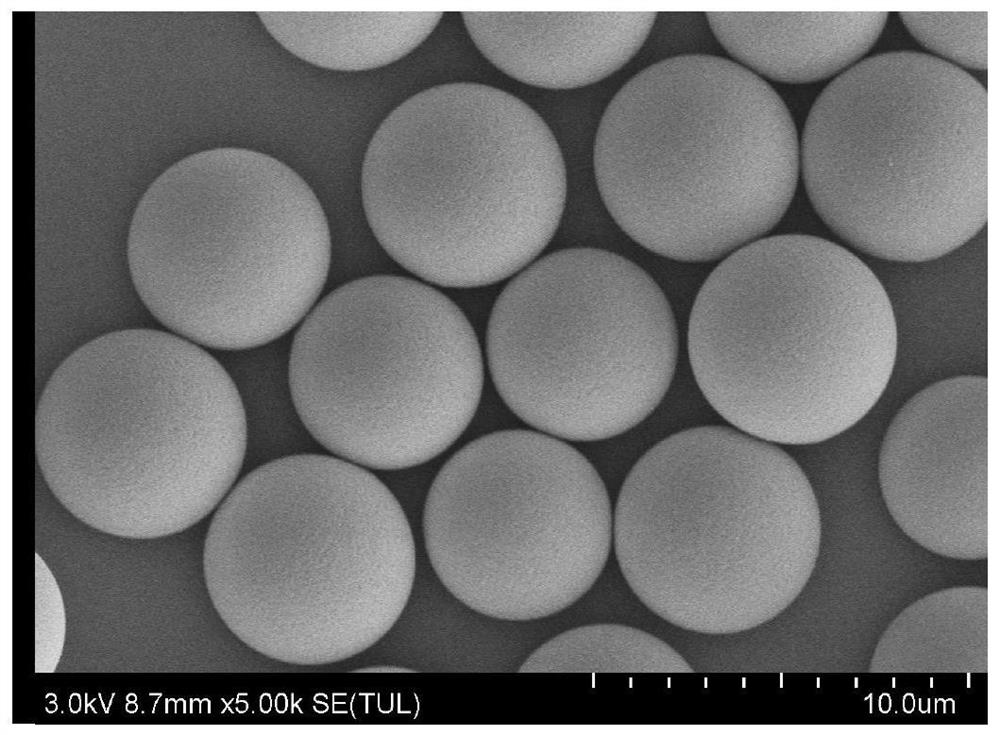

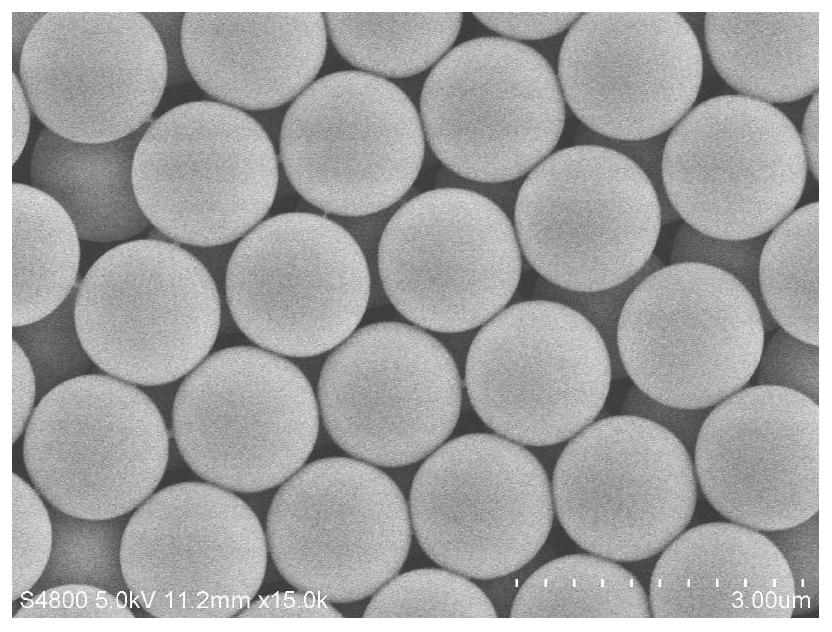

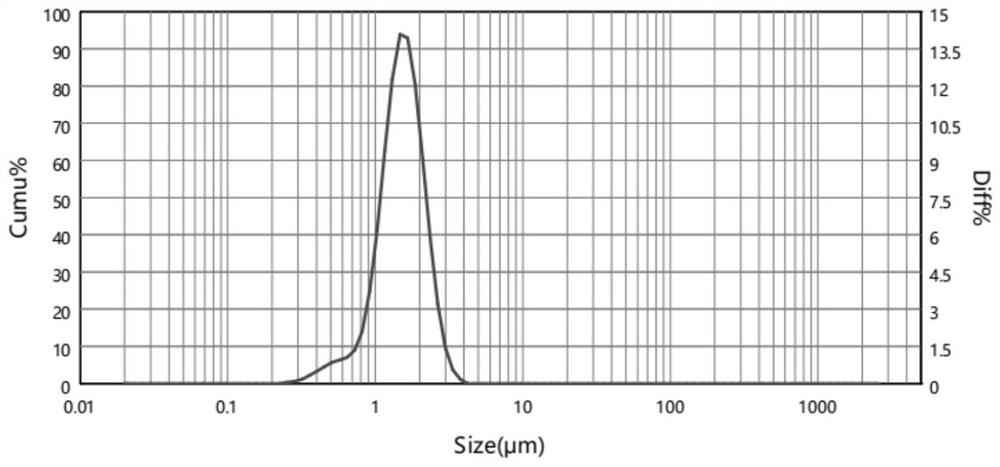

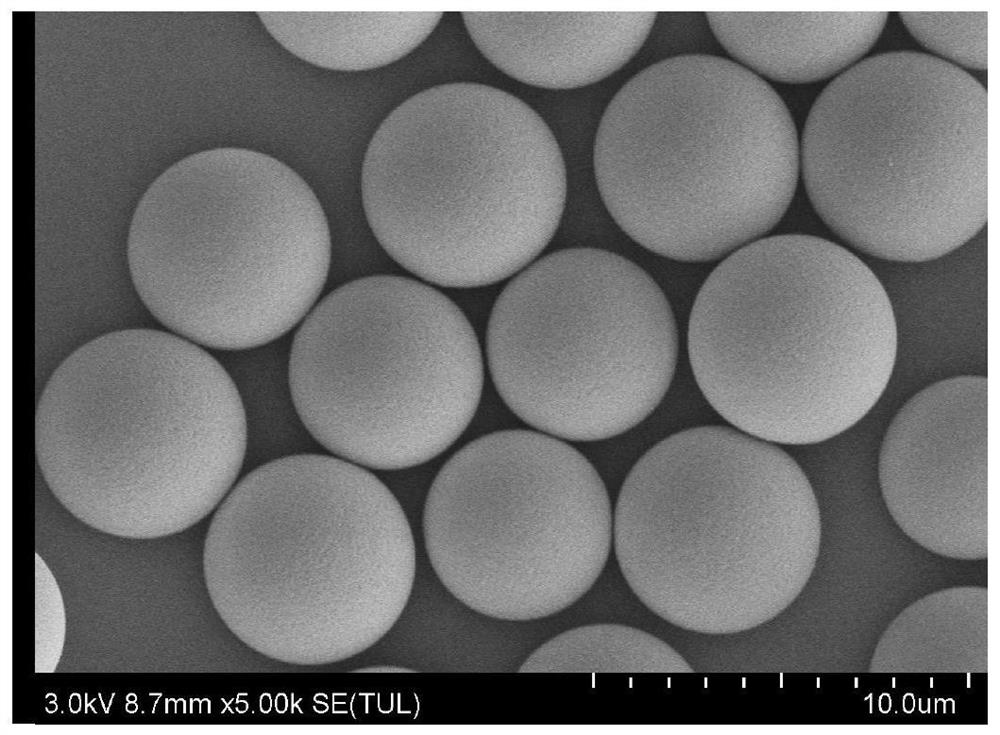

Vinyl monomer-polyvinyl cross-linking agent copolymer nonporous microsphere as well as preparation method and application thereof

ActiveCN113512152AMake up for the shortcomings of low specific surface area and low ion exchange capacityEasy to separateOther chemical processesComponent separationPolymer scienceIon exchange

The invention relates to a vinyl monomer-polyvinyl cross-linking agent copolymer nonporous microsphere as well as a preparation method and application thereof. The vinyl monomer-polyvinyl cross-linking agent copolymer non-porous microsphere comprises: a vinyl monomer-polyvinyl cross-linking agent copolymer mother sphere, wherein the vinyl monomer-polyvinyl cross-linking agent copolymer mother sphere is modified with a hydroxyl group; an epoxy compound, which is grafted to the vinyl monomer-polyvinyl cross-linking agent copolymer mother sphere through the hydroxyl group, wherein the epoxy compound comprises at least two epoxy groups. The vinyl monomer-polyvinyl cross-linking agent copolymer non-porous microsphere has good chemical and mechanical stability, excellent ion exchange performance, and high specific separation capability on hemoglobin and variants thereof.

Owner:SHENZHEN LIFOTRONIC TECH

Vinyl monomer-polyvinyl crosslinking agent copolymer non-porous microspheres and its preparation method and application

ActiveCN113512152BEasy to separateEfficient separationComponent separationOther chemical processesEpoxyPolymer science

The invention relates to a non-porous microsphere of a vinyl monomer-polyvinyl crosslinking agent copolymer, a preparation method and application thereof. Vinyl monomer-polyvinyl crosslinker copolymer non-porous microspheres include: vinyl monomer-polyvinyl crosslinker copolymer cue ball, vinyl monomer-polyvinyl crosslinker copolymer cue ball Modified with a hydroxyl group; an epoxy-based compound grafted to the vinyl monomer-polyvinyl cross-linking agent copolymer mother ball through the hydroxyl group, and the epoxy-based compound contains at least two epoxy groups. The vinyl monomer-polyvinyl cross-linking agent copolymer non-porous microsphere has good chemical and mechanical stability, has excellent ion exchange performance, and has high specific separation ability for hemoglobin and its variants.

Owner:SHENZHEN LIFOTRONIC TECH

Method and apparatus for improved resolution chromatography

ActiveUS20130313197A1Low drag on flowReduce resistanceIon-exchange process apparatusComponent separationHigh concentrationImage resolution

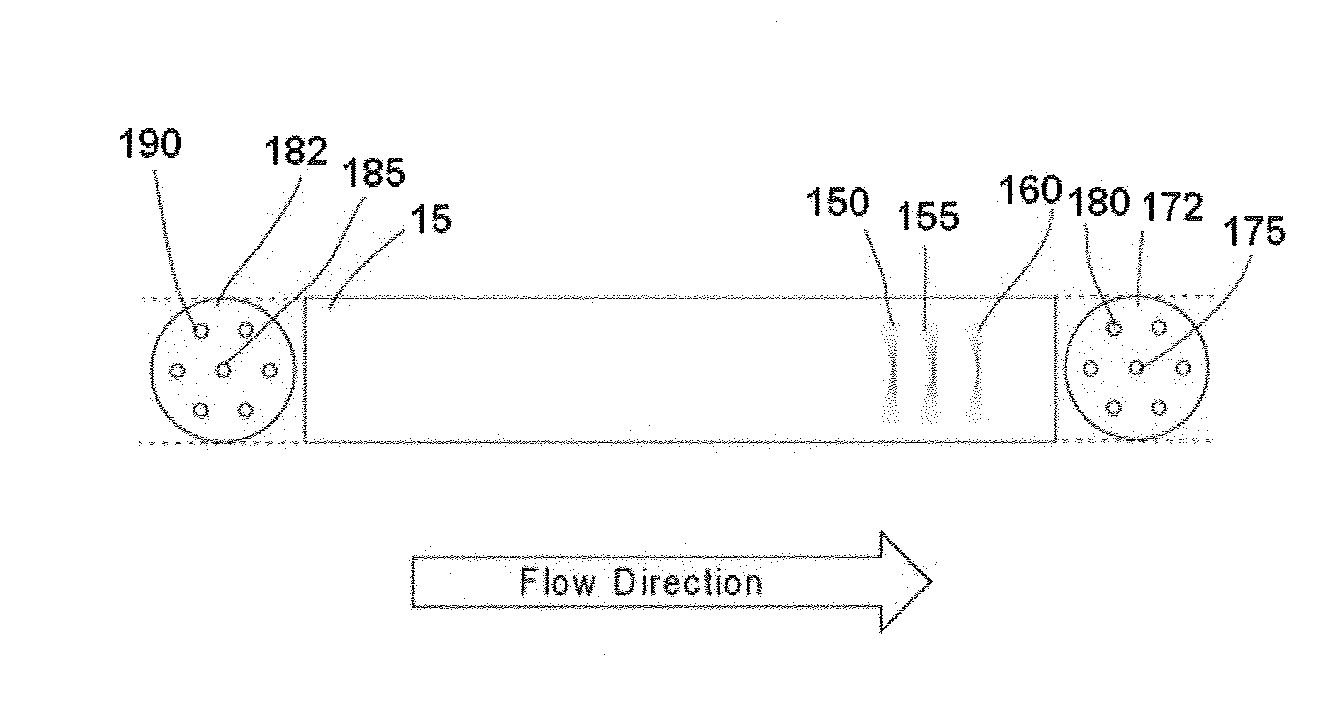

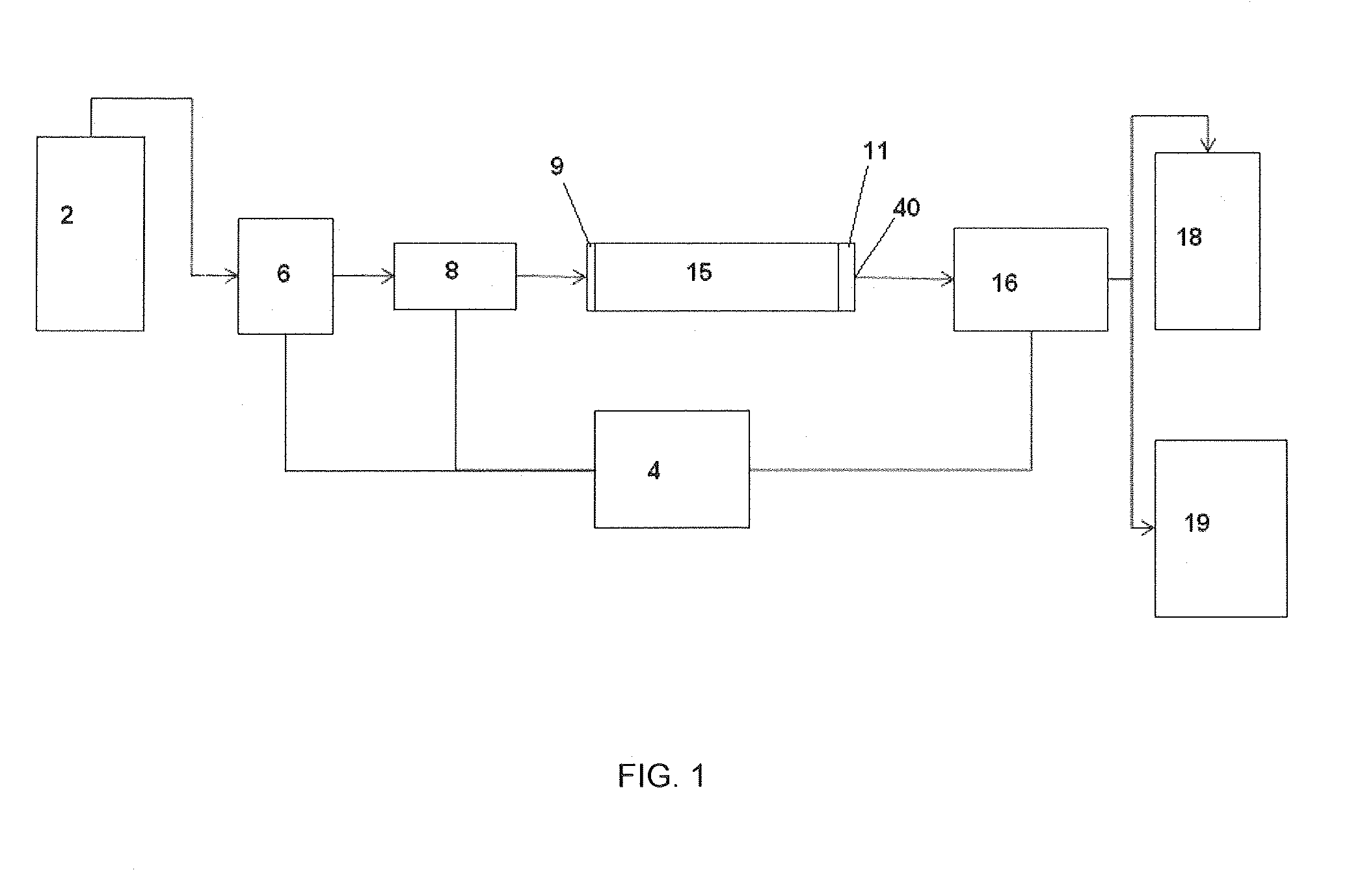

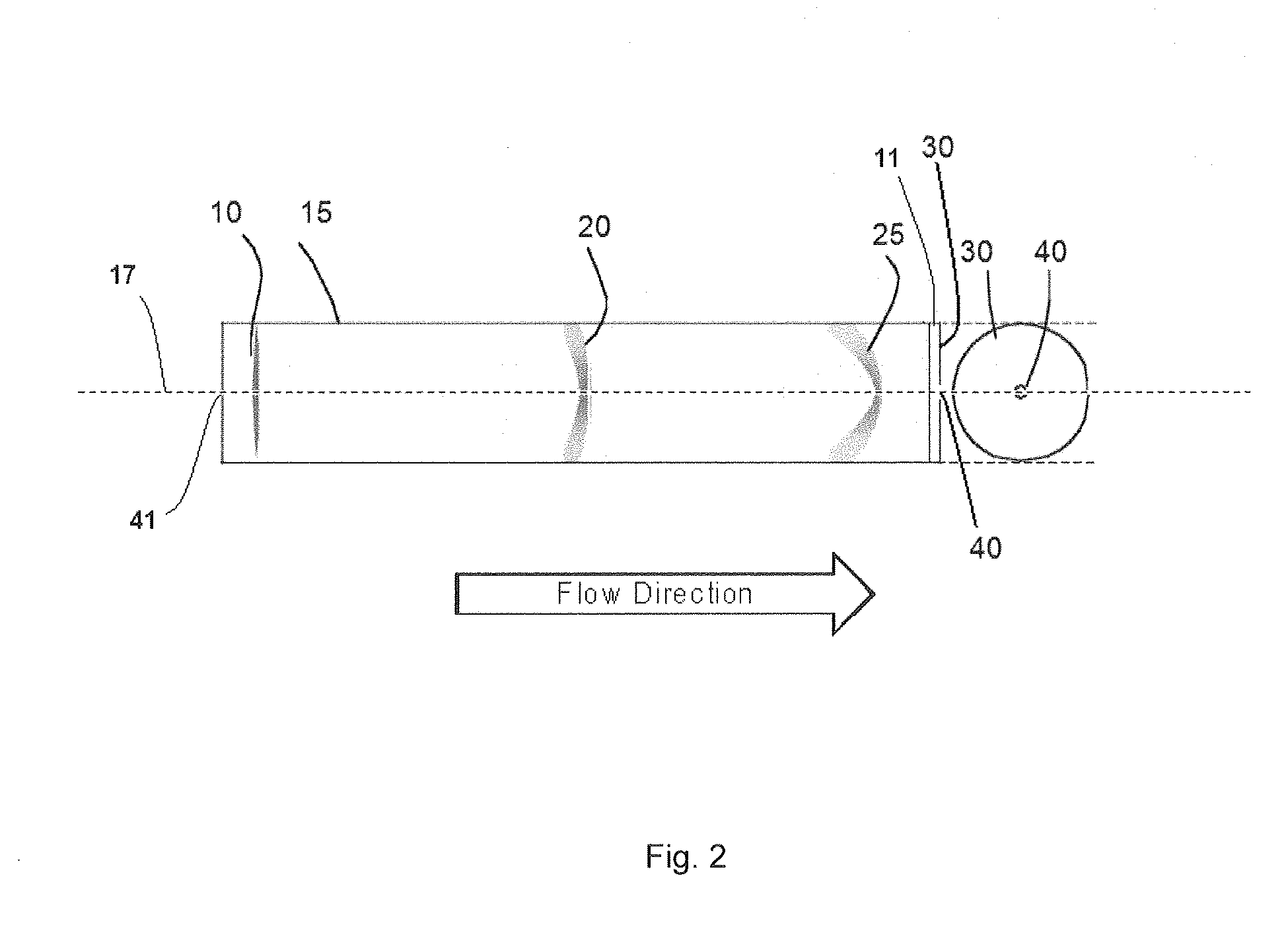

An apparatus and a method are provided for column chromatography, which provide improvements in separation resolution and detection sensitivity, comprising a chromatography column having an inlet and an outlet, wherein the inlet is configured to introduce a flow of mobile phase into the column carrying a sample, wherein the inlet is further configured to introduce the flow of mobile phase into the column in at least two separate portions which are independently controllable, and to introduce the portions into different radial regions of the column, such that the portions flow longitudinally through the column in different radial regions. The sample preferably is contained in one of the portions, especially a central portion, in a higher concentration than in the other portion(s). Preferably the flow velocities of the portions are independently controllable.

Owner:UNIVERSITY OF WESTERN SYDNEY +1