Structure and method for low Vss resistance and reduced dibl in a floating gate memory cell

一种浮动栅极、存储单元的技术,应用在电路、电气元件、半导体器件等方向,能够解决能障降低、存储单元临界电压降低、影响存储单元效能等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

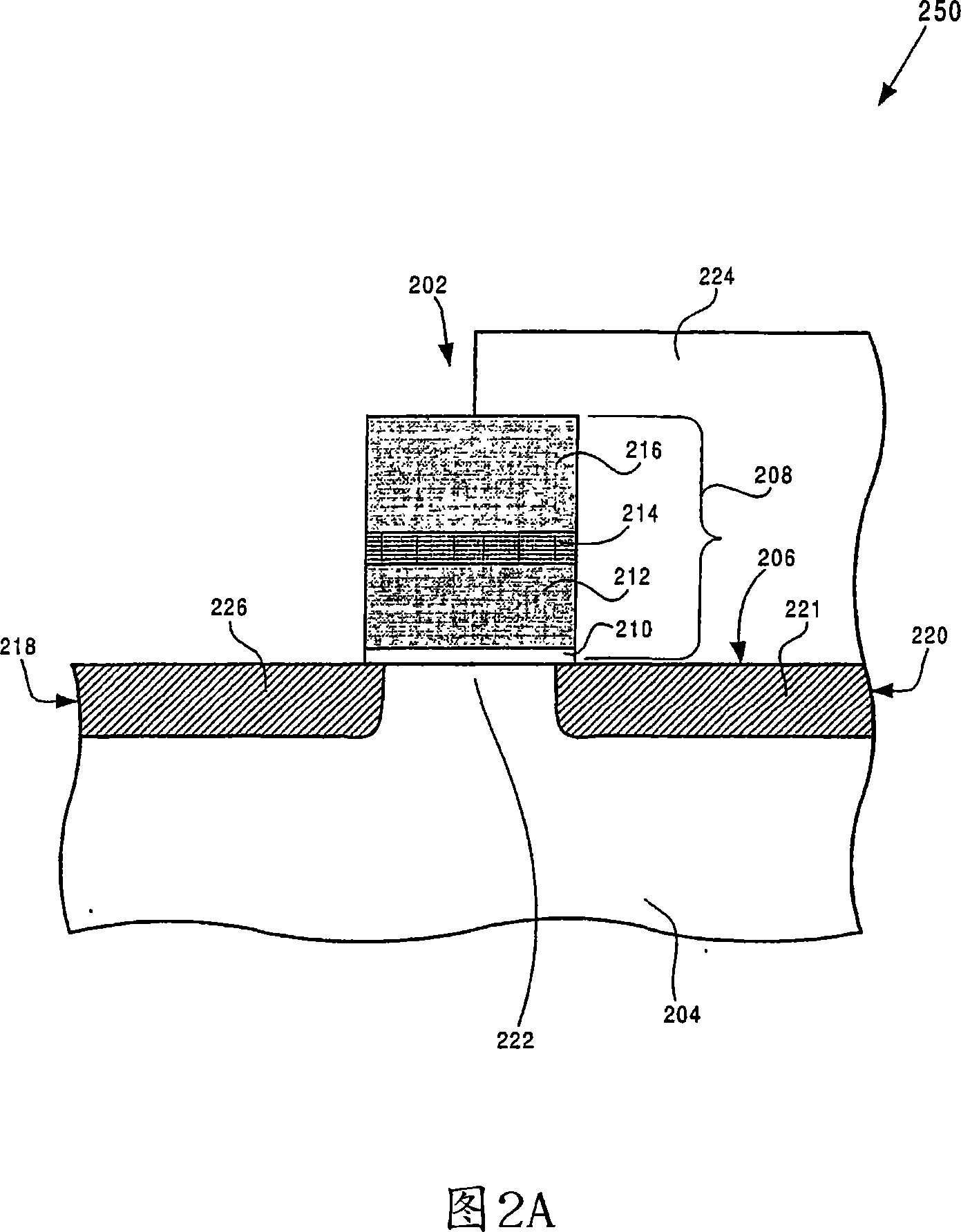

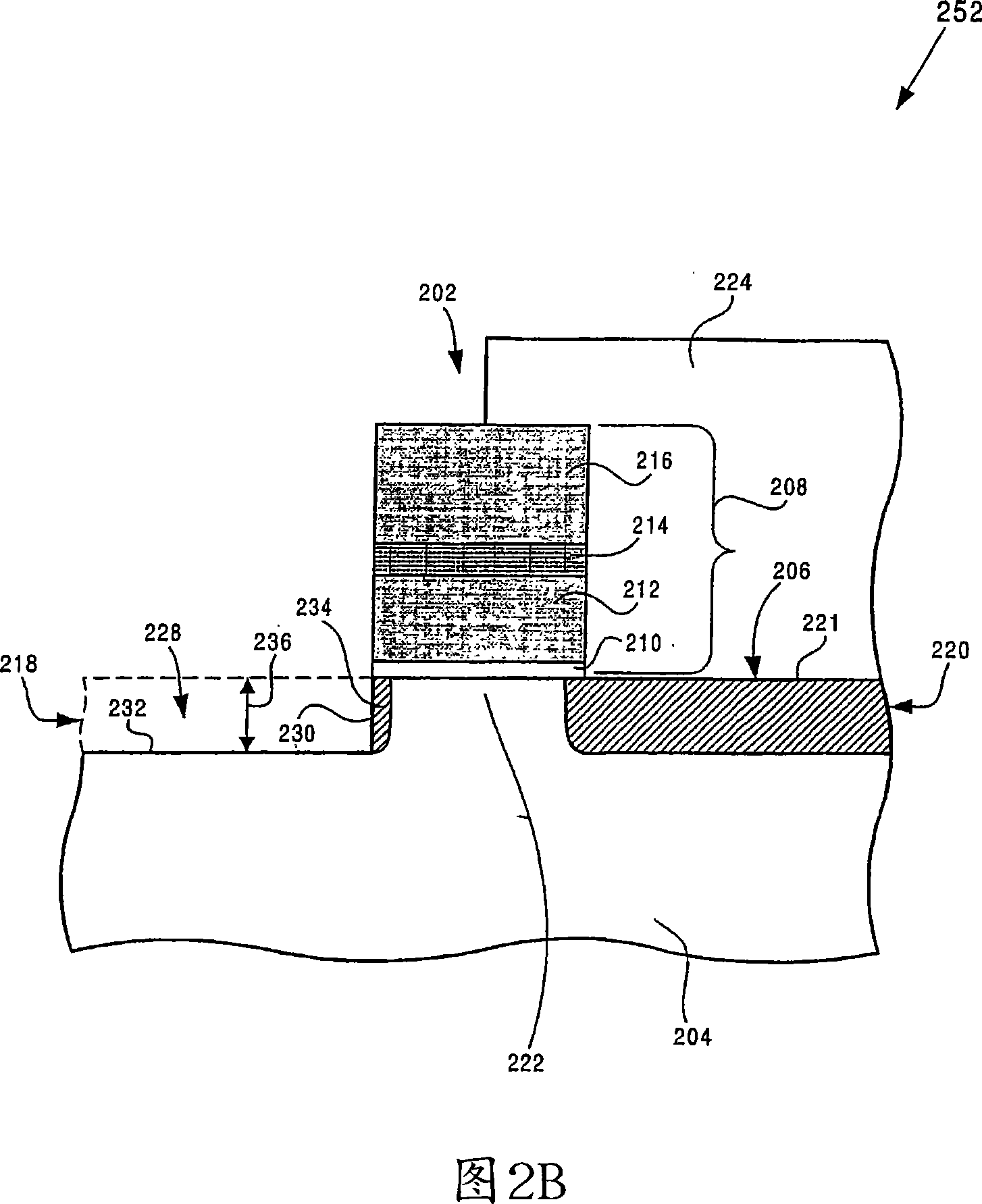

[0049] The present invention provides structures and methods for low Vss resistance and reduced drain induced energy barrier reduction in floating gate memory cells. The following description contains specific information pertaining to the practice of the invention. Those skilled in the art will appreciate that the present invention may be practiced otherwise than as specifically discussed in the present application. Additionally, some of the specific details of the invention are not discussed in order not to obscure the invention.

[0050] The drawings in this application and this additional detailed description provide merely illustrative embodiments of the invention. In order to maintain brevity, other embodiments of the invention are not specifically described in this application and not specifically illustrated by the drawings.

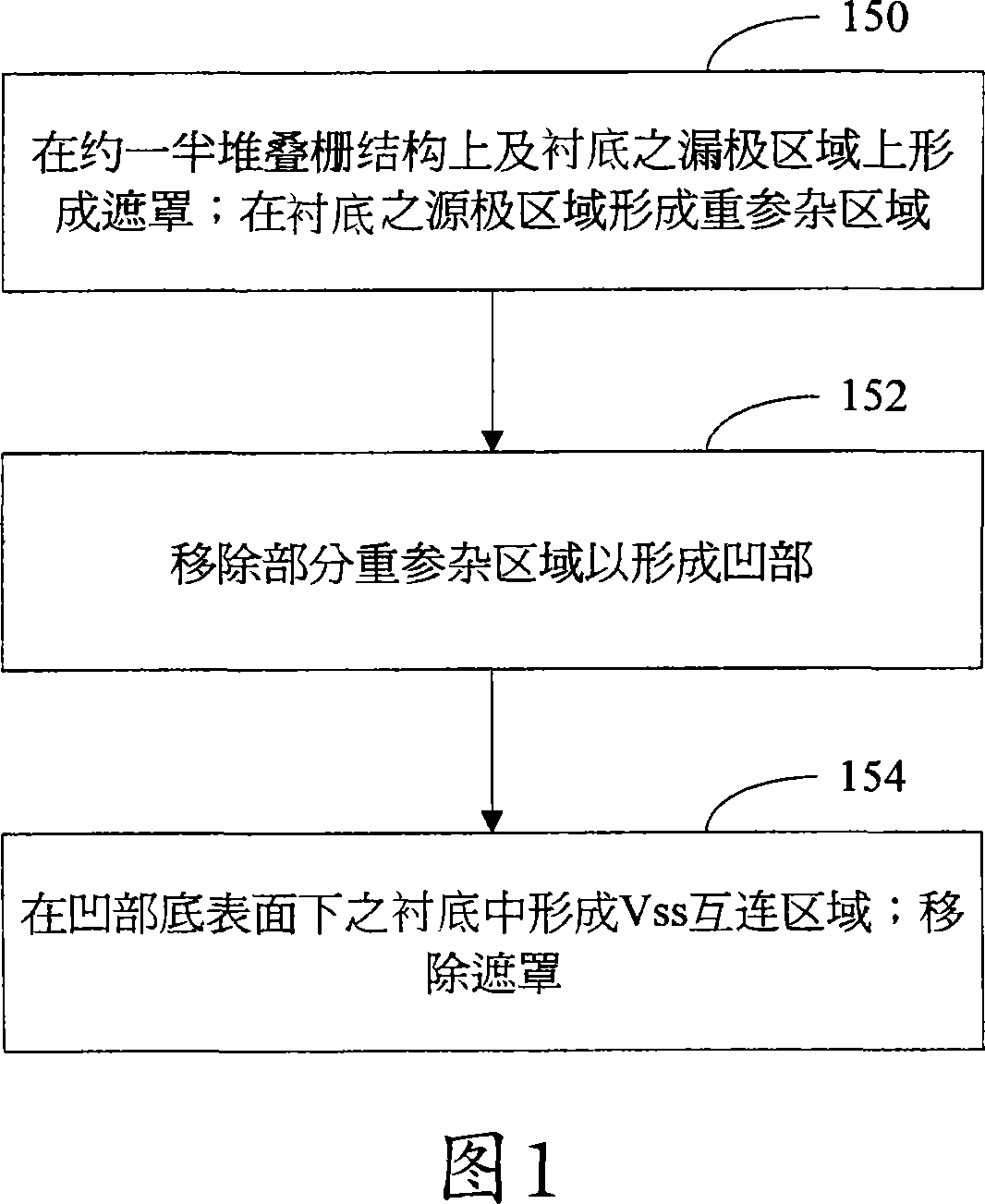

[0051]1 shows a flowchart illustrating an exemplary method for forming a floating gate flash memory cell including a recessed Vss implant regi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More