Thyristor chip with seven-layer p-n junction isolation structure and preparation method of thyristor chip

A through isolation, silicon chip technology, applied in the field of thyristor chips, can solve the problems of large isolation area width, increased process difficulty, short diffusion time, etc., and achieves small isolation area width, saving silicon wafer area, and short diffusion time. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

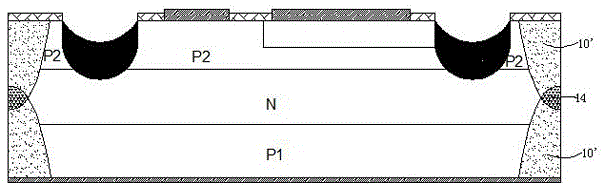

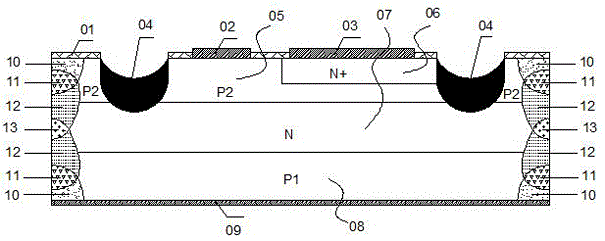

[0016] Such as Figure 4 , 5 A thyristor chip with a seven-layer on-through isolation structure and its preparation method are shown, including an anode region P18, an N-type long base region 7, a short base region P25, an N- + Type cathode region 6 and front oxide film 1, front gate metal electrode 2, front cathode metal electrode 3, back anode metal electrode 9, annular passivation trench 4 and glass passivation filled in the passivation trench chemical film and the isolation ring of the seven-layer isolation structure, the isolation ring of the seven-layer isolation structure is composed of boron impurity region 10, boron, aluminum mixed impurity region 11, aluminum impurity region 12, aluminum-aluminum The overlapping impurity region 13, the aluminum impurity region 12, the boron and aluminum mixed impurity region 11, and the boron impurity region constitute 10, and the isolation ring of the seven-layer through-isolation structure is arranged vertically on the oxide film ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More