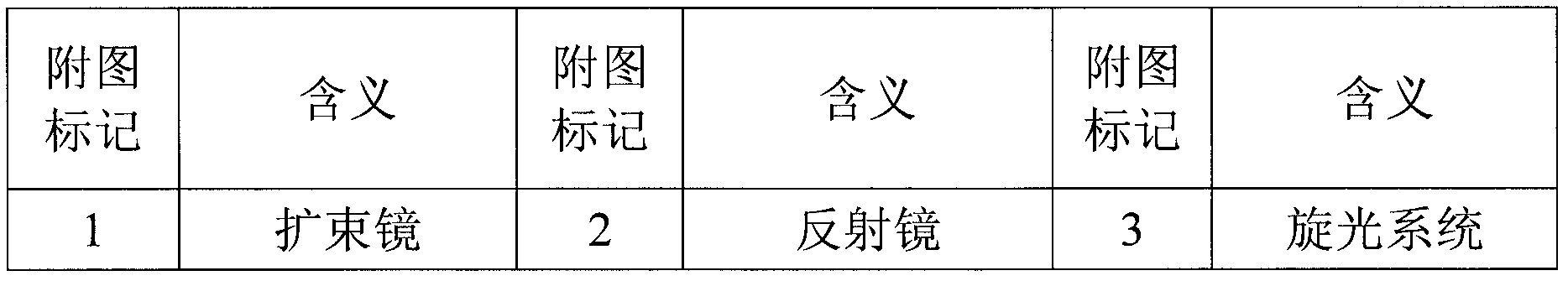

Patents

Literature

1390 results about "Laser drilling" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

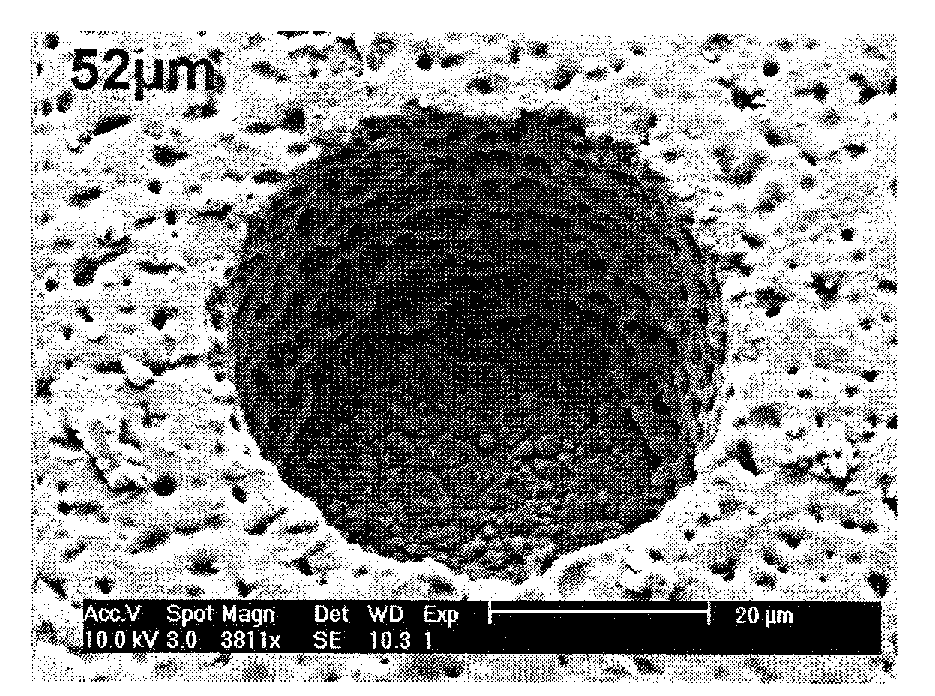

Laser drilling is the process of creating thru-holes, referred to as “popped” holes or “percussion drilled” holes, by repeatedly pulsing focused laser energy on a material. The diameter of these holes can be as small as 0.002” (~50 μm). If larger holes are required, the laser is moved around the circumference of the “popped” hole until the desired diameter is created; this technique is called “trepanning”.

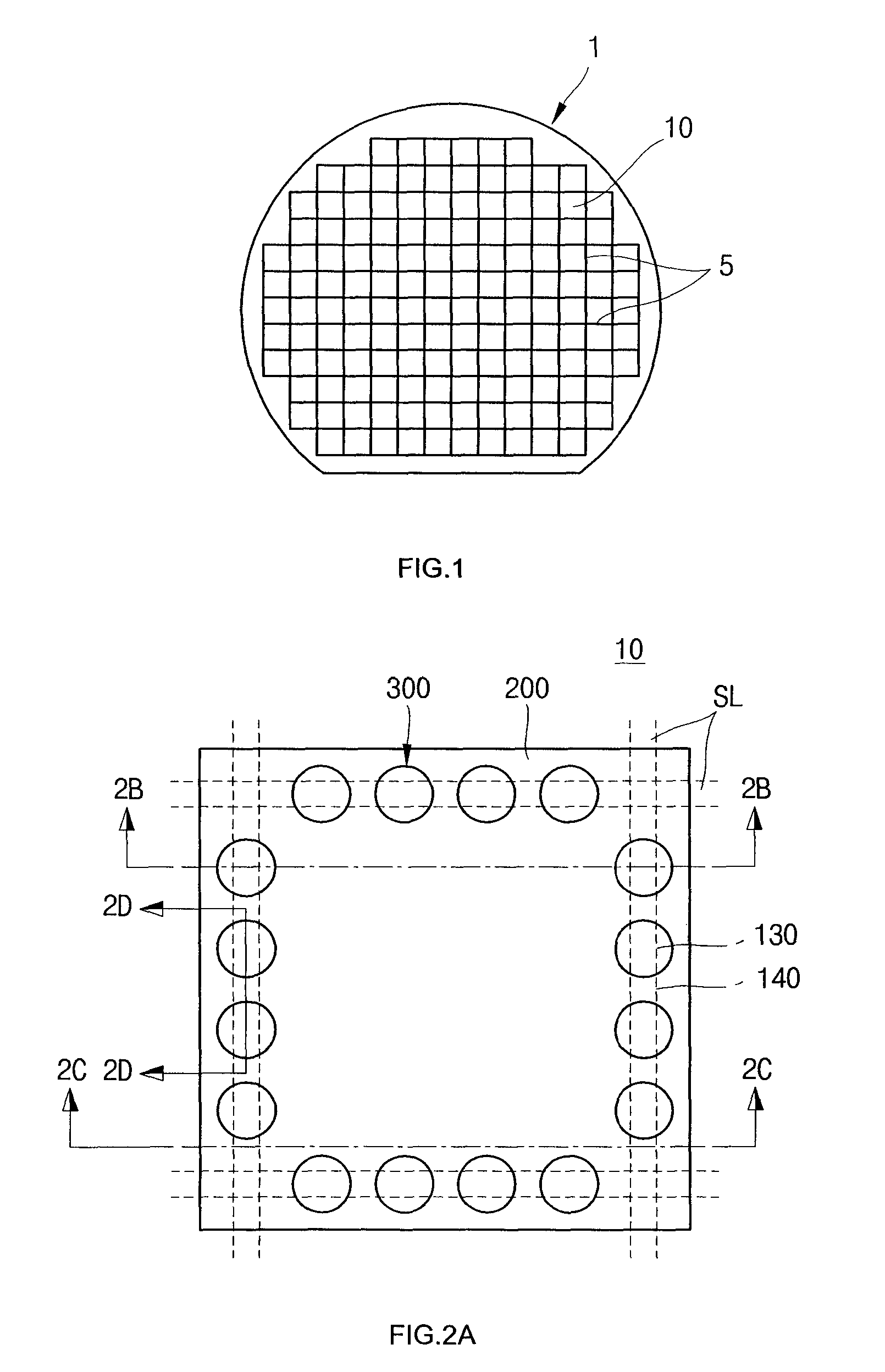

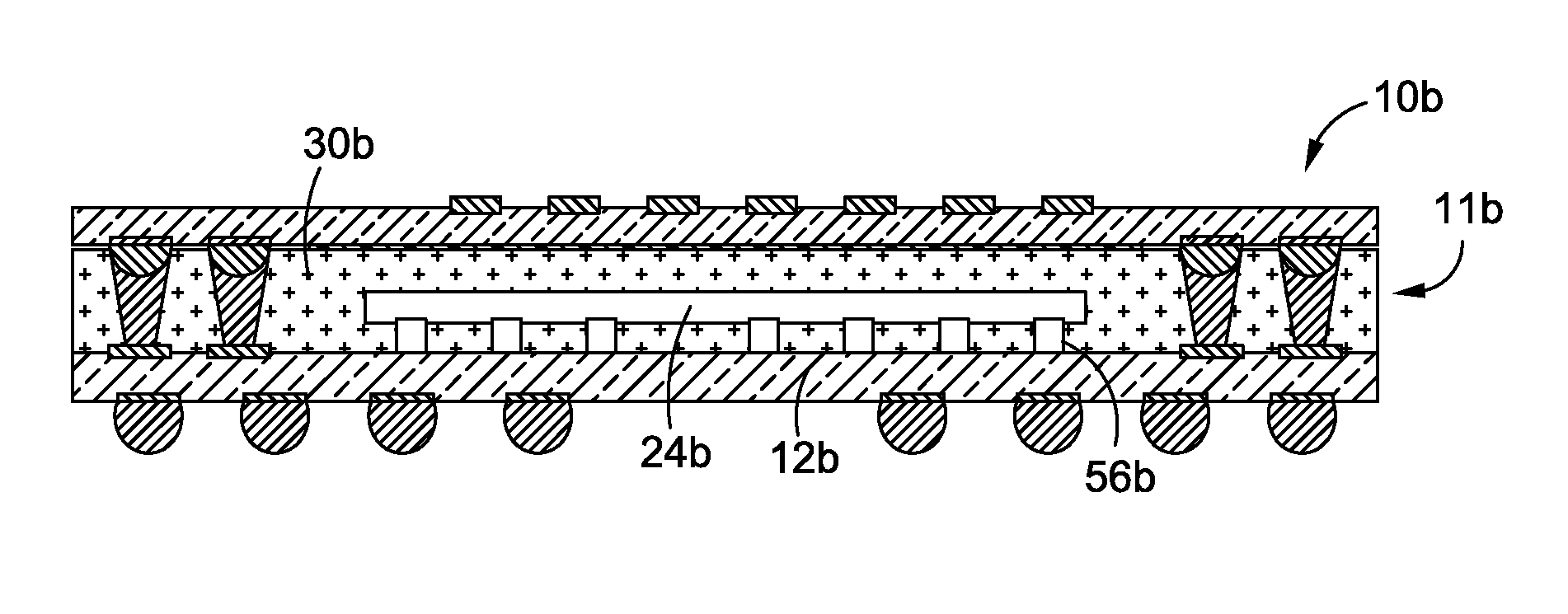

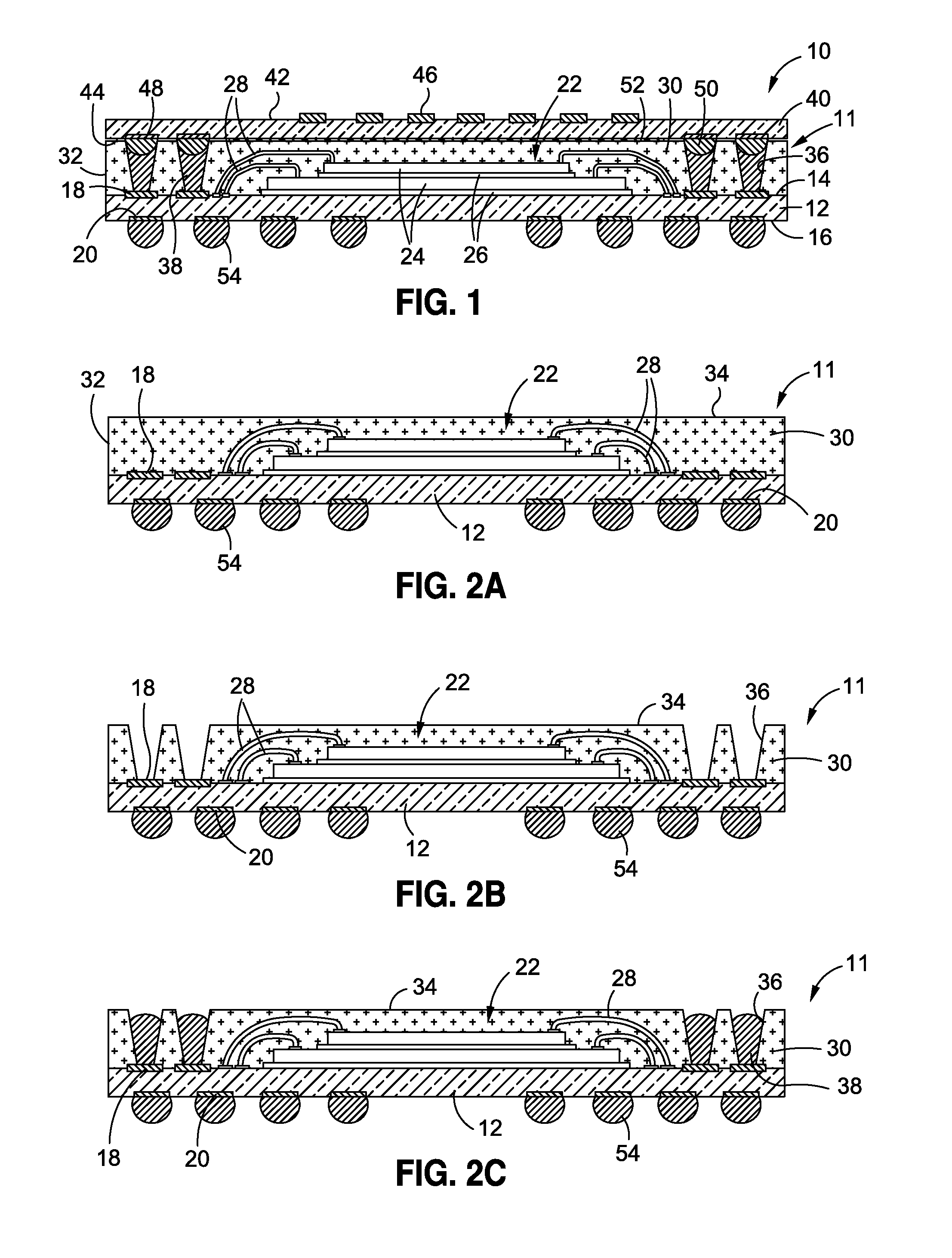

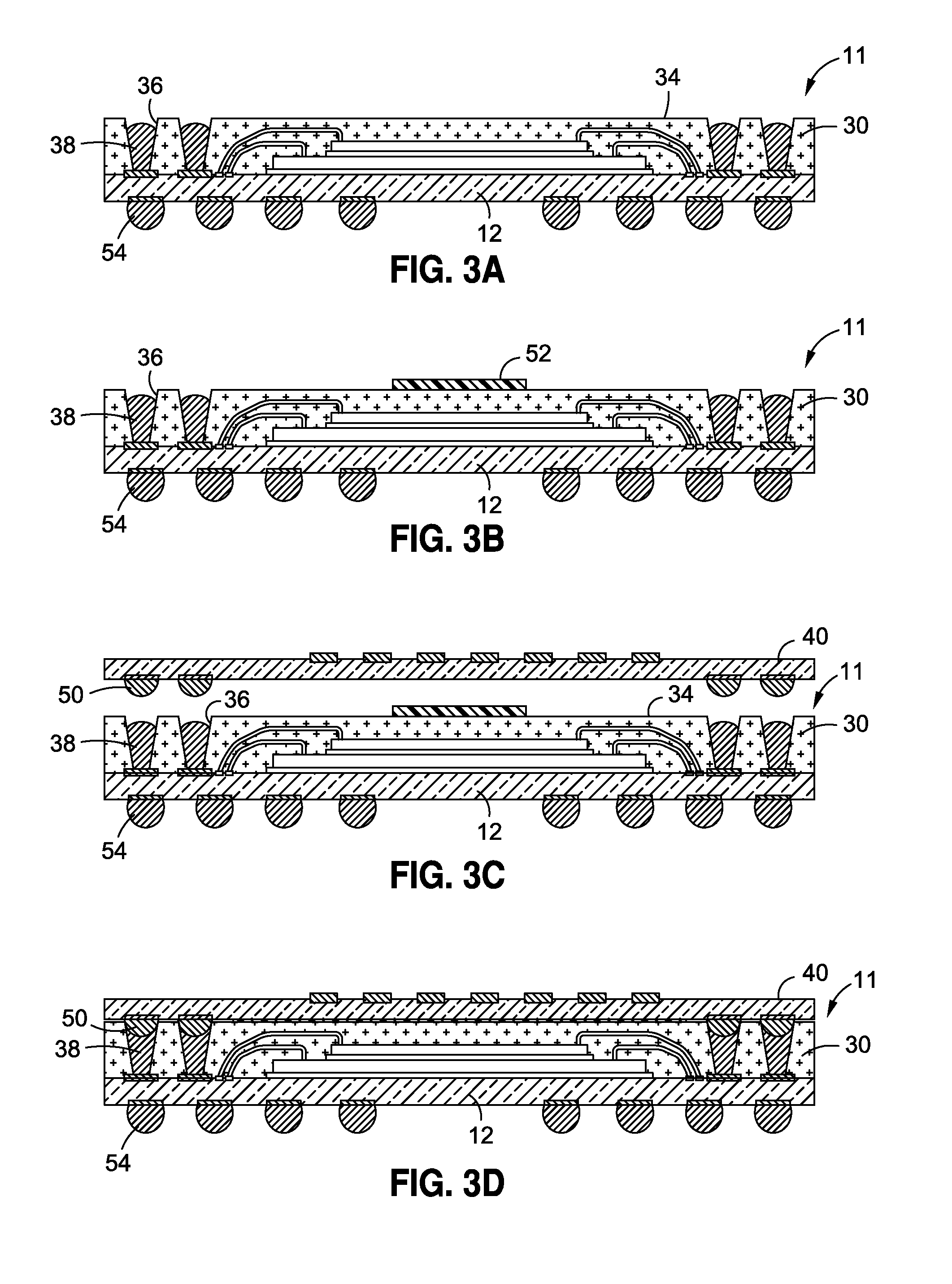

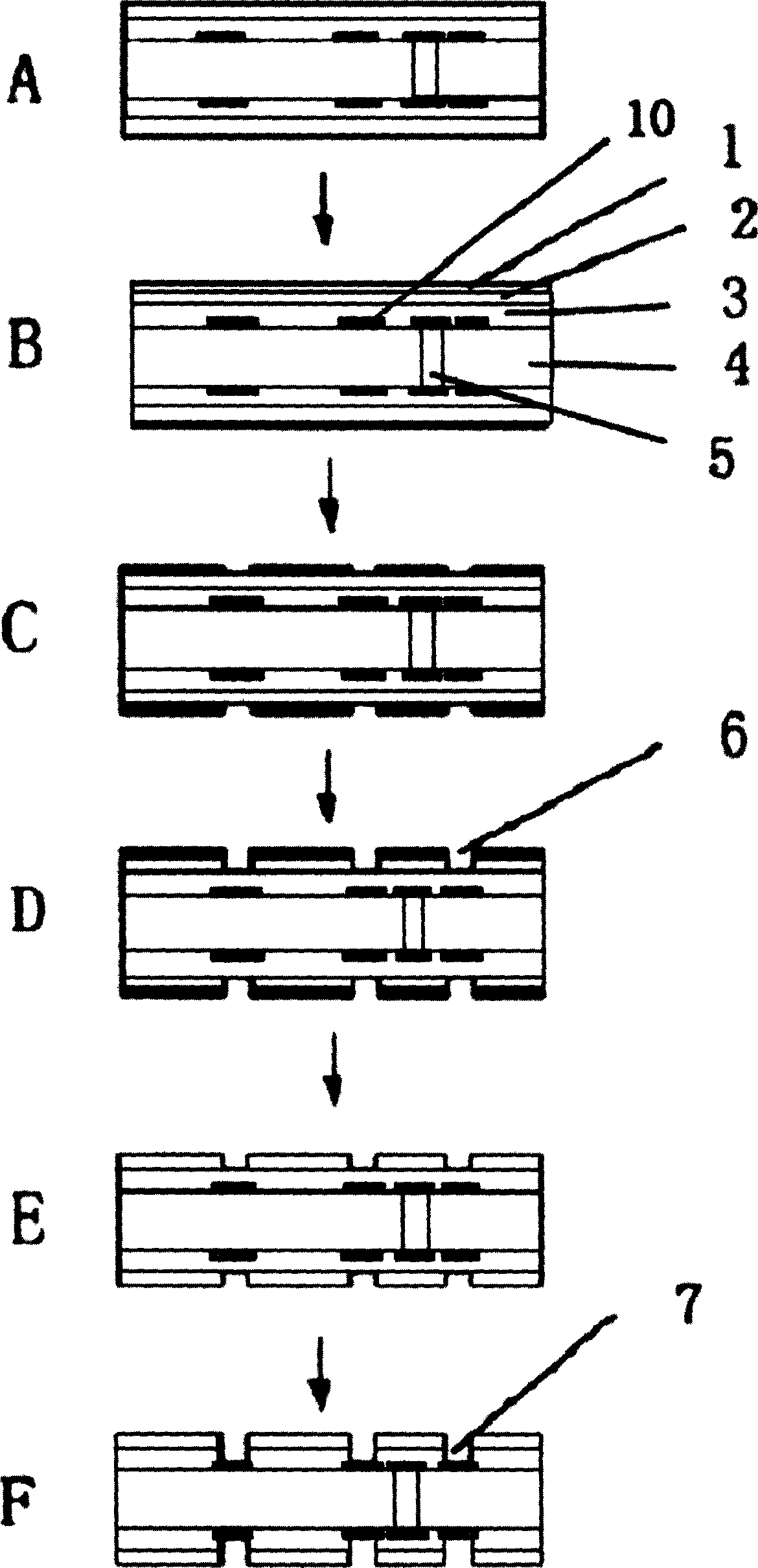

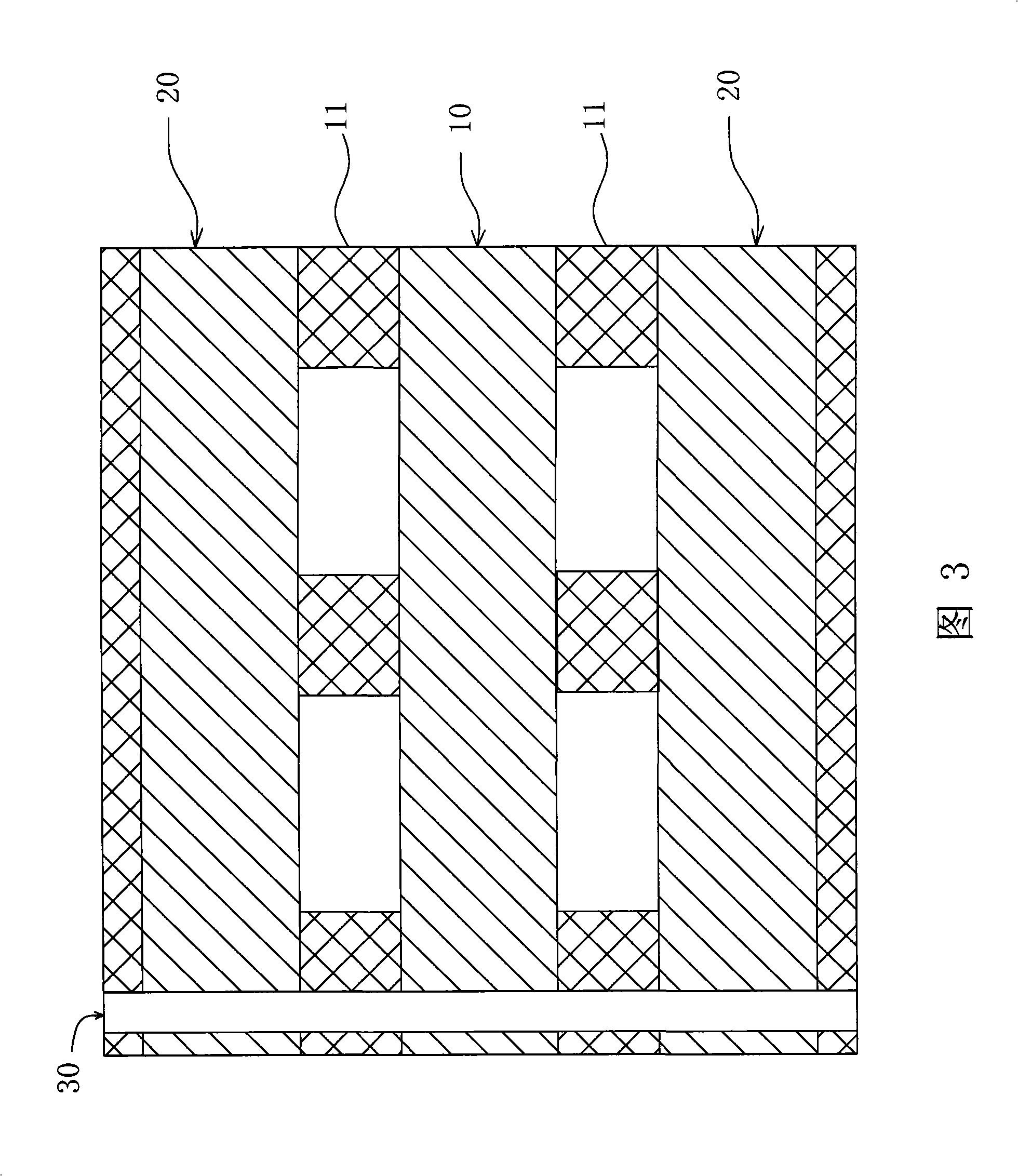

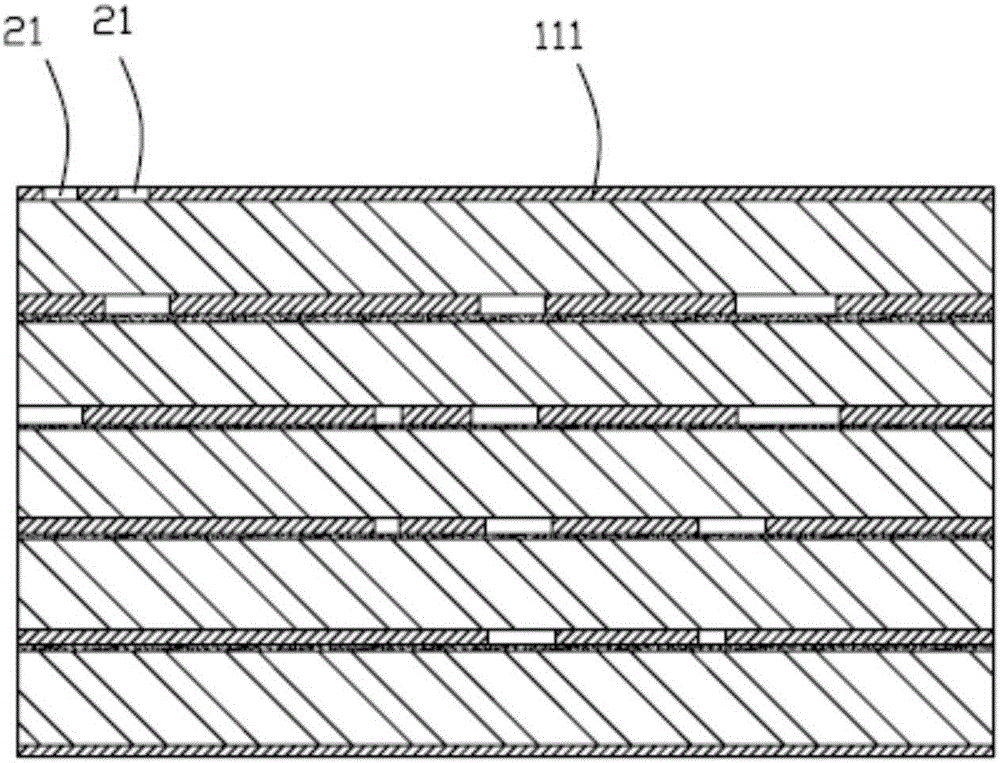

Thin stacked interposer package

ActiveUS7777351B1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor packageElectronic component

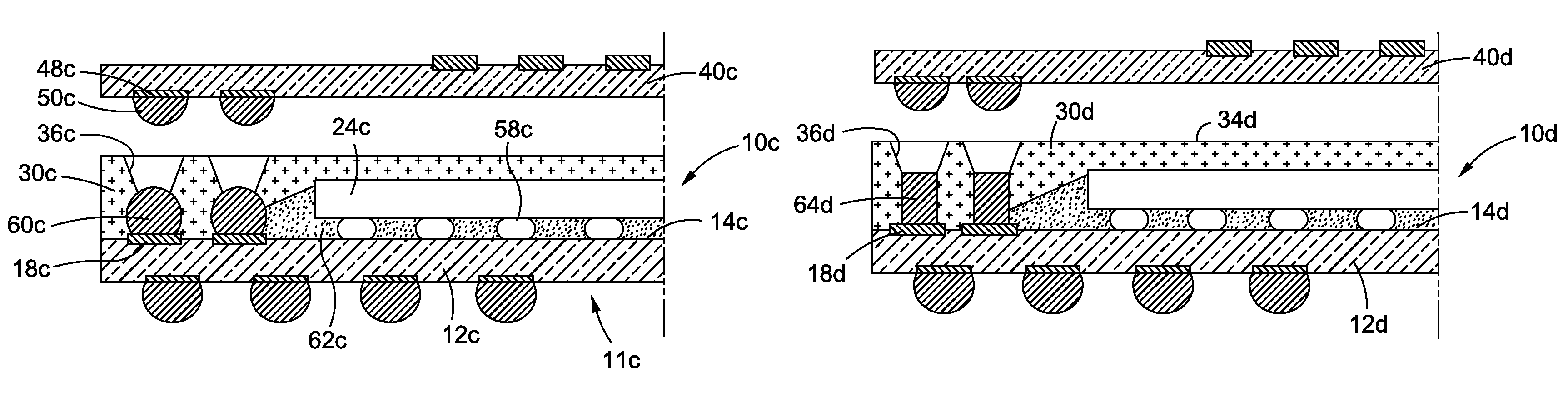

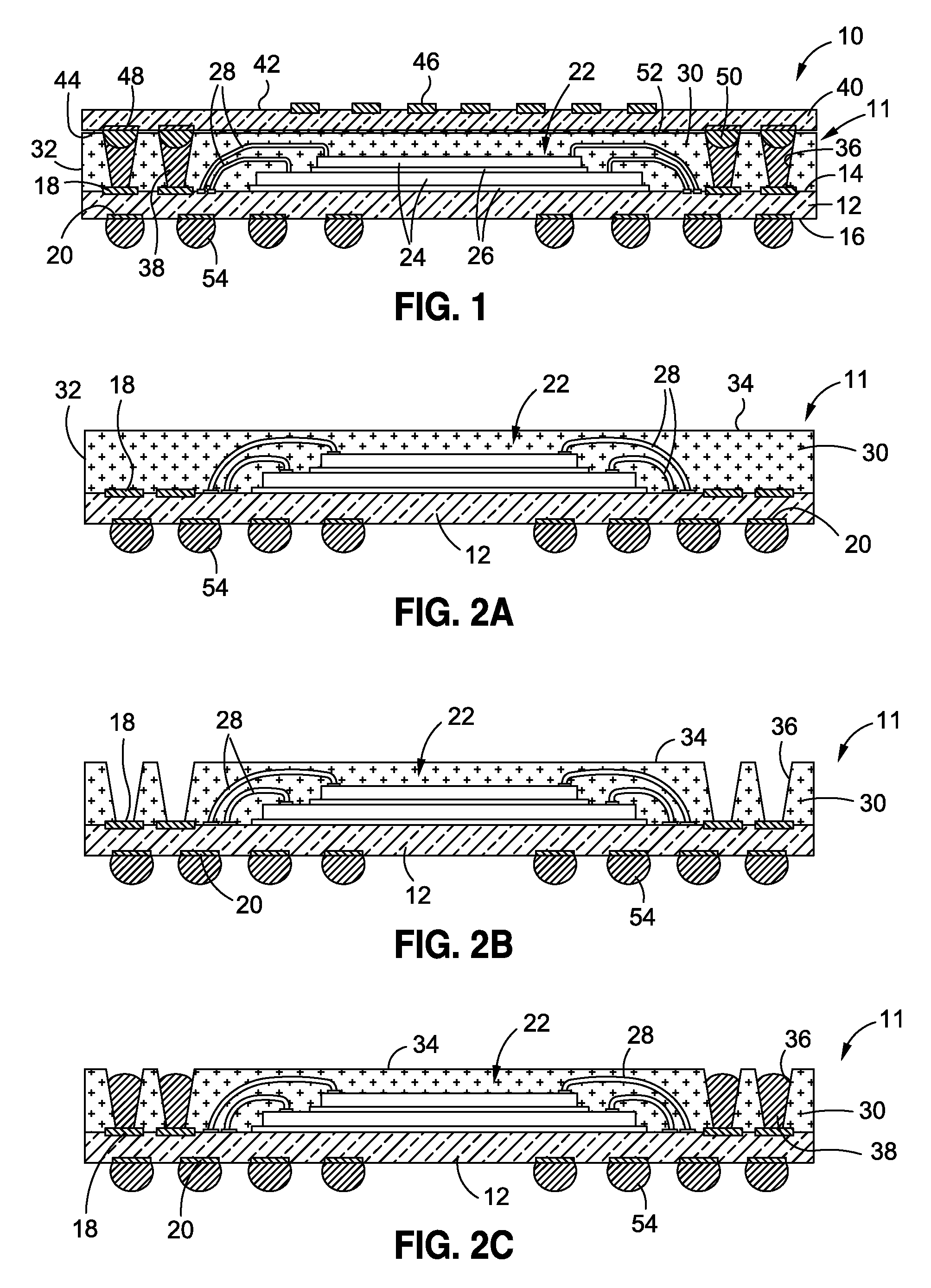

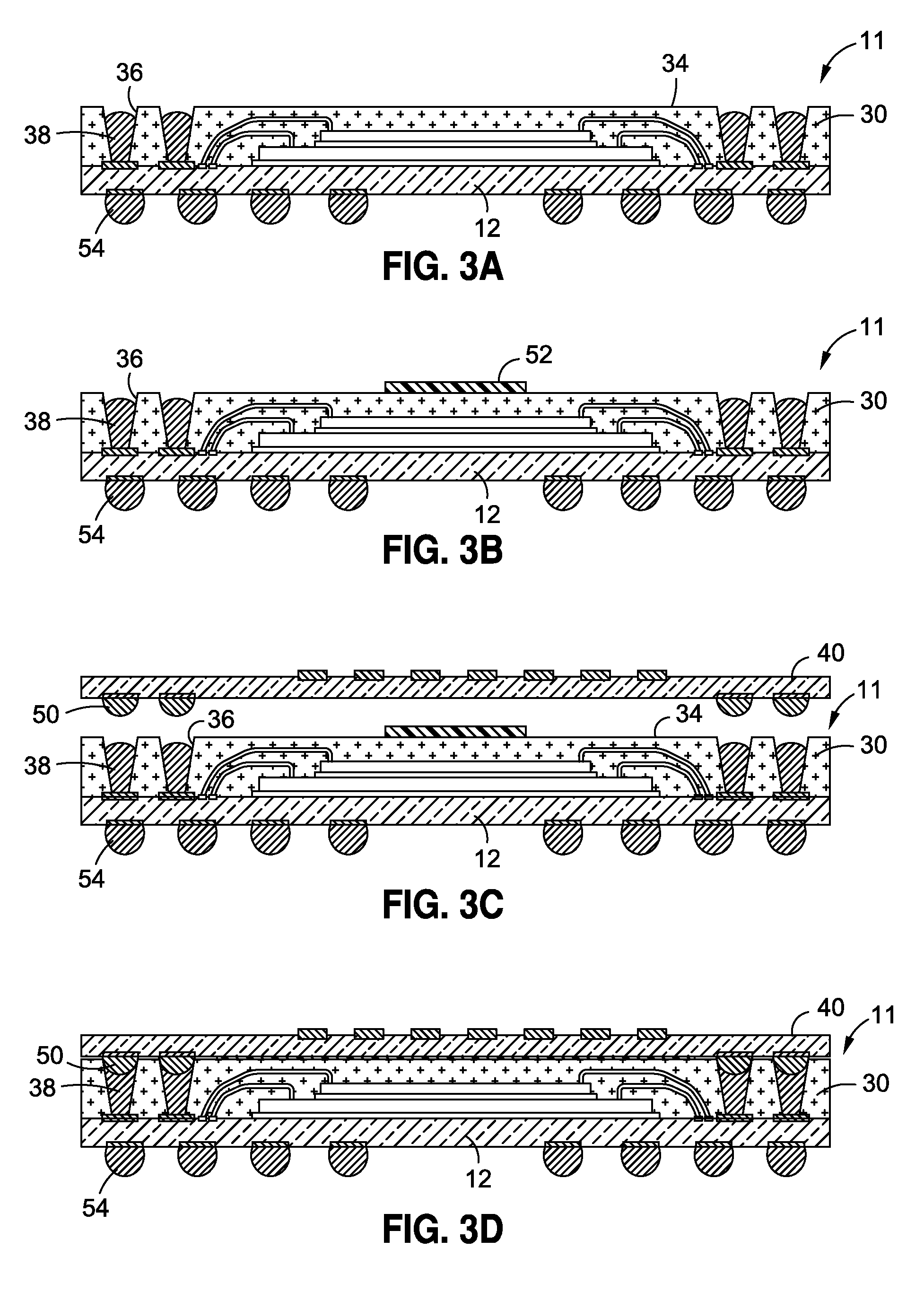

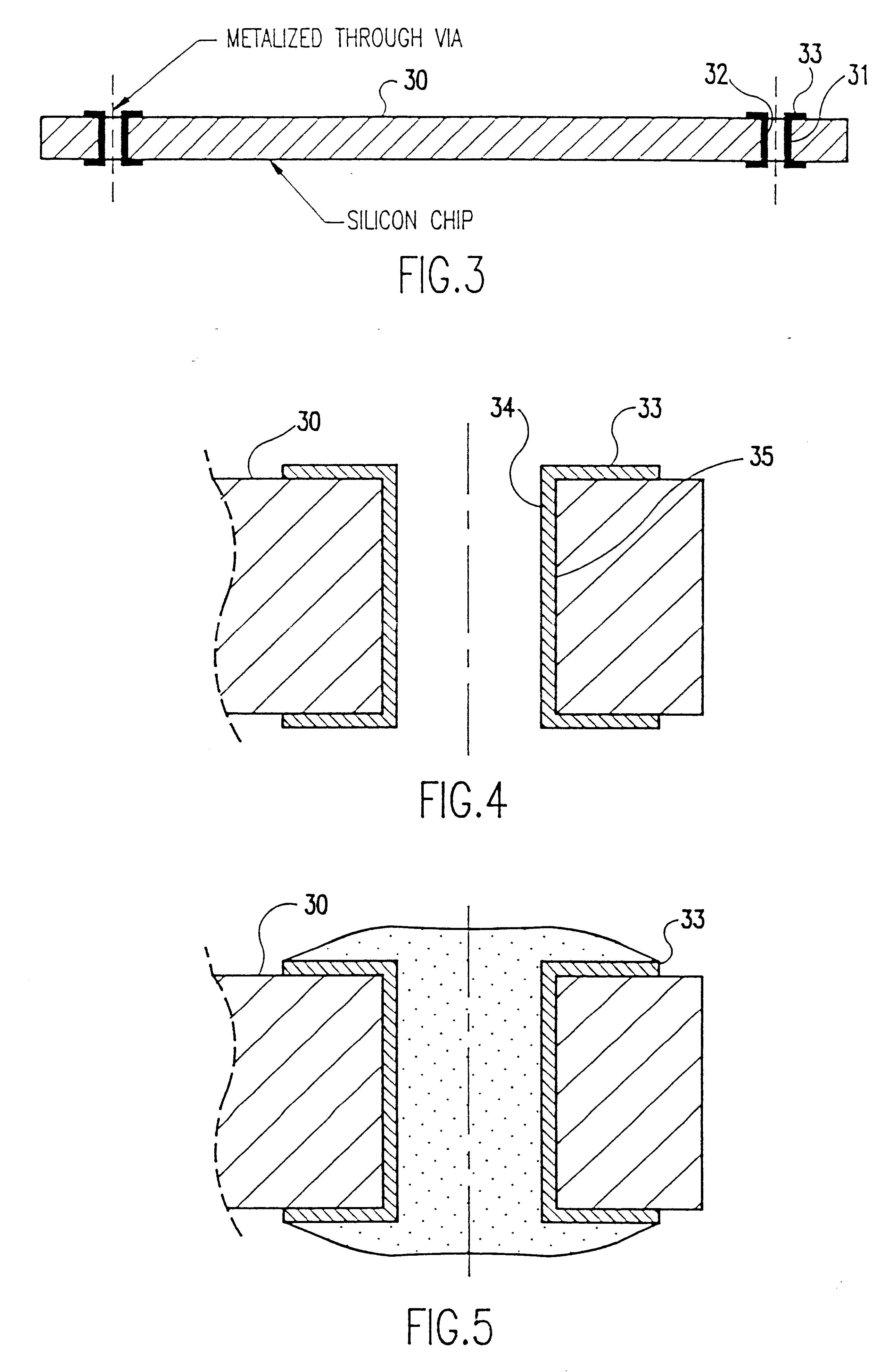

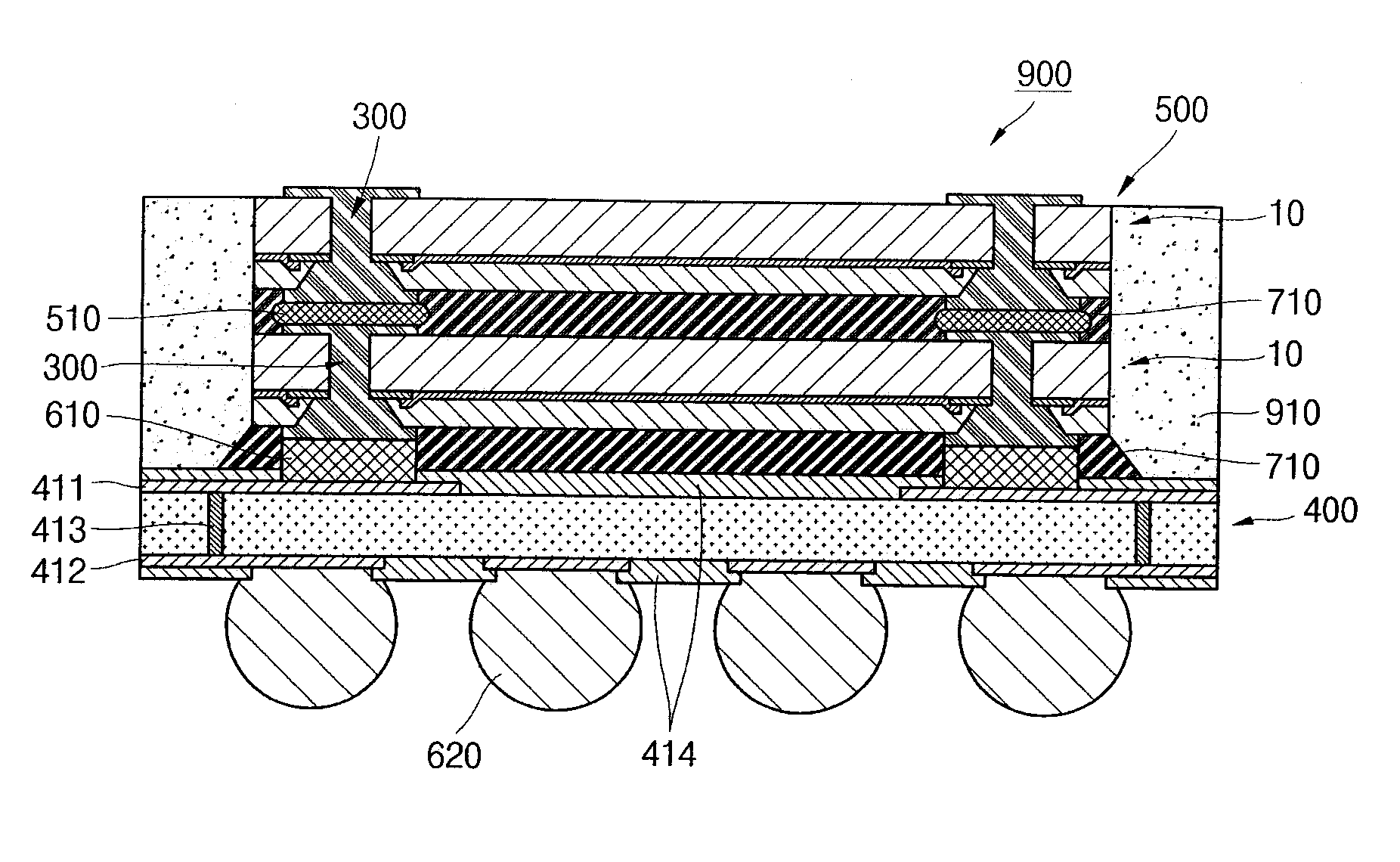

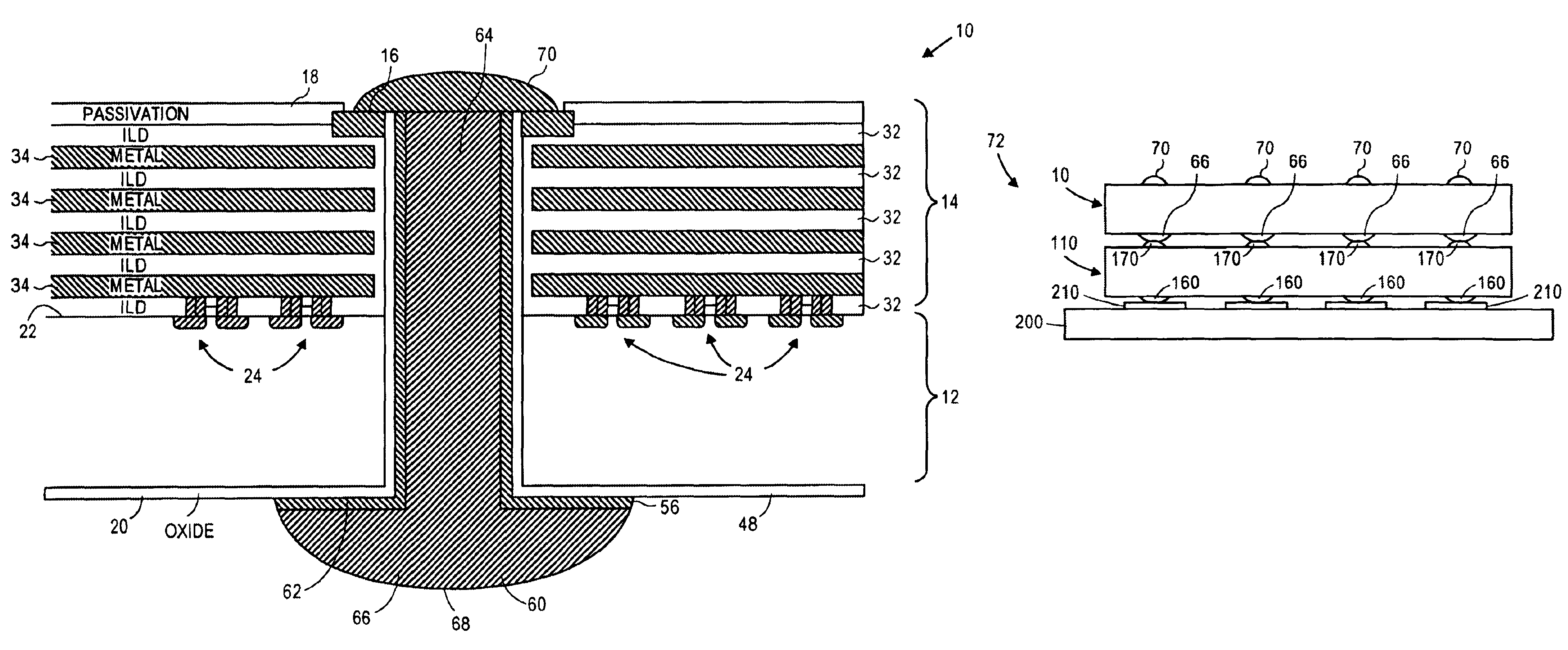

The present invention comprises a semiconductor package comprising a bottom semiconductor package substrate which is populated with one or more electronic components. The electronic component(s) of the bottom substrate are covered or encapsulated with a suitable mold compound which hardens into a package body of the semiconductor package. The package body is provided with one or more vias through the completion of laser drilling process, such via(s) providing access to one or more corresponding conductive contacts of the bottom substrate. These vias are either lined or partially filled with a conductive metal material. Subsequently, a top semiconductor package substrate (which may optionally be populated with one or more electronic components) is mounted to the package body and electrically connected to the conductive metal within the via(s) of the package body.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

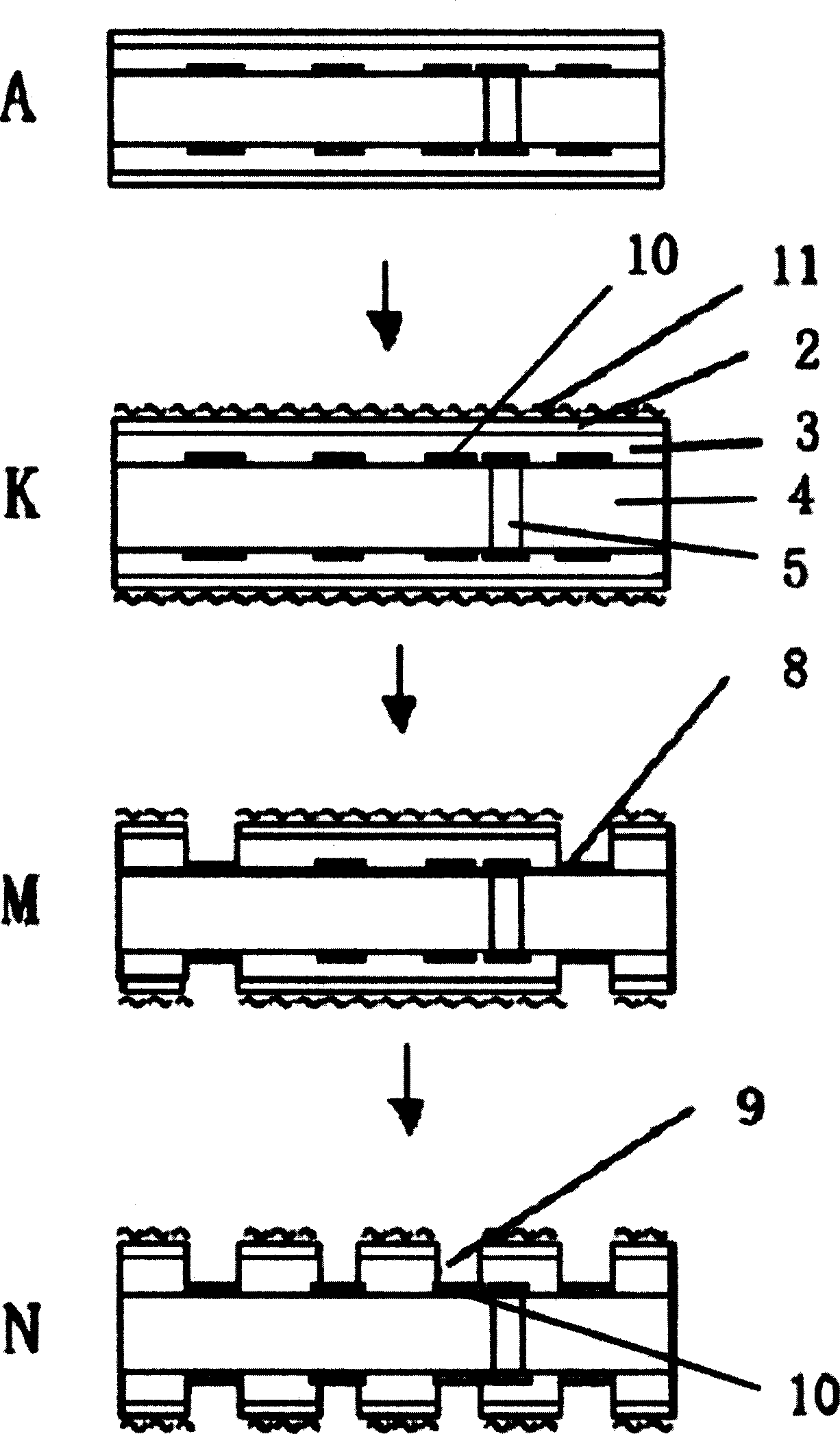

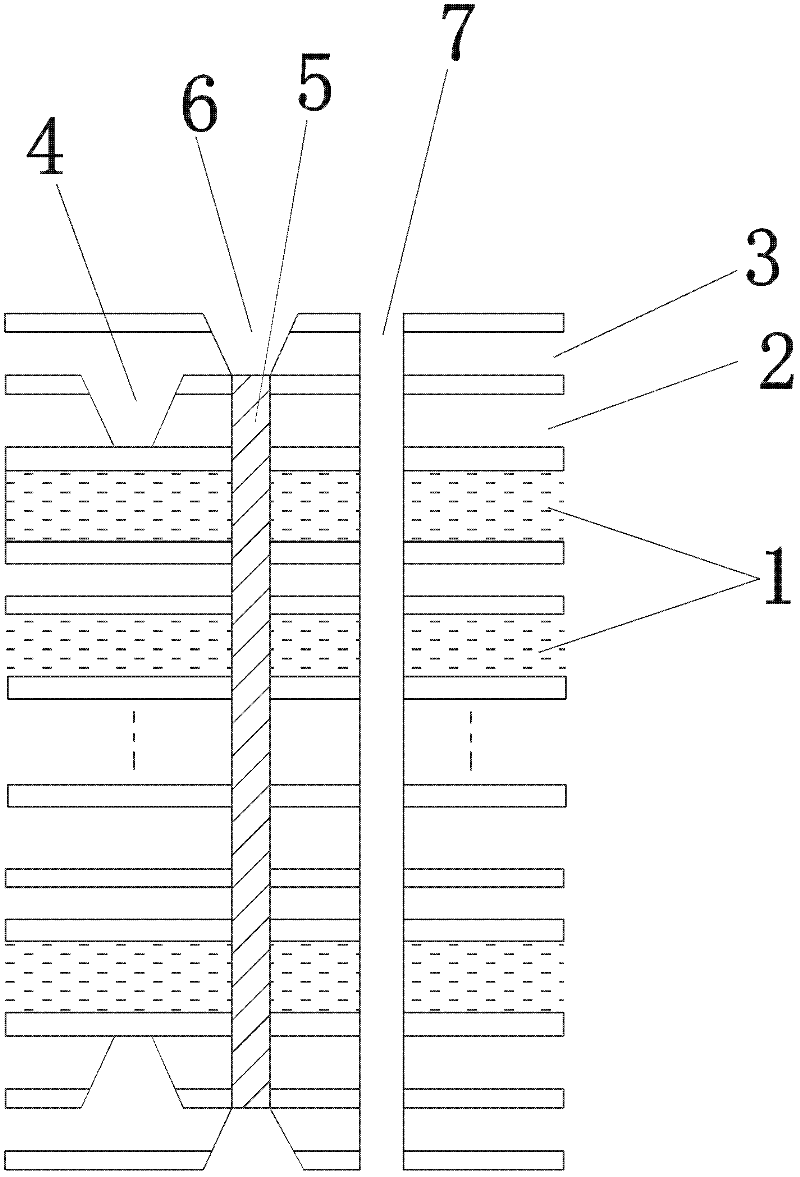

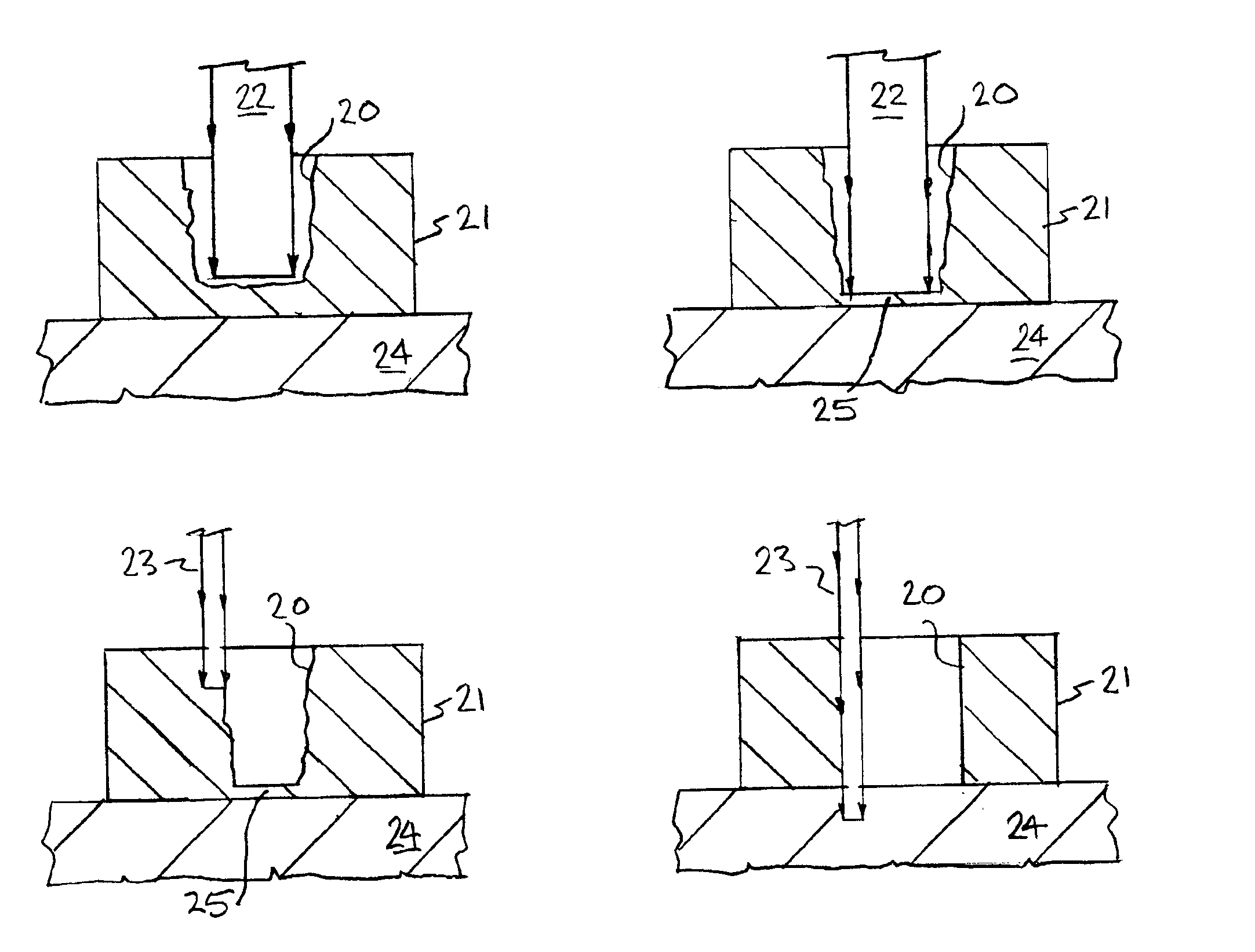

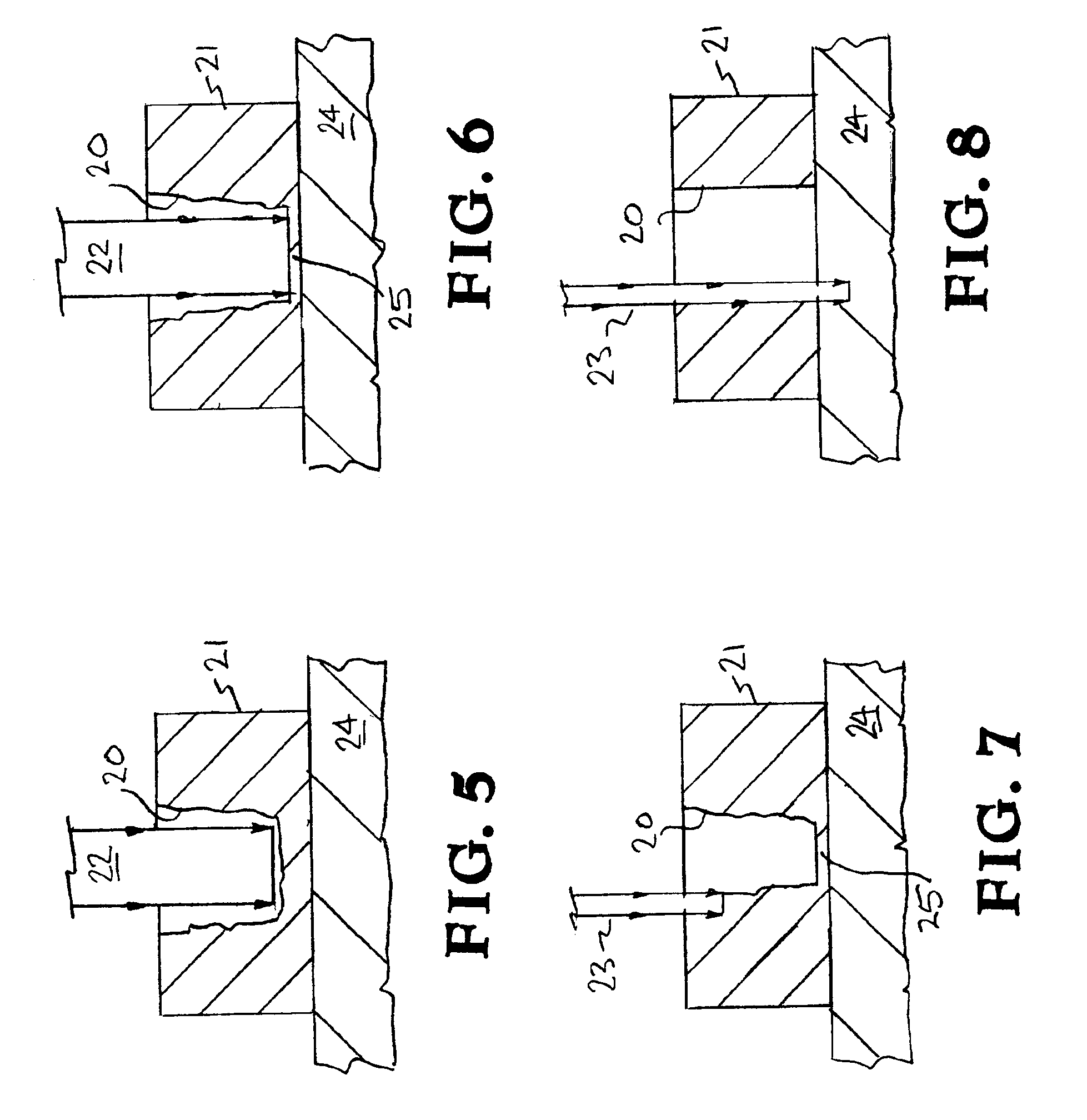

High density integrated circuit packaging with chip stacking and via interconnections

InactiveUS6236115B1Reduced connection exposureLarge capacitySemiconductor/solid-state device detailsSolid-state devicesEngineeringThermal expansion

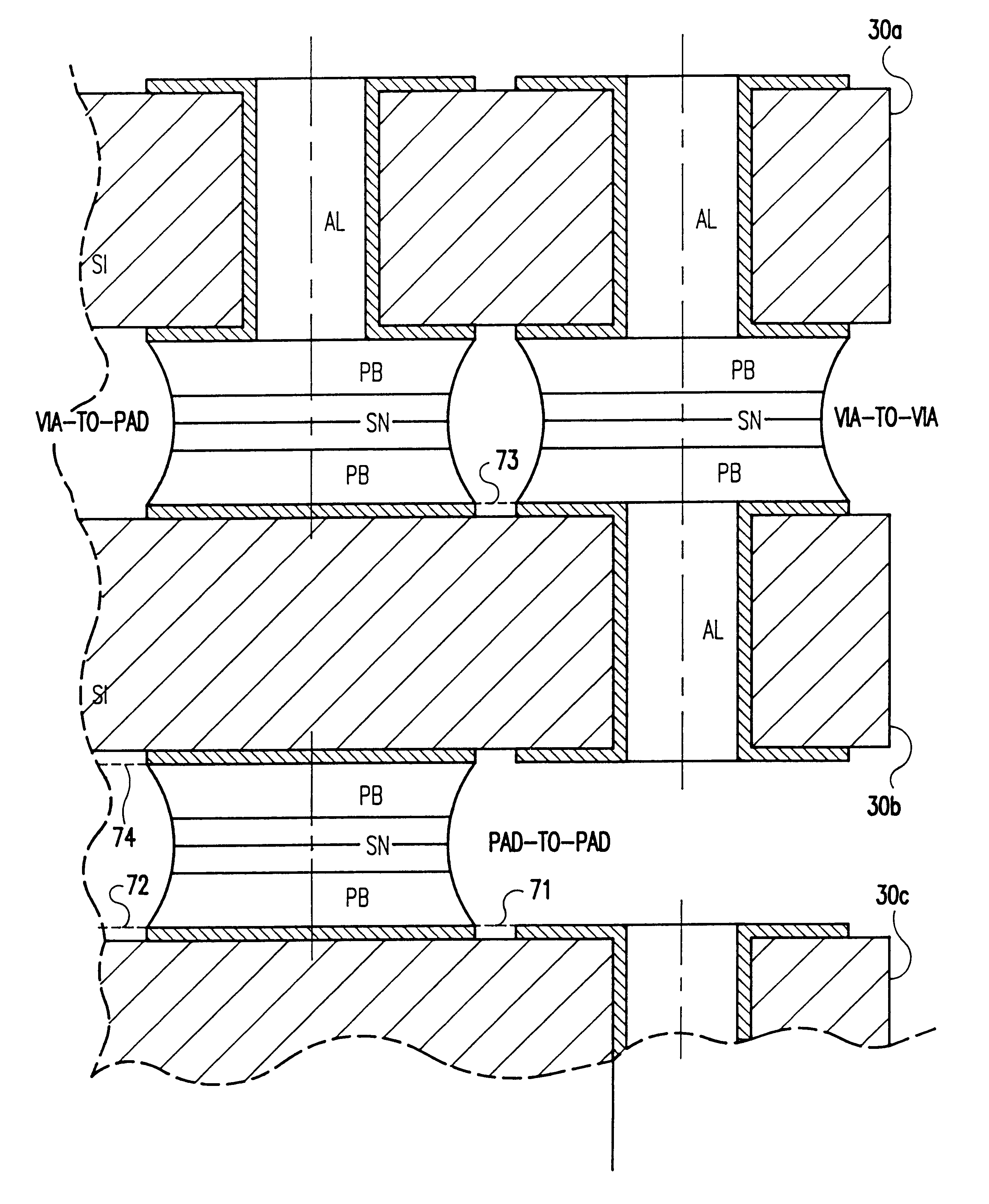

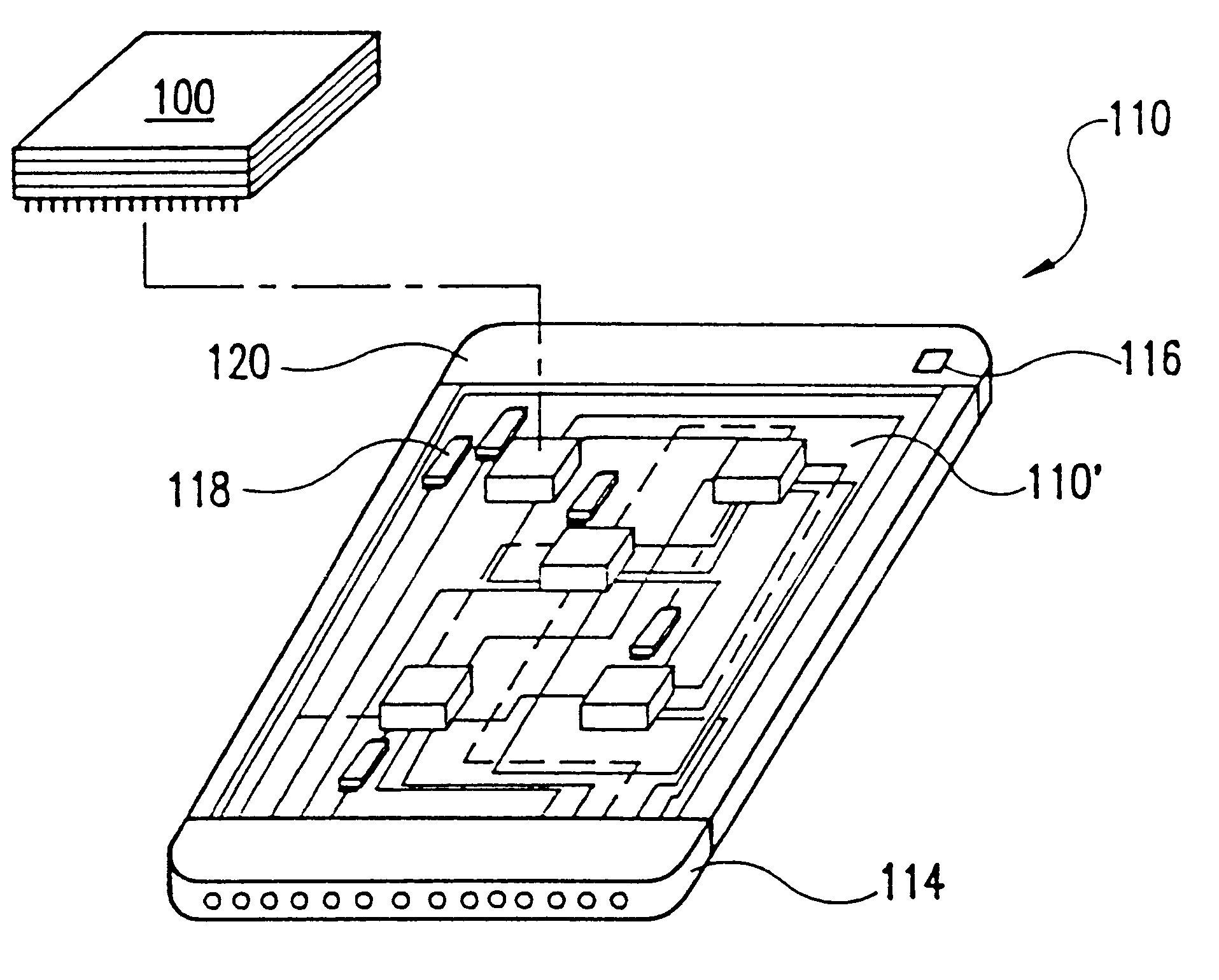

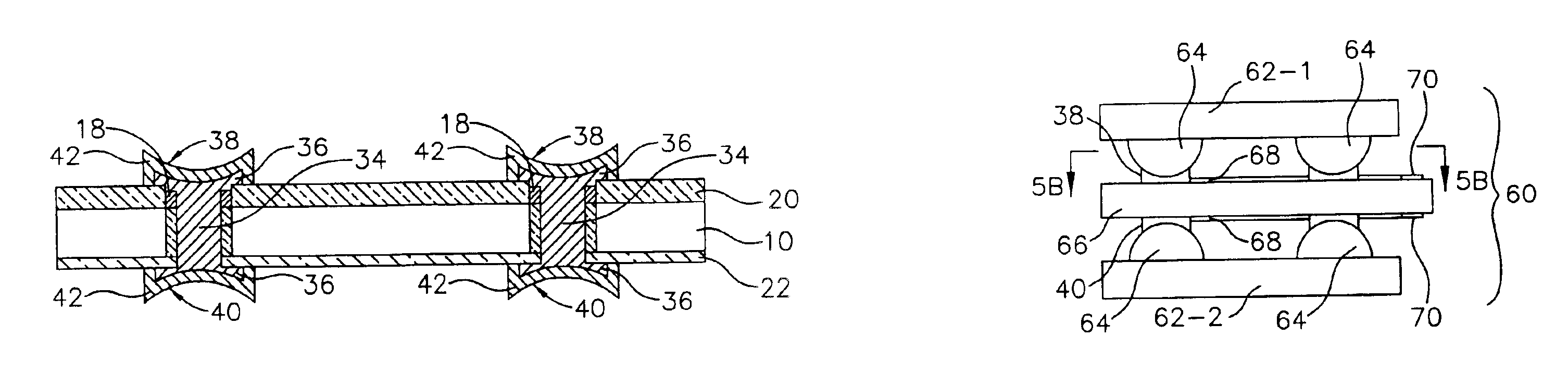

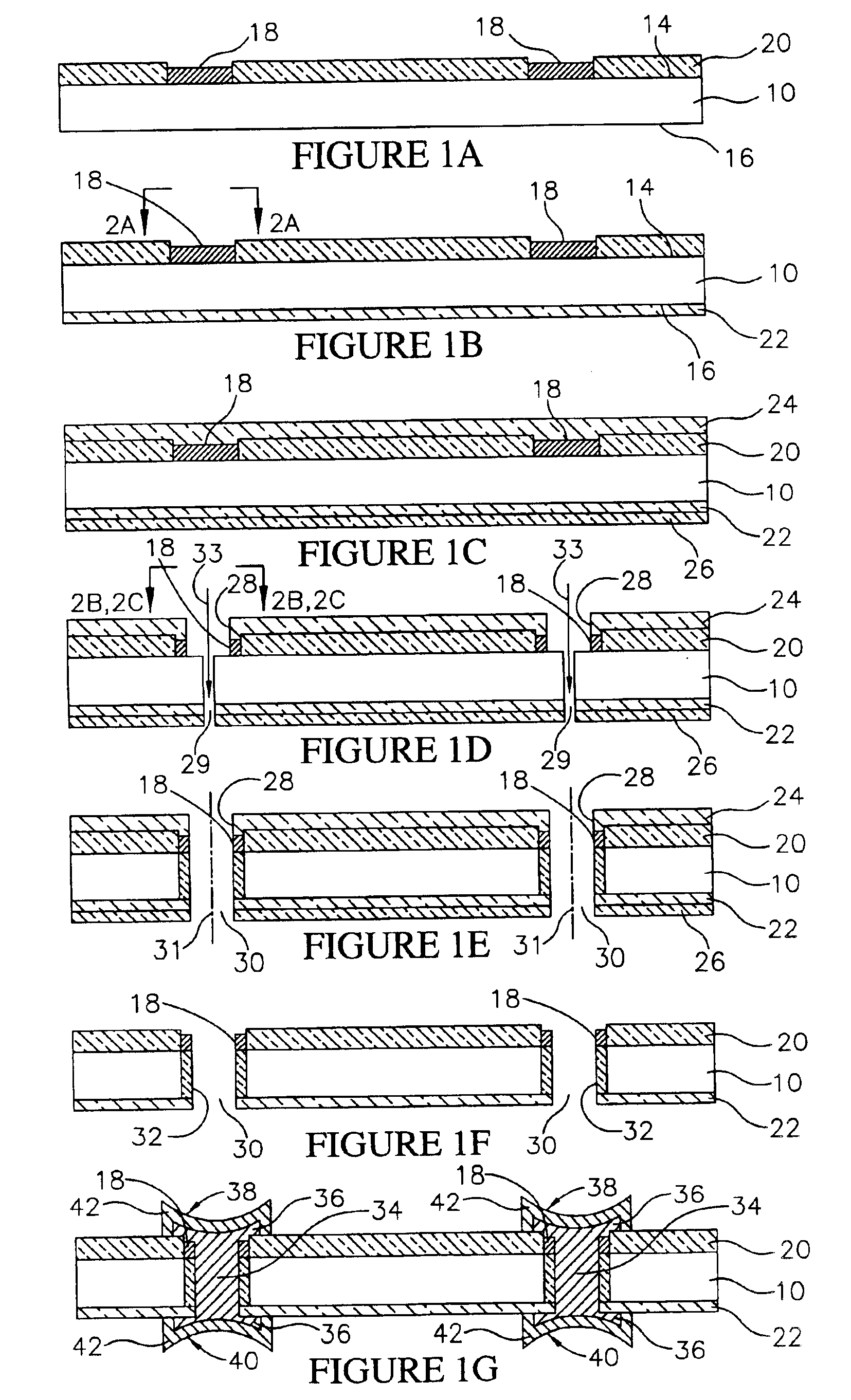

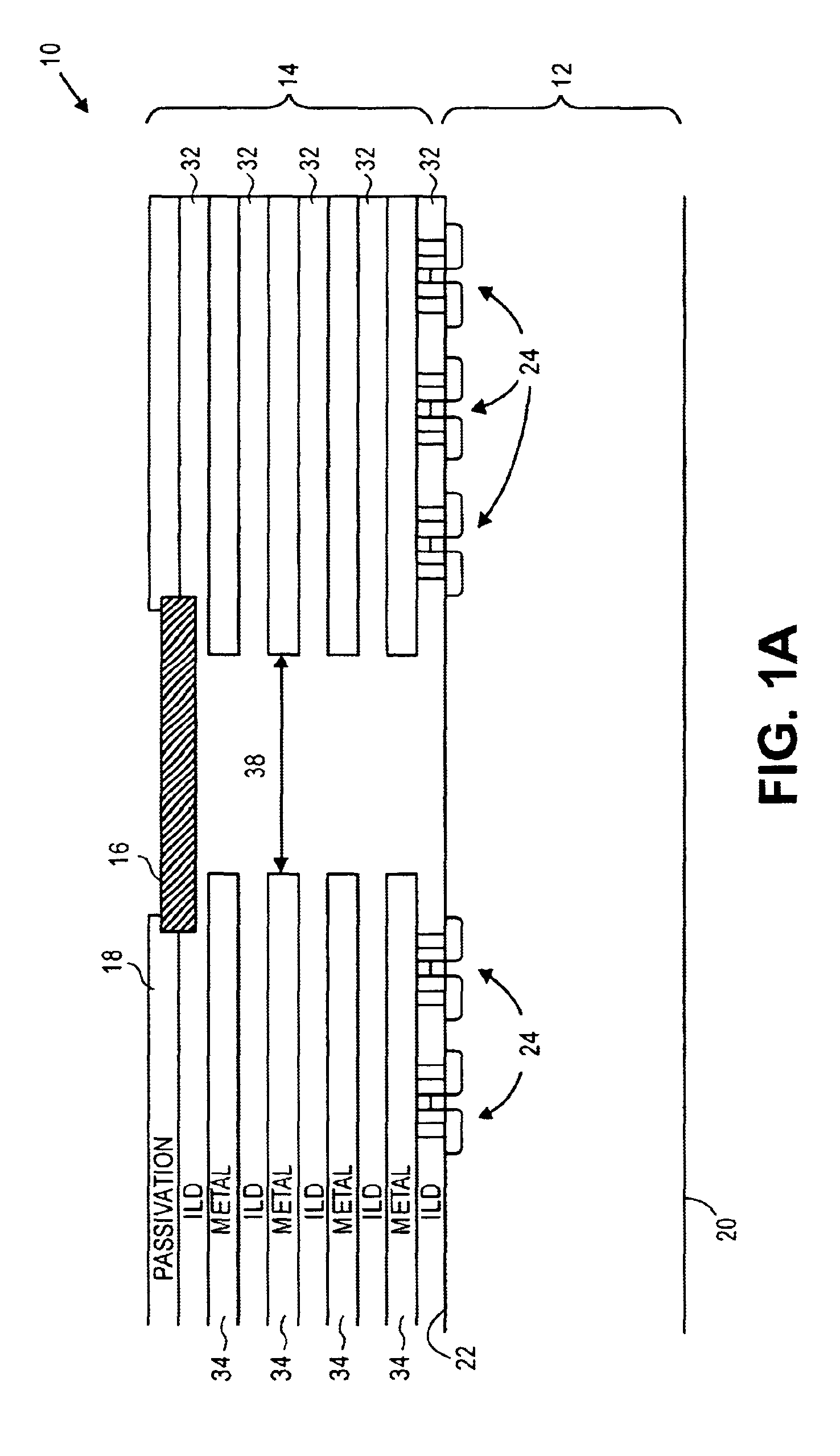

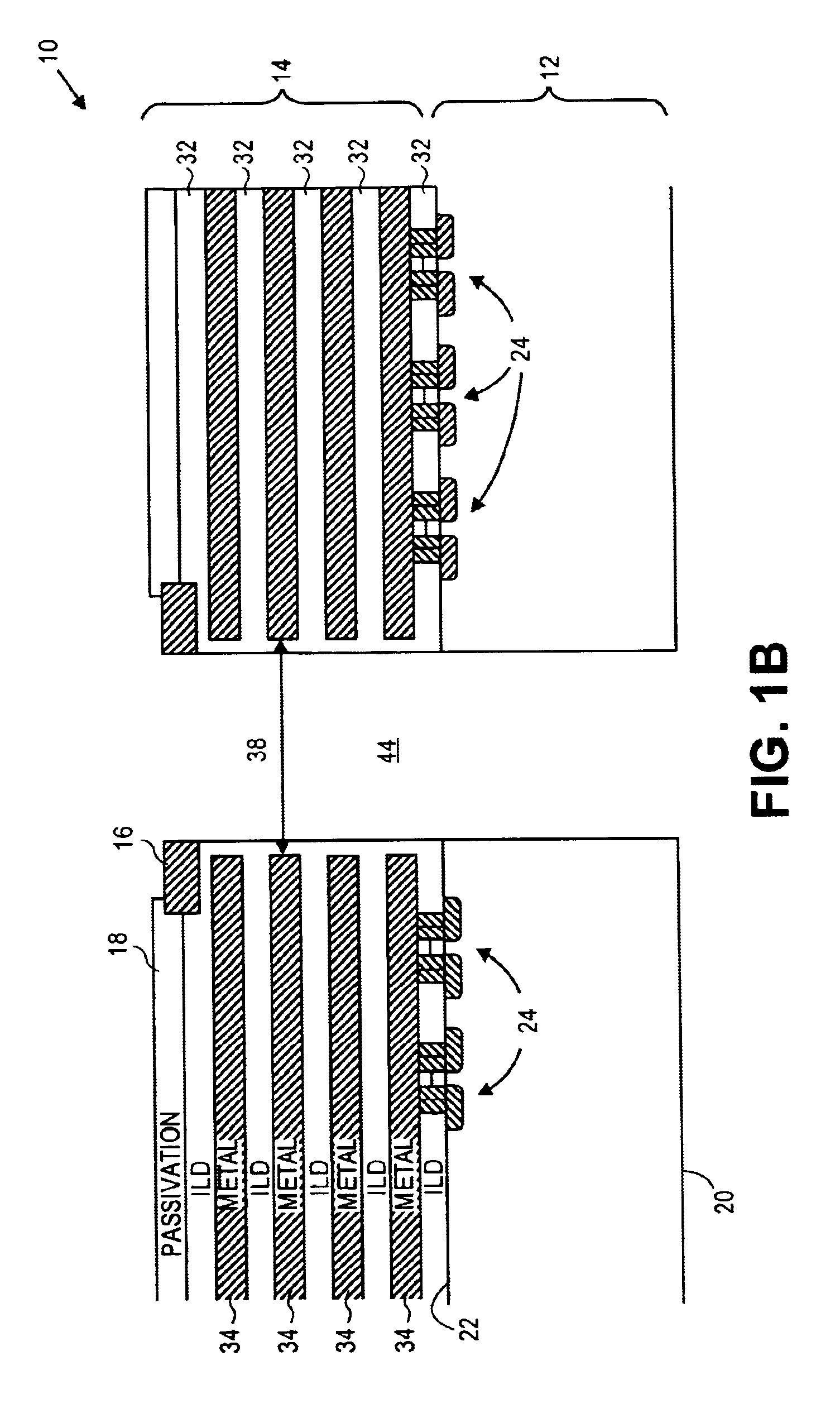

Chip stacks with decreased conductor length and improved noise immunity are formed by laser drilling of individual chips, such as memory chips, preferably near but within the periphery thereof, and forming conductors therethrough, preferably by metallization or filling with conductive paste which may be stabilized by transient liquid phase (TLP) processes and preferably with or during metallization of conductive pads, possibly including connector patterns on both sides of at least some of the chips in the stack. At least some of the chips in the stack then have electrical and mechanical connections made therebetween, preferably with electroplated solder preforms consistent with TLP processes. The connections may be contained by a layer of resilient material surrounding the connections and which may be formed in-situ. High density circuit packages thus obtained may be mounted on a carrier by surface mount techniques or separable connectors such as a plug and socket arrangement. The carrier may be of the same material as the chip stacks to match coefficients of thermal expansion. High-density circuit packages may also be in the form of removable memory modules in generally planar or prism shaped form similar to a pen or as a thermal conduction module.

Owner:INT BUSINESS MASCH CORP

High density integrated circuit packaging with chip stacking and via interconnections

InactiveUS6187678B1Reduced connection exposureLarge capacitySemiconductor/solid-state device detailsSolid-state devicesThermal expansionPrism

Chip stacks with decreased conductor length and improved noise immunity are formed by laser drilling of individual chips, such as memory chips, preferably near but within the periphery thereof, and forming conductors therethrough, preferably by metallization or filling with conductive paste which may be stabilized by transient liquid phase (TLP) processes and preferably with or during metallization of conductive pads, possibly including connector patterns on both sides of at least some of the chips in the stack. At least some of the chips in the stack then have electrical and mechanical connections made therebetween, preferably with electroplated solder preforms consistent with TLP processes. The connections may be contained by a layer of resilient material surrounding the connections and which may be formed in-situ. High density circuit packages thus obtained may be mounted on a carrier by surface mount techniques or separable connectors such as a plug and socket arrangement. The carrier may be of the same material as the chip stacks to match coefficients of thermal expansion. High-density circuit packages may also be in the form of removable memory modules in generally planar or prism shaped form similar to a pen or as a thermal conduction module.

Owner:IBM CORP

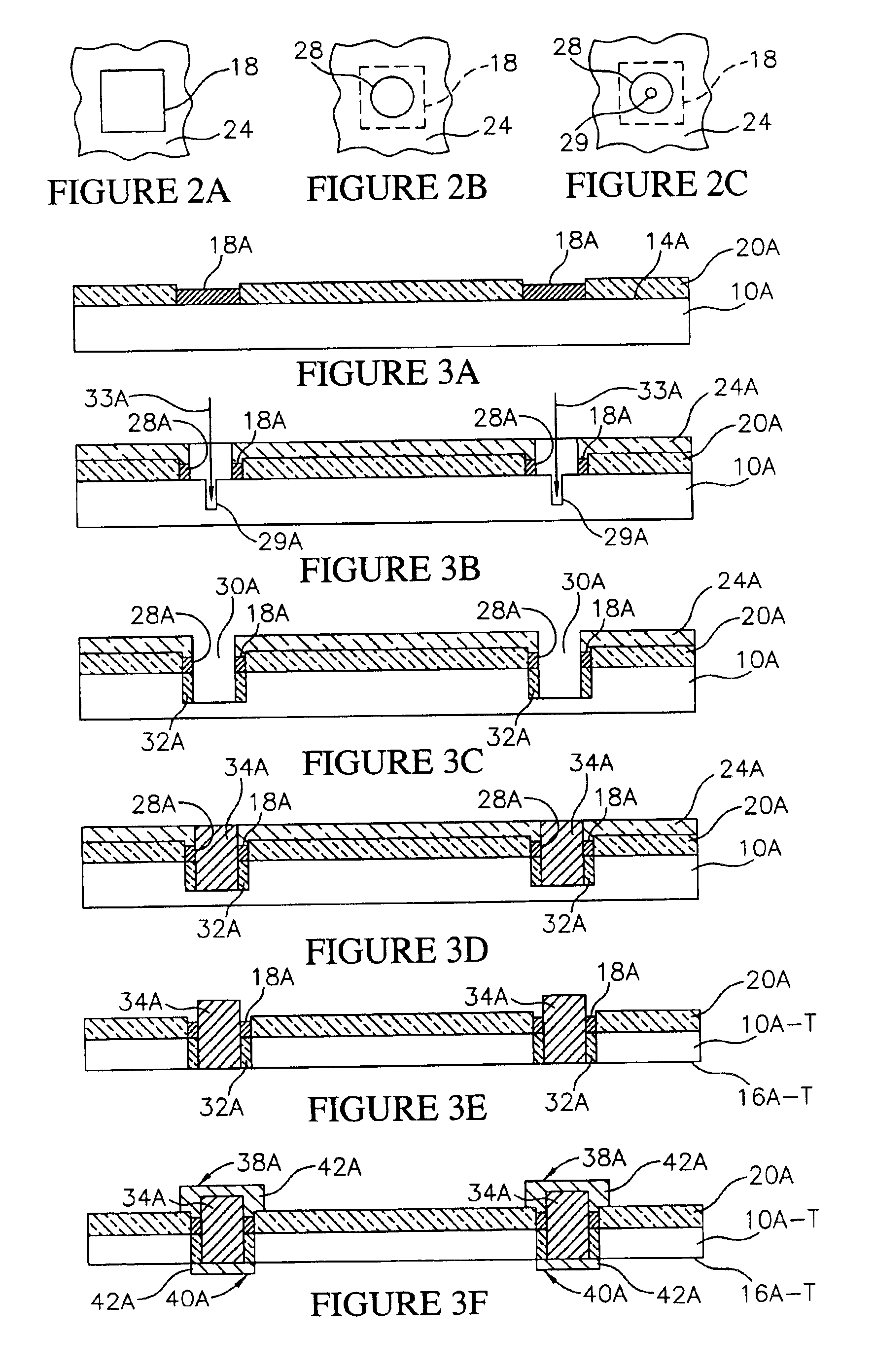

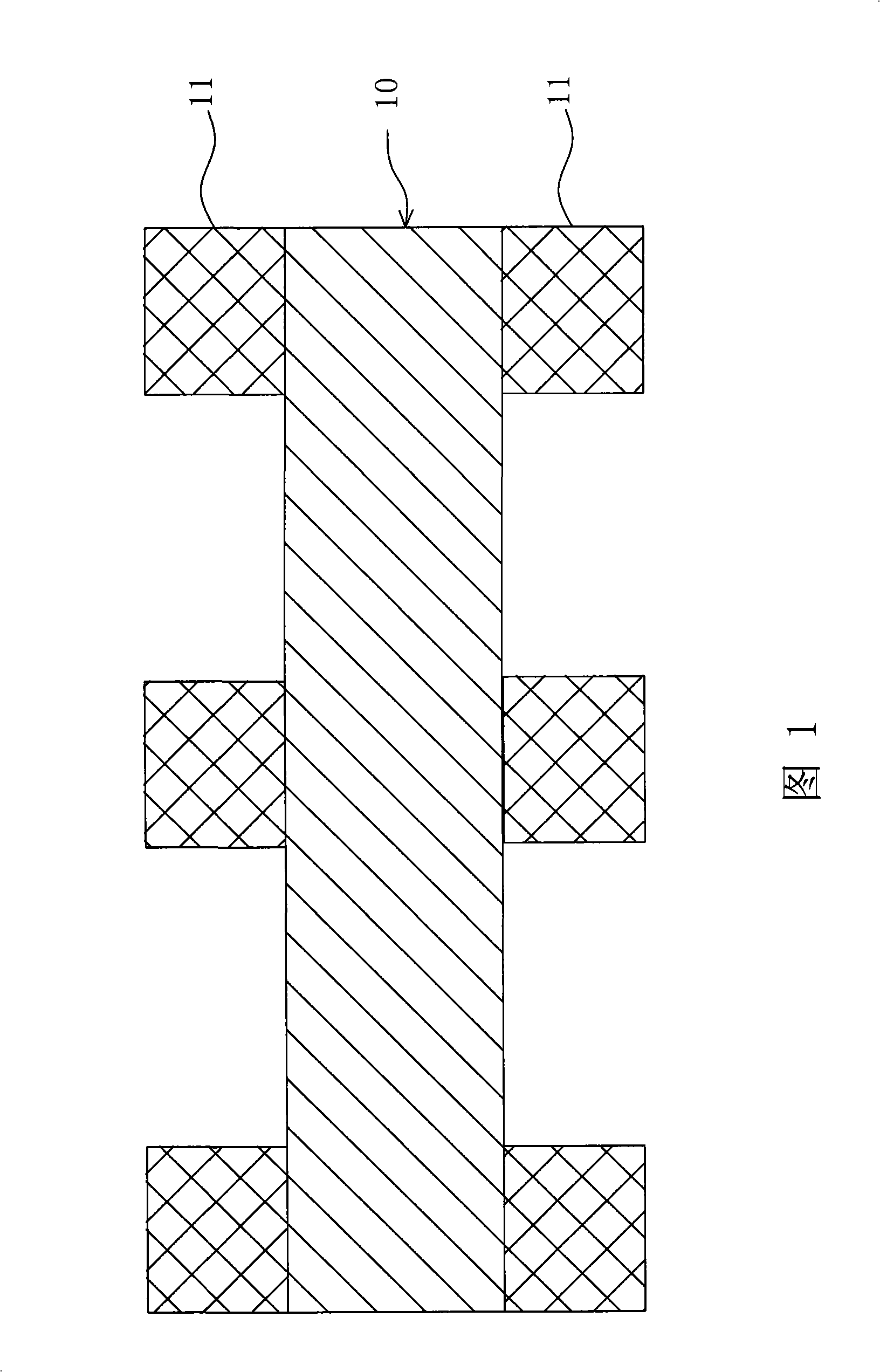

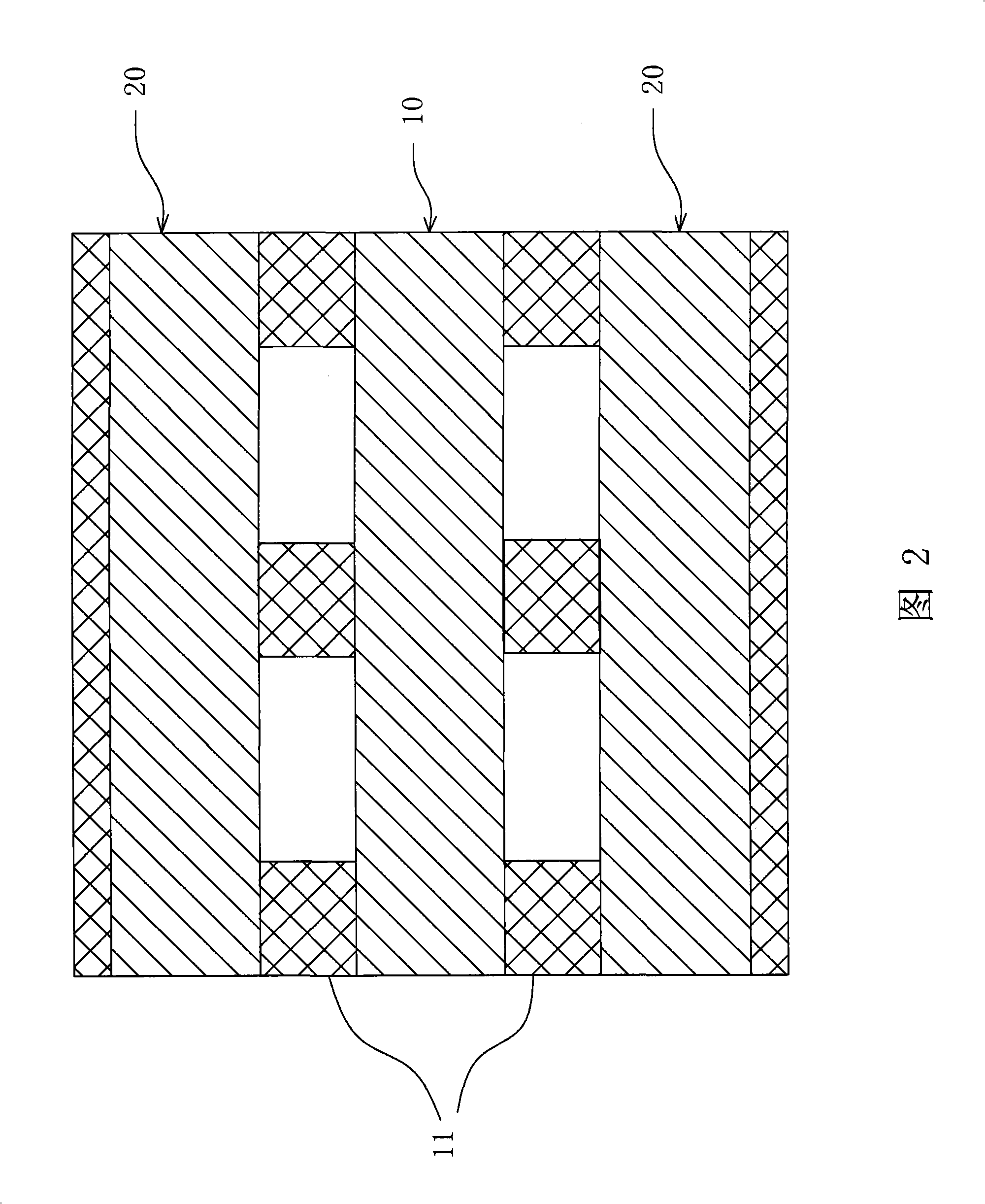

Semiconductor component and interconnect having conductive members and contacts on opposing sides

InactiveUS6903443B2Easy to manufactureSemiconductor/solid-state device detailsPrinted circuit aspectsSemiconductor packageElectronic assemblies

A method for fabricating semiconductor components and interconnects includes the steps of providing a substrate, such as a semiconductor die, forming external contacts on opposing sides of the substrate by laser drilling vias through the substrate, and forming conductive members in the vias. The conductive members include enlarged terminal portions that are covered with a non-oxidizing metal. The method can be used to fabricate stackable semiconductor packages having integrated circuits in electrical communication with the external contacts. The method can also be used to fabricate interconnects for electrically engaging packages, dice and wafers for testing or for constructing electronic assemblies.

Owner:ROUND ROCK RES LLC

Semiconductor package having through holes

ActiveUS7843072B1Save fabrication timeFabrication yield can be improvedSemiconductor/solid-state device detailsSolid-state devicesIonLaser drilling

Disclosed is a semiconductor package. The semiconductor package is configured to form a plurality of through holes for forming a through silicon via at once using a sawing device used for wafer sawing instead of a separate laser drilling equipment or a deep reactive ion etching (DRIE) equipment. Accordingly, the semiconductor package saves fabricating time and increases fabrication yield, saves costs for a laser drilling equipment or a DRIE equipment, and prevents various defects generated in an inner portion of a through hole in the case of using the laser drilling equipment or the DRIE equipment.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

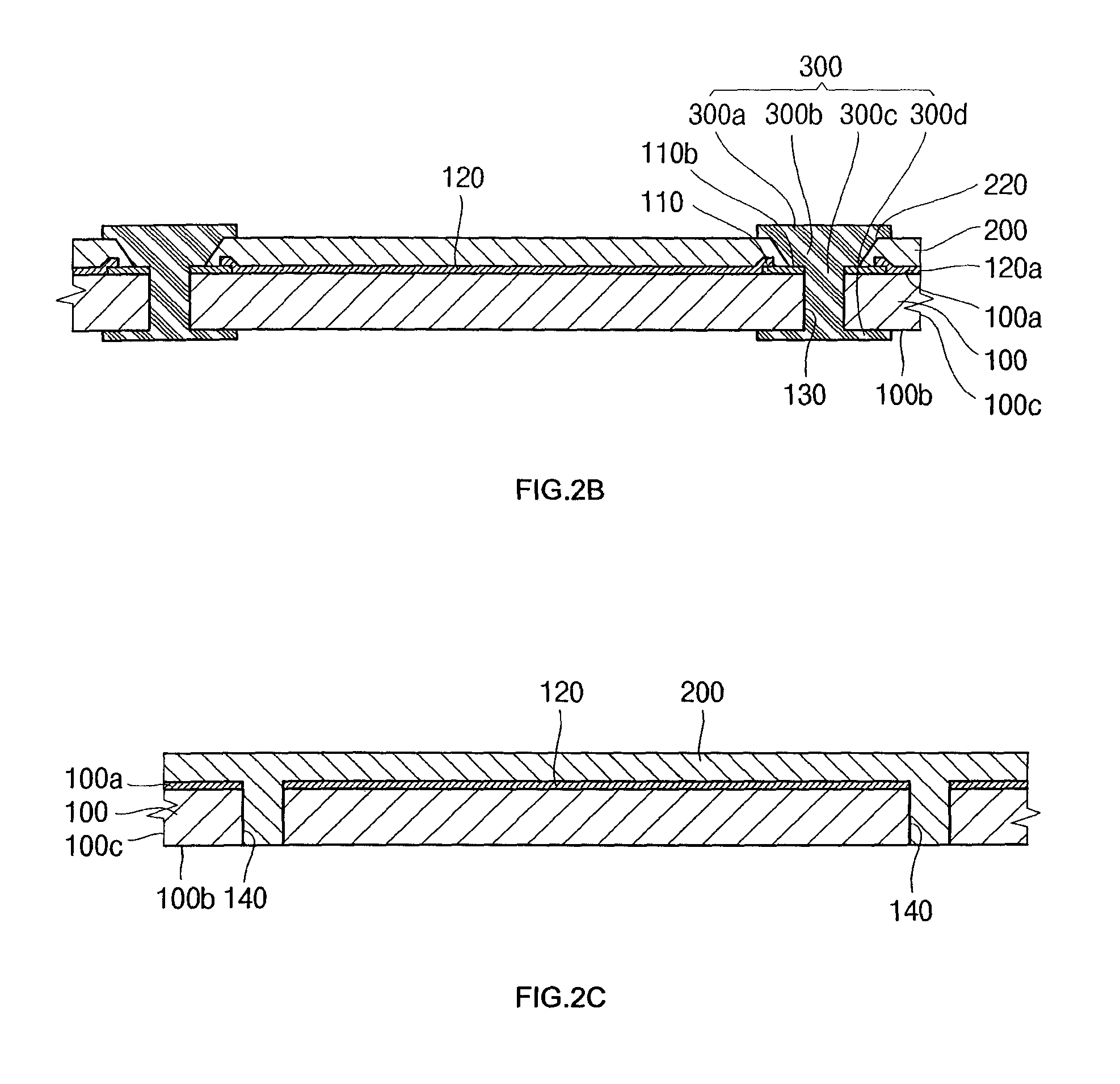

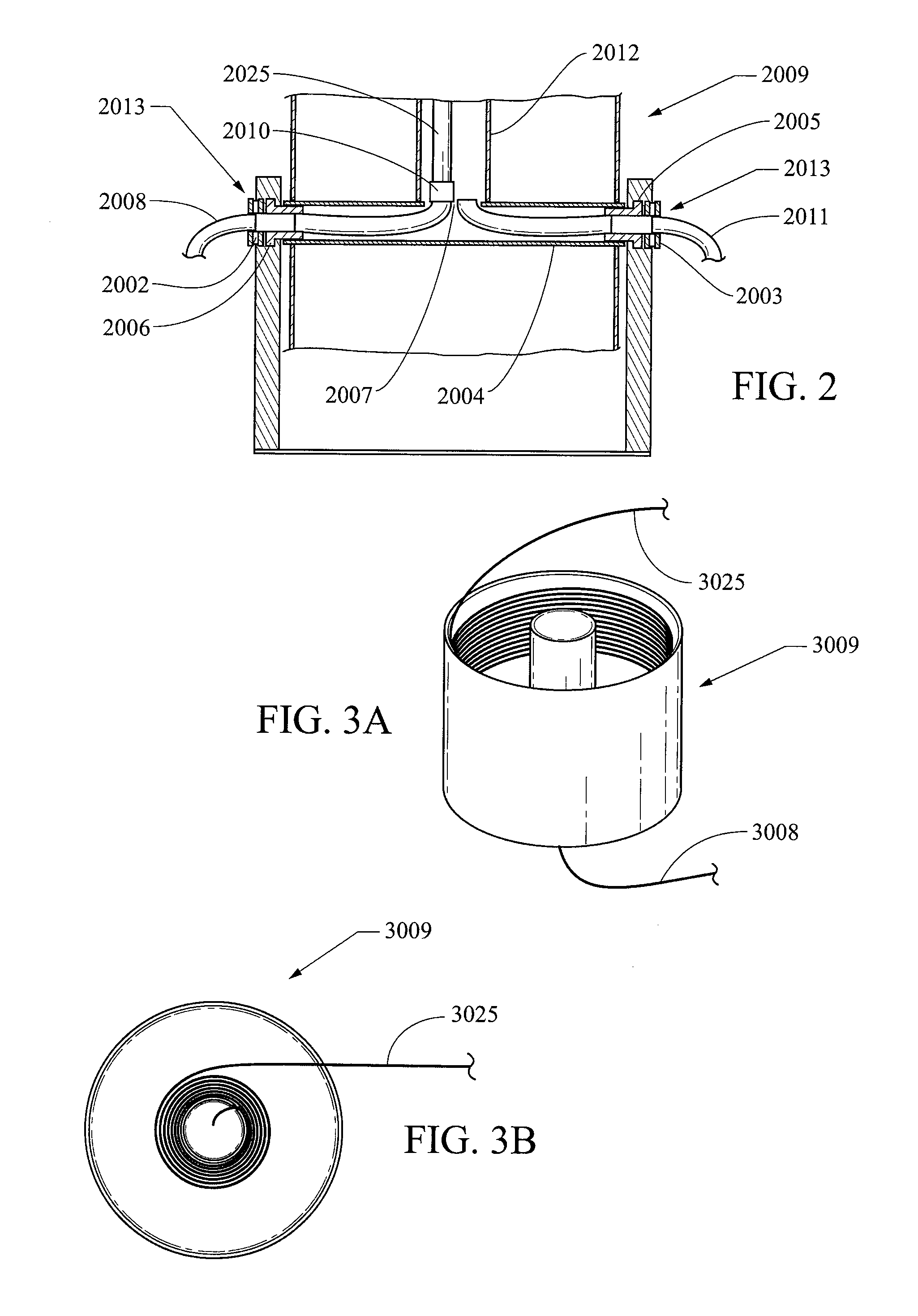

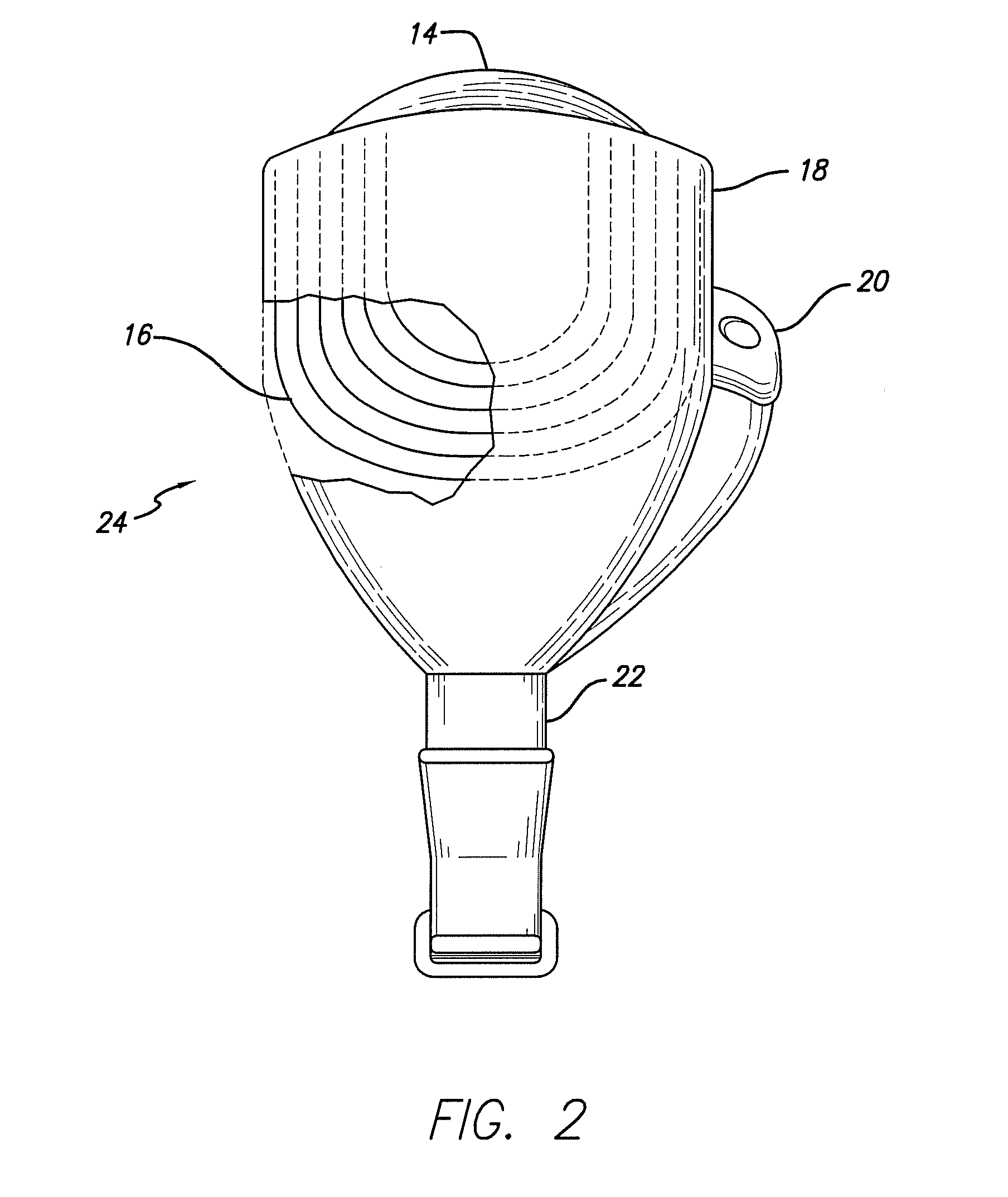

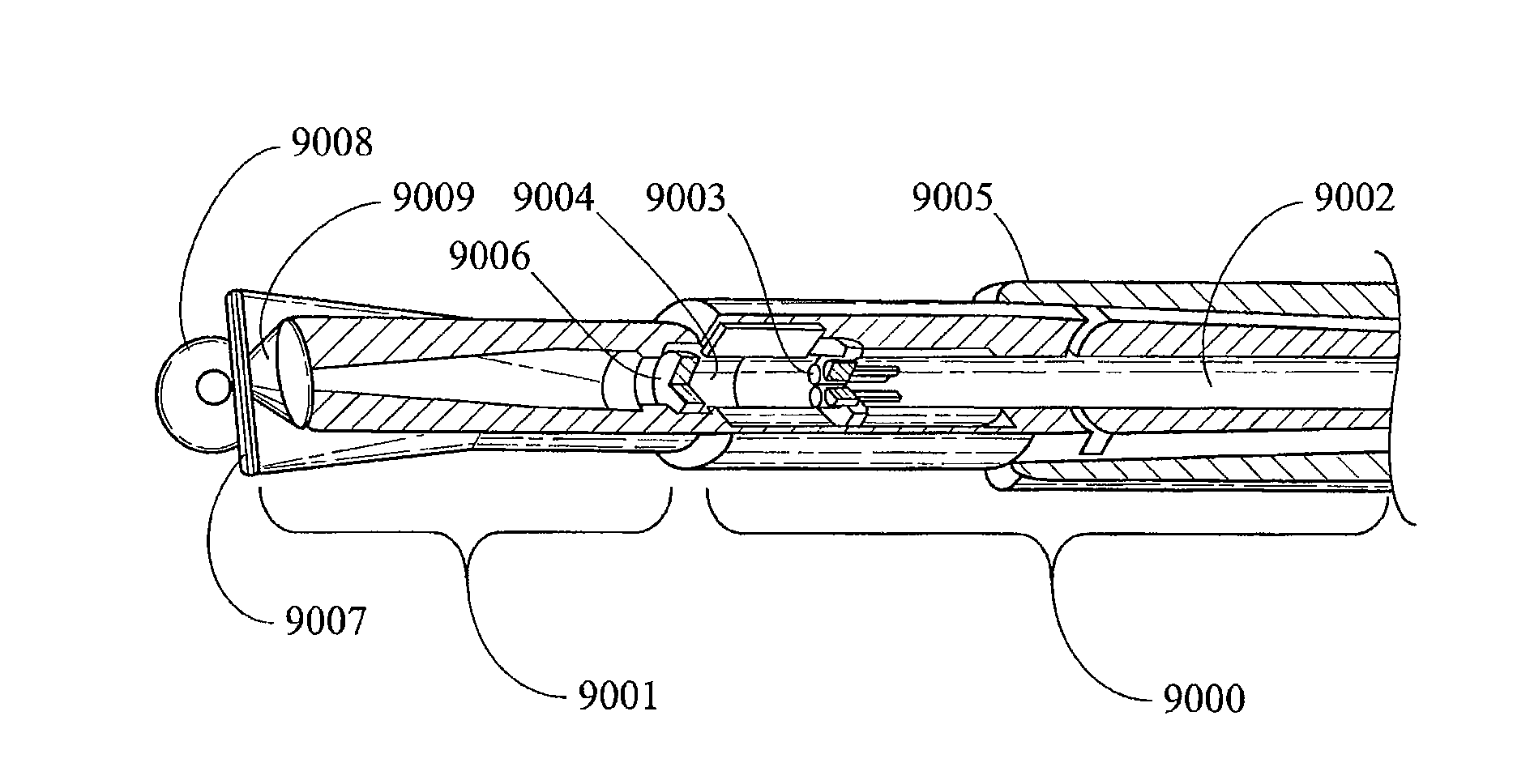

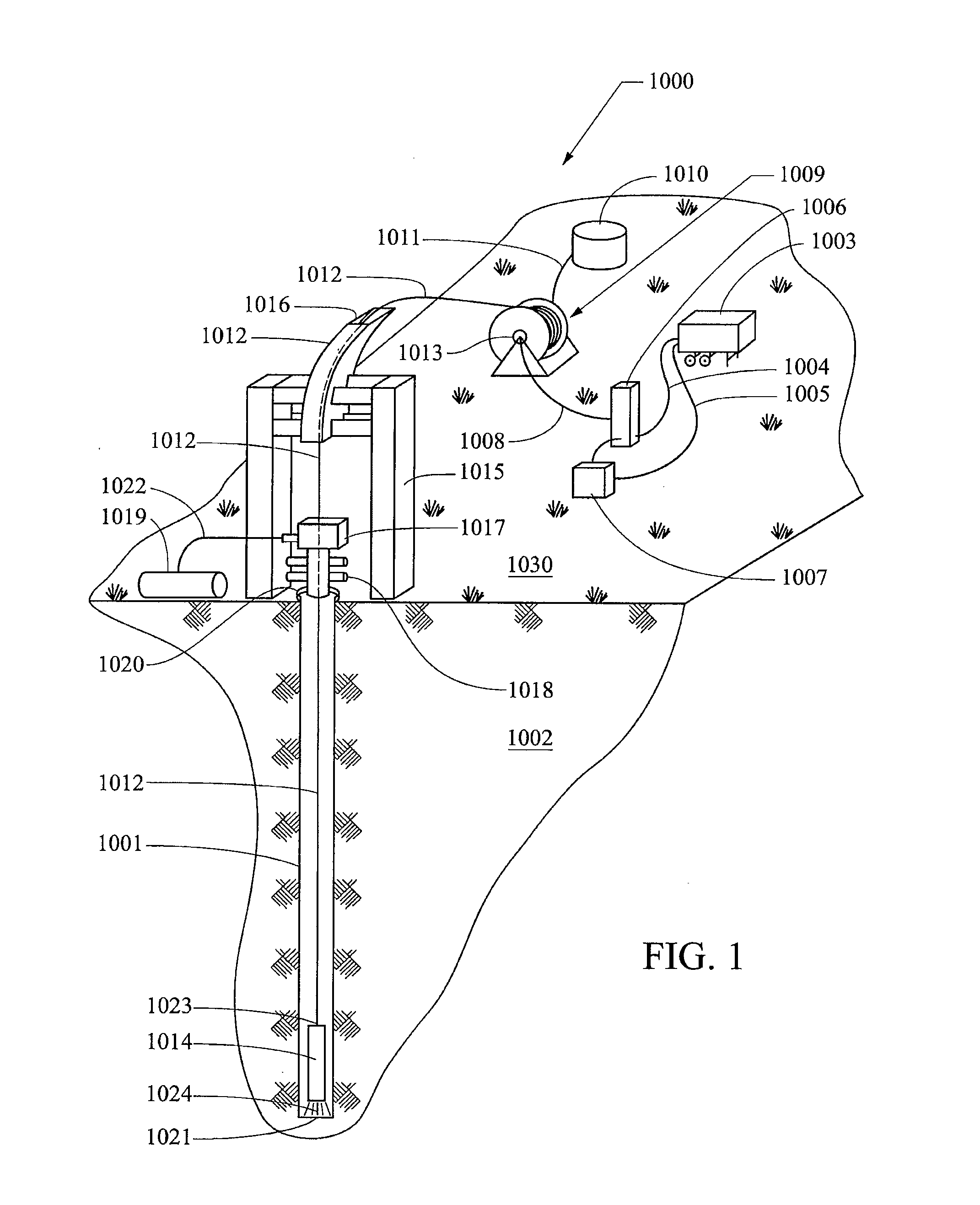

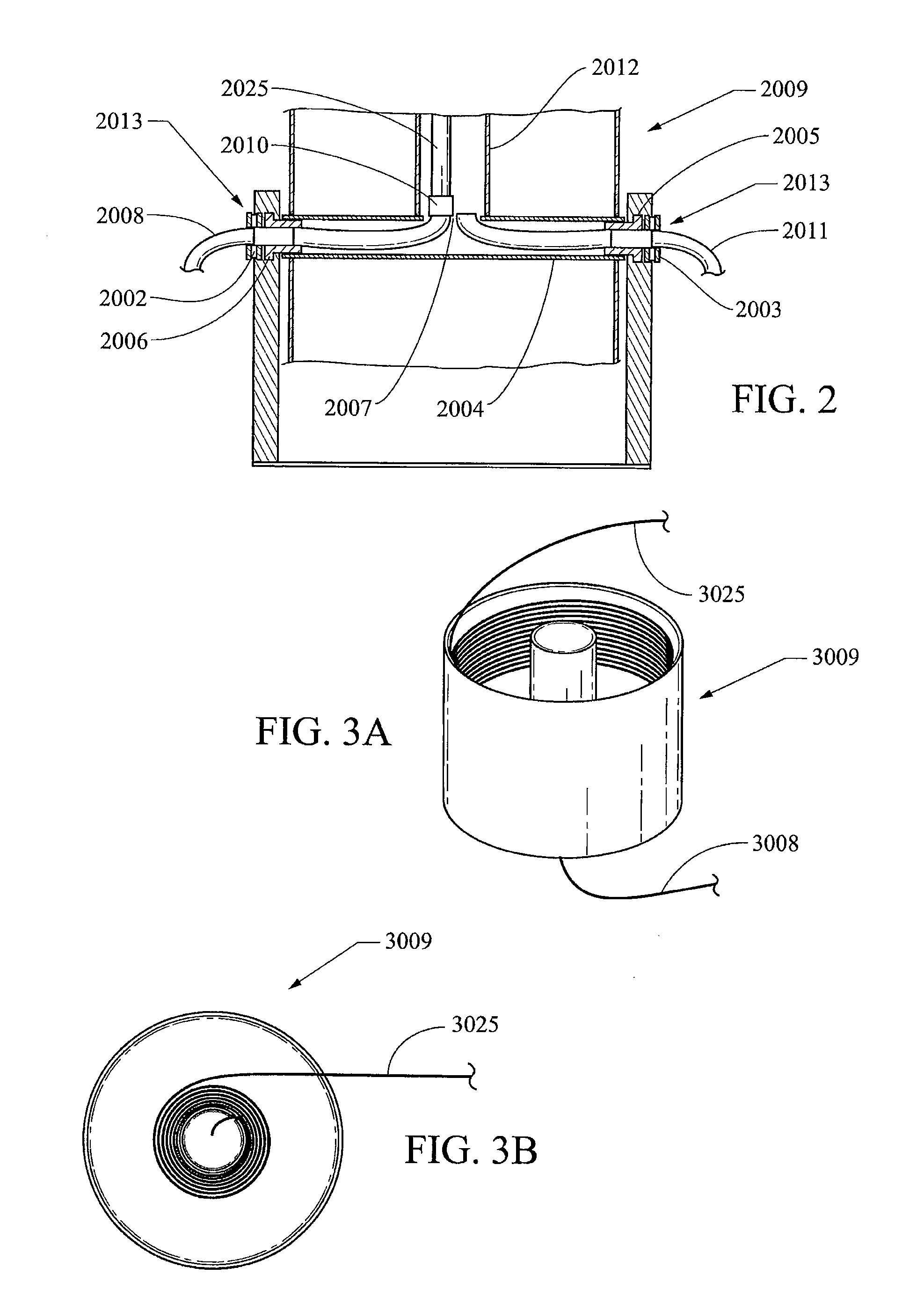

Method and apparatus for delivering high power laser energy over long distances

ActiveUS20100044106A1Suppressing nonlinear scattering phenomenonIncrease the lengthDrill bitsLaser using scattering effectsHigh power lasersOptoelectronics

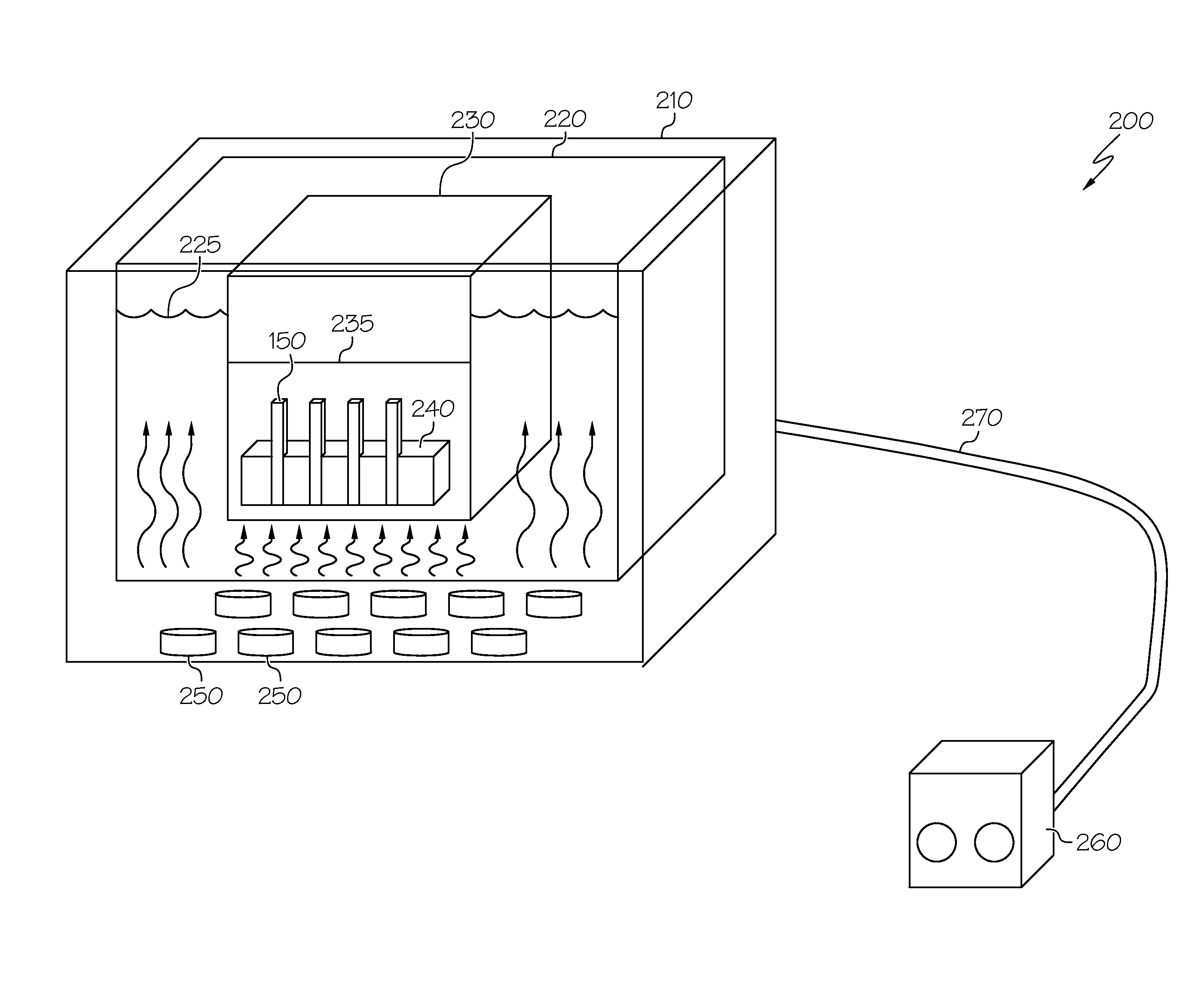

There is provided a system, apparatus and methods for the laser drilling of a borehole in the earth. There is further provided with in the systems a means for delivering high power laser energy down a deep borehole, while maintaining the high power to advance such boreholes deep into the earth and at highly efficient advancement rates.

Owner:FORO ENERGY

Thin stacked interposer package

ActiveUS8319338B1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor packageElectronic component

The present invention comprises a semiconductor package comprising a bottom semiconductor package substrate which is populated with one or more electronic components. The electronic component(s) of the bottom substrate are covered or encapsulated with a suitable mold compound which hardens into a package body of the semiconductor package. The package body is provided with one or more vias through the completion of laser drilling process, such via(s) providing access to one or more corresponding conductive contacts of the bottom substrate. These vias are either lined or partially filled with a conductive metal material. Subsequently, a top semiconductor package substrate (which may optionally be populated with one or more electronic components) is mounted to the package body and electrically connected to the conductive metal within the via(s) of the package body.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

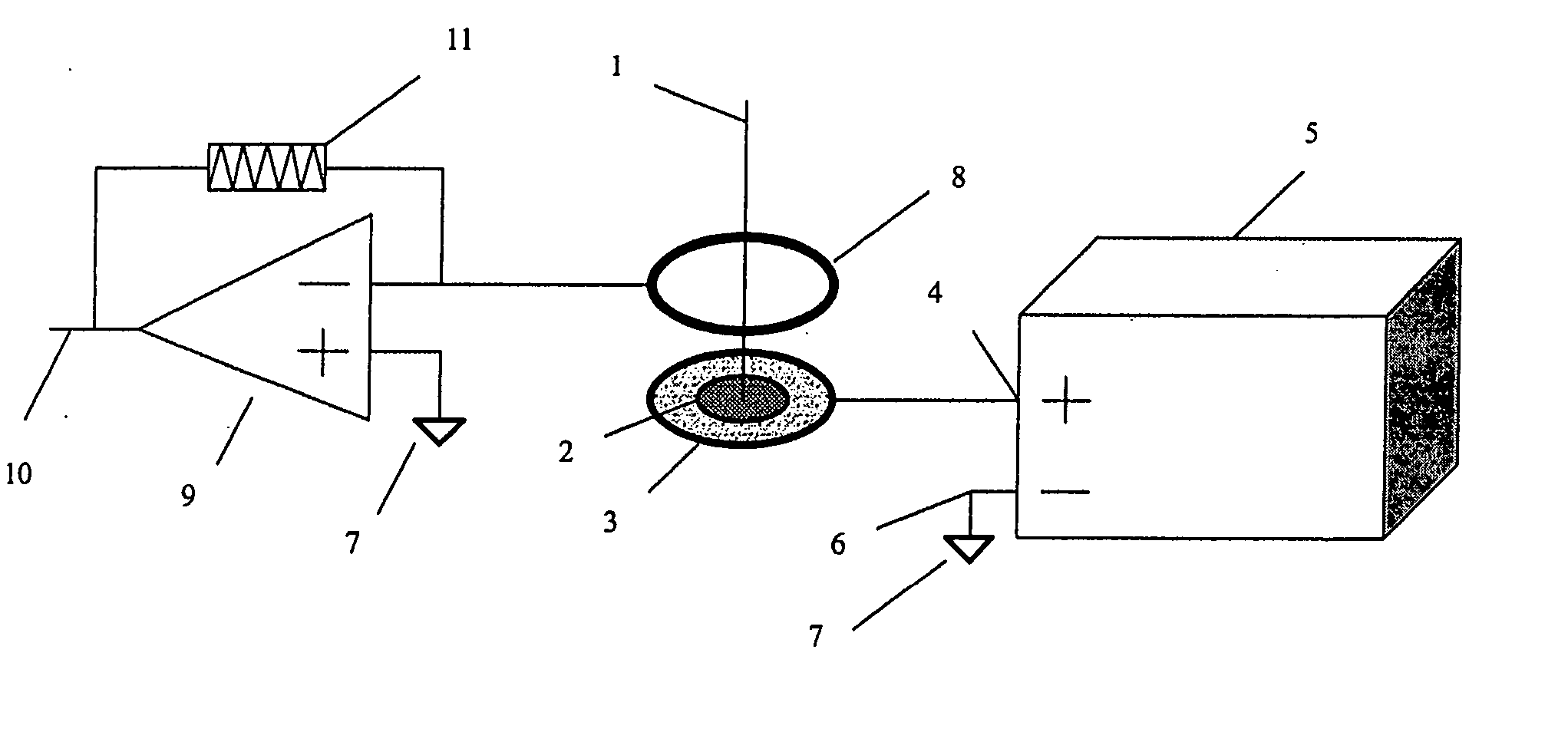

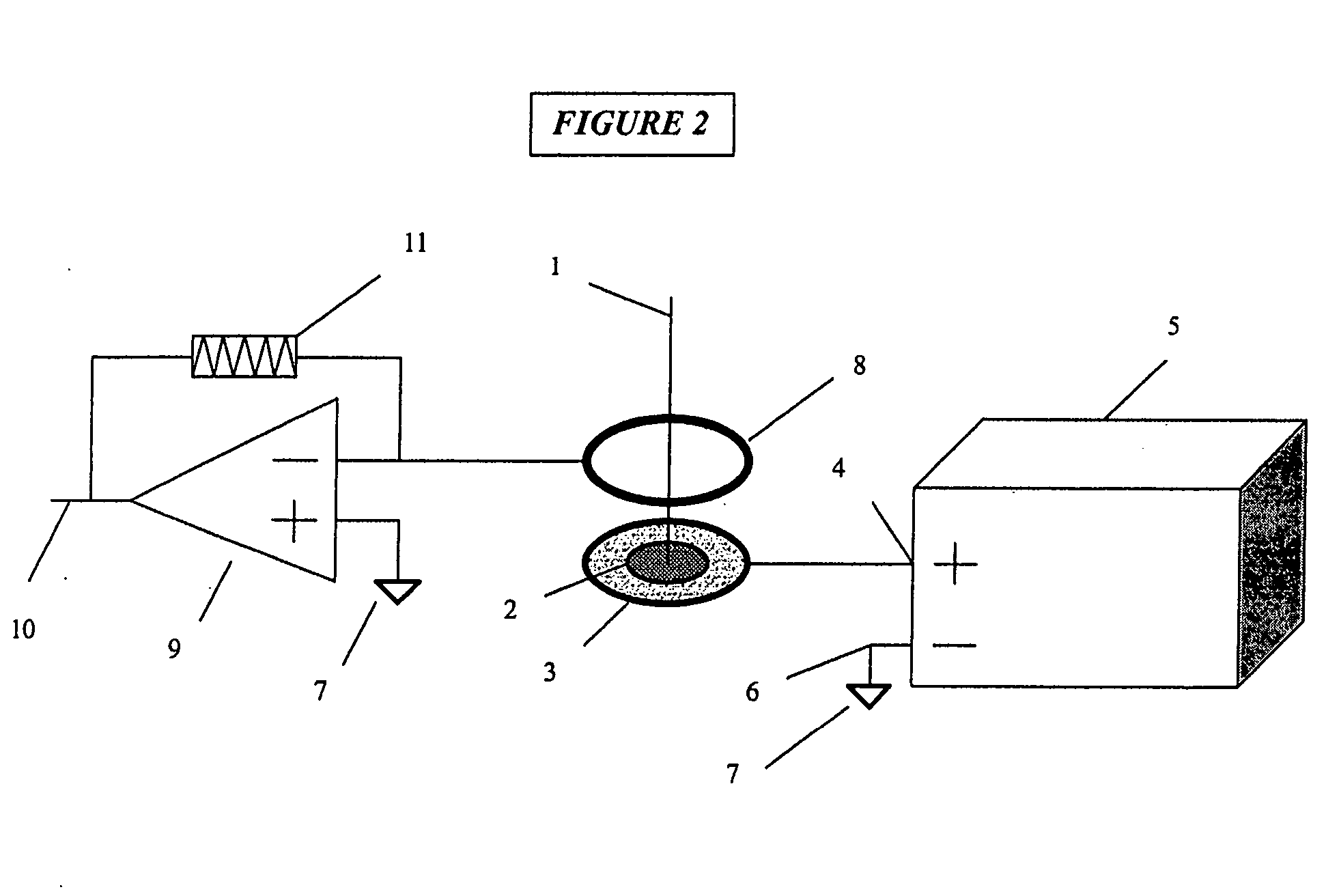

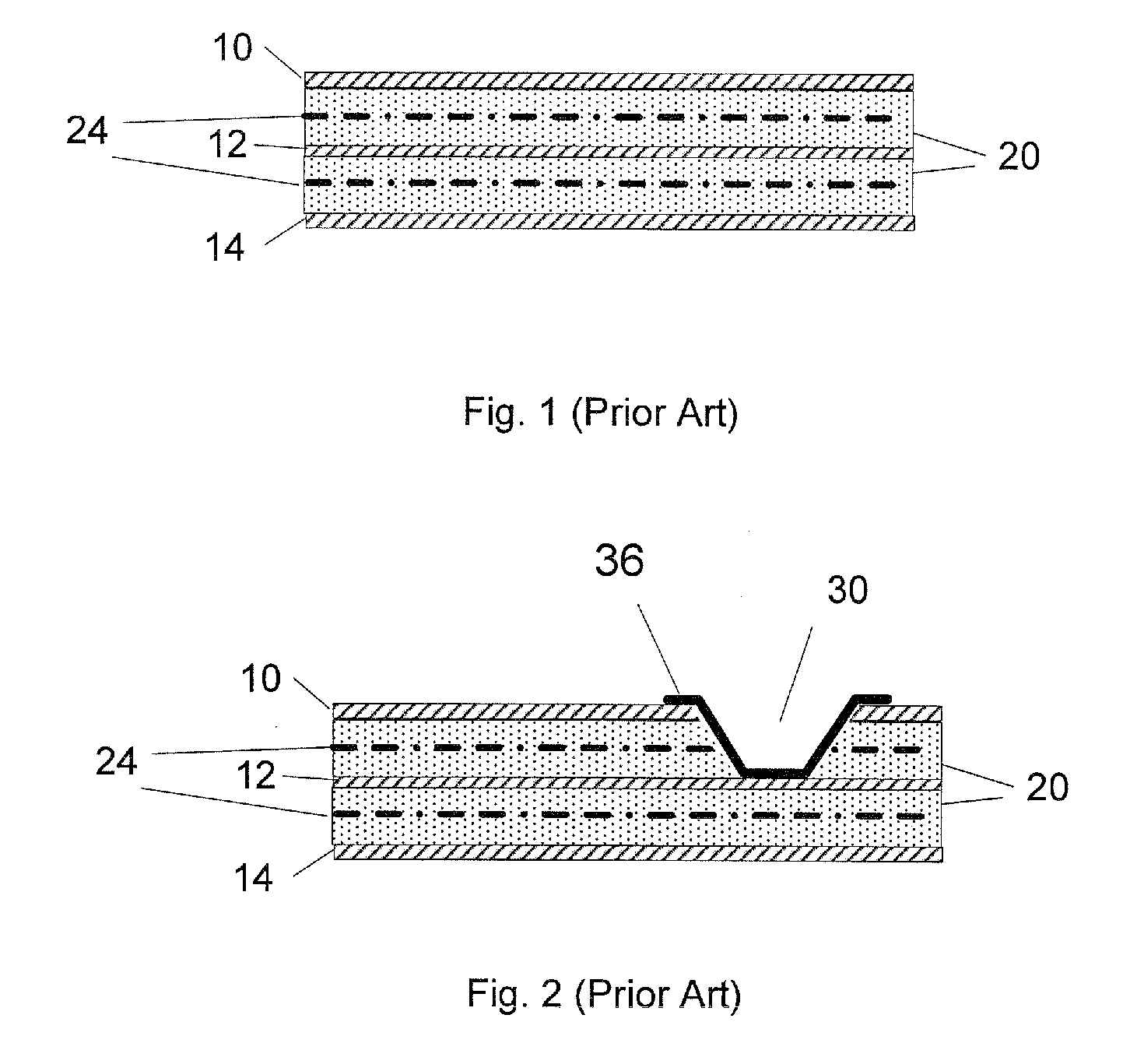

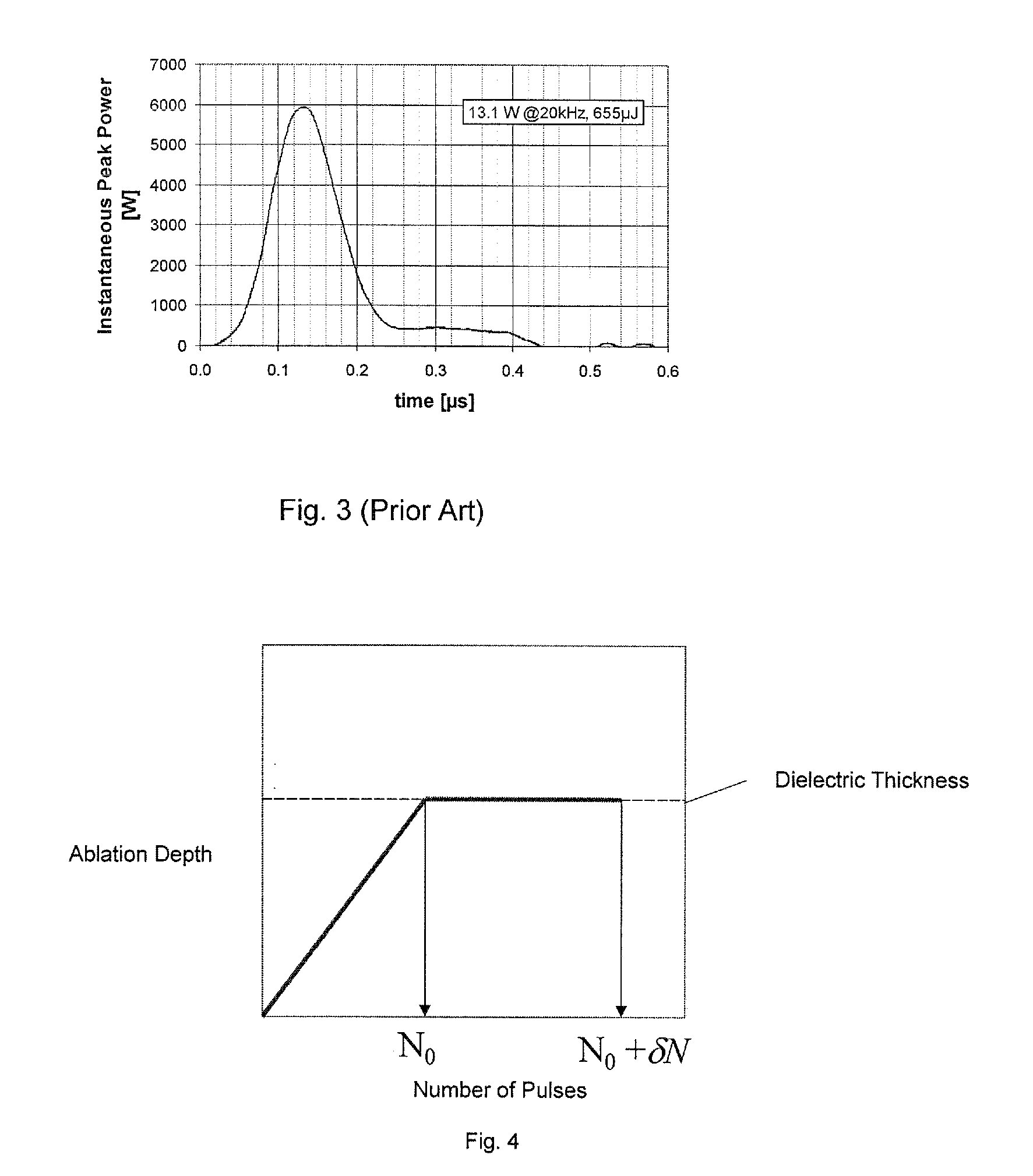

Laser ablation feedback spectroscopy

InactiveUS20050061779A1Precise depth controlReduce the amount requiredWelding/soldering/cutting articlesMetal working apparatusMass spectrometryAblation plasma

Methods, for use with a laser ablation or drilling process, which achieve depth-controlled removal of composite-layered work-piece material by real-time feedback of ablation plasma spectral features. The methods employ the use of electric, magnetic or combined fields in the region of the laser ablation plume to direct the ablated material. Specifically, the electric, magnetic or combined fields cause the ablated material to be widely dispersed, concentrated in a target region, or accelerated along a selected axis for optical or physical sampling, analysis and laser feedback control. The methods may be used with any laser drilling, welding or marking process and are particularly applicable to laser micro-machining. The described methods may be effectively used with ferrous and non-ferrous metals and non-metallic work-pieces. The two primary benefits of these methods are the ability to drill or ablate to a controlled depth, and to provide controlled removal of ablation debris from the ablation site. An ancillary benefit of the described methods is that they facilitate ablated materials analysis and characterization by optical and / or mass spectroscopy.

Owner:BLUMENFELD WALTER +2

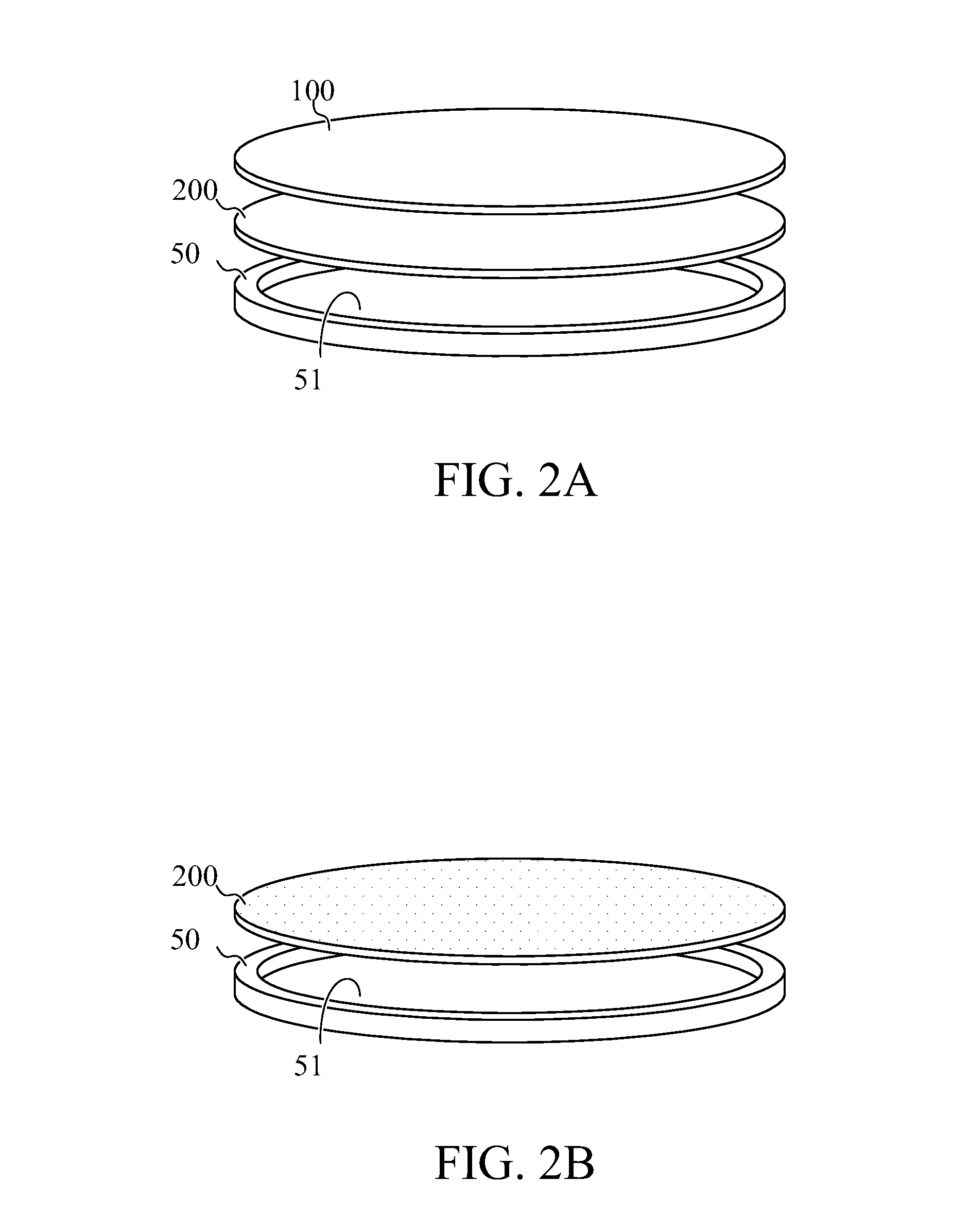

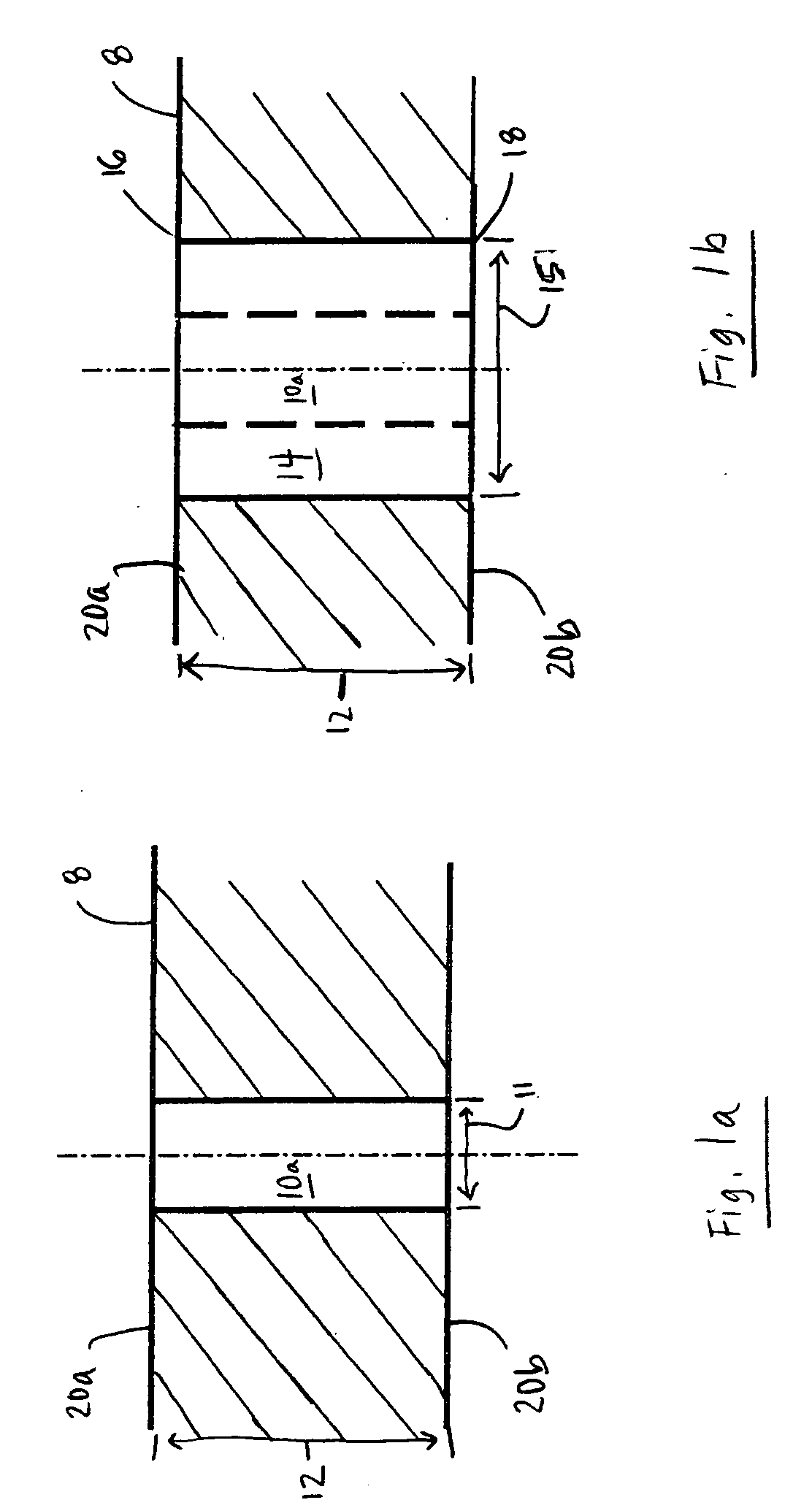

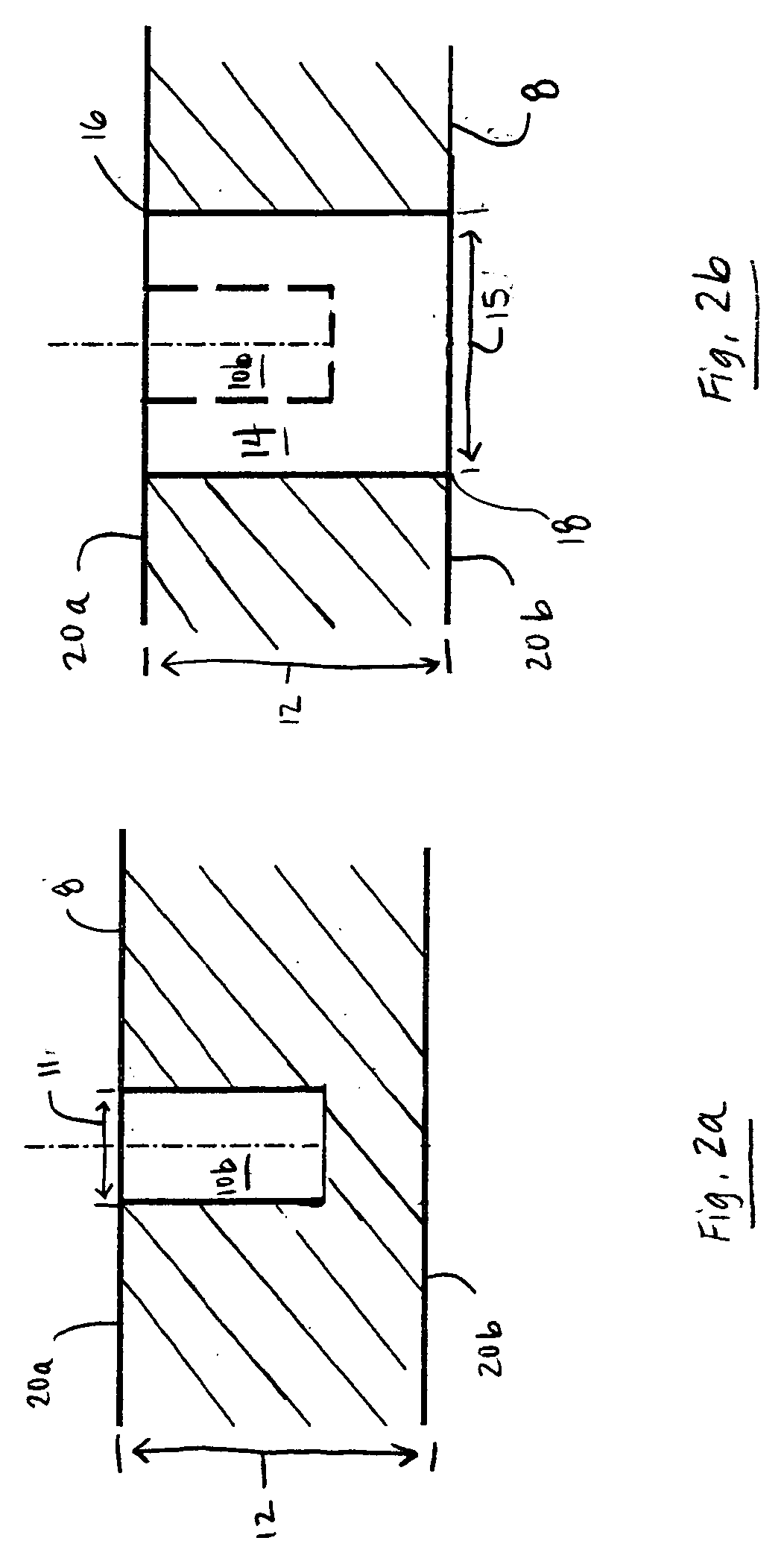

Sacrificial Cover Layers for Laser Drilling Substrates and Methods Thereof

InactiveUS20140147623A1Reduce violationsLayered productsPrinted circuit manufactureEngineeringLaser beams

A method for forming a plurality of precision holes in a substrate by drilling, including affixing a sacrificial cover layer to a surface of the substrate, positioning a laser beam in a predetermined location relative to the substrate and corresponding to a desired location of one of the plurality of precision holes, forming a through hole in the sacrificial cover layer by repeatedly pulsing a laser beam at the predetermined location, and pulsing the laser beam into the through hole formed in the sacrificial cover layer. A work piece having precision holes including a substrate having the precision holes formed therein, wherein a longitudinal axis of each precision hole extends in a thickness direction of the substrate, and a sacrificial cover layer detachably affixed to a surface of the substrate, such that the sacrificial cover layer reduces irregularities of the precision holes.

Owner:CORNING INC

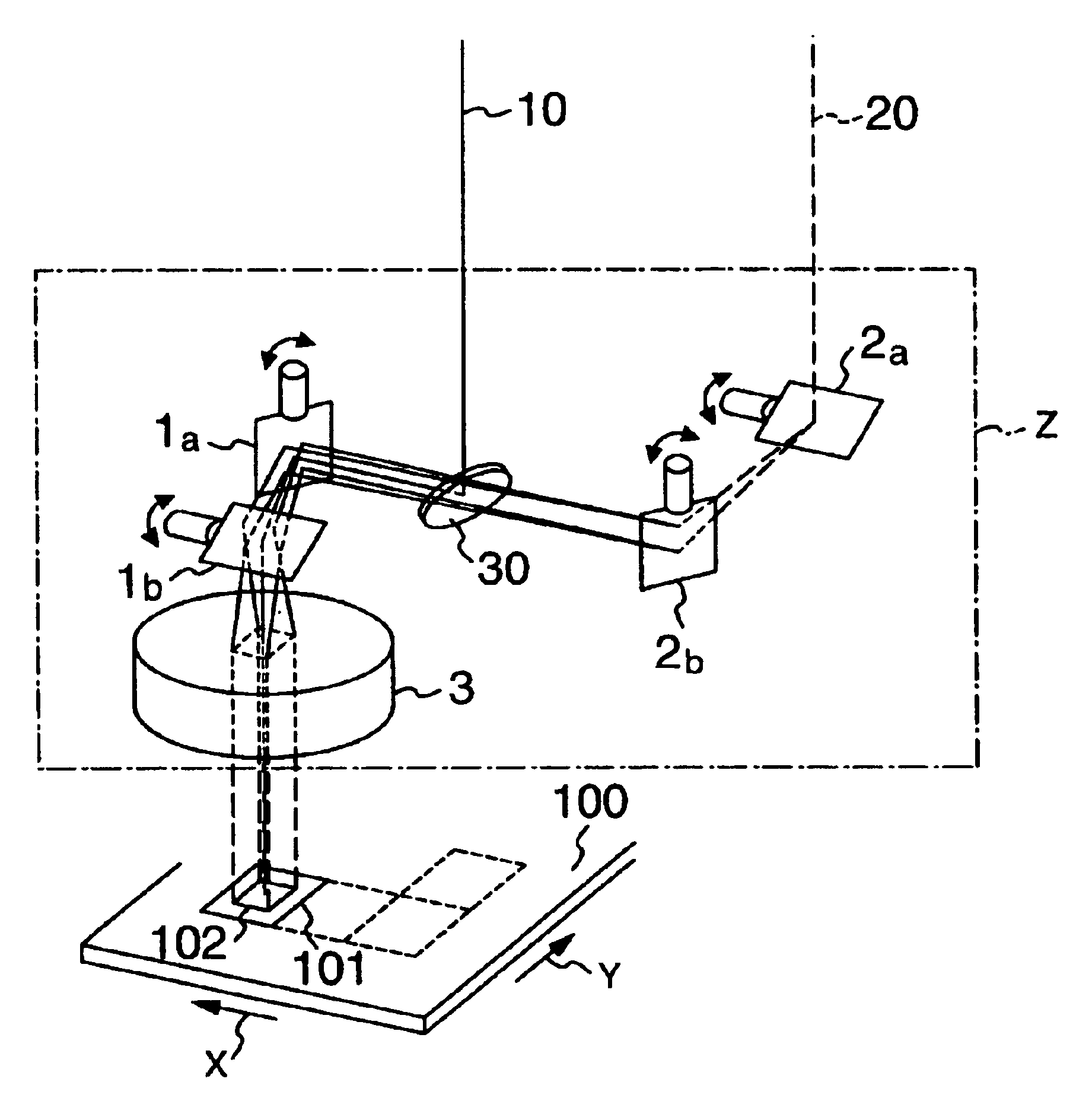

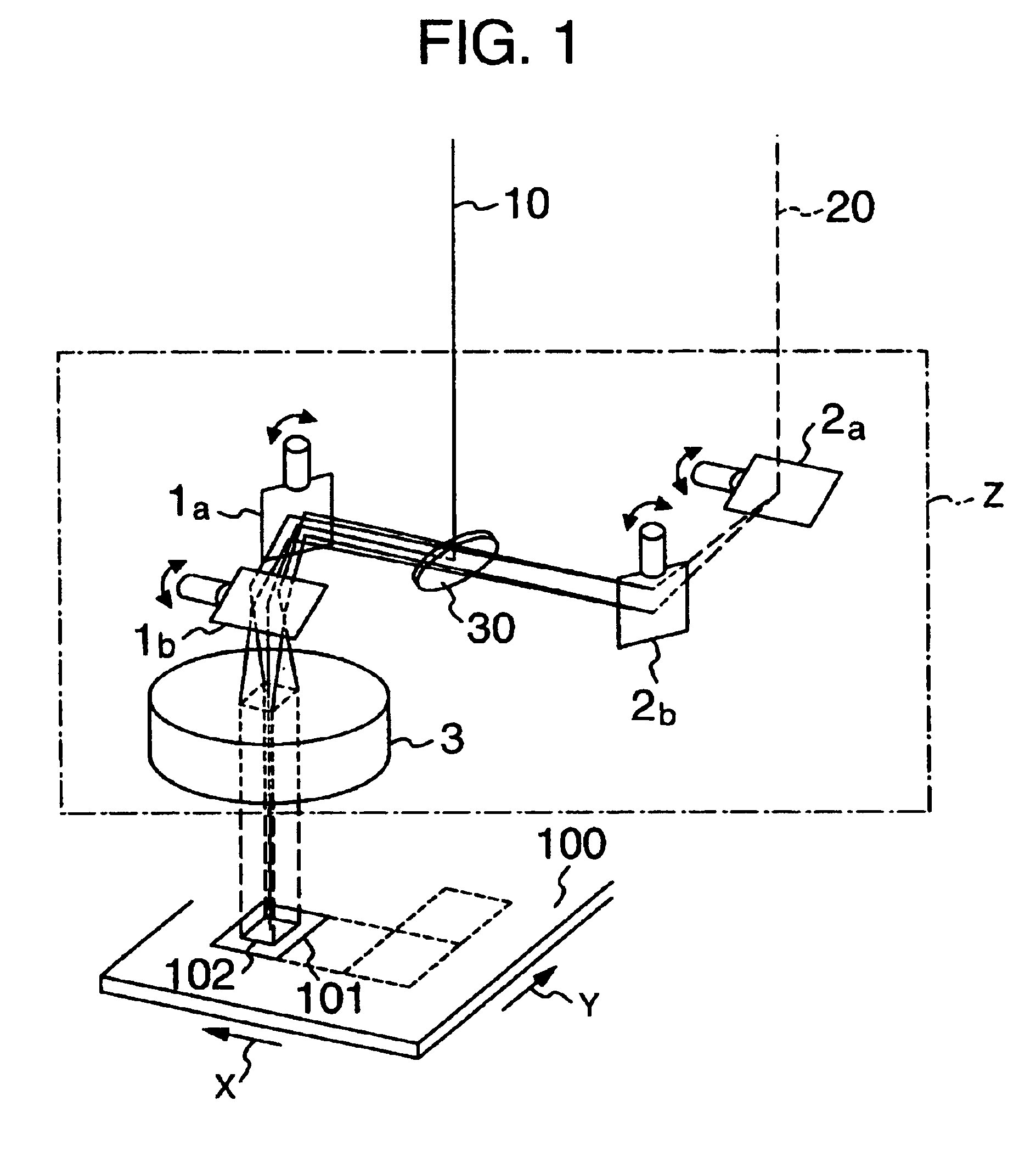

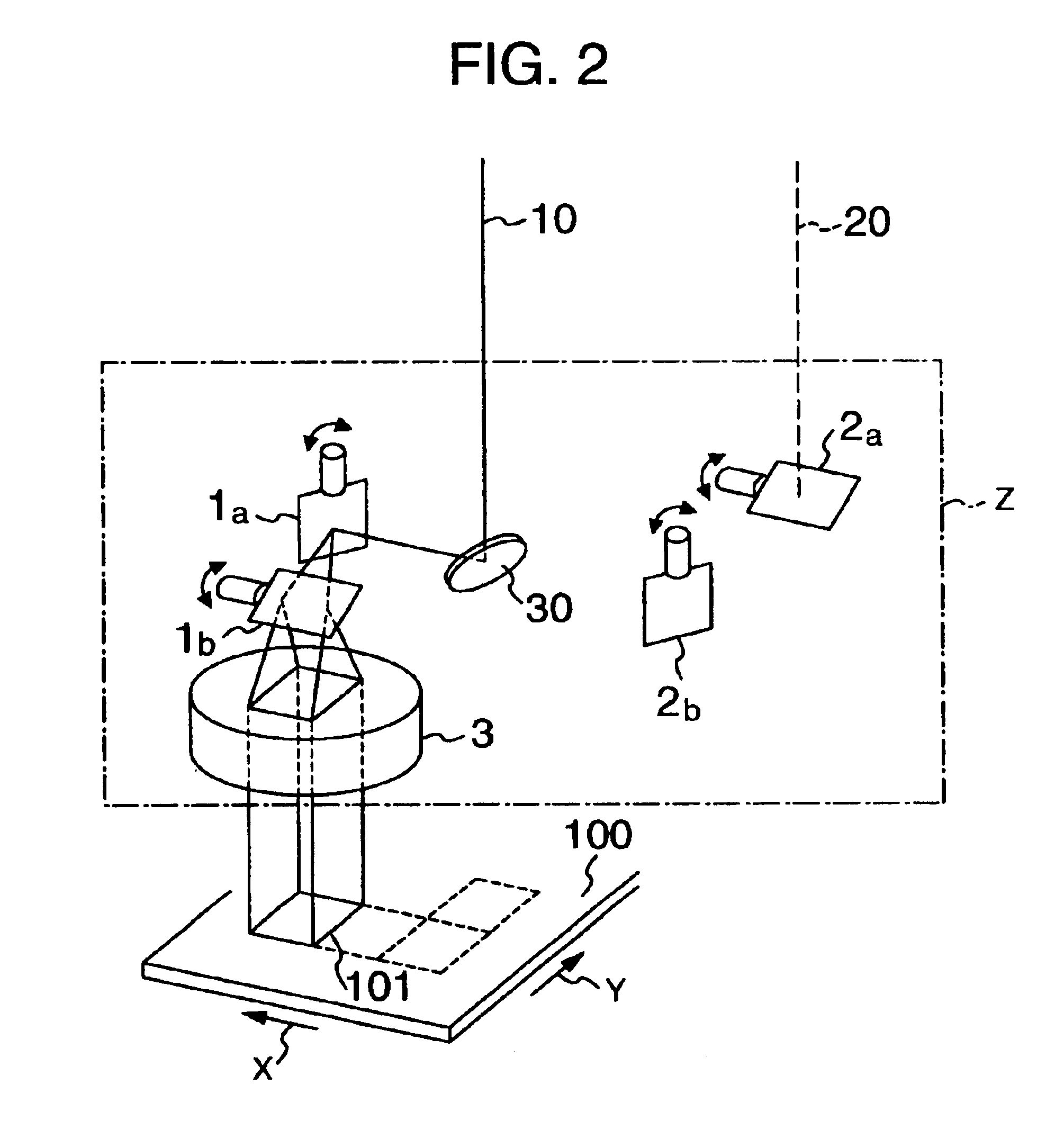

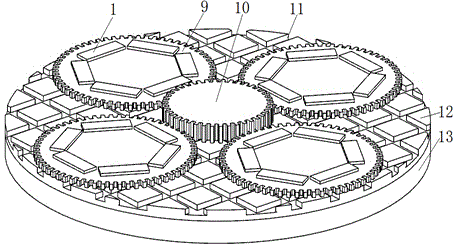

Multibeam laser drilling apparatus

ActiveUS6849824B2Avoid it happening againSuppress errorPrinted circuit manufactureWelding/soldering/cutting articlesPower flowGalvanometer

Provided is a multi-beam laser drilling apparatus for drilling a workpiece, simultaneously at two positions while telecentric errors are suppressed, in which a conventional optical system in which galvanometer mirrors are used for a first laser beam, and a galvanometer-mirror system is located close to an fθ lens in order to prevent occurrence of telecentric error. A second laser beam which has been deflected by a second galvanometer-mirror system, transmits through a polarized beam mixers and is incident upon the first galvanometer-mirror system and the fθ lens, and accordingly, the workpiece is drilled simultaneously at two positions with the use of both first and second laser beams.

Owner:HITACHI SEIKO LTD

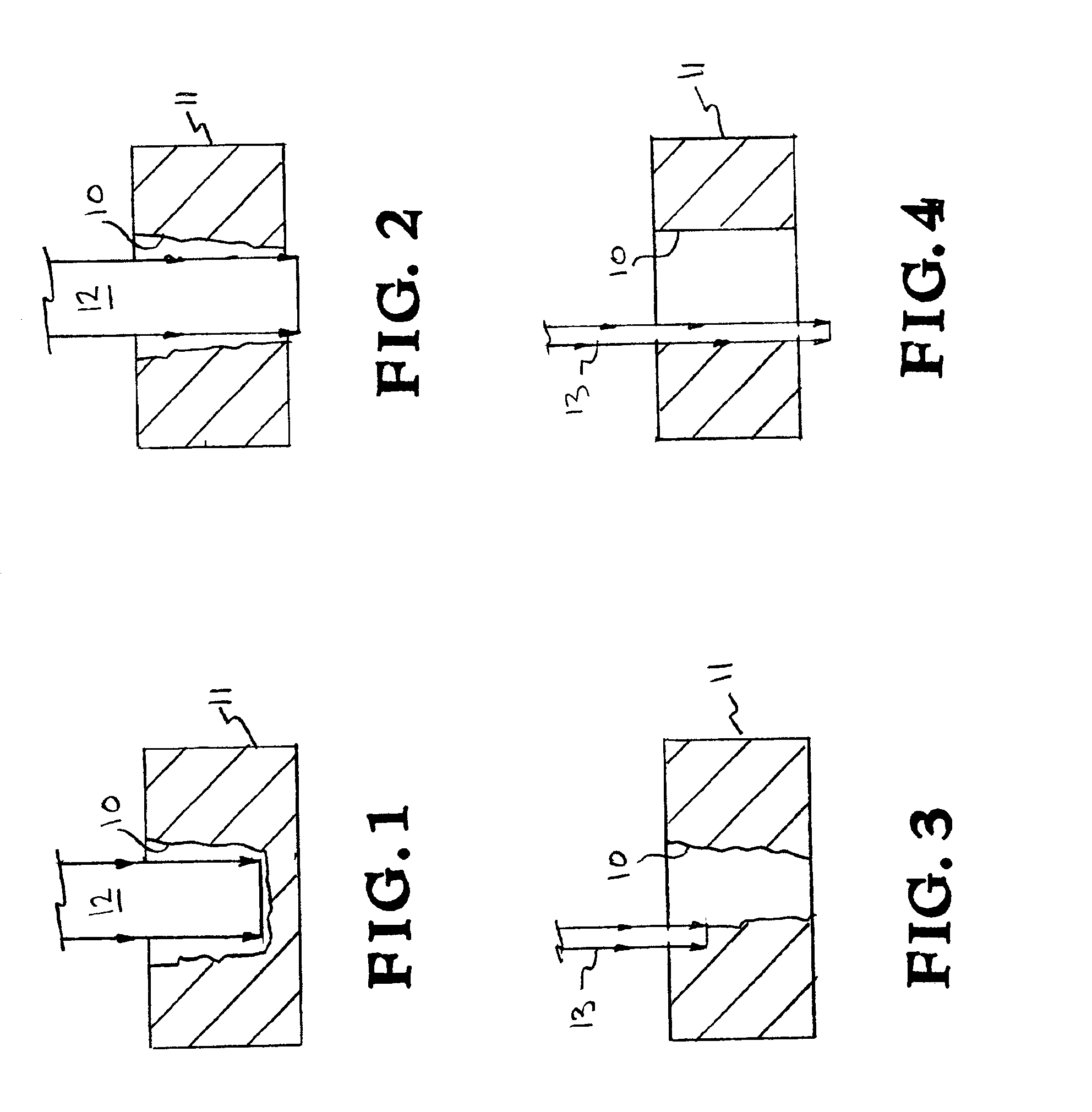

Integrated circuit die and an electronic assembly having a three-dimensional interconnection scheme

InactiveUS6848177B2Semiconductor/solid-state device detailsSolid-state devicesInterconnectionElectronic assemblies

An electronic assembly is assembled by stacking two or more integrated circuit dies on top of one another. Prior to singulation, an opening is laser-drilled into an upper die, and subsequently filled with a conductive member. The conductive member is located on a lower die and interconnects integrated circuits of the upper and lower dies. Laser-drilling allows for faster throughput when compared to, for example, etching, especially if a small number of openings has to be formed. The opening is laser-drilled from an upper surface of the upper die all the way through the die, which allows for the use of alignment marks on an upper surface of the upper die.

Owner:INTEL CORP

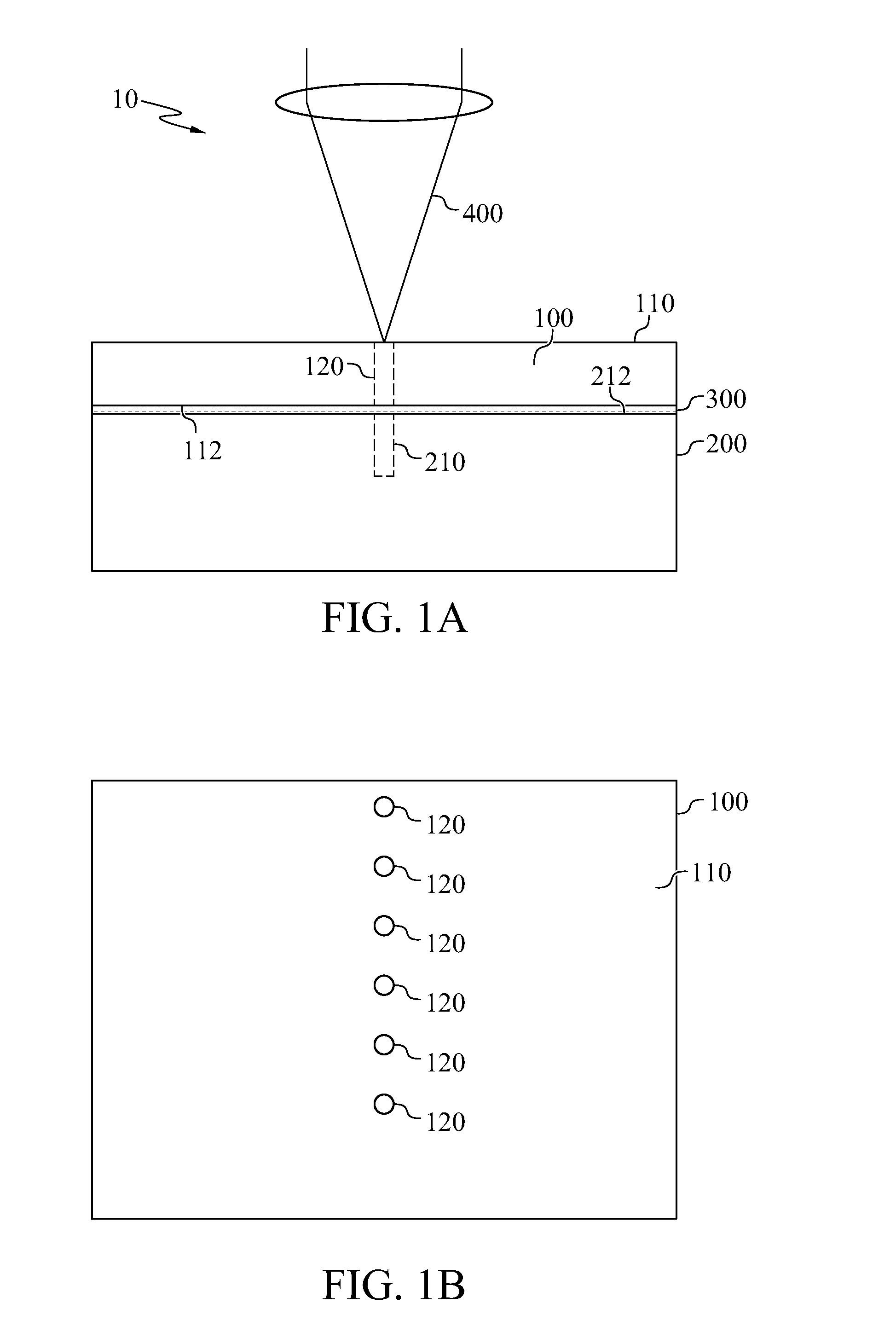

Methods for forming vias in glass substrates

ActiveUS20150060402A1Increase the diameterPaper/cardboard articlesDecorative surface effectsAcid etchingOptoelectronics

Methods for forming vias in glass substrates by laser drilling and acid etching are disclosed. In one embodiment, a method forming a via in a glass substrate includes laser drilling the via through at least a portion of a thickness of the glass substrate from an incident surface of the glass substrate. The method further includes etching the glass substrate for an etching duration to increase a diameter of an incident opening of the via and applying ultrasonic energy to the glass substrate during at least a portion of the etching duration. The applied ultrasonic energy has a frequency between 40 kHz and 192 kHz.

Owner:CORNING INC

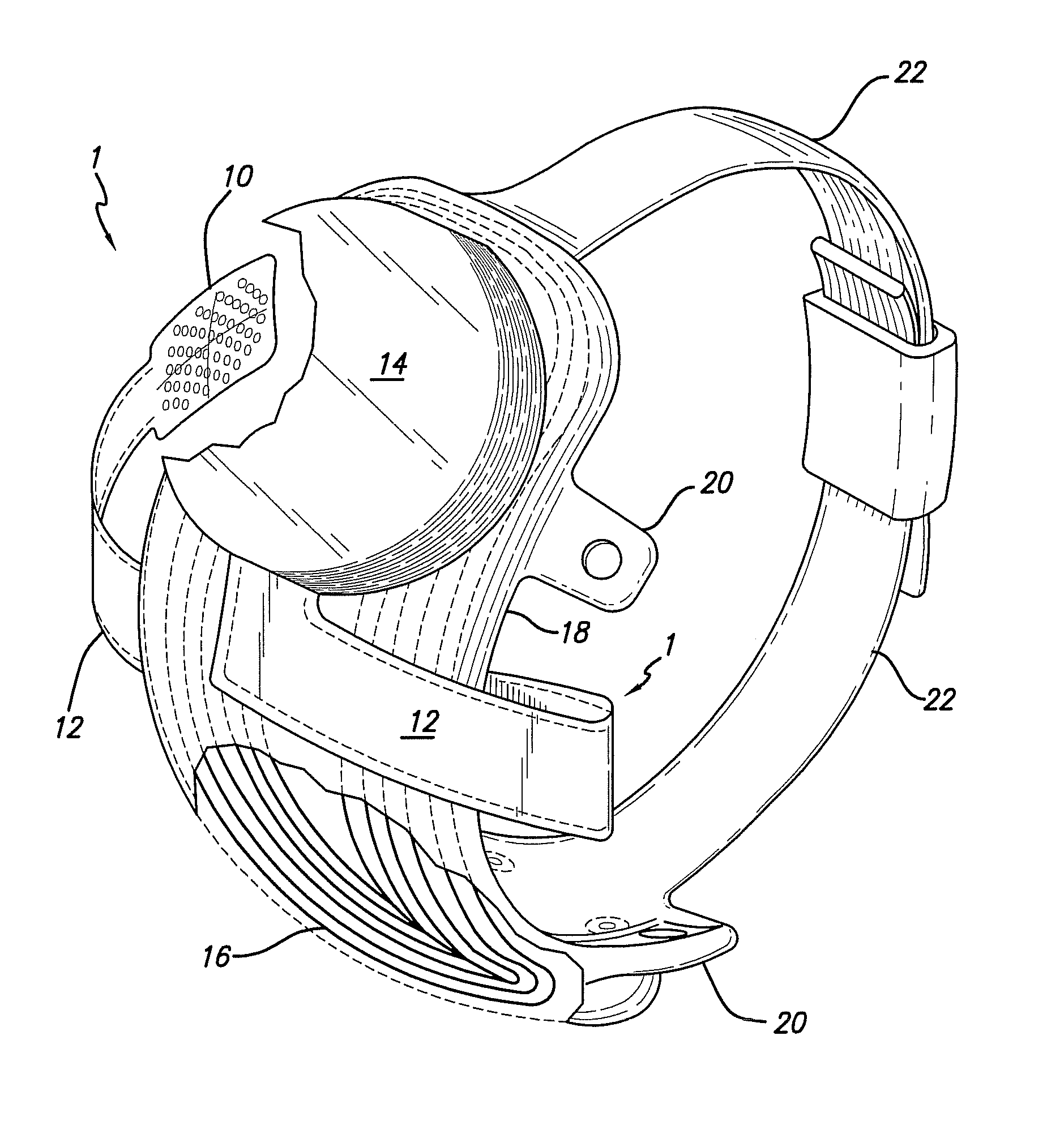

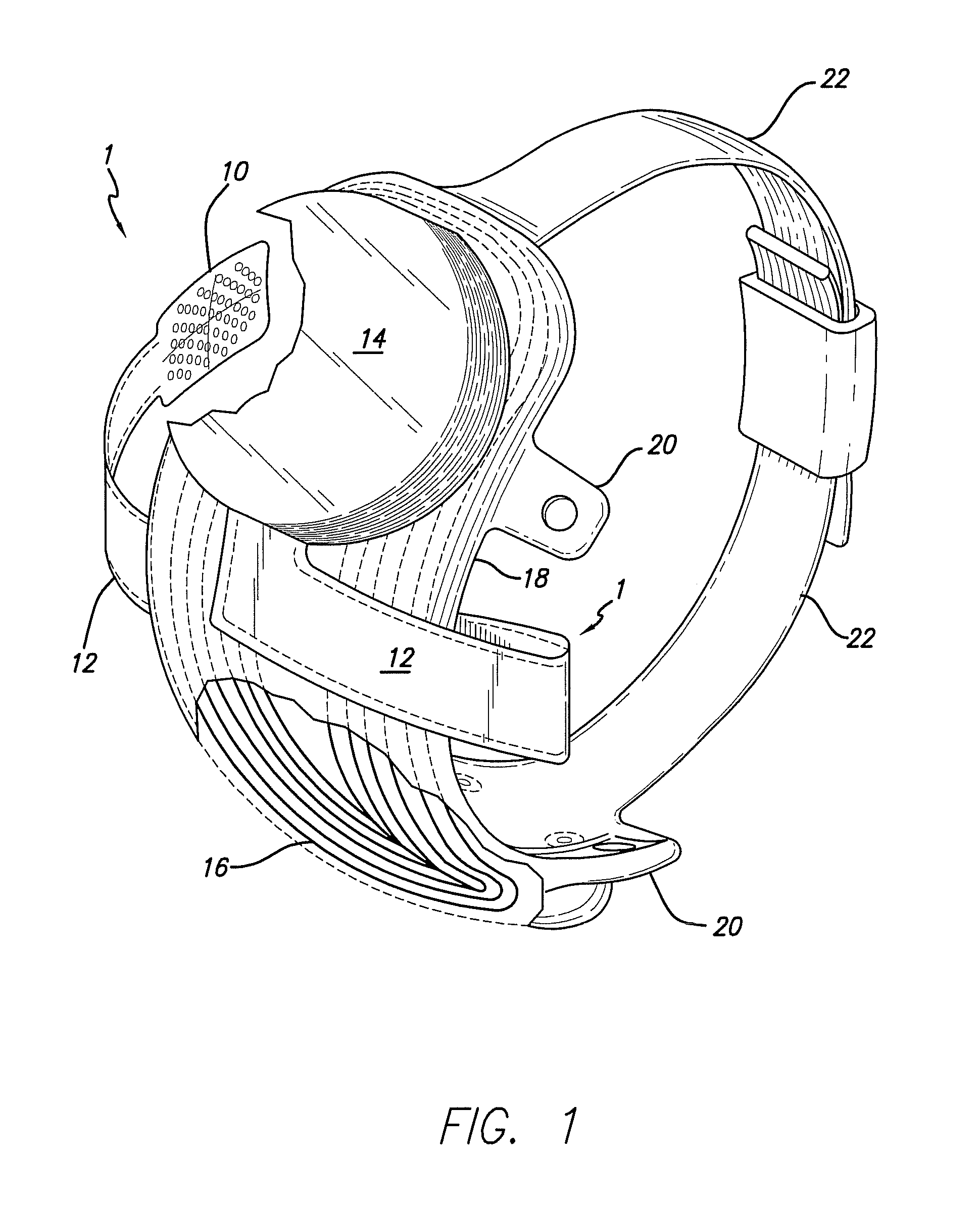

Flexible circuit electrode array device and a method for backside processing of a flexible circuit electrode device

The invention involves a flexible circuit electrode array device comprising: a polymer layer; wherein the polymer layer includes one or more metal traces, an electrode array; one or more bond pads; and the electrode array is located on the opposite side of the polymer layer.The invention further involves a method for backside processing of a flexible circuit electrode device, comprising: applying polymer film on a substrate; processing the front side; releasing the polymer film from substrate; flipping over the polymer film and fixing it onto the substrate; processing the backside; and final releasing of the polymer film from the substrate.The invention further involves a method for backside processing of a flexible circuit electrode device, comprising: processing the front side without releasing the polymer; processing the backside by sacrificial substrate method, or by laser drilling method; and releasing the polymer film from the substrate.

Owner:CORTIGENT INC

Method of drilling a hole through Co2 laser directly

InactiveCN1761378AHigh precisionGuaranteed alignmentConductive material chemical/electrolytical removalLaser beam welding apparatusEtchingCopper foil

Drilling method of carbon dioxide laser includes steps: preparing locating point on layer next to the outer layer; before pressfitting added layer, browning oxidizing surface of target bonding pad; after pressfitting added layer, milling location hole / polishing edge, washing surface under high pressure; browning front surface of copper, thinning and coursing the surface before drilling hole by layer; first time to drill hole by laser; positioning film perforation by using plate location hole in original etching method for making window of copper, burning through copper foil and resin above the locating point on layer next to the outer layer so as to expose the locating point; second time to drill hole by laser; using the exposed locating point as position fixing to make micro hole inplate; washing surface under high pressure to remove browning layer after drill hole. The invention saves dry film and etching liquid, and raises process precision.

Owner:WUS PRINTED CIRCUIT (KUNSHAN) CO LTD

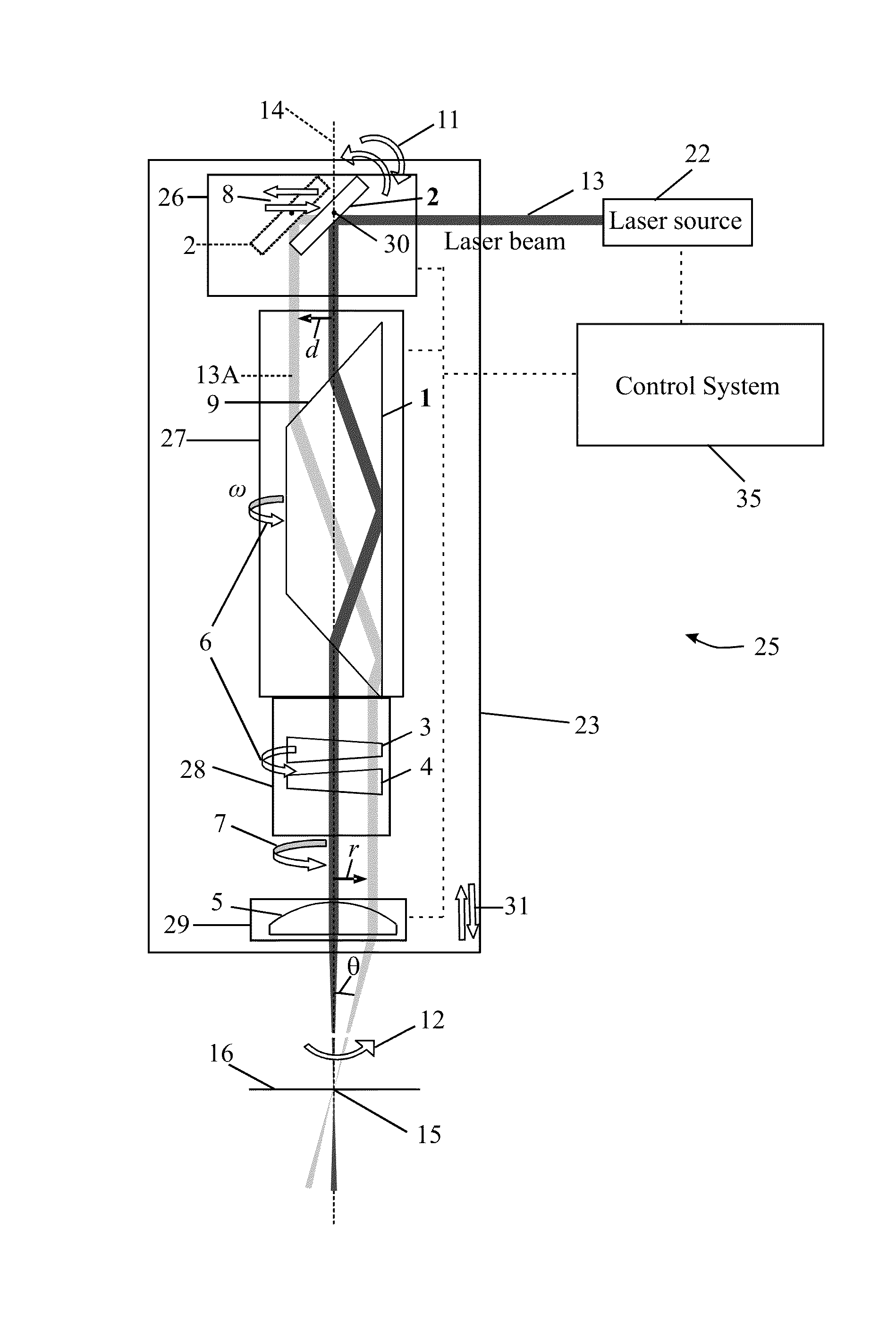

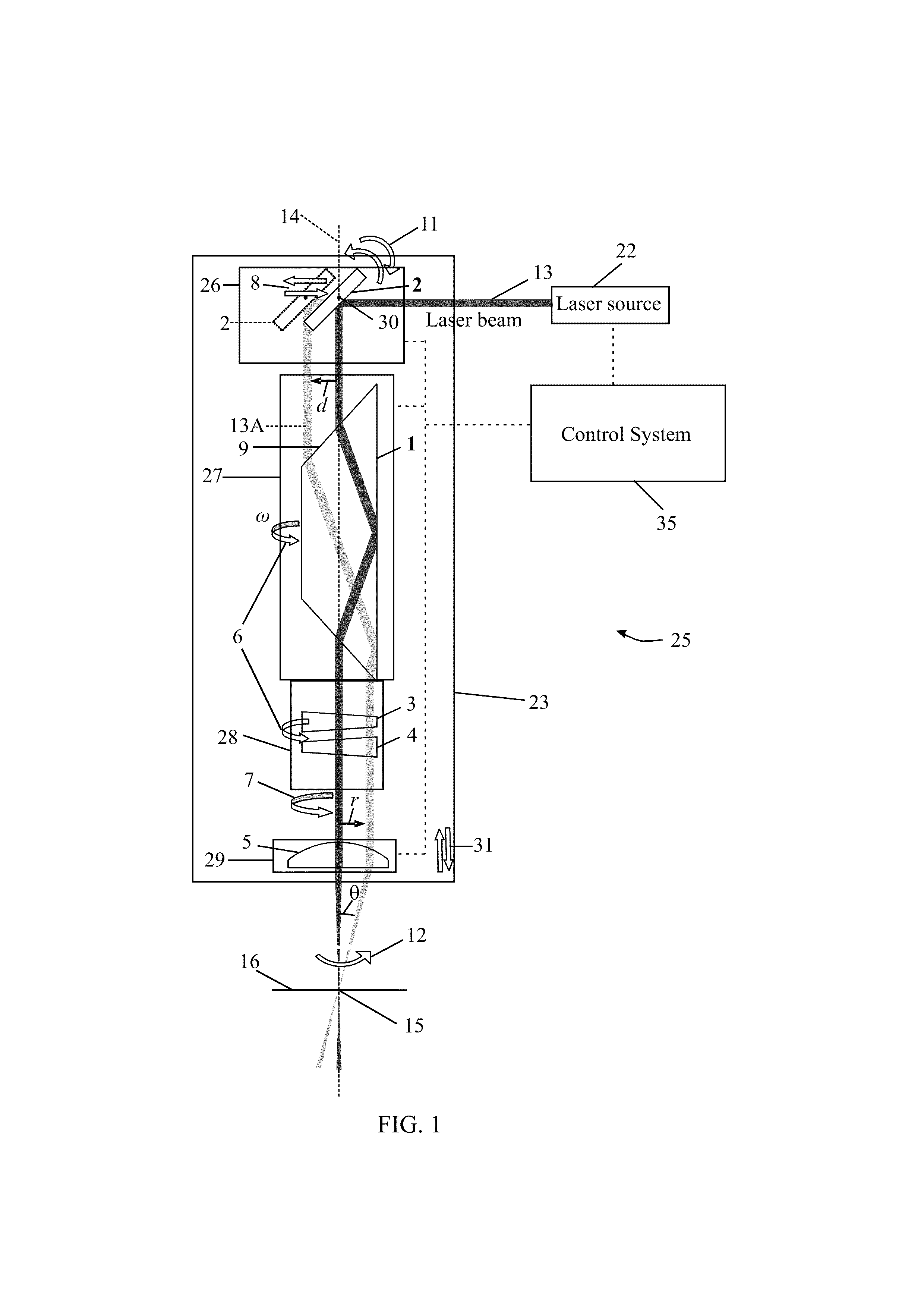

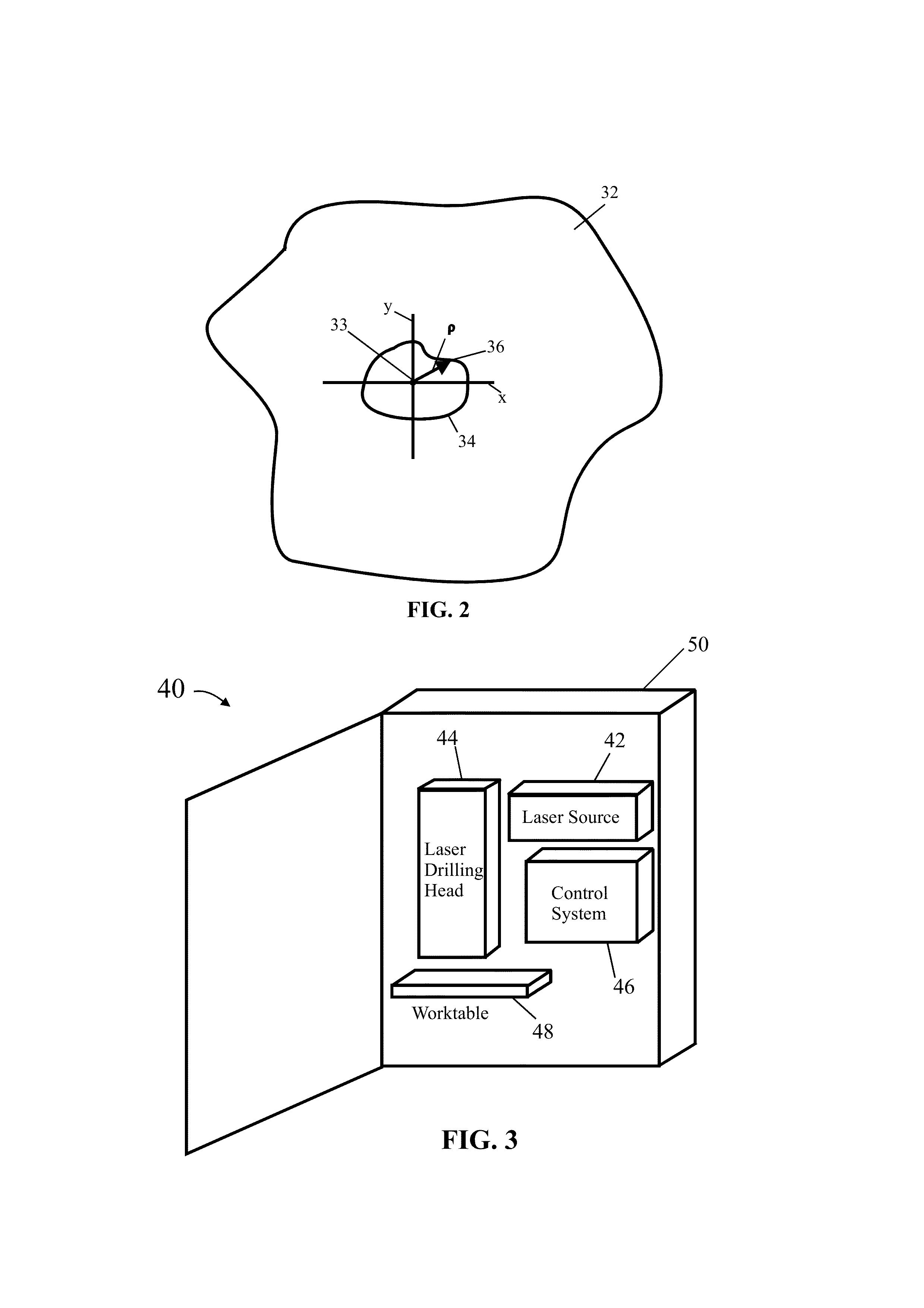

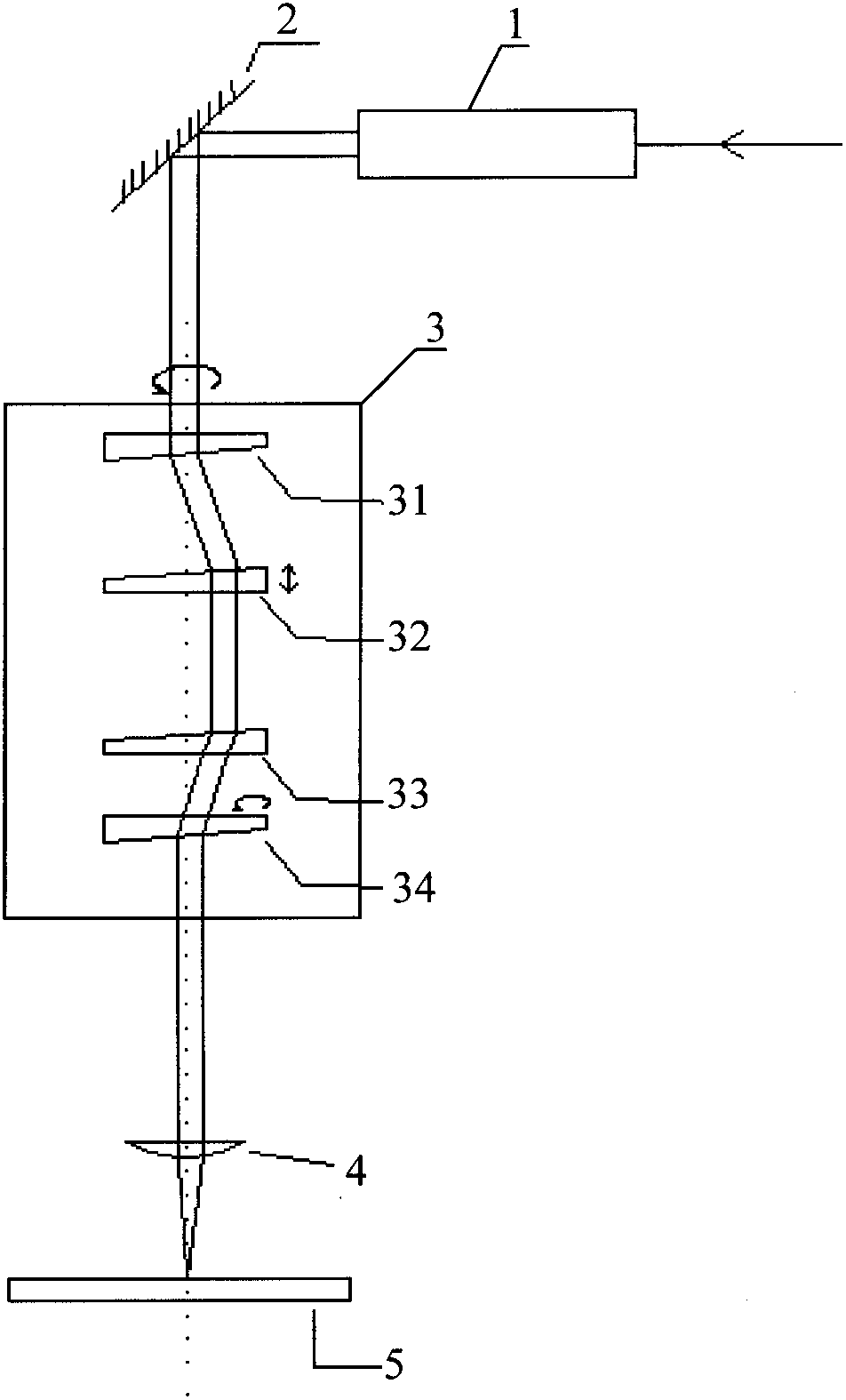

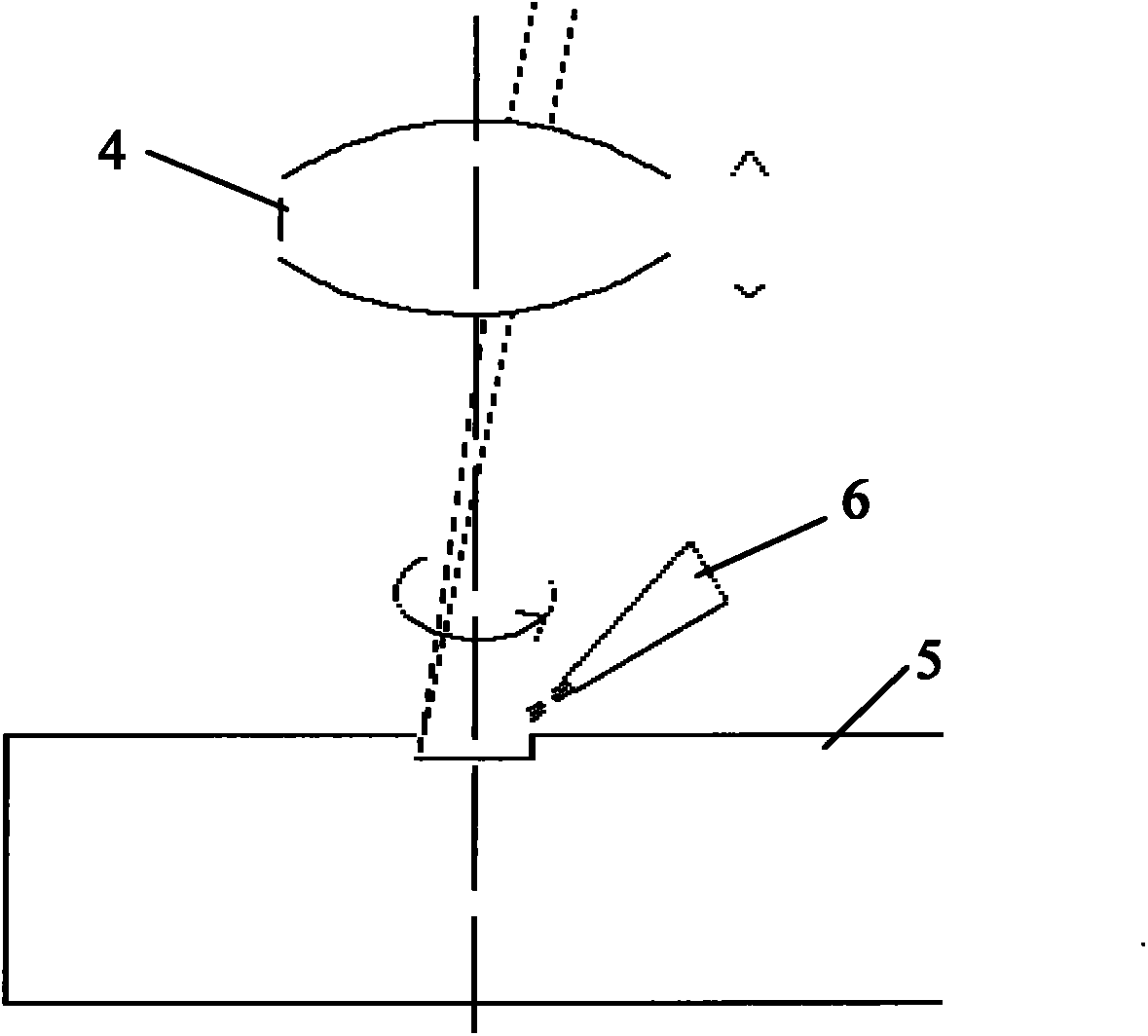

Laser Drilling and Trepanning Device

Laser drilling devices are disclosed which include a laser beam source and a laser drilling head. The laser drilling head includes a beam manipulator system in which the only dynamically moving optical element is a mirror. The mirror is dynamically and reciprocally translatable along the direction of the incoming laser beam and is also dynamically and reciprocally tiltable about an axis that is perpendicular to the nominal optical axis of the drilling head. The drilling head also includes a spinnable laser beam rotating system, a simplified compensation system, and a focusing system. The compensation system includes as its only laser beam path shifting optical elements on or two wedge plates which, if two, are fixably rotatable relative to one another in planes which are perpendicular to the nominal optical axis of the laser drilling device.

Owner:LUXCELIS TECH LLC

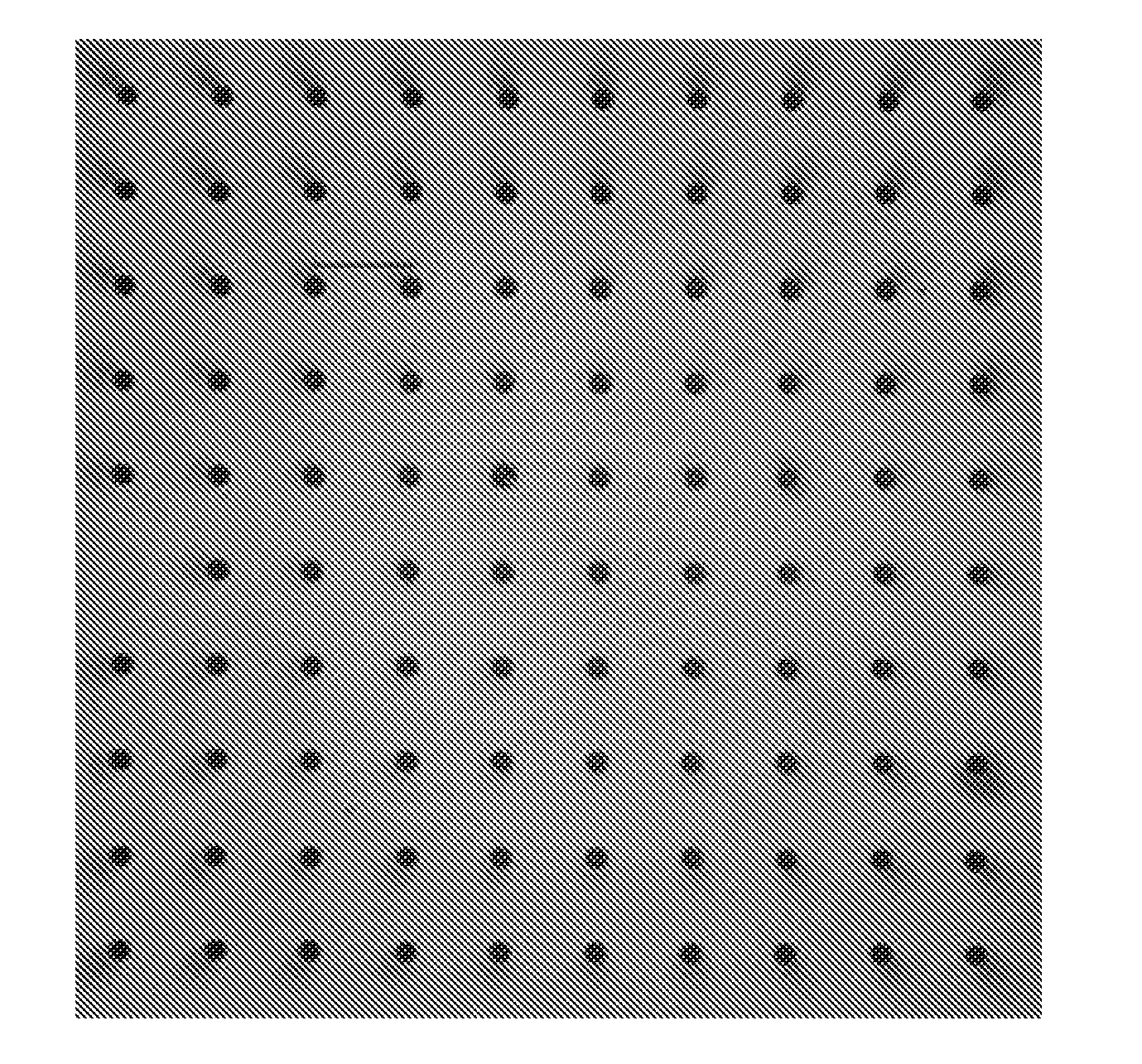

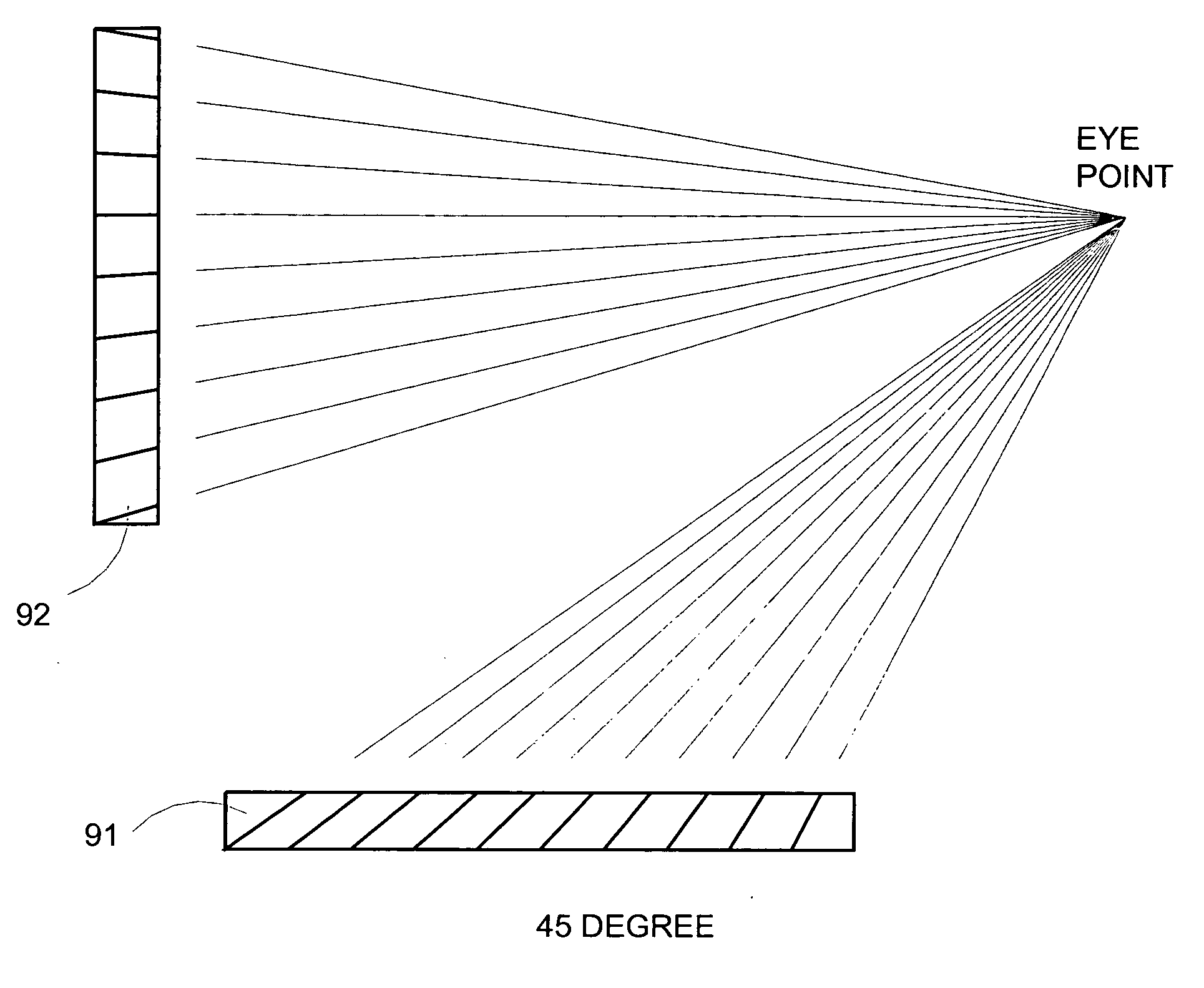

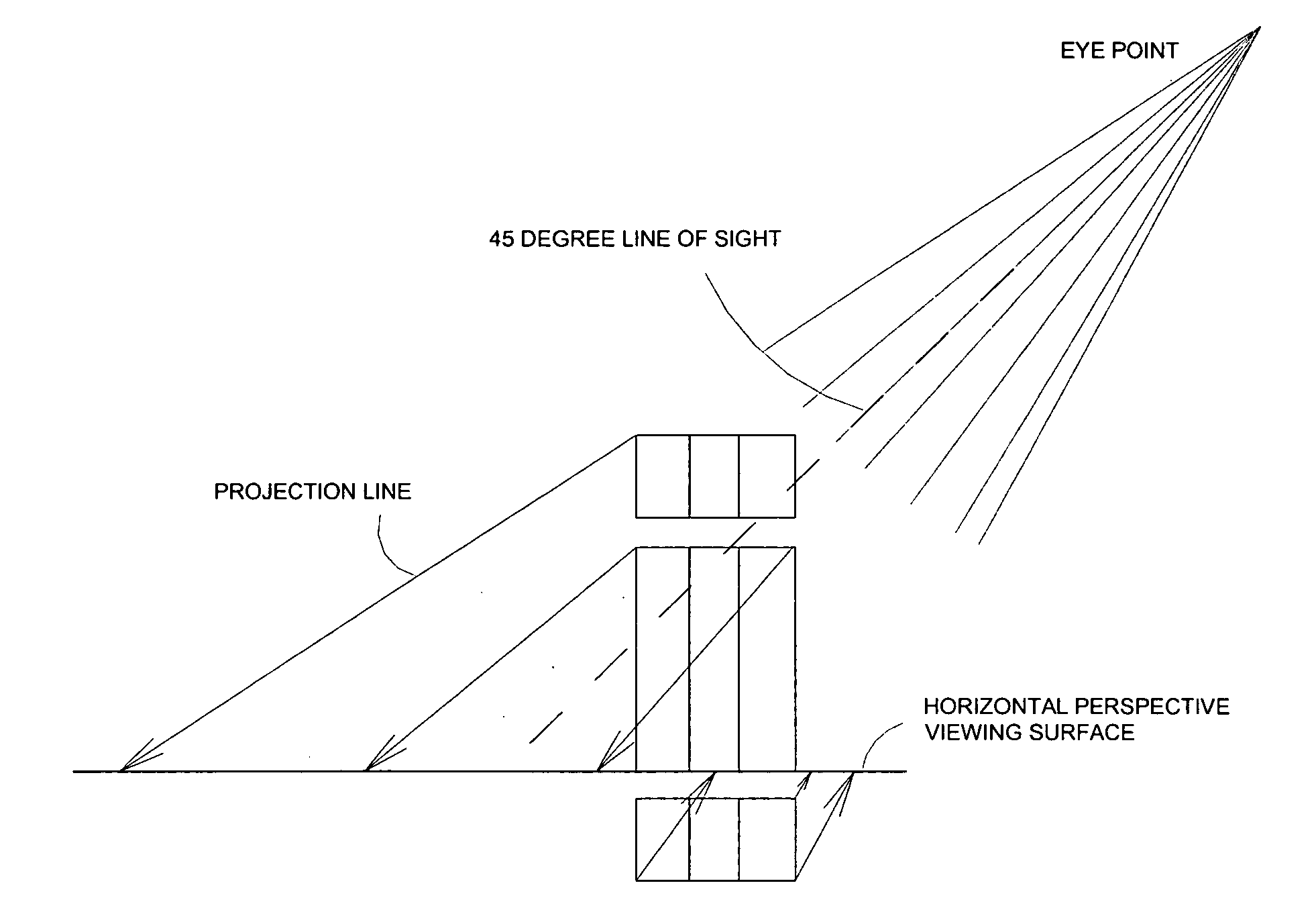

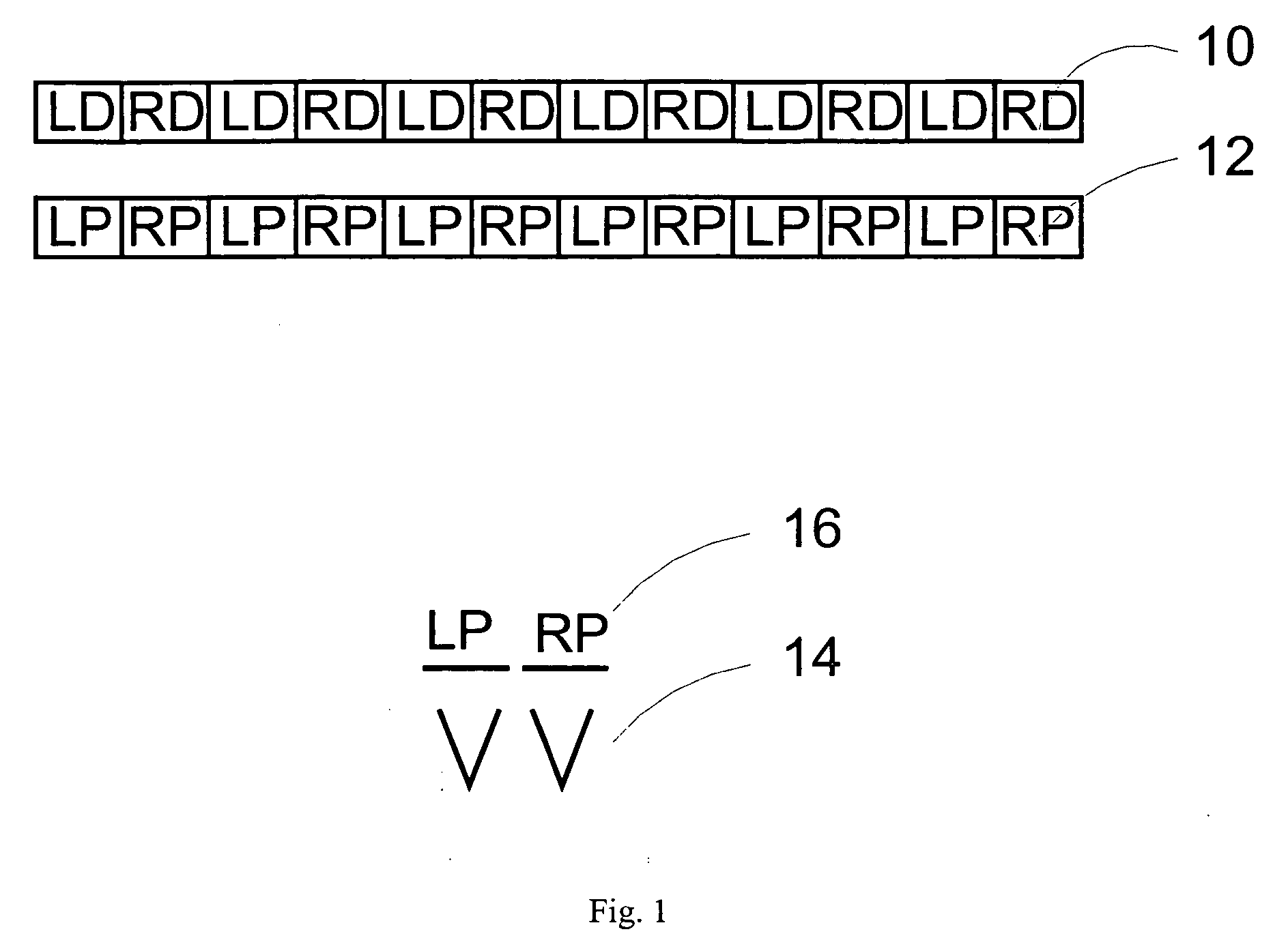

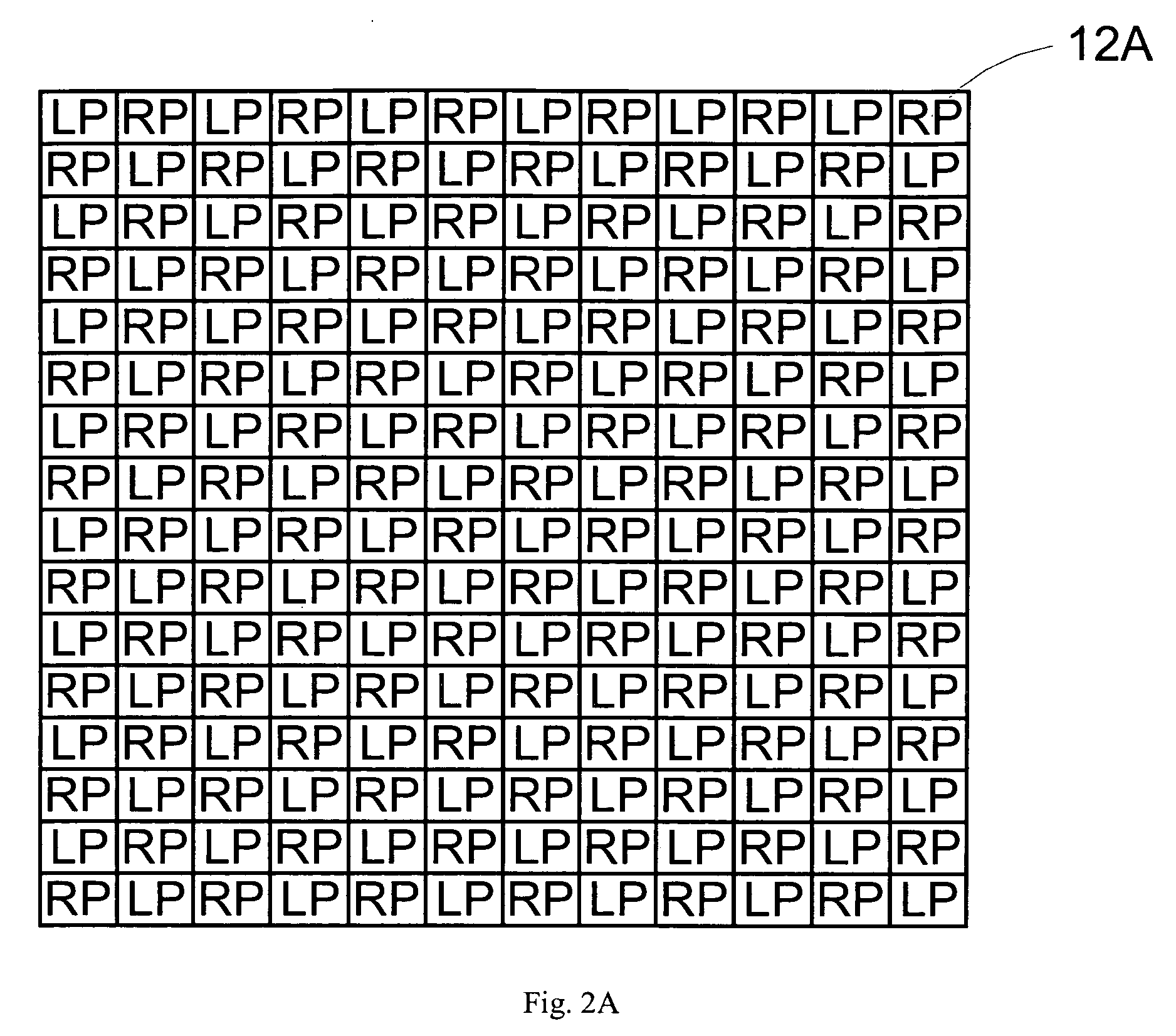

Stereoscopic display using polarized eyewear

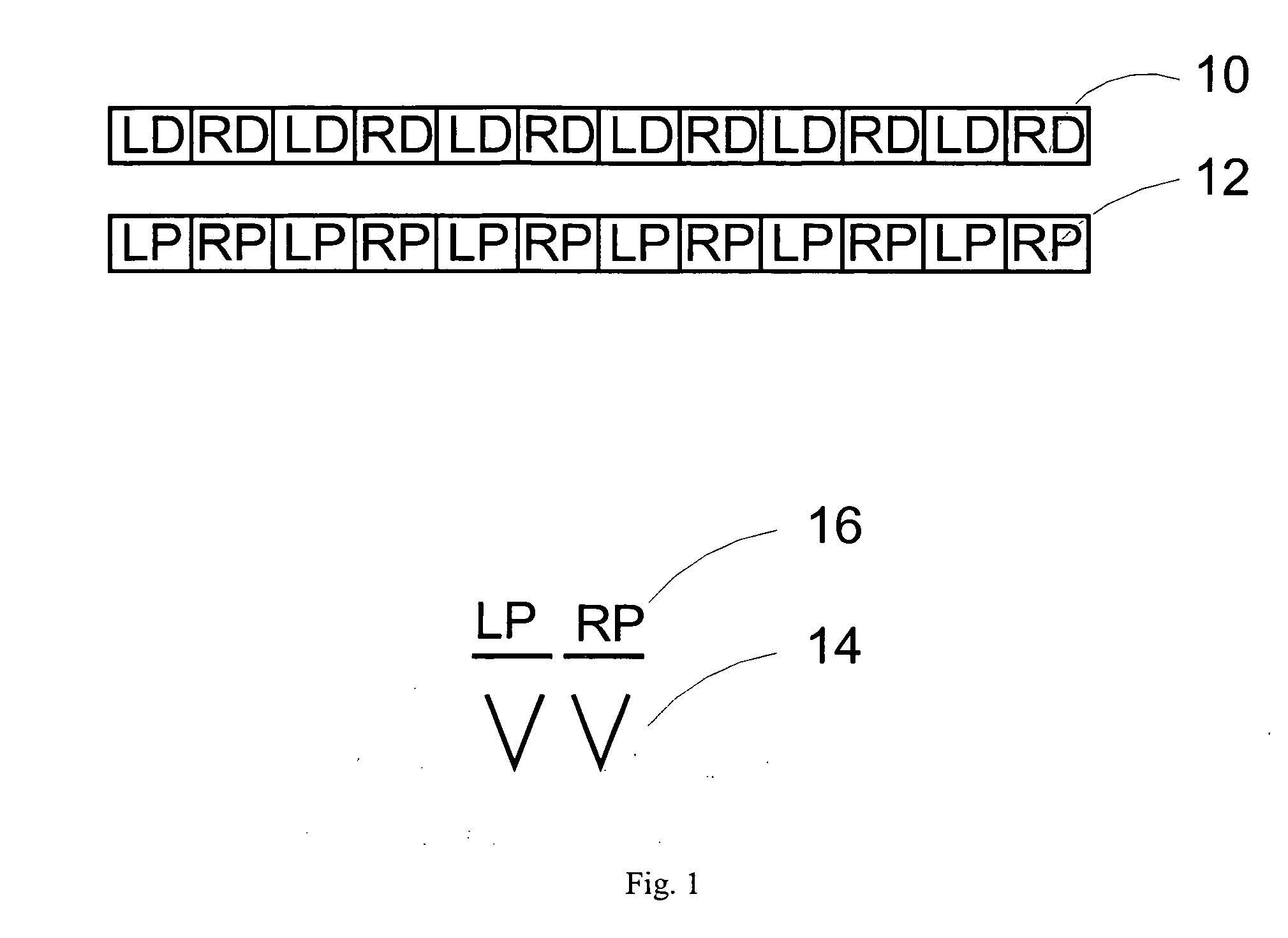

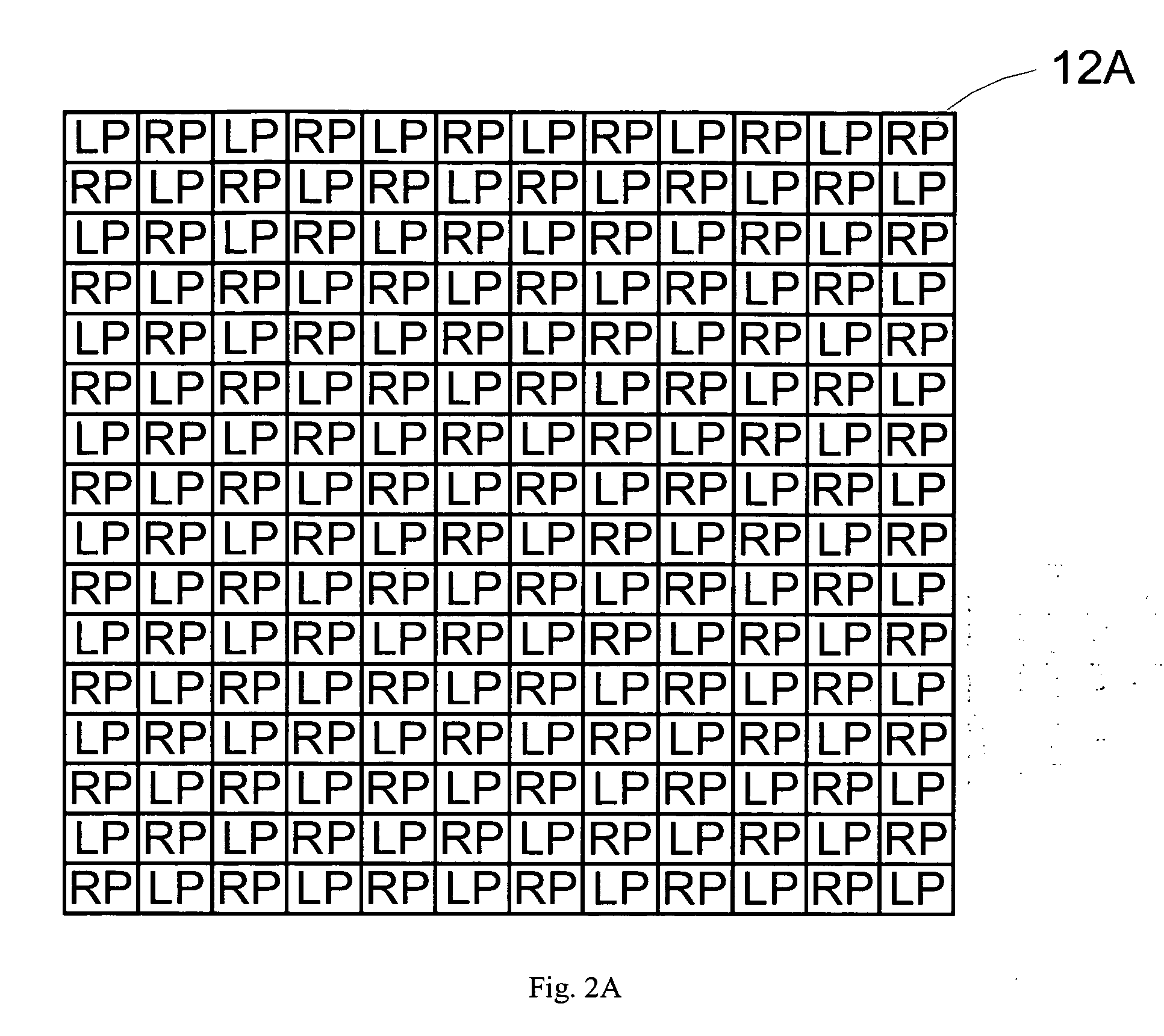

InactiveUS20070043466A1Minimize distortionMinimize discomfortColor television detailsSteroscopic systemsImage resolutionMicrometer

The present invention discloses a stereoscopic display employing polarized eyewear. The basic component of the present invention stereoscopic display is a stereopolarizer, which is a polarized screen comprising microscopic sections of mutually extinguishing polarizing filters dispersed throughout the screen. To achieve the proper resolution, the size of the microscopic polarizing filter needs to be in order of micrometer, from a few microns to a few hundred of microns. The arrangement of the microscopic polarizing filters can be alternating stripes in horizontal, vertical, or any arbitrarily direction. The microscopic polarizing filters can be arranged in alternating pattern, such as alternating square or circle. The polarizer screen can be one sheet or can be a composite sheet, comprising two distinct polarizer filter sheet laminated together. Laser drilling is used to fabricate the microscopic polarizing filters, primarily due to ease of operation and appropriate microscopic sizes. Further, laser drilling and cutting can form angle holes in the stereopolarizer, which provides optimum focus viewing for horizontal perspective display.

Owner:INFINITE Z

Control method for laser drilling contraposition accuracy of high-density lamination circuit board

ActiveCN101494954AResolve inconsistenciesSolve the accuracy problemMultilayer circuit manufactureLaser beam welding apparatusHigh densityX-ray

The invention relates to a positioning precision control method in laser boring on high density accumulation layer circuit board. The method comprises: a, making a circuit board, and disposing an electronic circuit layer at least on one side; b, forming a medium layer on the surface of the electronic circuit; c, positioning the bores on the circuit board with medium layer using X ray boring equipment by a target positioning drill; d, forming laser blind bore positioning bore on the circuit board by mechanical boring after positioning the bores by the target positioning drill; e, drilling blind bores on the circuit board using the laser blind bore positioning bore as reference. The method in the invention can align the centers of the mechanical through bore and the laser blind bore of the high density accumulation layer circuit board, can effectively improve the positioning precision of the high density accumulation layer circuit board, and achieves the advantages of simple processing technology, short time and no deformation of the circuit board in processing, and needs no positioning figure in drilling blind bore by etching laser.

Owner:SHENZHEN WUZHU TECH

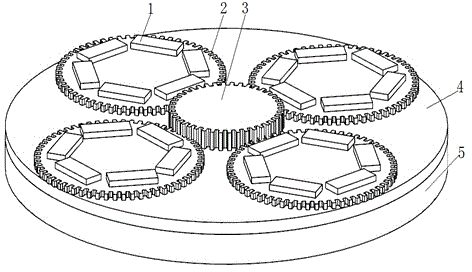

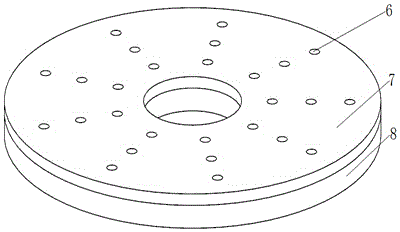

Laser rotary-cut drilling device

InactiveCN102218605AVariable sizeControllable taperLaser beam welding apparatusWedge angleBeam expander

The invention relates to a laser rotary-cut drilling device. The output end of a laser is provided with a beam expander; the output end of the beam expander is provided with a 45-degree total reflection mirror; the output end of the 45-degree total reflection mirror is provided with an optical rotation system; the optical rotation system comprises a first wedge prisma, a second wedge prisma, a third wedge prisma and a fourth wedge prisma; the first wedge prisma and the second wedge prisma have the same wedge angles; the first wedge prisma or the second wedge prisma is connected with a vertical straight-line motion mechanism; the third wedge prisma and the fourth wedge prisma have the same wedge angles; the third wedge prisma or the fourth wedge prisma is connected with a rotation mechanism; the output end of the optical rotation system is provided with a focus lens; and the focus lens is just opposite to a processing platform. The device is used for performing laser rotary-cut drilling on a workpiece, and can process straight holes, variable taper holes and irregular taper holes, so a laser drilling effect of variable sizes, controllable taper and smooth edges is achieved.

Owner:SUZHOU DELPHI LASER +1

Copper foil excellent in laser beam drilling performance and production method therefor

InactiveUS6638642B2Improve drilling effectFine surfaceRadiation applicationsExtrusion containersIndiumCopper foil

Owner:JX NIPPON MINING & METALS CORP

Method and apparatus for laser drilling holes with gaussian pulses

ActiveUS20090242528A1Increase path lengthDifficult to maintainWelding/soldering/cutting articlesLaser beam welding apparatusSurface finishOptoelectronics

An improved method and apparatus for drilling tapered holes in workpieces with laser pulses is presented which uses defocused laser pulses to machine the holes with specified taper and surface finish while maintaining specified exit diameters and improved system throughput. A system is described which can also drill holes with the desired taper and surface finish without requiring defocused laser pulses.

Owner:ELECTRO SCI IND INC

Methods of drilling through-holes in homogenous and non-homogeneous substrates

InactiveUS20050230365A1Minimum thermal damageImprove performanceSemiconductor/solid-state device detailsSolid-state devicesThermal energyPilot hole

A differential diameter hole drilling method by which through-holes having improved major surface quality are formed in a target material involves drilling a pilot hole having a diameter that is less than the desired diameter of the through-hole and then drilling a through-hole having the desired diameter. The pilot hole forms a channel from which thermal energy produced during laser drilling can diffuse into the environment, thereby reducing the amount of thermal energy diffusing into the surrounding target material matrix and the degree of thermal damage to the heat affected zone of the target material matrix. The pilot hole also forms a channel through which ablated target material may be removed, thereby increasing overall through-hole throughput. Pilot hole formation reduces the thermal energy required to form the remaining portion of the through-hole and thereby results in less thermal damage to the surrounding target material matrix.

Owner:ELECTRO SCI IND INC

Double-surface grinding and double-surface polishing high-efficiency ultraprecise processing method for large-sized A-directional sapphire mobile phone screen

ActiveCN104669106AQuality improvementReach processing costOther chemical processesLapping machinesManufacturing technologySurface layer

The invention discloses a double-surface grinding and double-surface polishing high-efficiency ultraprecise processing method for a large-sized A-directional sapphire mobile phone screen. The method comprises the steps of crystal ingot orientation, crystal plate slicing, crystal plate double-surface grinding, crystal plate cleaning, crystal plate annealing, crystal plate double-surface polishing, secondary crystal plate cleaning, laser drilling, crystal plate chamfering, triple crystal plate cleaning and crystal plate film plating. According to the method, optimal parameters, including constituents of polishing liquid, of the optimal processing technology and all the steps can be obtained by screening by a large quantity of experiments. By the method, the manufacturing technology of the large-sized (10 inches) sapphire mobile phone screen can be simplified, the processing stress on the surface layer can be effectively eliminated, the mechanical processing damaged layers can be eliminated, and the ultrasmooth surface with a complete surface crystal lattice, the flatness being less than 5 microns and the polishing surface roughness (RMS) being less than 0.2 nanometers can be obtained; the processing quality is high, the cost is low, and the efficiency is high; compared with the prior art, the method disclosed by the invention has the advantage that an extremely high technical progress is achieved.

Owner:江西伟嘉晶创光电科技有限公司

Method of and apparatus for laser drilling holes with improved taper

InactiveUS20080296273A1Improve abilitiesImprove efficiencyPrinted circuit aspectsPrinted circuit manufactureElectricityPulse parameter

A method of and an apparatus for drilling blind vias with selectable tapers in multilayer electronic circuits permit forming electrical connections between layers while maintaining quality and throughput. The method relies on recognizing that the top diameter of the via and the bottom diameter of the via, which define the taper, are functions of two separate sets of equations. Simultaneous solution of these equations yields a solution space that enables optimization of throughput while maintaining selected taper and quality using temporally unmodified Q-switched CO2 laser pulses with identical pulse parameters. Real time pulse tailoring is not required; therefore, system complexity and cost may be reduced.

Owner:ELECTRO SCI IND INC

Method and apparatus for delivering high power laser energy over long distances

ActiveUS20130175090A1Suppressing nonlinear scattering phenomenaIncrease the lengthDrill bitsDisloding machinesHigh power lasersOptoelectronics

There is provided a system, apparatus and methods for the laser drilling of a borehole in the earth. There is further provided with in the systems a means for delivering high power laser energy down a deep borehole, while maintaining the high power to advance such boreholes deep into the earth and at highly efficient advancement rates.

Owner:FORO ENERGY

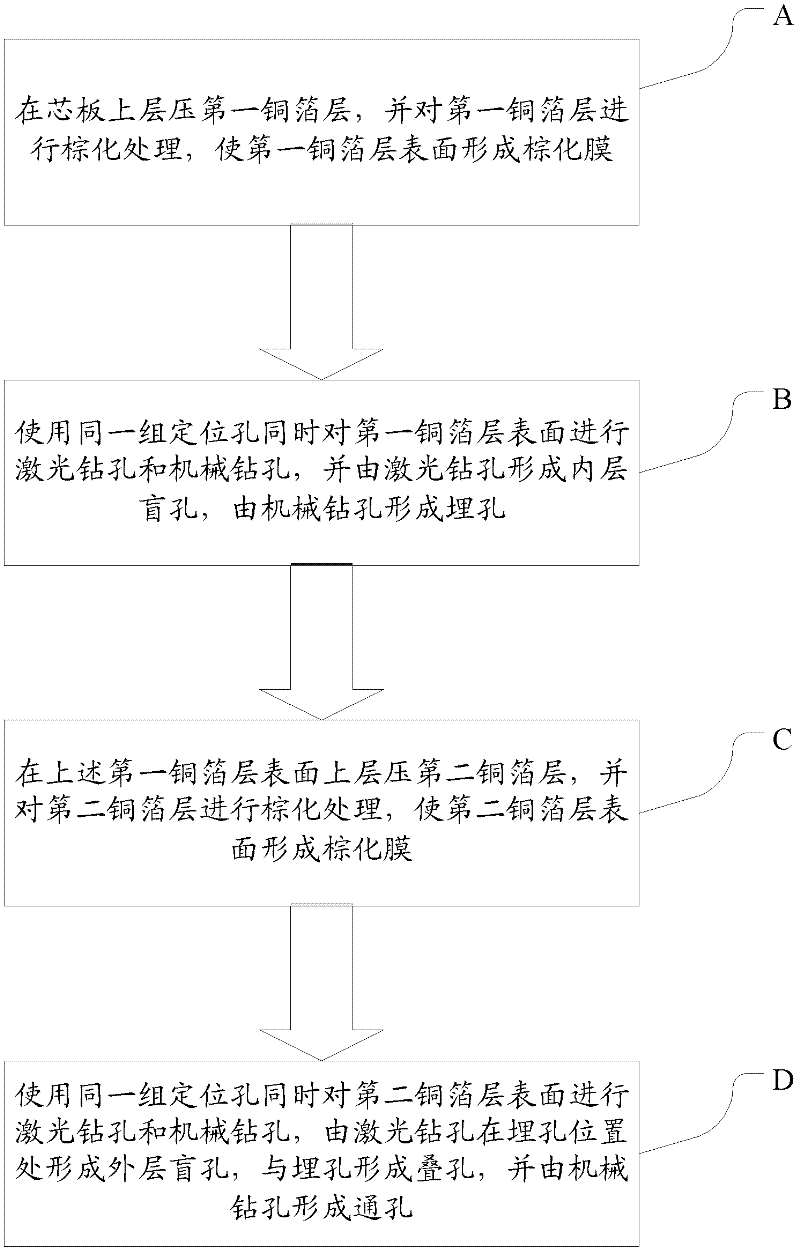

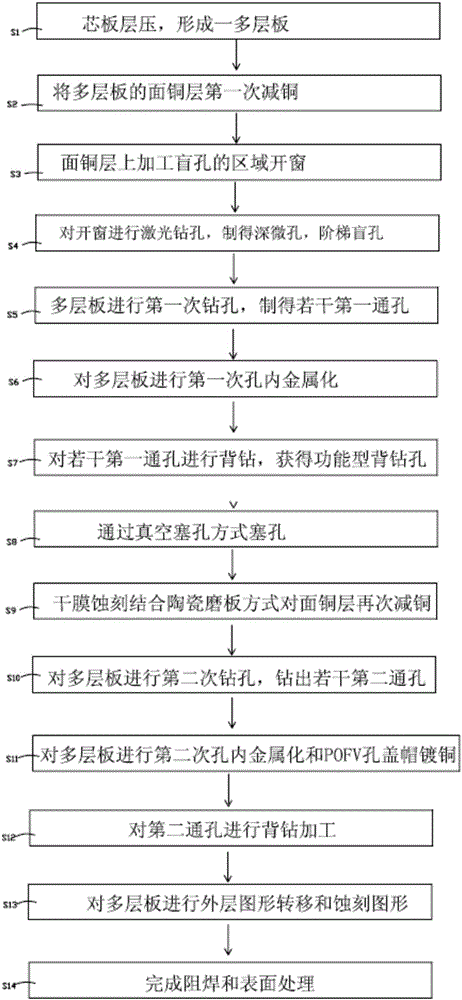

Production method of multi-stage HDI plate

ActiveCN102523704AGood dimensional stabilityAvoid processPrinted circuit aspectsMultilayer circuit manufactureCopper foilElectroplating

The invention discloses a production method of a multi-stage HDI plate. The method comprises the following steps: A. laminating a first copper foil layer on a core plate, carrying out multiband to the first copper foil layer so as to form a brown film on a surface of the first copper foil layer; B. using a same group of location holes to simultaneously carry out laser drilling and mechanical drilling to the surface of the first copper foil layer, forming an internal-layer blind hole through the laser drilling and forming a buried hole through the mechanical drilling; C. laminating a second copper foil layer on the surface of the first copper foil layer, carrying out the multiband to the second copper foil layer so as to form the brown film on the surface of the second copper foil layer; D. using the same group of location holes to simultaneously carry out the laser drilling and the mechanical drilling to the surface of the second copper foil layer, forming an outer-layer blind hole on the position of the buried hole through the laser drilling, forming a folded hole with the buried hole and forming a through hole through the mechanical drilling. At present, the blind hole and the buried hole are drilled separated so that the through hole and the blind hole are not matched with each other. According to the method of the invention, the above problem can be solved; processes of internal layer copper deposition, padpower, an internal layer plating hole graph, porefilling electroplating, film stripping, abrasive-belt grinding plate and the like can be reduced; a production period can be substantially shortened and production cost can be saved.

Owner:SHENZHEN SUNTAK MULTILAYER PCB

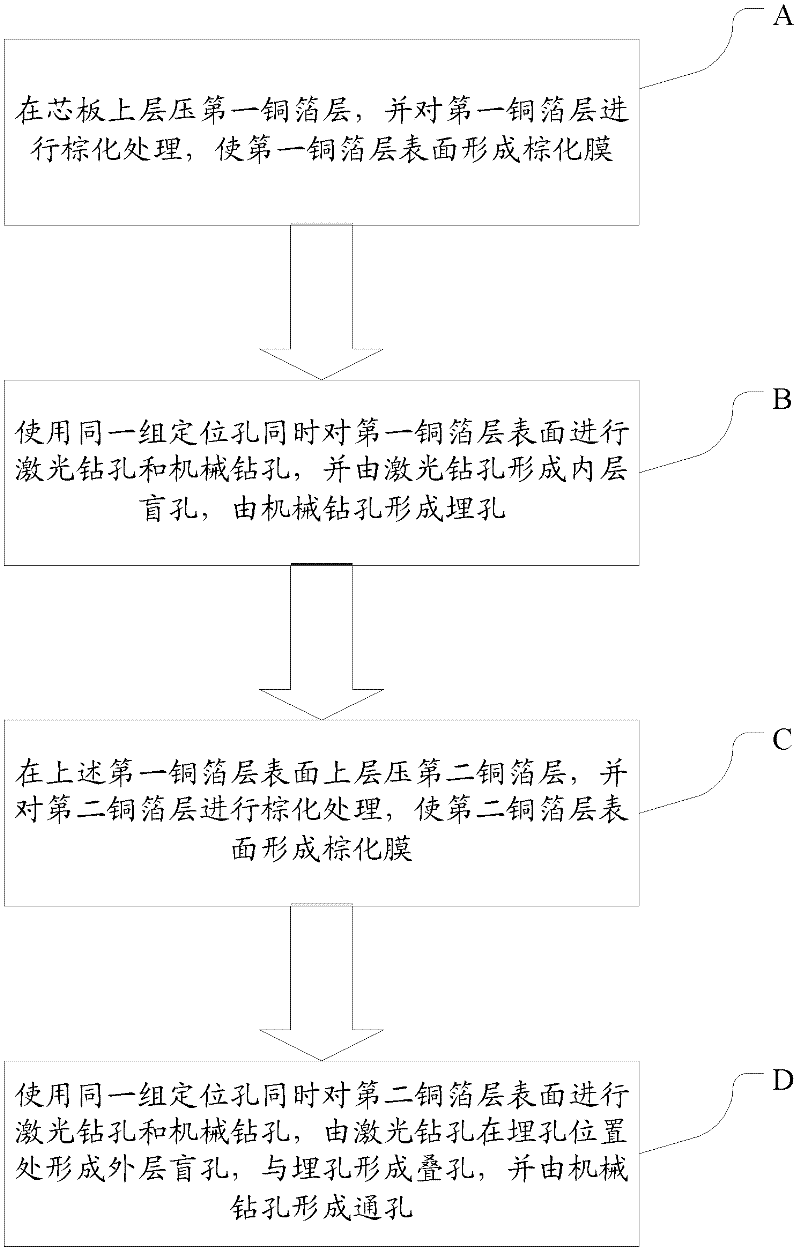

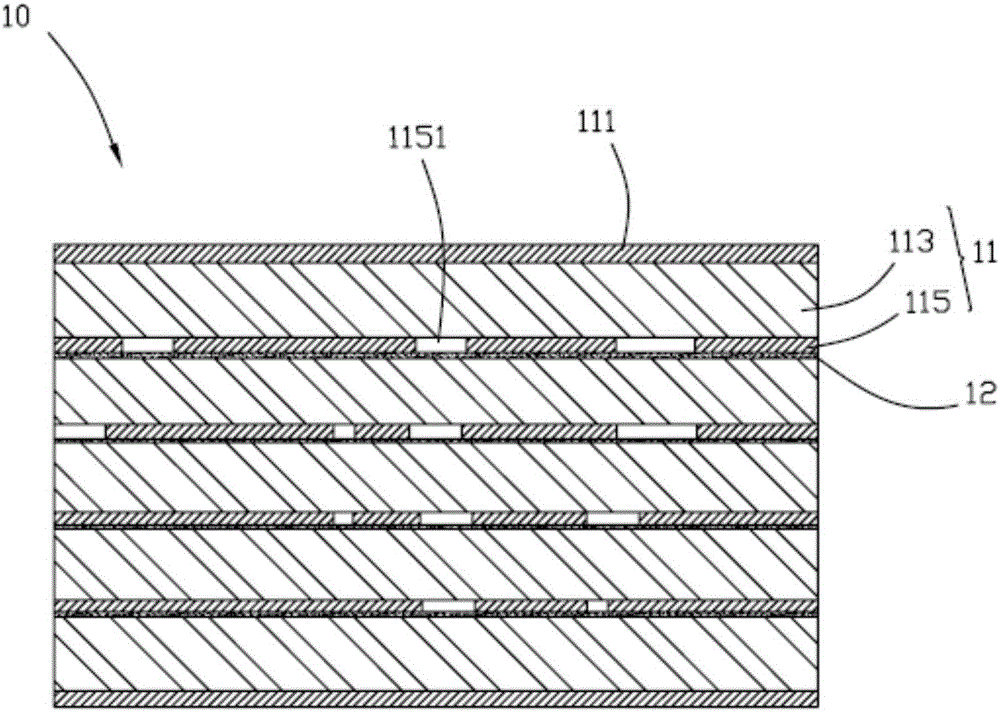

Manufacturing method of high-speed PCB and PCB

ActiveCN106793577AShort preparation cycleLow costPrinted circuit aspectsMultilayer circuit manufactureFine lineConnection type

The invention provides a manufacturing method of a high-speed PCB and the PCB. The manufacturing method includes the following steps that 1, lamination is carried out after a normal inner layer graph is manufactured; 2, copper reduction is carried out to achieve the size of 6 micrometers to 8 micrometers after lamination is completed; 3, +4.5 mil copper etching windowing is carried out on a deep micropore region and a first-order blind hole region overall; 4, laser drilling is carried out to complete deep micropore and first-order blind hole machining; 5, through holes needing resin hole plugging are mechanically drilled for the first time; 6, the interiors of the holes are metalized for the first time; 7, the through holes are back-drilled for the first time; 8, vacuum hole plugging is carried out; 9, the holes are covered with dry films, single side +5 mil dry film covering is carried out on deep micropores, first-order blind holes and the first through holes; 10, chemical copper reduction and ceramic grinding plate copper reduction are carried out to achieve the size of 20 micrometers to 25 micrometers; 11, second through holes are mechanically drilled; 12, the interiors of the holes are metalized for the second time, and POFV blocking is carried out; 13, the second through holes are back-drilled, and connection type functional holes are machined; 14, an outer layer graph is transferred, and a fine line graph is etched; 15, solder resisting and surface treatment are completed. The high-complexity high-speed PCB can be manufactured, the manufacturing period is short, and the cost is low.

Owner:DONGGUAN SHENGYI ELECTRONICS

High precision, rapid laser hole drilling

InactiveUS6864459B2Improve accuracyWelding/soldering/cutting articlesFilm packagingOptoelectronicsLaser beams

Owner:LAWRENCE LIVERMORE NAT SECURITY LLC

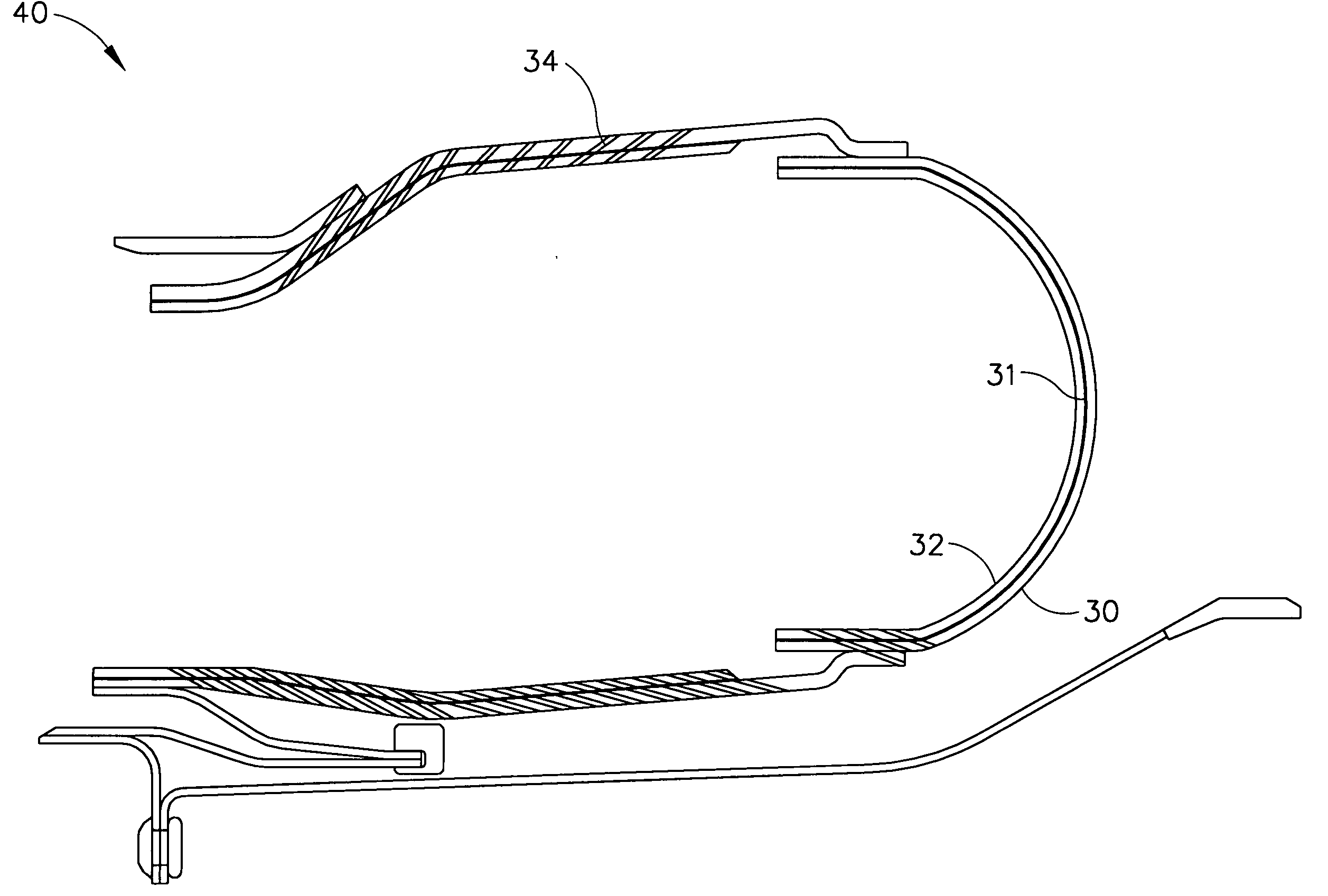

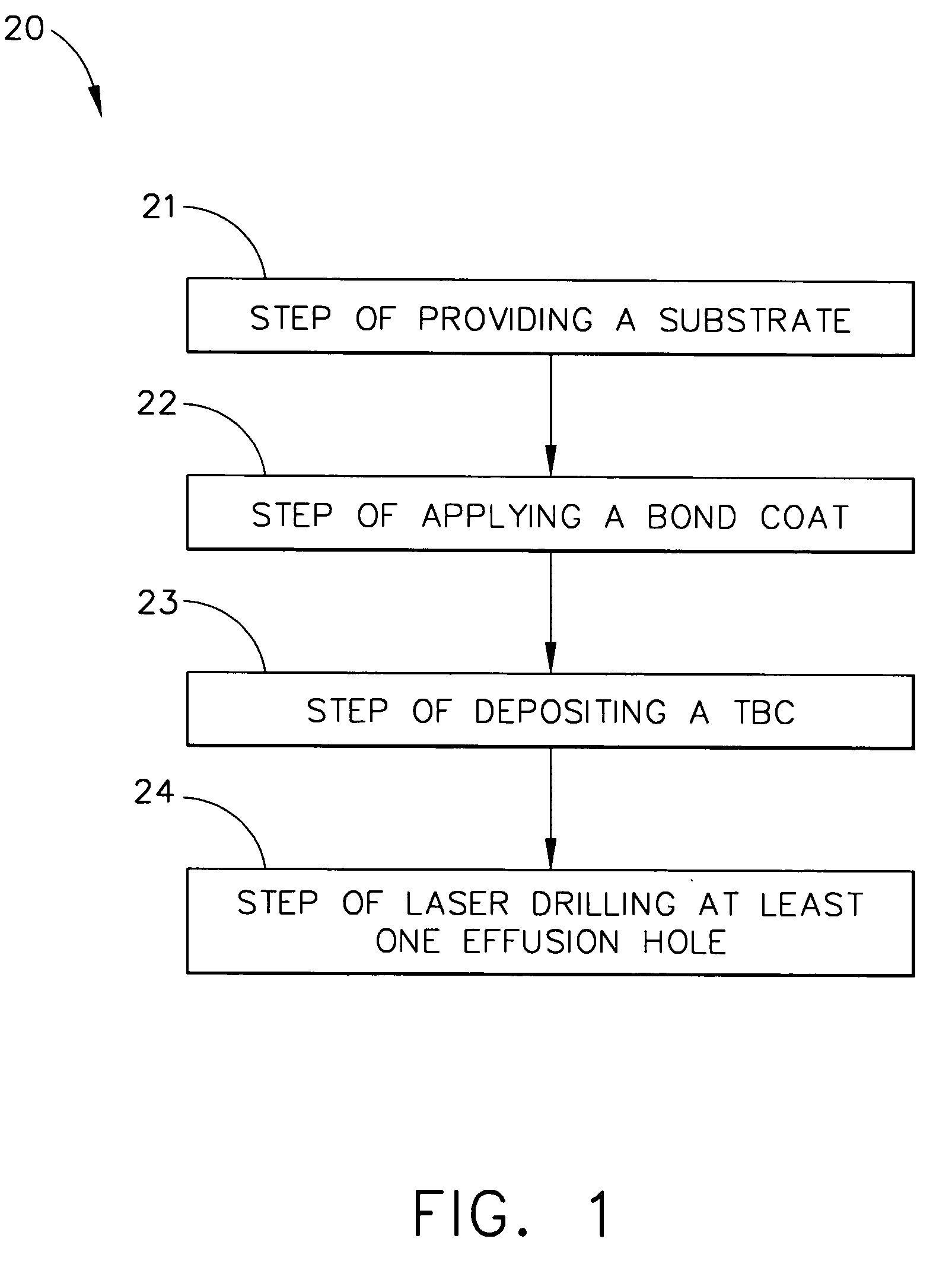

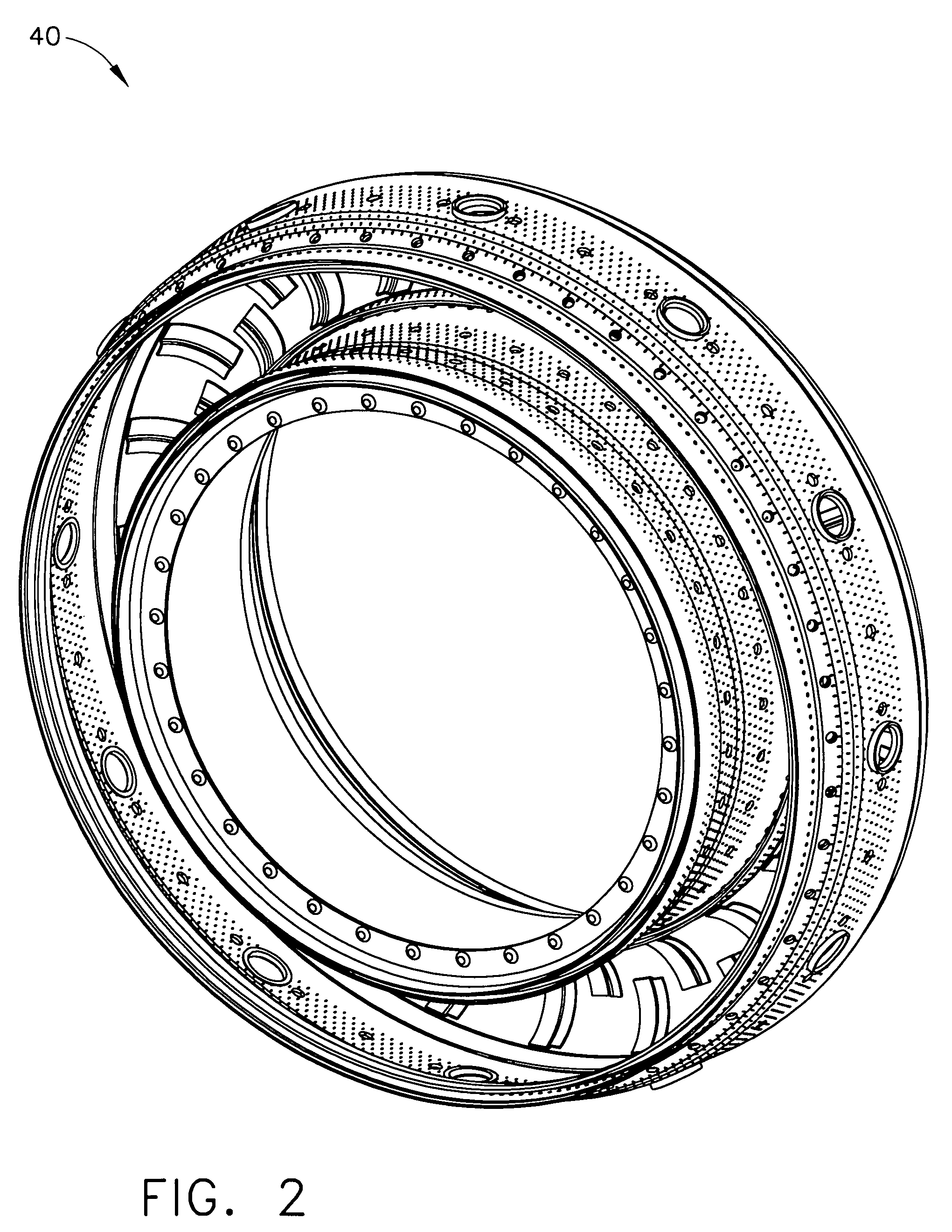

Combined effusion and thick TBC cooling method

A method for combined effusion and thick TBC cooling comprises a providing a substrate, depositing a thick TBC onto the substrate and laser drilling an array of effusion holes through the TBC coated substrate. The thick TBC has a columnar crack structure, which gives compliance and spall resistance. The microstructure of the segmentation microcracked TBC reduces cracking and chipping of the TBC during effusion hole laser drilling.

Owner:HONEYWELL INT INC

Stereoscopic display using polarized eyewear

InactiveUS20070040905A1Minimize distortionMinimize discomfortColor television detailsSteroscopic systemsMicrometerImage resolution

The present invention discloses a stereoscopic display employing polarized eyewear. The basic component of the present invention stereoscopic display is a stereopolarizer, which is a polarized screen comprising microscopic sections of mutually extinguishing polarizing filters dispersed throughout the screen. To achieve the proper resolution, the size of the microscopic polarizing filter needs to be in order of micrometer, from a few microns to a few hundred of microns. The arrangement of the microscopic polarizing filters can be alternating stripes in horizontal, vertical, or any arbitrarily direction. The microscopic polarizing filters can be arranged in alternating pattern, such as alternating square or circle. The polarizer screen can be one sheet or can be a composite sheet, comprising two distinct polarizer filter sheet laminated together. Laser drilling is used to fabricate the microscopic polarizing filters, primarily due to ease of operation and appropriate microscopic sizes. Further, laser drilling and cutting can form angle holes in the stereopolarizer, which provides optimum focus viewing for horizontal perspective display.

Owner:INFINITE Z

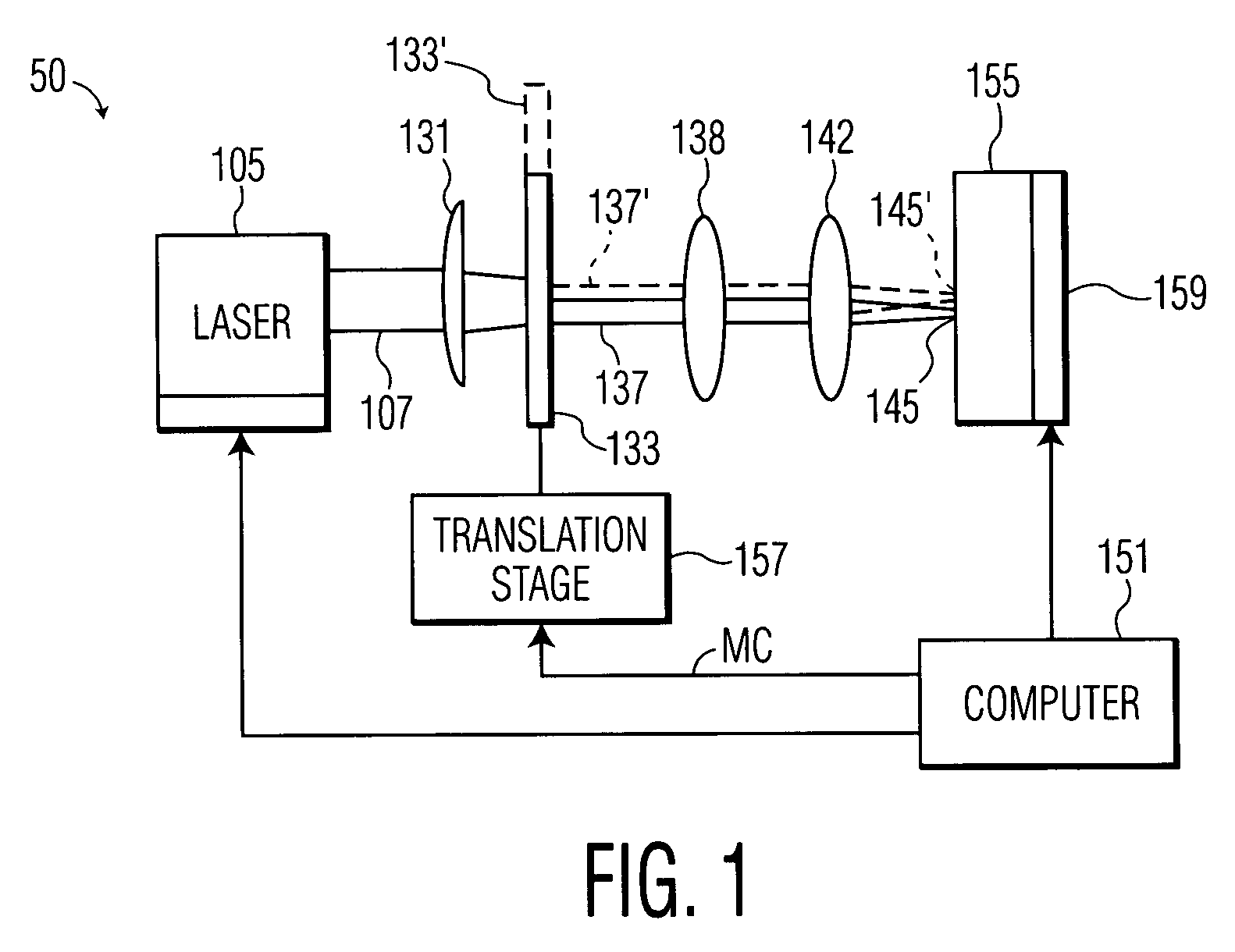

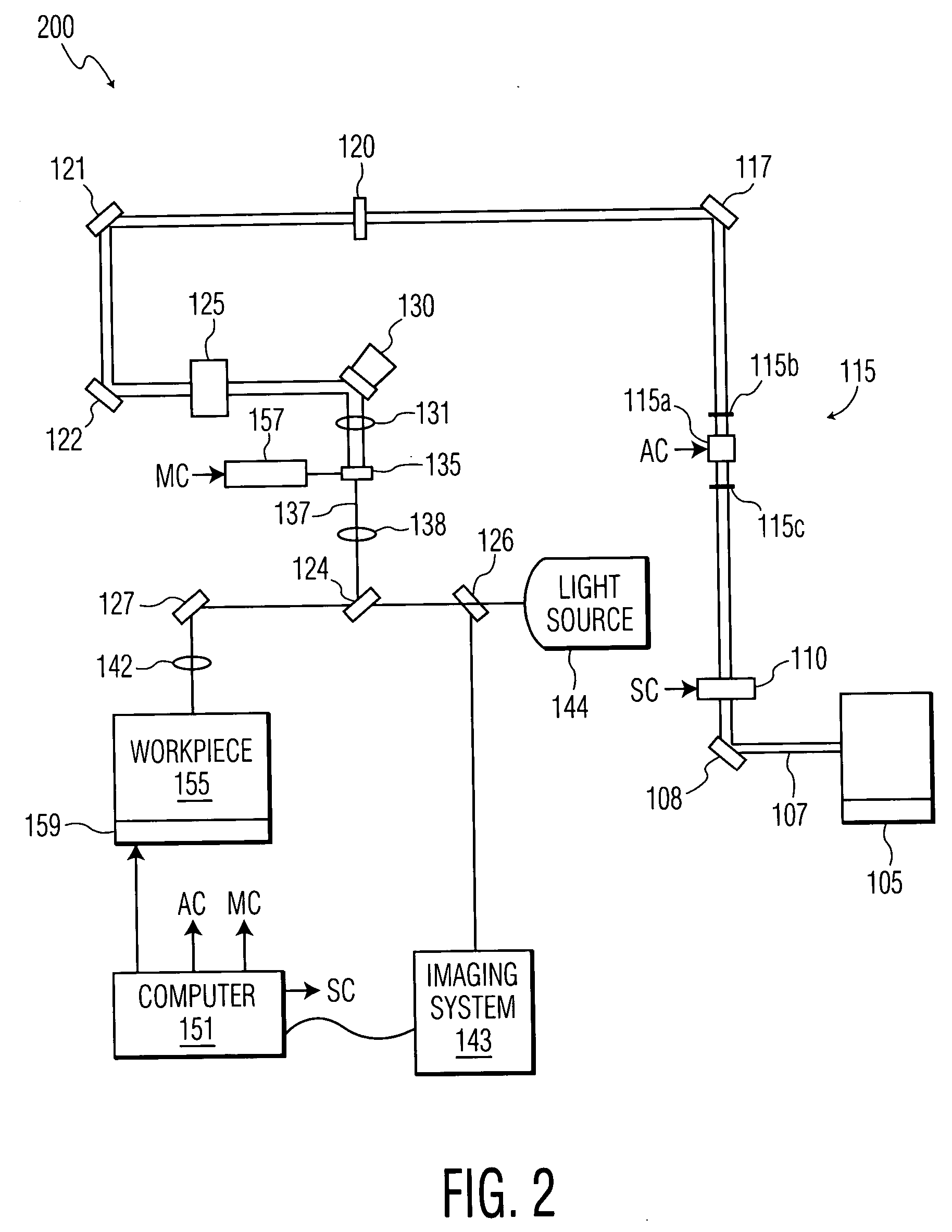

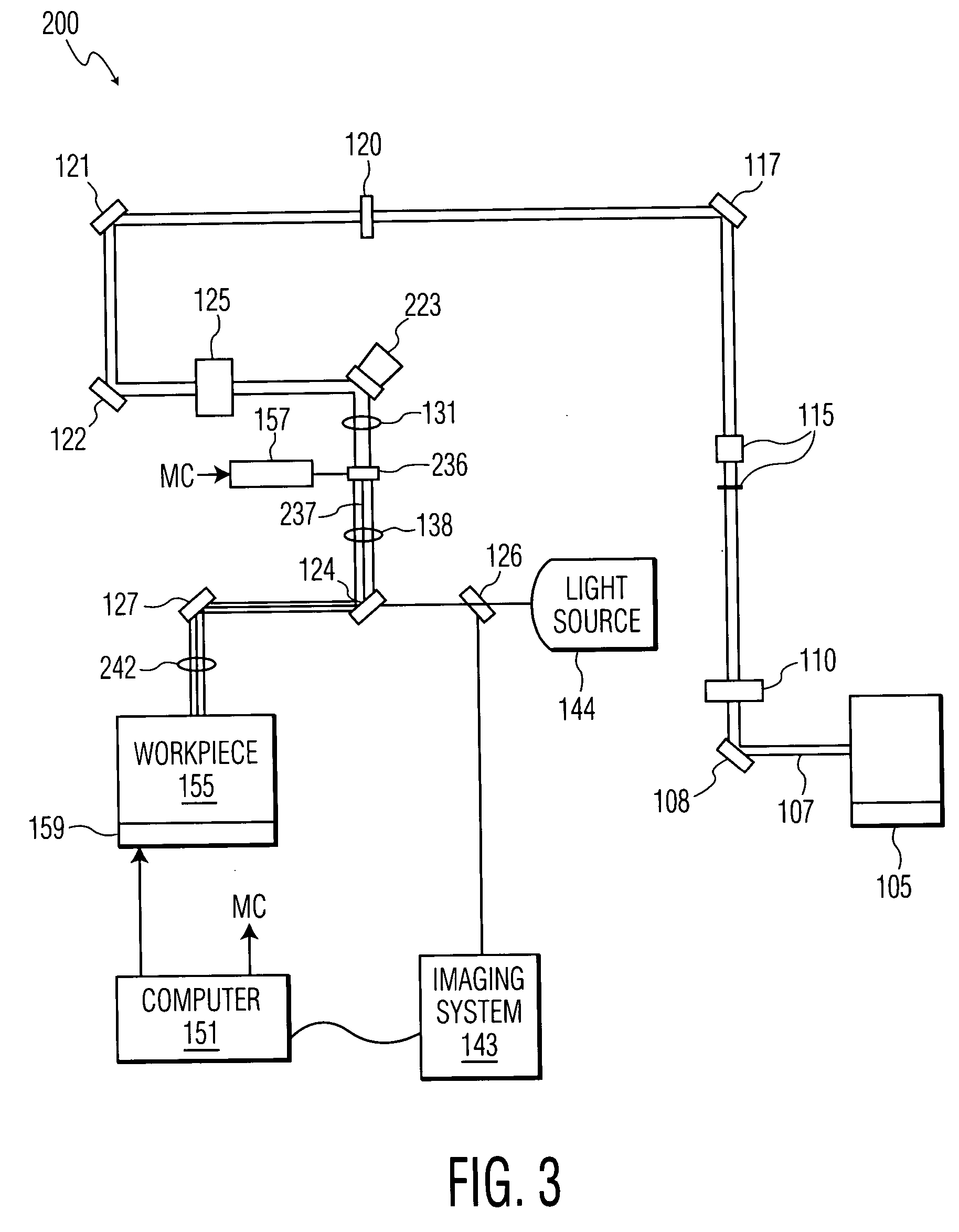

Precision laser micromachining system for drilling holes

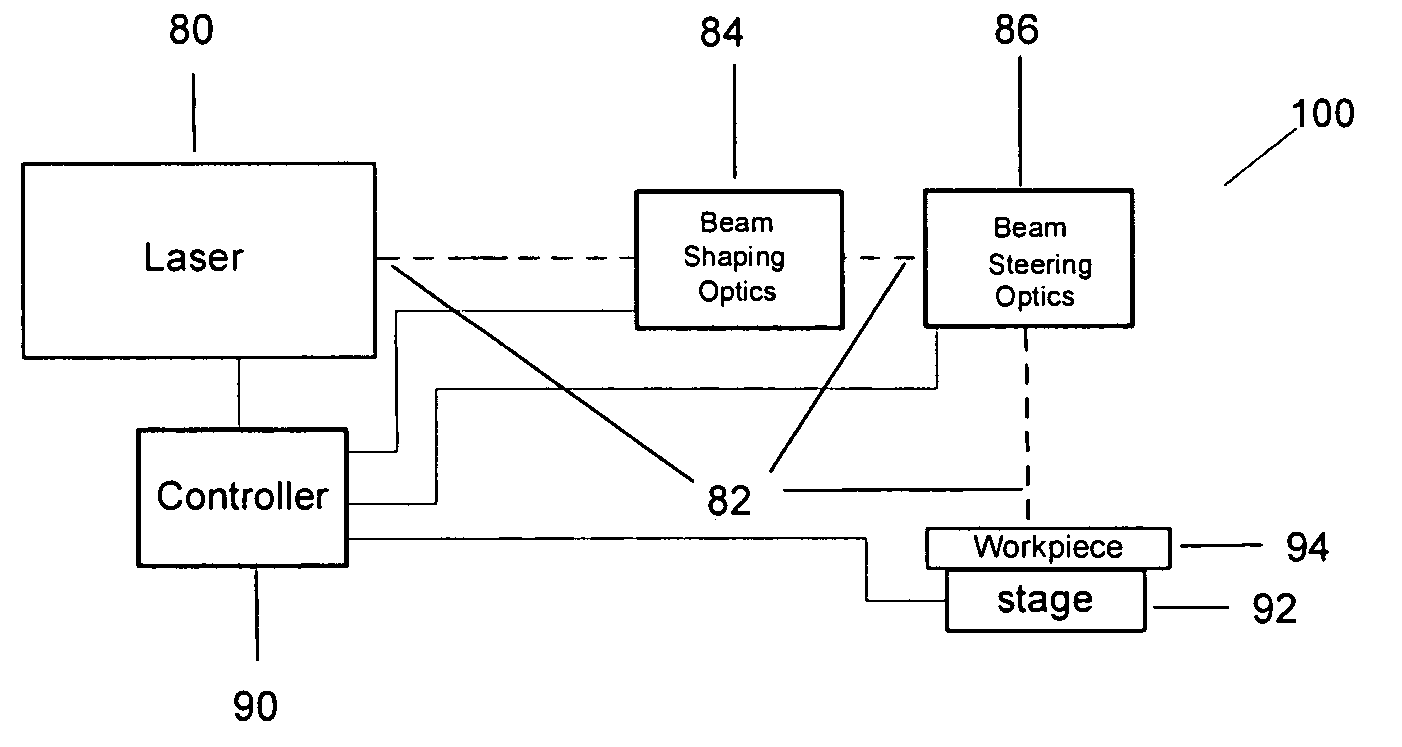

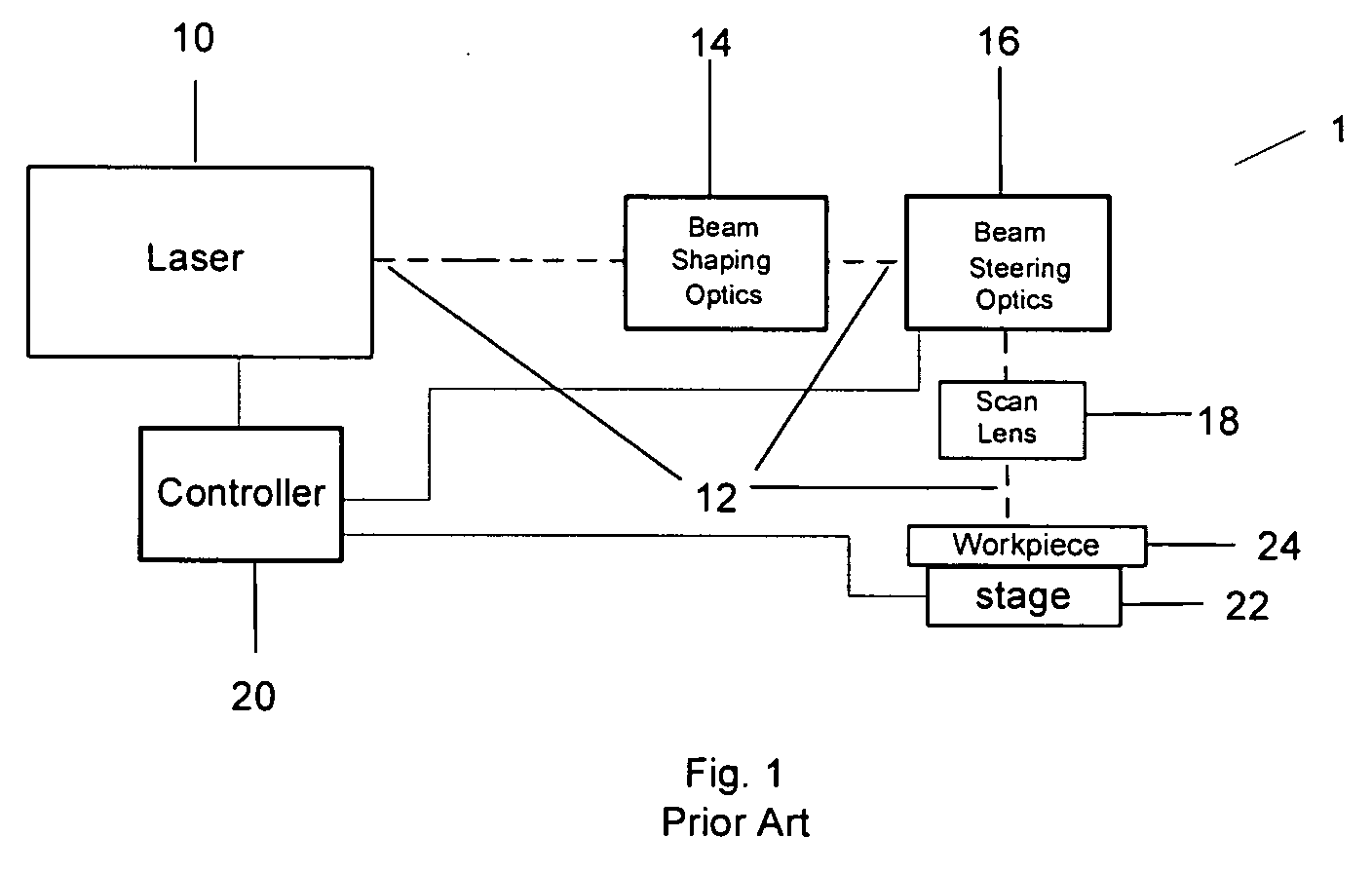

InactiveUS20050103759A1Optical resonator shape and constructionWelding/soldering/cutting articlesReduced sizeLight beam

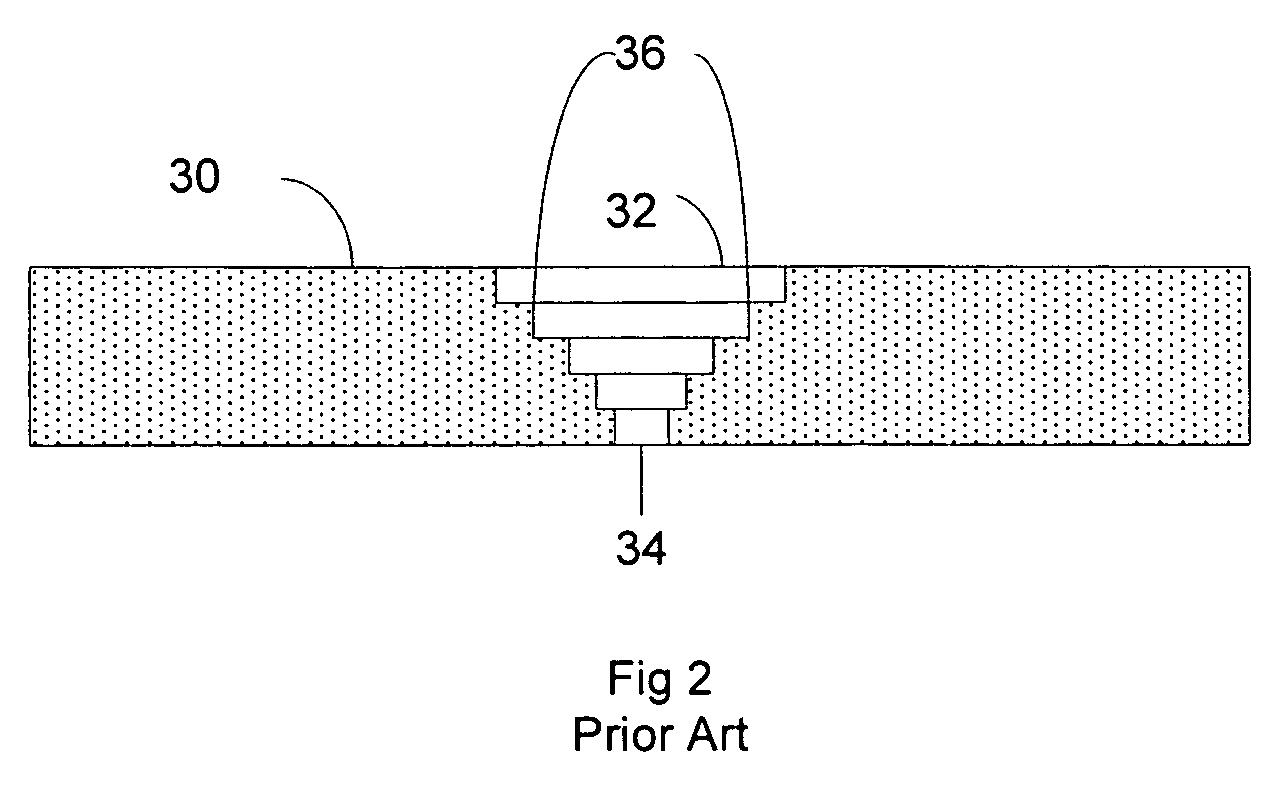

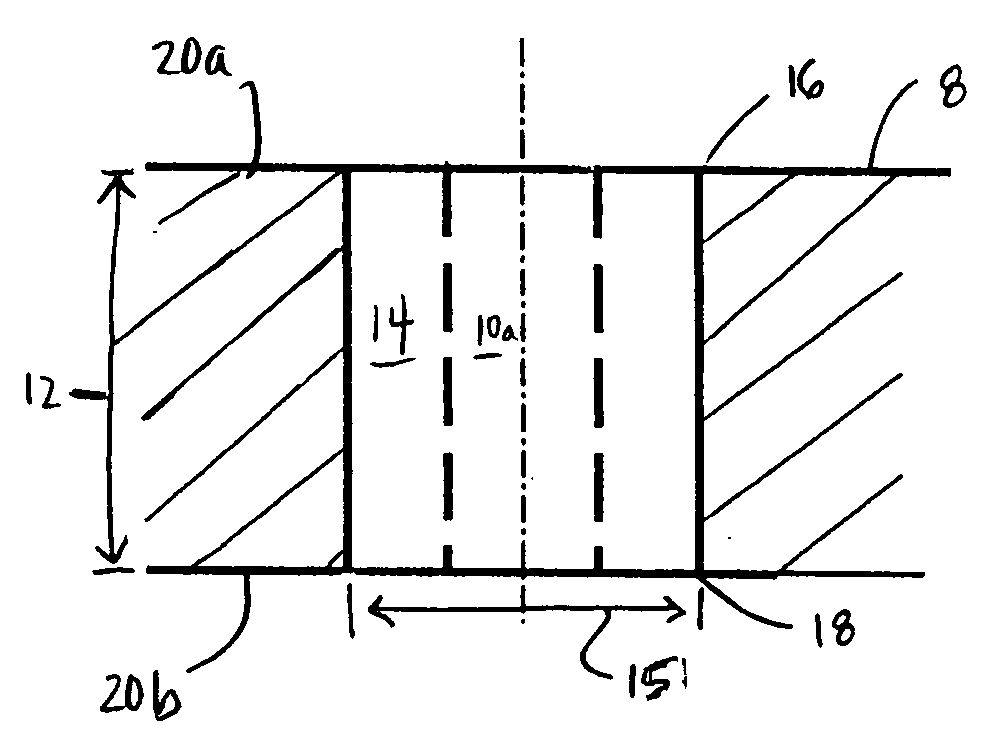

A laser drilling system for drilling holes in a work piece with a laser. The system includes: a laser for creating a laser beam and directing the laser beam along an optical path; a mask having at least one aperture, the mask and the aperture being located in the optical path to cause the creation of a sub-beam; a lens for forming a reduced-size image of the sub-beam onto the work piece and a translation stage for moving the mask to change the position of the sub-beam on the work piece. The laser beam has a wavefront cross-section with an area greater than the size of the aperture and is incident upon the mask and the aperture to create the sub-beam.

Owner:LI MING +2