Surface grid-type static induction transistor

An electrostatic induction and transistor technology, applied in the direction of transistors, circuits, electrical components, etc., can solve the problems of large gate cut-off current and drain cut-off current, weakened gate control sensitivity, low gate-source breakdown voltage, etc., to reduce gate-source parasitic capacitance , increasing gate control sensitivity and reducing gate-source area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The present invention is explained in detail below.

[0045] The process of the present invention is compatible with the traditional planar CMOS process, and the entire manufacturing process is as follows:

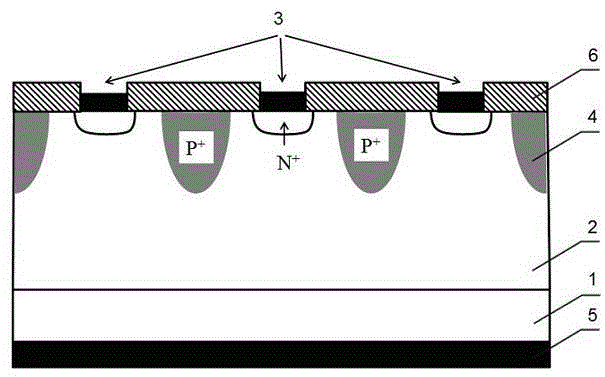

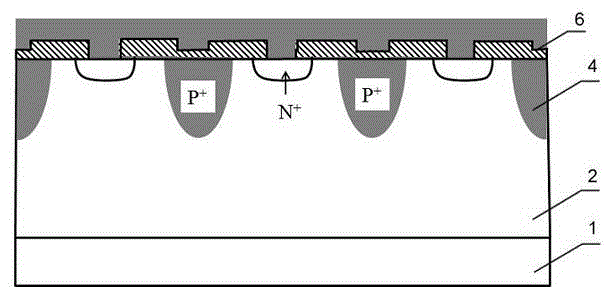

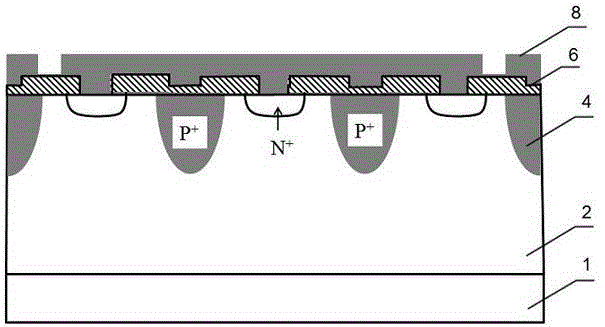

[0046] Silicon wafer cleaning - thermal oxidation - one photolithography (gate area, source area, gate wall window) - second photolithography (gate area, gate wall) - boron injection - one annealing - three photolithography - —Arsenic injection—second annealing (RTP)—LPCVD oxidation—densification annealing—four photolithography (ohmic contact window)—metallization—anti-etch gold—deposition of composite dielectric—five times Photolithography (lead hole) - triple annealing - backside thinning - backside metallization - dicing - packaging.

[0047] The invention can be formed by connecting 1500 to 2000 SIT units in parallel, and the current density of the device is greatly improved.

[0048] The following is an embodiment of the present invention, which will be descr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More