Heterogeneous metal stacked grid strained silicon-germanium on insulator p-channel metal oxide semiconductor field effect tube (SSGOI pMOSFET) device structure

A technology of heterogeneous metal and device structure, applied in the direction of semiconductor devices, electrical components, circuits, etc., to achieve the effects of suppressing leakage-induced barrier reduction, reducing the number of power lines, and reducing the DIBL effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

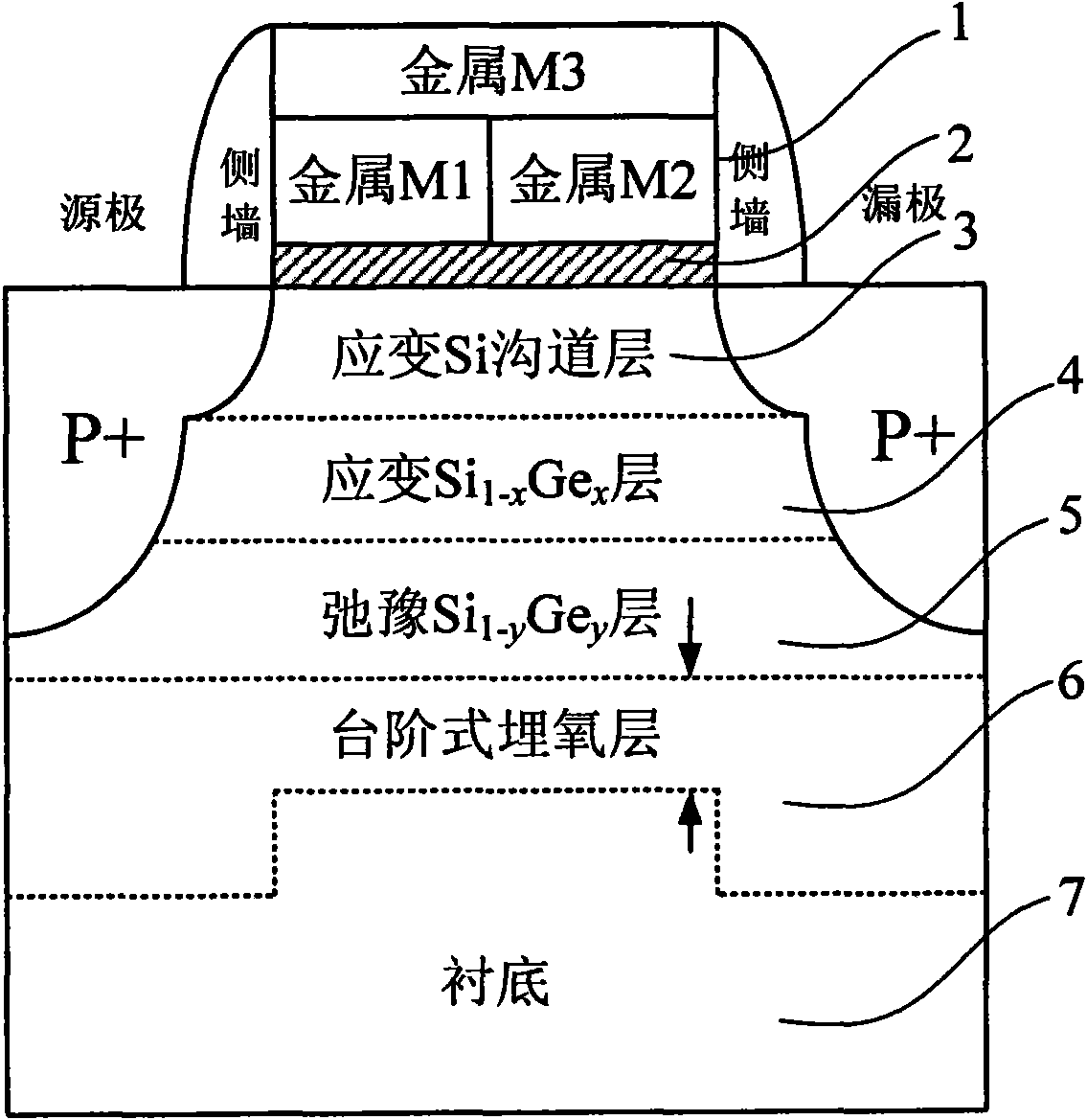

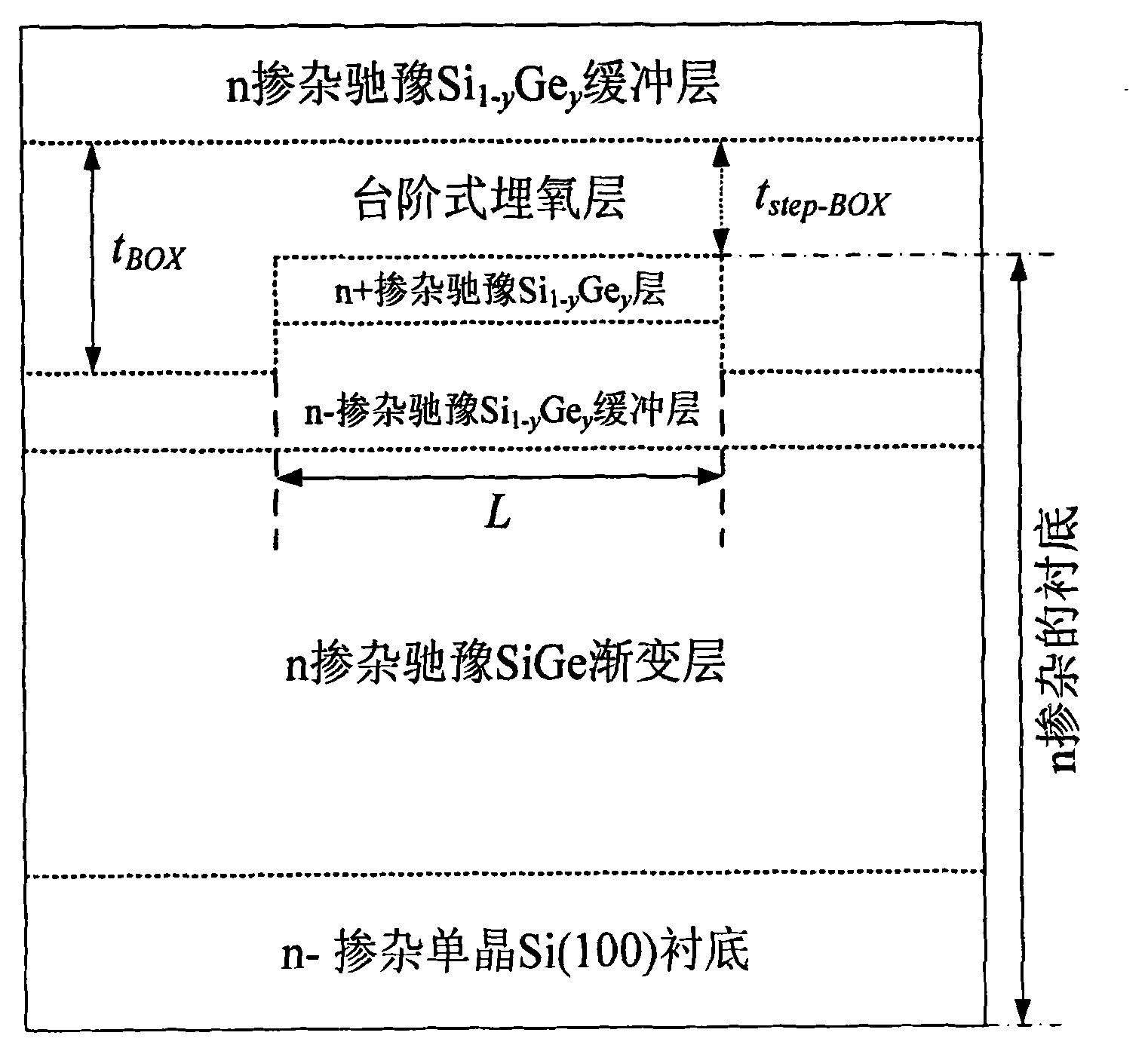

[0038] Such as figure 1 As shown, the heterogeneous metal stack gate SSGOI pMOSFET device structure of the present invention includes: a heterogeneous metal stack gate structure 1; gate insulating layer 2; intrinsic or n - Doped strained Si channel layer 3; intrinsic or n - Strained Si with Gradient Doping Composition 1-x Ge x Layer 4; n-doped relaxed Si 1-y Ge y layer 5; stepped buried oxide layer 6; n-doped substrate portion 7, ref. image 3 , the n-doped substrate part 7 is a thin layer (5-10 nanometers) of n + doped relaxed Si 1-y Ge y layer, n - doped relaxed Si 1-y Ge y buffer layer, n-doped relaxed SiGe graded layer and n - The doped single crystal Si (100) substrate consists of four parts.

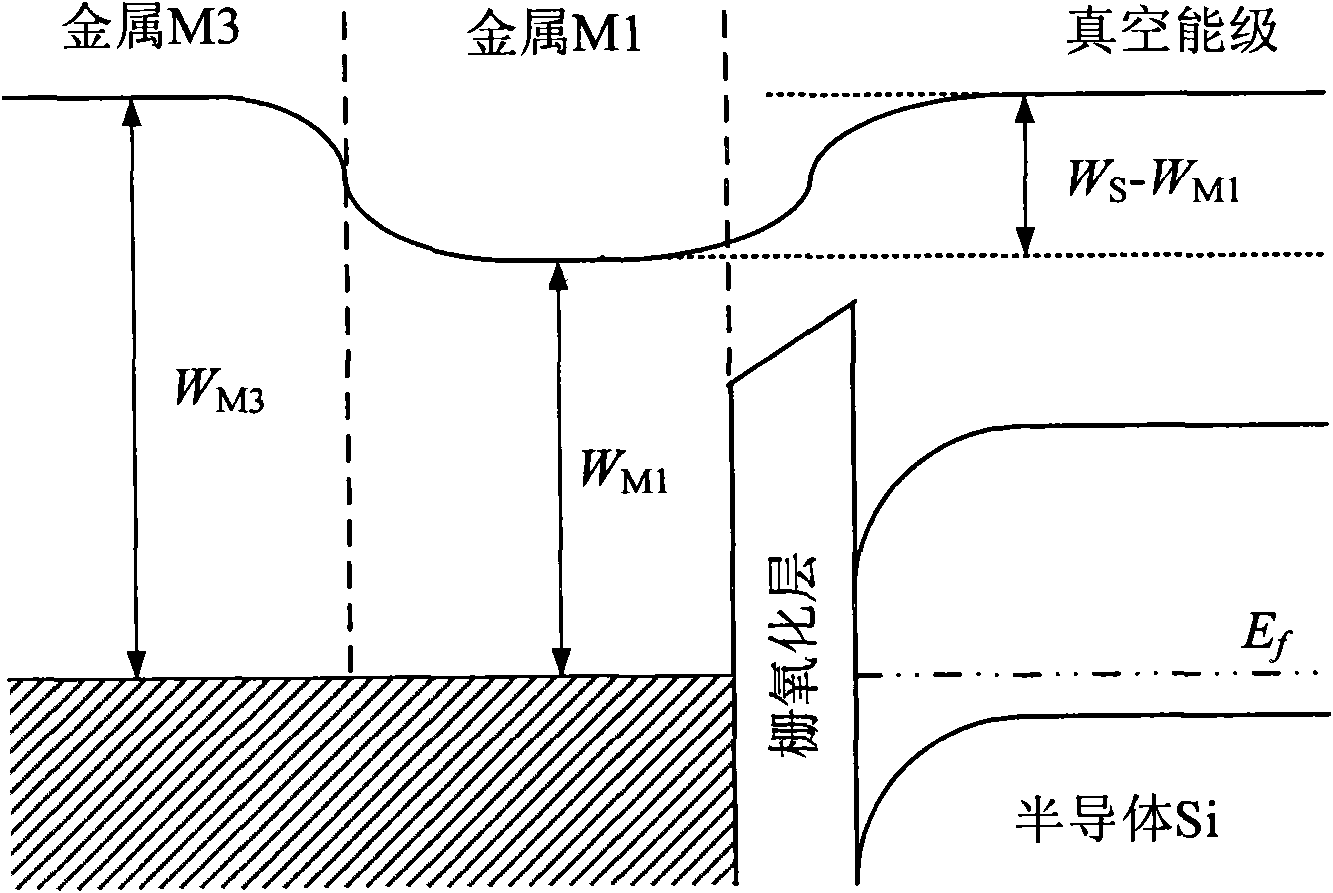

[0039] The heterogeneous metal stack gate structure includes a metal gate M1 near the source end, a metal gate M2 near the drain end, and a metal gate M3 above M1 and M2. M1 and M2 are completely covered by M3, and the work function W of the gate M1 M1 and the work f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More