Patents

Literature

45results about How to "Adjust Threshold Voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

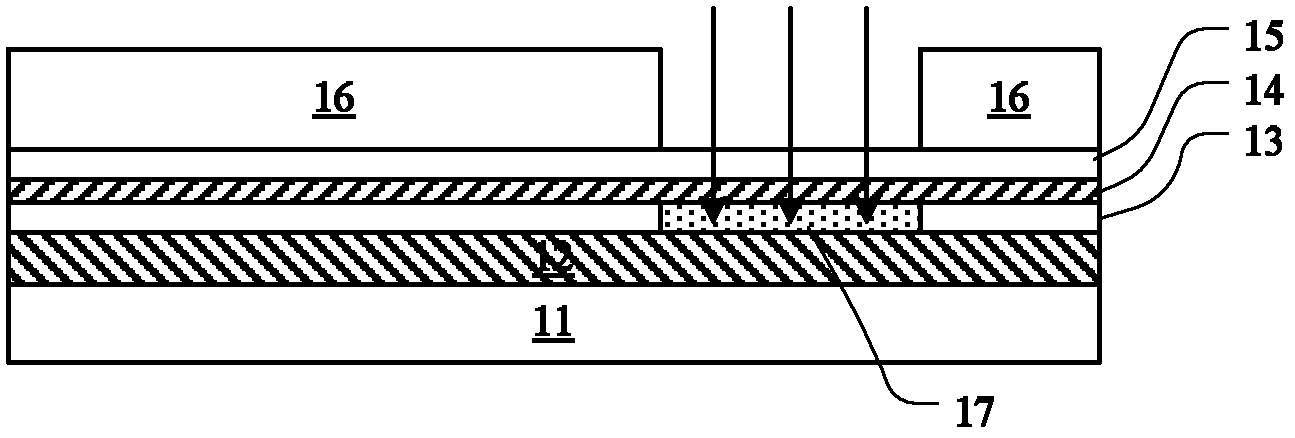

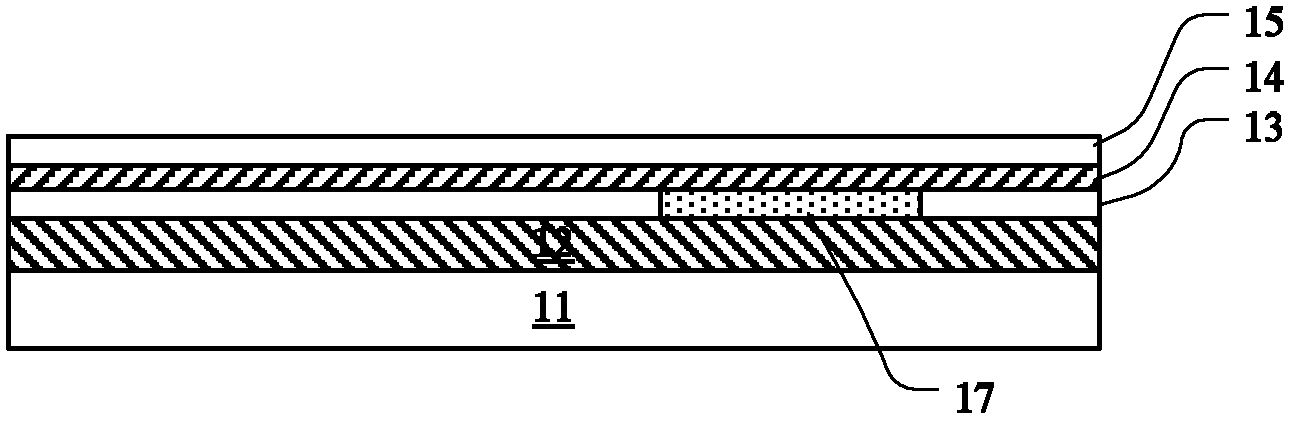

Thin film transistor on basis of metal oxide and preparation method and application thereof

InactiveCN102522429ALow costEasy for large area and mass productionTransistorSemiconductor/solid-state device manufacturingAnodic oxidationPhotoresist

The invention discloses a thin film transistor on the basis of metal oxide and a preparation method and application thereof. The preparation method comprises the following steps of: (1) making a buffer layer; (2) depositing a gate metal layer on the buffer layer; (3) preparing a gate insulation layer on the gate metal layer by using an anodic oxidation method, wherein the part in the gate metal layer, on which an oxide film does not need to be deposited, is protected by using a photoresist; (4) removing the photoresist; (5) removing an unrequired metal lead; (6) preparing an active layer on the gate insulation layer; and (7) according to the designed thin film transistor structure, depositing and patterning source and drain electrodes, a pixel electrode and a protection layer or an etched barrier layer. According to the invention, pure Al or Al alloy is used as gate metal and the gate insulation layer is prepared by using the anodic oxidation method. The performance of the gate insulation layer can be changed by regulating the components of the gate metal, so that the electrical properties of the thin film transistor are improved.

Owner:GUANG ZHOU NEW VISION OPTO ELECTRONICS TECH

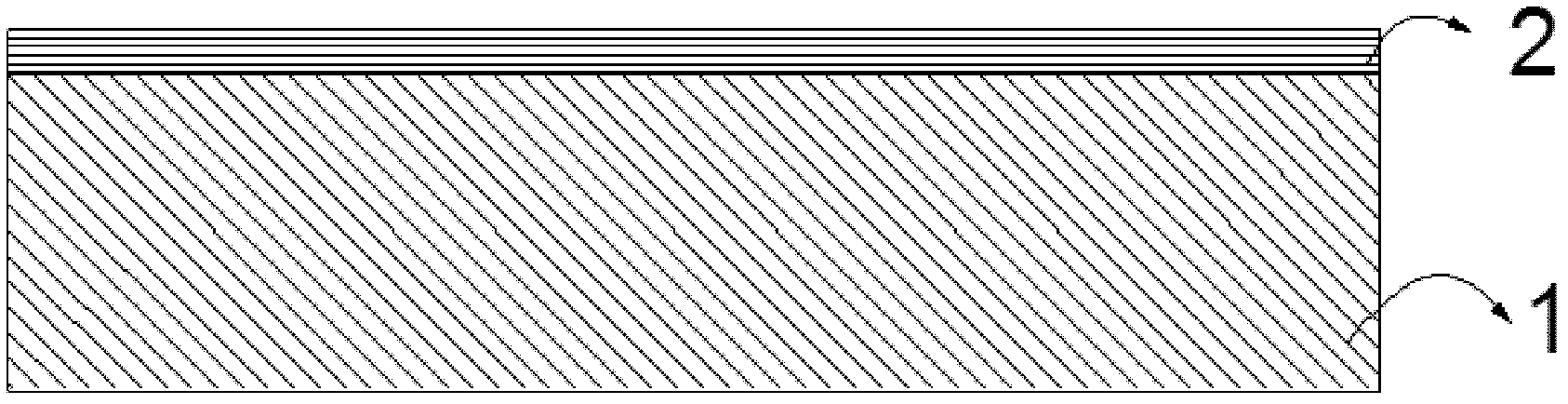

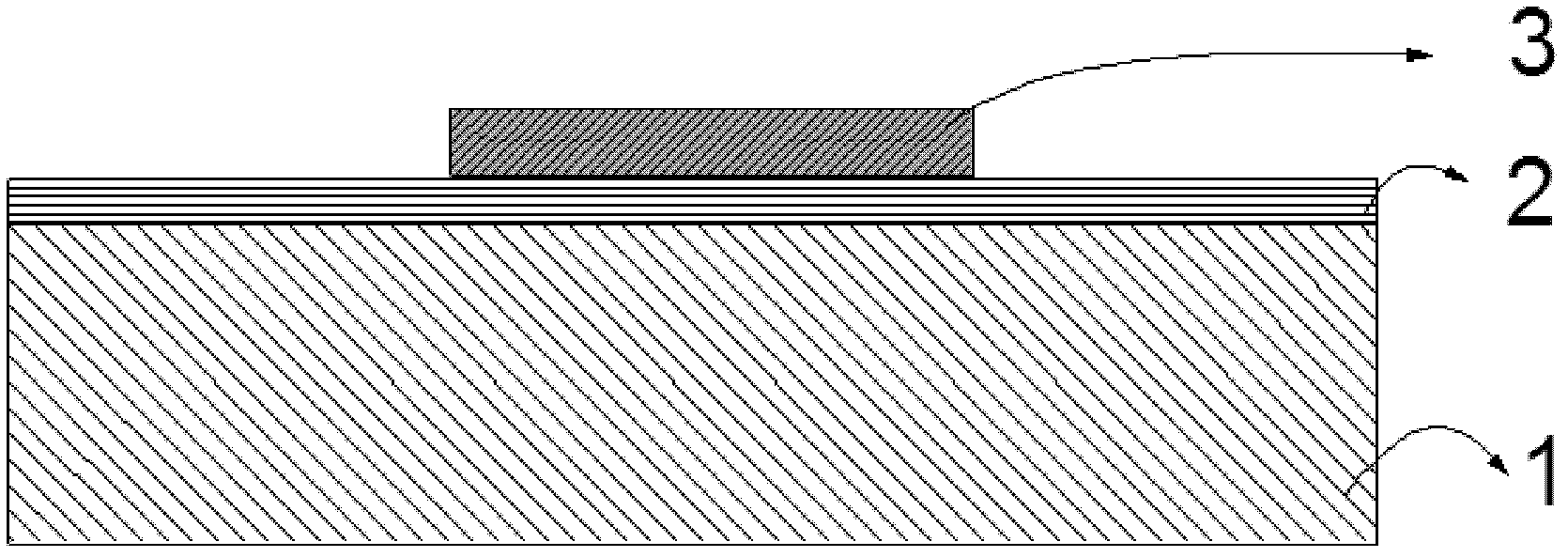

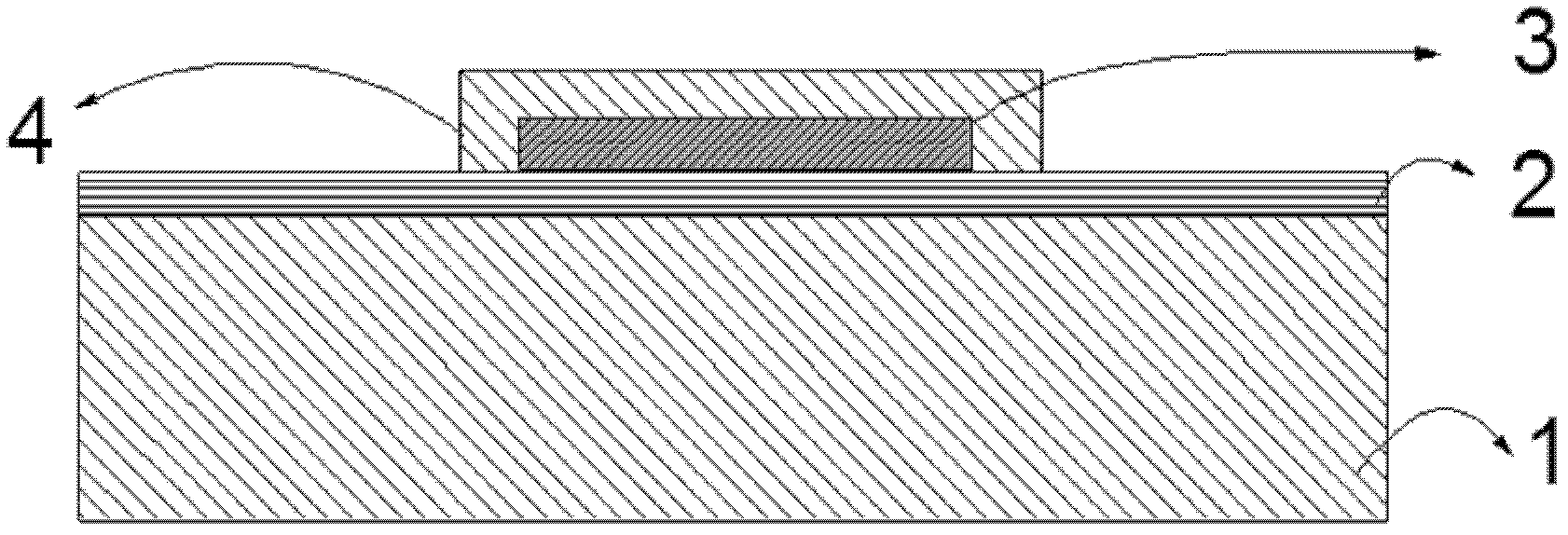

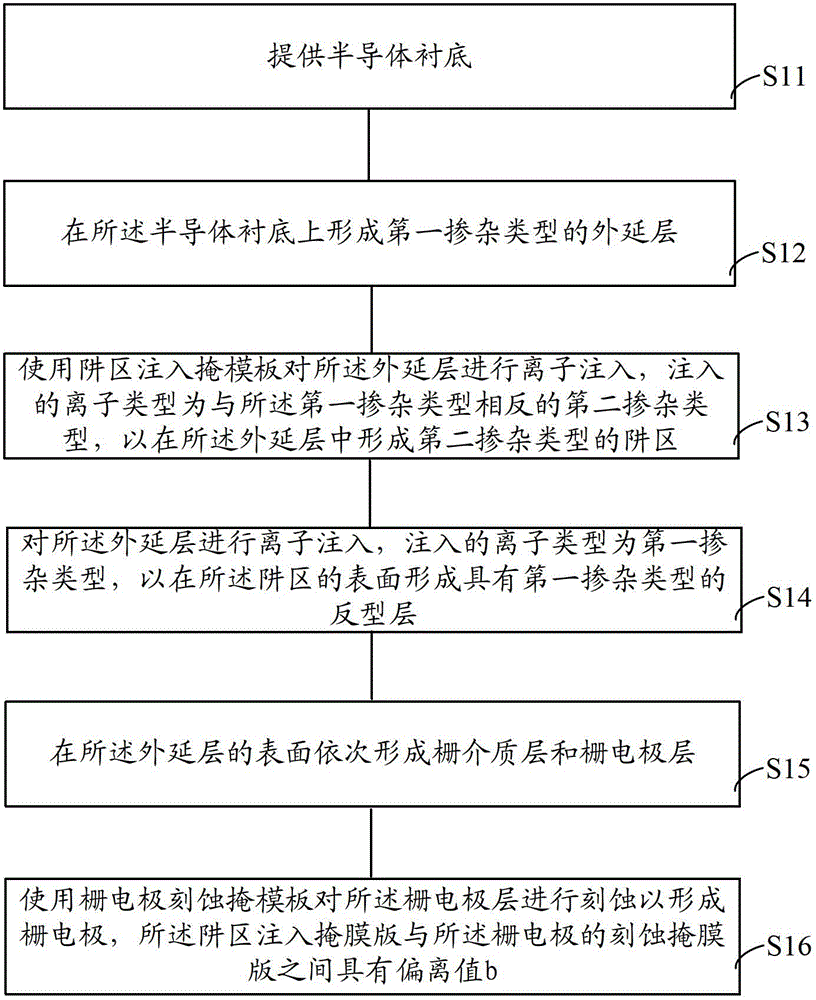

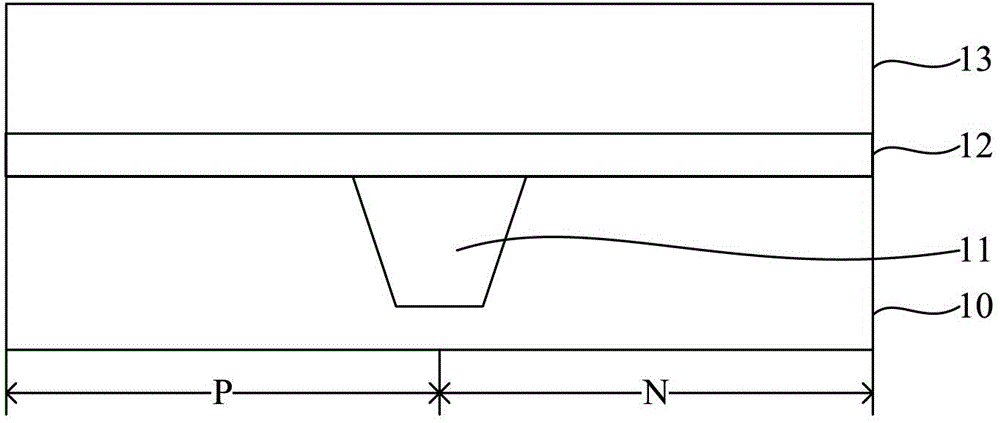

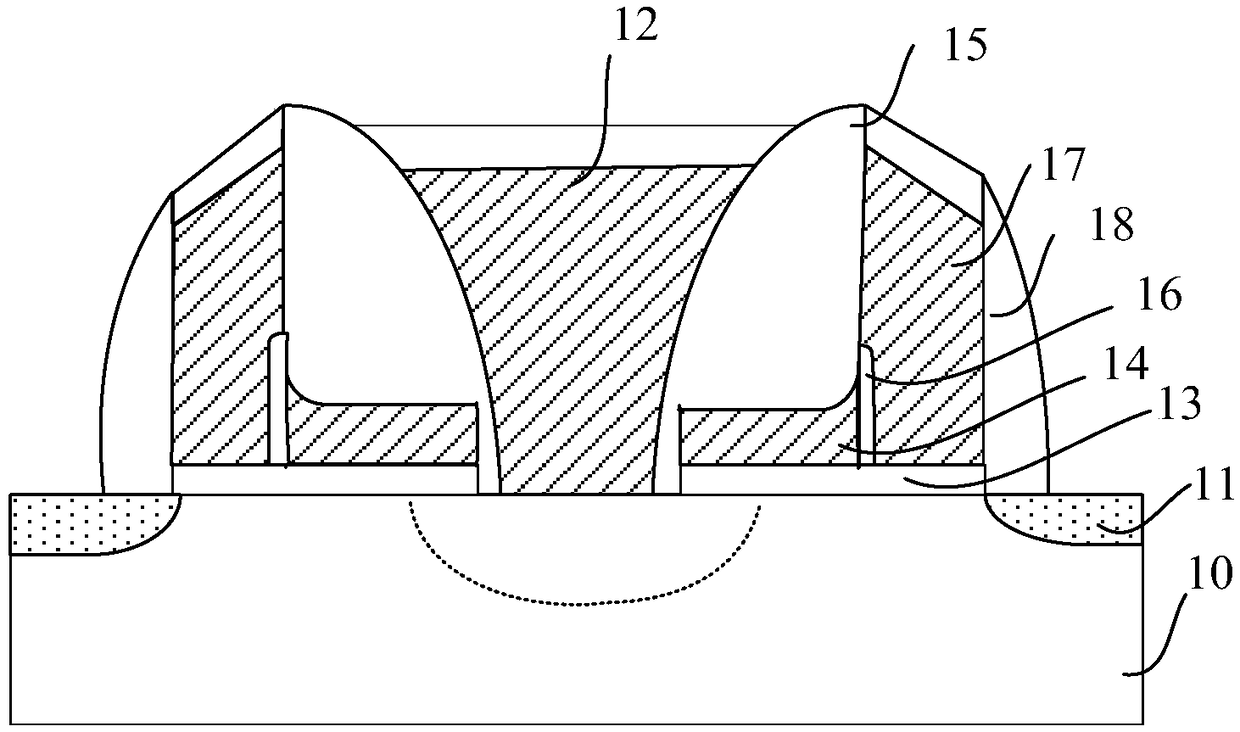

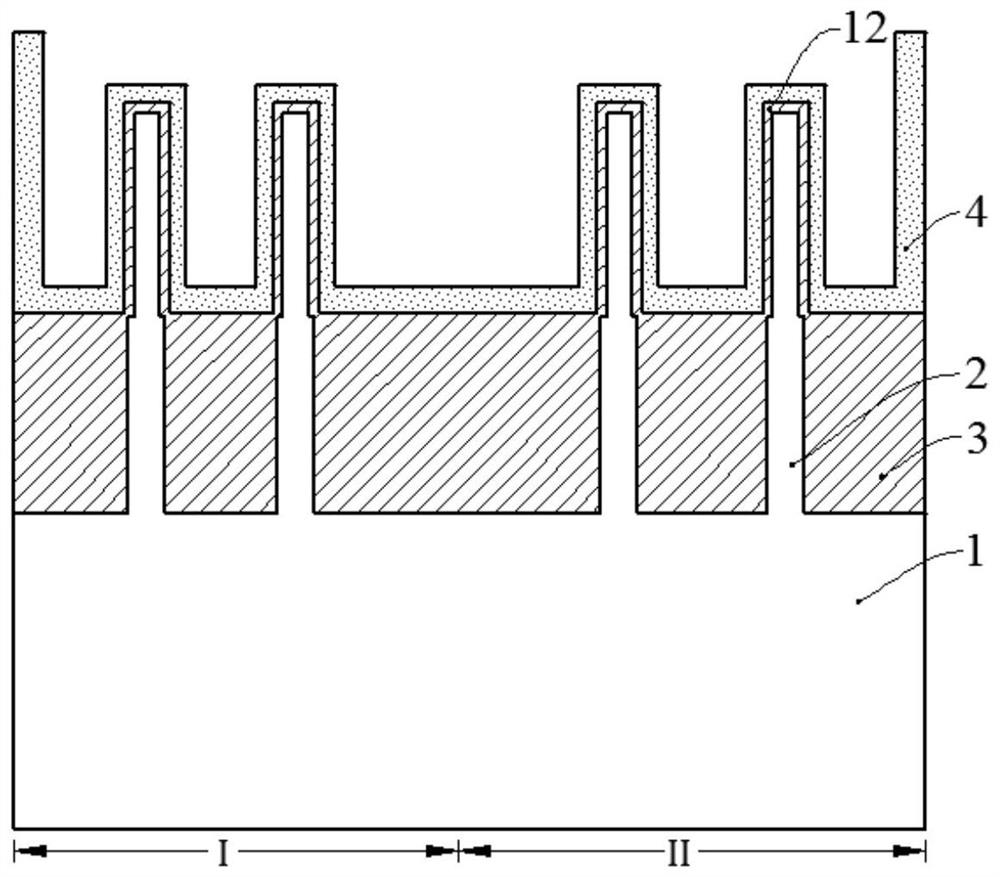

Depletion type power semiconductor device and manufacturing method thereof

ActiveCN102751332AAdjust Threshold VoltageEffective regulationSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceGate dielectric

The invention provides a depletion type power semiconductor device and a manufacturing method thereof. The device comprises a semiconductor substrate, an epitaxial layer of a first doping type, a well region of a second doping type, an inversion layer of the first doping type, a gate dielectric layer and a gate electrode. The well region of the second doping type is formed on the epitaxial layer which is positioned on the semiconductor substrate, the second doping type is opposite to the first dope type, the inversion layer of the first doping type is arranged on the surface of the well region, and the gate dielectric layer and the gate electrode are sequentially positioned on the epitaxial layer. The distance of the well region extending below the gate electrode is 0.75XXj+b, wherein Xj refers to the junction depth of the well region, and b is larger than or equal to -2 micrometers and smaller than or equal to 5 micrometers. The depletion type power semiconductor device and the manufacturing method thereof are simple in process procedure, low in cost and high in threshold voltage controllability.

Owner:HANGZHOU SILAN MICROELECTRONICS

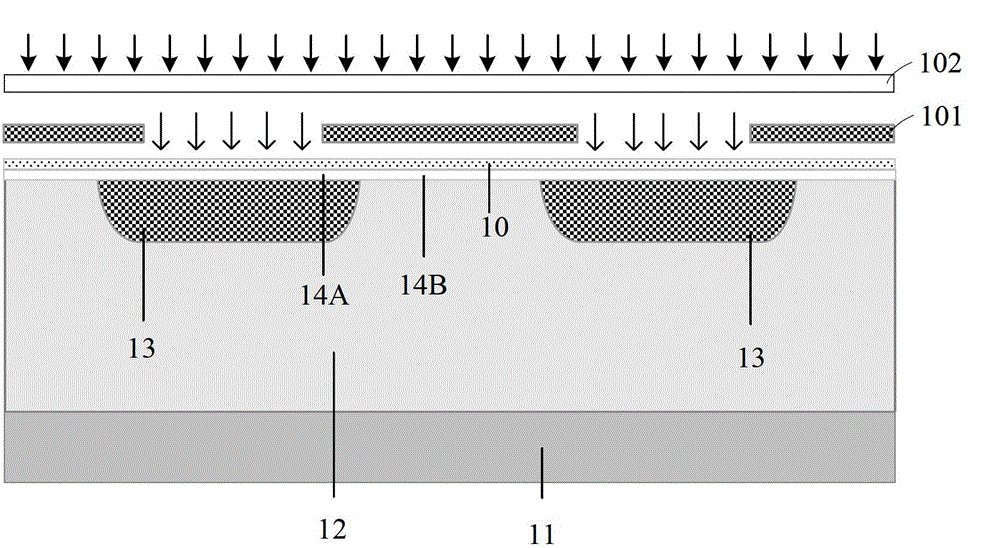

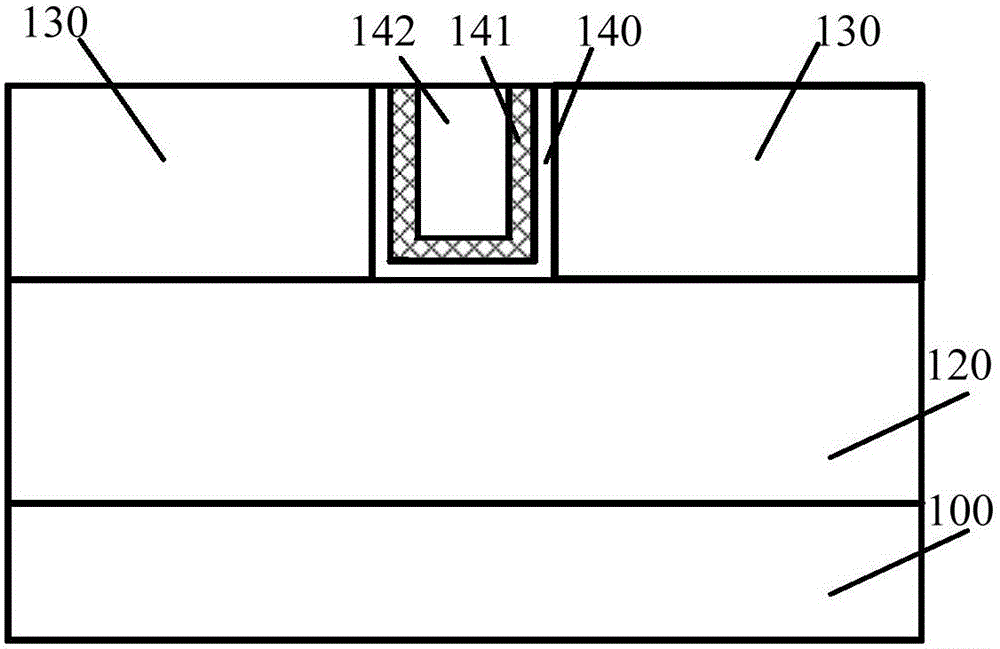

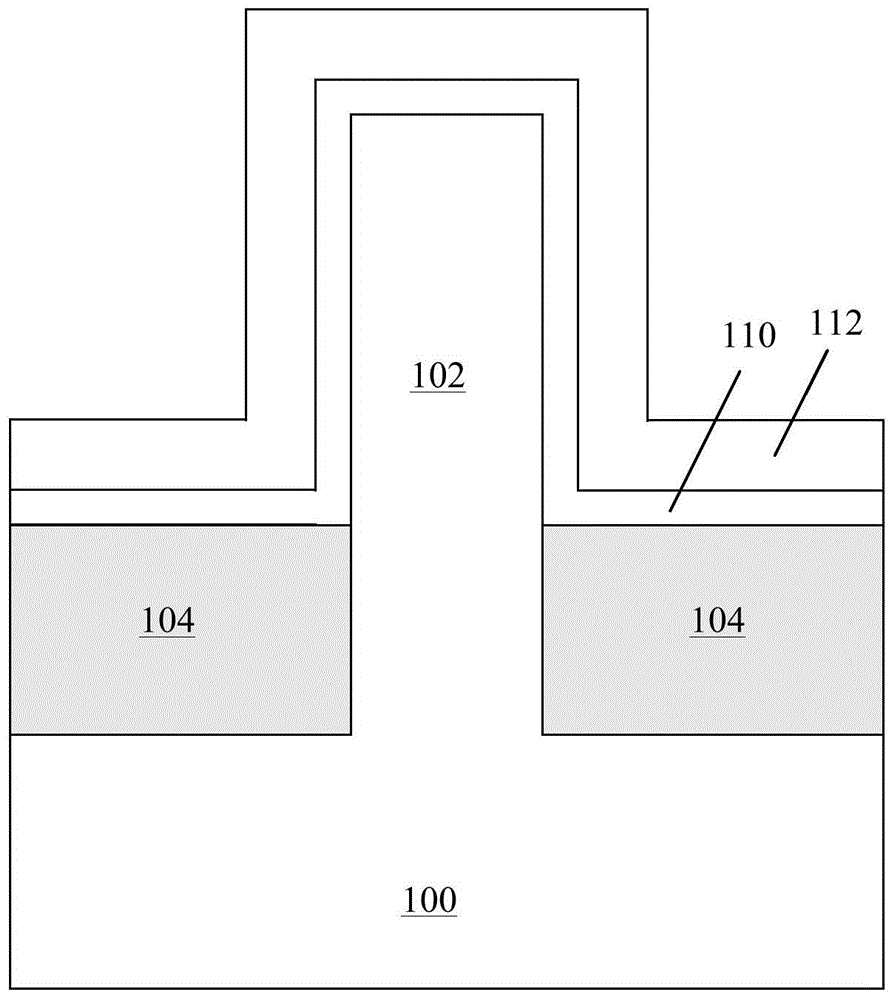

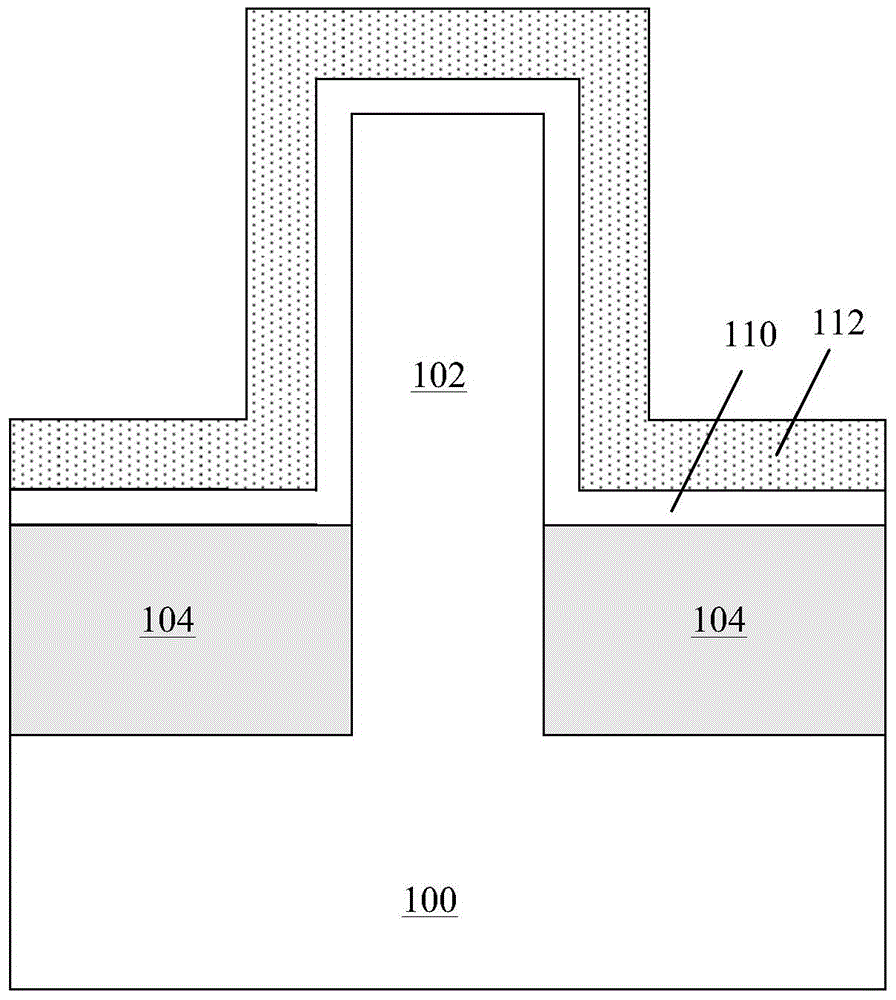

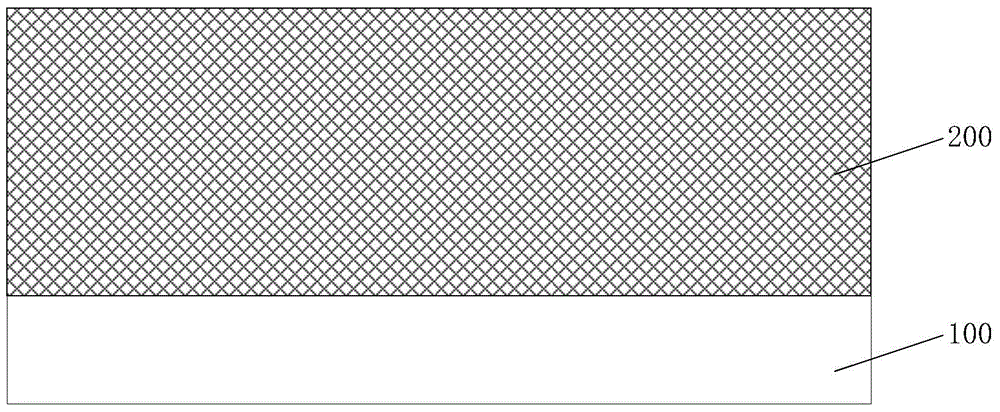

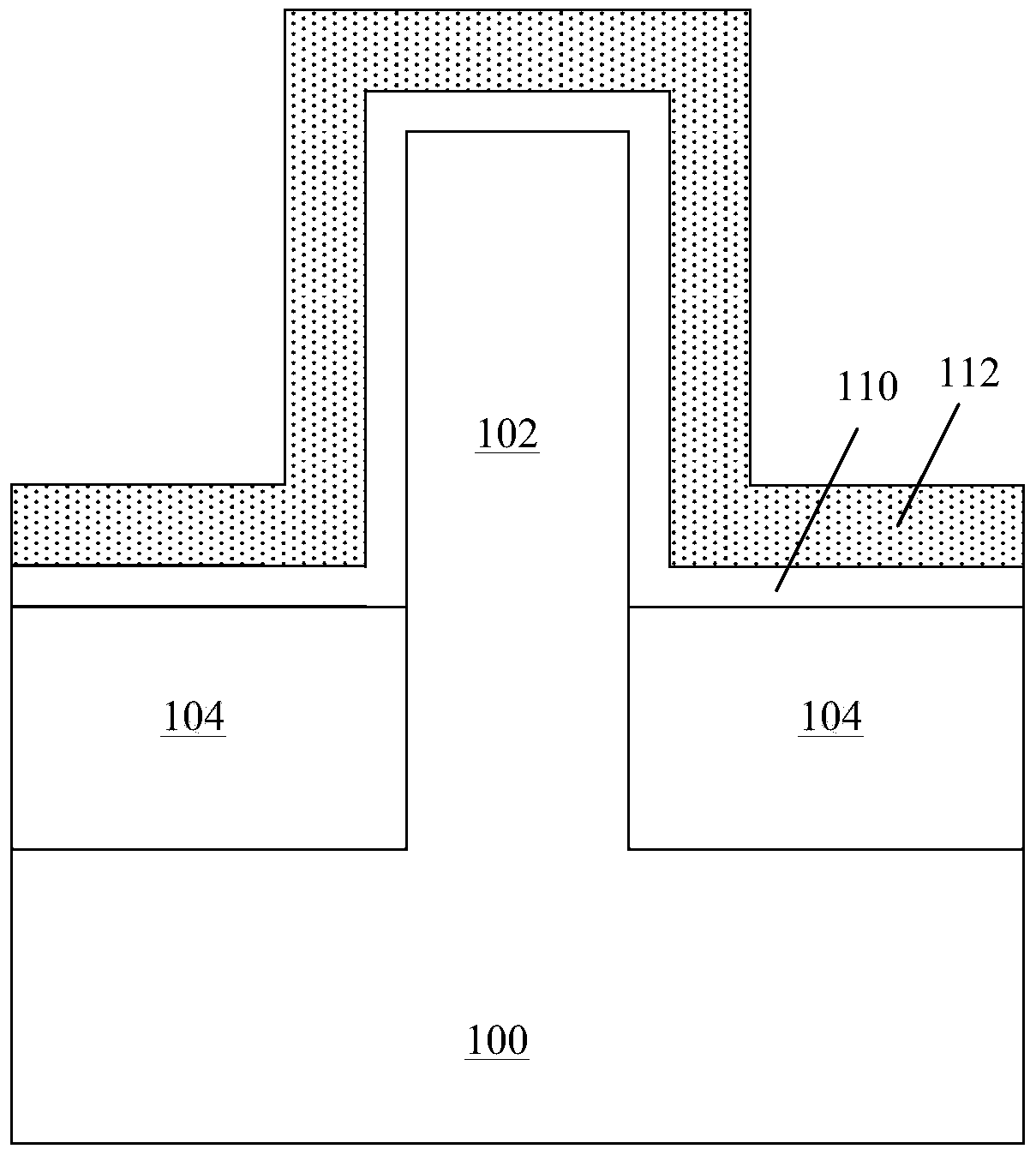

Semiconductor device and formation method thereof

ActiveCN106409677AAvoid accessImprove the blocking effectSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsSemiconductor

The invention provides a semiconductor device and a formation method thereof. The formation method of the semiconductor device comprises steps: providing a substrate, wherein the surface of the substrate is provided with an interlayer dielectric layer, a groove is arranged in the interlayer dielectric layer, and the surface of the substrate is exposed by the groove; forming a gate dielectric layer which covers the bottom and sidewalls of the groove; forming a first barrier layer which covers the gate dielectric layer; performing non-crystallization processing on the first barrier layer to convert the first barrier layer to a second barrier layer; and forming a metal layer which covers the second barrier layer, wherein the surface of the metal layer is aligned with the surface of the interlayer dielectric layer. According to the semiconductor device and the formation method thereof, the performance of the semiconductor device is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Oxide semiconductor thin film and thin film transistor

ActiveCN103325842AHigh electron mobilityAdjust Threshold VoltageTransistorPhysical chemistryThin membrane

The invention provides an oxide semiconductor thin film and a thin film transistor. The composition of the oxide semiconductor thin film is M[2x]In[2-2x]O[3-delta], wherein M is a III B family element, x is larger than or equal to 0.001 and small than or equal to 0.3, and delta is larger than or equal to 0 and small than 3. The III B family element is one or more arbitrary elements in a group consisting of Sc, Y, Ac, La, Ce, Pr, Nd, Pm, Sm, Eu, Gd, Tb, Dy, Ho, Er, Tm, Yb, and Lu. The thickness of the thin film is 5nm to 200nm. The carrier concentration of the oxide semiconductor thin film is less than 5*10<19>cm<-3>. The oxide semiconductor thin film is used as a channel layer material of the thin film transistor. The thin film transistor is provided with a gate, a channel layer, an insulated layer between the gate and the channel layer, a source electrode and a drain electrode, and the source electrode and the drain electrode are respectively connected to two ends of the channel layer. The channel layer is provided with the above oxide semiconductor thin film. The oxide semiconductor thin film and the oxide semiconductor thin film have the advantages of good performance, simple preparation and wide adaptation range.

Owner:SOUTH CHINA UNIV OF TECH

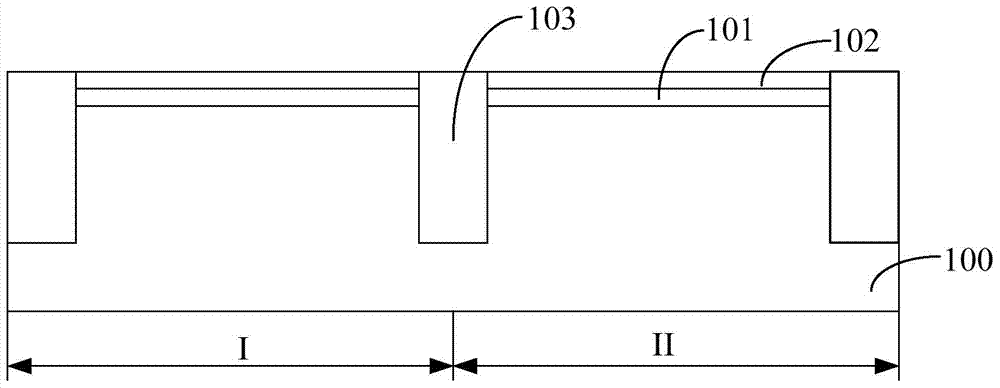

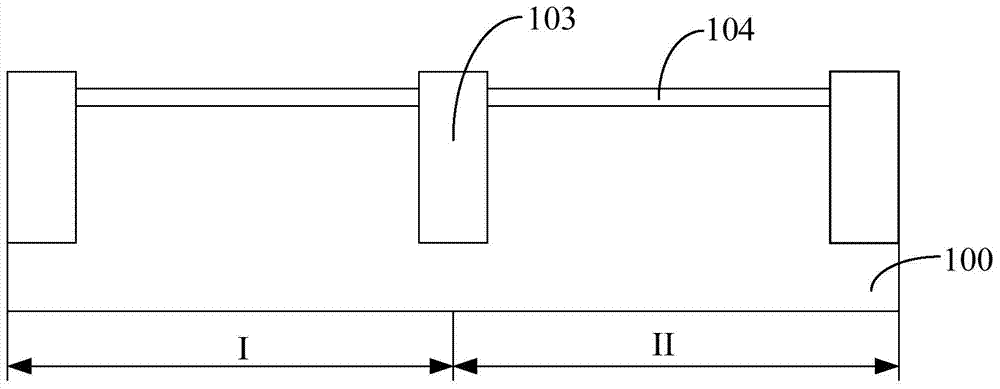

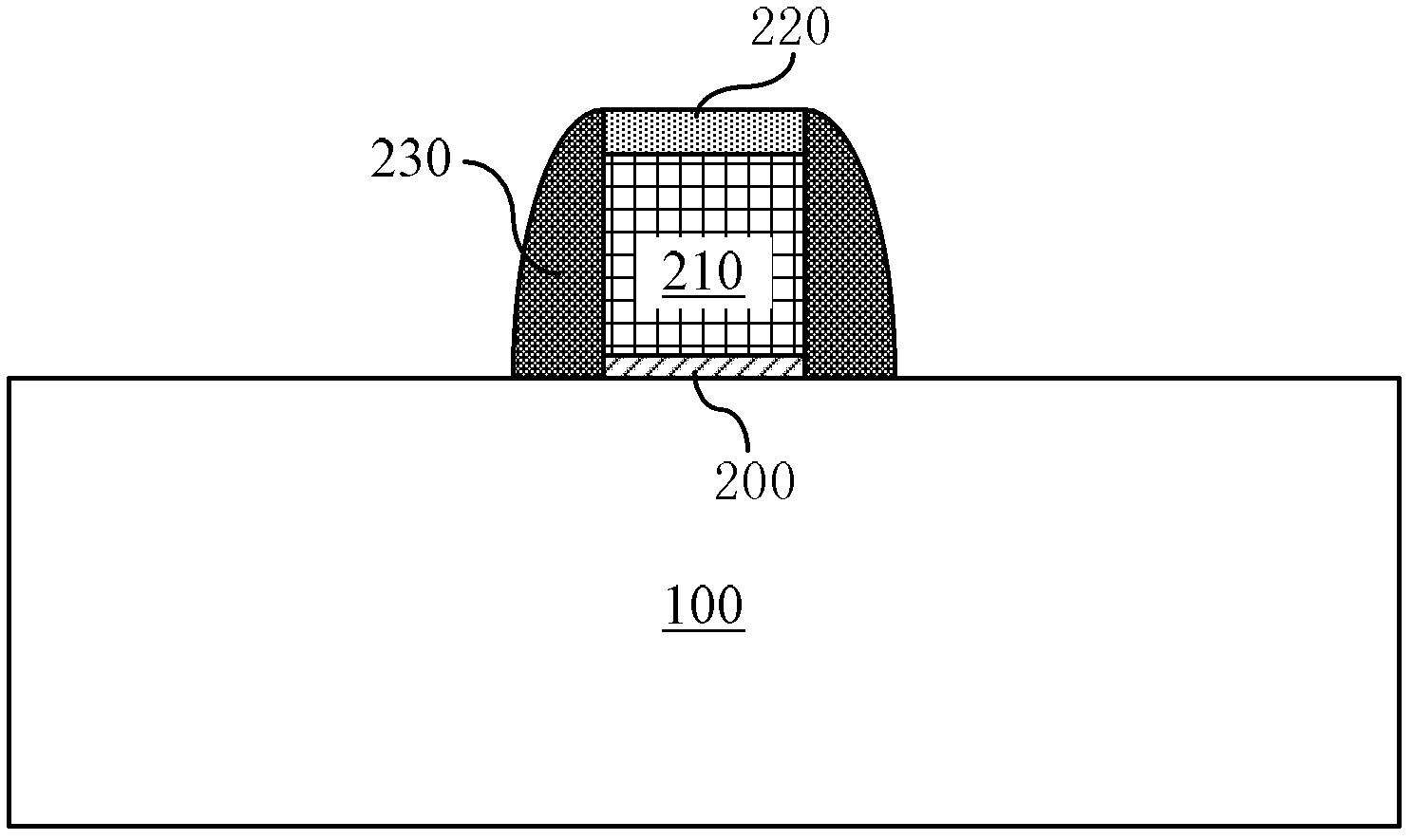

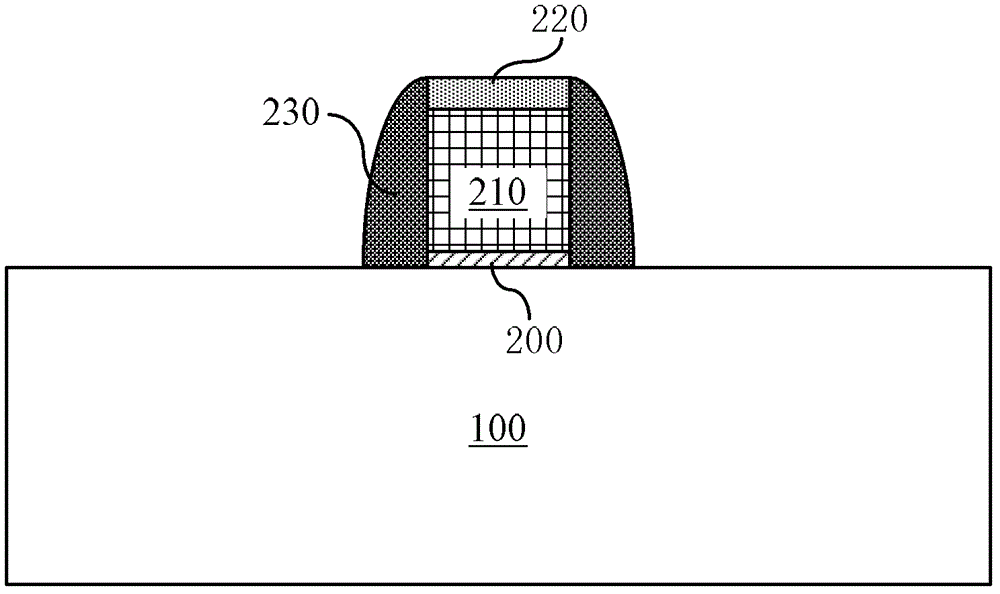

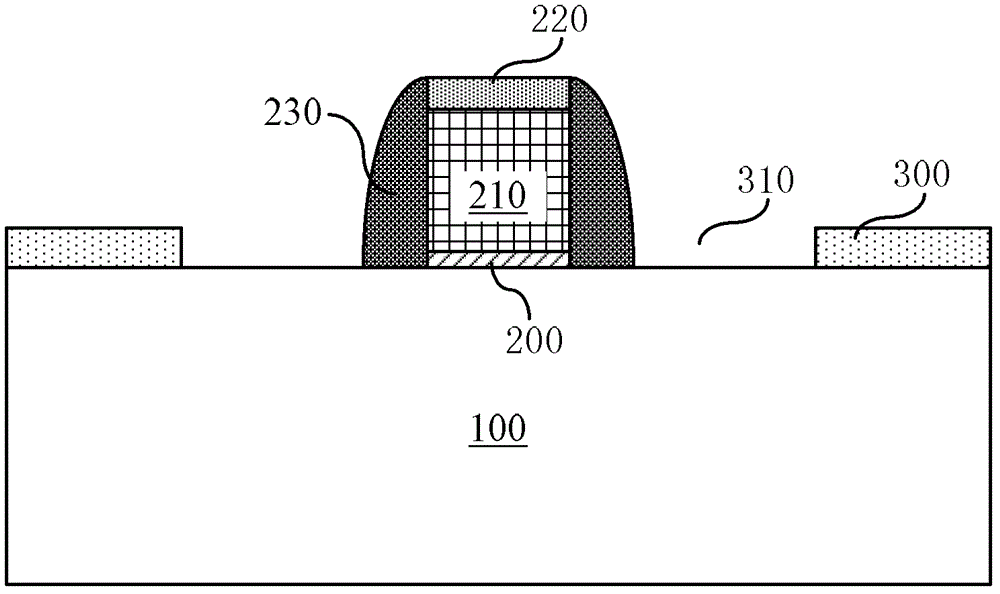

Buried channel transistor and forming method thereof

ActiveCN106935646AImprove performancePrevent flickering noiseSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricImpurity ions

The invention discloses a buried channel transistor and a forming method thereof. The forming method comprises steps: a semiconductor substrate is provided, and a well area is formed in the semiconductor substrate; an inversion doping area is formed in the well area, the doping type in the inversion doping area is opposite to that in the well area, and the depth of the inversion doping area is smaller than that of the well area; a gate structure is formed on the surface of the semiconductor substrate above the inversion doping area, wherein the gate structure comprises a gate dielectric layer and a gate located on the gate dielectric layer, impurity ions are doped in the gate, and the doping type in the gate is the same as that in the well area; a source area and a drain area are formed inside the semiconductor substrate at two sides of the gate structure, the doping type in the source area and the drain area is opposite to the type of the impurity ions in the well area, and the depth of the source area and the drain area is smaller than that of the well area and larger than that of the inversion doping area. The transistor formed by the method of the invention can prevent generation of flicker noise and improve the device performance.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

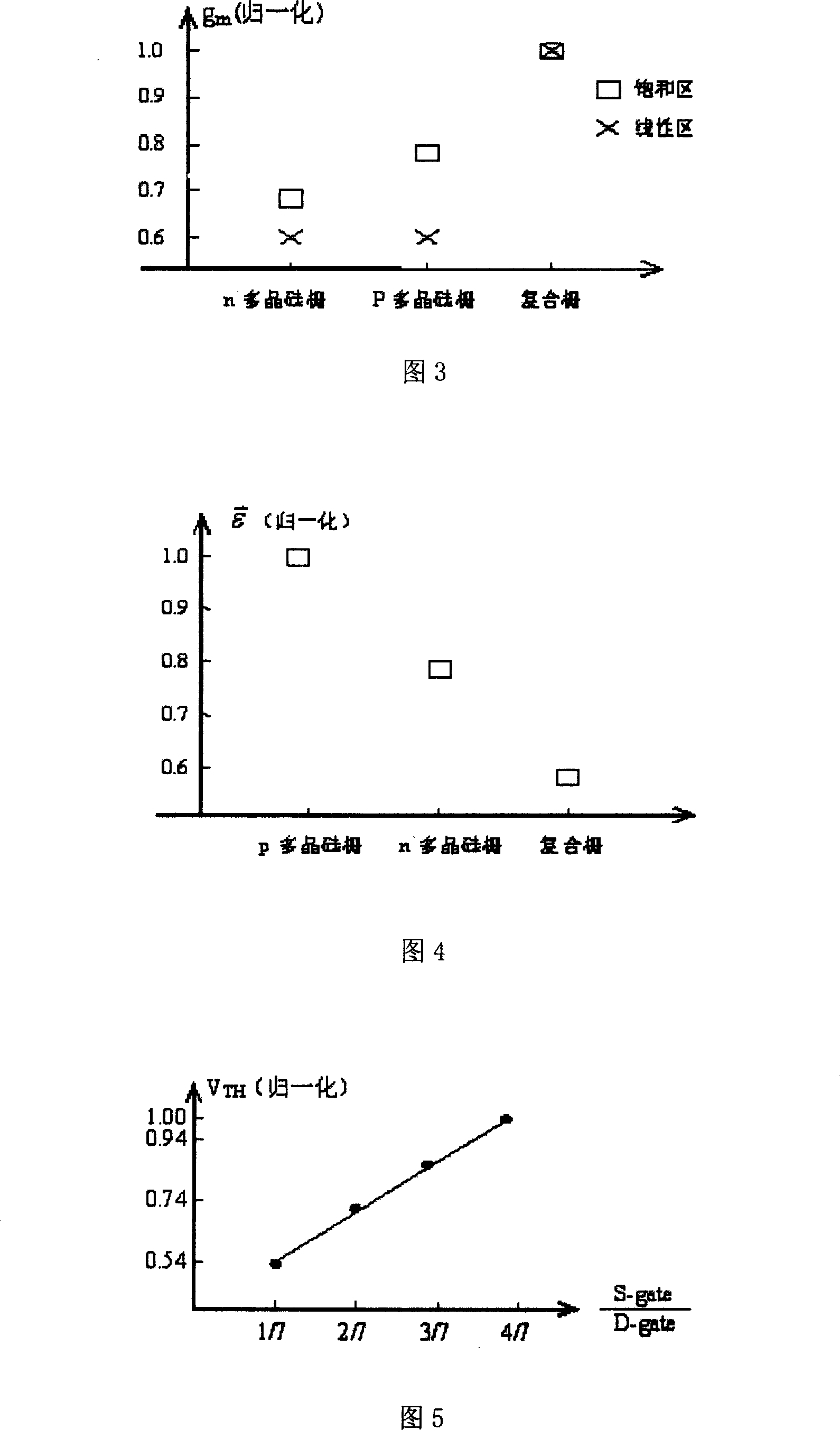

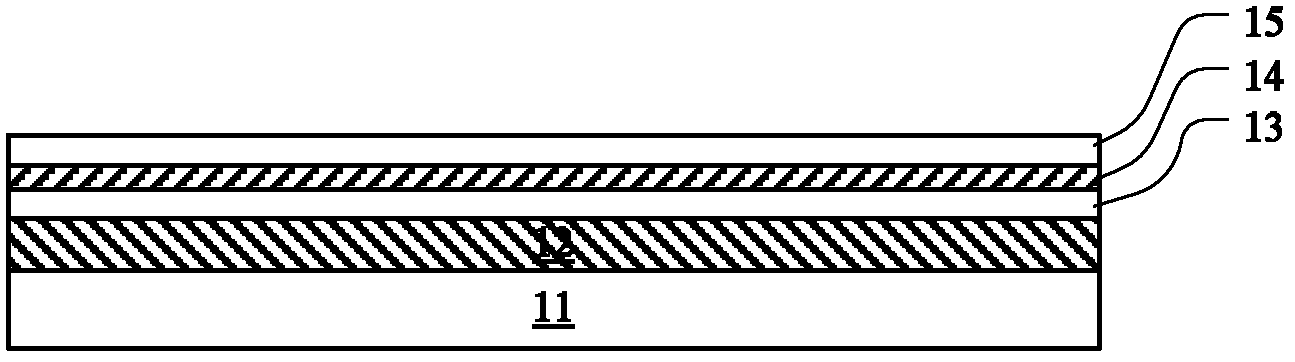

Homojunction combined gate field effect transistor

InactiveCN1953206AIncrease drive currentImprove transconductanceSemiconductor devicesDriving currentEngineering

The invention relates to a composite grid field effect transistor. Wherein, the grid, source, leak and substrate form the main body; the insulated layer is between grid and substrate; the groove is on the substrate between source and leak; the source extends shallow source extending area at the left end of groove; the grid extends shallow leak extending area at the right end; the invention is characterized in that the grid is composite grid and multi-crystal grid, while the left and right parts are different in conductive types; the left grid toward to source is P-type multi-crystal grid, while the left part toward leak is N-type multi-crystal grid. The invention can obtain radio MOSFET driving current, transconductance and cut-off frequency, and release the maximum field strength, thermal electronic effect and short-groove effect at the end of leak drift area.

Owner:ANHUI UNIVERSITY

MOSFET (metal oxide semiconductor field effect transistor) and manufacturing method thereof

ActiveCN102856201ASuppression of short channel effectsAdjust Threshold VoltageSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETField-effect transistor

The invention provides an MOSFET (metal oxide semiconductor field effect transistor) and a manufacturing method thereof. The MOSFET comprises a semiconductor substrate, a first insulating buried layer on the semiconductor layer, a back gate formed in a semiconductor layer on the first insulating buried layer, a second insulating buried layer on the first semiconductor layer, source / drain areas formed in a second semiconductor layer on the second insulating buried layer, a gate on the second semiconductor layer, and electric connection for the source / drain areas, the gate and the back gate. The back gate is located in one of the source / drain areas and below a groove area and not located below the other one of the source / drain areas. The electric connection includes a common conductive channel of the back gate and the source / drain areas. The short-channel channel inhibition effect is improved by the aid of the asymmetrical back gate of the MOSFET, and the area of a chip is reduced by the common conductive channel.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

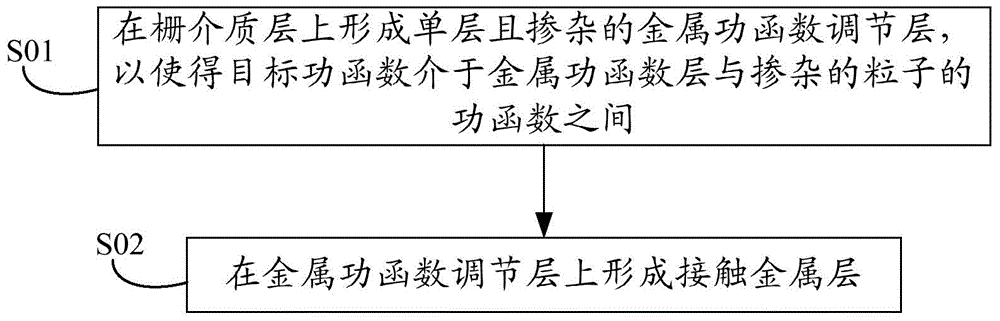

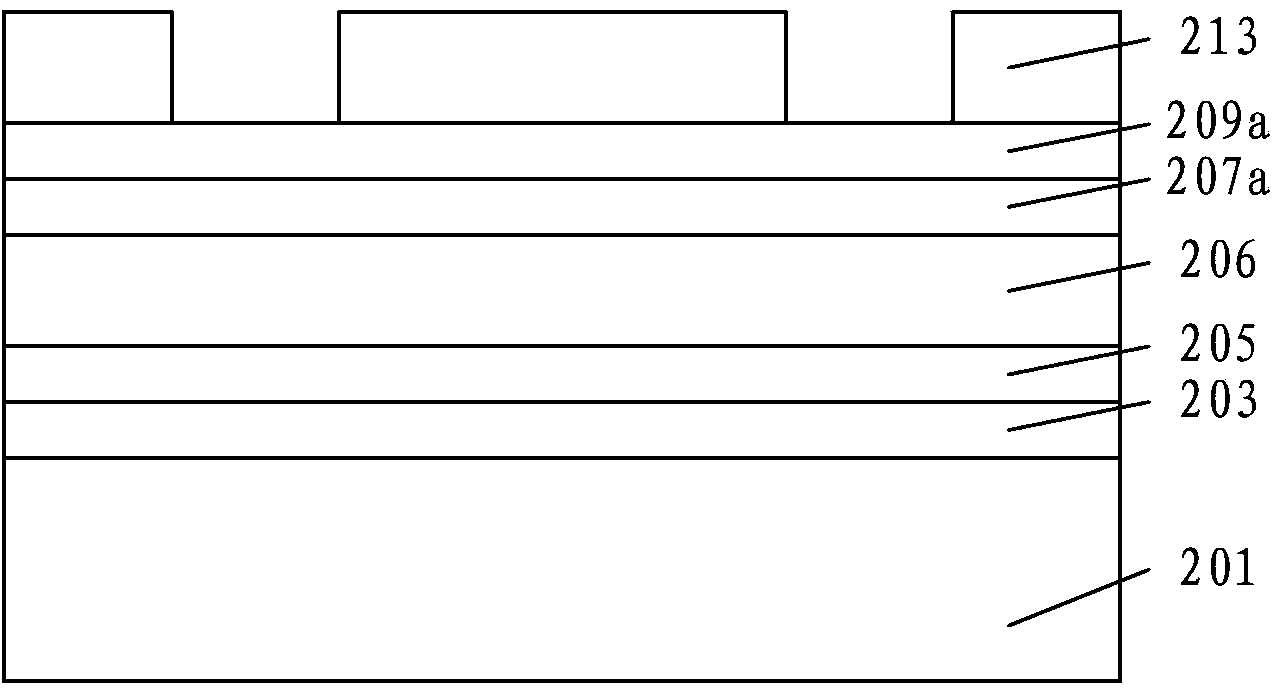

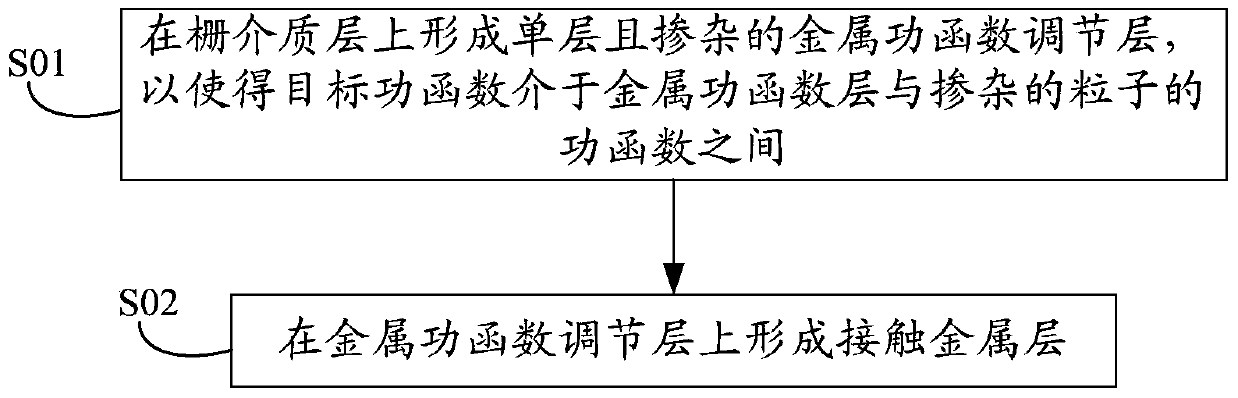

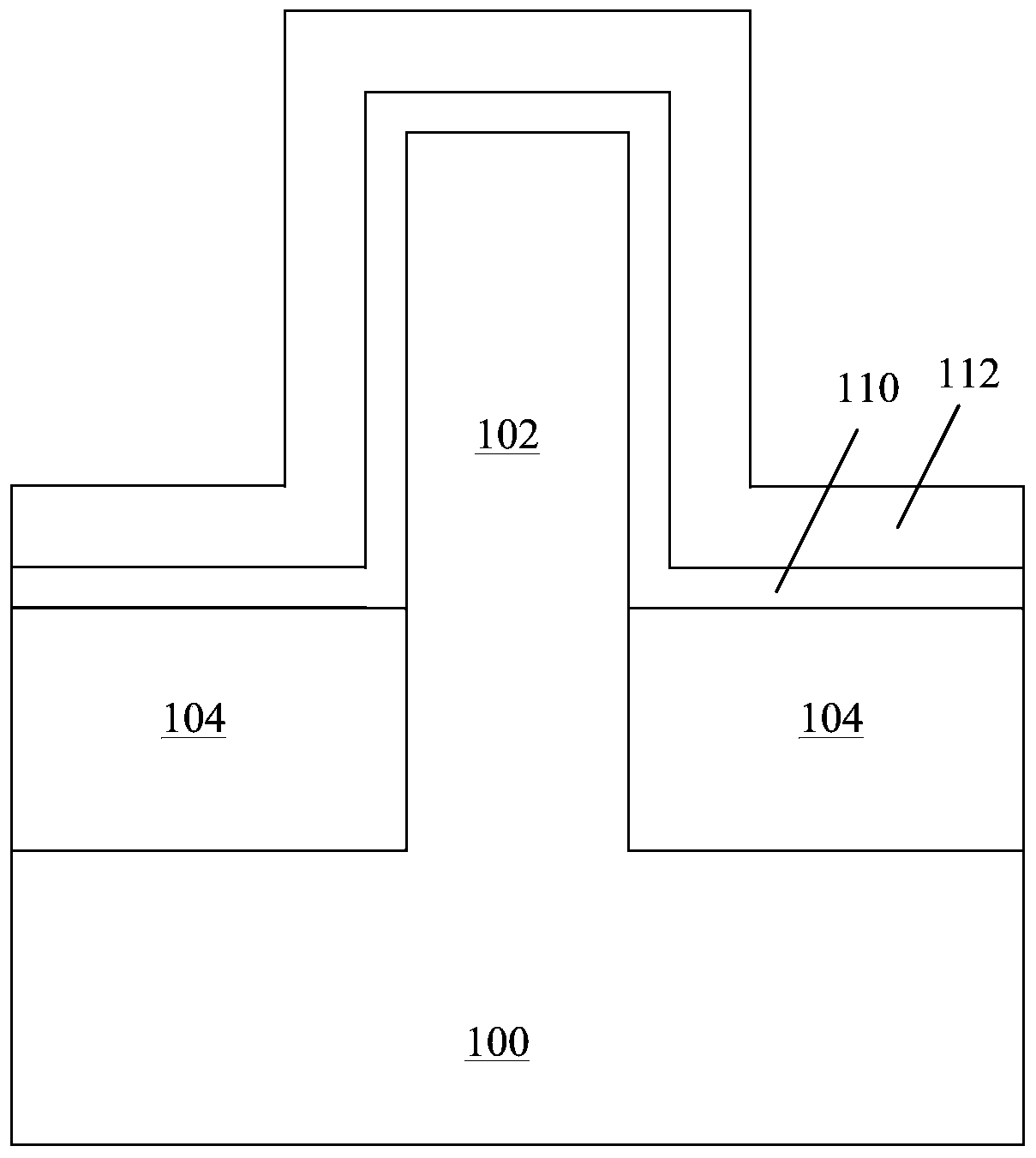

Gate and forming method thereof

ActiveCN105990403AAdjust Threshold VoltageEasy to adjustSemiconductor devicesGate dielectricWork function

The invention provides a gate forming method comprising the steps of forming a single doped metal work function adjustment layer on a gate dielectric layer to enable a target work function to be between the metal work function layer and a work function of doped particles, and forming other gate layers on the metal work function adjustment layer. Through the method, the threshold voltage can be adjusted easily, the process is simple and can be implemented without multiple metal gate layers, and the manufacturing cost is reduced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

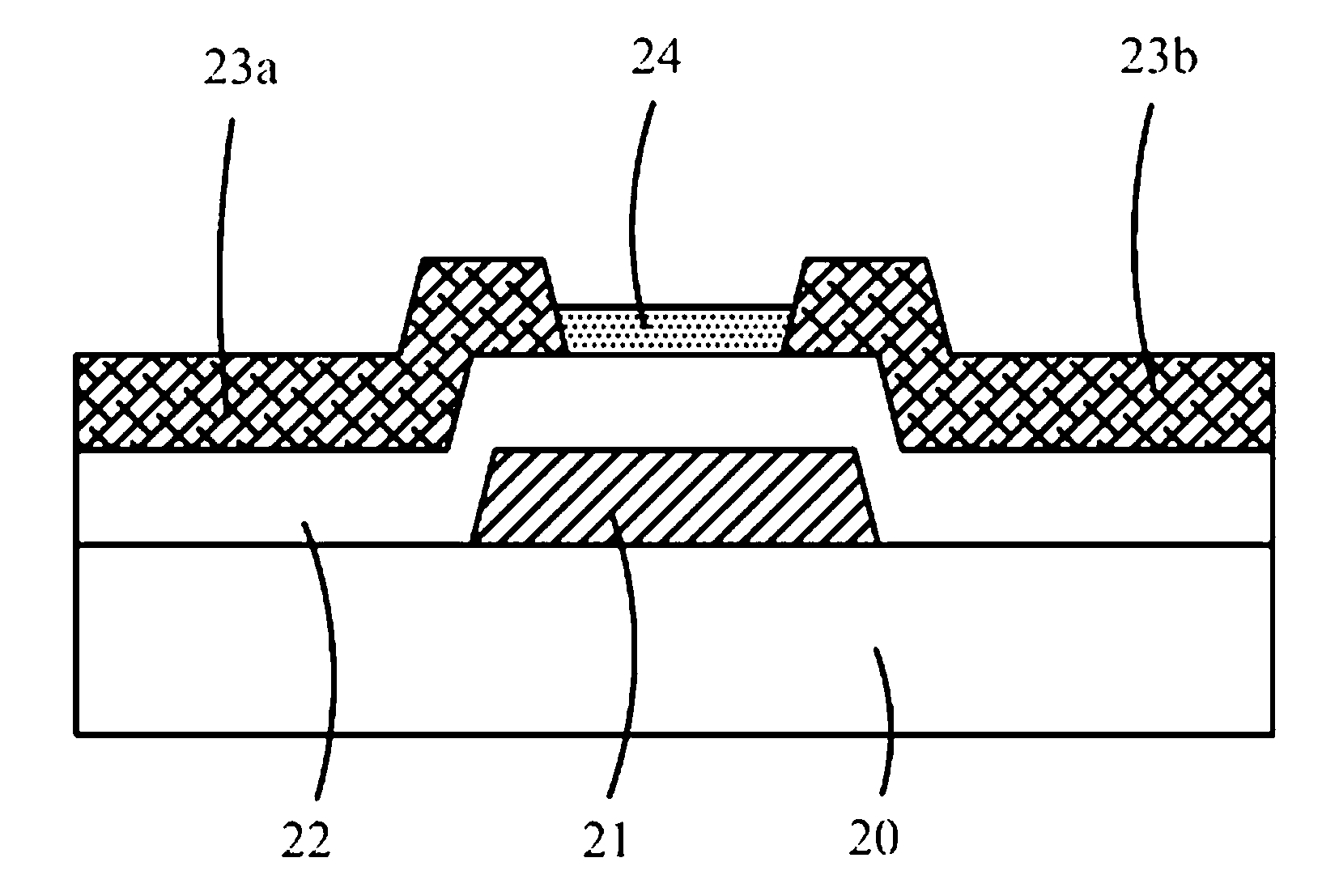

Method for forming MOS transistor

ActiveCN103632966AImproved adjustable range and stabilityImprove electrical performanceSemiconductor/solid-state device manufacturingSemiconductor devicesBody regionFiller metal

A method for forming an MOS transistor comprises providing a substrate; forming a back gate electrode, a back gate dielectric layer, a body region, a first functional layer and a front gate dielectric layer sequentially from the bottom surface of the substrate, the first functional layer being used for increasing the rate of migration of a carrier in a channel region; etching the front gate dielectric layer and the first functional layer and forming a first groove exposing a portion of the body region; conducting ion implantation on the first groove along the body region to form a heavily doped region; filling a metal layer in the first groove and forming a plug connected with the heavily doped region; and forming a second functional layer and a front gate on the surface of a front gate dielectric layer between the heavily doped regions sequentially from the bottom to the top, the second functional layer being used for reducing the leakage current of the channel region. The method for forming the MOS transistor can adjust the threshold voltage of the formed MOS transistor, improve the compatibility and matching rate of each MOS transistor in semiconductor devices and improve the performance of formed semiconductor devices.

Owner:SEMICON MFG INT (SHANGHAI) CORP

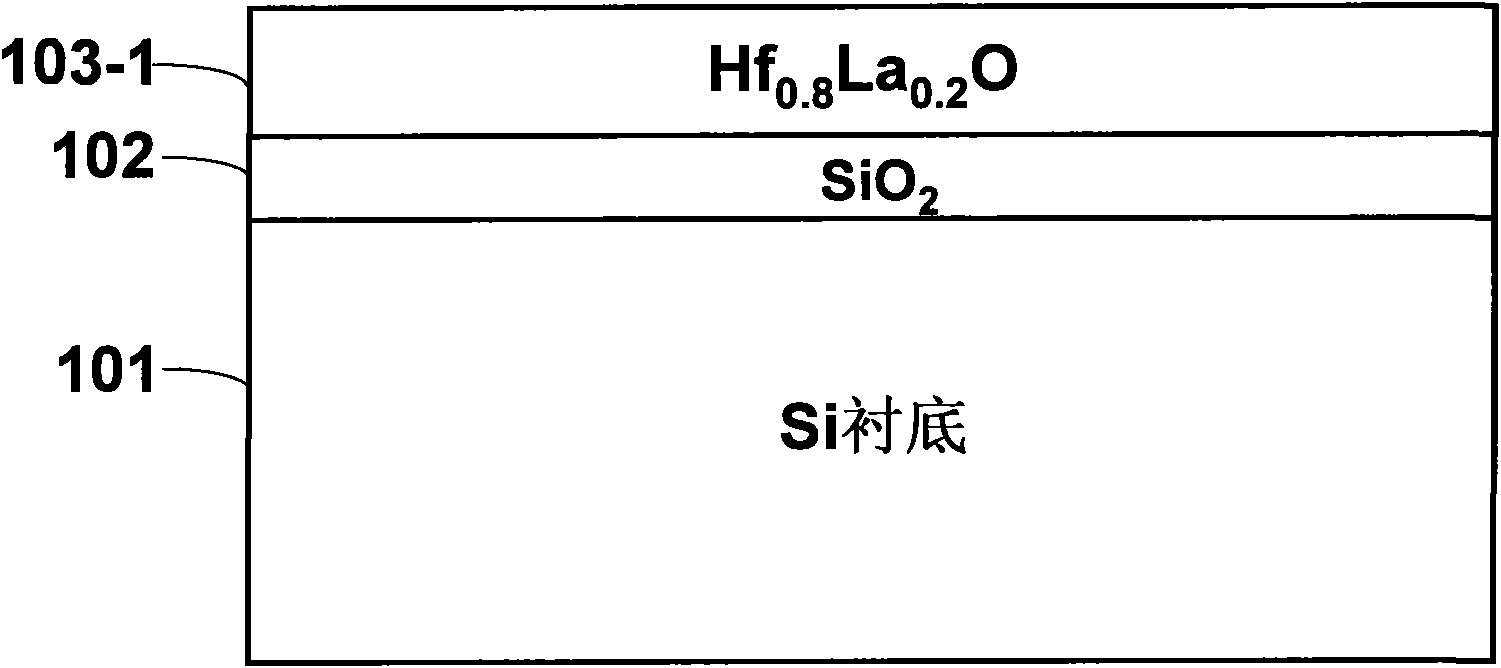

Method for forming stack gate of CMOS (Complementary Metal-Oxide-Semiconductor) device and stack gate sturcture

InactiveCN102074574AAdjust Threshold VoltageImprove channel mobilityTransistorOxide semiconductorCMOS

The invention provides a gate medium structure of an MOS ( Metal-Oxide-Semiconductor) device, which comprises a boundary layer film formed on the surface of a semiconductor substrate and at least two layers of insulating films formed on the surface of the boundary layer film, wherein each of the at least two layers of insulating films has element components and concentrations, which are different from that of other adjacent insulating films, the boundary layer film and the at least two layers of insulating films are processed by an optimized annealing process, and the optimized annealing process is related to the element components and the concentrations of the boundary layer film and the at least two layers of insulating films so as to realize ideal distribution of the element components and the concentrations. In the invention, the gate medium structure of the MOS device is formed by depositing multiple layers of different material components or different concentrations of films in a certain order, and then, the ideal distribution of all element components and the concentrations in the gate medium structure is realized by the optimized annealing process.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

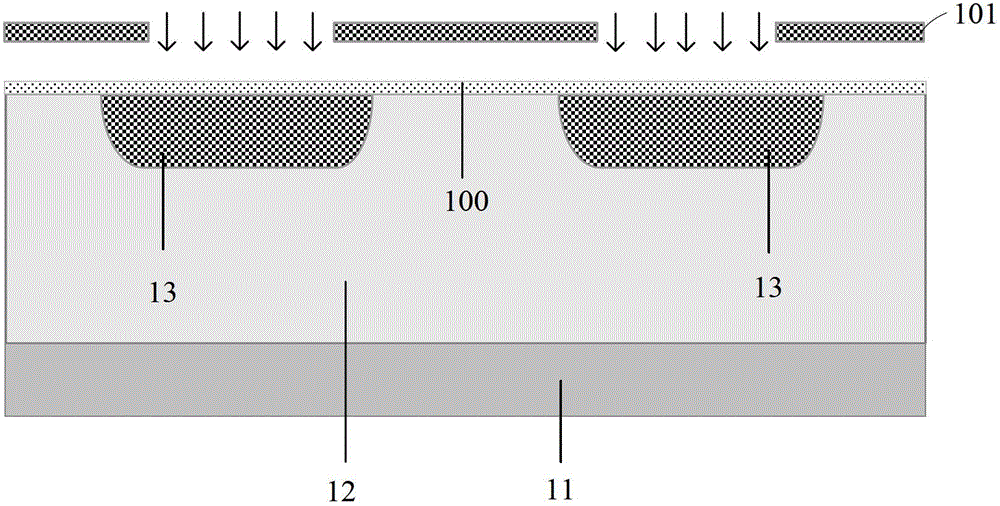

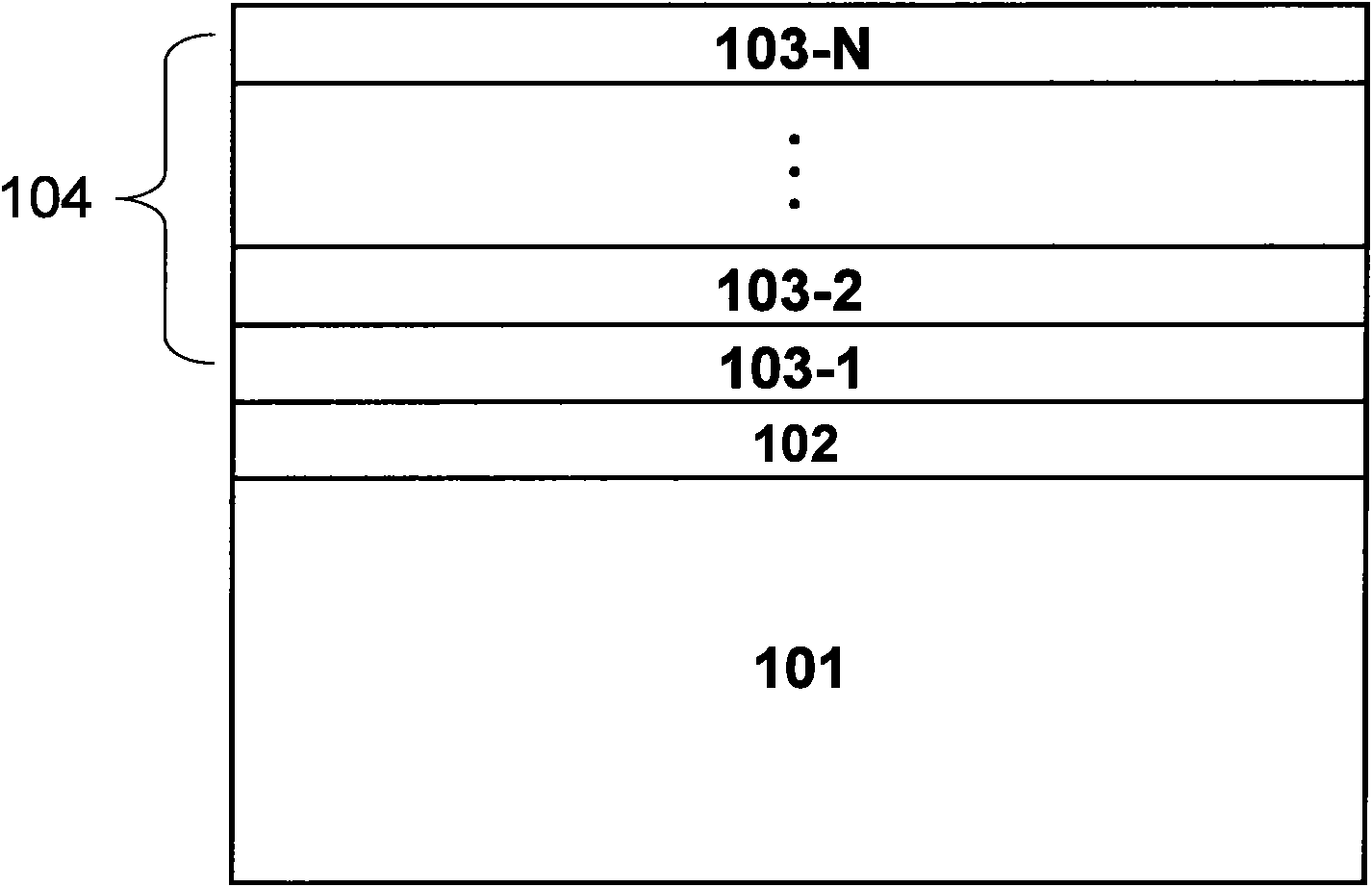

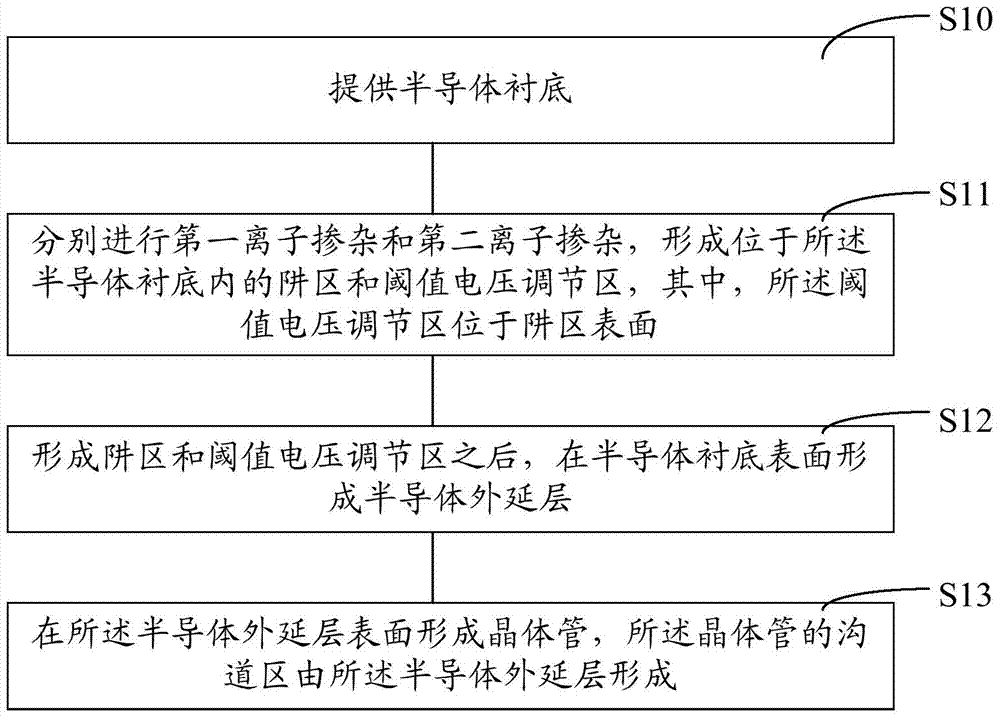

Method for forming semiconductor device

ActiveCN104733308AHigh carrier mobilityQuality improvementSemiconductor/solid-state device manufacturingPower semiconductor deviceCarrier scattering

The invention relates to a method for forming a semiconductor device, comprising the following steps: providing a semiconductor substrate; carrying out first ion doping and second ion doping to form a well region and a threshold voltage regulation region disposed in the semiconductor substrate, wherein the threshold voltage regulation region is disposed on the surface of the well region; forming a semiconductor epitaxial layer on the surface of the semiconductor substrate after the formation of the well region and the threshold voltage regulation region; and forming a transistor on the surface of the semiconductor epitaxial layer, wherein the channel region of the transistor is formed by the semiconductor epitaxial layer. According to the method for forming a semiconductor device, the semiconductor epitaxial layer, as the channel region of the transistor, avoids lattice damage caused by ion doping. Moreover, the semiconductor epitaxial layer used for forming the channel region is not doped or is lightly doped with boron. Thus, carrier scattering is reduced, the carrier migration rate of the transistor is high, and the device performance is superior.

Owner:SEMICON MFG INT (SHANGHAI) CORP

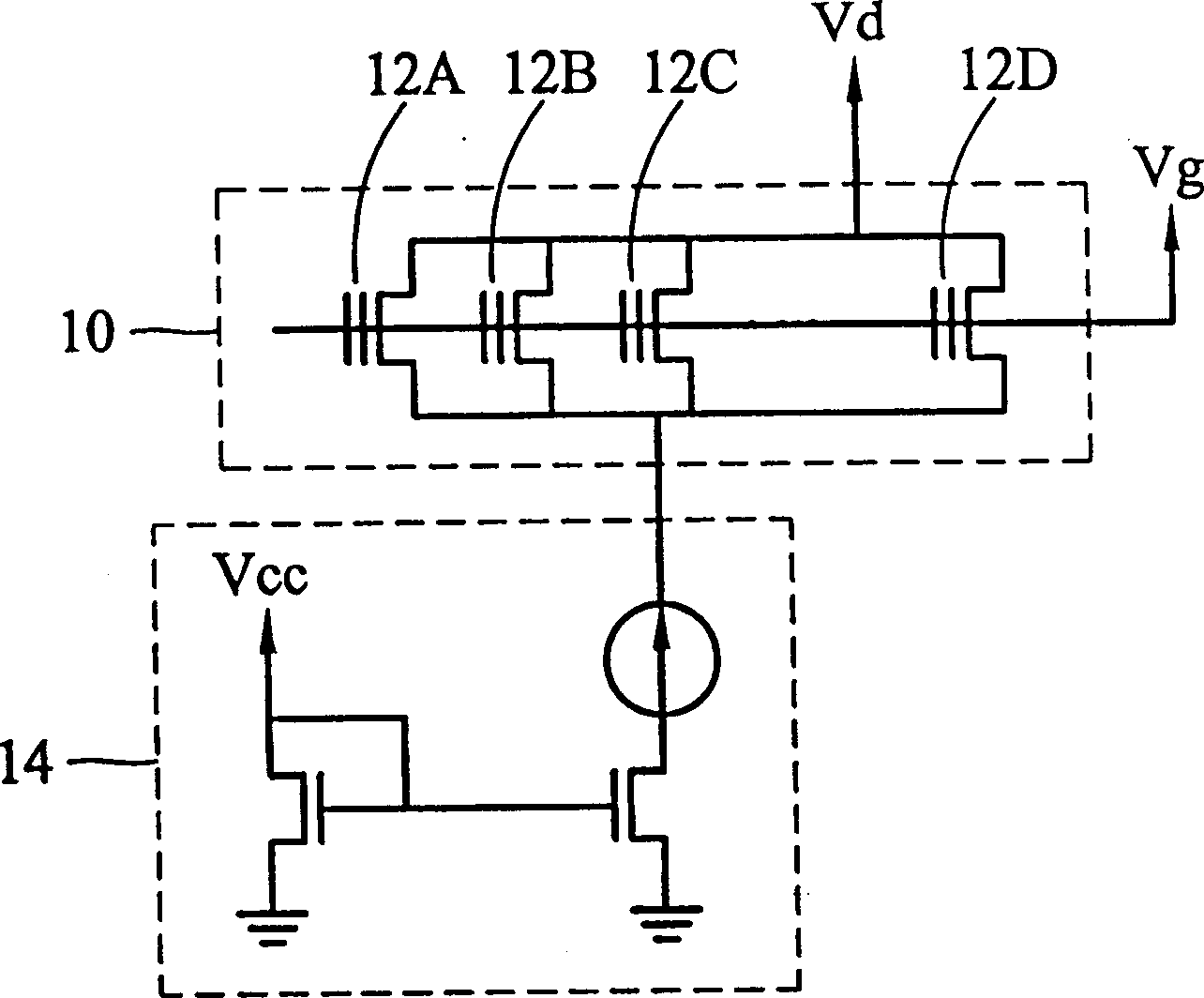

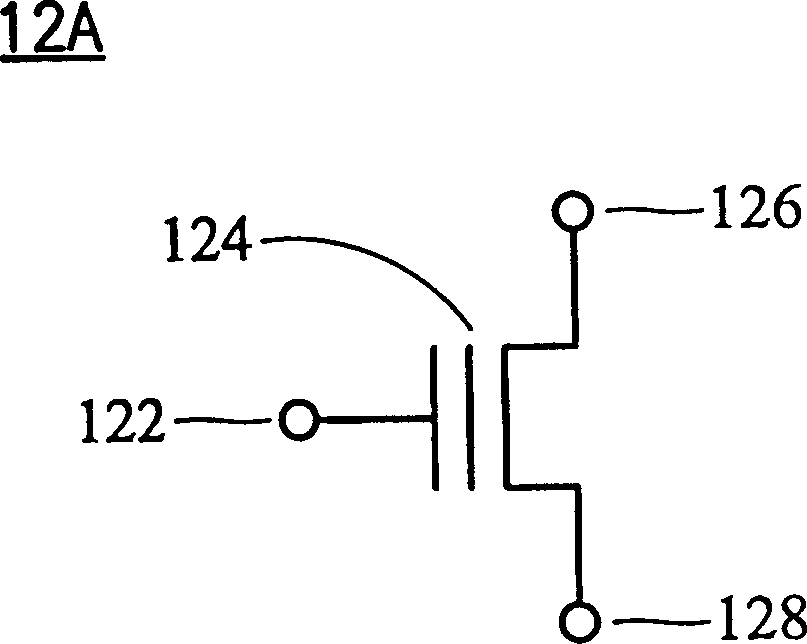

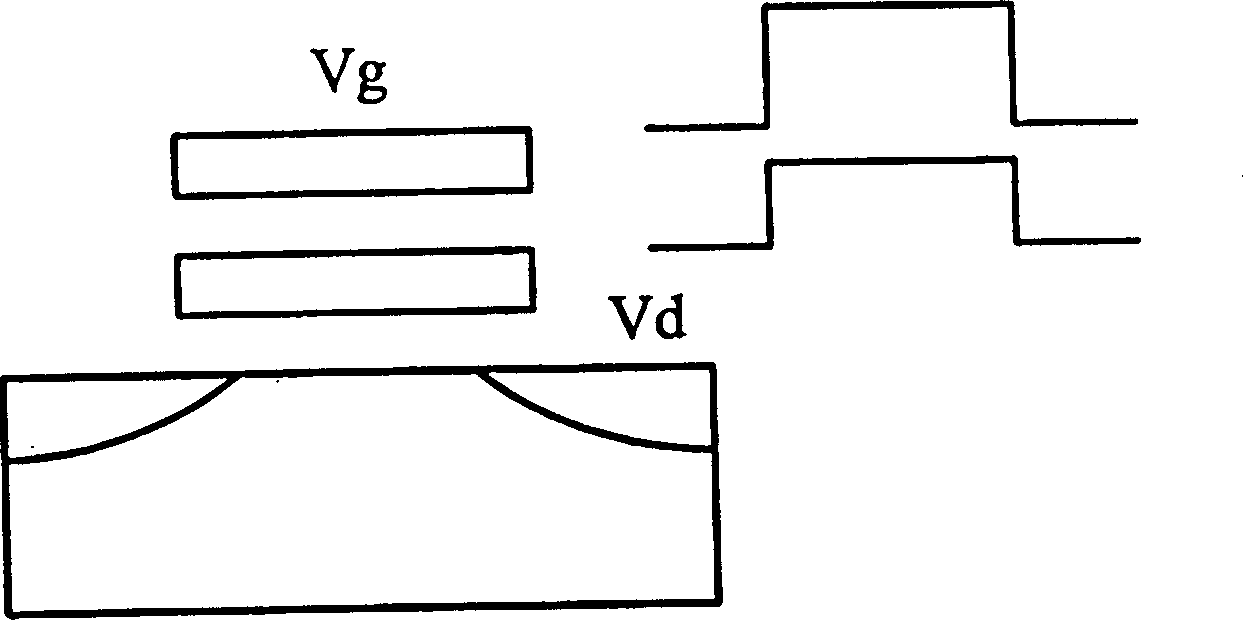

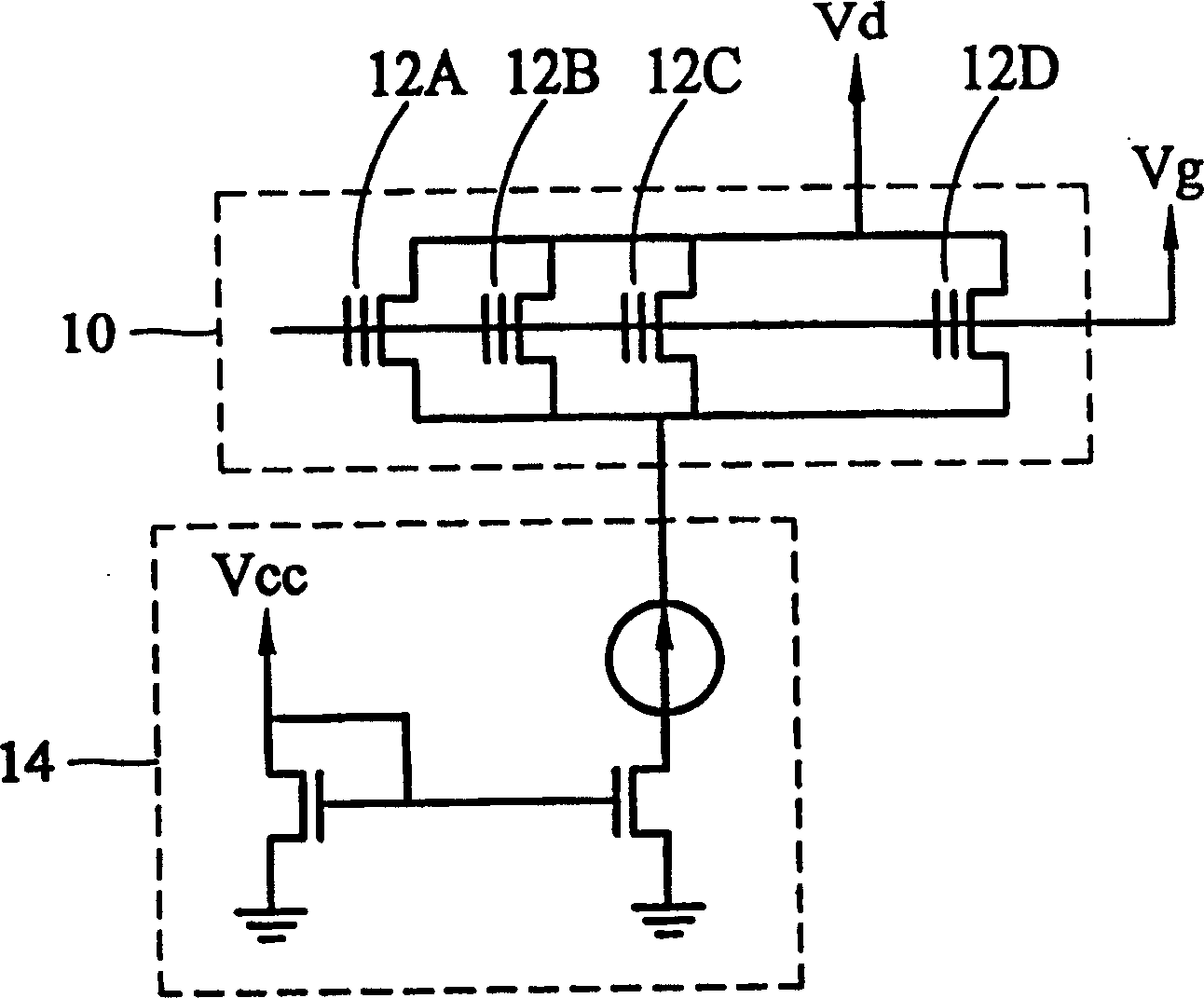

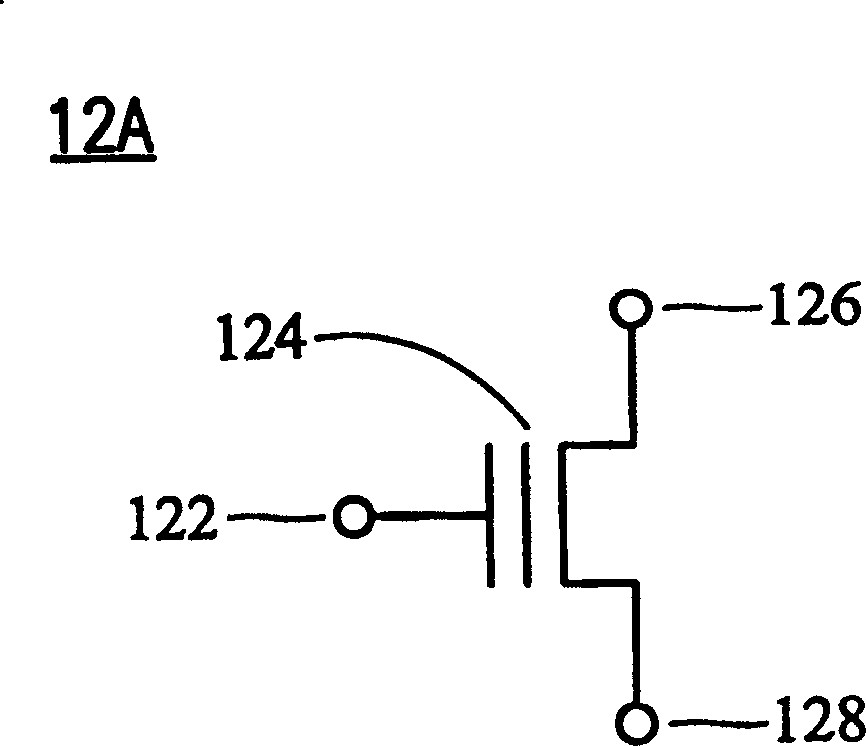

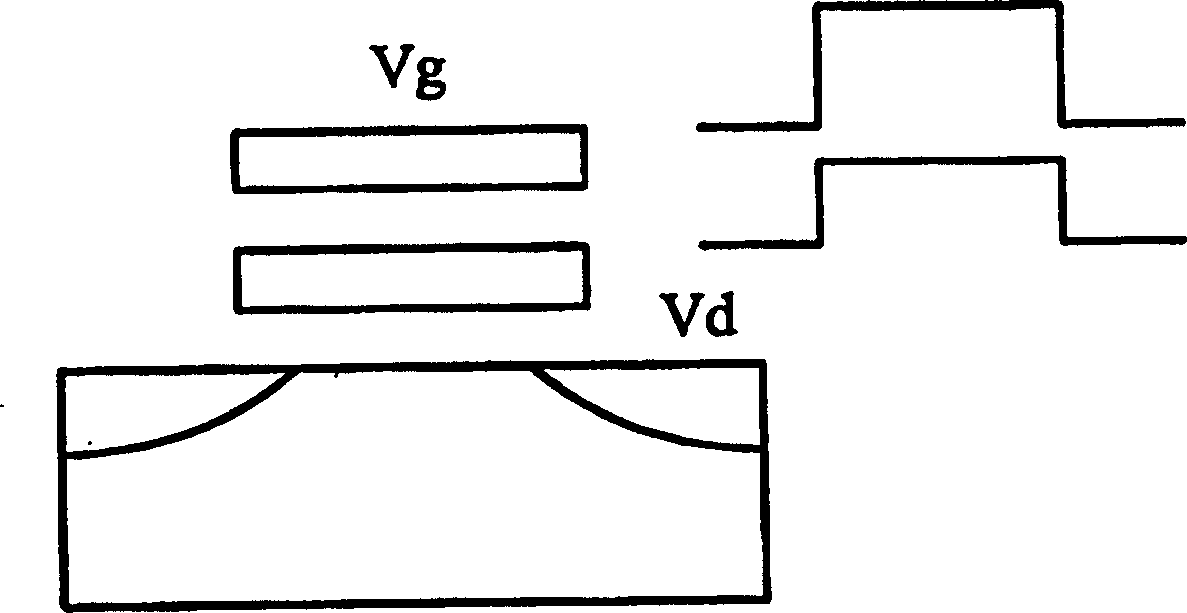

Adjusting device and method for flash memory array after erasion

InactiveCN1448955AReduce the numberAdjust Threshold VoltageRead-only memoriesCritical voltageConstant current source

The regulator suitable for memory array with several flash memory units, each of which includes one control grid, one floating grid, one source and one drain. The regulator includes one drain power source, constant current source and control grid source. The drain power source provides one positive voltage to the drain of the flash memory unit, the constant current source provides a source current to the source of the flash memory unit, and the control grid source provides a gradually raised grid voltage to the control grid of the flash memory unit to control the source current to the flashmemory unit and gradually change the critical voltage value of the flash memory unit.

Owner:MACRONIX INT CO LTD

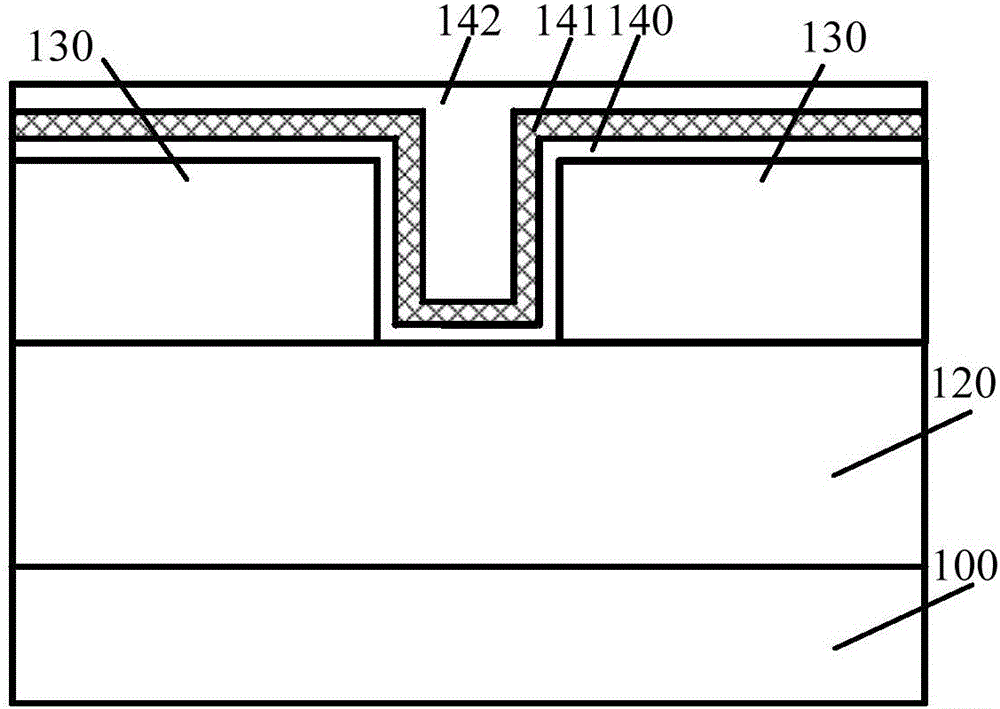

Formation method of semiconductor device

InactiveCN104064452AWon't hurtIntegrity guaranteedSemiconductor/solid-state device manufacturingSemiconductor devicesWork functionDielectric layer

Disclosed is a formation method of a semiconductor device. The method comprises: providing a semiconductor substrate, and forming an isolation structure in the substrate, wherein the isolation structure isolates the substrate to a first active area and a second active area, and the types of the first active area and the second active area are opposite; forming a high-k dielectric layer and a conducting layer on the high-k dielectric layer on the substrate, defining the conducting layer disposed in the first active area as a first conducting layer, and defining the conducting layer disposed on the second active area as a second conducting layer; carrying out work function adjustment on the first conducting layer and / or the second conducting layer; and after the work function adjustment is carried out, patterning the first conducting layer, the second conducting layer and the high-k dielectric layer, and forming a first grid electrode disposed in the first active area, a first high-k dielectric layer disposed below the first grid electrode, a second grid electrode disposed in the second active area and a second high-k dielectric layer disposed below the second grid electrode. According to the invention, the work function adjustment is carried out on the first conducting layer and / or the second conducting layer, an etching process is unnecessary, and the high-k dielectric layer is not damaged.

Owner:SEMICON MFG INT (SHANGHAI) CORP

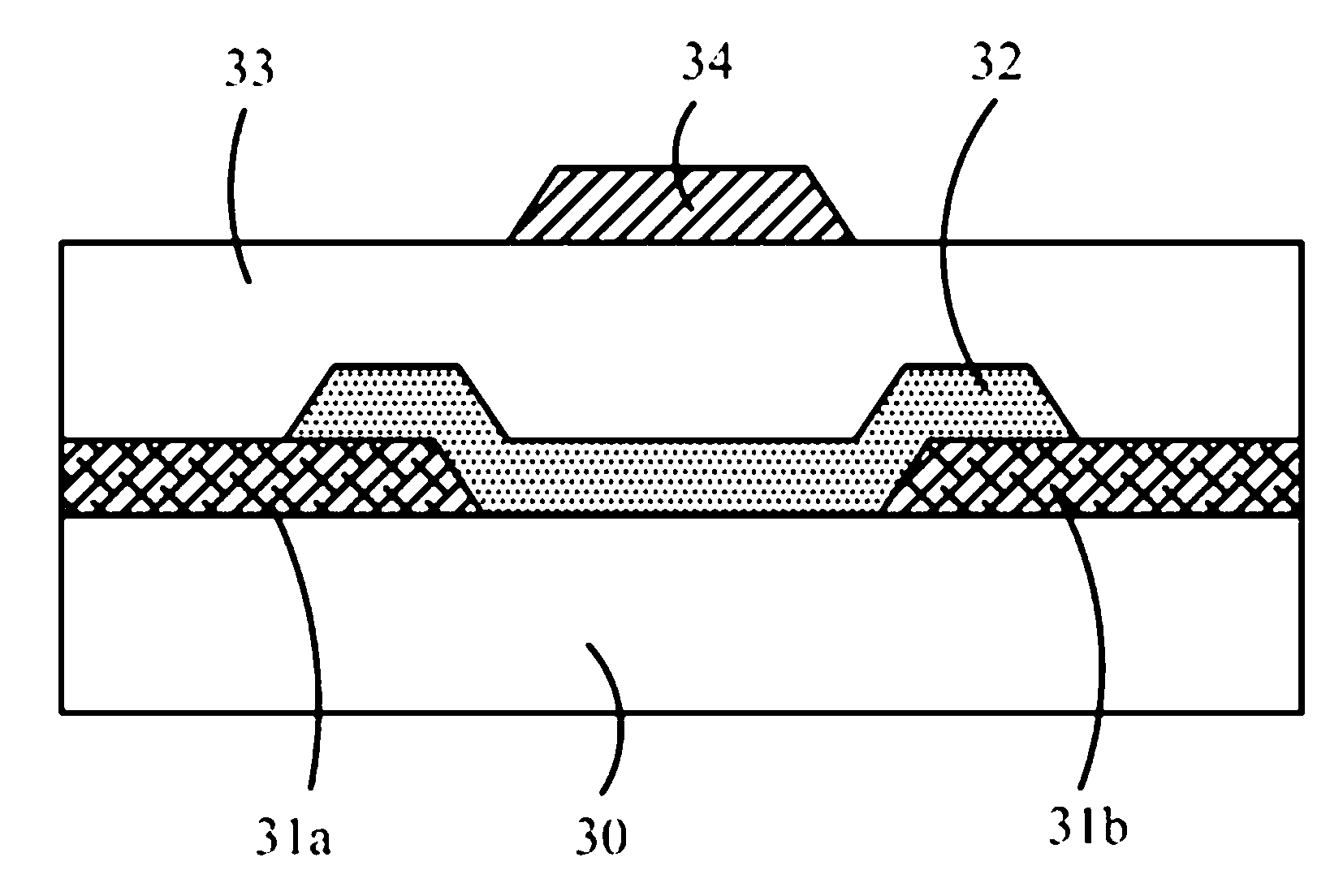

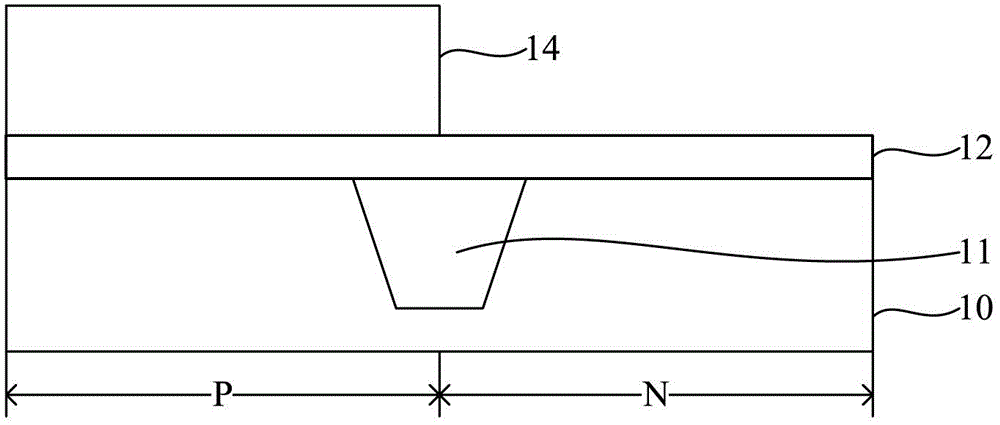

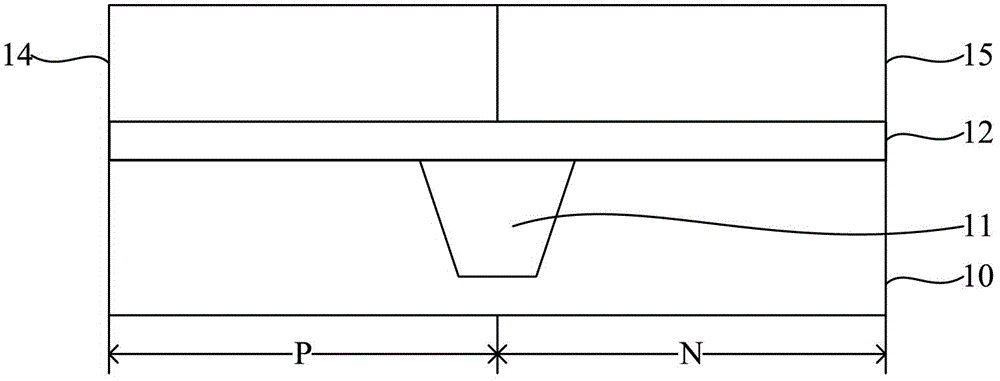

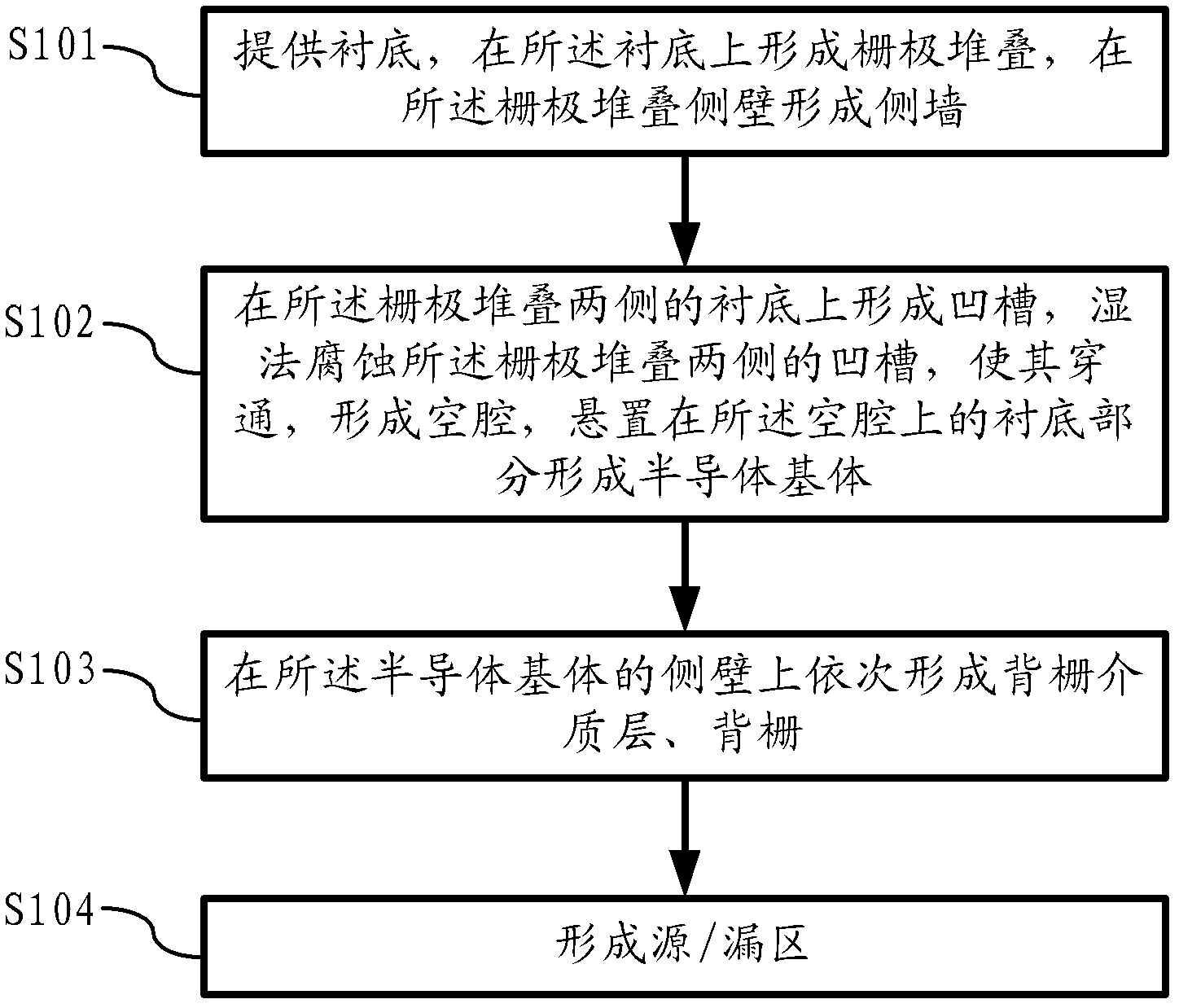

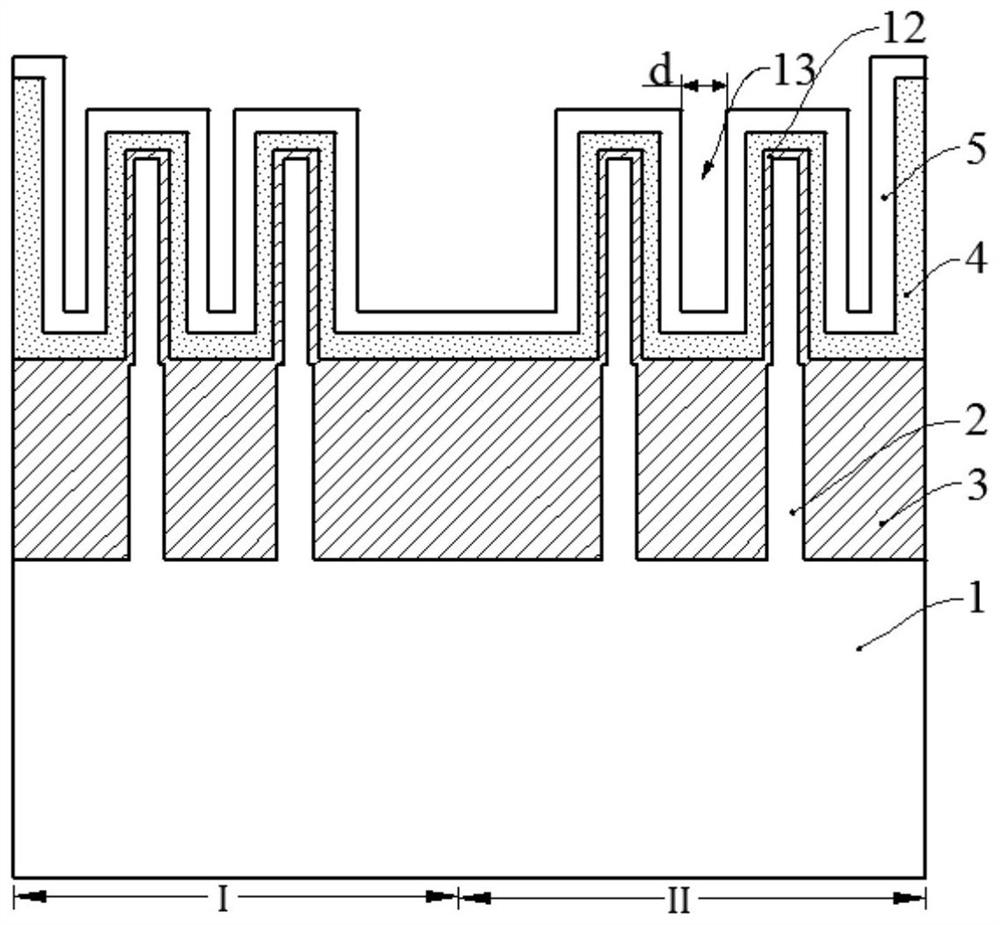

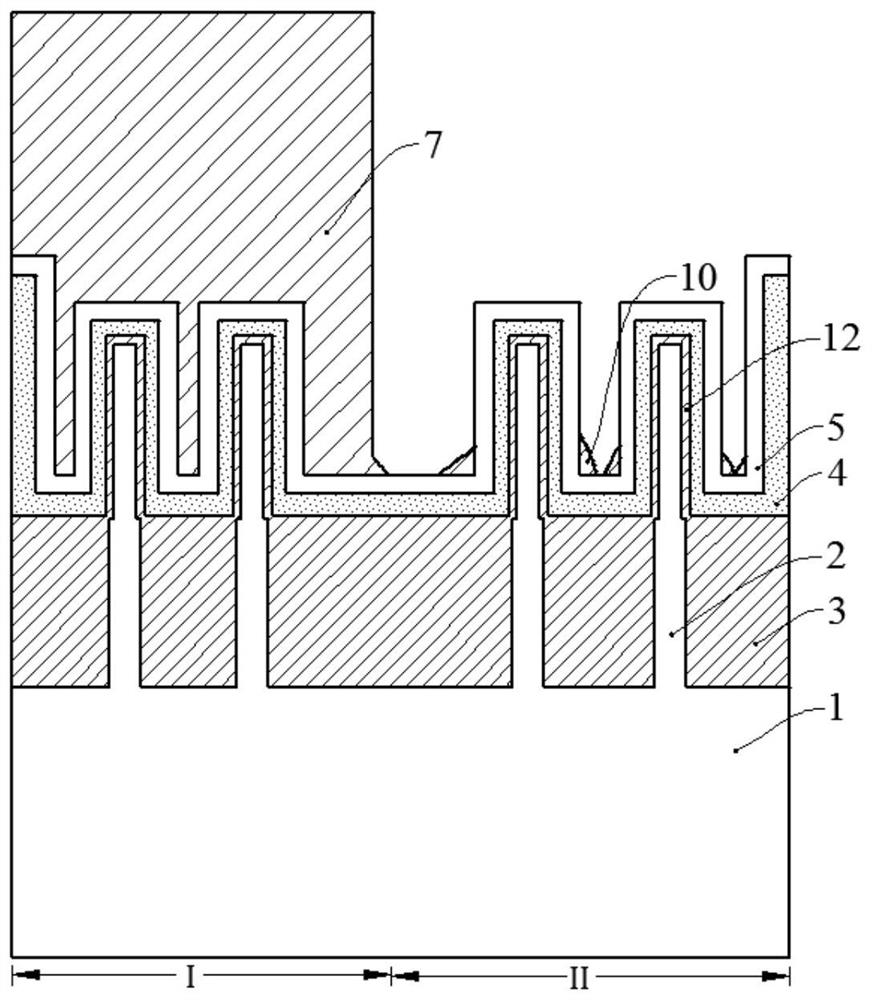

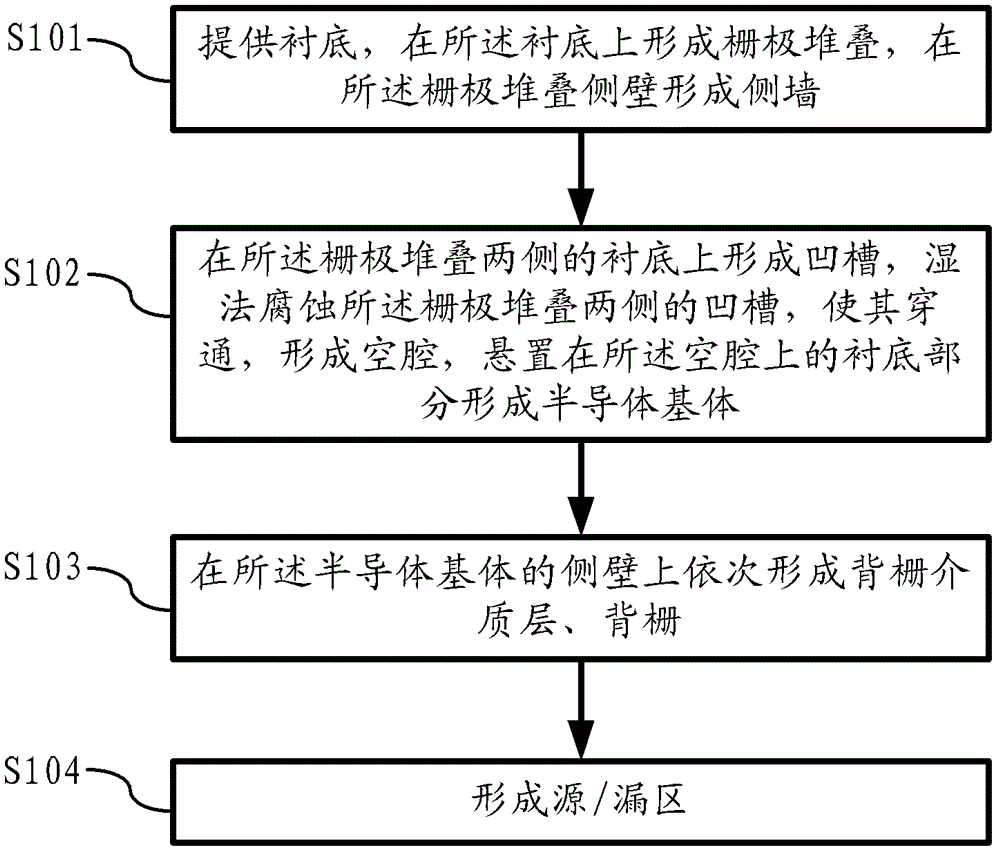

Semiconductor structure and preparation method thereof

ActiveCN102856360ASimple processLow costSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceShort-channel effect

The invention provides a semiconductor structure. The structure comprises a substrate, a semiconductor substrate, back gate dielectric layers, back gates, cavities, a gate stack, side walls and source / drain regions, wherein the gate stack is arranged on the semiconductor substrate; the side walls are arranged on the side walls of the gate stack; the source / drain regions are embedded in the semiconductor substrate and are arranged on the two sides of the gate stack; the cavities are embedded in the substrate; the semiconductor substrate is suspended above the cavities; in the direction of the gate length, the middle thickness of the semiconductor substrate is greater than the thickness of the two sides; in the direction of the gate width, the semiconductor substrate is connected with the substrate; the back gate dielectric layers are arranged on the side walls of the semiconductor substrate; and the back gates are arranged on the side walls of the back gate dielectric layers. Correspondingly, the invention also provides a preparation method of the semiconductor structure. The semiconductor structure and the preparation method are beneficial to suppressing the short channel effect, adjusting the threshold voltage of the semiconductor device, improving the device performances, reducing the cost and simplifying the process.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

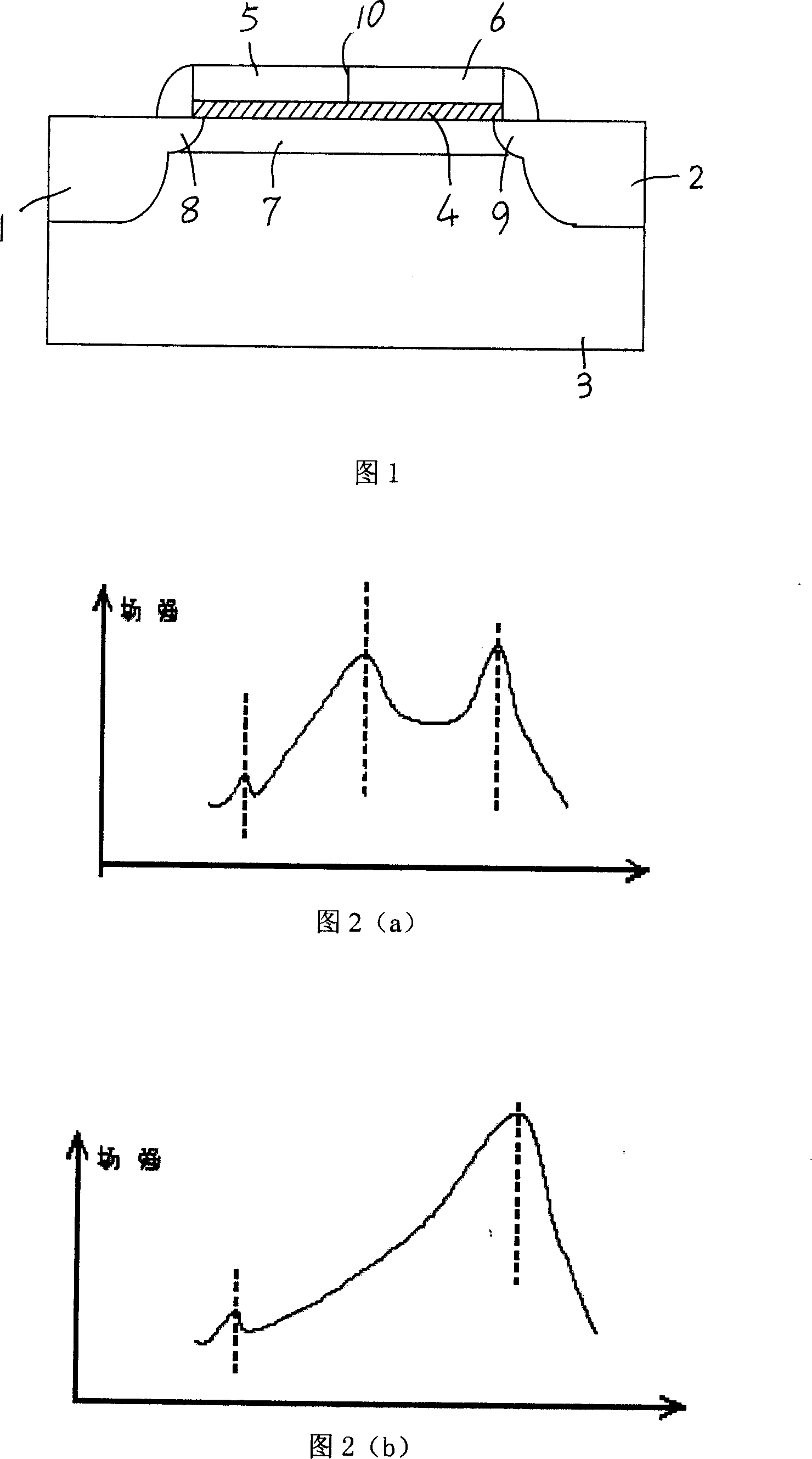

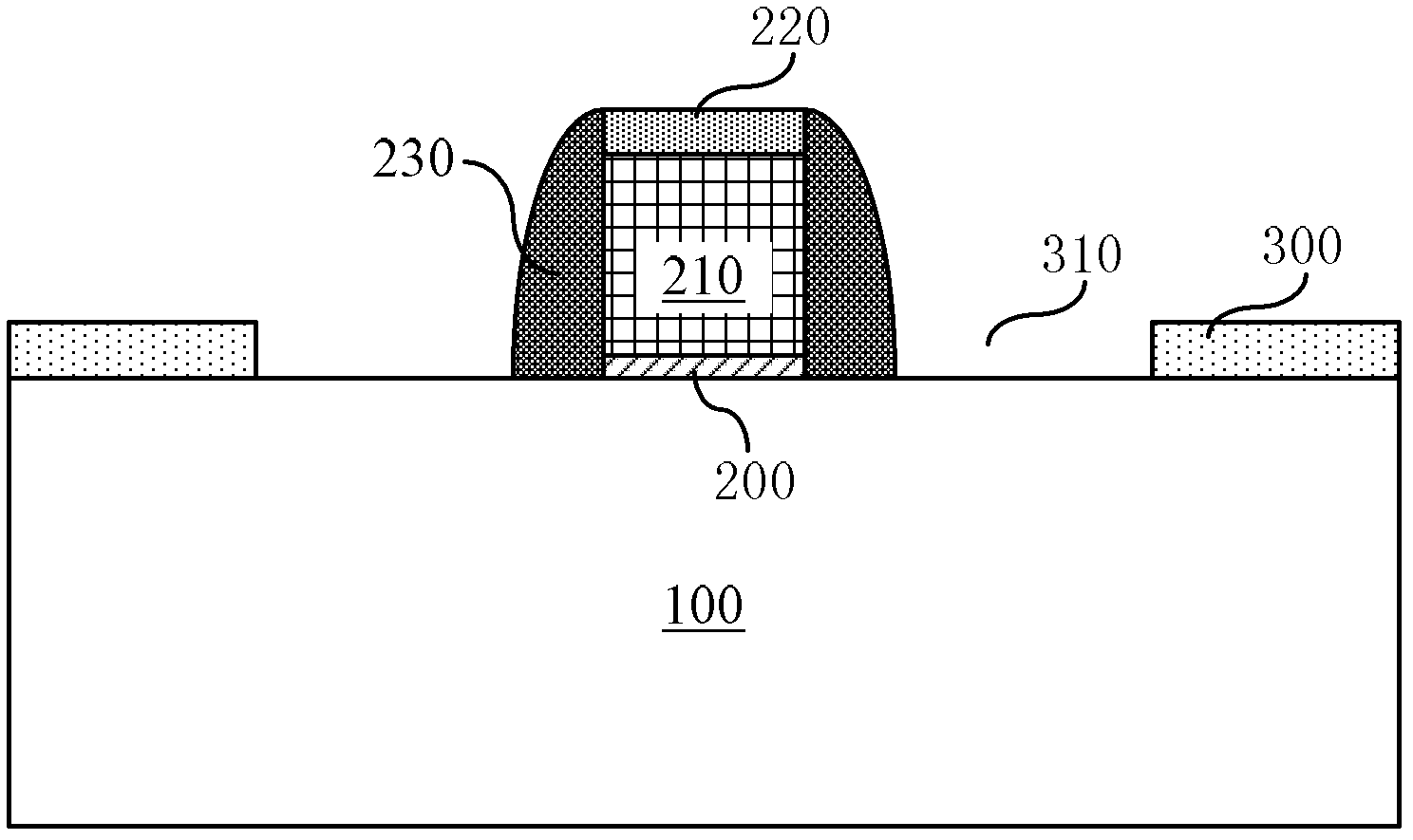

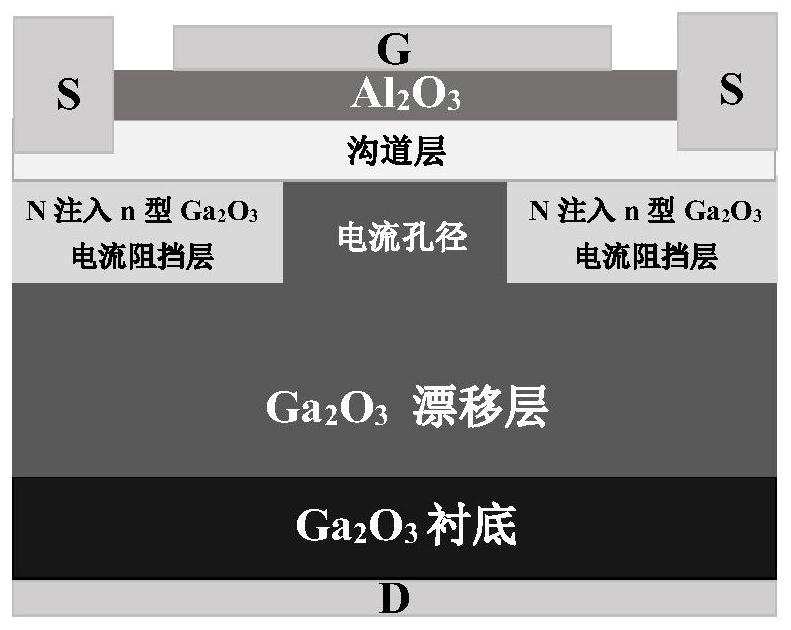

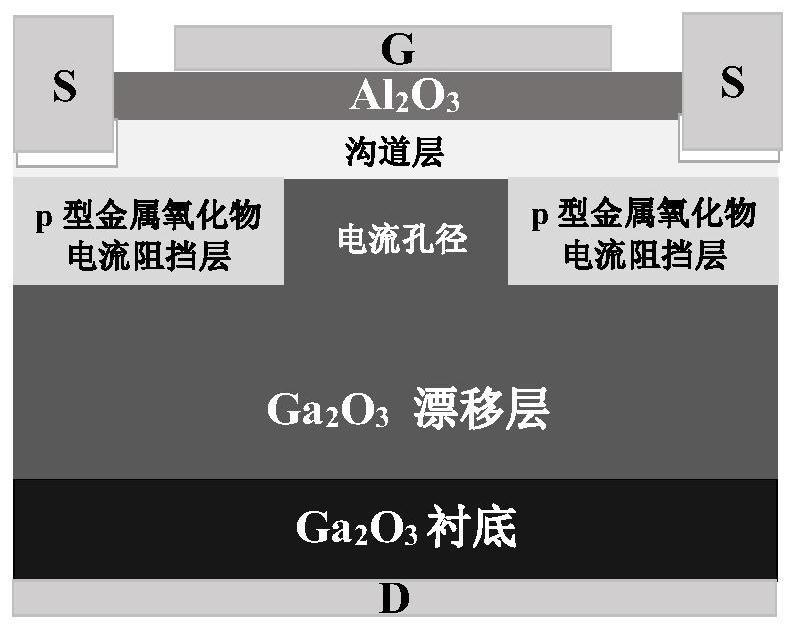

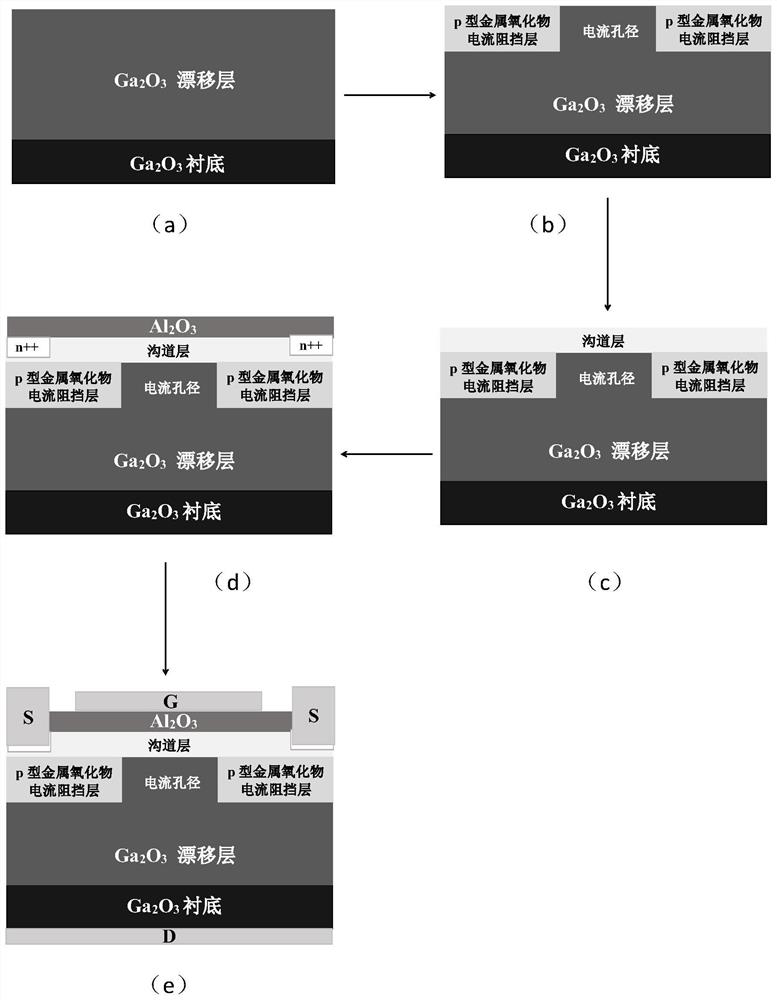

P-type metal oxide current blocking layer Ga2O3 vertical metal oxide semiconductor field effect transistor

ActiveCN113421914AImprove breakdown voltageAdjust Threshold VoltageSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsOxide semiconductor

The invention discloses a p-type metal oxide current barrier layer Ga2O3 vertical metal oxide semiconductor field effect transistor, which mainly solves the problem of low breakdown voltage caused by incapability of forming a pn junction in the prior art. The device comprises a drain electrode (1), a gallium oxide substrate (2), a gallium oxide drift layer (3), a gallium oxide channel layer (4), a gate dielectric layer (5) and a gate electrode (6) from bottom to top. Current blocking layers (7) are arranged on the two sides of the gallium oxide drift layer (3), a current aperture (8) is formed in the middle of the gallium oxide drift layer (3), and source electrodes (9) are arranged on the two sides of the gallium oxide channel layer (4) and the gate dielectric layer (5). The current blocking layer (7) is made of a p-type metal oxide material doped with boron element, and forms two heterojunctions with the gallium oxide drift layer (3) and the gallium oxide channel layer (4) respectively. The breakdown voltage of the device is greatly improved, and the device can be applied to high-power devices of industrial power and automobile power systems.

Owner:XIDIAN UNIV

Adjusting device and method for flash memory array after erasion

InactiveCN1225741CReduce the numberAdjust Threshold VoltageRead-only memoriesEngineeringCritical voltage

The regulator suitable for memory array with several flash memory units, each of which includes one control grid, one floating grid, one source and one drain. The regulator includes one drain power source, constant current source and control grid source. The drain power source provides one positive voltage to the drain of the flash memory unit, the constant current source provides a source current to the source of the flash memory unit, and the control grid source provides a gradually raised grid voltage to the control grid of the flash memory unit to control the source current to the flash memory unit and gradually change the critical voltage value of the flash memory unit.

Owner:MACRONIX INT CO LTD

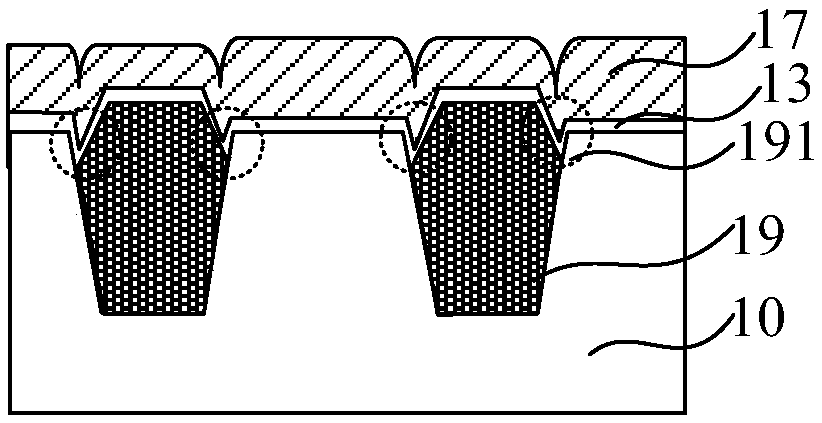

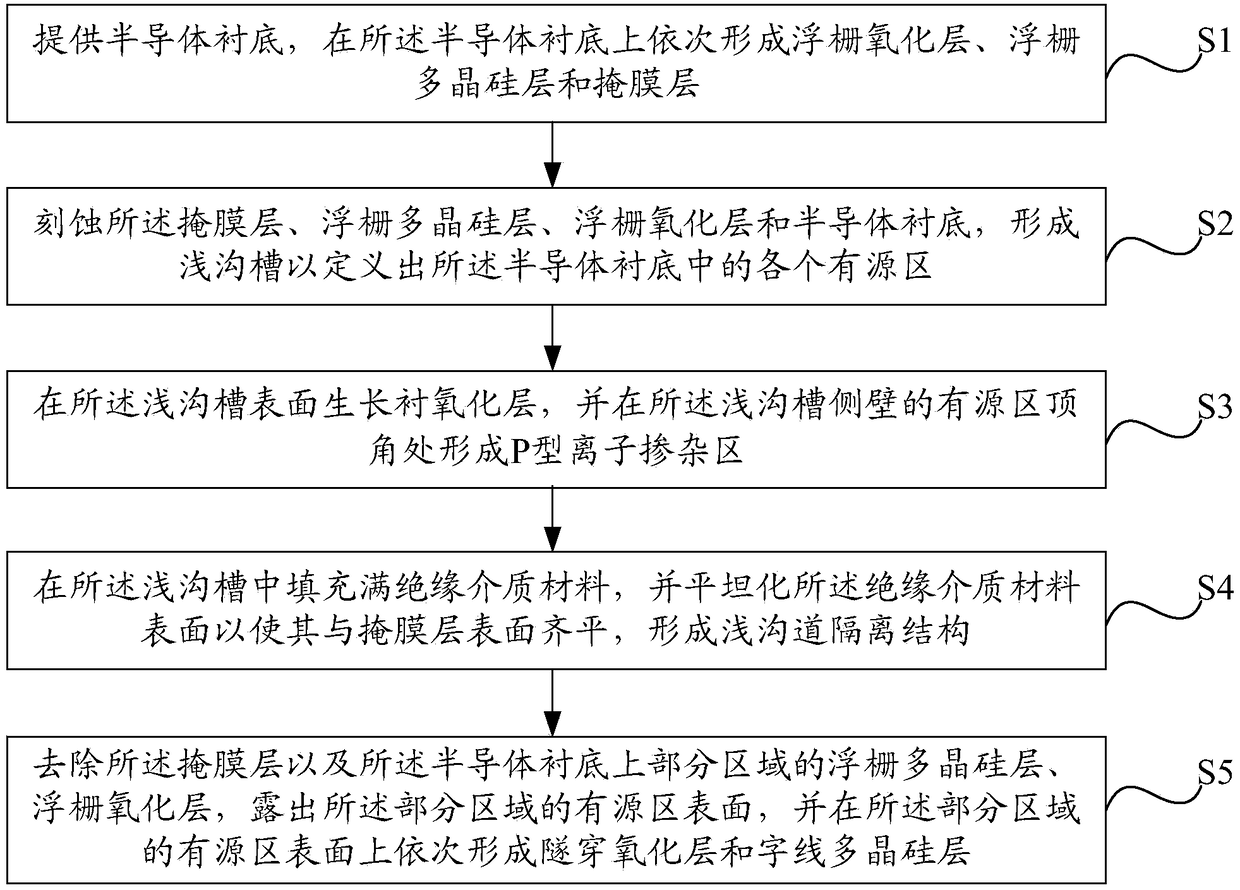

Flash memory device and manufacturing method thereof

ActiveCN105826273BImprove compactnessImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingPhysical chemistryIon implantation

The invention provides a flash memory device and a manufacturing method thereof. After the lining oxide layer is formed on the side wall of the shallow trench, P-type ion implantation is performed on the top corner of the active region of the side wall of the shallow trench to form P-type ion doping. area, to effectively improve the density of the liner oxide layer on the sidewall of the shallow trench, and to make the active area and the top boundary of the shallow trench isolation structure amorphized, with good corrosion resistance, which greatly reduces the impact of subsequent processes on the active area and the shallow trench isolation structure. The loss at the top of the top boundary of the shallow trench isolation structure reduces the depth of the pit at the top of the shallow trench isolation structure, reduces the distortion of the word line polysilicon layer formed subsequently and increases its height, and improves the narrow width effect. The off-state leakage current of the subsequently formed word line transistor is reduced and the threshold voltage thereof is increased, thereby increasing the program or program disturbance tolerance of the flash memory device. At the same time, the reliability and insulation of the subsequently formed shallow trench isolation structure are improved, and electric leakage of the shallow trench isolation structure is effectively prevented.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

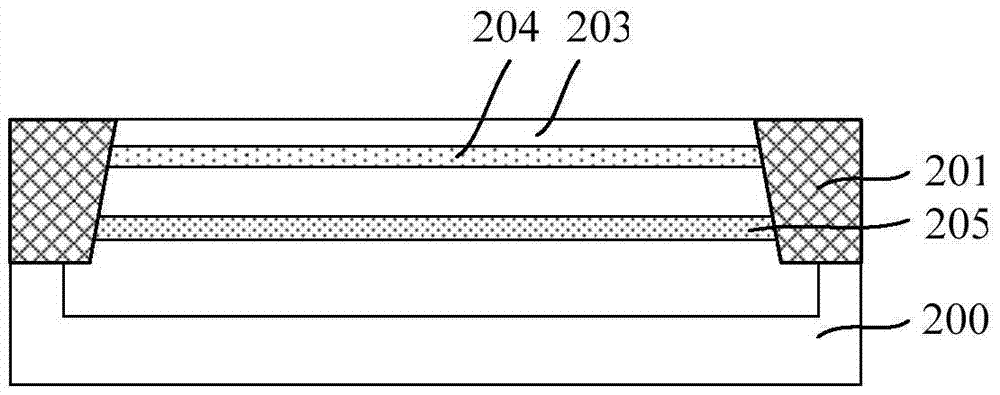

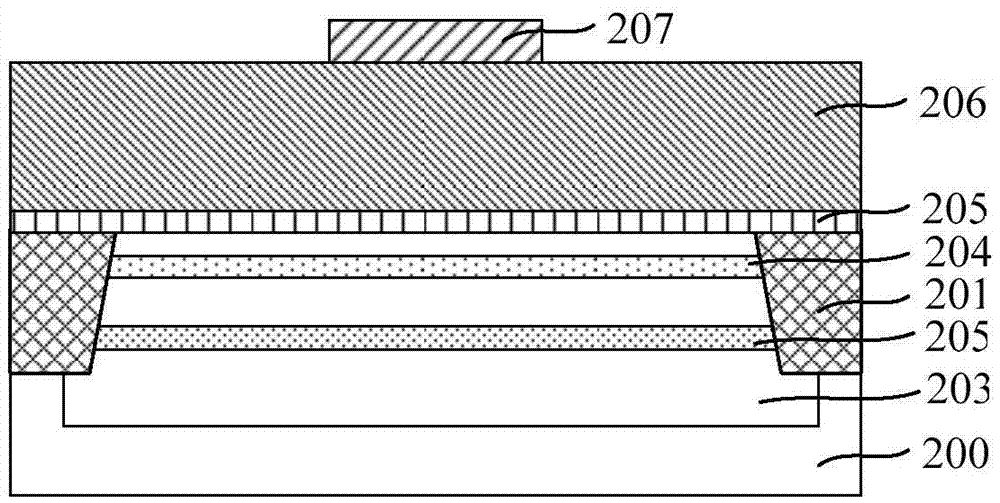

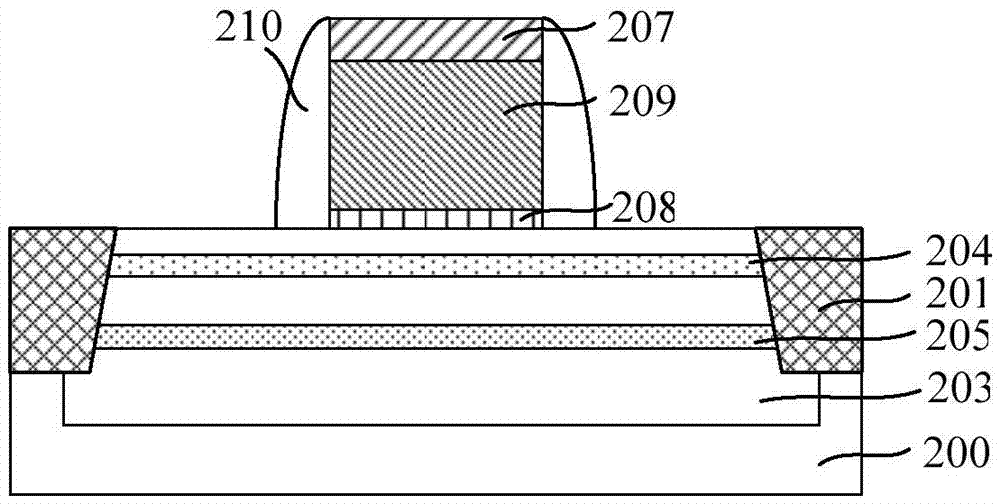

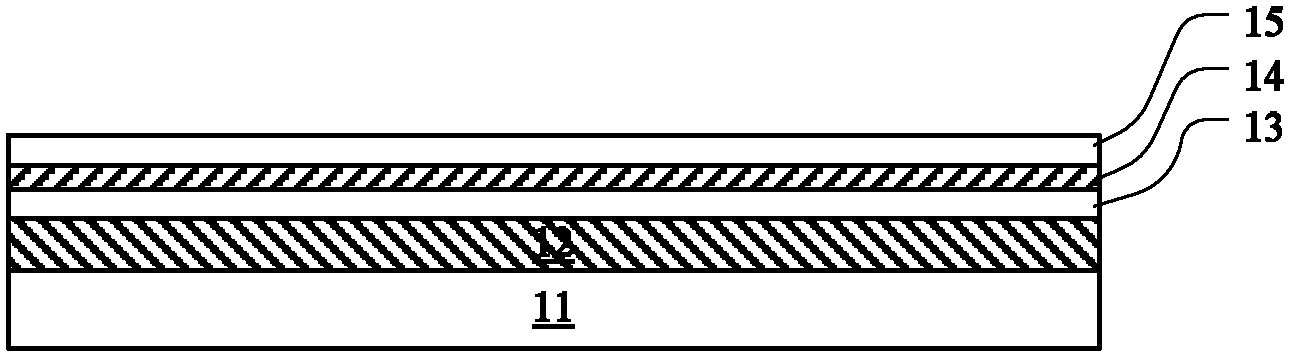

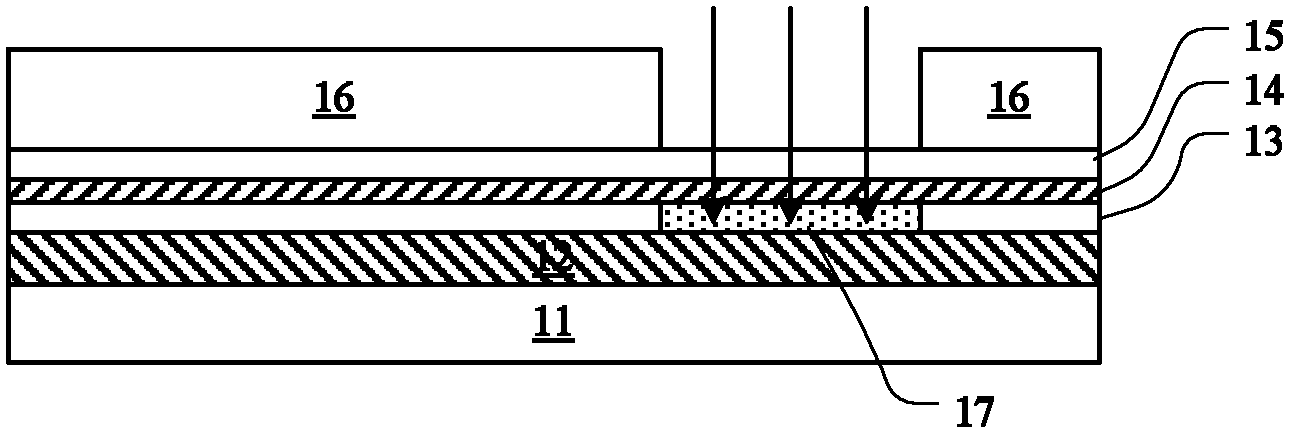

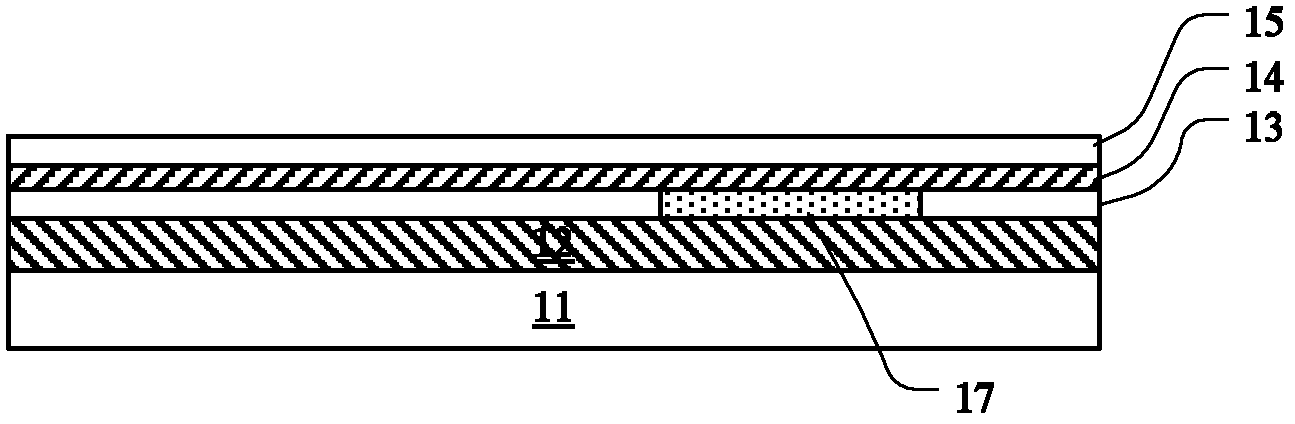

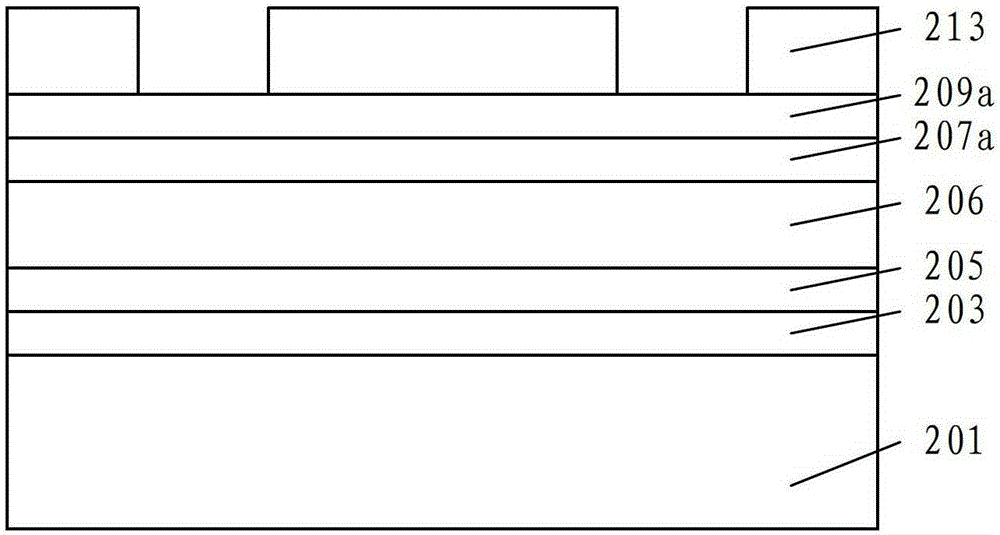

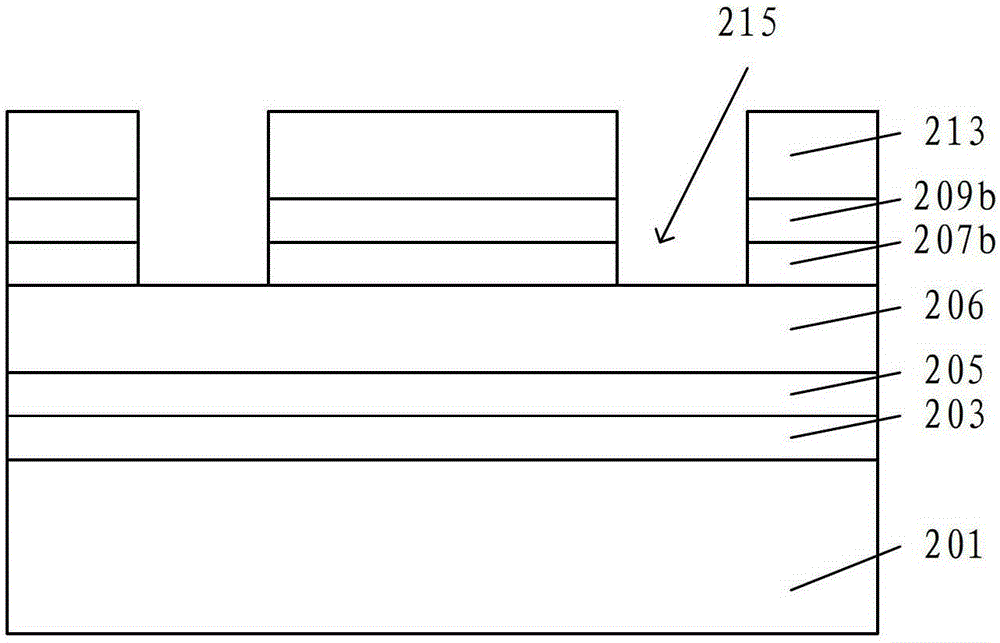

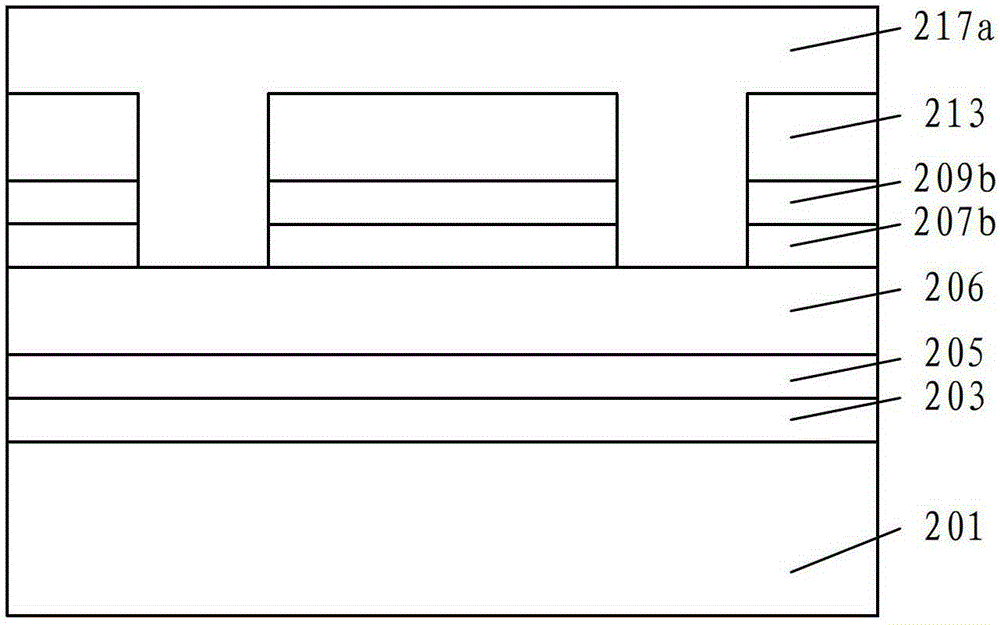

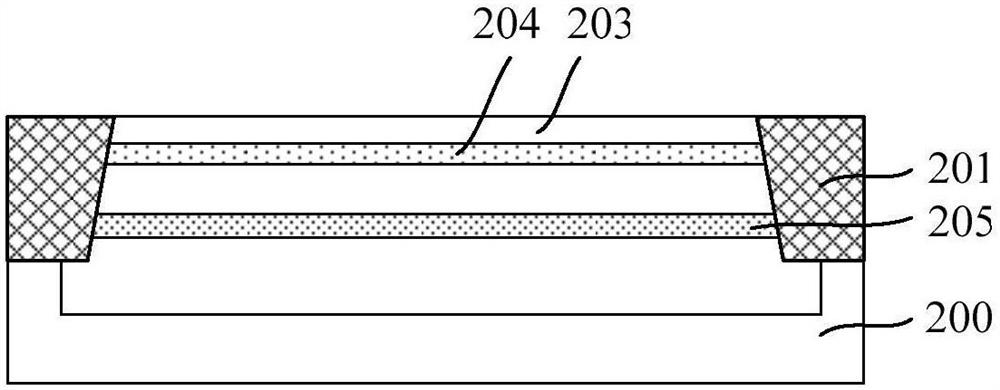

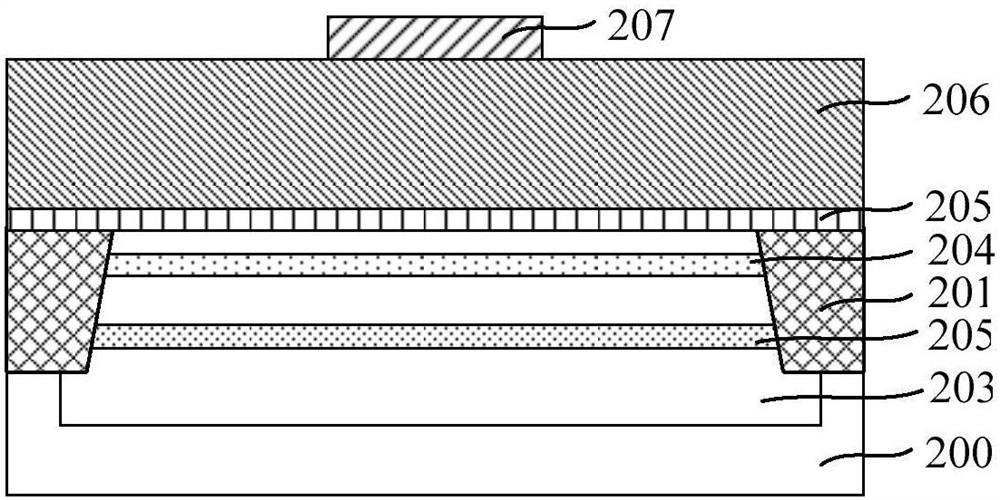

Thin film transistor and its preparation method, array substrate

ActiveCN106601786BAvoid depletion-type featuresImprove performanceTransistorSemiconductor/solid-state device manufacturingHeterojunctionField effect

The invention proposes a thin film transistor and preparation method thereof, and array substrate. The thin film transistor includes a substrate, an active layer, a gate insulating layer, a gate electrode, an interlayer insulating layer and source and drain electrodes, and is characterized in that the thin film transistor also includes at least one metal oxide semiconductor layer arranged on the active layer. According to the abovementioned thin film transistor and preparation method thereof, and the array substrate, through introduction of a metal oxide semiconductor, a weak inversion heterojunction is built in the vertical direction of the transistor, characteristics of longitudinal heterojunction weak inversion are introduced into a narrow-band high-resistance region in the horizontal direction, the depletion characteristic of a junction field effect transistor is avoided, and the purposes of suppressing leakage current and adjusting threshold voltage are achieved. At the same time, the characteristic of longitudinal heterojunction inversion charge accumulation shows a large current characteristic in the horizontal direction, and a high switch ratio is realized, thereby realizing improvement of an N channel thin film transistor in performance.

Owner:TRULY HUIZHOU SMART DISPLAY

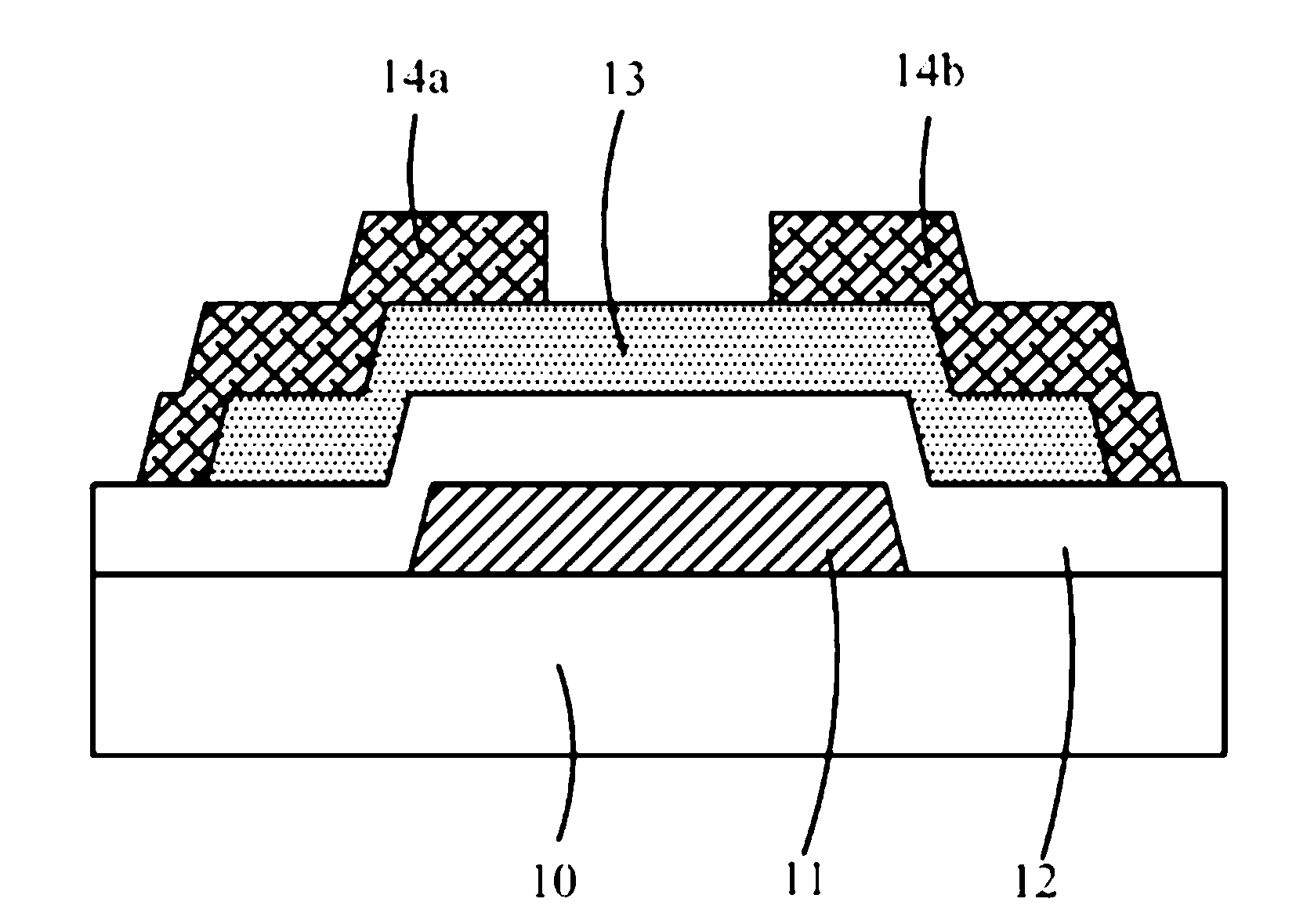

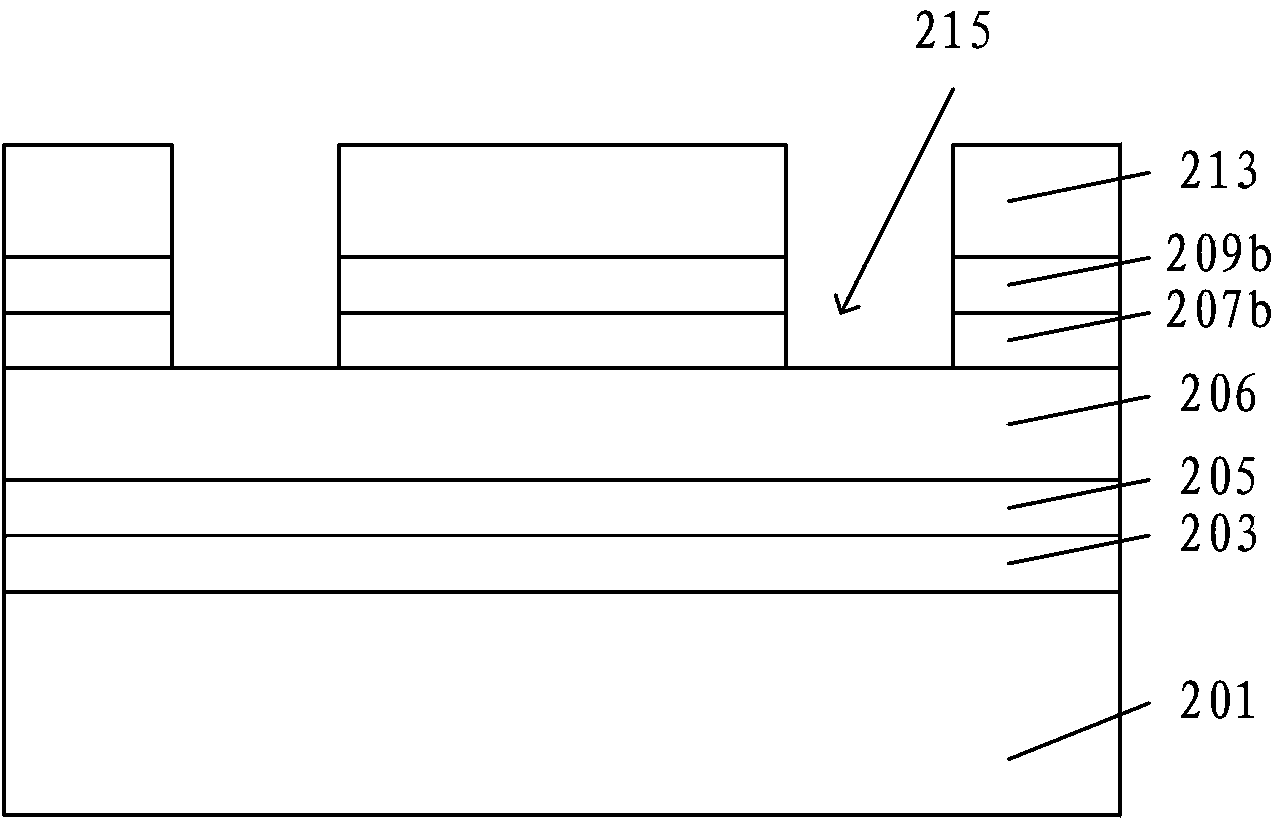

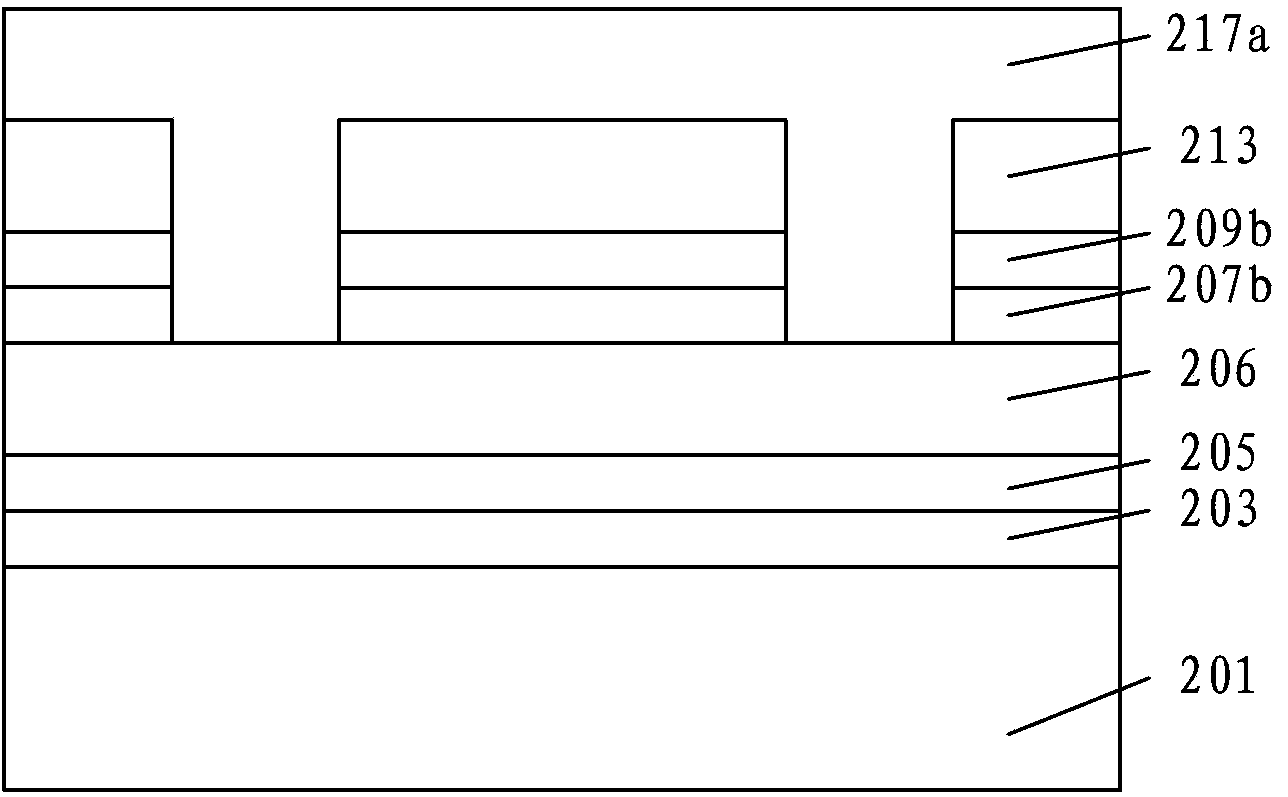

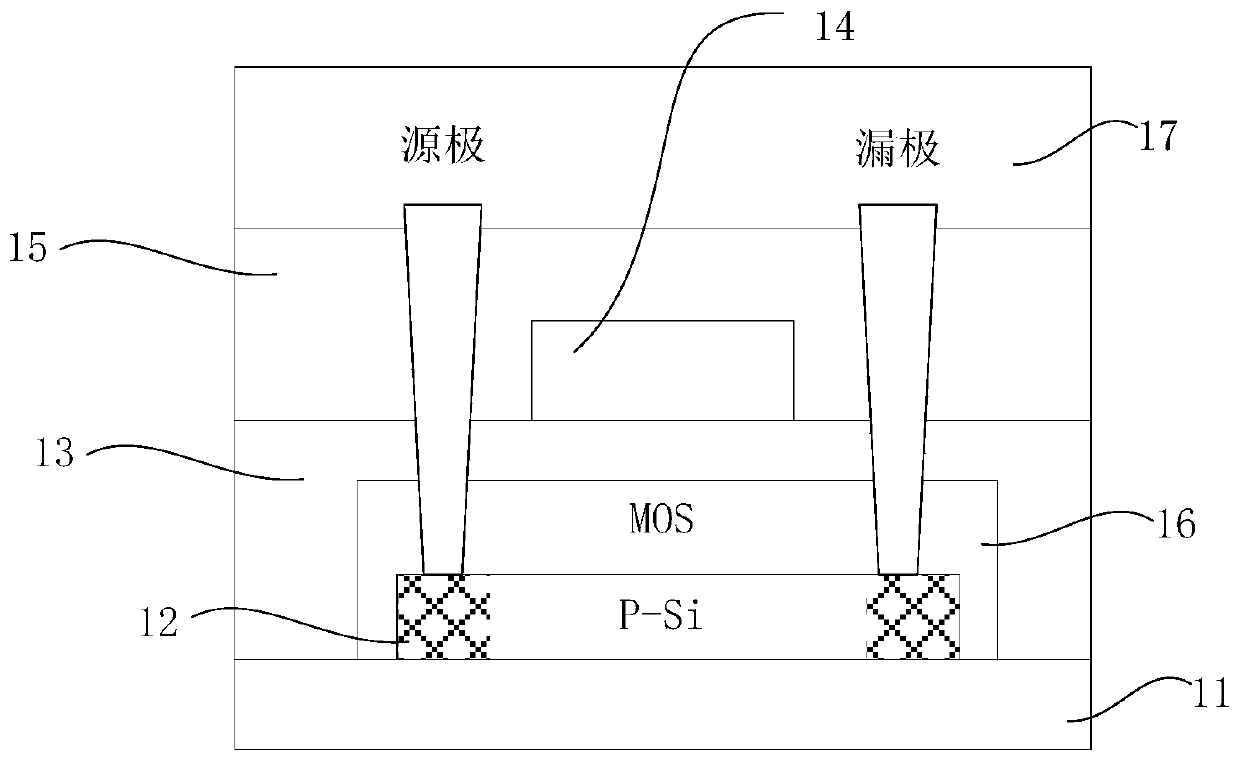

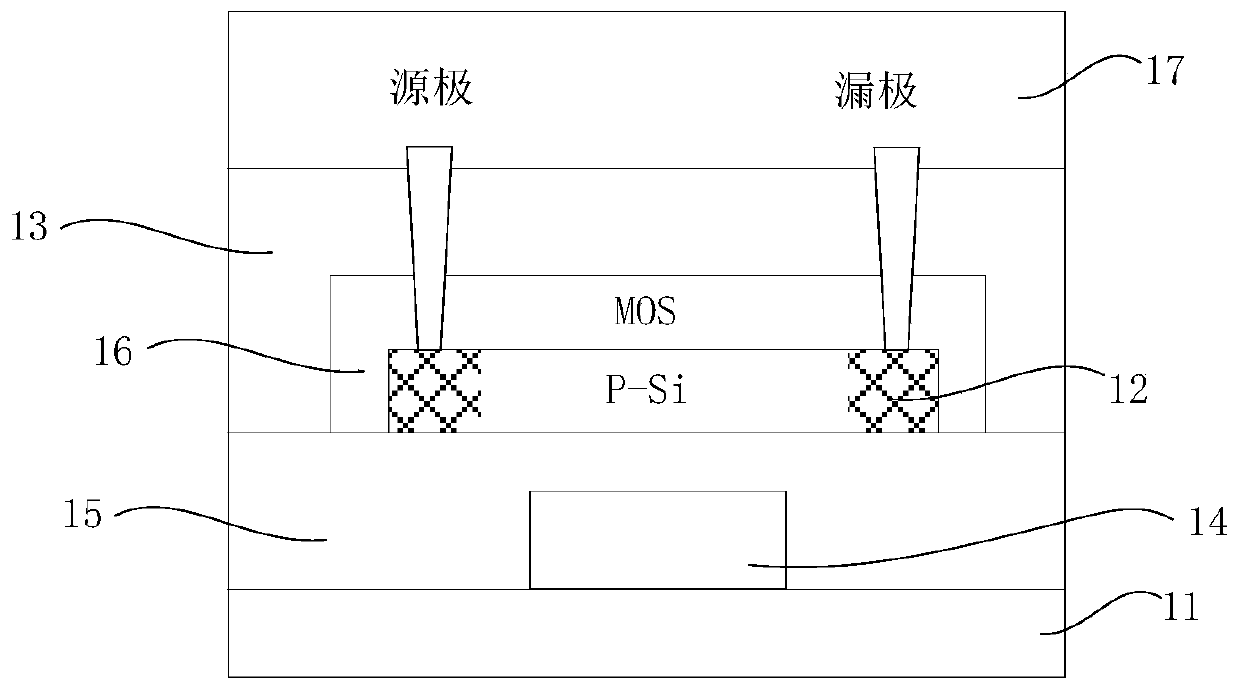

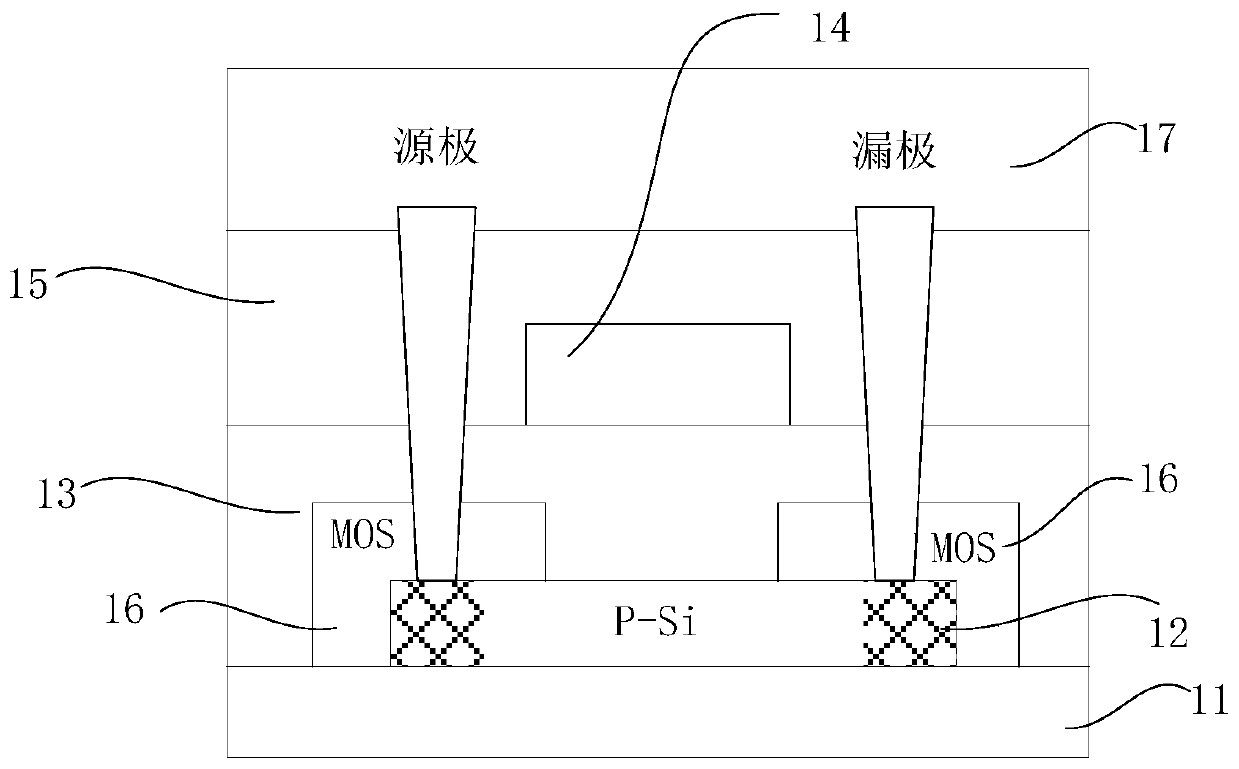

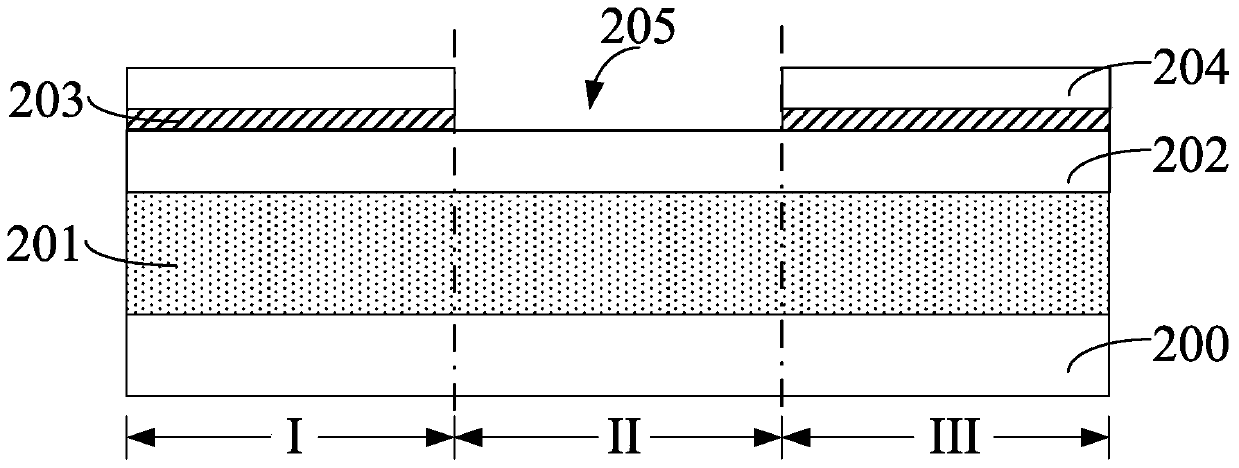

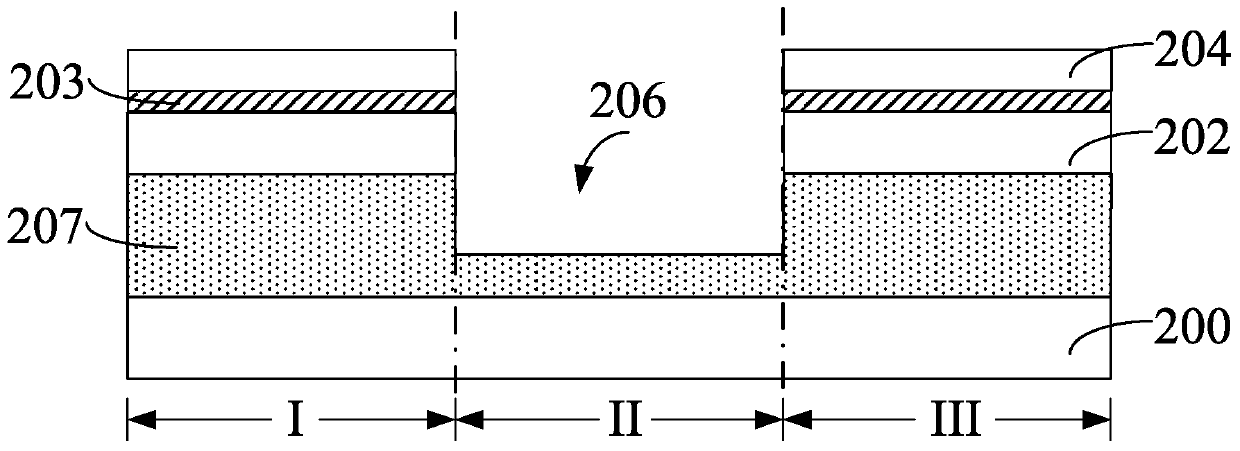

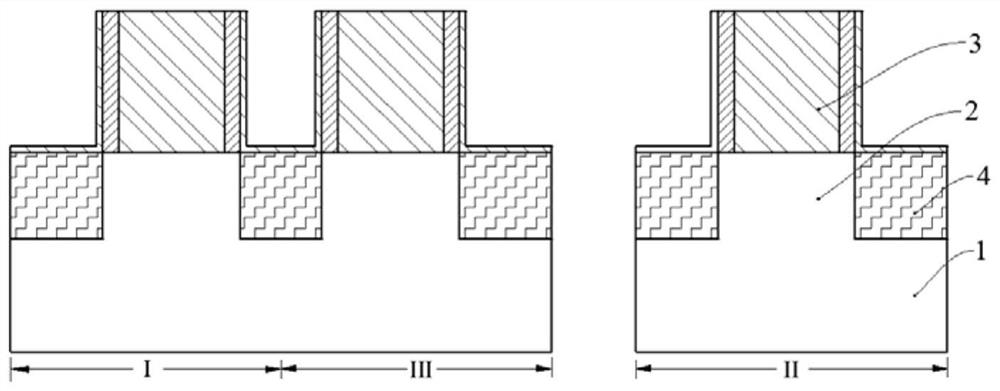

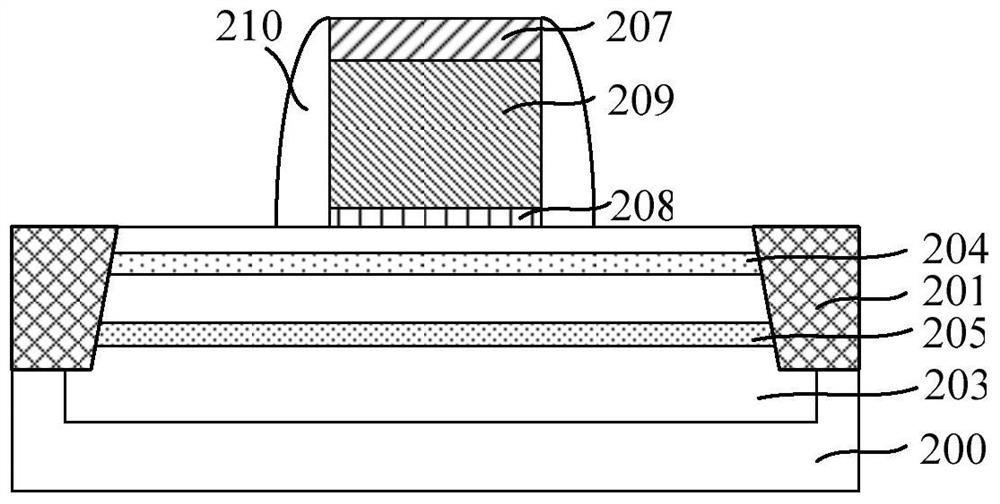

Semiconductor device and method of forming the same

ActiveCN105097711BAdjust Threshold VoltageImprove electrical performanceSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceElectrical conductor

A semiconductor device and a method for forming the same, wherein the method for forming the semiconductor device includes: providing a substrate, the substrate including a first semiconductor layer, an insulating layer positioned on the surface of the first semiconductor layer, and a second semiconductor layer positioned on the surface of the insulating layer, The substrate has a first region, a second region and a third region, the second region is adjacent to the first region and the third region, wherein the thickness of the insulating layer in the first region and the third region is greater than that of the insulating layer in the second region The bottom surface of the insulating layer in the first region, the second region and the third region is flush; the gate structure is formed on the surface of the second semiconductor layer in the second region; the first region and the third region on both sides of the gate structure A doped region is formed in the second semiconductor layer. The thickness of the insulating layer under the gate structure of the present invention is smaller than the thickness of the insulating layer under the doped region. Since the effective resistance of the insulating layer under the gate structure is small, the threshold voltage of the semiconductor device can be effectively improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

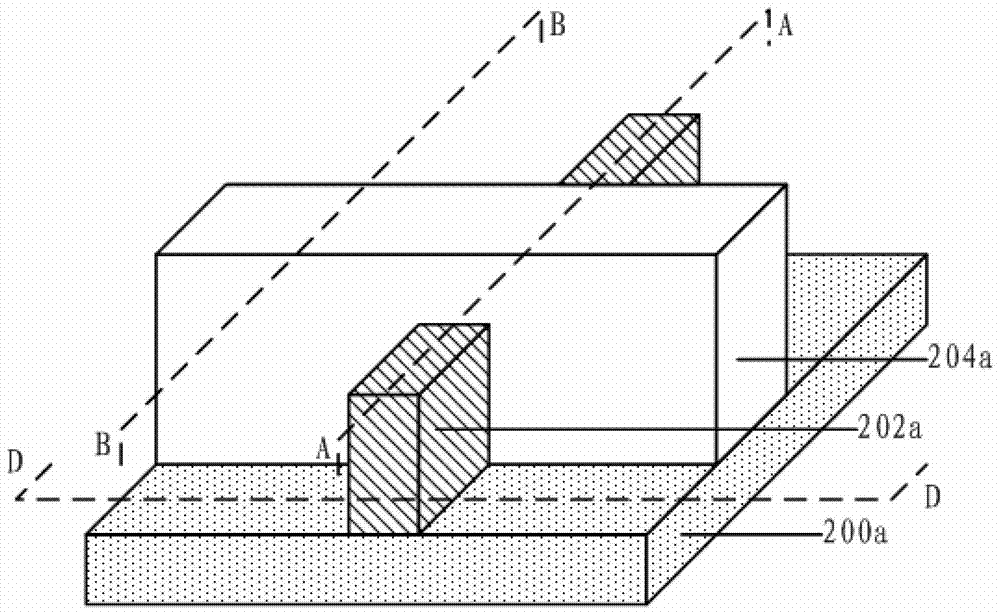

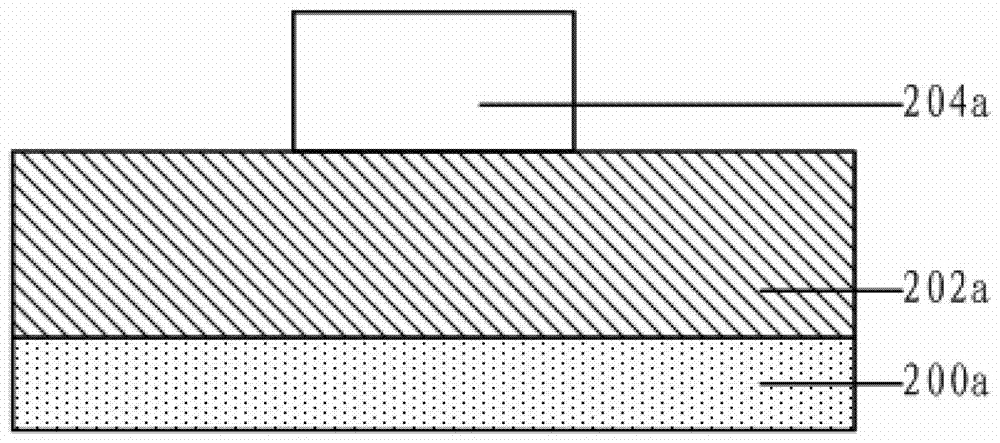

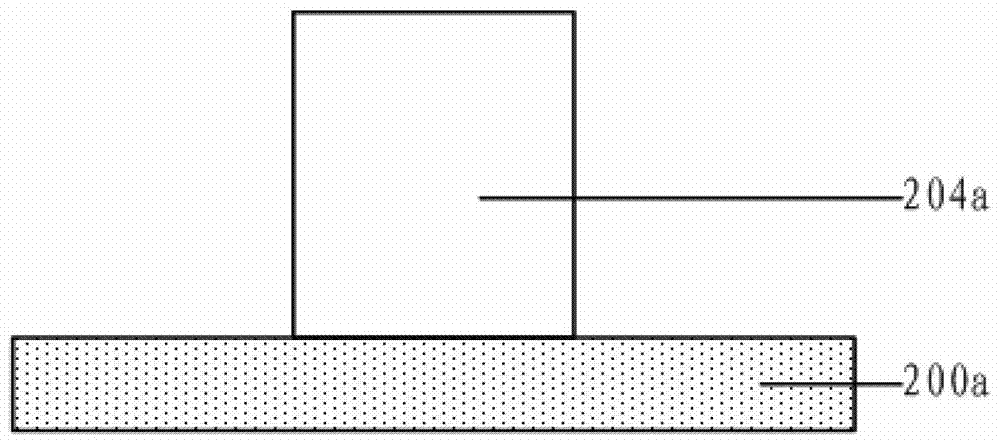

MOSFET (metal oxide semiconductor field effect transistor) and manufacturing method thereof

ActiveCN102856201BSuppression of short channel effectsAdjust Threshold VoltageSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical connectionEngineering

Provided are a MOSFET and a manufacturing method therefor. The MOSFET comprises: a semiconductor substrate, a first buried insulating layer on the semiconductor substrate, a backgate formed within a first semiconductor layer on the first buried insulating layer, a second buried insulating layer on the first semiconductor layer, source / drain regions formed within a second semiconductor layer on the second buried insulating layer, a gate on the second semiconductor layer, and an electrical connection of the source / drain regions, the gate, and the backgate. The backgate is only arranged below one in the source / drain regions and below a channel region, and not below the other in the source / drain regions. The electrical connection comprises a public conductive channel of the backgate and of the one in the source / drain regions. The MOSFET uses asymmetric backgate to improve the suppression of a short-channel effect, and uses the public conductive channel to reduce chip footprint.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Formation method of semiconductor structure

PendingCN114823533ANot easy to residueImprove removal efficiencyTransistorSolid-state devicesSemiconductor structureParasitic capacitance

A method for forming a semiconductor structure comprises the following steps: providing a substrate which comprises a first region and a second region, and forming an interlayer dielectric layer with a gate opening on the substrate; a shielding layer covering the gate opening of the second region and exposing the gate opening of the first region is formed, and the shielding layer occupies the gate opening of the second region, so that in the step of forming a first work function material layer in the gate opening of the first region, the first work function material layer is formed on the shielding layer; in the process of removing the shielding layer and the first work function material layer located on the shielding layer, the removal process window of the first work function material layer in the second area is large, residues do not exist easily, the removal efficiency is high, and the yield can be improved. Besides, a removal process window of the shielding layer is large, residues do not exist easily, the second work function layer can better adjust the threshold voltage of the transistor in the second area, parasitic capacitance in the transistor in the second area is reduced, and the electrical performance of the semiconductor structure is good.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

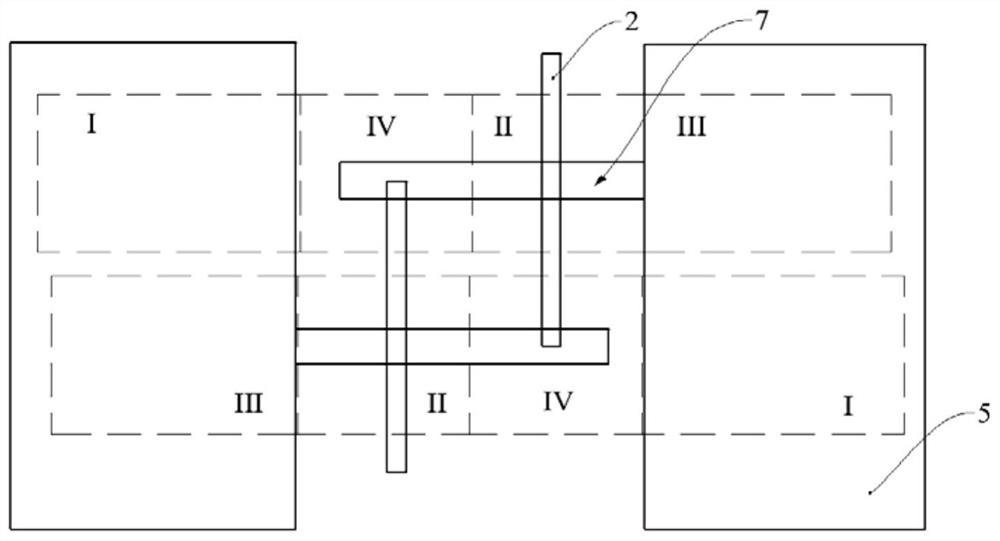

A kind of semiconductor structure and its manufacturing method

ActiveCN102856360BAdjust Threshold VoltageImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceGate dielectric

The invention provides a semiconductor structure. The structure comprises a substrate, a semiconductor substrate, back gate dielectric layers, back gates, cavities, a gate stack, side walls and source / drain regions, wherein the gate stack is arranged on the semiconductor substrate; the side walls are arranged on the side walls of the gate stack; the source / drain regions are embedded in the semiconductor substrate and are arranged on the two sides of the gate stack; the cavities are embedded in the substrate; the semiconductor substrate is suspended above the cavities; in the direction of the gate length, the middle thickness of the semiconductor substrate is greater than the thickness of the two sides; in the direction of the gate width, the semiconductor substrate is connected with the substrate; the back gate dielectric layers are arranged on the side walls of the semiconductor substrate; and the back gates are arranged on the side walls of the back gate dielectric layers. Correspondingly, the invention also provides a preparation method of the semiconductor structure. The semiconductor structure and the preparation method are beneficial to suppressing the short channel effect, adjusting the threshold voltage of the semiconductor device, improving the device performances, reducing the cost and simplifying the process.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

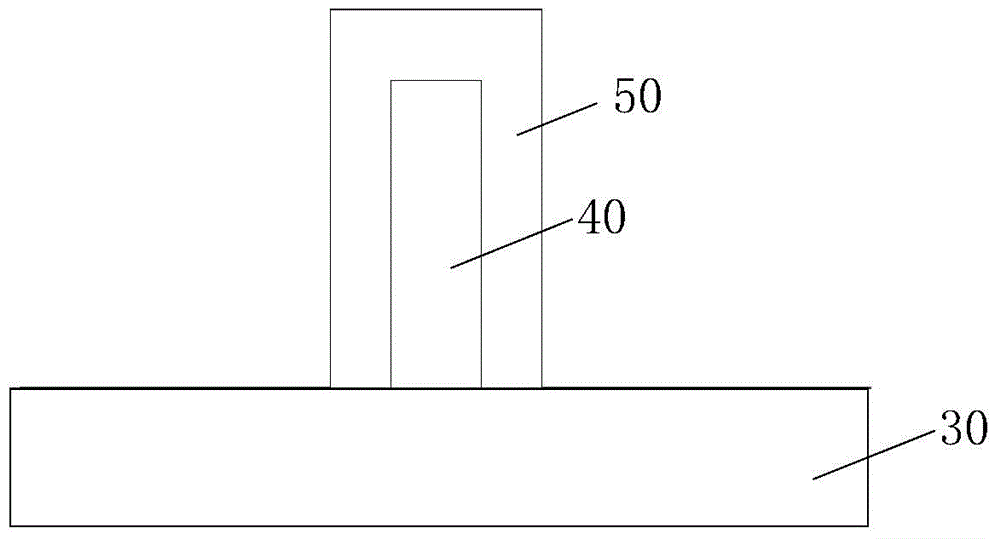

Semiconductor structure and formation method thereof

ActiveCN104952730AIncrease channel lengthImprove short channel effectSemiconductor/solid-state device manufacturingSemiconductor devicesMedia layerSemiconductor structure

The invention provides a semiconductor structure and a formation method thereof. The formation method of the semiconductor structure includes providing a substrate; forming a projecting grid on the surface of the substrate; forming gate medium layers on the surfaces of the side walls of the grid; forming a channel layer on the surface of the grid medium layer; forming a medium layer on the surface of the substrate; forming a first through hole in the medium layer on each side of the grid, wherein a part of the medium layer is arranged between the first through hole and the channel layer; and forming back grids in the first through holes. The semiconductor structure formed by adopting the above method has a comparatively large channel length and can adjust the threshold voltage of a transistor by exerting voltage on the channel layer through the back grids.

Owner:SEMICON MFG INT (SHANGHAI) CORP

How to form a mos transistor

ActiveCN103632966BIncrease migration rateAdjust Threshold VoltageSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricFiller metal

A method for forming an MOS transistor comprises providing a substrate; forming a back gate electrode, a back gate dielectric layer, a body region, a first functional layer and a front gate dielectric layer sequentially from the bottom surface of the substrate, the first functional layer being used for increasing the rate of migration of a carrier in a channel region; etching the front gate dielectric layer and the first functional layer and forming a first groove exposing a portion of the body region; conducting ion implantation on the first groove along the body region to form a heavily doped region; filling a metal layer in the first groove and forming a plug connected with the heavily doped region; and forming a second functional layer and a front gate on the surface of a front gate dielectric layer between the heavily doped regions sequentially from the bottom to the top, the second functional layer being used for reducing the leakage current of the channel region. The method for forming the MOS transistor can adjust the threshold voltage of the formed MOS transistor, improve the compatibility and matching rate of each MOS transistor in semiconductor devices and improve the performance of formed semiconductor devices.

Owner:SEMICON MFG INT (SHANGHAI) CORP

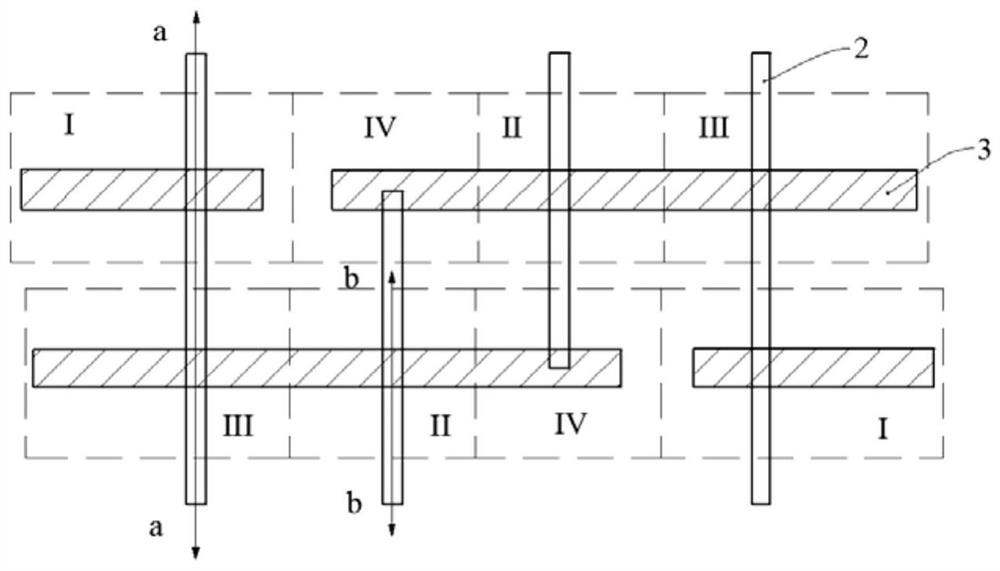

Semiconductor structure, forming method and mask

PendingCN114068558AImprove overlay accuracyImprove electrical performanceSolid-state devicesSemiconductor devicesSemiconductor structureEngineering

The invention discloses a semiconductor structure, a forming method and a mask, and the method comprises the steps: providing a substrate, wherein the substrate comprises a first device region, a pseudo device region, a second device region and a third device region which are sequentially arranged along a first row, and a third device region, a second device region, a pseudo device region and a first device region which are sequentially arranged along a second row. The first device region, the pseudo device region, the second device region and the third device region in the first row are in central symmetry with the first device region, the pseudo device region, the second device region and the third device region in the second row respectively According to the embodiment of the invention, a first shielding layer exposes the first device region and the pseudo device region, and the exposed area of the first shielding layer is large, so that the process window of the first shielding layer is large, the process difficulty of forming the first shielding layer is reduced, and the overlay precision of the first shielding layer is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

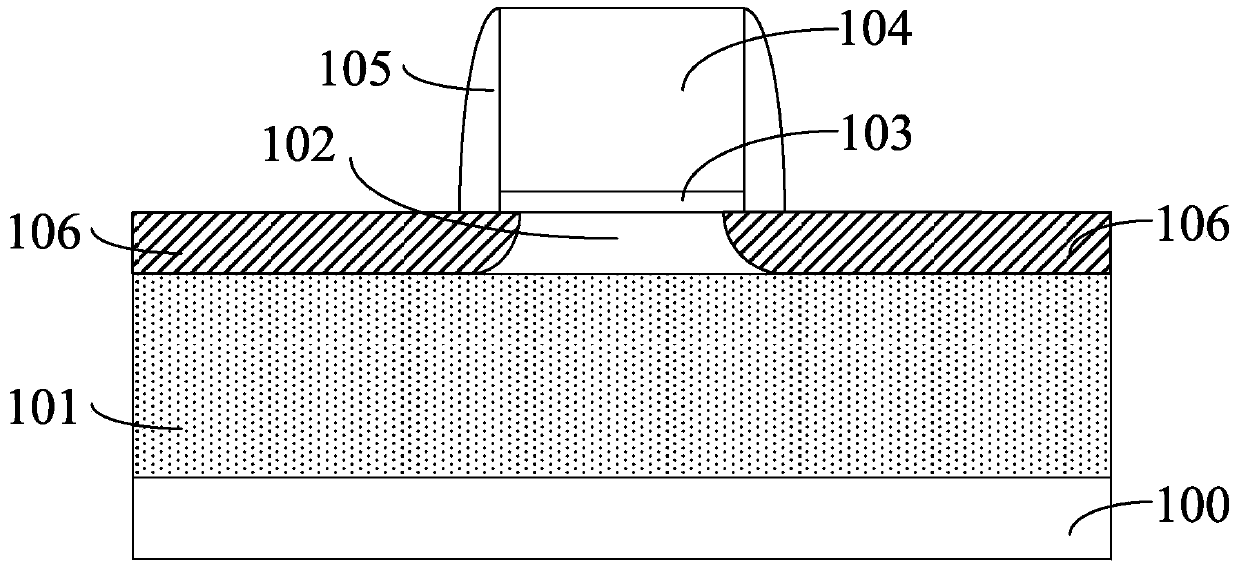

Buried channel transistor and method of forming same

ActiveCN106935646BImprove performancePrevent flickering noiseSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricEngineering

A buried channel transistor and a forming method thereof, the forming method comprising: providing a semiconductor substrate, forming a well region in the semiconductor substrate; forming an inversion doped region in the well region, and in the inversion doped region The type of doping is opposite to the type of doping in the well region, and the depth of the inversion doped region is smaller than the depth of the well region; a gate structure is formed on the surface of the semiconductor substrate above the inversion doped region, so The gate structure includes a gate dielectric layer and a gate electrode located on the gate dielectric layer, the gate electrode is doped with impurity ions, and the type of doping in the gate electrode is the same as that of the well region; A source region and a drain region are formed in the semiconductor substrate on both sides of the pole structure. The doping type in the source region and the drain region is opposite to the impurity ion type in the well region. The depth of the source region and the drain region is smaller than the depth of the well region and Greater than the depth of the inversion doped region. The transistor formed by the method of the invention prevents the generation of flicker noise and improves the performance of the device.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

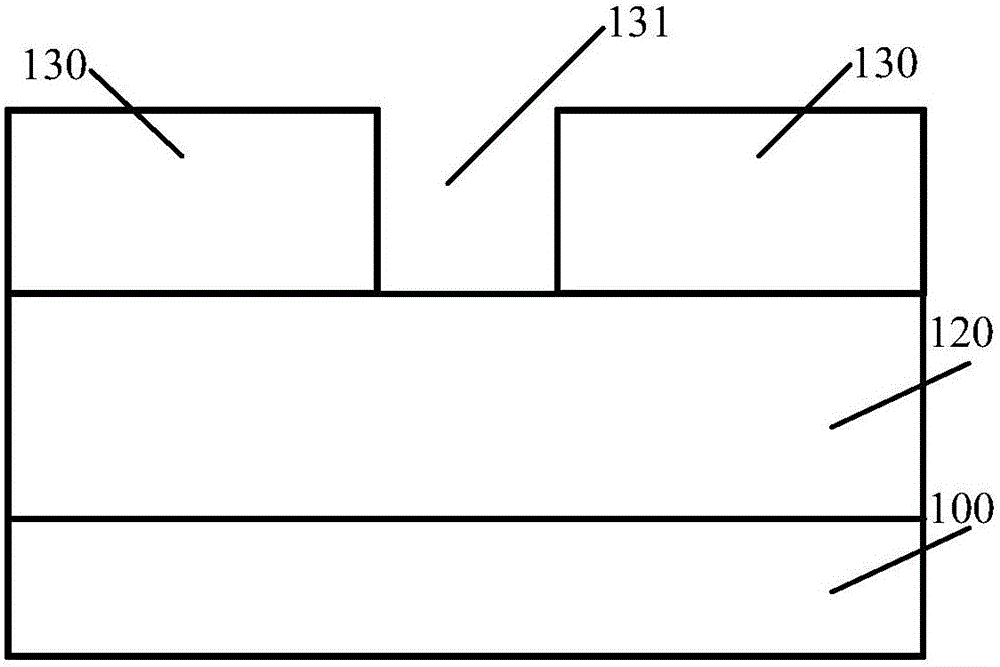

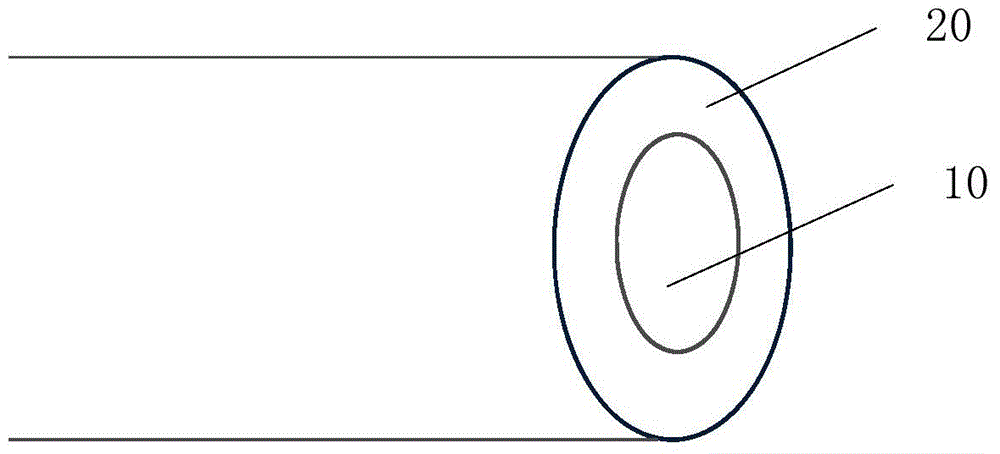

Method for forming fin field effect transistor

ActiveCN104022036BAdjust Threshold VoltageAdjust the on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringField-effect transistor

A forming method of a fin type field effect transistor comprises the following steps: providing a semiconductor substrate having a fin portion and a dummy grid electrode crossing a top portion and a side wall of the fin portion; forming an interlayer medium layer on the fin portion on two sides of the dummy grid electrode and the semiconductor substrate, and a top surface of the interlayer medium layer is flush with a top surface of the dummy grid electrode; etching the dummy grid electrode until the dummy grid electrode with partial thickness is left on the top of the fin portion, thereby forming a first groove; forming a first side wall on a side wall of the first groove; using the first side wall as a mask to continuously etch the dummy grid electrode through anistropic etching technology until the semiconductor substrate is exposed, thereby forming a second groove; processing the remained dummy grid electrode so as to form a second side wall; forming a metal grid electrode in the second groove comprising the second side wall. The threshold-voltage of the fin type field effect transistor formed by the method can be controlled, and the formed fin type field effect transistor has better performance.

Owner:SEMICON MFG INT (SHANGHAI) CORP

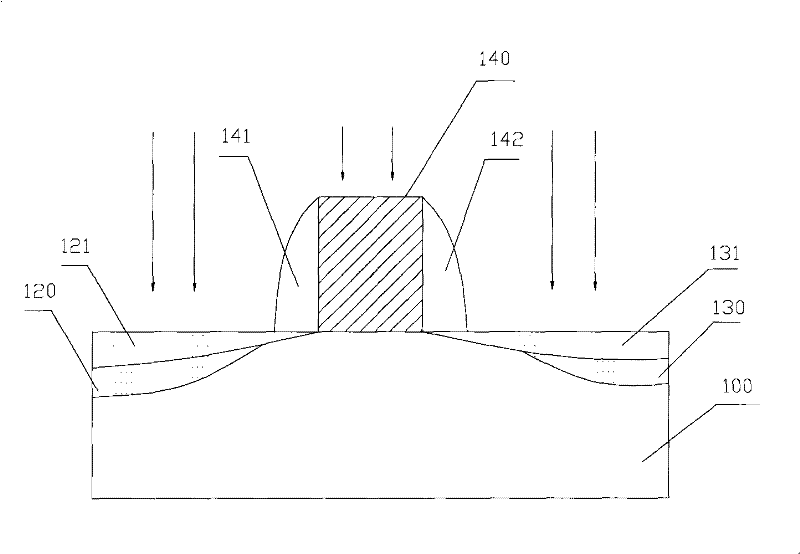

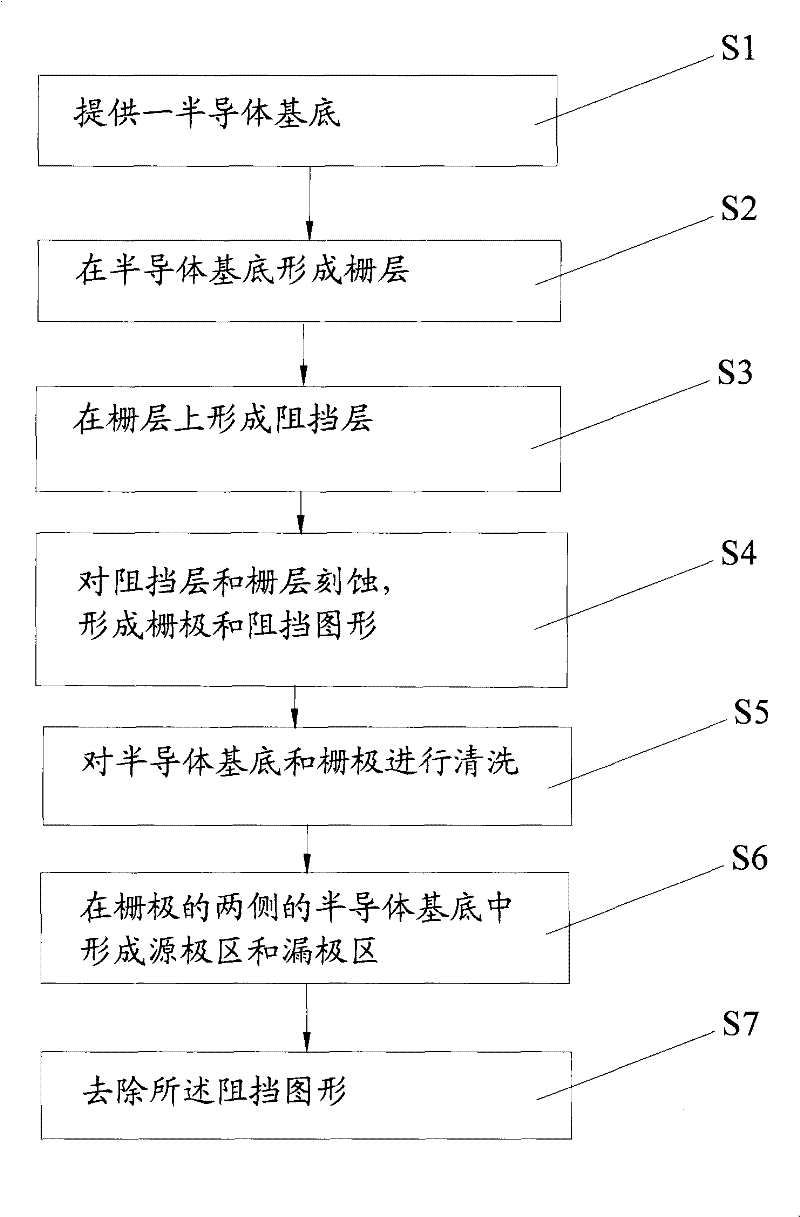

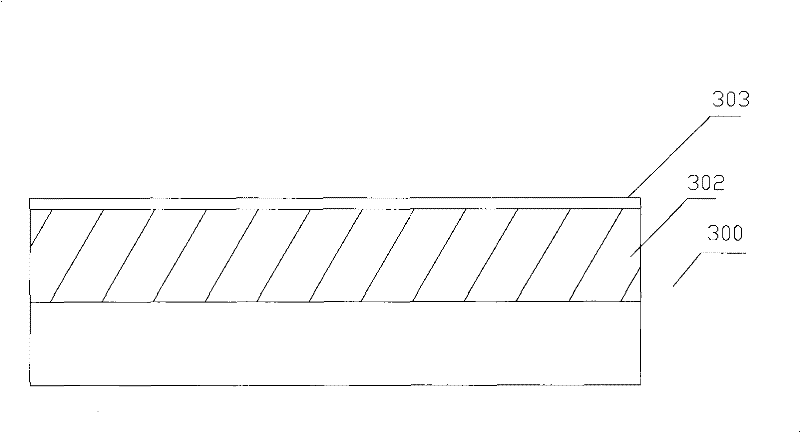

Method for manufacturing semiconductor device

ActiveCN101651103BImprove leakage currentAdjustment resistanceSemiconductor/solid-state device manufacturingElectrical conductorImpurity ions

The invention discloses a method for manufacturing a semiconductor device. The method comprises the following steps of: providing a semiconductor substrate; forming a gate layer on the semiconductor substrate; forming a blocking layer on the gate layer; etching the blocking layer and the gate layer to form a blocking pattern and a gate; washing the semiconductor substrate and the gate; forming a source electrode area and a drain electrode area in the semiconductor substrate on both sides of the gate; and removing the blocking pattern. In the method, with a blocking layer which is formed on the gate layer, impurity ions can be blocked from being filled in the semiconductor substrate below the gate layer in a process of forming the source electrode area and the drain electrode area in the semiconductor substrate on both sides of the gate, so the problem of drain current formed between the source electrode area and the drain electrode area can be solved.

Owner:SEMICON MFG INT (BEIJING) CORP

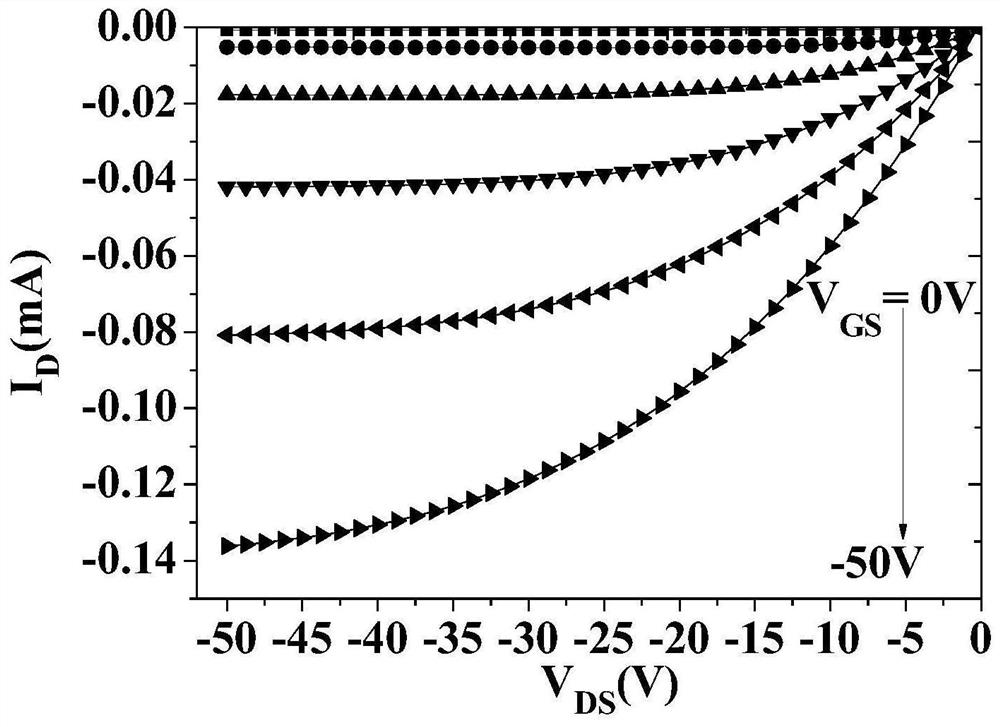

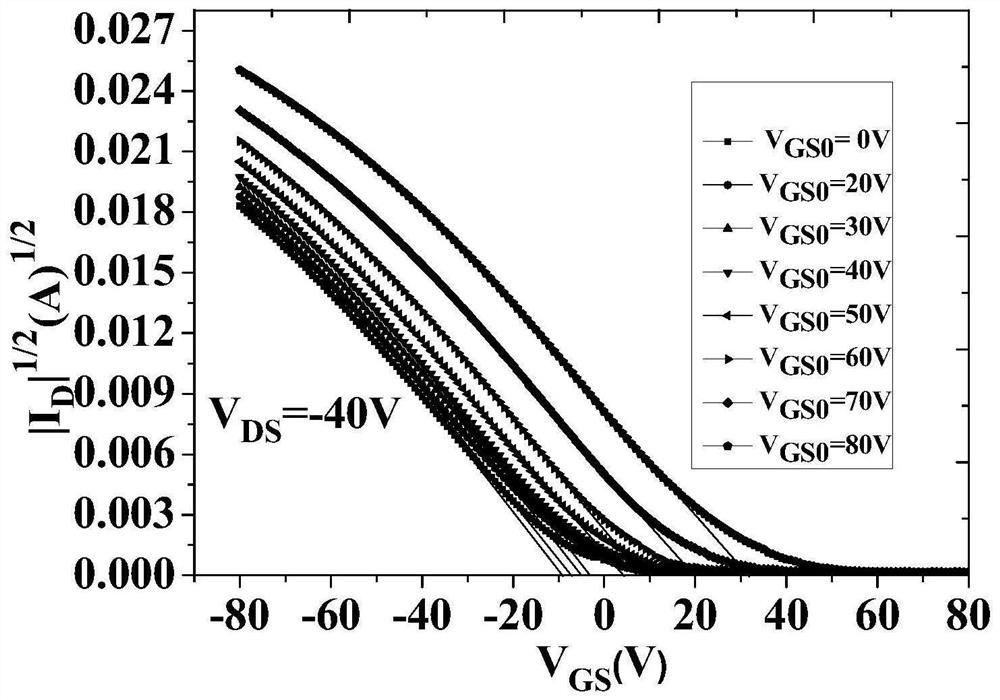

A kind of organic thin film transistor and its preparation method

ActiveCN113871535BAdjust Threshold VoltageSimple processMaterial nanotechnologyFinal product manufactureOrganic filmSemiconductor materials

The invention relates to an organic thin film transistor, which includes a mixed layer, wherein the mixed layer includes a semiconductor lower layer, a copper oxide layer and a semiconductor upper layer in order from bottom to top; the semiconductor lower layer and the semiconductor upper layer are the same or different semiconductor materials. The organic thin film transistor containing the copper oxide layer proposed by the invention can effectively adjust the threshold voltage of the organic thin film transistor. This regulation method does not need to rely on complex semiconductor doping and insulating layer surface modification technologies, and is a technology with simple processes and more suitable for commercial applications.

Owner:湖南工商大学

A gate and method for forming the same

ActiveCN105990403BAdjust Threshold VoltageEasy to adjustSemiconductor devicesGate dielectricWork function

The invention provides a gate forming method comprising the steps of forming a single doped metal work function adjustment layer on a gate dielectric layer to enable a target work function to be between the metal work function layer and a work function of doped particles, and forming other gate layers on the metal work function adjustment layer. Through the method, the threshold voltage can be adjusted easily, the process is simple and can be implemented without multiple metal gate layers, and the manufacturing cost is reduced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI