Homojunction combined gate field effect transistor

A technology of field-effect transistors and compound gates, which is applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of small-sized MOSFETs, high-work function materials, and difficult realization, so as to suppress short-channel effects, The effect of adjusting the threshold voltage and increasing the driving current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

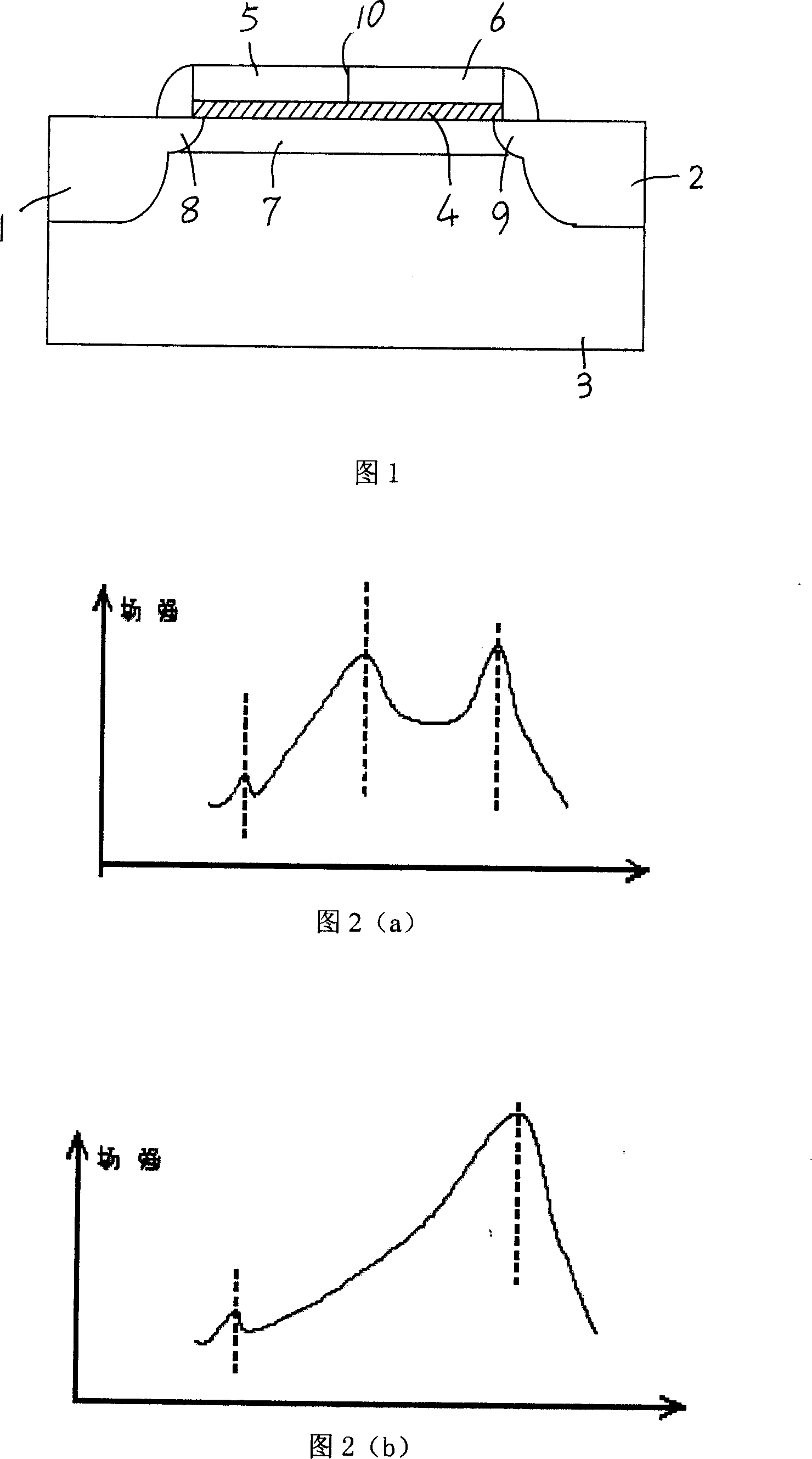

[0036] In embodiment 1, the channel length is set to 0.35um, and other related settings include:

[0037] The thickness of the insulating layer 4 is 7nm, and the doping concentrations of the source terminal 1 and the drain terminal 2 are both 1×10 20 cm -3 , the junction depth is 150nm; the doping concentration of shallow source extension region 8 and shallow drain extension region 9 is 1×10 20 cm -3 , the junction depth is 50nm, and the doping concentration of the substrate 3 is 3×10 17 cm -3 . The doping concentration of the P-type polysilicon gate 5 at the gate end is 1×10 20 cm -3 , the doping effect is P + And the doping concentration of the N-type polysilicon gate 6 is 1×10 20 cm -3 , the doping effect is N + , and the length ratio between them is 1:1.

Embodiment 2

[0038] Example 2: Set the channel length to 0.25um, other related settings include:

[0039] The thickness of the insulating layer 4 is 5nm, and the doping concentrations of the source terminal 1 and the drain terminal 2 are both 1×10 20 cm -3 , the junction depth is 150nm; the doping concentration of shallow source extension region 8 and shallow drain extension region 9 is 1×10 19 cm -3 , the junction depth is 50nm, and the doping concentration of the substrate 3 is 3×10 16 cm -3 . The doping concentration of the P-type polysilicon gate 5 at the gate end is 1×10 20 cm -3 , the doping effect is P + And the doping concentration of the N-type polysilicon gate 6 is 1×10 20 cm -3 , the doping effect is N + , and the length ratio between them is 1:1.

Embodiment 3

[0040] Example 3: Set the channel length to 0.13um, and other related settings include:

[0041] The thickness of the insulating layer 4 is 2nm, and the doping concentrations of the source terminal 1 and the drain terminal 2 are both 1×10 20 cm -3 , the junction depth is 150nm; the doping concentration of shallow source extension region 8 and shallow drain extension region 9 is 1×10 20 cm -3 , the junction depth is 50nm, and the doping concentration of the substrate 3 is 3×10 17 cm -3 . The doping concentration of the P-type polysilicon gate 5 at the gate end is 1×10 20 cm -3 , the doping effect is P + And the doping concentration of the N-type polysilicon gate 6 is 1×10 20cm -3 , the doping effect is N + , and the length ratio between them is 1:1.

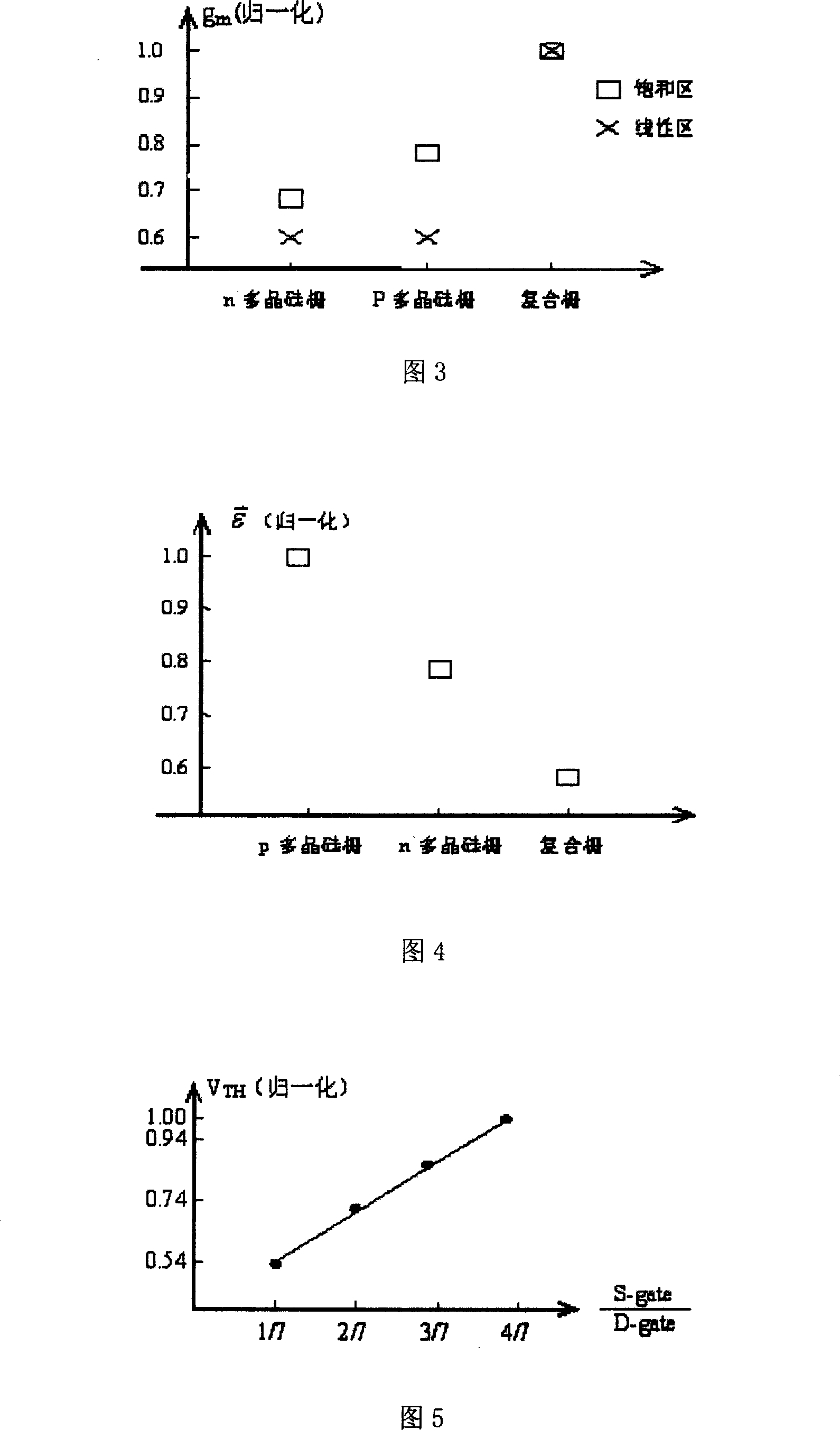

[0042] The characteristics of the device were simulated by the two-dimensional device simulation software - MEDICI, and the conclusions are as follows:

[0043] Table 1. Electrical characteristics of three gate electro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More