Fin field effect transistor and forming method thereof

A fin field effect and transistor technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as affecting transistor performance, increasing the parasitic capacitance of conductive plugs in source and drain regions, and reducing Effect of Small Parasitic Capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

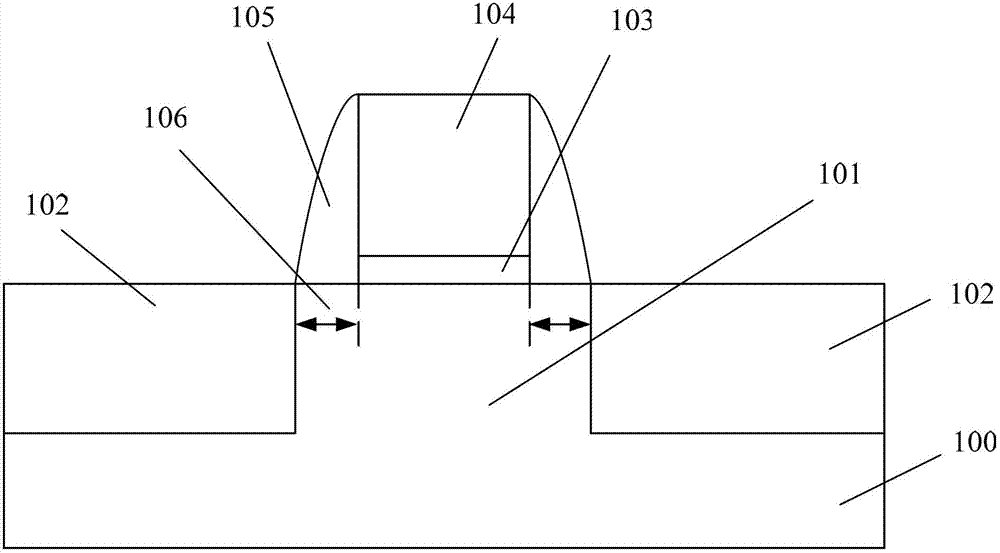

[0034] It can be seen from the background art that the parasitic capacitance between the gate electrode and the conductive plugs in the source region and the drain region of the fin field effect transistor with the negative cover region formed in the prior art is large.

[0035] The inventors of the present invention have studied the formation method of the fin field effect transistor with the negative cover region in the prior art, and found that the high dielectric constant sidewalls lead to large parasitic capacitance between the gate electrode and the conductive plugs in the source region and the drain region. the main reason. It can be seen from the formula C=εS / 4πkd that in a flat plate capacitor, the capacitance C is inversely proportional to the distance d between the plates, and is inversely proportional to the dielectric constant ε of the dielectric layer between the plates, so it can be reduced by reducing the dielectric of the sidewall material constant to reduce t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More