Depletion type power semiconductor device and manufacturing method thereof

A technology of power semiconductors and manufacturing methods, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as complex process, large threshold voltage drift, and poor threshold voltage controllability, and achieve simple process, Effect of effective threshold voltage and improvement of flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0062] The present invention will be further described below in conjunction with specific embodiments and accompanying drawings, but the protection scope of the present invention should not be limited thereby.

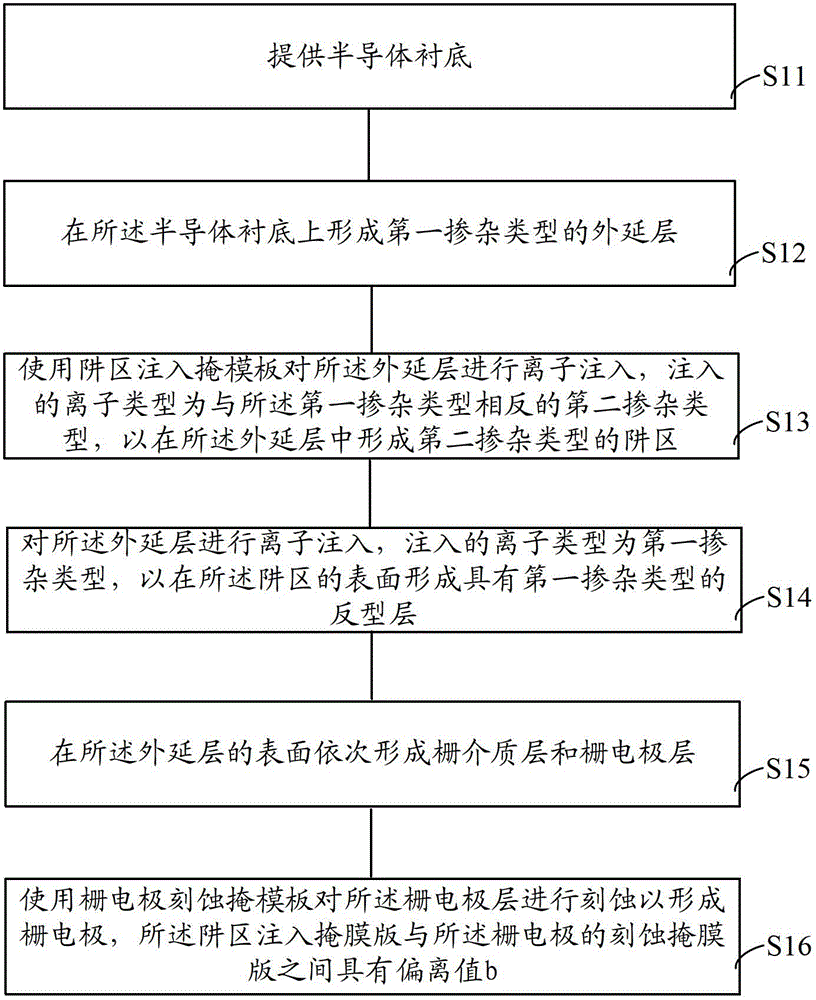

[0063] figure 1 A schematic flow chart showing a method for manufacturing a depletion-mode power semiconductor device in this embodiment includes the following steps:

[0064] Step S11, providing a semiconductor substrate;

[0065] Step S12, forming an epitaxial layer of the first doping type on the semiconductor substrate;

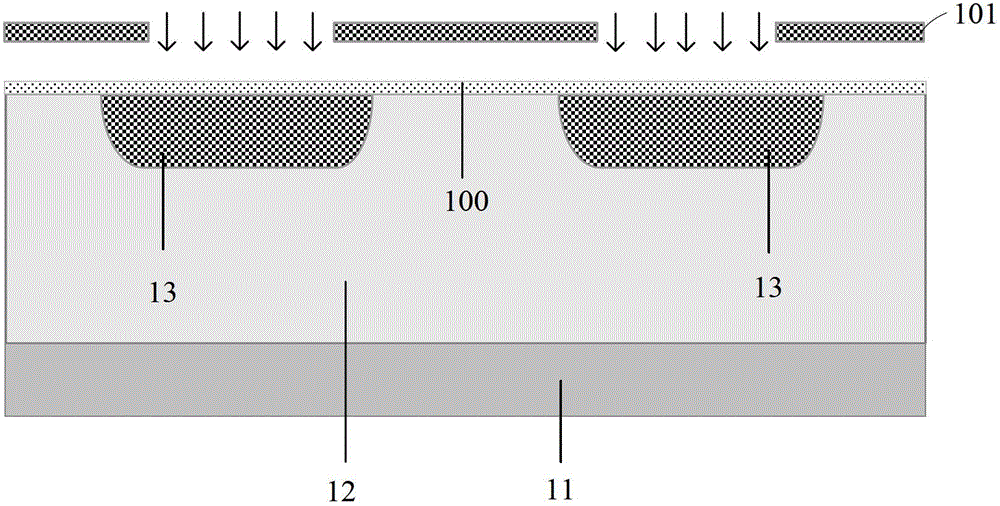

[0066] Step S13, using a well region implantation mask to perform ion implantation on the epitaxial layer, the implanted ion type is a second doping type opposite to the first doping type, so as to form a second doping type in the epitaxial layer. Doped type well region;

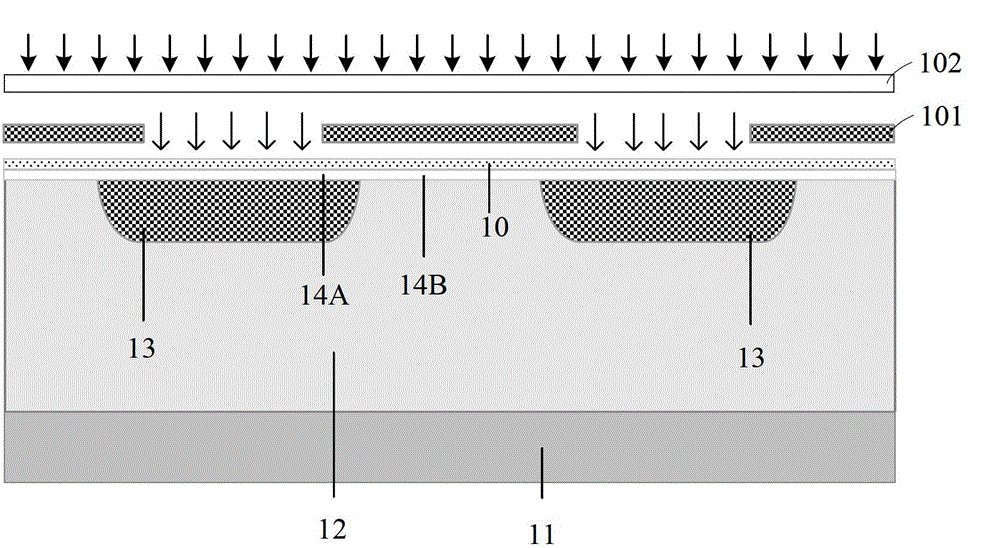

[0067] Step S14, performing ion implantation on the epitaxial layer, the implanted ion type is the first doping type, so as to form an inversion layer with the first doping t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More