Buried channel transistor and method of forming same

A transistor and channel technology, applied in the field of buried channel transistors and their formation, to prevent flicker noise and improve performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

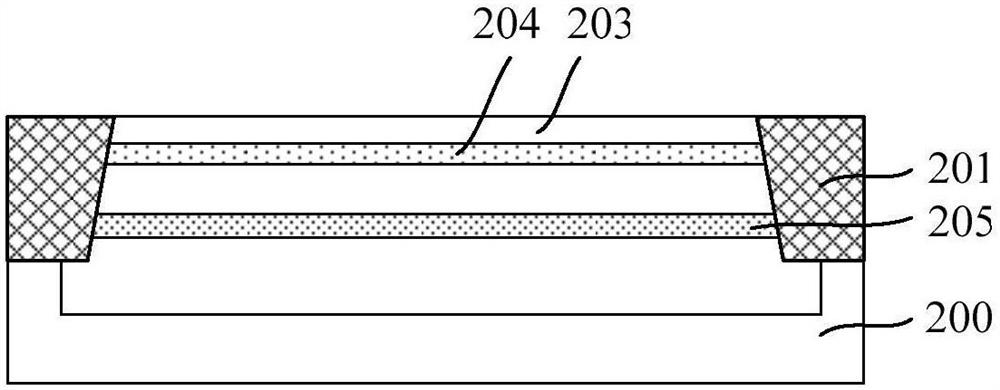

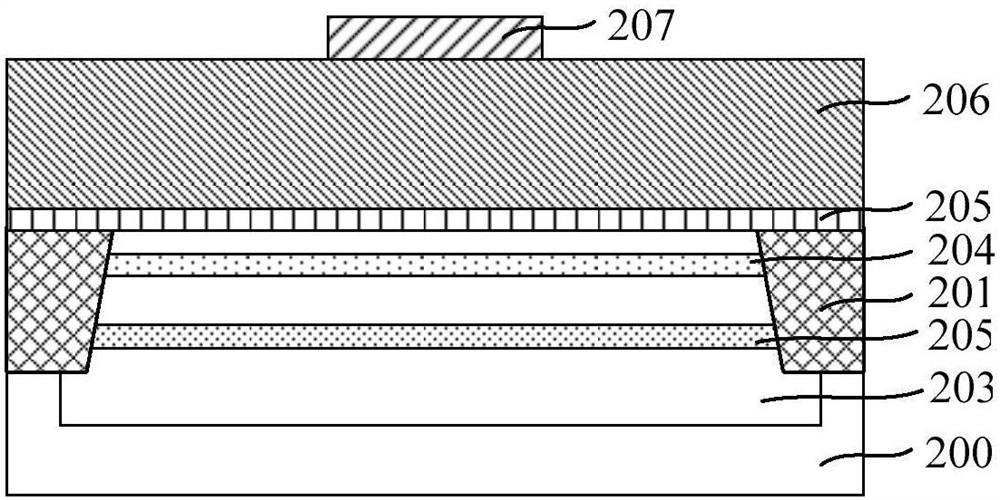

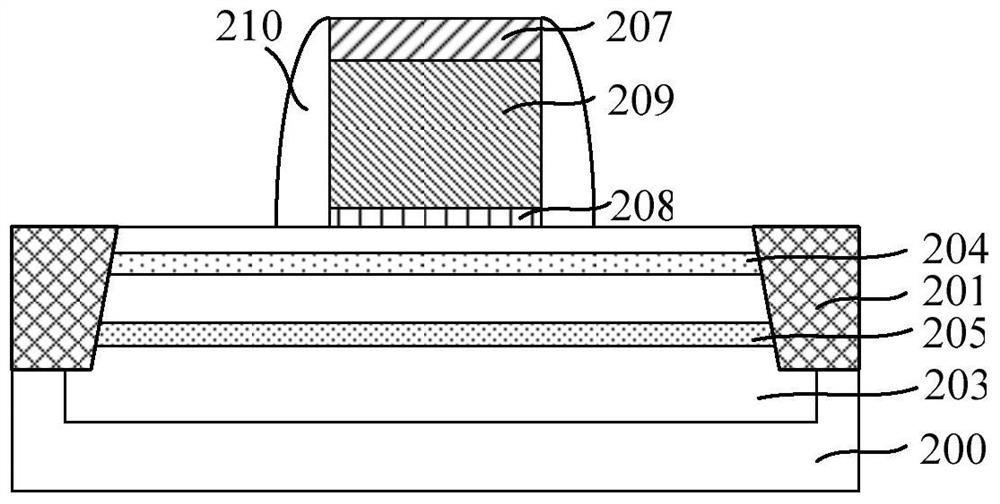

[0030] As mentioned in the background art, the performance of transistors formed in the prior art still needs to be improved. For example, the existing transistors have 1 / f noise or flicker noise during operation, and the generation of 1 / f noise or flicker noise is related to conduction. The smoothness of the channel has a great correlation, and the conductive channel formed by the existing transistor is basically a surface channel. In the manufacturing process, the smoothness of the substrate surface is difficult to ensure, and the substrate surface is inevitable. There will be defects, and the existence of defects will affect the transfer of carriers. Therefore, the existing transistors are prone to flicker noise during operation, which affects the performance of the device.

[0031] To this end, the present invention provides a buried channel transistor and a method for forming the same. By forming an inverse doped region in the well region, the carriers will travel along the g...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More