Method for forming stack gate of CMOS (Complementary Metal-Oxide-Semiconductor) device and stack gate sturcture

A technology of MOS devices and gate dielectrics, applied in semiconductor devices, electrical components, transistors, etc., can solve the problems of carrier mobility reduction, device performance degradation, large scattering of channel carriers, etc., and achieve improved channel migration rate, reduce gate leakage current, and adjust the effect of threshold voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

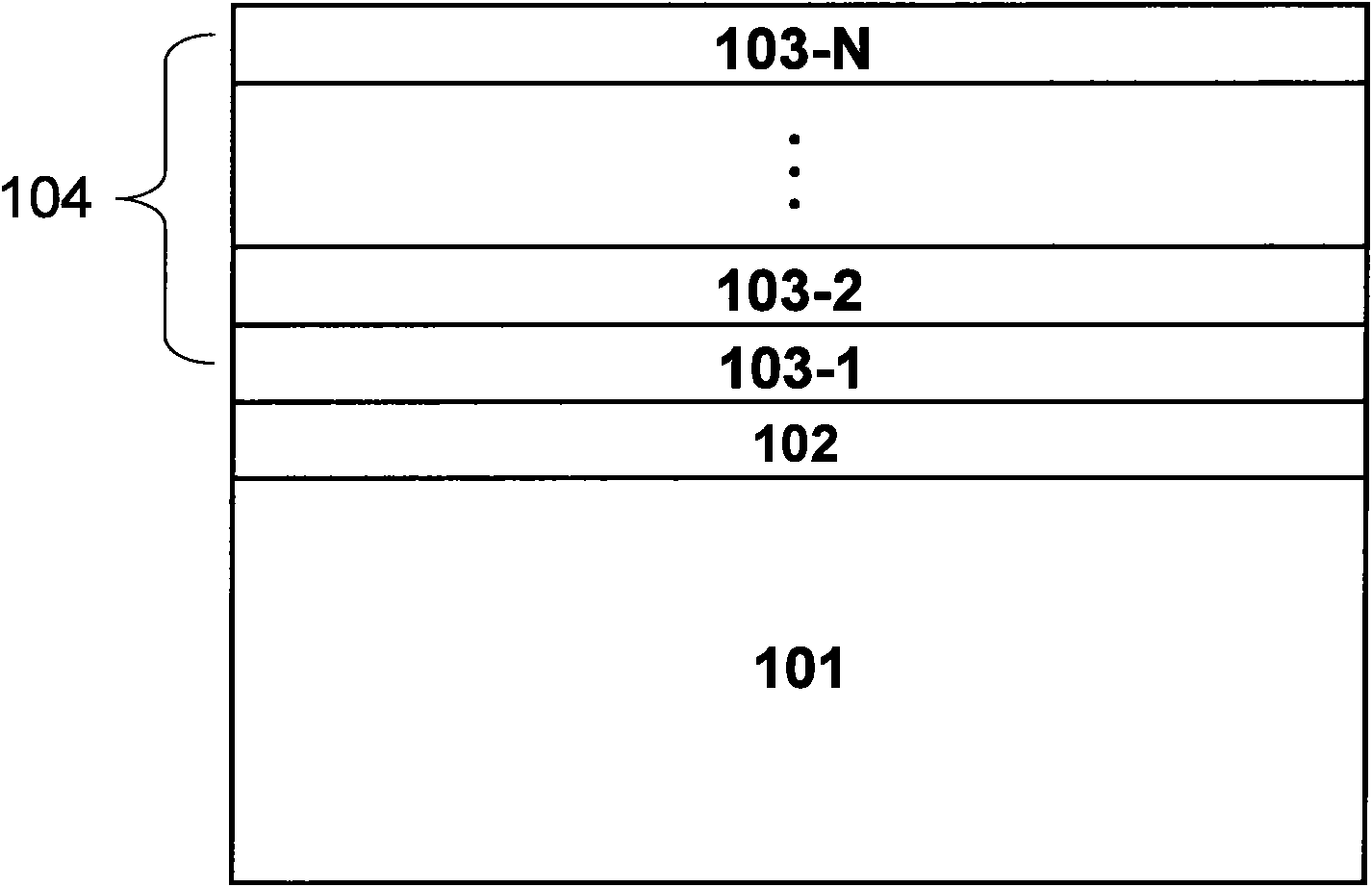

[0027] Such as Figure 2-5 As shown, it is a schematic diagram of forming the gate stack structure of the present invention in Embodiment 1 of the present invention. In this embodiment, the multi-layer insulating film is a three-layer film with the same thickness and different atomic percentages. Of course, in other embodiments, the insulating film It can also be different, including the following steps:

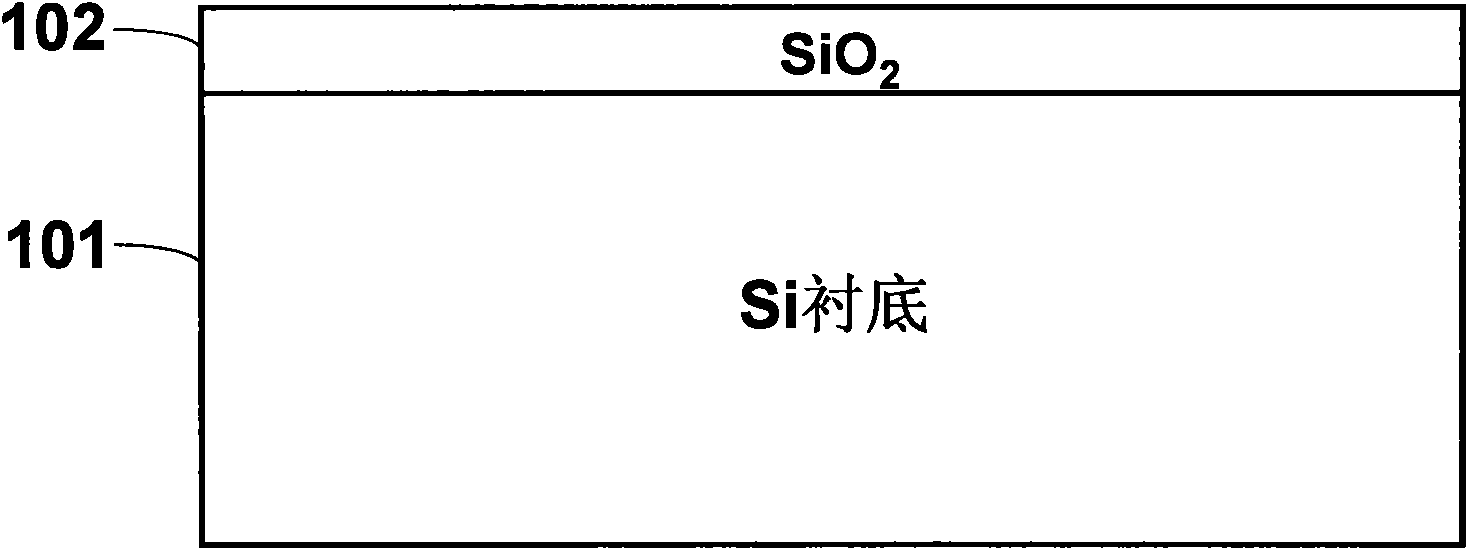

[0028] Step 1: If figure 2 As shown, the interface layer film 102 is grown on the silicon substrate 101 that has been processed in the early stage, and its thickness is about 0.5nm. In the embodiment of the present invention, the interface layer film 102 is SiO 2 interface layer film. In this embodiment, the interface layer film 102 is made of SiO 2 This is described as an example. In other embodiments, other materials mentioned above can be selected as the interface layer film 102 .

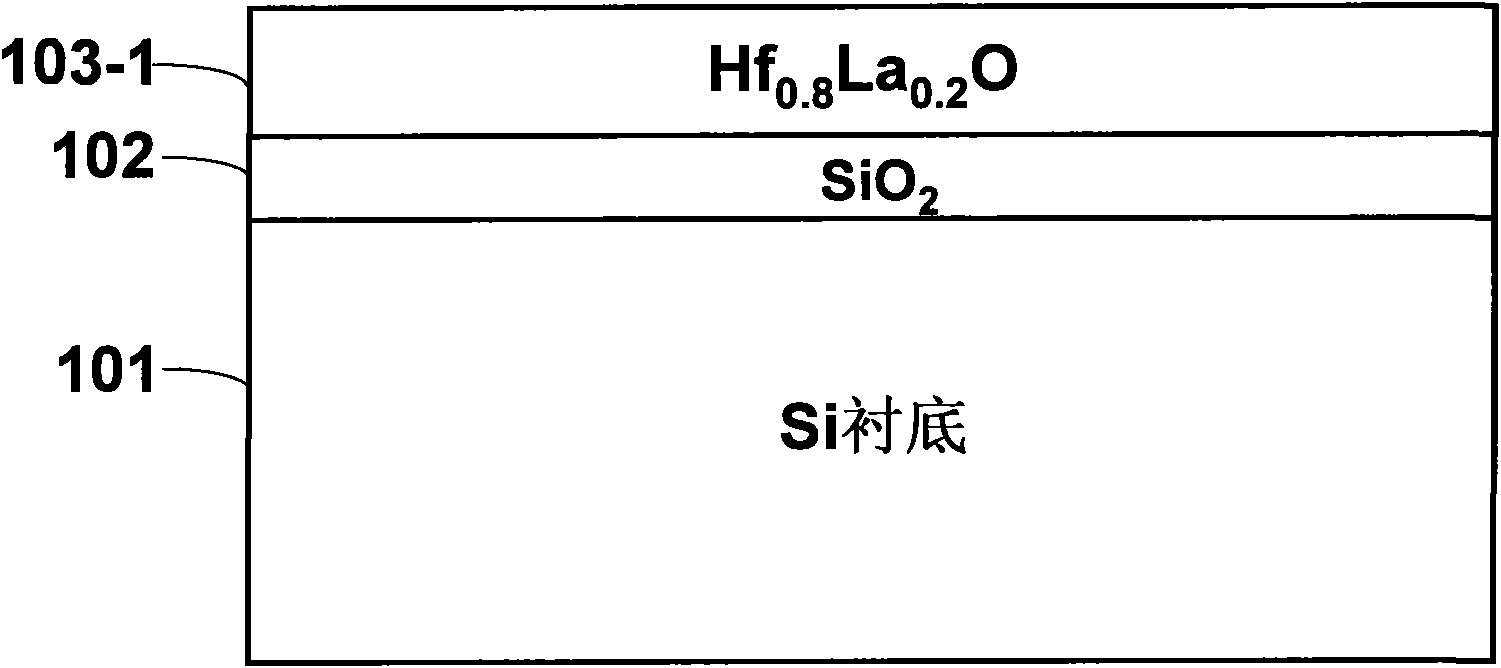

[0029] Step 2: If image 3 shown in SiO 2 ALD technology is used to grow the first ...

Embodiment 2

[0037] Such as Figure 6-11 As shown, it is a schematic diagram of forming the gate stack structure of the present invention according to Embodiment 2 of the present invention, which includes the following steps:

[0038] Step 1: grow a 0.5nm-thick interface layer film 102 on the silicon substrate 101 that has been processed in the previous stage, such as Image 6 As shown, in this embodiment the interface layer film 102 is SiO 2 . In this embodiment, the interface layer film 102 is made of SiO 2 This is described as an example. In other embodiments, other materials mentioned above can be selected as the interface layer film 102 .

[0039] Step 2: If Image 6 As shown, the first layer of insulating film 103-1 is grown by ALD technology on the interface layer film 102, and its thickness is about 1nm. In this embodiment, the first layer of insulating film 103-1 is HfO 2 film.

[0040] Step 3: If Figure 7 As shown, the second layer of insulating film 103-2 is grown by ALD...

Embodiment 3

[0050] Such as Figure 12-15 As shown, it is a schematic diagram of forming the gate stack structure of the present invention according to Embodiment 3 of the present invention, which includes the following steps:

[0051] Step 1: If Figure 12 As shown, a layer of 0.3nm thick HfO is grown by ALD technology on the silicon substrate 101 that has been processed in the early stage. 2 Film 102.

[0052] Step 2: In a nitrogen atmosphere, take the first annealing treatment of the structure at 700°C for 20s to form HfSiO x interface layer film 102, Figure 13 shown.

[0053] Step 3: If Figure 13 shown, in HfSiO x The first layer of insulating film 103-1 is grown on the interface layer film 102 by ALD technology, and its thickness is about 0.5nm. In this embodiment, the first layer of insulating film 103-1 is a HfLaON film.

[0054] Step 4: If Figure 14 As shown, the second layer of insulating film 103-2 is grown by ALD technology on the first layer of insulating film 103-1,...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More