Patents

Literature

130results about How to "Reduce gate leakage current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

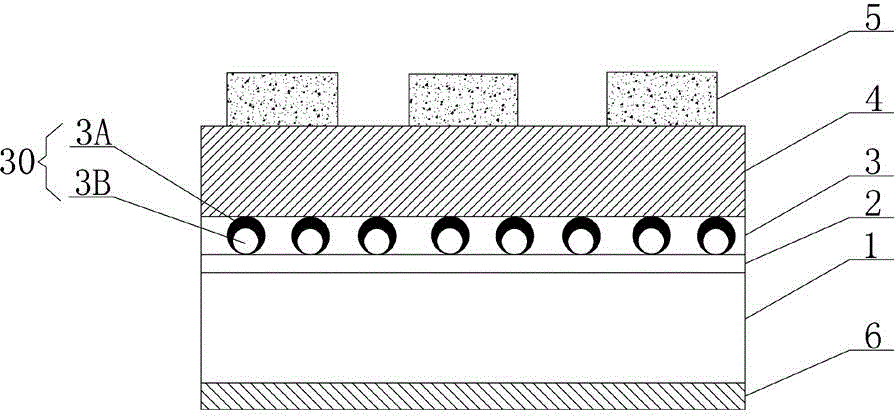

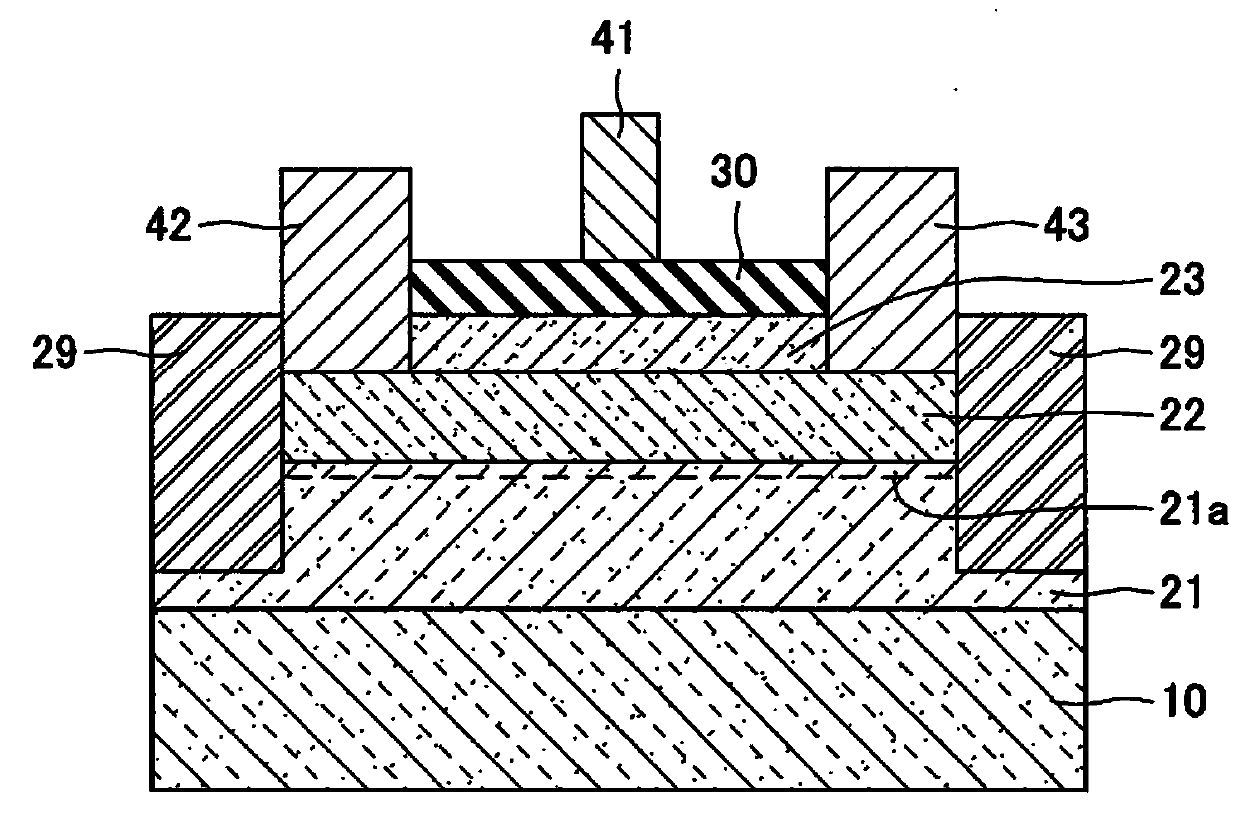

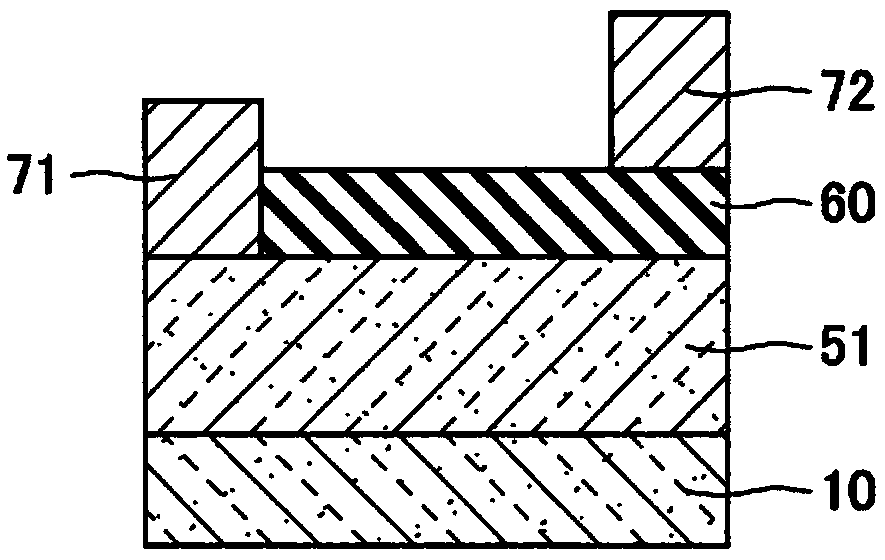

Field-effect semiconductor device

InactiveUS20080283870A1Reduce gate leakage currentLower turn-on resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductanceHeterojunction

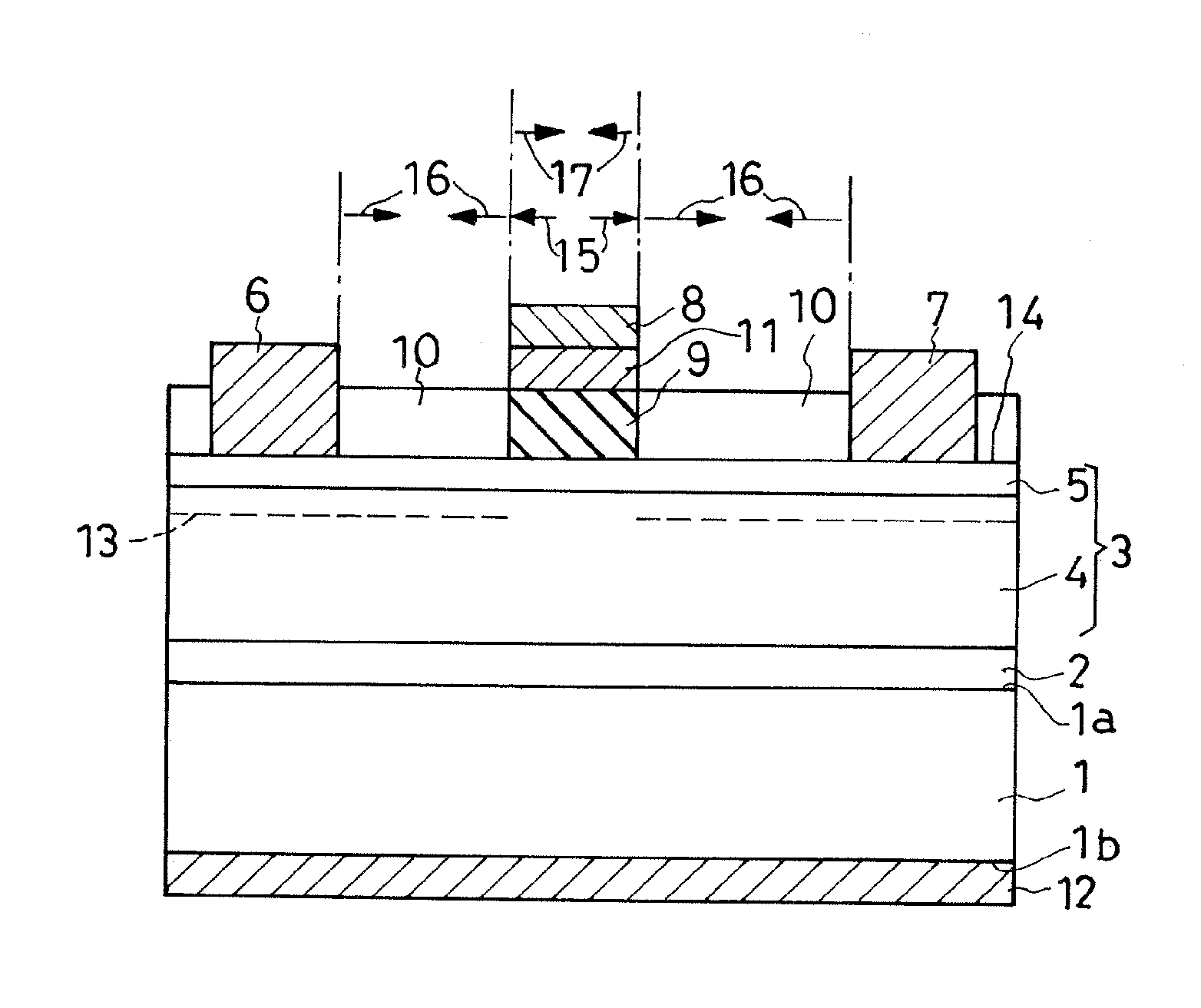

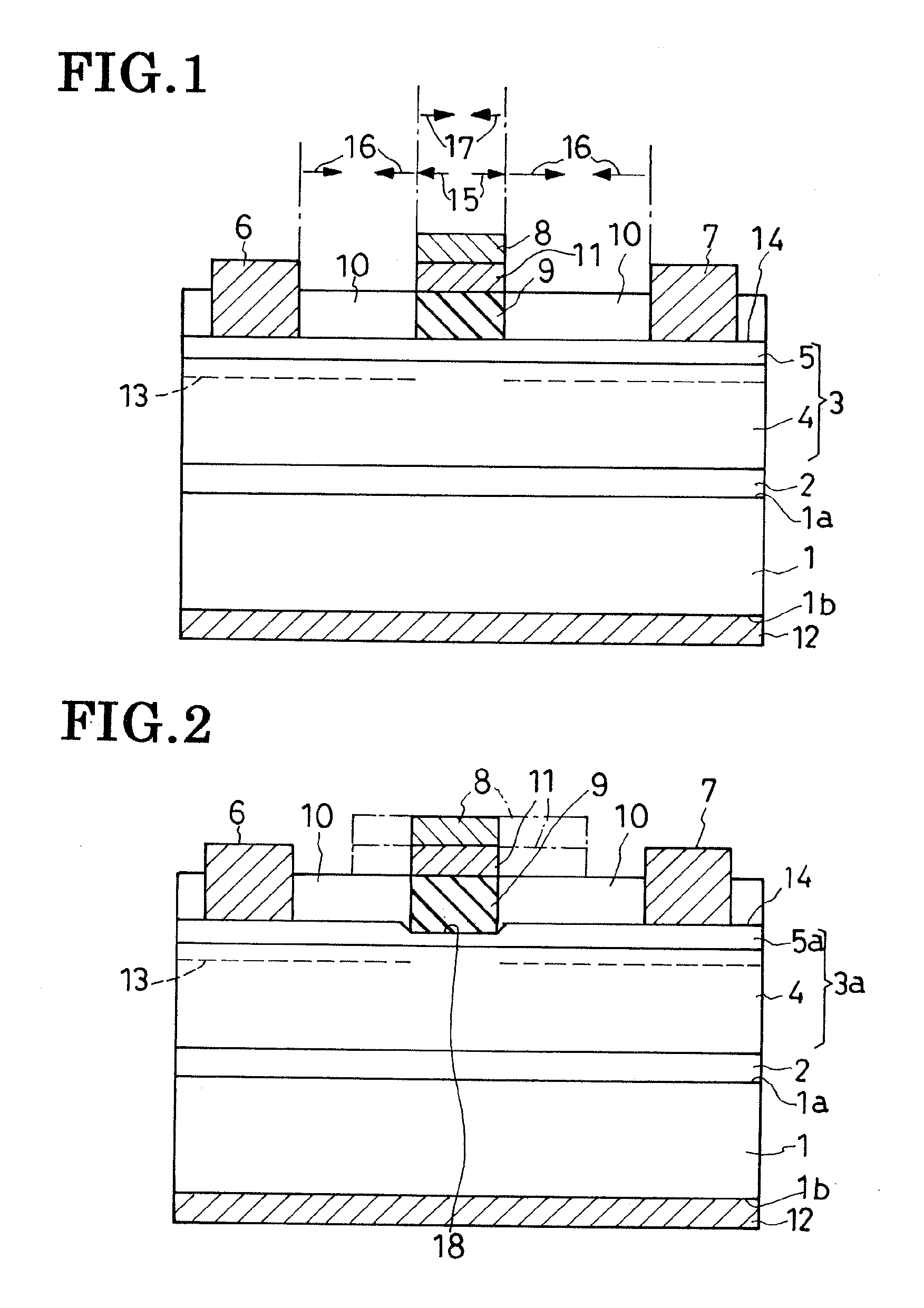

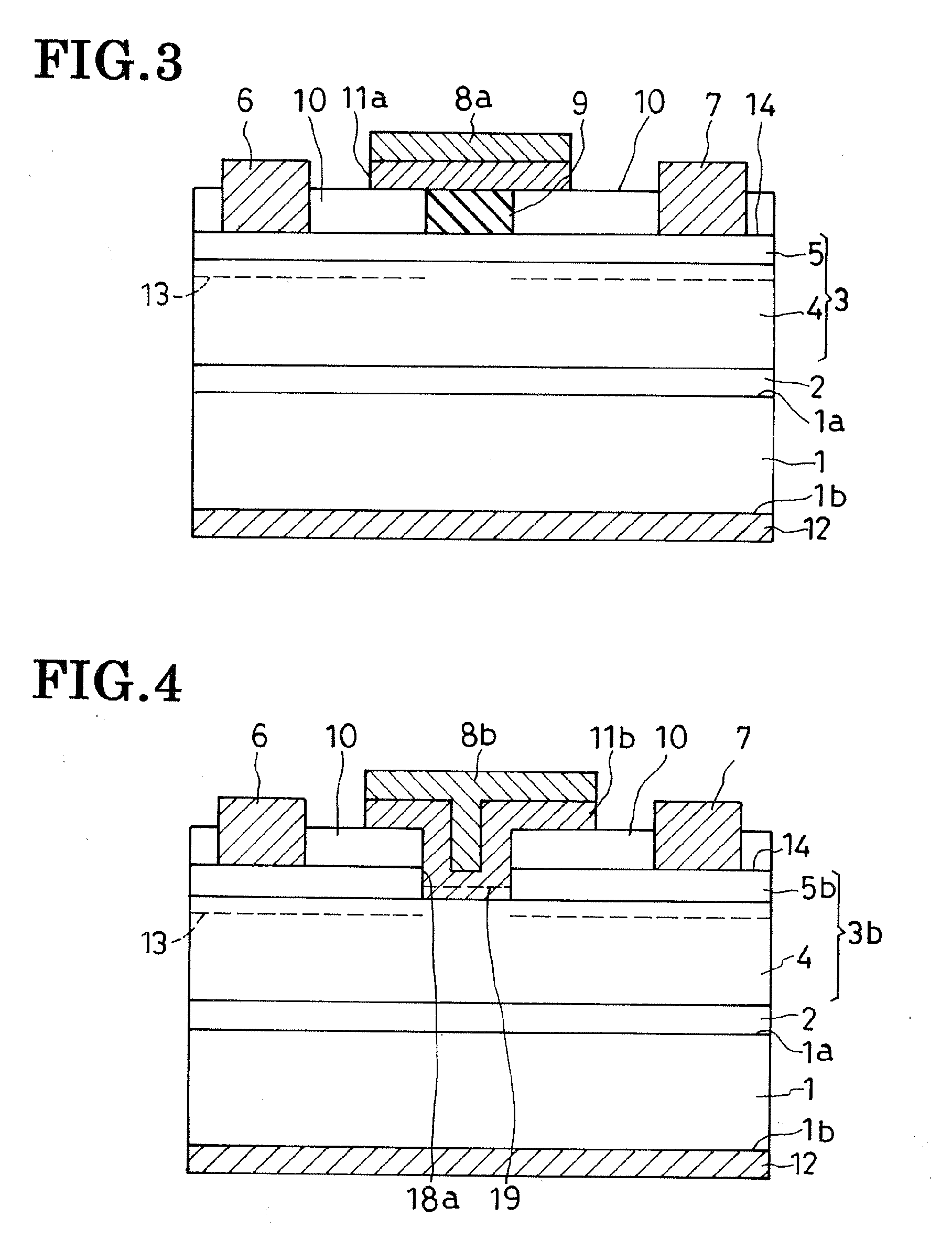

A HEMT-type field-effect semiconductor device has a main semiconductor region comprising two layers of dissimilar materials such that a two-dimensional electron gas layer is generated along the heterojunction between the two layers. A source and a drain electrode are placed in spaced positions on the main semiconductor region. Between these electrodes, with spacings therefrom, an insulator is provided with is made from a material capable of developing a stress to reduce carrier concentration in neighboring part of the two-dimensional electron gas layer, creating a discontinuity in this layer. A gate electrode overlies the insulator via a piezoelectric layer which is made from a material capable of developing, in response to a voltage applied to the gate electrode, a stress for canceling out the stress developed by the insulator. Thus the device is physically held off by the action of the insulator while no voltage is being impressed to the gate electrode and, upon voltage application thereto, piezoelectrically turns on by the action of the piezoelectric layer. The turn-on resistance of the device is relatively low as the insulator occupies only part of the source-drain spacing.

Owner:SANKEN ELECTRIC CO LTD

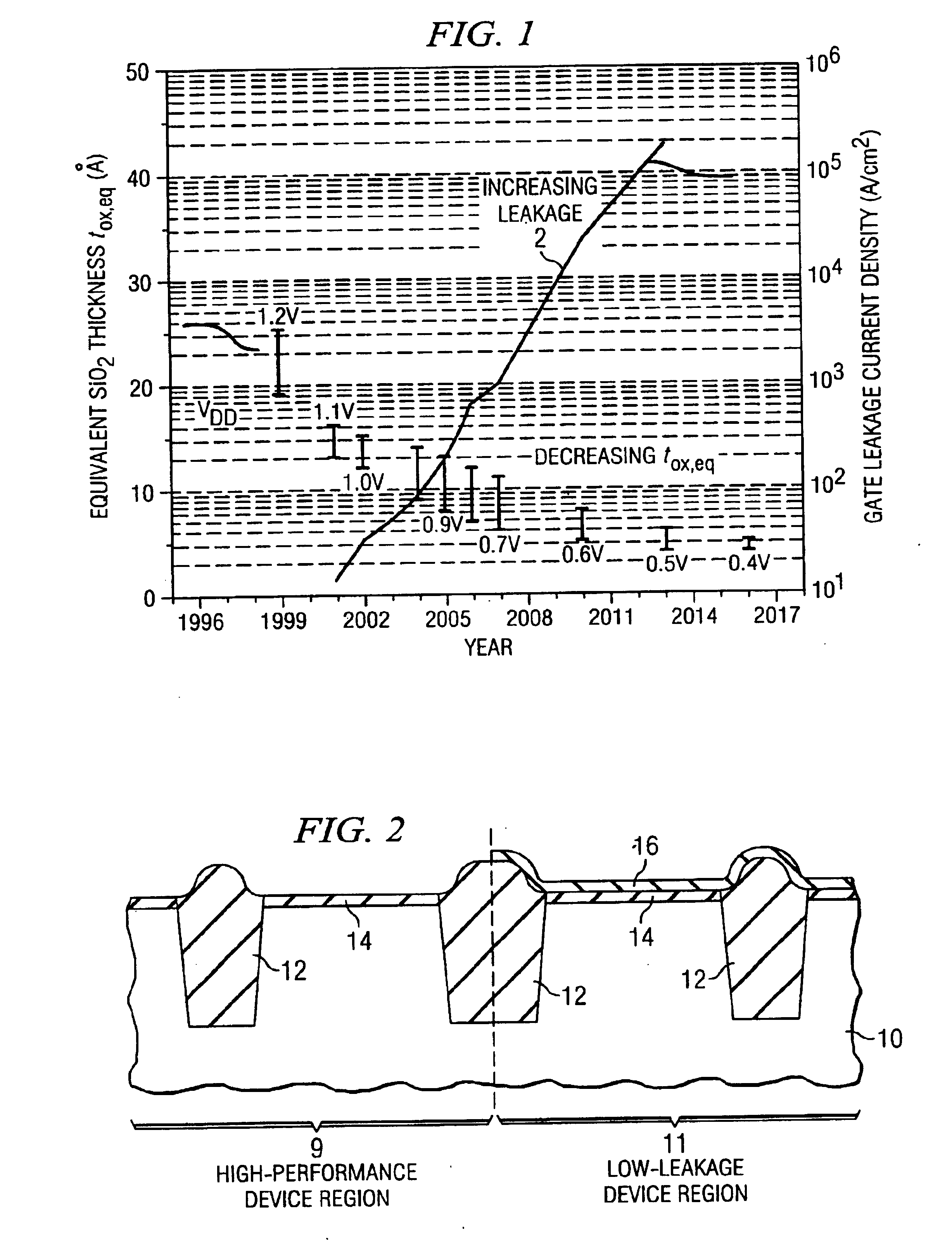

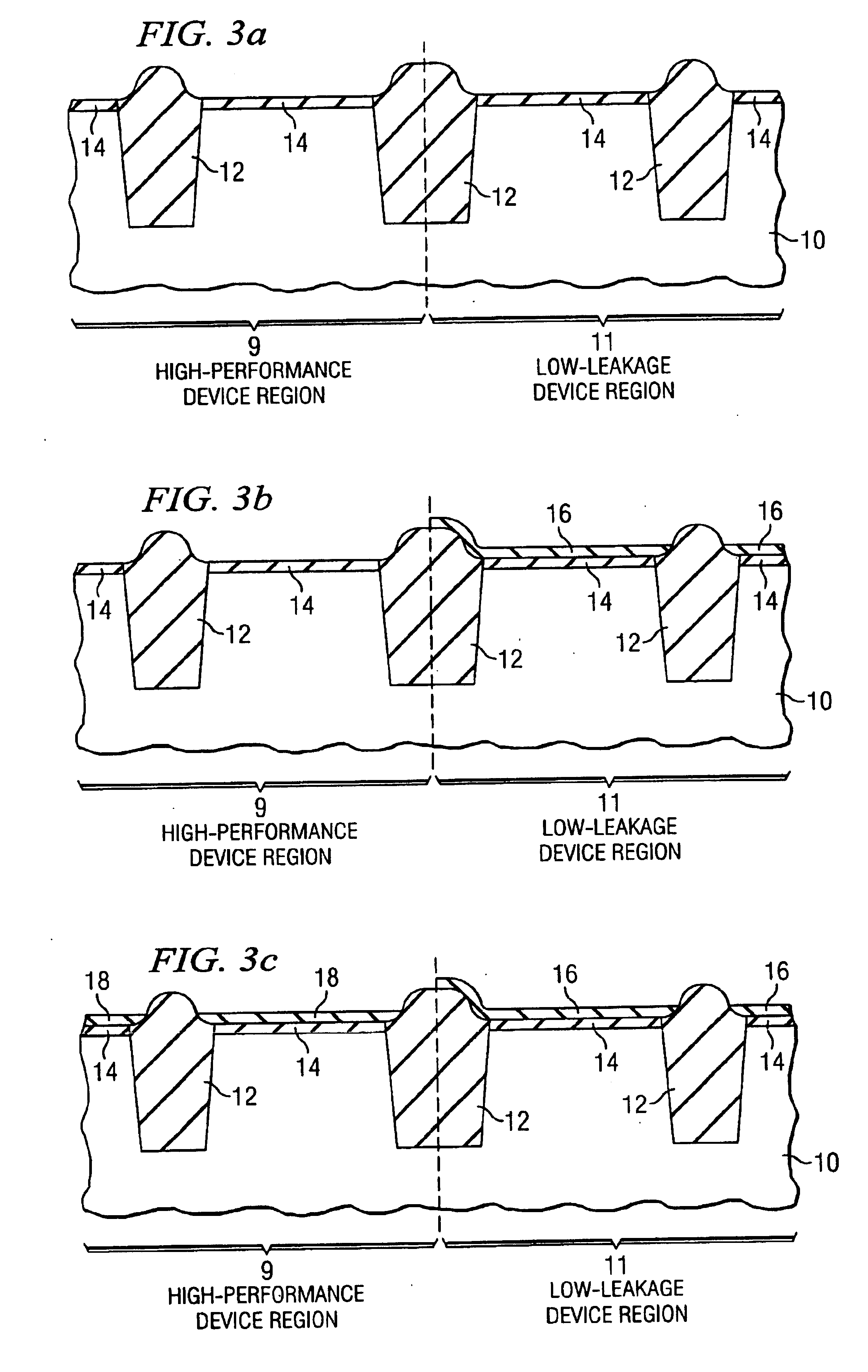

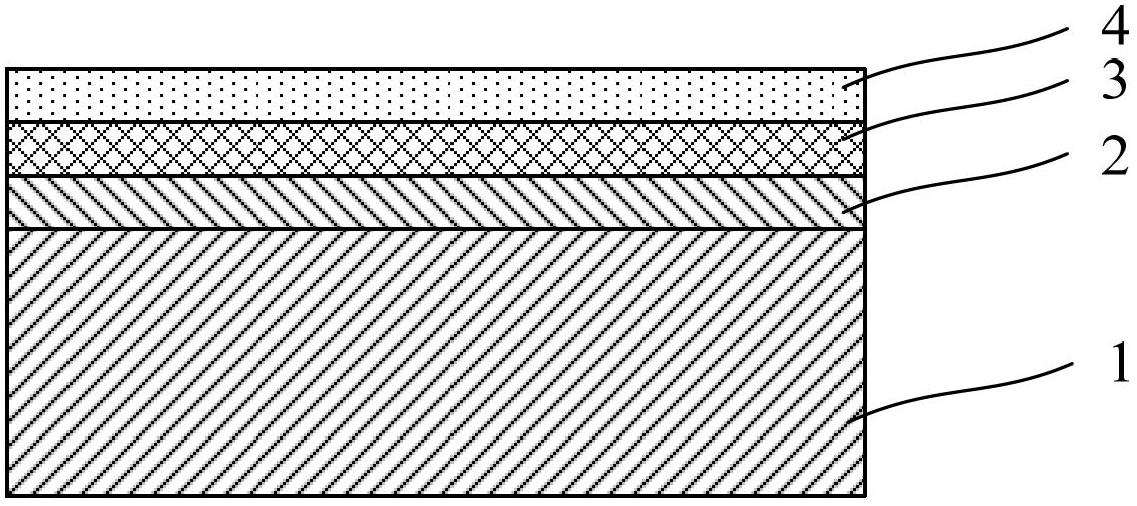

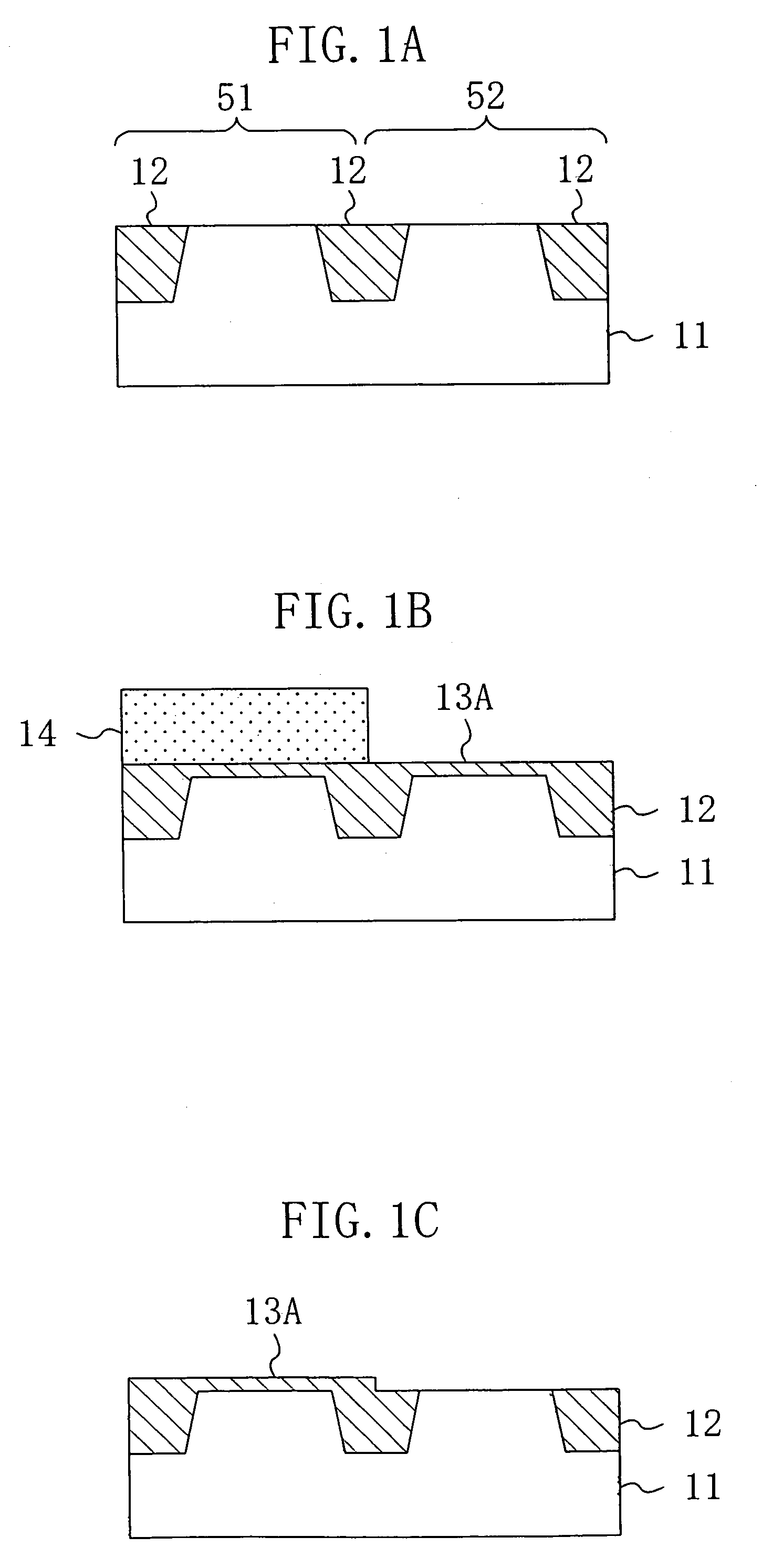

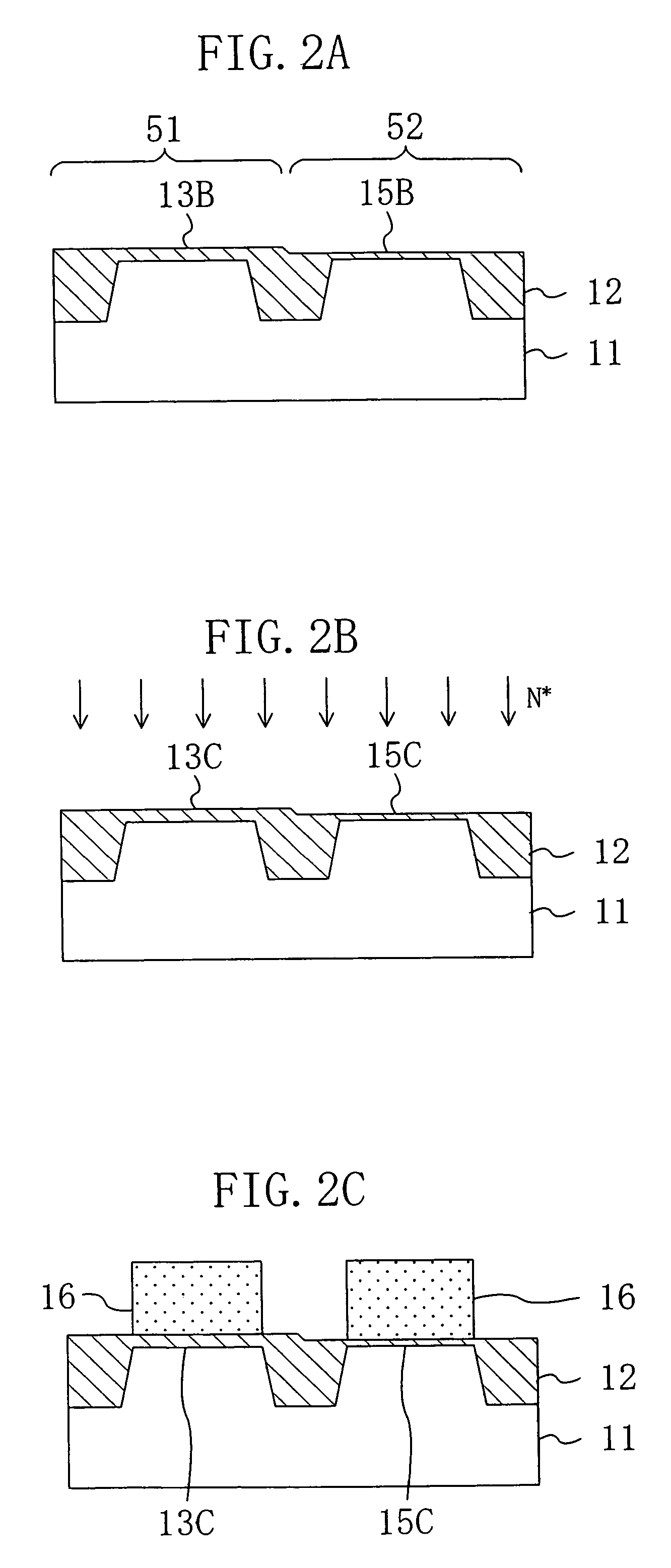

Semiconductor chip with gate dielectrics for high-performance and low-leakage applications

InactiveUS6906398B2Reduce gate leakage currentFast switching speedTransistorSolid-state devicesGate dielectricSemiconductor chip

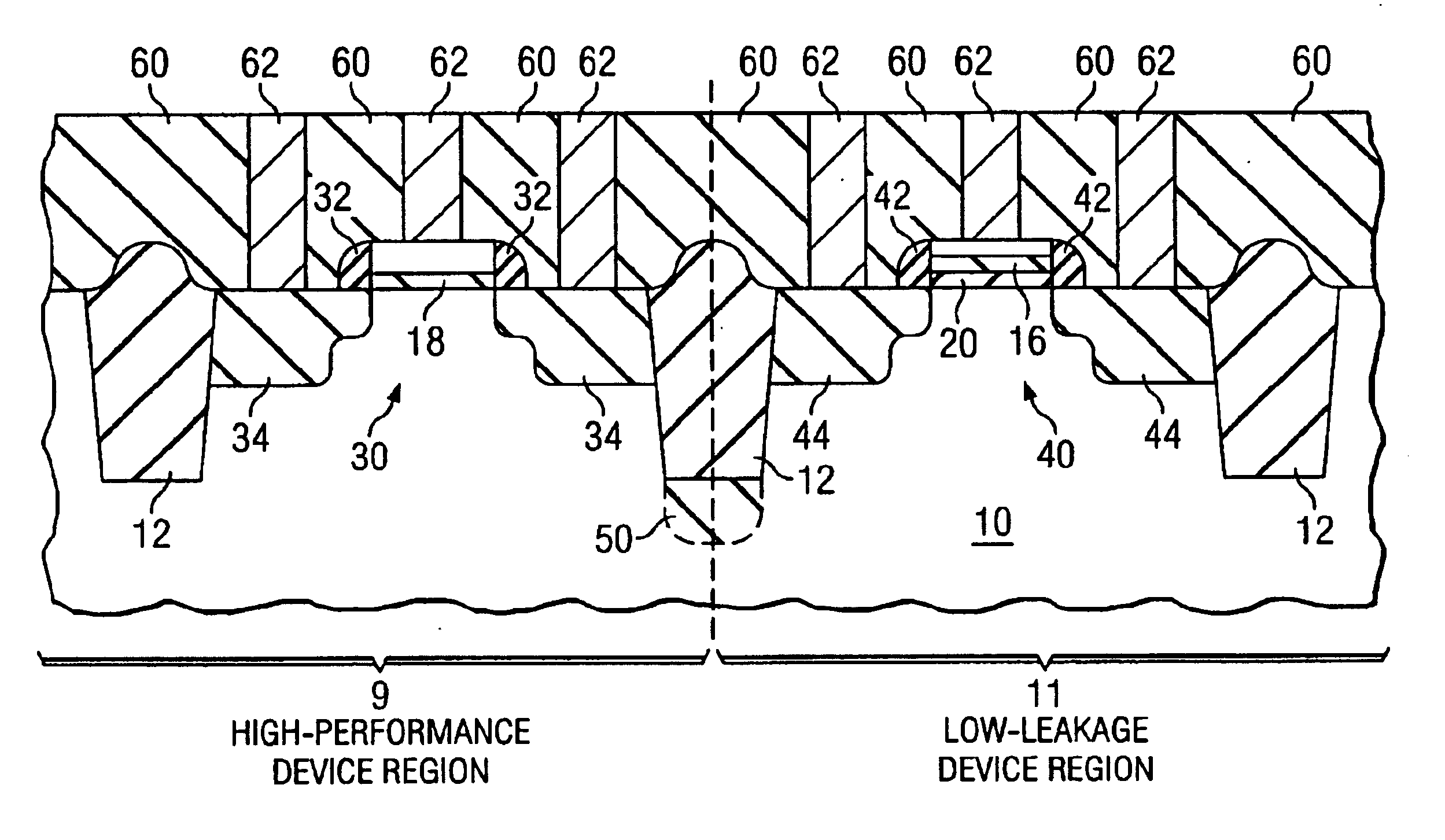

Both high performance and low leakage current devices can be formed on a single wafer without significant additional processing steps by the formation of an ultra-thin gate dielectric and a high-permittivity gate dielectric, respectively, in regions wherein switching speed and low leakage current, respectively, are desired. Logic and embedded memory regions can be performance optimized on the same integrated circuit.

Owner:TAIWAN SEMICON MFG CO LTD

Preparation method of graphite-based double-gate MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor)

InactiveCN102683217AAvoid destructionAvoid pollutionSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricField-effect transistor

The invention provides a preparation method of a graphite-based double-gate MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor), belonging to the fields of microelectronics and solid electronics. The preparation method comprises the following steps: forming a high-quality SiO2 layer on a monocrystalline silicon substrate; coating a layer of high polymer in a spinning way on the SiO2 layer, wherein the high polymer is used as a carbon source for preparing graphite; depositing a catalytic metal layer on the high polymer and performing high temperature annealing so at to form graphite at the junction face of the SiO2 layer and the catalytic metal layer; windowing the catalytic metal layer and forming a source and a drain of the transistor by using photolithography and an etching process; depositing a layer of high-K film in the windowed area by using an atomic deposition system and preparing a front metal gate above the high-K film; and finally preparing a back metal gate on the back of the Si substrate to obtain a double-gate MOSFET device based on a graphite trench material and a high-K gate dielectric medium.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

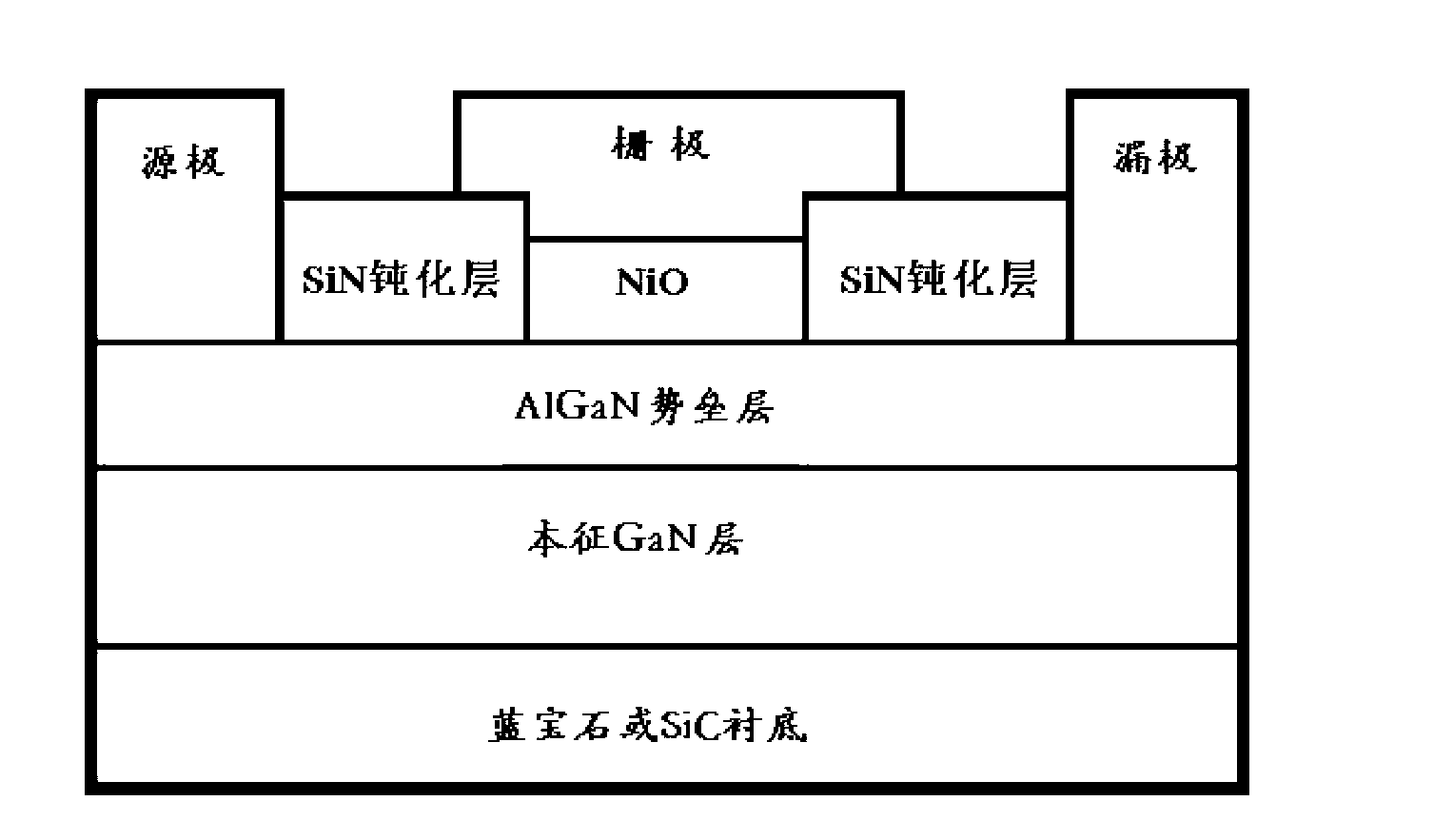

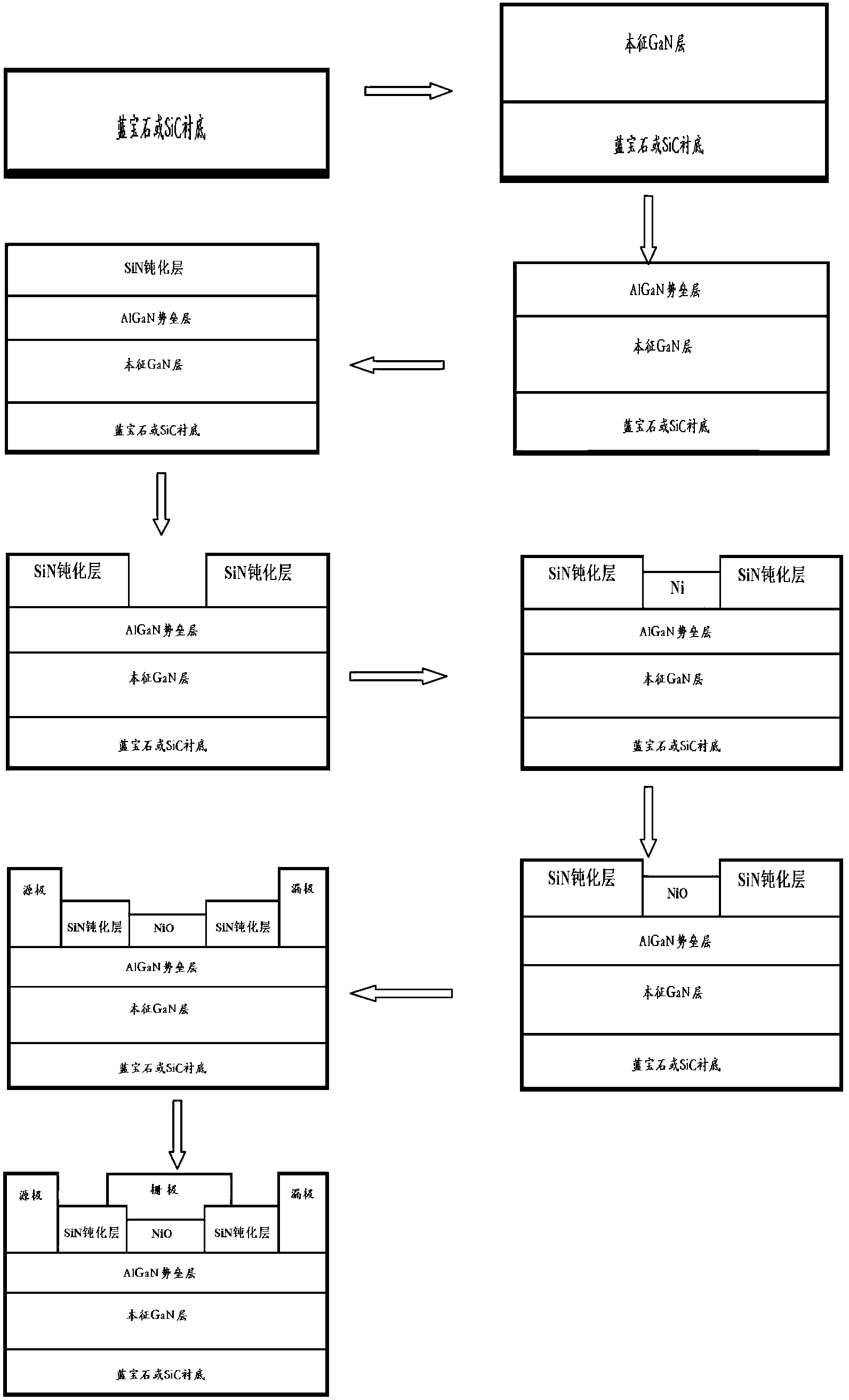

AlGaN/GaN heterojunction enhanced device and manufacturing method thereof

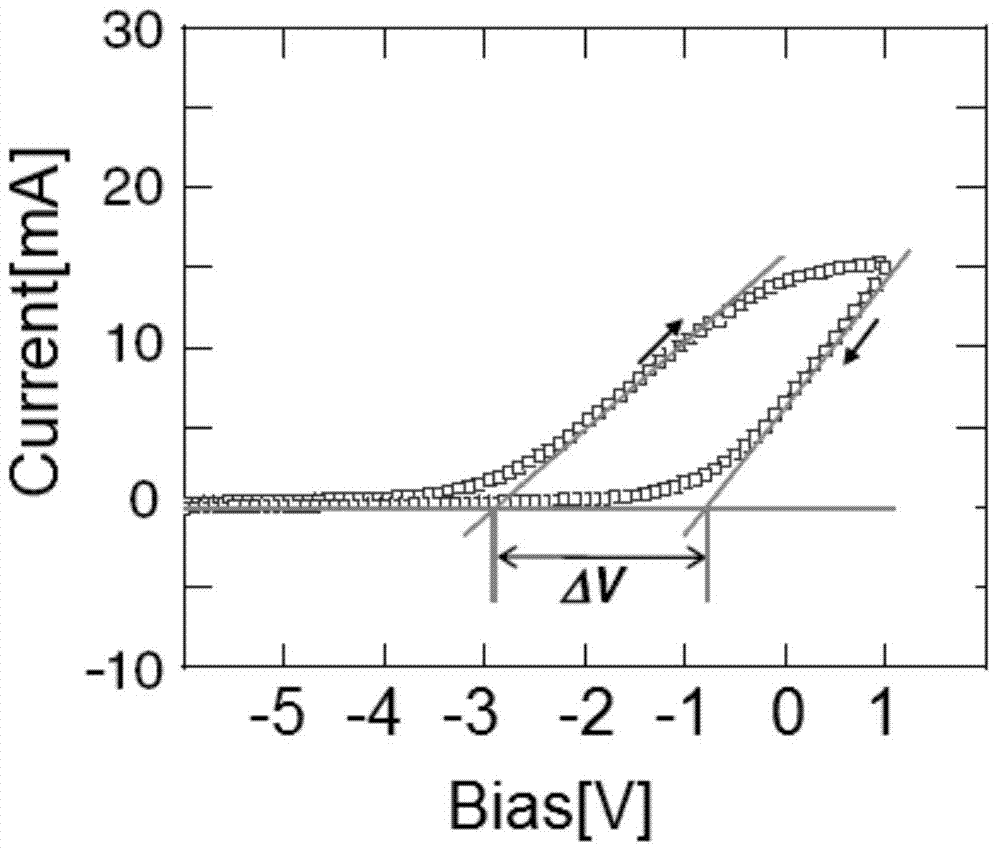

ActiveCN102938413ALow densityIncrease the forward threshold voltageSemiconductor/solid-state device manufacturingSemiconductor devicesHigh-electron-mobility transistorOhmic contact

The invention discloses a method for manufacturing an AlGaN / GaN heterojunction enhanced high-electron-mobility transistor. The method is mainly used for solving the problem that the current enhanced high-electron-mobility transistor is poor in threshold voltage uniformity and process repeatability. The method comprises the following manufacturing processes of: (1) growing AlGaN / GaN heterojunctions on a SiC or sapphire substrate, wherein the thickness of an AlGaN barrier layer is 8-16 nm, and the content of the component Al is 25-35%; (2) depositing a SiN layer on the surface of the AlGaN barrier layer so as to cover the AlGaN barrier layer, and carrying out grid groove etching so as to expose a grid area; (3) depositing metal Ni on the surface of the AlGaN barrier layer on which the grid area is exposed; (4) carrying out high-temperature heat treatment in an oxygen environment at the temperature of 800-860 DEG C by adopting a rapid thermal annealing furnace so as to form a NiO layer; and (5) carrying out active-area mesa isolation on the AlGaN barrier layer so as to finish source and drain ohmic contact electrodes, and manufacturing a grid electrode on the NiO layer. The method has the advantages of high device threshold voltage, low grid leakage current, simple manufacturing processes, and high process repeatability and controllability, and can be applied to high-working-voltage enhanced AlGaN / GaN heterojunction high-voltage switches and the basic units of GaN-based combinational logic circuits.

Owner:云南凝慧电子科技有限公司

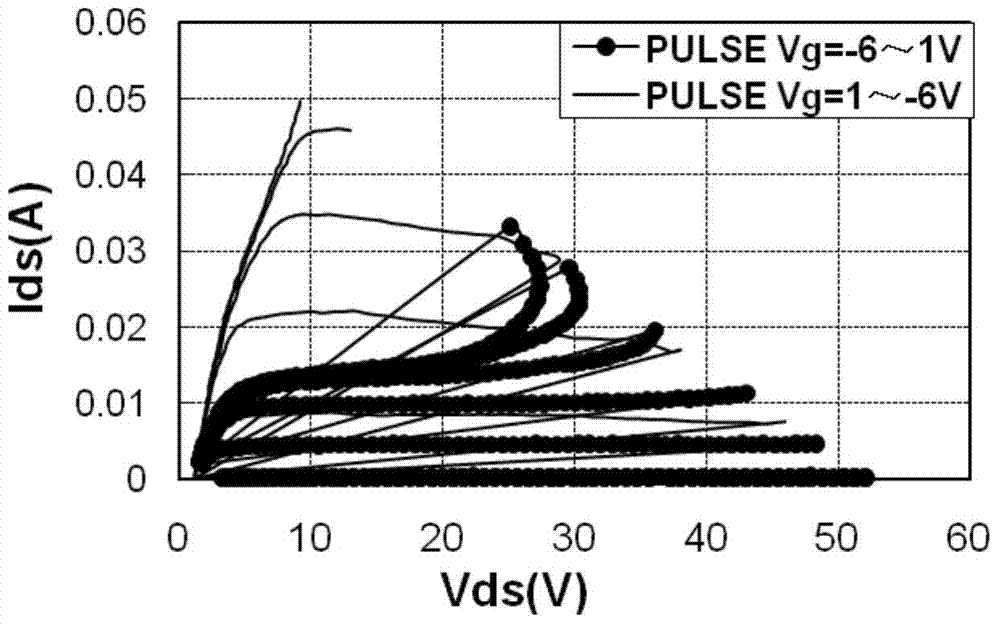

Radio frequency device and manufacturing method thereof

ActiveCN102810564AIncrease contentReduce contact resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactRadio frequency

The invention discloses a radio frequency device. A nitride barrier layer of the radio frequency device has two layers of aluminum-rich nitride, wherein aluminum content is more than 75 percent. The second nitride layer is silicon-containing nitride, and silicon content is high enough, so that metal electrodes of drain and source electrodes and the second nitride layer are in ohmic contact, and contact resistance of the drain and source electrodes is reduced; and because the silicon-containing nitride can provide more free electrons, concentration of two-dimensional electron gas is further increased, and radio frequency performance of the device is improved. Meanwhile, a dielectric layer used as a passivation layer of the nitride is grown on the silicon-containing nitride in situ, so that surface state intensity is reduced, and stress releasing is reduced. In the manufacturing process of a grid electrode, the passivation layer of a grid region is etched, and the exposed nitride barrier layer is oxidized. Oxide generated on the grid electrode greatly reduces leakage current of the grid electrode and the leakage current between the source and drain electrodes. In addition, the invention also provides a manufacturing method for the radio frequency device.

Owner:DYNAX SEMICON

Aluminium gallium nitride/gallium nitride high electronic migration rate transistor and its manufacturing method

InactiveCN1937249AReduce gate leakage currentImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorAluminum gallium nitride

Duplex conflicts exist in current semiconductor device: high breakdown voltage but small transconductance; or large transconductance but low breakdown voltage. The disclosed high electron mobility transistor of nitride of aluminum gallium / gallium nitride possesses advantages of both. The invention also discloses preparation method. The method includes steps and structures: the disclosed transistor includes channel layer, barrier layer as well as source pole and drain pole setup on the barrier layer; providing groove on the barrier layer between source pole and drain pole; quadrate or T type gate electrode is installed on groove covered by dielectric layer; function of dielectric layer is to reduce leakage current on gate electrode, and increase maximum current of device; function of groove is to raise transconductance of device. Advantages are: retaining large transconductance, small leakage current of gate electrode, and large drive current.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

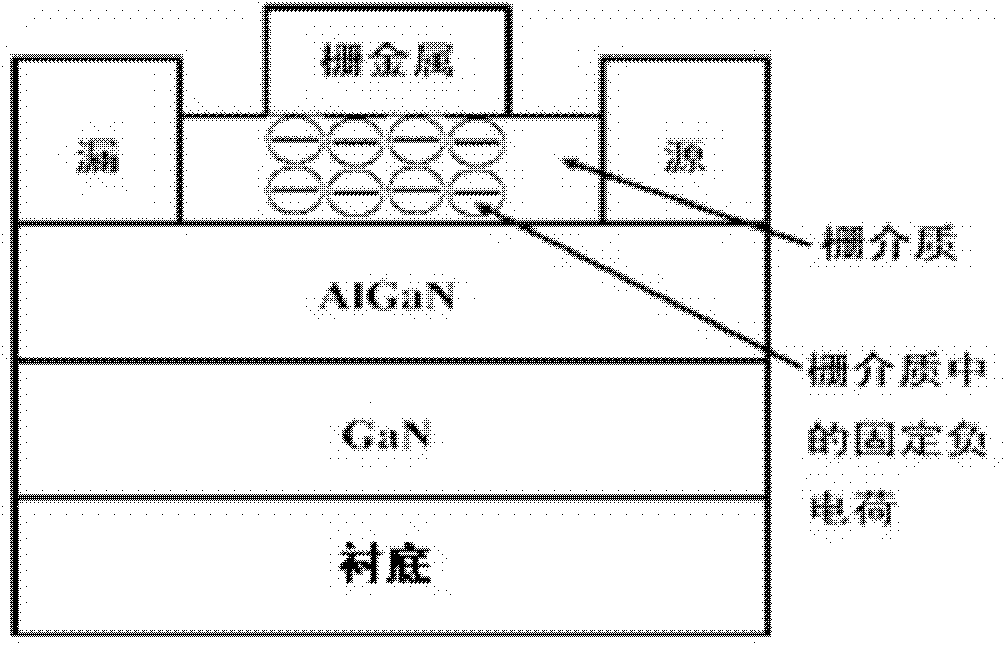

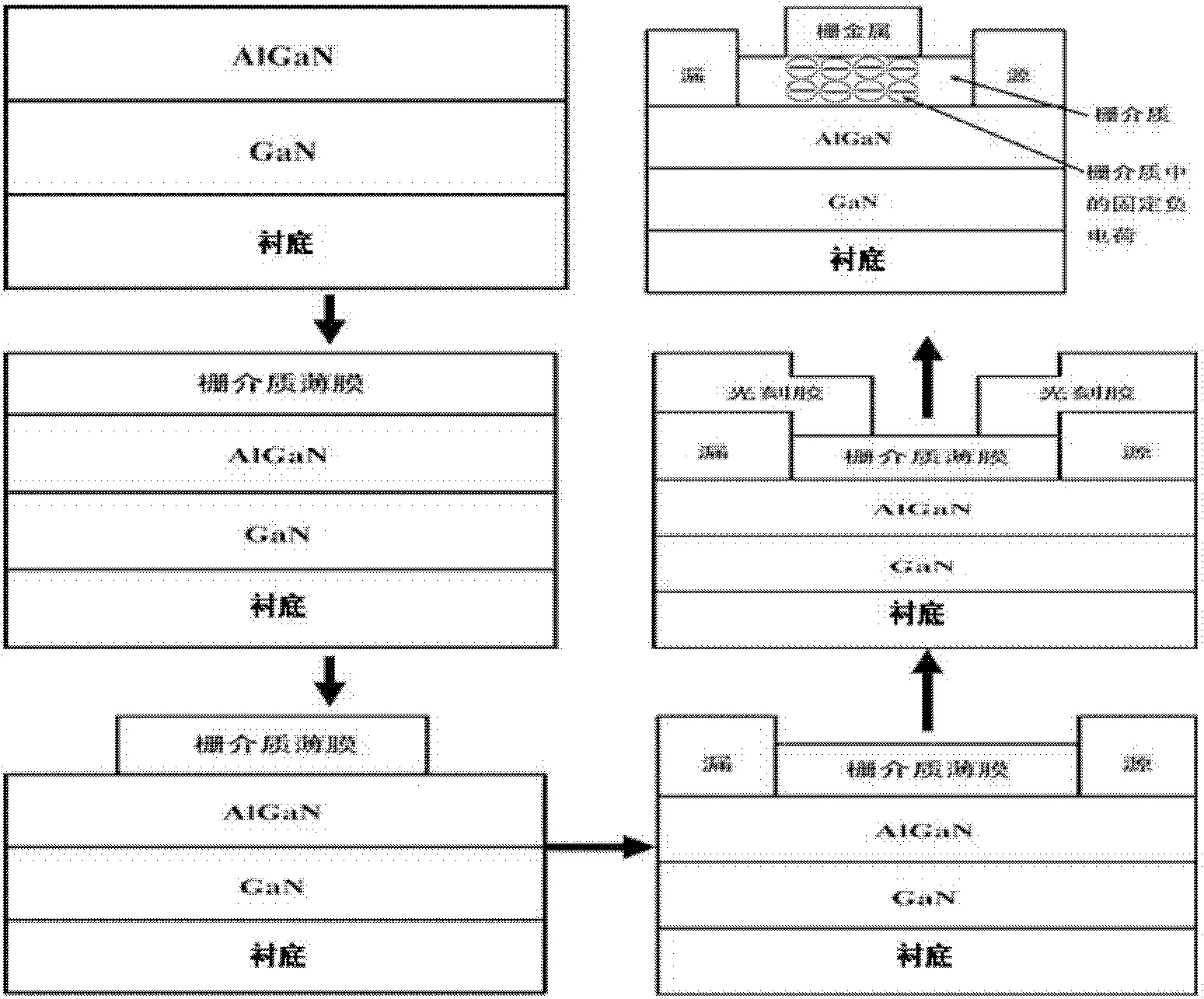

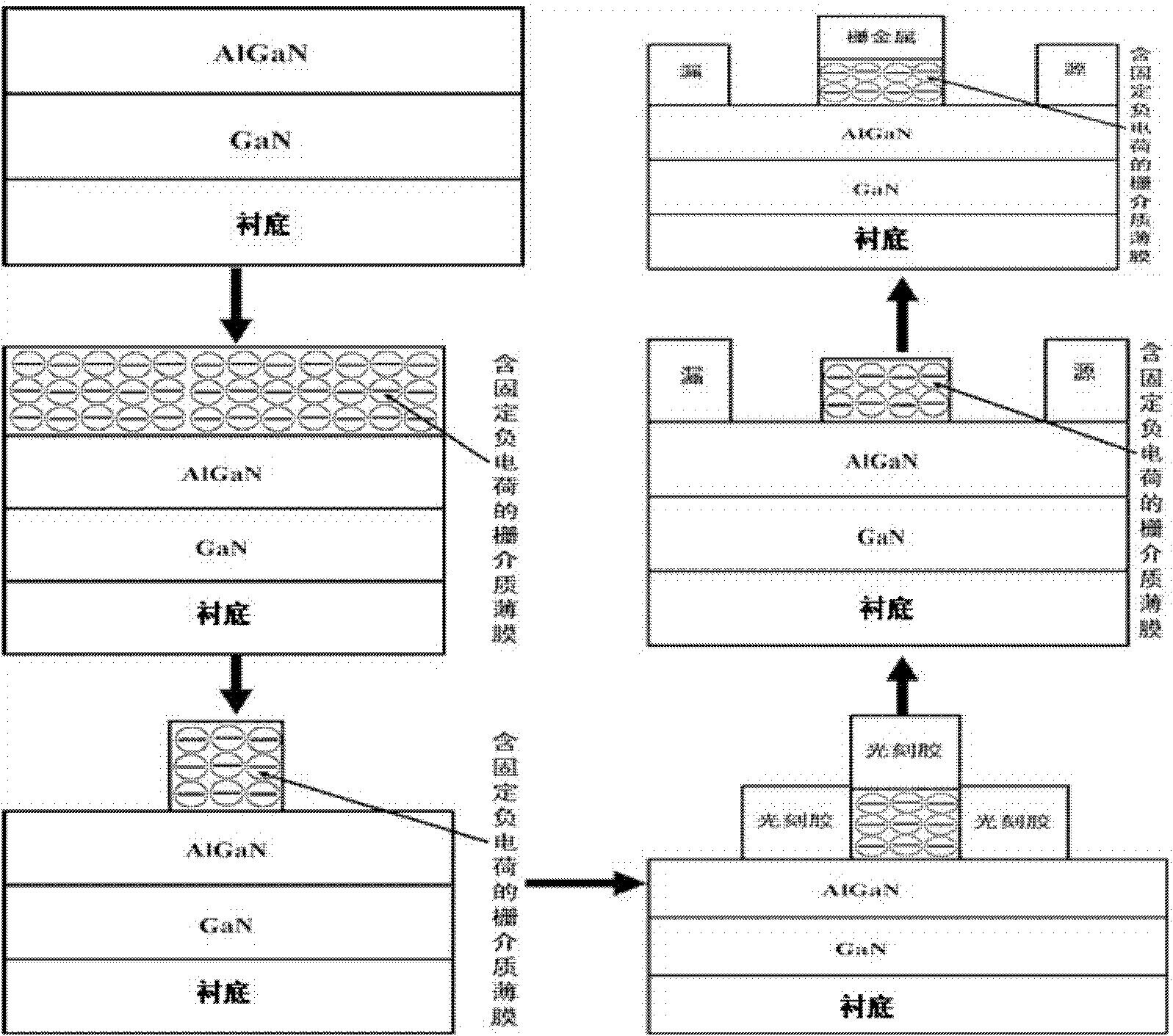

Enhanced AlGaN/GaN HEMT (High Electron Mobility Transistor) device and manufacturing method thereof

InactiveCN102184943AThe process is simple and easy to controlReduce gate leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionGate dielectric

The invention relates to an enhanced AlGaN / GaN HEMT (High Electron Mobility Transistor) device and a manufacturing method thereof, belonging to the technical field of semiconductor devices. The device comprises an AlGaN / GaN heterojunction structure located on the surface of a substrate and gate, source and drain electrode structures, wherein F ion or Cl ion fixed negative charges are arranged in a gate dielectric film material. In the invention, through introducing the F ion or Cl ion fixed negative charges into a gate dielectric film and controlling the electric charge quantity of the introduced fixed negative charges, the threshold voltage of a transistor is regulated and the enhanced AlGaN / GaN HEMT device with the threshold voltage greater than zero is realized. In the invention, the enhanced AlGaN / GaN HEMT device structure is obtained though a method of introducing the fixed negative charges into the gate dielectric film material; interface characteristics of the AlGaN / GaN heterojunction are not influenced so that the performance degeneration of the device is not caused; the process is simple and controllable and is compatible with the manufacturing process of a depletion mode (normally-on) AlGaN / GaN HEMT device; the source-drain saturation current density and the gate-drain current of the manufactured device for manufacturing a GaN enhanced effect transistor are small; and therefore, the device is particularly suitable for developing a GaN logic circuit.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Vacuum tube flash structure and manufacturing method thereof

InactiveCN106571367AEasy programmingExcellent gate control performanceSolid-state devicesSemiconductor/solid-state device manufacturingBlock effectEngineering

The invention provides a vacuum tube flash structure and a manufacturing method thereof. Vacuum is formed in a channel, and an oxide-nitride-oxide combined structure serves as a gate medium layer, wherein the nitride can better restrict electric charges, so as to provide insulation blocking effect between a grid electrode and vacuum. Since the oxide-nitride-oxide combined structure serves as a gate medium layer, a formed device has better programming, erasing speed and storage time. The grid electrode control performance can be improved, and the grid electrode current leakage can be minimized.

Owner:ZING SEMICON CORP

III-nitride semiconductor device and manufacturing method for same

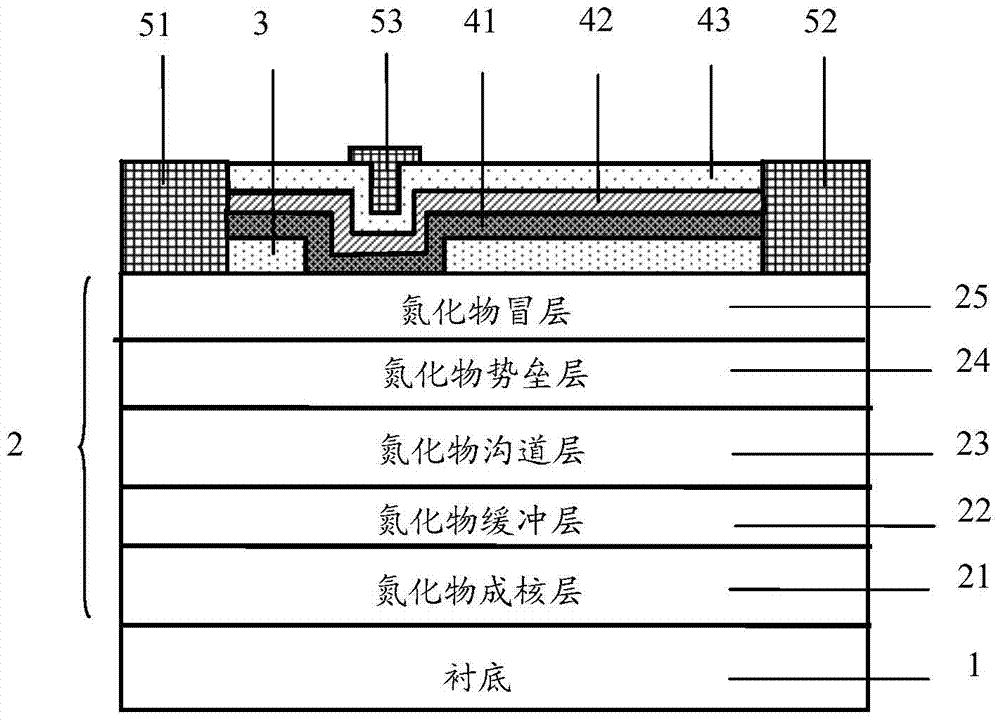

ActiveCN103500763AReduce gate leakage currentHigh gate withstand voltageSemiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingPower semiconductor deviceState density

The invention discloses an III-nitride semiconductor device and a manufacturing method for the same. The III-nitride semiconductor device comprises a nitride semiconductor layer, a passivation layer, a source, a drain and a gate, wherein the nitride semiconductor layer and the passivation layer are grown on a substrate; the gate is positioned between the source and the drain; the nitride semiconductor layer comprises a nitride nucleating layer, a nitride buffer layer, a nitride trench layer and a nitride potential barrier layer; the passivation layer is etched in a gate area until the nitride potential barrier layer is exposed, and a groove is formed in the gate. According to the device and the method, a combined structure of a composite dielectric layer is adopted between the nitride potential barrier layer and a gate metal layer, and the composite dielectric layer comprises a nitride dielectric layer, an oxynitride dielectric layer and an oxide dielectric layer, which are sequentially formed from the substrate, so that the increase of interface state density is avoided; compared with a conventional III-nitride semiconductor device with a single oxide dielectric layer, the III-nitride semiconductor device with the composite dielectric layer has the advantage that the electric leakage and current collapse effects of the semiconductor device can be simultaneously reduced.

Owner:ENKRIS SEMICON

Semiconductor device

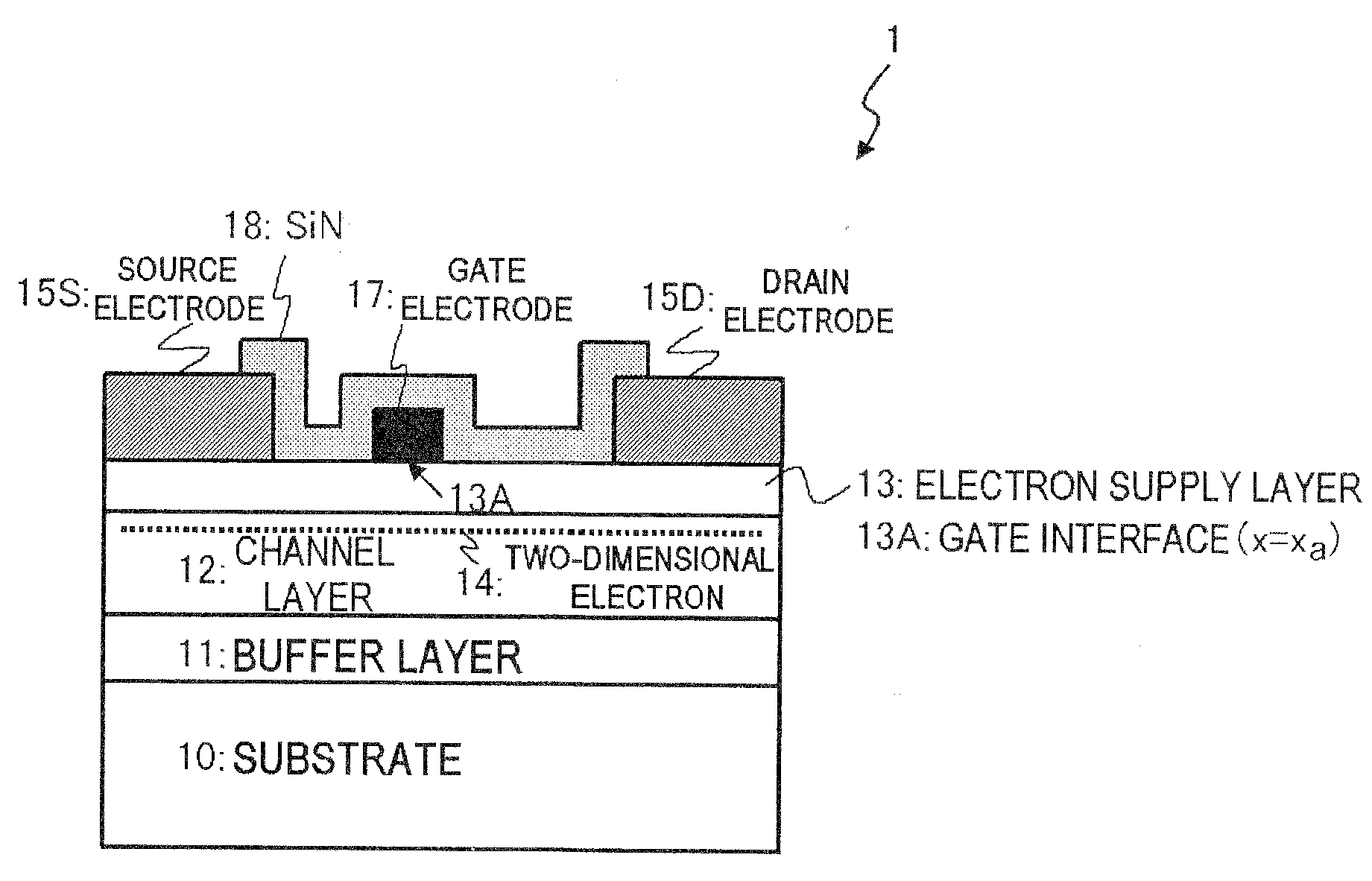

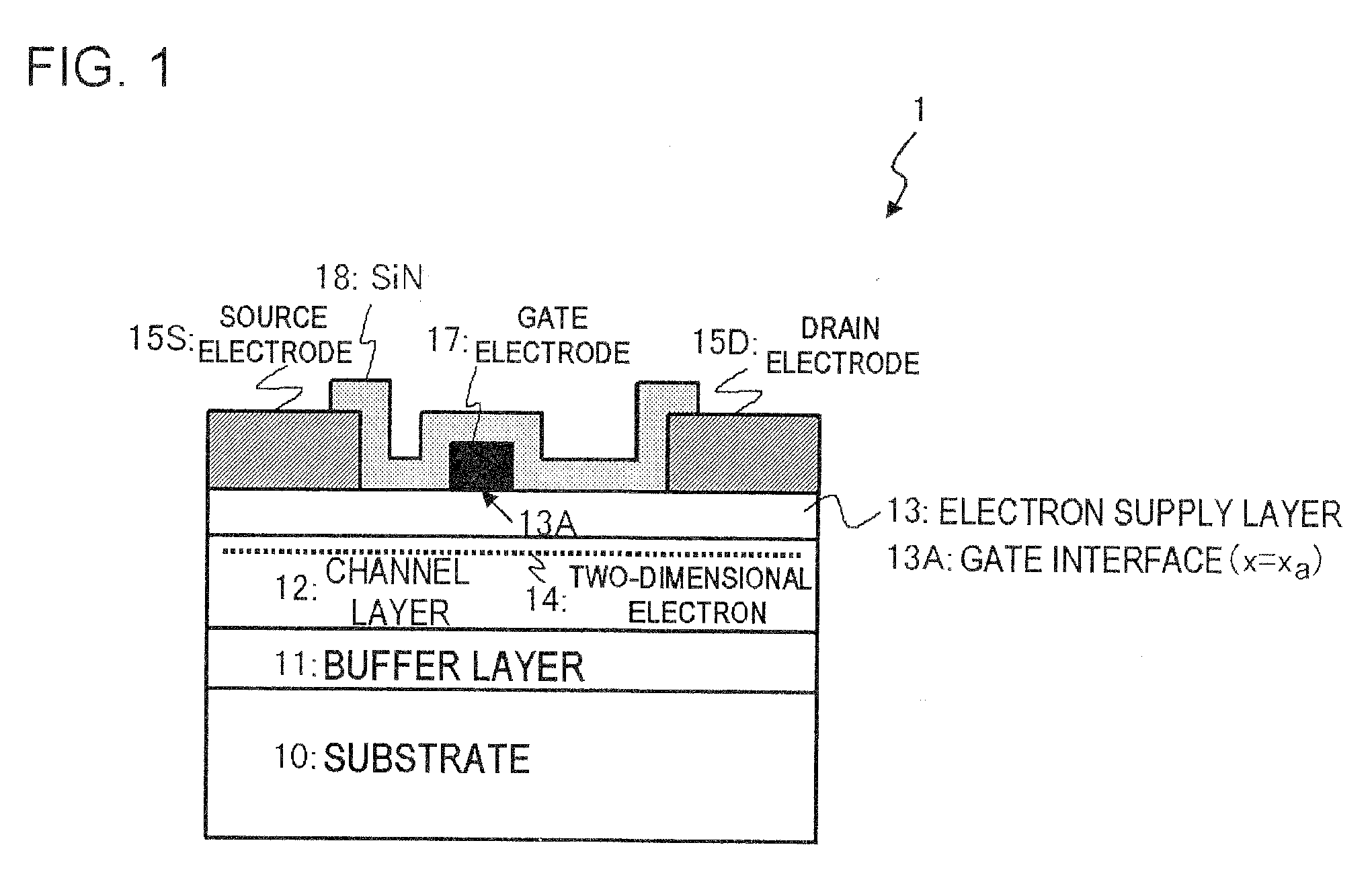

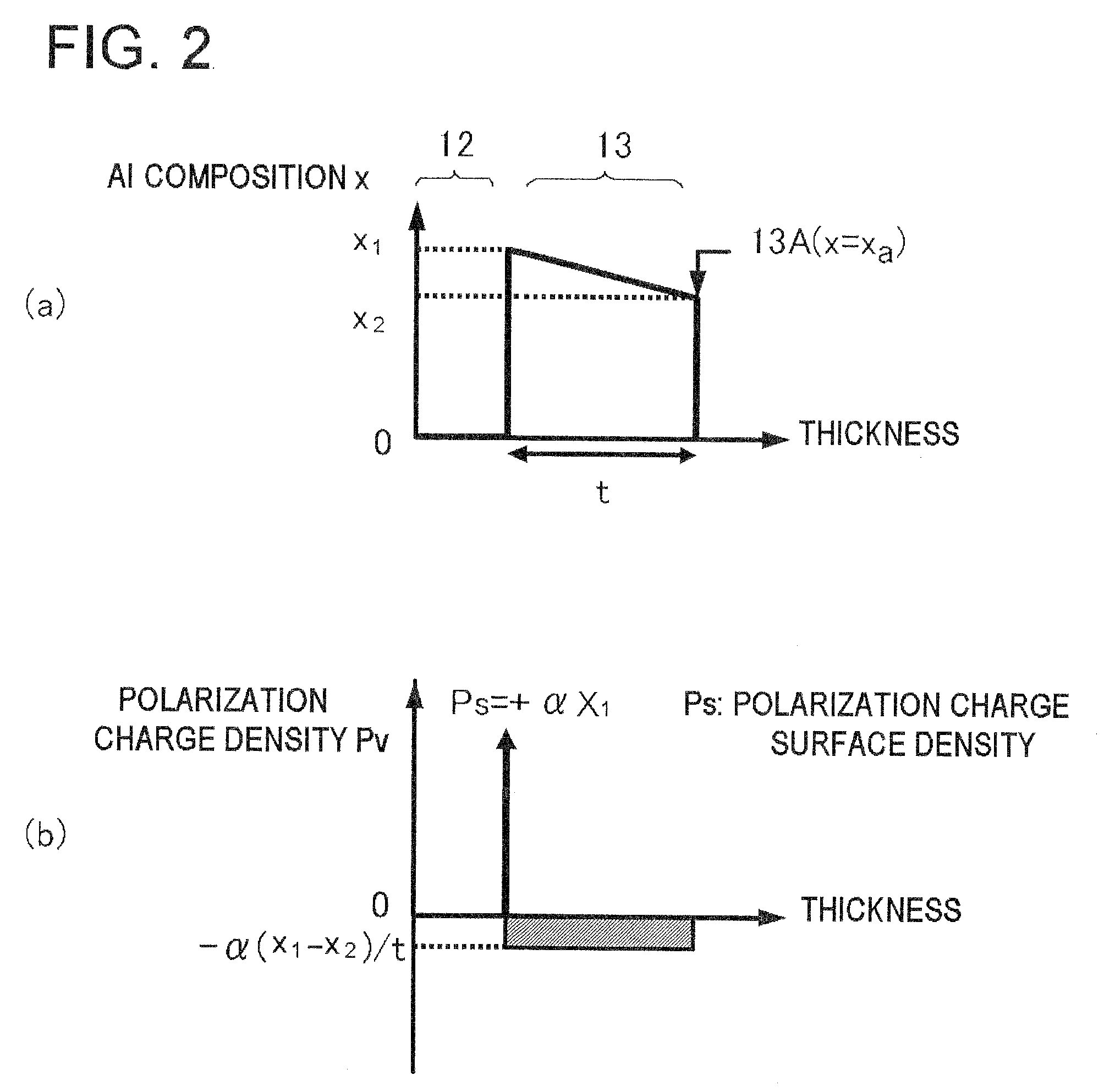

InactiveUS20090008678A1Reduce gate leakage currentSemiconductor devicesHeterojunctionDevice material

An electron supply layer (13) is a layer which forms a heterojunction with a channel layer (12) and contains InzAlxGa1-zxN (0≦z<1, 0<x<1, 0<x+z<1). On the electron supply layer (13), a gate electrode (17) is formed in contact with the electron supply layer (13). The Al composition ratio x1 at the interface between the electron supply layer (13) and the channel layer (12) and the Al composition ratio xa at the interface between the electron supply layer (13) and the gate electrode (17) satisfy the following conditions:x1 / 2≦xa<x1 andx1≦0.3.

Owner:NEC CORP

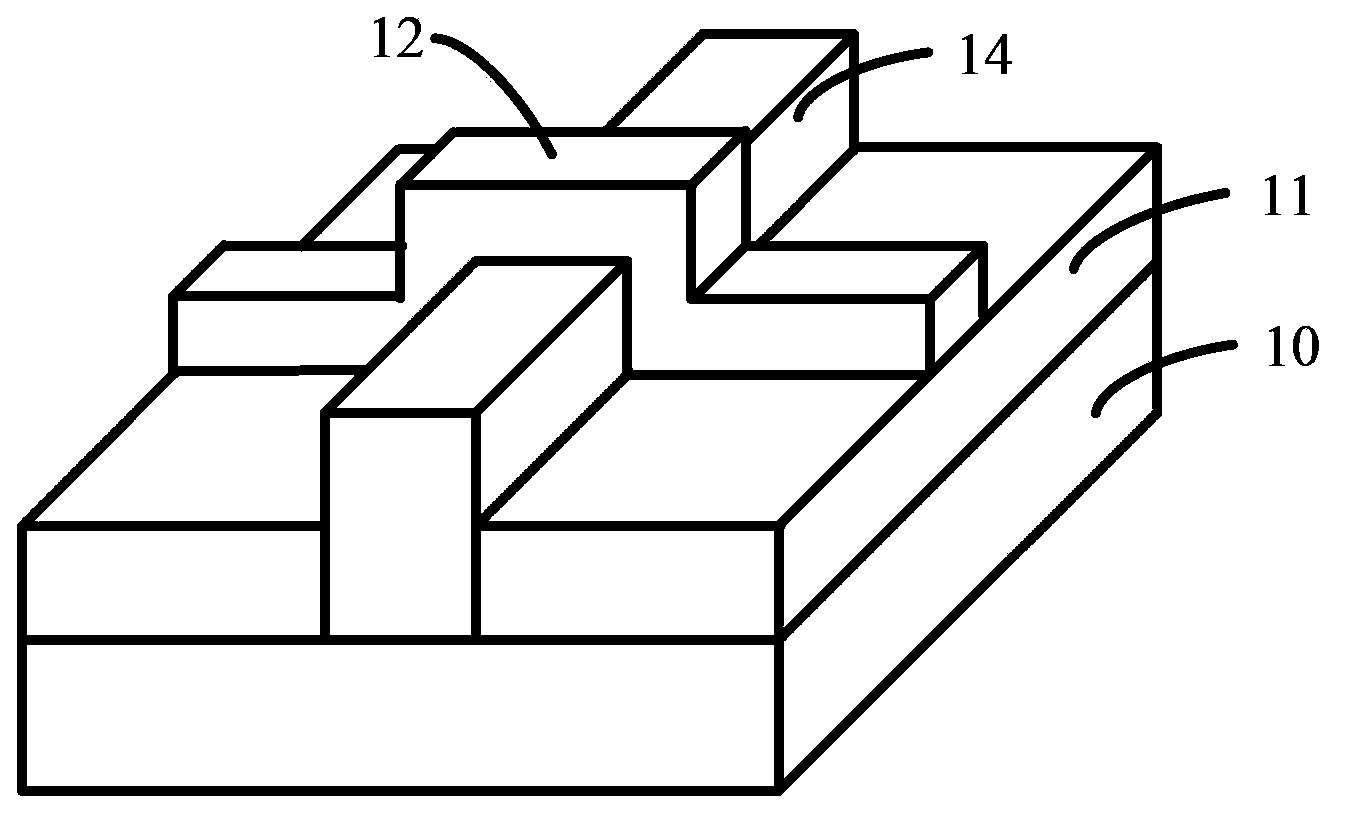

Fin field effect transistor and fabrication method

ActiveUS20130228832A1Improve bindingReduce gate leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesHydrogenEngineering

A fin field effect transistor and a method for forming the fin field effect transistor are provided. In an exemplary method, the Fin FET can be formed by forming a dielectric layer and a fin on a semiconductor substrate. The fin can be formed throughout an entire thickness of the dielectric layer and a top surface of the fin is higher than a top surface of the dielectric layer. The fin can be annealed using a hydrogen-containing gas and a repairing gas containing at least an element corresponding to a material of the fin. A gate structure can be formed on the top surface of the dielectric layer and at least on sidewalls of a length portion of the fin after the annealing process.

Owner:SEMICON MFG INT (SHANGHAI) CORP

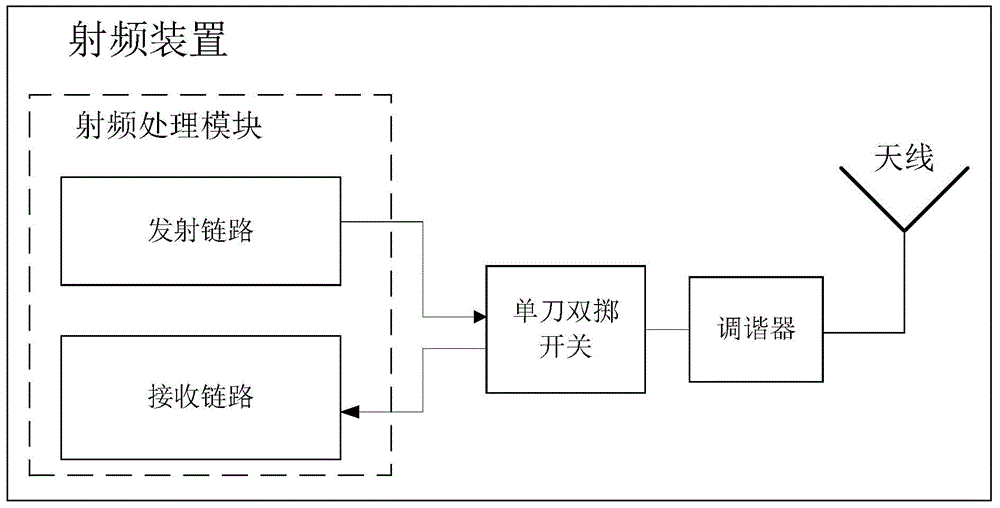

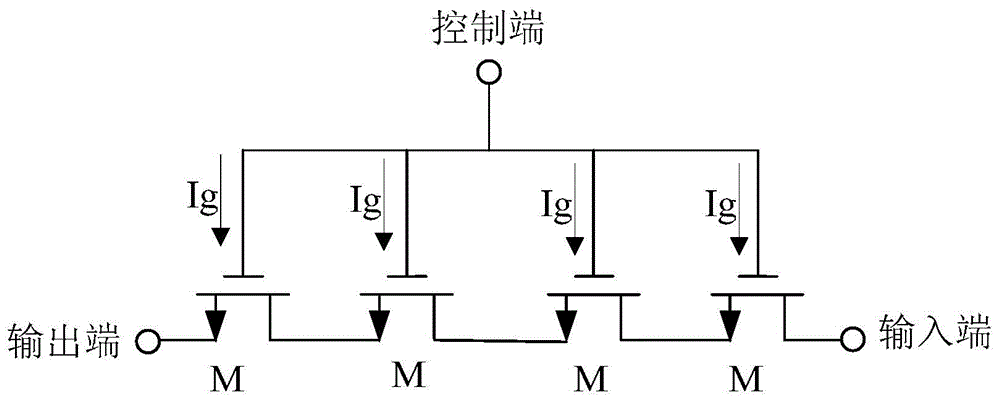

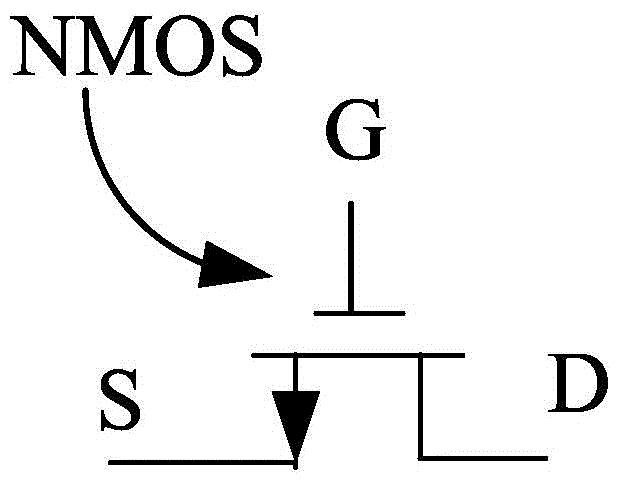

Switch, tuner of antenna and radio frequency device

ActiveCN103986450AReduce gate leakage currentReduce in quantityTransistorElectronic switchingControl signalControl switch

The embodiment of the invention discloses a switch, a tuner of an antenna and a radio frequency device, and therefore transmission efficiency of the switch comprising a plurality of series transistors is adjusted comprehensively, and a leakage current is restrained. The switch comprises the 2N transistors which are sequentially connected in series. According to the 2N transistors which are sequentially connected in series, the control ends of any two transistors with the odd sequence numbers closest to each other are coupled through a first resistor, and the control ends of any two transistors with the even sequence numbers closest to each other are coupled through a second resistor; the control end of the nth transistor is coupled to a first control signal in switch control signals, and the control end of the (n+1)th transistor is coupled to the first control signal, wherein n is an integer which is greater than or equal to one and less than or equal to 2N-1, N is an integer greater than or equal to two, and the first control signal is used for controlling switching-on or switching-off of the switch.

Owner:HUAWEI TECH CO LTD

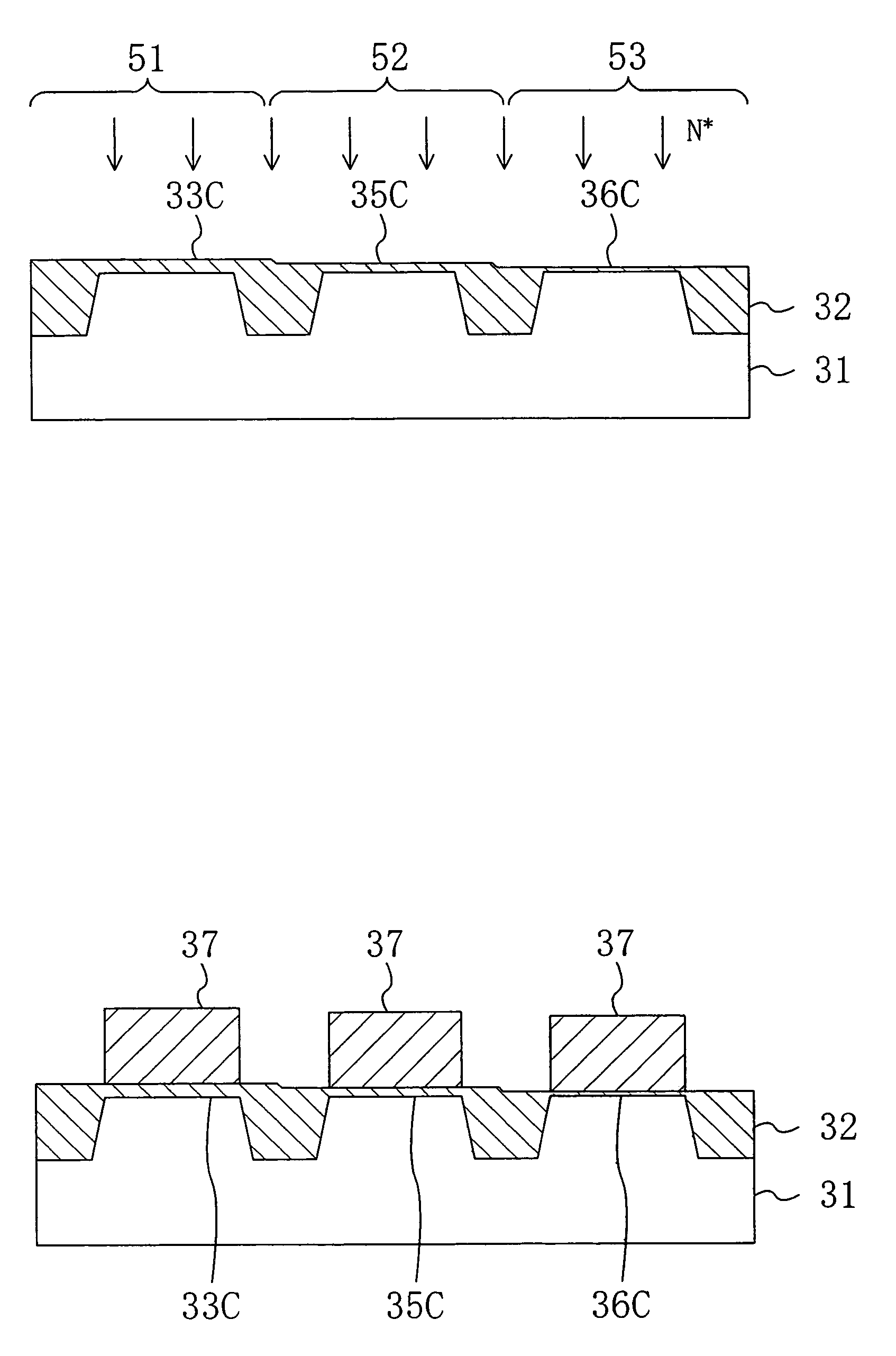

Semiconductor device and method for manufacturing the same

InactiveUS7164178B2Reduce gate leakage currentImprove the immunitySemiconductor/solid-state device manufacturingSemiconductor devicesPeak valueEngineering

A semiconductor device includes a gate insulating film formed on a semiconductor substrate, and a gate electrode formed on the gate insulating film. Nitrogen is introduced into the gate insulating film, and the nitrogen concentration distribution thereof has a peak near the surface of the gate insulating film or near the center of the gate insulating film in the thickness direction. The peak value of nitrogen concentration in the gate insulating film is equal to or greater than 10 atm % and less than or equal to 40 atm %.

Owner:PANNOVA SEMIC

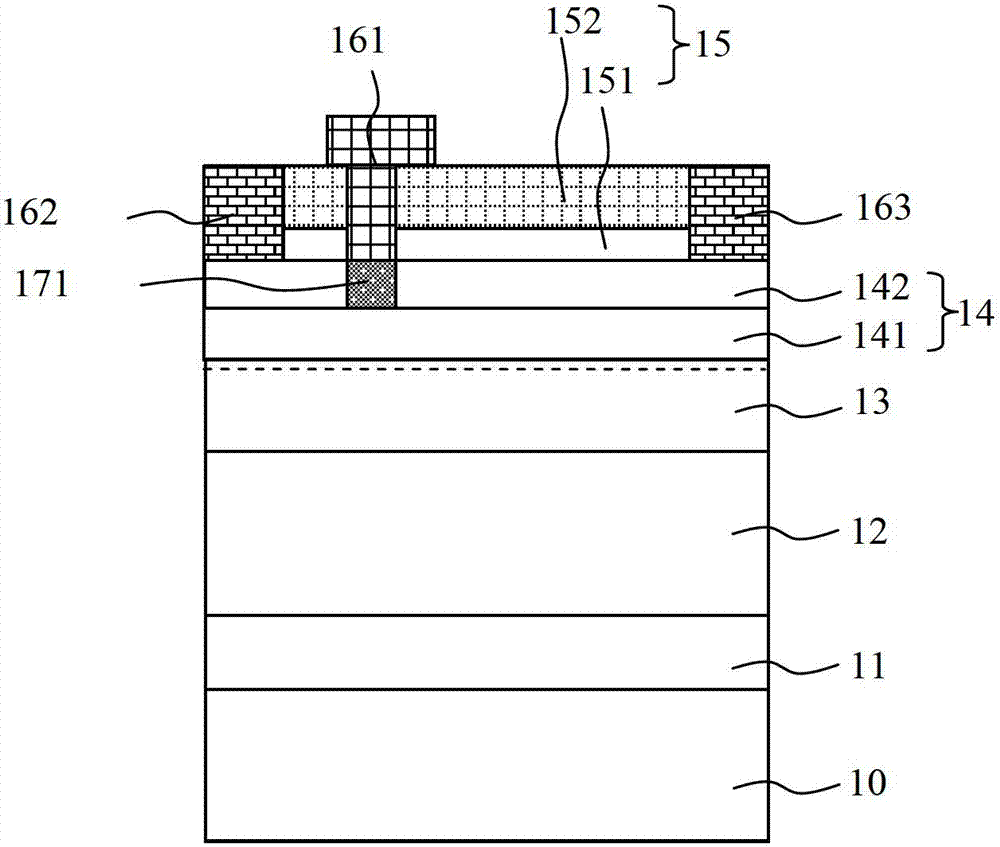

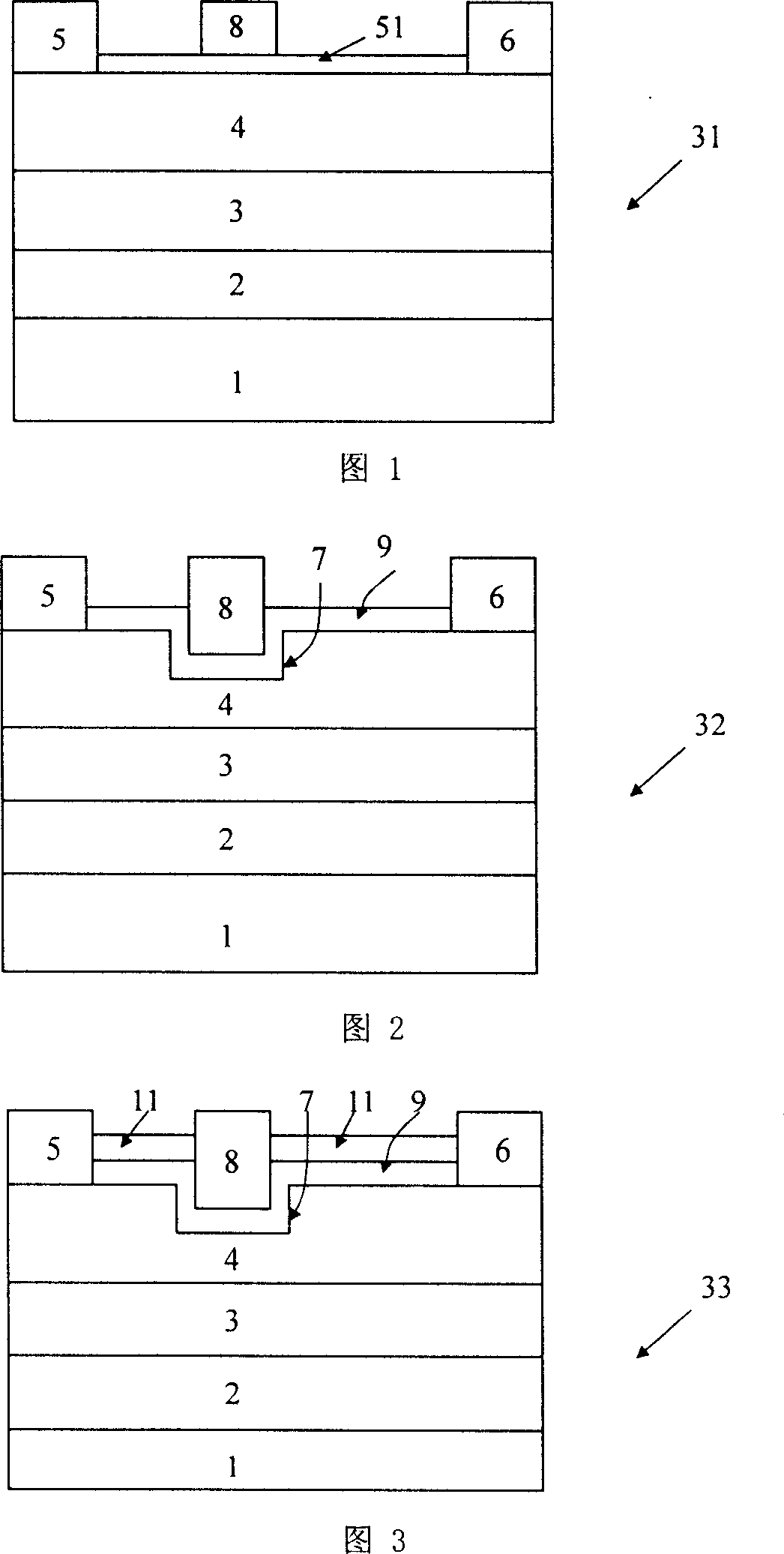

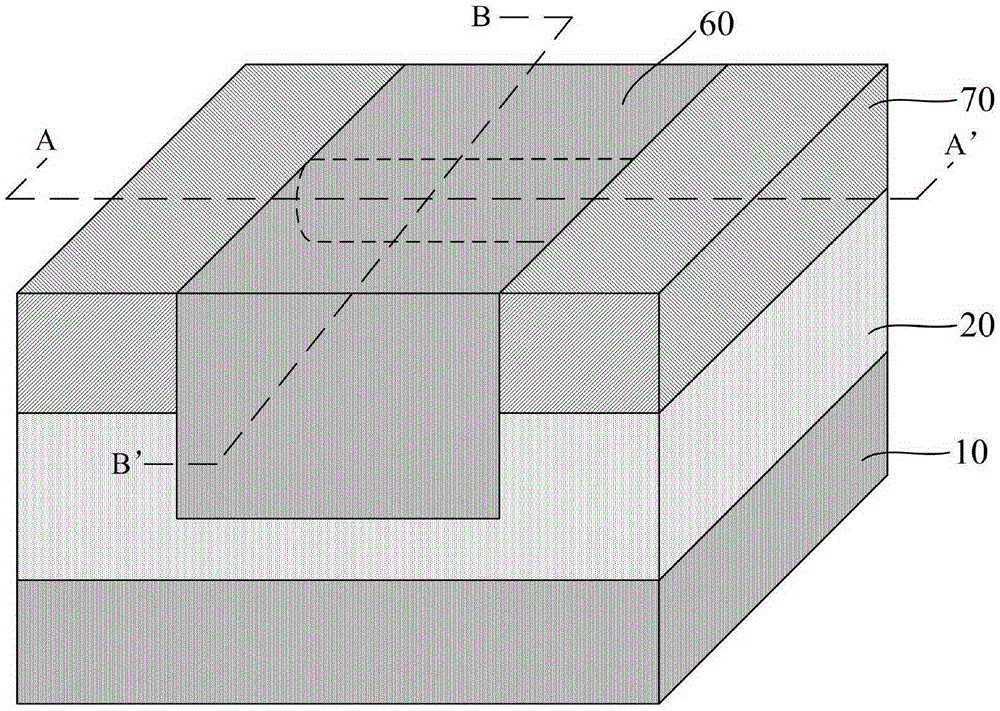

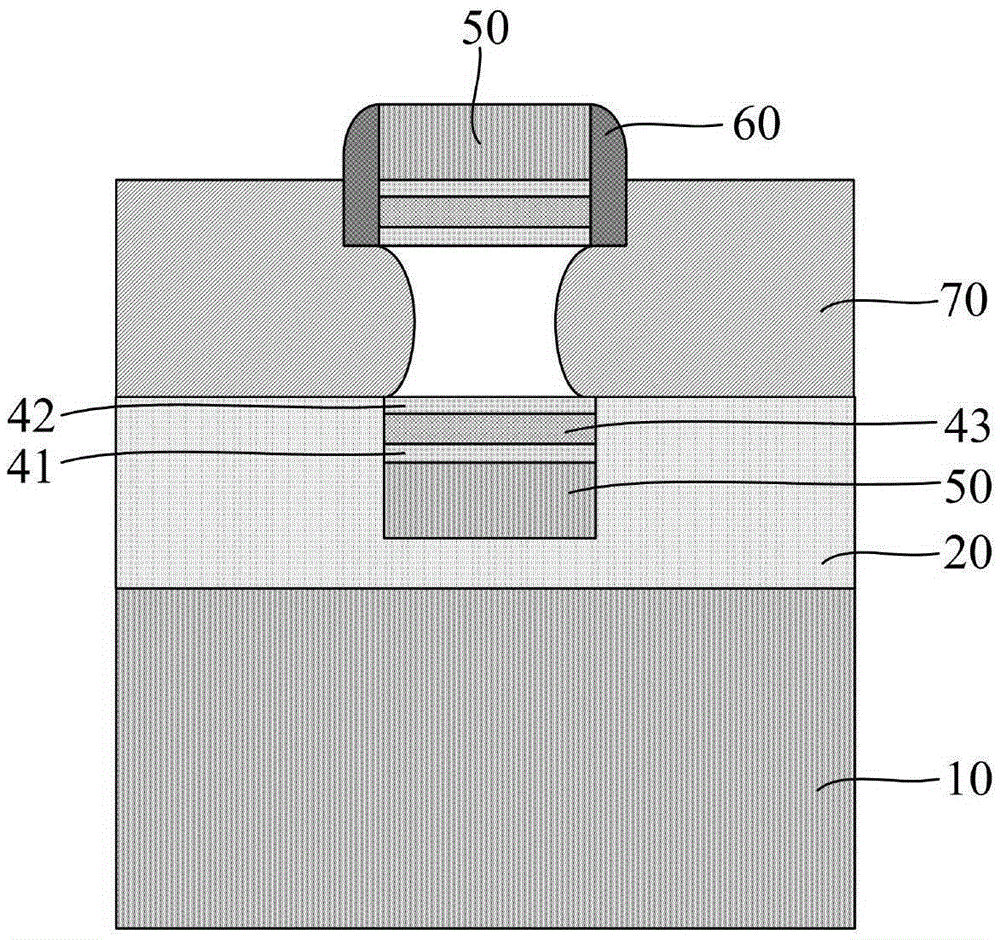

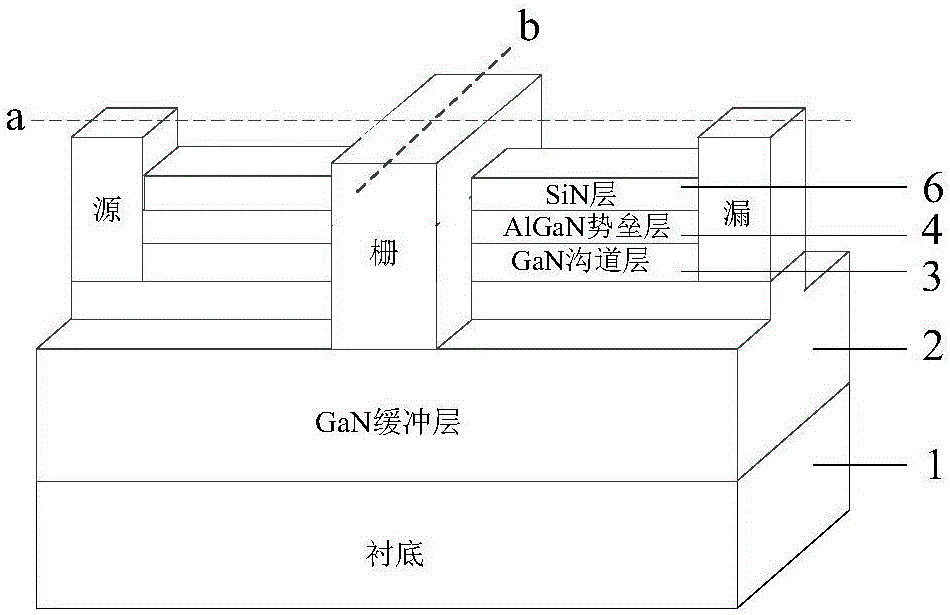

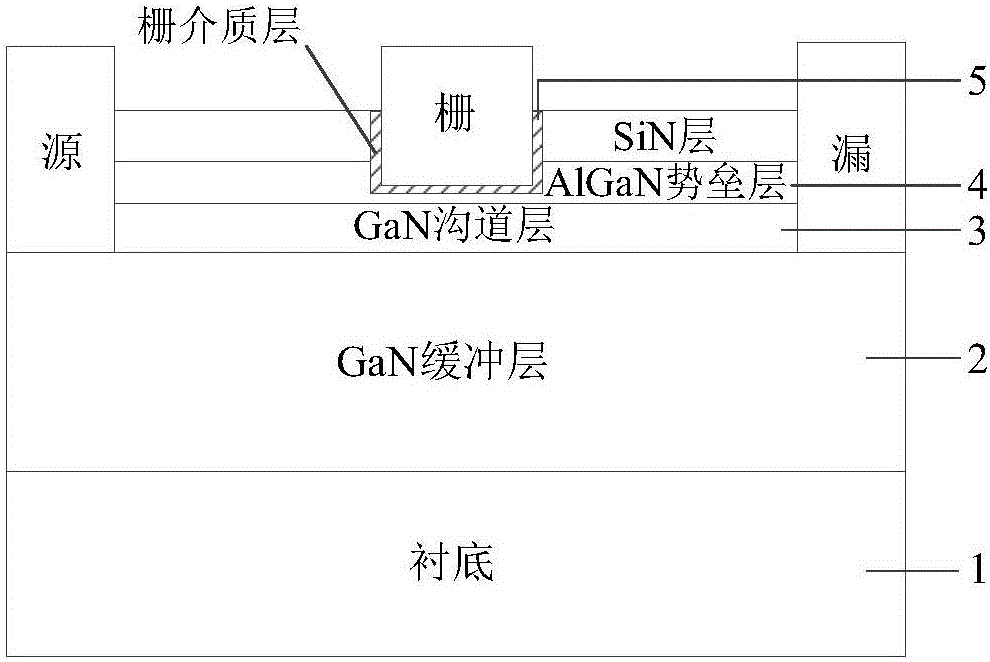

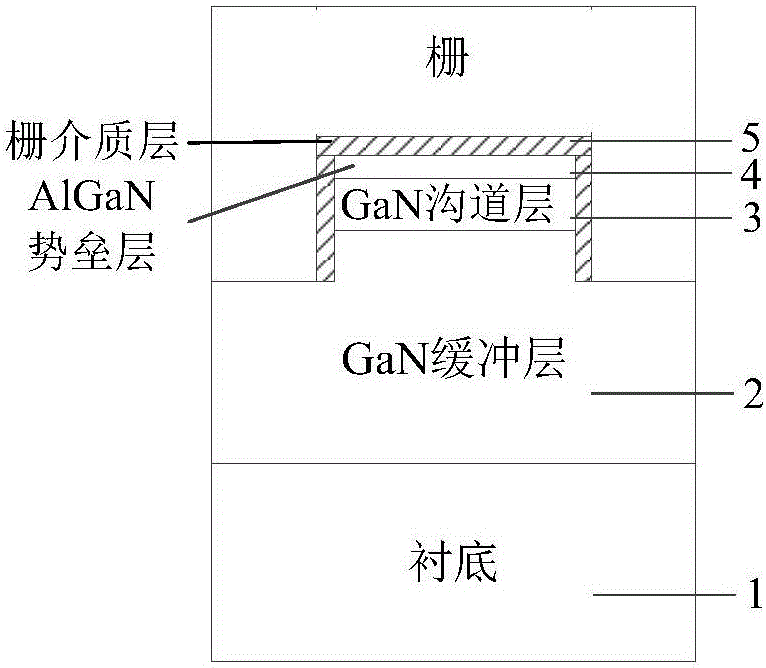

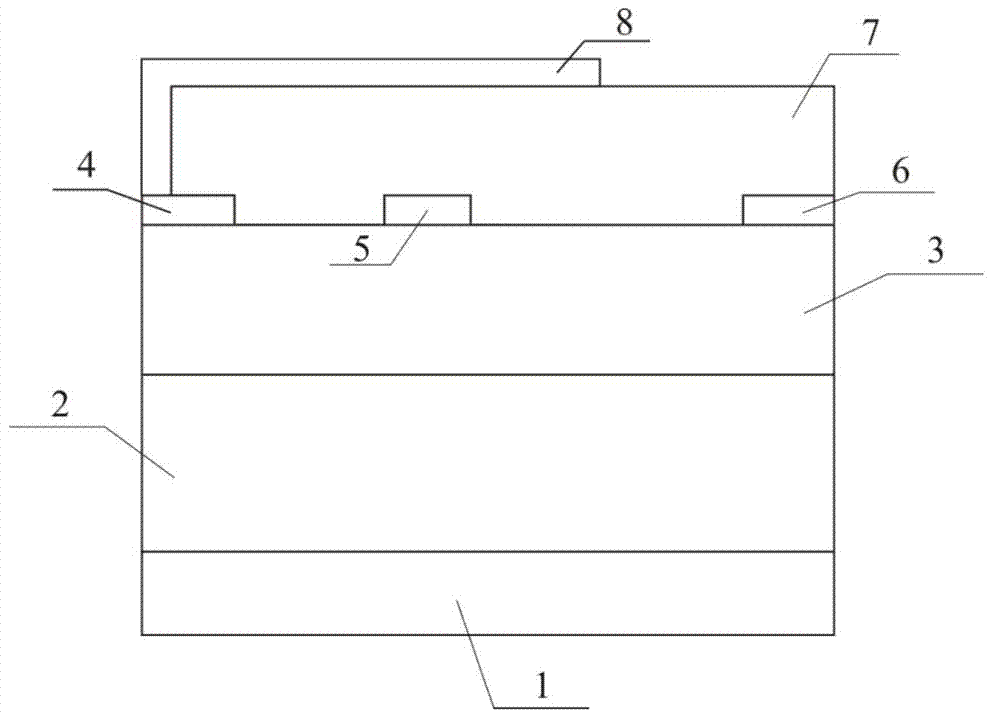

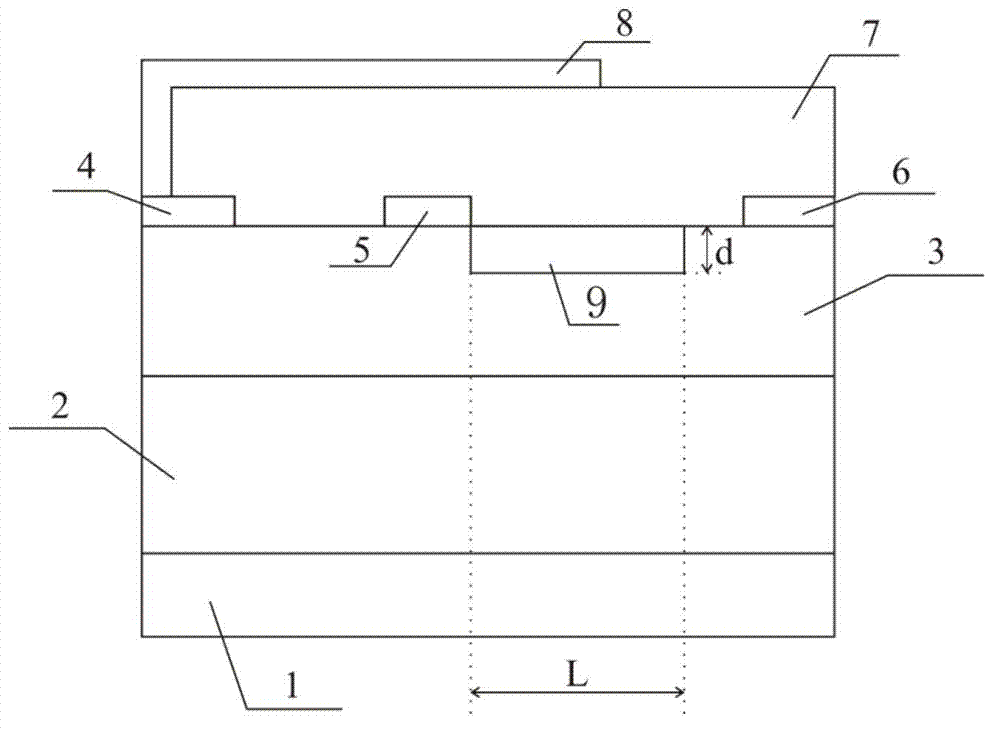

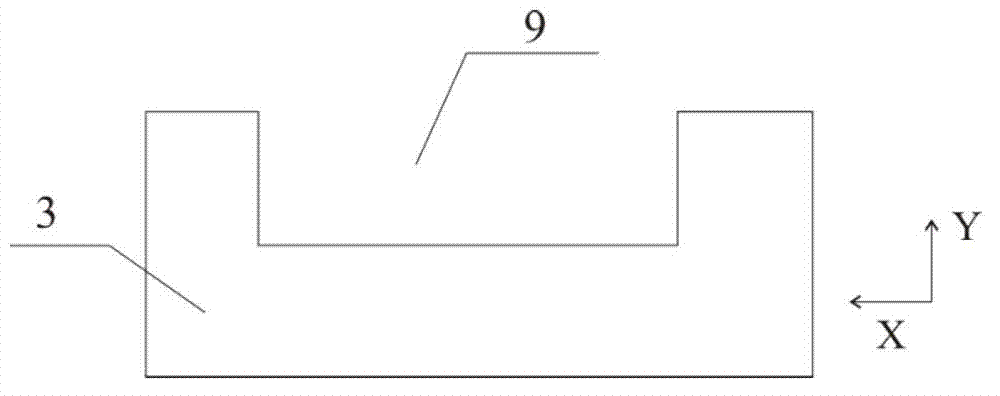

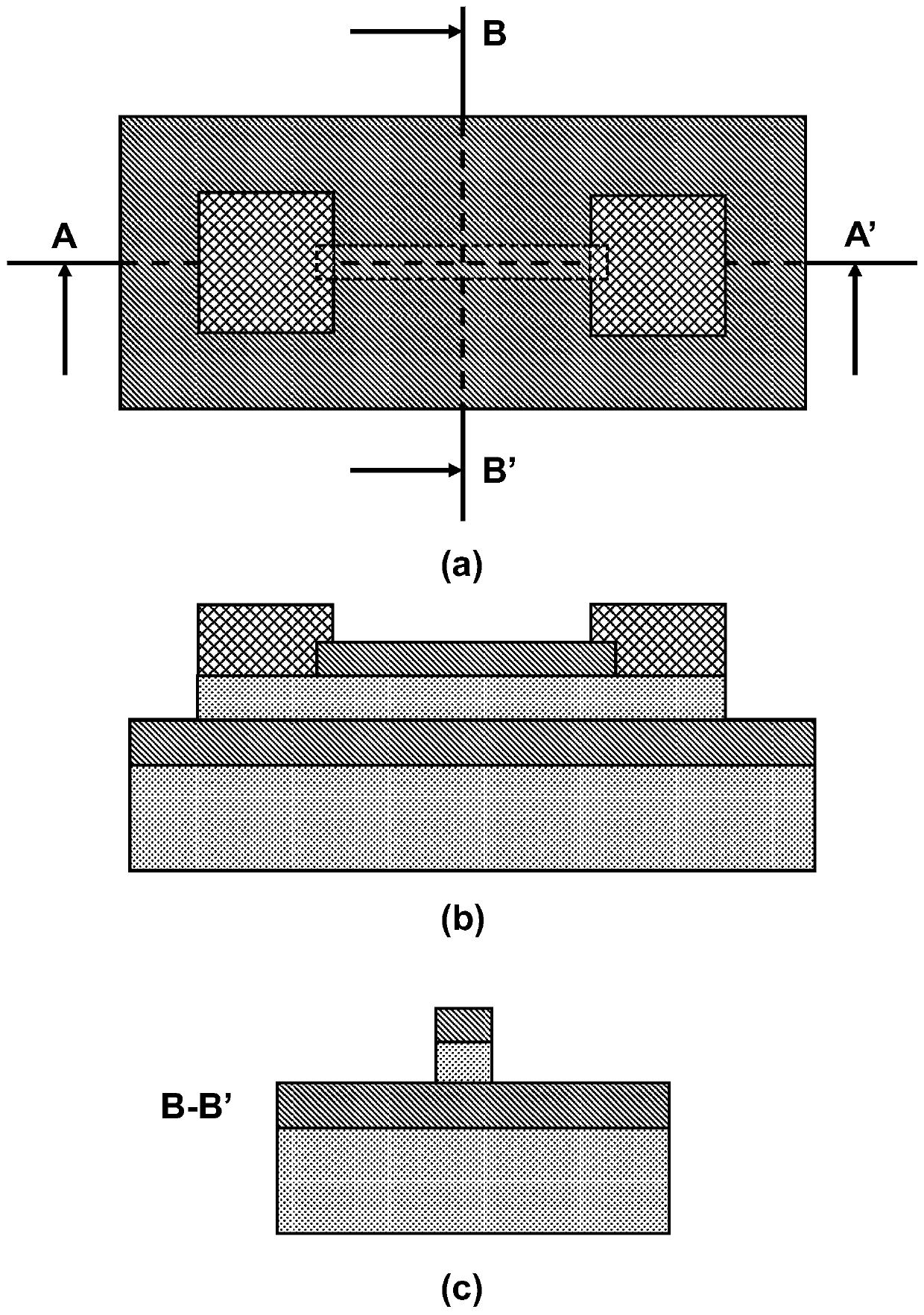

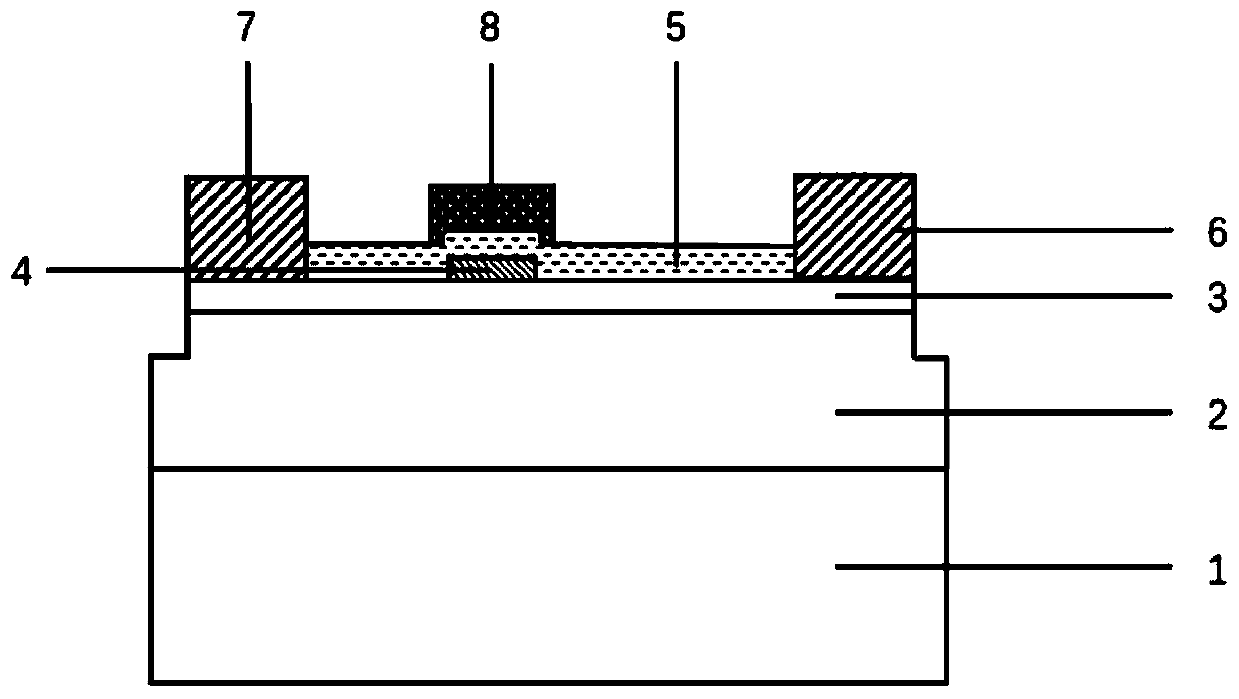

Enhanced fin-type insulated gate high-electronic mobility transistor

ActiveCN105810728AReduce gate leakage currentImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesElectron mobilityDrain resistance

The invention discloses an enhanced fin-type insulated gate high-electronic mobility transistor, which is mainly used for solving the problems of small threshold voltage and serious short channel effect of an existing enhanced device. The enhanced fin-type insulated gate high-electronic mobility transistor comprises a substrate (1), a GaN buffer layer (2), a GaN channel layer (3), an AlGaN barrier layer (4), a gate dielectric layer (5), a passivation layer (6), a source electrode, a drain electrode and a gate electrode from bottom to top, the GaN channel layer and the AlGaN barrier layer form an AlGaN / GaN heterojunction, and the source electrode and the drain electrode are arranged at the two ends of the AlGaN / GaN heterojunction. The device has the advantages of high threshold voltage, high gate control capability and small source / drain resistance, and can be taken as a small-size enhanced device.

Owner:XIDIAN UNIV

High electron mobility transistor (HEMT) with gate edge groove type source field plate structure

InactiveCN102738228AReduce gate leakage currentImprove breakdown voltageSemiconductor devicesElectric fieldElectron mobility

The invention discloses a high electron mobility transistor (HEMT) with a gate edge groove type source field plate structure and belongs to the field of semiconductor devices. The HEMT comprises a lining layer, a buffer layer, a barrier layer, a source, a gate, a drain, a passivation layer, the source field plate and a gate drainage region groove, wherein the gate drain region groove is formed along the edge of the gate in the gate drainage region and formed by etching the barrier layer in the width direction of the gate. Compared with the HEMT with the traditional source field plate, the HEMT with the gate edge groove type source field plate structure has the advantages that electric field wires collected at the periphery of one side, which is close to the drain, of the gate are reduced, so that the electric field at one side, which is close to the drain, of the gate can be reduced; and therefore, the breakdown voltage of the HEMT can be obviously increased.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

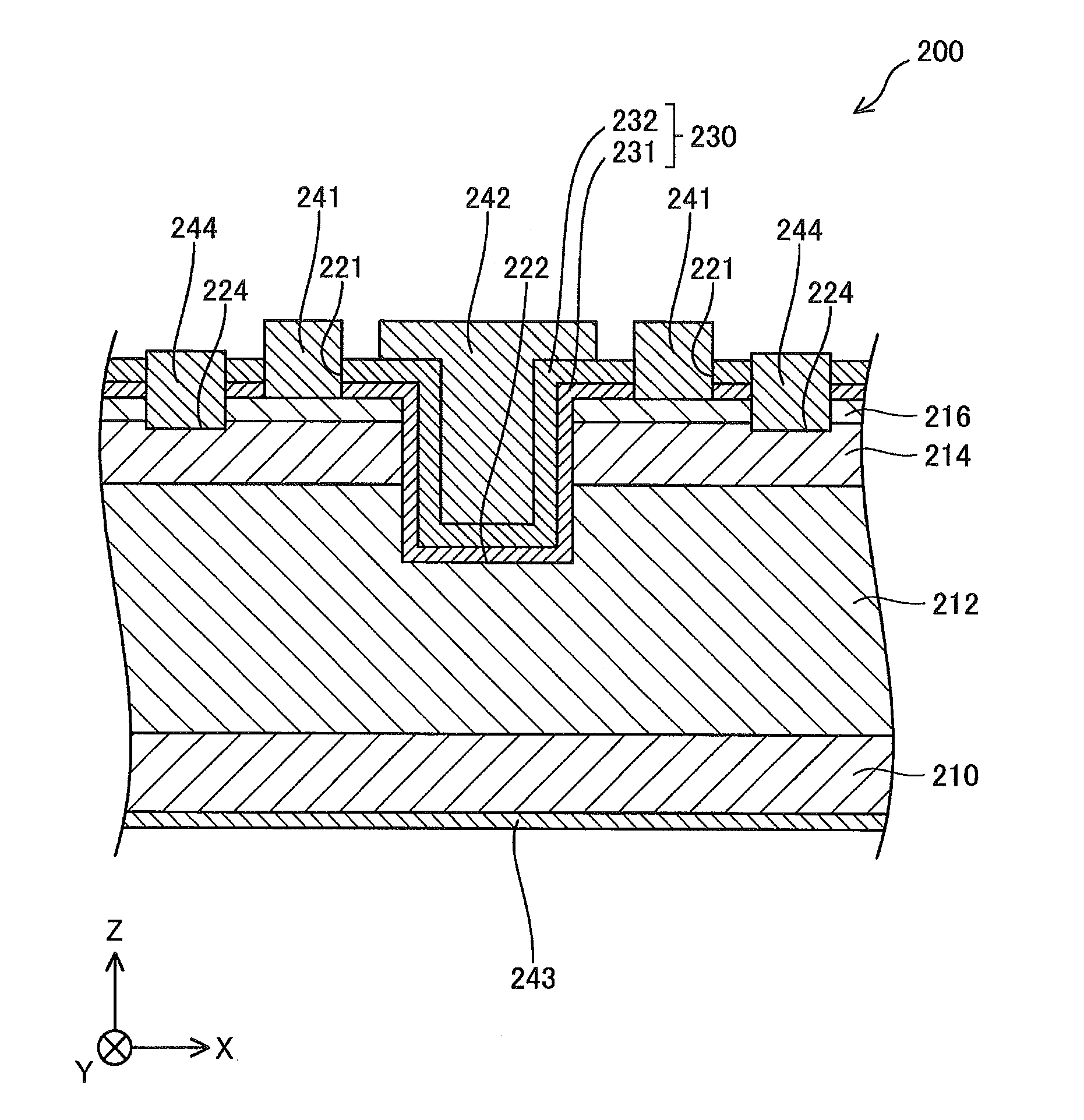

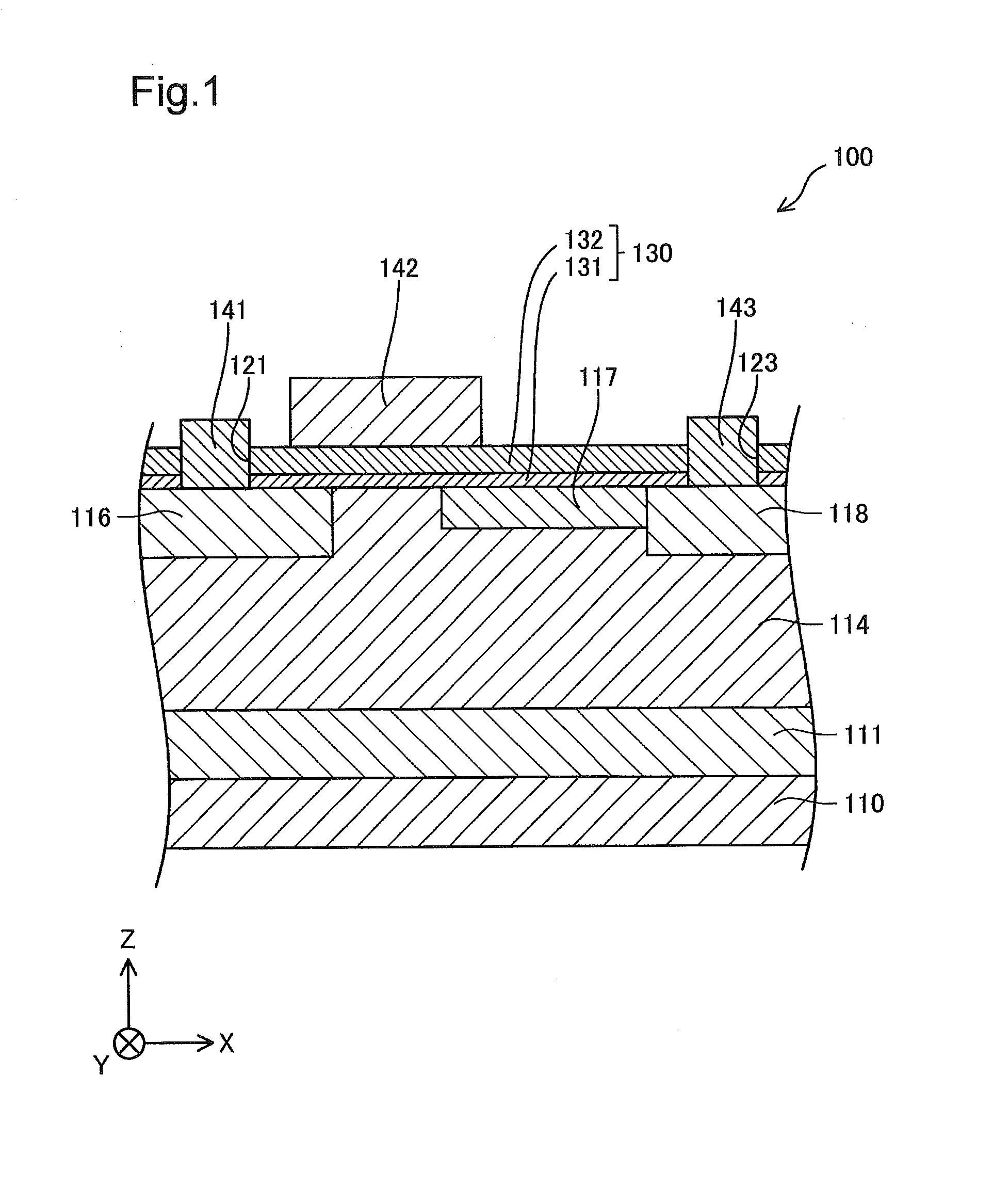

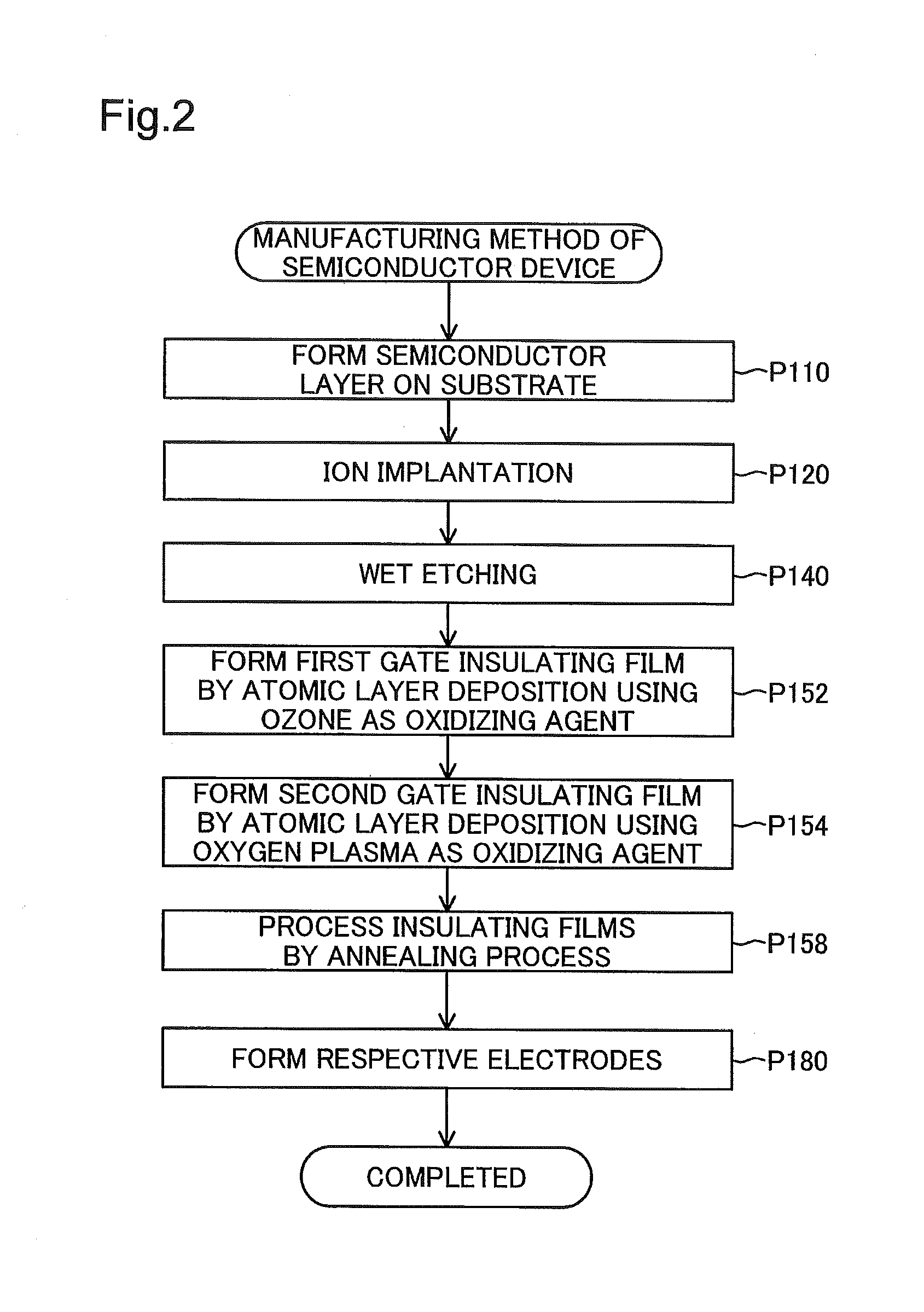

Semiconductor device and manufacturing method of the same

ActiveUS20160013282A1Improve film qualityHigh carrier mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesOxygen plasmaGallium nitride

A semiconductor device, comprises: a semiconductor layer, a first gate insulating film, a second gate insulating film and a gate electrode. The semiconductor layer is mainly made of gallium nitride (GaN). The first gate insulating film is formed on the semiconductor layer by atomic layer deposition using ozone as an oxidizing agent and is mainly made of an oxide. The second gate insulating film is formed on the first gate insulating film by atomic layer deposition using oxygen plasma as an oxidizing agent, and is mainly made of an oxide and contains carbon (C) at a lower concentration than that in the first gate insulating film. The gate electrode is formed on the second gate insulating film.

Owner:TOYODA GOSEI CO LTD

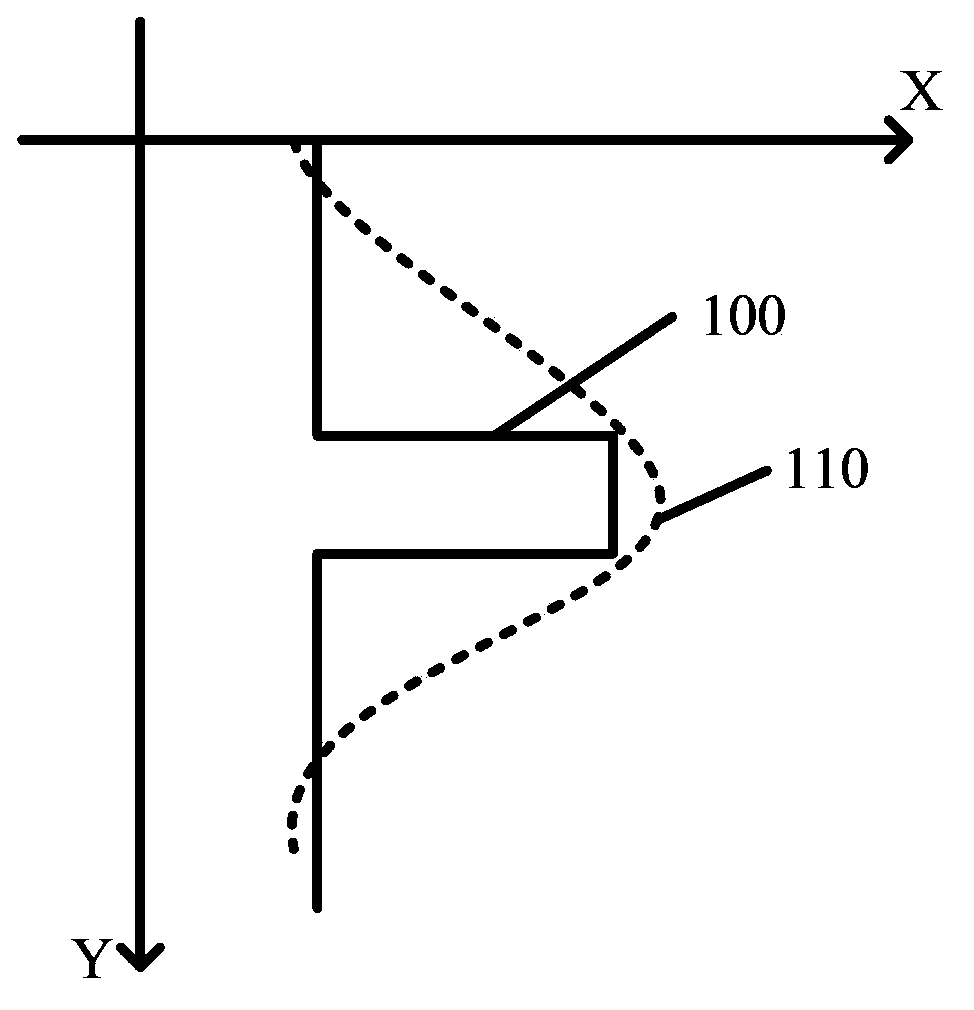

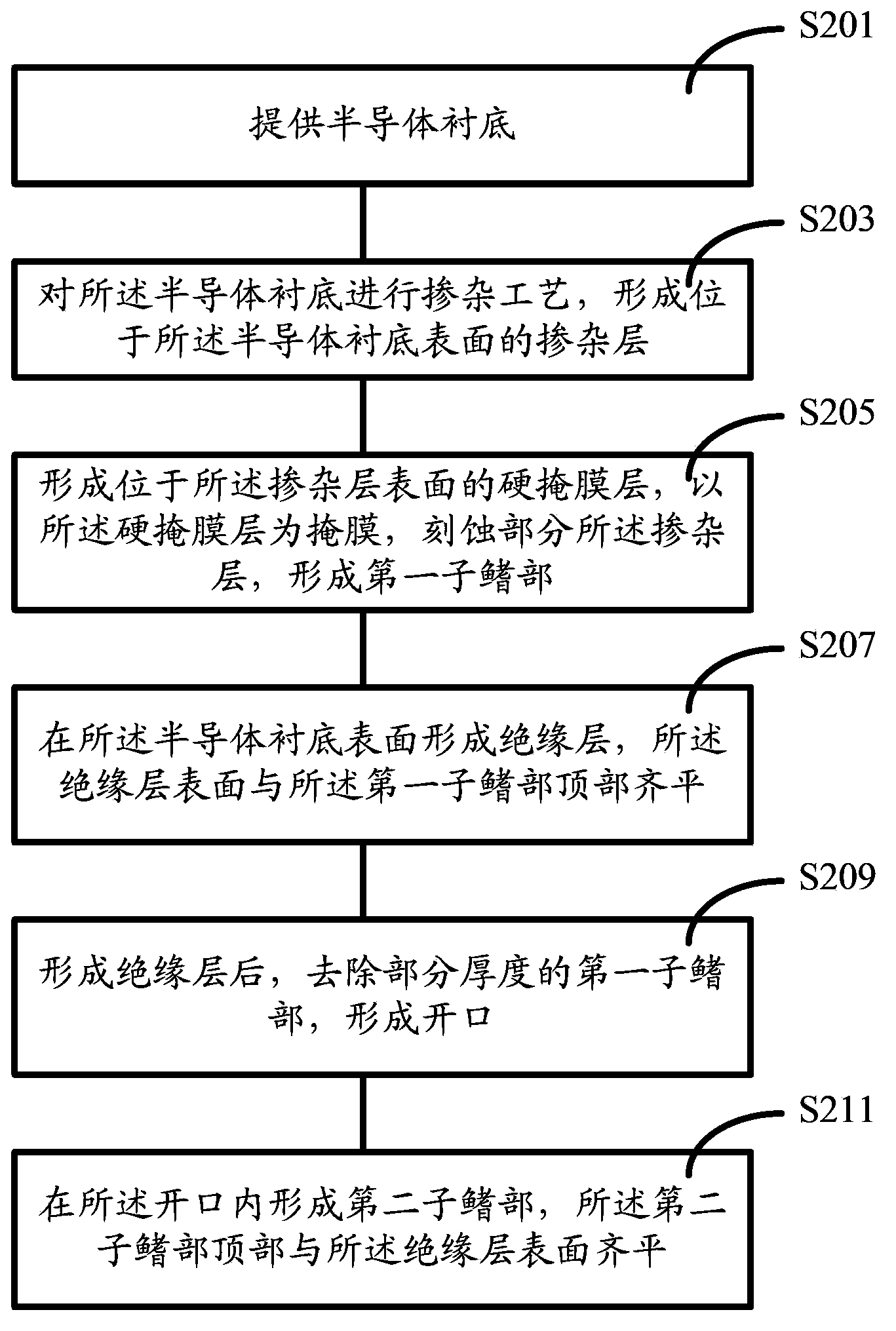

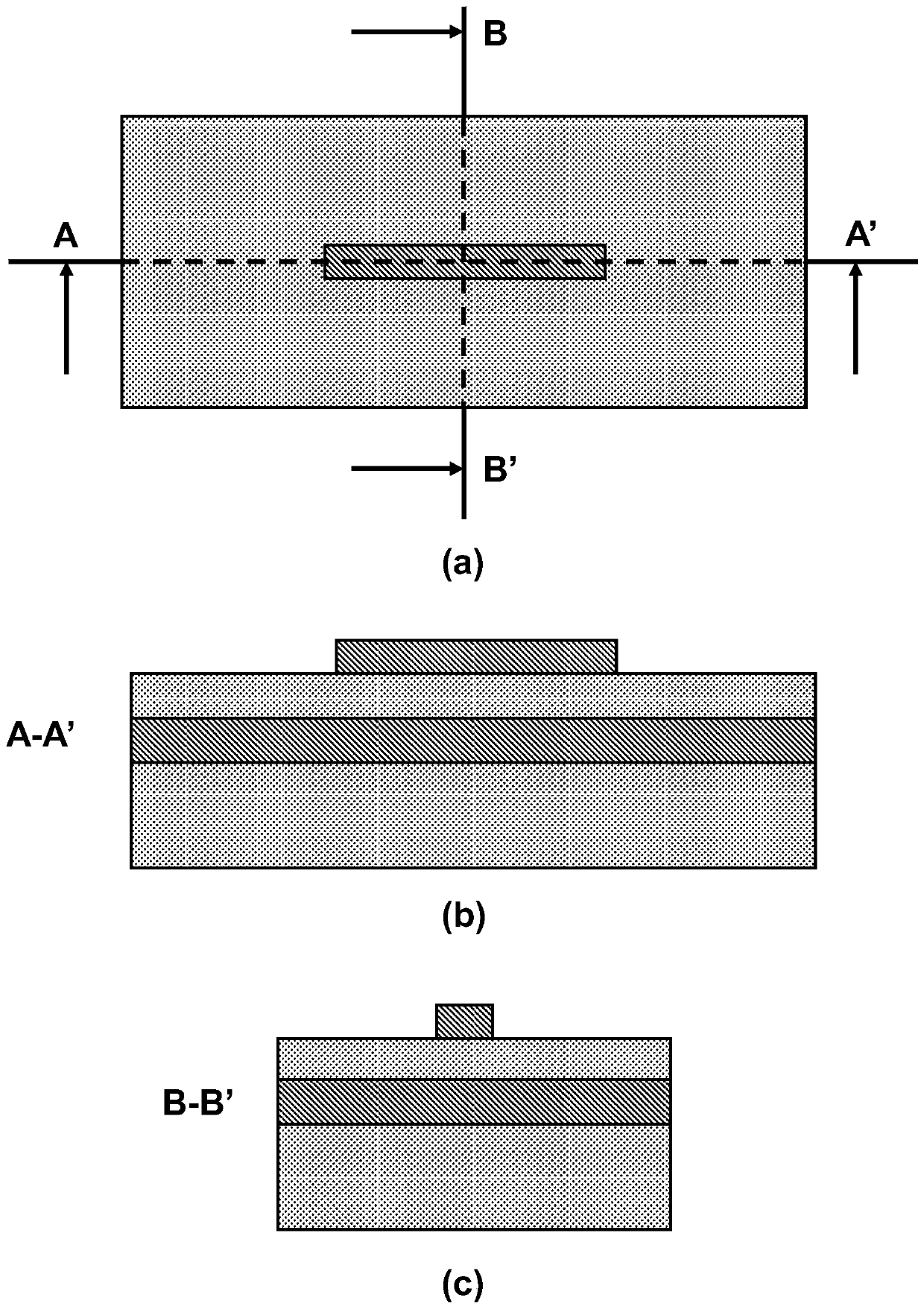

Forming method of semiconductor device and forming method of fin type field effect transistor

ActiveCN103426765ASimple forming processLower threshold voltageSolid-state devicesSemiconductor/solid-state device manufacturingGate leakage currentCharge carrier mobility

The invention provides the forming method of a semiconductor device. The forming method comprises the steps of providing a semiconductor substrate; carrying out a doping process on the semiconductor substrate; forming a doped layer on the surface of the semiconductor substrate; forming a hard mask layer located on the surface of the doped layer; etching a part of the doped layer by using the hard mask layer as a mask; forming a first sub fin part; forming an insulating layer on the surface of the semiconductor substrate, wherein the surface of the insulating layer is flush with the top of the first sub fin part; after the insulating layer is formed, removing the first sub fin part of part of thickness to form an opening; and forming a second sub fin part within the opening, wherein the top of the second sub fin part is flush with the surface of the insulating layer. The invention further provides a forming method of a fin type field effect transistor. Formed semiconductor device and the fin type field effect transistor have the advantages of large channel region stress, high carrier mobility ratio, low threshold voltage, small gate leakage current and stable performance.

Owner:SEMICON MFG INT (SHANGHAI) CORP

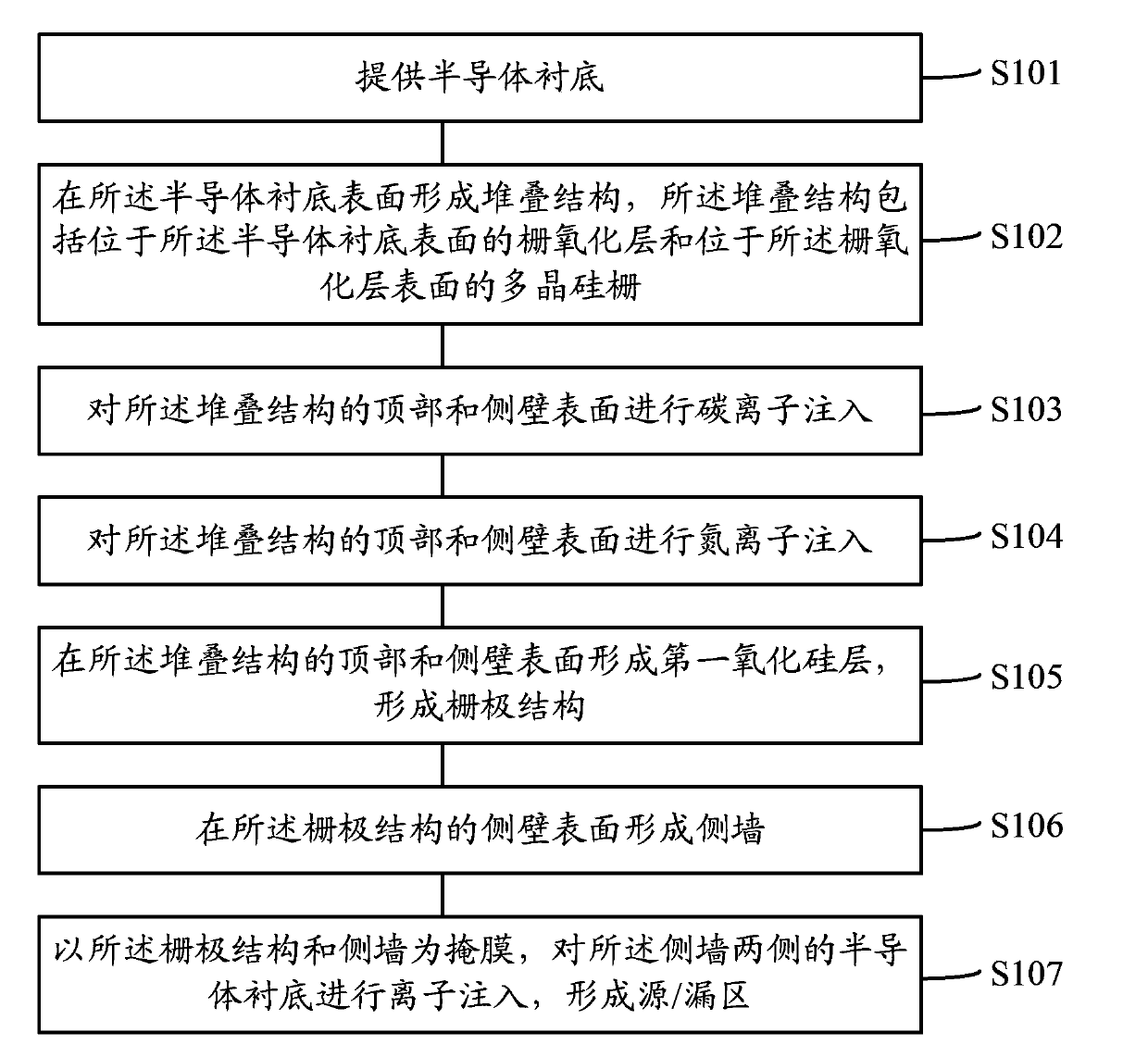

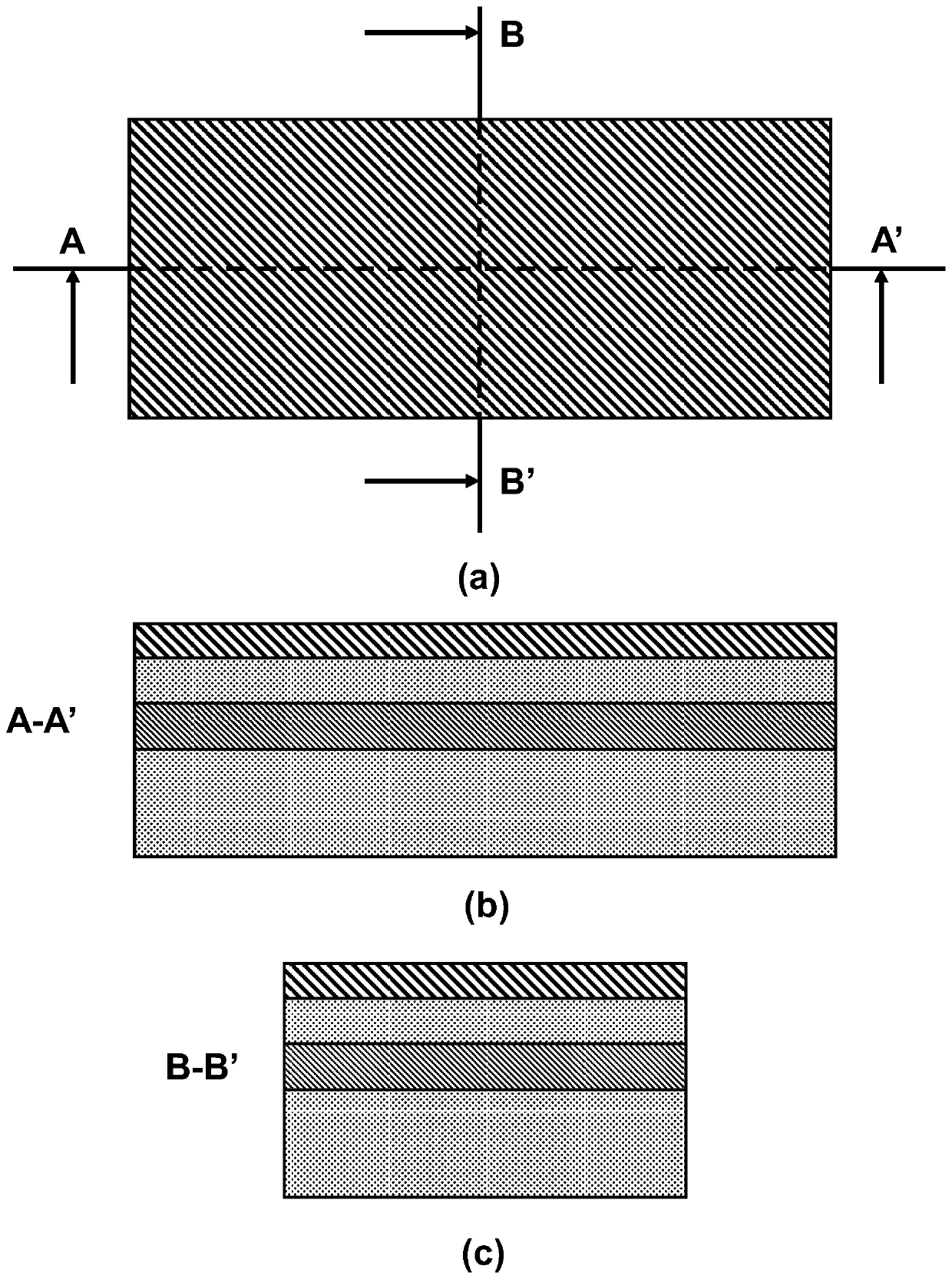

Gate structure and forming method thereof, semiconductor structure and forming method thereof

ActiveCN103378134AImprove the diffusion effectReduce gate leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureNitrogen

The invention discloses a gate structure, a forming method of the gate structure, a semiconductor structure with the gate structure and a forming method of the semiconductor structure. The forming method of the gate structure comprises the steps that a semiconductor substrate is provided; a stack structure is formed on the surface of the semiconductor substrate, wherein the stack structure comprises a gate oxide layer located on the surface of the semiconductor substrate and polysilicon gate located on the surface of the gate oxide layer; carbon ion implantation is conducted on the top of the stack structure and the surface of the side wall of the stack structure; nitrogen ion implantation is conducted on the top of the stack structure and the surface of the side wall of the stack structure; first monox layers are formed on the top of the stack structure and the surface of the side wall of the stack structure. Due to the fact that nitrogen ions and carbon ions implanted into the polysilicon gate can serve as impurity traps, the enhanced diffusion effect of foreign ions, close to the surface, of the polysilicon gate is restrained, the dosage concentration of the foreign ions, close to the surface, of the polysilicon gate and the dosage concentration of foreign ions inside the polysilicon gate are the same almost, and the resistance of the polysilicon gate will not improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Low-voltage multifunctional charge trapping synaptic transistor and preparation method thereof

ActiveCN111564499AEnhanced interfacial electric fieldConducive to tunnelingSemiconductor/solid-state device manufacturingSemiconductor devicesNanowireNeural network hardware

The invention discloses a low-voltage multifunctional charge trapping type synaptic transistor and a preparation method thereof, and belongs to the field of synaptic devices oriented to neural networkhardware application. According to the invention, a silicon nitride and hafnium oxide double-capture-layer structure is adopted to simultaneously realize short-long-time synaptic plasticity on a single device, so that the functions of the synaptic device are enriched; a three-gate nanowire structure is beneficial to enhancing an interface electric field, so that the FN tunneling width at the interface is reduced, the tunneling probability at the interface is enhanced, and the operation voltage and the device power consumption are reduced; and the device has complete CMOS material and processcompatibility, and due to the excellent device characteristics, the device has potential to be applied to a future large-scale neural network computing system.

Owner:PEKING UNIV

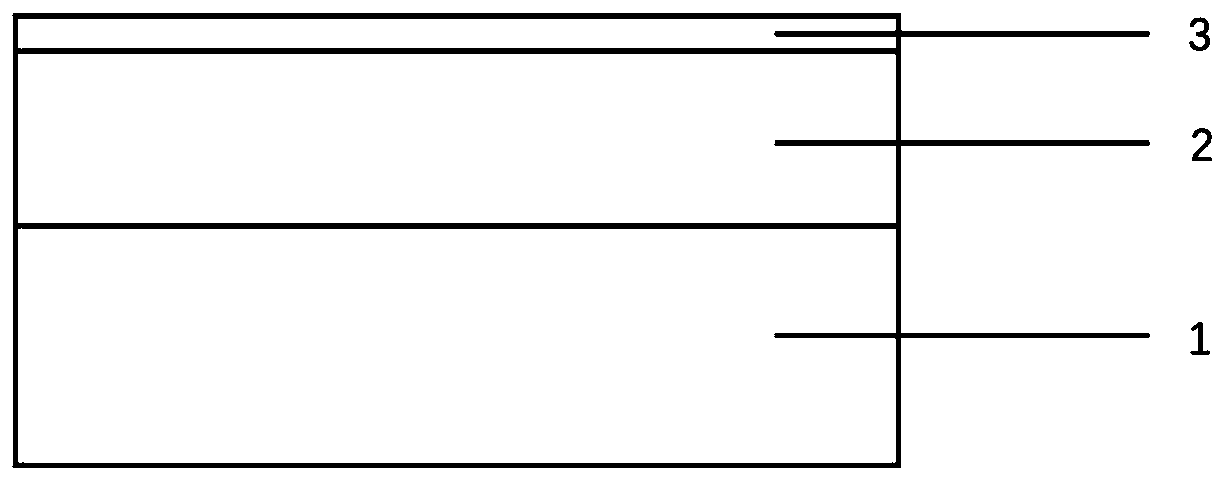

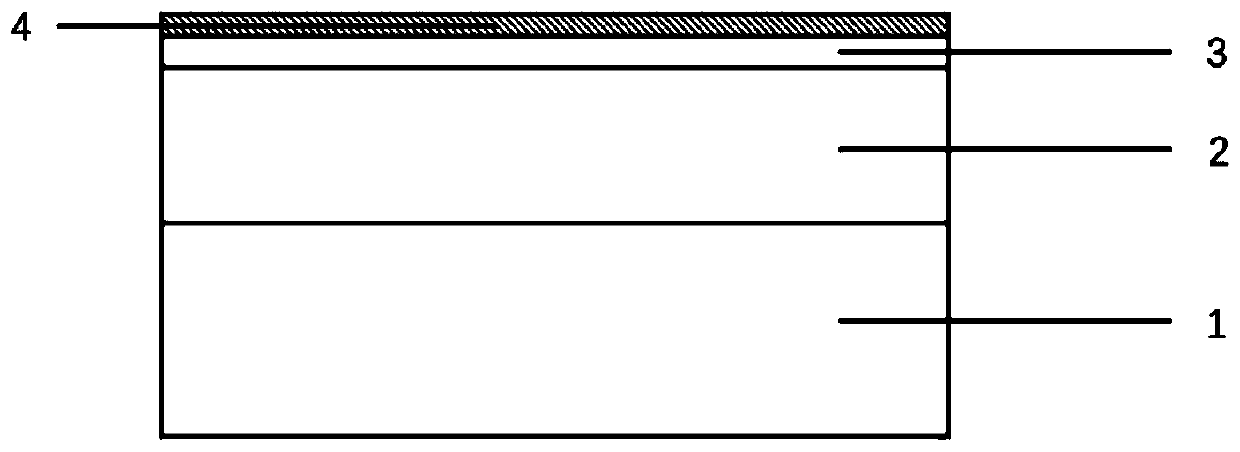

Enhanced AlN/AlGaN/GaN HEMT device and preparation method thereof

PendingCN110459595AImprove breakdown voltageReduce gate leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesGate leakage currentHeterojunction

The invention belongs to the field of semiconductor devices and discloses an enhanced AlN / AlGaN / GaN HEMT device and a preparation method thereof. The device includes a substrate, a GaN channel layer,an AlGaN ultra-thin barrier layer, an amorphous SiO2 layer, a single-crystal AlN layer, a drain metal electrode, a source metal electrode and a gate metal electrode. The enhanced device of the presentinvention is based on GaN and an ultra-thin AlGaN heterojunction, and the single-crystal AlN layer is epitaxially formed on the heterojunction after inserting an amorphous SiO2 layer in a region under a gate. The amorphous SiO2 layer under the gate can isolate the polarization enhancement effect of the highly polar single-crystal AlN layer on the AlGaN ultra-thin barrier layer, a two-dimensionalelectron gas under the gate is depleted, the device is turned off, and the enhanced device is realized. At the same time, the amorphous SiO2 under the gate and the single-crystal AlN can be used as adielectric layer under the gate, the reduction of the gate leakage current is facilitated, and the breakdown voltage of the device is increased.

Owner:SOUTH CHINA UNIV OF TECH

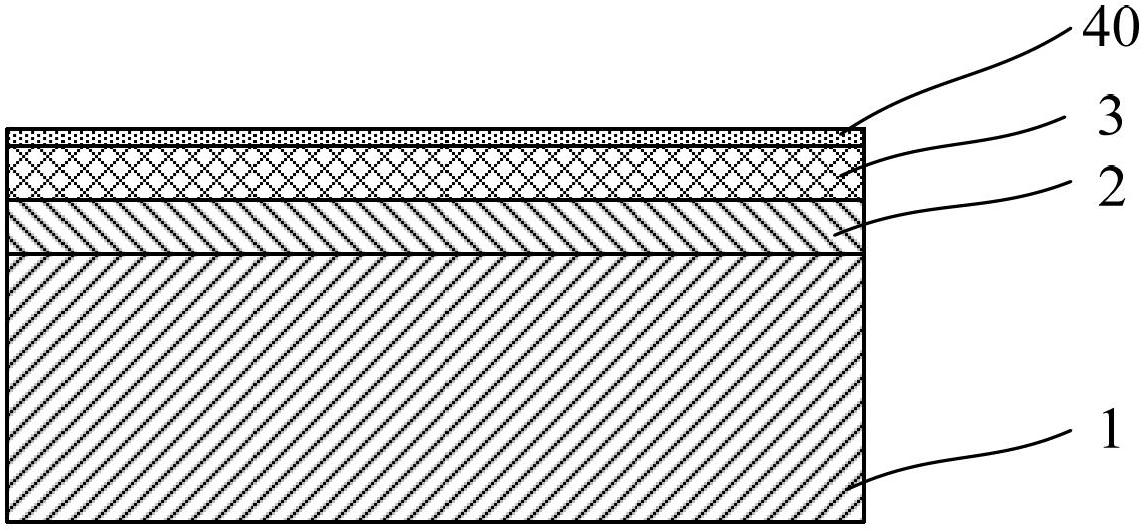

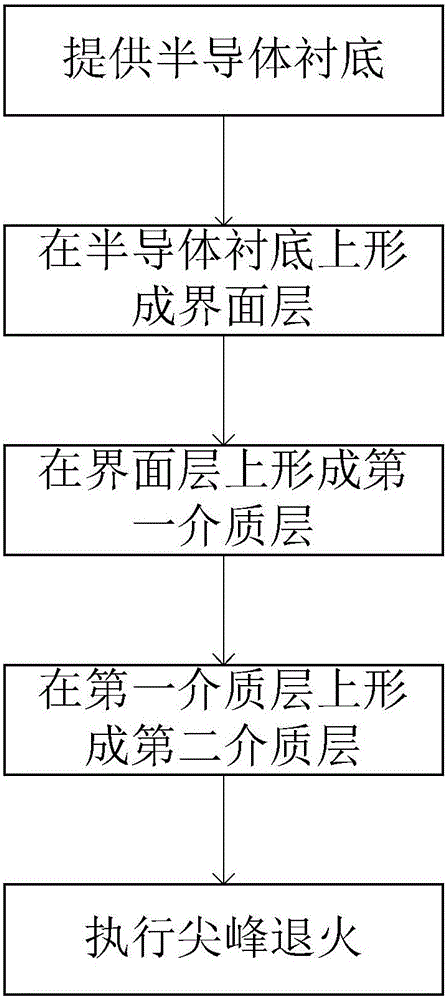

Semiconductor structure and forming method thereof

ActiveCN105932053AReduced oxygen vacanciesReduce gate leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesGate leakage currentOxygen vacancy

The invention provides a semiconductor structure, which comprises a semiconductor substrate, an interface layer, a first dielectric layer and a second dielectric layer, wherein the interface layer is formed on the semiconductor substrate; the first dielectric layer is formed on the interface layer; the second dielectric layer is formed on the first dielectric layer; and the phase-transition temperature of the second dielectric layer is lower than that of the first dielectric layer. By the semiconductor structure and the forming method thereof provided by the invention, the condition that external oxygen diffuses and passes through the second dielectric layer and enters the first dielectric layer is facilitated when dielectric constants of the dielectric layers are improved; and oxygen vacancies in the first dielectric layer are reduced, so that a gate leakage current is reduced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

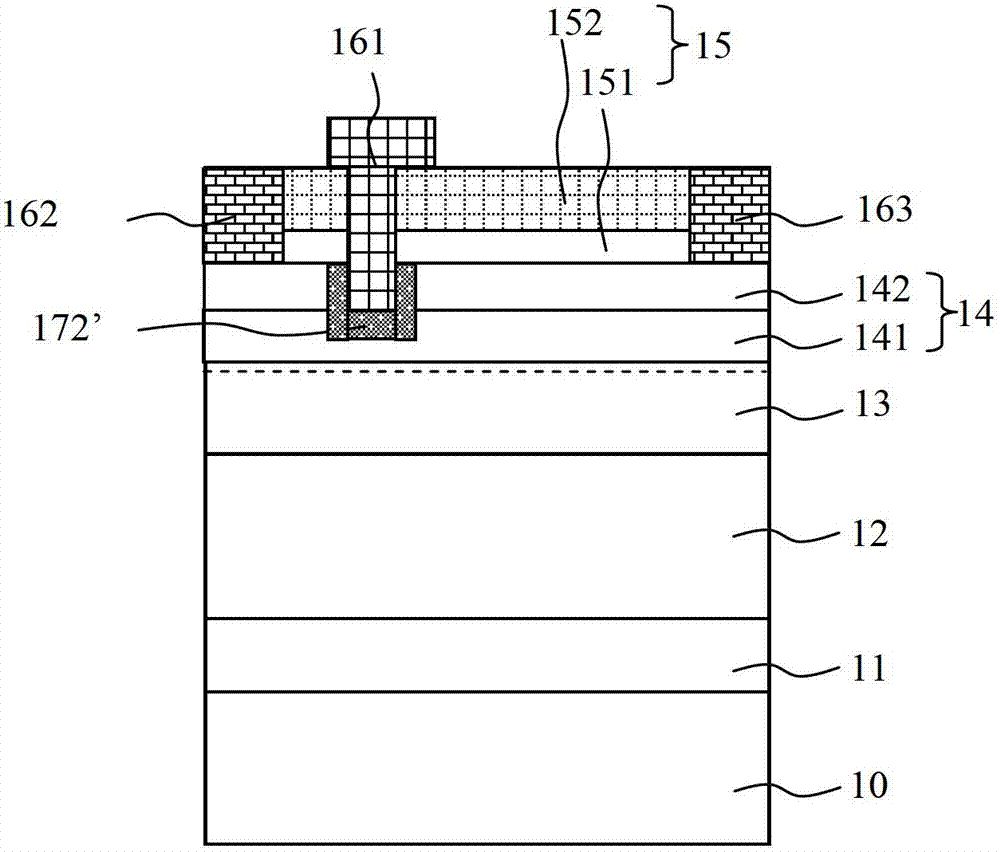

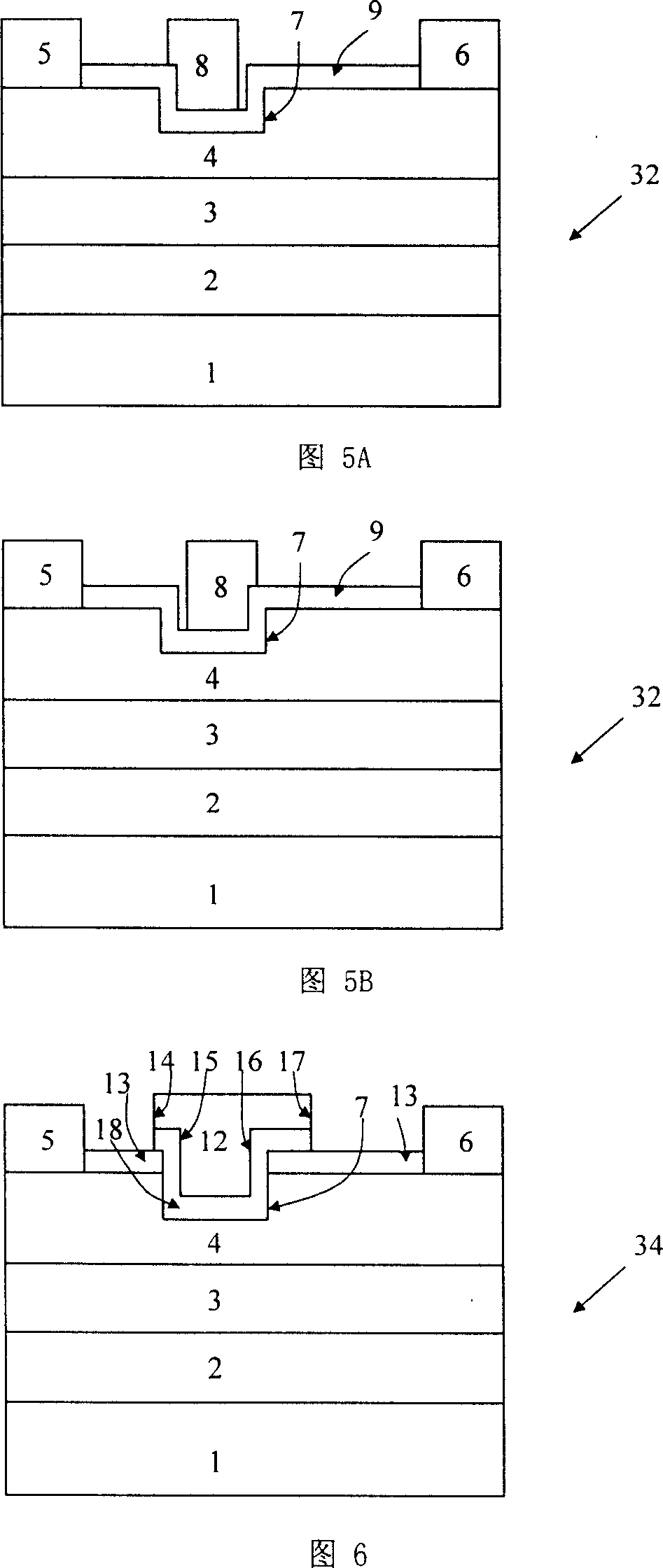

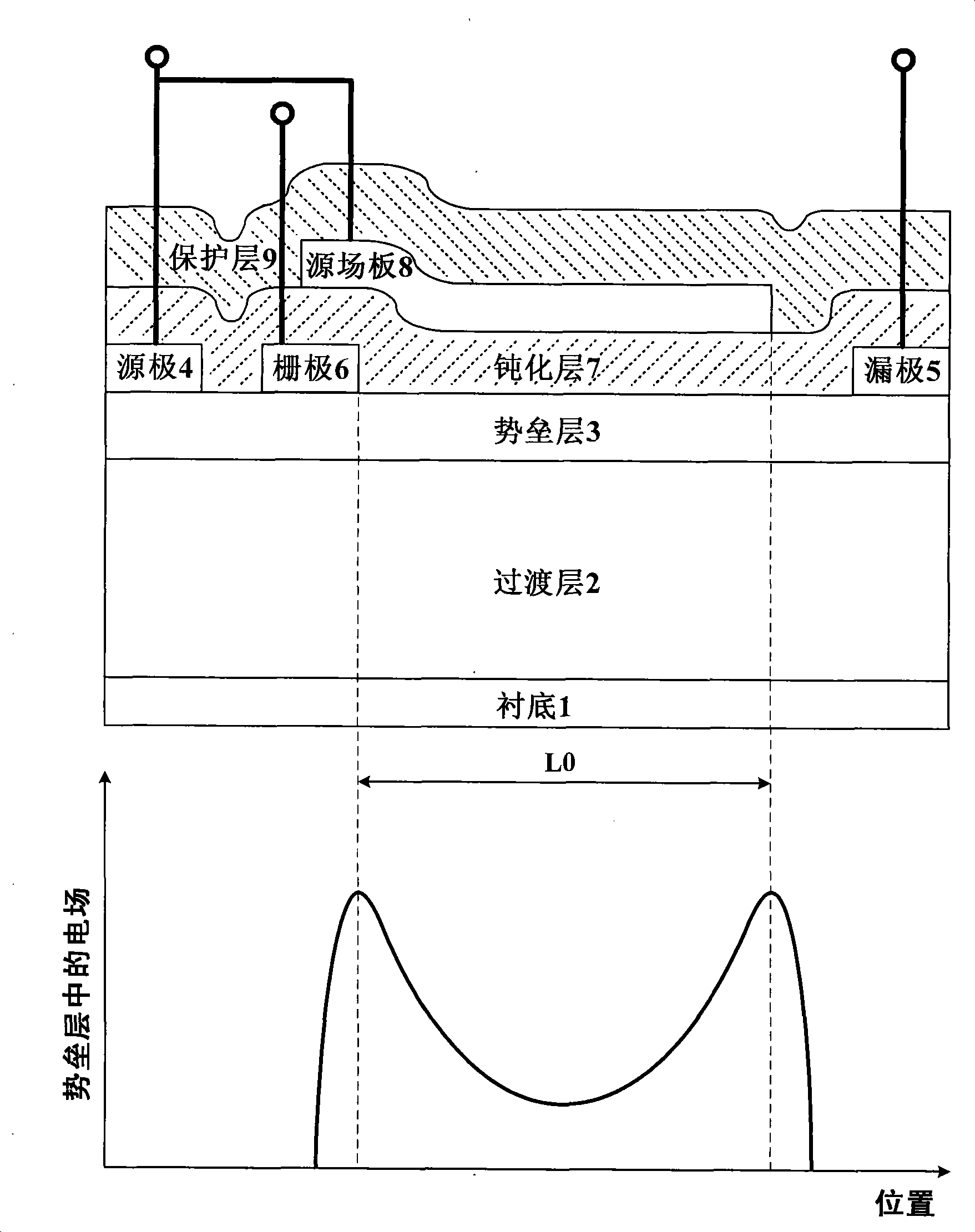

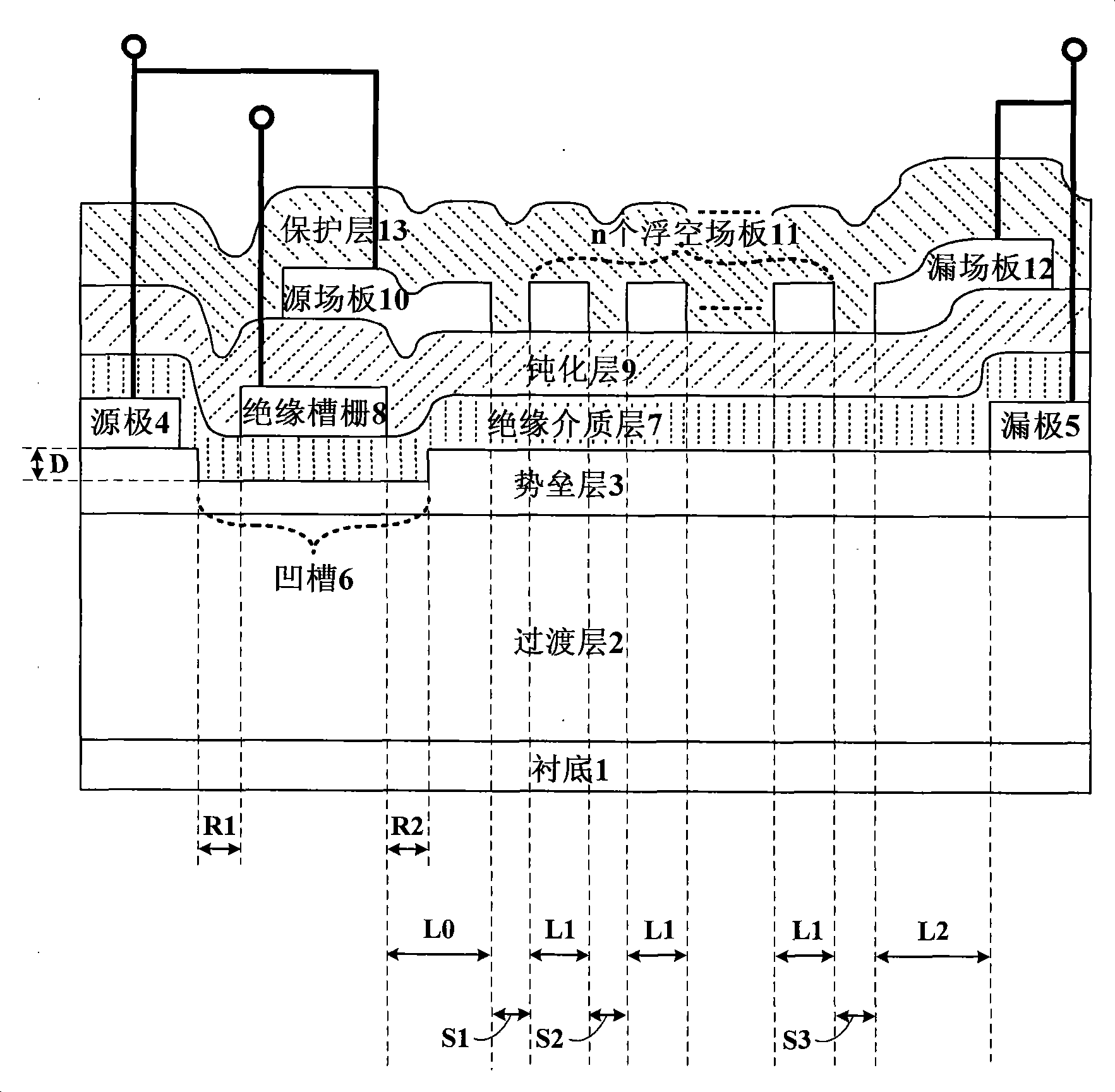

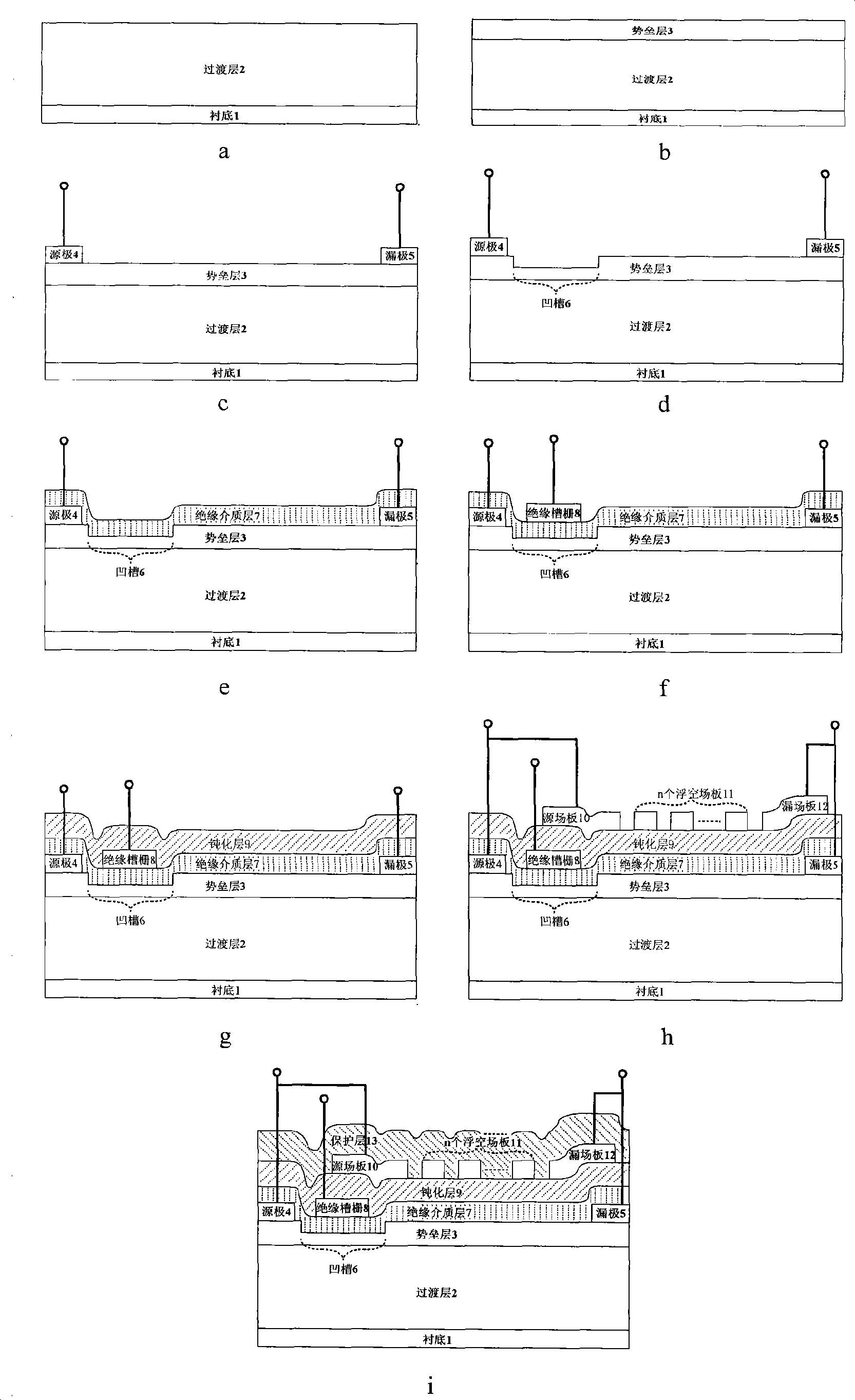

Groove insulated gate type source-leakage composite field plate transistor with high electron mobility

InactiveCN101414636AImprove breakdown voltageReduce gate leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesHigh-electron-mobility transistorComposite field

The invention discloses a groove-insulated gate type source-drain composite field plate transistor with high electron mobility. The transistor comprises, from bottom to top, a substrate (1), a transition layer (2), a barrier layer (3), a source electrode (4), a drain electrode (5), an insulation medium layer (7), an insulated groove gate (8), a passivation layer (9), a source field plate (10), a drain field plate (12) and a protection layer (13); the source field plate is electrically connected with source electrode, and the drain field plate is electrically connected with the drain electrode, wherein, a groove (6) is opened on the barrier layer; and n floating field plates (11) are deposited on the passivation layer arranged between the source field plate and the drain field plate. All the floating field plates have the same size and are mutually independent, and the floating field plates are equidistantly distributed between the source field plate and the drain field plate. The n floating field plates, the source field plate and the drain field plate are completed on the passivation layer by one-time process. The transistor has the advantages of simple process, strong reliability and high output power, and can be used for fabricating power devices based on a wide band gap compound semiconductor material heterojunction.

Owner:XIDIAN UNIV

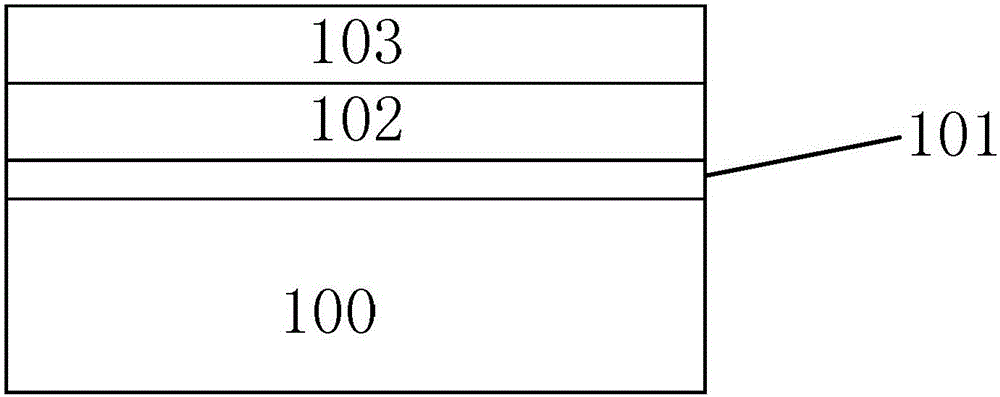

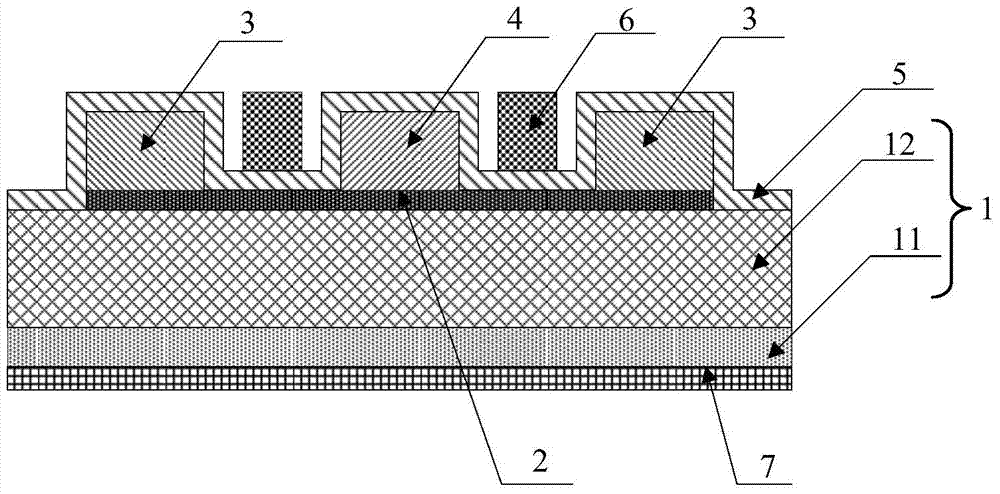

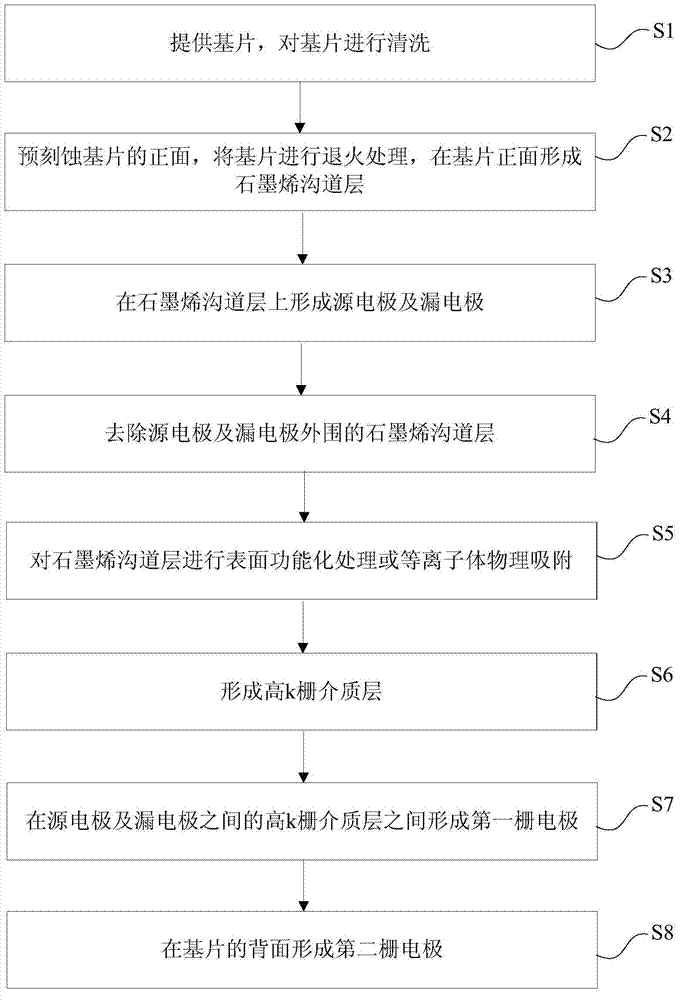

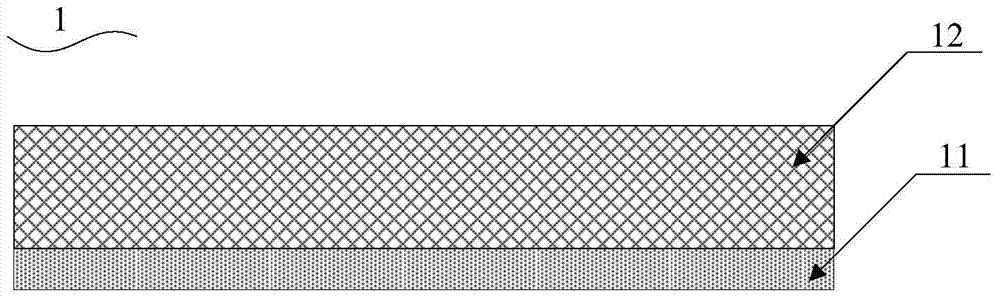

Double-gate and double-pole graphene field effect transistor and manufacturing method thereof

ActiveCN104716191AImprove breaking performanceAvoid destructionTransistorSemiconductor/solid-state device manufacturingGate leakage currentGate dielectric

The invention provides a double-gate and double-pole graphene field effect transistor and a manufacturing method thereof. The manufacturing method comprises the steps that a semiconductor substrate is provided, and a graphene channel layer is formed on the front face of the semiconductor substrate; a source electrode and a drain electrode are formed on the graphene channel layer; the portion, on the peripheries of the source electrode and the drain electrode, of the graphene channel layer is eliminated; surface functionalization processing or plasma physical adsorption is conducted on the graphene channel layer, and a high-k gate dielectric layer is formed; a first gate electrode is formed on the high-k gate dielectric layer between the source electrode and the drain electrode; a second gate electrode is formed on the back face of the semiconductor substrate. Graphene is directly attached to the substrate which needs graphene, troublesome transfer is not needed, and damage and impurity pollution to a graphene structure are avoided; the double-gate and double-pole graphene field effect transistor obtained through the method has the more excellent interruption performance, higher carrier mobility and smaller gate leakage current; the process procedure is simple, cost is low, and the method is suitable for large-scale production of the double-gate and double-pole graphene field effect transistor.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

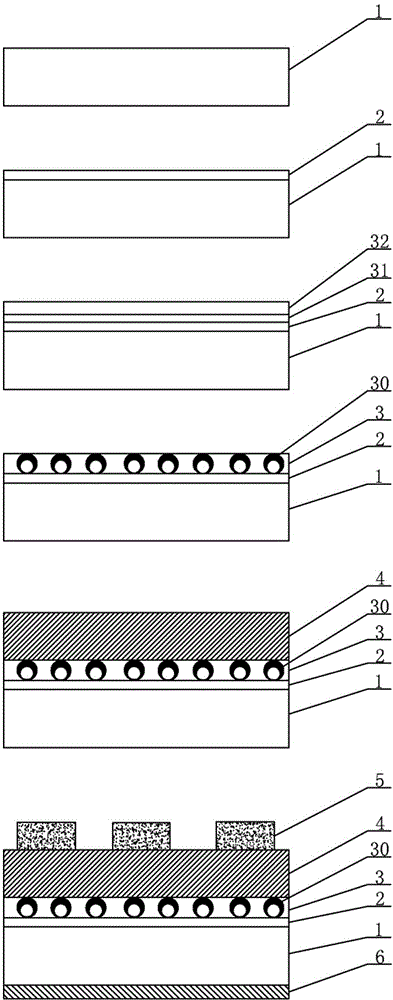

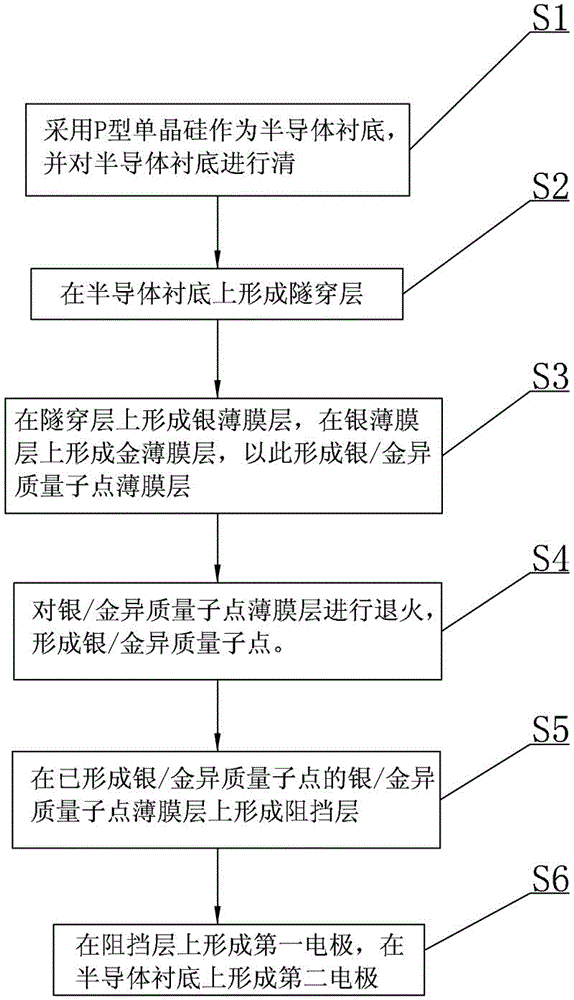

Floating gate memory based on metal heterogeneous quantum dots and preparation method therefor

InactiveCN104882490AExtended storage timeHigh densityTransistorSemiconductor/solid-state device manufacturingThin layerQuantum dot

The invention relates to a floating gate memory based on metal heterogeneous quantum dots and a preparation method therefor. The floating gate memory based on metal heterogeneous quantum dots comprises a semiconductor substrate. The semiconductor substrate is provided with a tunneling layer. The tunneling layer is provided with a silver / gold heterogeneous quantum dot thin layer. The silver / gold heterogeneous quantum dot thin layer is subjected to annealing to form silver / gold heterogeneous quantum dots. The silver / gold heterogeneous quantum dots achieve information storage by capturing tunneling charges. The silver / gold heterogeneous quantum dot thin layer is provided with a barrier layer for blocking captured charges by the silver / gold heterogeneous quantum dots for entering a first electrode. The barrier layer is provided with the first electrode for supplying power to the barrier layer. The semiconductor substrate is provided with a second electrode for supplying power to the semiconductor substrate. The floating gate memory based on the metal heterogeneous quantum dots is advantaged in that the charge storage density is high, the data holding property is good, the operation voltage is low, the erasing and writing speed is fast and the like.

Owner:SHAOXING UNIVERSITY

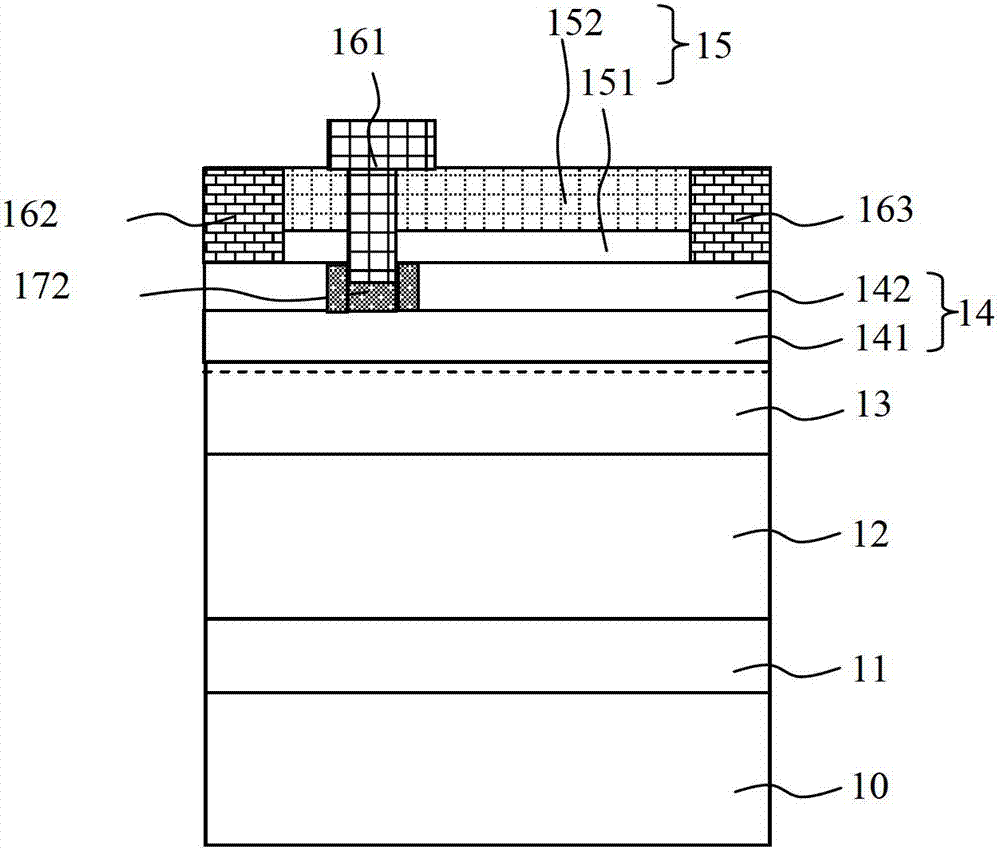

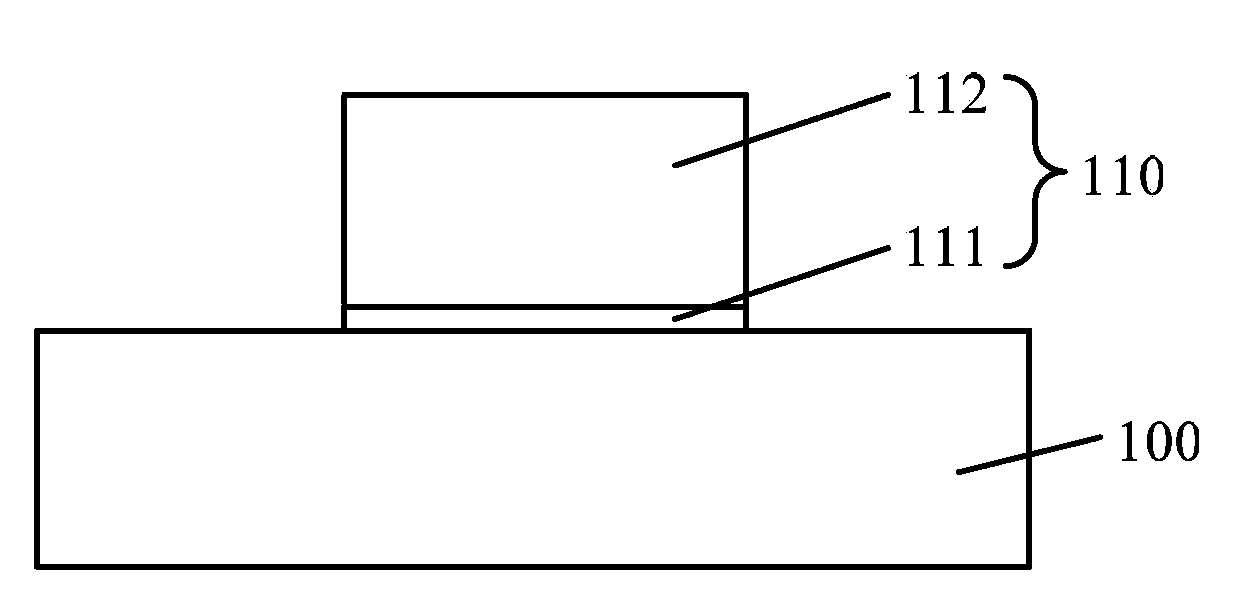

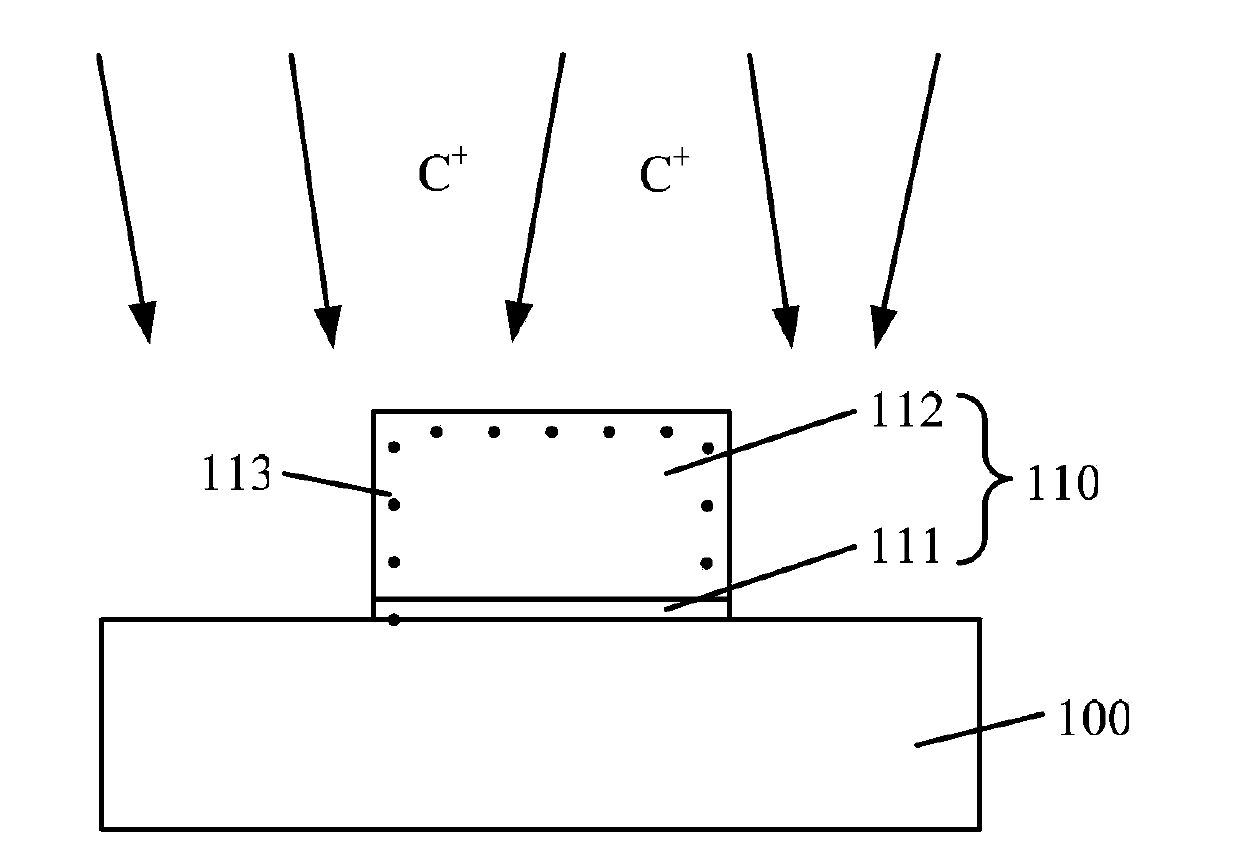

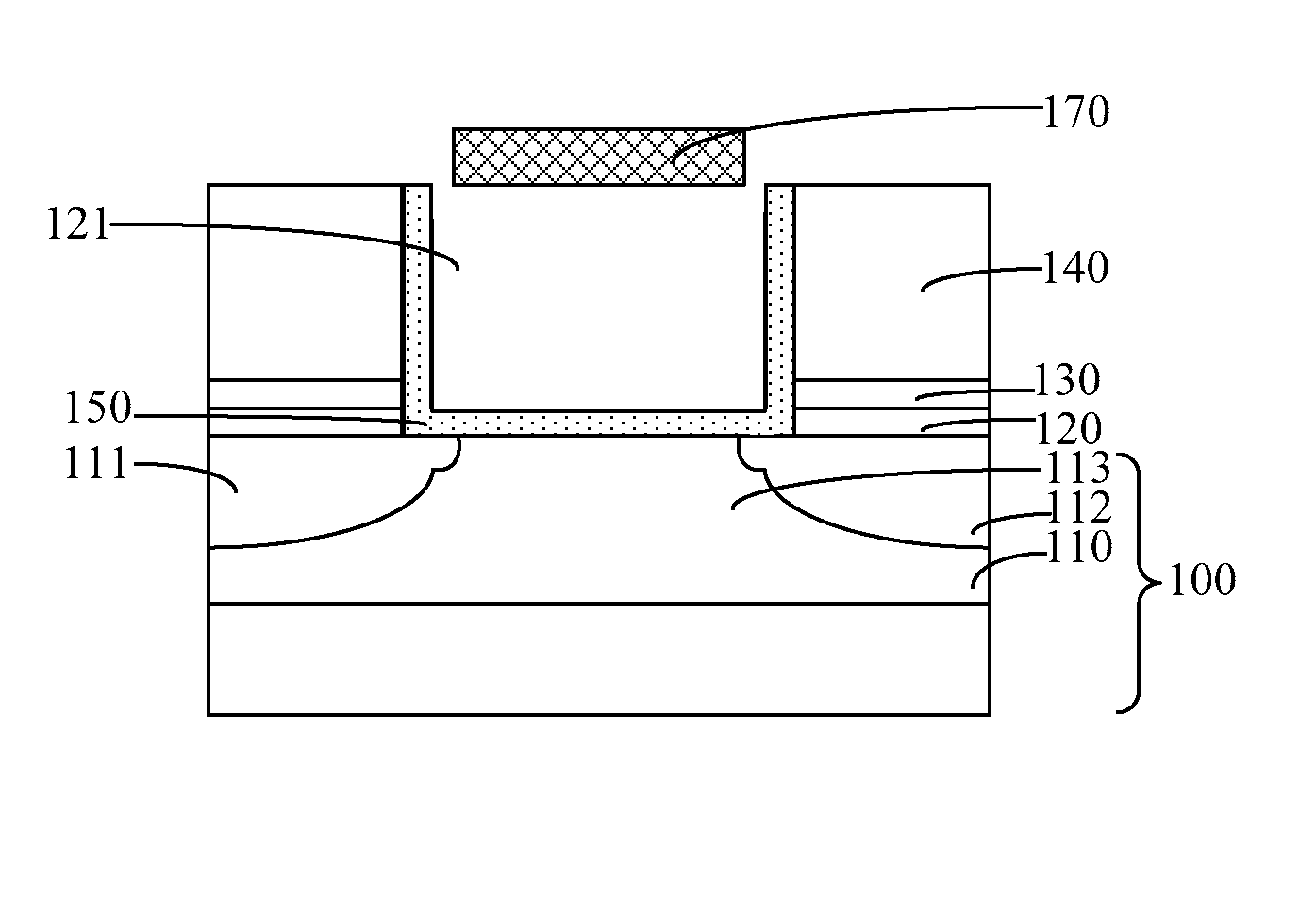

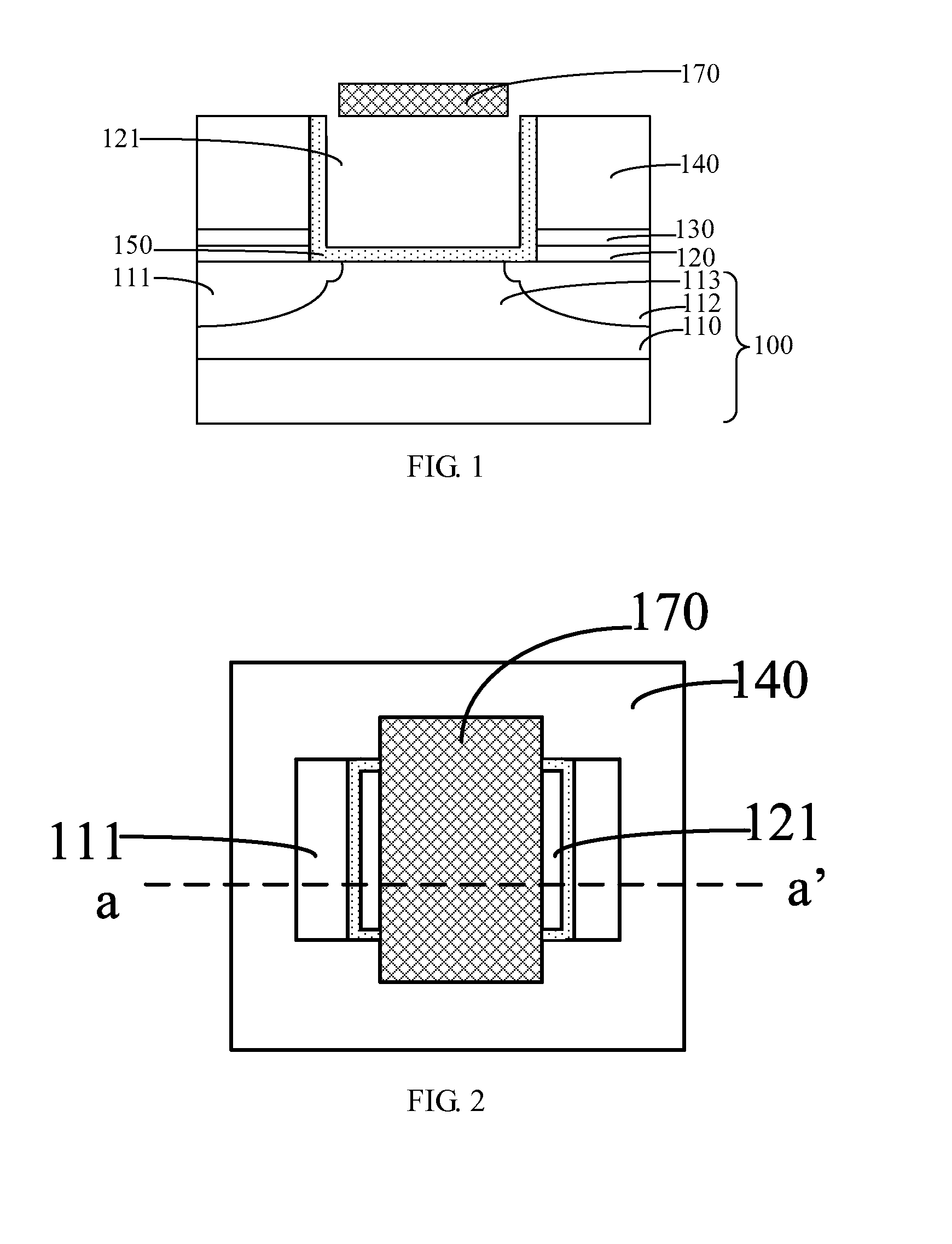

MEMS device and method of forming the same

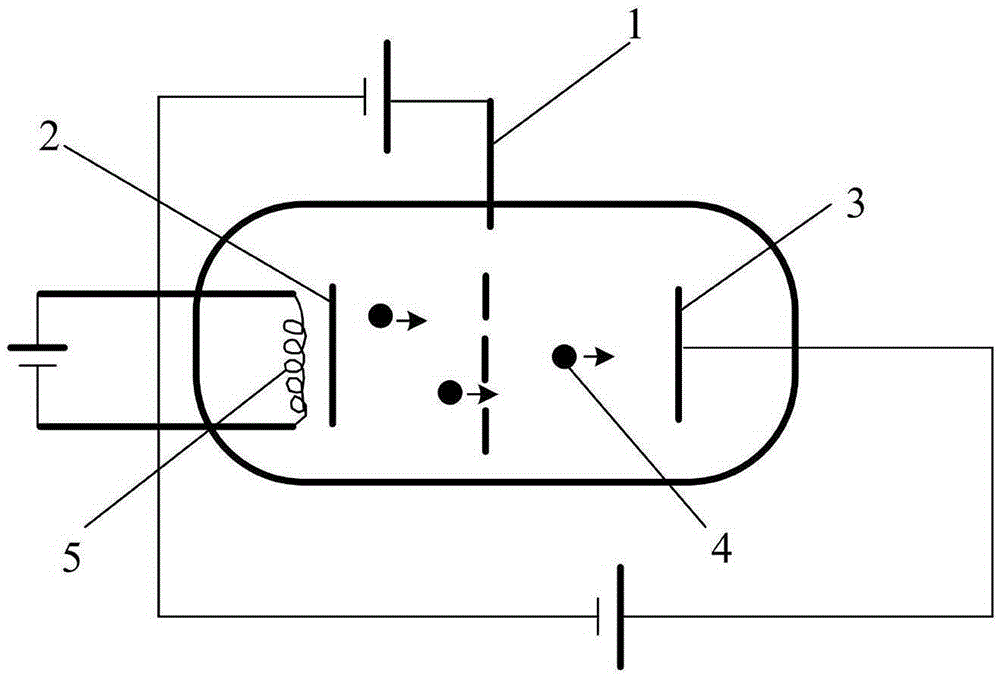

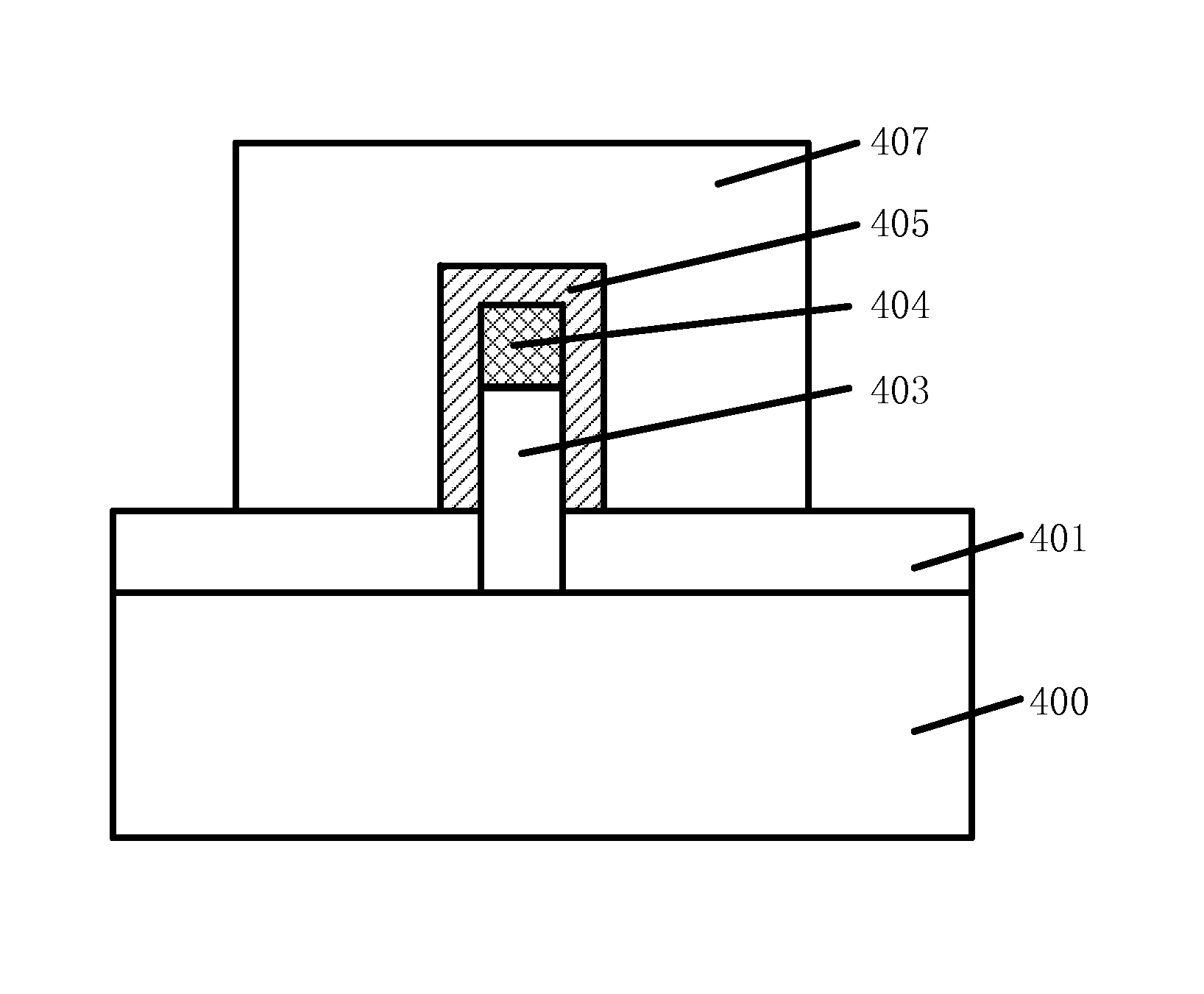

ActiveUS20130221450A1Reduce gate leakage currentReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsLow leakage

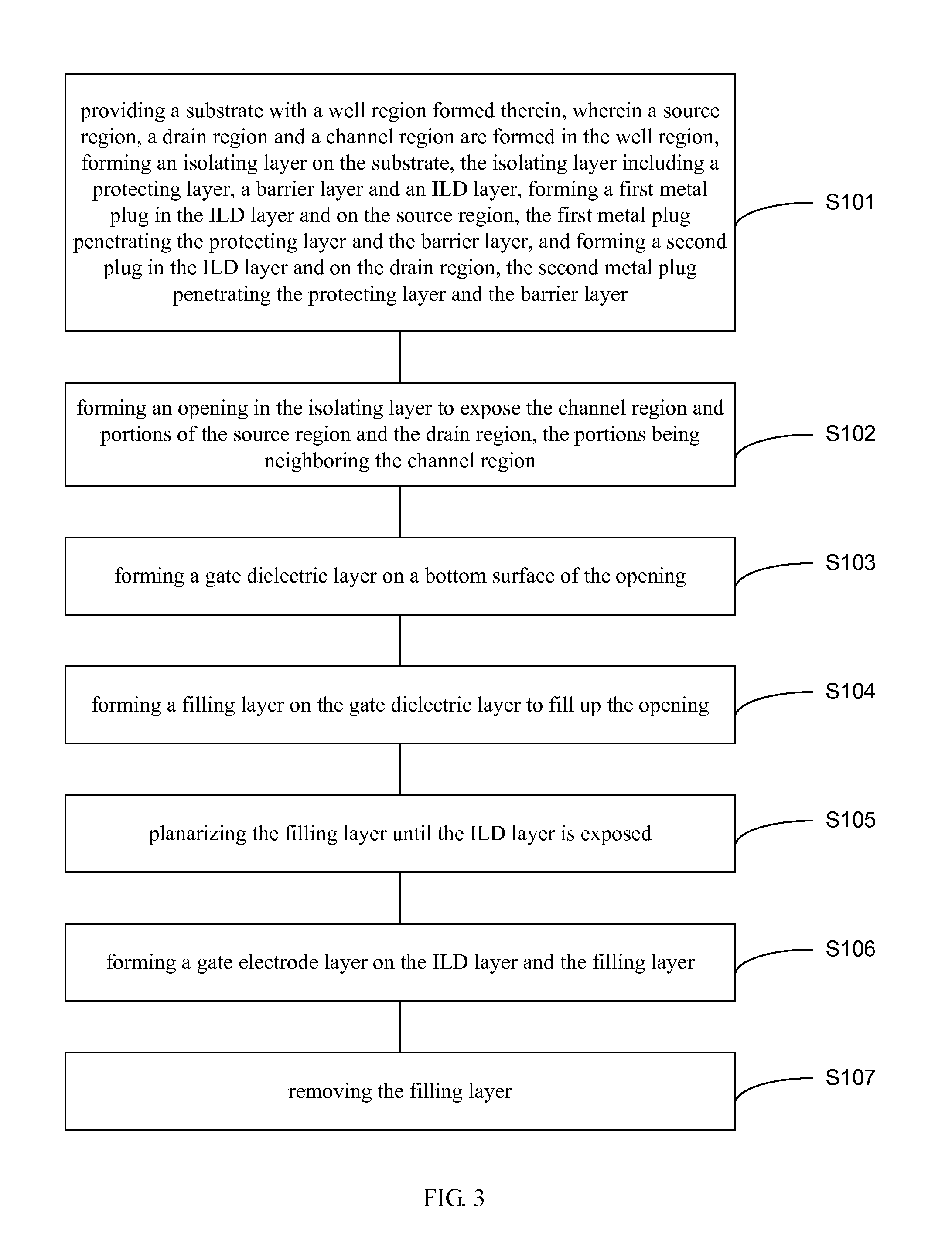

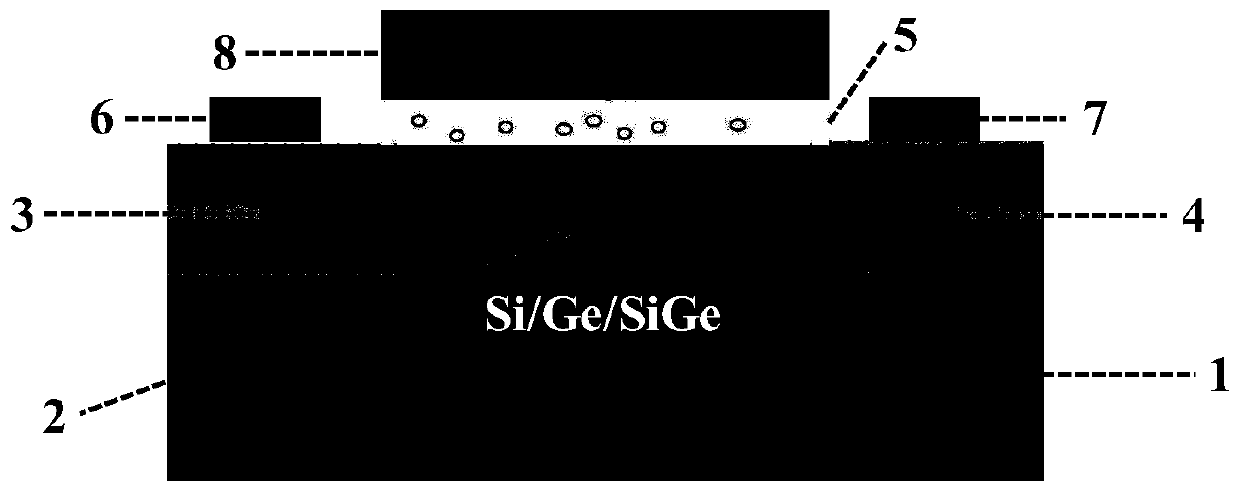

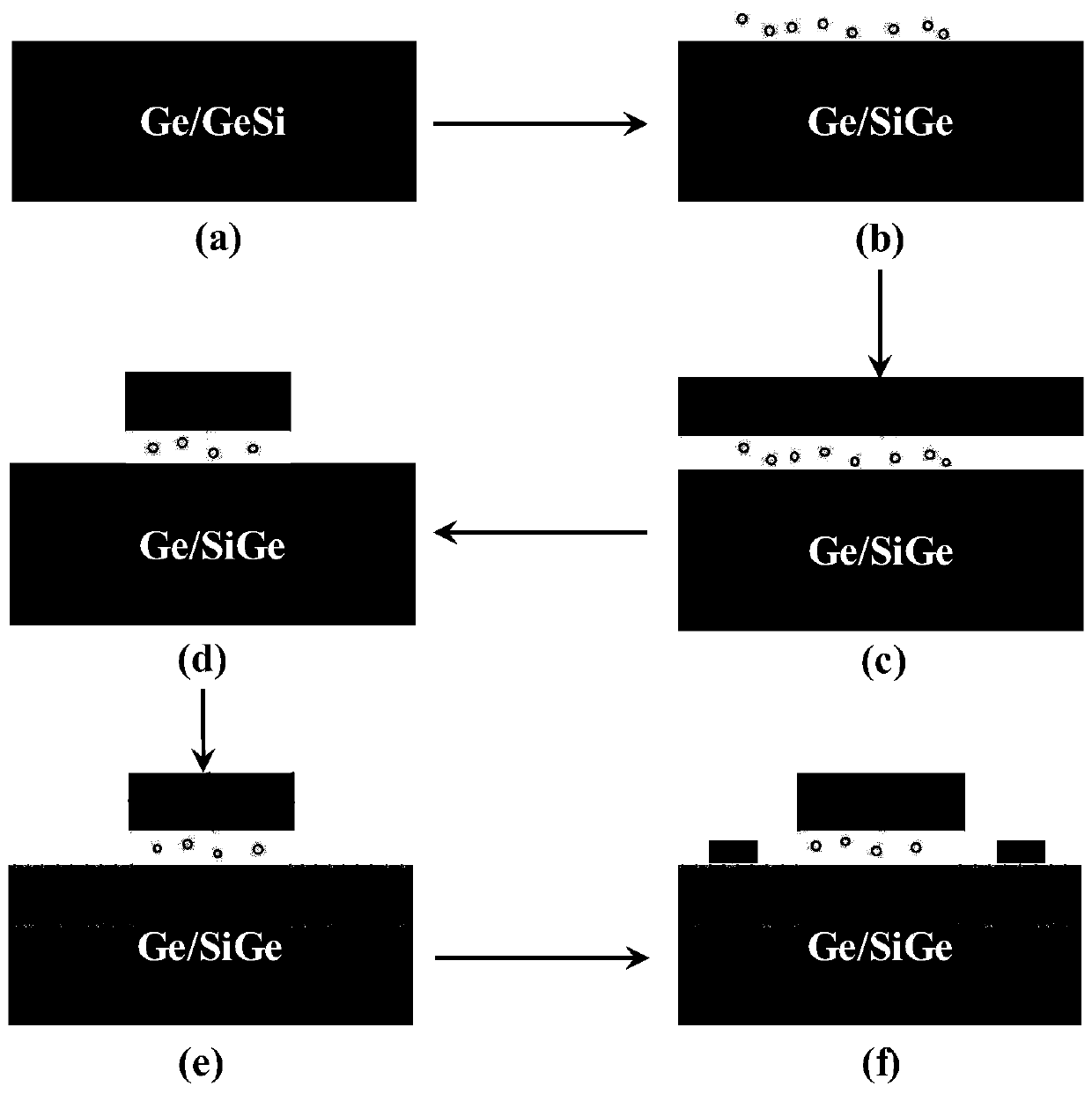

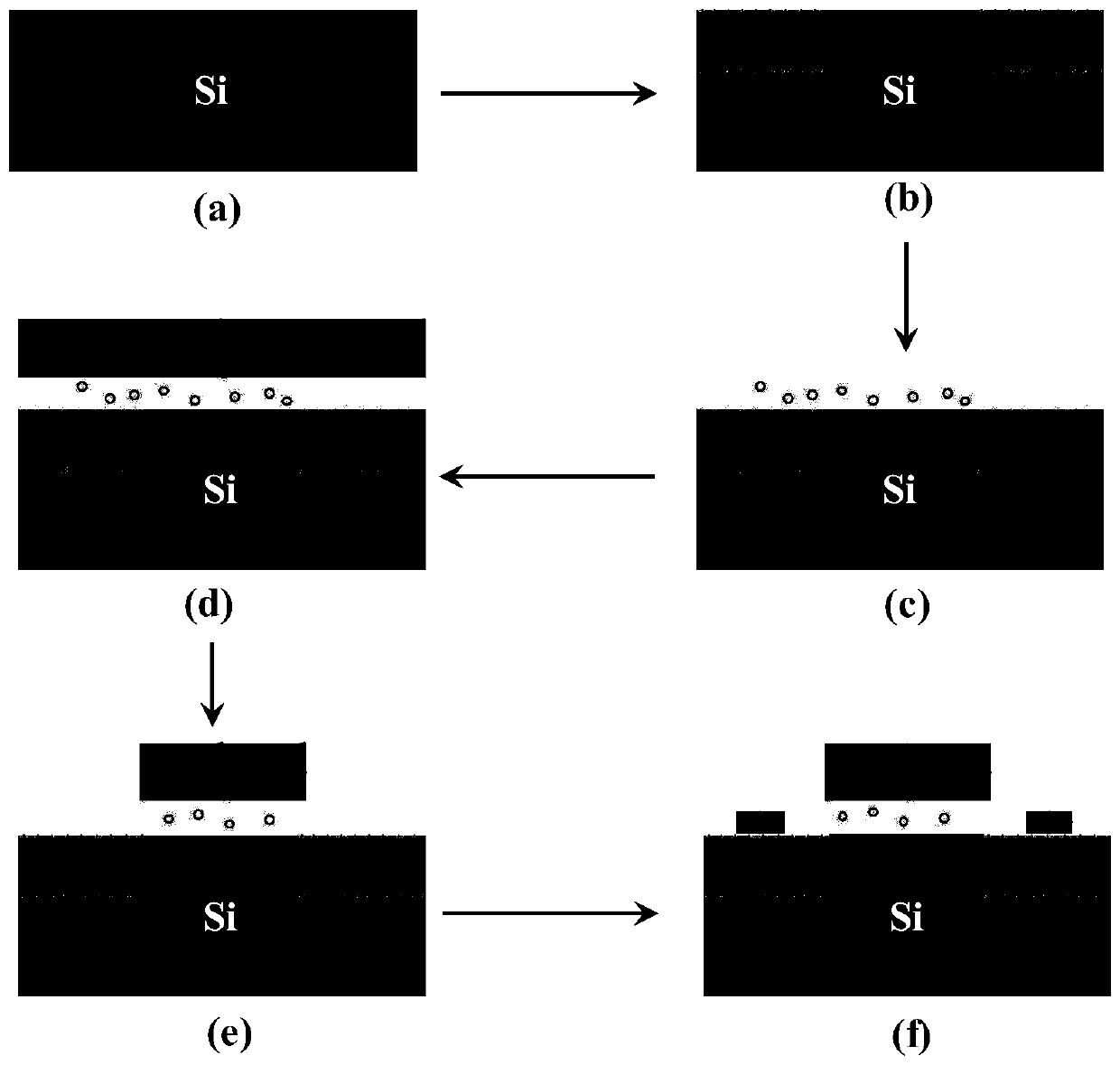

A micro electro mechanical system (MEMS) device and a method of forming the same are provided. The MEMS device comprises a semiconductor substrate (100); a well region (110) formed in the semiconductor substrate (100); a source region(111), a drain region (112) and a channel region (113) formed in the well region (110); an isolating layer (120,130,140) formed on the surface of the source region (111) and the drain region (112); a gate dielectric layer (150) formed on the surface of the channel region (113); and a gate electrode layer (170) formed above the gate dielectric layer (150), a gap is provided between the gate dielectric layer (150) and the gate electrode layer 170), and the gap width corresponds to the channel region width. The method of forming MEMS device can be compatible with a conventional semiconductor forming process, without redeveloping a new type material and a new fabrication process. The MEMS device has a high withstand voltage performance, and a low leakage current of the gate electrode.

Owner:SHANGHAI LEXVU OPTO MICROELECTRONICS TECH

Ferroelectric field effect transistor based on alumina material with embedded nanocrystalline and preparation method thereof

ActiveCN109728096AReduce thicknessStable characteristicsMaterial nanotechnologySemiconductor/solid-state device manufacturingGate dielectricOrganic field-effect transistor

The invention discloses a ferroelectric field effect transistor based on alumina material with embedded nanocrystalline and a preparation method thereof. The problems are mainly solved that a conventional ferroelectric gate dielectric in the current ferroelectric field effect transistor is incompatible with the prior art, and the hafnium oxide-based ferroelectric thin film generates large electricleakage. The ferroelectric field effect transistor comprises from bottom to top: a substrate (1), a channel (2), a gate dielectric layer (5) and a gate electrode (8); the two sides of the channel (2)are respectively provided with a source region (3) and a drain region (4); the upper portion of the source region (3) is provided with a source (6), and the upper portion of the drain region (4) is provided with a drain (7). The gate dielectric layer (5) employs an alumina ferroelectric film with an embedded nanocrystal. The ferroelectric field effect transistor based on alumina material with embedded nanocrystalline and the preparation method thereof can be compatible with the current integrated circuit process, can reduce the thickness of the gate dielectric layer below 4 nm, can reduce theelectric leakage of the gate dielectric layer, can improve the overall performances of the device and can be used for a large-scale integrated circuit.

Owner:XIDIAN UNIV

Circuit using dielectric unit capacitor

InactiveCN1851920AImprove reliabilityHigh Unit Capacitance ValueSolid-state devicesSemiconductor devicesDielectricCapacitor

This invention relates to a circuit using a thin dielectric unit condenser including one or more than one circuit modules and one or more than one decoupling modules coupled to said circuit modules, in which, every decoupling module has one or more decoupling thin dielectric unit condensers including: a first node coupled to a first circuit connecting point of the circuit module, a second node coupled to a second circuit connecting point of the circuit module and two or more thin dielectric condensers connected between the two nodes in series and at least the thickness of a grid dielectric of a thin dielectric condenser is less than 50.

Owner:TAIWAN SEMICON MFG CO LTD

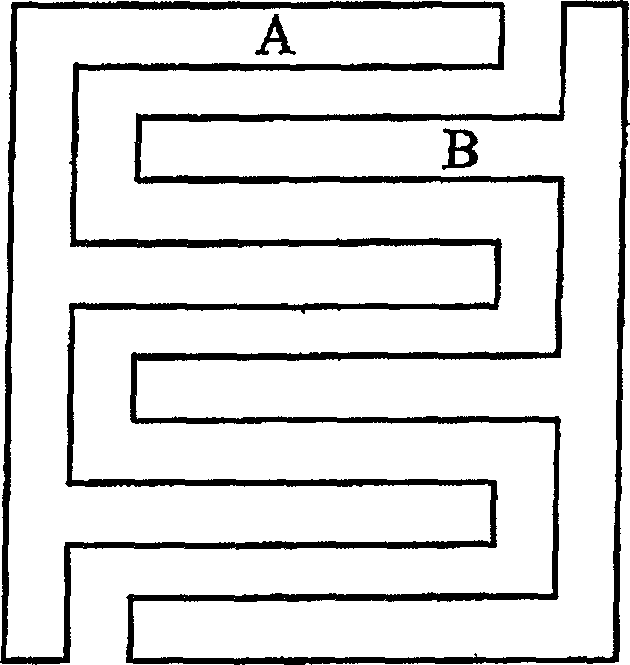

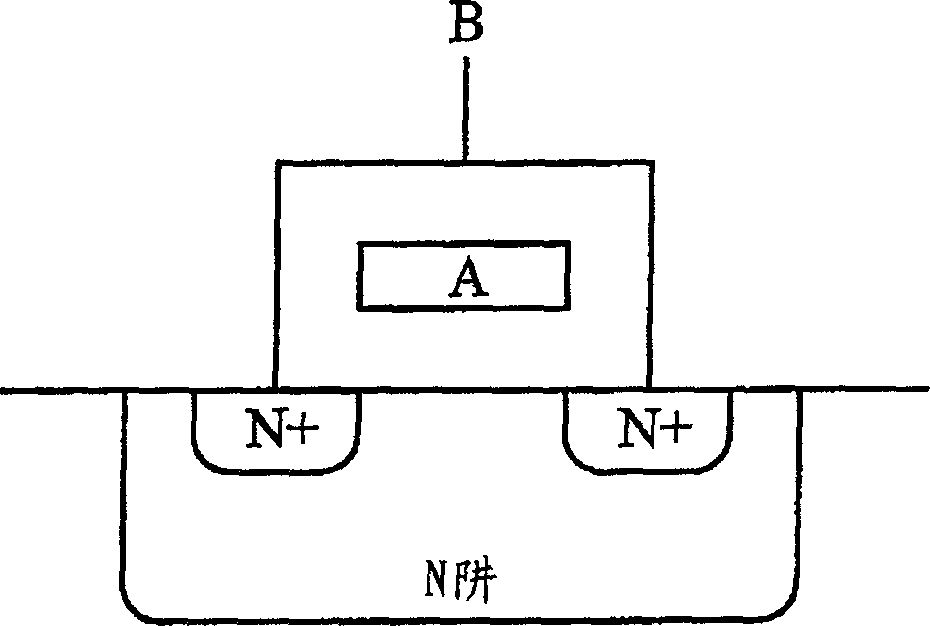

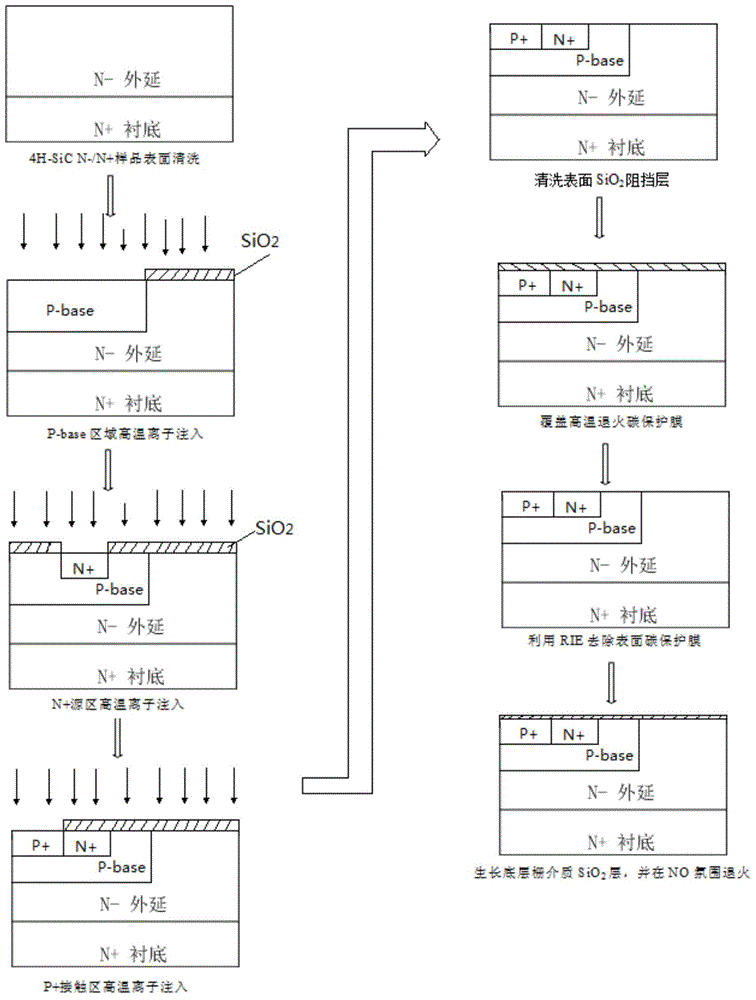

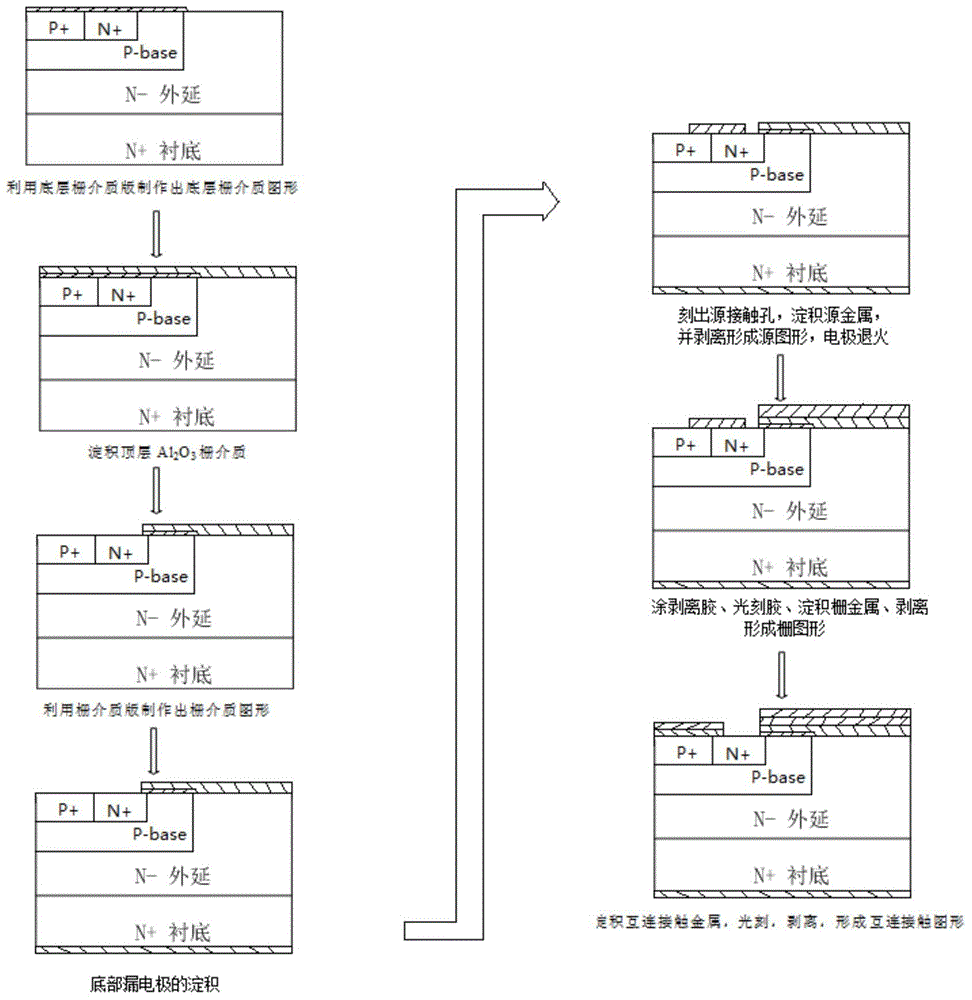

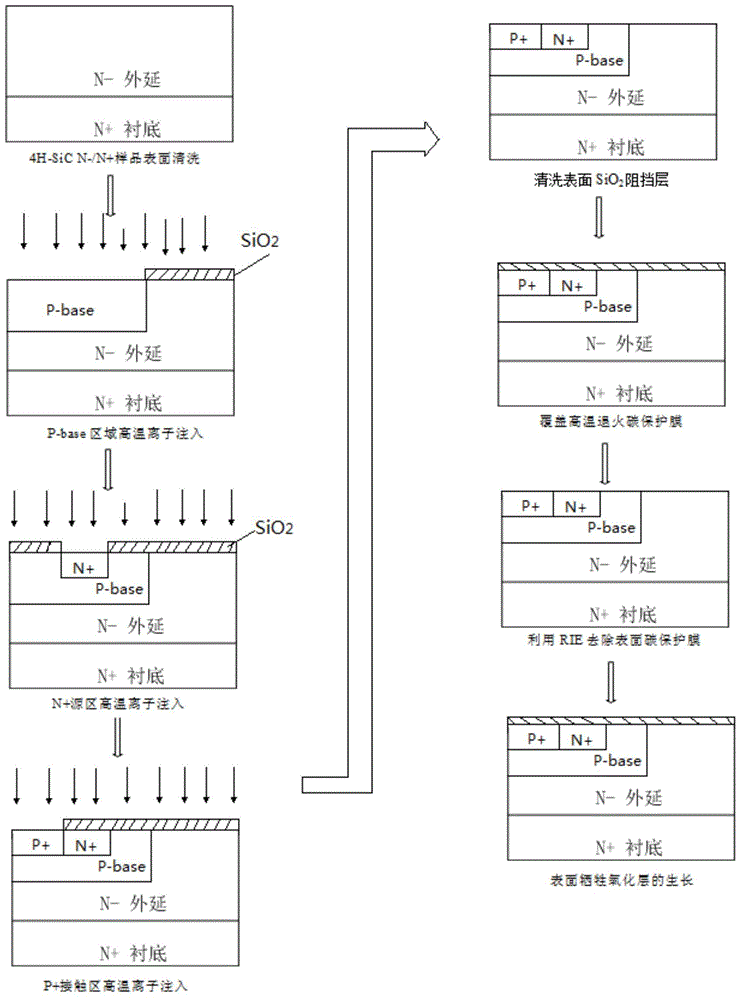

Manufacture method of SiC DMISFET device of partitioned composite gate structure

ActiveCN104810293AReduce interface state densityImprove interface propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesCarbon filmGate leakage current

The invention discloses a manufacture method of a SiC DMISFET device of a partitioned composite gate structure. The manufacture method comprises the steps that the surface of an N- / N+ type SiC epitaxial wafer is cleaned; a P-base area is etched, and Al ion implantation is carried out at high temperature; an N+ doped source area is etched, and N ion implantation is carried out at high temperature; a P type doped contact area is etched, and P type doped Al ion implantation is carried out at high temperature; a carbon protection film is formed at the surface of the N- / N+ type SiC epitaxial wafer; ion implantation annealing is carried out at the high temperature of 1600 DEG C; the carbon film at the surface is removed; acid cleaning is implemented; an Al2O3 / Nitrided-SiO2 composite gate dielectric layer is grown; a bottom drain electrode is grown; a peeling glue and a photoresist are coated, a source contact hole is etched, source metal is deposited, and a source pattern is peeled; gate electrode is formed on the SiC epitaxial wafer after annealing of the source and drain electrodes; and the source and drain interconnected electrode is formed, and a finished device is obtained. The manufacture method can effectively reduce the gate leakage current and improve the quality of the gate dielectric layer.

Owner:DALIAN UNIV OF TECH +1

Semiconductor device and method of manufacturing semiconductor device

ActiveCN104183638AGate Threshold Voltage StabilityReduce gate leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorNitride semiconductors

A semiconductor device includes a first semiconductor layer formed of a nitride semiconductor on a substrate; a second semiconductor layer formed of a nitride semiconductor on the first semiconductor layer; an insulating layer formed on the second semiconductor layer; a source electrode and a drain electrode formed on the second semiconductor layer; and a gate electrode formed on the insulating layer. The insulating layer is formed of a material including an oxide and is formed by laminating a first insulating layer and a second insulating layer in a positioning order of the first insulating layer followed by the second insulating layer from a side of the second semiconductor layer, and an amount of hydroxyl groups included in per unit volume of the first insulating layer is less than an amount of hydroxyl groups included in per unit volume of the second insulating layer.

Owner:FUJITSU LTD

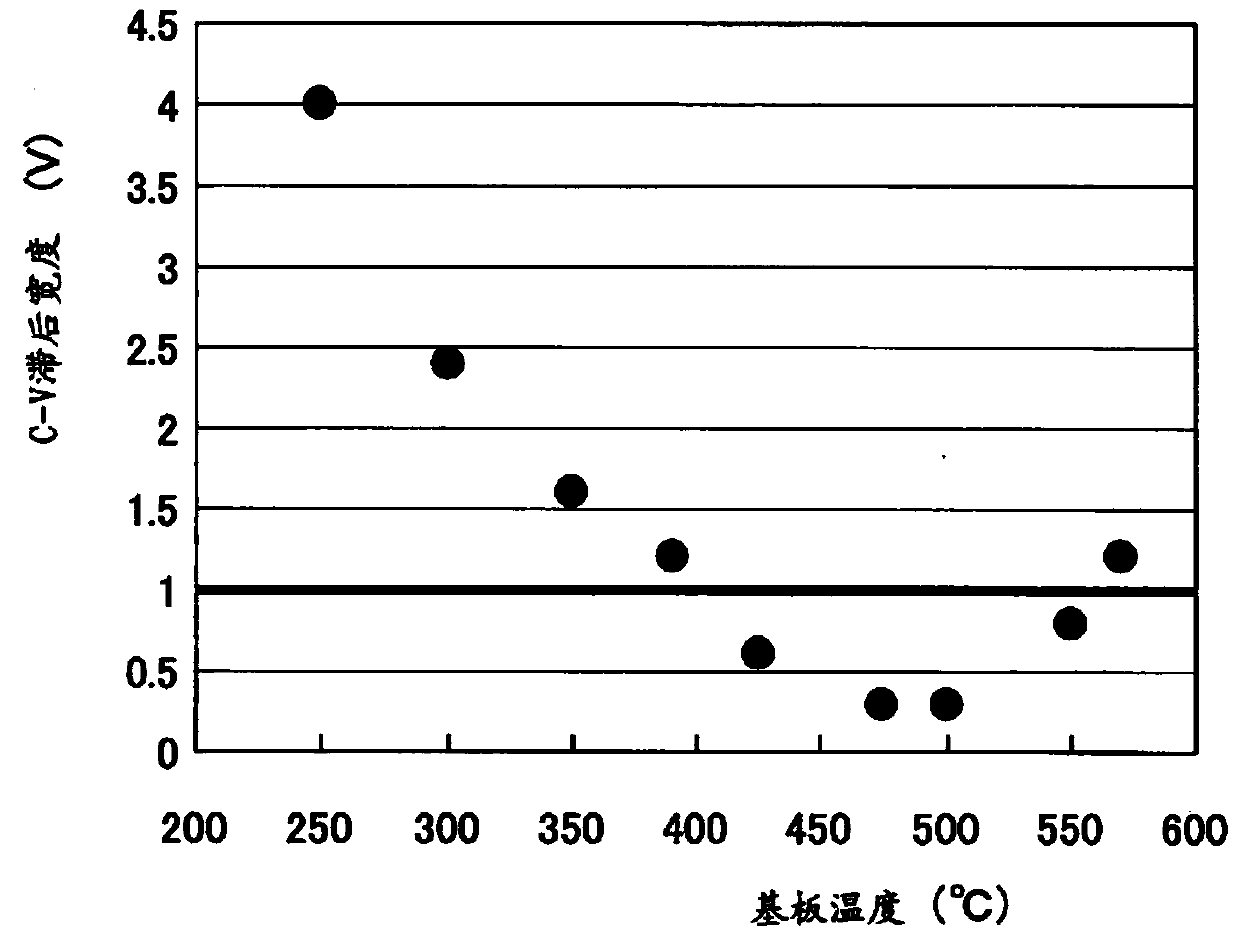

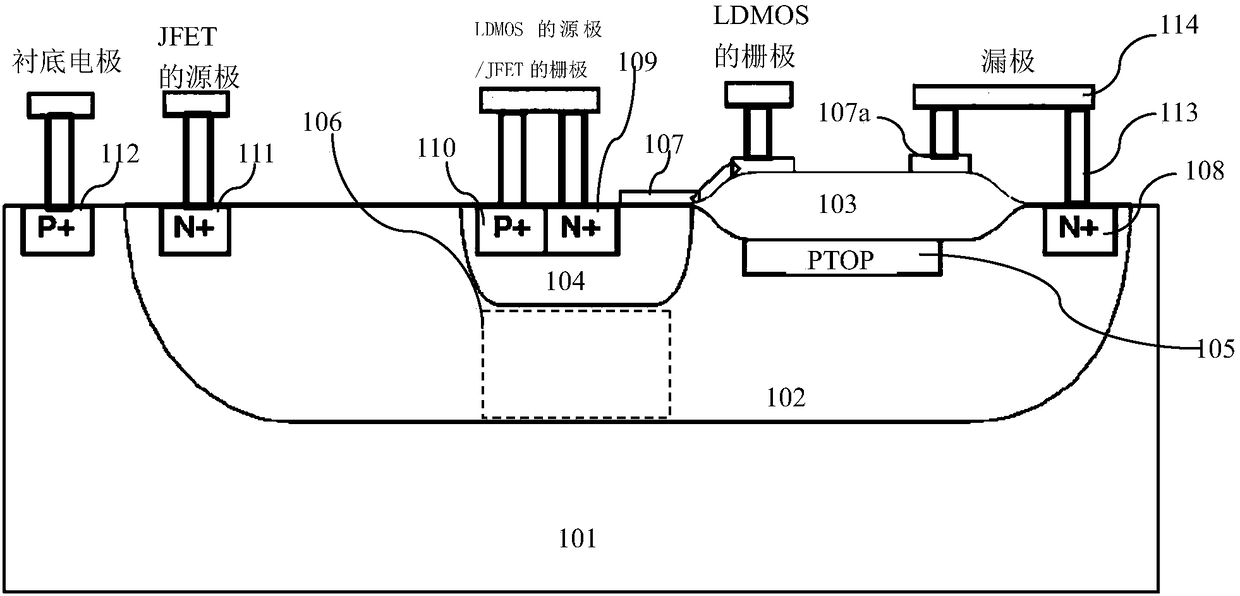

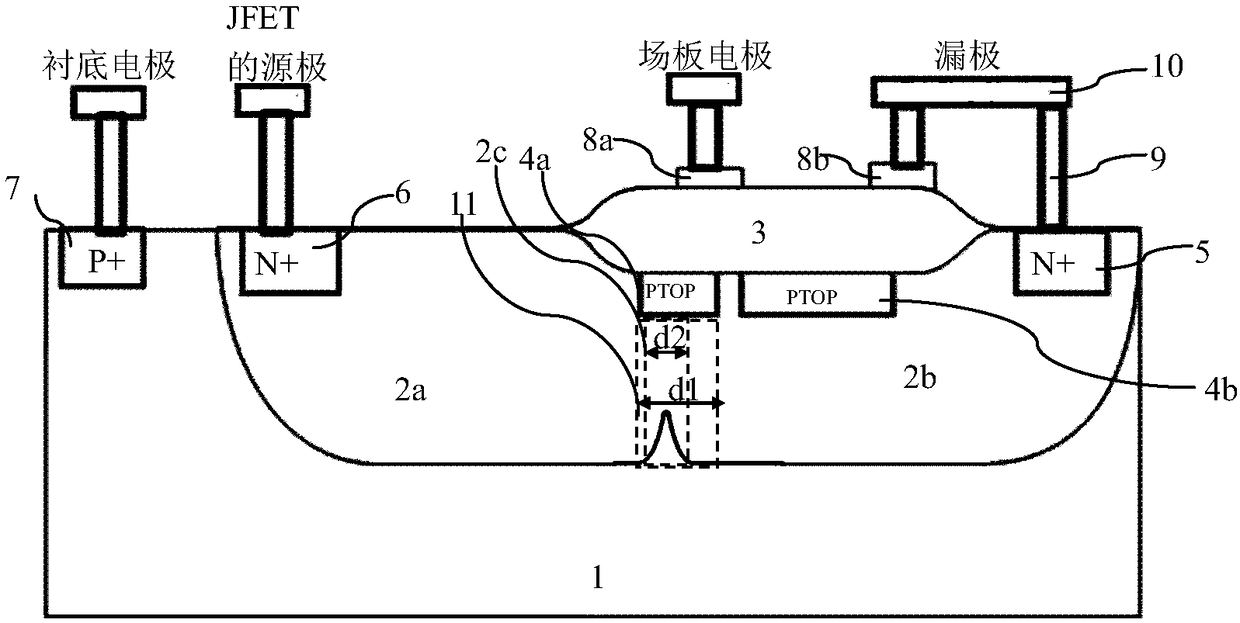

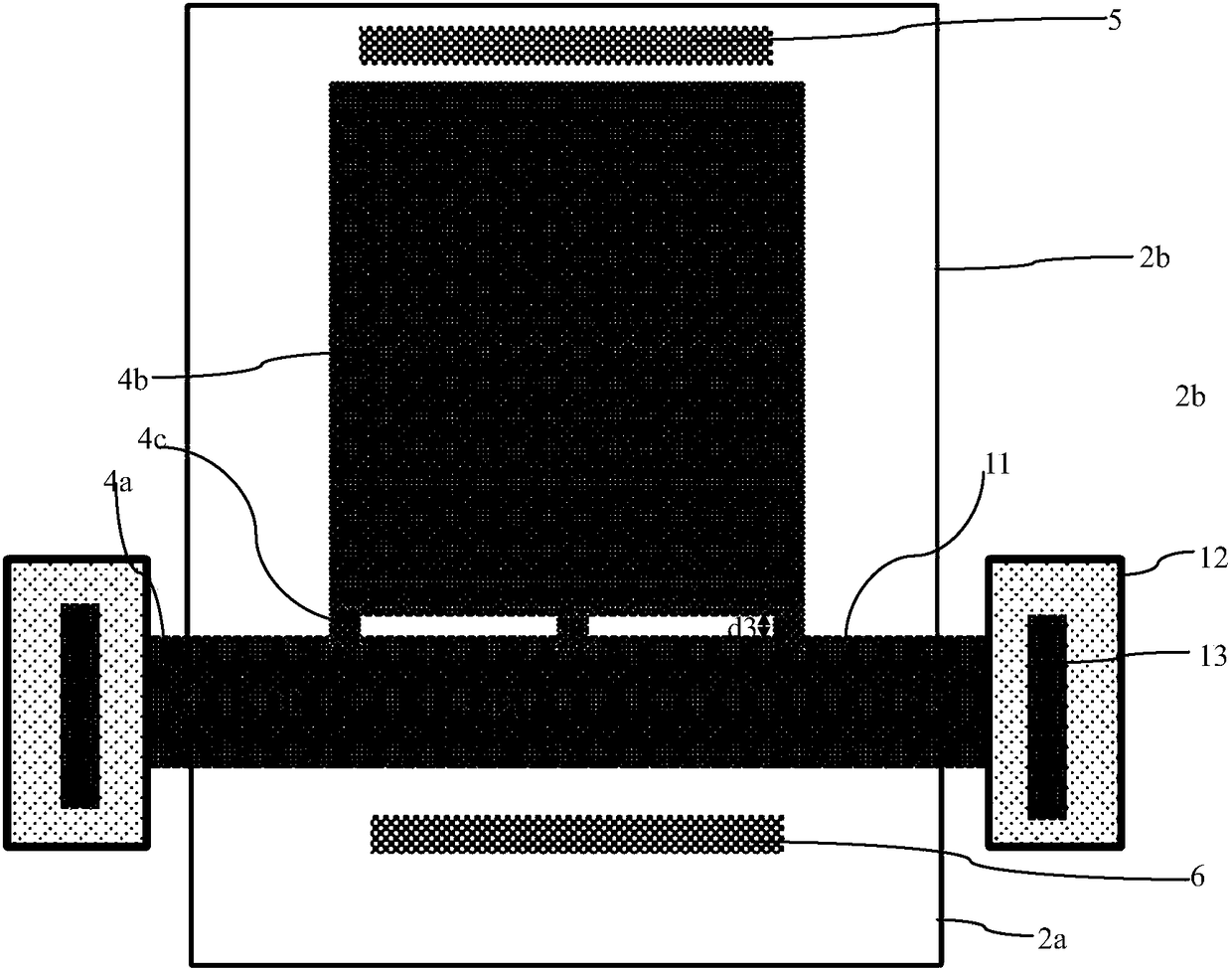

JFET and manufacturing method thereof

ActiveCN108305903AReduce gate leakage currentReduce areaSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSOxygen

The invention discloses a JFET. The JFET includes an N type deep well formed by transverse splicing of first and second deep well sections, and a channel resistance adjusting region of the JFET is formed between the two deep well sections; a P type top layer including a first top layer, a second top layer and a top layer connecting section is formed at the bottom of a drift region field oxygen thefirst top layer serves as a grid electrode region of the JFET, the N type deep well covered by the grid electrode region of the JFET serves as a channel region of the JFET, and the channel resistanceadjusting region is located in a channel region of the JFET; and the first top layer also extends into a semiconductor substrate on an outer side of the N type deep well and is connected to a grid electrode of the JFET through a contact hole. The invention also discloses a method for manufacturing a JFET. According to the JFET and manufacturing method thereof provided by the invention, pinch-offvoltage of a device can be increased, channel region resistance can be increased, and grid electrode leak current of the JFET can be reduced; and the JFET can be integrated with an LDMOS, and processcost is low.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP