Forming method of semiconductor device and forming method of fin type field effect transistor

一种鳍式场效应管、半导体的技术,应用在半导体器件、半导体/固态器件制造、电固体器件等方向,能够解决器件性能问题等问题,达到性能稳定、栅极漏电流小、沟道区载流子迁移率增加的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] As mentioned in the background, the performance of the prior art FinFET is not stable.

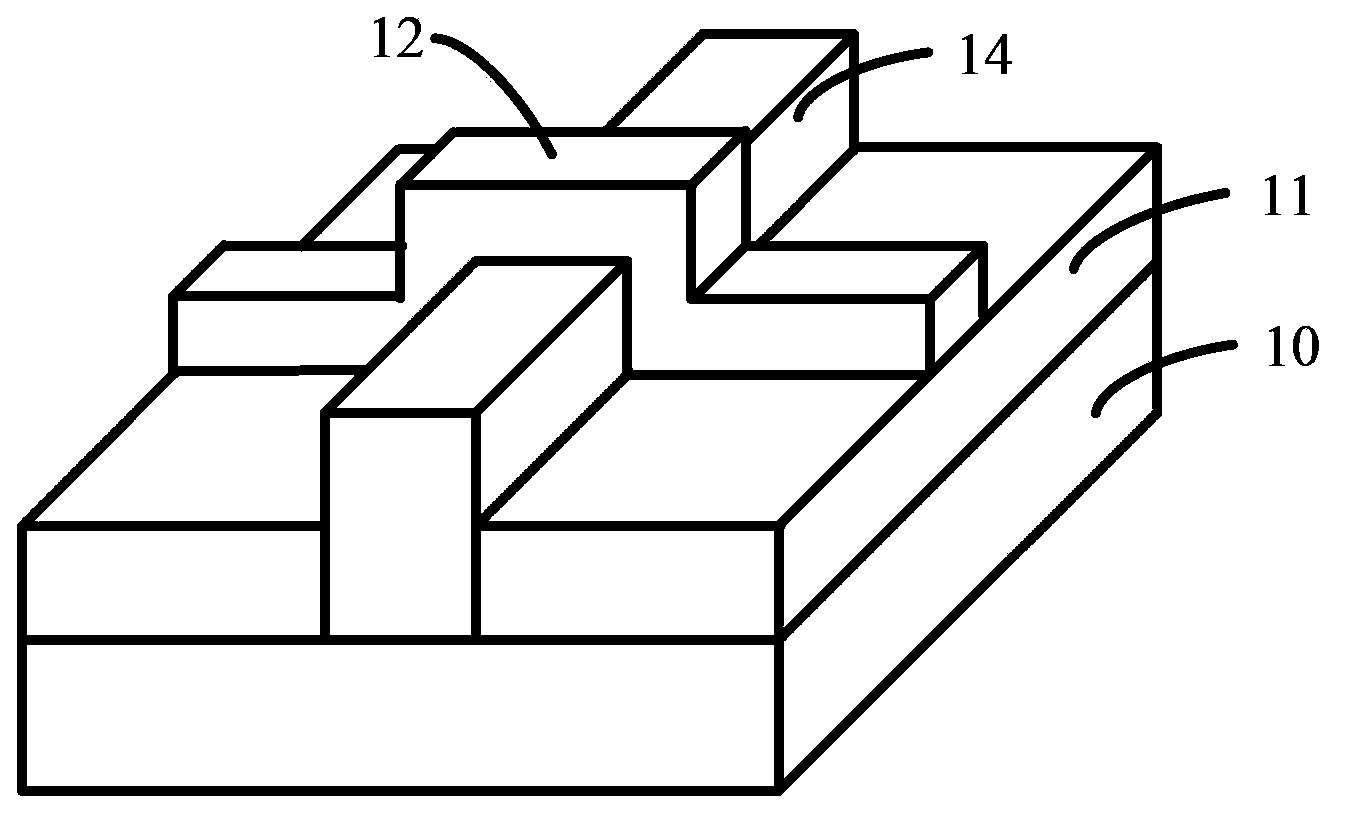

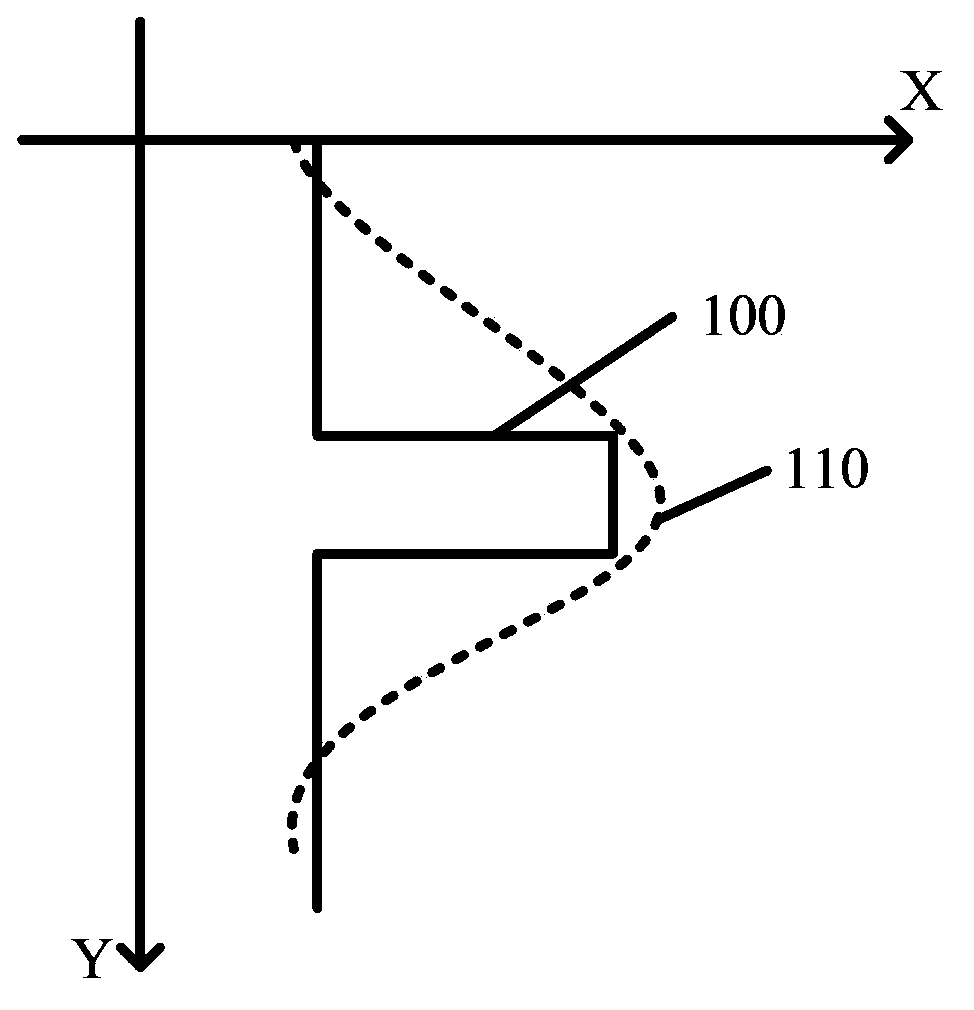

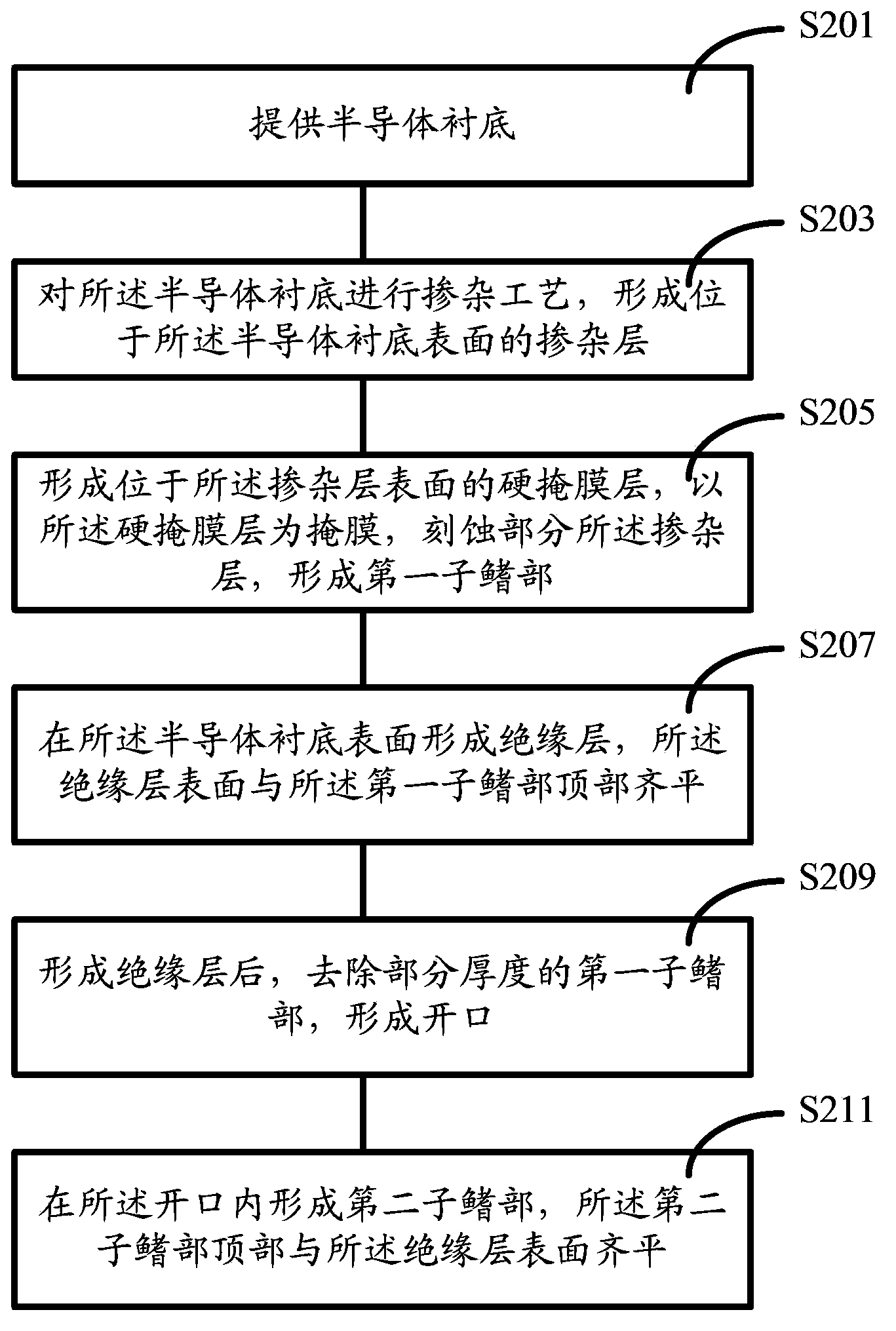

[0048] After research, the inventors found that there are many reasons affecting the performance stability of the fin field effect transistor, one of which is: the existing technology forms fins 14 on the surface of the semiconductor substrate (such as figure 1 As shown), when doping ions from the top surface of the fin 14 to the inside of the fin 14, as figure 2 as shown in figure 2 The middle X-axis represents the concentration of dopant ions in the fin 14, and the Y-axis represents the distance from any point in the fin 14 to the top of the fin 14. In the case of ideal doping, it is desired that the ion concentration after doping be within the fin 14 As shown in the curve 100, the dopant ions are concentrated in the middle of the fin 14, while the ion concentration at both ends of the fin 14 is less and evenly distributed; however, the actual doped ion concentration is in the ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| temperature | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More