Formation method for VDMOS (vertical double-diffused metal oxide semiconductor) device

A device and epitaxial layer technology, which is applied in the field of VDMOS device formation, can solve the problems of affecting the isolation effect, damaging the insulating performance of the second gate oxide layer, and being difficult to chemical mechanical polishing, and achieves the effect of improving electrical performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

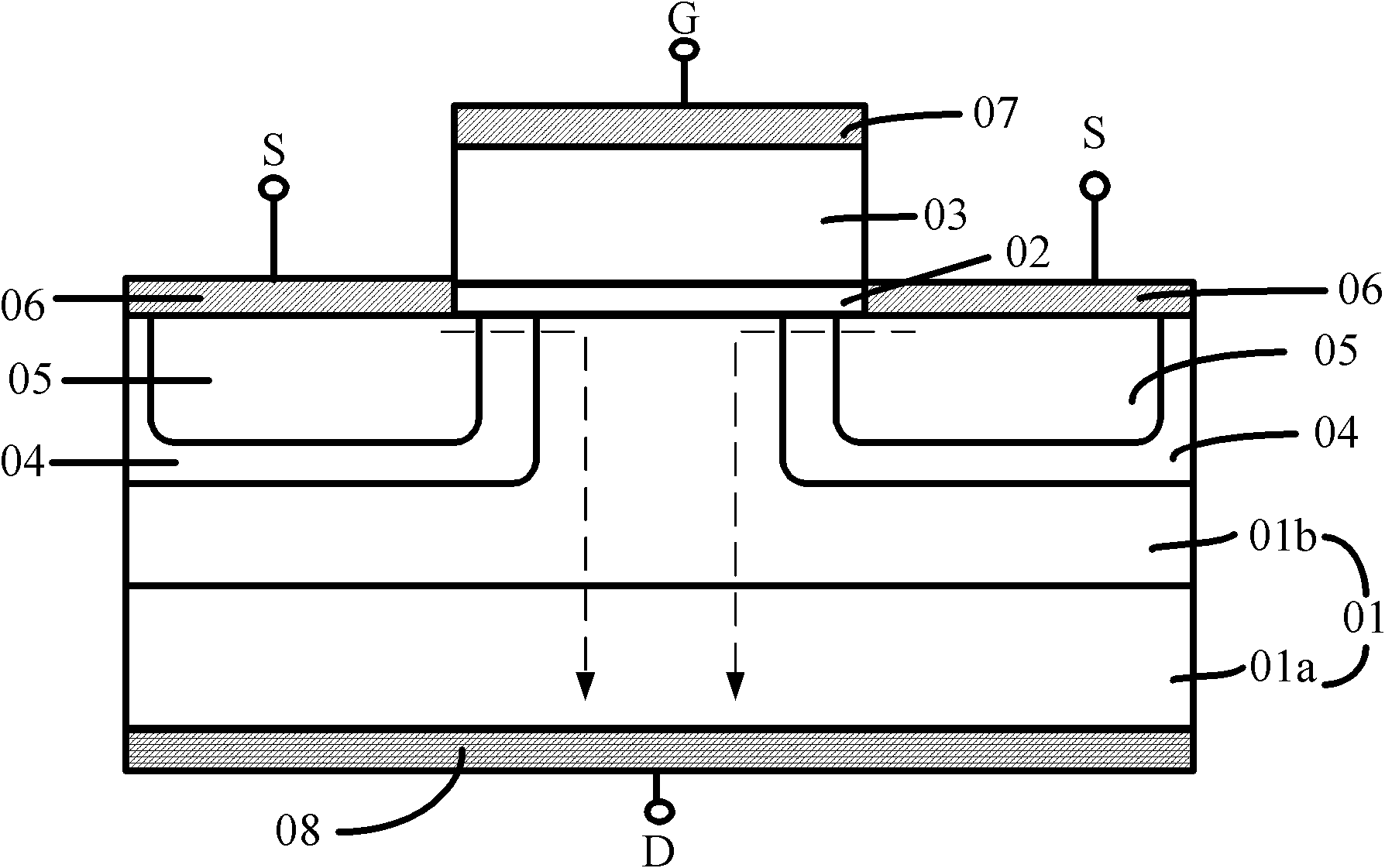

[0044] Such as Figure 7 As shown, the existing technology increases the thickness of the gate oxide layer between the drain D and the gate G by adding a second gate oxide layer 50 between the drain D and the gate G, and reduces the gap between the gate and the drain. The capacitor value increases the switching speed of VDMOS. However, the second gate oxide layer 50 is formed by deposition and chemical mechanical polishing, that is, the filled oxide needs to be chemical mechanical polishing to reach a predetermined thickness. Because the second gate oxide layer 50 is located in the recessed opening, it is not easy to perform chemical mechanical polishing.

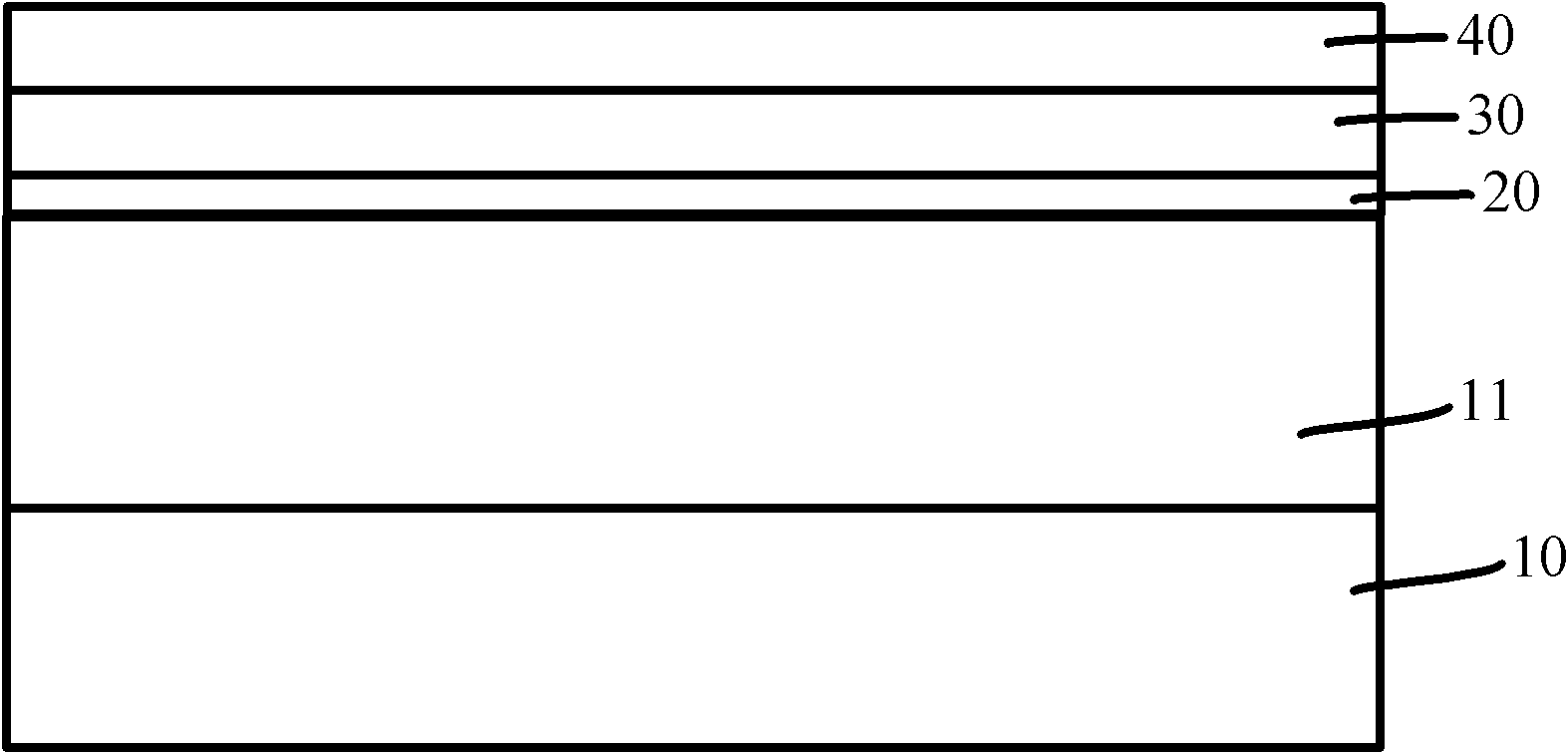

[0045]In order to solve the above problems, the present invention provides a method for forming a VDMOS device, comprising: providing a semiconductor substrate on which an epitaxial layer is formed; forming a sacrificial layer with an opening on the surface of the epitaxial layer, and the opening Exposing the surface of t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More