Patents

Literature

237results about How to "Reduce interface state density" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

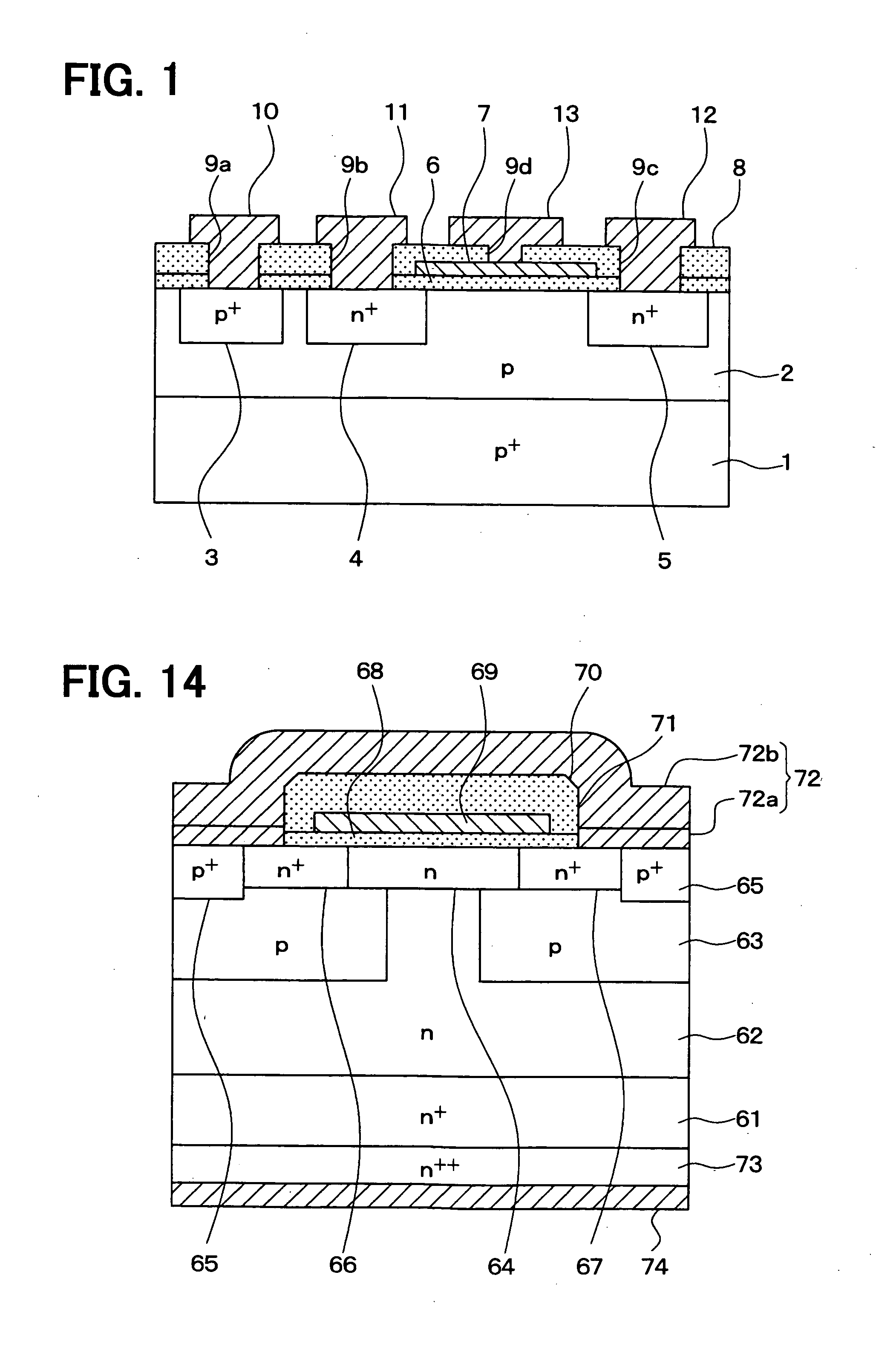

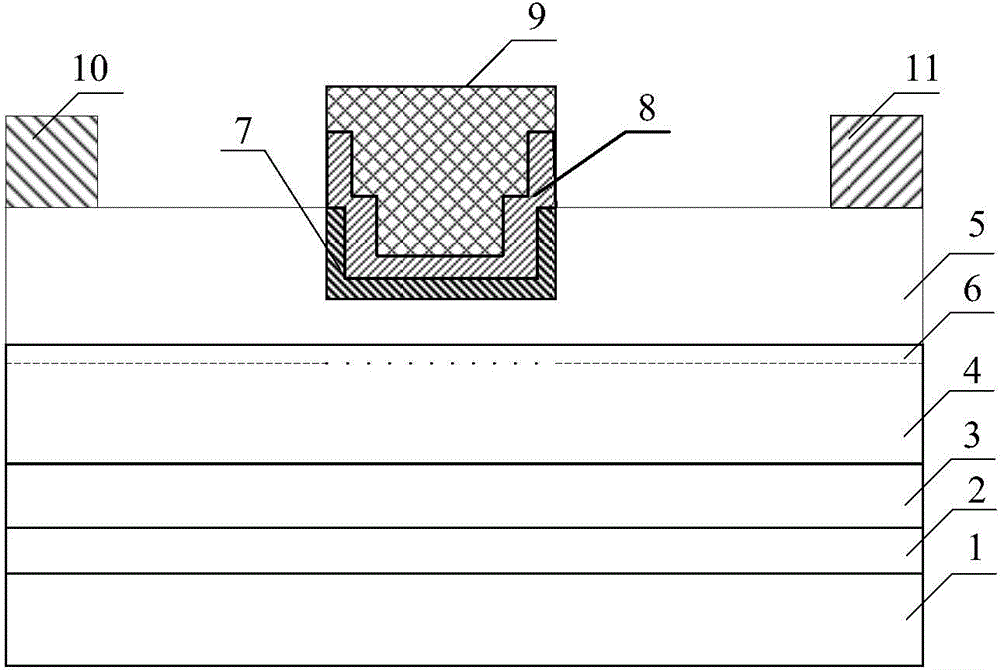

Semiconductor device and manufacturing method thereof

ActiveUS20160218219A1Excellent electrical propertiesEasy to manufactureTransistorSolid-state devicesSemiconductorSemiconductor device

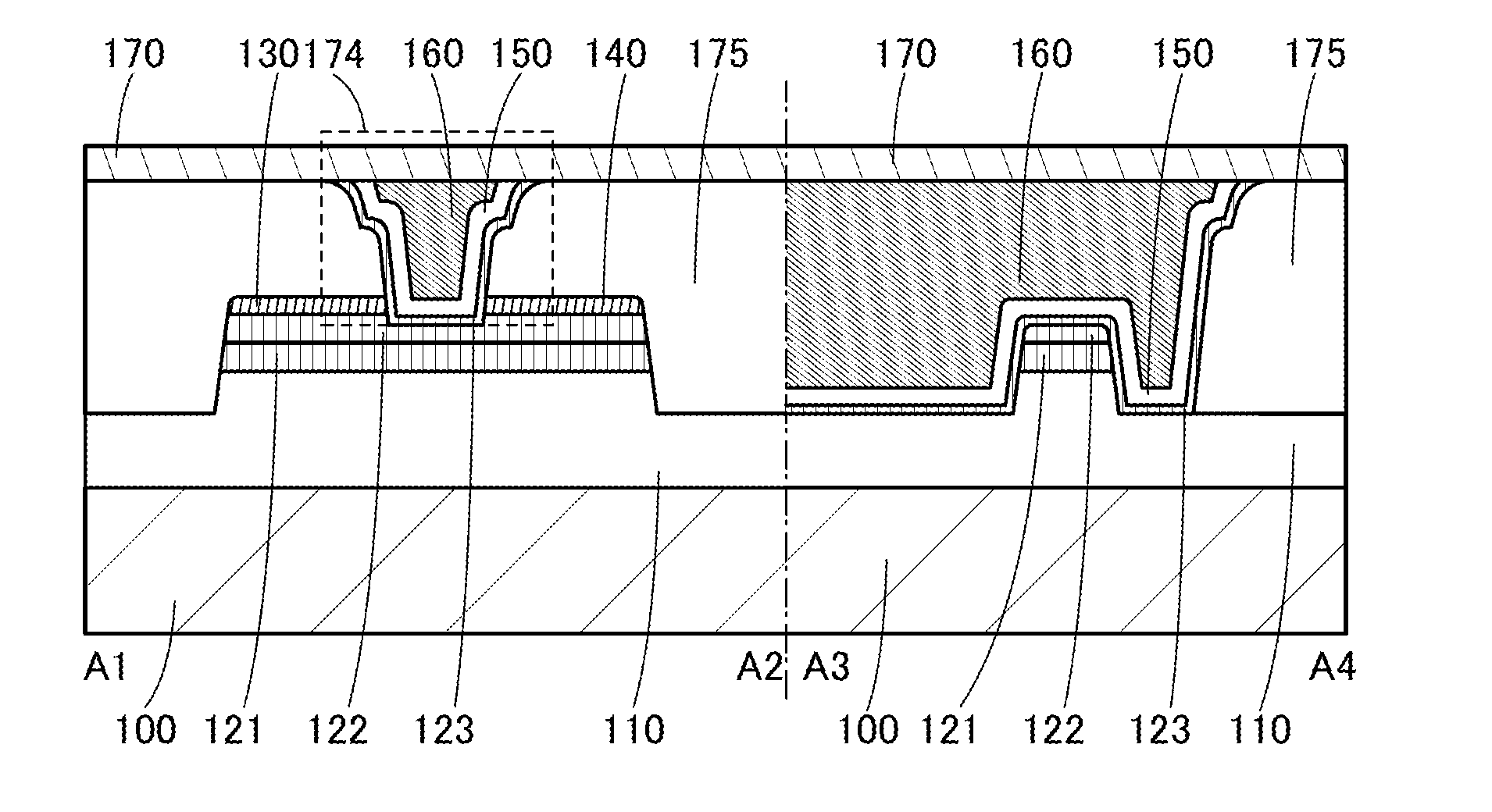

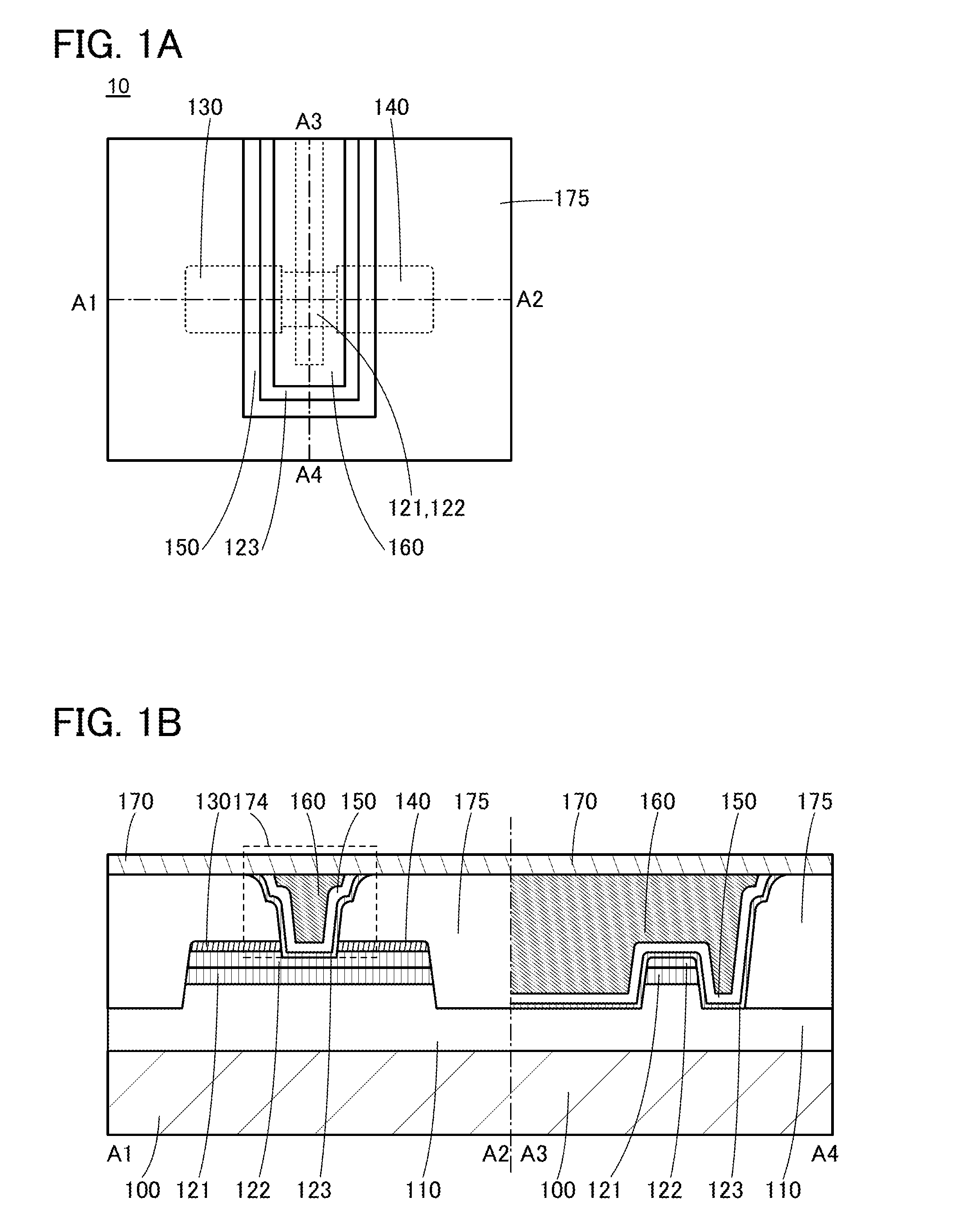

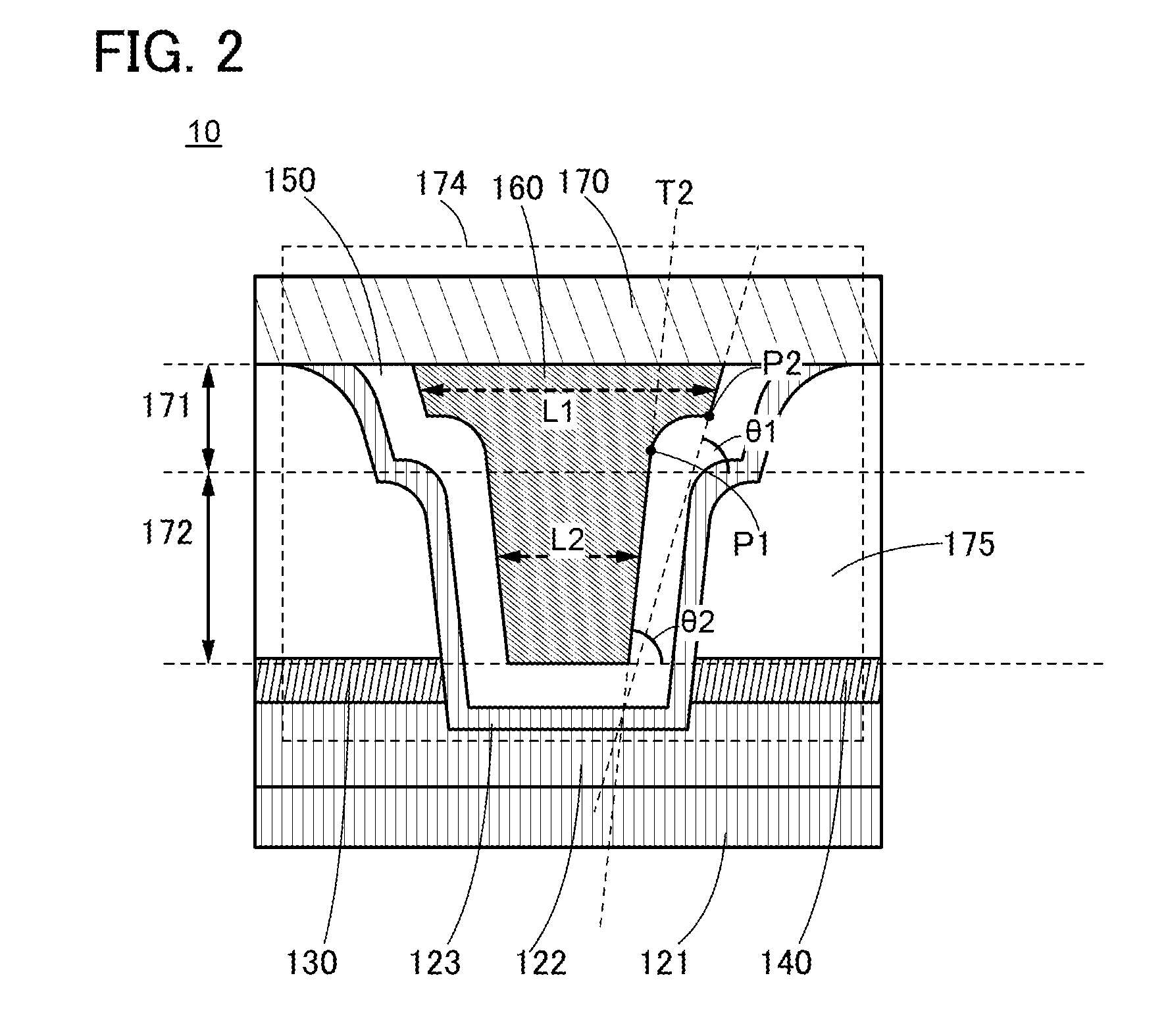

A semiconductor device includes a first oxide insulating layer over a first insulating layer, an oxide semiconductor layer over the first oxide insulating layer, a source electrode layer and a drain electrode layer over the oxide semiconductor layer, a second insulating layer over the source electrode layer and the drain electrode layer, a second oxide insulating layer over the oxide semiconductor layer, a gate insulating layer over the second oxide insulating layer, a gate electrode layer over the gate insulating layer, and a third insulating layer over the second insulating layer, the second oxide insulating layer, the gate insulating layer, and the gate electrode layer. A side surface portion of the second insulating layer is in contact with the second oxide insulating layer. The gate electrode layer includes a first region and a second region. The first region has a width larger than that of the second region.

Owner:SEMICON ENERGY LAB CO LTD

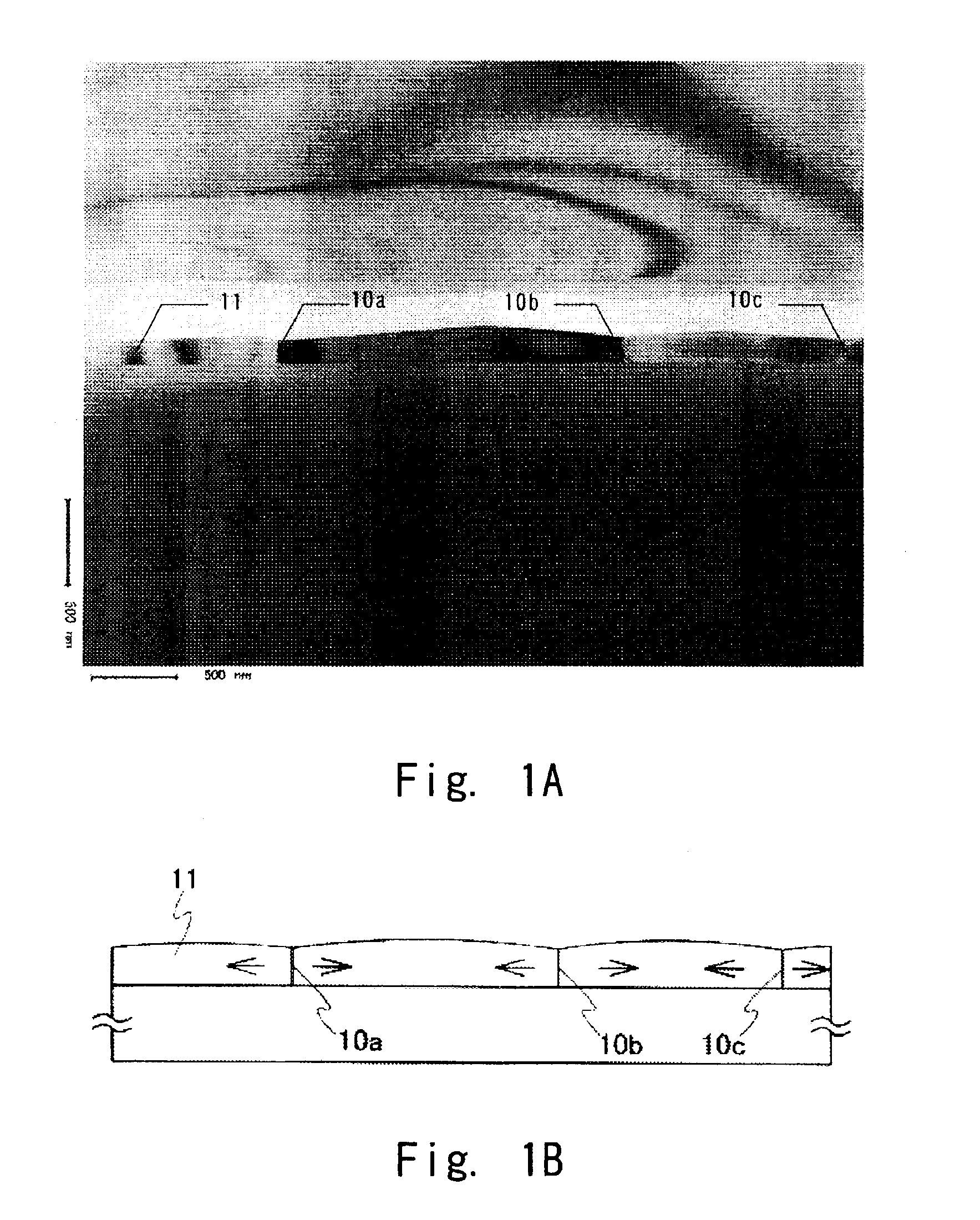

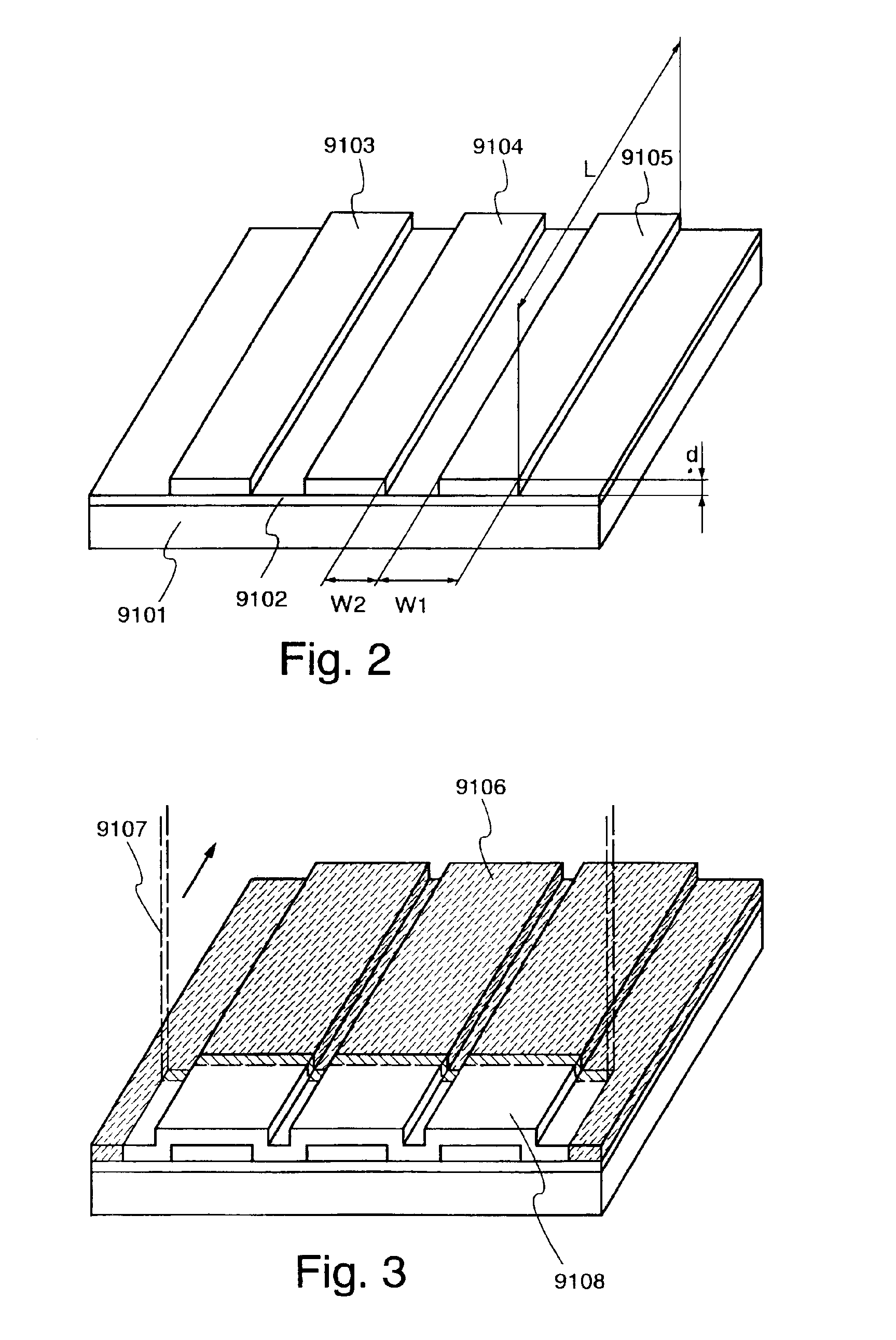

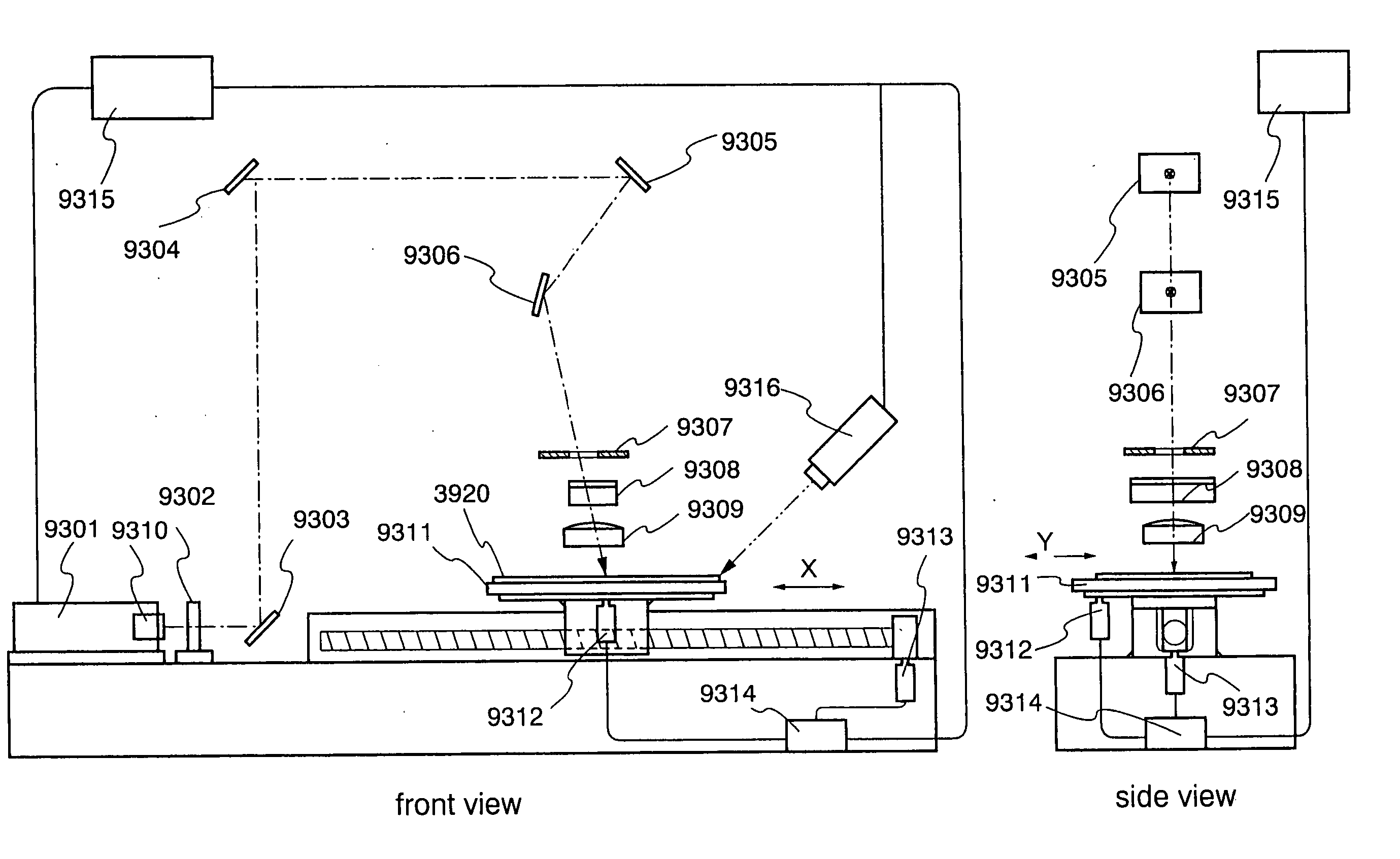

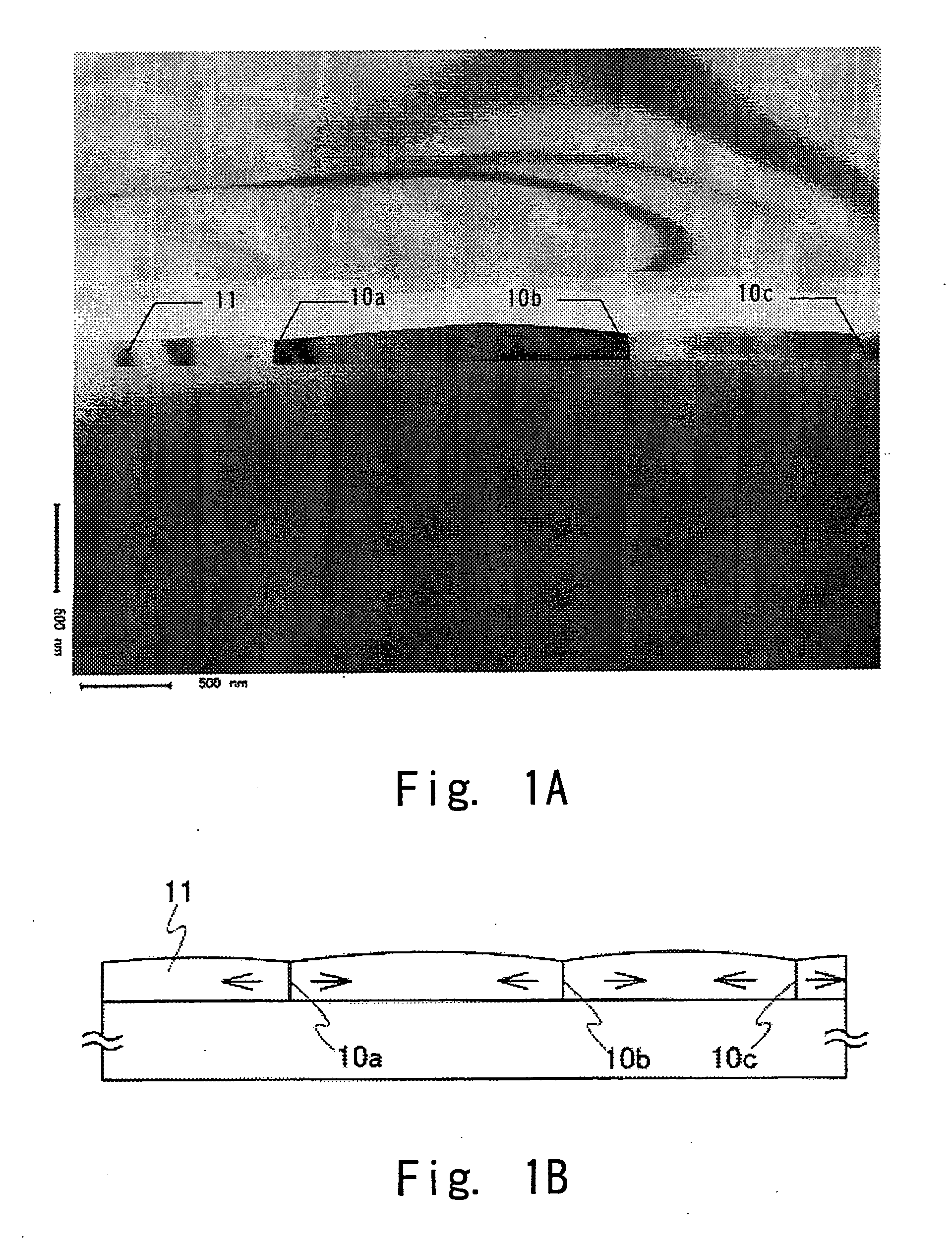

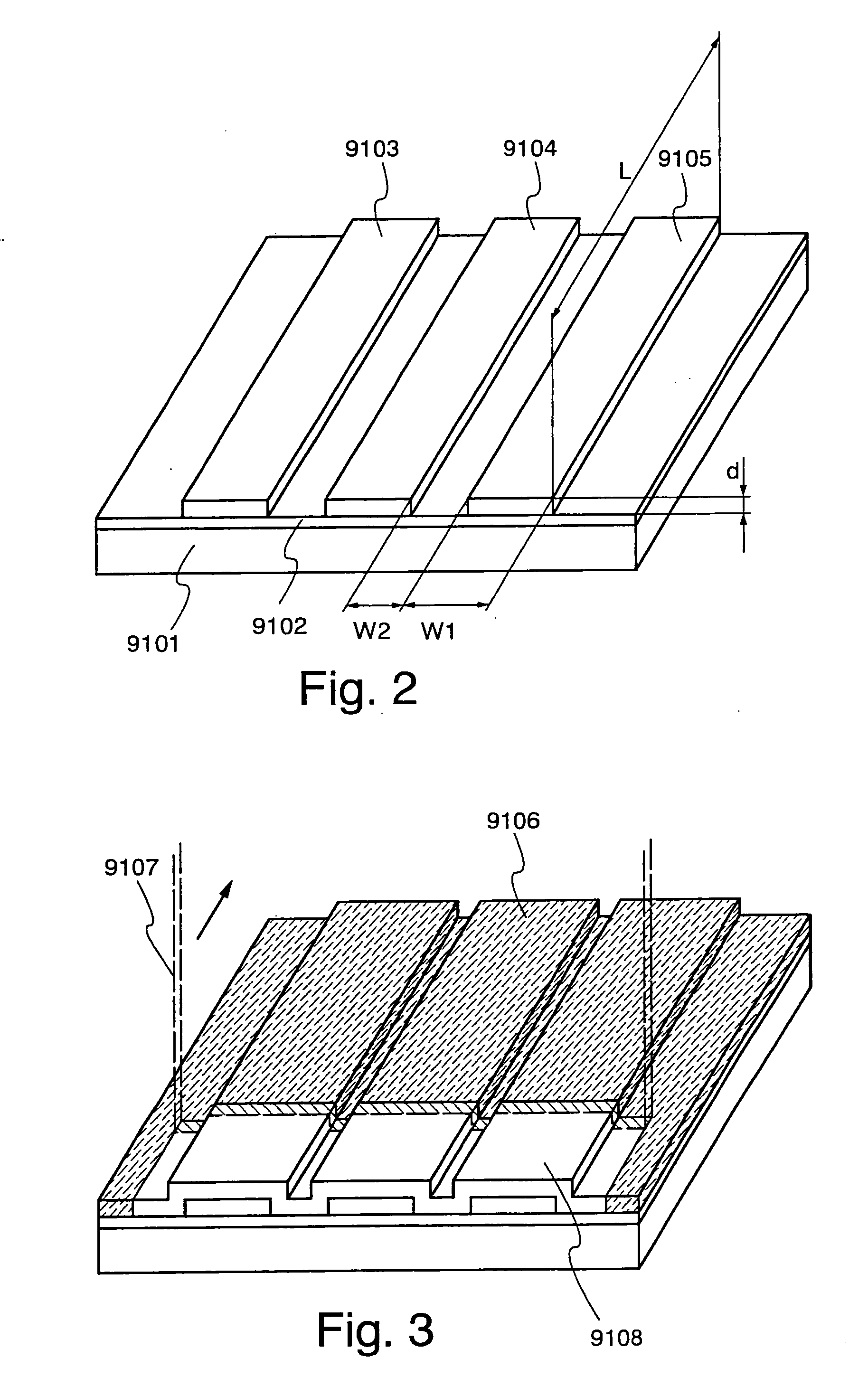

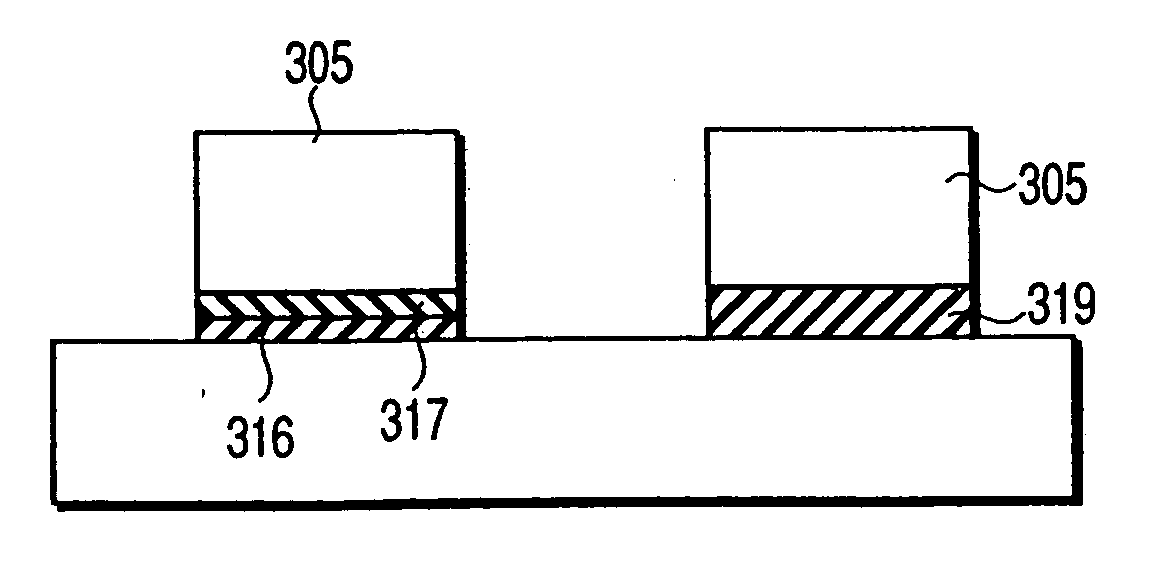

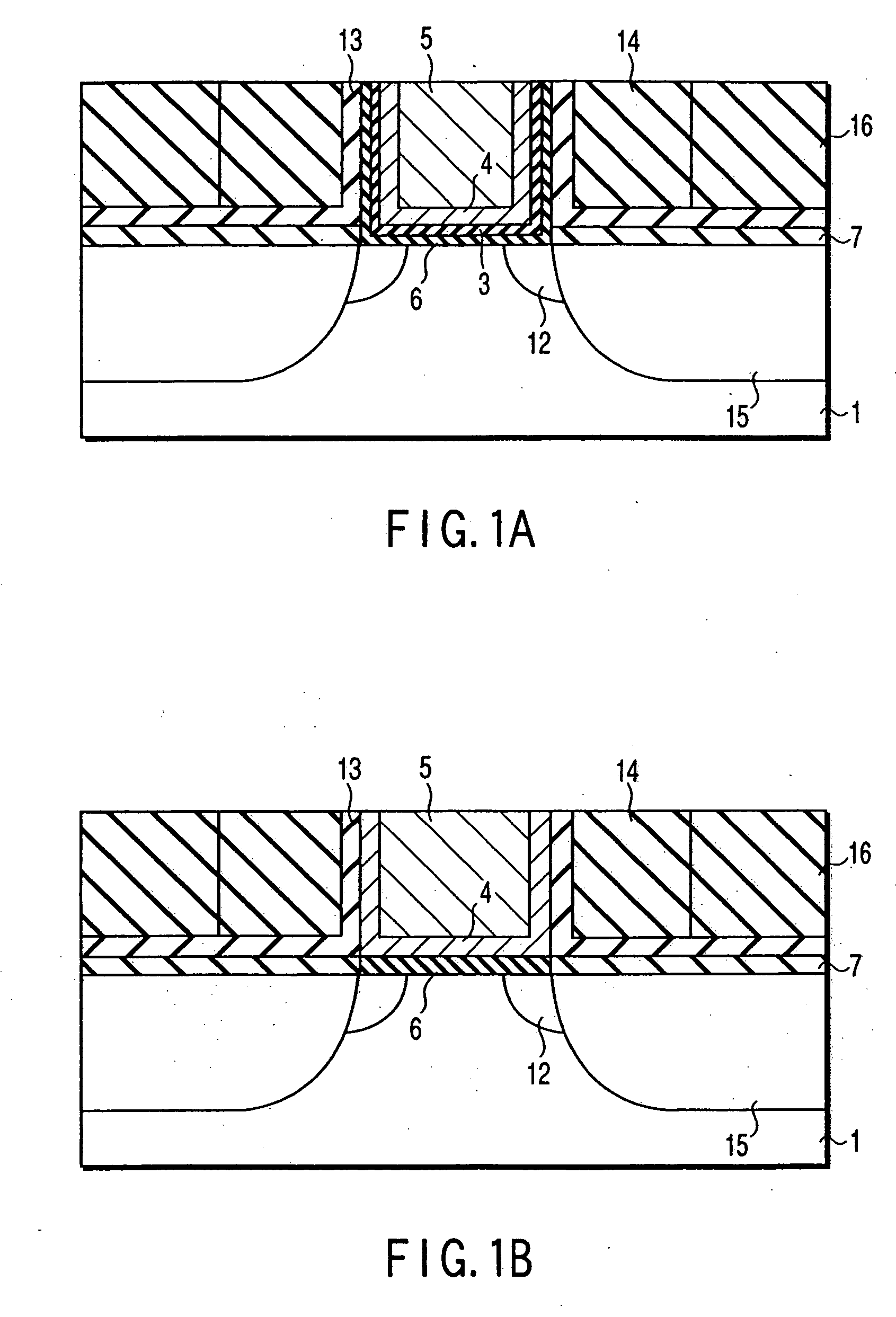

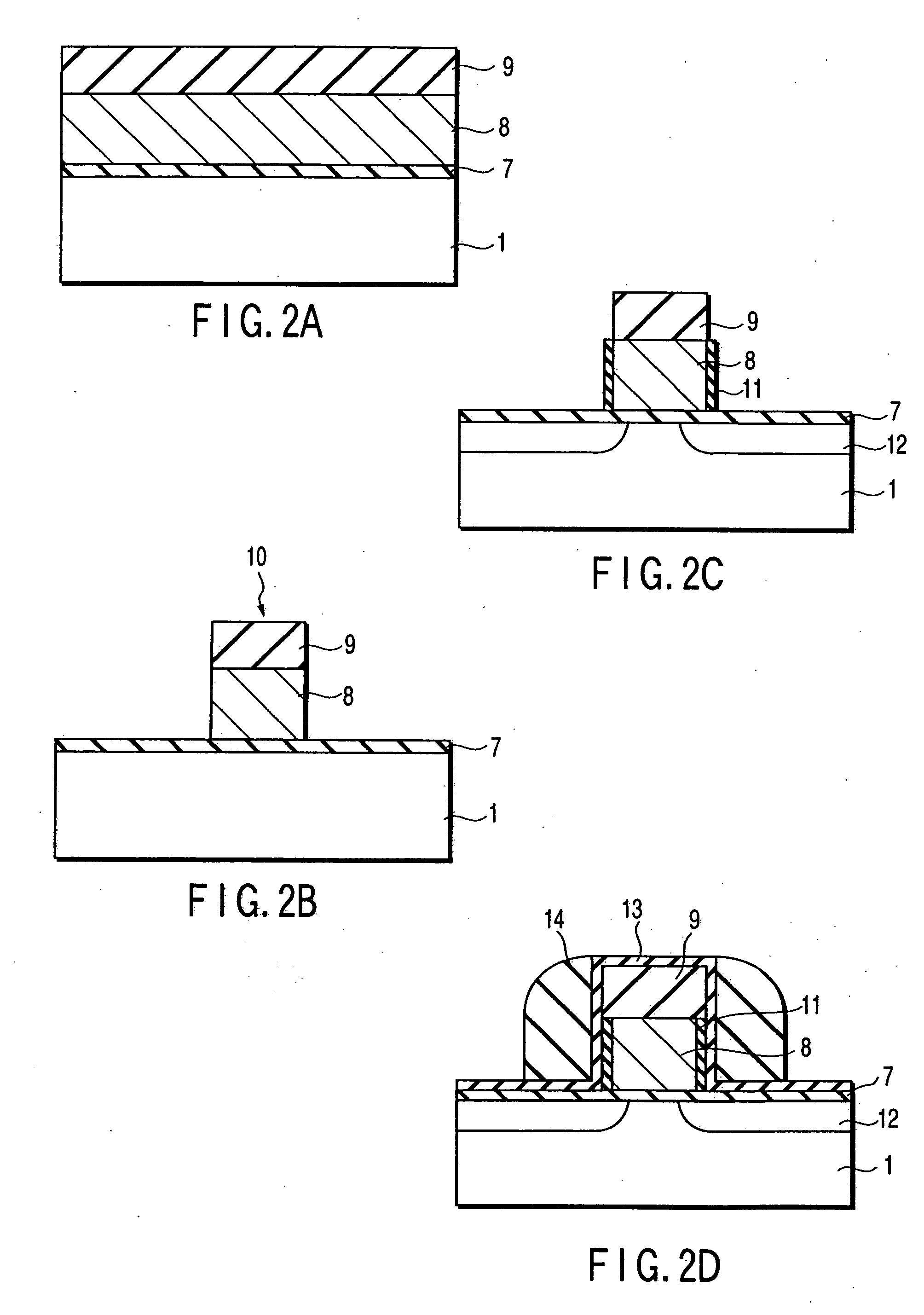

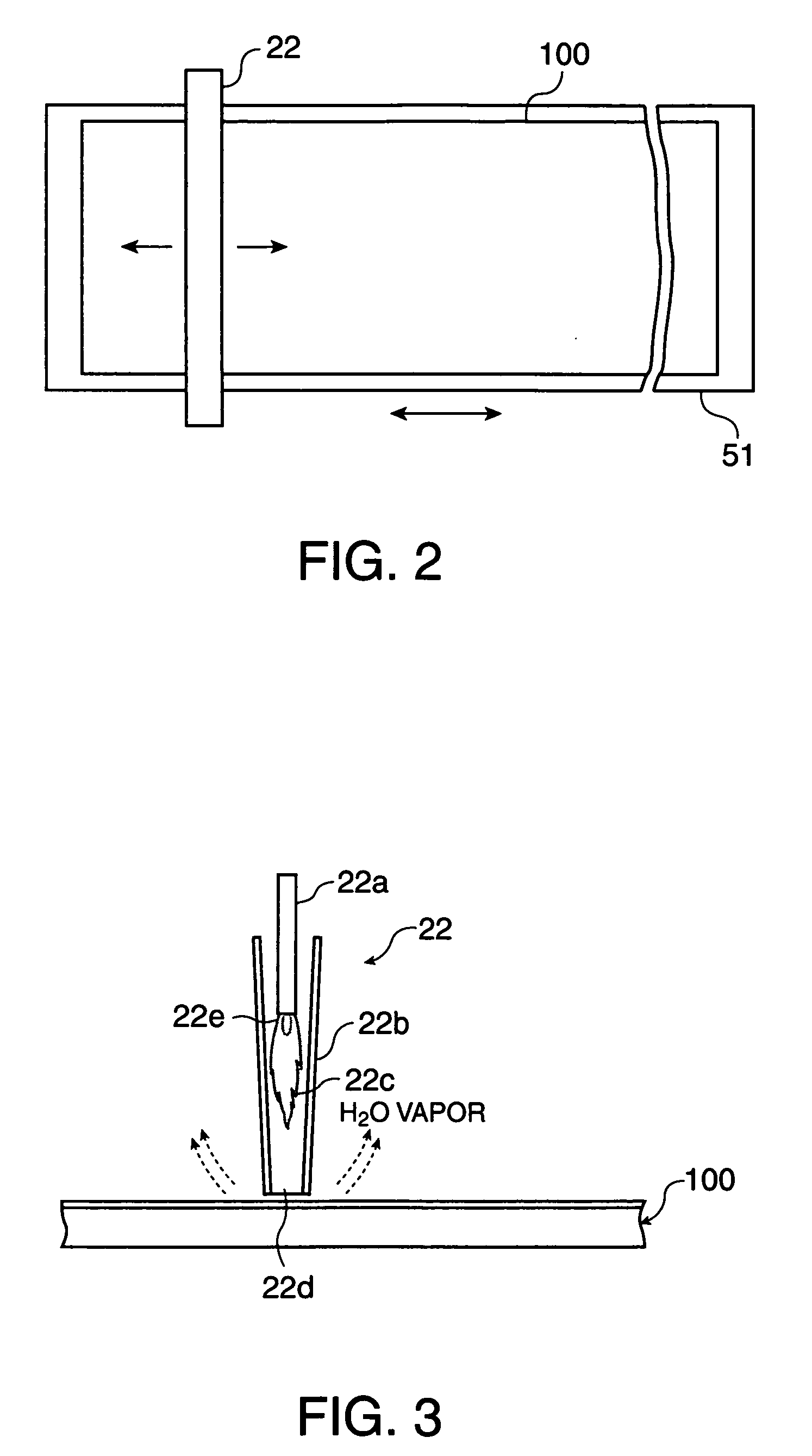

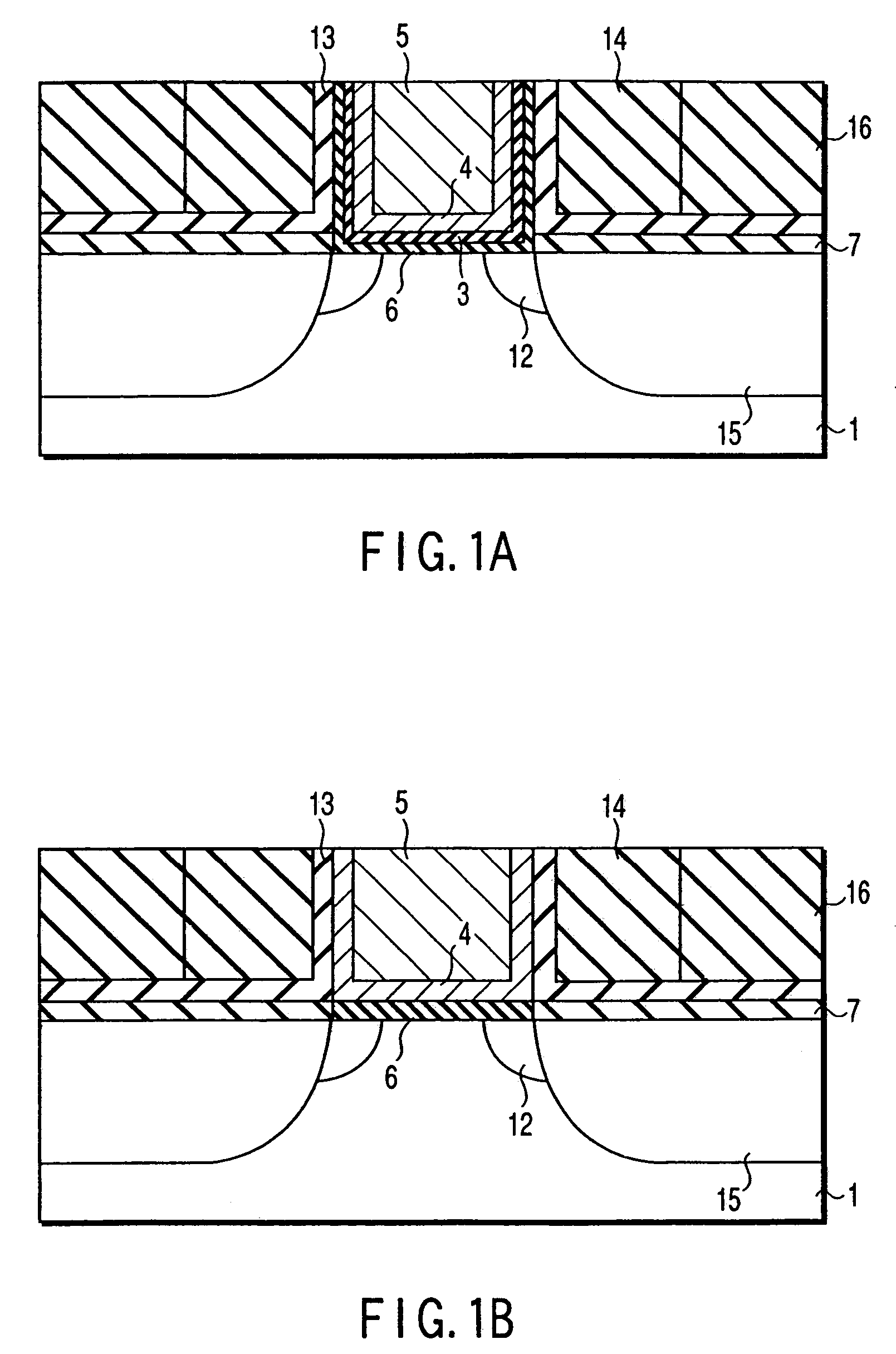

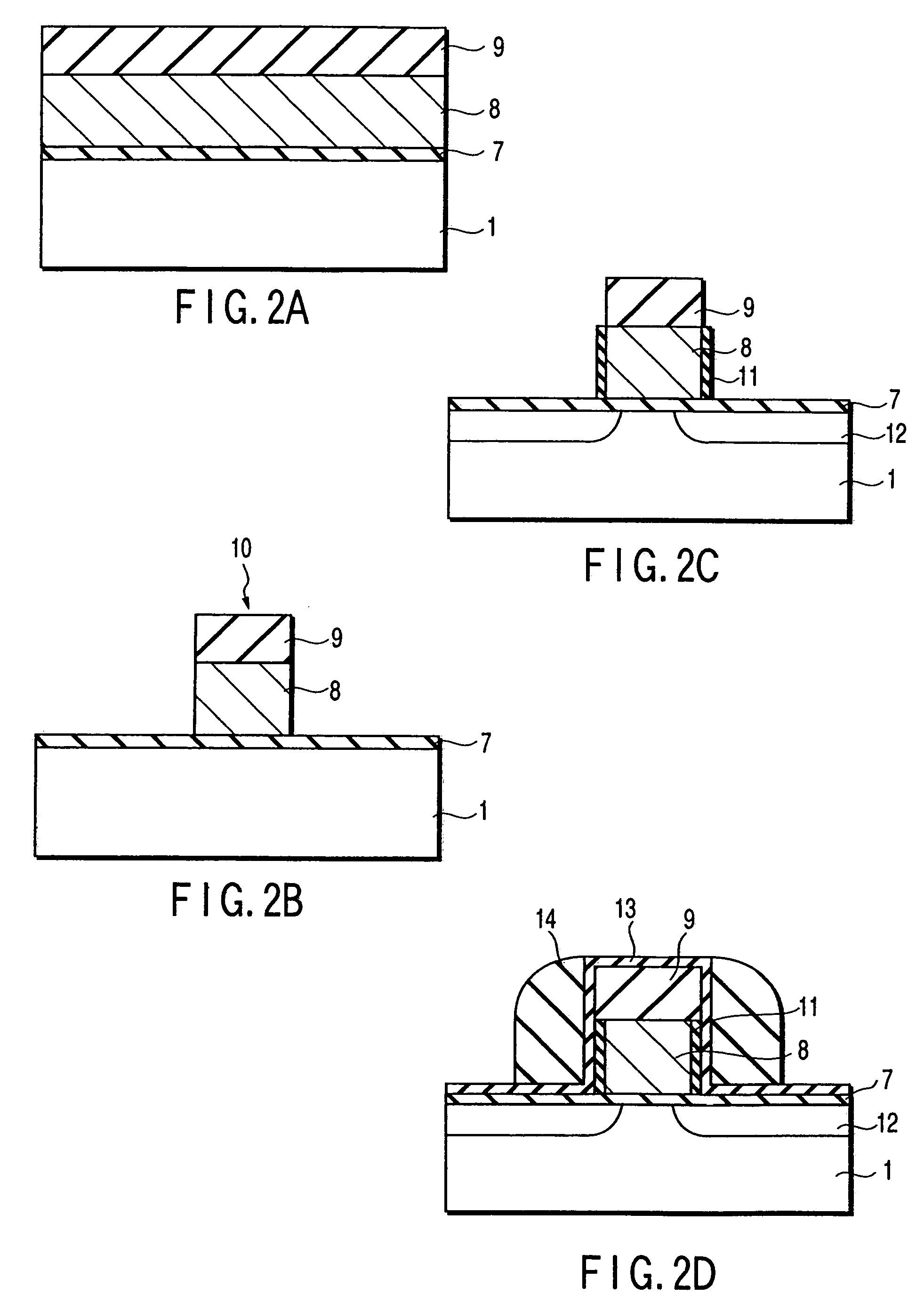

Semiconductor device and semiconductor device production system

InactiveUS6933527B2Improve barrier propertiesImprove stressTransistorSolid-state devicesStress concentrationLaser crystallization

It is a problem to provide a semiconductor device production system using a laser crystallization method capable of preventing grain boundaries from forming in a TFT channel region and further preventing conspicuous lowering in TFT mobility due to grain boundaries, on-current decrease or off-current increase. An insulation film is formed on a substrate, and a semiconductor film is formed on the insulation film. Due to this, preferentially formed is a region in the semiconductor film to be concentratedly applied by stress during crystallization with laser light. Specifically, a stripe-formed or rectangular concavo-convex is formed on the semiconductor film. Continuous-oscillation laser light is irradiated along the striped concavo-convex or along a direction of a longer or shorter axis of rectangle.

Owner:SEMICON ENERGY LAB CO LTD

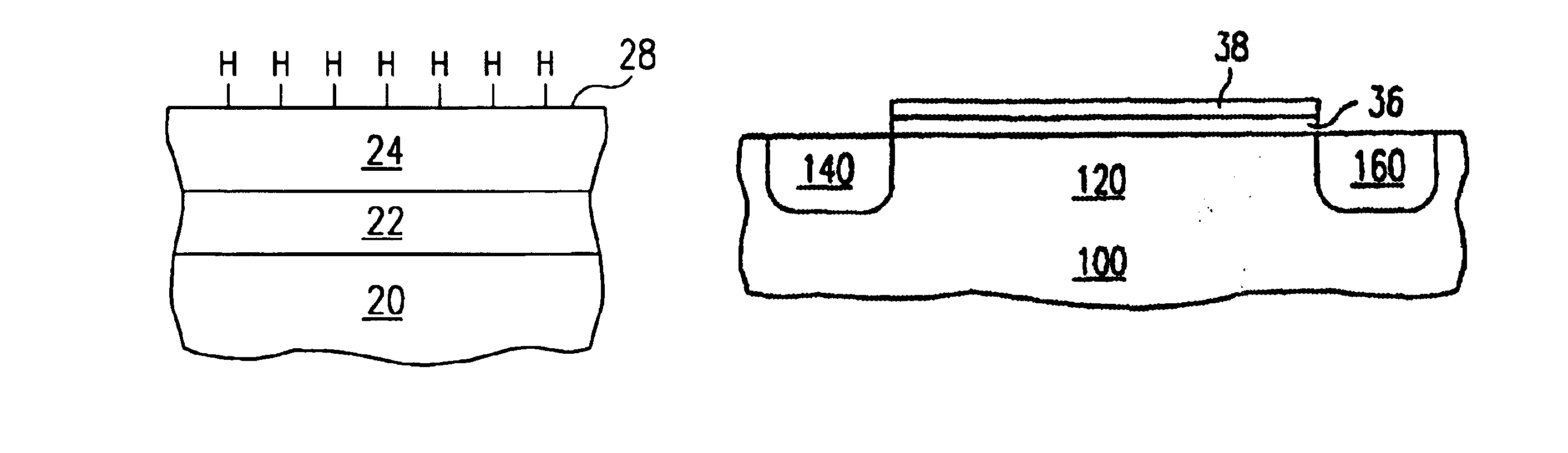

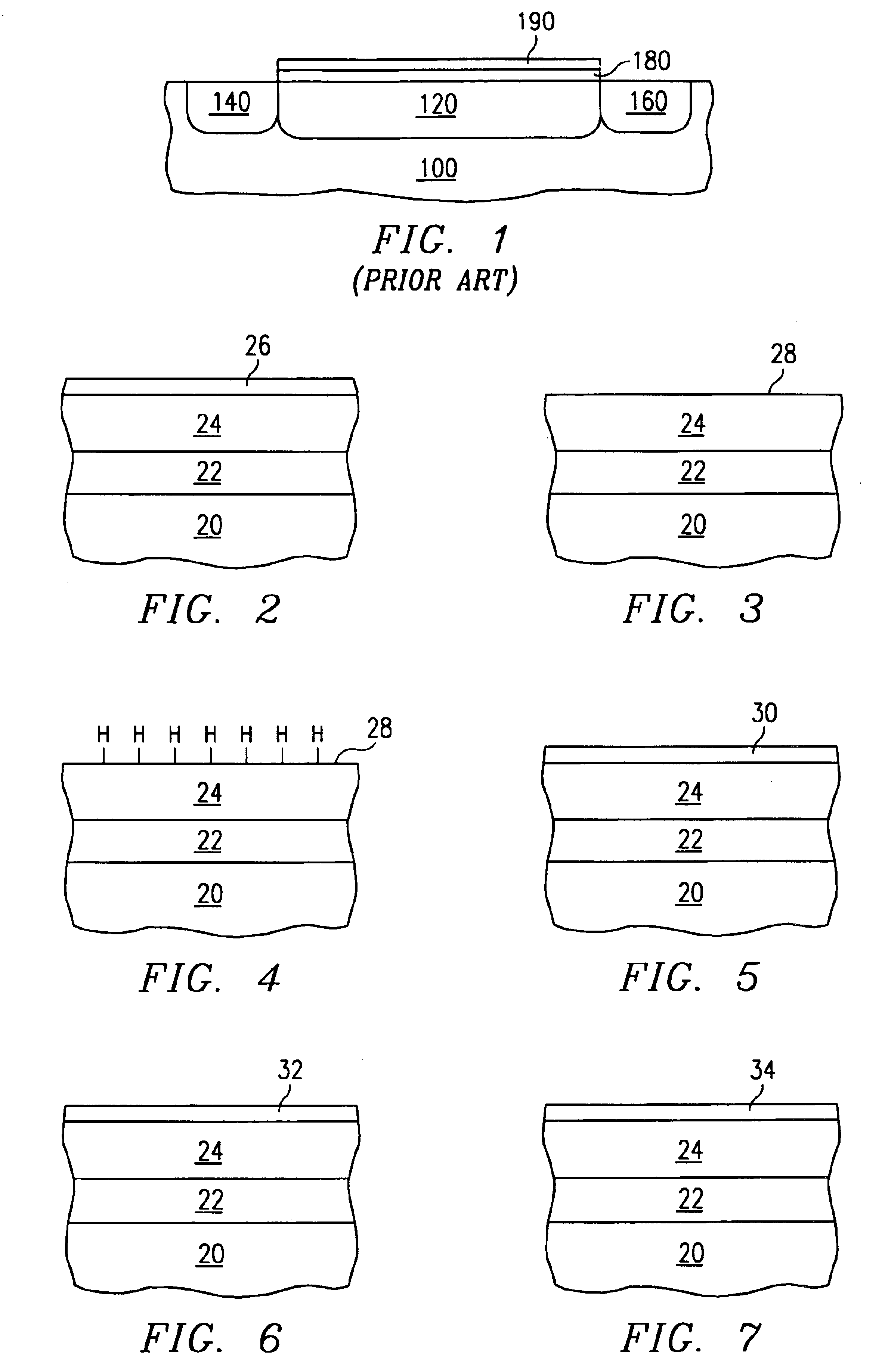

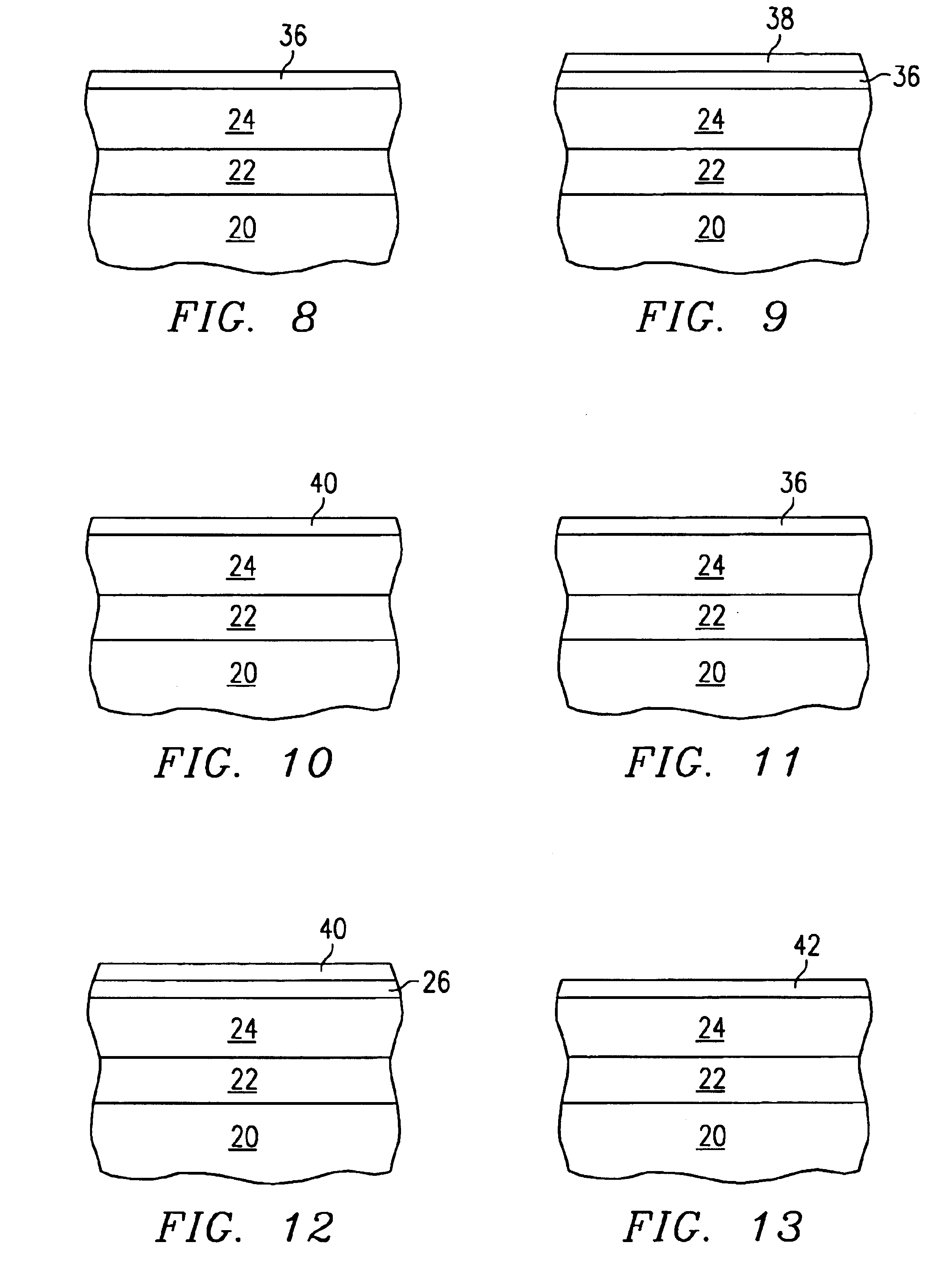

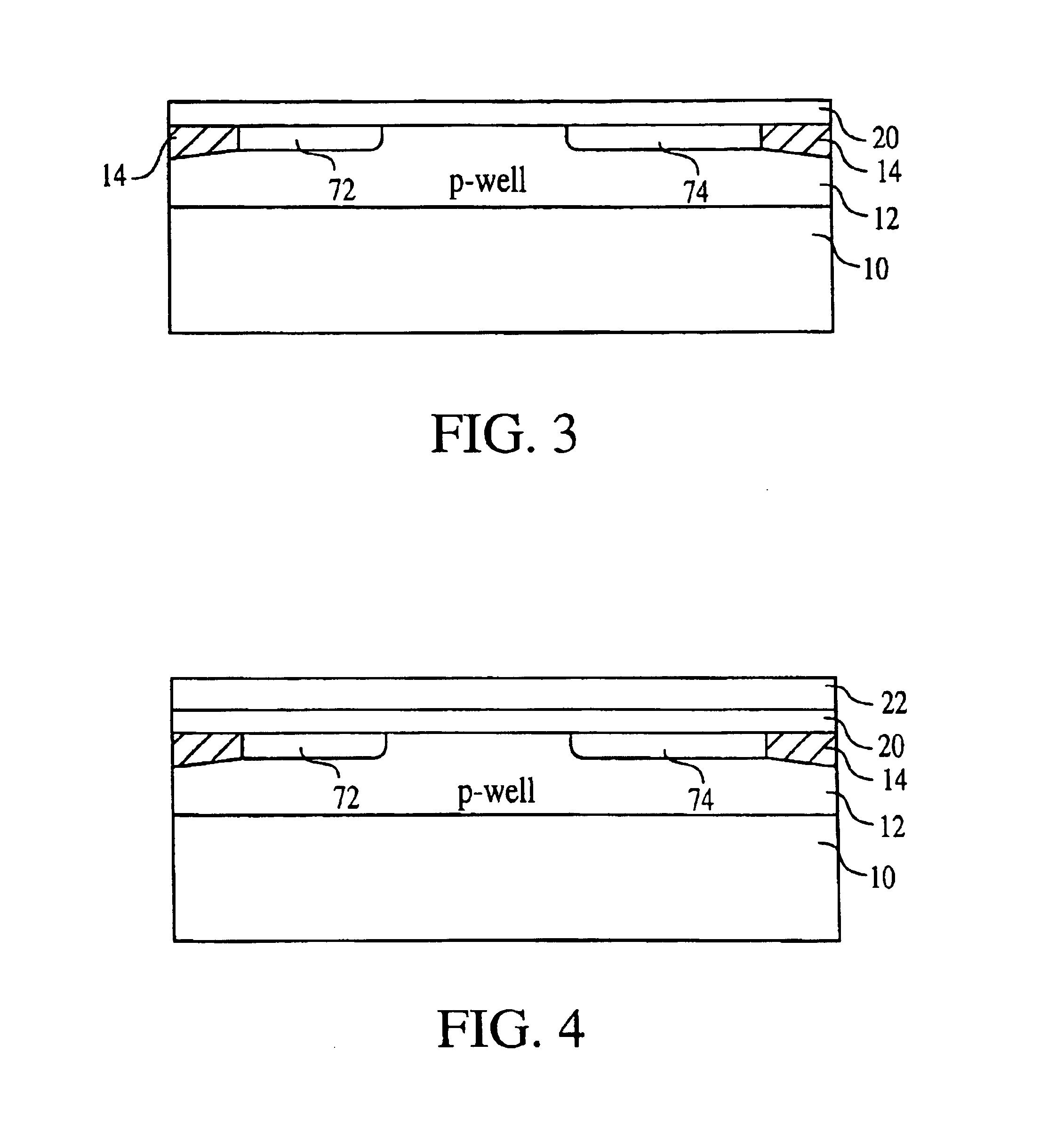

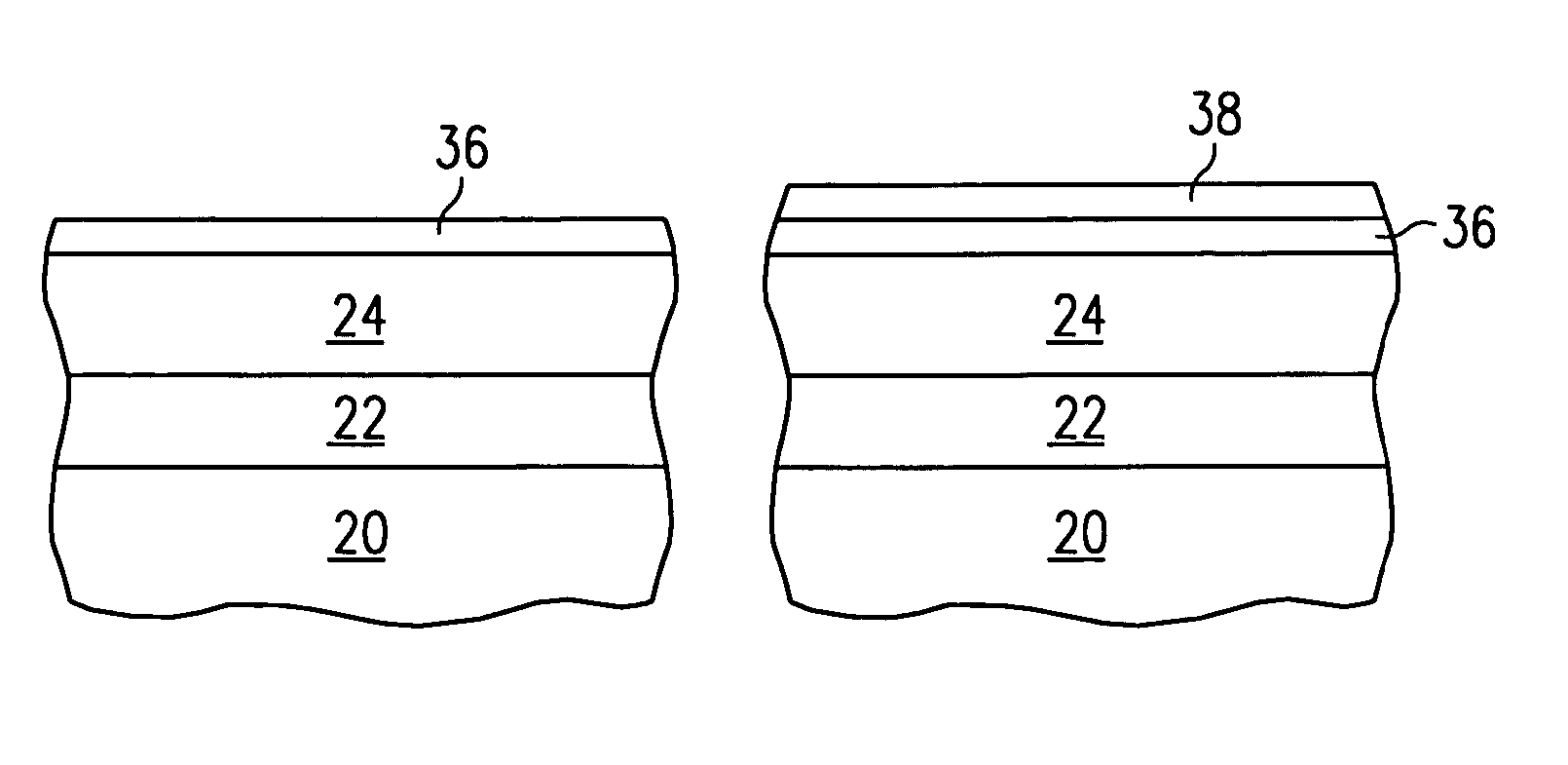

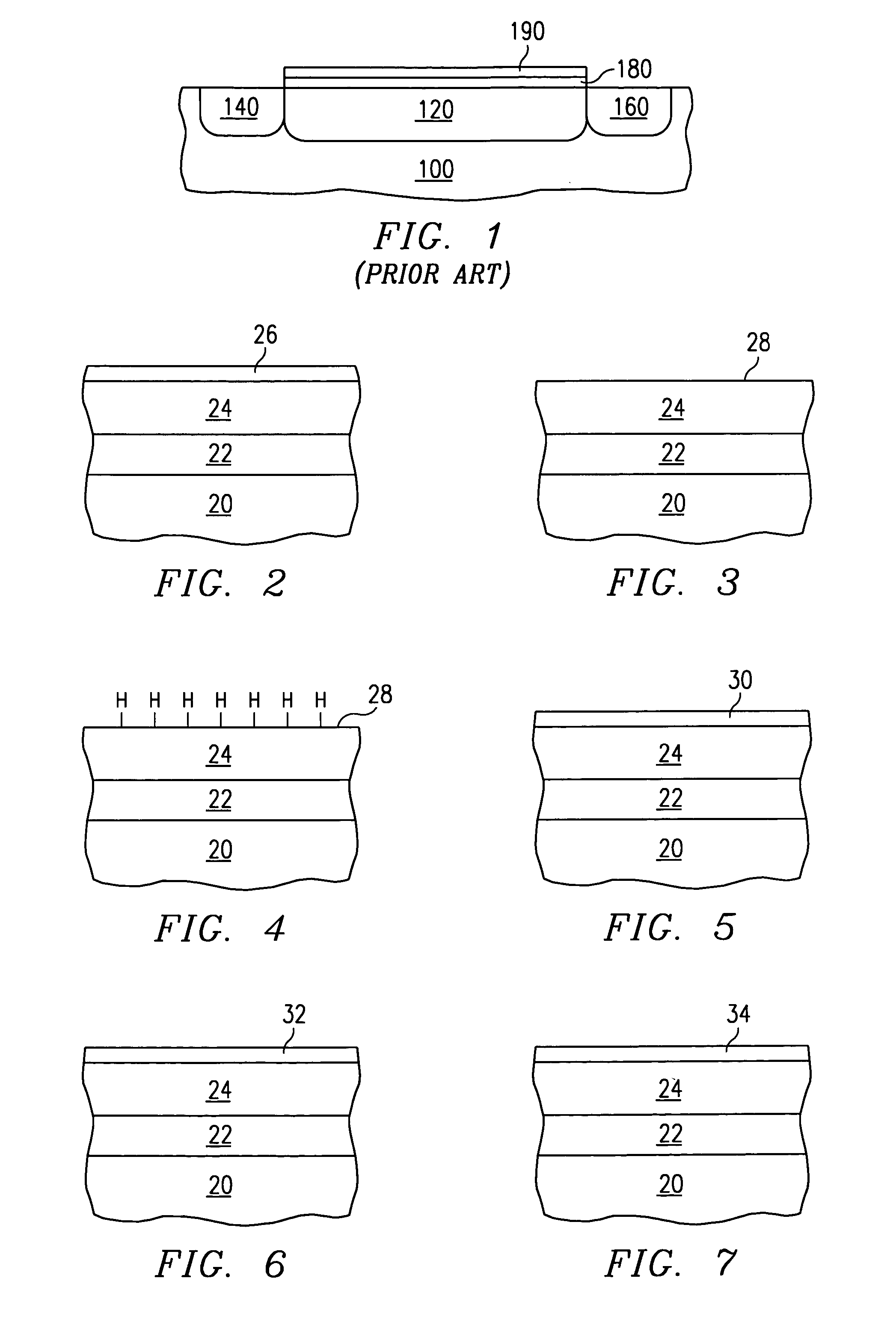

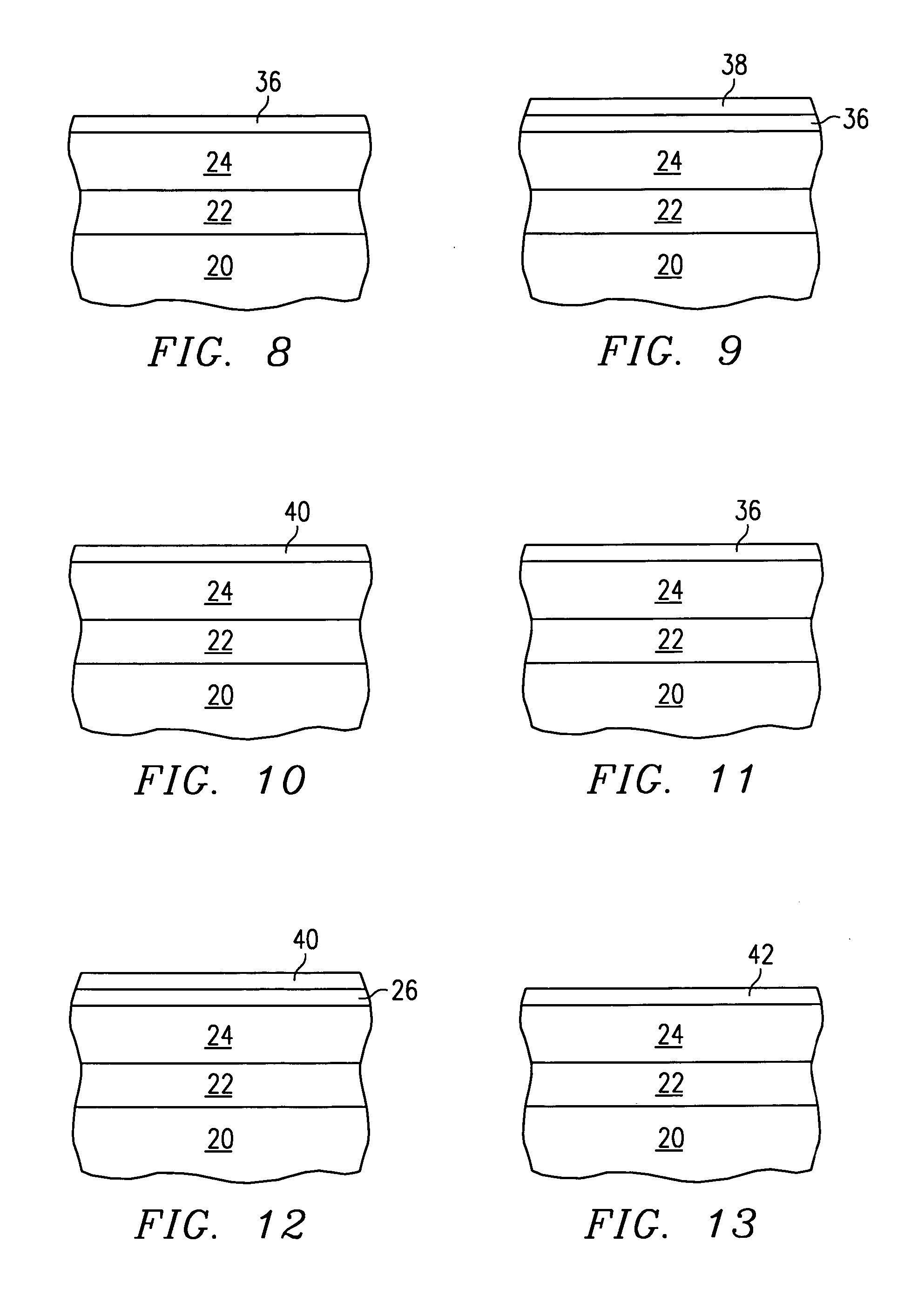

High permittivity silicate gate dielectric

InactiveUS6841439B1Great ratioHigh densitySemiconductor/solid-state device manufacturingSemiconductor devicesState densityHigh dielectric permittivity

A field effect semiconductor device comprising a high permittivity silicate gate dielectric and a method of forming the same are disclosed herein. The device comprises a silicon substrate 20 having a semiconducting channel region 24 formed therein. A metal silicate gate dielectric layer 36 is formed over this substrate, followed by a conductive gate 38. Silicate layer 36 may be, e.g., hafnium silicate, such that the dielectric constant of the gate dielectric is significantly higher than the dielectric constant of silicon dioxide. However, the silicate gate dielectric may also be designed to have the advantages of silicon dioxide, e.g. high breakdown, low interface state density, and high stability. The present invention includes methods for depositing both amorphous and polycrystalline silicate layers, as well as graded composition silicate layers.

Owner:TEXAS INSTR INC

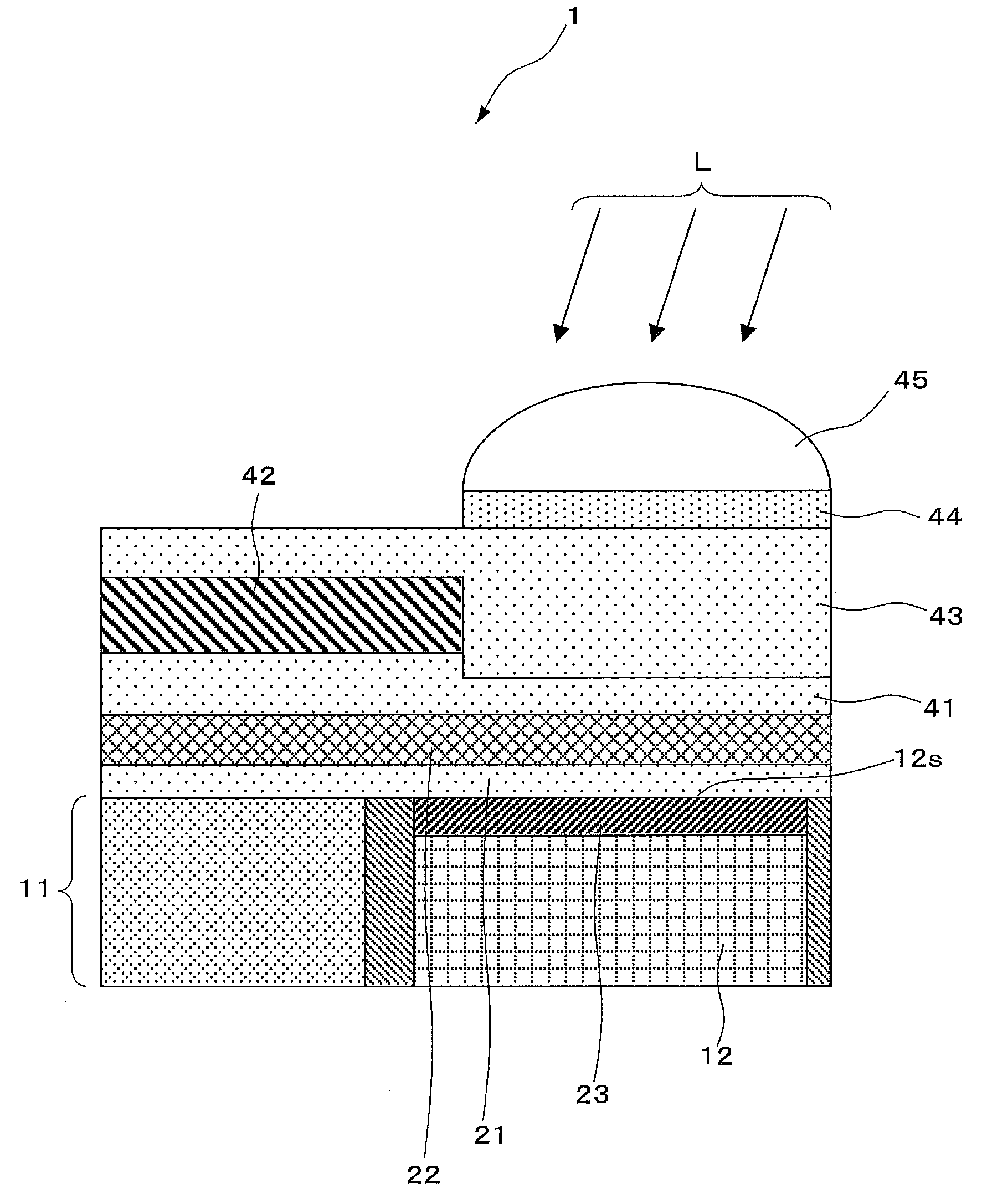

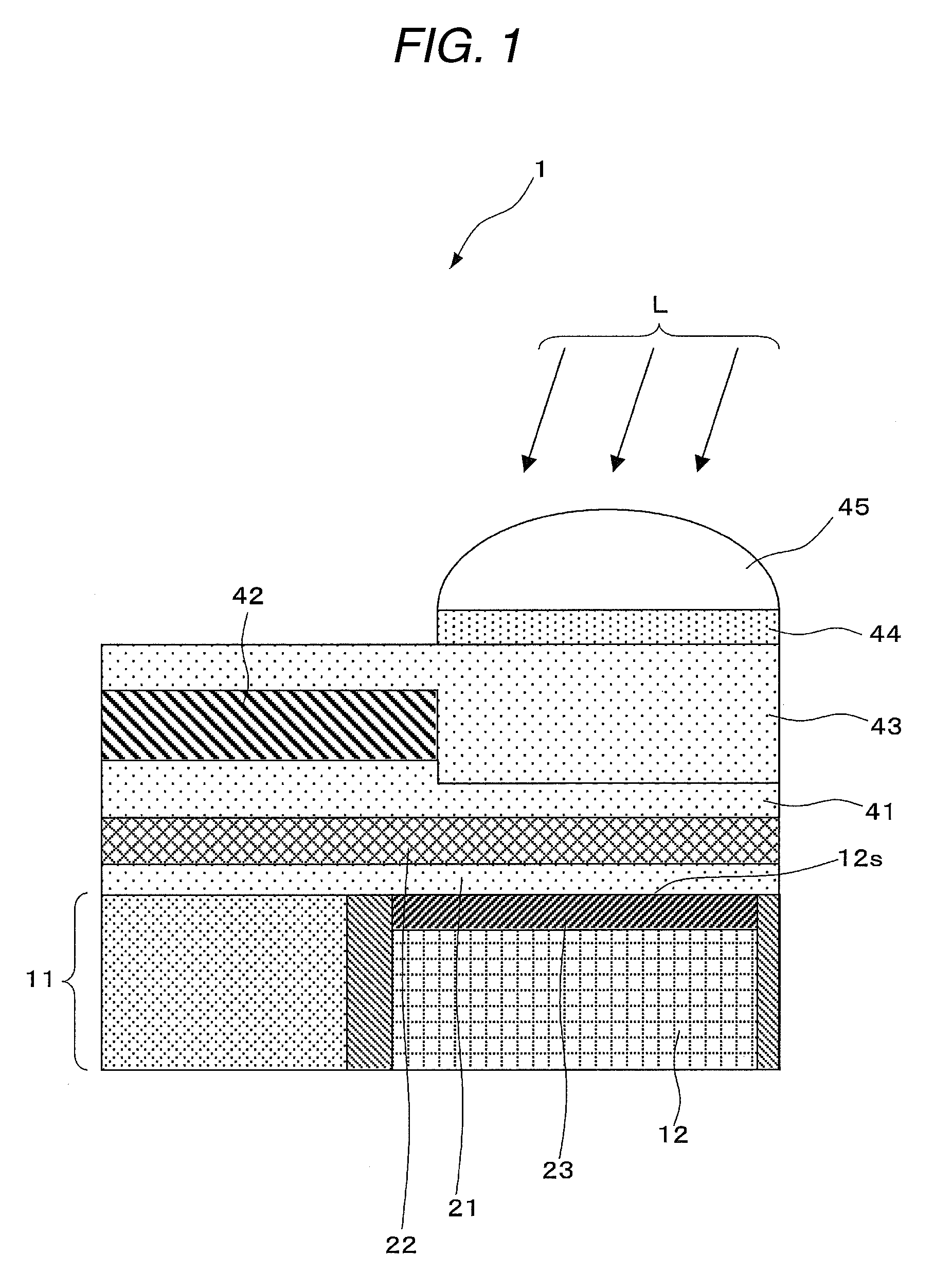

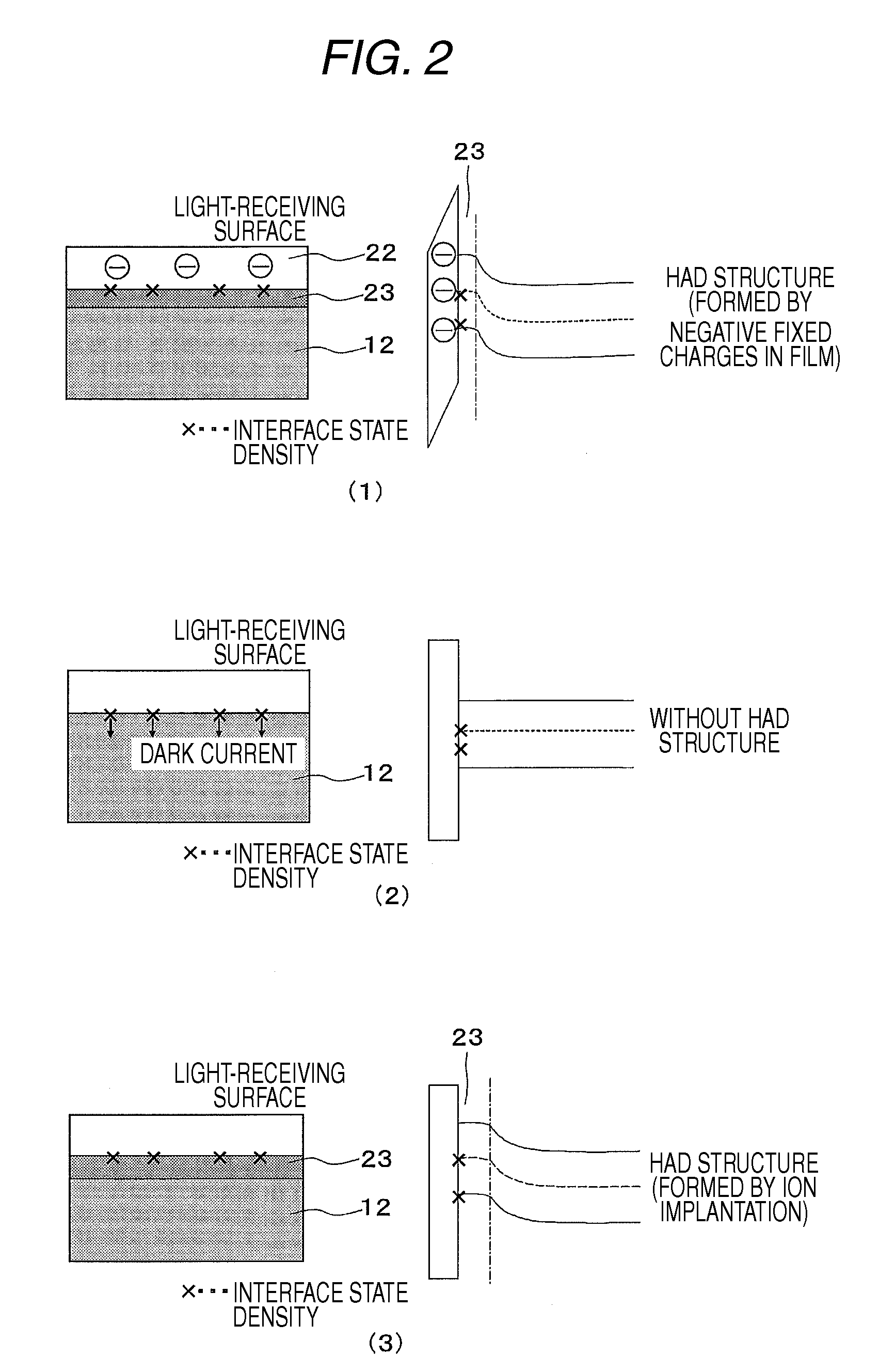

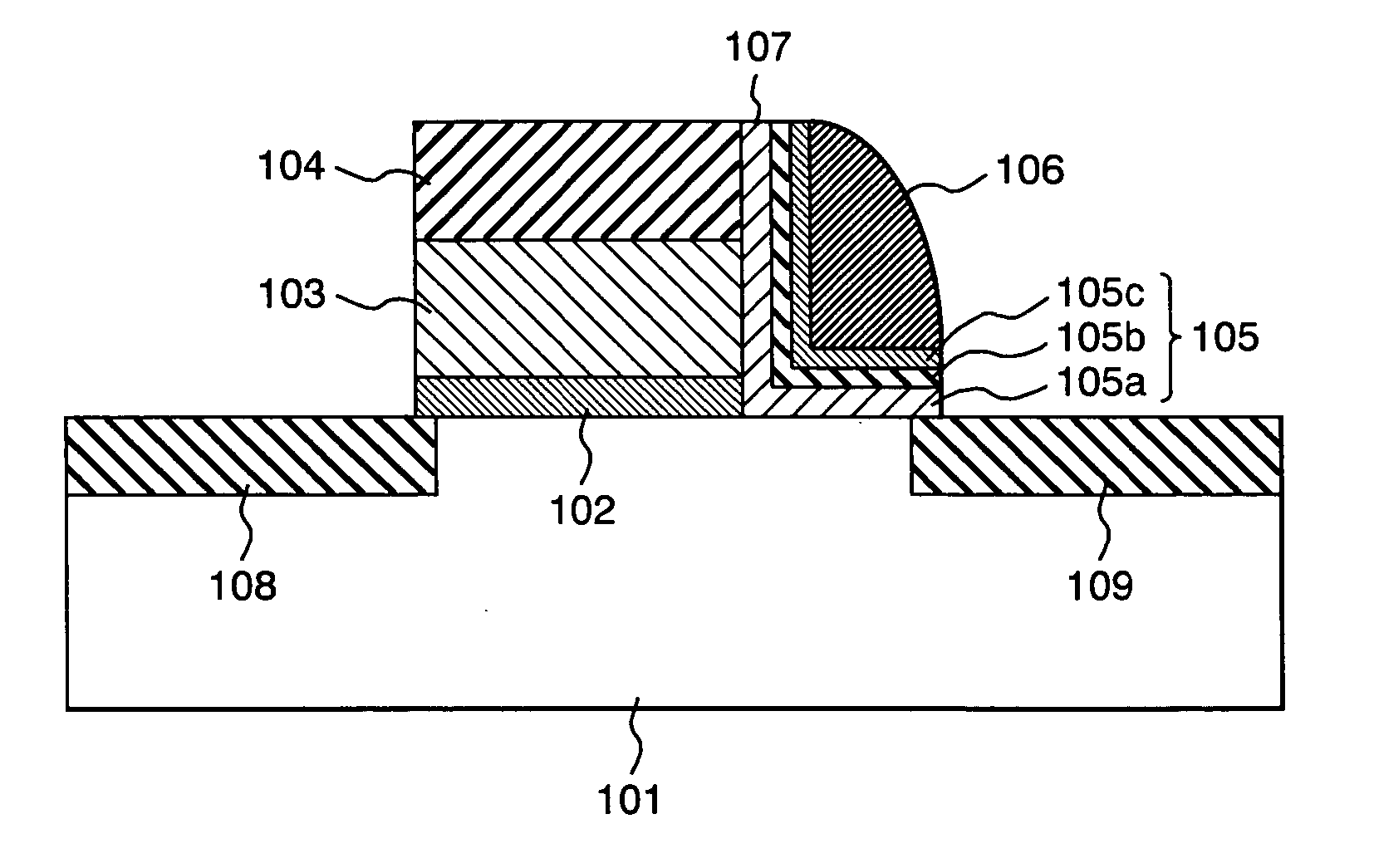

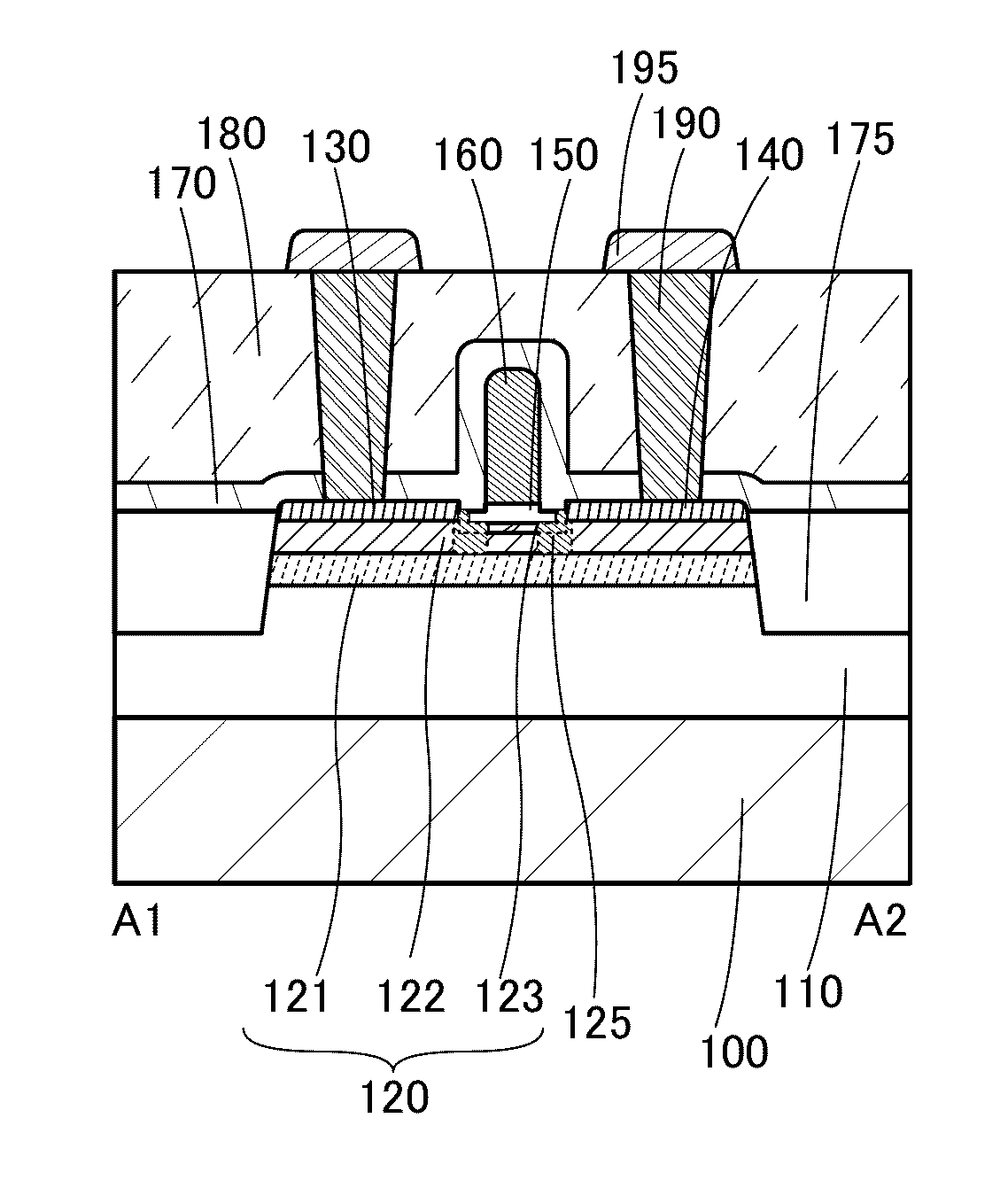

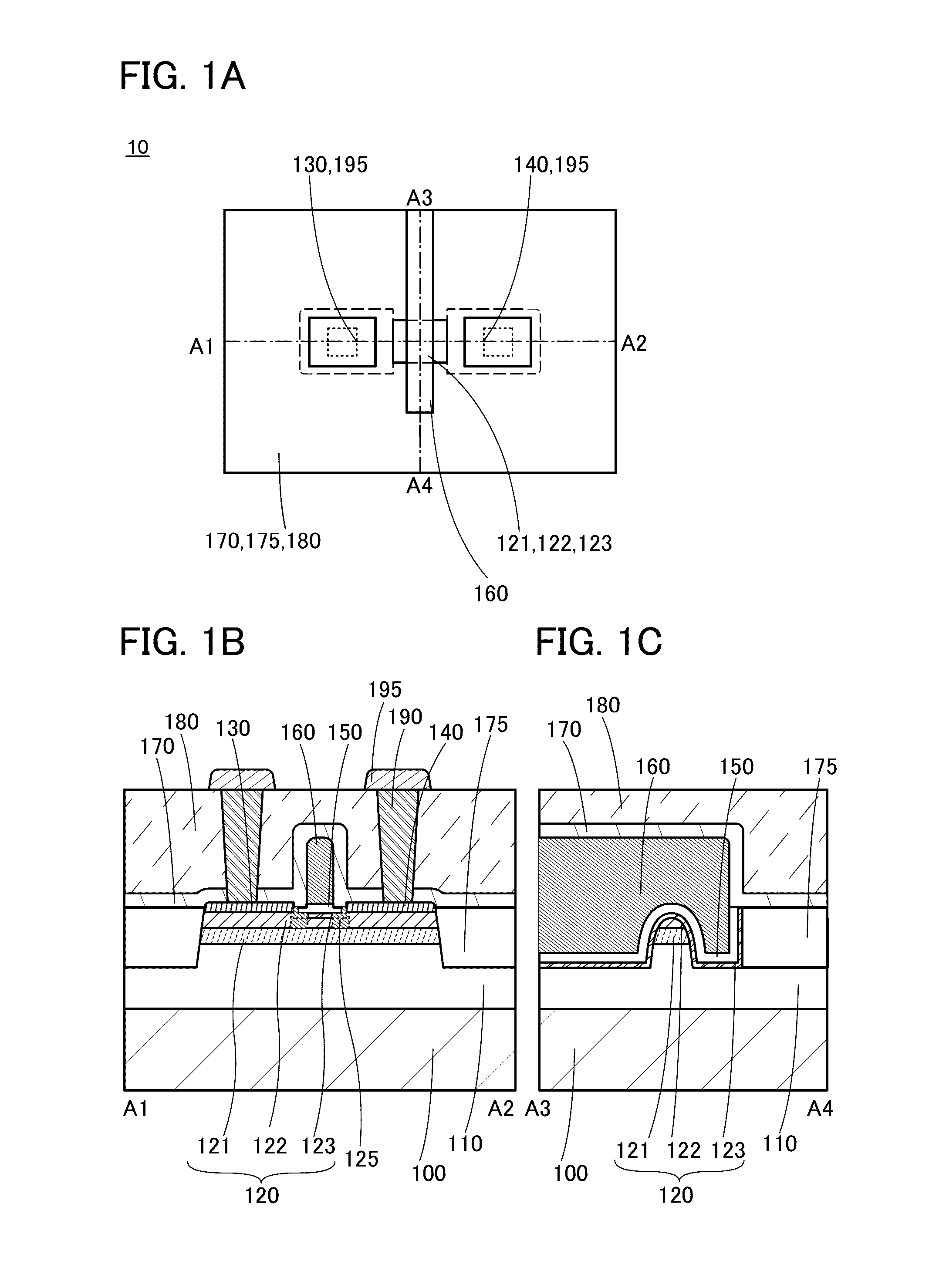

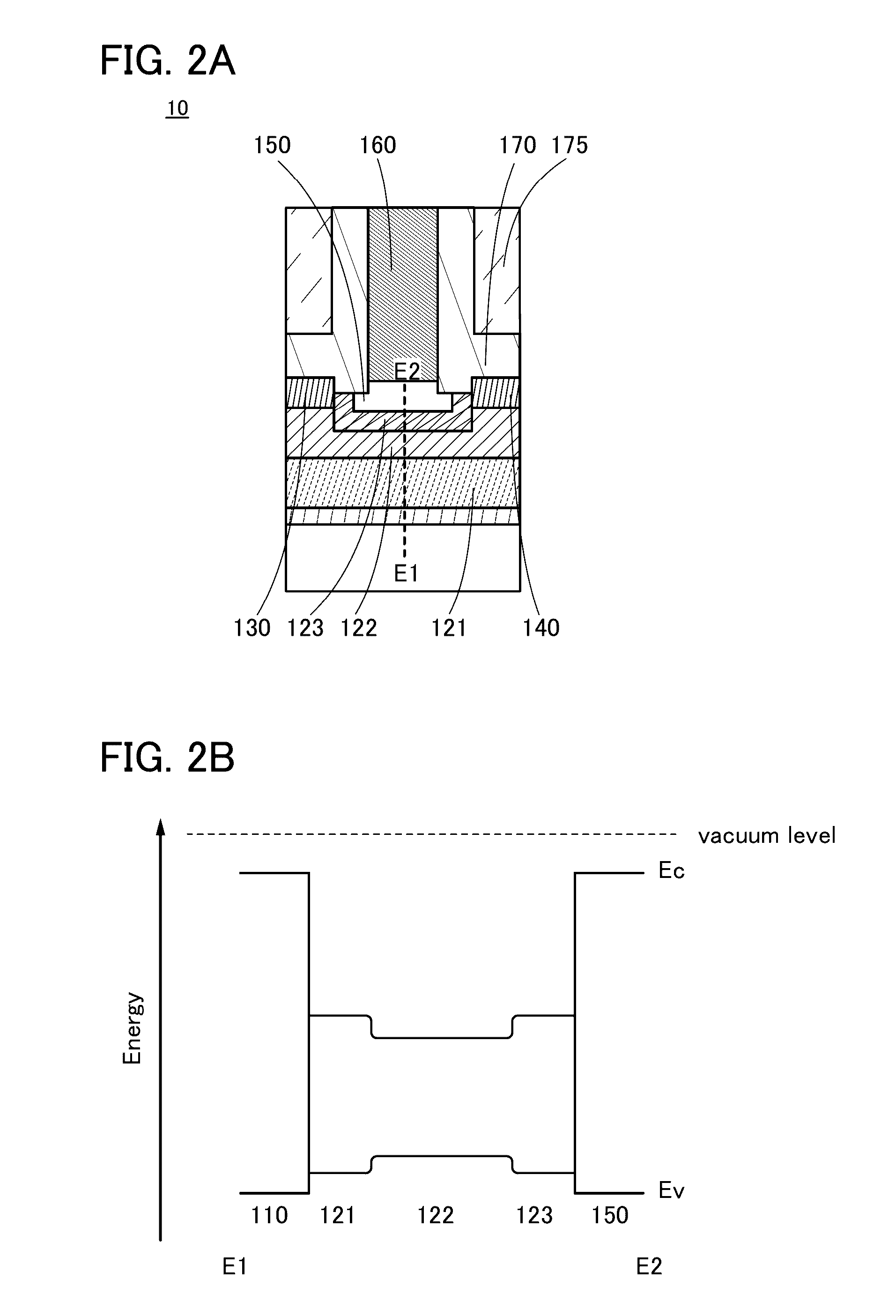

Solid-state imaging device, manufacturing method for the same, and imaging apparatus

ActiveUS20090189235A1Reduce interface state densityGeneration of charges (electrons) from the interface is suppressedTelevision system detailsSolid-state devicesEngineeringFixed charge

Owner:SONY CORP

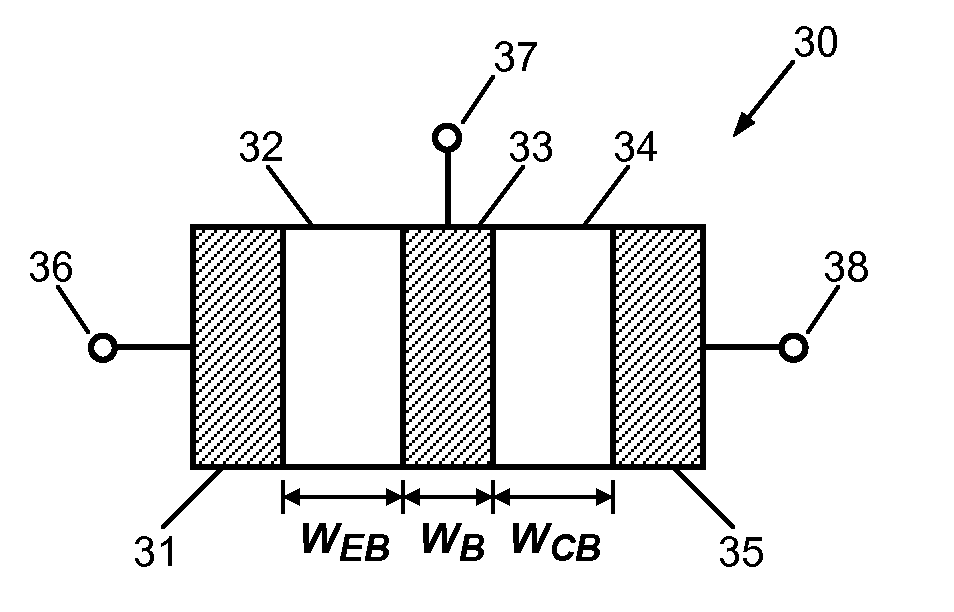

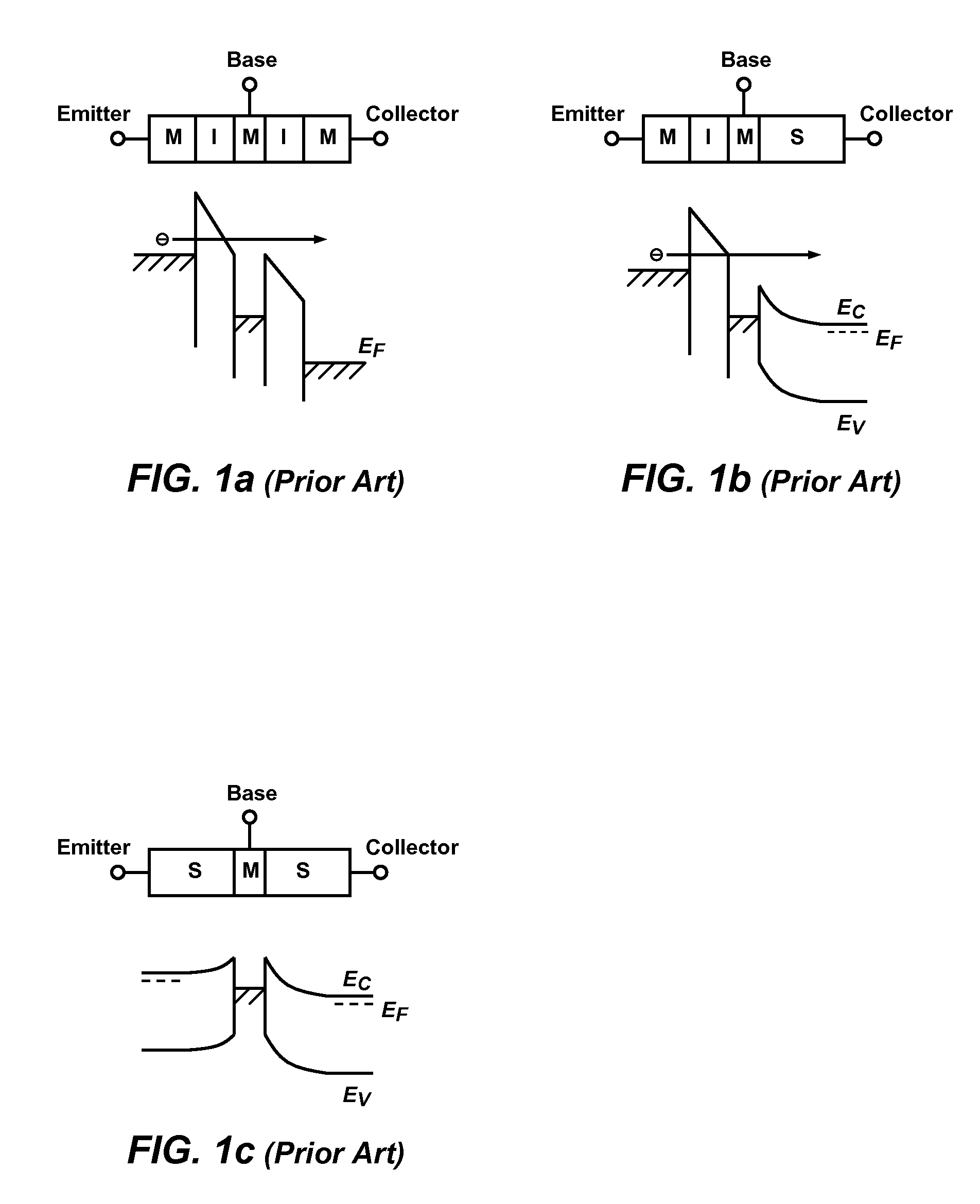

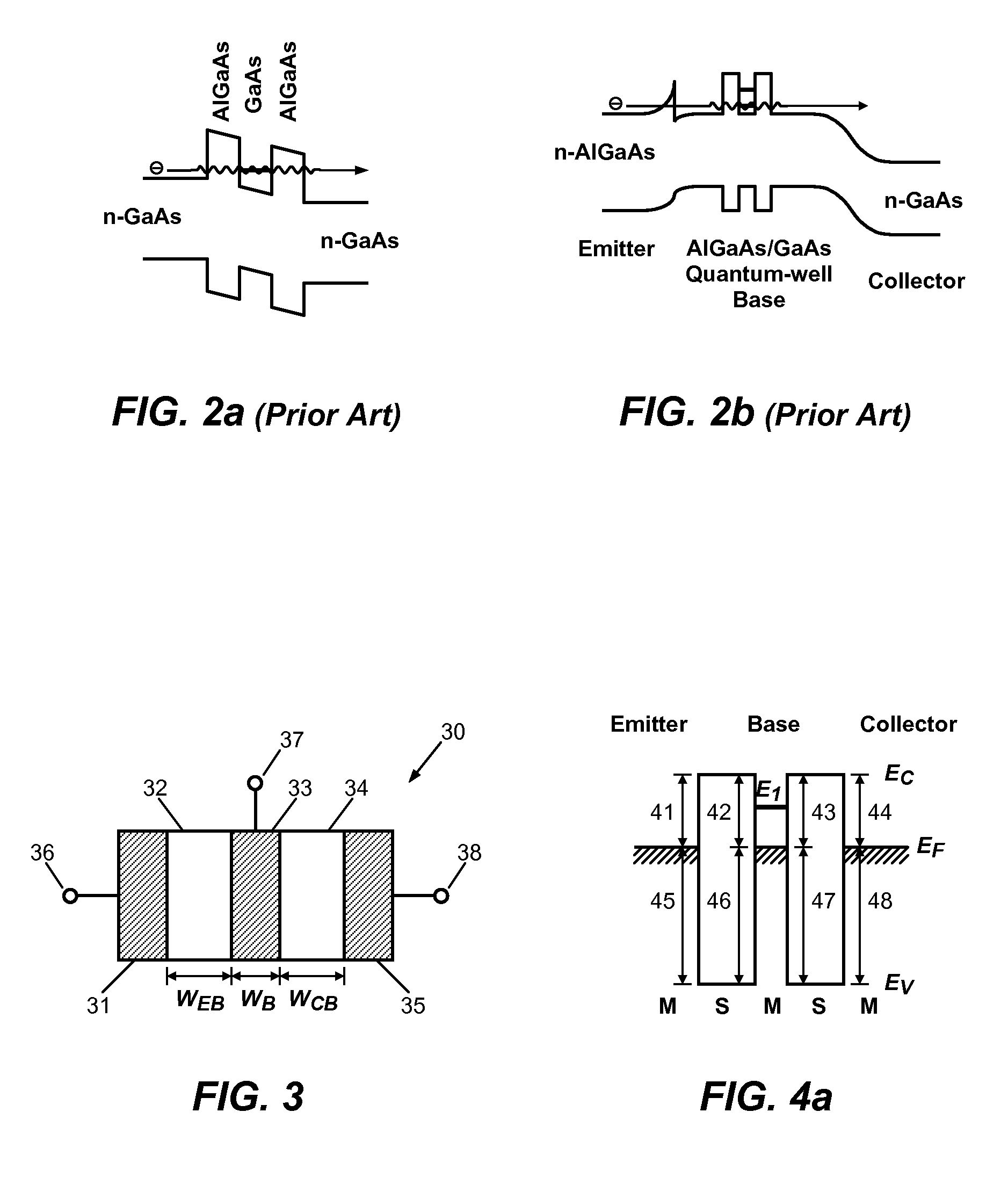

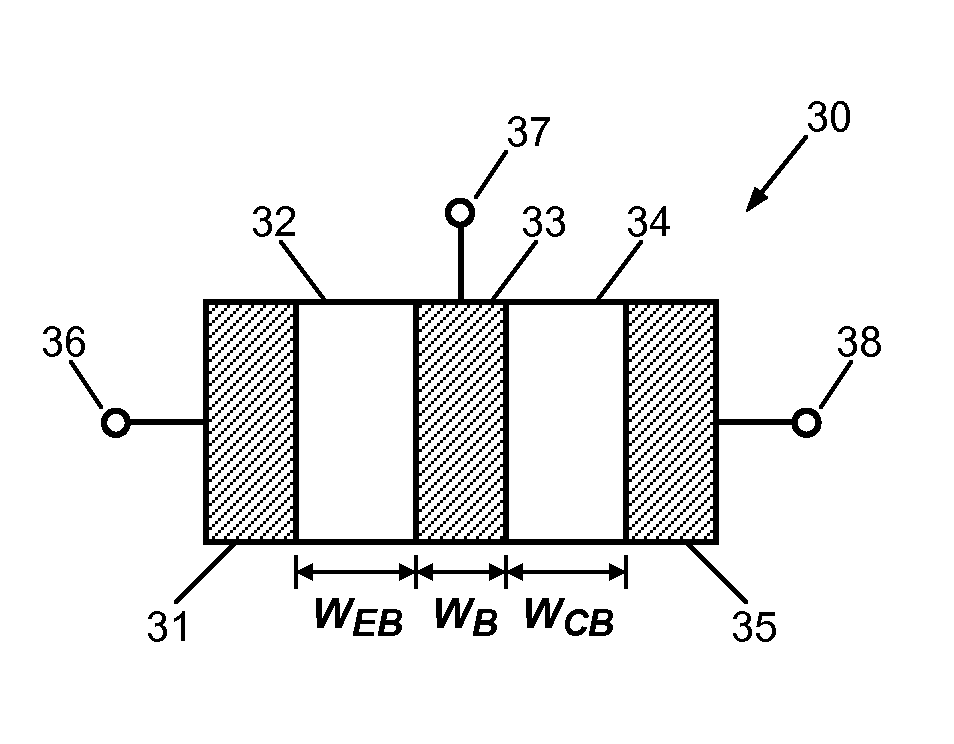

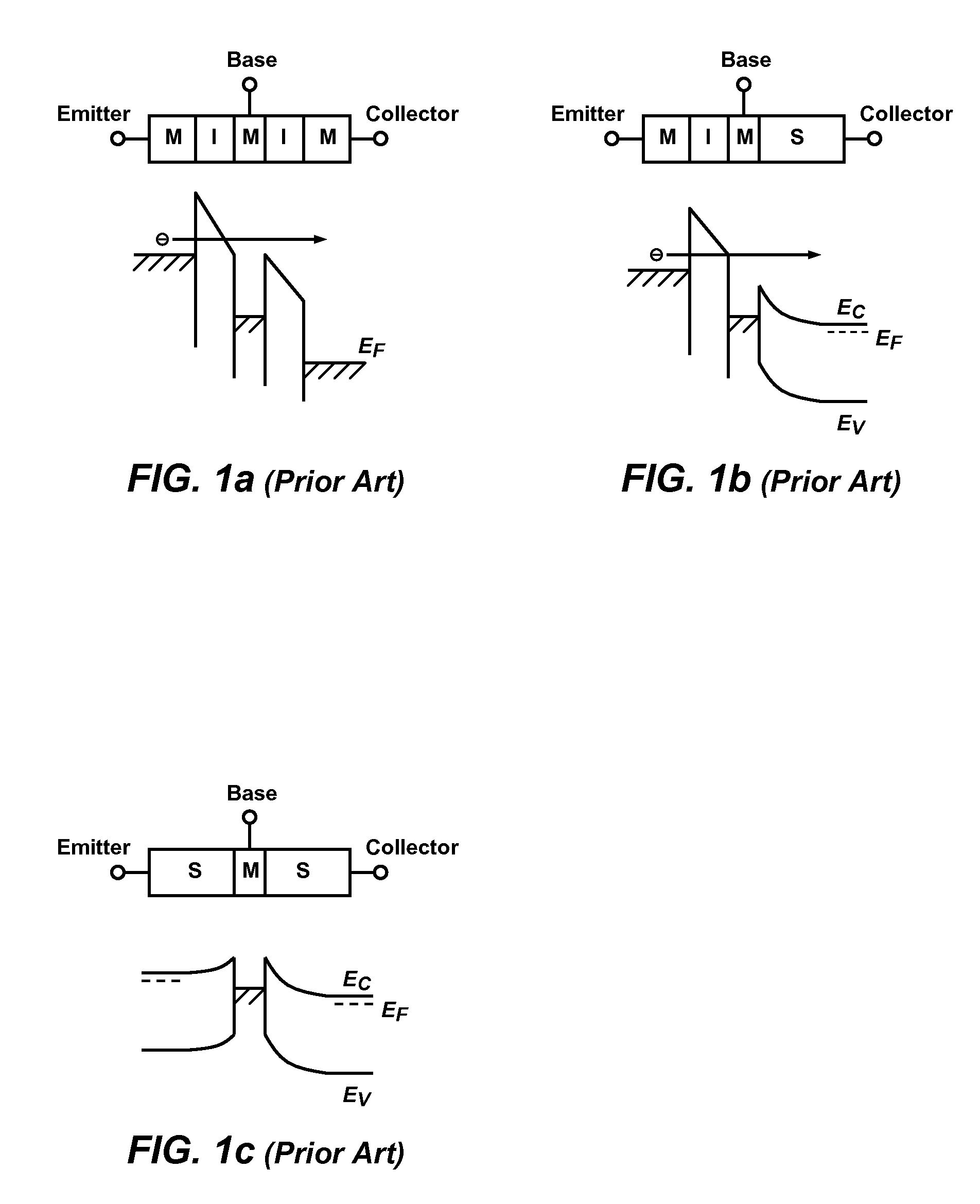

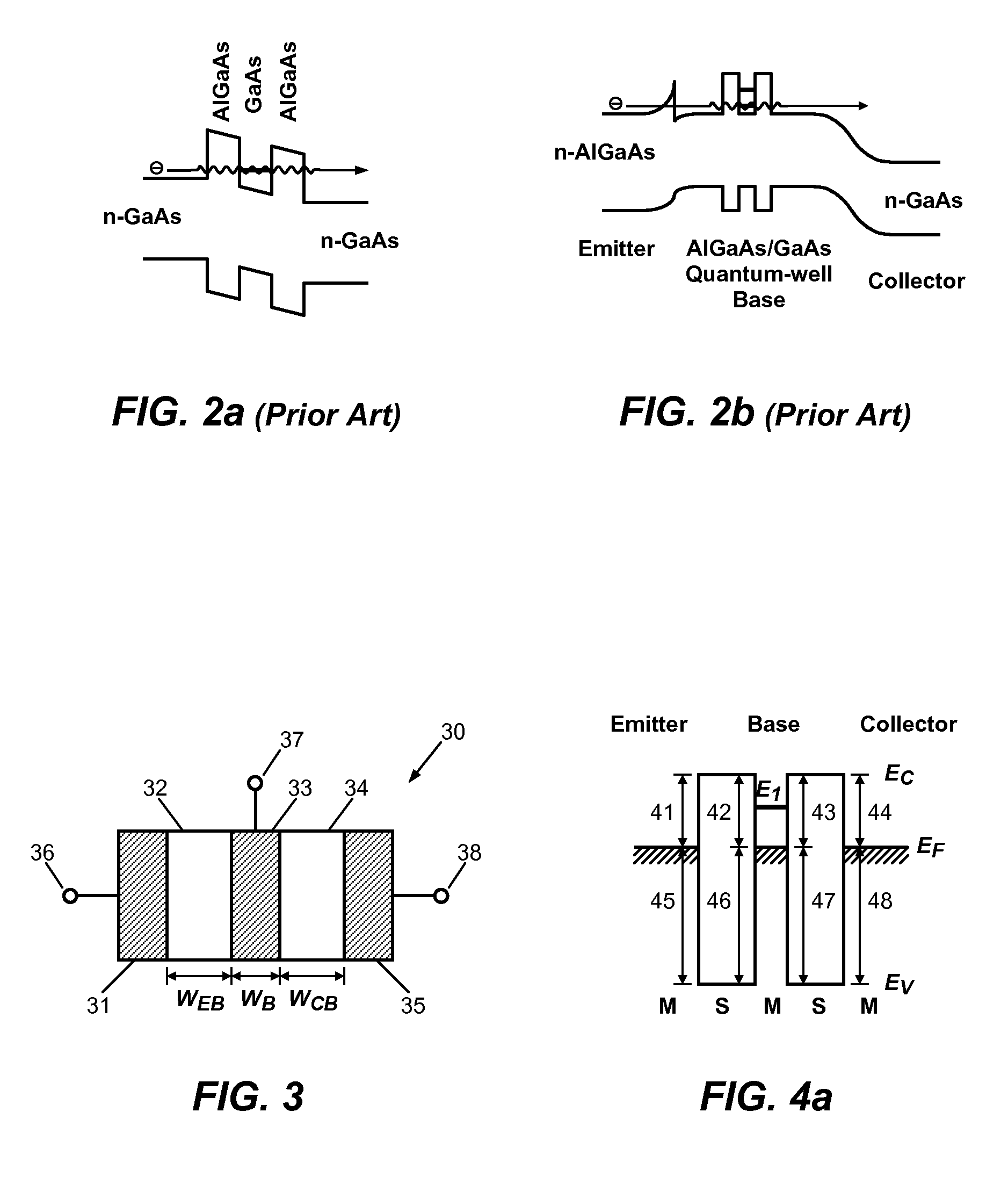

Schottky barrier quantum well resonant tunneling transistor

InactiveUS20100102298A1High speedReduce series resistanceTransistorSolid-state devicesQuantum wellSchottky barrier

A semiconductor transistor device includes one or more conductive base regions, a first semiconductor barrier region, a second semiconductor barrier region, a conductive emitter region, and a conductive collector region. The first semiconductor barrier region or the second semiconductor barrier region has a dimension smaller than 100 Å. A first Schottky barrier junction is formed at the interface of the first semiconductor barrier region and the one or more conductive base regions. A second Schottky barrier junction is formed at the interface of the second semiconductor barrier region and the one or more conductive base regions. A third Schottky barrier junction is formed at the interface of the conductive emitter region and the first semiconductor barrier region. A fourth Schottky barrier junction is formed at the interface of the conductive collector region and the second semiconductor barrier region.

Owner:WU KOUCHENG

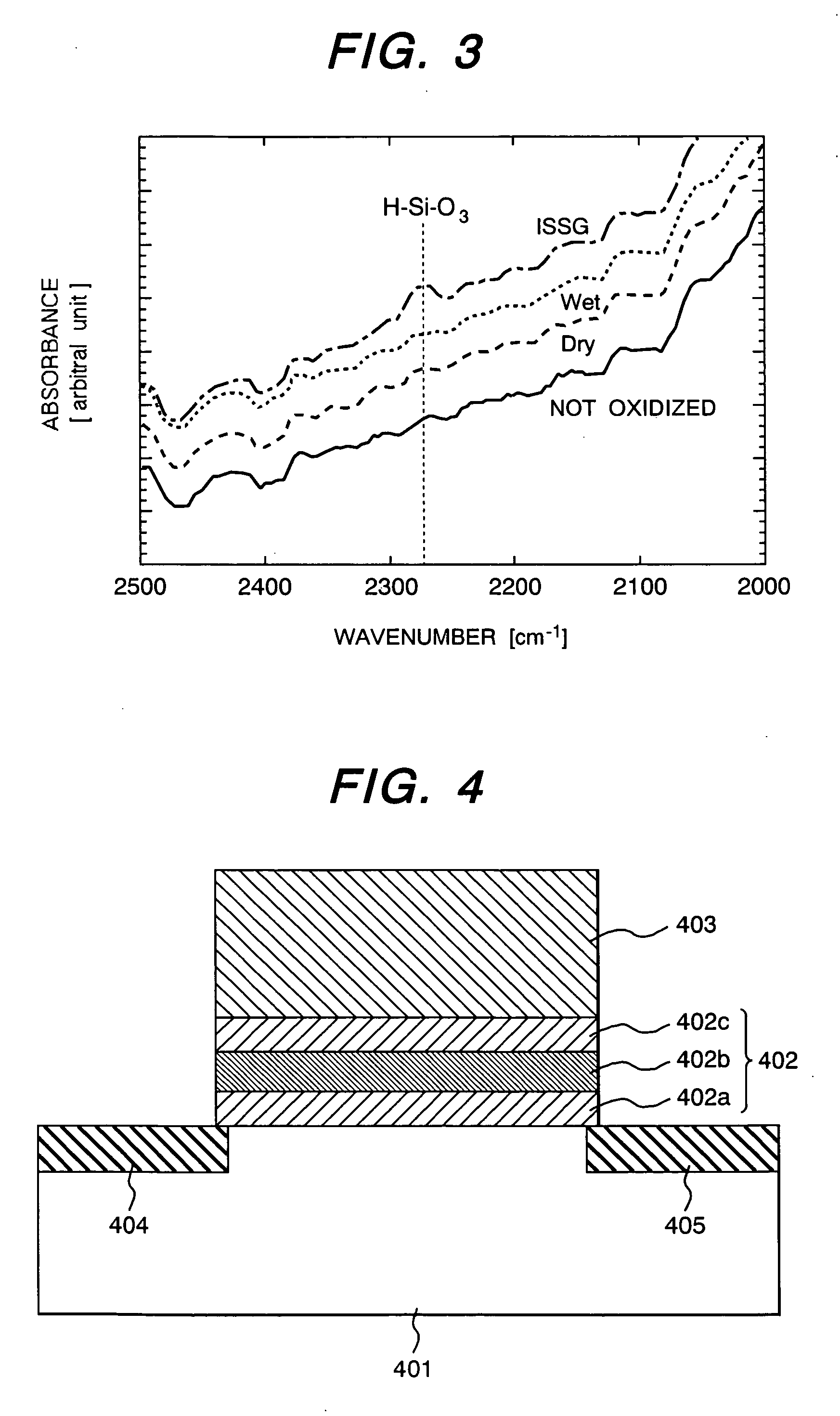

Method of manufacturing nonvolatile semiconductor memory device

ActiveUS20050272198A1Reduce in quantityImprove attributesTransistorSolid-state devicesHigh concentrationTrapping

Conventionally, a MONOS type nonvolatile memory is fabricated by subjecting a silicon nitride film to ISSG oxidation to form a top silicon oxide film of ONO structure. If the ISSG oxidation conditions are severe, repeats of programming / erase operation cause increase of interface state density (Dit) and electron trap density. This does not provide a sufficient value of the on current, posing a problem in that the deterioration of charge trapping properties cannot be suppressed. For the solution to the problem, the silicon nitride film is oxidized by means of a high concentration ozone gas to form the top silicon oxide film.

Owner:RENESAS ELECTRONICS CORP

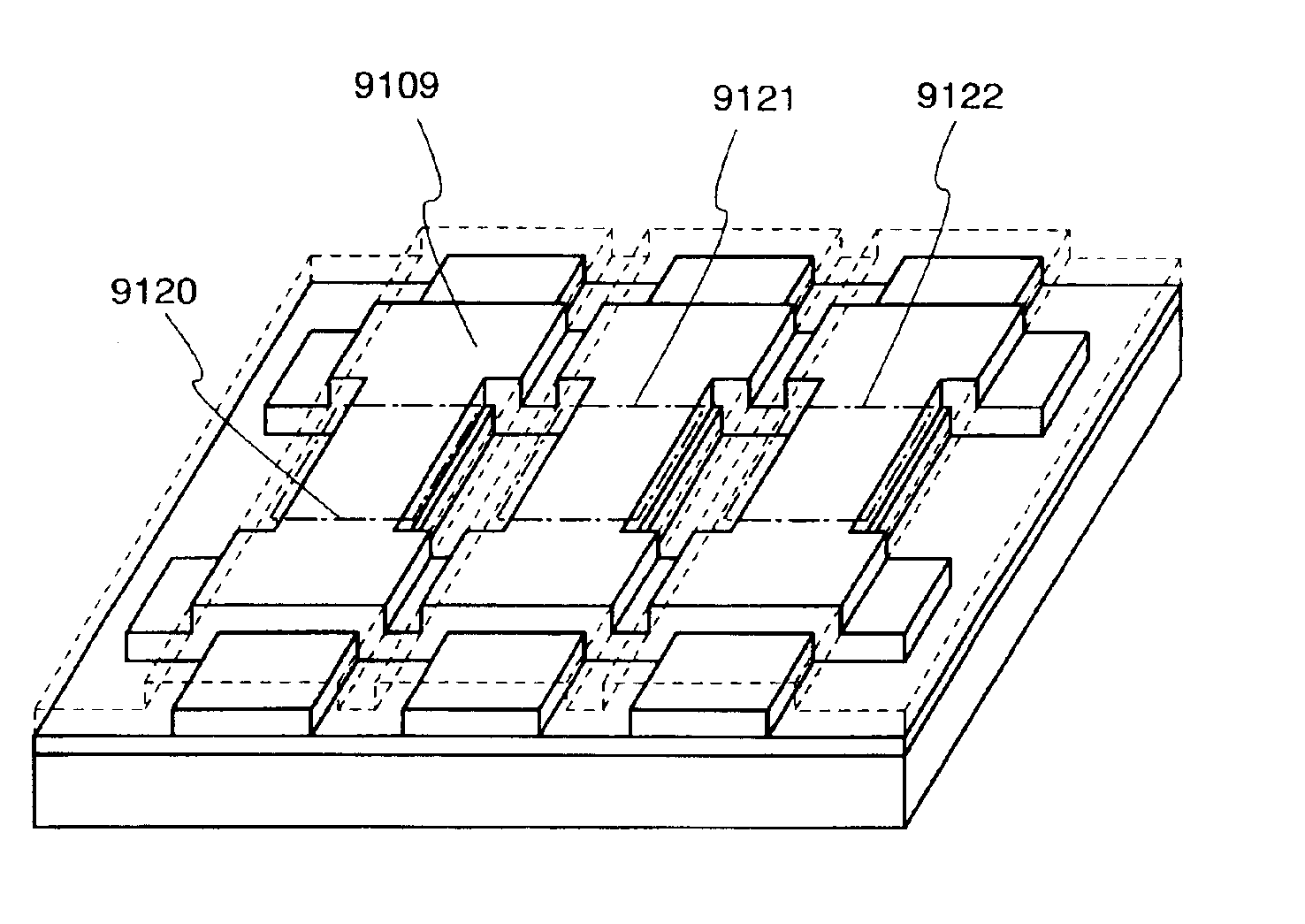

Semiconductor device and semiconductor device production system

InactiveUS20050161742A1Improve barrier propertiesImprove stressTransistorSolid-state devicesStress concentrationDevice material

It is a problem to provide a semiconductor device production system using a laser crystallization method capable of preventing grain boundaries from forming in a TFT channel region and further preventing conspicuous lowering in TFT mobility due to grain boundaries, on-current decrease or off-current increase. An insulation film is formed on a substrate, and a semiconductor film is formed on the insulation film. Due to this, preferentially formed is a region in the semiconductor film to be concentratedly applied by stress during crystallization with laser light. Specifically, a stripe-formed or rectangular concavo-convex is formed on the semiconductor film. Continuous-oscillation laser light is irradiated along the striped concavo-convex or along a direction of a longer or shorter axis of rectangle.

Owner:SEMICON ENERGY LAB CO LTD

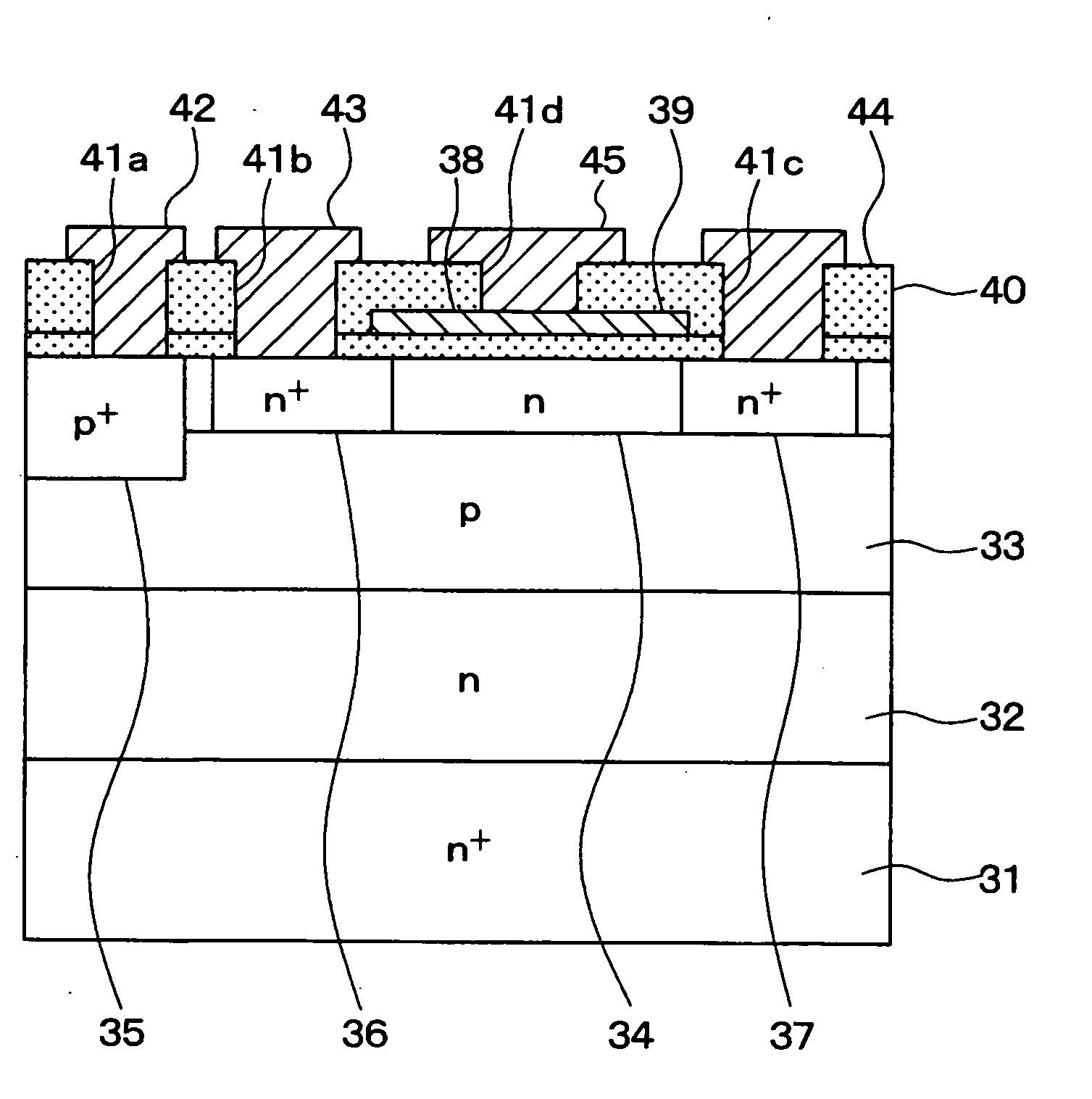

SiC semiconductor device and method for manufacturing the same

ActiveUS20080203441A1Improve channel mobilityReduce interface state densitySolid-state devicesSemiconductor/solid-state device manufacturingHydrogen concentrationEngineering

A SiC semiconductor device having a MOS structure includes: a SiC substrate; a channel region providing a current path; first and second impurity regions on upstream and downstream sides of the current path, respectively; and a gate on the channel region through the gate insulating film. The channel region for flowing current between the first and second impurity regions is controlled by a voltage applied to the gate. An interface between the channel region and the gate insulating film has a hydrogen concentration equal to or greater than 4.7×1020 cm−3. The interface provides a channel surface having a (000-1)-orientation surface.

Owner:DENSO CORP

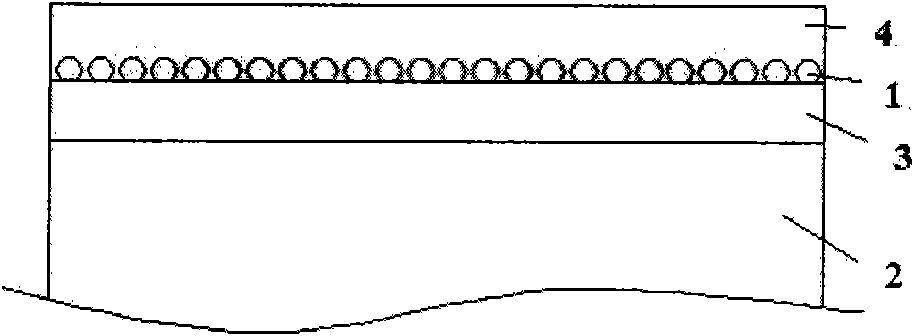

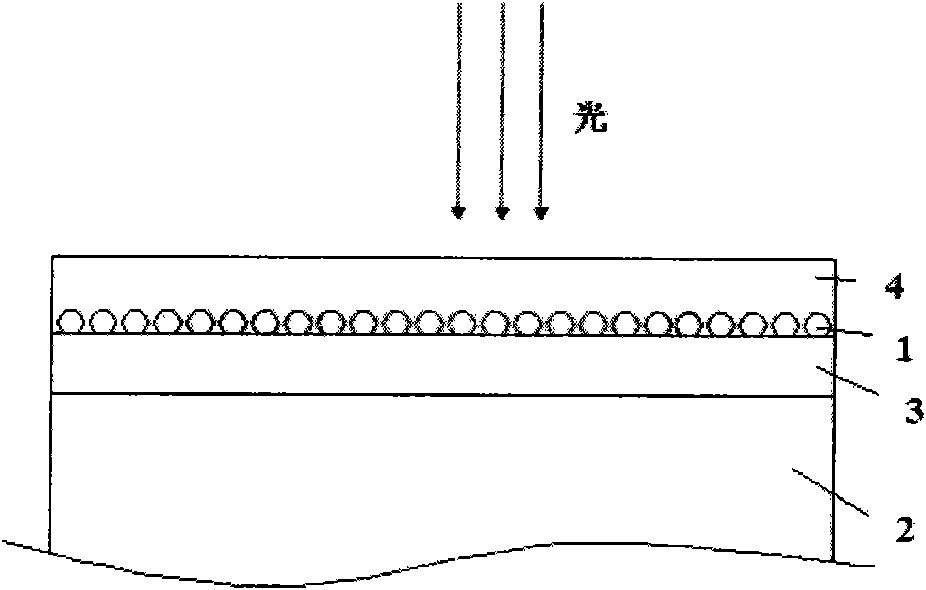

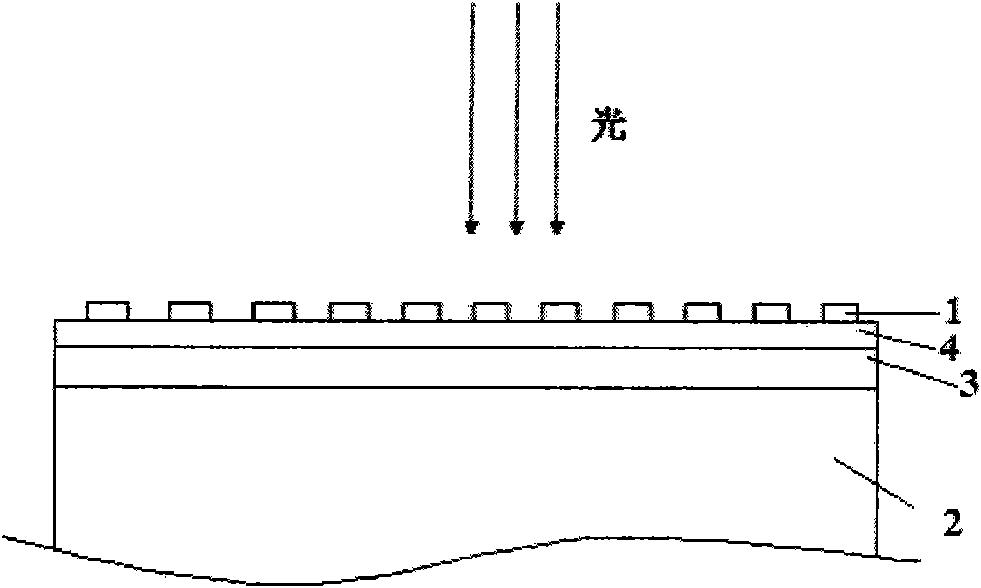

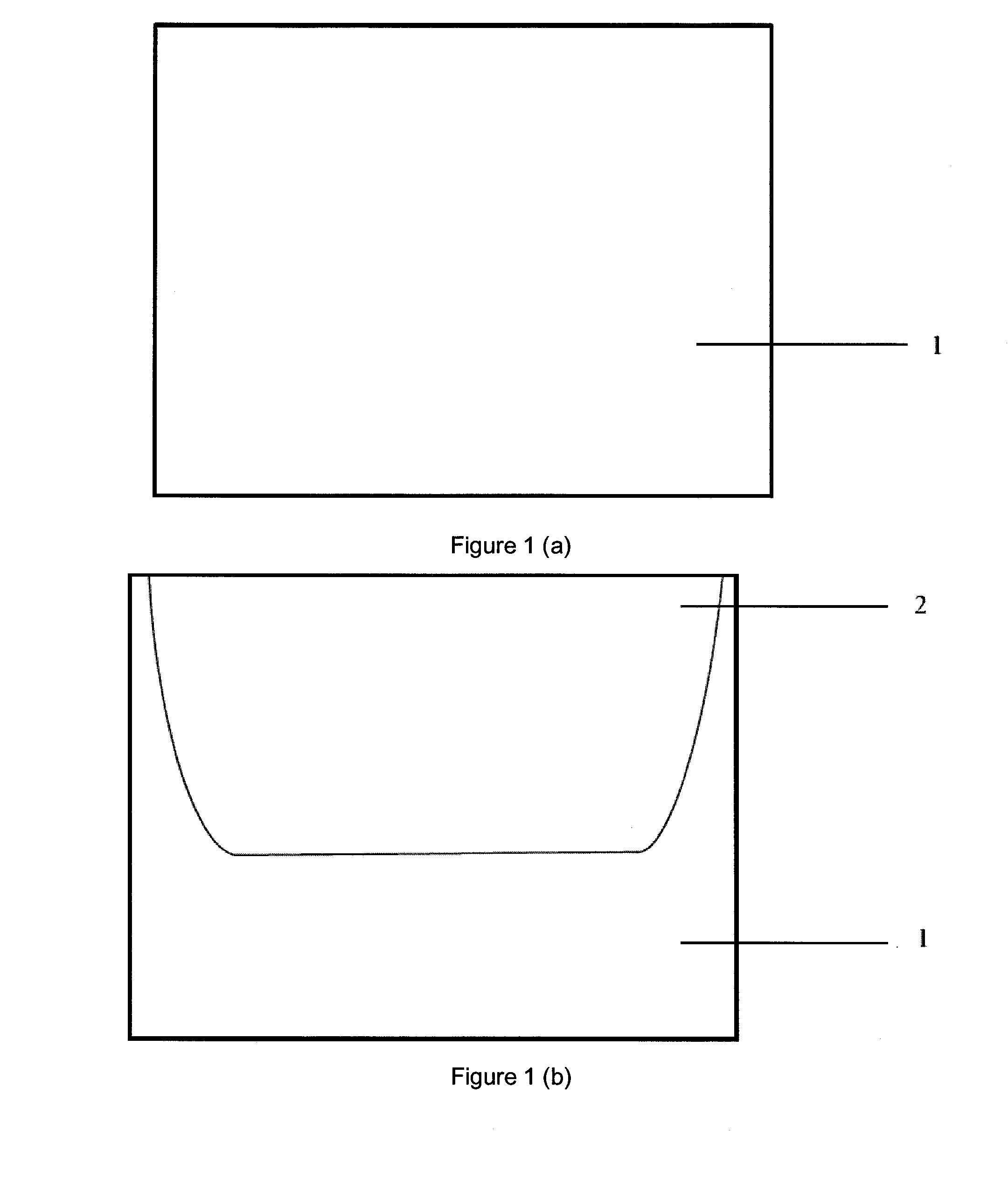

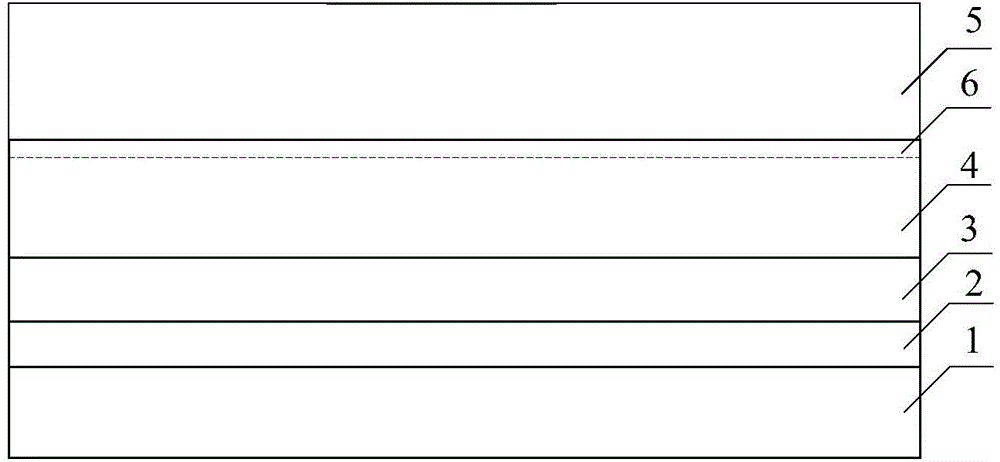

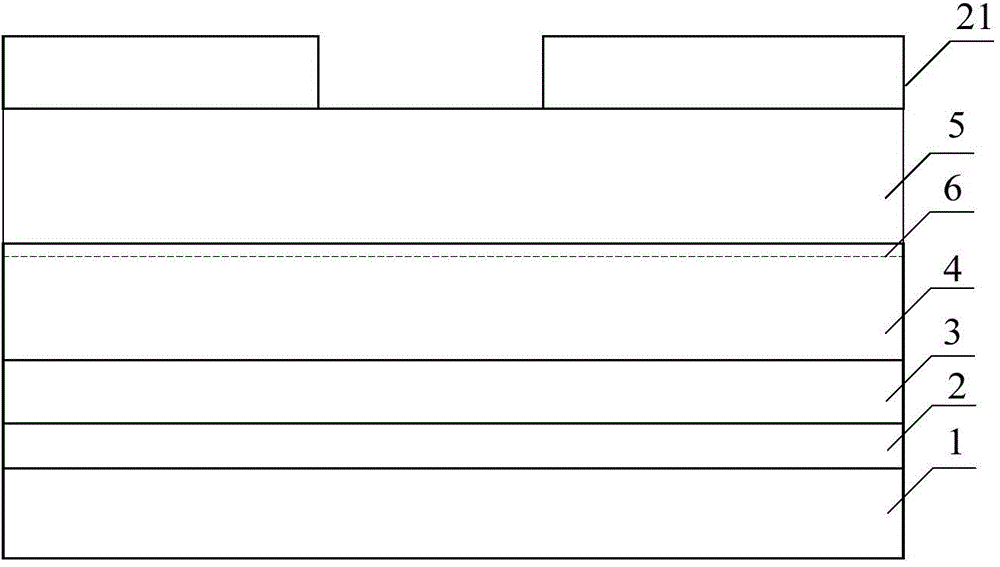

Light trapping structure for thin film silicon/crystalline silicon heterojunction solar battery

InactiveCN101866961AReduce interface state densityImprove performancePhotovoltaic energy generationSemiconductor devicesHeterojunctionSurface plasmon

The invention discloses a light trapping structure for a thin film silicon / crystalline silicon heterojunction solar battery, which comprises a crystalline silicon substrate (2), a doped thin film silicon layer (3) on the crystalline silicon substrate (2), a transparent conductive electrode (4) on the doped thin film silicon layer (3), and a metal nano-structure (1) between the doped thin film silicon layer (3) and the transparent conductive electrode (4), a metal nano-structure (1) above the transparent conductive electrode (4), or a metal nano-structure (1) inside the transparent conductive electrode (4). The connecting surface of the crystalline silicon substrate (2) and the crystalline silicon substrate (2) is not specially woven with velvet. The light trapping structure acquires a light trapping effect by using a surface plasmon effect of the metal nano-structure.

Owner:INST OF ELECTRICAL ENG CHINESE ACAD OF SCI

Method of forming a memory device and semiconductor device

InactiveUS6924186B2Good step coverageLow gate leakageSemiconductor/solid-state device manufacturingSemiconductor devicesNovel techniqueDielectric

A novel technique to quench electrical defects in CVD Al2O3 layers is disclosed. A small amount of silicon dopant to the aluminum oxide film reduces the leakage current as well as the gap interface trap density at the dielectric / silicon interface. The implanted silicon gives a better interface and improves the leakage characteristics of the dielectric.

Owner:MICRON TECH INC

Semiconductor device and method for manufacturing the same

ActiveUS20160284859A1ResponsivenessReduced responsivenessTransistorSolid-state devicesKryptonSemiconductor device modeling

A semiconductor device with low parasitic capacitance is provided. The semiconductor device includes a first oxide insulator, an oxide semiconductor, a second oxide insulator, a gate insulating layer, a gate electrode layer, source and drain electrode layers and an insulating layer. The oxide semiconductor includes first to fifth regions. The first region overlaps with the source electrode layer. The second region overlaps with the drain electrode layer. The third region overlaps with the gate electrode layer. The fourth region is between the first region and the third region. The fifth region is between the second region and the third region. The fourth region and the fifth region each contain an element N (N is hydrogen, nitrogen, helium, neon, argon, krypton, or xenon). A top surface of the insulating layer is positioned at a lower level than top surfaces of the source and drain electrode layers.

Owner:SEMICON ENERGY LAB CO LTD

Schottky barrier quantum well resonant tunneling transistor

InactiveUS7936040B2Simple device structureImprove good performanceTransistorSolid-state devicesSchottky barrierQuantum well

A semiconductor transistor device includes one or more conductive base regions, a first semiconductor barrier region, a second semiconductor barrier region, a conductive emitter region, and a conductive collector region. The first semiconductor barrier region or the second semiconductor barrier region has a dimension smaller than 100 Å. A first Schottky barrier junction is formed at the interface of the first semiconductor barrier region and the one or more conductive base regions. A second Schottky barrier junction is formed at the interface of the second semiconductor barrier region and the one or more conductive base regions. A third Schottky barrier junction is formed at the interface of the conductive emitter region and the first semiconductor barrier region. A fourth Schottky barrier junction is formed at the interface of the conductive collector region and the second semiconductor barrier region.

Owner:WU KOUCHENG

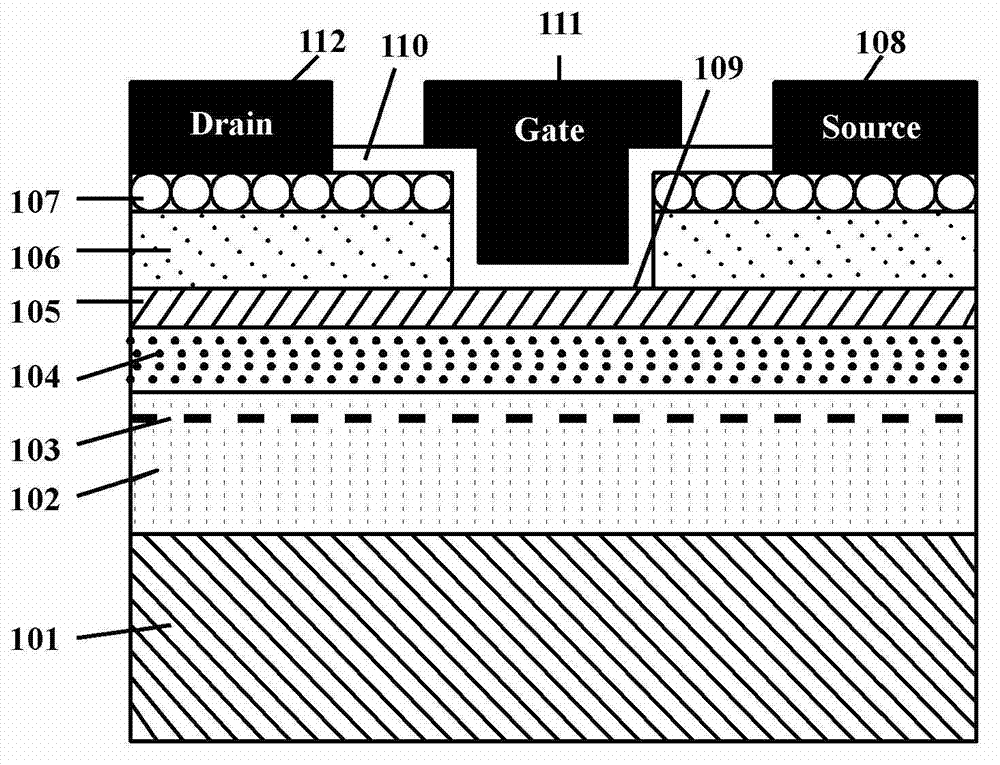

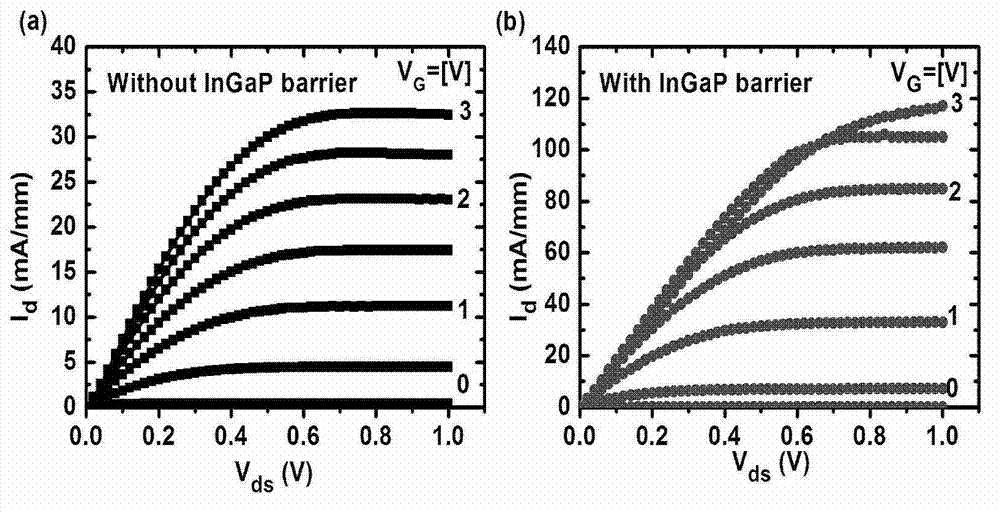

III-V group semiconductor MOS field effect transistor with high mobility

InactiveCN102931231AReduce scatterIncrease drive currentSemiconductor devicesControl layerLow voltage

The invention discloses a III-V group MOS (Metal-oxide Semiconductor) field effect transistor with high mobility, which comprises a single-crystal lining, a buffer layer formed on the single-crystal lining, a planar doped layer formed in the buffer layer, a high-mobility channel layer formed on the buffer layer, a doped interface control layer formed on the high-mobility channel layer, a high-doped semiconductor layer formed on the doped interface control layer, a narrow band gap ohm contact layer formed on the high-doped semiconductor layer, and a source-drain metal electrode formed on the narrow band gap ohm contact layer, wherein a grid groove etched to the doped interface control layer is located between two source drain metal electrodes; a high-K grid medium is uniformly covered on the inner surface of the grid groove structure; and a grid metal electrode is formed on the high-K grid medium. The III-V MOS device structure disclosed by the invention not only can lower MOS interface state density, and improve channel mobility, but also can improve channel two-dimensional electron (cavity) gas concentration, and satisfy the application demand of a high-speed lower voltage operation high mobility CMOS technology.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

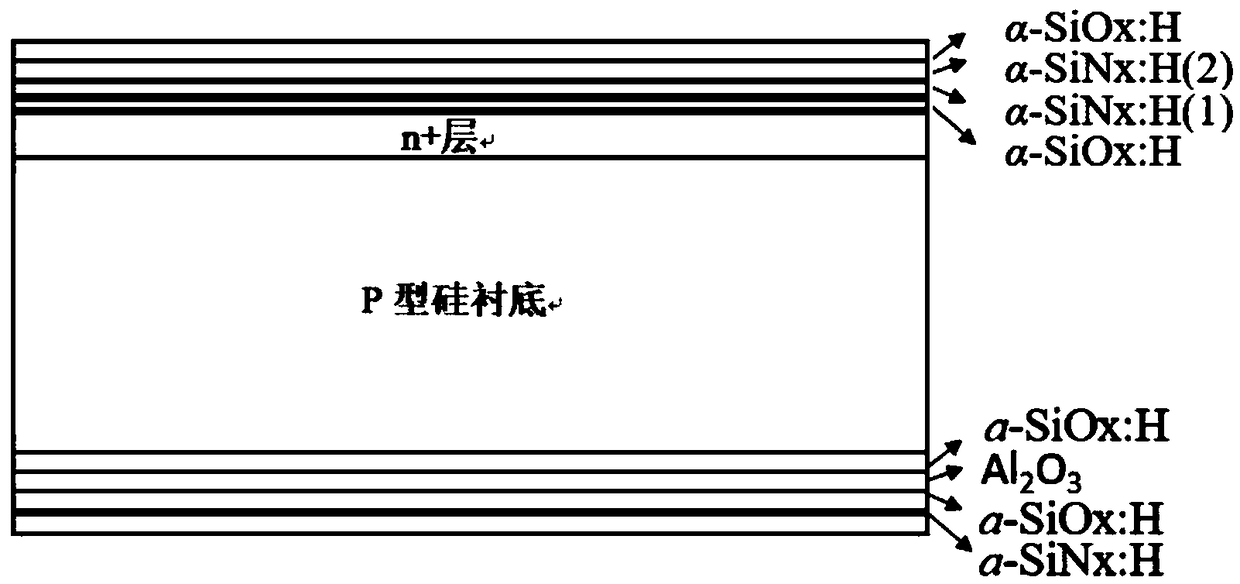

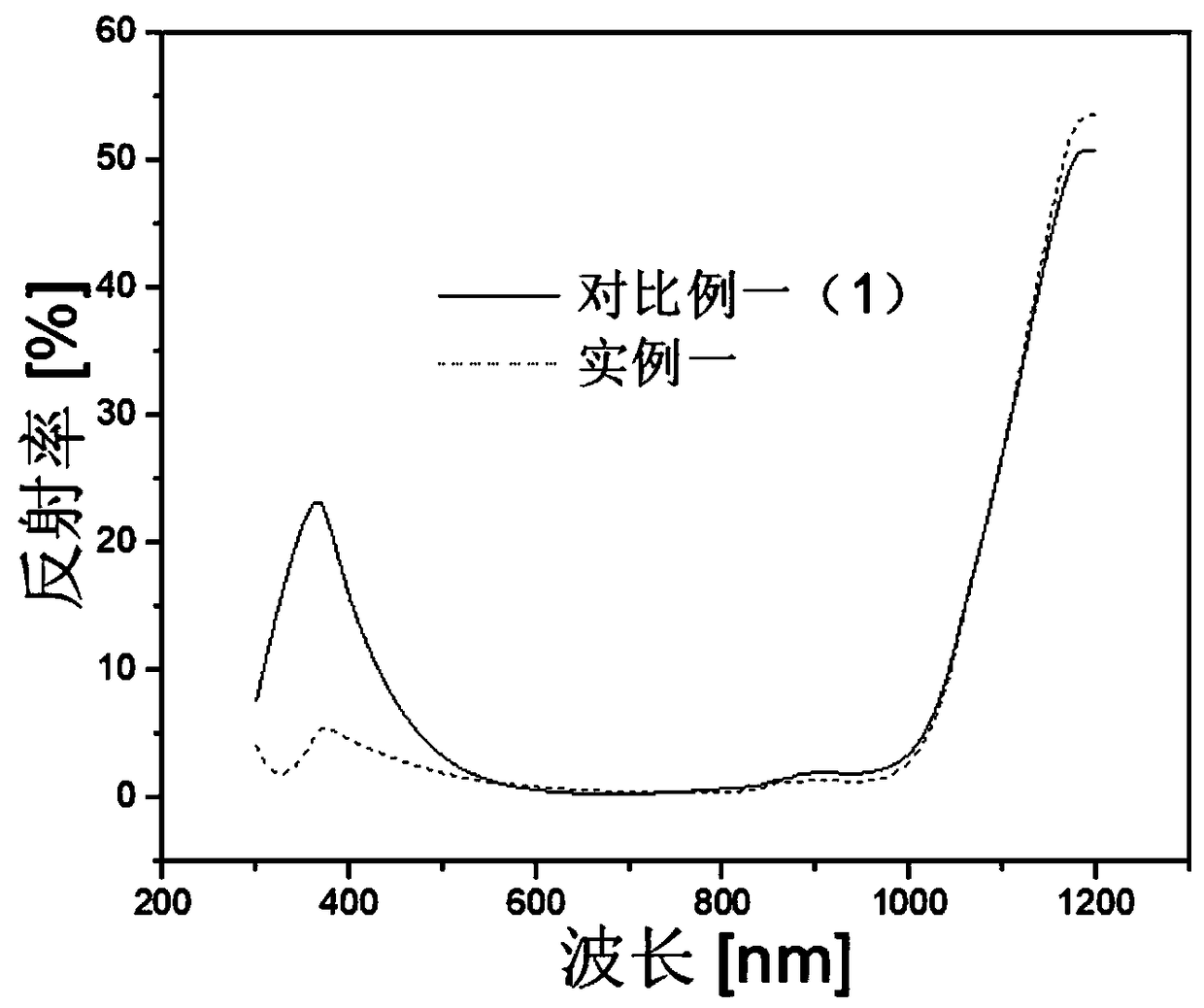

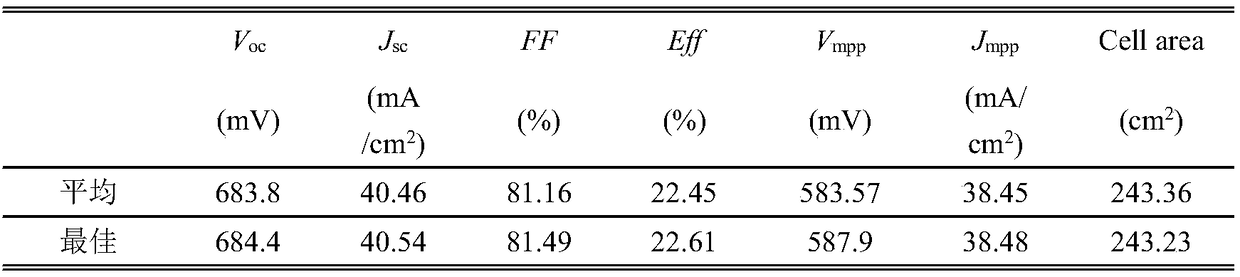

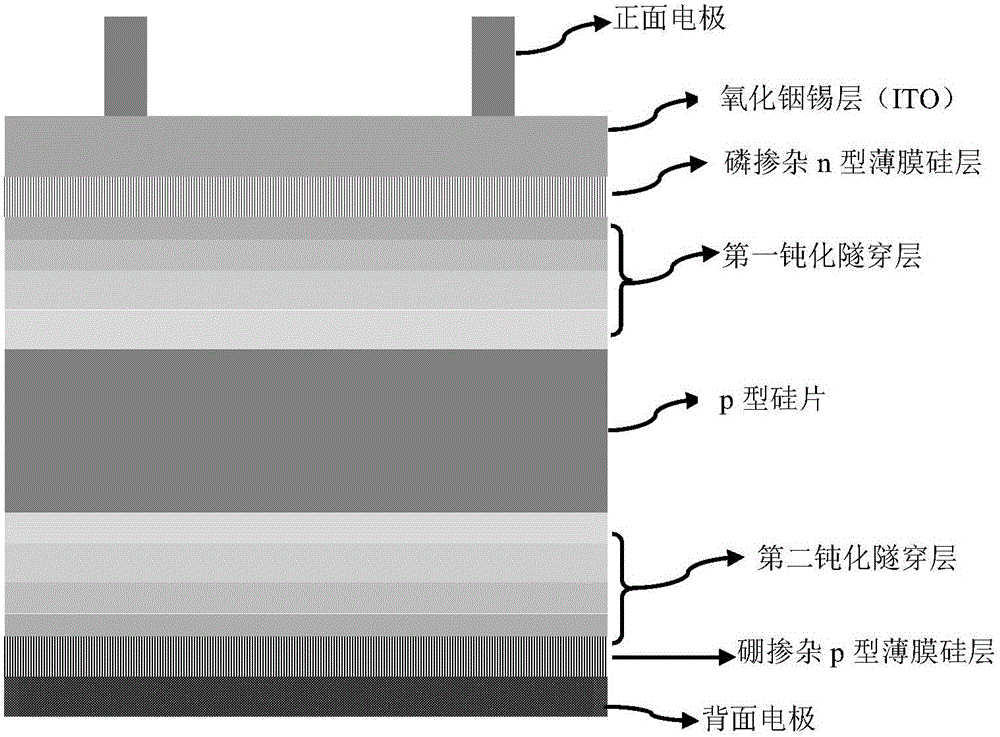

A surface interface passivation layer of an efficient crystalline silicon solar cell and a passivation method thereof

ActiveCN109216473AEasy to fixReduce interface state densityFinal product manufacturePhotovoltaic energy generationP type siliconCrystalline silicon

The invention discloses a surface interface passivation layer of a high-efficiency crystalline silicon solar cell and a passivation method thereof, belonging to the technical field of solar energy manufacturing. An n +-type doping layer is arranged on the front surface of the p-type crystal silicon battery, and the surface of the n +-type doping layer and the surface of the p-type layer on the back surface of the p-type silicon substrate are passivated respectively. Plasma enhanced chemical vapor deposition (PECVD) technique was used to prepare four-layer passivation film on the n + layer of P-type silicon substrate. Plasma enhanced chemical vapor deposition (PECVD) and atomic layer deposition (ALD) were used to prepare a four-layer passivation film on the p-type layer on the back surfaceof P-type silicon substrate, The structure order of the laminated passivation layer prepared by the patent of the invention has a vital effect on the passivation effect, and the laminated layers havemutual synergistic effect, and after passivation, the laminated passivation layer has excellent anti-reflection effect and good passivation effect, and the laminated passivation layer has excellent application prospect in p-type PERC batteries.

Owner:CHANGZHOU UNIV +1

Ge-based nmos device and method for fabricating the same

ActiveUS20140117465A1Alleviate Fermi level pinning effectReduce electron barrierSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierDielectric layer

The embodiments of the present invention provide a Ge-based NMOS device structure and a method for fabricating the same. By using the method, double dielectric layers of germanium oxide (GeO2) and metal oxide are deposited between the source / drain region and the substrate. The present invention not only reduces the electron Schottky barrier height of metal / Ge contact, but also improves the current switching ratio of the Ge-based Schottky and therefore, it will improve the performance of the Ge-based Schottky NMOS transistor. In addition, the fabrication process is very easy and completely compatible with the silicon CMOS process. As compared with conventional fabrication method, the Ge-based NMOS device structure and the fabrication method in the present invention can easily and effectively improve the performance of the Ge-based Schottky NMOS transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

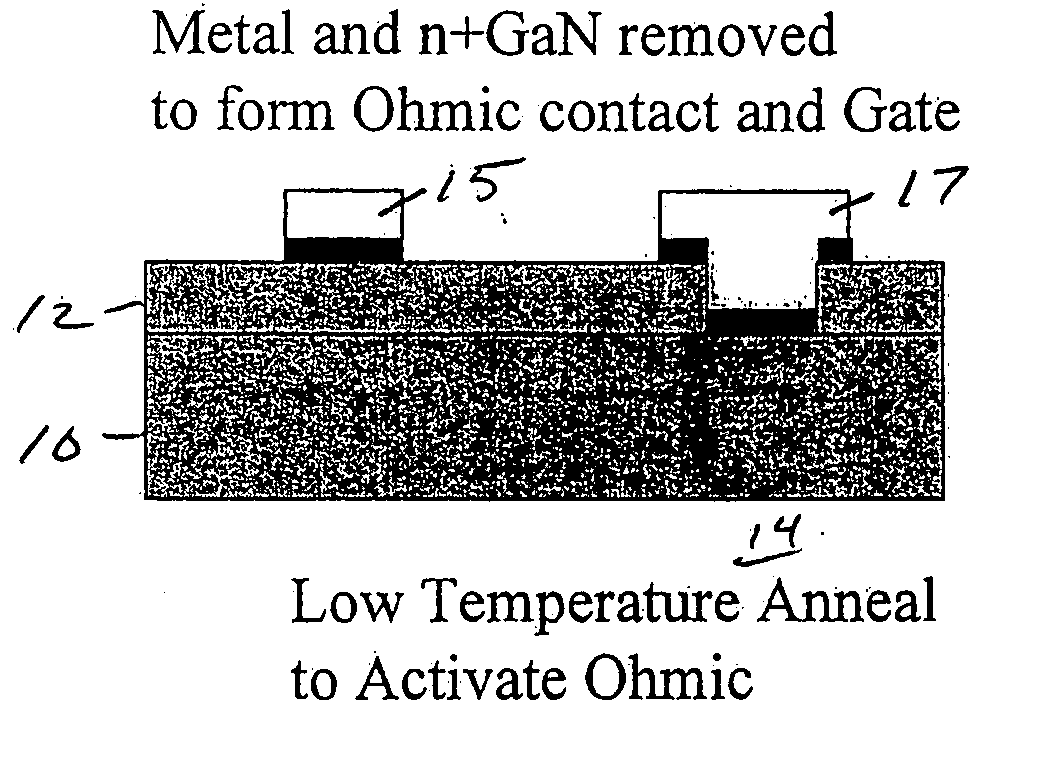

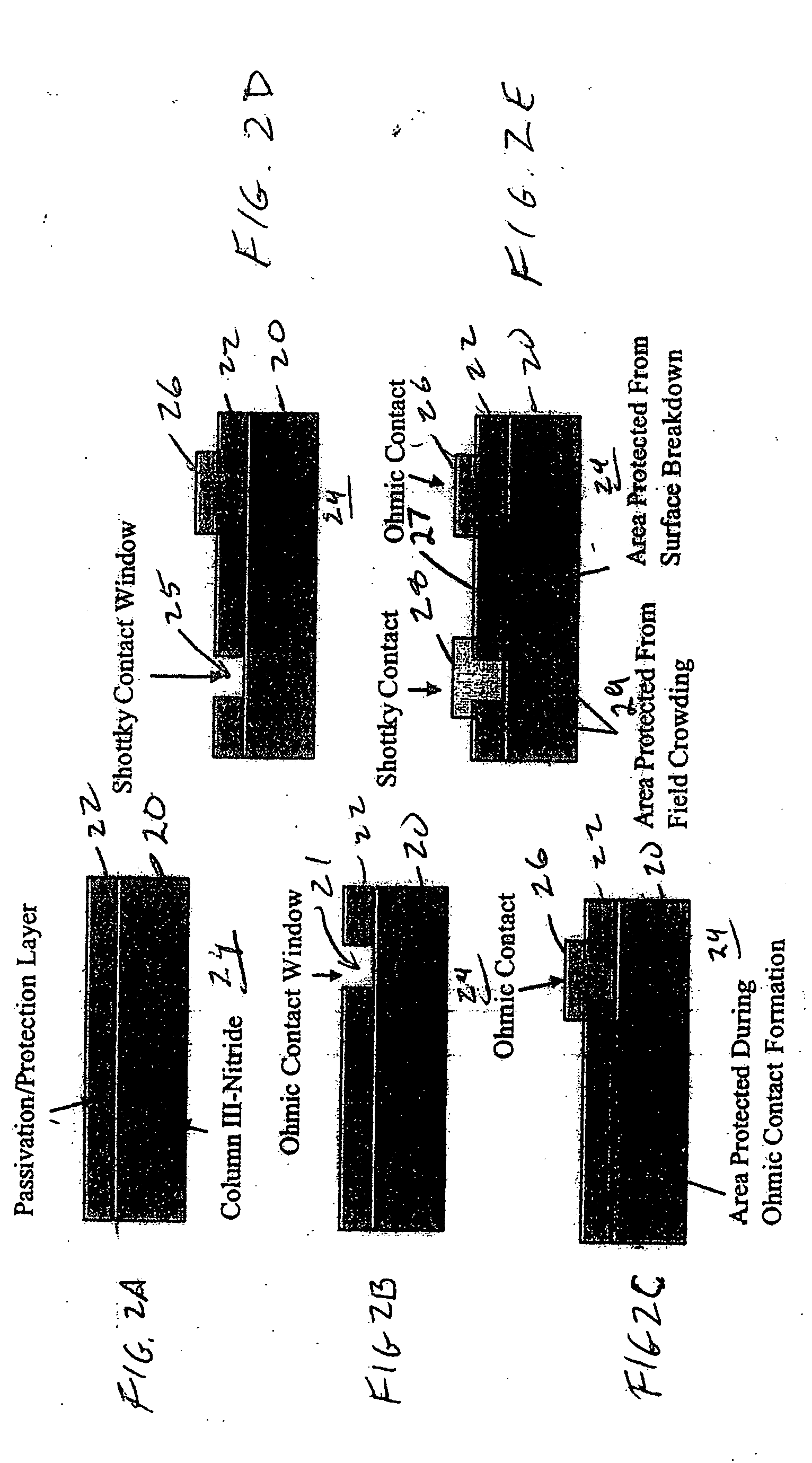

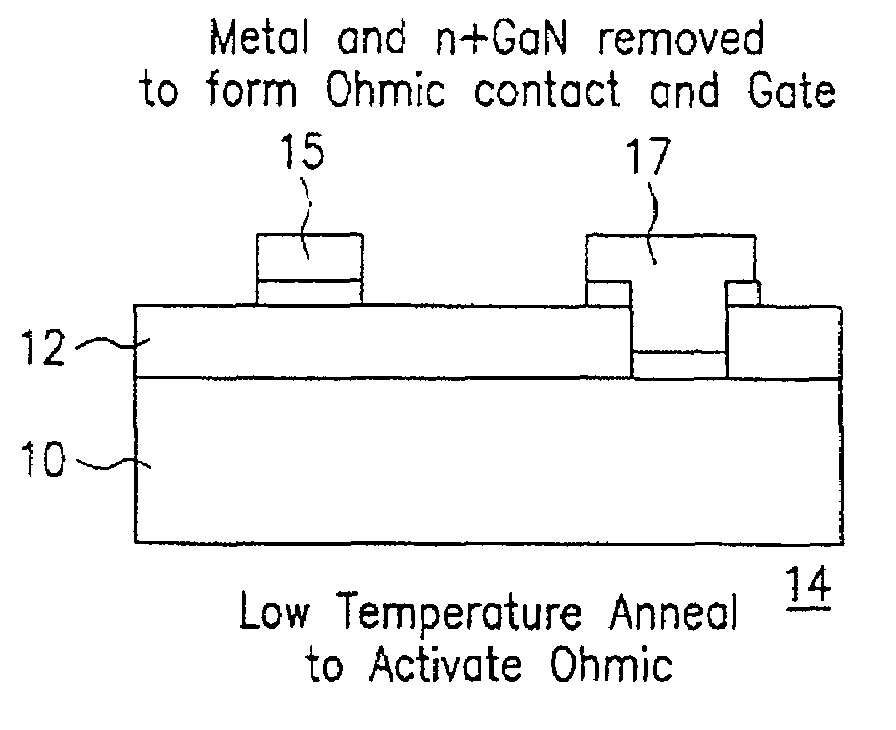

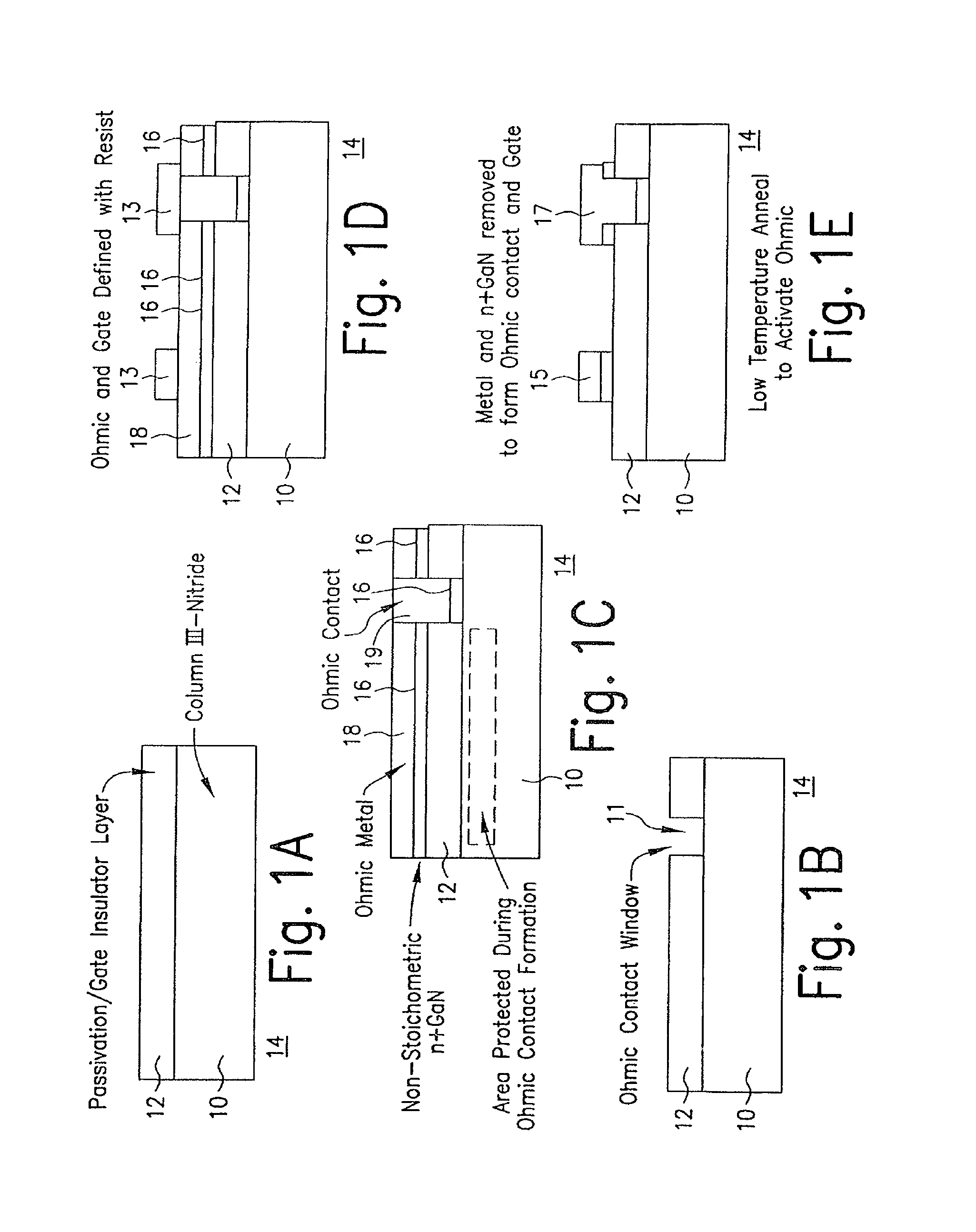

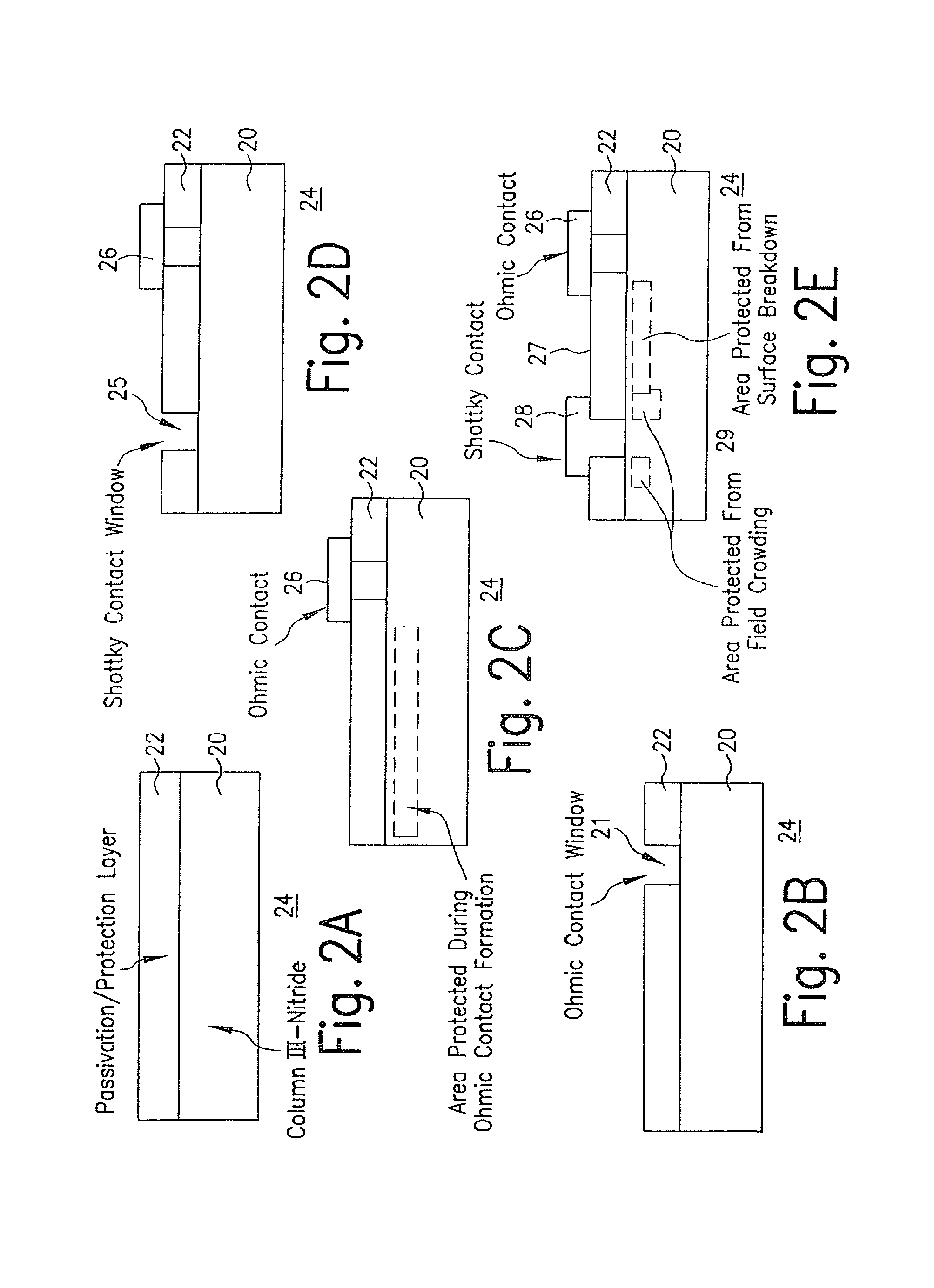

III-Nitride device passivation and method

ActiveUS20060006413A1Little and no damageQuality improvementSemiconductor/solid-state device detailsSolid-state devicesEngineeringActive layer

An embodiment of a III-nitride semiconductor device and method for making the same may include a low resistive passivation layer that permits the formation of device contacts without damage to the III-nitride material during high temperature processing. The passivation layer may be used to passivate the entire device. The passivation layer may also be provided in between contacts and active layers of the device to provide a low resistive path for current conduction. The passivation process may be used with any type of device, including FETs, rectifiers, schottky diodes and so forth, to improve breakdown voltage and prevent field crowding effects near contact junctions. The passivation layer may be activated with a low temperature anneal that does not impact the III-nitride device regarding outdiffusion.

Owner:INFINEON TECH AMERICAS CORP

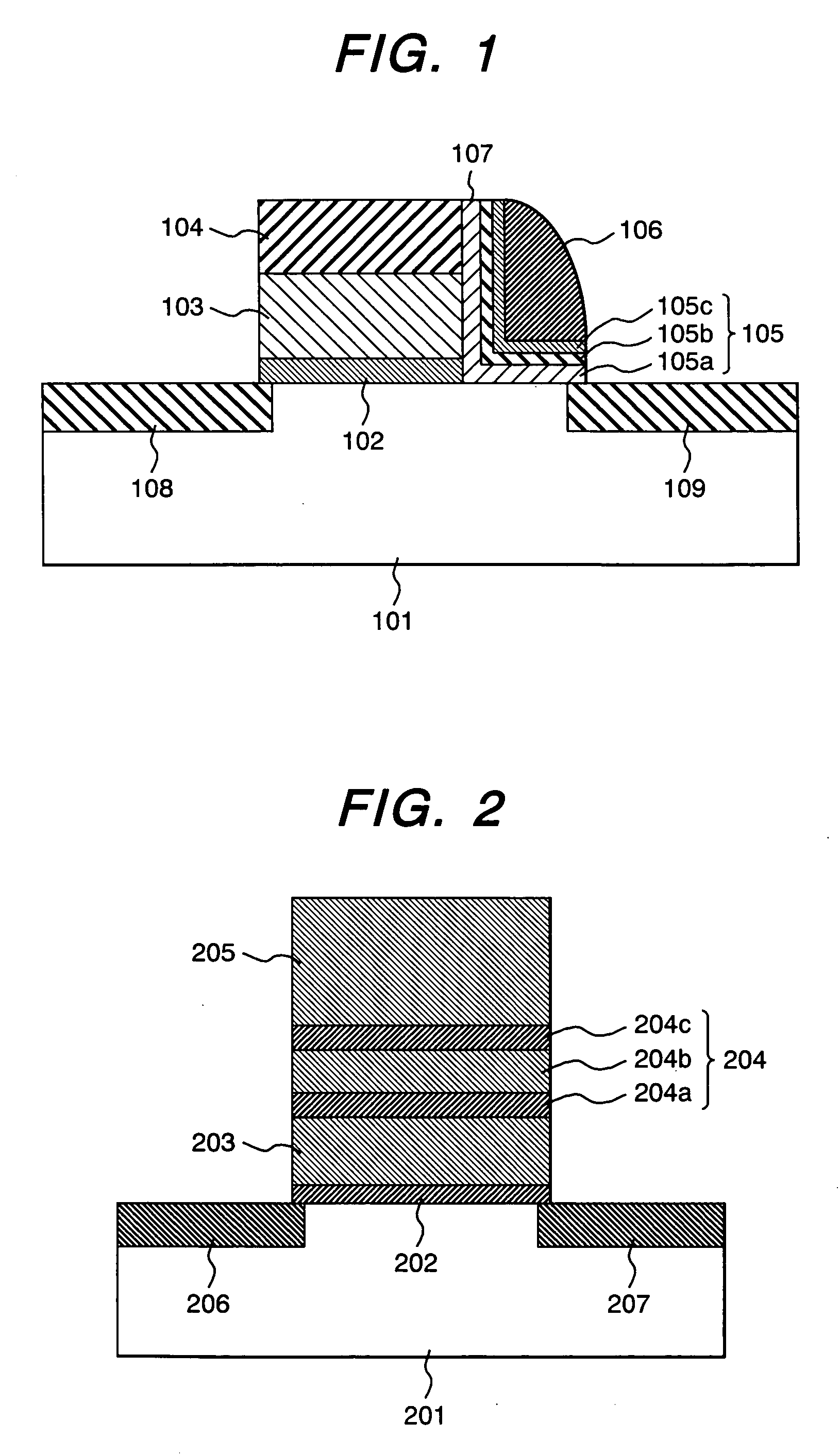

Semiconductor device having a gate insulating film structure including an insulating film containing metal, silicon and oxygen and manufacturing method thereof

InactiveUS20050006675A1Improve manufacturing productivityReduce interface state densityTransistorSolid-state devicesDevice materialOxygen

Claimed and disclosed is a semiconductor device including a transistor having a gate insulating film structure containing nitrogen or fluorine in a compound, such as metal silicate, containing metal, silicon and oxygen, a gate insulating film structure having a laminated structure of an amorphous metal oxide film and metal silicate film, or a gate insulating film structure having a first gate insulating film including an oxide film of a first metal element and a second gate insulating film including a metal silicate film of a second metal element.

Owner:HEAD TECHNOLOGY GMBH LTD +1

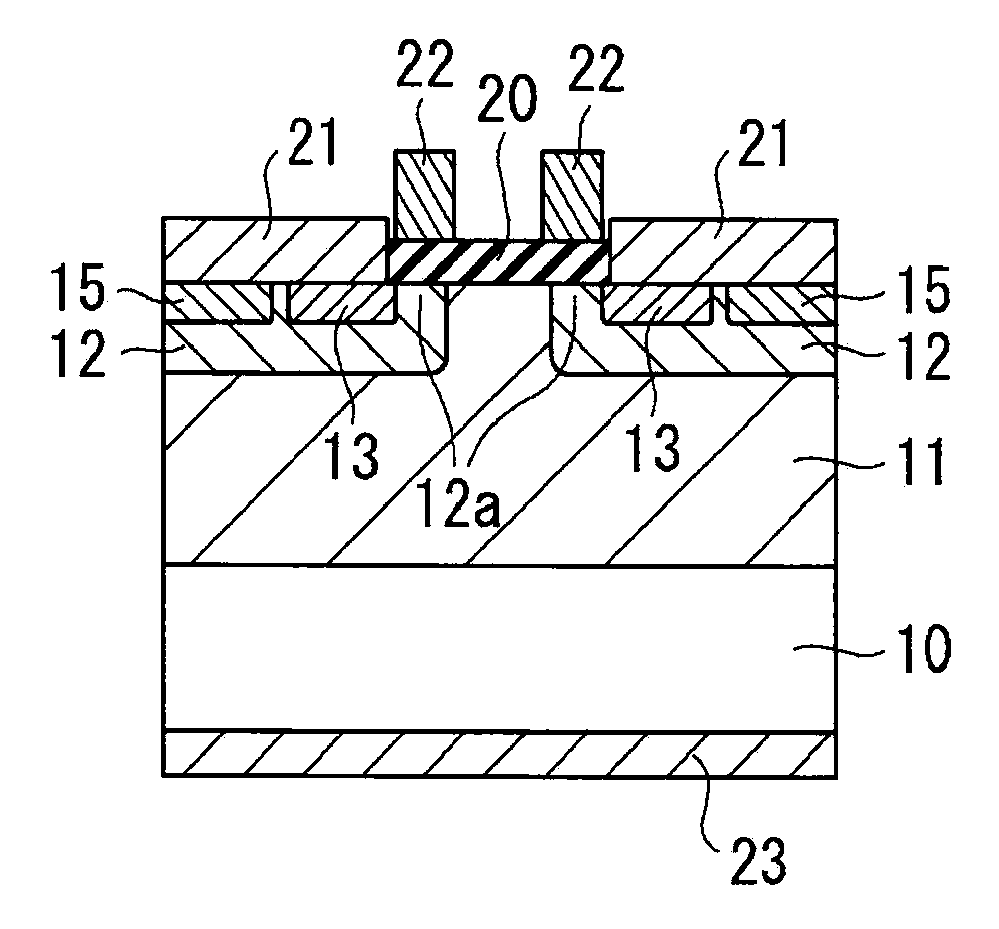

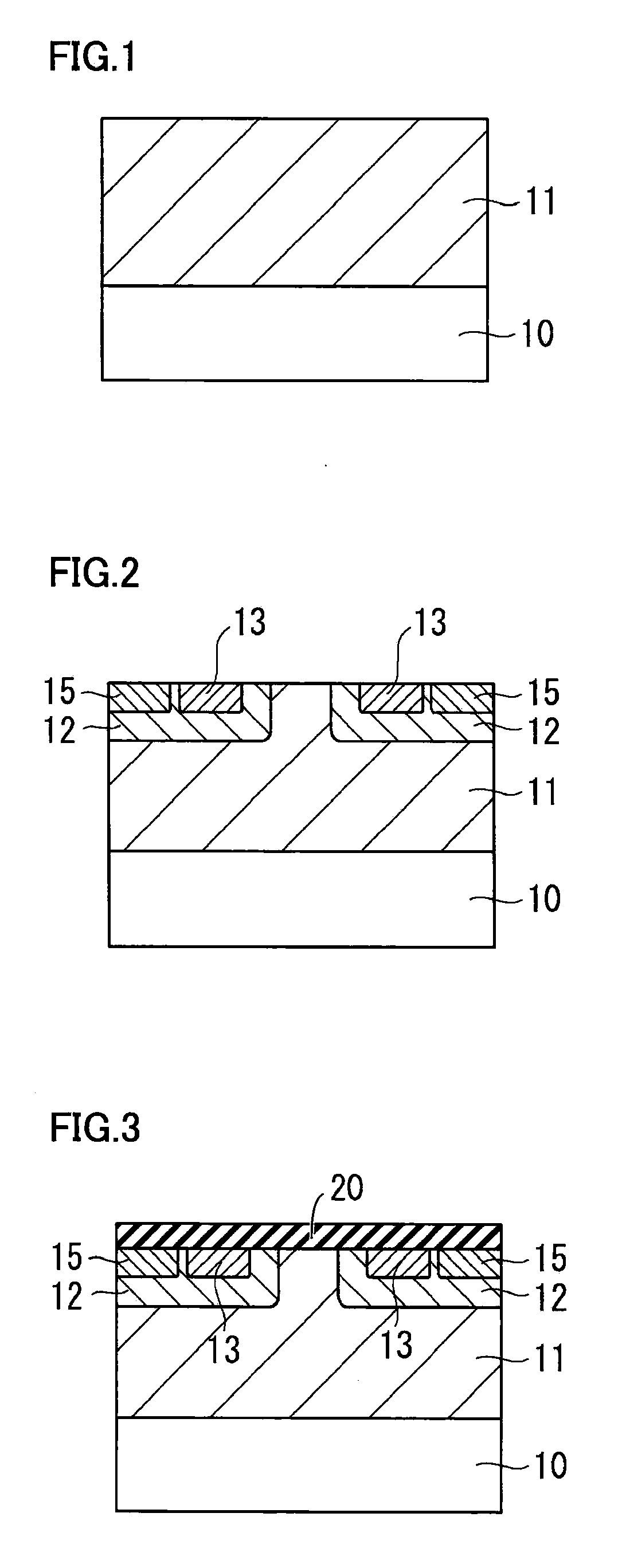

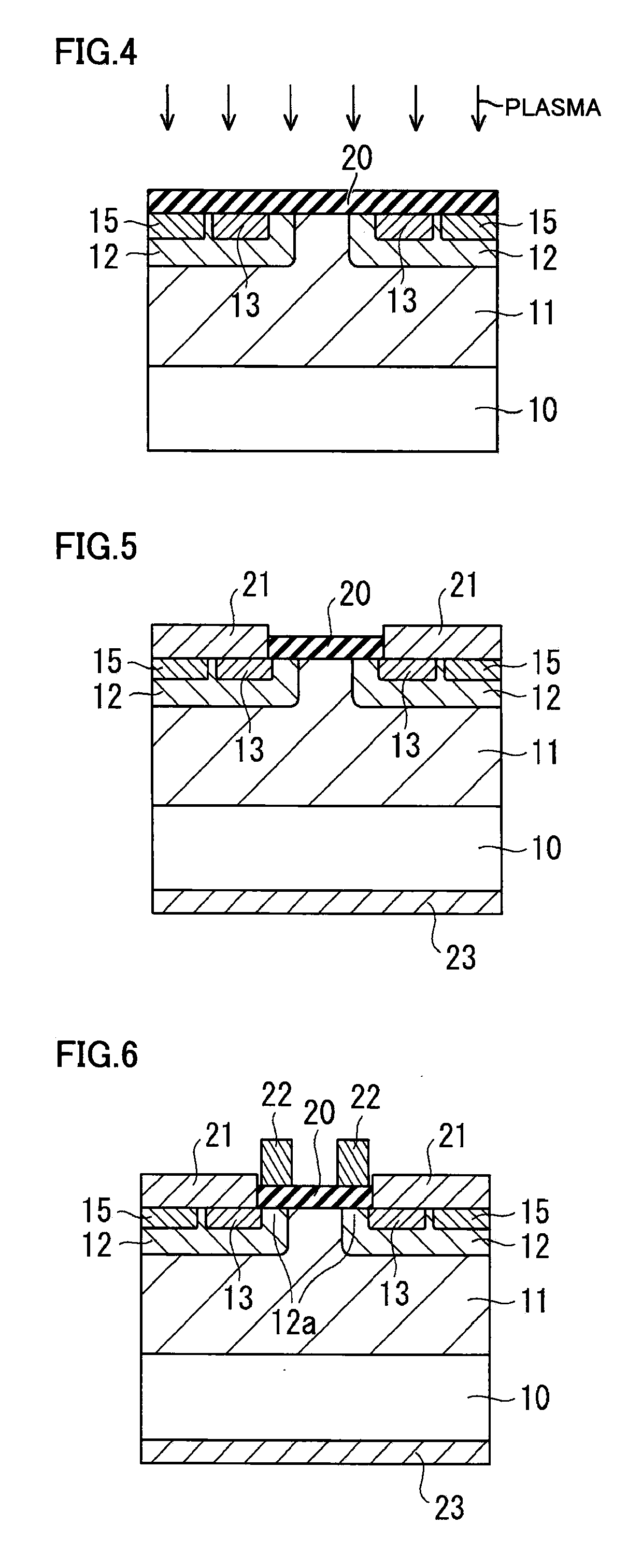

Method of manufacturing silicon carbide semiconductor device

InactiveUS20100221917A1Reduce interface state densityElectric discharge tubesSemiconductor/solid-state device manufacturingNitrogenSilicon oxide

A method of manufacturing a silicon carbide semiconductor device having low interface state density in an interface region between a gate insulating film and a silicon carbide layer is provided. An epitaxially grown layer is grown on a 4H-SiC substrate, and thereafter ion implantation is performed to form a p well region, a source region and a p+ contact region that are ion implantation layers. Thereafter, using thermal oxidation or CVD, the gate insulating film formed by a silicon oxide film is formed on the p well region, the source region and the p+ contact region. Then, plasma is generated using a gas containing N2O, which is the gas containing at least any one of oxygen and nitrogen, so as to expose the gate insulating film to plasma.

Owner:SUMITOMO ELECTRIC IND LTD

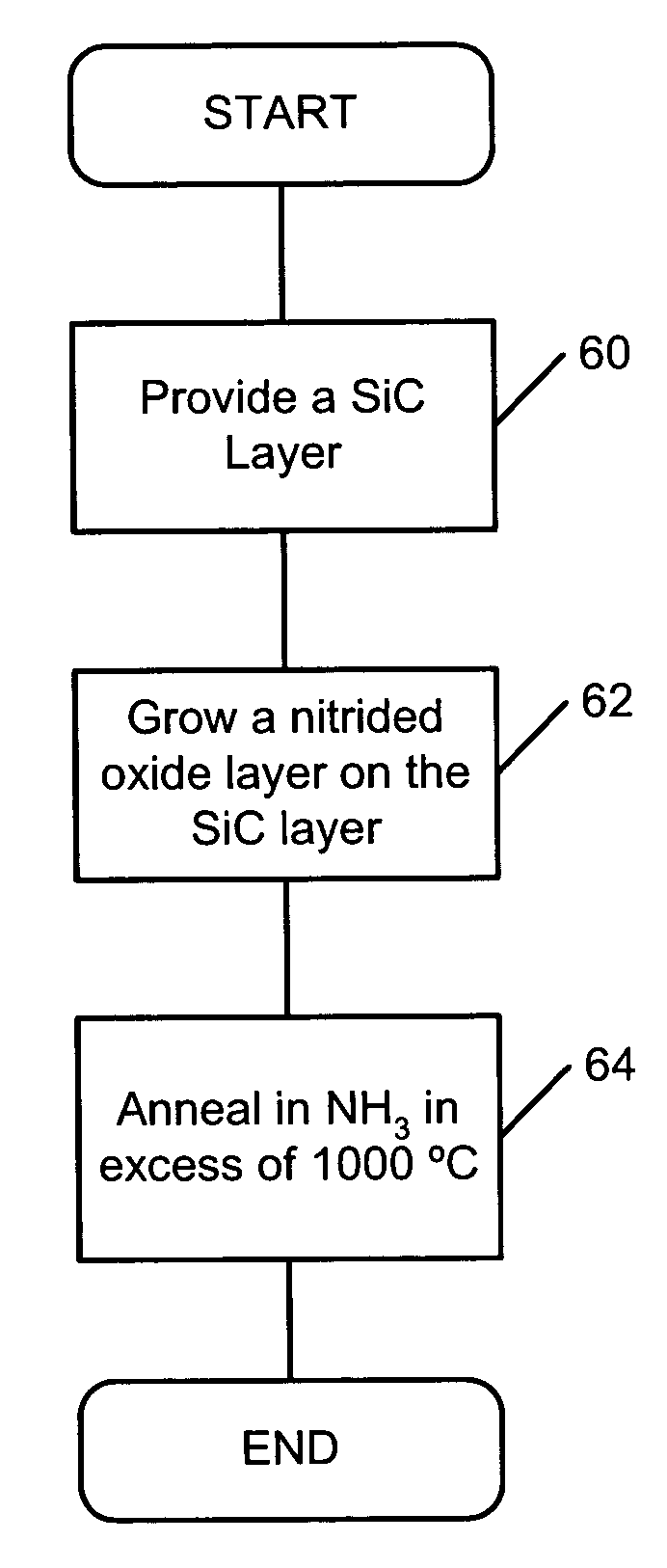

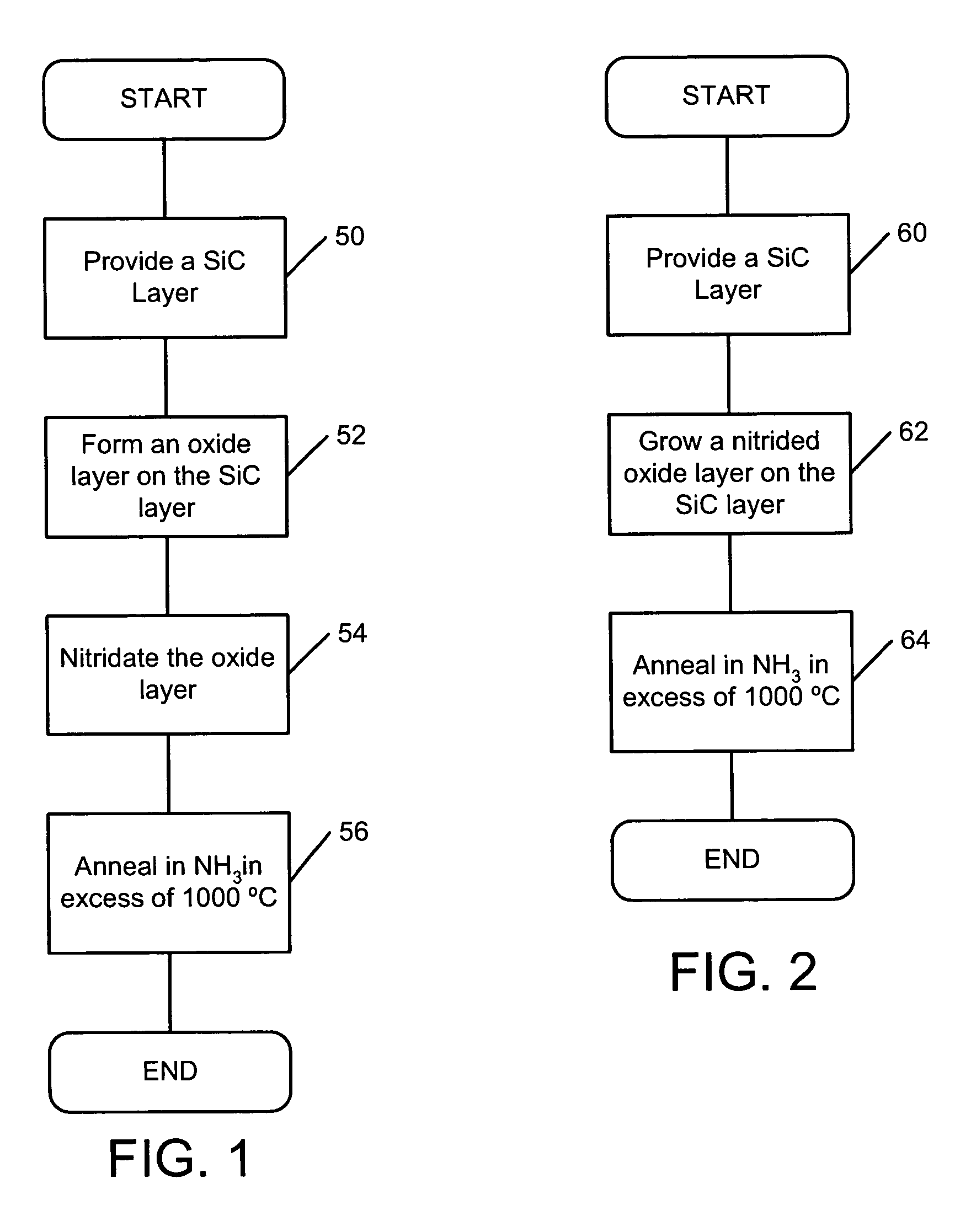

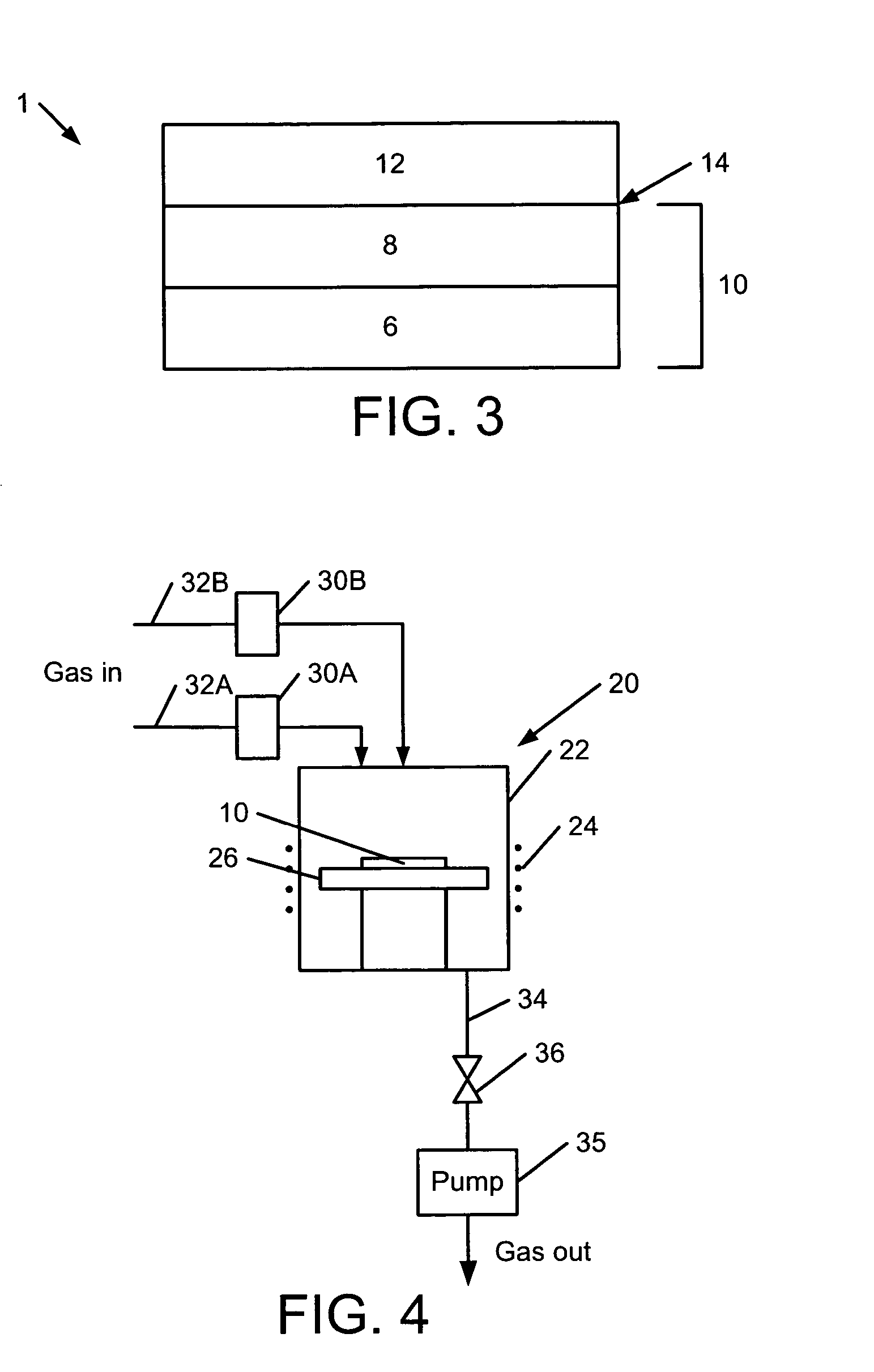

Nitrogen passivation of interface states in SiO2/SiC structures

InactiveUS7022378B2Reduce interface state densityReducing breakdown field strengthSemiconductor/solid-state device manufacturingPretreated surfacesNitrogenOxygen

A nitrided oxide layer on a silicon carbide layer is processed by annealing the nitrided oxide layer in a substantially oxygen-free nitrogen containing ambient. The anneal may be carried out at a temperature of greater than about 900° C., for example, a temperature of about 1100° C., a temperature of about 1200° C. or a temperature of about 1300° C. Annealing the nitrided oxide layer may be carried out at a pressure of less than about 1 atmosphere, for example, at a pressure of from about 0.01 to about 1 atm or, in particular, at a pressure of about 0.2 atm. The nitrided oxide layer may be an oxide layer that is grown in a N2O and / or NO containing ambient, that is annealed in a N2O and / or NO containing ambient or that is grown and annealed in a N2O and / or NO containing ambient.

Owner:CREE INC

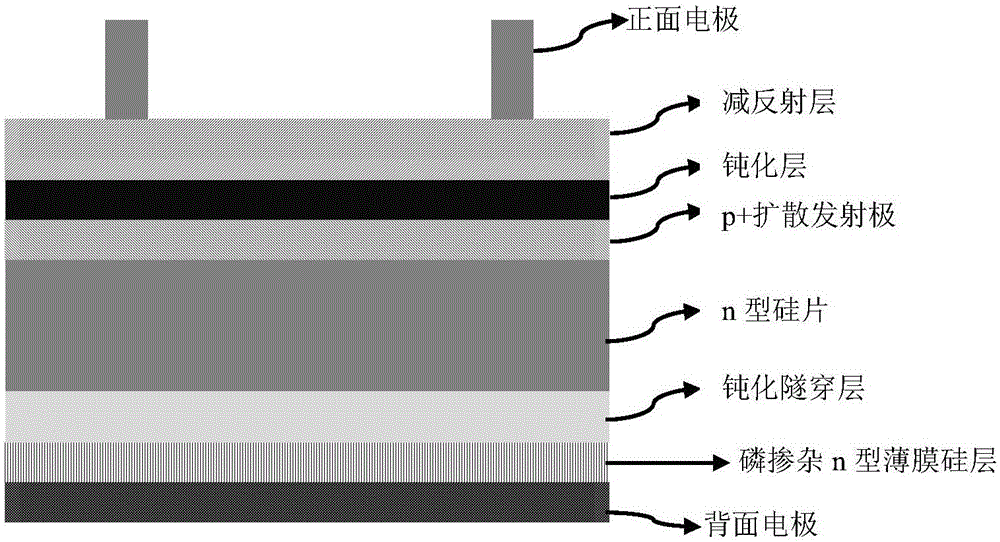

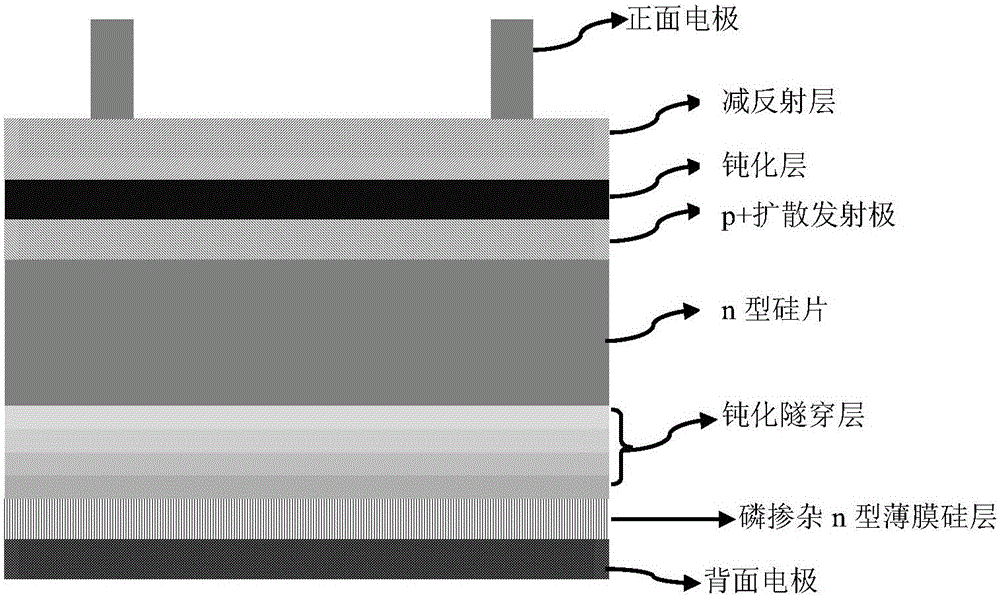

Tunnel silicon oxide passivated contact solar cell and preparation method thereof

ActiveCN105742391AReduce holesReduce generationPhotovoltaic energy generationSemiconductor devicesSilicon oxideSolar cell

The invention provides a solar cell. The solar cell comprises a silicon wafer, a passivated tunnel layer and a doping thin film silicon layer, wherein passivated tunnel layer is arranged between the silicon wafer and the doping thin film silicon layer, the passivated tunnel layer is one of a silicon oxide / silicon oxynitride gradient lamination layer, a silicon oxynitride / silicon nitride gradient lamination layer and a silicon oxide / silicon oxynitride / silicon nitride gradient lamination layer, the silicon oxynitride is nitrogen doping silicon oxide or oxygen doping silicon nitride, and the nitrogen concentration of the silicon oxide / silicon oxynitride gradient lamination layer, the silicon oxynitride / silicon nitride gradient lamination layer and the silicon oxide / silicon oxynitride / silicon nitride gradient lamination layer is gradiently reduced from a part far away from a silicon wafer side to the silicon wafer side. Since the tunnel barriers of silicon nitride and silicon oxynitride are relatively low, the thickness of the passivated tunnel layer can be appropriately widened on the premise of ensuring the tunnel efficiency, thus, the holes of the passivated tunnel layer are favorably reduced, the generation and combination rate of current leakage are reduced, the process window is expanded, and the process stability is improved.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI

III-nitride device passivation and method

ActiveUS7649215B2Little and no damageHigh quality interfaceSemiconductor/solid-state device detailsSolid-state devicesActive layerSchottky diode

Owner:INFINEON TECH AMERICAS CORP

Enhanced high electronic mobility transistor and manufacturing method thereof

ActiveCN105655395AImprove gate characteristicsImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesPower performanceState density

Owner:GPOWER SEMICON

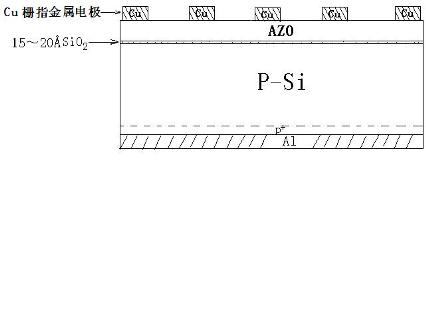

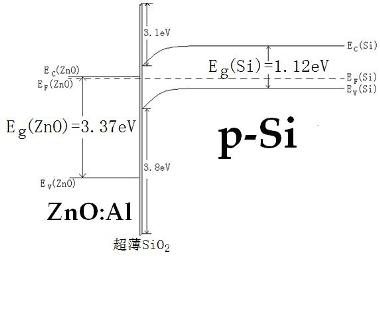

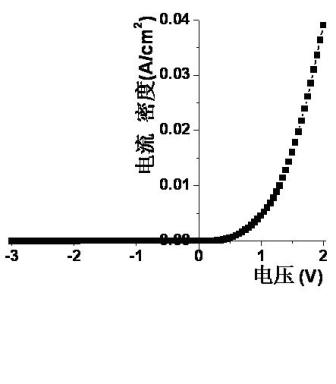

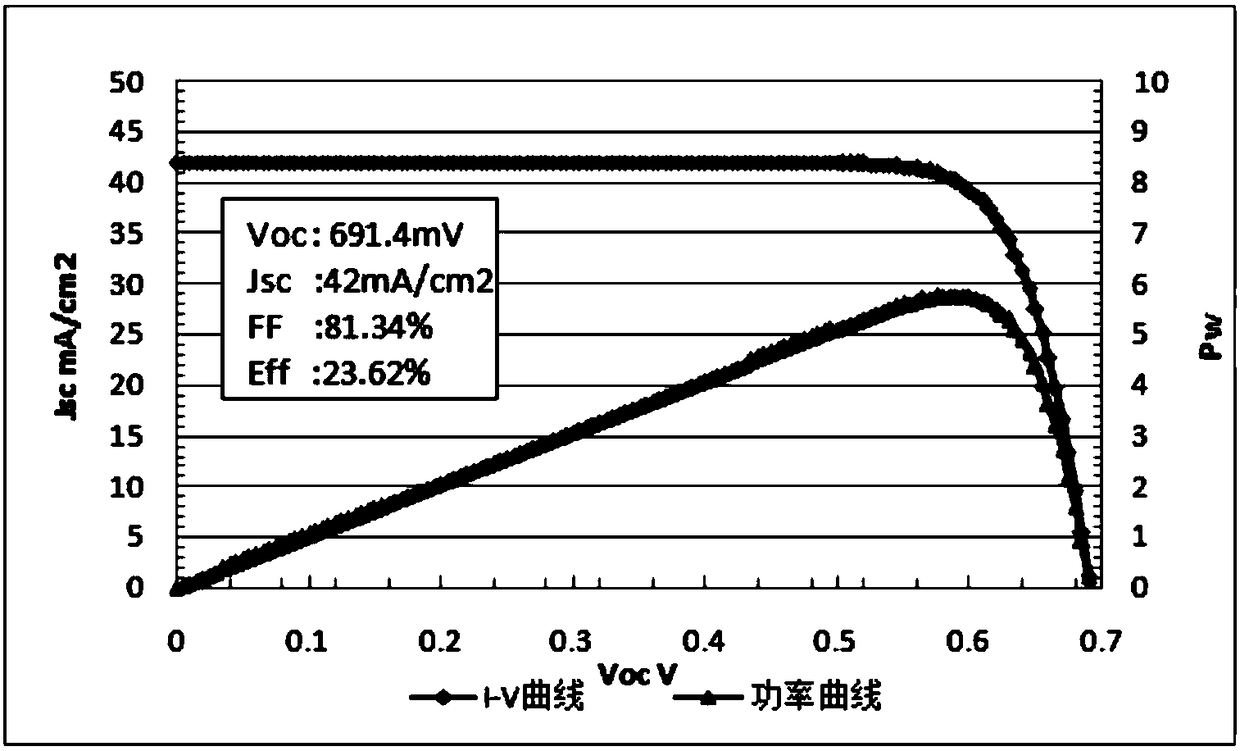

Method for preparing silicon-based SIS heterojunction photoelectric device

InactiveCN102034902AIncrease the open circuit voltageImprove conversion efficiencyFinal product manufactureSemiconductor devicesVisible near infraredPhotovoltaic effect

The invention relates to a method for preparing a direct current (DC) magnetron sputtering AZO / SiO2 / p-SiSIS heterojunction photoelectric device, and belongs to the technical field of methods for preparing silicon-based heterojunction photoelectric devices. By growth of an ultrathin SiO2 layer through low-temperature thermal oxidation, DC magnetron sputtering of an AZO emitter, antireflection and collection of an electrode film, a novel AZO / SiO2 / p-SiSIS ultraviolet-visible-near-infrared broad-spectrum heterojunction photoelectric device is successfully prepared. An I / V curve of the prepared AZO / SiO2 / p-SiSIS heterojunction has good rectification characterisitic and very low reverse dark current, so a good heterojunction diode is formed between AZO and p-Si. Under the condition of AM 1.5 illumination, the open-circuit voltage VOC is 230mV, the photoelectric conversion efficiency eta is 0.025 percent, and the photovoltaic effect is obvious. By combining different characteristics of a wide band gap of the AZO and a relatively narrow band gap of a Si material for mutual complementation, the SIS heterojunction can be developed into a low-cost solar cell, and also can become an excellent-performance ultraviolet-visible-near-infrared enhanced broad-spectrum photoelectric detector.

Owner:SHANGHAI UNIV

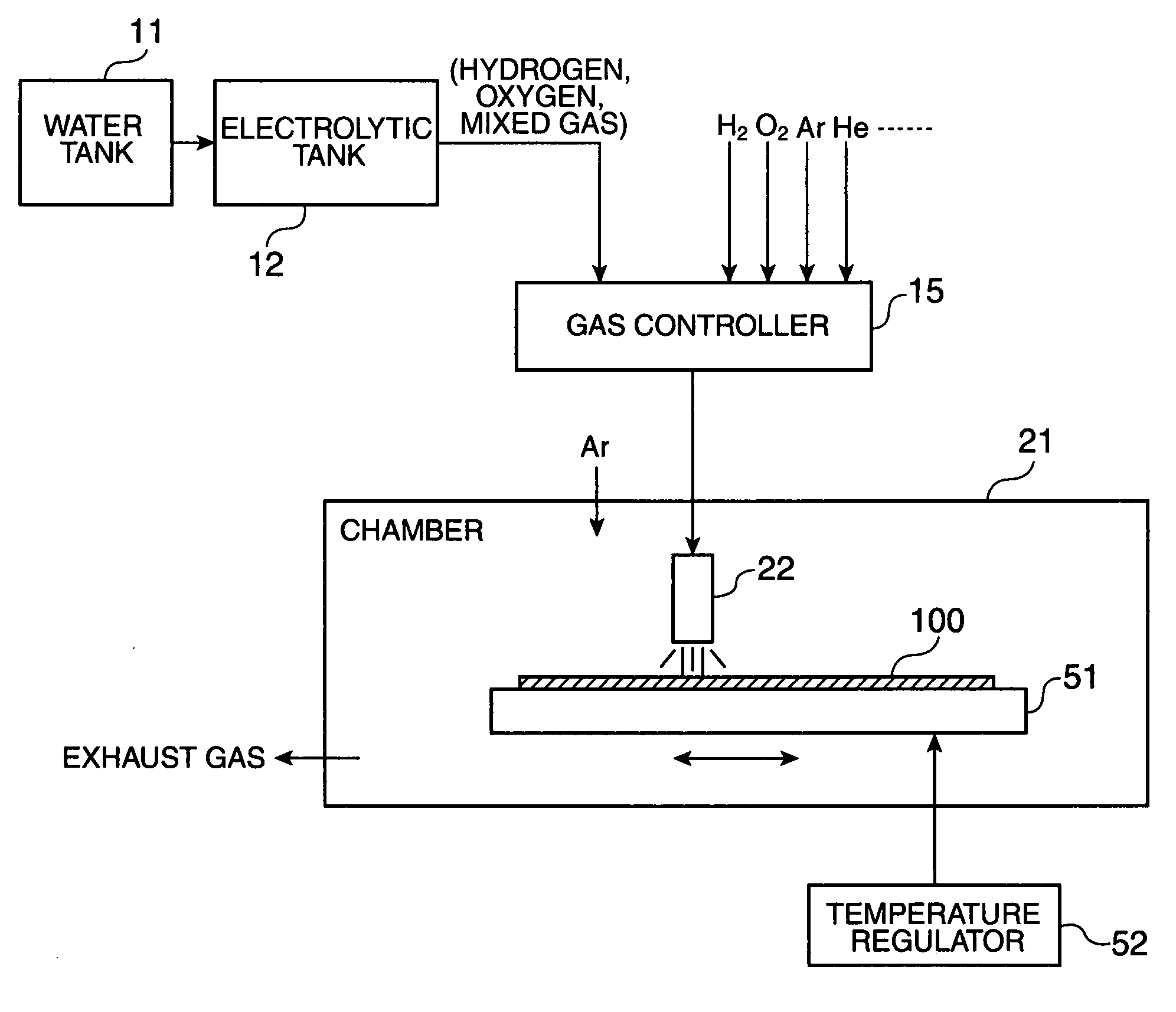

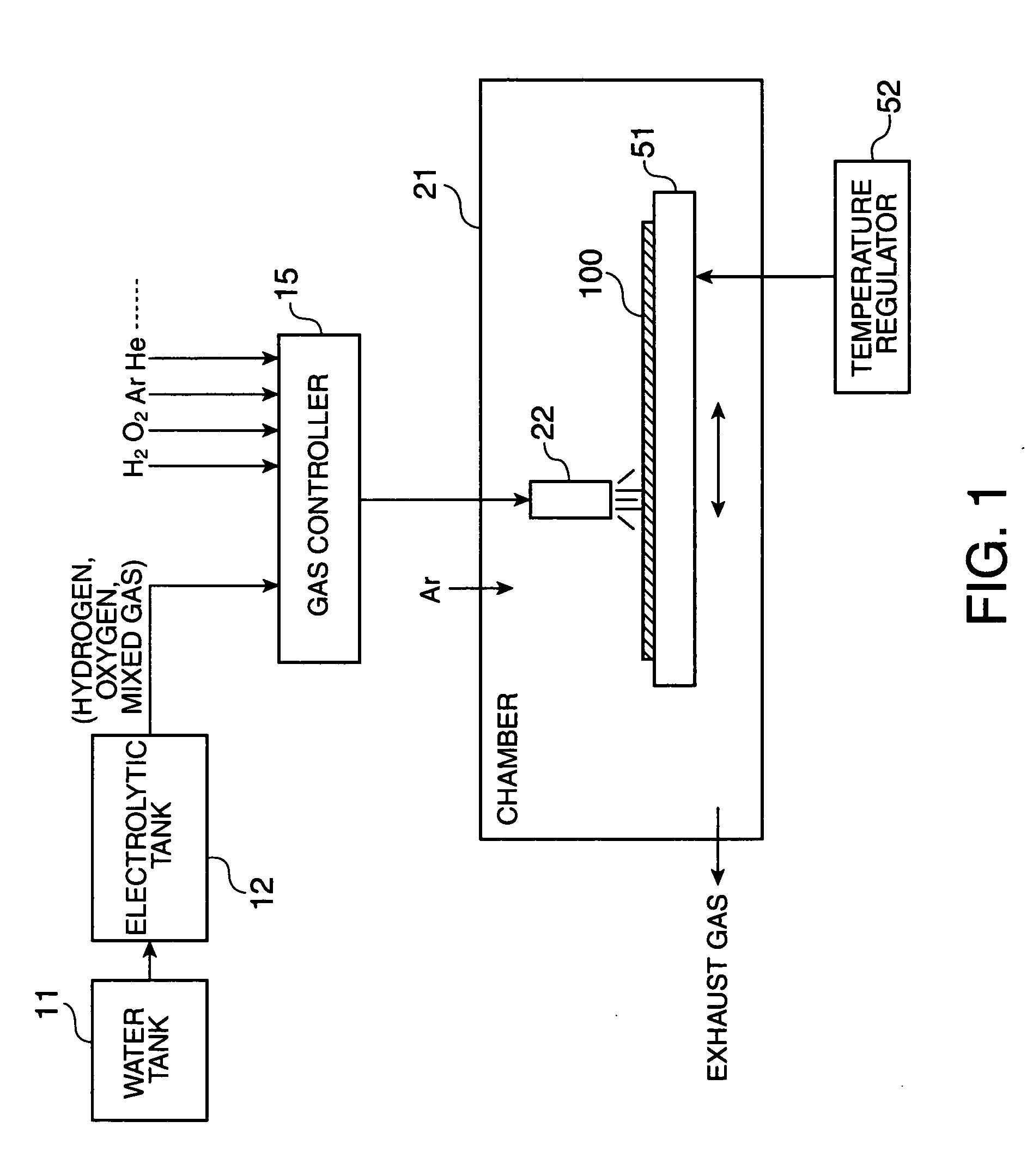

Apparatus and method for manufacturing semiconductor device, and electronic apparatus

ActiveUS20060223328A1Easily and economically availableLow densitySolid-state devicesSemiconductor/solid-state device manufacturingHydrogenDevice material

A method for manufacturing a semiconductor device, comprises providing a semiconductor layer deposited on a substrate with heat treatment by using a flame of a gas burner fueled by a hydrogen-and-oxygen mixed gas as a heat source.

Owner:138 EAST LCD ADVANCEMENTS LTD

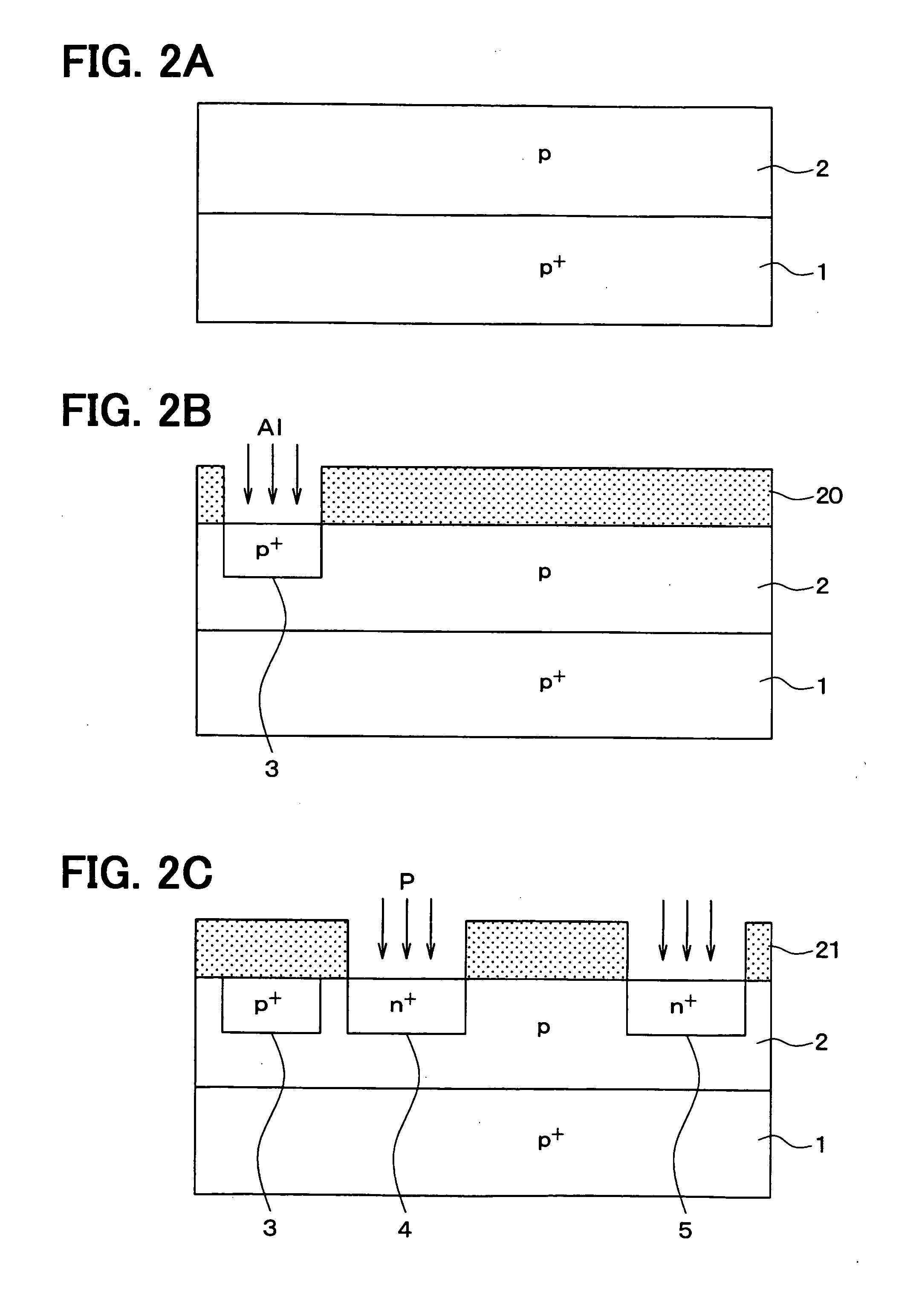

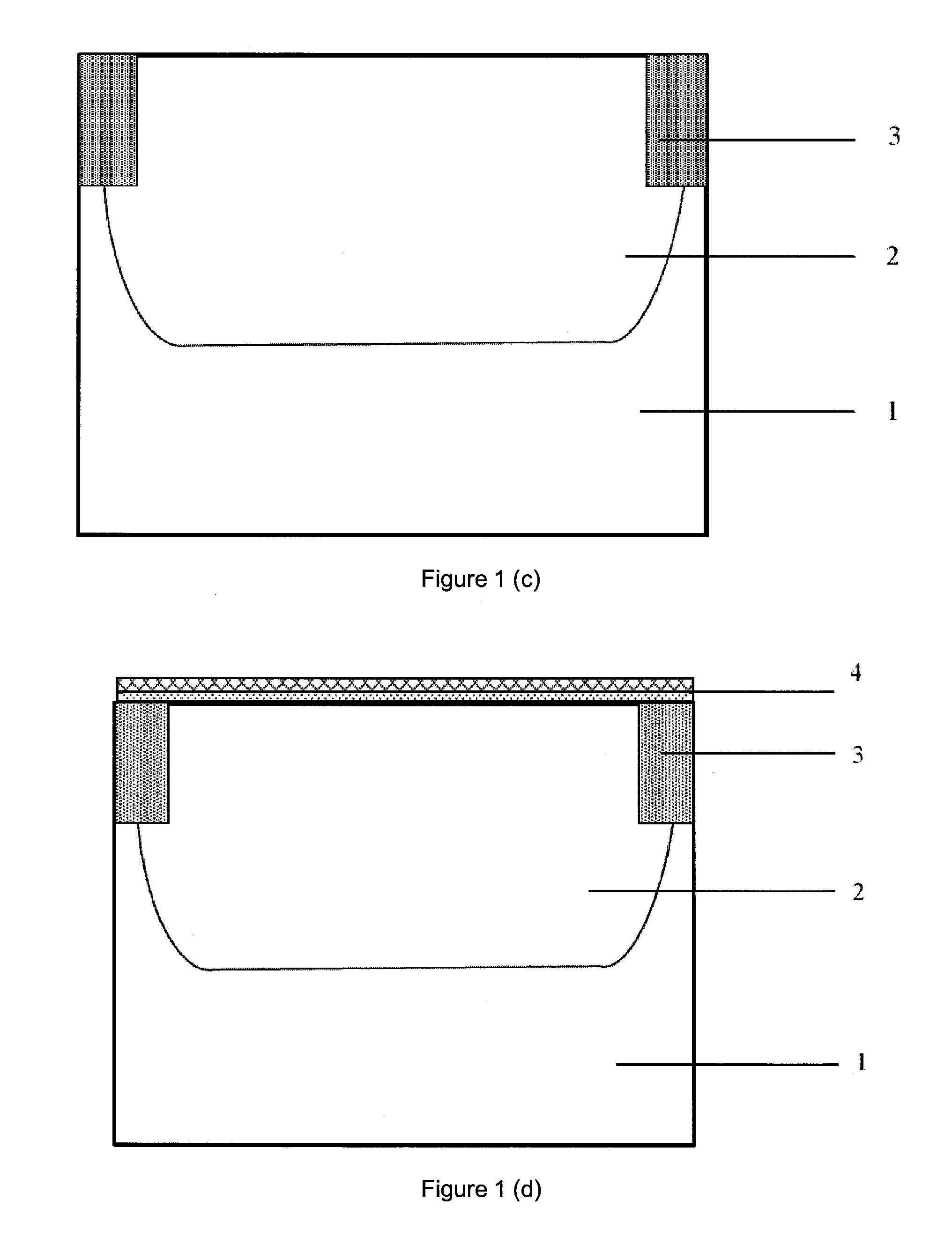

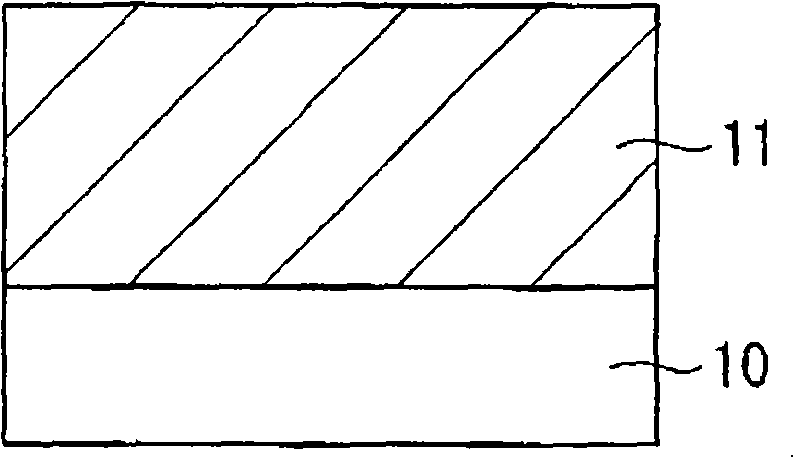

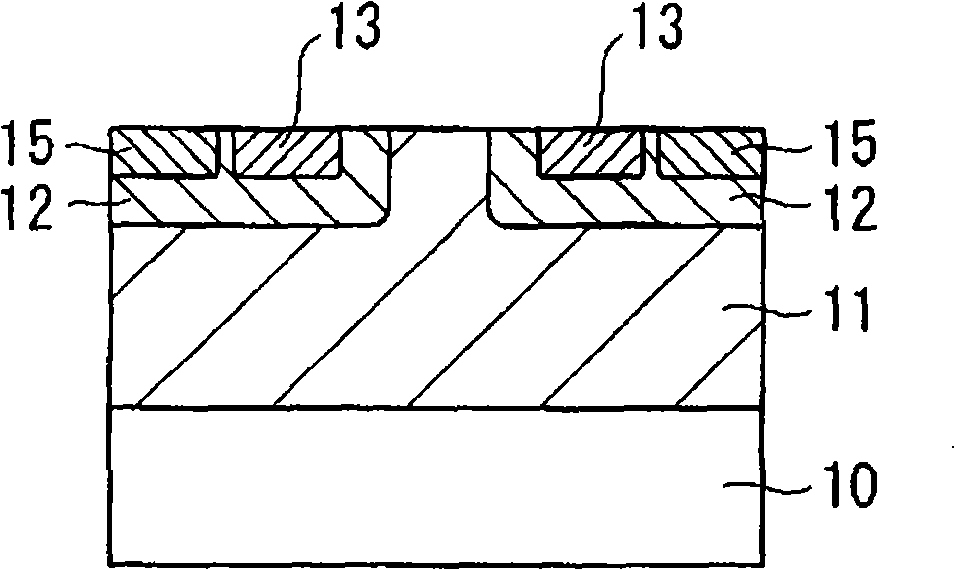

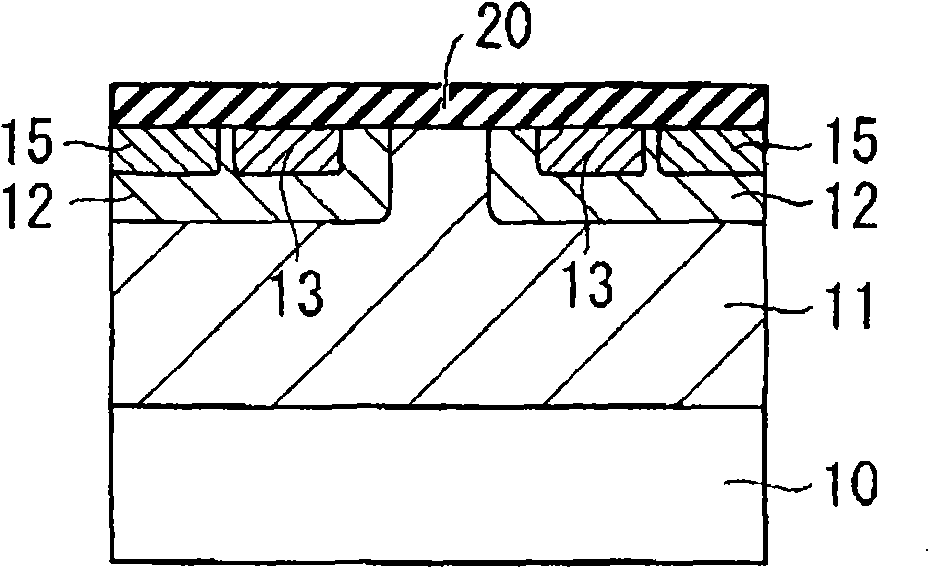

Method for manufacturing silicon carbide semiconductor device

InactiveCN101336473AReduce interface state densityElectric discharge tubesSemiconductor/solid-state device manufacturingNitrogenSilicon oxide

The invention provides a method for manufacturing a silicon carbide semiconductor device having a small interface state density in the interface region between a gate insulating film (20) and a silicon carbide layer (11). Specifically, an epitaxially grown layer (11) is formed on a 4H-SiC substrate (10), and after that a p well region (12), a source region (13) and a p<+> contact region (15) as ion implanted layers are formed by ion implantation. Then, a gate insulating film (20) composed of a silicon oxide film is formed on the p well region (12), the source region (13) and the p<+> contact region (15) by thermal oxidation or CVD. After that, a plasma is generated by using an N2O-containing gas, which is a gas containing at least one of oxygen and nitrogen, and the gate insulating film (20) is exposed to the plasma.

Owner:SUMITOMO ELECTRIC IND LTD

Silicon carbide semiconductor device and method for manufacturing same

ActiveUS20130099251A1Small on-resistanceHigh carrier mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesPlane orientationSemiconductor

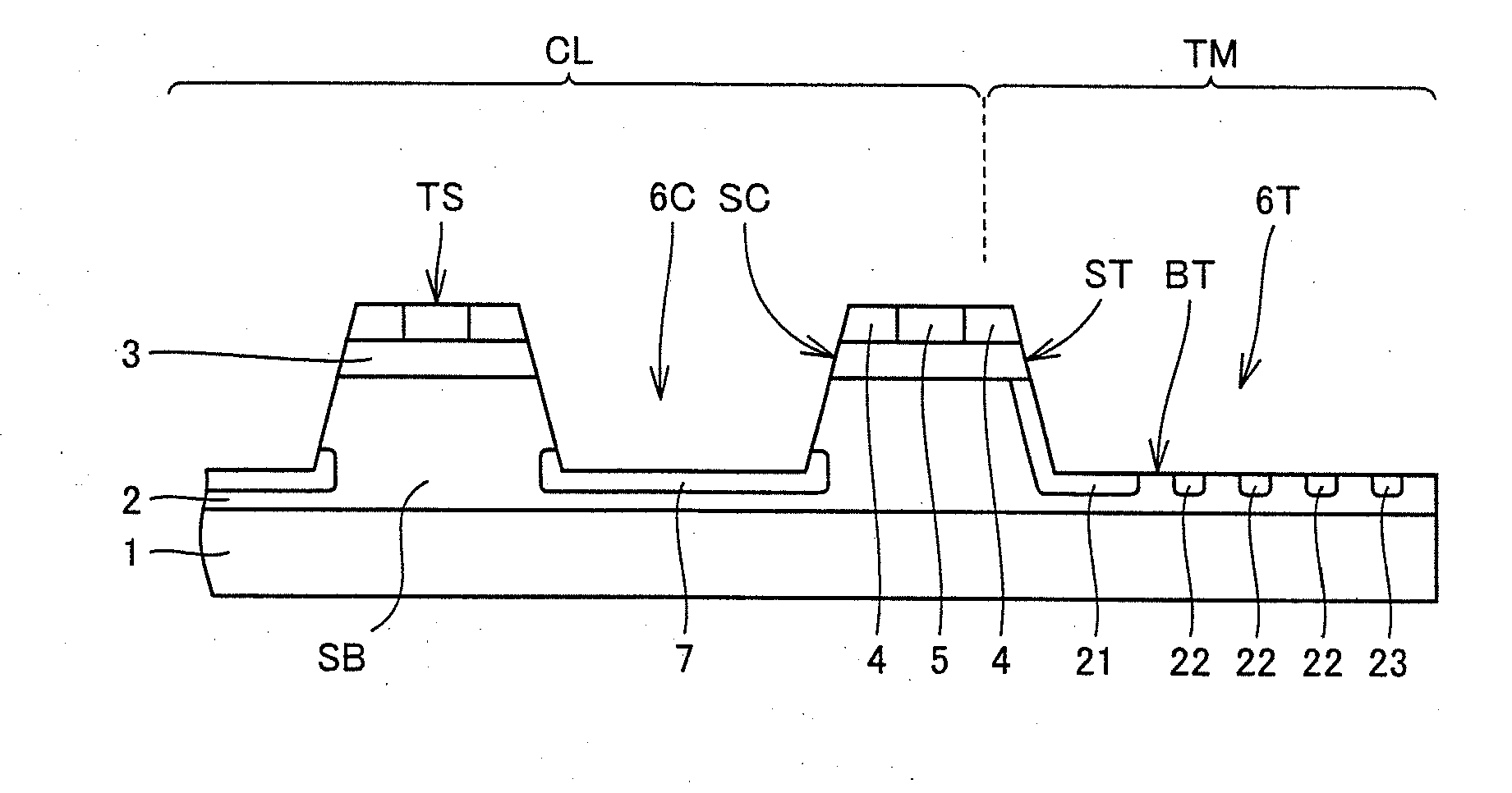

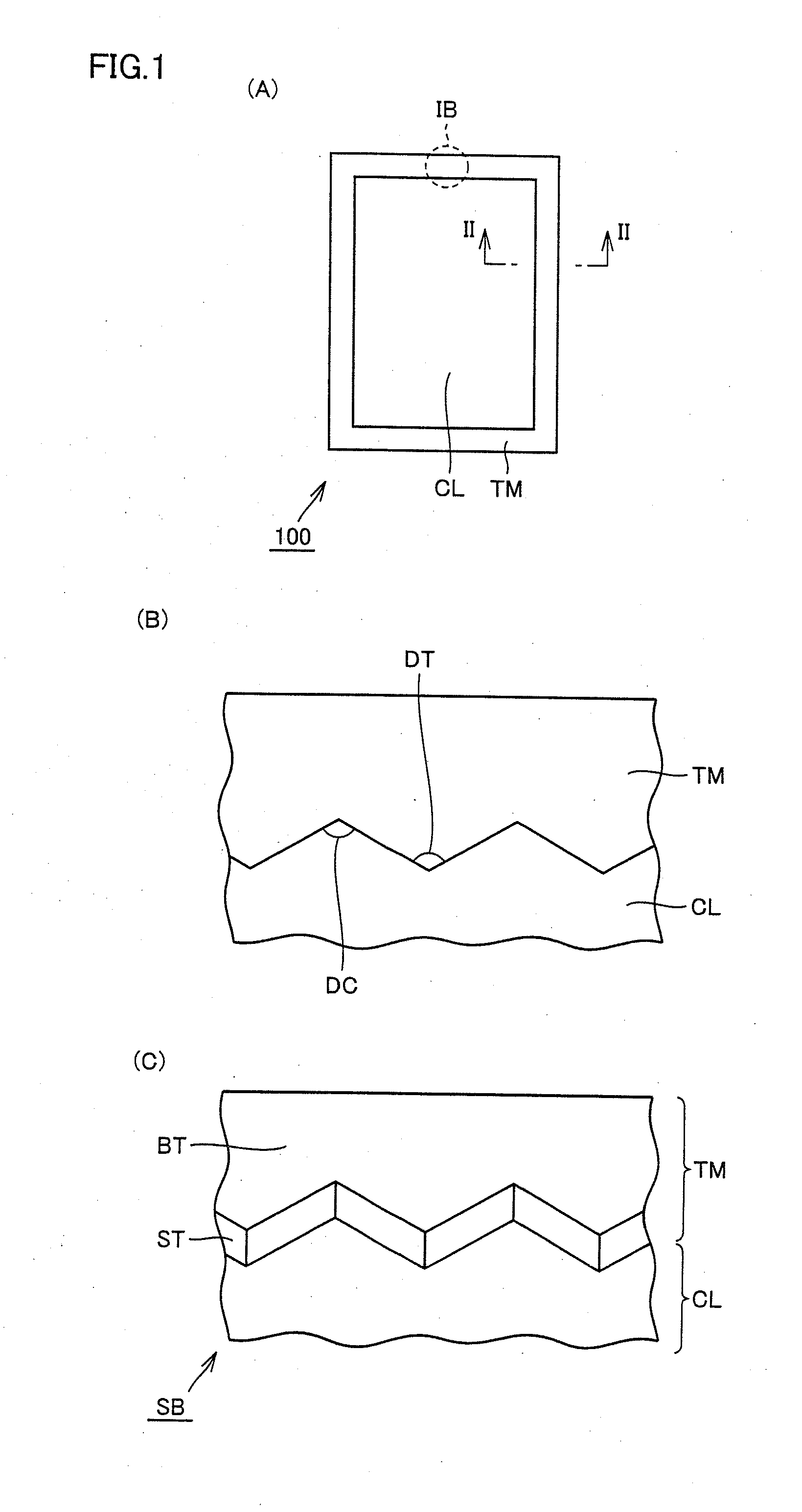

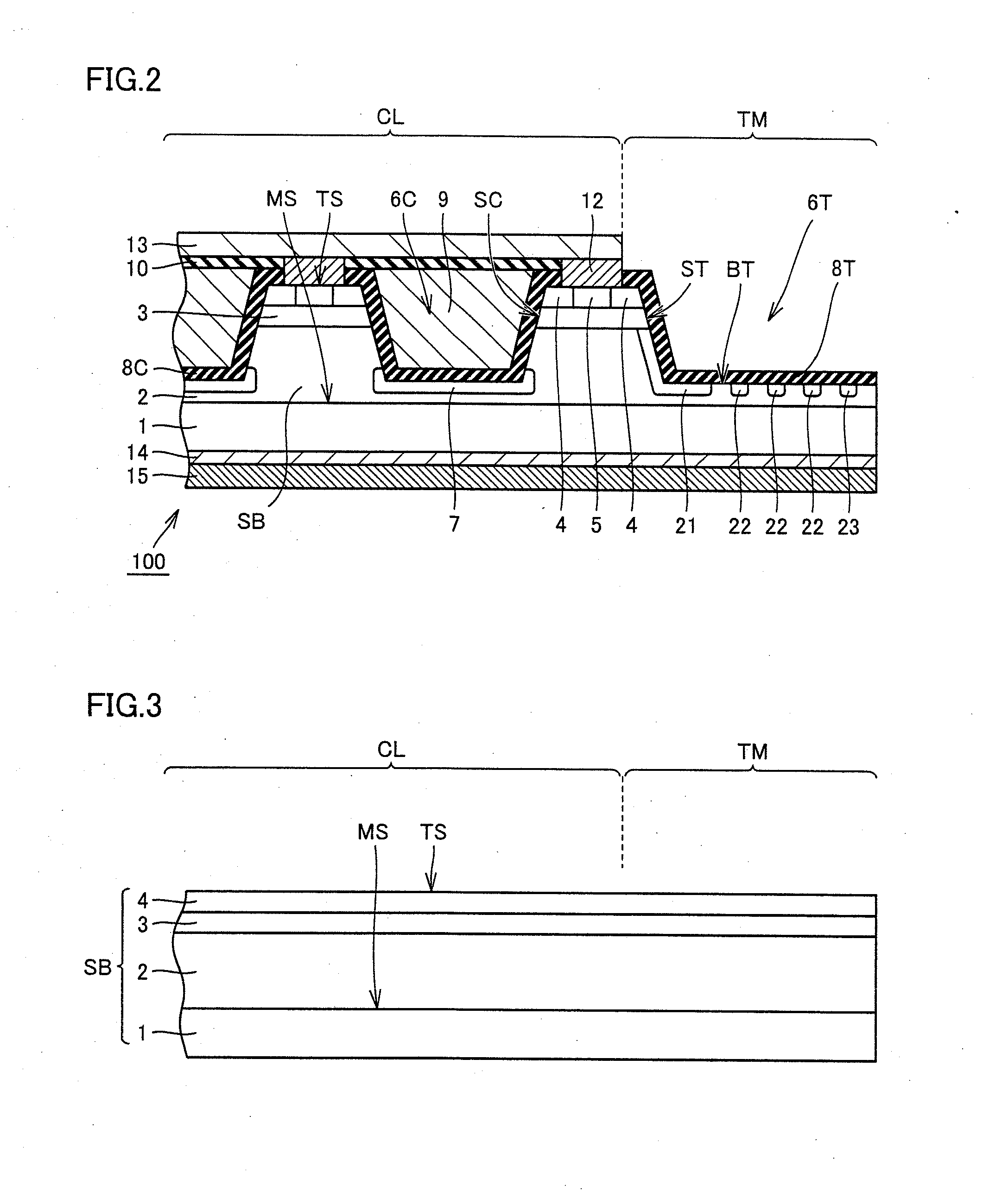

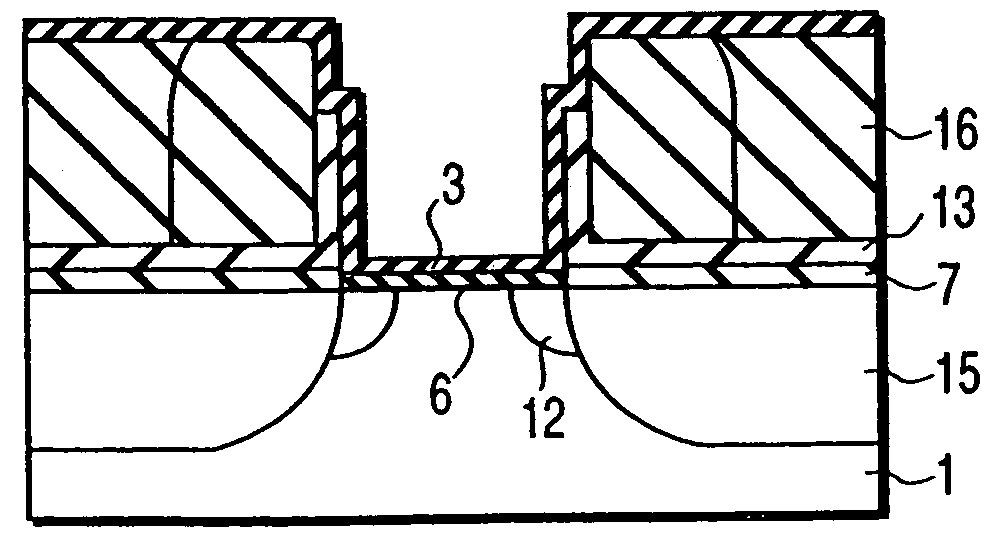

When viewed in a plan view, a termination region (TM) surrounds an element region (CL). A first side of a silicon carbide substrate (SB) is thermally etched to form a side wall (ST) and a bottom surface (BT) in the silicon carbide substrate (SB) at the termination region (TM). The side wall (ST) has a plane orientation of one of {0-33-8} and {0-11-4}. The bottom surface (BT) has a plane orientation of {000-1}. On the side wall (ST) and the bottom surface (BT), an insulating film (8T) is formed. A first electrode (12) is formed on the first side of the silicon carbide substrate (SB) at the element region (CL). A second electrode (14) is formed on a second side of the silicon carbide substrate (SB).

Owner:SUMITOMO ELECTRIC IND LTD

Semiconductor device having a gate insulating film structure including an insulating film containing metal, silicon and oxygen and manufacturing method thereof

InactiveUS7306994B2Improve manufacturing productivityReduce interface state densityTransistorSolid-state devicesOxygenAmorphous metal

Claimed and disclosed is a semiconductor device including a transistor having a gate insulating film structure containing nitrogen or fluorine in a compound, such as metal silicate, containing metal, silicon and oxygen, a gate insulating film structure having a laminated structure of an amorphous metal oxide film and metal silicate film, or a gate insulating film structure having a first gate insulating film including an oxide film of a first metal element and a second gate insulating film including a metal silicate film of a second metal element.

Owner:HEAD TECHNOLOGY GMBH LTD +1

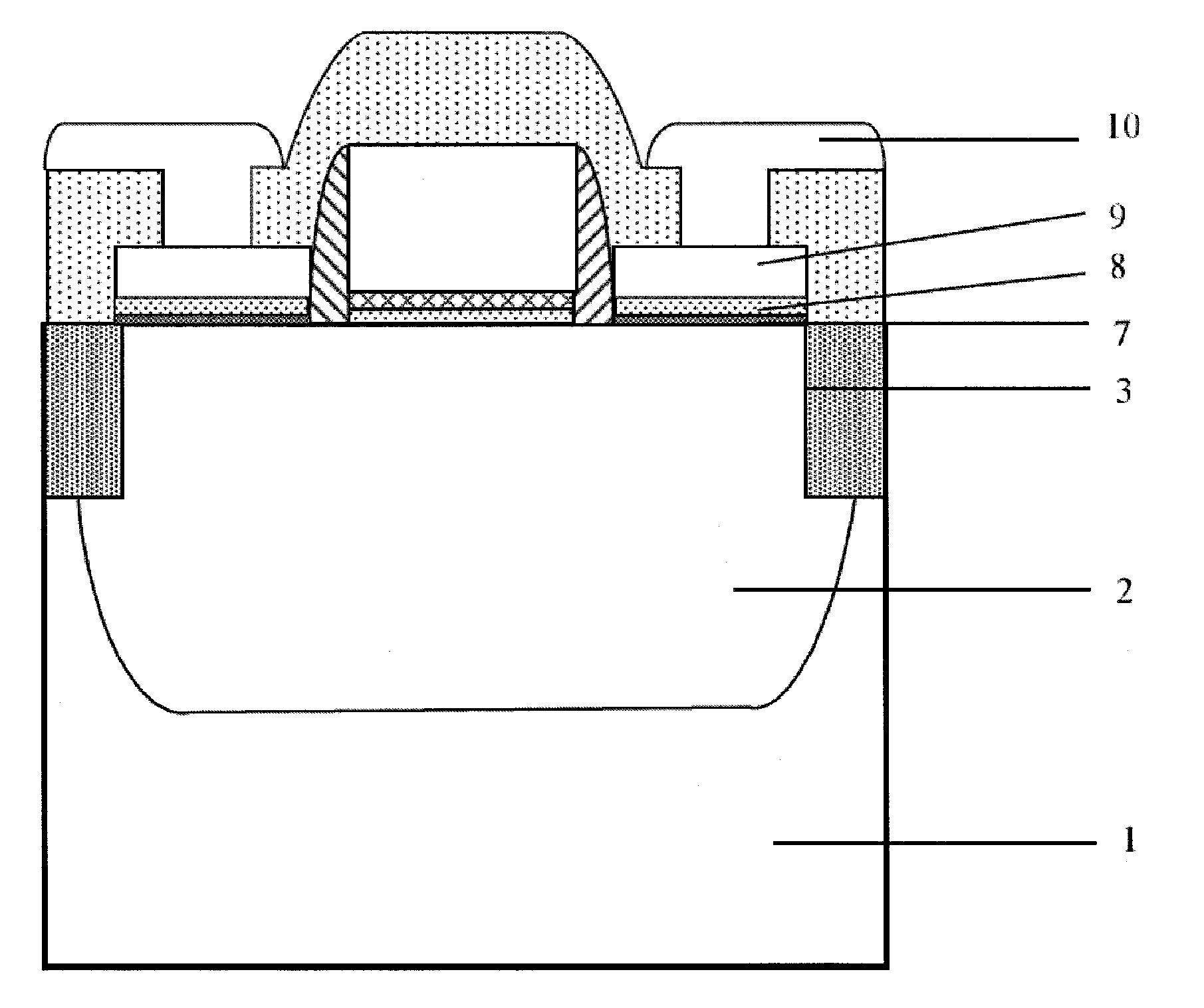

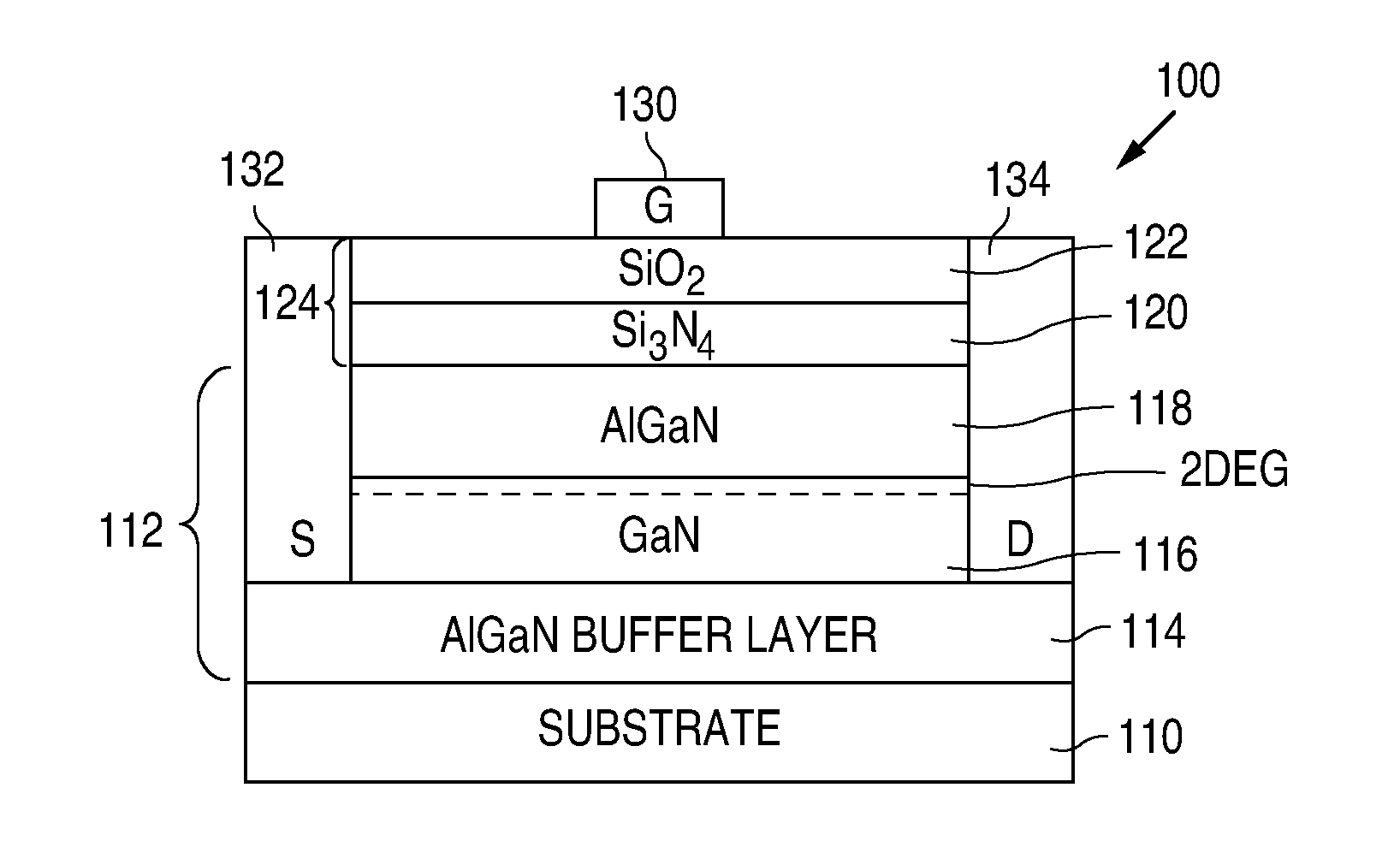

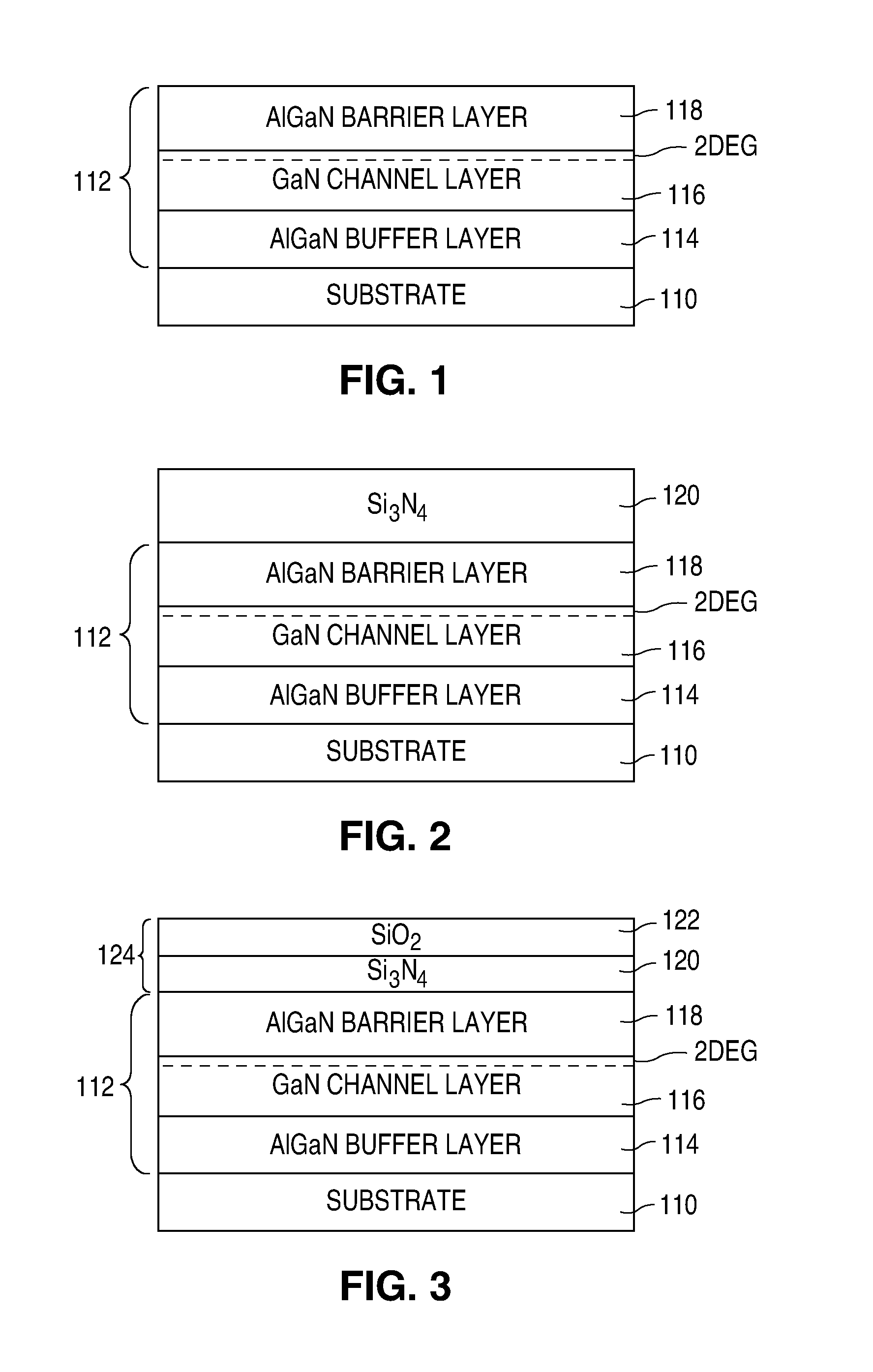

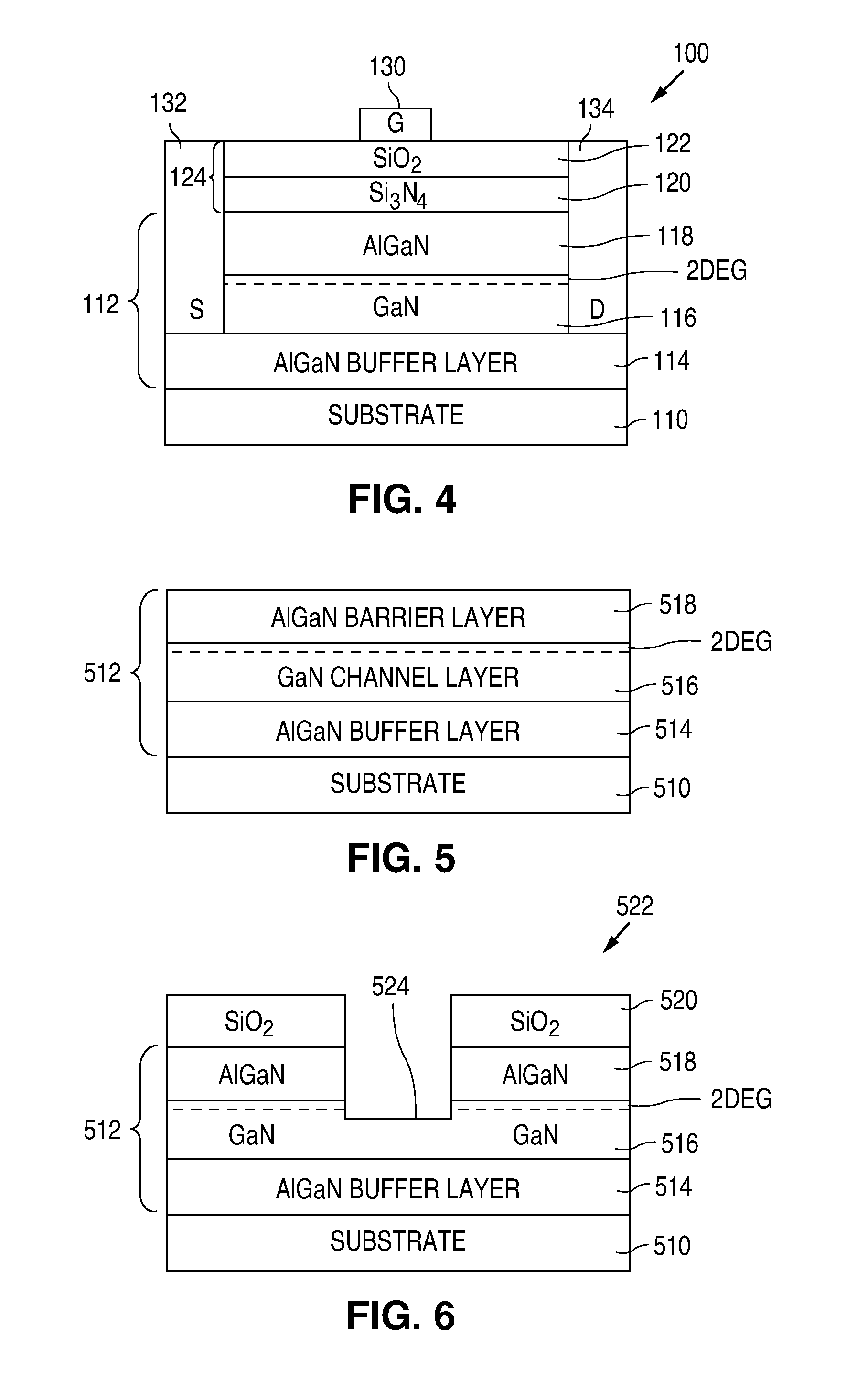

Enhancement-Mode GaN MOSFET with Low Leakage Current and Improved Reliability

ActiveUS20110186855A1Reduce formationReduce in quantitySemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETInsulation layer

An enhancement-mode GaN MOSFET with a low leakage current and an improved reliability is formed by utilizing a SiO2 / Si3N4 gate insulation layer on an AlGaN (or InAlGaN) barrier layer. The Si3N4 portion of the SiO2 / Si3N4 gate insulation layer significantly reduces the formation of interface states at the junction between the gate insulation layer and the barrier layer, while the SiO2 portion of the SiO2 / Si3N4 gate insulation layer significantly reduces the leakage current.

Owner:NAT SEMICON CORP

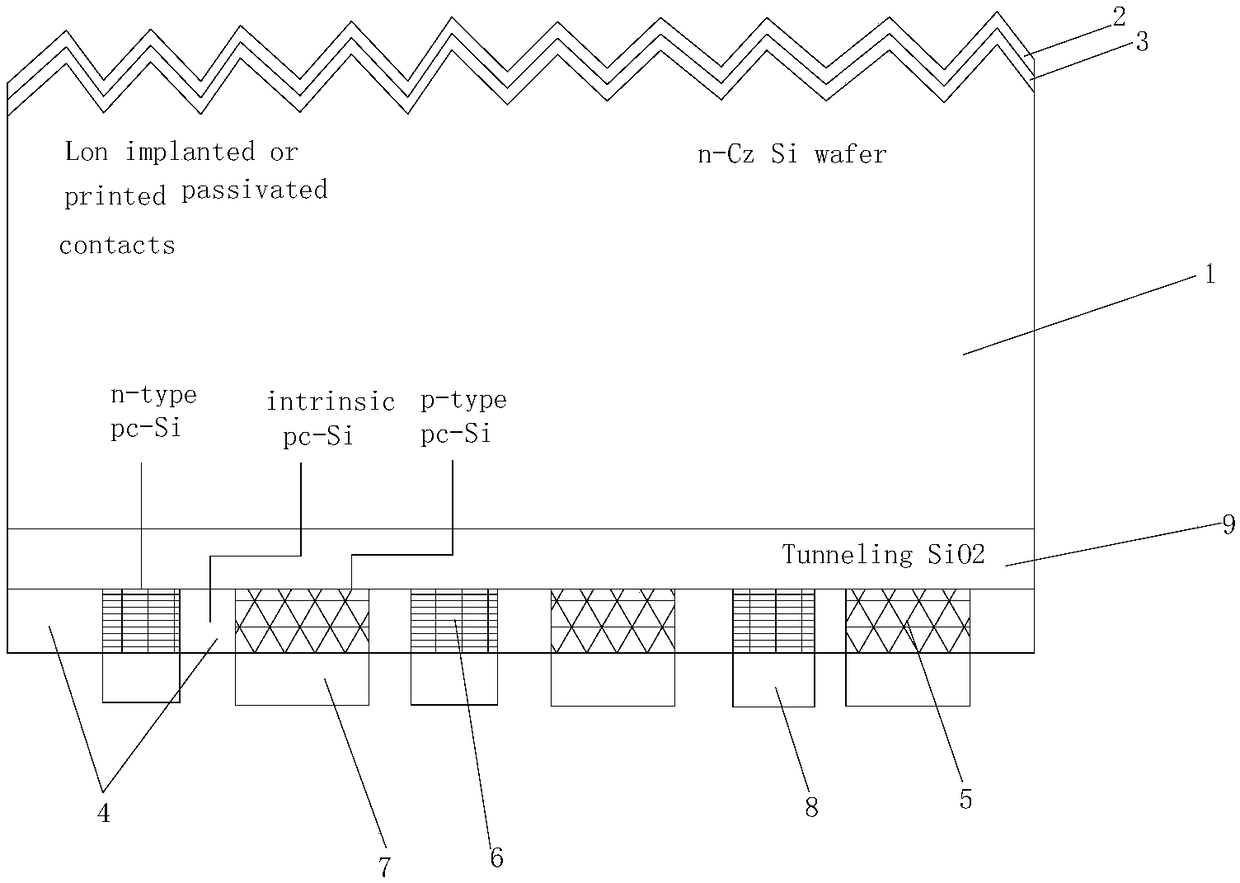

Novel composite structure full back-side heterojunction solar cell and preparation method thereof

ActiveCN108963005AReduce interface state densityIncrease short circuit current densityPhotovoltaic energy generationSemiconductor devicesSilicon nitridePolycrystalline silicon

The invention discloses a novel composite structure full back-side heterojunction solar cell and a preparation method thereof. The solar cell comprises an N-type silicon substrate, a silicon nitride film, an aluminum oxide film, intrinsic polycrystalline silicon, P-type polycrystalline silicon, and N-type polycrystalline silicon. The front surface of the N-type silicon substrate is coated with thealuminum oxide film. The aluminum oxide film is coated with the silicon nitride film. The intrinsic polycrystalline silicon, the P-type polycrystalline silicon, and the N-type polycrystalline siliconare deposited on the back surface of the N-type silicon substrate. The polycrystalline silicon layers are deposited by using horizontally placed silicon wafer LPCVD or horizontally placed silicon wafer PECVD, a homojunction layer can reduce an interface defect state and reduce interface recombination. A laser doping technology is used to realize the P-type polycrystalline silicon layer doping, ensure the service lives of minority carriers of the silicon substrate to the utmost extent and reduce the recombination current density of the contact of metal and silicon. In addition, the cell piecesof the cell with IBC structure fully utilize a solar spectrum to increase the short-circuit current density of the cell to the utmost extent.

Owner:拉普拉斯新能源科技股份有限公司

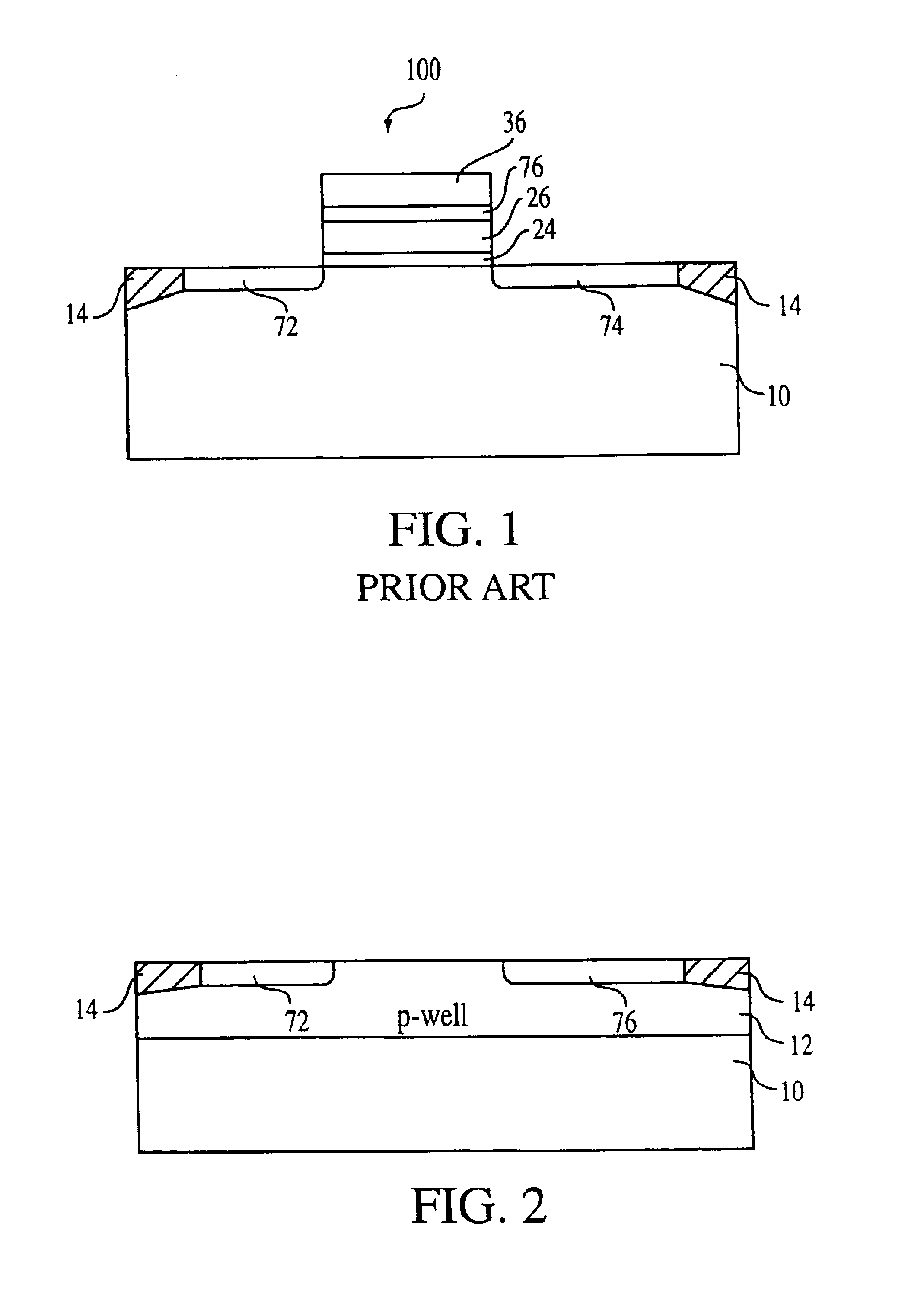

High permittivity silicate gate dielectric

InactiveUS7115461B2High densityHigh dielectric constantSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricHafnium

A field effect semiconductor device comprising a high permittivity silicate gate dielectric and a method of forming the same are disclosed herein. The device comprises a silicon substrate 20 having a semiconducting channel region 24 formed therein. A metal silicate gate dielectric layer 36 is formed over this substrate, followed by a conductive gate 38. Silicate layer 36 may be, e.g., hafnium silicate, such that the dielectric constant of the gate dielectric is significantly higher than the dielectric constant of silicon dioxide. However, the silicate gate dielectric may also be designed to have the advantages of silicon dioxide, e.g. high breakdown, low interface state density, and high stability. The present invention includes methods for depositing both amorphous and polycrystalline silicate layers, as well as graded composition silicate layers.

Owner:TEXAS INSTR INC