Enhanced high electronic mobility transistor and manufacturing method thereof

A high electron mobility, transistor technology, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve the problem of high interface state density in the dielectric layer, improve breakdown voltage and power performance, and reduce material damage and defects , Reduce the effect of current collapse effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

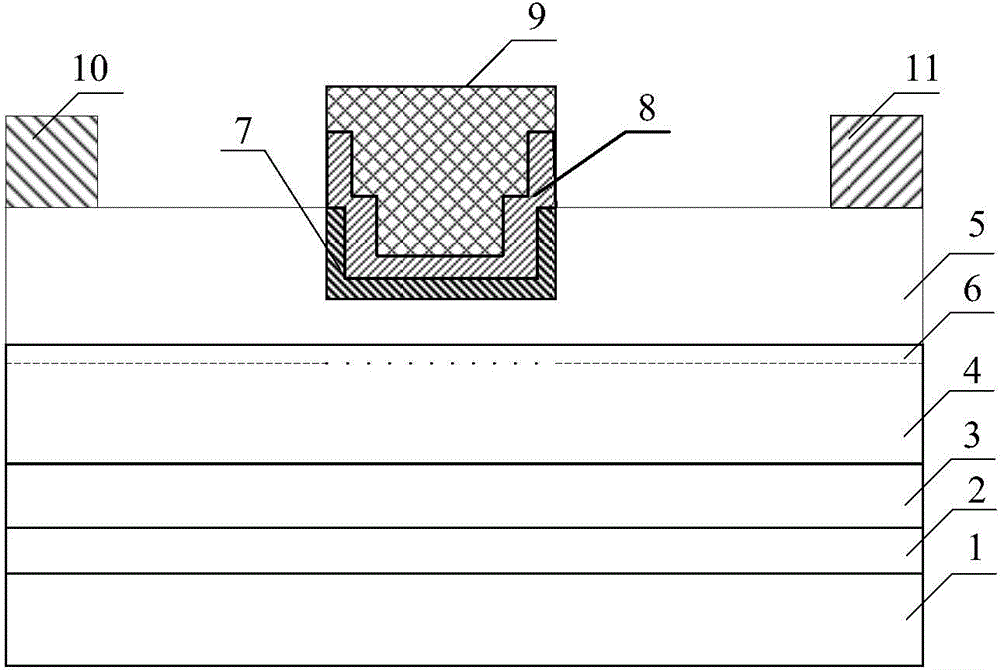

[0054] figure 1 It is a structural diagram of an enhancement-mode high electron mobility transistor provided in Embodiment 1 of the present invention. Such as figure 1 As shown, the enhanced high electron mobility transistor provided by Embodiment 1 of the present invention includes:

[0055] Substrate 1.

[0056] In this embodiment, the substrate material may be silicon, gallium nitride, silicon carbide or sapphire.

[0057] The nucleation layer 2 is located on the substrate 1 .

[0058] In this embodiment, the material of the nucleation layer may be aluminum nitride, gallium nitride or other III-V group compounds.

[0059] The buffer layer 3 is located on the nucleation layer 2 .

[0060] In this embodiment, the material of the buffer layer may be AlGaN or other III-V compounds.

[0061] The channel layer 4 is located on the buffer layer 3 .

[0062] In this embodiment, the material of the channel layer may be gallium nitride or other III-V compounds.

[0063] The ba...

Embodiment 2

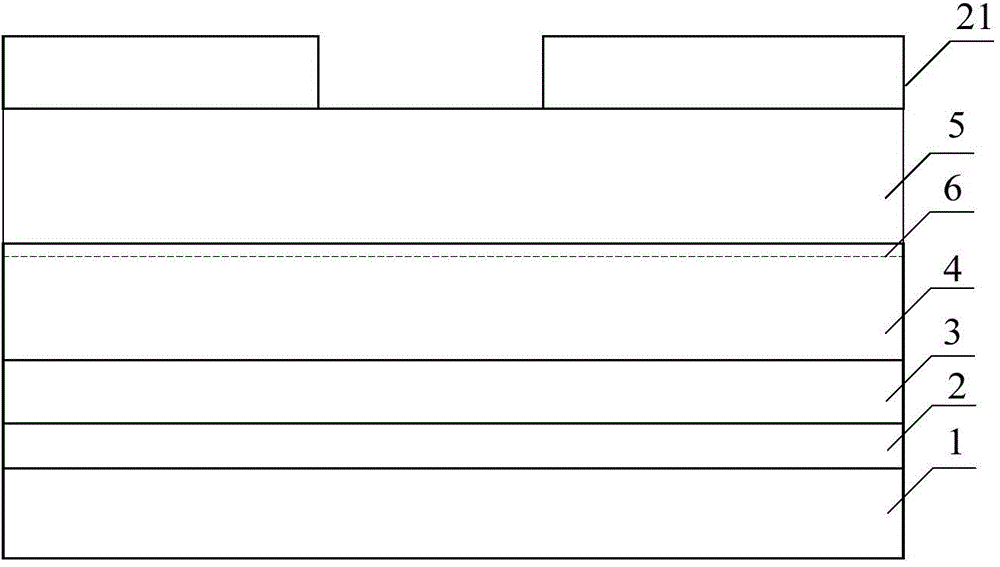

[0100] image 3 It is a structural diagram of the enhanced high electron mobility transistor provided in Embodiment 2 of the present invention. Such as image 3 As shown, the difference from the first embodiment of the present invention is that in the enhanced high electron mobility transistor provided by the second embodiment of the present invention, the secondary grown semiconductor epitaxial layer 7 expands toward the drain 11, and a junction termination structure is introduced, when When the Al composition in the secondary grown semiconductor epitaxial layer 7 is smaller than the Al composition in the barrier layer 5, it will have a certain depletion effect on the two-dimensional electron gas under the junction terminal, thereby reducing the The electric field spike increases the breakdown voltage of the device.

[0101] The manufacturing method of the enhanced high electron mobility transistor provided in the second embodiment of the present invention includes the foll...

Embodiment 3

[0123] Figure 5 It is a structural diagram of the enhanced high electron mobility transistor provided in Embodiment 3 of the present invention. Such as Figure 5 As shown, different from the second embodiment of the present invention, the enhanced high electron mobility transistor provided by the third embodiment of the present invention further includes: an in-situ mask layer 12 located on the barrier layer 5, an in-situ dielectric layer 8 It is located on the secondary grown semiconductor epitaxial layer 7 and the in-situ mask layer 12 .

[0124] In this embodiment, the in-situ mask layer is obtained by in-situ growth on the barrier layer by using the same preparation method without taking the wafer out of the growth chamber after the growth of the barrier layer is completed. This preparation method can obtain an in-situ mask layer with better crystal quality, and effectively reduce the interface state between the mask layer and the potential barrier layer.

[0125] Wher...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More