Patents

Literature

31results about How to "Improved Threshold Voltage Stability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

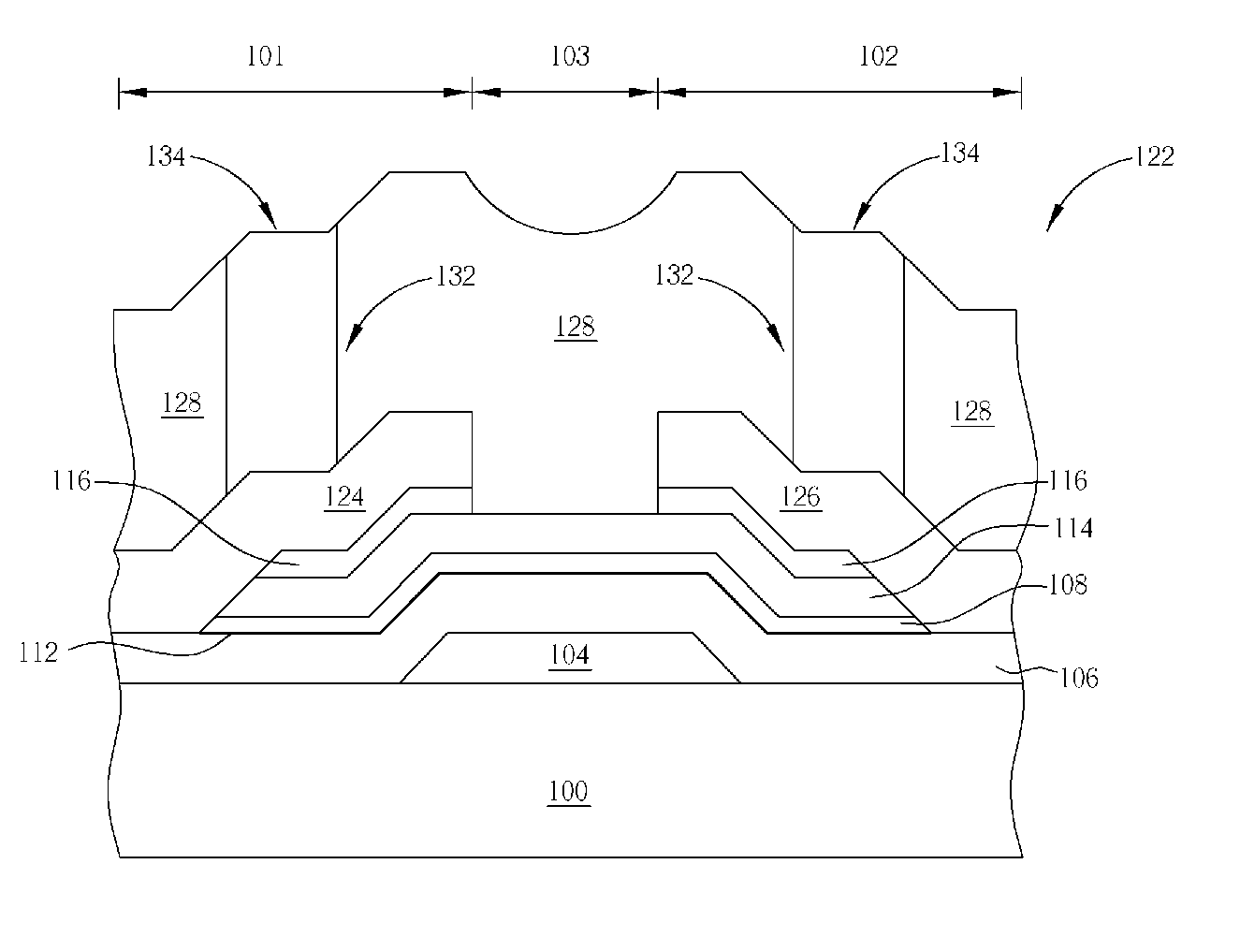

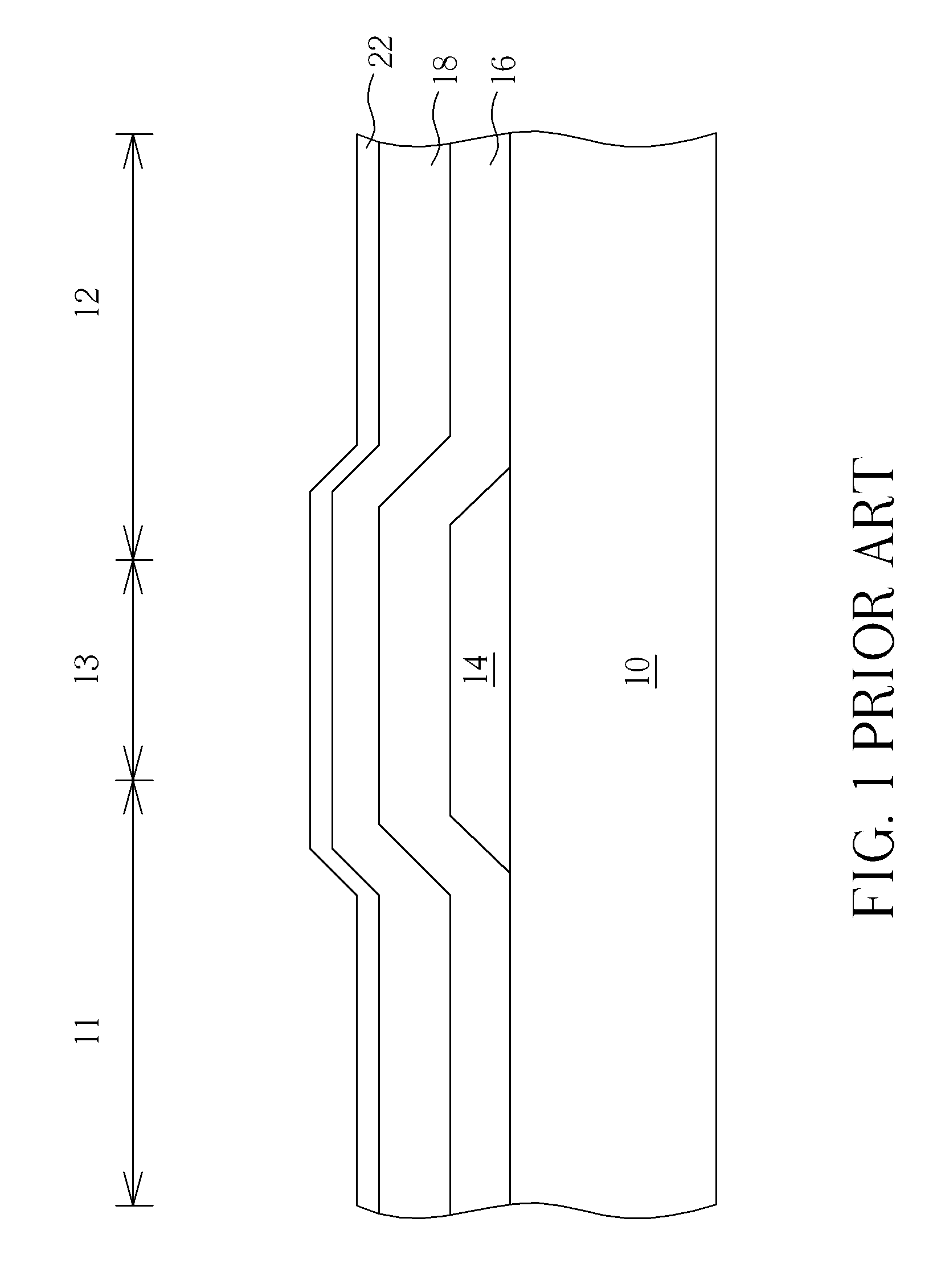

Thin film transistor and method for fabricating same

ActiveUS20060024866A1Excellent characteristicsImprove functionalityTransistorSemiconductor/solid-state device manufacturingInsulation layerHydrogen

A method for forming a thin film transistor on a substrate is disclosed. A gate electrode and a gate insulation layer are disposed on a surface of the substrate. A deposition process is performed by utilizing hydrogen diluted silane to form a silicon-contained thin film on the gate insulation layer first. A hydrogen plasma etching process is thereafter performed. The deposition process and the etching process are repeated for at least one time to form an interface layer. Finally, an amorphous silicon layer, n+ doped Si layers, a source electrode, and a drain electrode are formed on the interface layer.

Owner:AU OPTRONICS CORP

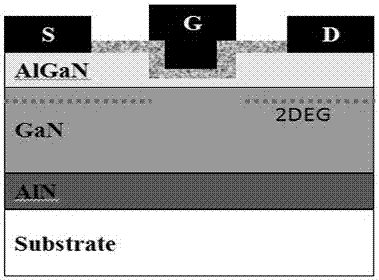

Enhanced high electronic mobility transistor and manufacturing method thereof

ActiveCN105655395AImprove gate characteristicsImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesPower performanceState density

Owner:GPOWER SEMICON

GaN-based field effect transistor with high quality MIS structure and preparation method of GaN-based field effect transistor

InactiveCN105336789AImprove performanceThreshold voltage stability is remarkableSemiconductor/solid-state device manufacturingSemiconductor devicesPartial oxidationVoltage stability

The invention belongs to the semiconductor material and device field and discloses a GaN-based field effect transistor with a high quality MIS structure and a preparation method of the GaN-based field effect transistor, in particular, a GaN MISFET device gate dielectric layer and an improvement method of a dielectric layer and GaN interface. The device includes a substrate, an epitaxial layer grown on the substrate as well as a gate electrode, a source electrode, a drain electrode and an insulating layer; the epitaxial layer includes a stress buffer layer which is formed through primary epitaxial growth, a GaN epitaxial layer as well as a second epitaxial layer and a third epitaxial layer which are grown on selective regions on the GaN epitaxial layer; a GaN / AlGaN heterostructure is formed through secondary epitaxial growth, and groove channels are formed; an AlN thin layer is formed through third epitaxial growth; the AlN thin layer is partially oxidized so as to form an AlN / oxide dielectric layer stack structure; gate metal covers the groove channels; a source electrode region and a drain electrode region are formed at two ends; and the source electrode region and the drain electrode region are covered with metal, so that the source electrode and the drain electrode can be formed. The device and preparation process of the invention are simple and reliable. With the preparation method adopted, the high quality MIS structure can be formed, and the performance of the GaN MISFET device can be improved. The preparation method can play a key role in decreasing the electric leakage of the gate electrode, decreasing the resistance of the channels and stabilizing threshold voltage.

Owner:SUN YAT SEN UNIV

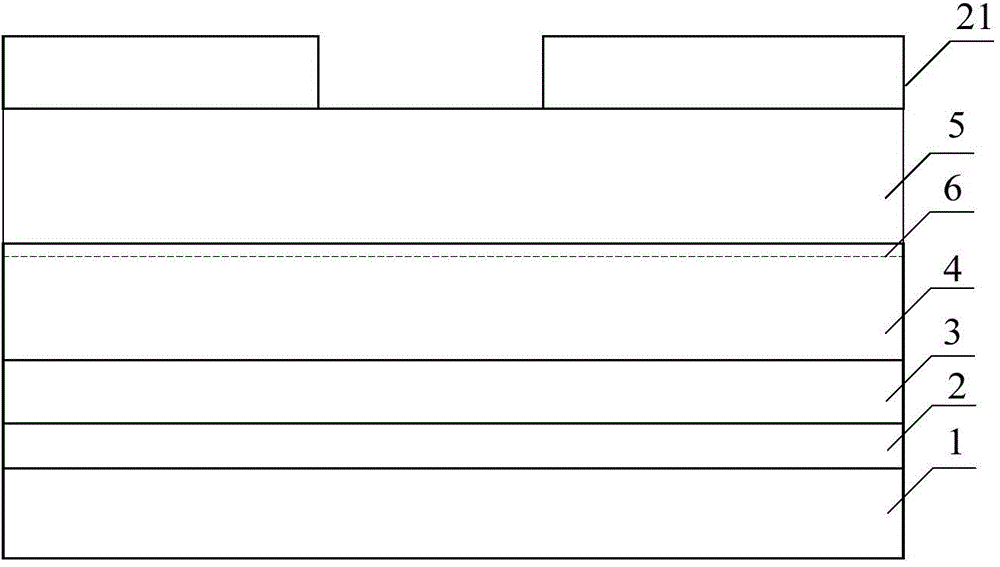

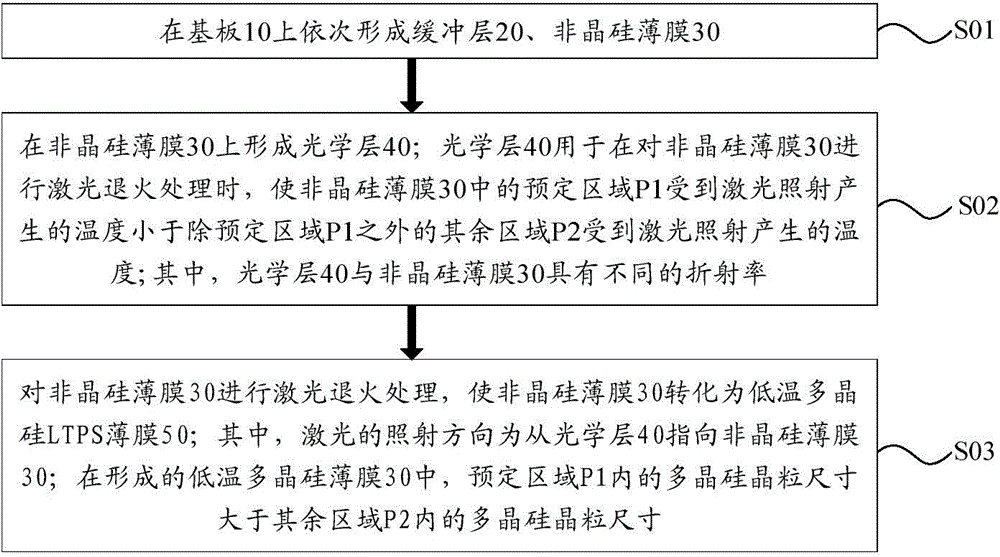

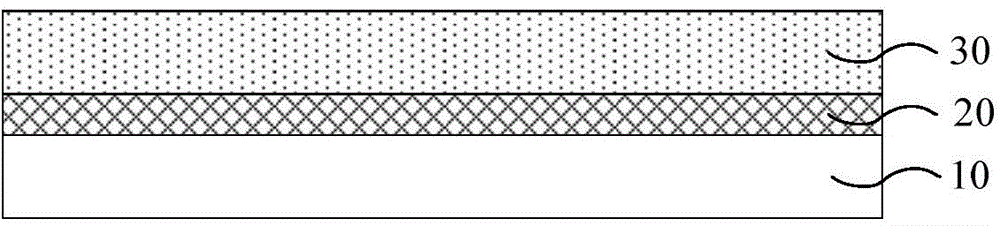

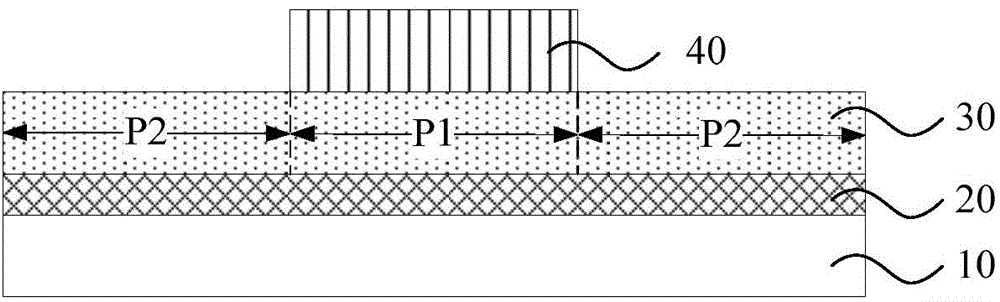

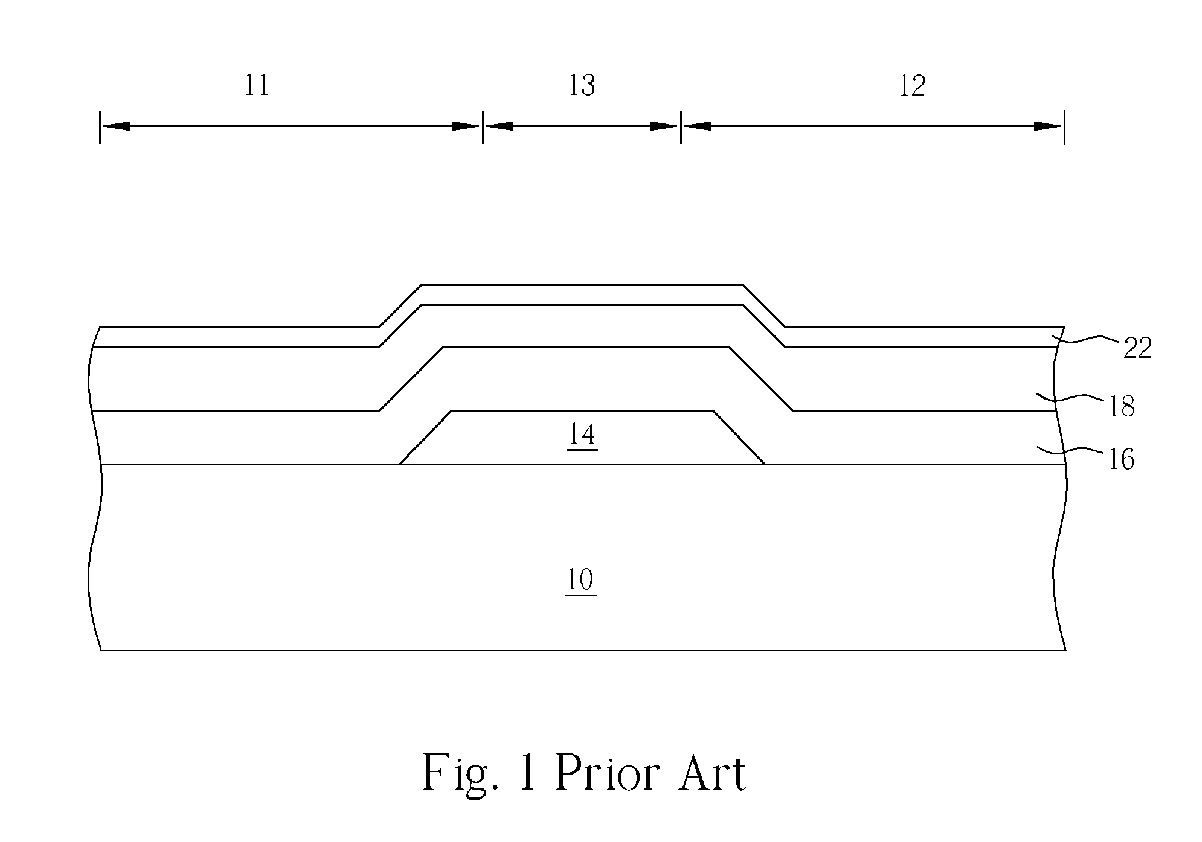

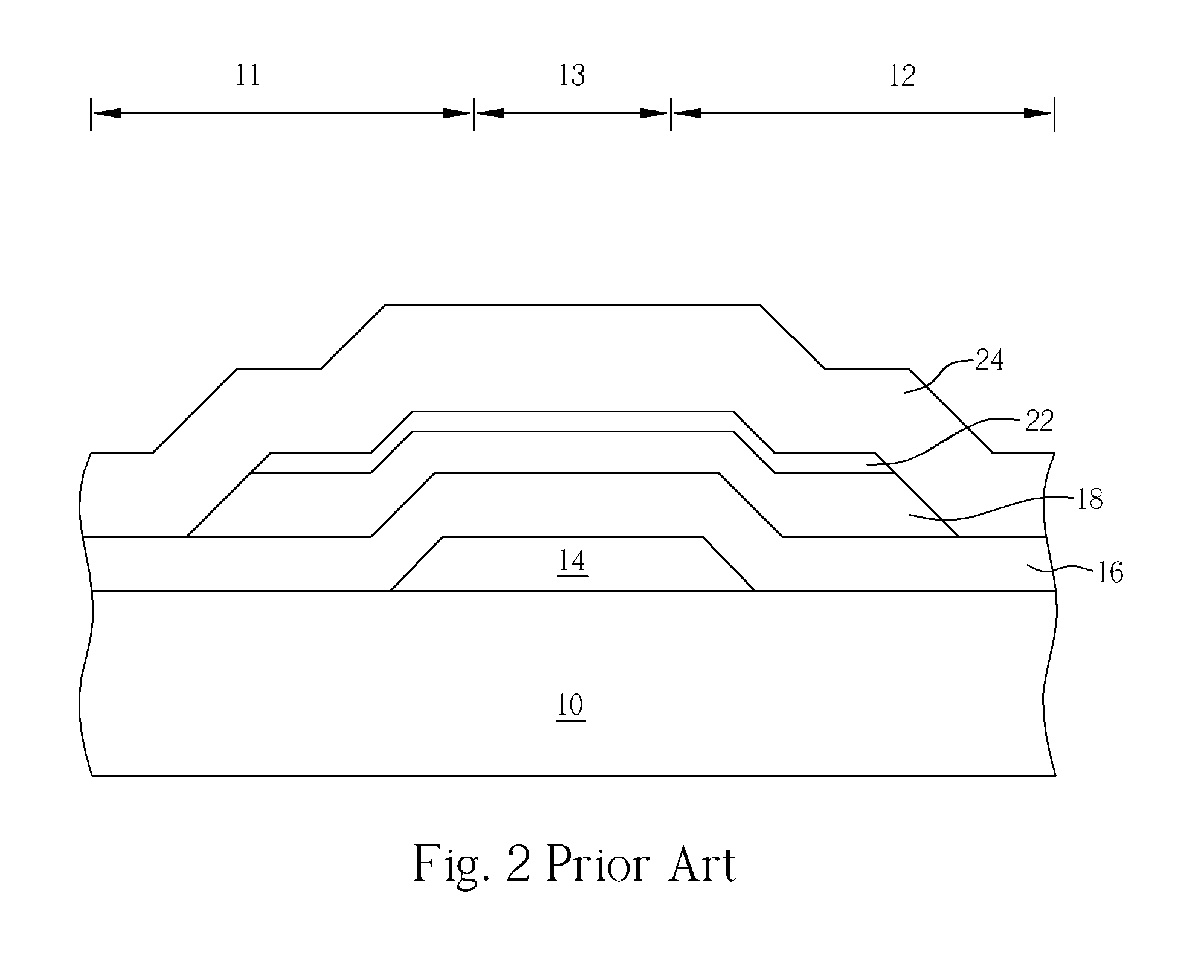

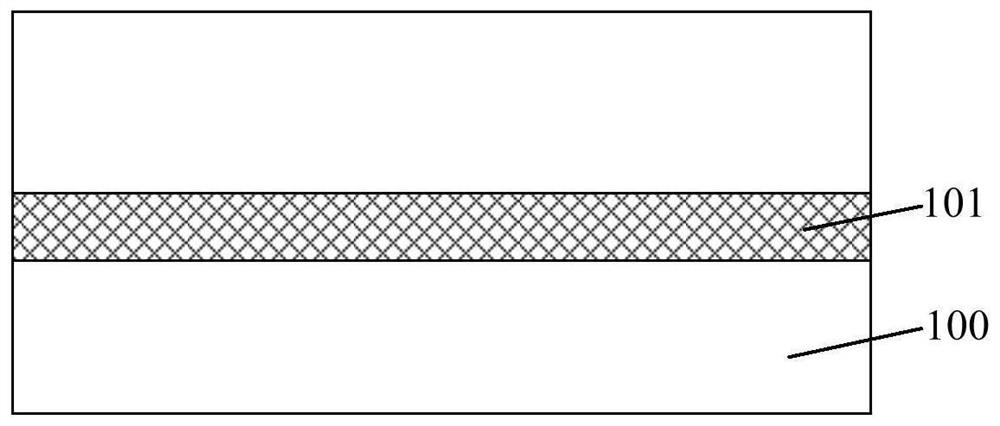

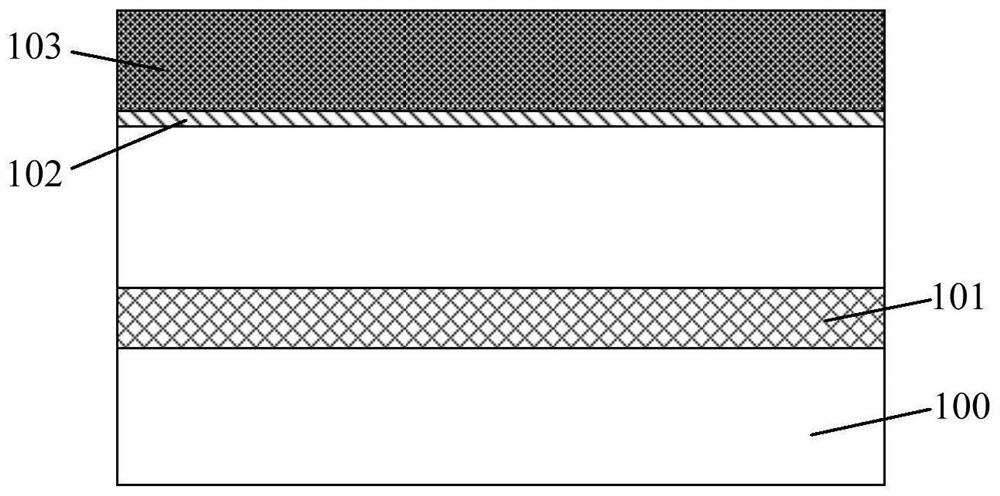

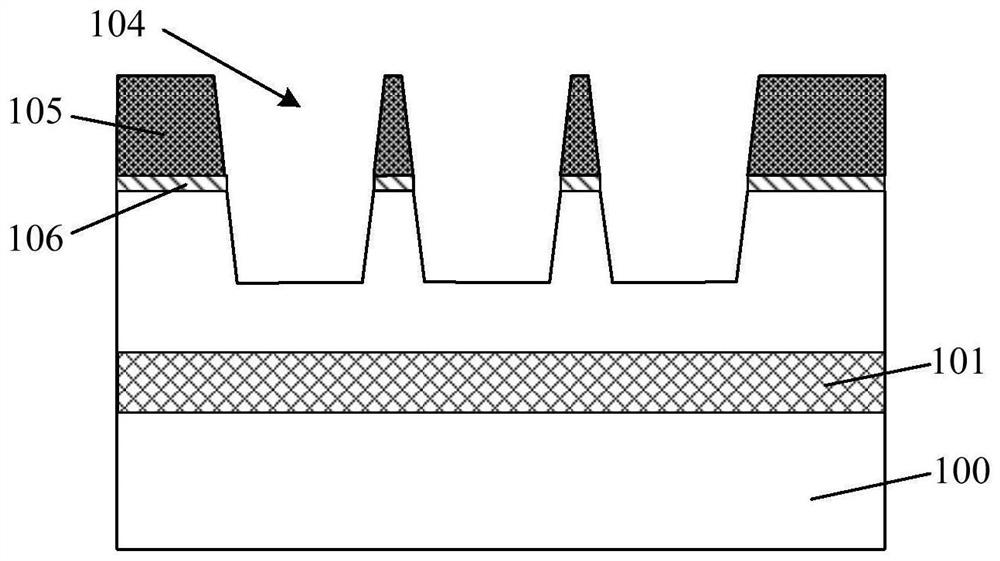

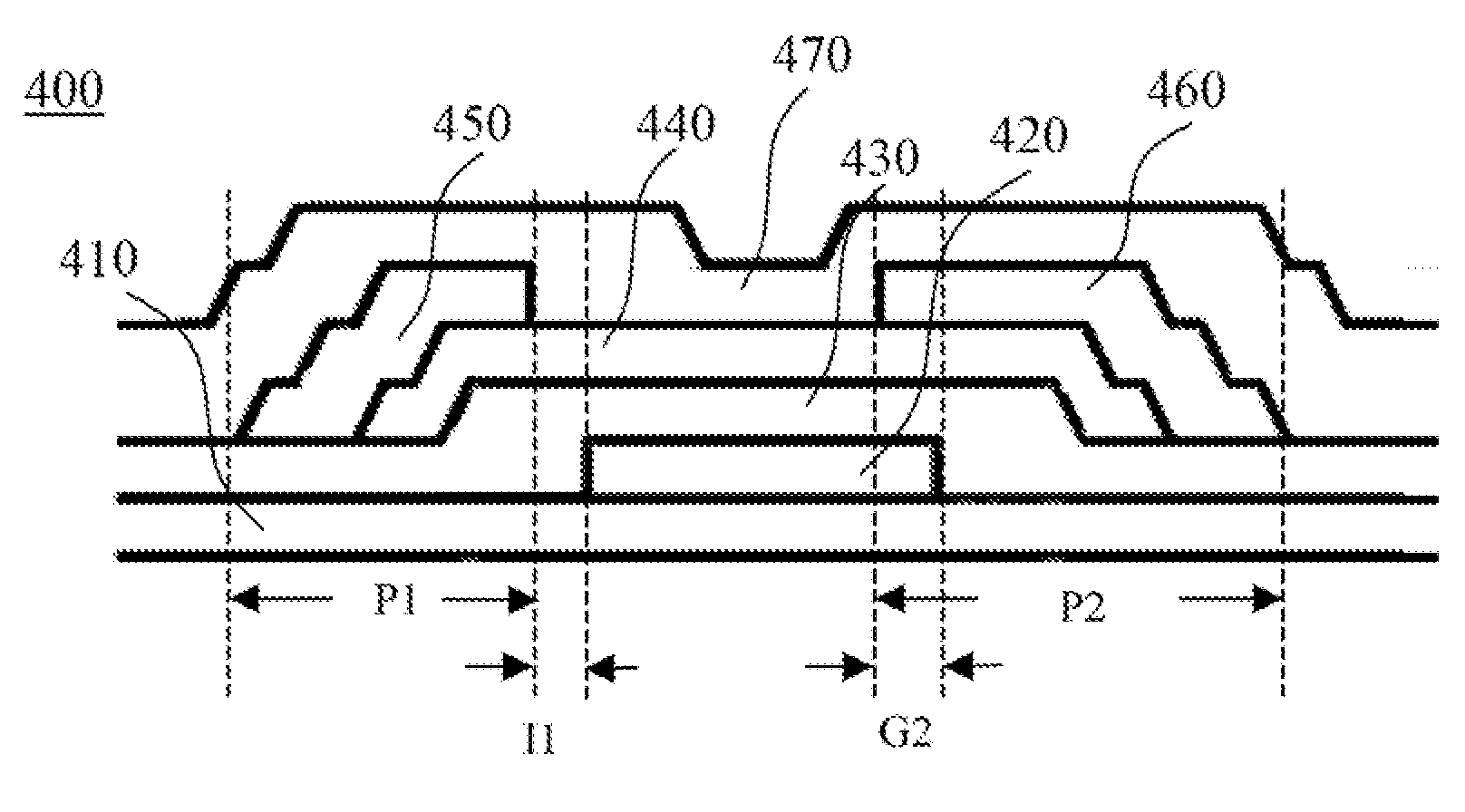

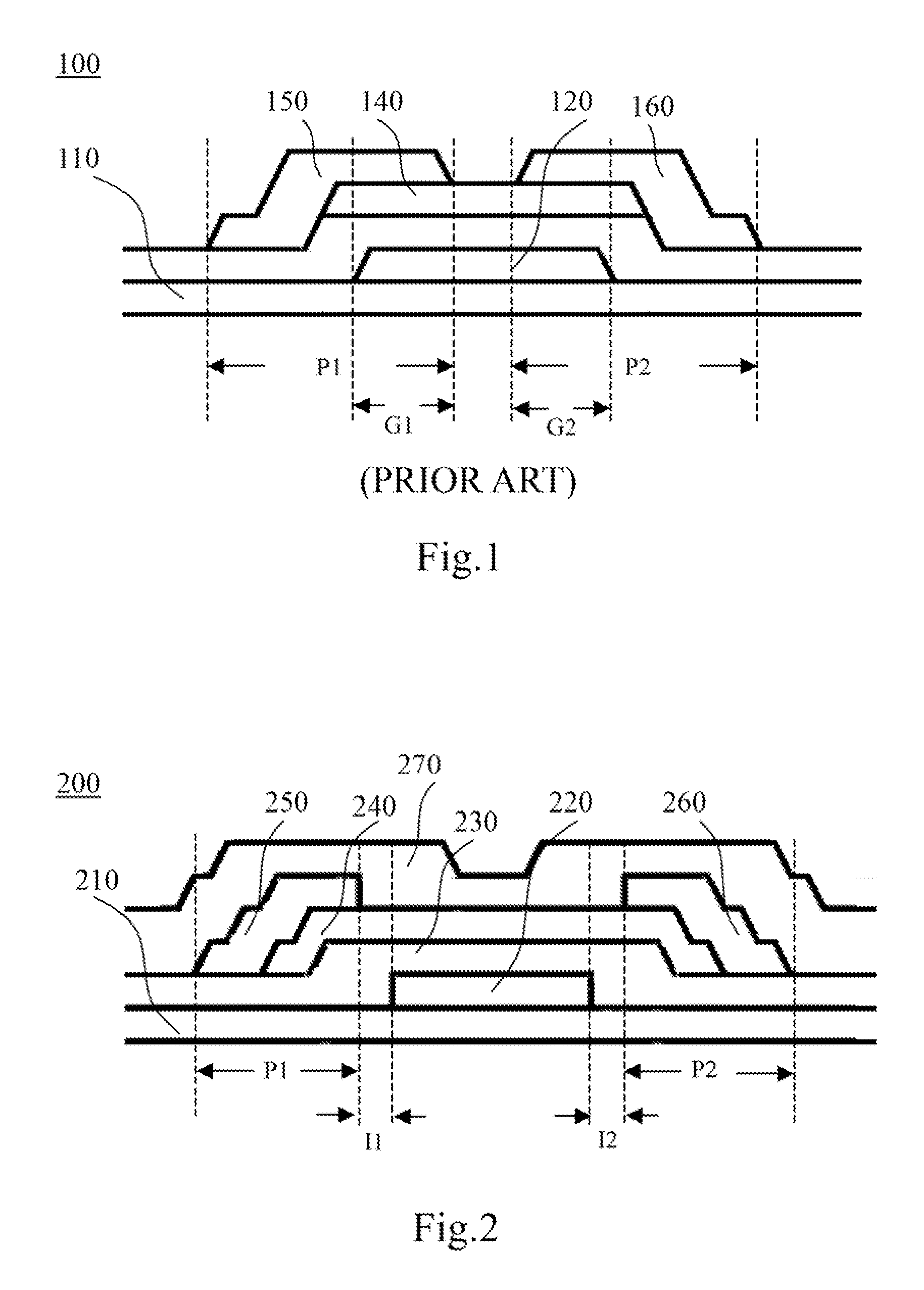

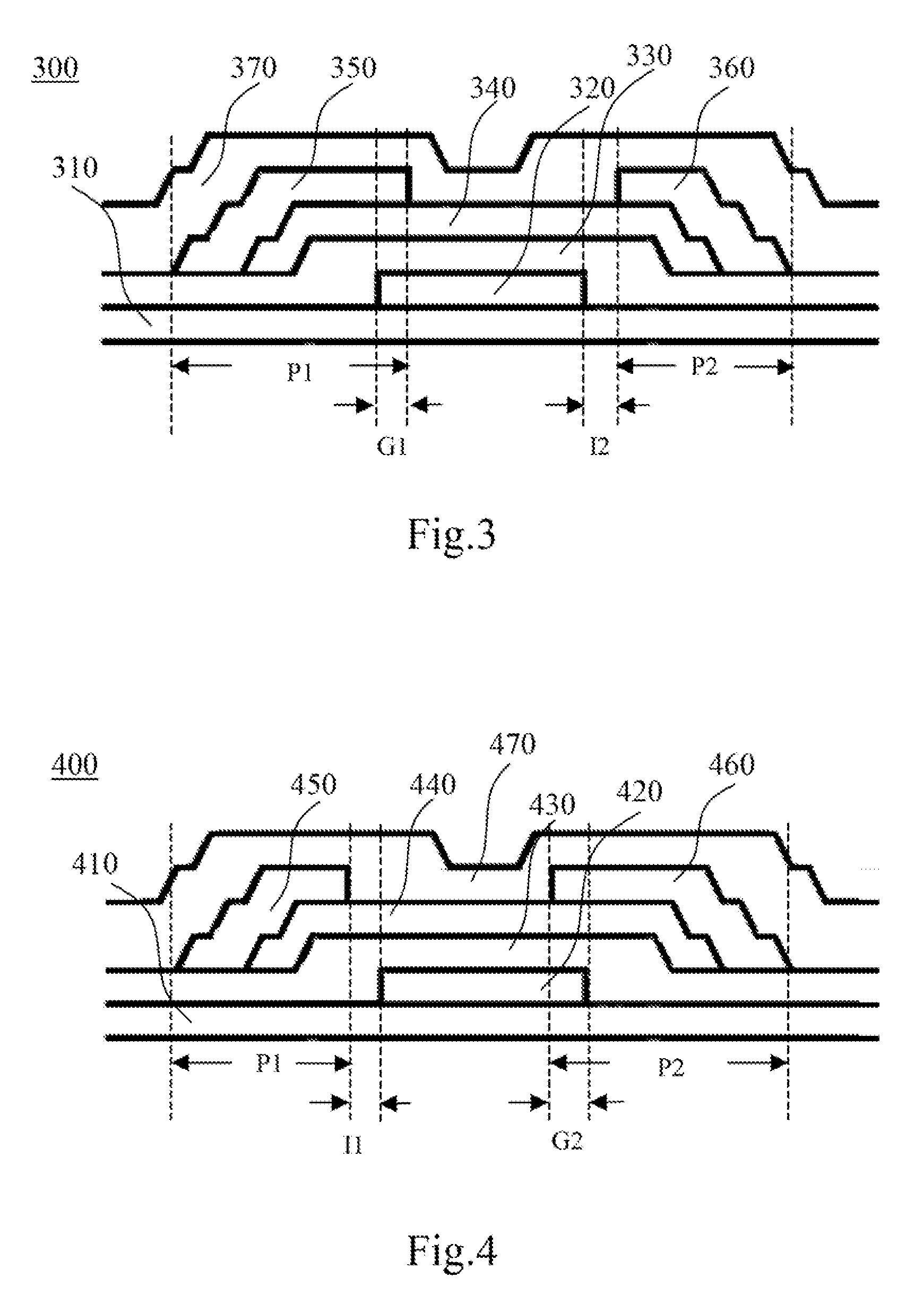

Preparation method of low-temperature polycrystalline silicon film, TFT, array base plate and display device

InactiveCN104538310ARefine the grain sizeImproved Threshold Voltage StabilityTransistorSolid-state devicesDisplay deviceRefractive index

The invention provides a preparation method of a low-temperature polycrystalline silicon film, a TFT, an array base plate and a display device, relates to the technical field of display, and aims at achieving the purposes that an LTPS film prepared by using an ELA method is relatively large in crystal grain size and relatively small in crystal boundary in an area between a source and a drain corresponding to the TFT, the TFT drain current is reduced, and the threshold voltage stability is improved. The preparation method comprises the following steps: forming a buffer layer and an amorphous silicon film; forming an optical layer on the amorphous silicon film, so that the temperature generated when a preset area is radiated by laser is smaller than that generated when other areas are radiated by laser when the amorphous silicon film is subjected to laser annealing treatment; supplying different refractive indexes to the optical layer and the amorphous silicon film; performing laser annealing treatment on the amorphous silicon film so as to convert the amorphous silicon film into a low-temperature polycrystalline silicon film; enabling the size of polycrystalline silicon grains inside the preset area to be greater than that of the polycrystalline silicon grains in other areas. The preparation method is adopted to prepare low-temperature polycrystalline silicon films and thin film transistors with the low-temperature polycrystalline silicon films.

Owner:BOE TECH GRP CO LTD

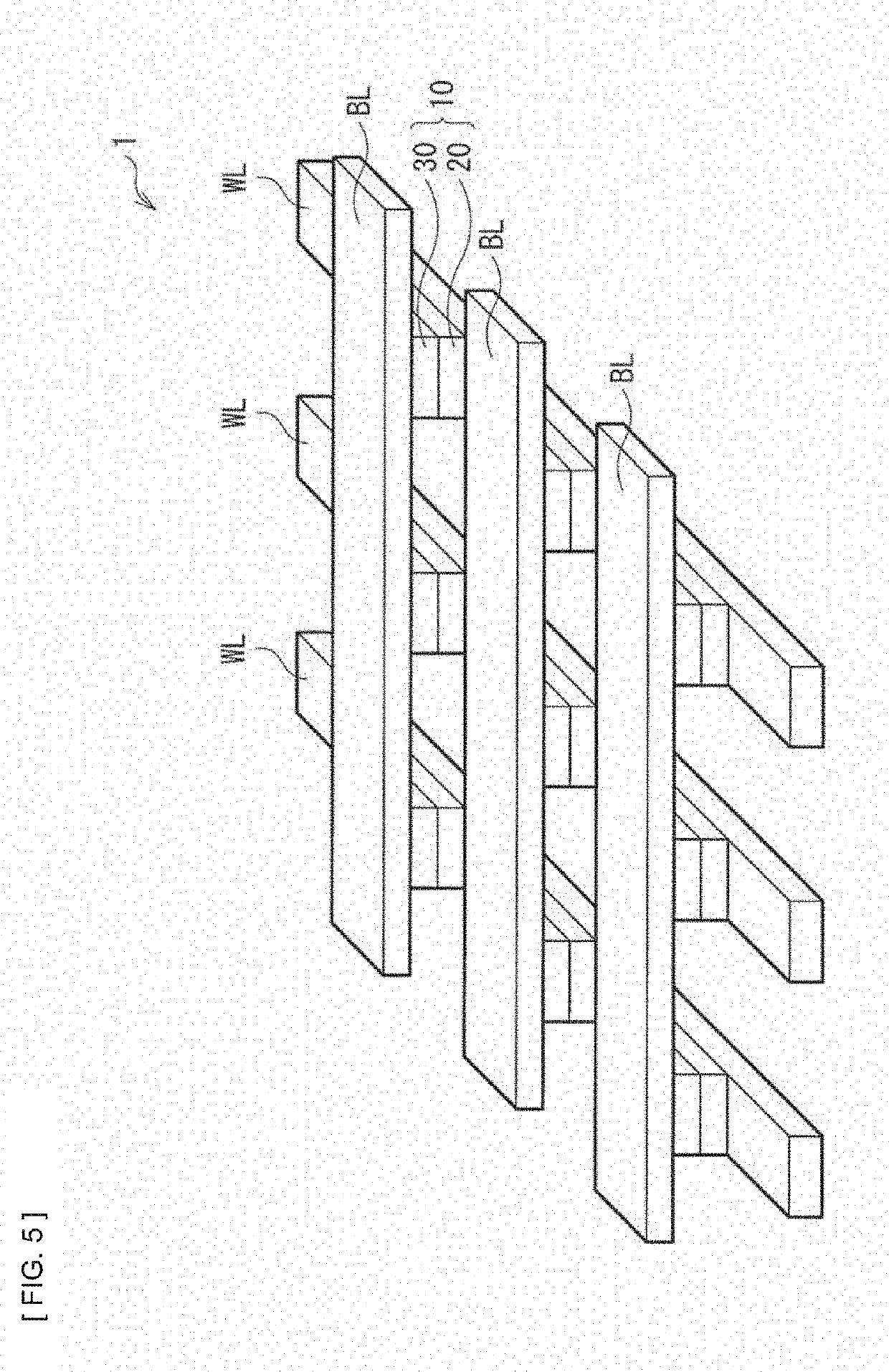

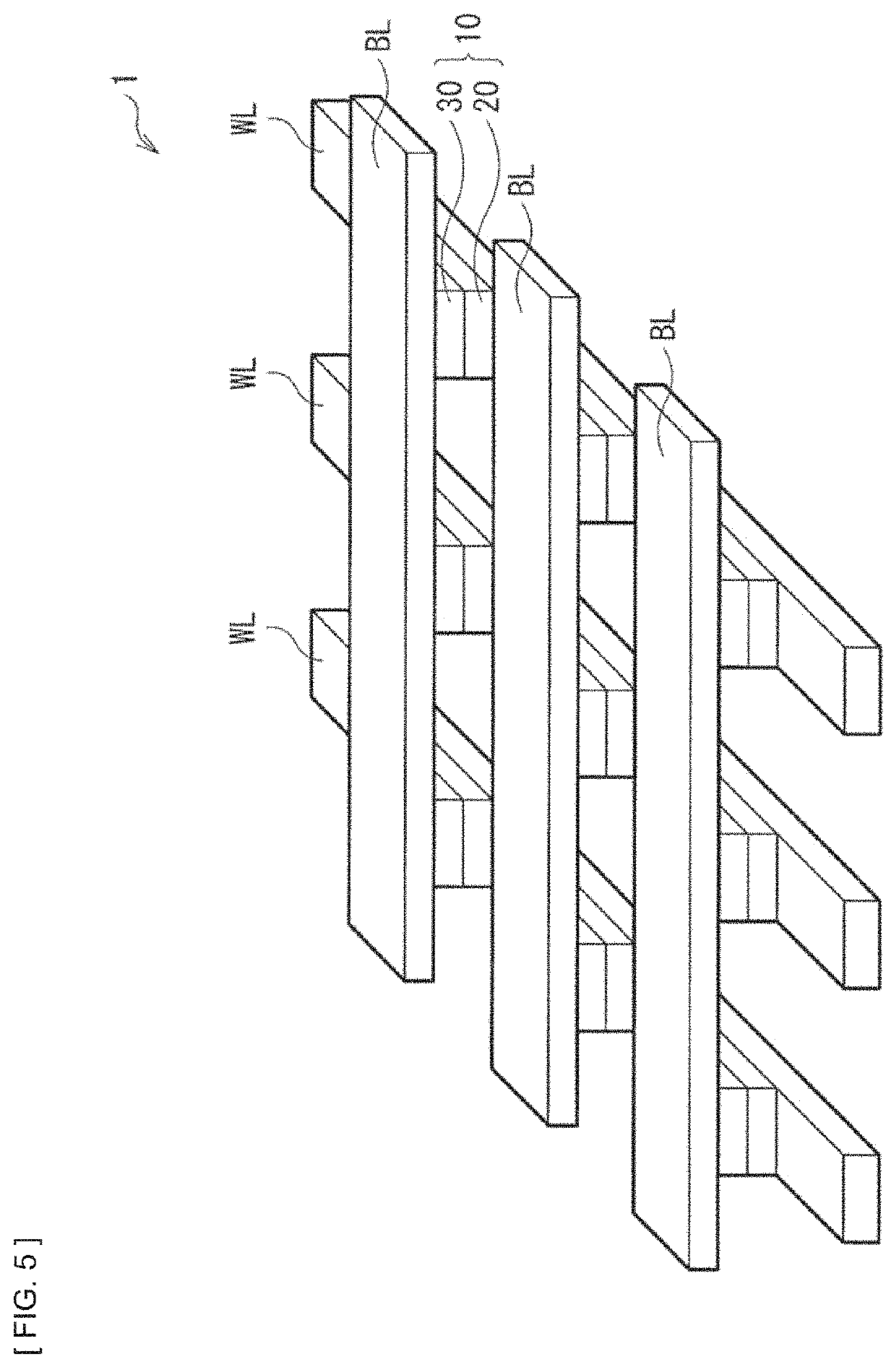

Switch device, storage apparatus, and memory system

ActiveUS20190252609A1Improved Threshold Voltage StabilityStable structureSolid-state devicesRead-only memoriesPhysicsGallium

A switch device according to an embodiment of the present disclosure includes: a first electrode; a second electrode opposed to the first electrode; and a switch layer provided between the first electrode and the second electrode, and the switch layer includes one or more kinds of chalcogen elements selected from tellurium (Te), selenium (Se), and sulfur (S) and one or more kinds of first elements selected from phosphorus (P) and arsenic (As), and further includes one or both of one or more kinds of second elements selected from boron (B) and carbon (C) and one or more kinds of third elements selected from aluminum (Al), gallium (Ga), and indium (In).

Owner:SONY SEMICON SOLUTIONS CORP

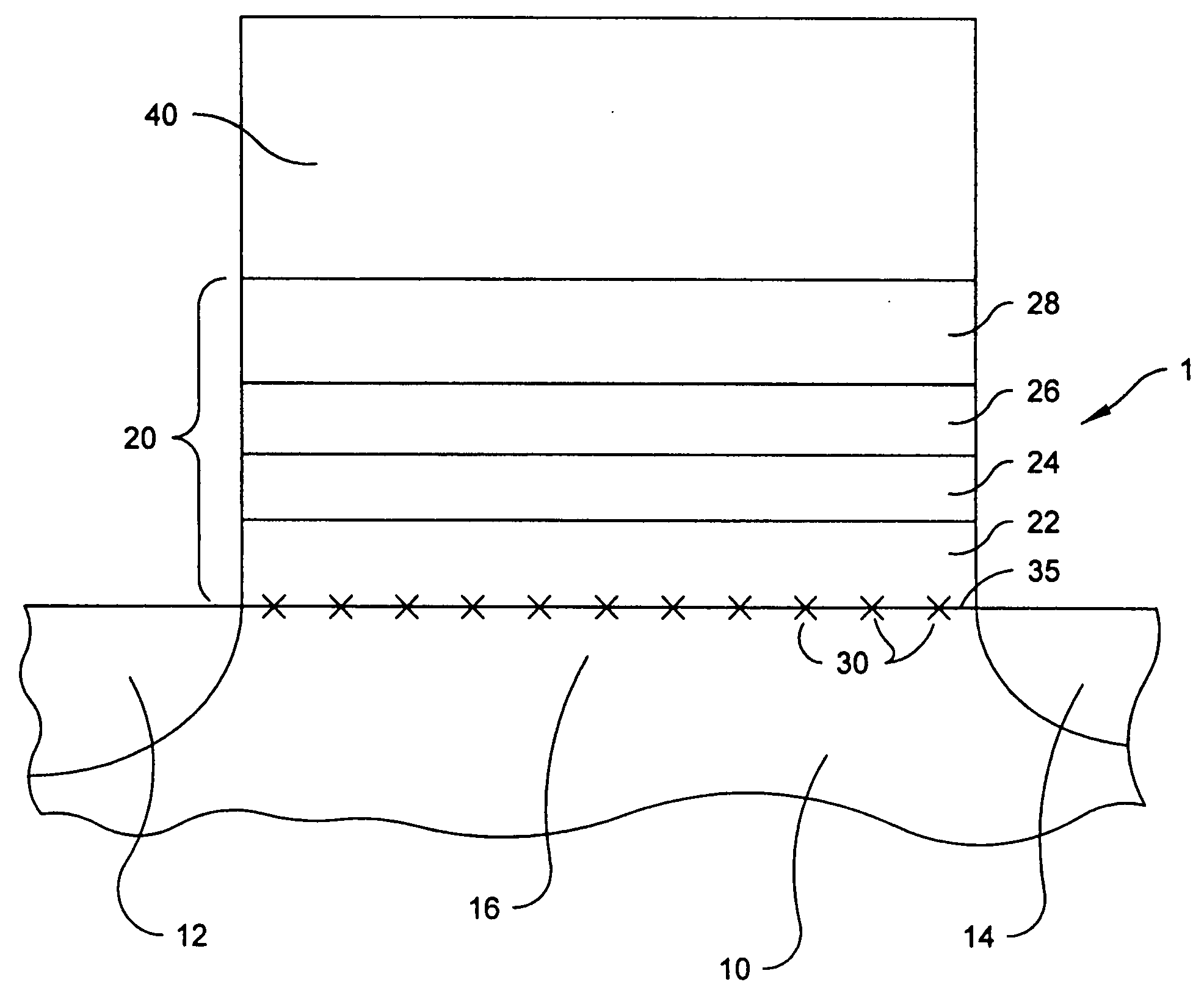

Low hydrogen concentration charge-trapping layer structures for non-volatile memory and methods of forming the same

ActiveUS20070108497A1Improved Threshold Voltage StabilityImproved data retention propertyTransistorSemiconductor/solid-state device manufacturingHydrogen concentrationTrapping

Memory cells comprising: a semiconductor substrate having at least two source / drain regions separated by a channel region; a charge-trapping structure disposed above the channel region; and a gate disposed above the charge-trapping structure; wherein the charge-trapping structure comprises a bottom insulating layer, a first charge-trapping layer, and a second charge-trapping layer, wherein an interface between the bottom insulating layer and the substrate has a hydrogen concentration of less than about 3×1011 / cm−2, and methods for forming such memory cells.

Owner:MACRONIX INT CO LTD

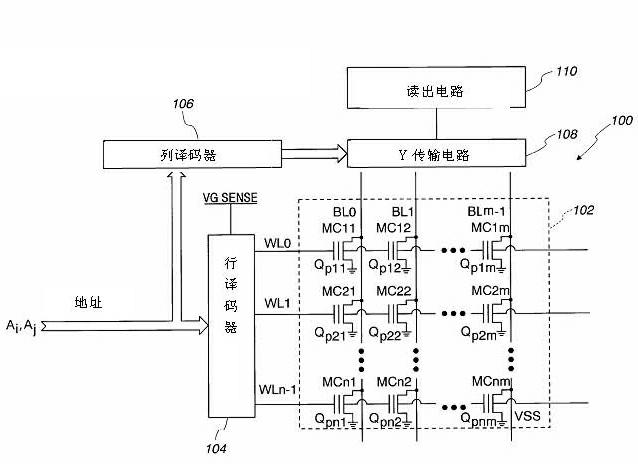

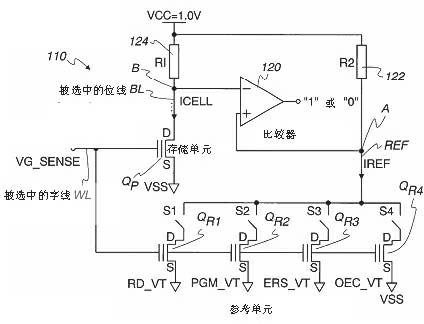

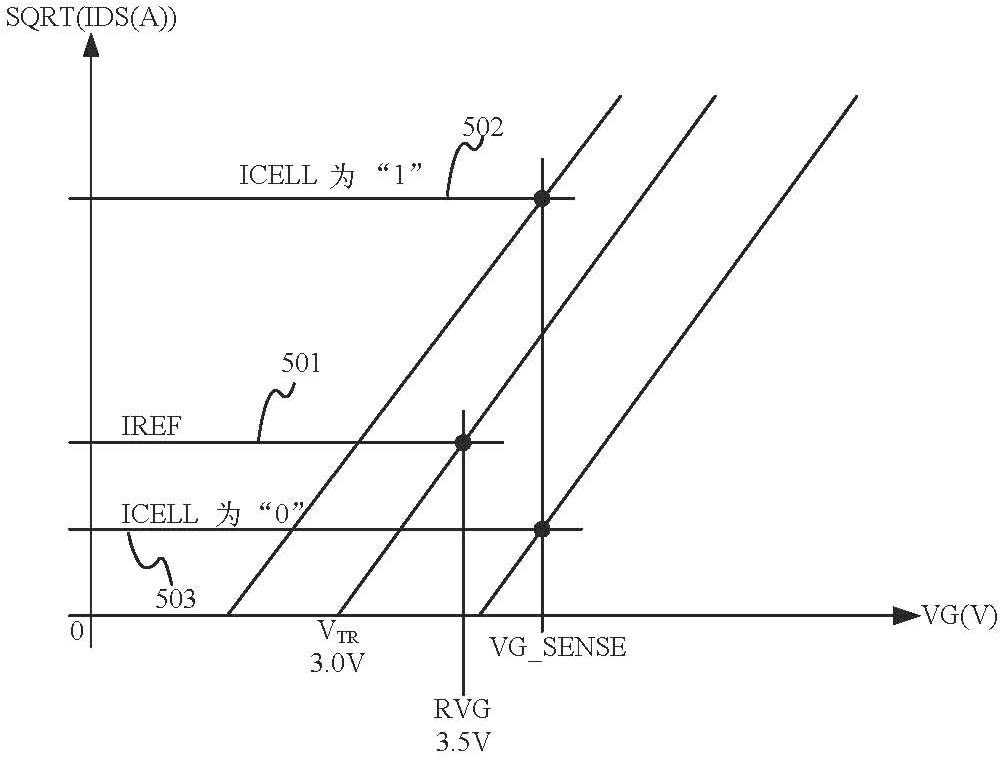

Readout circuit and readout method for electrically erasable read-only memory

ActiveCN102467967AImproved Threshold Voltage StabilitySave configuration timeRead-only memoriesElectricityComputer science

The invention relates to a readout circuit and a readout method for an electrically erasable read-only memory. The readout circuit comprises a comparator, a reference resistor, a sensing resistor, a reference unit and a storage unit, wherein the readout circuit is only configured with one reference unit, and the same reference unit is used in the process of reading operation; the threshold voltage of the reference unit is set into neutral threshold voltage; and the voltage on a reference unit control grid is set into a fixed value, so that the configuration time in the manufacturing process is obviously reduced, and the threshold added on a storage unit control grid is changed along with operating modes. Meanwhile, the voltage added on the storage unit control grid during the reading operation and programming verification operation is lower than that in the prior art, so that a stress effect of grid voltage is reduced, and the threshold voltage of the reference unit is set to a value approaching the neutral threshold voltage so as to be more stable.

Owner:SHANGHAI FUDAN MICROELECTRONICS GROUP

Thin film transistor and method for fabricating same

ActiveUS7541229B2Enhance characteristic functionalityEasy to controlTransistorSemiconductor/solid-state device manufacturingInsulation layerHydrogen

A method for forming a thin film transistor on a substrate is disclosed. A gate electrode and a gate insulation layer are disposed on a surface of the substrate. A deposition process is performed by utilizing hydrogen diluted silane to form a silicon-contained thin film on the gate insulation layer first. A hydrogen plasma etching process is thereafter performed. The deposition process and the etching process are repeated for at least one time to form an interface layer. Finally, an amorphous silicon layer, n+ doped Si layers, a source electrode, and a drain electrode are formed on the interface layer.

Owner:AU OPTRONICS CORP

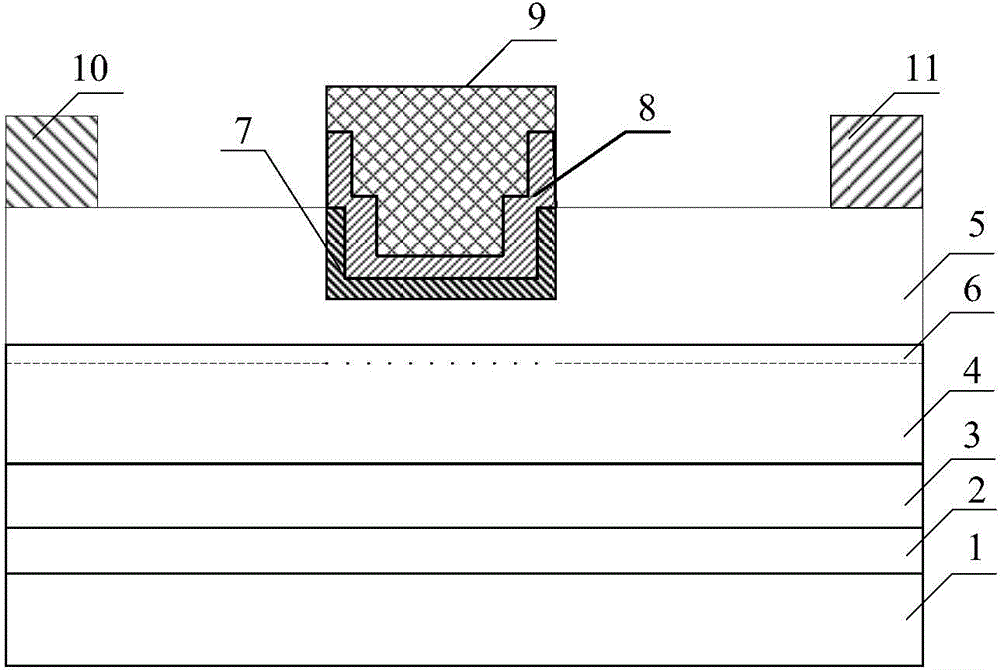

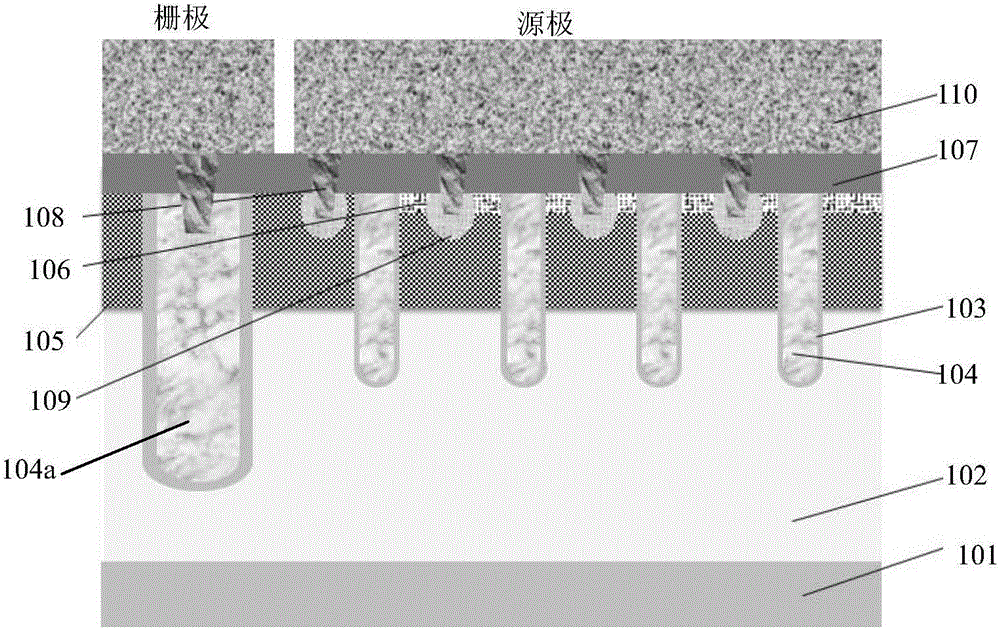

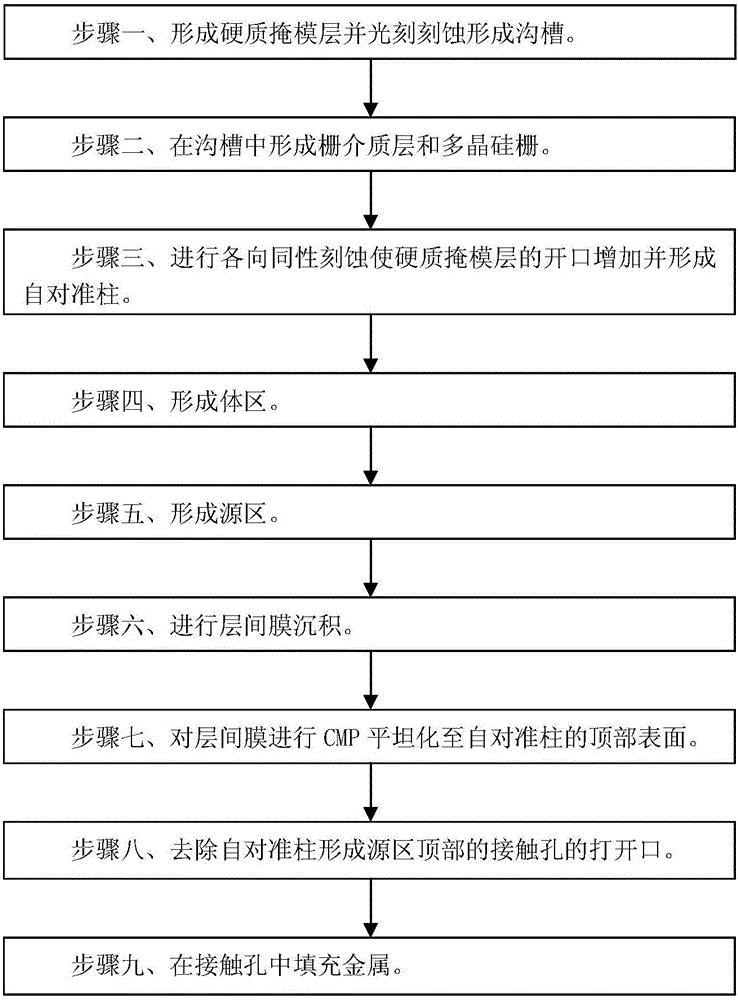

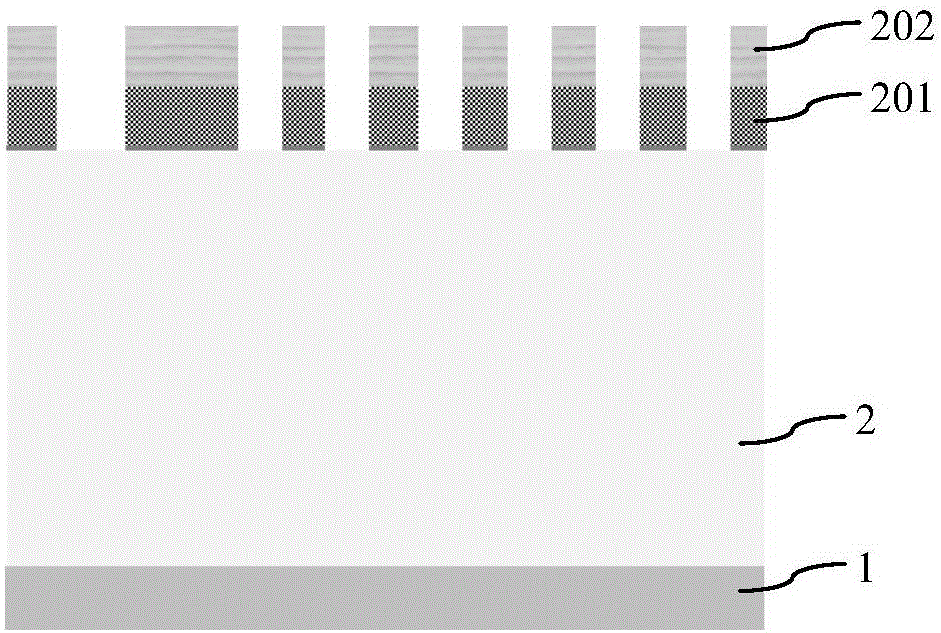

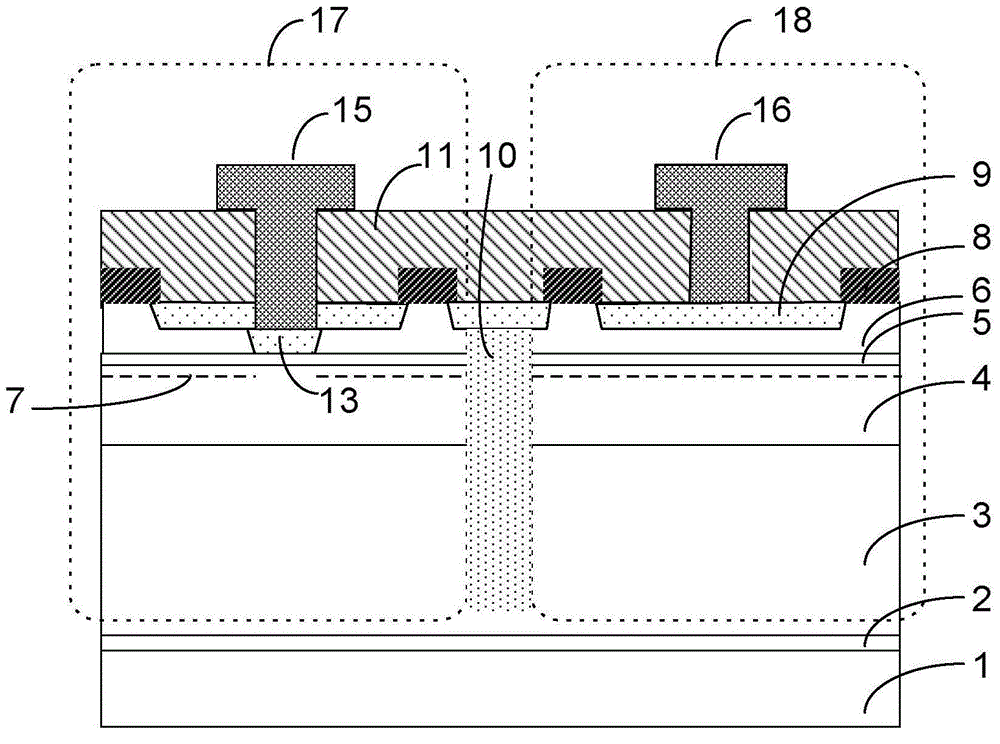

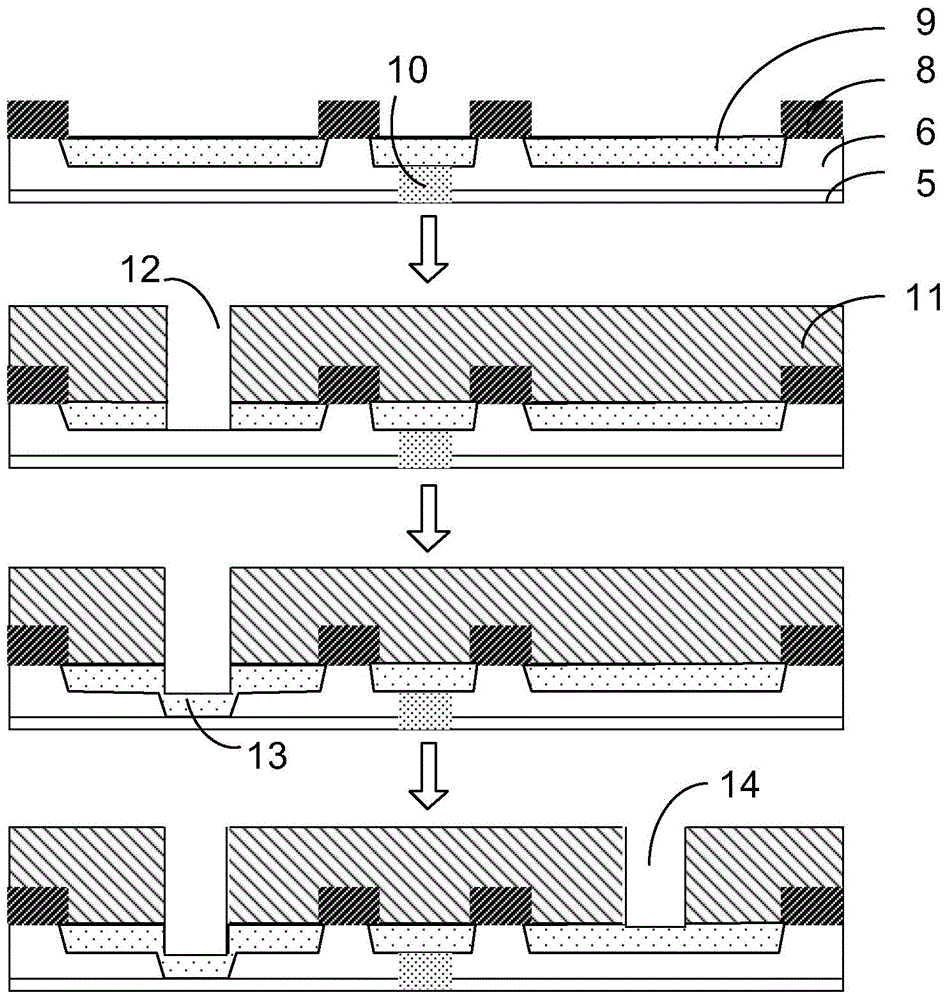

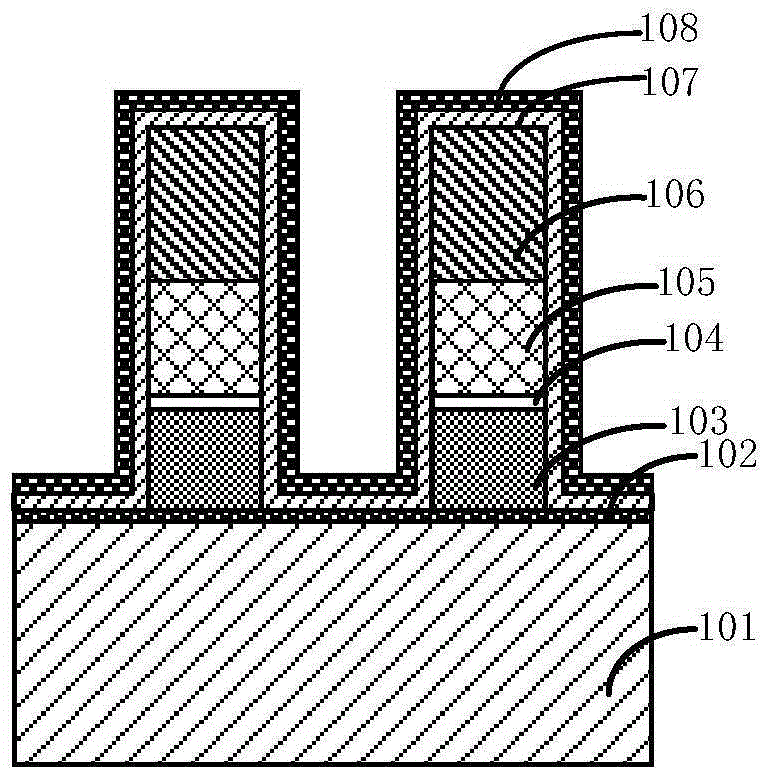

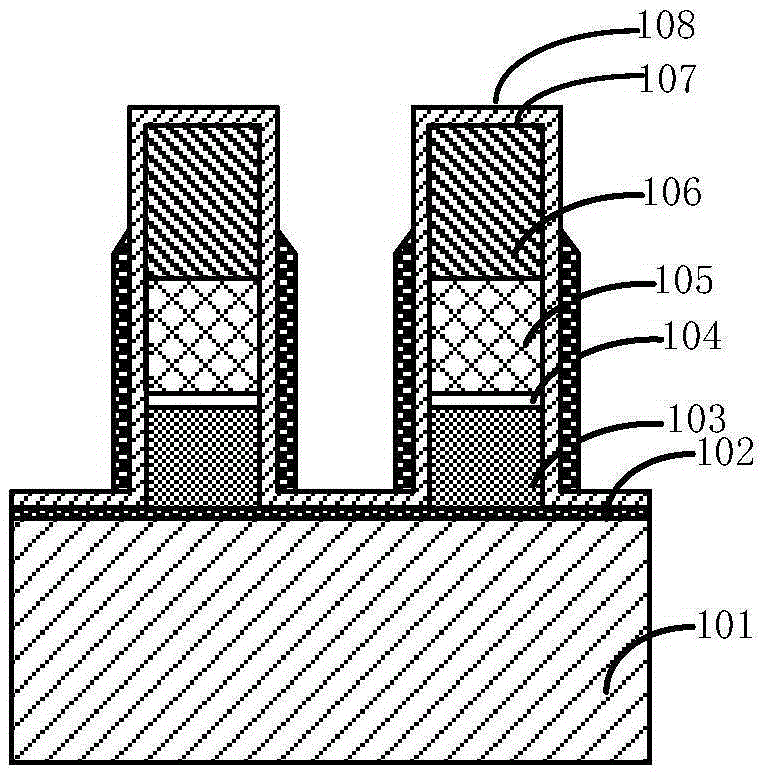

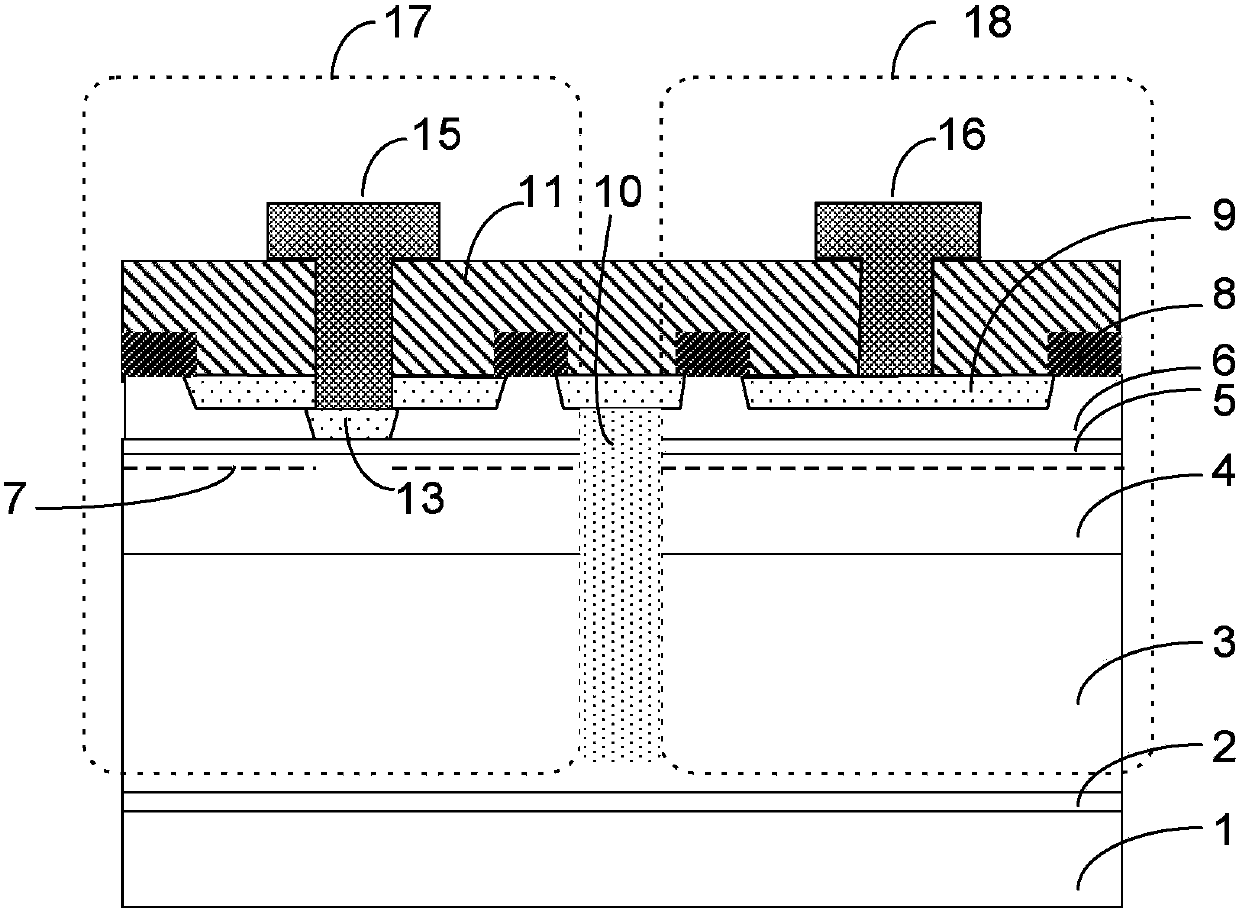

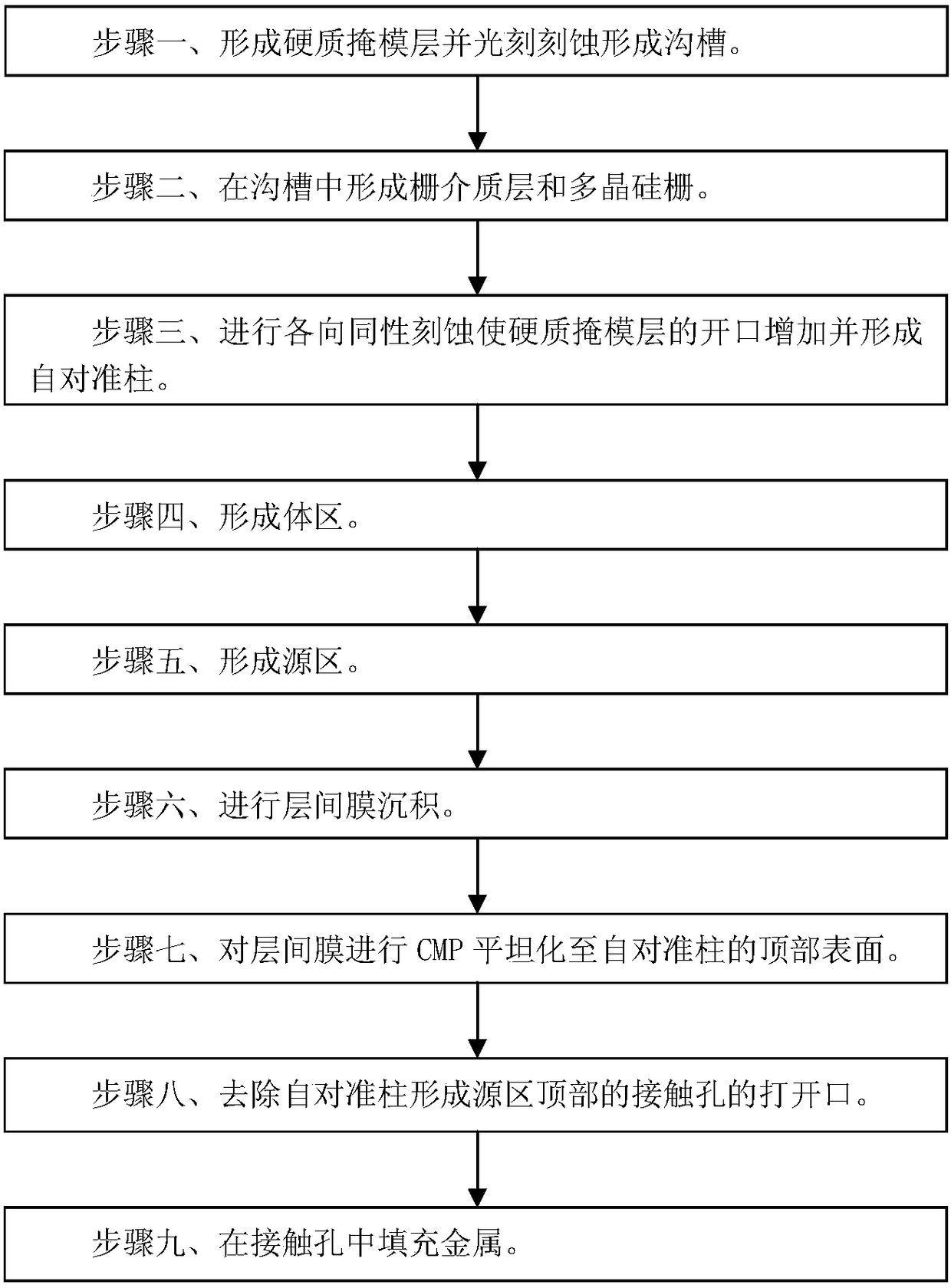

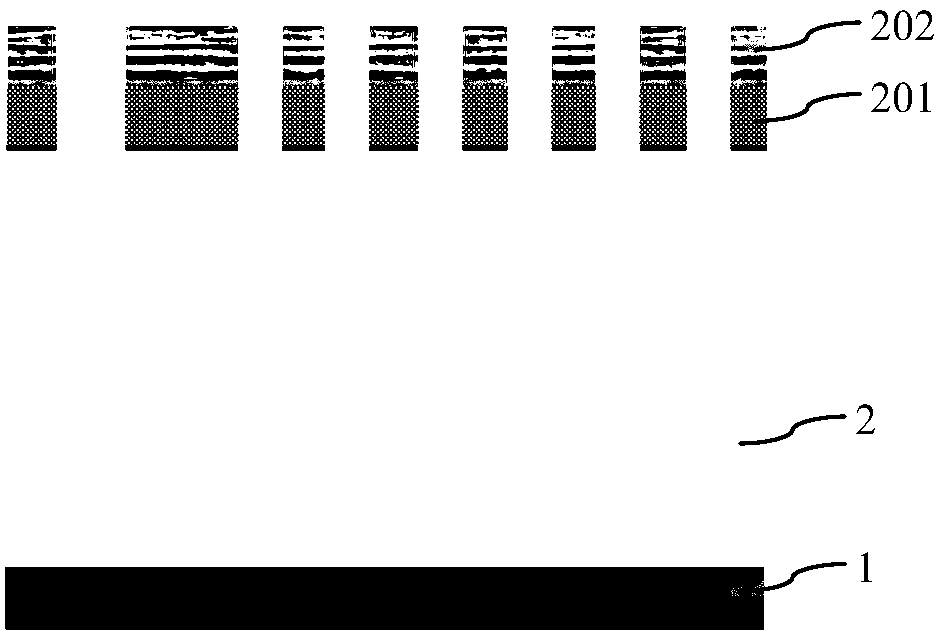

Manufacturing method for groove grid power device and structure

ActiveCN105826205AAchieve self-alignment definitionLow costSemiconductor/solid-state device manufacturingSemiconductor devicesMechanical engineeringPolysilicon gate

The invention discloses a manufacturing method for a groove grid power device. Formation steps of each cell of a conduction region comprise that a hard mask layer is formed, and a groove is formed through photolithographic etching; a grid medium layer and a polysilicon grid are formed in the groove; an opening of the hard mask layer is enlarged through isotropic etching, and a self-aligning column is formed; a body region is formed; a source region is formed; deposition of an interlayer film is carried out; chemical mechanical grinding planarization for the interlayer film is carried out to the surface of the top portion of the self-aligning column; an opening of a contact hole at the top portion of the source region formed at the self-aligning column is removed; and metal is filled into the contact hole. The invention further discloses a groove grid power device. According to the manufacturing method, self-aligning definition of the contact hole can be realized, registration redundancy is not needed to consider, the contact hole does not require the exposure technology, manufacturing cost is saved, so threshold voltage stability of the device can be improved, unit dimensions of the device are reduced, and conduction resistance is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

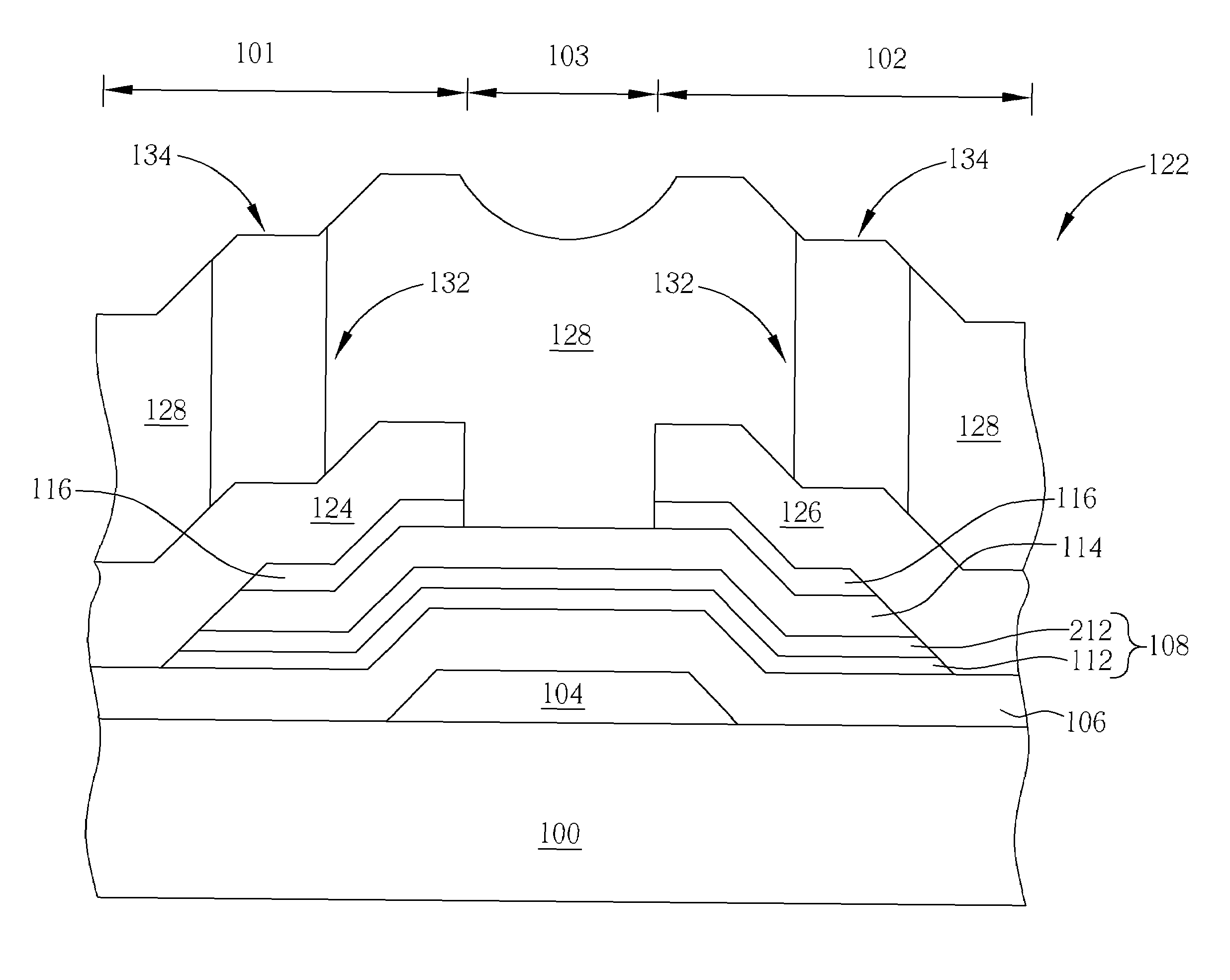

Thin film transistor and method for fabricating same

ActiveUS20090212289A1Enhance characteristic functionalityEasy to controlTransistorSolid-state devicesInsulation layerHydrogen

A method for forming a thin film transistor on a substrate is disclosed. A gate electrode and a gate insulation layer are disposed on a surface of the substrate. A deposition process is performed by utilizing hydrogen diluted silane to form a silicon-contained thin film on the gate insulation layer first. A hydrogen plasma etching process is thereafter performed. The deposition process and the etching process are repeated for at least one time to form an interface layer. Finally, an amorphous silicon layer, n+ doped Si layers, a source electrode, and a drain electrode are formed on the interface layer.

Owner:AU OPTRONICS CORP

Tunneling field effect transistor 3D NAND data cell structure and method for forming the same

ActiveUS20190081068A1Reduce distractionsImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorDielectric layer

Owner:YANGTZE MEMORY TECH CO LTD

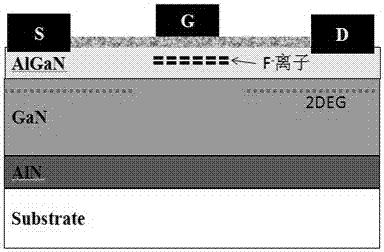

GaN E/D integrated device production method based on two-step oxidation method

ActiveCN104835819AReduce gate leakageImproved Threshold Voltage StabilitySolid-state devicesSemiconductor/solid-state device manufacturingHeterojunctionHigh concentration

The invention discloses a GaN E / D integrated device production method based on a two-step oxidation method. Based on the traditional depletion A1GaN(A1InN) / A1N / GaN heterostructure, the barrier layer thickness can be controlled accurately by using the oxidation method, and the thickness of the barrier layer can be reduced to a half of the original thickness after the first oxidation process, and the high concentration electron gas can be maintained in the channel, and the medium generated by the oxidation can be used as the D-mode device gate dielectric. The medium of the E-mode device gate dielectric area can be removed, and the barrier layer can be consumed completely after the second oxidation process, and the two-dimensional electron gas can be consumed in the channel, and at the same time, the E-mode device gate dielectric can be generated. The same two-step oxidation technologies can be completed, the E-mode device technology and the D-mode device technology can be completely compatible, and the thicknesses of the gate dielectrics are the same, and therefore the device structures and the device performances can be cooperated with each other. The production of the E-mode device can be realized by using the oxidation method to reduce the thickness of the barrier layer, and the processing controllability is high; the E-mode technology and the D-mode technology can be completely compatible, and the thickness of the E-mode device gate dielectric and the thickness of the D-mode device gate dielectric are the same, the performances are cooperated with each other, and then the yield of the GaN E / D integrated circuit can be improved.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

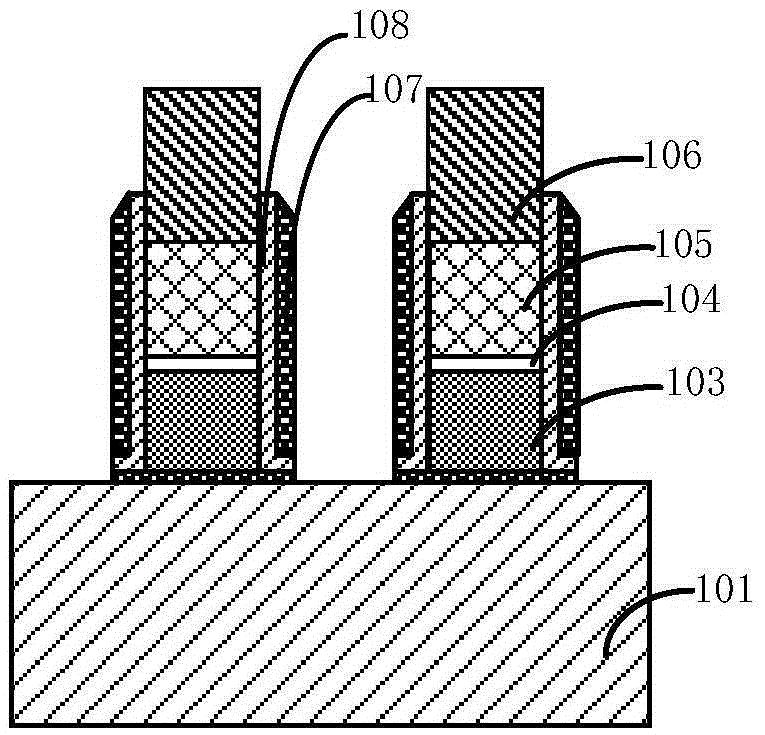

GaNHEMT cell structure with graphene buried source and longitudinal gate and preparation method

PendingCN107195674ALower turn-on resistanceIncrease the areaSemiconductor/solid-state device manufacturingSemiconductor devicesHigh densityGraphite

The invention discloses a GaNHEMT cell structure with a graphene buried source and a longitudinal gate. The source is connected with a graphene buried cooling layer through a metal material; the device adopts a longitudinal gate structure, a long transverse channel opening mode in the traditional HEMT device is turned to a short longitudinal channel opening mode, a long transverse current control channel is turned to a short longitudinal current control channel for the gate, the device uses a short gate side wall channel to realize switch control, and the on resistance of the device can be effectively reduced. A high-density cell structure can be realized, and the effective using area and the unit area power density of the device are improved; and by using the excellent thermal conductivity of the graphene, heat generated in an active area of the device can be conducted rapidly, the high-power GaNHEMT device can be realized, and the high-temperature reliability of the device can be enhanced.

Owner:BEIJING HUAJINCHUANGWEI ELECTRONICS CO LTD

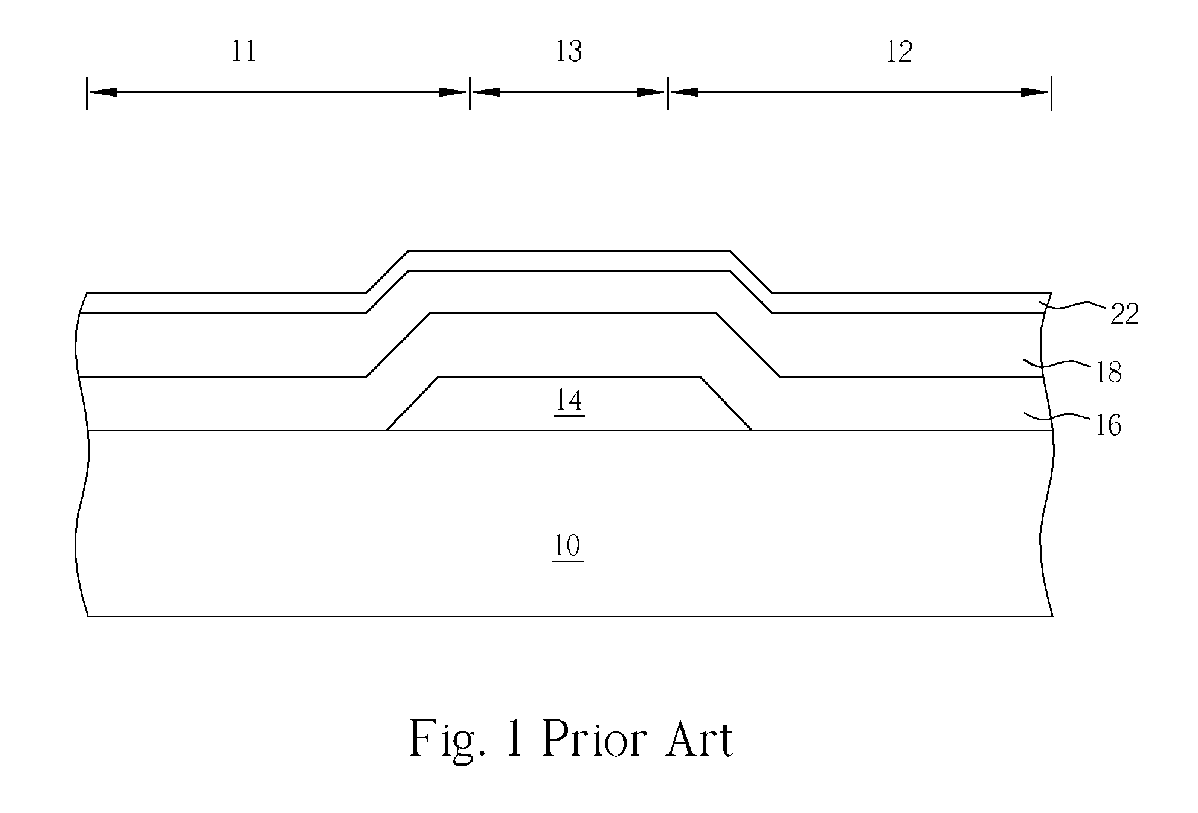

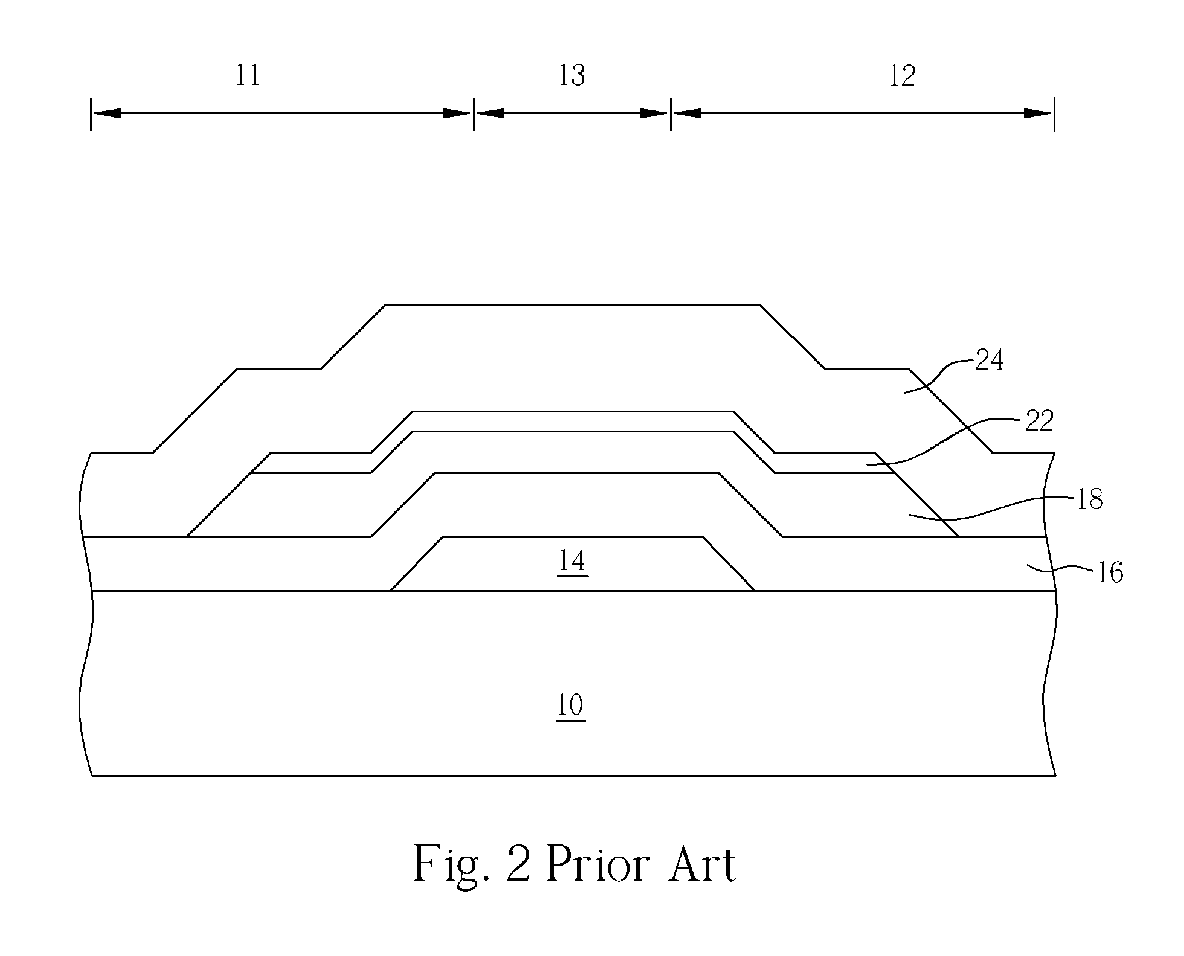

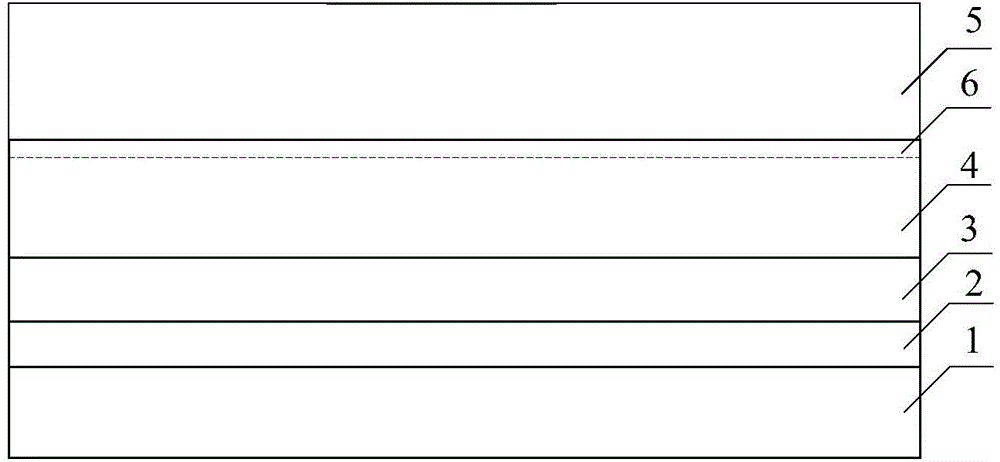

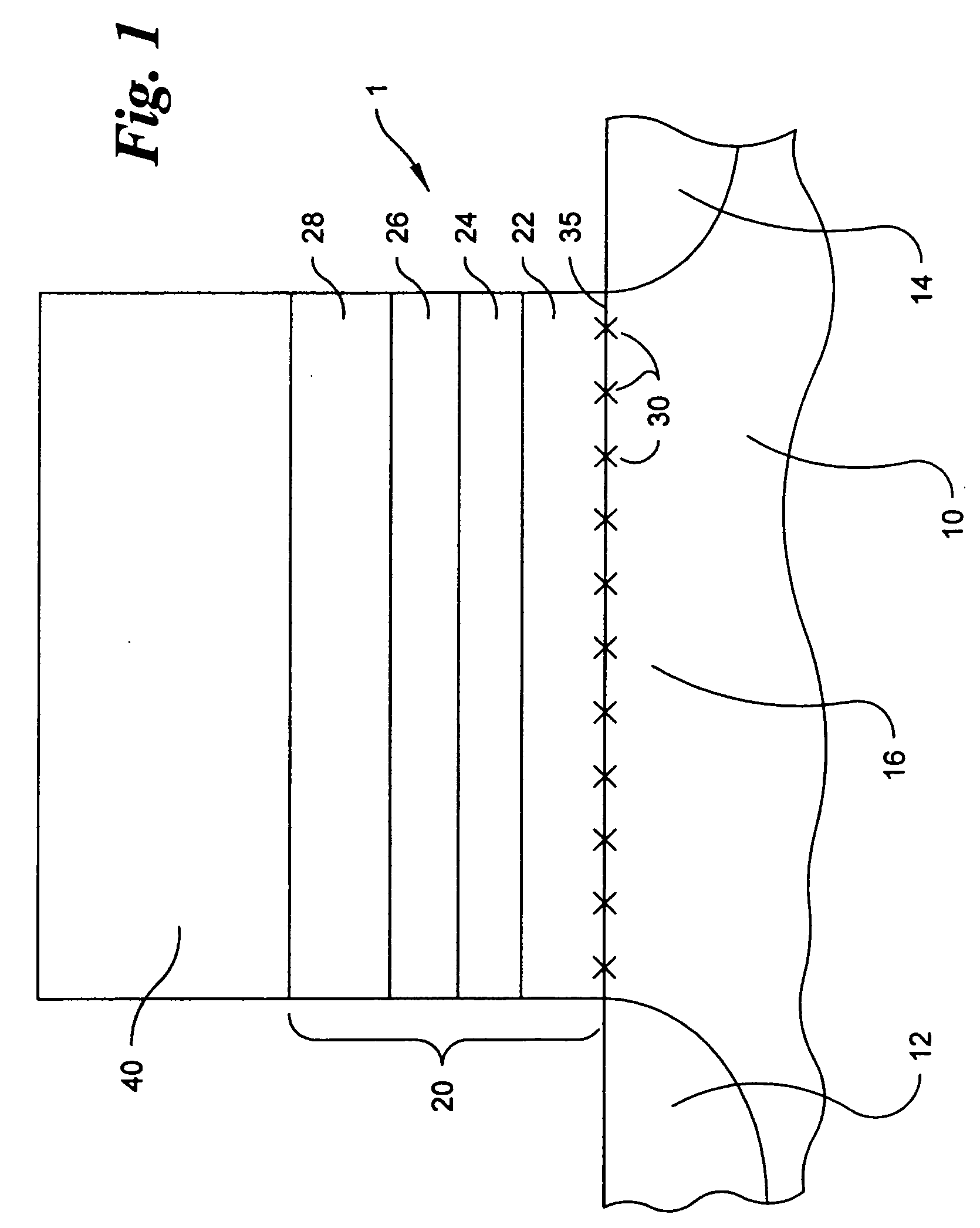

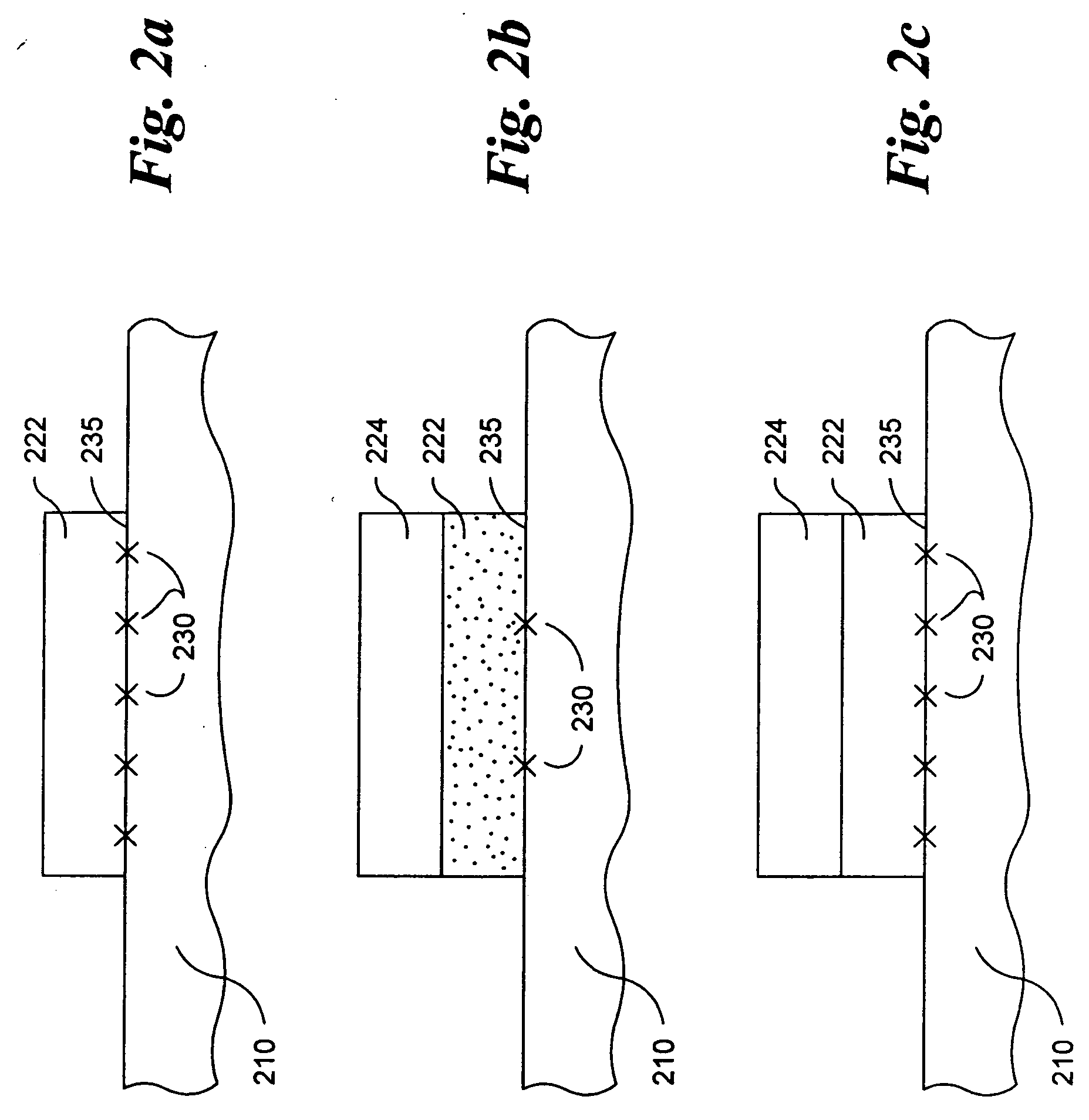

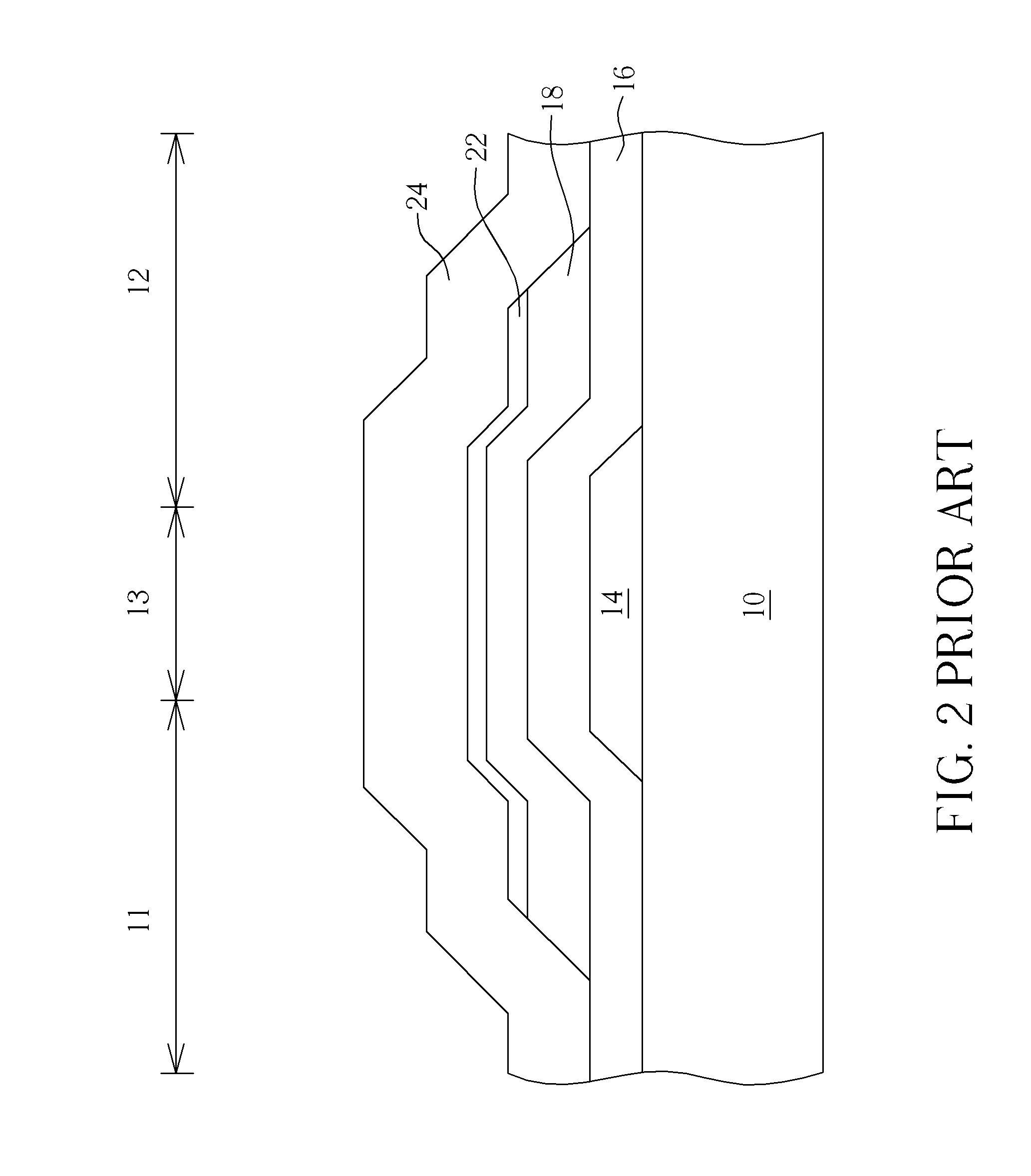

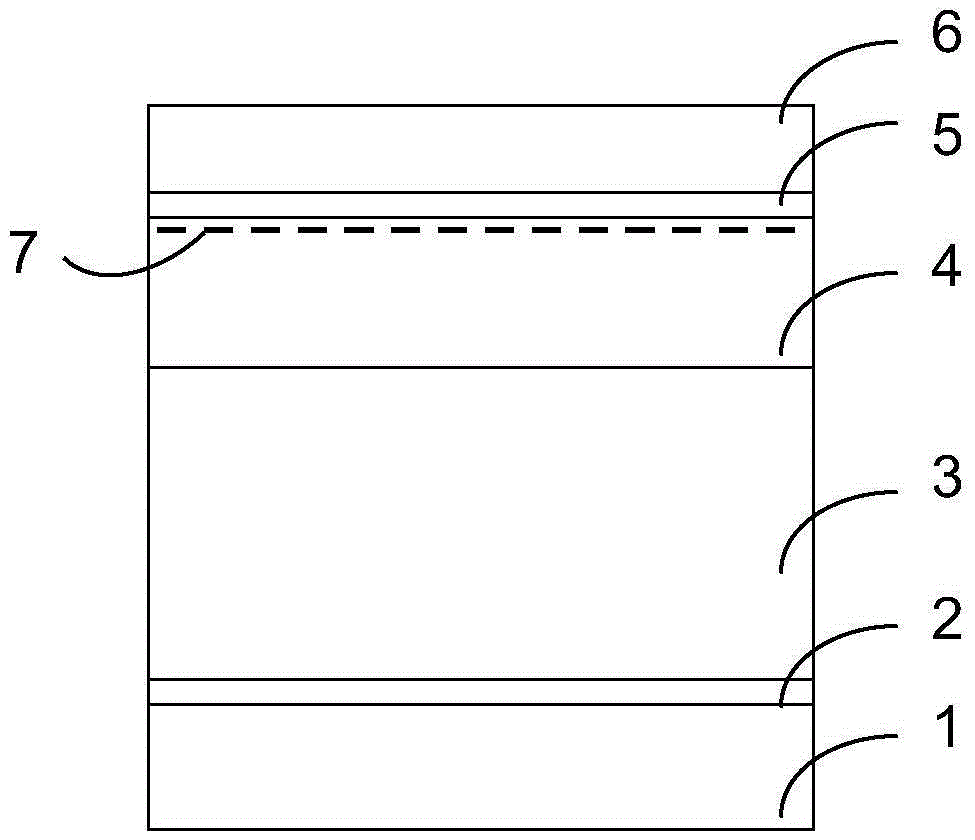

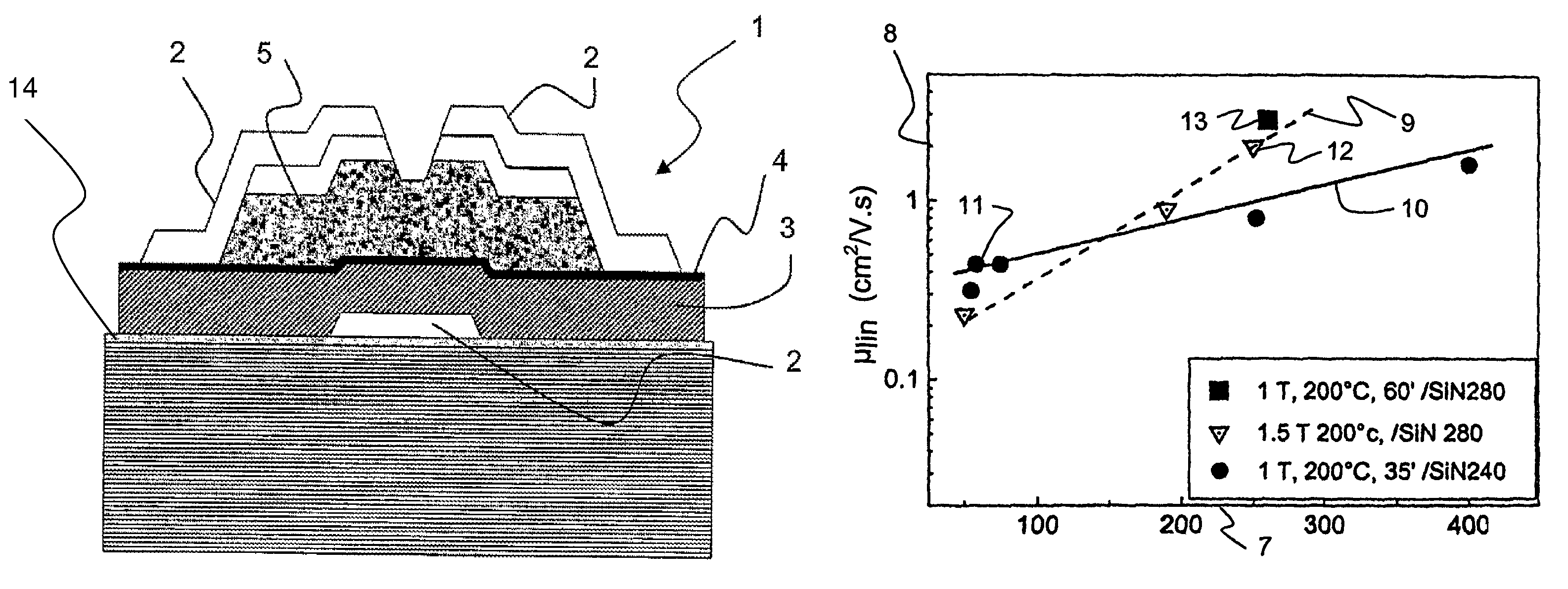

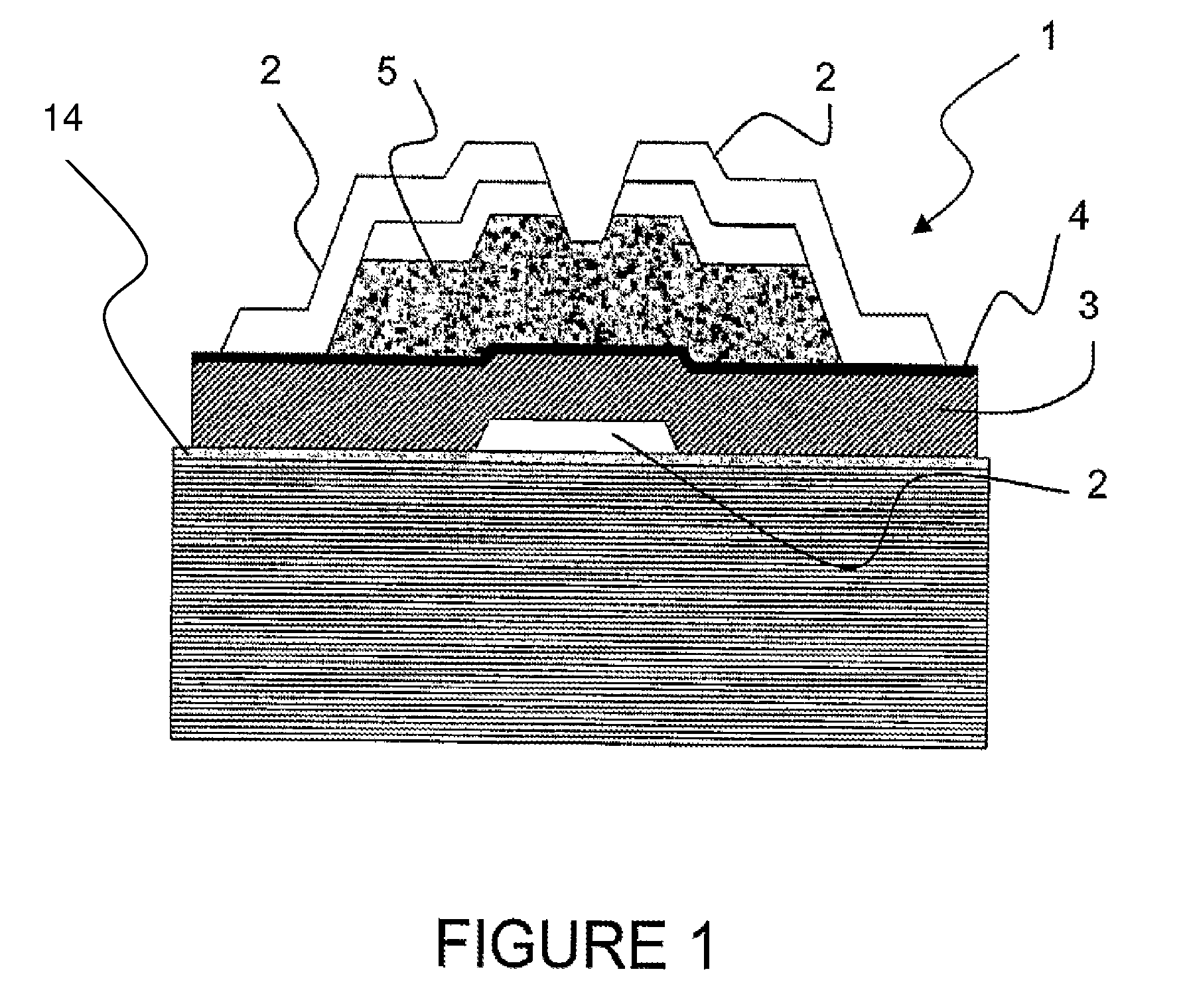

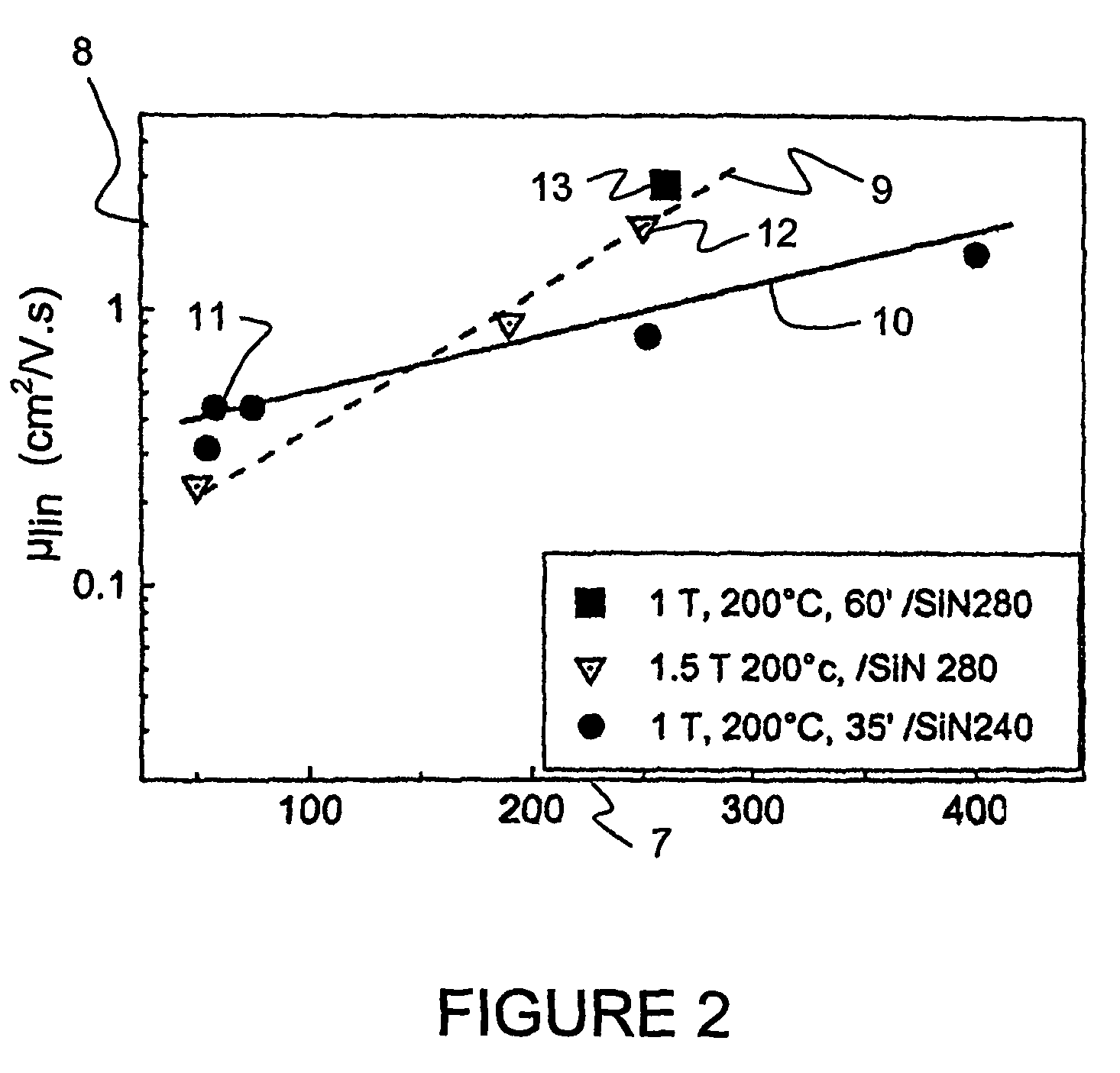

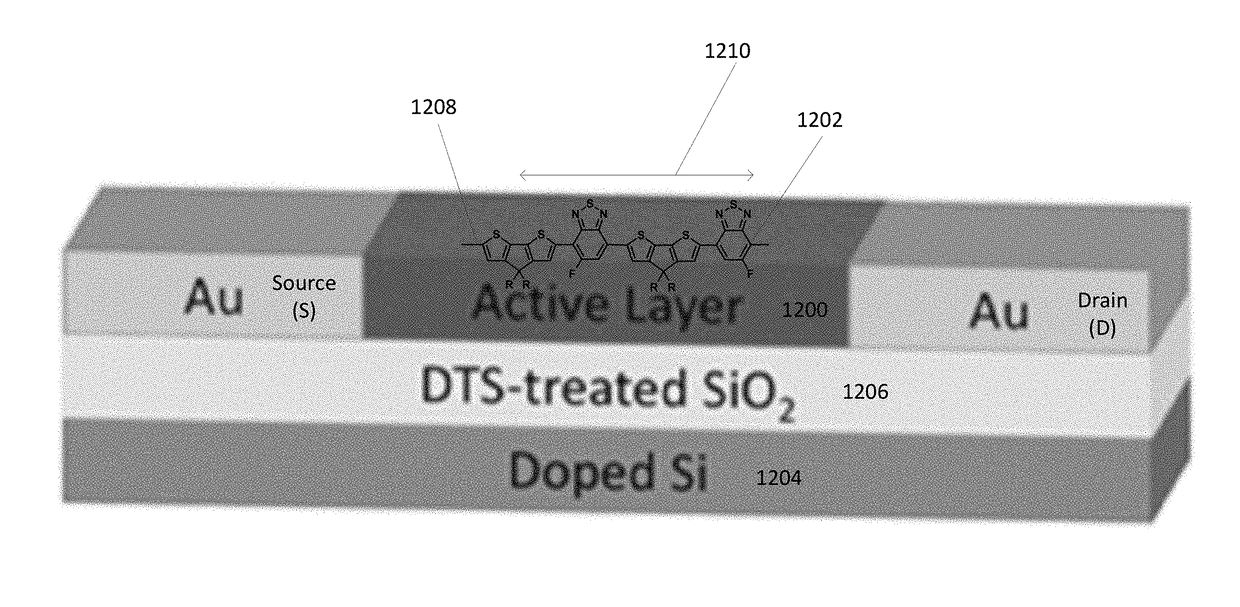

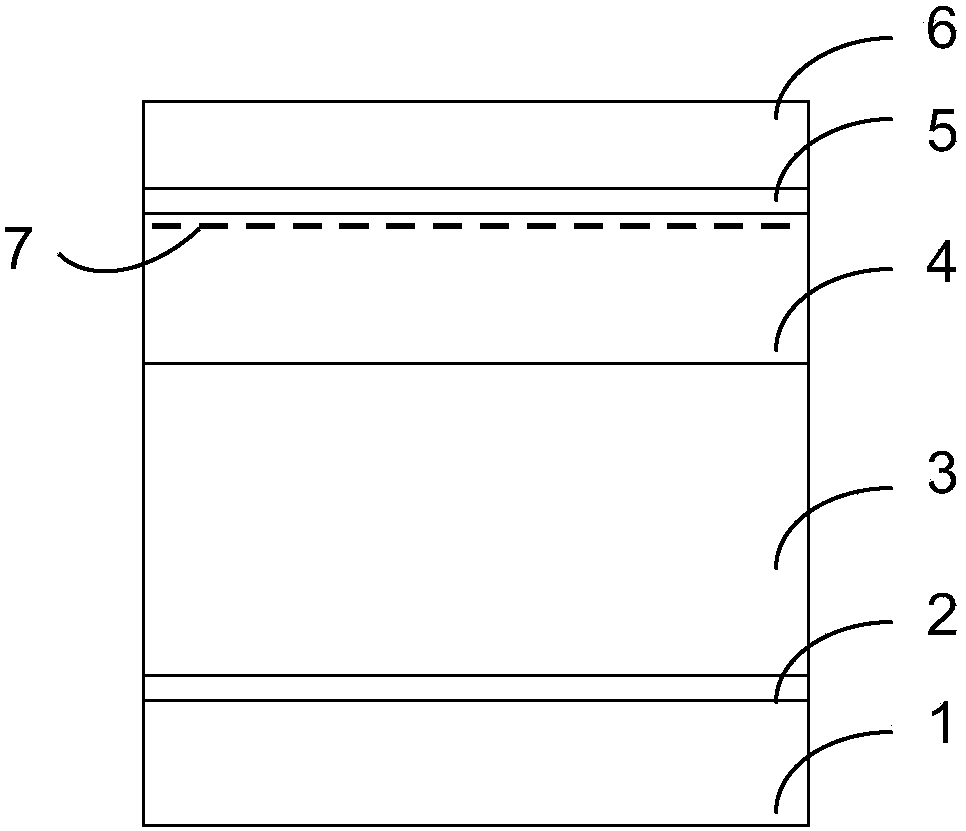

Transistor for active matrix display and a method for producing said transistor

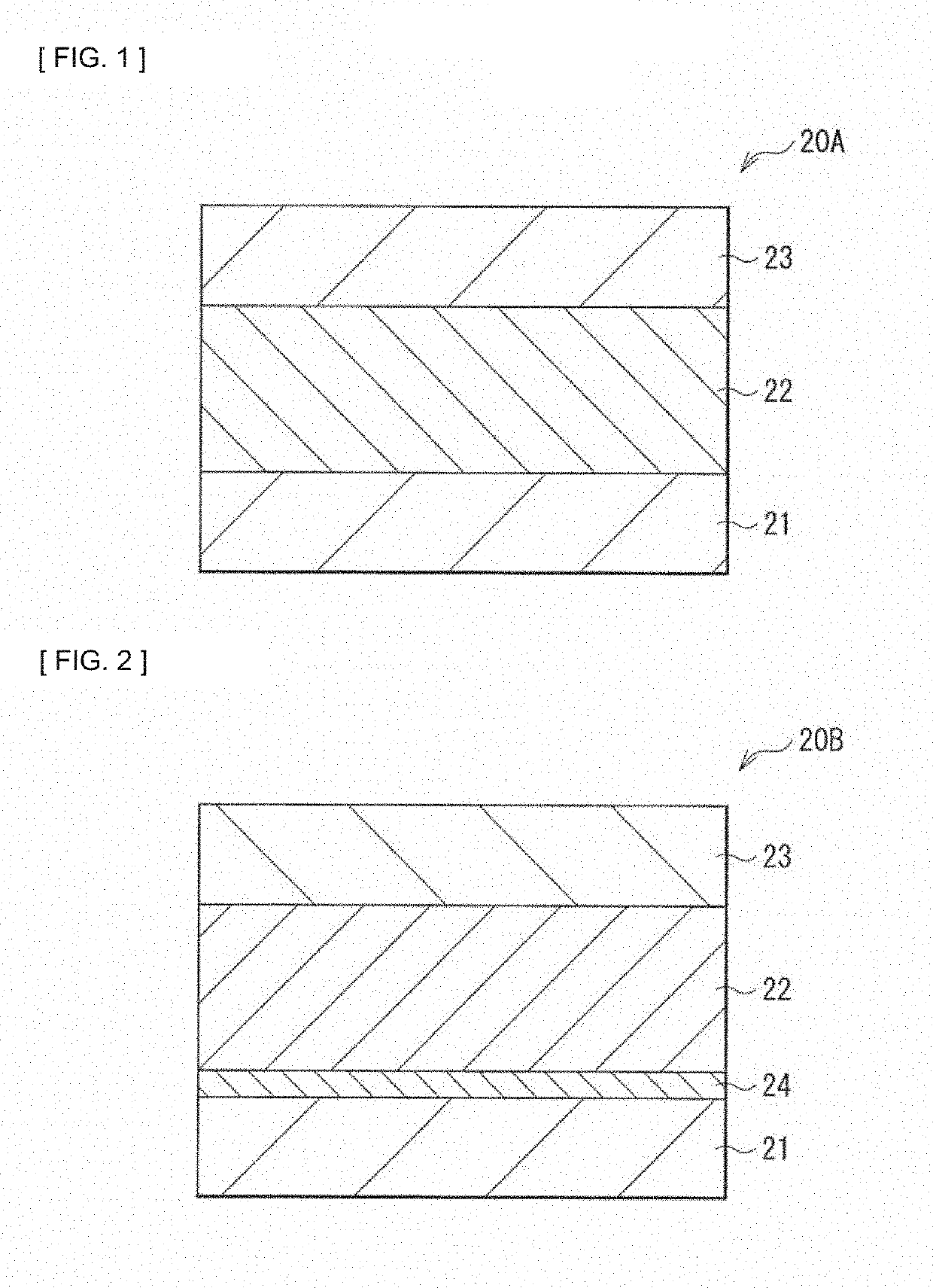

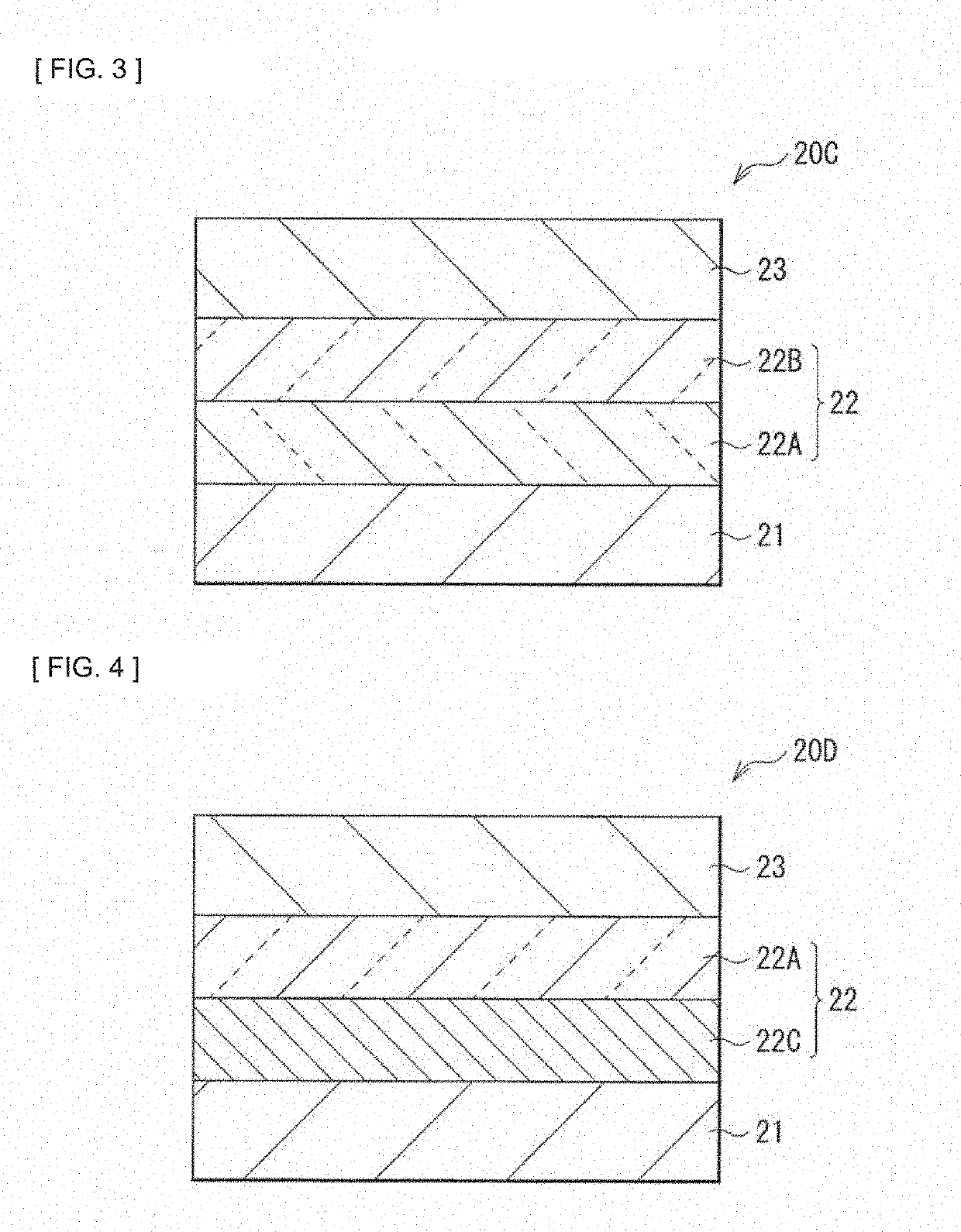

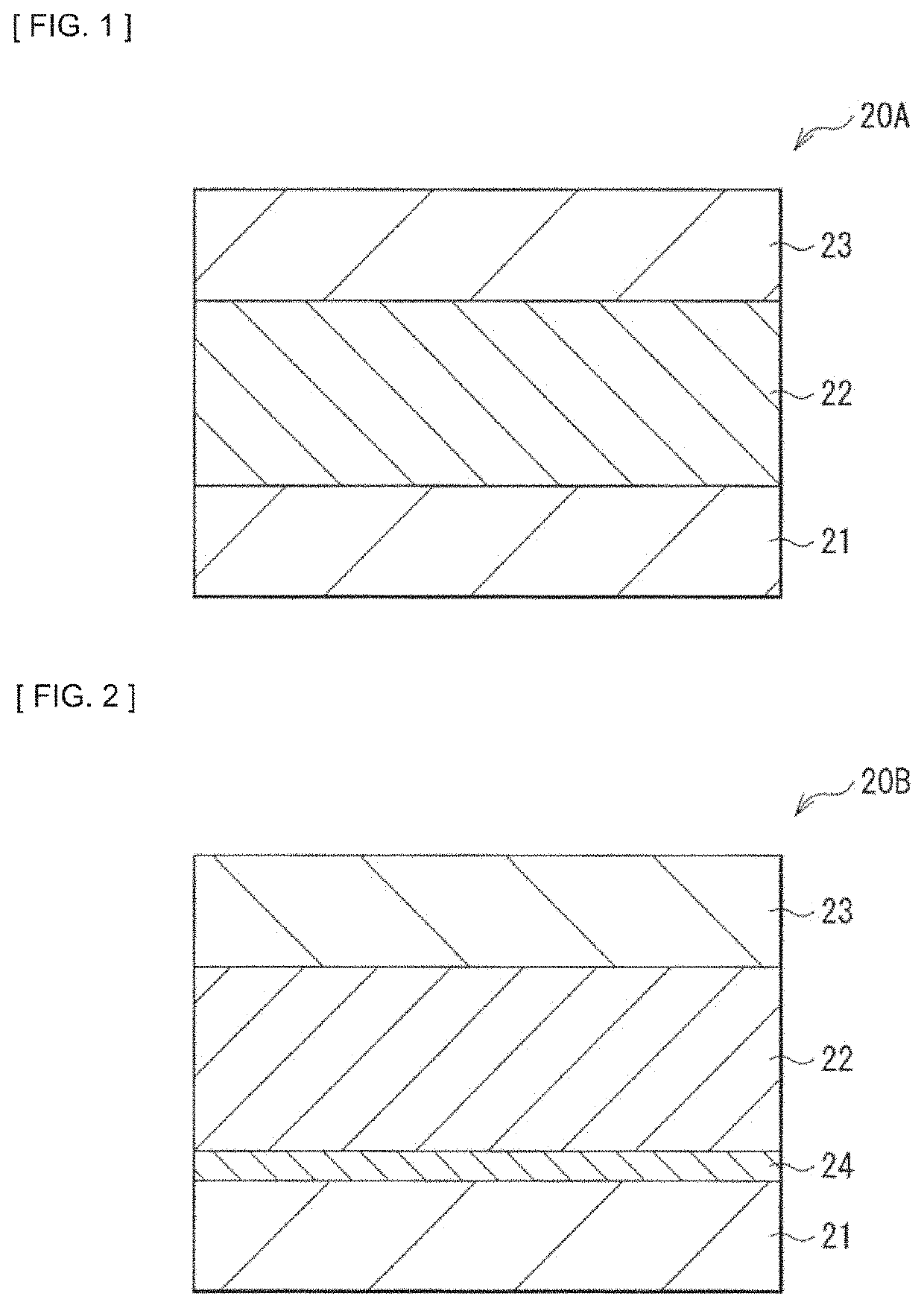

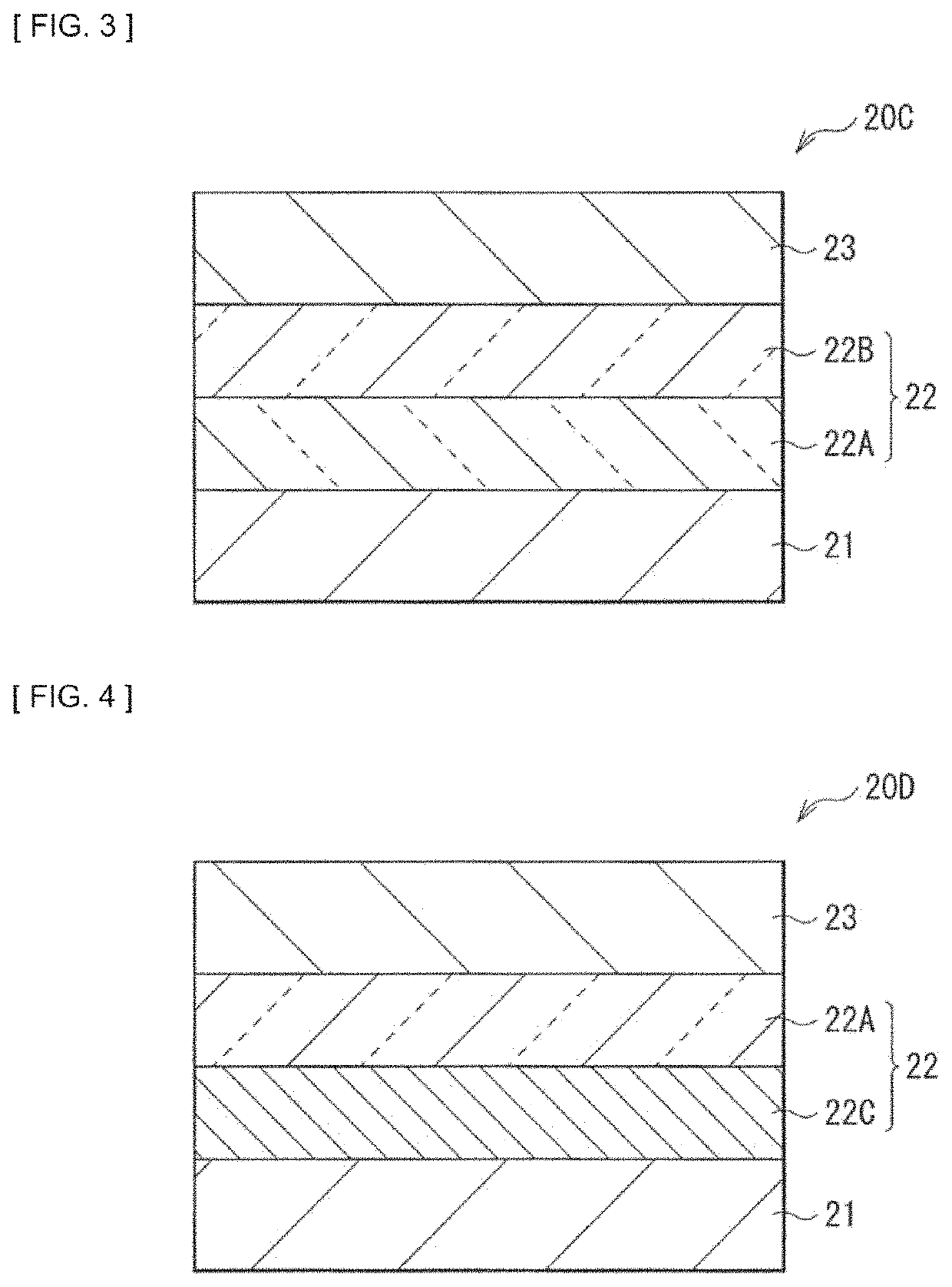

InactiveUS7863113B2Improve mobilityImproved Threshold Voltage StabilityTransistorSemiconductor/solid-state device manufacturingActive matrixEngineering

A transistor for active matrix display and a method for producing the transistor (1). The transistor (1) includes a microcrystalline silicon film (5) and an insulator (3). The crystalline fraction of the microcrystalline silicon film (5) is above 80%. According to the invention, the transistor (1) includes a plasma treated interface (4) located between the insulator (3) and the microcrystalline silicon film (5) so that the transistor (1) has a linear mobility equal or superior to 1.5 cm2V−1s−1, shows threshold voltage stability and wherein the microcrystalline silicon film (5) includes grains (6) whose size ranges between 10 nm and 400 nm. The invention concerns as well a display unit having a line-column matrix of pixels that are actively addressed, each pixel comprising at least a transistor as described above.

Owner:CENT NAT DE LA RECHERCHE SCI +1

Semiconductor device and preparation method thereof, and electronic apparatus

ActiveCN106611709AImprove cycle performanceImproved Threshold Voltage StabilitySolid-state devicesSemiconductor/solid-state device manufacturingIsolation layerSemiconductor

The invention relates to a semiconductor device and a preparation method thereof, and an electronic apparatus. The method comprises the following steps: S1, providing a semiconductor substrate, wherein a plurality of gate laminations are formed on the semiconductor substrate, and the gate laminations include a floating gate, an isolation layer, a control gate and a mask layer which are laminated in turn; S2, sequentially forming a first gap wall material layer and a second gap wall material layer on the semiconductor substrate and the gate laminations to cover the gate laminations, wherein the first gap wall material layer is made of oxide; S3, etching the second gap wall material layer to expose the first gap wall material layer on the semiconductor substrate and on the upper sidewall of the mark layer; S4, removing the exposed first gap wall material layer through etching to form a gap wall on the sidewall of the gate laminations; and S5, depositing a stop layer to cover the gap wall and the mask layer. Through the method, the yield and performance of NOR flash memories are improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

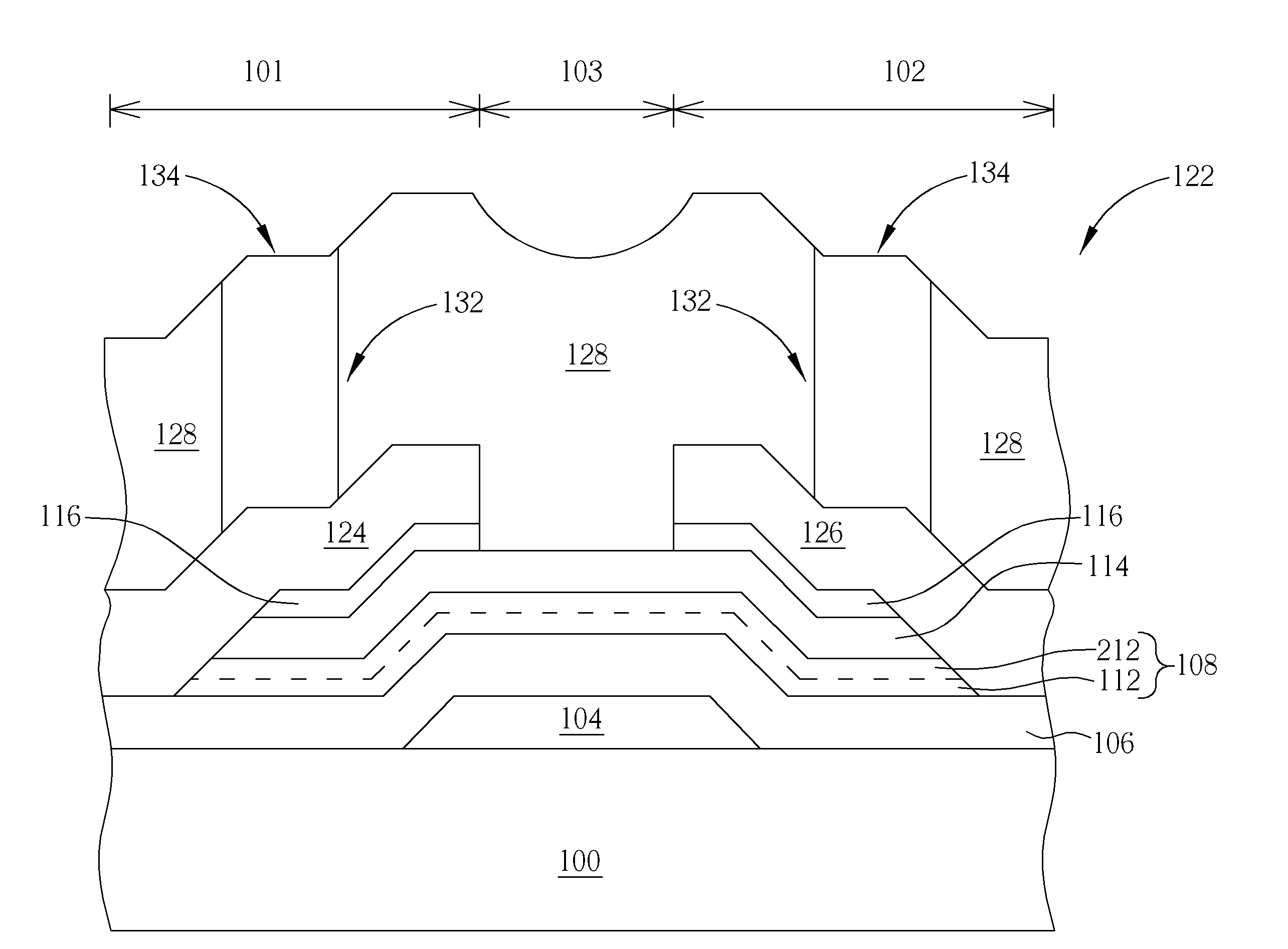

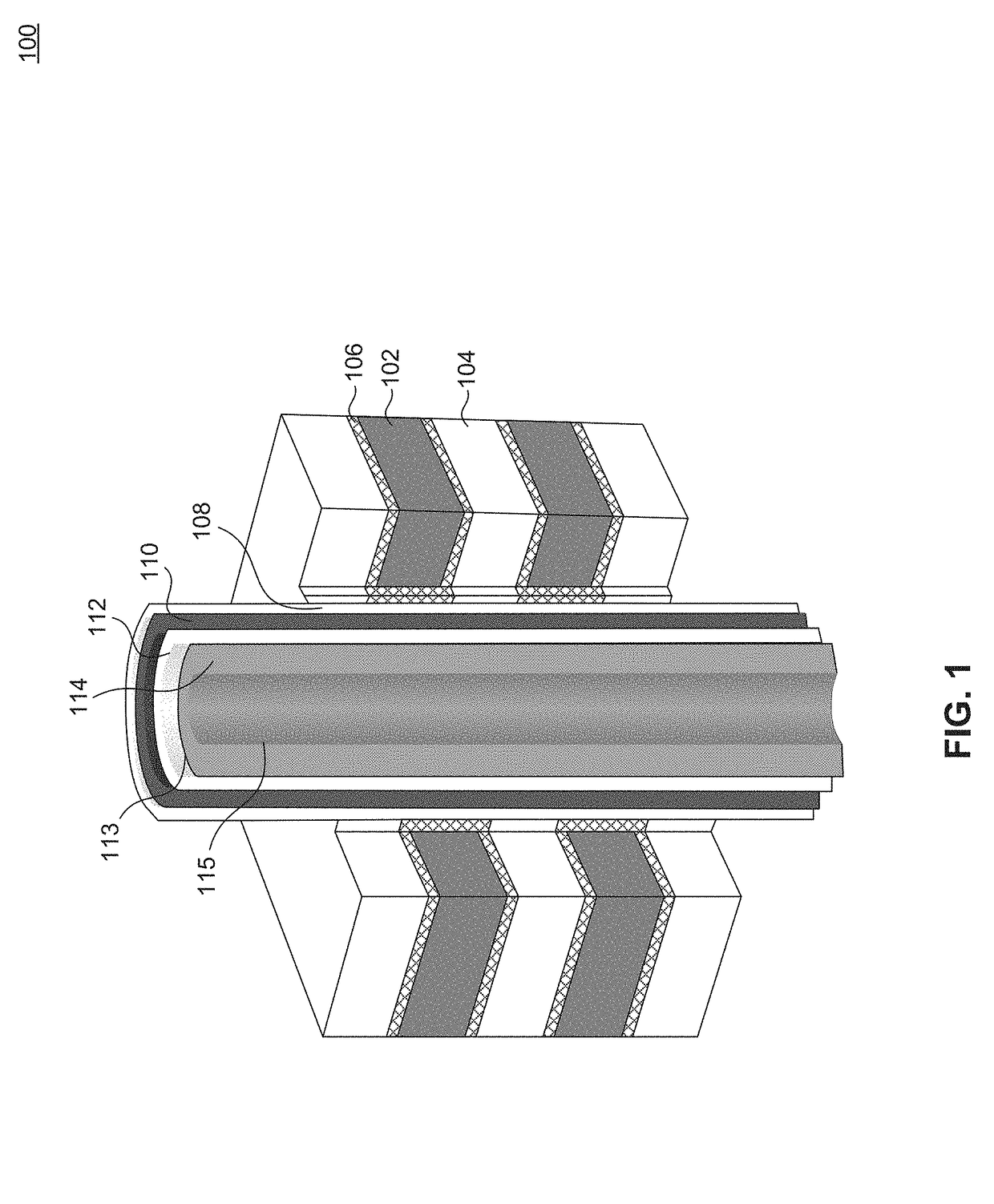

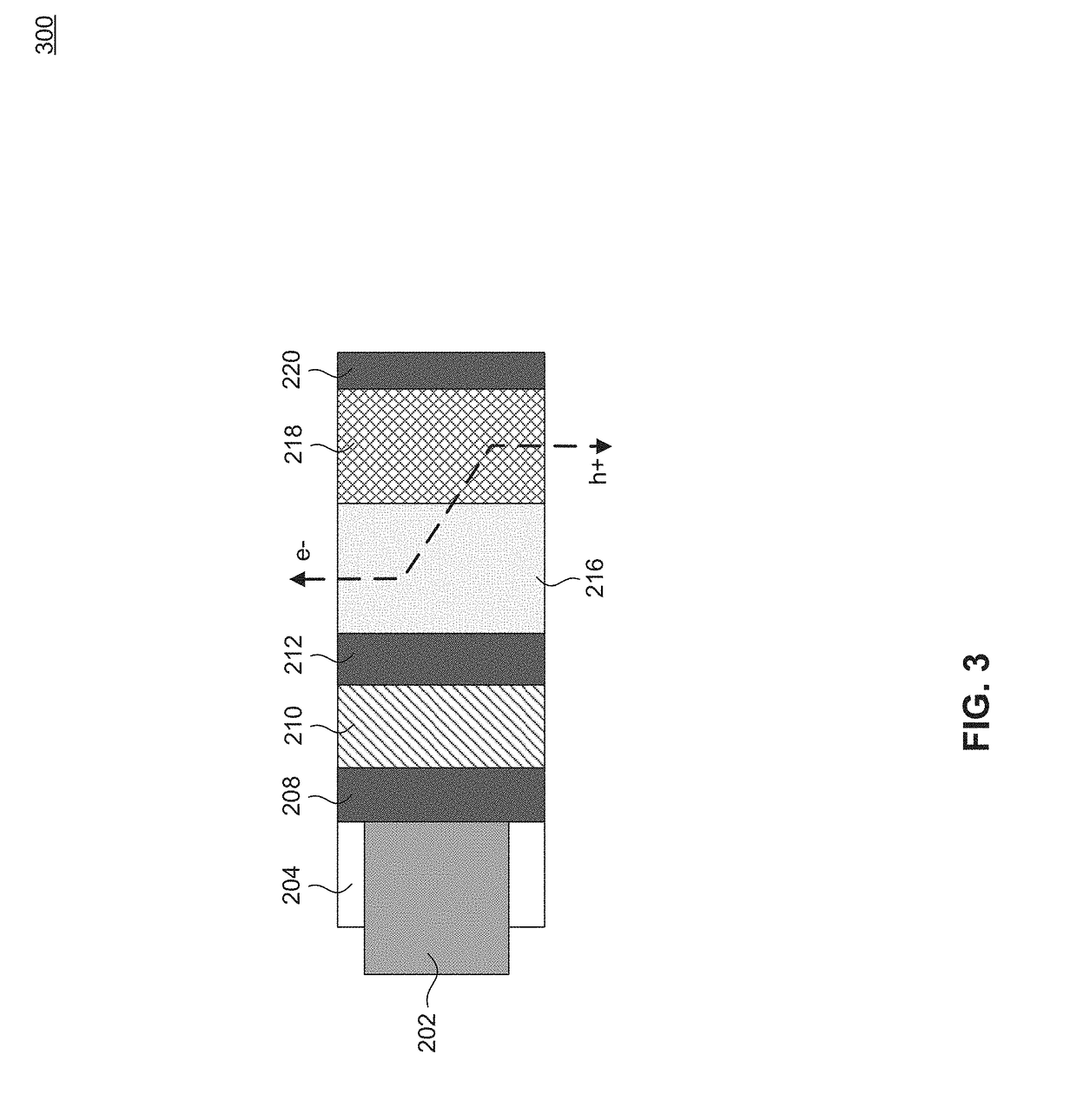

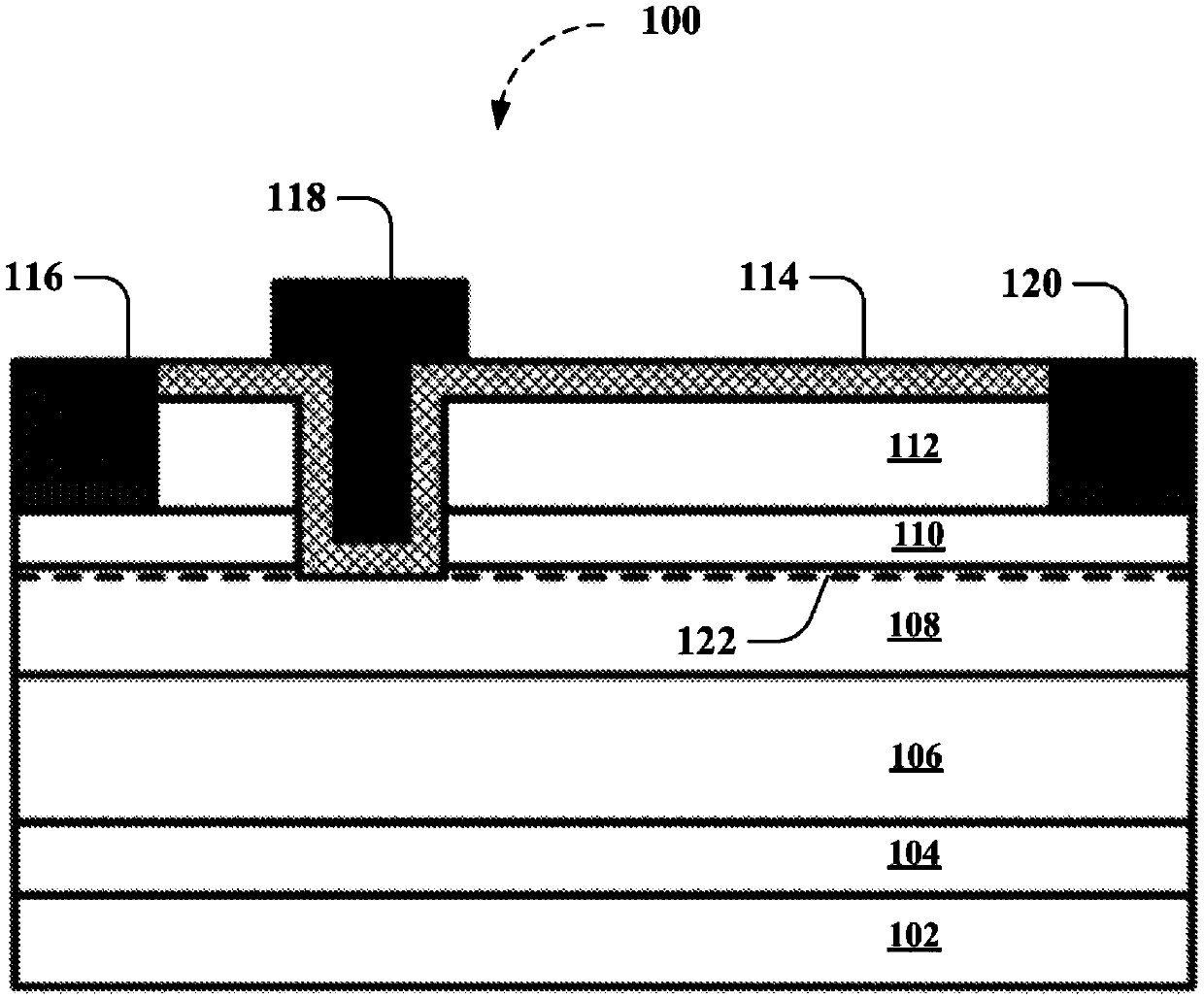

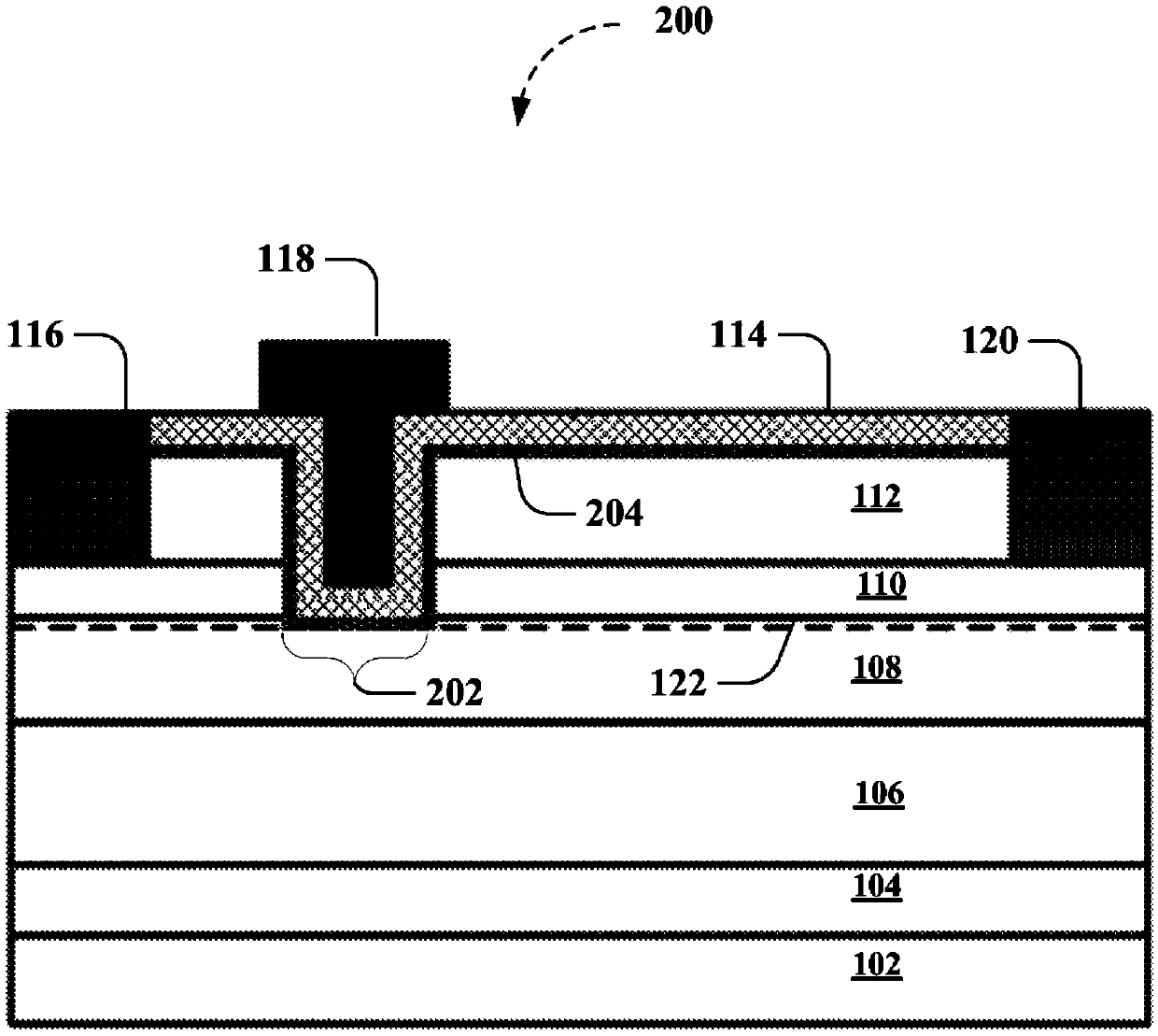

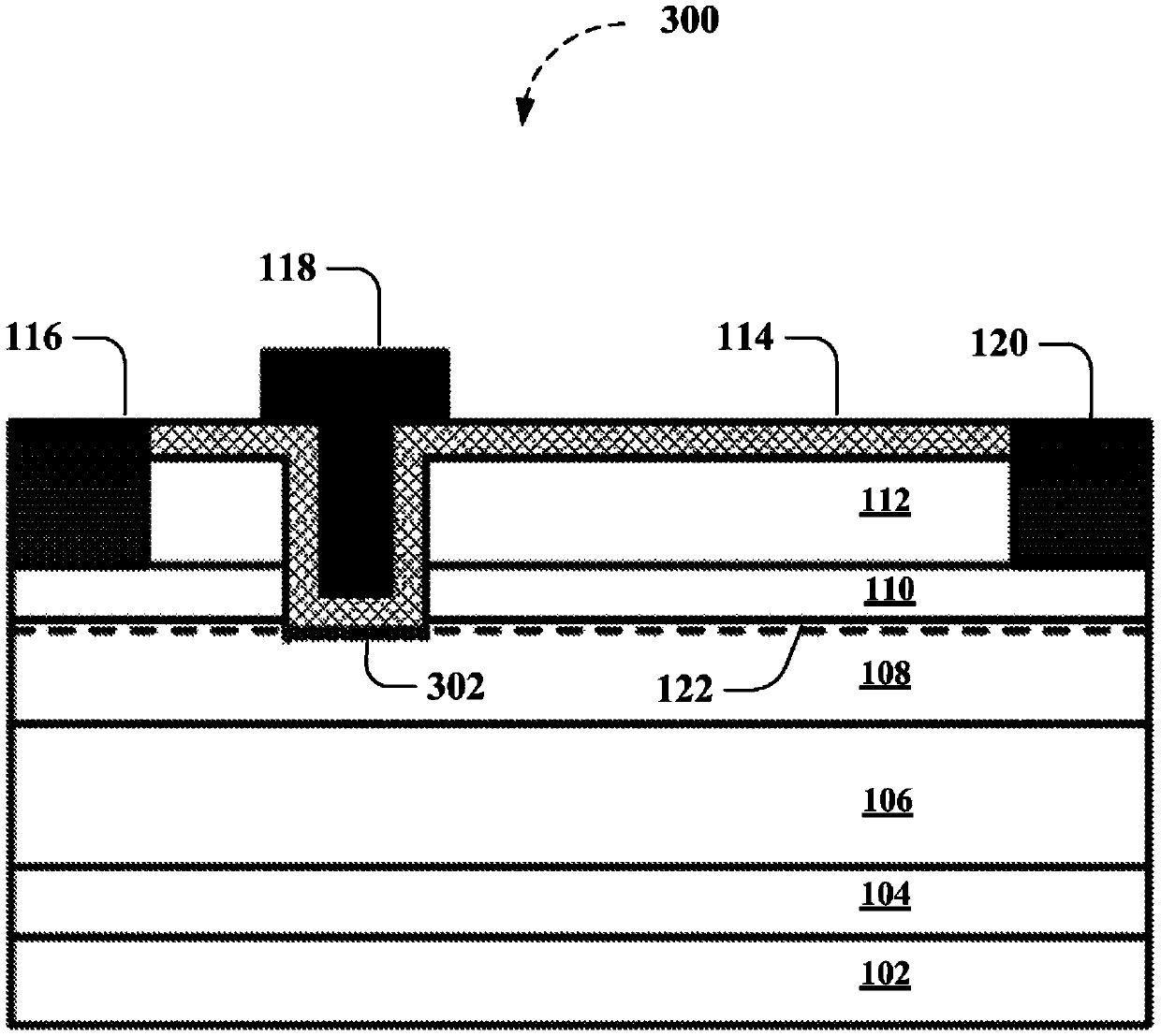

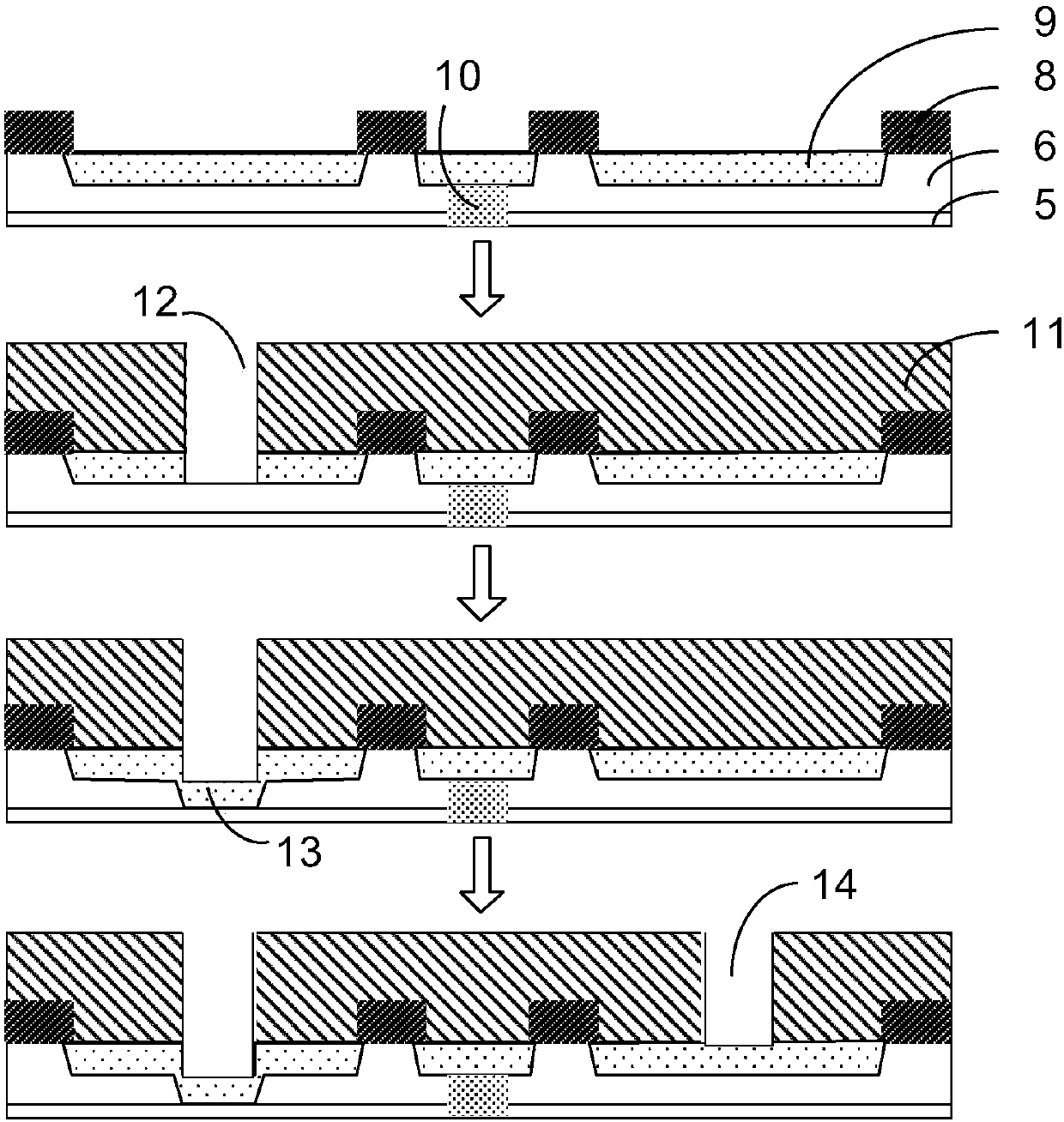

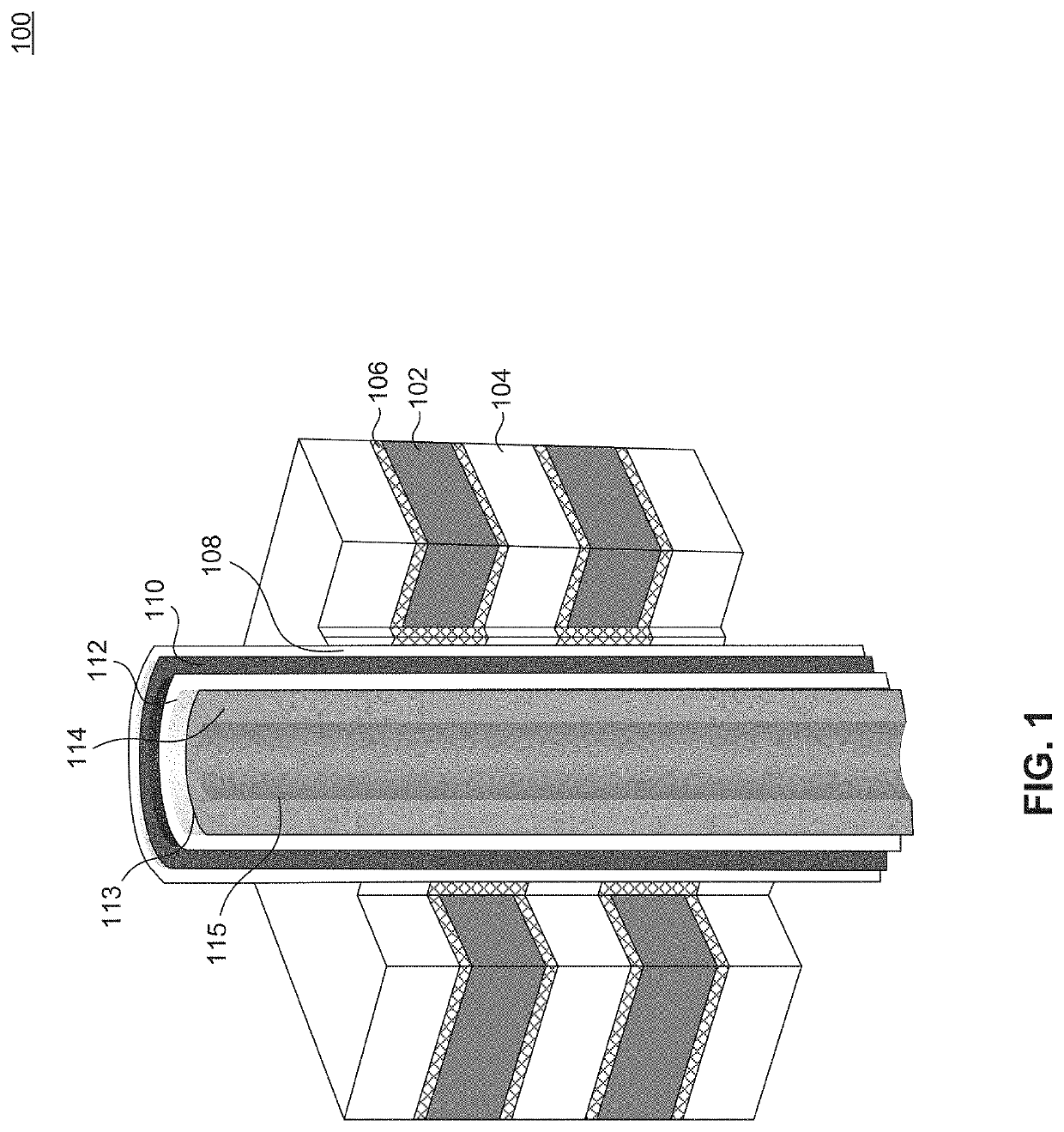

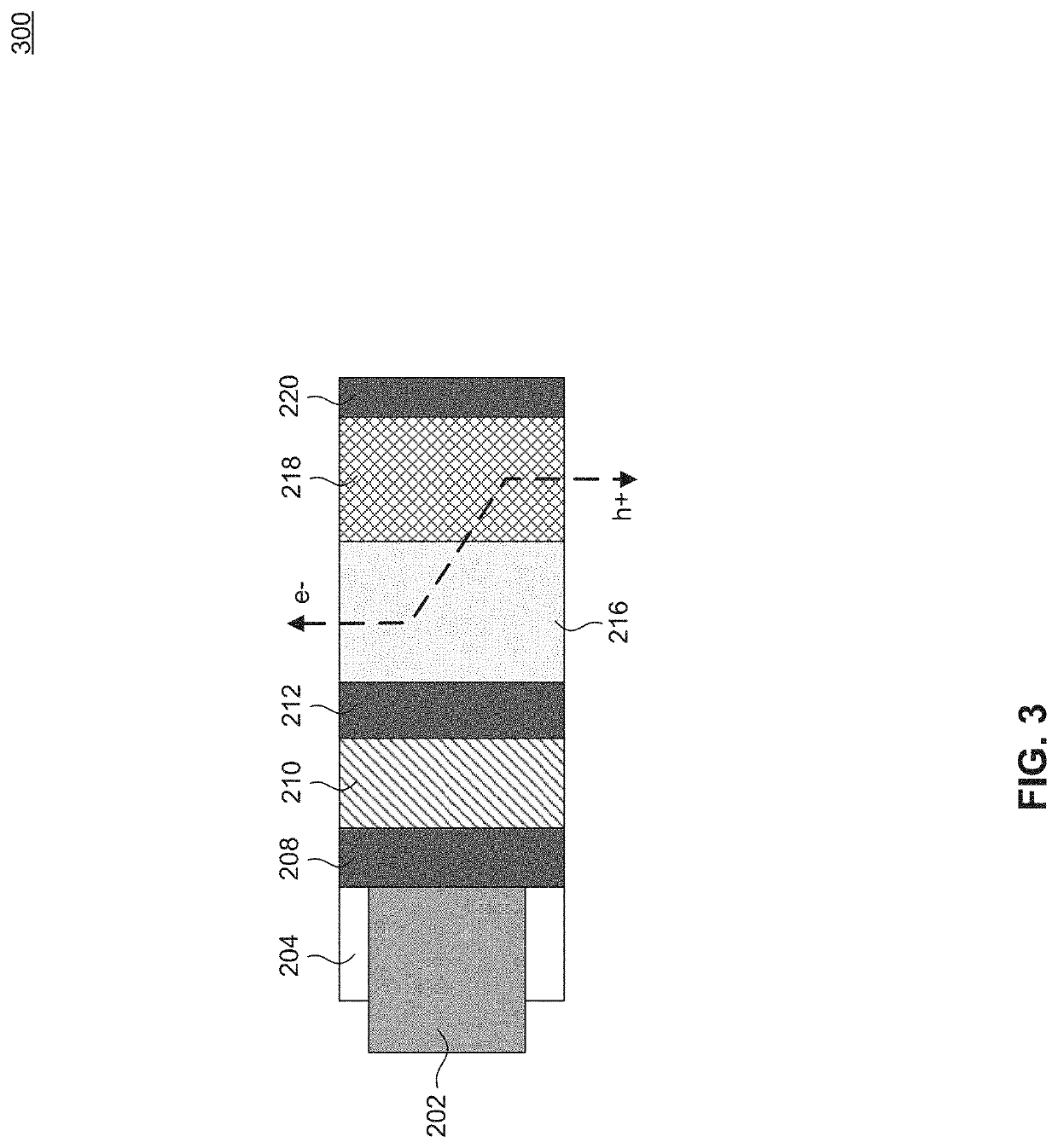

Metal-insulator-semiconductor transistors with gate-dielectric/semiconductor interfacial protection layer

InactiveCN109690784AImproved Threshold Voltage StabilityHigh Gate Dielectric ReliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesDielectricGate dielectric

Structures, devices and methods are provided for forming an interface protection layer (204) adjacent to a fully or partially recessed gate structure (202) of a group III nitride, a metal-insulator-semiconductor high-electron-mobility transistor (MIS-HEMT) device or a metal-insulator-semiconductor field-effect transistor (MIS-FET) device, and forming a gate dielectric (114) disposed on the interface protection layer (204).

Owner:THE HONG KONG UNIV OF SCI & TECH

Semiconductor structure and forming method thereof

PendingCN114334986AIncrease channel widthImproved Threshold Voltage StabilityTransistorSolid-state devicesSemiconductor structureIsolation layer

The invention discloses a semiconductor structure and a forming method thereof. The method comprises the following steps: providing an initial substrate; a substrate and a plurality of active regions located on the substrate and arranged in the first direction are formed, the first direction is parallel to the surface of the substrate, each active region comprises a first region and second regions located on the two sides of the first region respectively, and the first region and the second regions are arranged in the first direction, the top surface of the second region is lower than the top surface of the first region; forming a plurality of floating gates on the surfaces of the plurality of active regions; and forming an isolation layer between the adjacent active regions, wherein the isolation layer is also located on a part of the side wall of the floating gate. The channel width of the formed device is increased, the threshold voltage stability of the device is improved, the influences of the short channel effect and the drain induced barrier reduction effect of the device are improved, and therefore the performance of the device is improved.

Owner:HUA HONG SEMICON WUXI LTD

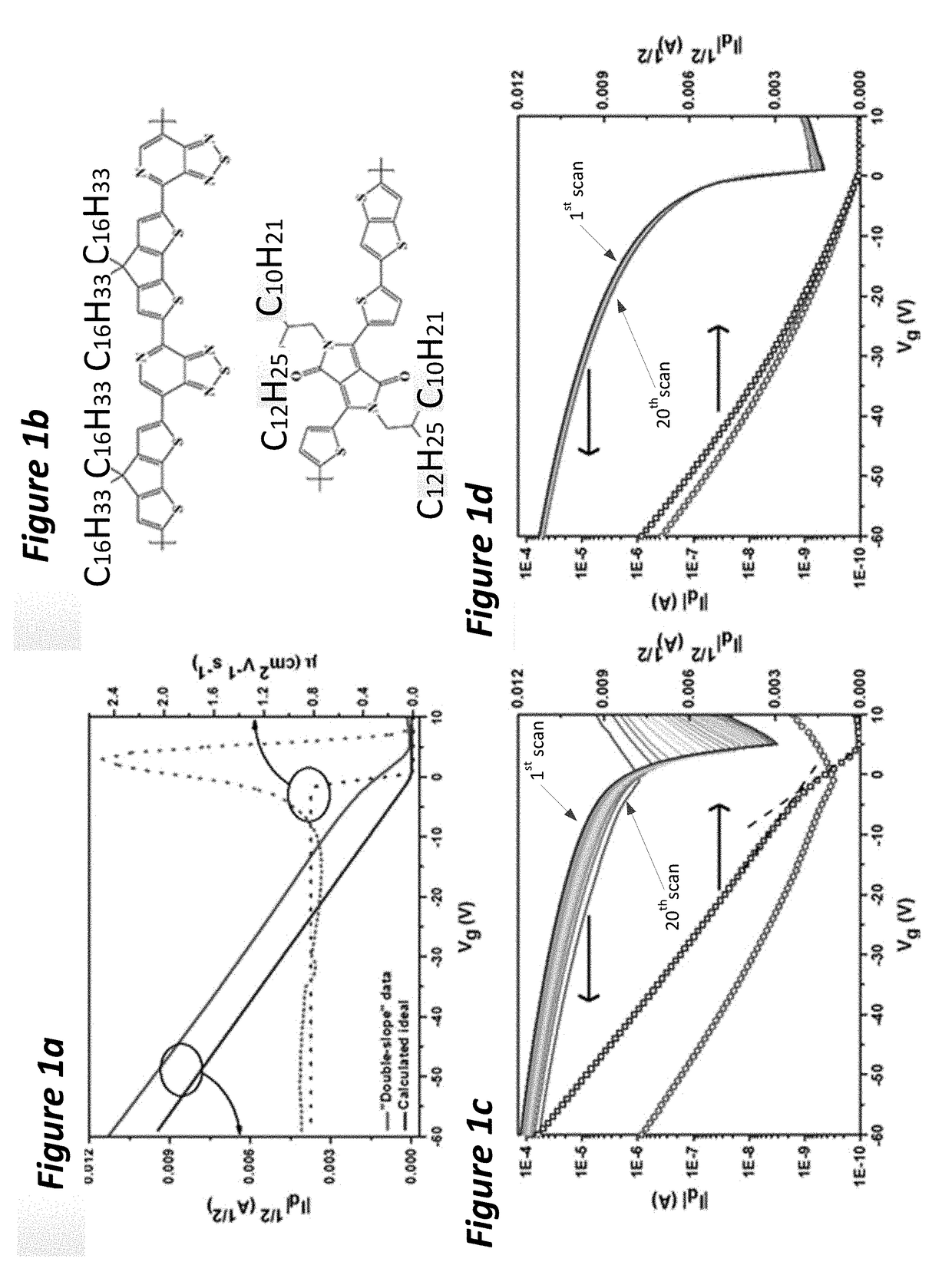

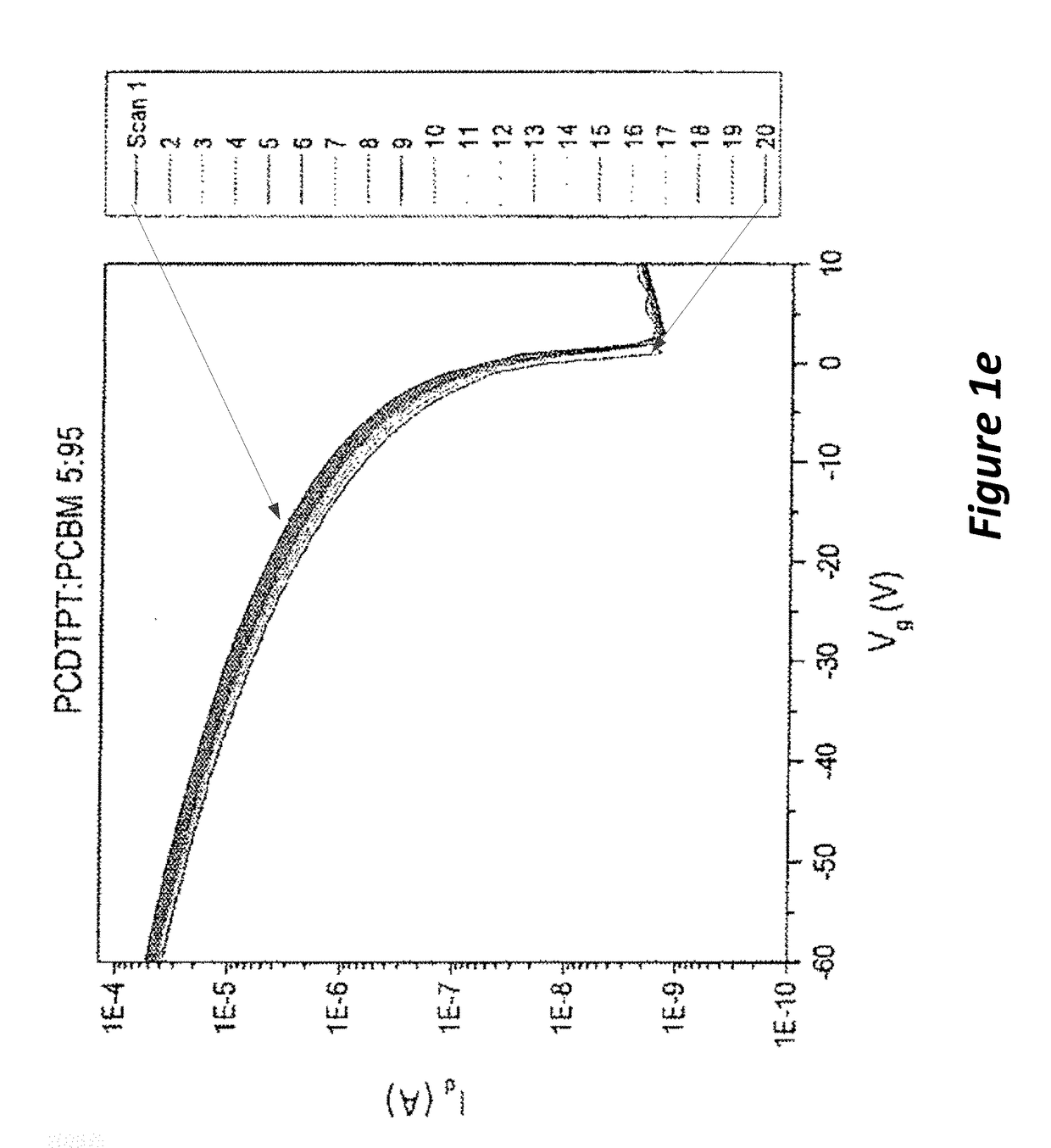

Stable organic field-effect transistors by incorporating an electron-accepting molecule

ActiveUS20170200894A1General applicabilitySuppress instabilitySolid-state devicesSemiconductor/solid-state device manufacturingOrganic field-effect transistorInstability

Owner:RGT UNIV OF CALIFORNIA

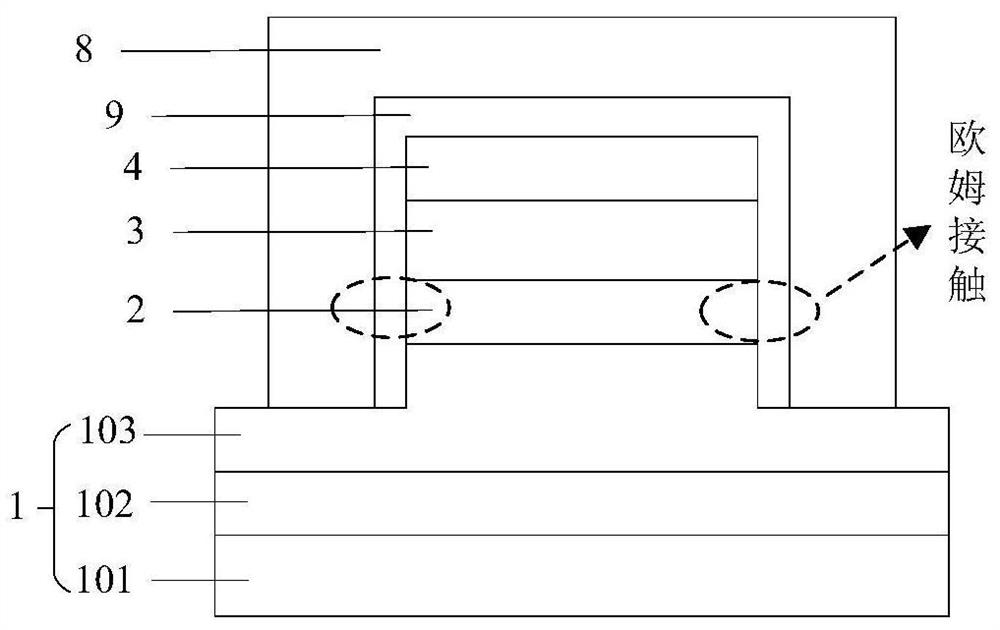

GaN MISFET device with high-quality gate interface and preparation method thereof

PendingCN109755301AQuality improvementOmit removal stepSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricDielectric layer

The invention relates to a GaN MISFET device with a high-quality gate interface and a preparation method thereof. The device comprises a substrate, and an epitaxial layer, a gate dielectric layer, a source, a drain and a gate which grown on the substrate. The epitaxial layer comprises a stress buffer layer and a GaN epitaxial layer which are grown in a primary epitaxial mode; a secondary epitaxiallayer is grown on a reselection area thereon, and a groove channel is formed; a high-quality SiO2 mask layer subjected to high-temperature annealing in the secondary epitaxy is retained as a first gate dielectric layer, and a second gate dielectric layer is grown on the mask layer. Gate metal covers the gate dielectric layer of the groove channel, and two ends of the gate are covered with metal to form the source and the drain. Compared with an existing method, in which the SiO2 mask layer is removed and then a gate dielectric layer is deposited; the device structure and the preparation process of the invention are simpler and more reliable, and the quality of the gate dielectric layer and the dielectric layer / GaN interface are better optimized, so that the performance of the GaN MISFET device is improved, and particularly, it is very critical to improvement of the problems in reduction of the channel resistance, the gate electric leakage, the threshold voltage stability and the like.

Owner:SUN YAT SEN UNIV

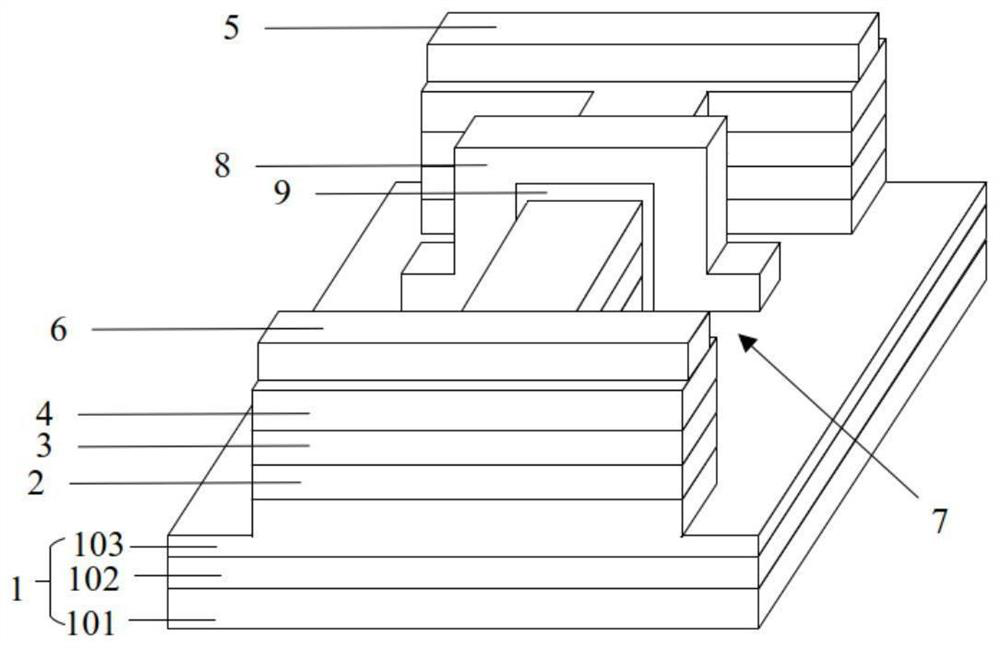

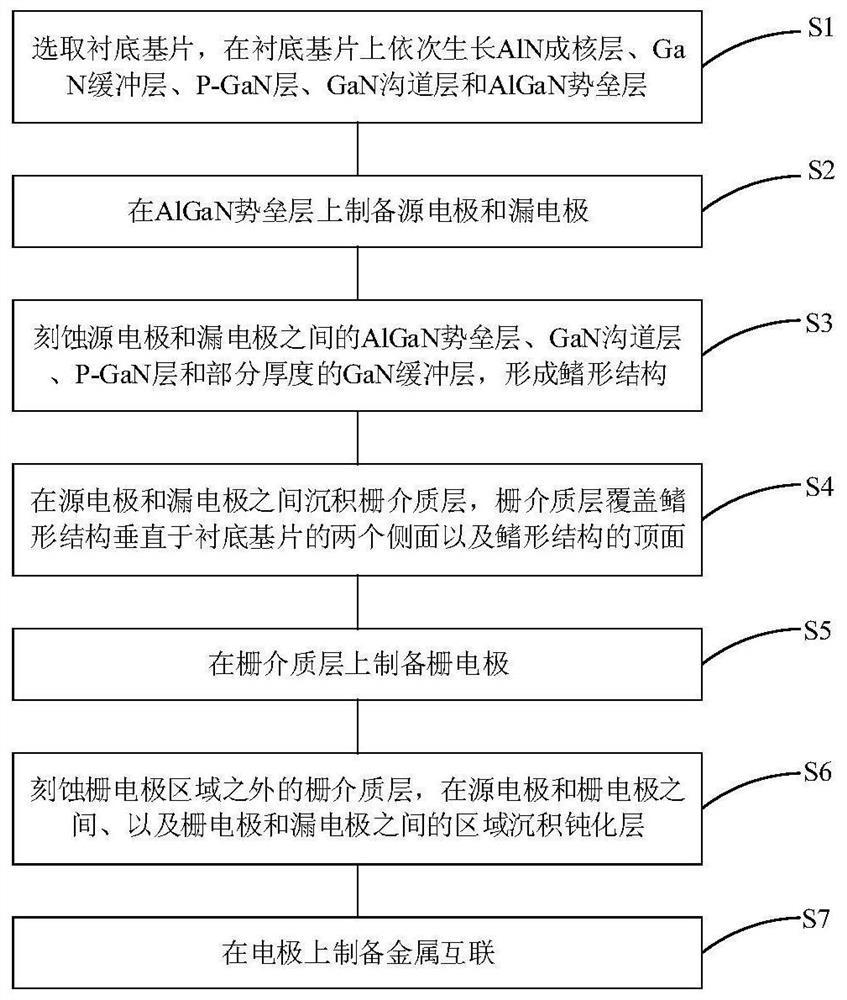

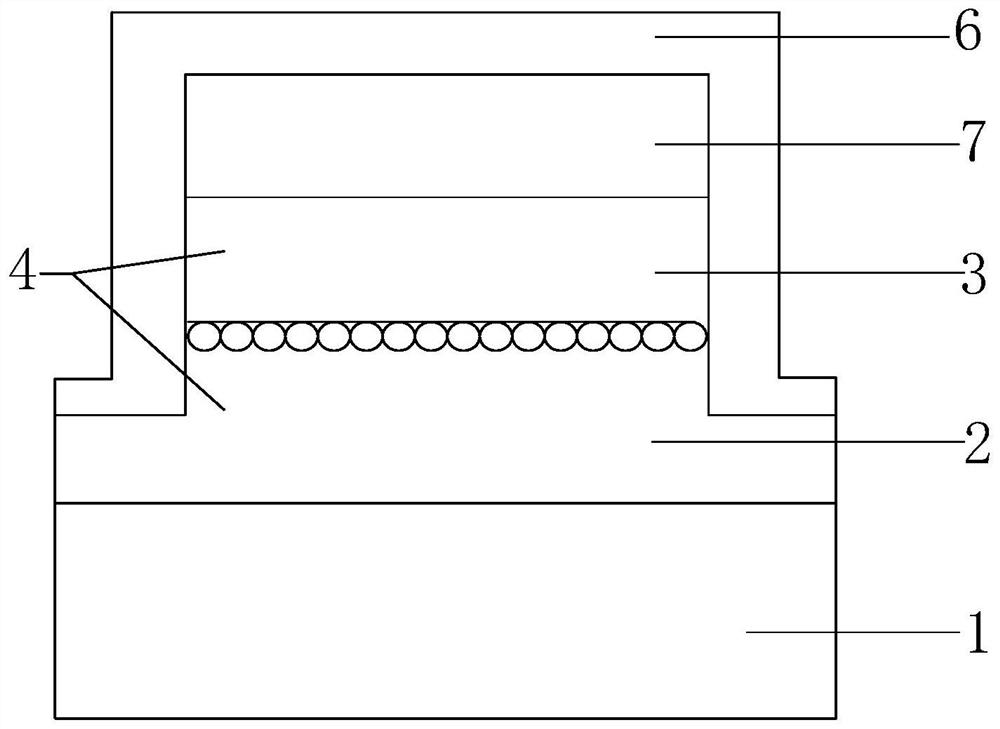

Back gate full-controlled AlGaN/GaN heterojunction enhanced power HEMT device and preparation method thereof

ActiveCN112768508AImprove breakdown voltageReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionGate dielectric

The invention relates to a back gate full-controlled AlGaN / GaN heterojunction enhanced power HEMT device and a preparation method thereof. The HEMT device comprises: a substrate, a P-GaN layer, a GaN channel layer and an AlGaN barrier layer which are sequentially stacked from bottom to top; a source electrode disposed on one side of the AlGaN barrier layer; a drain electrode arranged on the other side of the AlGaN barrier layer and opposite to the source electrode, wherein the substrate, the P-GaN layer, the GaN channel layer and the AlGaN barrier layer with partial thickness between the source electrode and the drain electrode form a fin-shaped structure; a gate electrode located between the source electrode and the drain electrode and covering the two side faces, perpendicular to the substrate, of the fin-shaped structure and the top face of the fin-shaped structure, wherein ohmic contact is formed between the gate electrode and the P-GaN layer; and a gate dielectric layer arranged between the gate electrode and the fin-shaped structure. According to the back gate full-controlled AlGaN / GaN heterojunction enhanced power HEMT device, the mode that the P-GaN layer and the gate metal form the back gate is adopted, an AlGaN / GaN heterojunction gate electric field is adjusted, and the breakdown voltage of the device can be improved.

Owner:XIDIAN UNIV

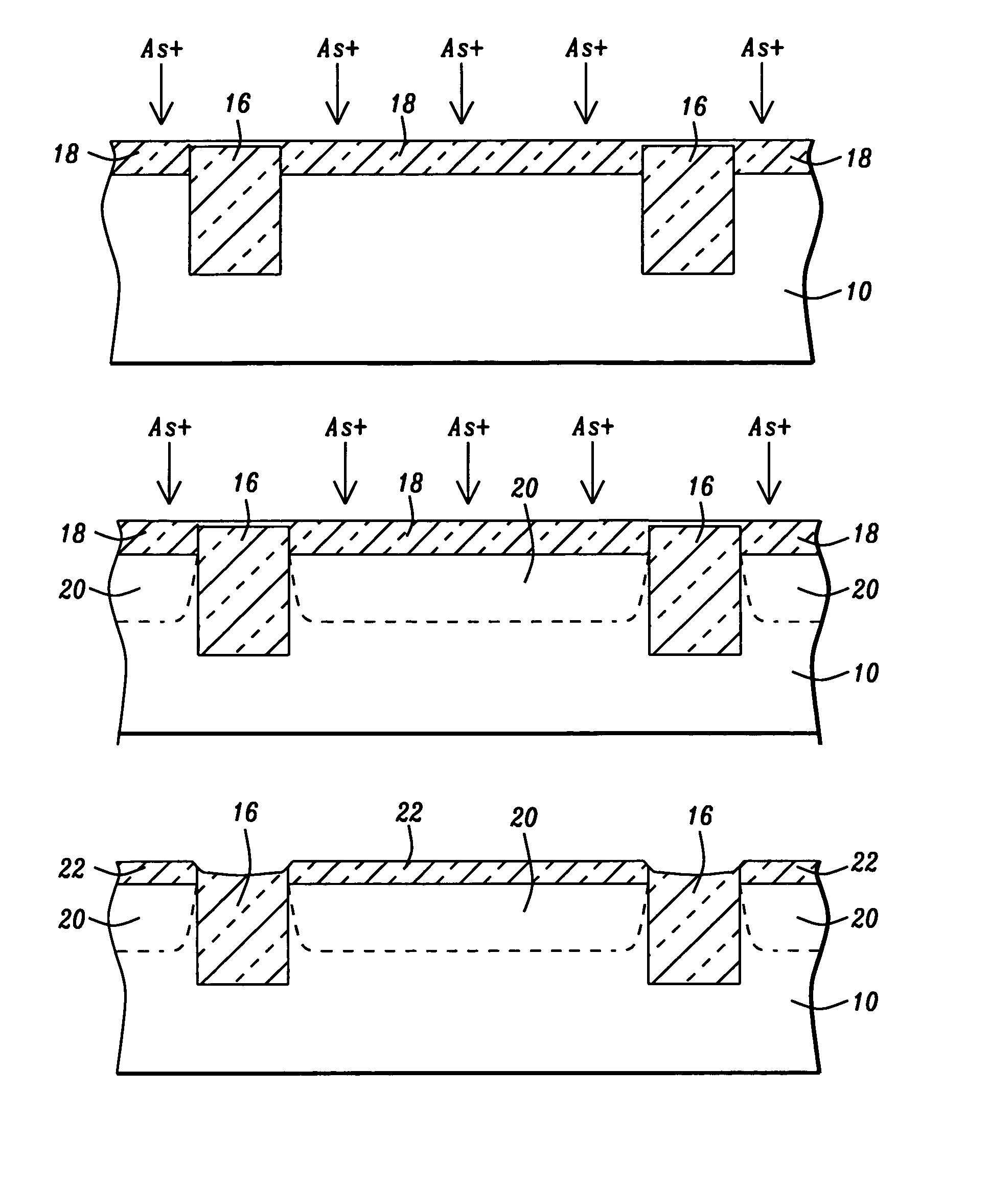

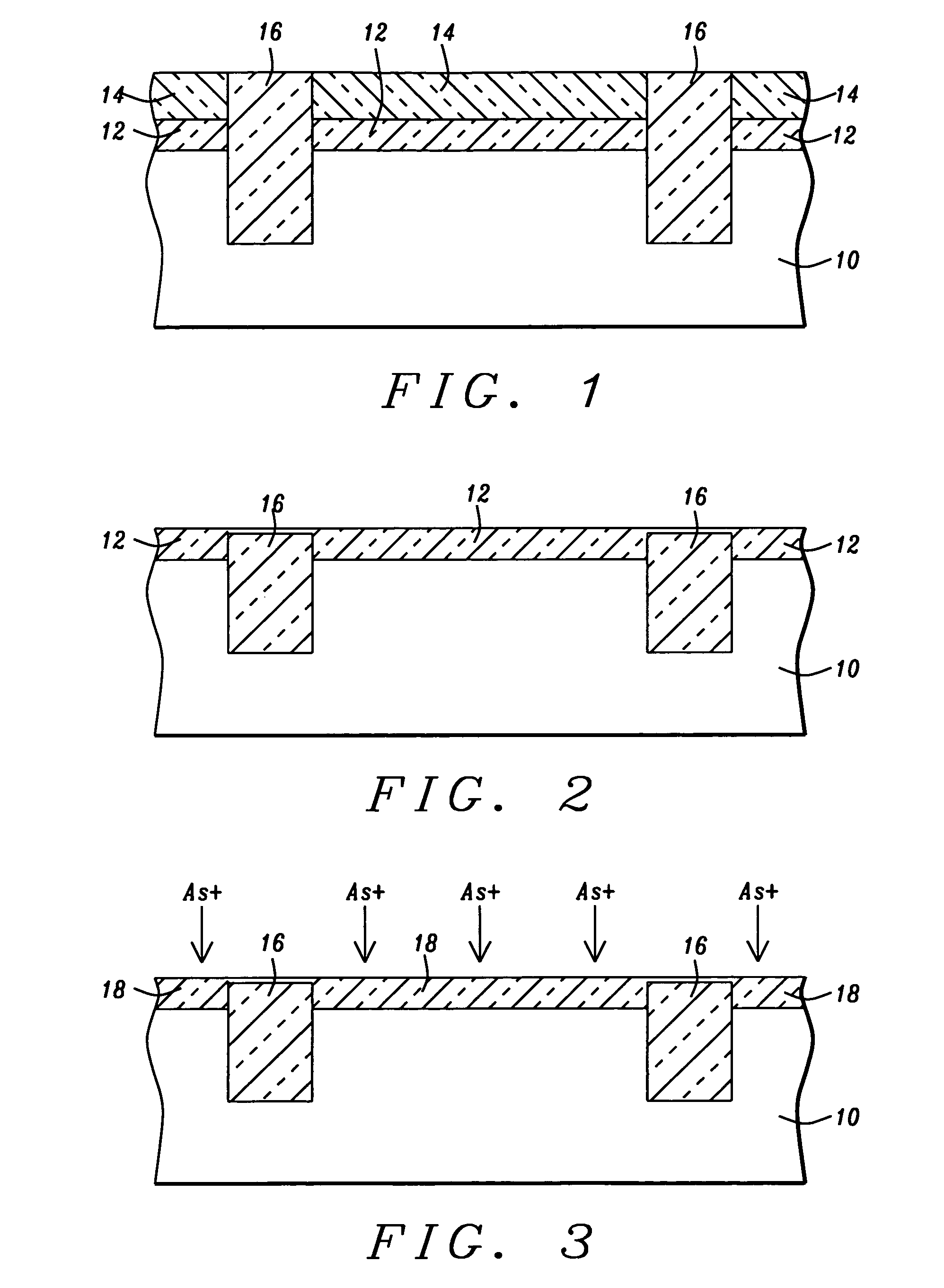

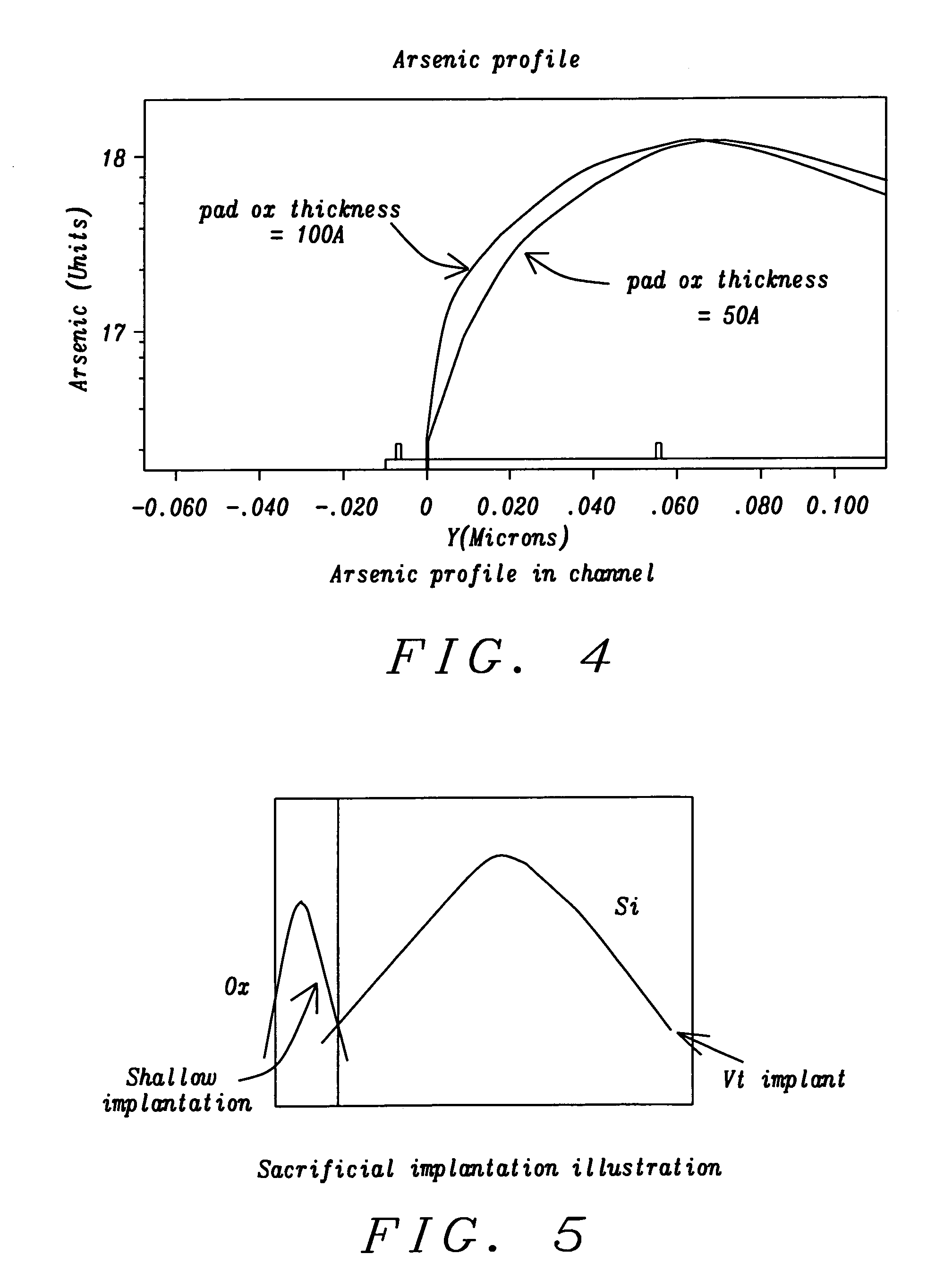

Shallow low energy ion implantation into pad oxide for improving threshold voltage stability

InactiveUS7259072B2Improved Threshold Voltage StabilitySemiconductor/solid-state device manufacturingSemiconductor devicesDopantMOSFET

A method is described to fabricate a MOSFET device with increased threshold voltage stability. After the pad oxide and pad nitride are deposited on the silicon substrate and shallow trenches are patterned and the pad nitride removed. As+ or P+ species are then implanted using low energy ions of approximately 5 keV into the pad oxide. Conventional As+ or P+ implant follows the shallow implant to form the n-wells. With this procedure of forming a sacrificial shallow implantation oxide layer, surface dopant concentration variation at pad oxide:silicon substrate interface is minimized; and threshold voltage stability variation of the device is significantly decreased.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

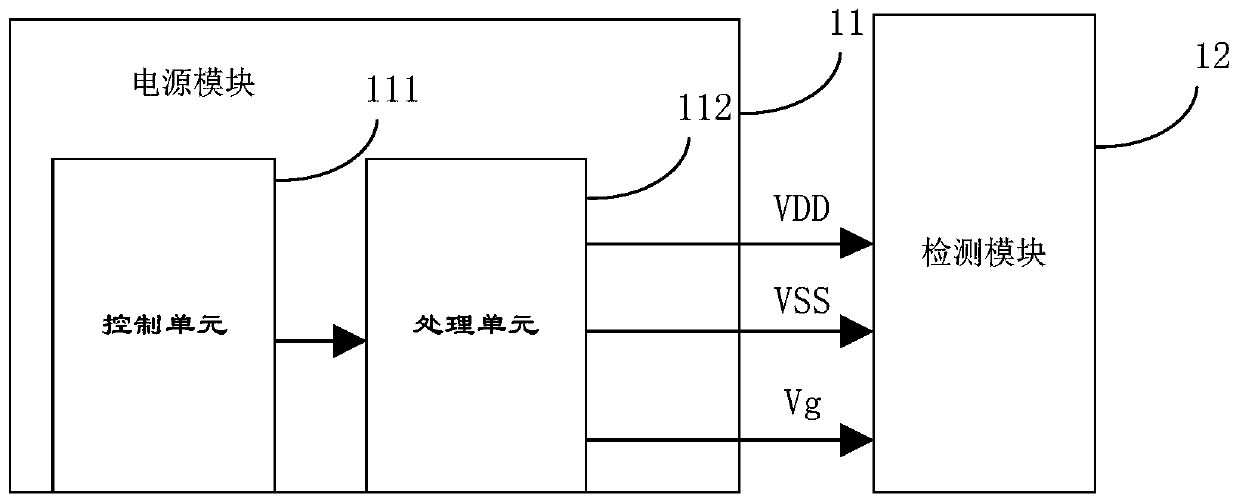

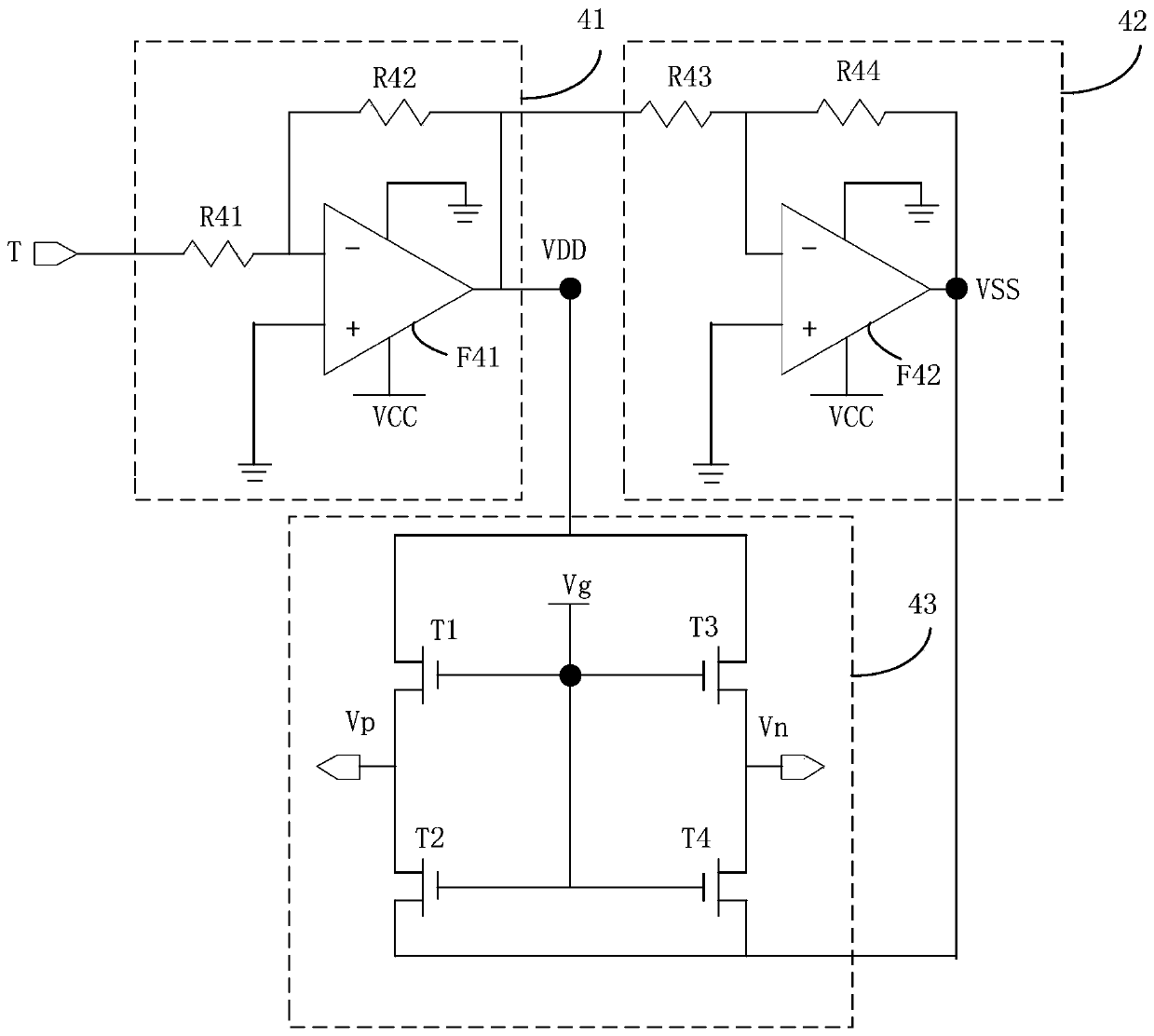

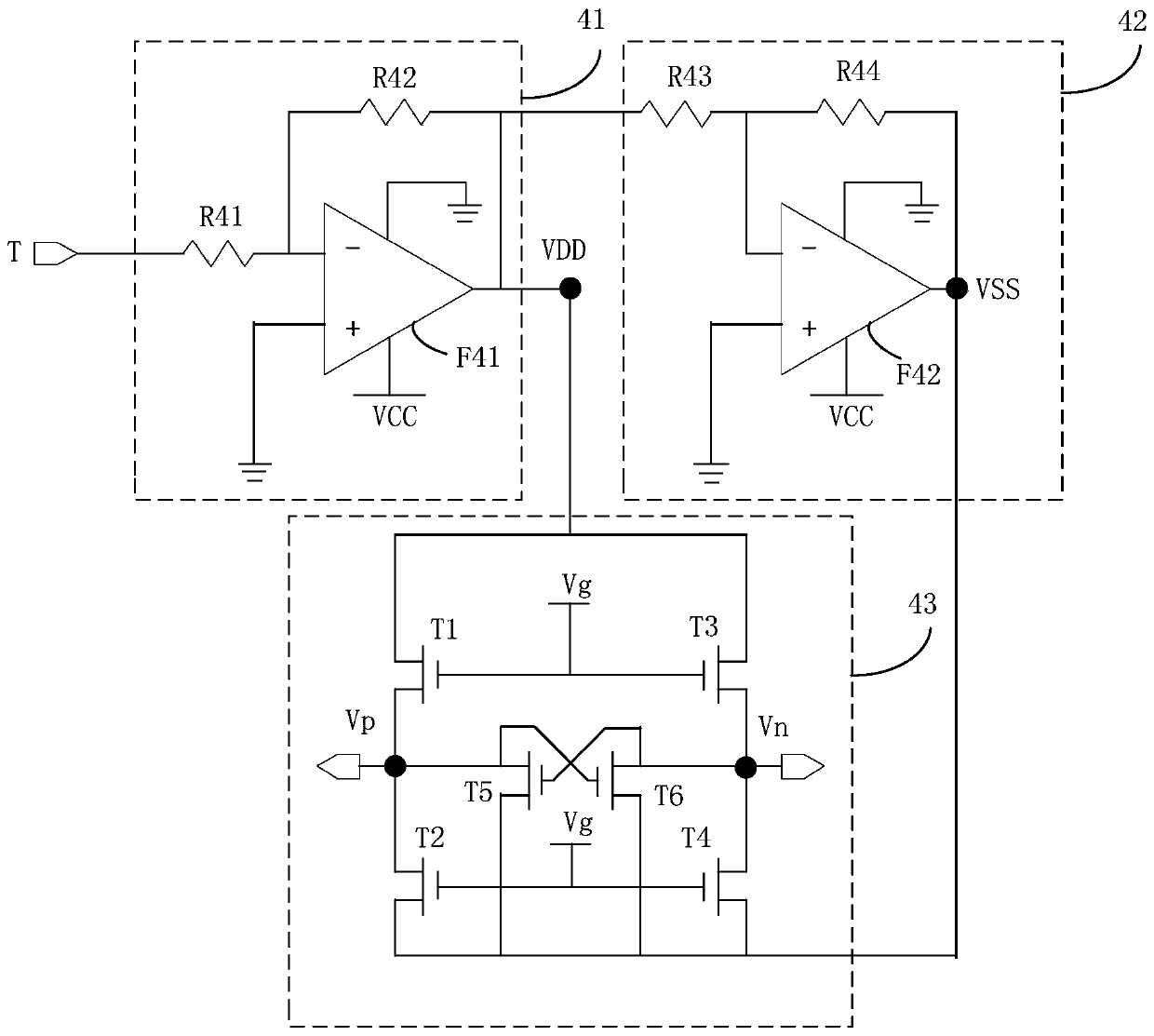

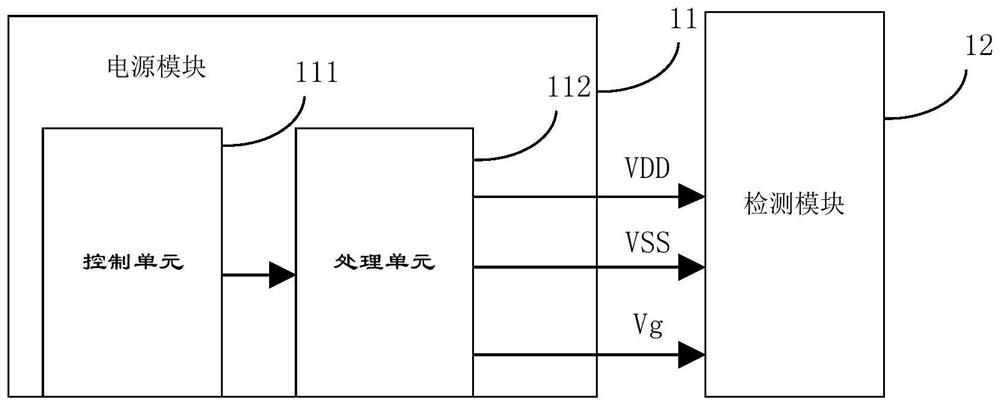

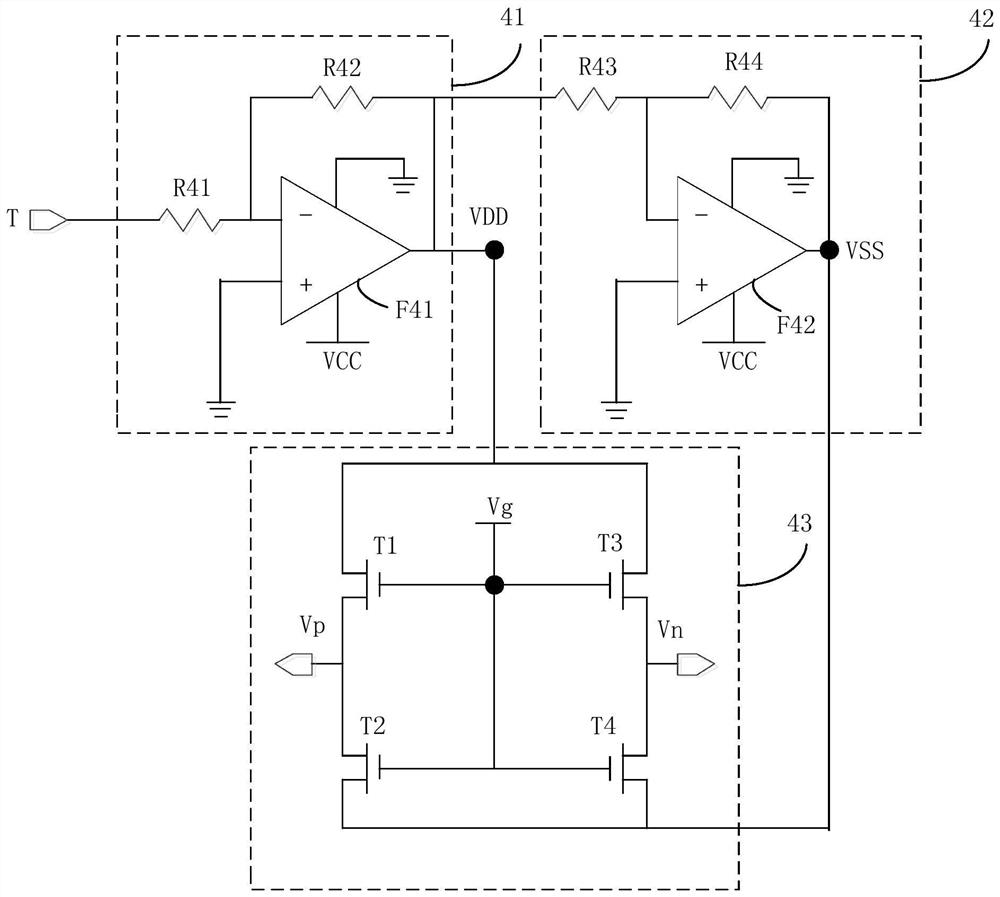

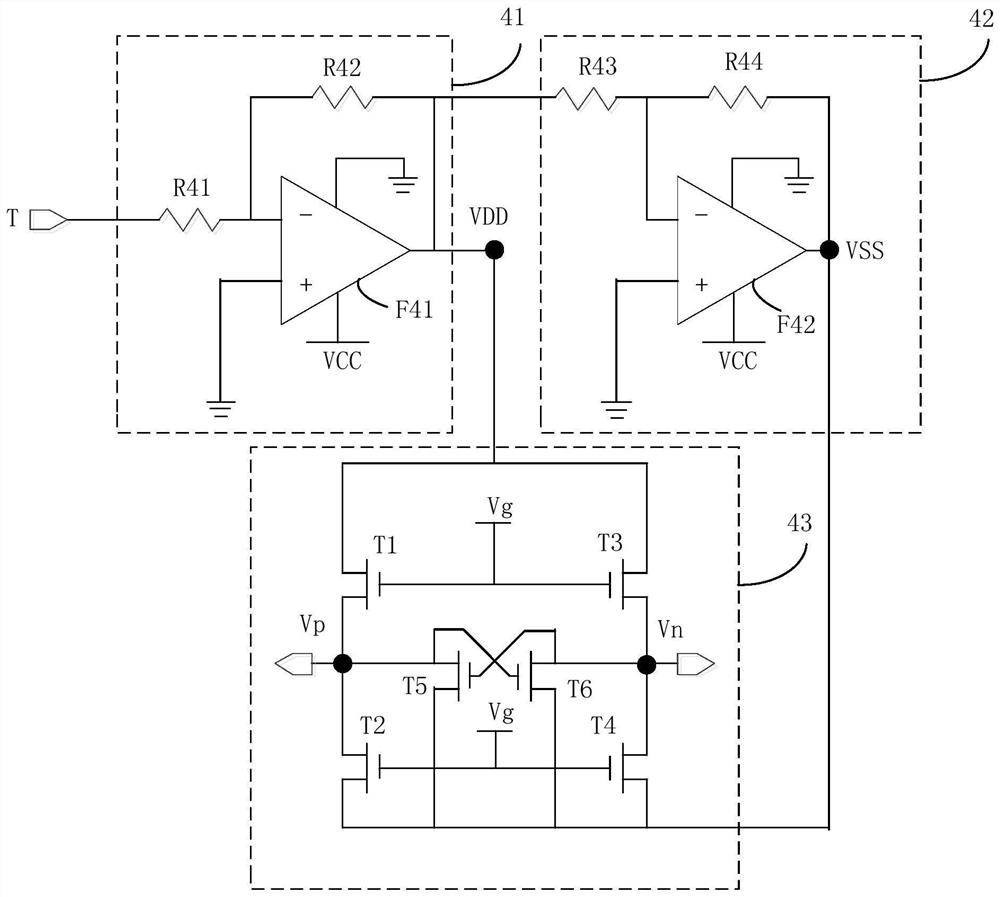

Light sensation detection device and display terminal

ActiveCN110849472AReduce mistakesEnhanced Threshold Voltage StabilityPhotometry electrical circuitsElectrical and Electronics engineeringComputer science

The invention provides a light sensation detection device and a display terminal which are applied to the technical field of display. In the light sensation detection device, a power supply module comprises a control unit and a processing unit which are connected with each other to output a first voltage, a second voltage and a third voltage; a detection module is connected with the power supply module, and comprises a first bridge arm and a second bridge arm which are connected in parallel to receive a first voltage, a second voltage and a third voltage, an upper switching tube of the first bridge arm and a lower switching tube of the second bridge arm are photoinduction switching tubes, the midpoint of the first bridge arm outputs a first detection signal, and the midpoint of the secondbridge arm outputs a second detection signal; and the work period of the light sensation detection device comprises a first time period and a second time period, and the first voltage is higher than the second voltage in the first time period and lower than the second voltage in the second time period. According to the light sensation detection device and the display terminal, light sensation errors can be reduced, the device stability is enhanced, and the sensitivity of an automatic backlight system of the display terminal is improved.

Owner:KUSN INFOVISION OPTOELECTRONICS

Metal oxide thin film transistor

A metal oxide thin film transistor (TFT) includes a gate electrode, a gate insulating layer, a metal oxide active layer, a source electrode, and a drain electrode. The gate electrode is formed on a substrate. The gate insulating layer is formed on the substrate and covers the gate electrode. The metal oxide active layer is formed on the gate insulating layer. The drain electrode and the source electrode are formed on two opposite ends of the metal oxide active layer in a spaced-apart manner, in which at least one of the orthographic projection of the source electrode and the orthographic projection of the drain electrode on the substrate does not overlap the gate electrode.

Owner:E INK HLDG INC

A photosensitive detection device and a display terminal

ActiveCN110849472BReduce mistakesImproved Threshold Voltage StabilityPhotometry electrical circuitsLight sensingEngineering

Owner:KUSN INFOVISION OPTOELECTRONICS

Switch device, storage apparatus, and memory system

ActiveUS11183633B2Improved Threshold Voltage StabilityStable structureSolid-state devicesRead-only memoriesIndiumPhysical chemistry

A switch device includes: a first electrode; a second electrode opposed to the first electrode; and a switch layer provided between the first electrode and the second electrode, and the switch layer includes one or more kinds of chalcogen elements selected from tellurium (Te), selenium (Se), and sulfur (S) and one or more kinds of first elements selected from phosphorus (P) and arsenic (As), and further includes one or both of one or more kinds of second elements selected from boron (B) and carbon (C) and one or more kinds of third elements selected from aluminum (Al), gallium (Ga), and indium (In).

Owner:SONY SEMICON SOLUTIONS CORP

A preparation method of gan E/D integrated device based on secondary oxidation method

ActiveCN104835819BReduce gate leakageImproved Threshold Voltage StabilitySolid-state devicesSemiconductor/solid-state device manufacturingHigh concentrationFoot region

The invention discloses a method for preparing a GaN E / D integrated device based on a secondary oxidation method. Based on the traditional depletion-type AlGaN (AlInN) / AlN / GaN heterostructure, the oxidation method is used to precisely control the thickness of the barrier layer. Oxidation thins the barrier layer to half of its original thickness, and the channel still maintains a high concentration of two-dimensional electron gas. The dielectric generated by oxidation is used as the gate dielectric of the D-mode device; then the dielectric in the gate foot area of the E-mode device is removed, and then the second The secondary oxidation completely consumes the barrier layer, depletes the two-dimensional electron gas in the channel, and generates the gate foot dielectric of the E-mode device at the same time. The two oxidation processes are the same, so that the E and D-mode device processes are fully compatible and the thickness of the gate dielectric is the same. It ensures that the device structure matches the device performance. The invention adopts an oxidation method to thin the barrier layer to realize the preparation of the E-mode device, and the process is highly controllable; the E-mode and D-mode processes are fully compatible, and the gate dielectrics of the E and D-mode devices have the same thickness and performance matching, which is beneficial to improve the GaN E / D integrated circuit yield.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

Tunneling field effect transistor 3D NAND data cell structure and method for forming the same

ActiveUS10720442B2Reduce distractionsImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringField effect

Owner:YANGTZE MEMORY TECH CO LTD

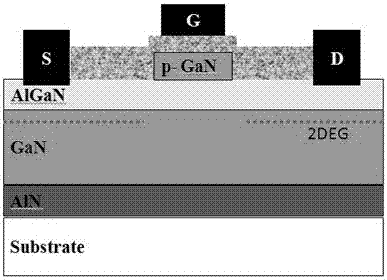

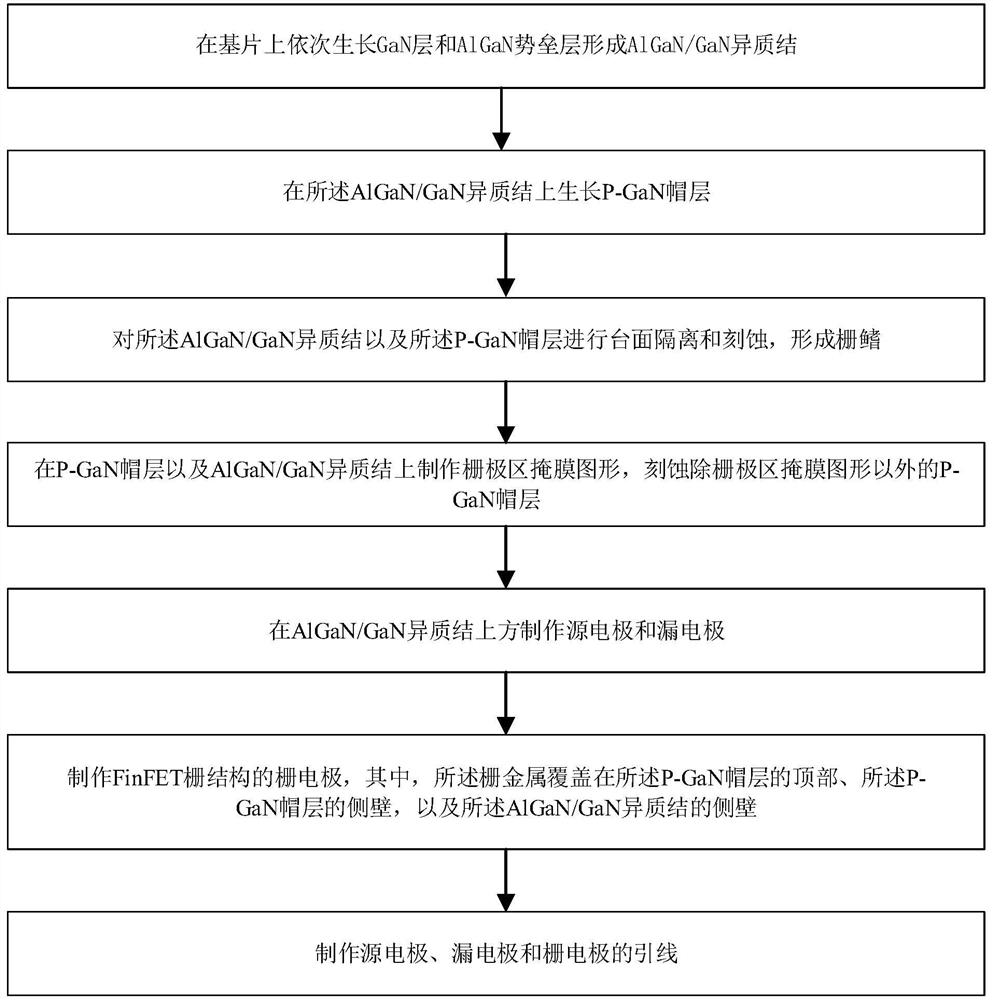

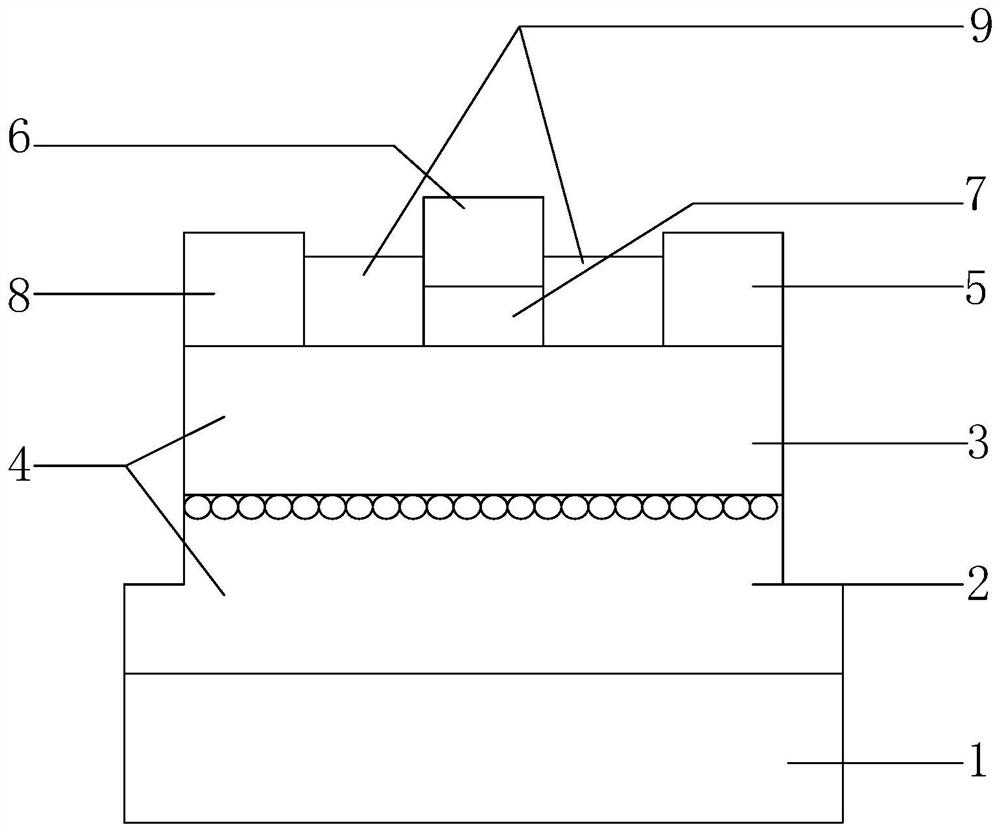

Finfet enhanced device and manufacturing method of p-gan cap layer

ActiveCN110676166BHigh Forward Threshold VoltageImprove gate control abilitySemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionTransconductance

The invention relates to a FinFET enhanced device of a P-GaN cap layer and a manufacturing method. The manufacturing method comprises the steps of enabling a GaN layer and an AlGaN barrier layer sequentially to grow on a substrate to form an AlGaN / GaN heterojunction; enabling a P-GaN cap layer to grow on the heterojunction; performing mesa isolation and etching on the heterojunction to form a gatefin; forming a gate region mask pattern on the surfaces of the P-GaN cap layer and the heterojunction, and etching the P-GaN cap layer except the gate region mask pattern; manufacturing a source electrode and a drain electrode on two sides of the heterojunction; depositing gate metal in the region of the P-GaN cap layer to form a FinFET gate structure gate electrode, the gate metal covering the top and the sidewall of the P-GaN cap layer and covering the sidewall of the heterojunction; manufacturing an electrode lead. According to the device and the manufacturing method, a P-GaN cap layer structure is adopted, and a three-dimensional grid-controlled FinFET structure is combined, so that the transconductance and grid-control capabilities of the device are enhanced, and the threshold voltage and stability of the device are improved.

Owner:XIDIAN UNIV

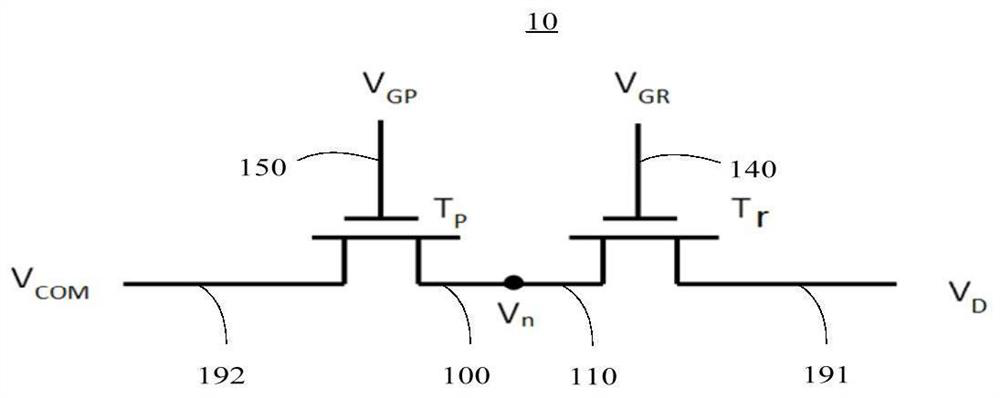

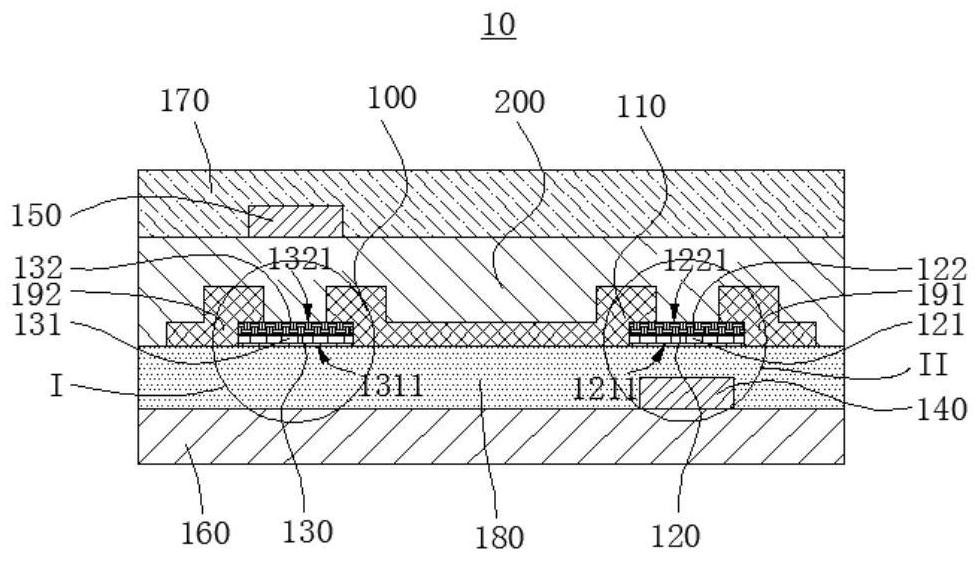

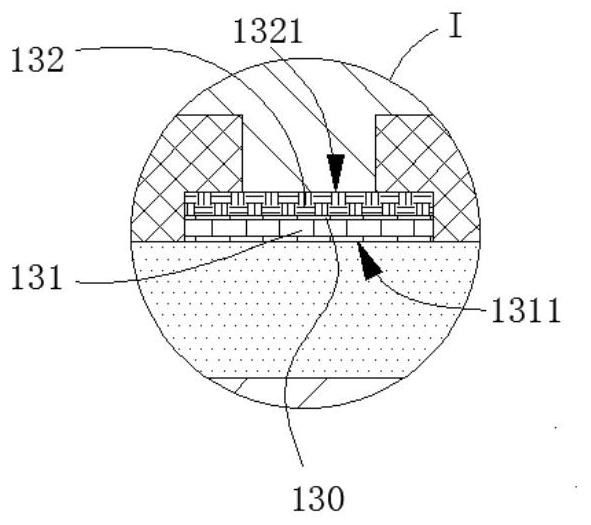

Photosensitive circuit, method for preparing photosensitive circuit, and display device

ActiveCN110914749BHigh electron mobilityReduced electron mobilityNon-linear opticsIdentification meansDisplay deviceHemt circuits

A photosensitive circuit (10), a method for preparing the photosensitive circuit (10), and a display device. The photosensitive circuit (10) includes a first thin film transistor (Tr) and a second thin film transistor (Tp), the drain (100) of the second thin film transistor is electrically connected to the source (110, 191) of the first thin film transistor, and the first thin film transistor The transistor includes a first active layer (120), the second thin film transistor includes a second active layer (130), the first active layer (120) includes a first semiconductor portion (121), and the second active layer (130) It includes a second semiconductor portion (131), the first and second semiconductor portions (131) are arranged in the same layer and spaced apart, the first active layer (120) includes a third semiconductor portion (122), and the third semiconductor portion (122) is arranged On the first semiconductor portion (121), the second active layer (130) includes a fourth semiconductor portion (132), the fourth semiconductor portion (132) is arranged on the second semiconductor portion (131), the third and fourth The semiconductor parts (132) are arranged on the same layer at intervals, the first semiconductor part (121) is adjacent to the gate (140) of the first thin film transistor, the fourth semiconductor part (132) is adjacent to the gate (150) of the second thin film transistor, and the second semiconductor part (132) is adjacent to the gate (150) of the second thin film transistor. The defect state density of the third semiconductor portion (122) is higher than the defect state density of the first semiconductor portion (121), and the defect state density of the fourth semiconductor portion (132) is higher than the defect state density of the second semiconductor portion (131) density of.

Owner:SHENZHEN ROYOLE TECH CO LTD

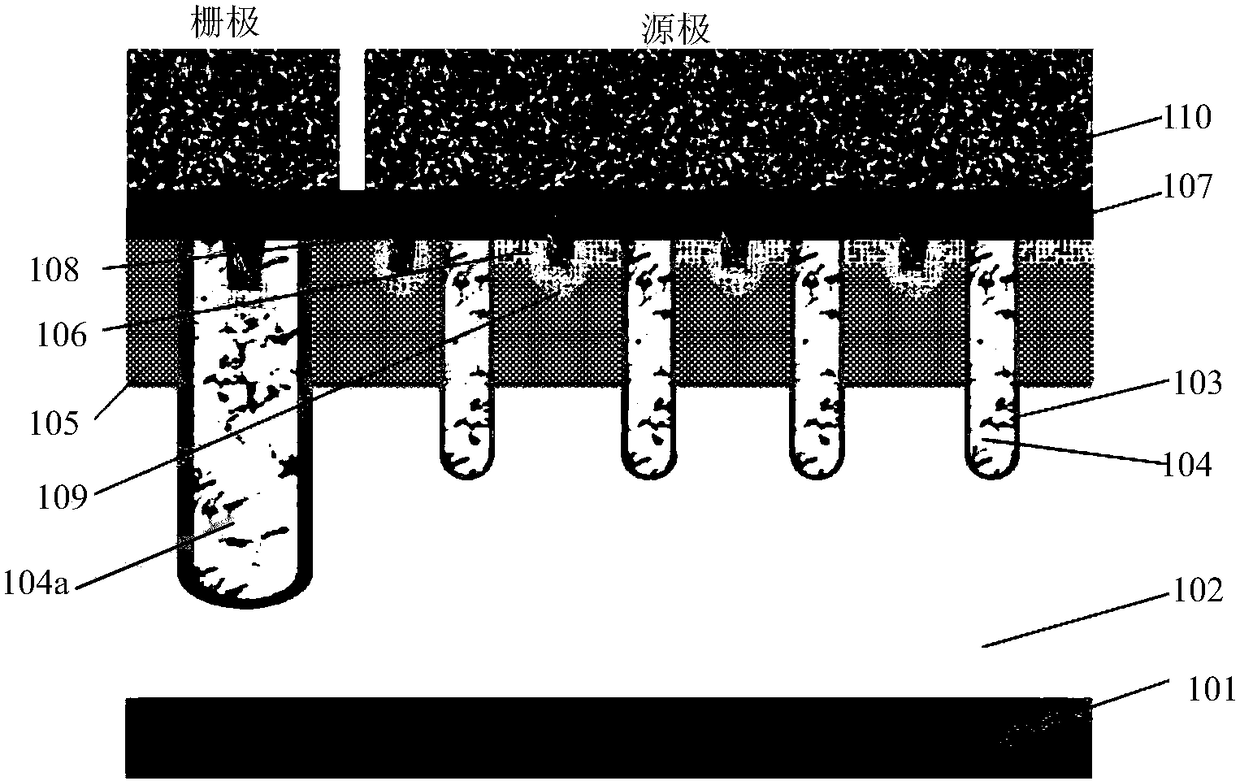

Manufacturing method and structure of trench gate power device

ActiveCN105826205BAchieve self-alignment definitionLow costSemiconductor/solid-state device manufacturingSemiconductor devicesMedia layerFiller metal

The invention discloses a manufacturing method for a groove grid power device. Formation steps of each cell of a conduction region comprise that a hard mask layer is formed, and a groove is formed through photolithographic etching; a grid medium layer and a polysilicon grid are formed in the groove; an opening of the hard mask layer is enlarged through isotropic etching, and a self-aligning column is formed; a body region is formed; a source region is formed; deposition of an interlayer film is carried out; chemical mechanical grinding planarization for the interlayer film is carried out to the surface of the top portion of the self-aligning column; an opening of a contact hole at the top portion of the source region formed at the self-aligning column is removed; and metal is filled into the contact hole. The invention further discloses a groove grid power device. According to the manufacturing method, self-aligning definition of the contact hole can be realized, registration redundancy is not needed to consider, the contact hole does not require the exposure technology, manufacturing cost is saved, so threshold voltage stability of the device can be improved, unit dimensions of the device are reduced, and conduction resistance is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP