Readout circuit and readout method for electrically erasable read-only memory

A read-only memory and readout circuit technology, which is applied in the field of readout circuits, can solve the problems of threshold shift, charge loss, multi-time, etc., and achieve the effect of reducing gate voltage stress effect, reducing configuration time, and stabilizing threshold voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0062] based on the following Figure 4 and Figure 5 , specify the preferred embodiment of the present invention:

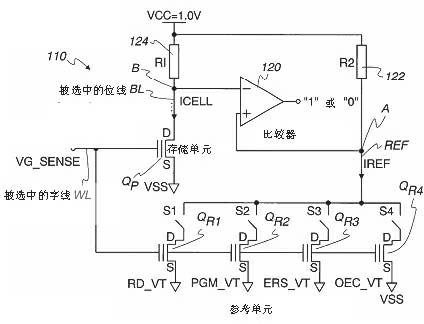

[0063] like Figure 4 Shown is a circuit diagram of a readout circuit for an EEPROM provided by the present invention, the readout circuit includes a comparator 420, a reference resistor 412 with a resistance value of R402, and a sensing resistor with a resistance value of R401 414, R402=R401.

[0064] The readout circuit also contains a reference cell Q R and memory cell Q C .

[0065] One end of the reference resistor 412 is connected to a voltage source VCC, a typical value of VCC is +1.0V, and the other end is connected to the non-inverting input end of the comparator 420 at the reference node Y. The reference node Y is connected to the reference cell Q through the reference bit line REF R connected to the drain terminal. One terminal of the sensing resistor 414 is connected to VCC, and the other terminal is connected to the inverting input terminal ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More