A preparation method of gan E/D integrated device based on secondary oxidation method

A technology of secondary oxidation and integrated devices, which is applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc. Process consistency and controllability are not high, etching damage reduces device saturation current, etc., to achieve high process stability and consistency, low interface state density, and good on-chip consistency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

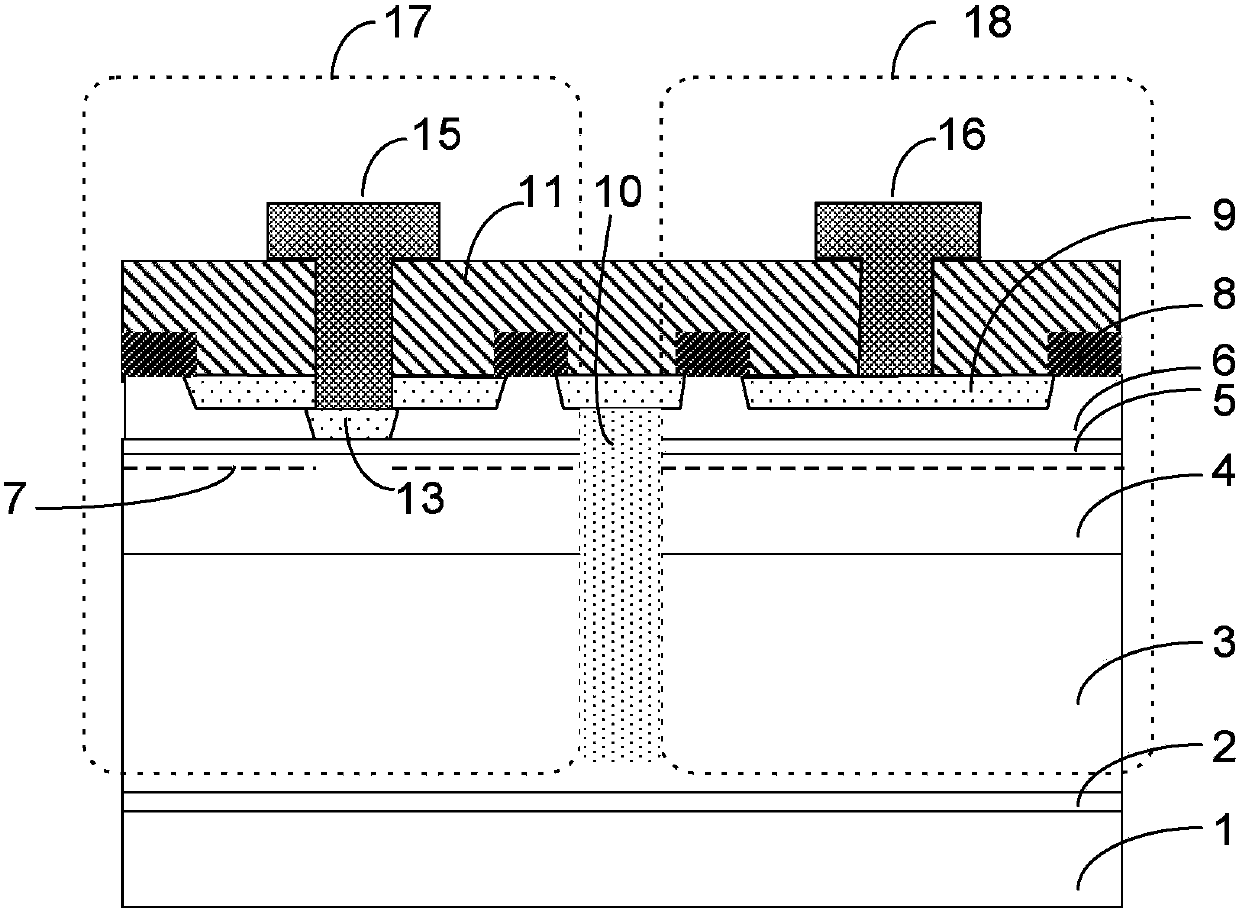

[0026] like Figures 1~3 As shown, a method for preparing a GaN E / D integrated device based on a secondary oxidation method, the preparation steps of which include the following steps:

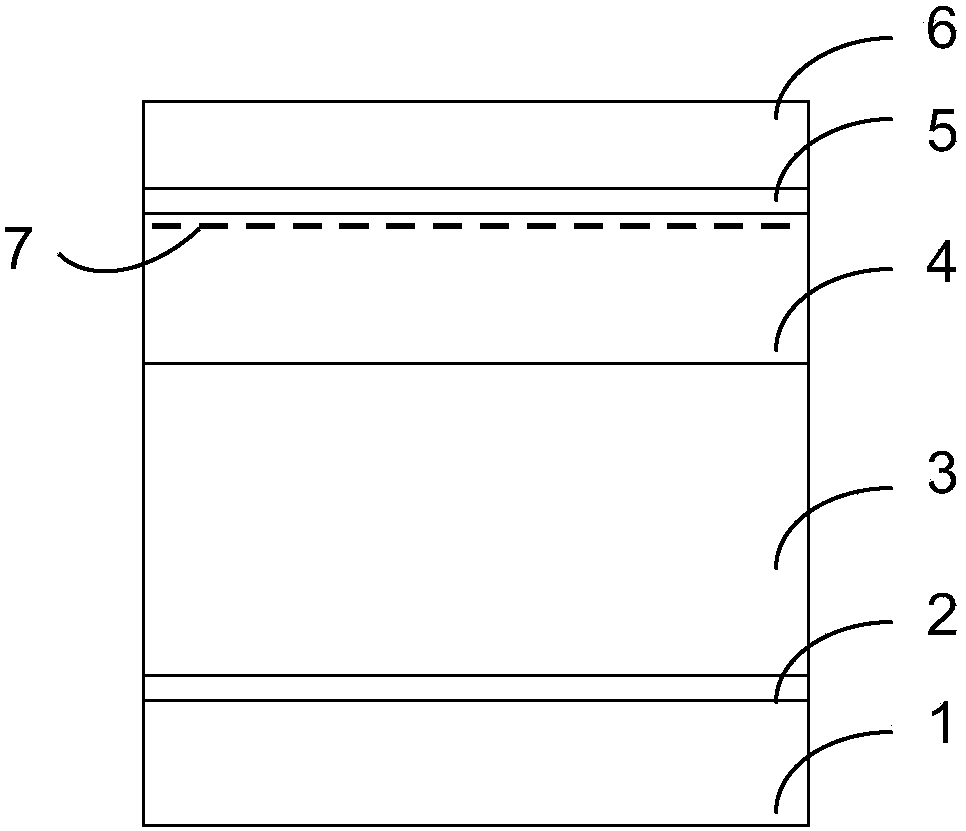

[0027] a) A nucleation layer 2, an AlyGa1-yN buffer layer 3, a GaN channel layer 4, an AlN insertion layer 5, and a barrier layer 6 are sequentially grown on the substrate 1 to form a GaN HEMT heterostructure, and the hetero interface forms a two-dimensional electronic gas 7;

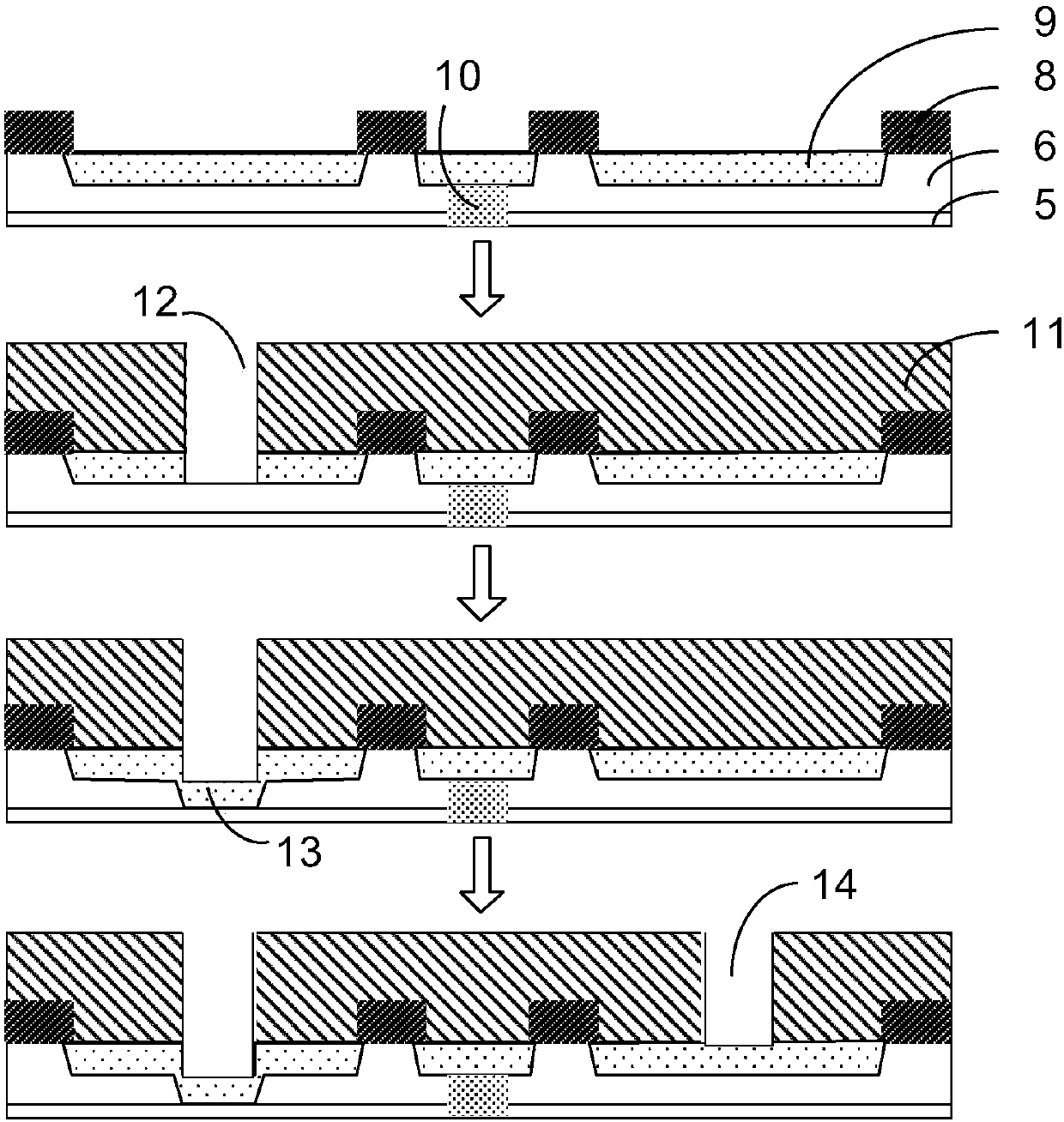

[0028] b) After the conventional ohmic metal electrode 8 is completed, the oxygen plasma treatment method is used for the first oxidation, which consumes part of the barrier layer 6 and reduces its thickness to half of the original thickness, and at the same time generates a first layer of oxide medium 9 on the surface; this The two-dimensional electron gas 7 is still retained in the channel;

[0029] c) Perform device isolation 10, make a mask 11, open holes in the area 12 reserved for making the gate feet of the E-m...

Embodiment 1

[0034] AlN nucleation layer 2 is grown on SiC substrate, 1μm GaN is grown as buffer layer 3, 40nm undoped GaN is used as channel layer 4, 1.5nm AlN insertion layer 5, and finally 6nm undoped Al0.72In0.18N is covered. barrier layer 5, in which the concentration of two-dimensional electron gas 7 is 1.87×10 13 cm -2, constituting an AlInN / AlN / GaN heterostructure material for E / D integration. After the conventional ohmic metal electrode 8 is completed, the first oxidation treatment is carried out. This oxidation condition can consume the 3nm Al0.72 In0.18N barrier layer 5 to generate the first layer of oxide medium 9, and then use the B ion implantation method to carry out Isolate 10, make a mask 11, open a window by photolithography in the area 12 reserved for making the gate foot of the E-mode device, remove the gate foot dielectric 9 of the E-mode device, and then perform a second oxidation, and the oxidation conditions are the same as the first oxidation conditions. It is ex...

Embodiment 2

[0036] AlN nucleation layer 2 is grown on the SiC substrate, 1μm Al0.08Ga0.92N is grown as buffer layer 3, 20nm undoped GaN is grown as channel layer 4, 2nm AlN insertion layer 5, and finally 4nm undoped Al0 is covered. 5Ga0.5N barrier layer 5, in which the concentration of two-dimensional electron gas 7 is 1.32×10 13 cm -2 , constituting an AlGaN / AlN / GaN heterostructure material for E / D integration. After the conventional ohmic metal electrode 8 is completed, the first oxidation treatment is carried out. This oxidation condition can consume the 2nm Al0.5Ga0.5N barrier layer 5 to generate a first layer of oxide medium 9, and then use B ion implantation for isolation. 10. Make a mask 11, open a window by photolithography in the area 12 reserved for making the gate foot of the E-mode device, remove the gate foot dielectric 9 of the E-mode device, and then perform a second oxidation. The oxidation conditions are completely the same as the first oxidation conditions. The same, t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More