Patents

Literature

382results about How to "Improve interface properties" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

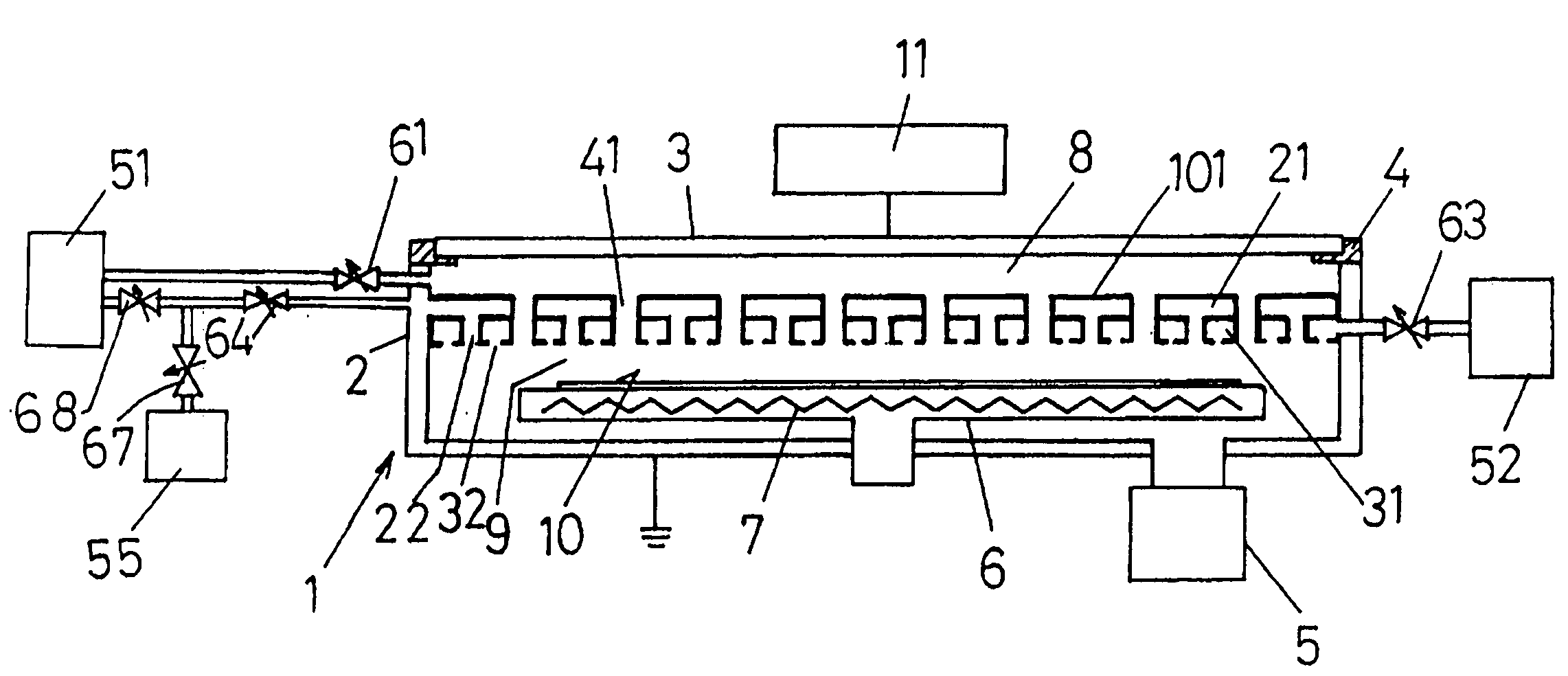

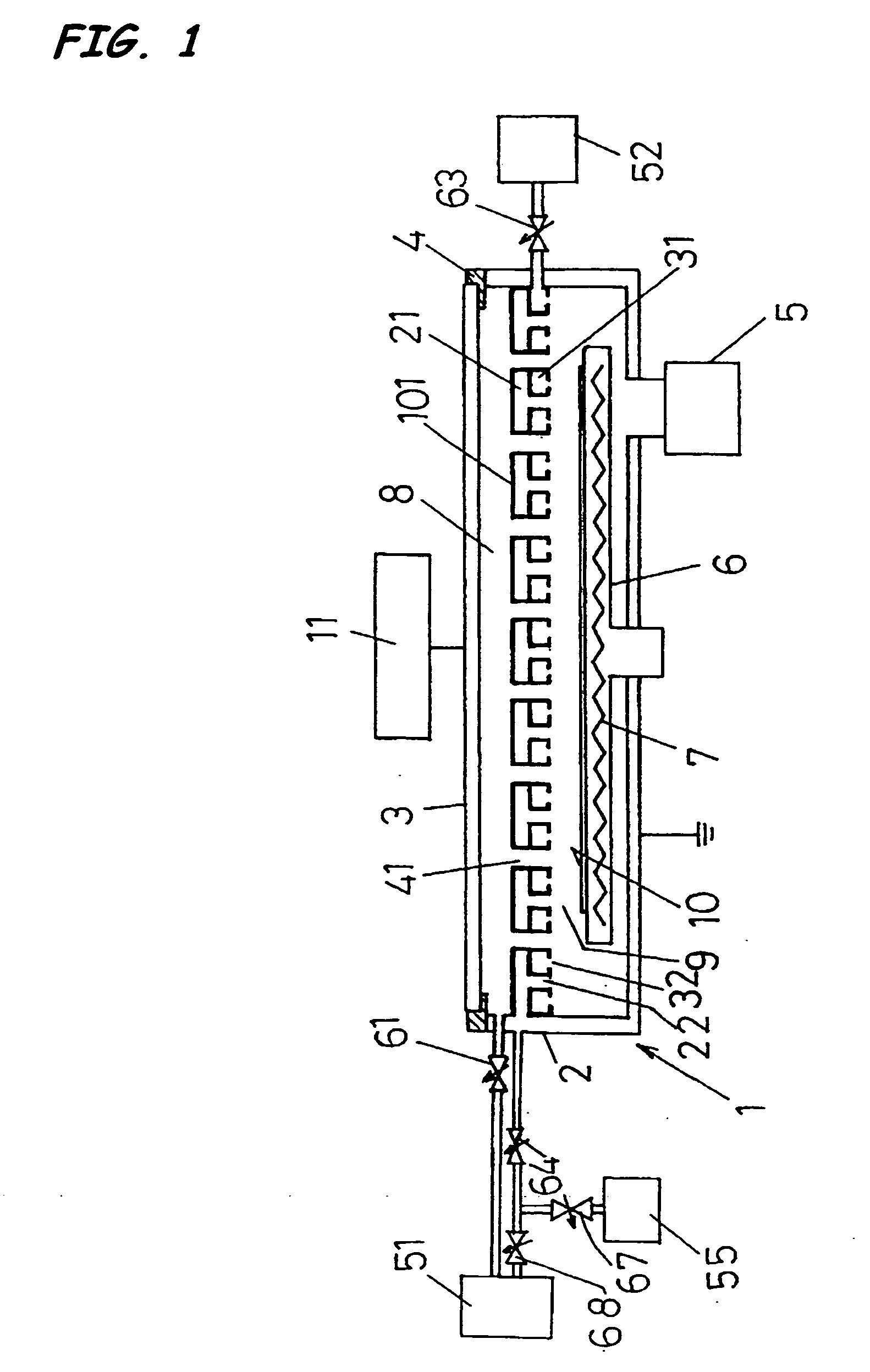

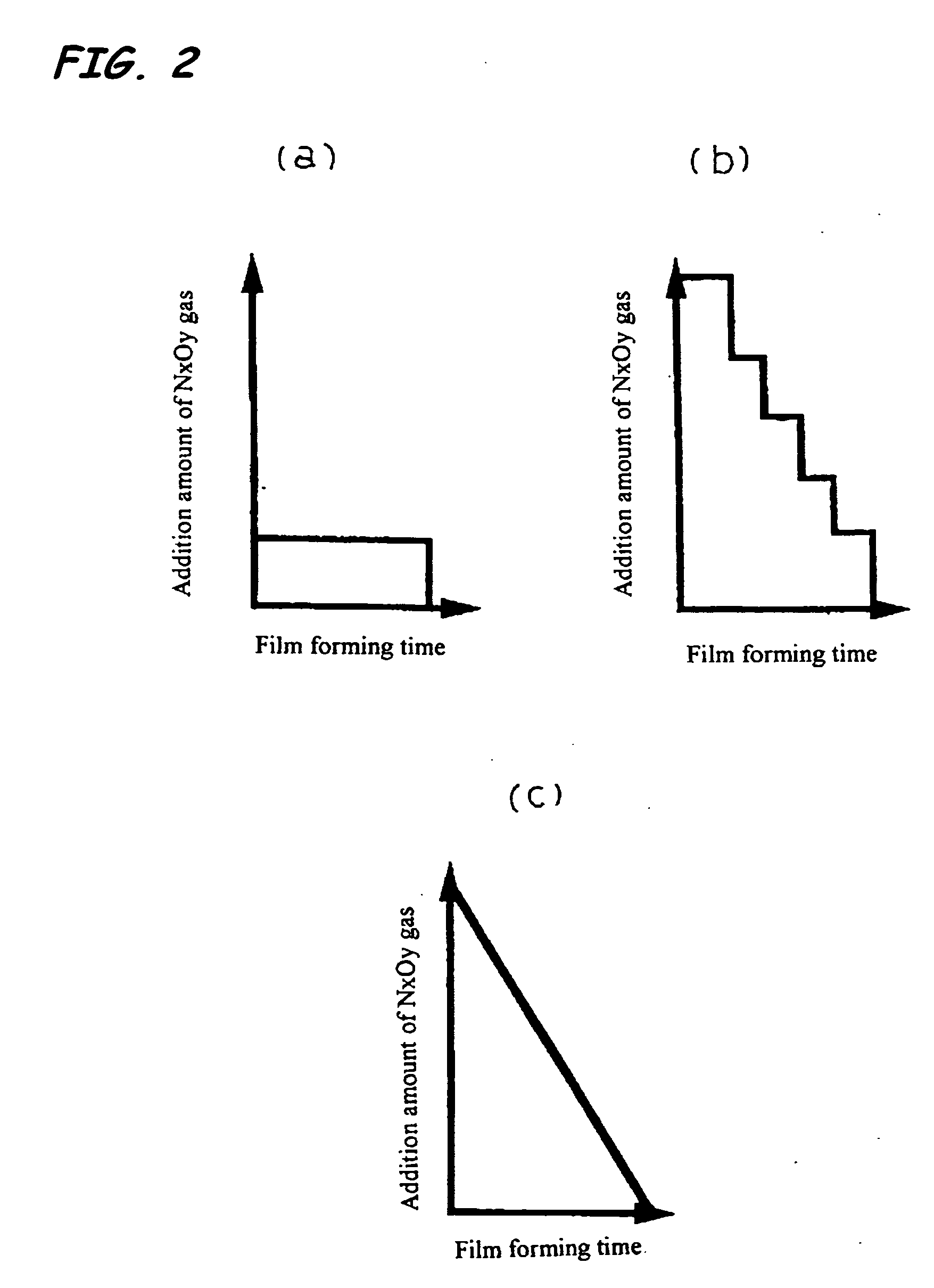

Method for Thin Film Formation

InactiveUS20090202721A1Improve interface propertiesLow densitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingNitrogenSilicon oxide

A method for thin film formation that can form, at a low temperature, a good thin film having a good interfacial property between a silicon substrate and a silicon oxide film and having a low interfacial trap density is provided.The method for thin film formation comprises generating plasma within a vacuum vessel to generate an active species (radical) and forming a silicon oxide film on a silicon substrate using this active species and a material gas, wherein, in addition to the material gas, a nitrogen atom-containing gas is introduced into the vacuum vessel in its film forming space where the active species (radical) and the material gas come into contact with each other for the first time and are reacted with each other to form a silicon film on the silicon substrate, and wherein the flow rate of the nitrogen atom-containing gas during the formation of the silicon oxide film on the silicon substrate is regulated so as to be the maximum value at least at the time of the start of formation of the silicon film on the silicon substrate.

Owner:NEC CORP

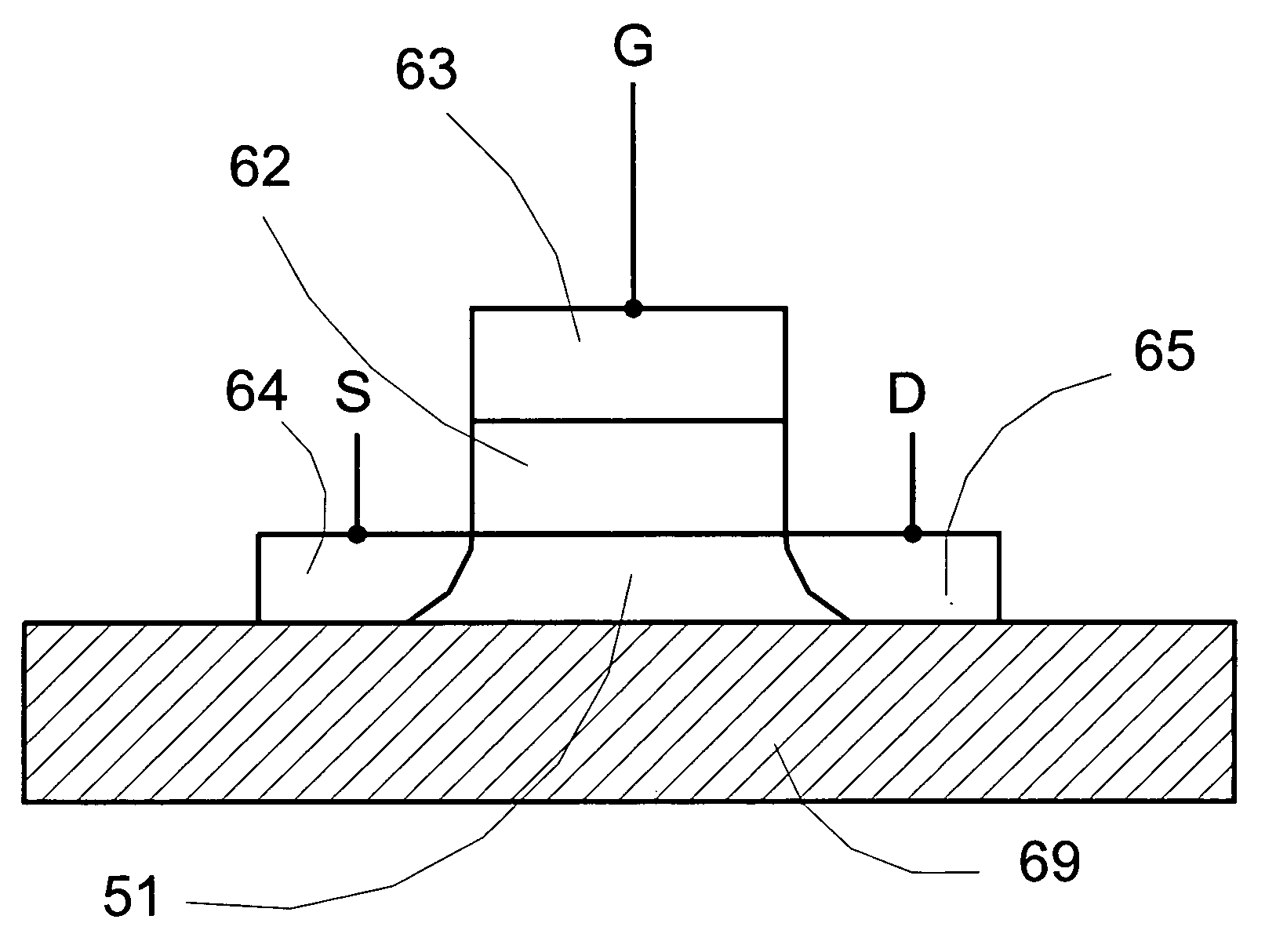

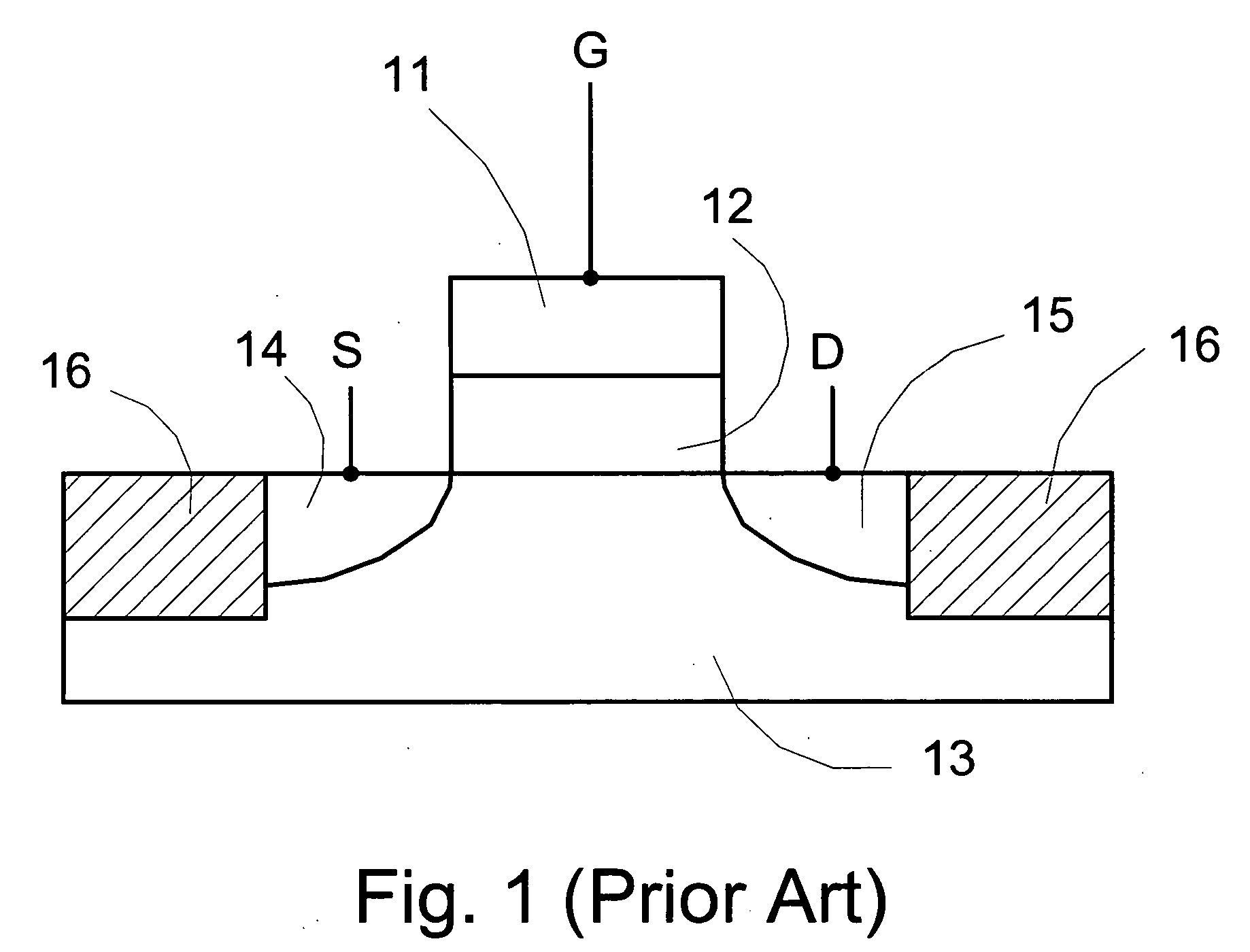

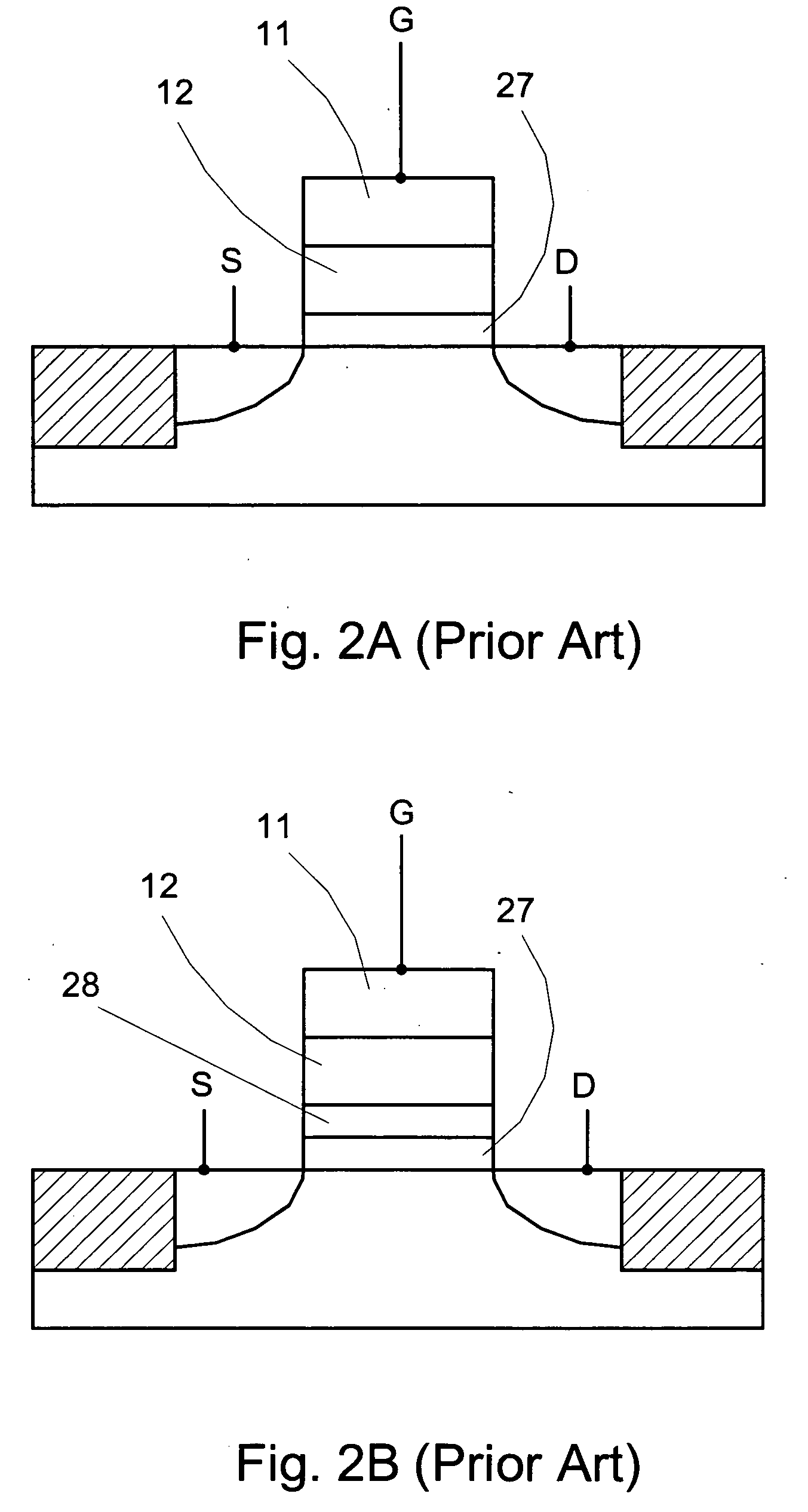

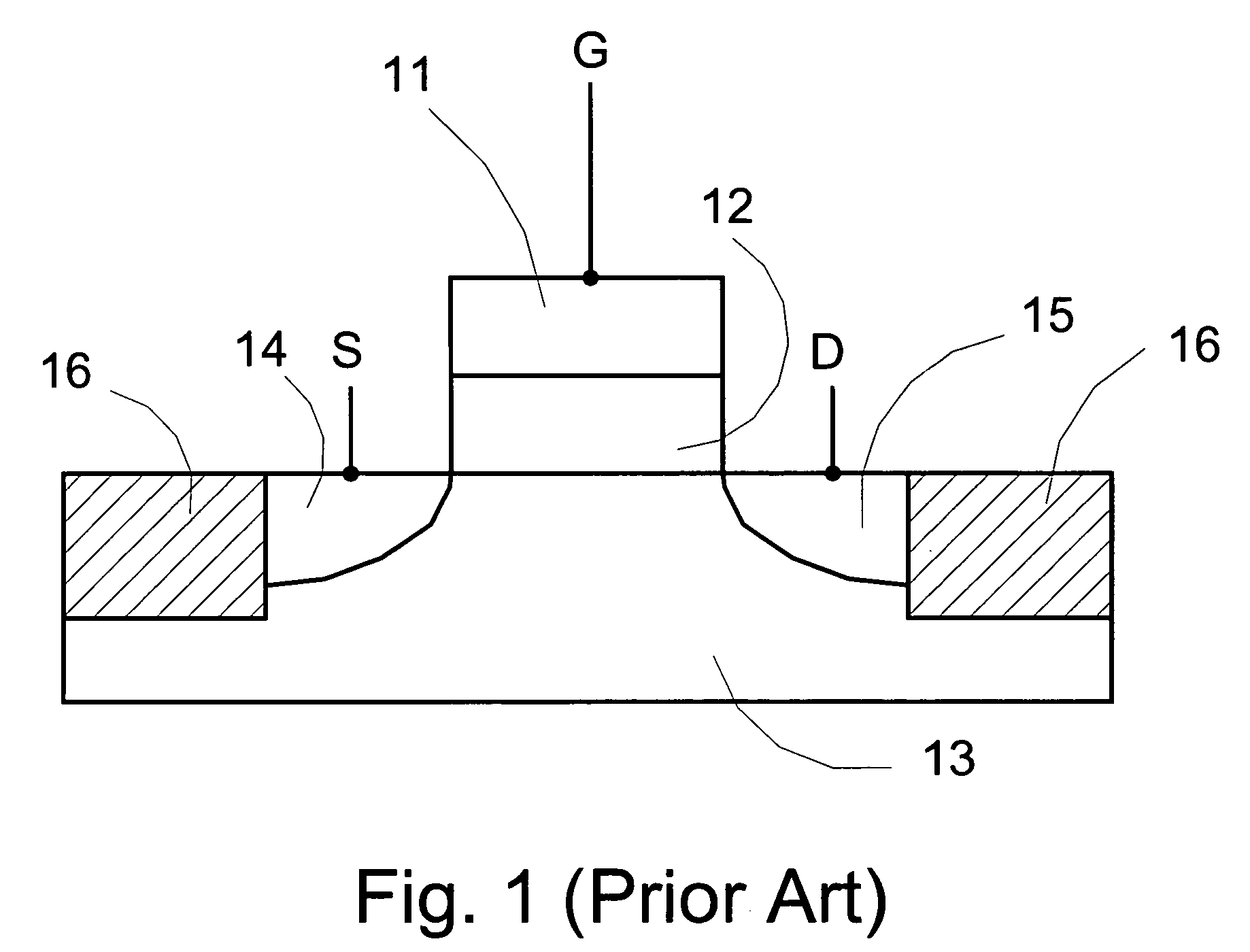

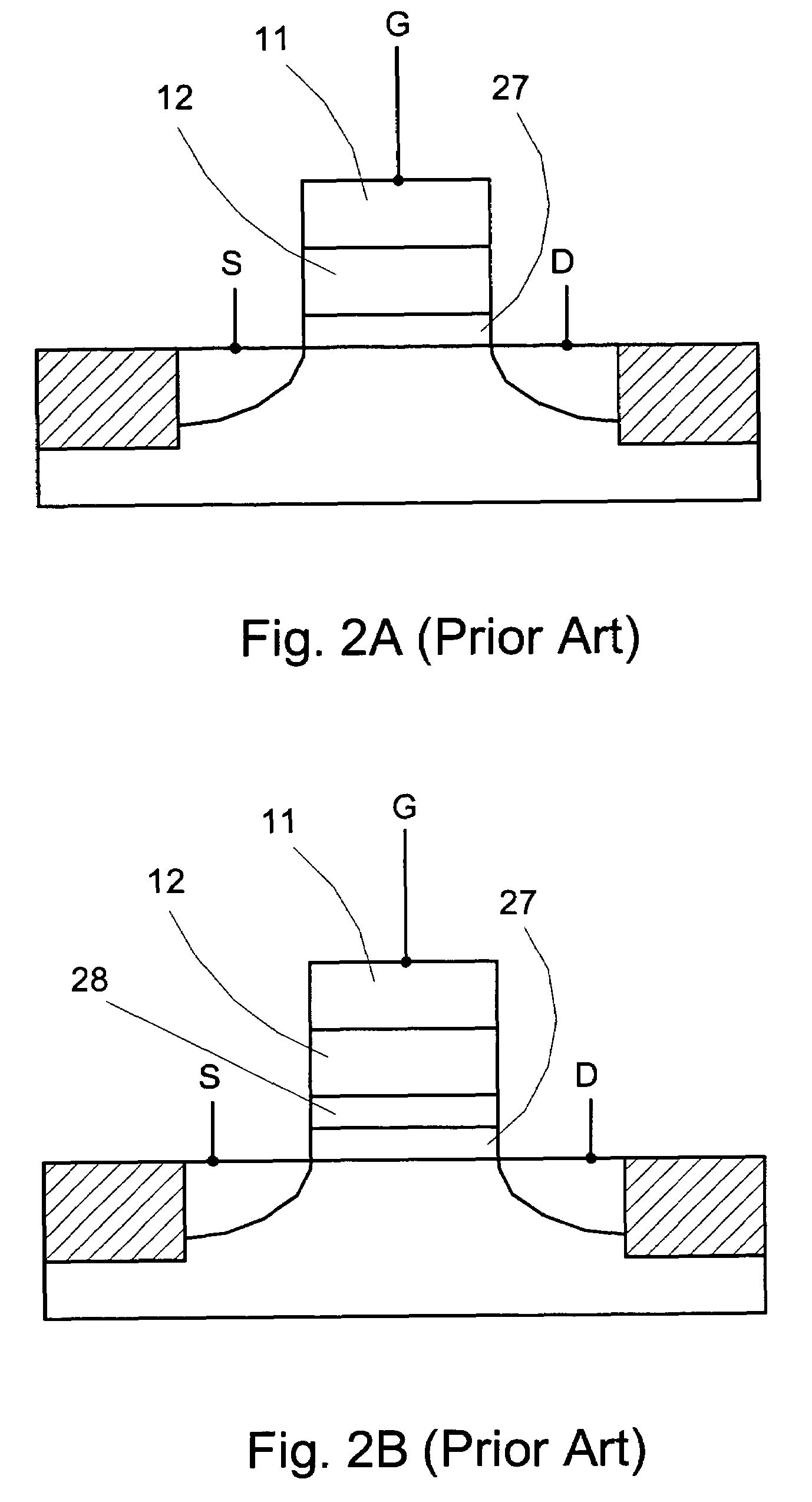

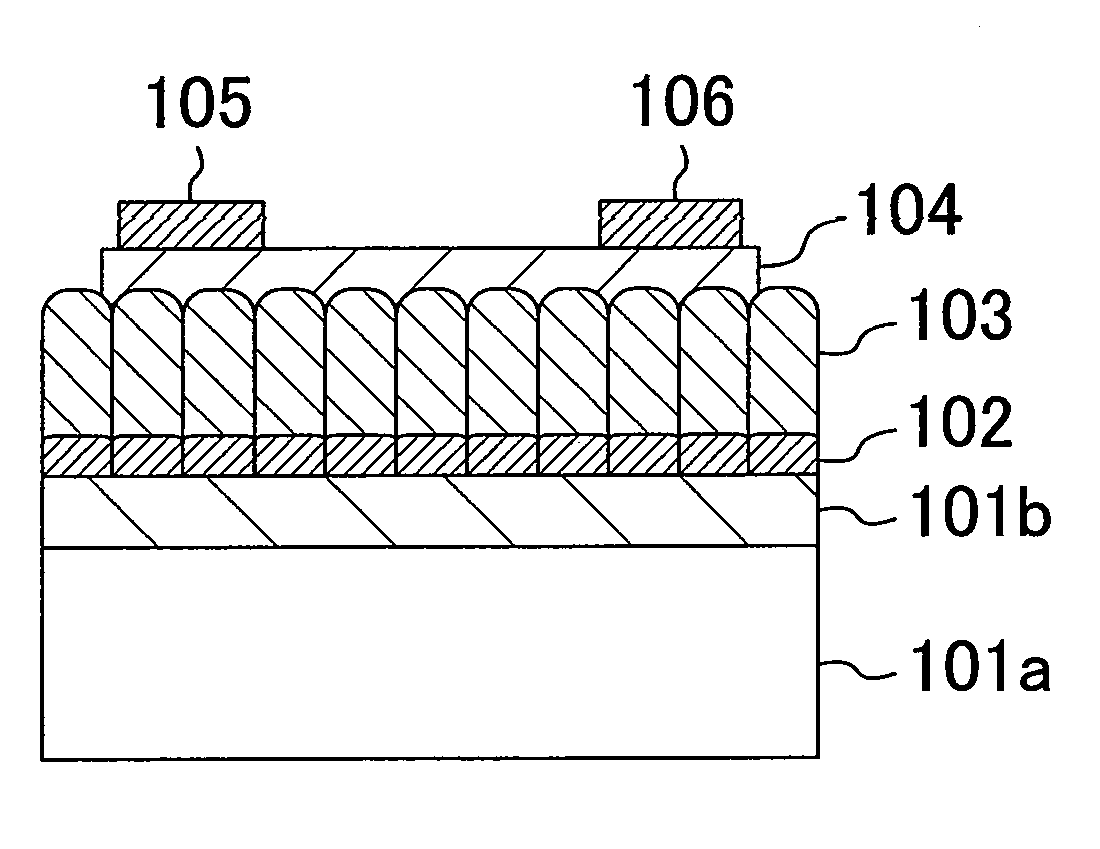

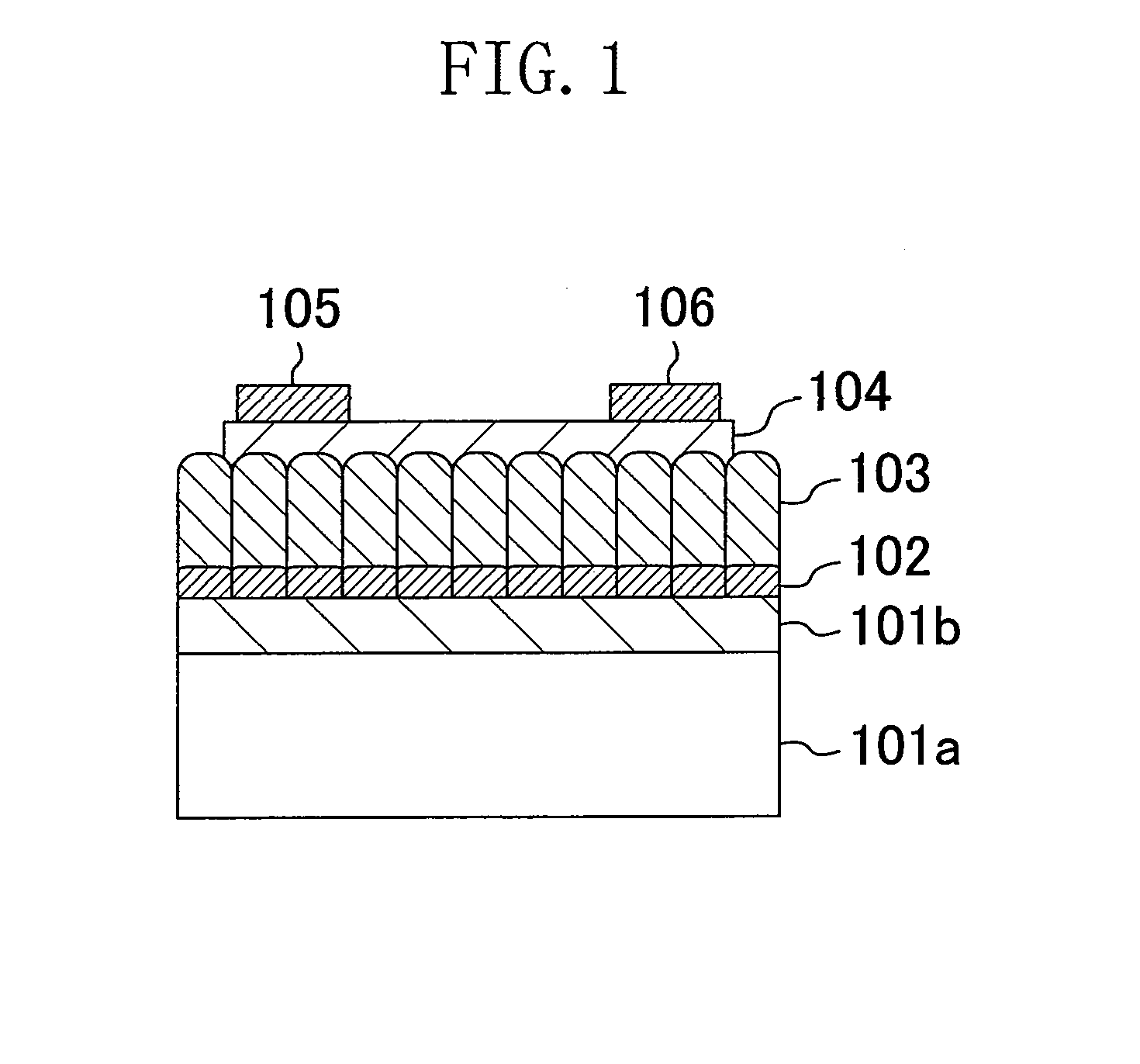

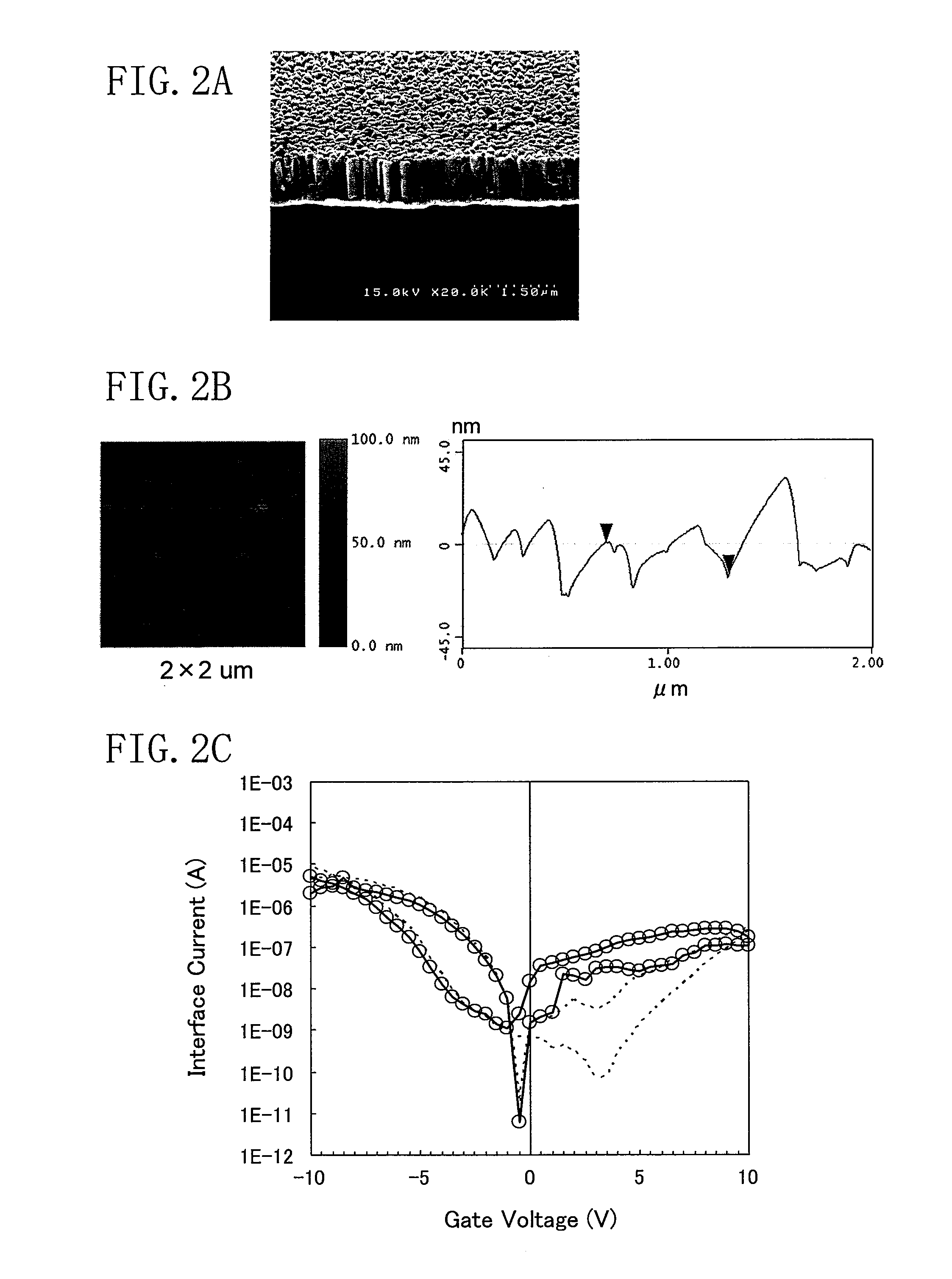

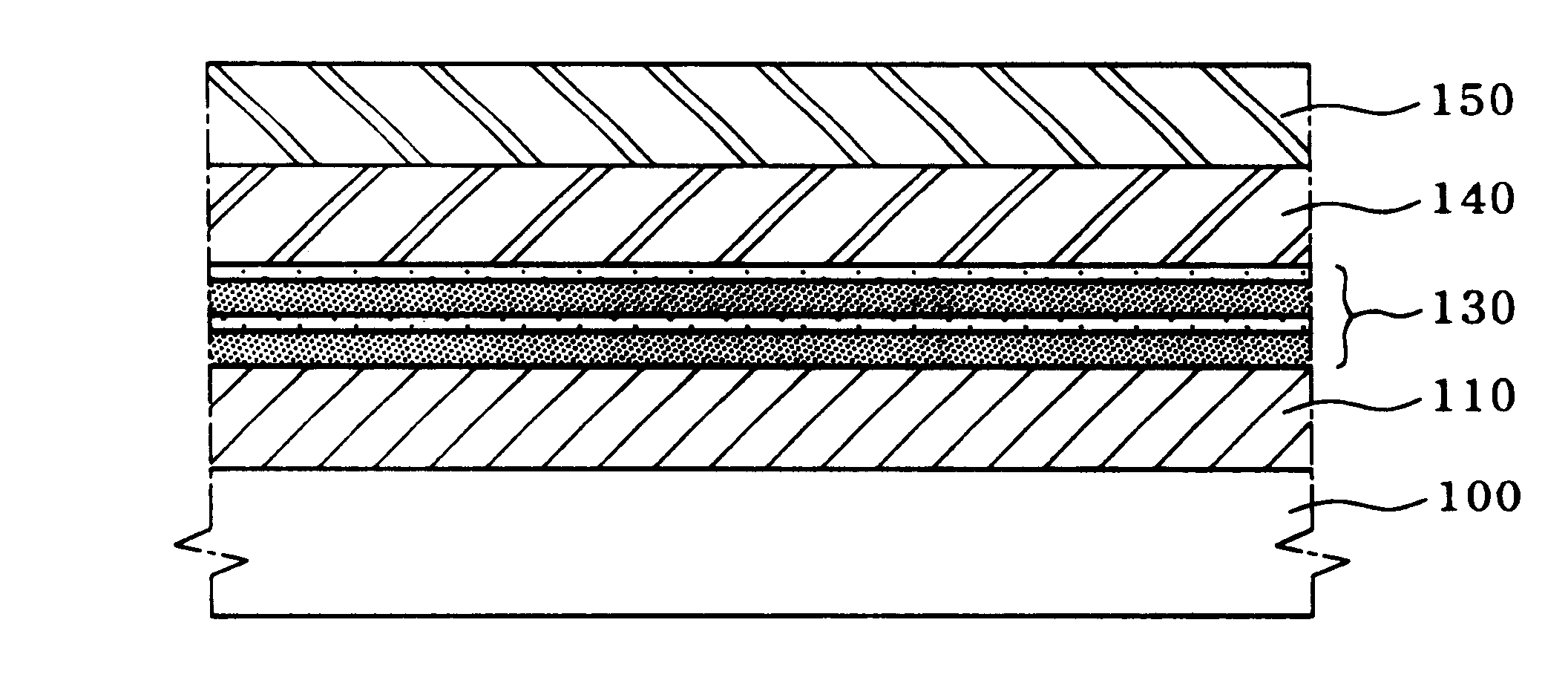

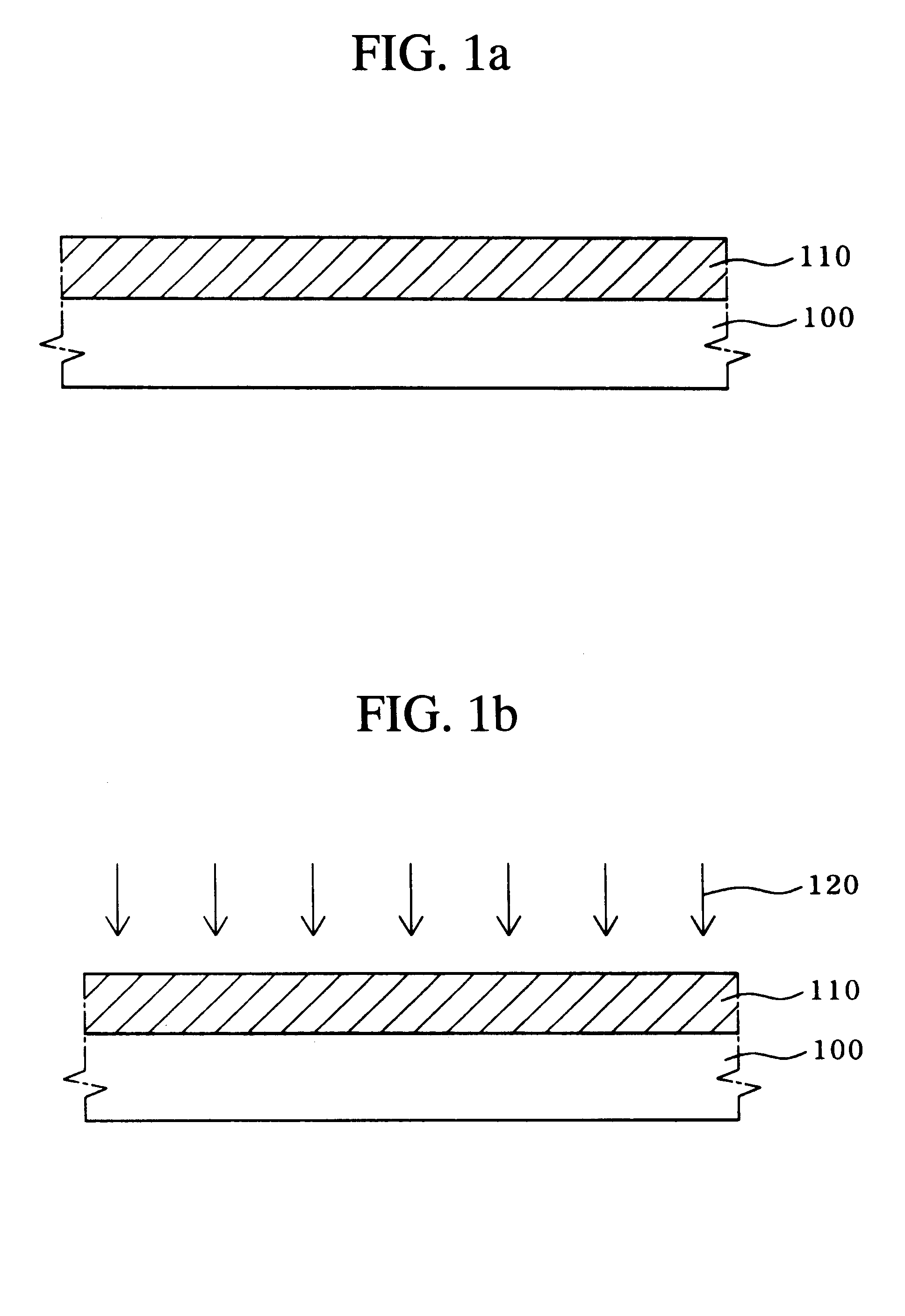

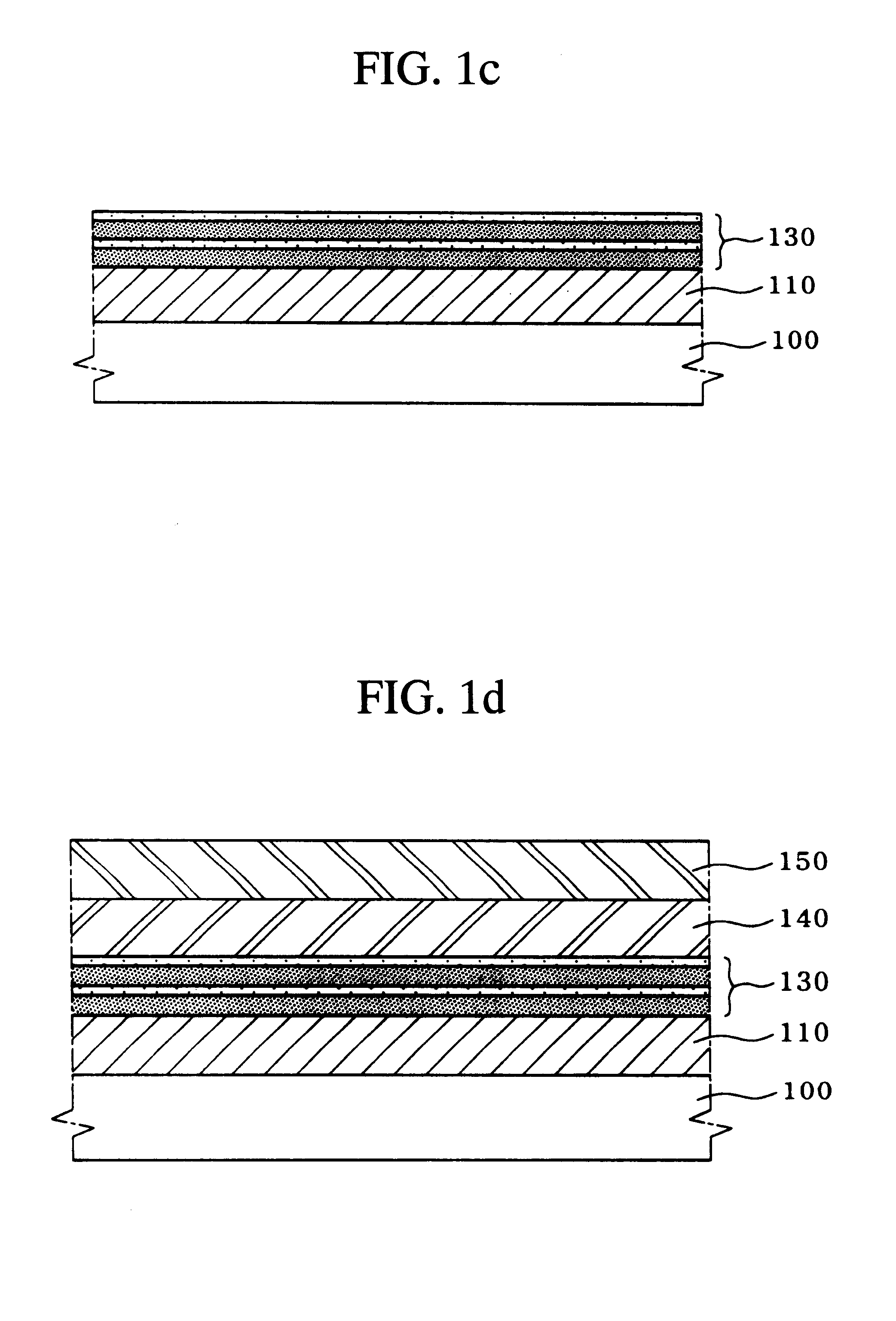

Semiconductive metal oxide thin film ferroelectric memory transistor

InactiveUS20060038242A1Simplify the manufacturing processHigh densitySemiconductor/solid-state device manufacturingSemiconductor devicesDielectricGate dielectric

The present invention discloses a novel transistor structure employing semiconductive metal oxide as the transistor conductive channel. By replacing the silicon conductive channel with a semiconductive metal oxide channel, the transistors can achieve simpler fabrication process and could realize 3D structure to increase circuit density. The disclosed semiconductive metal oxide transistor can have great potential in ferroelectric non volatile memory device with the further advantages of good interfacial properties with the ferroelectric materials, possible lattice matching with the ferroelectric layer, reducing or eliminating the oxygen diffusion problem to improve the reliability of the ferroelectric memory transistor. The semiconductive metal oxide film is preferably a metal oxide exhibiting semiconducting properties at the transistor operating conditions, for example, In2O3 or RuO2. The present invention ferroelectric transistor can be a metal-ferroelectric-semiconductive metal oxide FET having a gate stack of a top metal electrode disposed on a ferroelectric layer disposed on a semiconductive metal oxide channel on a substrate. Using additional layer of bottom electrode and gate dielectric, the present invention ferroelectric transistor can also be a metal-ferroelectric-metal (optional)-gate dielectric (optional)-semiconductive metal oxide FET.

Owner:SHARP KK

Semiconductive metal oxide thin film ferroelectric memory transistor

InactiveUS7378286B2Simplify the manufacturing processHigh densityTransistorSemiconductor/solid-state device manufacturingDielectricGate dielectric

The present invention discloses a novel transistor structure employing semiconductive metal oxide as the transistor conductive channel. By replacing the silicon conductive channel with a semiconductive metal oxide channel, the transistors can achieve simpler fabrication process and could realize 3D structure to increase circuit density. The disclosed semiconductive metal oxide transistor can have great potential in ferroelectric non volatile memory device with the further advantages of good interfacial properties with the ferroelectric materials, possible lattice matching with the ferroelectric layer, reducing or eliminating the oxygen diffusion problem to improve the reliability of the ferroelectric memory transistor. The semiconductive metal oxide film is preferably a metal oxide exhibiting semiconducting properties at the transistor operating conditions, for example, In2O3 or RuO2. The present invention ferroelectric transistor can be a metal-ferroelectric-semiconductive metal oxide FET having a gate stack of a top metal electrode disposed on a ferroelectric layer disposed on a semiconductive metal oxide channel on a substrate. Using additional layer of bottom electrode and gate dielectric, the present invention ferroelectric transistor can also be a metal-ferroelectric-metal (optional)-gate dielectric (optional)-semiconductive metal oxide FET.

Owner:SHARP KK

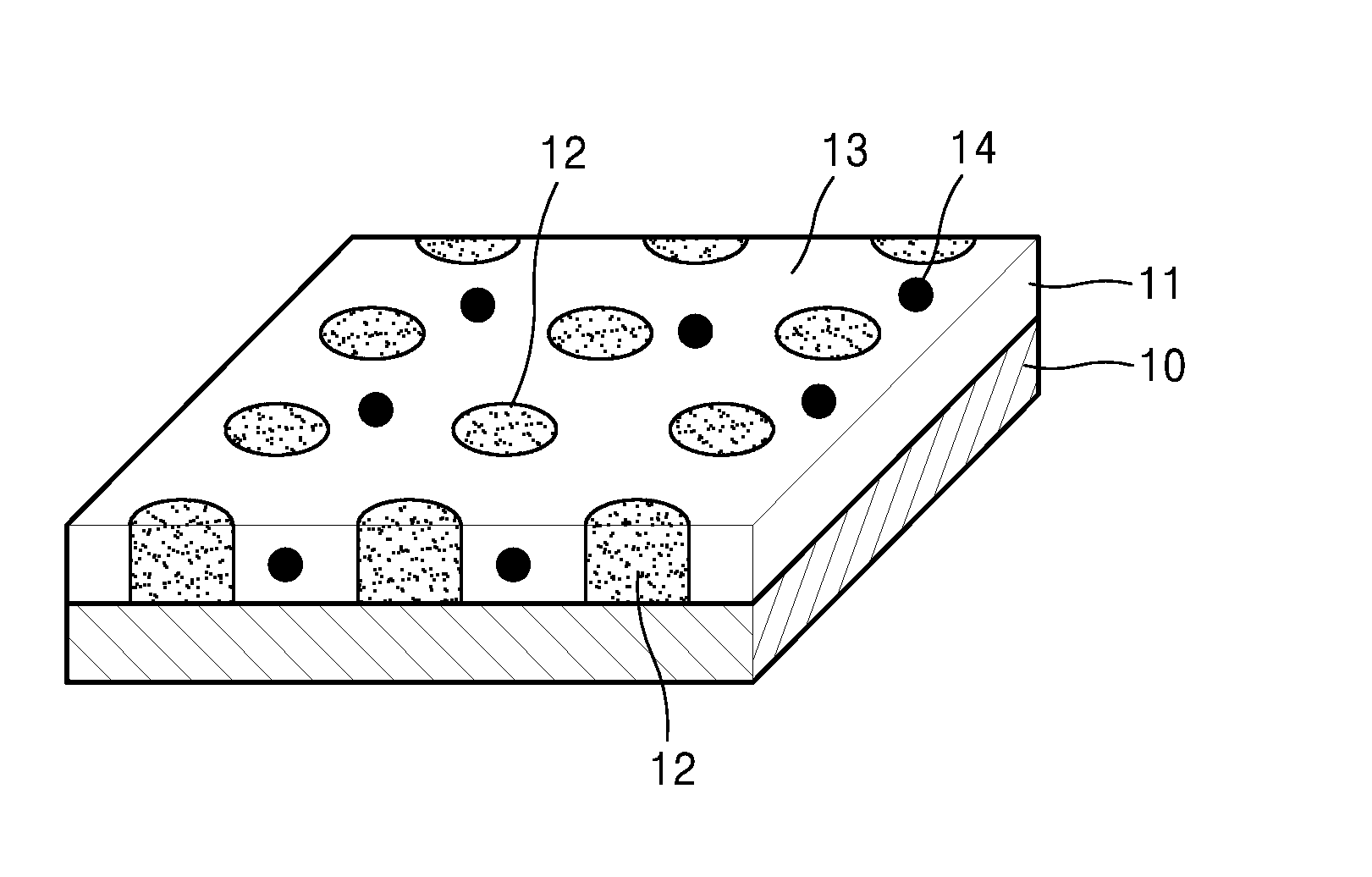

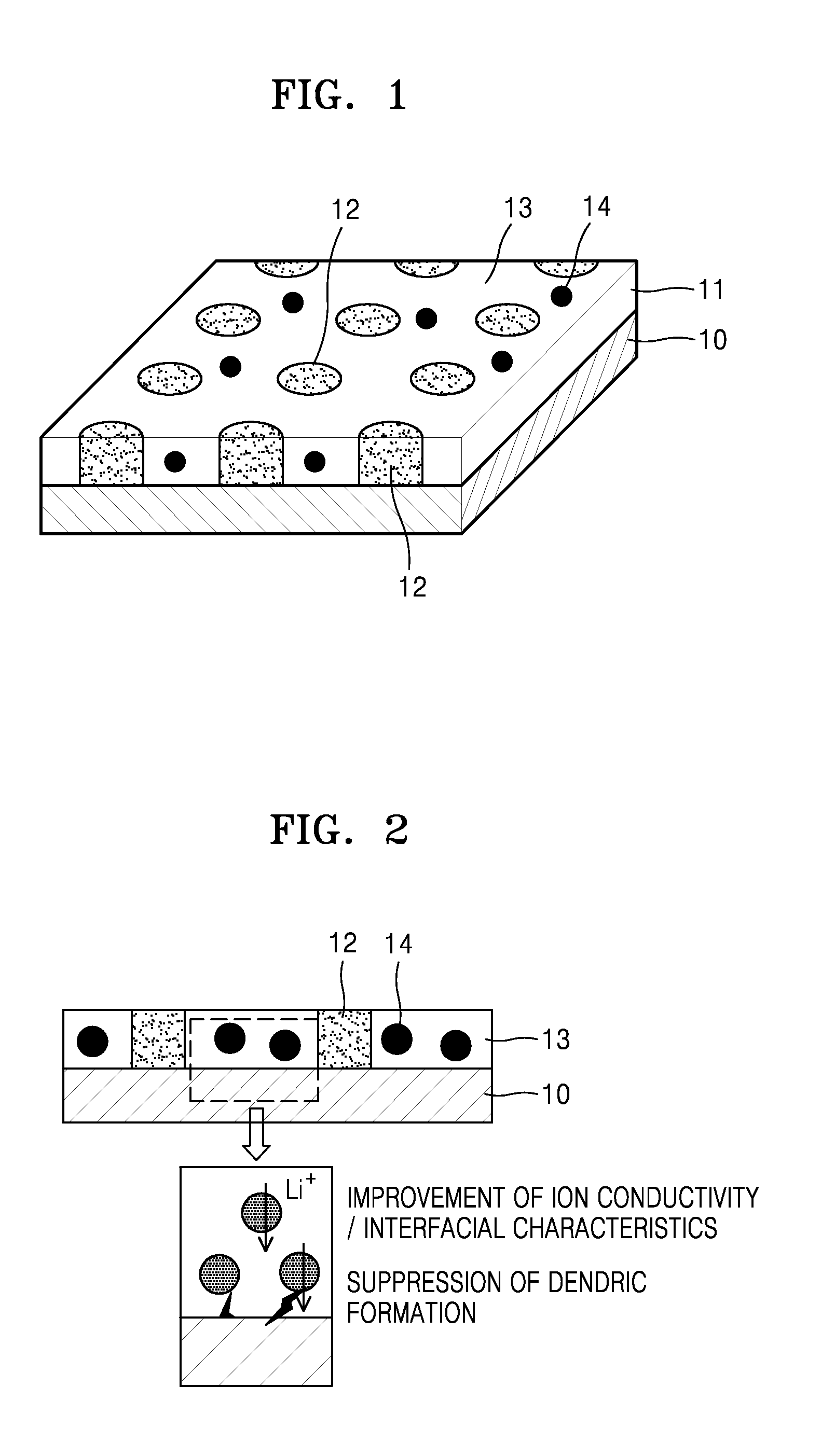

Electrolyte composite and negative electrode and lithium second battery including the electrolyte composite

ActiveUS20160336618A1Improve interface propertiesImprove conductivitySolid electrolytesSecondary cellsLithiumElectrical conductor

An electrolyte composite including a first block copolymer and a lithium ion conductor, wherein the first block copolymer includes i) a structural domain and ii) at least one of a rubbery domain and an ion conductive domain, wherein the structural domain includes a polymer segment including a structural repeating unit, wherein the rubbery domain includes a polymer segment including a rubbery repeating unit, and wherein the ion conductive domain includes a polymer segment including an ion conductive repeating unit.

Owner:SAMSUNG UNIV +1

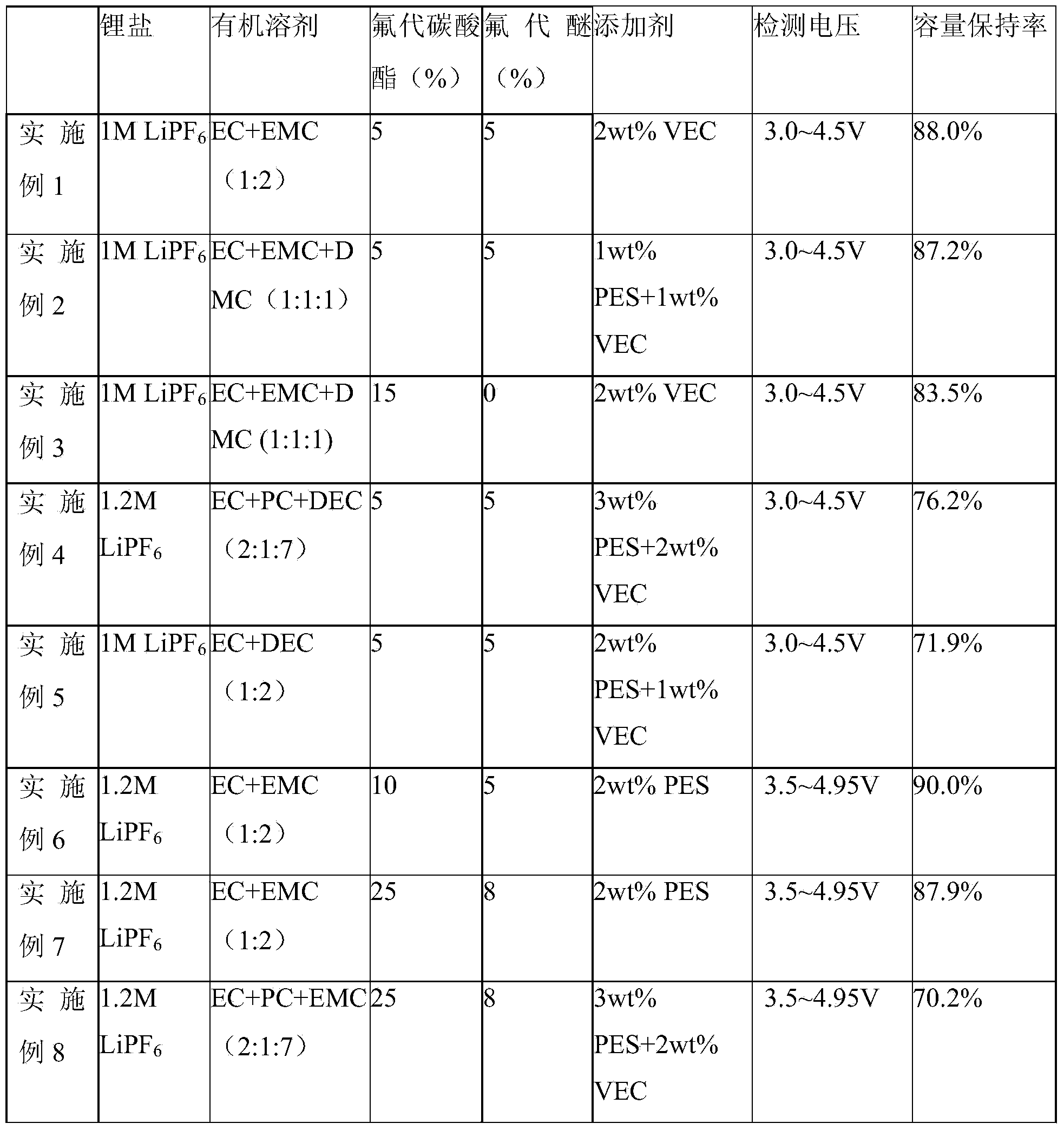

Lithium-ion battery electrolyte and lithium ion battery with the same

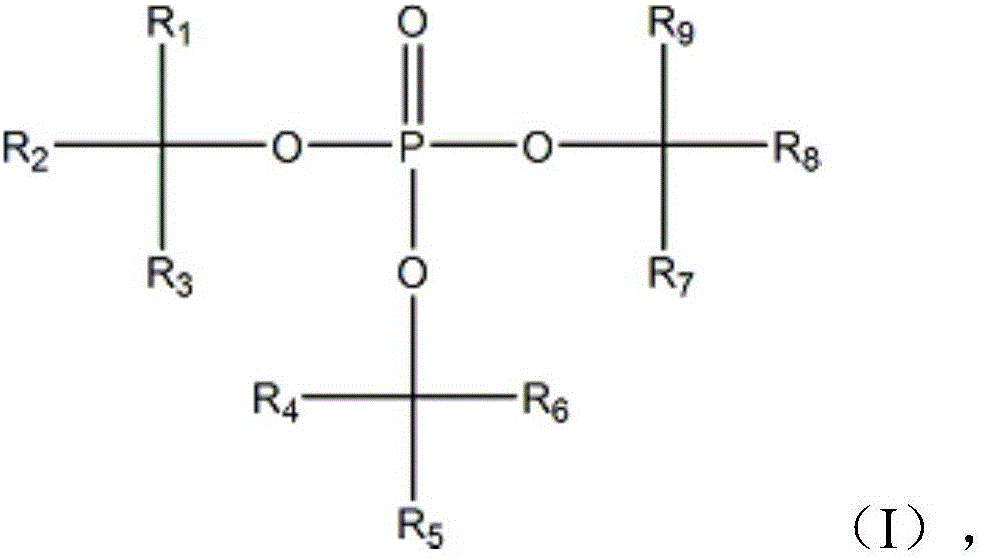

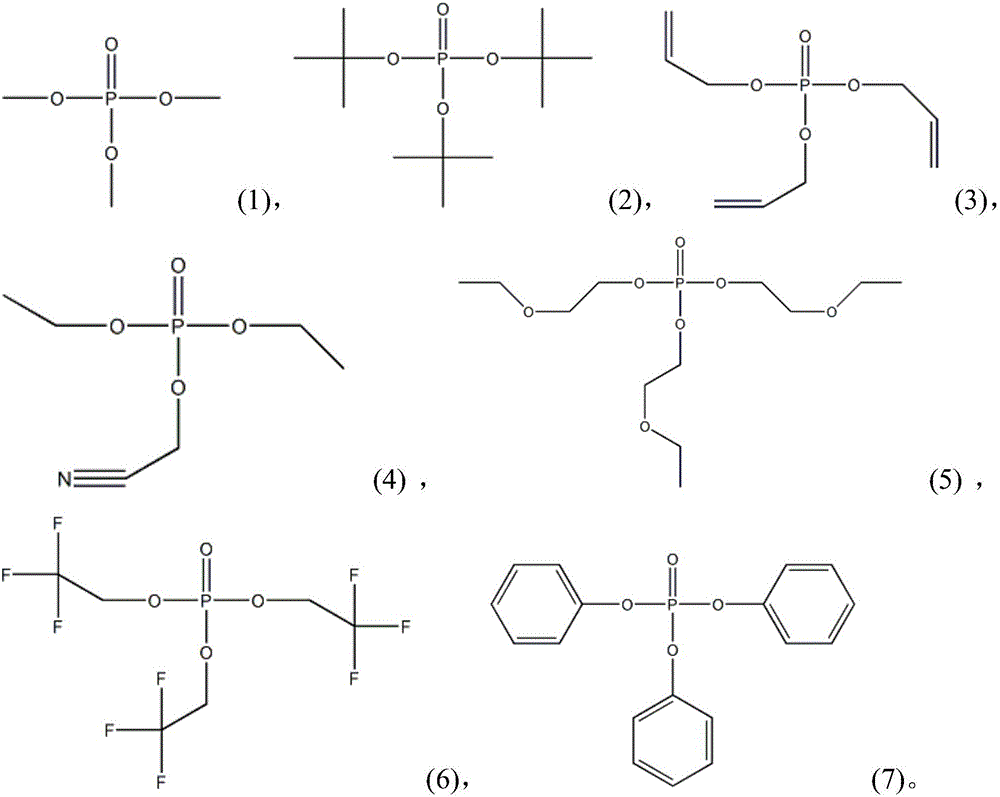

InactiveCN106450438AImprove interface propertiesImprove stabilitySecondary cellsDecompositionLithium electrode

The invention belongs to the technical field of lithium-ion batteries, and discloses a lithium-ion battery electrolyte and a lithium ion battery with the same. The lithium-ion battery electrolyte is prepared from an organic solvent, conductive lithium salt and an additive; the additive is prepared from a common additive and a phosphoric acid ester additive, and the phosphoric acid ester additive has the structural formula shown in the formula (I) (please see the specification). According to the lithium-ion battery electrolyte, the phosphoric acid ester additive is added, the interface characteristics of the electrode / electrolyte of the lithium-ion battery can be improved, the stability is improved, interface impedance is reduced, the cycling stability, the high-temperature performance and the high-voltage performance of the lithium ion battery are improved accordingly, gas generation caused by organic solvent decomposition is inhibited, and expansion of the battery is reduced.

Owner:GUANGZHOU TINCI MATERIALS TECH

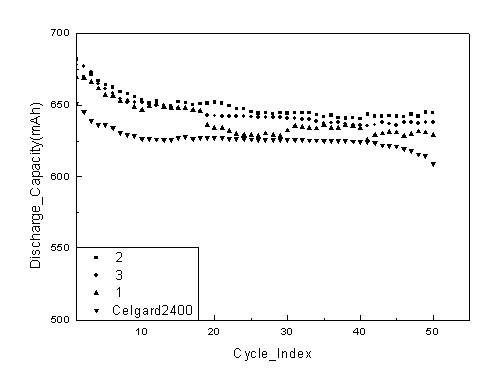

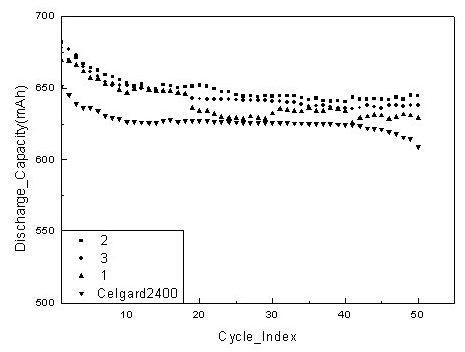

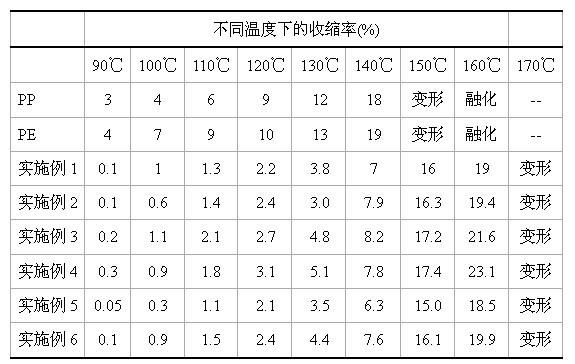

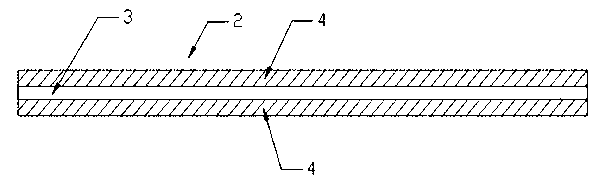

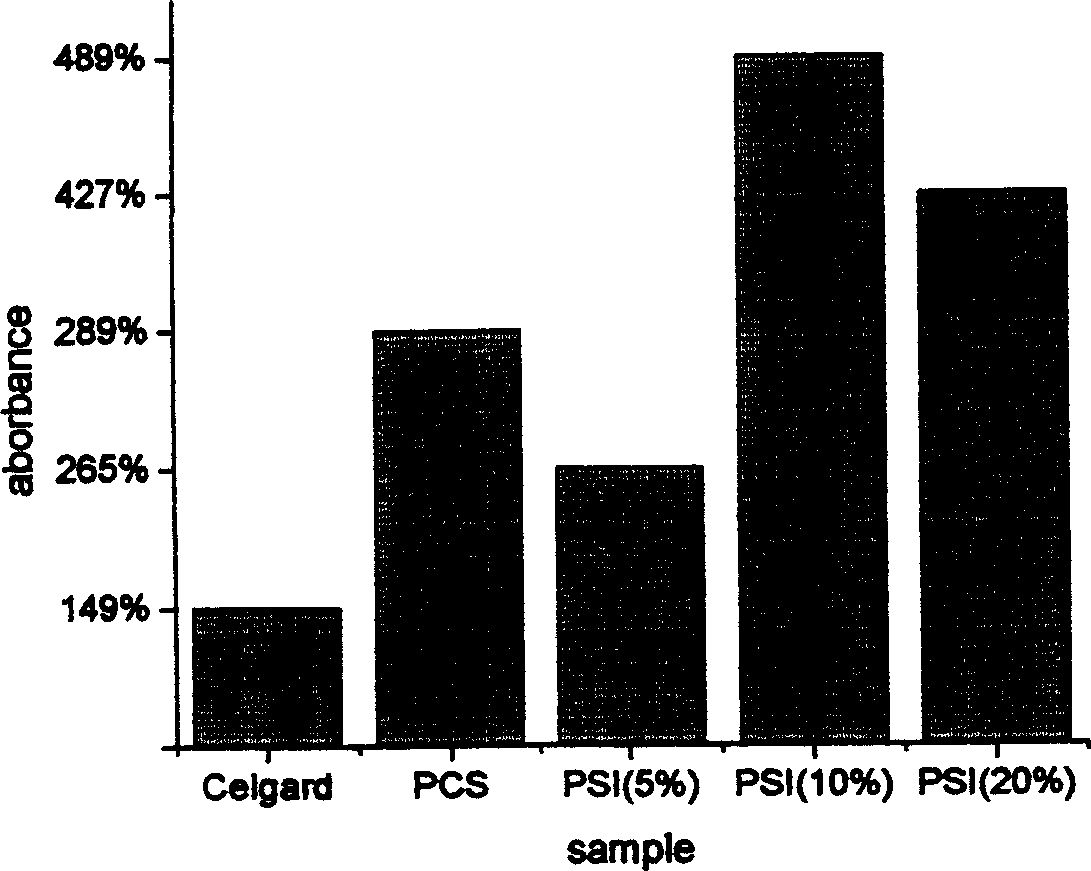

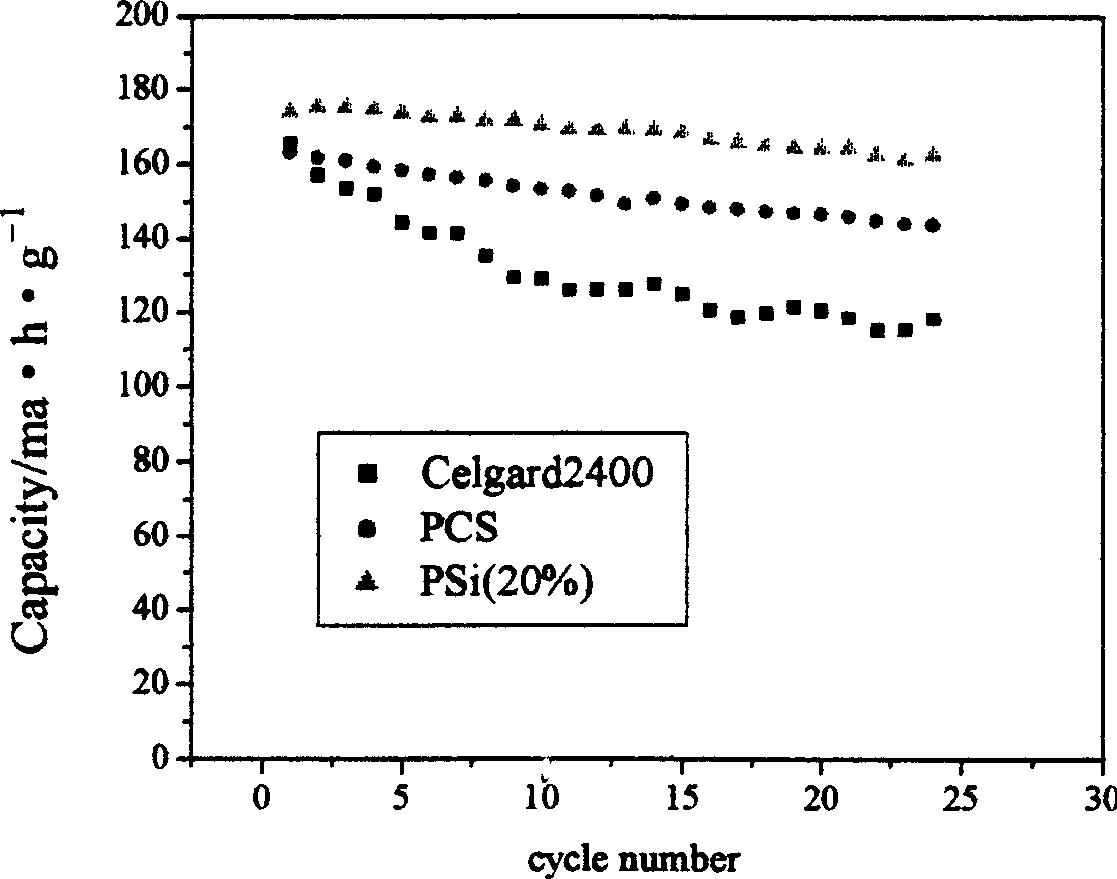

Compound modified polyolefin lithium ion battery separator and manufacturing method thereof

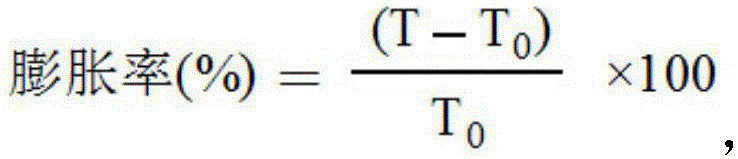

InactiveCN102306726AImprove wettabilityImprove interface propertiesSynthetic resin layered productsCell component detailsPolyolefinPolymer science

The invention provides a compound modified polyolefin lithium ion battery separator and a manufacturing method thereof. The battery separator is formed by compounding a one-sided or double-sided polyolefin microporous membrane with a layer of thin film, wherein the thin film is formed by dissolving a polymer and inorganic fillers in a solvent; the polymer is polyvinylidene fluoride-hexafluoropropylene, and the inorganic fillers are oxides; and the weight ratio of the polymer to the inorganic fillers is 100:(2-30). The battery separator prepared by the method provided by the invention has the advantages of good wettability, thermal blackout effect and low heat shrinkage, thus the interfacial characteristics between the cathode and anode materials and the separator can be improved, and the safety performance and cycle performance of the battery can be enhanced.

Owner:CANGZHOU MINGZHU PLASTIC

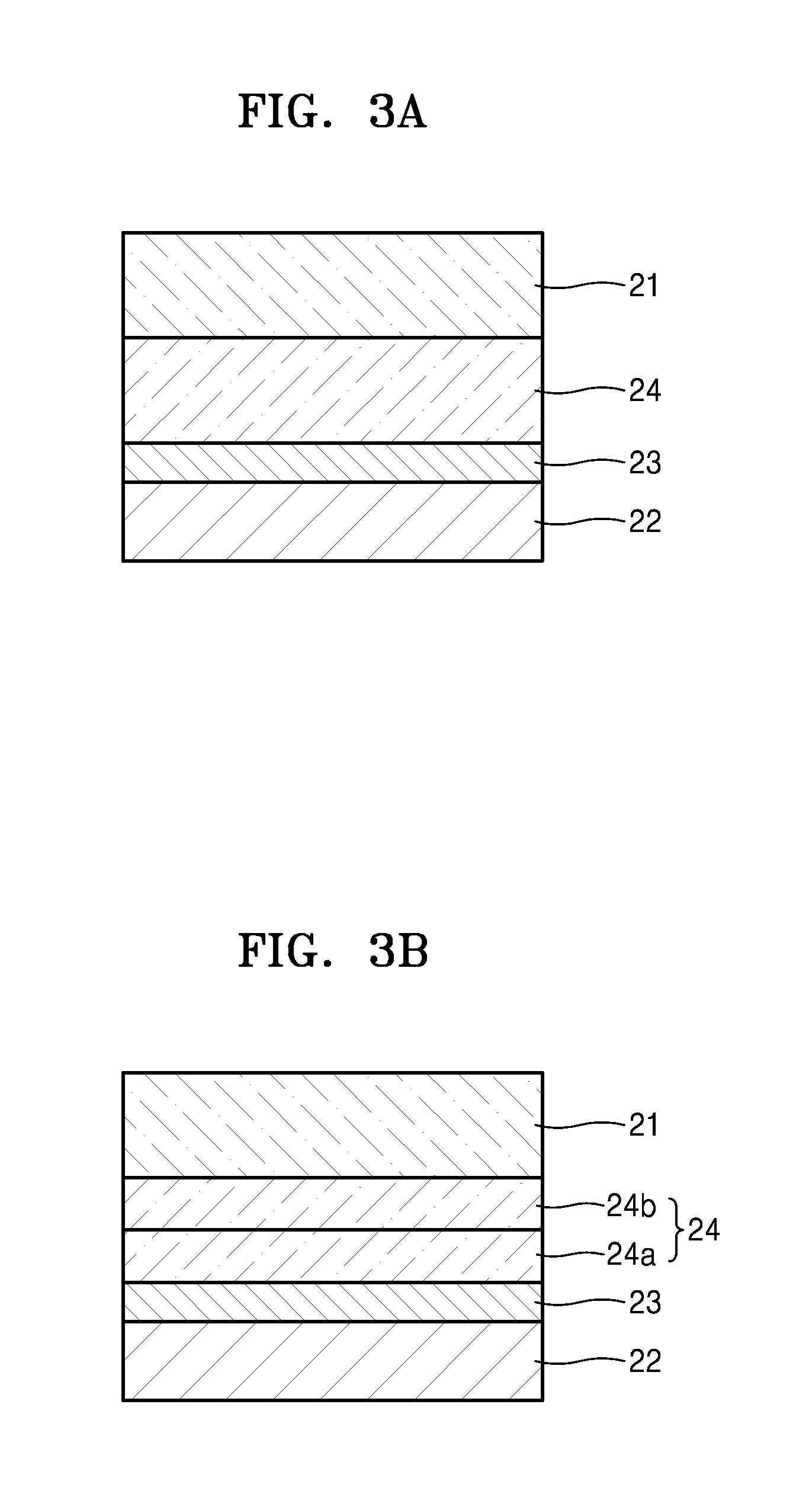

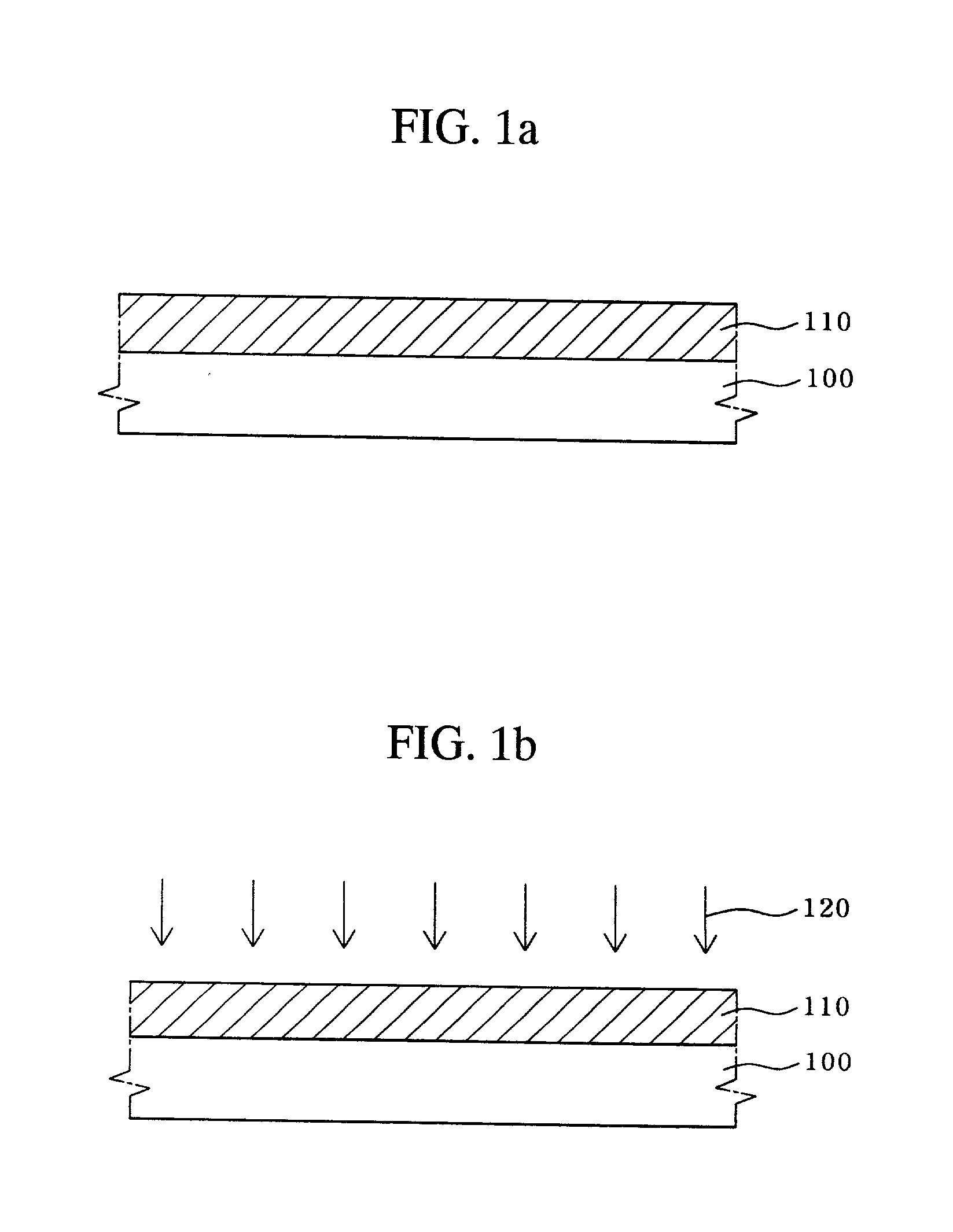

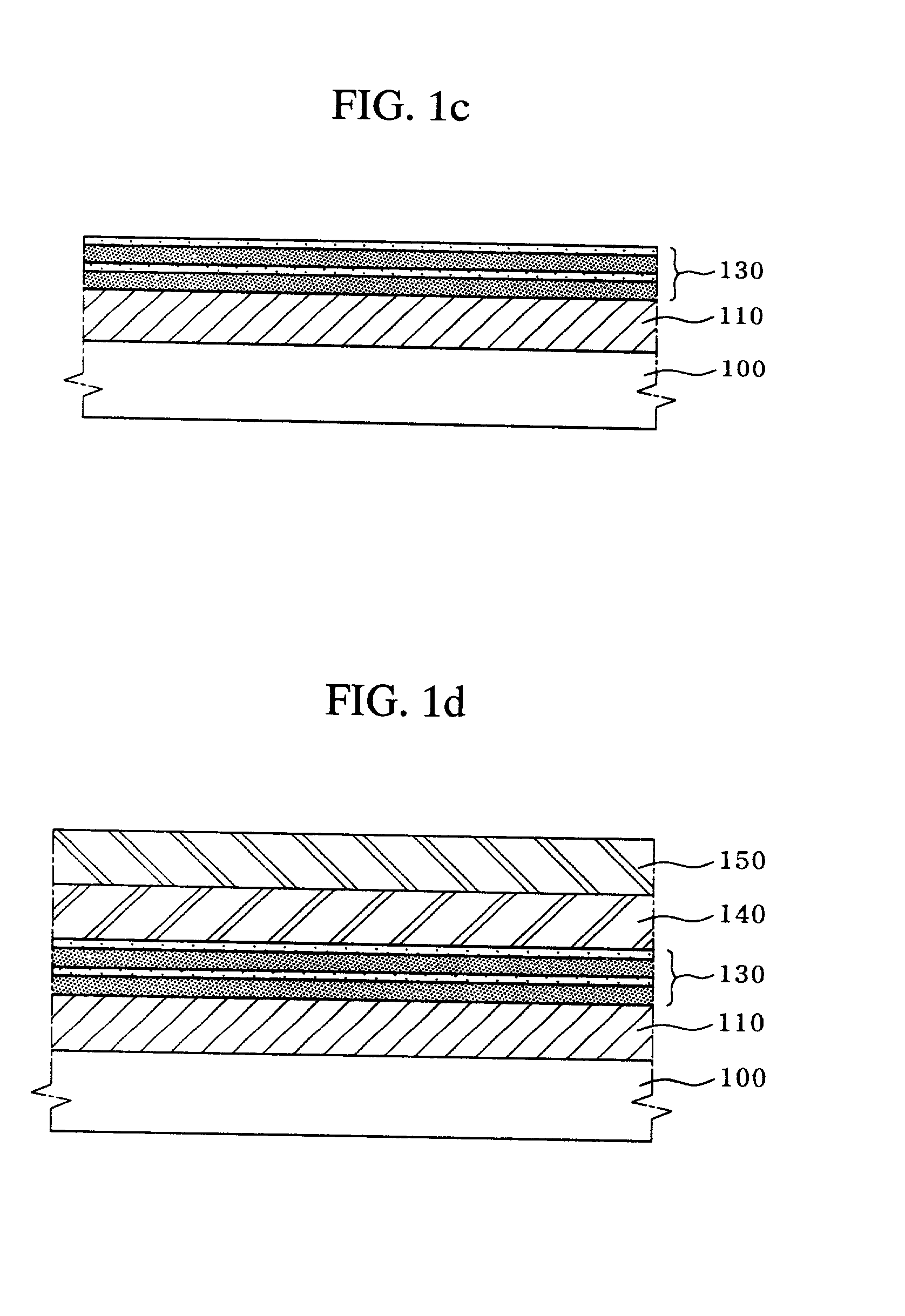

Ferroelectric stacked-layer structure, field effect transistor, and ferroelectric capacitor and fabrication methods thereof

InactiveUS20090152607A1Improve interface propertiesReduced carrier trap levelFixed capacitor dielectricStacked capacitorsFerroelectric thin filmsCrystal structure

A ferroelectric stacked-layer structure is fabricated by forming a first polycrystalline ferroelectric film on a polycrystalline or amorphous substrate, and after planarizing a surface of the first ferroelectric film, laminating on the first ferroelectric film a second thin ferroelectric film having the same crystalline structure as the first ferroelectric film. A field effect transistor or a ferroelectric capacitor includes the ferroelectric stacked-layer structure as a gate insulating film or a capacitor film.

Owner:PANASONIC CORP

Method for forming cell capacitor for high-integrated DRAMs

InactiveUS6573547B2Improve interface propertiesIncrease capacitanceTransistorSolid-state devicesCapacitanceHigh capacitance

A method for forming a cell capacitor used for a high-integrated DRAM is disclosed which guarantees interfacial properties of aluminum oxide and excellent leakage current preventive properties by depositing an aluminum oxide layer and a mixed layer of TiON and TiO2 as dielectric layers on a semiconductor substrate having a predetermined lower substructure by an atomic layer deposition (ALD) method and thus forming a double layer structure, and simultaneously providing a high capacitance by using a high dielectric property of a mixed layer of TiON and TiO2.

Owner:SK HYNIX INC

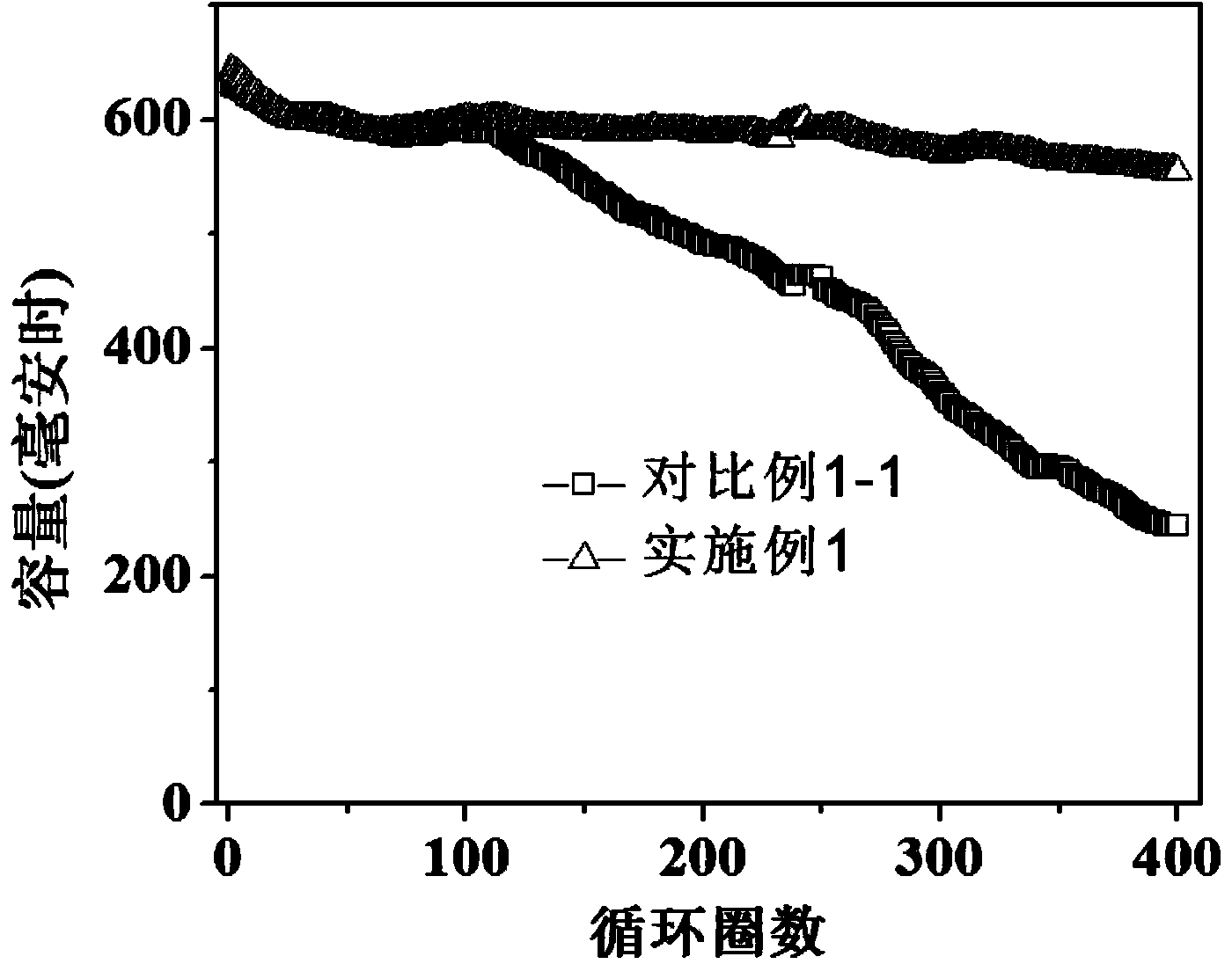

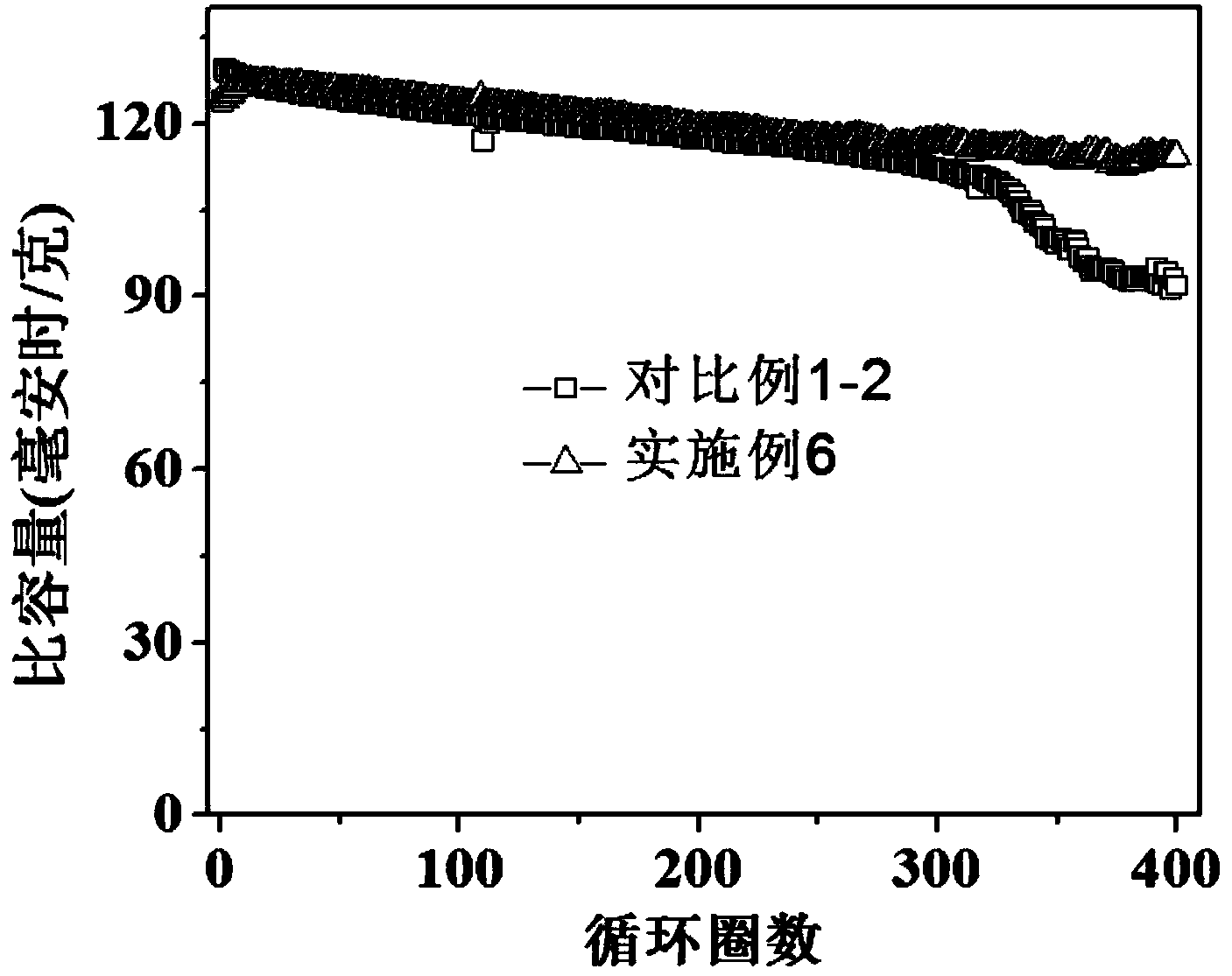

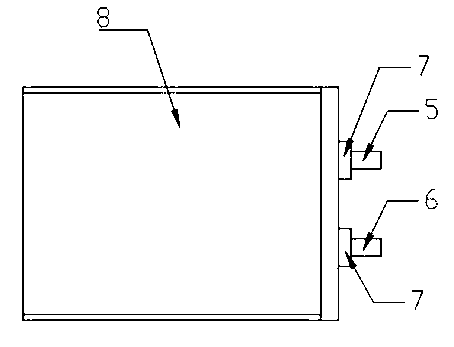

High-multiplying power lithium ion battery and preparation method thereof

InactiveCN105591055ASimple structural designImprove interface propertiesFinal product manufactureCell component detailsPorosityCooking & baking

The invention discloses a high-multiplying power lithium ion battery and a preparation method thereof. The lithium ion battery comprises a cathode plate, an anode plate, a composite diaphragm and an electrolyte solution, and the surfaces of the diaphragm are coated with composite conductive layers; each composite conductive layer is composed of a bonding agent, a conductive agent and micropores; the cathode plate and the anode plate are each of a full-tab structure. The preparation method comprises the steps that the diaphragm coated with the composite conductive layers, the cathode plate and the anode plate are subjected to a winding process to prepare a wound core, and the wound core is subjected to the processes of packaging, baking, liquid injecting, hot-cold pressing, forming and capacity grading to prepare the high-multiplying power lithium ion battery. According to the high-multiplying power lithium ion battery and the preparation method thereof, by improving the characteristics of the interfaces between the diaphragm and cathode and anode membranes and optimizing the structural design of the battery, the bonding performance of the contact interfaces between the diaphragm and the cathode and anode plates is improved, the lithium ion transfer resistance between the different interfaces is decreased, the electronic conductivity of the cathode and anode plates is enhanced, the porosity and the air permeability of the composite diaphragm are improved, wetting of the electrolyte solution to the diaphragm is improved, the retaining capacity of the electrolyte solution in the battery is improved, the high-multiplying power performance of the lithium ion battery is greatly improved, the high-multiplying power discharge capacity retention rate is increased by 10% or above compared with the prior art, and the high-multiplying power lithium ion battery is suitable for industrialized production.

Owner:CENT SOUTH UNIV

IGZO (indium gallium zinc oxide) thin film transistor and preparing method thereof

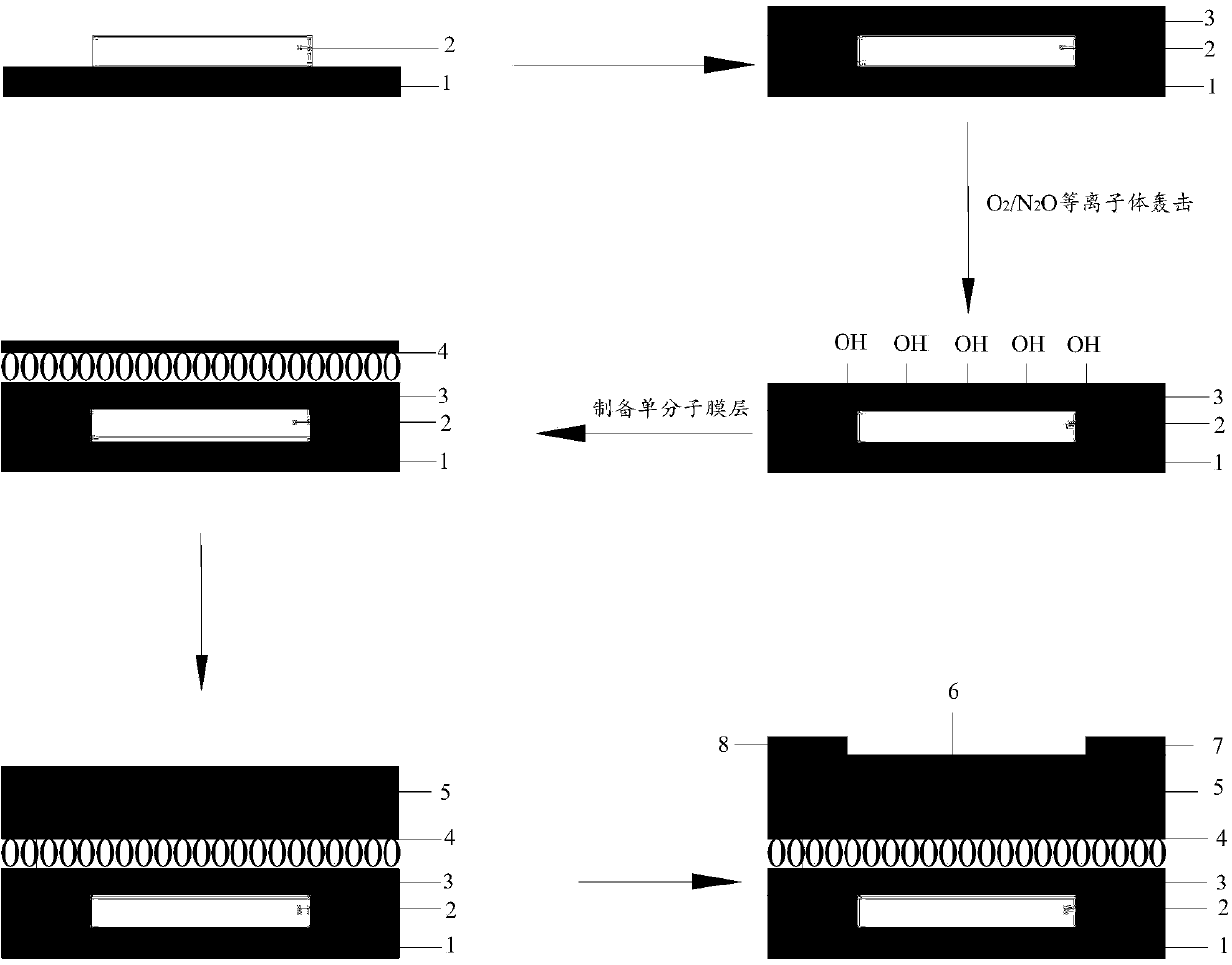

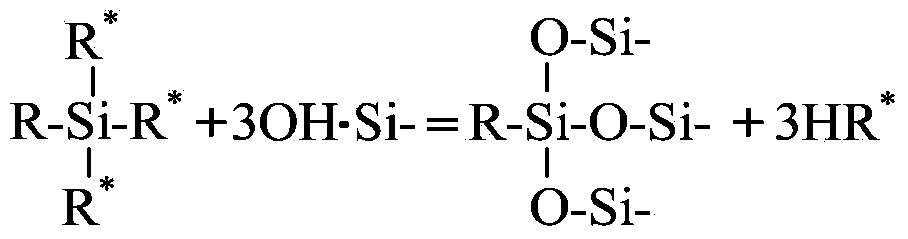

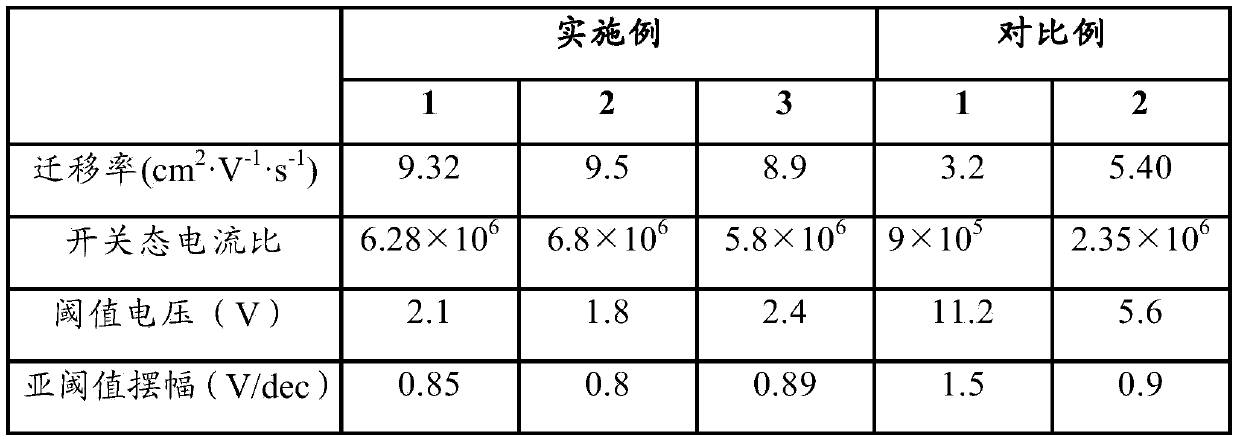

ActiveCN103700710AImprove mobilityImprove performanceTransistorSemiconductor/solid-state device manufacturingInsulation layerIndium gallium zinc oxide

The invention discloses an IGZO (indium gallium zinc oxide) thin film transistor and a preparing method thereof, wherein the IGZO thin film transistor comprises a substrate, a grid combined on the substrate surface and a silicide grid insulation layer covering the outer surfaces of the substrate and the grid, wherein the surface of the silicide grid insulation layer is subjected to O2 / N2O plasma bombardment processing; the surface of the silicide grid insulation layer subjected to the O2 / N2O plasma bombardment processing is also combined with a self-assembly single-molecule film layer in a laminating mode, so the film defect state of the silicide grid insulation layer can be reduced after the O2 / N2O plasma bombardment, the charge trap action is inhibited, the roughness of the surface of the insulation layer is reduced by the self-assembly single-molecule film layer, the interface property between the insulation layer and an active layer is well improved, charges are prevented from being captured by an interface defect, the carrier mobility of a device is reduced, the threshold voltage is reduced, leak current is reduced and the performance of the device is more stable.

Owner:TCL CORPORATION

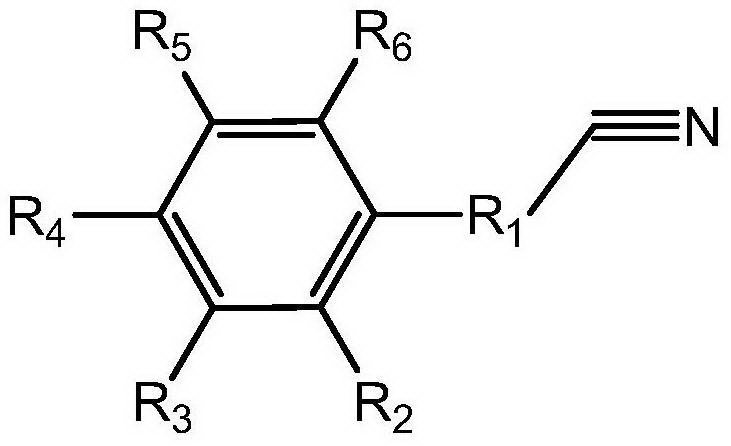

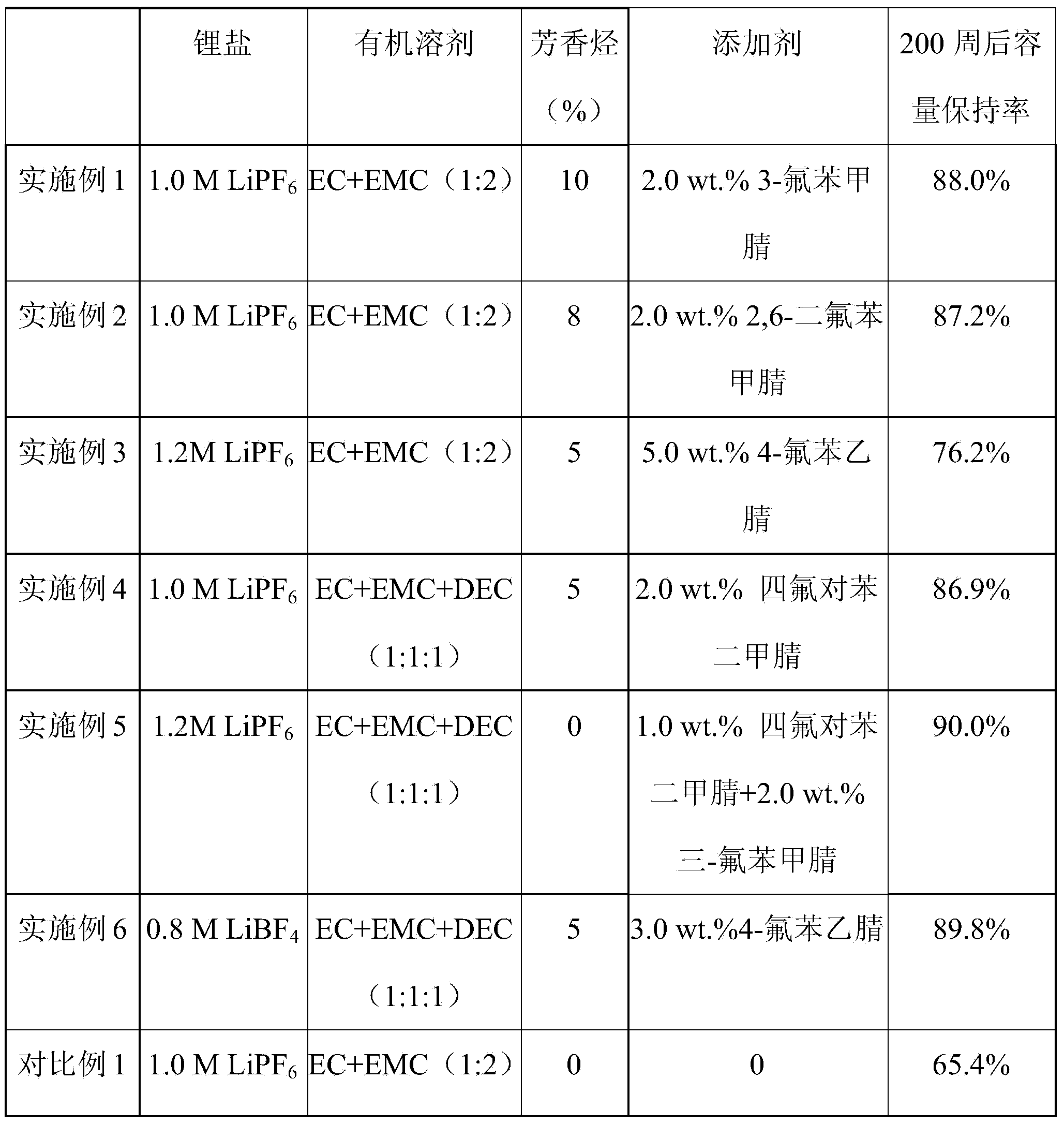

Electrolyte, preparation method for same and high-voltage lithium ion battery

ActiveCN104051786AReduce polarizationImprove interface propertiesElectrolyte accumulators manufactureOrganic solventDecomposition

The invention discloses electrolyte, a preparation method for the same and a high-voltage lithium ion battery. The electrolyte mainly comprises an organic solvent, conductive lithium salt and an additive, wherein the organic solvent is prepared from more than one of a cyclic carbonate solvent, an aromatic hydrocarbon solvent and a linear solvent; the concentration of the conductive lithium salt in the organic solvent is 0.8 to 1.5mol / L; the using amount of the additive is 0.1 to 10.0 percent based on the weight of the organic solvent, and the additive is a halogenated cyanophenyl compound. After the additive is added into the electrolyte, a polymer film can be formed on the surface of each of a positive electrode and a negative electrode, so that the interface impedance of the electrodes / electrolyte is reduced, the decomposition of the electrolyte on the surface of an electrode material is suppressed, and the prolonging of cycle life of the high-voltage lithium ion battery (higher than 4.4V), the improvement of high / low-temperature performance of the high-voltage lithium ion battery and the suppression of gas expansion of the battery are facilitated.

Owner:GUANGZHOU TINCI MATERIALS TECH

Light high-strength buoyancy material and preparation method thereof

The invention provides a light high-strength buoyancy material and a preparation method thereof. The material comprises the following components in part by weight: 100 parts of low-viscosity epoxy resin, 5 to 10 parts of thermoplastic resin, 16 to 48 parts of hollow microspheres and 10 to 20 parts of curing agent. The preparation method comprises the following steps of: (1) putting 100 weight parts of epoxy resin and 5 to 10 weight parts of engineering plastic into a reaction kettle, and performing prepolymerization reaction on the epoxy resin to obtain epoxy resin prepolymer; and (2) adding 16 to 48 weight parts of hollow microspheres treated by a silane coupling agent and 10 to 20 weight parts of curing agent into 48 to 90 weight parts of epoxy resin prepolymer, uniformly mixing, putting into a vacuum drying oven, vacuumizing, kneading the mixed material by using a grinder, defoaming in vacuum, curing for forming, putting the formed material into a drying box, heating to the curing temperature of an epoxy resin system, and thus obtaining a finished light high-strength buoyancy material product. The material meets the requirements of a deep ocean material on density and strength and the requirements of ocean development and submarine exploration.

Owner:CHINA NAT OFFSHORE OIL CORP +3

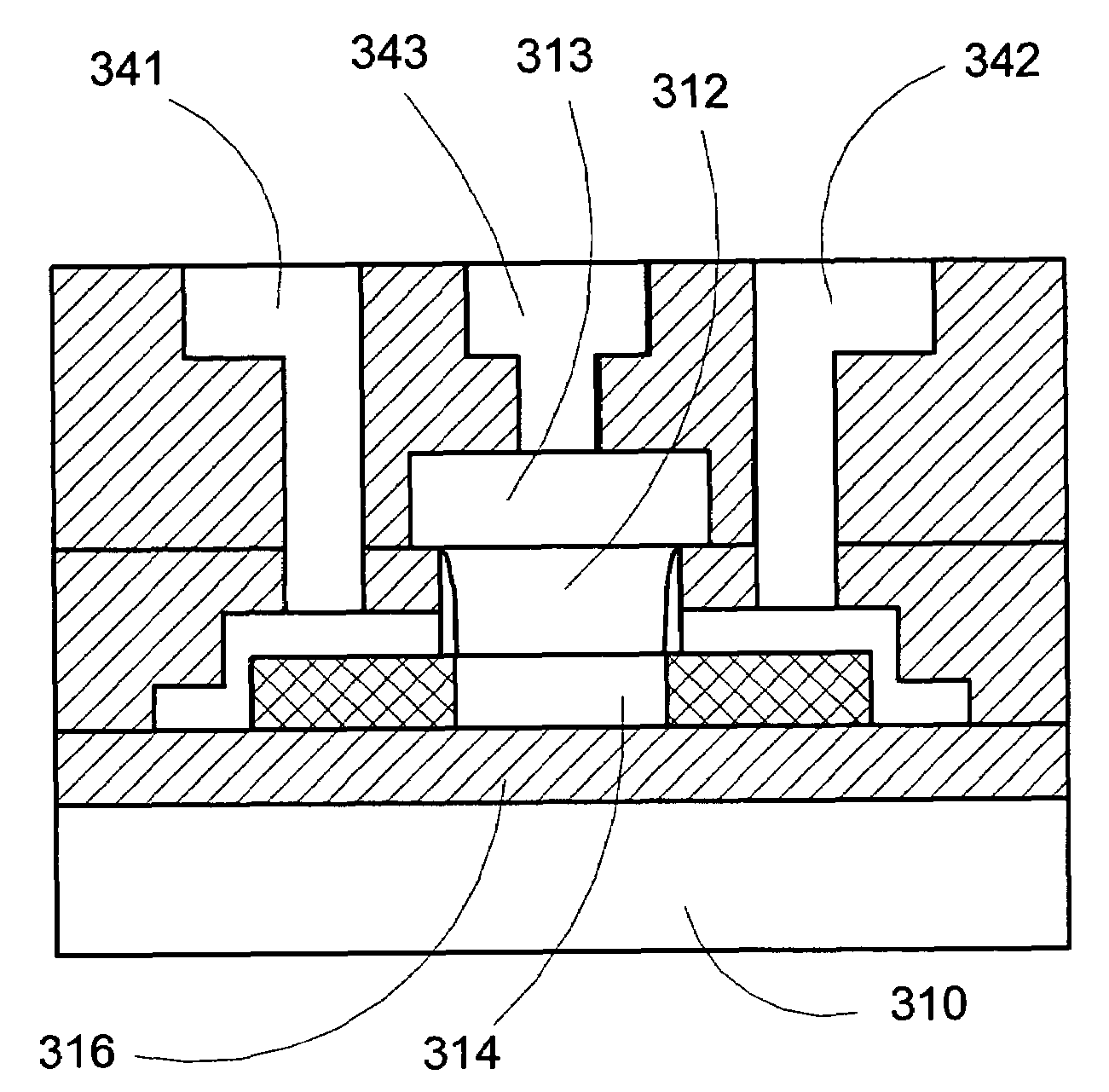

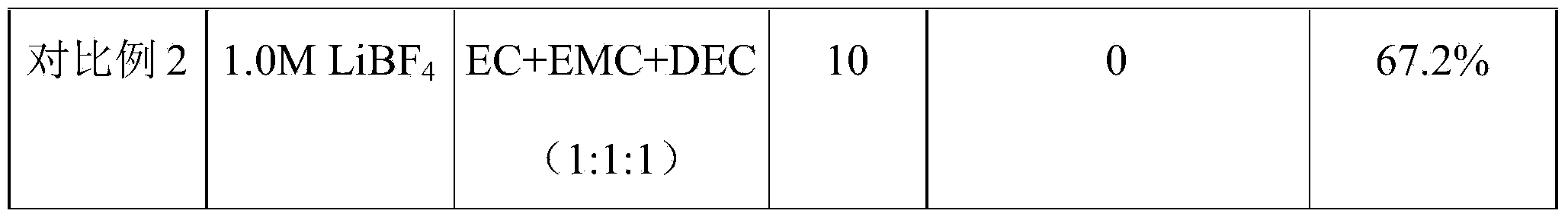

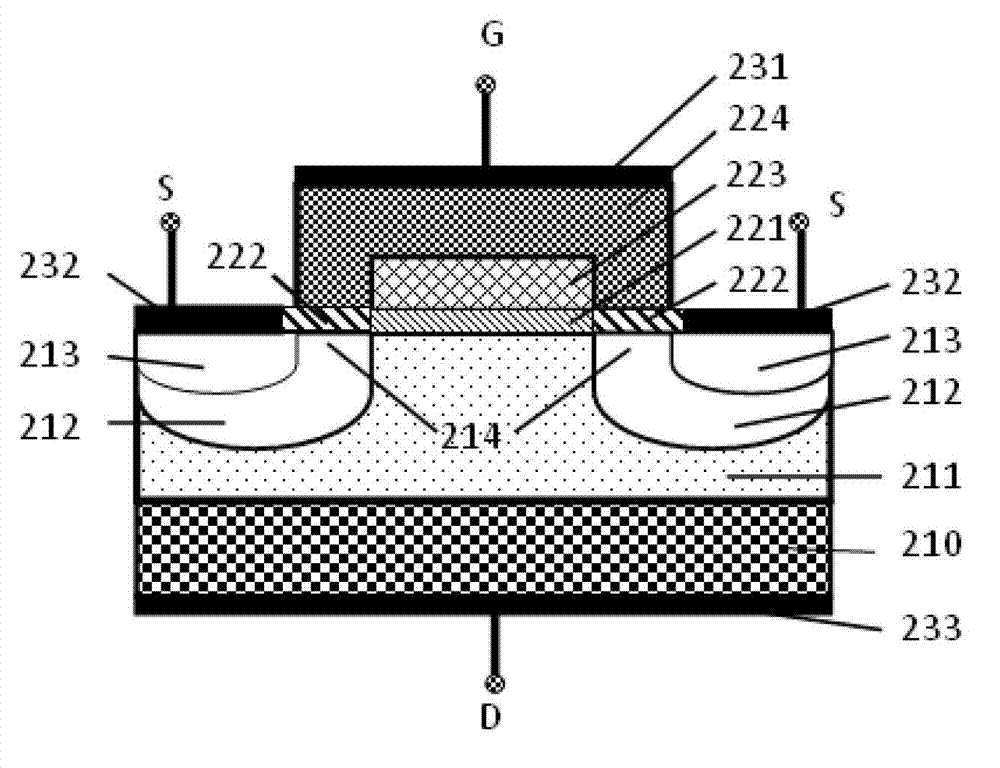

VDMOS transistor and preparation method thereof

InactiveCN103035732AIncreasing the thicknessReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceSilicon dioxide

The invention discloses a VDMOS transistor and a preparation method thereof and belongs to the field of semiconductors. The VDMOS transistor comprises a first conduction type substrate, a first conduction type epitaxial layer, a second conduction type injection region, a first conduction type highly doped source region and a grid structure, the second conduction type injection region and the first conduction type highly doped source region are arranged in the epitaxial layer, and the grid structure comprises a grid insulating layer, a semi-insulating polycrystalline silicon layer, a silicon oxynitride layer and a polycrystalline silicon layer. The grid insulating layer is arranged above a drift region of the epitaxial layer, the semi-insulating polycrystalline silicon layer is arranged above the grid insulating layer, the silicon oxynitride layer is arranged above a channel region, and the polycrystalline silicon layer is covered on the semi-insulating polycrystalline silicon layer and the silicon oxynitride layer. A heat nitriding silicon oxynitride layer is introduced into the preparation method, a traditional silica layer which is used as a gate medium layer on a channel is replaced, and the semi-insulating polycrystalline silicon layer is added on an oxide layer which is arranged above the drift region of the epitaxial layer. The VDMOS transistor and the preparation method thereof can obviously reduce grid-drain capacitance and achieve overcoming the defects that insulating performance of the grid insulating layer is poor, current leaking of a grid electrode is increased, and degeneration of the VDMOS performance is unreliable.

Owner:SOUTH CHINA UNIV OF TECH

High-voltage lithium ion battery electrolyte, preparation method and application of electrolyte

InactiveCN103956517AReduce decompositionImprove high voltage performanceFinal product manufactureElectrolyte accumulators manufactureOrganic solventSolvent

The invention discloses high-voltage lithium ion battery electrolyte, a preparation method and application of electrolyte. The high-voltage lithium ion battery electrolyte comprises an organic solvent, conductive lithium salt and a functional additive, wherein the organic solvent is prepared from a cyclic carbonate solvent, a fluoro solvent and a linear carbonic ester solvent, the content of the fluoro solvent in the high-voltage lithium ion battery electrolyte is 0.1-40wt.%, the content of the functional additive is 0.01-5wt.%, and the concentration of the conductive lithium salt in the organic solvent is 0.8-1.5mol / L. According to the high-voltage lithium ion battery electrolyte, the interfacial property of the anode and the cathode of the battery and the electrolyte can be improved, and the stability of the electrolyte can be improved, so that the cycle life of the high-voltage lithium ion battery is prolonged, the high-temperature property of the high-voltage lithium ion battery is improved and the working voltage of the high-voltage lithium ion battery is increased to be above 4.5V.

Owner:SOUTH CHINA NORMAL UNIVERSITY

Epsilon-polylysine bionic antibacterial membrane, preparation and application thereof

ActiveCN108066805AGood antibacterial effectImprove adhesionAbsorbent padsBandagesCross-linkEpsilon-Polylysine

The invention relates to an epsilon-polylysine bionic antibacterial membrane and a preparation method and application thereof. The method for preparing the epsilon-polylysine bionic antibacterial membrane is characterized by comprising the following steps: preparing a gelatinous aqueous solution containing epsilon-polylysine, chitosan, hyaluronic acid, gelatin, polyvinyl alcohol and glycerol, thenadding a cross-linking agent to perform a cross-linking reaction in a patterned template to obtain a gel, and then neutralizing, washing, and drying. The epsilon-polylysine bionic antibacterial membrane has good antibacterial and moisturizing properties, and the composition approximates an extracellular matrix and has a patterned surface that can promote epithelial cell adhesion, growth and migration. Therefore, the epsilon-polylysine bionic antibacterial membrane can be used as a skin wound dressing to improve the wound healing effect.

Owner:大连敏慧精益科技有限公司

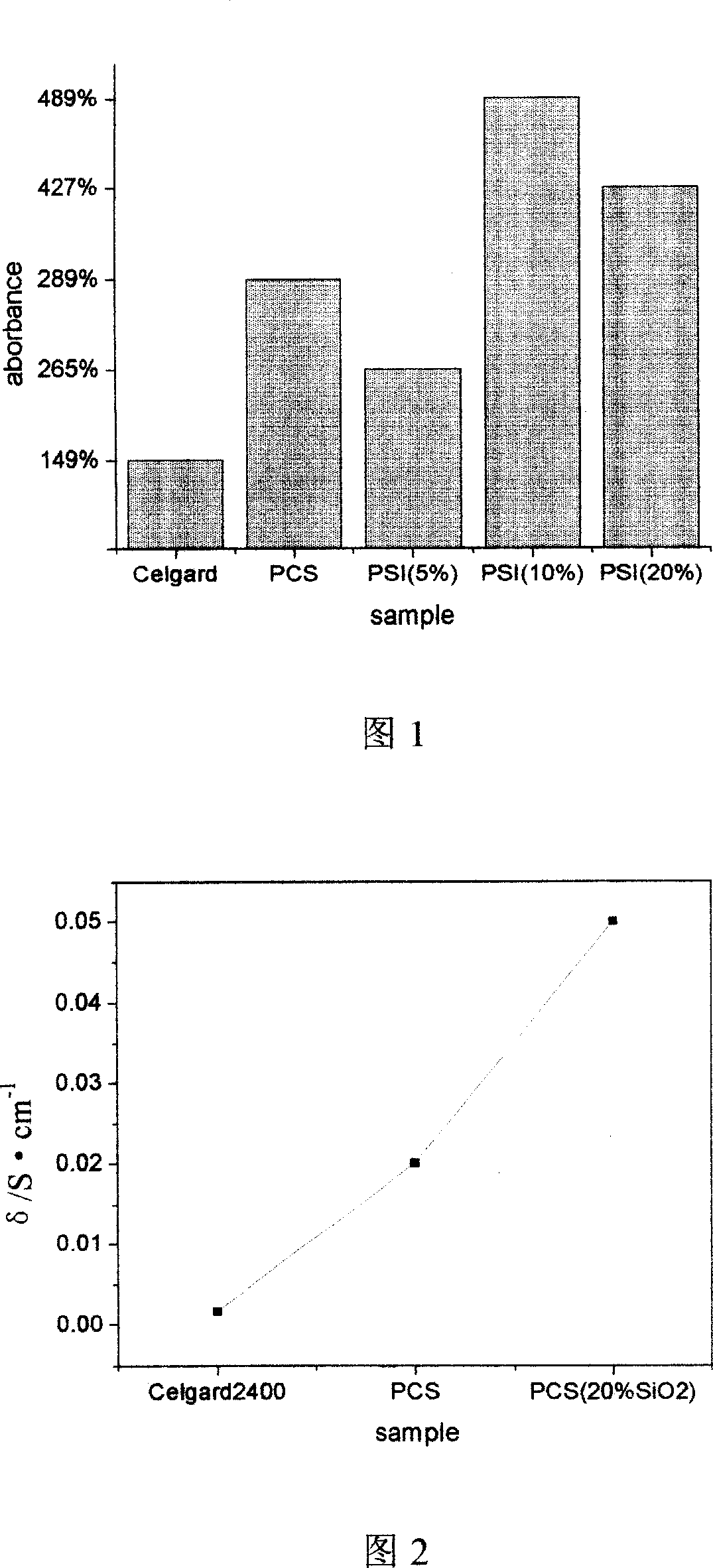

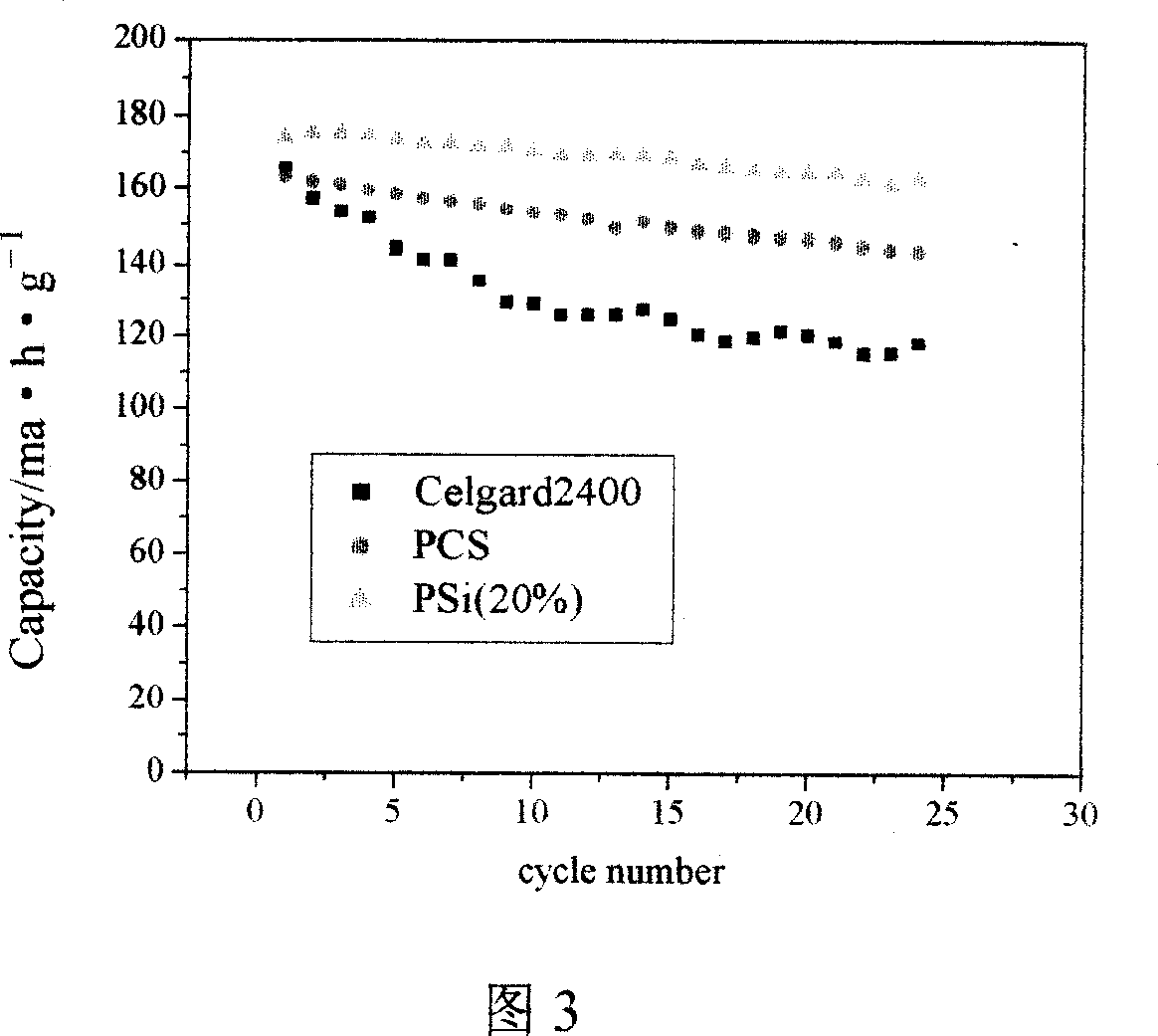

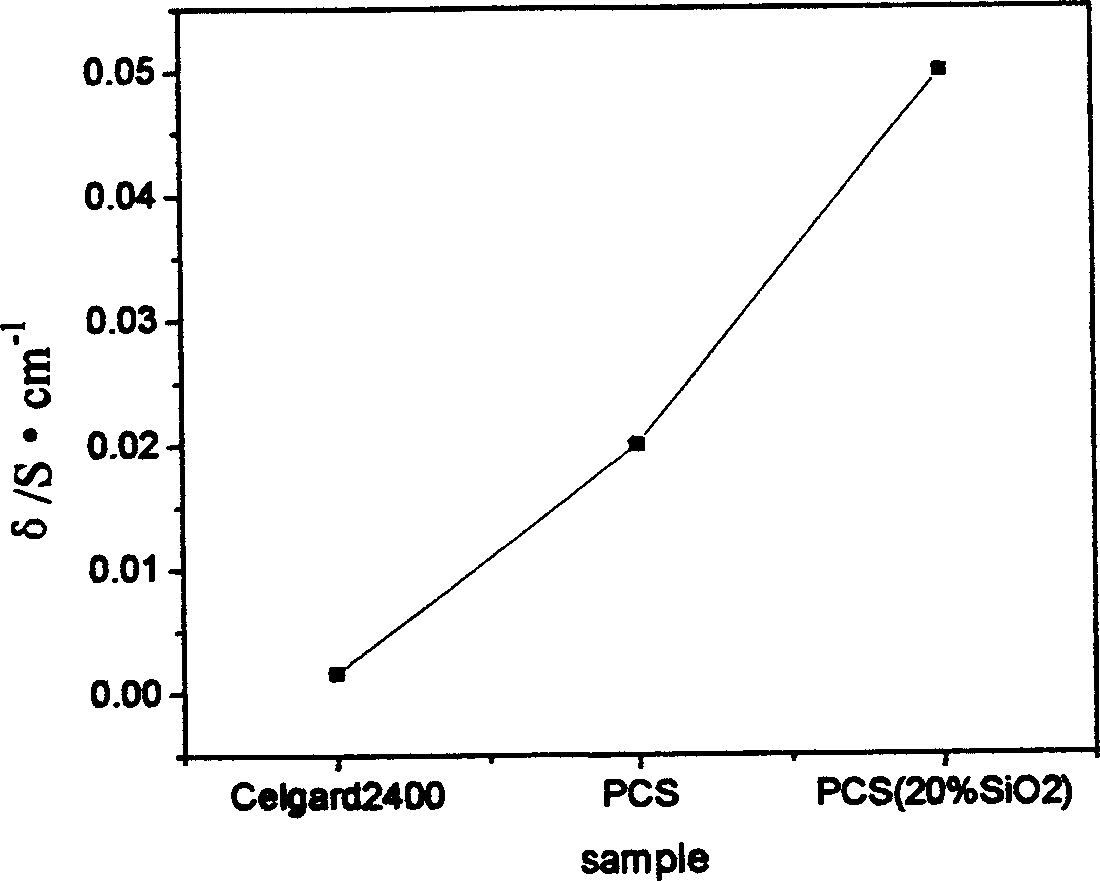

Composite lithium battery membrane and method for making same

InactiveCN1312789CImprove interface propertiesHigh conductivity at room temperatureCell component detailsElectrical batteryNano sio2

The invention refers to a manufacturing method for a kind of compound polypropylene lithium membrane. The materials are base membrane, polymer and nano SiO2 fillers; the step is: the materials are solved in the solvent, the sol compound can be acquired, and then they are transferred to the culture dish, the membrane is immersed in them; the membrane is taken out and transferred to the template, the solvent is absorbed by the molecular sift, then they are transferred into the vacuum drying box to be dried. The invention emphasizes the humidity to membrane by the polymer and the improvement to the interface performance, the organic group component of the SiO2 surface is important to the performance of the compound membrane. The compound membrane upgrades the room temperature conductivity, and improves the interface performance of the positive material / membrane, lithium / membrane. The assembled battery has an excellent circular performance.

Owner:XIAMEN UNIV

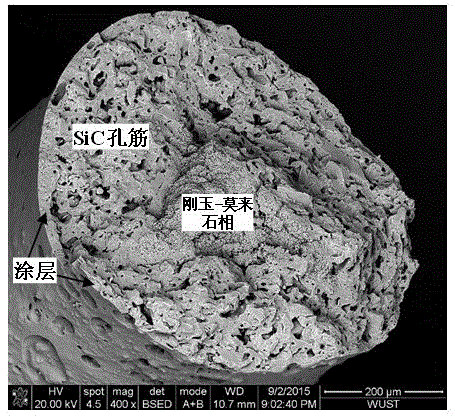

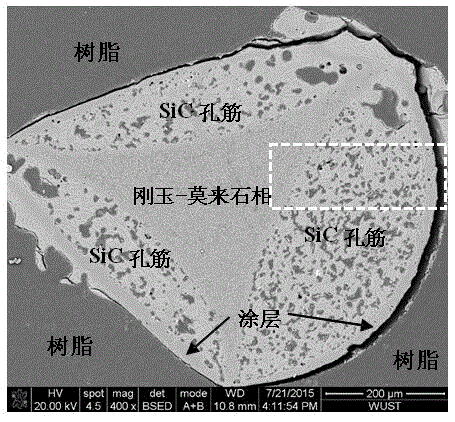

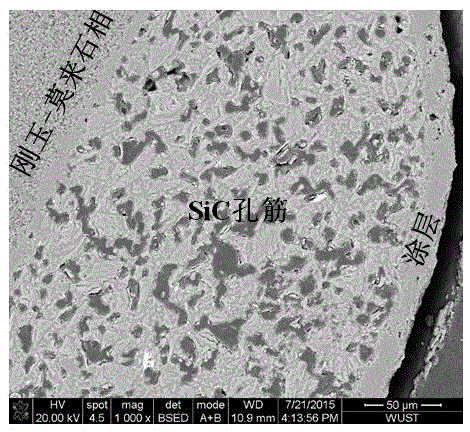

Silicon carbide-based composite foamed ceramic of multilayer hole rib structure and preparation method thereof

The invention discloses a silicon carbide-based composite foamed ceramic of a multilayer hole rib structure and a preparation method thereof. The preparation method comprises the following steps: uniformly mixing silicon carbide, micro alumina powder, silicon powder, ammonium lignosulfonate, polycarboxylate and water so as to prepare slurry I; uniformly mixing micro alumina powder, a silicon source polycarboxylate and water so as to prepare slurry II; then dipping polyurethane sponge in the slurry I, and successively carrying out extruding or slurry centrifugation, drying and heat preservation at 600 to 850 DEG C for 0.5 to 3 h so as to obtain a presintered body of silicon carbide foamed ceramic; subjecting the presintered body of silicon carbide foamed ceramic to vacuum dipping in the slurry II and successively carrying out slurry centrifugation and drying so as to obtain a green body of silicon carbide-based composite foamed ceramic; and carrying out heat preservation at 1300 to 1500 DEG C in an air atmosphere for 2 to 4 h so as to prepare the silicon carbide-based composite foamed ceramic of the multilayer hole rib structure. The preparation method has the characteristics of simple process and low cost; and the prepared silicon carbide-based composite foamed ceramic of the multilayer hole rib structure has high mechanical strength, good thermal shock resistance and excellent high-temperature anti-oxidation performance.

Owner:WUHAN UNIV OF SCI & TECH

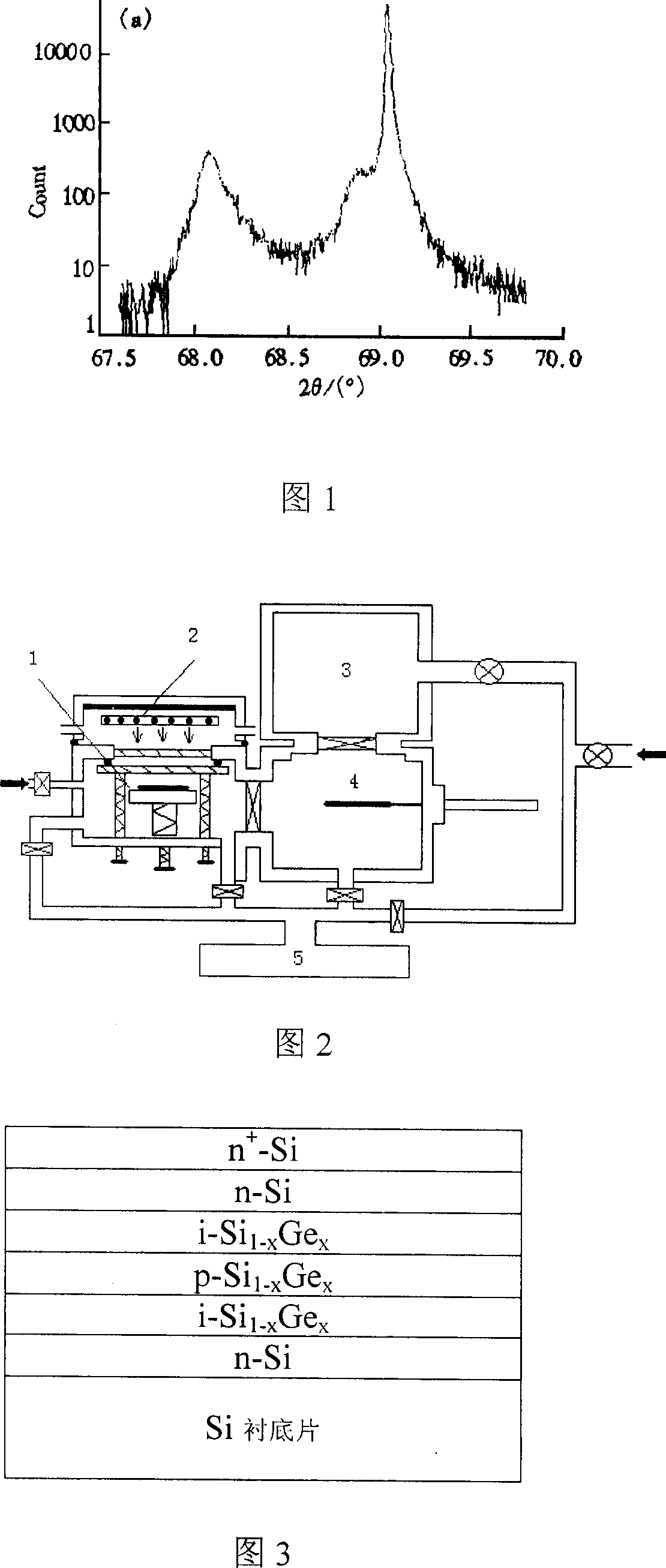

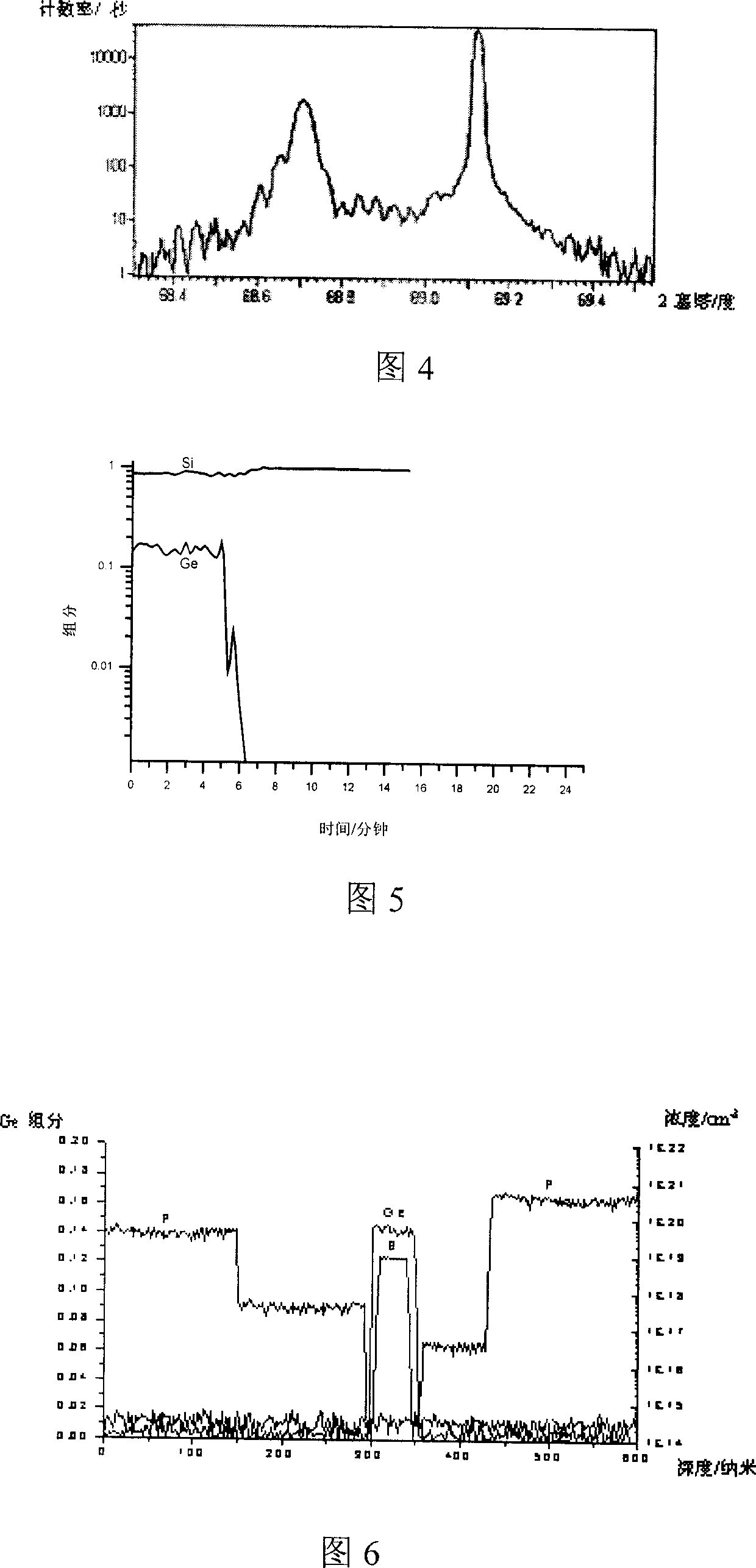

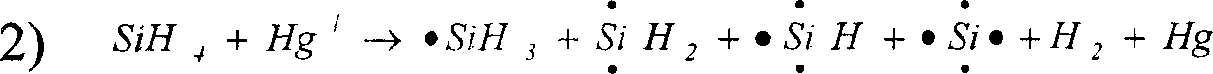

SiGe/Si Chemical vapor deposition growth process

InactiveCN1417844AAvoid unclear material interfaceReduce material interface unclearSemiconductor/solid-state device manufacturingMaterial growthSilicon-germanium

The present invention discloses an epitaxial growth process of SiGe / Si material with optochemical vapor deposition equipment in low-temperature and high-background vacuum environment. The main feature of the present invention is organic combinatino of UHV / CVD technology and CVD technology. The SiGe / Si material is grown through reaction in background vacuum superior to 1E(-7) Pa, reaction temperature of 400-450 deg.c and reaction pressure of 1-10 Pa. The SiGe / Si material growth in the process of the present invention has less tress, complete crystal structure, good interface characteristic andhigh practicability.

Owner:XIDIAN UNIV

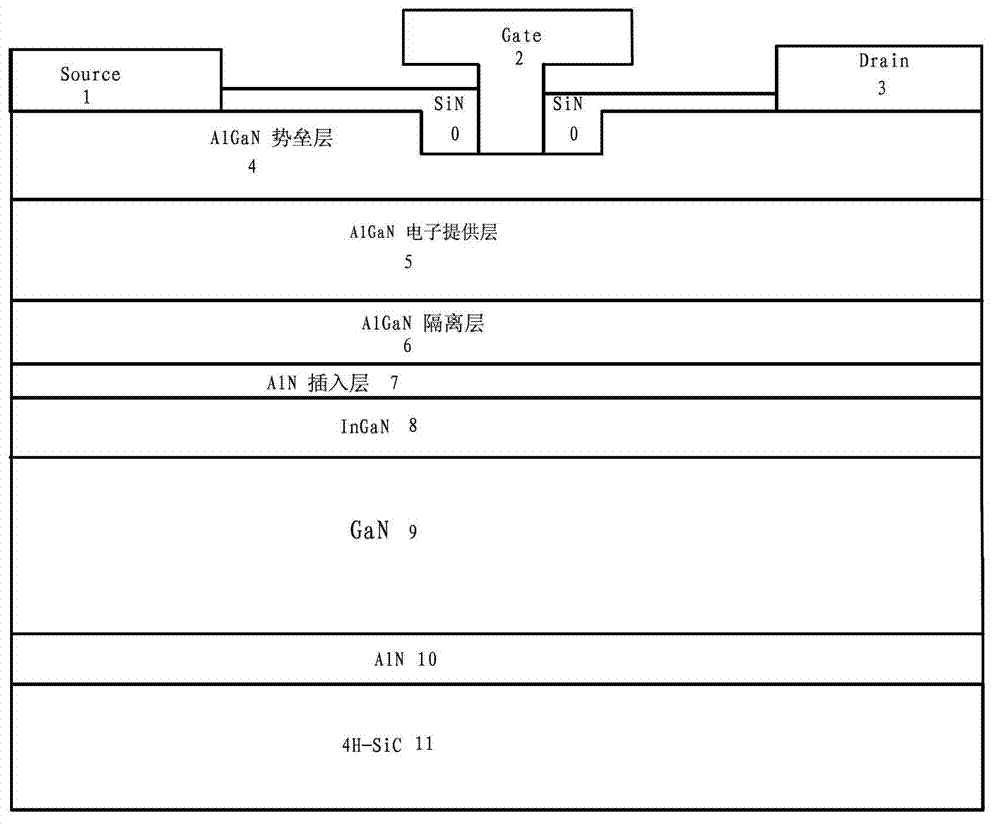

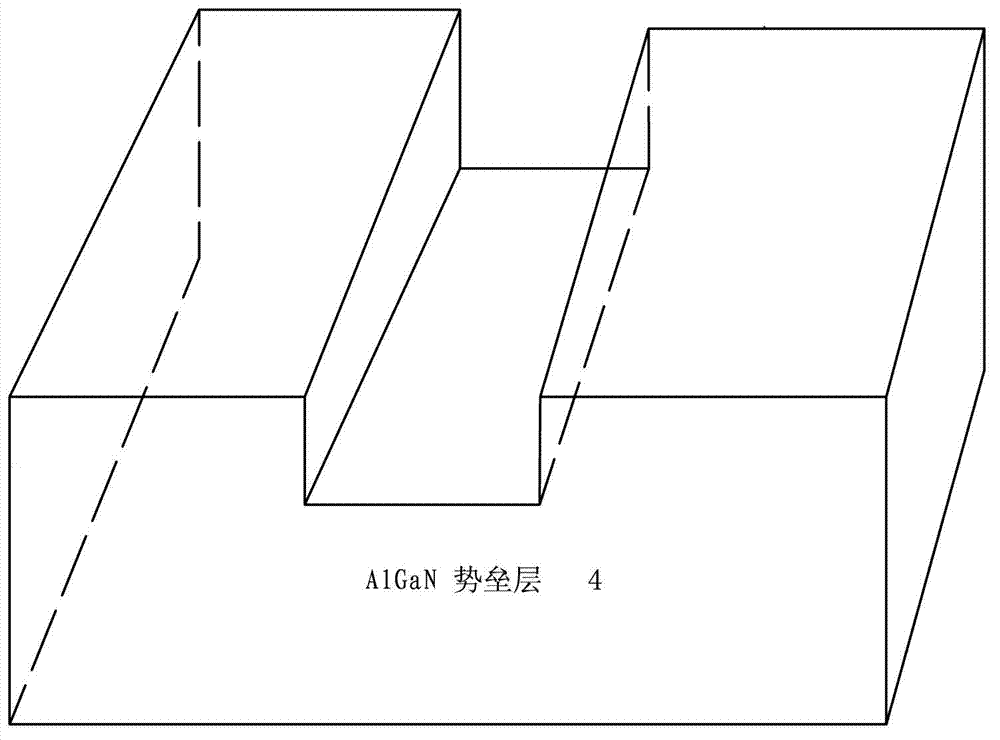

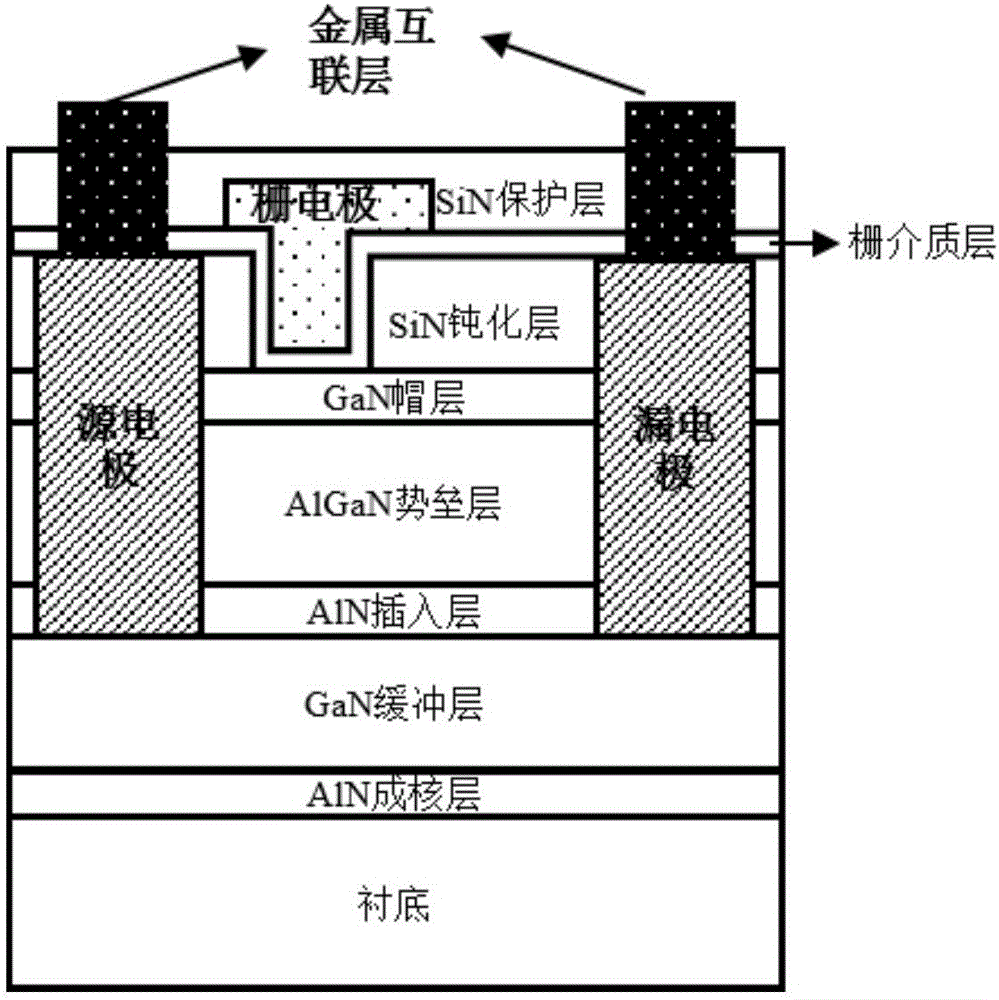

High-frequency and low-noise gallium nitride transistor structure with high electronic mobility

InactiveCN102881715AImprove interface propertiesImprove Noise PerformanceSemiconductor devicesLow noisePotential well

The invention relates to a high-frequency and low-noise gallium nitride transistor structure with high electronic mobility. The structure comprises a substrate, an aluminium nitride nucleating layer arranged on the substrate and a gallium nitride cushioning layer arranged on the aluminium nitride nucleating layer; the substrate, the aluminium nitride nucleating layer and the gallium nitride cushioning layer are sequentially overlapped from bottom to top; the high-frequency and low-noise gallium nitride transistor structure with the high electronic mobility is characterized in that an InGaN inserting layer for improving roughness of a component interface, an aluminium nitride inserting layer for improving a potential barrier, an AlGaN isolating layer, an AlGaN electronic providing layer, an AlGaN potential barrier layer as well as a source electrode, a grid electrode and a drain electrode which are respectively in ohm connection with the AlGaN potential barrier layer are sequentially overlapped on the gallium nitride cushioning layer. The high-frequency and low-noise gallium nitride transistor structure has the beneficial effects that two-dimensional electronic gas is better bound in a potential well, therefore, scattering of the two-dimensional electronic gas caused by impurities in a channel layer is reduced, and a saturated rate and a mobility ratio of the two-dimensional electronic gas are increased, and a noise performance of a device is improved, particularly a high-frequency noise performance.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Grid structure from material with high dielectric constant and preparing technique

InactiveCN1540769AEffective isolation of diffusionPrevent penetrationTransistorSemiconductor/solid-state device manufacturingDielectricThin layer

Oxidizing surface of silicon chip grows a very thin silicon oxynitride layer as a buffer of interface between material with high dielectric constant and silicon substrate in order to insulate diffusion between impurity element in material with high dielectric constant and silicon substrate. Carrying out nitrogen treatment for surface of material with high dielectric constant or depositing a thin layer of silicon nitride covers material with high dielectric constant. The nitrogen treated surface or deposited thin layer as interface layer between material with high dielectric constant and polysilicon blocks off penetration from boron P+ polycrystal. In the invention , grid structure is in sandwich type. The invention is applicable to not more than 65 Nano CMOS technique.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT +1

Cement-based composite material for steel box girder bridge deck, as well as preparation and pavement thereof

ActiveCN103449786AImprove toughnessLimit extensionBridge erection/assemblyBridge materialsEpoxyBridge deck

The invention relates to a cement-based composite material for pavement of a steel box girder bridge deck, as well as a preparation method and a pavement method thereof. The invention aims at providing a lightweight and high-toughness cement-based composite material which is suitable for pavement of larger-span steel box girder bridge decks, and the cement-based composite material comprises the following components in parts by weight: 849-881 parts of cement, 339-425 parts of quartz sand, 215-273 parts of pottery sand, 100-226 parts of fly ash, 30-56 parts of silica fume, 275-295 parts of water, 10-13 parts of water reducing agent, 40-80 parts of steel fiber, 6.5-13 parts of organic fiber and 20-30 parts of epoxy resin. Through material optimization, the durability of a bridge deck paving layer is improved, the overall dead weight is reduced, the cost of a project is simultaneously saved, and the cement-based composite material is suitable for pavement of the larger-span steel box girder bridge decks.

Owner:WUHAN UNIV OF TECH

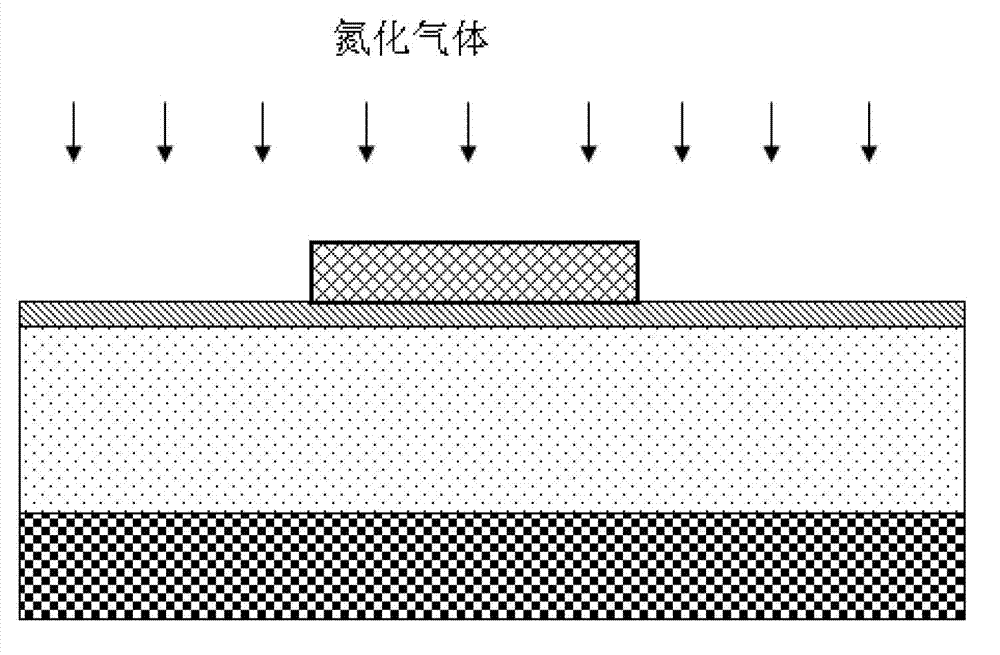

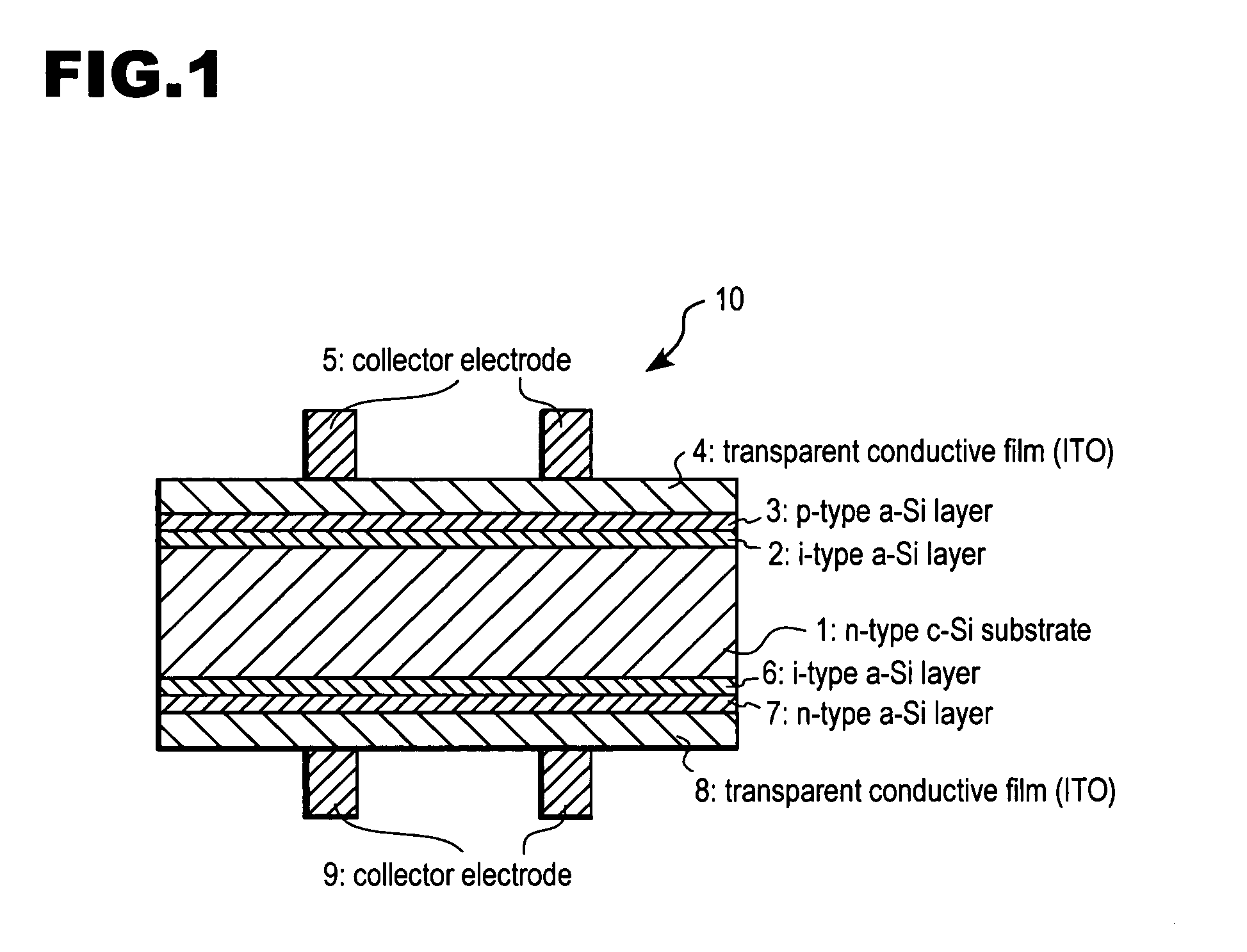

Nitrided barrier layers for solar cells

InactiveCN101999176AImprove interface propertiesEnhanced electric fieldFinal product manufacturePhotovoltaic energy generationLithographic artistSolar cell

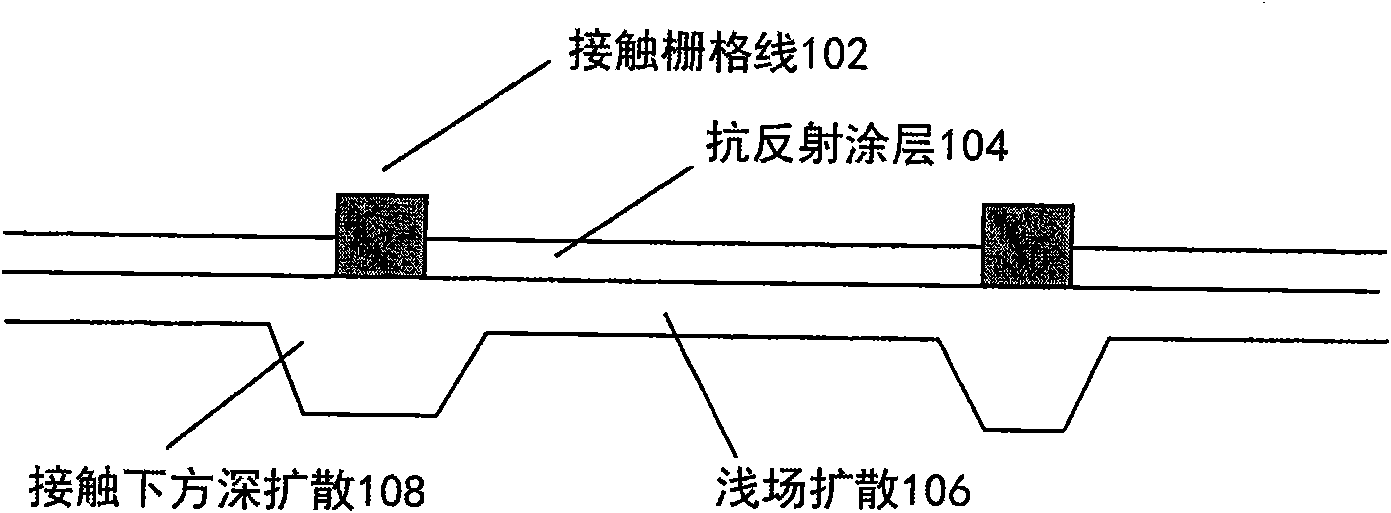

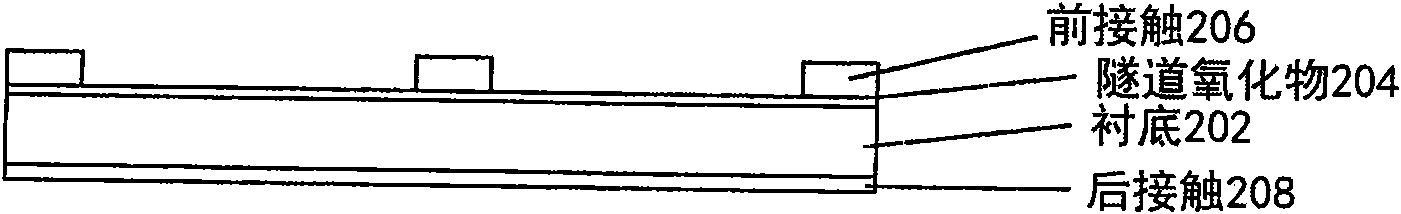

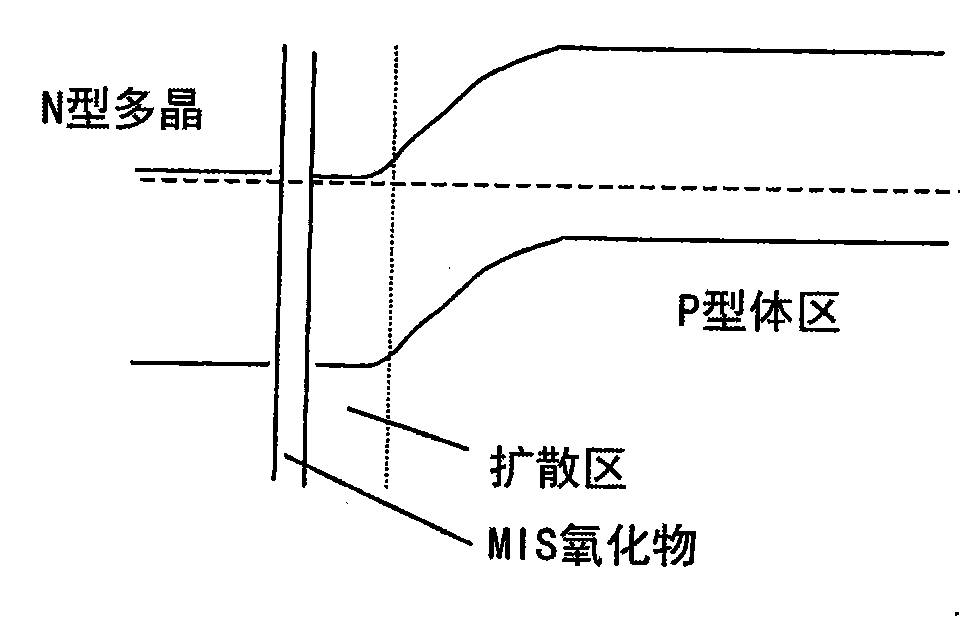

The present invention relates to polysilicon emitter solar cells, and more particularly to polysilicon emitter solar cells with hyperabrupt junctions, and methods for making such solar cells. According to one aspect, a polysilicon emitter solar cell according to the invention includes a nitrided tunnel insulator. The nitridation prevents boron diffusion, enabling a hyperabrupt junction for a p-poly on n-Si device. According to another aspect, a nitrided oxide (DPN) is used in a tunnel oxide layer of a MIS solar cell structure. The DPN layer minimizes plasma damage, resulting in improved interface properties. An overlying polysilicon emitter can then provide a low sheet resistance emitter without heavy doping effects in the substrate, excess recombination, or absorption, and is a significant improvement over a conventional diffused emitter or TCO. According to another aspect, the invention includes a method for making a solar cell structure that is functionally equivalent to a selective emitter, but without the requirement for multiple diffusions, long diffusions, aligned lithography, or fine contact holes.

Owner:APPLIED MATERIALS INC

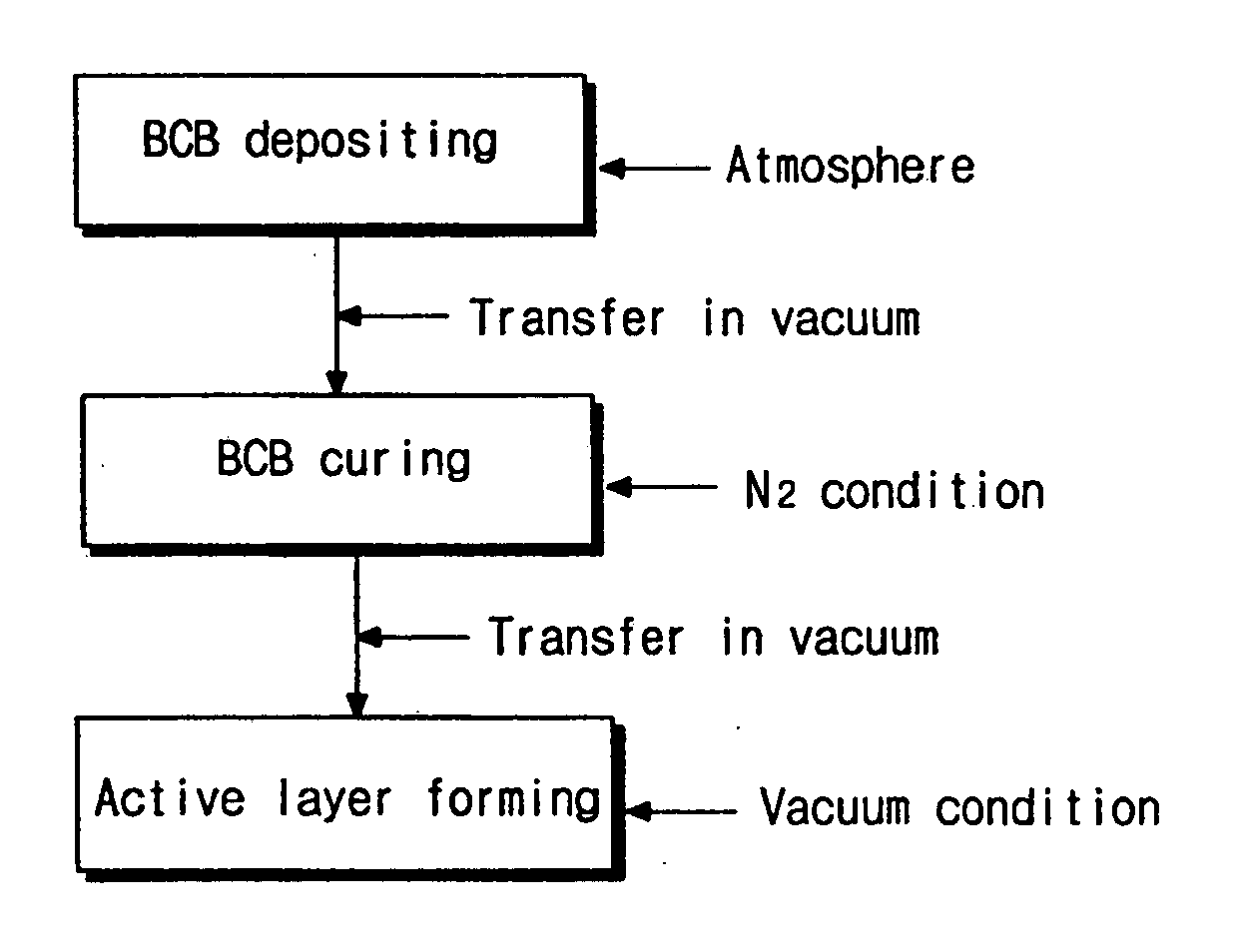

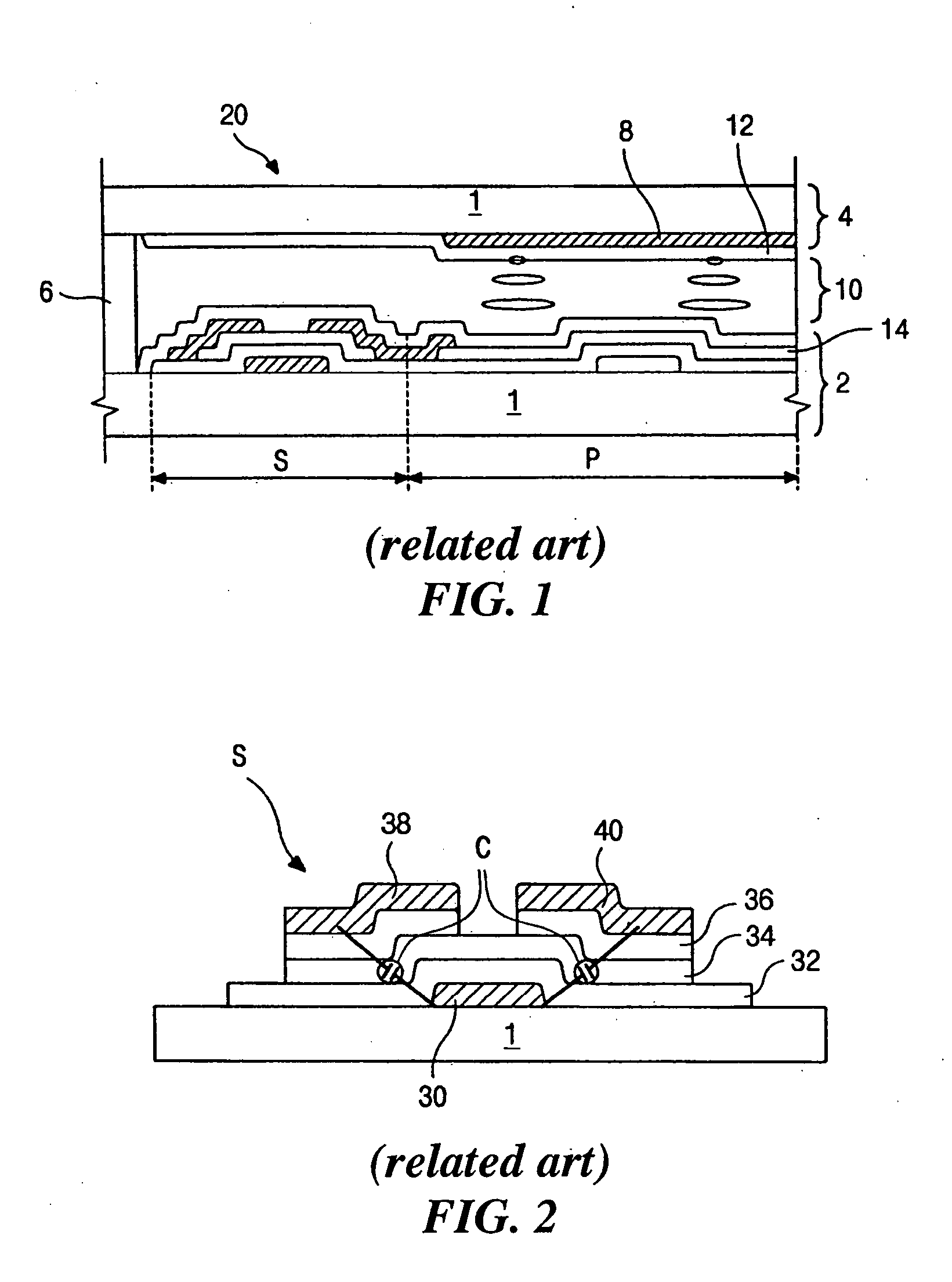

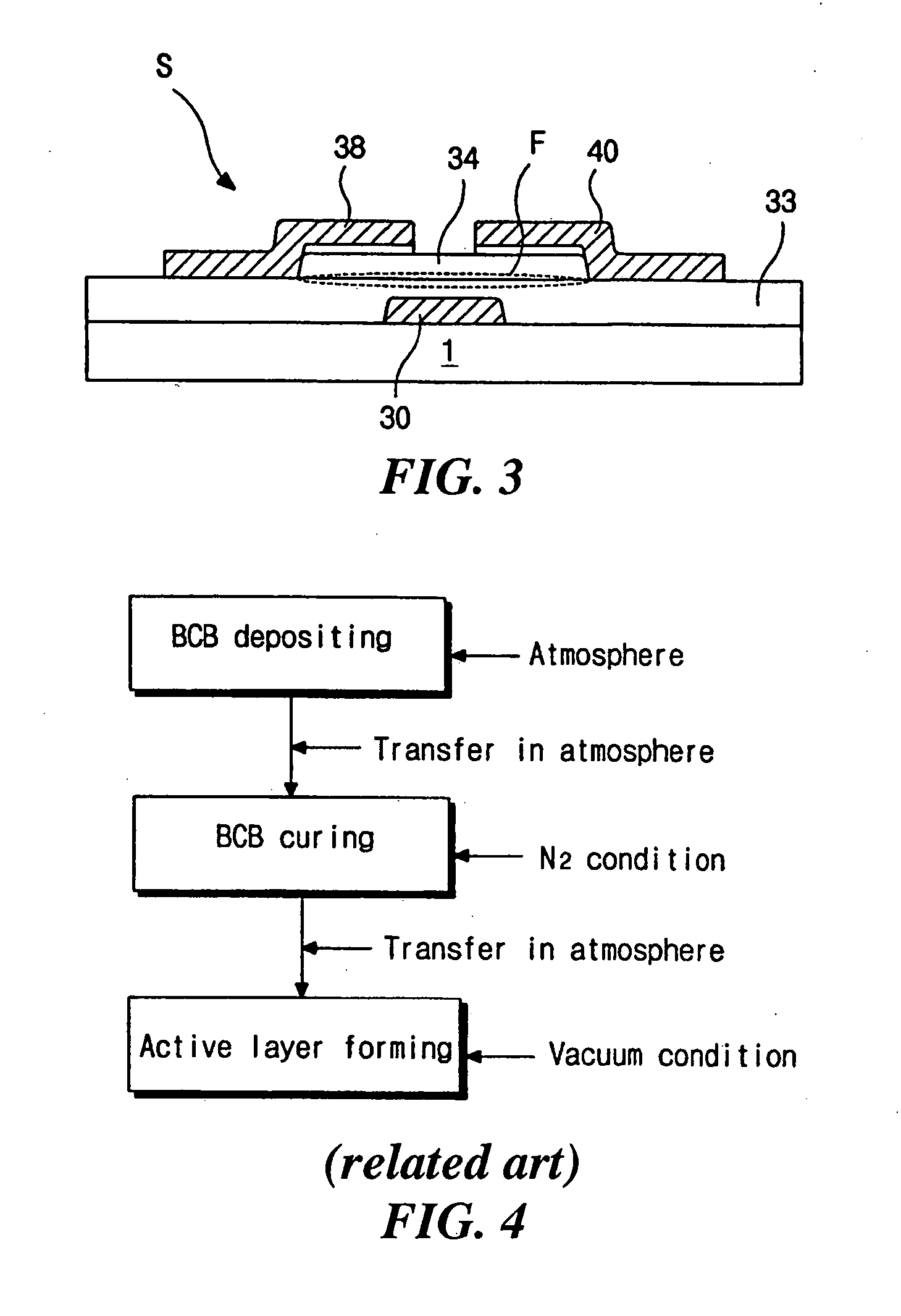

Method of fabricating a thin film transistor and manufacturing equipment

InactiveUS20050087137A1Improve interface propertiesTransistorSemiconductor/solid-state device manufacturingOrganic layerOptoelectronics

A method of forming a thin film transistor includes forming a gate electrode on a substrate, forming an organic layer over the substrate having the gate electrode, curing the organic layer in a first chamber, transferring the substrate having the organic layer from the first chamber to a second chamber without exposing the substrate having the organic layer to oxygen atmosphere during transfer, forming an active layer on the organic layer in the second chamber; and forming source and drain electrodes on the active layer.

Owner:LG DISPLAY CO LTD

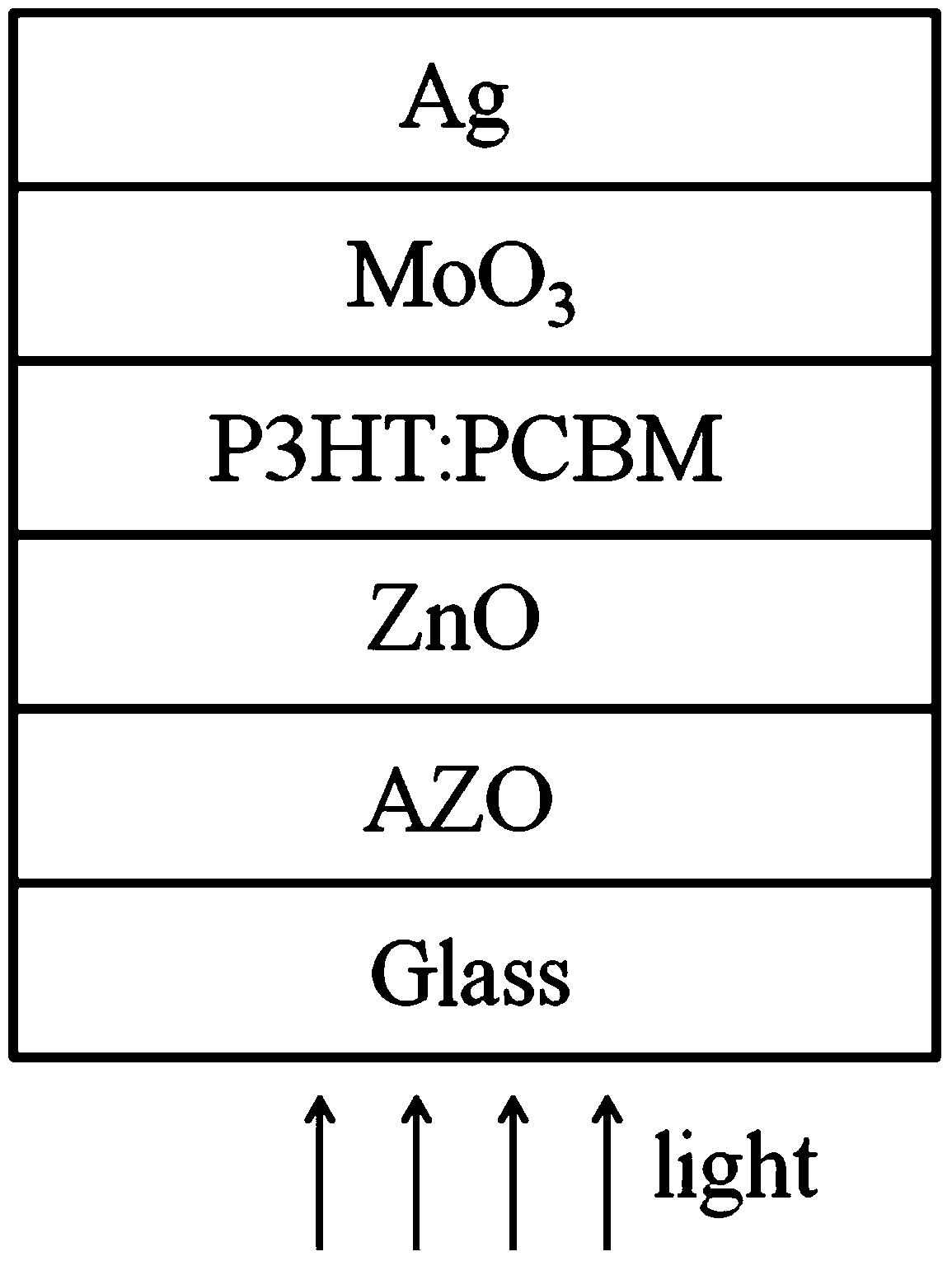

Polymer solar cell based on AZO/ZnO cathode and manufacturing method of polymer solar cell

InactiveCN104051625ALower work functionSimple manufacturing processFinal product manufactureSolid-state devicesWork functionElectron transfer

The invention discloses a polymer solar cell based on an AZO / ZnO cathode and a manufacturing method of the polymer solar cell. The manufacturing method comprises the following steps that (1) a substrate is washed, (2) a ZnO electron transfer layer is deposited, (3) a P3HT: PCBM organic light active layer is deposited, (4) pre-annealing is conducted, (5) a MoO3 hole transfer layer is deposited, and (6) an Ag metal anode is deposited. The ZnO electron transfer layer is prepared according to a low-temperature water solution method, the work function of an AZO electrode is lowered through the ZnO electron transfer layer, energy level matching between AZO and P3HT: PCBM is achieved, the interface characteristic is improved, energy loss is reduced, and the energy conversion efficiency of the polymer solar cell of a reversed structure is effectively improved.

Owner:XIDIAN UNIV

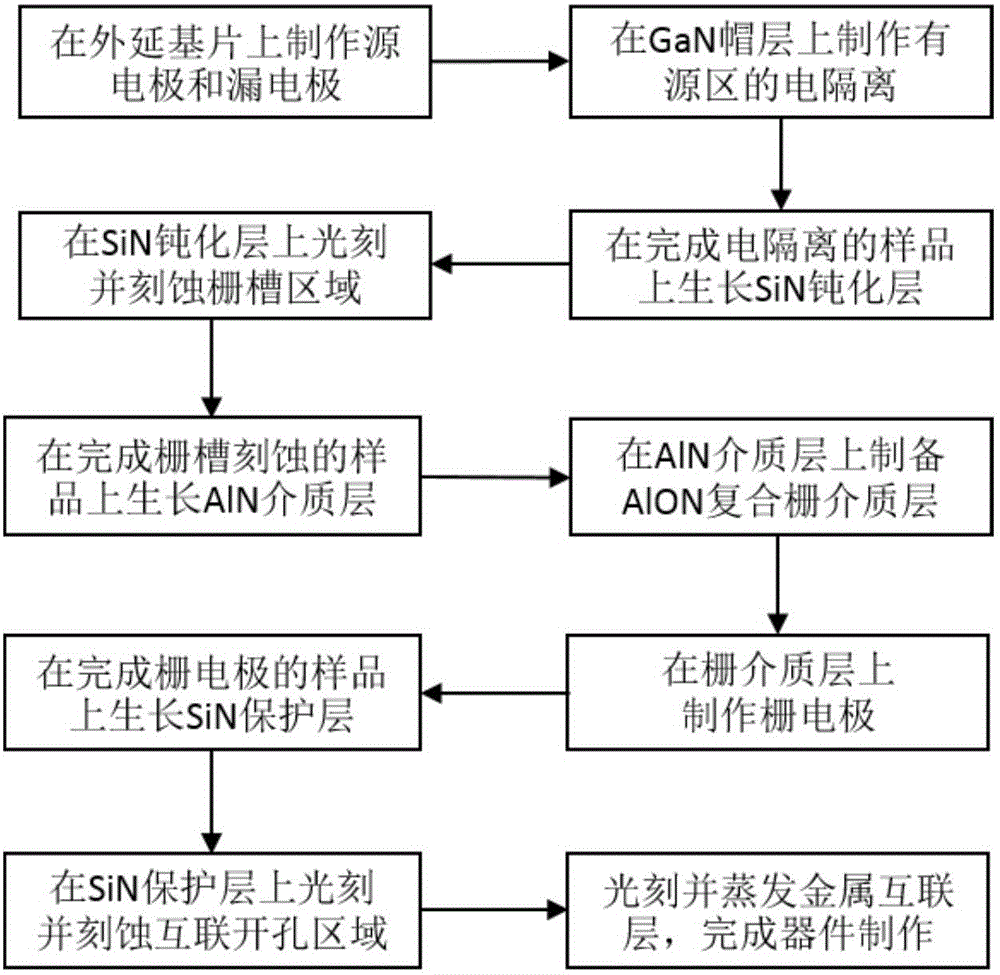

Fabrication method for transistor with composite gate dielectric GaN-based insulating gate and high electron mobility

ActiveCN106373884ALow process temperatureImprove compatibilitySemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricHigh electron

The invention discloses a fabrication method for a transistor with a composite gate dielectric GaN-based insulating gate and high electron mobility, mainly aims to solve the problem of low reliability a similar device. The fabrication method comprises the steps of manufacturing a source electrode, a drain electrode and an electric isolating region of an active region on an epitaxial wafer, and enabling an SiN passivation layer to be grown; photoetching and etching a gate slot region in the SiN passivation layer; enabling an AlN dielectric layer to be grown on the gate slot and the SiN passivation layer, and oxidizing the AlN dielectric layer into an AlON composite gate dielectric layer through thermal oxidization or plasma auxiliary oxidization process; manufacturing a gate electrode on the gate dielectric layer; enabling an SiN protection layer to be grown on the gate electrode and the gate dielectric layer out of the gate electrode region; photoetching and etching a metal interlinked open pore region in the SiN protection layer; and manufacturing a metal interlinking layer on the interlinked open pore region and the unopened and non-etched SiN protection layer to complete the manufacturing of the device. By adoption of the fabrication method, the interface characteristic of the device is improved, the reliability of the device is improved, and the device can be used as an efficient microwave power device.

Owner:XIDIAN UNIV

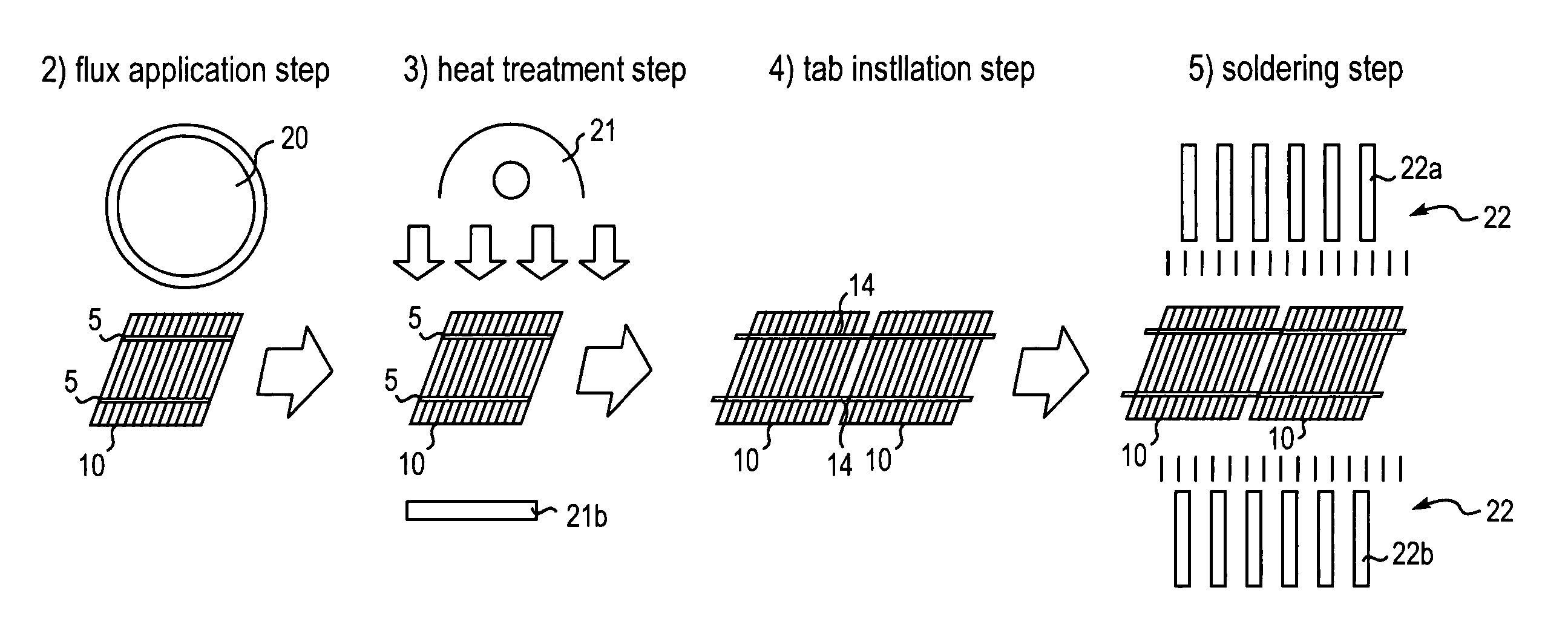

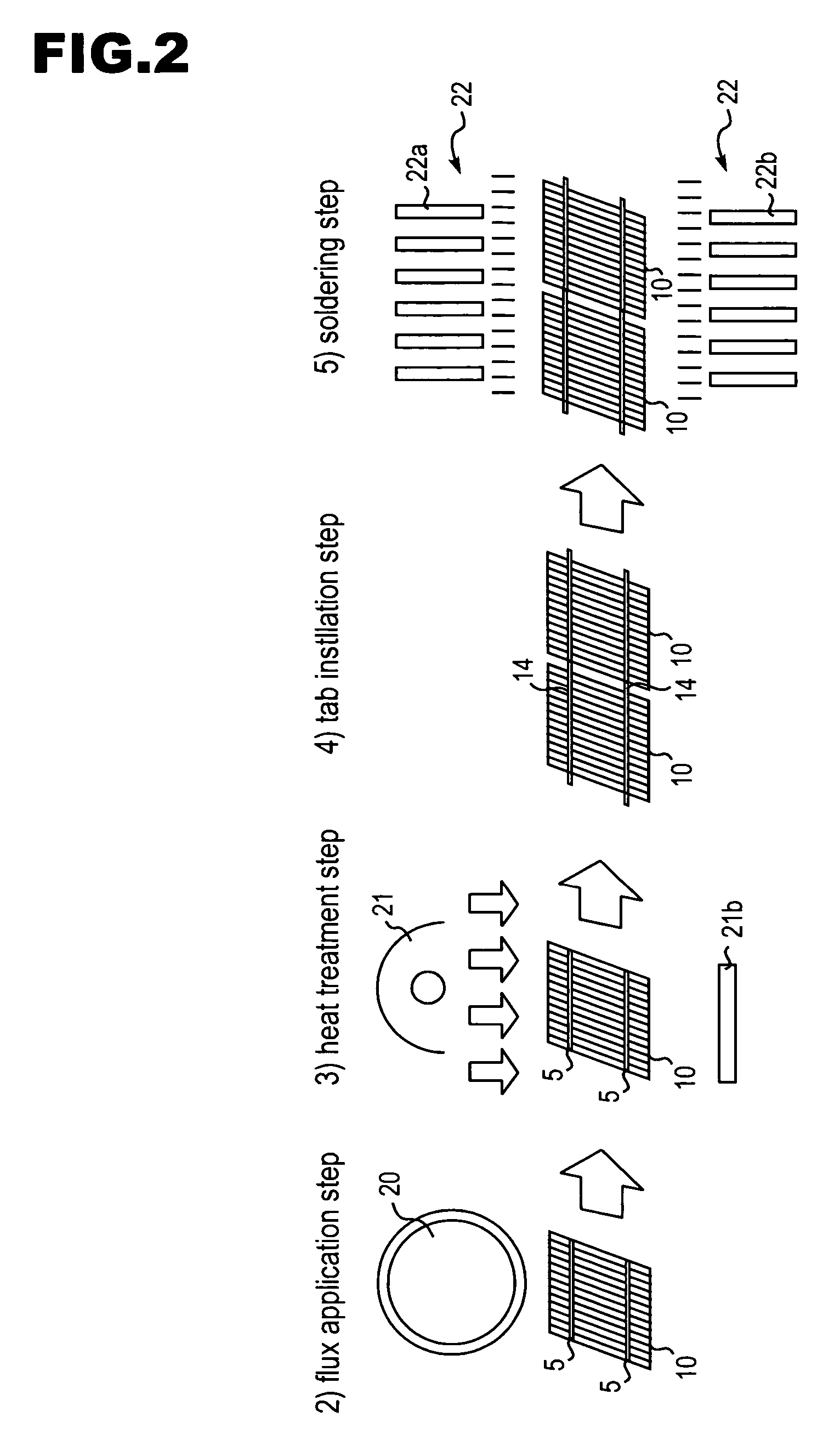

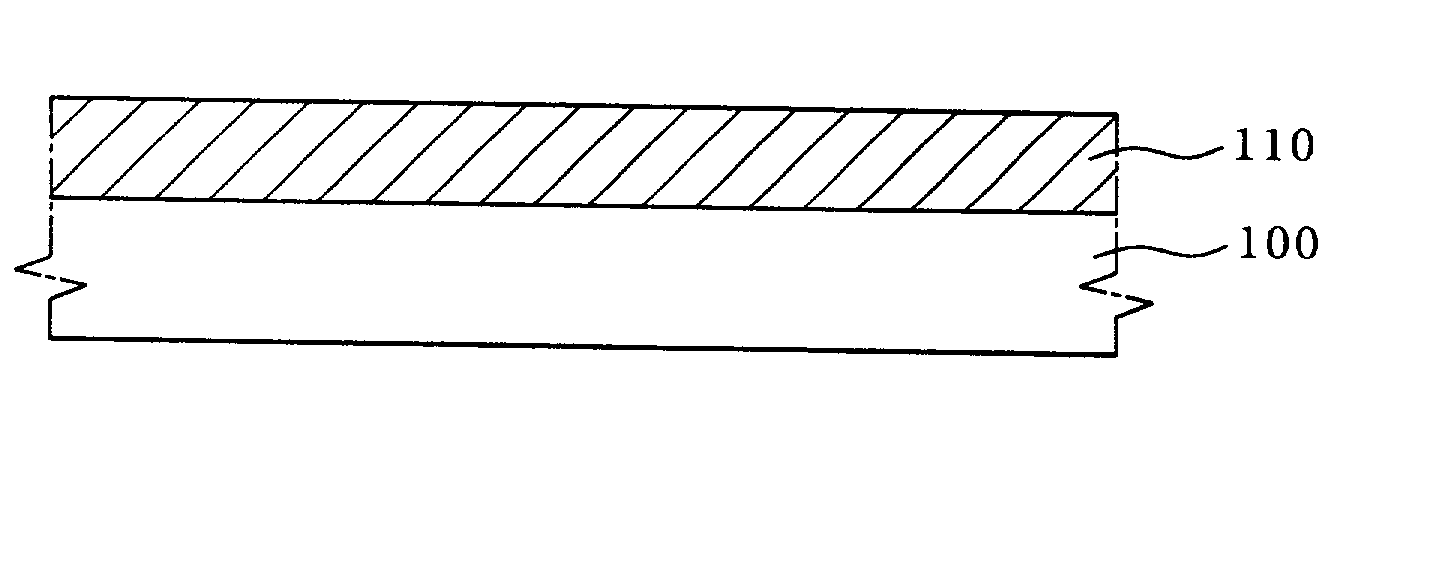

Method for manufacturing photovoltaic module

InactiveUS7754962B2Control heating temperatureImprove output characteristicsPV power plantsFinal product manufactureHeterojunctionAmorphous silicon

This invention is made to improve the characteristics of a photovoltaic module in which a plurality of solar cells are electrically connected to each other with connecting members such as tabs or connecting leads. The present invention provides a method for manufacturing a photovoltaic module comprising a plurality solar cells each including a semiconductor heterojunction made by combining amorphous silicon and crystalline silicon and connecting members for connecting the plurality solar cells in which the connecting members are connected to the solar cells by soldering after a high-temperature heat treatment is applied to the solar cells, and the plurality of solar cells are electrically connected to each other with the connecting members.

Owner:SANYO ELECTRIC CO LTD

Method for forming cell capacitor for high-integrated DRAMs

InactiveUS20020094624A1Improve interface propertiesIncrease capacitanceSemiconductor/solid-state device manufacturingCapacitorsCapacitanceHigh capacitance

A method for forming a cell capacitor used for a high-integrated DRAM is disclosed which guarantees interfacial properties of aluminum oxide and excellent leakage current preventive properties by depositing an aluminum oxide layer and a mixed layer of TiON and TiO2 as dielectric layers on a semiconductor substrate having a predetermined lower substructure by an atomic layer deposition (ALD) method and thus forming a double layer structure, and simultaneously providing a high capacitance by using a high dielectric property of a mixed layer of TiON and TiO2.

Owner:SK HYNIX INC

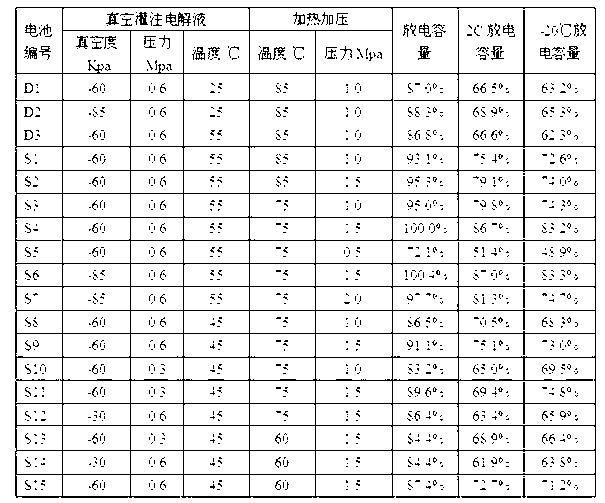

Manufacturing method of lithium ion battery containing gel electrolyte

ActiveCN103000956AEasy to prepareImprove ionic conductivityFinal product manufactureElectrolyte accumulators manufactureElectrolytic agentElectrical battery

The invention belongs to the technical field of a lithium ion battery, and particularly relates to a manufacturing method of a lithium ion battery containing gel electrolyte. The manufacturing method comprises the steps of preparation of a micro-pore isolating diaphragm plate, preparation of a cell, pouring of the electrolyte, after-treatment and the like. Compared with the prior art, the manufacturing method provided by the invention adopts a two-step method to polymerize gel; a good cathode pole sheet / electrolyte interface and a good anode pole sheet / electrolyte interface are formed on the cell by a pre-gelling step; in a formation process, a cathode activity material and an anode activity material can be sufficiently activated; the lithium ion battery is pressurized in a heating process after the formation is completed, so that air bubbles generated in the formation process of the battery and existing between the cathode pole sheet / electrolyte interface and the anode pole sheet / electrolyte interface can be removed; and an interface gap can be smaller, thereby being beneficial to the generation of the cathode pole sheet / electrolyte interface and the anode pole sheet / electrolyte interface. Therefore, the battery has better electrochemical performance.

Owner:DONGGUAN AMPEREX TECH

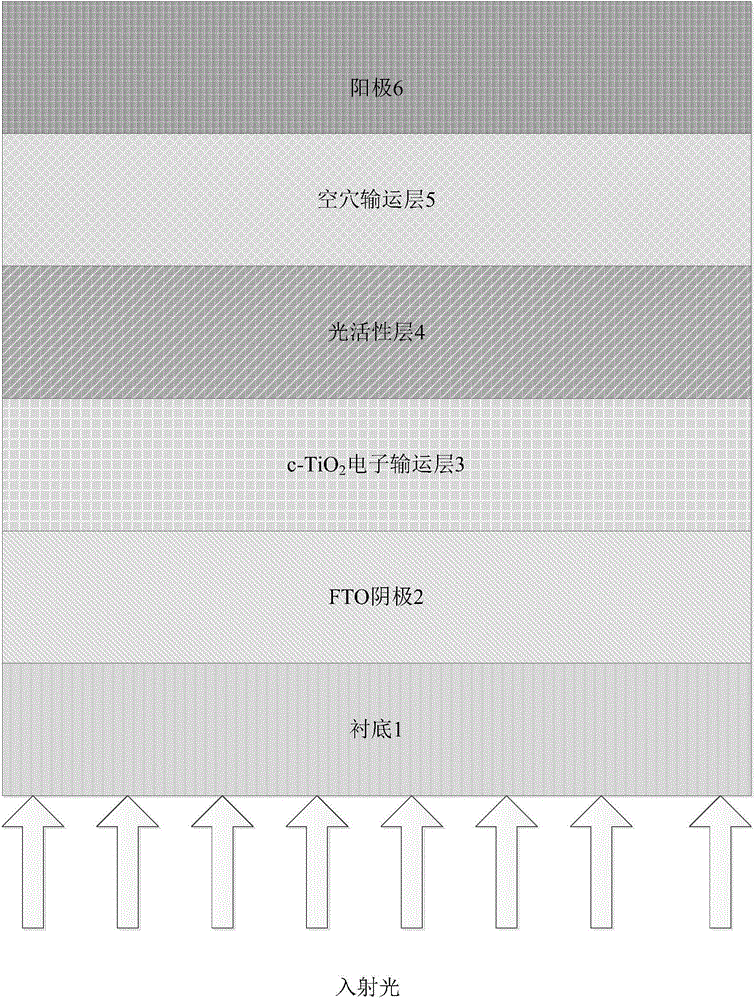

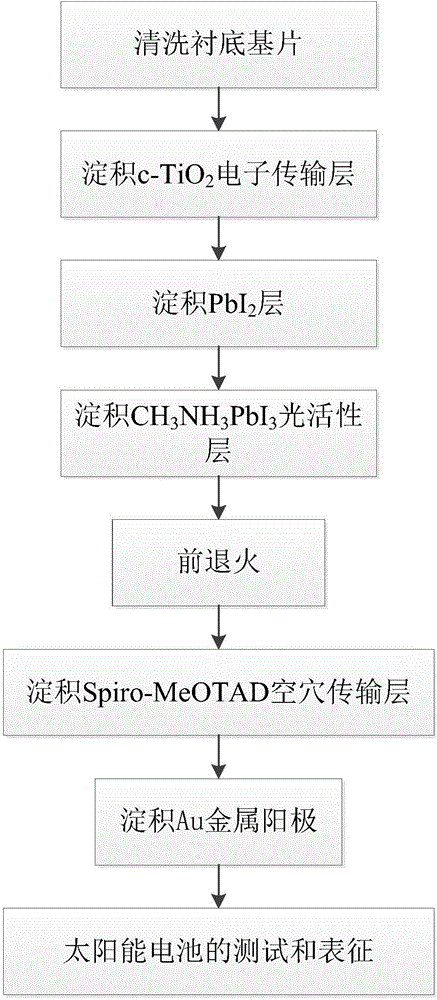

Plane perovskite solar cell based on FTO/c-TiO2 cathode and manufacturing method of plane perovskite solar cell

InactiveCN104538551AImprove energy conversion efficiencyHigh light transmittanceFinal product manufactureSolid-state devicesPerovskite solar cellWork function

The invention discloses a plane perovskite solar cell based on an FTO / c-TiO2 cathode and a manufacturing method of the plane perovskite solar cell. The problems that an existing perovskite solar cell is not matched in energy level and poor in interfacial characteristic are mainly solved. The plane perovskite solar cell comprises a liner (1), the cathode (2), an electron transmission layer (3), an optical active layer (4), a hole transmission layer (5) and an anode (6) from bottom to top, wherein the cathode (2) is made of fluorine-doped tin oxide (FTO) and is used for collecting electrons, and the electron transmission layer is made of compact titanium dioxide c-TiO2 and is used for modifying an interface, blocking holes and transmitting electrons. The electron transmission layer made of the c-TiO2 is manufactured through a spin coating precursor solution, and therefore the work function of the cathode made of the FTO is reduced, the energy level matching between the FTO and CH3NH3PbI3 is achieved, the interface characteristic is improved, and the performance of the plane-structure perovskite solar cell is effectively improved.

Owner:XIDIAN UNIV

Composite lithium battery membrane and method for making same

InactiveCN1547270AImprove interface propertiesHigh conductivity at room temperatureCell component detailsElectrical batteryNano sio2

The invention refers to a manufacturing method for a kind of compound polypropylene lithium membrane. The materials are base membrane, polymer and nano SiO2 fillers; the step is: the materials are solved in the solvent, the sol compound can be acquired, and then they are transferred to the culture dish, the membrane is immersed in them; the membrane is taken out and transferred to the template, the solvent is absorbed by the molecular sift, then they are transferred into the vacuum drying box to be dried. The invention emphasizes the humidity to membrane by the polymer and the improvement to the interface performance, the organic group component of the SiO2 surface is important to the performance of the compound membrane. The compound membrane upgrades the room temperature conductivity, and improves the interface performance of the positive material / membrane, lithium / membrane. The assembled battery has an excellent circular performance.

Owner:XIAMEN UNIV