IGZO (indium gallium zinc oxide) thin film transistor and preparing method thereof

A thin film transistor and film layer technology, applied in the field of microelectronics, can solve the problems of reducing the electrical performance of the device and affecting the charge transfer in the device, and achieve the effects of low cost, easy control of conditions and high mobility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

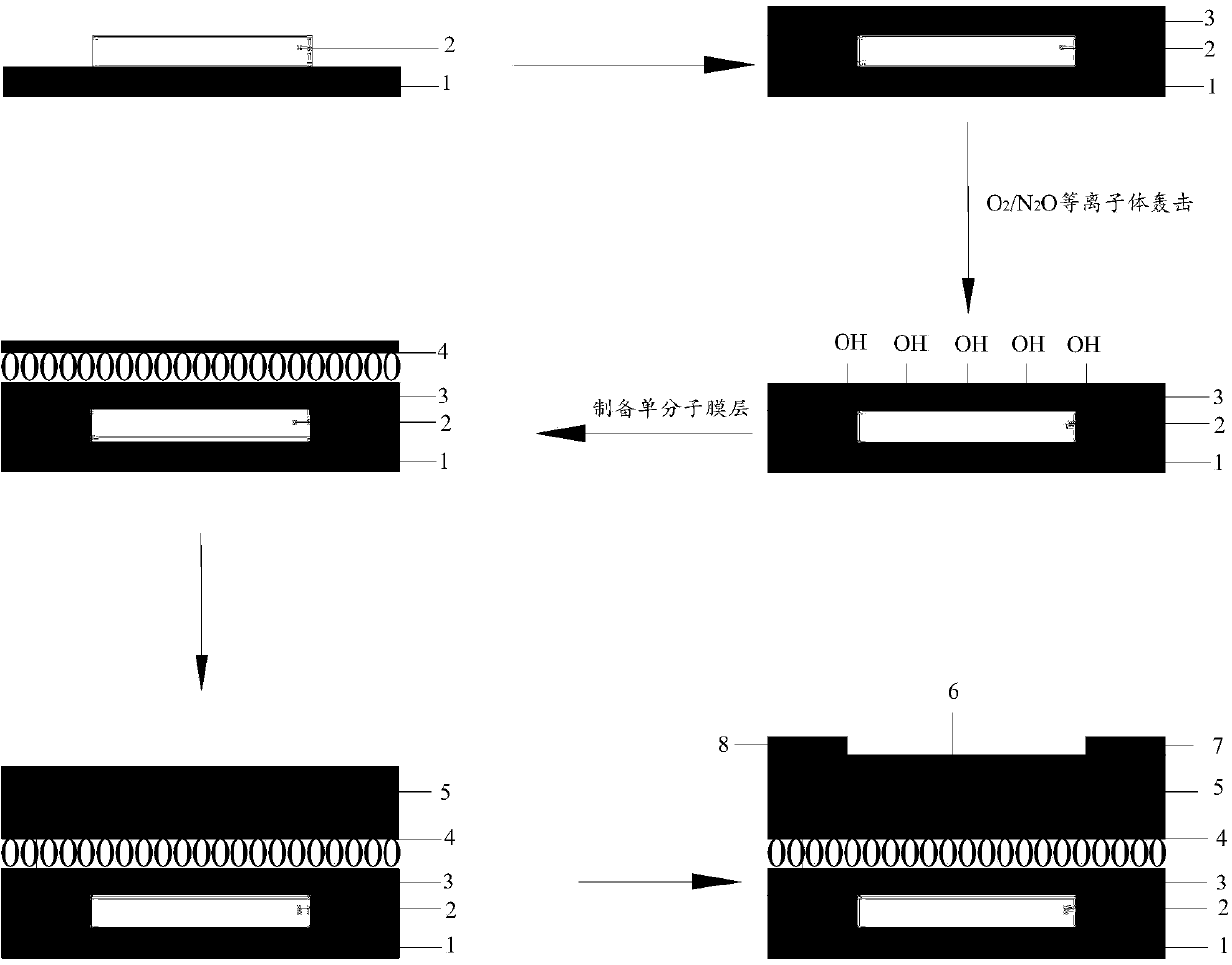

[0030] Correspondingly, a method for preparing an IGZO thin film transistor with high mobility and excellent device performance comprises the following steps:

[0031] S01. Covering the outer surface of the substrate 1 combined with the gate 2 and the outer surface of the gate 2 with silicide to form a silicide gate insulating layer 3;

[0032] S02. Use O 2 / N 2 O plasma bombards the silicide gate insulating layer 3 to obtain a modified silicide gate insulating layer;

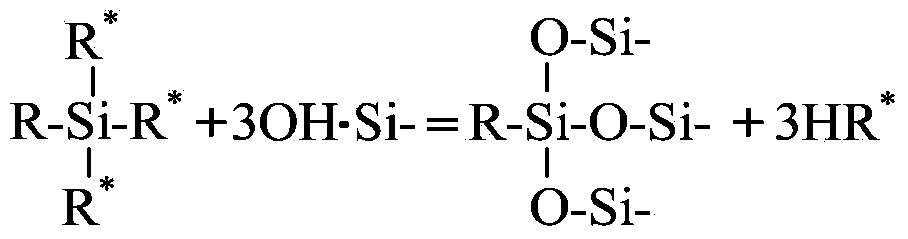

[0033] S03. Prepare a self-assembled monomolecular film layer 4 on the outer surface of the modified silicide gate insulating layer;

[0034] S04. Prepare an IGZO active layer 5 on the outer surface of the self-assembled monomolecular film layer 4, and prepare an etching stopper layer 6, a source electrode 7 and a drain electrode 8 on the IGZO active layer 5 to obtain a prepared IGZO thin film transistor, Afterwards, it is annealed to obtain the above-mentioned IGZO thin film transistor.

[0035] The proces...

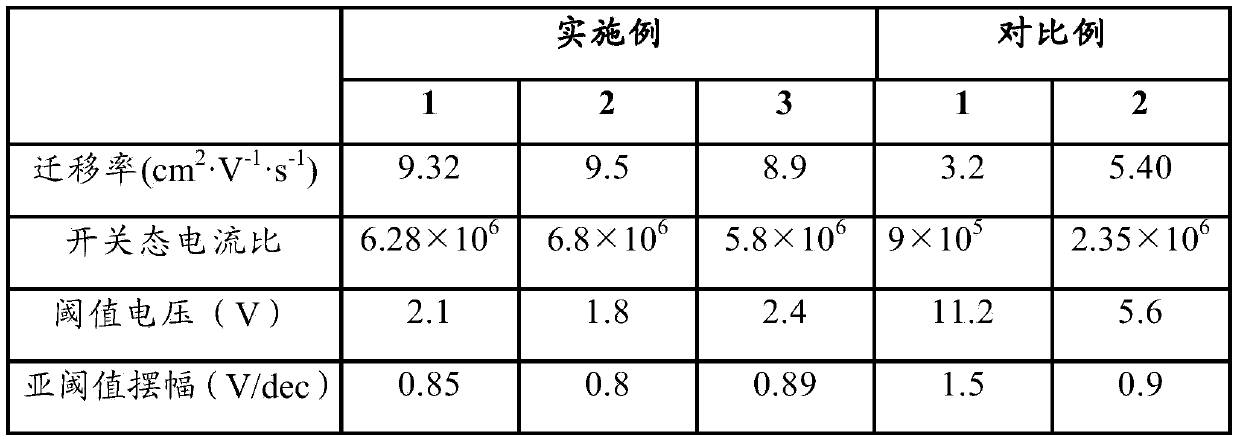

Embodiment 1

[0048] A preparation method for an IGZO thin film transistor, comprising the steps of:

[0049] S11. Using a heavily doped N-type silicon wafer as a substrate, prepare a silicide gate insulating layer on the heavily doped N-type silicon wafer substrate by a thermal oxidation method, and then use HF to clean the back side of the insulating layer;

[0050] S121. First take the absorbent cotton ball dipped in acetone and repeatedly scrub the silicide gate insulating layer to erase the pollutants left on the surface of the silicide gate insulating layer; then clean the entire substrate combined with the silicide gate insulating layer with Cleaning solution, acetone, isopropanol and deionized water were ultrasonically cleaned for 20 minutes, and dried in an oven to obtain a clean and dry heavily doped N-type silicon wafer substrate with a silicide gate insulating layer;

[0051]S122. Adopt PECVD equipment, set the air pressure in the cavity to 200mtorr, and process for 3 minutes, O...

Embodiment 2

[0059] A kind of preparation method of IGZO thin film transistor, its concrete steps are similar to embodiment 1, difference is: the O 2 The flow rate is 100 sccm, and the processing time is 1.5 minutes; when self-assembling a monomolecular film layer at the same time, the silane mixed solution is prepared from phenylethyltrichlorosilane and a mixed solvent composed of chloroform and cyclohexane with a volume ratio of 3:7 , and the concentration is 5mg / ml, placed on a hot stage at 60°C, and the reaction time is 40 minutes. Specific steps are as follows:

[0060] S222. Adopt PECVD equipment, and set the air pressure in the chamber to be 200mtorr, the processing time is 1.5 minutes, O 2 The flow rate is 100sccm, the processing power is 40W, and the surface of the silicide gate insulating layer is O 2 Plasma bombardment.

[0061] S231. Prepare a mixed solvent of phenethyltrichlorosilane and chloroform and cyclohexane with a volume ratio of 3:7 to form a mixed solution with a c...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More