Patents

Literature

187 results about "Indium zinc oxide" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Indium Gallium Zinc Oxide, also known as IGZO, or a-IGZO in its amorphous form (In 2Ga 2ZnO 7) is a transparent amorphous oxide semiconductor (TAPS) used in thin-film transitors (TFTs) and LED devices. IGZO is generally immediately available in most volumes. High purity, submicron and nanopowder forms may be considered.

Semiconductor device and manufacturing method thereof

ActiveUS20140042437A1Avoid changeImprove reliabilityTransistorSolid-state devicesDevice materialCrystal structure

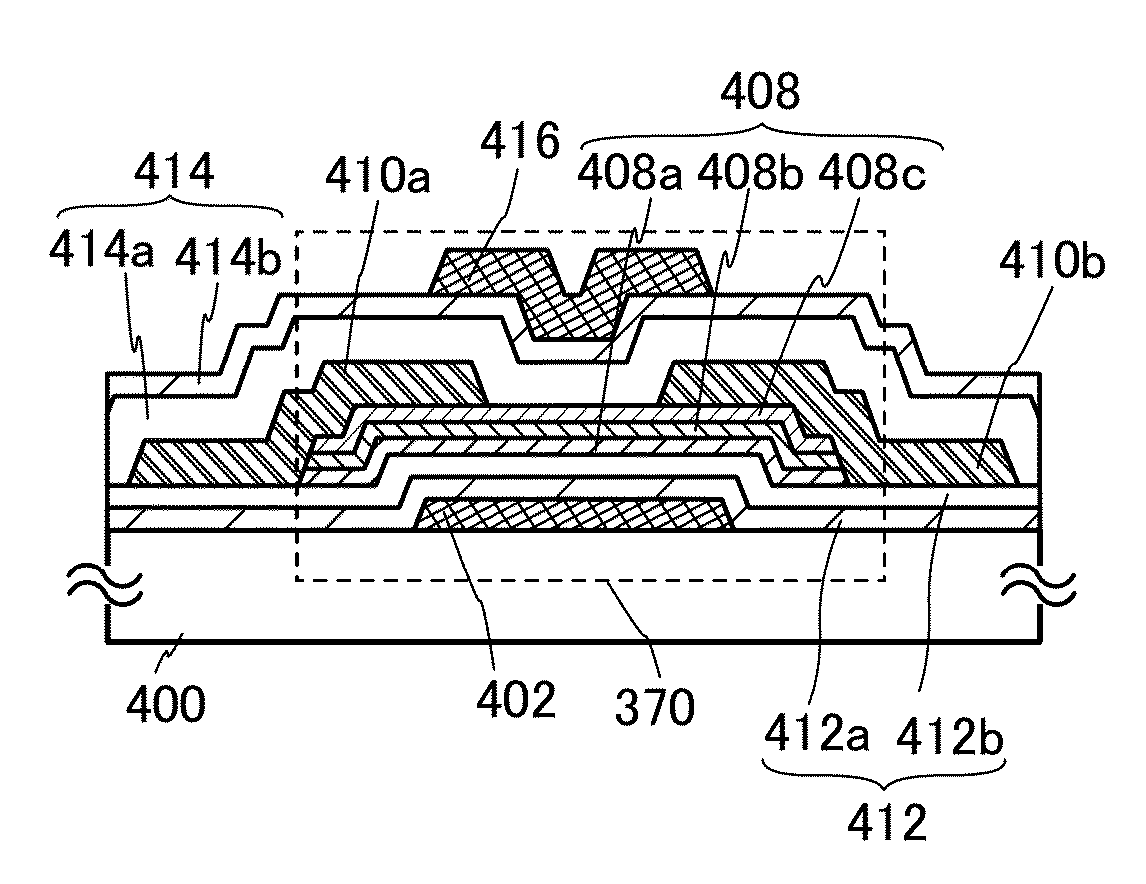

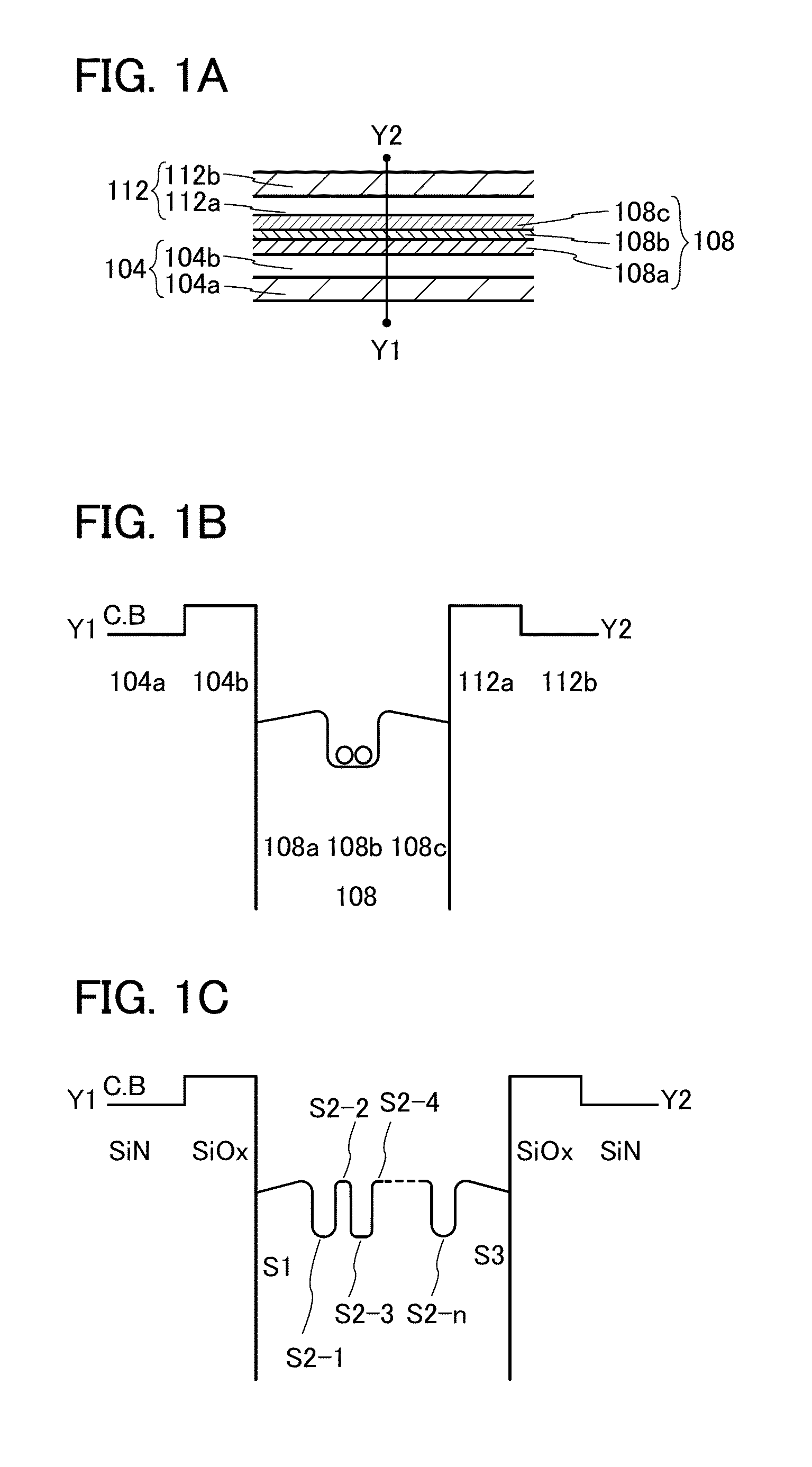

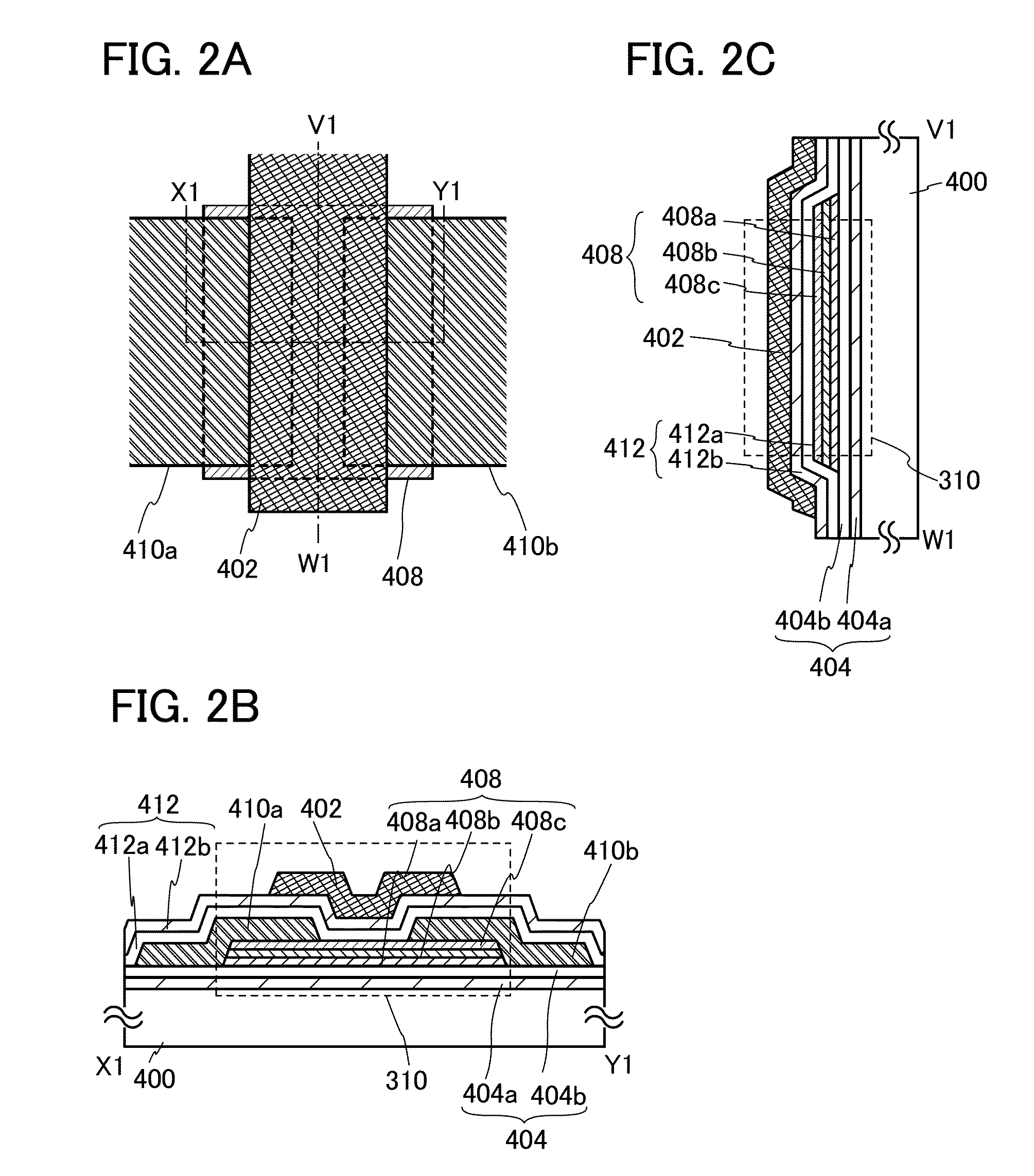

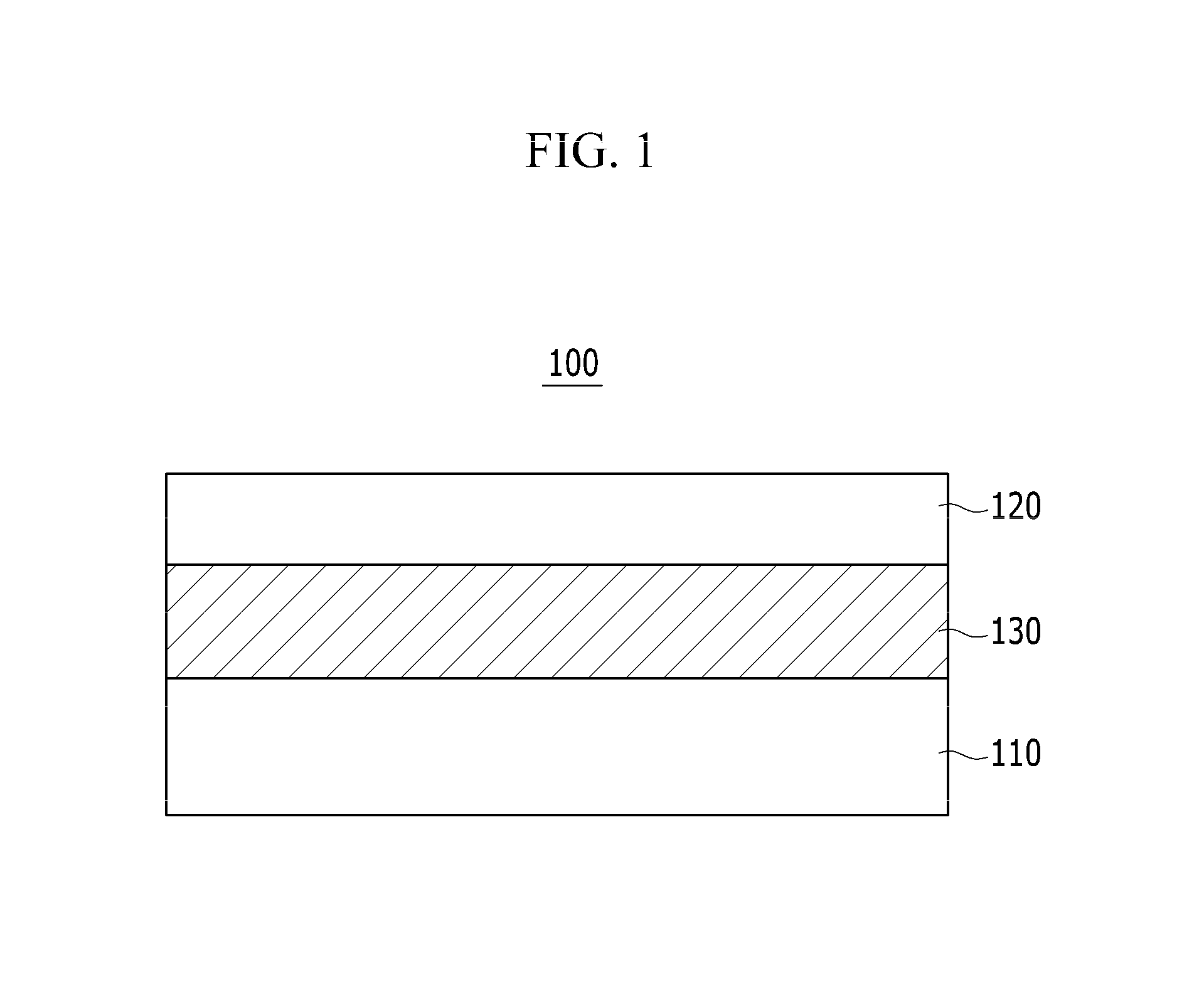

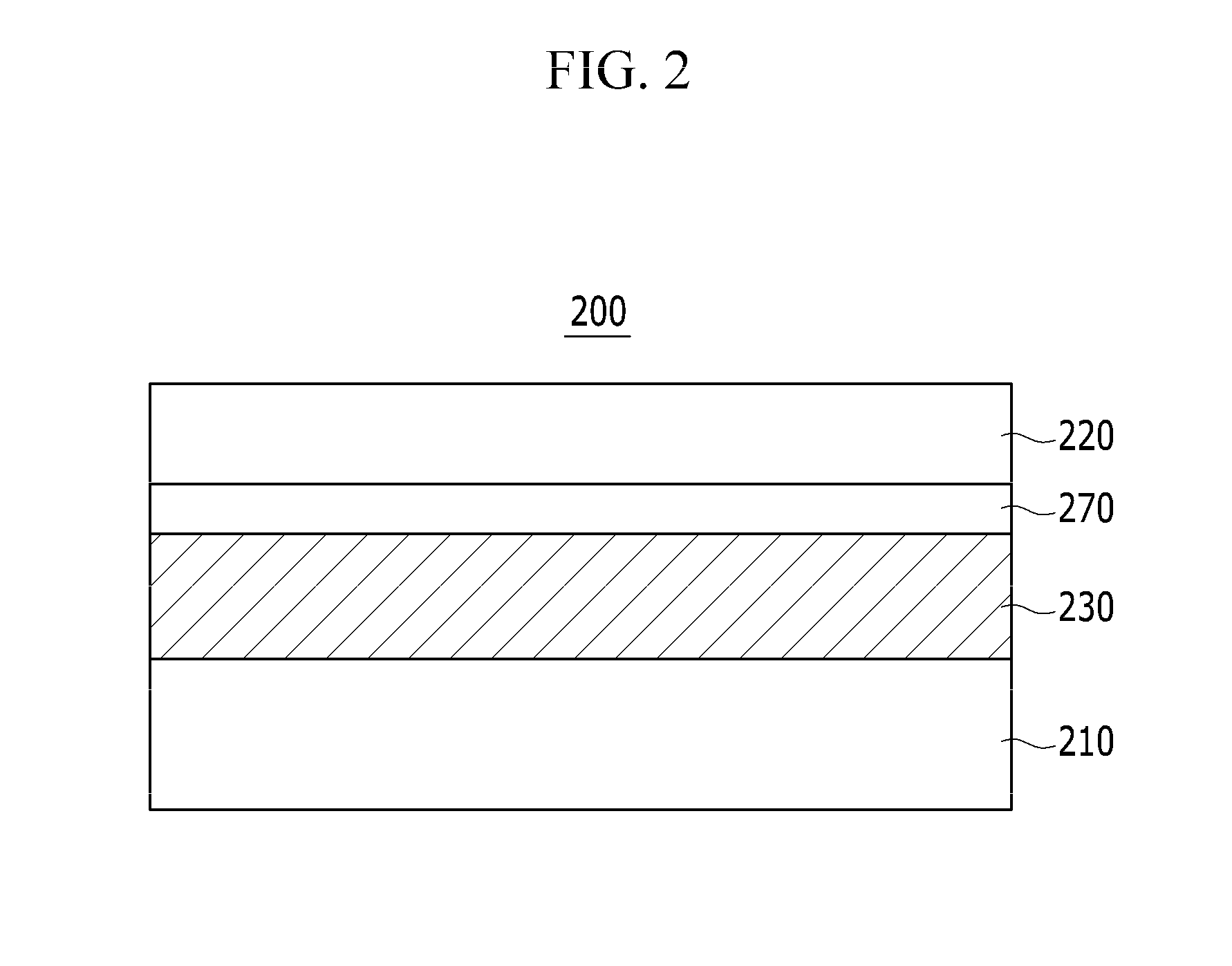

A transistor having a multi-layer structure of oxide semiconductor layers is provided in which a second oxide semiconductor layer having a crystalline structure including indium zinc oxide is formed over a first oxide semiconductor layer having an amorphous structure, and at least a third oxide semiconductor layer is formed stacked over the second oxide semiconductor layer. The second oxide semiconductor layer mainly serves as a carrier path for the transistor. The first oxide semiconductor layer and the third oxide semiconductor layer each serve as a barrier layer for suppressing entrance of impurity states of an insulating layer in contact with the multi-layer structure to the carrier path.

Owner:SEMICON ENERGY LAB CO LTD

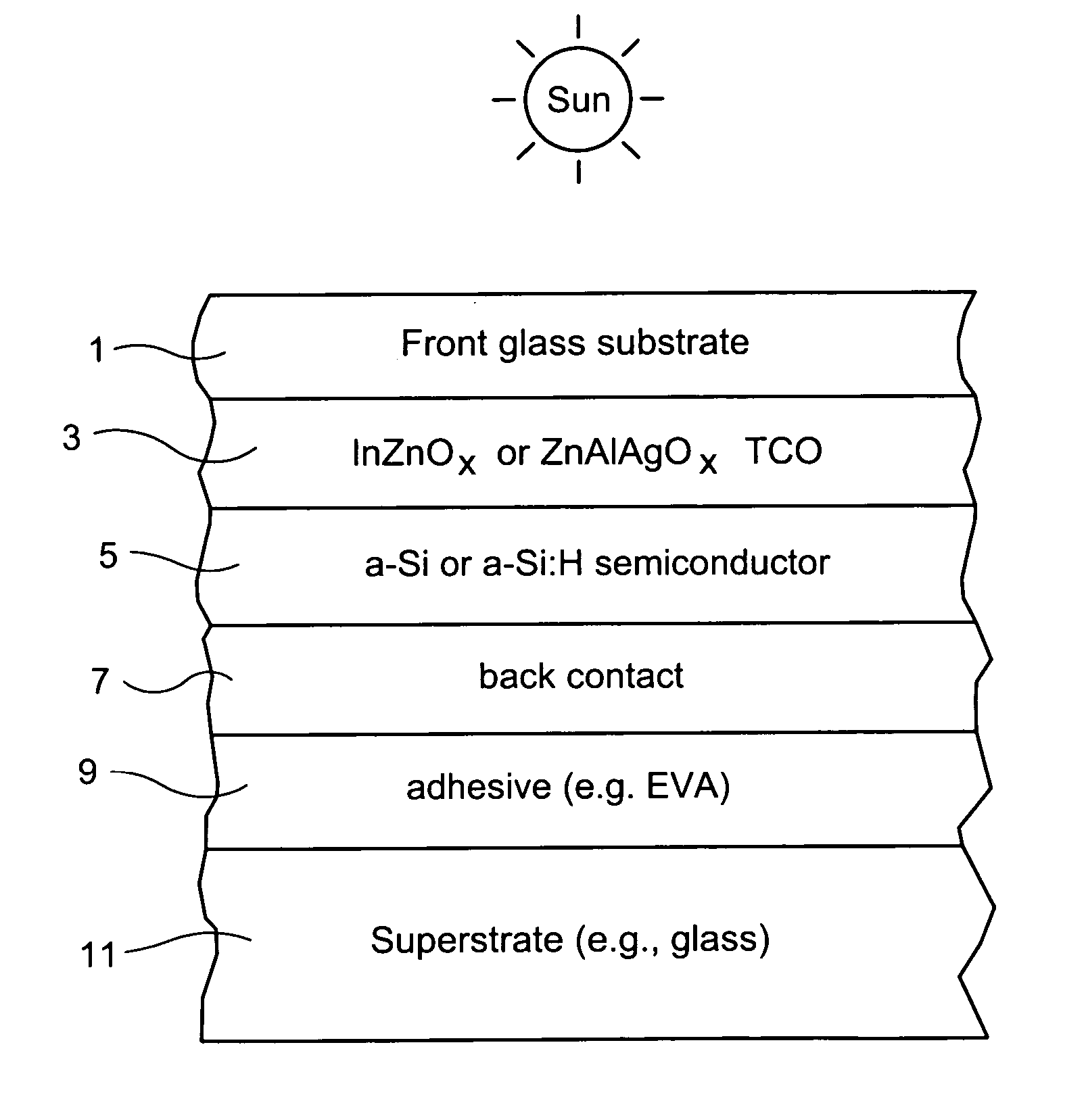

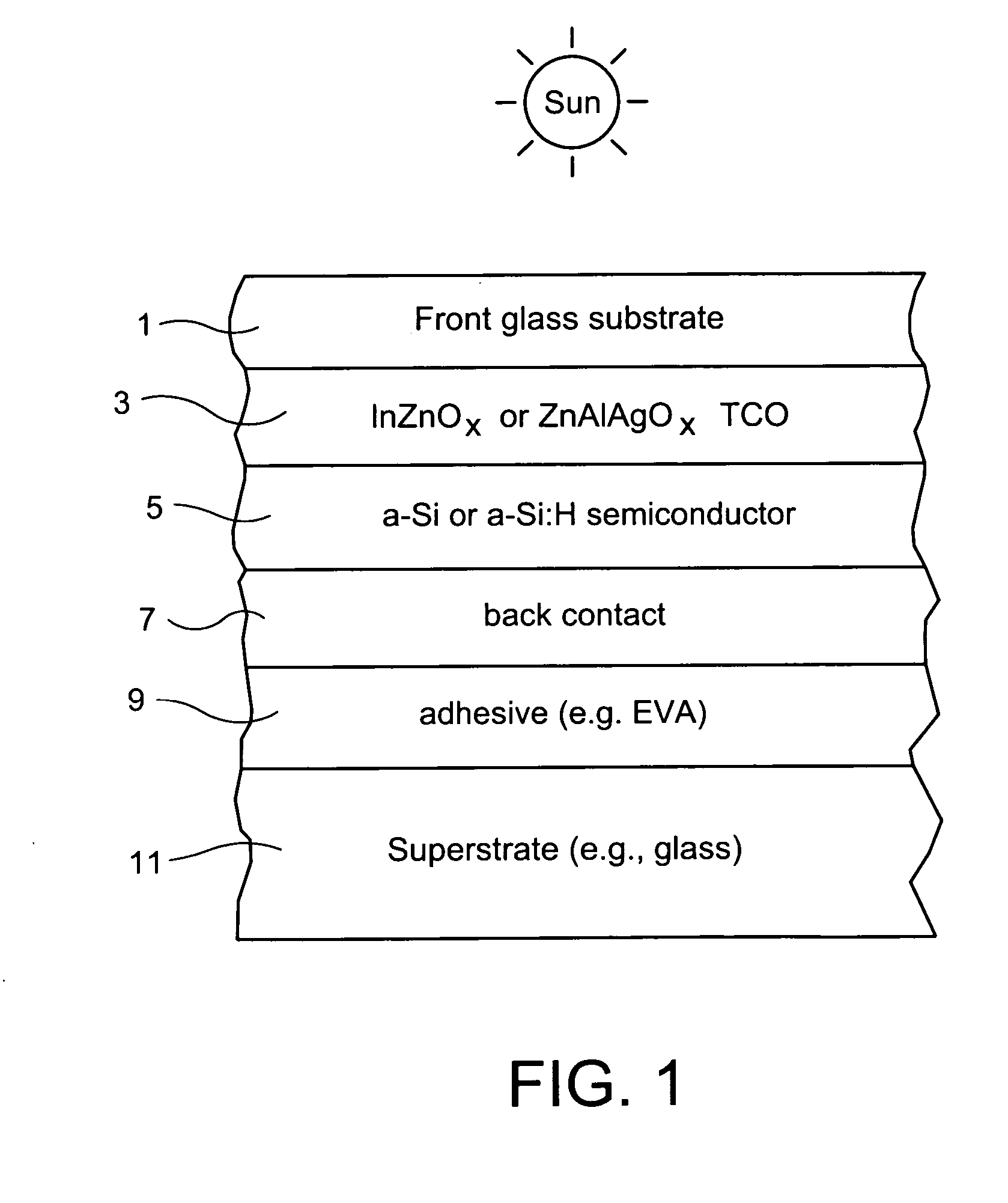

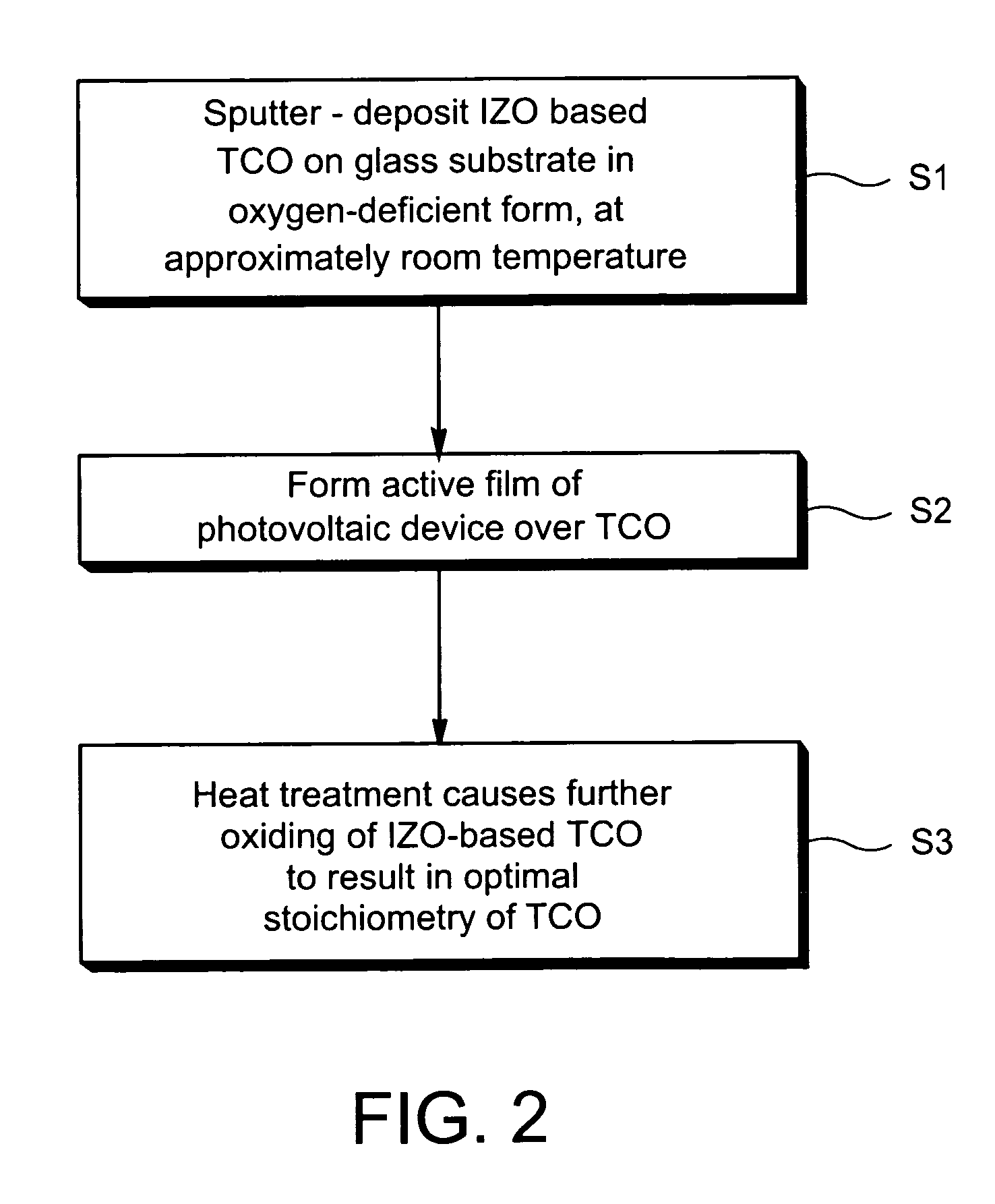

Indium zinc oxide based front contact for photovoltaic device and method of making same

InactiveUS20070193624A1Low resistivityPhotovoltaic energy generationSemiconductor devicesCooking & bakingIndium zinc oxide

This invention relates to a photovoltaic device including a front contact and / or a method of making the same. In certain example embodiments, the transparent conductive oxide (TCO) front contact is of indium zinc oxide (IZO). In other example embodiments, the IZO may have other element(s) such as silver (Ag) added thereto so that the front contact may be of or include zinc aluminum silver oxide (ZnAlAgO) for example. Moreover, in certain example embodiments the front contact (e.g., IZO or ZnAlAgO) may be sputter-deposited in an oxygen deficient form (substoichiometric); so that subsequent heat treatment or baking used in the photovoltaic device manufacturing (e.g., for subsequent layer formation) results in an optimal stoichiometry which may or may not be substoichiometric in the final product.

Owner:GUARDIAN GLASS LLC

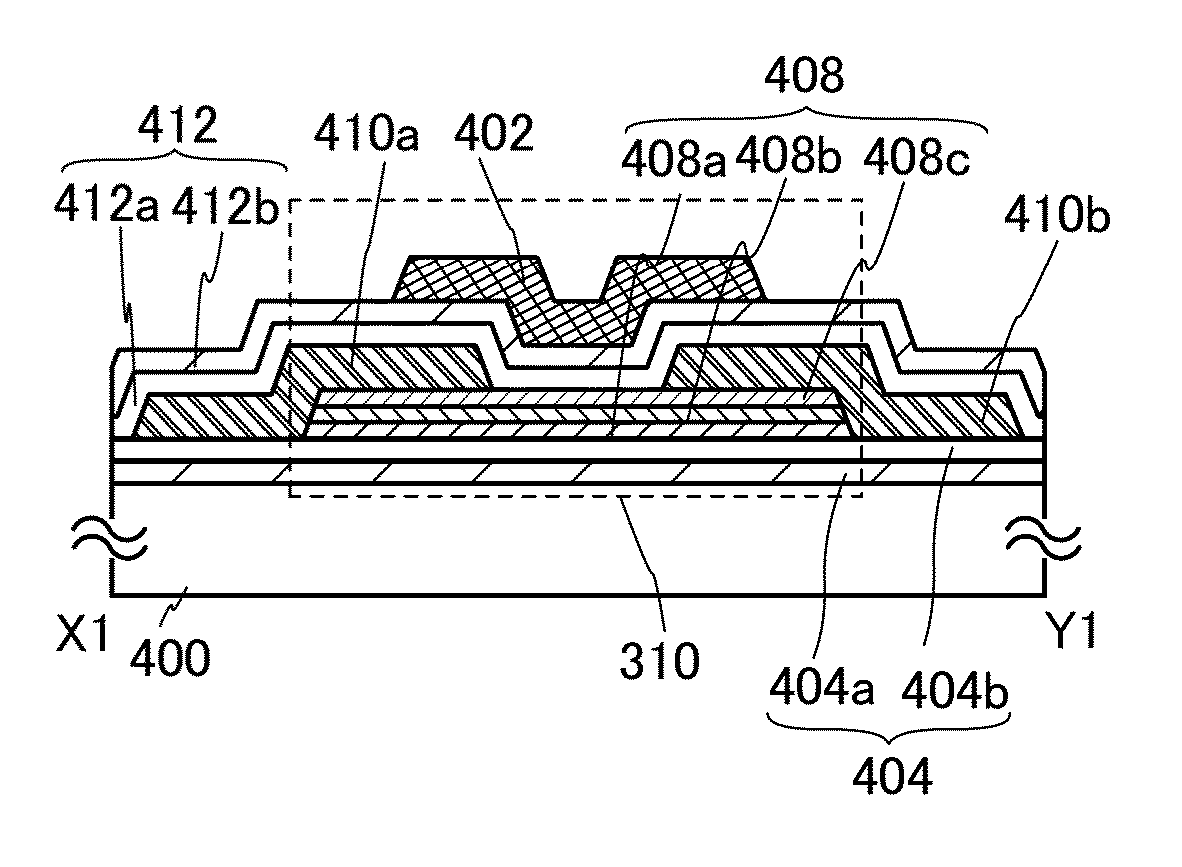

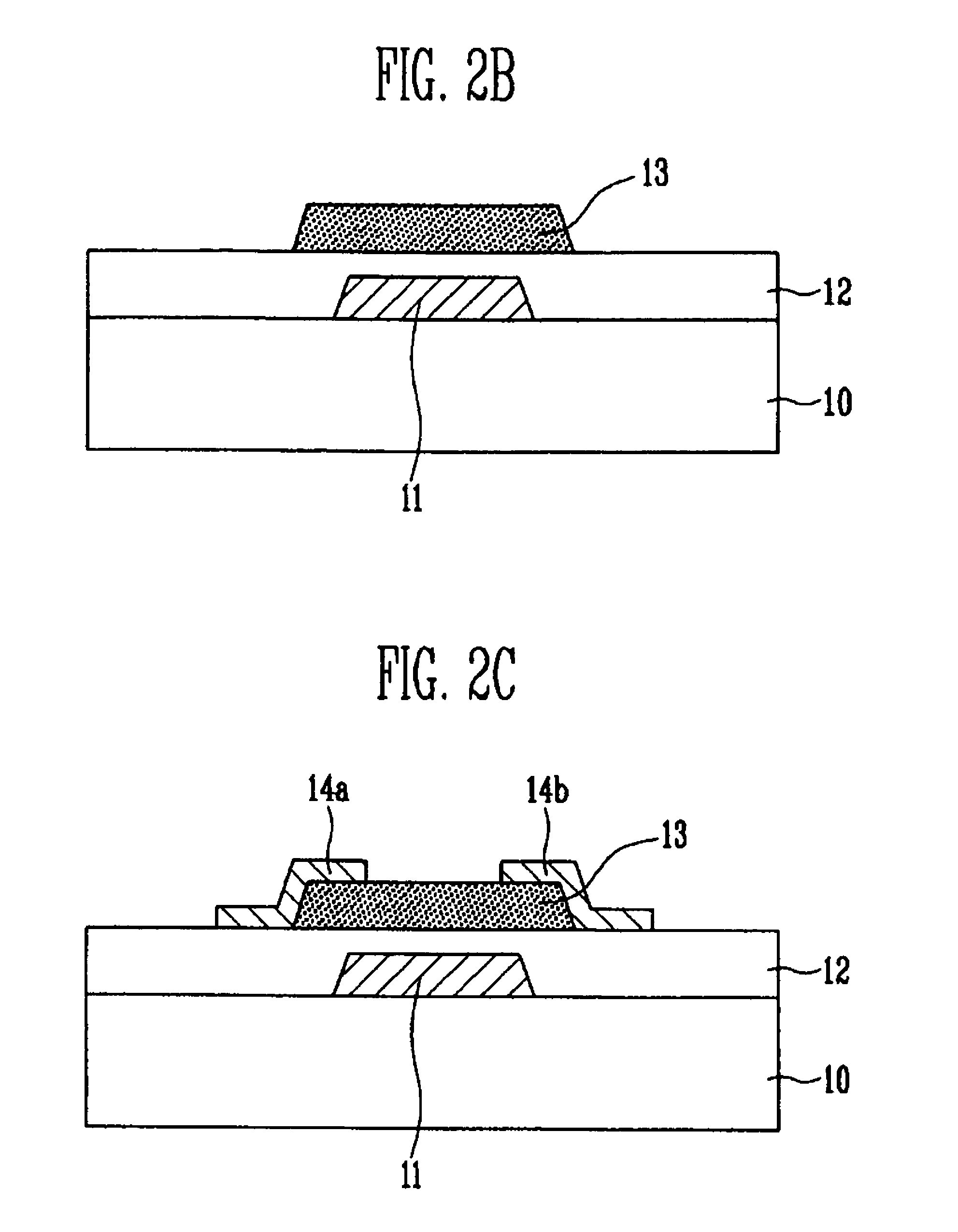

Semiconductor device and manufacturing method thereof

ActiveUS9293602B2Avoid changeImprove reliabilityTransistorSolid-state devicesCharge carrierCrystal structure

A transistor having a multi-layer structure of oxide semiconductor layers is provided in which a second oxide semiconductor layer having a crystalline structure including indium zinc oxide is formed over a first oxide semiconductor layer having an amorphous structure, and at least a third oxide semiconductor layer is formed stacked over the second oxide semiconductor layer. The second oxide semiconductor layer mainly serves as a carrier path for the transistor. The first oxide semiconductor layer and the third oxide semiconductor layer each serve as a barrier layer for suppressing entrance of impurity states of an insulating layer in contact with the multi-layer structure to the carrier path.

Owner:SEMICON ENERGY LAB CO LTD

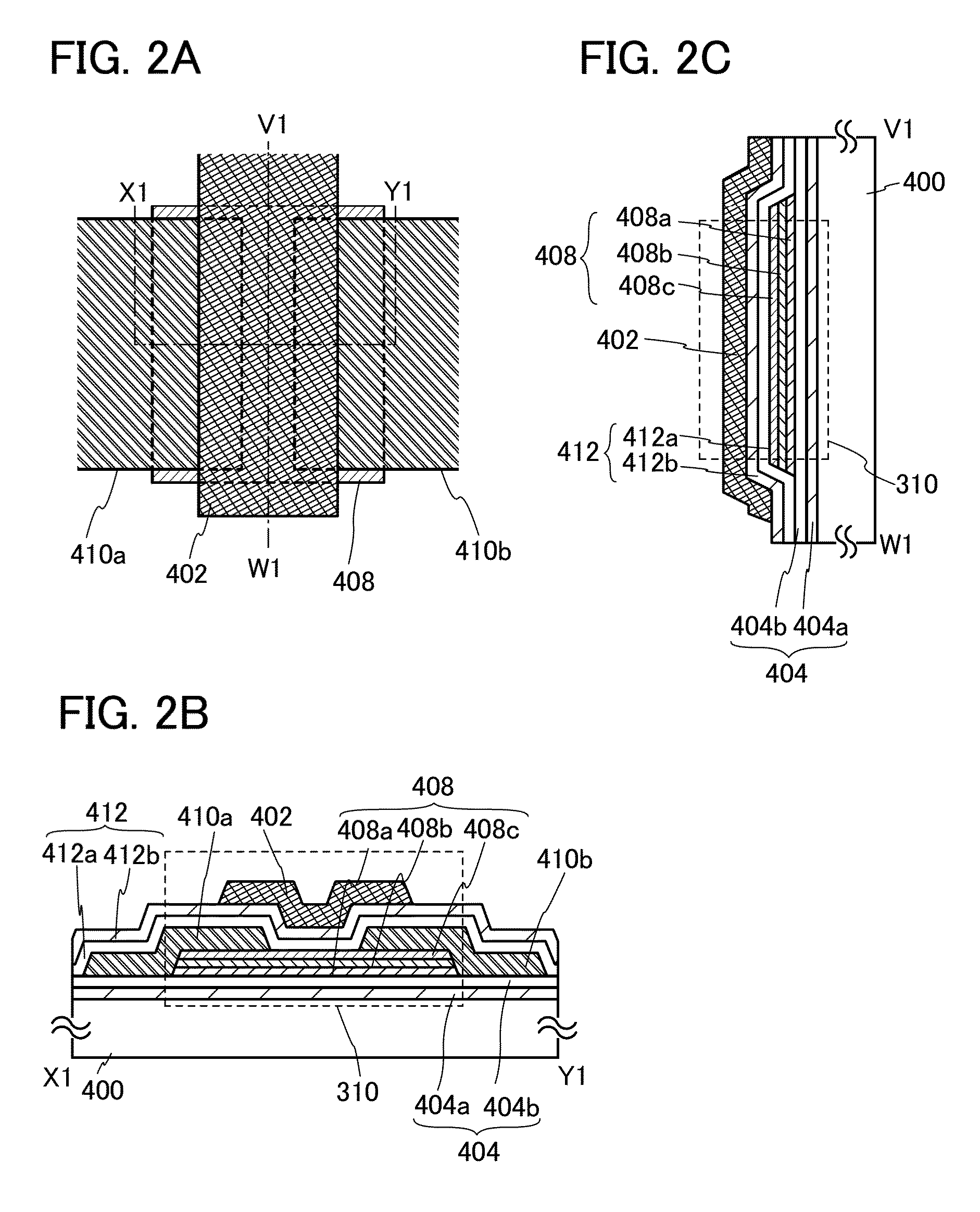

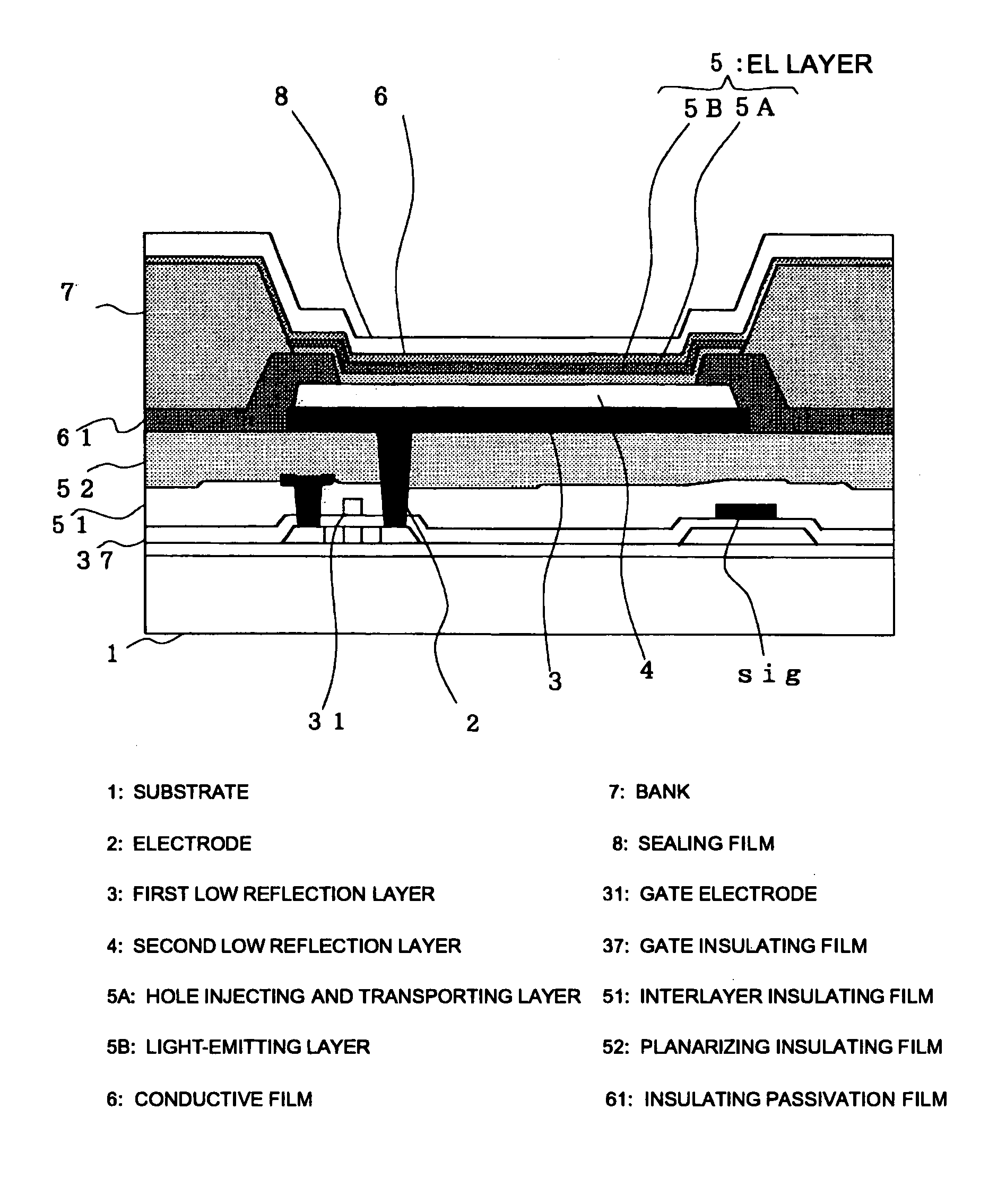

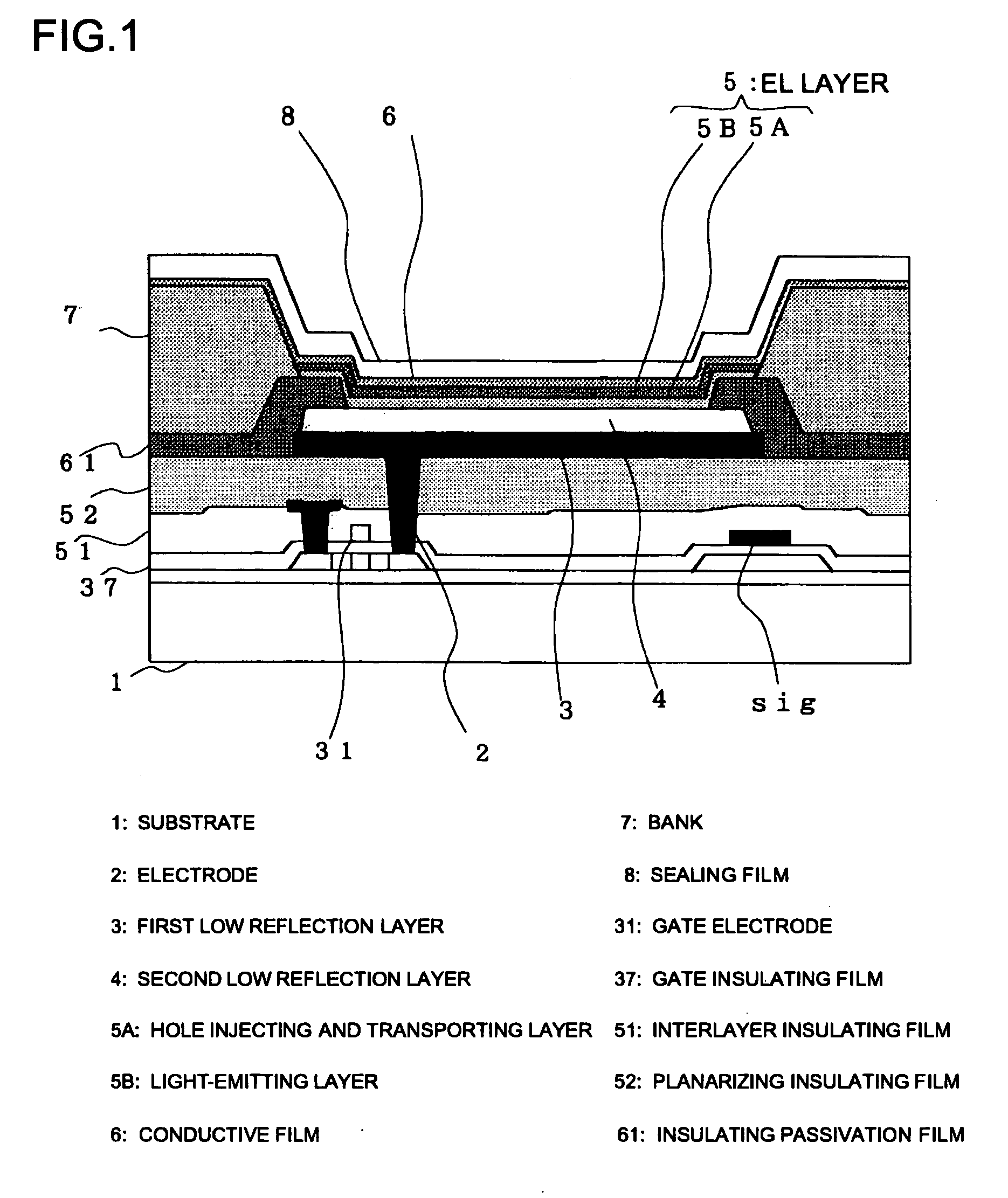

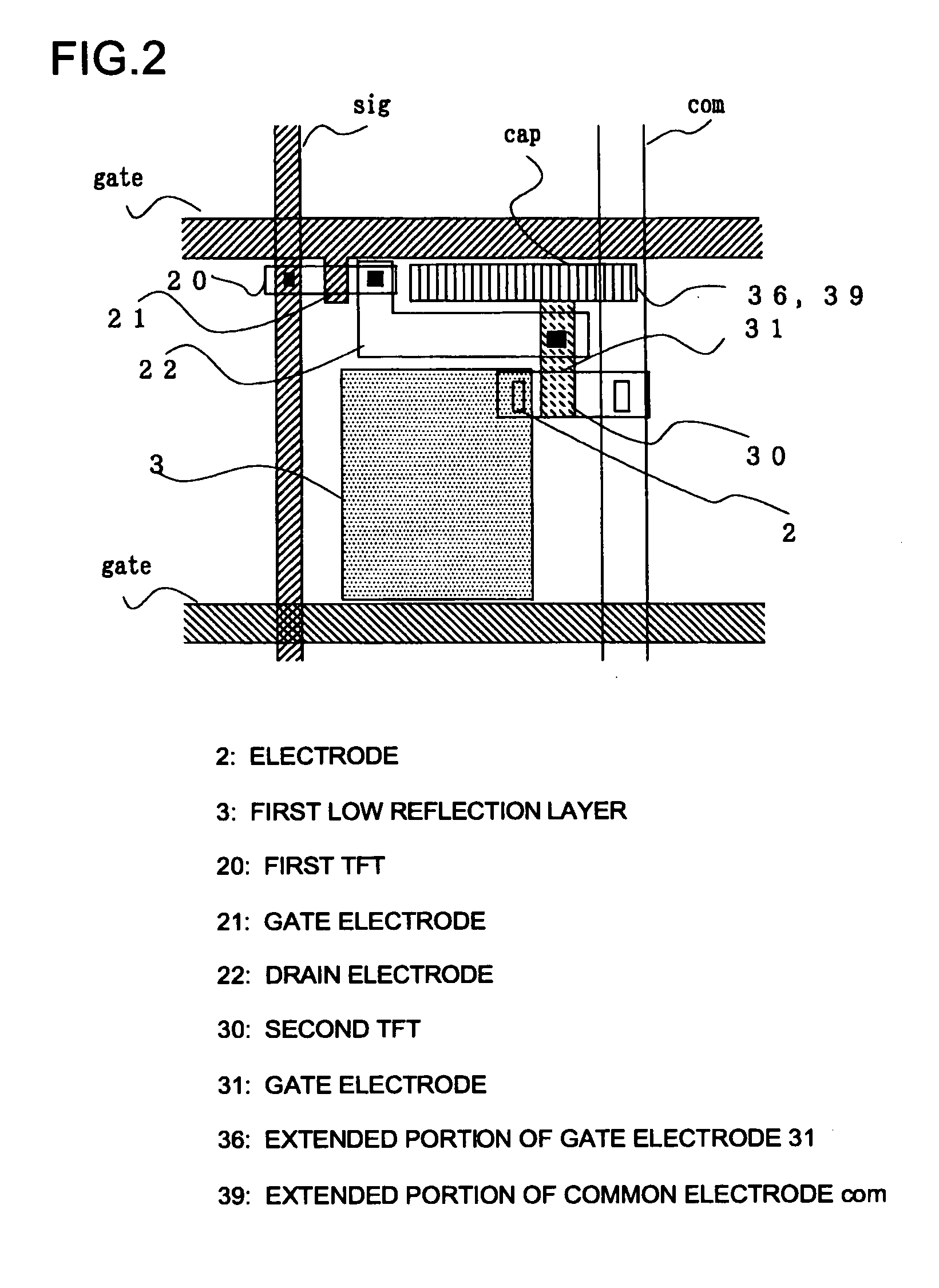

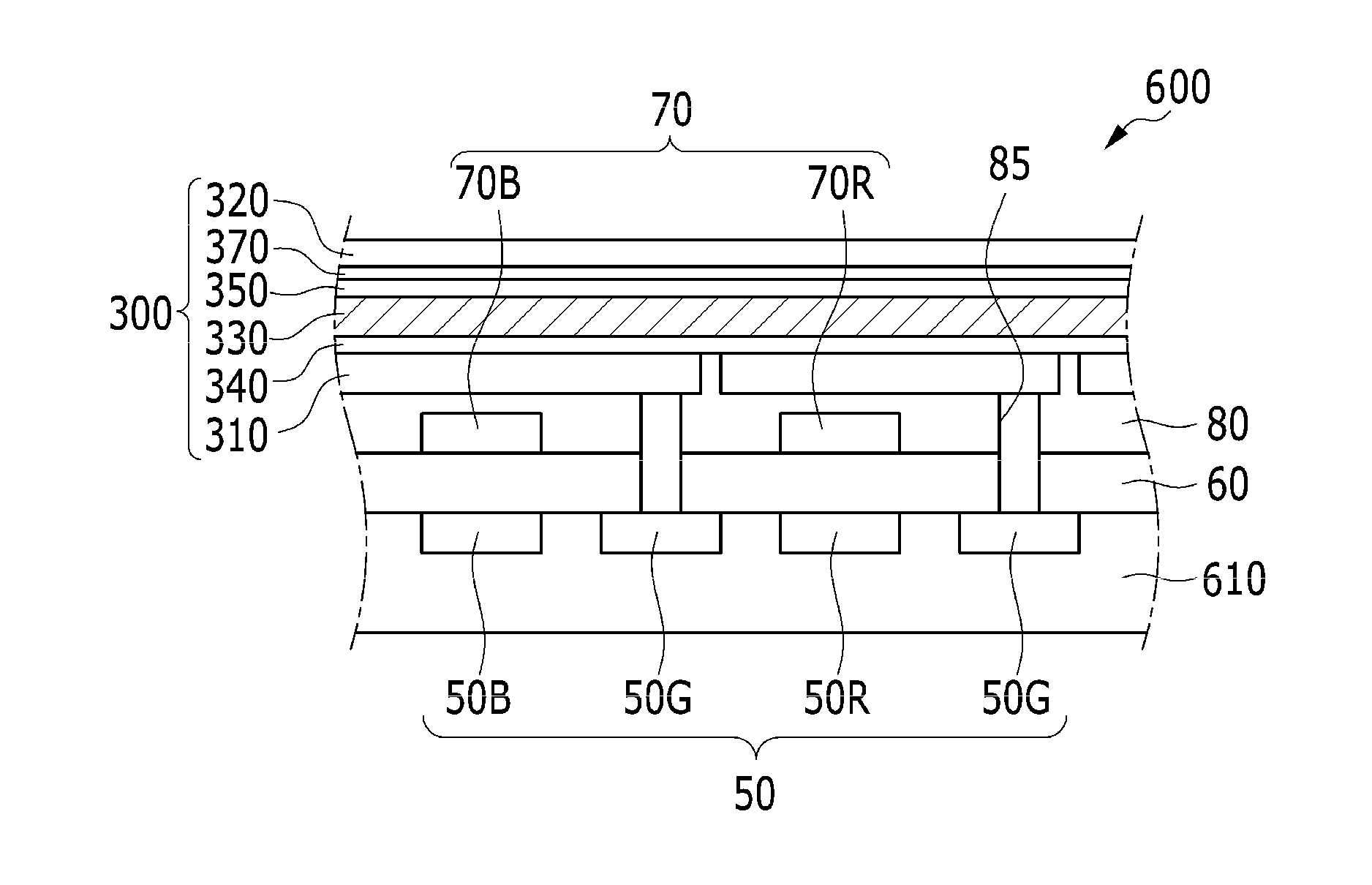

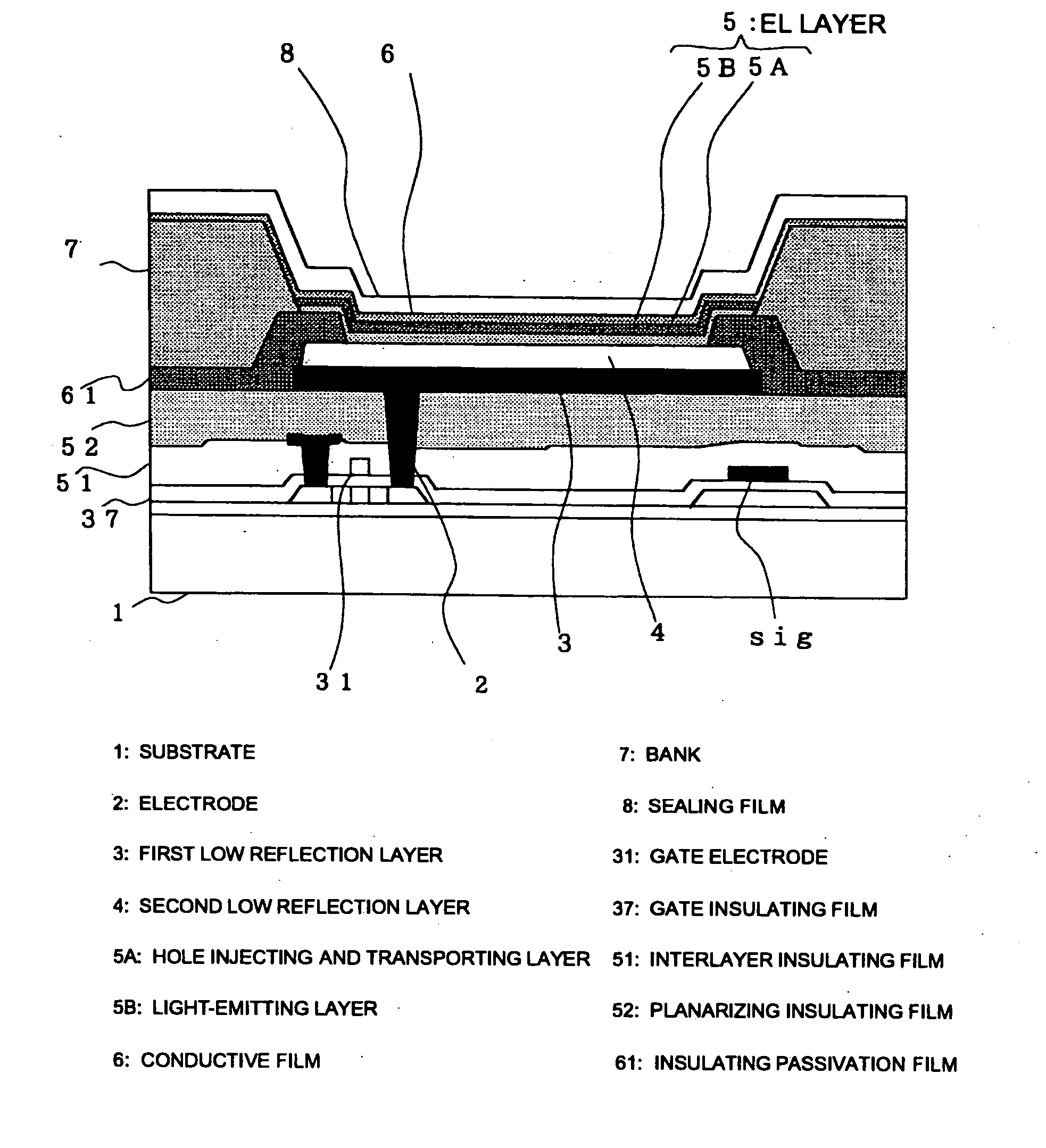

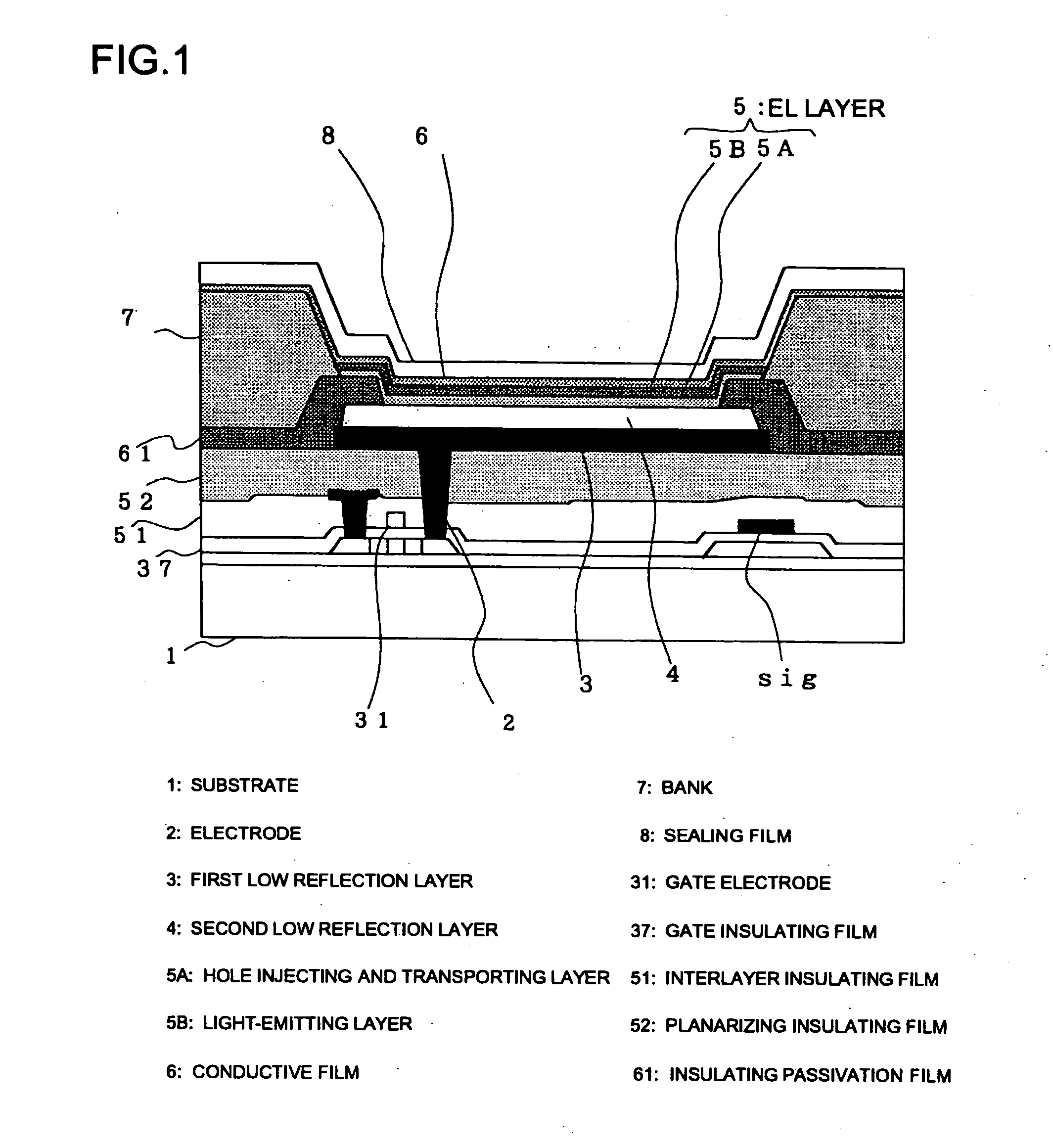

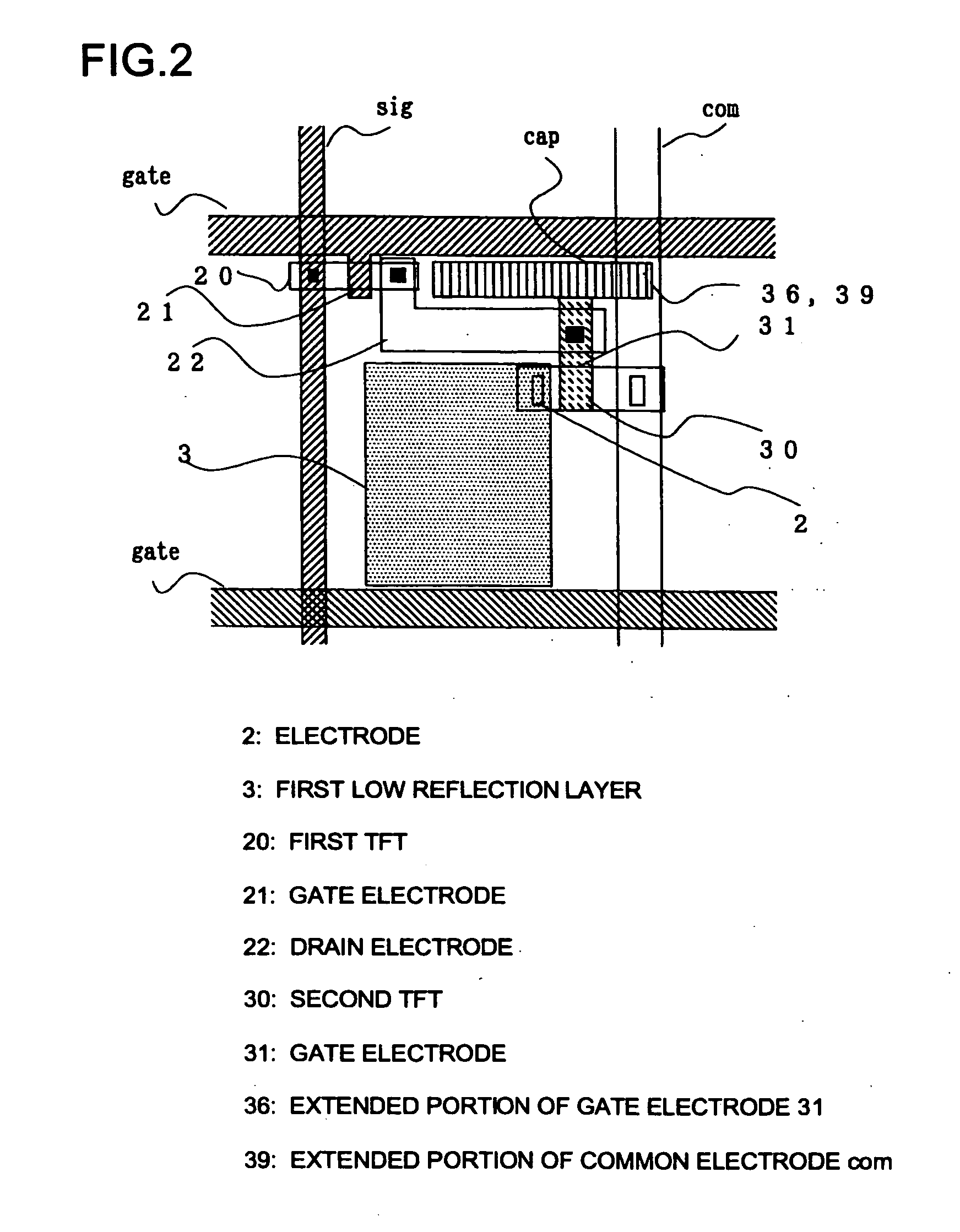

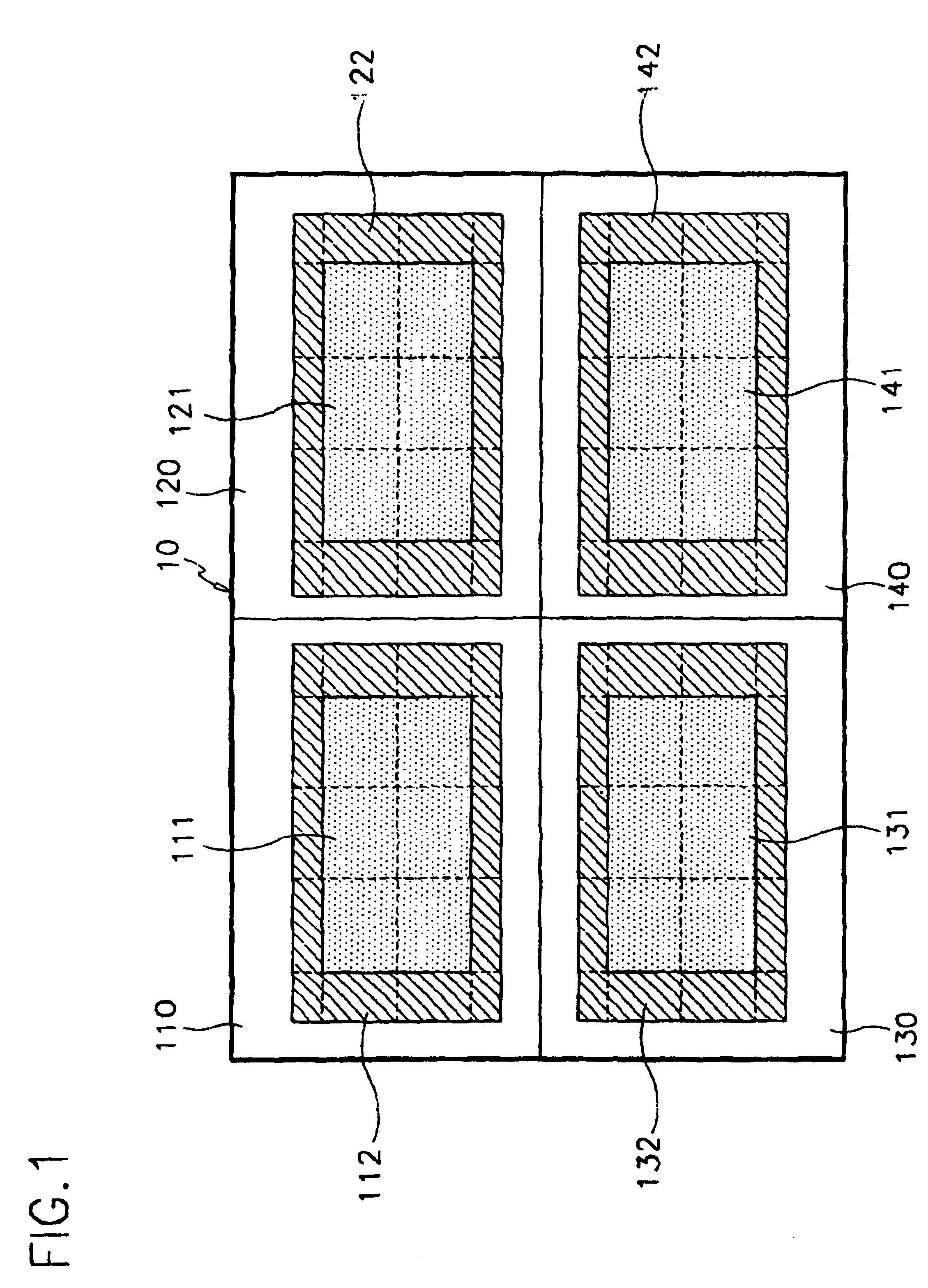

Display panel, electronic apparatus with the same, and method of manufacturing the same

ActiveUS20040178725A1Efficient preparationHigh integration of elementDischarge tube luminescnet screensElectroluminescent light sourcesVisibilityTitanium nitride

There is provided a display panel that is capable of improving visibility outdoors and which can be easily manufactured. In a display panel in which at least one side thereof serves as a display surface, the display panel includes a first reflectance layer 3, which is made of titanium, titanium nitride, or an alloy of titanium and tungsten and a second reflectance layer 4, which is made of indium tin oxide, indium zinc oxide, or gallium zinc oxide, wherein the first and second low reflection layer 3 and 4 are deposited at positions corresponding to pixels on a substrate 1.

Owner:SEIKO EPSON CORP

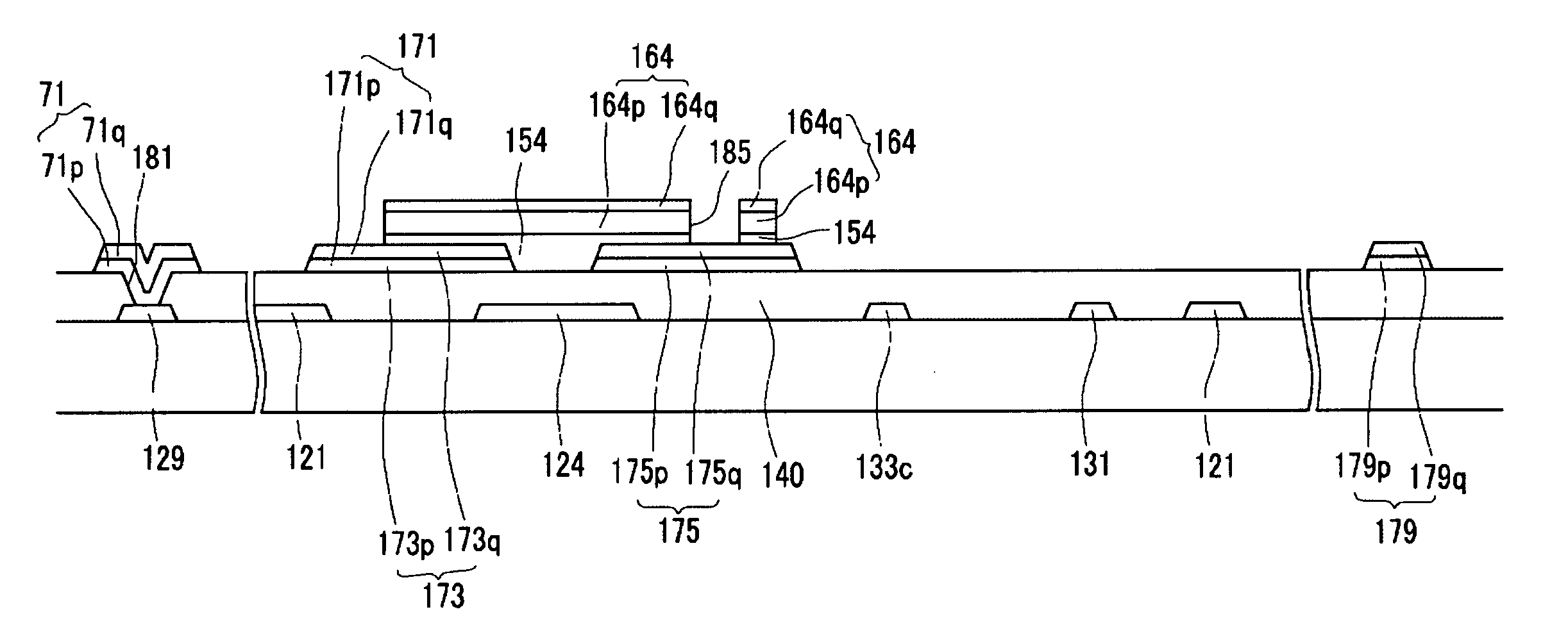

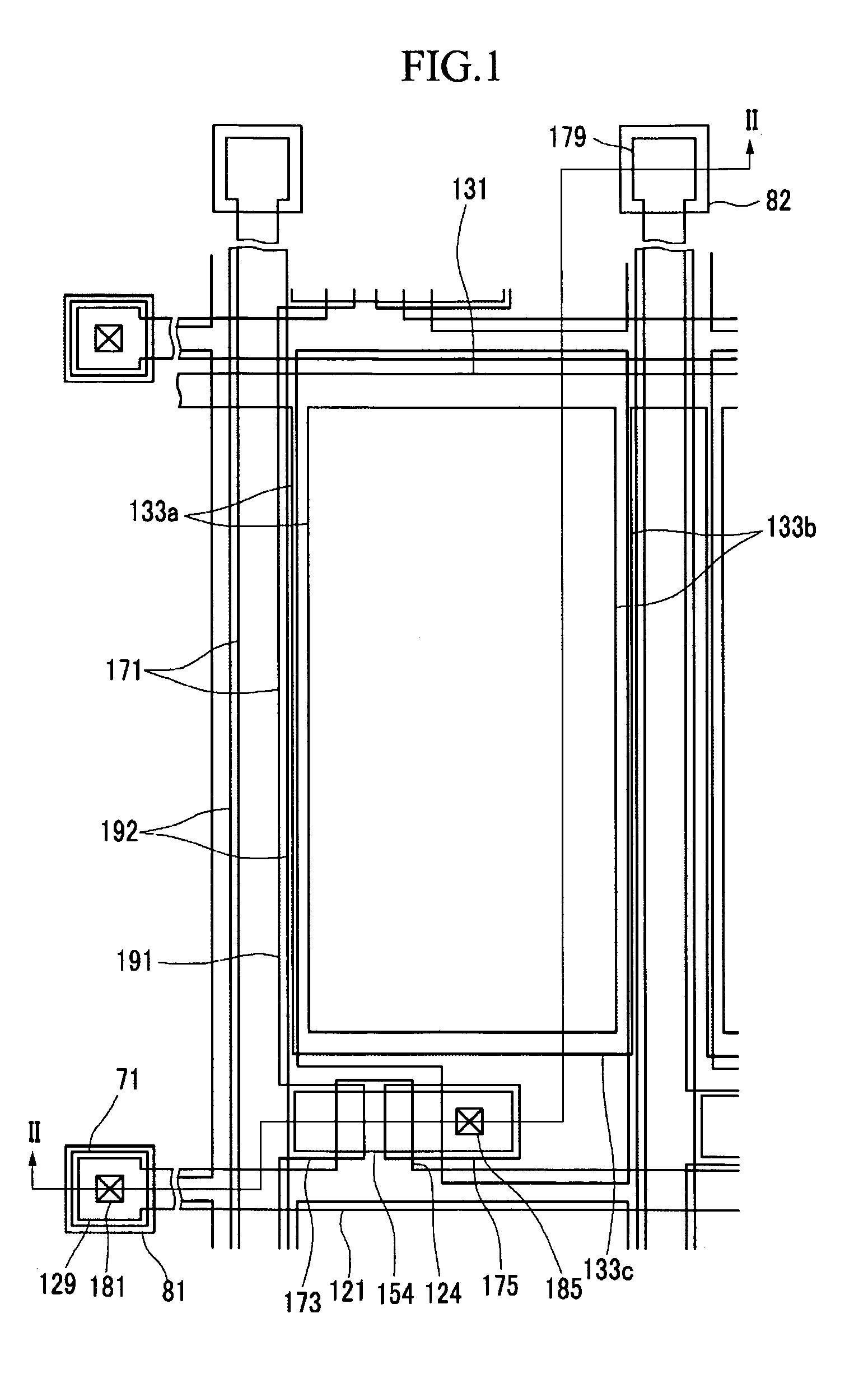

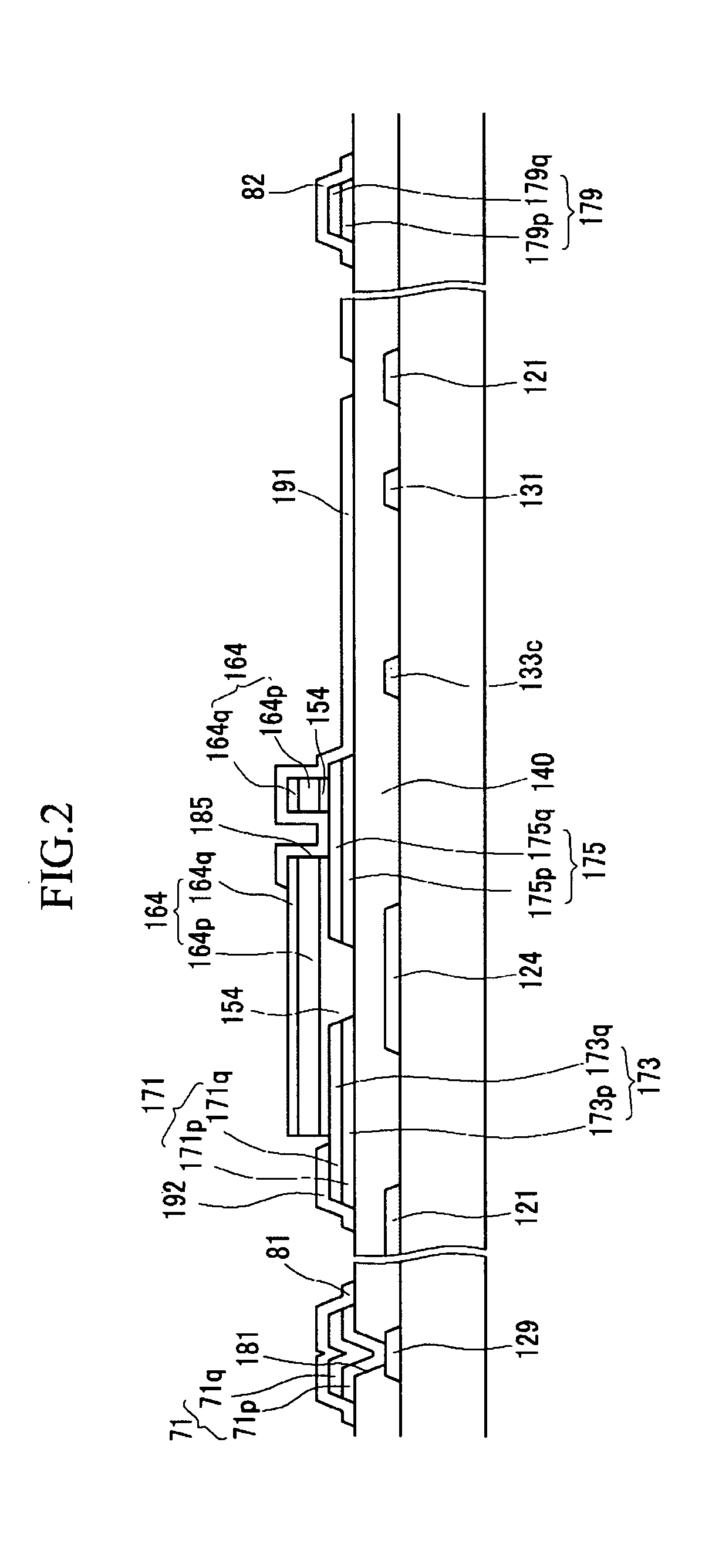

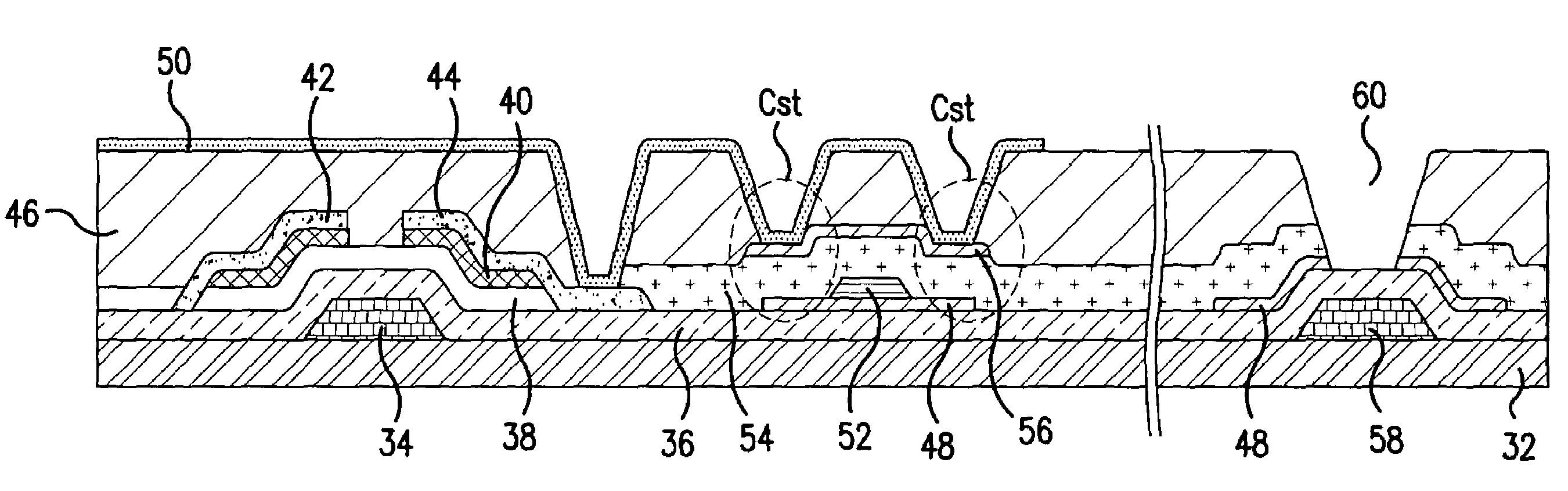

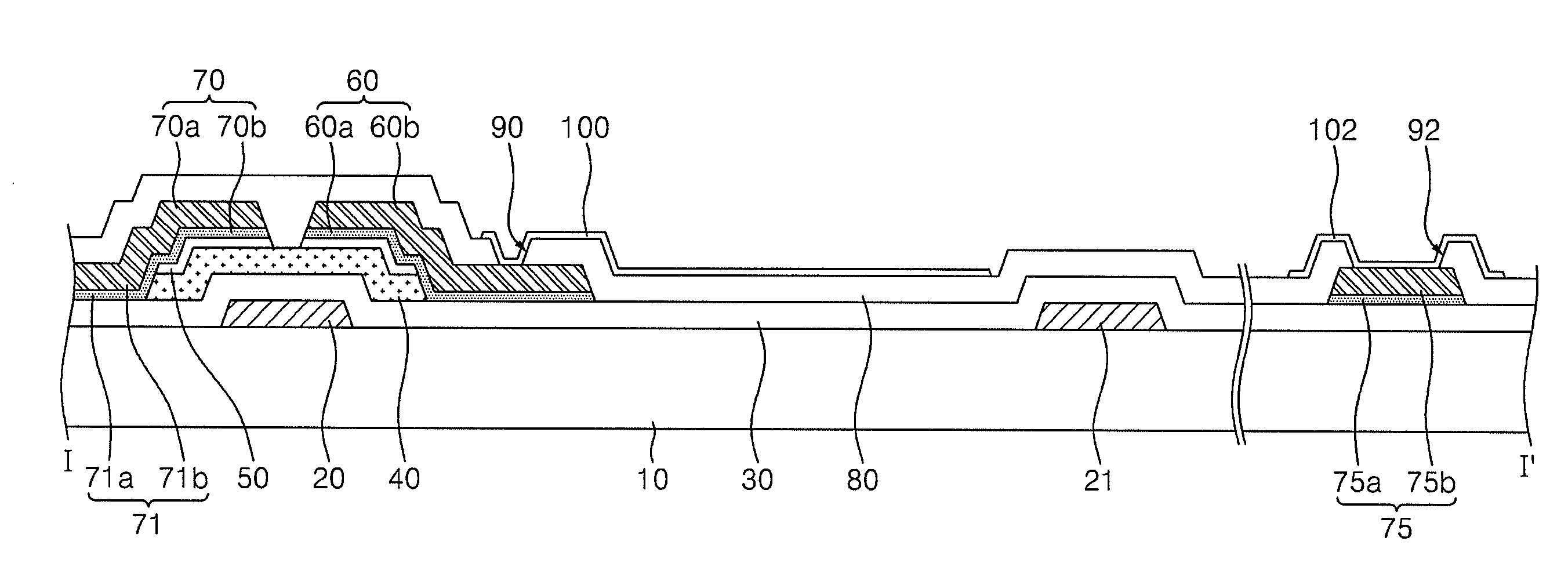

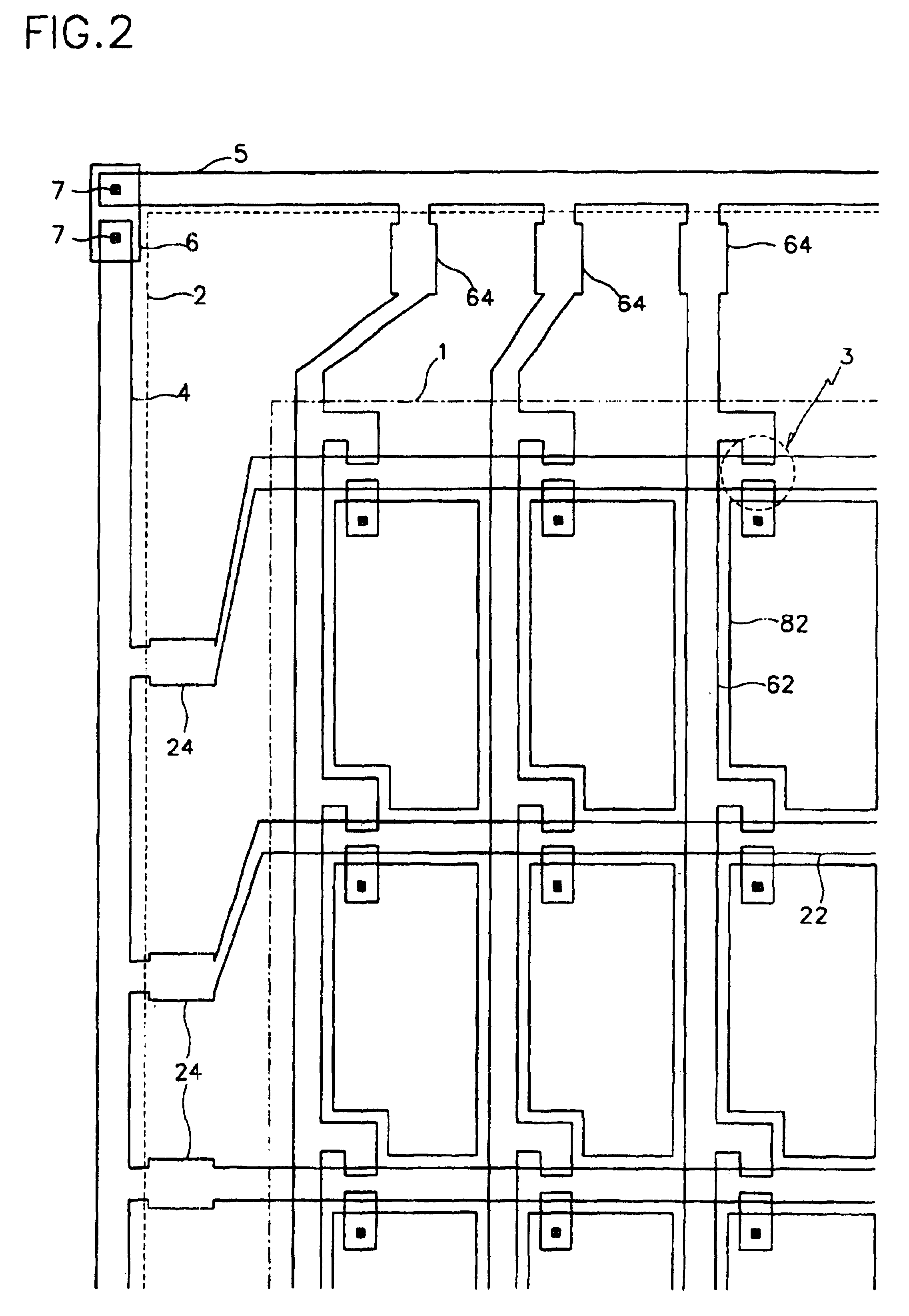

Wiring line assembly and method for manufacturing the same, and thin film transistor array substrate having the wiring line assembly and method for manufacturing the same

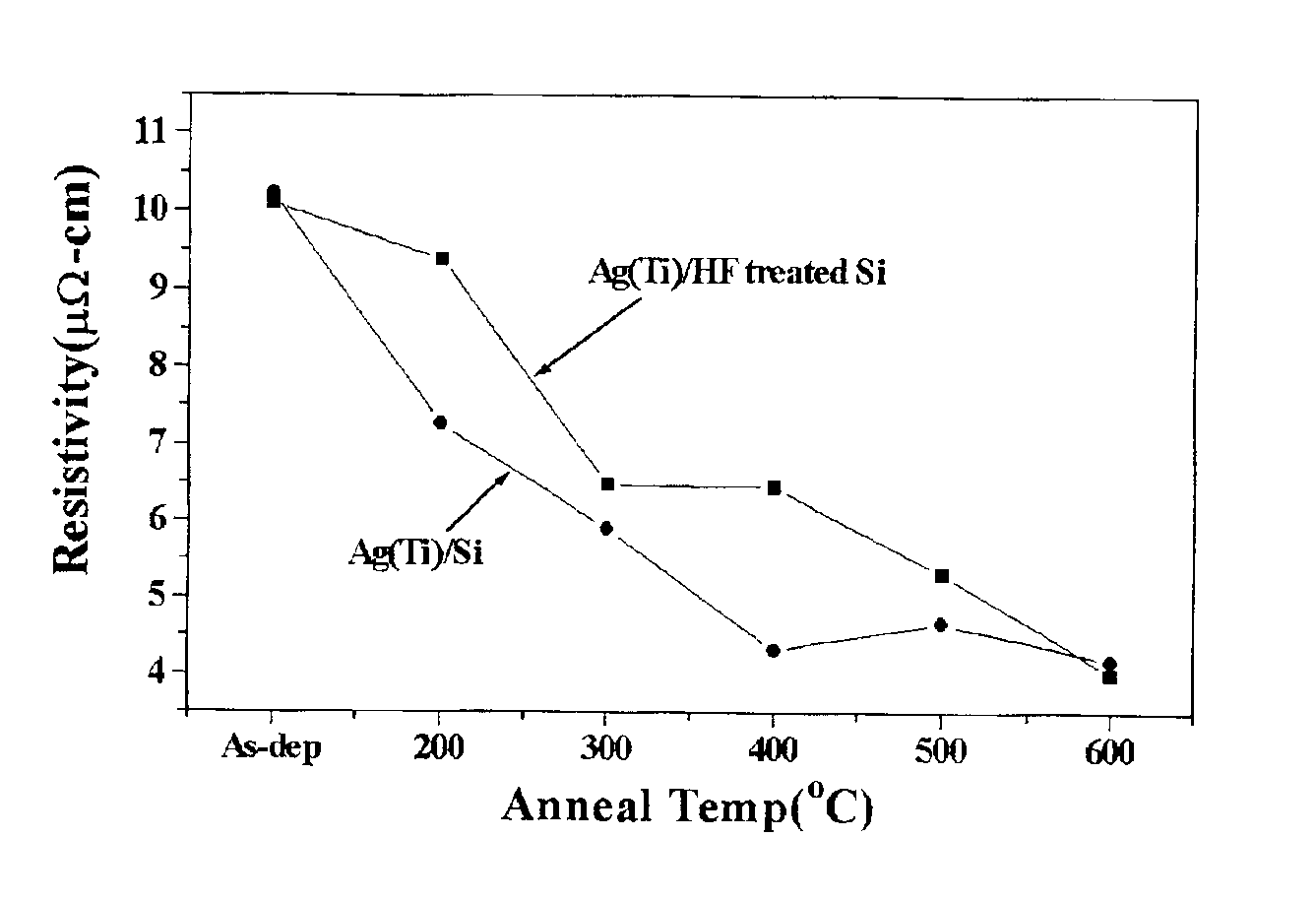

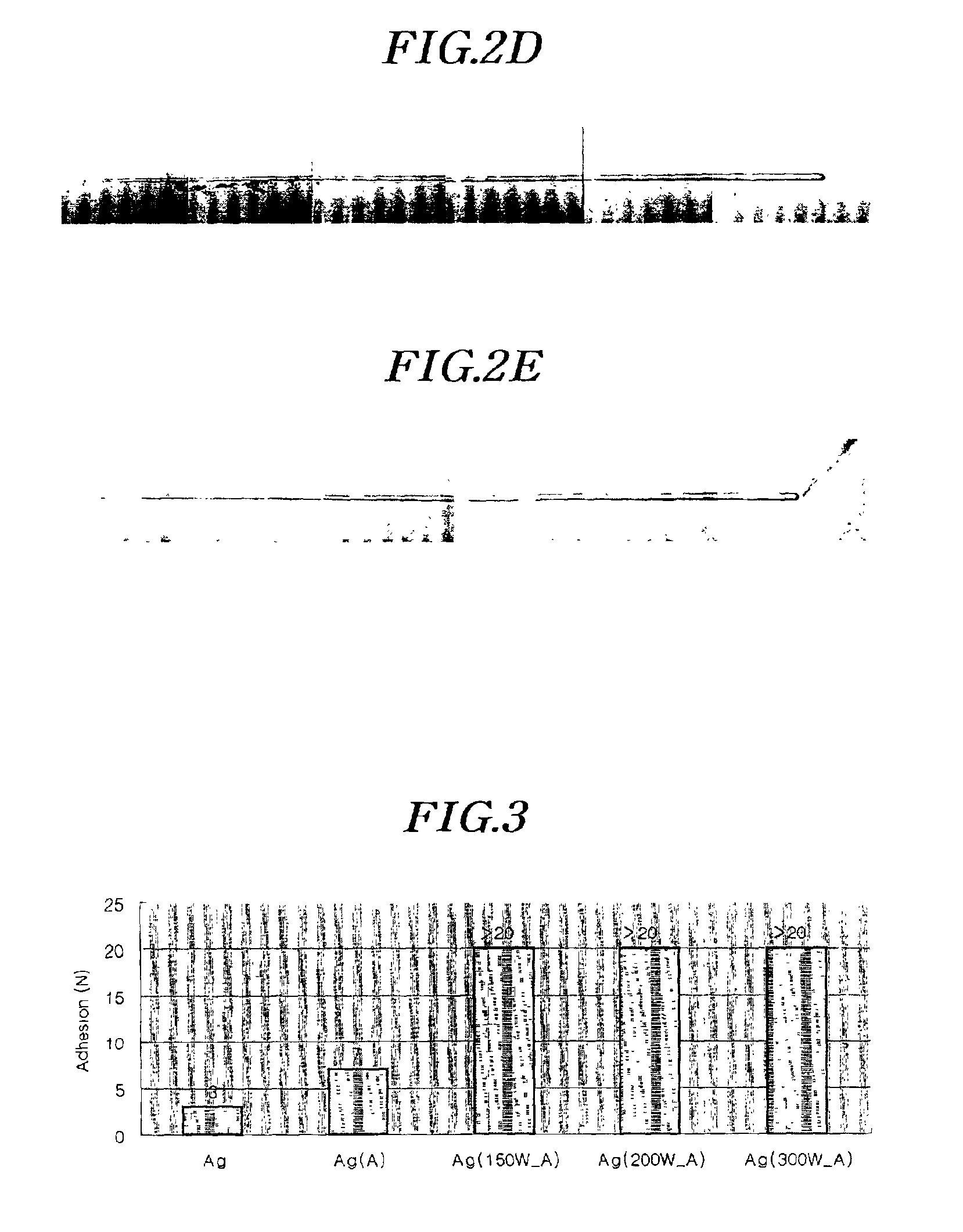

InactiveUS6867108B2Lower resistanceGood adhesion characteristicTransistorSemiconductor/solid-state device detailsIndium zinc oxideEngineering

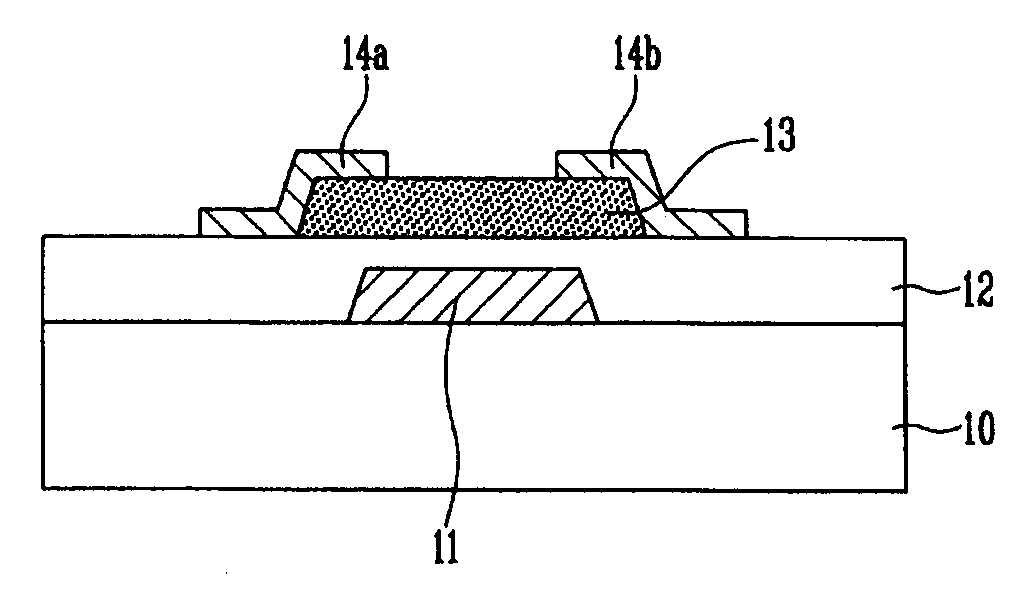

In a method for fabricating a thin film transistor array substrate, a glass substrate undergoes an oxygen plasma treatment. A silver or silver alloy-based conductive layer is deposited onto the substrate, and patterned to thereby form a gate line assembly proceeding in the horizontal direction. The gate line assembly includes gate lines, gate electrodes, and gate pads. Thereafter, a silicon nitride-based gate insulating layer is deposited onto the substrate, and a semiconductor layer and an ohmic contact layer are sequentially formed on the gate insulating layer. The semiconductor layer and the ohmic contact layer are HF-treated. A silver alloy-based conductive layer is deposited onto the substrate, and patterned to thereby form a data line assembly. The data line assembly includes data lines crossing over the gate lines, source electrodes, drain electrodes, and data pads. A protective layer based on silicon nitride or an organic material is deposited onto the substrate, and patterned through dry etching such that the protective layer bears contact holes exposing the drain electrodes, the gate pads and the data pads, respectively. An indium zinc oxide or indium tin oxide-based layer is deposited onto the substrate, and patterned to thereby form pixel electrodes, and subsidiary gate and data pads. The pixel electrodes are electrically connected to the drain electrodes, and the subsidiary gate and data pads to the gate and data pads.

Owner:SAMSUNG DISPLAY CO LTD

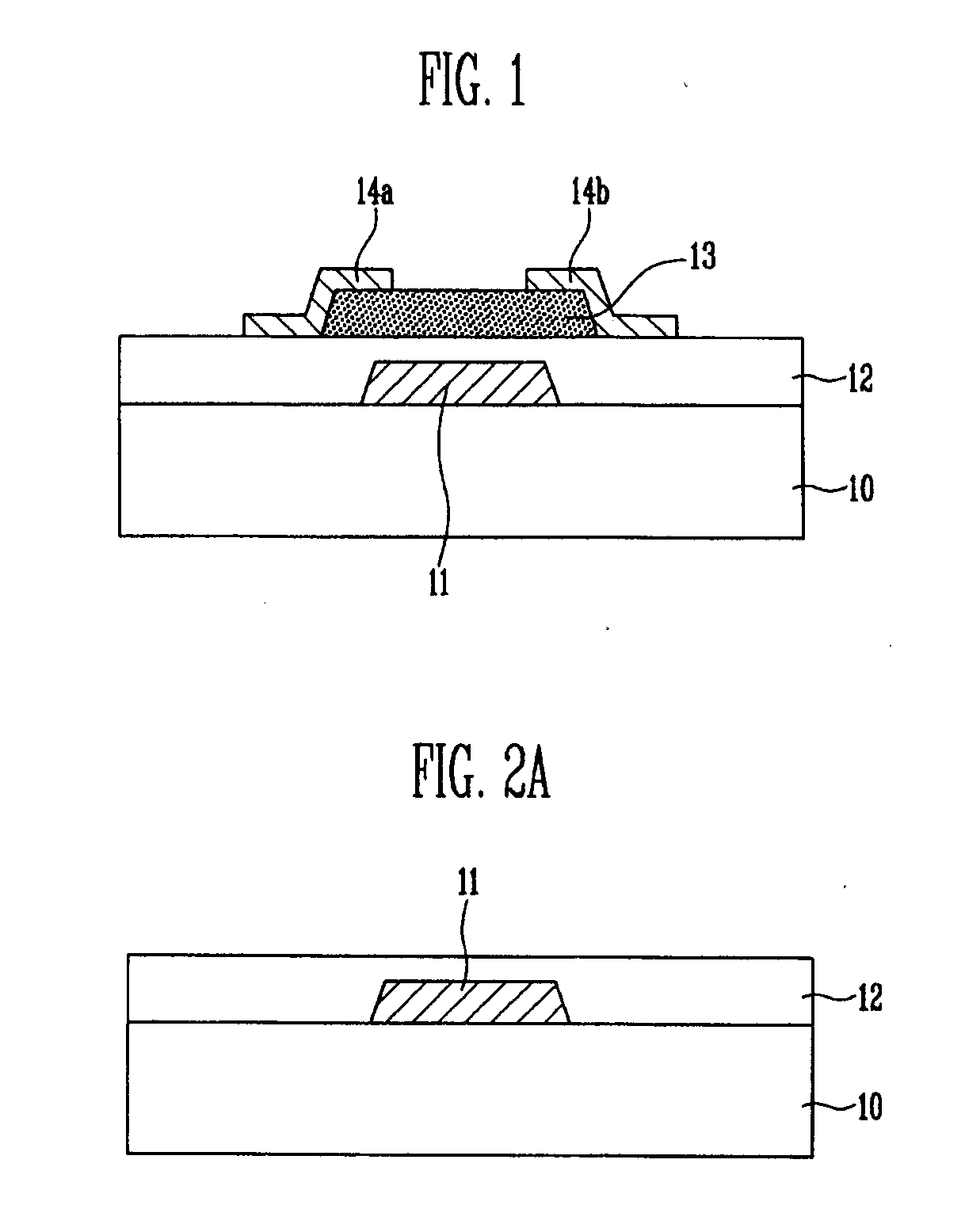

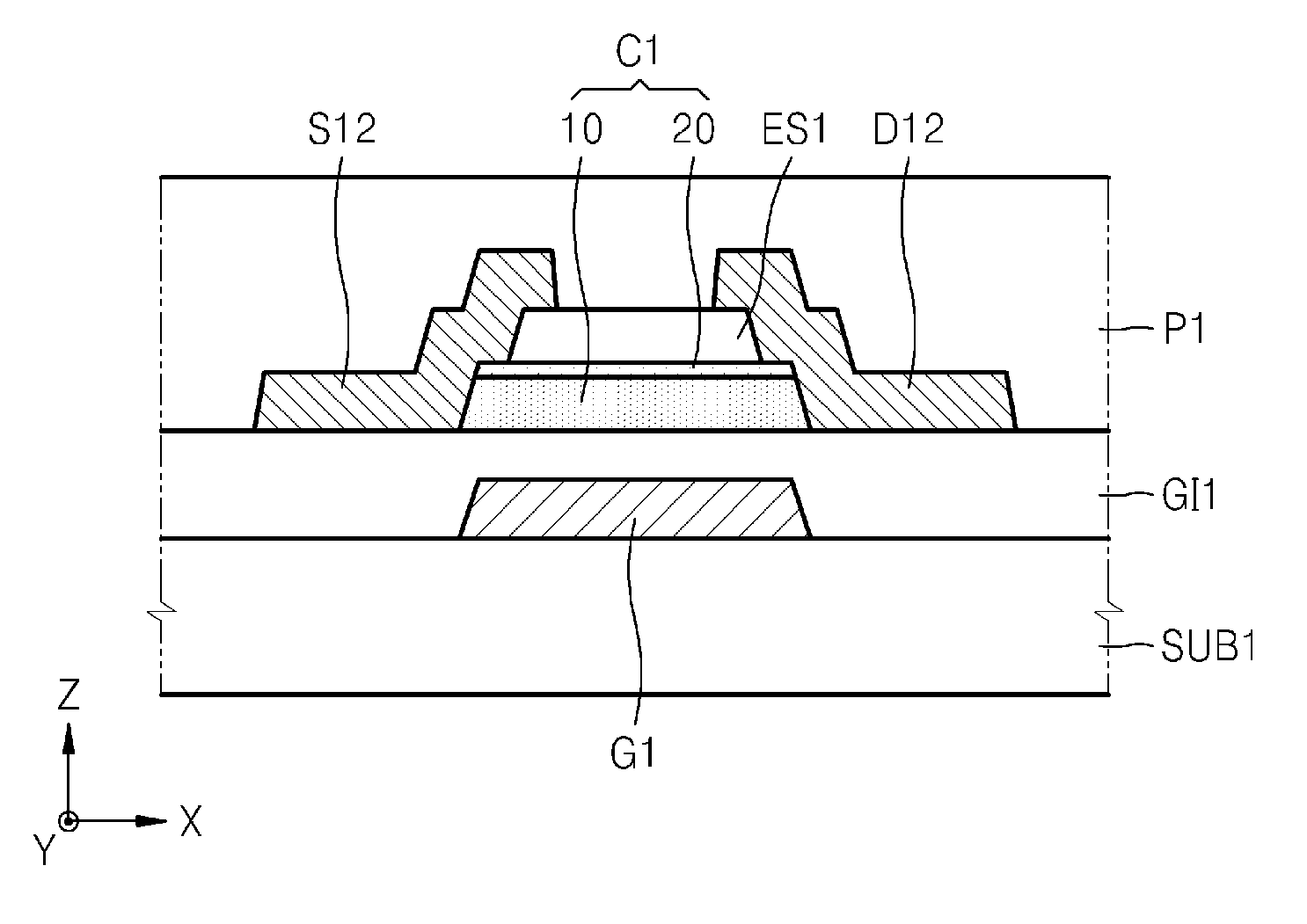

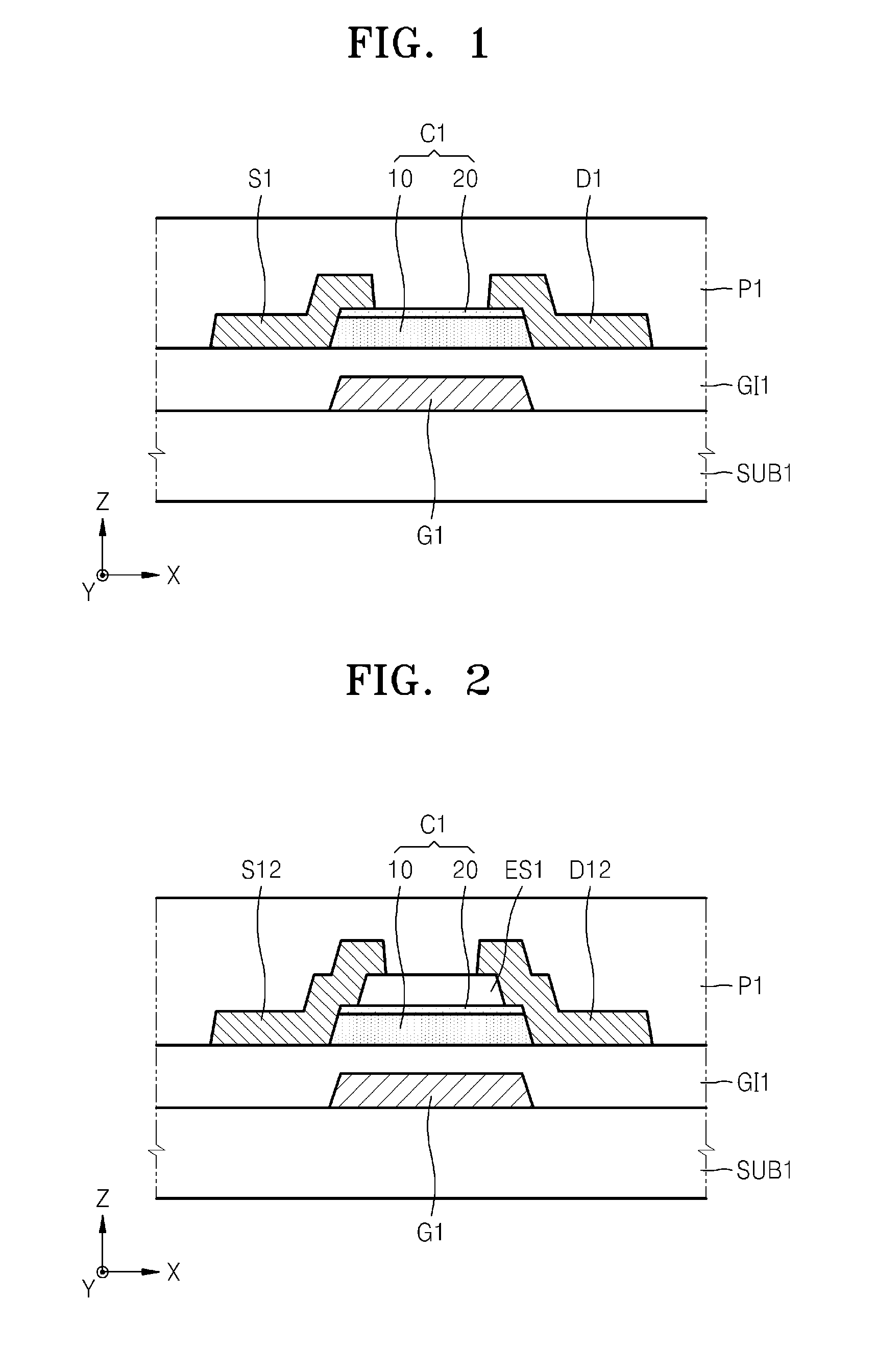

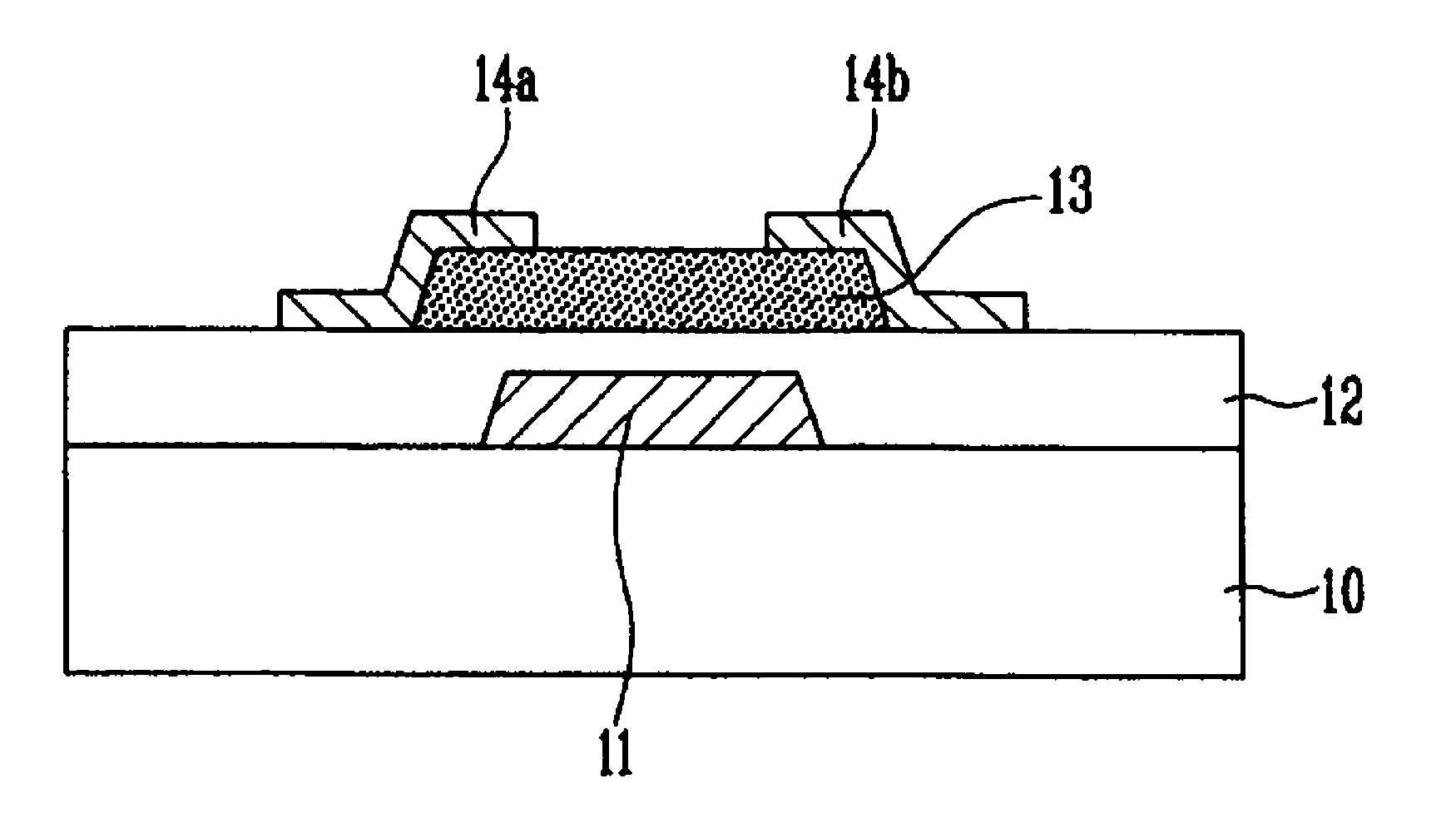

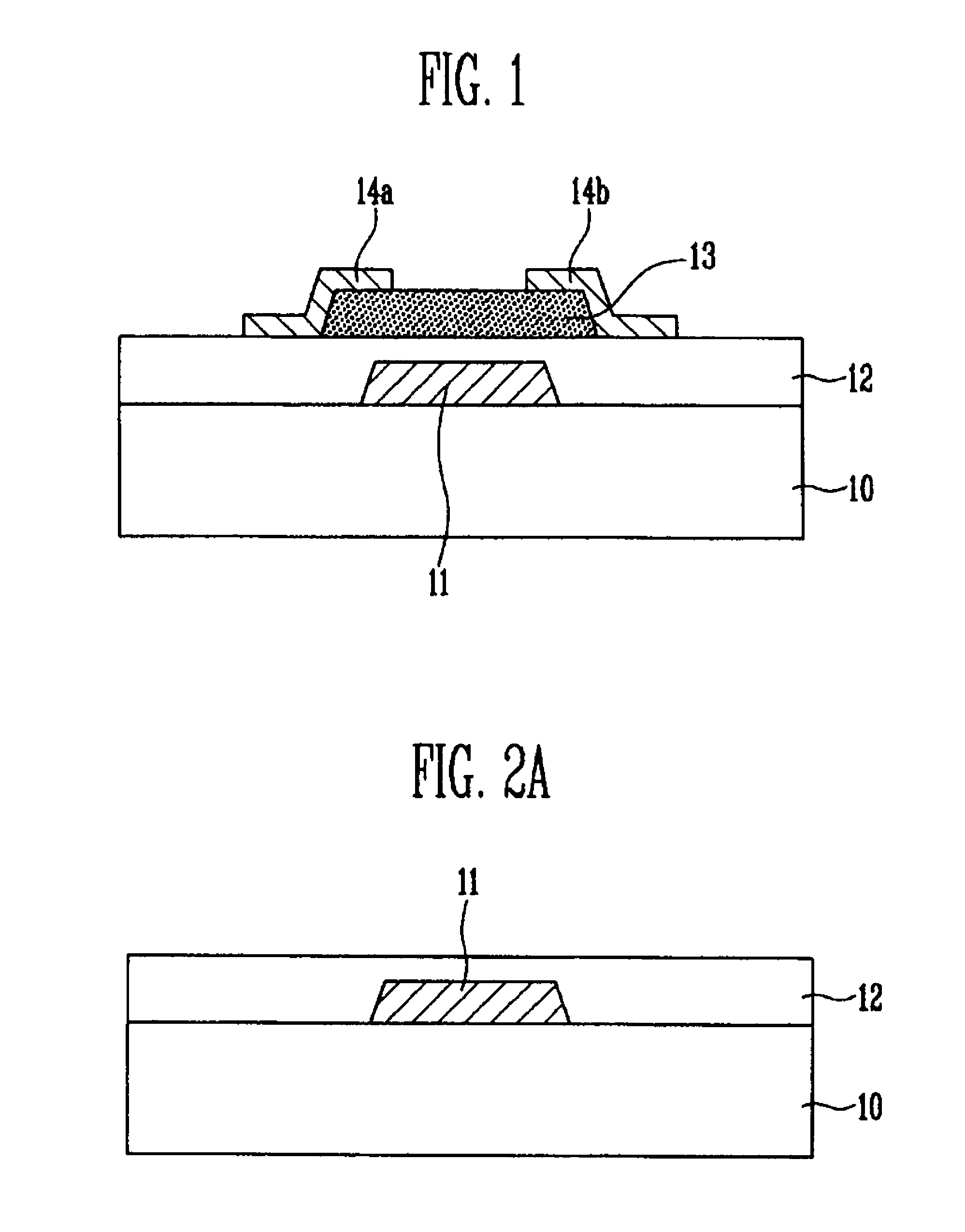

Thin film transistor, method of manufacturing the same, and flat panel display device having the same

ActiveUS20090194766A1Improve featuresEasy to controlTransistorSolid-state devicesDisplay deviceIndium zinc oxide

A thin film transistor (TFT) using an oxide semiconductor layer as an active layer, a method of manufacturing the TFT, and a flat panel display (FPD) including the TFT are taught. The TFT includes a gate electrode formed on a substrate, an oxide semiconductor layer electrically insulated from the gate electrode by a gate insulating layer, and the oxide semiconductor layer including a channel region, a source region, and a drain region, and a source electrode and a drain electrode respectively electrically contacting the source region and the drain region. The oxide semiconductor layer is formed of an InZnO or IZO layer (indium zinc oxide layer) including Zr. The carrier density of the IZO layer is controlled to be 1×1013 to 1×1018 #cm−3 by controlling an amount of Zr.

Owner:SAMSUNG DISPLAY CO LTD

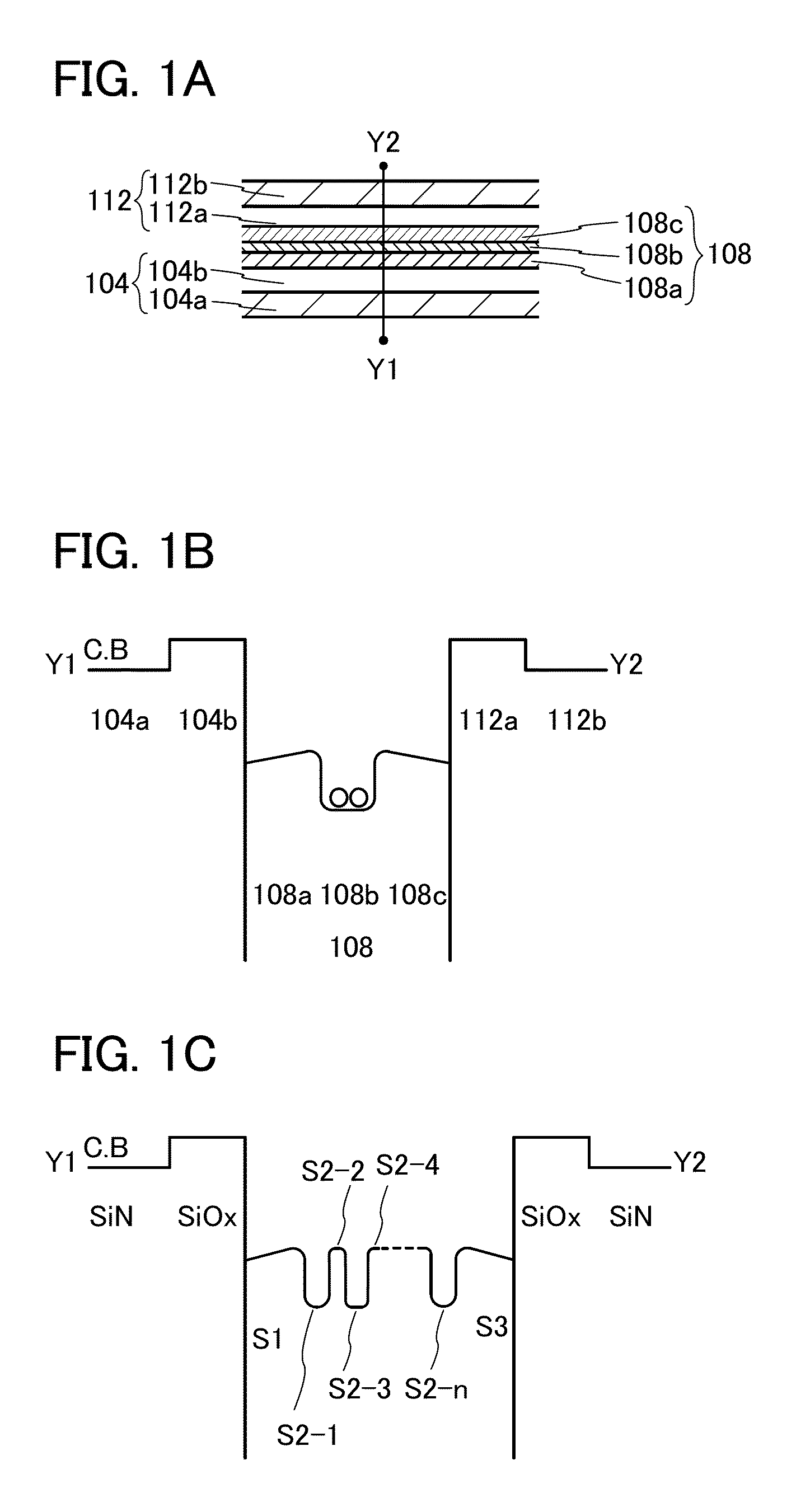

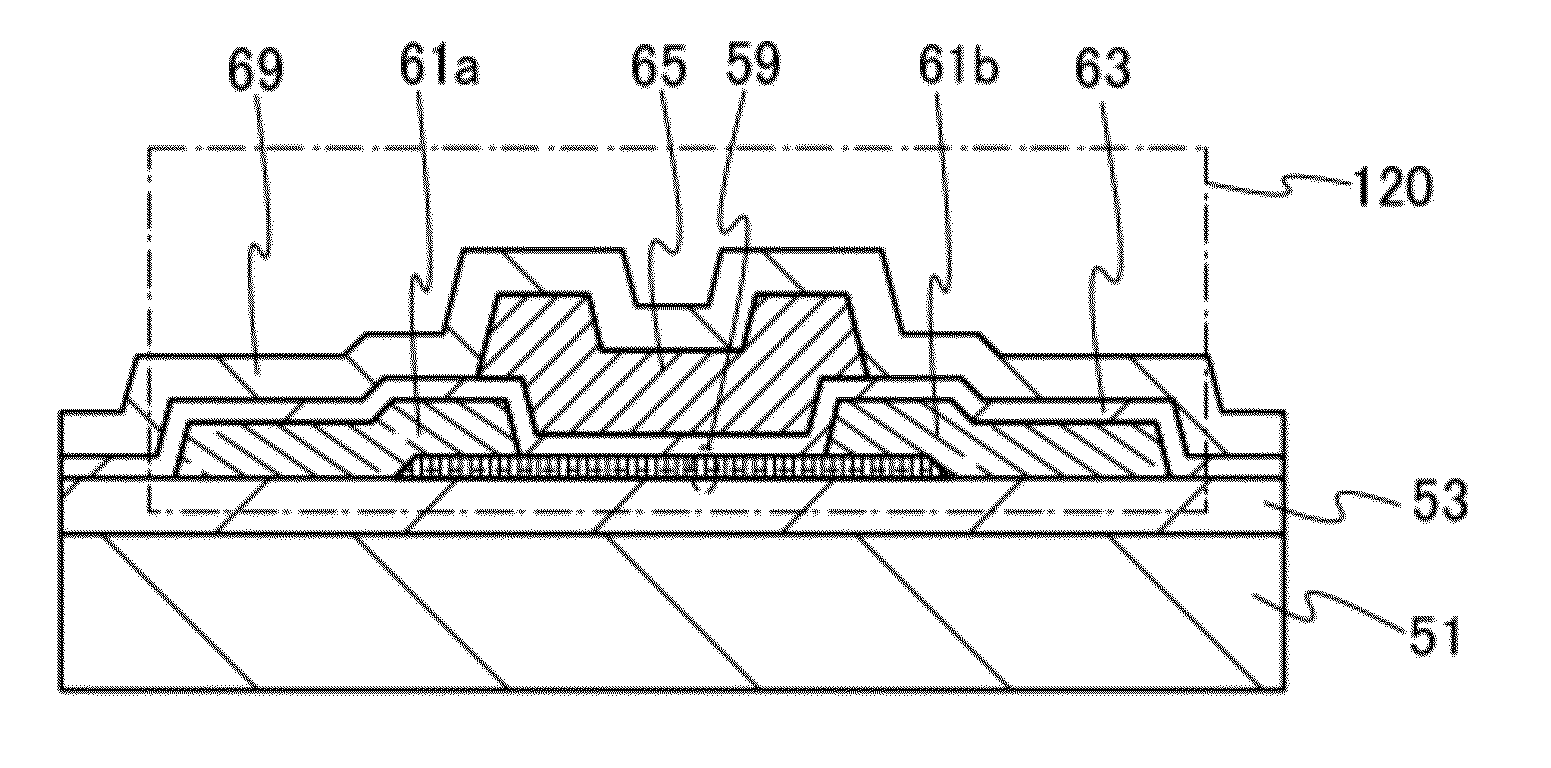

Oxide semiconductor film and semiconductor device

ActiveUS20120241735A1Stable electrical characteristicsStable characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialCrystal structure

Provided is an oxide semiconductor film which has more stable electric characteristics and essentially consists of indium zinc oxide. In addition, provided is a highly reliable semiconductor device which has stable electric characteristics by using the oxide semiconductor film. The oxide semiconductor film essentially consisting of indium zinc oxide has a hexagonal crystal structure in which the a-b plane is substantially parallel to a surface of the oxide semiconductor film and a rhombohedral crystal structure in which the a-b plane is substantially parallel to the surface of the oxide semiconductor film.

Owner:SEMICON ENERGY LAB CO LTD

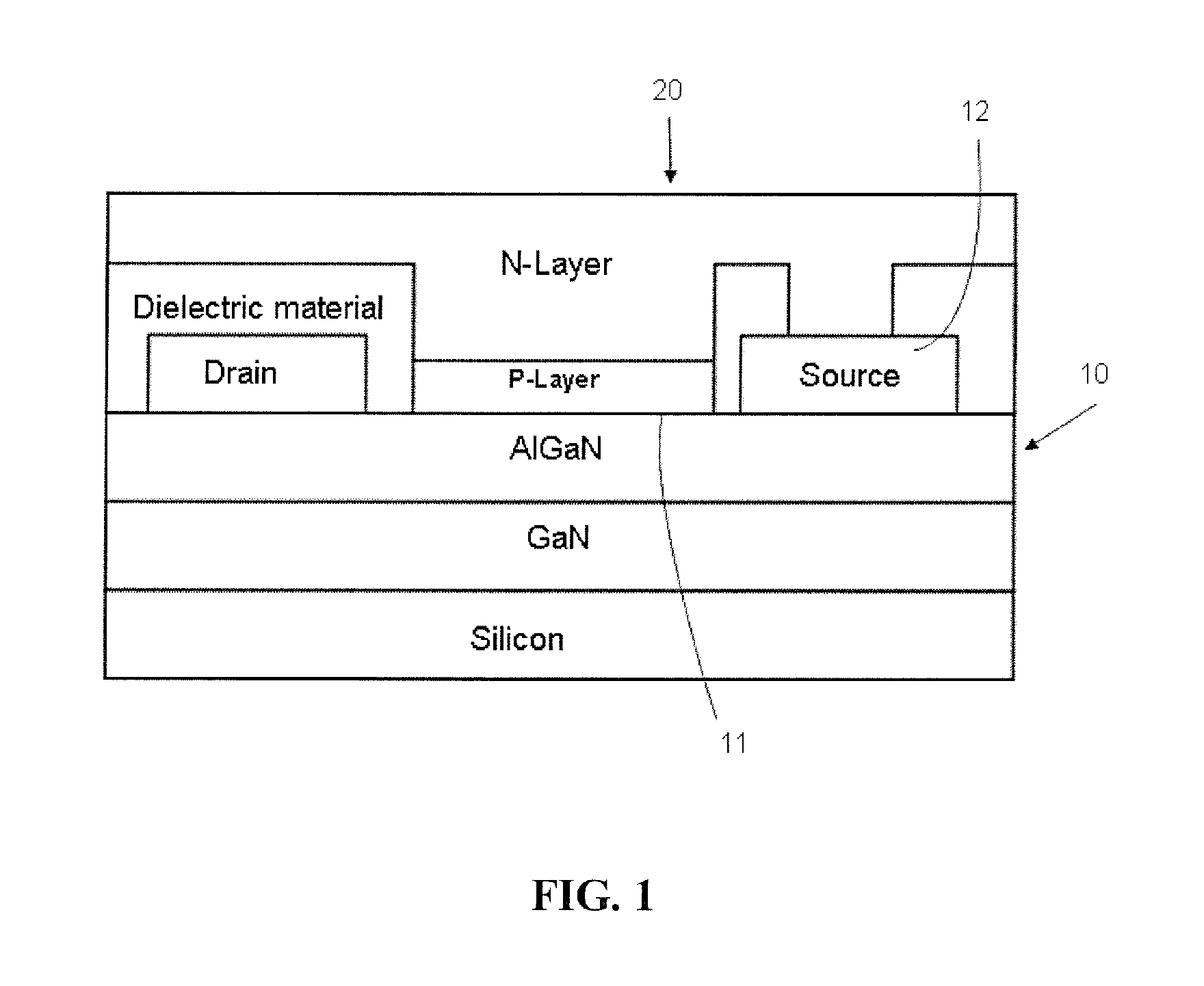

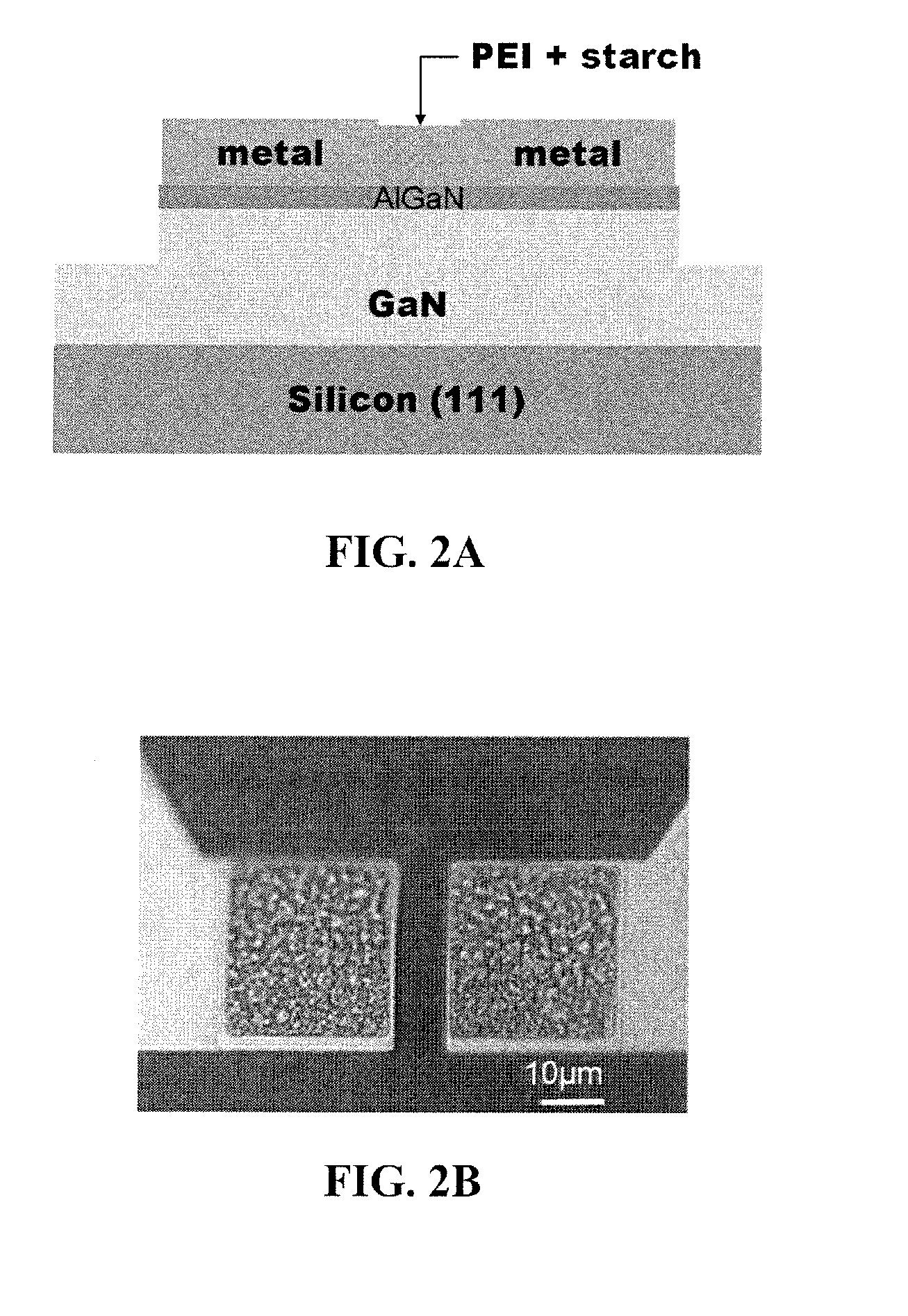

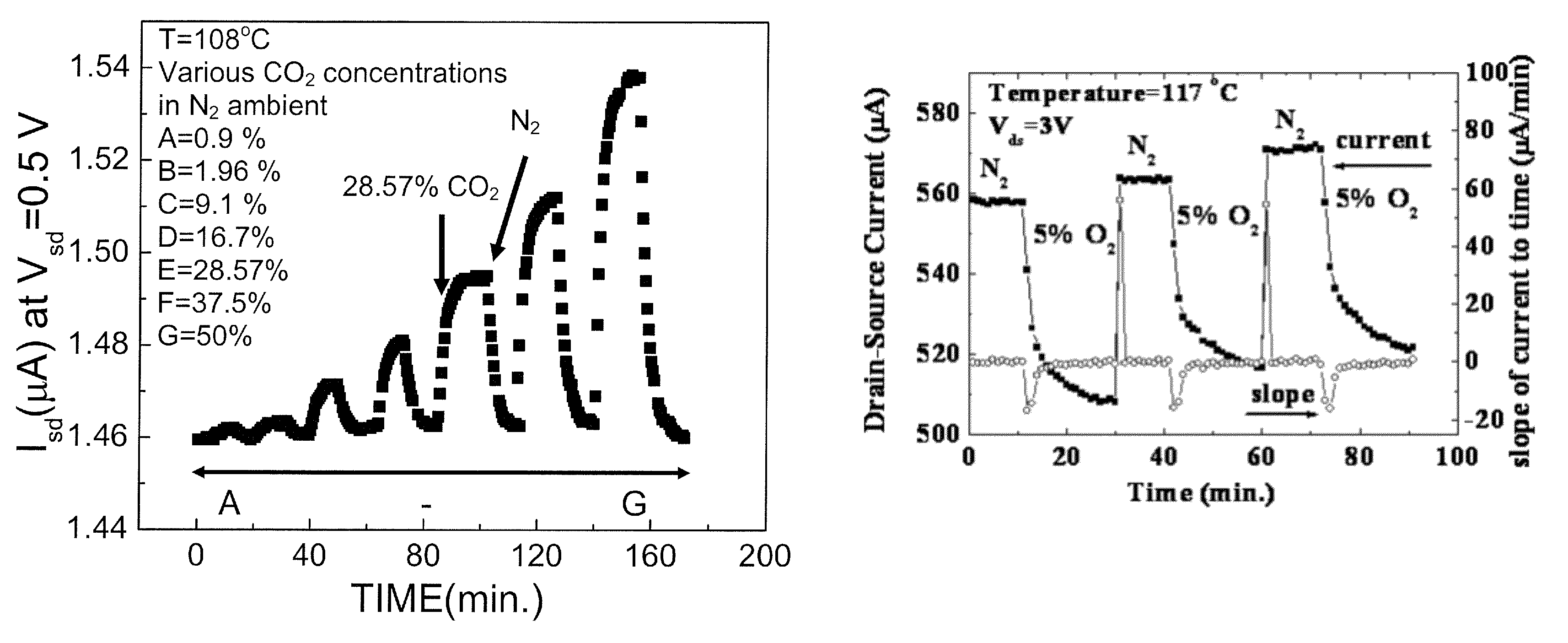

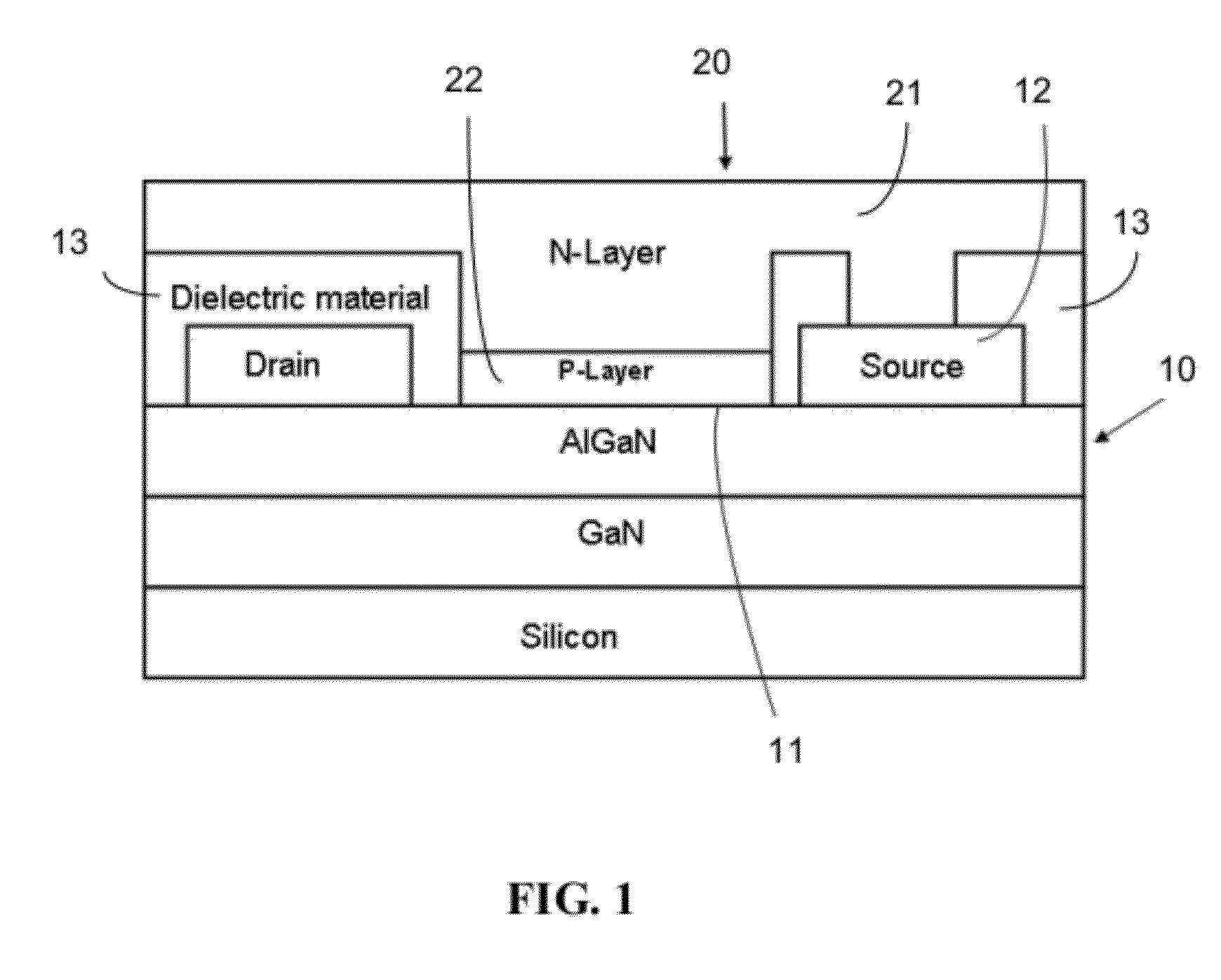

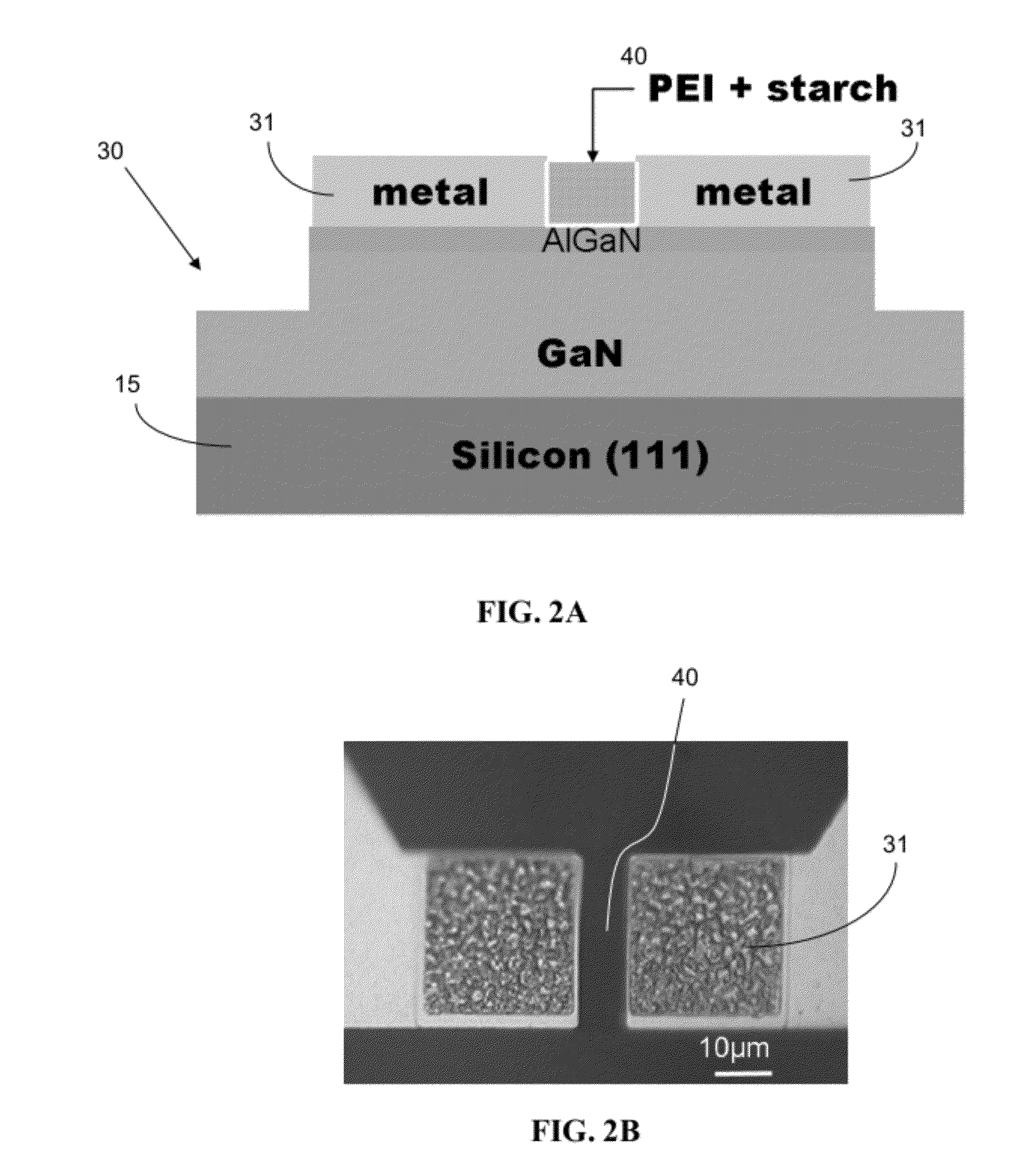

Oxygen and carbon dioxide sensing

InactiveUS20110045600A1Component separationWithdrawing sample devicesIndium zinc oxidePolymer solar cell

A high electron mobility transistor (HEMT) capable of performing as a CO2 or O2 sensor is disclosed, hi one implementation, a polymer solar cell can be connected to the HEMT for use in an infrared detection system. In a second implementation, a selective recognition layer can be provided on a gate region of the HEMT. For carbon dioxide sensing, the selective recognition layer can be, in one example, PEI / starch. For oxygen sensing, the selective recognition layer can be, in one example, indium zinc oxide (IZO). In one application, the HEMTs can be used for the detection of carbon dioxide and oxygen in exhaled breath or blood.

Owner:UNIV OF FLORIDA RES FOUNDATION INC

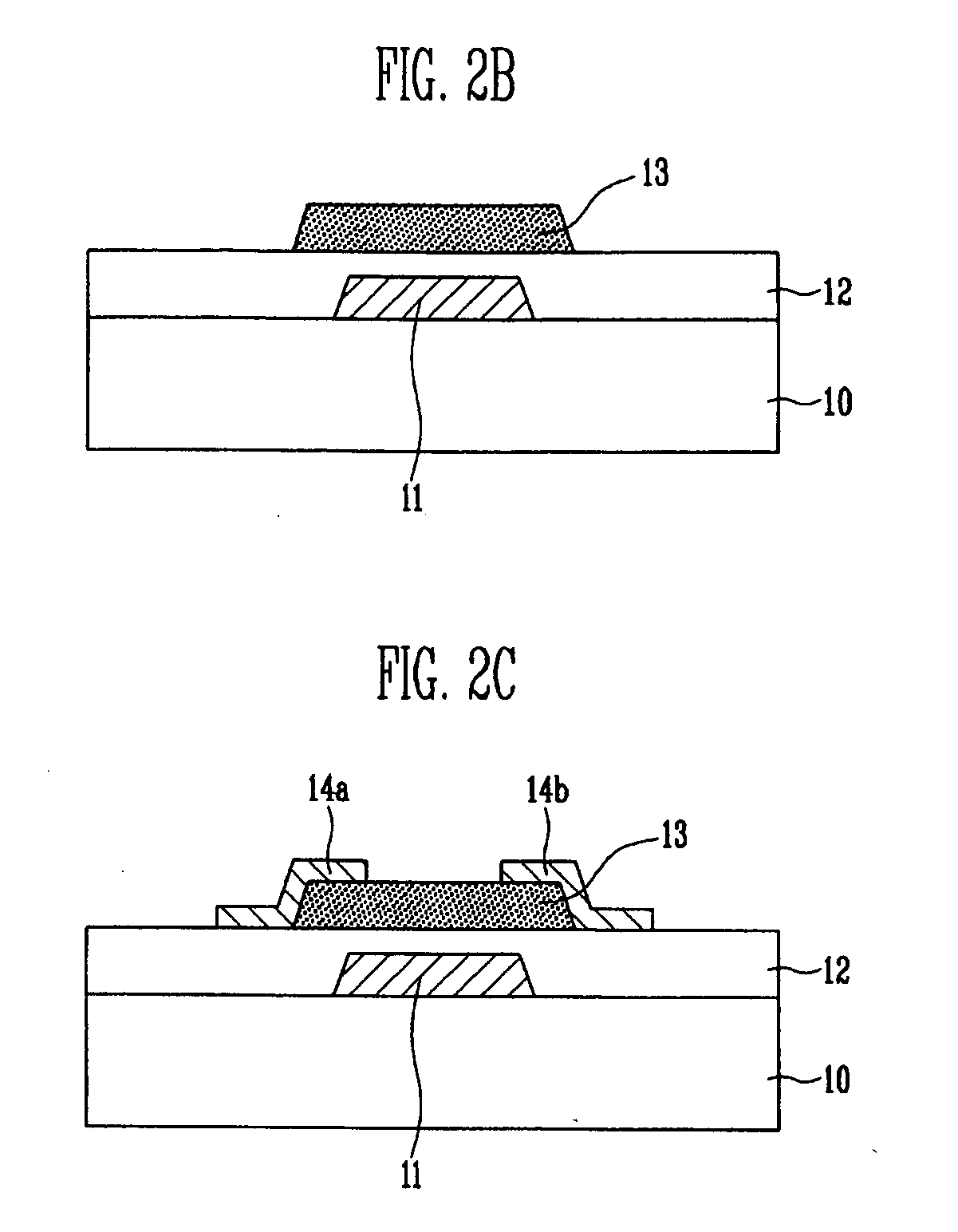

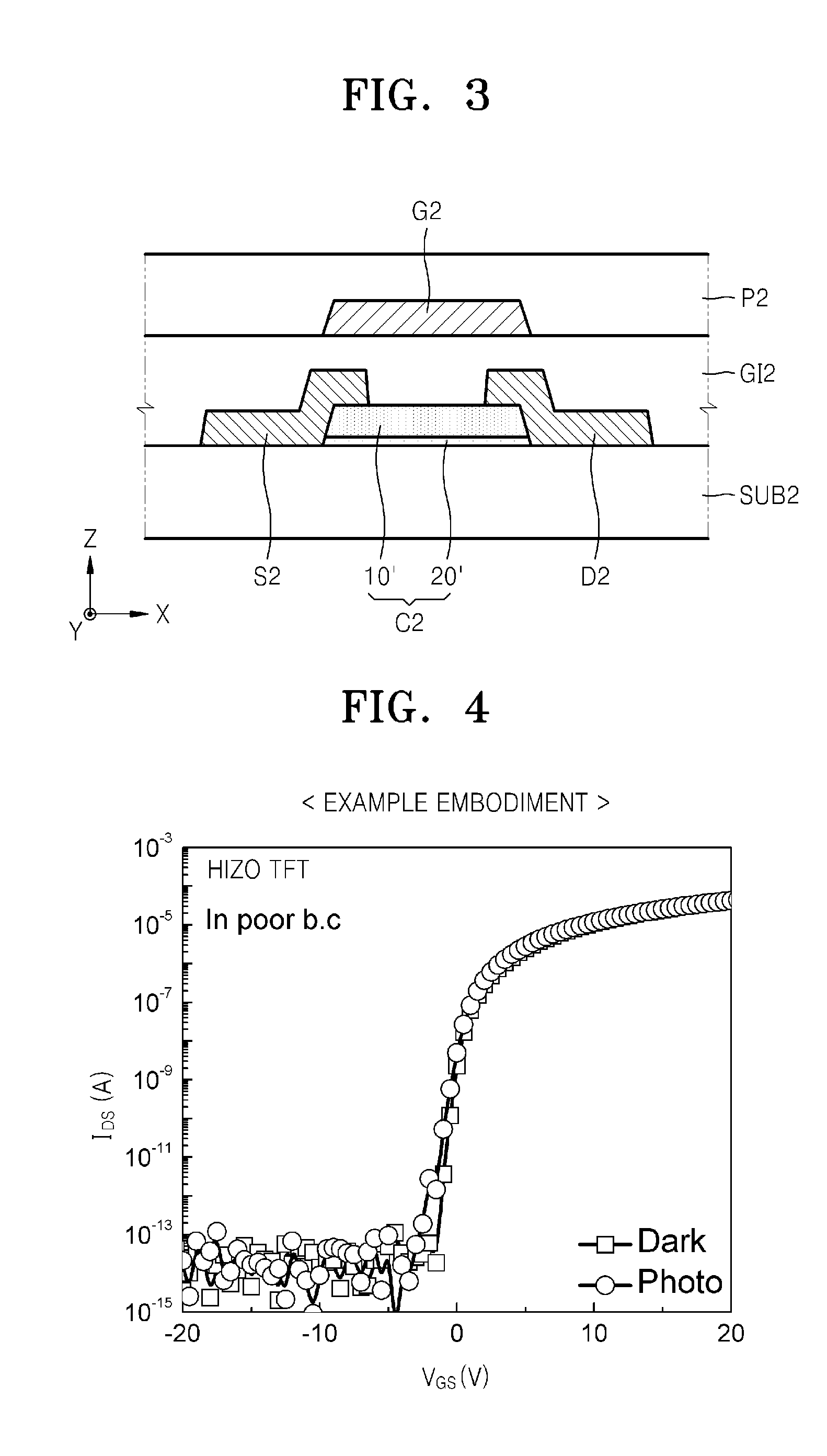

Transistors, methods of manufacturing the same and electronic devices including transistors

ActiveUS20120126223A1Improve performanceInhibition of characteristic changesTransistorSemiconductor/solid-state device manufacturingIndium zinc oxideElectrode Contact

An oxide transistor includes: a channel layer formed of an oxide semiconductor; a source electrode contacting a first end portion of the channel layer; a drain electrode contacting a second end portion of the channel layer; a gate corresponding to the channel layer; and a gate insulating layer disposed between the channel layer and the gate. The oxide semiconductor includes hafnium-indium-zinc-oxide (HfInZnO). An electrical conductivity of a back channel region of the channel layer is lower than an electrical conductivity of a front channel region of the channel layer.

Owner:SAMSUNG ELECTRONICS CO LTD

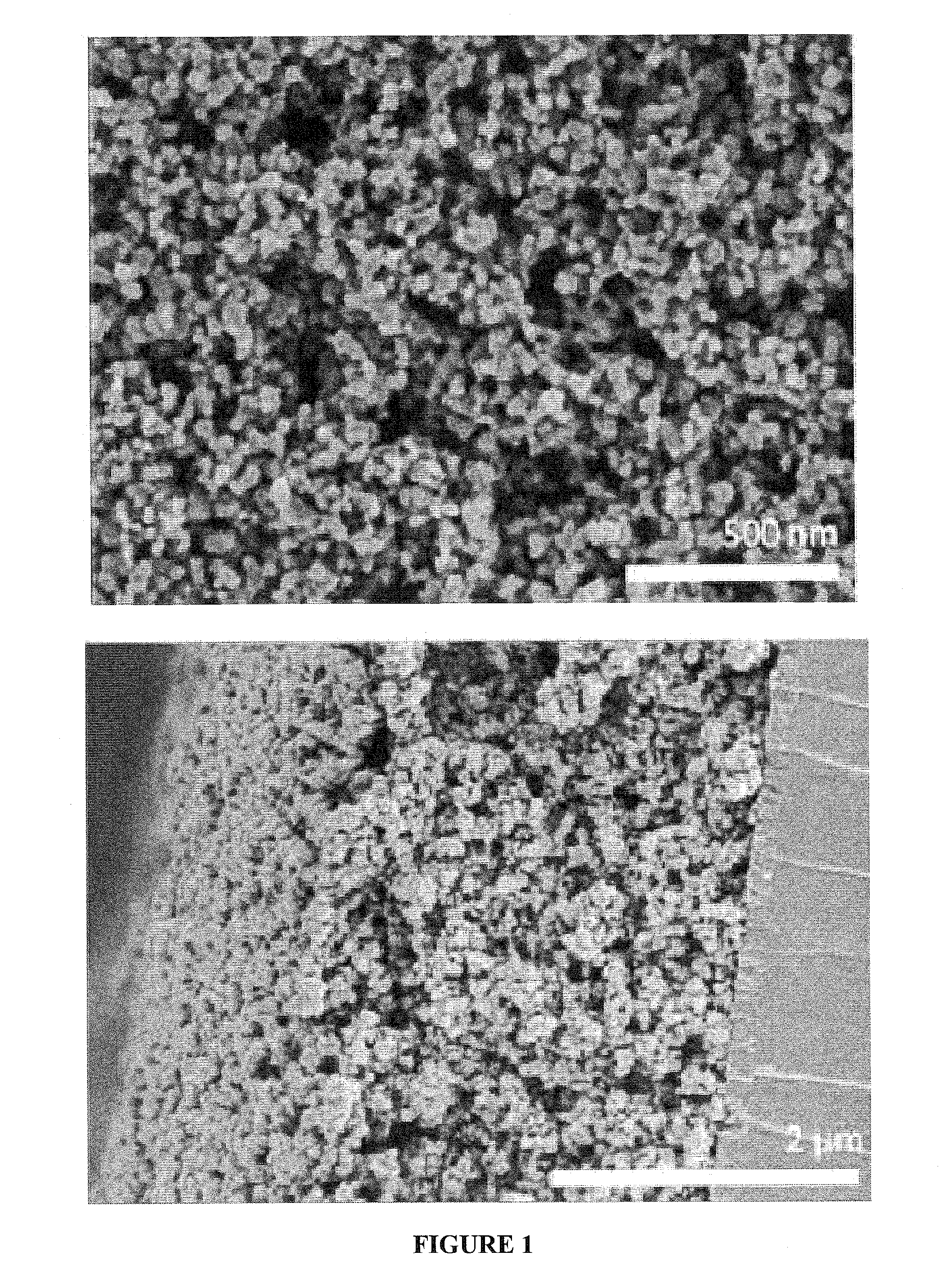

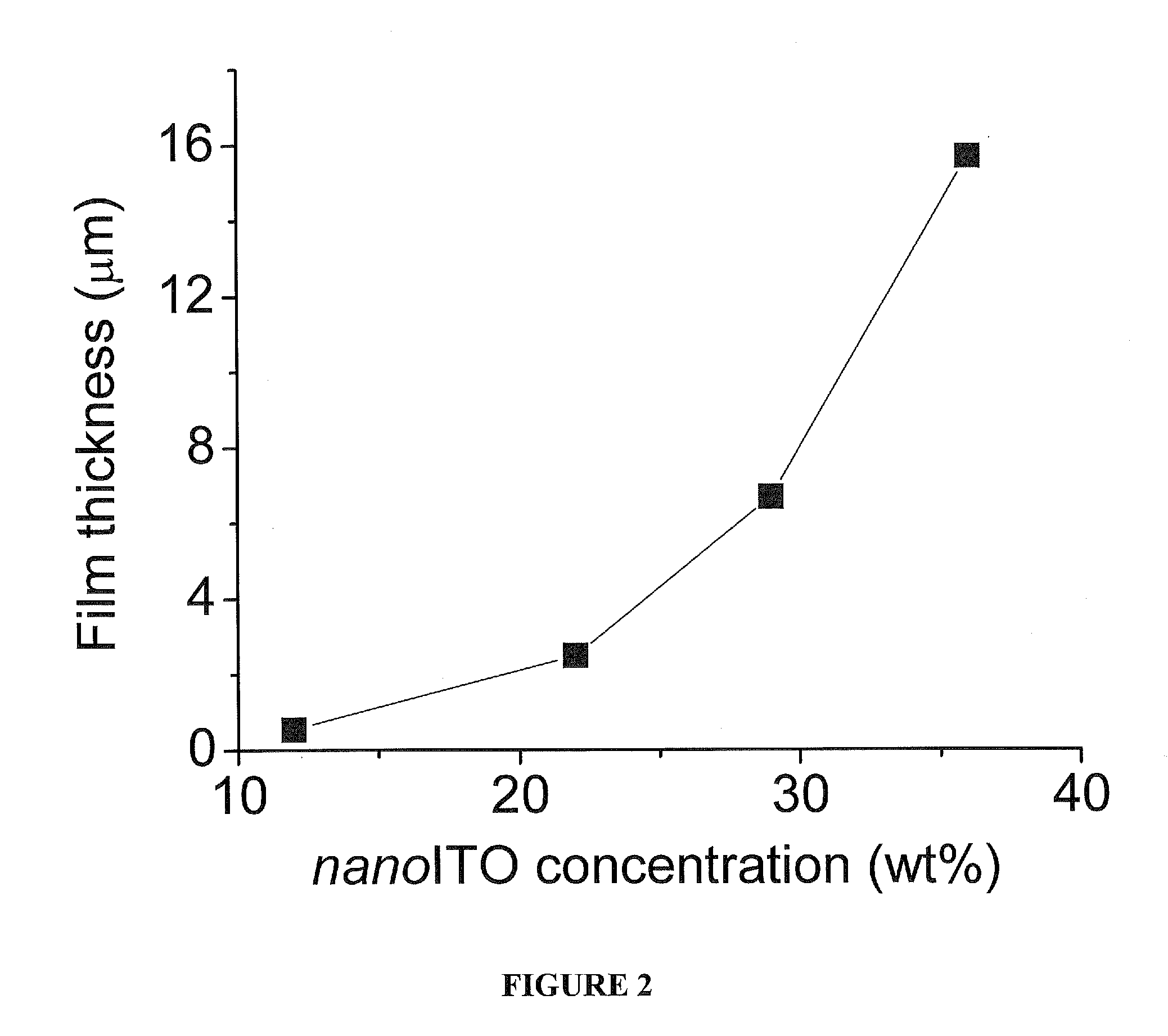

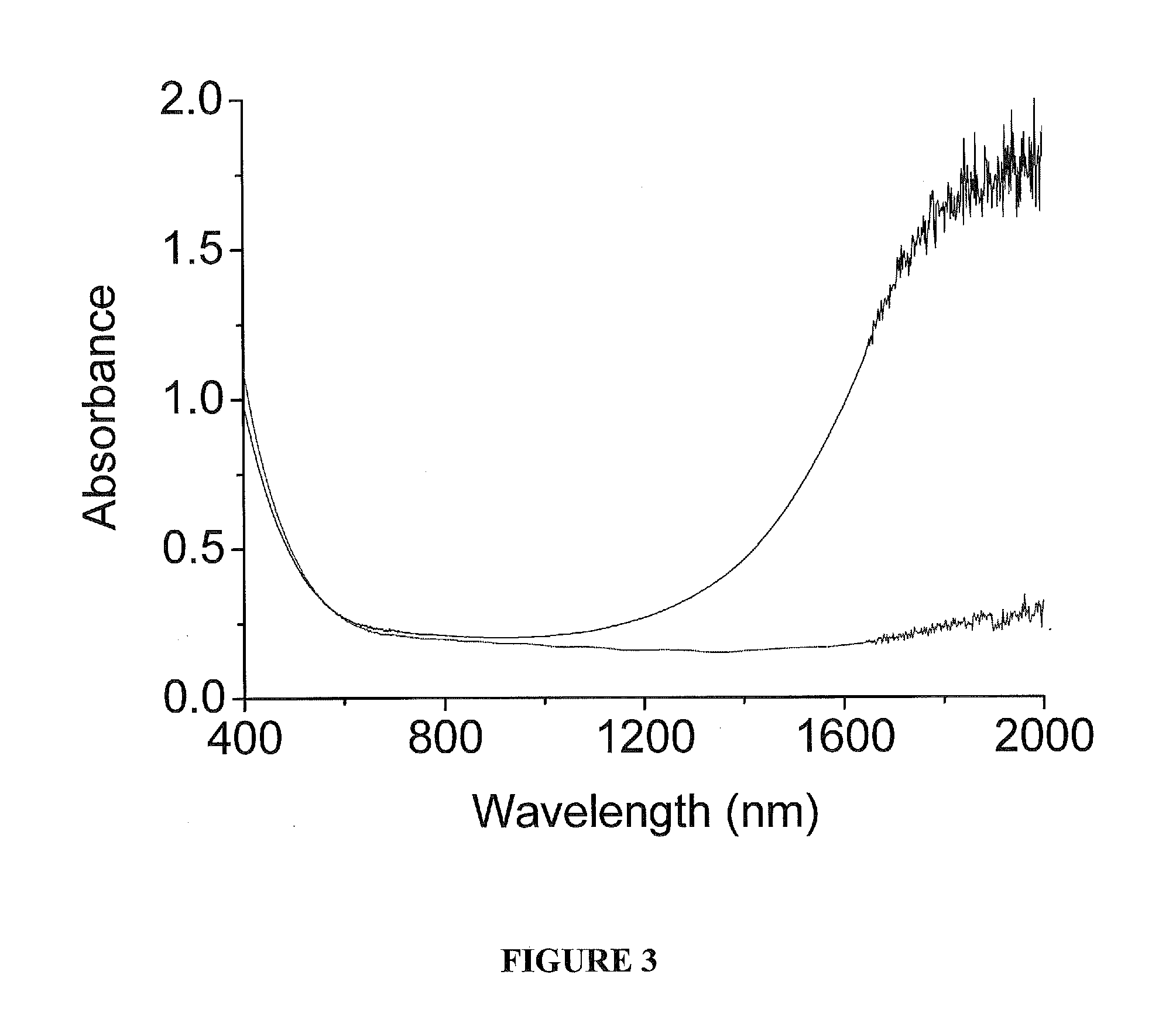

Nanoparticle Electrodes and Methods of Preparation

The present invention provides an electrode which comprises (a) a supporting substrate, and (b) nanoparticle composition comprising optically transparent conductive nanoparticles. In one embodiment, the nanoparticles are selected from tin-doped indium oxide (ITO), fluorine doped tin oxide (FTO), antimony tin oxide (ATO), gallium zinc oxide (GZO), indium zinc oxide (IZO), copper aluminum oxide, fluorine-doped zinc oxide and aluminum zinc oxide (AZO) nanoparticles and combinations thereof. In one embodiment, the electrode further comprises a transition metal catalyst, and the catalyst is absorbed to the surface of the nanoparticles. Another aspect of the invention relates to methods for preparing the electrode described herein which comprises the step of (1) preparing a suspension of nanoparticles; (2) applying the suspension of the nanoparticles to a support substrate; and (3) annealing the supporting substrate with the nanoparticle for a period of time and at a temperature sufficient to produce nanoparticle film on the electrode.

Owner:CORBEA JAVIER JESUS CONCEPCION +3

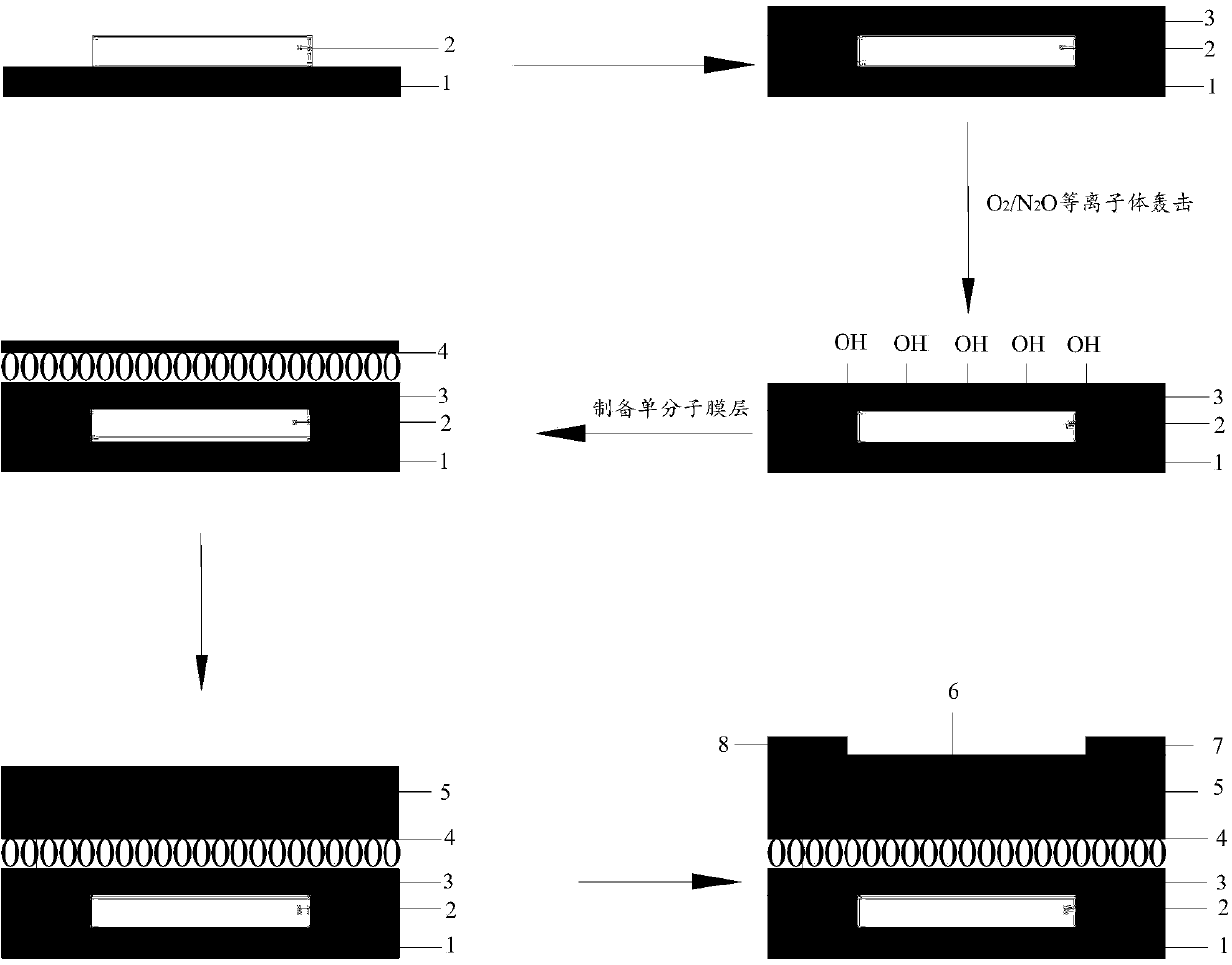

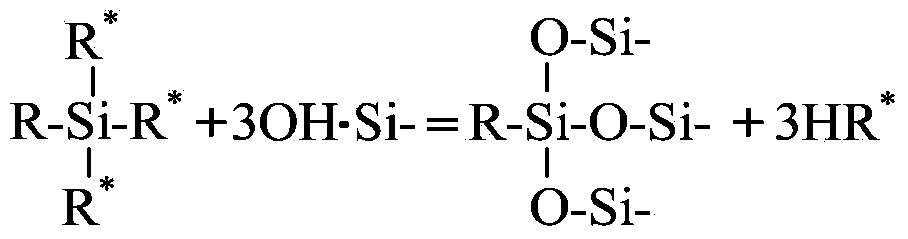

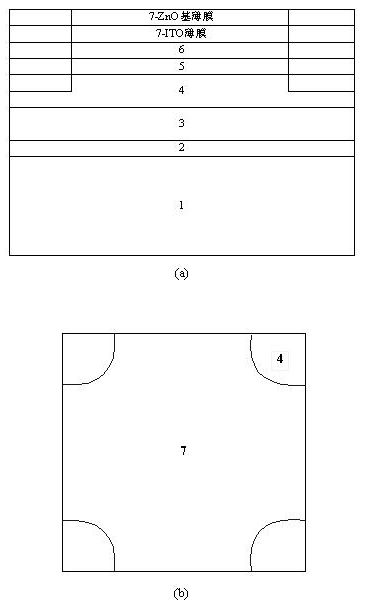

IGZO (indium gallium zinc oxide) thin film transistor and preparing method thereof

ActiveCN103700710AImprove mobilityImprove performanceTransistorSemiconductor/solid-state device manufacturingInsulation layerIndium gallium zinc oxide

The invention discloses an IGZO (indium gallium zinc oxide) thin film transistor and a preparing method thereof, wherein the IGZO thin film transistor comprises a substrate, a grid combined on the substrate surface and a silicide grid insulation layer covering the outer surfaces of the substrate and the grid, wherein the surface of the silicide grid insulation layer is subjected to O2 / N2O plasma bombardment processing; the surface of the silicide grid insulation layer subjected to the O2 / N2O plasma bombardment processing is also combined with a self-assembly single-molecule film layer in a laminating mode, so the film defect state of the silicide grid insulation layer can be reduced after the O2 / N2O plasma bombardment, the charge trap action is inhibited, the roughness of the surface of the insulation layer is reduced by the self-assembly single-molecule film layer, the interface property between the insulation layer and an active layer is well improved, charges are prevented from being captured by an interface defect, the carrier mobility of a device is reduced, the threshold voltage is reduced, leak current is reduced and the performance of the device is more stable.

Owner:TCL CORPORATION

Indium zinc oxide based sputtering target, method of manufacturing the same, and indium zinc oxide based thin film

InactiveUS20090211903A1Lower resistanceReduce the temperatureCellsTransportation and packagingIndiumTitanium

Disclosed are an indium (In) zinc (Zn) oxide based sputtering target, a method of manufacturing the same, and an In Zn oxide based thin film deposited using the In Zn oxide based sputtering target. The In Zn oxide based sputtering target has a composition of (MO2)x(In2O3)y(ZnO)z, in which x:y is about 1:0.01 to 1:1, y:z is about 1:0.1 to 1:10, and M is at least one metal selected from a group consisting of hafnium (Hf), zirconium (Zr), and titanium (Ti).

Owner:SAMSUNG CORNING PRECISION MATERIALS CO LTD

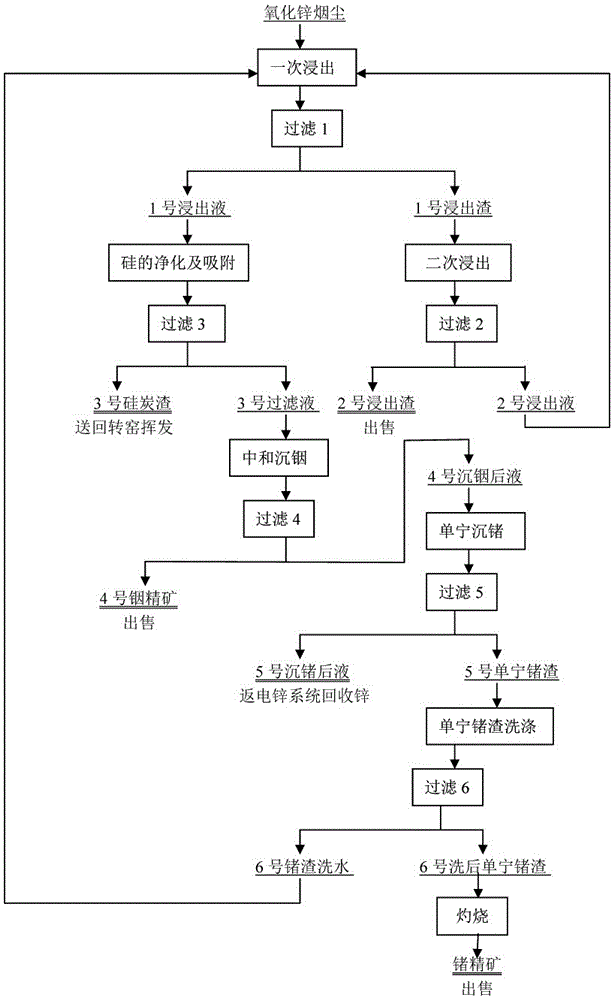

Method for recovering valuable metals from high-silicon low-germanium and low-indium zinc oxide soot

ActiveCN105838891AEasy to recycleSmooth recyclingProcess efficiency improvementIndiumIndium zinc oxide

A method for recovering valuable metals from high-silicon low-germanium and low-indium zinc oxide soot includes the steps of (1) primary leaching, (2) secondary leaching, (3) silicon purification and adsorption, (4) indium deposition through neutralization and (5) germanium deposition through tannin. Through the simple and convenient method, purification and removal of silicon and the adsorption performance of amorphous carbon are combined, so that full recycling of resources is achieved. Through the adsorbability of the amorphous carbon, the filtering performance in solid-liquid separation during silicon purification is well improved, an effective carrier is provided for suspended matter in a solution, and therefore filter liquor is clear and free of suspended matter. By means of the method, the influence of silicon and suspended matter on indium and germanium deposition is eliminated, and the effects of burning heat generation and reduction of the added amorphous carbon can be played normally in the volatilization process of a rotary kiln. Under the conditions that the grade of indium and germanium in raw materials is low and the grade of silicon dioxide is high, interference of silicon and suspended matter is avoided, and germanium and indium are smoothly recovered.

Owner:YUNNAN LUOPING ZINC & ELECTRICITY

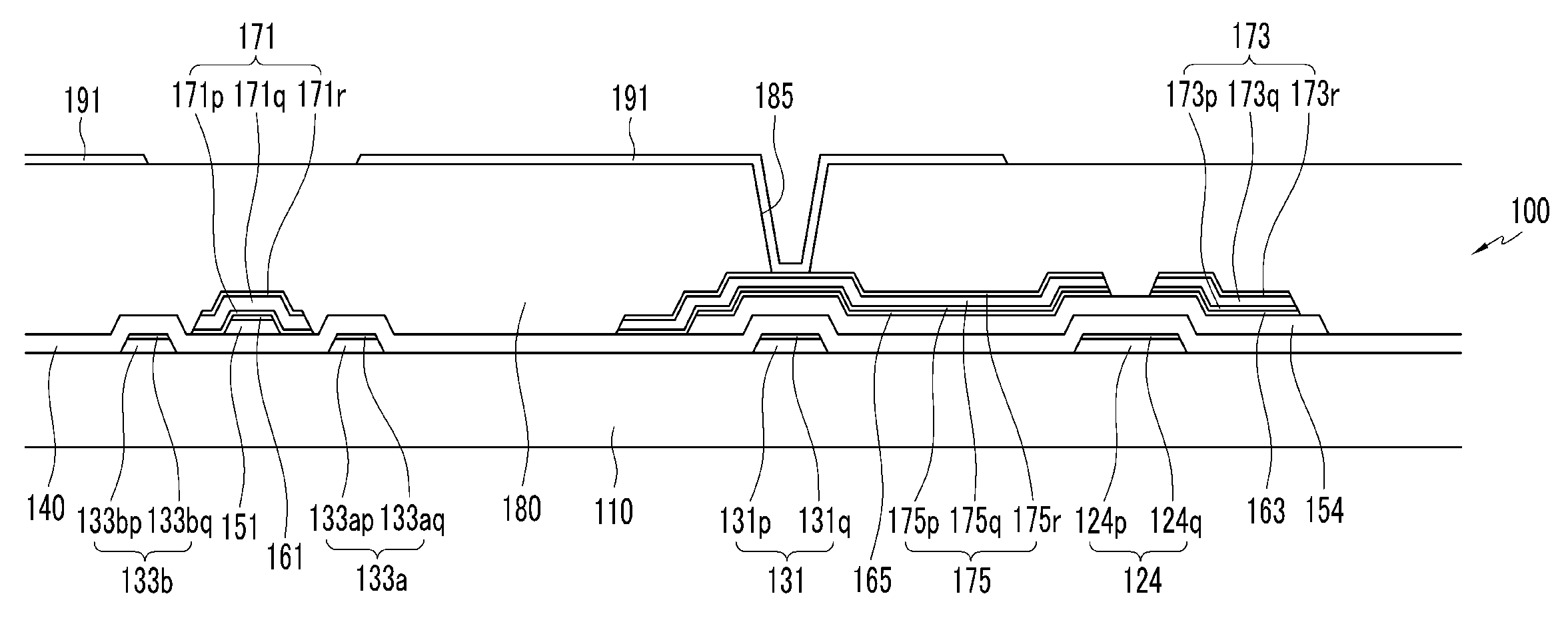

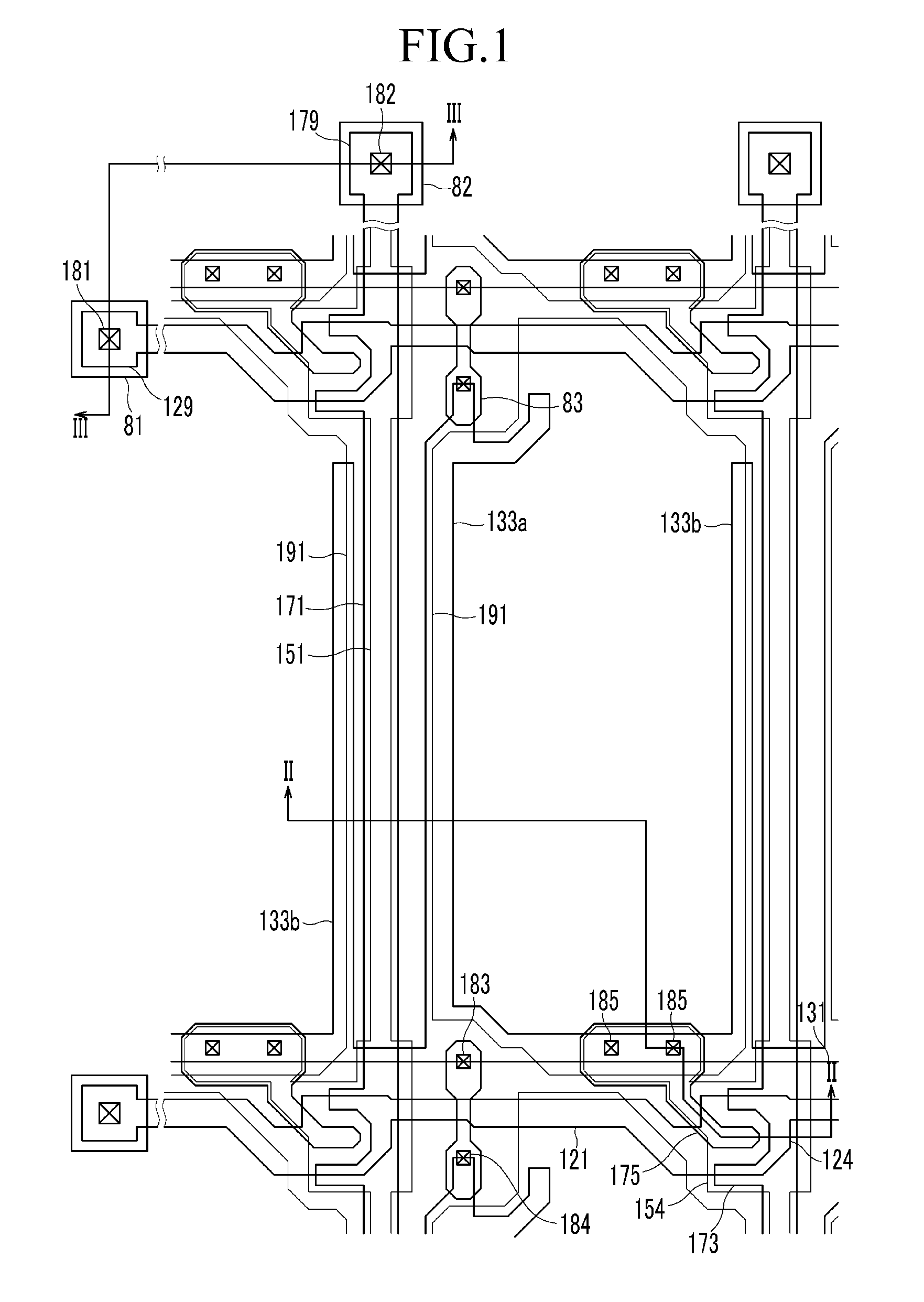

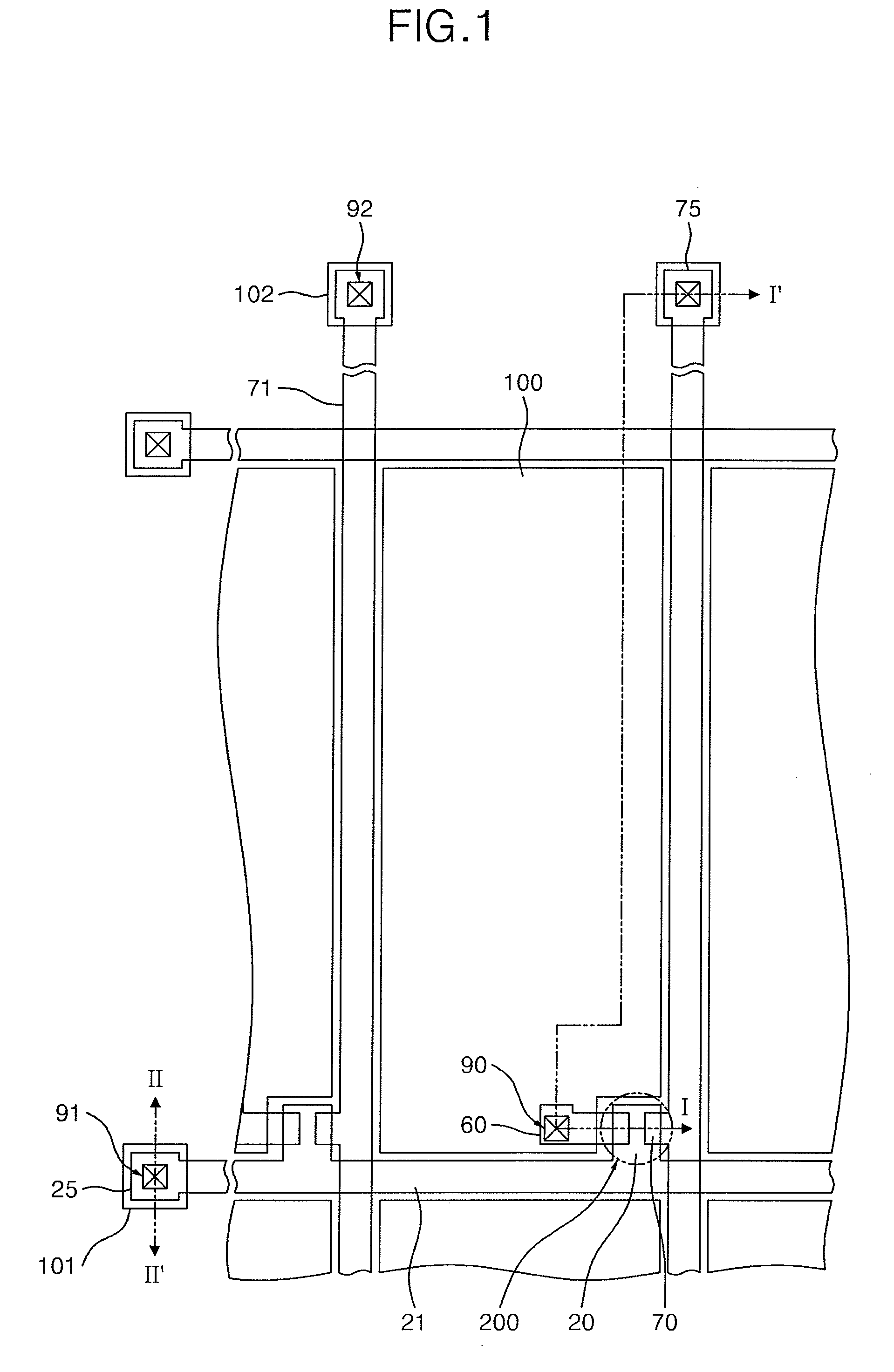

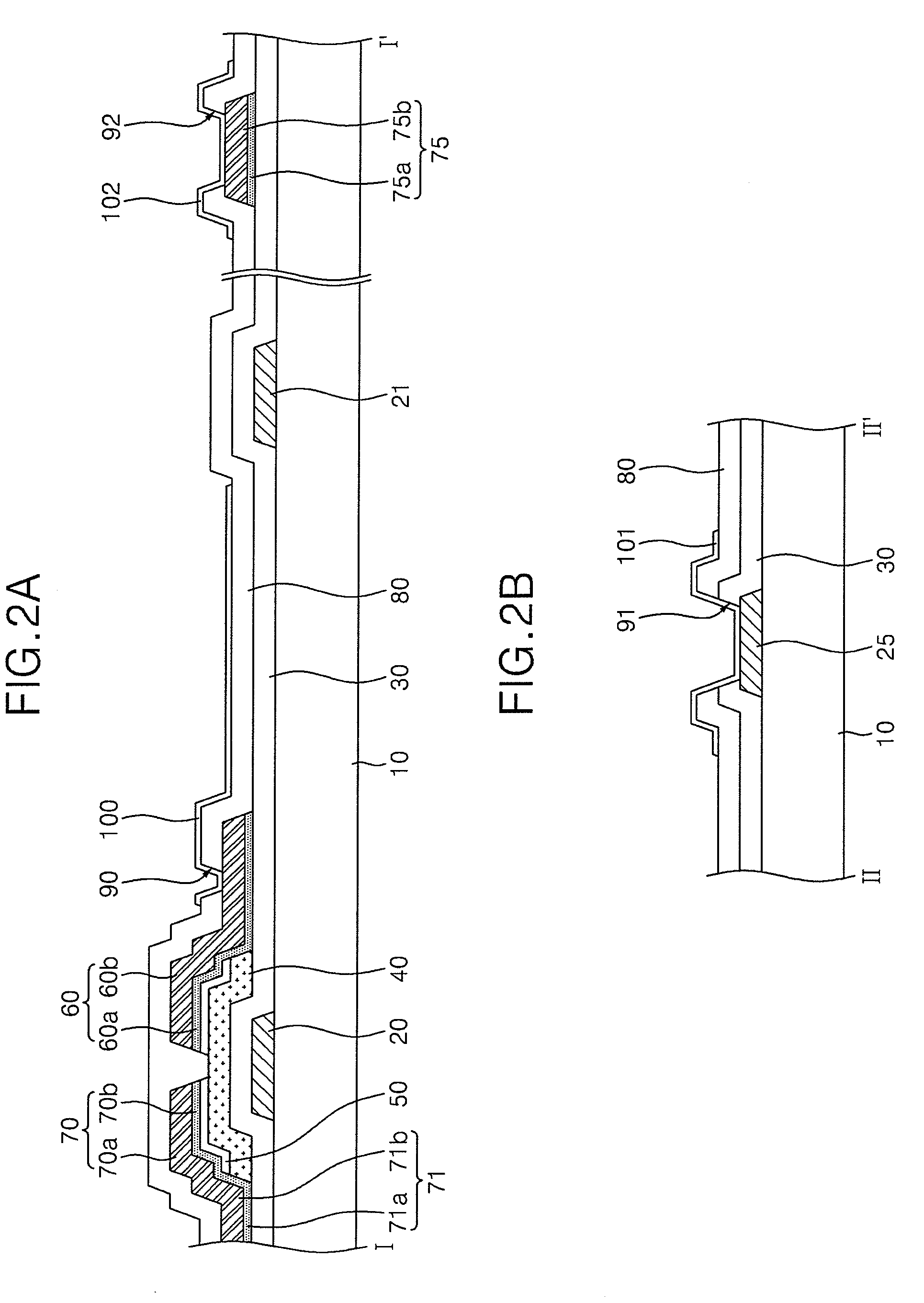

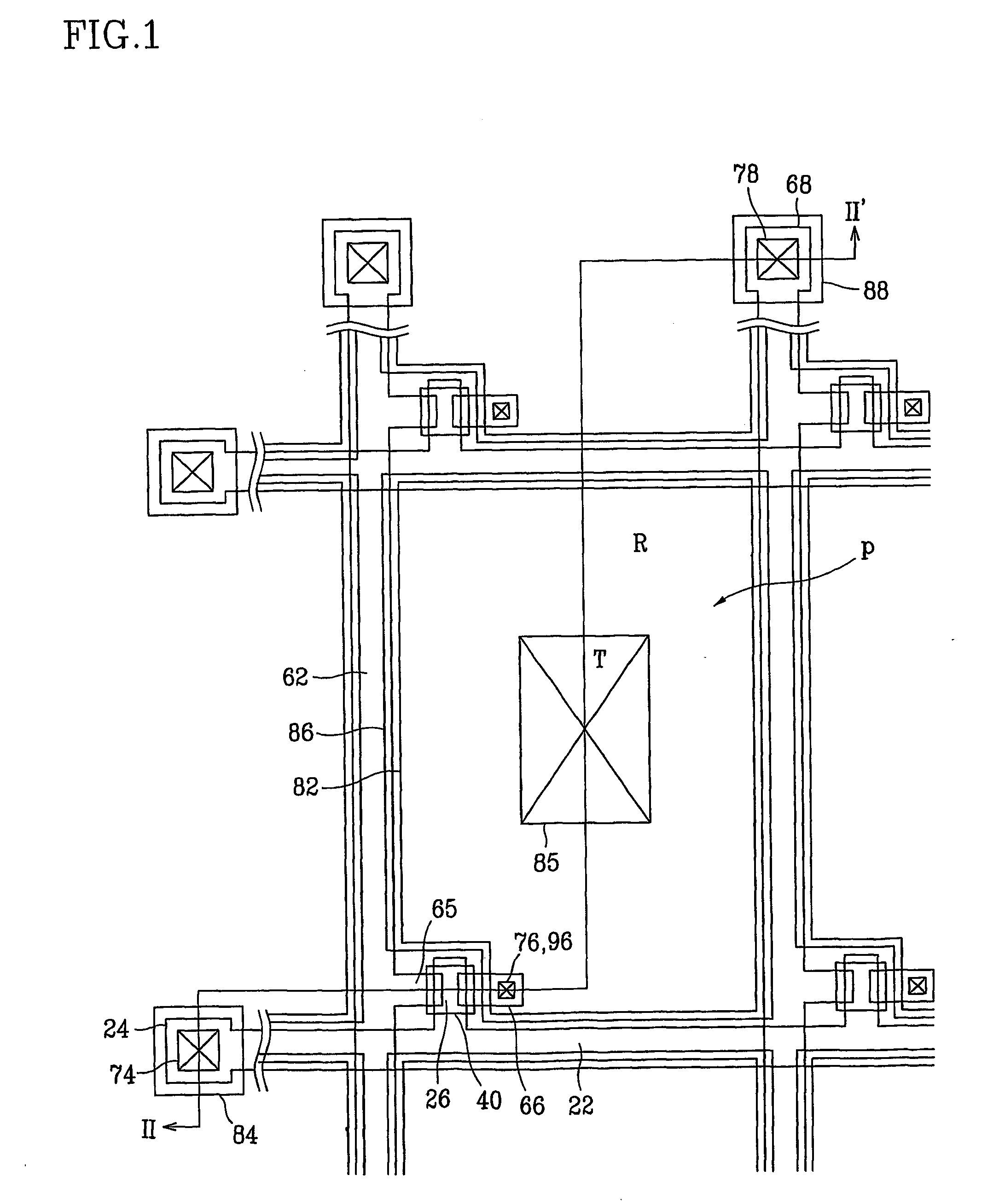

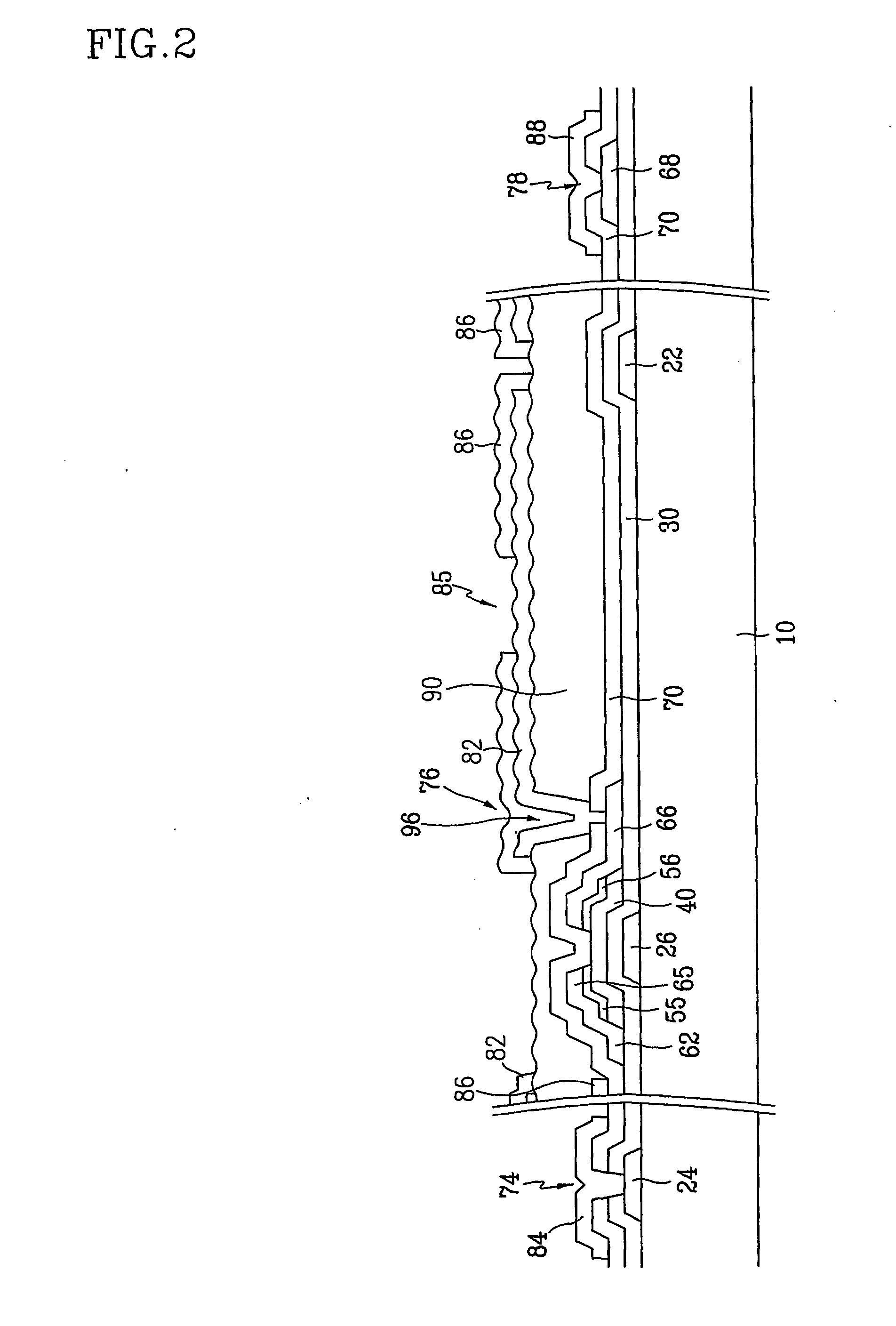

Thin film transistor panel and method of manufacturing the same

ActiveUS20100044717A1Reduce yieldIncrease production costTransistorSolid-state devicesIndium zinc oxideOptoelectronics

After forming a signal line including aluminum, an upper layer of an oxide layer including aluminum that covers the signal line is formed in the same chamber and by using the same sputtering target as the signal line, or a buffer layer of an oxide layer including aluminum is formed in a contact hole exposing the signal line during the formation of the contact hole. Accordingly, the contact characteristic between an upper layer including indium tin oxide (“ITO”) or indium zinc oxide (“IZO”) and the signal line may be improved to enhance the adhesion therebetween while not increasing the production cost of the thin film transistor (“TFT”) array panel.

Owner:SAMSUNG DISPLAY CO LTD

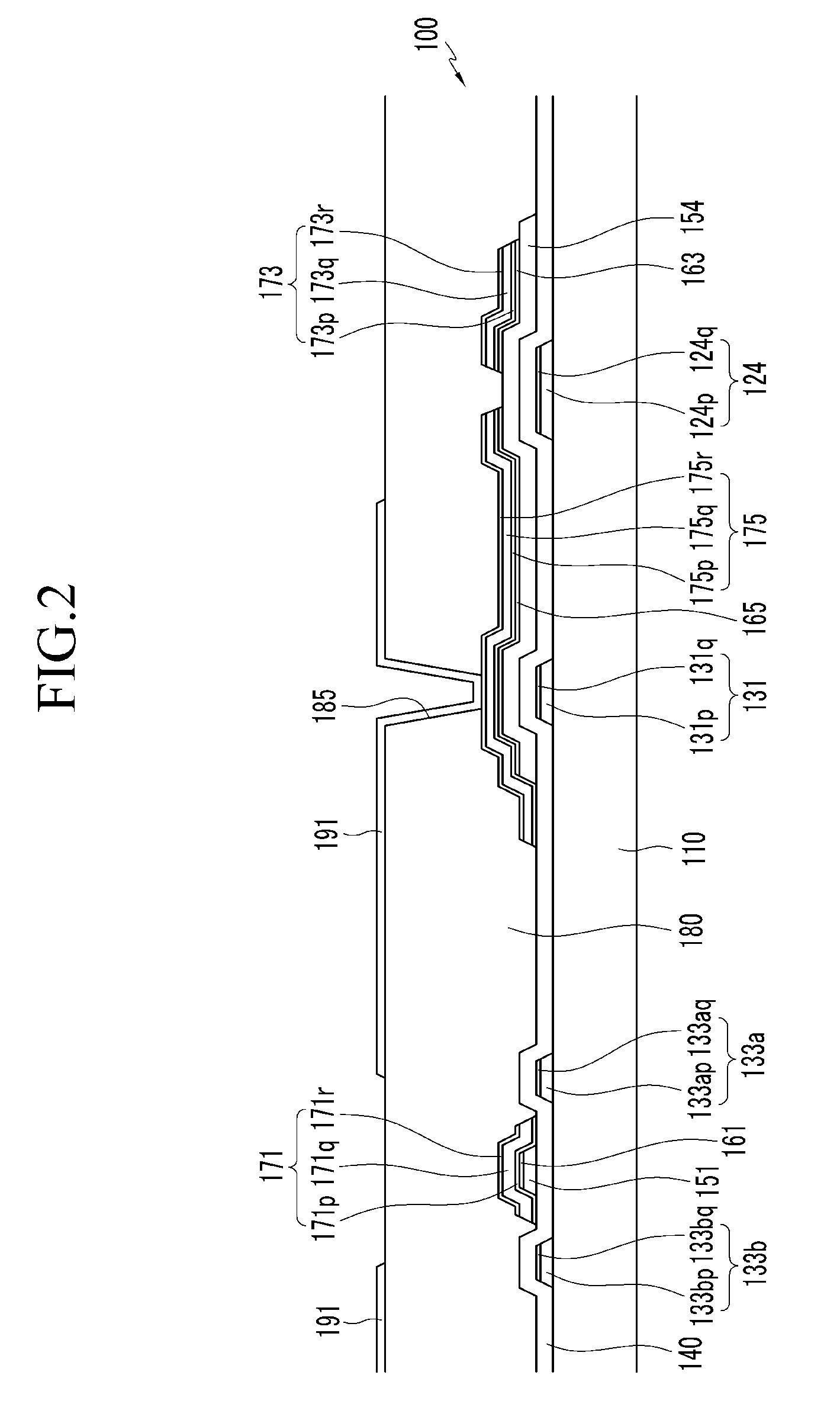

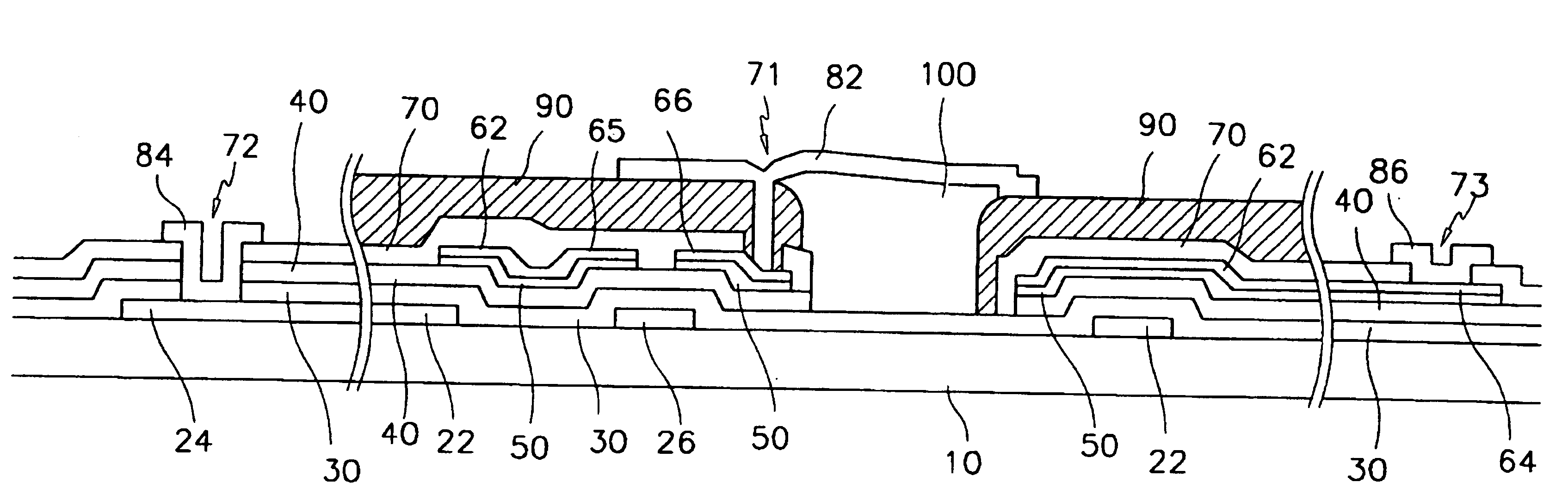

Organic thin film transistor display panel

InactiveUS20070024766A1Electroluminescent light sourcesSolid-state devicesWork functionOrganic semiconductor

An organic thin film transistor array panel according to an embodiment of the present invention includes forming a gate line on an insulating plastic or glass substrate; forming a gate insulating layer on the gate line; forming a data line and a drain electrode on the gate insulating layer, the data line and the drain electrode comprising a first conductive film and a second conductive film of indium tin oxide (ITO) or indium zinc oxide (IZO) that has a work function similar to that of the organic semiconductor that is deposited overlapping the data line and the drain electrode; forming a passivation layer on the organic semiconductor; and forming a pixel electrode connected to the drain electrode on the passivation and the gate insulating layer.

Owner:SAMSUNG ELECTRONICS CO LTD

Organic photoelectronic device and image sensor

ActiveUS20150188064A1Reduce lossesEnsuring photoelectric conversion efficiencySolid-state devicesSemiconductor/solid-state device manufacturingIndium zinc oxideZinc

Disclosed are an organic photoelectronic device including a first light-transmitting electrode, an active layer positioned on one side of the first light-transmitting electrode, and a second light-transmitting electrode positioned on one side of the active layer, wherein the first light-transmitting electrode and the second light-transmitting electrode independently comprise at least one of indium tin oxide (ITO), indium zinc oxide (IZO), tin oxide (SnO), aluminum tin oxide (ATO), aluminum zinc oxide (AZO), and fluorine-doped tin oxide (FTO). Also disclosed is an image sensor including the organic photoelectronic device.

Owner:SAMSUNG ELECTRONICS CO LTD

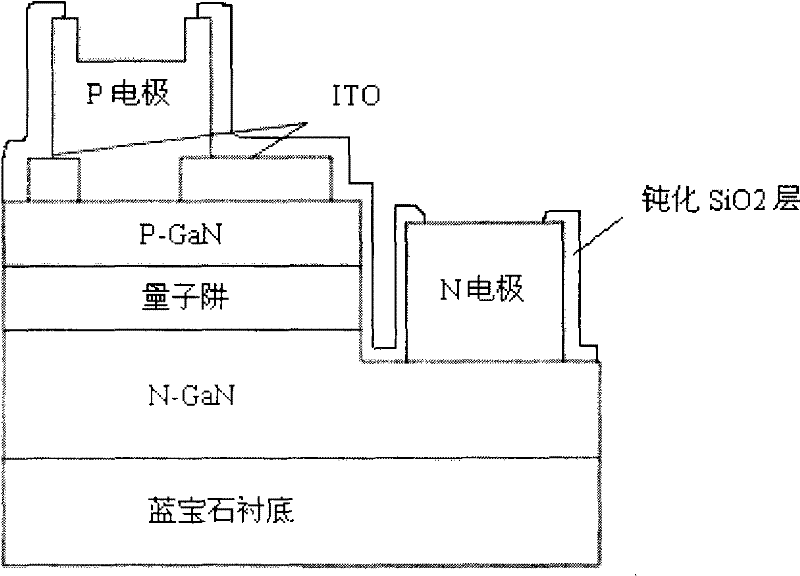

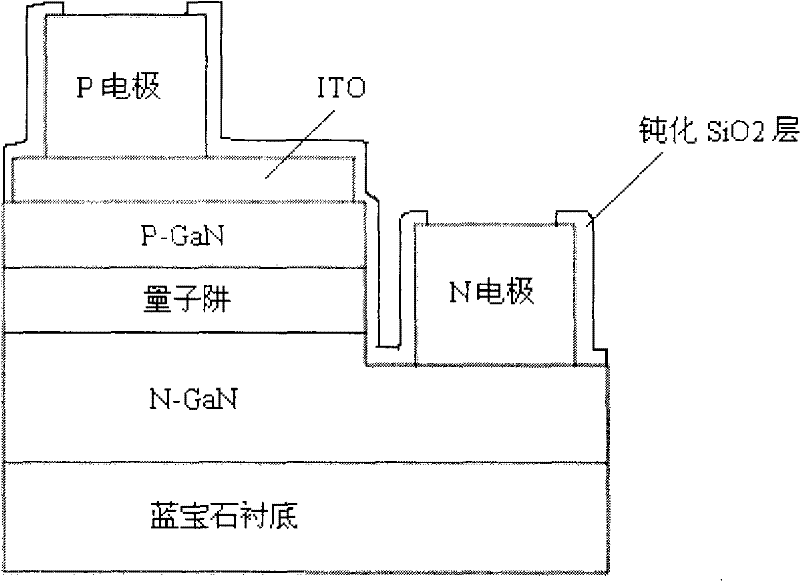

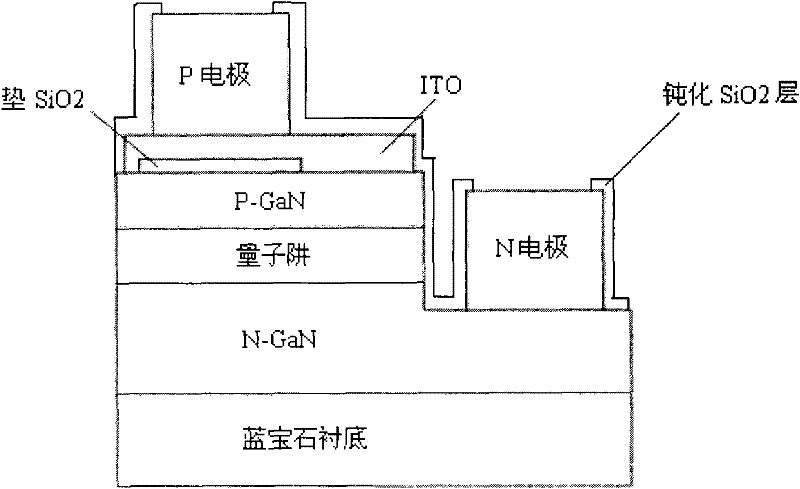

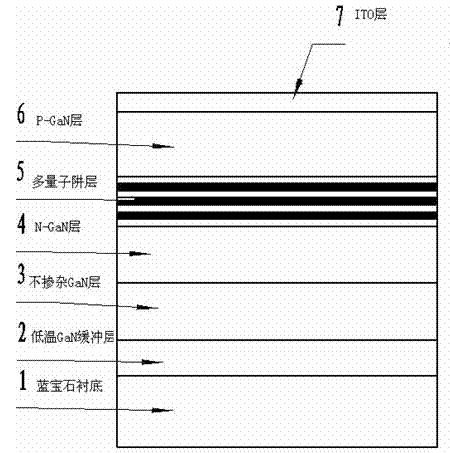

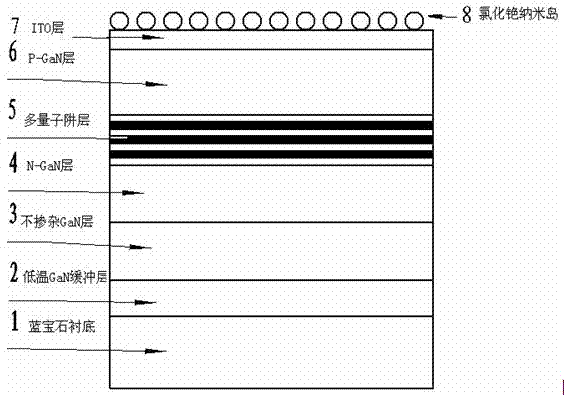

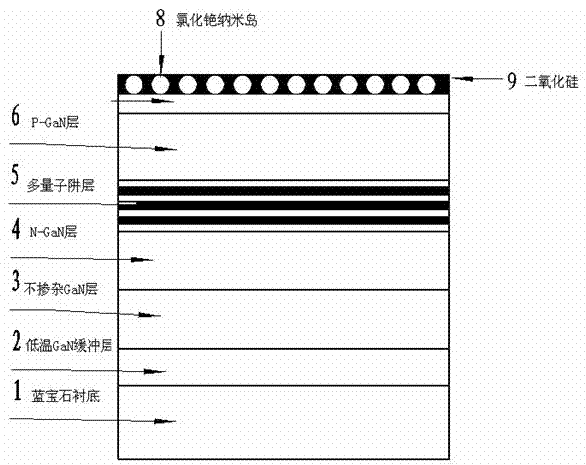

Light-emitting diode (LED) with indium tin oxide (ITO)/zinc oxide based composite transparent electrode and preparation method of LED

InactiveCN102169943AReduce contact resistanceSpread evenlySemiconductor devicesEvaporationIndium zinc oxide

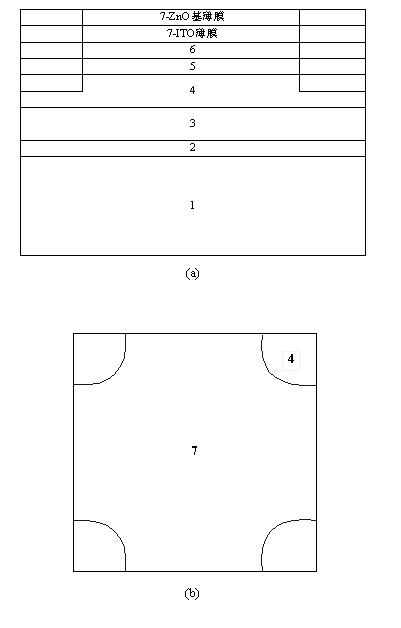

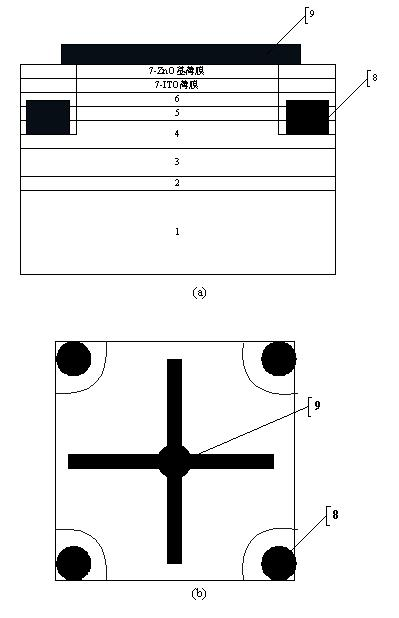

The invention relates to a light-emitting diode (LED) with an indium tin oxide (ITO) / zinc oxide based composite transparent electrode and a manufacturing process of the LED. The LED comprises a buffer layer, an intrinsic layer, an n-gallium nitride (GaN), a quantum well, a p-GaN and an ITO / zinc oxide based composite current expansion layer which are arranged on a sapphire substrate; an n-metal electrode (PAD) is connected with the n-GaN; and a p-metal electrode (PAD) is connected with the ITO / zinc oxide based composite current expansion layer. The manufacturing process comprises the following steps of: finishing sequential growth of the buffer layer, the intrinsic layer, the n-GaN, the quantum well and the p-GaN in metal organic chemical vapour deposition (MOCVD) equipment; sequentially depositing an ITO film and a zinc oxide film on a surface of the p-GaN by electron beam evaporation and magnetron sputtering to form the ITO / zinc oxide based composite current expansion layer; exposing the n-GaN by dry etching; and growing the metal electrodes by thermal evaporation after annealing. The size of a chip is 1mm*1mm. The composite transparent electrode improves contact between the p-GaN and an electrode layer, improves the light extraction efficiency of an LED chip and improves the reliability of the LED chip.

Owner:SHANGHAI UNIV

Method of Recovering Valuable Metals from IZO Scrap

InactiveUS20100288645A1Good effectIncrease productivityPhotography auxillary processesProcess efficiency improvementElectrolysisIndium

Provided is a method of recovering valuable metals from IZO scrap in which valuable metals are recovered as indium and zinc metals or suboxides by performing electrolysis using an insoluble electrode as an anode and an IZO scrap as a cathode. Specifically, this method enables the efficient recovery of indium and zinc from IZO scrap such as an indium-zinc oxide (IZO) sputtering target or IZO mill ends that arise during the manufacture of such a sputtering target.

Owner:JX NIPPON MINING & METALS CORP

Method of Recovering Valuable Metals from IZO Scrap

InactiveUS20100288646A1Simple and efficient recoveryIncrease productivityPhotography auxillary processesElectrolysis componentsIndiumElectrolysis

Provided are a method of recovering valuable metals from IZO scrap, wherein indium and zinc are recovered as hydroxides by using an IZO scrap as both an anode and a cathode, and performing electrolysis while periodically reversing polarity; and a method of recovering valuable metals from IZO scrap, wherein the hydroxides of indium and zinc obtained by the electrolysis are roasted and indium and zinc are recovered as oxides. Specifically, provided is a method which enables the efficient recovery of indium and zinc from IZO scrap such as a spent indium-zinc oxide (IZO) sputtering target and IZO mill ends arising during the manufacture of such a sputtering target.

Owner:JX NIPPON MINING& METALS CORP

Method of Recovering Valuable Metals from IZO Scrap

ActiveUS20100282615A1Simple and efficient recoveryIncrease productivityPhotography auxillary processesElectrolysis componentsIndiumElectrolysis

Provided are a method of recovering valuable metals from IZO scrap, wherein valuable metals are recovered as hydroxides of indium and zinc by using an insoluble electrode as an anode or a cathode and an IZO scrap as the other cathode or anode as the opposite electrode, and performing electrolysis while periodically reversing polarity; and a method of recovering valuable metals from IZO scrap, wherein the hydroxides of indium and zinc obtained by the electrolysis are roasted and valuable metals are recovered as oxides of indium and zinc. Specifically, provided is a method which enables the efficient recovery of indium and zinc from IZO scrap such as a spent indium-zinc oxide (IZO) sputtering target and IZO mill ends arising during the manufacture of such a sputtering target.

Owner:JX NIPPON MINING& METALS CORP

Oxygen and carbon dioxide sensing

InactiveUS8222041B2Component separationWithdrawing sample devicesIndium zinc oxidePolymer solar cell

A high electron mobility transistor (HEMT) capable of performing as a CO2 or O2 sensor is disclosed, hi one implementation, a polymer solar cell can be connected to the HEMT for use in an infrared detection system. In a second implementation, a selective recognition layer can be provided on a gate region of the HEMT. For carbon dioxide sensing, the selective recognition layer can be, in one example, PEI / starch. For oxygen sensing, the selective recognition layer can be, in one example, indium zinc oxide (IZO). In one application, the HEMTs can be used for the detection of carbon dioxide and oxygen in exhaled breath or blood.

Owner:UNIV OF FLORIDA RES FOUNDATION INC

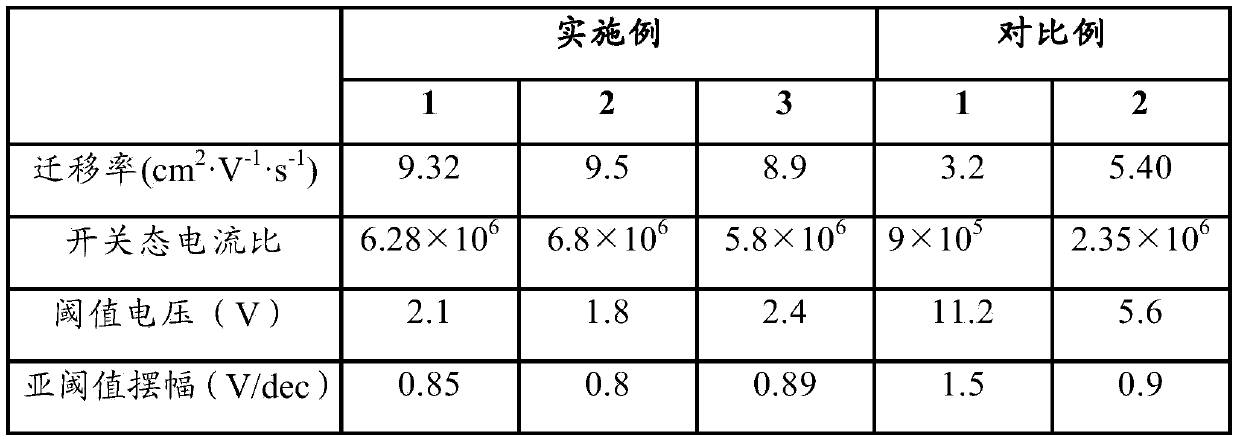

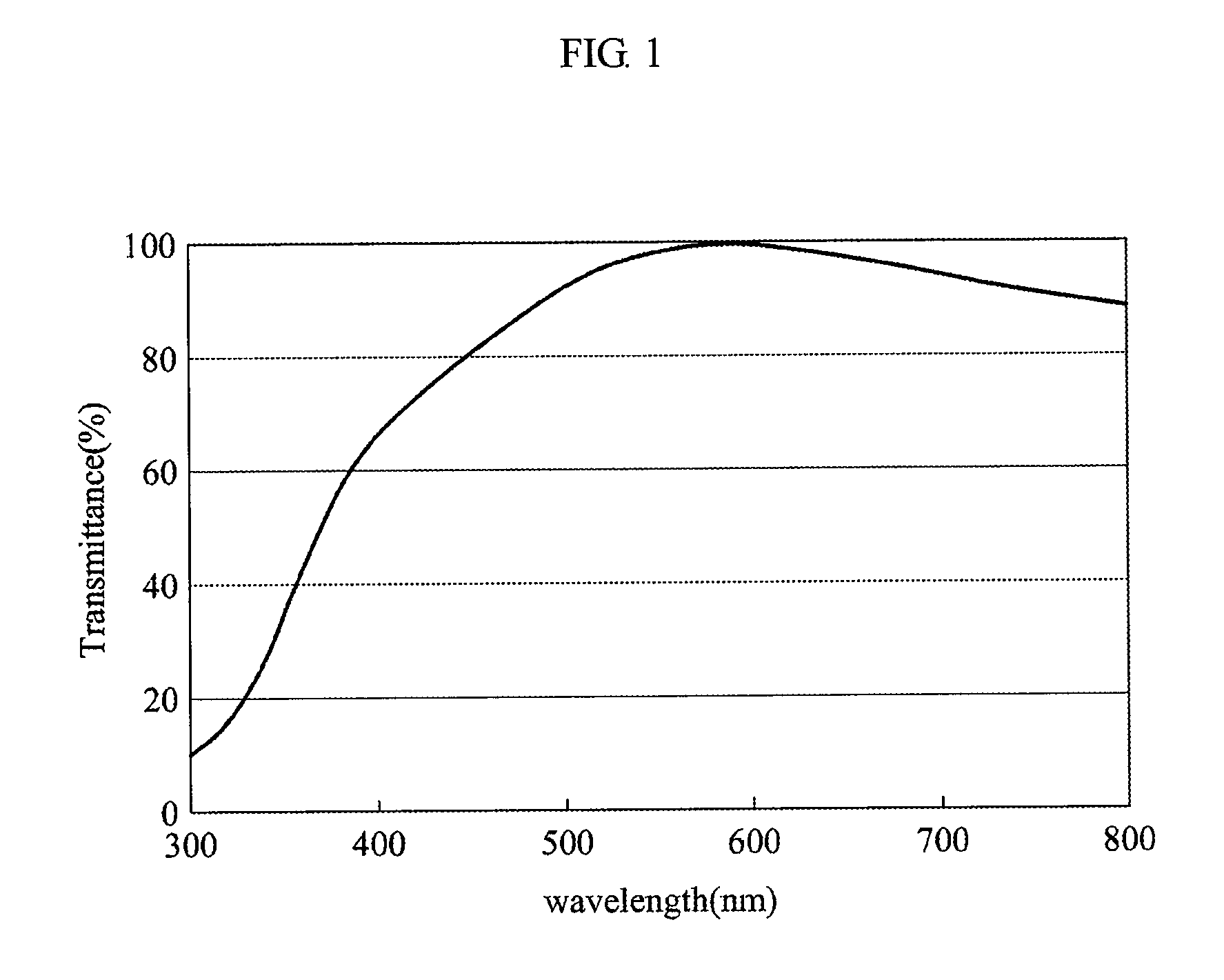

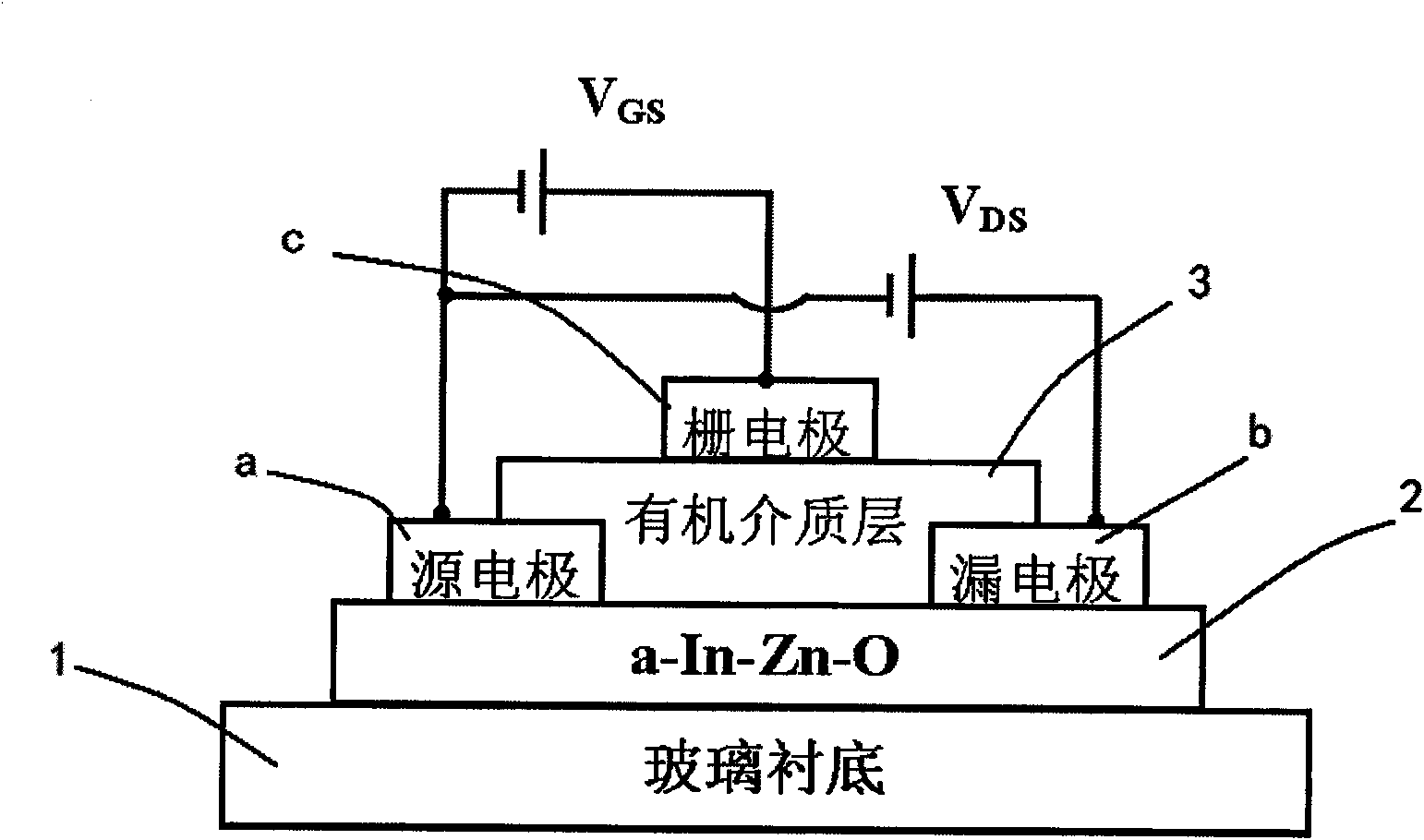

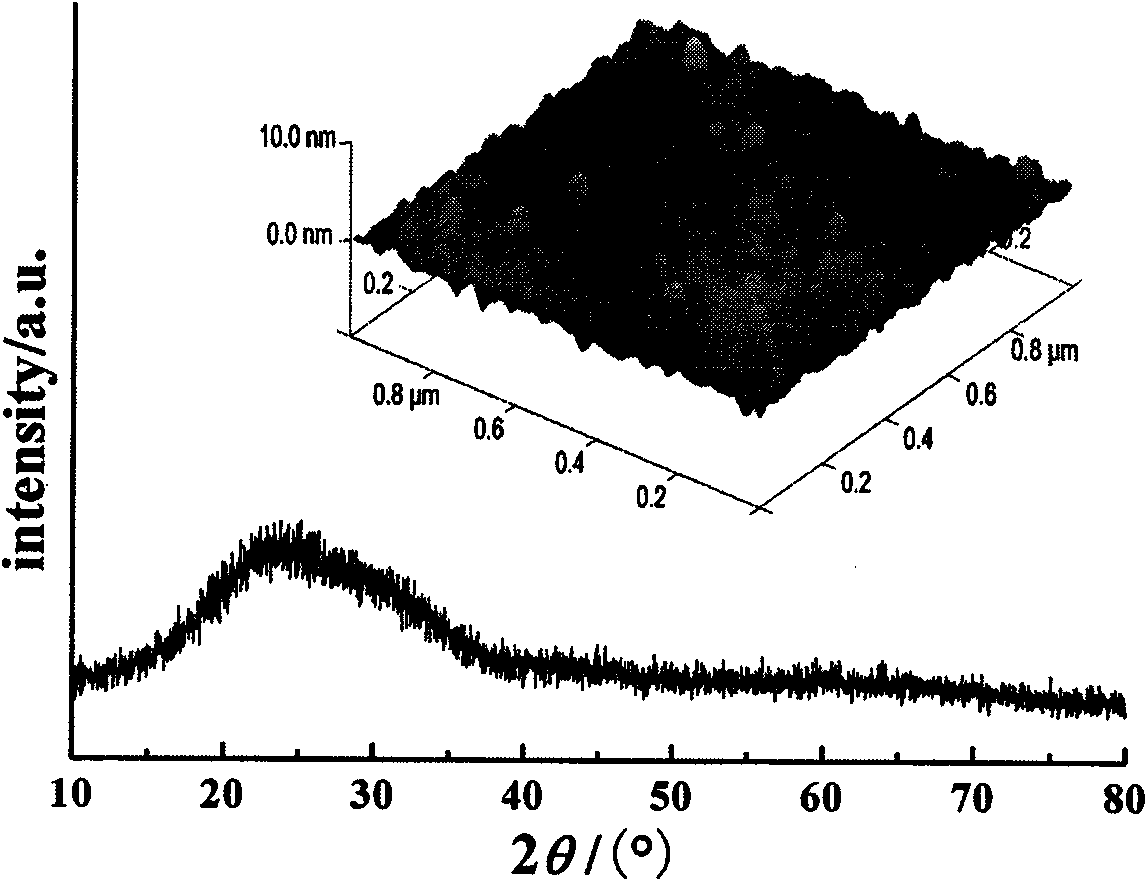

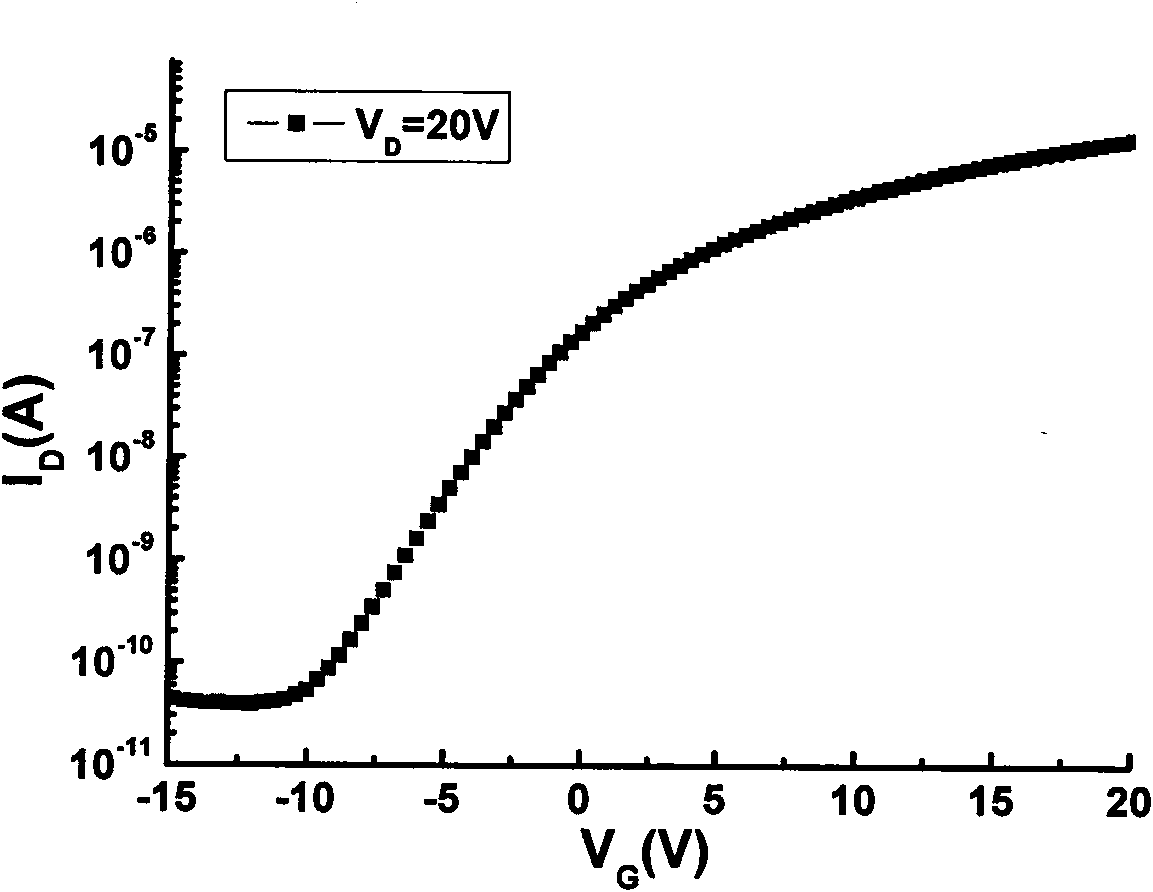

Method for preparing thin film transistor

InactiveCN101599437AImprove mobilityHigh switching ratioSemiconductor/solid-state device manufacturingIndiumEvaporation

The invention belongs to the technical field of thin film transistors, and relates to a method for preparing a thin film transistor. The method comprises the following steps: by adopting indium-zinc alloy or indium-zinc oxide as a target material, under the room temperature, growing an indium-zinc oxide semiconductor thin film with a transparent amorphous structure on a substrate through magnetron sputtering technology, and forming a channel layer of the thin film transistor; preparing a source electrode and a drain electrode by adopting a thermal evaporation method; covering a layer of organic medium layer thin film manufactured by polyvinylpyrrolidone organic solution on the source electrode and the drain electrode by adopting a hauling or spinning method; and preparing a gate electrode on the organic medium layer thin film by adopting the thermal evaporation method. The atomic ratio of In to Zn in the target material is 0.5 to 5.0. The method can prepare a novel transparent thin film transistor with good electronic optical performance, has low preparation temperature and simple process, is favorable for large-area production, and has wide application prospect.

Owner:FUDAN UNIV

Transparent electrode made from indium-zinc-oxide and etchant for etching the same

InactiveUS7279765B2Excellent etching propertiesShort timeAfter-treatment detailsElectrolytic capacitorsLiquid-crystal displayIndium zinc oxide

A pixel electrode employs a transparent electrode made from indium-zinc-oxide (IZO) that is capable of preventing damage and bending thereof. In a liquid crystal display device containing pixel electrodes, the transparent electrode is made from indium-zinc-oxide (IZO) having an amorphous structure so that it can be etched within a short period of time with a low concentration of etchant. Accordingly, it is possible to prevent damage and bending of the transparent electrode upon the patterning thereof.

Owner:LG DISPLAY CO LTD

Method for evaporating indium tin oxide (ITO)

ActiveCN102194956AIncrease brightnessHigh light transmittanceVacuum evaporation coatingSputtering coatingSemiconductor structureOptical transmittance

The invention provides a method for evaporating indium tin oxide (ITO). The method comprises the following steps: putting a semi-conductor structure on which the ITO is to be evaporated on a wafer-bearing disk; vacuumizing until the vacuum degree of a cavity of a electron beam evaporation machine is above 5*10<-6> Torr, then rotating the wafer-bearing disk, and preheating the wafer-bearing disk to a preset temperature and stabilizing for 10-30 minutes; then opening an oxygen valve, and pre-plating the semi-conductor for 1-5 minutes when oxygen flow is stabilized to a preset flow; and finally, evaporating the ITO at a preset evaporation speed, so that the ITO with a preset thickness is evaporated out on the semi-conductor structure. In the method, the ITO resistance is controlled through controlling oxygen flow, evaporation temperature, ITO thickness and evaporation rate, and simultaneously, the high light transmittance is maintained, so that the ITO resistance is matched with the epitaxial GaN layer, and current is more evenly expanded, thereby effectively improving the brightness of the chip.

Owner:EPILIGHT TECH

Display panel, electronic apparatus with the same, and method of manufacturing the same

ActiveUS20060202610A1Easy to manufactureEfficiently formedDischarge tube luminescnet screensLamp detailsVisibilityTitanium nitride

There is provided a display panel that is capable of improving visibility outdoors and which can be easily manufactured. In a display panel in which at least one side thereof serves as a display surface, the display panel includes a first reflectance layer 3, which is made of titanium, titanium nitride, or an alloy of titanium and tungsten and a second reflectance layer 4, which is made of indium tin oxide, indium zinc oxide, or gallium zinc oxide, wherein the first and second low reflection layer 3 and 4 are deposited at positions corresponding to pixels on a substrate 1.

Owner:SEIKO EPSON CORP

Thin film transistor, thin film transistor substrate including the same and method of manufacturing the same

InactiveUS20100022055A1Solid-state devicesSemiconductor/solid-state device manufacturingOhmic contactNitrogen

A thin film transistor showing desirable contact characteristics during contact with indium tin oxide (ITO) or indium zinc oxide (IZO), in which a first conductive pattern including a gate electrode and a second conductive pattern including a source electrode and a drain electrode are formed without an etching process, a TFT substrate including the TFTs, and a method of manufacturing the same. The thin film transistor includes a gate electrode formed of a first conductive layer, a gate insulating layer covering the gate electrode, a semiconductor layer forming a channel on the gate insulating layer; an ohmic contact layer formed on the semiconductor layer, and a source electrode and a drain electrode formed of a second conductive layer and of a third conductive layer. The second conductive layer includes an aluminum-nickel alloy and nitrogen and is formed on the semiconductor layer. The third conductive layer includes an aluminum-nickel alloy and is formed on the second conductive layer.

Owner:SAMSUNG DISPLAY CO LTD

Thin film transistor array substrate for a liquid crystal display

InactiveUSRE40162E1Improve performanceReduce in quantityTransistorSolid-state devicesResistLiquid-crystal display

A thin film transistor substrate for a liquid crystal display includes an insulating substrate, and a gate line assembly formed on the substrate. The gate line assembly has a double-layered structure with a lower layer exhibiting good contact characteristics with respect to indium tin oxide, and an upper layer exhibiting low resistance characteristics. A gate insulating layer, a semiconductor layer, a contact layer, and first and second data line layers are sequentially deposited onto the substrate with the gate line assembly. The first and second data line layers are patterned to form a data line assembly, and the contact layer is etched through the pattern of the data line assembly such that the contact layer has the same pattern as the data line assembly. A passivation layer is deposited onto the data line assembly, and a photoresist pattern is formed on the passivation layer by using a mask of different light transmissties mainly at a display area and a peripheral area. The passivation layer and the underlying layers are etched through the photoresist pattern to form a semiconductor pattern and contact windows. A pixel electrode, a supplemental gate pad and a supplemental data pad are then formed of indium tin oxide or indium zinc oxide. The gate and data line assemblies may be formed with a single layered structure. A black matrix and a color filter may be formed at the structured substrate before forming the pixel electrode, and an opening portion may be formed between the pixel electrode and the data line to prevent possible short circuits.

Owner:SAMSUNG DISPLAY CO LTD

Method for manufacturing thin film transistor array panel for display device

InactiveUS20050170548A1Improve adhesionMinimized contact resistanceSemiconductor/solid-state device manufacturingNon-linear opticsDisplay deviceConductive materials

A gate wire including gate lines, gate electrodes, and gate pads and extending in a transverse direction is formed on a substrate. A gate insulating layer is formed thereafter, and a semiconductor layer and an ohmic contact layer are sequentially formed thereon. A conductive material is deposited and patterned to form a data wire inducing data lines intersecting the gate lines, source electrodes, drain electrodes, and data pads. A protective layer made of silicon nitride is deposited on the substrate, and an organic insulating layer made of a photosensitive organic insulating material is coated on the protective layer. The organic insulating layer is patterned to form an unevenness pattern on its surface and first contact holes exposing the protective layer opposite the drain electrodes. Subsequently, the surface of the organic insulating layer is treated using inactive gas such as Ar, and then the protective layer is patterned together with the gate insulating layer by photo etch using a photoresist pattern to form contact holes respectively exposing the drain electrodes, the gate pads, and the data pads. Next, indium-tin-oxide or indium-zinc-oxide is deposited and patterned to form transparent electrodes, subsidiary gate pads, and subsidiary data pads respectively connected to the drain electrodes, the gate pads and the data pads. Finally, a reflective conductive material is deposited and patterned to form reflecting films having respective apertures in the pixel area on the transparent electrodes.

Owner:SAMSUNG DISPLAY CO LTD

Thin film transistor, method of manufacturing the same, and flat panel display device having the same

ActiveUS8008658B2Improve featuresEasy to controlSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceIndium zinc oxide

A thin film transistor (TFT) using an oxide semiconductor layer as an active layer, a method of manufacturing the TFT, and a flat panel display (FPD) including the TFT are taught. The TFT includes a gate electrode formed on a substrate, an oxide semiconductor layer electrically insulated from the gate electrode by a gate insulating layer, and the oxide semiconductor layer including a channel region, a source region, and a drain region, and a source electrode and a drain electrode respectively electrically contacting the source region and the drain region. The oxide semiconductor layer is formed of an InZnO or IZO layer (indium zinc oxide layer) including Zr. The carrier density of the IZO layer is controlled to be 1×1013 to 1×1018 #cm−3 by controlling an amount of Zr.

Owner:SAMSUNG DISPLAY CO LTD

Production method of gallium nitride (GaN)-based light emitting diode (LED) chip with indium tin oxide (ITO) surface roughness

The invention relates to a production method of a gallium nitride (GaN)-based light emitting diode (LED) chip with indium tin oxide (ITO) surface roughness, which relates to the technical field of the production of a semiconductor. The production method comprises following steps of firstly forming a GaN epitaxial wafer; preparing an ITO film layer on the surface of a phosphorus gallium nitride (P-GaN) layer of the epitaxial wafer; roughening the surface of the film layer; performing inductively coupled plasma (ICP) etching on one side of the GaN epitaxial wafer, and forming an ITO transparent electrode on a P-type table-board; forming a positive (P) electrode and a negative (N) electrode; and thinning a semiconductor substrate, and then slicing the semiconductor substrate into independent chips. The production method is characterized in that when the surface roughening is performed on the surface of the ITO film layer, a nano bowl-shaped roughened surface layer is produced, and the nano bowl-shaped roughened surface layer is formed by joining a plurality of back surfaces respectively to bowl-shaped grooves on the P-GaN layer, wherein the back surfaces are connected with each other. The size and the depth of each bowl-shaped groove in the nano bowl-shaped roughened surface layer are controllable, and the bowl-shaped structure is more favorable for the light extraction.

Owner:YANGZHOU ZHONGKE SEMICON LIGHTING