Patents

Literature

73results about How to "Minimized contact resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

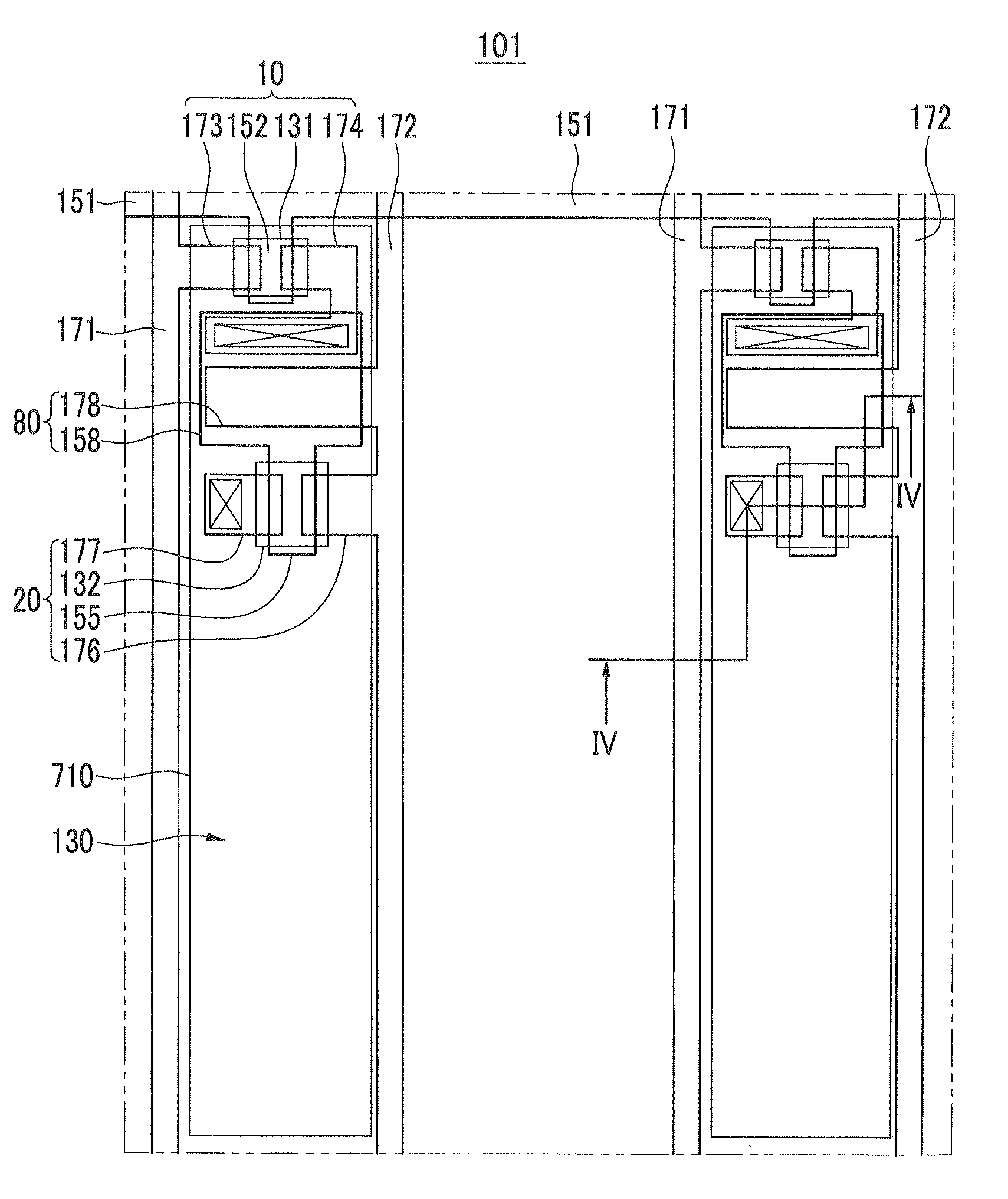

Organic light emitting diode display and method of manufacturing the same

InactiveUS20110133215A1Efficient removalImproved light emissionElectroluminescent light sourcesSolid-state devicesDisplay deviceConductive materials

A method of manufacturing an organic light emitting diode (OLED) display includes forming an upper electrode power source line outside of a pixel area over a substrate, forming a lower electrode in the pixel area, forming at least one layer of an organic material layer in the pixel area and areas outside of the pixel area, forming an upper electrode in the pixel area, selectively removing portions of the organic material layer that are exposed outside of the upper electrode, thereby exposing the upper electrode power source line, and coating a conductive material between the upper electrode and the upper electrode power source line in a normal pressure condition such that the conductive material overlaps the upper electrode and the upper electrode power source line, thereby forming a connection portion.

Owner:SAMSUNG DISPLAY CO LTD

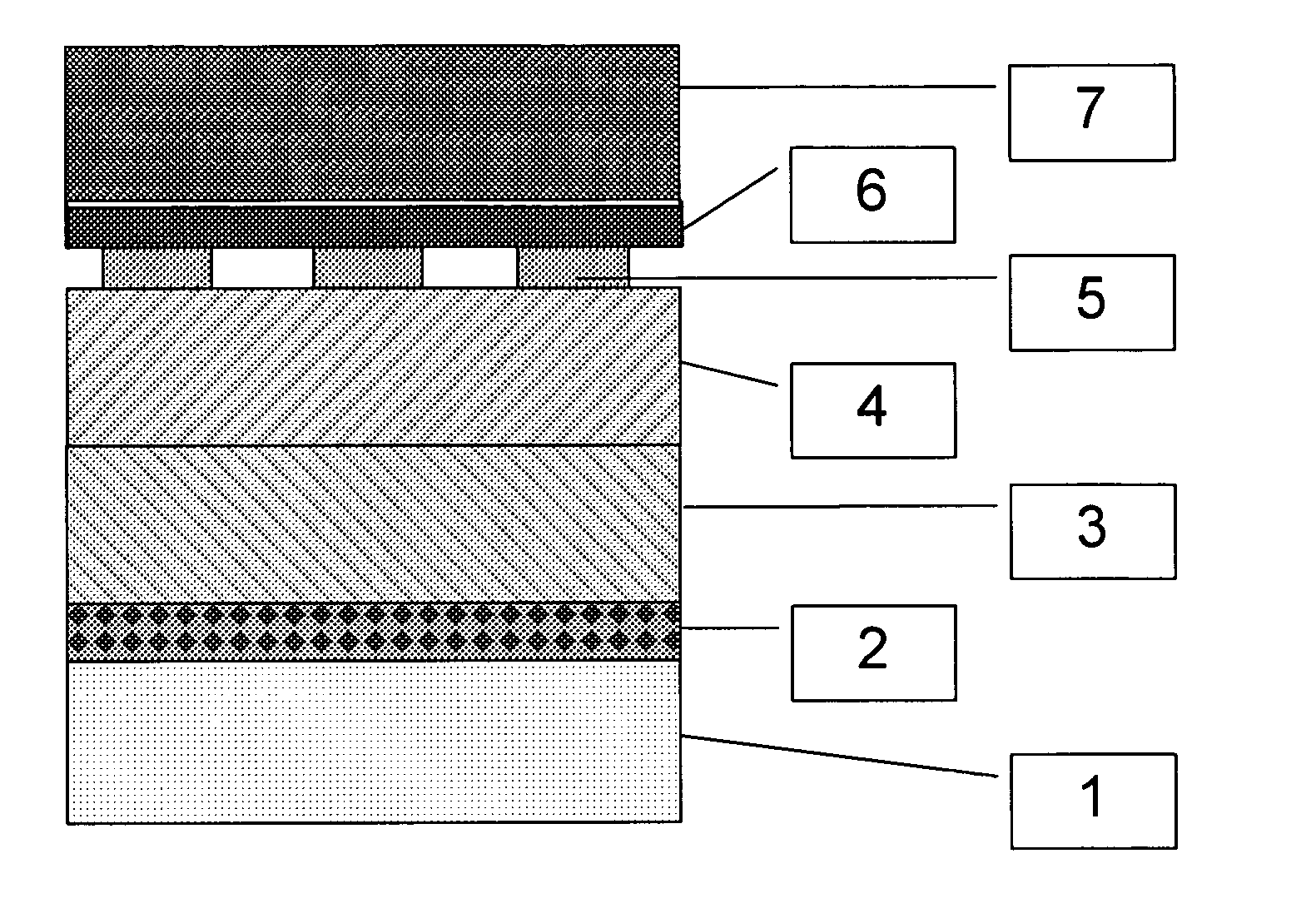

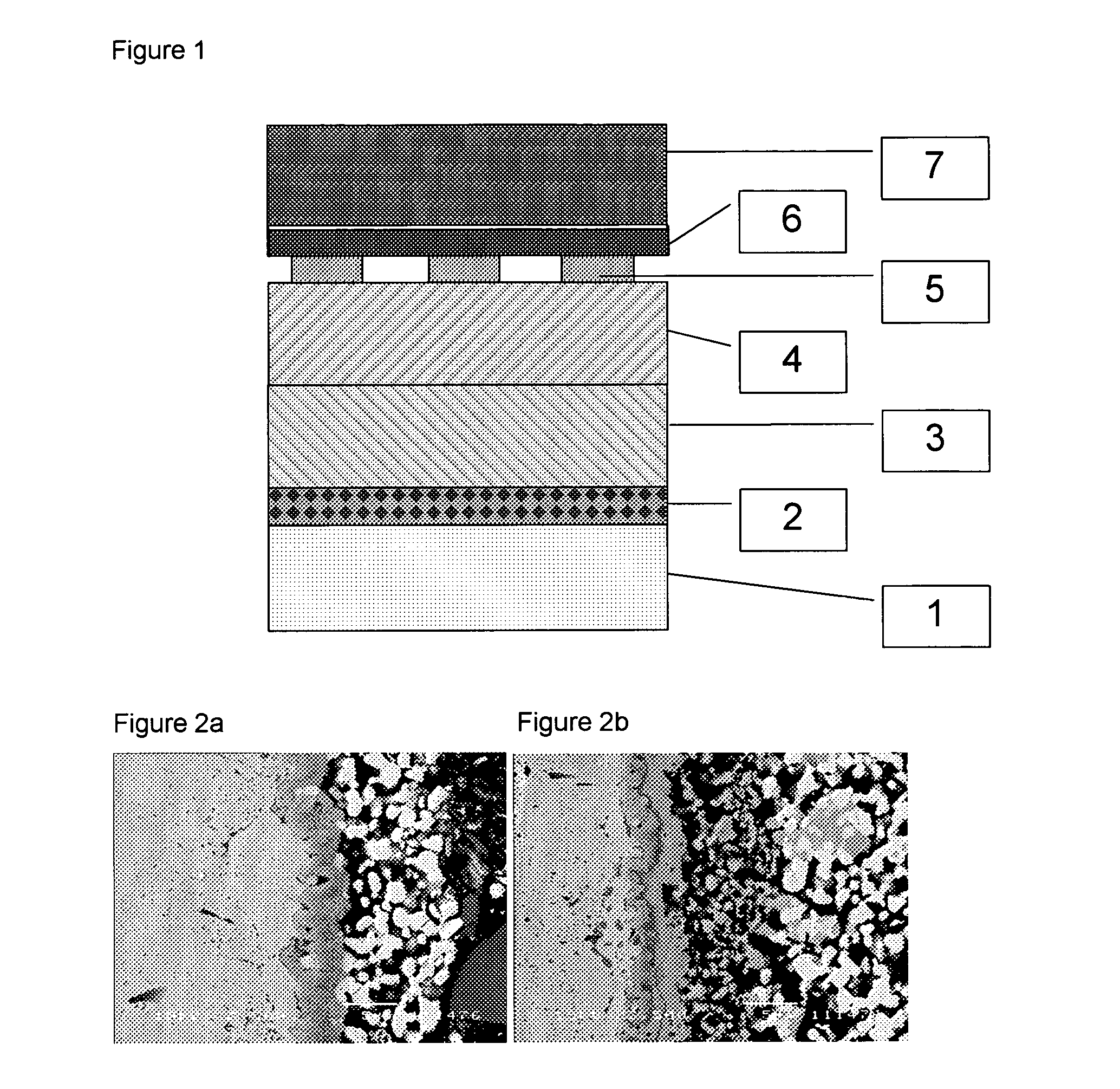

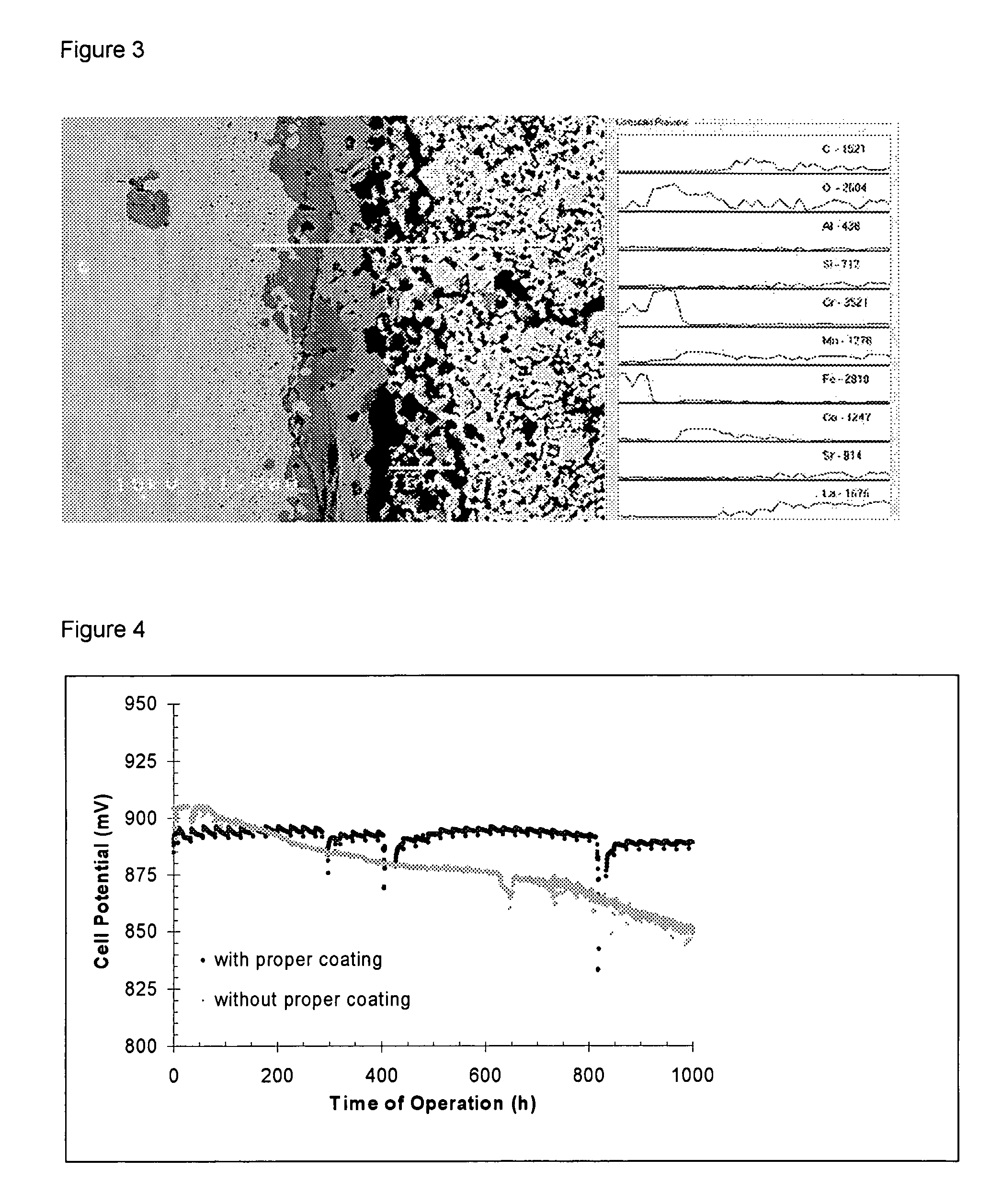

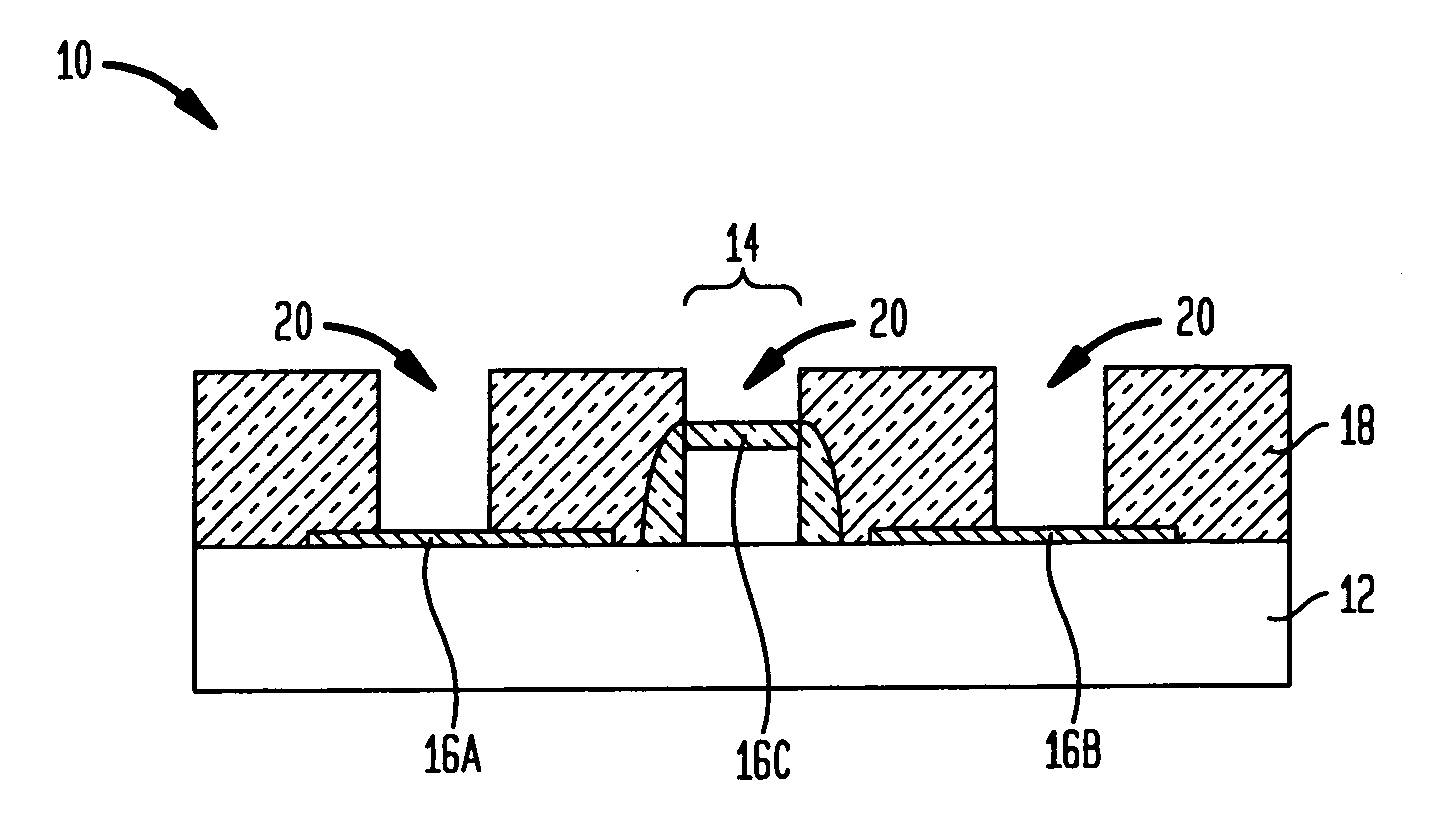

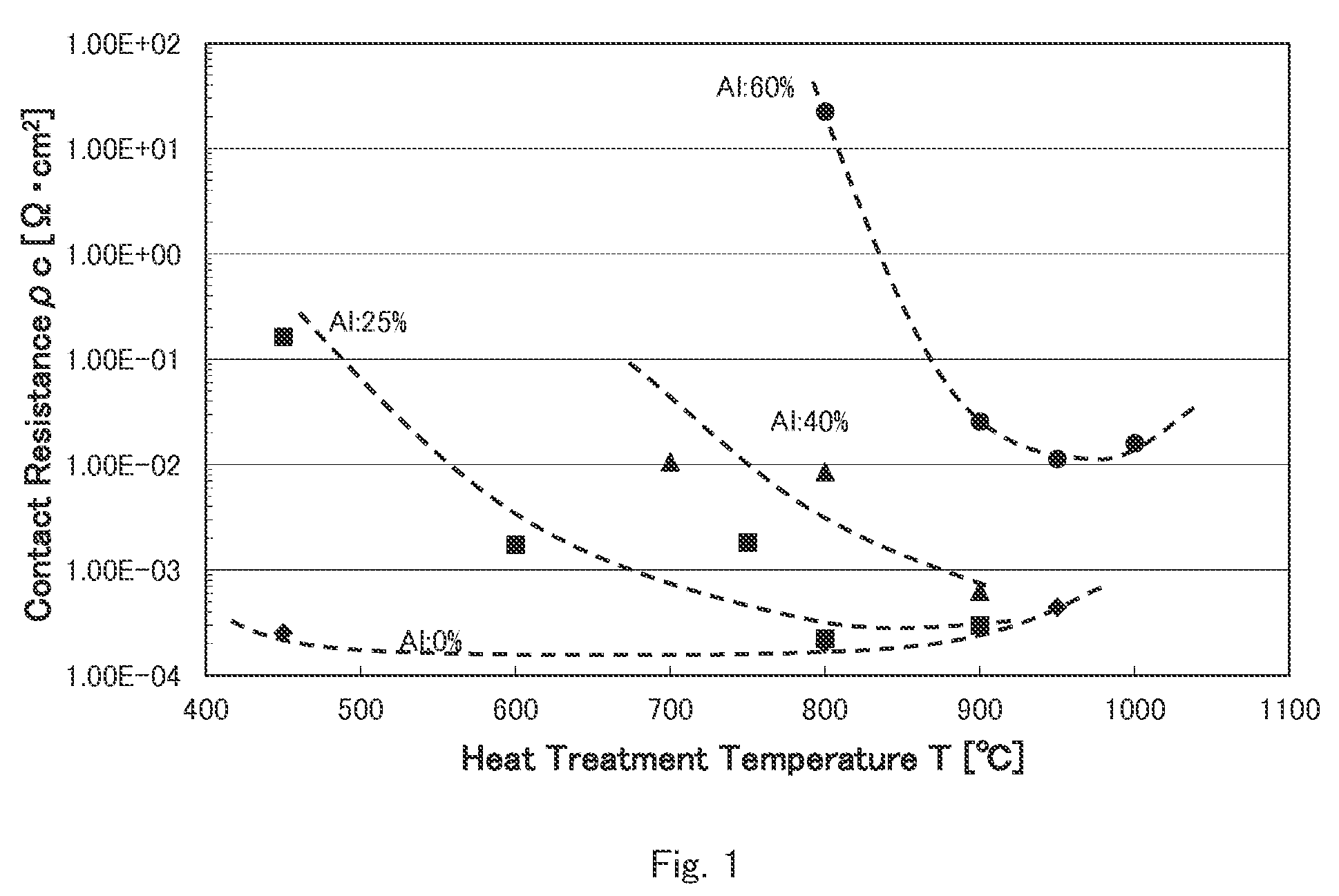

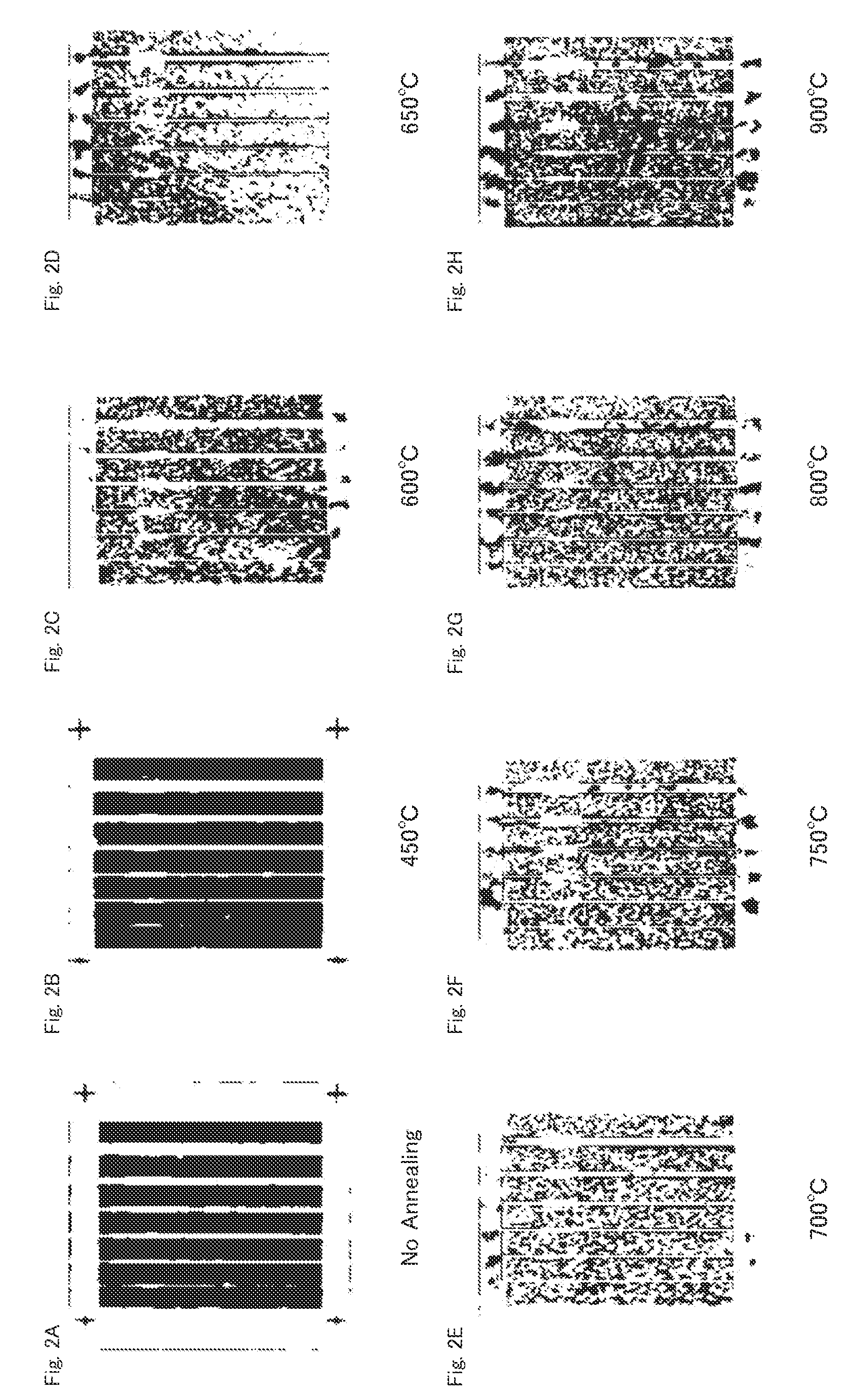

Method of producing a multilayer barrier structure for a solid oxide fuel cell

InactiveUS20100119886A1Minimized contact resistanceFuel cells groupingFinal product manufactureCurrent loadFuel cells

The present invention provides a method of producing a multilayer barrier structure in a solid oxide cell stack, comprising the steps of: -providing a metal interconnect; -applying a first metal oxide layer on said metal interconnect; -applying a second metal oxide layer on top of said first metal oxide layer; -applying a third metal oxide layer on top of said second metal oxide layer; -forming a solid oxide cell stack comprising said metal interconnect having said metal oxide layers thereon; and -reacting the metal oxide in said first metal oxide layer with the metal of said metal interconnect during the SOC-stack initialisation, and a solid oxide stack comprising an anode contact layer and support structure, an anode layer, an electrolyte layer, a cathode layer, a cathode contact layer, a metallic interconnect, and a multilayer barrier structure which is obtainable by the above method and through an initialisation step, which is carried out under controlled conditions for atmosphere composition and current load, which depends on the layer composition facilitating the formation of the desired reaction products as a dense barrier layer without chromium species migrating to the air-electrode.

Owner:TOPSOE FUEL CELL +1

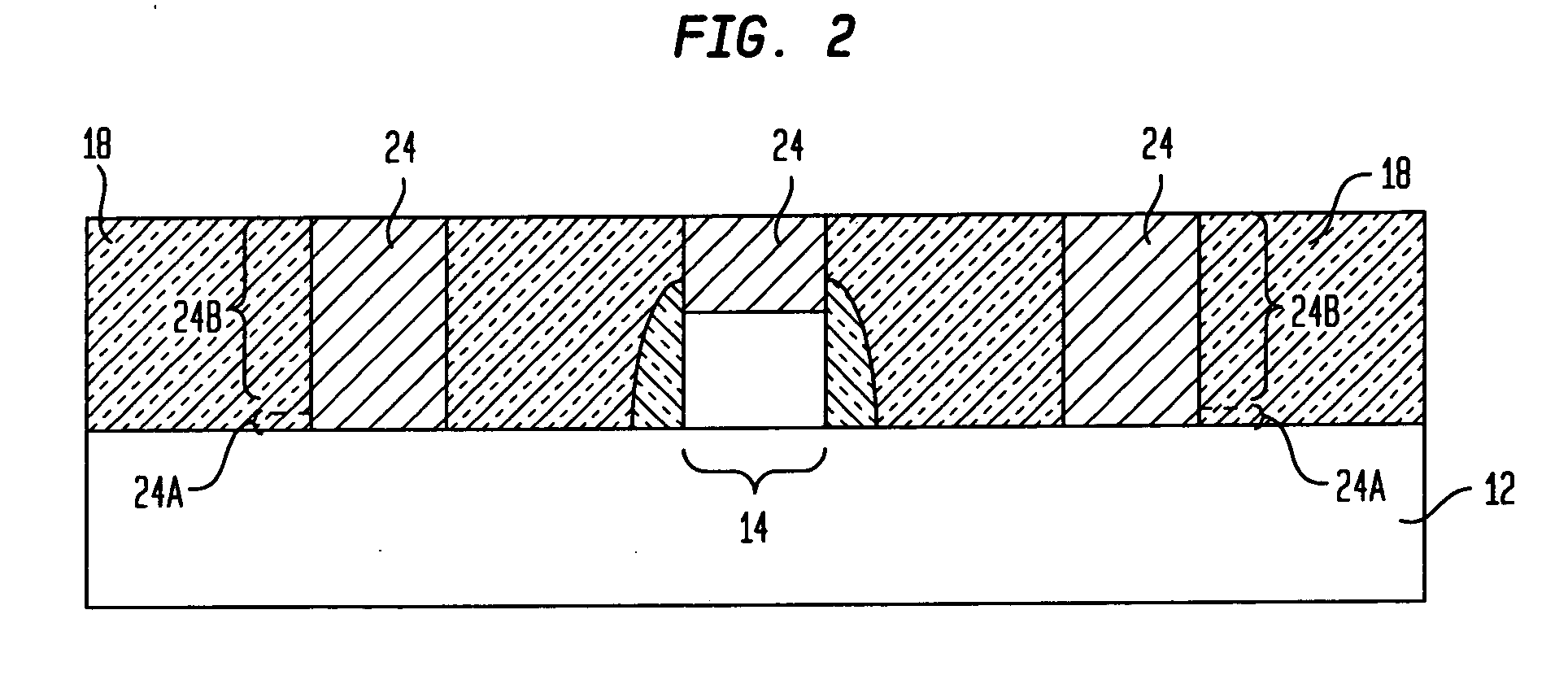

Method and structure for reducing contact resistance between silicide contact and overlying metallization

InactiveUS20070275548A1Lower resistance contactReduce contact resistanceSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureMetal silicide

A semiconductor structure in which the contact resistance in the contact opening is reduced as well as a method of forming the same are provided. This is achieved in the present invention by replacing conventional contact metallurgy, such as tungsten, or a metal silicide, such as Ni silicide or Cu silicide, with a metal germanide-containing contact material. The term “metal germanide-containing” is used in the present application to denote a pure metal germanide (i.e., MGe alloy) or a metal germanide that includes Si (i.e., MSiGe alloy).

Owner:GLOBALFOUNDRIES INC

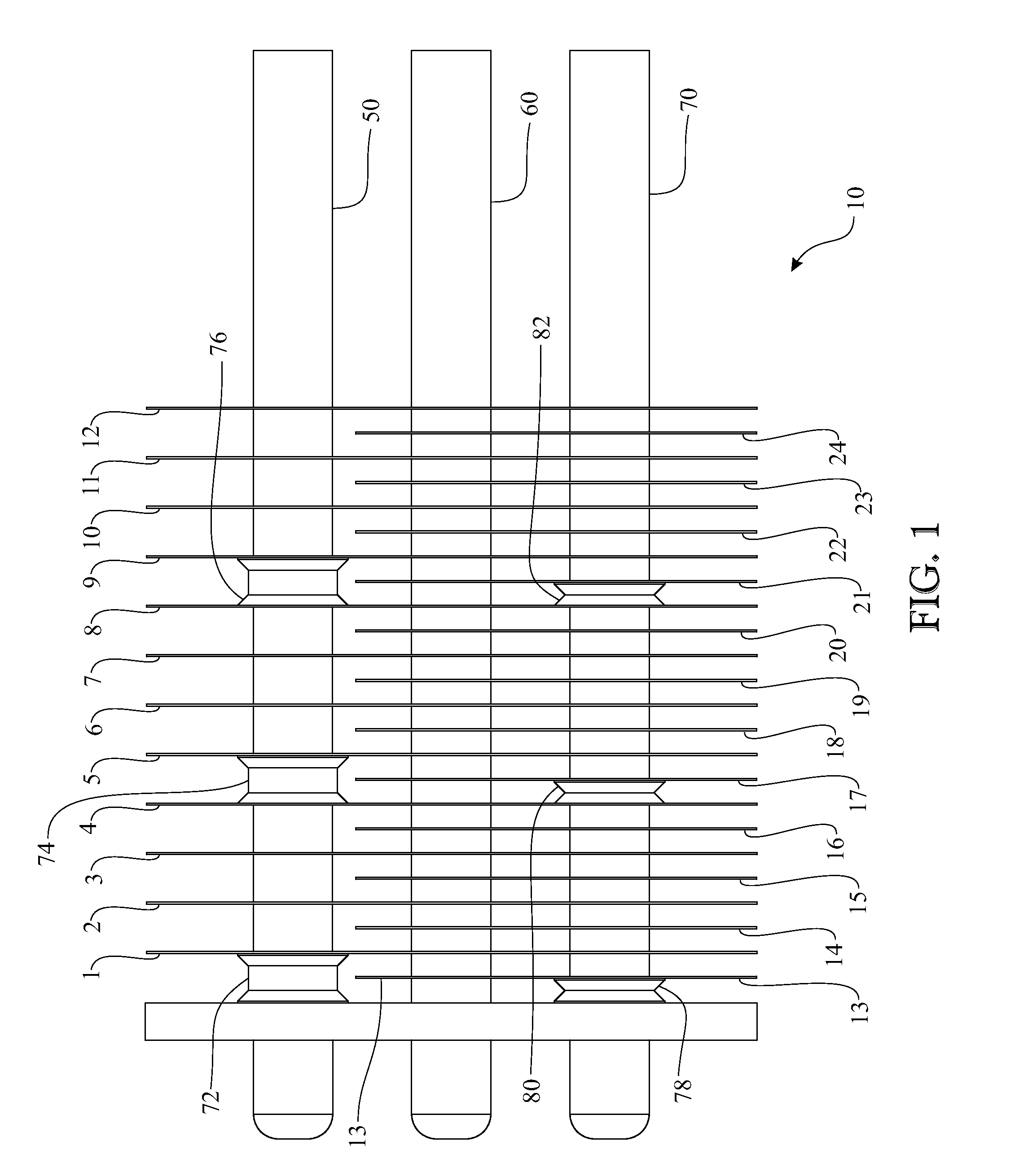

High density integral test probe

InactiveUS7276919B1Minimized contact resistanceEasy alignmentElectrical measurement instrument detailsIndividual semiconductor device testingHigh densityContact position

Owner:GLOBALFOUNDRIES INC

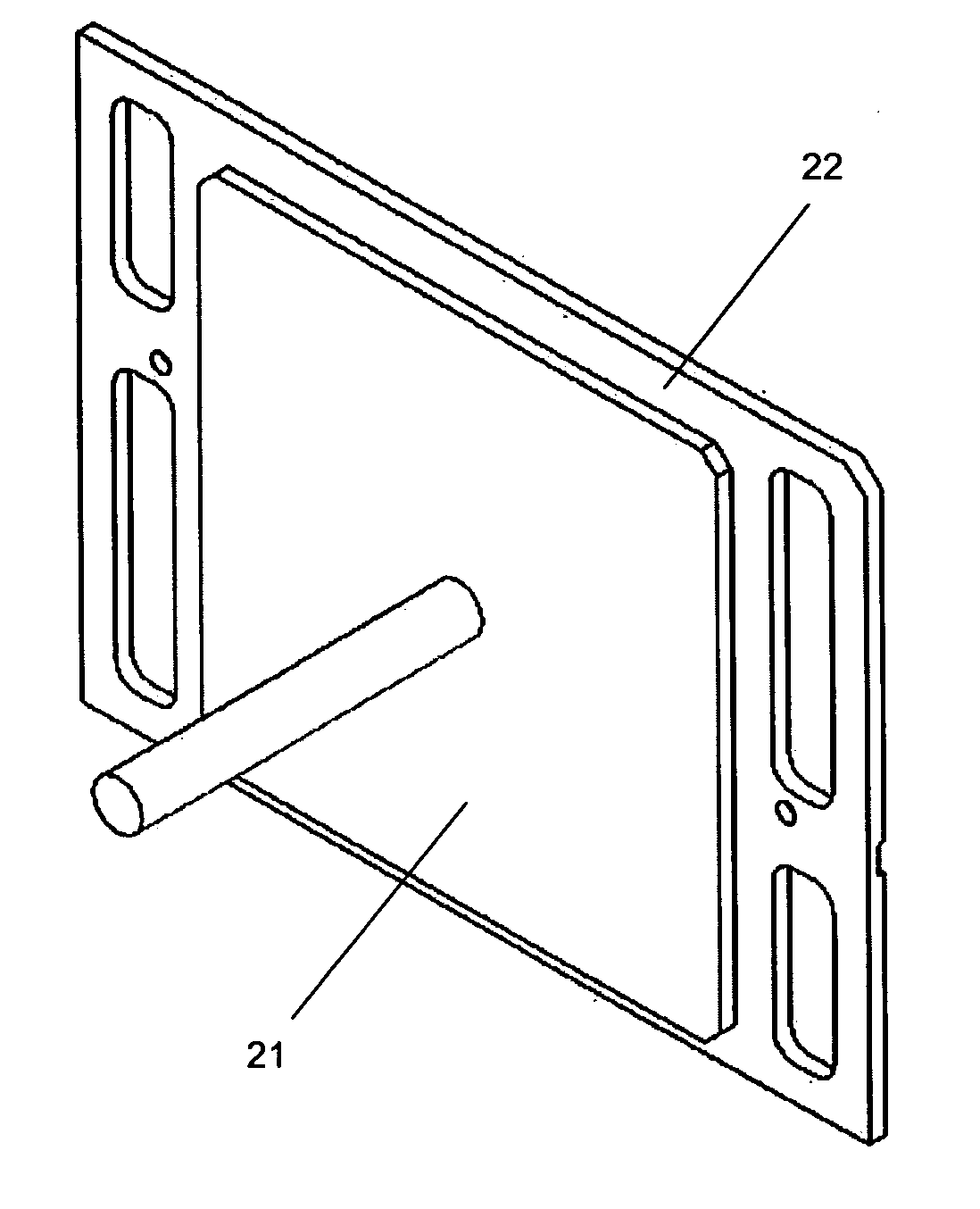

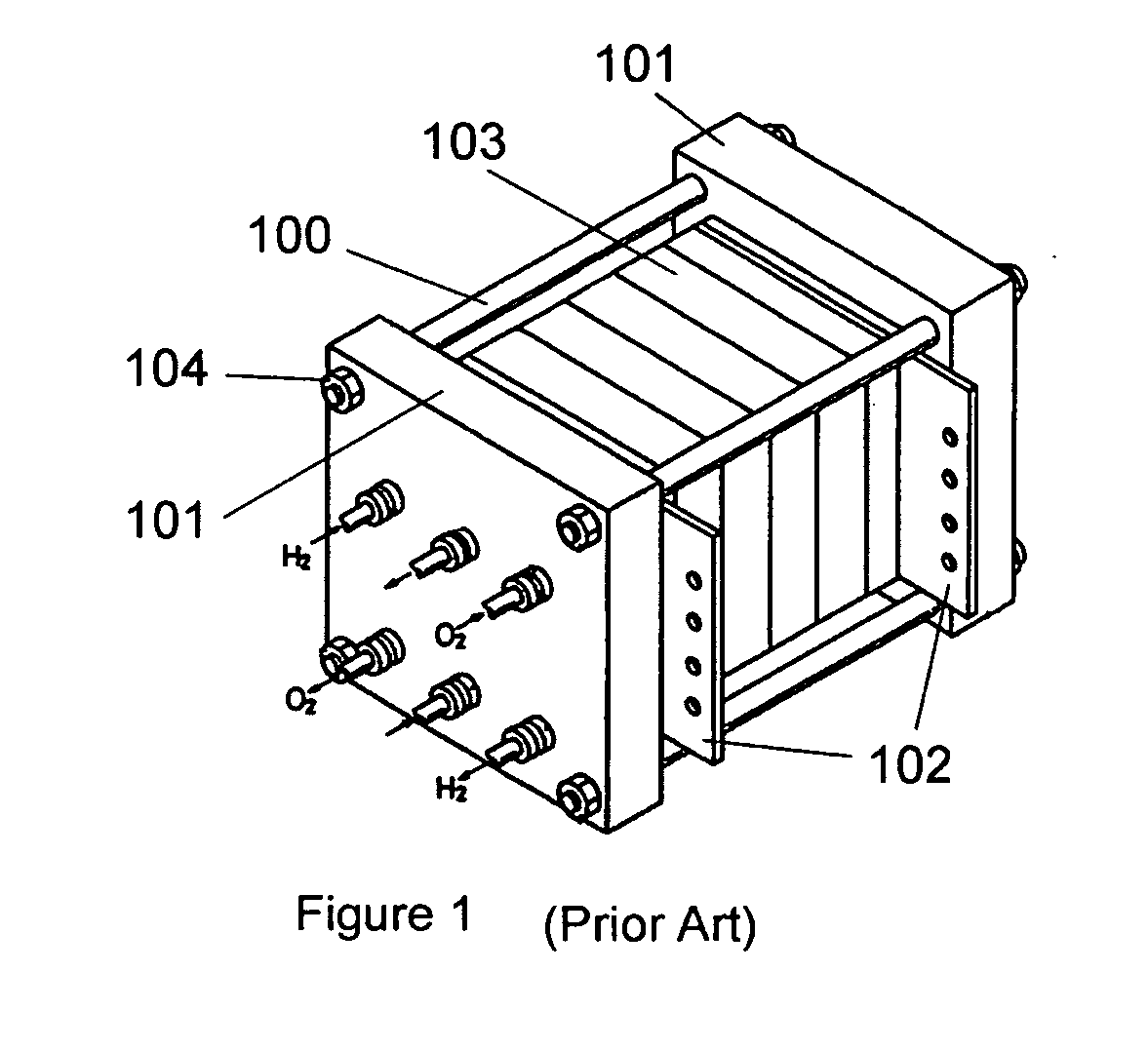

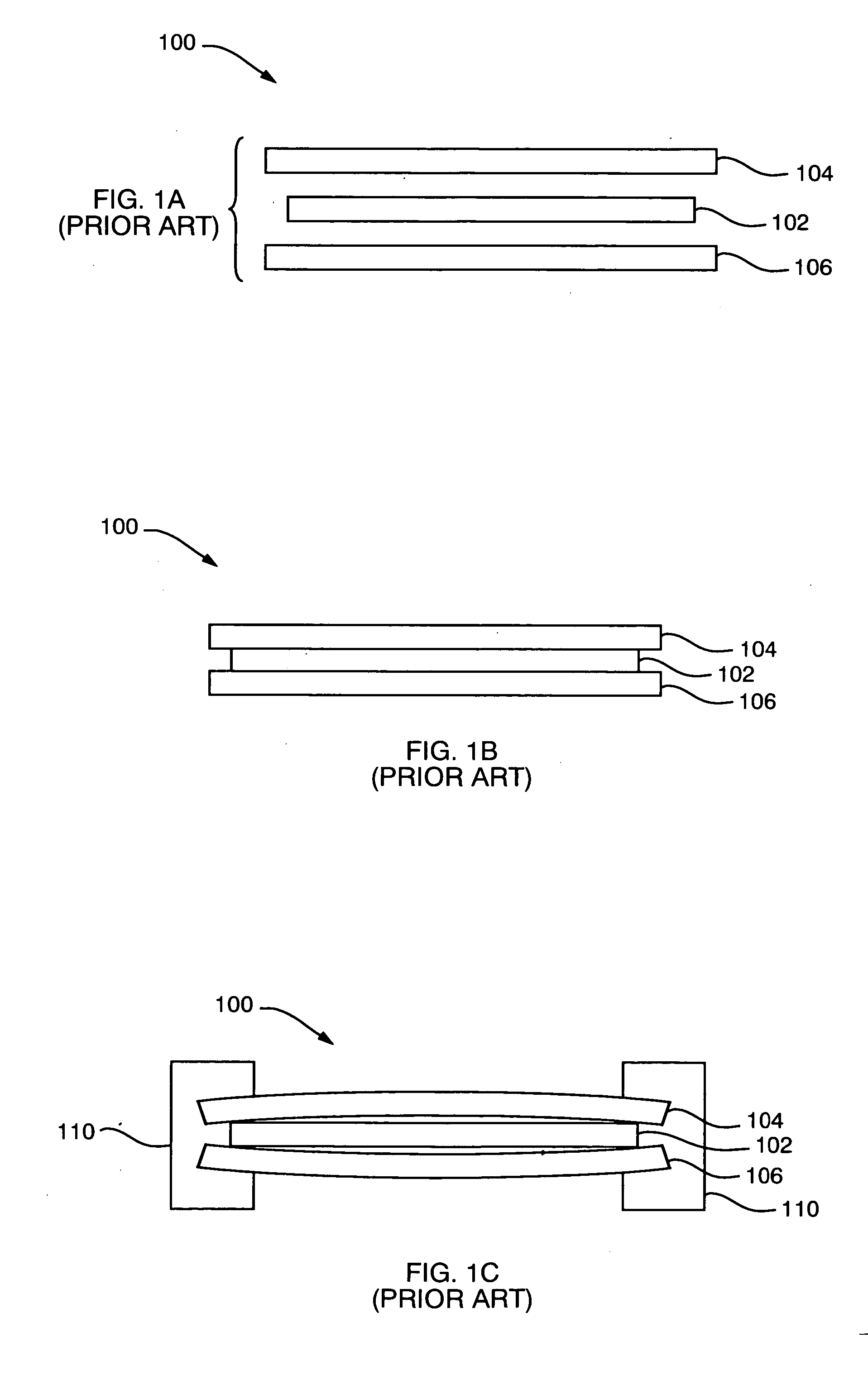

PEM fuel cell stack with floating current collector plates

InactiveUS20050186462A1Minimizing contact resistance therebetweenMinimized contact resistanceFuel cells groupingCell component detailsElectrical resistance and conductanceFuel cells

A proton exchange membrane (PEM) fuel cell end plate assembly provides an axial direction electric lead on an end plate of the assembly, and minimizes the contact resistance between an end fluid separator plate of a fuel cell stack and a current collector of the assembly. The current collector comprises an electrically conductive flat plate and a solid member connected together. The member goes through an opening on the end plate and provides an axial direction electric lead from the fuel cell stack. Means are provided to firmly contact the current collector and the fluid separator plate to maintain good contact across the entire area between the two components. The means of firmly contacting include moulding or bonding the separator plate and current collector together, or applying pressure to the separator plate and current collector such that firm contact is maintained between the two components.

Owner:PALCAN POWER SYST

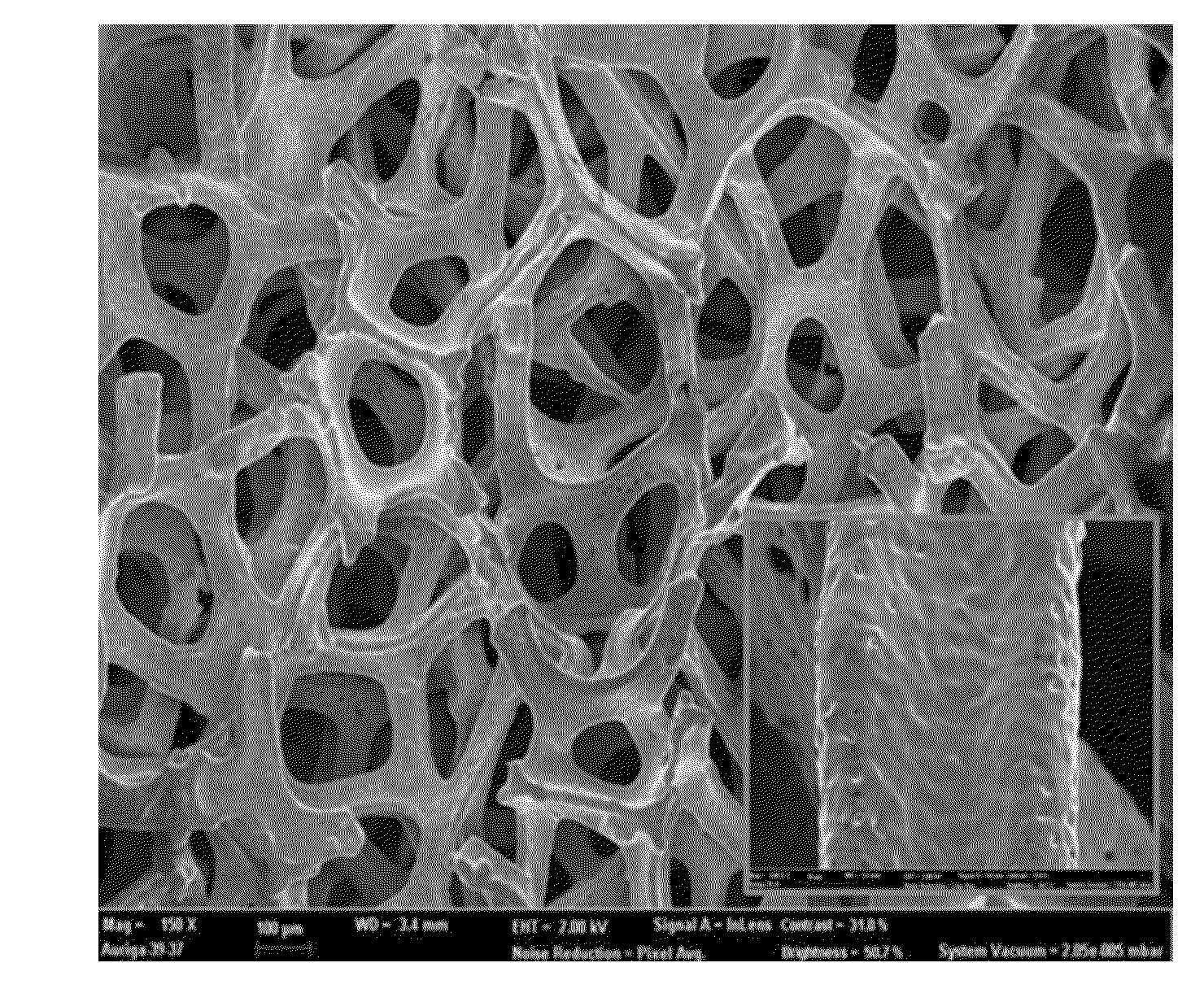

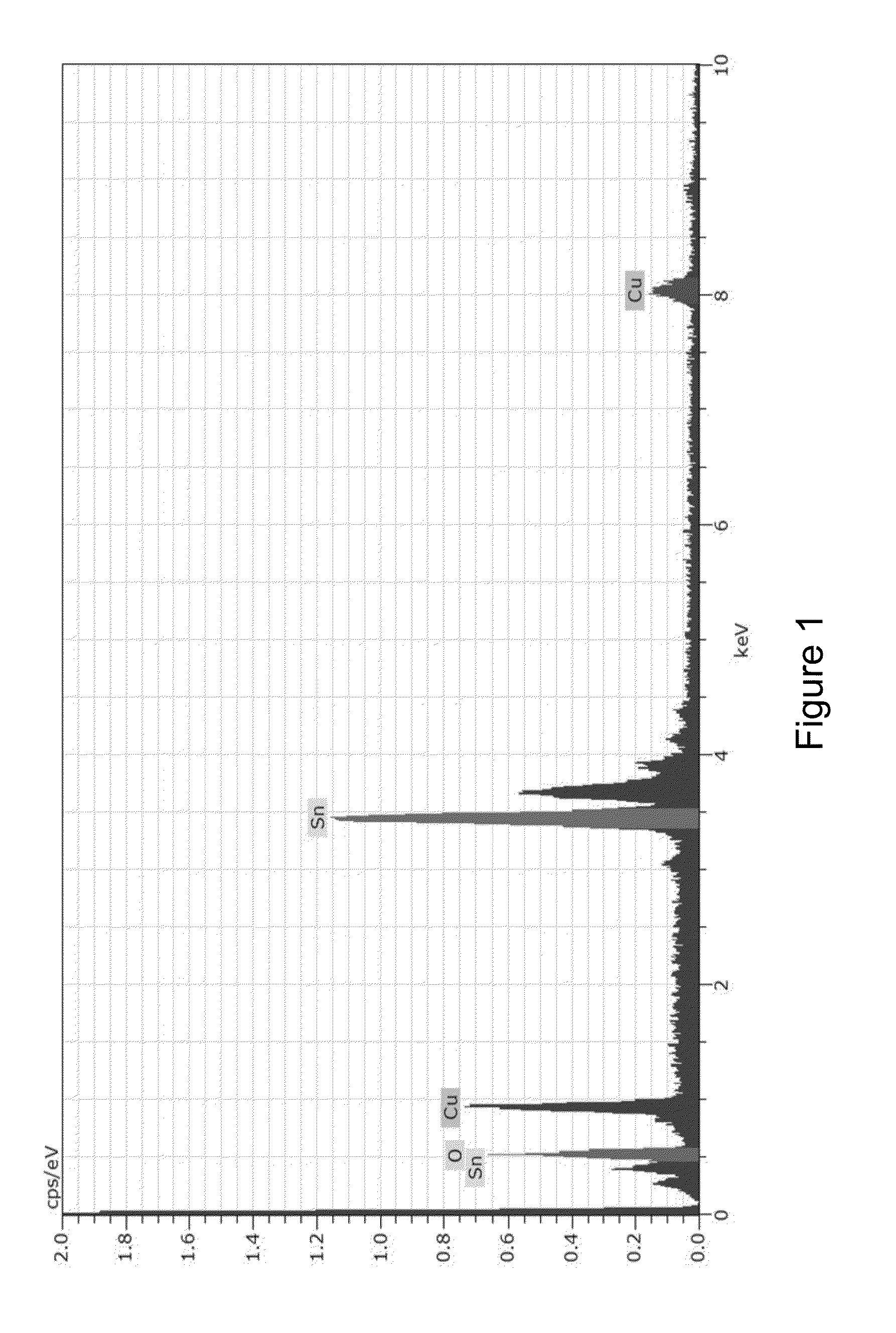

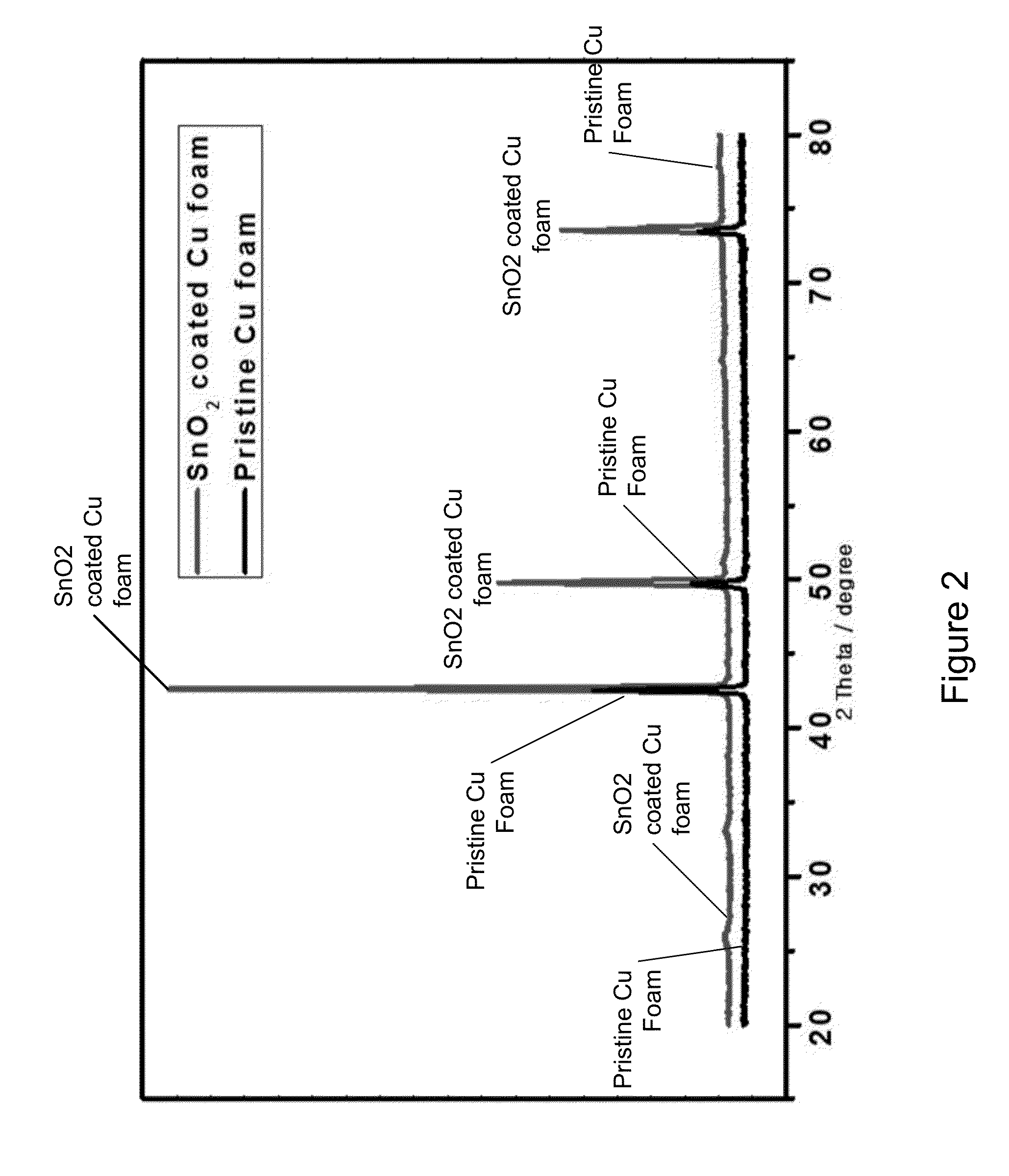

Metal Foam for Electrode of Secondary Lithium Battery, Preparing Method Thereof, and Secondary Lithium Battery Including the Metal Foam

ActiveUS20150072236A1Improve abilitiesImprove featuresSilver accumulatorsElectrode thermal treatmentMetal foamMaterials science

Using metal foams for the electrode of secondary lithium battery, preparing method thereof, and secondary lithium battery including the metal foam. A metal foam is used in an electrode of secondary lithium battery where the surface and the inner pore walls are coated with the active materials, a method of manufacturing such metal foam, and secondary lithium battery including the metal foam.

Owner:CELLMO MATERIALS INNOVATION INC

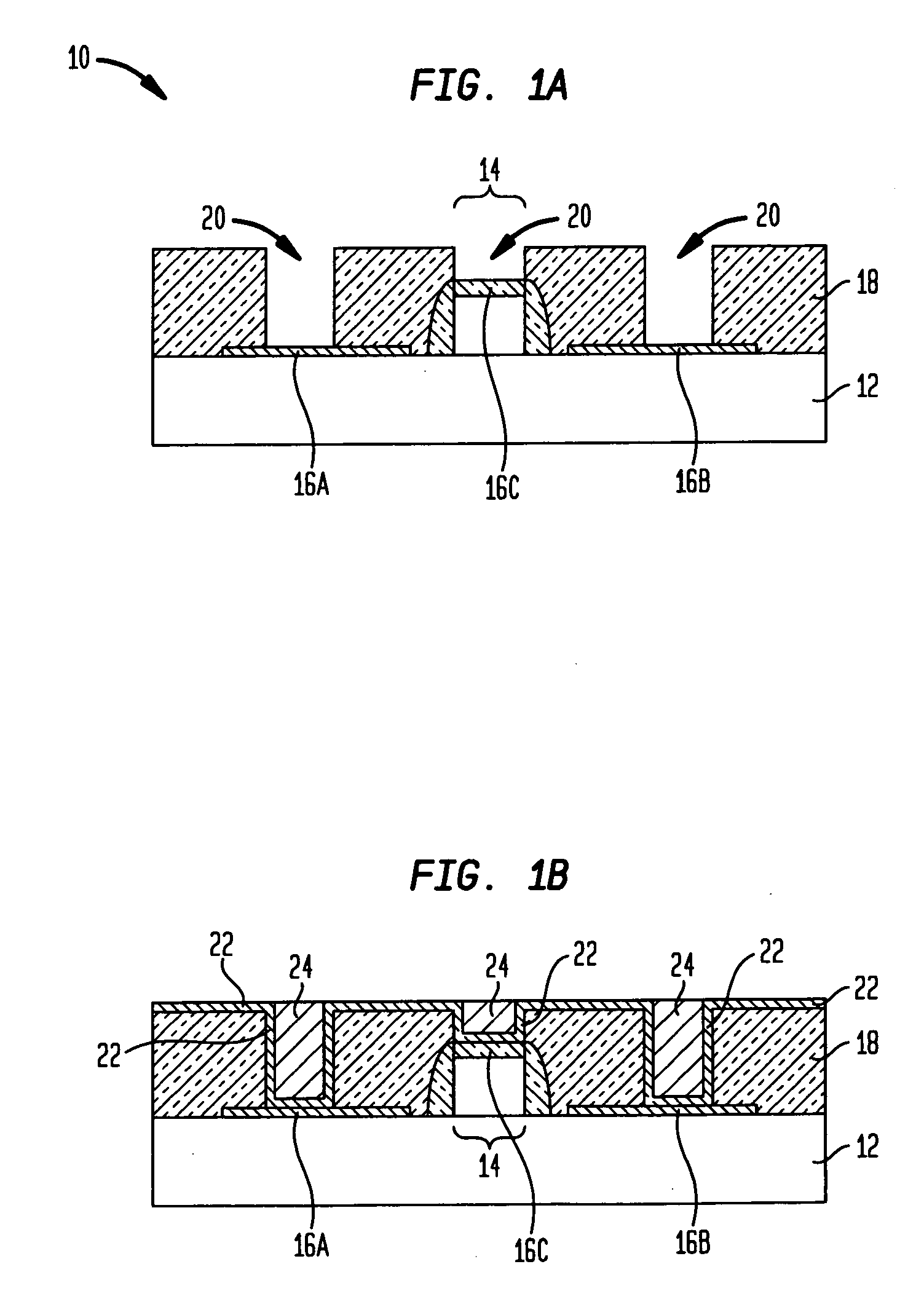

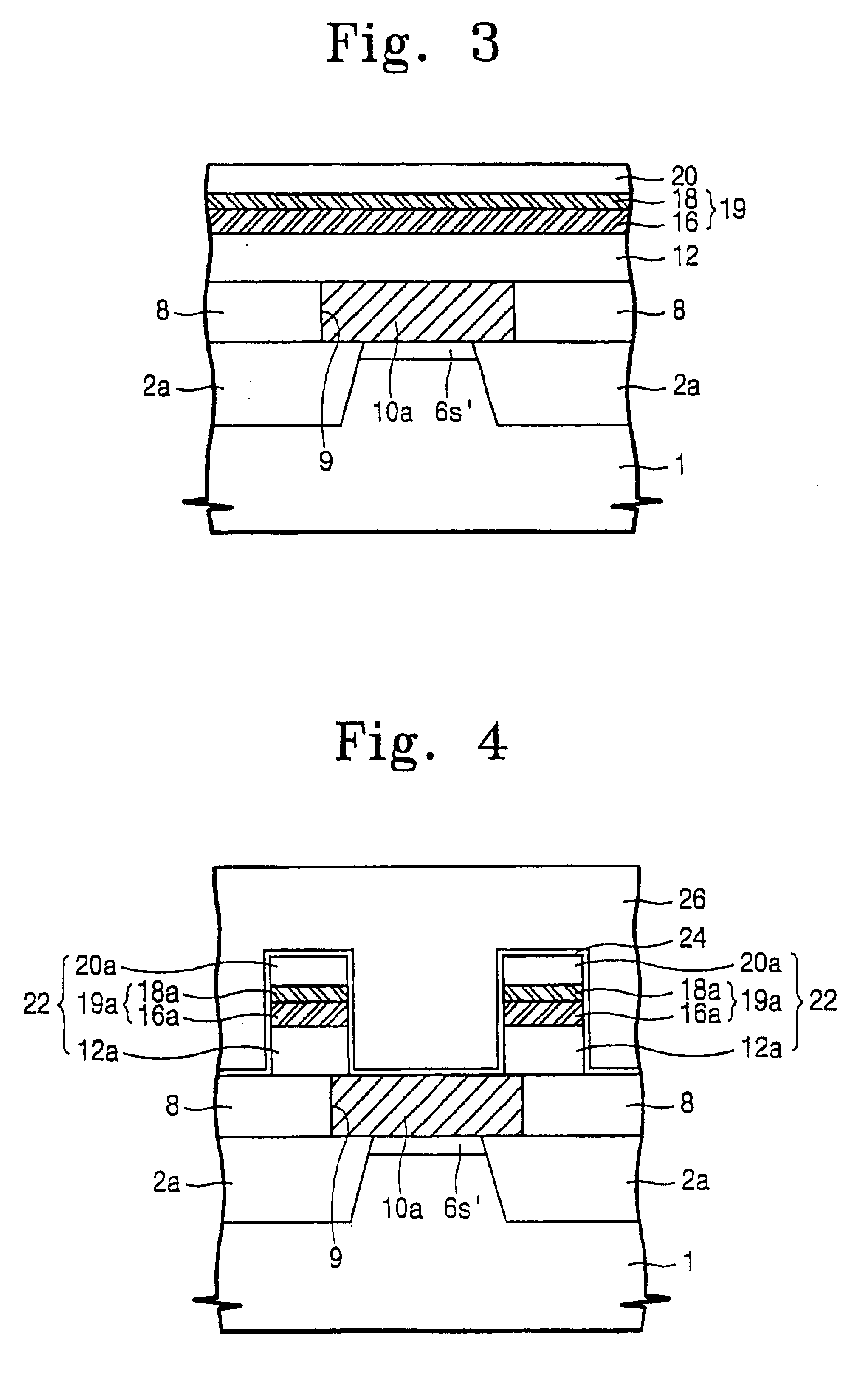

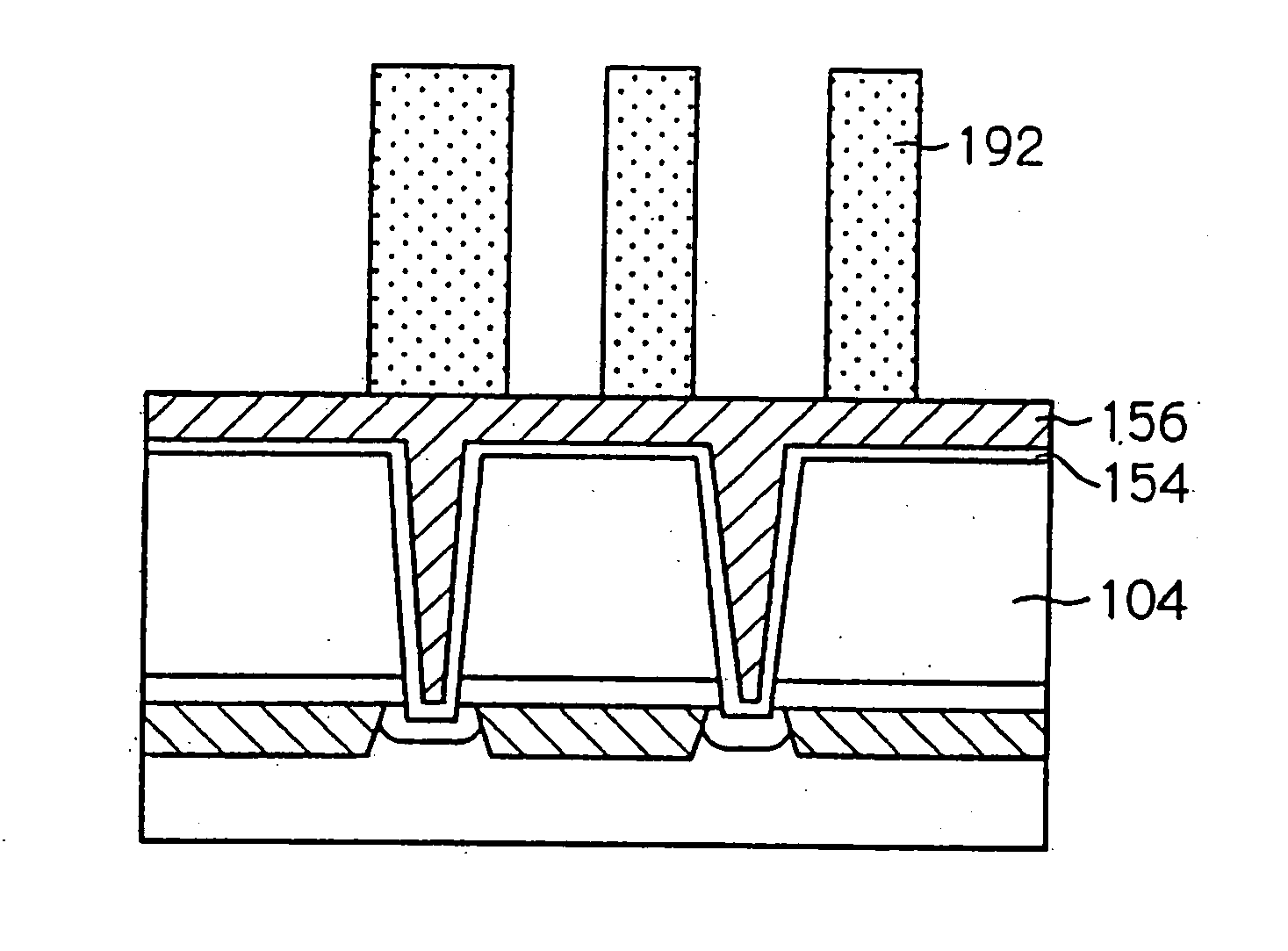

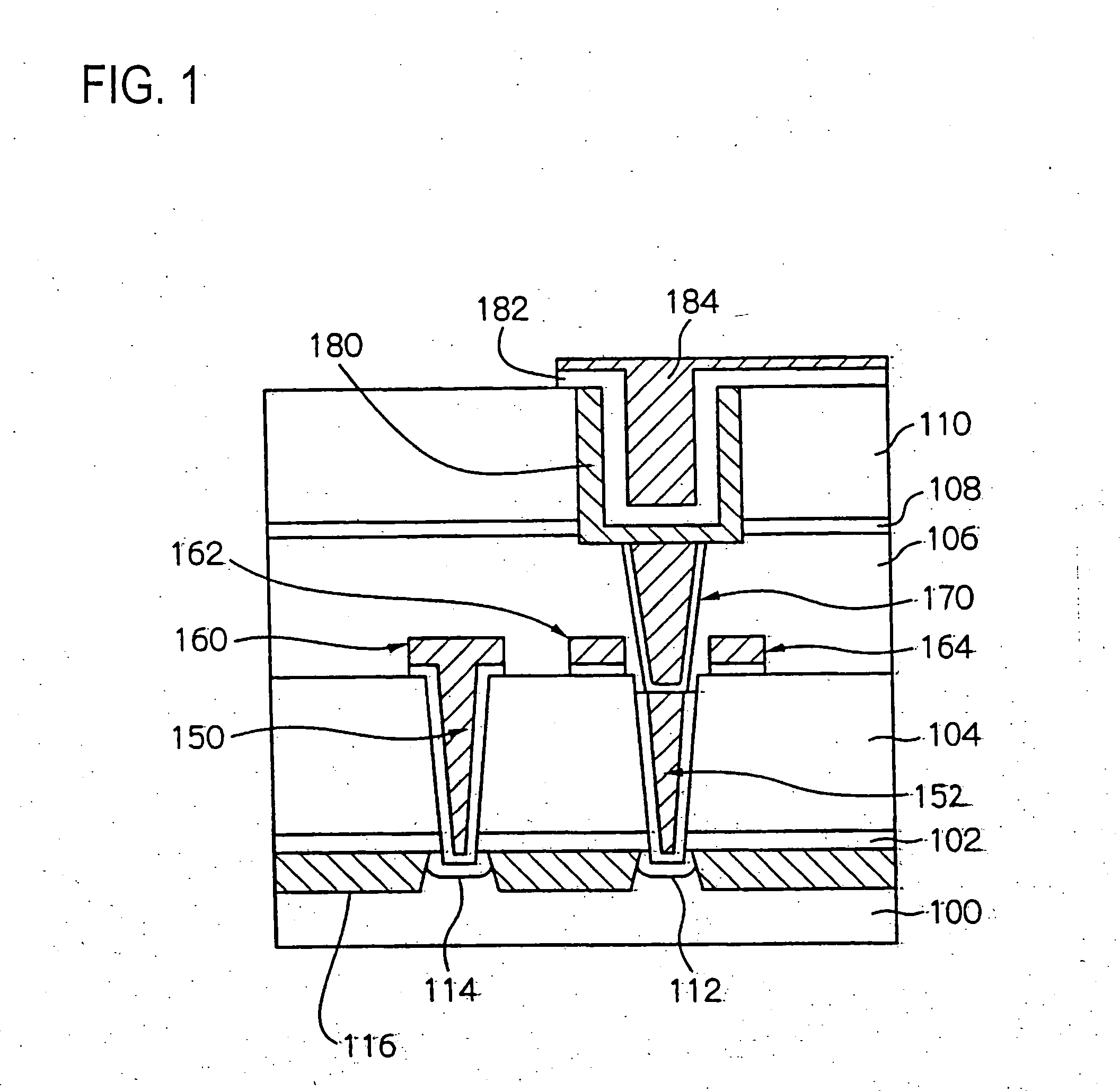

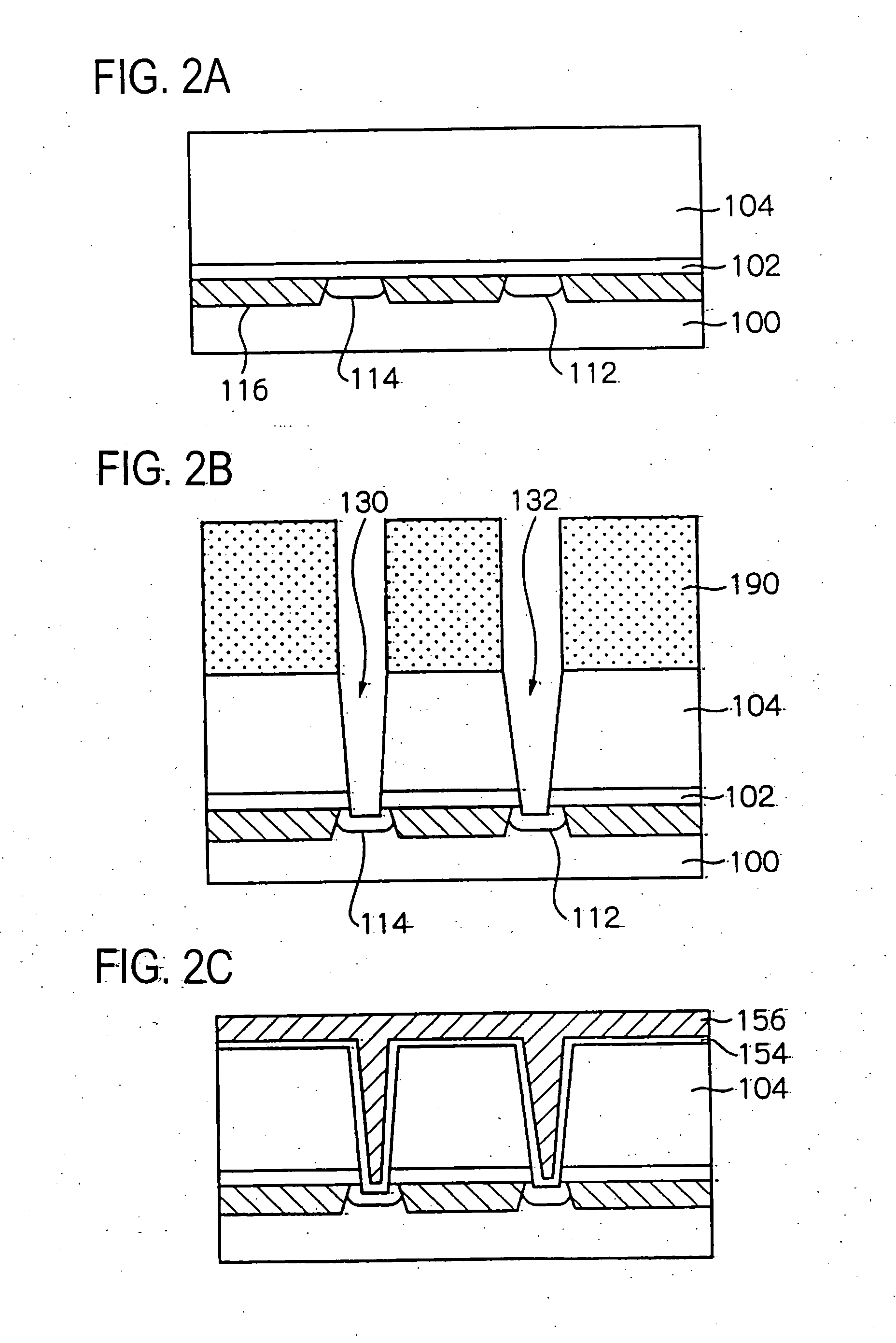

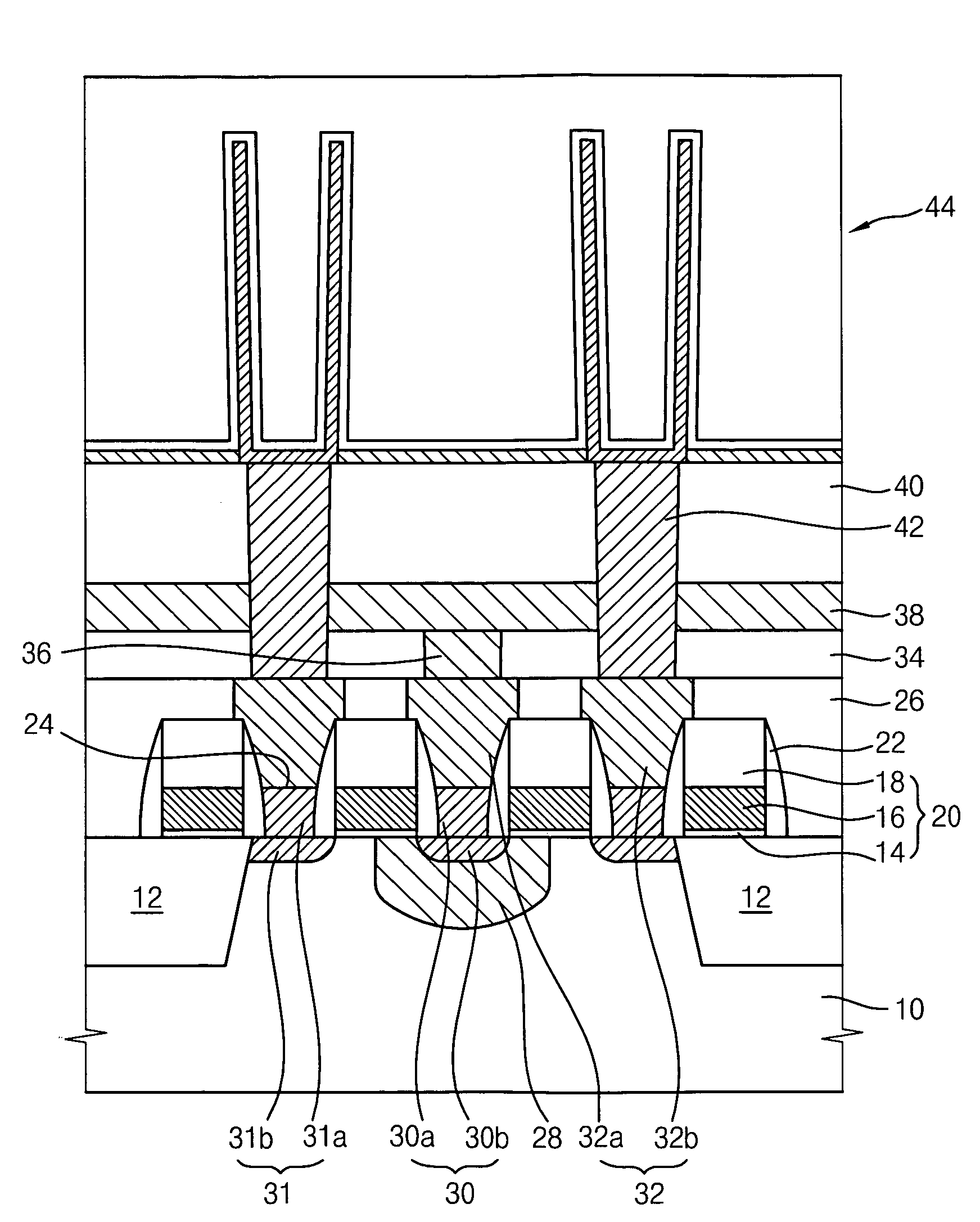

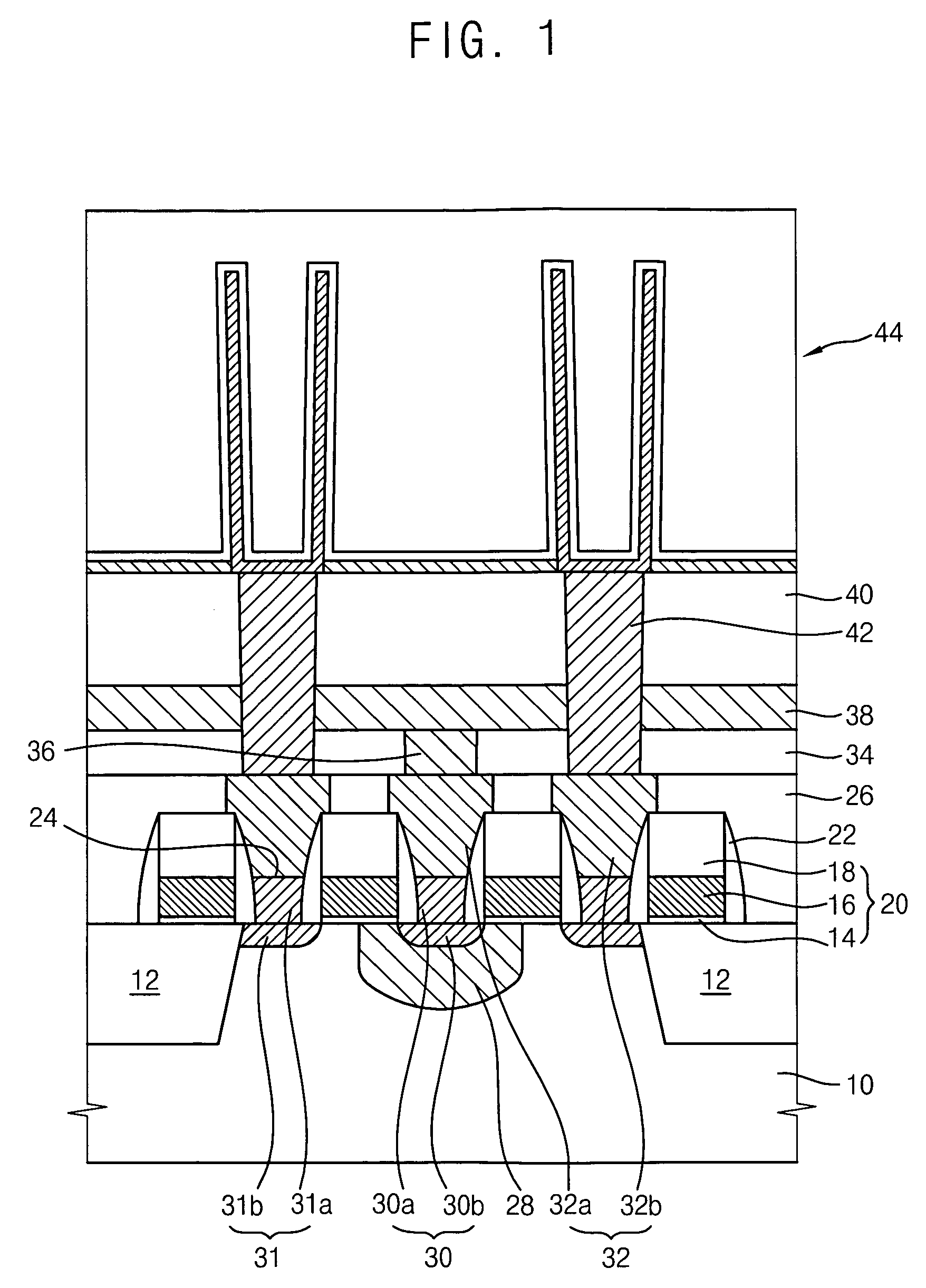

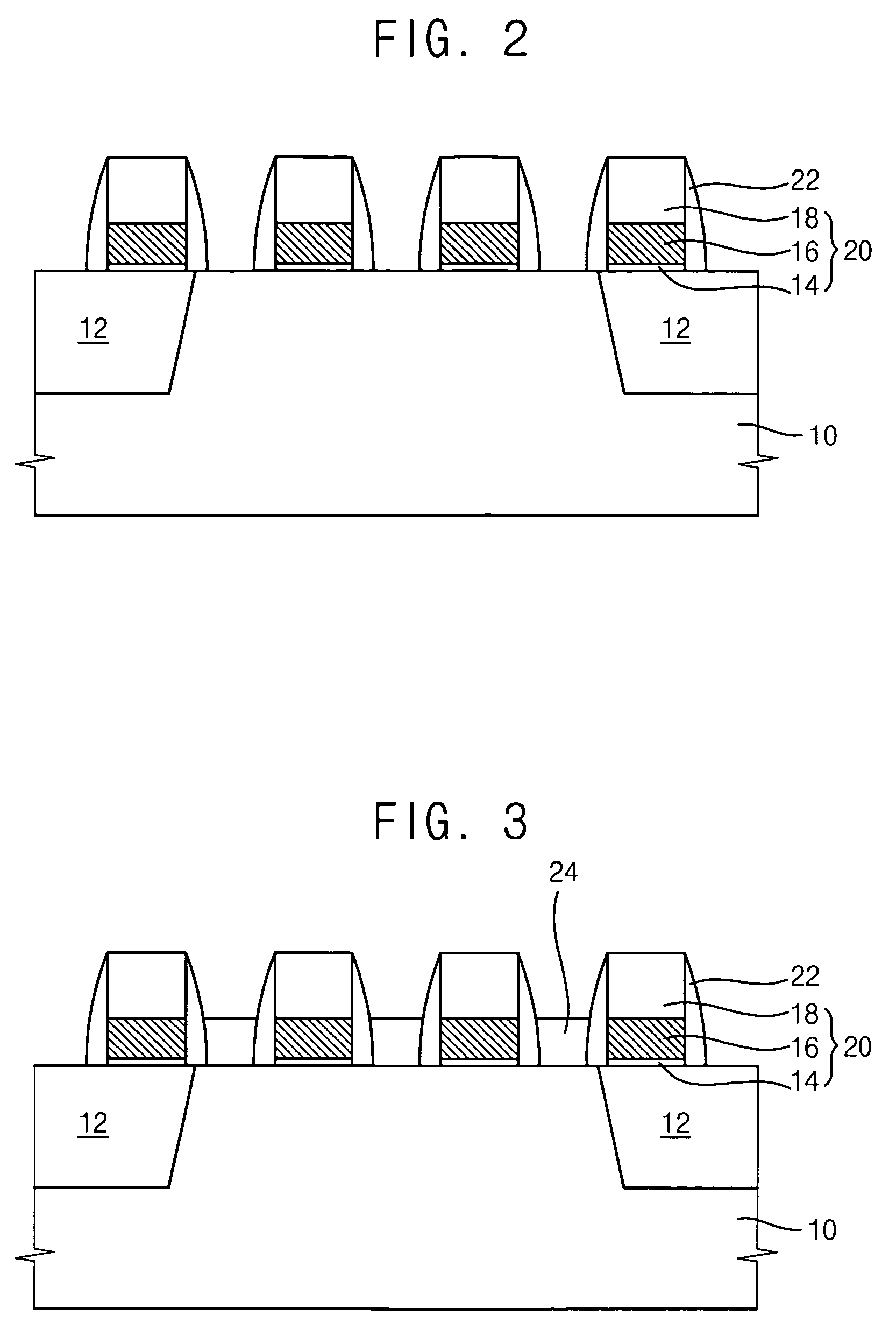

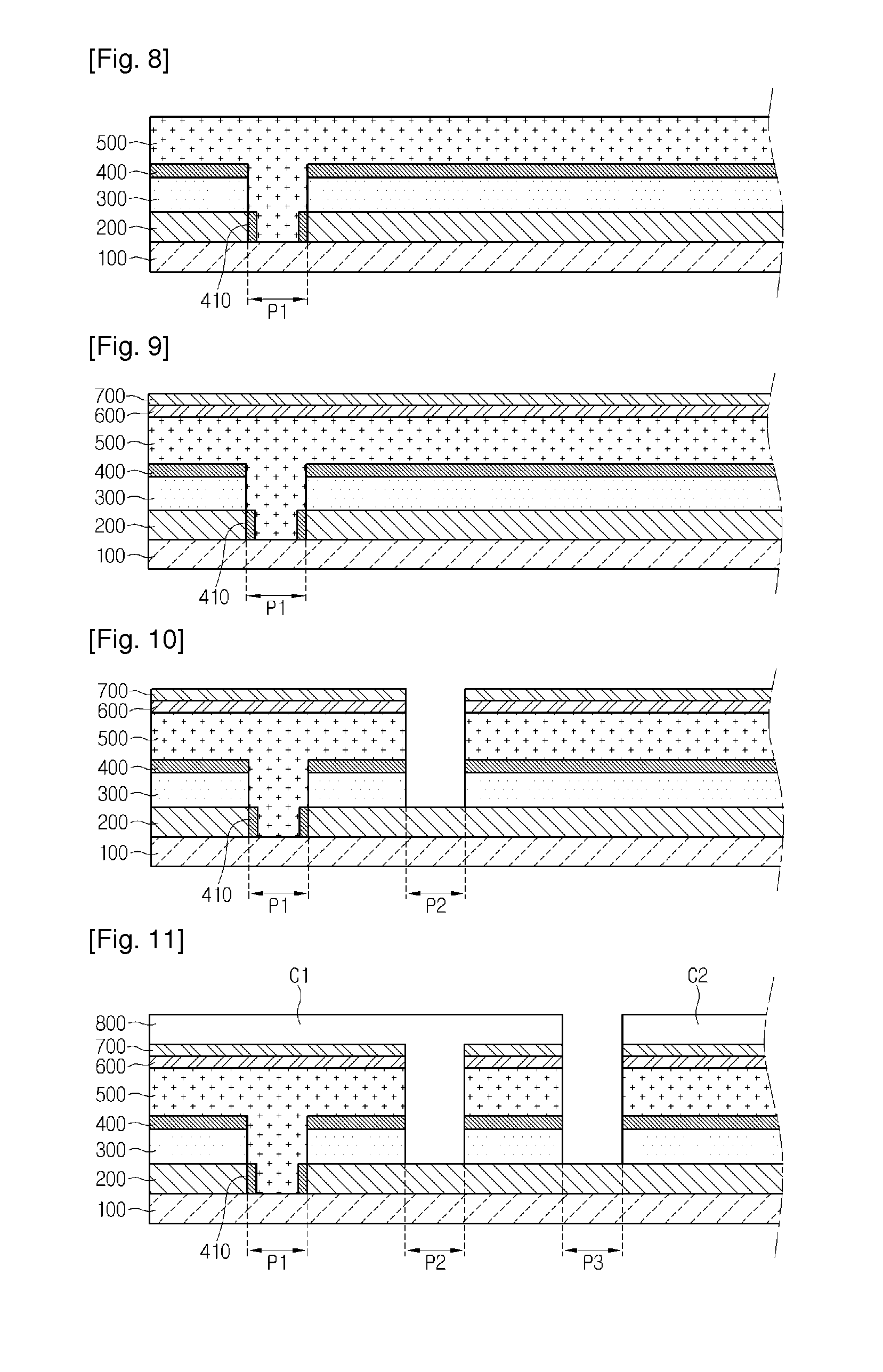

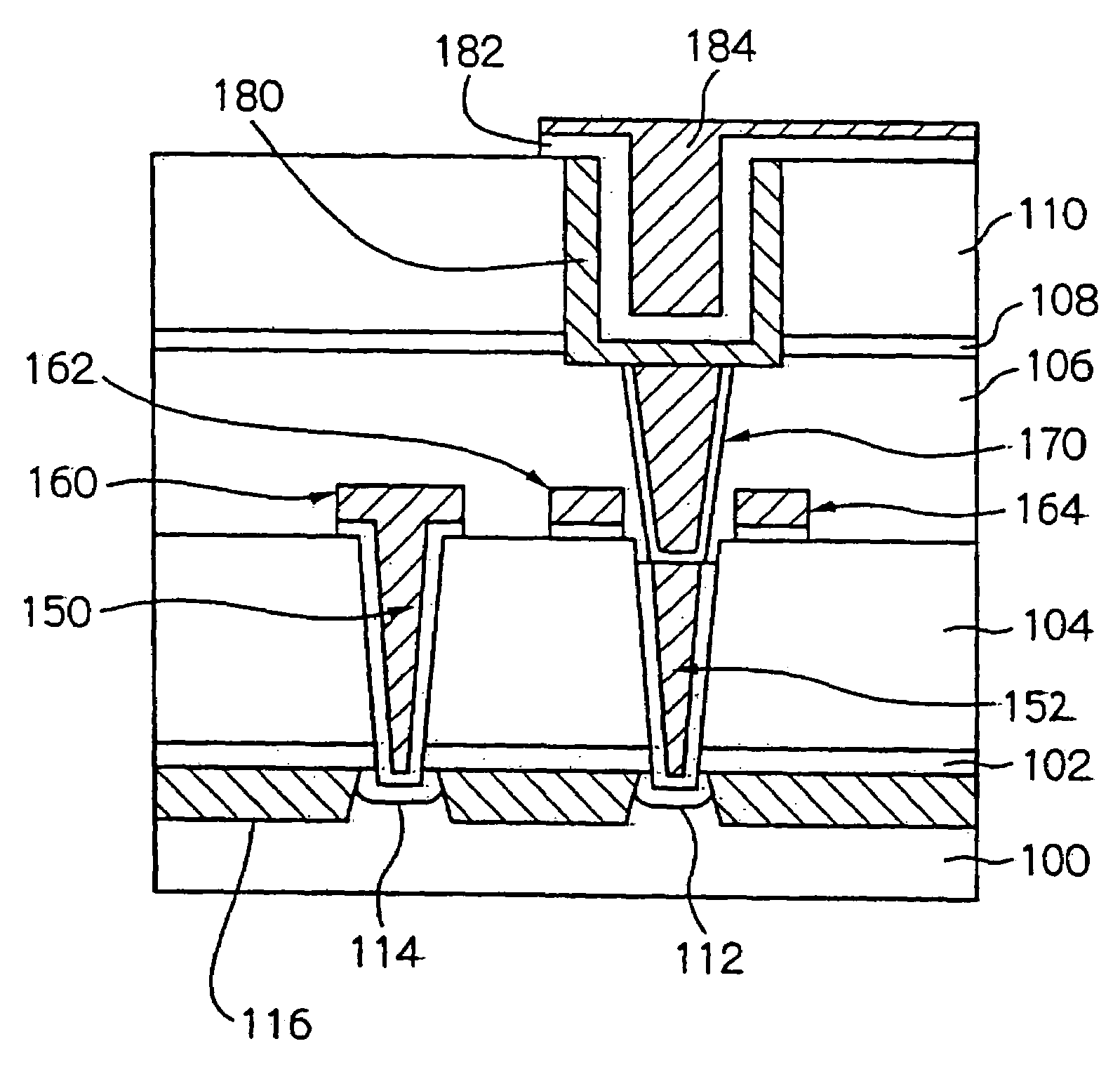

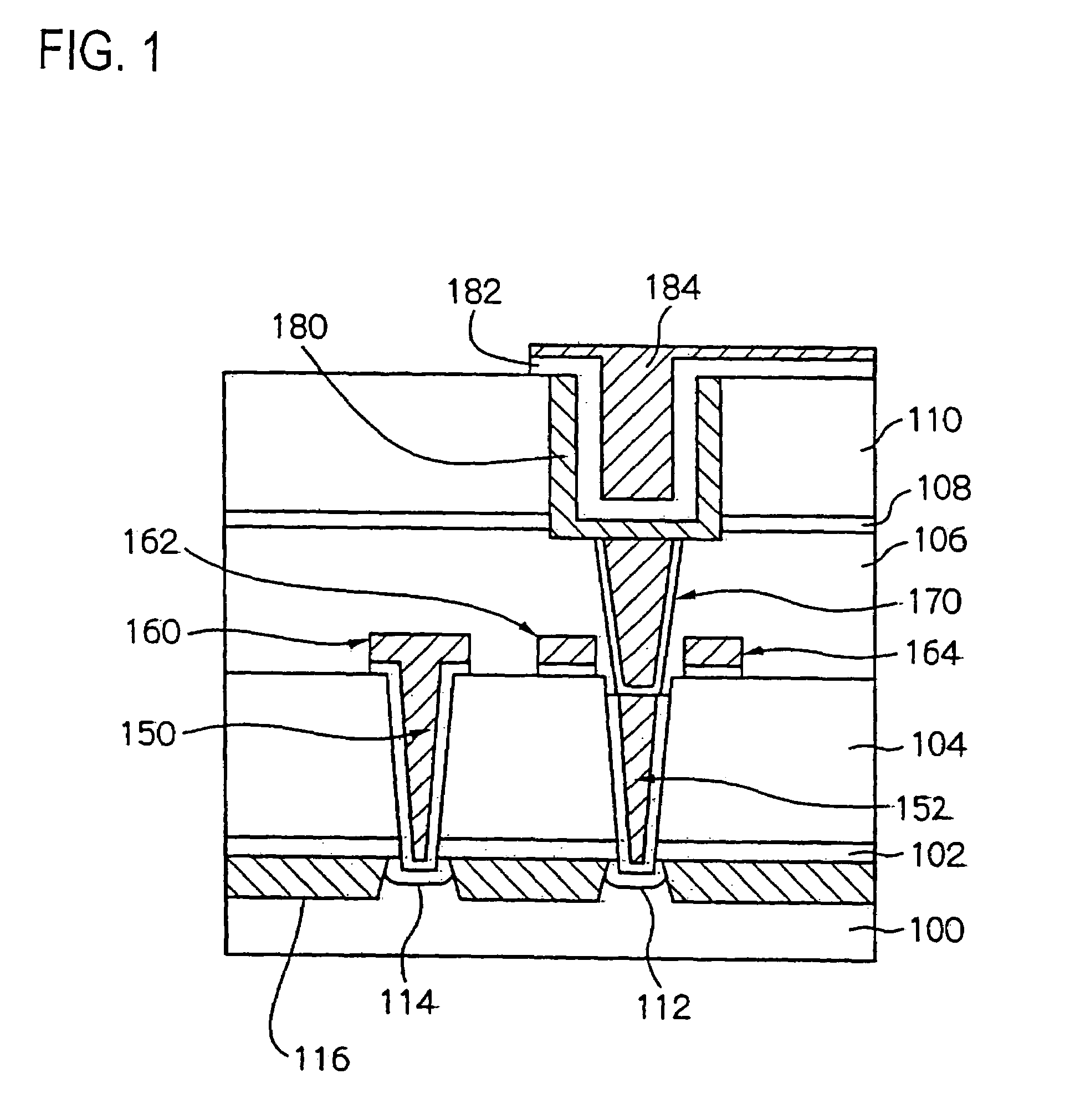

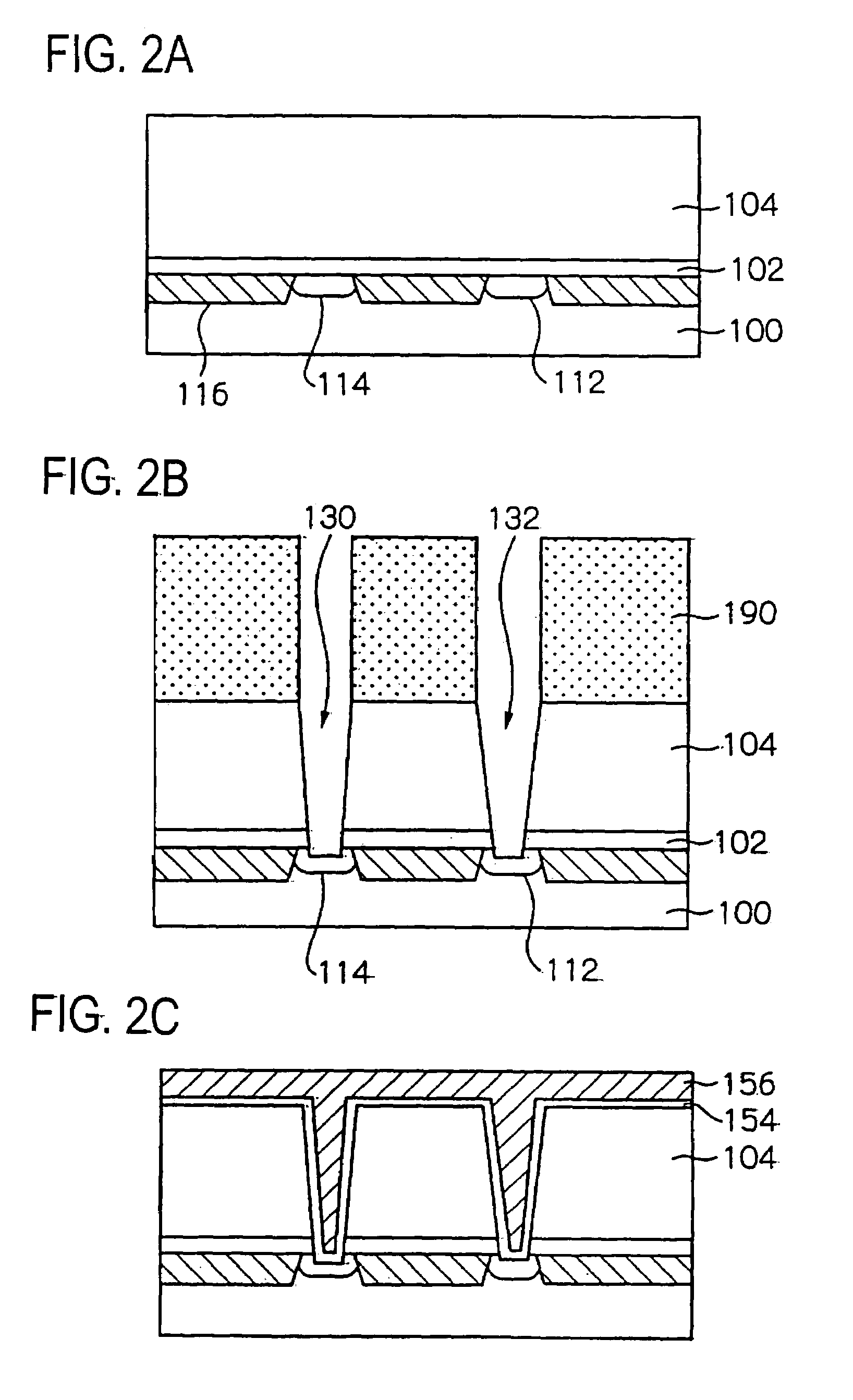

Methods of forming self-aligned contact structures in semiconductor integrated circuit devices

InactiveUS6881659B2Minimize parasitic capacitanceImprove reliabilityTransistorSolid-state devicesEtchingInterconnection

Methods of forming integrated circuit devices (e.g., memory devices) include the use of preferred self-aligned contact hole fabrication steps. These steps improve process reliability by reducing the likelihood that contact holes will become misaligned to underlying integrated circuit device structures and thereby potentially expose the structures in an adverse manner. Typical methods include the steps of forming a plurality of interconnection patterns on a substrate and then covering a surface of the interconnection patterns and a portion of the substrate with a capping insulating layer such as silicon nitride layer. The capping insulating layer is then covered with an upper interlayer insulating layer different from the capping insulating layer. The upper interlayer insulating layer and the capping insulating layer are then dry-etched in sequence to form a first narrow contact hole that exposes the substrate, but preferably does not expose the interconnection patterns. The first contact hole is then widened in a self-aligned manner using the capping insulating layer as an etch-stop layer. This widening step is performed by wet etching sidewalls of the first contact hole using an etchant that etches the upper interlayer insulating layer faster than the capping insulating layer. In this manner, the first contact hole may be formed to initially compensate for potential misalignment errors and then a self-aligned wet etching step may be performed to widen the first contact hole into a second contact hole so that low resistance contacts (e.g., contact plugs) can be provided therein.

Owner:SAMSUNG ELECTRONICS CO LTD

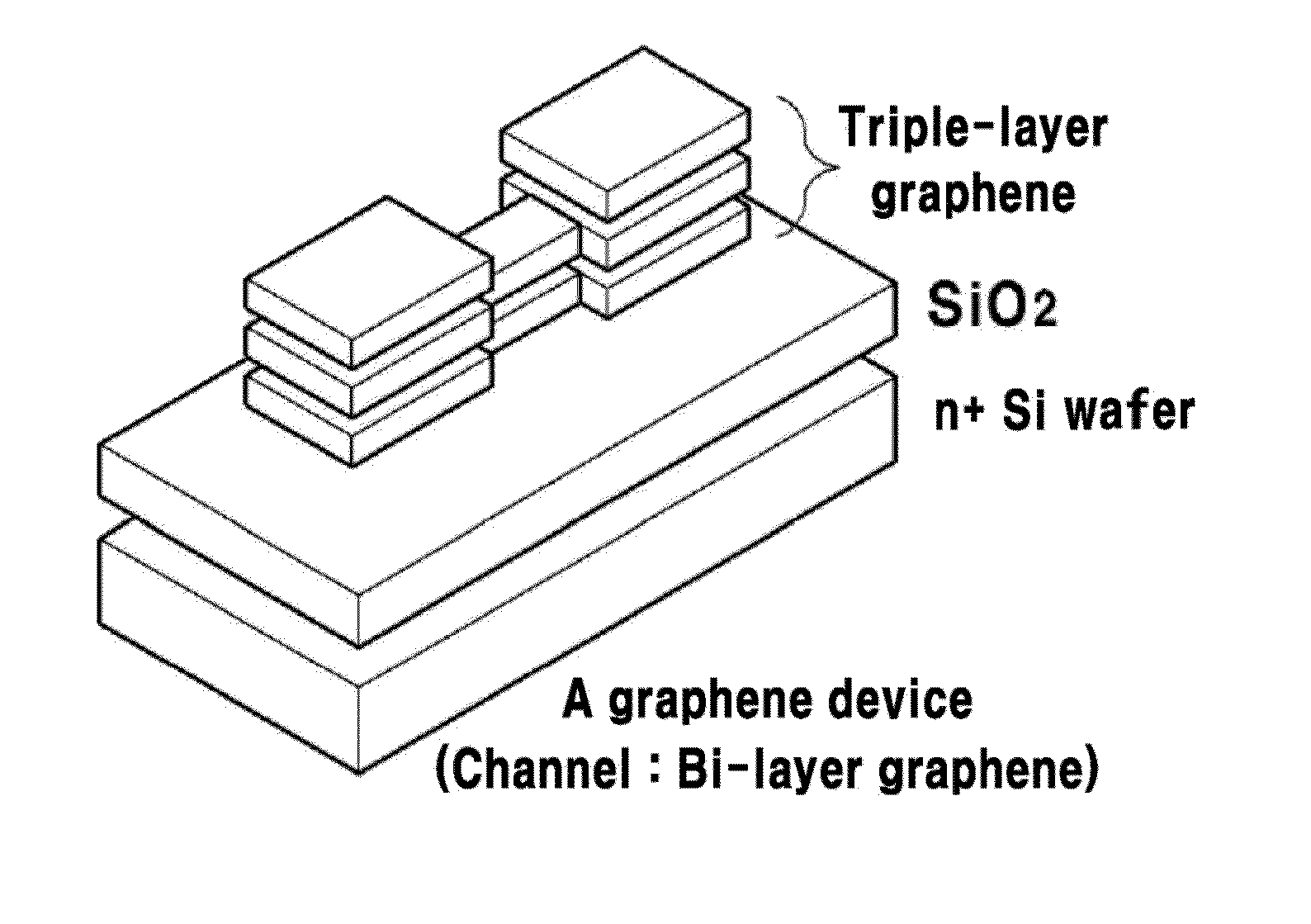

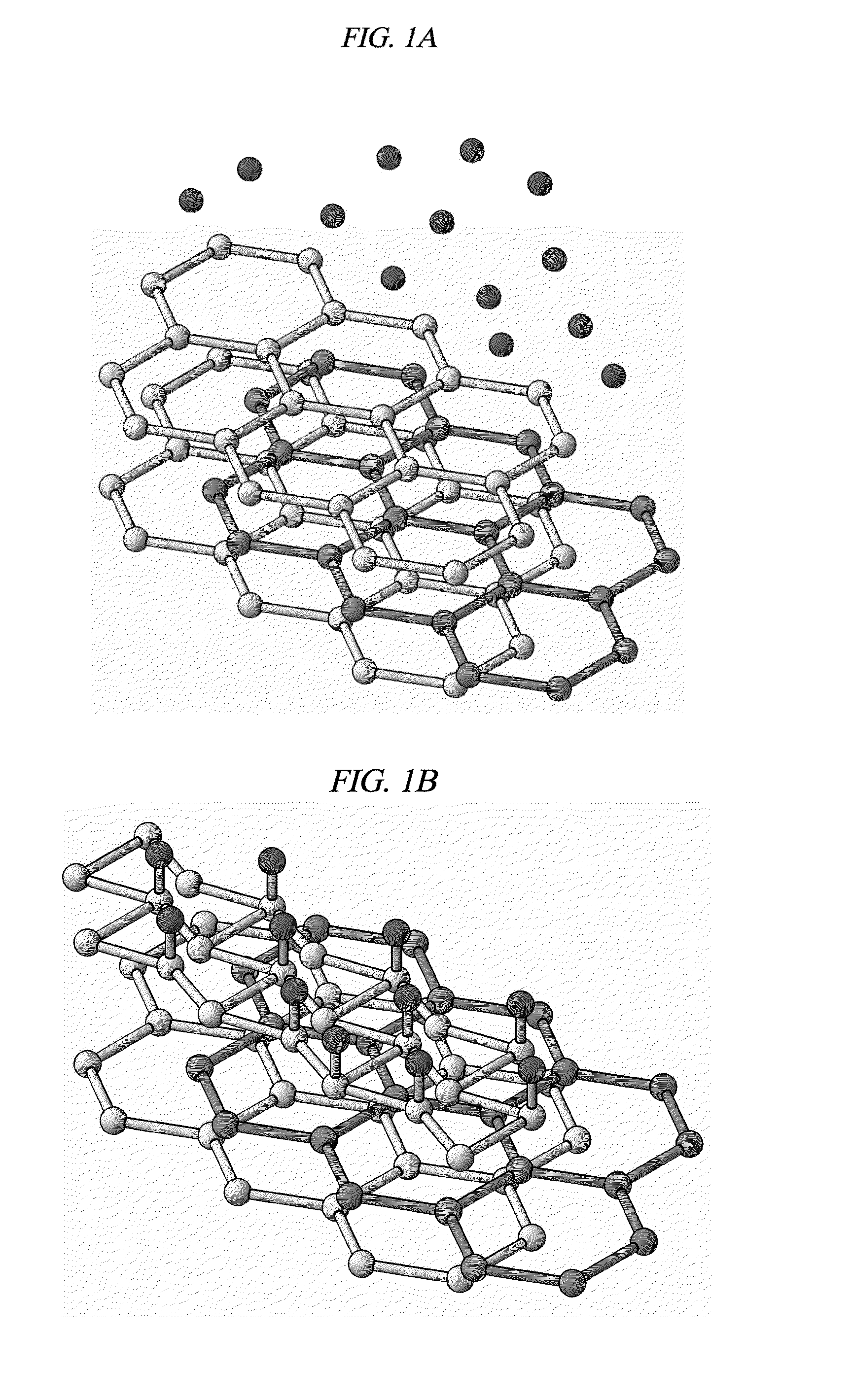

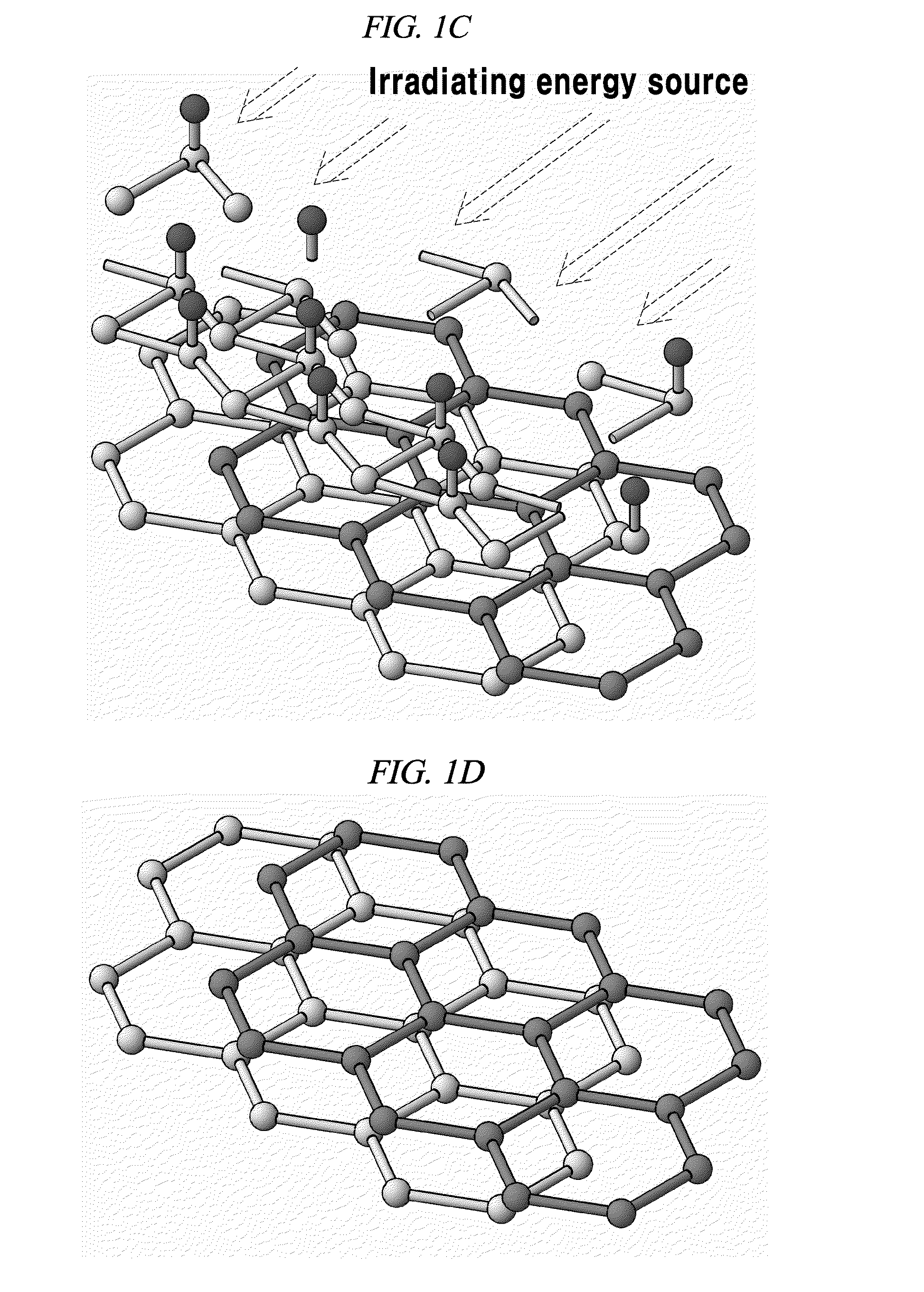

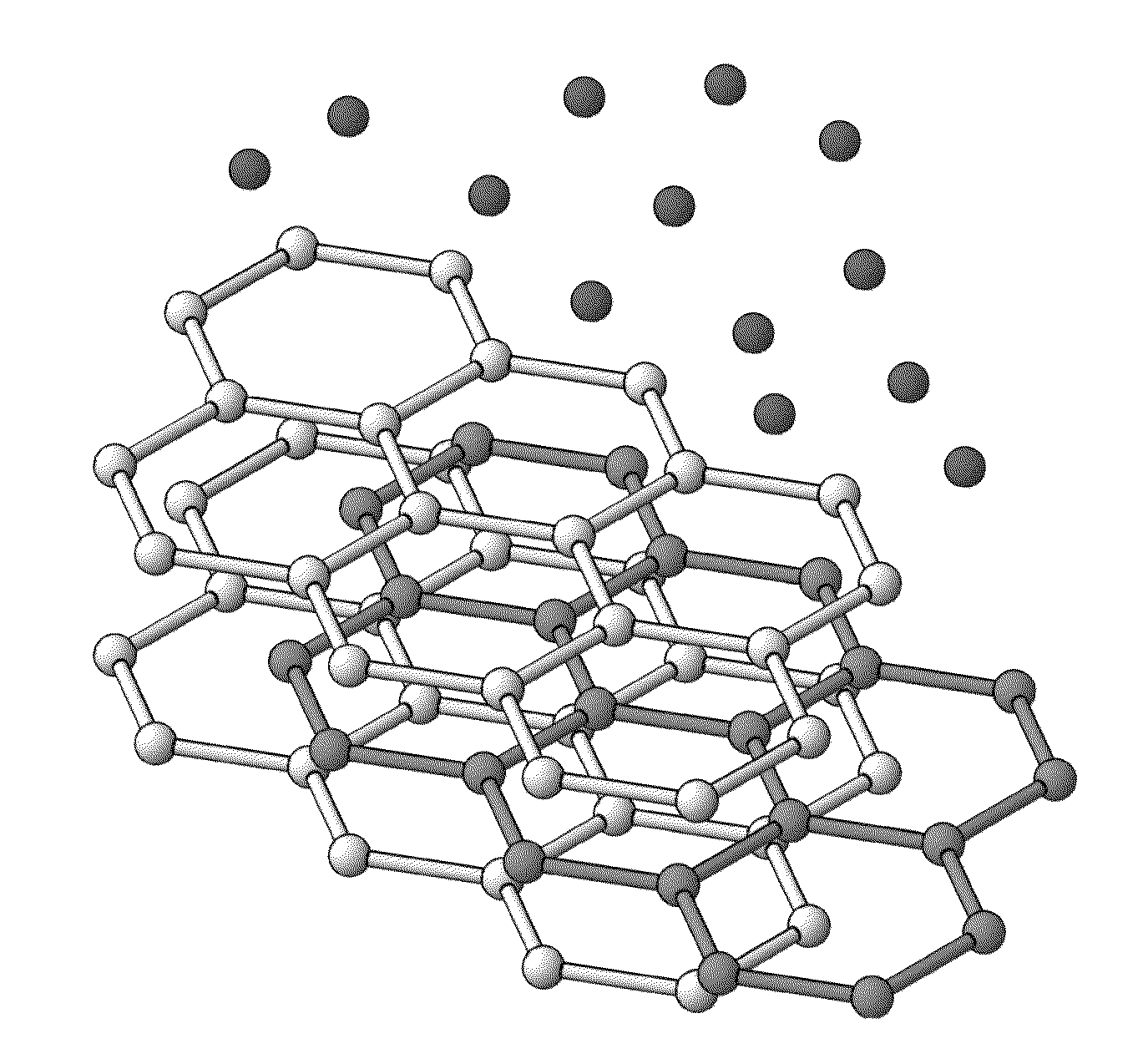

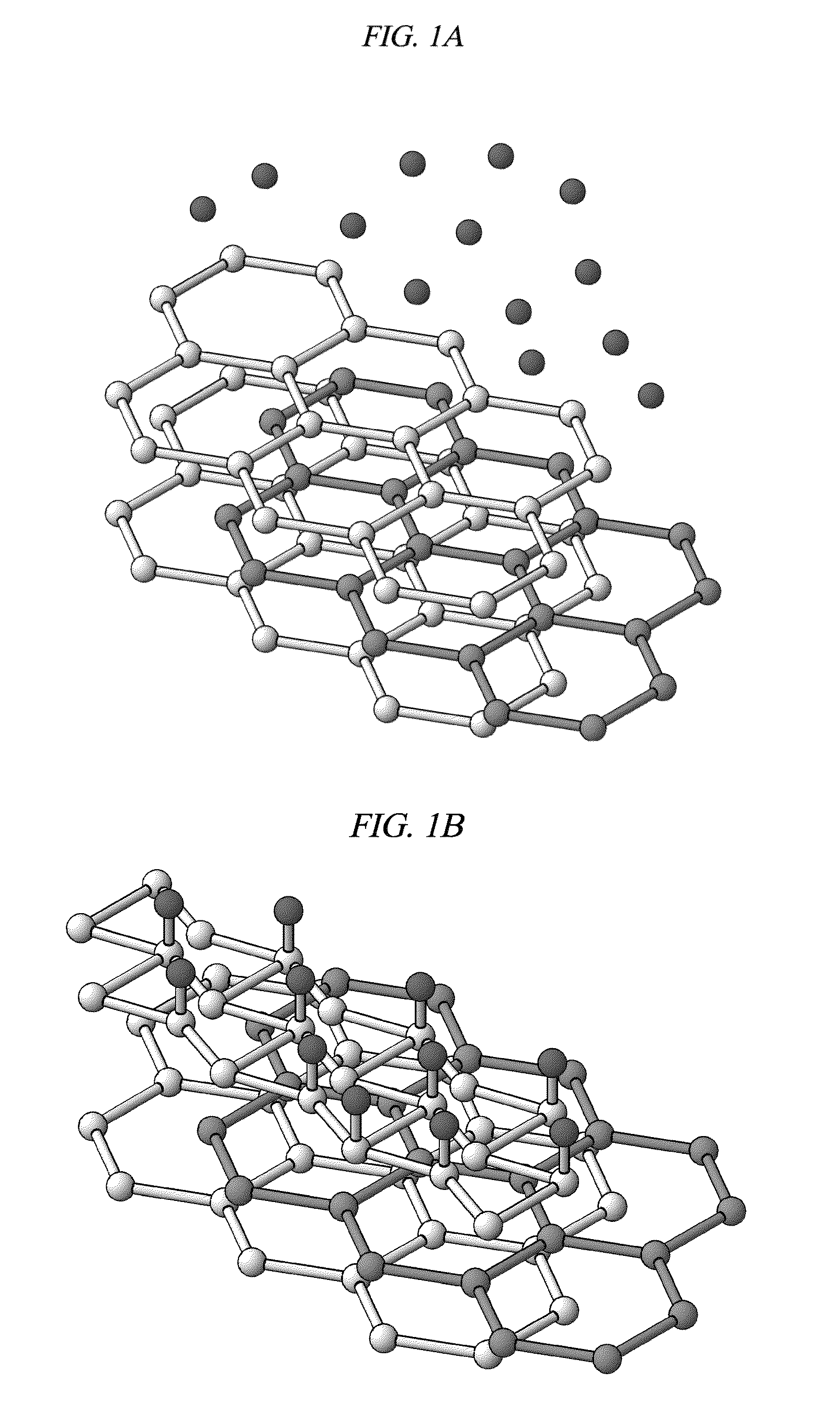

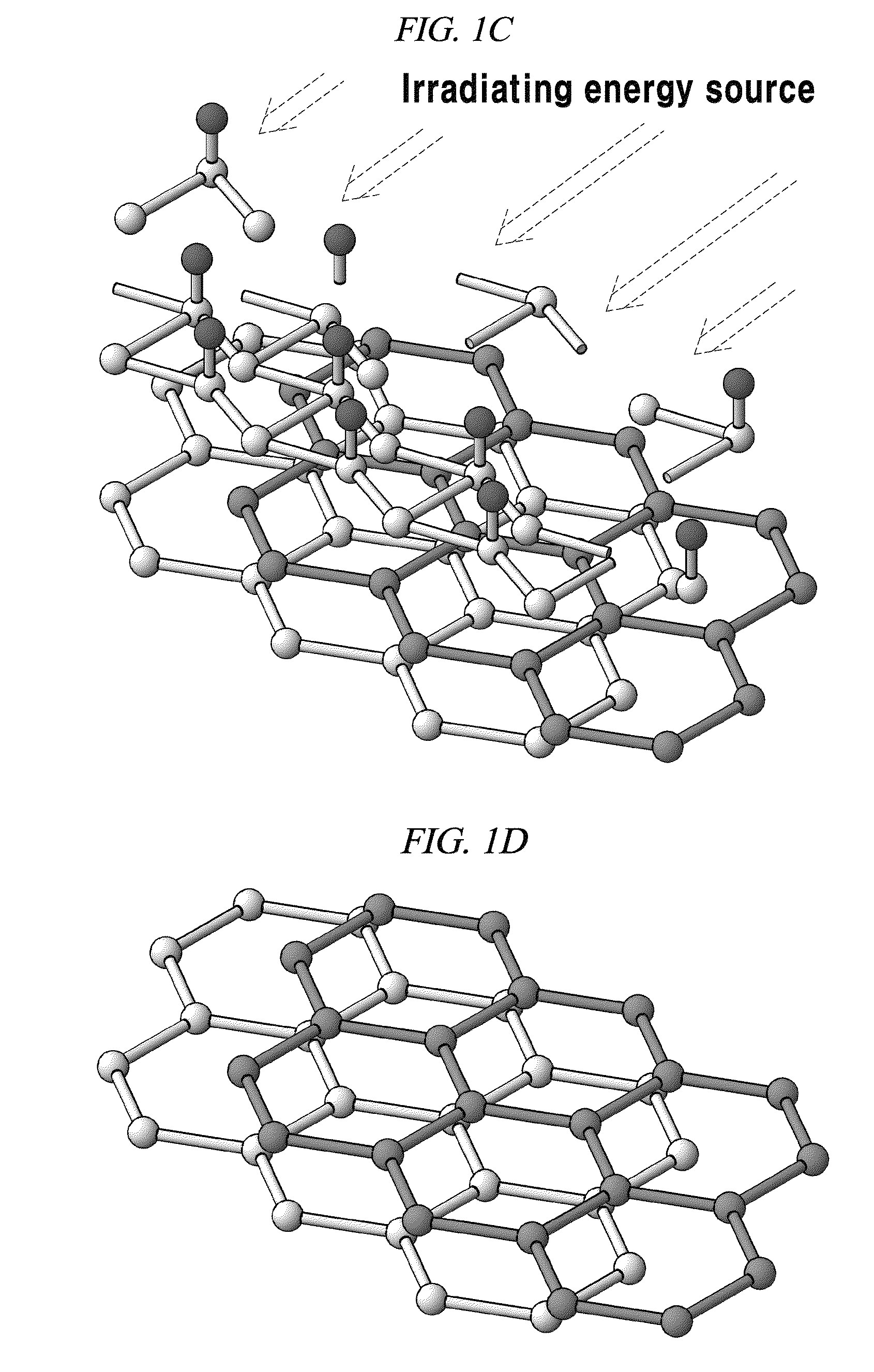

Method for etching atomic layer of graphine

ActiveUS20140206192A1Minimize damageMinimizing physical and electrical damageSemiconductor/solid-state device manufacturingGrapheneEtchingGraphite

This present disclosure relates to an atomic layer etching method for graphene, including adsorbing reactive radicals onto a surface of the graphene and irradiating an energy source to the graphene on which the reactive radicals are adsorbed.

Owner:RES & BUSINESS FOUND SUNGKYUNKWAN UNIV

Semiconductor device and method of manufacturing thereof

ActiveUS20050001253A1Minimized contact resistanceEfficiently and stably provideTransistorSolid-state devicesDielectricLithography process

There is provided a method of manufacturing a semiconductor device that can reduce the number of processes, and decrease contact resistance between plugs. The method comprises forming a first interlayer dielectric film having a first opening where a contact plug is to be formed; uniformly forming a first conductive layer on the first interlayer dielectric film and in the first opening; forming a resist defining an interconnect pattern by a lithography process on a region excluding the first opening; performing first anisotropic etching to remove a region of the first conductive layer not covered with the resist until an upper face of the first interlayer dielectric film is exposed, thus to form an interconnect and the contact plug.

Owner:RENESAS ELECTRONICS CORP

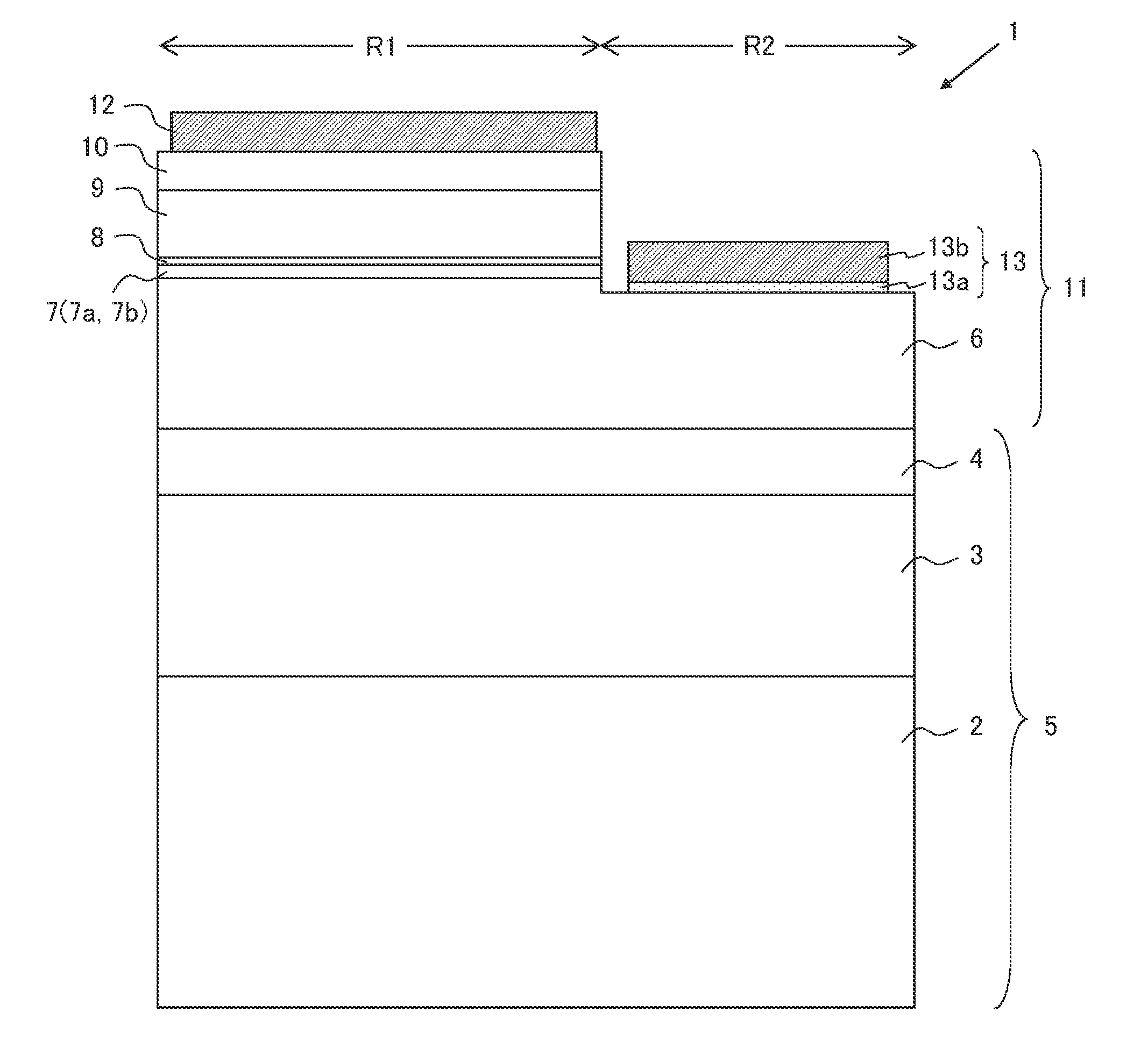

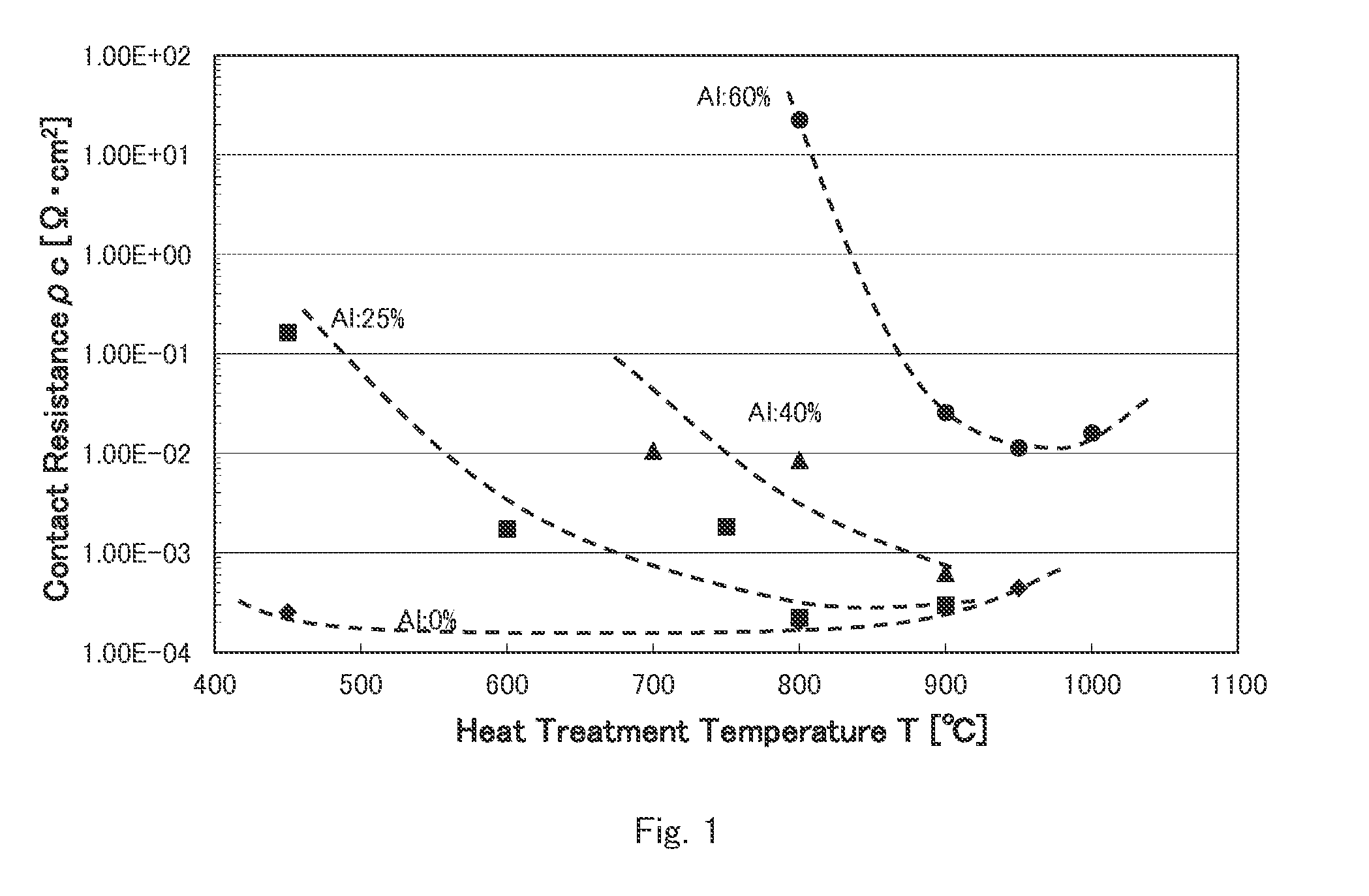

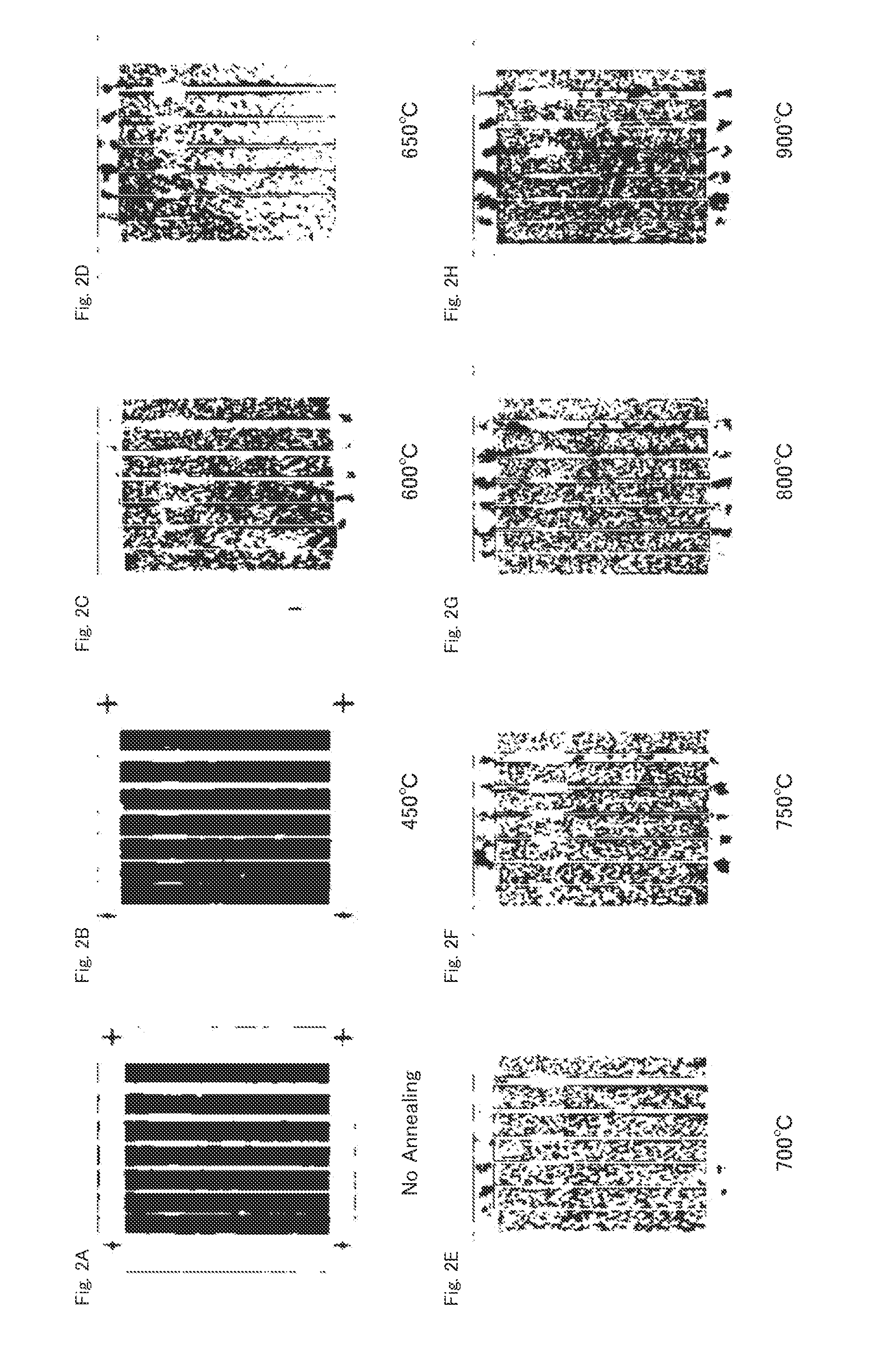

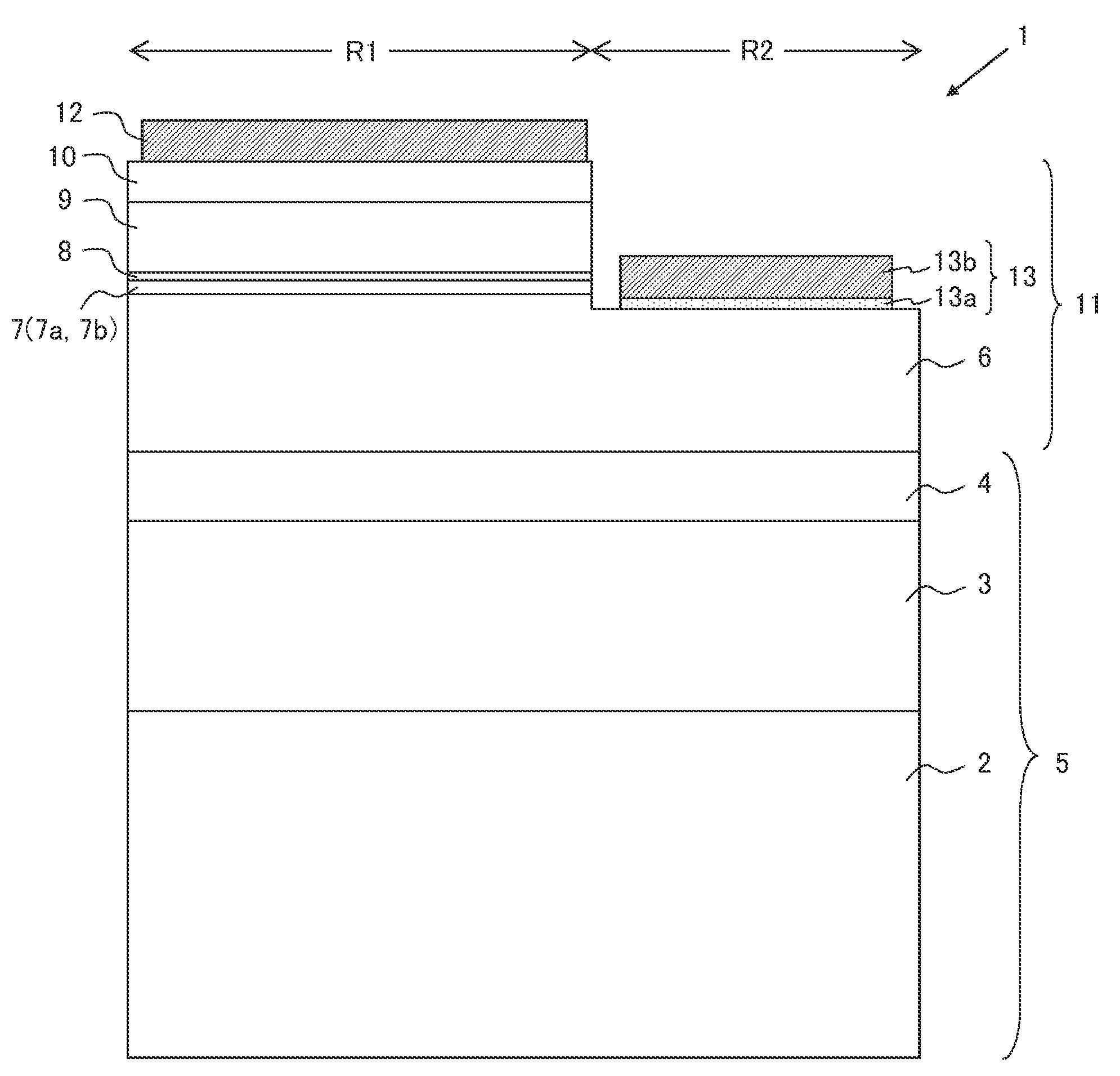

Nitride semiconductor element and method for producing same

ActiveUS20150048304A1Increase consumptionHigh production costSemiconductor/solid-state device manufacturingSemiconductor devicesElectrode ContactNitride semiconductors

A nitride semiconductor element 1 includes a base structure part 5, and an element structure part 11 formed on the base structure part 5 and having at least an n-type AlGaN based semiconductor layer 6, and p-type AlGaN based semiconductor layers 8, 9, 10, and further includes an n-electrode contact part 13a formed on the n-type AlGaN based semiconductor layer 6, an n-electrode pad part 13b formed on the n-electrode contact part 13a, and a p-electrode 12 formed on the p-type AlGaN based semiconductor layers 8, 9, 10, in which an AlN mole fraction in the n-type AlGaN based semiconductor layer 6 is 20% or more, the n-electrode contact part 13a includes one or more metal layers, and the p-electrode 12 and the n-electrode pad part 13b have a common laminated structure of two or more layers having an Au layer as an uppermost layer, and an Au diffusion preventing layer composed of conductive metal oxide and formed under the uppermost layer to prevent Au diffusion.

Owner:NIKKISO COMPANY

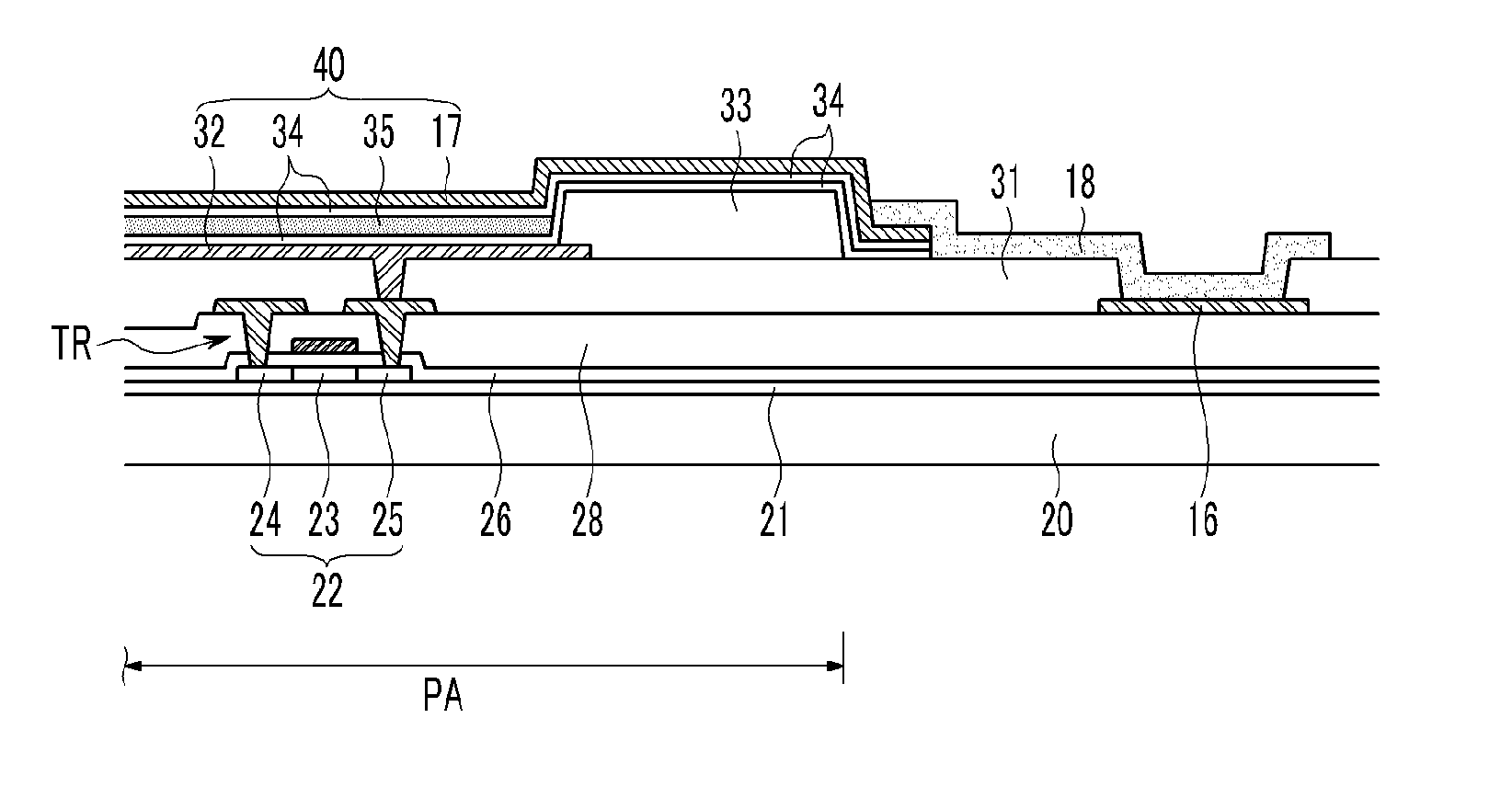

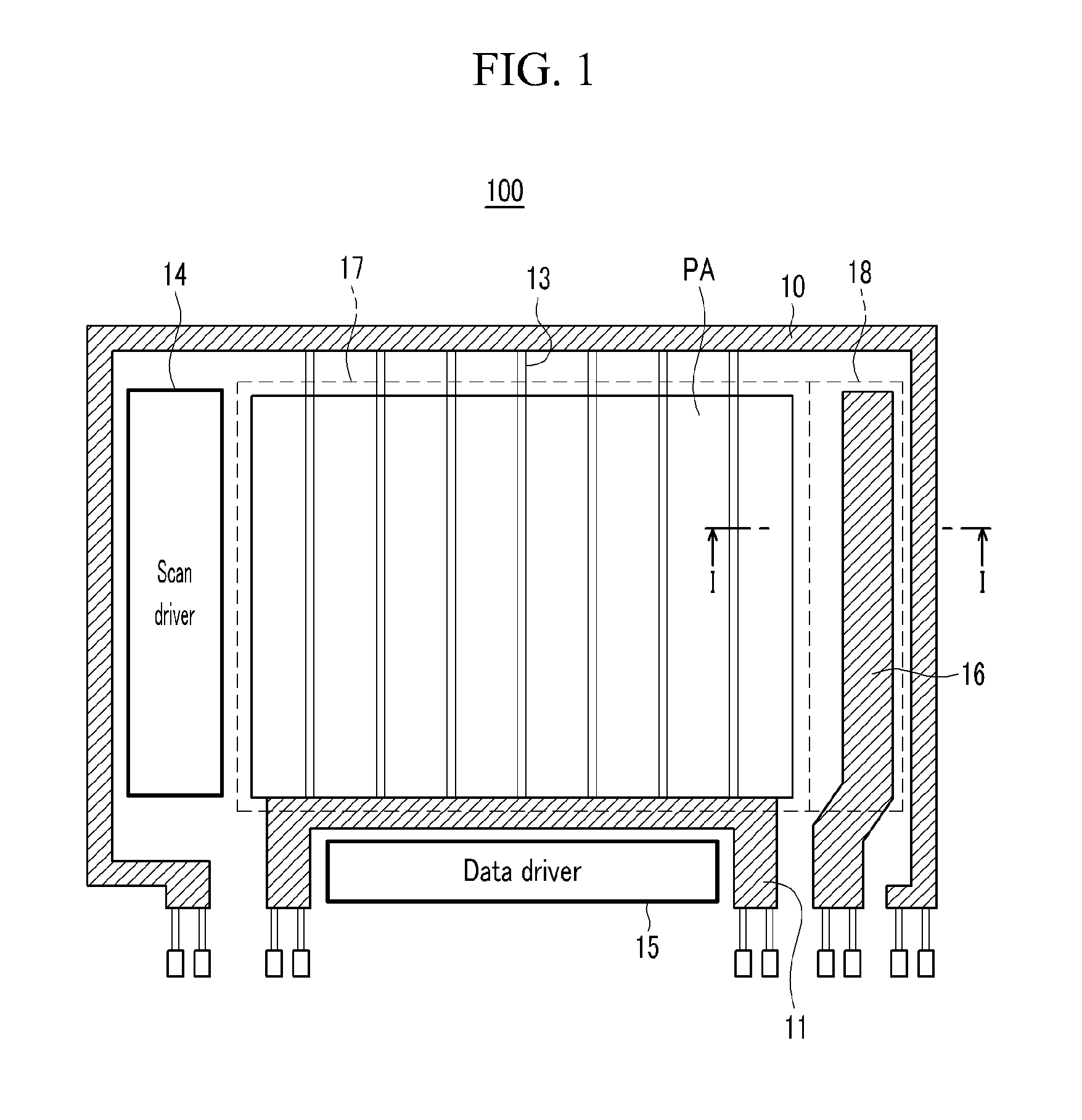

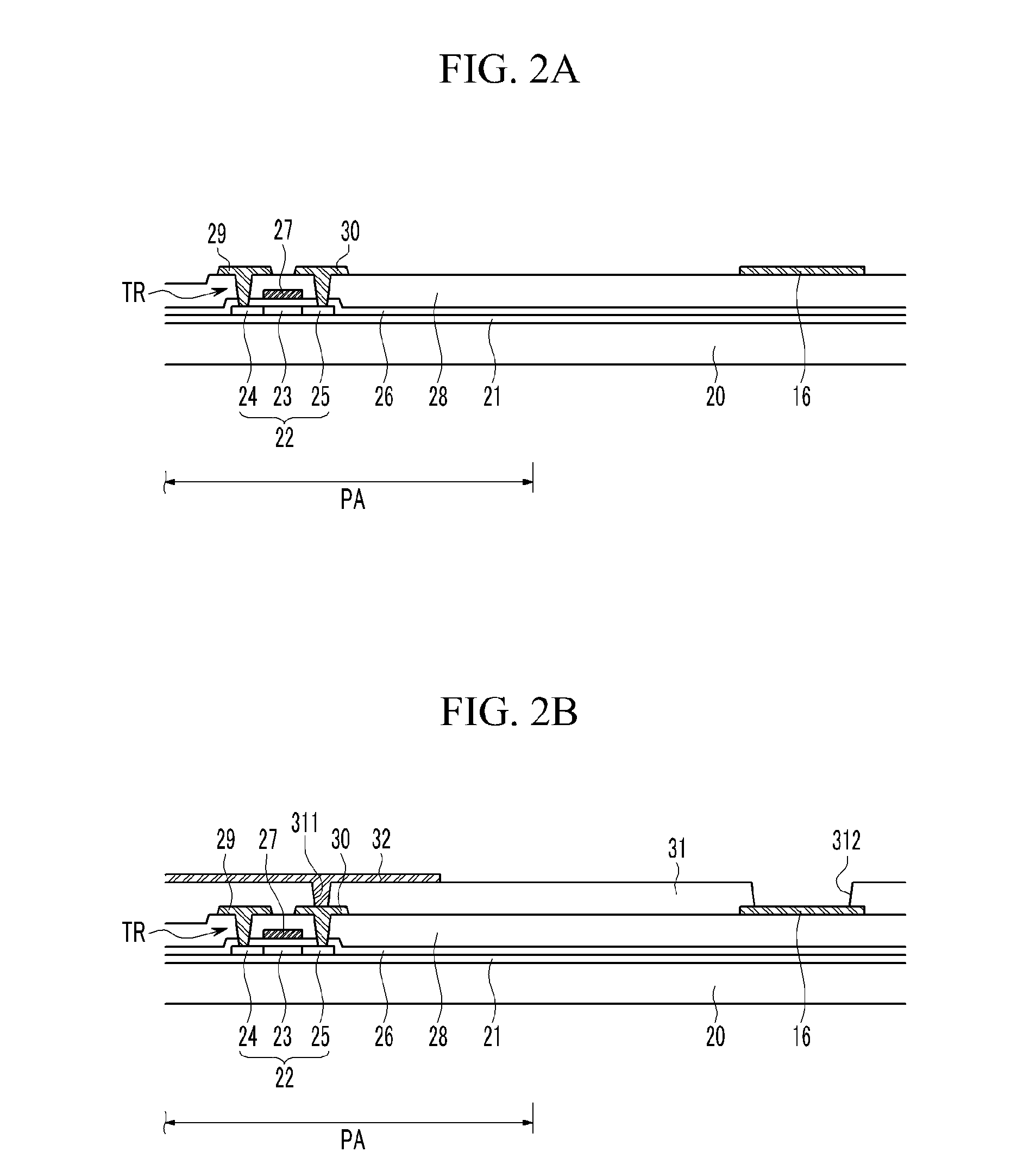

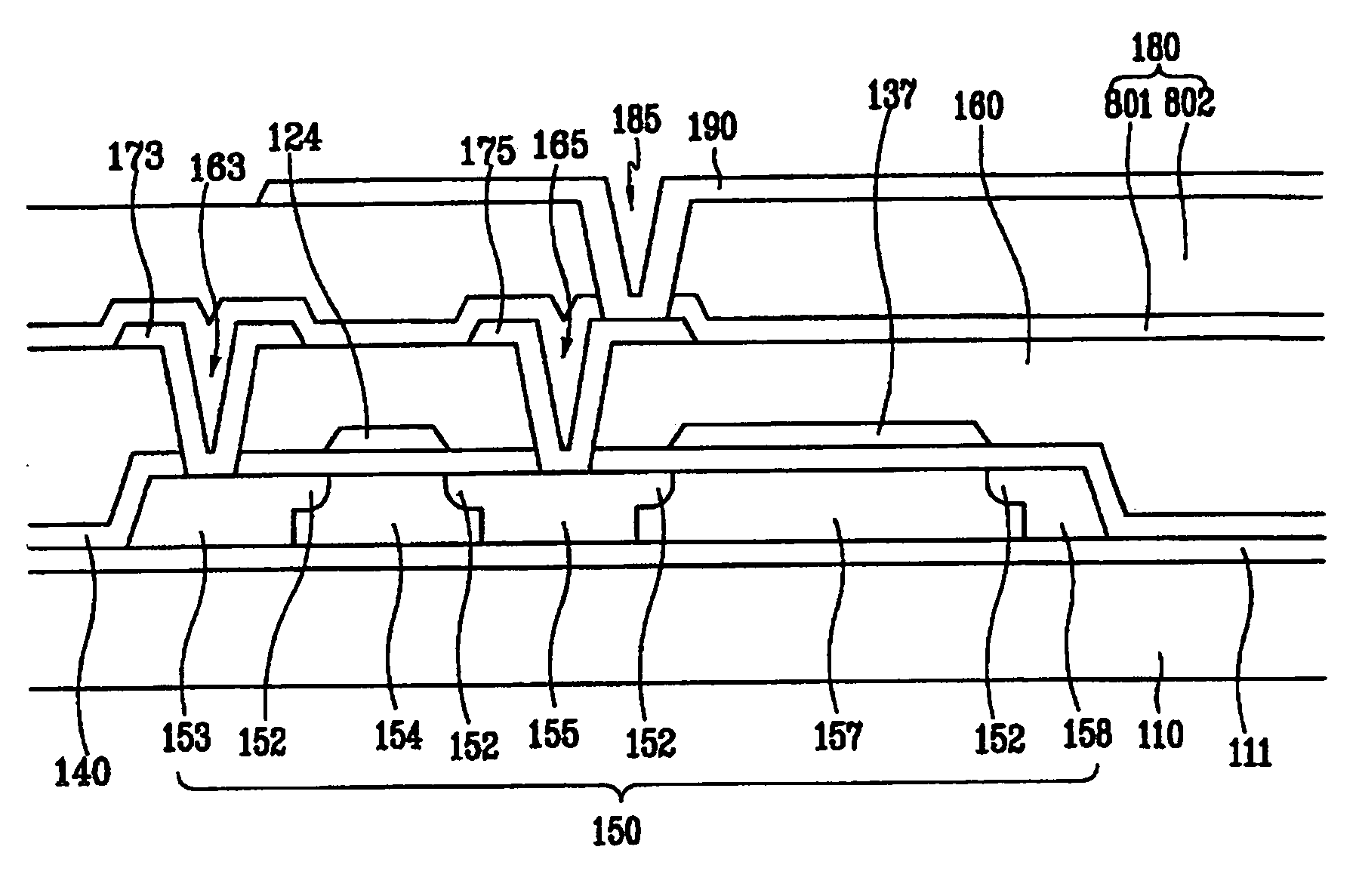

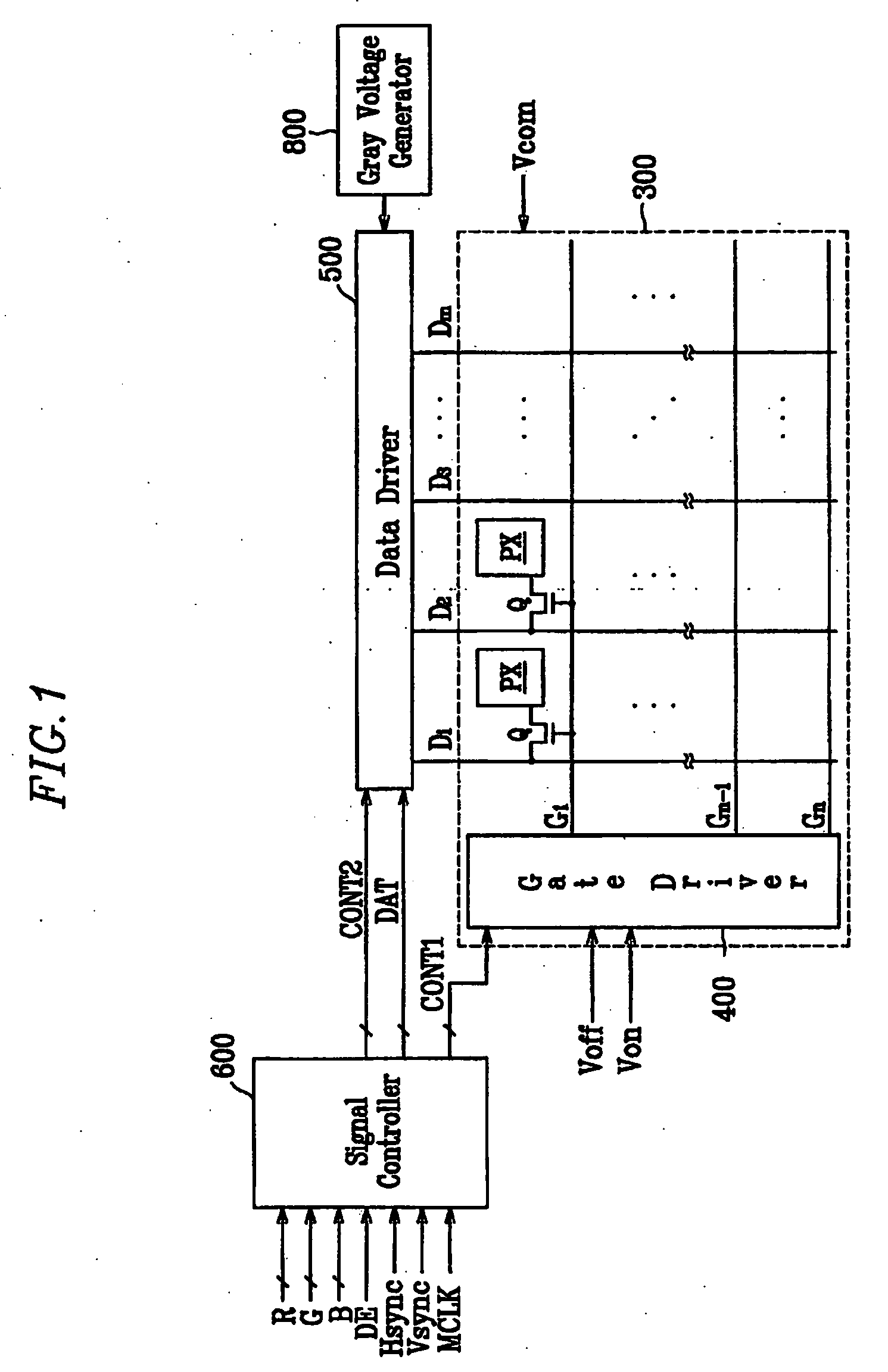

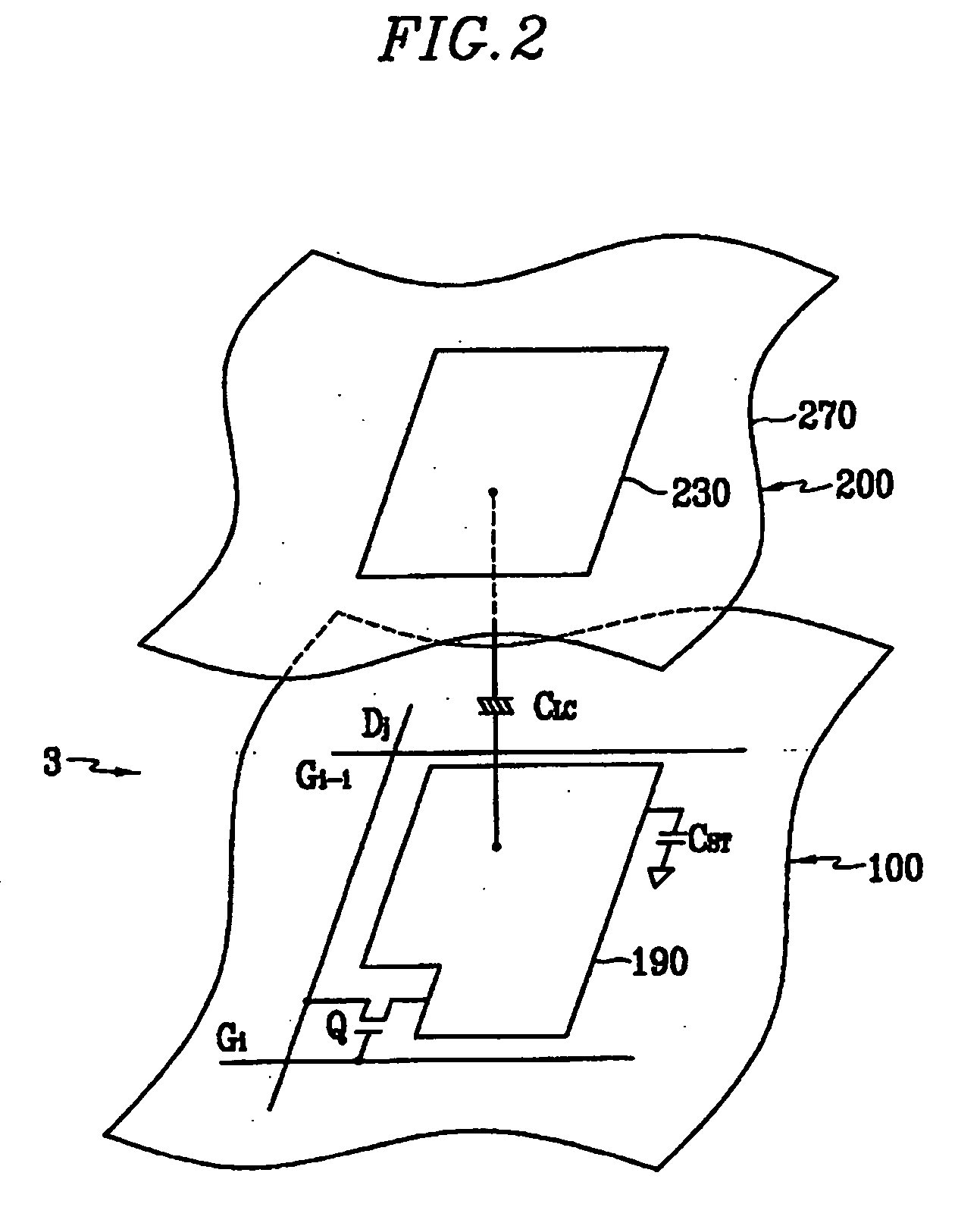

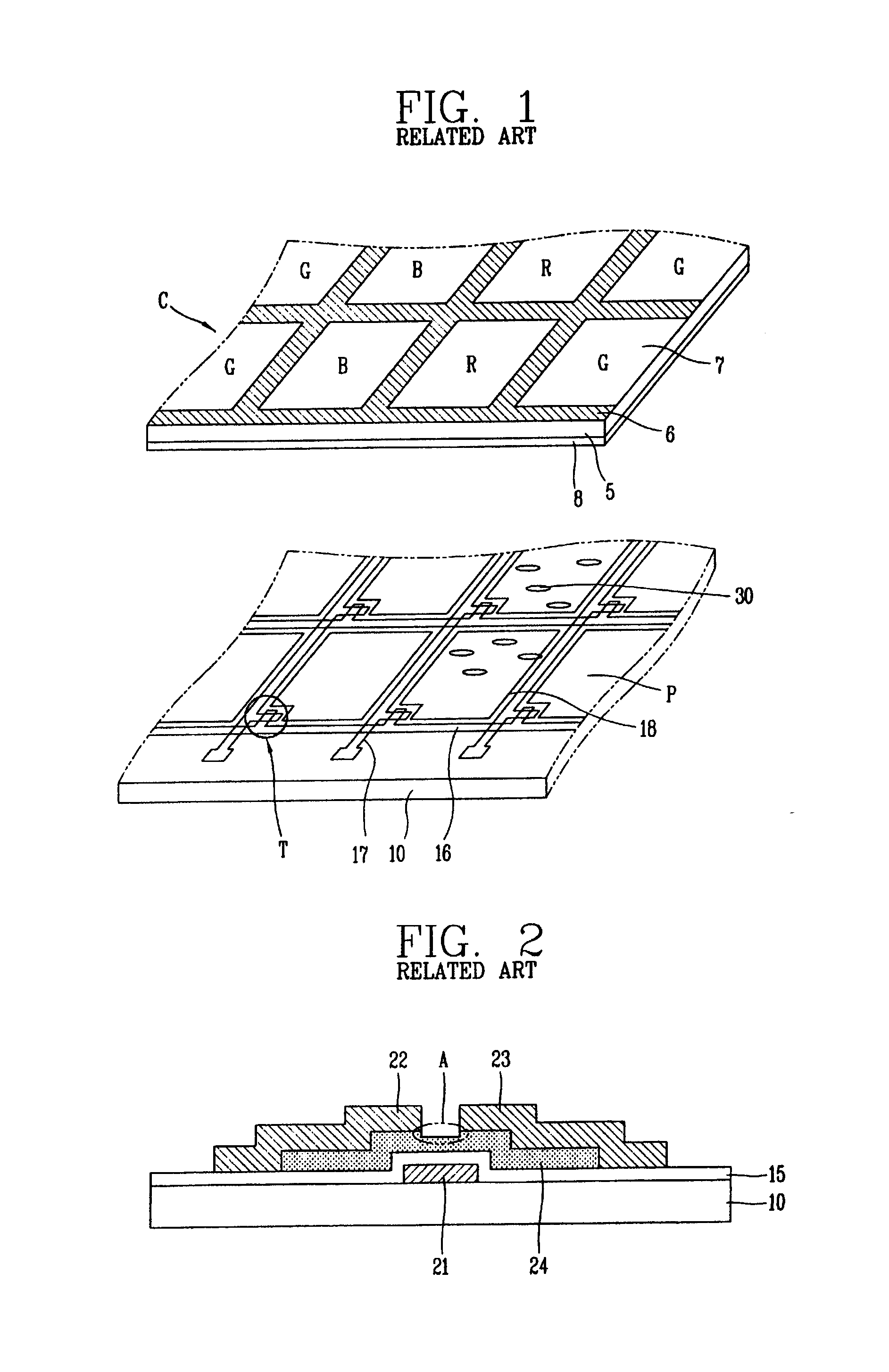

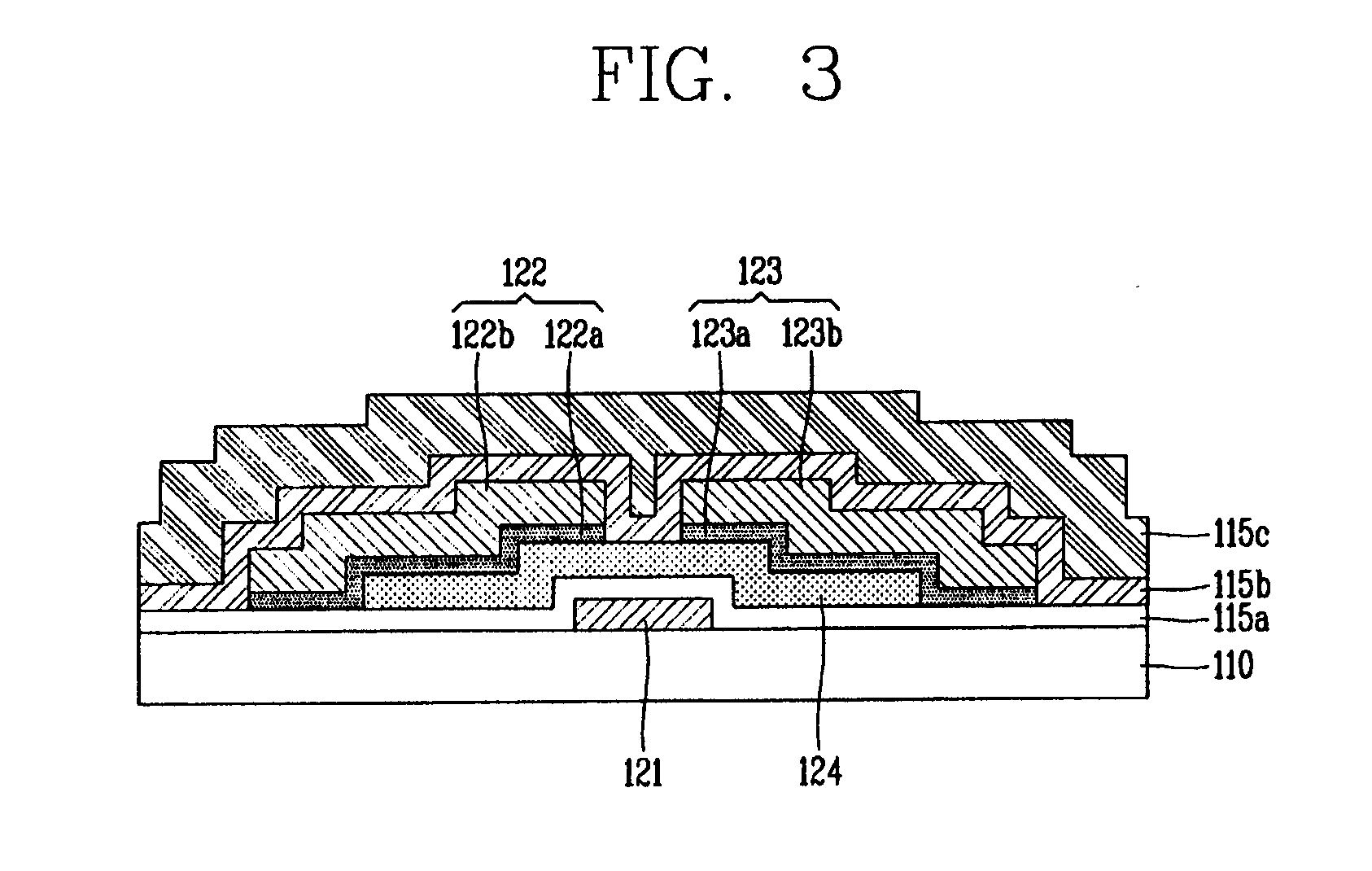

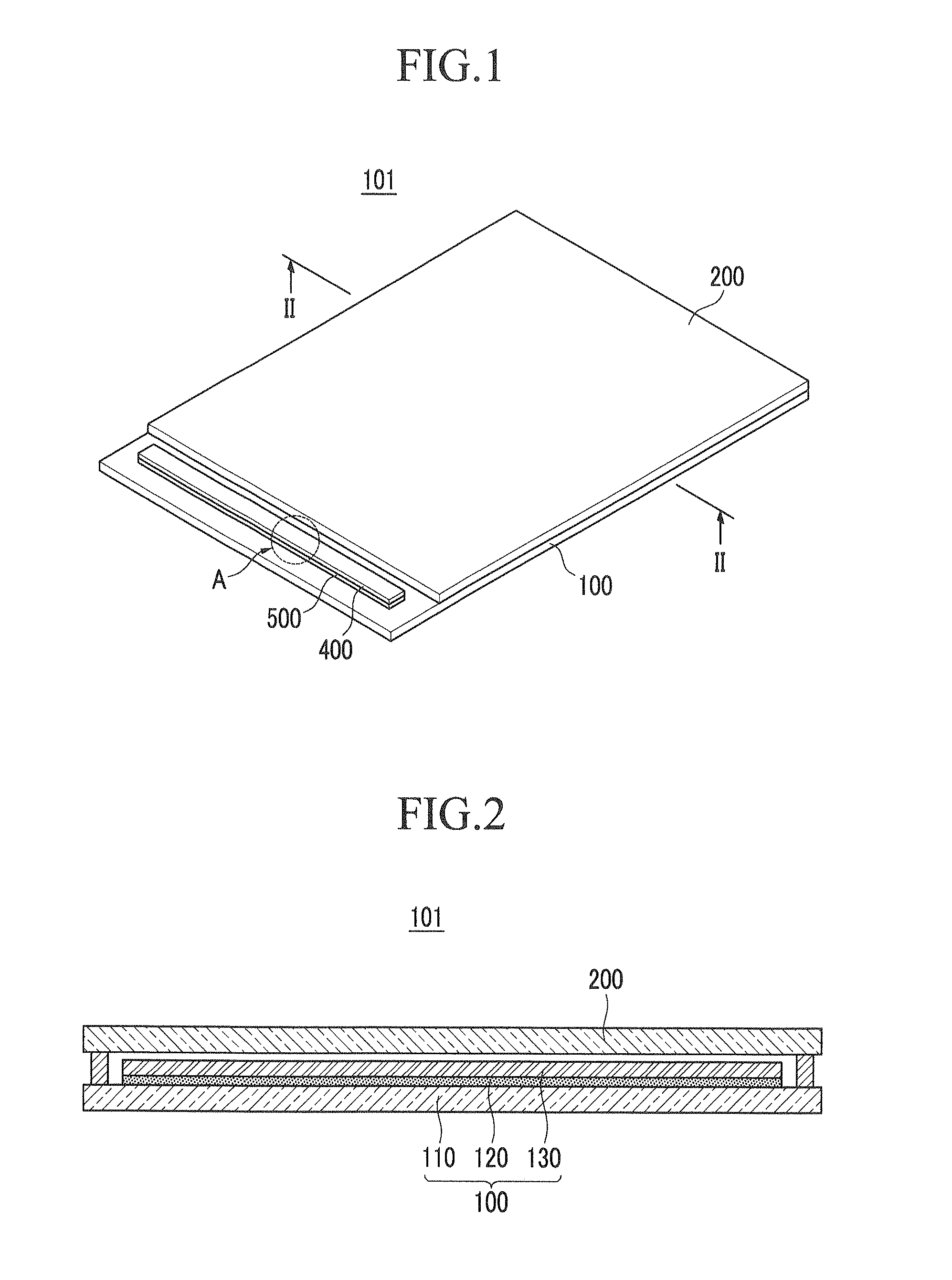

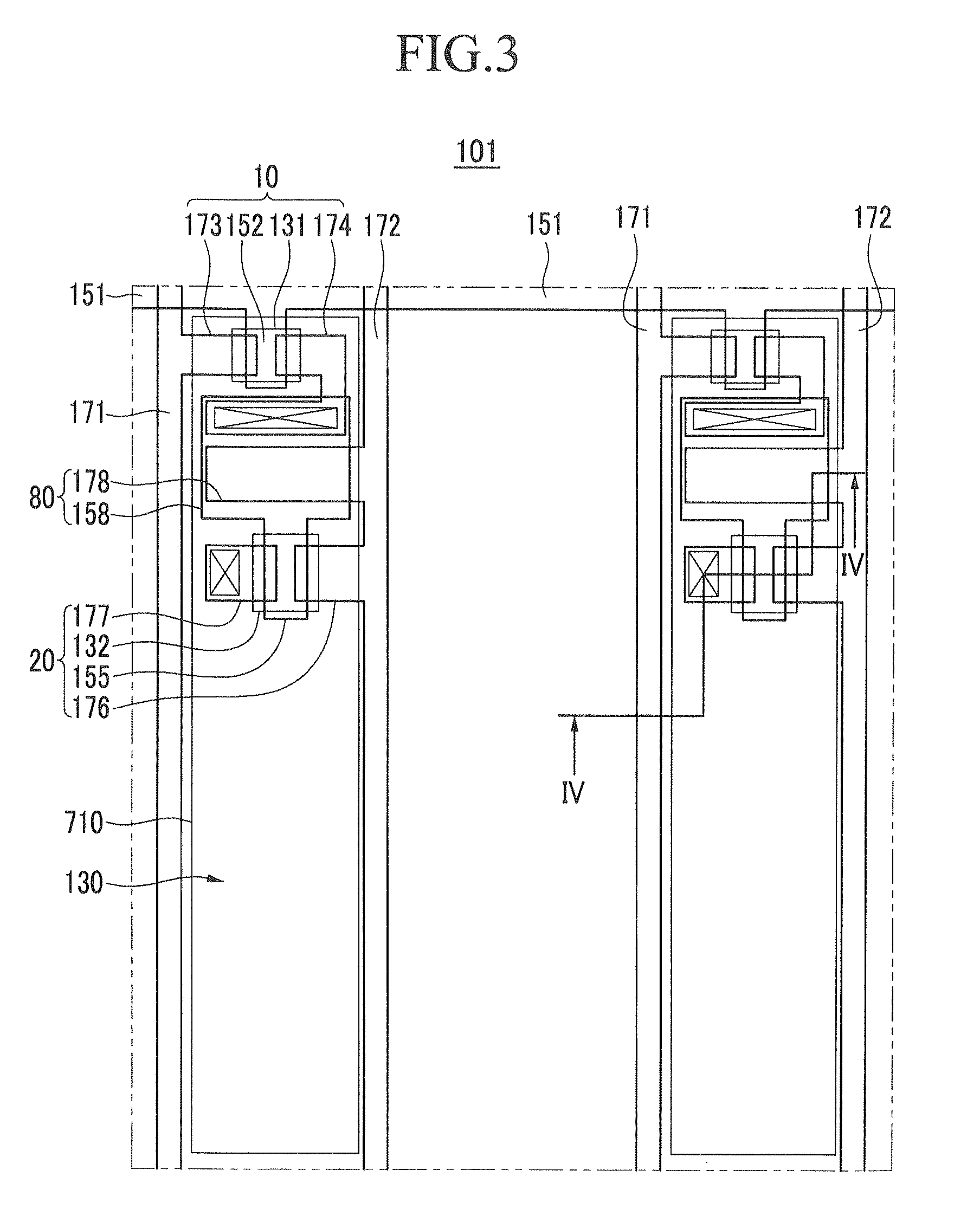

Thin film transistor array panel

ActiveUS20060049407A1Low resistivityAvoid signal delaySolid-state devicesNon-linear opticsTransistorElectrical and Electronics engineering

Improved thin film transistor array panels are provided. In one embodiment, a panel includes a plurality of gate lines, data lines, and a plurality of switching elements connected to the gate lines and the data lines. An interlayer insulating layer is formed between the gate lines and the data lines. A passivation layer covering the gate lines, the data lines, and the switching elements is also provided having a plurality of first contact holes exposing portions of the data lines, wherein the switching elements and the pixel electrodes are connected through the first contact holes. A plurality of contact assistants are formed on the passivation layer and are connected to the data lines through a plurality of second contact holes in the passivation layer. A plurality of auxiliary lines are connected to the data lines through a plurality of third contact holes in the interlayer insulating layer.

Owner:SAMSUNG DISPLAY CO LTD

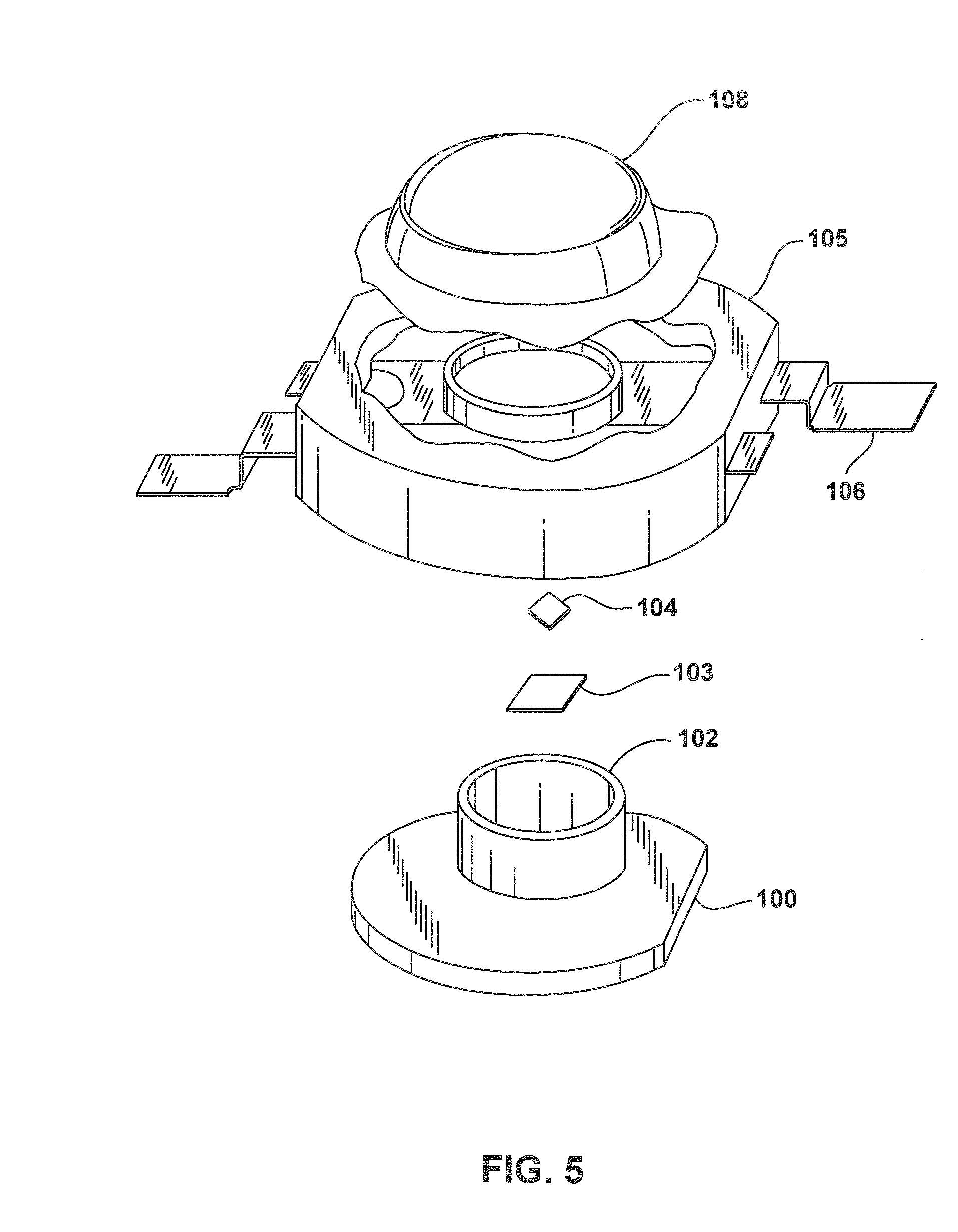

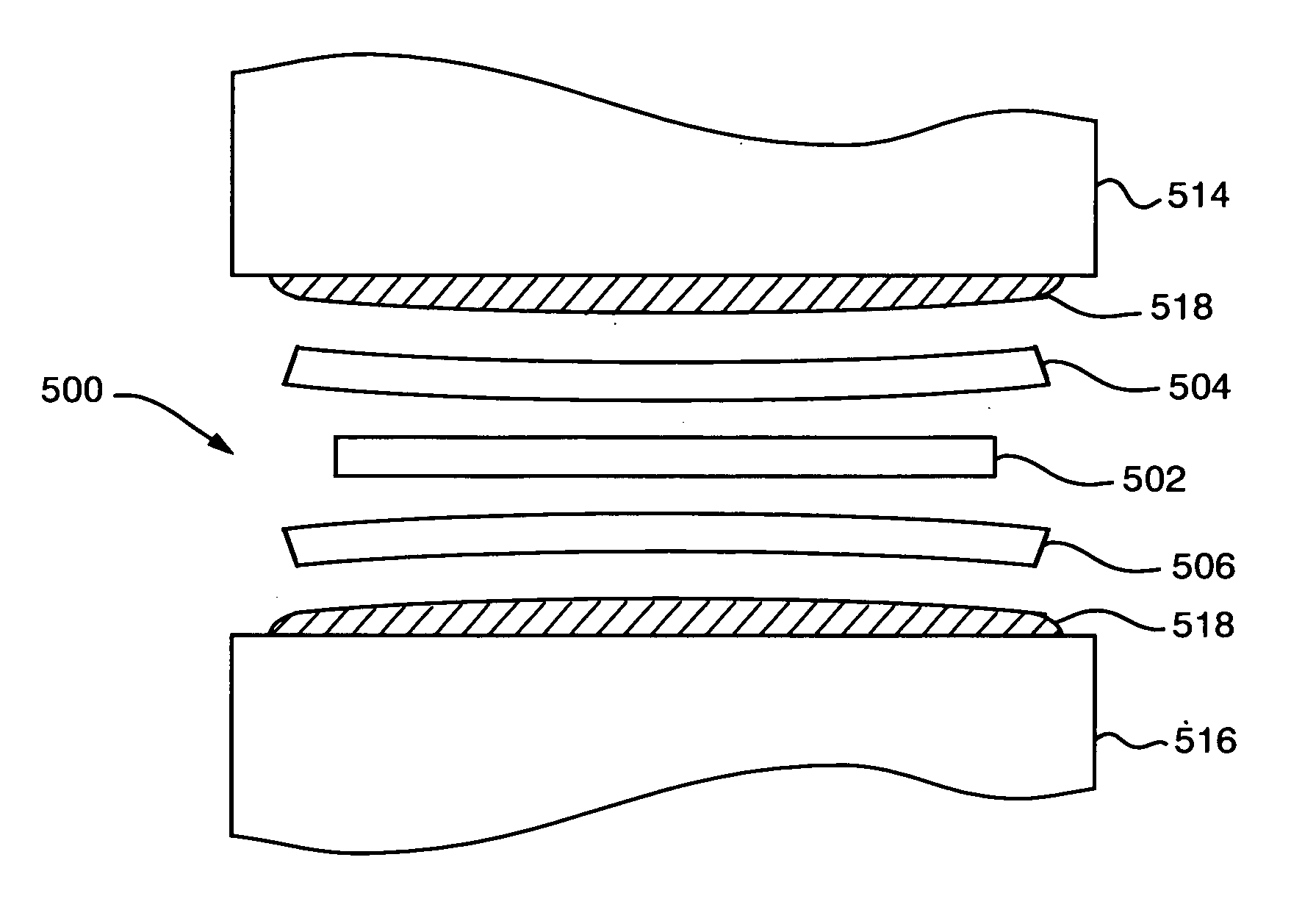

Contact for a semiconductor light emitting device

InactiveUS20090173956A1Minimized contact resistanceImprove reflectivitySolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureTotal thickness

An AlGaInP light emitting device is formed as a thin, flip chip device. The device includes a semiconductor structure comprising an AlGaInP light emitting layer disposed between an n-type region and a p-type region. N- and p-contacts electrically connected to the n- and p-type regions are both formed on the same side of the semiconductor structure. The semiconductor structure is connected to the mount via the contacts. The growth substrate is removed from the semiconductor structure and the thick transparent substrate is omitted, such that the total thickness of semiconductor layers in the device is less than 15 μm in some embodiments, less than 10 μm in some embodiments. The top side of the semiconductor structure may be textured.

Owner:LUMILEDS

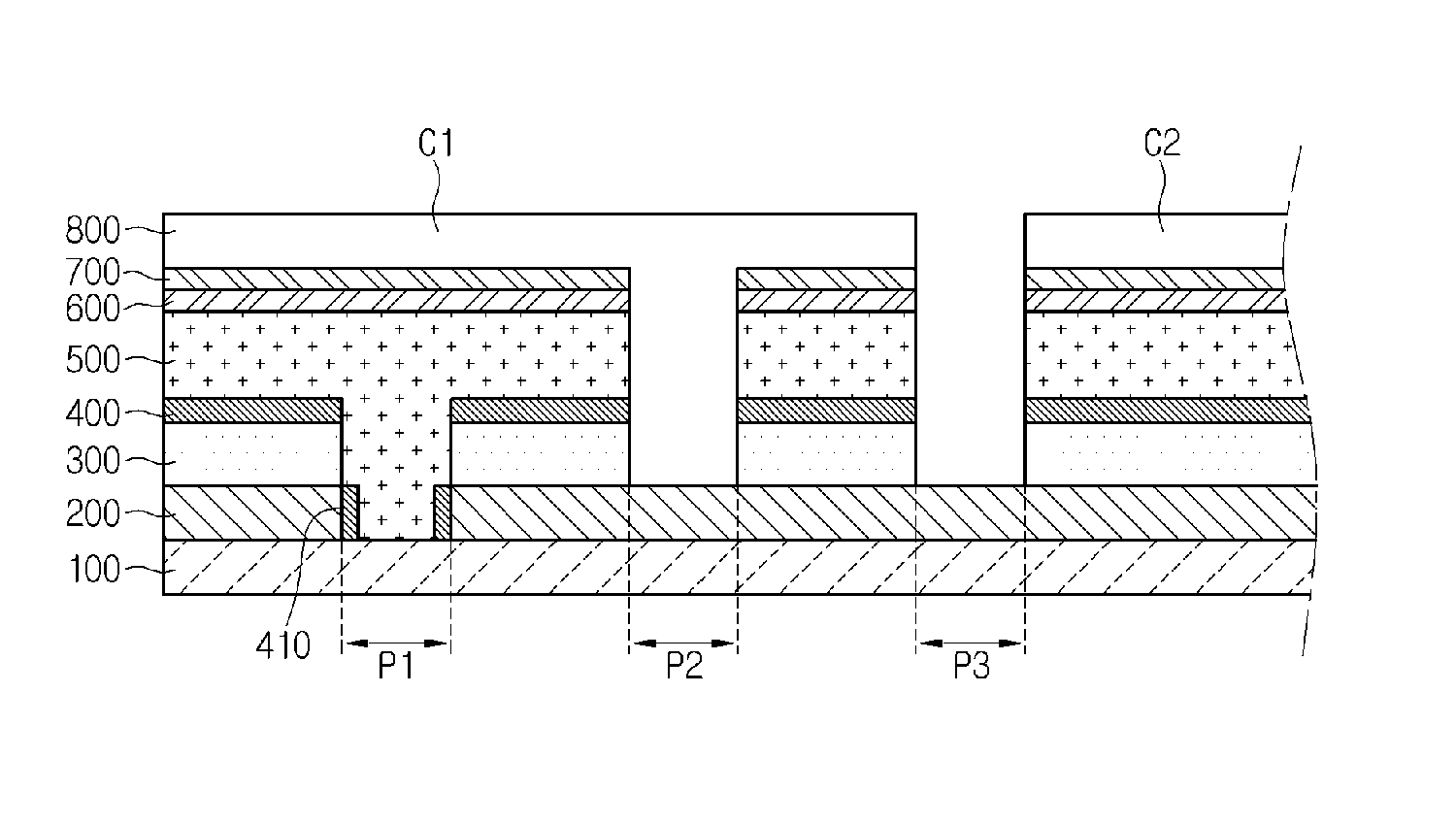

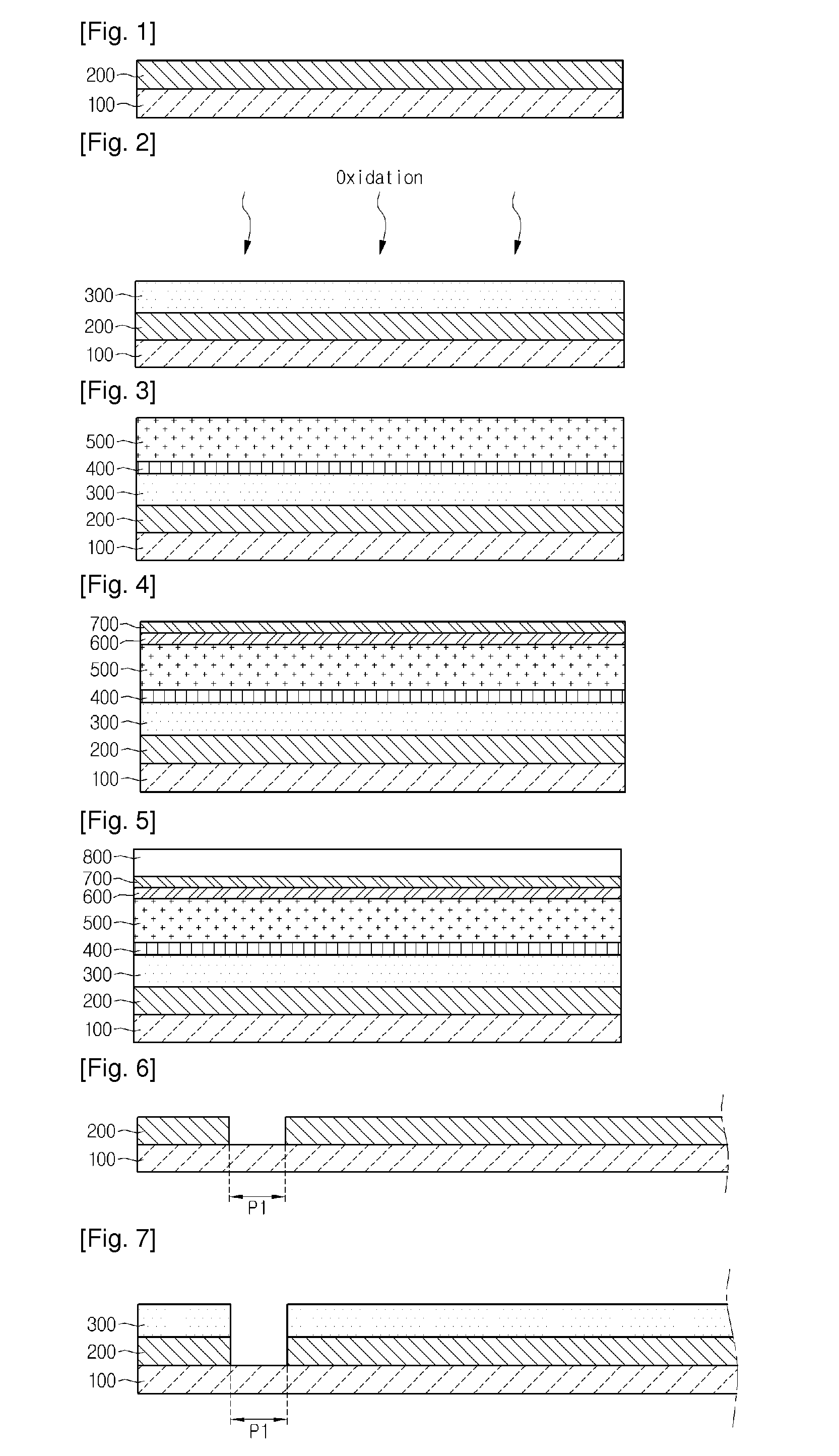

Oxide thin film transistor and method of fabricating the same

ActiveUS20140339537A1Avoid damageImprove stabilityTransistorSemiconductor/solid-state device manufacturingOxide thin-film transistorActive layer

The present disclosure relates to an oxide thin film transistor and a fabricating method thereof. In the oxide thin film transistor, which uses amorphous zinc oxide (ZnO) semiconductor as an active layer, damage to the oxide semiconductor due to dry etching may be minimized by forming source and drain electrodes in a multilayered structure having at least two layers, and improving stability and reliability of a device by employing a dual passivation layer structure, which includes a lower layer for overcoming a deficiency and an upper layer for minimizing external affection, on the multilayered source and drain electrodes.

Owner:LG DISPLAY CO LTD

Nitride semiconductor element and method for producing same

ActiveUS9281439B2Increase consumptionHigh production costSemiconductor devicesElectrode ContactNitride semiconductors

A nitride semiconductor element 1 includes a base structure part 5, and an element structure part 11 formed on the base structure part 5 and having at least an n-type AlGaN based semiconductor layer 6, and p-type AlGaN based semiconductor layers 8, 9, 10, and further includes an n-electrode contact part 13a formed on the n-type AlGaN based semiconductor layer 6, an n-electrode pad part 13b formed on the n-electrode contact part 13a, and a p-electrode 12 formed on the p-type AlGaN based semiconductor layers 8, 9, 10, in which an AlN mole fraction in the n-type AlGaN based semiconductor layer 6 is 20% or more, the n-electrode contact part 13a includes one or more metal layers, and the p-electrode 12 and the n-electrode pad part 13b have a common laminated structure of two or more layers having an Au layer as an uppermost layer, and an Au diffusion preventing layer composed of conductive metal oxide and formed under the uppermost layer to prevent Au diffusion.

Owner:NIKKISO COMPANY

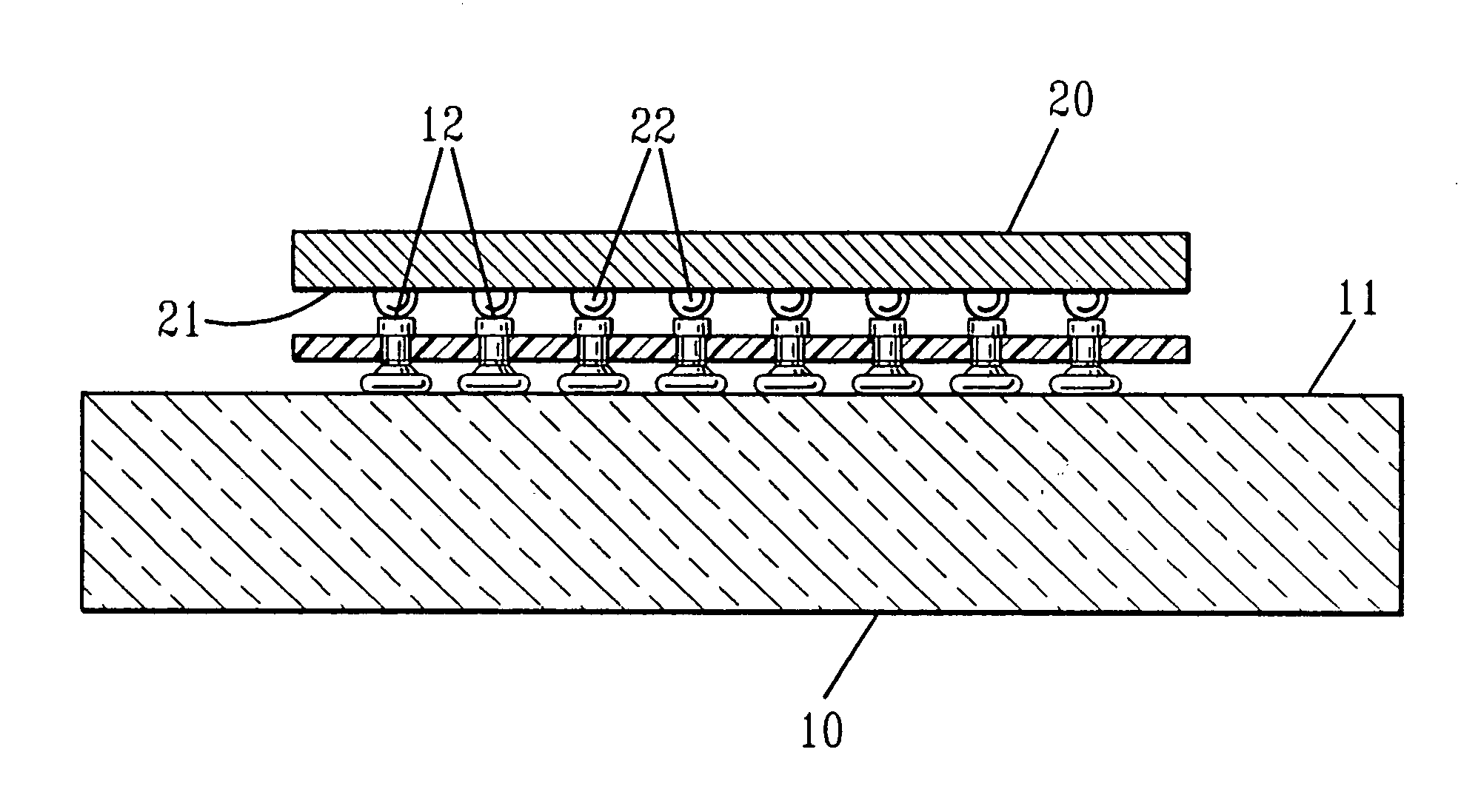

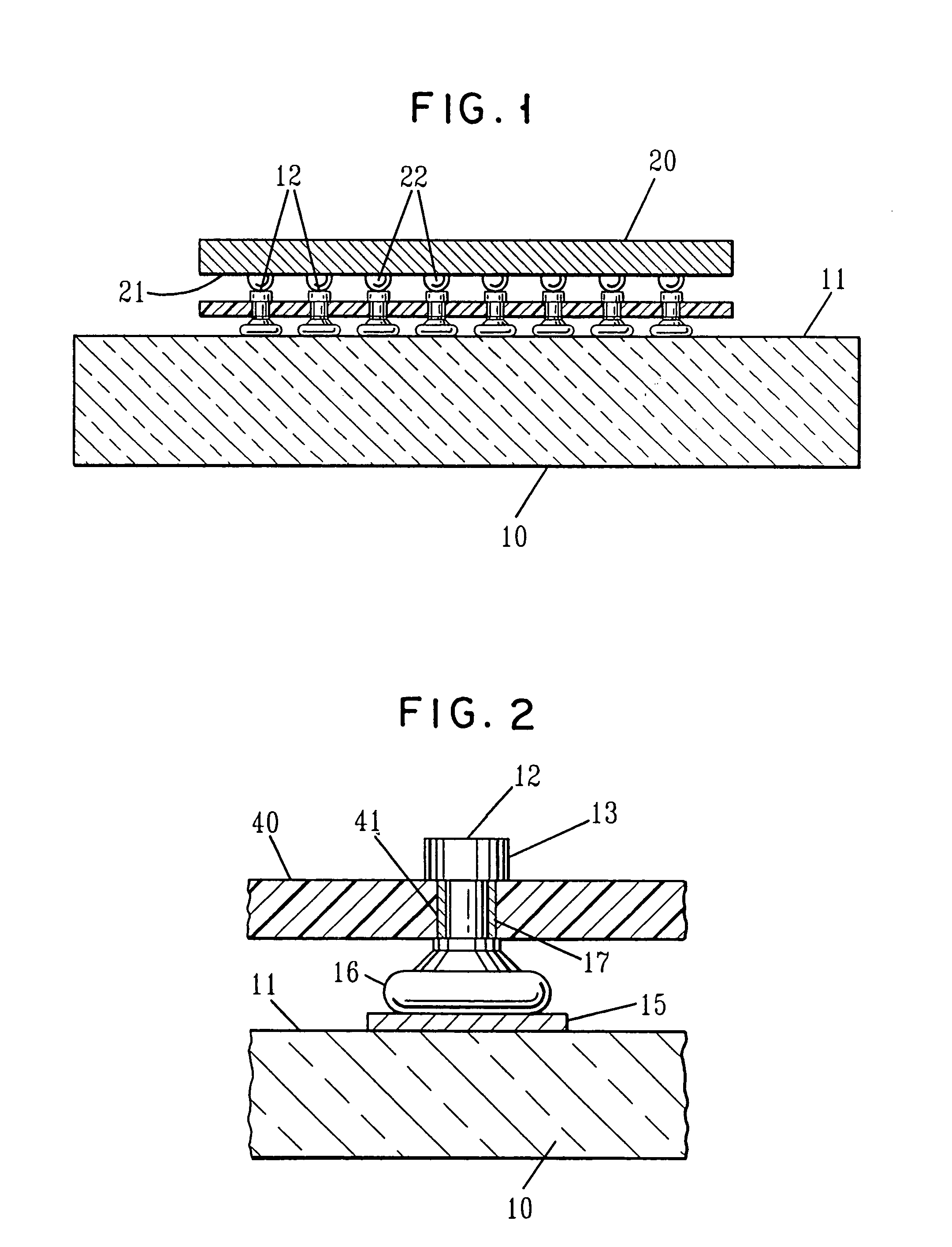

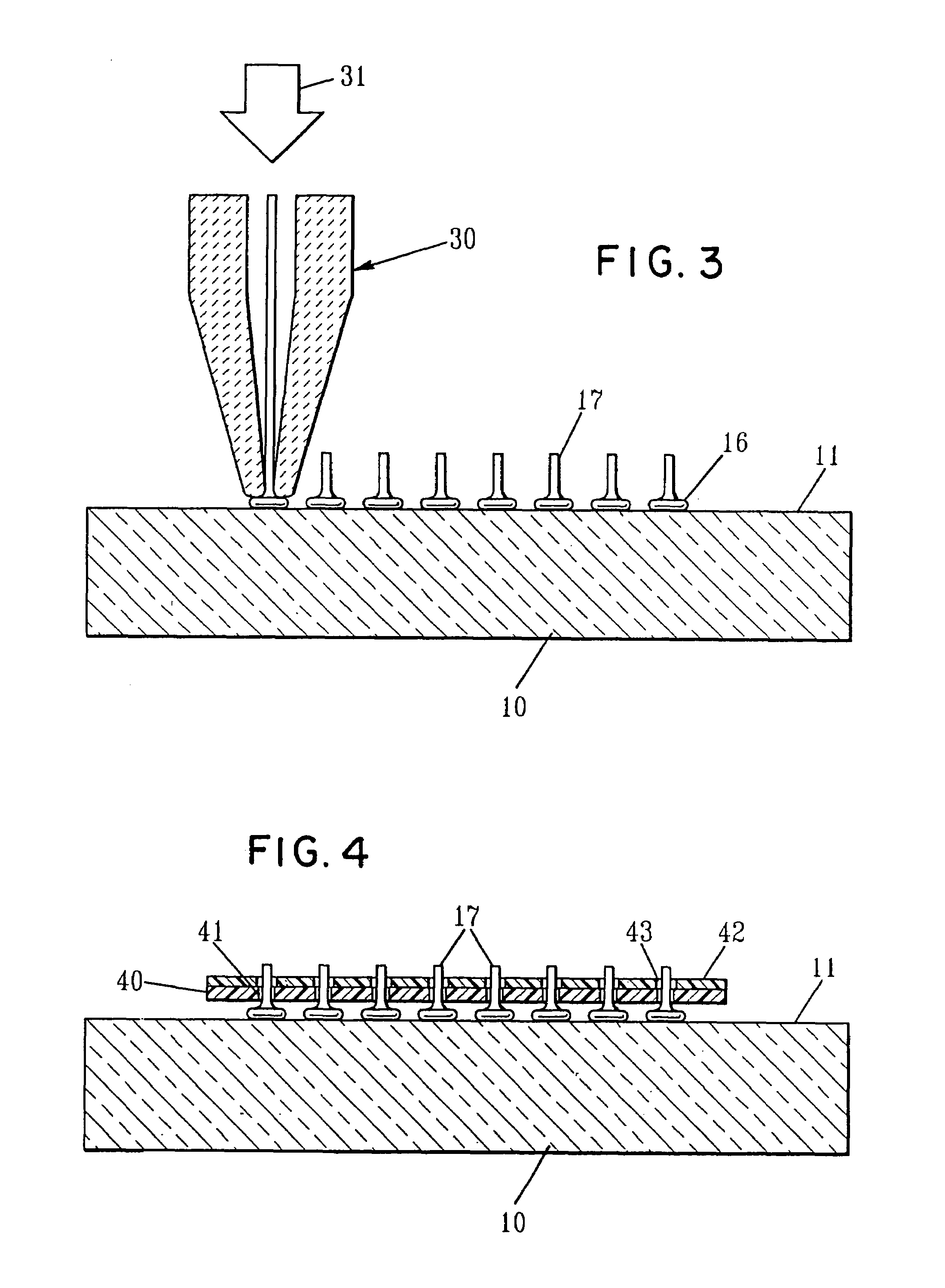

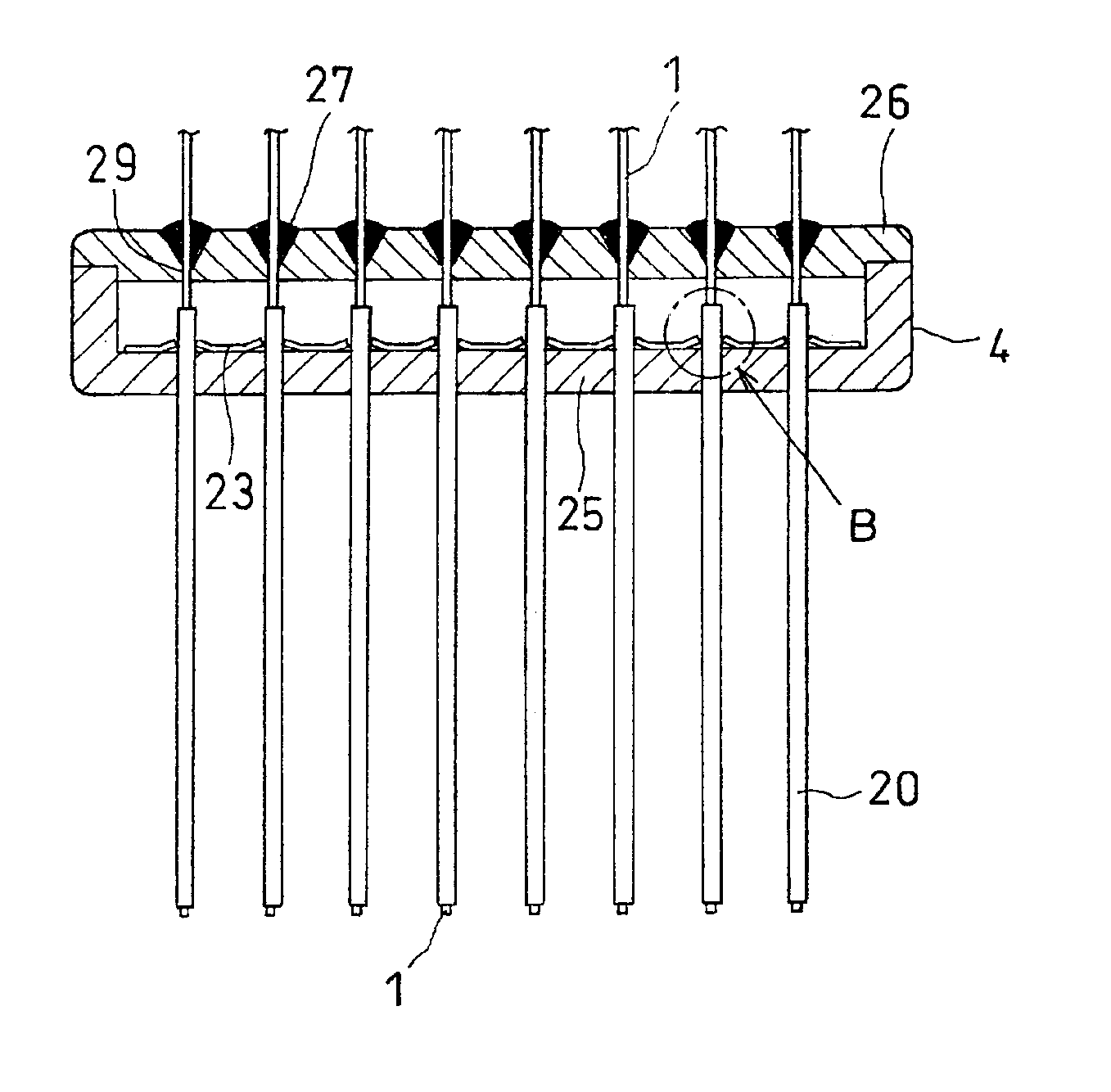

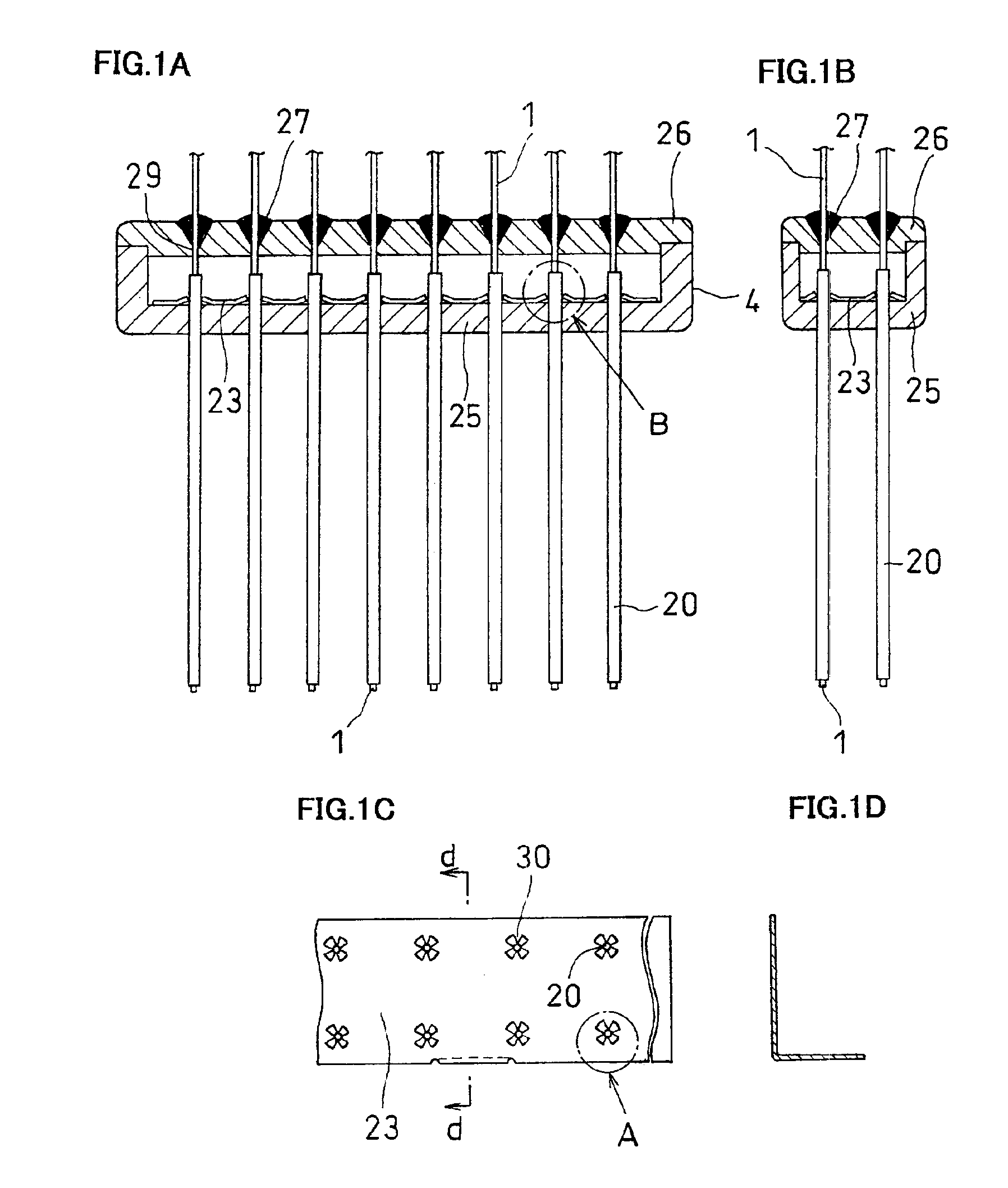

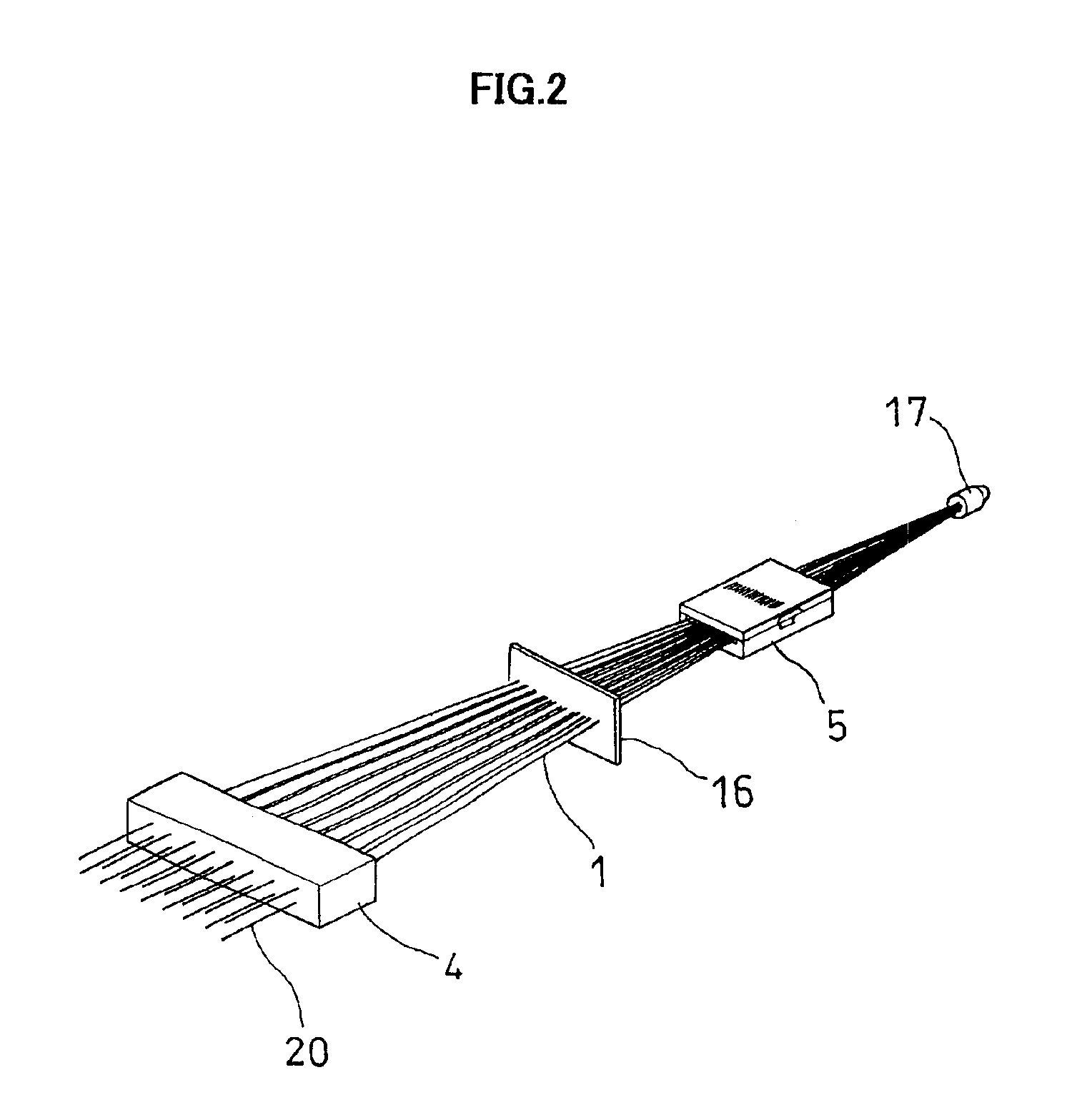

Capillary array device

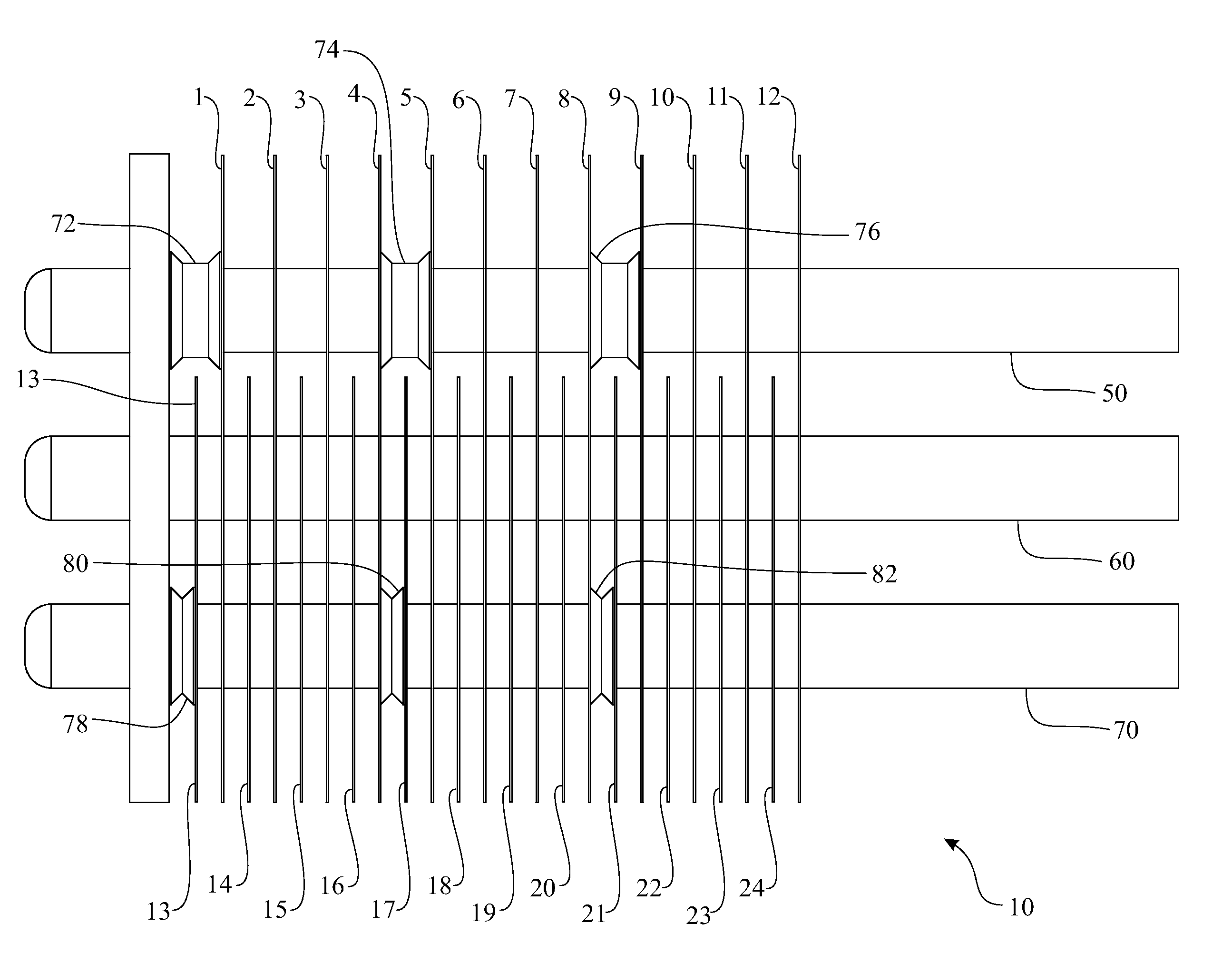

InactiveUS6878256B2Minimized contact resistancePressure bondingSludge treatmentVolume/mass flow measurementSpring forceHigh voltage

The present invention easies a connection between electrodes of a capillary array device and a connection plate for supplying a high voltage to the electrodes.According to the present invention, a connection plate 23 and hollow electrodes 20 are connected without solder but via a spring force. Alternatively, the hollow electrodes 20 can be connected to the connection plate 23 by utilizing volume elasticity of the connection plate.

Owner:HITACHI LTD

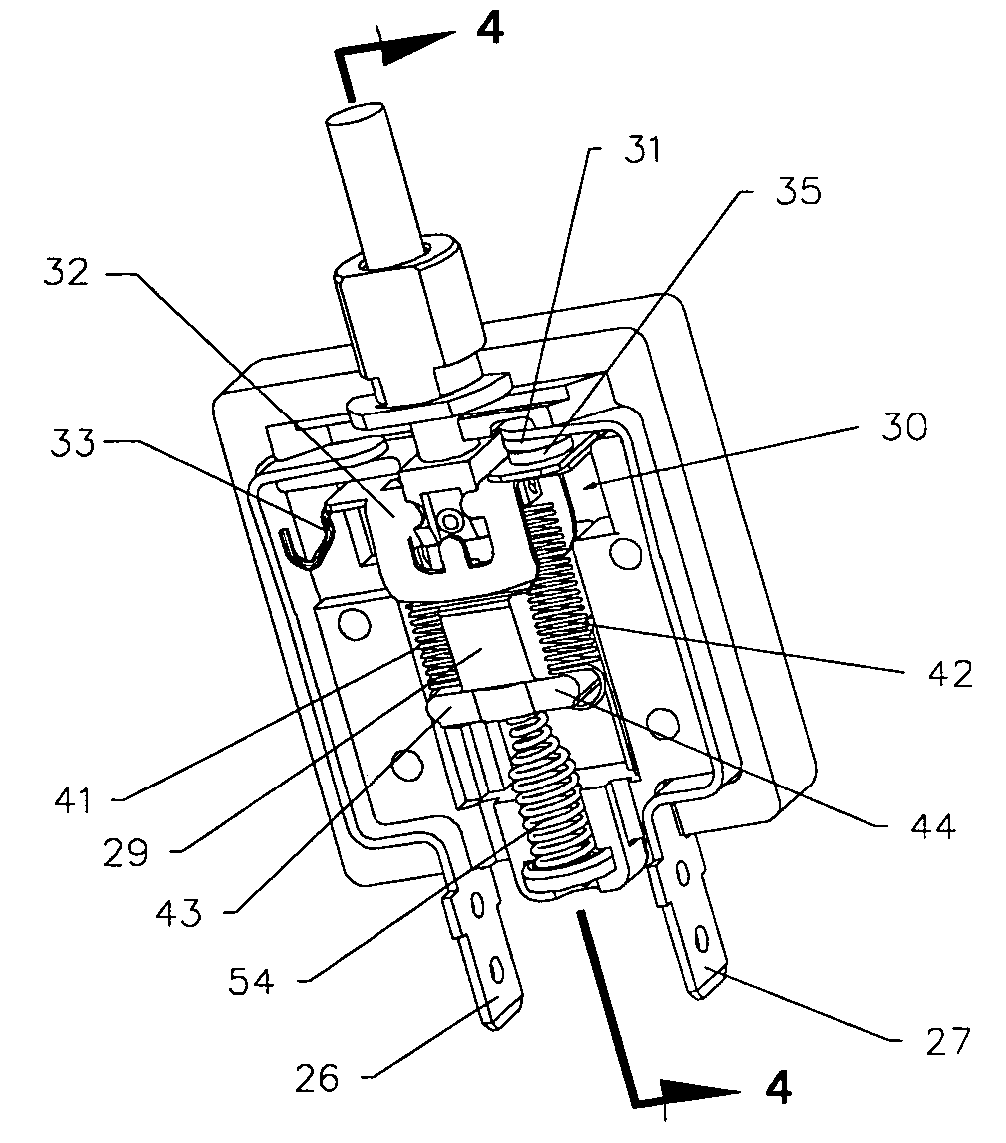

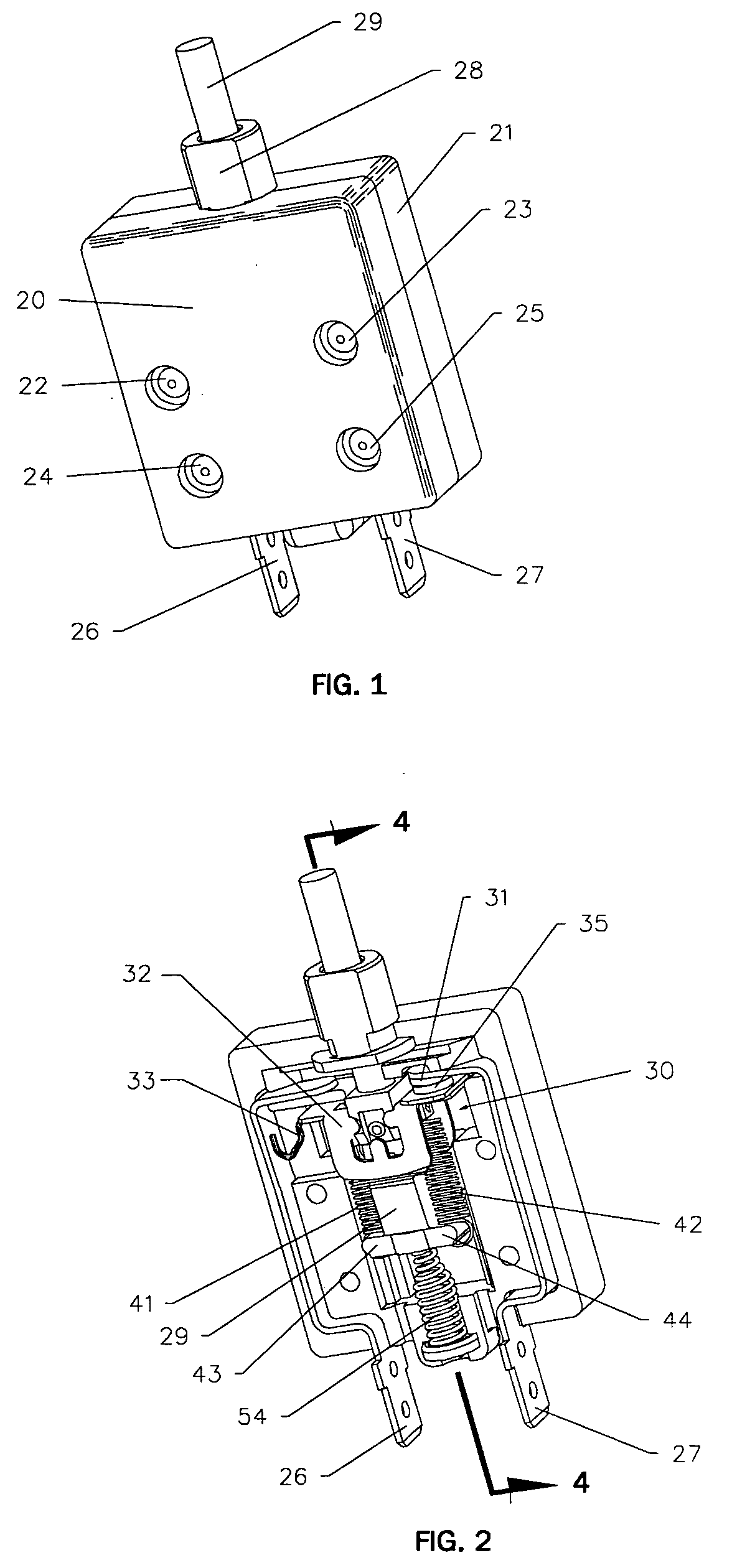

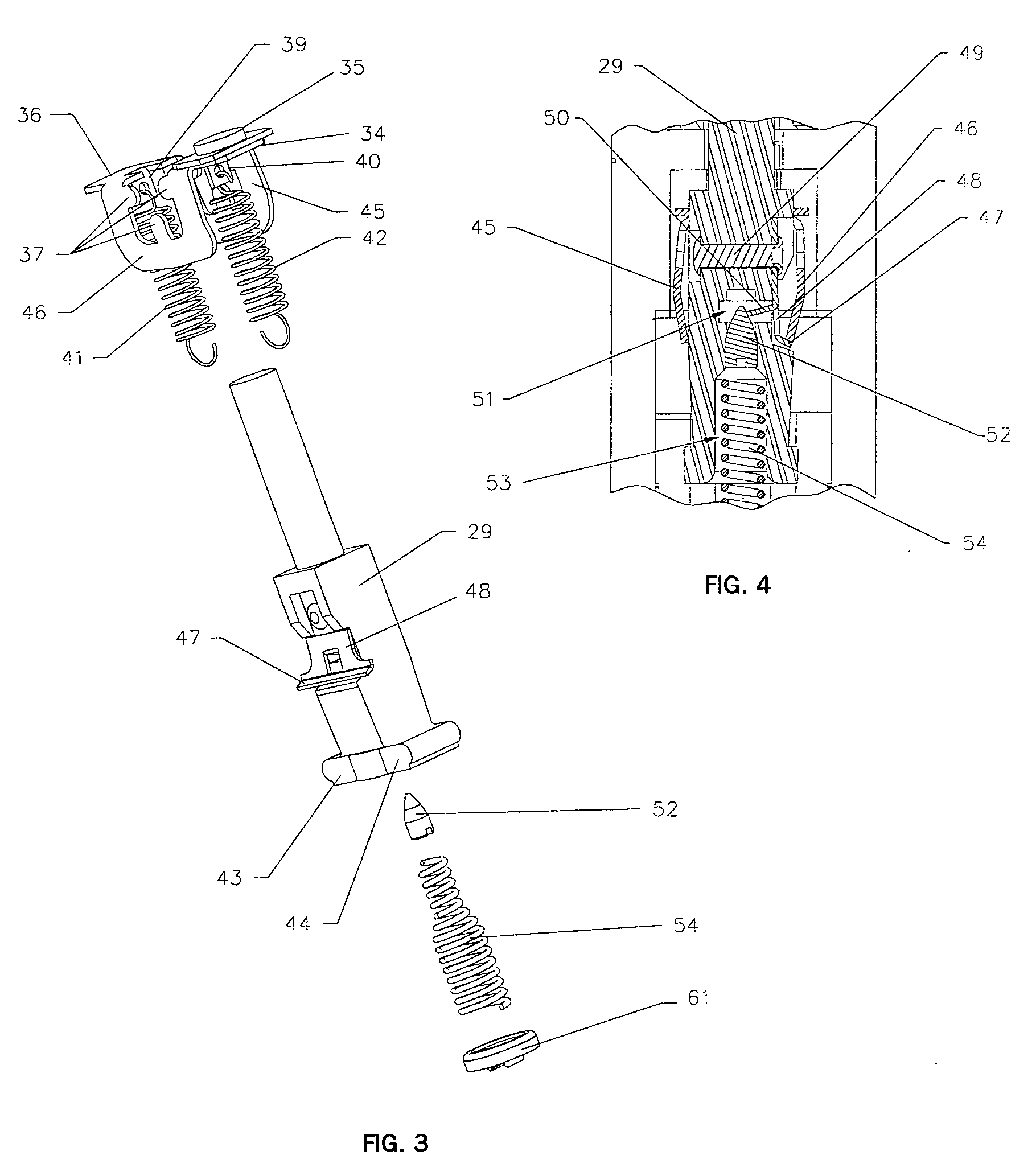

Circuit breaker

ActiveUS20060109073A1Reduce contact resistanceLow production costSwitches with electrothermal openingSwitches with electrothermal releaseSingle phaseEngineering

The invention relates to a re-settable, single-phase, thermo / electric circuit breaker utilizing a U-shape bimetallic element of substantial resistance properties in the circuit, so that when a predetermined overload current occurs the bimetallic element self heats and moves to trip a mechanism that opens the breaker circuit. The invention replaces the double-contact break configuration normally associated with a breaker of this type, with a single contact break configuration designed to produce a sliding action between contacts during the normal reset operation, providing a more reliable continuity at the moveable and stationary contact interface that is also less expensive to produce.

Owner:MP HOLLYWOOD

Fin Spacing On An Evaporative Atmospheric Water Condenser

InactiveUS20140262188A1Altering overall heat transfer coefficientDifferent spacingSpacing meansHeat exhanger finsFrostPotable water

An improvement in atmospheric evaporative water condenser is disclosed. The apparatus includes tubes through which a refrigerant would pass and a variety of generally rectangular or circular fins are in contact with the tubes which causes the fins to cool. This permits water in its vapor form which exists in atmospheric air to condense on the fins and the condensate is collected as potable water. The improvement includes a plurality of different width spacers which are toleranced to be placed over the tubes and secured in desired positions. The fins are placed between the spacers allowing different fin spacing configurations on the apparatus. The different fin configurations optimize airflow for different coil and fin sections and help prevent water flooding or frost buildup on the fins which impair efficiency. Also, the spacers allow the fins to be placed far enough apart that non-frozen condensate does not block the air flow through the space between the fins.

Owner:AVYA GREEN TECH PVT LTD

Fuel cell bipolar plate

InactiveUS20060263670A1Improve hydrophilicityImprove power generation efficiencyNon-metal conductorsConductive materialBody shapeFuel cells

A fuel cell bipolar plate obtained by subjecting a body shaped from a specific composition to surface roughening treatment and atmospheric pressure plasma treatment has a gas flow channel face with specific surface characteristics which endow the bipolar plate with an excellent and long-lasting hydrophilicity that enables water which forms during power generation by the fuel cell to be easily drained off, and which also provide the bipolar plate with a low contact resistance with electrodes in the fuel cell.

Owner:NISSHINBO IND INC

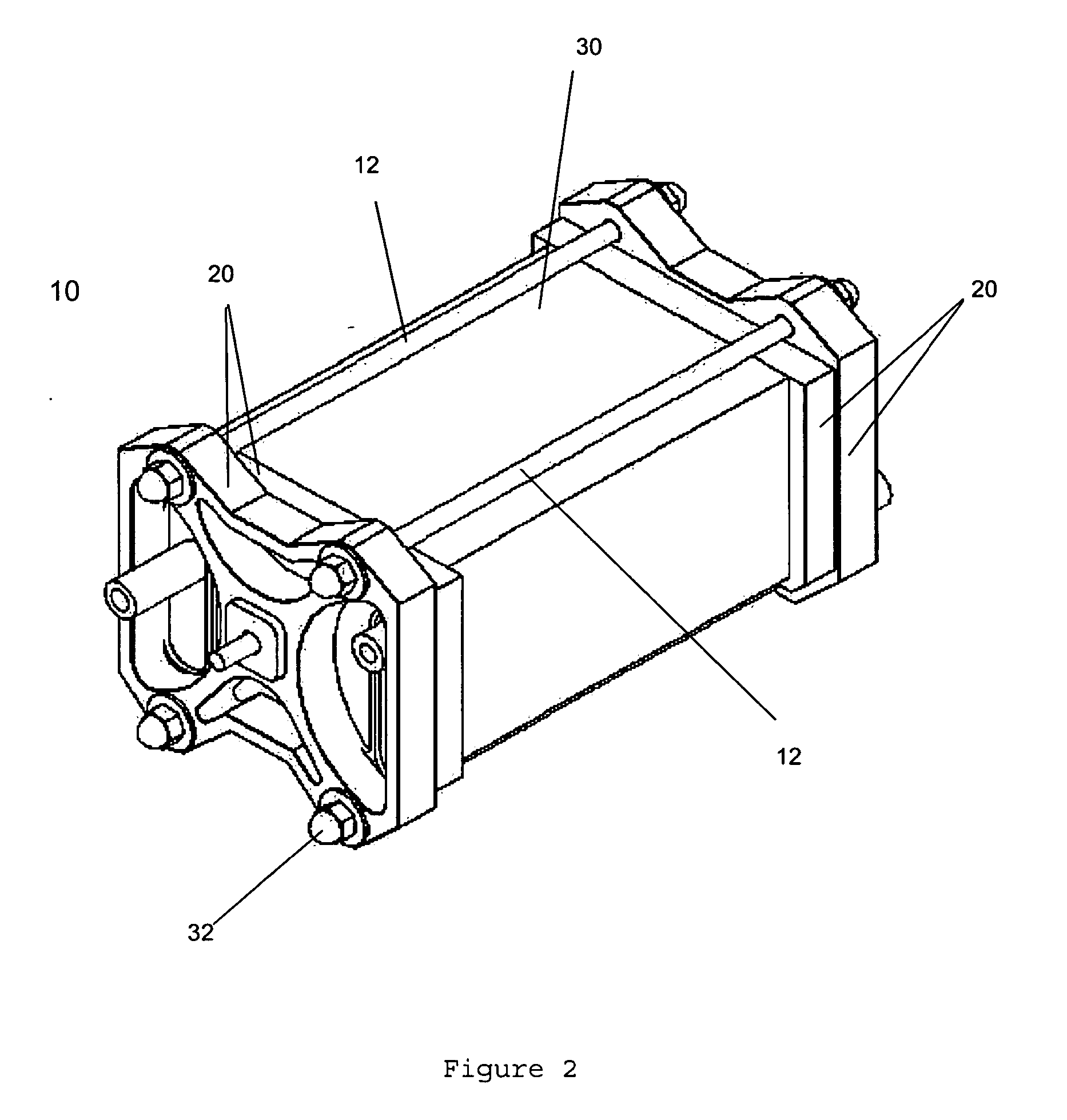

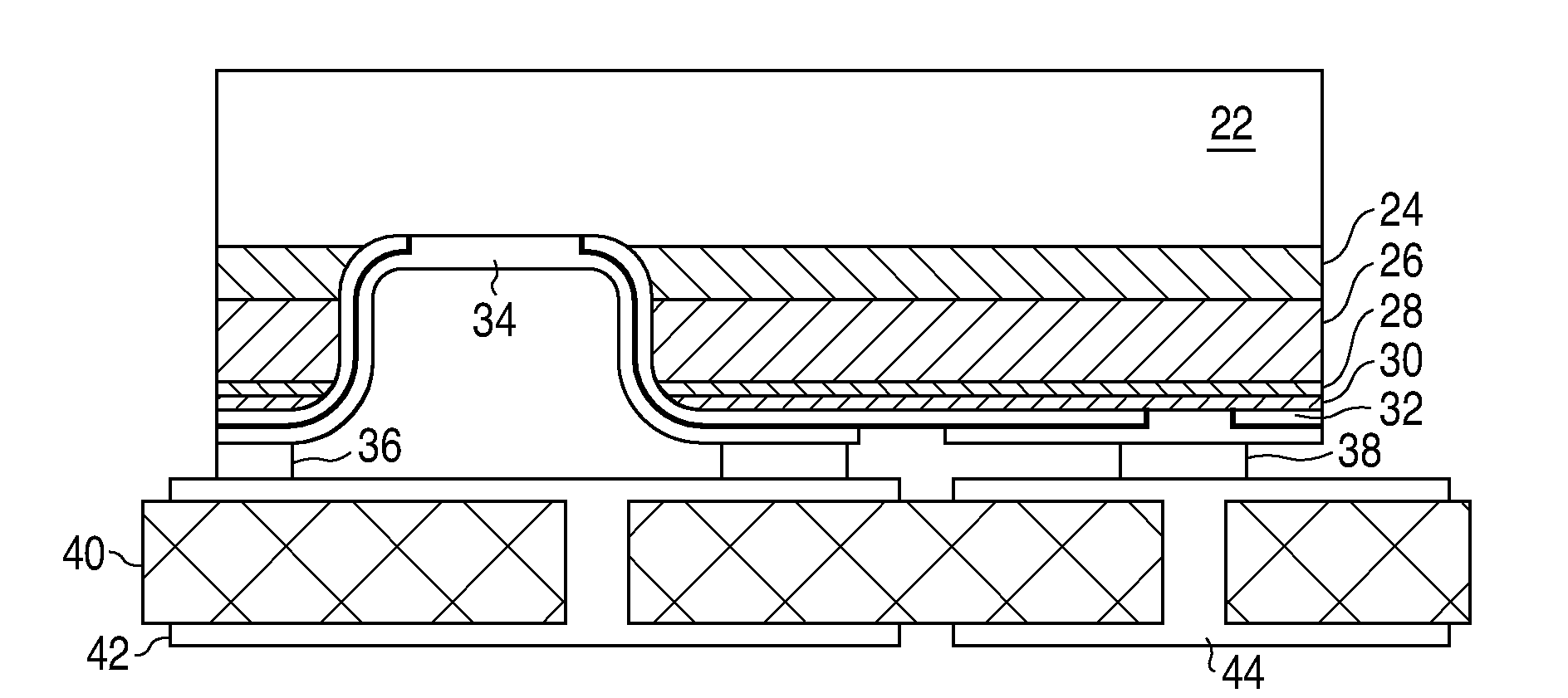

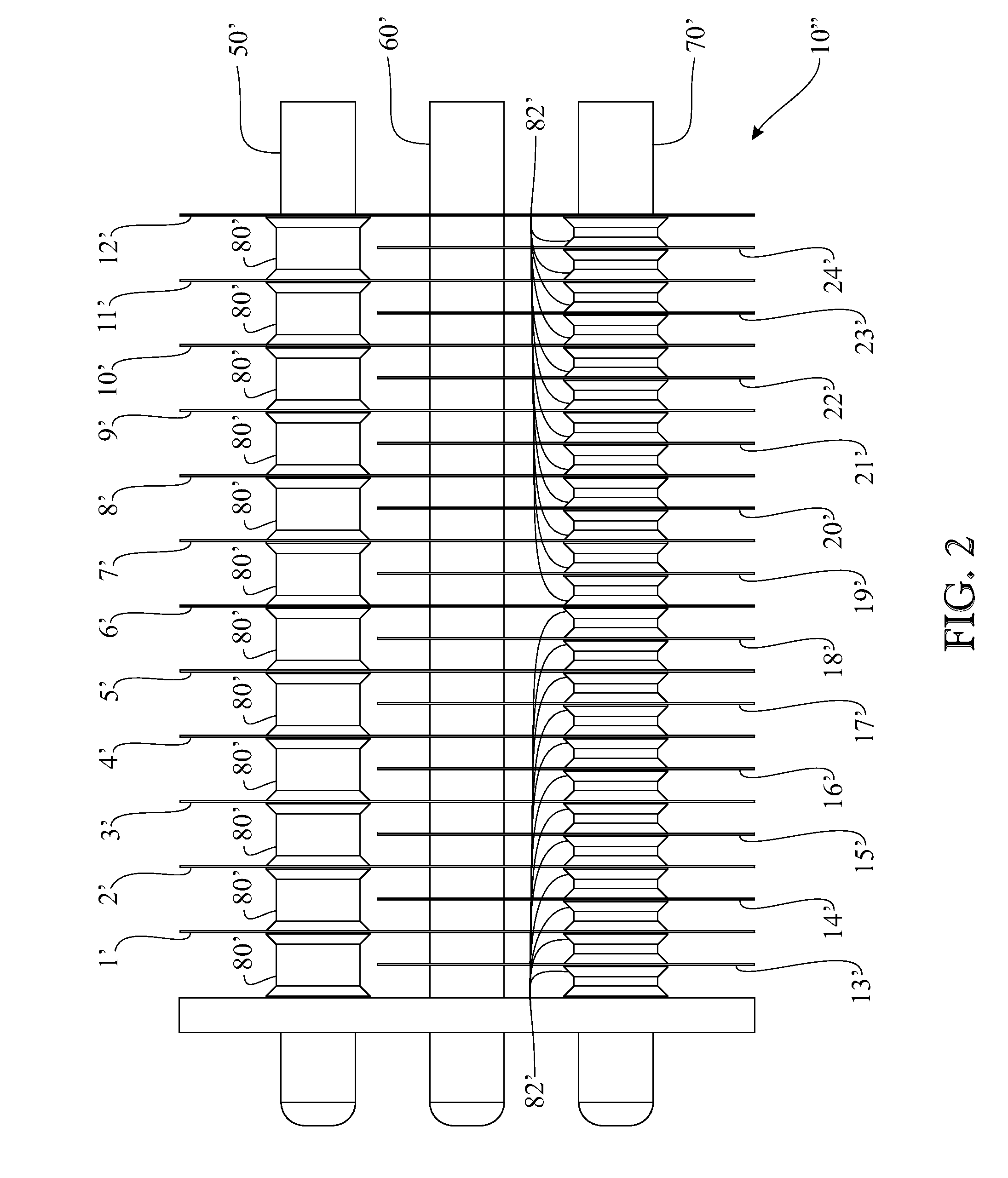

Fuel cell with pre-shaped current collectors

InactiveUS20050249998A1Reduce needMinimized contact resistanceFuel cells groupingFinal product manufactureFuel cellsEngineering

The present invention discloses a process for manufacturing a fuel cell and an associated fuel cell array that includes novel pre-shaped current collectors and conforming compression plates. The current collectors are pre-shaped to counteract any deflection of the fuel cell after compression is released during manufacture. The pre-shaped current collectors may bend outwards by the same amount as previously, however, the overall compression relaxation may be much lower because the pre-shaped current collectors are bending back into the flat position, as opposed to away from it. Also provided with the present invention are associated mold plates that induce the desired pre-shaping to the current collectors.

Owner:MTI MICROFUEL CELLS

Display device

ActiveUS20110068346A1Avoid excessive hardnessContact resistanceSemiconductor/solid-state device detailsElectroluminescent light sourcesDisplay deviceIntegrated circuit

A display device includes a wire substrate including a wire unit for driving the display device, an integrated circuit chip mounted at the wire substrate, and a pad unit extended from the wire unit to be disposed between the wire substrate and the integrated circuit chip. The pad unit is connected to the integrated circuit chip. The pad unit includes a first conductive layer extended from the wire unit, and a second conductive layer disposed on the first conductive layer. The hardness of the second conductive layer is less than the hardness of the first conductive layer.

Owner:SAMSUNG DISPLAY CO LTD

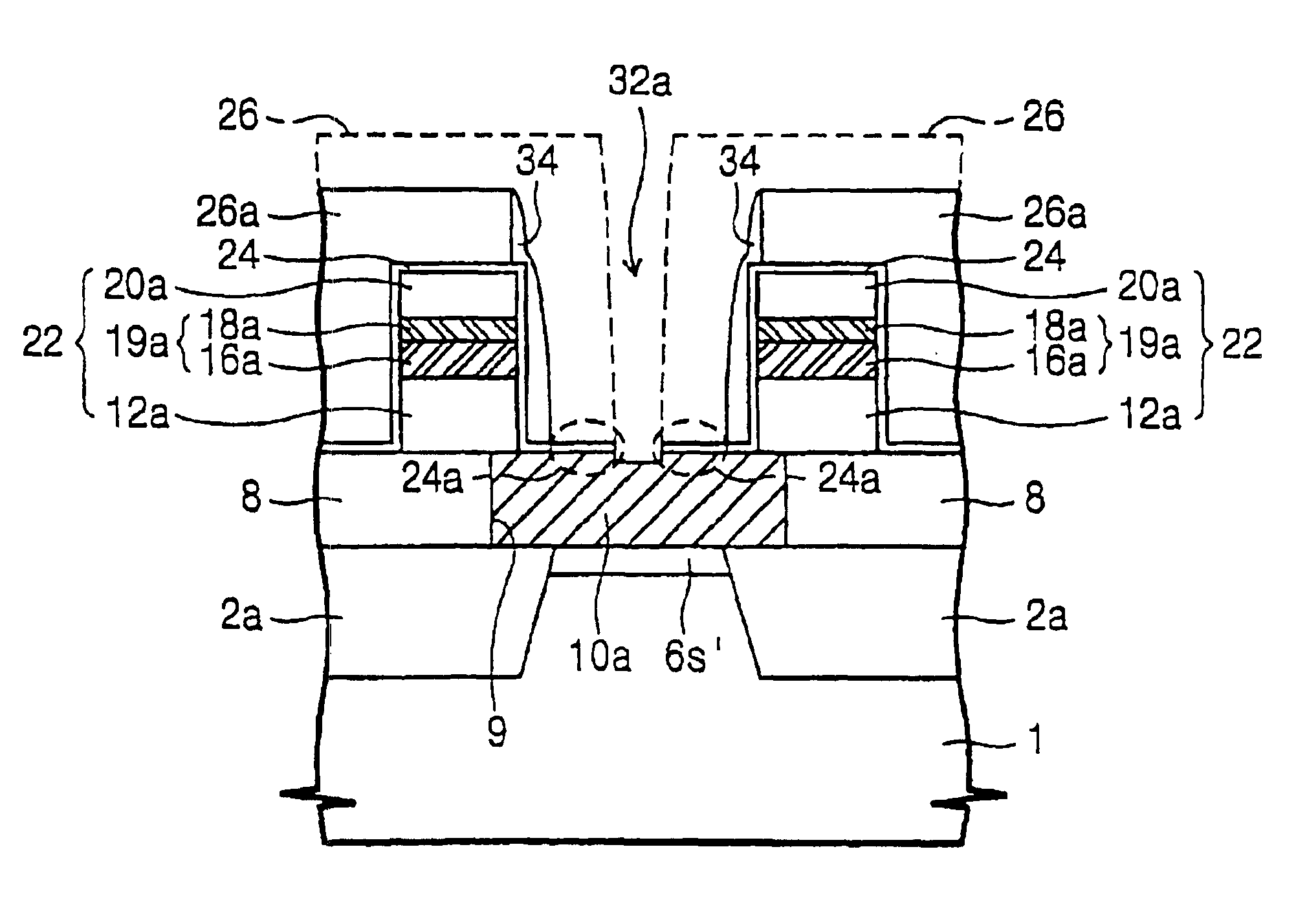

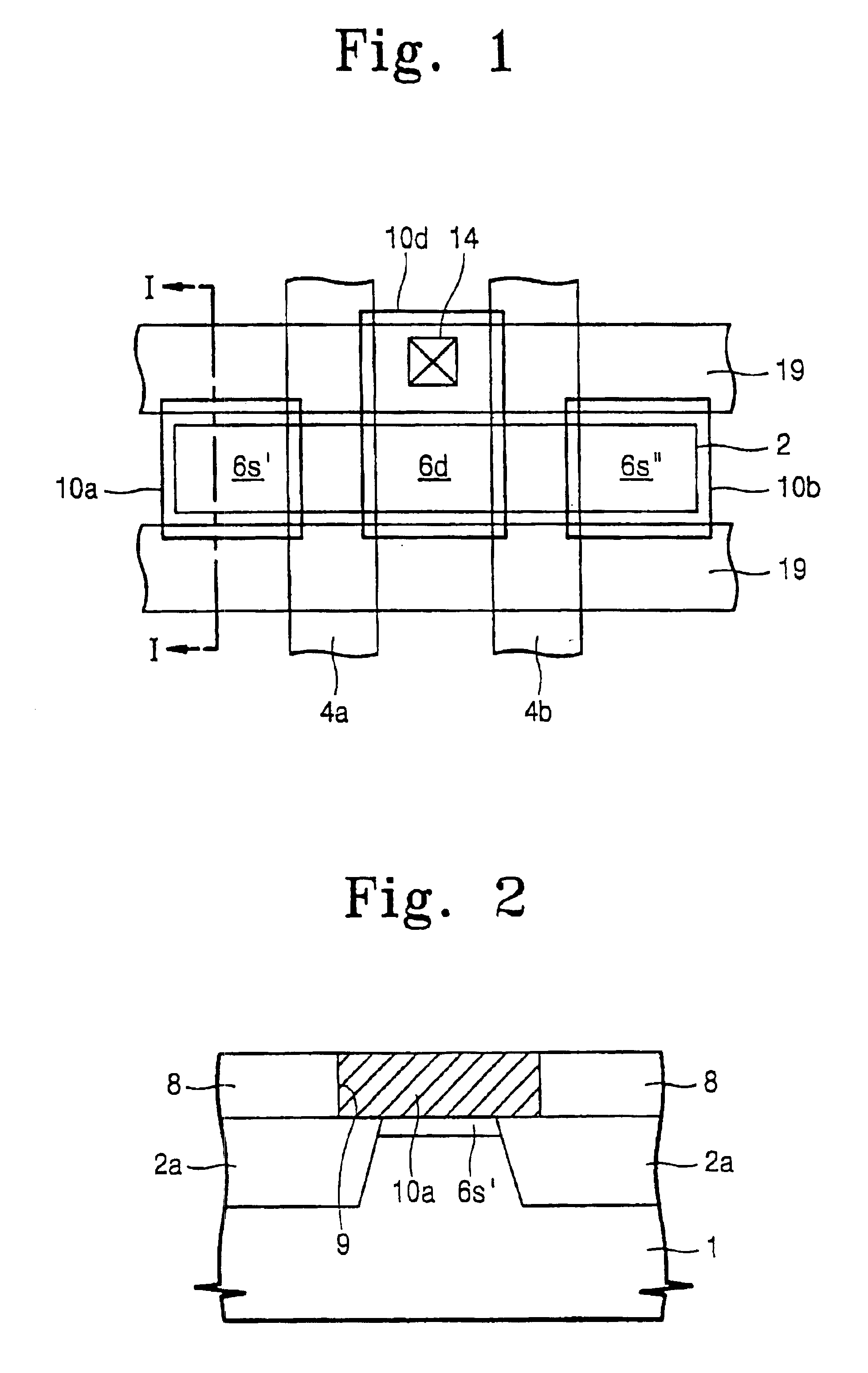

Method of manufacturing a semiconductor memory device including a transistor

InactiveUS7247541B2Total current dropReduce resistanceTransistorSolid-state devicesDevice materialSemiconductor

A semiconductor device comprises a plurality of gate structures formed on a substrate, a gate spacer formed on a sidewall of the gate structures, a semiconductor pattern formed on the substrate between the gate structures, a first impurity region and a second impurity region formed in the semiconductor pattern and at surface portions of the substrate, respectively, wherein the first and second impurity regions include a first conductive type impurity, and a channel doping region surrounding the first impurity region, wherein the channel doping region includes a second conductive type impurity.

Owner:SAMSUNG ELECTRONICS CO LTD

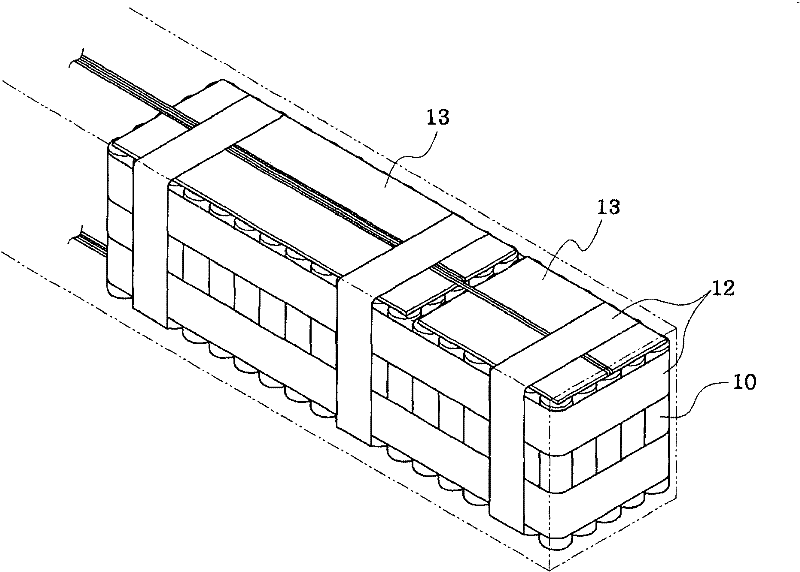

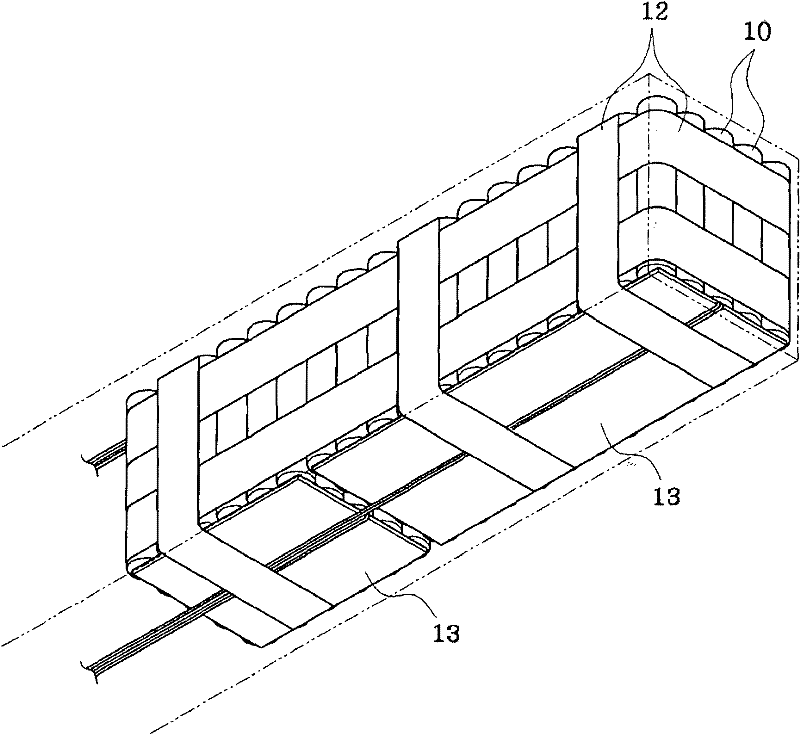

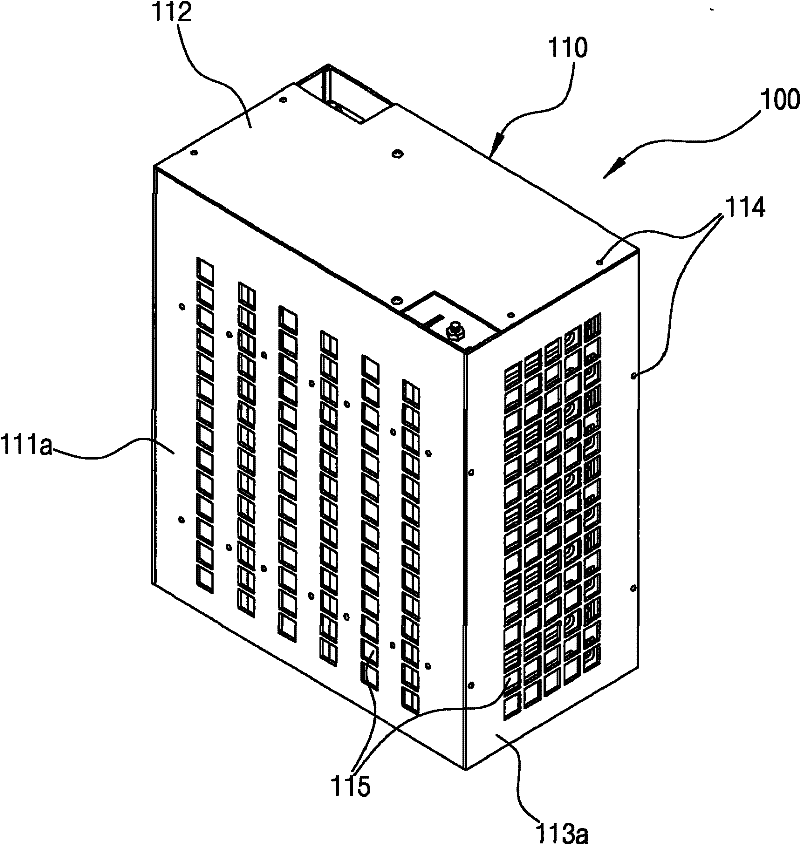

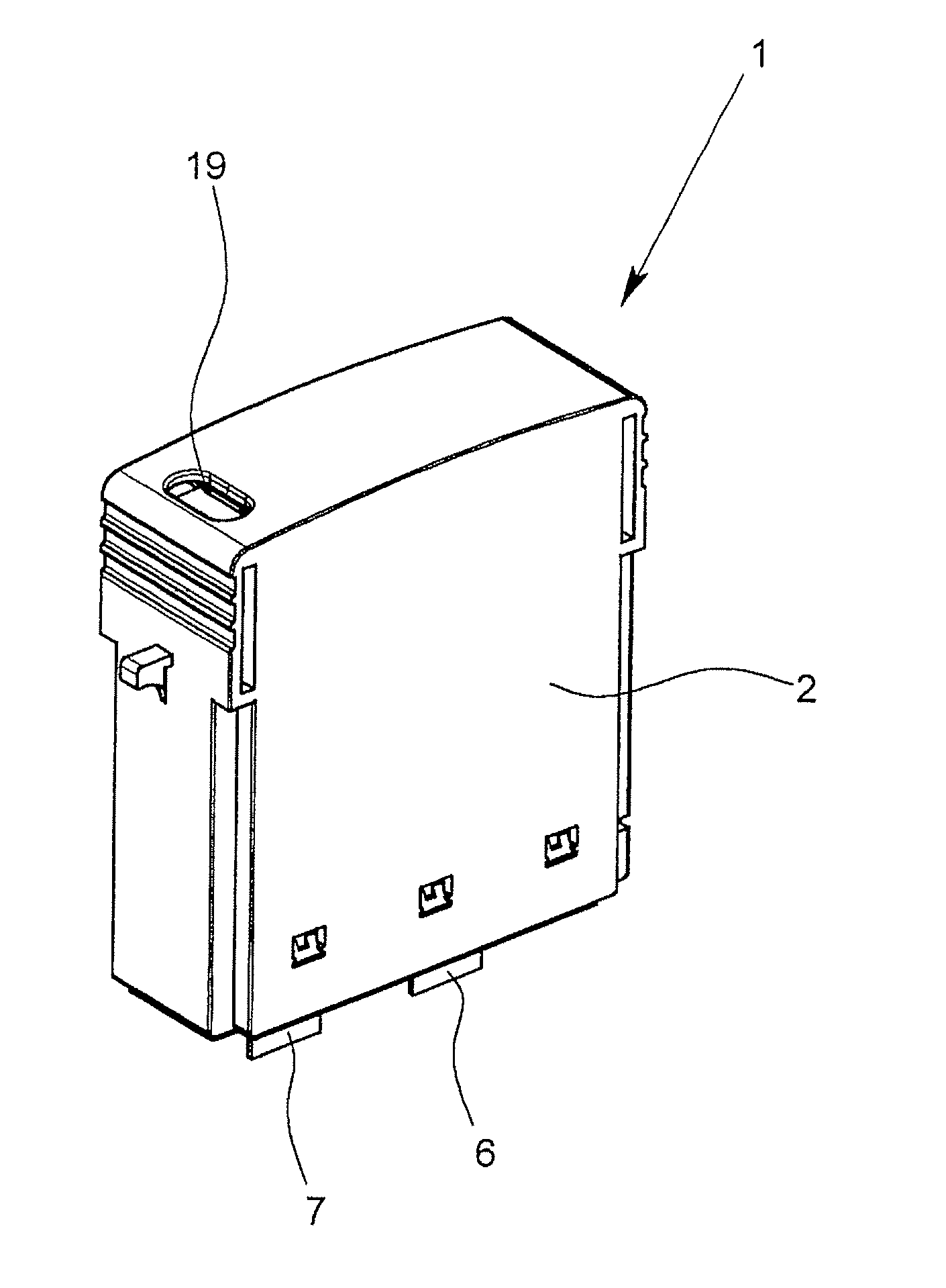

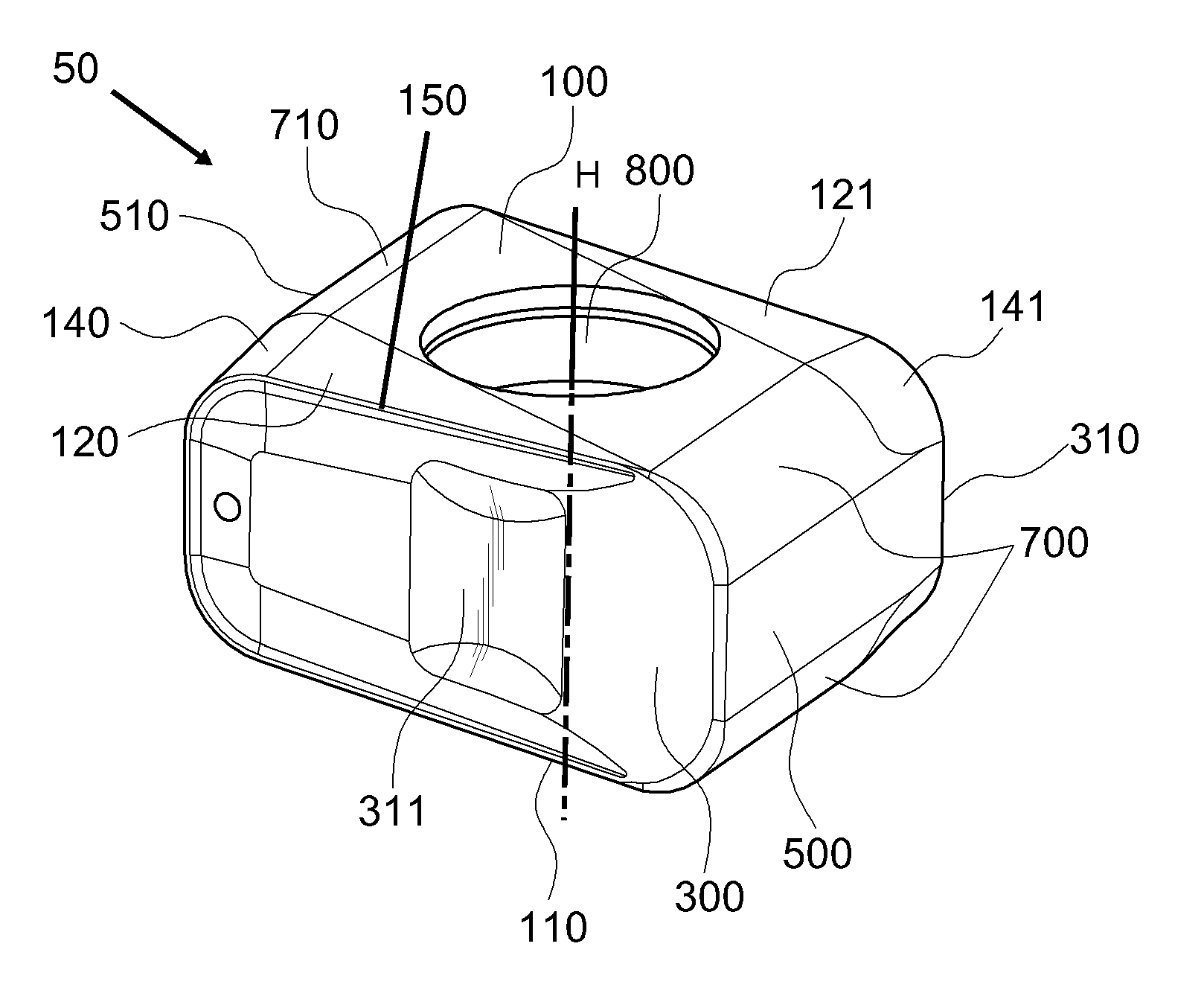

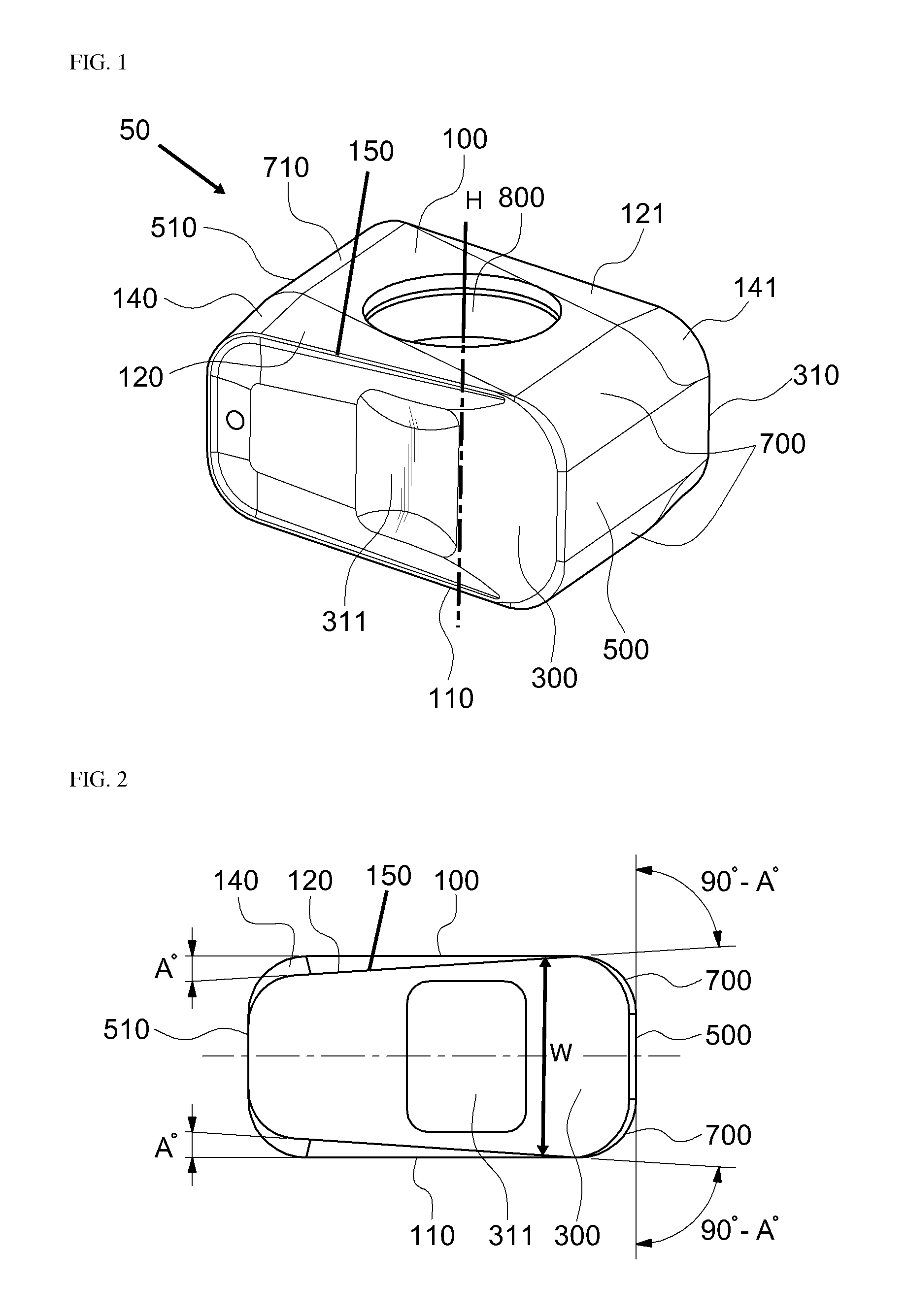

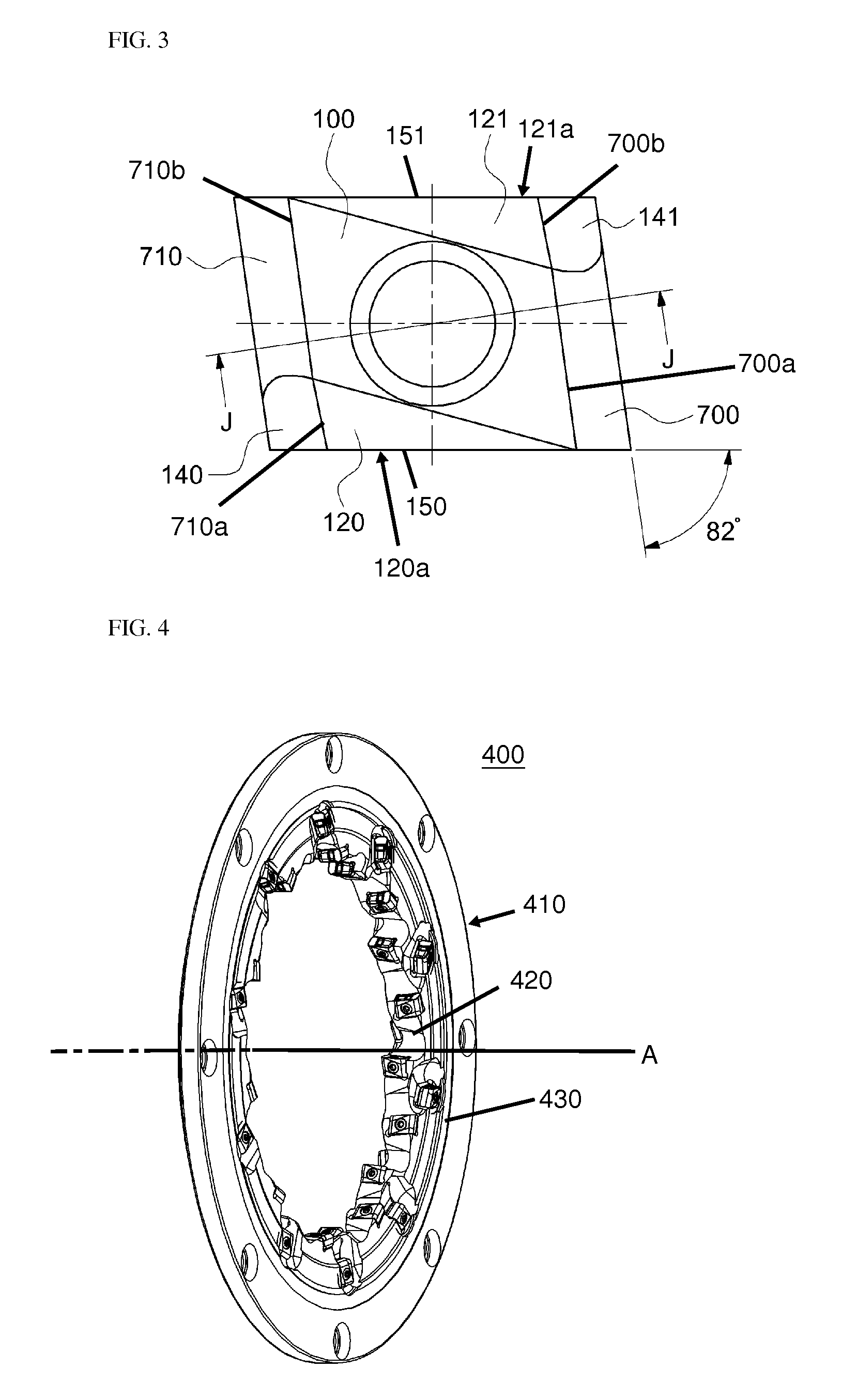

Instrument connection type unit pack combined cell cartridge

InactiveCN102460813AEasy to changeEasy to assembleSecondary cellsCell component detailsConnection typeProduction rate

The present invention relates to an instrument connection type unit pack combined cell cartridge assembled into a compound cell interconnection mesh, and to a combined cartridge electricity storage device assembled into a compound unit interconnection mesh in which a plurality of cell cartridges are electrically interconnected. The unit pack combined cell cartridge of the present invention is configured such that a plurality of cells are interconnected into a unit pack using a suitable device (bus bar), and a plurality of unit packs are interconnected into a unitary cartridge using a suitable device (intermediate conductor plate).The combined cartridge electricity storage device of the present invention is configured such that a plurality of unit pack combined cartridges are accommodated in an outer case and interconnected into a serial or parallel compound interconnection structure to form a unitary system. The present invention interconnects cells, unit packs and cartridges using an easily connectible or separable instrument, to thereby allow for ease of assembly and improve productivity. In addition, the number of cells used in a unit pack, the number of unit packs used in a cartridge, and the number of cartridges used in an electricity storage device can be adjusted and changed to change current capacity and voltage capacity with ease.

Owner:MEGABESS +1

Solar cell and preparing method of the same

ActiveUS20140305505A1Improve responseMinimized contact resistanceFinal product manufactureEnergy conversion devicesOptoelectronicsSolar cell

Disclosed are a solar cell and preparing method of the same. The solar cell includes a back electrode layer on a support substrate, a molybdenum oxide layer on the back electrode layer, a light absorbing layer on the molybdenum oxide layer, and a front electrode layer on the light absorbing layer.

Owner:LG INNOTEK CO LTD

Fuel cell separator

InactiveUS20050130022A1Stable power generation efficiencyHigh hydrophilicityNon-metal conductorsConductive materialEngineeringGraphite

Fuel cell separators which are made by shaping a composition that includes a thermosetting resin, an artificial graphite with an average particle size of 20 to 70 μm and an internal mold release agent and which have a surface with an average roughness Ra of 1.0 to 5.0 μm are very hydrophilic, and thus facilitate the removal of water that forms during power generation by the fuel cell. Such separators also have a low contact resistance with electrodes in the fuel cell.

Owner:NISSHINBO IND INC

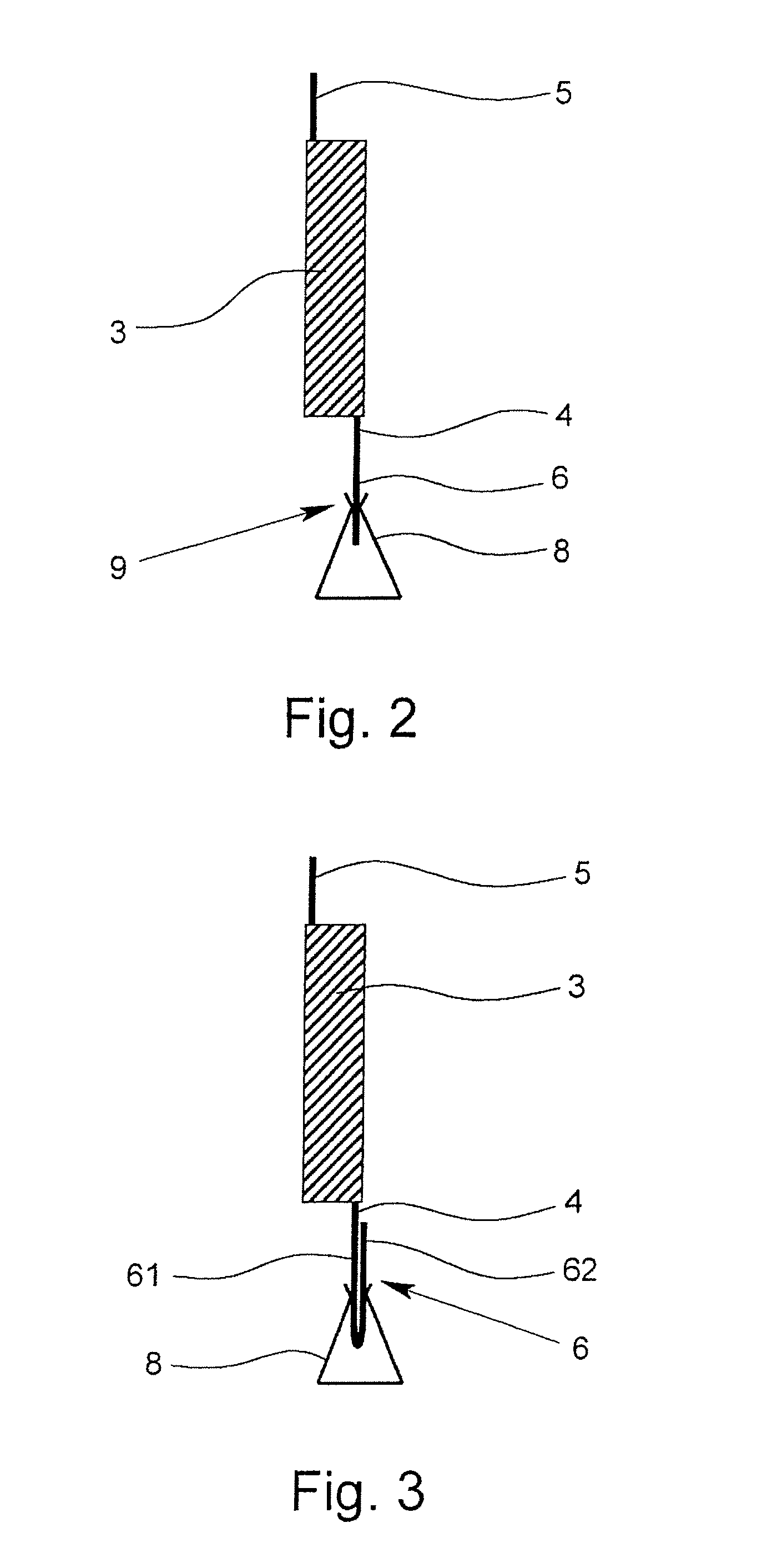

Overvoltage protection element

ActiveUS20110026184A1Easy to produceMore economicallyEmergency protective arrangement detailsOvervoltage protection resistorsElectricityOvervoltage

An overvoltage protection element with a housing, with at least one overvoltage limiting component which is located in the housing, especially a varistor, with two terminal lugs which are each connected to a respective pole of the overvoltage limiting component in an electrically conductive manner, especially soldered or welded, and with two connecting elements for electrical connection of the overvoltage protection element to the current path or signal path to be protected. In the normal state of the overvoltage protection element, the connecting elements are each in electrically conductive contact with a respective terminal lug. The overvoltage protection element can be produced especially easily and economically by the first terminal lug and the first connecting element being integrally connected to one another and by the free end of the first connecting element which faces away from the overvoltage limiting component being made as a plug-in contact.

Owner:PHOENIX CONTACT GMBH & CO KG

Pin miller inserts and a cutter using same

ActiveUS20130266392A1Minimized contact resistanceHigh strengthMilling cuttersAttachable milling devicesMechanical engineeringWedge shape

An indexable hexahedral cutting insert has opposing top and bottom abutting faces, opposing rake faces connecting to opposing side faces, and a central hole passing through the abutting faces. Each rake face is wider in the top-to-bottom direction at a different one of the side faces. Arcuate corner portions with one-directional curvature are formed along intersecting portions between the abutting faces and the side faces. Each abutting face has first and second wedge-shaped inclined planes adjoining and inclining toward corresponding first and second rake faces. Each inclined plane has a base side at a cutting edge formed at the border with one of the rake faces, and a width which gradually increases from one corner portion to the opposite corner portion along the abutting face. Each corner portion has an associated inclined arcuate surface adjacent to the wide end of the wedge-shaped inclined planes.

Owner:TAEGUTEC

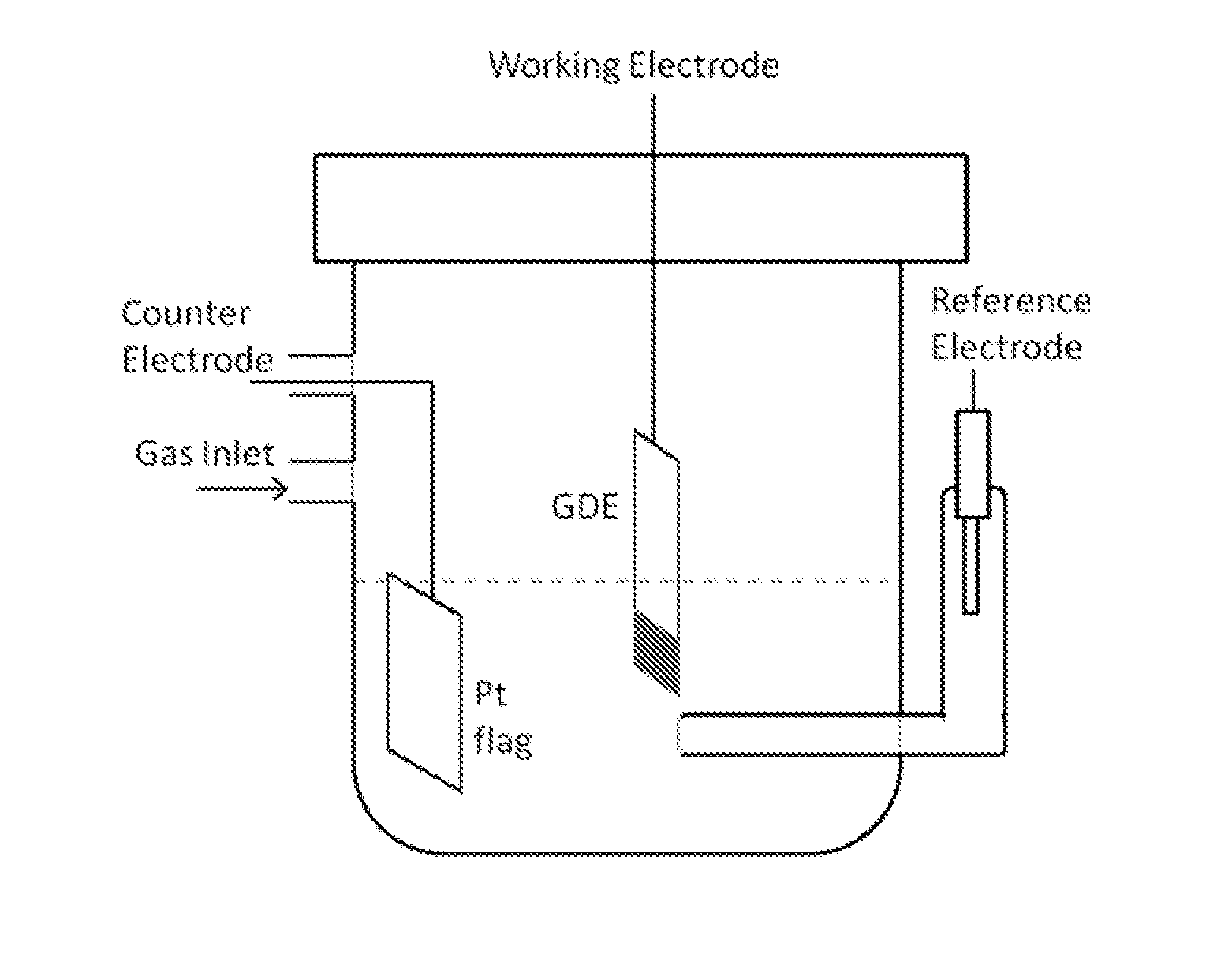

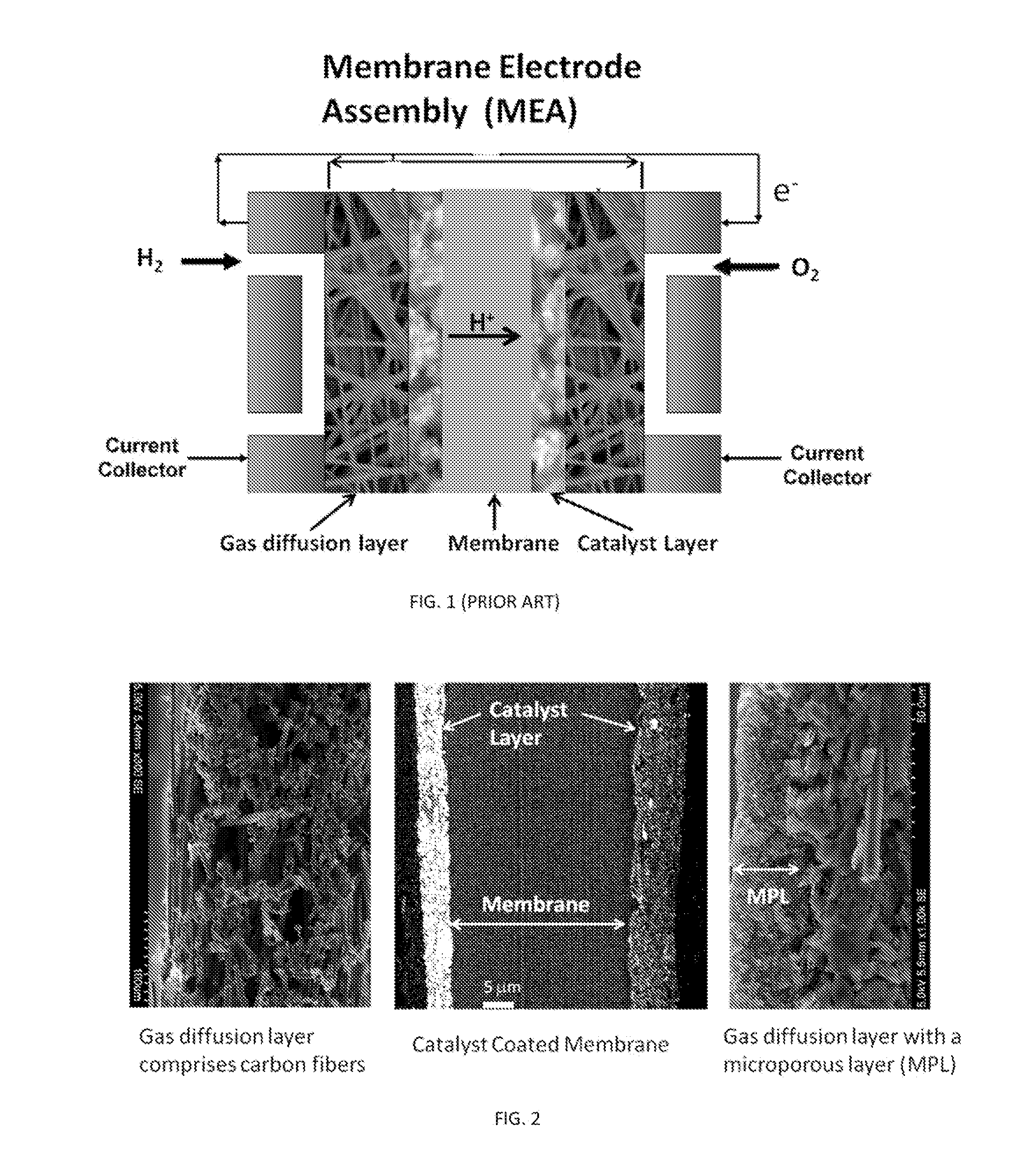

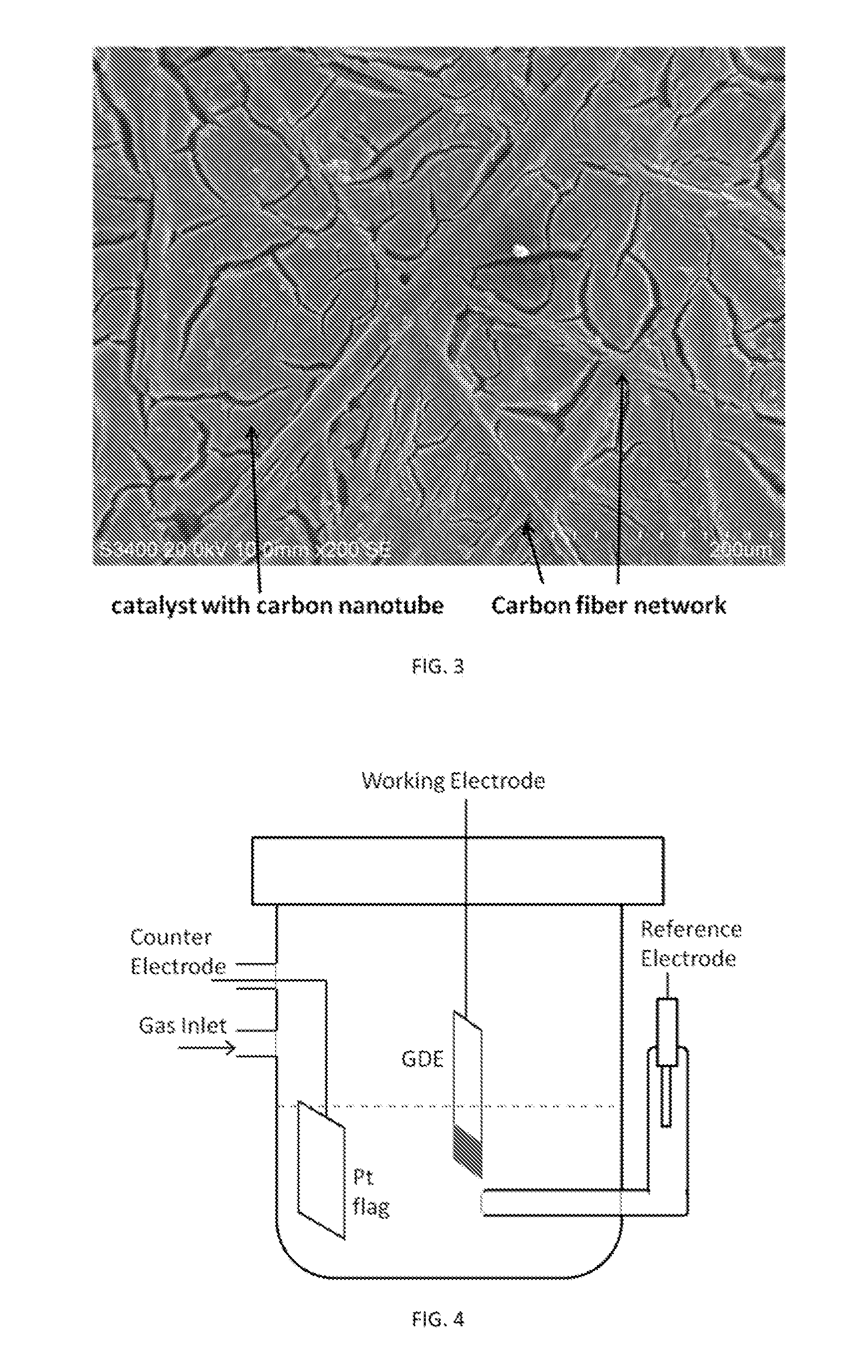

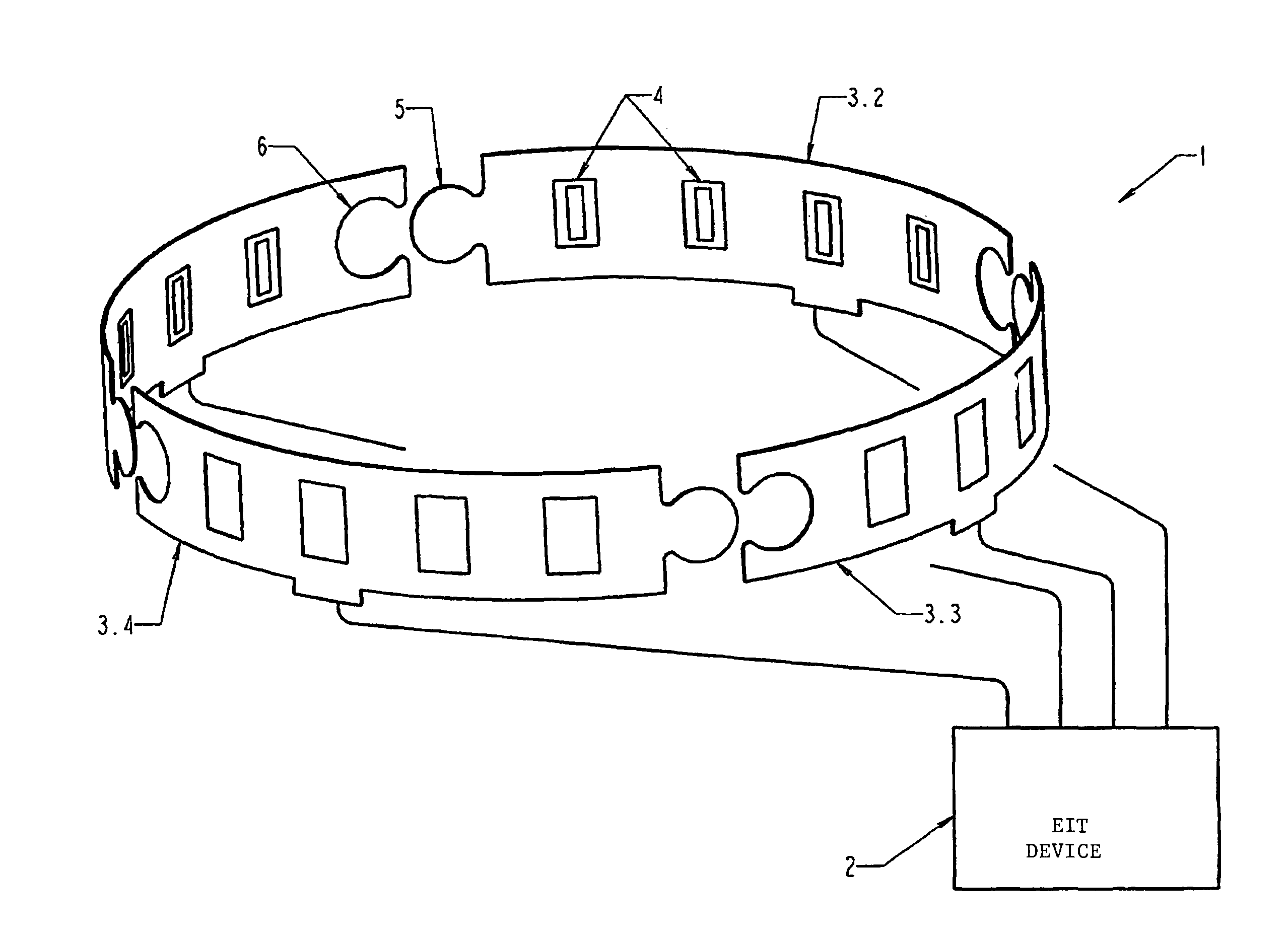

Gas Diffusion Electrodes and Methods for Fabricating and Testing Same

InactiveUS20150376803A1Improve performanceLow costCellsMachining electrodesDiffusion resistanceCurrent range

Highly effective, standalone gas-diffusion electrodes (GDEs) and the methods for their manufacture and test are disclosed, Nanocataiysis are directly bonded on a gas diffusion layer, so that the integrity of the catalyst layer holds without polymer electrolyte membrane, facilitating minimization of electronic, prottmtc, and diffusion resistances in the catalyst layer. The devised embodiments provide examples showing a facile hanging-strip method for testing the standalone GDEs in a solution electrochemical cell, which removes the mA-cm−2-scale mass transport limited currents on rotating disk electrodes to allow studies of reaction kinetics on single electrode over sufficiently wide current ranges (up to A cm−2) without mass transport limitation. Ultralow-Pi-content GDEs are fabricated as the cathode for hydrogen evolution in water eiectrolyzers and as the anode for hydrogen oxidation in hydrogen fuel cells. High performance GDEs with low loadings of platinum group metals are being developed for oxygen evolution reaction at the anode of water electrolyzers and for the oxygen reduction reaction at the cathode of fuel cells.

Owner:BROOKHAVEN SCI ASSOCS

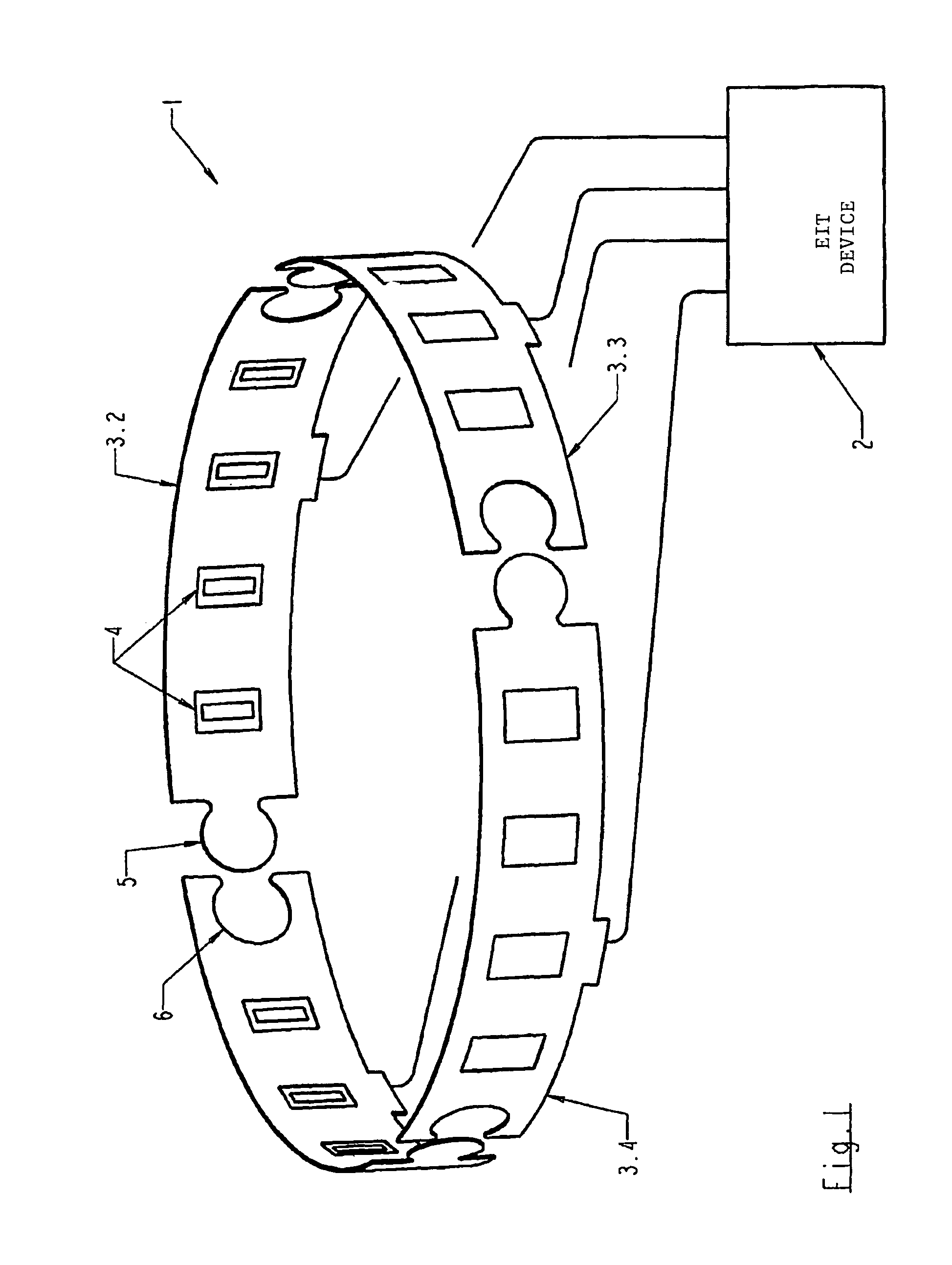

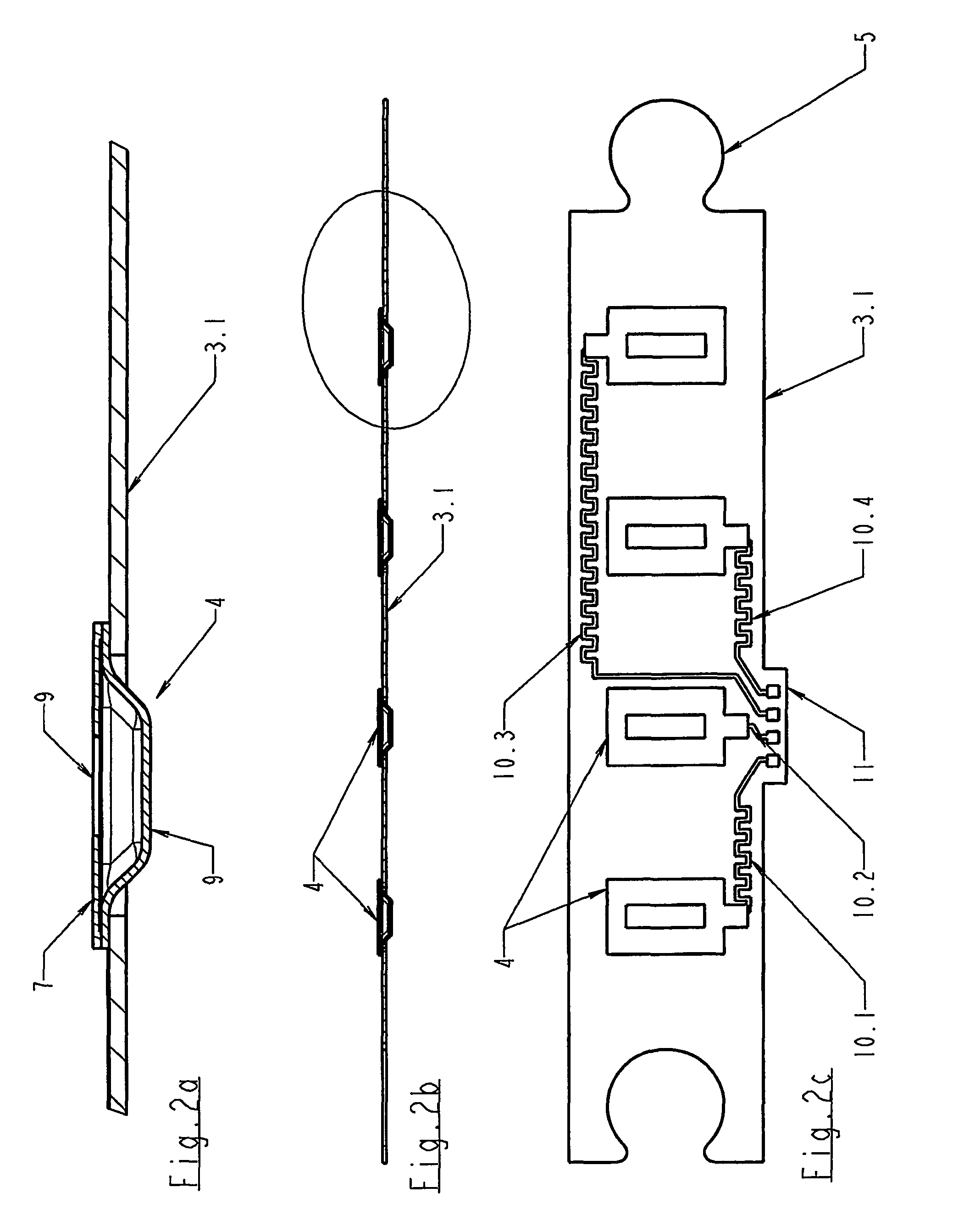

Electrode system

InactiveUS7747303B2Stretch smoothlyMinimized contact resistanceConnections to liquidInternal electrodesElectrical and Electronics engineeringElectrode

This invention relates to an electrode arrangement (1), in particular for electroimpedance tomography, having multiple electrodes (4) for electric contacting of measurement object and a belt-shaped electrode carrier (3.1-3.4) for encompassing the measurement object, with the electrodes (4) being attached to the belt-shaped electrode carrier (3.1-3.4). It is proposed that the electrodes (4) be positionable on the belt-shaped electrode carrier (3.1-3.4) in the longitudinal direction of the belt-shaped electrode carrier (3.1-3.4). In addition, this invention relates to a method for applying such an electrode arrangement to a measurement object.

Owner:VYAIRE MEDICAL GMBH

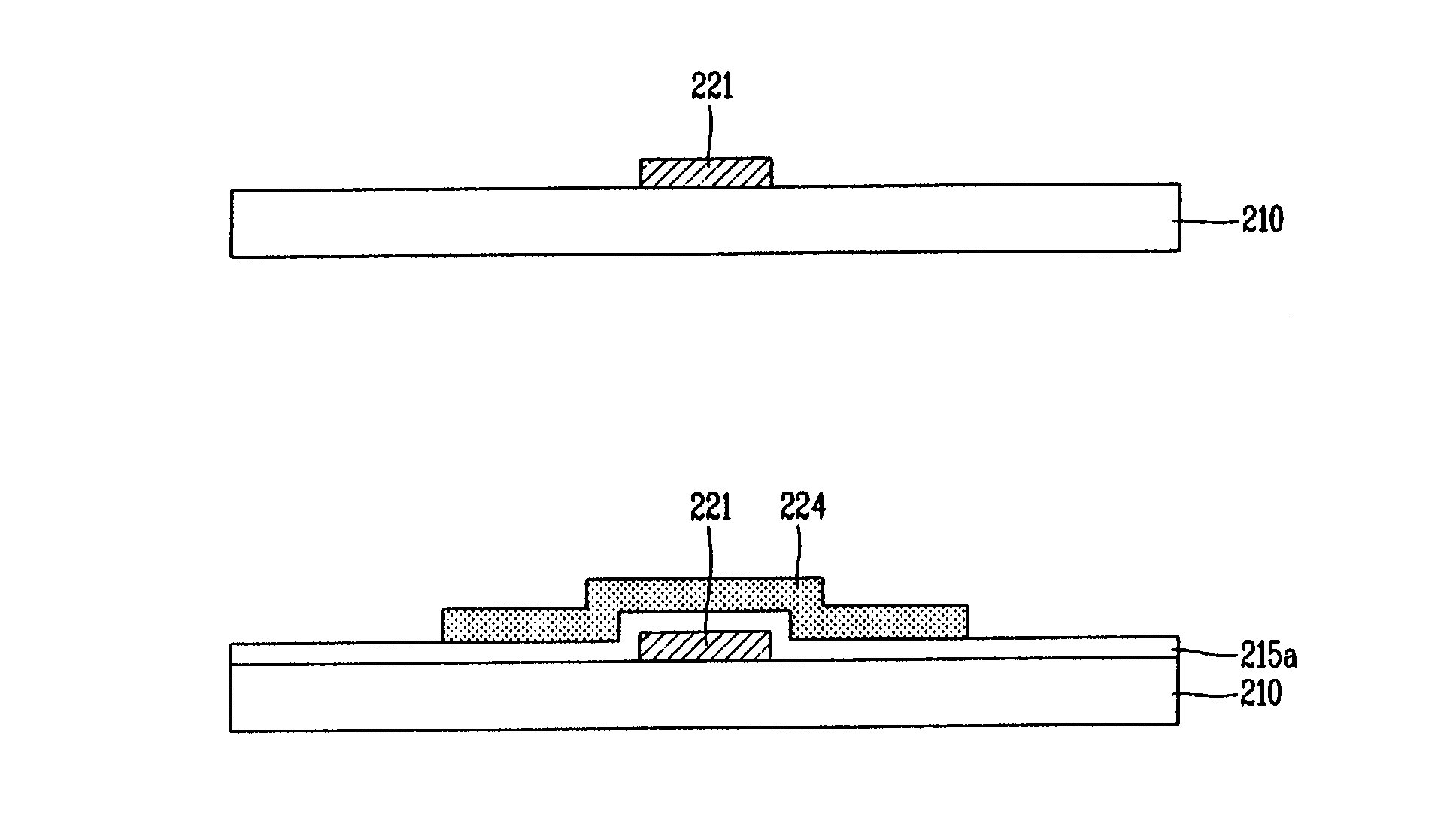

Semiconductor device and method of manufacturing thereof

ActiveUS7157369B2Minimized contact resistanceEfficiently and stably provideTransistorSolid-state devicesDielectricLithography process

There is provided a method of manufacturing a semiconductor device that can reduce the number of processes, and decrease contact resistance between plugs. The method comprises forming a first interlayer dielectric film having a first opening where a contact plug is to be formed; uniformly forming a first conductive layer on the first interlayer dielectric film and in the first opening; forming a resist defining an interconnect pattern by a lithography process on a region excluding the first opening; performing first anisotropic etching to remove a region of the first conductive layer not covered with the resist until an upper face of the first interlayer dielectric film is exposed, thus to form an interconnect and the contact plug.

Owner:RENESAS ELECTRONICS CORP

Method for etching atomic layer of graphene

ActiveUS9245752B2Minimizing physical and electrical damageMinimized contact resistanceSemiconductor/solid-state device manufacturingGrapheneEtchingCvd graphene

This present disclosure relates to an atomic layer etching method for graphene, including adsorbing reactive radicals onto a surface of the graphene and irradiating an energy source to the graphene on which the reactive radicals are adsorbed.

Owner:RES & BUSINESS FOUND SUNGKYUNKWAN UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com