Patents

Literature

205results about How to "High switching ratio" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

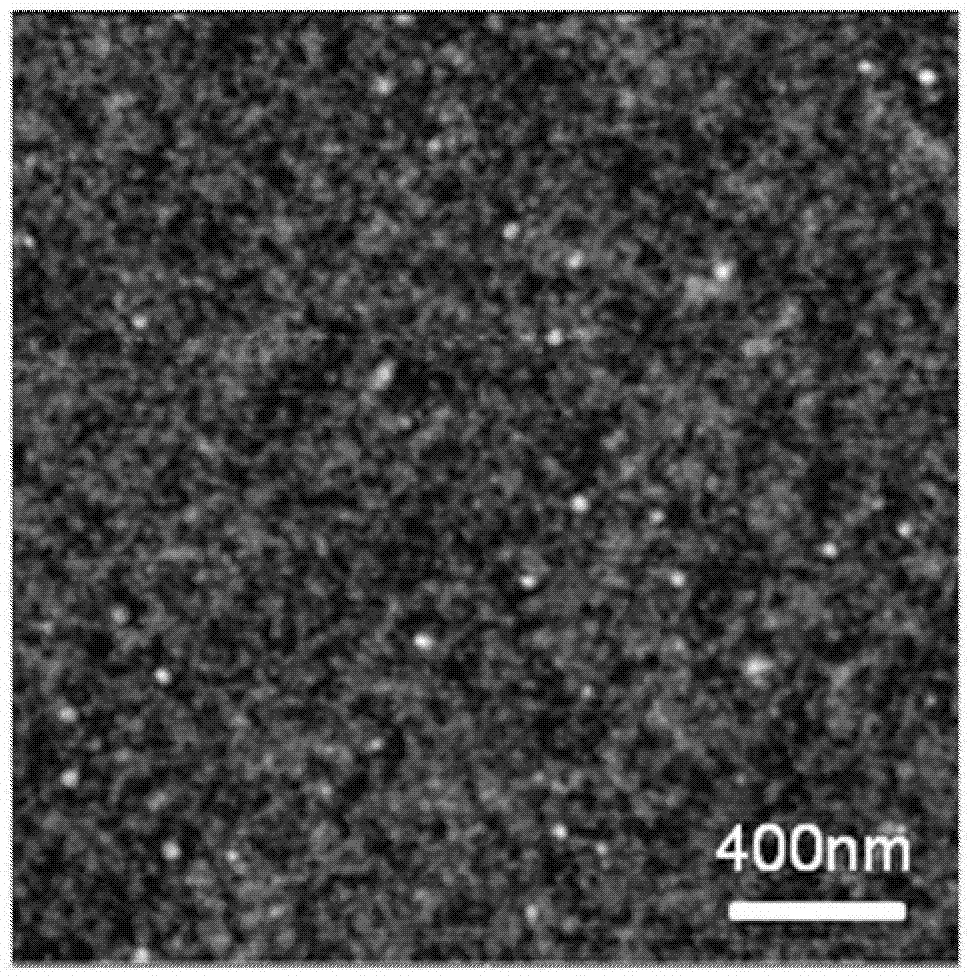

Method for preparing metal chalcogenide film

ActiveCN103194729AControl thicknessSmall sizeChemical vapor deposition coatingDeposition temperatureSulfur

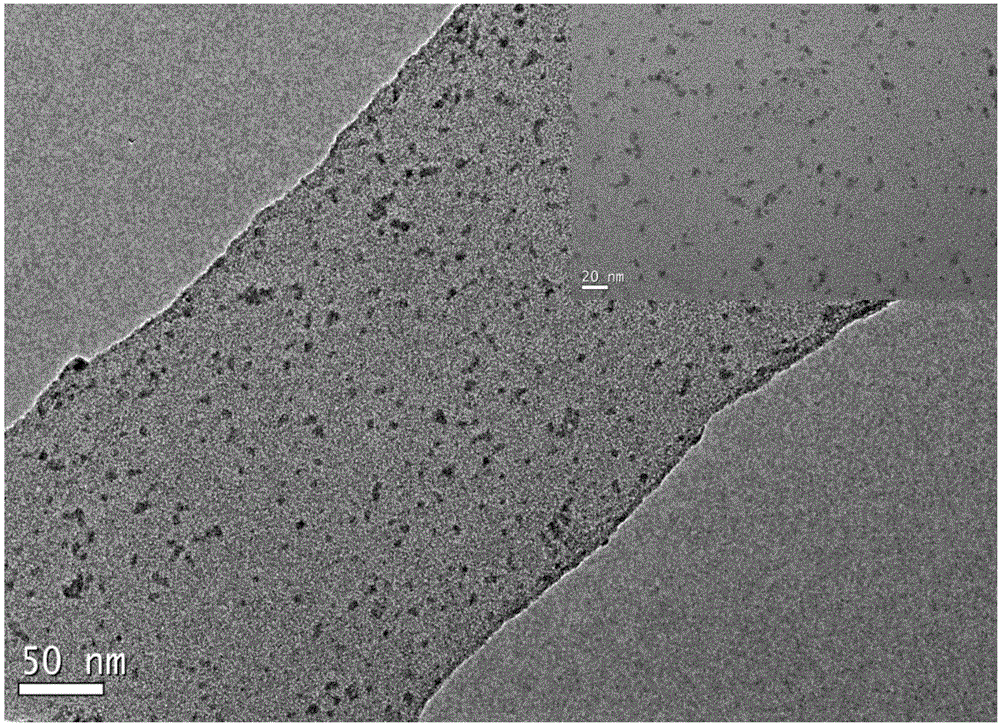

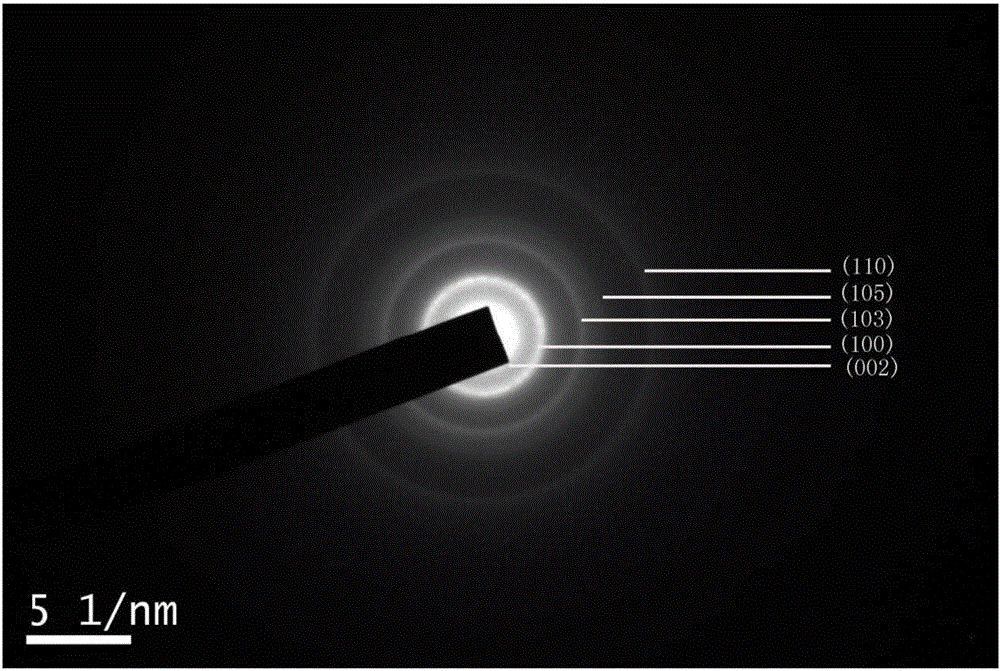

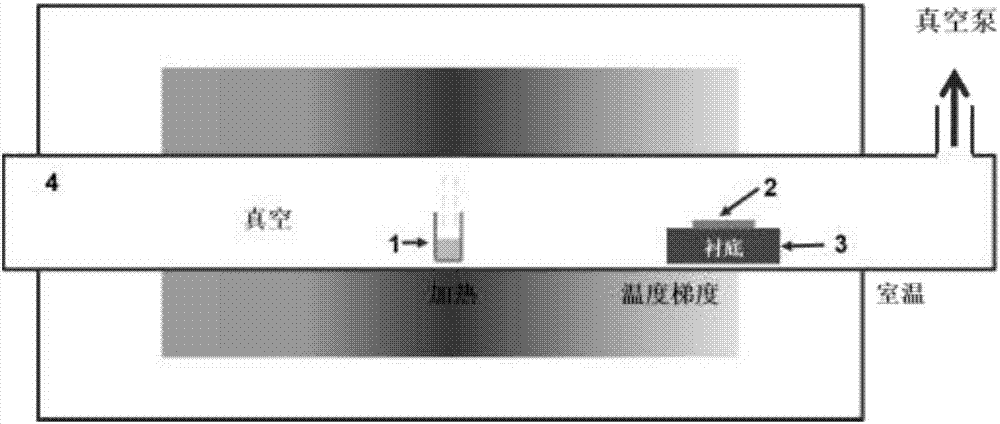

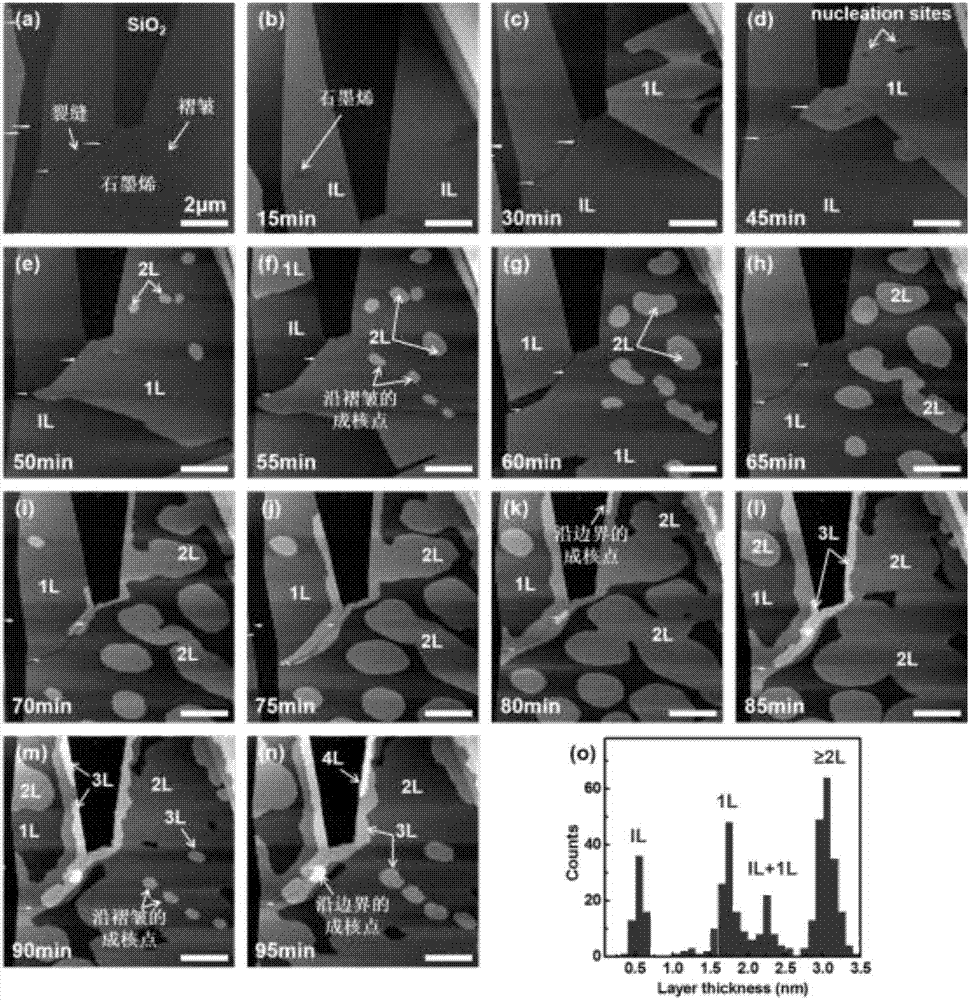

The invention discloses a method for preparing a metal chalcogenide film. The method is used for growing the metal chalcogenide film on a substrate with the vapor deposition process by using a chalcogen source and a metal element source and comprises the following steps of: providing three temperature zones, wherein the temperature of the three temperature zones can be controlled independently, and the chalcogen source, the metal element source and the substrate are put in the three temperature zones respectively; controlling the three temperature zones, evaporating the chalcogen source to generate the chalcogen source steam, evaporating the metal element source to generate the metal element source steam, and heating the substrate to the predetermined deposition temperature; providing a carrier gas, and enabling the carrier gas to flow through the three temperature zones in sequence to deliver the metal element source steam to the substrate to deposit and grow so as to form the metal chalcogenide film. The method disclosed by the invention is simple, dispenses with the original complex step of introducing a nucleation site and effectively ensures the purity and the surface cleanness of a sample. The metal chalcogenide film prepared by adopting the method has high quality.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

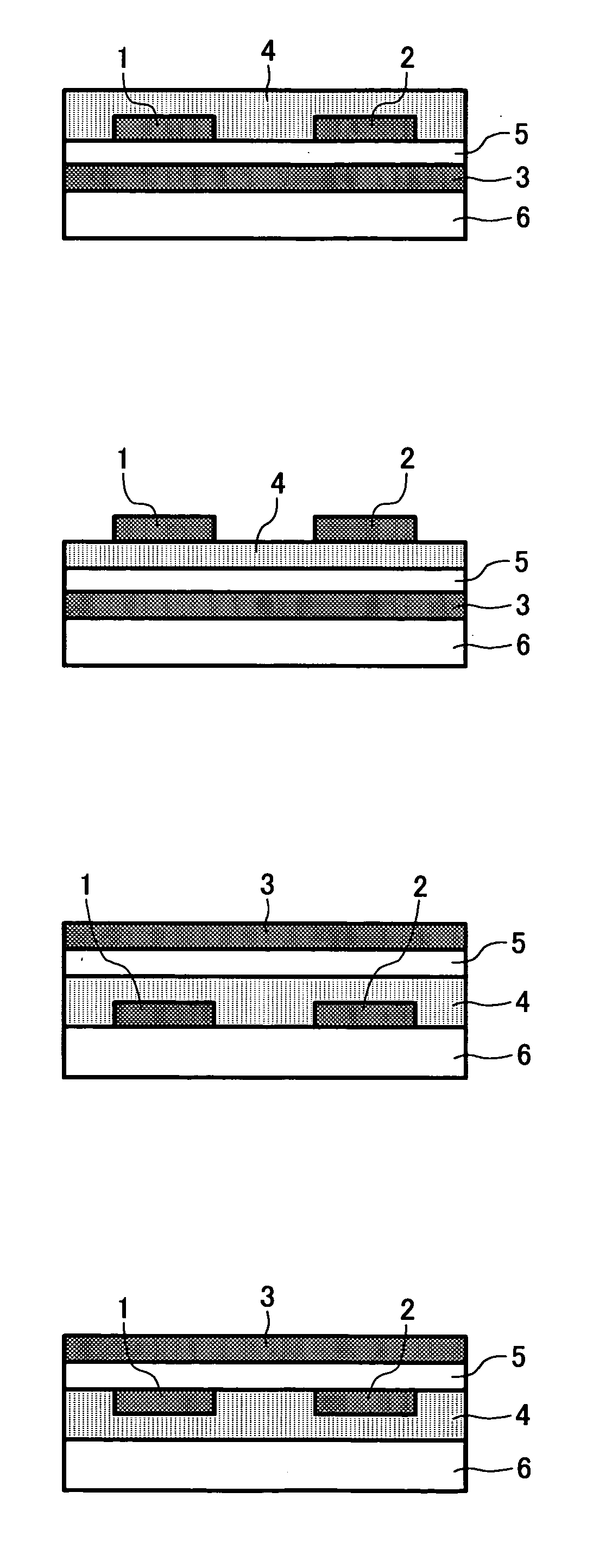

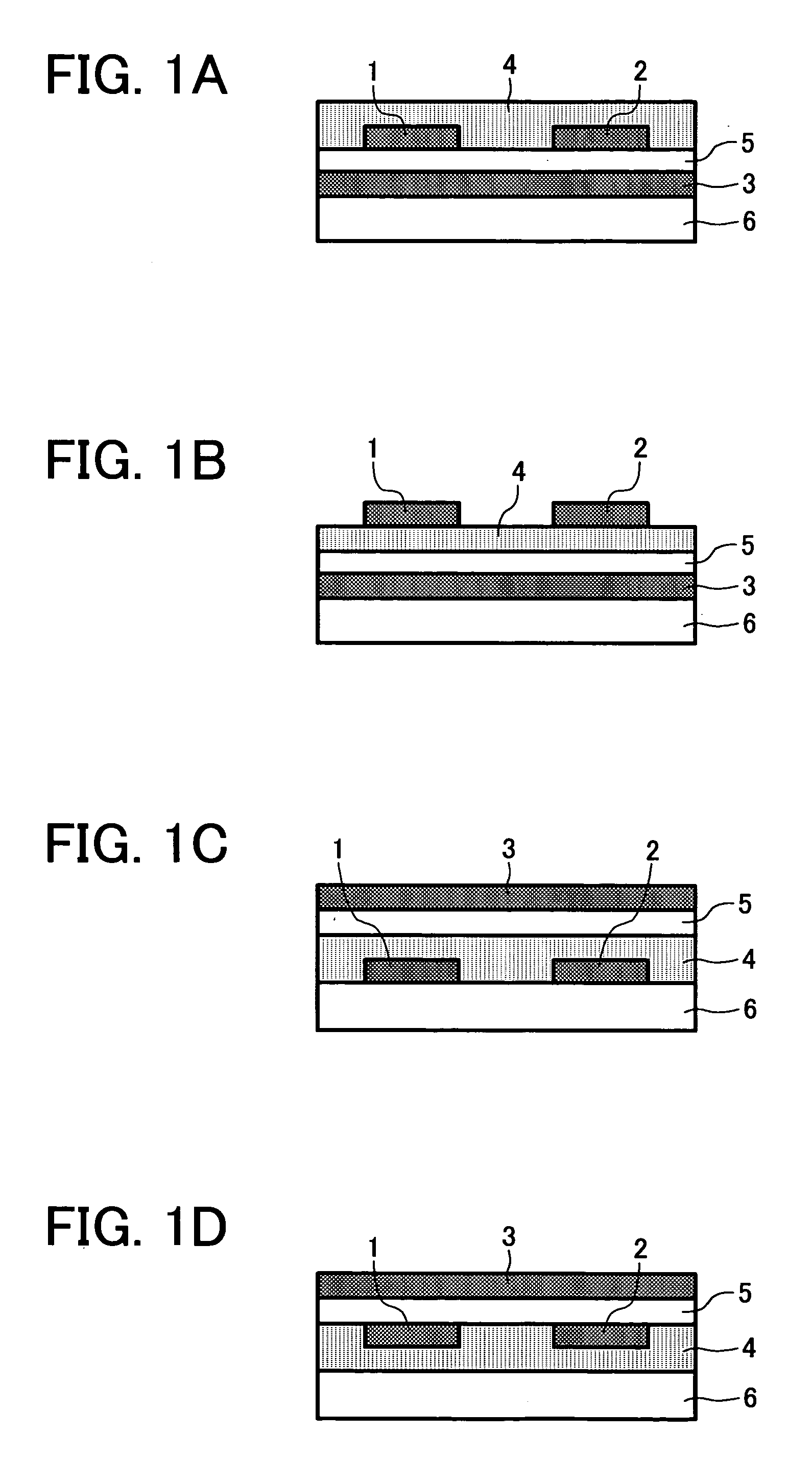

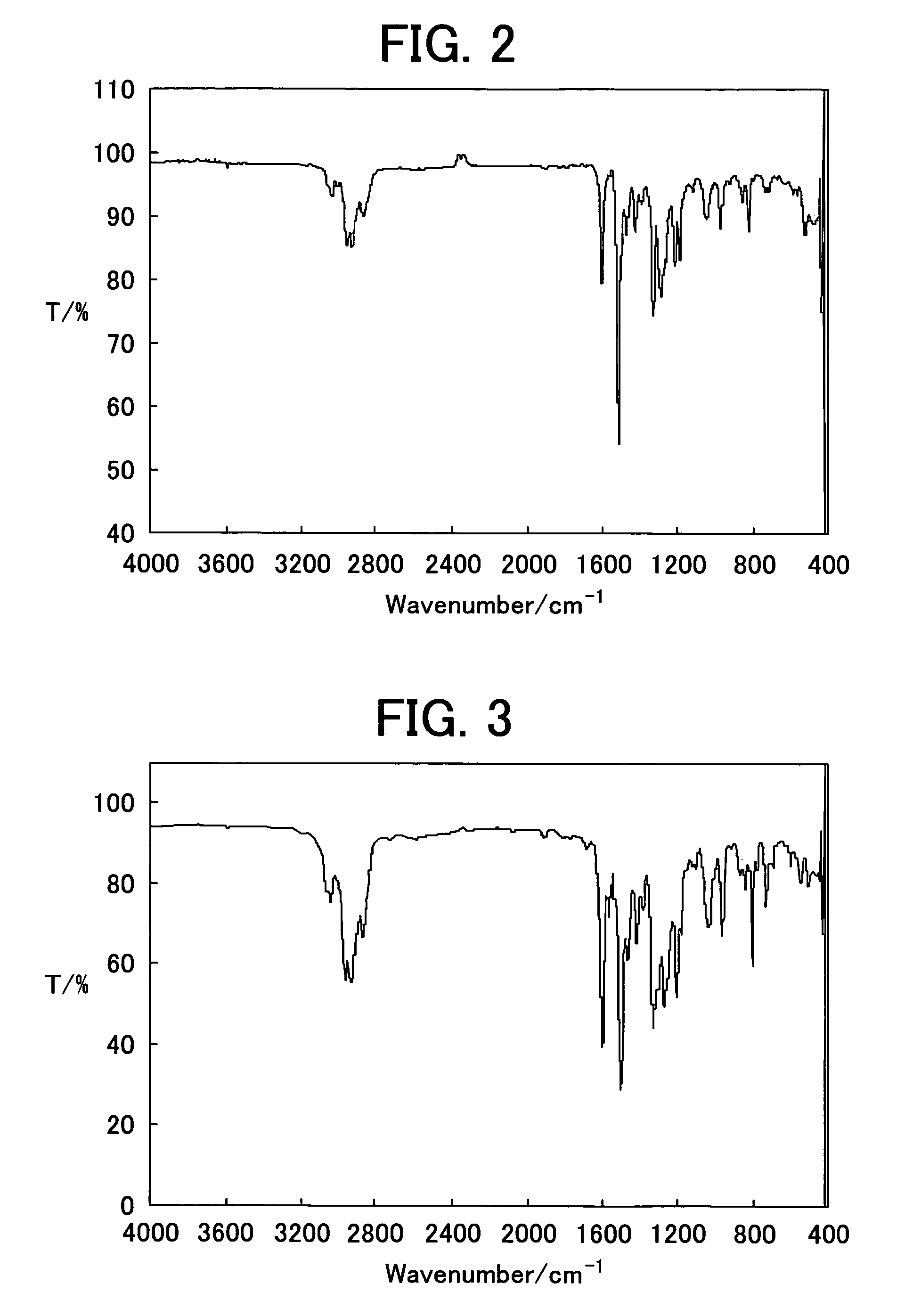

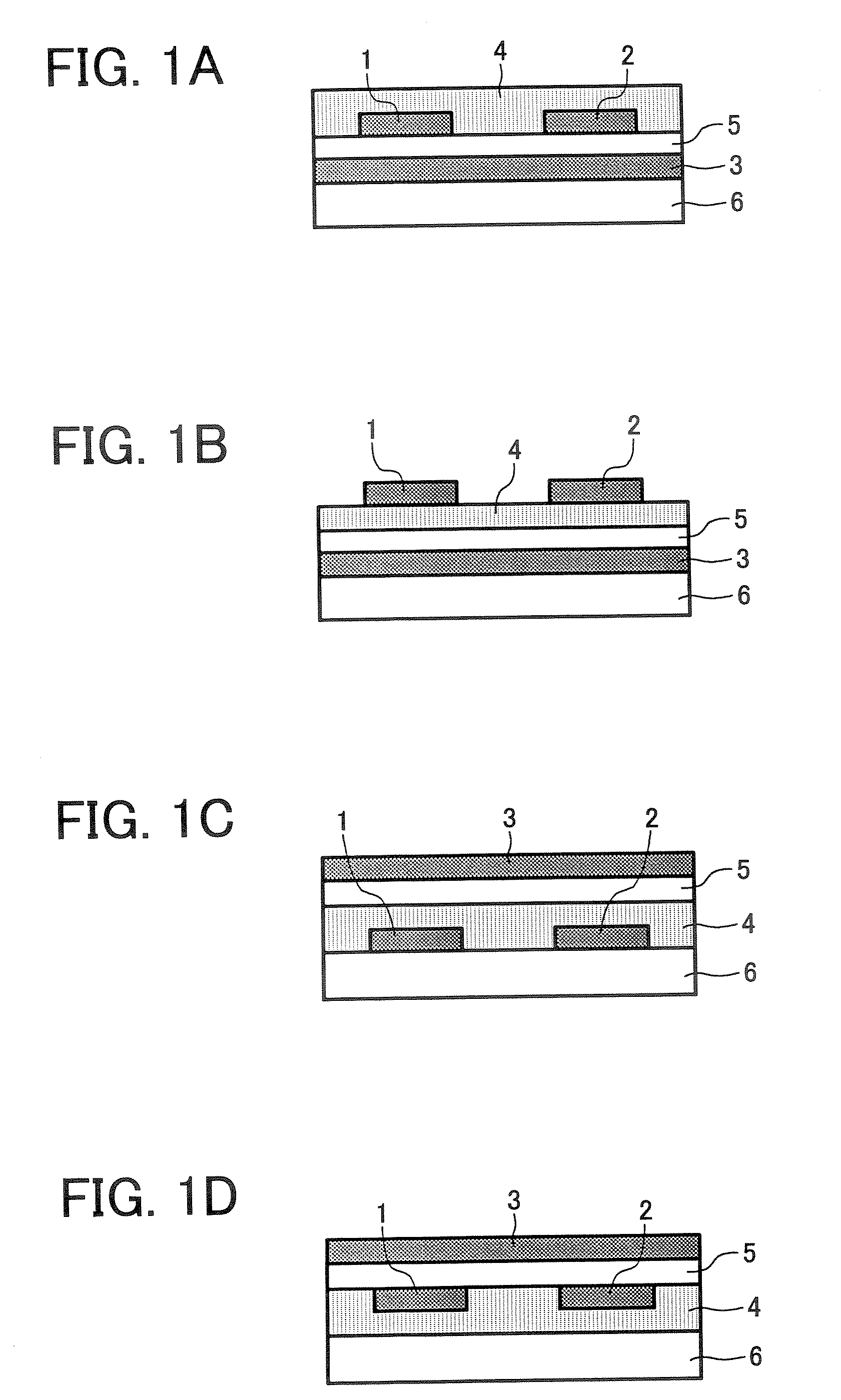

Aryl amine polymer, thin film transistor using the aryl amine polymer, and method of manufacturing the thin film transistor

ActiveUS7166689B2High carrier mobilityHigh switching ratioTransistorCell electrodesArylSemiconductor materials

An aryl amine polymer is provided which contains a specific repeat unit, its use in preparing an organic semiconductor material which contains the aryl amine polymer and an additional specific compound and in the preparation of organic light emitting devices (OLED), organic thin film transistors (TFT) and so on, along with an organic TFT including a substrate, an organic semiconductor layer which contains the organic semiconductor material and is located overlying the substrate, an electrode pair of a source electrode and a drain electrode; and a third electrode.

Owner:RICOH KK

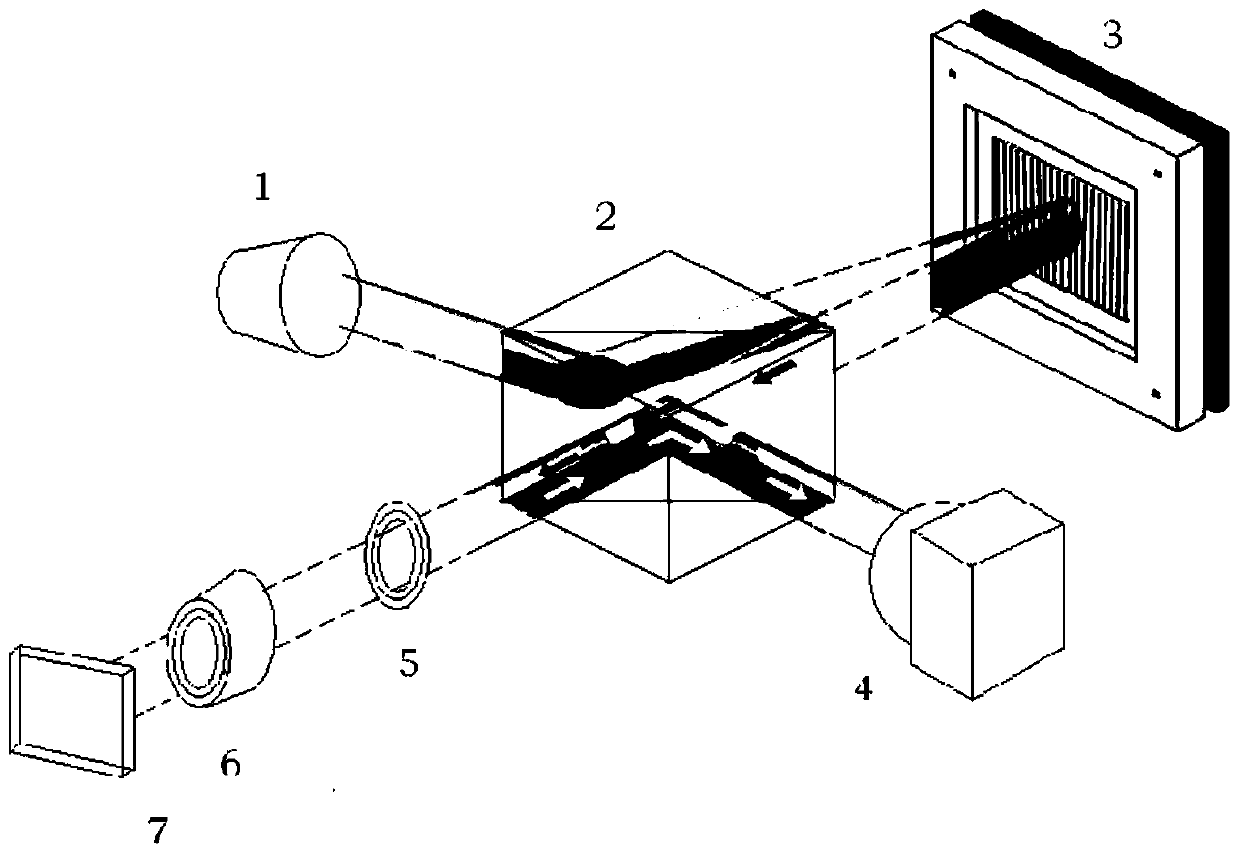

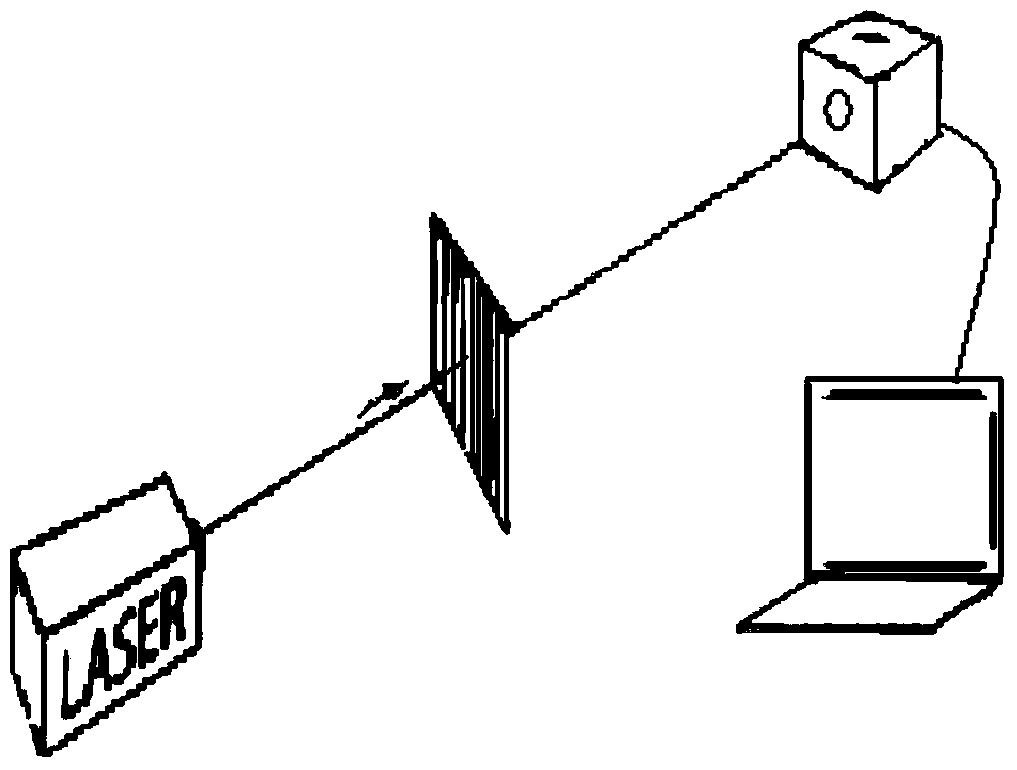

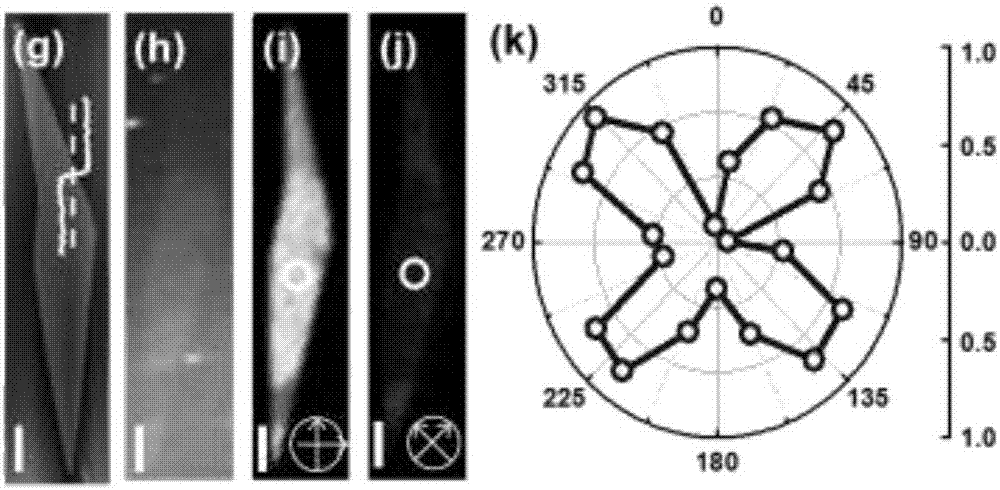

Forked liquid crystal grating preparation method and application of forked liquid crystal grating in vortex beam

InactiveCN103792605AImprove light energy conversion efficiencyChange in real timeDiffraction gratingsNon-linear opticsLithographic artistOptical axis

A forked liquid crystal grating is characterized in that liquid crystal orientation of adjacent liquid crystal areas of the forked liquid crystal grating is controlled differently such that the following three types of forked liquid crystal gratings can be formed, namely a TN / PA-type forked liquid crystal grating, an orthogonal PA-type liquid crystal grating and an orthogonal HAN-type liquid crystal grating; 90-degree twisted phase microcells of liquid crystal and parallel-oriented microcells of and the liquid crystal are alternately arranged so as to form the TN / PA-type forked liquid crystal grating; uniformly parallel microcells of the liquid crystal of which optical axes are in the same region and microcells in an adjacent region which are orthogonal to each other are alternately arranged to form the orthogonal PA-type liquid crystal grating. According to the preparation of the forked liquid crystal grating, a photoalignment method is adopted to control liquid crystal micro orientation so as to control the director distribution of the liquid crystal. Since a digital?micro-mirror device (DMD)-based micro projection-type lithography system is realized, a digital control device outputs liquid crystal forked gritting pattern signals to control the reflected light of each pixel of a digital?micro-mirror device (DMD), such that the imaging of a liquid crystal forked grating pattern can be realized; and after being narrowed through a micro objective, light beams are projected to photoalignment material agent conductive glass through a polarizing film.

Owner:NANJING UNIV

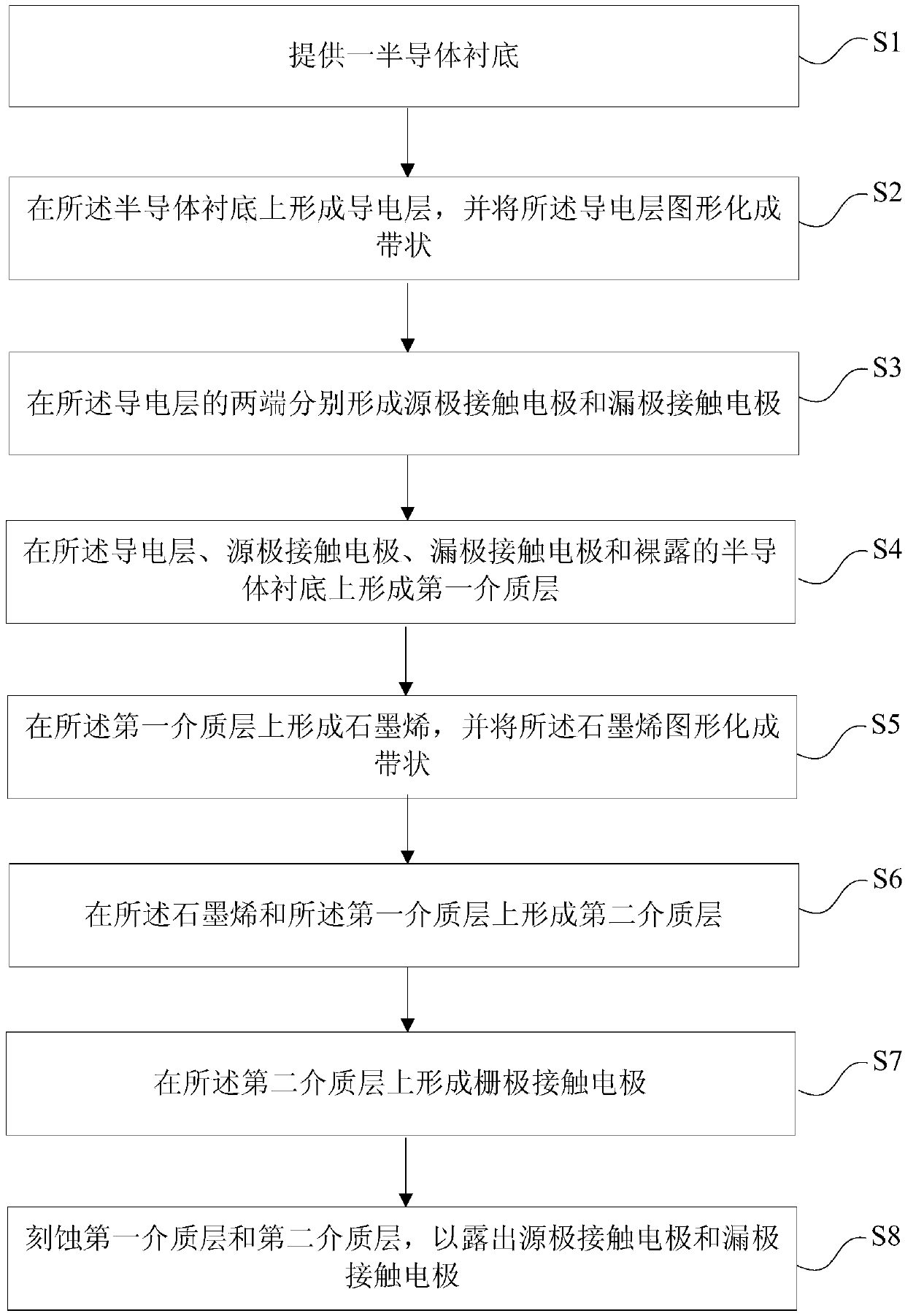

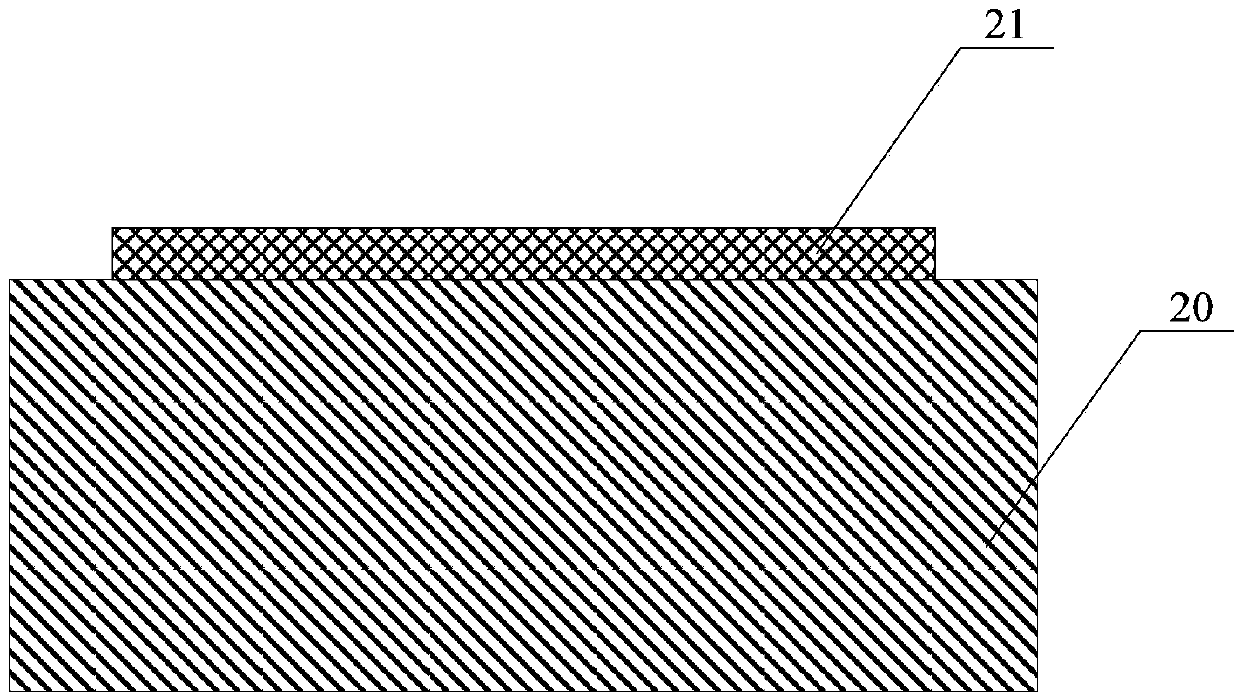

Preparation method of graphene flash memory

InactiveCN104192835ASimple processSimple and fast operationSemiconductor/solid-state device manufacturingCapacitancePhysical space

The invention provides a preparation method of a graphene flash memory. According to the method, a single-layer or multi-layer continuous graphene thin film replaces a polysilicon gate or nitric oxide to store electric charges, the storage capacity of the electric charges is improved within a limited physical space, and as the graphene is relatively thin, the influence of capacity coupling in a device is eliminated while the longitudinal dimension of the device is diminished, so that the problem of crosstalk of adjacent storage units in work is effectively avoided. The graphene flash memory is simple in process and convenient in operation, and the data of the graphene flash memory are rapidly written, erased and read at the low power consumption.

Owner:浙江鸿盟杉海智能科技有限公司

High-dielectric-constant gate dielectric composite channel field effect transistor and preparing method thereof

InactiveCN104766888AImprove electrical performanceImprove mobilityTransistorSemiconductor/solid-state device manufacturingDielectricGate dielectric

The invention relates to a high-dielectric-constant gate dielectric composite channel field effect transistor device and belongs to the technical field of micro-electronics new materials and devices. The device comprises a substrate, a high-dielectric-constant gate dielectric, a graphical graphene conducting channel and a graphical molybdenum sulfide (MoS2) conducting channel which are sequentially stacked, and comprises a metal source electrode and a metal drain electrode which are arranged on the composite conducting channel. According to a preparing method, the mode of the atomic layer deposition technology (ALD) is directly utilized, and a high-dielectric-constant (high-k) material grows on the Si substrate. As the graphene / molybdenum sulfide (MoS2) composite channels are adopted, the larger migration rate and the larger switch ratio can be obtained, and the electric property of the device is improved.

Owner:TSINGHUA UNIV

New aryl amine polymer, thin film transistor using the new aryl amine polymer, and method of manufacturing the thin film transistor

InactiveUS20070092760A1High carrier mobilityHigh switching ratioTransistorCell electrodesArylOrganic light emitting device

An aryl amine polymer is provided which contains a specific repeat unit, its use in preparing an organic semiconductor material which contains the aryl amine polymer and an additional specific compound and in the preparation of organic light emitting devices (OLED), organic thin film transistors (TFT) and so on, along with an organic TFT including a substrate, an organic semiconductor layer which contains the organic semiconductor material and is located overlying the substrate, an electrode pair of a source electrode and a drain electrode; and a third electrode.

Owner:RICOH KK

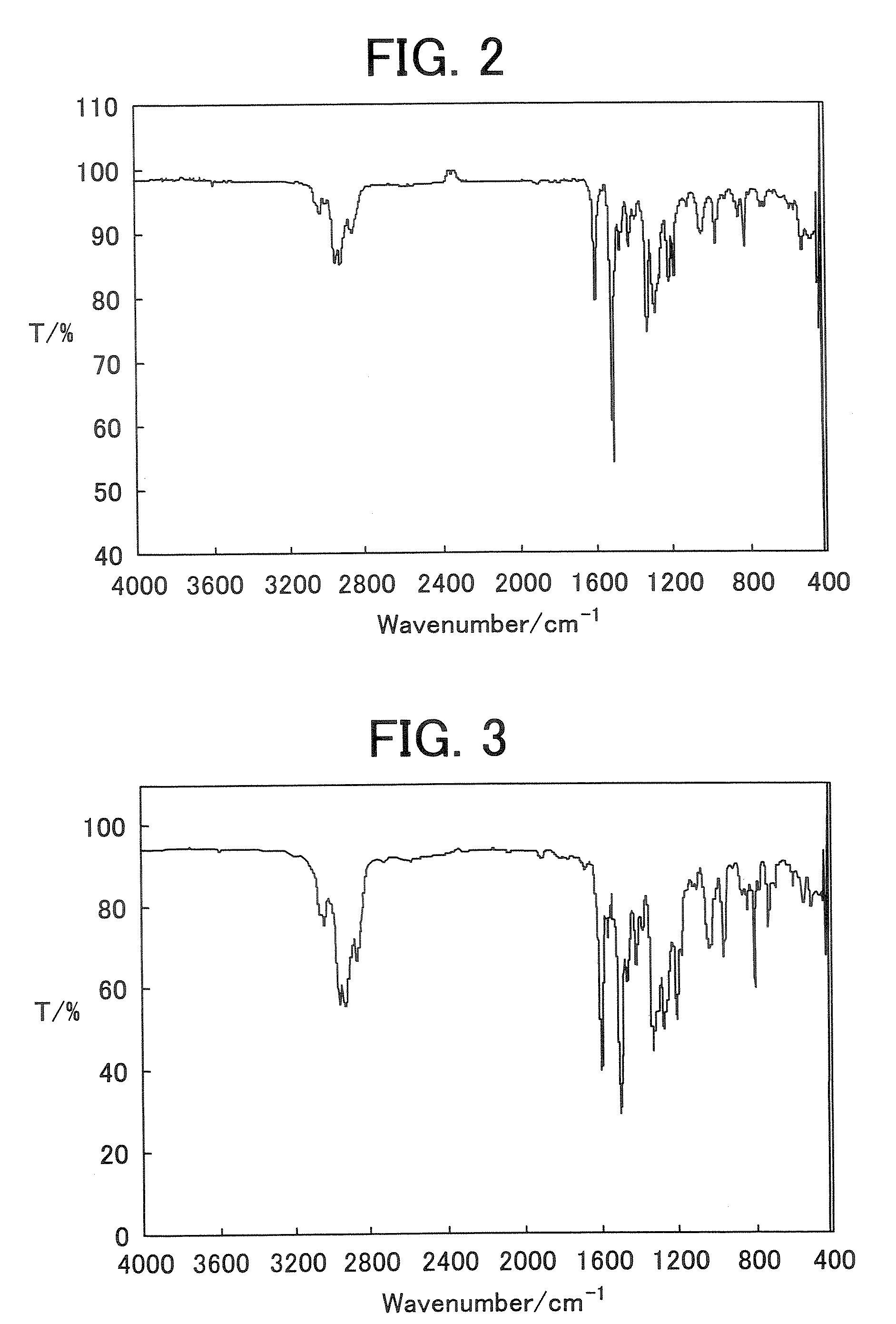

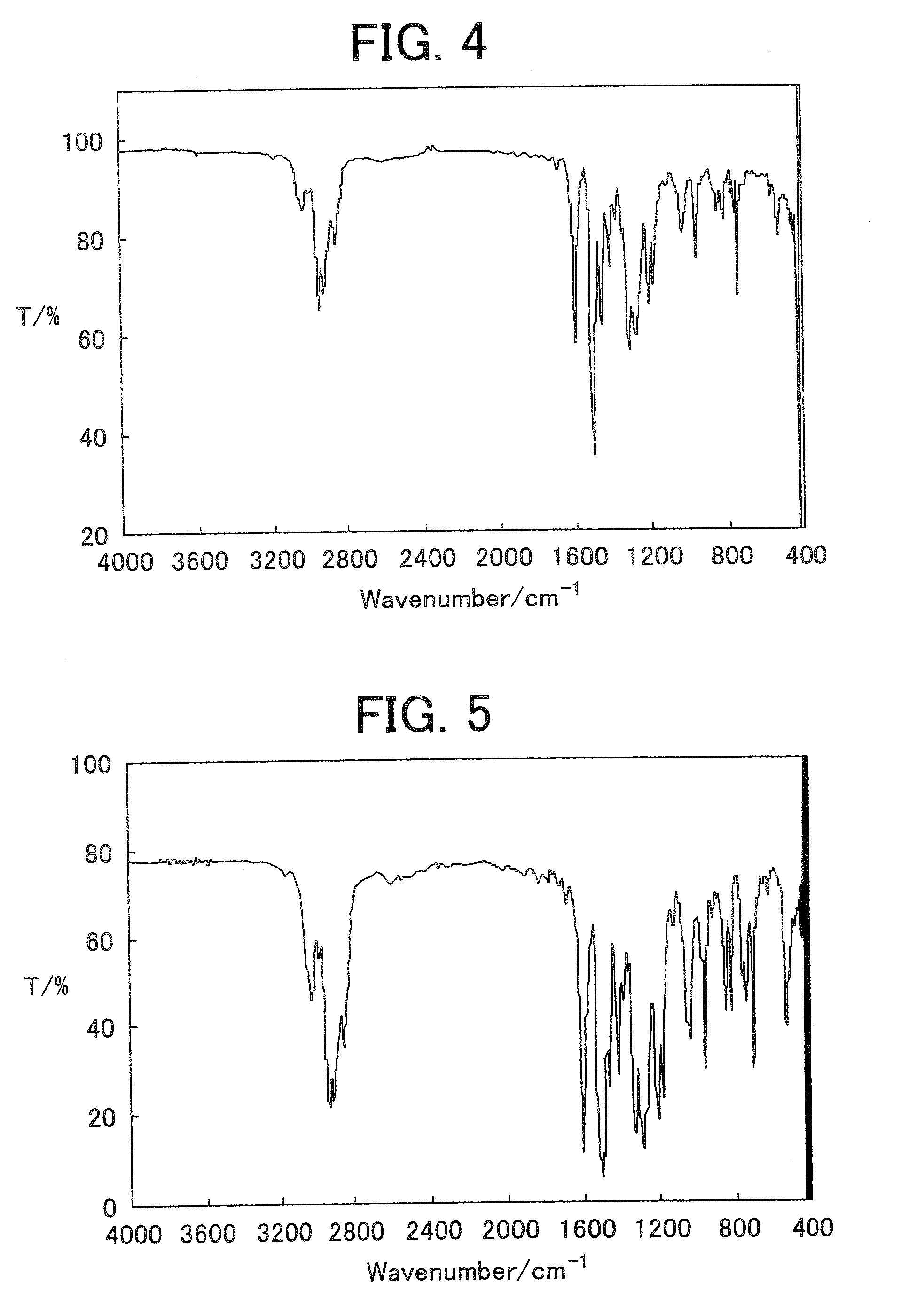

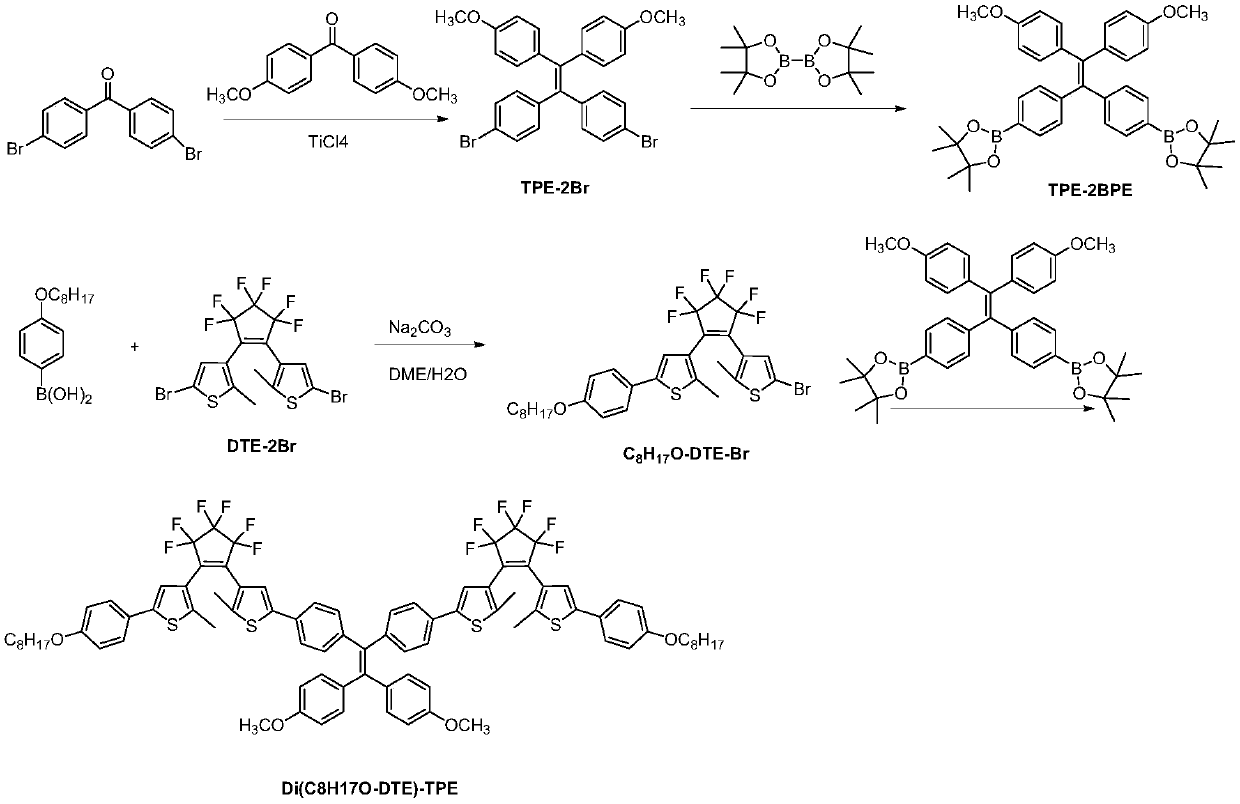

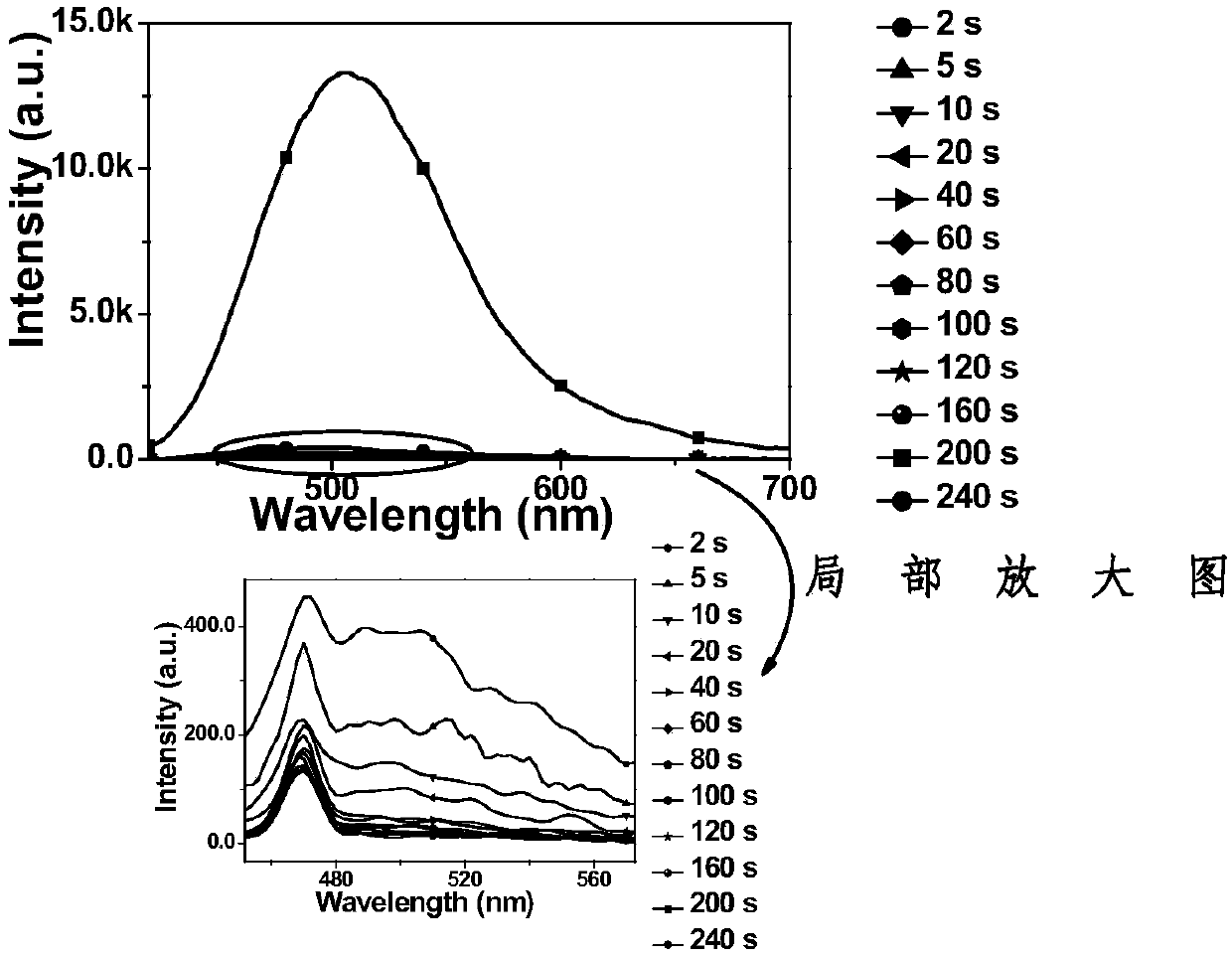

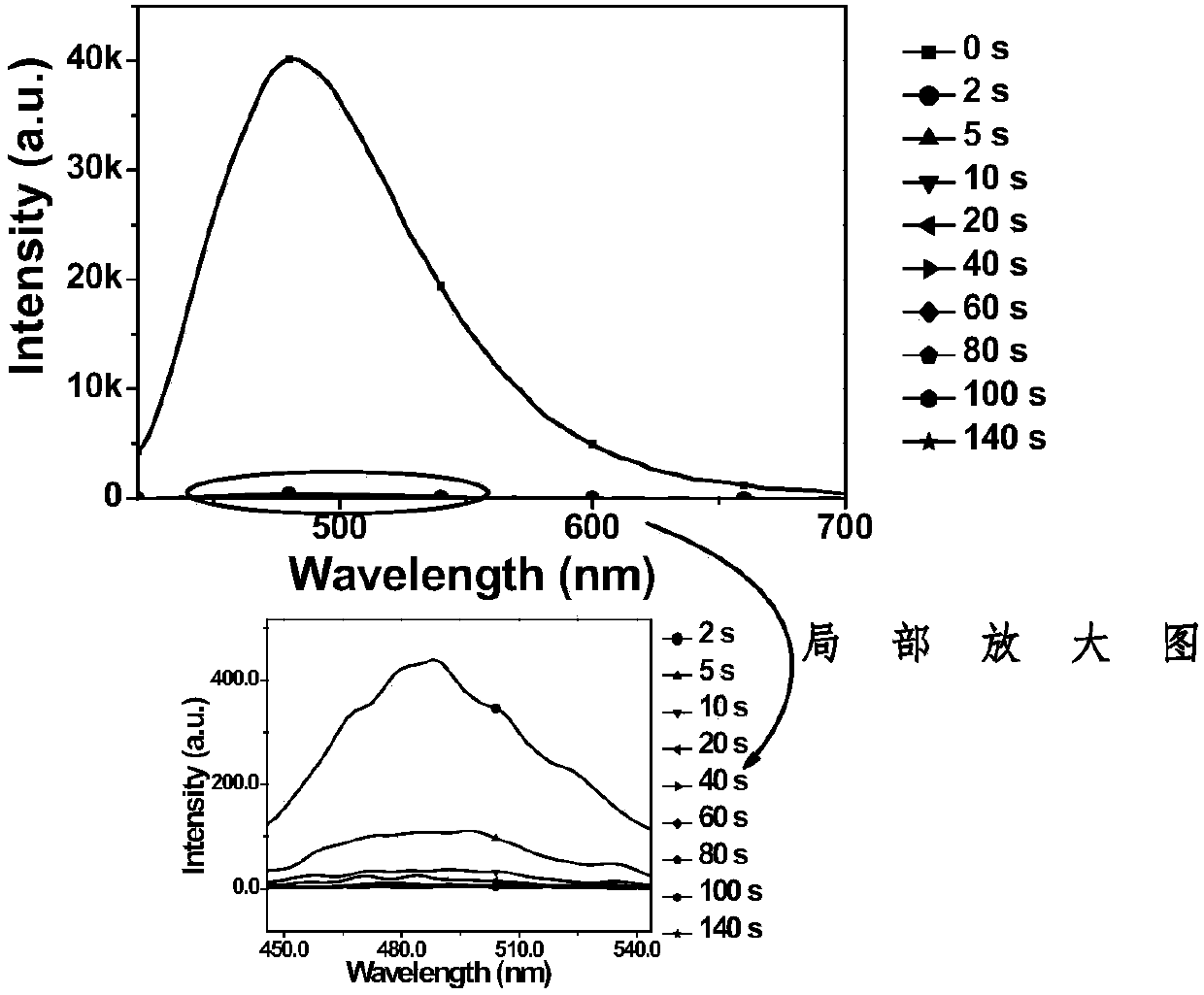

Diarylethene fluorescent molecular switch and preparation method and application thereof

ActiveCN107652279AEasy to synthesizeImprove thermal stabilityOrganic chemistryFluorescence/phosphorescenceAggregation-induced emissionMolecular switch

The invention discloses an aggregation-induced emission type diarylethene fluorescent molecular switch and a preparation method and application thereof. The aggregation-induced emission type diarylethene fluorescent molecular switch is characterized in that an AIE radical is introduced to gain solid or aggregation strong emission capacity; two diarylethene can be used for quickly quenching fluorescence of fluorescent radicals which aggregate in the surrounding under the irradiation of ultraviolet rays or visible light, thus achieving the purpose of high fluorescent switch ratio. According to the light control type AIE-effect fluorescent molecular switch, the limitation that traditional fluorescent chromophore leads to fluorescence quenching is broken; in addition, the fluorescent molecularswitch in solid and aggregation state has the advantages of being high in switch ratio and high in fluorescence quenching efficiency by being compared with the fluorescent molecular switch in solution state; the fluorescent molecular switch is applicable to information storage under solid state and photoelectric devices and has potential application in biosensing and fluorescence imaging.

Owner:HUAZHONG UNIV OF SCI & TECH

Graphene/silicon/graphene-based avalanche photodetector and manufacturing method thereof

ActiveCN104157721AHigh gainLarge light signal currentFinal product manufactureSemiconductor devicesIonizationCvd graphene

The invention discloses a graphene / silicon / graphene-based avalanche photodetector and a manufacturing method thereof. The avalanche photodetector comprises an n-type silicon substrate, a silicon dioxide isolation layer, a silicon dioxide window, a silicon dioxide insulation layer, a top electrode, a graphene interdigital electrode film and an anti-reflection layer. Graphene serves the transparent interdigital electrode and together with the silicon substrate, the photodetector of an MSM-type structure is formed. The photodetector can carry out wide spectrum detection, the problem that the traditional silicon-based PIN junction is low to ultraviolet light detection response can be solved; the anti-reflection layer enhances absorption of incident lights, and photocurrent is enhanced; under the effect of large reverse bias, a strong electric field is generated among the grapheme interdigital electrodes, collision ionization is likely to happen to photocarrier and silicon lattice, and high gain is obtained. The graphene / silicon / graphene-based avalanche photodetector and a manufacturing method thereof have the advantages of high response degree, quick response speed, large internal gain, small switch ratio and low power consumption.

Owner:ZHEJIANG UNIV

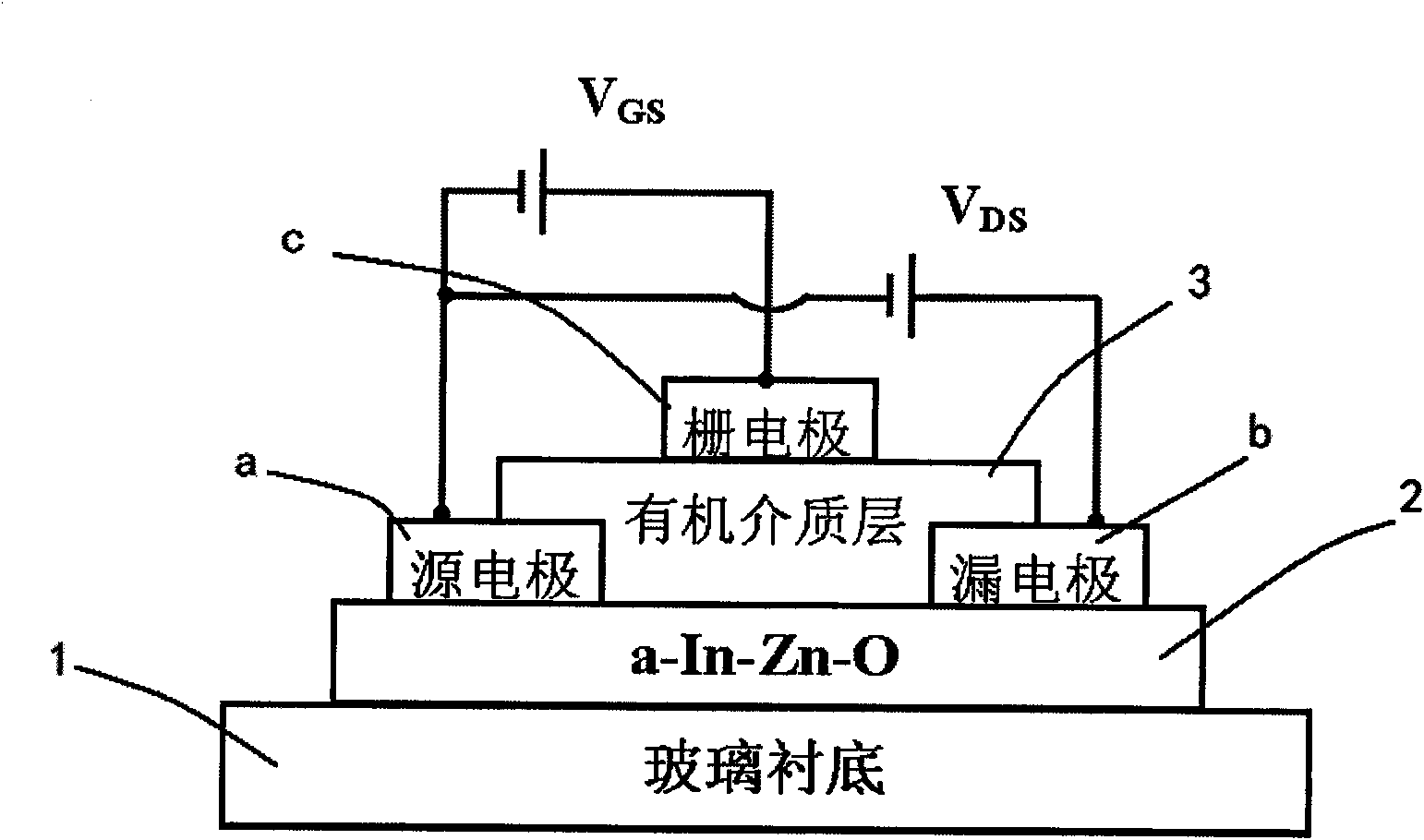

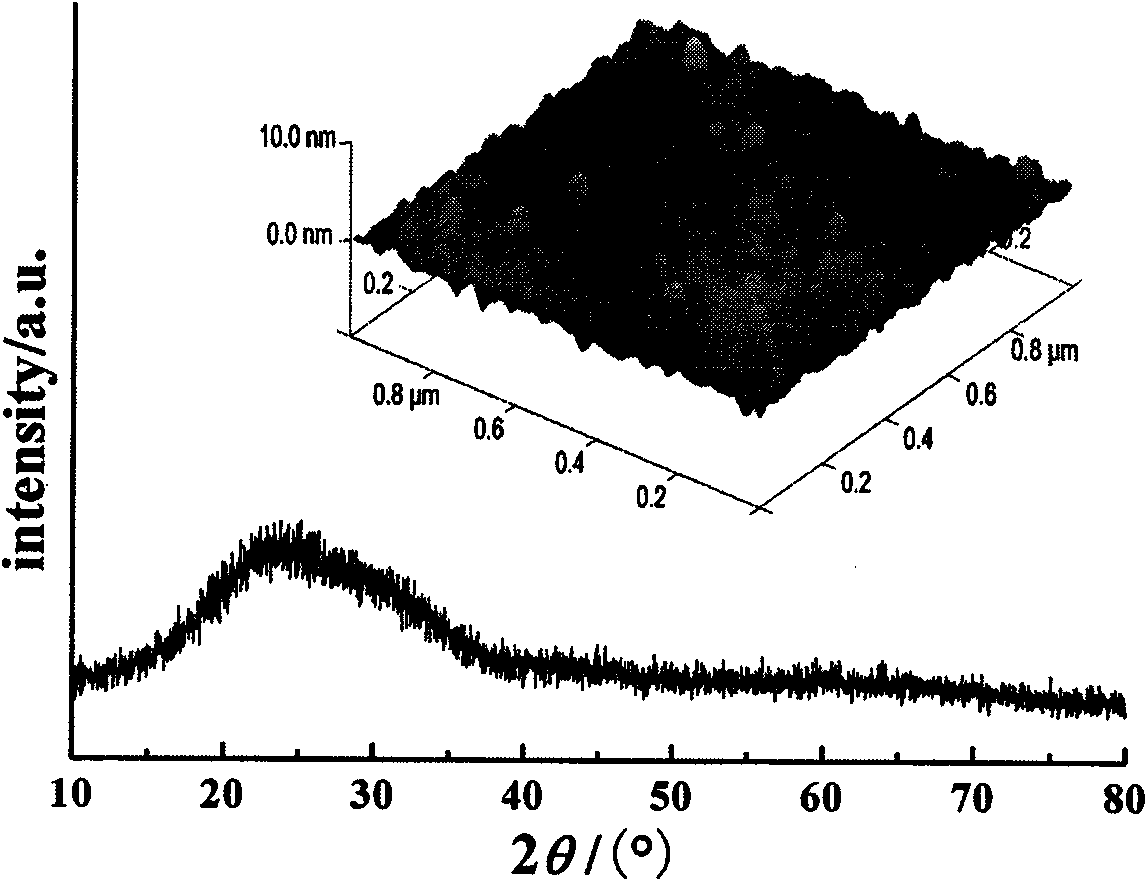

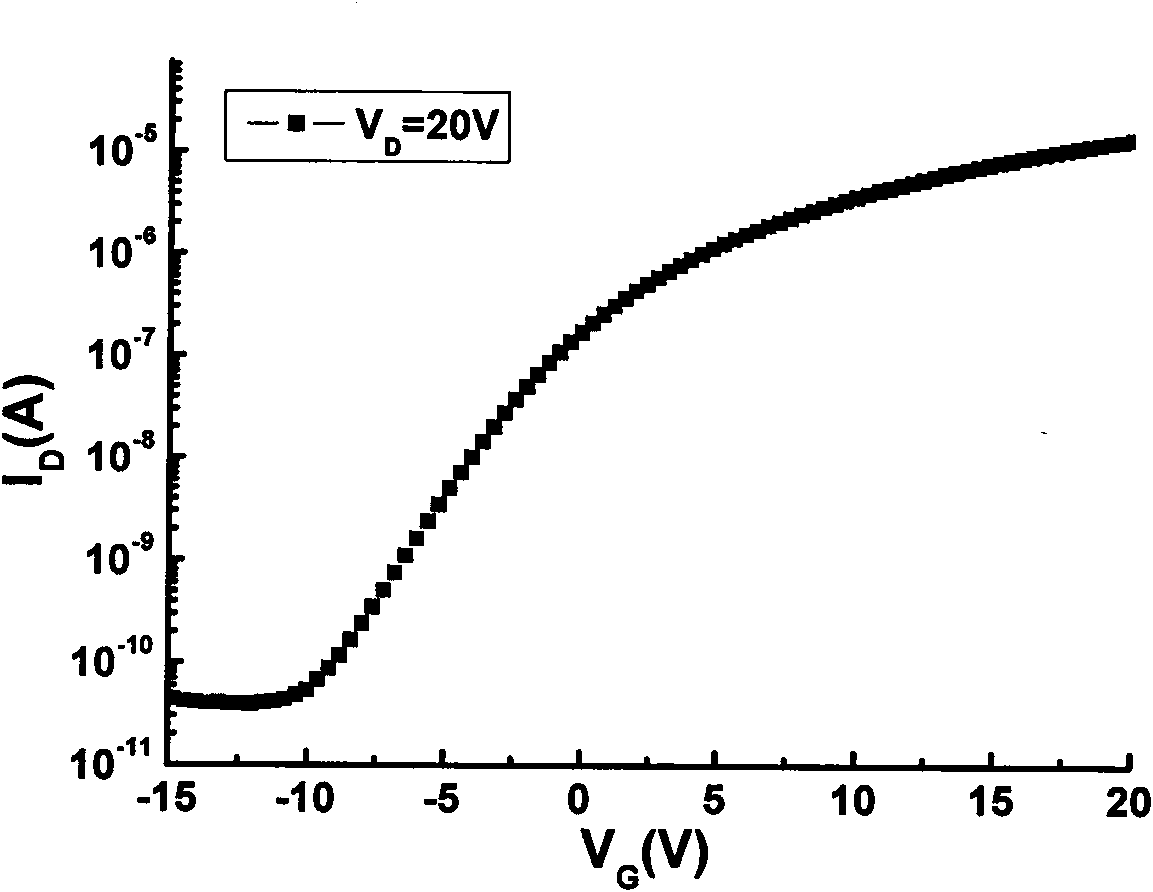

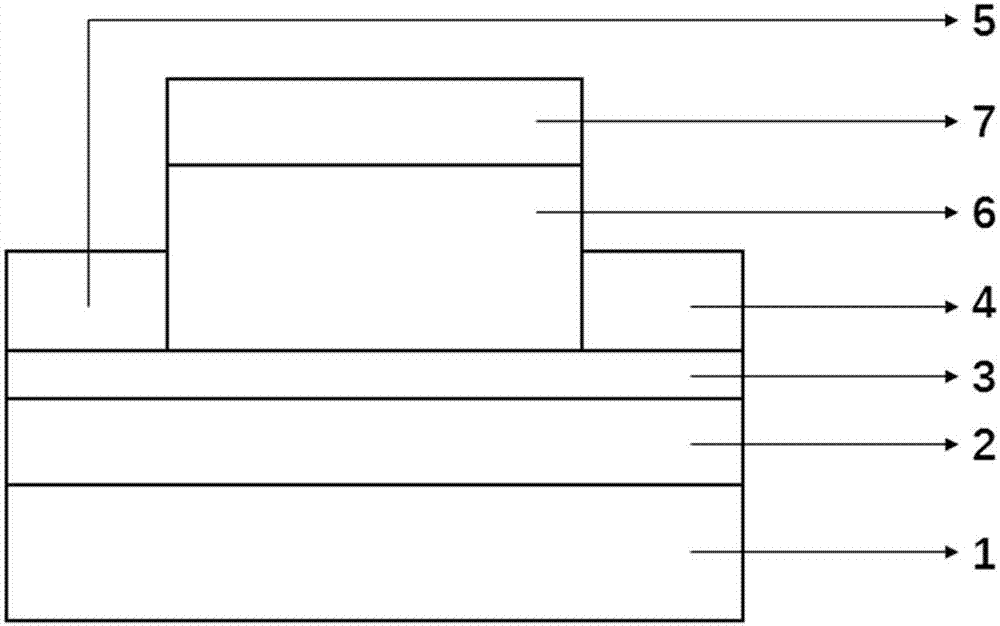

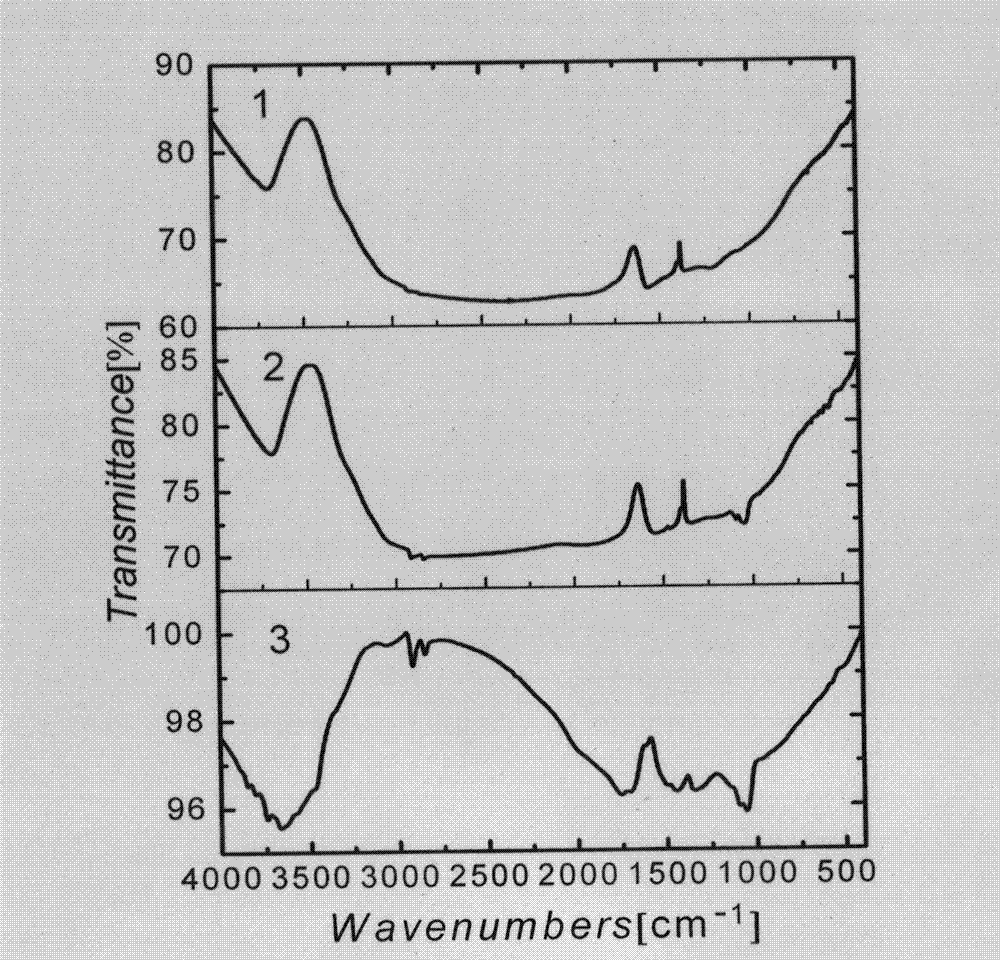

Method for preparing thin film transistor

InactiveCN101599437AImprove mobilityHigh switching ratioSemiconductor/solid-state device manufacturingIndiumEvaporation

The invention belongs to the technical field of thin film transistors, and relates to a method for preparing a thin film transistor. The method comprises the following steps: by adopting indium-zinc alloy or indium-zinc oxide as a target material, under the room temperature, growing an indium-zinc oxide semiconductor thin film with a transparent amorphous structure on a substrate through magnetron sputtering technology, and forming a channel layer of the thin film transistor; preparing a source electrode and a drain electrode by adopting a thermal evaporation method; covering a layer of organic medium layer thin film manufactured by polyvinylpyrrolidone organic solution on the source electrode and the drain electrode by adopting a hauling or spinning method; and preparing a gate electrode on the organic medium layer thin film by adopting the thermal evaporation method. The atomic ratio of In to Zn in the target material is 0.5 to 5.0. The method can prepare a novel transparent thin film transistor with good electronic optical performance, has low preparation temperature and simple process, is favorable for large-area production, and has wide application prospect.

Owner:FUDAN UNIV

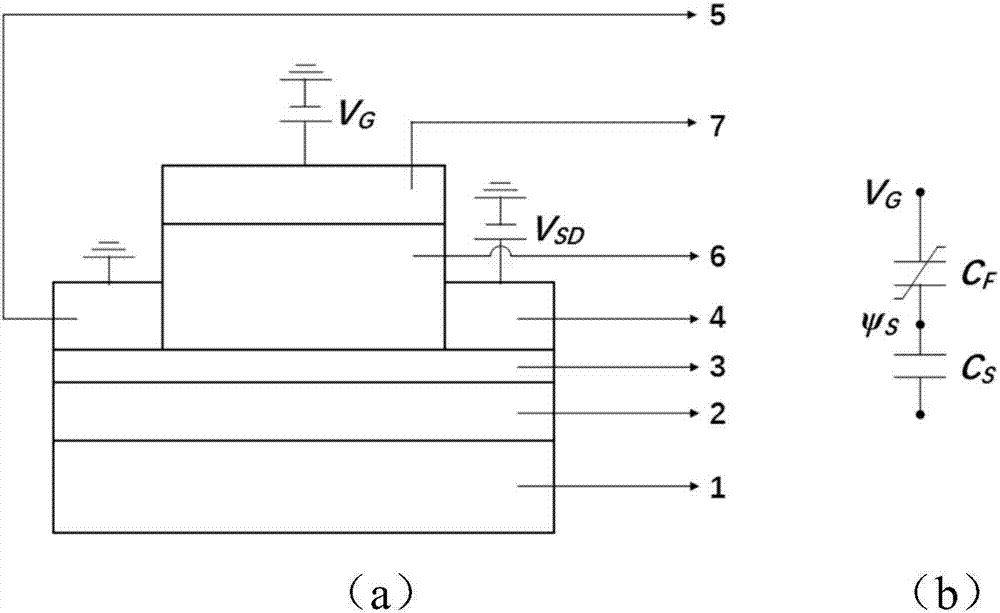

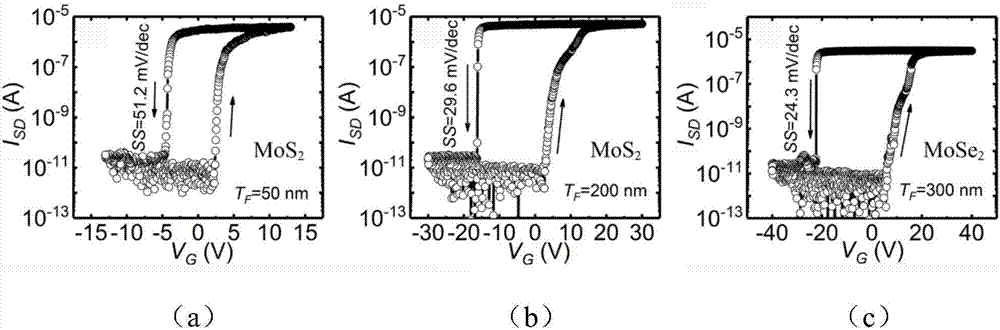

Two-dimensional semiconductor negative capacitance field-effect transistor and preparation method thereof

PendingCN107195681ASimple structureEasy to manufactureSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceCapacitive effect

The invention discloses a two-dimensional semiconductor negative capacitance field-effect transistor and a preparation method thereof. The device structure sequentially comprises a substrate, a two-dimensional semiconductor, a metal source-drain electrode, a ferroelectric gate medium with a negative capacitance effect and a metal gate electrode from bottom to top. The preparation method comprises the steps of firstly, preparing the transition metal chalcogenide two-dimensional conductor on a substrate; secondly, preparing the metal source-drain electrode by employing an electron beam lithography technology and combining a stripping process; thirdly, preparing a ferroelectric thin film with the negative capacitance effect on the structure; and finally, preparing the metal gate electrode on the thin film to form ferroelectric-controlled two-dimensional semiconductor negative capacitance field-effect transistor. Different from other two-dimensional semiconductor negative capacitance field-effect device structures, the metal-ferroelectric-semiconductor structure has the advantages that a high-performance negative capacitance field-effect device can be achieved; and an electrical test result shows that the subthreshold swing of the device is far smaller than 60mV / dec, the Boltzmann limit is broken through, and the two-dimensional semiconductor negative capacitance field-effect device simultaneously has the characteristics of extremely low power consumption, high-speed turnover and the like.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

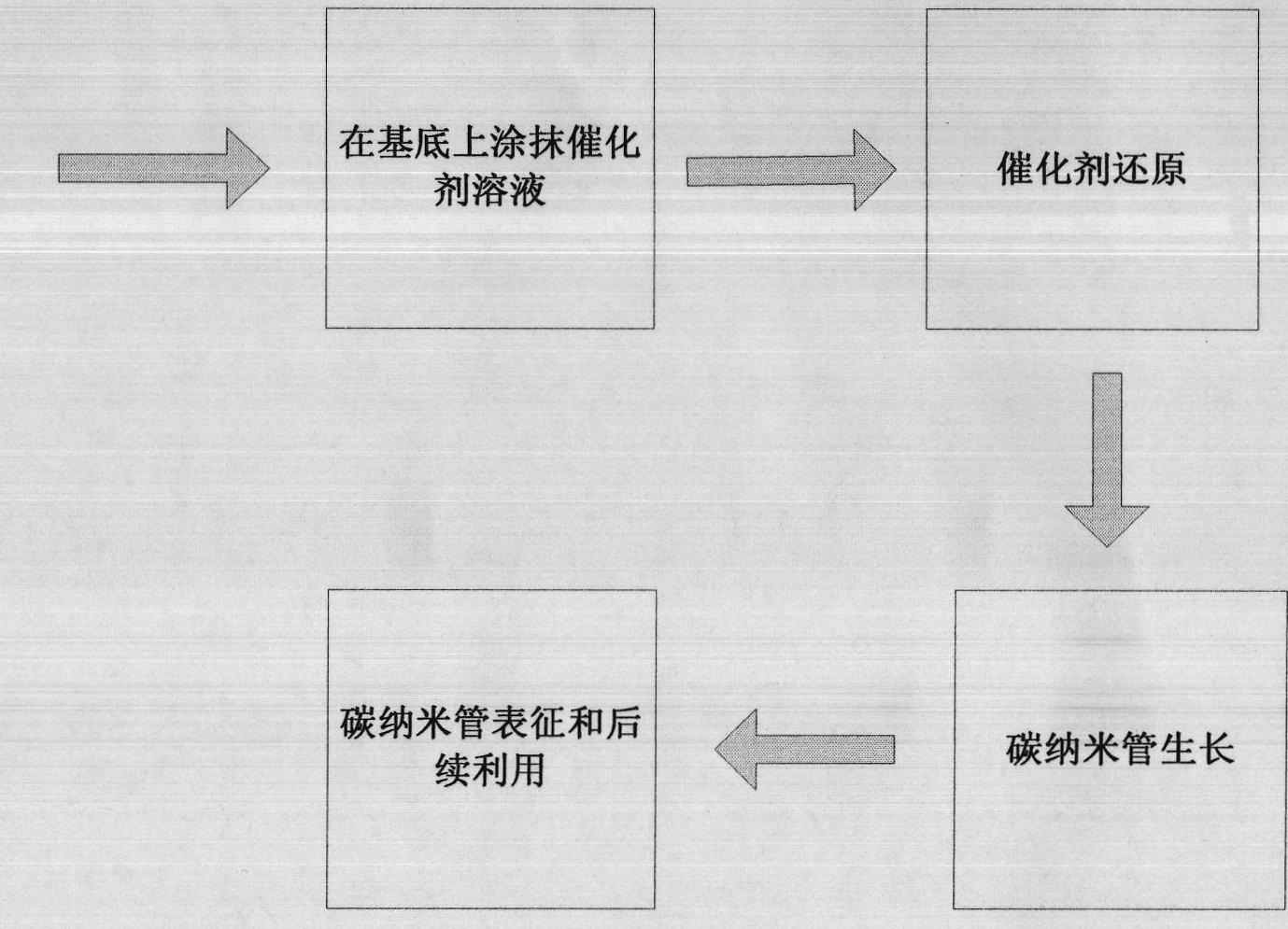

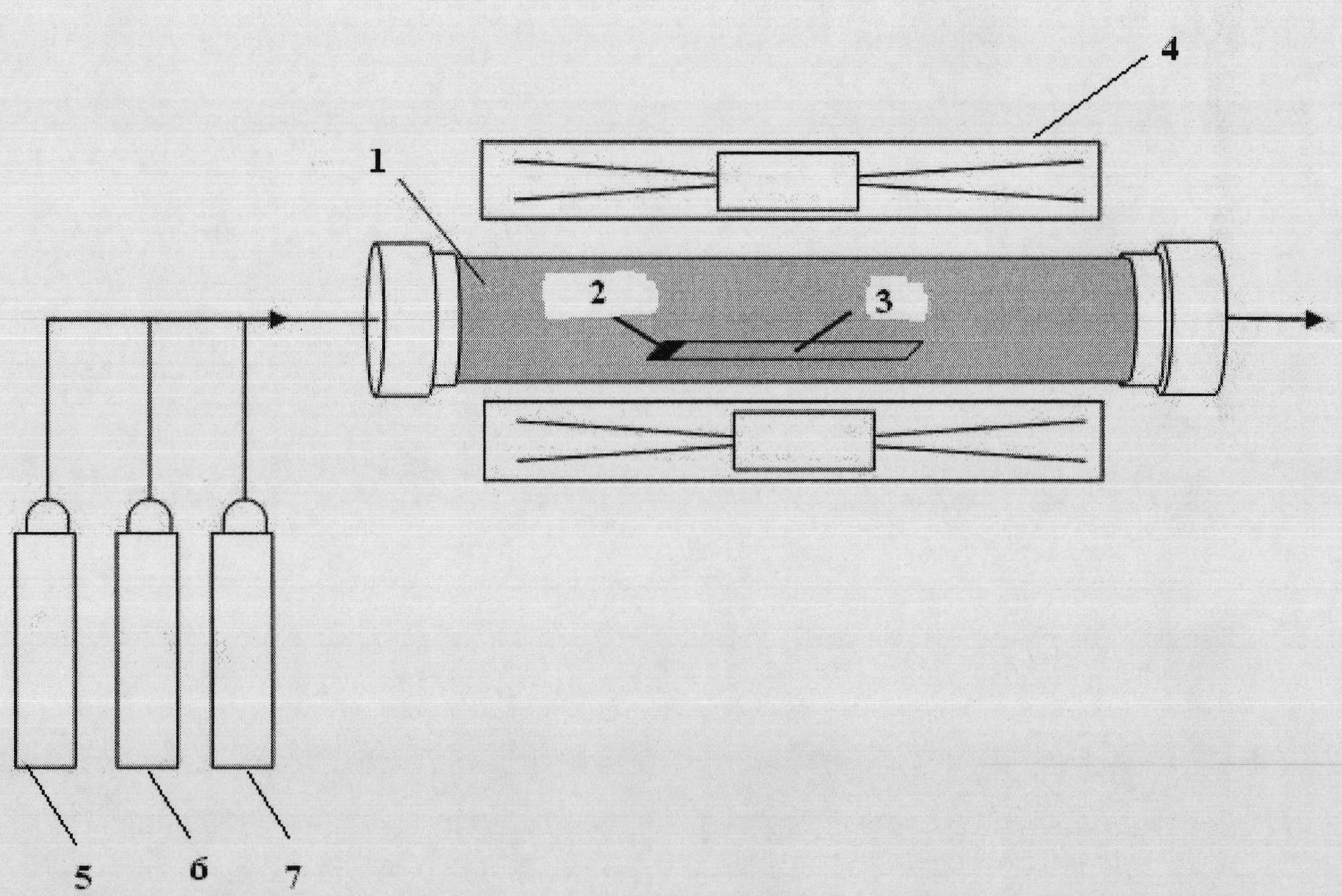

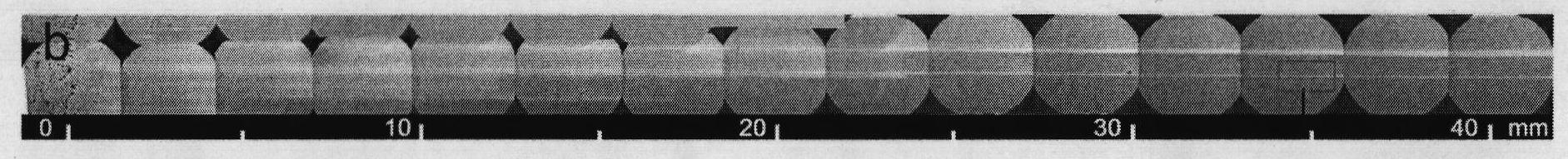

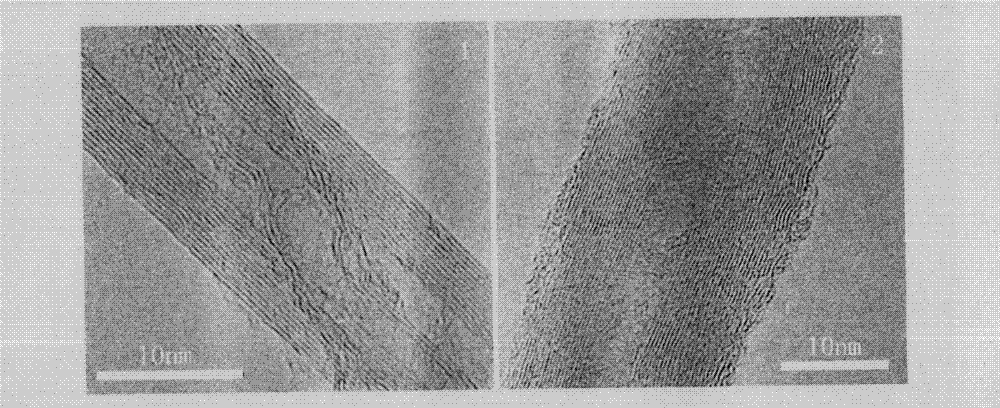

Overlong carbon nanotubes and preparation method thereof

The invention provides overlong carbon nanotubes and a preparation method thereof. The method provided by the invention comprises the following steps of: 1) coating ethanol solution or aqueous solution of a metal chloride of at least one of Fe, Mo, Cu and Cr on a substrate, placing the substrate in a reactor and heating the reactor to 600 to 1,000 DEG C, introducing a hydrogen gas or mixed gas ofthe hydrogen gas and an inert gas into the reactor to perform reduction reaction; and 2) heating the reactor to 800 to 1,100 DEG C after the reduction reaction is finished, and introducing mixed gas of a carbon source gas, the hydrogen gas and vapor into the reactor and reacting to obtain the carbon nanotubes. The overlong carbon nanotubes prepared by the method have perfect structures and superior electric and mechanical properties.

Owner:TSINGHUA UNIV

Tunneling field effect transistor

InactiveCN102832256AImprove performanceIncrease the on-state currentTransistorSub thresholdCondensed matter physics

The invention relates to the technical field of field effect transistors and discloses a tunneling field effect transistor. The tunneling field effect transistor comprises a source region, a channel region and a drain region, wherein the source region and the drain region are respectively formed on the two sides of the channel region, and a contact region between the source region and the channel region is made of extrinsic materials and different from the doping type of the source region. According to the invention, the contact area between the source region and the channel region is doped differently from the source region, so that the device is relatively narrow in a tunneling layer from the source end to the channel in an ON state, and the ON-state current is increased. As the thickness of a tunneling layer from the source end to the drain end in an OFF state is not changed with the method, a relatively low OFF-state current can be kept, as a result, a higher switch ratio and a relatively low sub-threshold slope can be acquired with the method, so that a better device performance can be acquired.

Owner:PEKING UNIV

Phase change storage unit based on VOx gate tube

ActiveCN106992251AAchieve High Density StorageSimple preparation processElectrical apparatusDigital storagePhase-change memoryLow voltage

The invention discloses a phase change storage unit based on a VOx gate tube. The storage unit comprises a lower electrode layer, a VOx gating layer, a phase change function layer and an upper electrode layer. According to the invention, by use of the VOx, the gating of the phase change function layer is achieved; storage of the data is achieved on the basis of gating of the phase change function layer; by imposing voltage on the VOx, the state switching of the VOx is controlled, so an objective that the phase change storage unit is in a non-gating state during low voltage and in a gating system during high voltage can be achieved; through the switch control of the VOx, leakage current of the a phase change memory array can be effectively reduced and enough big Reset current is provided; a high-temperature technique condition is not required; preparation technique of the phase change memory is simplified; cost is reduced; and it is possible to commercialize the highly integrated phase change memory.

Owner:HUAZHONG UNIV OF SCI & TECH

Amorphous semiconductor film and preparation method and application thereof

InactiveCN104218074AImprove driving abilityMinus interface defect statesTransistorSemiconductor/solid-state device manufacturingRare-earth elementMetallurgy

The invention discloses an aluminum zinc oxide amorphous semiconductor film material and a preparation method and application thereof and belongs to the technical field of semiconductor integrated circuits and manufacture thereof. The amorphous semiconductor film comprises, by mole percent content, 85-98% of zinc element, 1-10% of aluminum element and 1-14% of rare earth element, wherein the rare earth element is at least one of Gd, Lu, Y and Sc. A radio frequency magnetron sputtering method is adopted to prepare the aluminum zinc oxide film material doped with the rare earth element, the voltage division ratio of oxygen atmosphere is adjusted in the sputtering process to form a channel material which has amorphous characteristics and is high in migration rate. The preparation method is compatible with a traditional complementary metal oxide semiconductor (CMOS) process, and a rare earth doped oxide semiconductor film transistor can be prepared, is high in practical value and can be applied to future thin film transistor (TFT) integrated circuits.

Owner:PEKING UNIV

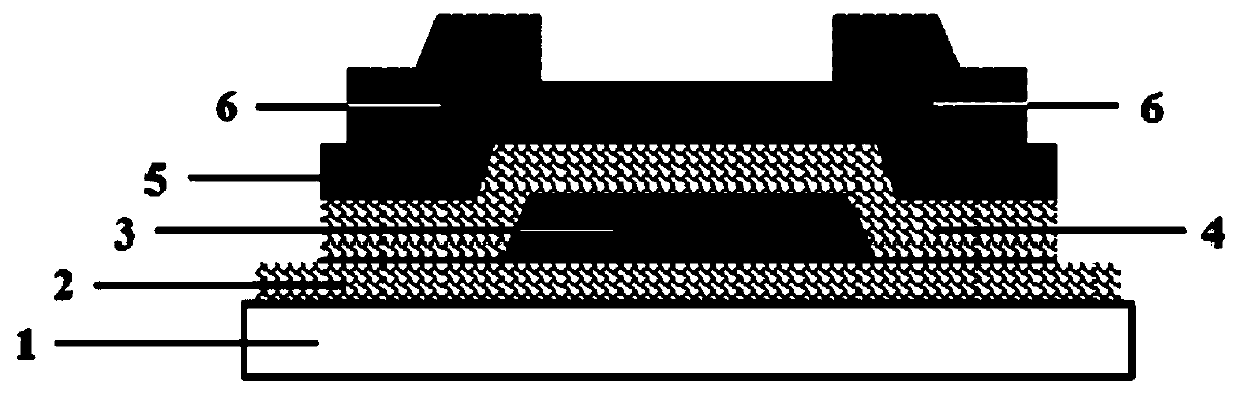

Stepped gate-dielectric double-layer graphene field effect transistor and production method thereof

ActiveCN104218089AReduce the tunneling windowSuppresses off-state currentSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricBottom gate

A stepped gate-dielectric double-layer graphene field effect transistor comprises a bottom gate electrode, a bottom gate dielectric layer, a double-layer graphene active region, a metal source electrode, a metal drain electrode, a stepped top gate dielectric layer and a top gate electrode. The bottom gate dielectric layer is located on the bottom gate electrode, the double-layer graphene active region is located on the bottom gate dielectric layer, the metal source electrode and the metal drain electrode are located at two ends of the double-layer graphene active region respectively and cover the bottom gate dielectric layer and part of the double-layer graphene active region at the same time, the stepped top gate dielectric layer covers the metal source electrode, the metal drain electrode and graphene between the two electrodes, the top gate electrode only covers the top of the stepped top gate dielectric layer partially, and the distance between the top gate electrode and the edge of the metal source electrode is equal to that between the top gate electrode and the edge of the metal drain electrode. By introduction of the stepped top gate dielectric layer, a tunneling window between a source region and a gate-controlled trench under an off state is reduced effectively, so that small off-state current is obtained, and on-off ratio of a device is increased.

Owner:PEKING UNIV

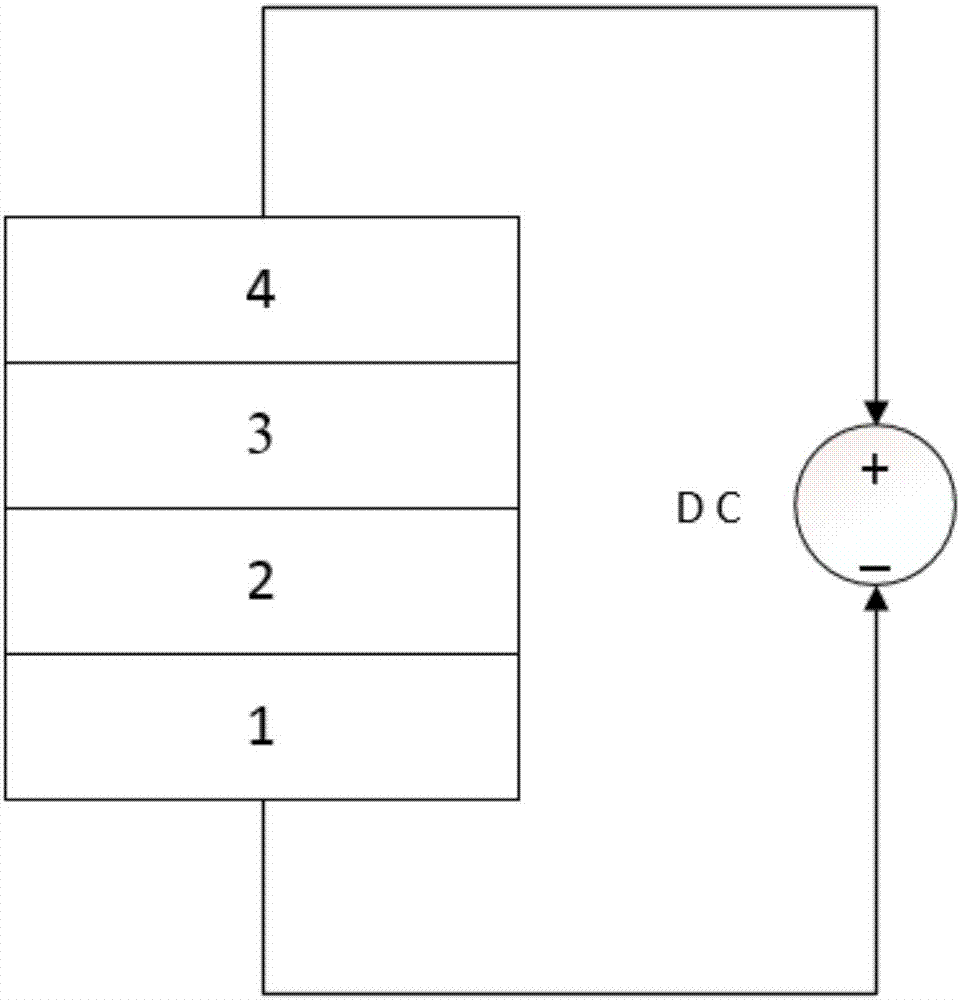

Resistive random access memory based on MoS2 quantum dot embedded organic polymer and preparation method of resistive random access memory

ActiveCN106449974AEasy to prepareImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingMass storageStatic random-access memory

The invention provides a resistive random access memory based on a MoS2 quantum dot embedded organic polymer and a preparation method of the resistive random access memory. The resistive random access memory comprises a bottom electrode, a top electrode, and a resistive random functional composite layer clamped between the bottom electrode and the top electrode; the resistive random functional composite layer includes a first organic polymer film layer, a second organic polymer film layer and a MoS2 quantum dot / organic polymer composite film layer clamped between the first organic polymer film layer and the second organic polymer film layer, and the bottom electrode and the top electrode are connected with the first organic polymer film layer and the second organic polymer film layer respectively in a stacking mode. The resistive random access memory has the advantages of being high in repeatability, stable in device performance, high in response speed and the like, and can be used in the highly integrated large capacity memory field.

Owner:SOUTH CHINA NORMAL UNIVERSITY

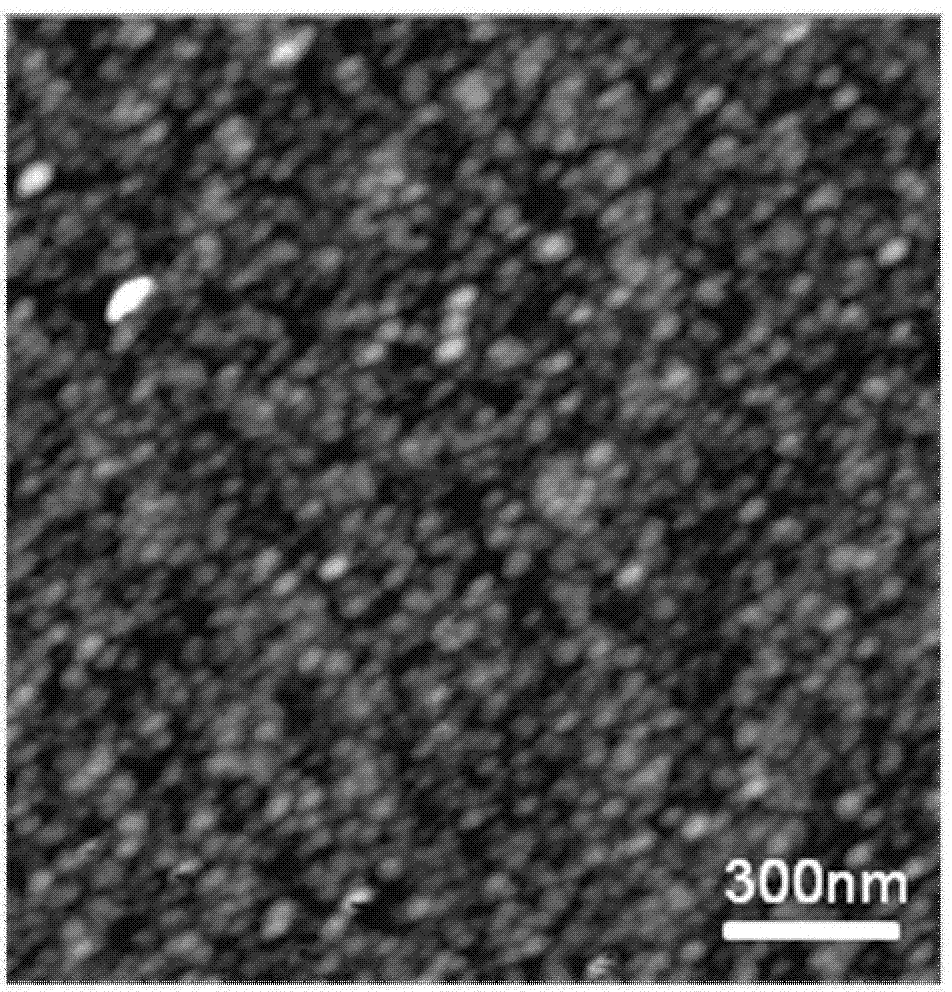

Flexible low-voltage organic field effect transistor and manufacturing method thereof

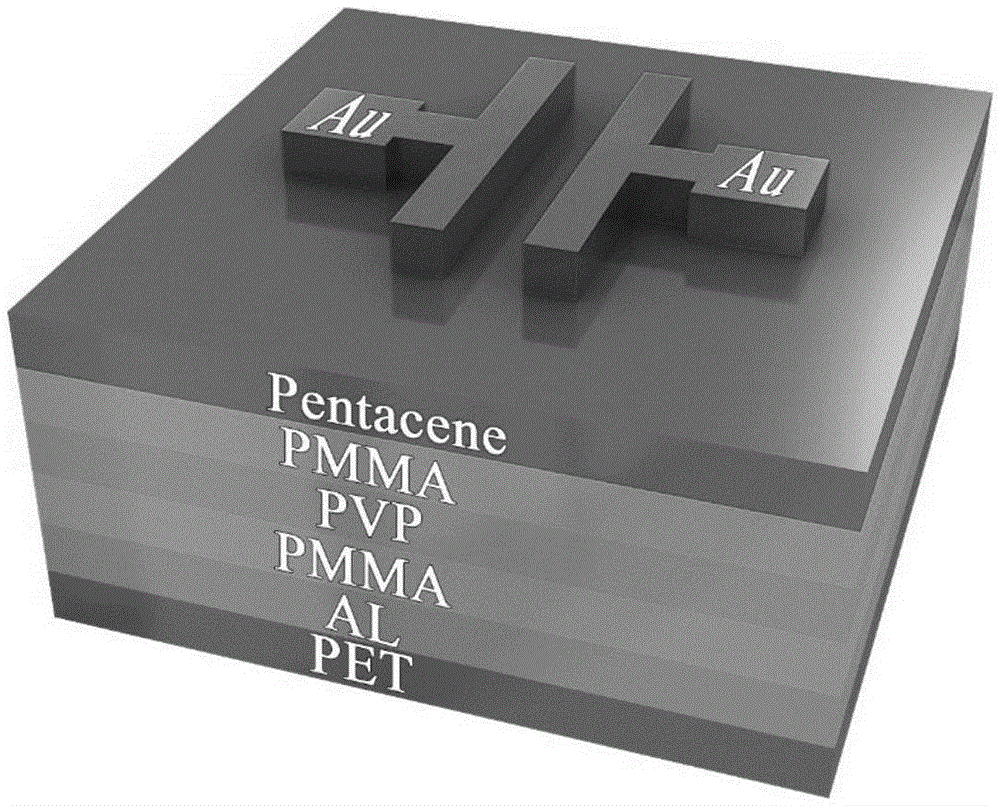

InactiveCN105336860AGood electrical propertiesImprove mobilitySolid-state devicesSemiconductor/solid-state device manufacturingOrganic field-effect transistorLow voltage

The invention discloses a flexible low-voltage organic field effect transistor and a manufacturing method thereof. Three layers of polymers are added between a gate and a semiconductor layer interface to serve as an insulated layer; the overall device comprises a source and drain electrode, a semiconductor, a high-insulation polymer, a high-dielectric constant material polymer, a high-insulation polymer, a gate, and a flexible transparent plastic substrate sequentially from top to bottom; and the dielectric layer with the structure has excellent insulation and good stability. Through measuring electrical properties and a semiconductor particle growth shape, whether the device is a flexible low-voltage organic field effect transistor can be judged. The organic field effect transistor has the advantages of realizing high mobility and large switch ratio under low voltage, maintaining good performance when bias voltage is applied and in a high temperature condition, and having good stability features in different bending modes.

Owner:NANJING UNIV OF POSTS & TELECOMM

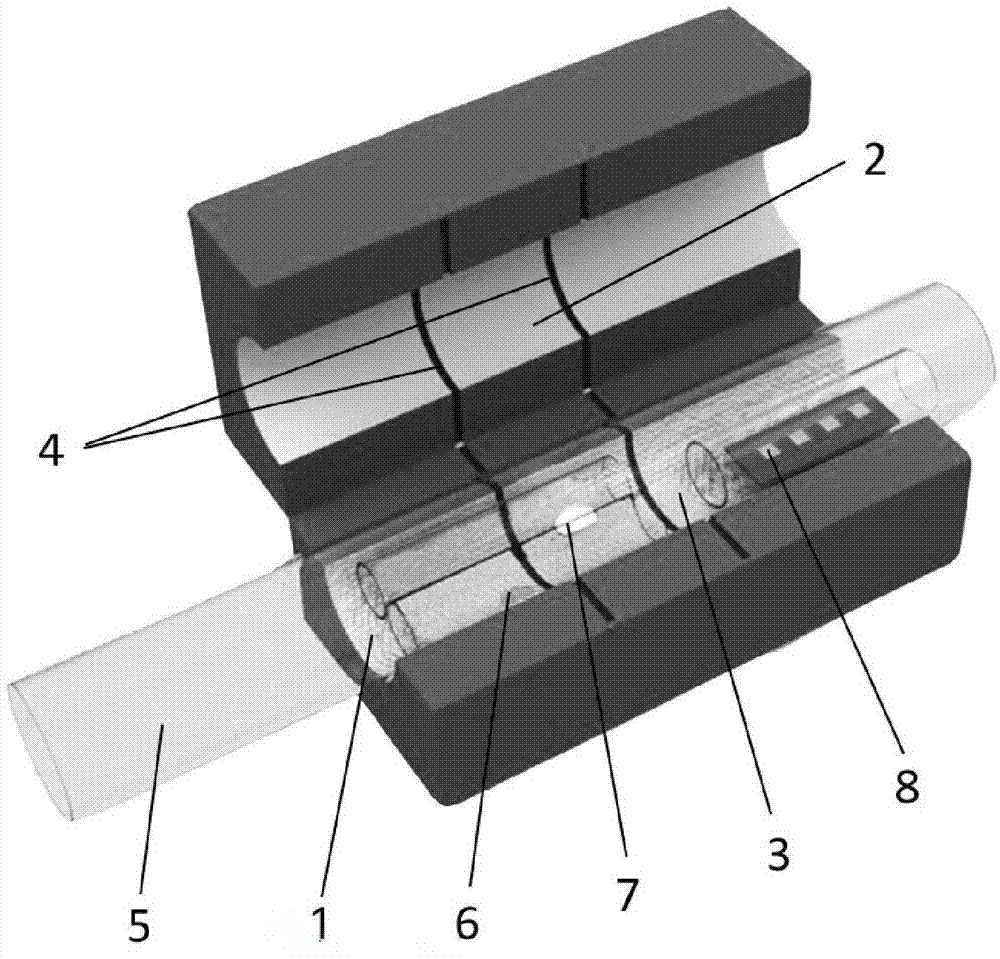

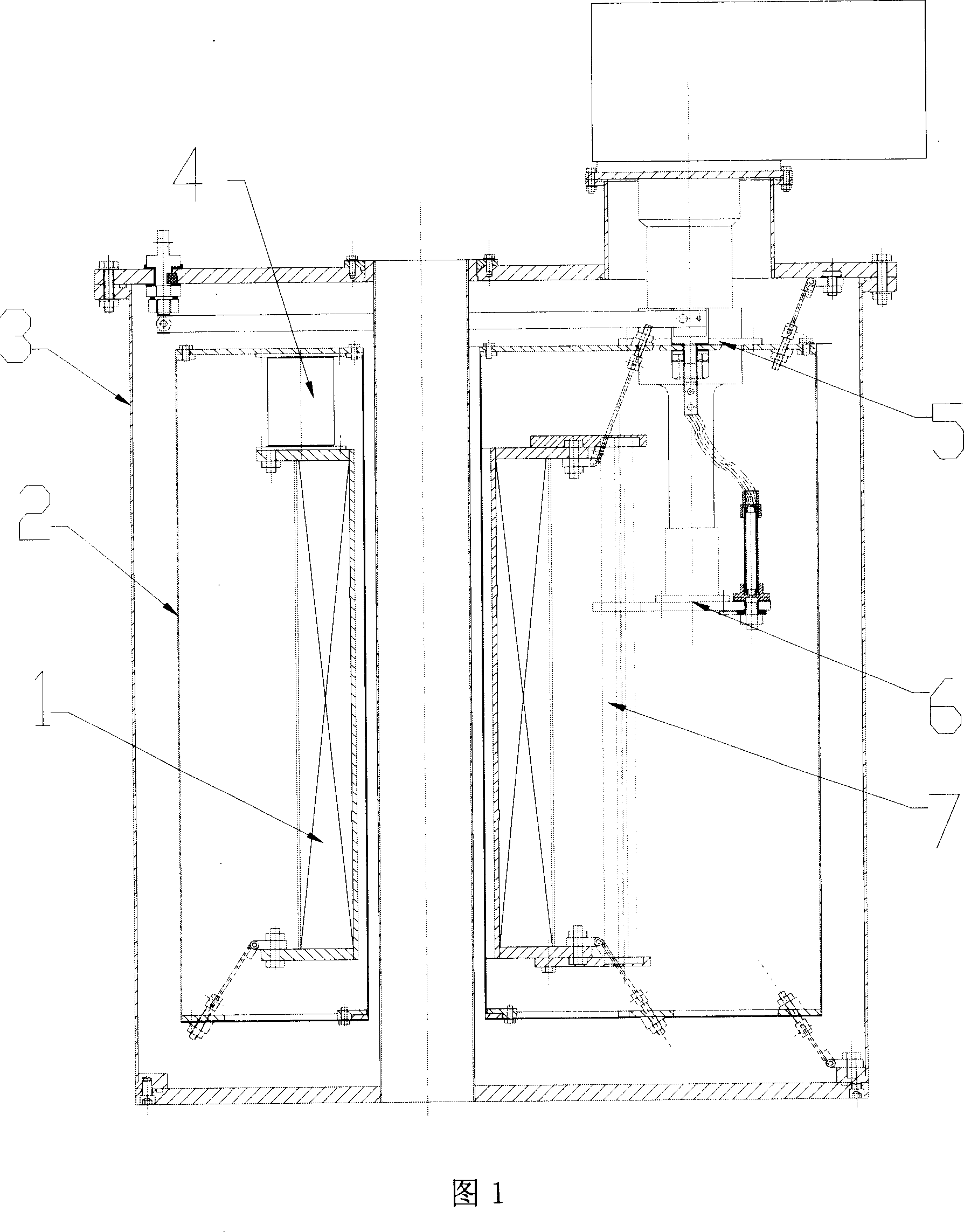

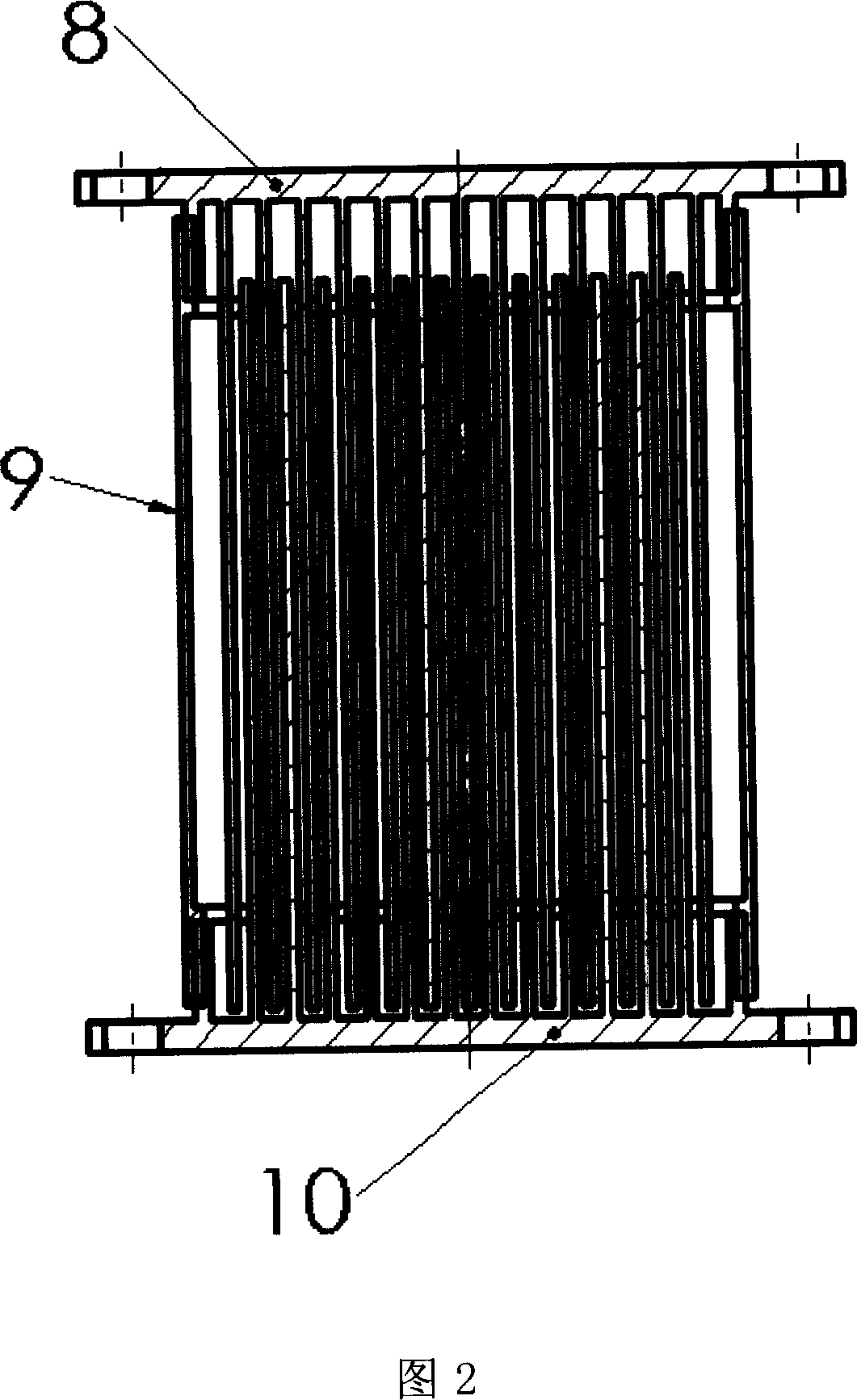

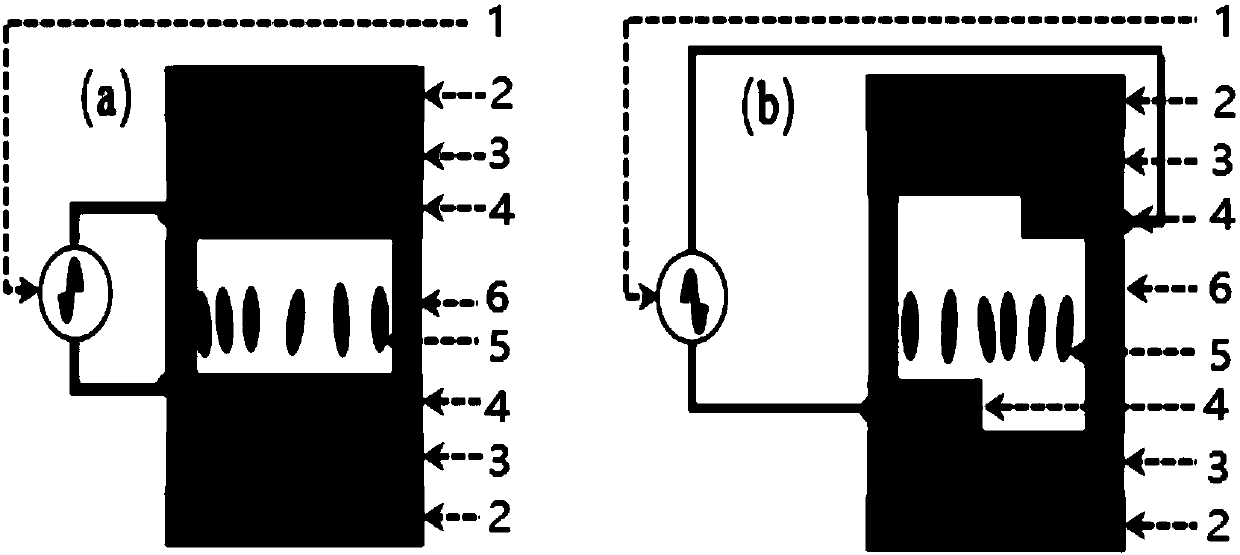

Thermal switch for conduction cooling superconducting magnet

InactiveCN1991287AStrong conduction abilityHigh switching ratioIndirect heat exchangersSuperconducting CoilsThermal conductivity

The invention relates to a thermal switch for conduction-cooled superconducting magnet, characterized in that it is the cylinder closed accommodator, comprising upper round plate [8], low round plate [10] and cylinder with thin wall [9]; the cylinder with thin wall [9] is the wall surface of cylinder closed accommodator; parallel red copper fins arranged in certain distance are set on inner surfaces of upper round plate [8] and lower round plate [10], fins on upper and lower round plates insert in cross and there is gap between adjacent fins; upper round plate [8] and lower round plate [10] are made of high thermal conductivity material and the cylinder with thin wall [9] is made of low thermal conductivity material; upper round plate [8], lower round plate [10] and cylinder with thin wall [9] are connected by positive and negative screw thread and the length of thermal switch [4] on the axial direction is controlled by the rotating depth of cylinder with thin wall [9]. The invention is provided with no need to vacuum pumping, strong conduction ability, big on-off ratio and no need to be controlled by outside. It can shorten the cooling time of prior conducting cooled magnet system.

Owner:INST OF ELECTRICAL ENG CHINESE ACAD OF SCI

Method for epitaxially growing ultrathin organic crystalline layers on surface and its applications

ActiveCN107109697AHigh switching ratioQuality improvementPolycrystalline material growthVacuum evaporation coatingLogic gateVacuum chamber

Disclosed is a method for depositing ultrathin layers of an organic semiconductor material on a support, and its applications in fabrication of electronic devices like OEFT and diodes. In the method, a source of an organic semiconductor material and a support are spaced from each other in a vacuum chamber and subjected to a temperature gradient, and the epitaxy initiates due to a van der Waals interaction between the organic molecules and the support. The ultrathin crystalline layers of the organic semiconductor material can be only a-few-molecule thick and even one-molecule thick in total. Further disclosed is a layered structure produced by said method and use of the layered structure in fabrication of logic gates.

Owner:NANJING UNIV

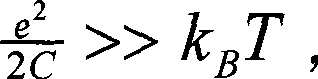

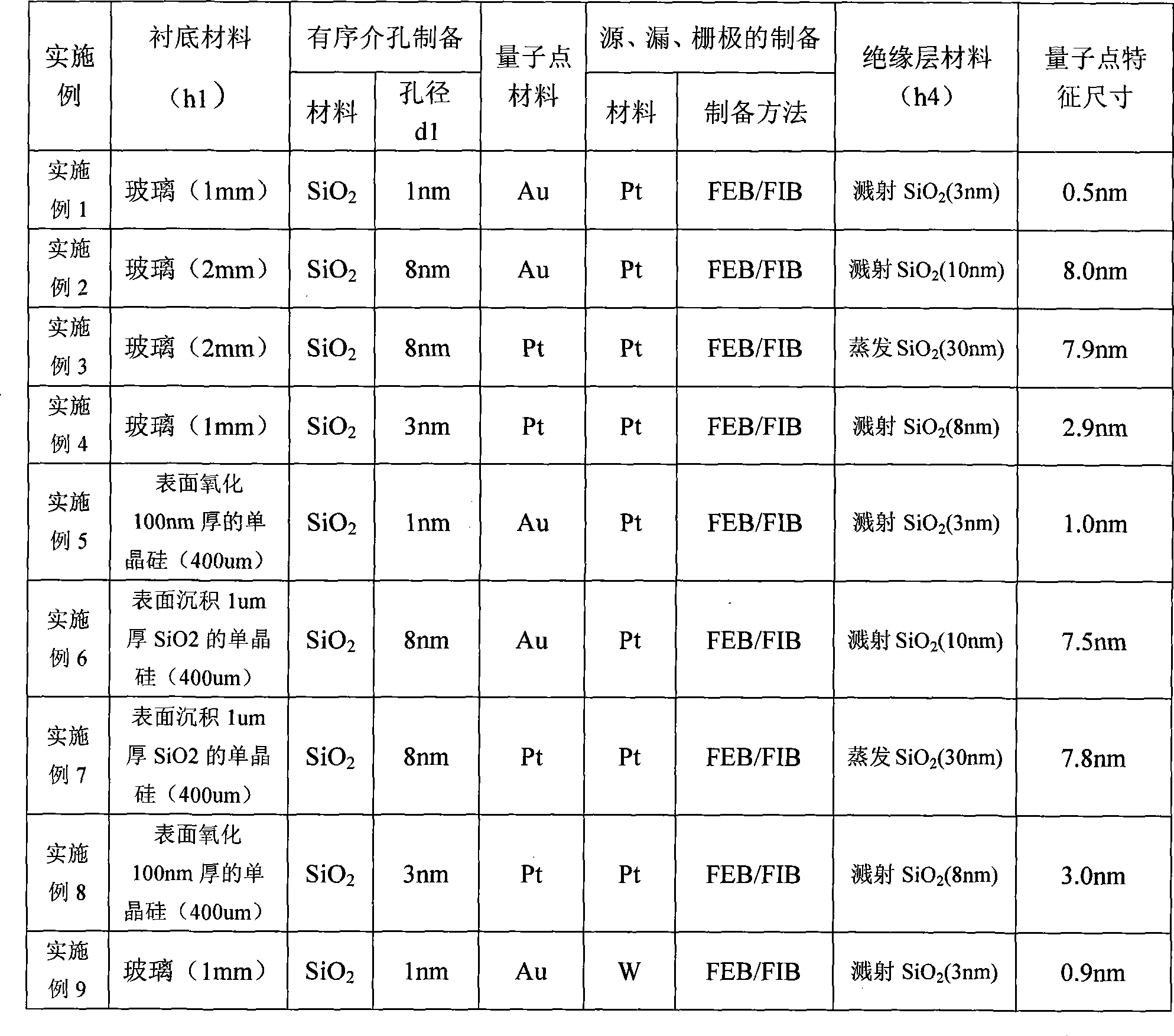

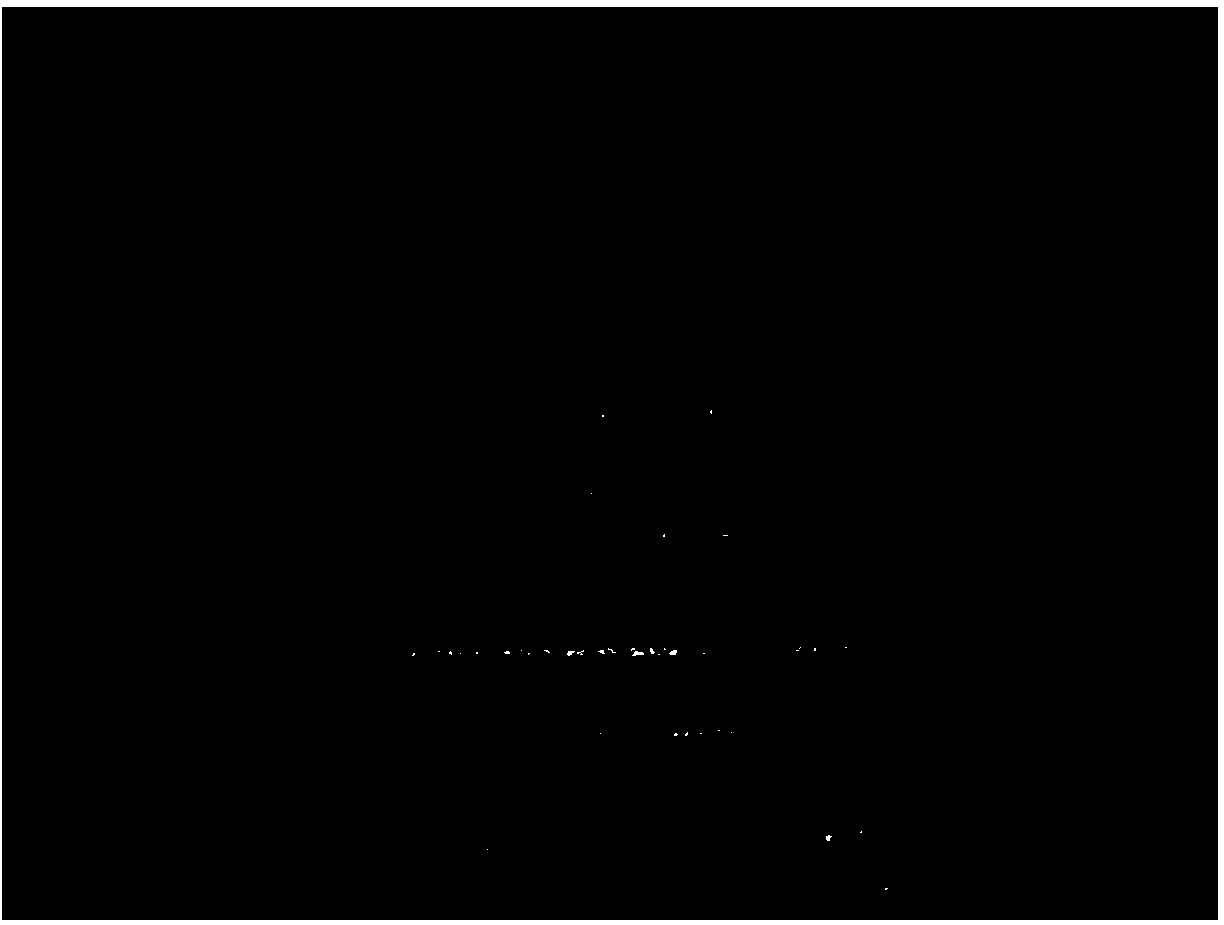

Single electron transistor based on ordered mesoporous and preparation thereof

InactiveCN101478003AAchieve normal workGuaranteed orderNanostructure manufactureSemiconductor/solid-state device manufacturingSingle electronNanoparticle

The invention discloses a single-electron transistor based on ordered mesopores and the fabrication method thereof, which can solve the problems of the prior single-electron transistors, such as large quantum dot size, disordered arrangement of the quantum dots and poor isolation performance of the quantum dots. The single-electron transistor based on ordered mesopores consists of a substrate, a source, a drain, a gate and an ordered mesopore layer and an insulation layer, wherein nanoparticles serving as the quantum dots of the single-electron transistor are assembled in the ordered mesopores of the ordered mesopore layer. The fabrication method comprises the following steps: preparing the substrate; then fabricating the ordered mesopore layer, the source and the drain; fabricating the insulation layer next; and finally fabricating the gate. With the adoption of the method, quantum dots with the size of 0.5 to 0.8 nm and ordered arrangement, so that the single-electron transistor can operate at normal temperature with the advantages of high reliability and convenient fabrication and integration.

Owner:NAT UNIV OF DEFENSE TECH

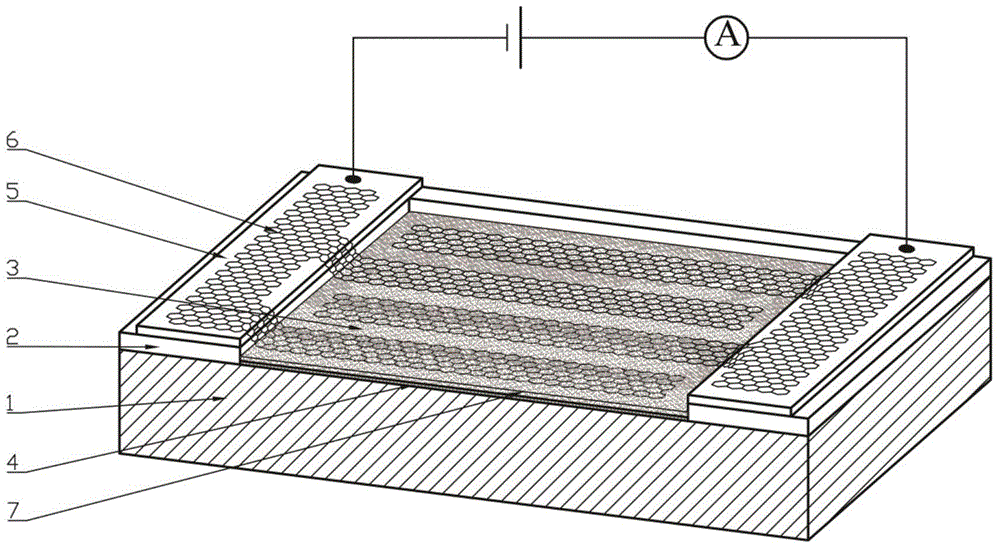

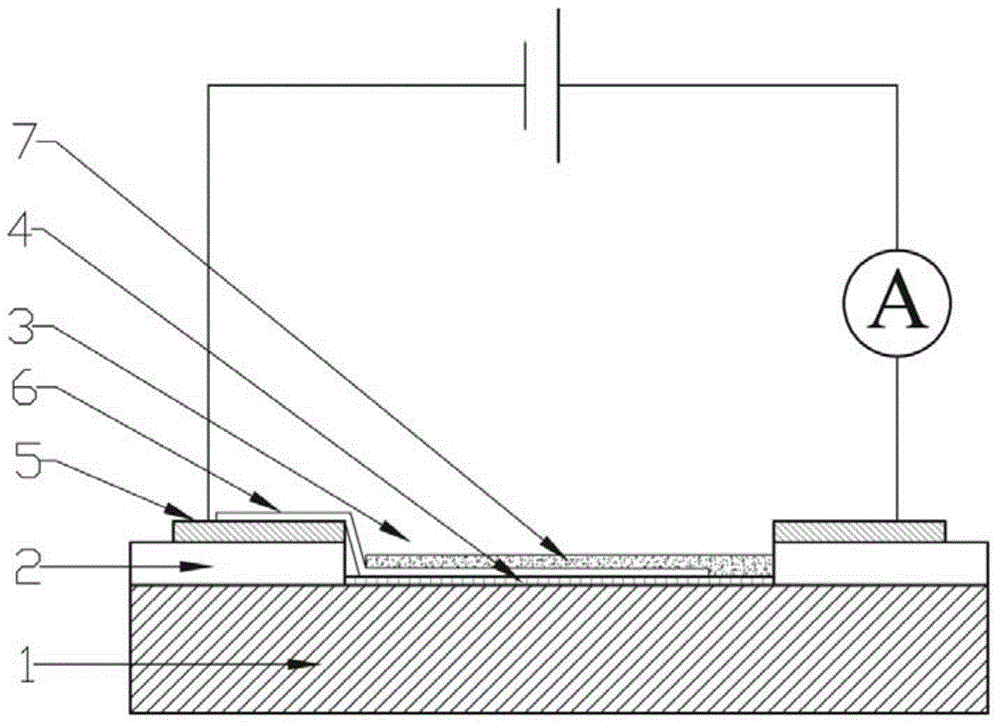

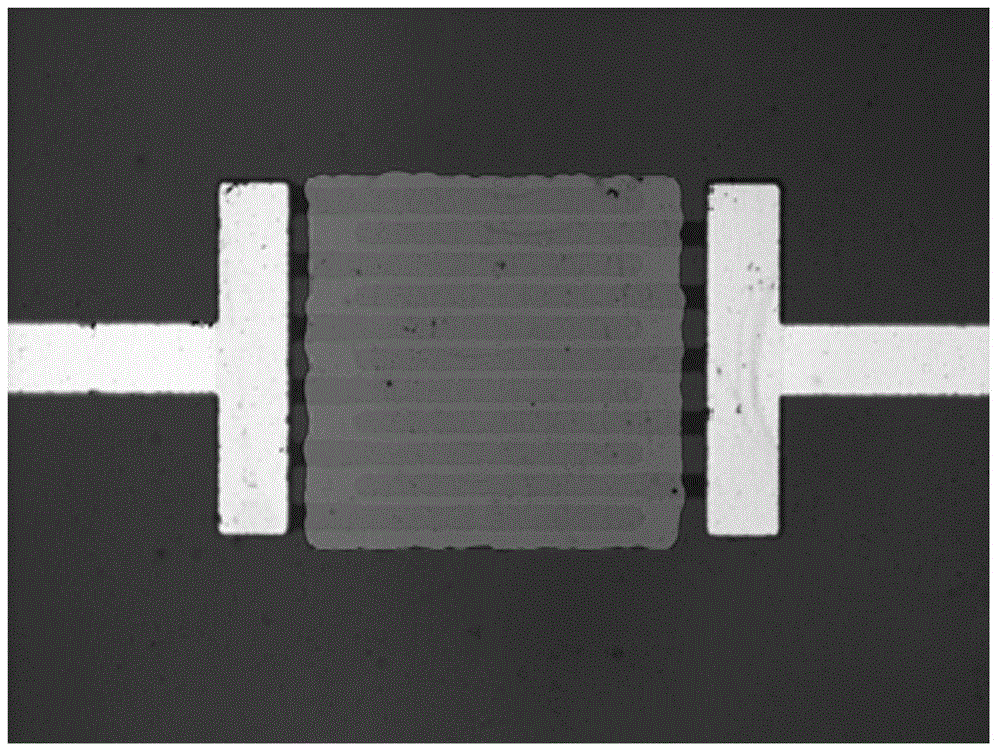

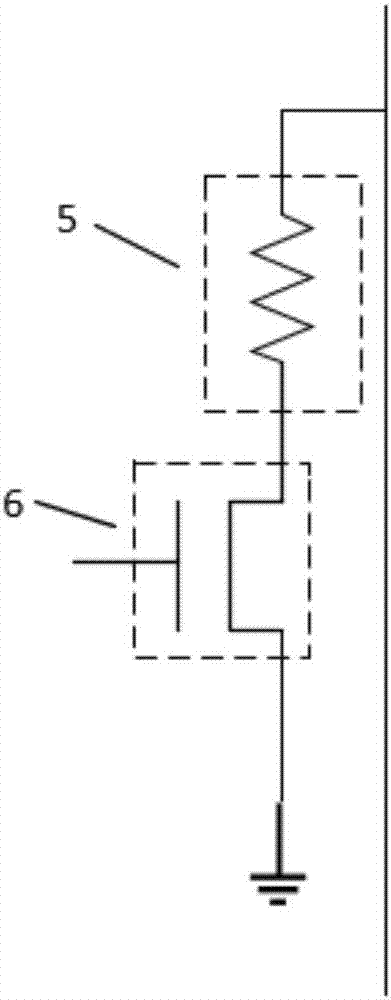

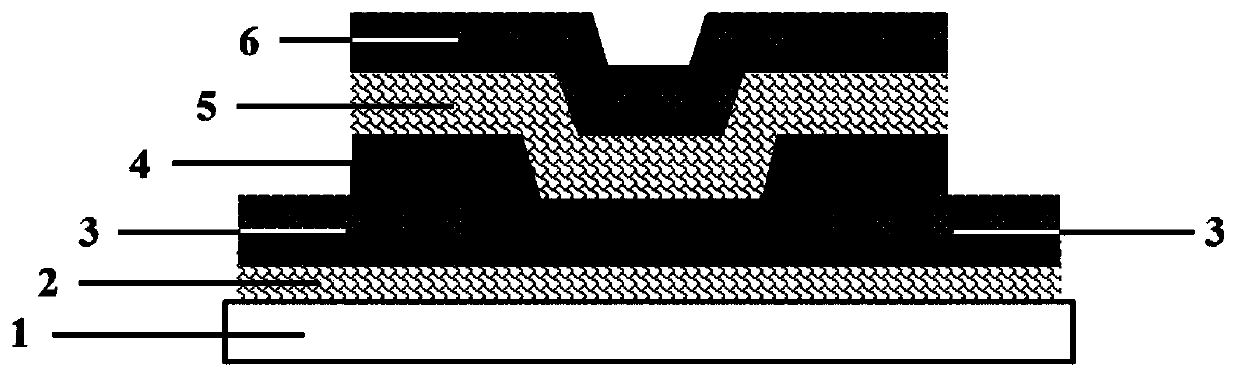

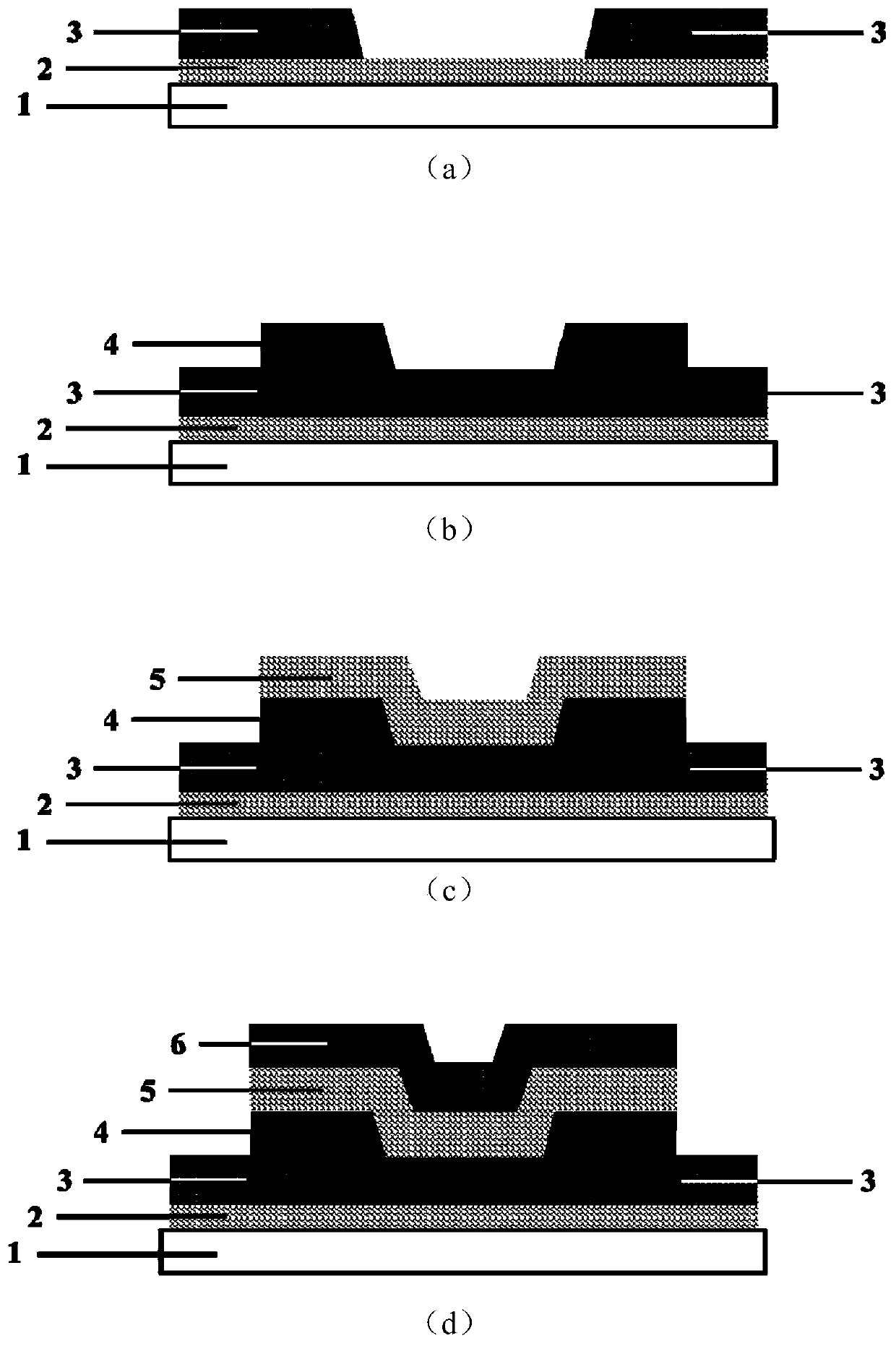

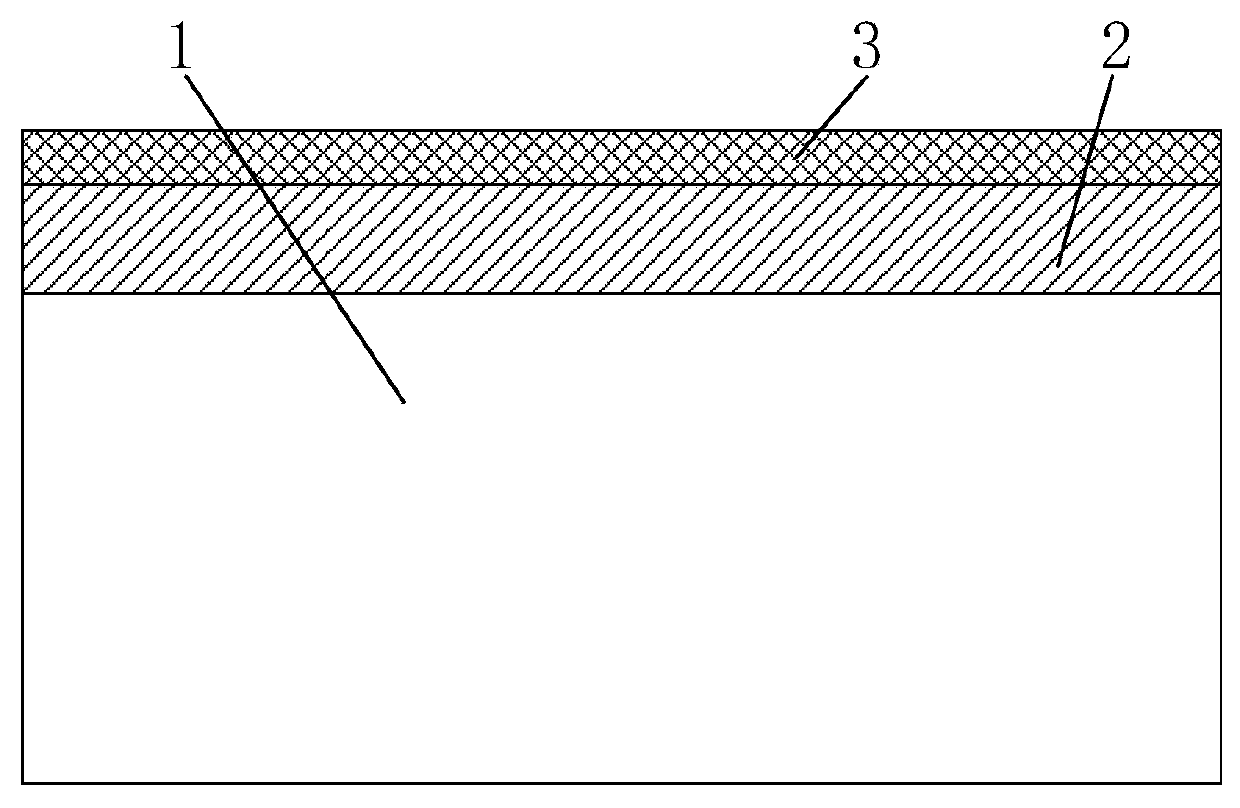

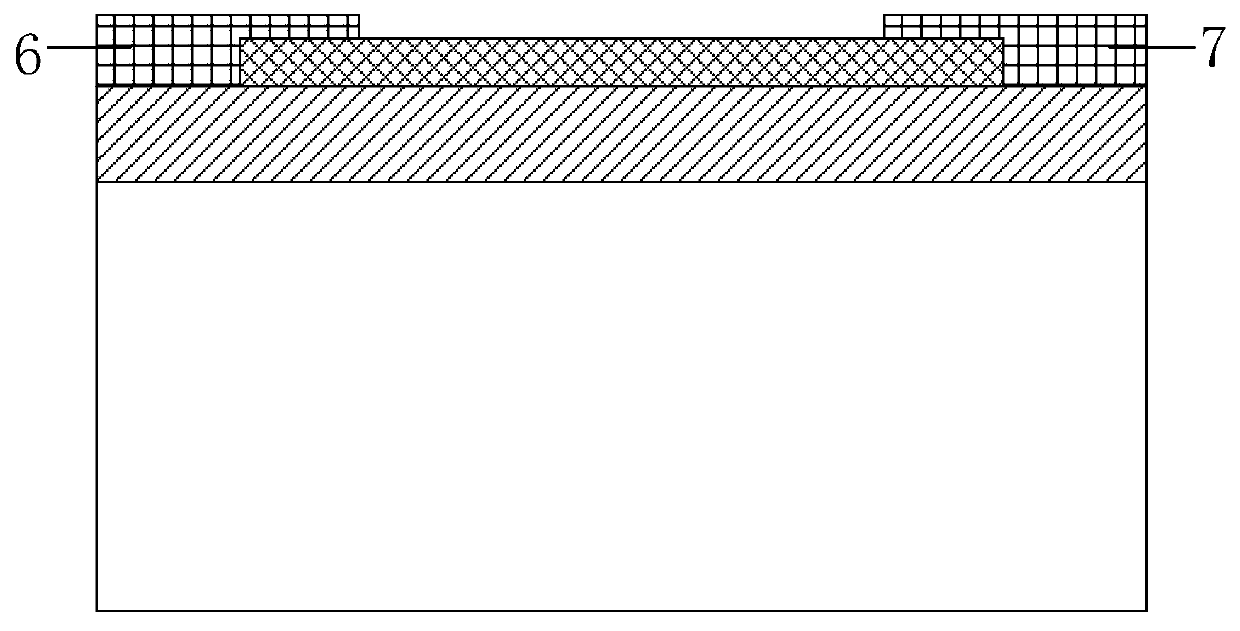

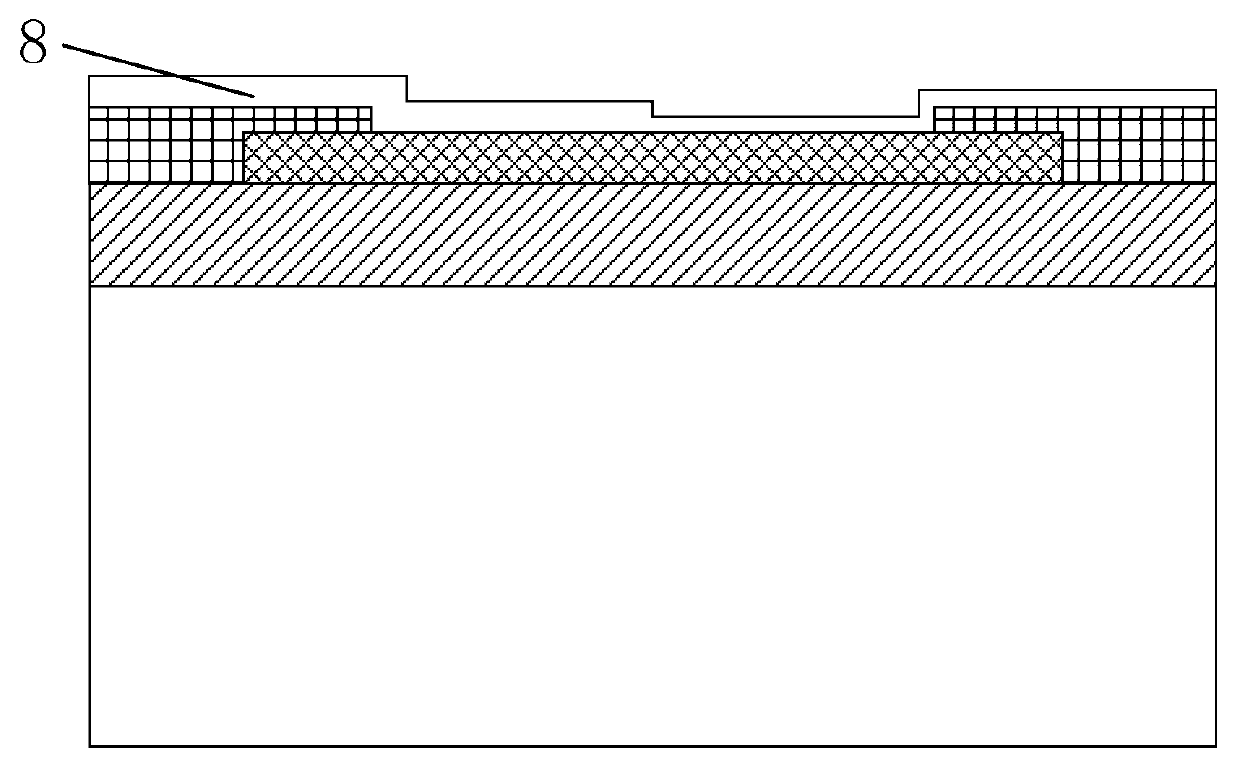

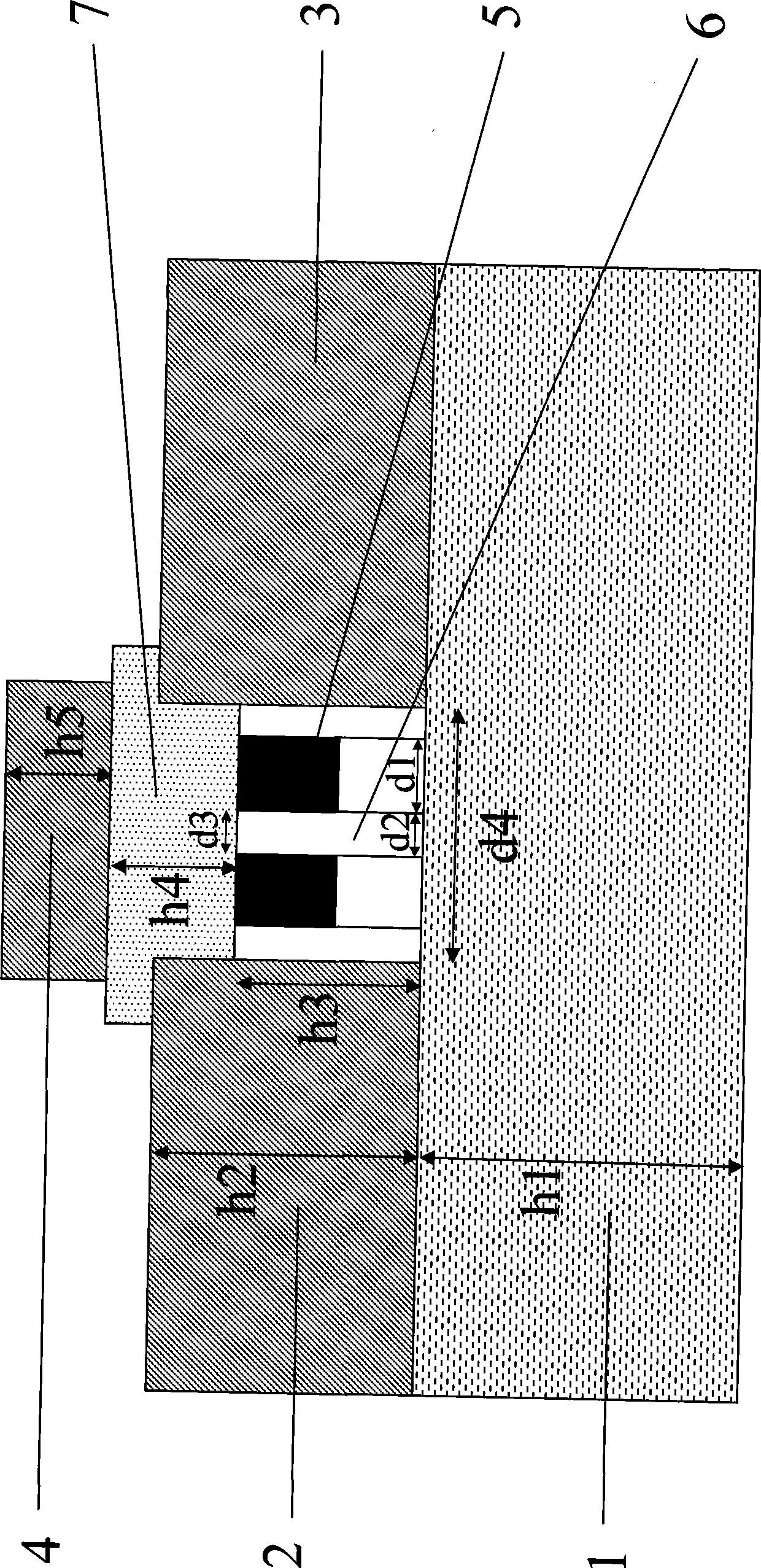

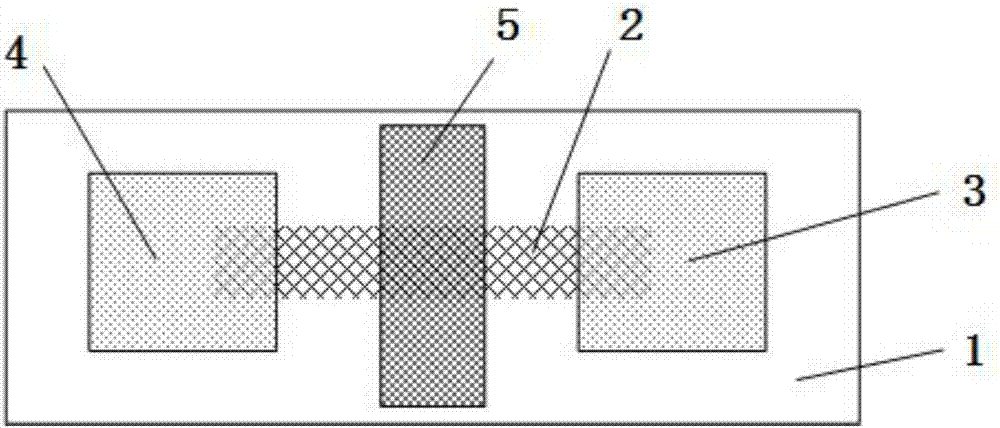

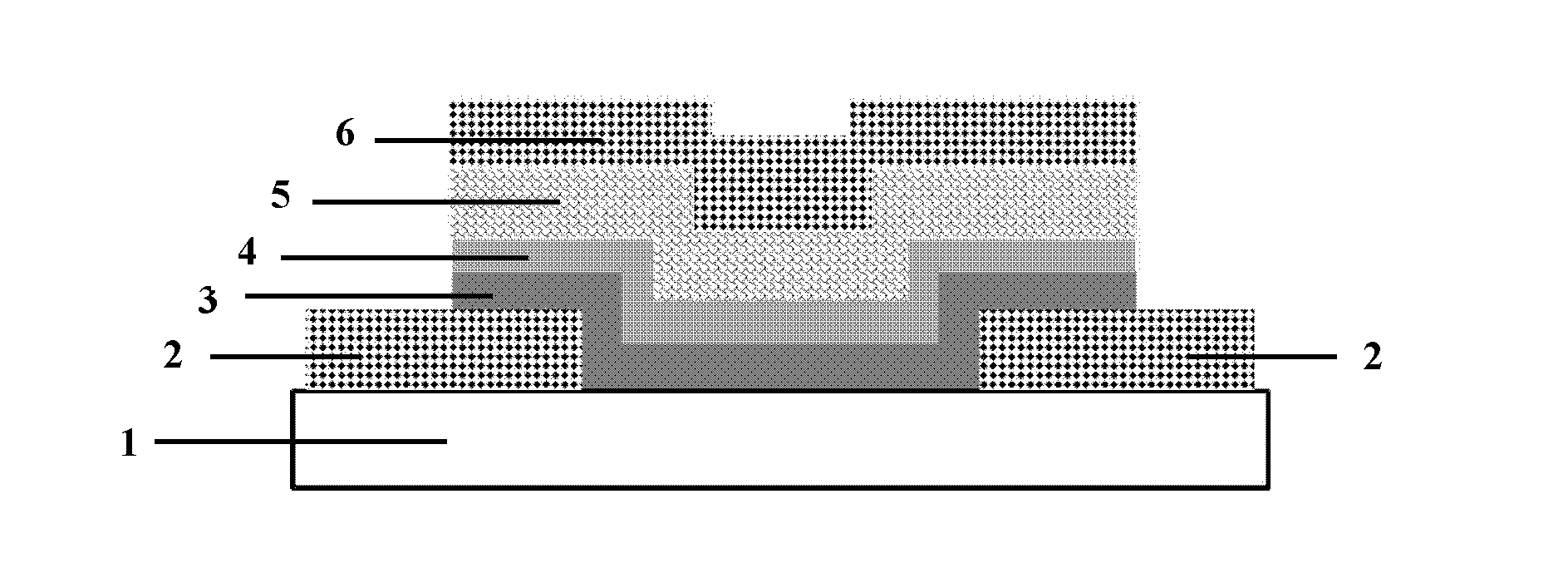

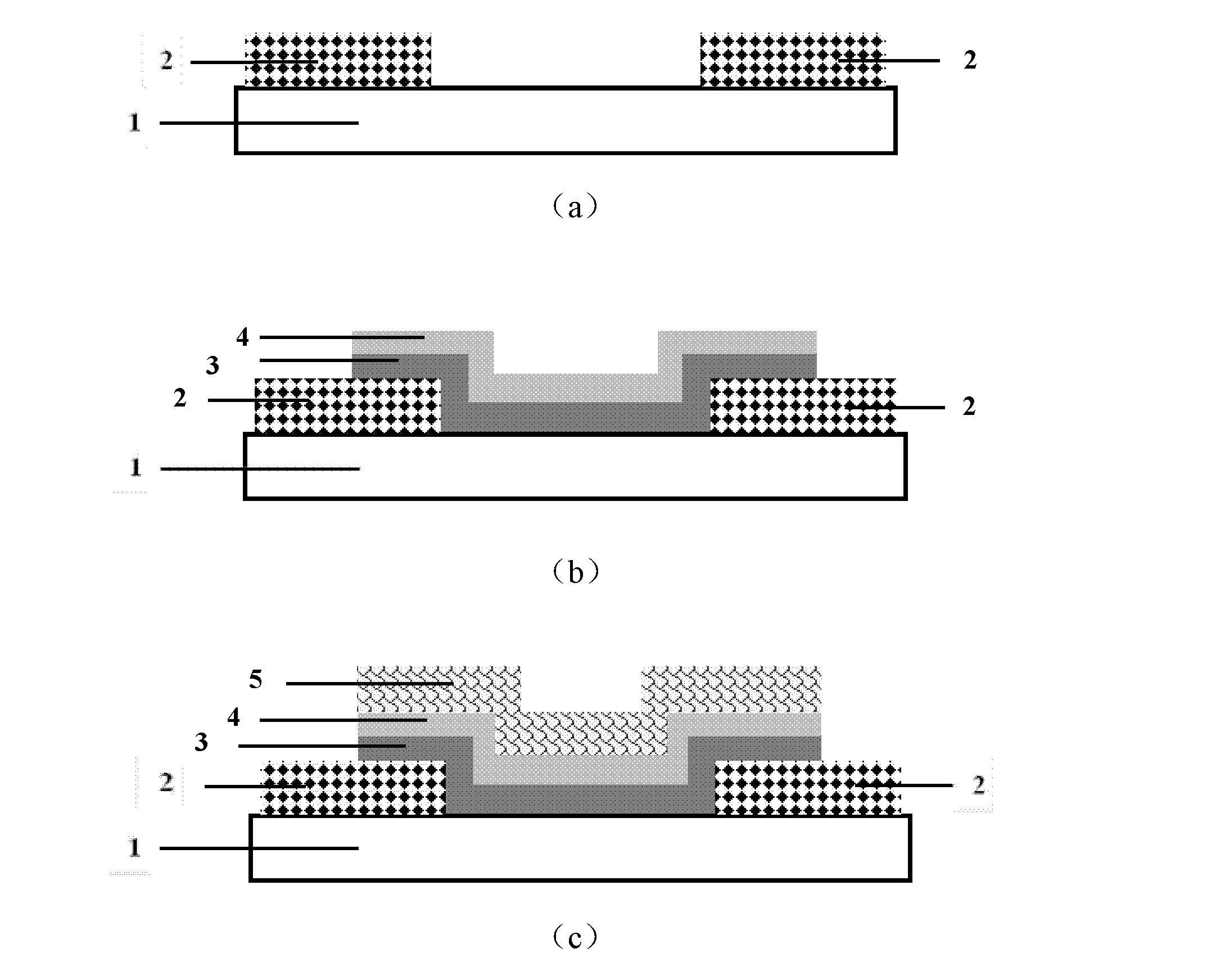

Ferro-electric field effect transistor based on structured carbon nano tube striped array and manufacturing method thereof

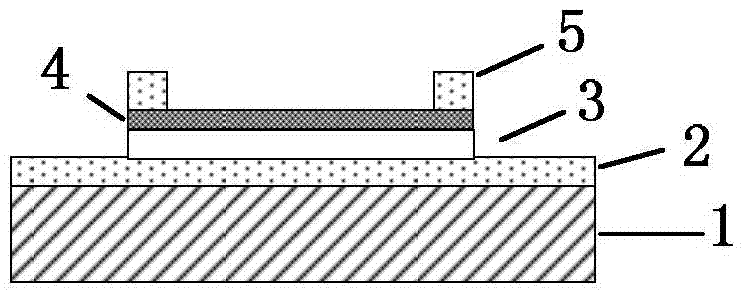

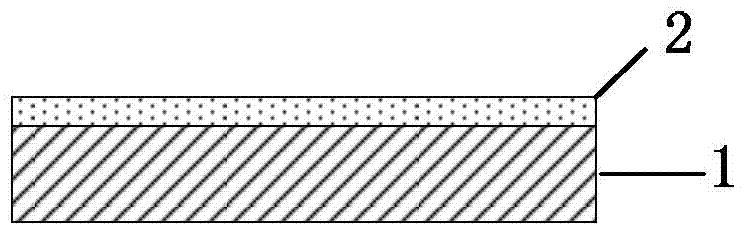

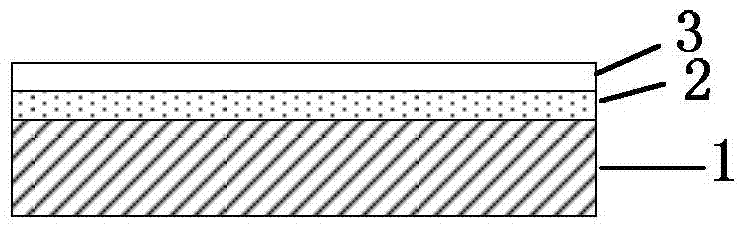

InactiveCN104009091AIncrease the on-state currentHigh switching ratioNanoinformaticsSemiconductor/solid-state device manufacturingOrganic field-effect transistorCharge carrier mobility

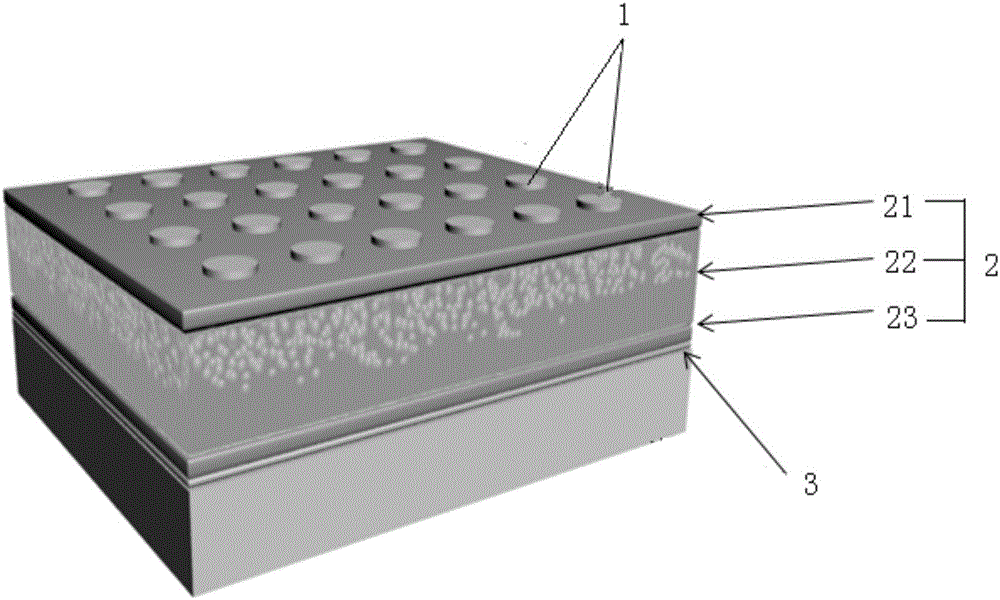

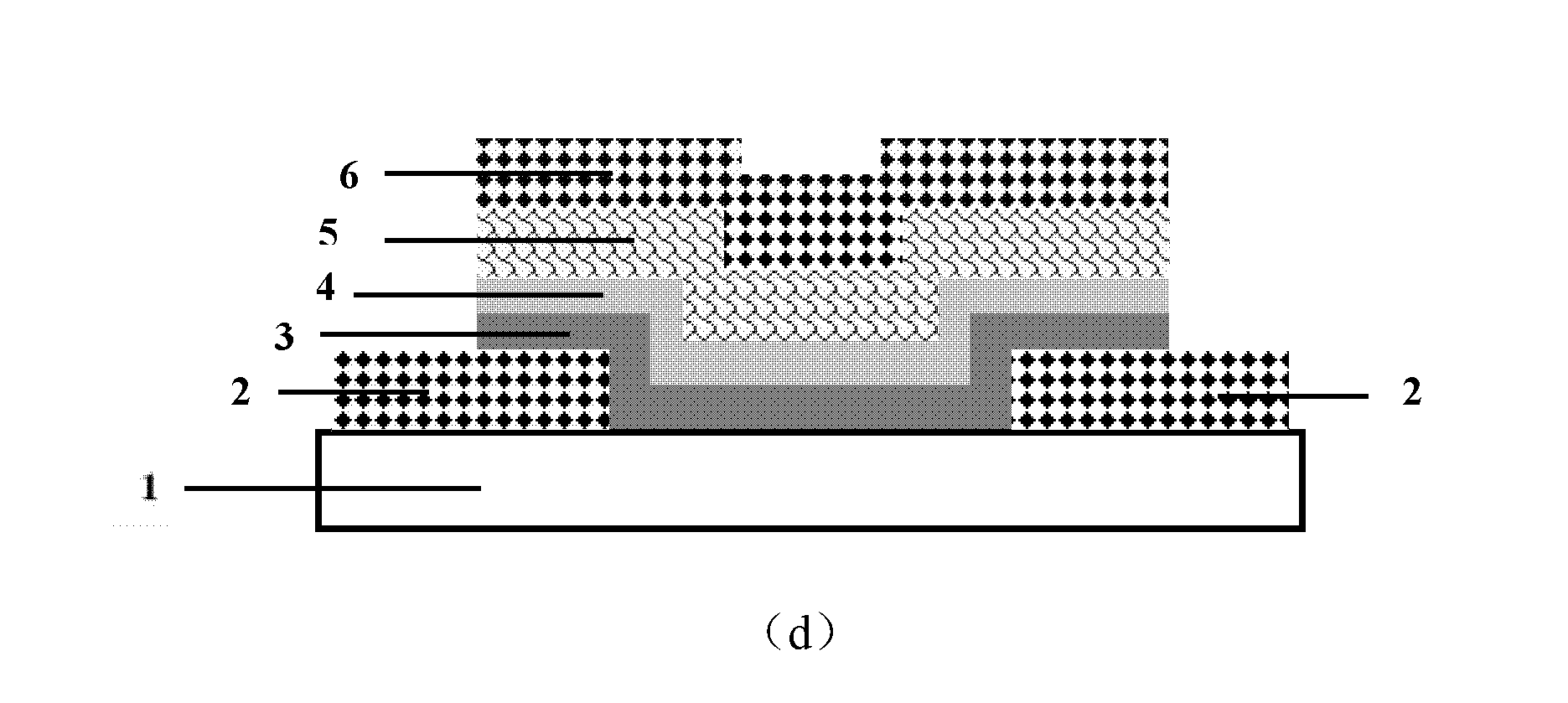

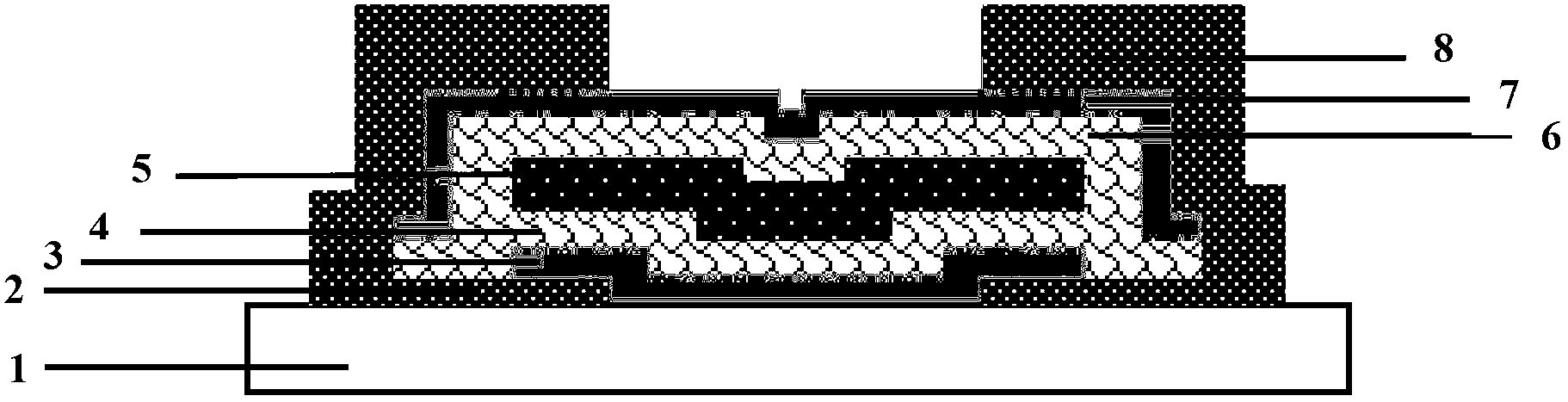

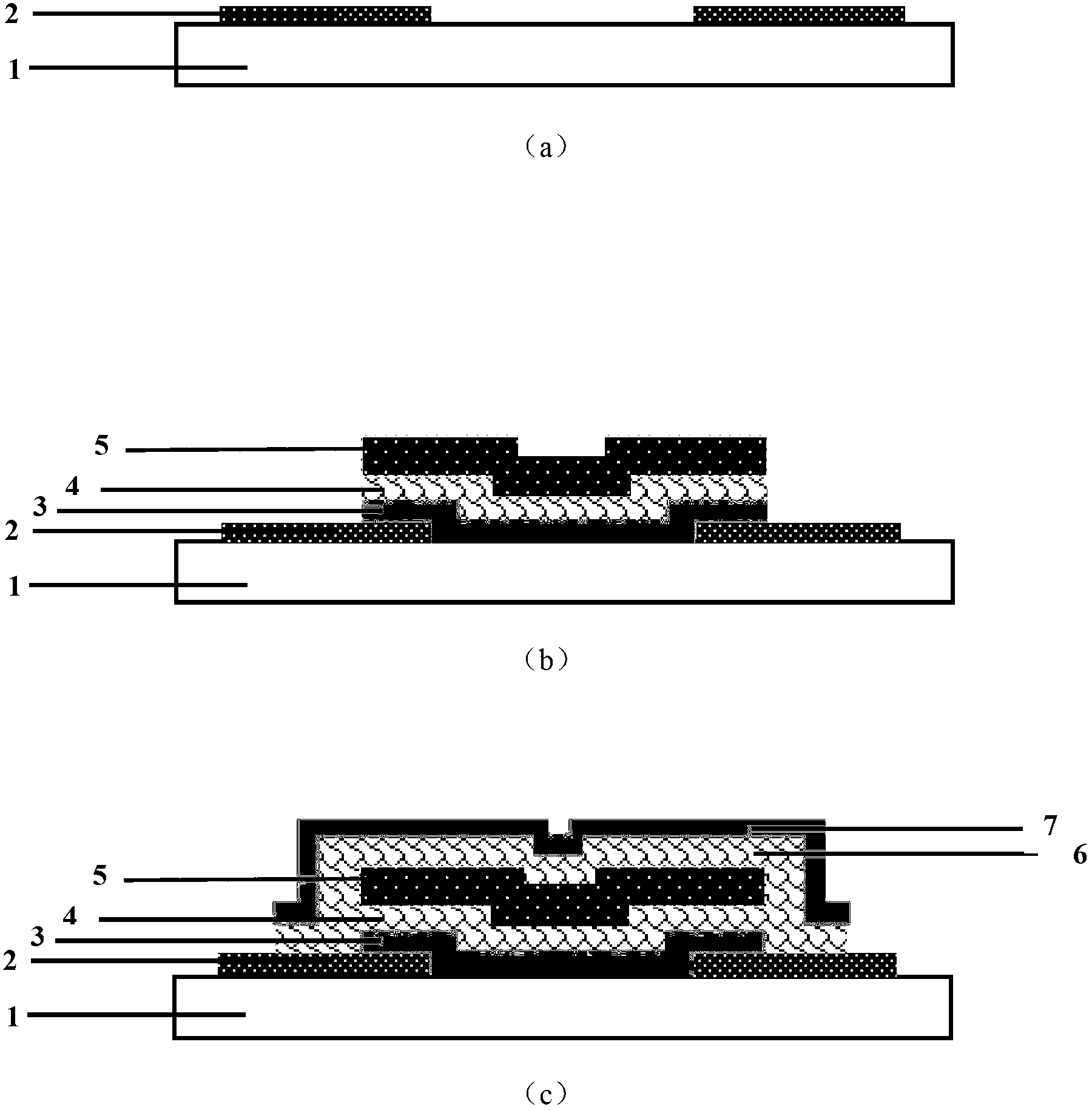

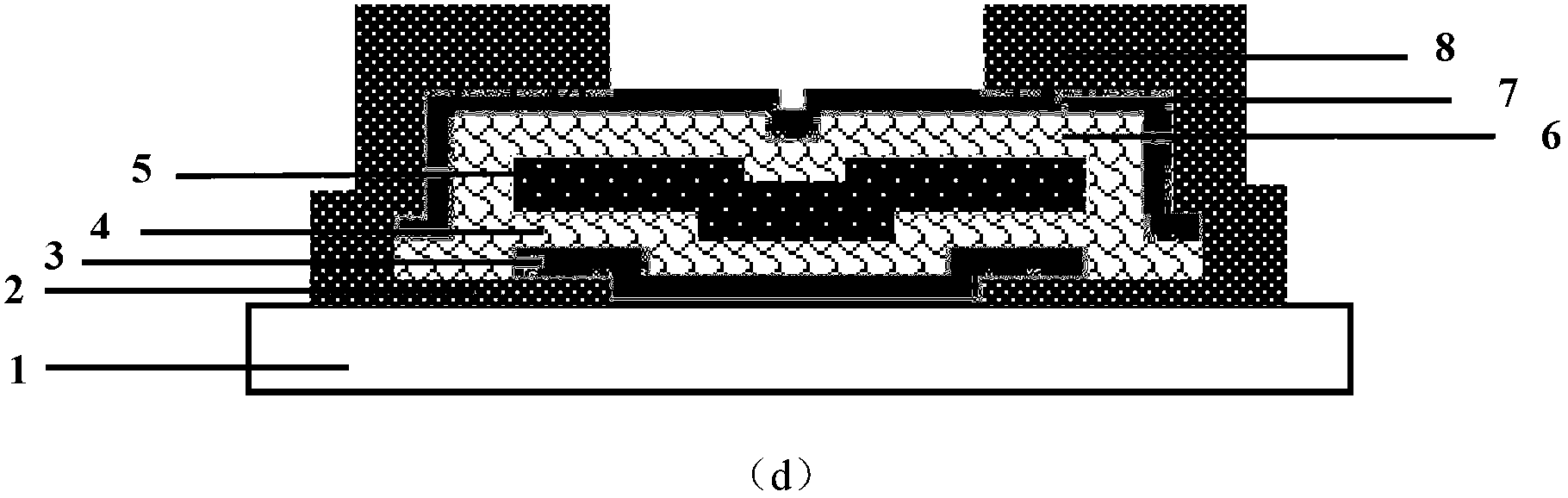

The invention discloses a ferro-electric field effect transistor based on a structured carbon nano tube striped array and a manufacturing method of the ferro-electric field effect transistor. According to the unit structure of the transistor, a bottom electrode layer (1) is arranged on the bottom layer, a ferro-electric film insulated gate layer (2) and a structured carbon nano tube striped array channel layer (3) are sequentially arranged on the middle layer, and a top layer is arranged on the structured carbon nano tube striped array channel layer (3) and comprises a transistor source electrode (4) and a transistor drain electrode (5); carbon nano tubes are single-walled carbon nano tubes, or double-walled carbon nano tubes or multi-walled carbon nano tubes. According to the ferro-electric field effect transistor, the on-state current and the switch ratio are large, carrier mobility is high, the starting voltage is small, the storage window is wide, and meanwhile the ferro-electric field effect transistor has the advantages of being simple in structure and a buffering layer is not needed, interface contact between a ferro-electric layer and a semiconductor layer is good, and large-area soft devices are easy to obtain. The manufacturing method is simple in technology, convenient to operate and low in cost and dispense with expensive equipment, and large-area and large-scale industrial production is easy to realize.

Owner:XIANGTAN UNIV

Memory device, method for manufacturing memory device, and electronic device

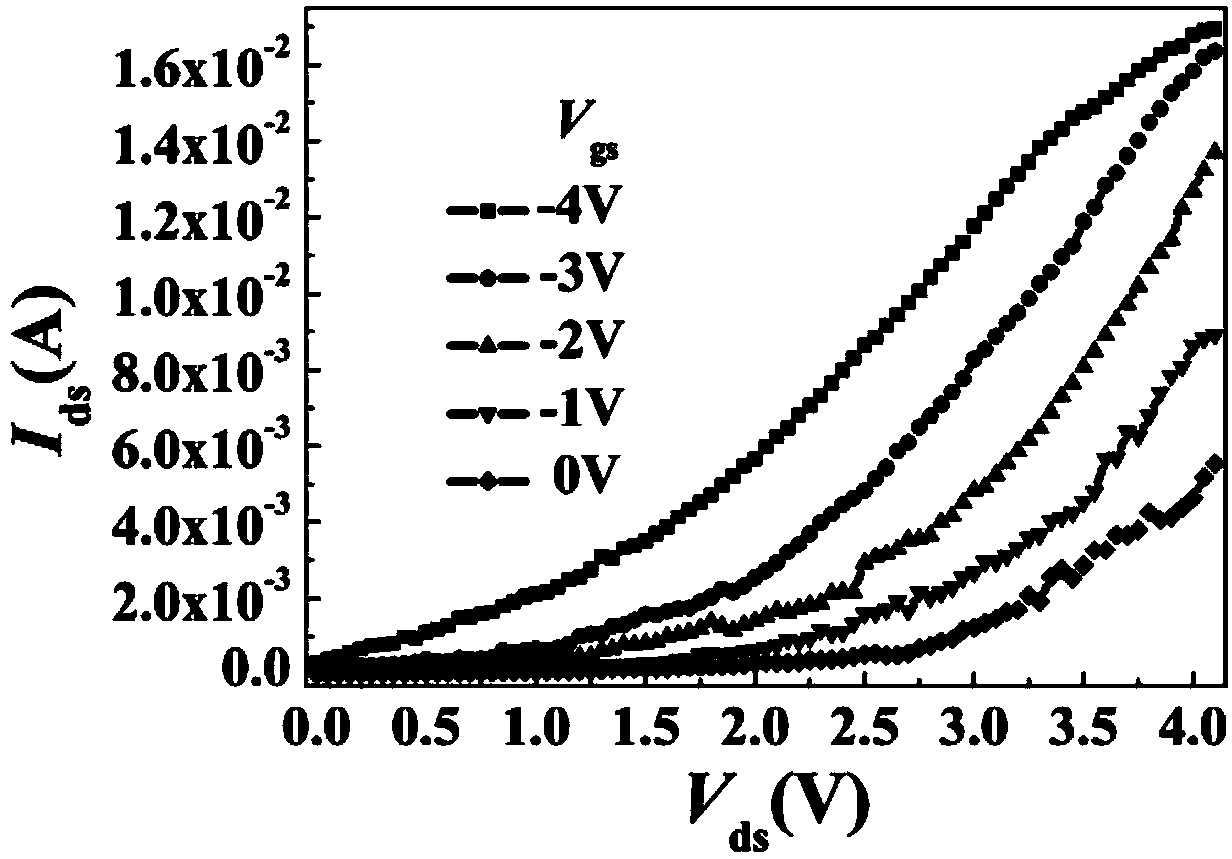

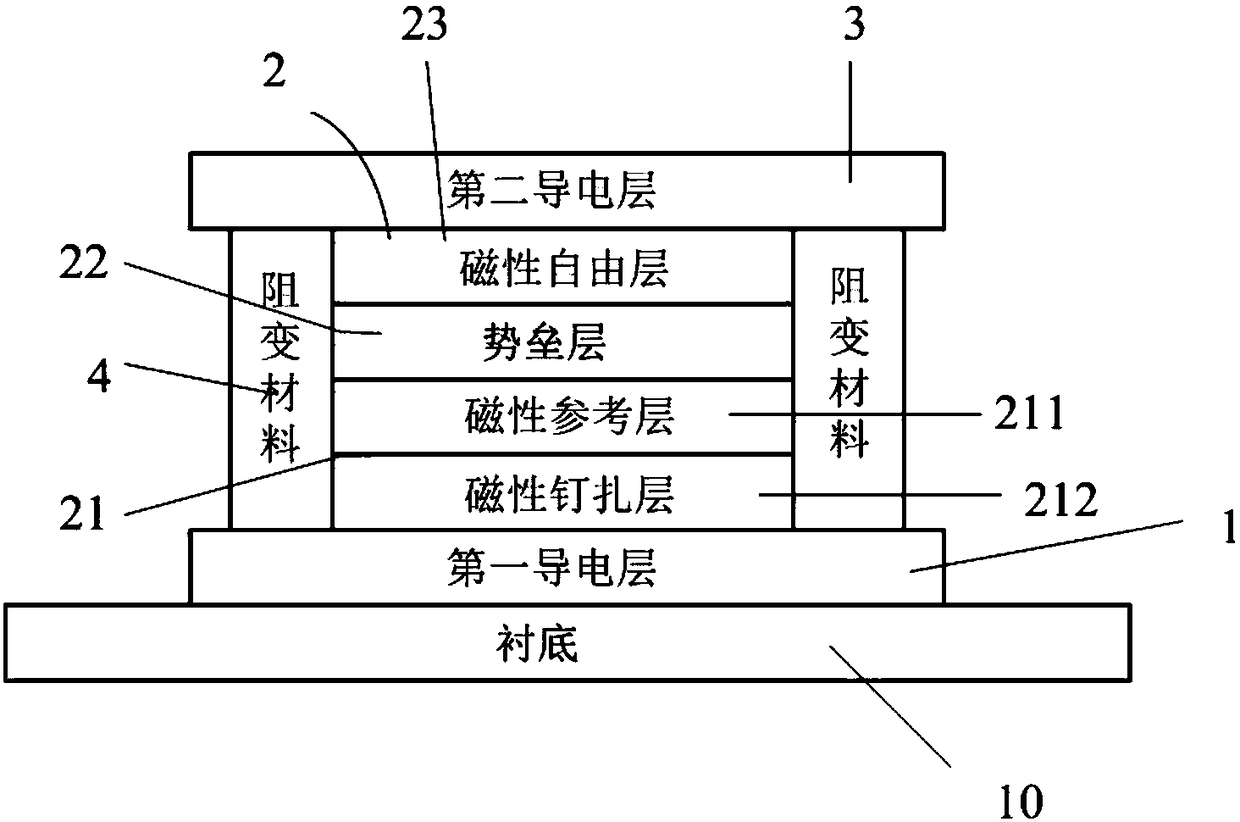

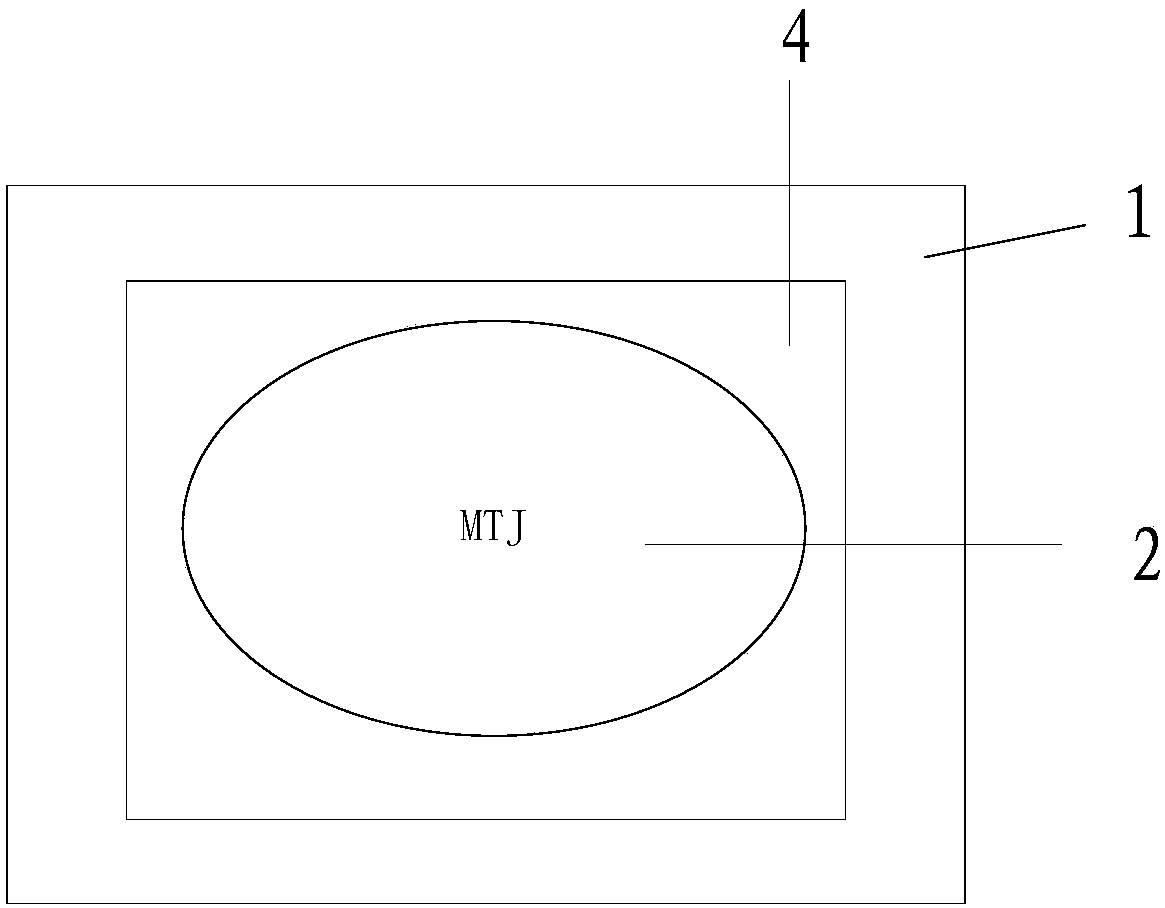

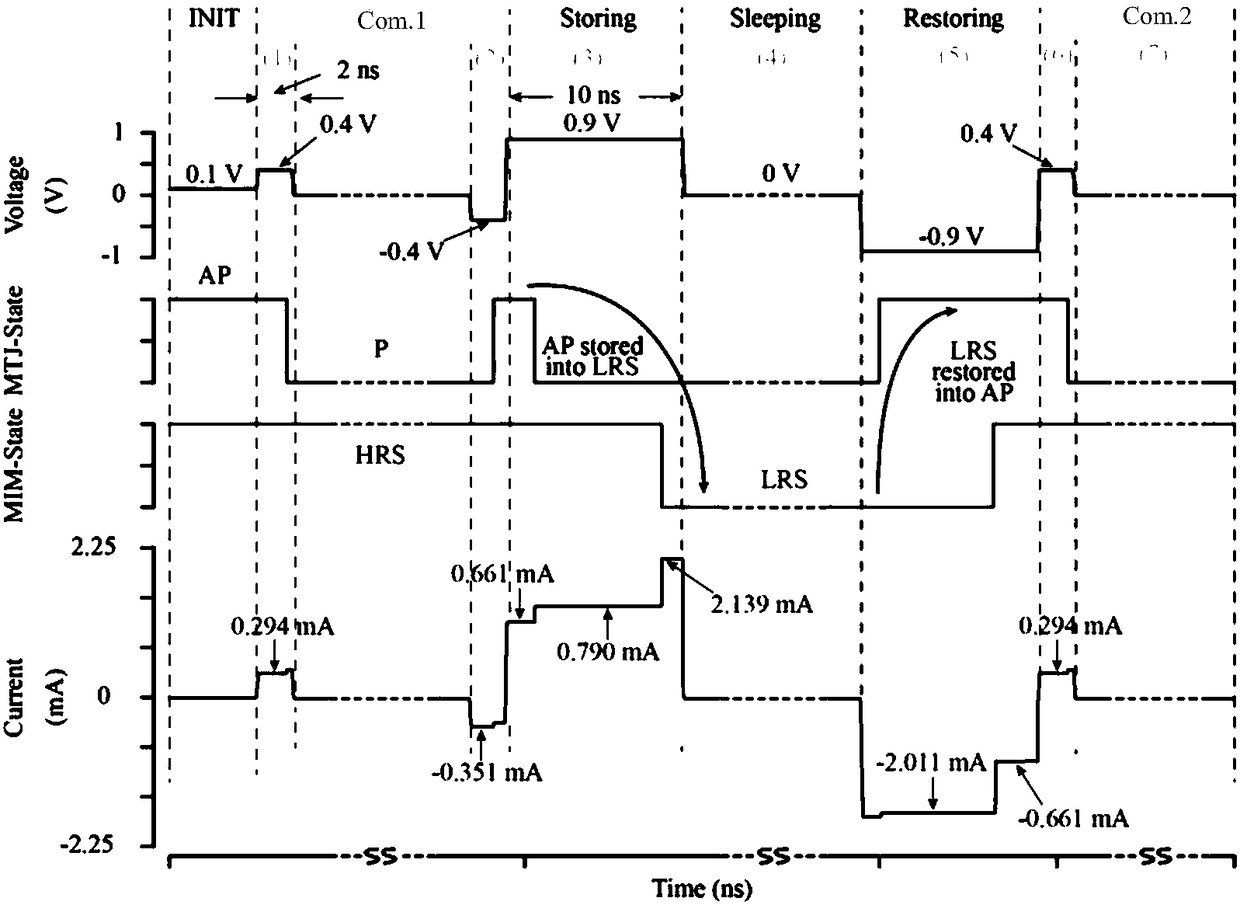

PendingCN108336223AHigh switching ratioMagnetic-field-controlled resistorsGalvano-magnetic device manufacture/treatmentMagnetic memoryEngineering

The embodiment of the invention provides a memory device, a manufacturing method of the memory device and an electronic device. The memory device comprises a resistive material, a first conductive layer sequentially stacked, a magnetic tunnel junction and a second conductive layer, wherein the first conductive layer, the magnetic tunnel junction and the second conductive layer are sequentially stacked; the resistive material is positioned between the first conductive layer and the second conductive layer; the resistive material is adhered to the edge of the magnetic tunnel junction to wrap themagnetic tunnel junction; the magnetic tunnel junction comprises a magnetic fixing layer, a barrier layer and a magnetic free layer which are sequentially stacked; a conductive channel is formed in the region near the magnetic tunnel junction in the resistive material and two ends of the conductive channel are respectively connected to the magnetic fixing layer and the magnetic free layer. The memory device provided by the embodiment of the invention can equivalently be the parallel connection of the magnetic memory unit and the impedance memory unit in the electrical structure, and has the advantages of high read-write speed, unlimited read-write operation, high switching ratio and the like.

Owner:QINGDAO RES INST OF BEIHANG UNIV

Schottky gate field effect transistor and preparation method and application thereof

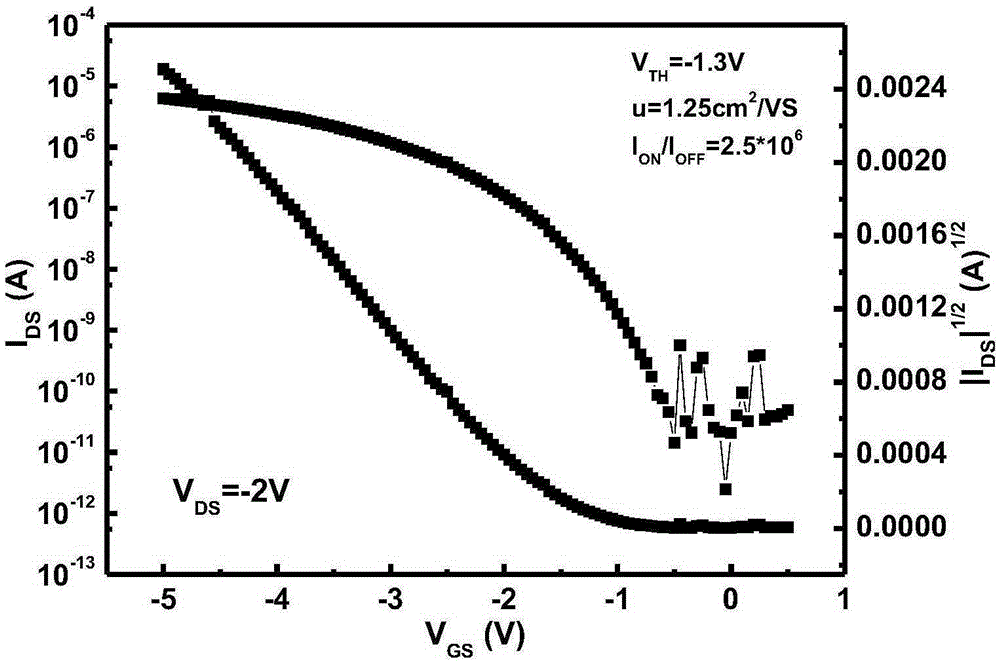

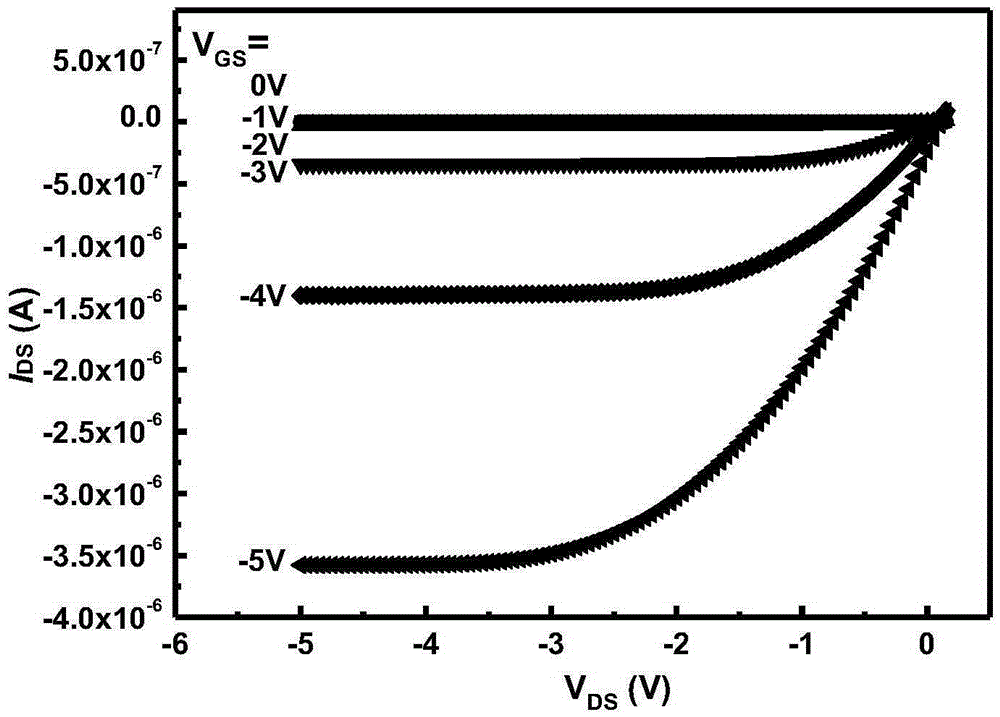

InactiveCN107146815ASimple preparation processImplement the arraySemiconductor/solid-state device manufacturingSemiconductor devicesApplication areasPhotoresist

The invention discloses a preparation method of a schottky gate field effect transistor. According to the preparation method, a two-dimensional material is prepared on a substrate firstly, then the substrate and the two-dimensional material are coated with photoresist in a spin coating manner, and photoetching exposure and developing are performed to expose source and drain electrode windows; metal is coated, and the photoresist is washed off, and next, annealing in gas atmosphere is performed to form a source electrode and a drain electrode; next, the whole piece of a sample is coated with photoresist in a spin coating manner, and photoetching exposure and developing are performed to expose a gate electrode window; and next, metal is coated, and the photoresist is washed off to form the schottky gate field effect transistor. The schottky gate field effect transistor has the advantages of small dimensions, high switch ratio, high mobility, capability of well eliminating a short-channel effect and the like, so that the application field of a two-dimensional material device can be expanded.

Owner:GUANGDONG UNIV OF TECH

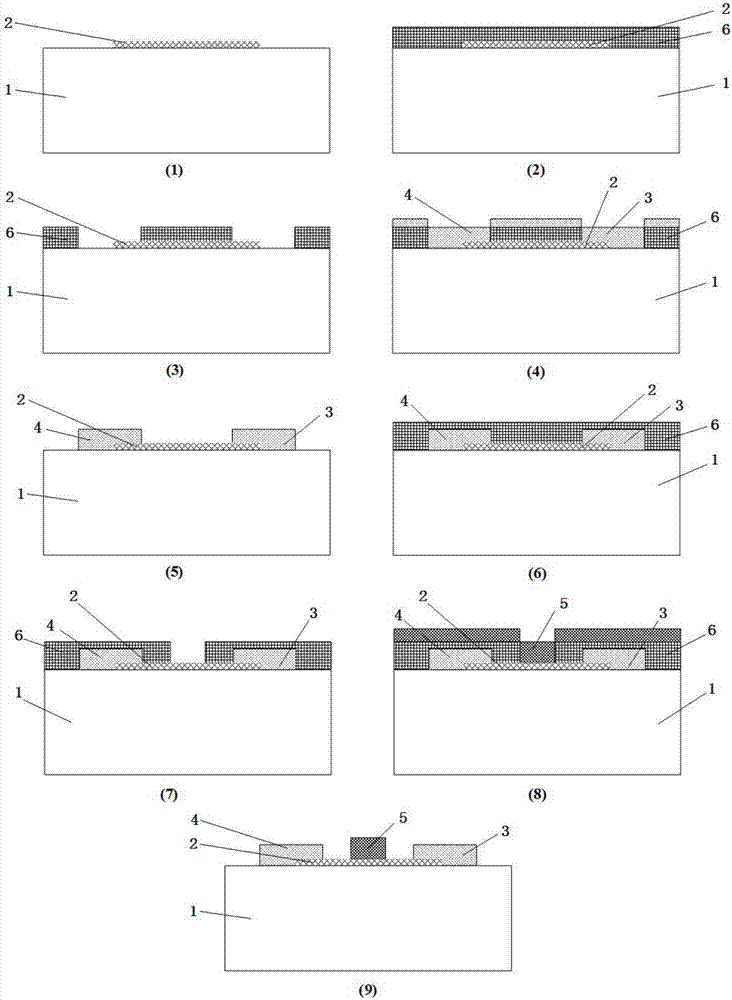

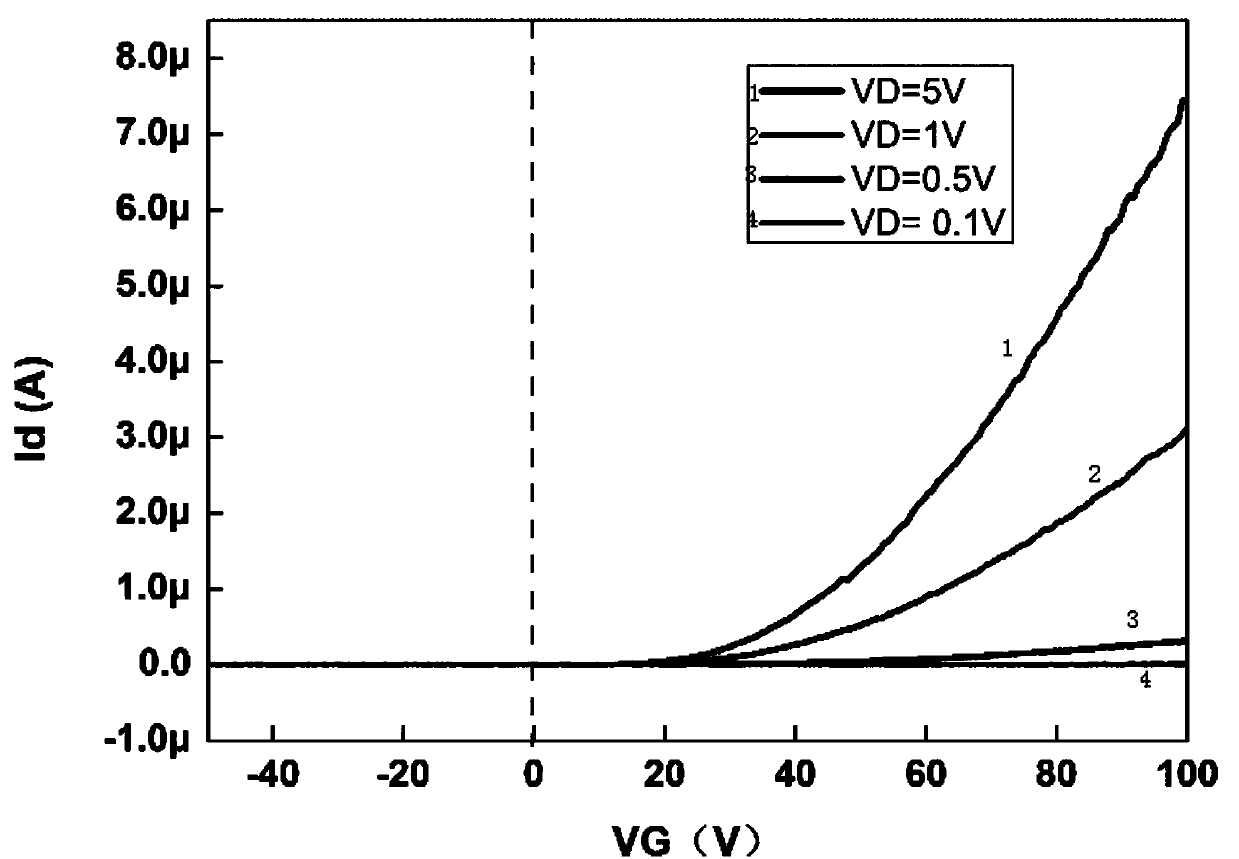

Preparation method of enhanced field effect transistor based on two-dimensional planar heterojunction

InactiveCN107818921AEasy to integrateEase of mass productionTransistorSemiconductor/solid-state device manufacturingHeterojunctionIn plane

The invention relates to a preparation method of an enhanced field effect transistor based on a two-dimensional planar heterojunction, and relates to the application field of microelectronic devices.The preparation method comprises the steps of transferring a graphene film to a monocrystalline silicon wafer substrate with an oxide layer by adopting wet transfer; uniformly spinning a photoresist on the graphene film, and transferring a pattern to the photoresist through exposure; etching the graphene film into graphene strips, and removing the photoresist; enabling the substrate with the graphene strips to serve as a substrate for growth, growing an MX2 type single-layer or few-layer material according to a CVD method, and forming a graphene-MX2-graphene in-plane heterojunction; and evaporating and depositing Ti / Au metal on the graphene-MX2-graphene in-plane heterojunction to obtain a two-dimensional planar heterojunction enhanced field effect transistor. The field effect transistor with a high switching ratio is obtained by combining the semi-metal material graphene with high carrier mobility and the MX2 two-dimensional material with the band gap being adjustable along with variations in number of layers, and the field effect transistor has excellent characteristics of very small dark current when being applied to photoelectric detection.

Owner:BEIJING UNIV OF TECH

Novel liquid crystal material as well as preparation method and light modulator

InactiveCN107815320AEasy to assembleColor adjustableLiquid crystal compositionsNon-linear opticsPermeationElectron

The invention discloses a novel liquid crystal material as well as a preparation method and a light modulator. The novel liquid crystal material is mainly prepared from a stable solution of an inorganic two-dimensional material; the light modulator is mainly composed of a transparent liner, a polaroid, a transparent conductive electrode and a driving power supply; and the stable solution of the inorganic two-dimensional material is sealed in a liquid crystal material accommodation cavity formed by the transparent liner. The invention discloses that an inorganic two-dimensional material is adopted as a liquid crystal activated layer for a first time, the novel liquid crystal material has the advantages of being free of orientated layer, convenient to assemble, adjustable in color and permeation rate, high in on-off ratio, high in stability, low in cost, good in environmental friendliness, and the like, and is applicable to fields such as large-scale electronic curtains, flat displays, mobile phone screens, camera screens, personal electronic and photoelectron equipment screens, game facility screens and light memory storage.

Owner:TSINGHUA BERKELEY SHENZHEN INST

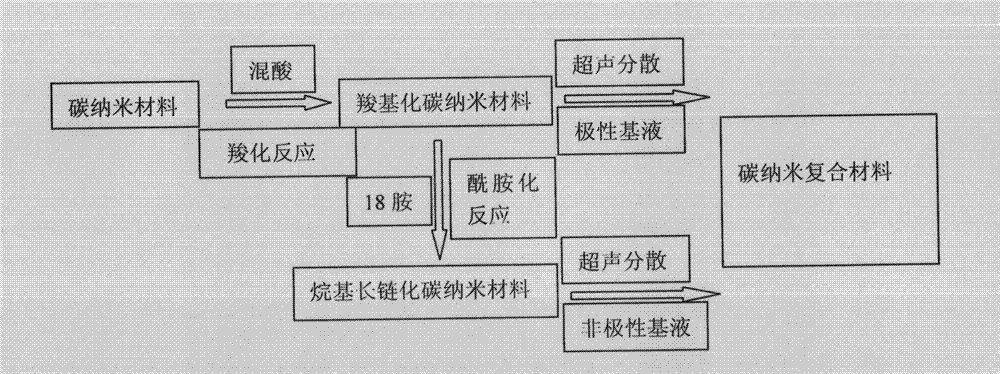

High-temperature coefficient and high-stability room temperature switch nanocomposite

ActiveCN102766439AHigh switching ratioEnhance interface affinityThermometers using electric/magnetic elementsConductive materialTemperature coefficientNanometre

The invention relates to a method for preparing a high-temperature coefficient and high-stability room temperature switch nanocomposite and the performance of the high-temperature coefficient and high-stability room temperature switch nanocomposite. The high-temperature coefficient and high-stability room temperature switch nanocomposite is a novel intelligent nano composite functional material. According to the method, a nano material with high heat, electric and magnetic transmission characteristics and an insulating base solution with a fixed crystallization point are combined flexibly to prepare the switch nanocomposite; and the interface affinity of the switch nanocomposite and the base solution is enhanced by the surface modification of the nano material, so that the switch ratio and stability of the nanocomposite are improved greatly. The intelligent nano composite functional material with high practicality has a broad application prospect in fields of energy, biological medical treatment and the like.

Owner:BEIJING NORMAL UNIVERSITY

Oxide semiconductor thin-film transistor and preparation method thereof

InactiveCN102637742AImprove driving abilityMinus interface defect statesSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSRadio frequency magnetron sputtering

The invention discloses an oxide semiconductor thin-film transistor and a preparation method for the oxide semiconductor thin-film transistor, belonging to the technical fields of semiconductor integrated circuits and manufacturing of the semiconductor integrated circuits. Two layers of AlZnO thin-film materials are formed as active areas by adoption of a radio frequency magnetron sputtering method, and the two layers of the AlZnO thin-film materials contain different oxygen ion contents. The oxide semiconductor thin-film transistor disclosed by the invention has the advantages of high migration rate. The preparation method disclosed by the invention and the existing CMOS (complementary metal-oxide-semiconductor transistor) technology are compatible, so that the preparation method has higher practical value, and can be applied in future TFT (thin-film transistor) integrated circuits.

Owner:PEKING UNIV

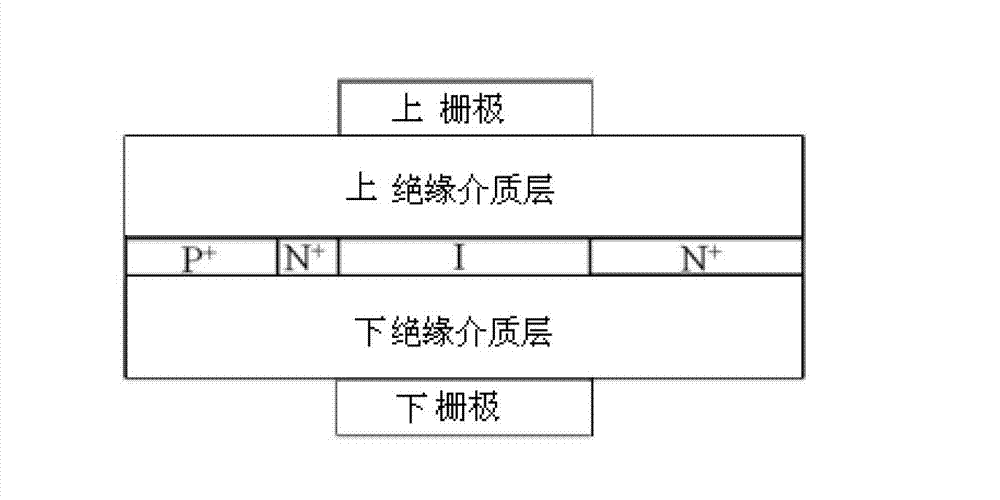

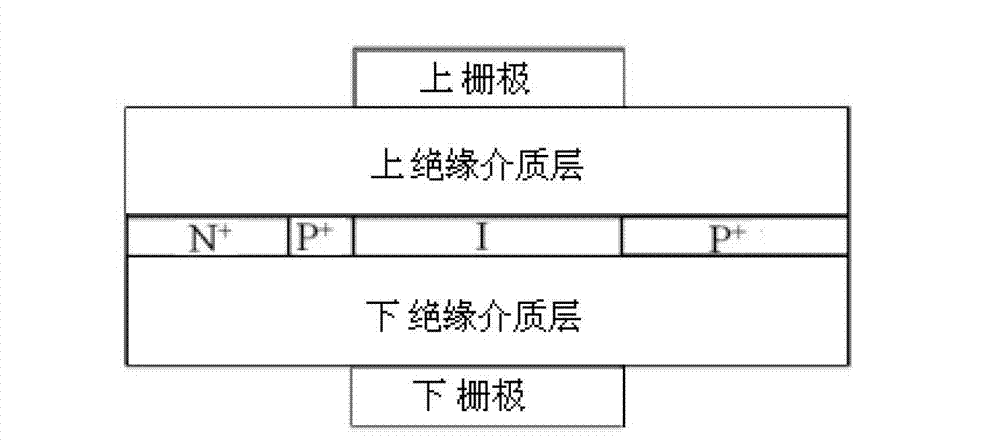

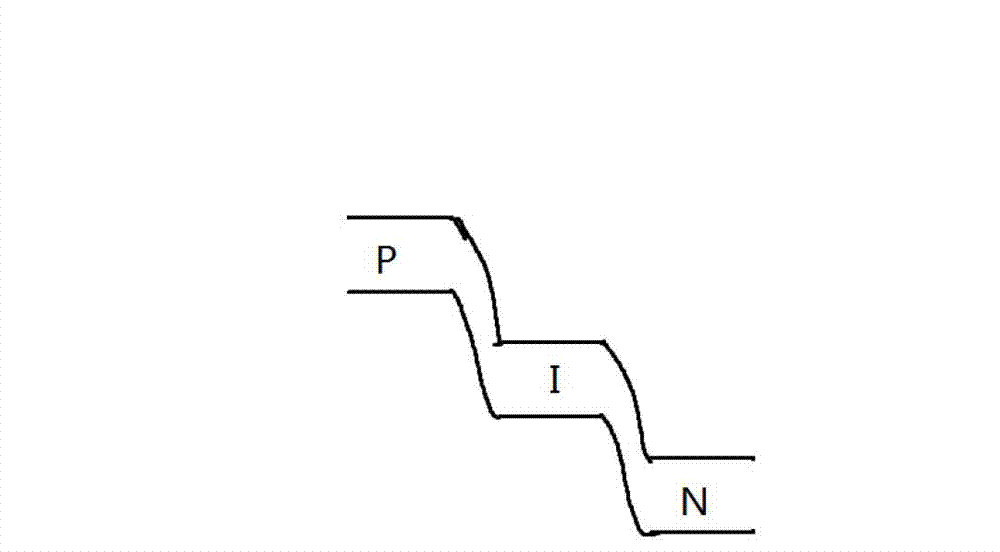

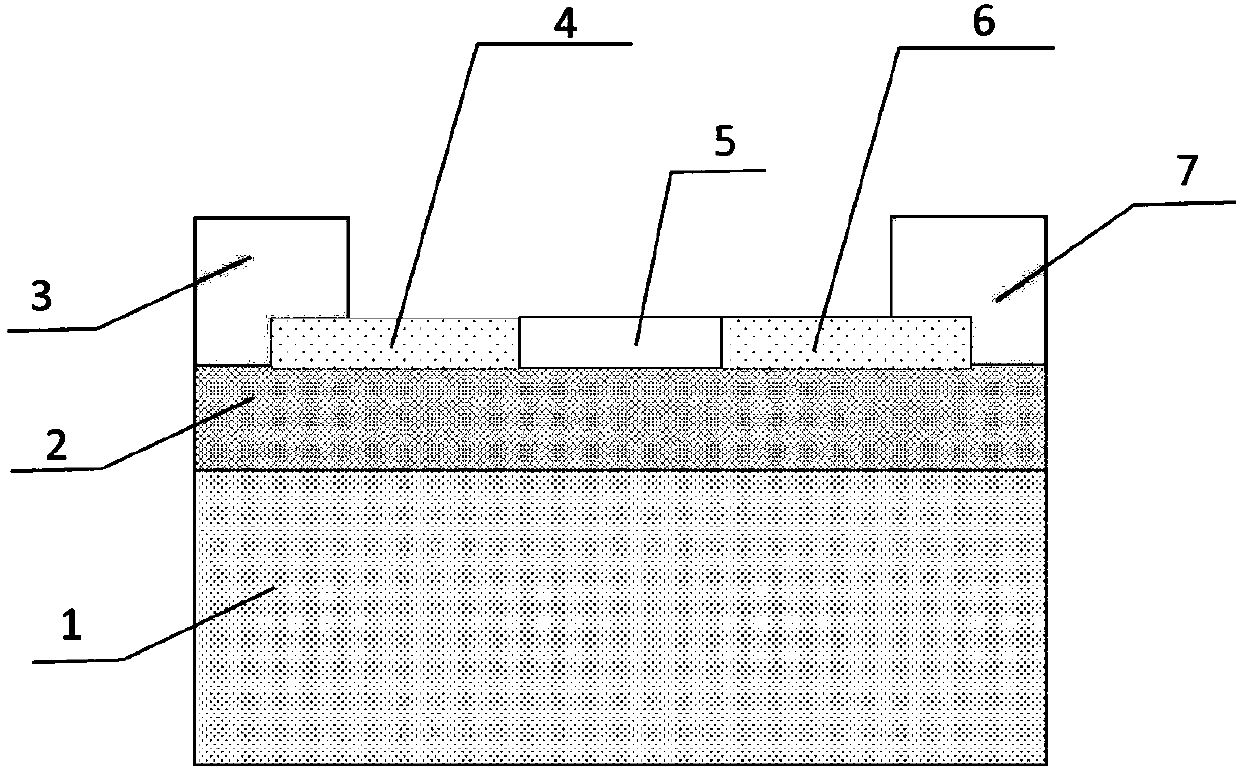

Three-dimensional (3D) oxide semiconductor thin film transistor and preparation method thereof

ActiveCN102709316AImprove driving abilityReduce interface defect statesTransistorSemiconductor/solid-state device manufacturingGate dielectricSub threshold

The invention discloses a three-dimensional (3D) oxide semiconductor thin film transistor (TFT) and a preparation method thereof. According to the TFT, the continuous growth of a lower-layer active area, a lower-layer gate dielectric and a gate electrode and the continuous growth of an upper-layer gate dielectric and an upper-layer active area are adopted, so that the interface deficiency state of an active layer and the gate dielectric can be greatly reduced to greatly improve the driving capability of the (TFT). Moreover, the same gate electrode can simultaneously control the upper-layer and lower-layer active areas, so that the driving capability of the TFT is further improved. The TFT prepared by the method has the good characteristics of high switch ratio, high on-state current, abrupt sub-threshold slope and the like. Therefore, the TFT and the preparation method thereof have high practical value, and are expected to be widely used for microelectronic and flat panel display industries. Furthermore, if the upper-layer and lower-layer active areas are controlled by different threshold voltages, a multi-threshold technology can be integrated into the same TFT, and the integration of the multi-threshold technology into the TFT is expected to widely used for pixel driving unit circuits.

Owner:BOE TECH GRP CO LTD

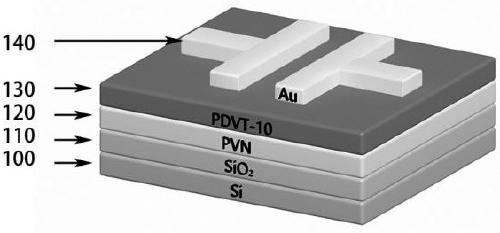

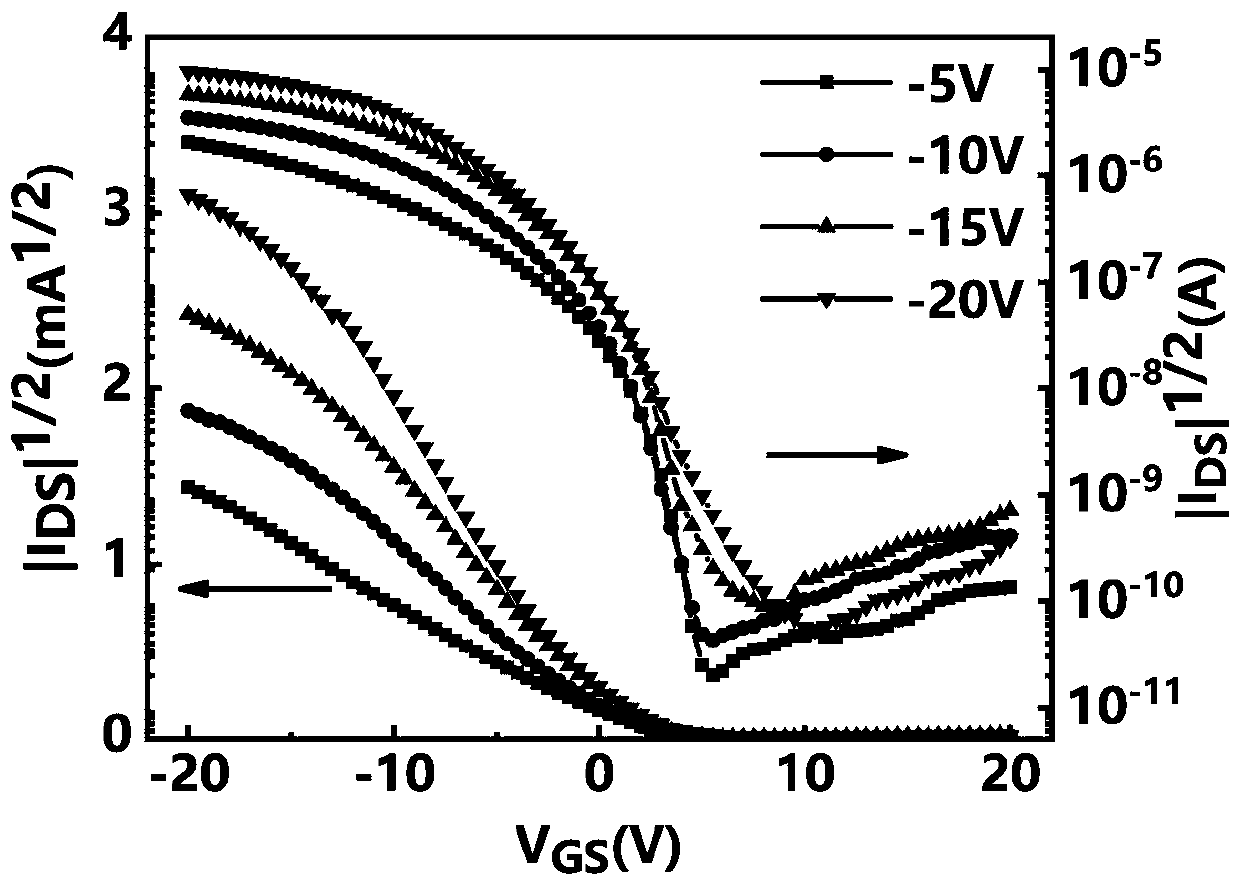

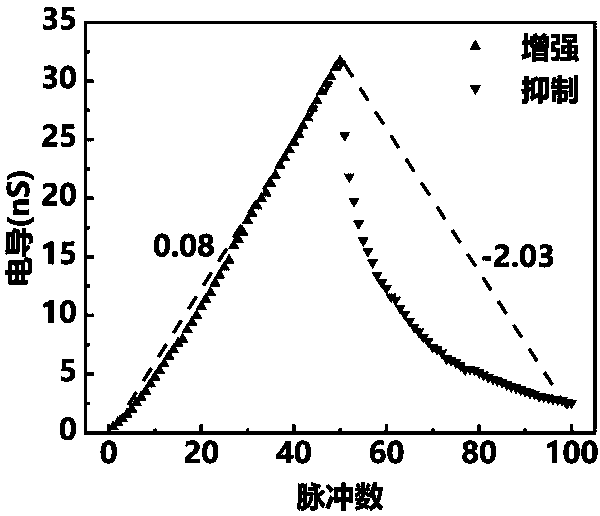

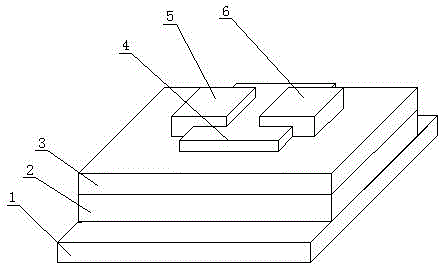

Electret-based synapse transistor and preparation method thereof

ActiveCN111180582AAct as a gate regulatorHigh switching ratioSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringComputational physics

The invention relates to an electret-based synapse transistor and a preparation method thereof. The transistor is composed of a substrate with an insulating layer, an electret dielectric layer, an organic semiconductor layer and a top electrode from bottom to top. The electret dielectric layer forms an interface capture layer between the insulating layer and the semiconductor, and the interface capture layer is used for capturing electrons and holes, forming an additional electric field and playing an additional grid regulation and control role on the semiconductor layer. The transistor has ahigh switching ratio and a large conductance regulation and control range, the conductance increase and the regulated and controlled pulse number are in a good linear relation, the transistor is suitable for neuromorphic calculation, the pattern recognition precision is effectively improved, and an application prospect is provided for future artificial synapses.

Owner:FUZHOU UNIV

Indium tin zinc oxide homogeneous thin film transistor and preparation method thereof

InactiveCN103943683AHigh field-induced mobilityHigh switching ratioTransistorSemiconductor/solid-state device manufacturingOxide ceramicIndium

Provided is an indium tin zinc oxide homogeneous thin film transistor and a preparation method of the thin film transistor. The thin film transistor comprises a substrate, a grid electrode, an insulating layer, a channel layer, a source electrode and a drain electrode. The thin film transistor is characterized in that material of the channel layer, the source electrode and the drain electrode is indium tin zinc oxide. The indium tin zinc oxide is indium tin zinc oxide ceramic target material made of In2O3, SnO2 and ZnO powders via ball grinding and uniform mixing, and technologies of molding, sintering, etc. The atomic number ratio of indium, tin and zinc in the indium tin zinc oxide ceramic target material is a: b: c=35-88: 8-35: 2-25. The indium tin zinc oxide ceramic target material is deposited into a thin film by utilizing a magnetron sputtering mode. The thin film transistor is simple in preparation technology and suitable for industrial production. The surface of an amorphous electrode is great in flatness so as to be better in contact with the interface of the channel layer. Therefore, injection of carriers is easier, mobility is high and on-off ratio is high.

Owner:山东大学(威海)