Patents

Literature

48results about How to "Processing technology compatible" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

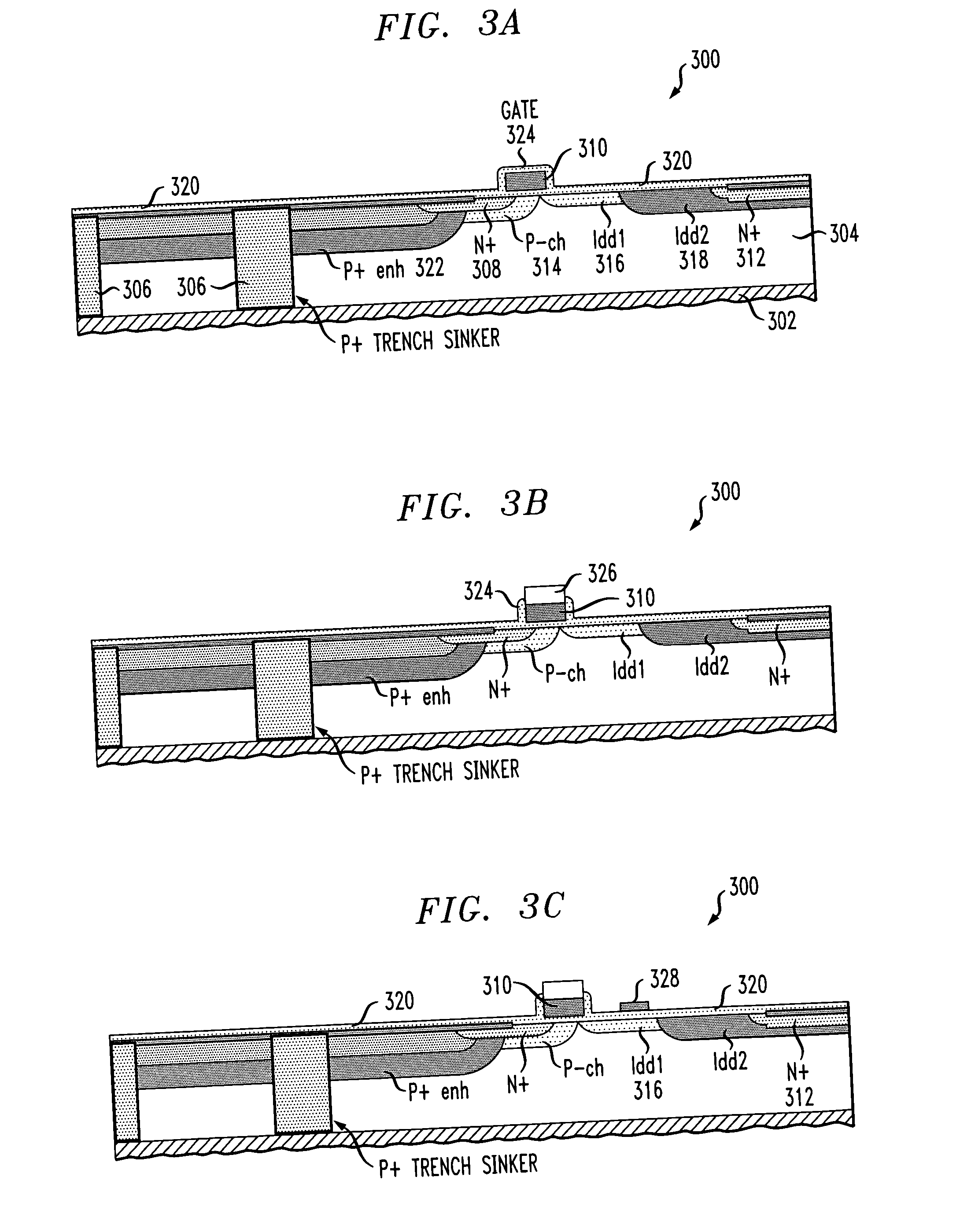

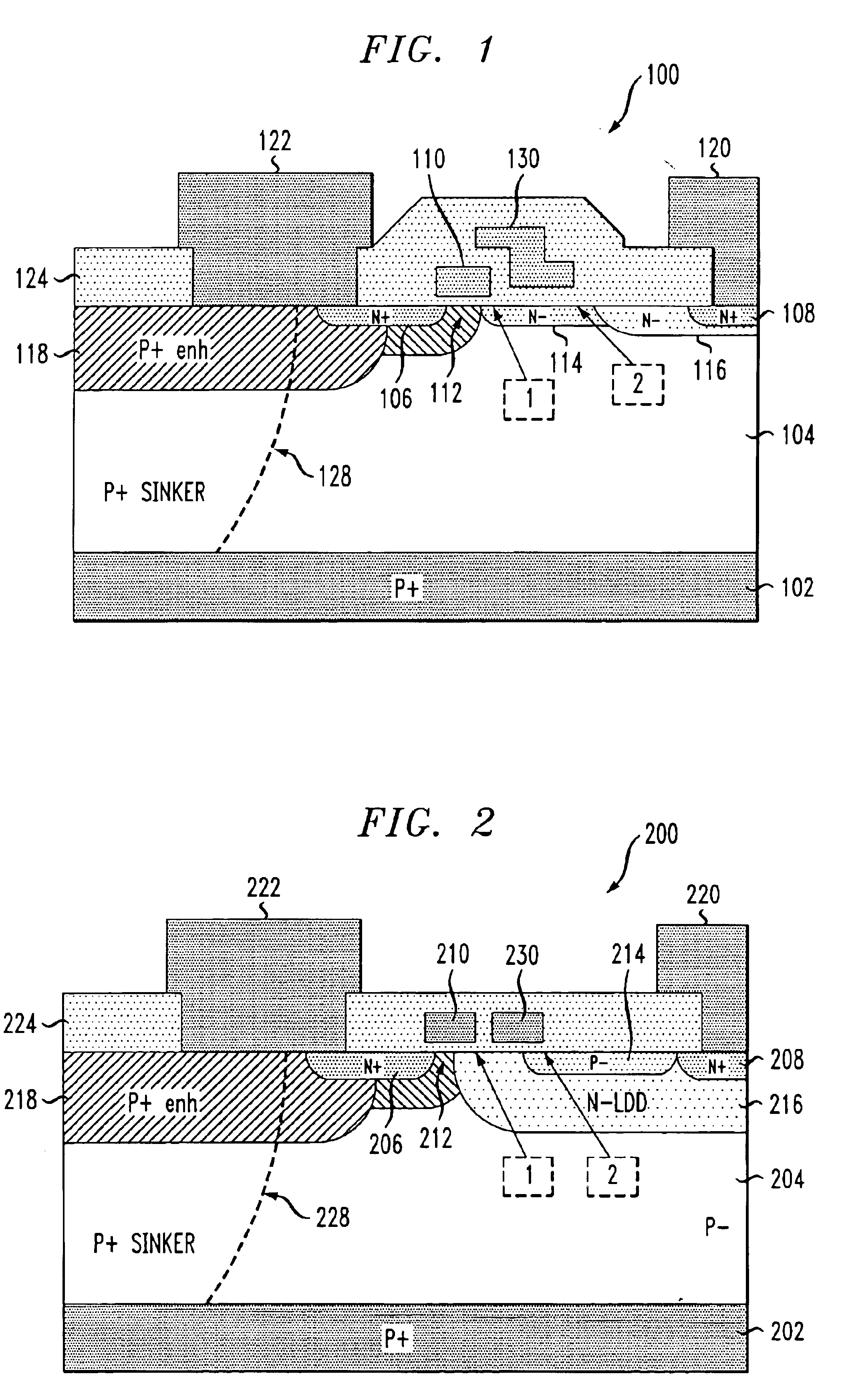

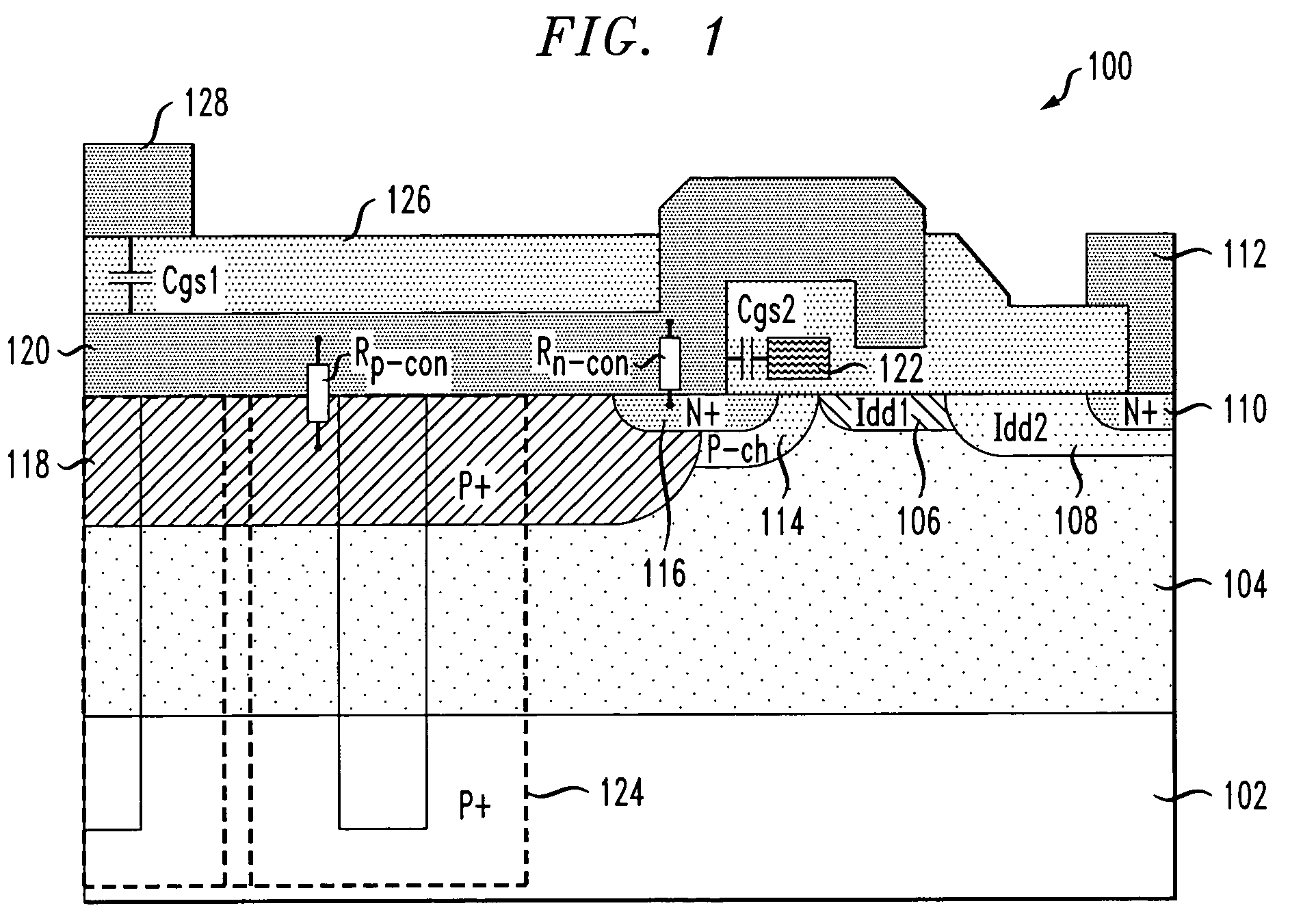

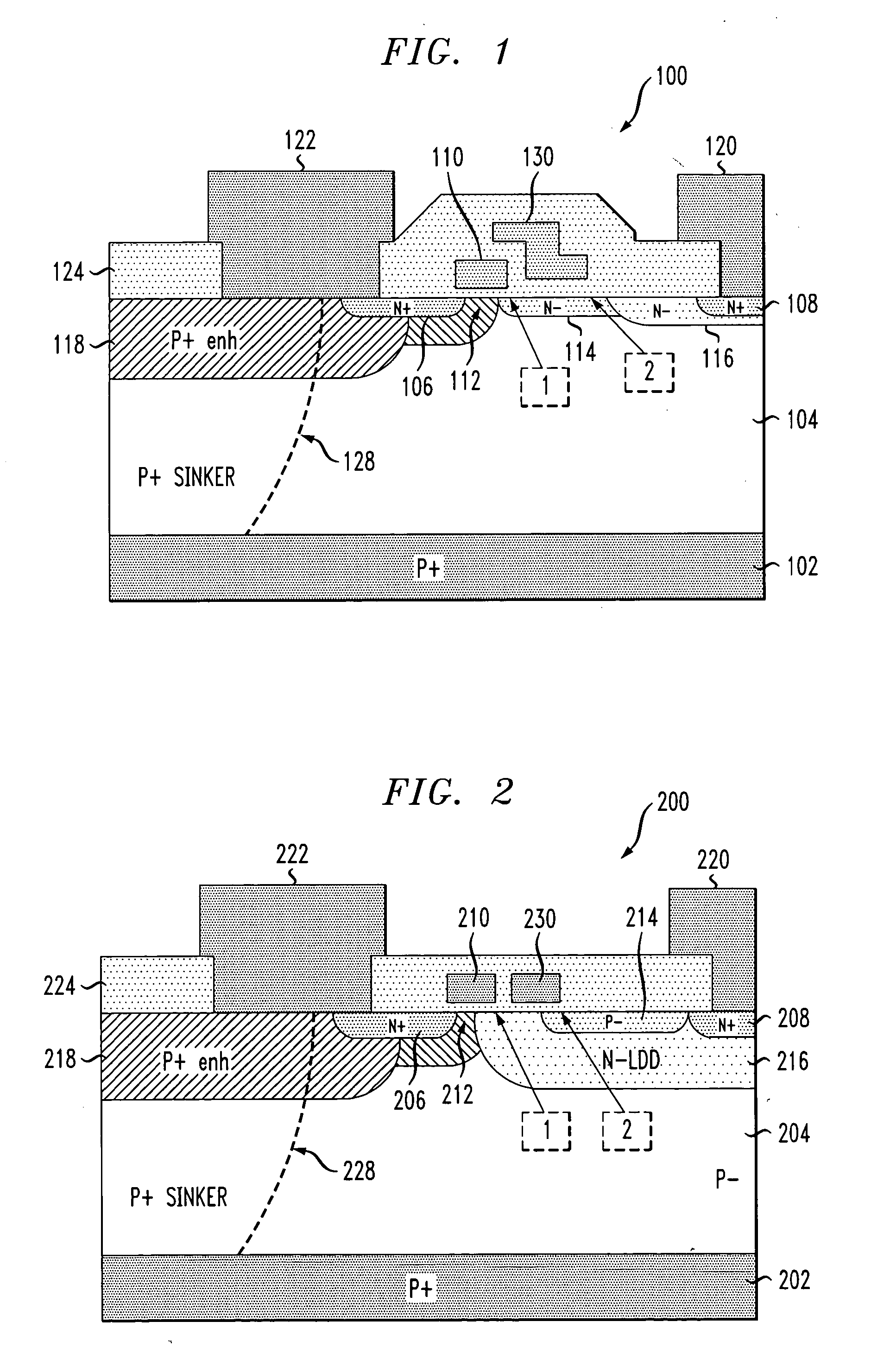

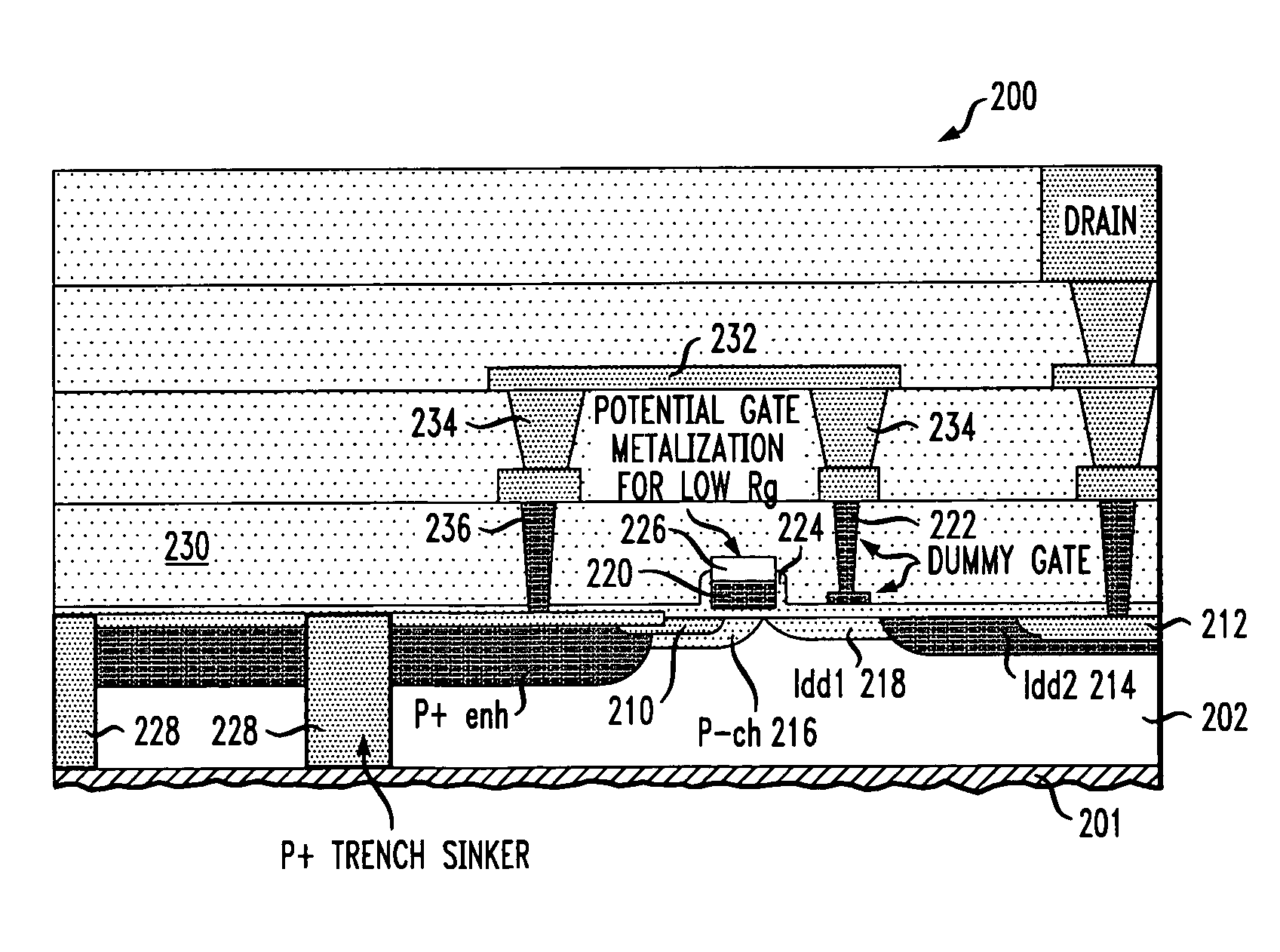

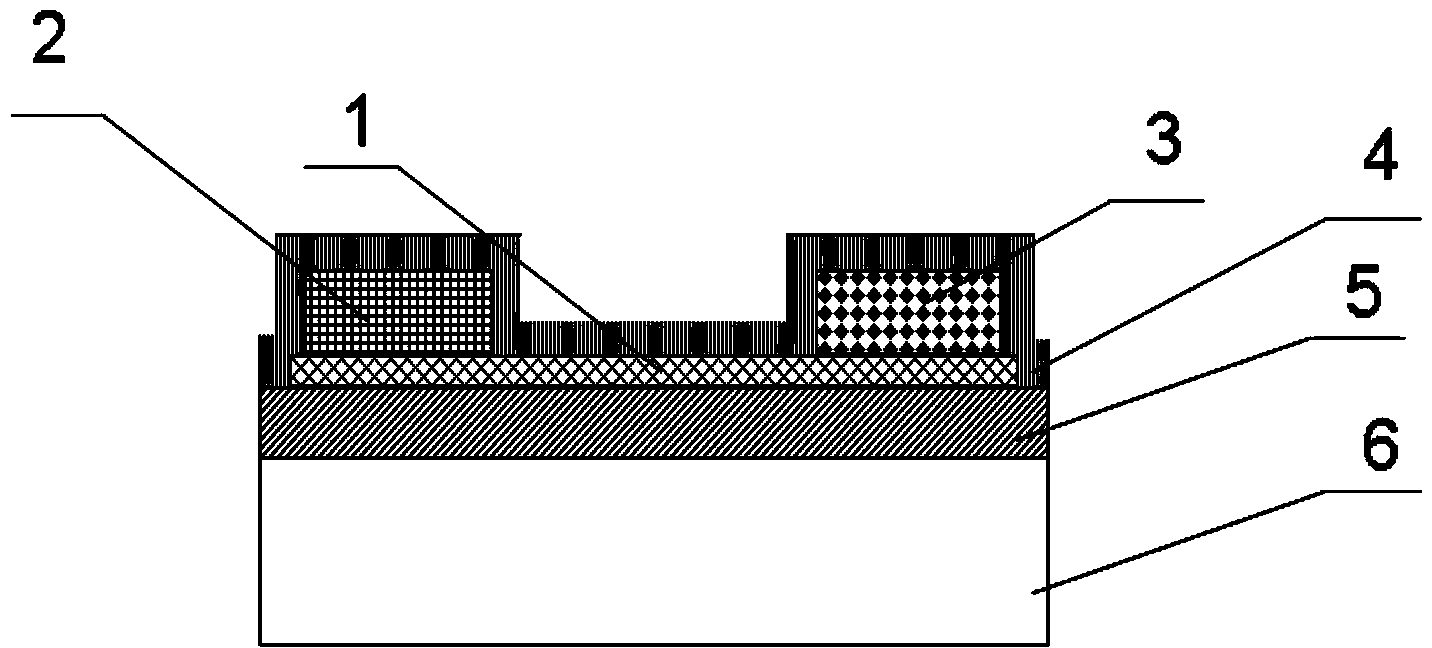

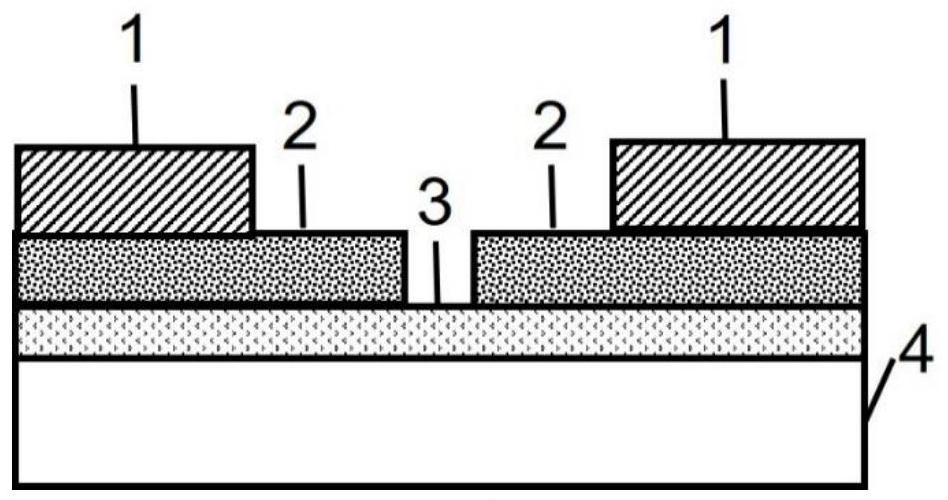

Shielding structure for use in a metal-oxide-semiconductor device

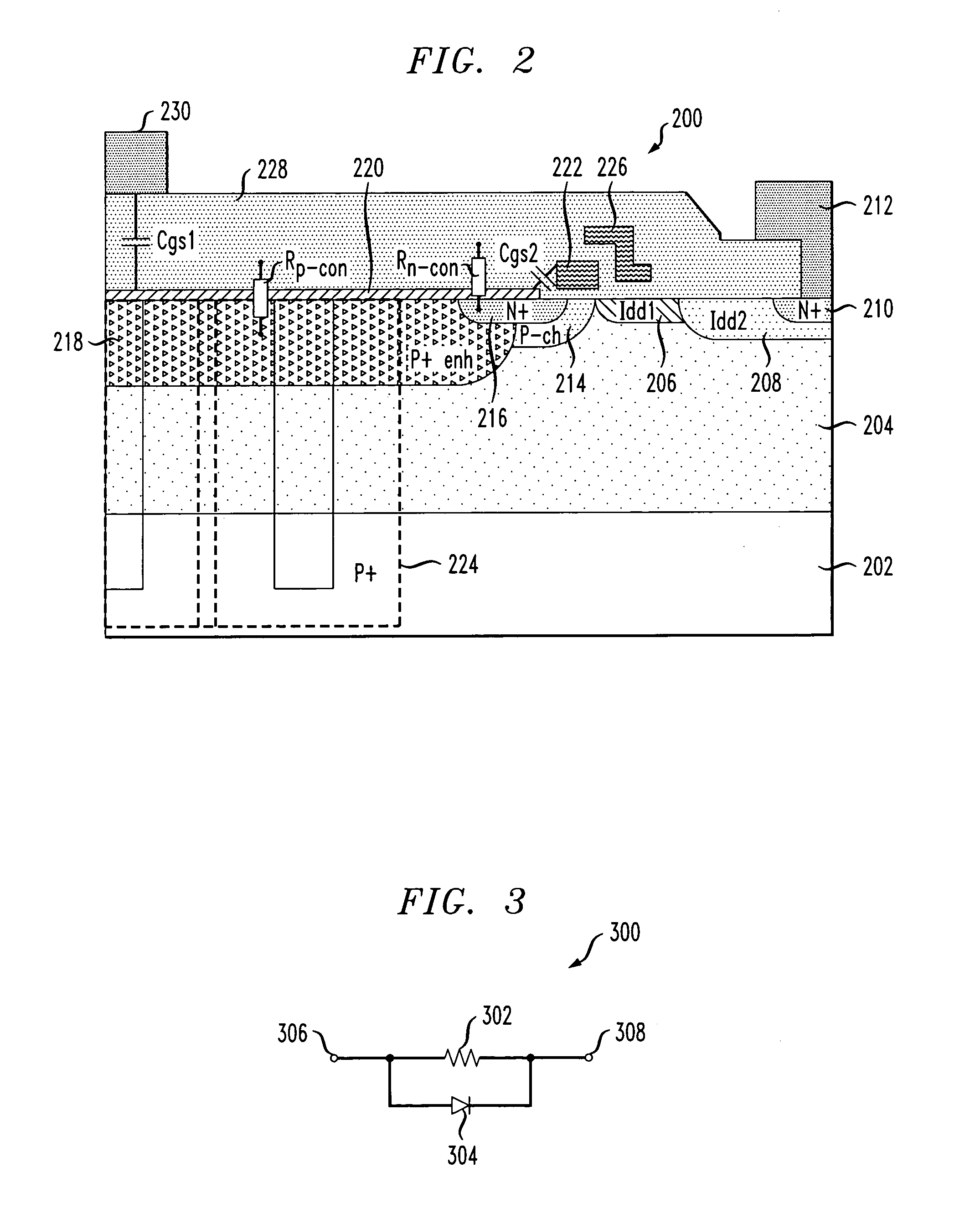

InactiveUS20050017298A1Improve high frequency performanceLow costTransistorSemiconductor/solid-state device detailsSemiconductorCmos process

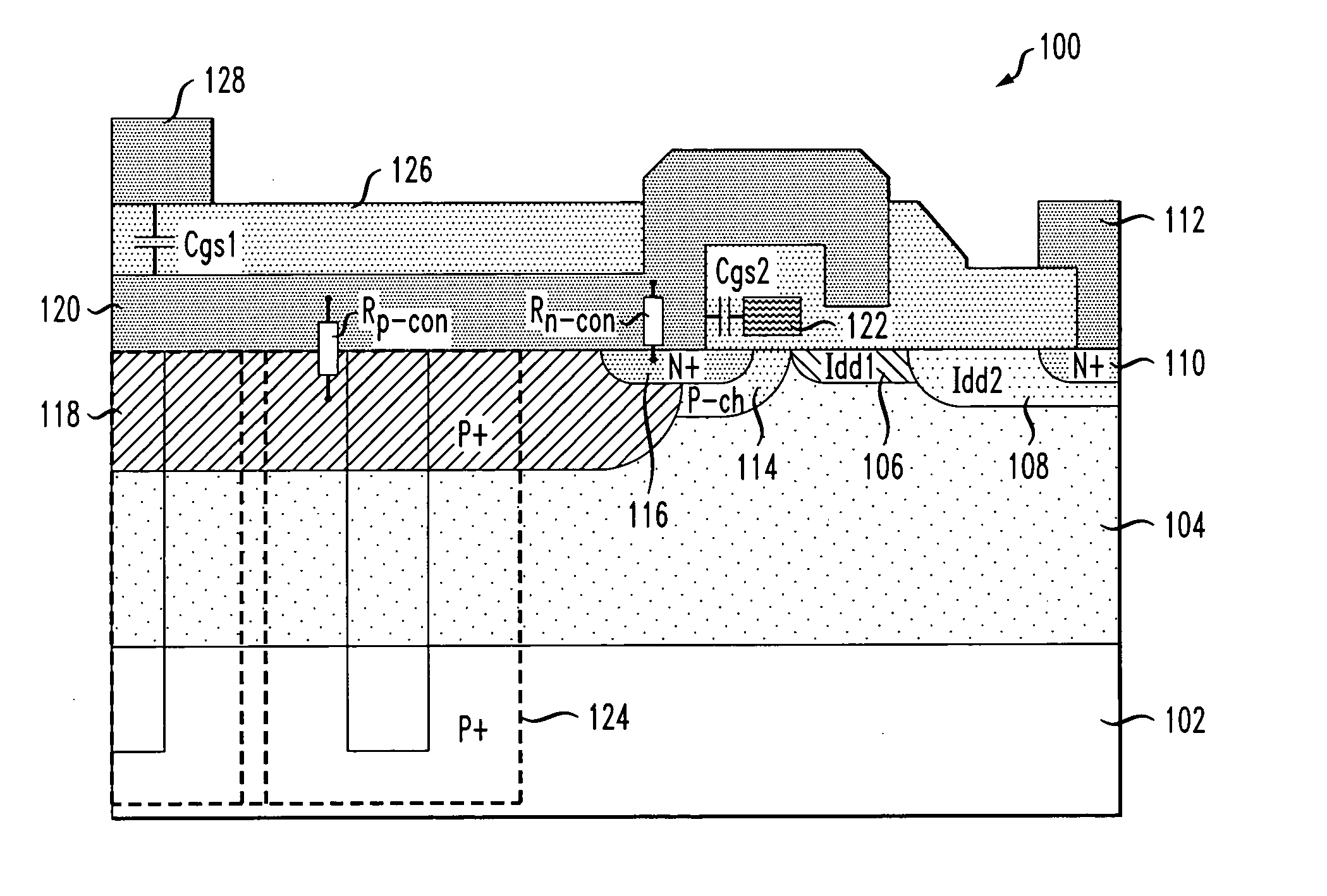

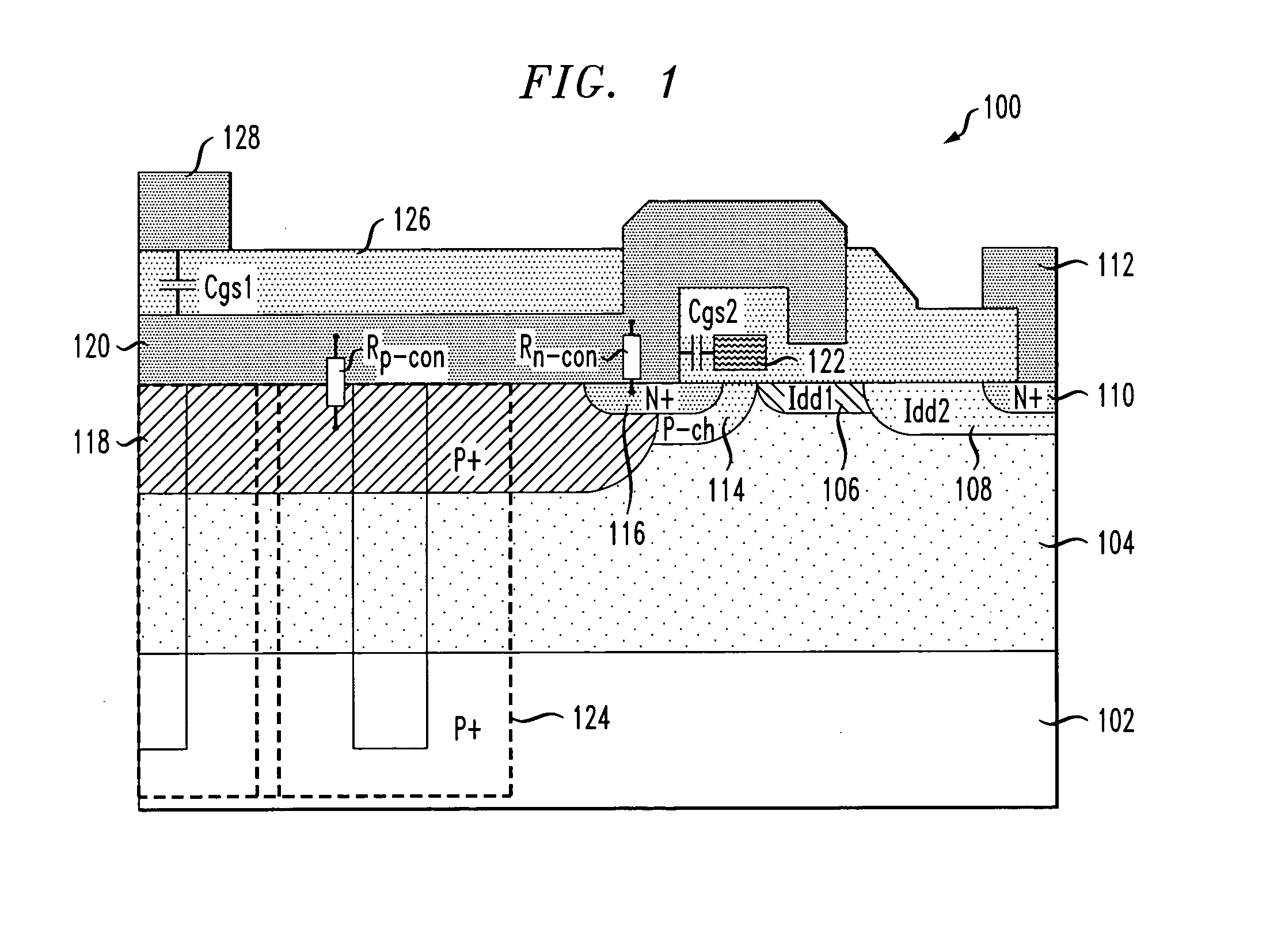

An MOS device is formed comprising a semiconductor layer of a first conductivity type, a first source / drain region of a second conductivity type formed in the semiconductor layer, and a second source / drain region of the second conductivity type formed in the semiconductor layer and spaced apart from the first source / drain region. The MOS device further comprises a gate formed proximate an upper surface of the semiconductor layer and at least partially between the first and second source / drain regions, and a shielding structure formed proximate the upper surface of the semiconductor layer and between the gate and the second source / drain region, the shielding structure being electrically connected to the first source / drain region, the shielding structure being spaced laterally from the gate and being non-overlapping relative to the gate. In this manner, the MOS device is substantially compatible with a CMOS process technology.

Owner:BELL SEMICON LLC

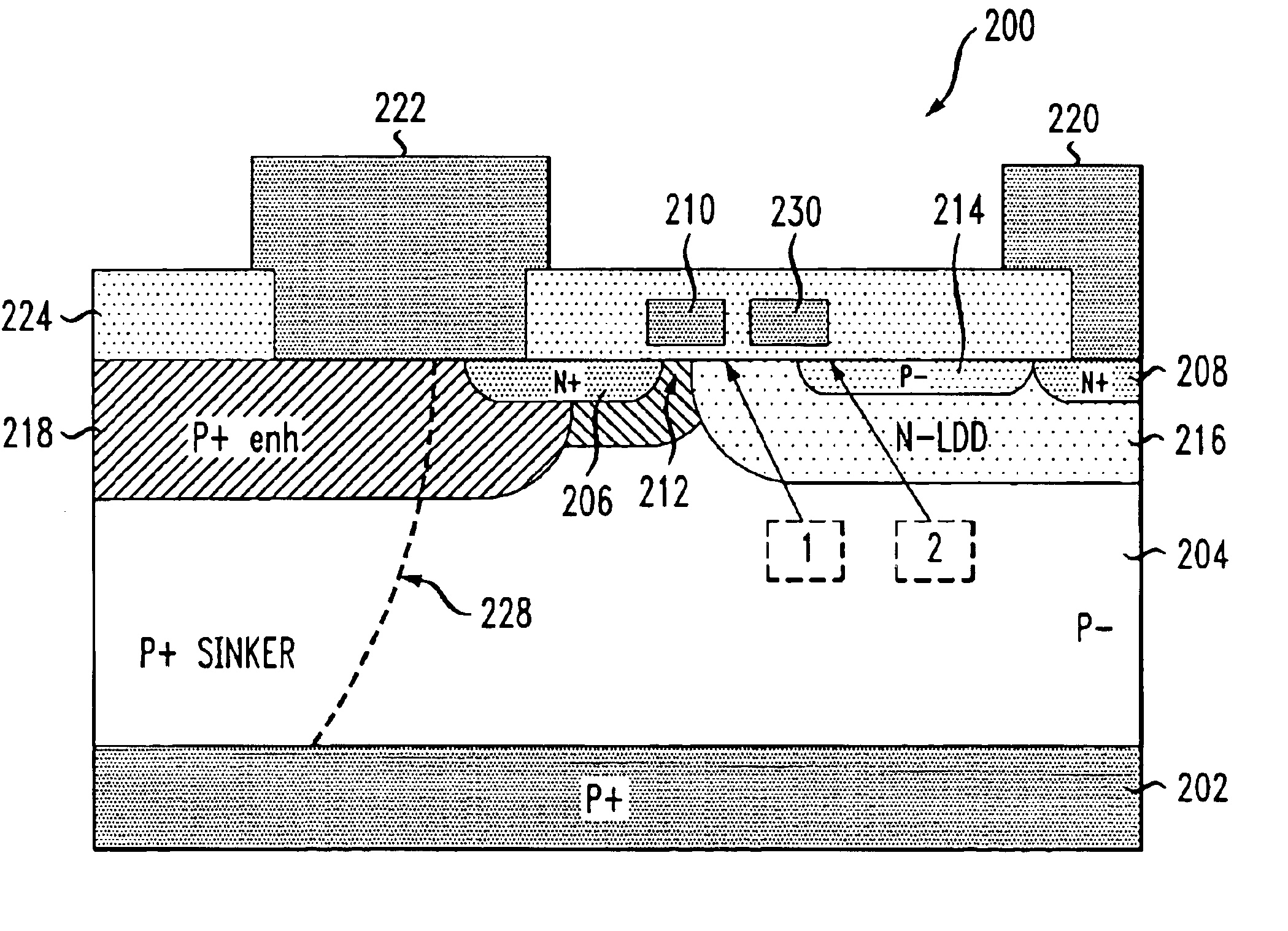

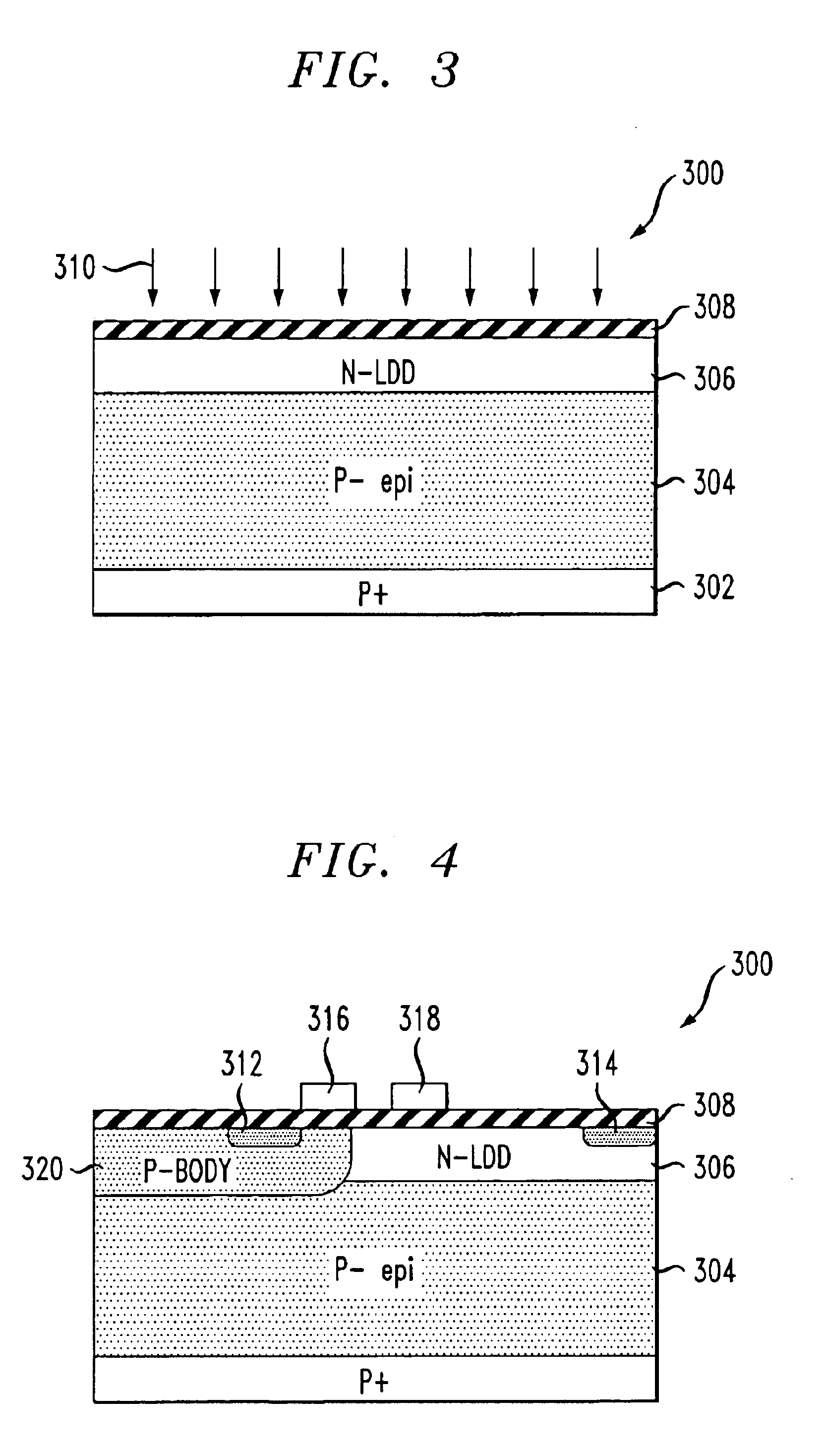

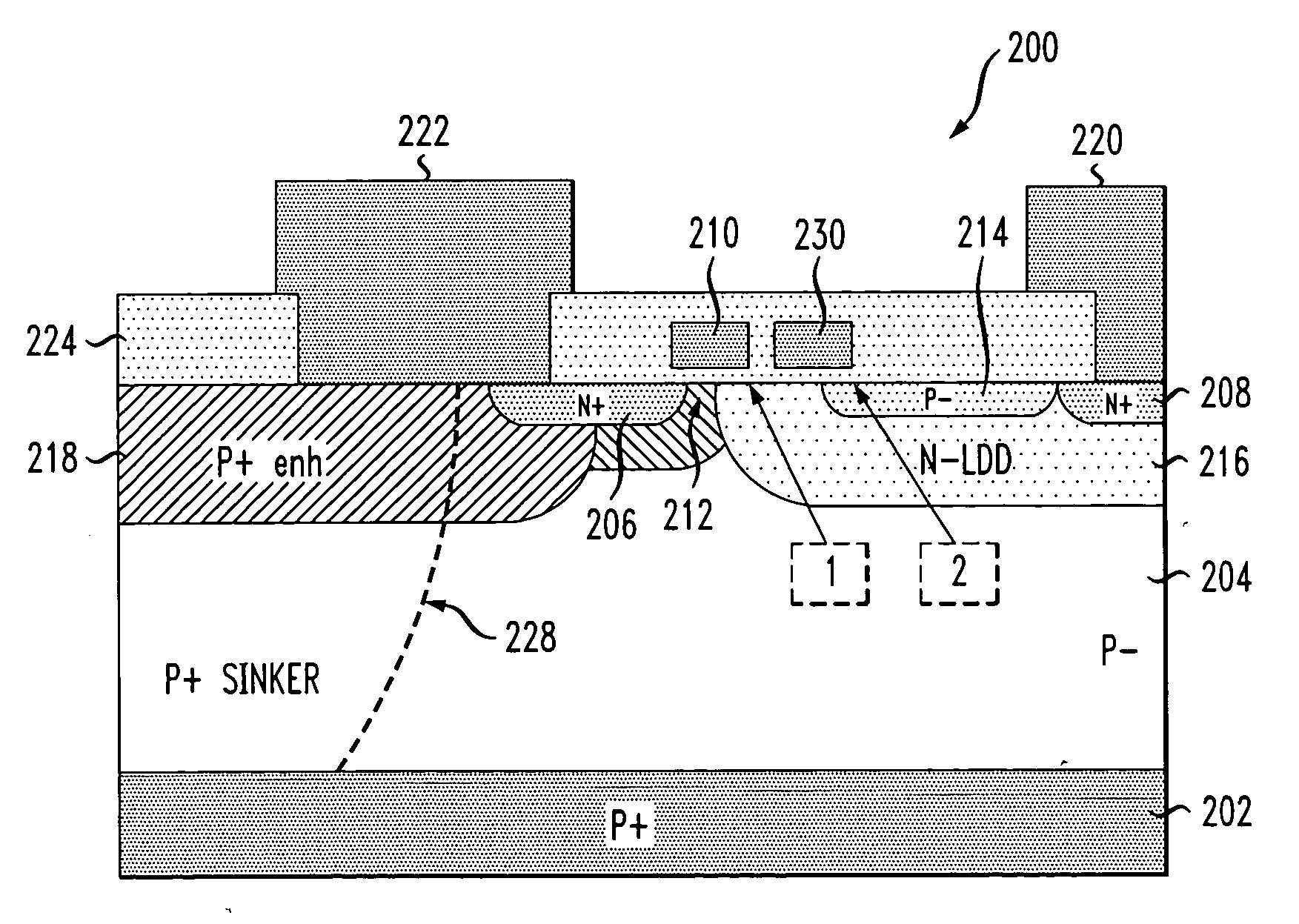

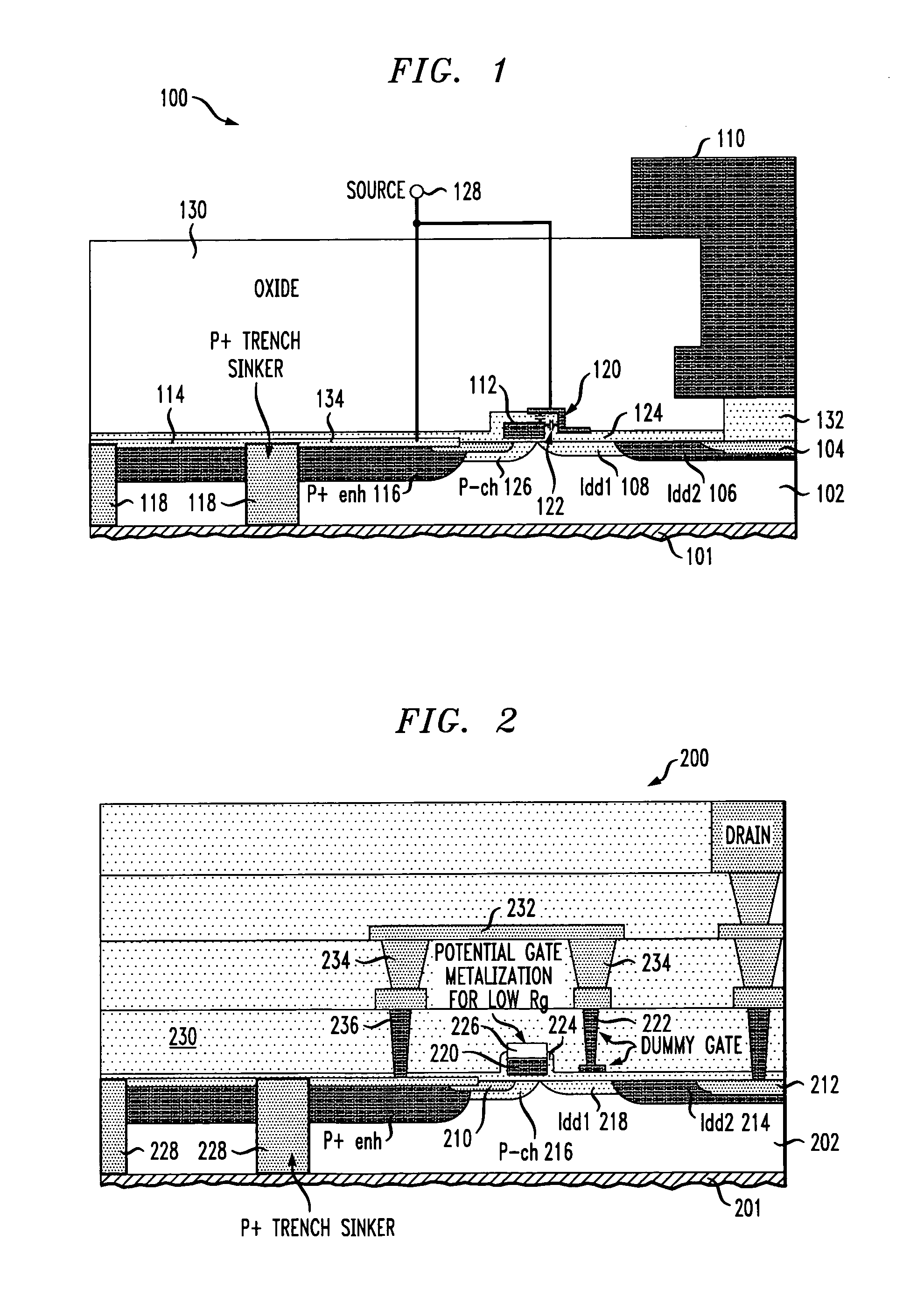

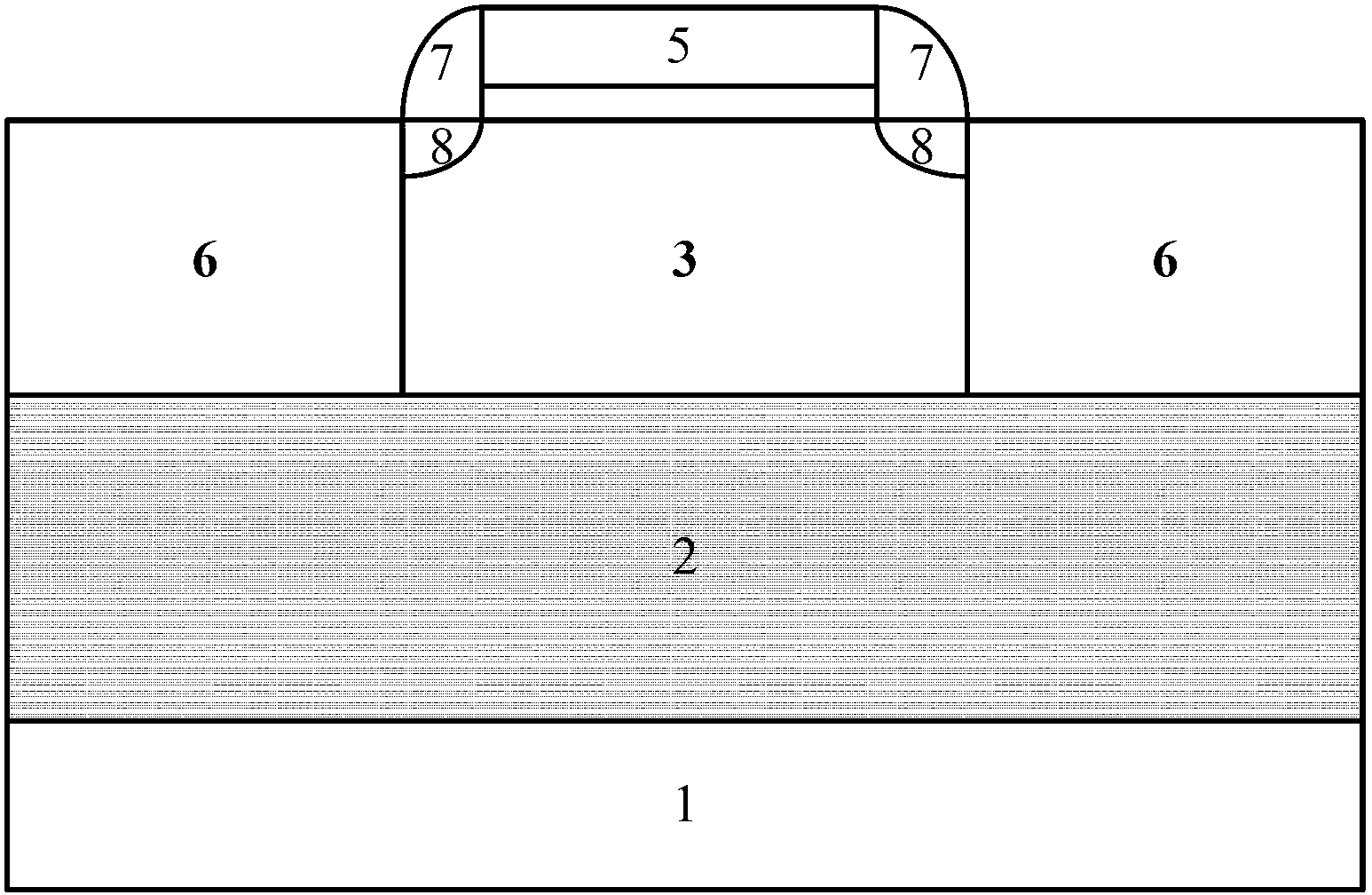

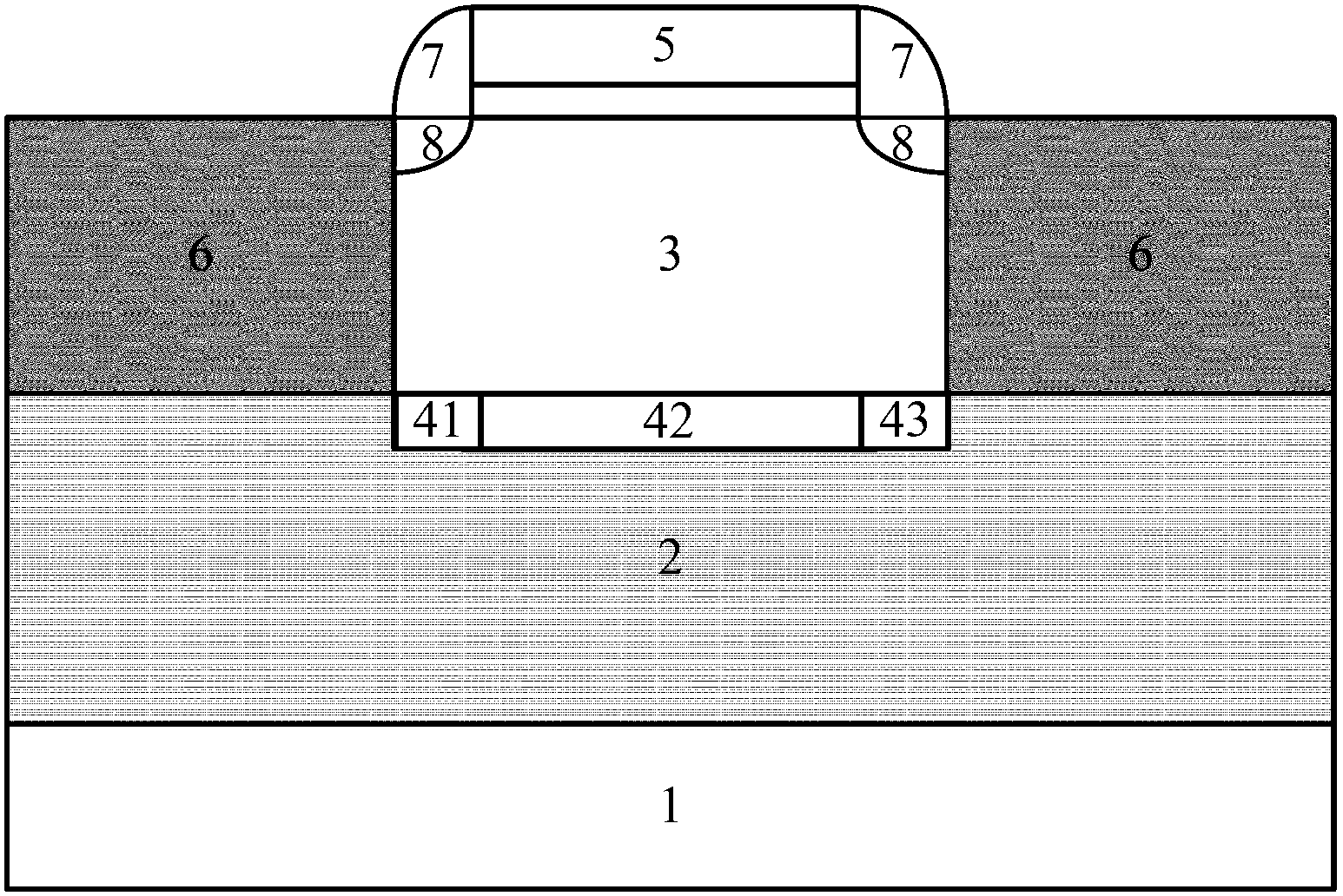

Metal-oxide-semiconductor device including a buried lightly-doped drain region

InactiveUS6927453B2Improve performanceImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesCondensed matter physicsSemiconductor

Owner:BELL SEMICON LLC

Method for preparing metal chalcogenide film

ActiveCN103194729AControl thicknessSmall sizeChemical vapor deposition coatingDeposition temperatureSulfur

The invention discloses a method for preparing a metal chalcogenide film. The method is used for growing the metal chalcogenide film on a substrate with the vapor deposition process by using a chalcogen source and a metal element source and comprises the following steps of: providing three temperature zones, wherein the temperature of the three temperature zones can be controlled independently, and the chalcogen source, the metal element source and the substrate are put in the three temperature zones respectively; controlling the three temperature zones, evaporating the chalcogen source to generate the chalcogen source steam, evaporating the metal element source to generate the metal element source steam, and heating the substrate to the predetermined deposition temperature; providing a carrier gas, and enabling the carrier gas to flow through the three temperature zones in sequence to deliver the metal element source steam to the substrate to deposit and grow so as to form the metal chalcogenide film. The method disclosed by the invention is simple, dispenses with the original complex step of introducing a nucleation site and effectively ensures the purity and the surface cleanness of a sample. The metal chalcogenide film prepared by adopting the method has high quality.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

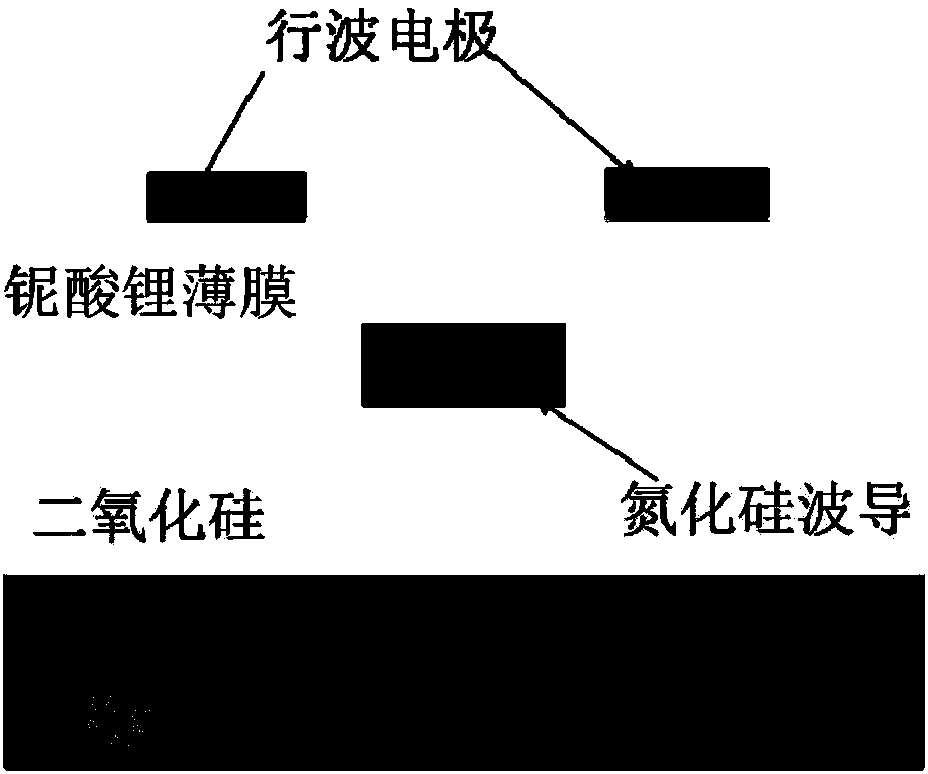

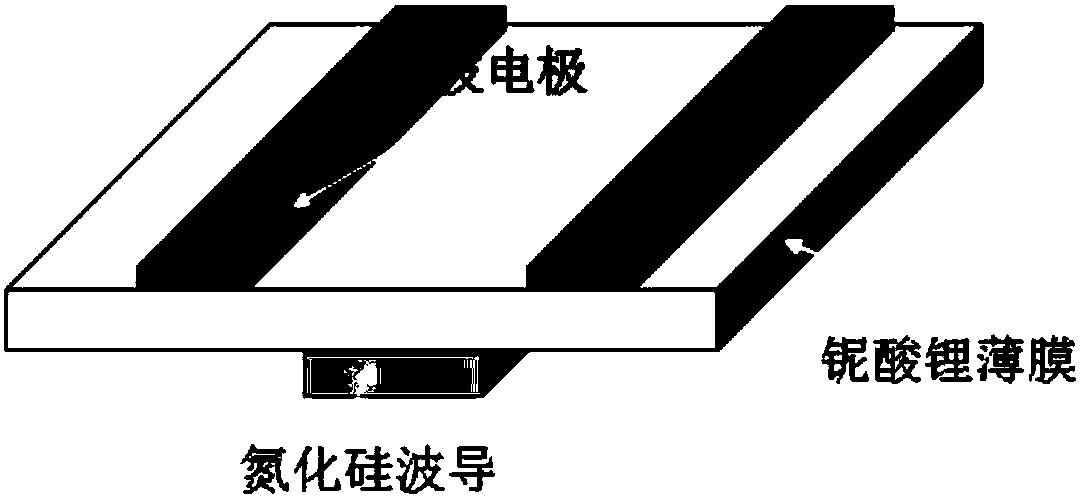

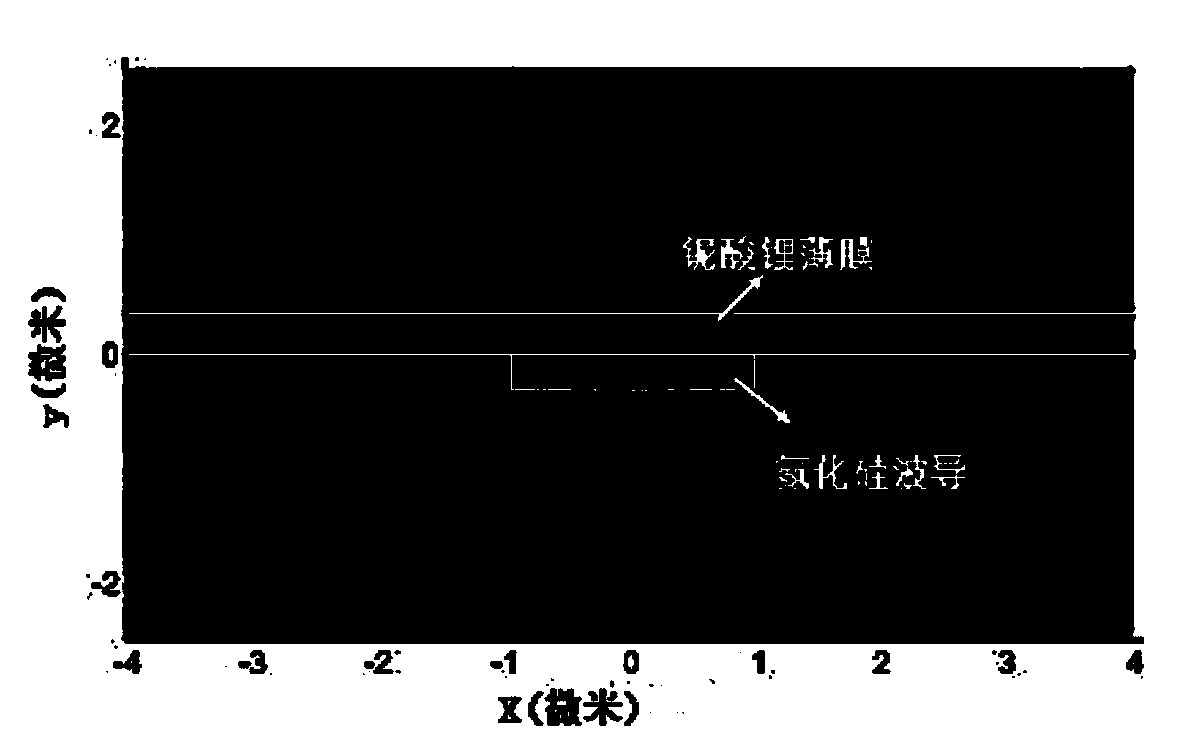

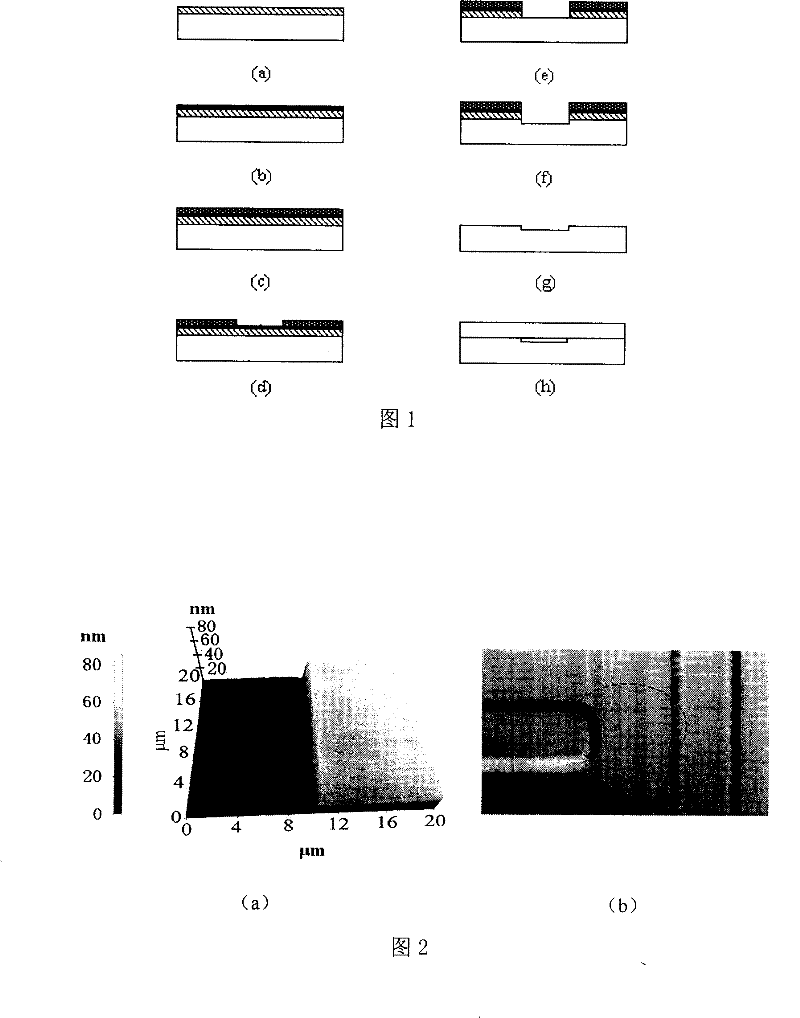

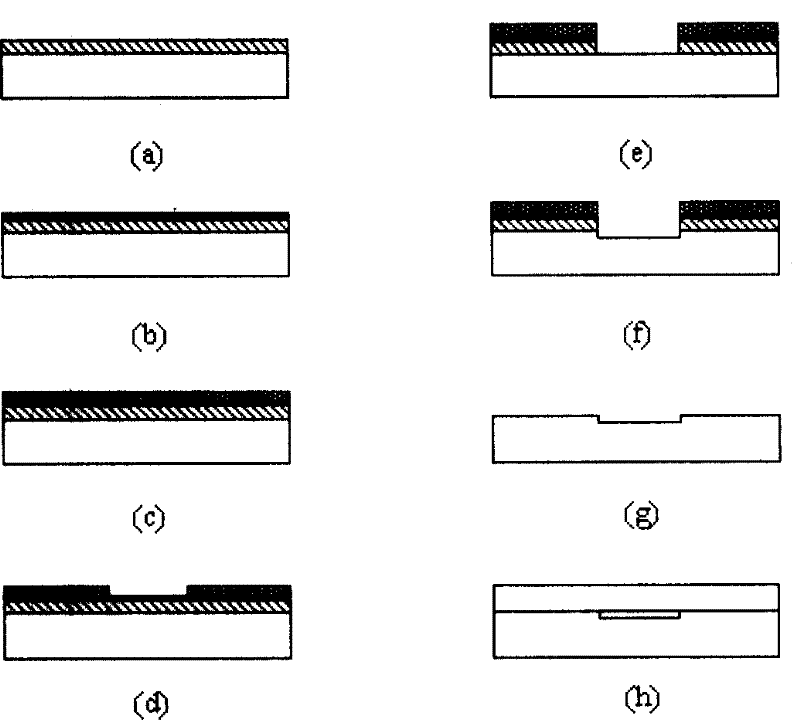

Silicon nitride-lithium niobate heterogeneous integrated waveguide device structure and preparation method of the same

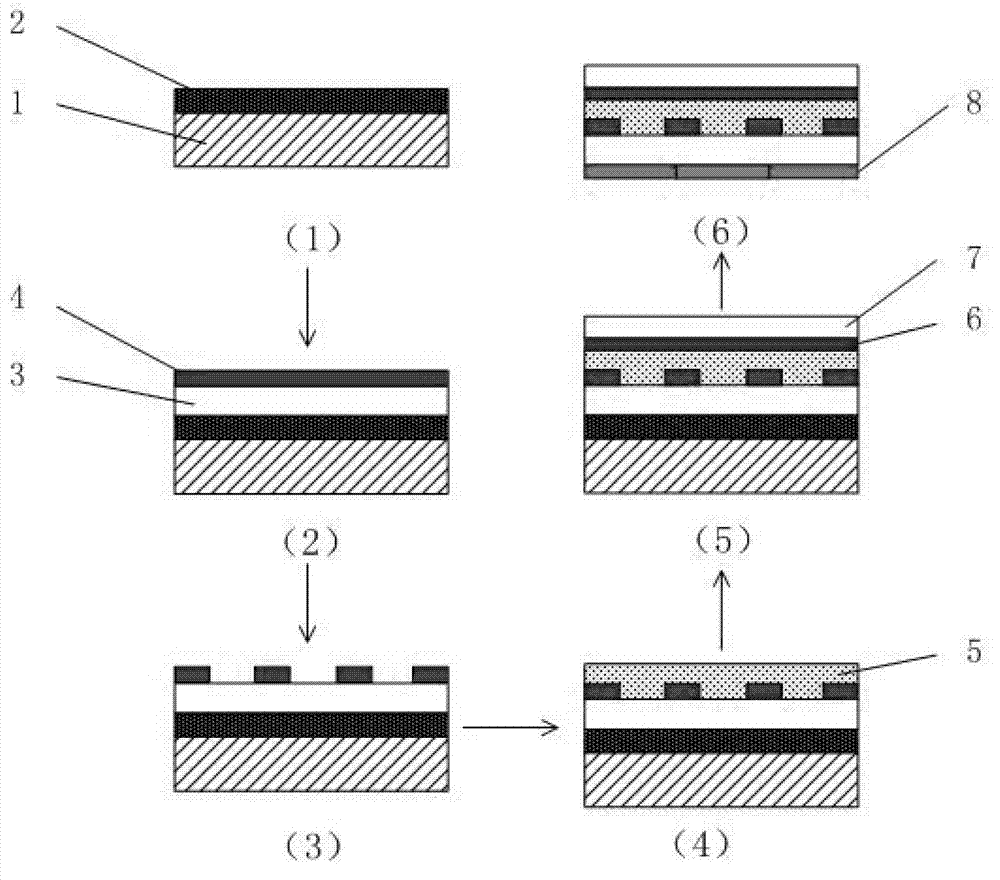

InactiveCN107843957AReduce energy consumptionImprove modulation efficiencyOptical waveguide light guideNon-linear opticsManufacturing technologySilica coating

The invention relates to a silicon nitride-lithium niobate heterogeneous integrated waveguide device structure and a preparation method of the same. The silicon nitride-lithium niobate heterogeneous integrated waveguide device structure is characterized in that a silicon nitride waveguide in a silica coating layer and a lithium niobate film on the upper surface of the silicon nitride waveguide areheterogeneously integrated to form a ridge waveguide; a traveling wave electrode is arranged on the upper surface of the lithium niobate film; the silicon nitride waveguide is crossed and coupled with the lithium niobate film on the upper surface of the silicon nitride waveguide, and a high speed electric signal is applied to the traveling wave electrode to control the phase of the light wave passing through the lithium niobate film to realize conversion from amplitude modulation of the loaded electric signal to phase modulation of an optical signal; and three-dimensional vertical integrateddesign is utilized to enable integration of the chip to be more compact, so that the space is saved; at the same time insertion loss of the light waveguide can be reduced; 100G light modulation rate can be realized; high speed modulation of the light wave in the lithium niobate film can be realized and the characteristic of low loss propagation through the silicon nitride waveguide is realized; and light modulation with excellent performance is completed. The manufacturing technology of the silicon nitride-lithium niobate heterogeneous integrated waveguide device structure is compatible with the semiconductor processing technology, is high in the modulation efficiency and low in energy consumption, and has important application prospects in the optical signal processing field and other fields.

Owner:UNIV OF SHANGHAI FOR SCI & TECH

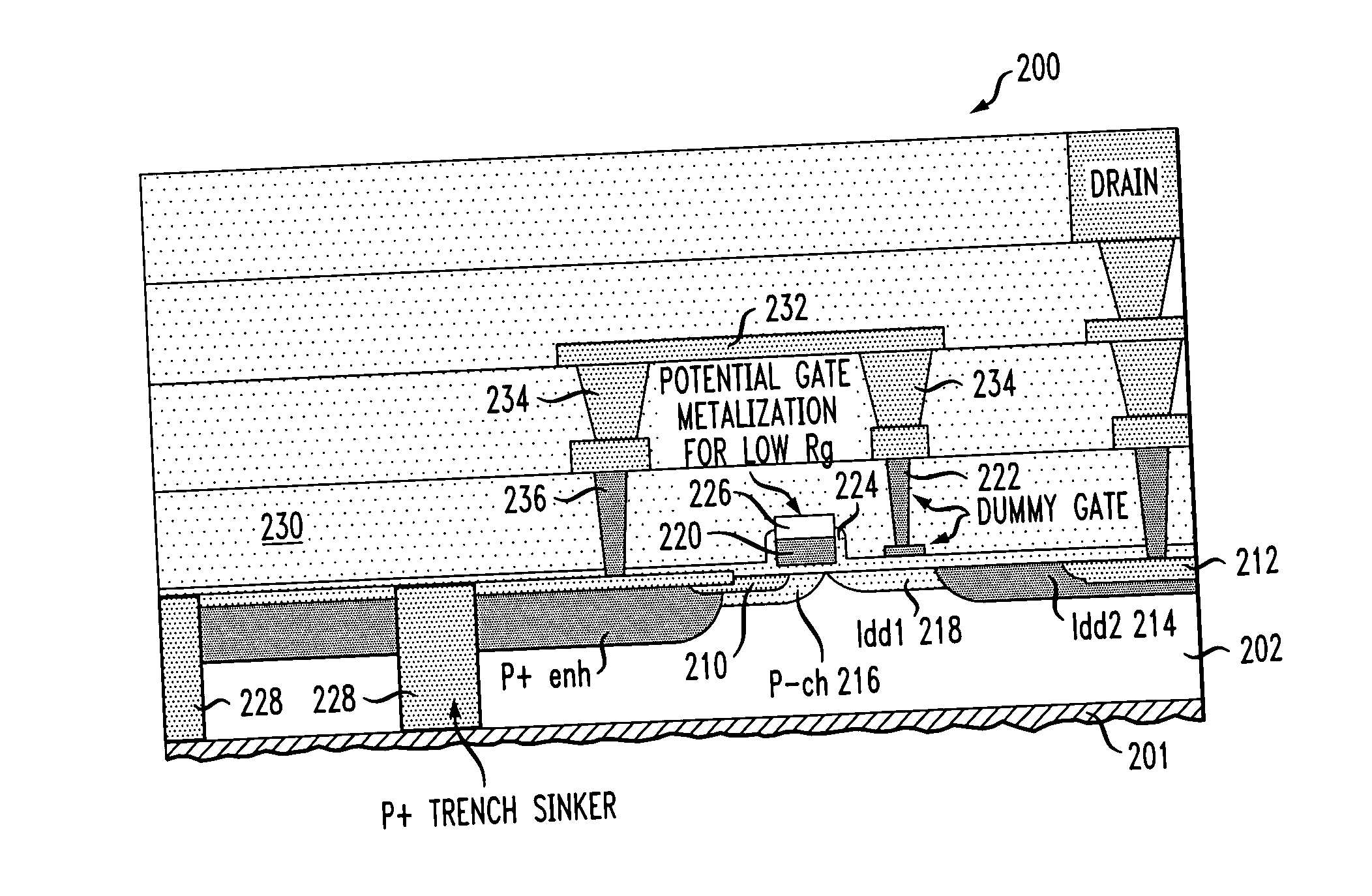

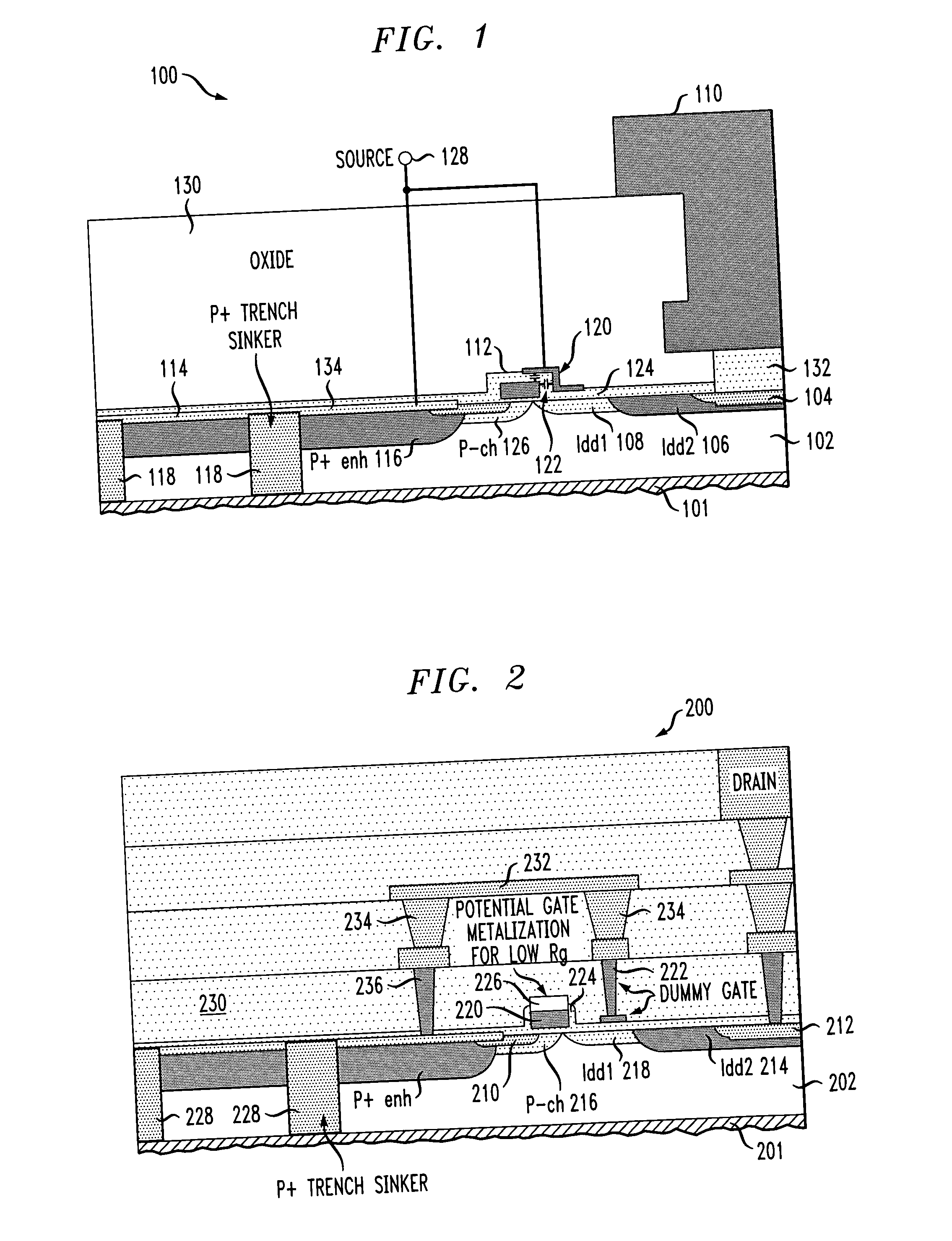

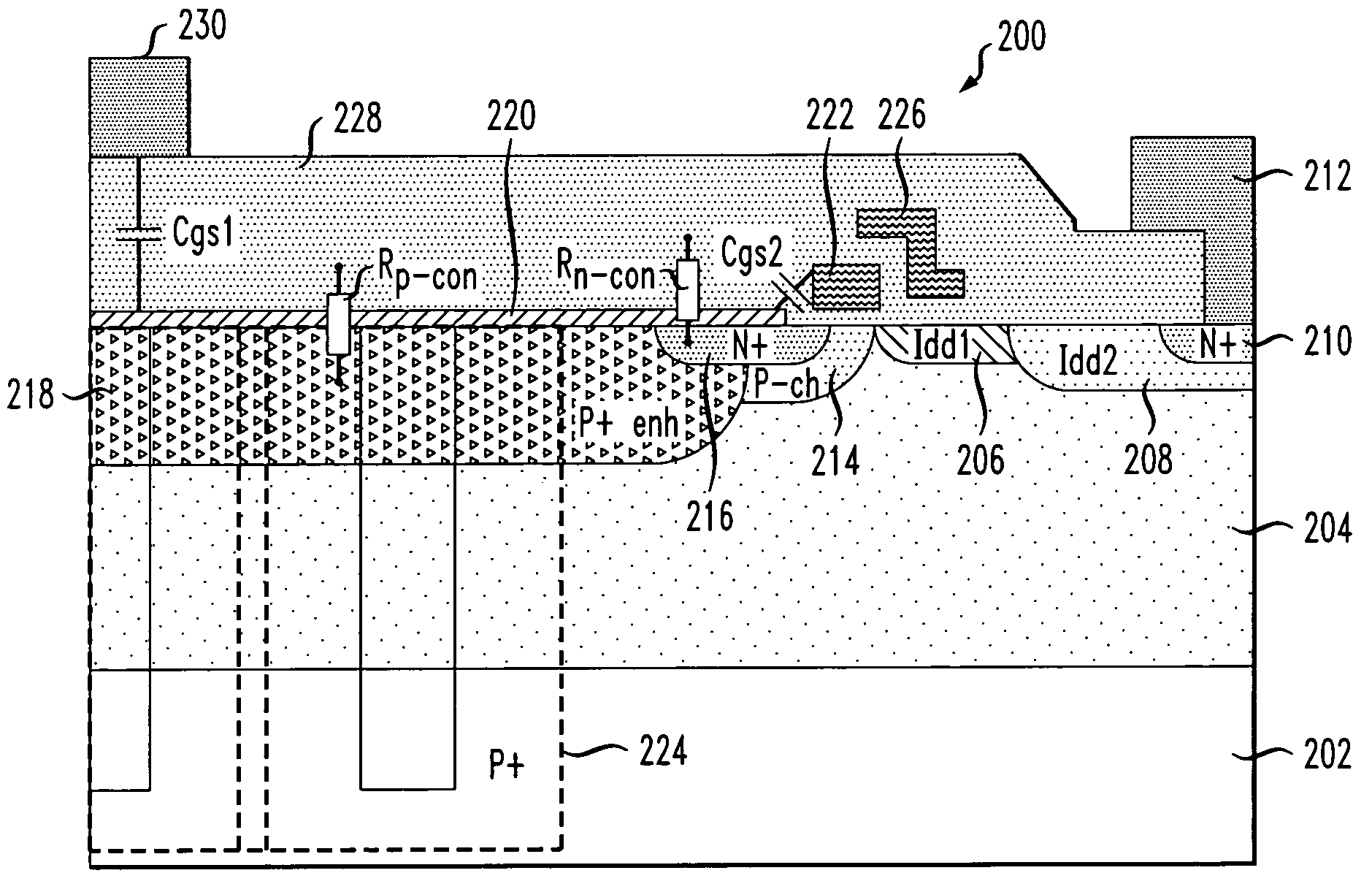

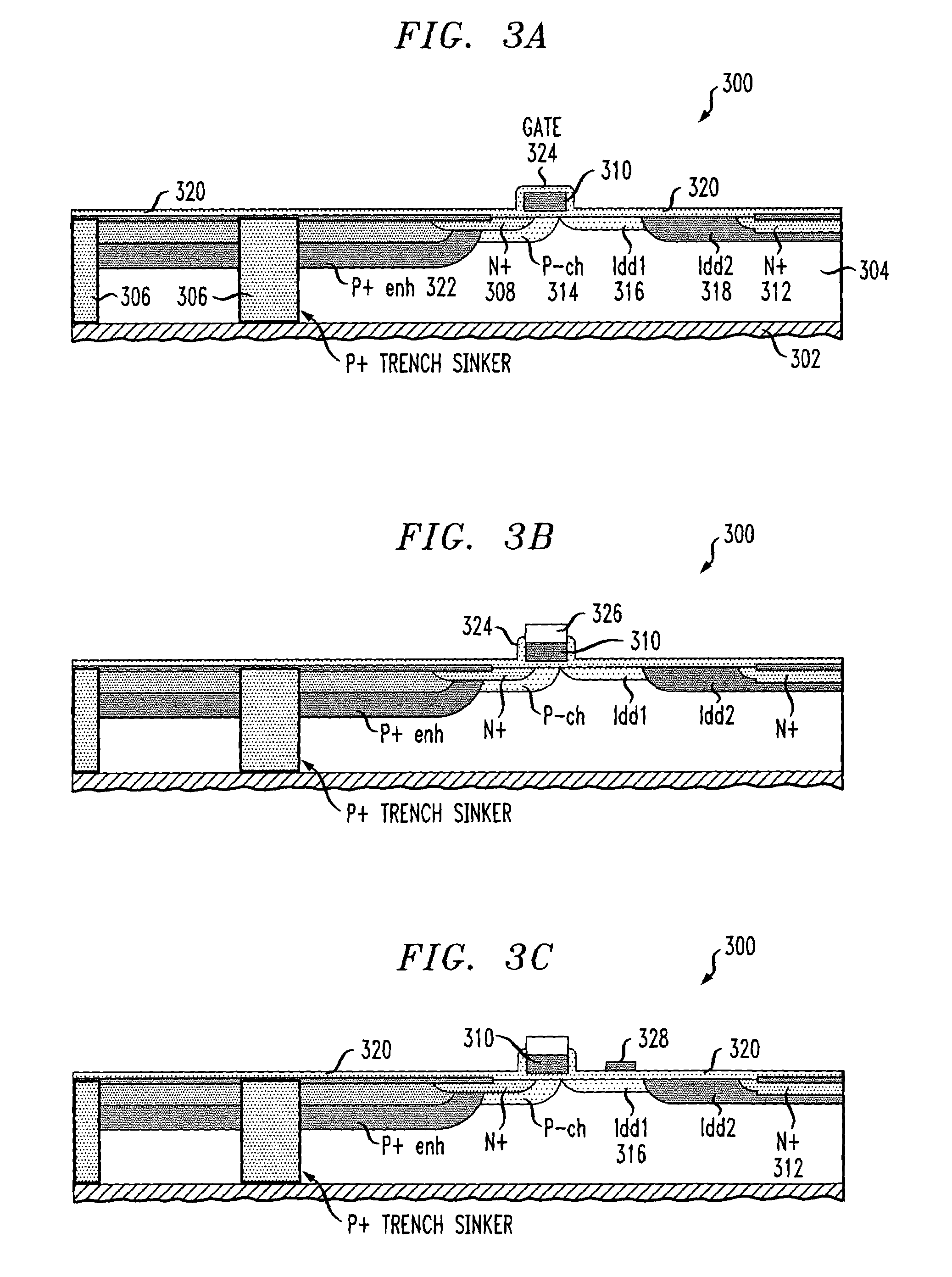

Metal-oxide-semiconductor device with enhanced source electrode

ActiveUS7126193B2Reduce input capacitanceImprove device performanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical connectionSemiconductor

An MOS device is formed including a semiconductor layer of a first conductivity type, a first source / drain region of a second conductivity type formed in the semiconductor layer, and a second source / drain region of the second conductivity type formed in the semiconductor layer and spaced apart from the first source / drain region. A gate is formed proximate an upper surface of the semiconductor layer and at least partially between the first and second source / drain regions. The MOS device further includes at least one contact, the at least one contact including a silicide layer formed on and in electrical connection with at least a portion of the first source / drain region, the silicide layer extending laterally away from the gate. The contact further includes at least one insulating layer formed directly on the silicide layer.

Owner:CICLON SEMICON DEVICE

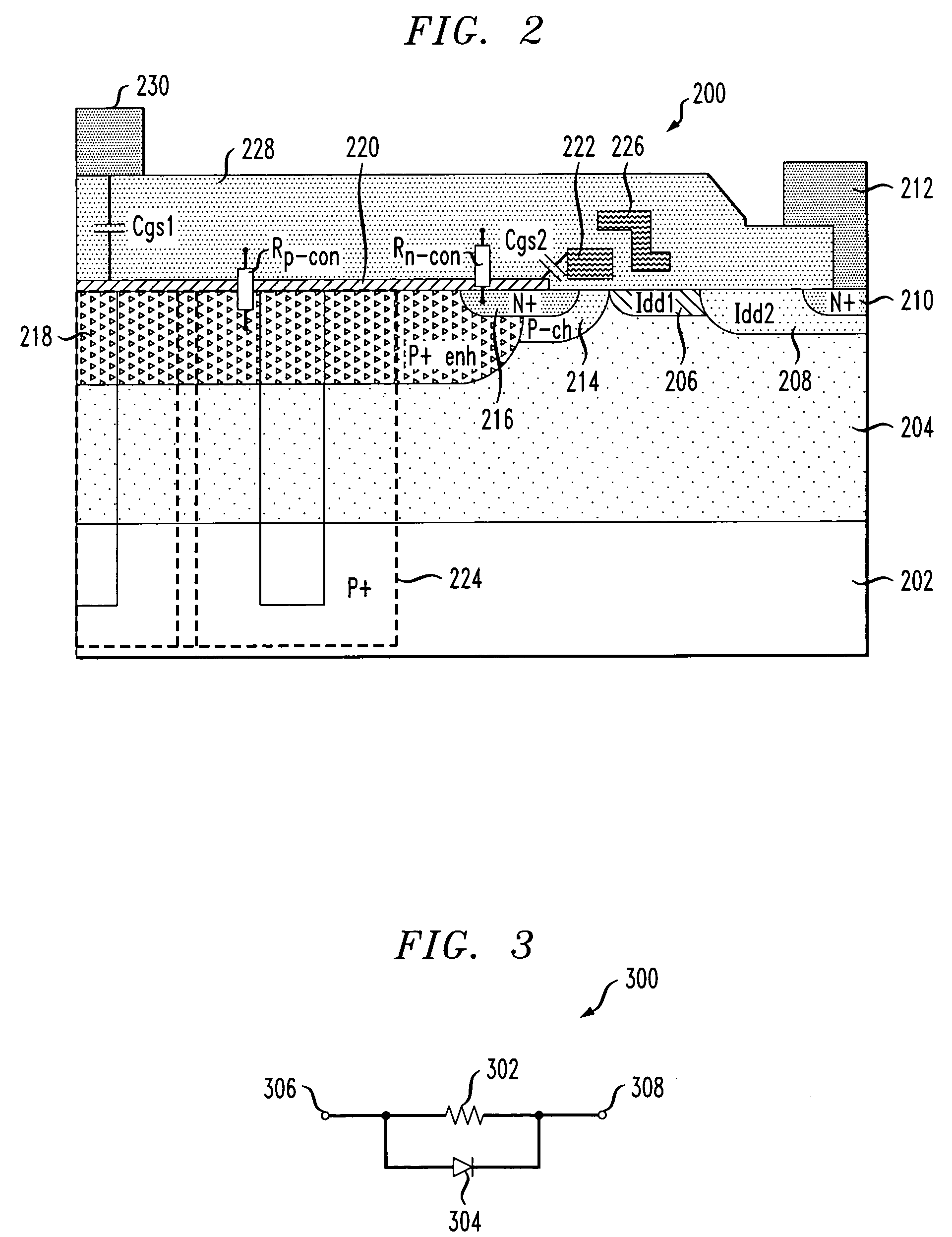

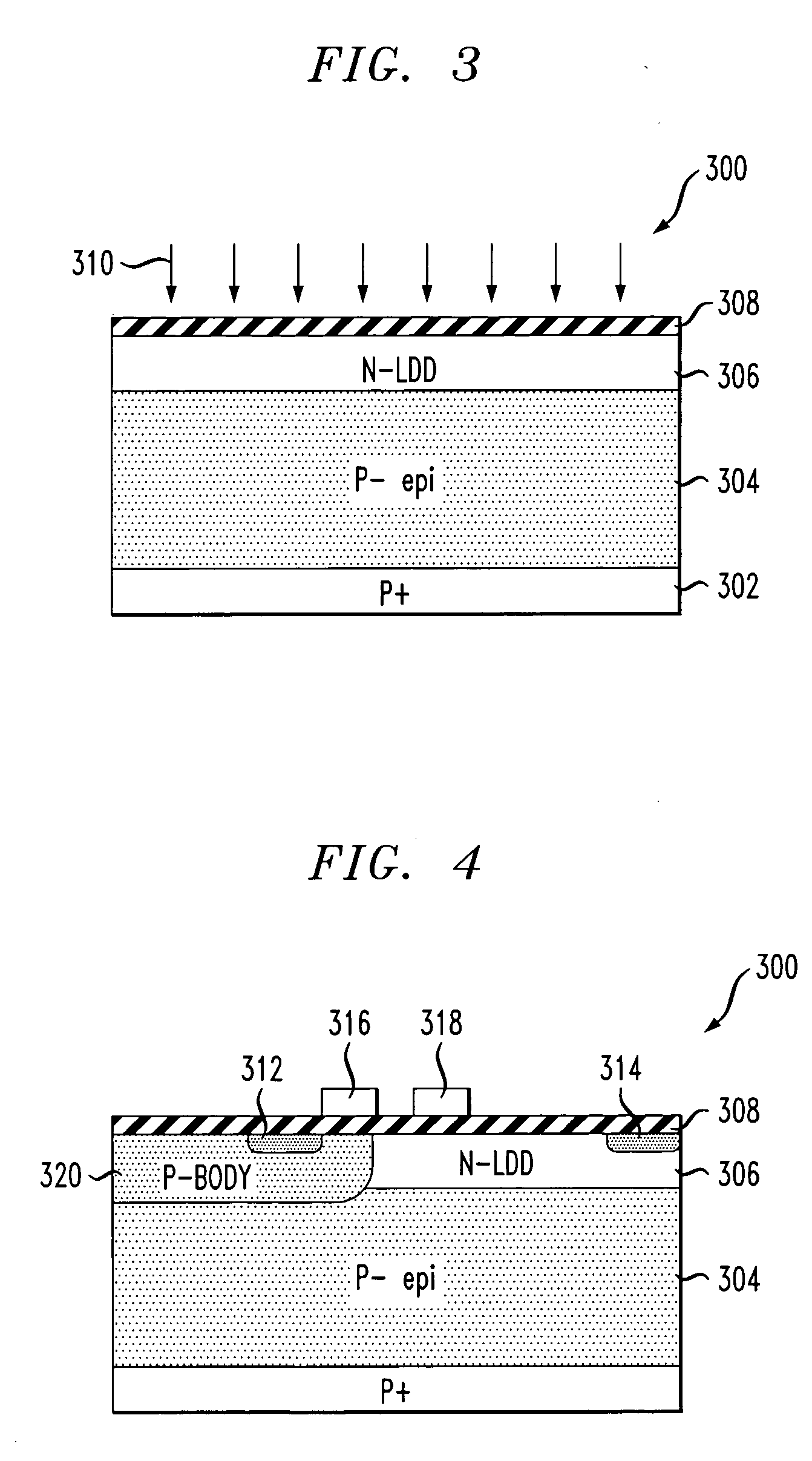

Metal-oxide-semiconductor device including a buried lightly-doped drain region

InactiveUS20050067655A1Lower on-resistanceIncreases gate-to-drain capacitanceSemiconductor/solid-state device detailsSolid-state devicesCondensed matter physicsSemiconductor

An MOS device includes a semiconductor layer of a first conductivity type, a source region of a second conductivity type formed in the semiconductor layer, and a drain region of the second conductivity type formed in the semiconductor layer and spaced apart from the source region. A gate is formed proximate an upper surface of the semiconductor layer and at least partially between the source and drain regions. The MOS device further includes a buried LDD region of the second conductivity type formed in the semiconductor layer between the gate and the drain region, the buried LDD region being spaced laterally from the drain region, and a second LDD region of the first conductivity type formed in the buried LDD region and proximate the upper surface of the semiconductor layer. The second LDD region is self-aligned with the gate and spaced laterally from the gate such that the gate is non-overlapping relative to the second LDD region.

Owner:BELL SEMICON LLC

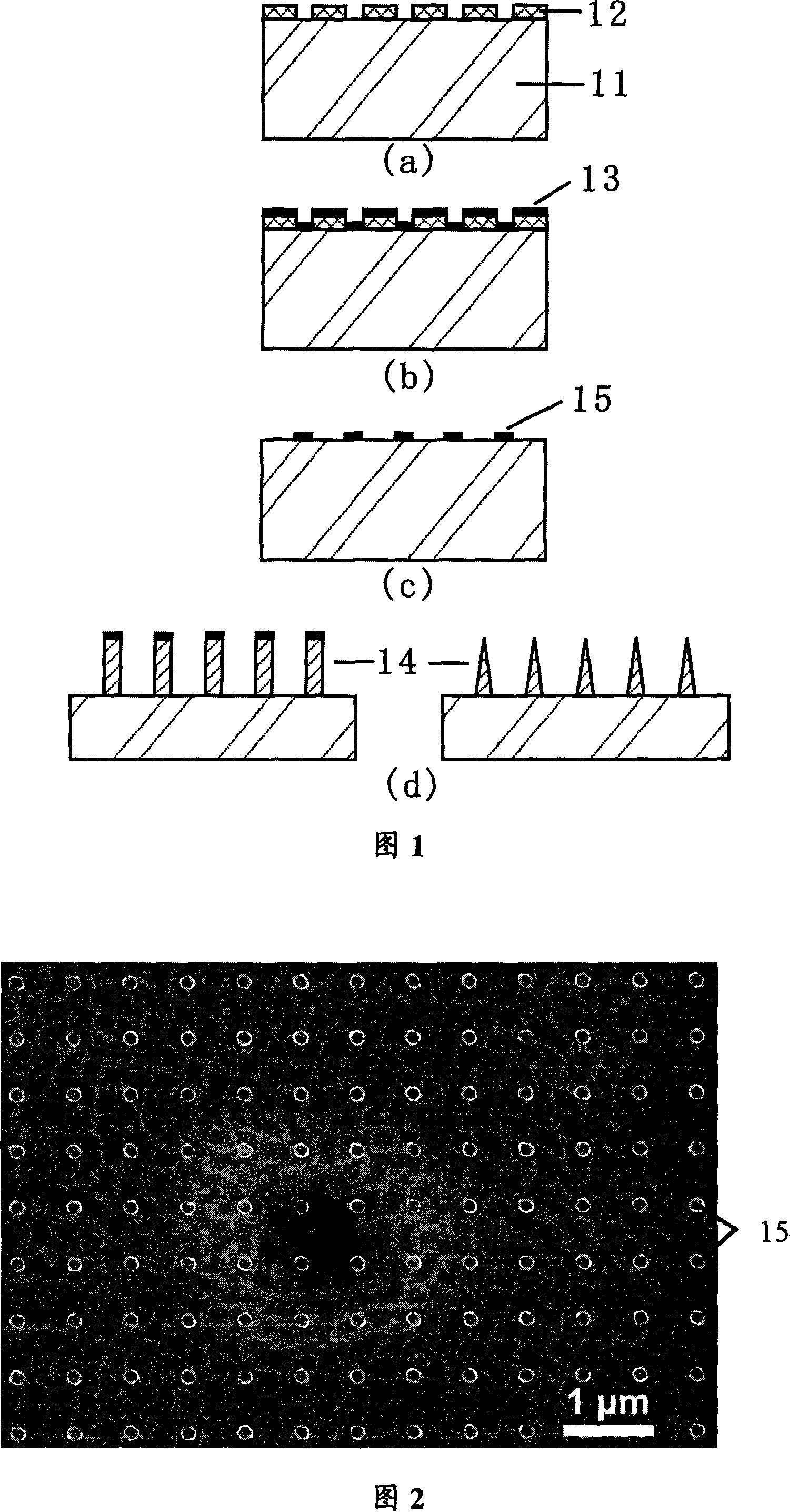

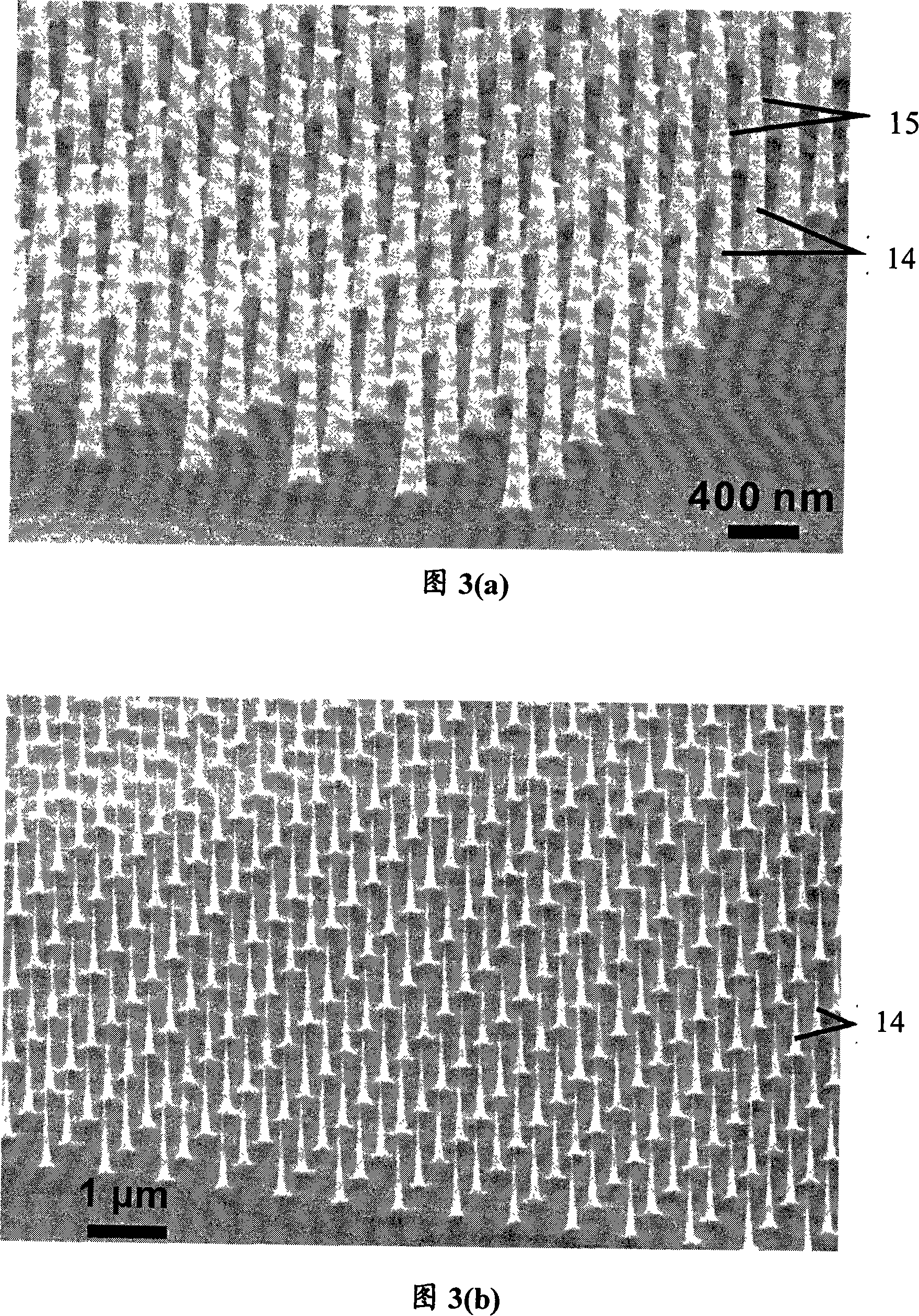

Method for preparation of one-dimensional silicon nanostructure

InactiveCN101117208APosition is easy to controlEasy to manufactureNanostructure manufactureNanoparticleSilicon nanowires

The invention discloses a method for preparing one-dimensional silicon nanostructure. The order of the processing steps adopted by the invention is as follows: (A) nanometer particle mould is prepared on the surface of backing material; (B) etching of the backing material is completed by use of plasma etching technology. The step (A) includes the following procedures: (i) the surface of backing material is coated with one layer of photoresist through spin coating at first, and then micropores are formed at the surface of backing material through adopting electronic photoetching technique; (ii) one layer of mask film is deposited on the surface of backing material; (iii) photoresist peeling-off of the surface of backing material deposited with the mask film is completed so as to form the nanometer particle mask at the micropores of procedure (i). In addition, step (A) can also be as follows: one layer of metallic film is firstly deposited on the surface of backing material and then heat treatment of the metallic film is completed to obtain metallic nanometer particle mask on the surface of backing material. The silicon nano wire / tip prepared by the invention is characterized in erection, order and controllable position and diameter etc., thereby being particularly favorable to manufacture and assembly of device.

Owner:SUN YAT SEN UNIV

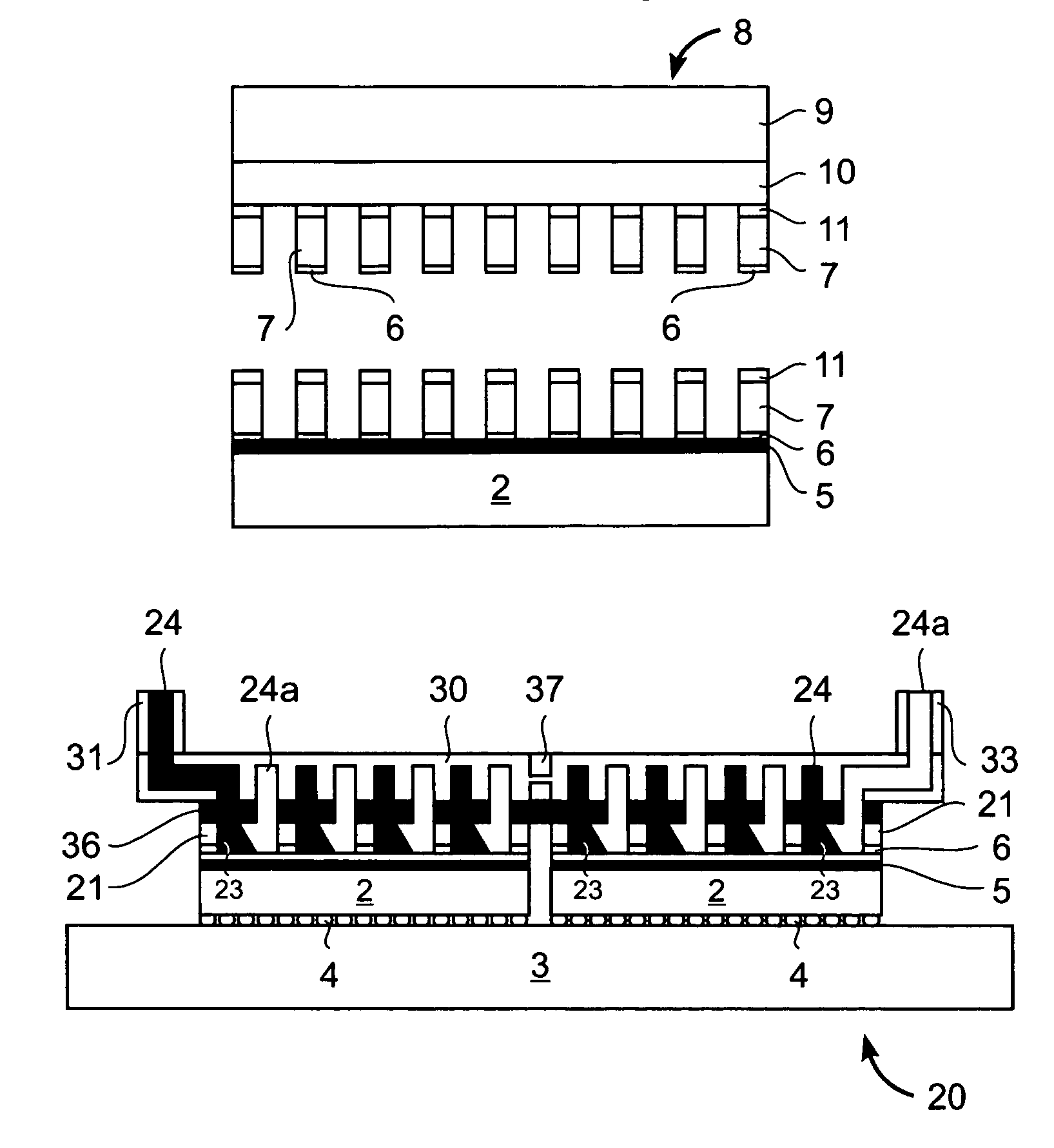

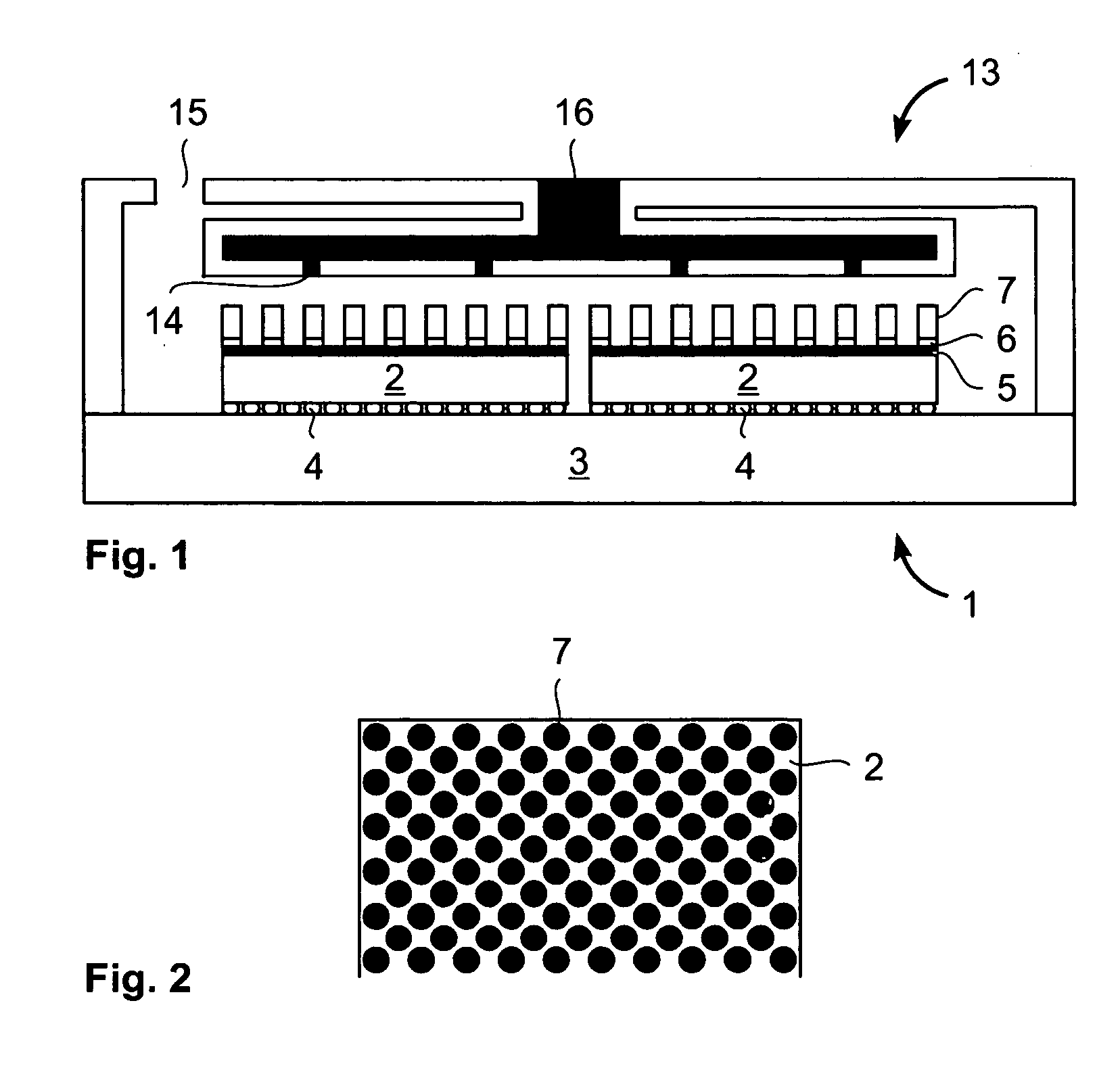

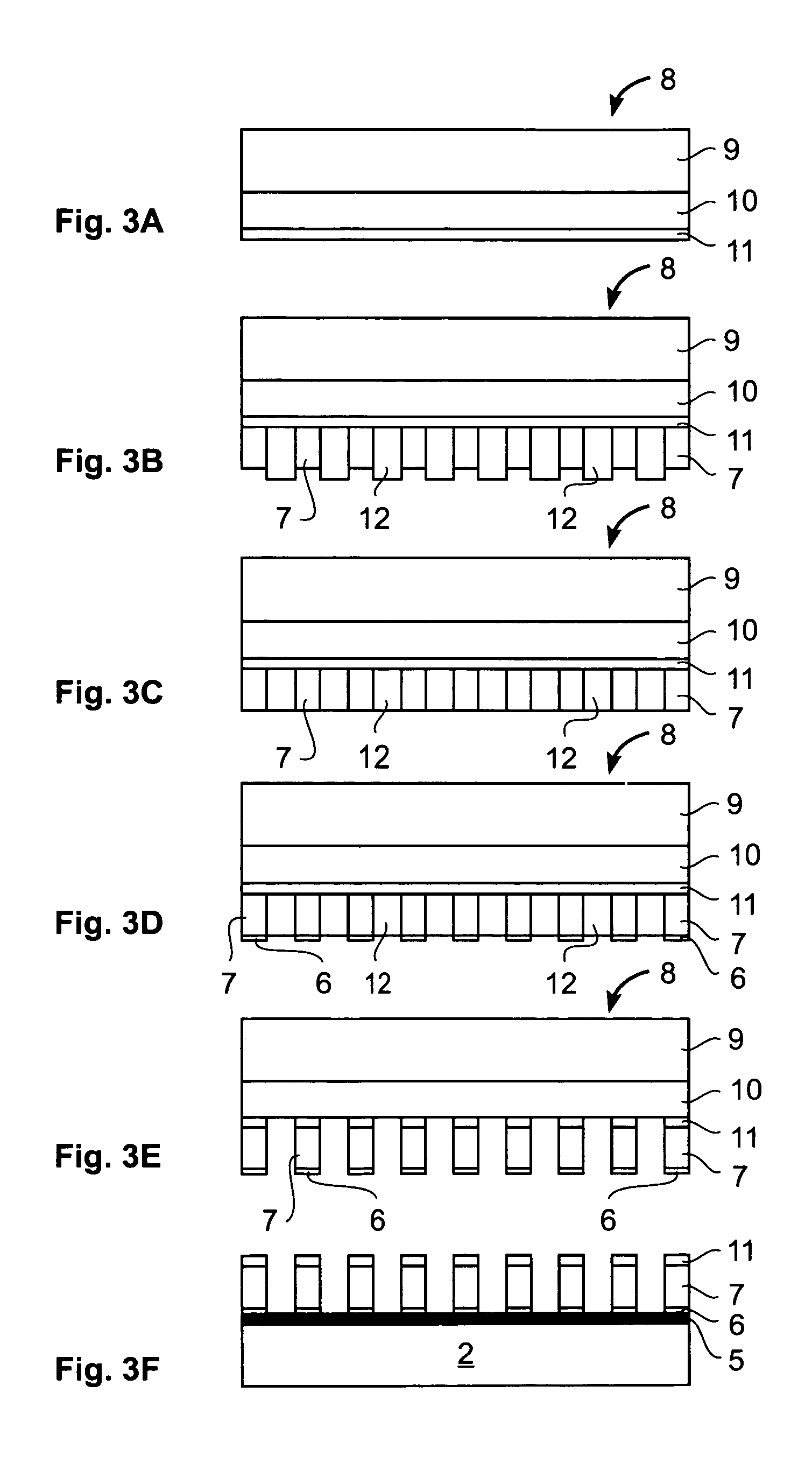

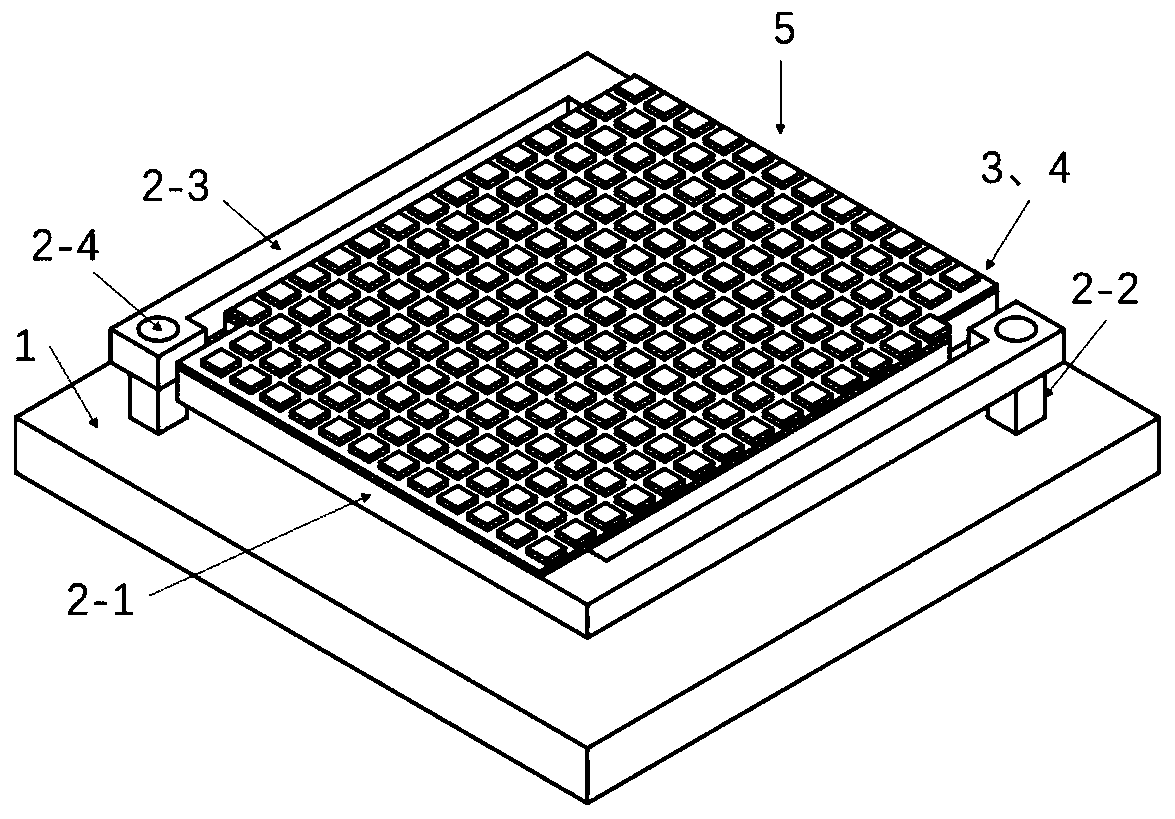

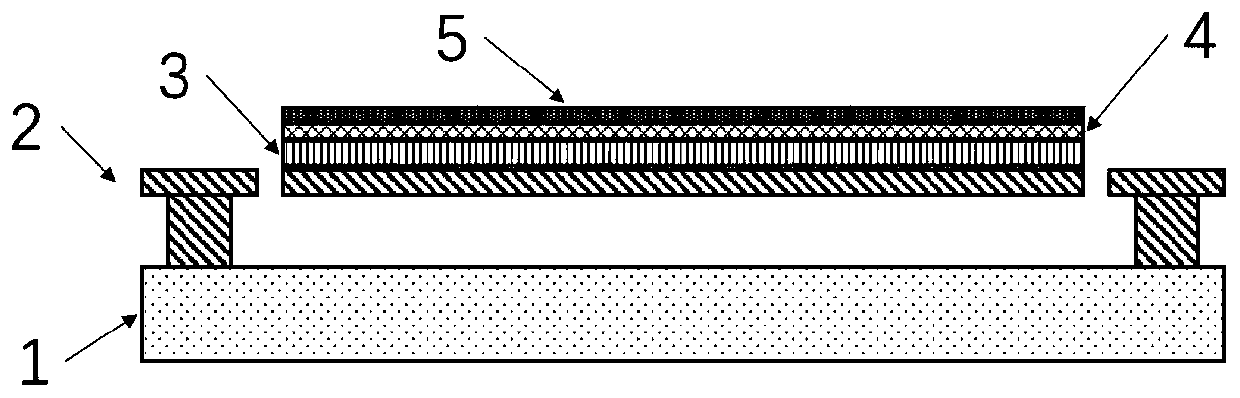

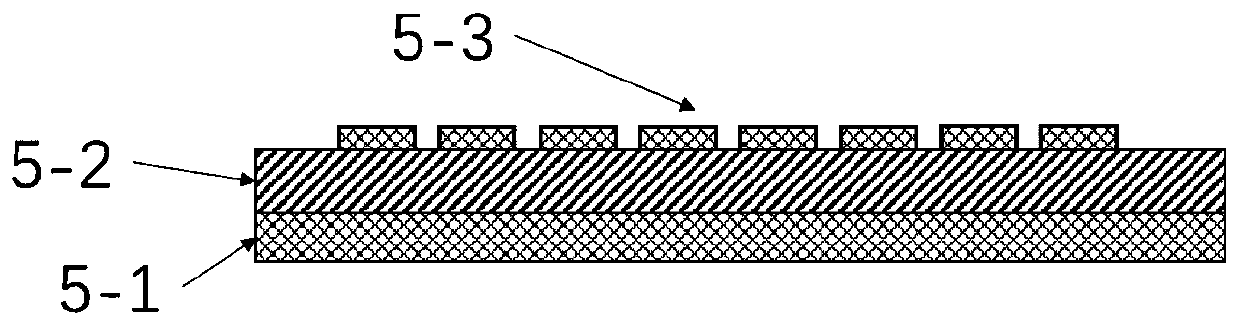

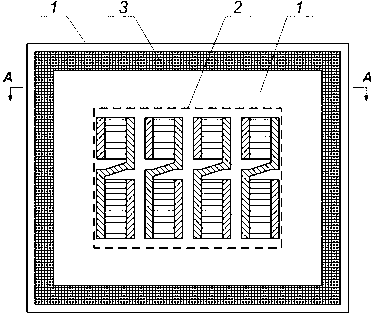

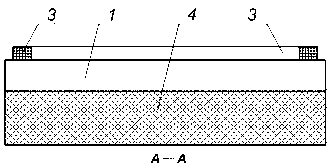

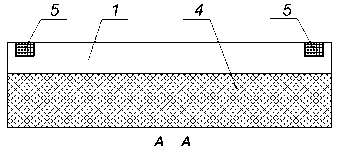

Semiconductor device with a high thermal dissipation efficiency

ActiveUS7271034B2High thermal dissipation efficiencyImprove mechanical stabilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringSoldering

Provides semiconductor devices and method for fabricating devices having a high thermal dissipation efficiency. An example device comprises a thermally conducting structure attached to a surface of the semiconductor device via soldering. The thermally conducting structure is essentially formed of a thermally conducting material and comprises an array of freestanding fins, studs or frames, or a grid of connected fins. A process for fabricating such a semiconductor device includes forming a thermally conducting structure on a carrier and attaching the thermally conducting structure formed on the carrier to a surface of the semiconductor device via soldering.

Owner:GLOBALFOUNDRIES US INC

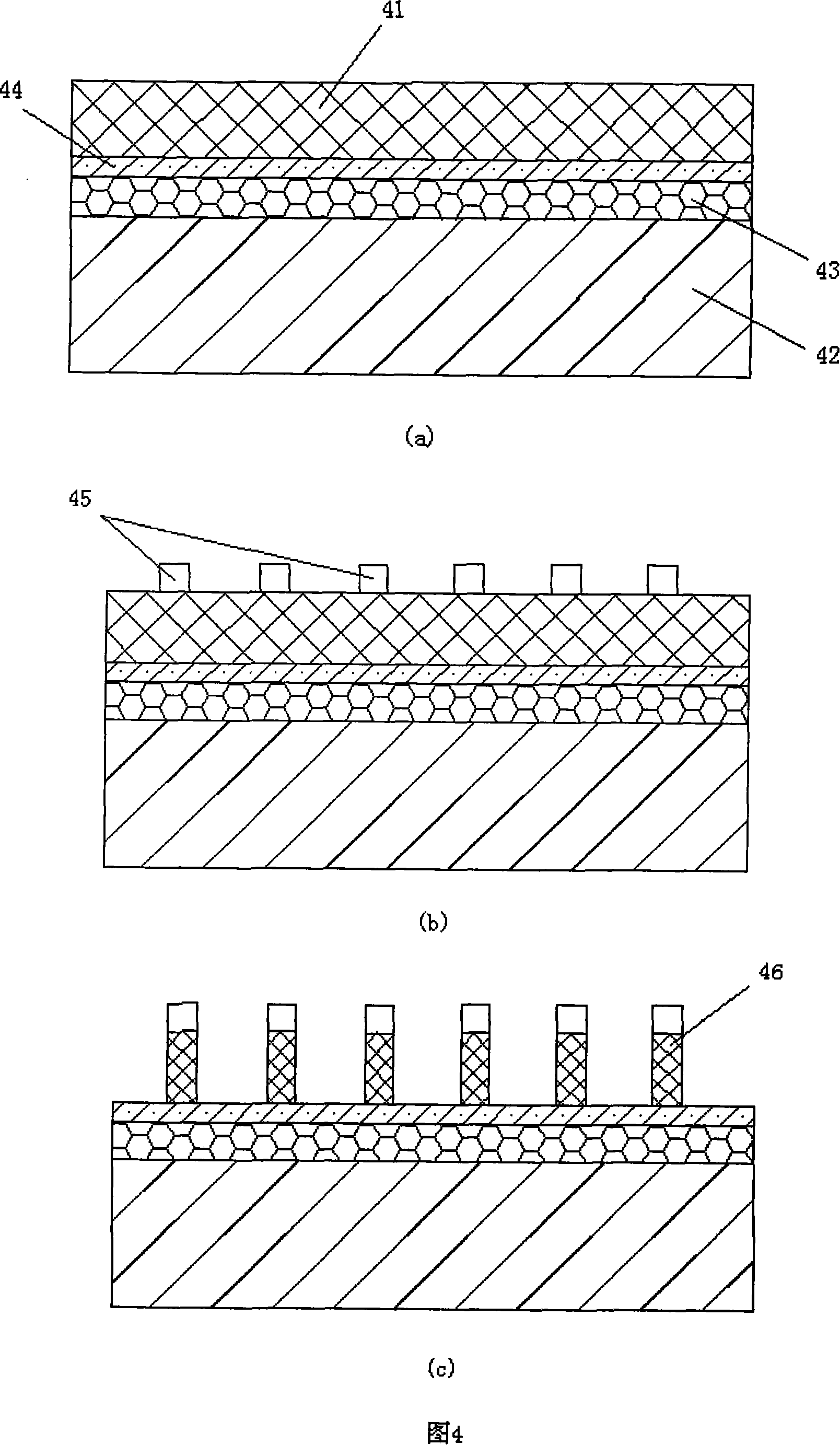

Method for preparing flexible display module based on PDLC

InactiveCN103033968AGuaranteed machining accuracyProcessing technology compatibleNon-linear opticsElectrode arrayMagenta

The invention provides a method for preparing a flexible display module based on PDLC (Polymer Dispersed Liquid Crystal). The method comprises the following steps: selecting a single-face polished silicon wafer or glass sheet with high evenness as a rigid chip, and adopting an adhesion layer to evenly fix a flexible substrate with a transparent conducting layer on the rigid chip; etching the transparent conducting layer into an electrode array composed of mutually-parallel transparent conducting grids with a photoetching and etching process, and then adopting a coating process to coat a layer of PDLC membrane on one surface with the electrode array of the flexible substrate; and utilizing a coating machine to evenly and compactly cover a transparent flexible chip on the surface of the PDLC membrane and photocure the PDLC membrane, and then stripping the rigid chip from a device; and adopting a printing process to airbrushing a CMKY (cyan, magenta, yellow black) ink layer on the back of the flexible substrate. According to the preparation method, the processing precision of products is ensured, and the processing craft is compatible with the processing craft of micro-electronics, so that the production cost of the product is reduced.

Owner:BEIJING SAN WU JIU INVESTMENT

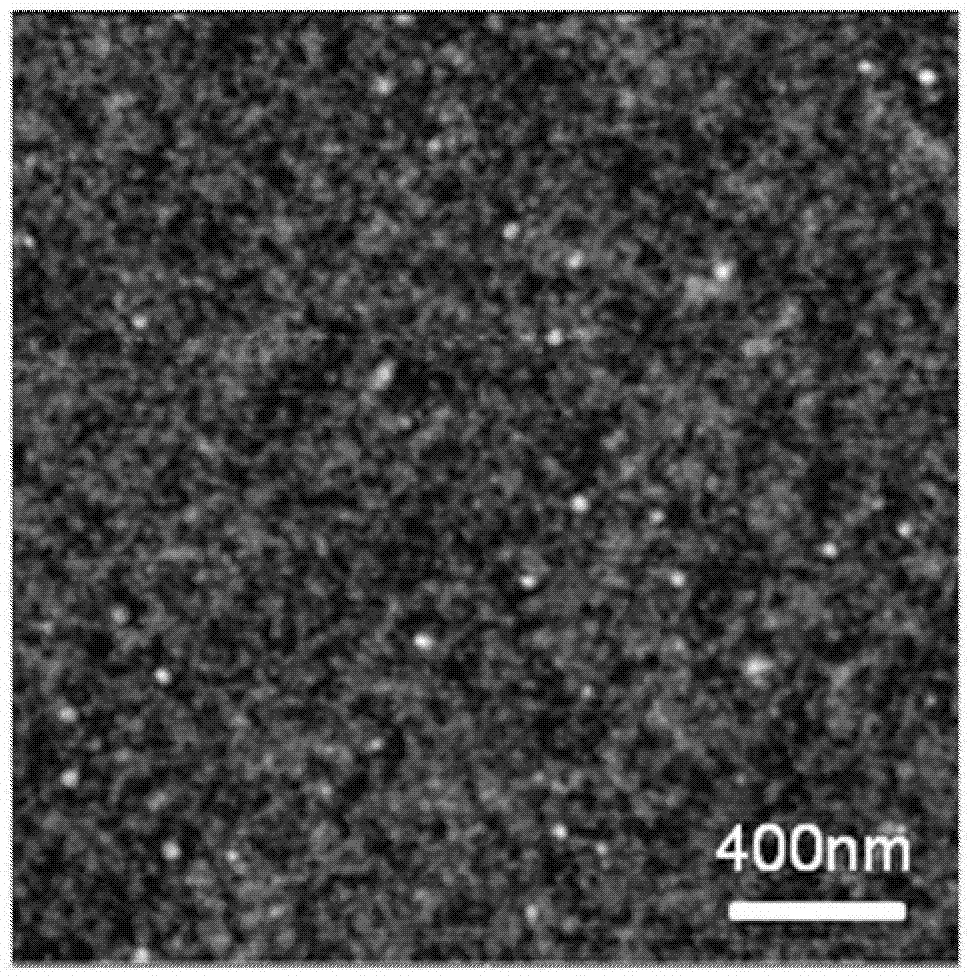

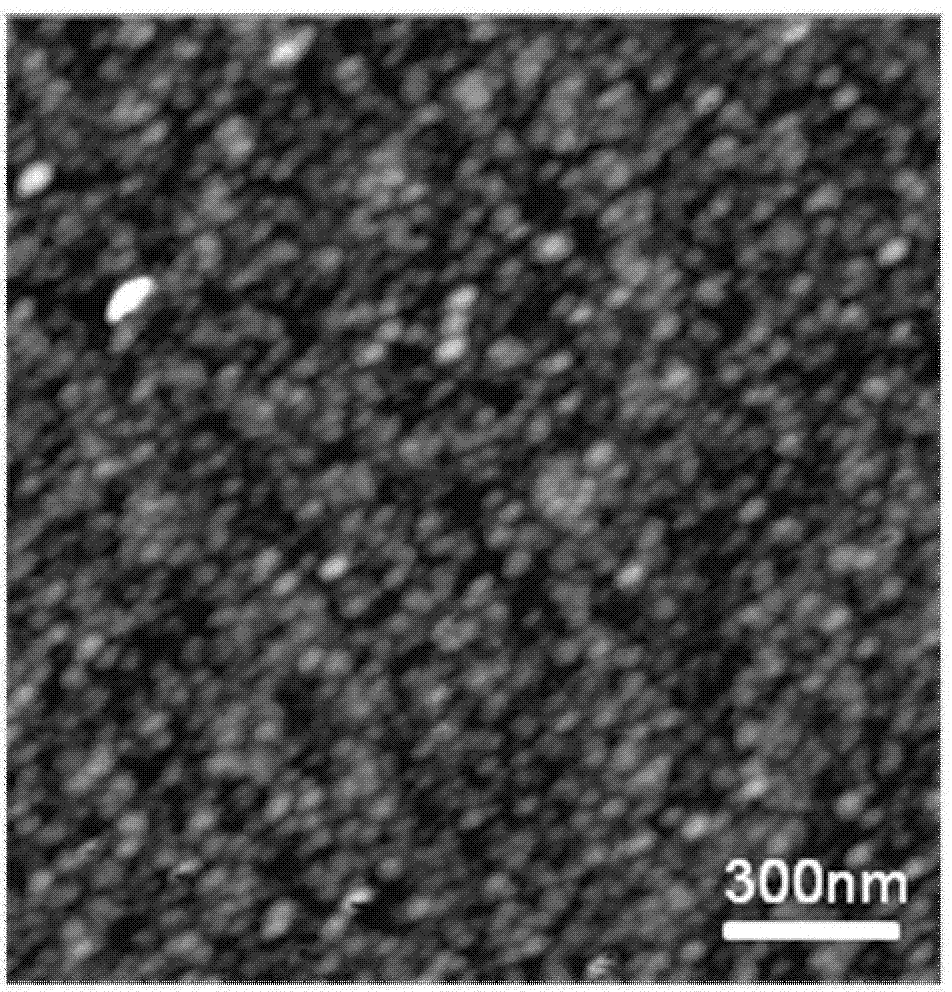

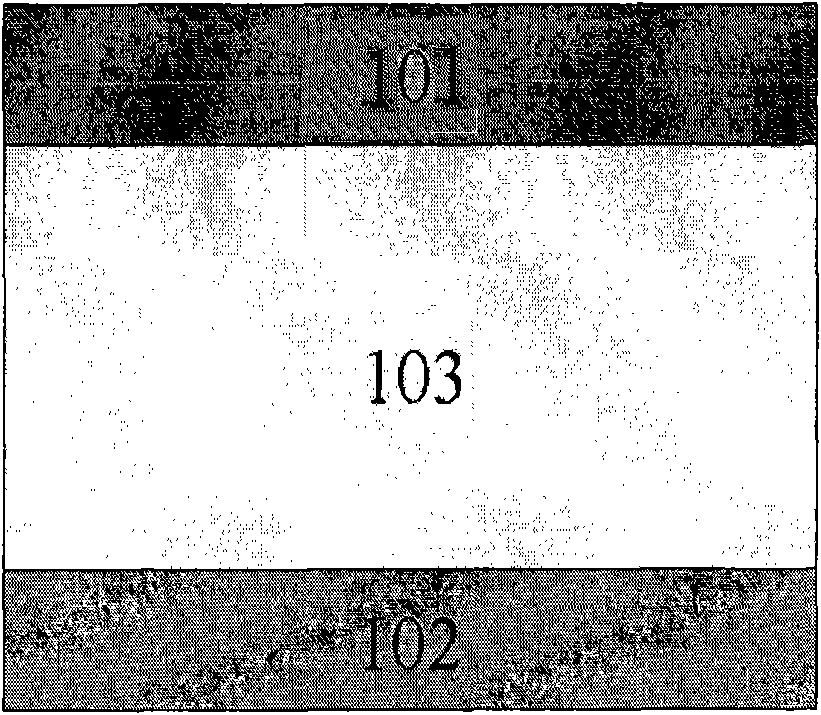

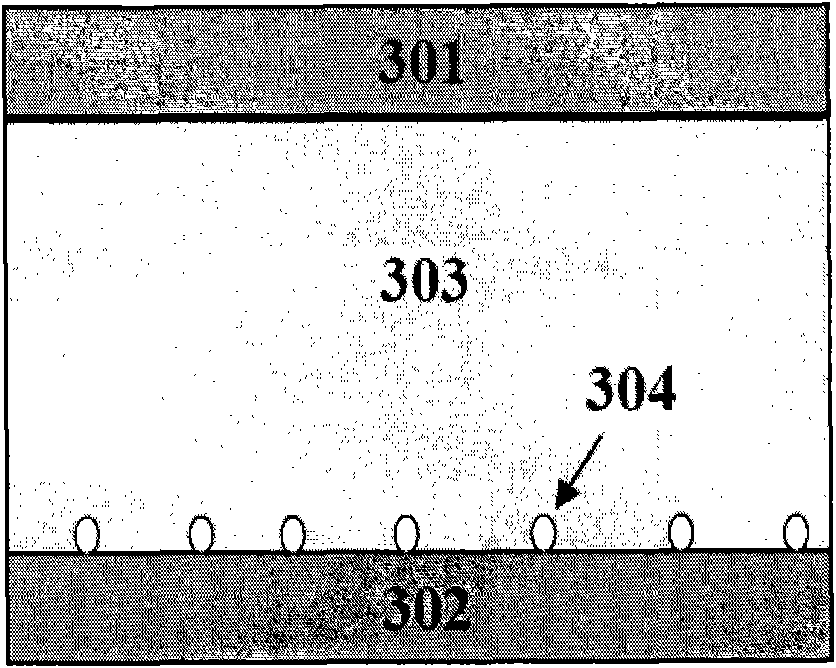

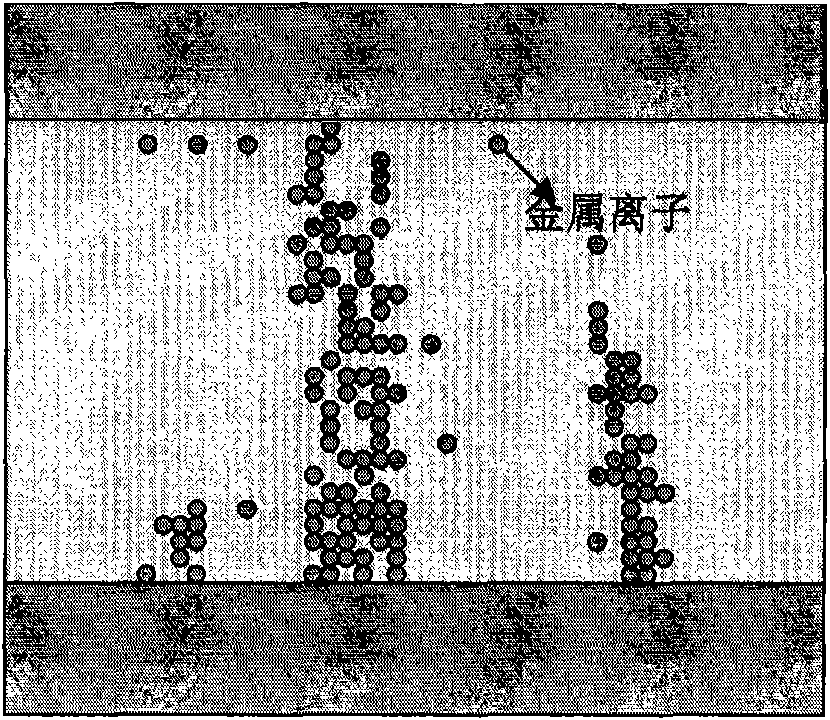

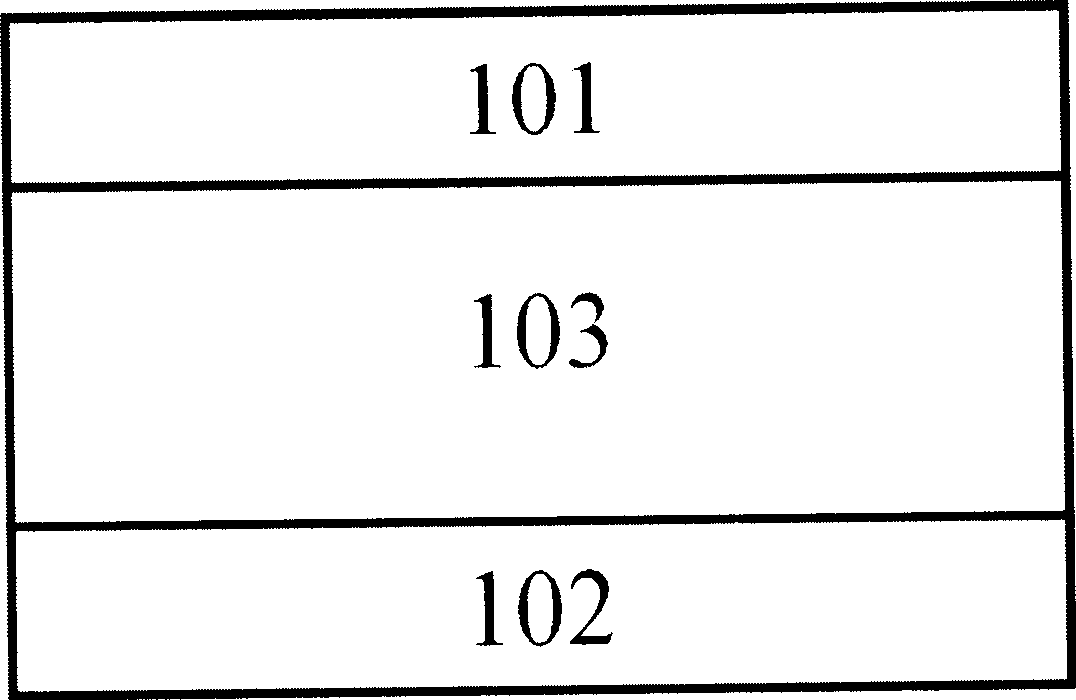

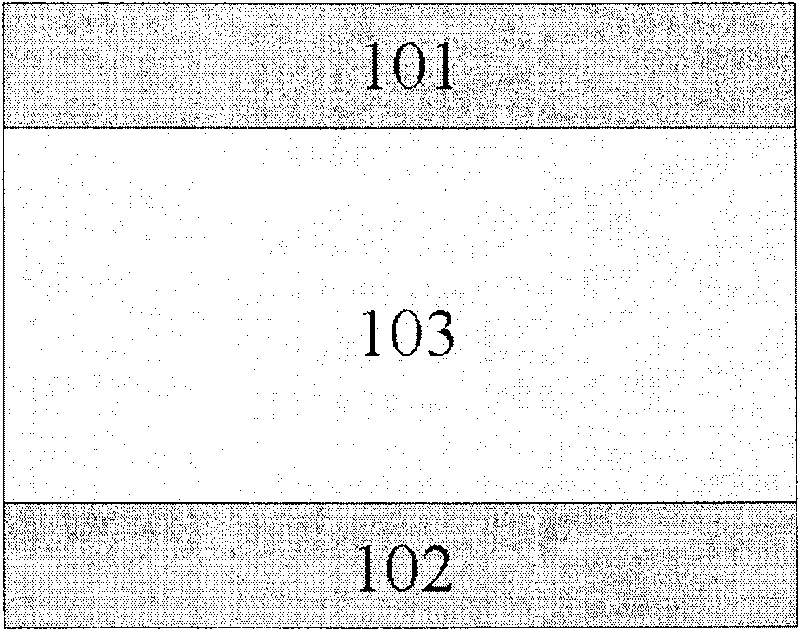

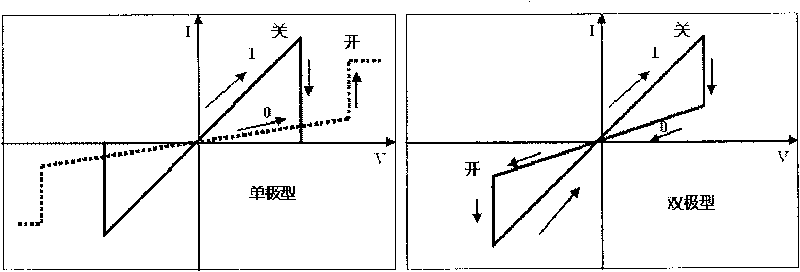

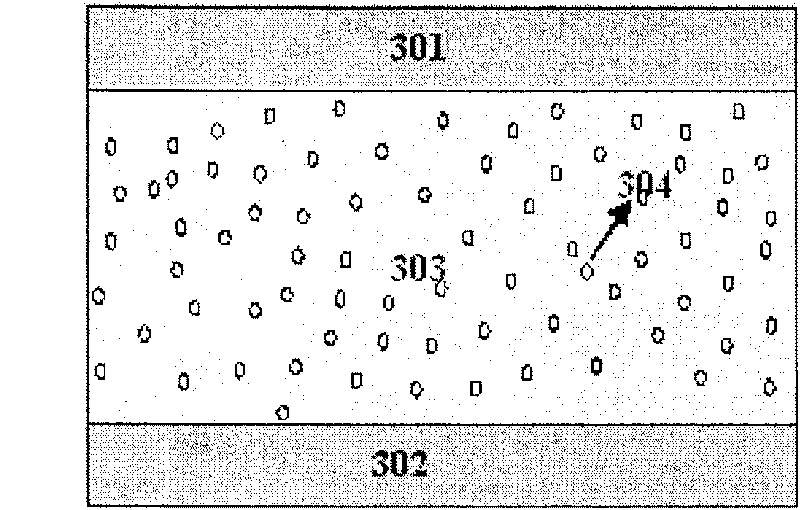

Resistor-type nonvolatile storage device and manufacturing method thereof

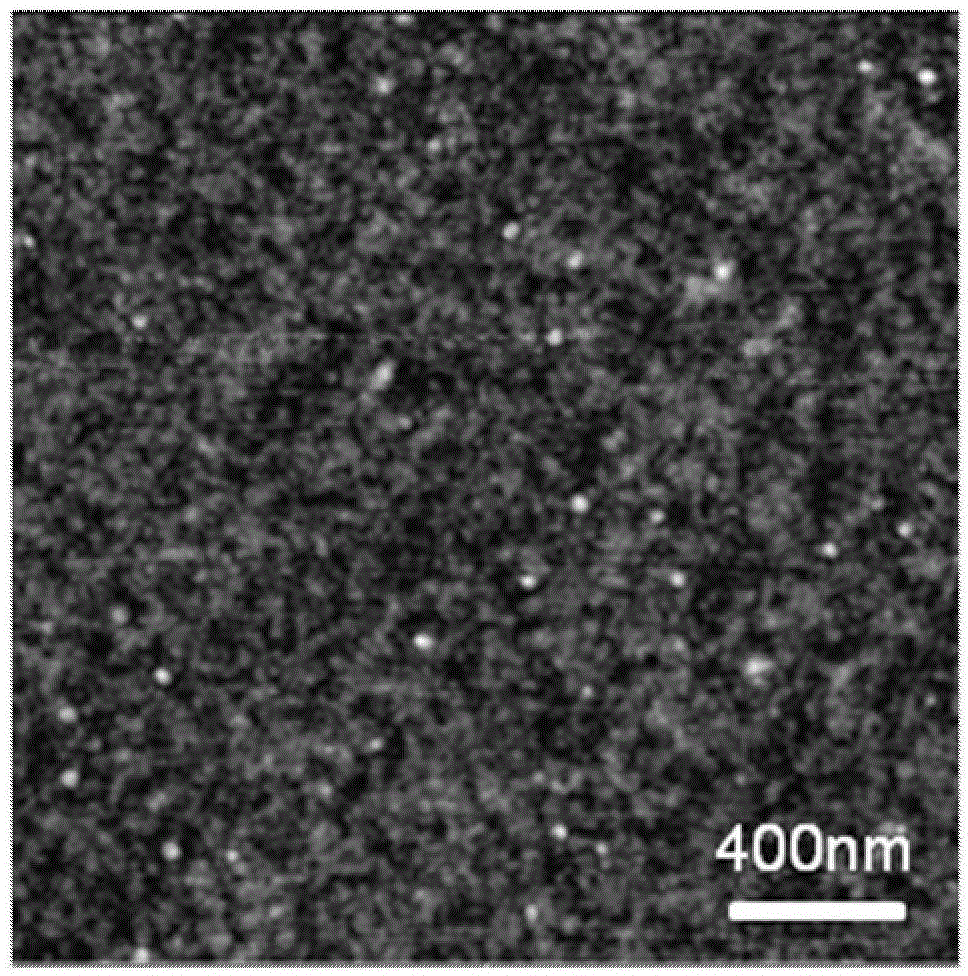

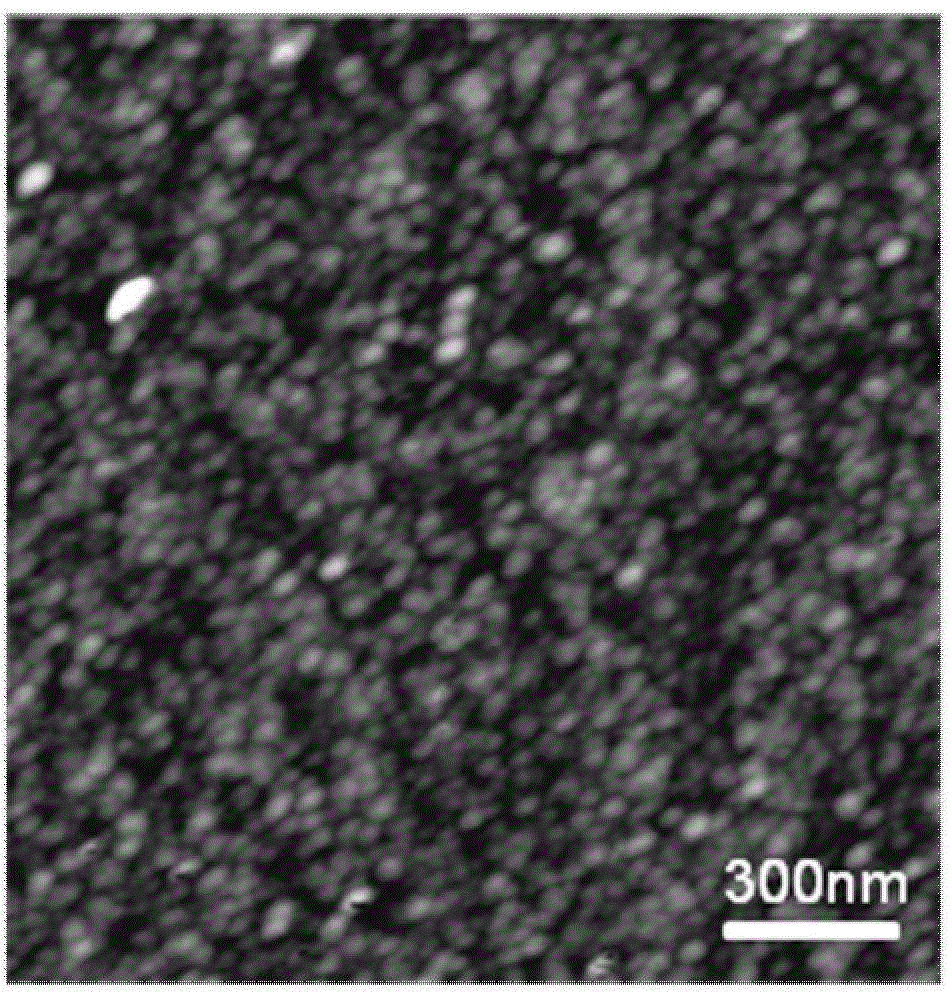

InactiveCN101872836AProcessing technology compatibleExcellent electrical propertiesElectrical apparatusDigital storageSolid state electrolyteElectrical field strength

The invention discloses a resistor-type nonvolatile storage device, comprising an upper conducting electrode, a lower conducting electrode, a solid-state electrolyte film or a binary oxide film, and metal nanocrystalline, wherein the solid-state electrolyte film or the binary oxide film is contained between the upper conducting electrode and the lower conducting electrode; and the metal nanocrystalline is positioned on the upper surface of the lower conducting electrode. The invention discloses a method for manufacturing the resistor-type nonvolatile storage device simultaneously. Aiming at the current situation that the randomness in the formation process of a conducting channel exists in two categories, i.e. fuse / antifuse and ion conduction-type in a resistor transitional type storage at present, the invention changes the electric-field strength in local parts by changing the appearance for the lower conducting electrode, thus achieving the purpose of controlling the formed position of the conducting channel. The resistor transitional type storage manufactured by the method has the characteristics of low programming voltage, little discreteness of the programming voltage, low power consumption, fast programming speed and the like.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Non-volatile resistor transition type memory embedded into nano-crystalline granule

The invention relates to the technical field of microelectronic devices and memories and discloses a non-volatile resistive transition memory based on embedded nano-crystalline particles of binary transition metal oxides. The memory comprises an upper conductive electrode layer, a lower conductive electrode layer, a binary transition metal oxide film between the upper conductive electrode layer and the lower conductive electrode layer and nano-crystalline particles embedded in the binary transition metal oxides. With the invention, the processing technology of devices is compatible with the traditional CMOS technology, which can greatly increase the production of the devices and lay foundations for large-scale integration of the devices.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

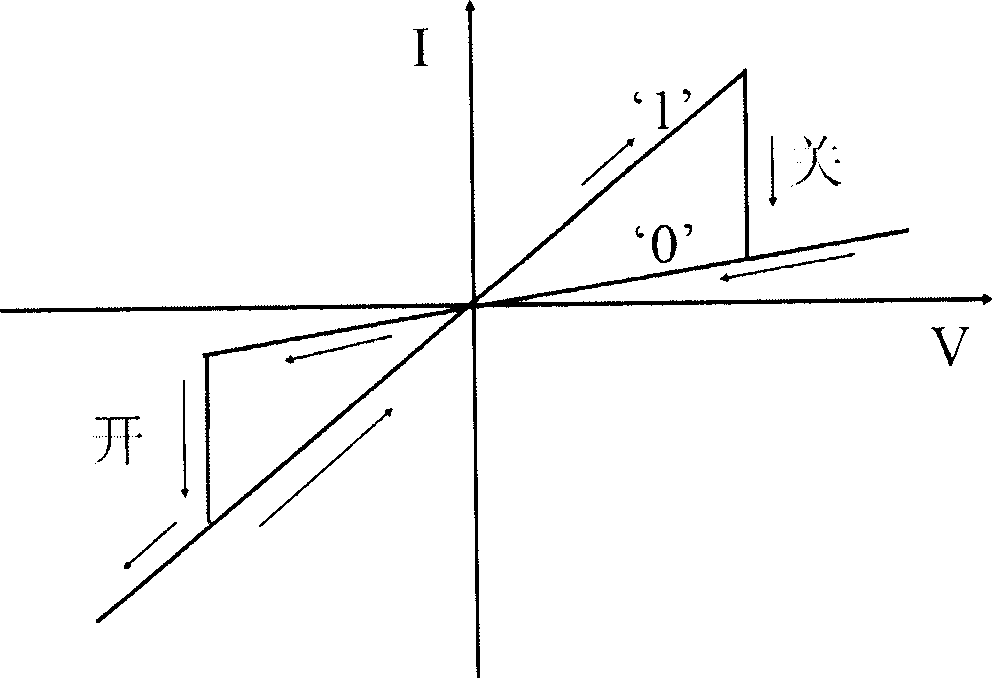

Non-volatile resistor change type memory with self-rectification effect

InactiveCN101783388AProcessing technology compatibleImprove storage densityDigital storageSemiconductor devicesCMOSChange Type

The invention discloses a non-volatile resistor change type memory with the self-rectification effect. The non-volatile resistor change type memory comprises an upper Pt electrode, a lower Pt electrode, a binary transition metal oxide thin film and a PtOx boundary layer, wherein the binary transition metal oxide thin film is positioned between the upper Pt electrode and the lower Pt electrode, and the PtOx boundary layer is positioned between the binary transition metal oxide thin film and the lower Pt electrode. The non-volatile resistor change type memory with the self-rectification effect has the advantages of simple structure, easy integration, low cost, compatible process with the traditional silicon planer CMOS, and the like, and is beneficial to the wide popularization and the application of the invention.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Metal-oxide-semiconductor device with enhanced source electrode

ActiveUS20050077552A1Reduce input capacitanceImprove device performanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical connectionSemiconductor

An MOS device is formed including a semiconductor layer of a first conductivity type, a first source / drain region of a second conductivity type formed in the semiconductor layer, and a second source / drain region of the second conductivity type formed in the semiconductor layer and spaced apart from the first source / drain region. A gate is formed proximate an upper surface of the semiconductor layer and at least partially between the first and second source / drain regions. The MOS device further includes at least one contact, the at least one contact including a silicide layer formed on and in electrical connection with at least a portion of the first source / drain region, the silicide layer extending laterally away from the gate. The contact further includes at least one insulating layer formed directly on the silicide layer.

Owner:CICLON SEMICON DEVICE

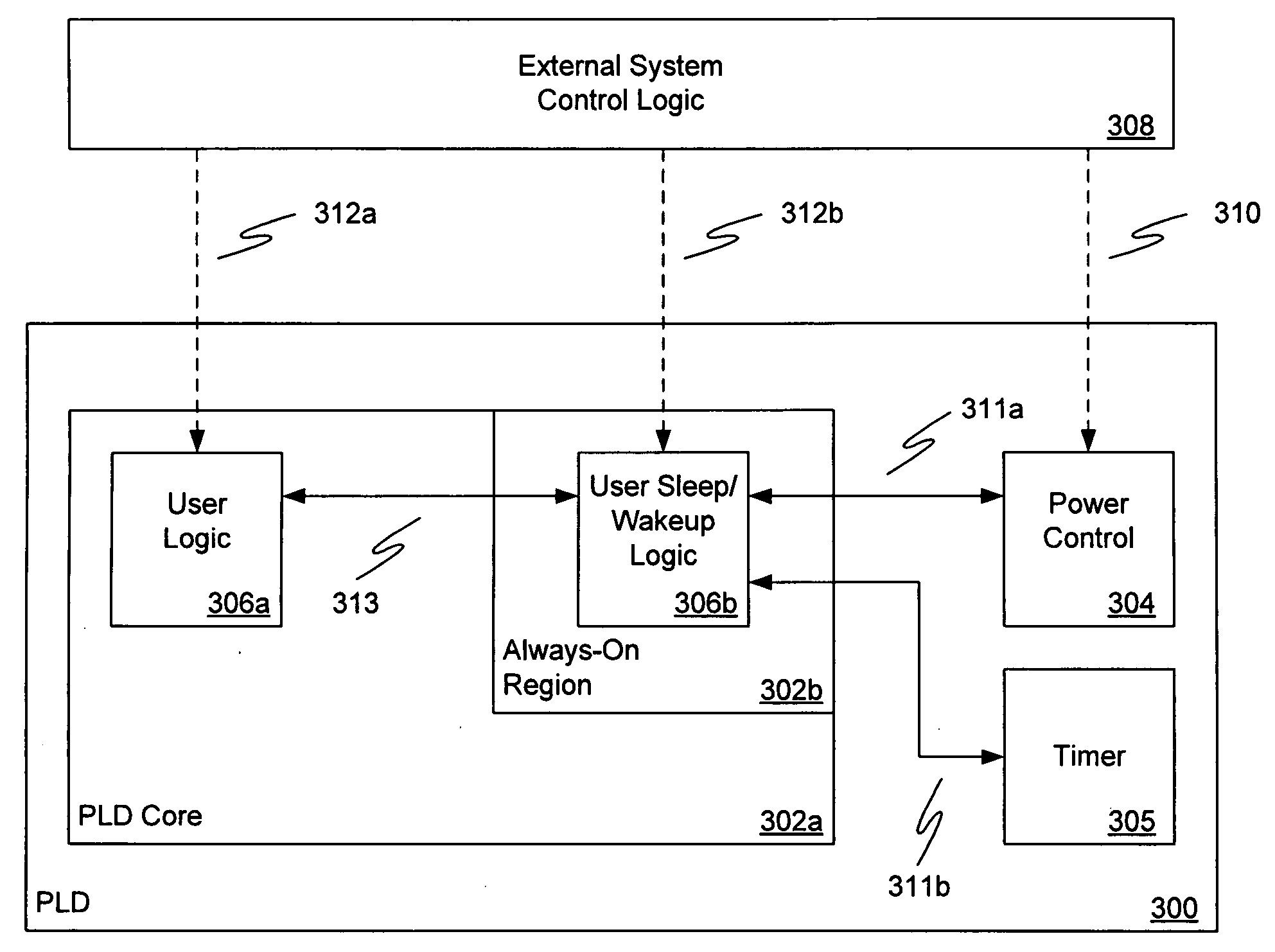

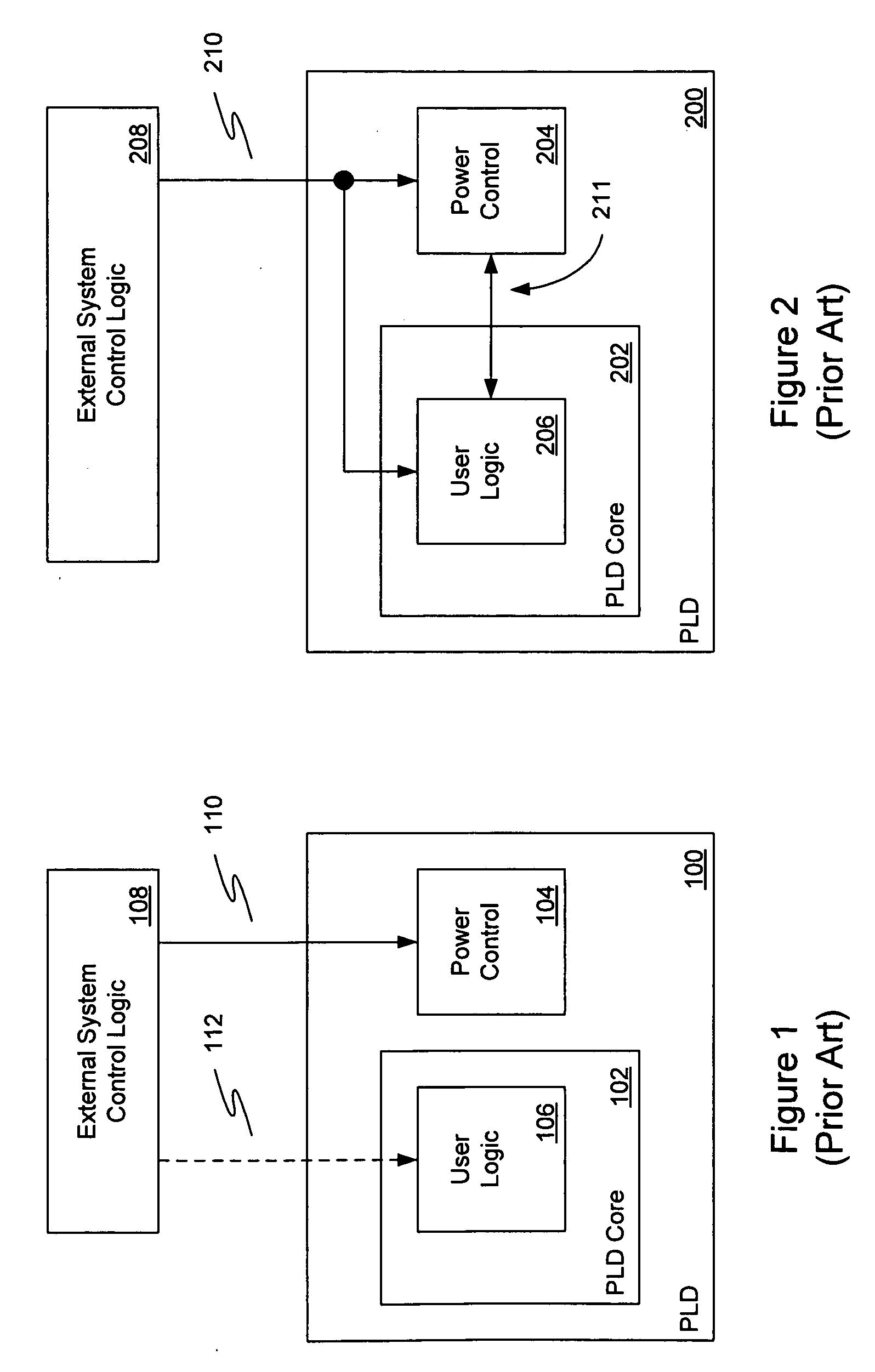

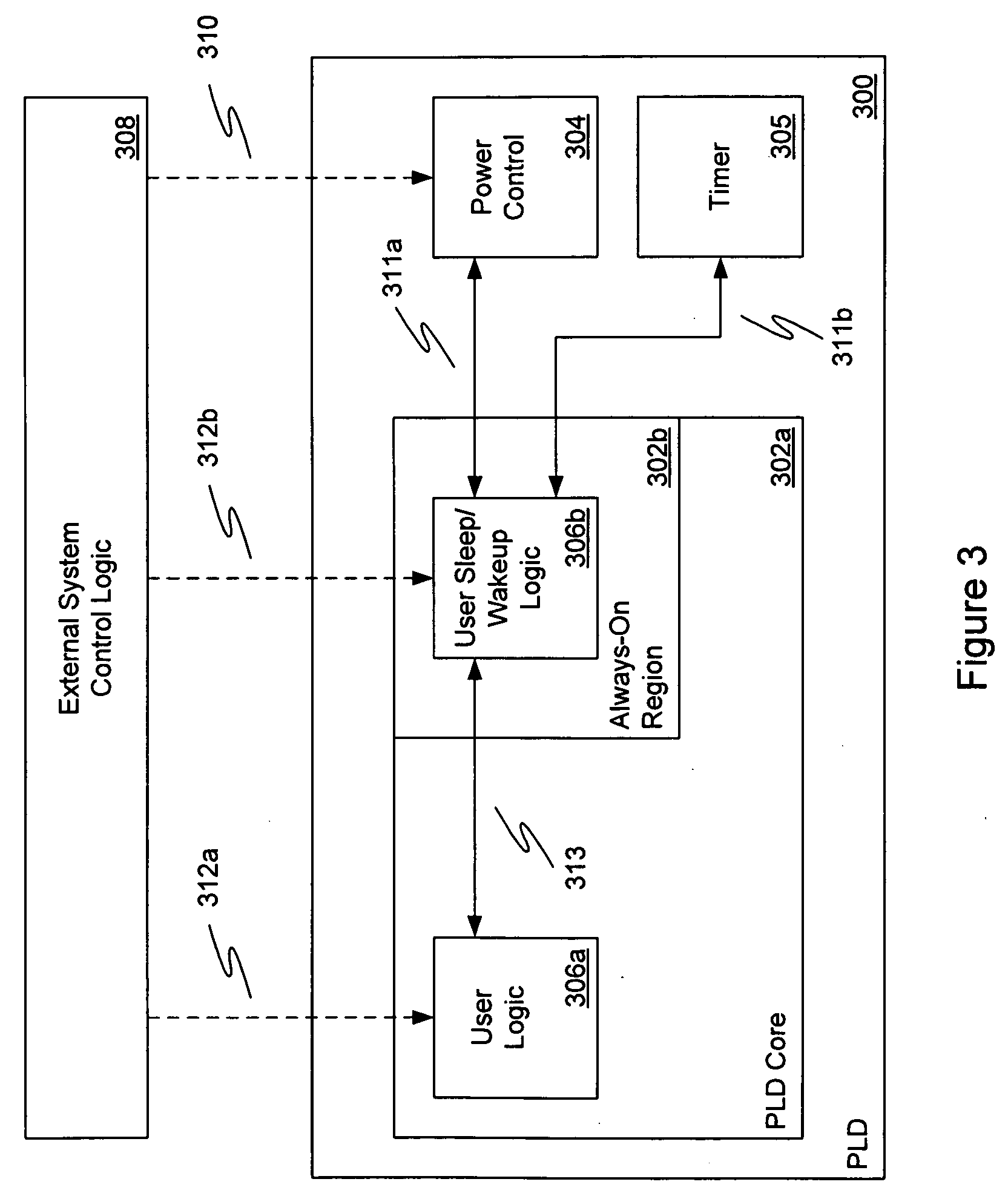

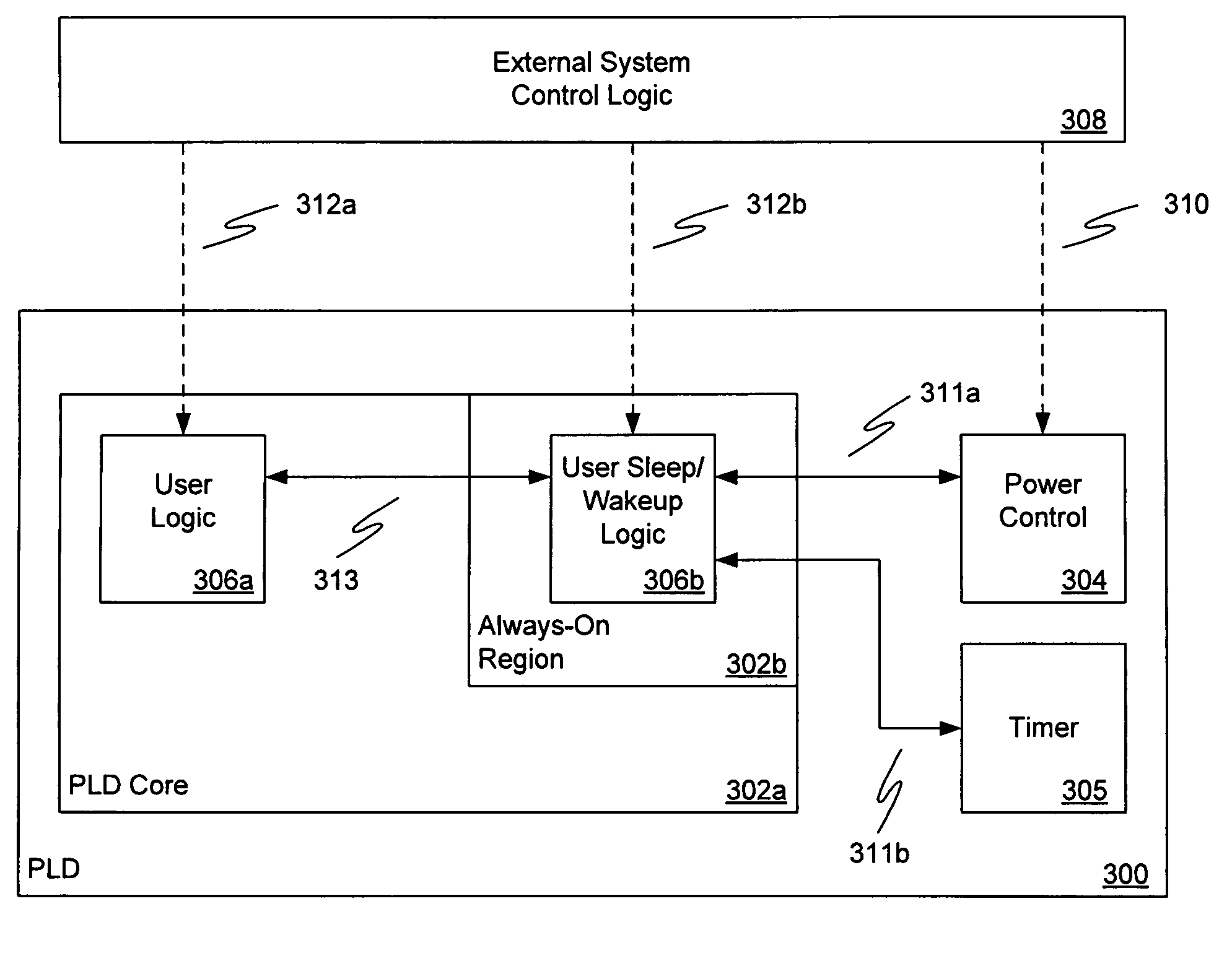

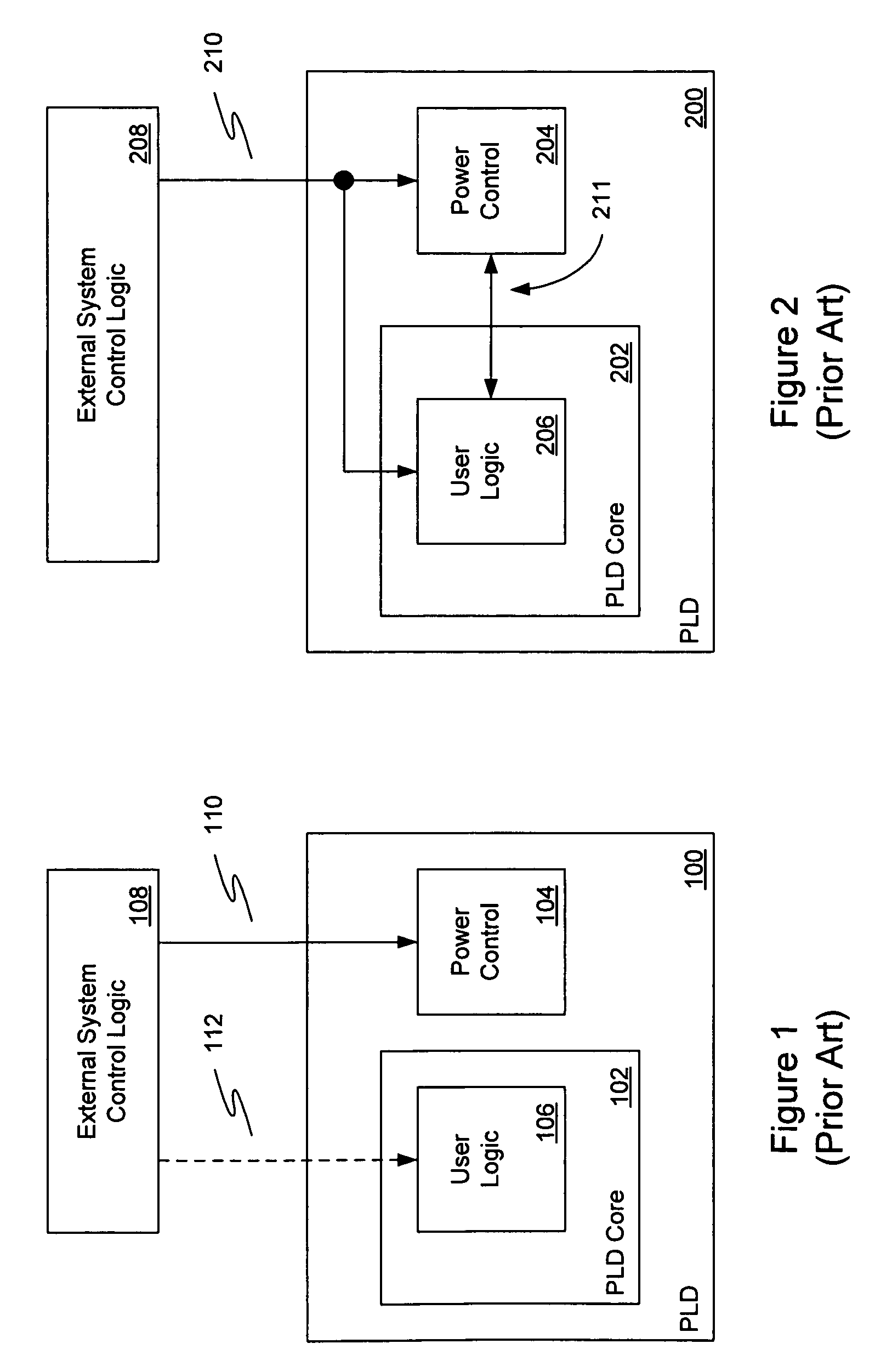

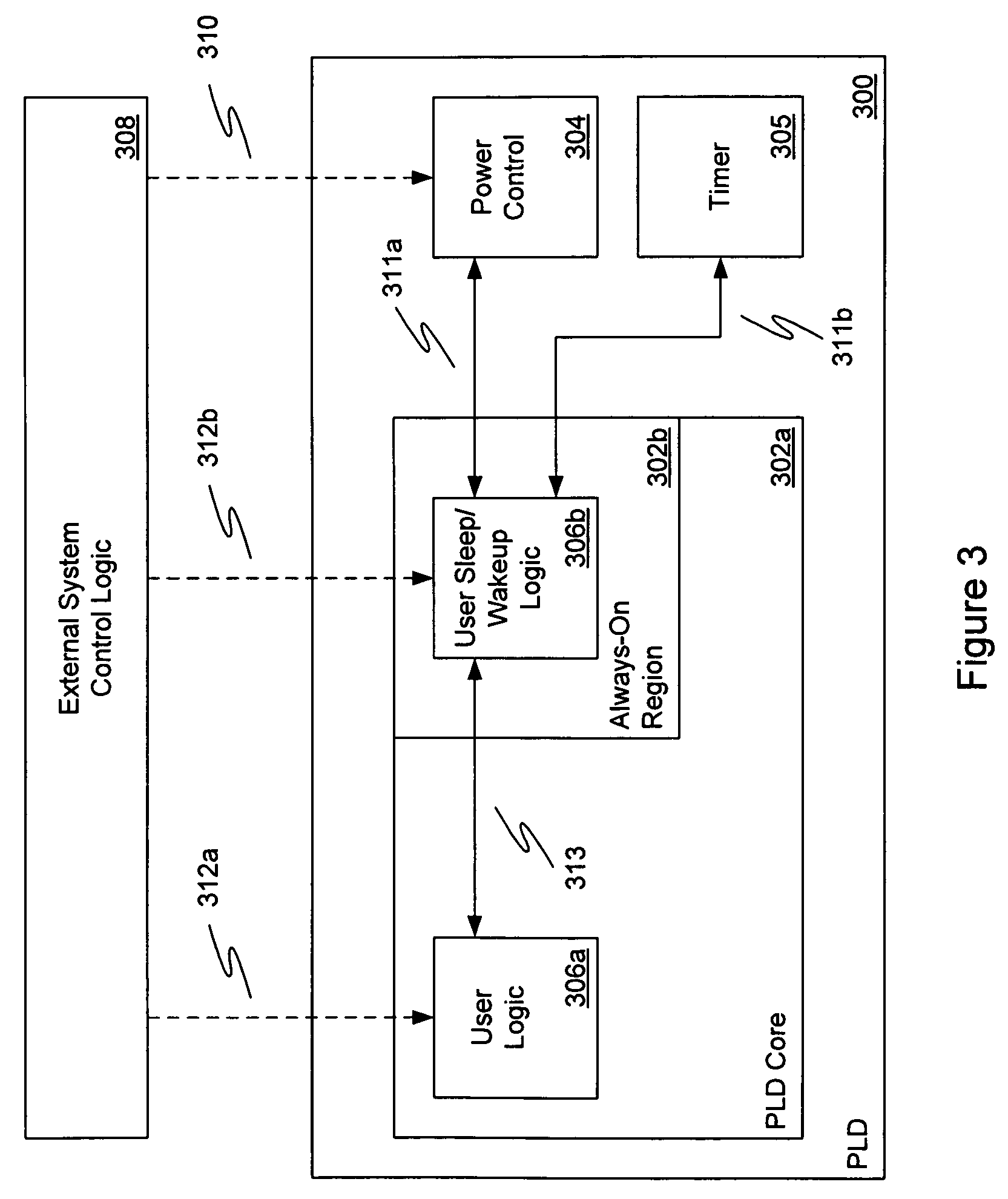

Pld providing soft wakeup logic

ActiveUS20100156457A1Reduce power consumptionReduce voltageReliability increasing modificationsSolid-state devicesPower modeProgrammable logic device

A programmable logic device (PLD) with a plurality of programmable regions is disclosed. Some of the programmable regions have switch power or ground supplies to allow them to be put into a low-power state in one or more low-power modes. At least one of the programmable regions always remains on during the low-power modes to enable the user to design custom PLD power management logic that may be placed in the always-on programmable region.

Owner:MICROSEMI SOC

Shielding structure for use in a metal-oxide-semiconductor device

InactiveUS7138690B2Improve high frequency performanceLow costTransistorSemiconductor/solid-state device detailsSemiconductorCmos process

An MOS device is formed comprising a semiconductor layer of a first conductivity type, a first source / drain region of a second conductivity type formed in the semiconductor layer, and a second source / drain region of the second conductivity type formed in the semiconductor layer and spaced apart from the first source / drain region. The MOS device further comprises a gate formed proximate an upper surface of the semiconductor layer and at least partially between the first and second source / drain regions, and a shielding structure formed proximate the upper surface of the semiconductor layer and between the gate and the second source / drain region, the shielding structure being electrically connected to the first source / drain region, the shielding structure being spaced laterally from the gate and being non-overlapping relative to the gate. In this manner, the MOS device is substantially compatible with a CMOS process technology.

Owner:BELL SEMICON LLC

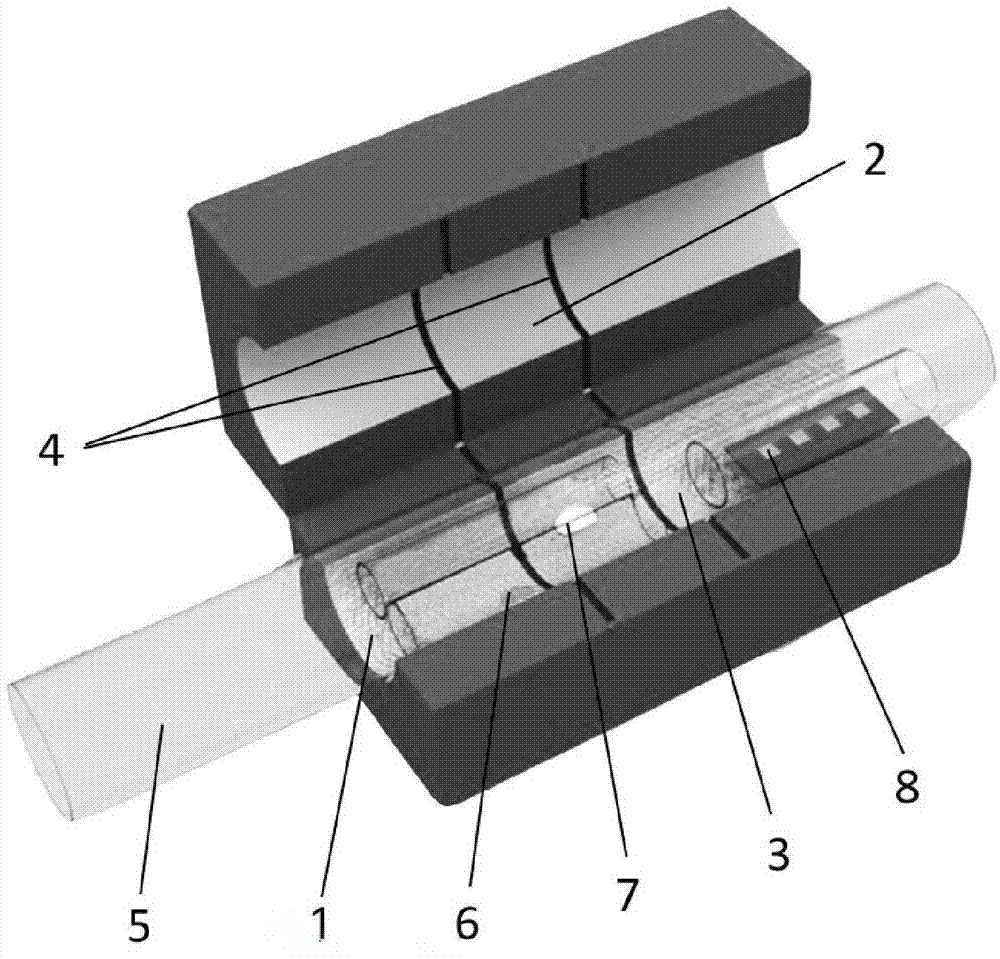

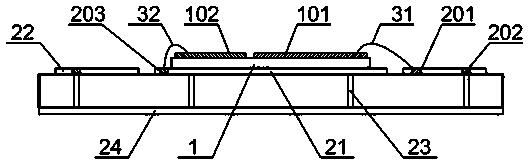

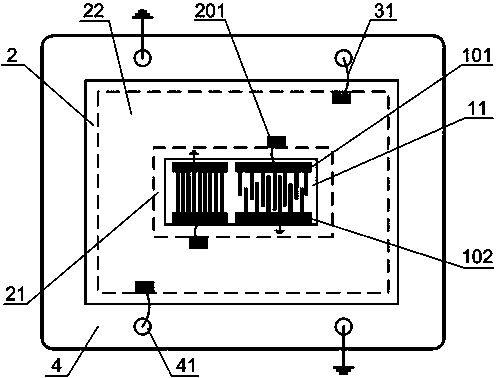

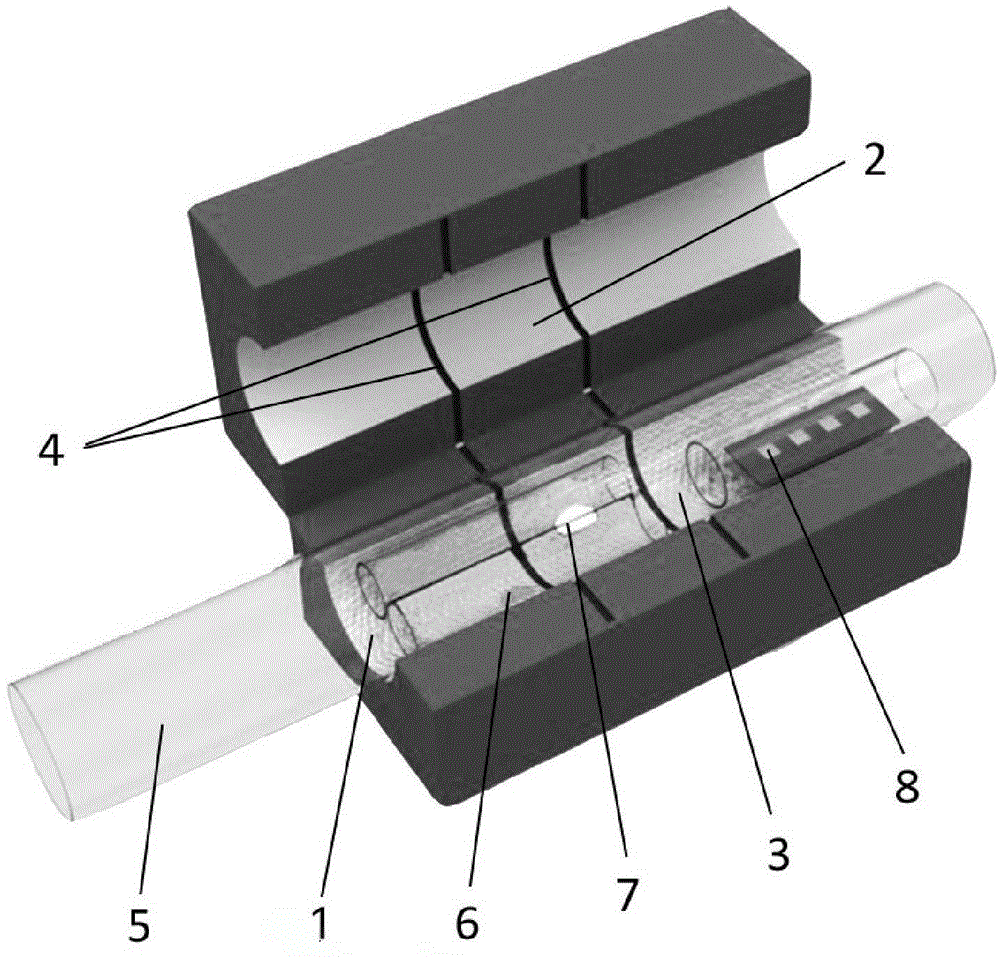

Integrated packaging structure of surface acoustic wave filter and packaging method thereof

InactiveCN103441746ASimplify the interconnect structureImprove performanceImpedence networksEngineeringSurface acoustic wave

The invention discloses an integrated packaging structure of a surface acoustic wave filter and a packaging method thereof and belongs to the technical field of surface acoustic waves. The integrated packaging structure comprises a surface acoustic wave filter chip, a matching tuned circuit and a packaging shell. The packaging shell is composed of a packaging base, outer pins of the packaging base, and a sealing cap. The sealing cap covers the packaging base. The integrated packaging structure is characterized in that a tuned substrate is arranged, the matching tuned circuit is manufactured on the tuned substrate, the surface acoustic wave filter chip is adhered to the tuned substrate and is electrically connected with the matching tuned circuit through a bonding wire, and the tuned substrate is adhered to the packaging base and is electrically connected with the outer pins of the packaging base through bonding wires. According to the integrated packaging structure, the surface acoustic wave filter chip and the matching tuned circuit are integrated and packaged in the same packaging body, so that mutual connection structures between the surface acoustic wave filter chip and an application circuit, and between the matching tuned circuit and an application circuit are simplified. Consequently, the integrated packaging structure has the advantages of being compact in structure, small in consumption, strong in antijamming capability, and the like, and helps to improve the overall performance of an application system of a surface acoustic wave filter.

Owner:YANGZHOU UNIV

PLD providing soft wakeup logic

ActiveUS7884640B2Reduce power consumptionReduce gate leakageReliability increasing modificationsSolid-state devicesPower modeProgrammable logic device

Owner:MICROSEMI SOC

Double-spectrum super-surface integrated uncooled infrared detector and manufacturing method thereof

ActiveCN109813448AAchieving Bispectral ResponsesReduce equivalent heat capacityPyrometry using electric radation detectorsHigh absorptionTemperature resistance

The invention discloses a double-spectrum super-surface integrated uncooled infrared detector and a manufacturing method thereof, relates to the technical field of infrared detection and imaging, andsolves the problems that an existing uncooled focal plane increases the thickness of an absorption layer for achieving high absorption rate, and the performance is reduced due to the increase of equivalent heat capacity. The focal plane comprises an array consisting of a plurality of picture elements, wherein each picture element sequentially comprises: a readout circuit, which is a silicon-basedor germanium-based CMOS integrated circuit with the functions of amplifying and reducing noise, and a readout electrode pair is arranged on the CMOS integrated circuit; an adiabatic microbridge, whichcomprises a microbridge deck, two microsupport structures and two microcantilever beams; a thermistor layer, which is a material with the absolute value of a temperature resistance coefficient higherthan 2%; a readout electrode is connected with the thermistor layer through a through hole; the thermistor layer is protected by a passivation insulating layer; the bispectral absorption film layer comprises a metal layer, a dielectric layer and a metal microarray; the manufacturing method is compatible with the traditional uncooled infrared detector processing technology, and the process is simple, so that large-scale and low-cost preparation are facilitated.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

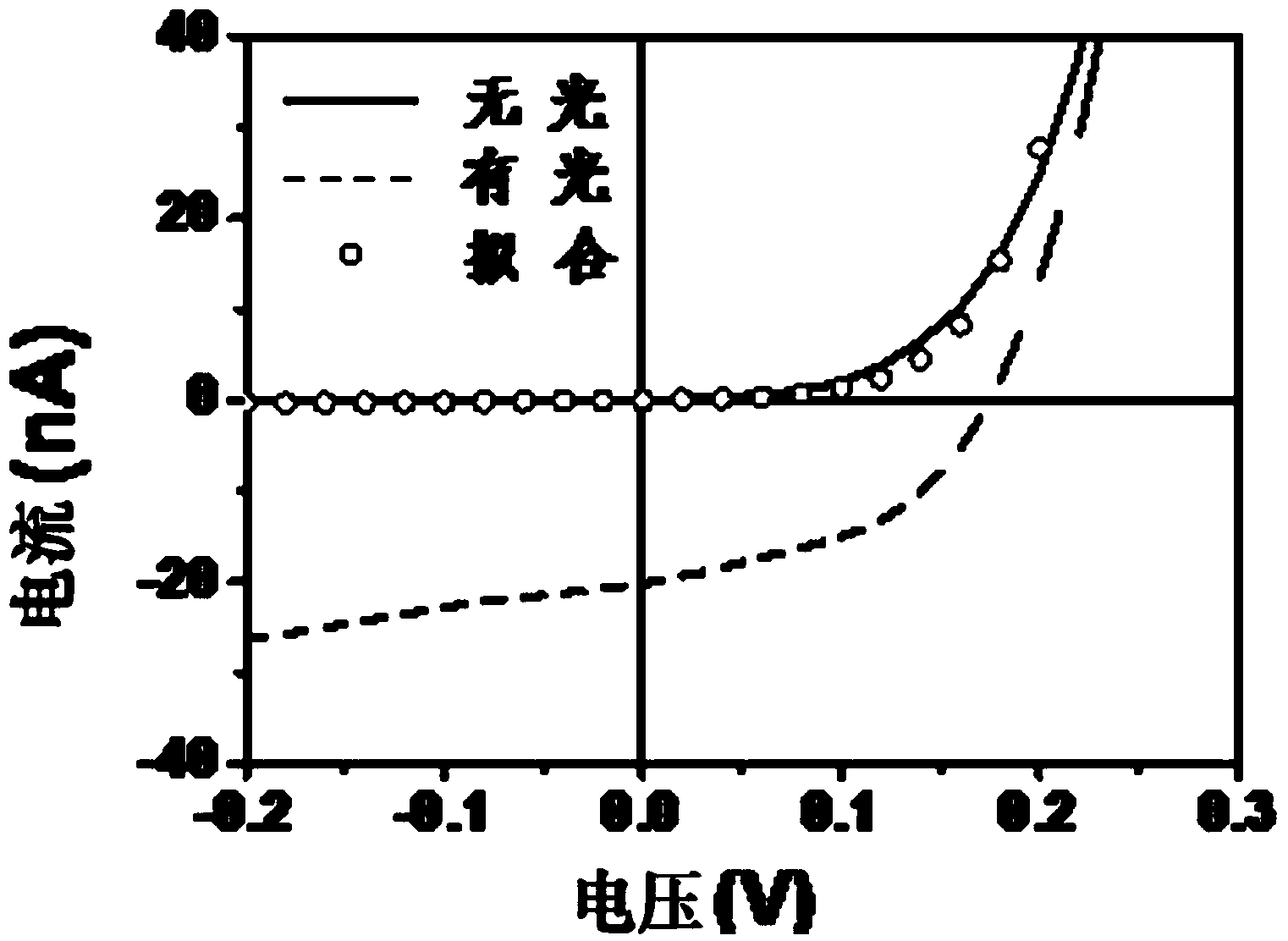

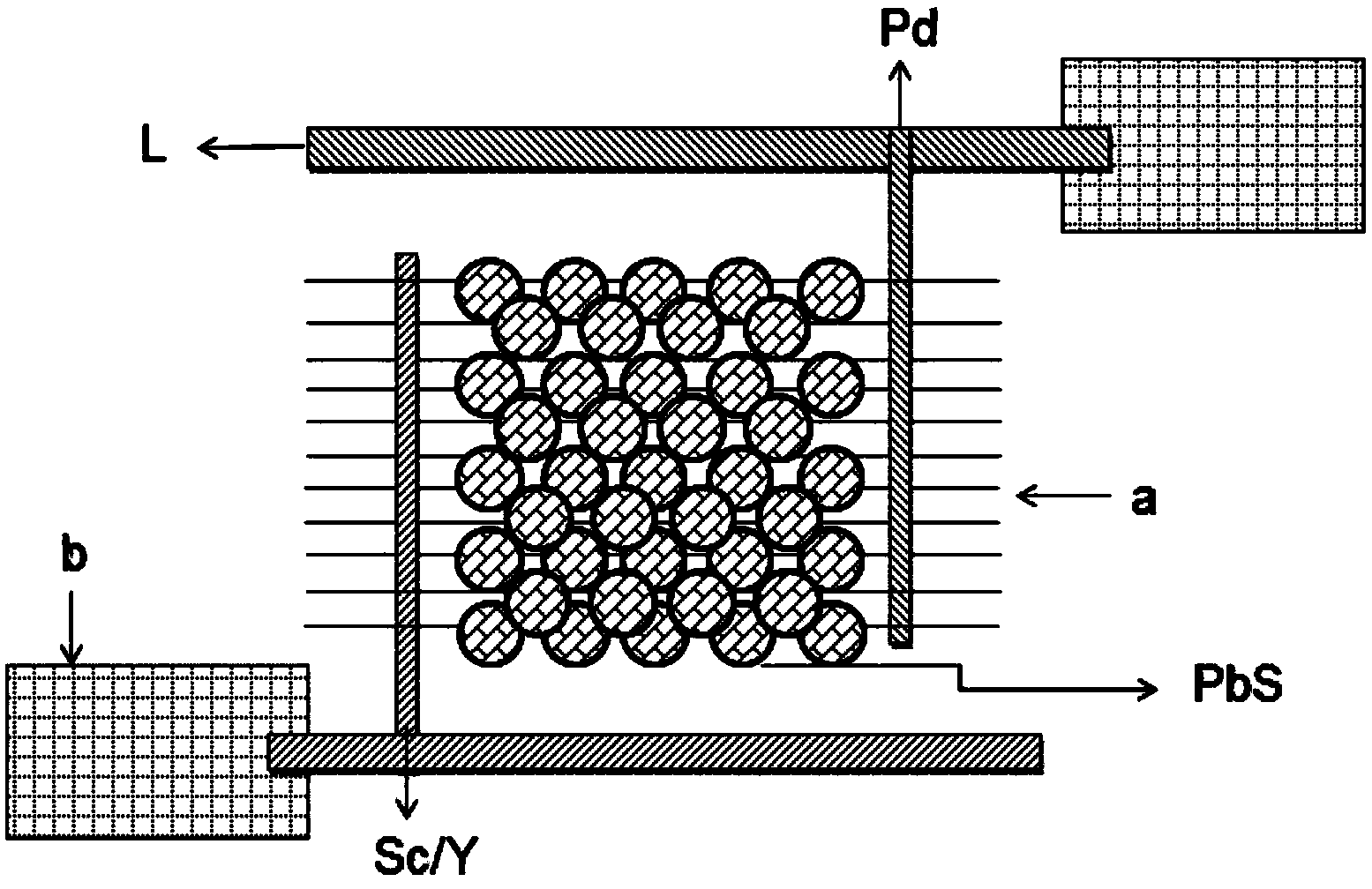

Infrared imaging detector carbon nanotube based on quantum dots and preparation method for the same

InactiveCN104167451AImprove performanceReduce dark current levelsFinal product manufactureSemiconductor devicesElectron holeCarbon nanotube

The invention discloses an infrared imaging detector carbon nanotube based on quantum dots and a preparation method for the same. The infrared imaging detector comprises a substrate, a plurality of one dimensional semiconductor carbon nanotubes or semiconductor carbon nanotube thin film strips which are positioned on the substrate, an asymmetric contact electrode for forming contact of electrons and electron hole ohmics and a plurality of Pbs quantum dots, wherein the asymmetric contact electrode comprises a plurality of first electrodes and a plurality of second electrodes. A plurality of one dimensional semiconductor carbon nanotubes or a plurality of semiconductor carbon nanotube thin film strips are arranged on the substrate by the evaporation drive self-assembling method; a first electrode, a second electrode and pattern shapes of metal connection lines are formed on the substrate; the metal layer of the electrode is evaporated; and the quantum dots are deposited on the carbon nanotube thin film in the middle of the conducting channel. The invention can obtain high detection efficiency, can solve the unstable problem of the short chain converted from the quantum dot, and can provide convenience to production.

Owner:PEKING UNIV

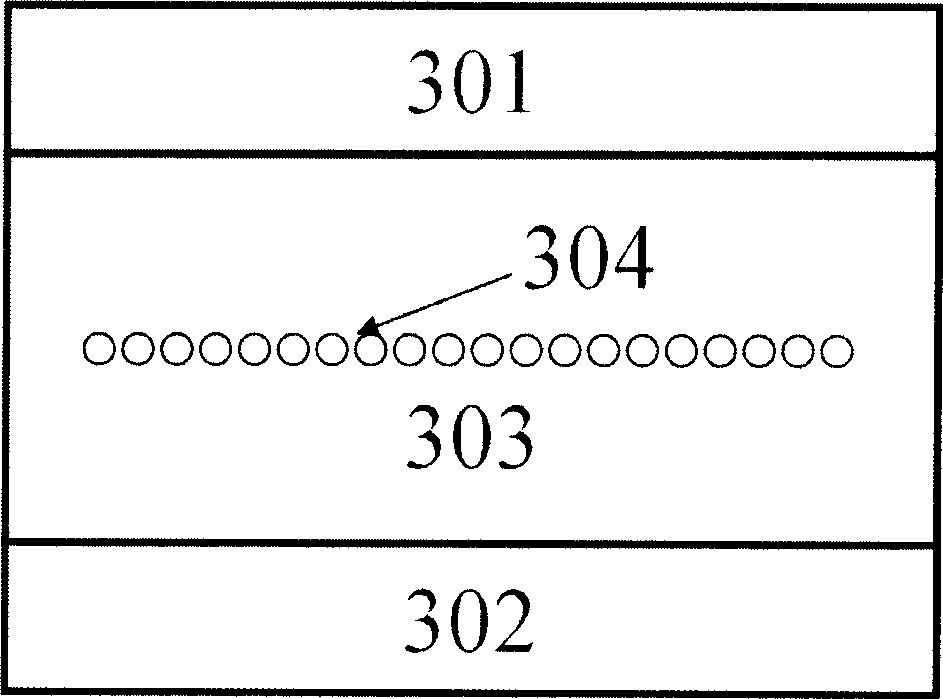

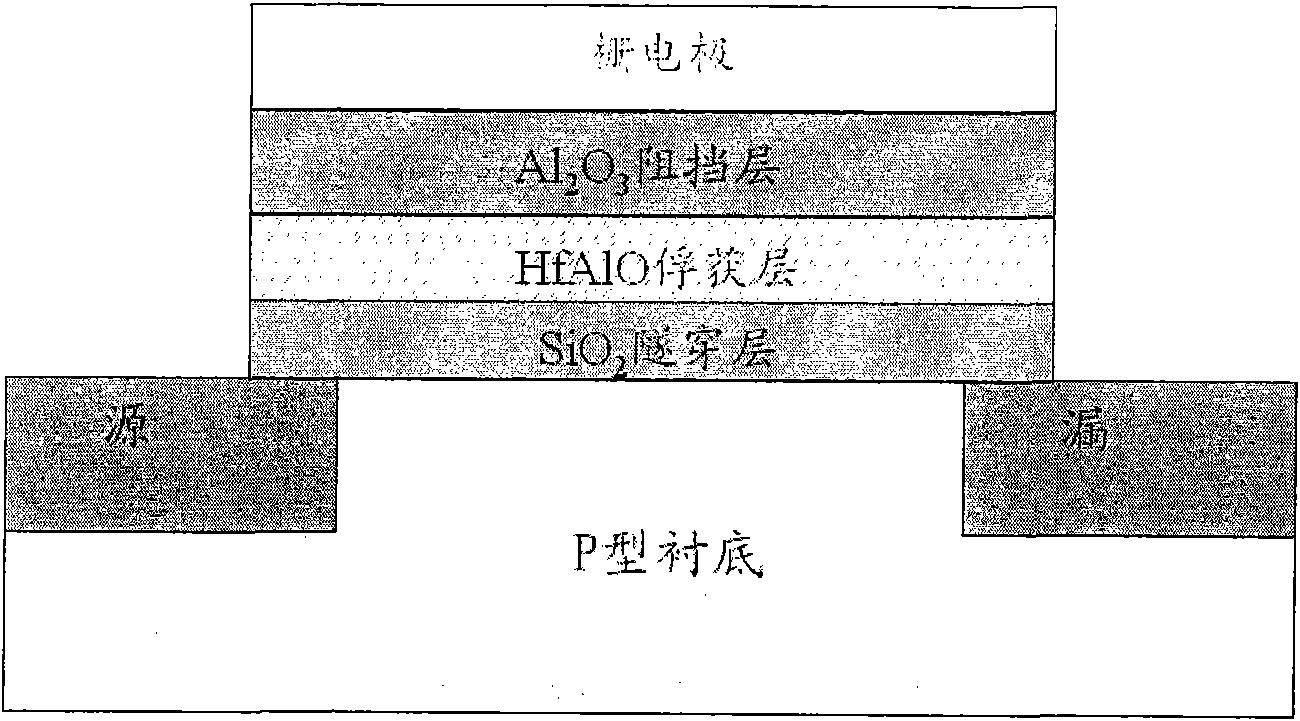

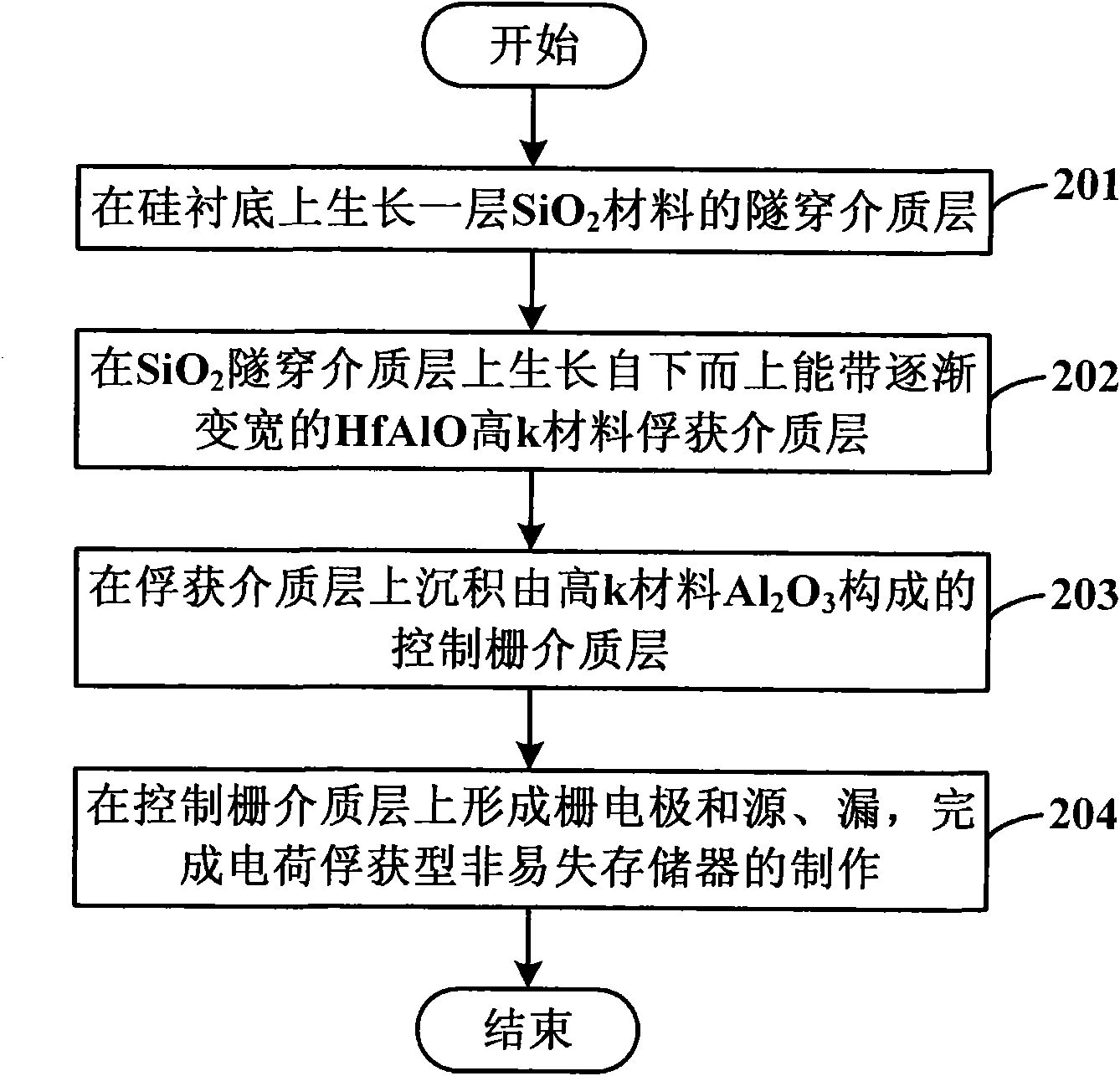

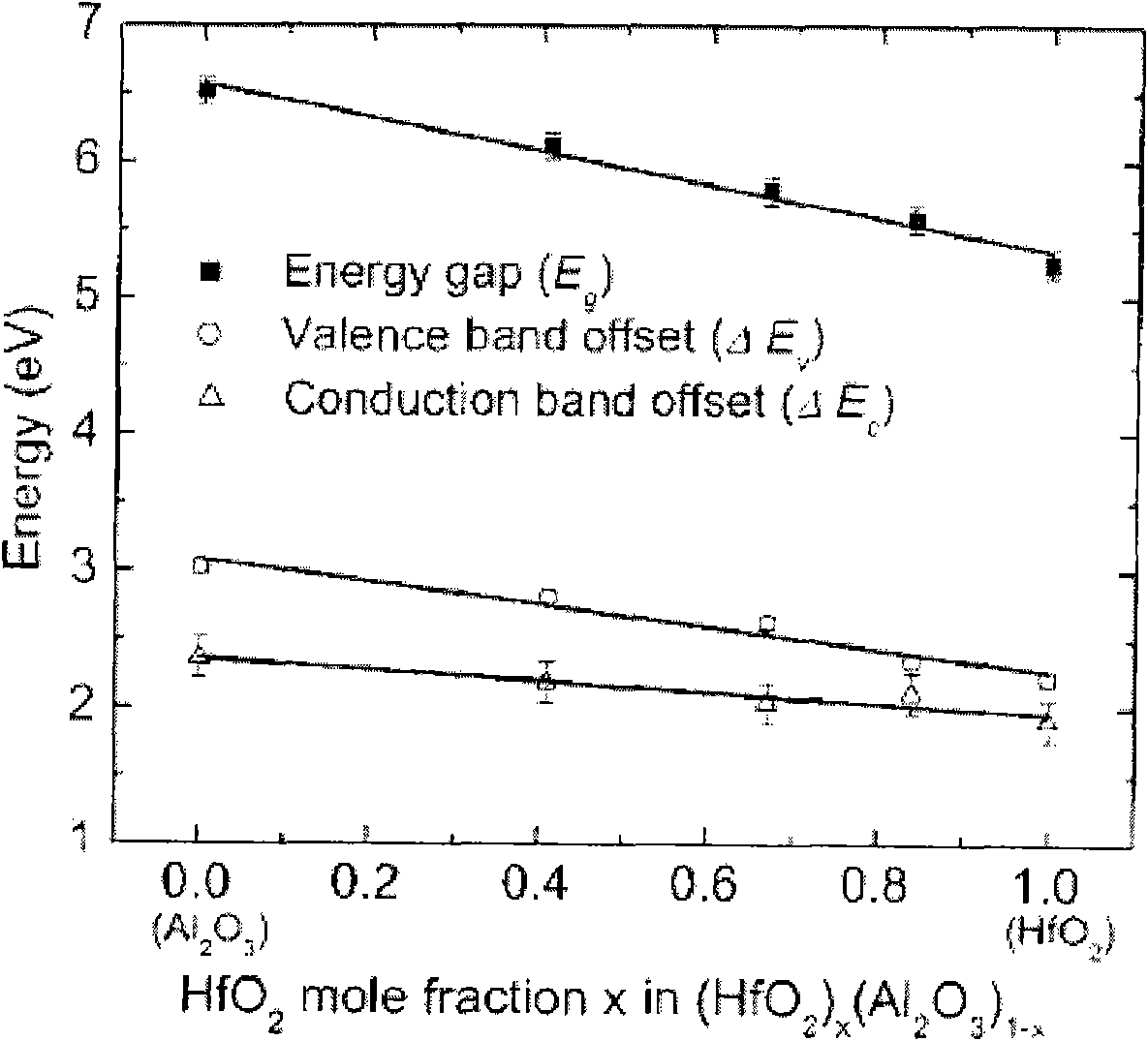

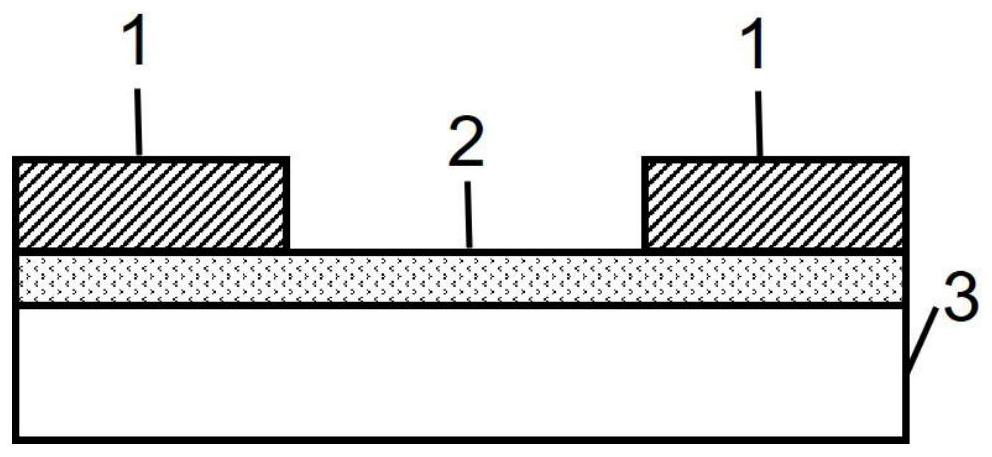

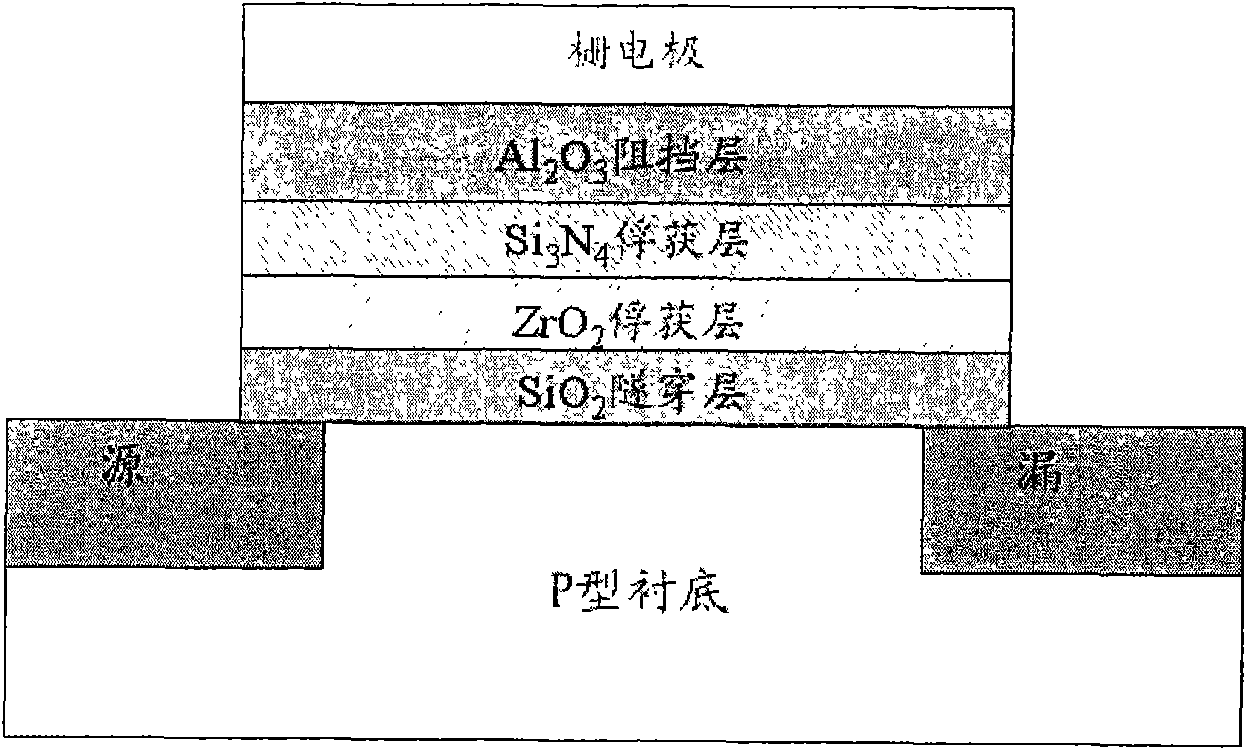

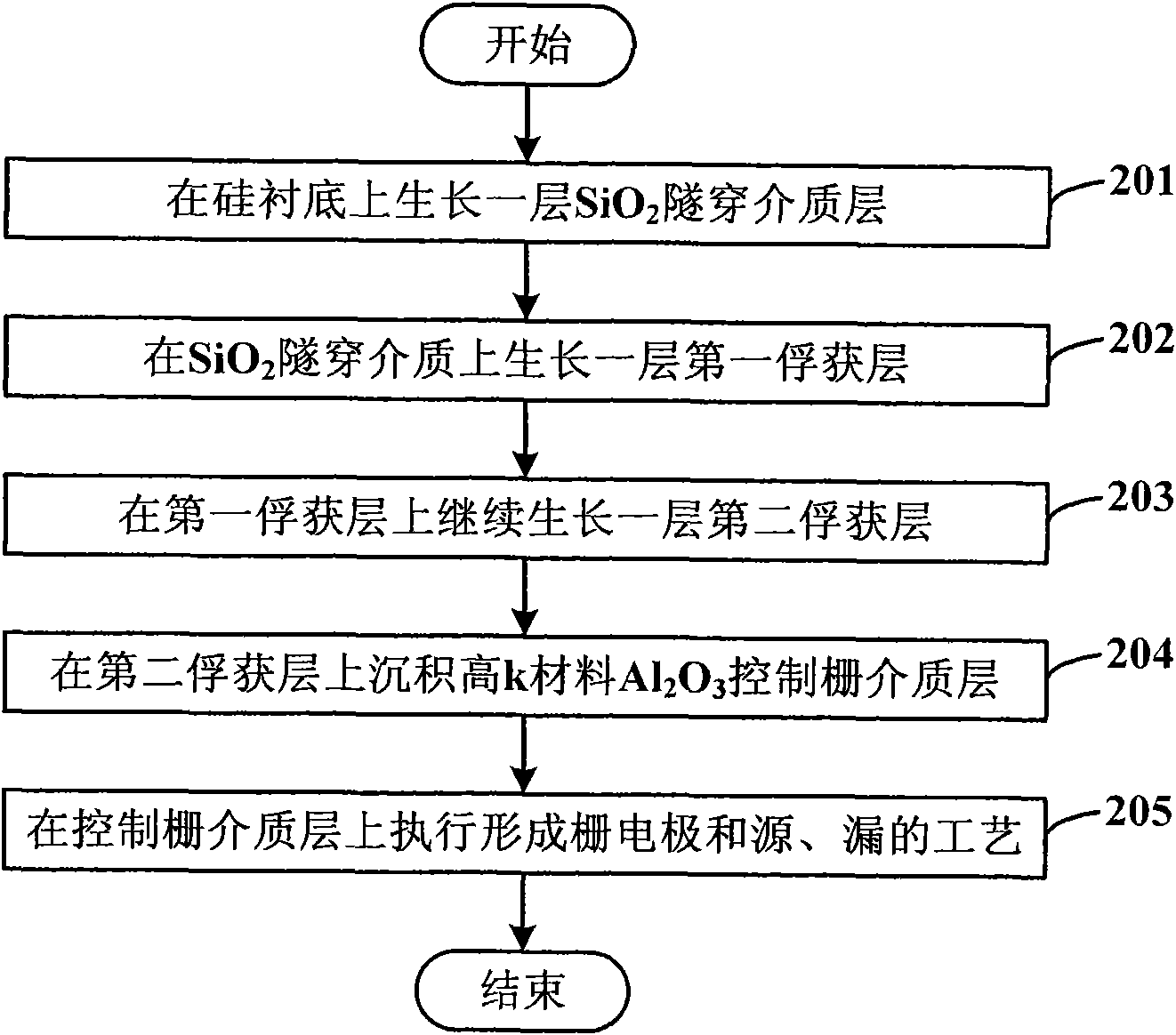

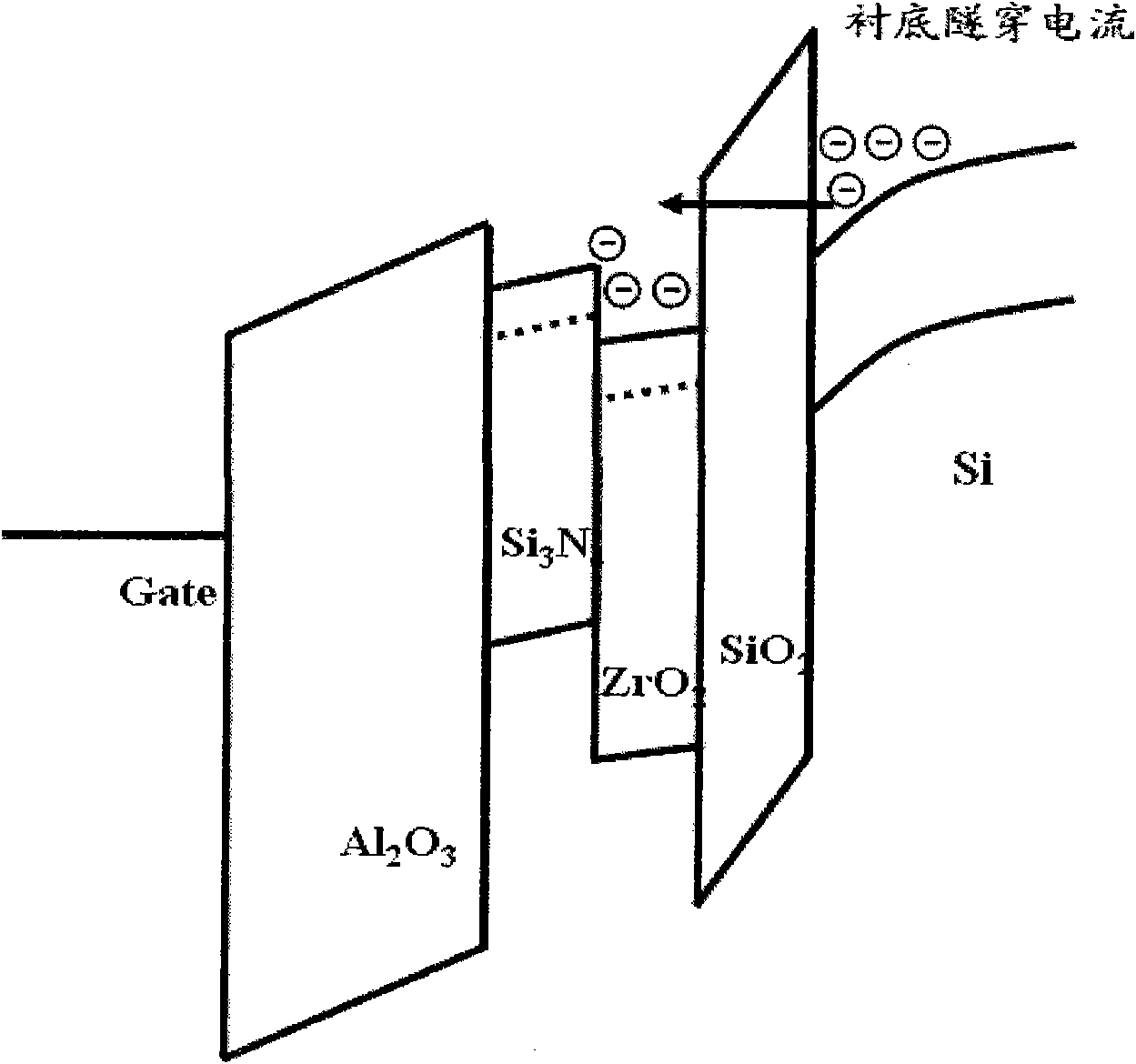

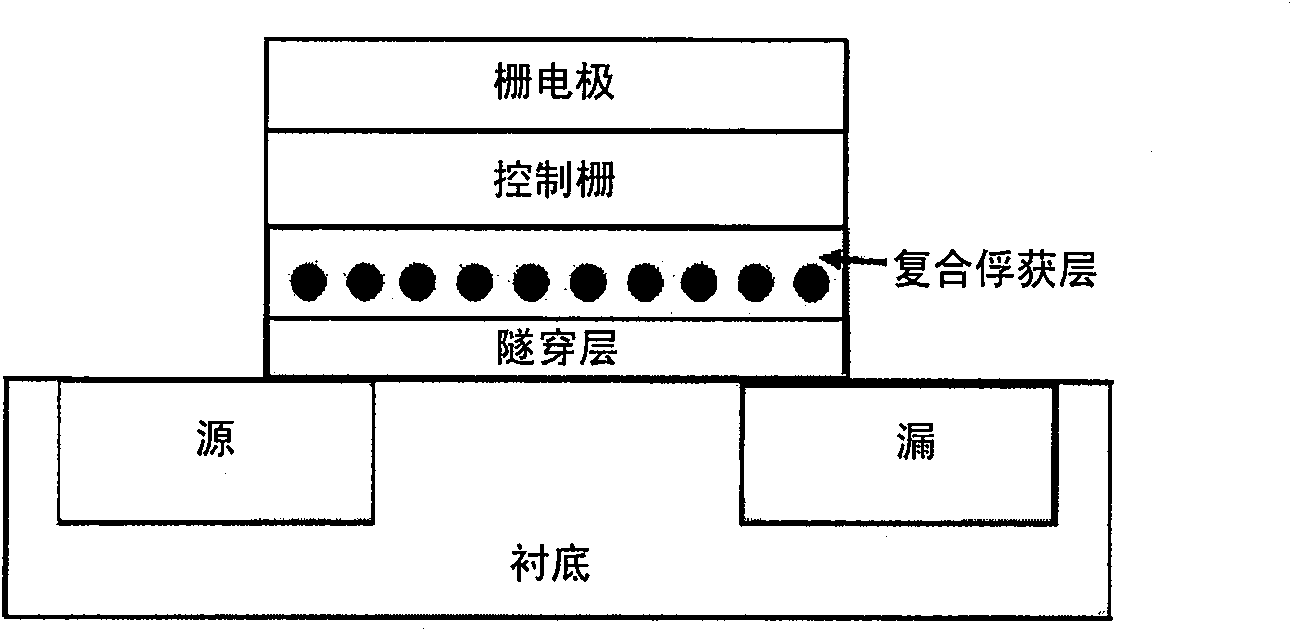

Charge trapping type nonvolatile memory and manufacturing method thereof

InactiveCN102117810AProcessing technology compatibleReduce the chance of leaksSolid-state devicesSemiconductor/solid-state device manufacturingPhysicsElectronic band structure

The invention discloses a charge trapping type nonvolatile memory and a manufacturing method thereof. The memory comprises a silicon substrate, a source conduction region, a drain conduction region, a tunneling dielectric layer, an HfAlO high-K material trapping dielectric layer with a tapered band structure, a control grid dielectric layer and a grid material layer, wherein the source conduction region and the drain conduction region are heavily doped on the silicon substrate; the tunneling dielectric layer is made of SiO2 materials and covers a current carrier channel arranged between the source conduction region and the drain conduction region; the HfAlO high-K material trapping dielectric layer with the tapered band structure covers the tunneling dielectric layer; the control grid dielectric layer is made of high-k Al2O3 materials and covers the trapping dielectric layer; and the grid material layer covers the control grid dielectric layer. By utilizing the charge trapping type nonvolatile memory, the charge retaining characteristic of the charge trapping type nonvolatile memory is effectively improved, the storage window is favorably enlarged, the erasing and writing speeds are increased, and the storage performance of the charge trapping type nonvolatile memory is improved comprehensively, thereby laying the foundation for further microminiaturizing devices.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

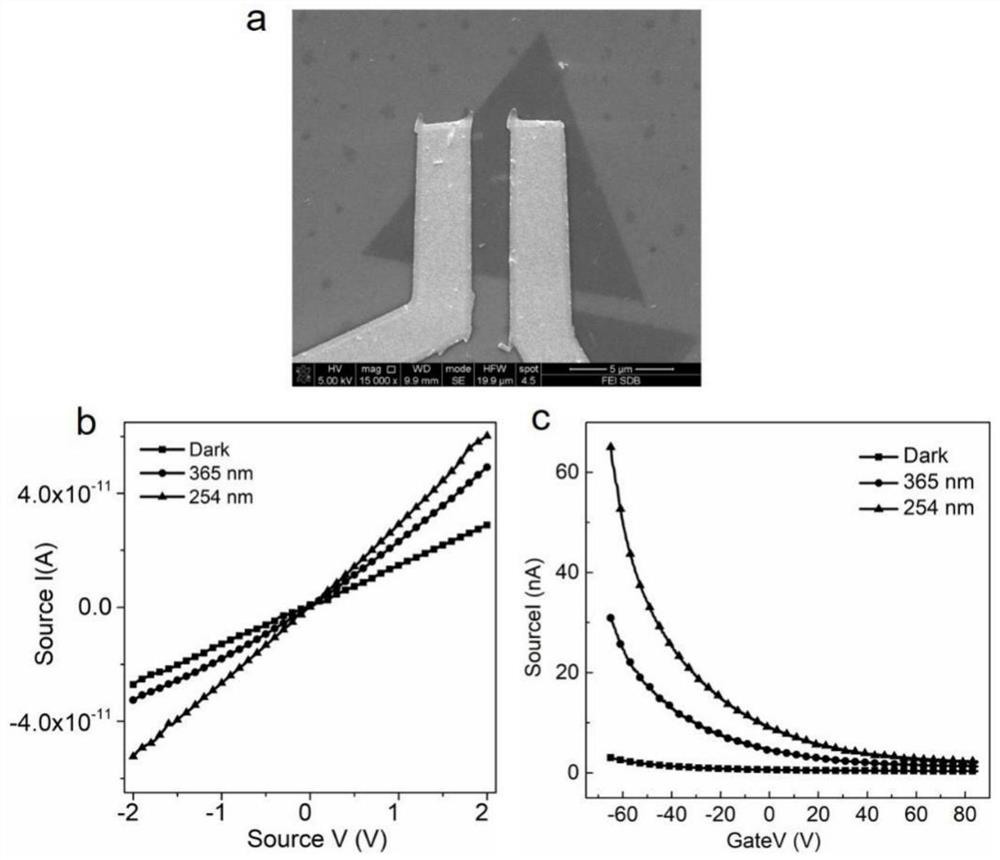

Zinc oxide ultraviolet photoelectric detector with adjustable gate voltage and preparation method thereof

ActiveCN113193071ALower channel resistanceGrid voltage adjustableFinal product manufactureNanosensorsPhotovoltaic detectorsUltraviolet

The invention relates to the technical field of ultraviolet photoelectric detectors, in particular to a zinc oxide ultraviolet photoelectric detector with adjustable gate voltage and a preparation method thereof. The zinc oxide ultraviolet photoelectric detector with the adjustable gate voltage comprises an insulating silicon substrate arranged on a bottom layer, a two-dimensional zinc oxide nanosheet layer arranged on the insulating silicon substrate and an electrode layer arranged on the two-dimensional zinc oxide nanosheet layer, wherein the electrode layer is composed of two metal electrodes which are not intersected with each other, and a zinc oxide channel is formed in the interval position of the two metal electrodes. Furthermore, a two-dimensional material layer is arranged between the two-dimensional zinc oxide nanosheet layer and each metal electrode, and the two-dimensional material has metallic property or semi-metallic property. According to the invention, the ultra-thin zinc oxide nanosheet is synthesized by using an ion layer epitaxial method, and the ultra-thin zinc oxide ultraviolet photoelectric detector capable of regulating and controlling the performance of the photoelectric detector through an external electric field is designed.

Owner:UNIV OF SCI & TECH BEIJING

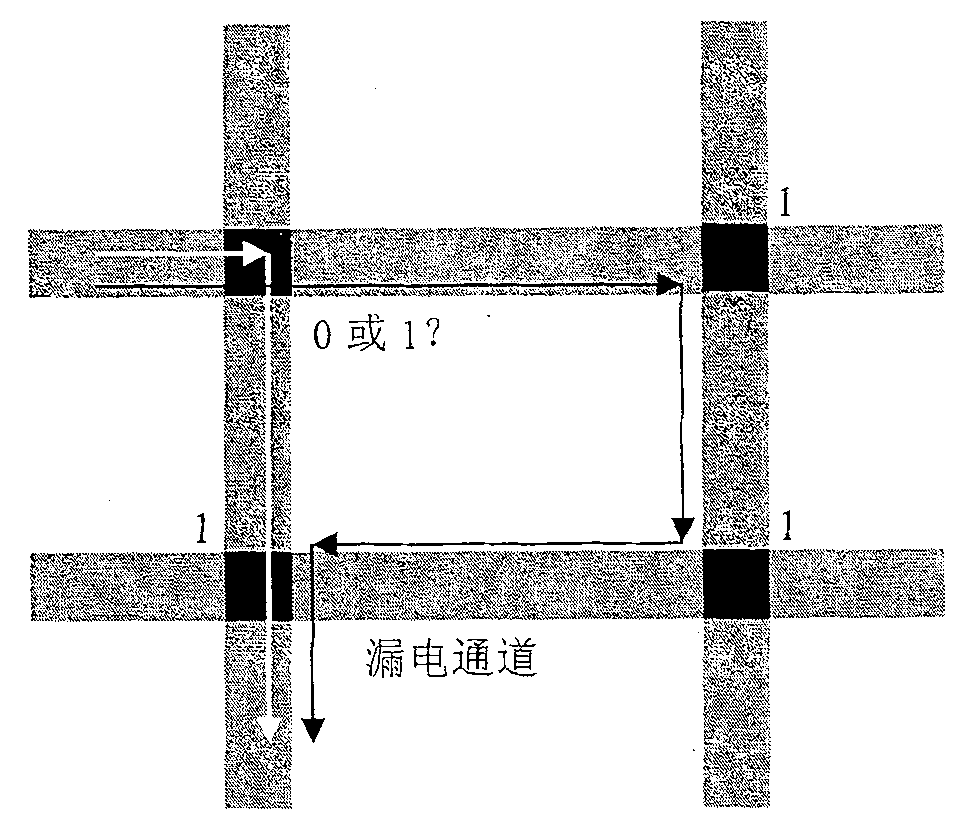

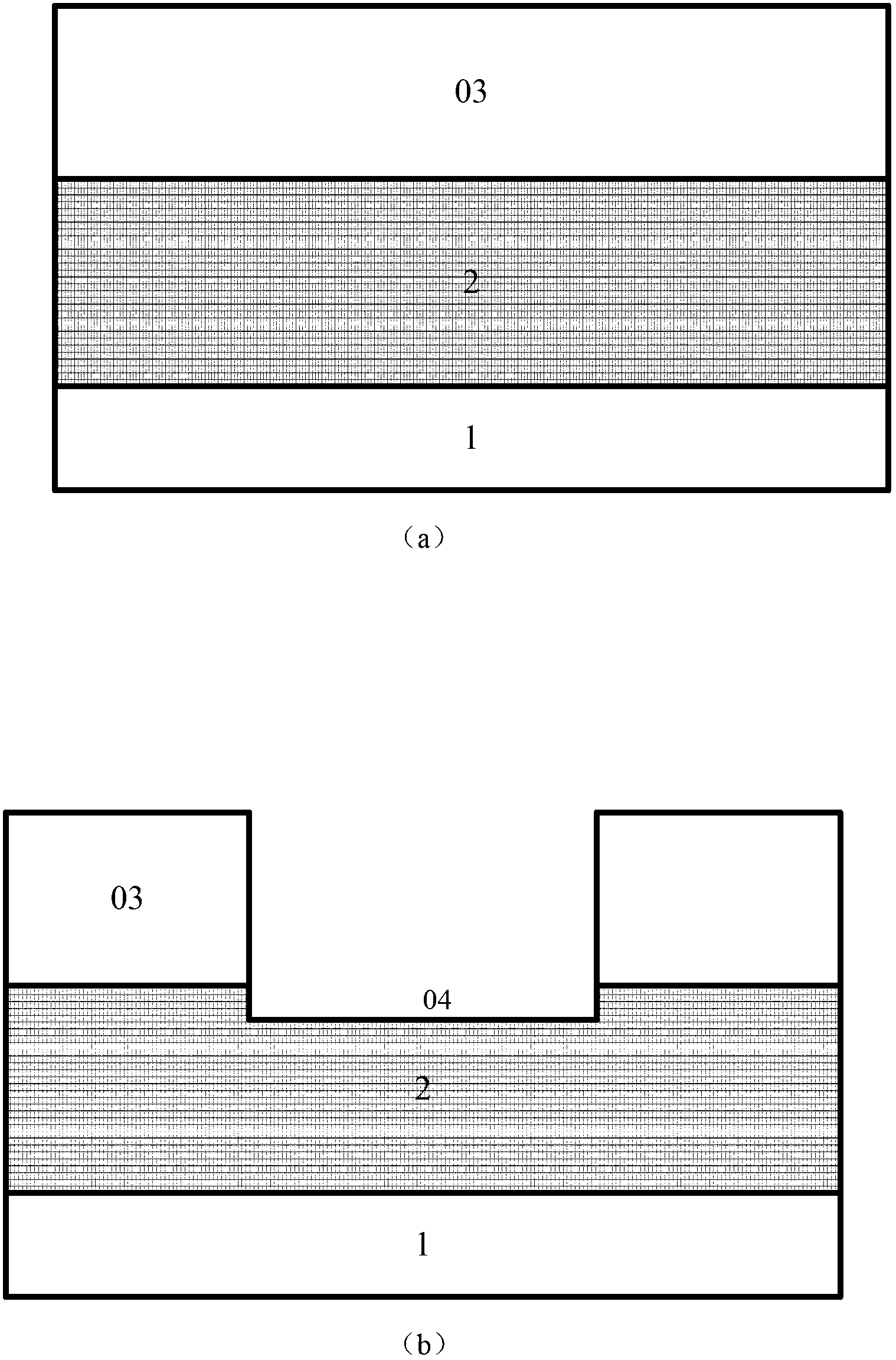

Silicon-on-insulator (SOI) device capable of restraining back gate leakage current caused by radiation and preparation method of SOI device

ActiveCN102938418ASuppress back gate leakage currentImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesBody regionBuried oxide

The invention discloses an SOI device capable of restraining back gate leakage current caused by radiation and a preparation method of the SOI device. The SOI device comprises a substrate, a buried oxide layer, a semiconductor body region, a grid region, a source region, a drain region, a grid side wall, a lightly doped drain (LDD) region and a leakproof region, wherein the leakproof region is sunk in the buried oxide layer and is located below the semiconductor body region. According to the photoetching SOI device, the buried oxide layer forms a sunk region, a semiconductor material is grown in an epitaxial mode and is doped regionally to form the leakproof region, the second portion in the middle is a heavily-doped region and is not easily radiated by positively charged trapped charge transoid formed by buried oxide, the back gate leakage current of the SOI device, which is caused by radiation, can be effectively restrained, and the reliability of the SOI device in a radiation environment is improved. According to the SOI device and the preparation method, only conventional processes such as photoetching, epitaxy and ion implantation doping are introduced during preparation of the conventional SOI device, so that the process is simple and compatible with existing technologies.

Owner:PEKING UNIV

Charge trapping type nonvolatile memory and manufacturing method thereof

InactiveCN102117838AProcessing technology compatibleReduce the chance of leaksSolid-state devicesSemiconductor/solid-state device manufacturingCharge retentionTrapping

The invention discloses a charge trapping type nonvolatile memory and a manufacturing method thereof. The memory comprises a silicon substrate, a source conducting region and a drainage conducting region heavily doped on the silicon substrate, a tunneling dielectric layer formed by covering an SiO2 medium on a carrier channel between the source conducting region and the drainage conducting region, a first trapping layer covering on the tunneling dielectric layer, a second trapping layer covering on the first trapping layer, a control grid dielectric layer formed by high-k AI2O3 covering on a ZrO2 / Si3N4 stacked trapping layer which is formed by the first trapping layer and the second trapping layer, and a grid material layer covering on the control grid dielectric layer. The charge trapping type nonvolatile memory effectively improves the charge maintaining characteristic, is beneficial to the increasing of the memory window, improves the erasing speed, improves the memorizing characteristic comprehensively, and lays the foundation for further shrinkage of the charge trapping type nonvolatile memory.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Preparation method of metal chalcogenide film

ActiveCN103194729BControl thicknessSmall sizeChemical vapor deposition coatingDeposition temperatureSulfur

The invention discloses a method for preparing a metal chalcogenide film. The method is used for growing the metal chalcogenide film on a substrate with the vapor deposition process by using a chalcogen source and a metal element source and comprises the following steps of: providing three temperature zones, wherein the temperature of the three temperature zones can be controlled independently, and the chalcogen source, the metal element source and the substrate are put in the three temperature zones respectively; controlling the three temperature zones, evaporating the chalcogen source to generate the chalcogen source steam, evaporating the metal element source to generate the metal element source steam, and heating the substrate to the predetermined deposition temperature; providing a carrier gas, and enabling the carrier gas to flow through the three temperature zones in sequence to deliver the metal element source steam to the substrate to deposit and grow so as to form the metal chalcogenide film. The method disclosed by the invention is simple, dispenses with the original complex step of introducing a nucleation site and effectively ensures the purity and the surface cleanness of a sample. The metal chalcogenide film prepared by adopting the method has high quality.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

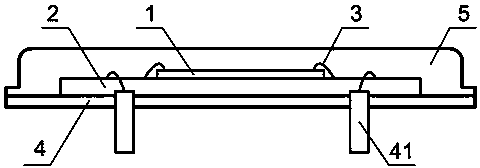

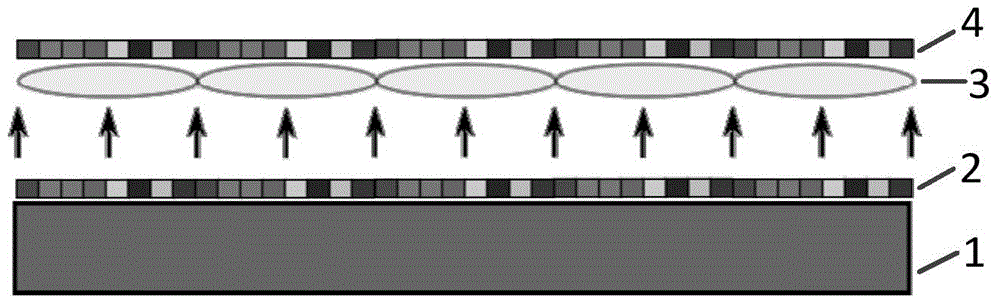

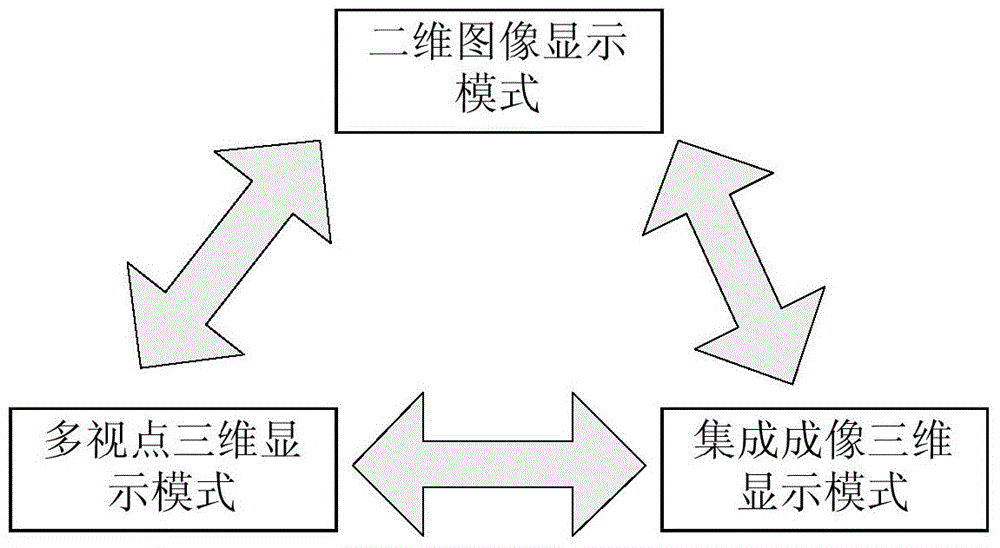

Two-dimensional display mode and three-dimensional display mode switchable display device and method

InactiveCN104320648AMeet the needs of different viewing modesProcessing technology compatibleSteroscopic systemsOptical elementsParallaxComputer science

The invention discloses a two-dimensional display mode and three-dimensional display mode switchable device and method. The problem that an existing display device is simple in display mode is mainly solved. The two-dimensional display mode and three-dimensional display mode switchable device comprises a backlight source (1), a built-in liquid crystal layer (3), an external liquid crystal layer (2) and a lens array (4). When the built-in liquid crystal layer is in an all-pass state, the backlight source, the built-in liquid crystal layer and the lens array form a new backlight source, and light intensity is modulated through the external liquid crystal layer to achieve two-dimensional image display. The built-in liquid crystal layer, the backlight source and the lens array form a directional backlight source, and a two-dimensional anaglyph is displayed through the external liquid crystal layer to achieve multi-view three-dimensional display. When the external liquid crystal layer is in the all-pass state, unit image arrays are displayed through the built-in liquid crystal layer to achieve integrated imaging three-dimensional display. The two-dimensional display mode and three-dimensional display mode switchable device and method can achieve free switching of two-dimensional image display, multi-view three-dimensional display and integrated imaging three-dimensional display and can be used for display of televisions, computers and the like.

Owner:XIDIAN UNIV

Method for reducing thermal strain of surface acoustic wave device chip packaging

InactiveCN103346753AEnsure consistencyGuaranteed complianceImpedence networksElectricitySurface layer

The invention discloses a method for reducing thermal strain of surface acoustic wave device chip packaging. A set of ring-shaped structure which is synchronously manufactured with a surface acoustic wave device is manufactured in the edge area of a piezoelectric single-crystal substrate of a surface acoustic wave device chip, the ring-shaped structure is made of materials with a certain thermo-mechanical characteristic, a compound structure with complementary thermo-mechanical characteristics is formed by the ring-shaped structure, the piezoelectric single-crystal substrate and a packaging base, and the ring-shaped structure is a ring-shaped band manufactured on the surface of the piezoelectric single-crystal substrate, or a ring-shaped strip embedded into the surface layer of the piezoelectric single-crystal substrate. A thermal strain reducing structure is simple and compact, is arranged in a non-device area on the edge of the surface acoustic wave device chip, and cannot cause direct influence on parameters of a geometric structure of the surface acoustic wave device, electrical parameters of the surface acoustic wave device cannot degrade, consistency, conformance and reliability of the surface acoustic wave device can be ensured, and a manufacturing method for the thermal strain reducing structure can be compatible with a conventional processing technology of the surface acoustic wave device, and can be easily achieved with the surface acoustic wave device in a synchronous mode.

Owner:YANGZHOU UNIV

Dyadic transition group metallic oxide non-volatilization electric resistance transition type memory

InactiveCN101471421BProcessing technology compatibleHigh yieldSolid-state devicesRead-only memoriesHigh resistanceElectrical resistance and conductance

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Method for making nano-groove on quartz glass

InactiveCN101037185BGood micromachining propertiesProcessing technology compatibleDecorative surface effectsLaboratory glasswaresGraphicsReactive-ion etching

The invention relates to a nano-channel preparing method on a piece of quartz glass, characterized in that the crucial technology for preparing comprises three steps of photoetching, wet etching and linking, wherein the wet etching solution preparation is one of the crucial steps of the MEMS processing technology, and can directly influence the graphic structure of the nano-channels. The invention employs the quartz glass as the substrate material, the technology is simple and has no need of reactive ion etching equipment, and the depth error of the nano-channel can be precisely controlled tobe + / -1nm or so by regulating the etching time and temperature on the basis of the prepared etching solution.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Method for preparing flexible display module based on PDLC

InactiveCN103033968BGuaranteed machining accuracyProcessing technology compatibleNon-linear opticsMagentaElectrode array

Owner:BEIJING SAN WU JIU INVESTMENT

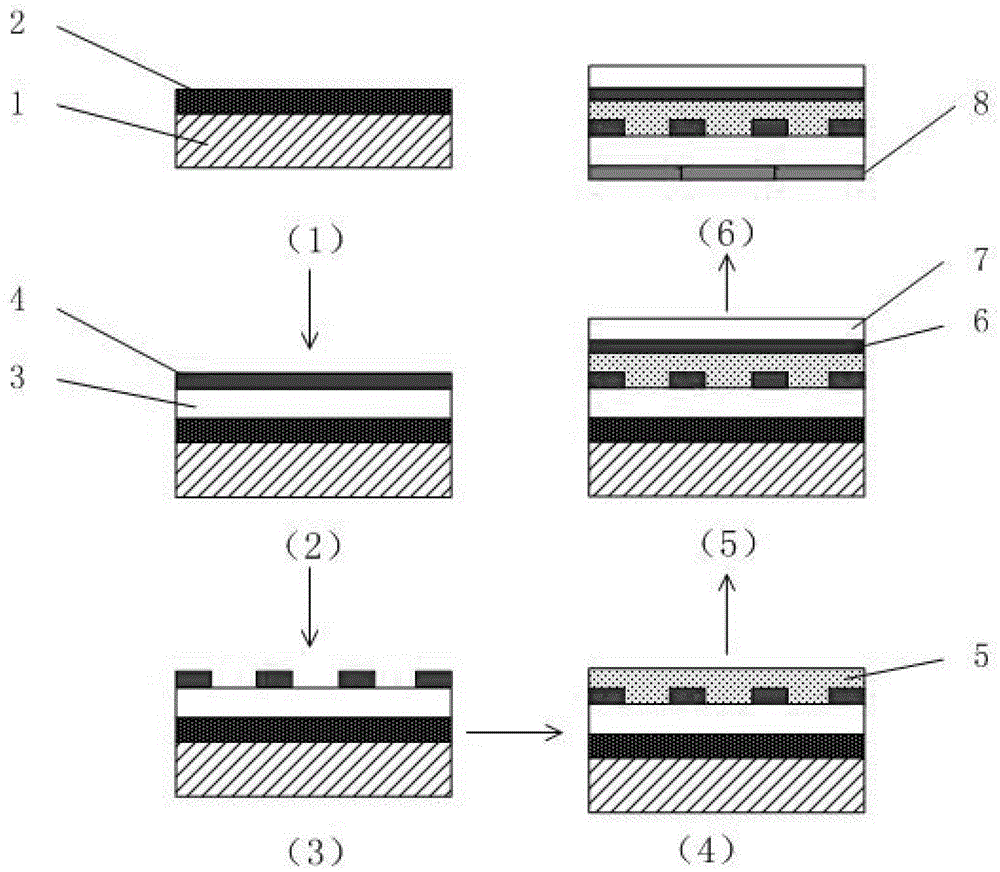

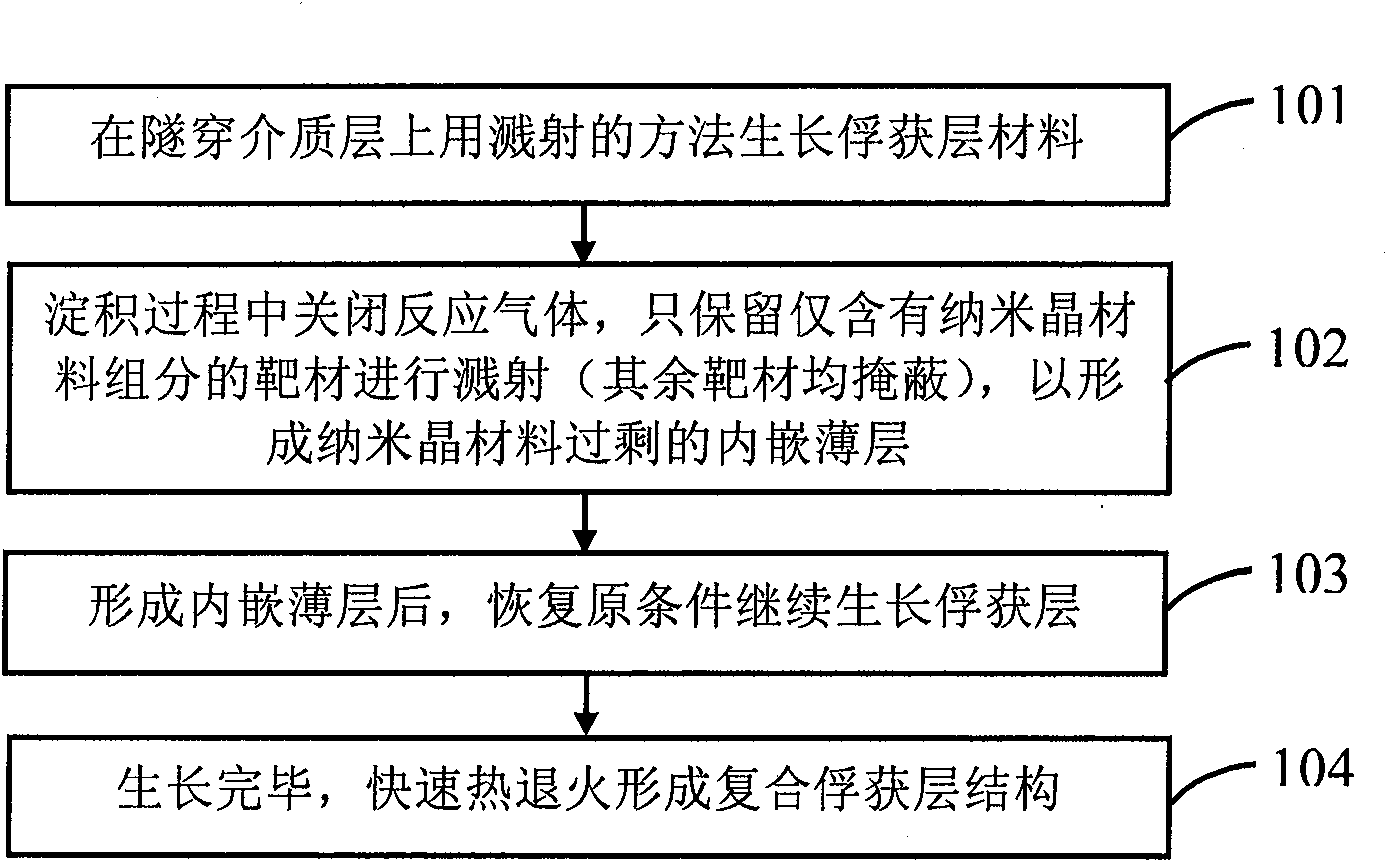

Method for preparing of compound trapping layer in floating gate type nonvolatile storage

ActiveCN101807521AProcessing technology compatibleSimple processNanostructure manufactureVacuum evaporation coatingCMOSTrapping

The invention discloses a method for preparing a compound trapping layer in a floating gate type nonvolatile storage, comprising the following steps of: co-sputtering a plurality of target materials on a tunneling medium layer by a sputtering process to deposit and grow a trapping layer medium; concealing other target materials and independently sputtering a certain target material in the sputtering process to form an embedded nanocrystalline thin-layer with surplus nanocrystalline materials in the trapping layer; after the embedded nanocrystalline thin-layer is formed, by recovering original process conditions to continuously grow trapping layer materials; and after the trapping layer materials are completely grown, forming a compound trapping layer structure stacked by nanocrystalline and the trapping layer through heat treatment. In the invention, the processing process of a device is compatible with the traditional CMOS (Complementary Metal-Oxide-Semiconductor Transistor) process, thereby greatly simplifying the process course, reducing the manufacturing cost and laying a foundation for the device to be trending towards practical application.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI