Patents

Literature

82results about How to "Reduce gate leakage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

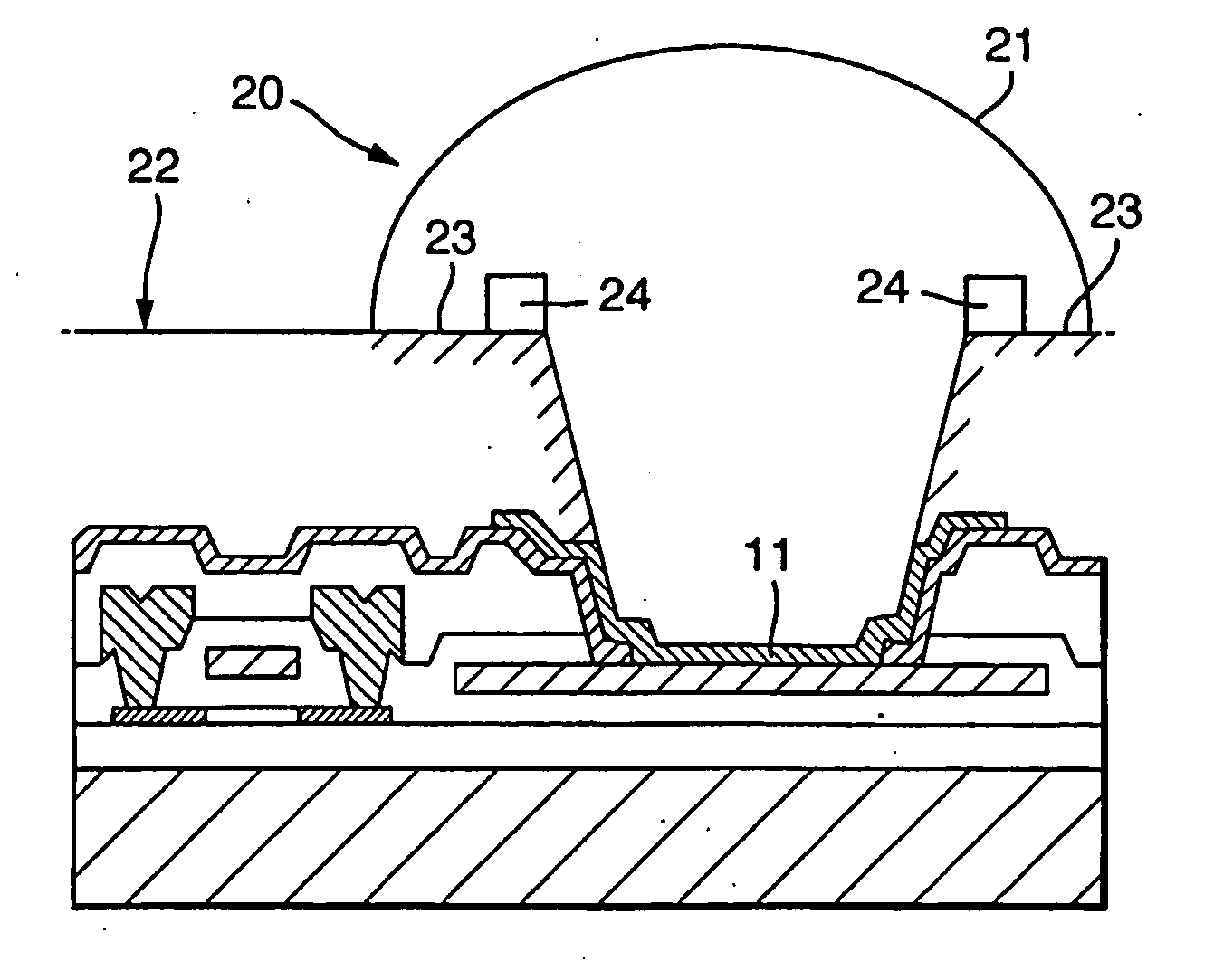

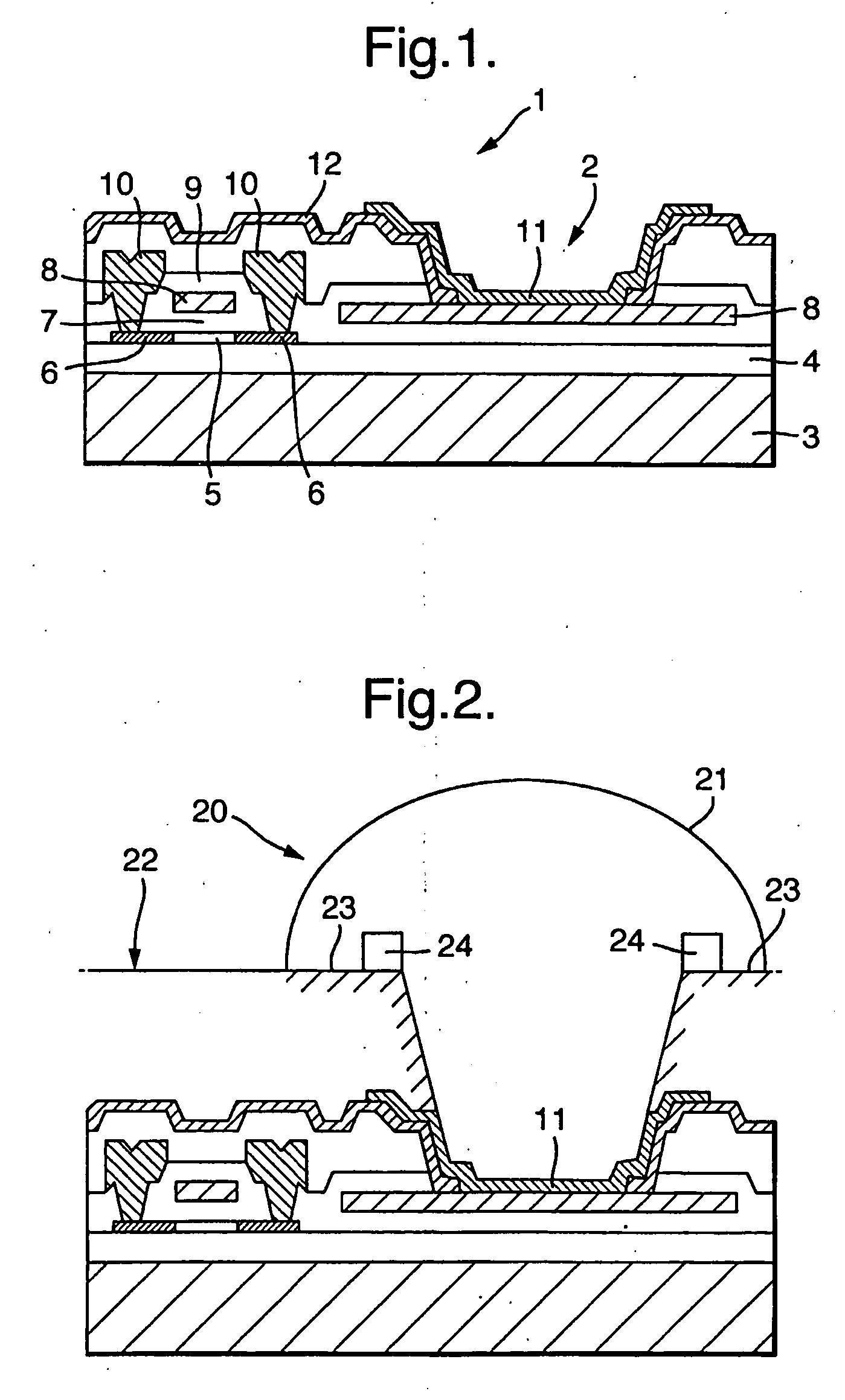

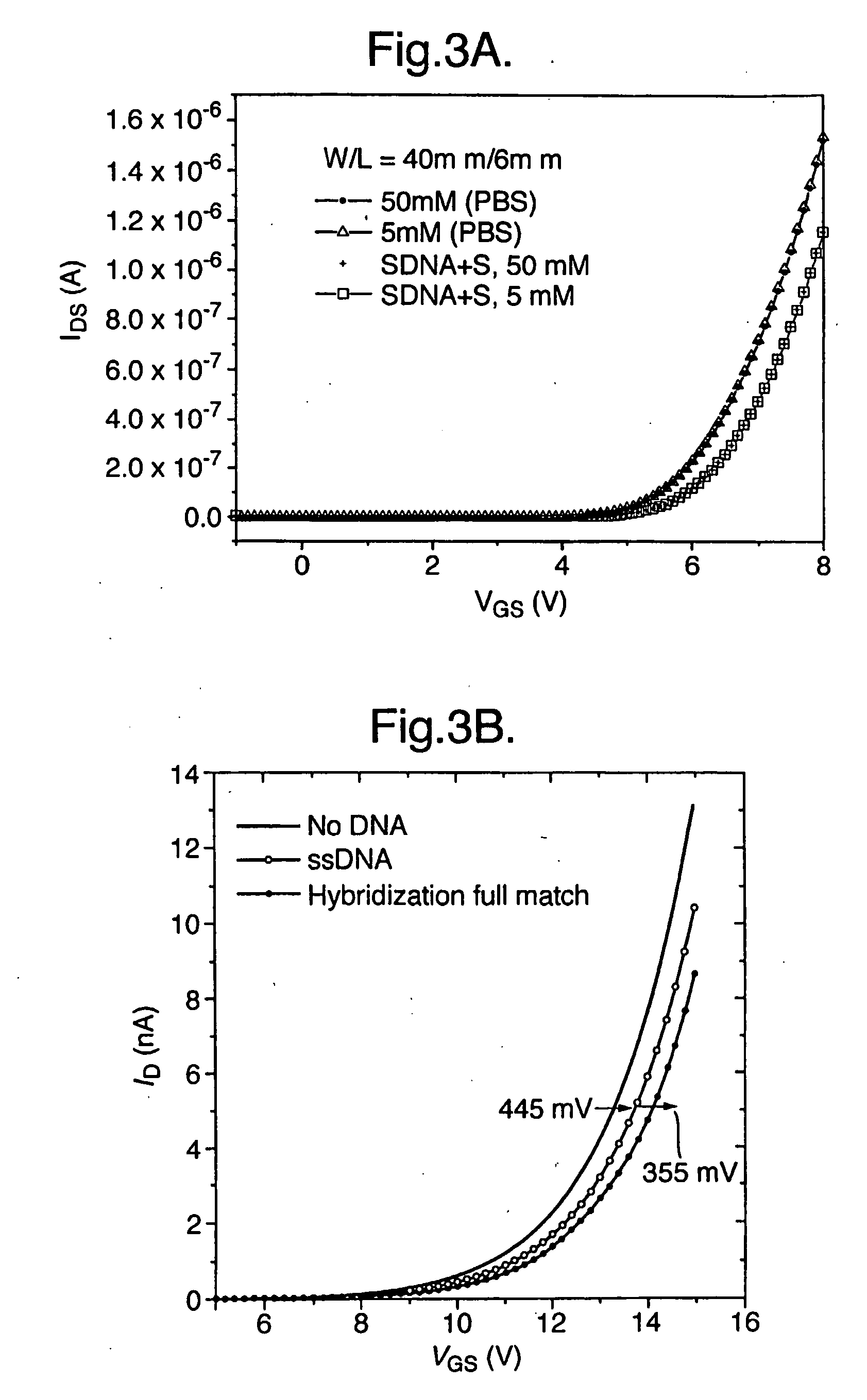

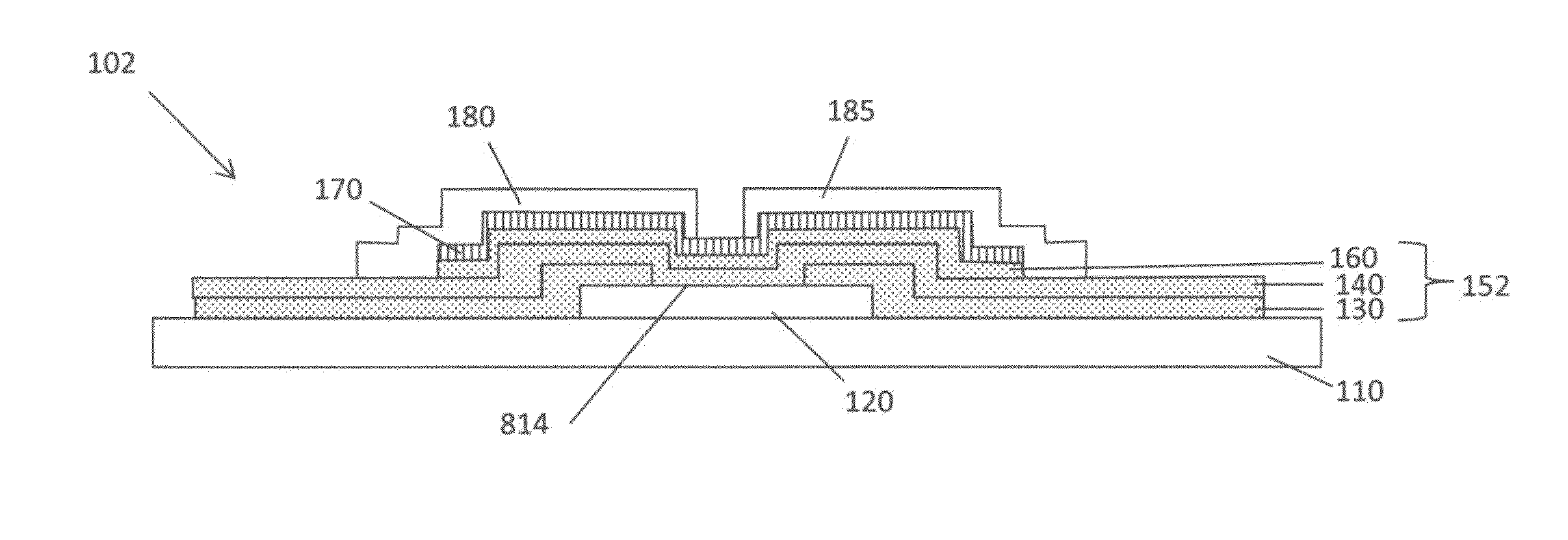

Detection of molecular interactions using a field effect transistor

InactiveUS20060197118A1Operation may changeHigh impedanceSemiconductor/solid-state device detailsSolid-state devicesField-effect transistorDNA

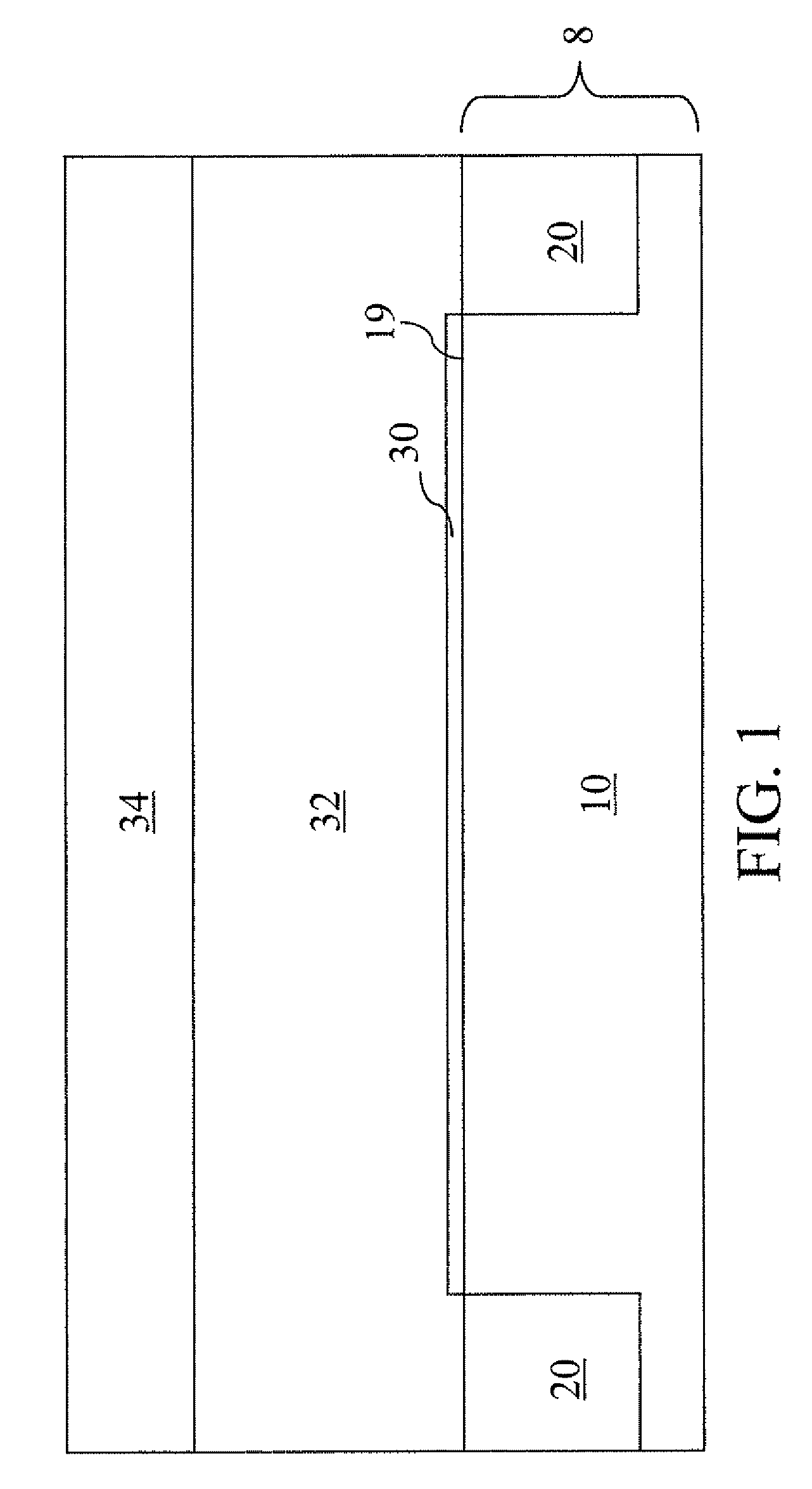

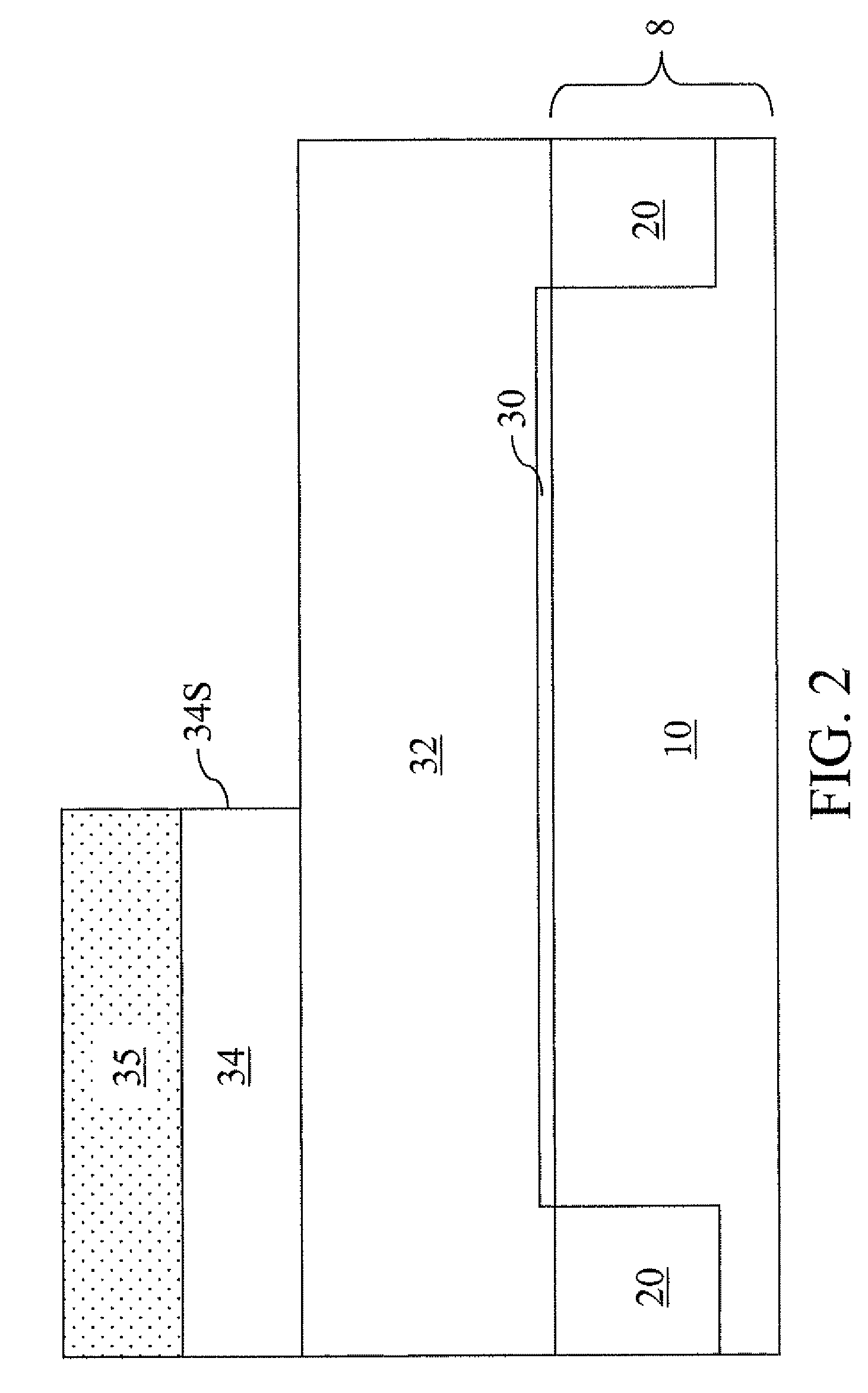

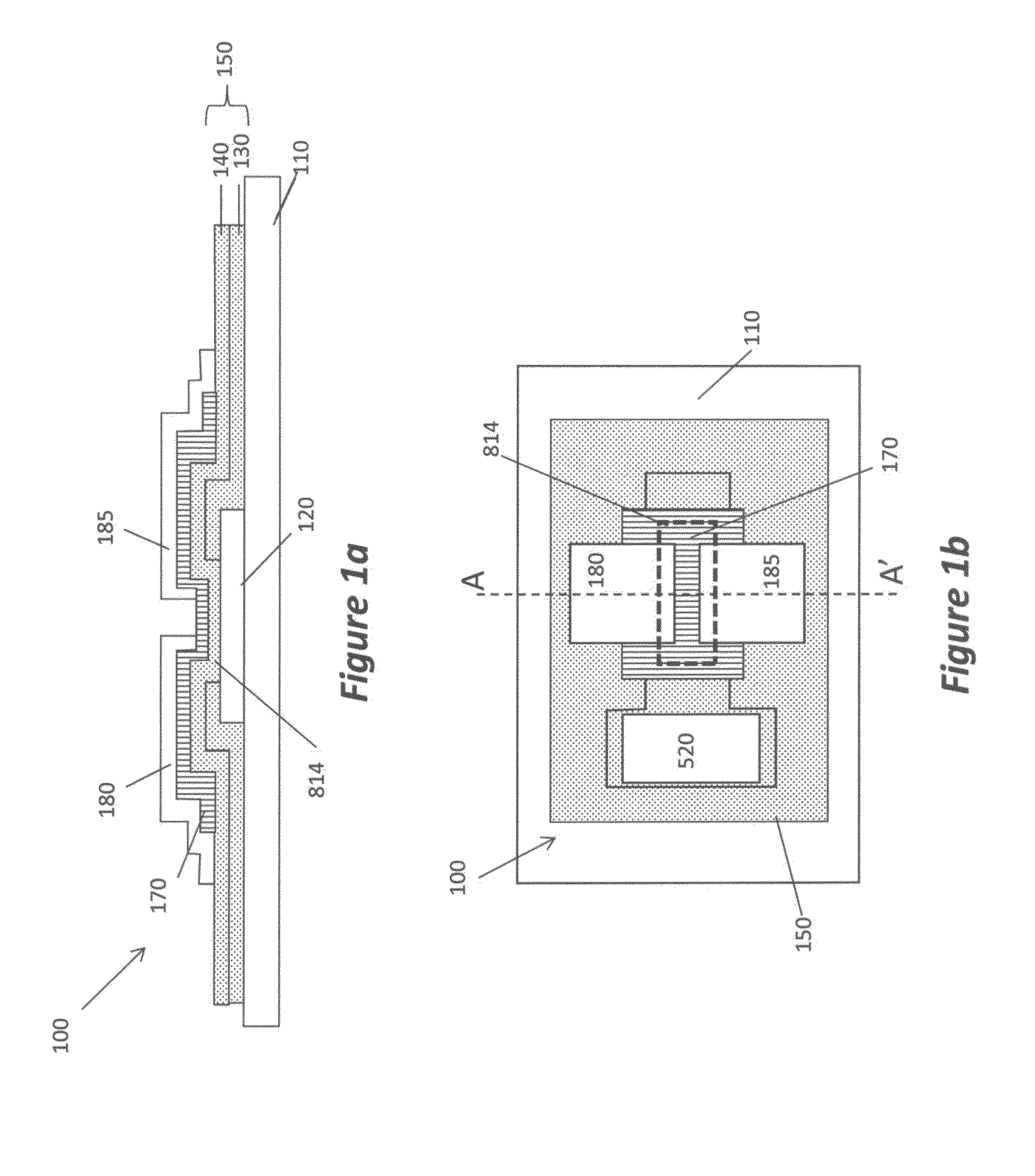

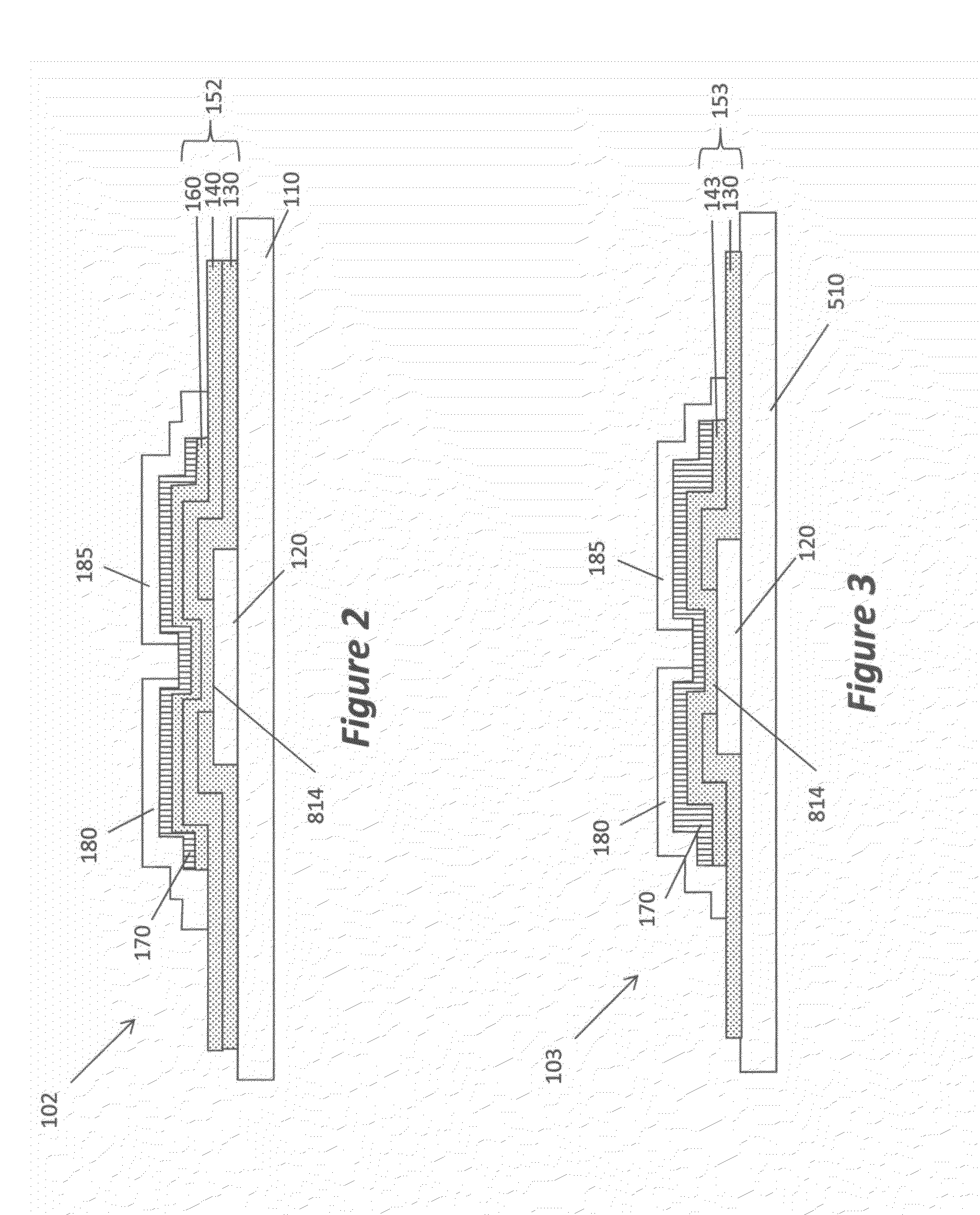

A sensor for use in the detection of a molecular interaction comprises a field effect transistor (FET) having a core structure and an extended gate structure, the core structure and the extended gate structure being located on substantially separate regions of a substrate, the extended gate structure including an exposed metal sensor electrode on which probe molecules can be immobilized, wherein, in use, the sensor is operative to produce a change in an electrical characteristic of the FET in response to molecular interaction at the exposed surface of the metal sensor electrode. The sensor is particularly suitable for detecting biomolecular interactions such as the hybridization of DNA, when the sensor is prepared with suitable probe molecules immobilized on the exposed gate metal.

Owner:CAMBRIDGE ENTERPRISE LTD

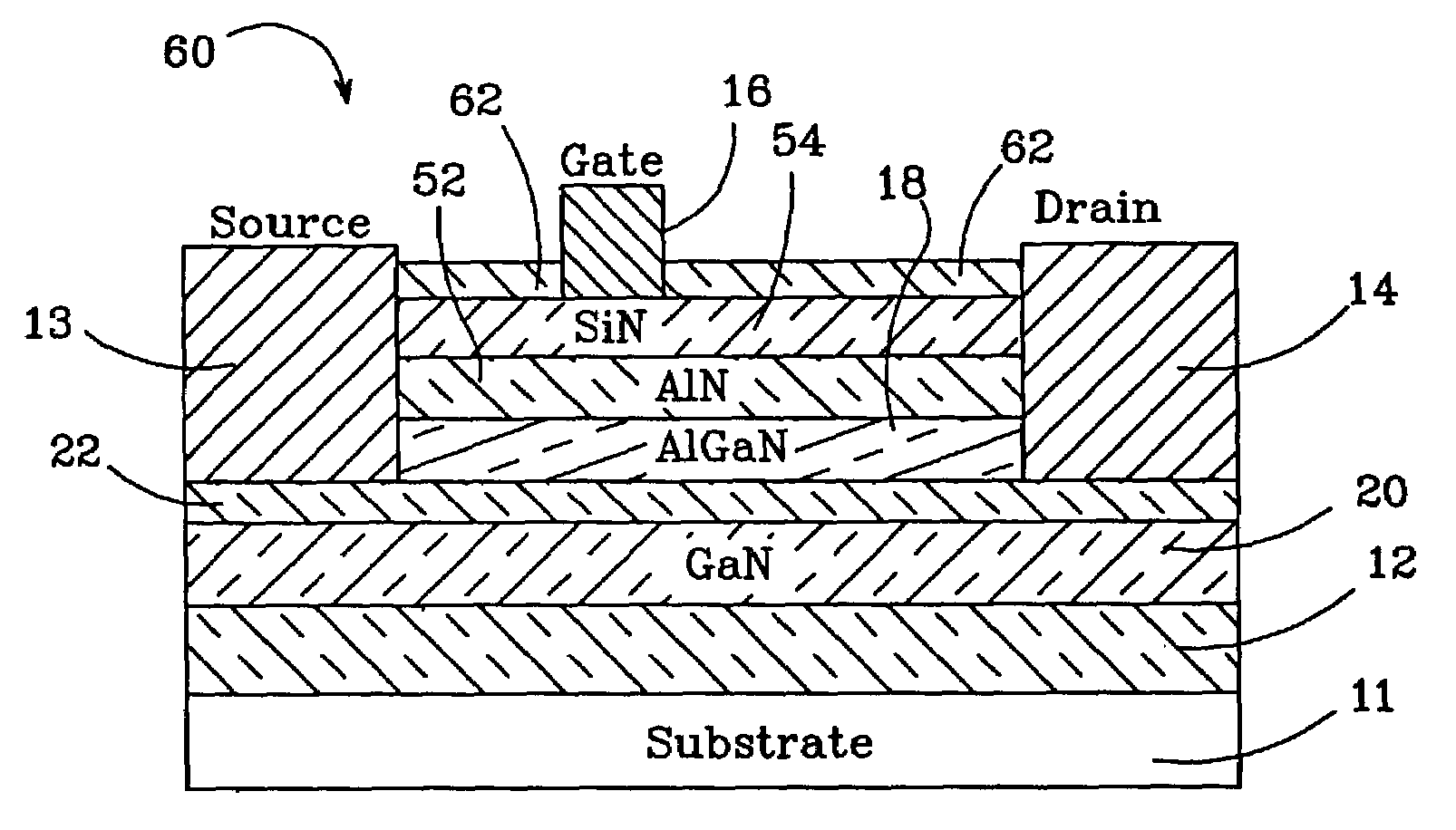

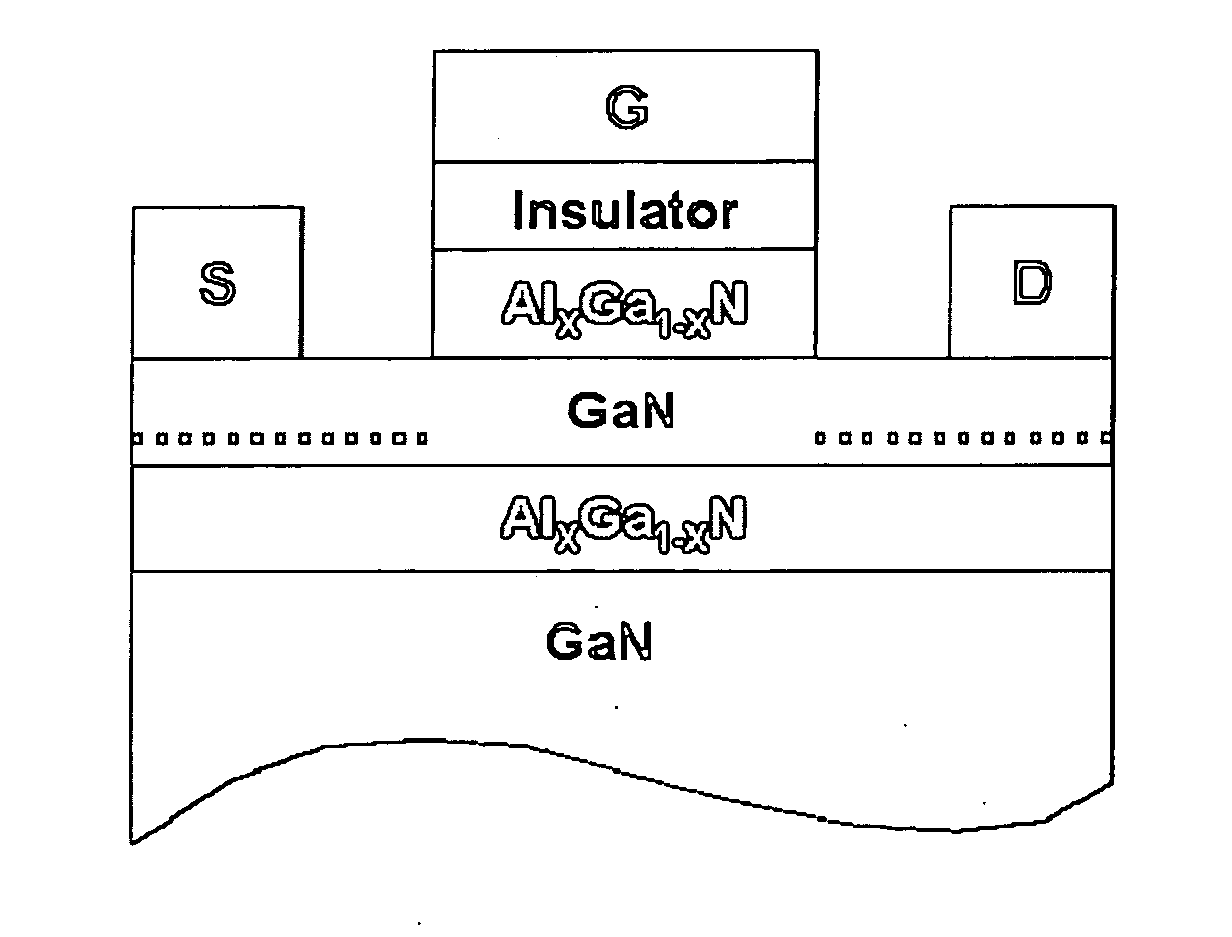

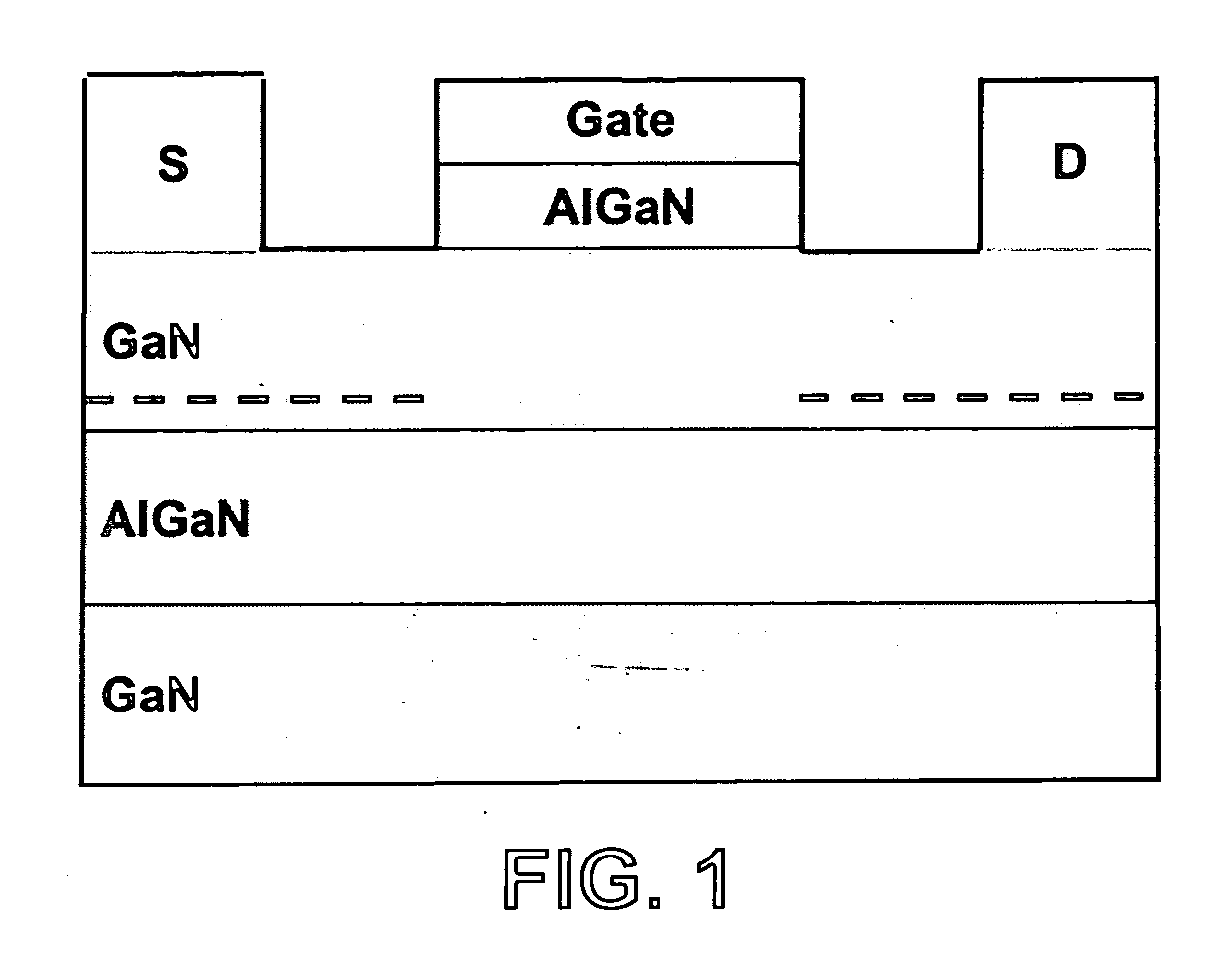

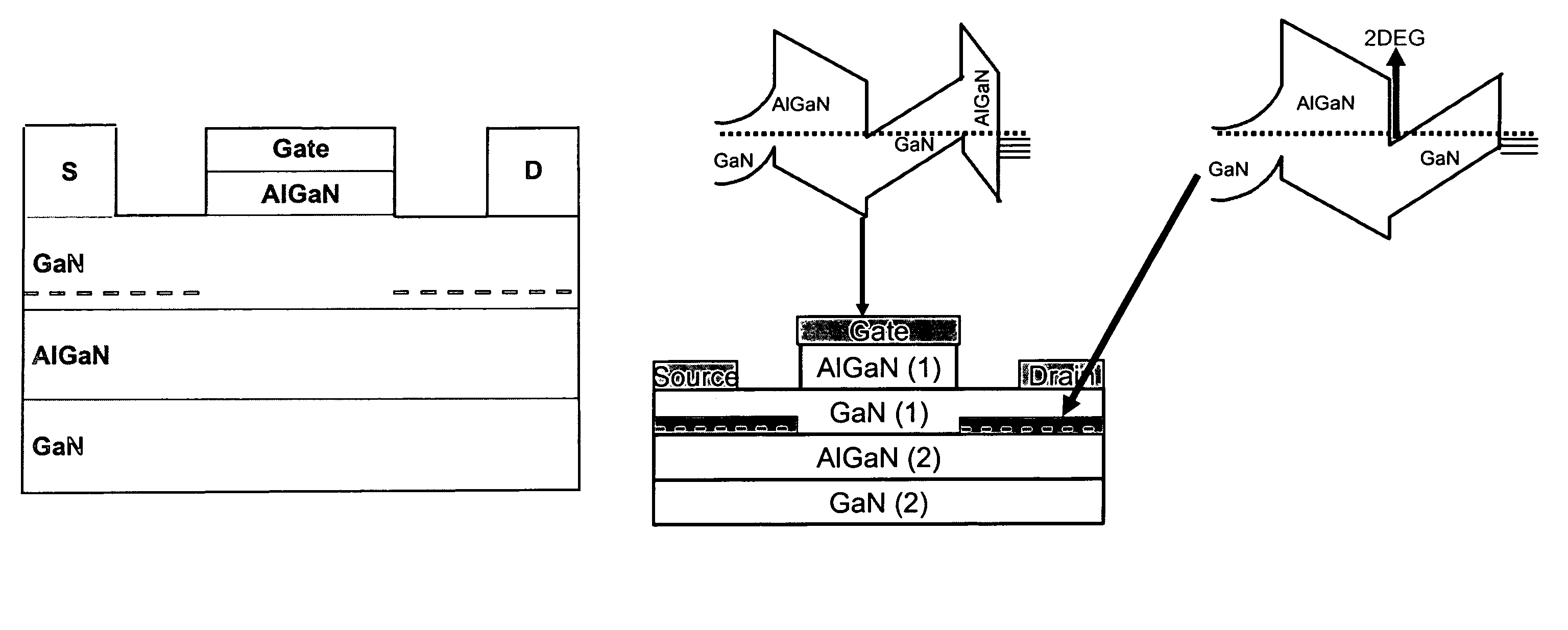

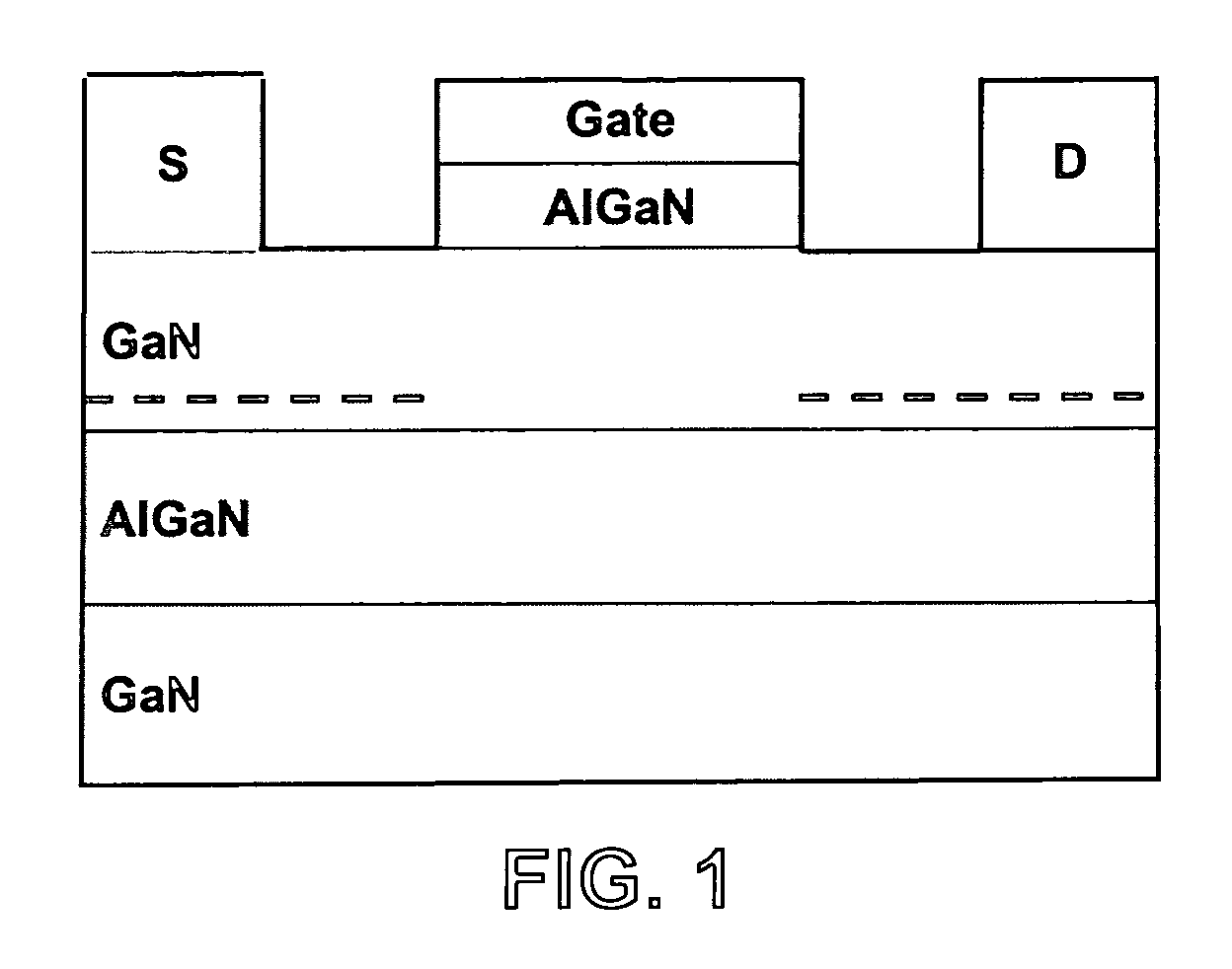

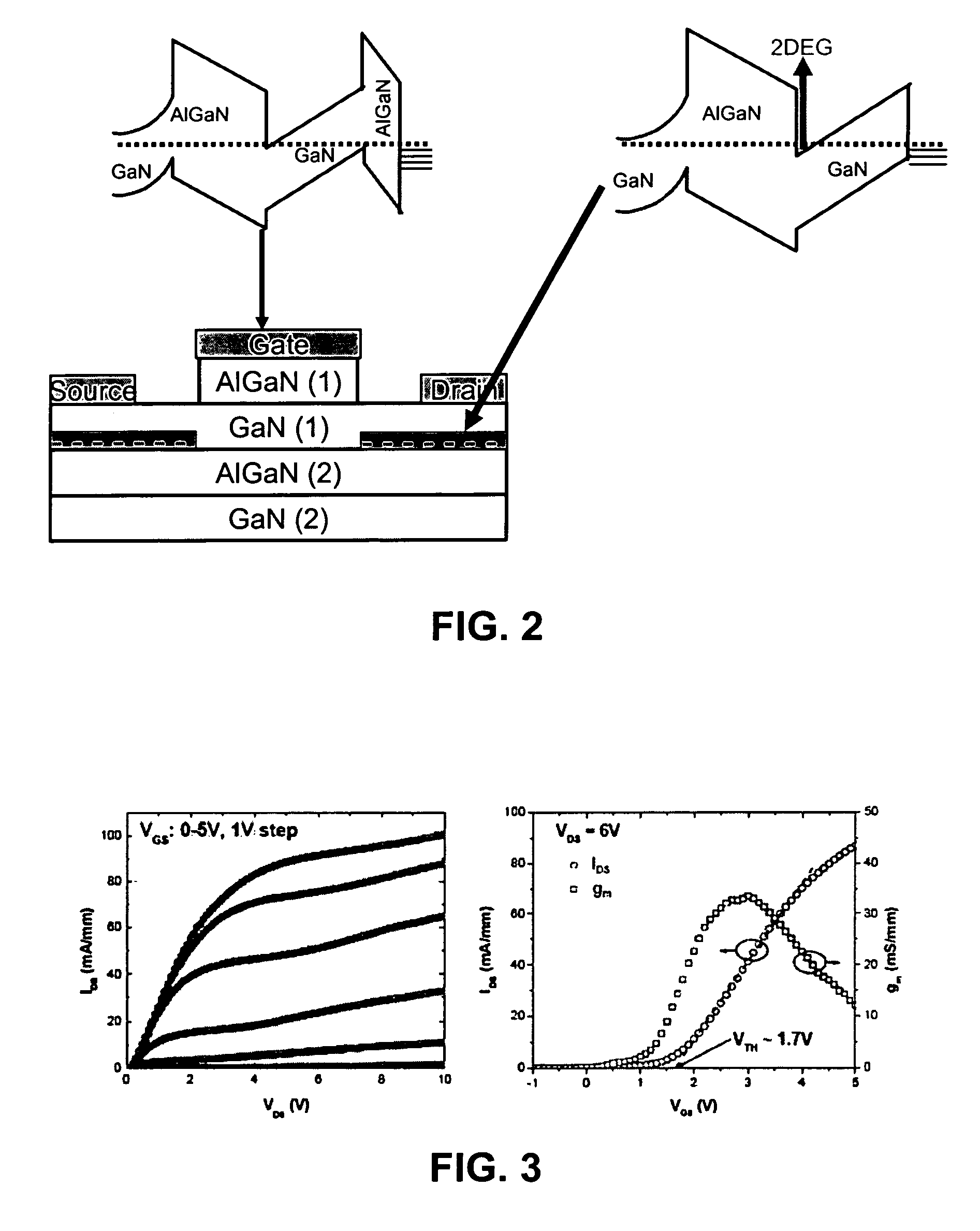

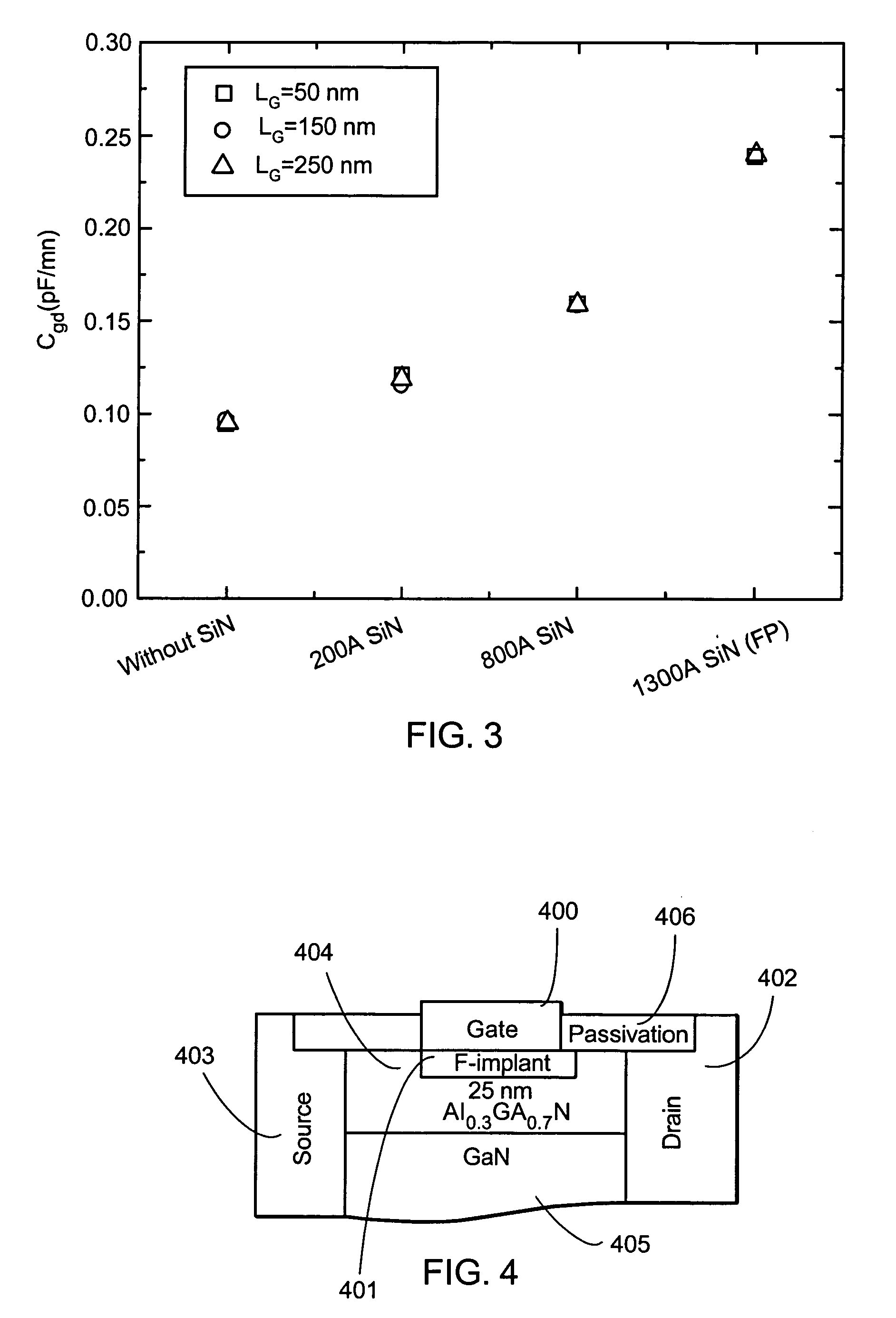

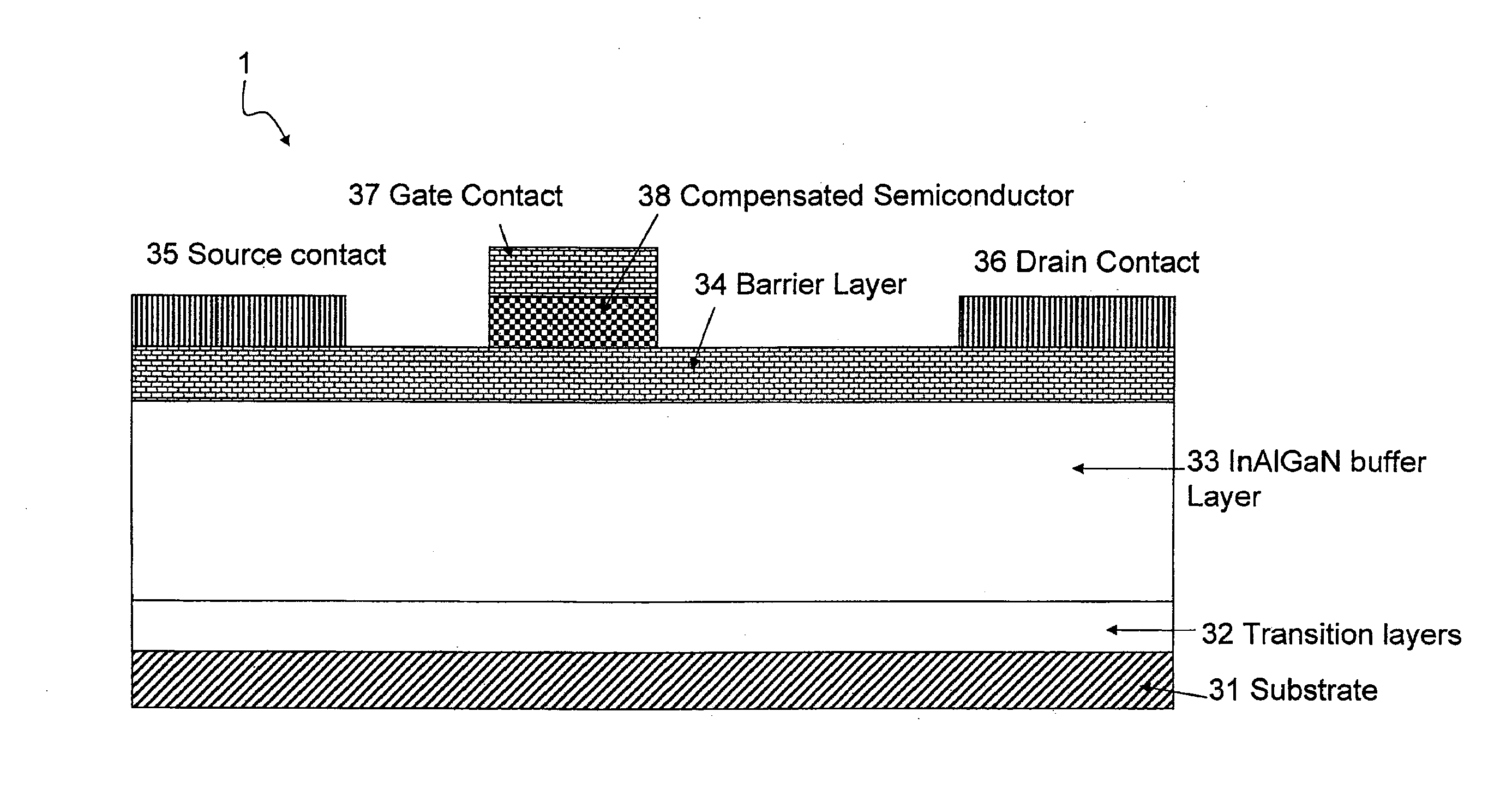

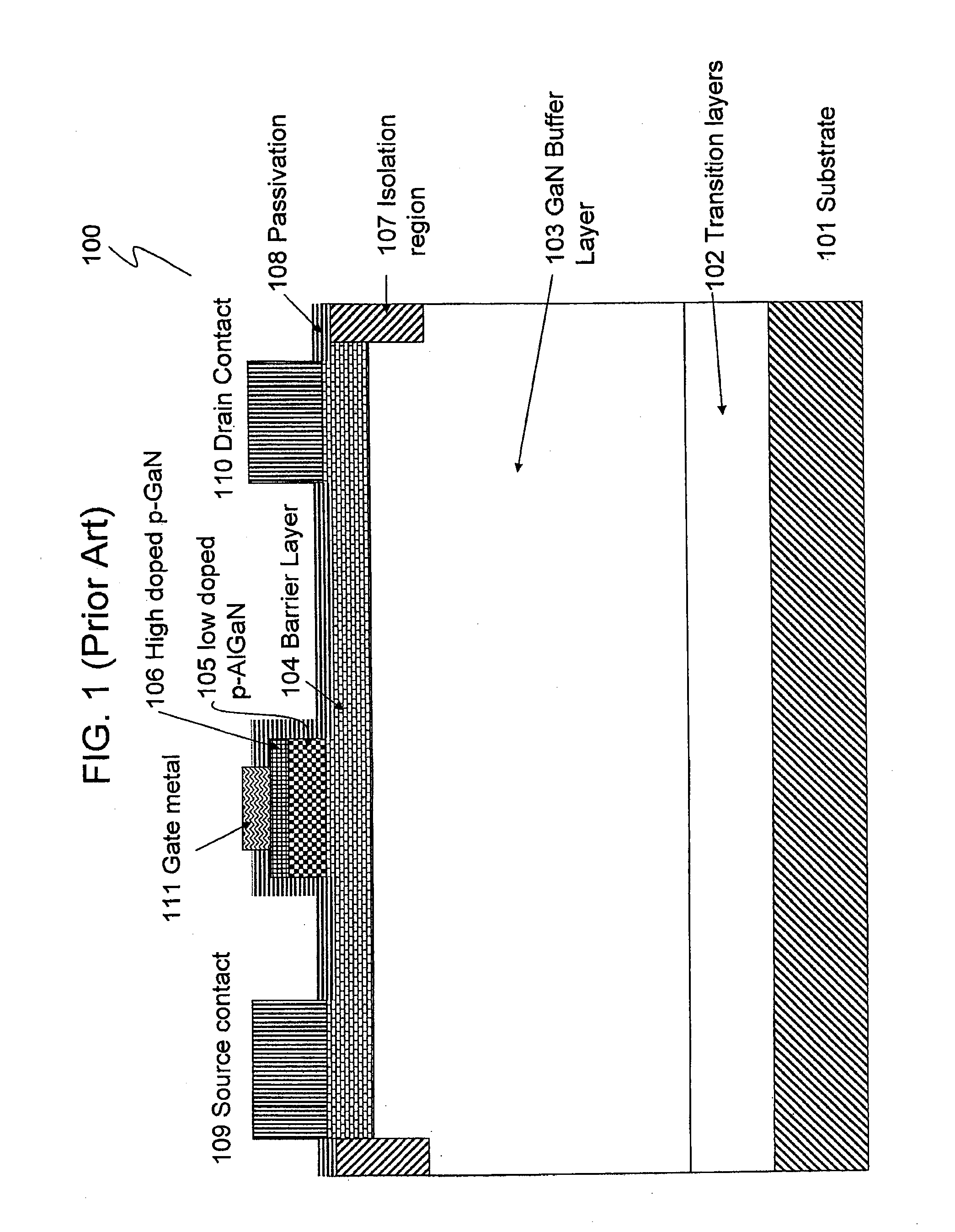

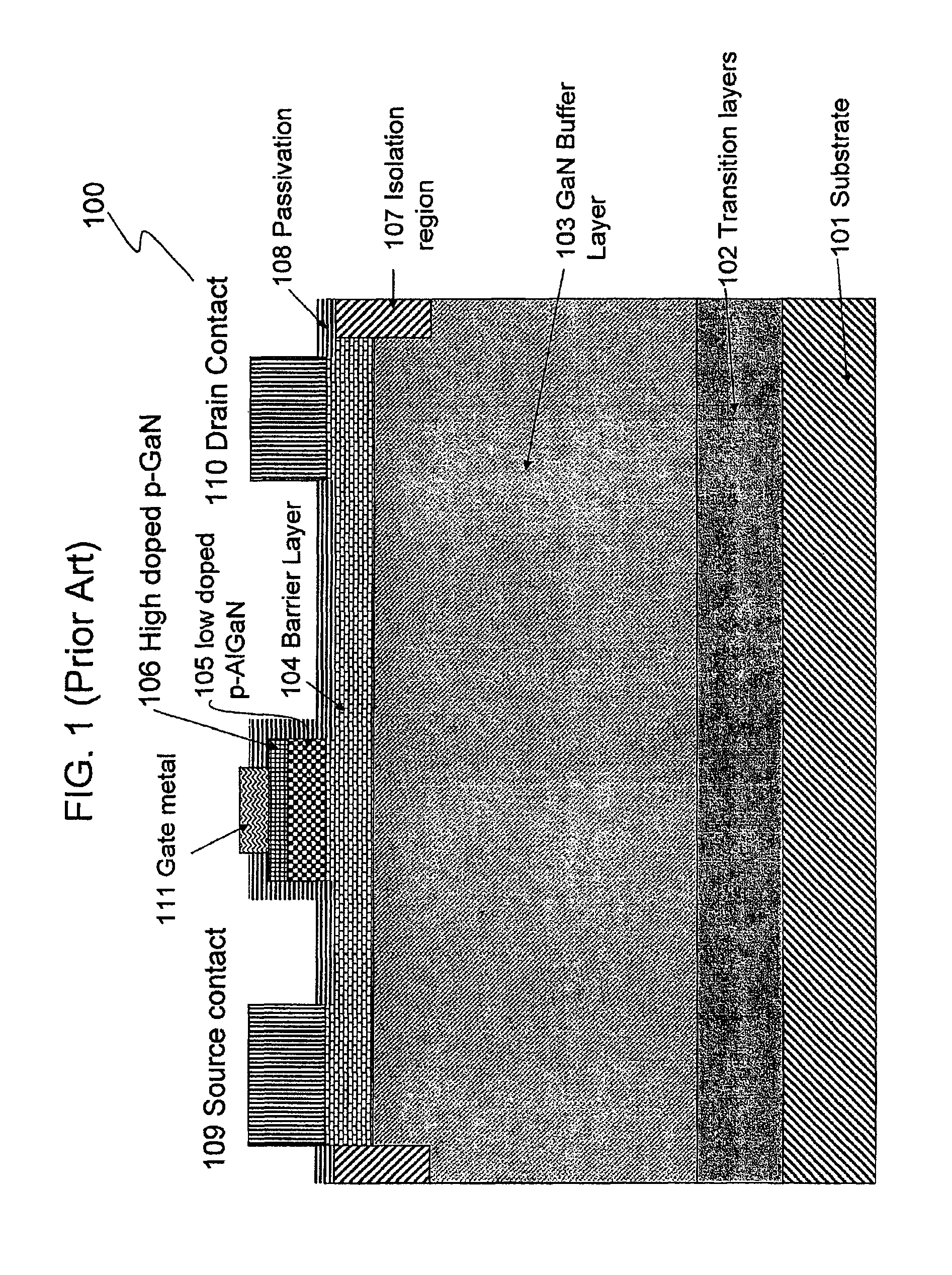

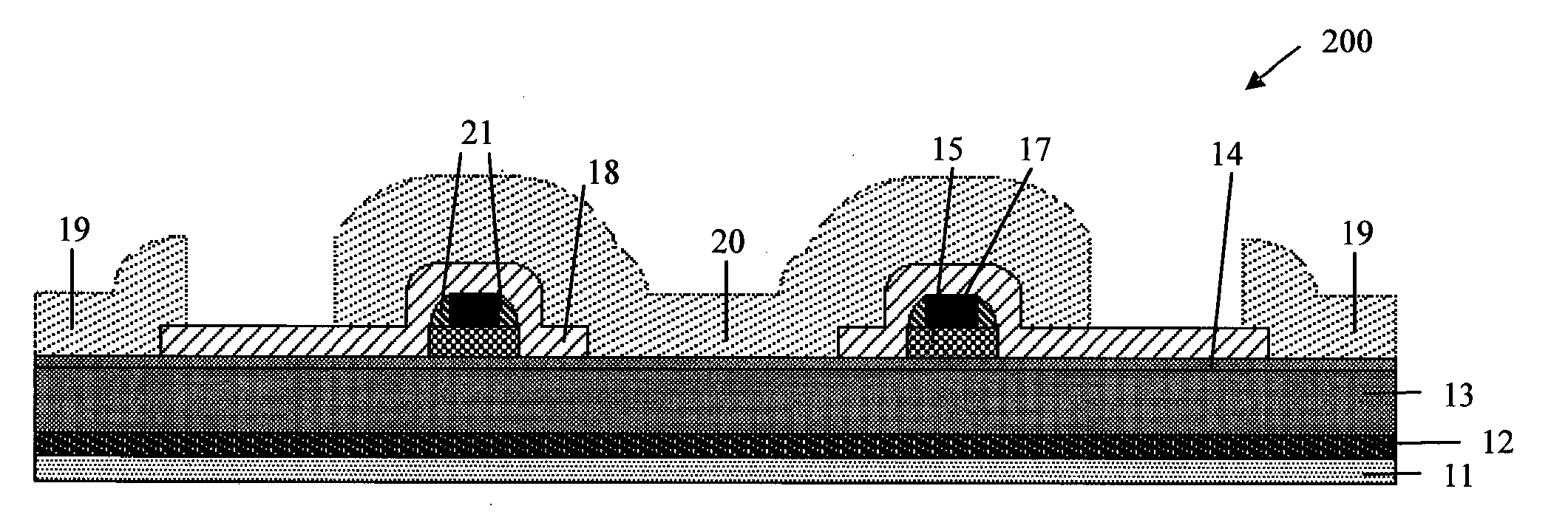

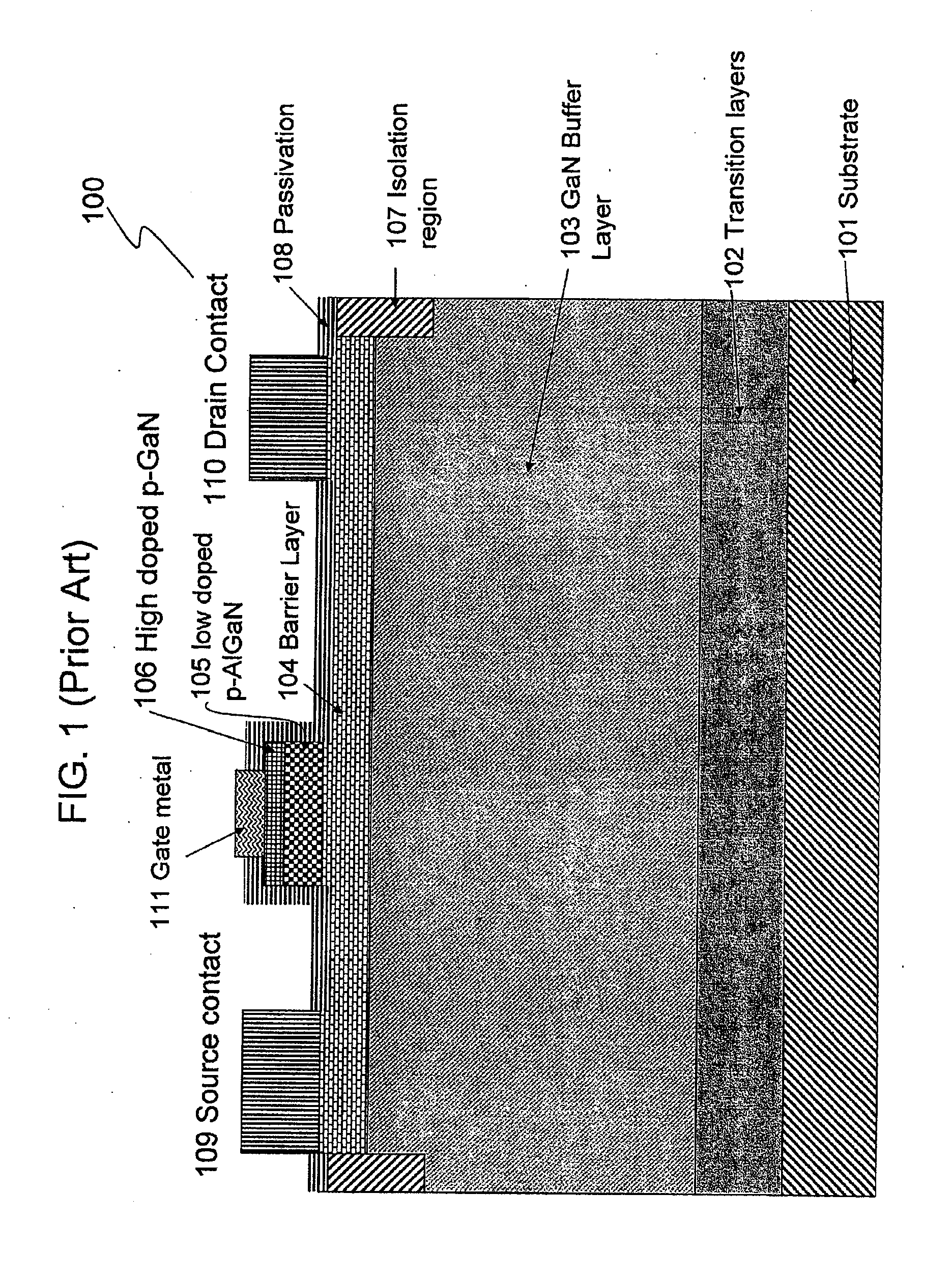

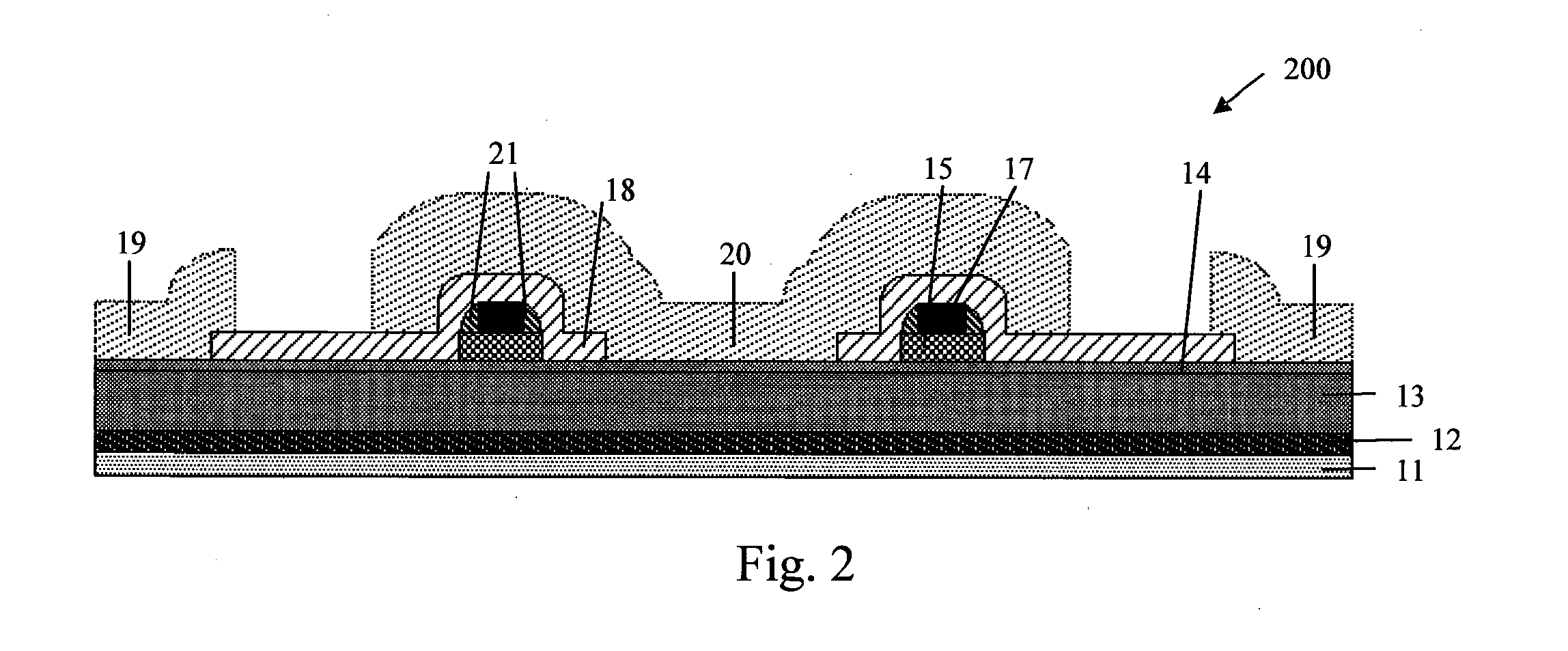

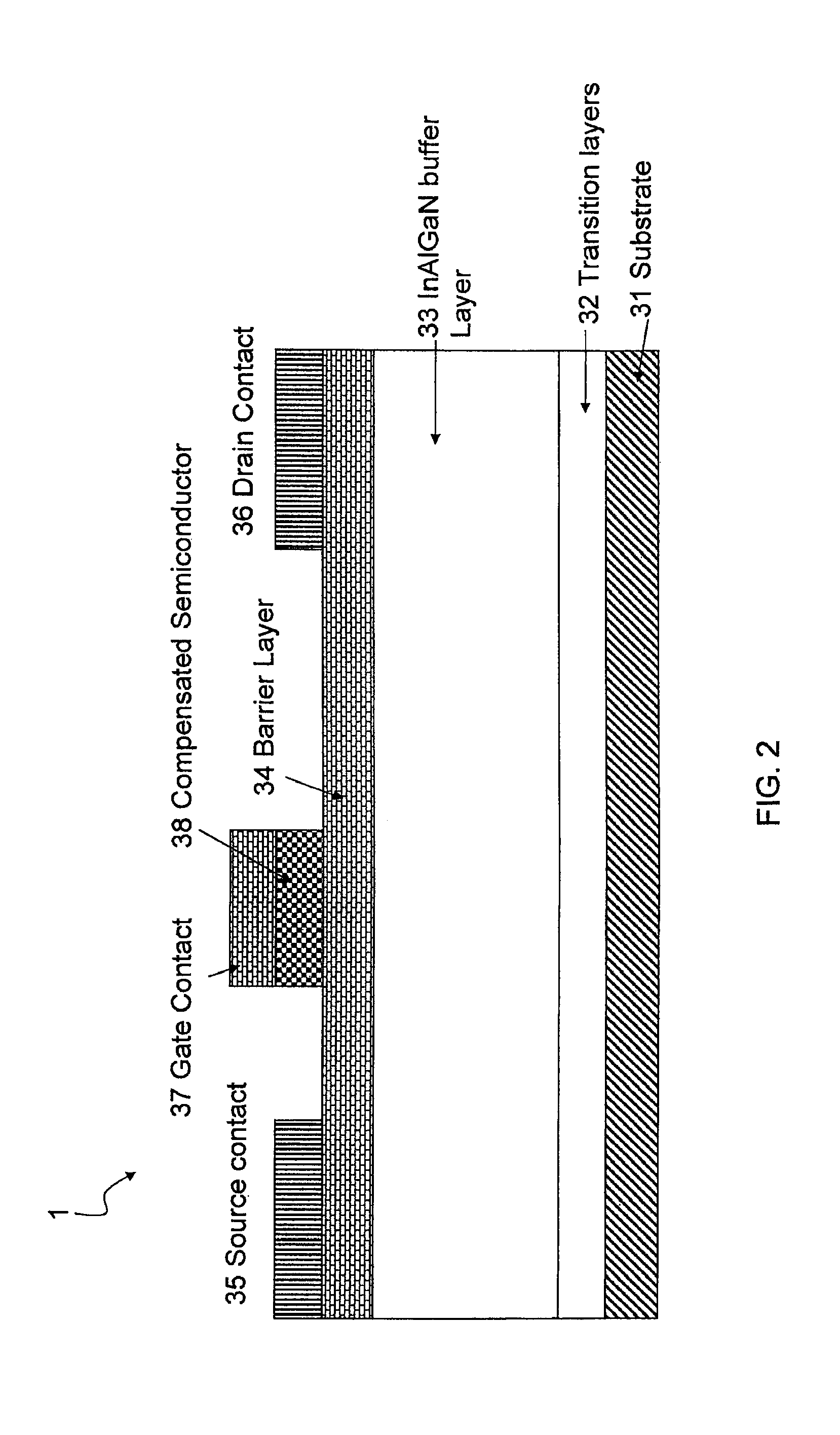

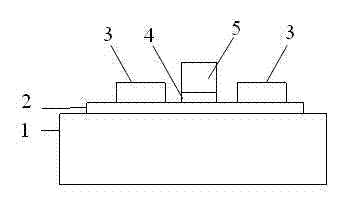

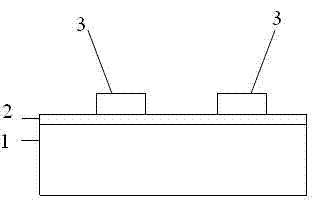

Insulating gate AlGaN/GaN HEMT

InactiveUS7230284B2Reduce trappingReduce gate leakageSemiconductor/solid-state device detailsSolid-state devicesGate leakage currentDriving current

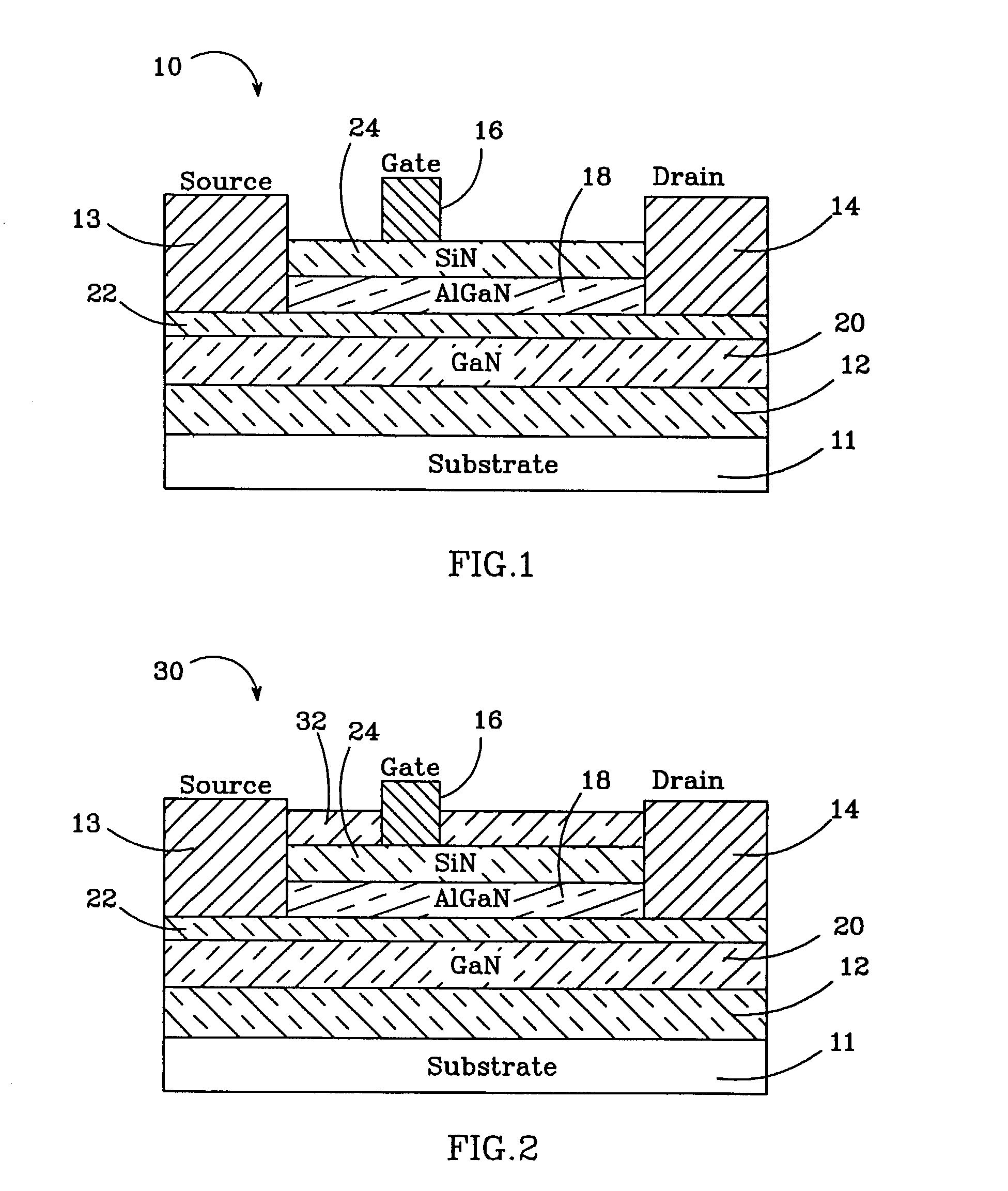

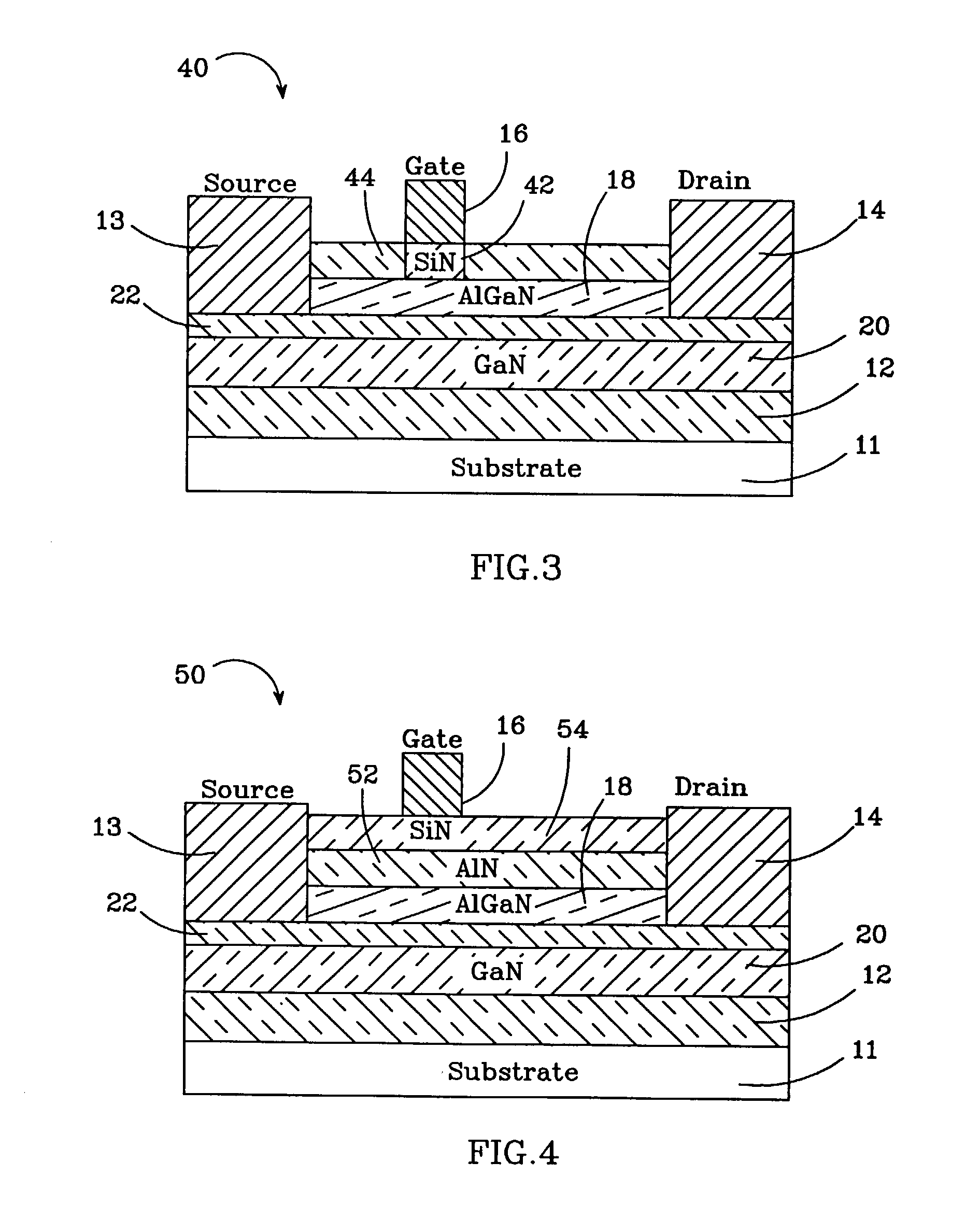

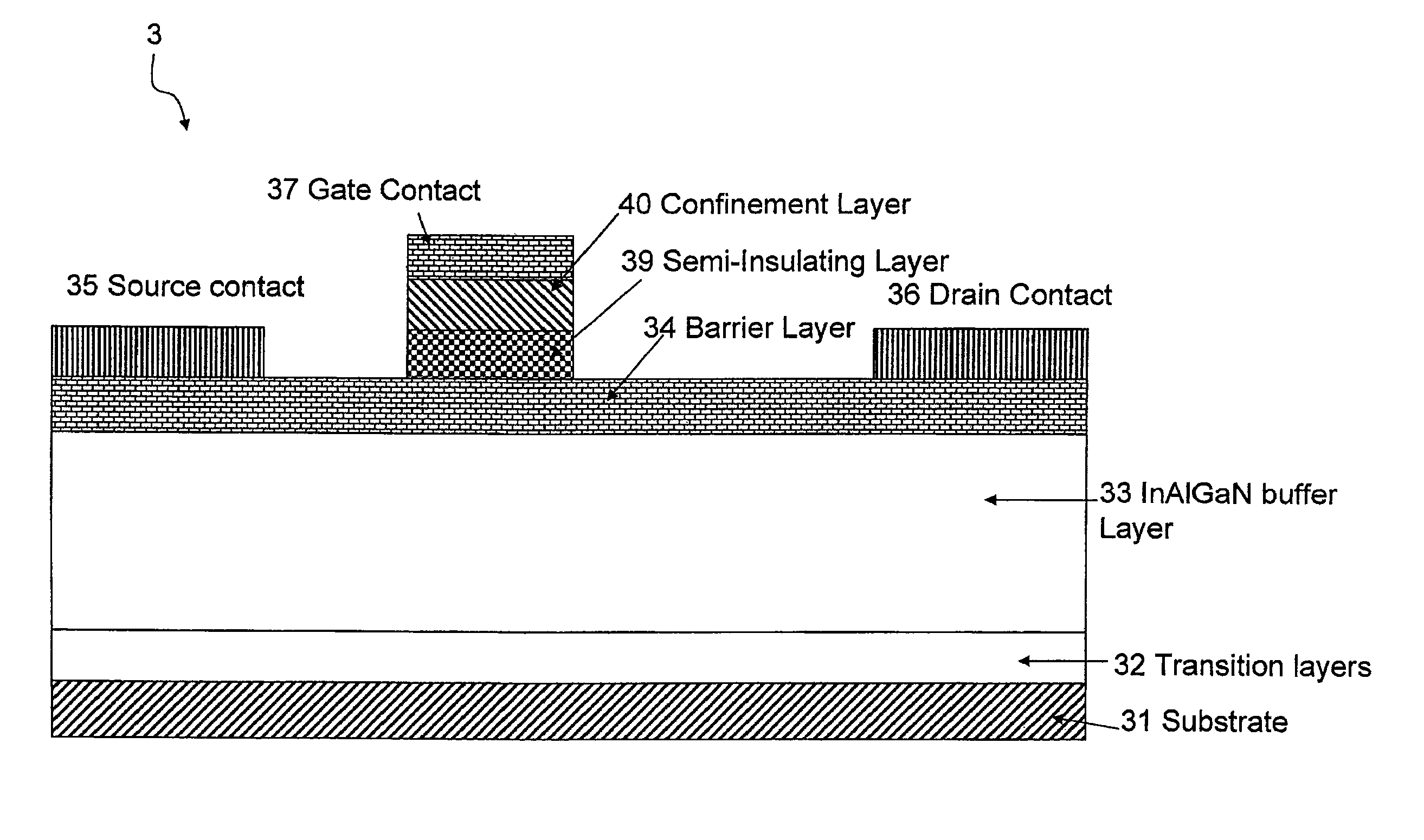

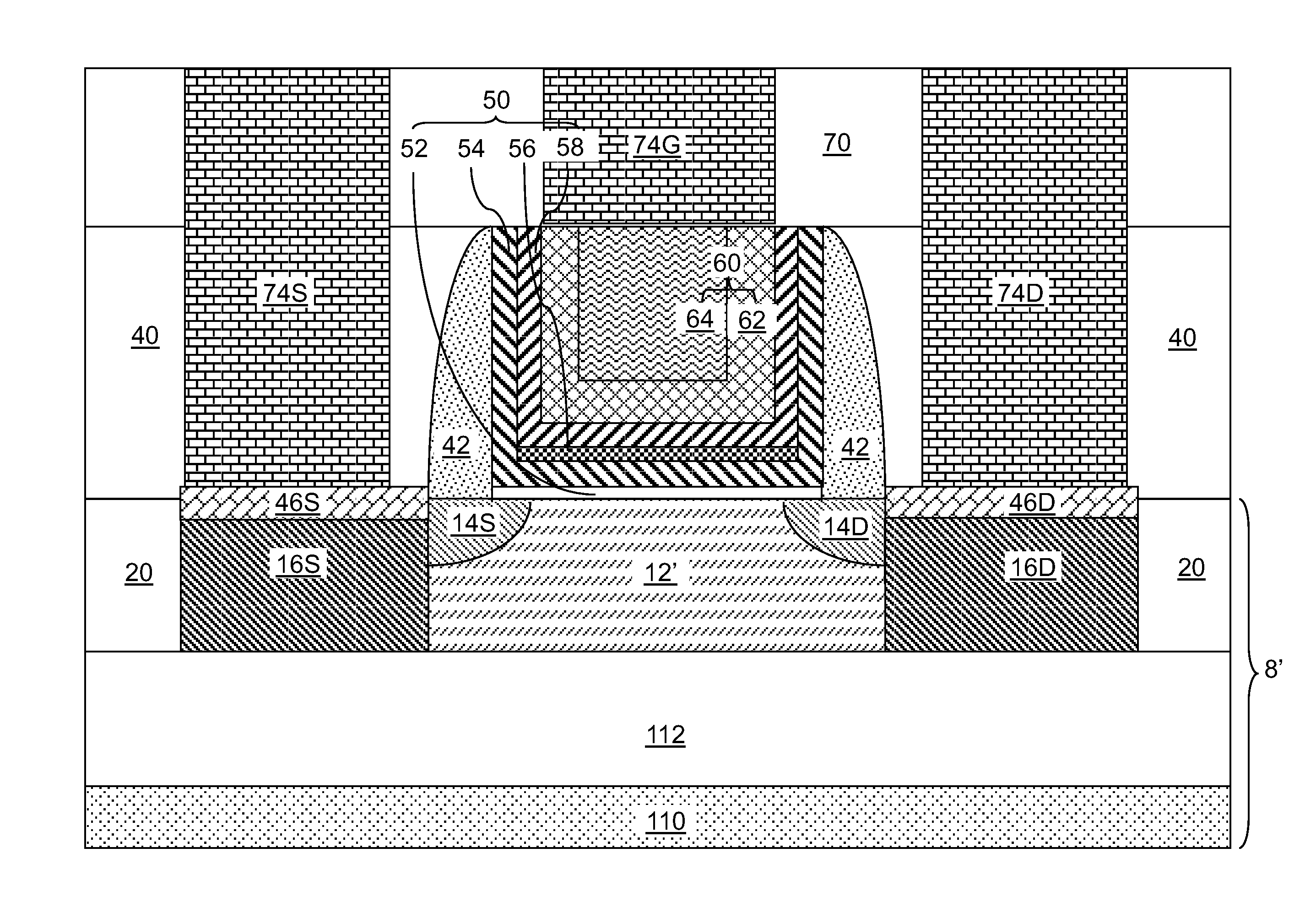

AlGaN / GaN HEMTs are disclosed having a thin AlGaN layer to reduce trapping and also having additional layers to reduce gate leakage and increase the maximum drive current. One HEMT according to the present invention comprises a high resistivity semiconductor layer with a barrier semiconductor layer on it. The barrier layer has a wider bandgap than the high resistivity layer and a 2DEG forms between the layers. Source and drain contacts contact the barrier layer, with part of the surface of the barrier layer uncovered by the contacts. An insulating layer is included on the uncovered surface of the barrier layer and a gate contact is included on the insulating layer. The insulating layer forms a barrier to gate leakage current and also helps to increase the HEMT's maximum current drive. The invention also includes methods for fabricating HEMTs according to the present invention. In one method, the HEMT and its insulating layer are fabricated using metal-organic chemical vapor deposition (MOCVD). In another method the insulating layer is sputtered onto the top surface of the HEMT in a sputtering chamber.

Owner:CREE INC

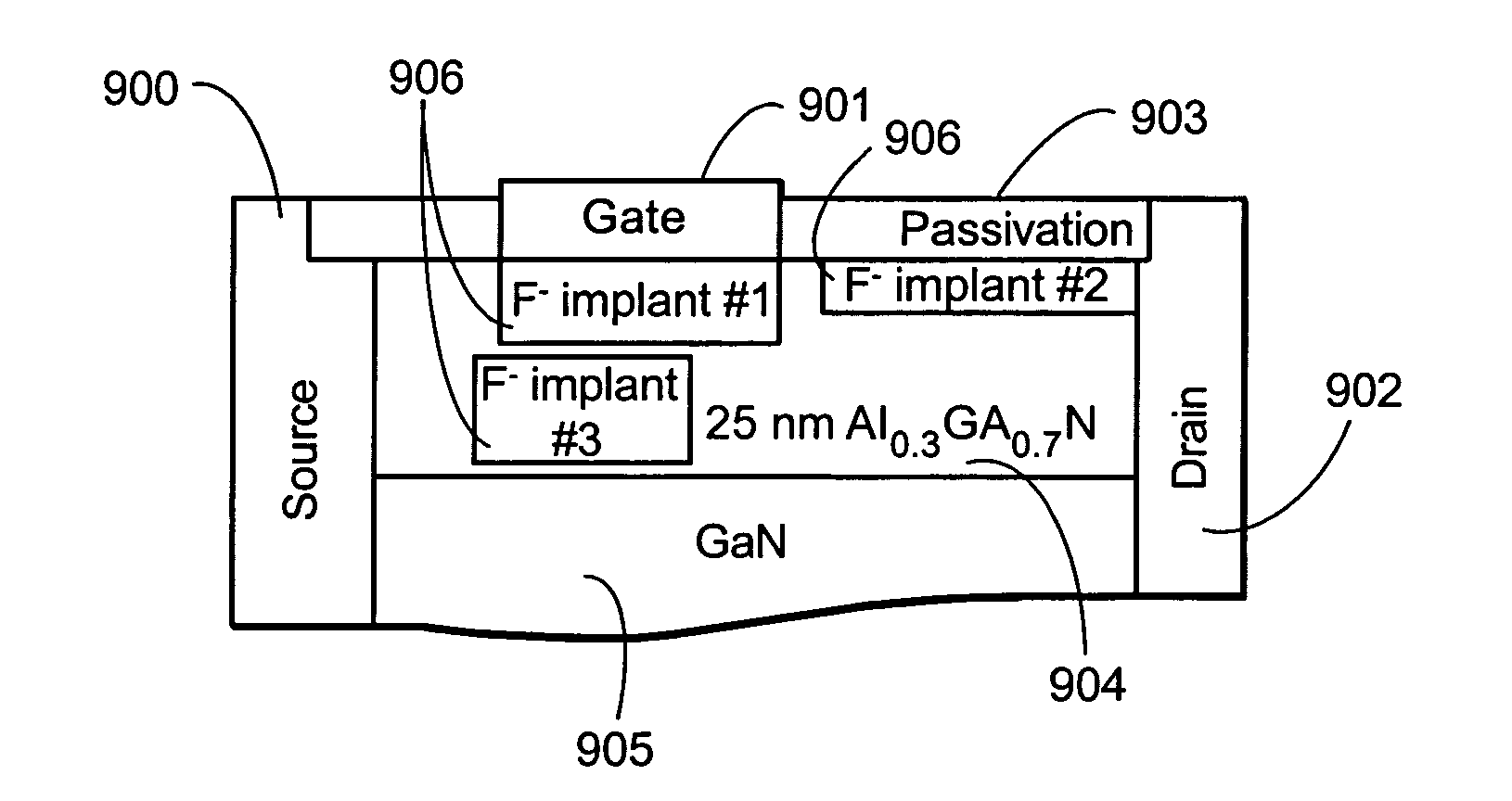

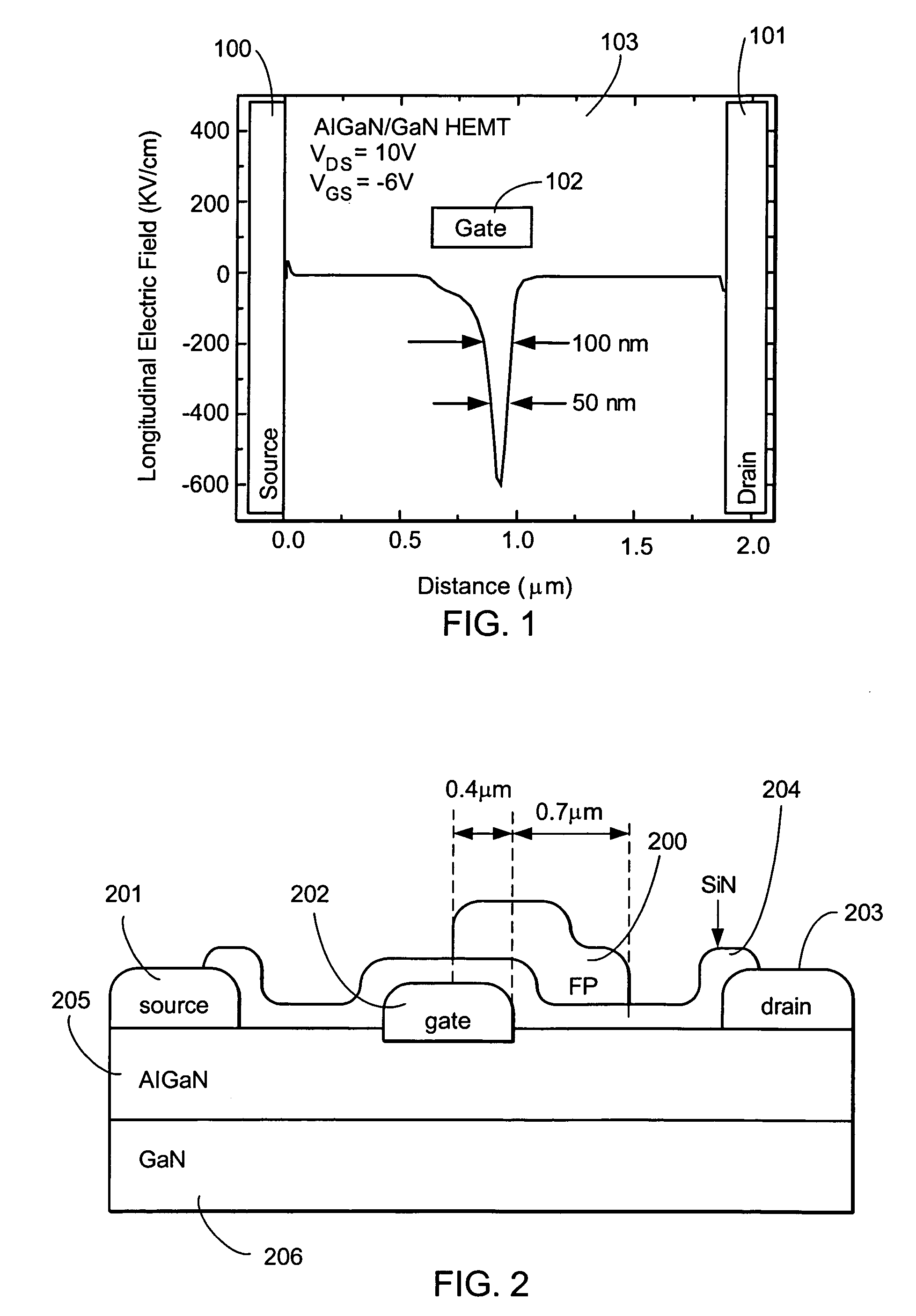

Methods to shape the electric field in electron devices, passivate dislocations and point defects, and enhance the luminescence efficiency of optical devices

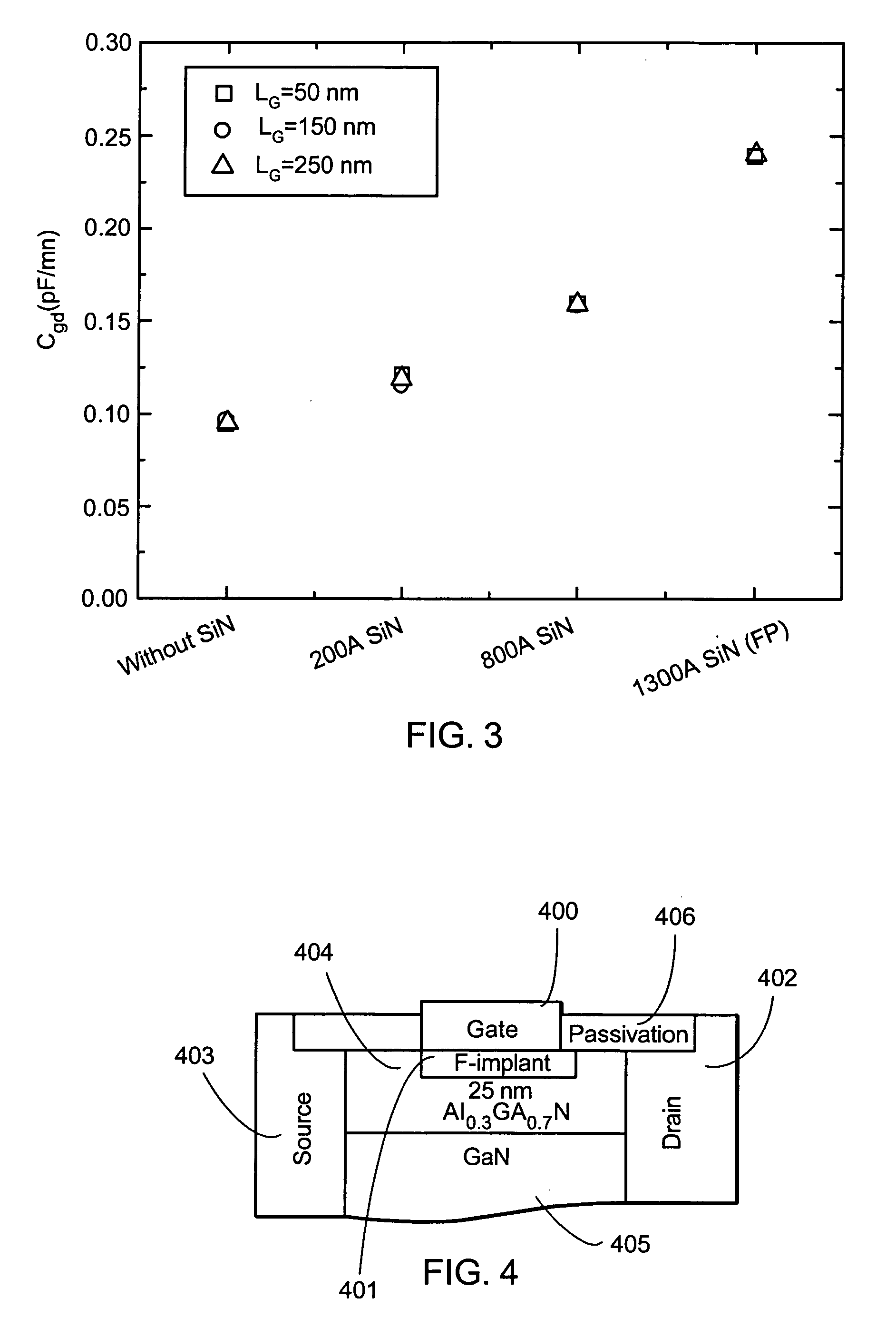

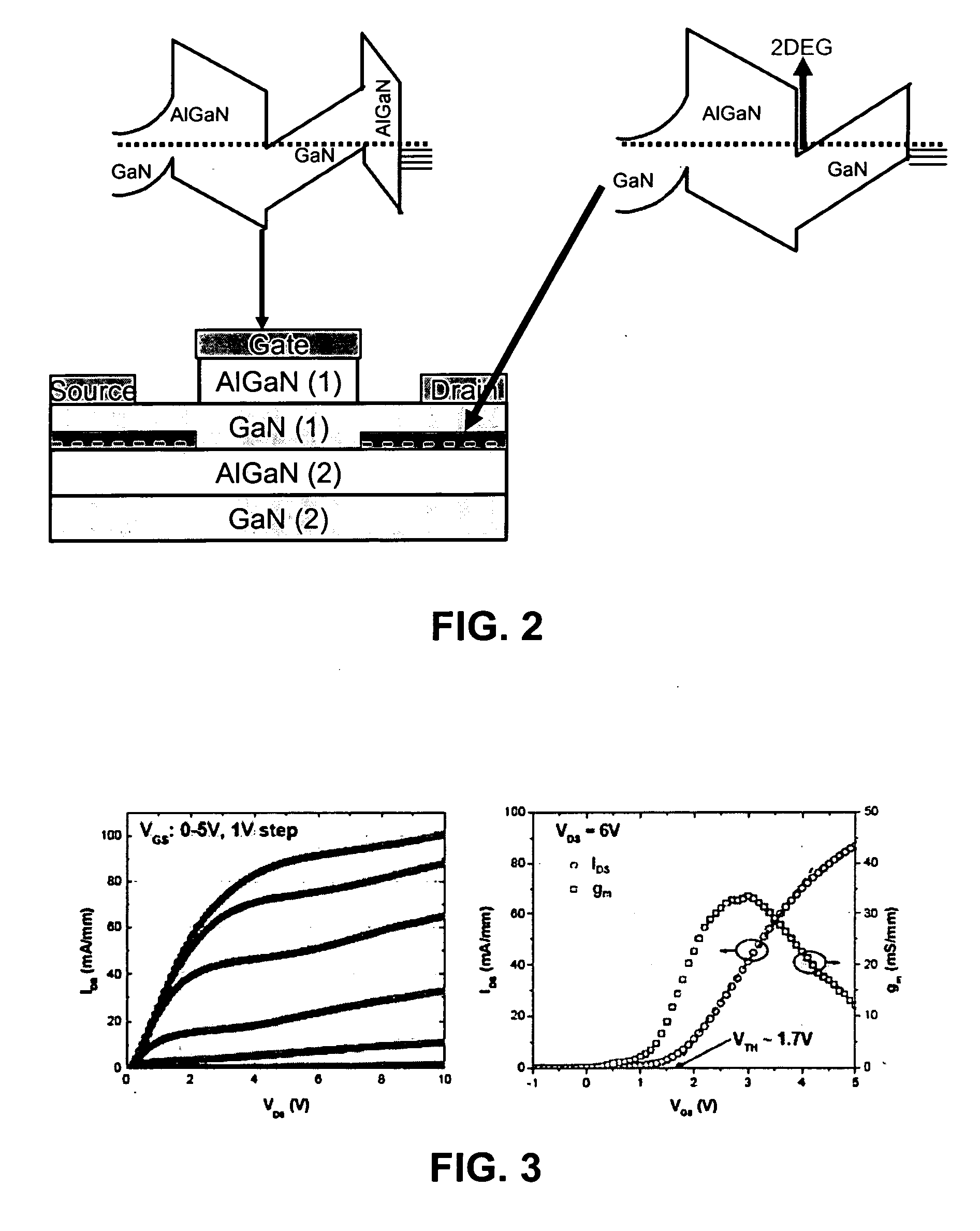

ActiveUS20070224710A1Increase output powerReduce gate leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesPeak valueDislocation

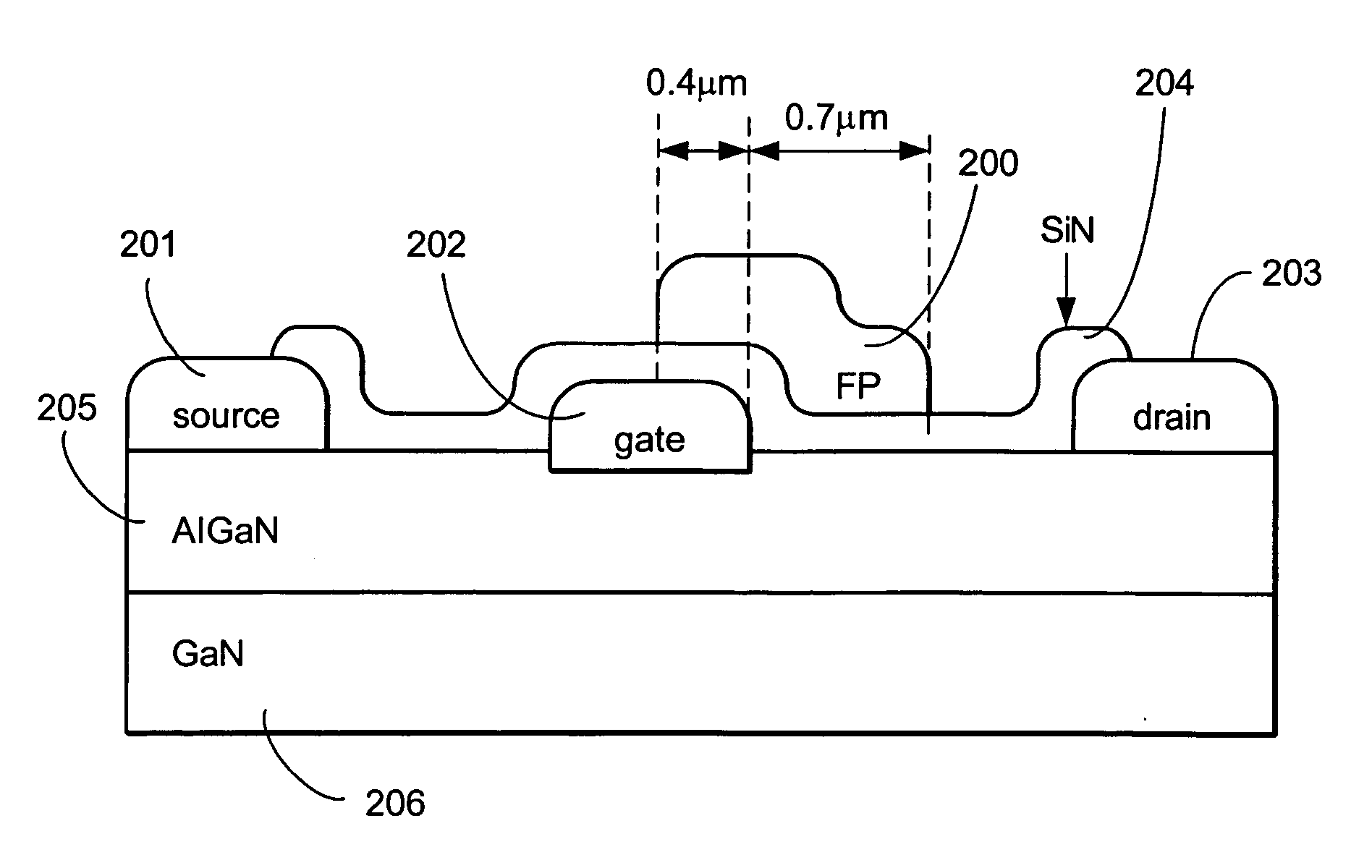

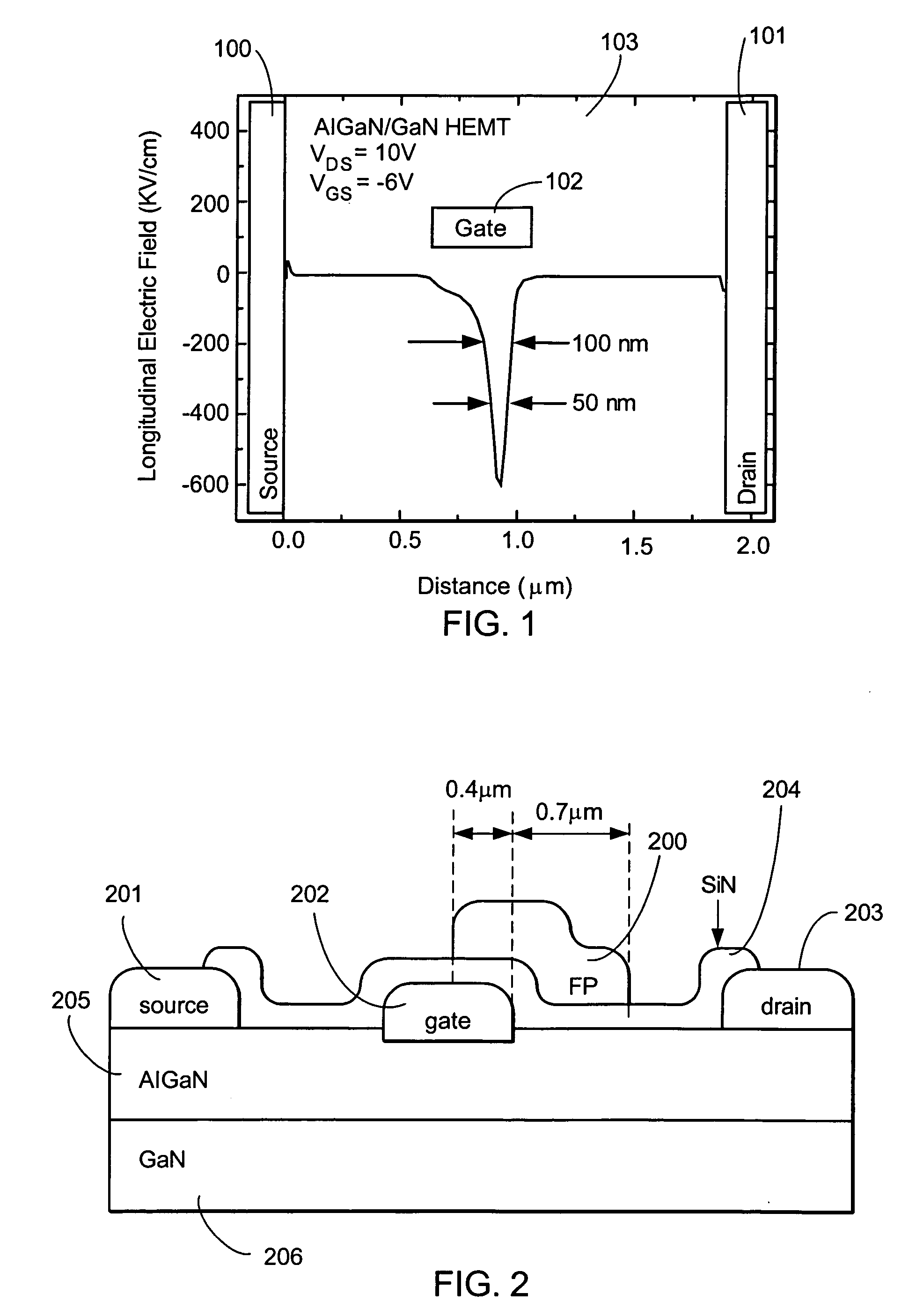

A fluorine treatment that can shape the electric field profile in electronic devices in 1, 2, or 3 dimensions is disclosed. A method to increase the breakdown voltage of AlGaN / GaN high electron mobility transistors, by the introduction of a controlled amount of dispersion into the device, is also disclosed. This dispersion is large enough to reduce the peak electric field in the channel, but low enough in order not to cause a significant decrease in the output power of the device. In this design, the whole transistor is passivated against dispersion with the exception of a small region 50 to 100 nm wide right next to the drain side of the gate. In that region, surface traps cause limited amounts of dispersion, that will spread the high electric field under the gate edge, therefore increasing the breakdown voltage. Three different methods to introduce dispersion in the 50 nm closest to the gate are described: (1) introduction of a small gap between the passivation and the gate metal, (2) gradually reducing the thickness of the passivation, and (3) gradually reducing the thickness of the AlGaN cap layer in the region close the gate.

Owner:RGT UNIV OF CALIFORNIA

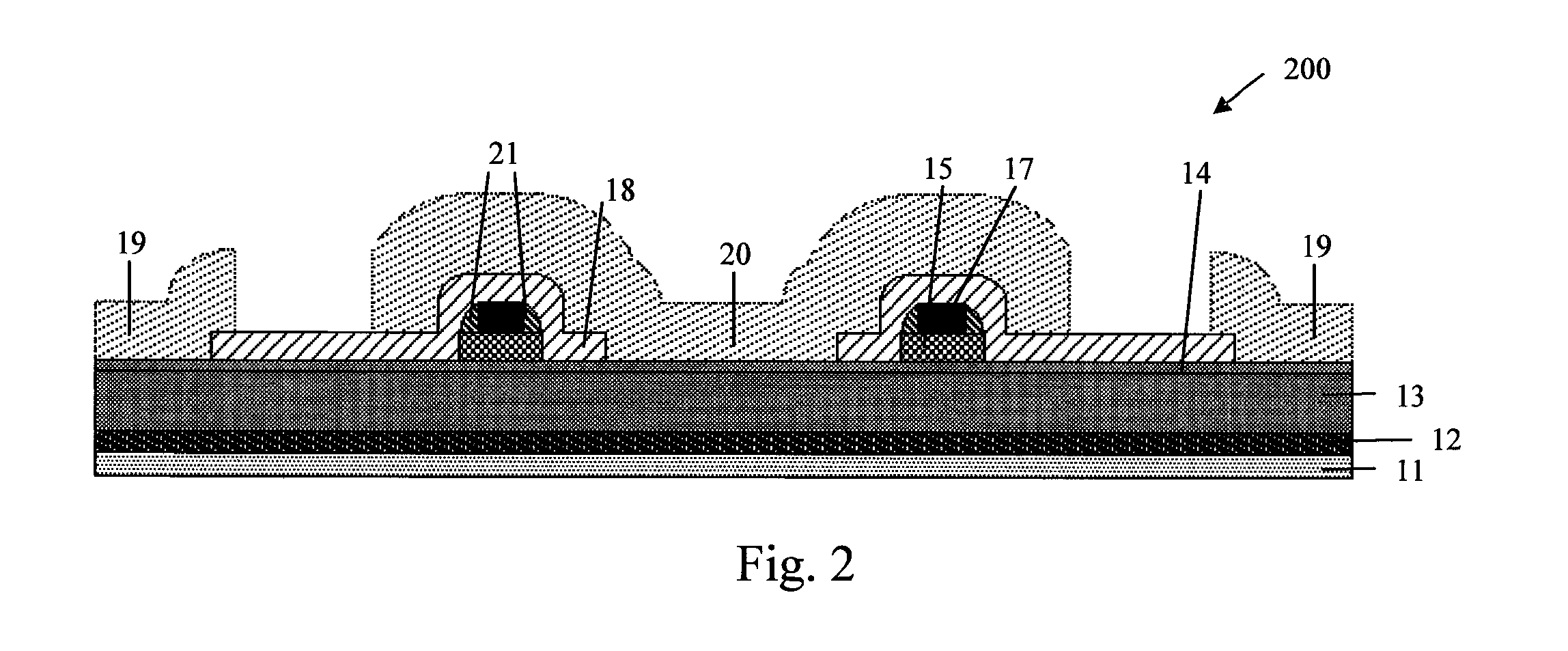

N-polar aluminum gallium nitride/gallium nitride enhancement-mode field effect transistor

ActiveUS20100264461A1High electron mobilityGood dispersionSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical polarityField effect

A novel enhancement mode field effect transistor (FET), such as a High Electron Mobility Transistors (HEMT), has an N-polar surface uses polarization fields to reduce the electron population under the gate in the N-polar orientation, has improved dispersion suppression, and low gate leakage.

Owner:RGT UNIV OF CALIFORNIA

N-polar aluminum gallium nitride/gallium nitride enhancement-mode field effect transistor

ActiveUS7948011B2High electron mobilityGood dispersionSemiconductor/solid-state device manufacturingSemiconductor devicesField effectHigh electron

A novel enhancement mode field effect transistor (FET), such as a High Electron Mobility Transistors (HEMT), has an N-polar surface uses polarization fields to reduce the electron population under the gate in the N-polar orientation, has improved dispersion suppression, and low gate leakage.

Owner:RGT UNIV OF CALIFORNIA

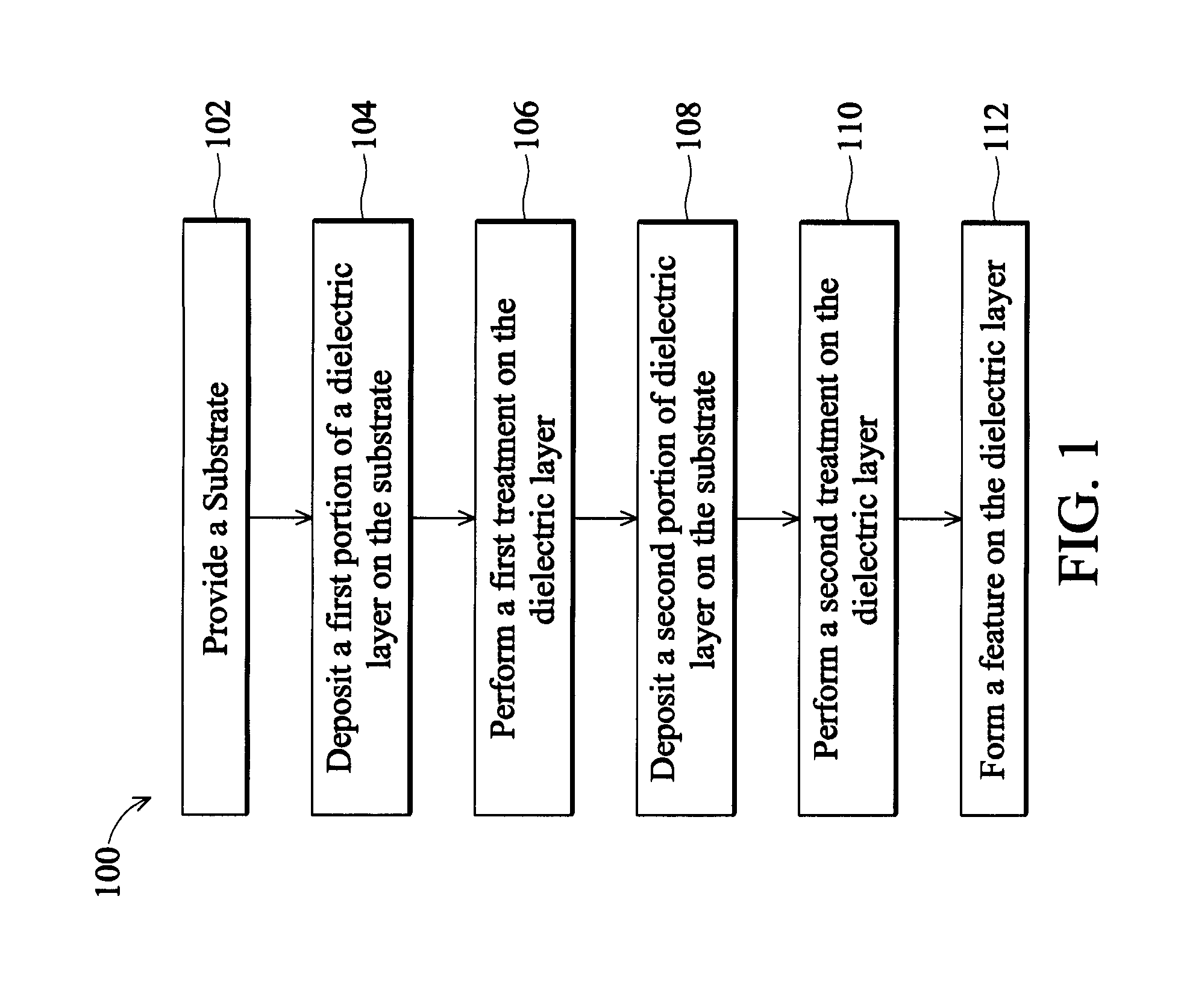

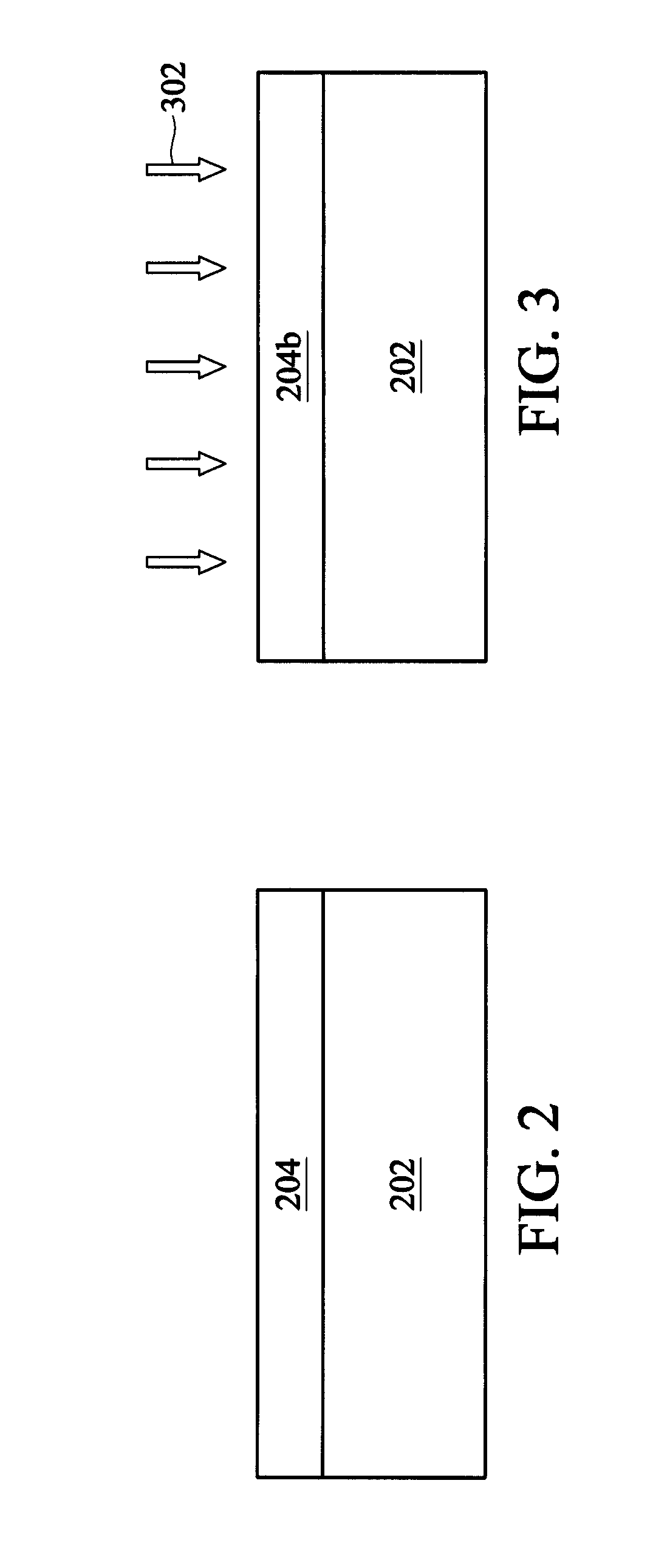

Multiple Deposition, Multiple Treatment Dielectric Layer For A Semiconductor Device

InactiveUS20110256682A1Improve device performanceSmall sizeSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricMultiple treatments

A method is provided for fabricating a semiconductor device. A semiconductor substrate is provided. A first high-k dielectric layer is formed on the semiconductor substrate. A first treatment is performed on the high-k dielectric layer. In an embodiment, the treatment includes a UV radiation in the presence of O2 and / or O3. A second high-k dielectric layer is formed on the treated first high-k dielectric layer. A second treatment is performed on the second high-k dielectric layer. In an embodiment, the high-k dielectric layer forms a gate dielectric layer of a field effect transistor.

Owner:TAIWAN SEMICON MFG CO LTD

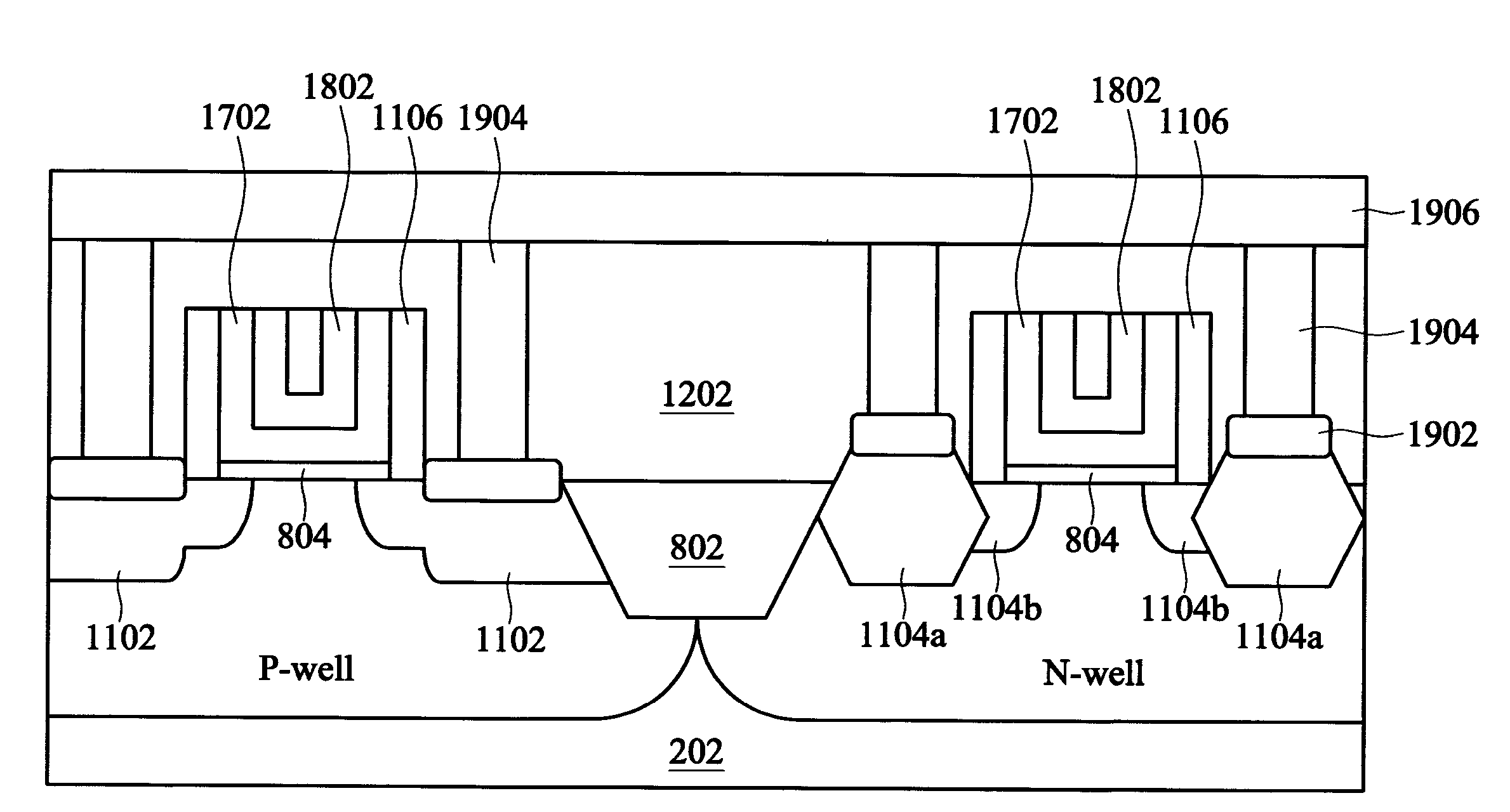

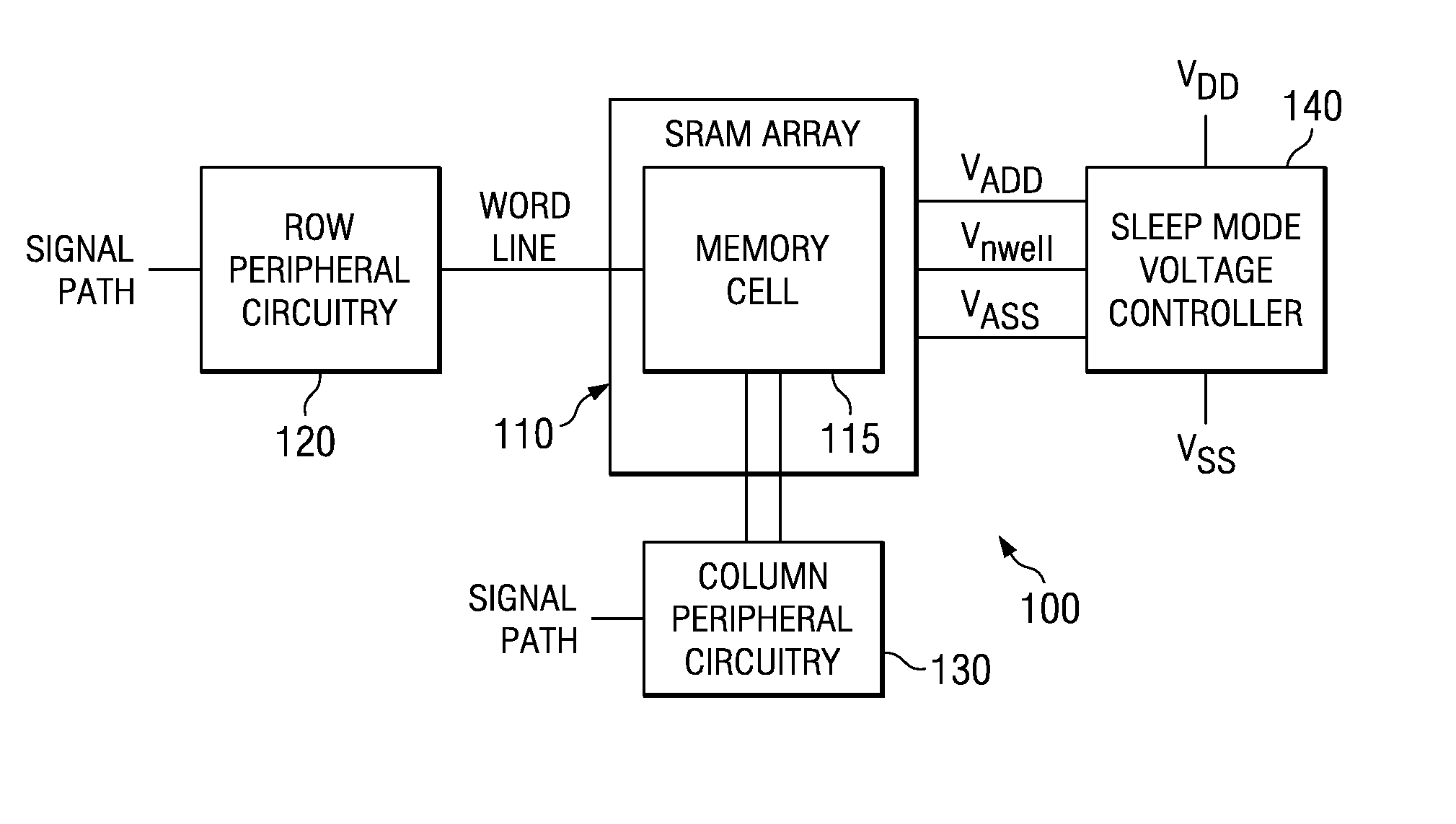

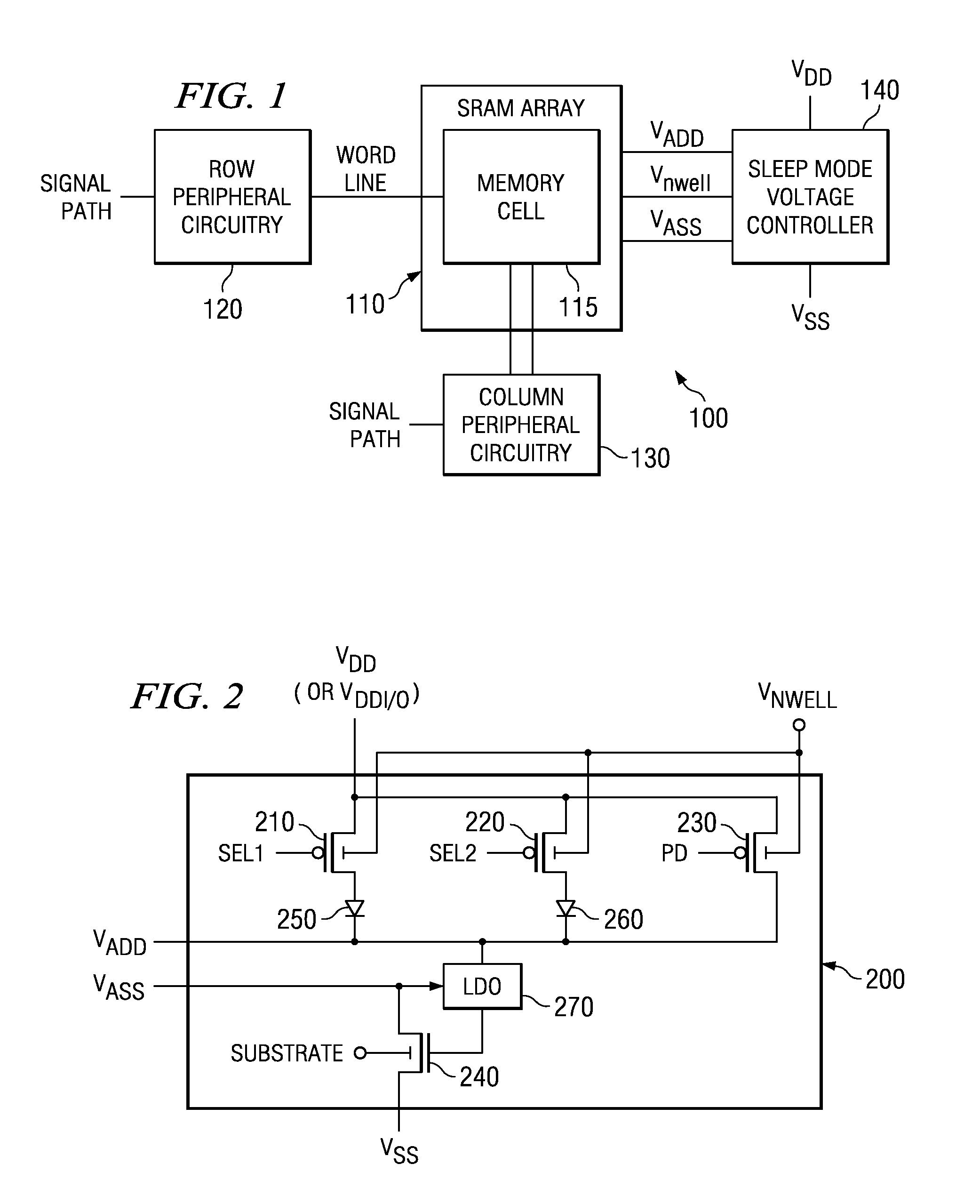

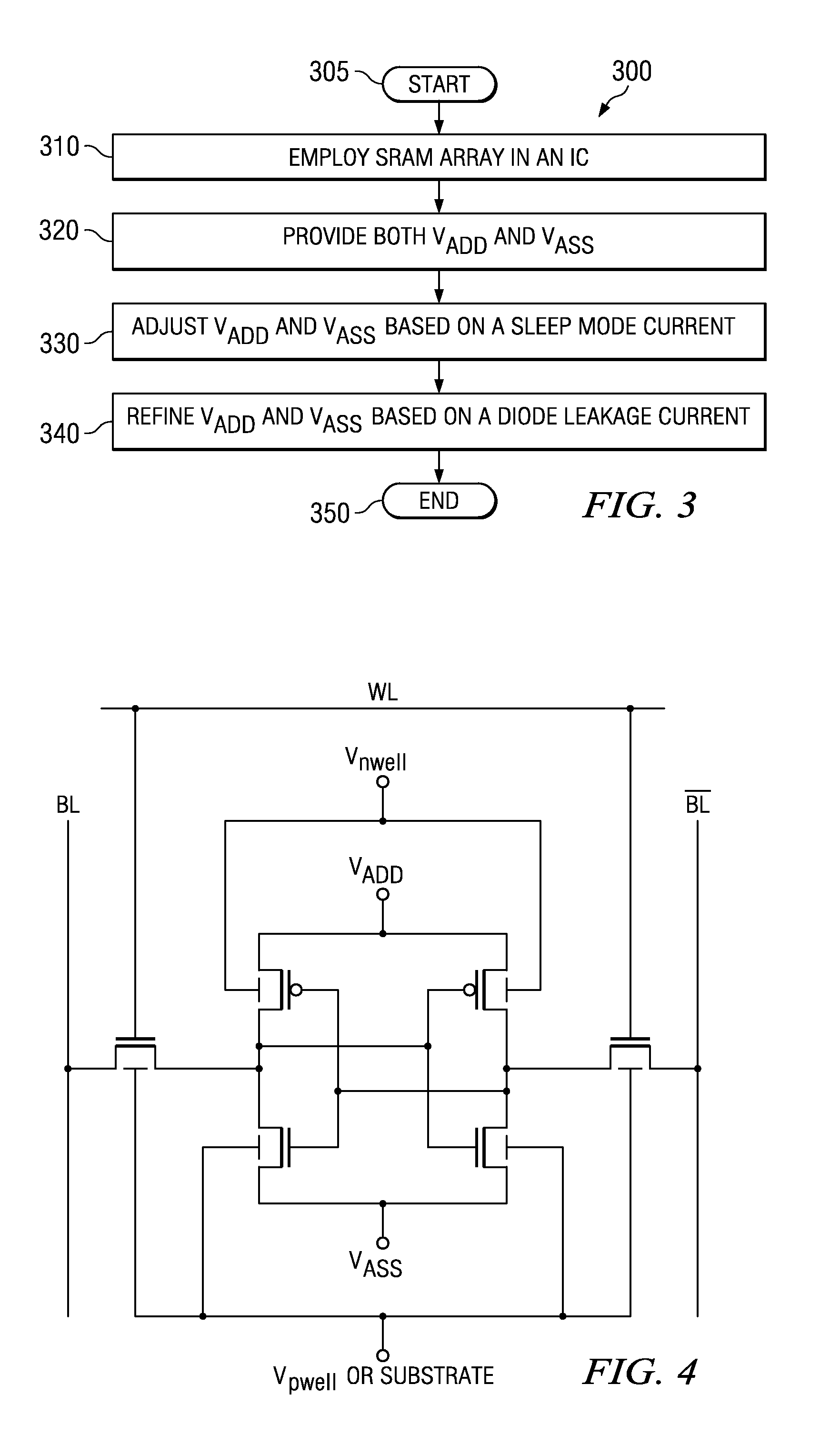

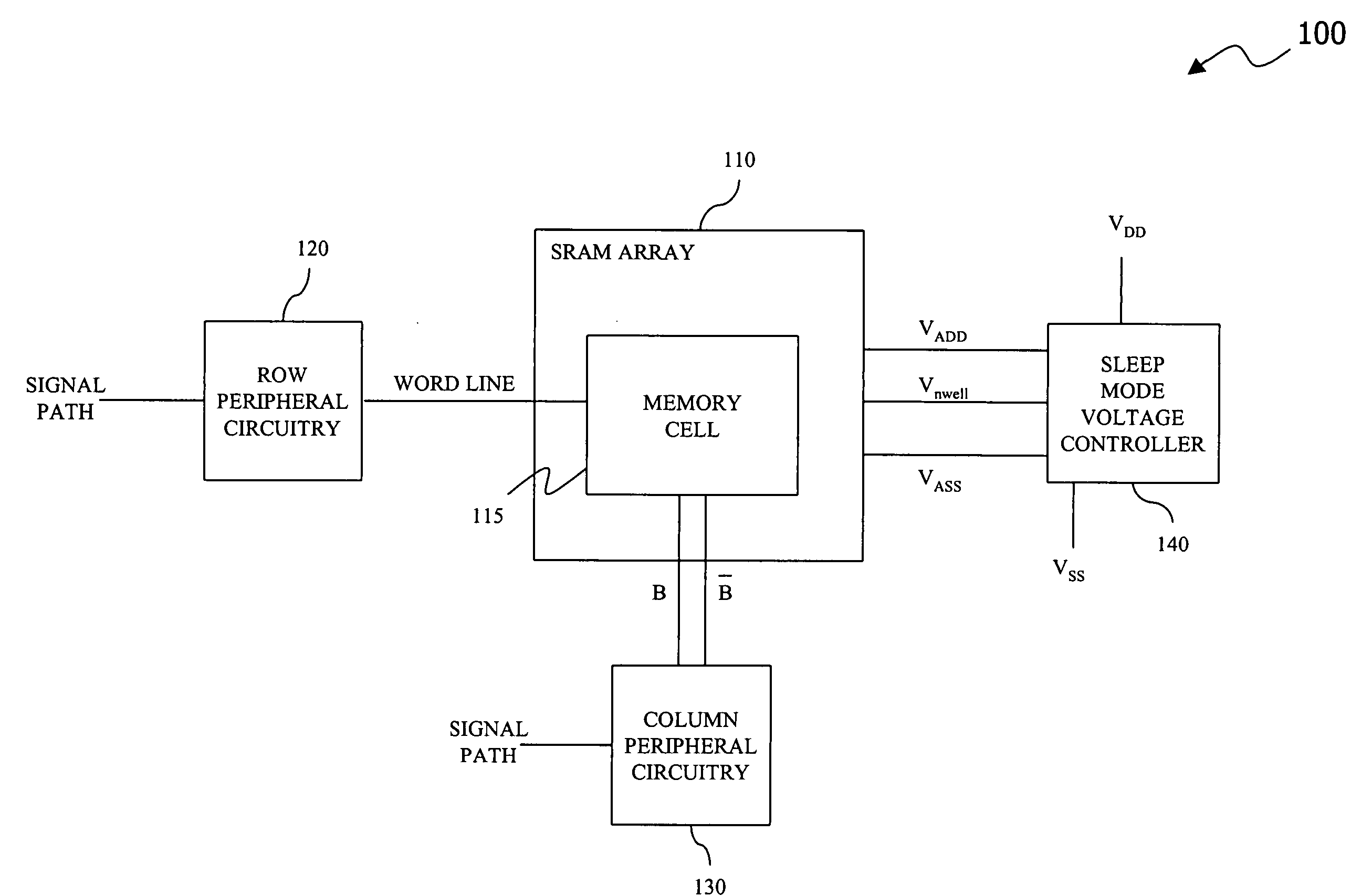

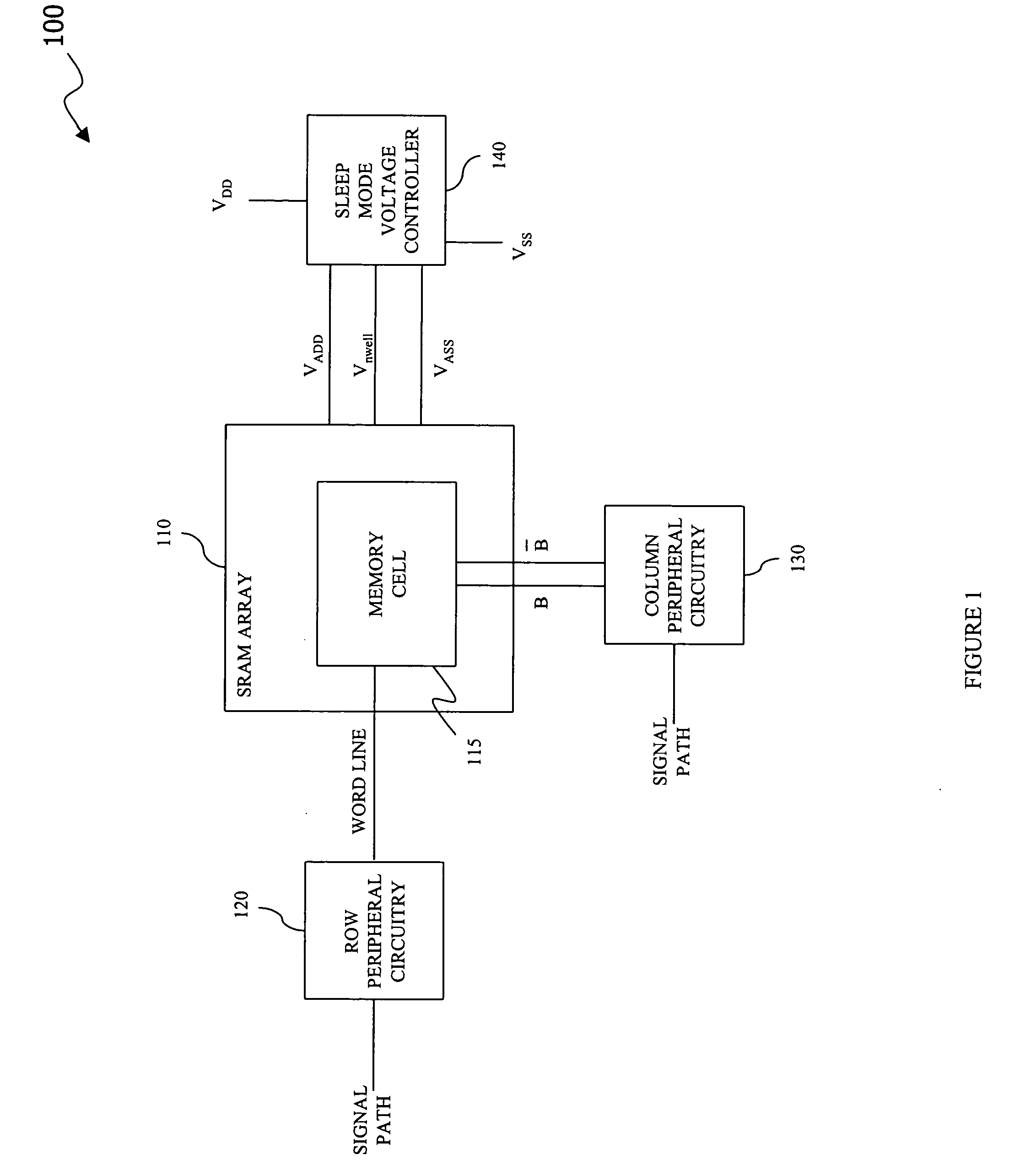

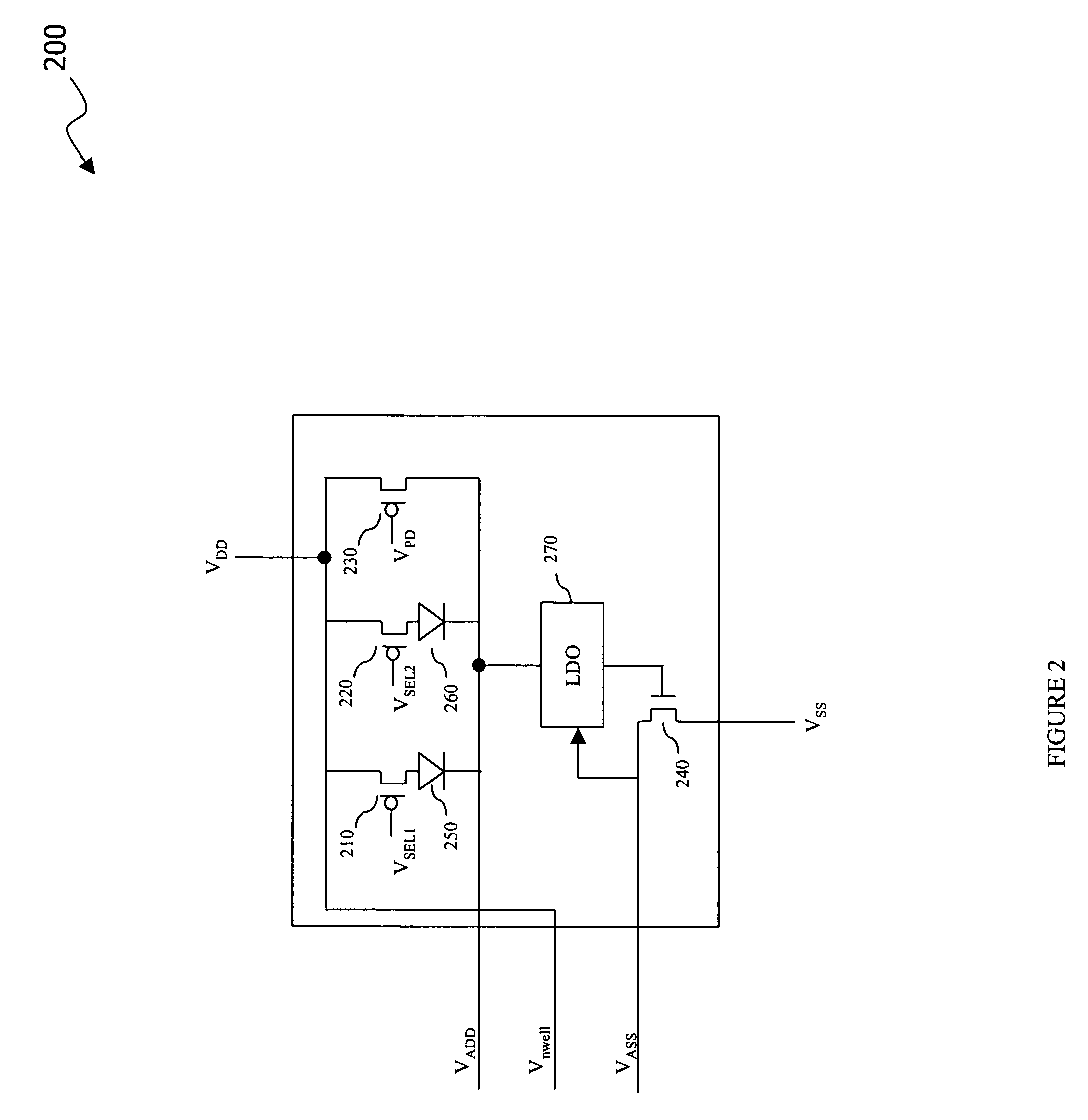

SRAM device and a method of operating the same to reduce leakage current during a sleep mode

An SRAM device and a method of operating an SRAM device. In one embodiment, the SRAM device includes (1) an SRAM array coupled to row peripheral circuitry by a word line and coupled to column peripheral circuitry by bit lines and (2) a sleep mode voltage controller configured to provide both an array high supply voltage VADD that is lower than a high operating voltage VDD and an array low supply voltage VASS that is higher than a low operating voltage VSS to the SRAM array during a sleep mode.

Owner:TEXAS INSTR INC

SRAM device and a method of operating the same to reduce leakage current during a sleep mode

ActiveUS20050128789A1Reducing subthreshold current leakageIncreasing diode gate leakageDigital storageBit lineHemt circuits

An SRAM device and a method of operating an SRAM device. In one embodiment, the SRAM device includes (1) an SRAM array coupled to row peripheral circuitry by a word line and coupled to column peripheral circuitry by bit lines and (2) a sleep mode voltage controller configured to provide both an array high supply voltage VADD that is lower than a high operating voltage VDD and an array low supply voltage VASS that is higher than a low operating voltage VSS to the SRAM array during a sleep mode.

Owner:TEXAS INSTR INC

Methods to shape the electric field in electron devices, passivate dislocations and point defects, and enhance the luminescence efficiency of optical devices

ActiveUS8114717B2Reduction in a peak electric fieldImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPeak value

A fluorine treatment that can shape the electric field profile in electronic devices in 1, 2, or 3 dimensions is disclosed. A method to increase the breakdown voltage of AlGaN / GaN high electron mobility transistors, by the introduction of a controlled amount of dispersion into the device, is also disclosed. This dispersion is large enough to reduce the peak electric field in the channel, but low enough in order not to cause a significant decrease in the output power of the device. In this design, the whole transistor is passivated against dispersion with the exception of a small region 50 to 100 nm wide right next to the drain side of the gate. In that region, surface traps cause limited amounts of dispersion, that will spread the high electric field under the gate edge, therefore increasing the breakdown voltage. Three different methods to introduce dispersion in the 50 nm closest to the gate are described: (1) introduction of a small gap between the passivation and the gate metal, (2) gradually reducing the thickness of the passivation, and (3) gradually reducing the thickness of the AlGaN cap layer in the region close the gate.

Owner:RGT UNIV OF CALIFORNIA

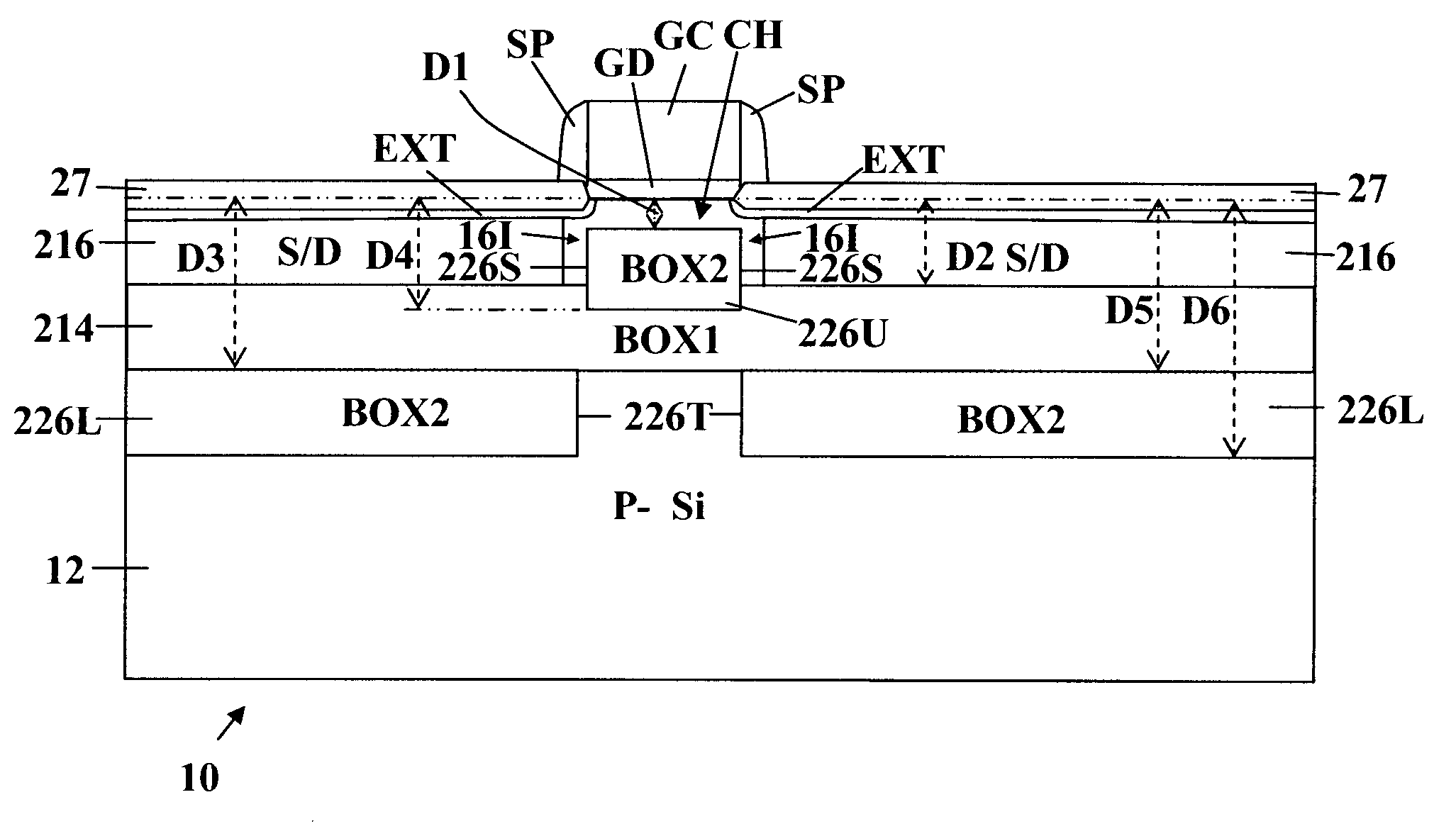

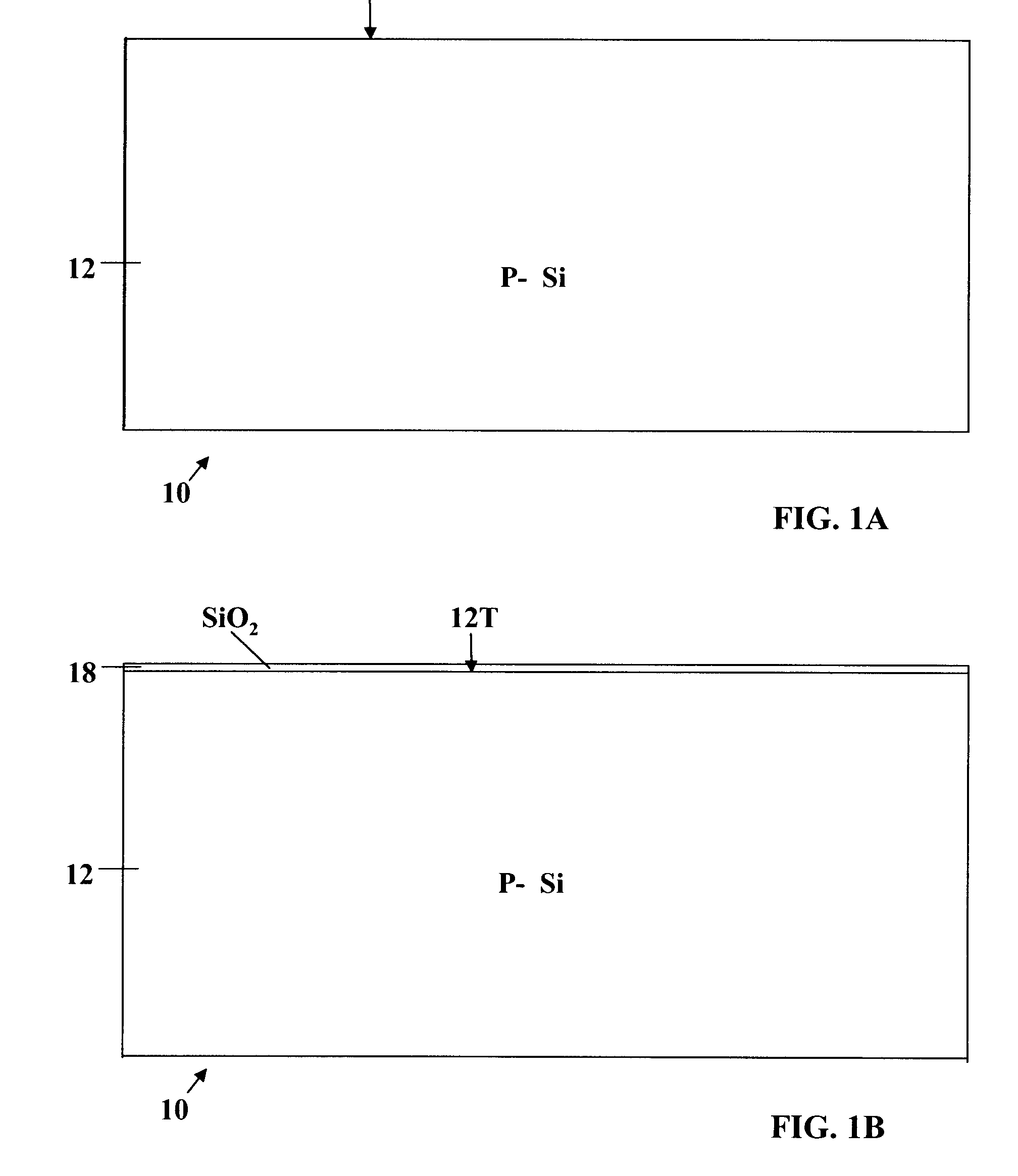

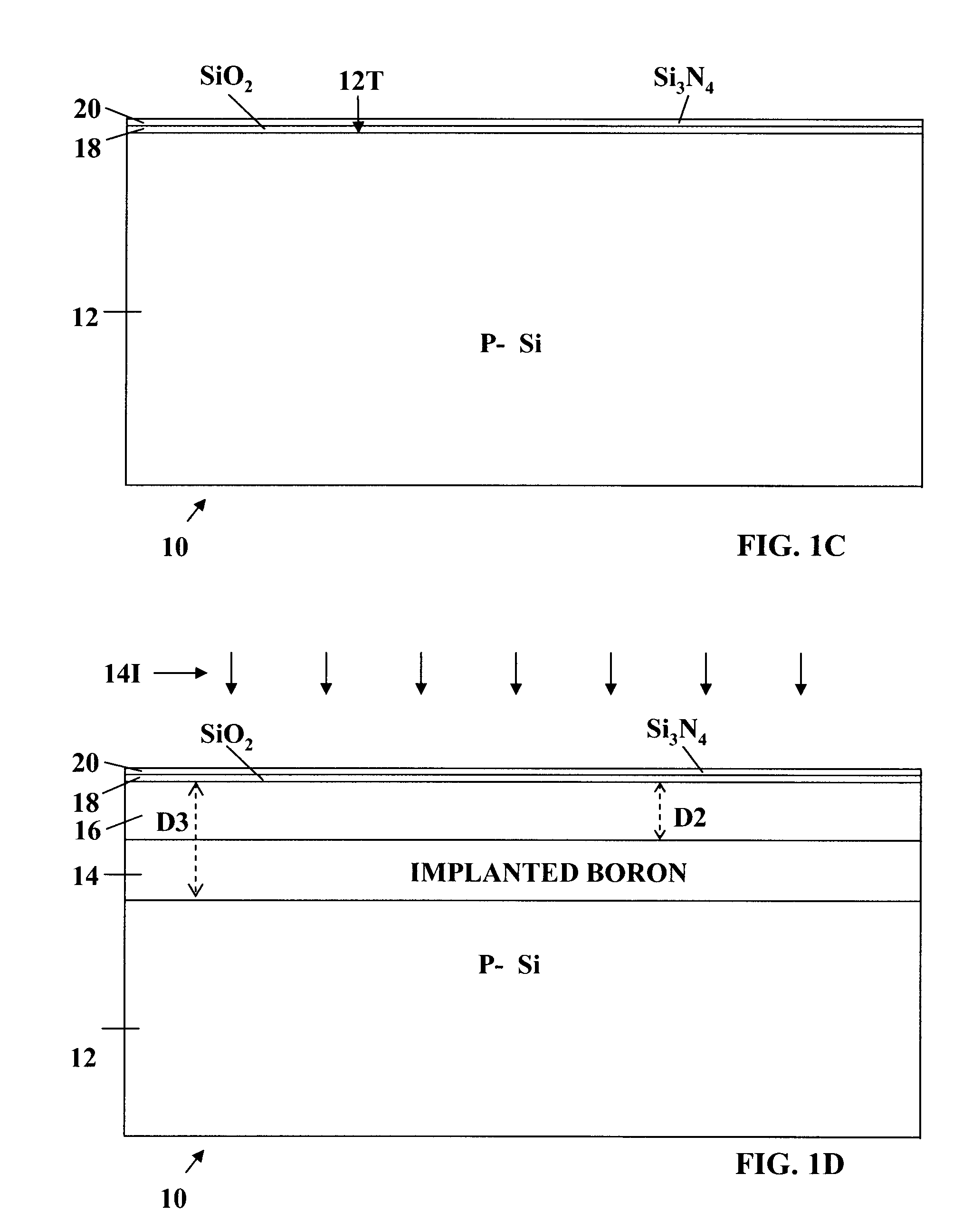

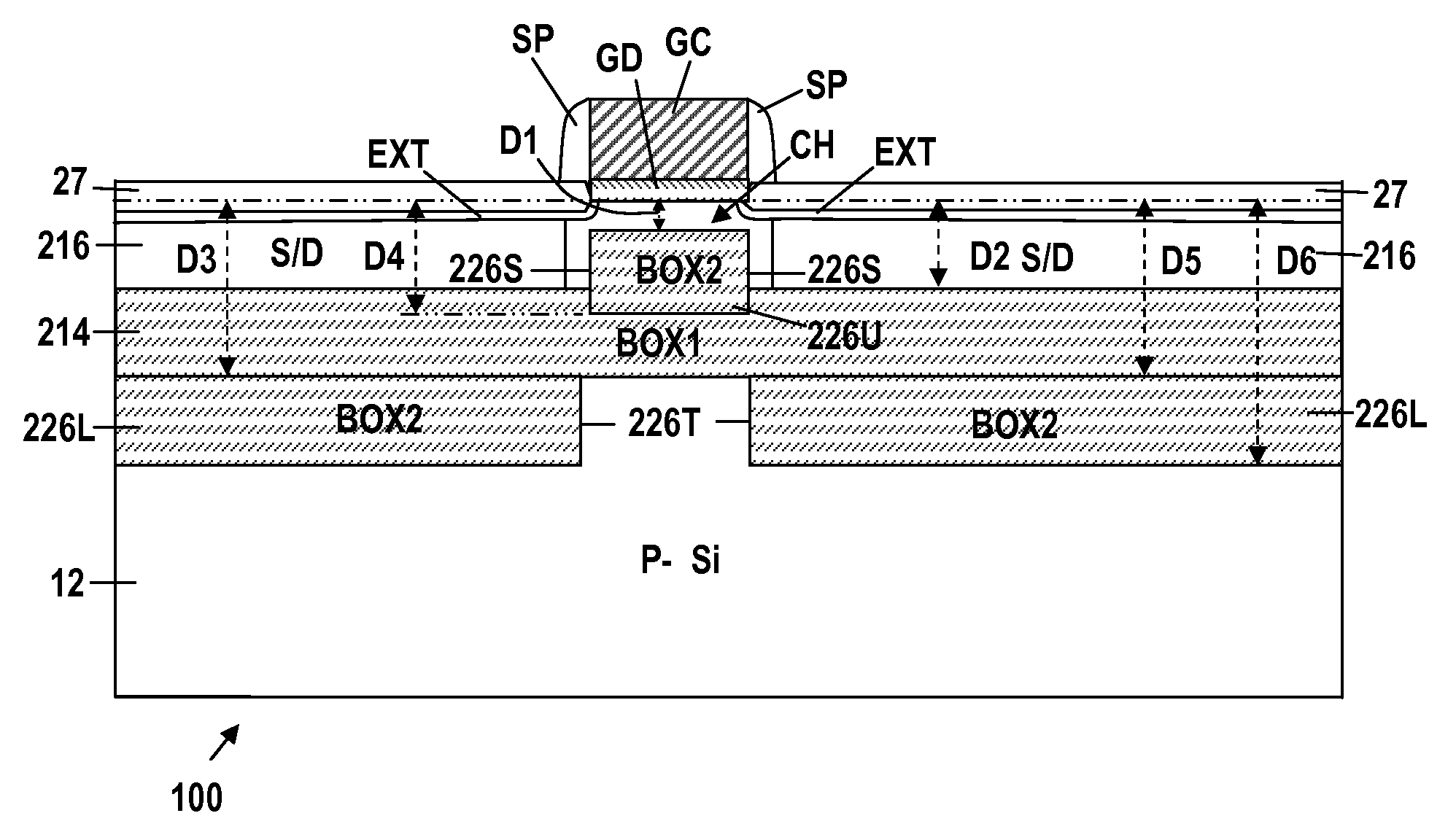

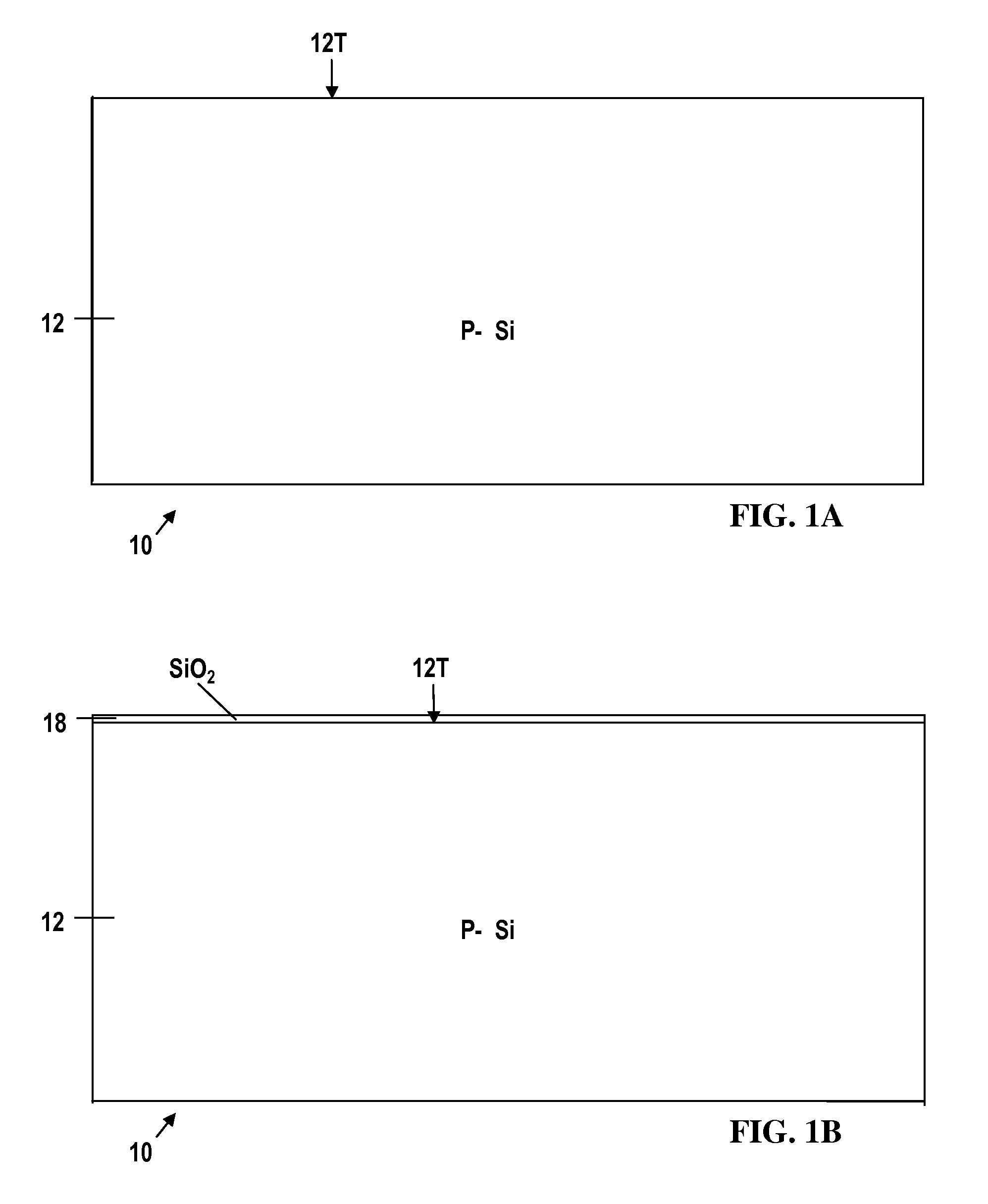

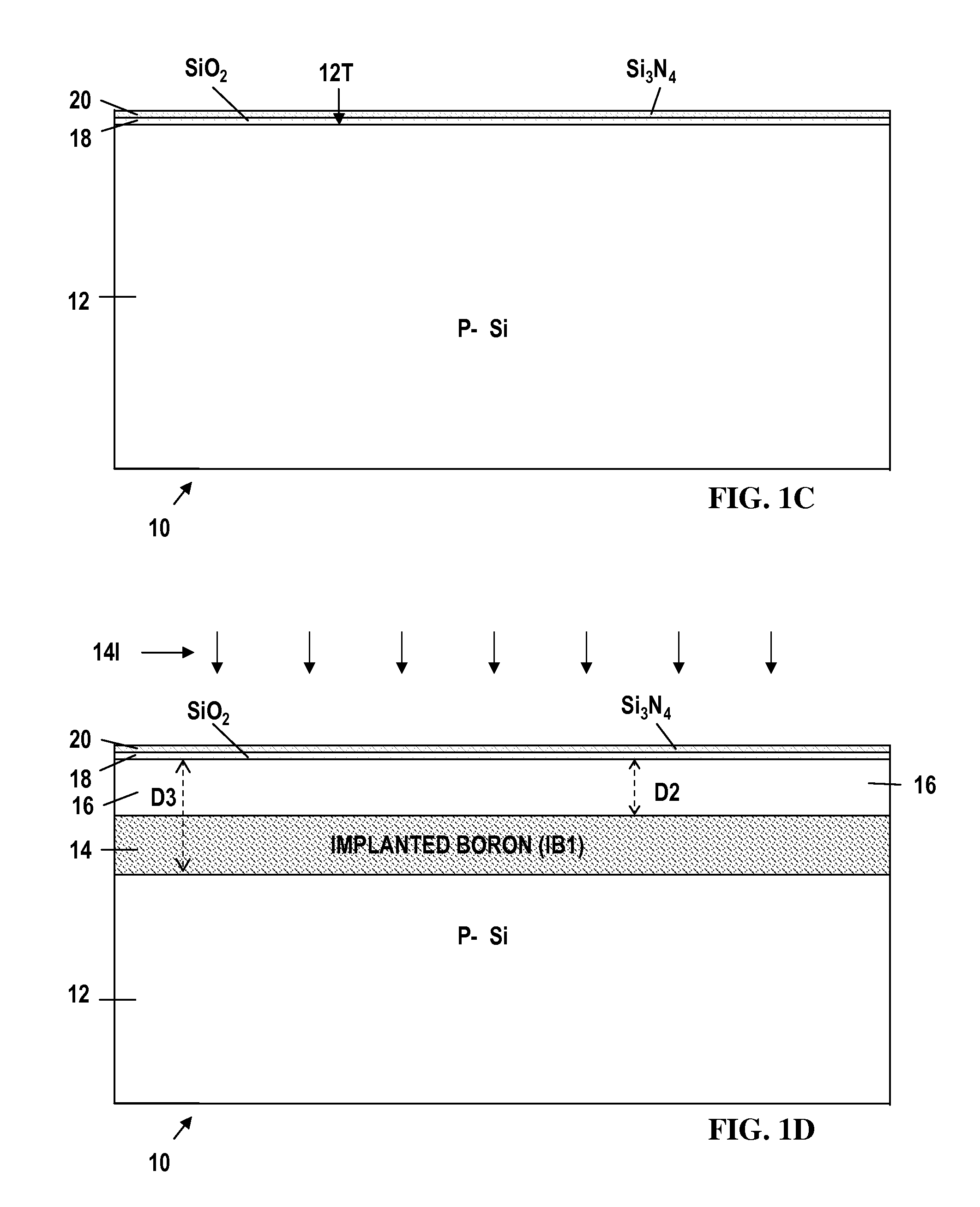

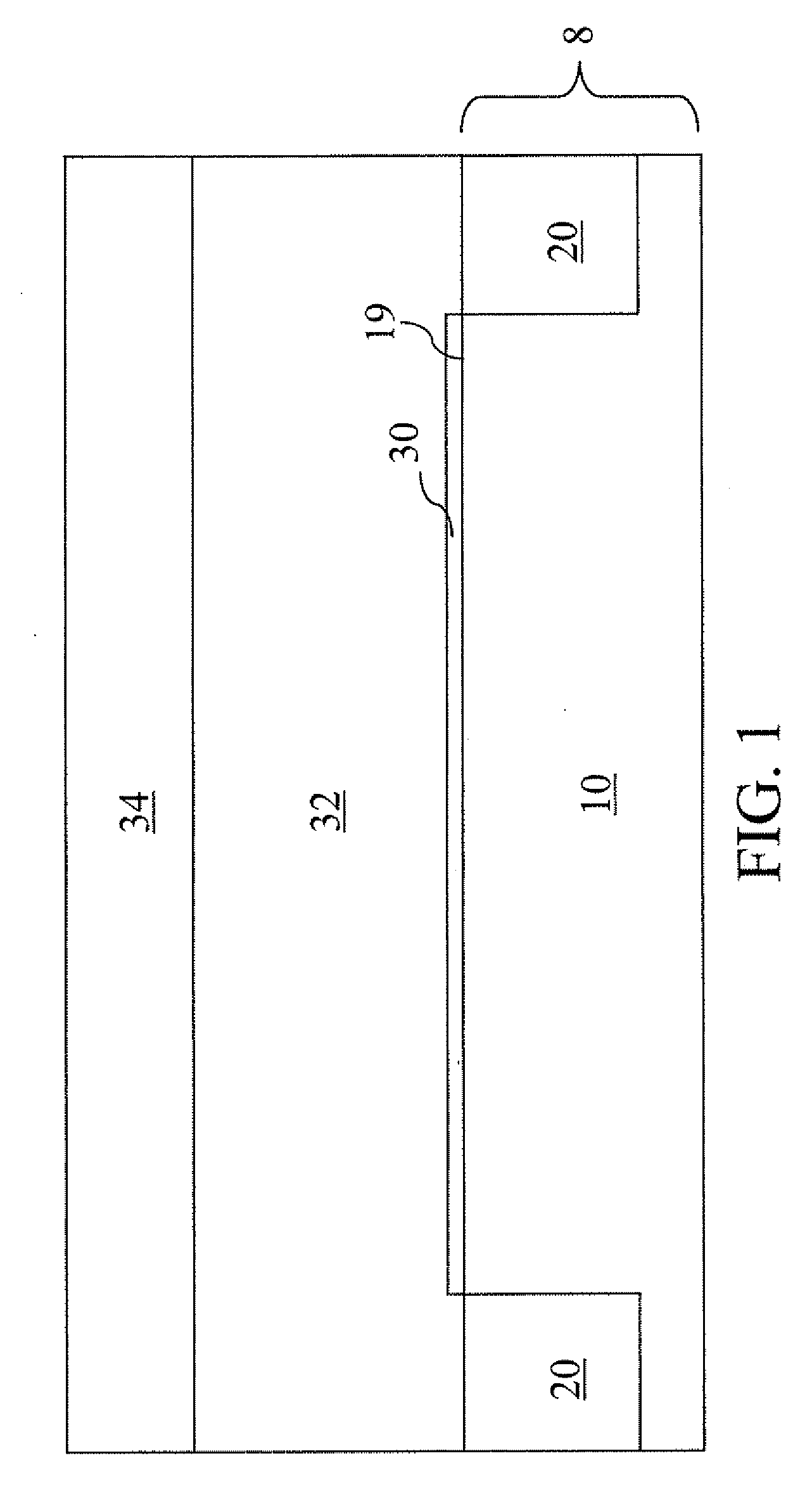

Planar ultra-thin semiconductor-on-insulator channel mosfet with embedded source/drain

InactiveUS20070069300A1Eliminate variationReduce Overlap CapacitanceTransistorSemiconductor/solid-state device manufacturingMOSFETGate dielectric

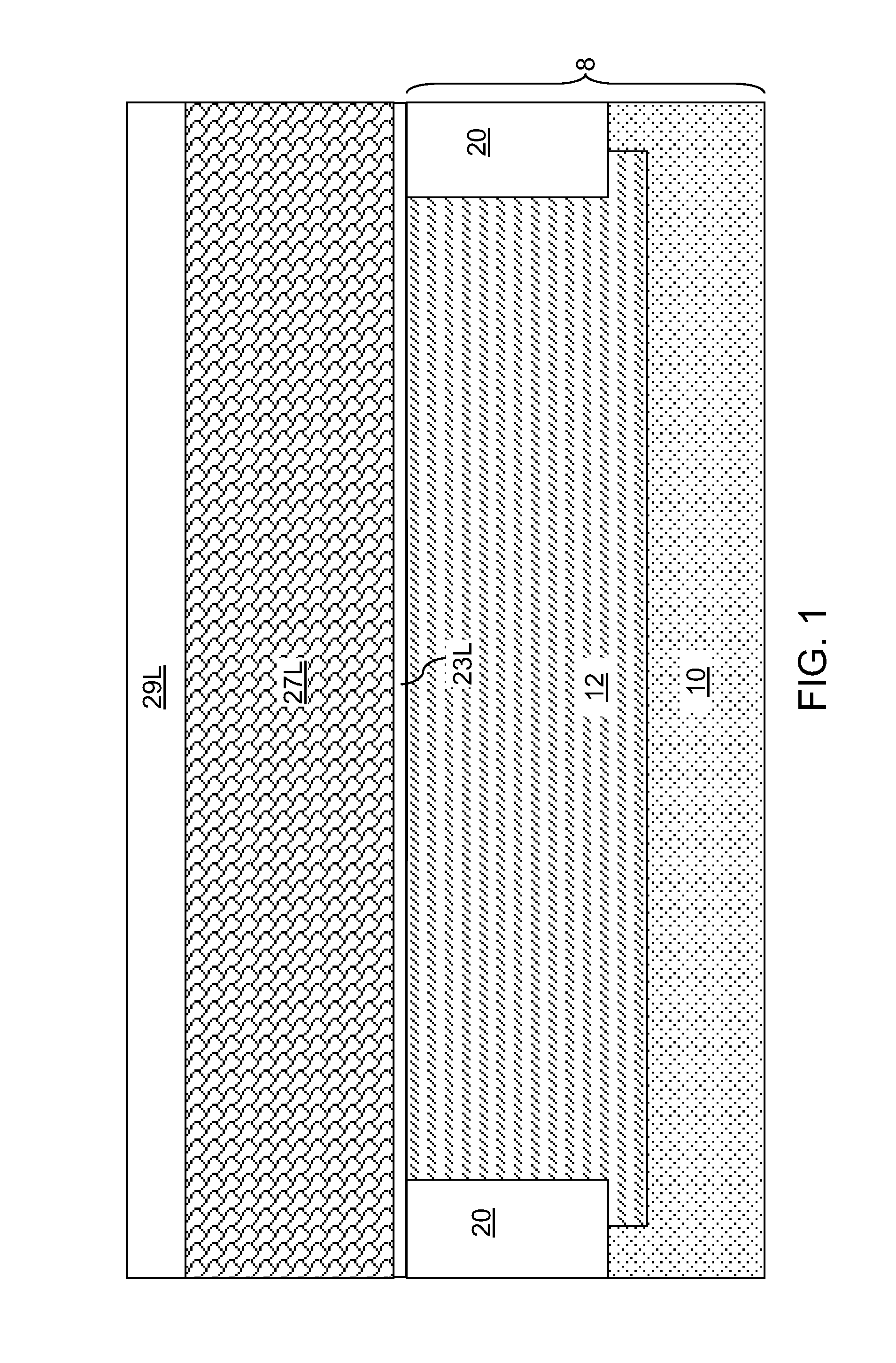

A MOSFET structure includes a planar semiconductor substrate, a gate dielectric and a gate. An ultra-thin (UT) semiconductor-on-insulator channel extends to a first depth below the top surface of the substrate and is self-aligned to and is laterally coextensive with the gate. Source-drain regions, extend to a second depth greater than the first depth below the top surface, and are self-aligned to the UT channel region. A first BOX region extends across the entire structure, and vertically from the second depth to a third depth below the top surface. An upper portion of a second BOX region under the UT channel region is self-aligned to and is laterally coextensive with the gate, and extends vertically from the first depth to a third depth below the top surface, and where the third depth is greater than the second depth.

Owner:GLOBALFOUNDRIES INC

Stratified gate dielectric stack for gate dielectric leakage reduction

InactiveUS20130277743A1Reduce leakageReduce gate leakageTransistorSolid-state devicesEngineeringBand gap

A stratified gate dielectric stack includes a first high dielectric constant (high-k) gate dielectric comprising a first high-k dielectric material, a band-gap-disrupting dielectric comprising a dielectric material having a different band gap than the first high-k dielectric material, and a second high-k gate dielectric comprising a second high-k dielectric material. The band-gap-disrupting dielectric includes at least one contiguous atomic layer of the dielectric material. Thus, the stratified gate dielectric stack includes a first atomic interface between the first high-k gate dielectric and the band-gap-disrupting dielectric, and a second atomic interface between the second high-k gate dielectric and the band-gap-disrupting dielectric that is spaced from the first atomic interface by at least one continuous atomic layer of the dielectric material of the band-gap-disrupting dielectric. The insertion of the band-gap disrupting dielectric results in lower gate leakage without resulting in any substantial changes in the threshold voltage characteristics and effective oxide thickness.

Owner:IBM CORP

Method of forming a memory device and semiconductor device

InactiveUS6924186B2Good step coverageLow gate leakageSemiconductor/solid-state device manufacturingSemiconductor devicesNovel techniqueDielectric

A novel technique to quench electrical defects in CVD Al2O3 layers is disclosed. A small amount of silicon dopant to the aluminum oxide film reduces the leakage current as well as the gap interface trap density at the dielectric / silicon interface. The implanted silicon gives a better interface and improves the leakage characteristics of the dielectric.

Owner:MICRON TECH INC

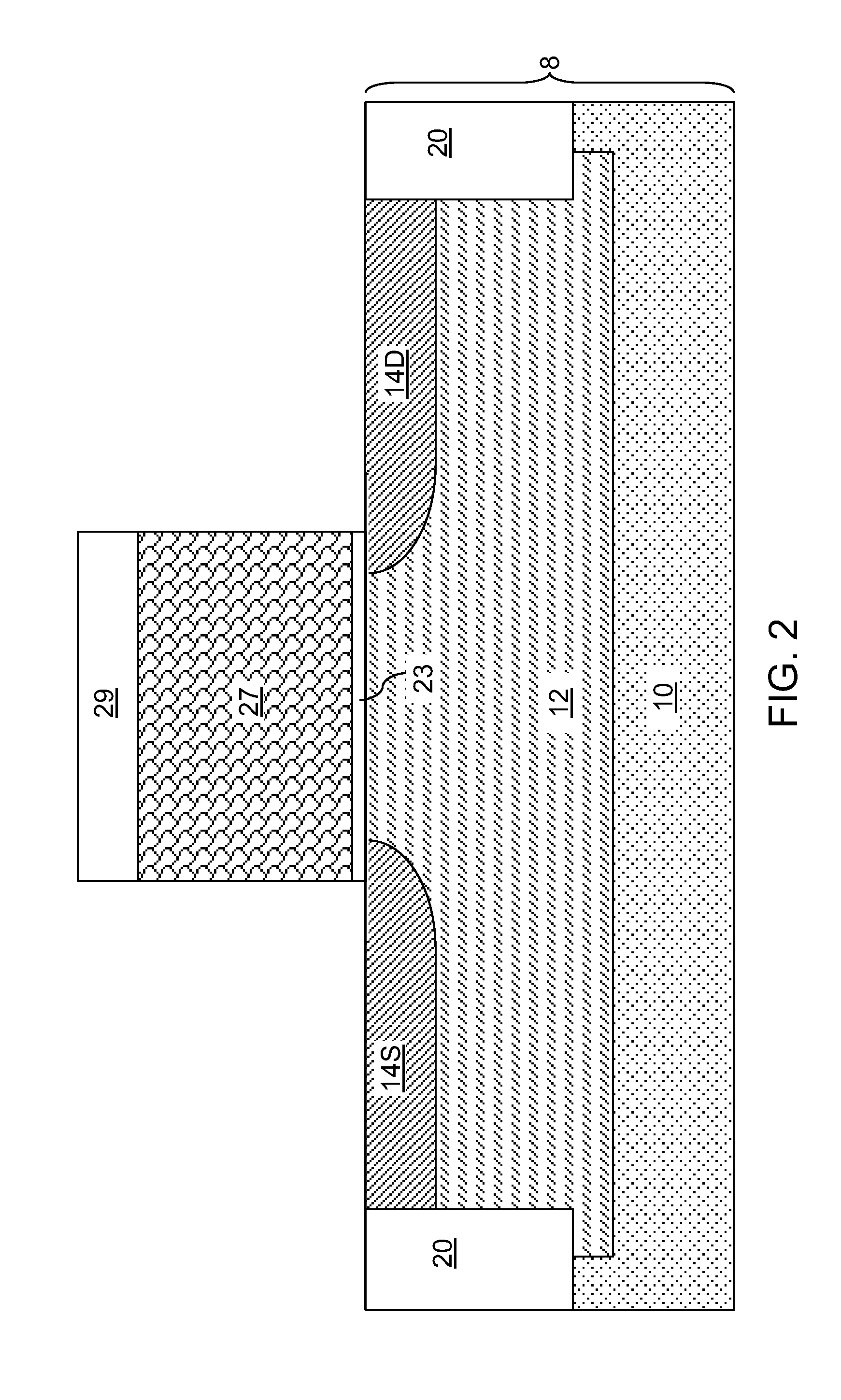

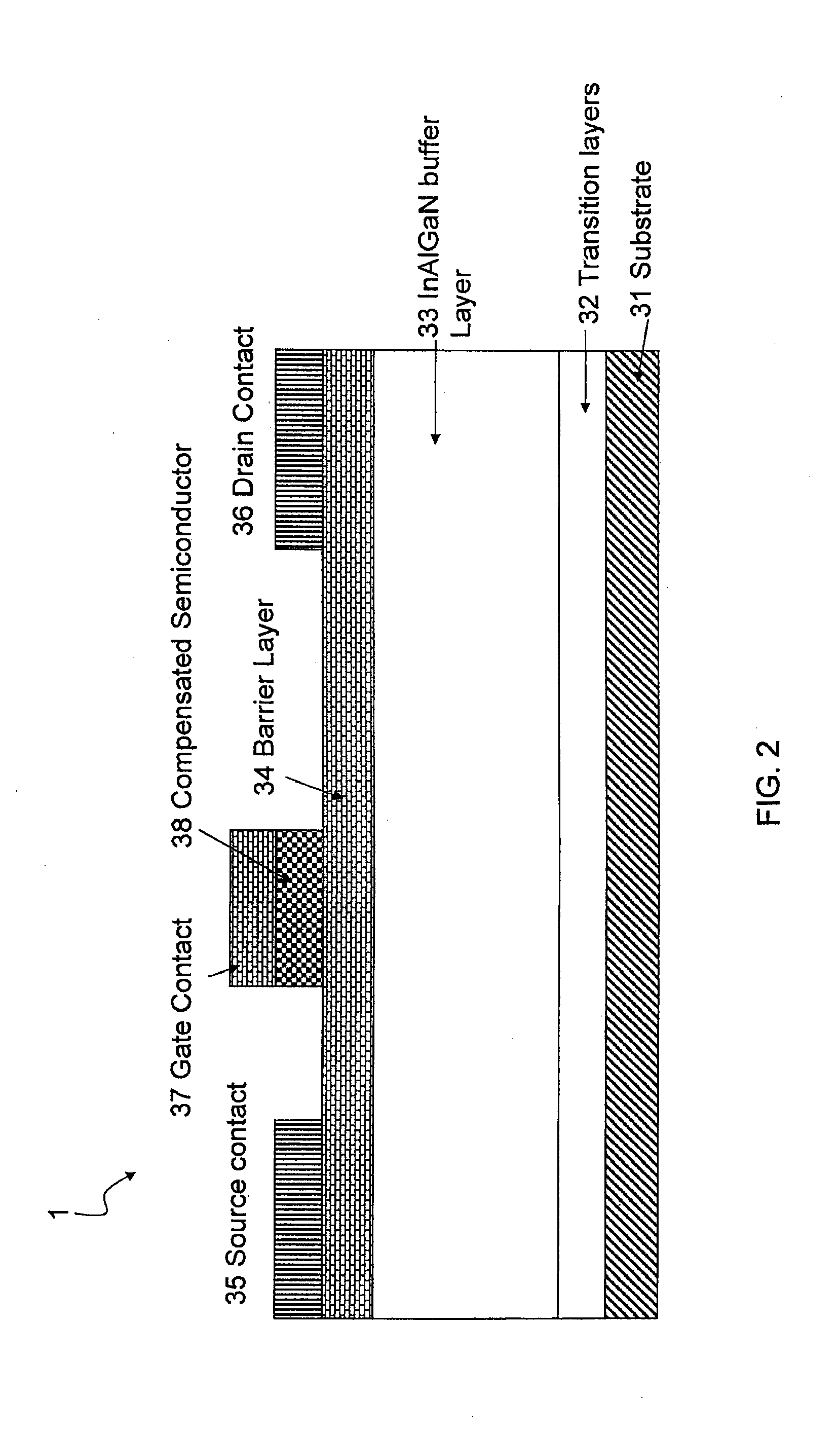

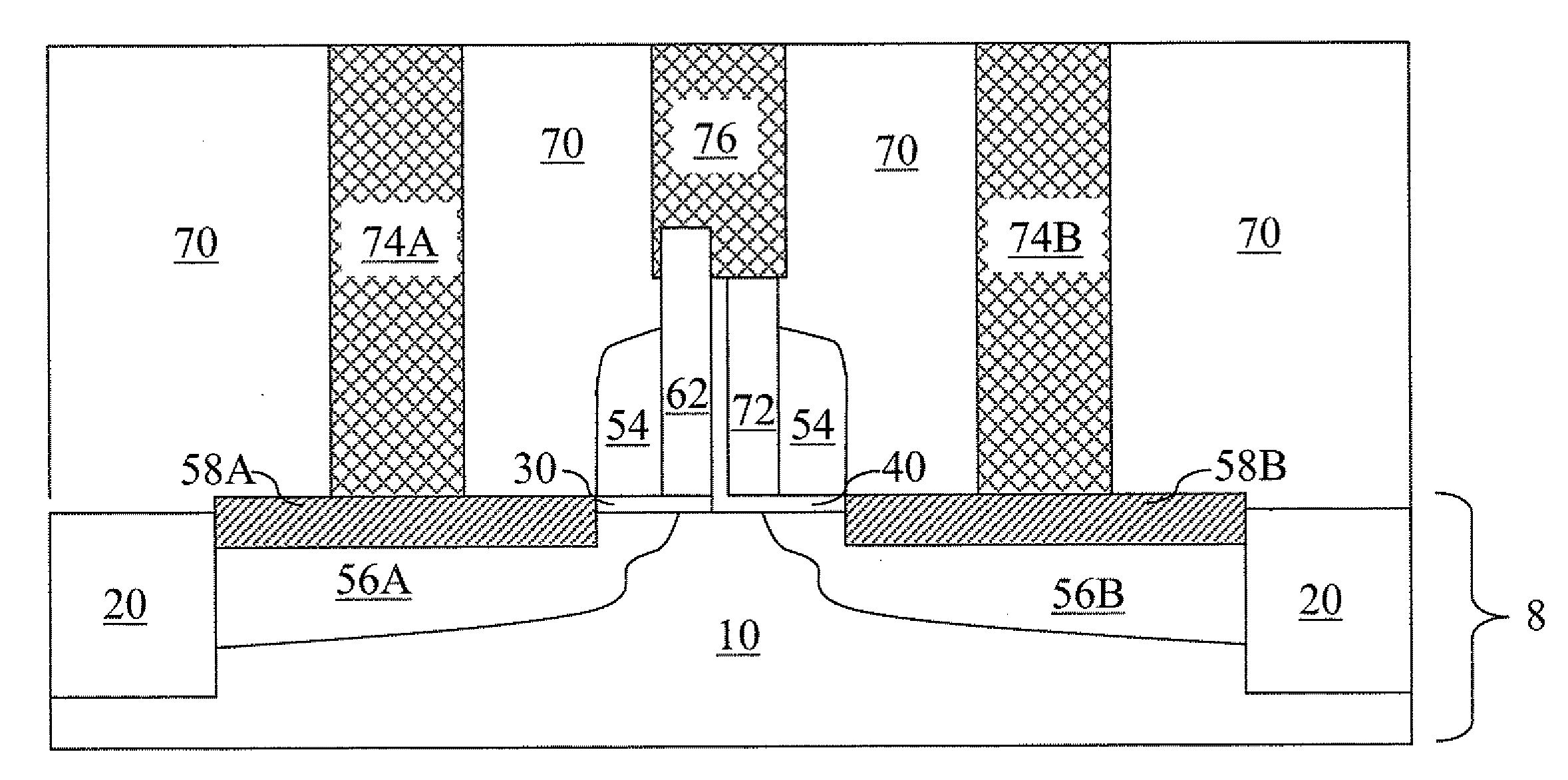

Compensated gate misfet and method for fabricating the same

ActiveUS20100258848A1Reduce gate leakageTransistorSemiconductor/solid-state device manufacturingEngineeringSemi insulating

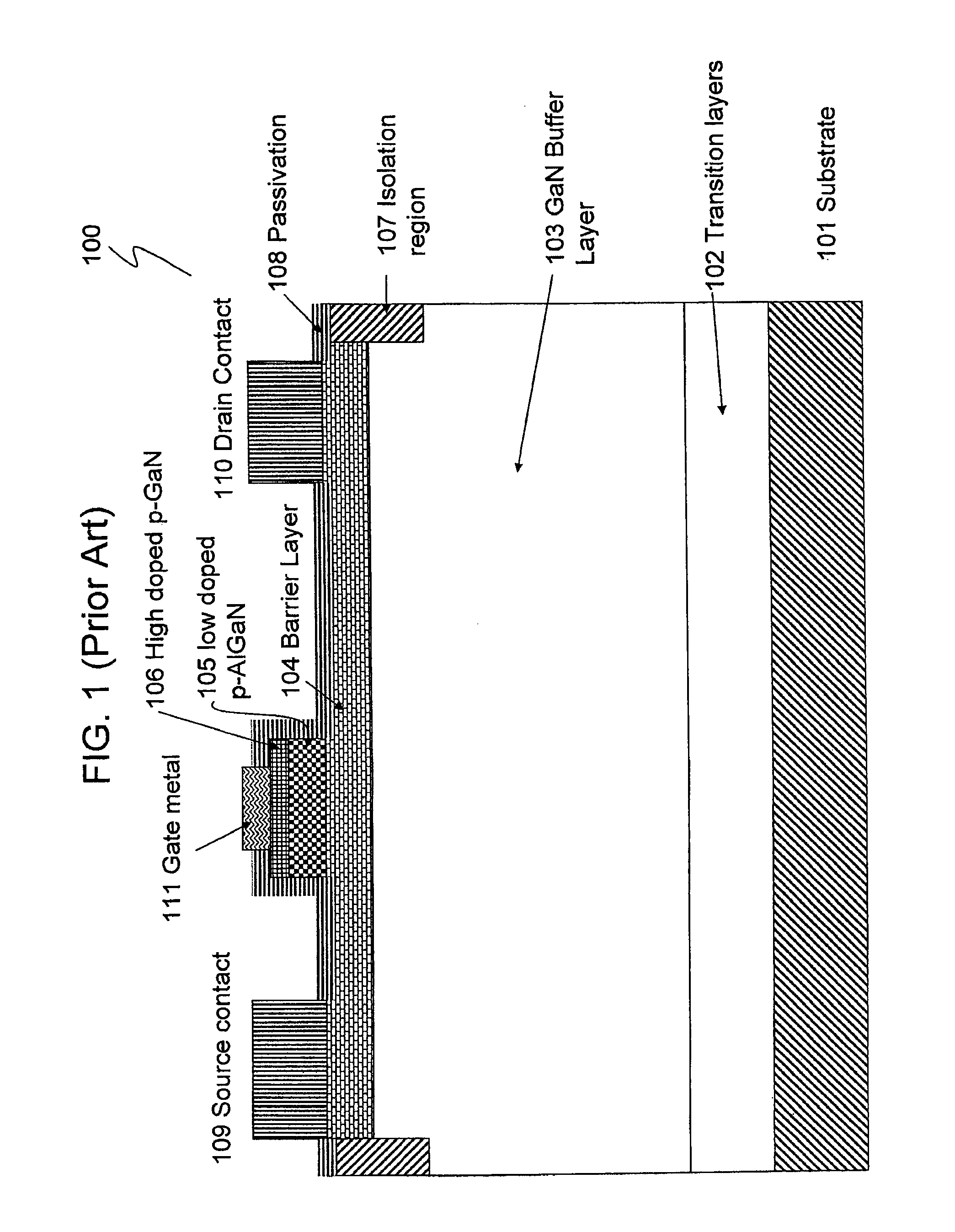

A MISFET, such as a GaN transistor, with low gate leakage. In one embodiment, the gate leakage is reduced with a compensated GaN layer below the gate contact and above the barrier layer. In another embodiment, the gate leakage is reduced by employing a semi-insulating layer below the gate contact and above the barrier layer.

Owner:EFFICIENT POWER CONVERSION CORP

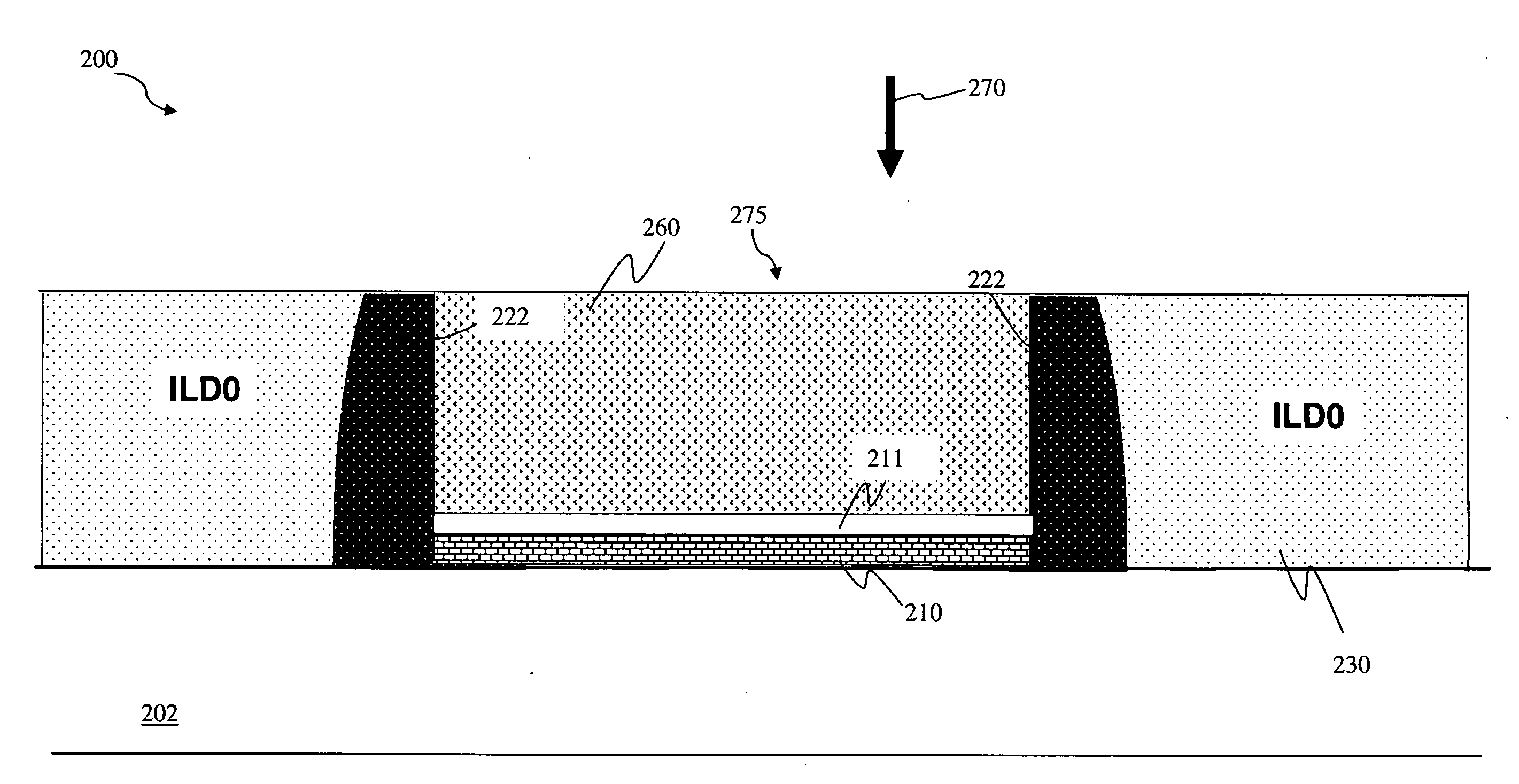

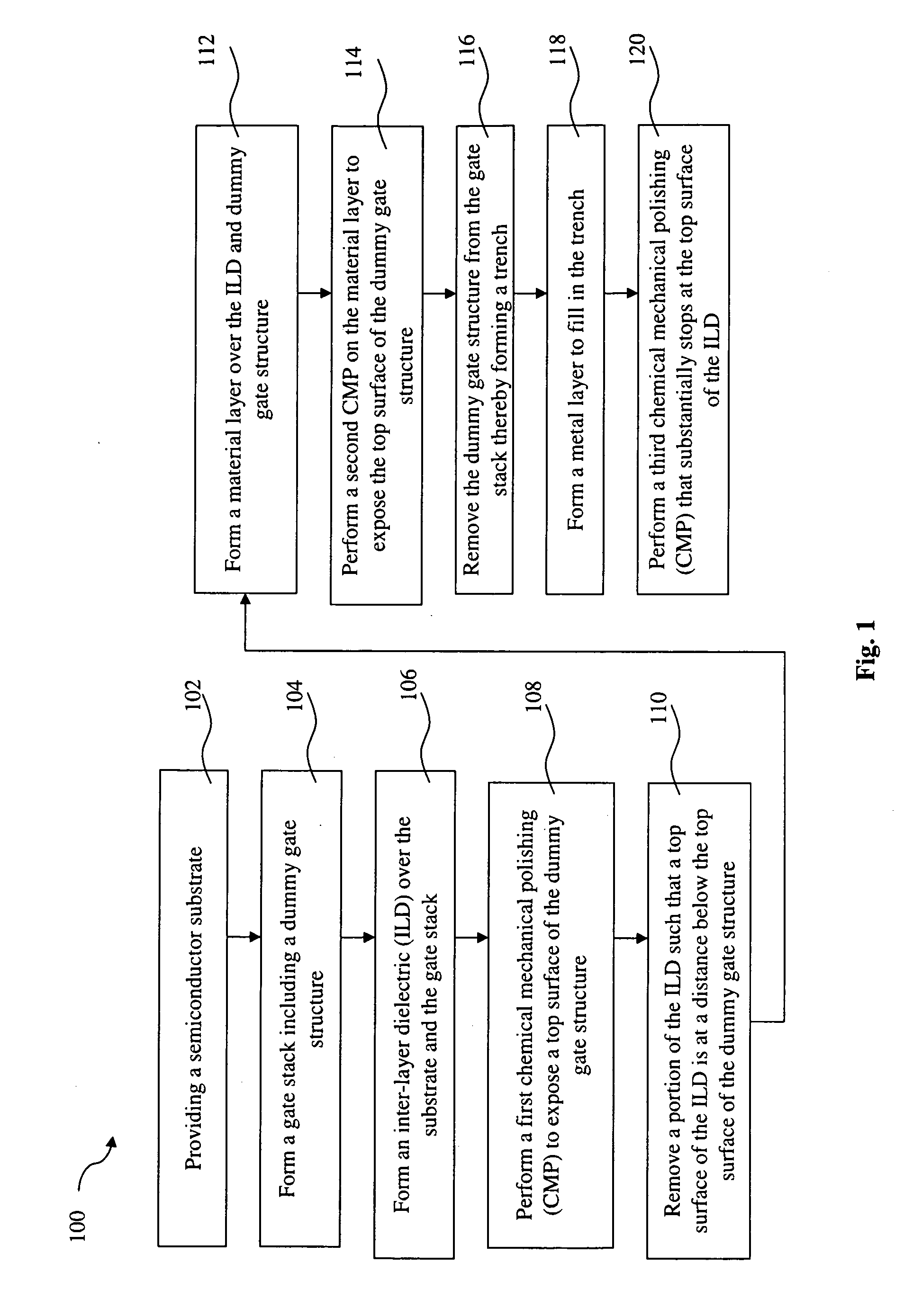

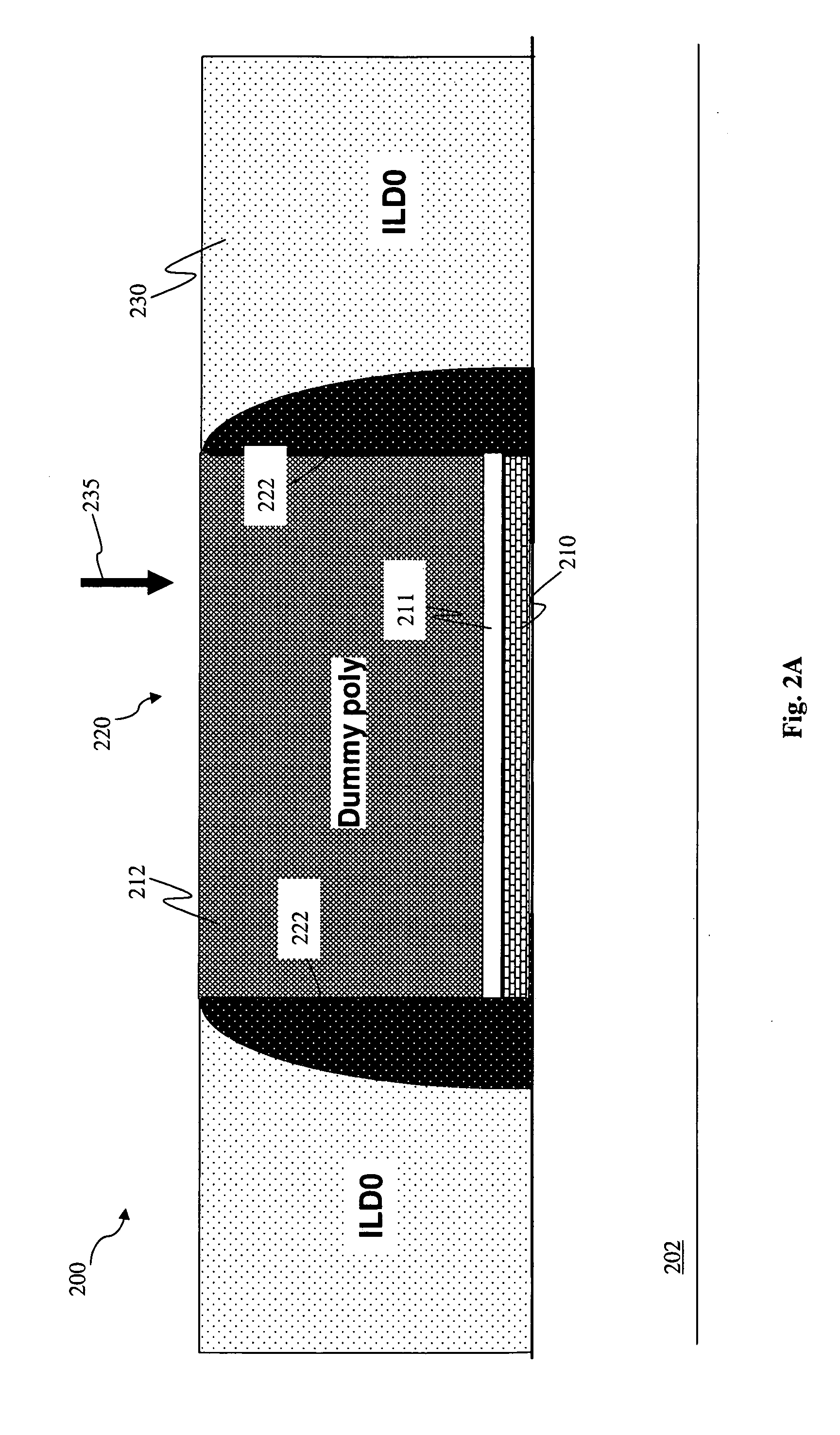

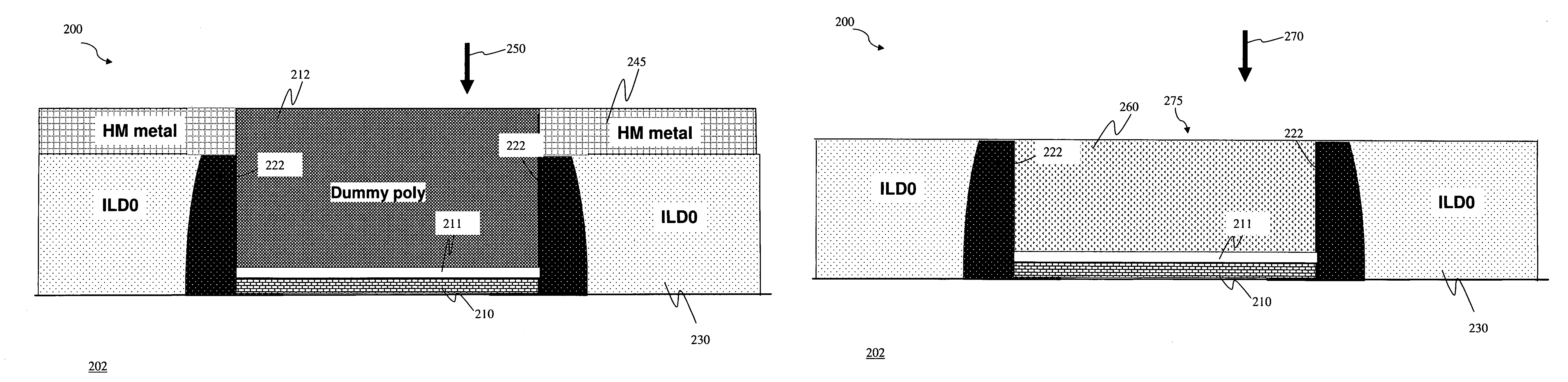

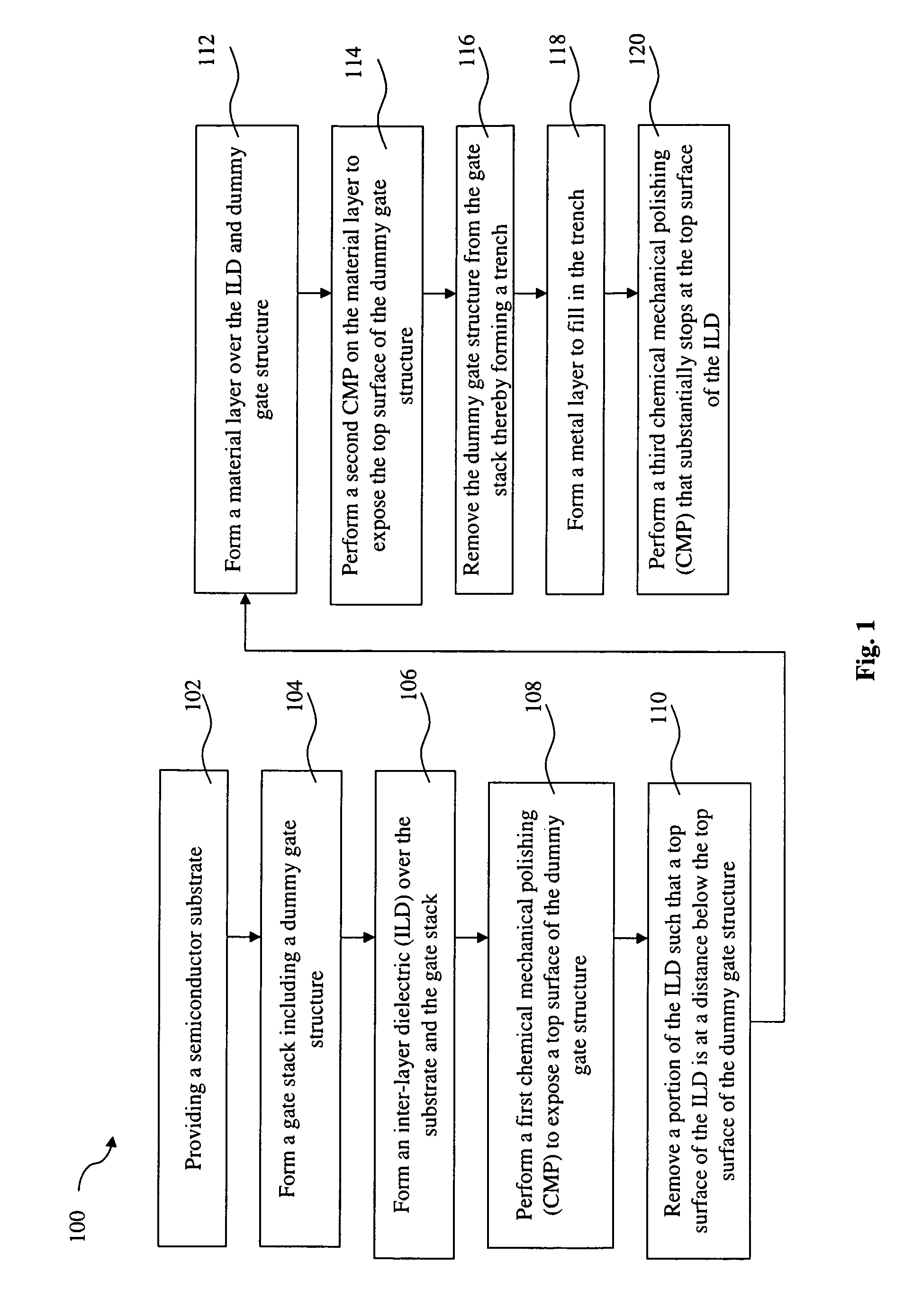

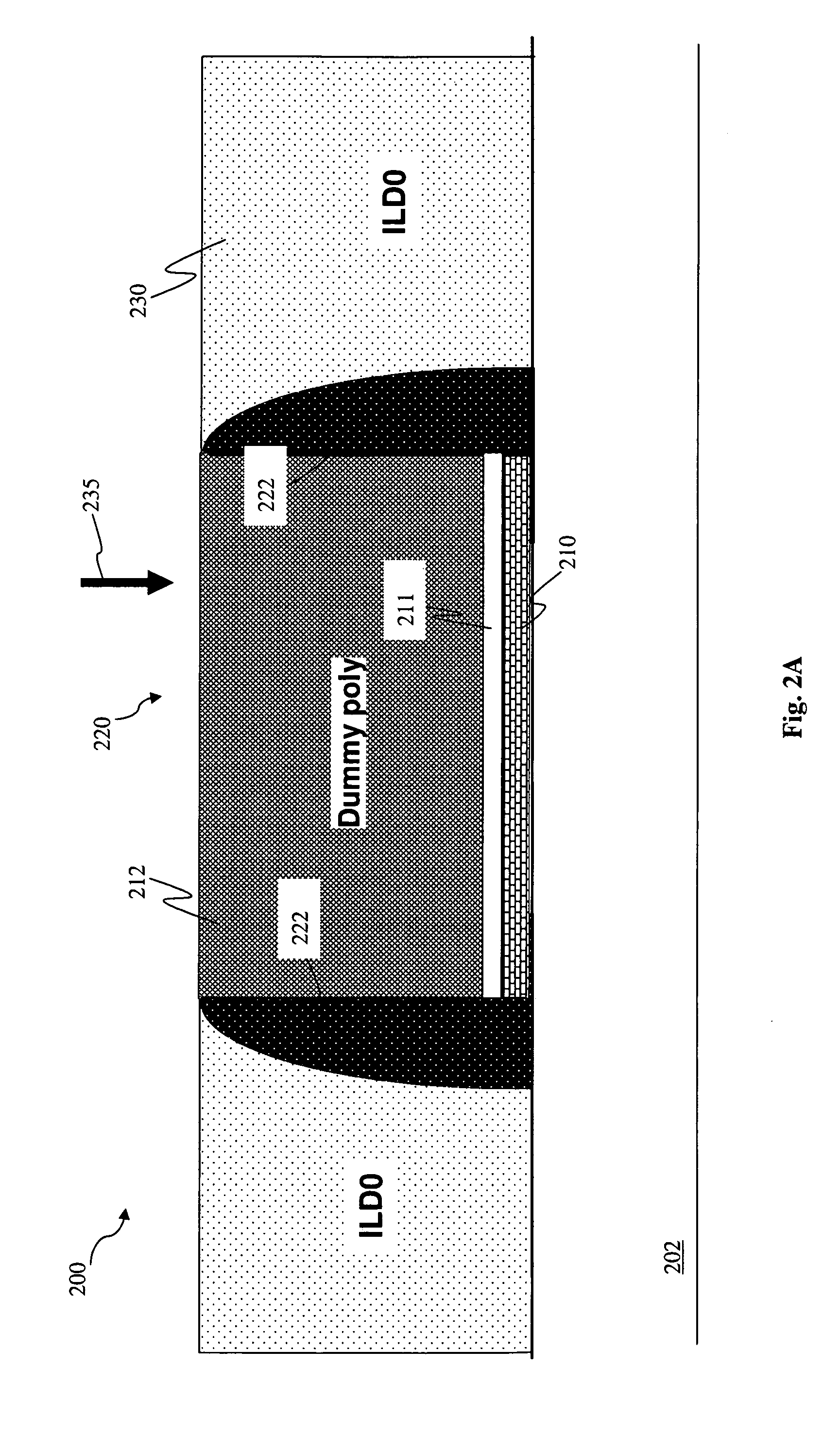

Method for gate height control in a gate last process

InactiveUS20100087056A1Improve device performanceSmall sizeSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricInter layer

A method is provided for fabricating a semiconductor device that includes providing a semiconductor substrate, forming a transistor in the substrate, the transistor having a gate structure that includes a dummy gate structure, forming an inter-layer dielectric (ILD), performing a first chemical mechanical polishing (CMP) to expose a top surface of the dummy gate structure, removing a portion of the ILD such that a top surface of the ILD is at a distance below the top surface of the dummy gate structure, forming a material layer over the ILD and dummy gate structure, performing a second CMP on the material layer to expose the top surface of the dummy gate structure, removing the dummy gate structure thereby forming a trench, forming a metal layer to fill in the trench, and performing a third CMP that substantially stops at the top surface of the ILD.

Owner:TAIWAN SEMICON MFG CO LTD

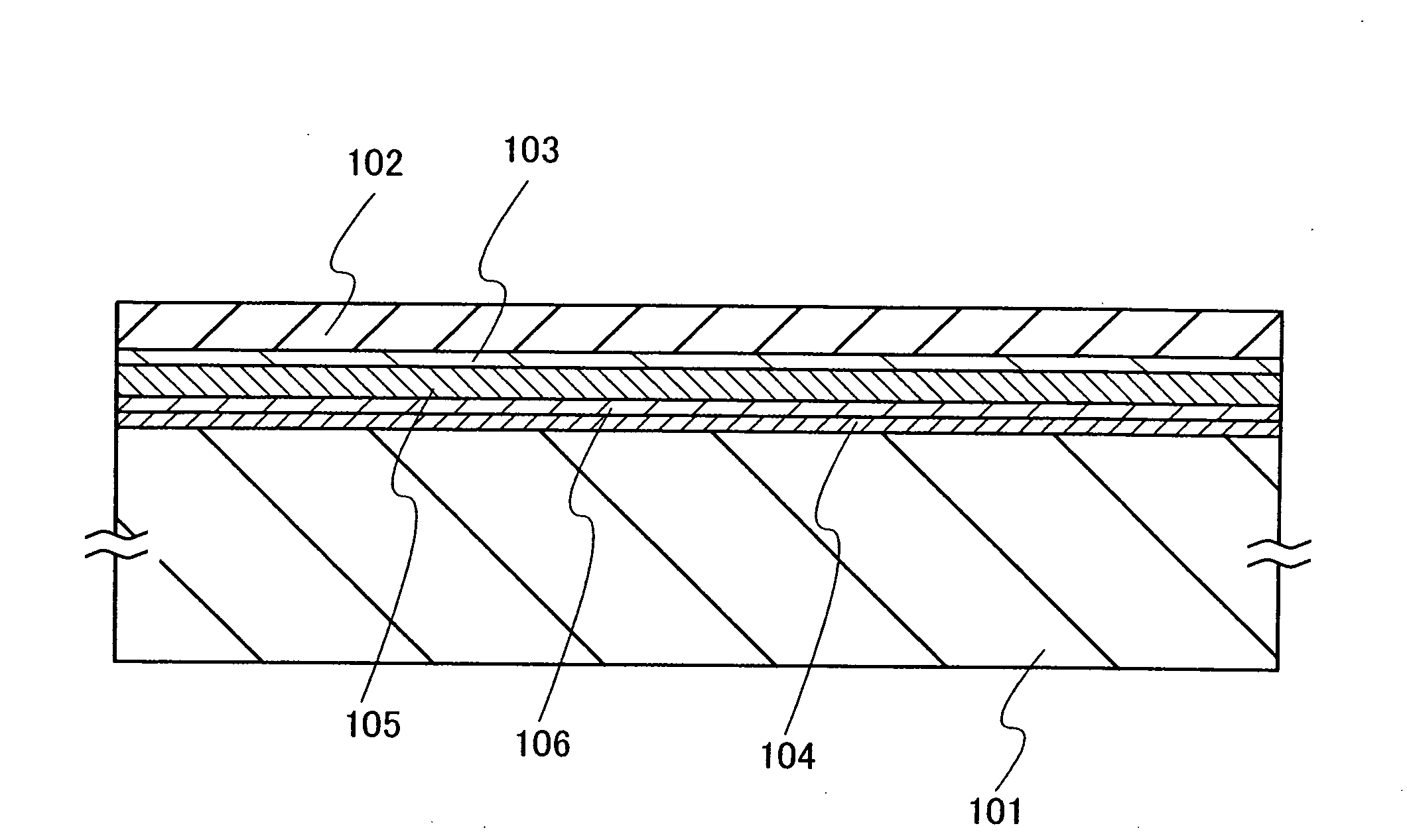

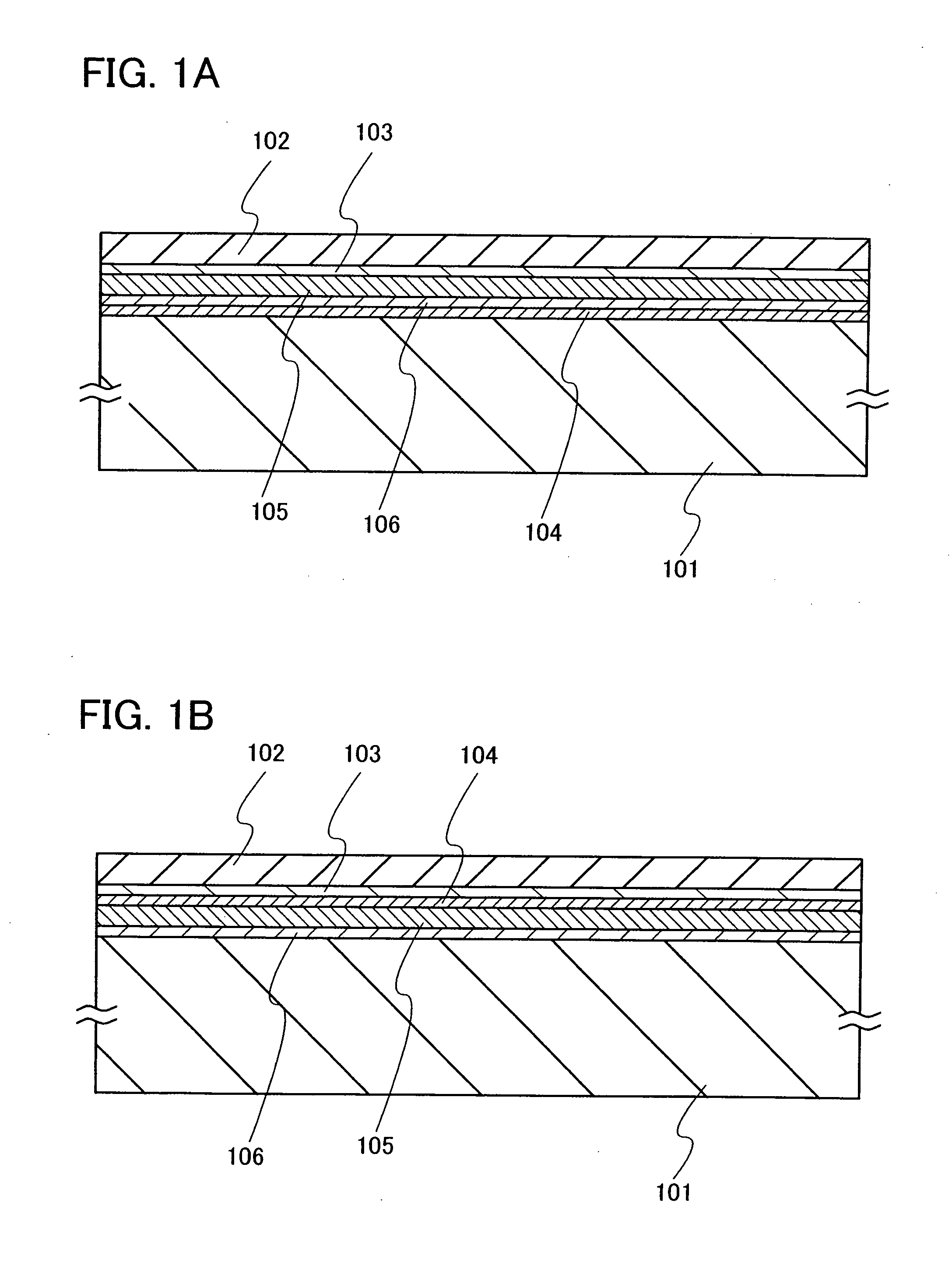

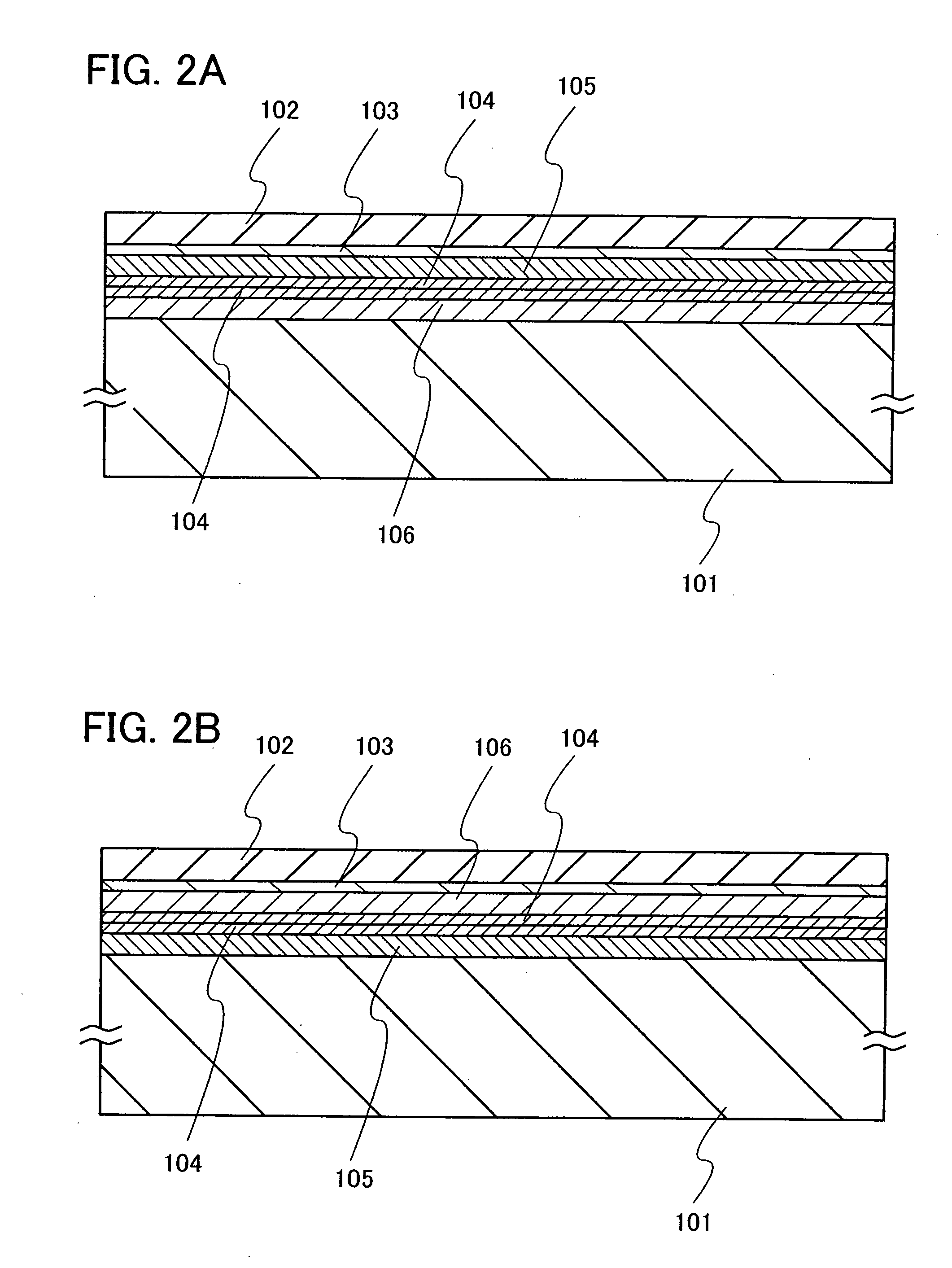

Semiconductor substrate and manufacturing method of semiconductor device

InactiveUS20080296724A1Impurity contaminationSuppress generationSemiconductor/solid-state device detailsSolid-state devicesMicrowaveHydrogen

To provide a semiconductor substrate including a crystalline semiconductor layer which is suitable for practical use, even if a material different from that of the semiconductor layer is used for a supporting substrate, and a semiconductor device using the semiconductor substrate. The semiconductor substrate includes a bonding layer which forms a bonding plane, a barrier layer formed of an insulating material containing nitrogen, a relief layer which is formed of an insulating material that includes nitrogen at less than 20 at. % and hydrogen at 1 at. % to 20 at. %, and an insulating layer containing a halogen, between a supporting substrate and a single-crystal semiconductor layer. The semiconductor device includes the above-described structure at least partially, and a gate insulating layer formed by a microwave plasma CVD method using SiH4 and N2O as source gases is in contact with the single-crystal semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

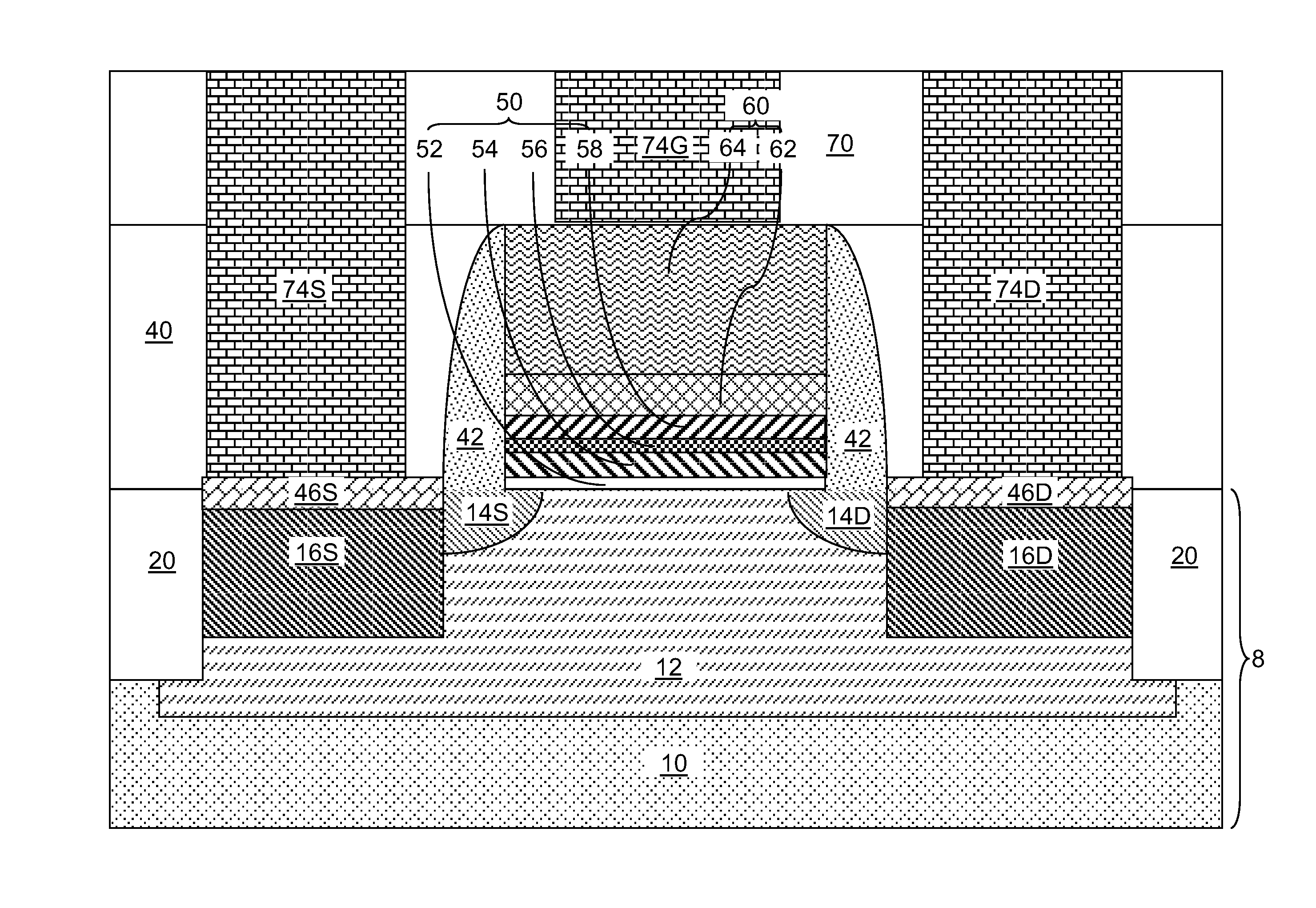

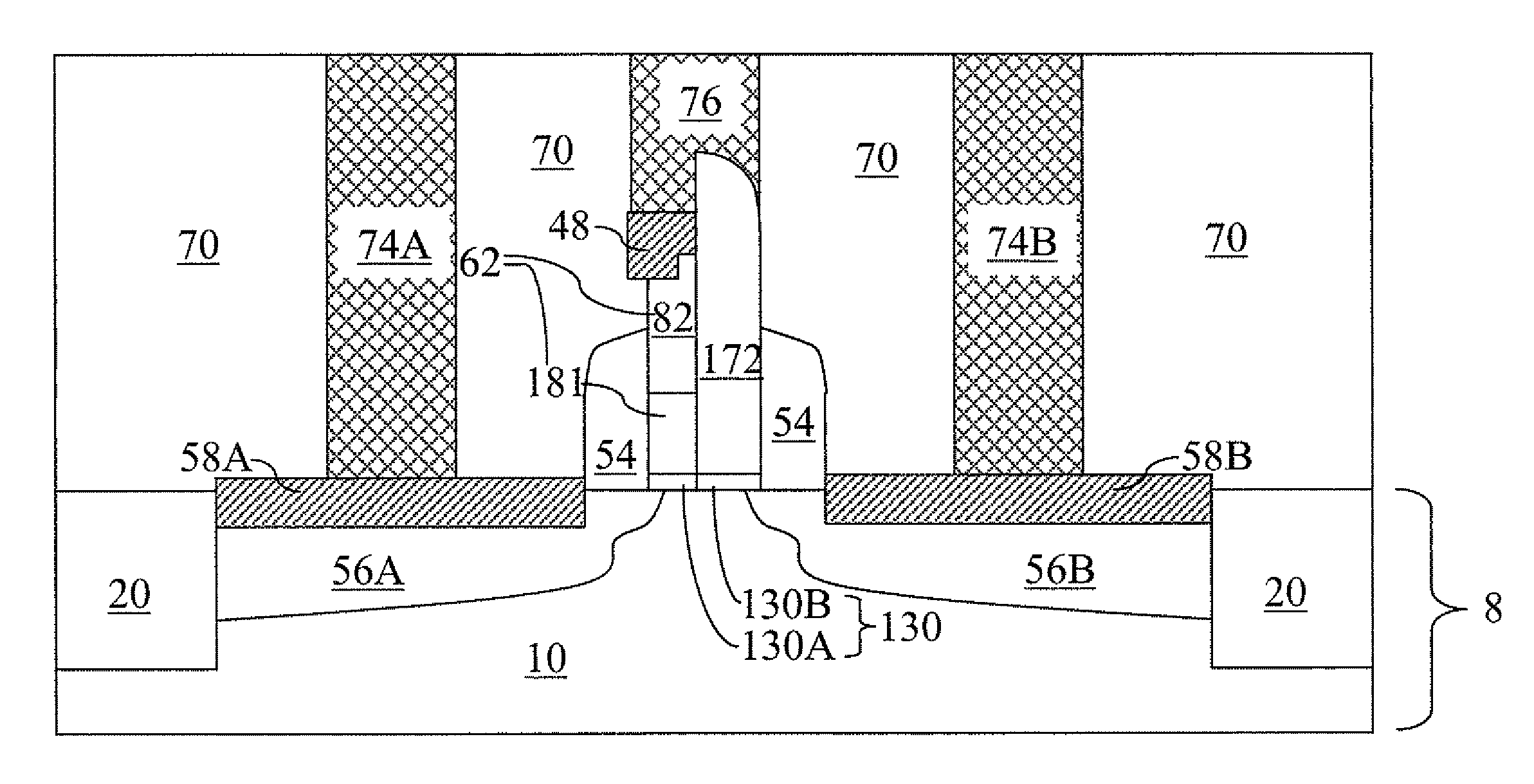

Ultra Thin Channel (UTC) MOSFET Structure Formed on BOX Regions Having Different Depths and Different Thicknesses Beneath the UTC and SourceDrain Regions and Method of Manufacture Thereof

ActiveUS20080283918A1Eliminate variationReduce Overlap CapacitanceTransistorSolid-state devicesMOSFETGate dielectric

A MOSFET structure includes a planar semiconductor substrate, a gate dielectric and a gate. A UT SOI channel extends to a first depth below the top surface of the substrate and is self-aligned to and is laterally coextensive with the gate. Source-drain regions, extend to a second depth greater than the first depth below the top surface, and are self-aligned to the UT channel region. A BOX1 region extends across the entire structure, and vertically from the second depth to a third depth below the top surface. An upper portion of a BOX2 region under the UT channel region is self-aligned to and is laterally coextensive with the gate, and extends vertically from the first depth to a third depth below the top surface, and where the third depth is greater than the second depth.

Owner:GLOBALFOUNDRIES US INC

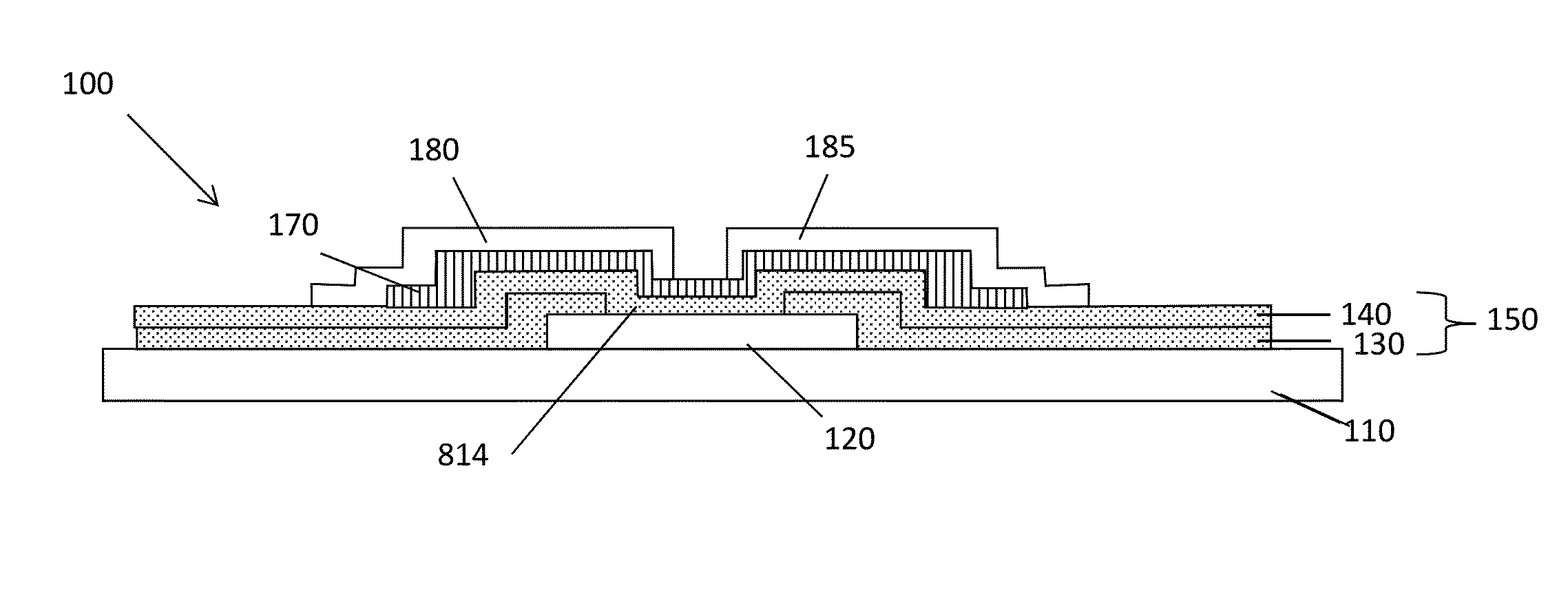

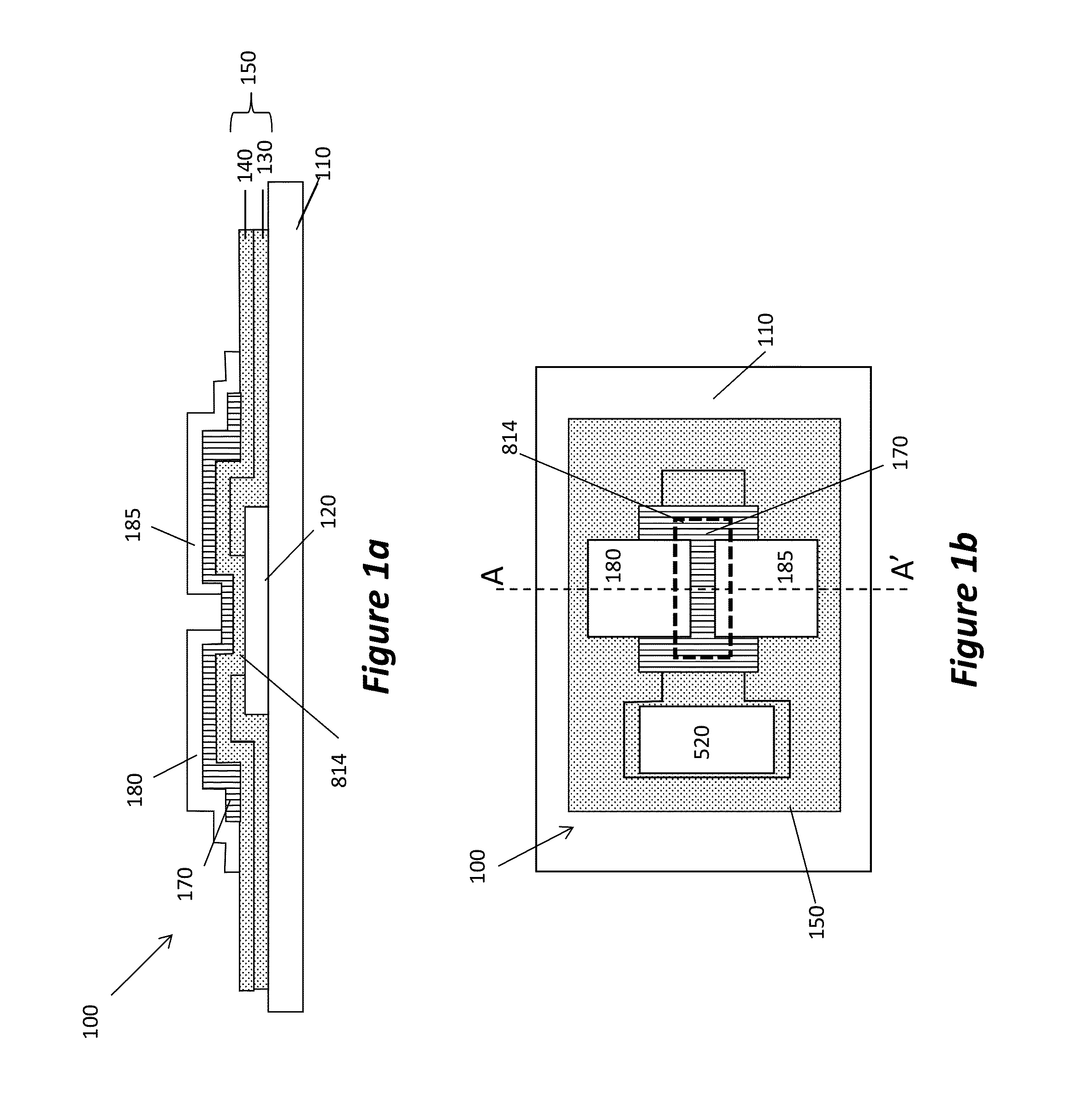

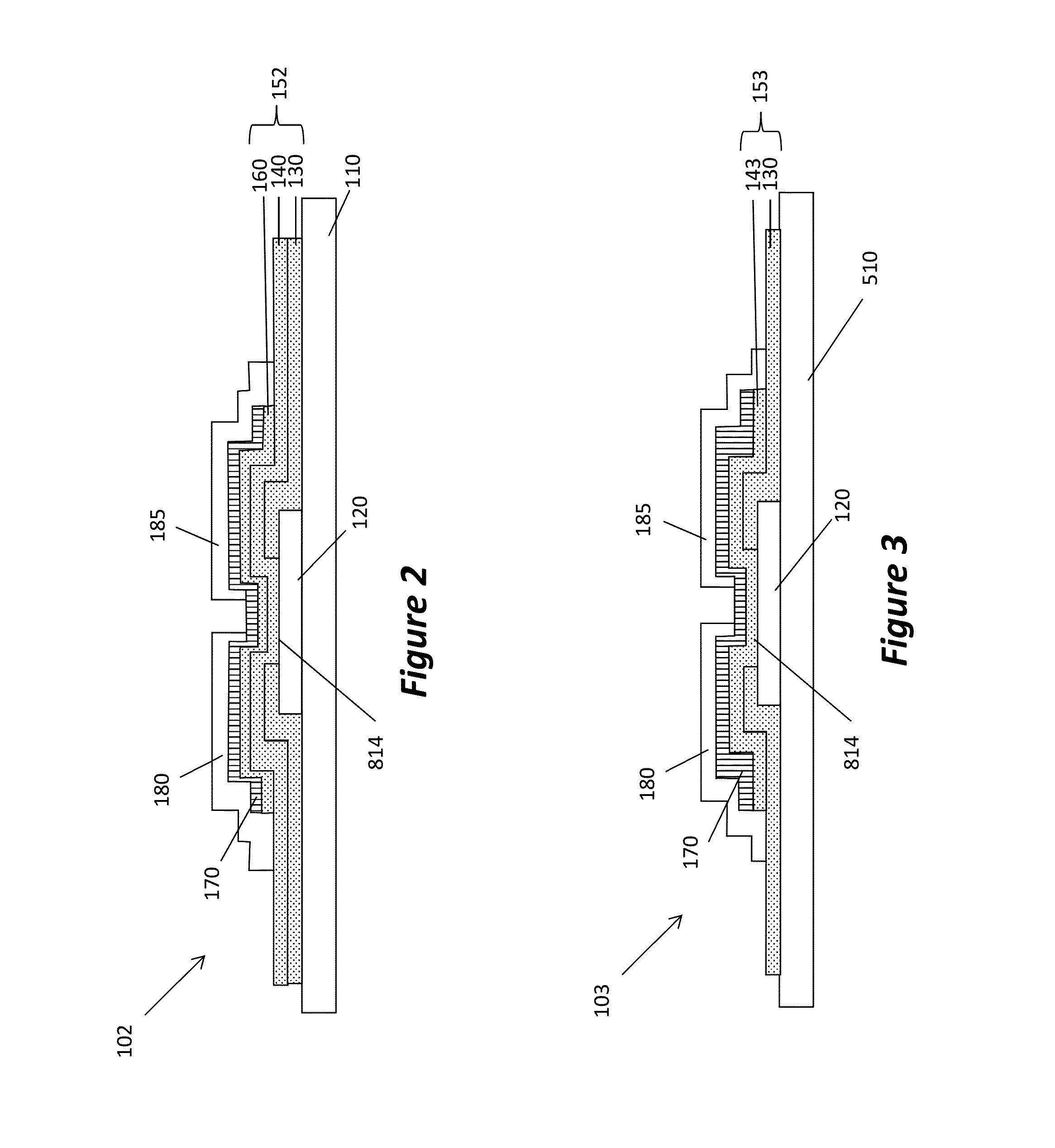

Enhancement mode GaN HEMT device with gate spacer and method for fabricating the same

ActiveUS8823012B2Reduce leakageReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesGate leakage currentOhmic contact

Enhancement-mode GaN devices having a gate spacer, a gate metal material and a gate compound that are self-aligned, and a methods of forming the same. The materials are patterned and etched using a single photo mask, which reduces manufacturing costs. An interface of the gate spacer and the gate compound has lower leakage than the interface of a dielectric film and the gate compound, thereby reducing gate leakage. In addition, an ohmic contact metal layer is used as a field plate to relieve the electric field at a doped III-V gate compound corner towards the drain contact, which leads to lower gate leakage current and improved gate reliability.

Owner:EFFICIENT POWER CONVERSION CORP

Field effect transistor having an asymmetric gate electrode

InactiveUS20090032889A1Improve short channel effectHigh carrier mobilityTransistorRead-only memoriesGate dielectricElectrical conductor

The gate electrode of a metal oxide semiconductor field effect transistor (MOSFET) comprises a source side gate electrode and a drain side gate electrode that abut each other near the middle of the channel. In one embodiment, the source side gate electrode comprises a silicon oxide based gate dielectric and the drain side gate electrode comprises a high-k gate dielectric. The source side gate electrode provides high carrier mobility, while the drain side gate electrode provides good short channel effect and reduced gate leakage. In another embodiment, the source gate electrode and drain gate electrode comprises different high-k gate dielectric stacks and different gate conductor materials, wherein the source side gate electrode has a first work function a quarter band gap away from a band gap edge and the drain side gate electrode has a second work function near the band gap edge.

Owner:GLOBALFOUNDRIES INC

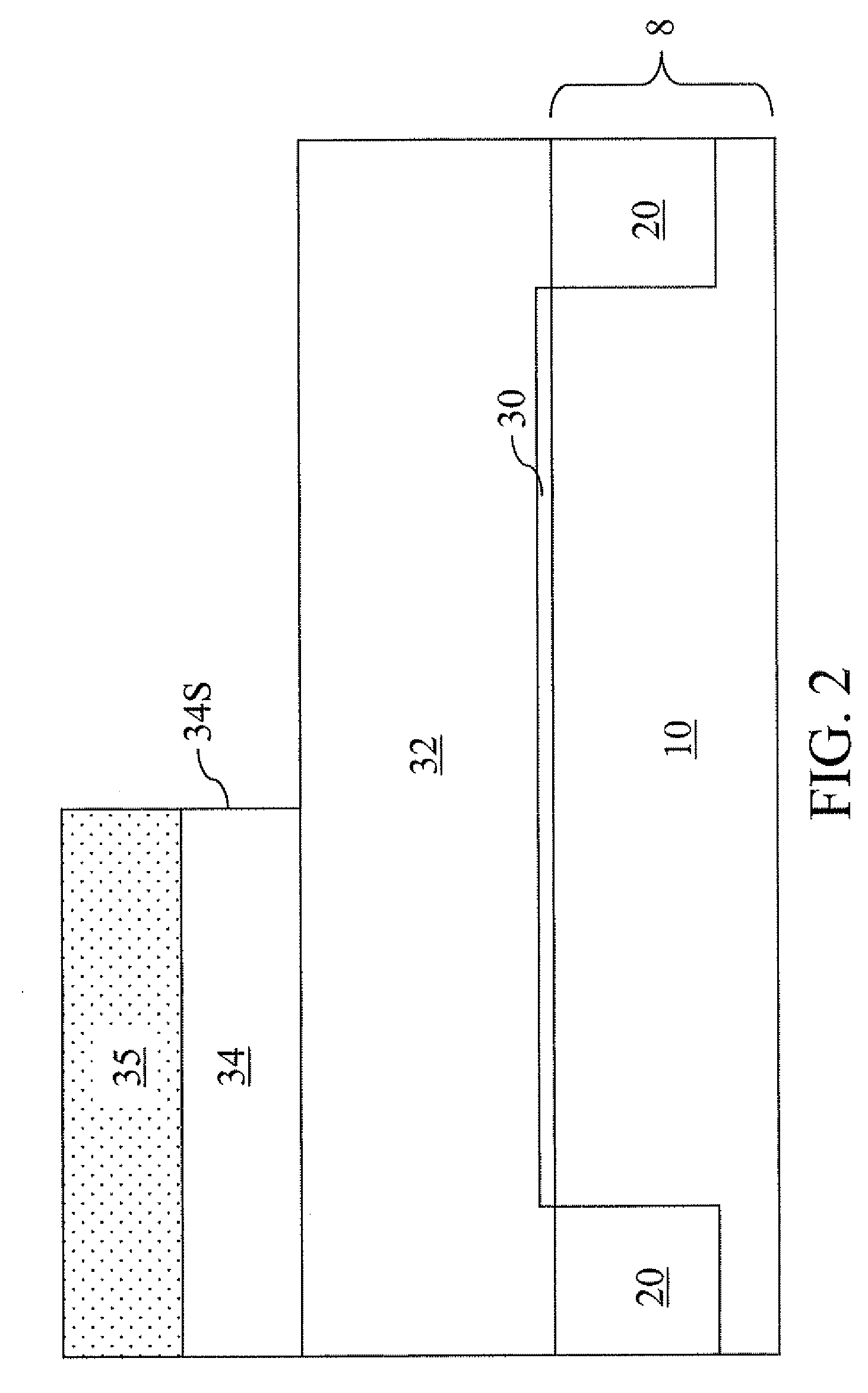

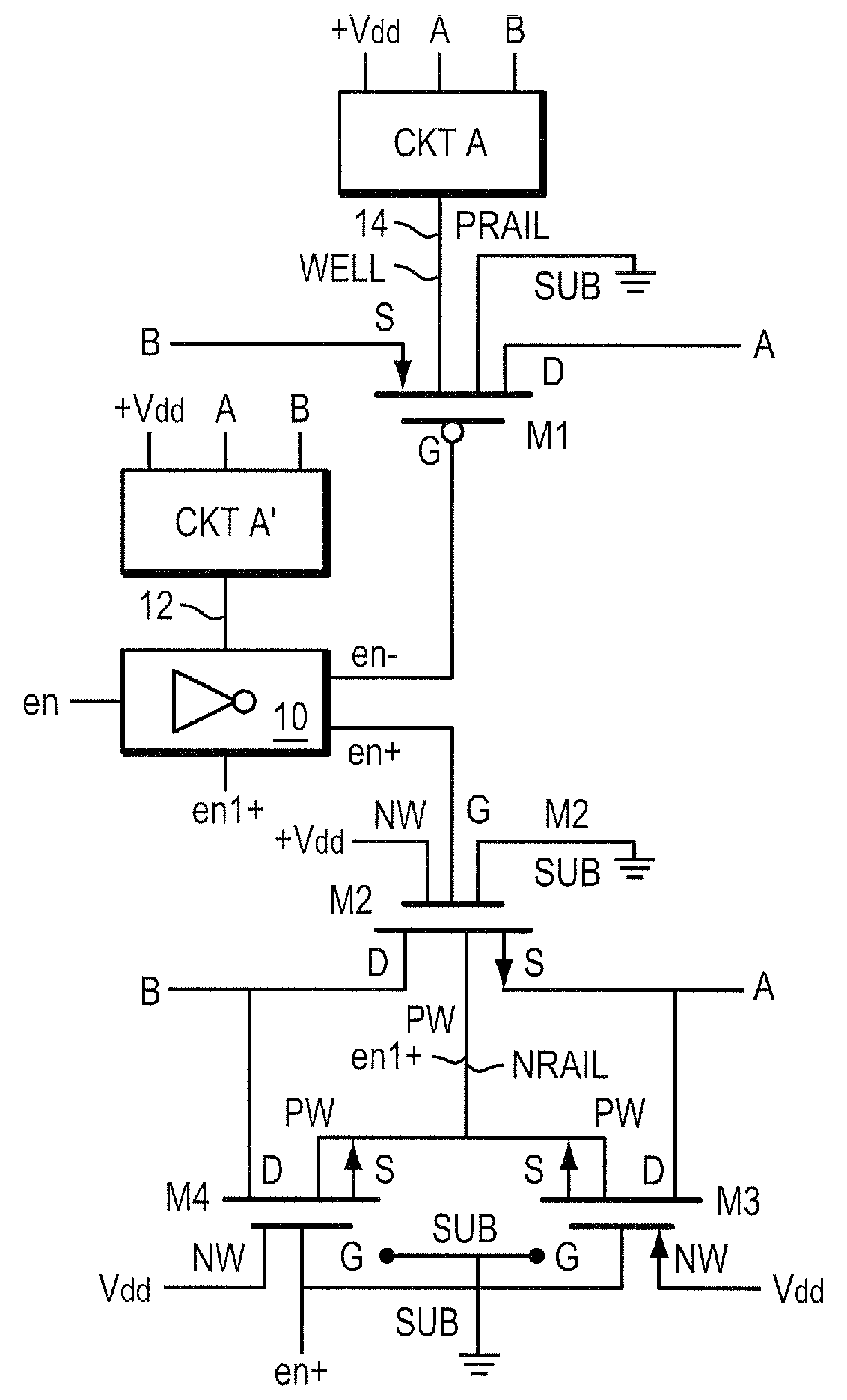

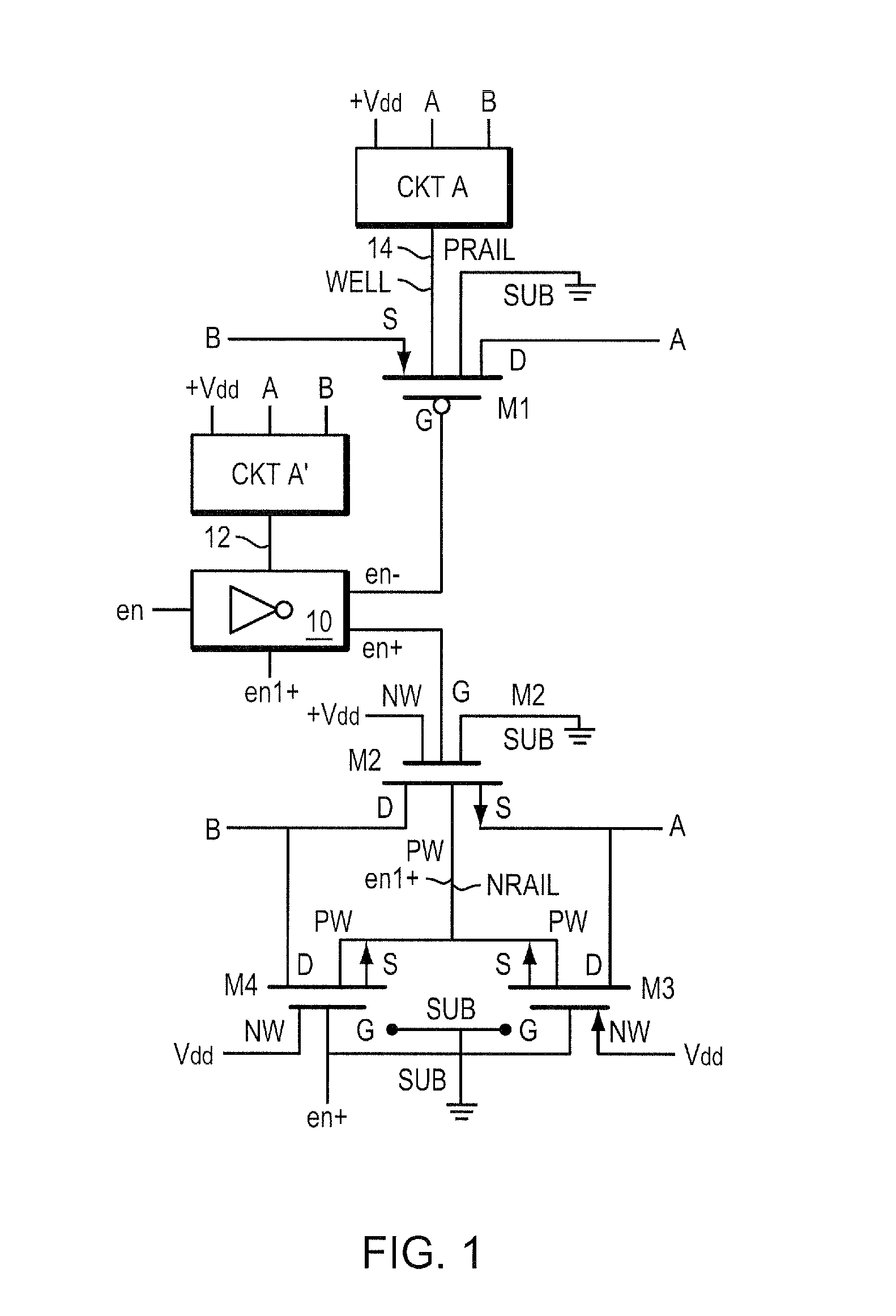

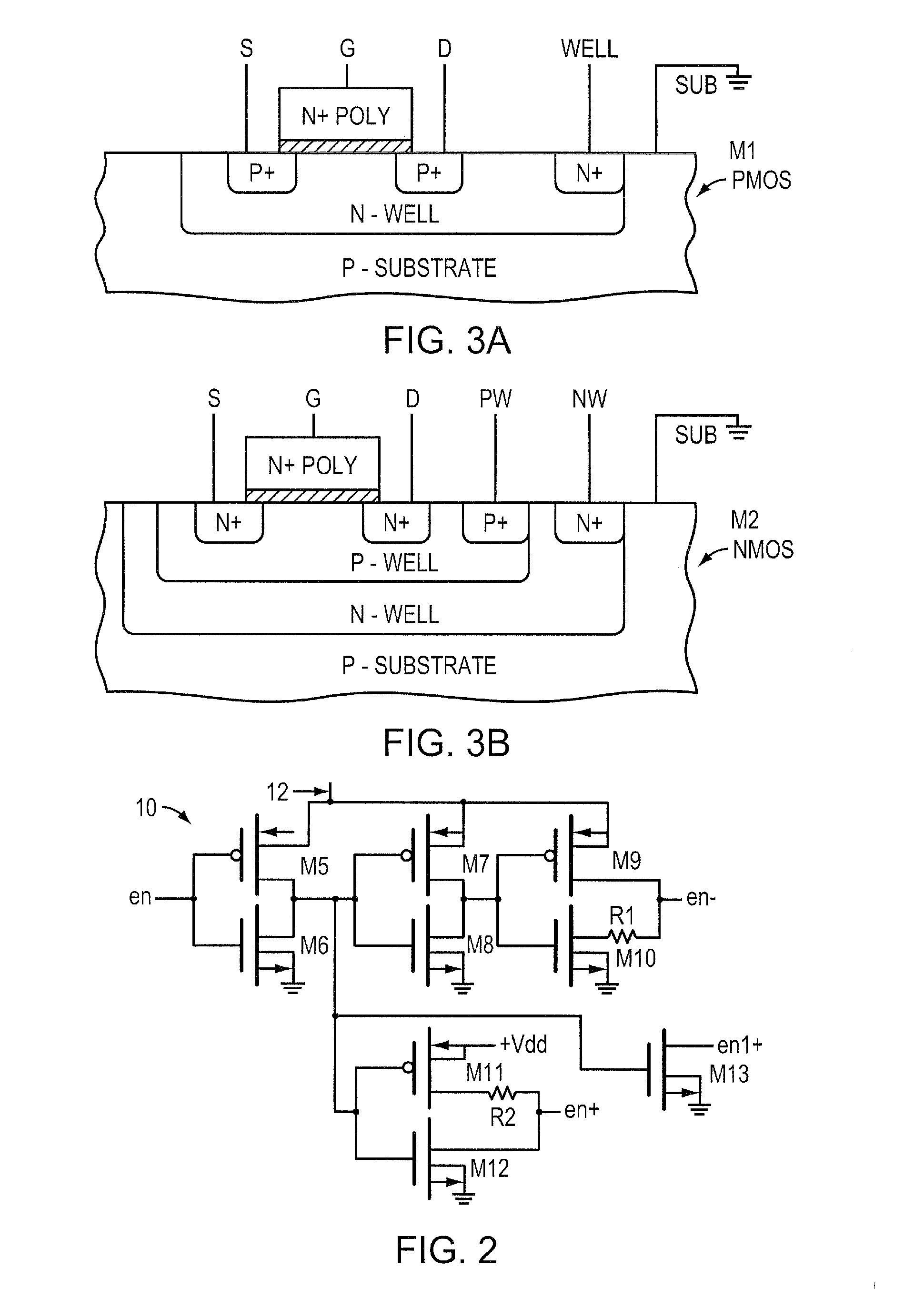

Over-voltage tolerant pass-gate

ActiveUS7514983B2Improve leakageNegatively reductionTransistorElectronic switchingSchottky diodePass gate

A pass-gate having a single or parallel opposite polarity FETs is disclosed. The wells of the primary transistor switches are driven from circuitry that reduces over-voltage leakage and other malfunctions. A circuit that drives the wells is also used to power enable circuits that drive the gates of the pass transistors. The use of separate circuits to the gate and the wells further reduces leakage. In the condition of power supply voltage and signal levels that are near the thresholds of the FETs involved, one or more Schottky diodes may be used across pn junctions in the FETs that will prevent turning on the pn junctions.

Owner:SEMICON COMPONENTS IND LLC

ENHANCEMENT MODE GaN HEMT DEVICE WITH GATE SPACER AND METHOD FOR FABRICATING THE SAME

ActiveUS20120175631A1Reduce leakageReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesGate leakage currentDielectric membrane

Enhancement-mode GaN devices having a gate spacer, a gate metal material and a gate compound that are self-aligned, and a methods of forming the same. The materials are patterned and etched using a single photo mask, which reduces manufacturing costs. An interface of the gate spacer and the gate compound has lower leakage than the interface of a dielectric film and the gate compound, thereby reducing gate leakage. In addition, an ohmic contact metal layer is used as a field plate to relieve the electric field at a doped III-V gate compound corner towards the drain contact, which leads to lower gate leakage current and improved gate reliability.

Owner:EFFICIENT POWER CONVERSION CORP

Field effect transistor having an asymmetric gate electrode

InactiveUS8110465B2Improve short channel effectHigh carrier mobilityTransistorRead-only memoriesElectrical conductorGate dielectric

The gate electrode of a metal oxide semiconductor field effect transistor (MOSFET) comprises a source side gate electrode and a drain side gate electrode that abut each other near the middle of the channel. In one embodiment, the source side gate electrode comprises a silicon oxide based gate dielectric and the drain side gate electrode comprises a high-k gate dielectric. The source side gate electrode provides high carrier mobility, while the drain side gate electrode provides good short channel effect and reduced gate leakage. In another embodiment, the source gate electrode and drain gate electrode comprises different high-k gate dielectric stacks and different gate conductor materials, wherein the source side gate electrode has a first work function a quarter band gap away from a band gap edge and the drain side gate electrode has a second work function near the band gap edge.

Owner:GLOBALFOUNDRIES INC

Compensated gate MISFET and method for fabricating the same

ActiveUS8350294B2Reduce gate leakageTransistorSemiconductor/solid-state device manufacturingEngineeringSemi insulating

A MISFET, such as a GaN transistor, with low gate leakage. In one embodiment, the gate leakage is reduced with a compensated GaN layer below the gate contact and above the barrier layer. In another embodiment, the gate leakage is reduced by employing a semi-insulating layer below the gate contact and above the barrier layer.

Owner:EFFICIENT POWER CONVERSION CORP

GaN-based field effect transistor with high quality MIS structure and preparation method of GaN-based field effect transistor

InactiveCN105336789AImprove performanceThreshold voltage stability is remarkableSemiconductor/solid-state device manufacturingSemiconductor devicesPartial oxidationVoltage stability

The invention belongs to the semiconductor material and device field and discloses a GaN-based field effect transistor with a high quality MIS structure and a preparation method of the GaN-based field effect transistor, in particular, a GaN MISFET device gate dielectric layer and an improvement method of a dielectric layer and GaN interface. The device includes a substrate, an epitaxial layer grown on the substrate as well as a gate electrode, a source electrode, a drain electrode and an insulating layer; the epitaxial layer includes a stress buffer layer which is formed through primary epitaxial growth, a GaN epitaxial layer as well as a second epitaxial layer and a third epitaxial layer which are grown on selective regions on the GaN epitaxial layer; a GaN / AlGaN heterostructure is formed through secondary epitaxial growth, and groove channels are formed; an AlN thin layer is formed through third epitaxial growth; the AlN thin layer is partially oxidized so as to form an AlN / oxide dielectric layer stack structure; gate metal covers the groove channels; a source electrode region and a drain electrode region are formed at two ends; and the source electrode region and the drain electrode region are covered with metal, so that the source electrode and the drain electrode can be formed. The device and preparation process of the invention are simple and reliable. With the preparation method adopted, the high quality MIS structure can be formed, and the performance of the GaN MISFET device can be improved. The preparation method can play a key role in decreasing the electric leakage of the gate electrode, decreasing the resistance of the channels and stabilizing threshold voltage.

Owner:SUN YAT SEN UNIV

Field effect transistor with diamond metal-insulator-semiconductor structure and preparation method thereof

InactiveCN102903756AMeet the requirements of developmentReduce gate leakageSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricSemiconductor structure

The invention provides a field effect transistor with a diamond metal-insulator-semiconductor structure and prepared by means of an auto-oxidation method and a preparation method thereof. The field effect transistor with the diamond metal-insulator-semiconductor structure is structurally characterized in that a conducting channel is formed on a diamond after diamond surface is hydrogenated, two symmetrical Au are arranged on the conducting channel, a Al2O3 / TiO2 composite medium film is arranged between the two symmetrical Au, and a metal gate is arranged on the composite medium film. The preparation method comprises the steps of performing surface hydrogenation, performing ohmic contact, performing device isolation, preparing an Al2O3 / TiO2 multi-layer composite oxidization film, forming an insulating layer and forming a management information system (MIS) structure. The field effect transistor with the diamond metal-insulator-semiconductor structure has the advantages of effectively protecting the conducting channel layer on the surface of the diamond, adopting a TiO2 material with high dielectric constant to reduce the influence of the medium thickness on transconductance and frequency characteristics of a device, using a separating method to achieve an under-gate medium method, reducing the influence of a parasitic capacitor formed by a gate-side medium on the frequency performance of the device and obtaining a low-gate leakage range and a high-gate working voltage range.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

Enhancement-depletion mode inverter with two transistor architectures

ActiveUS20160126241A1Easy injectionReduces the possibility of short circuitsTransistorSolid-state devicesGate dielectricElectrical conductor

An enhancement-depletion-mode inverter includes a load transistor and a drive transistor. The load transistor has a top gate architecture with a first source, a first drain, a load channel region, a first semiconductor layer, and a first gate electrode. A load gate dielectric is in the load channel region, and has a load dielectric thickness. The load transistor is configured to operate in a depletion mode. The drive transistor has a bottom gate architecture with a second source, a second drain, a drive channel region, a second semiconductor layer, and a second gate electrode. A drive gate dielectric is in the drive channel region, and has a drive dielectric thickness that is different from the load dielectric thickness. The drive transistor is configured to operate in a normal mode or an enhancement mode. The first source is electrically connected to the second drain and the first gate.

Owner:EASTMAN KODAK CO

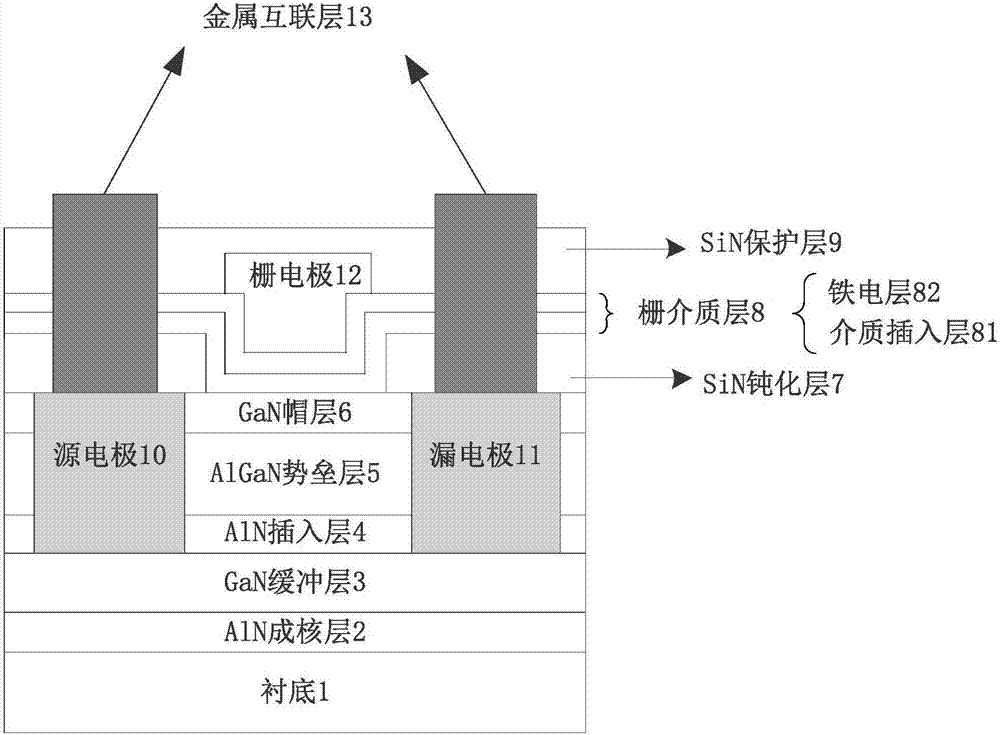

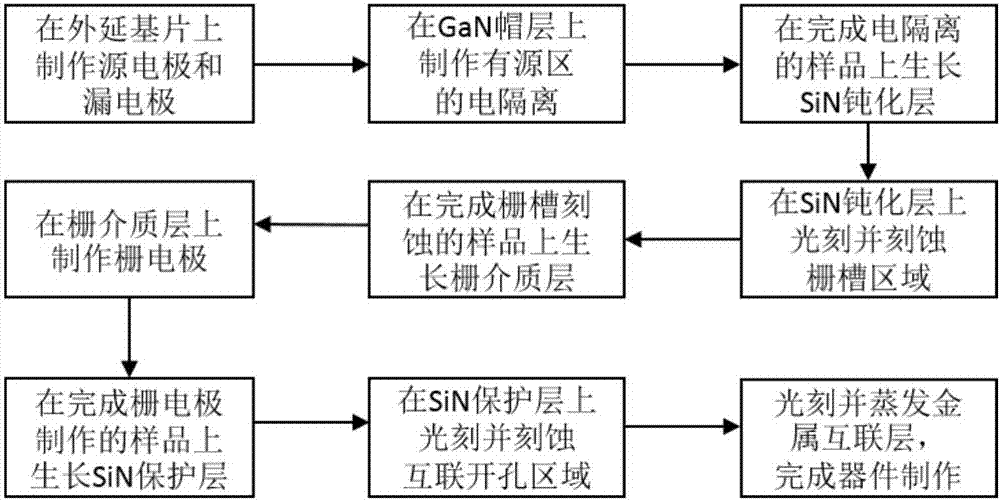

Stack gate enhanced GaN high-electron-mobility transistor containing ferroelectric gate dielectric and preparation method

ActiveCN107369704AImprove interface propertiesImprove compatibilitySemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricEngineering

The invention discloses a stack gate enhanced GaN high-electron-mobility transistor containing a ferroelectric gate dielectric, which mainly solves a problem of poor reliability of the existing similar devices. The stack gate enhanced GaN high-electron-mobility transistor comprises a substrate, an AlN nucleation layer, a GaN buffer layer, an AlN insertion layer, an AlGaN barrier layer, a GaN cap layer, an SiN passivation layer, a gate dielectric layer and an SiN protection layer from the bottom up, wherein the SiN passivation layer is provided with a concave structure, the inner wall of the concave structure and the surface of the SiN passivation layer are provided with the gate dielectric layer, the gate dielectric layer comprises an AlN or Al2O3 dielectric insertion layer and an HfZrO ferroelectric layer, two ends of the GaN buffer layer are provided with a source electrode and a drain electrode respectively, the middle of the gate dielectric layer is provided with a gate electrode, the source electrode and the drain electrode are provided with a metal interconnection layer, and the gate electrode and the gate dielectric layer at the surface of the passivation layer are covered with the SiN protection layer. According to the invention, the reliability of the device is improved, gate leakage of the enhanced device is reduced, and the transistor can be used as a switching device requiring high threshold voltage.

Owner:XIDIAN UNIV

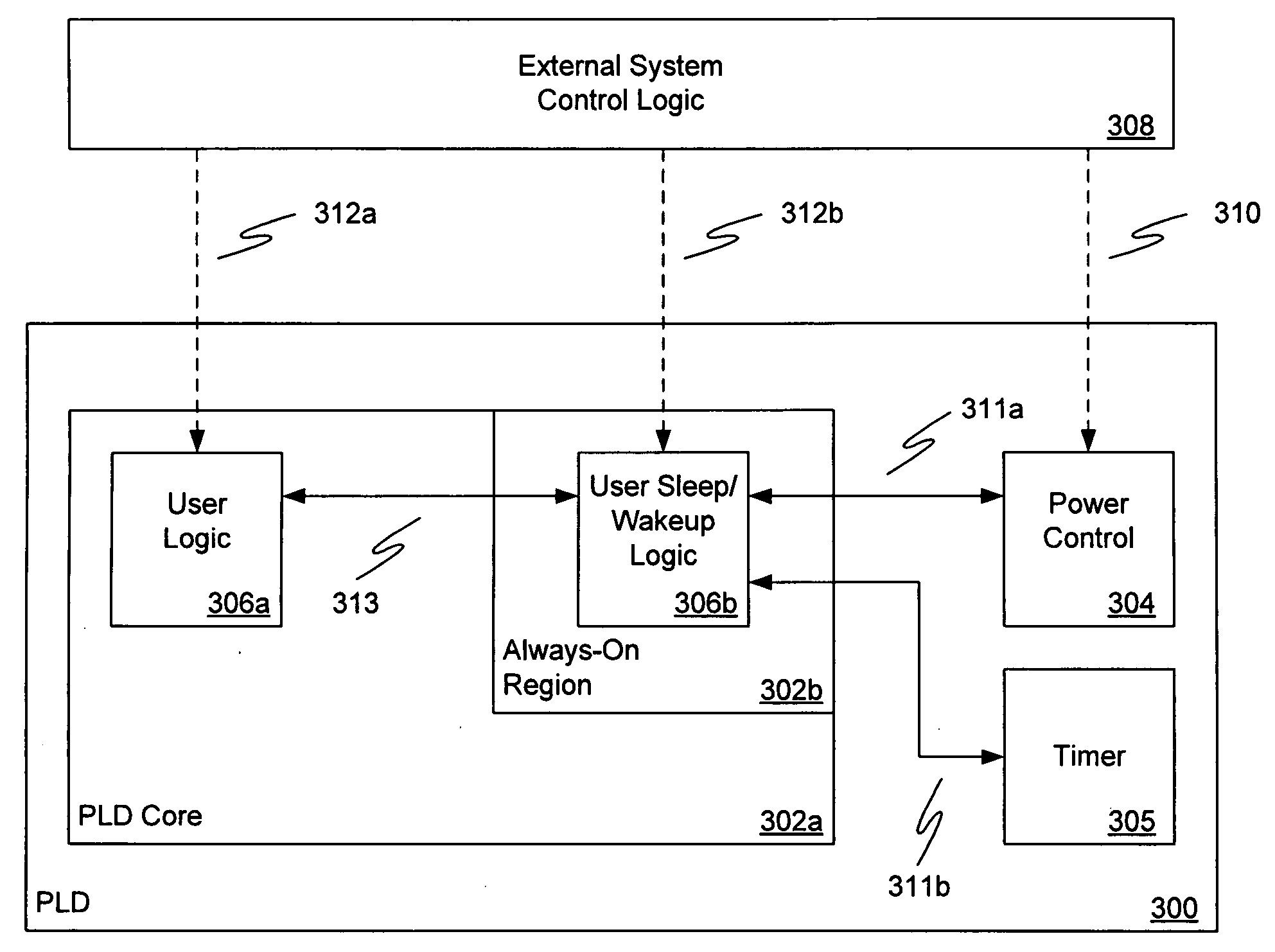

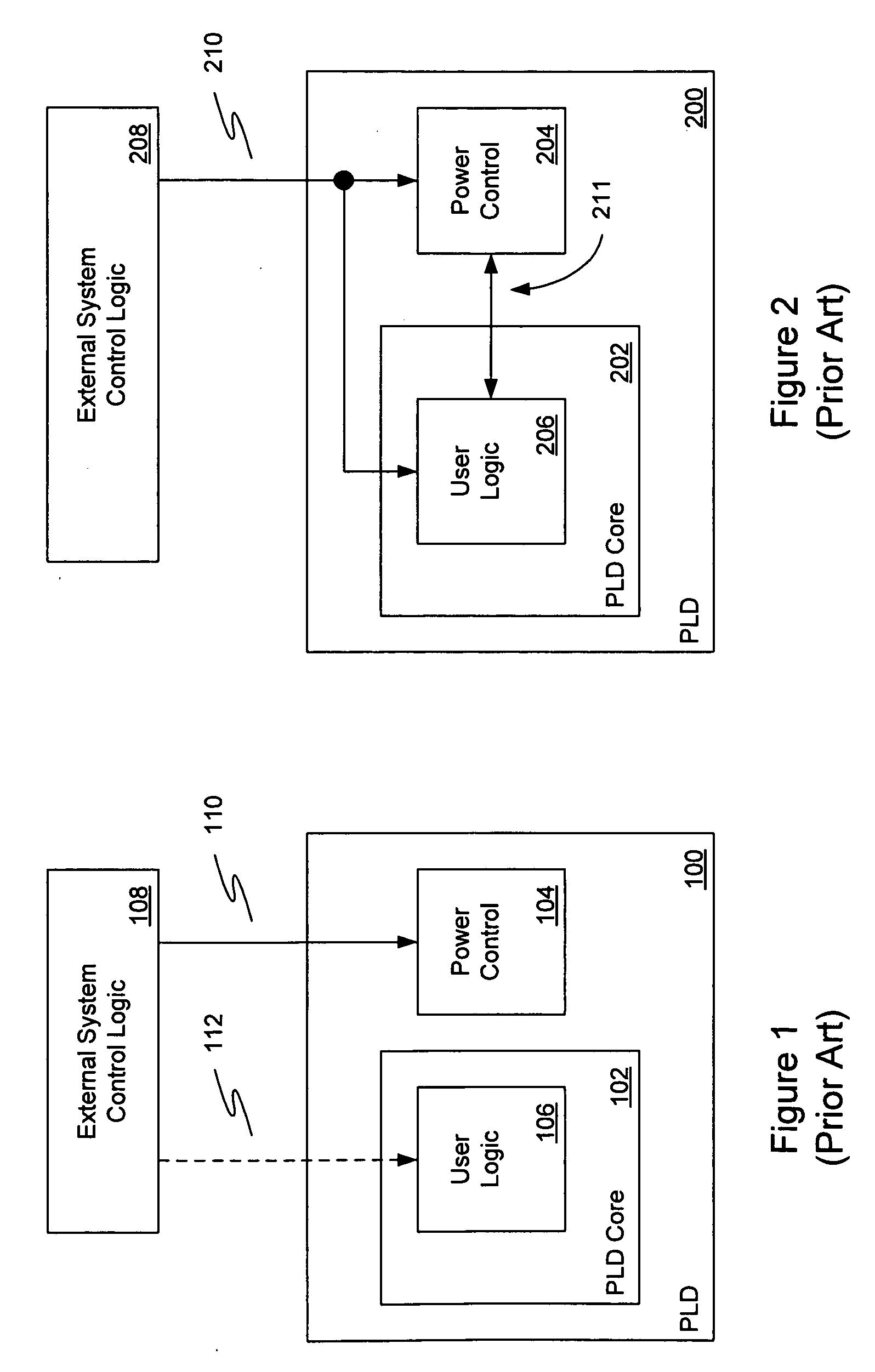

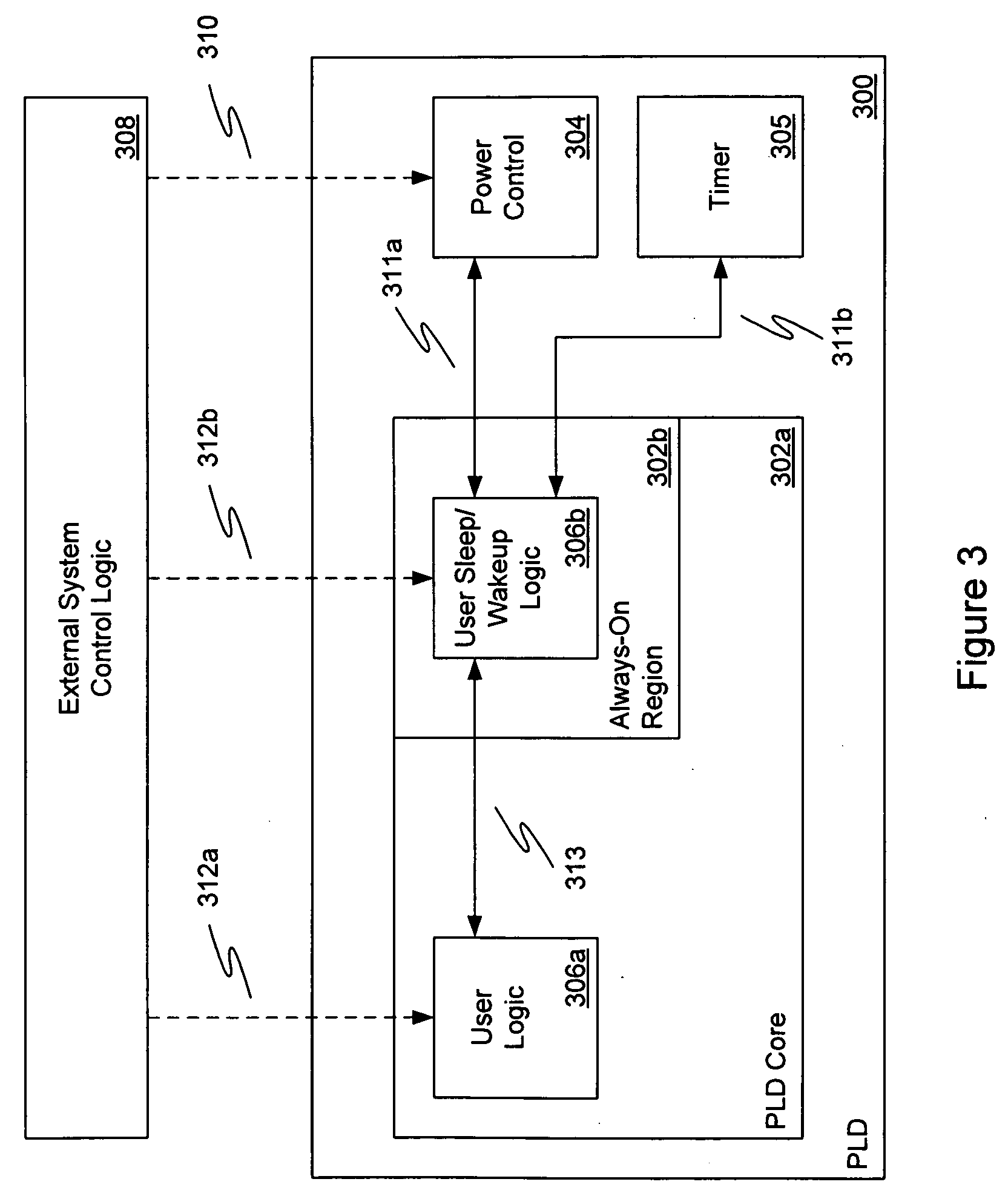

Pld providing soft wakeup logic

ActiveUS20100156457A1Reduce power consumptionReduce voltageReliability increasing modificationsSolid-state devicesPower modeProgrammable logic device

A programmable logic device (PLD) with a plurality of programmable regions is disclosed. Some of the programmable regions have switch power or ground supplies to allow them to be put into a low-power state in one or more low-power modes. At least one of the programmable regions always remains on during the low-power modes to enable the user to design custom PLD power management logic that may be placed in the always-on programmable region.

Owner:MICROSEMI SOC

Method for forming a variable thickness dielectric stack

InactiveUS20160126101A1Easy injectionReduces the possibility of short circuitsSolid-state devicesSemiconductor/solid-state device manufacturingVariable thicknessDielectric layer

Producing a variable thickness dielectric stack includes providing a substrate with a first patterned conductive layer thereon. A first dielectric thin film is deposited using ALD and a first patterned deposition inhibitor layer, which is subsequently removed, to form a first patterned conformal dielectric layer having a first pattern. A second dielectric thin film is deposited using ALD and a second patterned deposition inhibitor layer to form a second patterned conformal dielectric layer having a second pattern. A second patterned conductive layer is formed with at least a portion of the first and second patterned conductive layers overlapping each other forming an overlap region. A portion of the first or second pattern extends into the overlap region such that one portion of the overlap region includes the first and second dielectric thin films, and another portion of the overlap region includes only the first or second dielectric thin film.

Owner:EASTMAN KODAK CO

Stratified gate dielectric stack for gate dielectric leakage reduction

ActiveUS9006094B2Reduce gate leakageTransistorSemiconductor/solid-state device manufacturingGate dielectricDielectric layer

A stratified gate dielectric stack includes a first high dielectric constant (high-k) gate dielectric comprising a first high-k dielectric material, a band-gap-disrupting dielectric comprising a dielectric material having a different band gap than the first high-k dielectric material, and a second high-k gate dielectric comprising a second high-k dielectric material. The band-gap-disrupting dielectric includes at least one contiguous atomic layer of the dielectric material. Thus, the stratified gate dielectric stack includes a first atomic interface between the first high-k gate dielectric and the band-gap-disrupting dielectric, and a second atomic interface between the second high-k gate dielectric and the band-gap-disrupting dielectric that is spaced from the first atomic interface by at least one continuous atomic layer of the dielectric material of the band-gap-disrupting dielectric. The insertion of the band-gap disrupting dielectric results in lower gate leakage without resulting in any substantial changes in the threshold voltage characteristics and effective oxide thickness.

Owner:INT BUSINESS MASCH CORP

Method for gate height control in a gate last process

InactiveUS7939392B2Improve device performanceSmall sizeSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricInter layer

A method is provided for fabricating a semiconductor device that includes providing a semiconductor substrate, forming a transistor in the substrate, the transistor having a gate structure that includes a dummy gate structure, forming an inter-layer dielectric (ILD), performing a first chemical mechanical polishing (CMP) to expose a top surface of the dummy gate structure, removing a portion of the ILD such that a top surface of the ILD is at a distance below the top surface of the dummy gate structure, forming a material layer over the ILD and dummy gate structure, performing a second CMP on the material layer to expose the top surface of the dummy gate structure, removing the dummy gate structure thereby forming a trench, forming a metal layer to fill in the trench, and performing a third CMP that substantially stops at the top surface of the ILD.

Owner:TAIWAN SEMICON MFG CO LTD