GaN-based field effect transistor with high quality MIS structure and preparation method of GaN-based field effect transistor

A MIS structure, high-quality technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as degraded device stability, threshold voltage drift, etc., and achieve high process repeatability and reliability, high threshold Voltage stability, effect of improving mobility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0037] Such as Picture 11 Shown is a schematic diagram of the device structure of this embodiment. The structure includes substrate 1, stress buffer layer 2, GaN epitaxial layer 3, secondary epitaxial layer 4, secondary epitaxial formation grooves, and tertiary epitaxial layer 5 from bottom to top. , The surface of the tertiary epitaxial layer 5 is oxidized to form an insulating oxide dielectric layer 6 with a source 7 and a drain 8 formed at both ends, and a gate 9 is covered on the insulating layer 6 at the groove channel.

[0038] The manufacturing method of the above-mentioned high-quality MIS structure GaN-based field effect transistor is as follows Figure 1-Figure 10 As shown, including the following steps:

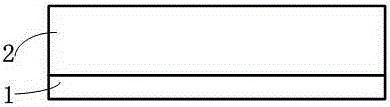

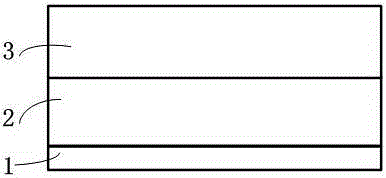

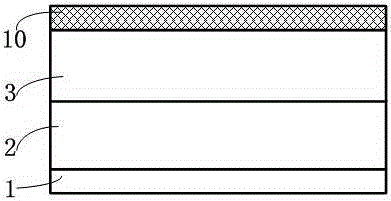

[0039] S1. Using metal organic chemical vapor deposition method to grow a layer of stress buffer layer (2) on Si substrate (1), such as figure 1 Shown

[0040] S2, using the metal organic chemical vapor deposition method to grow a GaN epitaxial layer (3) on the stress b...

Embodiment 2

[0052] Such as Picture 12 Shown is a schematic diagram of the device structure of this embodiment, which differs from the structure of Embodiment 1 only in that: the GaN / AlGaN heterostructure in Embodiment 1 is formed by secondary epitaxy and the gate groove region is naturally formed at the same time, while Embodiment 2 The medium GaN / AlGaN heterostructure is formed by one-time epitaxial formation and the gate groove area is formed by dry (or wet) etching. The reference number 11 is the primary epitaxial GaN / AlGaN heterostructure layer.

Embodiment 3

[0054] Such as Figure 13 Shown is a schematic diagram of the device structure of this embodiment, which is different from the structure of Embodiment 1 only in that: Embodiment 1 is a lateral conduction device structure, and Embodiment 2 is a vertical conduction device structure. The substrate 12 is a heavily doped GaN free-standing substrate or a low-resistance silicon substrate or a low-resistance silicon carbide substrate, etc., 13 is a buffer layer, 14 is a lightly doped GaN drift layer, and 15 is a p-type doped GaN layer Or AlGaN layer. The vertical structure improves the chip power per unit area and effectively increases the breakdown voltage of the device.

[0055] In addition, it should be noted that the drawings of the above embodiments are only for illustrative purposes, and therefore it is not necessary to draw to scale.

[0056] Obviously, the above-mentioned embodiments of the present invention are merely examples to clearly illustrate the present invention, and are ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More