Patents

Literature

222results about How to "Improve short channel effect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

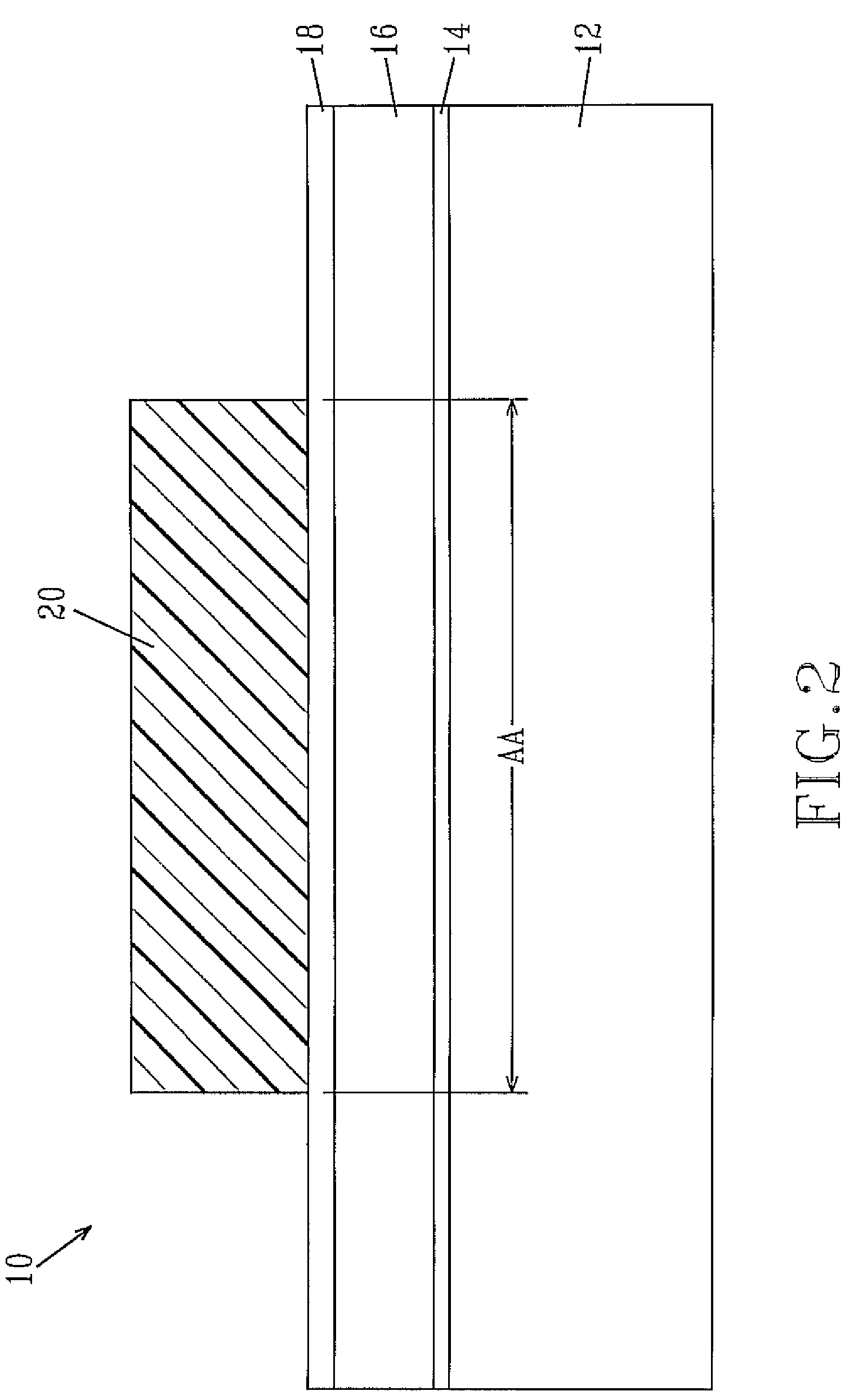

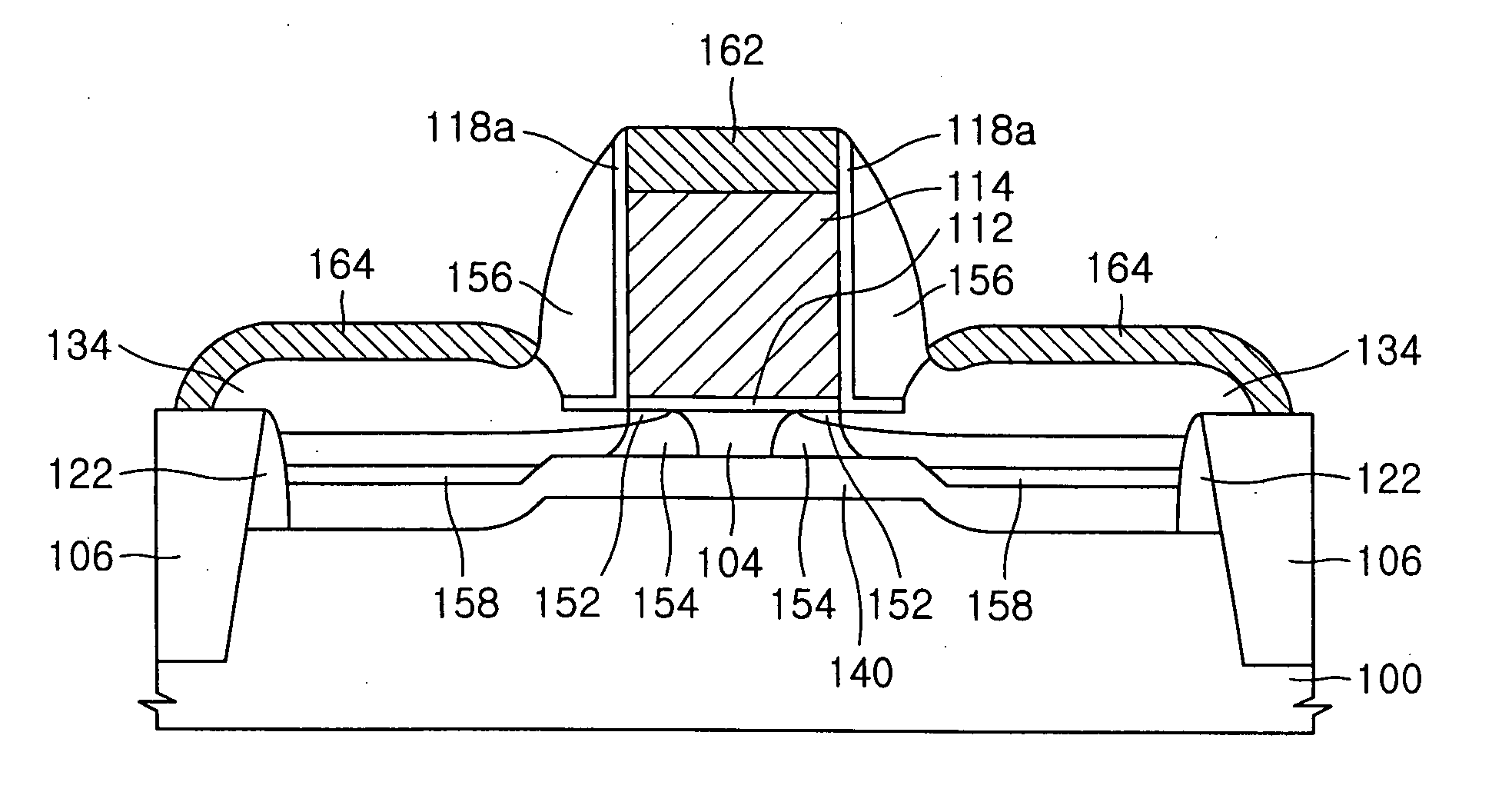

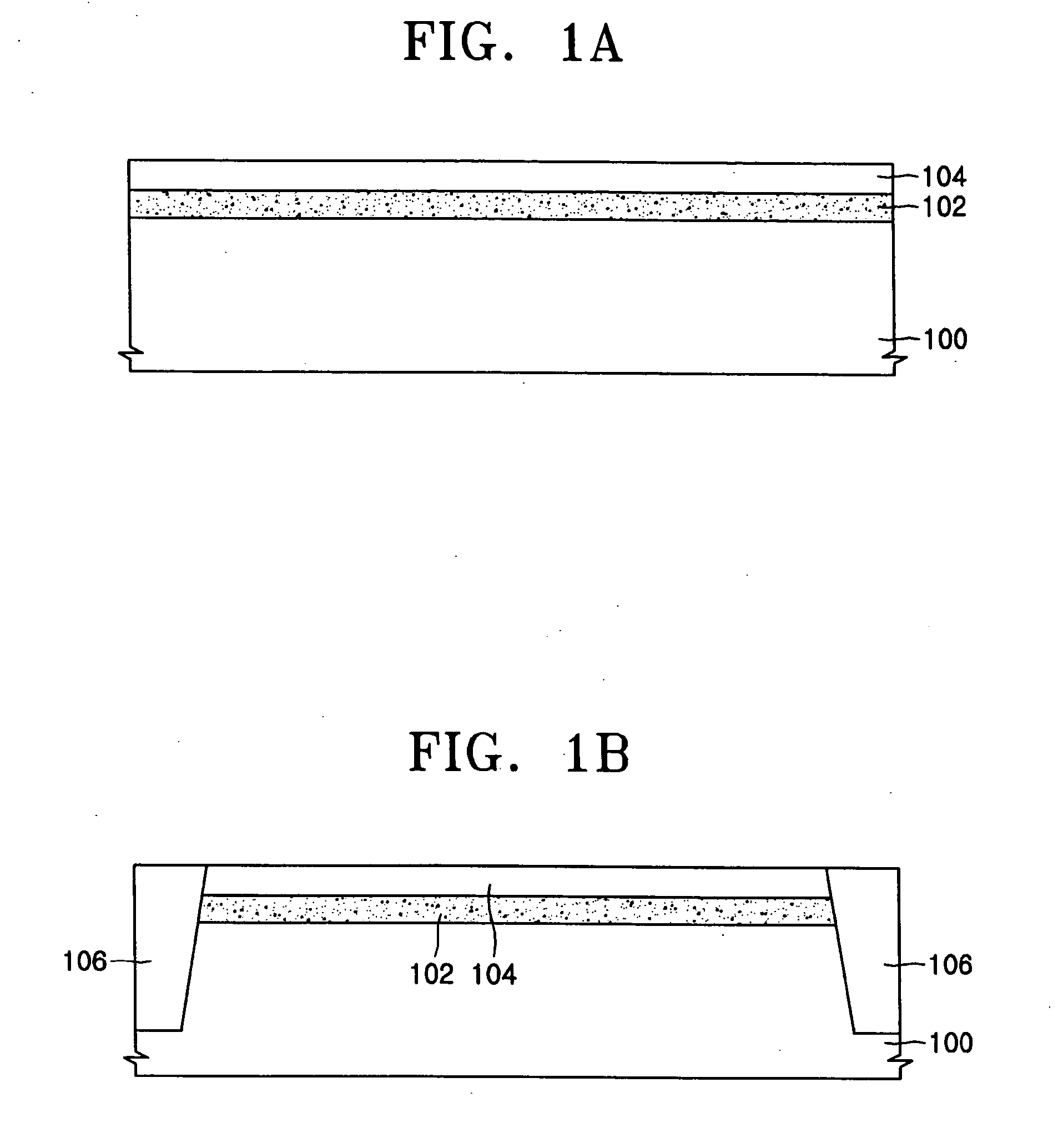

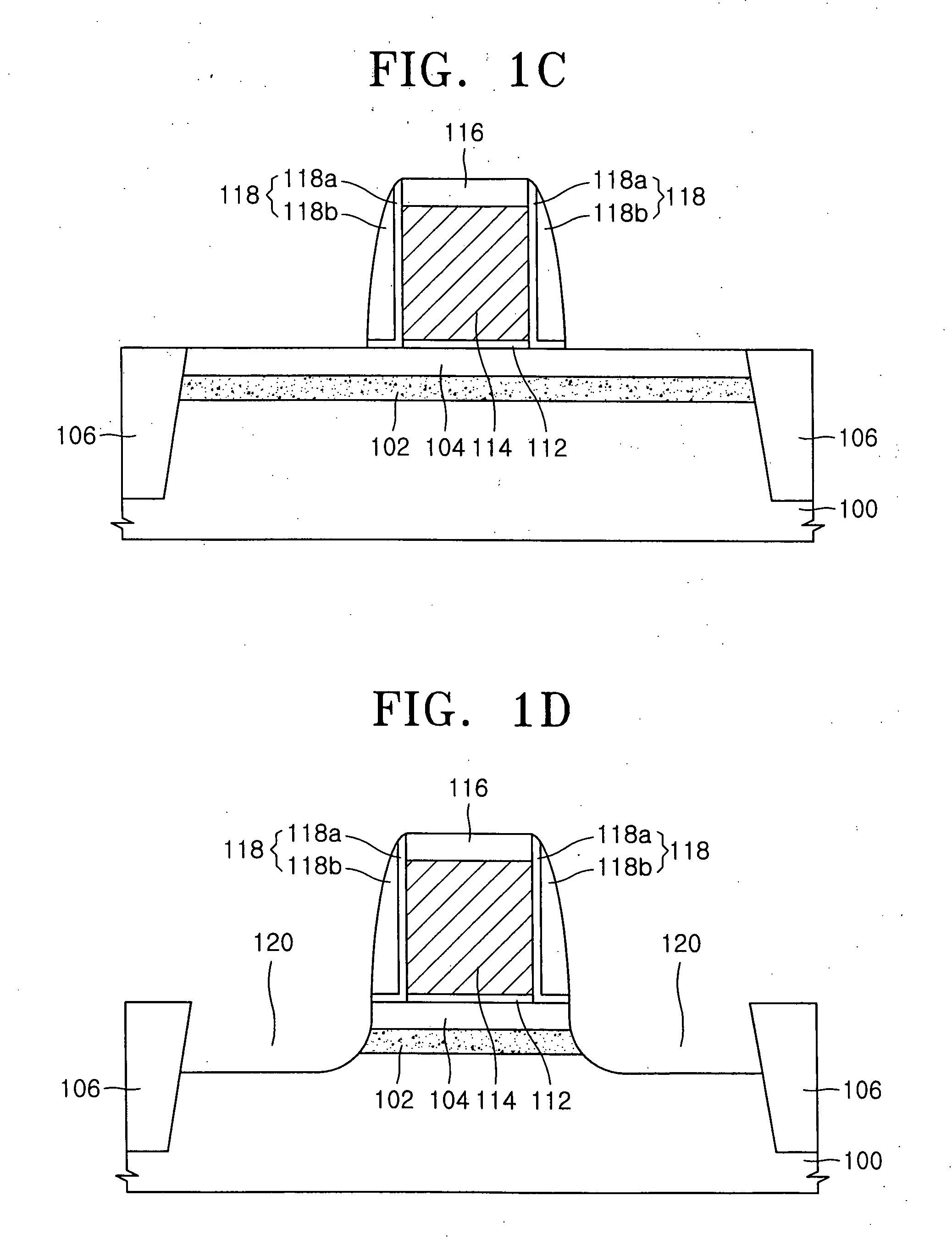

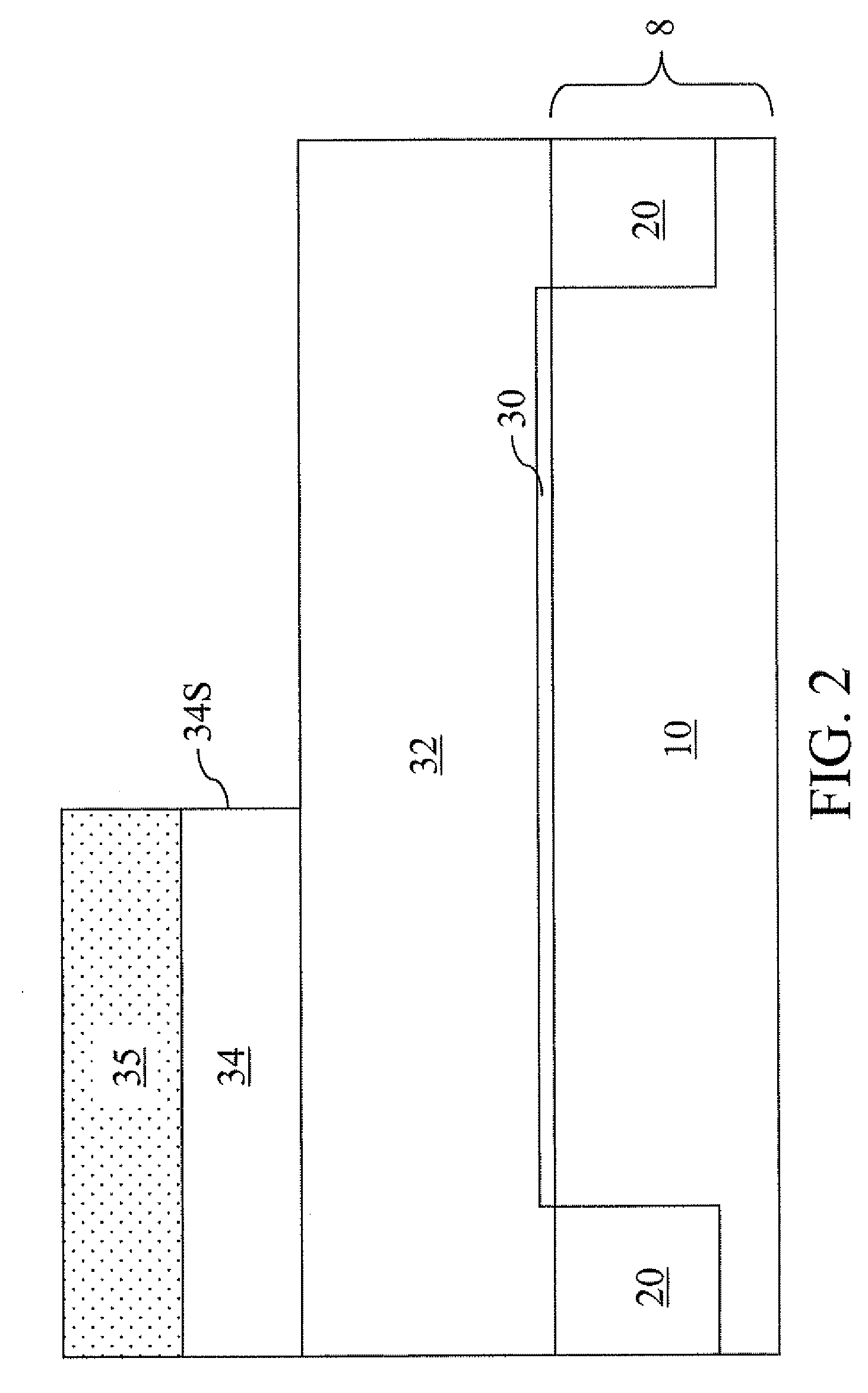

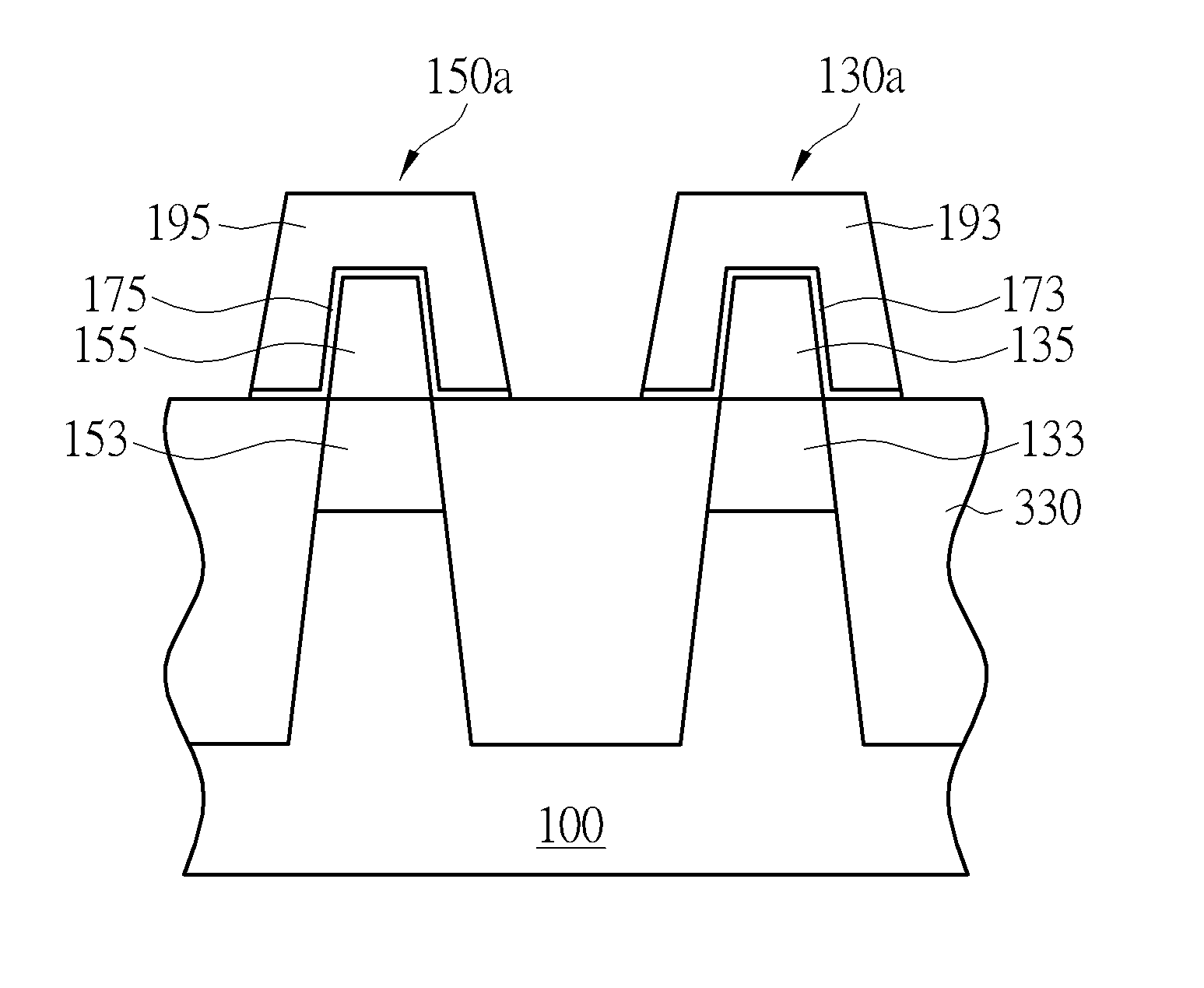

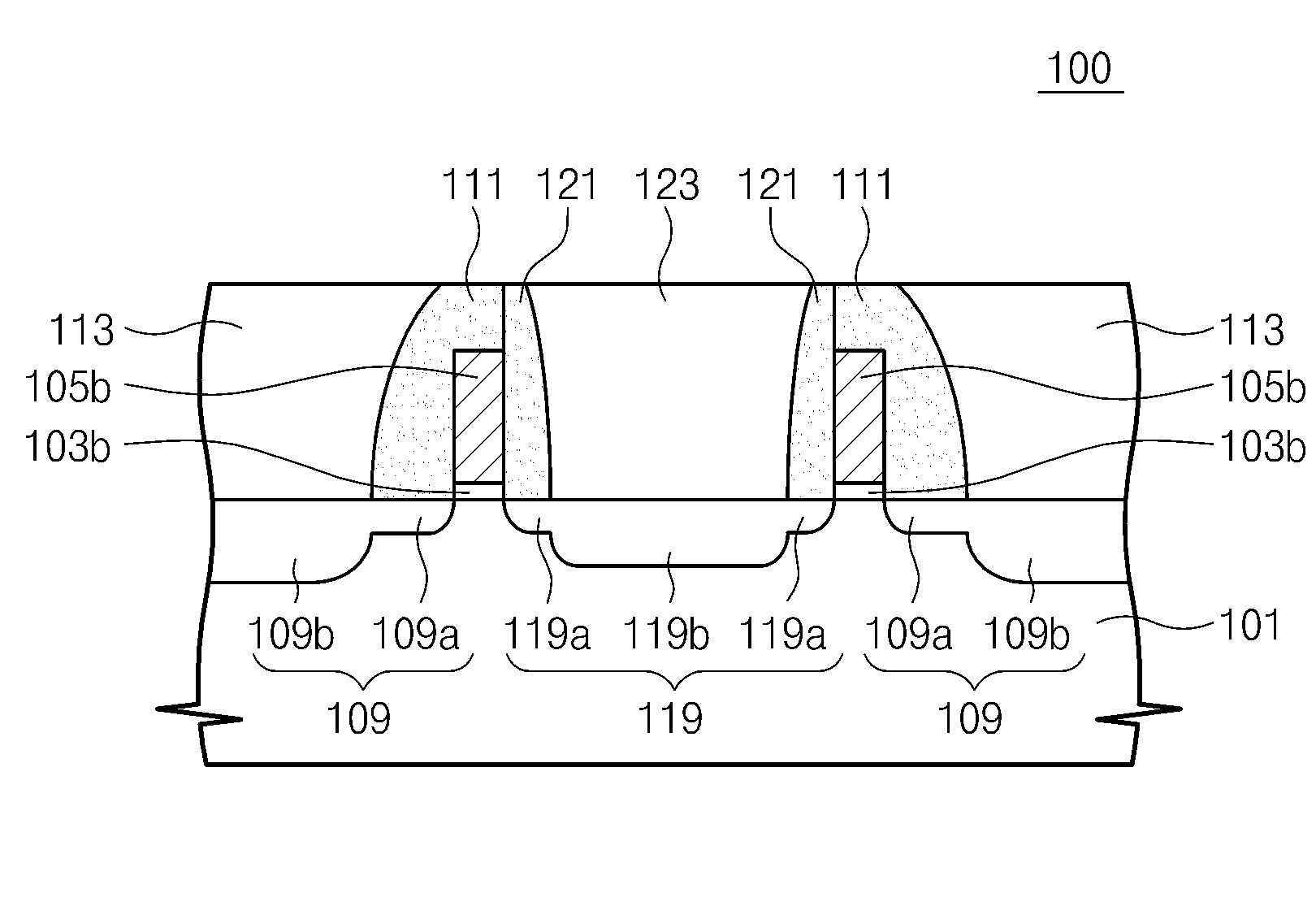

Non-volatile memory device and method of manufacturing the same

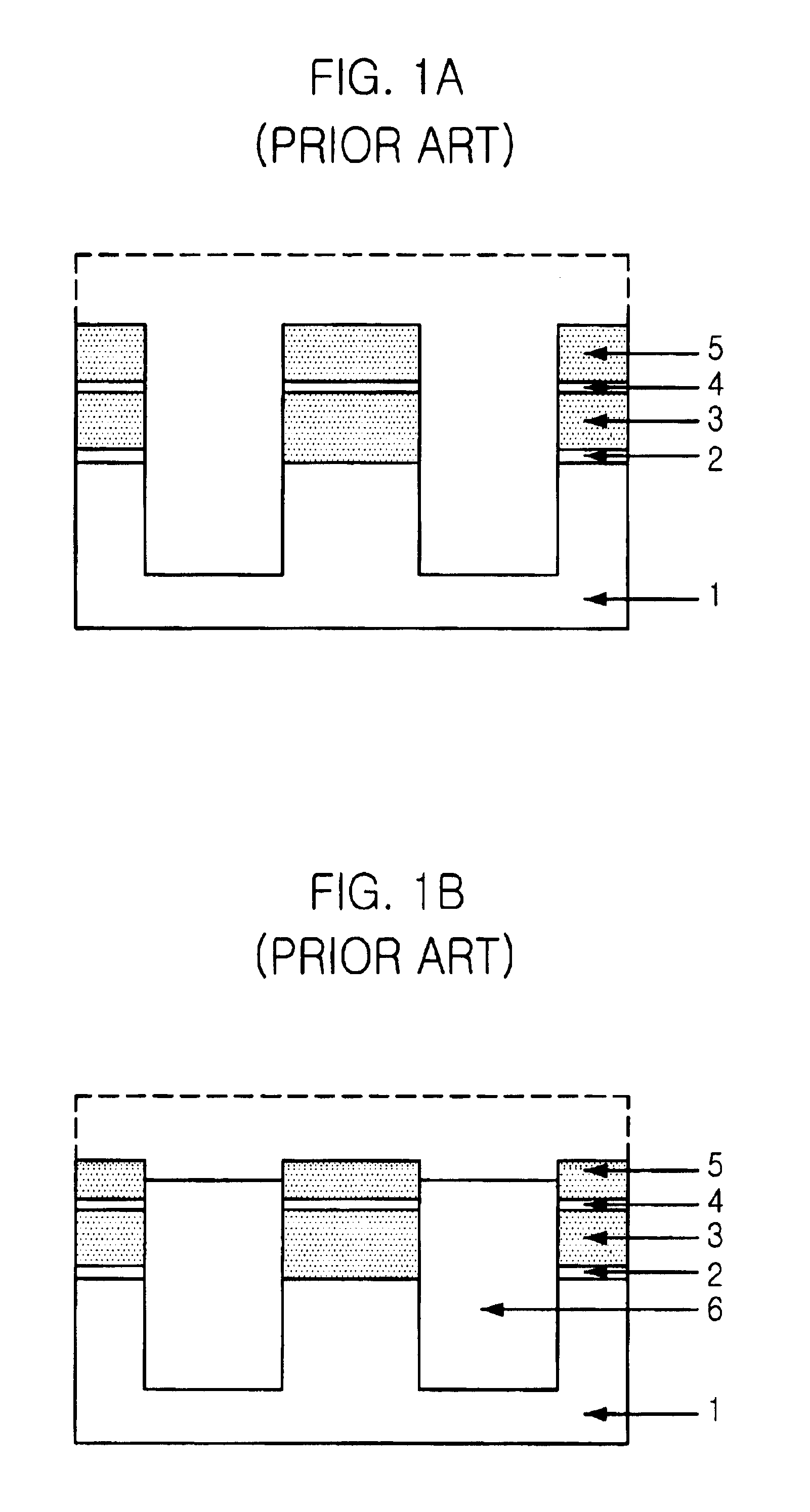

InactiveUS7622761B2Less susceptibleImprove short channel effectTransistorSolid-state devicesSemiconductorNon-volatile memory

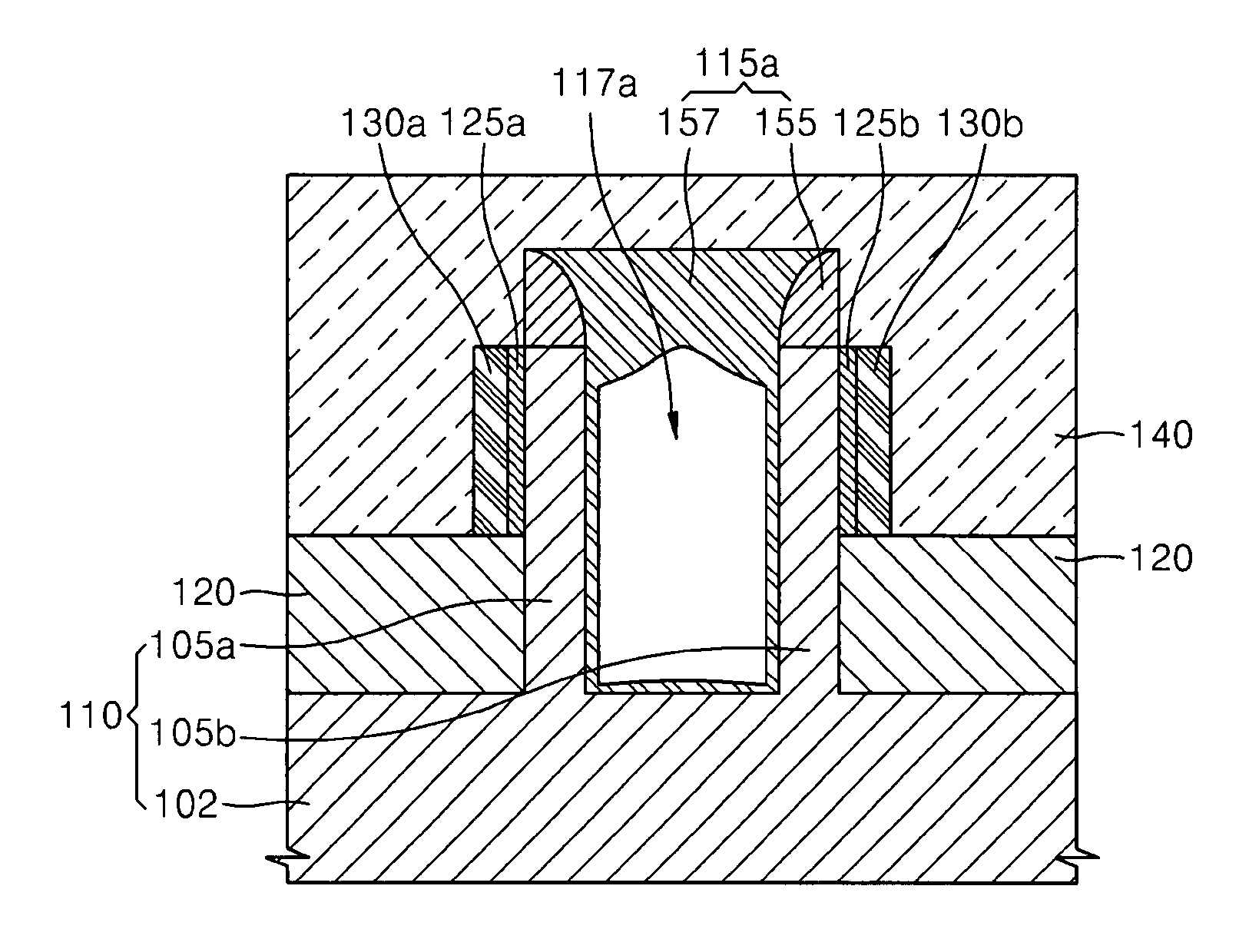

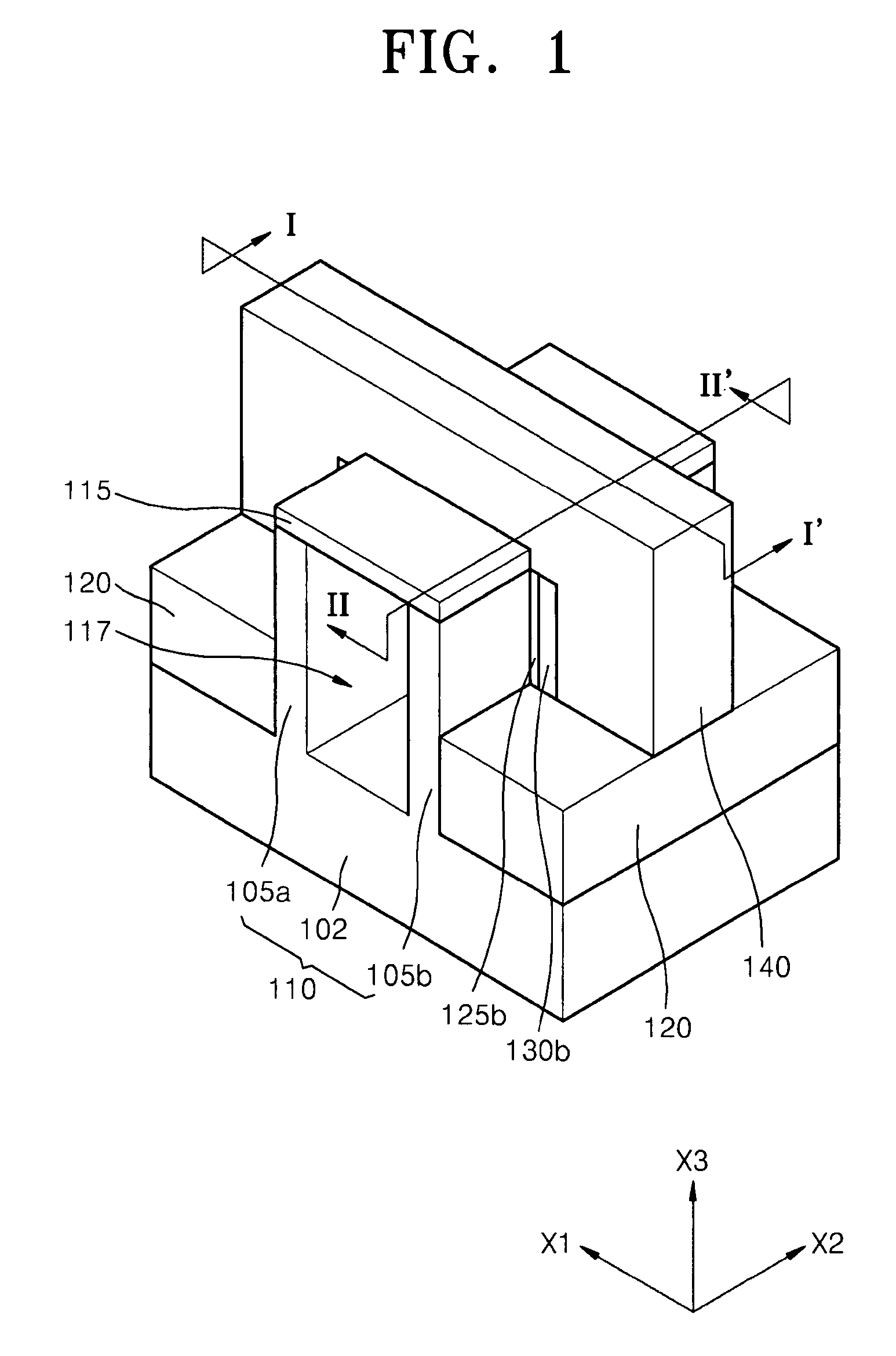

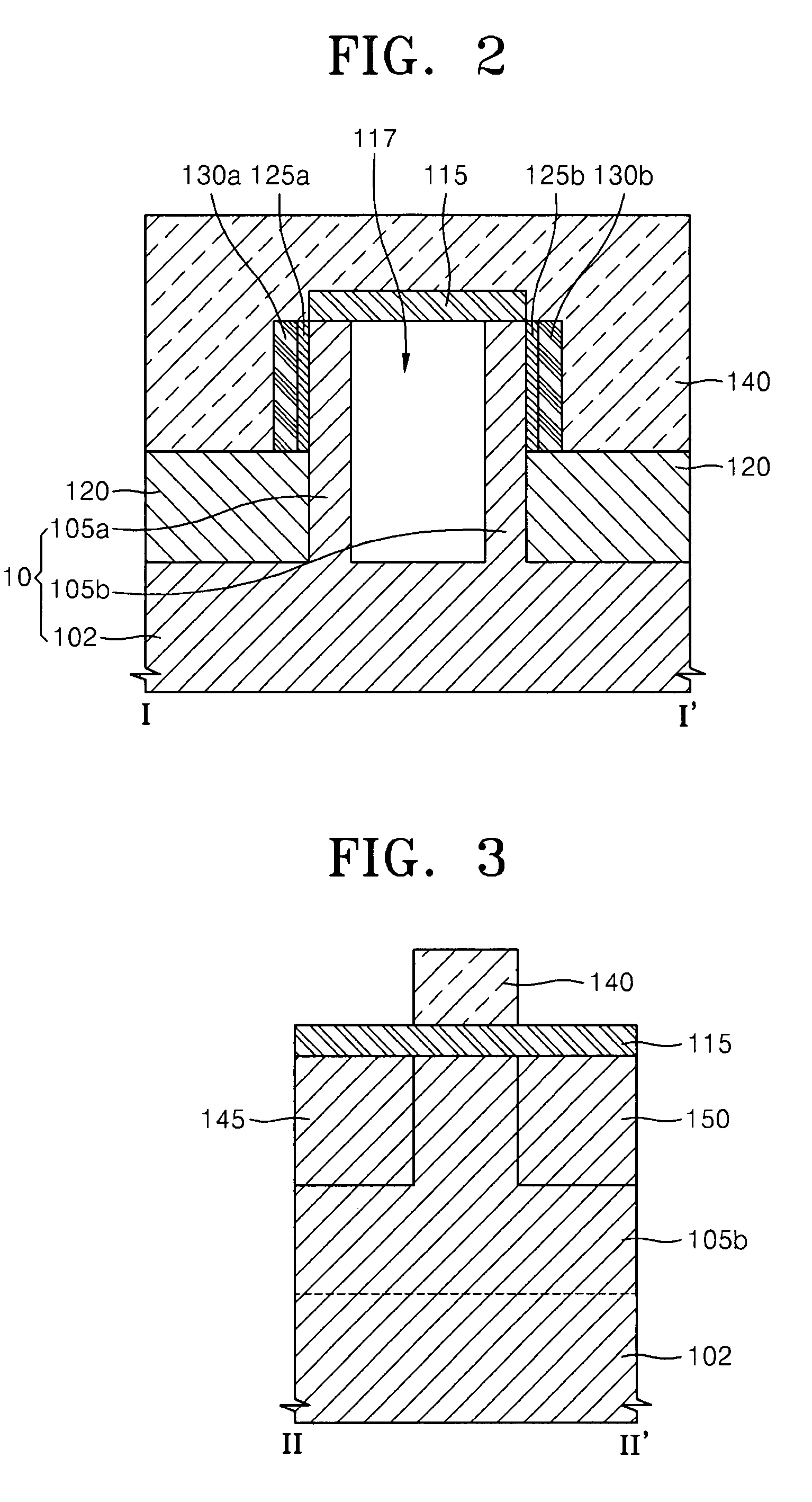

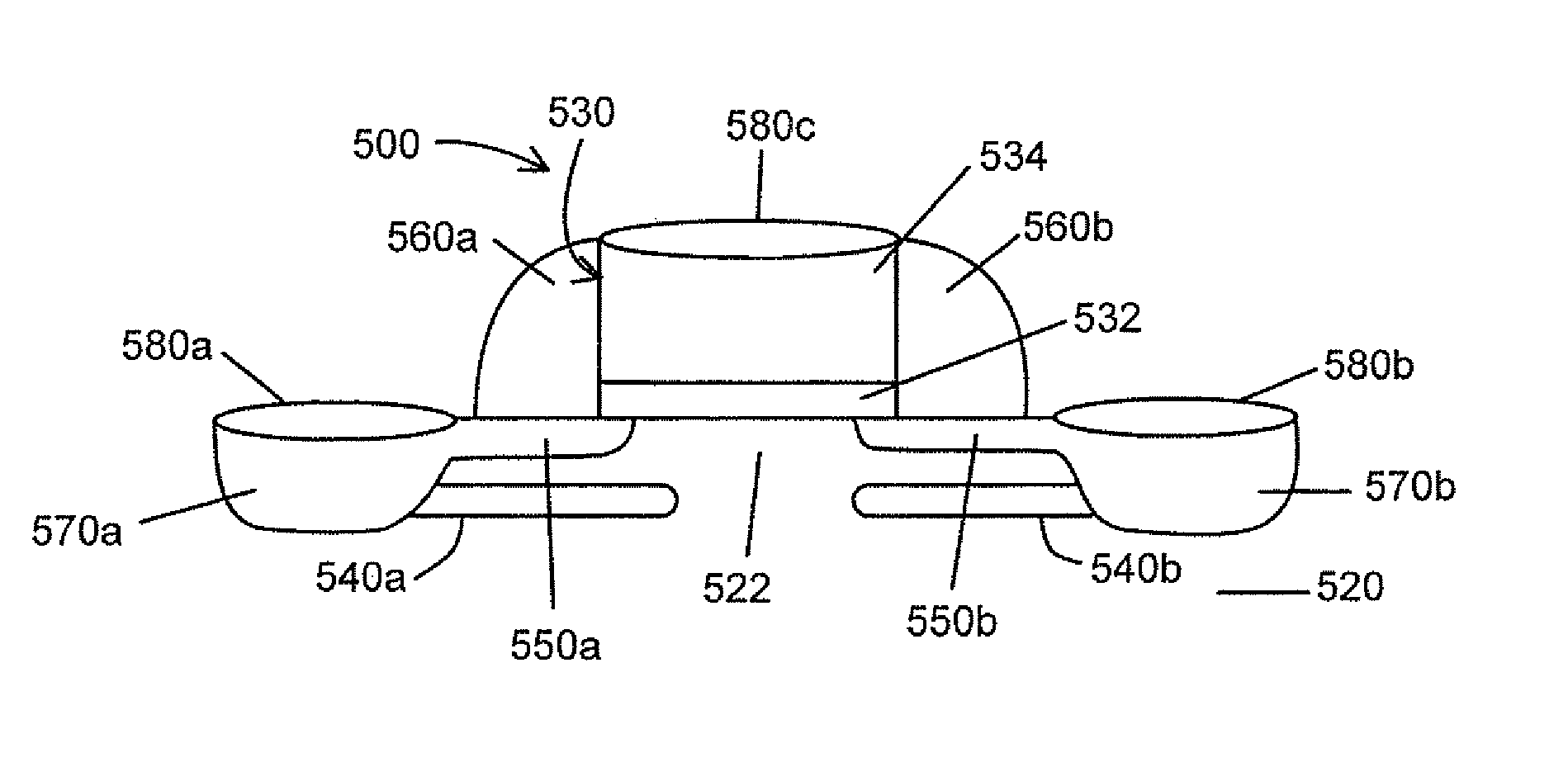

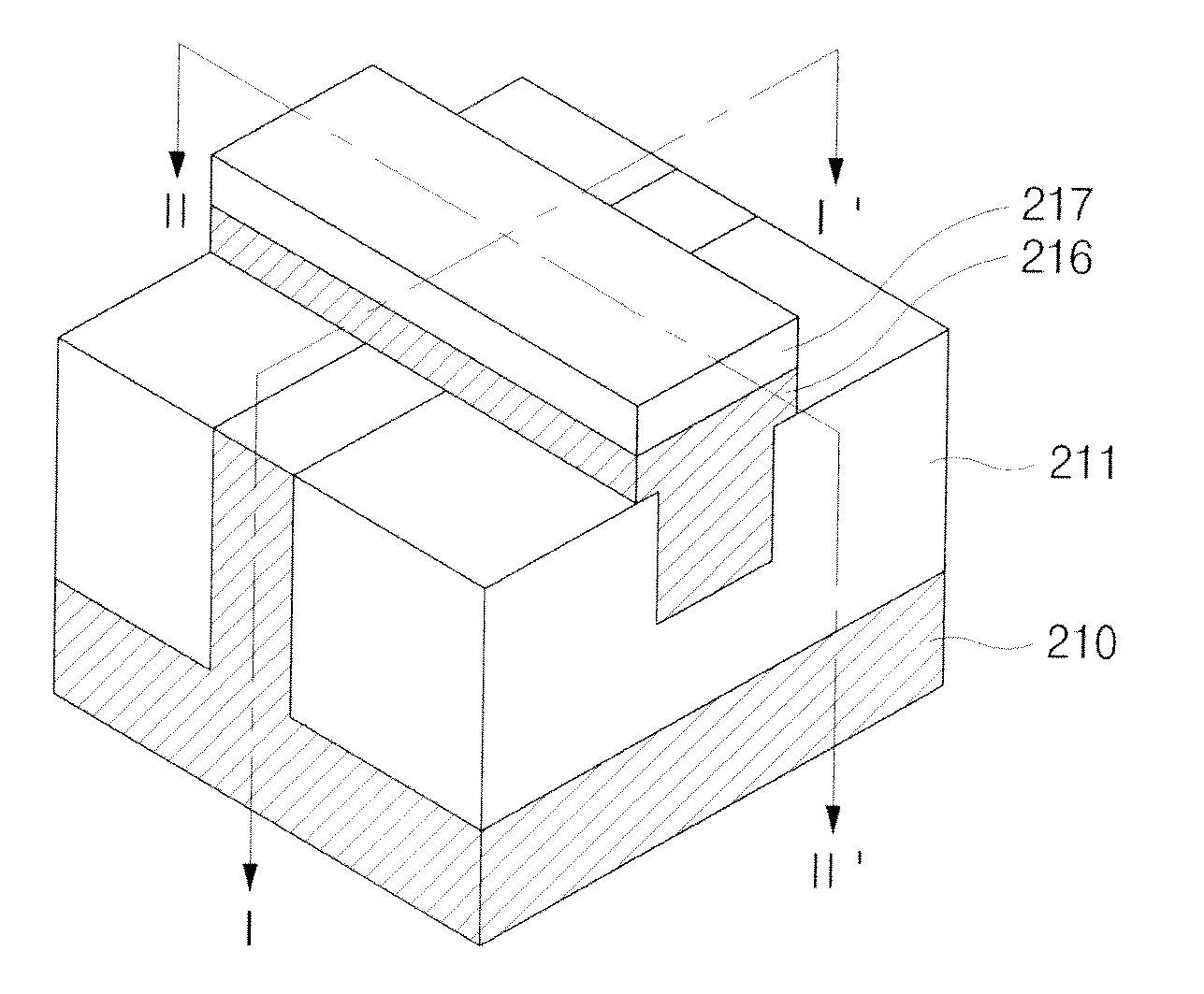

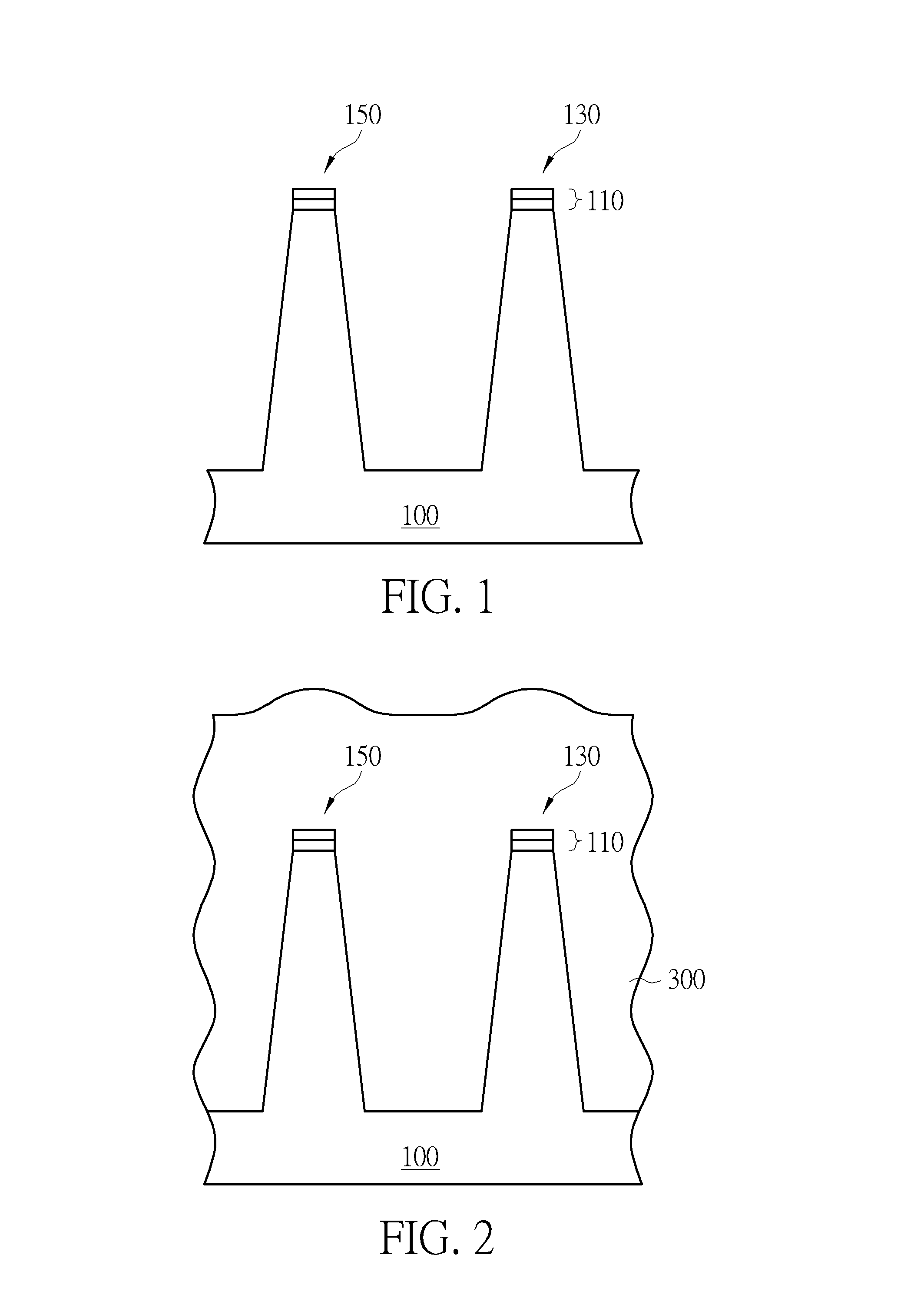

The non-volatile memory device may include a semiconductor substrate having a body and a pair of fins. A bridge insulating layer may non-electrically connect upper portions of the pair of fins to define a void between the pair of fins. Outer surfaces of the pair of fins are the surfaces of the pair of fins that do not face the void and inner surfaces of the pair of fins are the surfaces of the pair of fins that do face the void. The non-volatile memory device may further include at least one control gate electrode that may cover at least a portion of outer surfaces of the pair of fins, may extend over the bridge insulating layer, and may be isolated from the semiconductor substrate. At least one pair of gate insulating layers may be between the at least one control gate electrode and the pair of fins, and at least one pair of storage nodes may be between the at least one pair of gate insulating layers and the at least one control gate electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

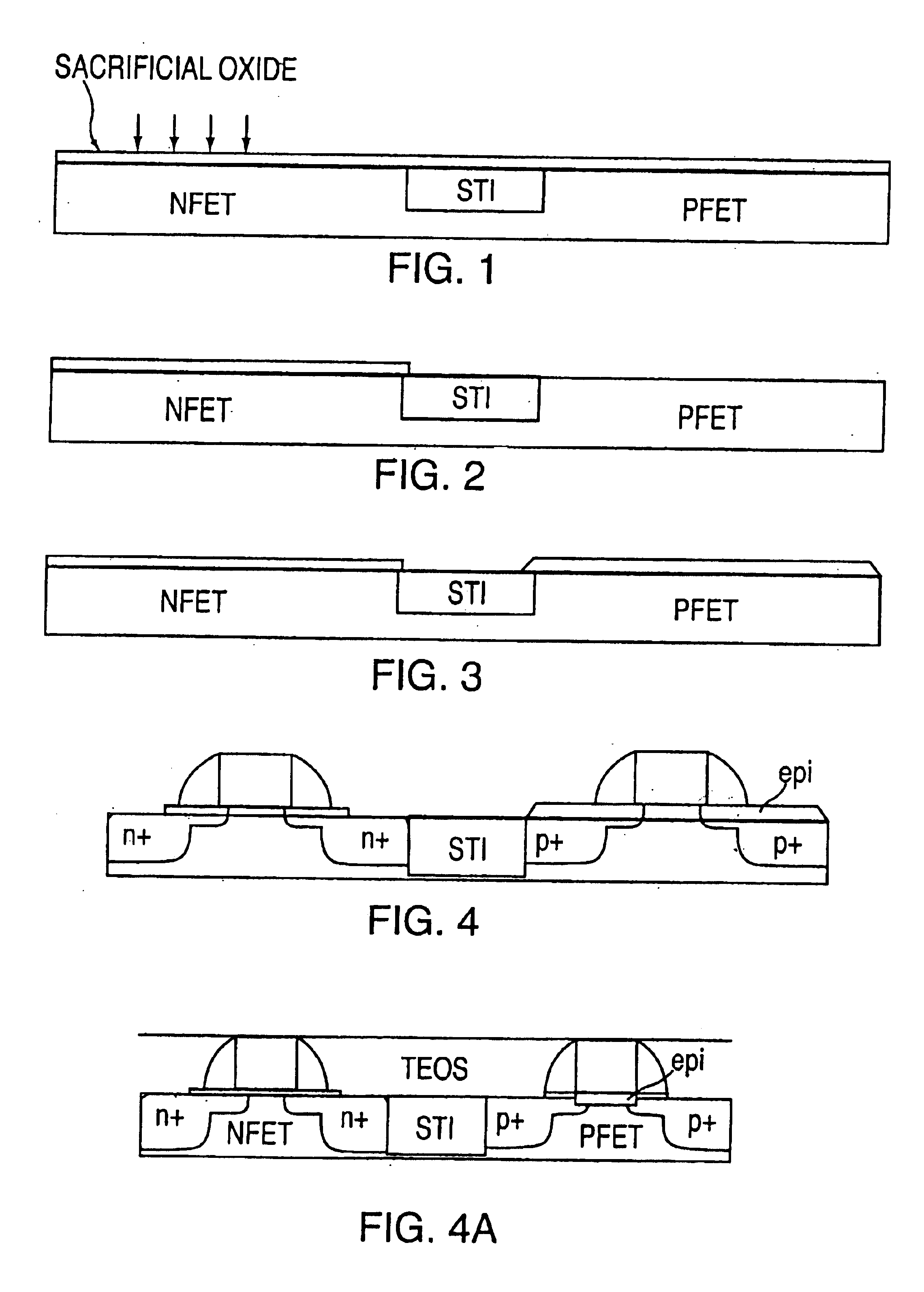

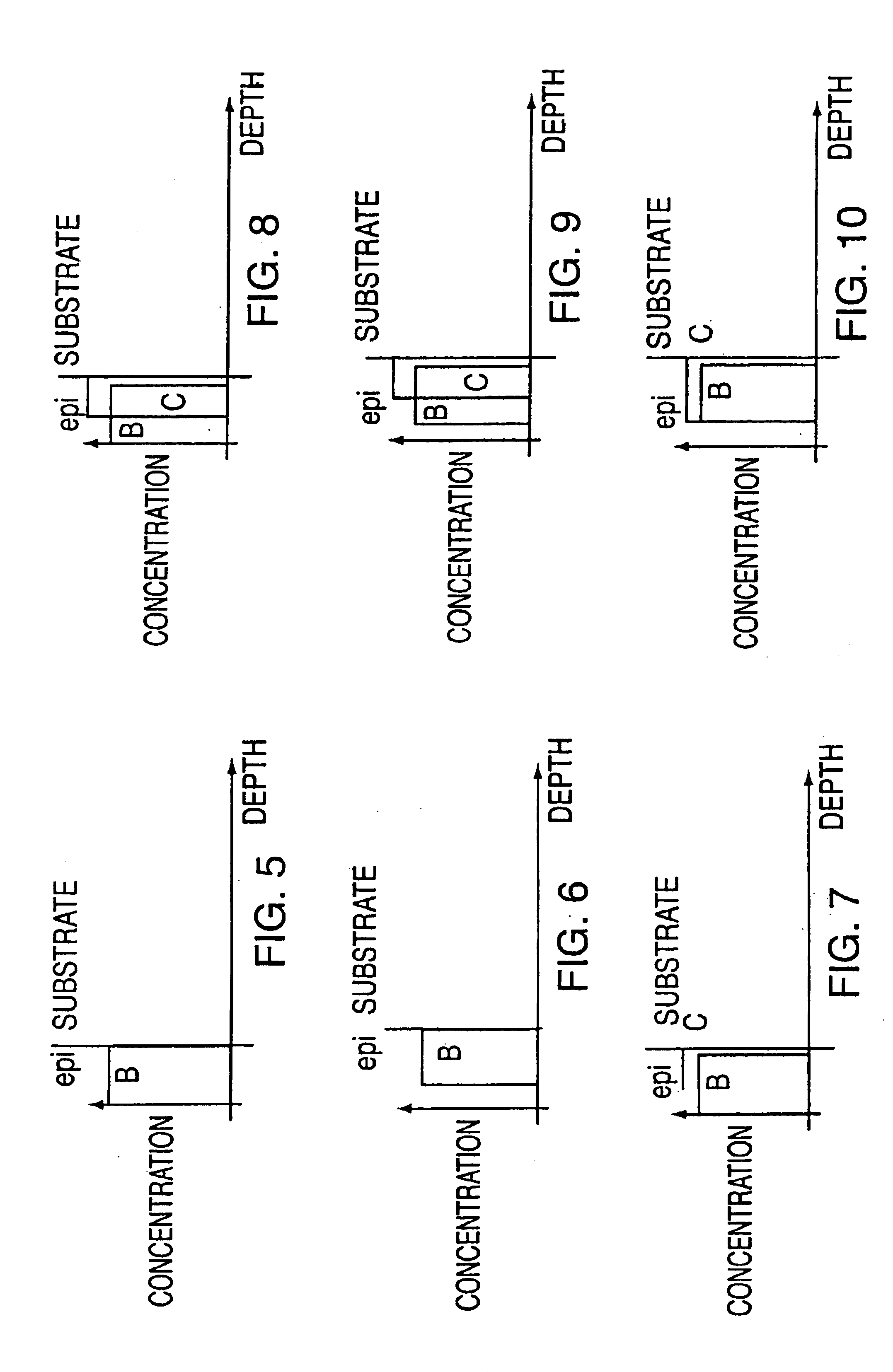

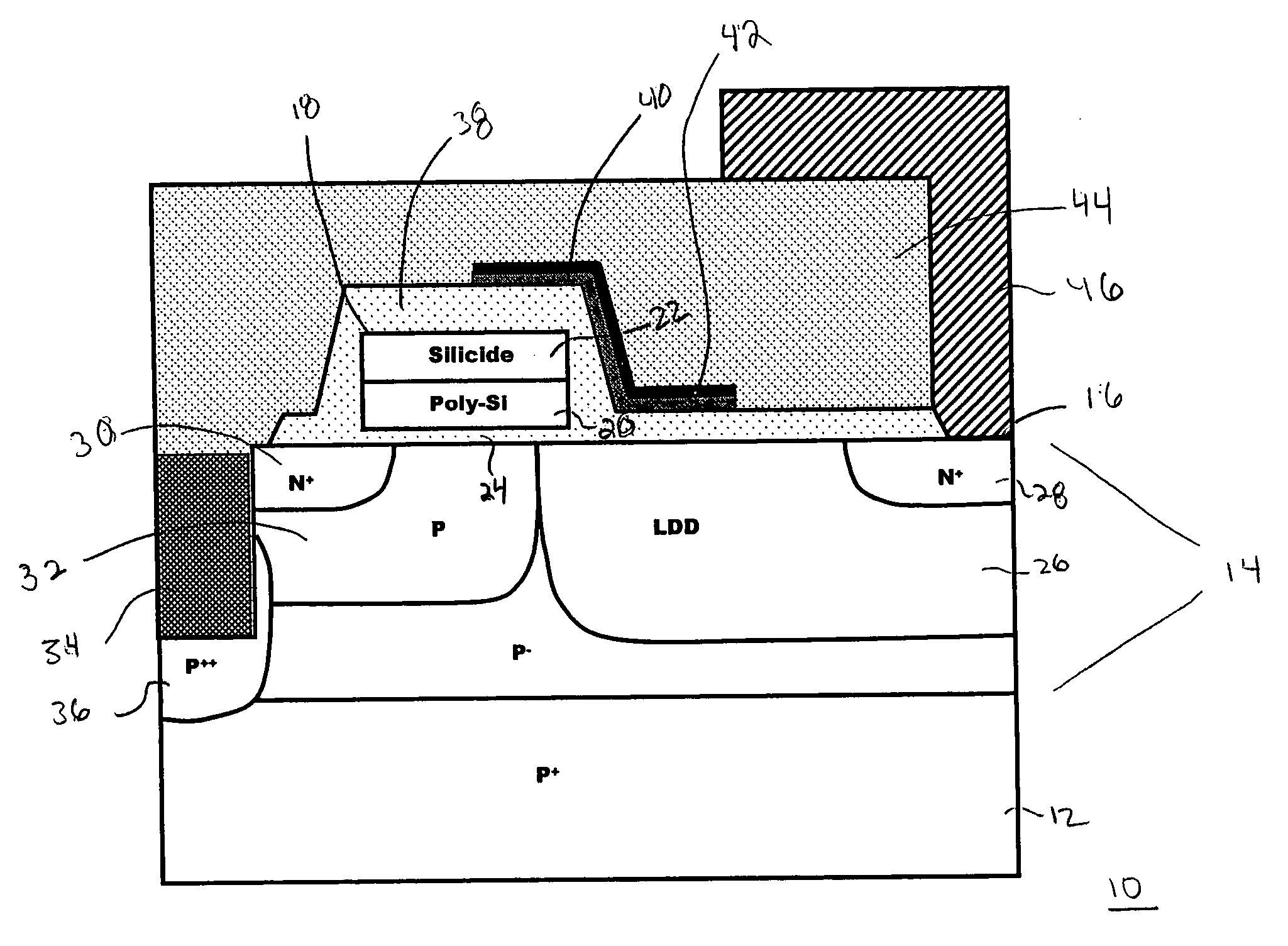

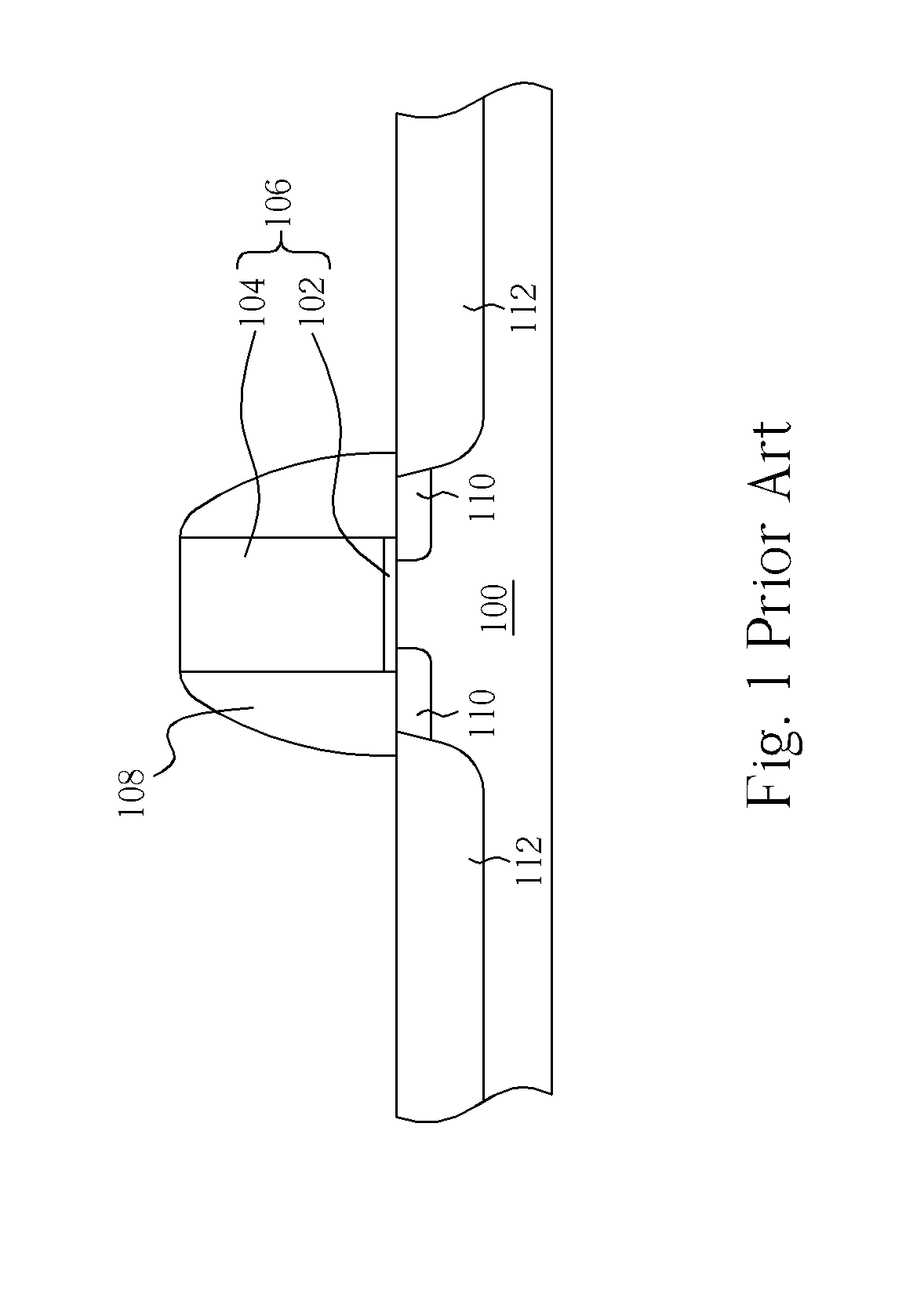

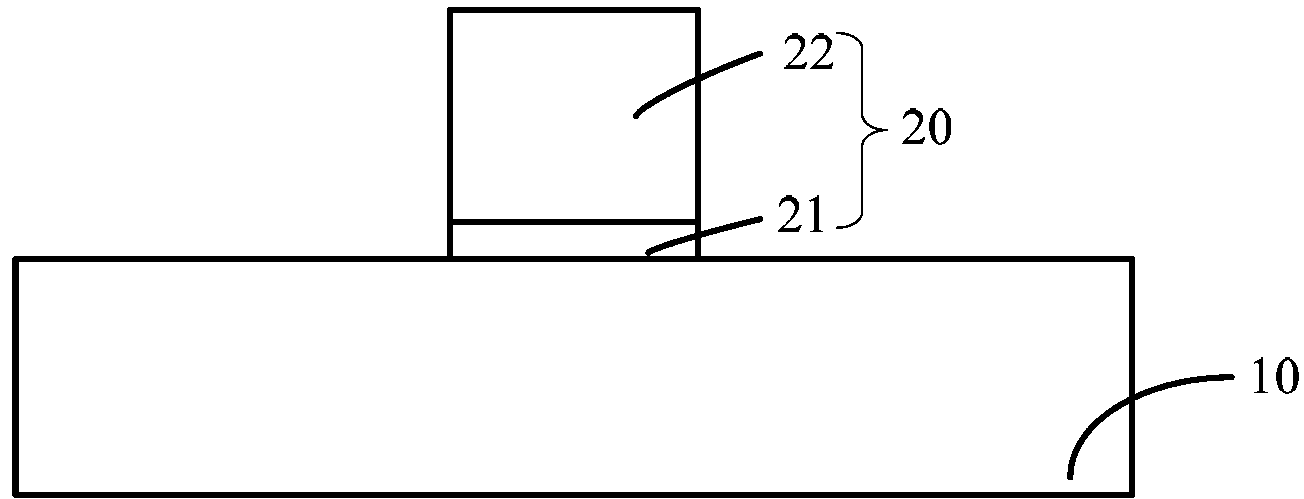

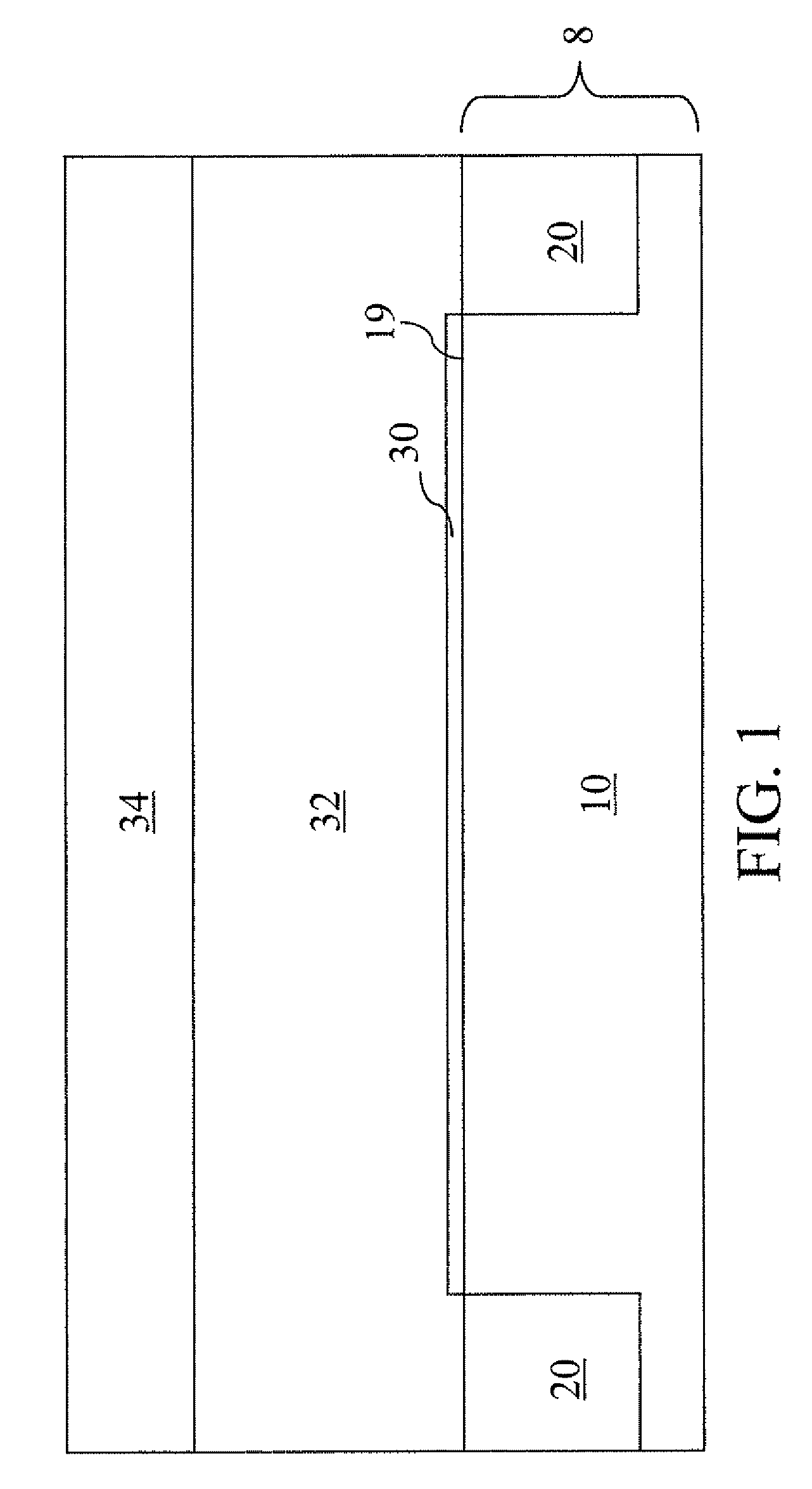

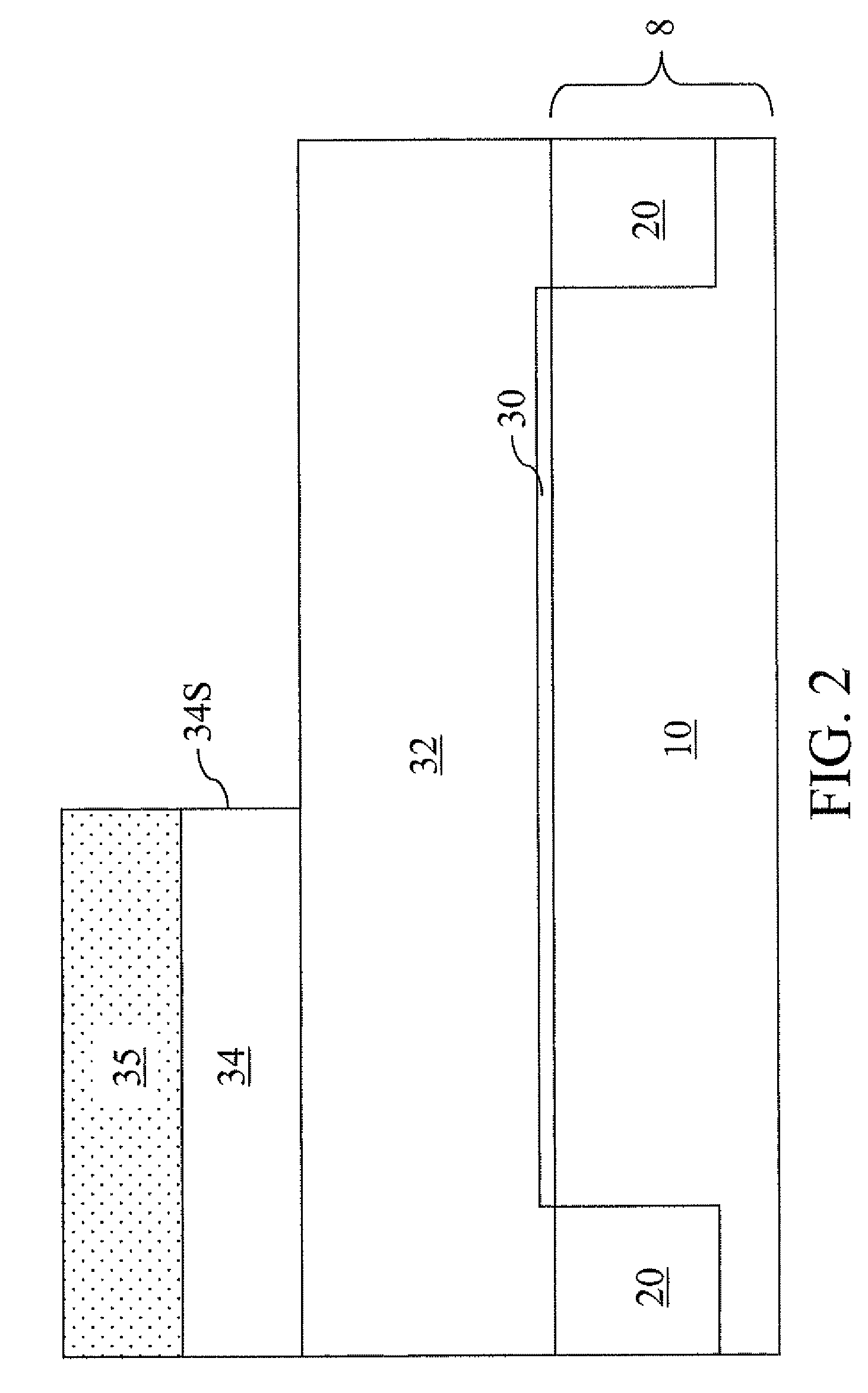

High performance CMOS device structure with mid-gap metal gate

InactiveUS6916698B2Improve performanceReduce diffuseTransistorSemiconductor/solid-state device manufacturingCMOSWork function

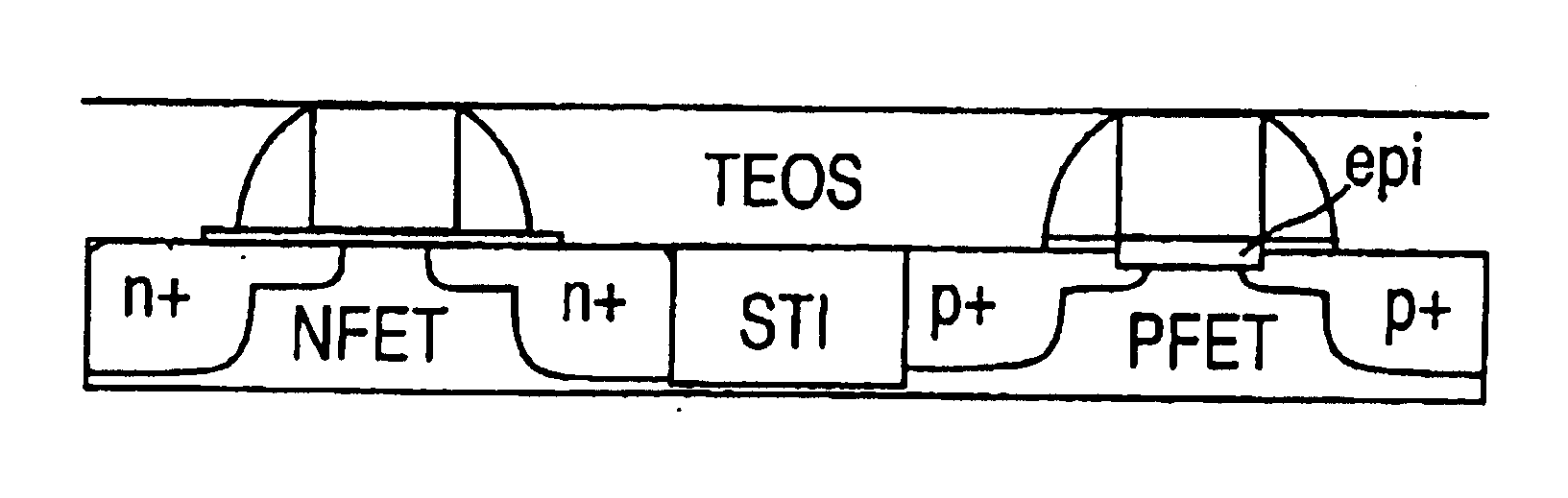

High performance (surface channel) CMOS devices with a mid-gap work function metal gate are disclosed wherein an epitaxial layer is used for a threshold voltage Vt adjust / decrease for the PFET area, for large Vt reductions (˜500 mV), as are required by CMOS devices with a mid-gap metal gate. The present invention provides counter doping using an in situ B doped epitaxial layer or a B and C co-doped epitaxial layer, wherein the C co-doping provides an additional degree of freedom to reduce the diffusion of B (also during subsequent activation thermal cycles) to maintain a shallow B profile, which is critical to provide a surface channel CMOS device with a mid-gap metal gate while maintaining good short channel effects. The B diffusion profiles are satisfactorily shallow, sharp and have a high B concentration for devices with mid-gap metal gates, to provide and maintain a thin, highly doped B layer under the gate oxide.

Owner:IBM CORP

High performance MOSFET

InactiveUS7704844B2Improve device performanceImprove short channel effectSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationDopant

A semiconductor structure which exhibits high device performance and improved short channel effects is provided. In particular, the present invention provides a metal oxide semiconductor field effect transistor (MOFET) that includes a low dopant concentration within an inversion layer of the structure; the inversion layer is an epitaxial semiconductor layer that is formed atop a portion of the semiconductor substrate. The inventive structure also includes a well region of a first conductivity type beneath the inversion layer, wherein the well region has a central portion and two horizontally abutting end portions. The central portion has a higher concentration of a first conductivity type dopant than the two horizontally abutting end portions. Such a well region may be referred to as a non-uniform super-steep retrograde well.

Owner:GLOBALFOUNDRIES INC

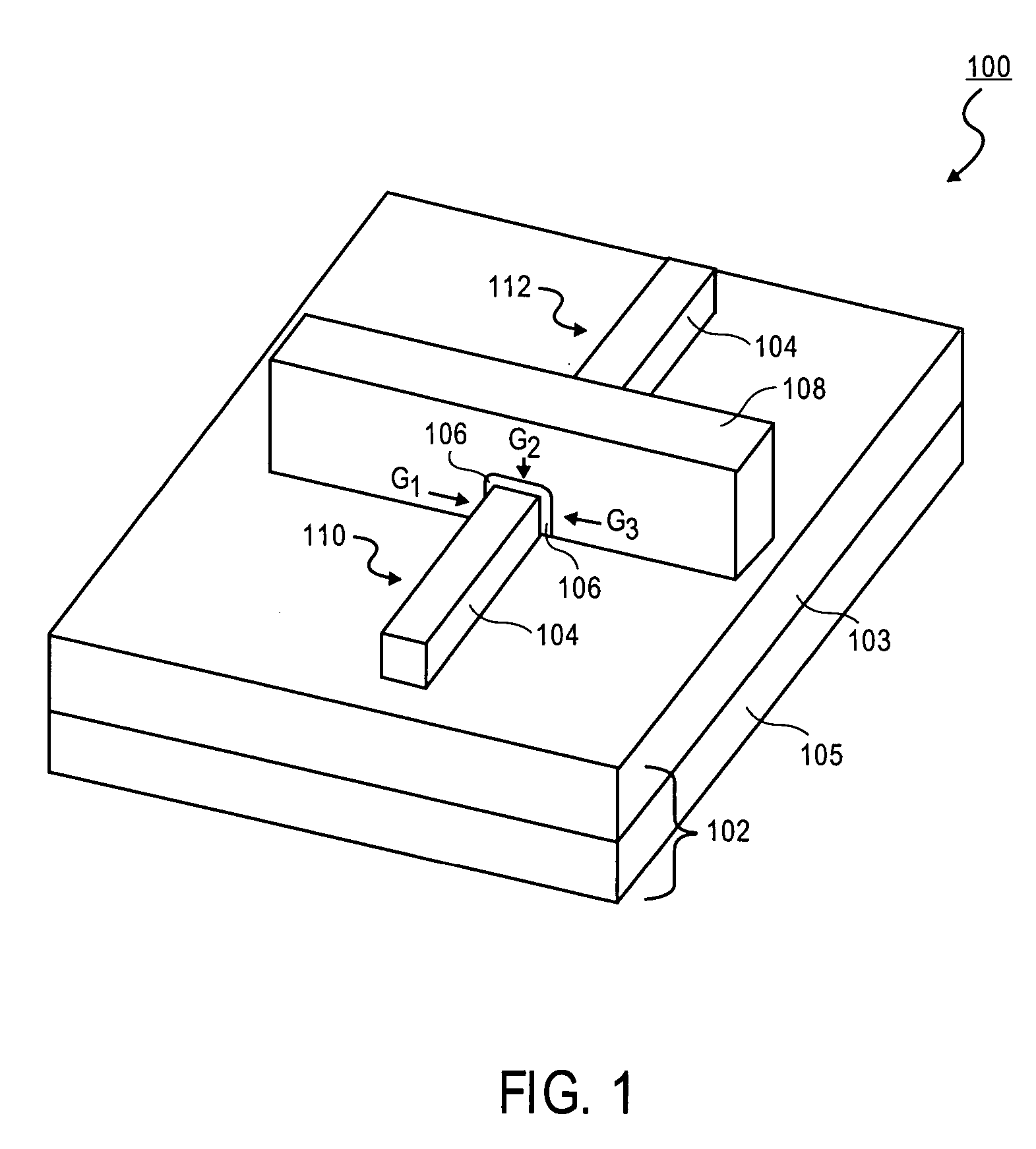

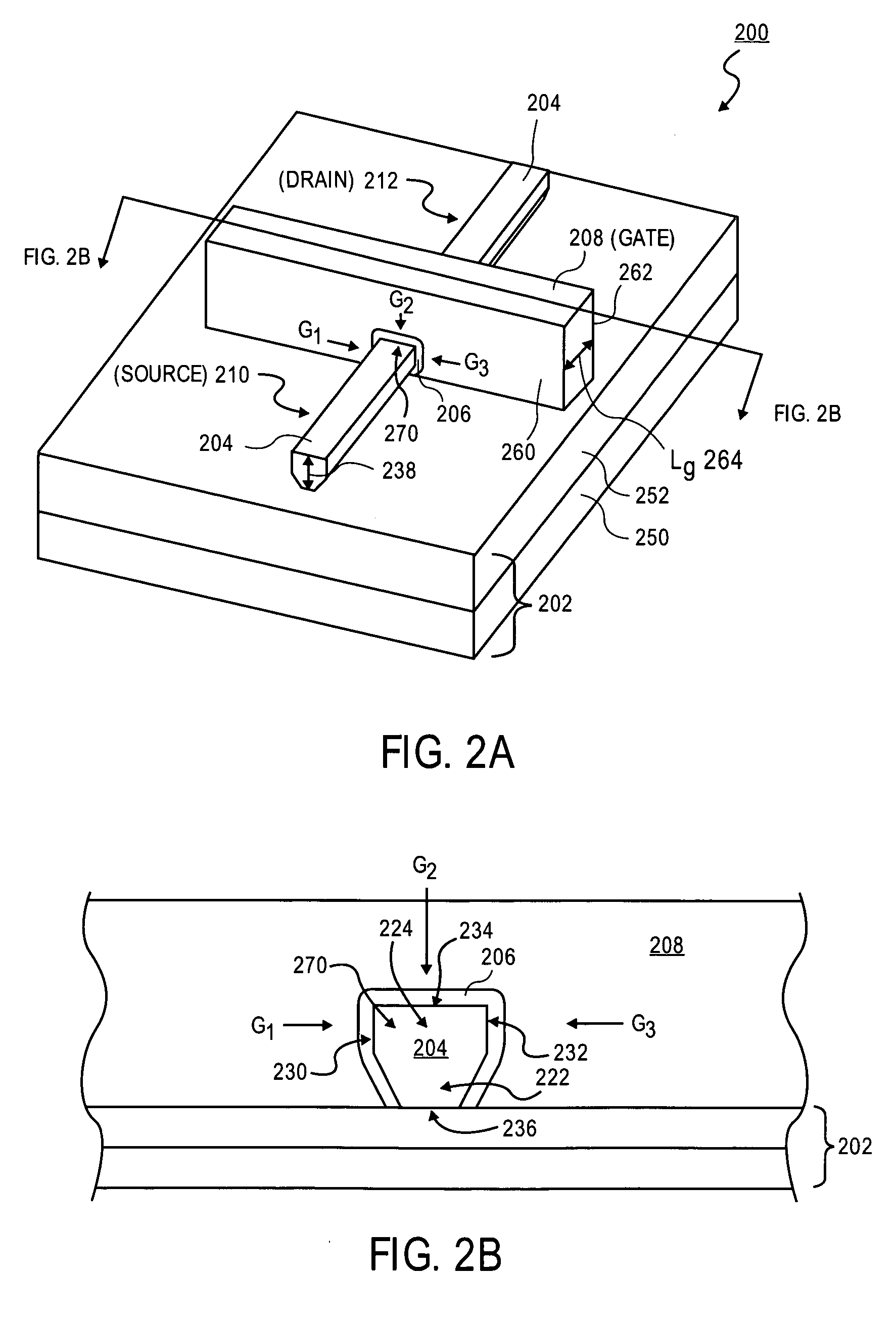

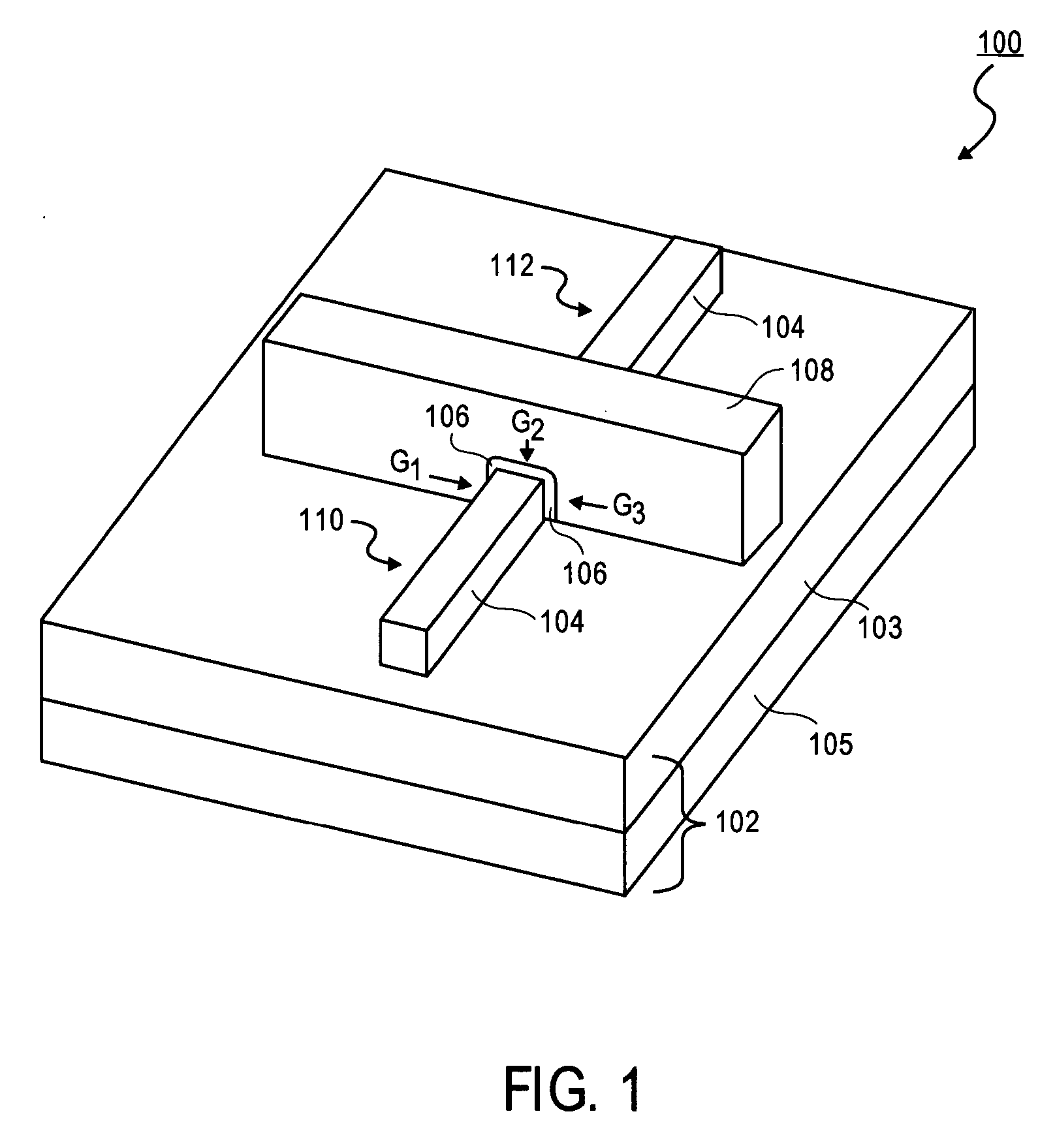

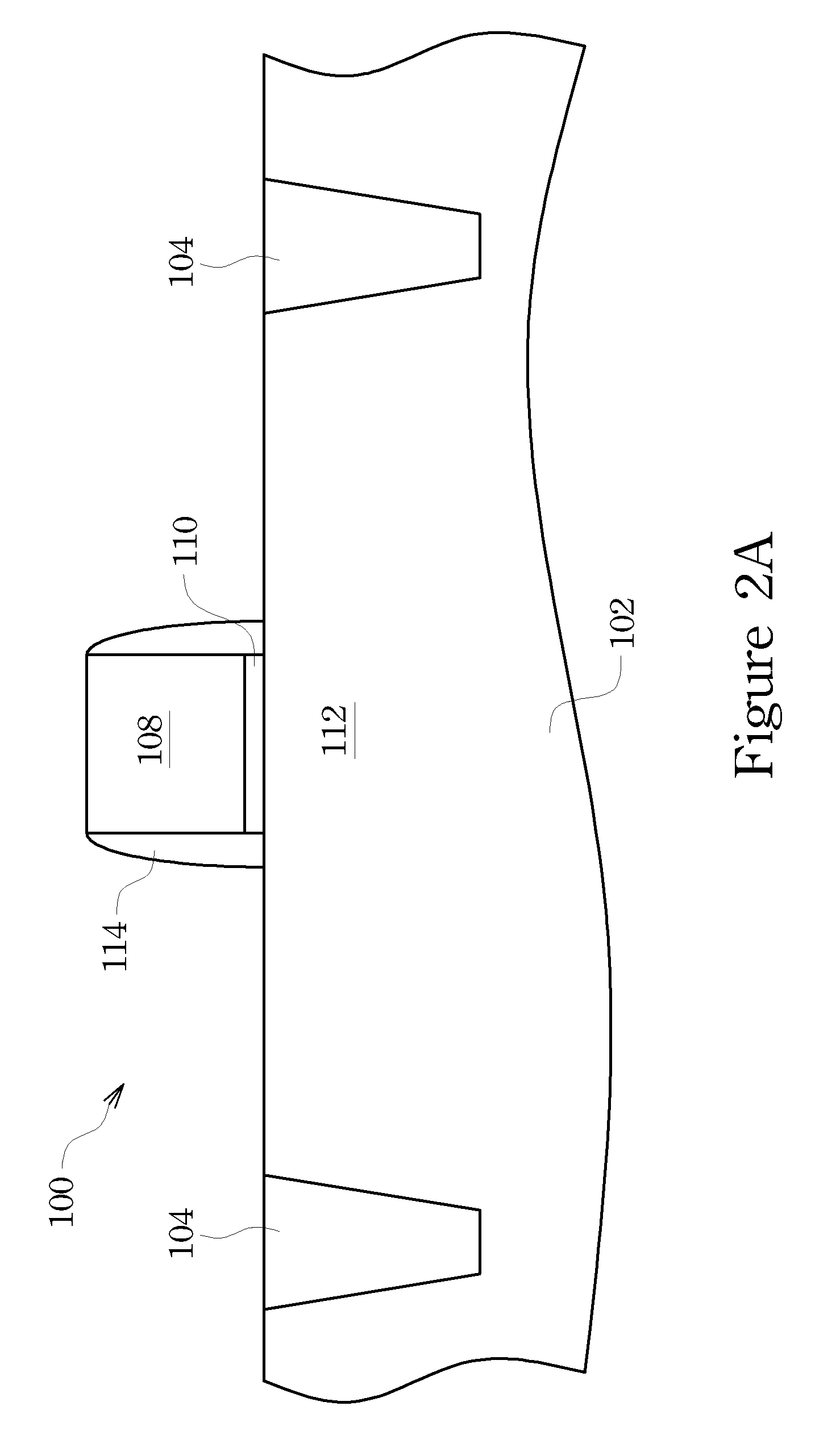

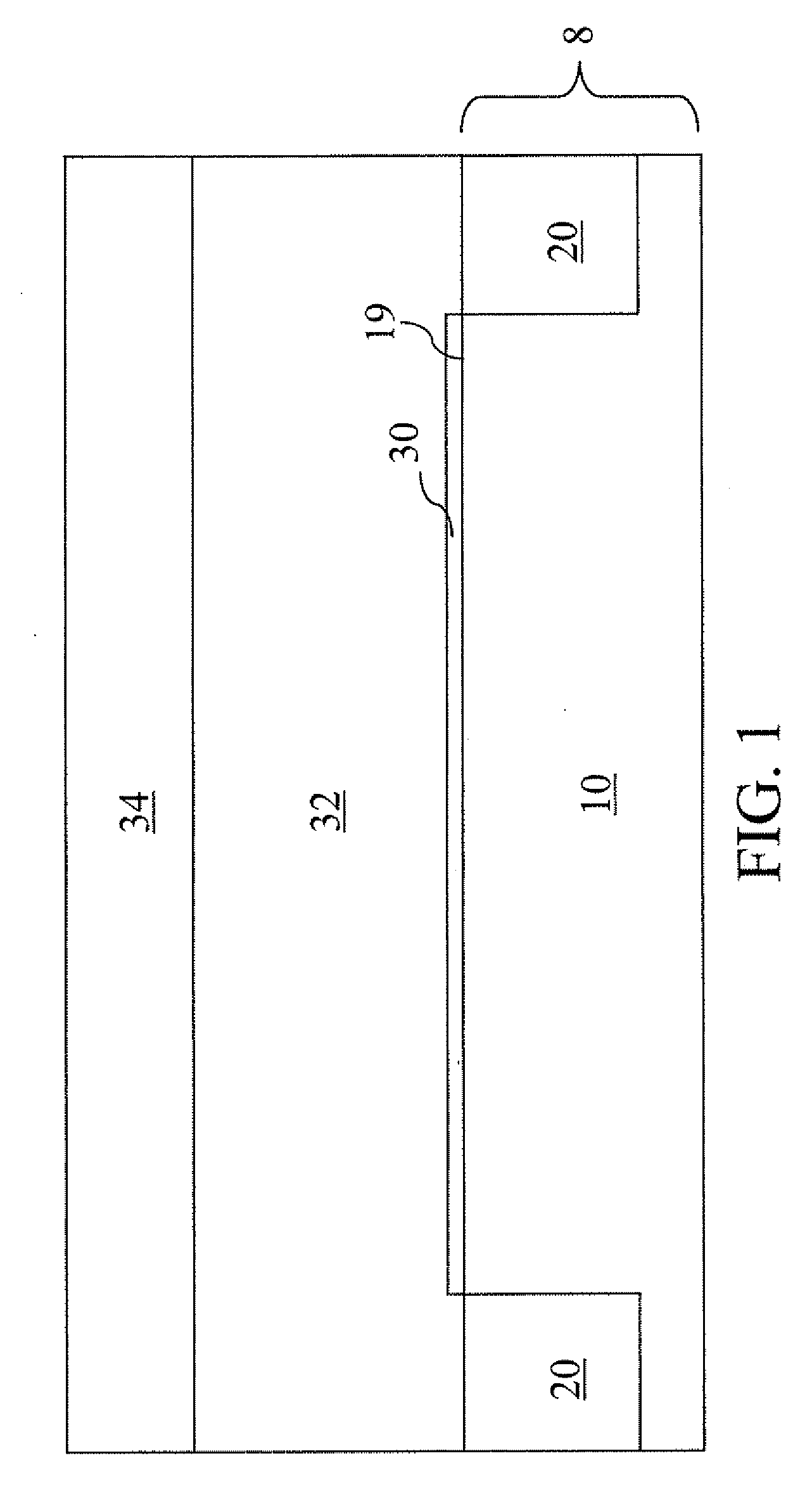

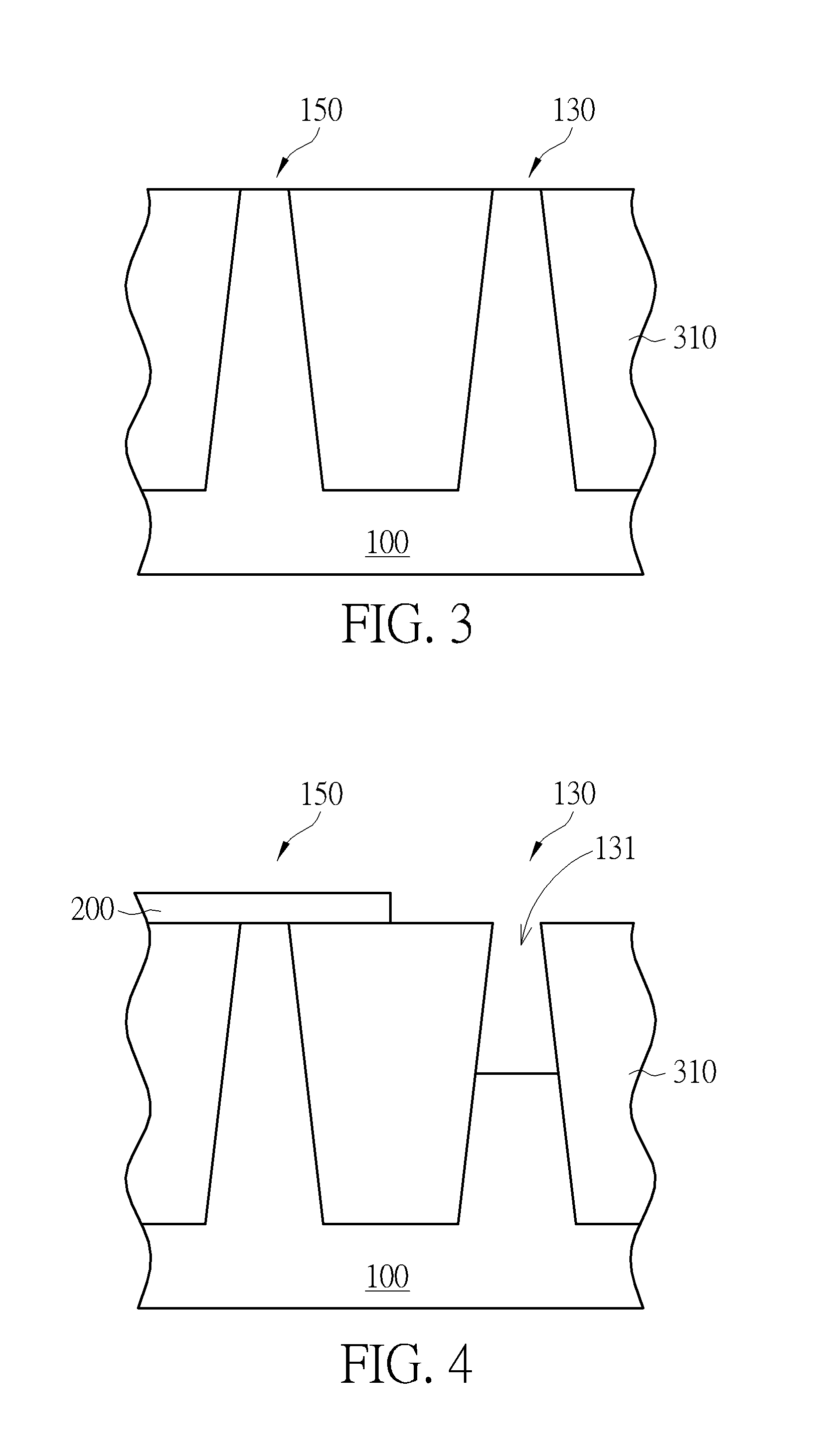

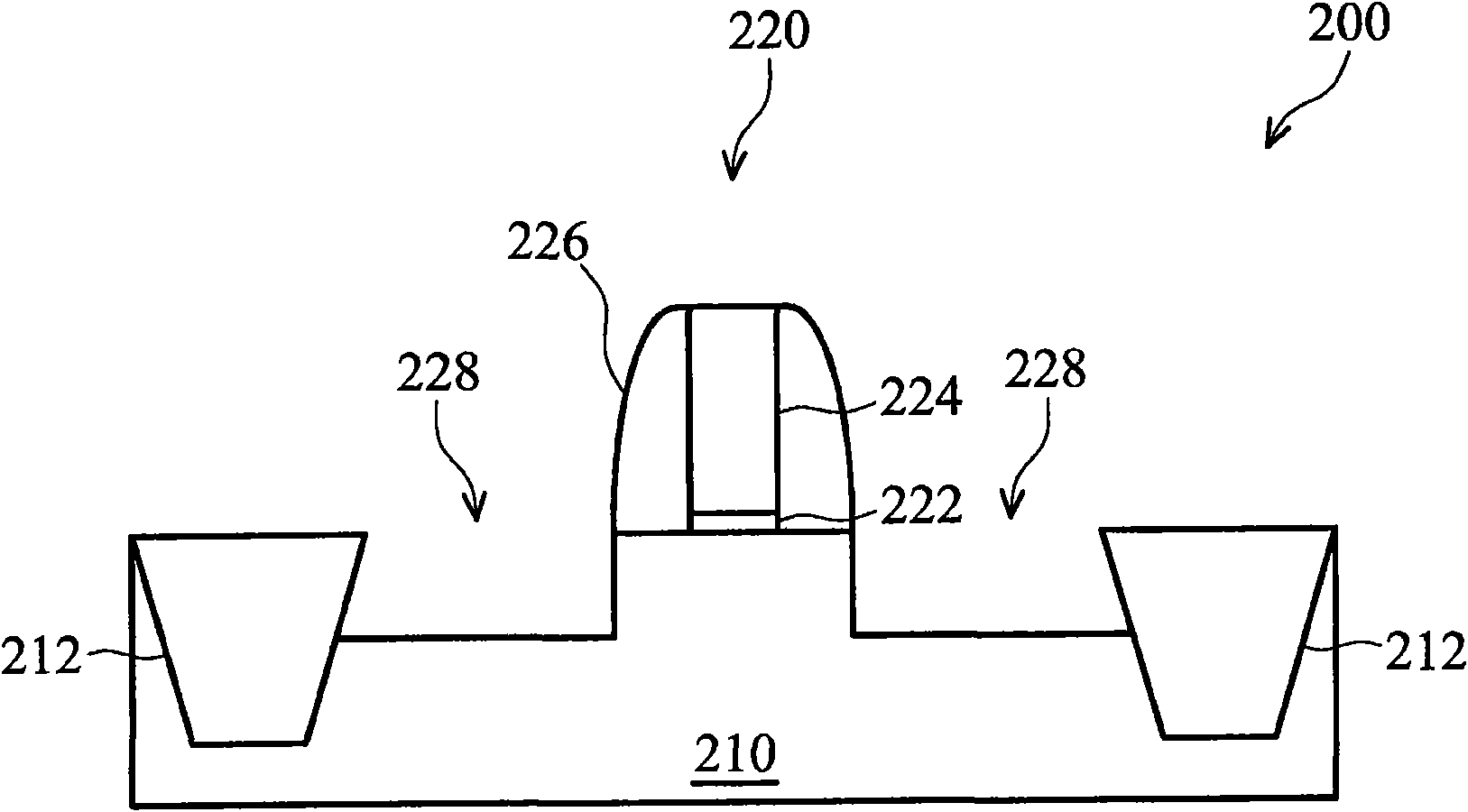

Nonplanar device with thinned lower body portion and method of fabrication

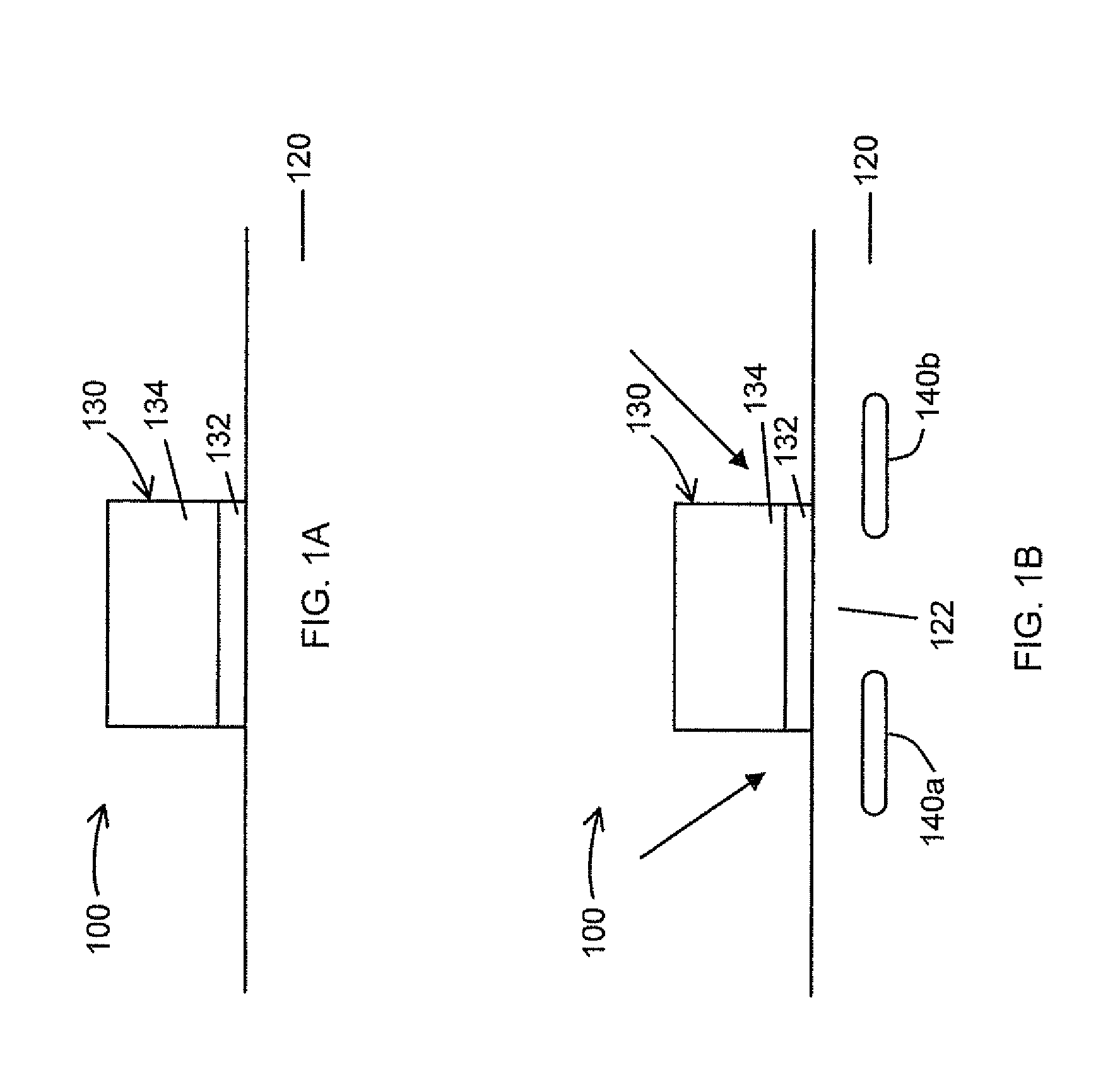

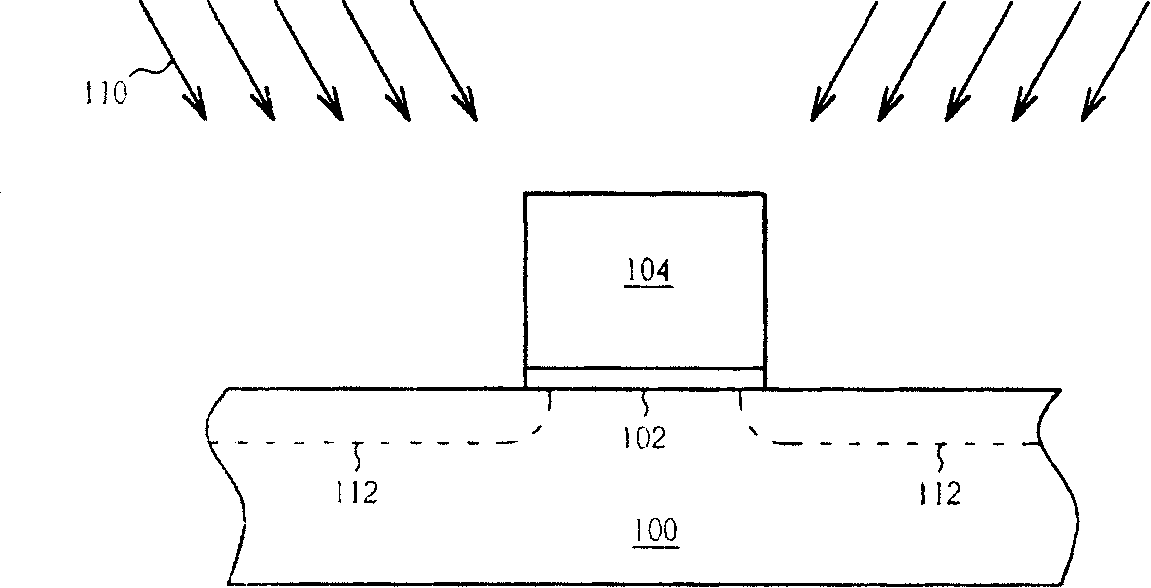

InactiveUS20060086977A1Improve short channel effectSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricDevice material

A nonplanar semiconductor device having a semiconductor body formed on an insulating layer of a substrate. The semiconductor body has a top surface opposite a bottom surface formed on the insulating layer and a pair of laterally opposite sidewalls wherein the distance between the laterally opposite sidewalls at the top surface is greater than at the bottom surface. A gate dielectric layer is formed on the top surface of the semiconductor body and on the sidewalls of the semiconductor body. A gate electrode is formed on the gate dielectric layer on the top surface and sidewalls of the semiconductor body. A pair of source / drain regions are formed in the semiconductor body on opposite sides of the gate electrode.

Owner:INTEL CORP

High performance CMOS devices and methods for making same

ActiveUS8067280B2Improve performanceImprove short channel effectTransistorSemiconductor/solid-state device manufacturingCapacitanceCMOS

An integrated circuit having high performance CMOS devices with good short channel effects may be made by forming a gate structure over a substrate; forming pocket implant regions and source / drain extensions in the substrate; forming spacers along sides of the gate structure; and thermal annealing the substrate when forming the spacers, the thermal annealing performed at an ultra-low temperature. An integrated circuit having high performance CMOS devices with low parasitic junction capacitance may be made by forming a gate structure over a substrate; forming pocket implant regions and source / drain extensions in the substrate; forming spacers along sides of the gate structure; performing a low dosage source / drain implant; and performing a high dosage source / drain implant.

Owner:TAIWAN SEMICON MFG CO LTD

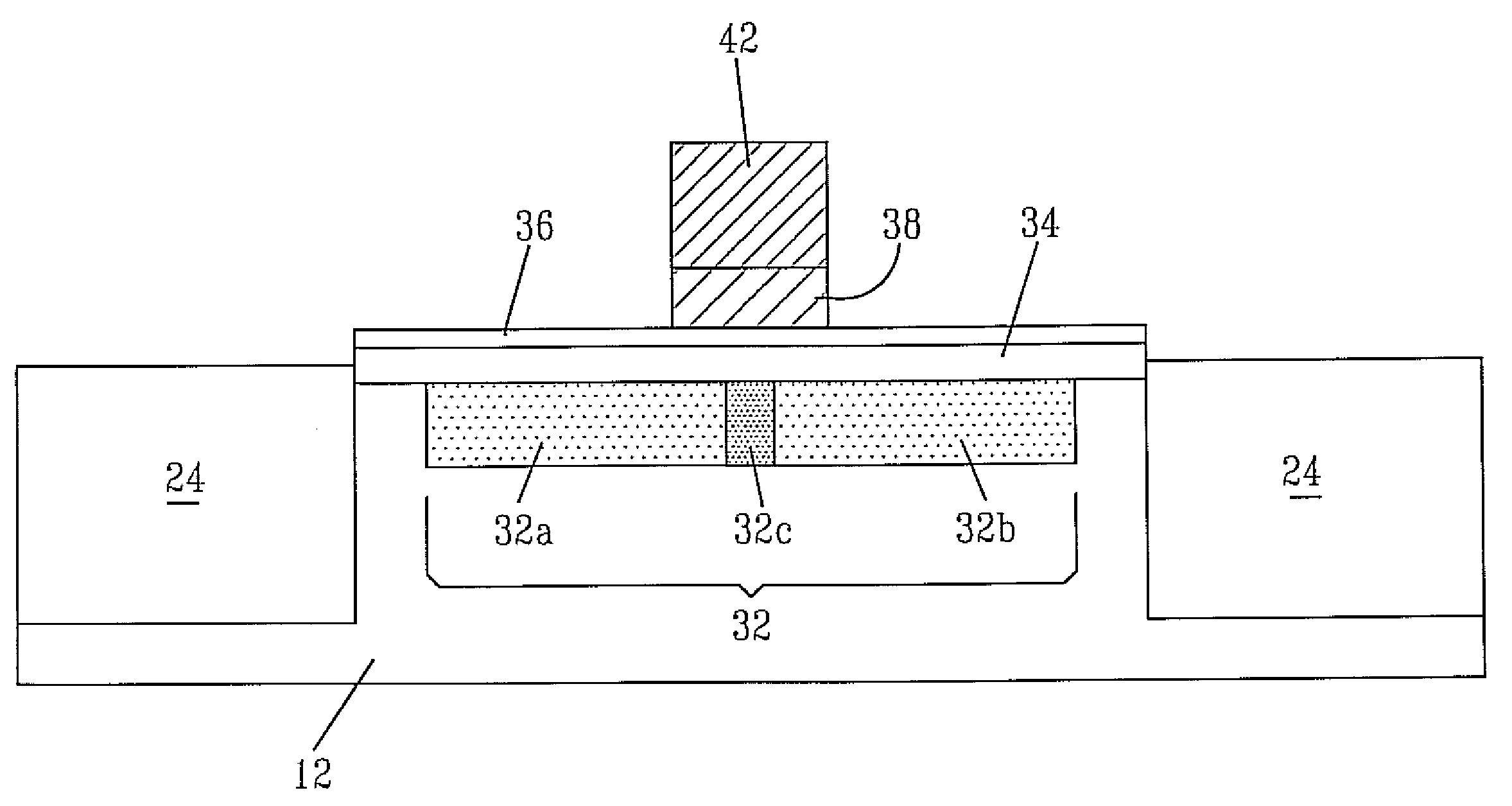

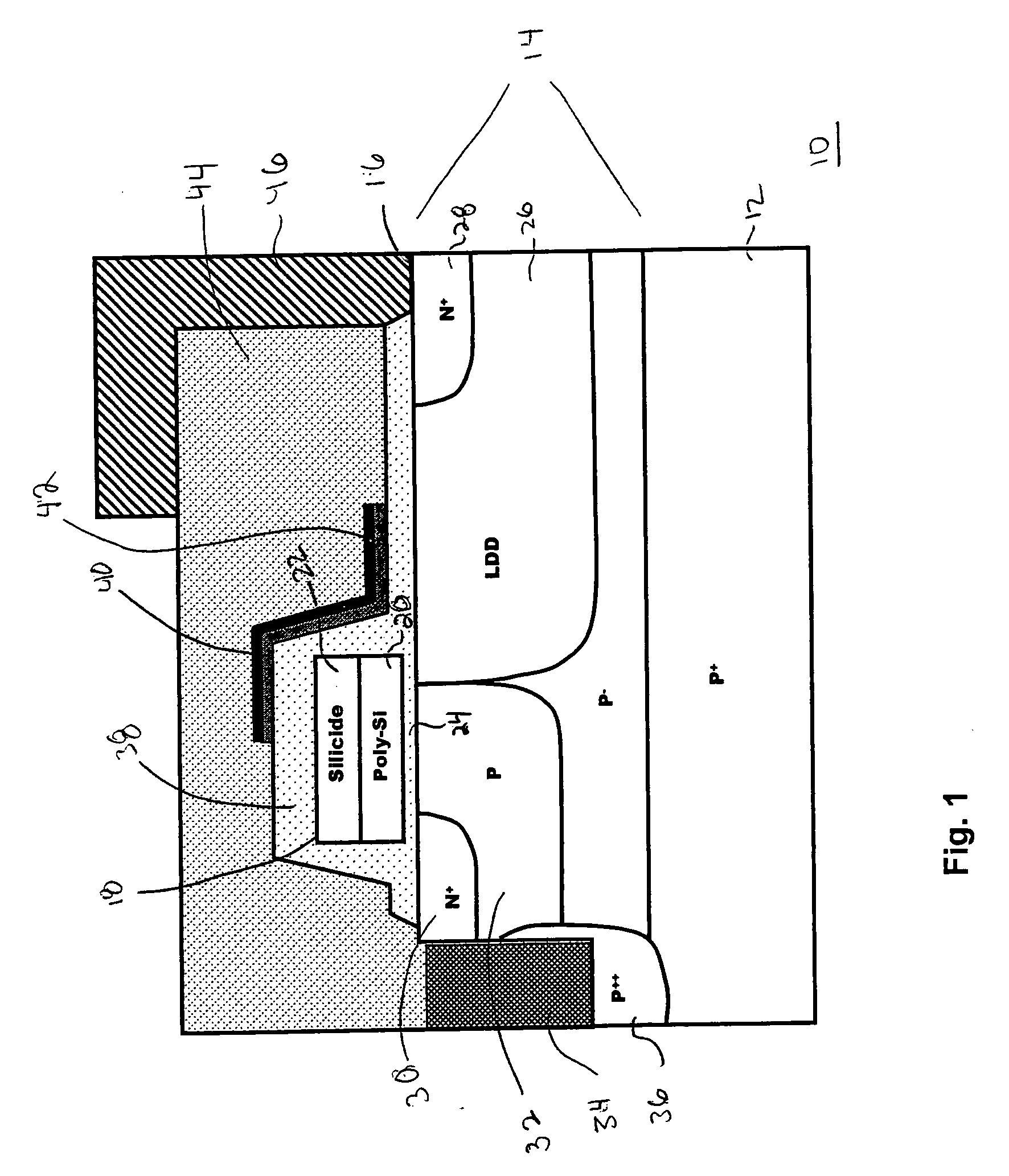

Power LDMOS transistor

A laterally diffused metal-oxide-semiconductor (LDMOS) transistor device includes a doped substrate having an epitaxial layer thereover having source and drain implant regions and body and lightly doped drain regions formed therein. The channel region and lightly doped drain regions are doped to a depth to abut the top surface of the substrate. In alternative embodiments, a buffer region of the second conductivity type and having dopant concentration greater than or equal to about the channel region is formed over the top surface of the substrate between the top surface of the substrate and the channel region and lightly doped drain region, wherein the channel region and lightly doped drain regions are doped to a depth to abut the buffer region.

Owner:CICLON SEMICON DEVICE

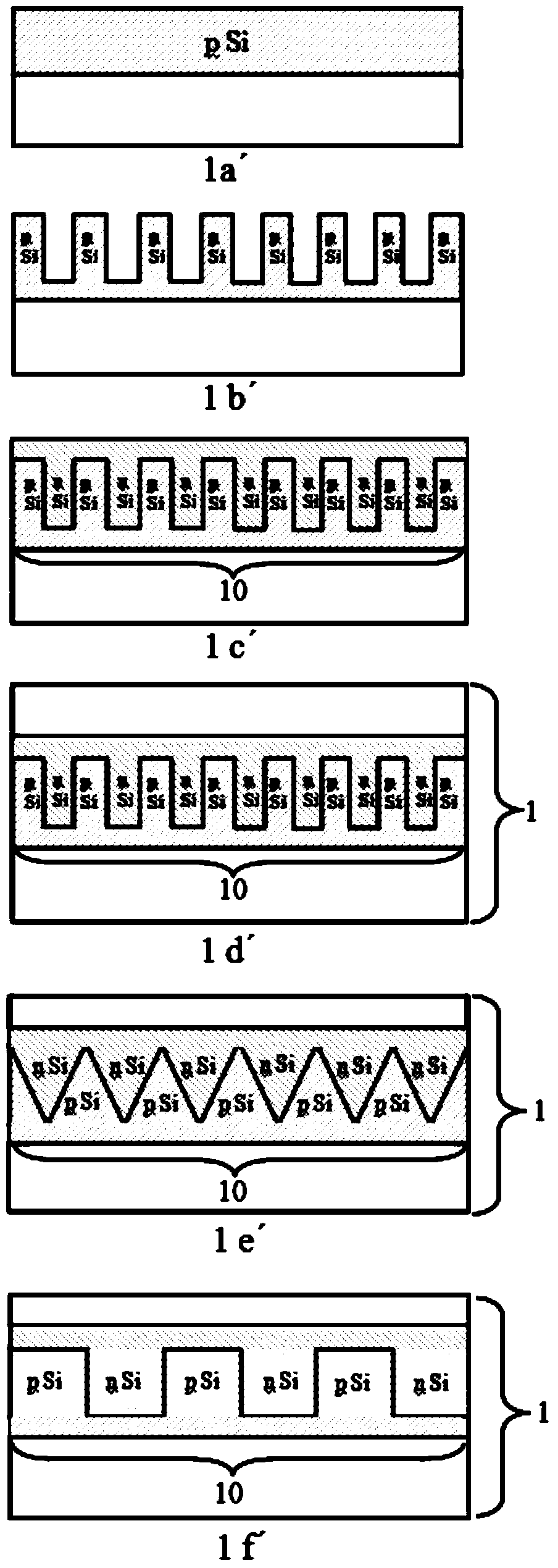

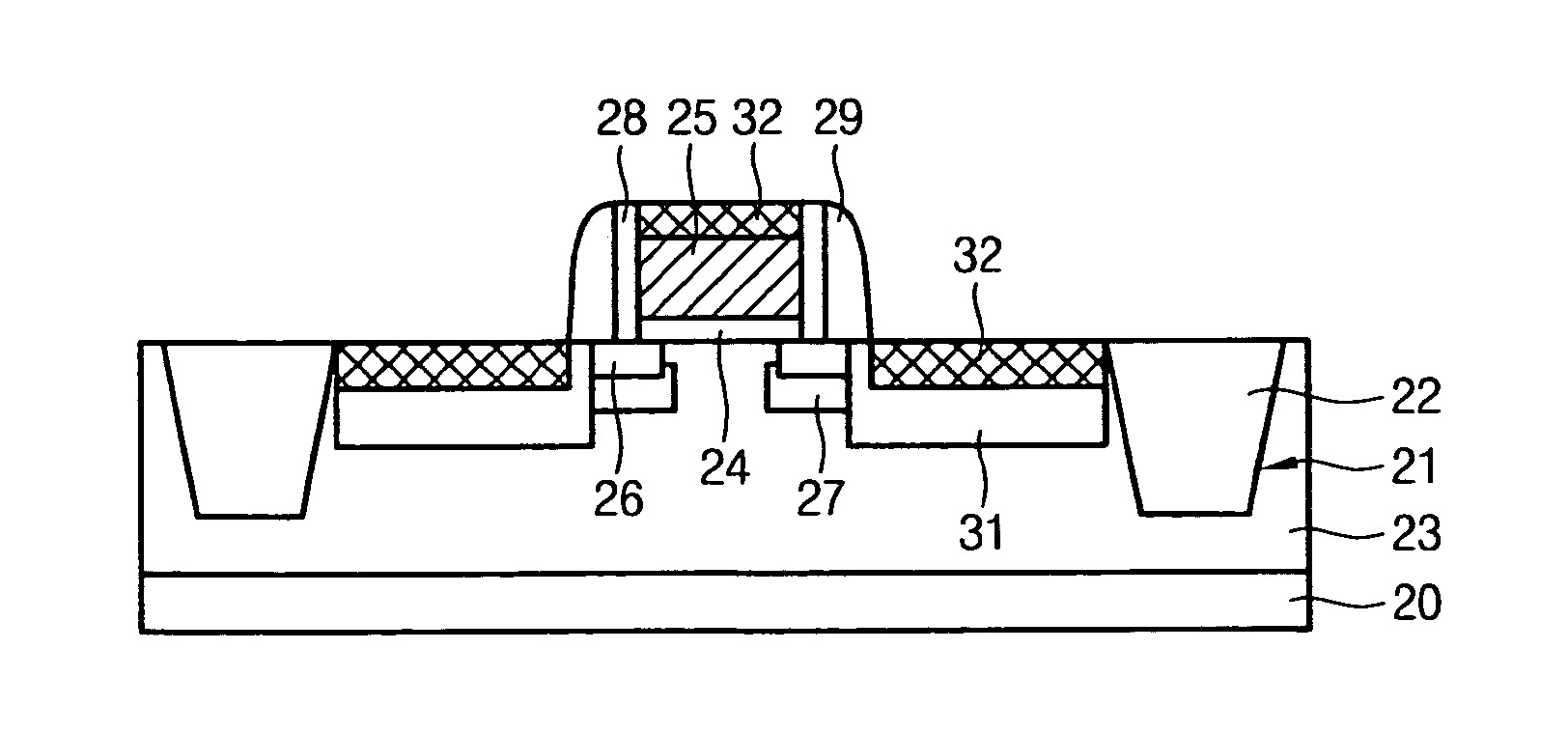

Semiconductor device and method of manufacturing same

InactiveUS20050285193A1Efficient solutionHigh carrier mobilityTransistorSolid-state devicesDevice materialEngineering

A semiconductor device and related method of manufacture are disclosed. The semiconductor device comprises a gate electrode formed on a semiconductor substrate, an active region containing spaces formed below the gate electrode, a channel region formed between the gate electrode and the spaces, and source and drain regions formed on opposite sides of the gate electrode within the active region. The spaces are formed by etching a semiconductor layer formed below the gate electrode in the active region.

Owner:SAMSUNG ELECTRONICS CO LTD

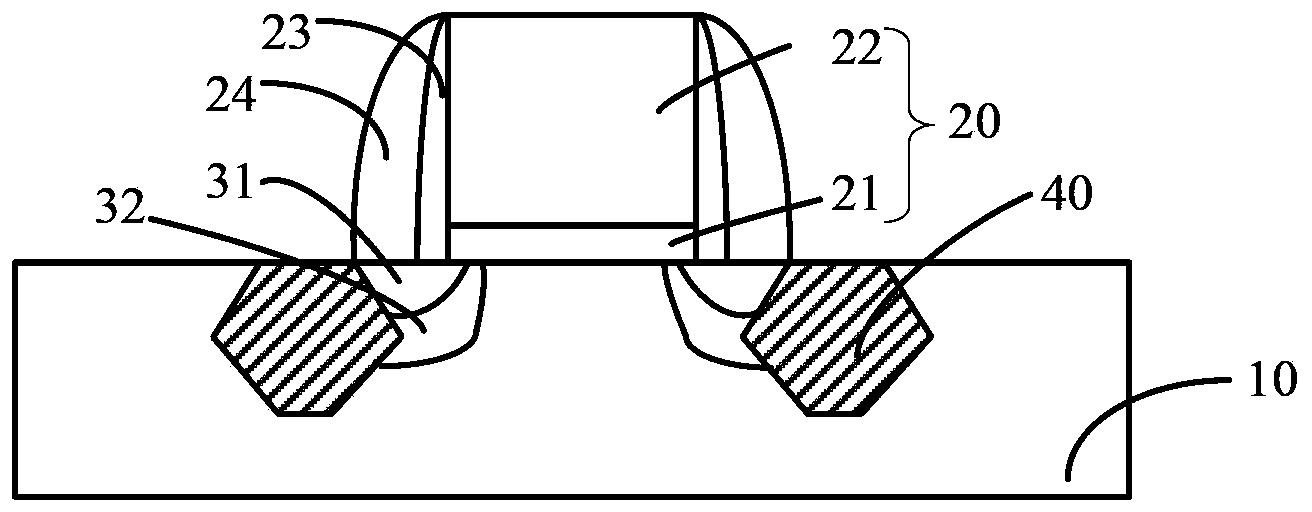

Source/Drain Carbon Implant and RTA Anneal, Pre-SiGe Deposition

ActiveUS20090273034A1Avoid damageImprove short channel effectSemiconductor/solid-state device manufacturingBulk negative resistance effect devicesDopantDevice material

A semiconductor device system, structure, and method of manufacture of a source / drain to retard dopant out-diffusion from a stressor are disclosed. An illustrative embodiment comprises a semiconductor substrate, device, and method to retard sidewall dopant out-diffusion in source / drain regions. A semiconductor substrate is provided with a gate structure, and a source and drain on opposing sides of the gate structure. Recessed regions are etched in a portion of the source and drain. Doped stressors are embedded into the recessed regions. A barrier dopant is incorporated into a remaining portion of the source and drain.

Owner:TAIWAN SEMICON MFG CO LTD

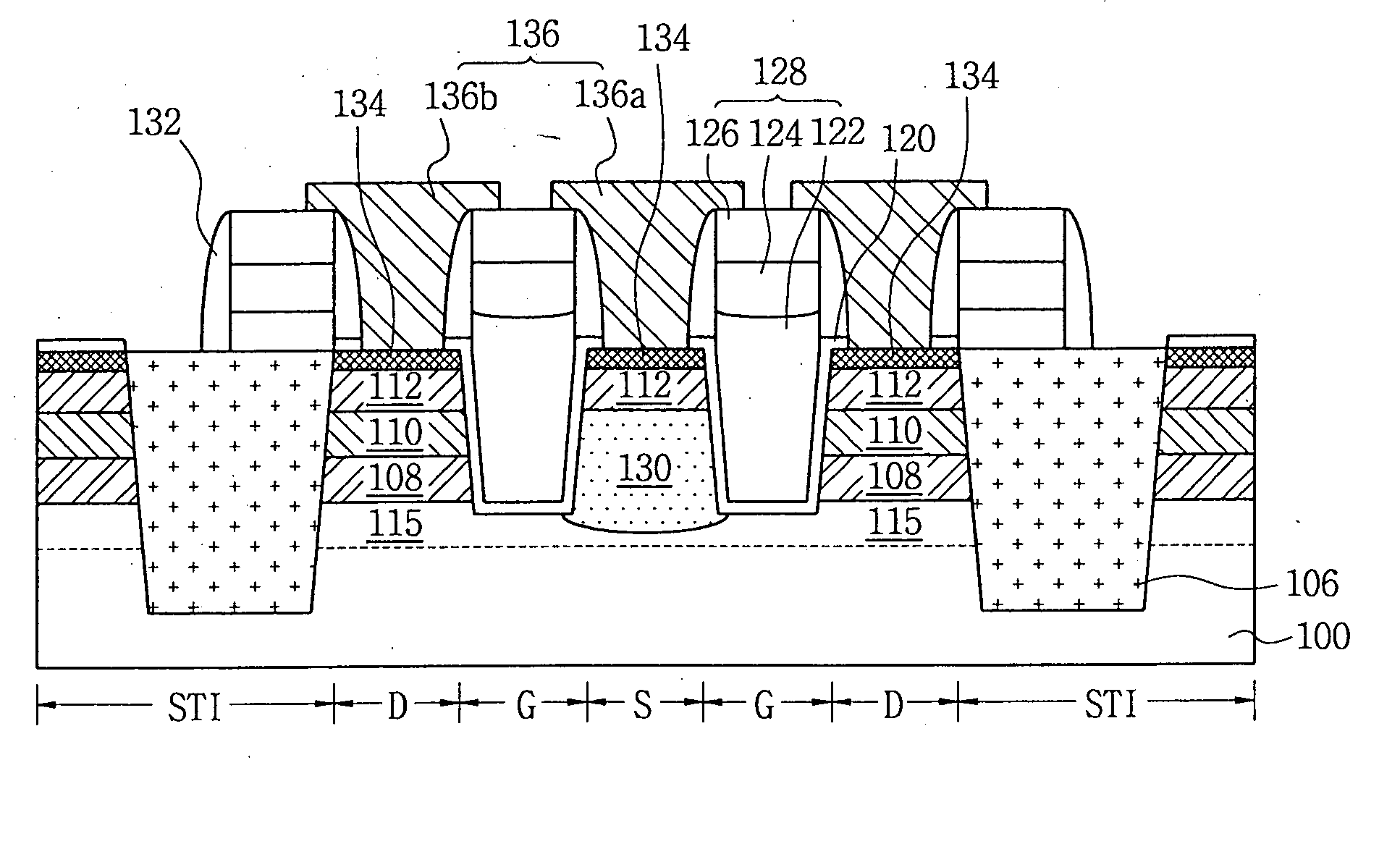

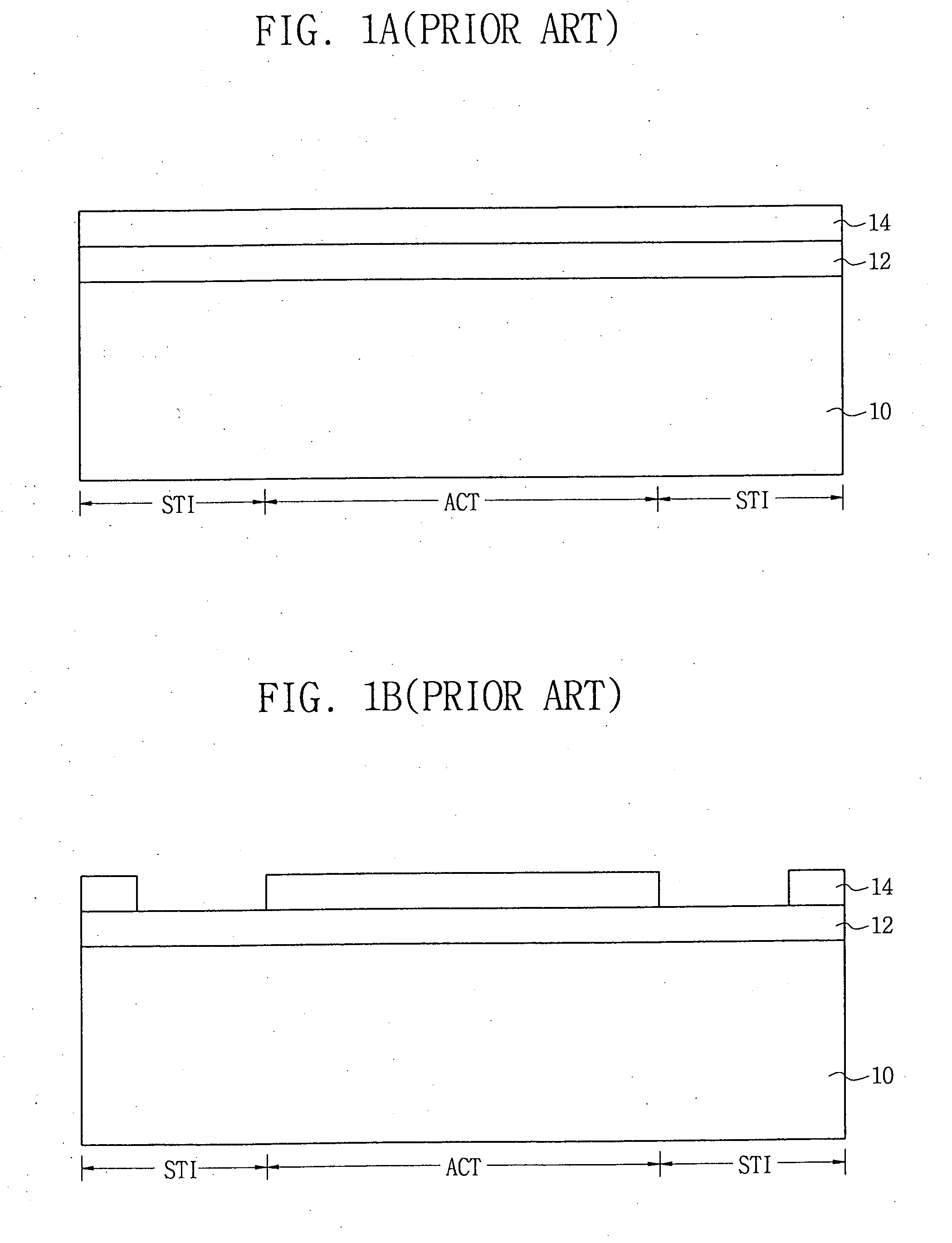

Semiconductor device having a trench gate and method of fabricating the same

InactiveUS20070190712A1Easy to controlImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesTrench gateSemiconductor

A method of fabricating a semiconductor device having a trench gate is provided. First, a semiconductor substrate having a trench etch mask thereon is provided. The semiconductor substrate is etched to form a trench having a sidewall and a bottom using the trench etch mask as a shield. Impurities are doped into the semiconductor substrate through the trench to form a doped region. The semiconductor substrate underlying the trench is etched to form an extended portion. A gate insulating layer is formed on the trench and the extended portion. A trench gate is formed in the trench and the extended portion.

Owner:NAN YA TECH

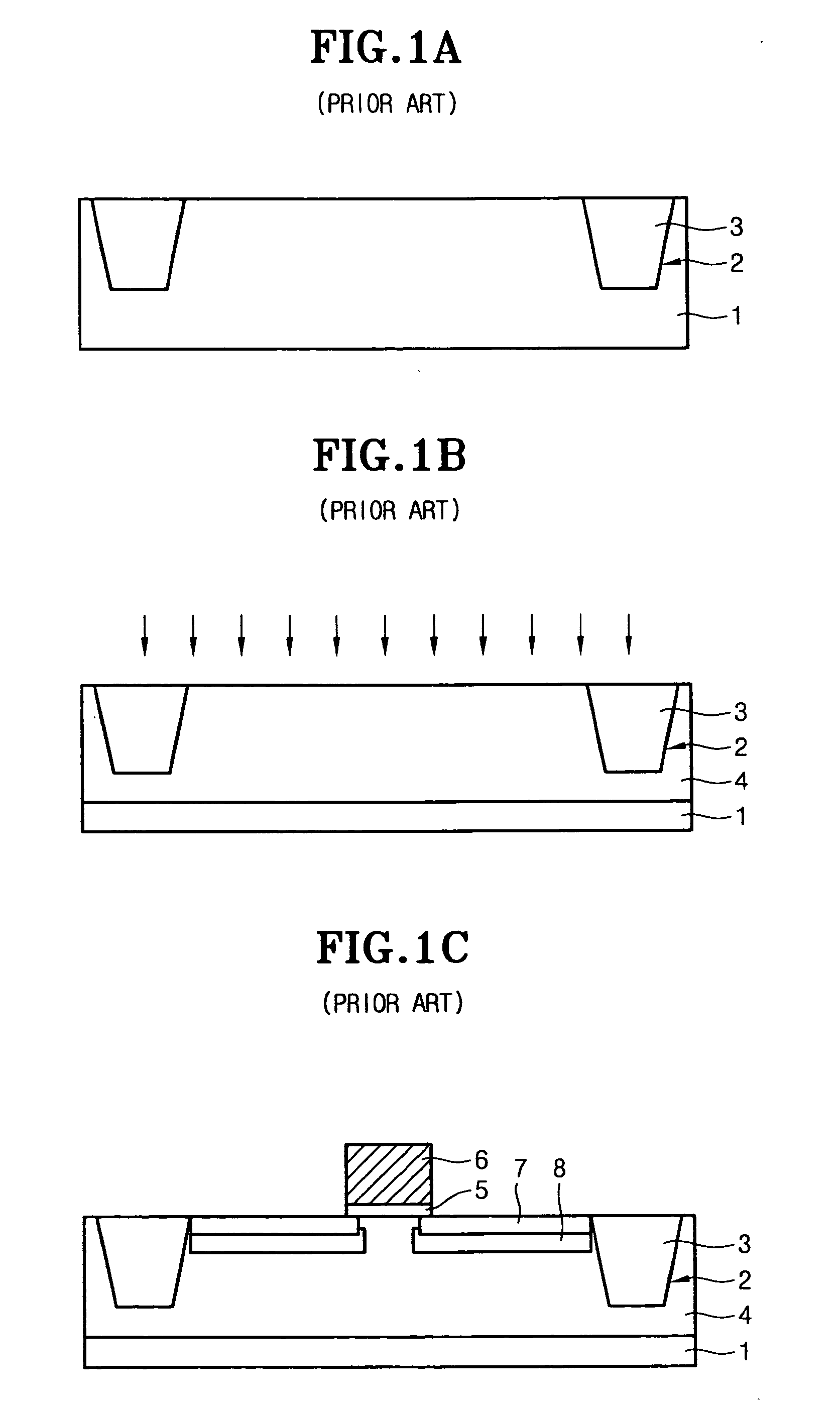

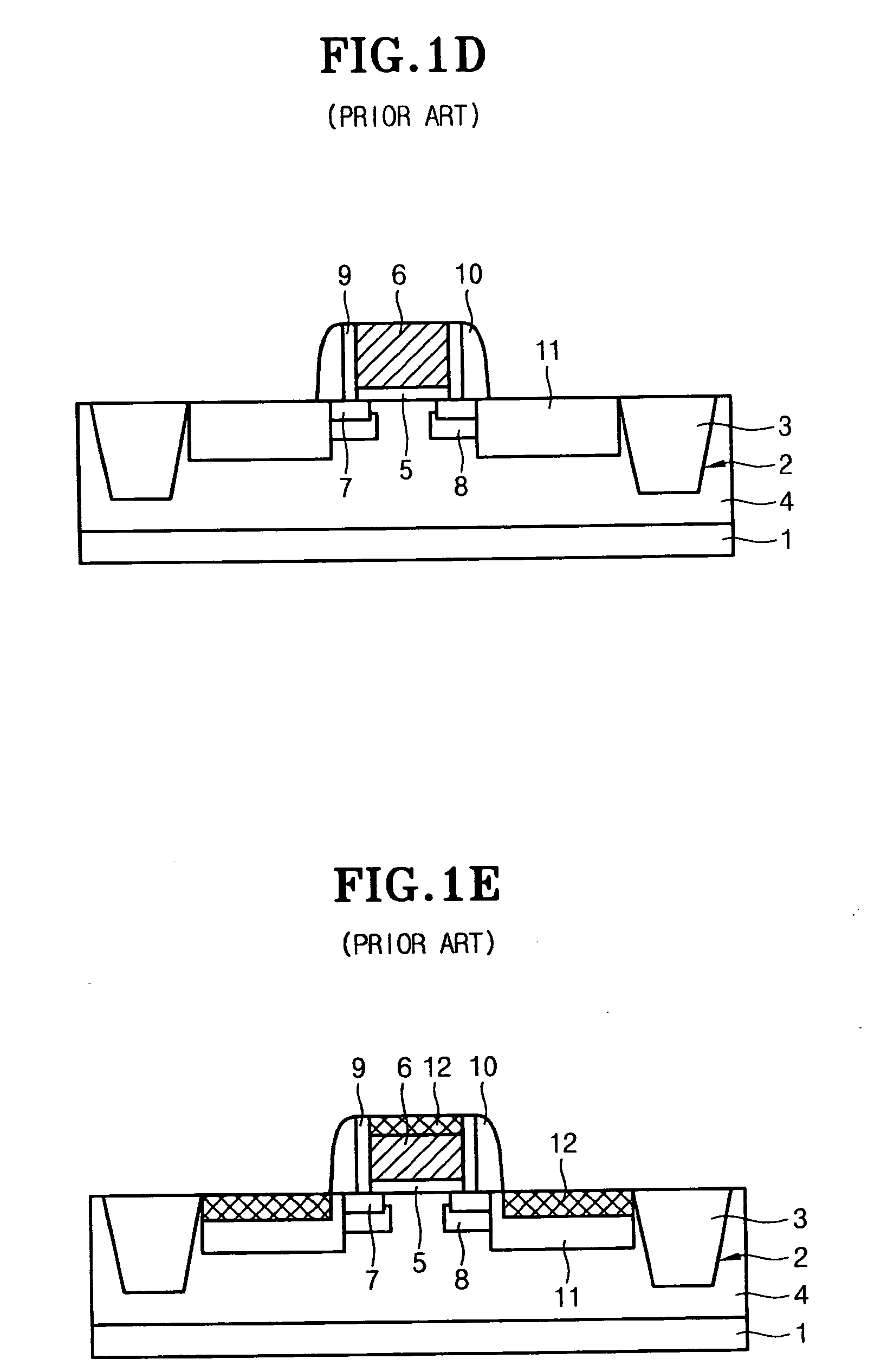

Recess type MOS transistor and method of manufacturing same

ActiveUS20050196947A1Improve featuresLeakage currentSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerGate stack

The method of manufacturing a recess type MOS transistor improves a refresh characteristic. In the method, a channel impurity region is formed by ion implanting a first conductive impurity in an active region of a semiconductor substrate. Thereon, a second conductive impurity and the first conductive impurity are ion-implanted each alternately into the active region, to thus sequentially form first to third impurity regions having a dual diode structure on the channel impurity region, the second conductive impurity having conductivity opposite to the first conductive impurity. A trench is formed, and a gate insulation layer is formed in a gate region to produce a gate stack. The first conductive impurity is selectively ion-implanted in a source region, to thus form a fourth impurity region. A spacer is then formed in a sidewall of the gate stack, and the second conductive impurity is ion-implanted in the source / drain regions, to form a fifth impurity region.

Owner:SAMSUNG ELECTRONICS CO LTD

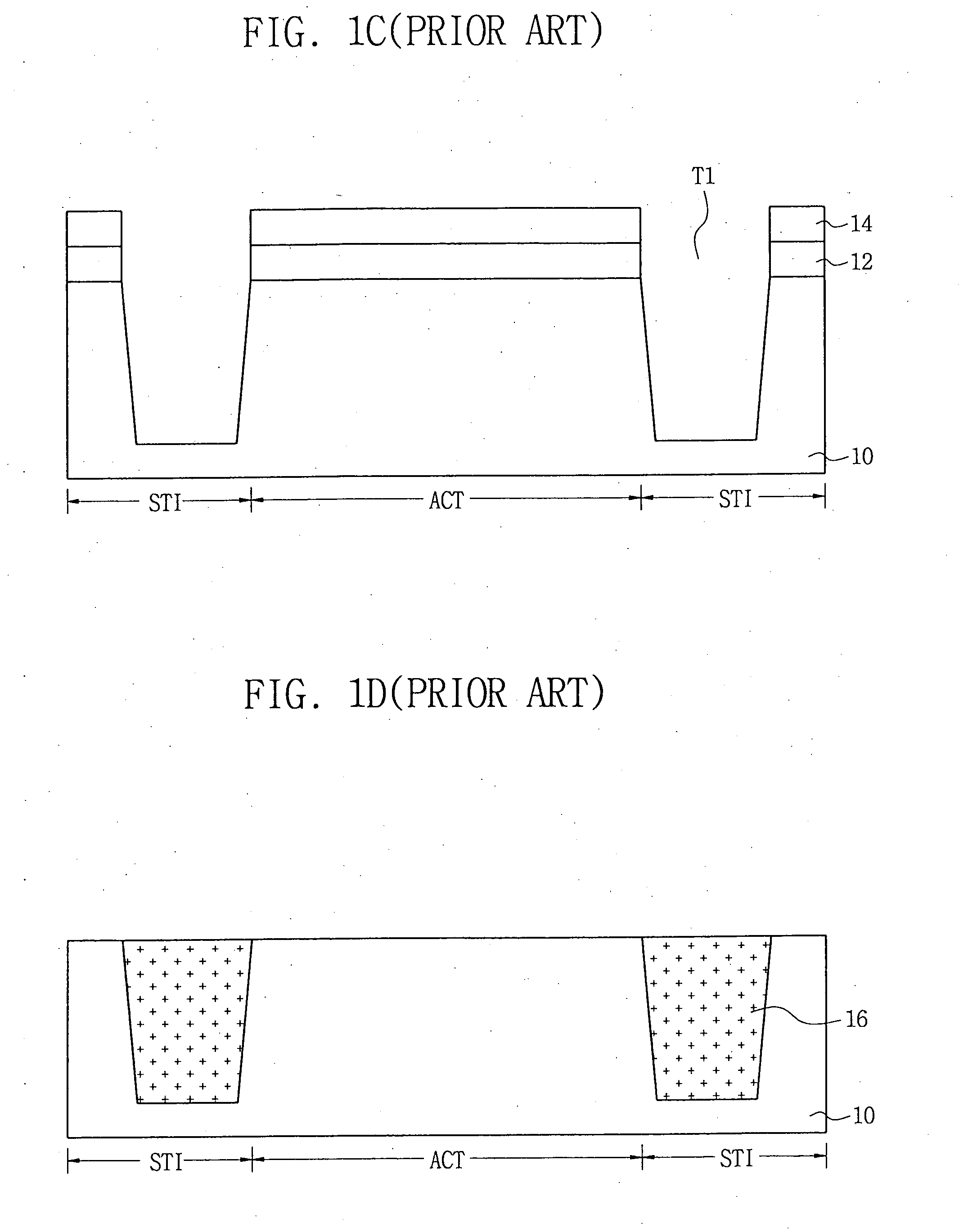

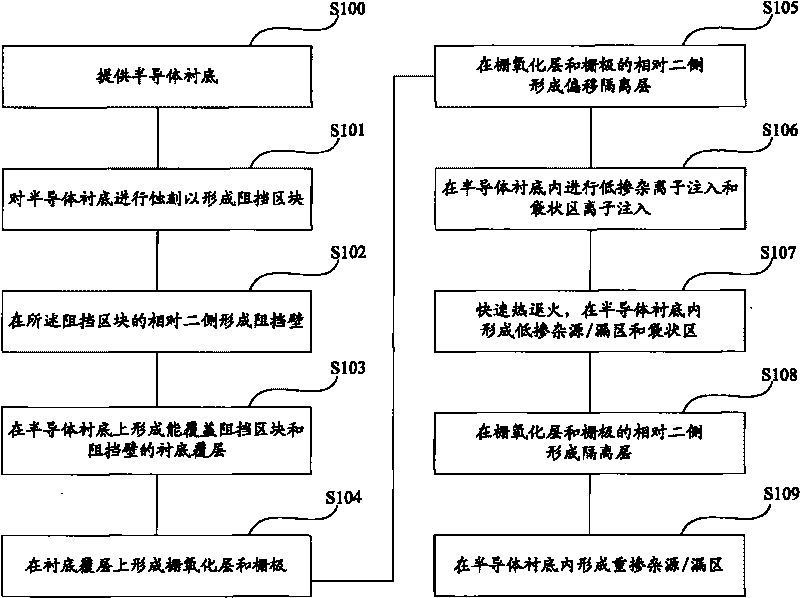

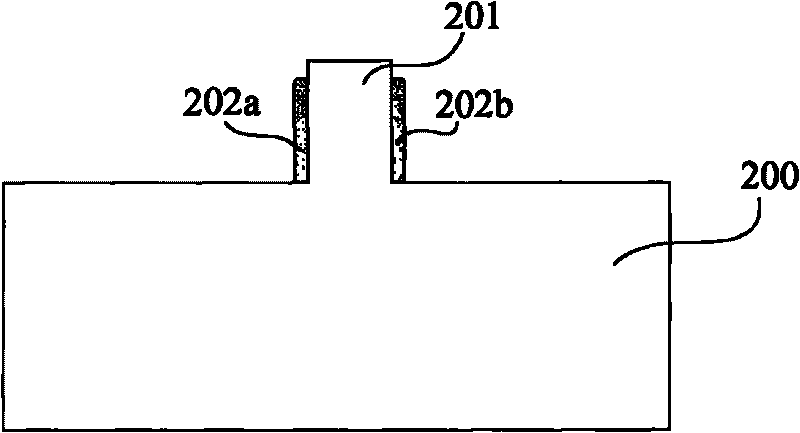

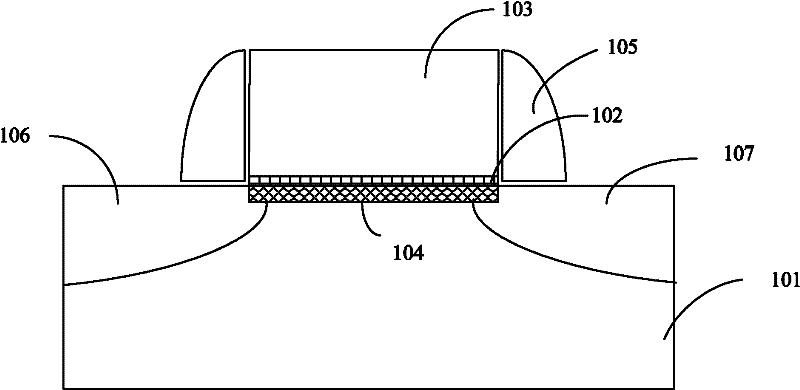

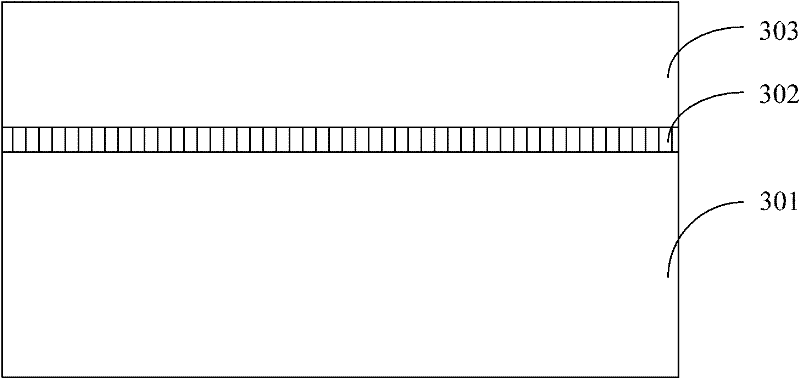

Semiconductor device and manufacture method thereof

InactiveCN101740393AInterpenetration barrierImprove short channel effectSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceRapid thermal annealing

The invention relates to a semiconductor device and a manufacture method thereof, wherein the manufacture method comprises the following steps of: providing a semiconductor underlay; etching the semiconductor underlay so as to form a barrier region block; forming barrier walls at both sides of the barrier region block; forming an underlay coating on the semiconductor underlay, wherein the barrier walls and the surface of the underlay coating have fall; forming a gate oxide and a grid electrode on the underlay coating and the semiconductor underlay; carrying out low-doping ion implantation in the semiconductor underlay; carrying out rapid thermal annealing to form a low-doping source / drain region in the semiconductor underlay; forming isolation layers at opposite sides of the gate oxide and the grid electrode; and forming a heavy-doping source / drain region in the semiconductor underlay. The invention has technical scheme that the barrier walls are formed in the semiconductor underlay, thereby effectively separating the interpenetration between the source region and the drain region, obviously improving the short channel effect of the semiconductor device, avoiding the generation of a punch-through effect between the source region and the drain region and improving the electrical behaviour of the semiconductor device. Meanwhile, a bigger process regulating space is provided for the reduction of junction capacitance and the enlargement of process window in the ultra shallow junction process.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Nonplanar device with thinned lower body portion and method of fabrication

InactiveUS20060214231A1Improve short channel effectSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricDevice material

Owner:INTEL CORP

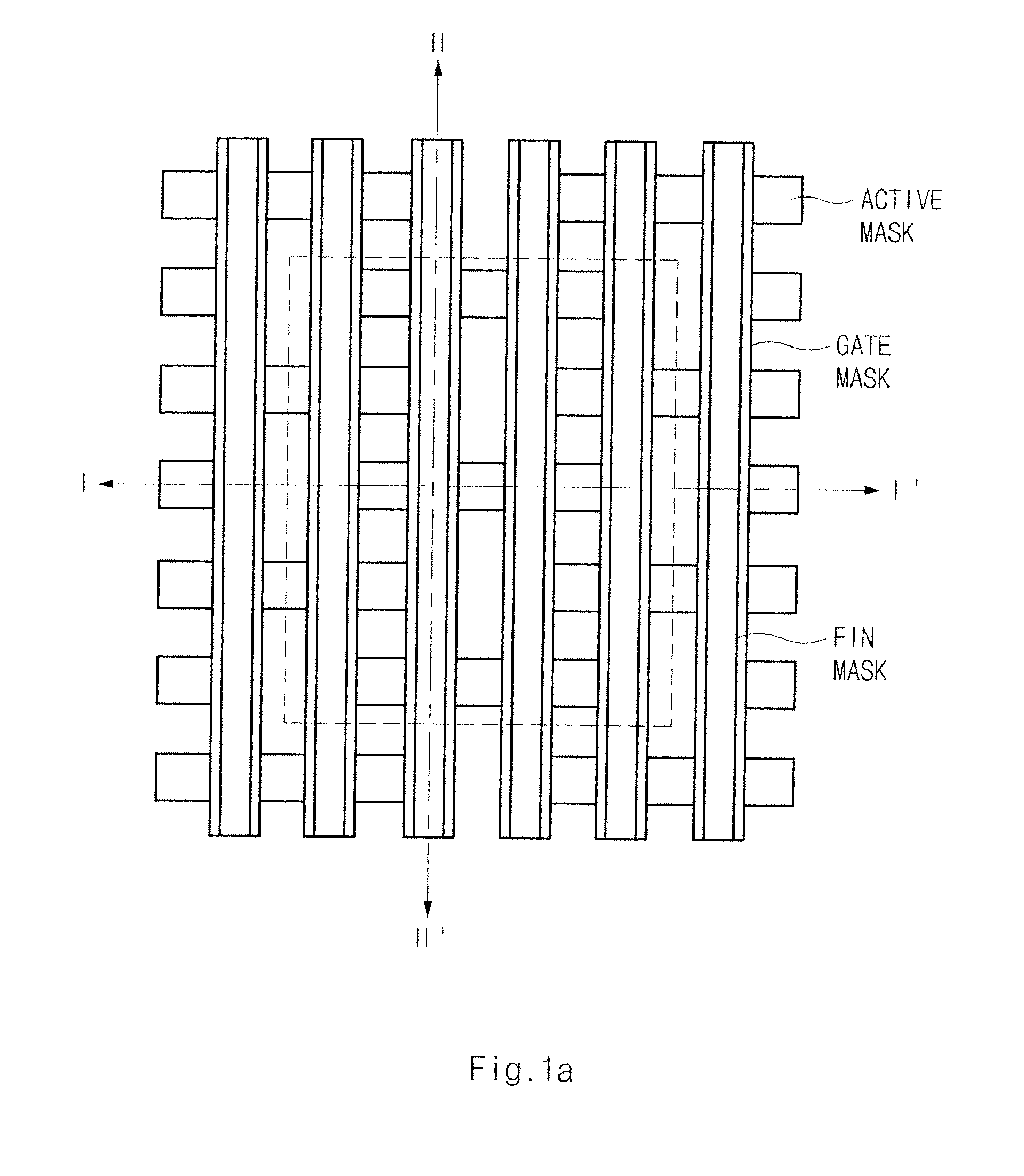

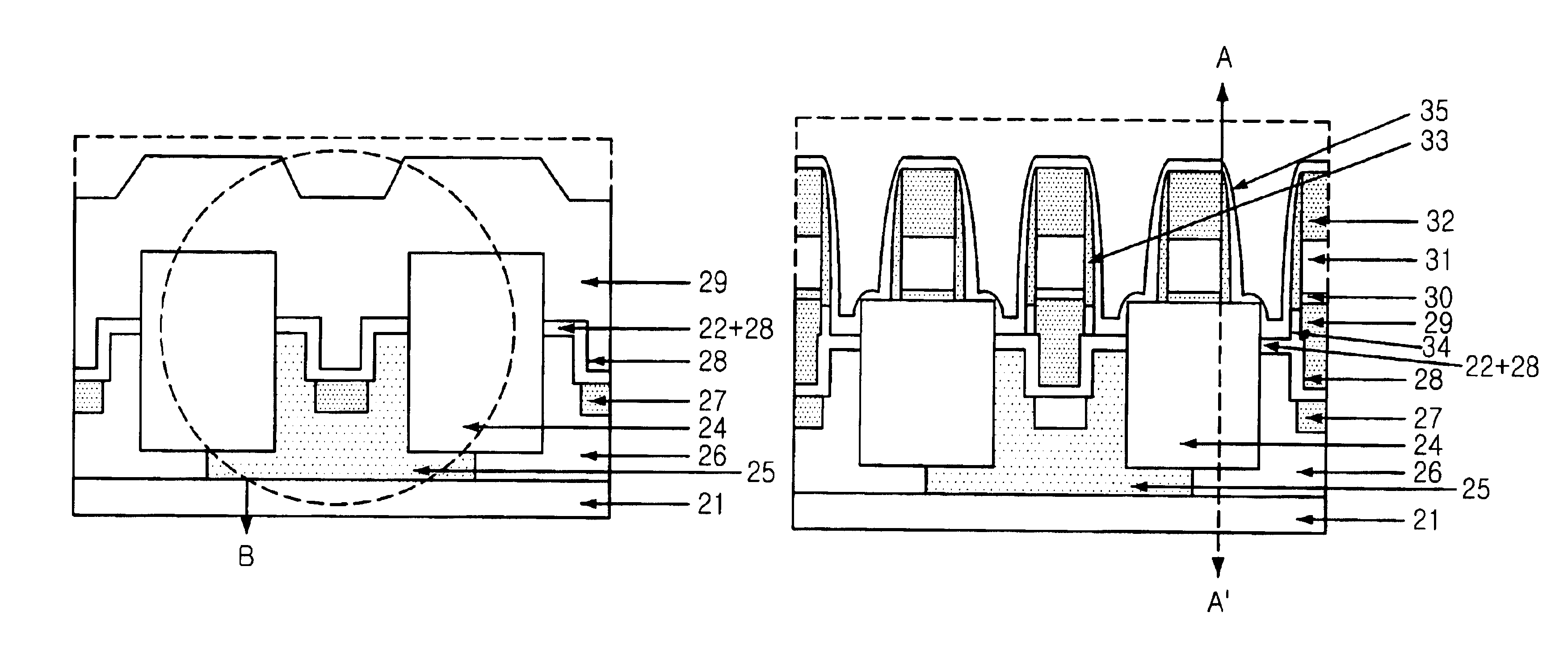

Method for Manufacturing Semiconductor Apparatus Having Saddle-Fin Transistor and Semiconductor Apparatus Fabricated Thereby

ActiveUS20090294857A1Reduce misalignmentImprove short channel effectSolid-state devicesSemiconductor/solid-state device manufacturingCell regionSemiconductor

A method for manufacturing a semiconductor memory apparatus may include forming a channel region and a gate region through a self-alignment etching process on a cell region; and forming a three-dimensional multi-channel region through an etching process using a first multi-channel mask on a core region and a peripheral region and forming a gate region through an etching process using a second multi-channel mask, thereby preventing mis-arrangement of gates.

Owner:SK HYNIX INC

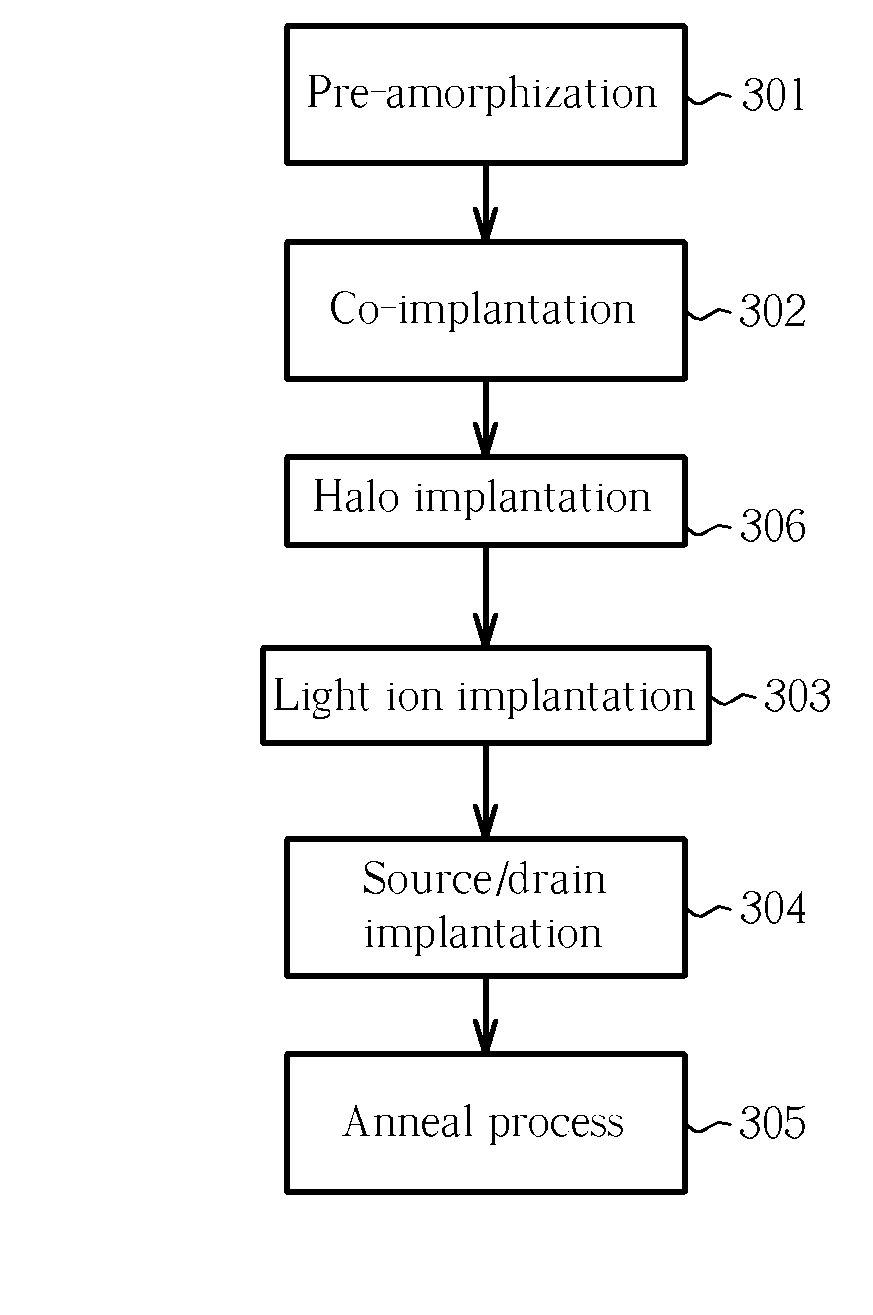

Method of forming a MOS transistor

ActiveUS20070238234A1Improve short channel effectFacilitated DiffusionTransistorSemiconductor/solid-state device manufacturingDopantEngineering

A method of forming a MOS transistor, in which a co-implantation is performed to implant an implant into a source region and a drain region or a halo implanted region to effectively prevent dopants from over diffusion in the source region and the drain region or the halo implanted region, for obtaining a good junction profile and improving short channel effect. The implant comprises carbon, a hydrocarbon, or a derivative of the hydrocarbon, such as one selected from a group consisting of C, CxHy+, and (CxHy)n+, wherein x is a number of 1 to 10, y is a number of 4 to 20, and n is a number of 1 to 1000.

Owner:MARLIN SEMICON LTD

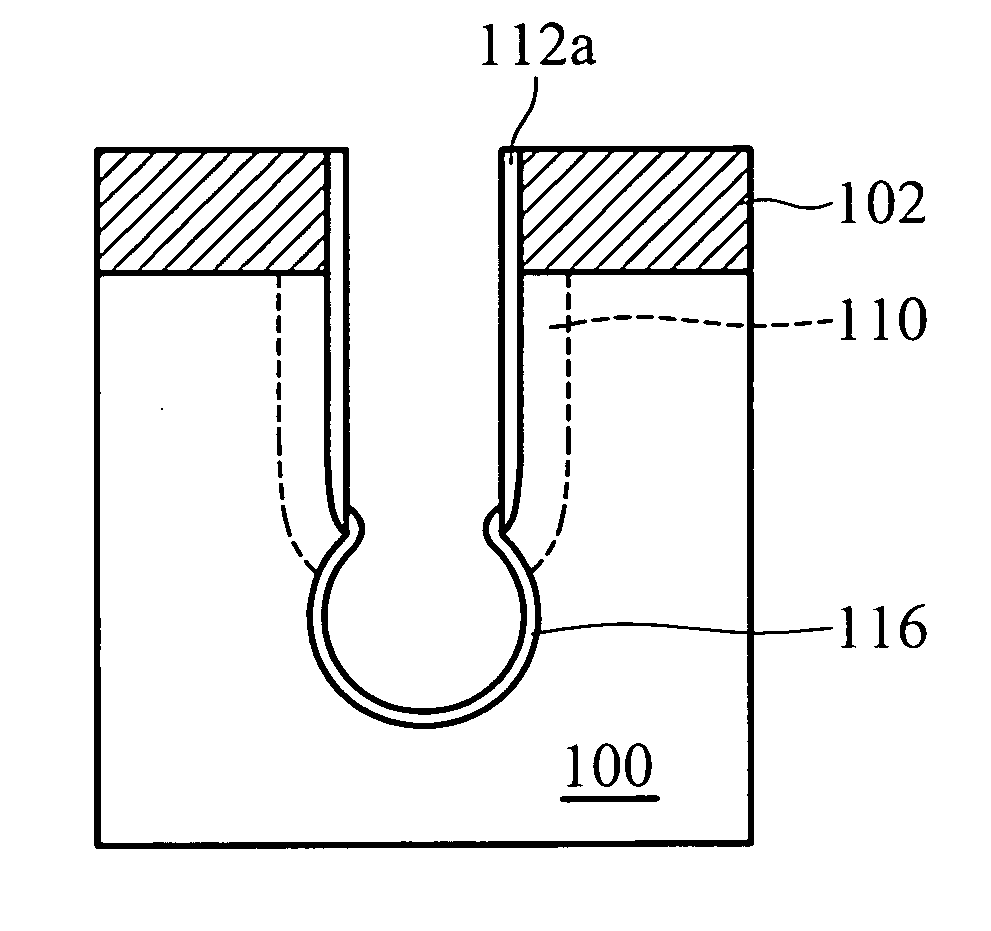

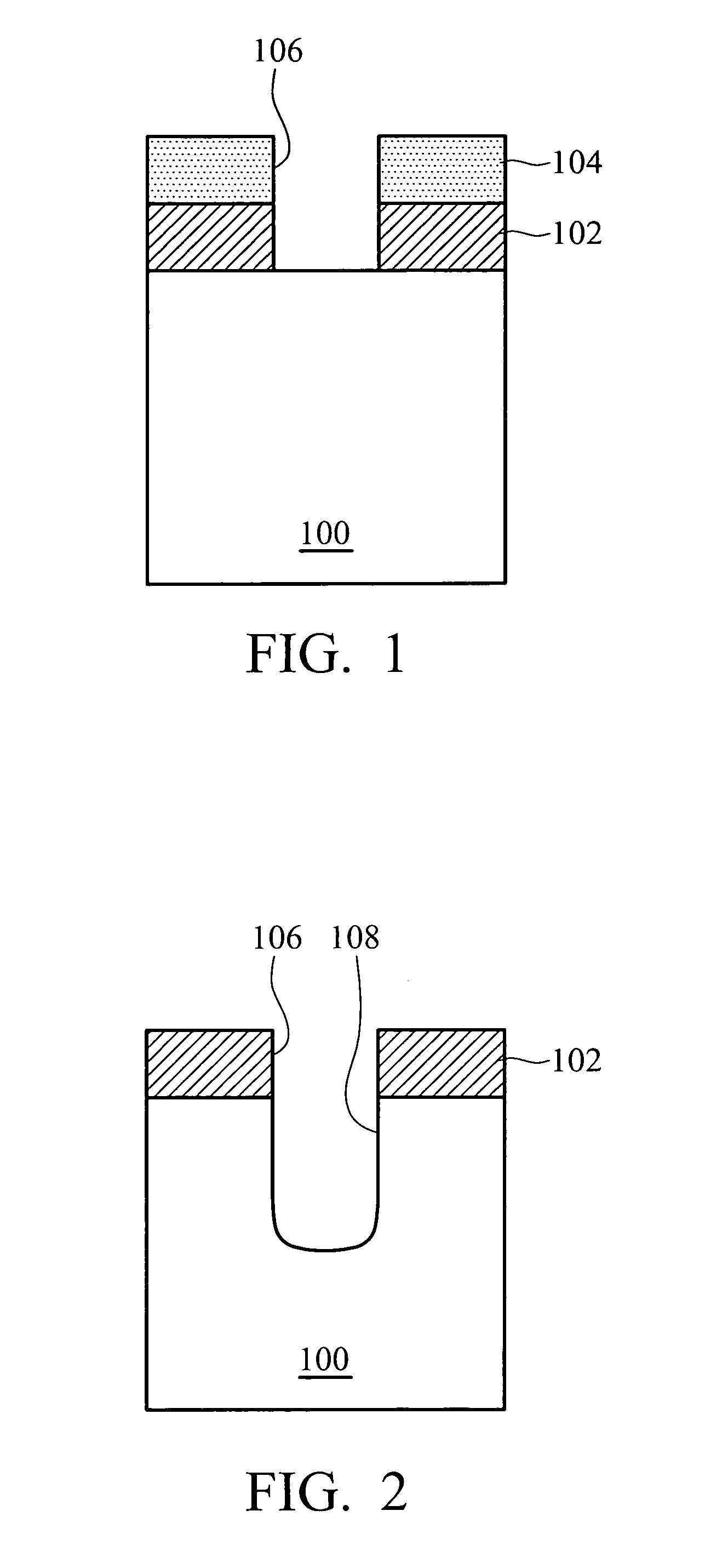

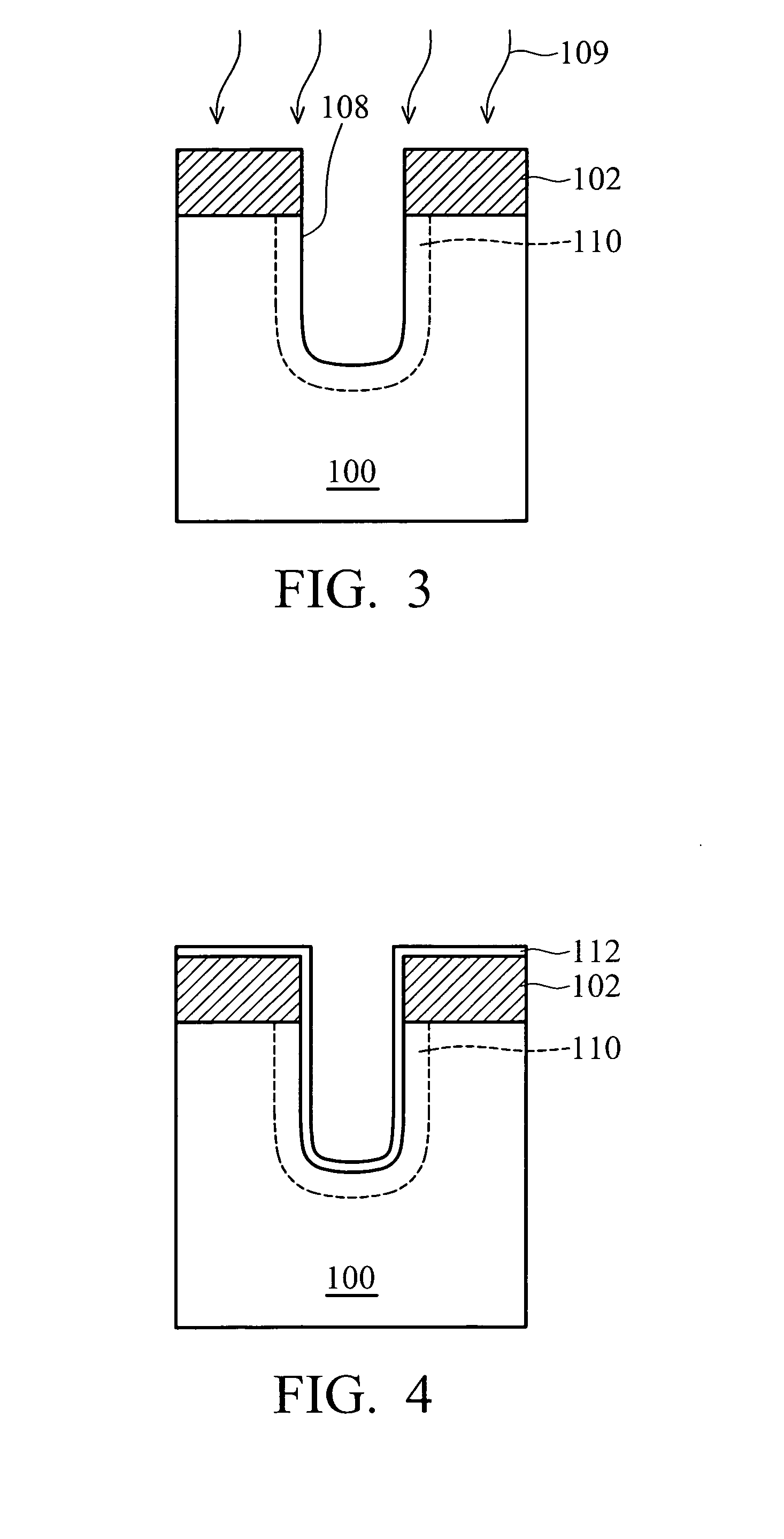

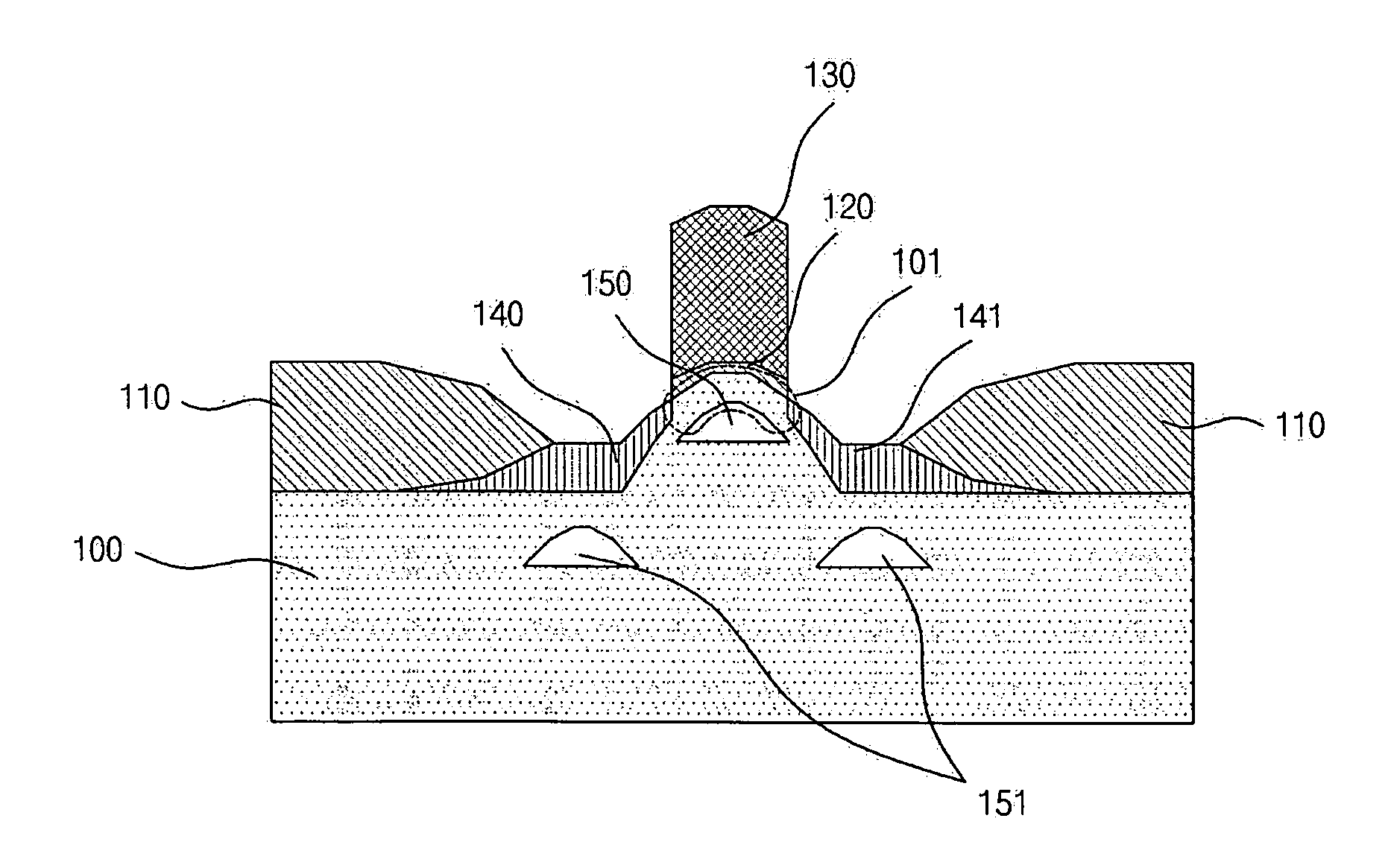

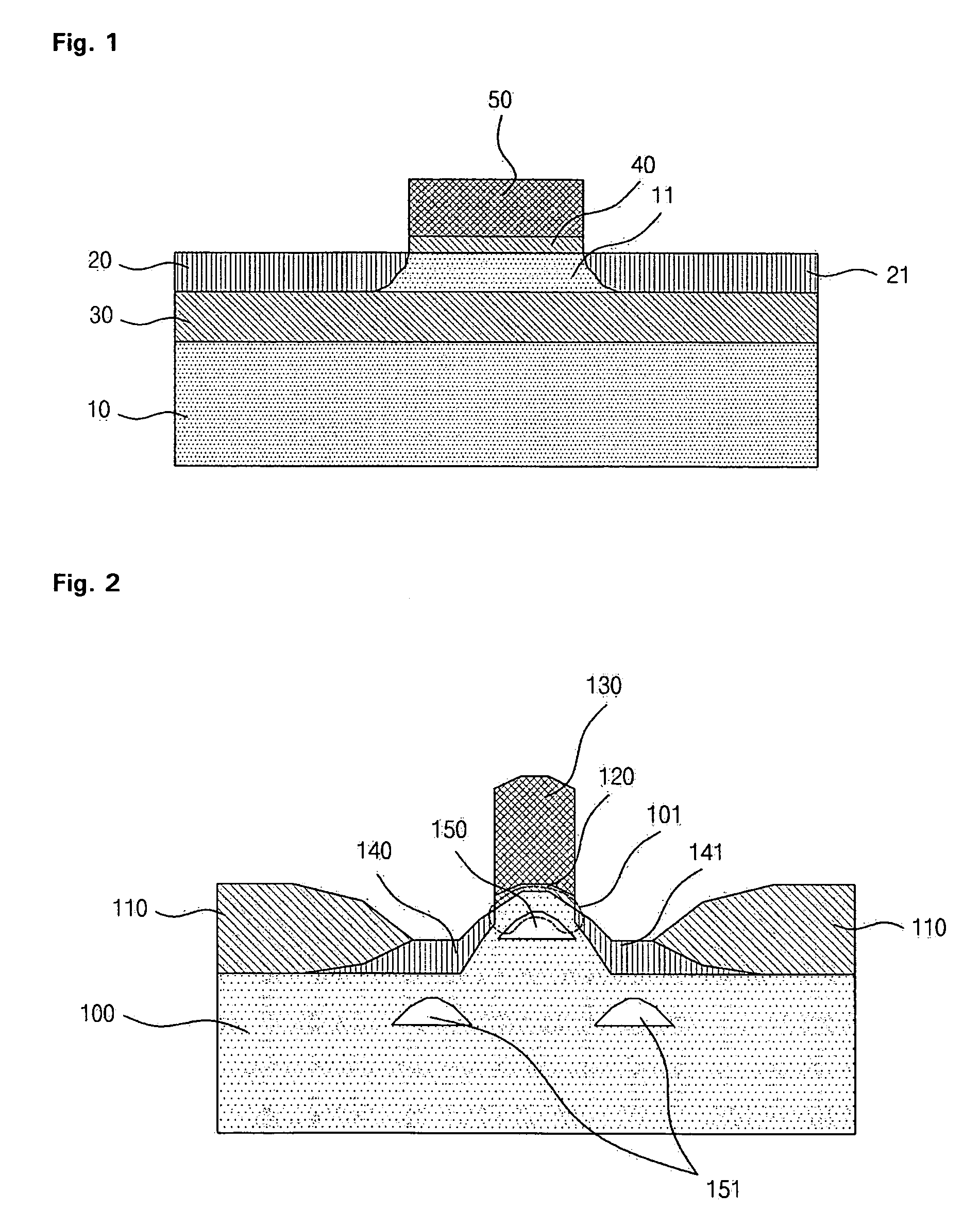

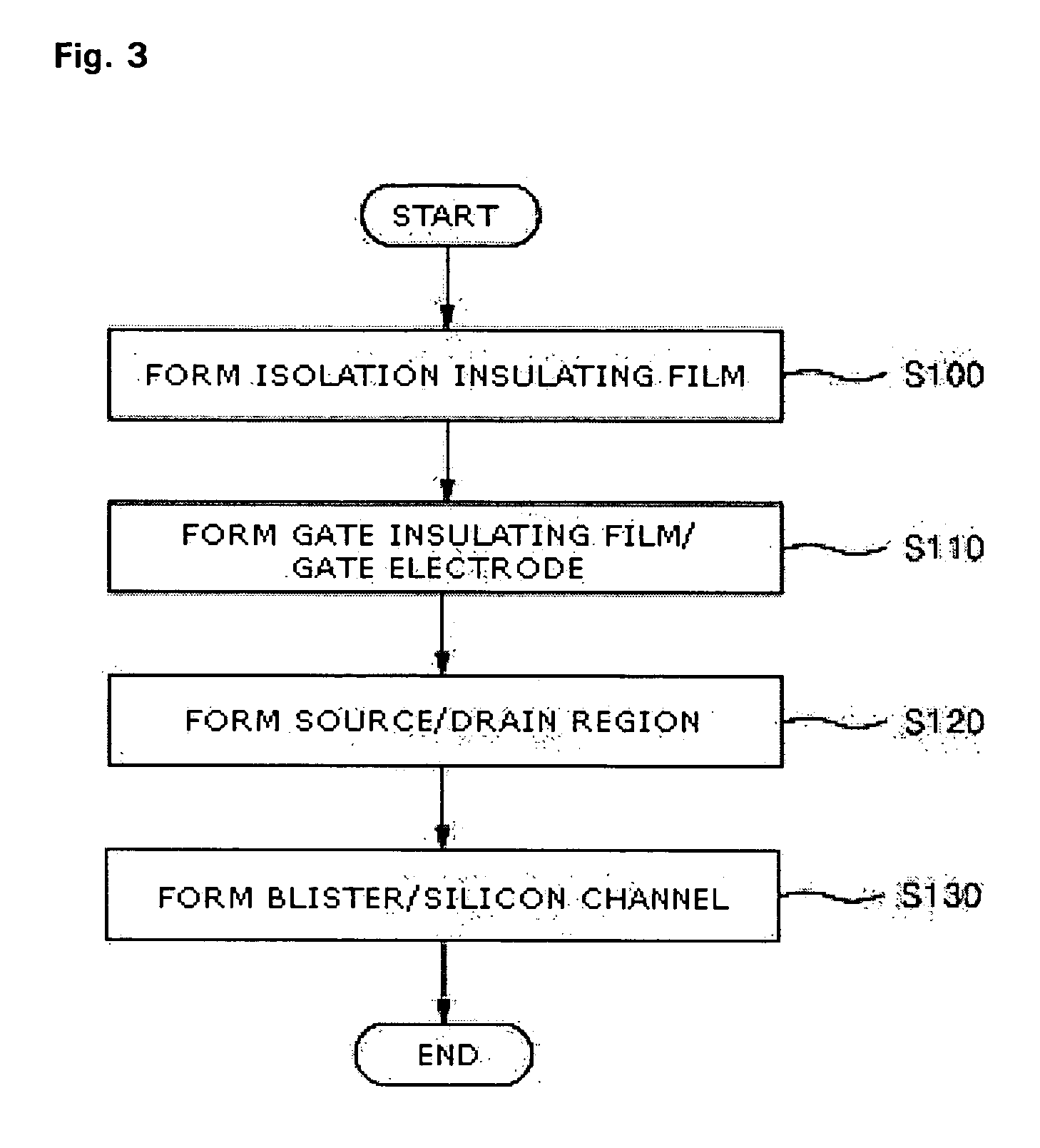

Silicon-on-nothing metal oxide semiconductor field effect transistor and method of manufacturing the same

InactiveUS20060208342A1Maximize advantageImprove featuresSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETHydrogen

The present invention relates to a SON MOSFET and method of manufacturing the same, in which a blister is formed within a silicon substrate, thus improving the disadvantages of a bulk structure and a Silicon-On-Insulator (SOI) structure at the same time. The SON MOSFET according to the present invention comprises isolation insulating films formed at both upper sides of a silicon substrate, a gate insulating film and a gate electrode that are sequentially formed on a surface of the silicon substrate between the isolation insulating films, a source region and a drain region that are formed on the silicon substrate between the gate insulating film and the isolation insulating films, a blister formed within the silicon substrate under the gate insulating film, and a silicon channel, which is surrounded by the blister, the source region and the drain region, within the silicon substrate, wherein the blister is formed of hydrogen or helium ion.

Owner:KOREA ADVANCED INST OF SCI & TECH

Source/drain carbon implant and RTA anneal, pre-SiGe deposition

ActiveUS7838887B2Avoid damageImprove short channel effectSemiconductor/solid-state device manufacturingBulk negative resistance effect devicesDopantSemiconductor

Owner:TAIWAN SEMICON MFG CO LTD

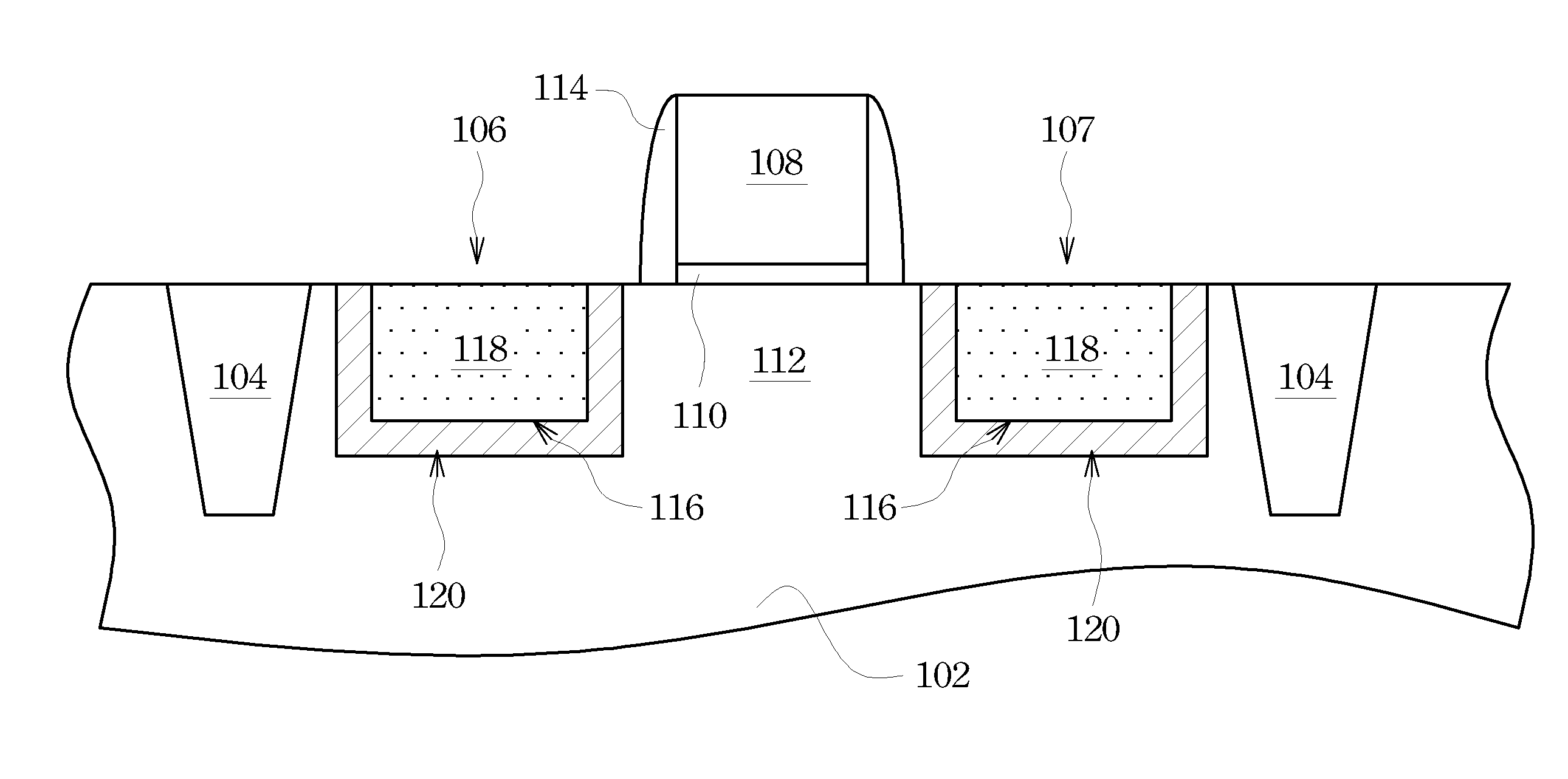

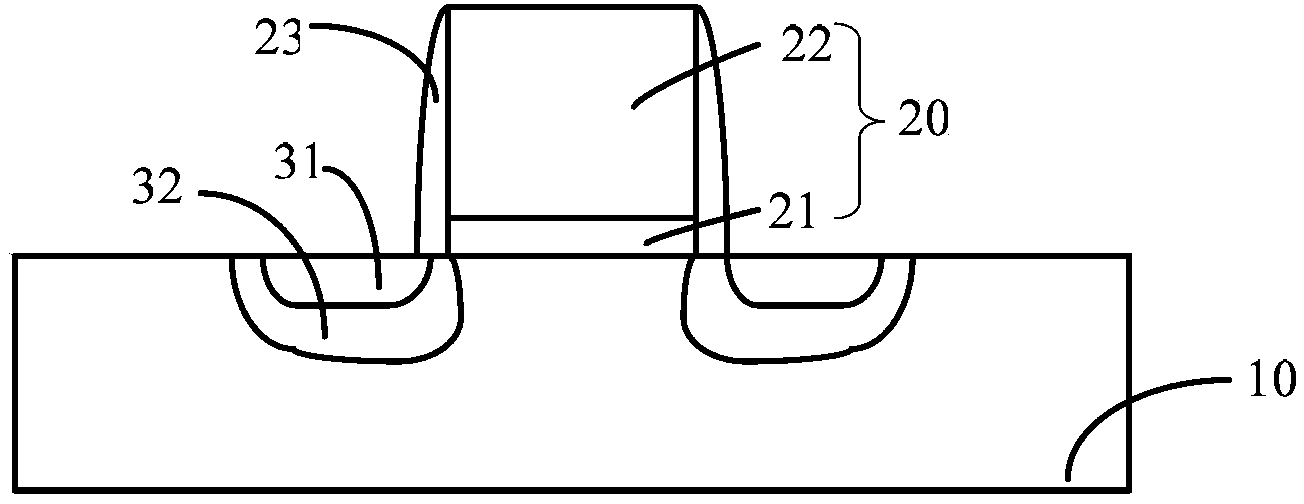

MOS transistor and forming method thereof

InactiveCN104124167AAvoid source-drain punch-through effectImprove short channel effectSemiconductor/solid-state device manufacturingSemiconductor devicesShort-channel effectSemiconductor

Provided are an MOS transistor and a forming method thereof. The method for forming the MOS transistor comprises the steps of providing a semiconductor substrate and enabling the surface of the semiconductor substrate to be provided with a grid structure; etching the semiconductor substrate on two sides of the grid structure to form grooves; forming a diffusion barrier layer on the surface of a side wall of one side of each groove close to the grid structure, enabling the diffusion barrier layer to cover two sides of a channel area; and forming sources and drains in the grooves. The method for forming the MOS transistor can improve short channel effect of the transistor and improve performance of the transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP

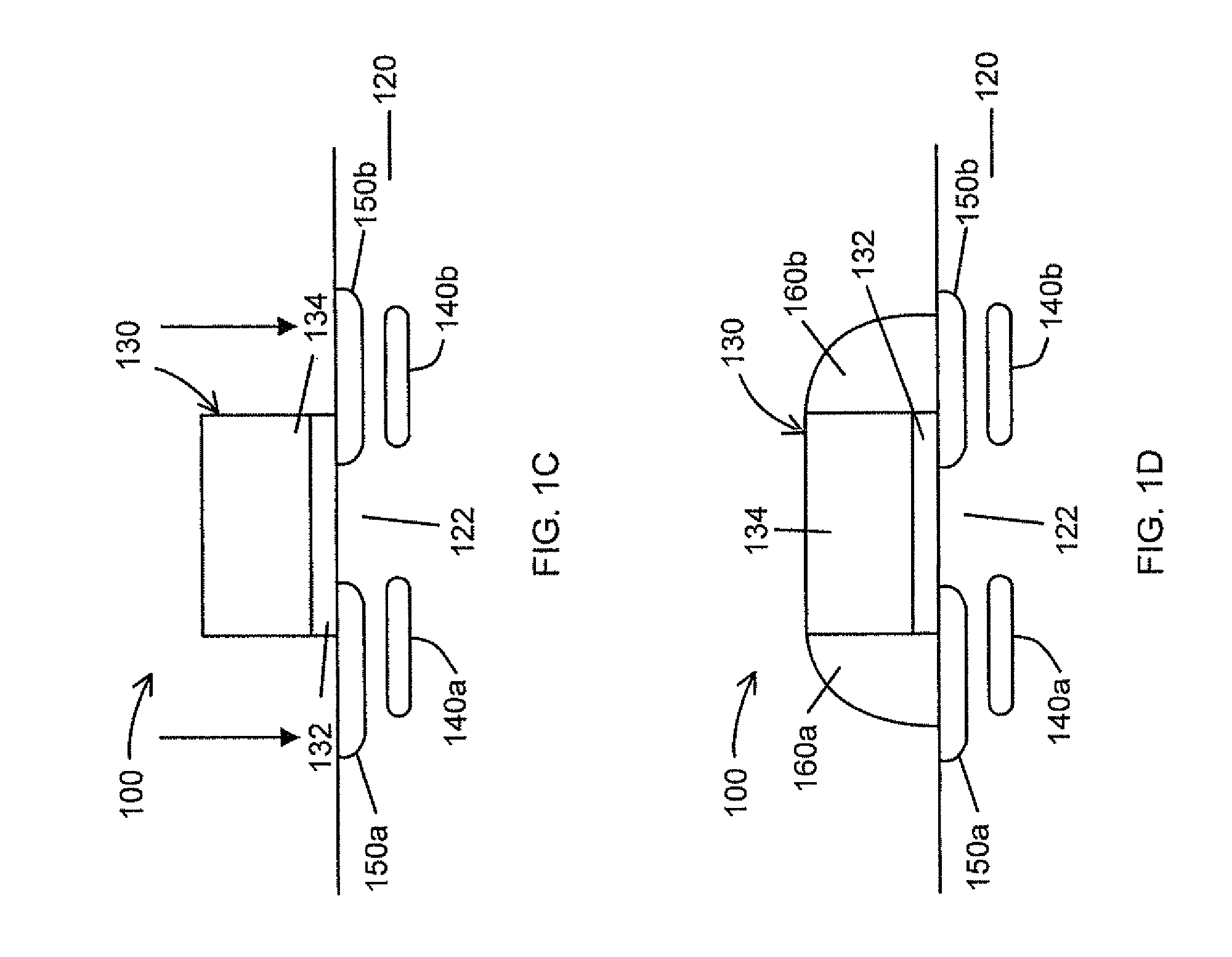

Field effect transistor having an asymmetric gate electrode

InactiveUS20090032889A1Improve short channel effectHigh carrier mobilityTransistorRead-only memoriesGate dielectricElectrical conductor

The gate electrode of a metal oxide semiconductor field effect transistor (MOSFET) comprises a source side gate electrode and a drain side gate electrode that abut each other near the middle of the channel. In one embodiment, the source side gate electrode comprises a silicon oxide based gate dielectric and the drain side gate electrode comprises a high-k gate dielectric. The source side gate electrode provides high carrier mobility, while the drain side gate electrode provides good short channel effect and reduced gate leakage. In another embodiment, the source gate electrode and drain gate electrode comprises different high-k gate dielectric stacks and different gate conductor materials, wherein the source side gate electrode has a first work function a quarter band gap away from a band gap edge and the drain side gate electrode has a second work function near the band gap edge.

Owner:GLOBALFOUNDRIES INC

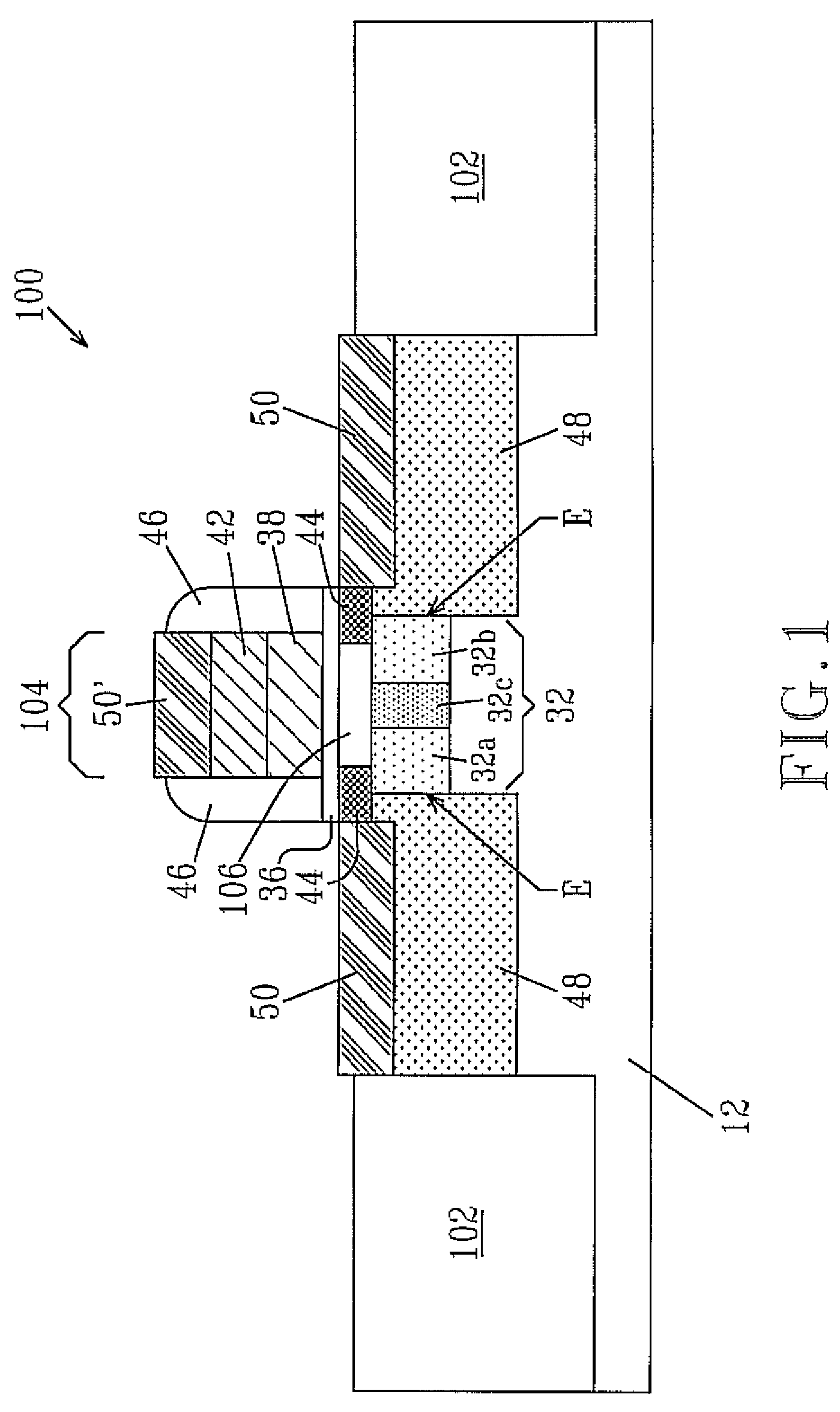

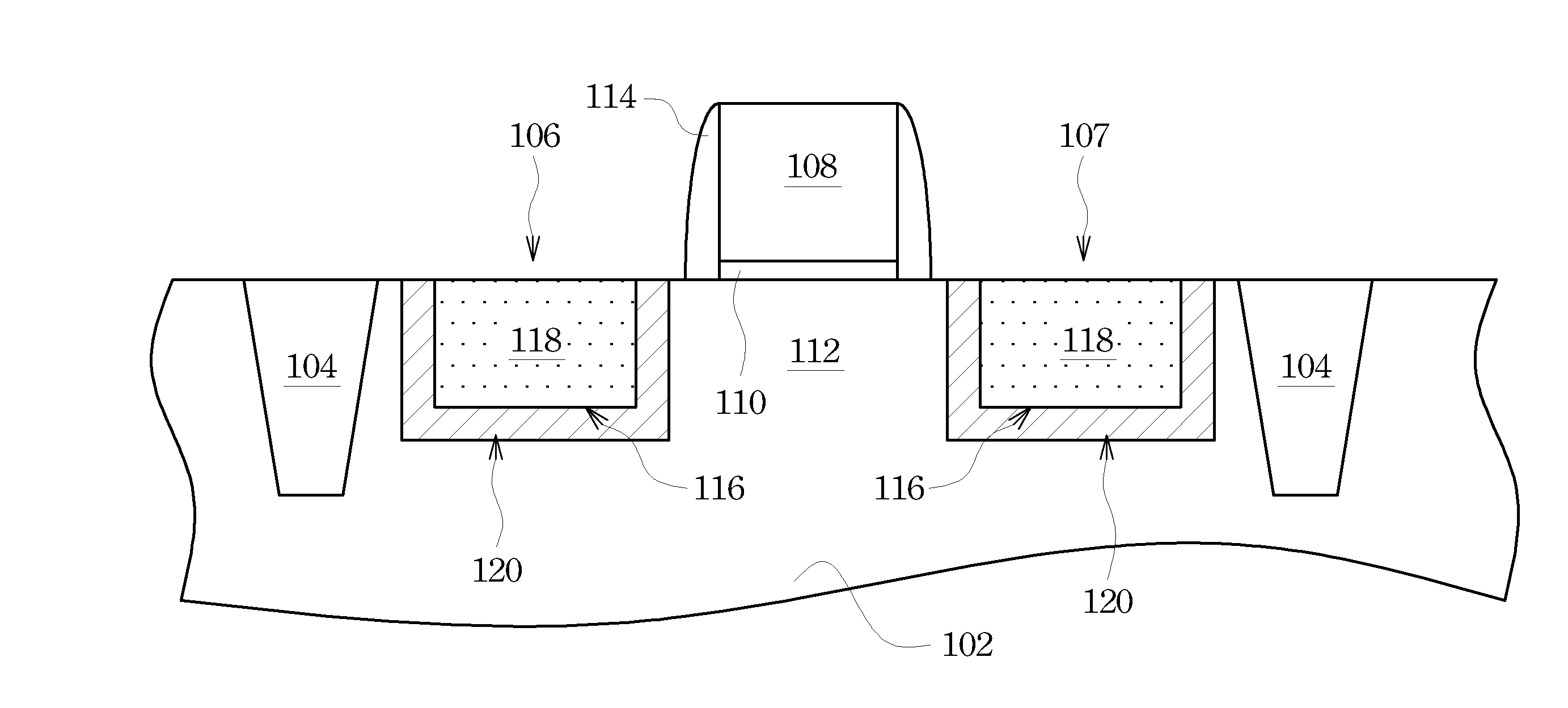

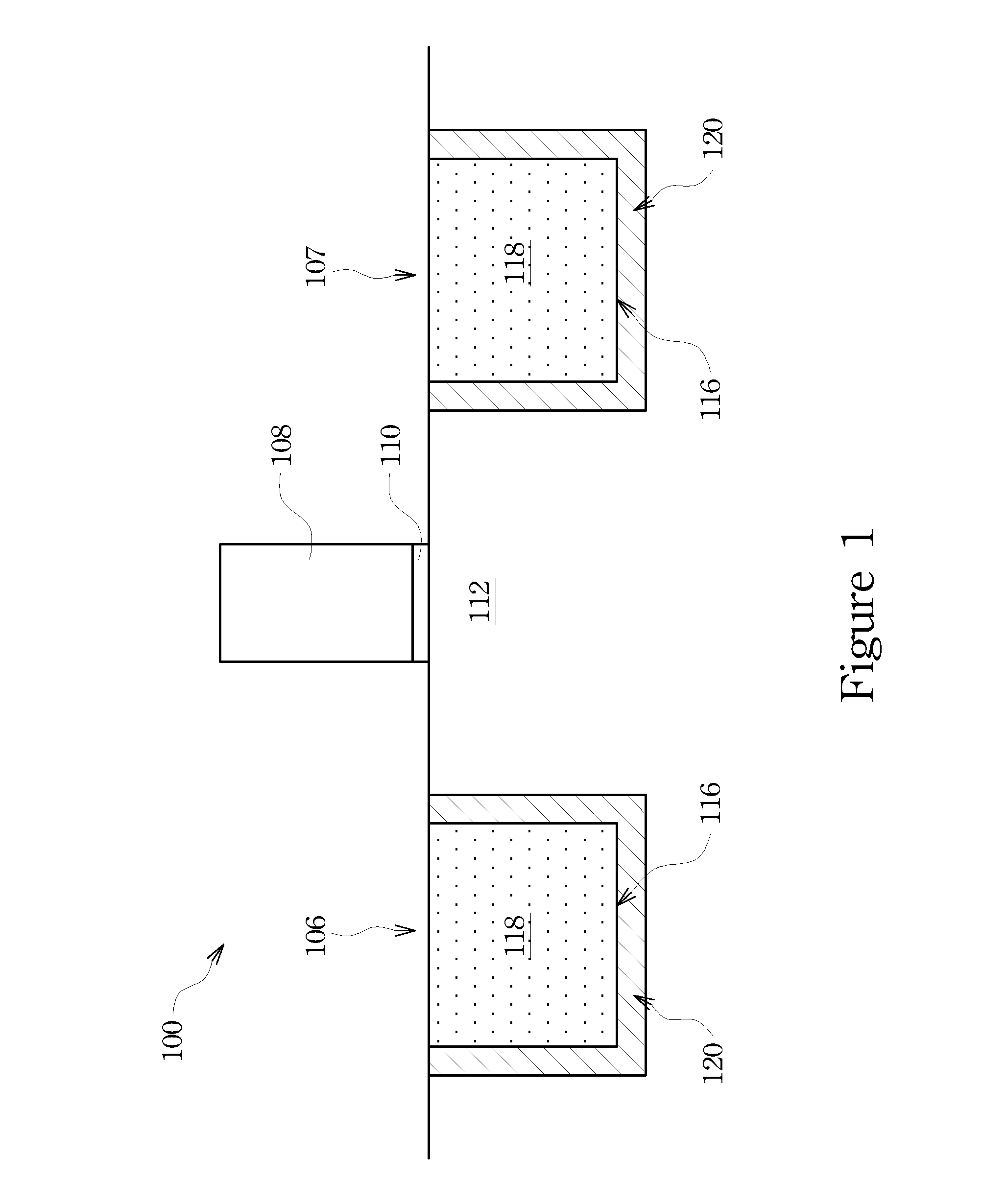

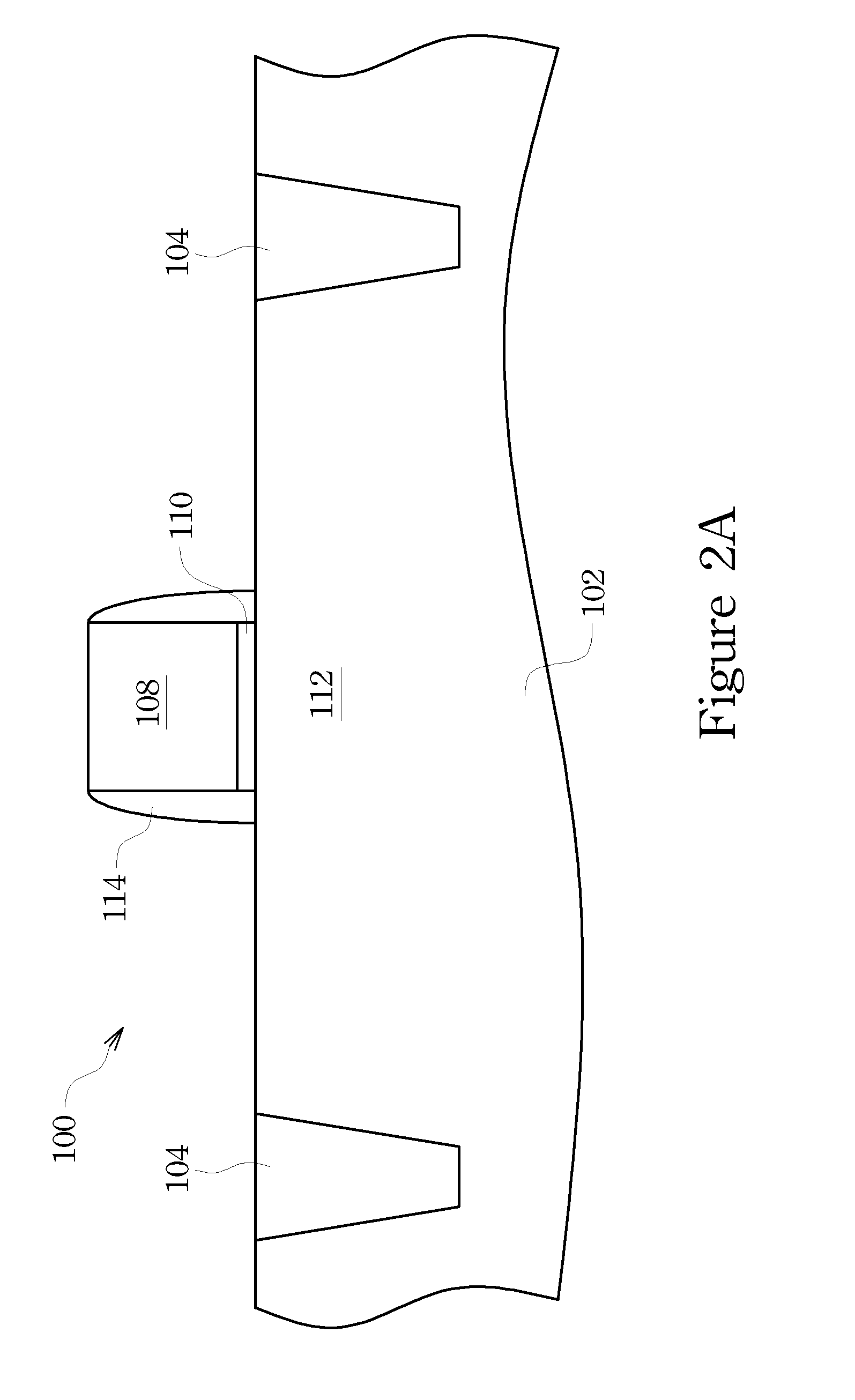

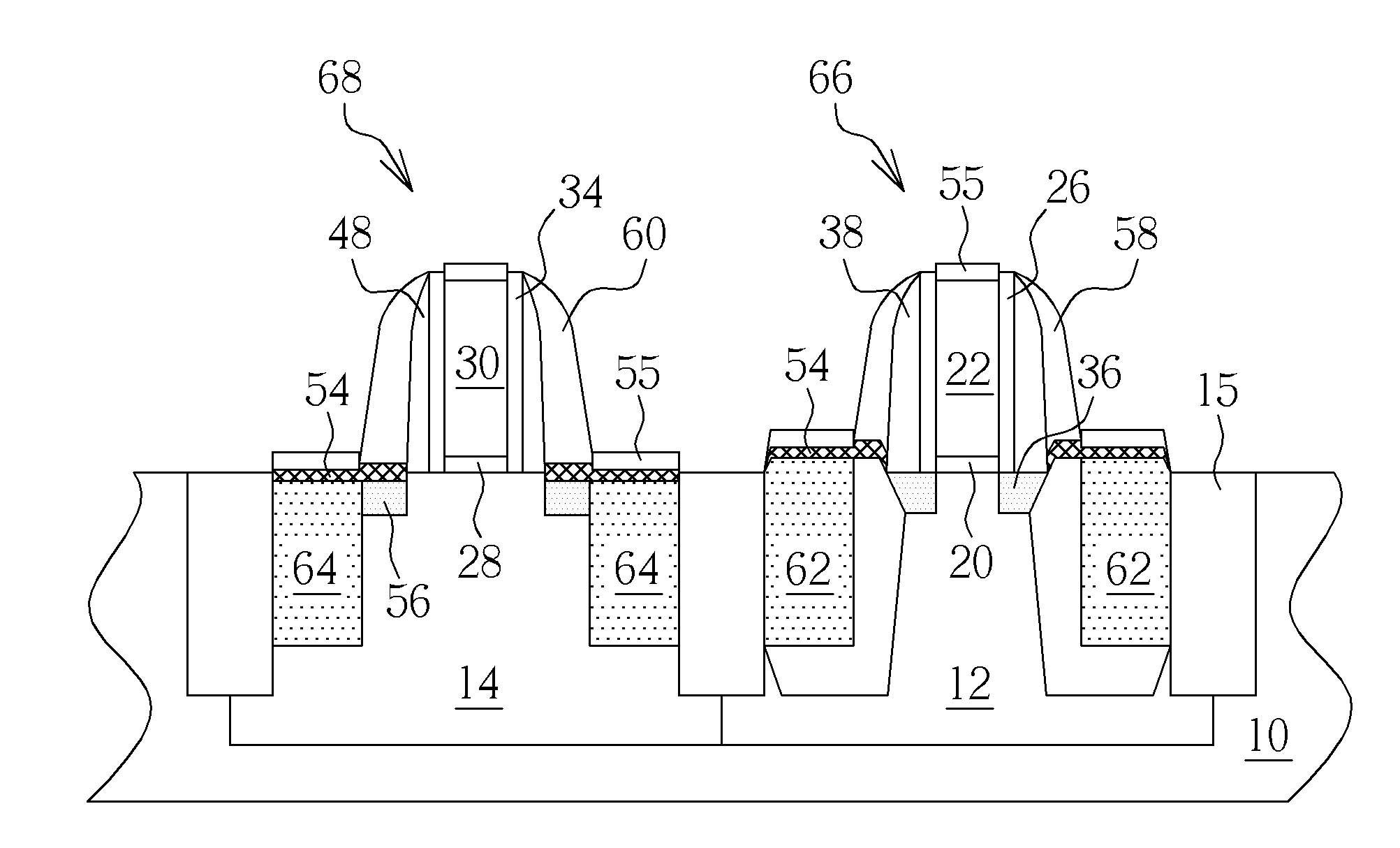

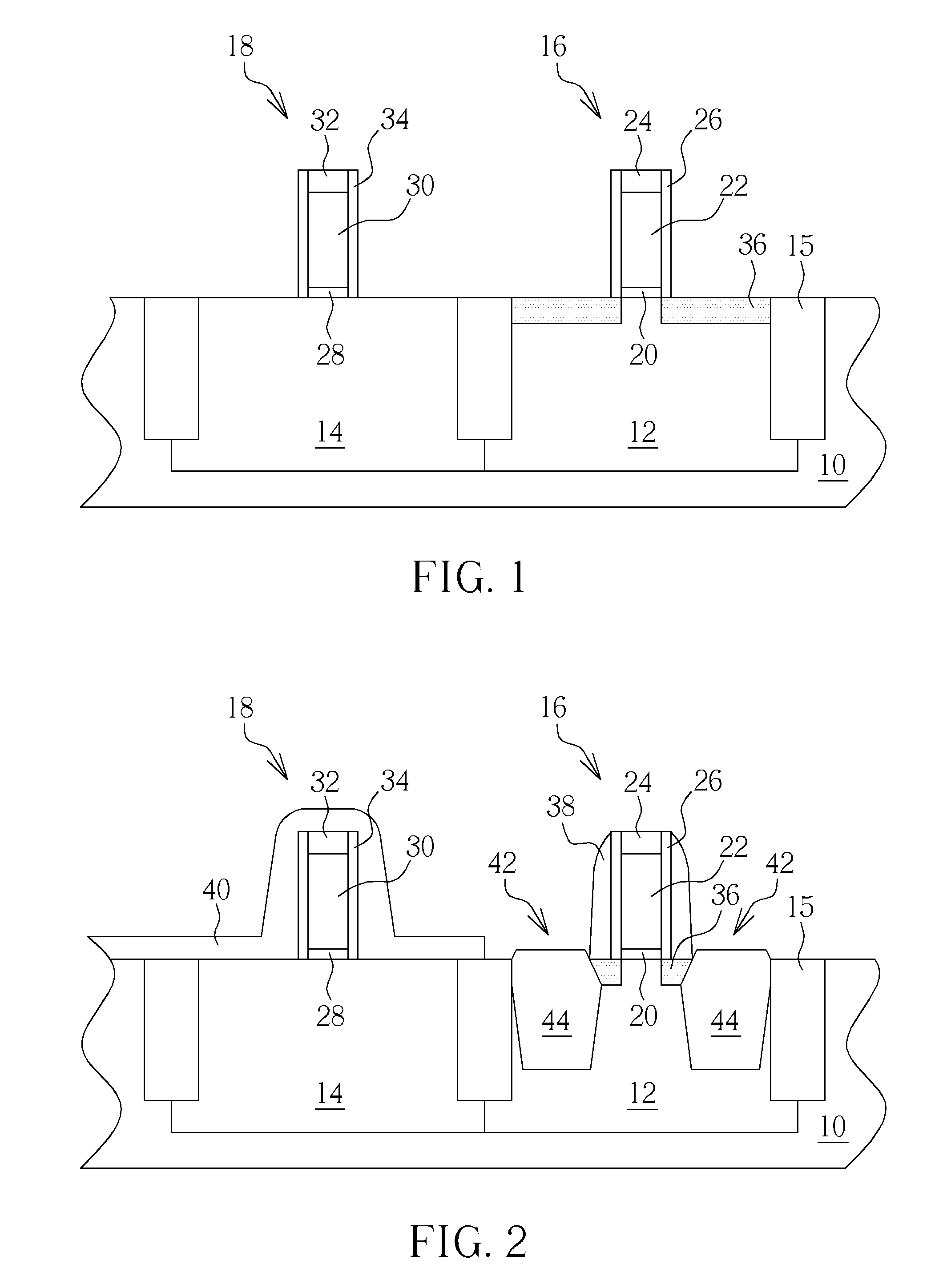

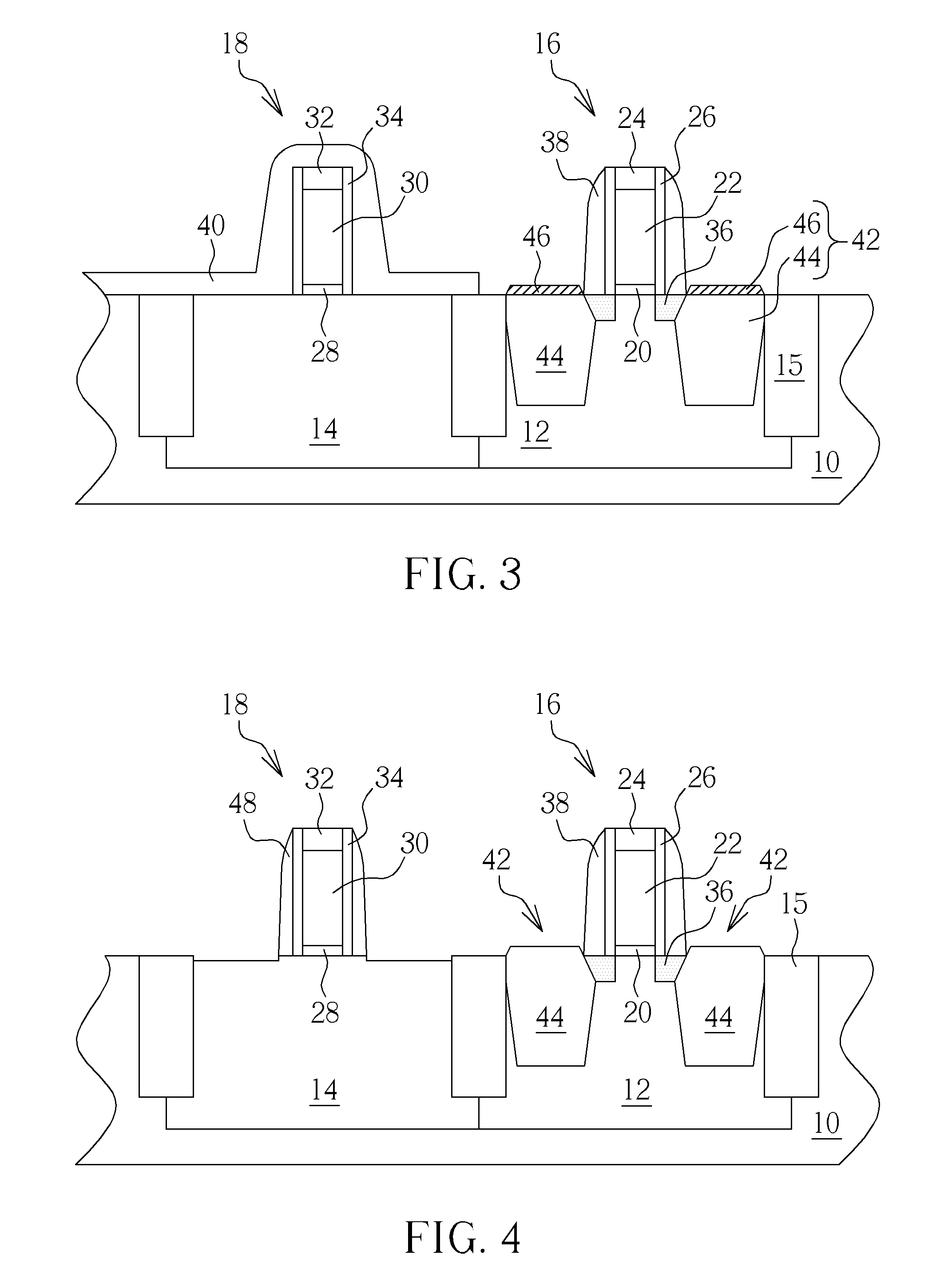

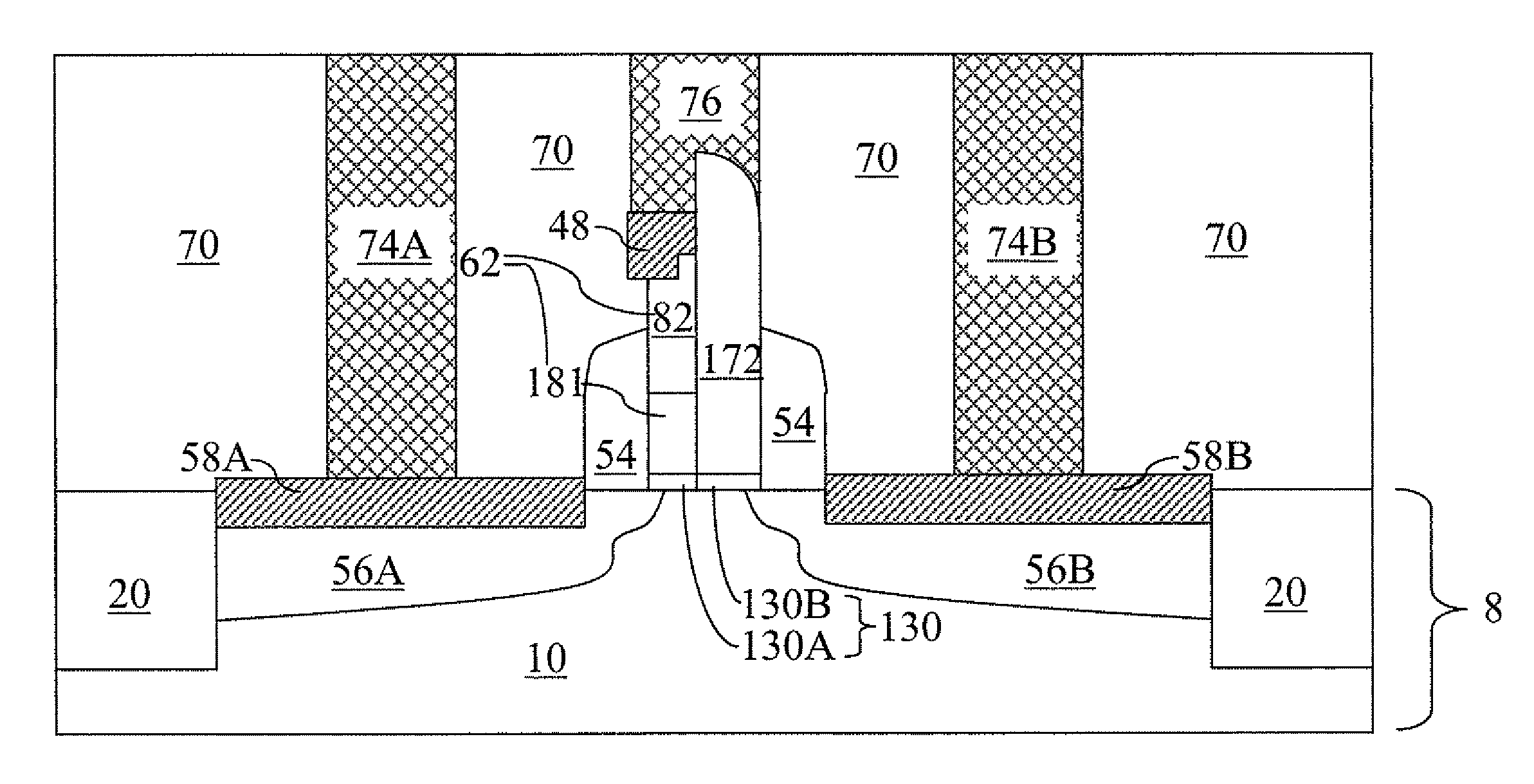

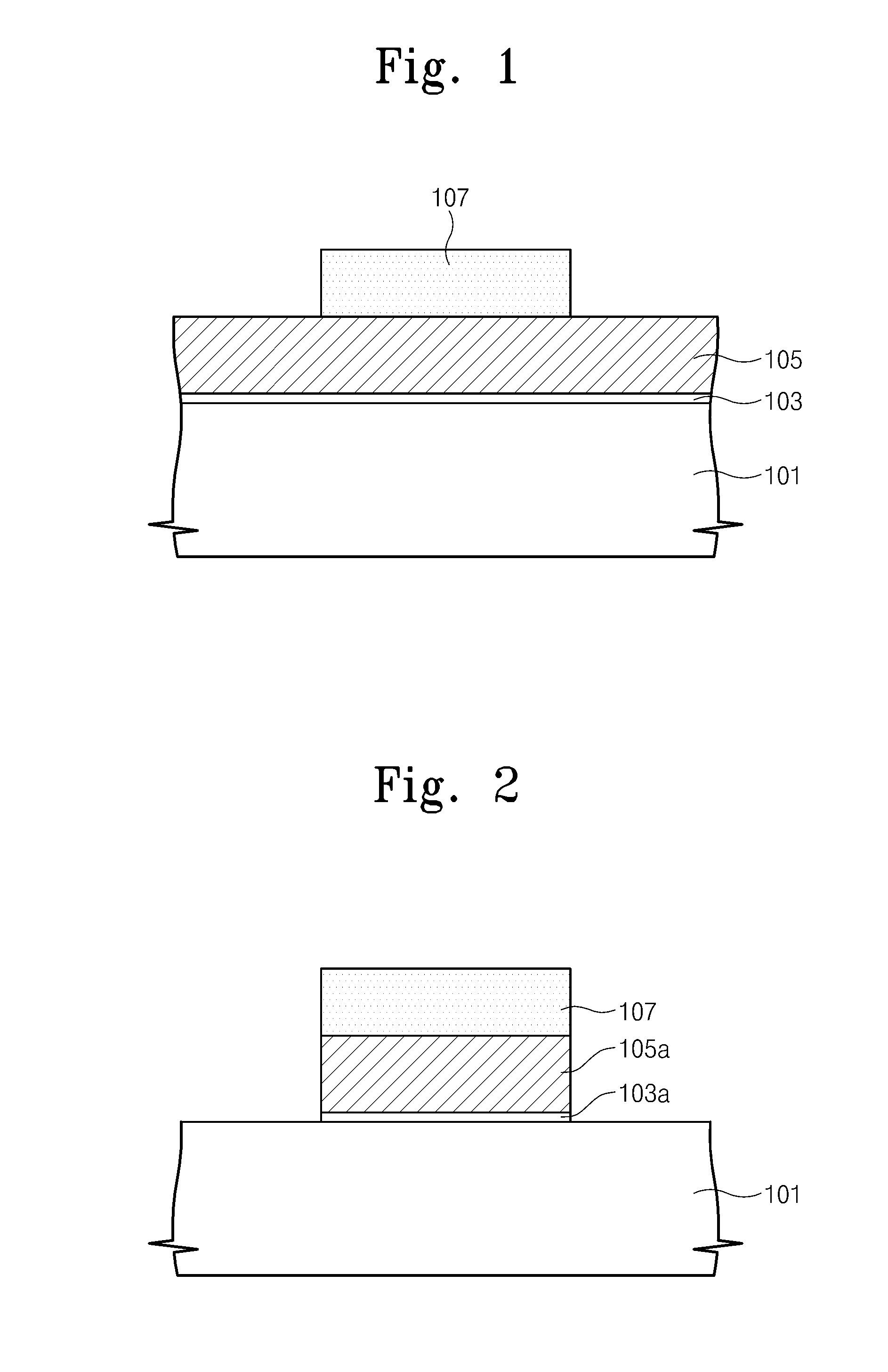

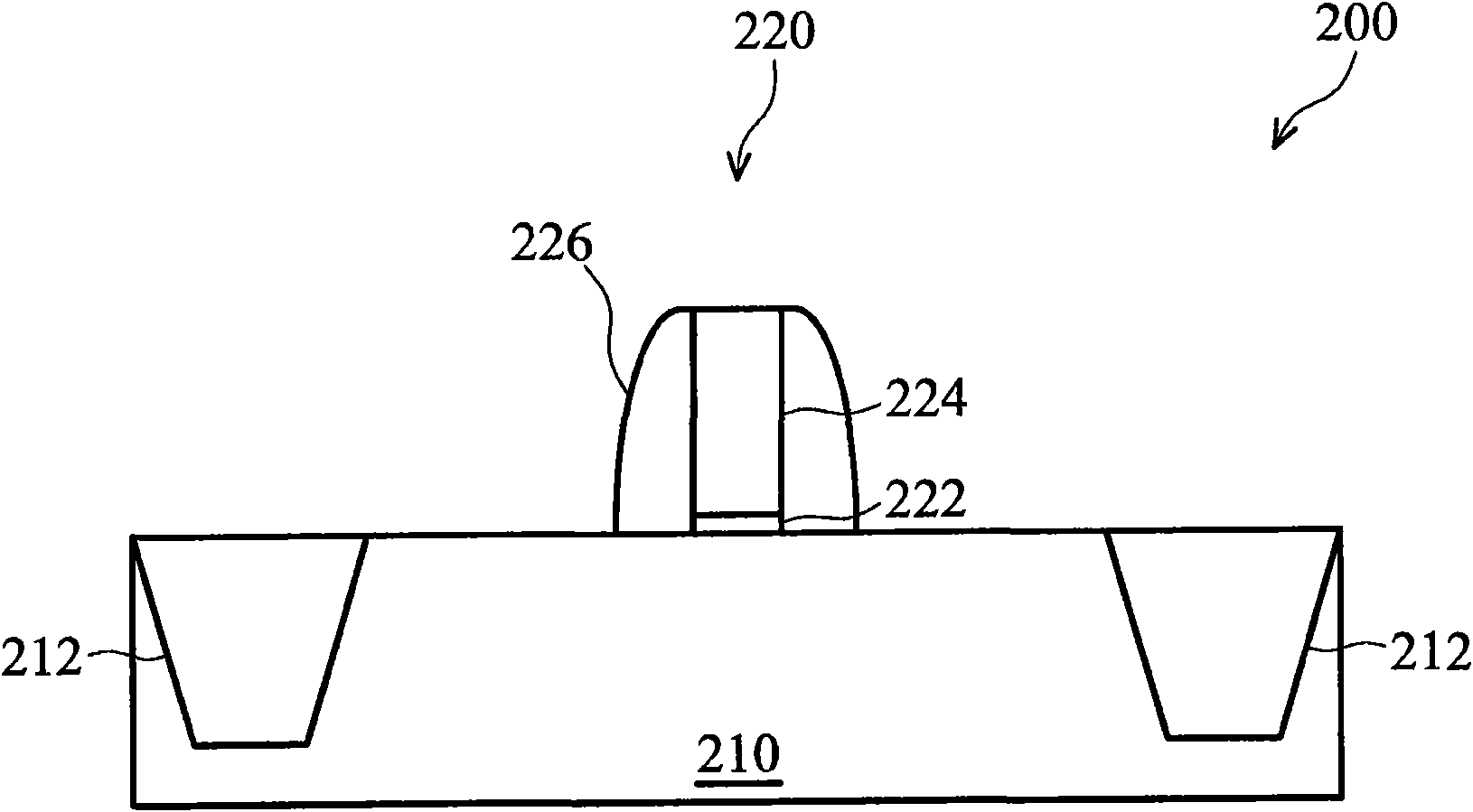

Method of fabricating transistors and a transistor structure for improving short channel effect and drain induced barrier lowering

ActiveUS20110012197A1Improve short channel effectImproving drain induced barrier loweringTransistorSemiconductor/solid-state device manufacturingSiliconShort-channel effect

A method of fabricating transistors includes: providing a substrate including an N-type well and P-type well; forming a first gate on the N-type well and a second gate on the P-type well, respectively; forming a third spacer on the first gate; forming an epitaxial layer in the substrate at two sides of the first gate; forming a fourth spacer on the second gate; forming a silicon cap layer covering the surface of the epitaxial layer and the surface of the substrate at two sides of the fourth spacer; and forming a first source / drain doping region and a second source / drain doping region at two sides of the first gate and the second gate respectively.

Owner:UNITED MICROELECTRONICS CORP

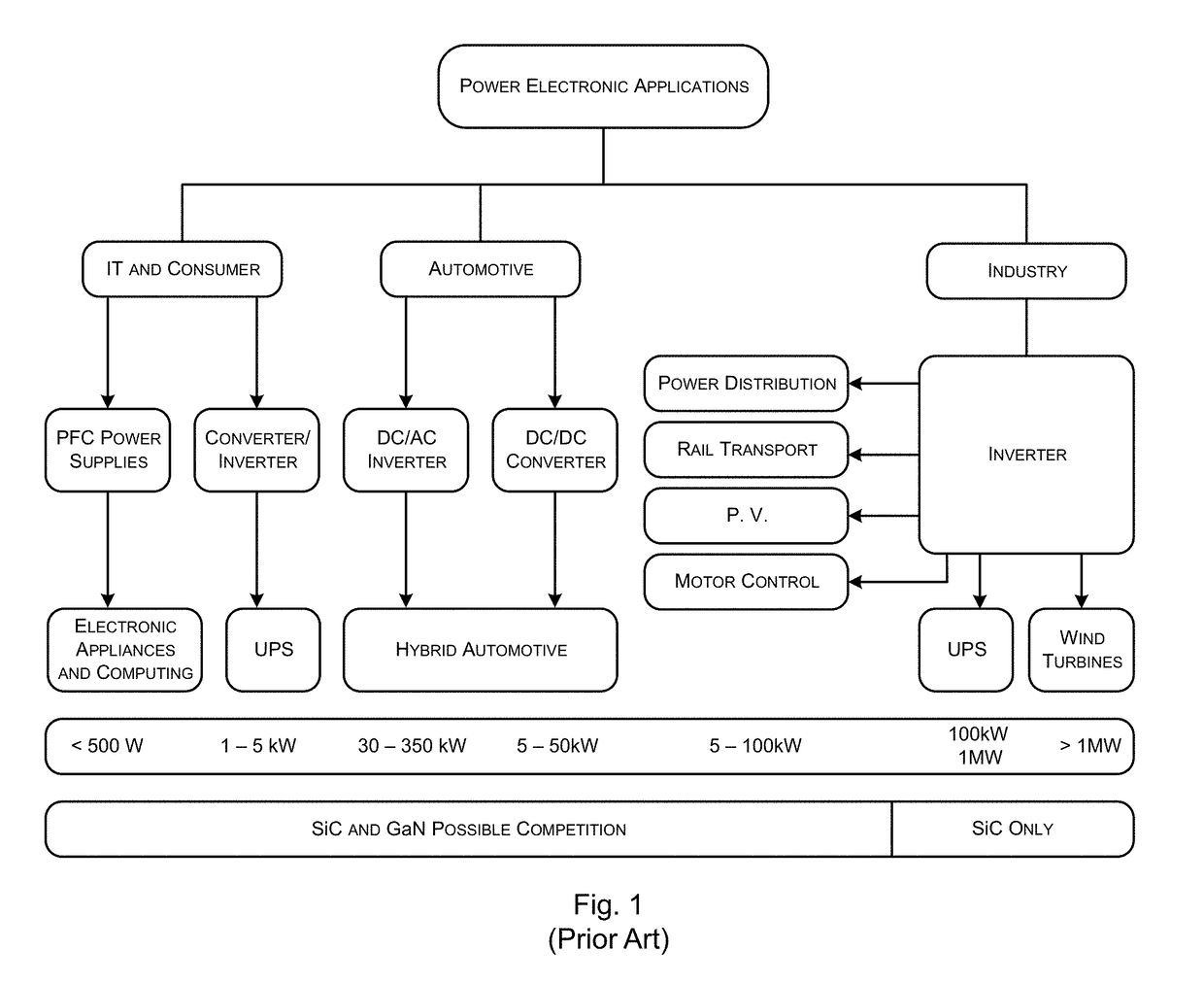

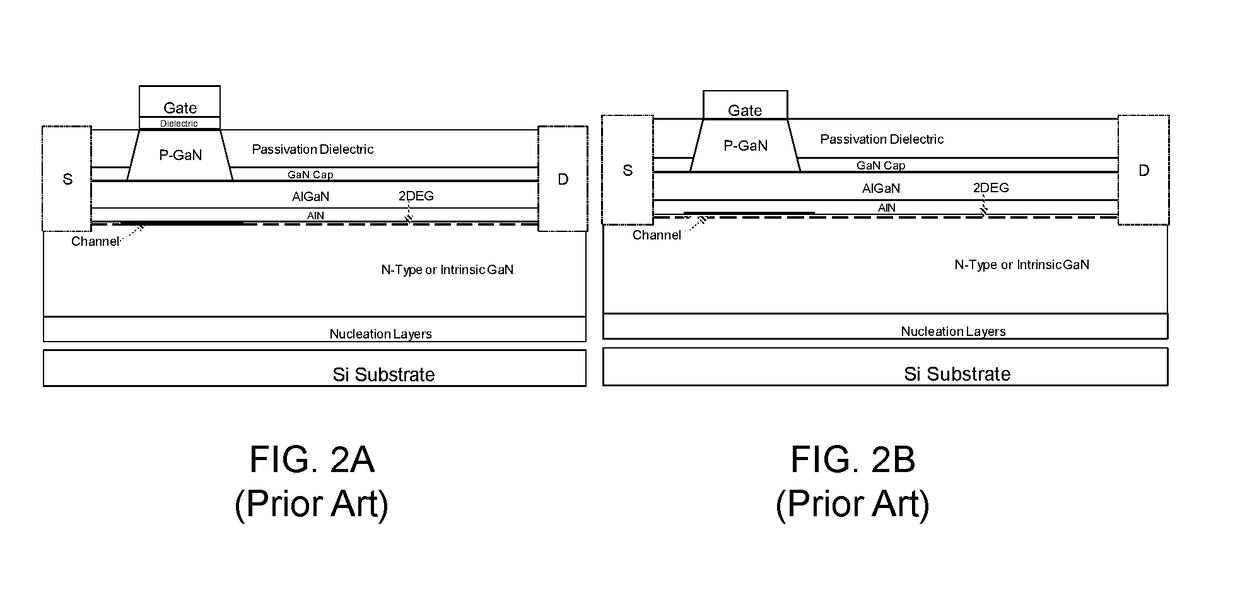

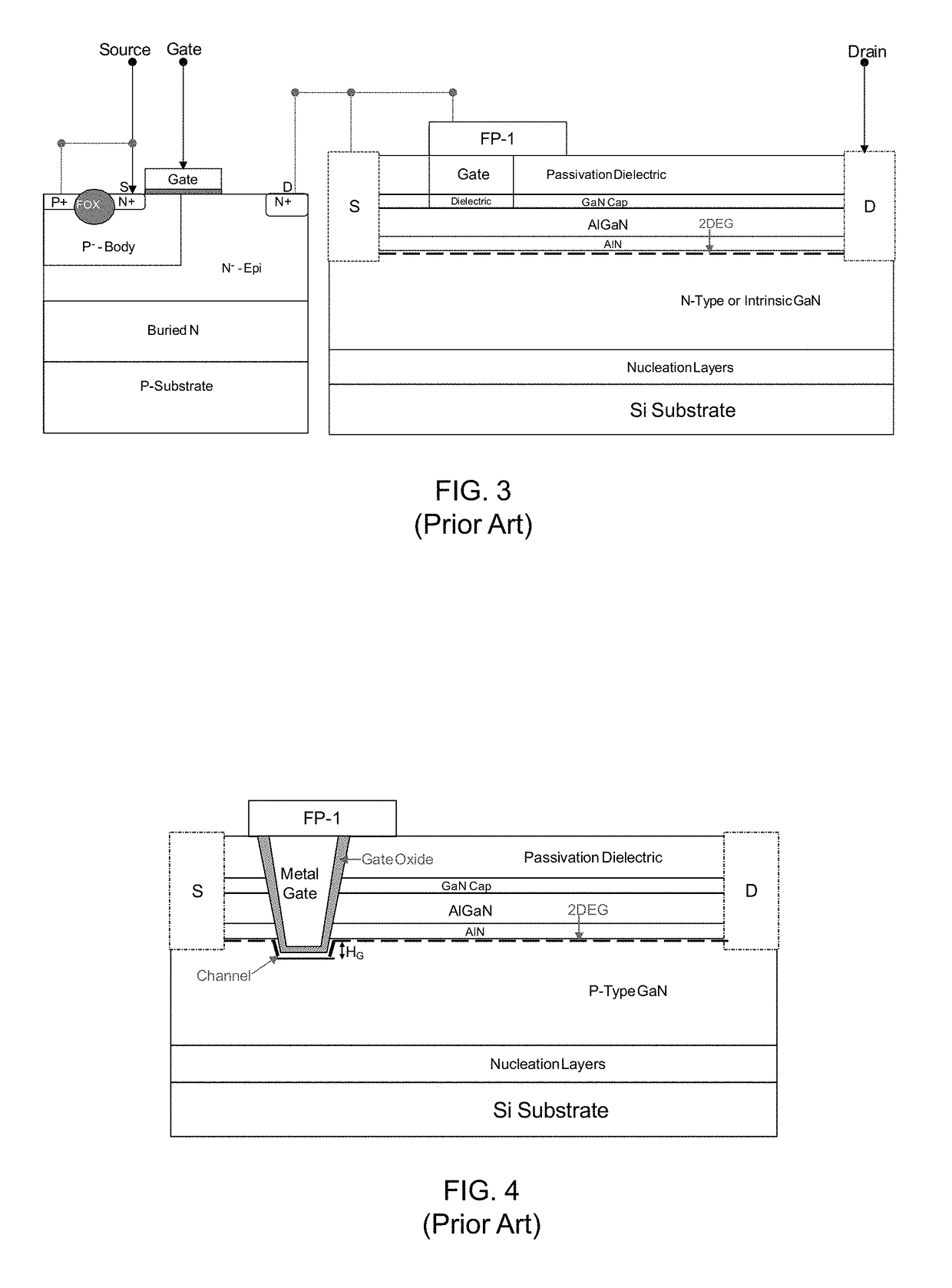

A High-electron-mobility transistor (HEMT)

ActiveUS20190081164A1Improve short channel effectFast switching speedSemiconductor/solid-state device detailsSolid-state devicesCapacitanceElectrical resistance and conductance

The present disclosure provides a superjunction based design for normally-OFF HEMT that has two key components: (i) a recessed high-K metal gate and (ii) a superjunction layer under the gate, which is embedded within the N-type GaN buffer layers and separated from recessed gate. Recess gate is to deplete the 2DEG from the channel region (under the gate) when the transistor is under OFF state. The present disclosure provides a new, improved, efficient and technically advanced HEMT device which can provide higher breakdown voltage, when compared to designs available in the prior-art, without affecting the performance figure of merits. Further, the new HEMT device offers improved breakdown voltage as compared to ON-resistance trade-off, improved the short channel effects, improved gate control over channel, improved switching speed for a given breakdown voltage, and improved device reliability. Furthermore, the new HEMT device lowers gate-to-drain (miller) capacitance and is available at low cost.

Owner:INDIAN INSTITUTE OF SCIENCE

Fin shape structure

ActiveUS20160141288A1Great band offsetImprove short channel effectTransistorSolid-state devicesEngineering

Owner:MARLIN SEMICON LTD

Nitride power transistor and manufacturing method thereof

InactiveCN103531615AImprove breakdown voltageImprove mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesCompound structureSpace charge

The invention discloses a nitride power transistor and a manufacturing method thereof. The nitride power transistor comprises a silicon substrate, a nitride nucleating layer which is arranged on the silicon substrate, a nitride buffering layer which is arranged on the nitride nucleating layer, a nitride channel layer which is arranged on the nitride buffering layer, a source and a drain which are in contact with the nitride channel layer, and a grid which is arranged between the source and the drain, wherein the silicon substrate comprises a differently doped semiconductor composite structure which is used for forming a space charge depletion region. By introducing the differently doped semiconductor compound structure which can form the space charge depletion region in the silicon substrate of the nitride power transistor, the nitride power transistor is enabled to be able to withstand higher external voltage and the breakdown voltage of a device is improved.

Owner:ENKRIS SEMICON

Field effect transistor having an asymmetric gate electrode

InactiveUS8110465B2Improve short channel effectHigh carrier mobilityTransistorRead-only memoriesElectrical conductorGate dielectric

The gate electrode of a metal oxide semiconductor field effect transistor (MOSFET) comprises a source side gate electrode and a drain side gate electrode that abut each other near the middle of the channel. In one embodiment, the source side gate electrode comprises a silicon oxide based gate dielectric and the drain side gate electrode comprises a high-k gate dielectric. The source side gate electrode provides high carrier mobility, while the drain side gate electrode provides good short channel effect and reduced gate leakage. In another embodiment, the source gate electrode and drain gate electrode comprises different high-k gate dielectric stacks and different gate conductor materials, wherein the source side gate electrode has a first work function a quarter band gap away from a band gap edge and the drain side gate electrode has a second work function near the band gap edge.

Owner:GLOBALFOUNDRIES INC

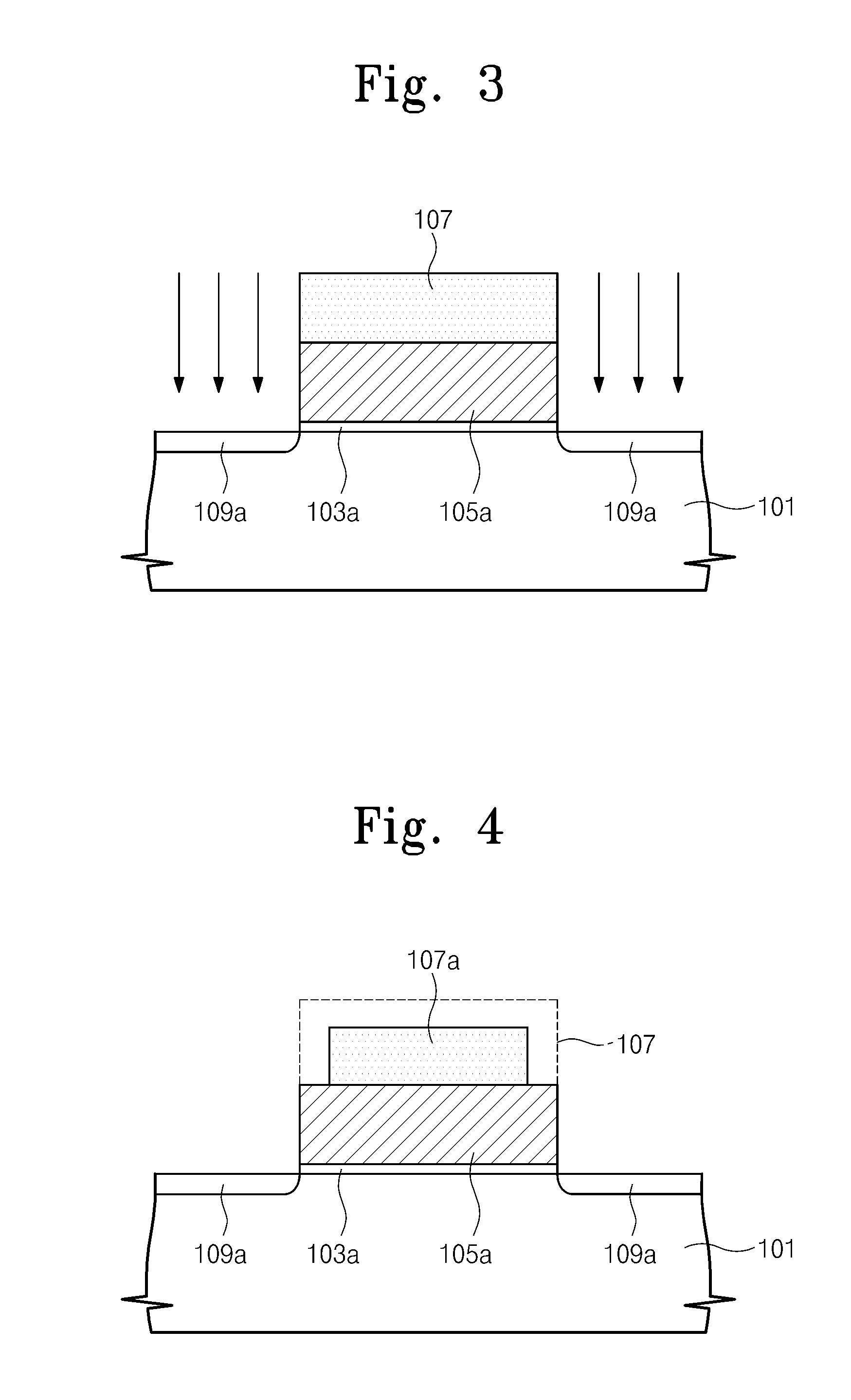

Method of fabricating a semiconductor device

InactiveUS20090197383A1Improve short channel effectForming of the inner and outer junction regions is facilitatedSemiconductor/solid-state device manufacturingNanotechnologyEngineeringSemiconductor

A method of fabricating a semiconductor device forms a micro-sized gate, and mitigates short channel effects. The method includes a pull-back process to form the gate on a substrate. The method also includes forming inner and outer spacers on the gate that are asymmetric to one another with respect to the gate, and using the spacers in forming junction regions in the substrate on opposite sides of the gate. In particular, the inner and outer spacers are formed on opposite sides of the gate so as to have different thicknesses at the bottom of the gate. The inner and outer junction regions are formed by doping the substrate before and after the spacers are formed. Thus, the inner and outer junction regions have extension regions under the inner and outer spacers, respectively, and the extension regions have different lengths.

Owner:SAMSUNG ELECTRONICS CO LTD

Method for fabricating metal-oxide semiconductor transistor

InactiveUS6855604B2Improve short channel effectImprove featuresSemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentTungsten nitride

The present invention relates to a method for fabricating a metal-oxide semiconductor (MOS) transistor having a gate electrode with a stack structure of a polysilicon layer, a tungsten nitride barrier layer and a tungsten layer. According to the present invention, a depth from a lastly deposited nitride layer to a bottom surface of a trench is shallower, and thereby decreasing incidences of a void generation. Also, the present invention provides an advantage of an elaborate manipulation of well and channel dopings by performing ion-implantations with two different approaches. Furthermore, it is possible to enhance device characteristics by decreasing gate induced drain leakage (GIDL) currents and improving a capability of driving currents. This decrease of the GIDL currents and the improved driving current capability are obtained by forming the gate oxide layer with different thicknesses.

Owner:MOSAID TECH

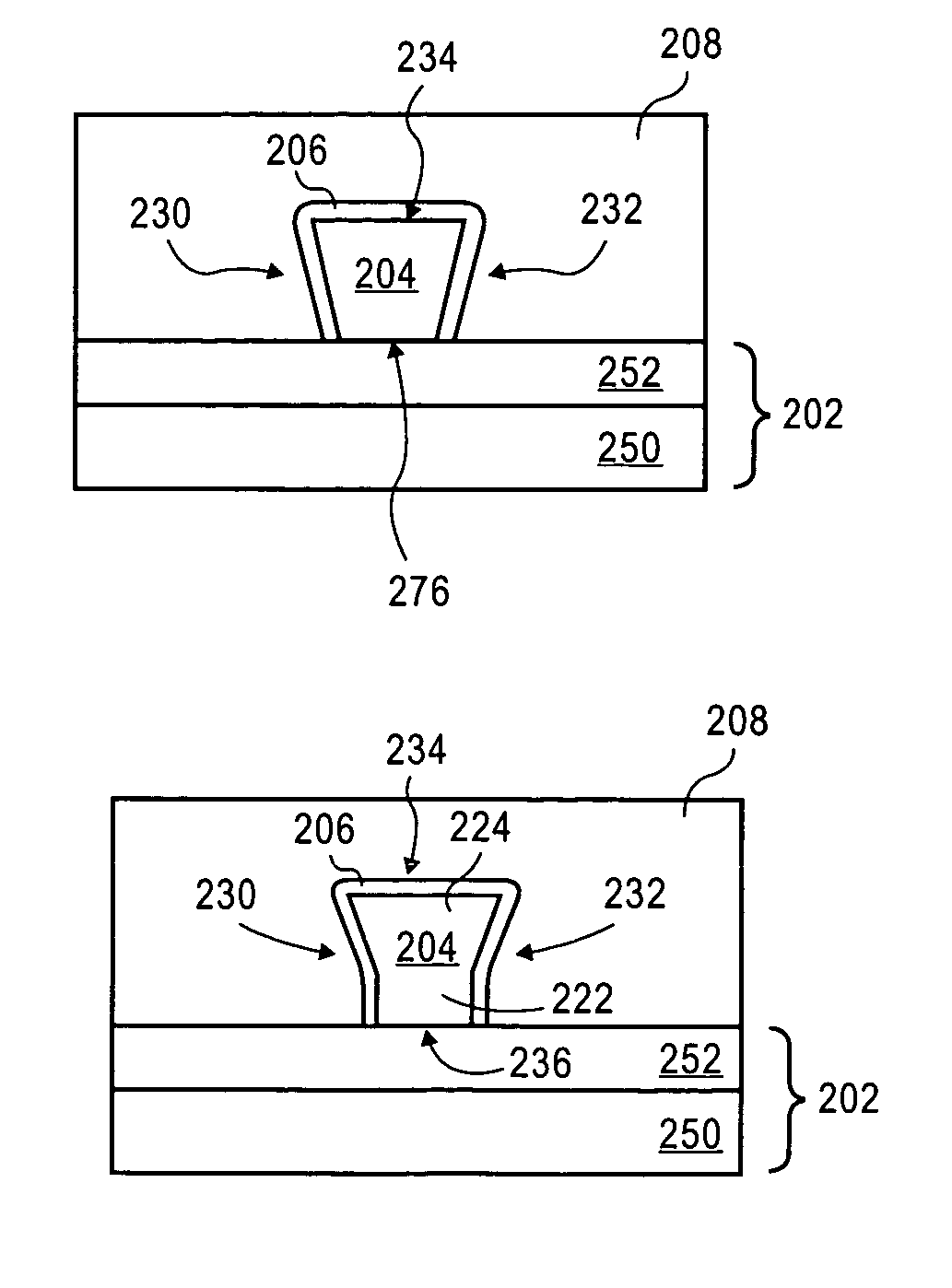

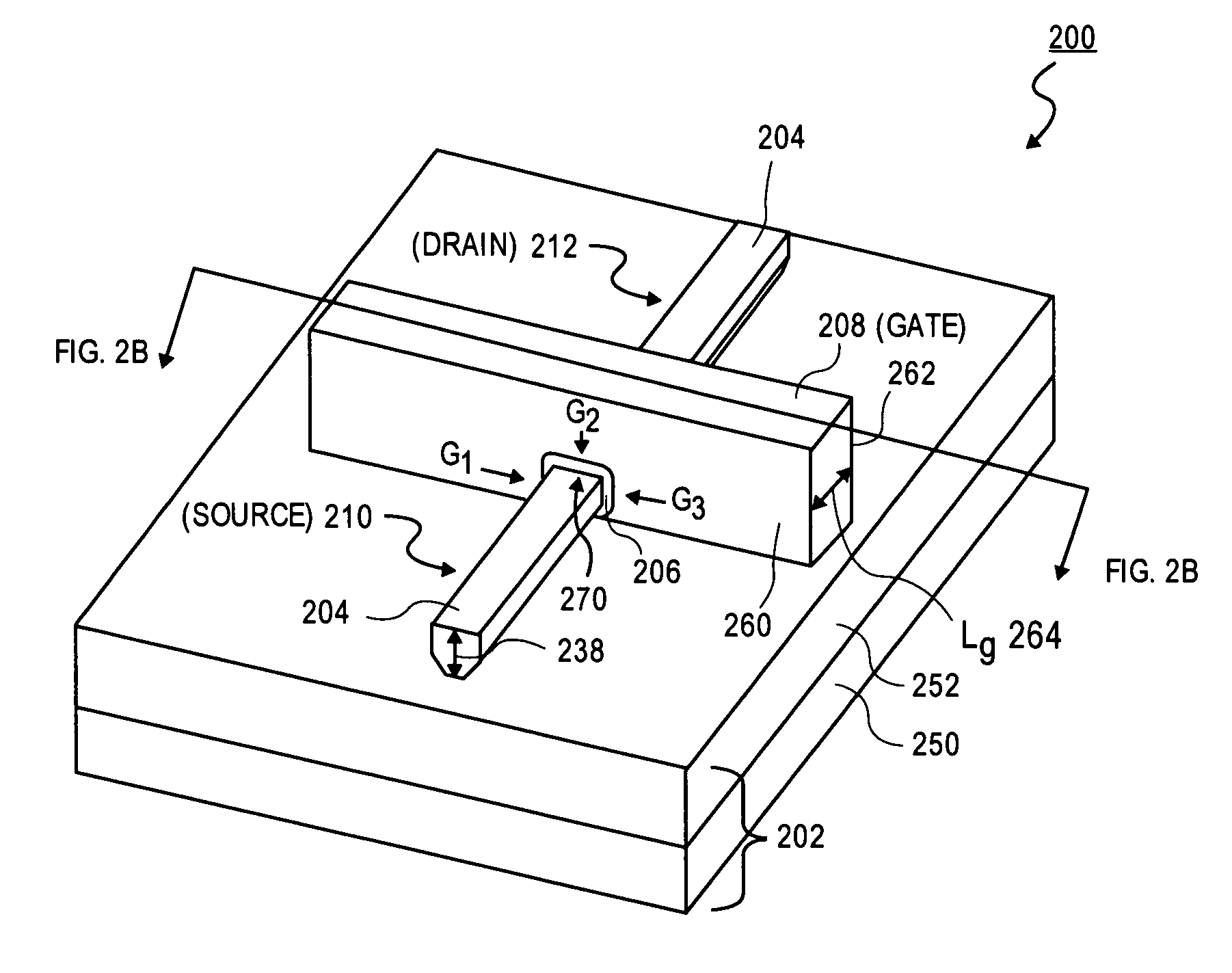

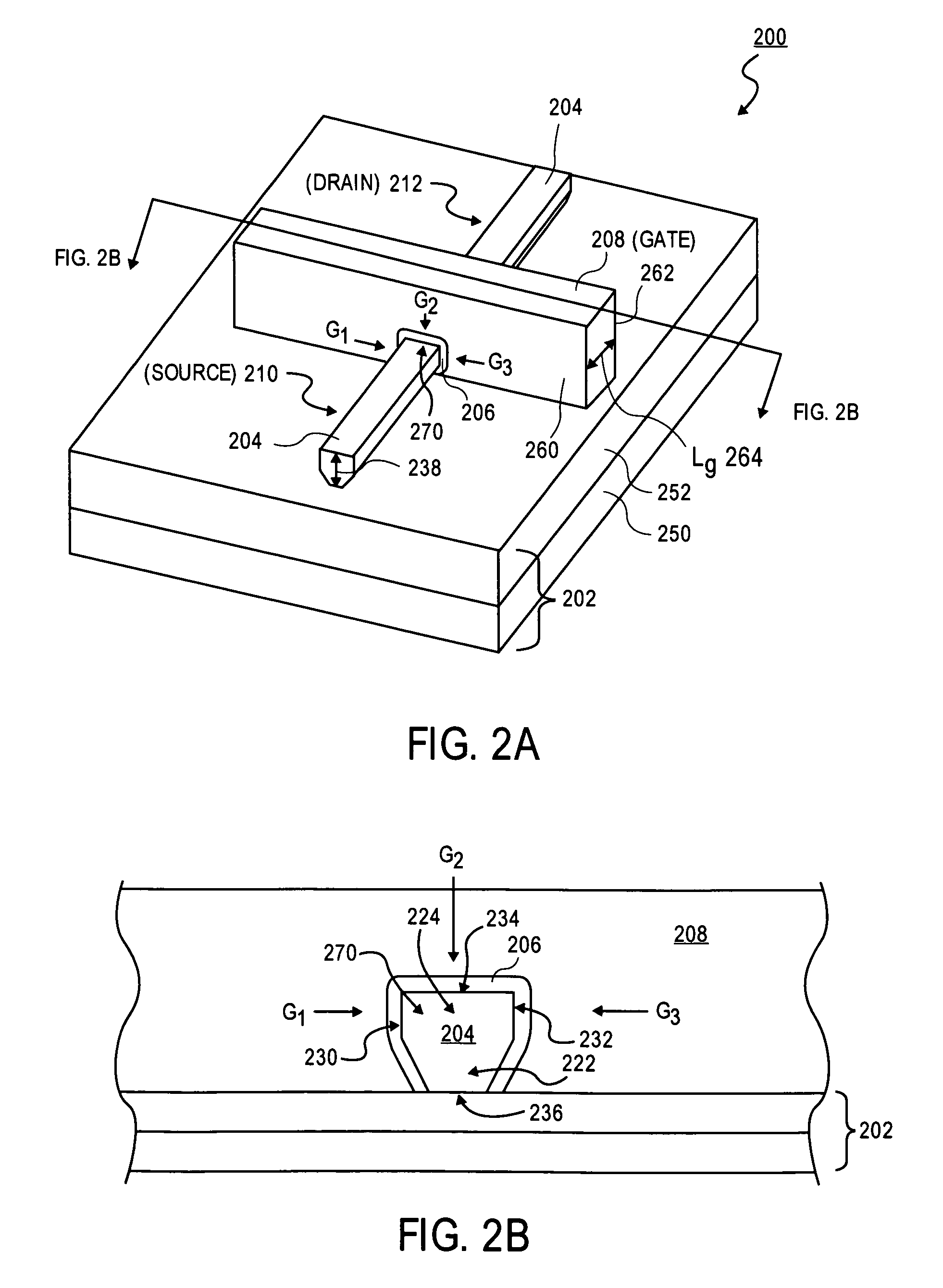

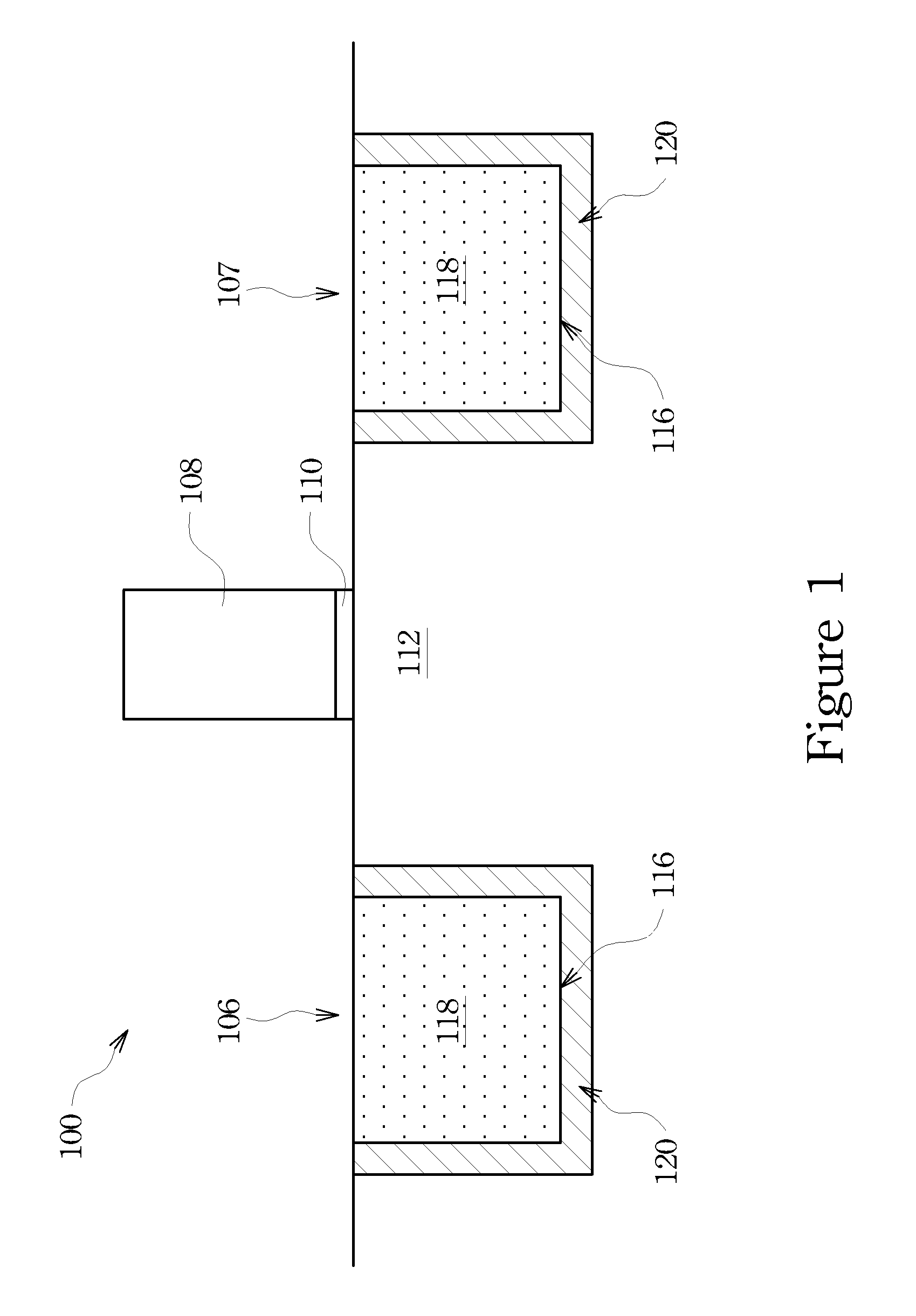

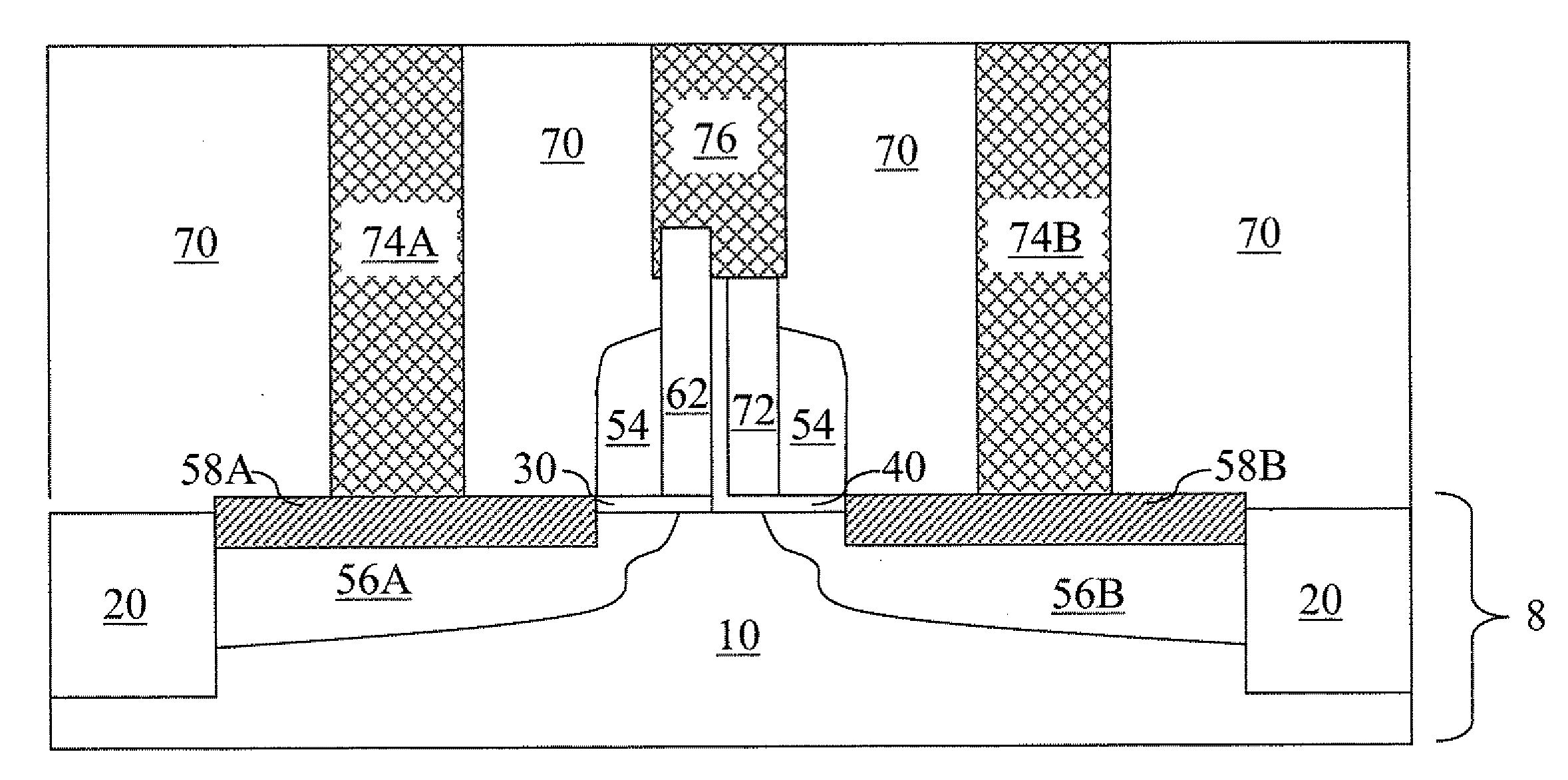

Semiconductor apparatus and method for fabricating the same

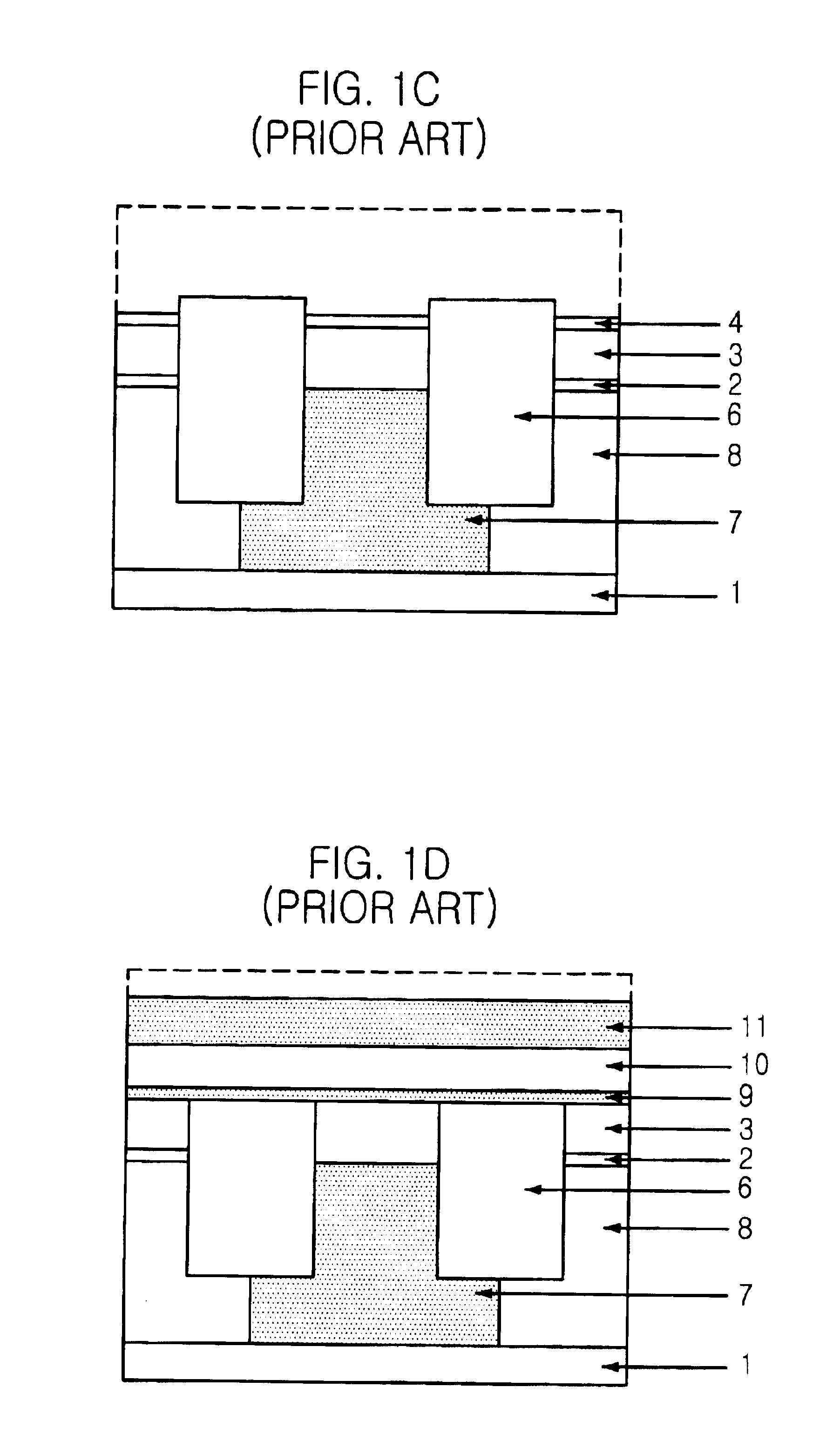

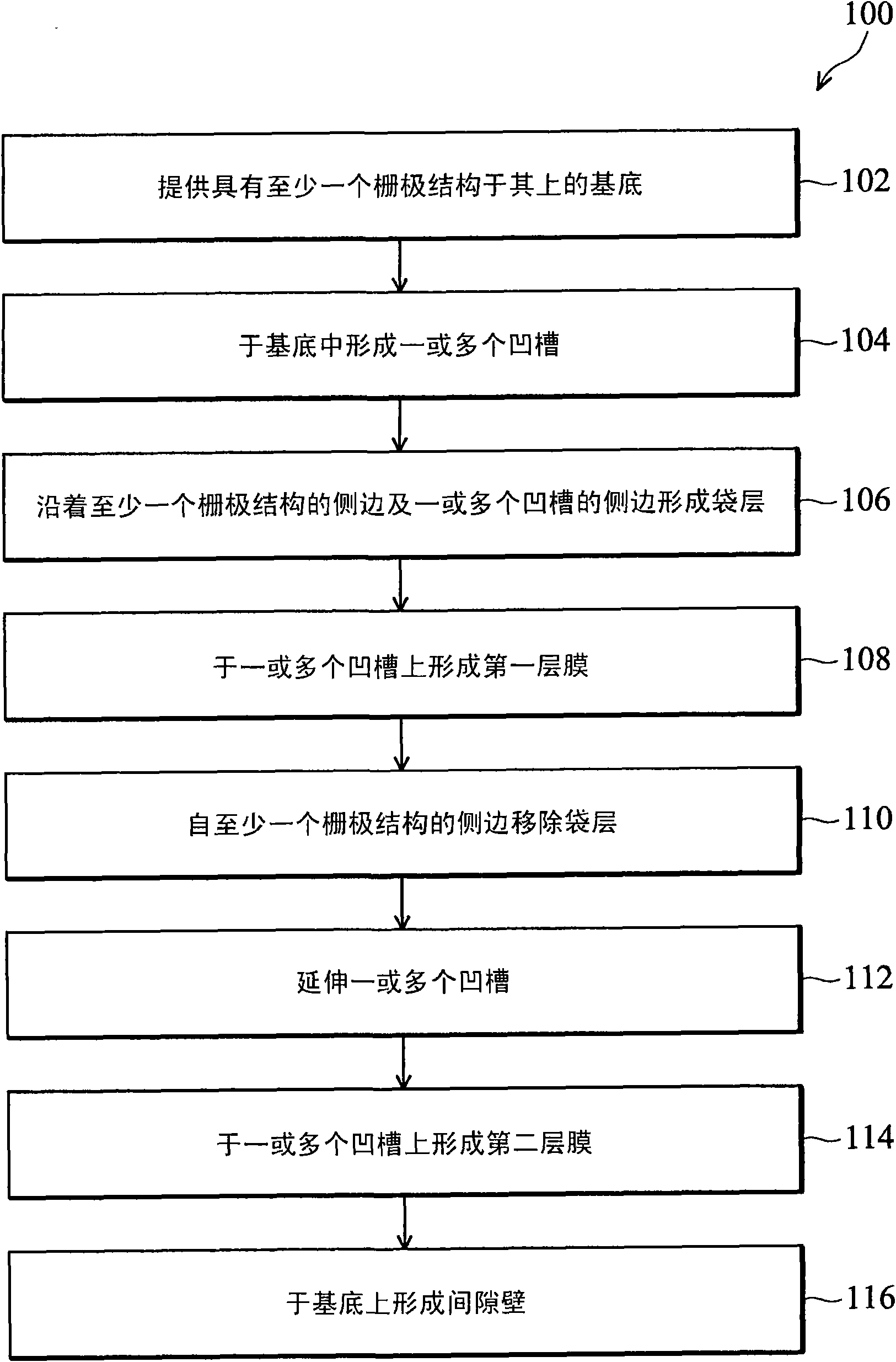

ActiveCN101908506AReduce dopingImprove short channel effectTransistorSemiconductor/solid-state device manufacturingElectrical junctionEngineering

The invention provides a semiconductor apparatus and method for fabricating the same. The method comprises providing a substrate comprising a first material; forming at least one gate stack over the substrate; forming one or more recesses in the substrate, wherein the one or more recesses define at least one source region and at least one drain region; and forming a pocket, a first layer comprising a second material, and a second layer comprising a third material in the one or more recesses, the pocket being disposed between the first layer and the substrate. The pockets 234 of the invention,essentially providing an abrupt junction between the source / drain region and substrate interface, may lead to significant improvement in SCEs (short channel effect) and / or reduce current leakage. Improvement in SCEs can allow continual semiconductor device scaling down. Further, in the present embodiment, the method may reduce strain relaxation within the SiGe portions of the source / drain regions, which can improve the performance of semiconductor device. the invention also reduces the channel doping degree.

Owner:TAIWAN SEMICON MFG CO LTD

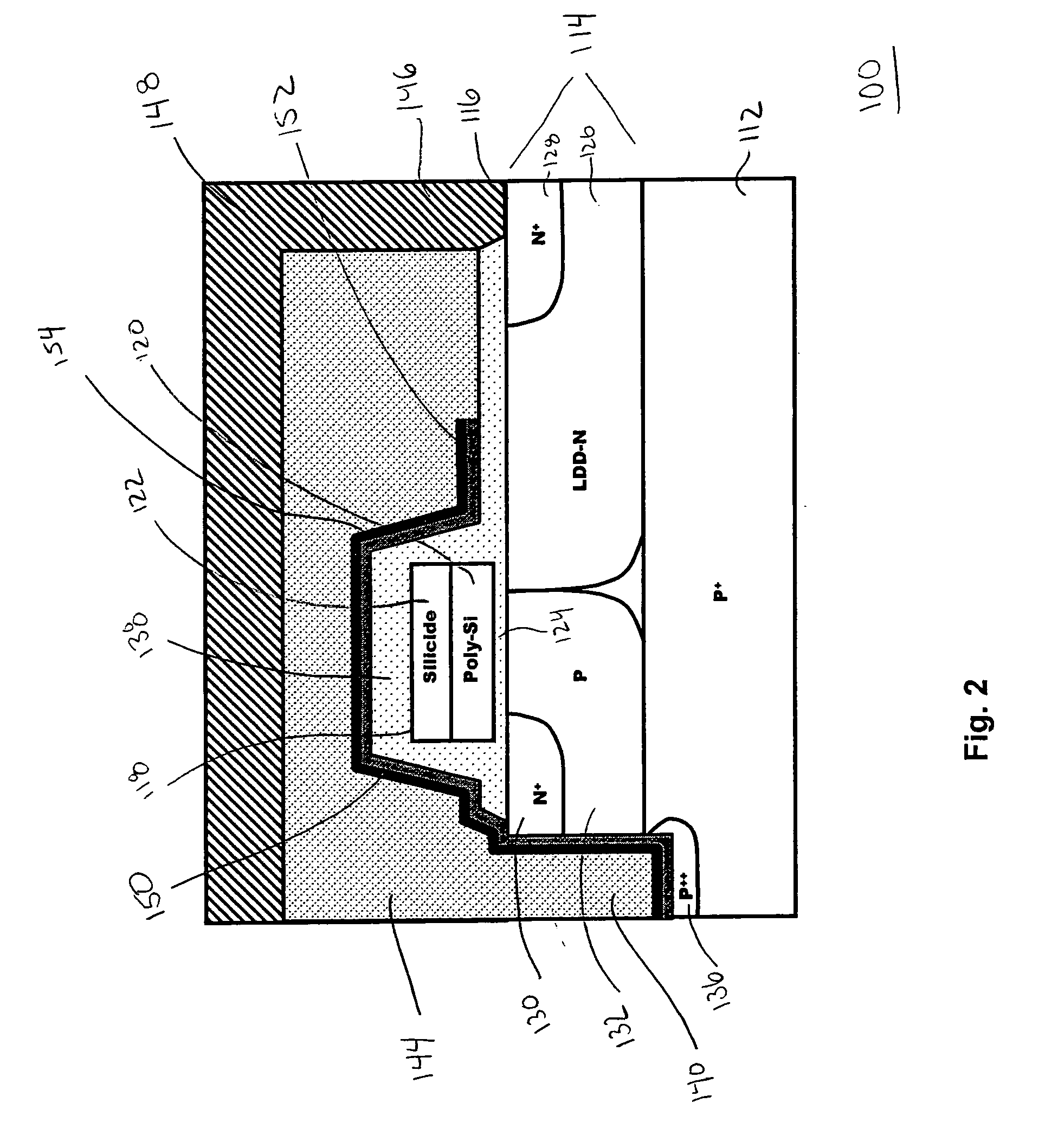

Method for fabricating transistor of semiconductor device

ActiveUS20050112835A1Slow down the spreadImprove short channel effectTransistorSemiconductor/solid-state device manufacturingSalicideHigh density

Disclosed is a method for fabricating a transistor of a semiconductor device, the method comprising the steps of: providing a semiconductor; forming a gate electrode; performing a low-density ion implantation process with respect to the substrate, thereby forming an LDD ion implantation layer; forming an insulation spacer on a sidewall of the gate electrode; forming a diffusion barrier; performing a high-density ion implantation process with respect to the substrate, thereby forming a source / drain; performing a first thermal treatment process with respect to a resultant structure, so as to activate impurities in the source / drain, and simultaneously causing a diffusion velocity of the impurities in the source / drain to be reduced by the diffusion barrier; and forming a salicide layer.

Owner:ATRIA TECH INC

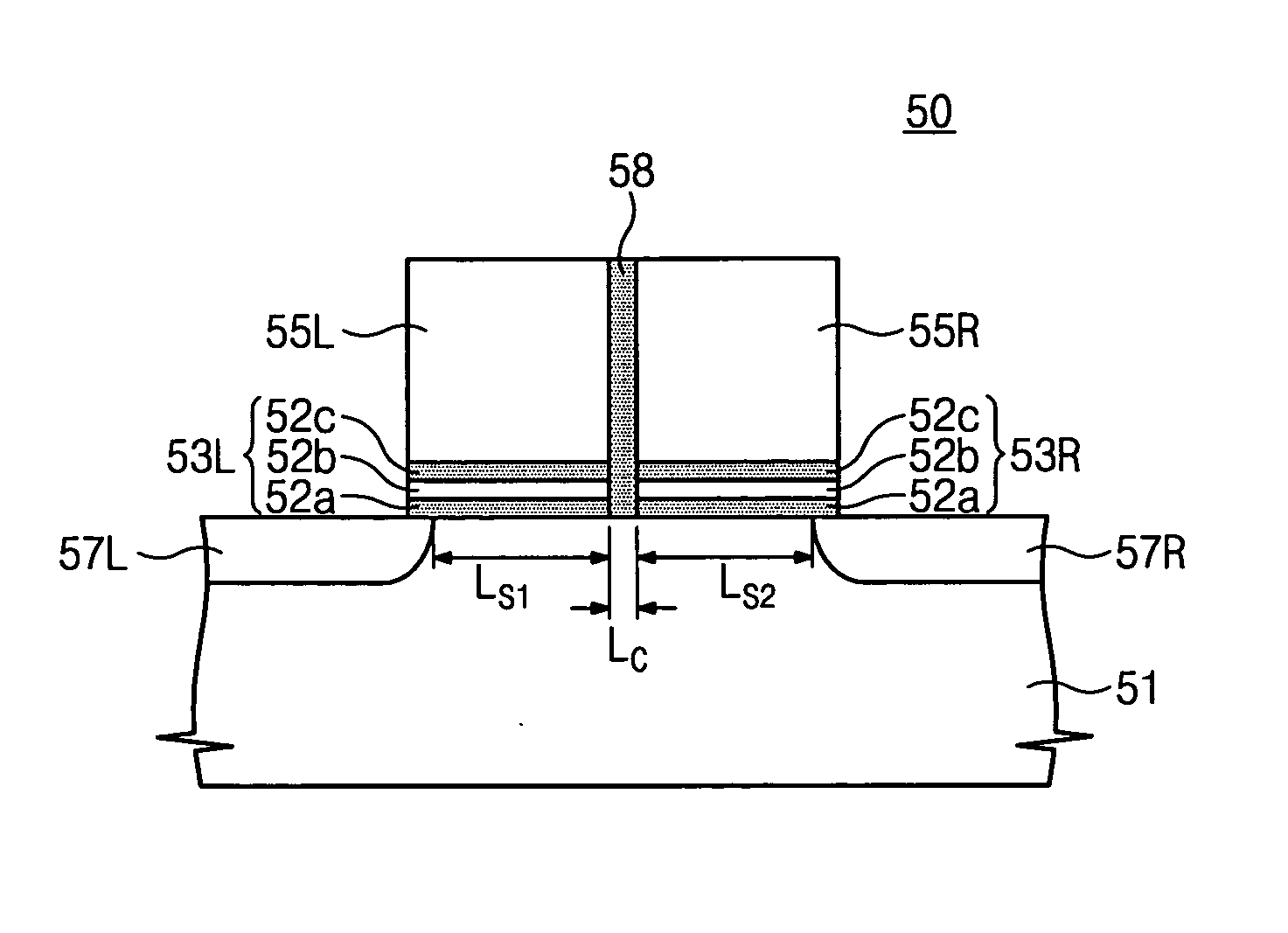

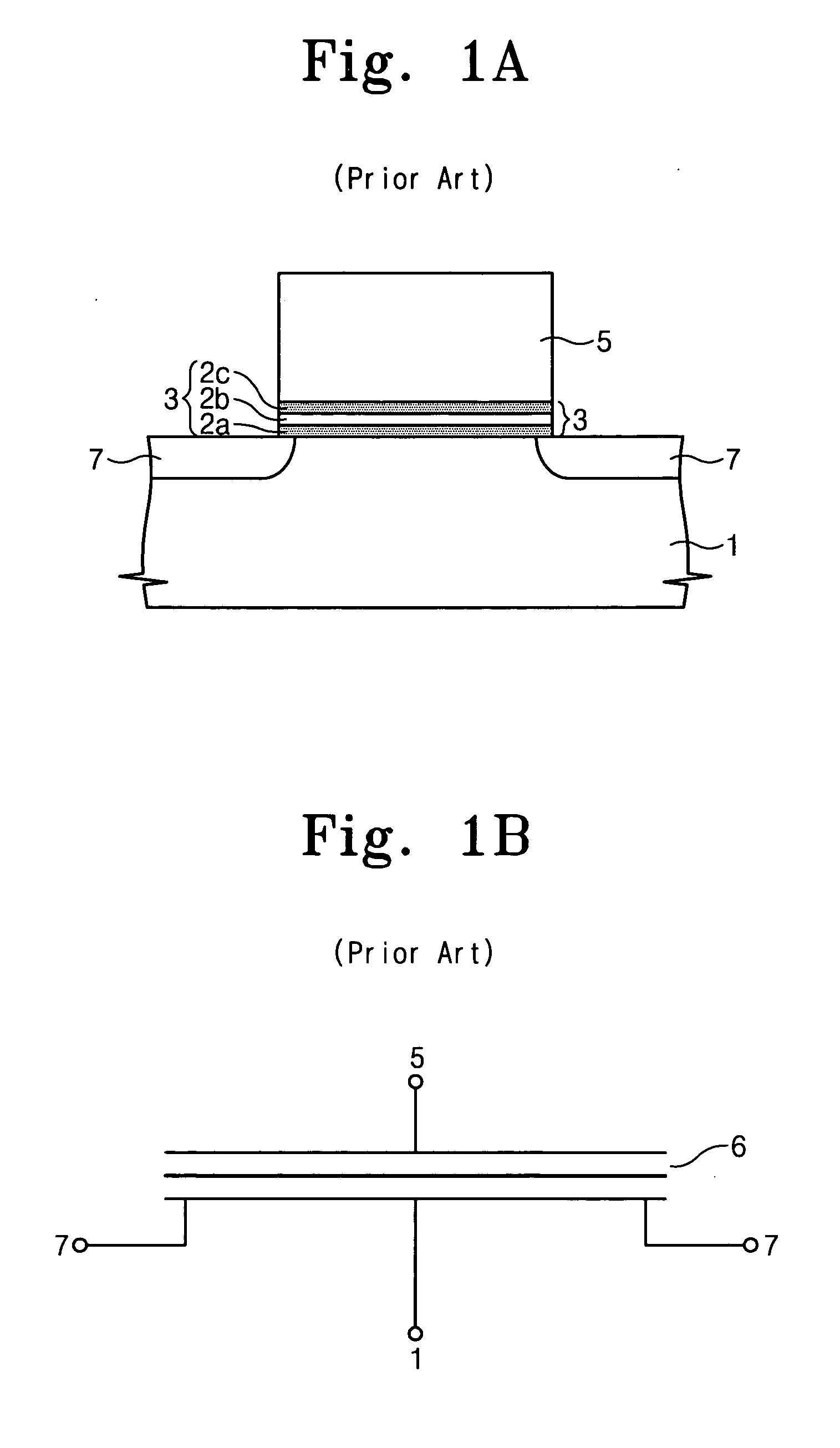

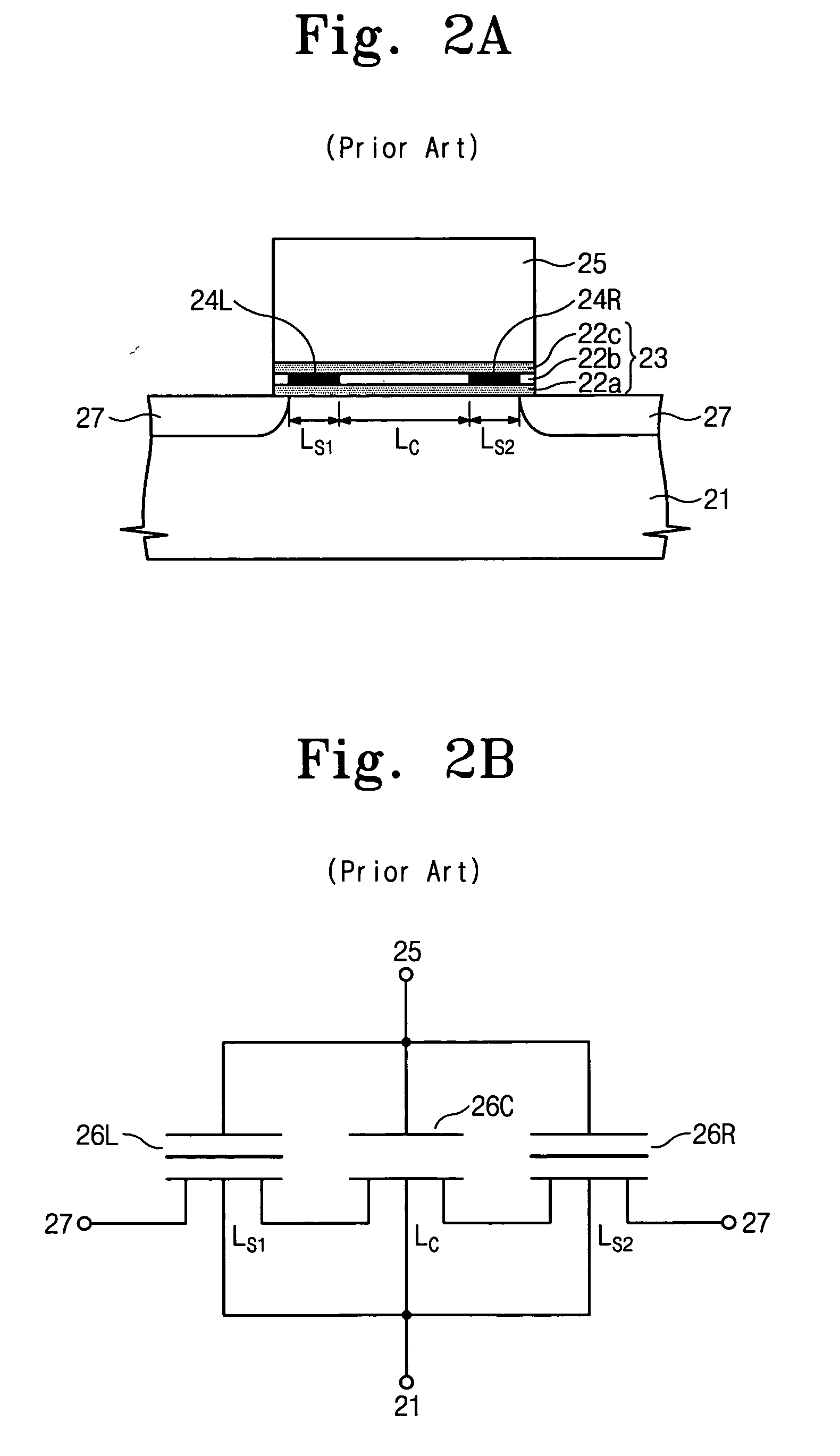

Two-bit non-volatile memory devices including independently-controllable gate electrodes and methods for fabricating the same

InactiveUS20060180847A1Unnecessary couplingLower threshold voltageSolid-state devicesSemiconductor/solid-state device manufacturingTrappingEngineering

A non-volatile integrated circuit memory device includes a substrate including first and second source / drain regions therein and a channel region therebetween, a first memory cell on the channel region adjacent the first source / drain region, and a second memory cell on the channel region adjacent the second source / drain region. The first memory cell includes a first conductive gate on the channel region and a first multi-layered charge storage structure therebetween. Similarly, the second memory cell includes a second conductive gate on the channel region and a second multi-layered charge storage structure therebetween. A single-layer insulating layer on the channel region extends between the first and second memory cells along sidewalls thereof. The single-layer insulating layer may not include a charge-trapping layer, and may separate the first and second conductive gates by a distance of less than a thickness of the first multi-layered charge storage structure. Related fabrication methods are also discussed.

Owner:SAMSUNG ELECTRONICS CO LTD

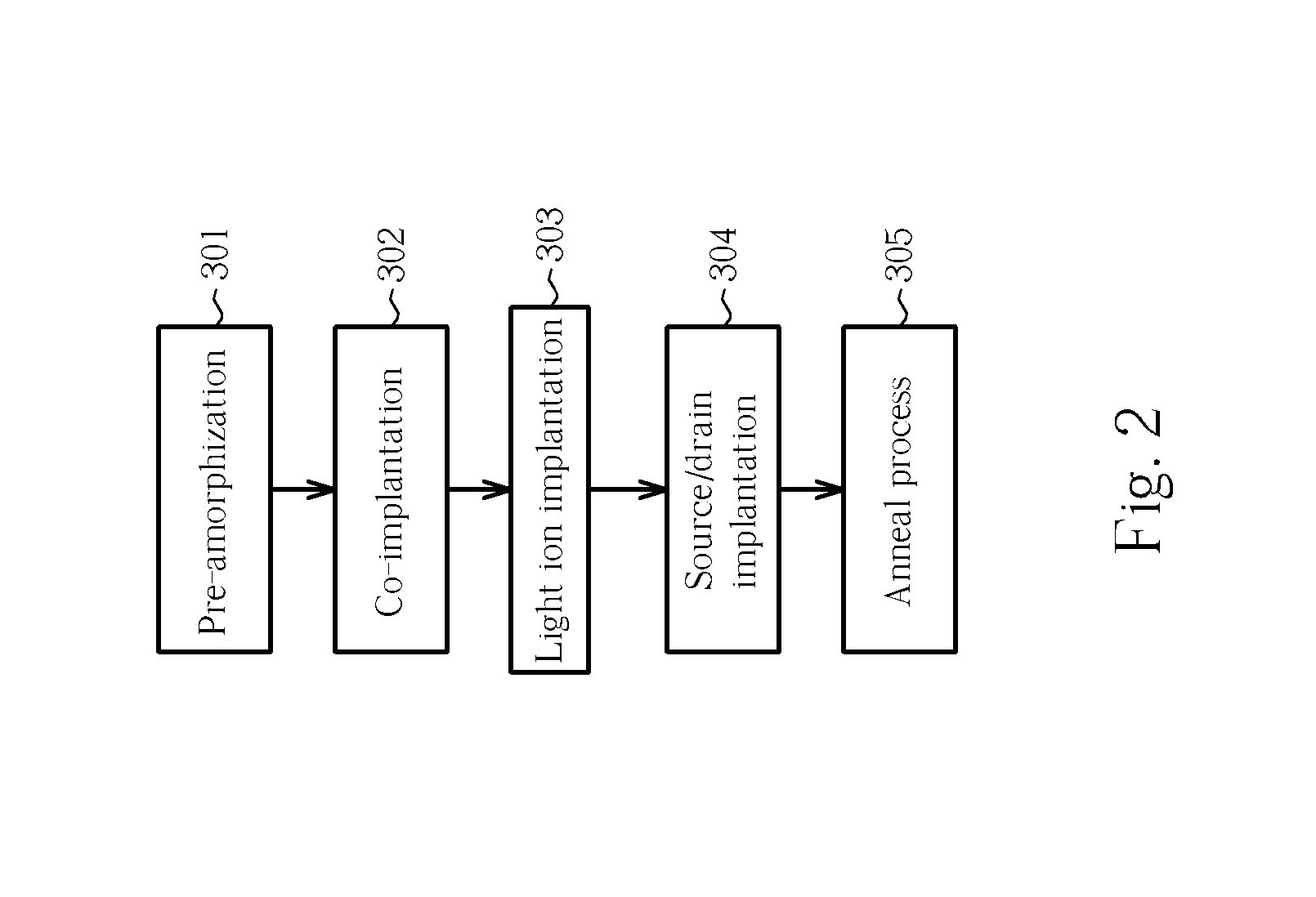

Method for manufacturing metal-oxide-semiconductor transistor

ActiveCN101179027AReduce lateral spreadReduced TED effectSemiconductor/solid-state device manufacturingEngineeringCo injection

The invention provides a method for manufacturing an MOS transistor. The method provides a substrate including a gate structure. Then a pre-non-crystallization technology is carried out and a non-crystallization region is formed in the substrate at two sides of the gate structure; the co-injection technology is carried out, and the impurity for co-injection is injected in the non-crystallization region. A first ion injection technology and a first quick-annealing technology are carried out in such a manner that a slight-doping drain electrode is formed. Finally, a separation wall is respectively formed at two sides of the gate structure in such a manner that a source cathode or a drain electrode is formed.

Owner:UNITED MICROELECTRONICS CORP

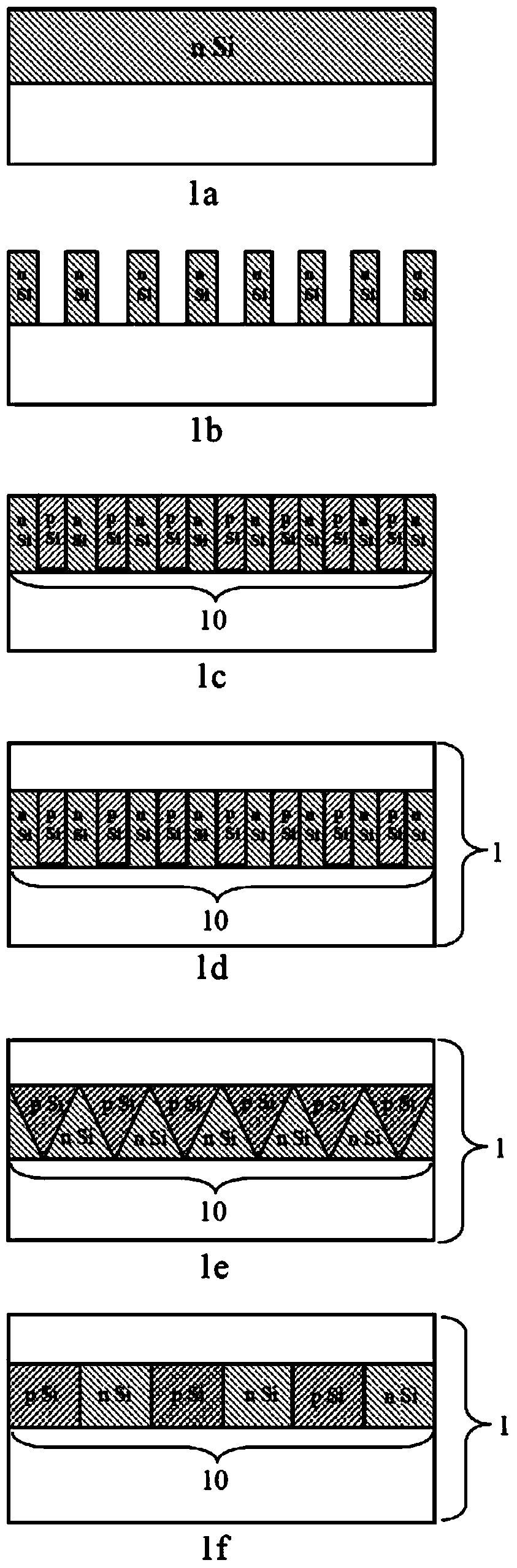

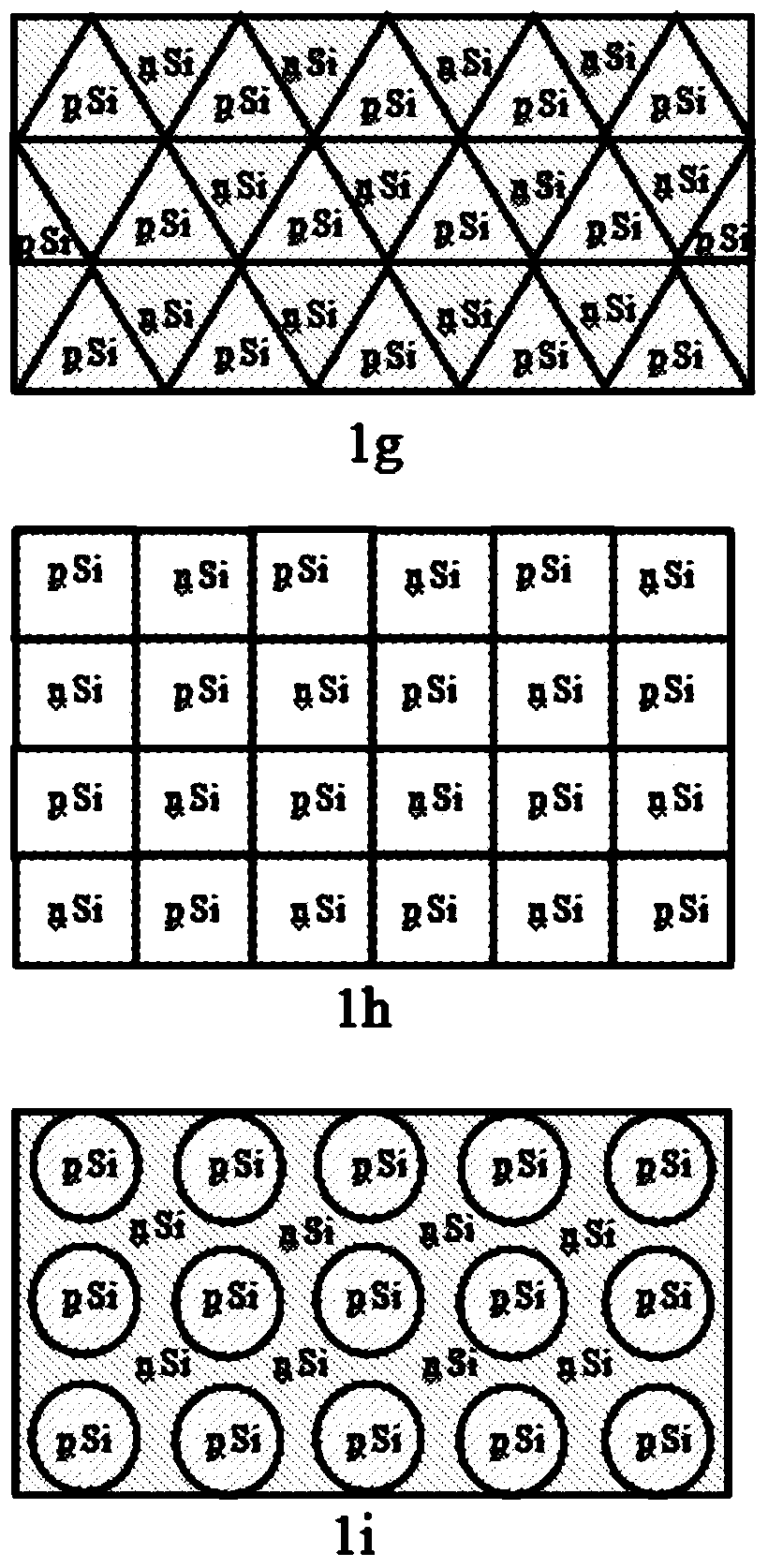

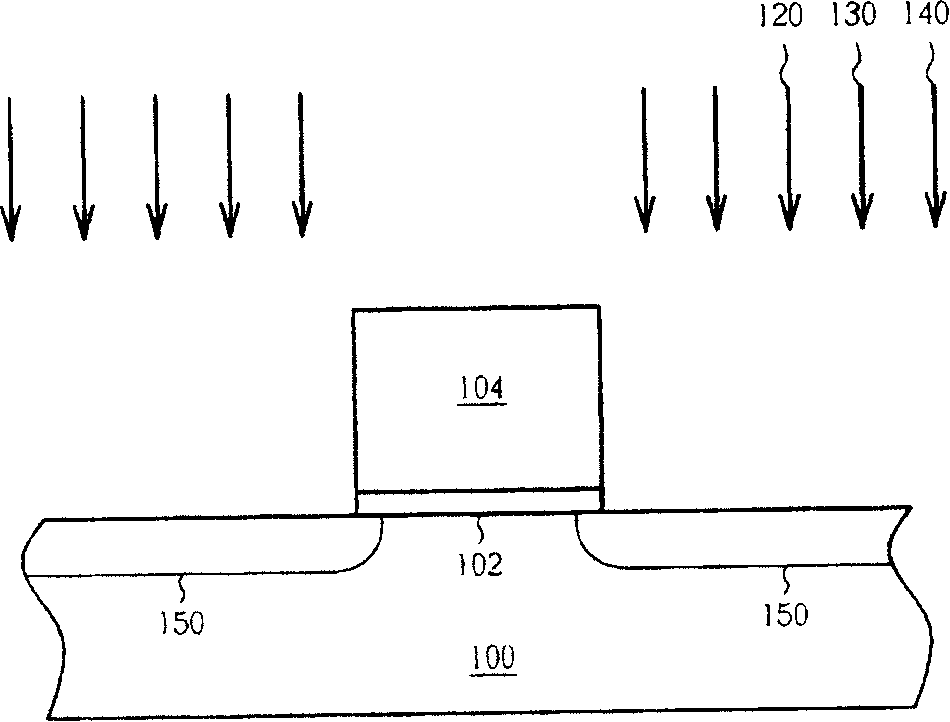

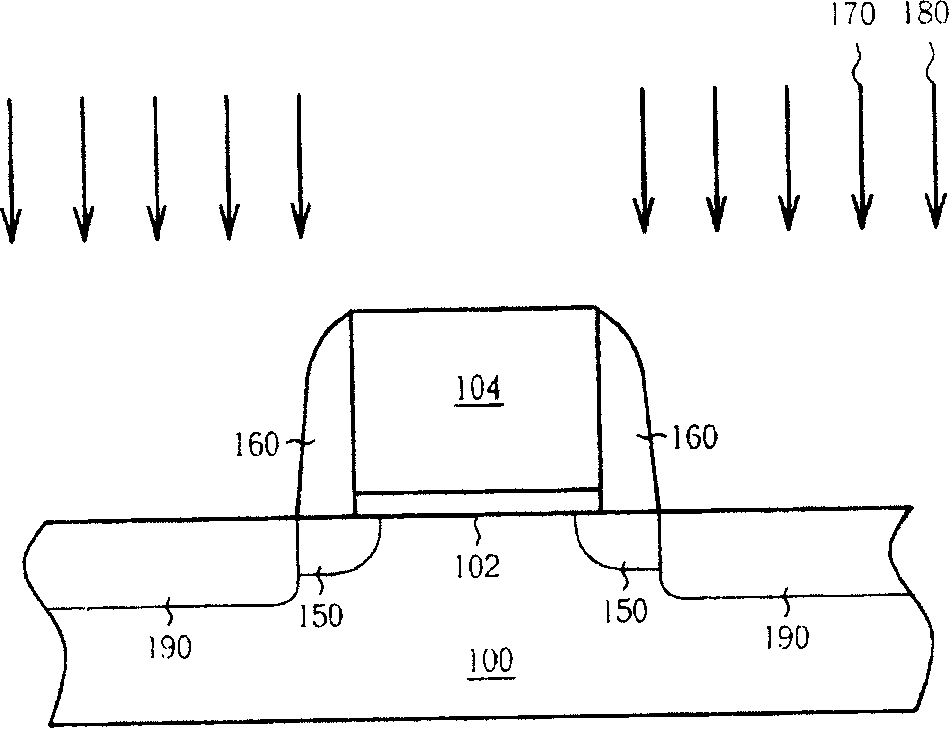

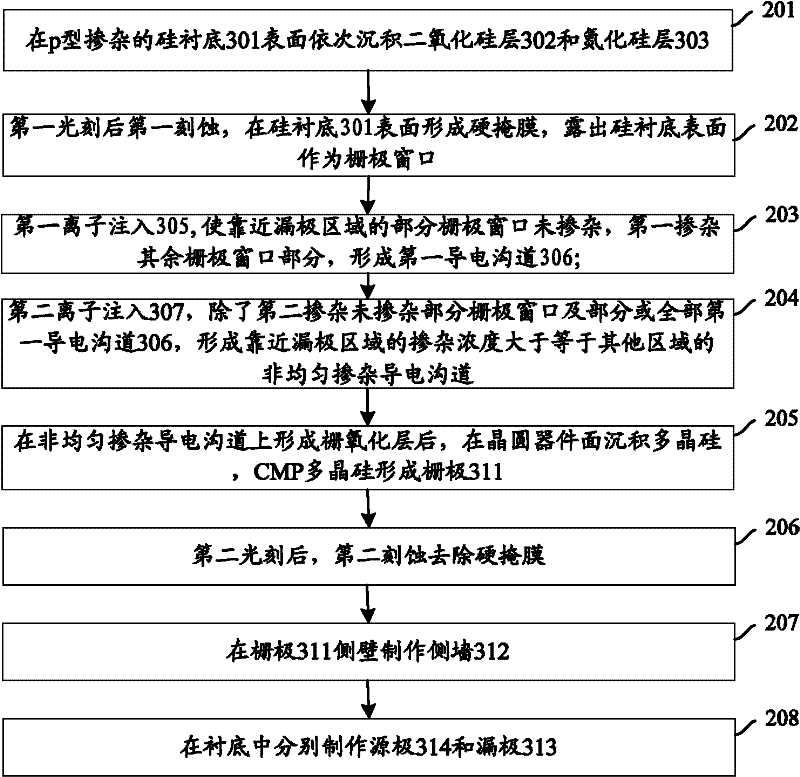

Manufacturing method of metal-oxide-semiconductor field effect transistor (MOSFET)

ActiveCN102479718AReduce doping concentrationImprove short channel effectSemiconductor/solid-state device manufacturingOxide semiconductorPhysics

The invention provides a manufacturing method of a metal-oxide-semiconductor field effect transistor (MOSFET), comprising the following steps: manufacturing a hard mask on the surface of a silicon substrate on a source region and a drain region before a conductive channel is formed, and carrying out ion implantation at twice from different angles by using the hard mask as a shield in the process for forming the conductive channel through ion implantation to form a nonuniform conductive channel, thus, the doping concentration of the part of the conductive channel near the edge of the drain region is reduced on the premise that the whole doping concentration of the nonuniform conductive channel is not remarkably changed, on the one hand, the short channel effect of the MOSFET is prevented from increasing, and on the other hand, the band-gap tunneling effect and drain leakage current are reduced, shutdown current is reduced, and the service life of the MOSFET device is prolonged.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1