Nonplanar device with thinned lower body portion and method of fabrication

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0012] The present invention is a novel nonplanar device with a thinned lower body portion and a method of fabrication. In the following description, numerous specific details are set forth in order to provide a thorough understanding of the present invention. In other instances, well known semiconductor processes and manufacturing techniques have not been described in particular detail in order to not unnecessarily obscure the present invention.

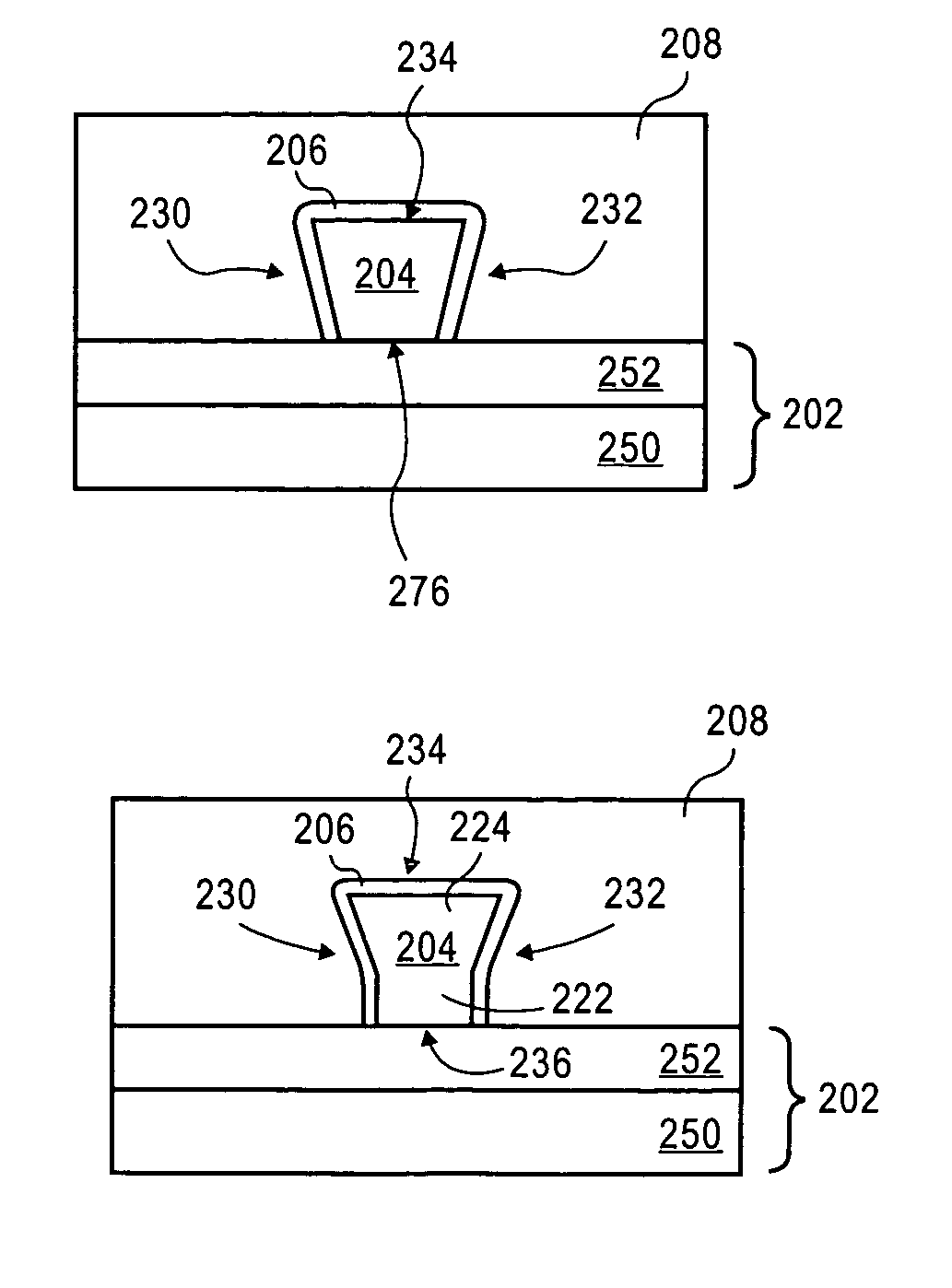

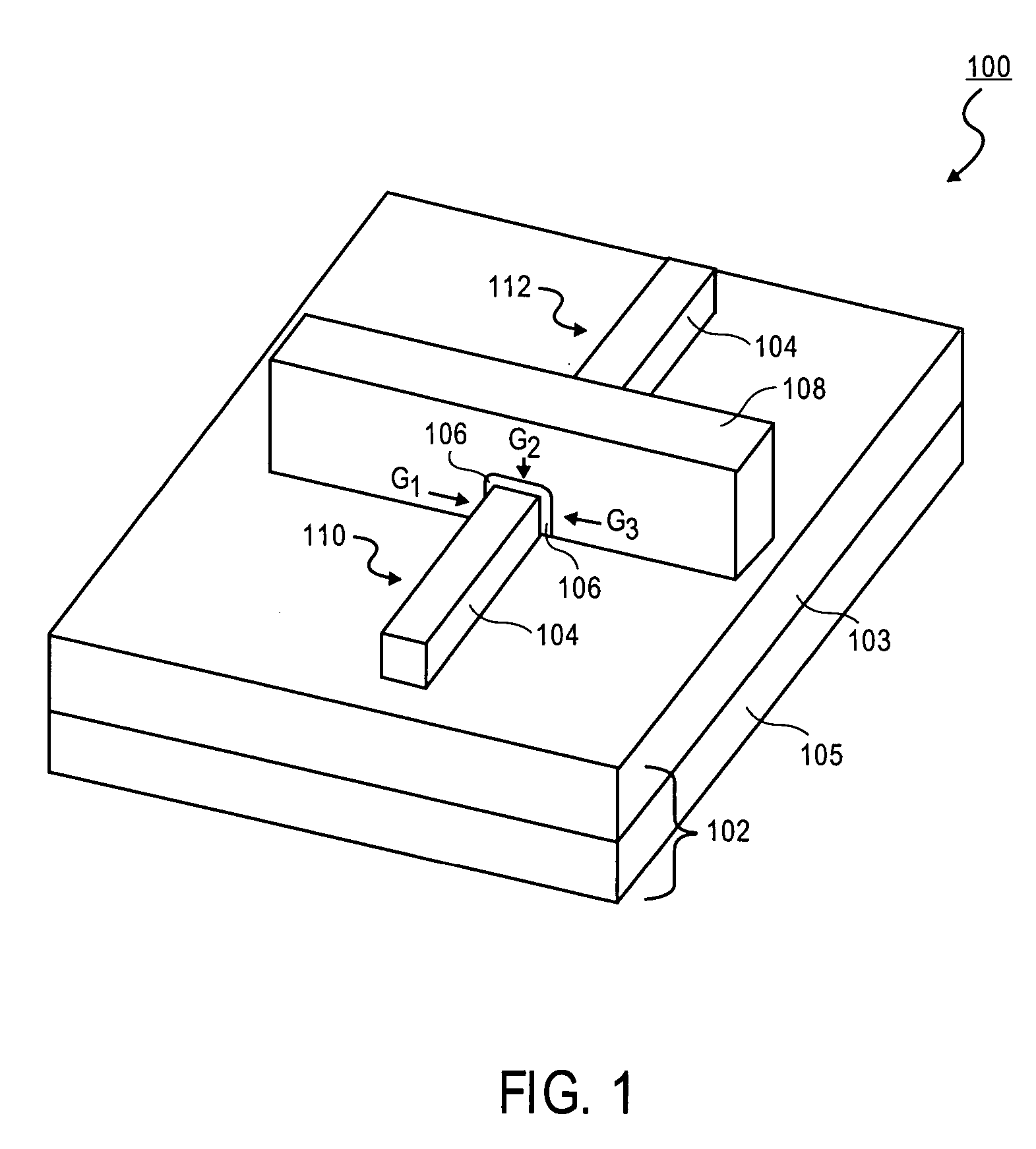

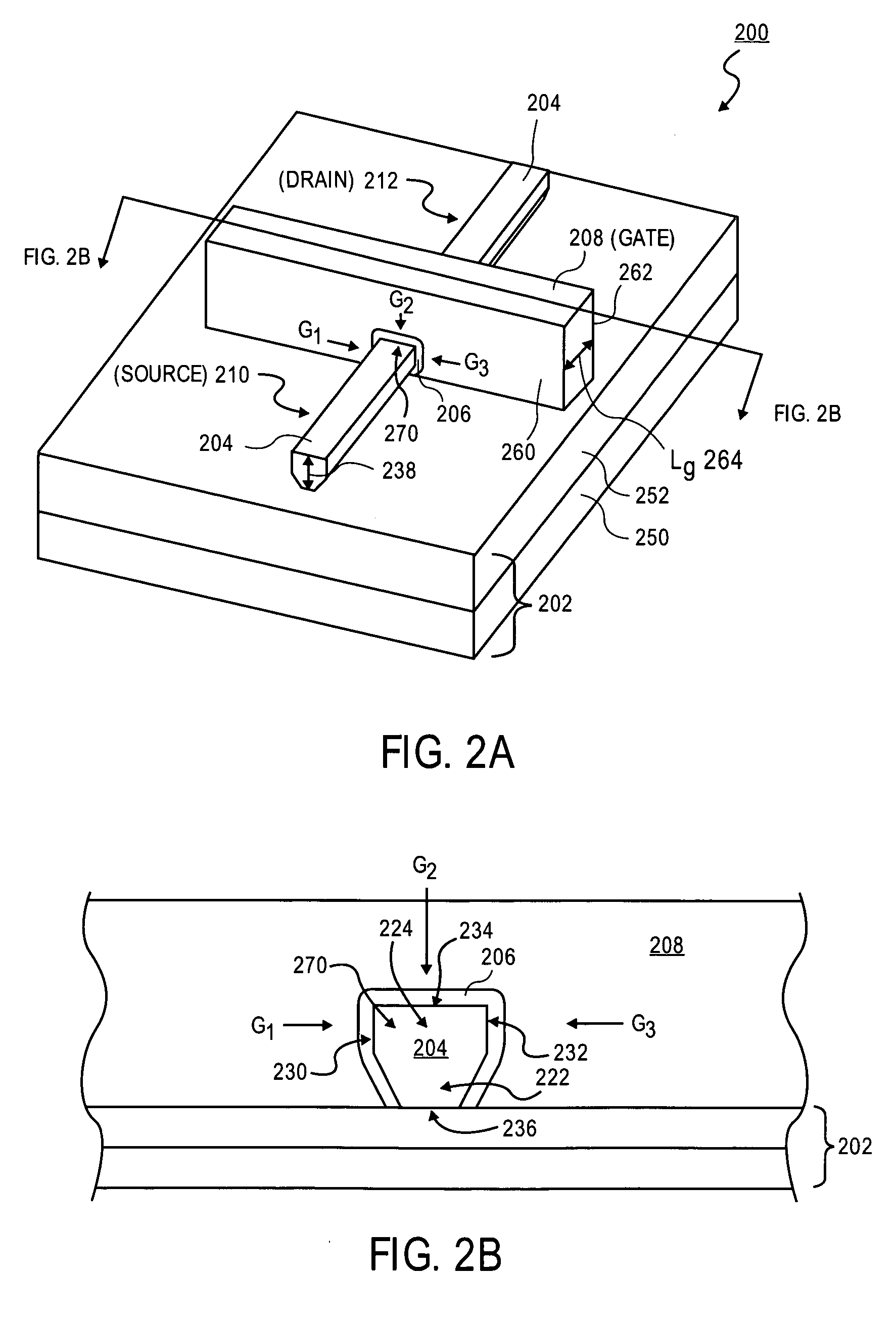

[0013] Embodiments of the present invention include a nonplanar or tri-gate transistor having a semiconductor body which is wrapped around on three sides by a gate dielectric layer and a gate electrode. In embodiments of the present invention, the bottom portion of the semiconductor body is made thinner than the top portion of the semiconductor body. Making the bottom portion of the semiconductor body thinner than the top portion increases the gate control over the bottom portion of the body resulting in better short channel effects. In an ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More