Method for manufacturing metal-oxide-semiconductor transistor

An oxide semiconductor and transistor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as unsatisfactory lateral diffusion of P-type dopants, and achieve improved short-channel effects and good junction profiles. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

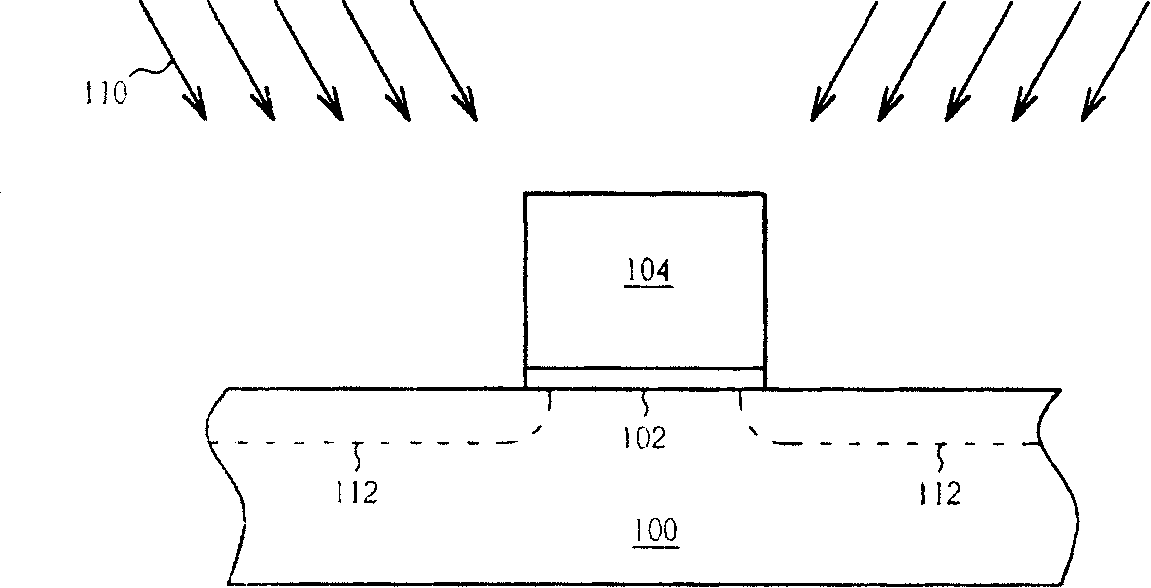

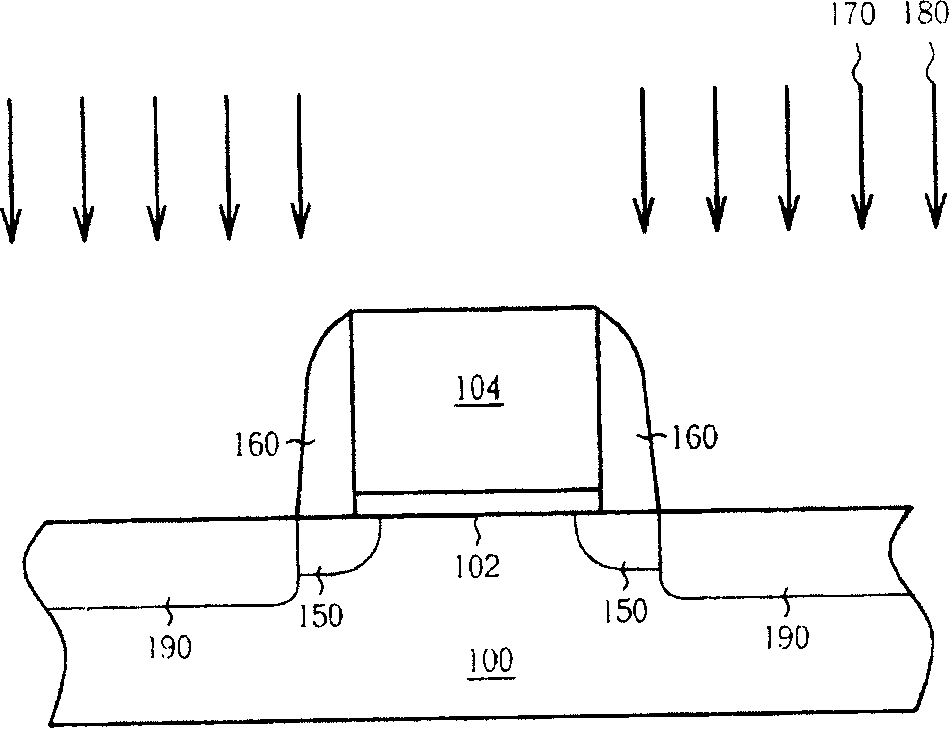

[0043] see Figure 4 to Figure 8 , Figure 4 to Figure 8 It is a schematic diagram of the first preferred embodiment of the method for manufacturing a MOS transistor provided by the present invention. Such as Figure 4 As shown, a substrate 200 is firstly provided. The substrate 200 can be a semiconductor wafer, a silicon-on-insulator (SOI wafer), etc. The substrate 200 has completed the shallow trench isolation (STI) process and the doping of the well (well). complex process, and a gate structure 210 at least composed of a gate dielectric layer 212 and a gate 214 has been formed on the substrate 200 . Then, a pre-amorphization (PAI) process 220 is performed. The PAI process 220 can be a right-angle or angled PAI process to form an amorphized region 222 in the substrate 200 on both sides of the gate structure 210. .

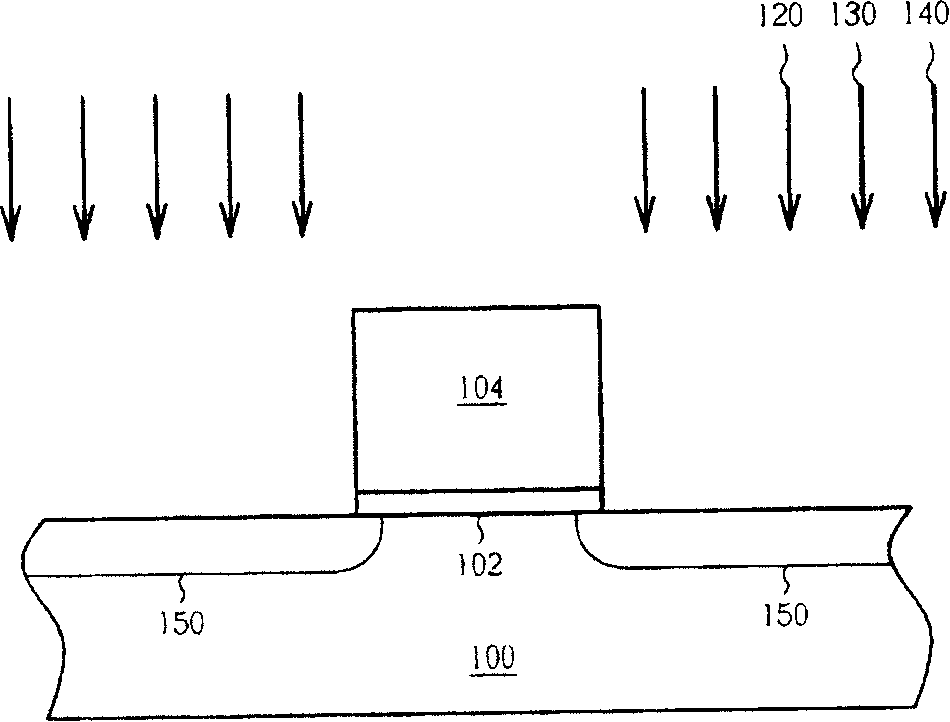

[0044] see Figure 5 . Next, a co-implantation process 230 is performed to implant a co-implantation dopant 232 into the amorphized region 222 . It should...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More