MOS transistor and forming method thereof

A MOS transistor and semiconductor technology, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of drain induction barrier reduction, affecting transistor performance and reliability, source-drain punch-through, etc., to avoid source Drain punch-through effect, the effect of improving the short channel effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

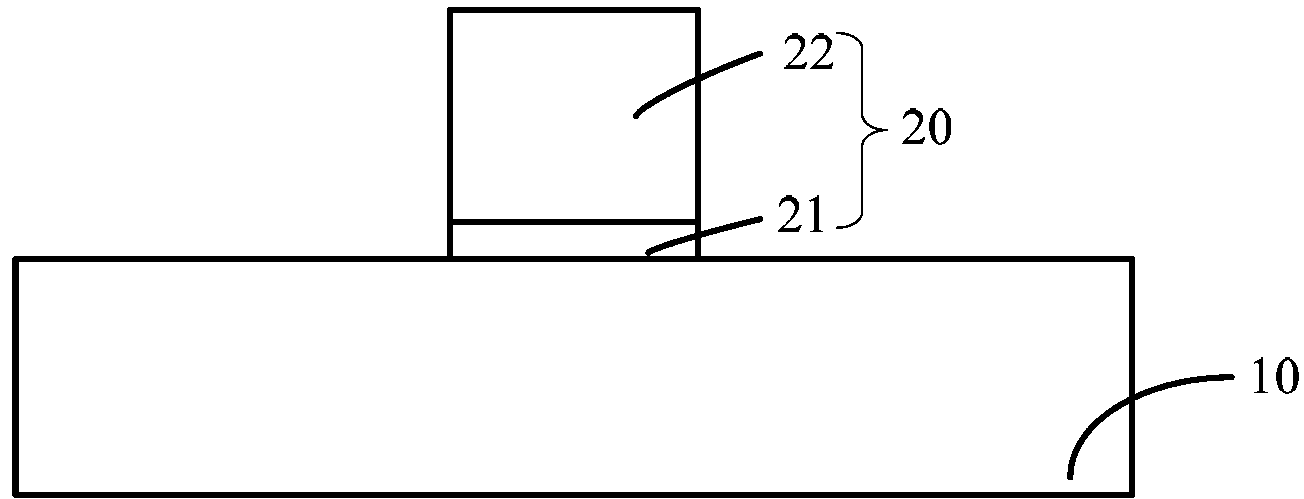

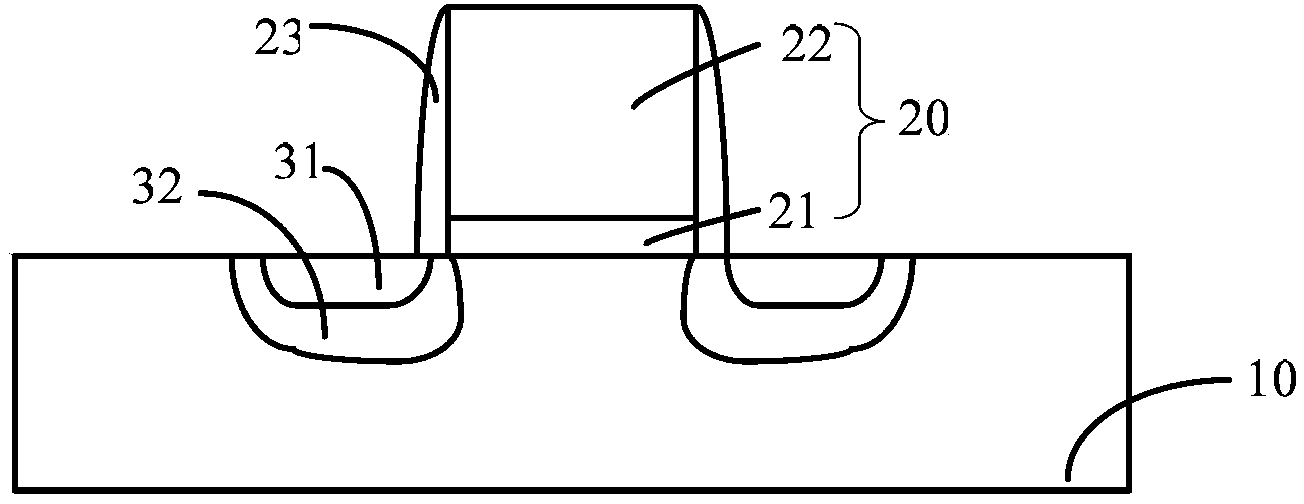

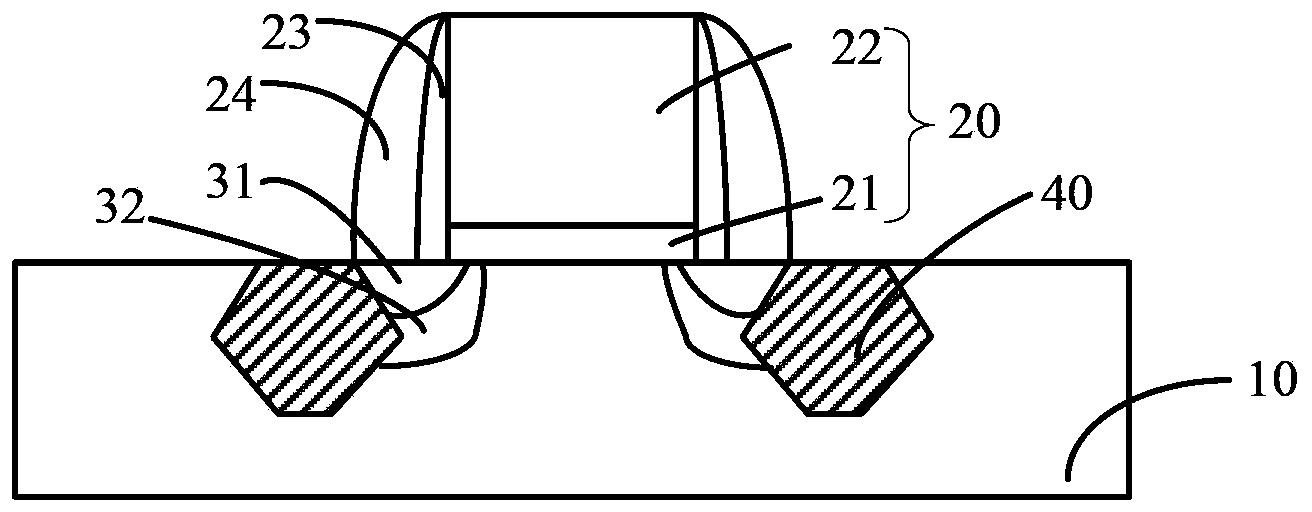

[0035] As mentioned in the background art, phenomena such as source-drain punch-through and drain induction barrier reduction of MOS transistors formed in the prior art will seriously affect the performance and reliability of the transistor.

[0036] Research has found that in the prior art, after the lightly doped region and the halo region of the transistor are formed, the source and drain of the transistor are formed using a SiGe or SiC source-drain process, and the short channel effect of the transistor is serious. The main reason is that in the process of forming the source and drain of the transistor, the semiconductor substrate needs to be etched to form grooves. When the semiconductor substrate is etched to form grooves, part of the previously formed halos will inevitably be removed. region, resulting in a reduction in the area of the halo region, and a corresponding reduction in the diffusion barrier effect on source and drain dopant ions; After the halo region, par...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More