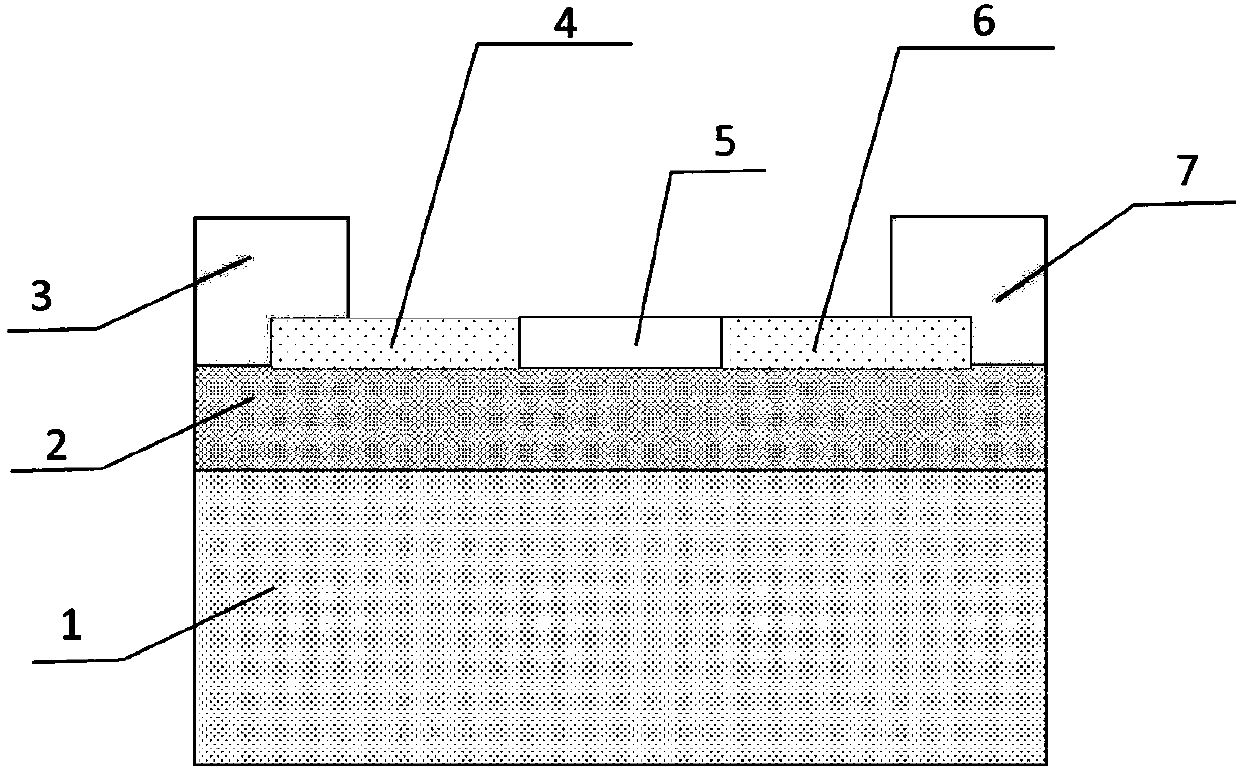

Preparation method of enhanced field effect transistor based on two-dimensional planar heterojunction

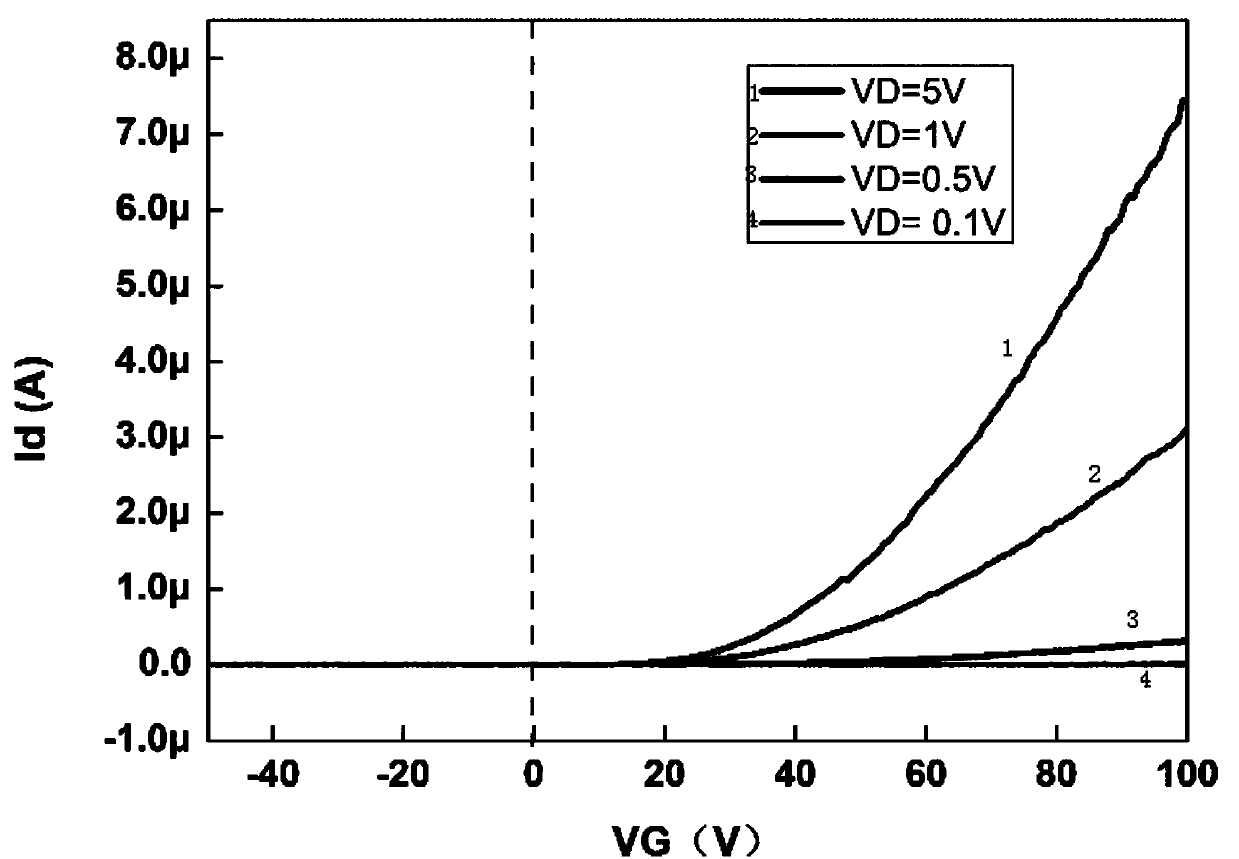

A field-effect transistor, two-dimensional planar technology, applied in transistors, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problem of not being able to control device turn-off well, the carrier mobility has a great influence, and low switching. ratio and other issues, to achieve the effects of low power consumption, easy mass production, and low dark current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0028] Embodiment 1 A preparation method based on a two-dimensional planar heterojunction enhanced field effect transistor is carried out according to the following steps:

[0029] The graphene grown on copper foil prepared by CVD method was transferred to the single crystal silicon wafer substrate with oxide layer by wet transfer method. During the experiment, ammonium persulfate solution was used as the etching solution for copper foil, and the concentration of the solution was 0.1mol / L. After the etching was completed, the graphene film was transferred to a new silicon dioxide / silicon substrate;

[0030] Spin photoresist evenly on the transferred graphene film, and then transfer the pattern on the mask plate to the photoresist by exposure through photolithography; then clean the unexposed part of the photoresist by developing solution Rinse off and tumble dry.

[0031] The non-patterned part is etched by plasma, and the part outside the pattern is etched away. After the e...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More