Two-dimensional semiconductor negative capacitance field-effect transistor and preparation method thereof

A two-dimensional semiconductor and capacitive field technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, circuits, etc., can solve the problem of inability to break through the sub-threshold swing of devices, mutual constraints of power consumption-performance-scale, and high-integration power consumption Unable to solve other problems, achieve the effect of reducing the sub-threshold swing, simple structure, and high switching ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

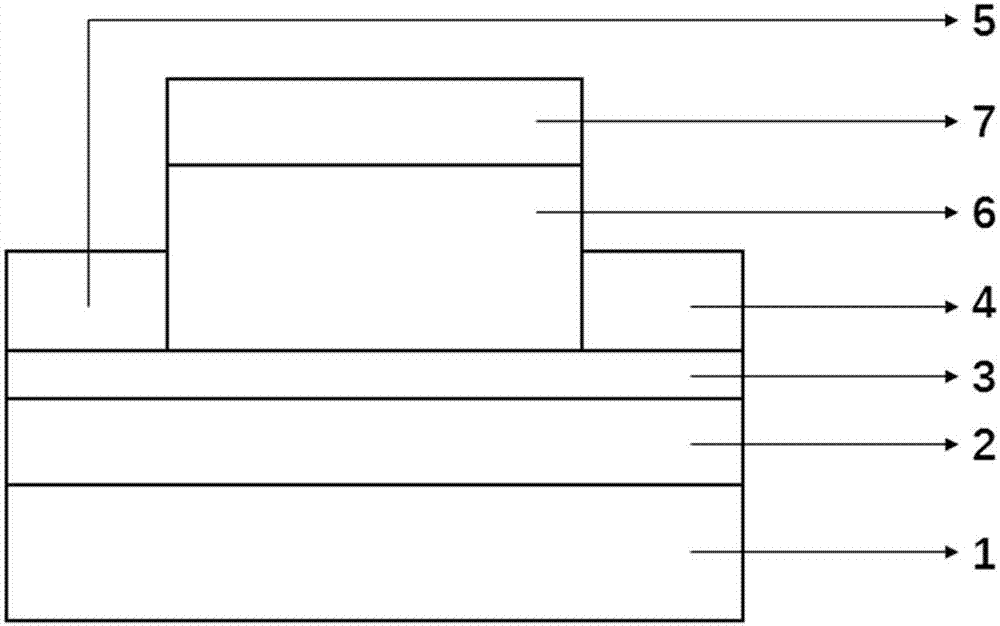

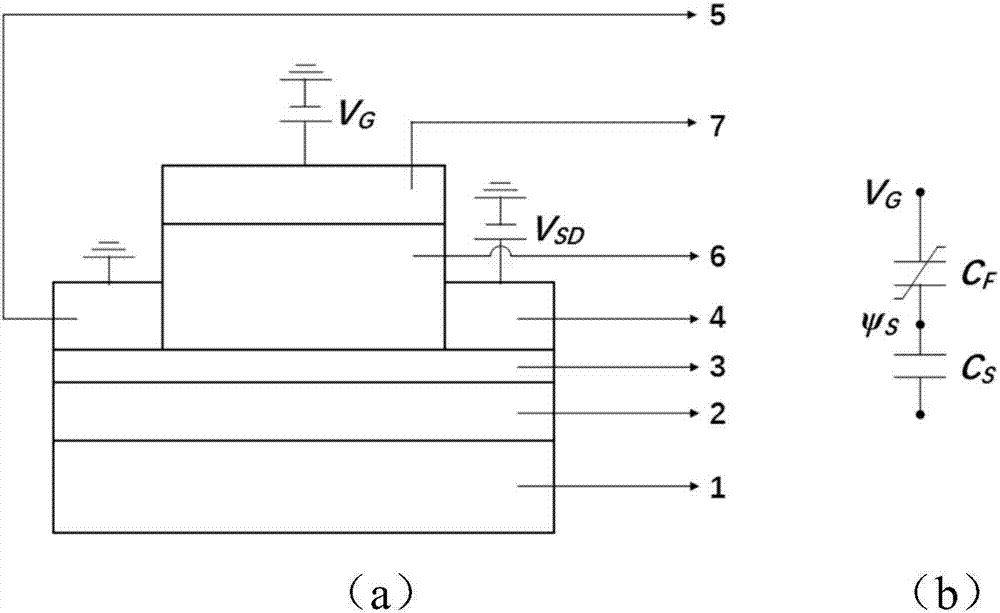

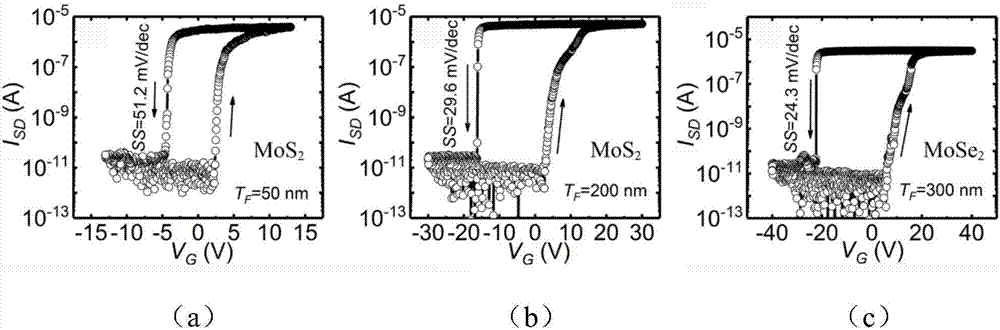

[0041] Example 1 of the present invention is described in detail below in conjunction with accompanying drawing:

[0042] The invention develops a two-dimensional semiconductor negative capacitance field effect transistor. Utilize the negative capacitance effect of P(VDF-TrFE) ferroelectric polymer material to amplify the externally applied gate voltage, strengthen the control of the carrier and energy band of the two-dimensional semiconductor material, so as to effectively reduce the sub-scale of the field effect transistor device. Threshold swing, increase the device turnover rate, reduce the overall power consumption of the device.

[0043] Specific steps are as follows:

[0044] 1. Substrate selection

[0045] A heavily doped p-type silicon with a thickness of 0.5 mm is selected as the substrate.

[0046] 2. Preparation of oxide dielectric layer

[0047] The silicon dioxide with a thickness of 285±5 nanometers is oxidized on the surface of the silicon substrate by a th...

example 2

[0059] Example 2 of the present invention is described in detail below in conjunction with accompanying drawing:

[0060] The invention develops a two-dimensional semiconductor negative capacitance field effect transistor. Utilize the negative capacitance effect of P(VDF-TrFE) ferroelectric polymer material to amplify the externally applied gate voltage, strengthen the control of the carrier and energy band of the two-dimensional semiconductor material, so as to effectively reduce the sub-scale of the field effect transistor device. Threshold swing, increase the device turnover rate, reduce the overall power consumption of the device.

[0061] Specific steps are as follows:

[0062] 5. Substrate selection

[0063] A heavily doped p-type silicon with a thickness of 0.5 mm is selected as the substrate.

[0064] 6. Preparation of oxide dielectric layer

[0065] The silicon dioxide with a thickness of 285±5 nanometers is oxidized on the surface of the silicon substrate by a th...

example 3

[0077] Example 3 of the present invention is described in detail below in conjunction with accompanying drawing:

[0078] The invention develops a two-dimensional semiconductor negative capacitance field effect transistor. Utilize the negative capacitance effect of P(VDF-TrFE) ferroelectric polymer material to amplify the externally applied gate voltage, strengthen the control of the carrier and energy band of the two-dimensional semiconductor material, so as to effectively reduce the sub-scale of the field effect transistor device. Threshold swing, increase the device turnover rate, reduce the overall power consumption of the device.

[0079] Specific steps are as follows:

[0080] 1. Substrate selection

[0081] A heavily doped p-type silicon with a thickness of 0.5 mm is selected as the substrate.

[0082] 2. Preparation of oxide dielectric layer

[0083] The silicon dioxide with a thickness of 285±5 nanometers is oxidized on the surface of the silicon substrate by a th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More