Patents

Literature

46results about How to "Increase switching speed" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

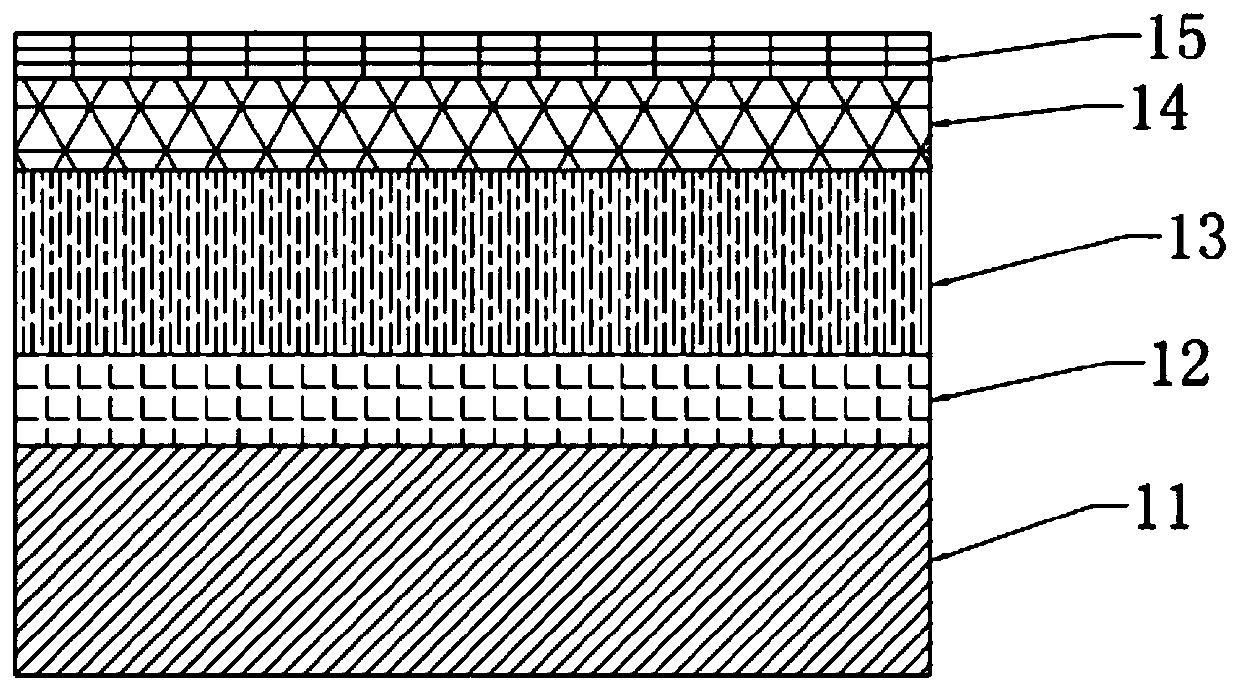

Light-operated terahertz modulator based on graphene/silicon-doped compound double-layer structure

ActiveCN105824138AShort lifeIncrease switching speedNon-linear opticsCommunications systemRoom temperature

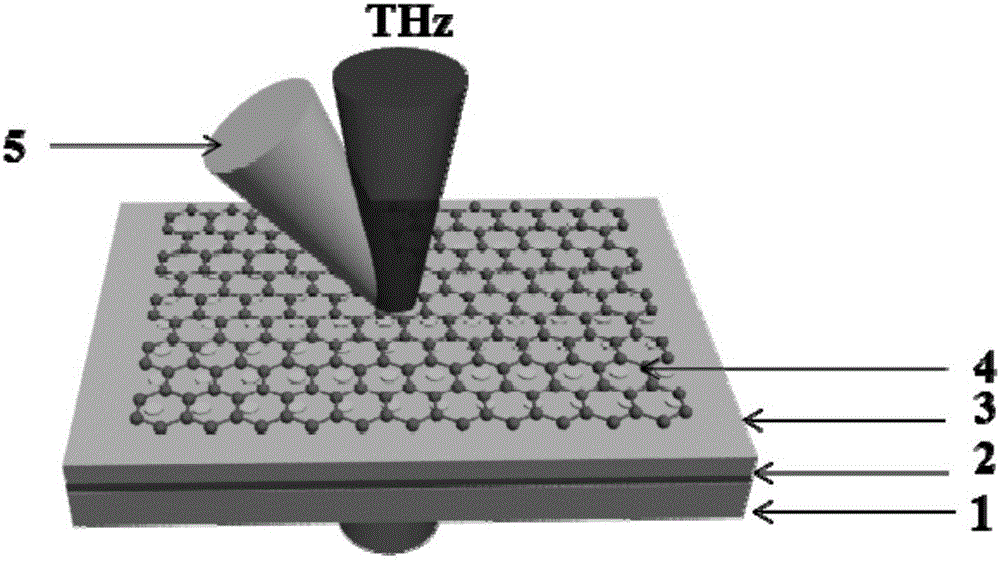

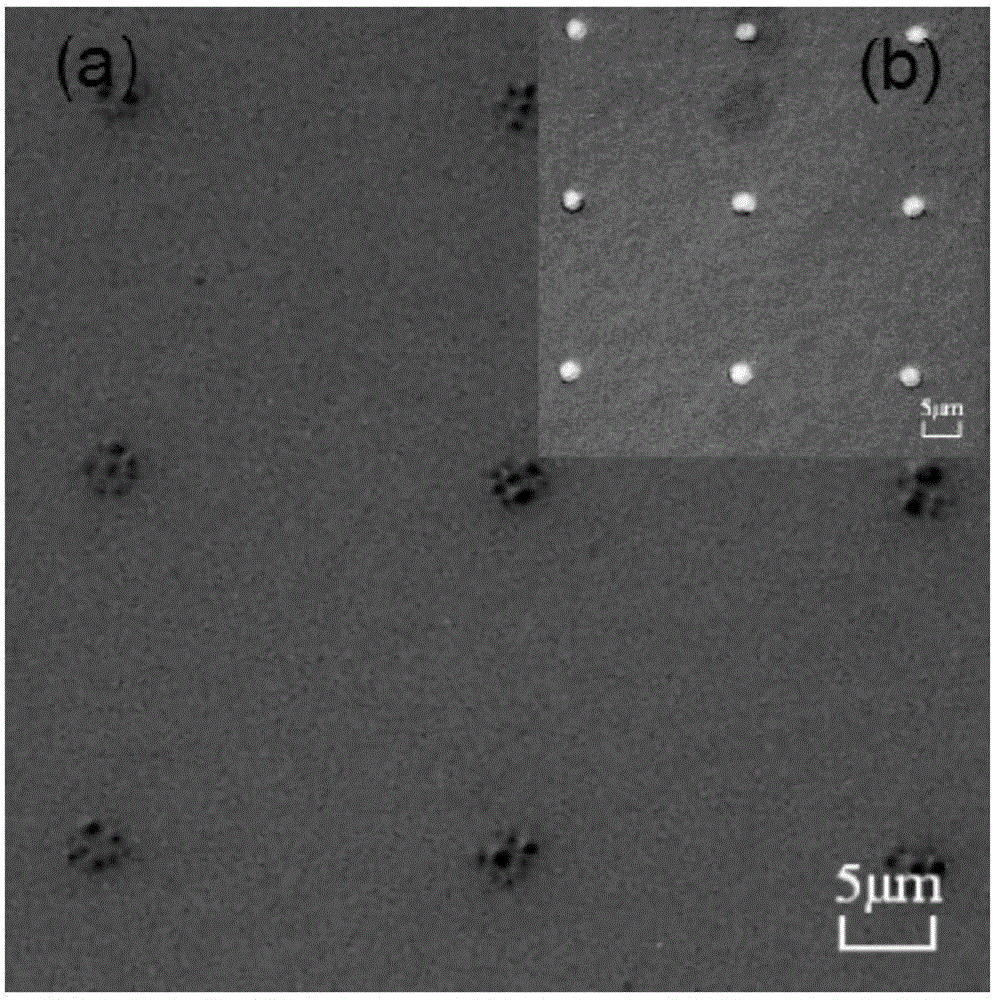

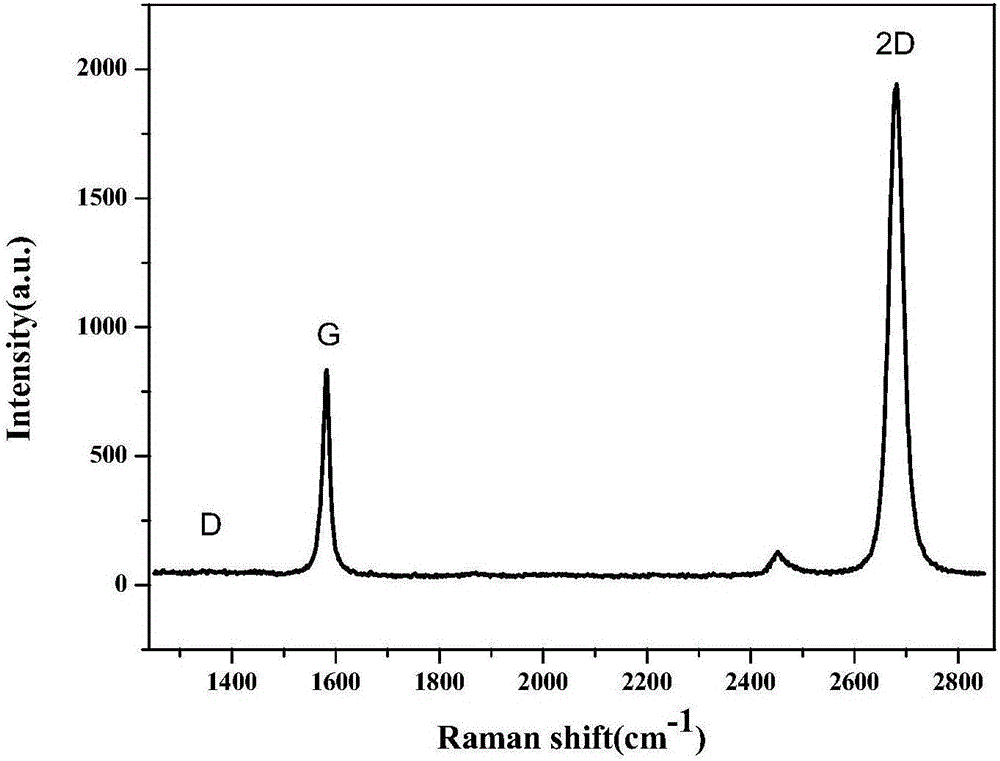

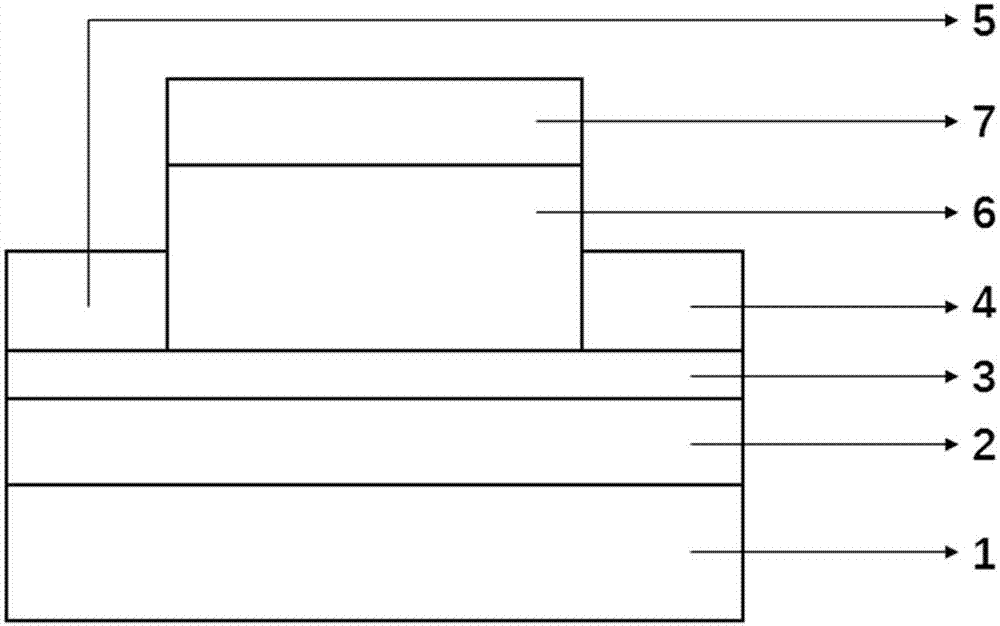

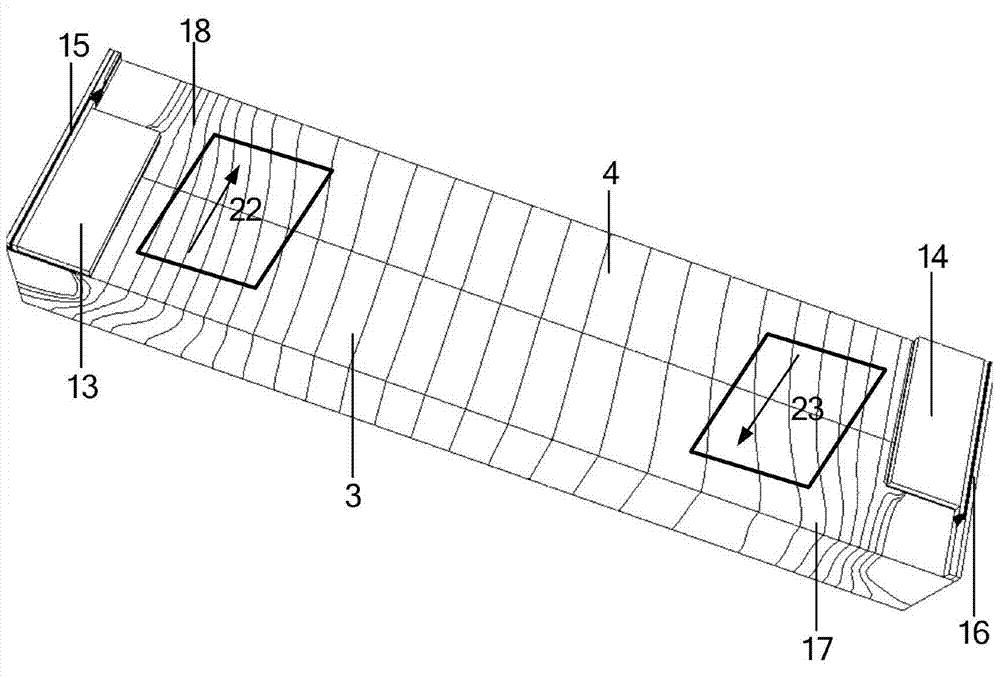

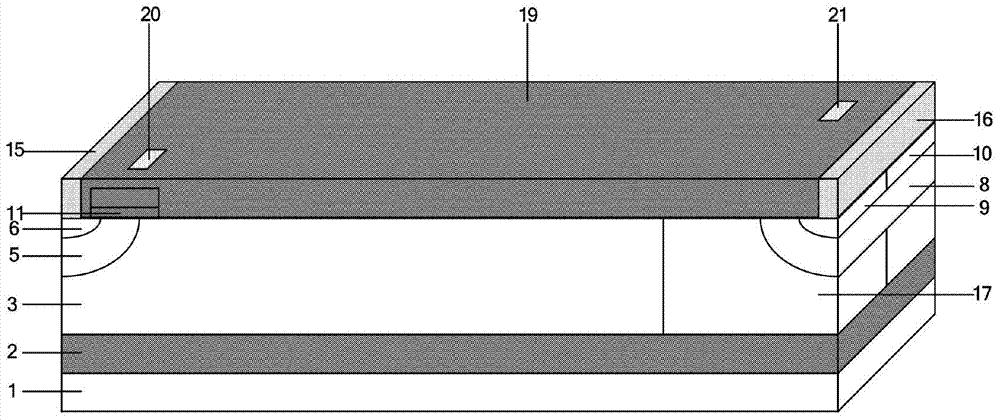

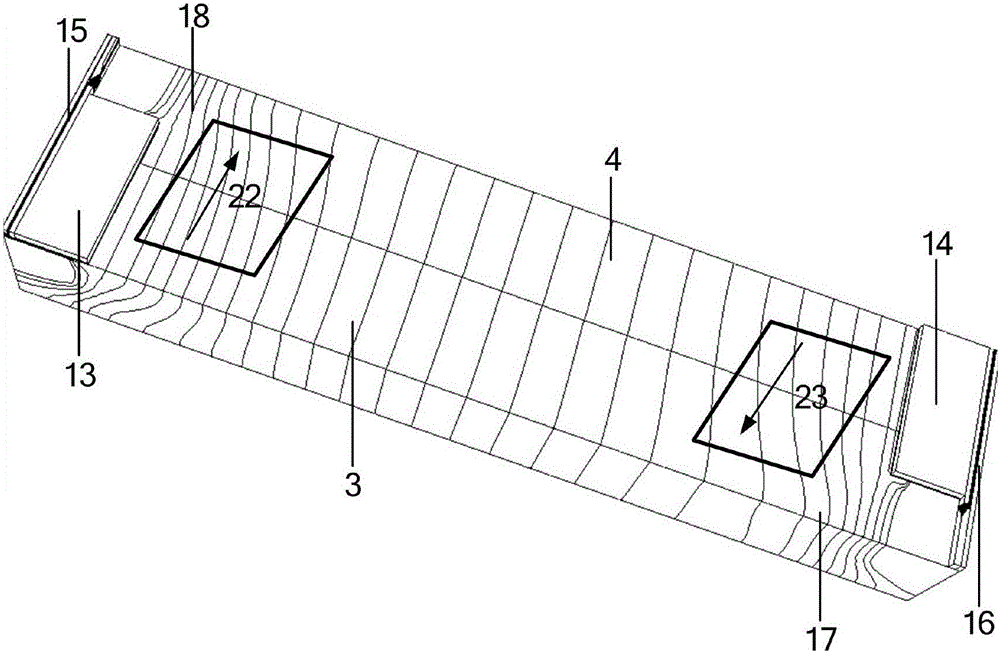

The invention belongs to the technical field of terahertz wave application and provides a light-operated terahertz modulator based on a graphene / silicon-doped compound double-layer structure. The light-operated terahertz modulator is used for simultaneously acquiring large modulation rate and modulation depth and comprises a substrate 1, an insulating layer 2, a metal doping Si semiconductor layer 3, a graphene film 4 and a pumping laser beam 5 which are successively arranged from bottom to top. The light-operated terahertz modulator is characterized in that the metal doping Si semiconductor layer 3 and the graphene film 4 form the graphene / silicon-doped compound double-layer structure. The light-operated terahertz modulator provided by the invention has the characteristics of high speed, broadband, large-amplitude modulation and room-temperature work, can work under the conditions of 0.2-2.6THz, the modulation frequency being 10MHz and the maximum modulation depth being 50% and above, and can be applied to a terahertz high-speed wireless communication system and also can be used as a high-speed broadband terahertz wave modulator in a plurality of application systems for terahertz imaging and detection.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

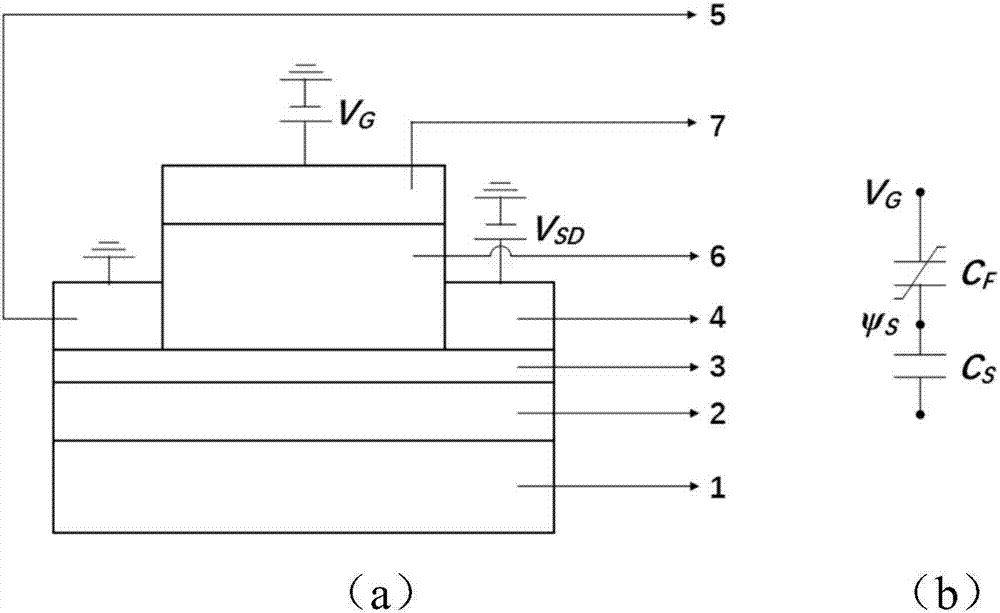

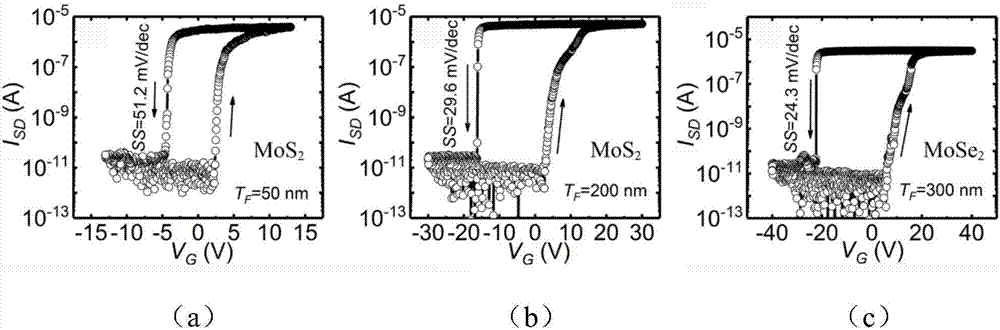

Two-dimensional semiconductor negative capacitance field-effect transistor and preparation method thereof

PendingCN107195681ASimple structureEasy to manufactureSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceCapacitive effect

The invention discloses a two-dimensional semiconductor negative capacitance field-effect transistor and a preparation method thereof. The device structure sequentially comprises a substrate, a two-dimensional semiconductor, a metal source-drain electrode, a ferroelectric gate medium with a negative capacitance effect and a metal gate electrode from bottom to top. The preparation method comprises the steps of firstly, preparing the transition metal chalcogenide two-dimensional conductor on a substrate; secondly, preparing the metal source-drain electrode by employing an electron beam lithography technology and combining a stripping process; thirdly, preparing a ferroelectric thin film with the negative capacitance effect on the structure; and finally, preparing the metal gate electrode on the thin film to form ferroelectric-controlled two-dimensional semiconductor negative capacitance field-effect transistor. Different from other two-dimensional semiconductor negative capacitance field-effect device structures, the metal-ferroelectric-semiconductor structure has the advantages that a high-performance negative capacitance field-effect device can be achieved; and an electrical test result shows that the subthreshold swing of the device is far smaller than 60mV / dec, the Boltzmann limit is broken through, and the two-dimensional semiconductor negative capacitance field-effect device simultaneously has the characteristics of extremely low power consumption, high-speed turnover and the like.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

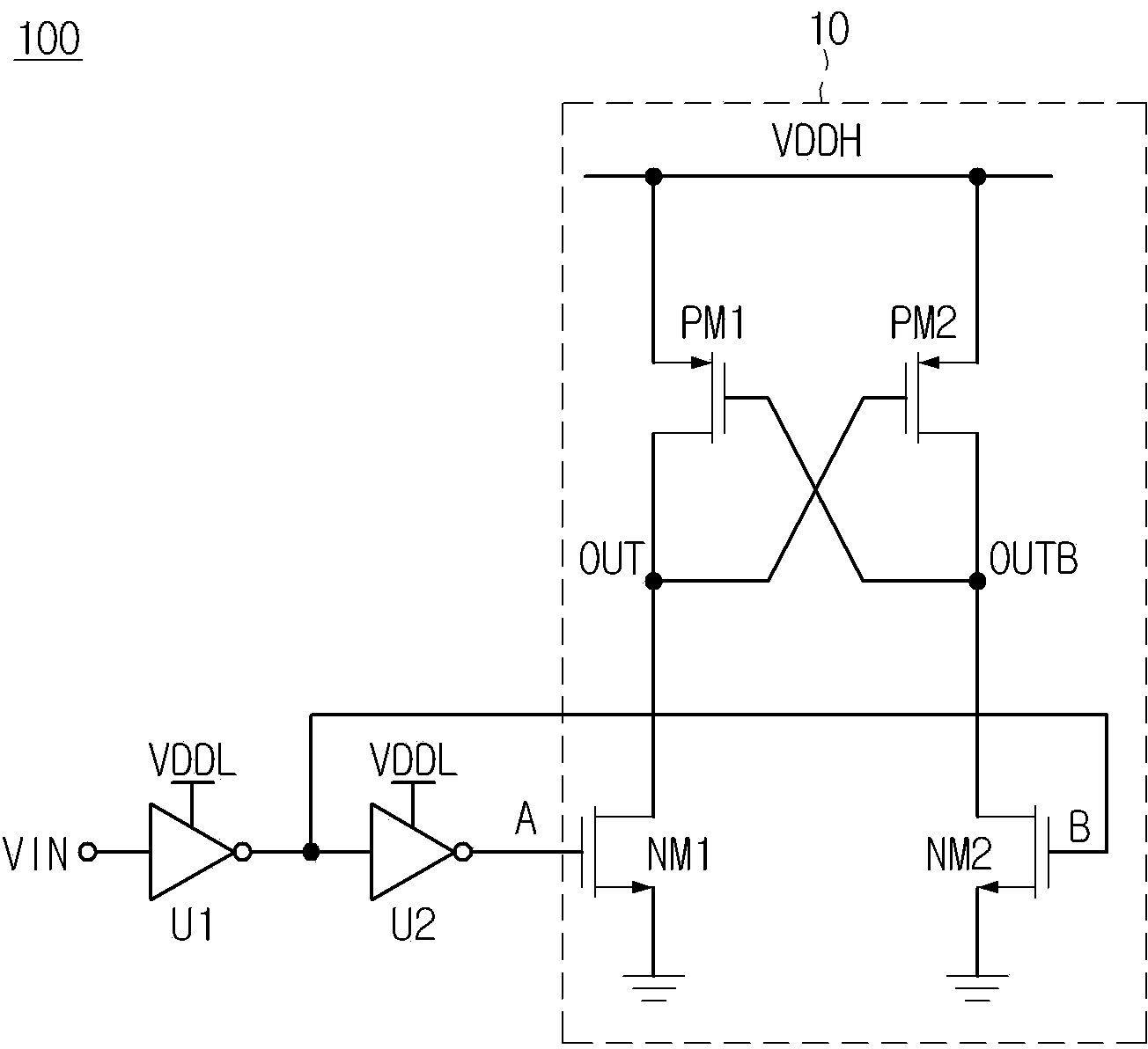

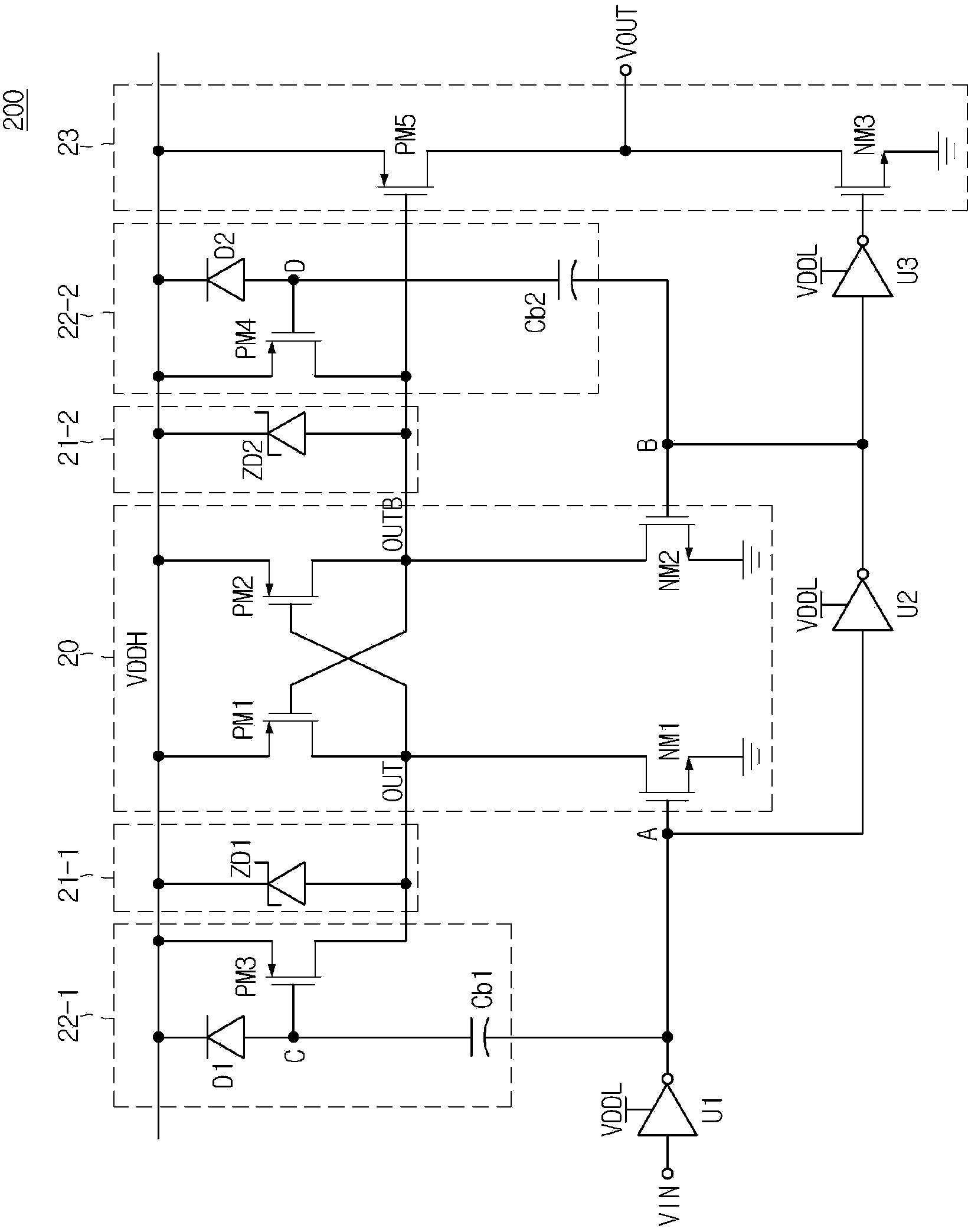

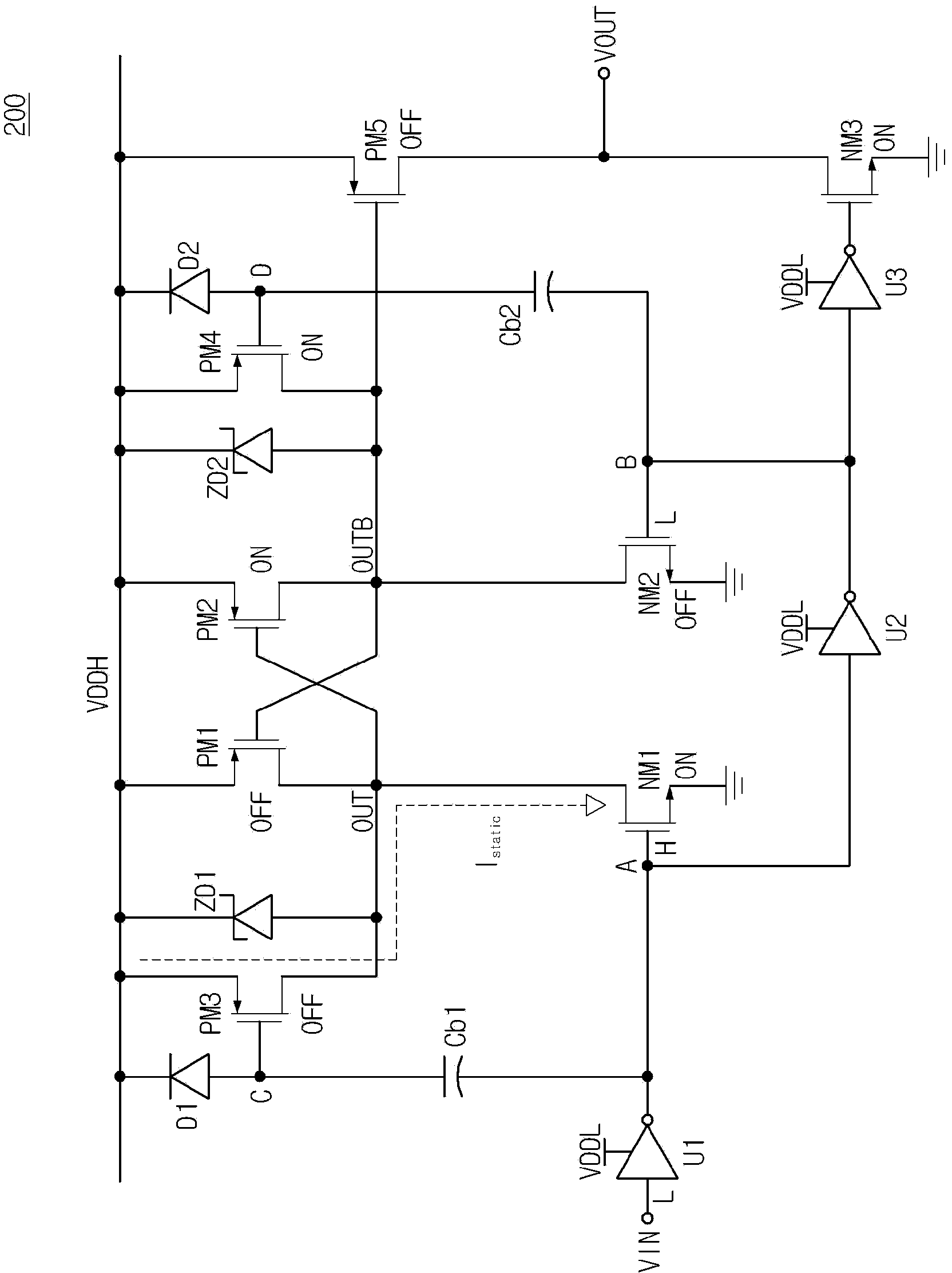

Level shift device

InactiveCN103684412APrevent Vgs breakdown phenomenonReduce power consumptionStatic indicating devicesLogic circuits coupling/interface using field-effect transistorsVoltage generatorLow voltage

Disclosed is a level shift device. The level shift device to convert an input signal having a low-voltage level into an output signal having a high-voltage level includes a latch-type level shifter and a voltage generator. The latch-type level shifter includes two upper pull-up P channel transistors and two lower P channel transistors to prevent the gate-source voltage breakdown of the two upper pull-up P channel transistors. The two upper pull-up P channel transistors and the two lower P channel transistors form a latch structure. The voltage generator generates a voltage to prevent the gate-source voltage brake down of the two upper pull-up P channel transistors and provides the voltage to the gate electrodes of the two lower P channel transistors.

Owner:LSIS CO LTD

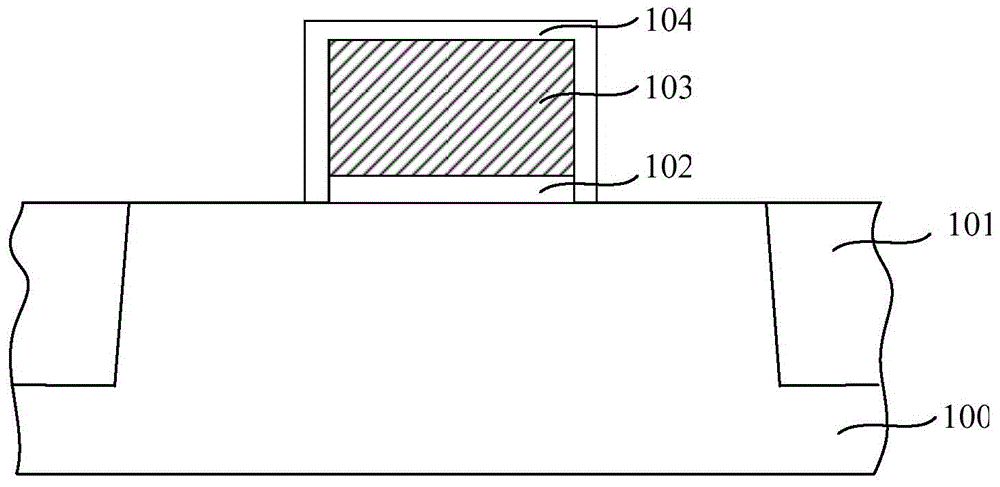

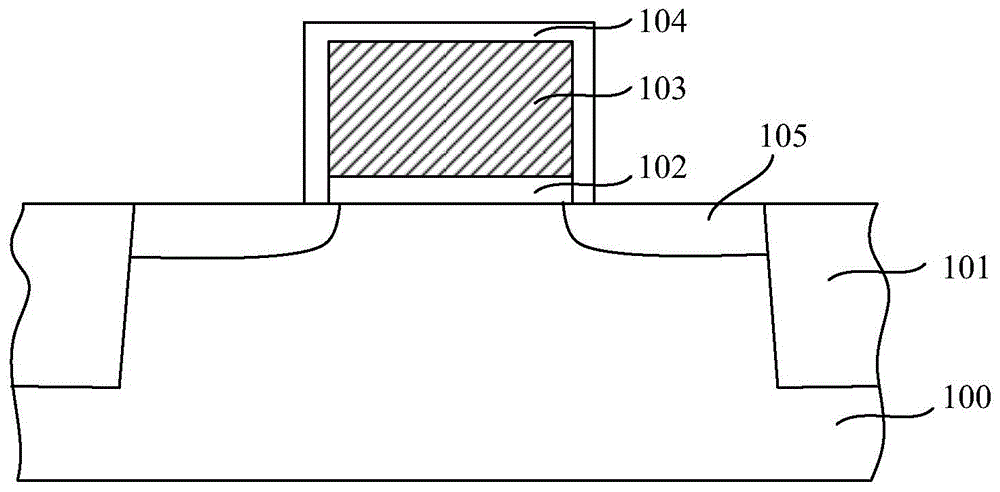

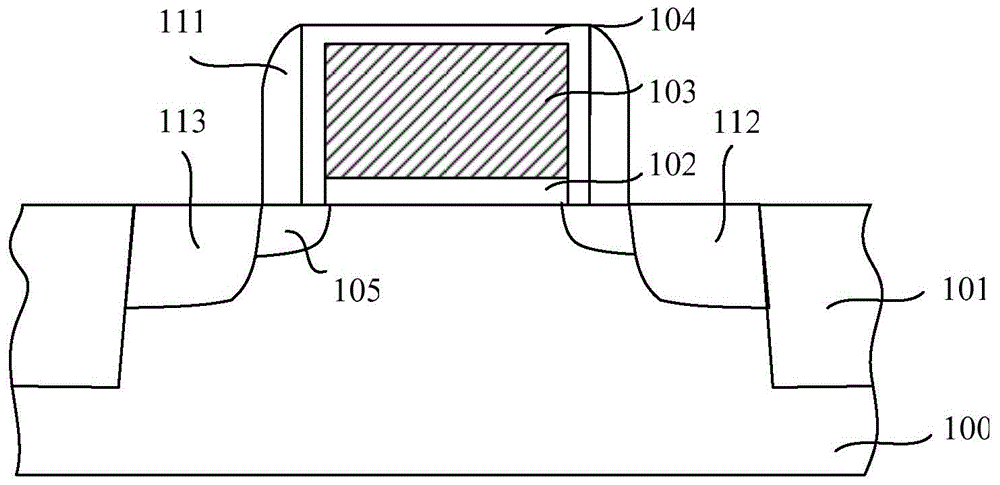

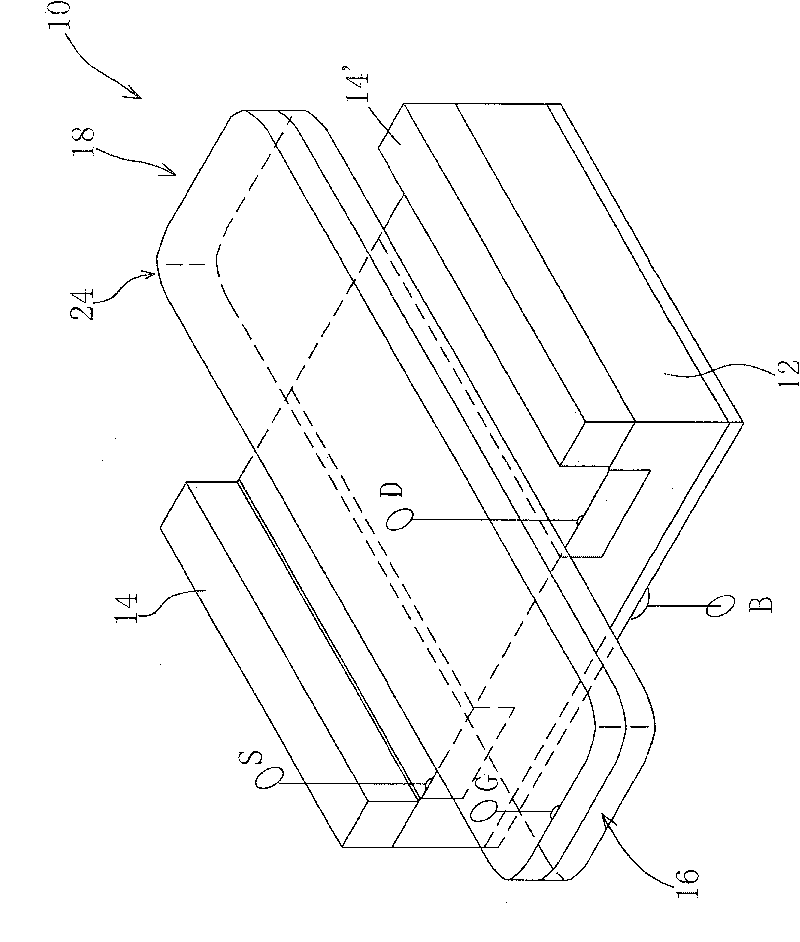

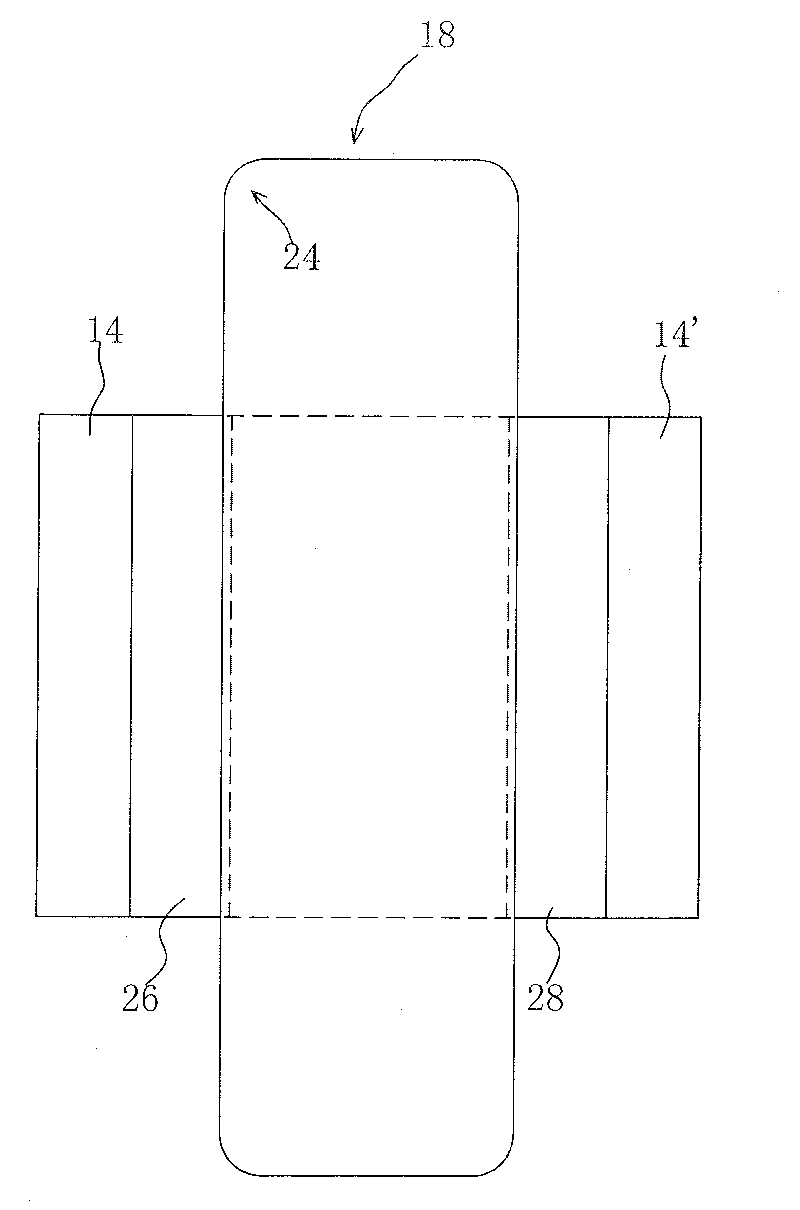

Transistor and method of forming same

ActiveCN105448916AIncrease switching speedReduce contact areaTransistorSemiconductor/solid-state device manufacturingParasitic capacitanceSemiconductor

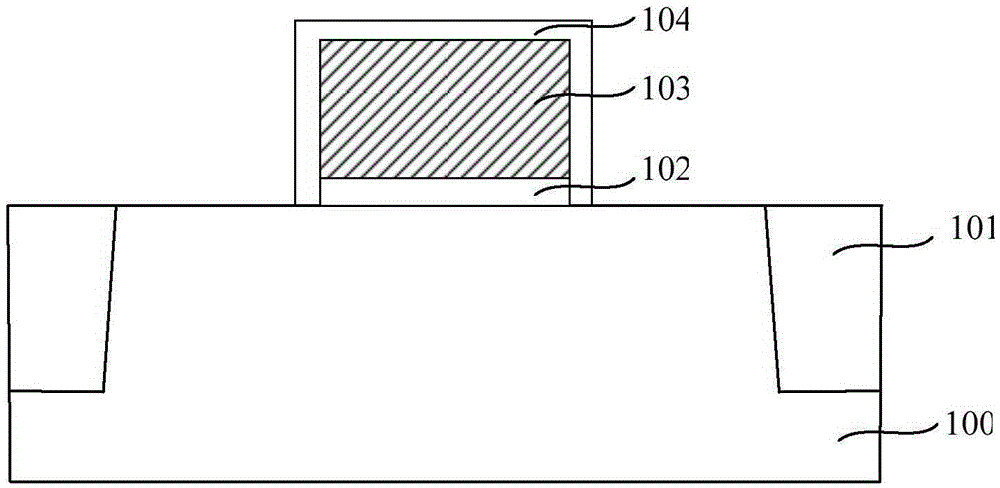

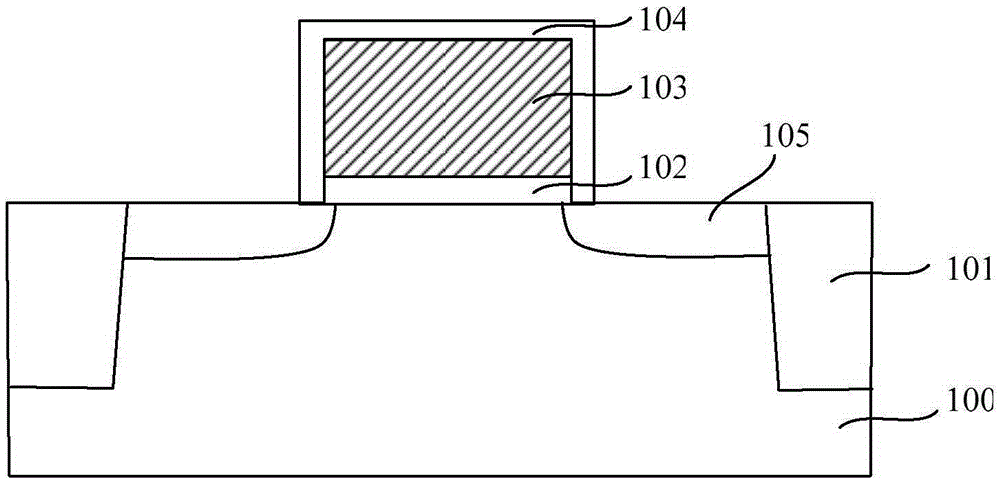

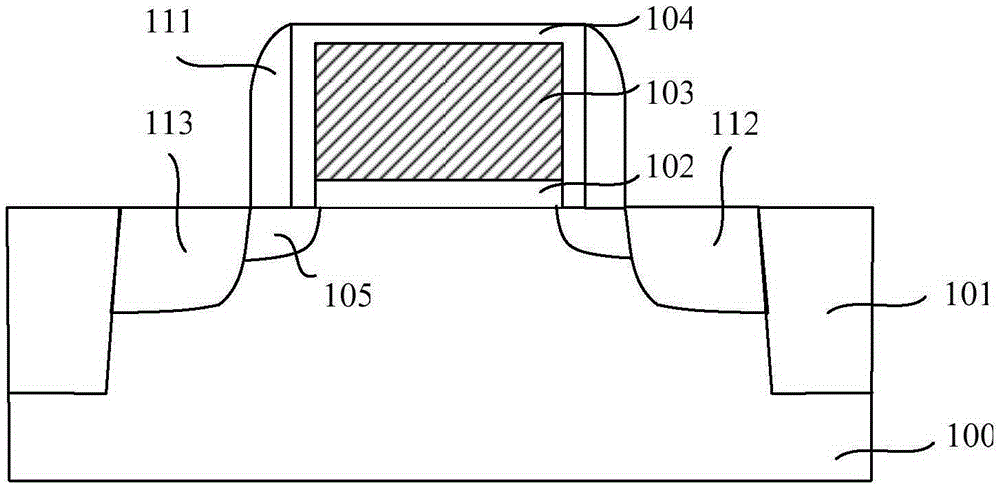

A transistor and a method of forming the same are disclosed. The method of forming the transistor comprises the steps of providing a semiconductor substrate consisting of a first region, a second region and a third region which are adjacent to one another; carrying out well region ion implantation, and forming a well region in the semiconductor substrate; carrying out channel ion implantation, and forming a first doped region in the surface of the well region in the first region; forming a gate structure on the semiconductor substrate and in the first region, the gate structure covering the first doped region in the first region; carrying out shallow doped ion implantation, forming a shallow doped source region in the semiconductor substrate and in the second region at one side of the gate structure, and forming a shallow doped drain region in the semiconductor substrate and in the third region at the other side of the gate structure; and forming an elevated source region on the shallow doped source region, and forming an elevated drain region on the shallow doped drain region. The method of the invention reduces the parasitic capacitance between the source and drain regions and the channel region and the substrate.

Owner:SEMICON MFG INT (SHANGHAI) CORP

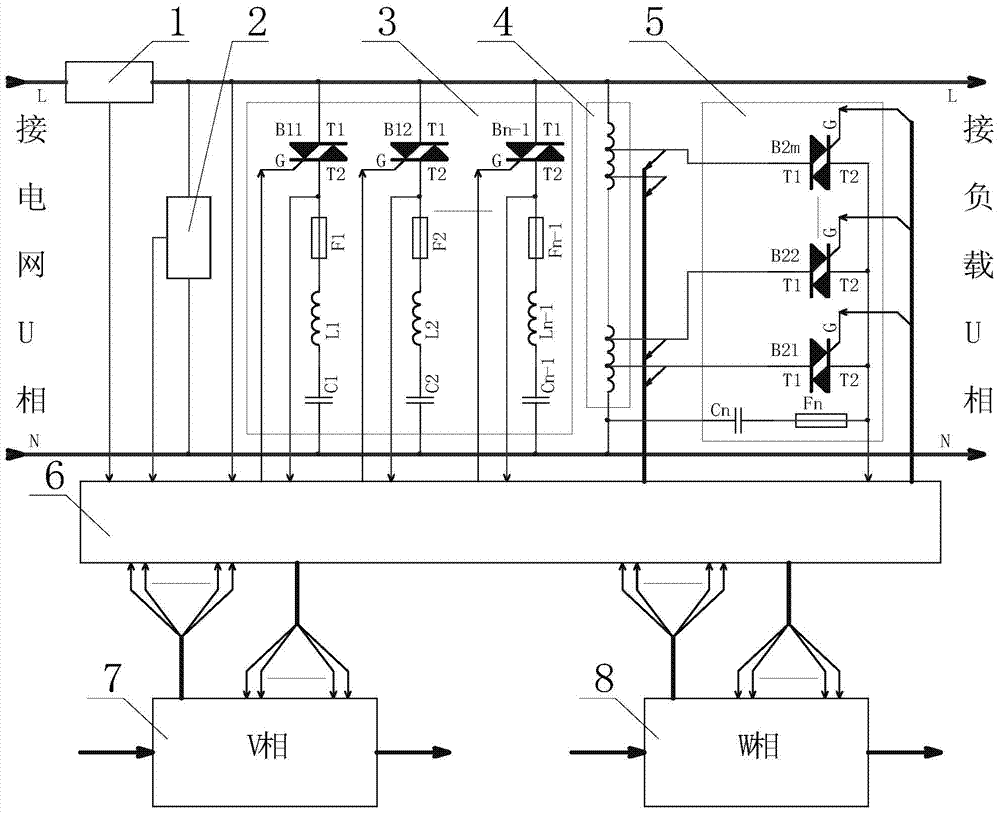

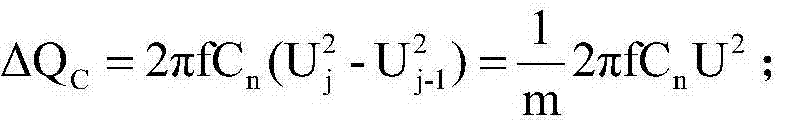

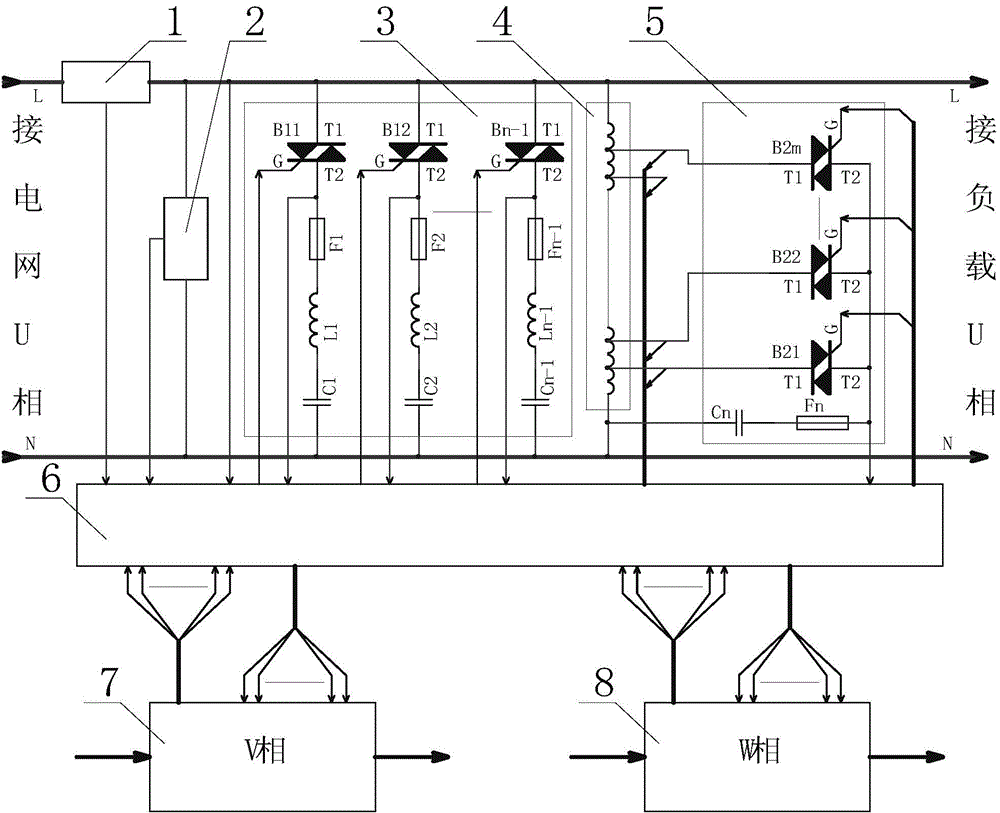

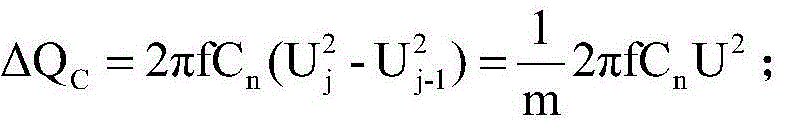

Reactive compensation device and method for partially regulating voltages and capacitance of three-phase four-wire power grid

ActiveCN103490432AReduce capacityReduce lossReactive power adjustment/elimination/compensationReactive power compensationCapacitanceAutotransformer

The invention discloses a reactive compensation device and method for partially regulating voltages and capacitance of a three-phase four-wire power grid. The reactive compensation device comprises a U-phase voltage and capacitance regulating reactive compensation unit, a V-phase voltage and capacitance regulating reactive compensation unit, a W-phase voltage and capacitance regulating reactive compensation unit and a control unit. Each phase of voltage and capacitance regulating reactive compensation unit is mainly composed of a current detection element, a voltage detection element, a full-voltage compensation capacitor bank, an auto-transformer and a voltage-regulating capacitor bank. The control mode of independent reactive compensation in each phase is used in the three-phase four-wire power grid, total capacitance in each phase is uniform, the capacitance in each phase is evenly divided into n sets, wherein one set of the capacitance is subjected to voltage and capacitance regulation through the auto-transformer which totally has m levels of output voltages, each phase has n*m grades of compensation, and multi-level fine compensation for the power grid is achieved.

Owner:GUILIN UNIV OF ELECTRONIC TECH

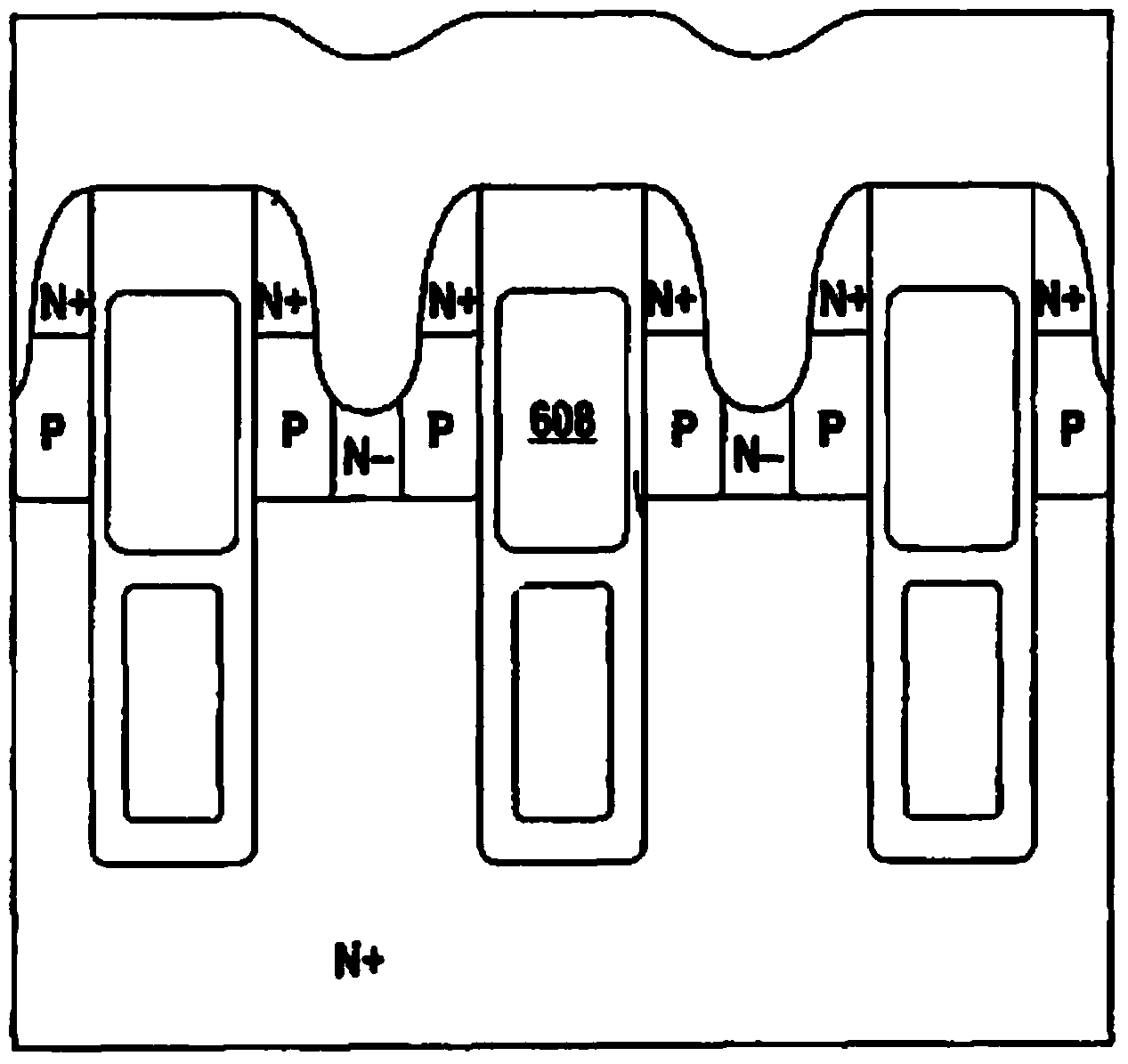

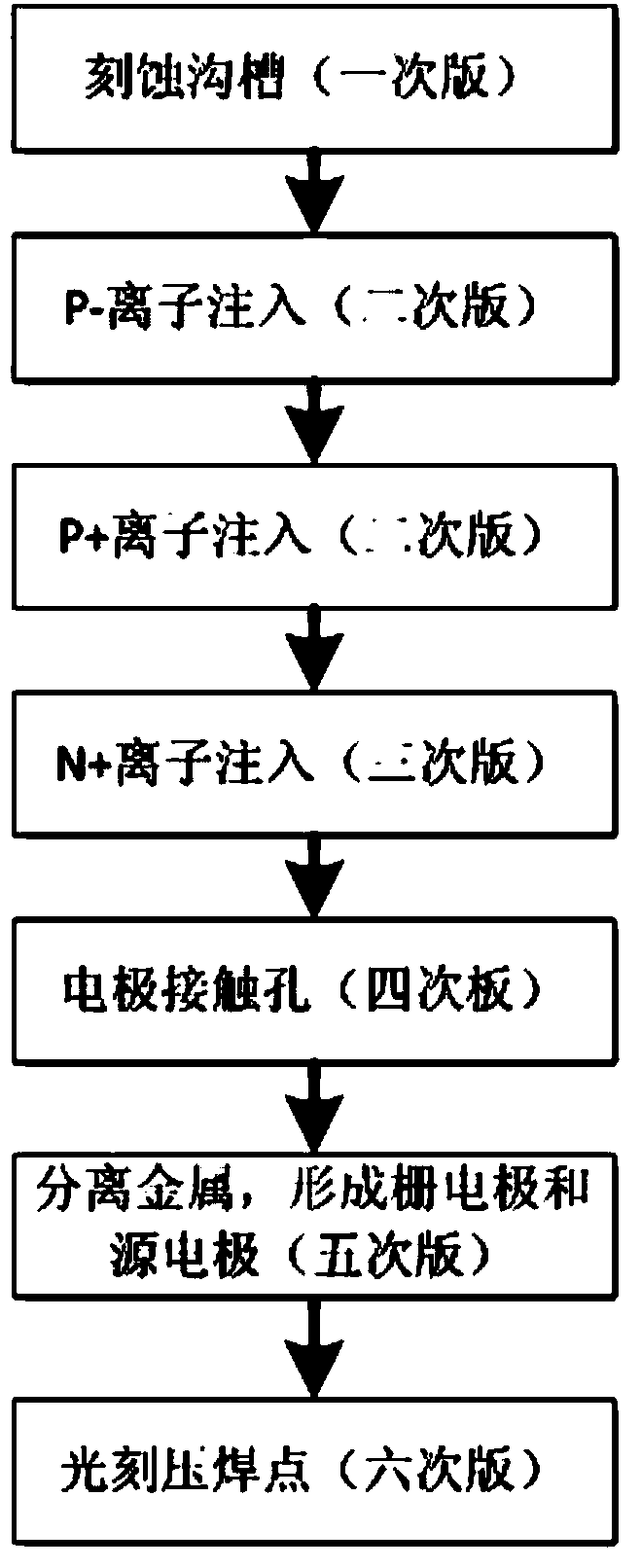

Manufacturing method of integrated Schottky split-gate type power MOS device

InactiveCN103594377ALower on-resistanceDoes not affect breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesChannel powerEngineering

The invention discloses a manufacturing method of an integrated Schottky split-gate type power MOS device. The integrated Schottky split-gate type power MOS device is manufactured by utilizing 6 mask templates. Compared with a traditional manufacturing process of a split-gate type channel power MOS device, the manufacturing method of the integrated Schottky split-gate type power MOS device can reduce process steps and process difficulty.

Owner:HARBIN ENG UNIV

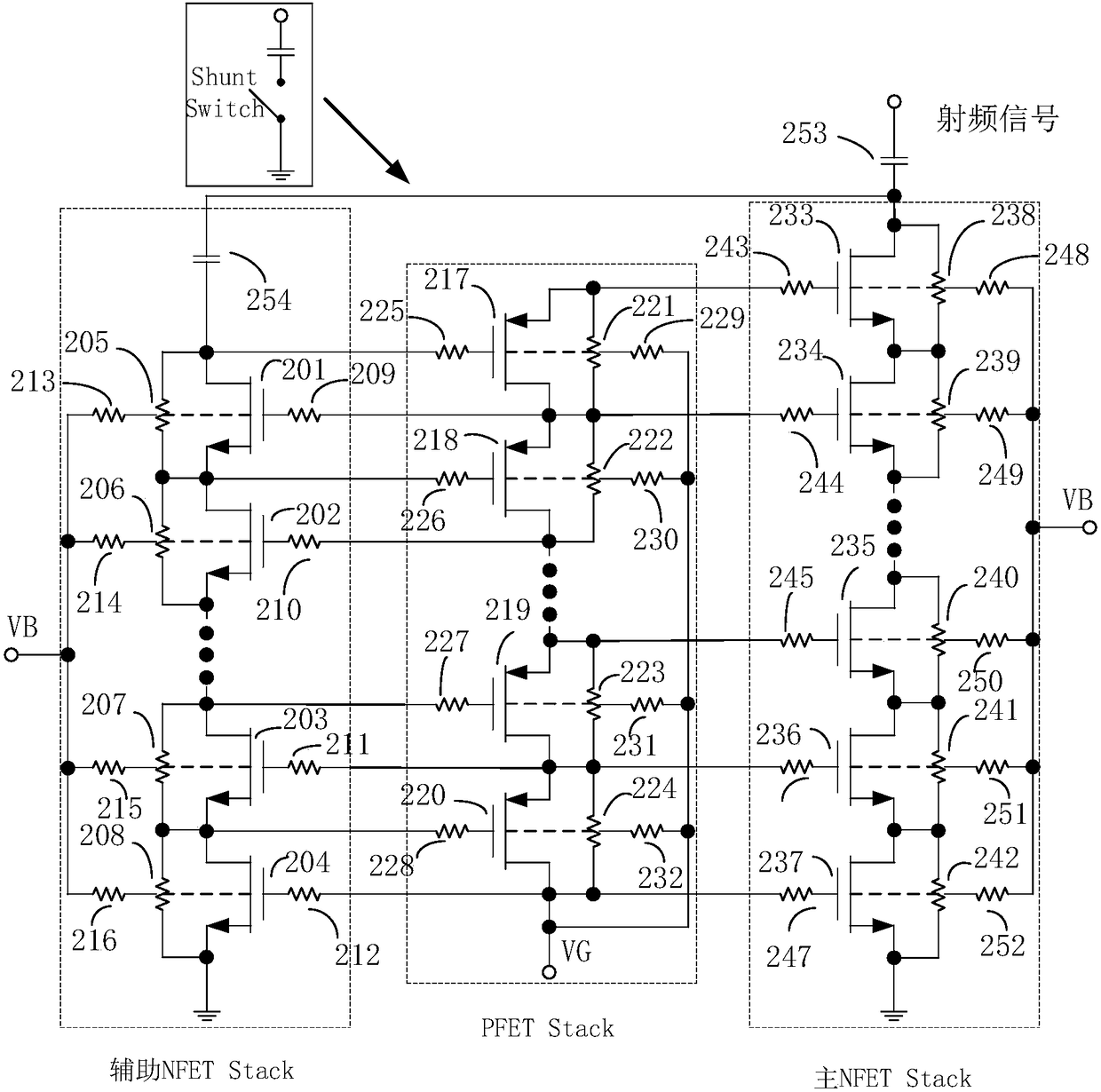

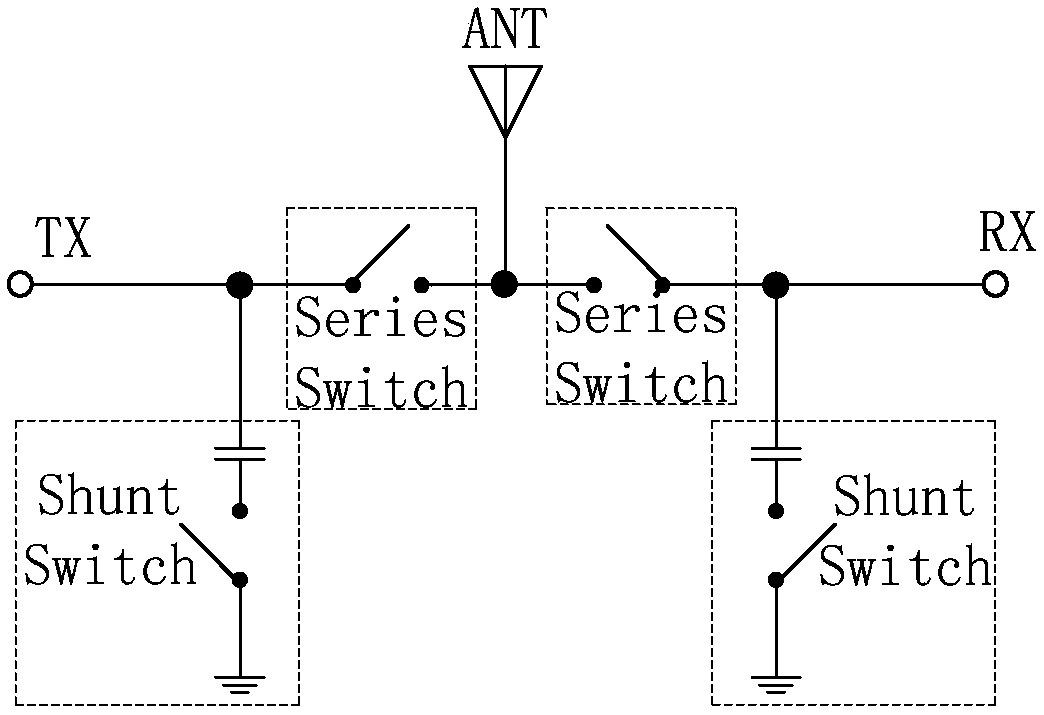

CMOS SOI radio frequency switching circuit

ActiveCN108736866AReduce power consumptionIncrease switching speedTransistorElectronic switchingCapacitanceRadio frequency

The invention discloses a CMOS SOI radio frequency switching circuit. The CMOS SOI radio frequency switching circuit comprises a main NFET Stack, an auxiliary NFET Stack, a PFET Stack, a first capacitor and a second capacitor; grid electrodes of the main NFET Stack and the auxiliary NFET Stack are connected to a drain electrode and a source electrode of the PFET Stack step by step; one end of themain NFET Stack is connected to the auxiliary NFET Stack and the first capacitor, and the other end thereof is grounded; one end of the auxiliary NFET Stack is connected to the main NFET Stack and thesecond capacitor, and the other end thereof is grounded; the PFET Stack connection controls a second bias voltage; and the on-off state of the CMOS SOI radio frequency switching circuit is controlledby a first bias voltage and the second bias voltage. The CMOS SOI radio frequency switching circuit provided by the invention can increase the switching speed of a switch without reducing the grid capacitance of an NFET.

Owner:SANECHIPS TECH CO LTD

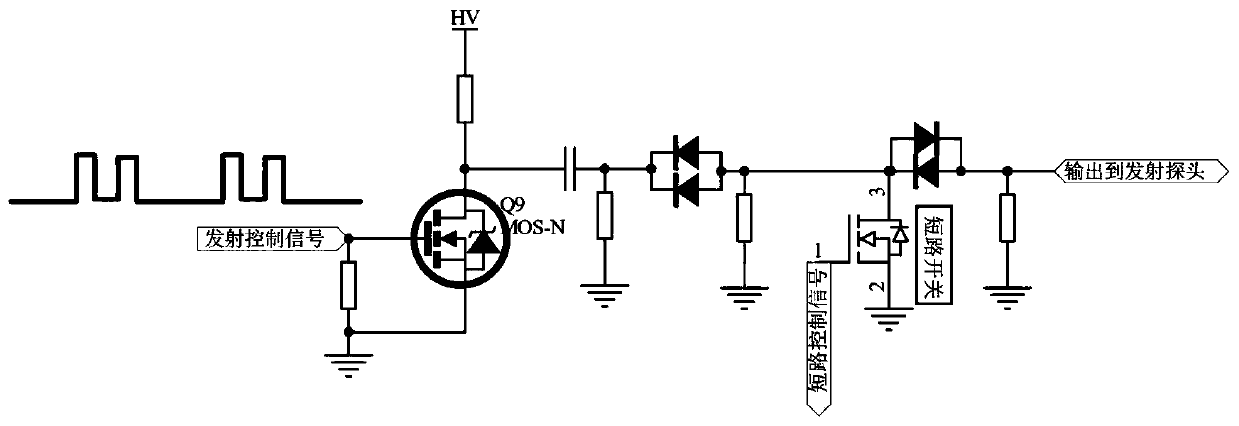

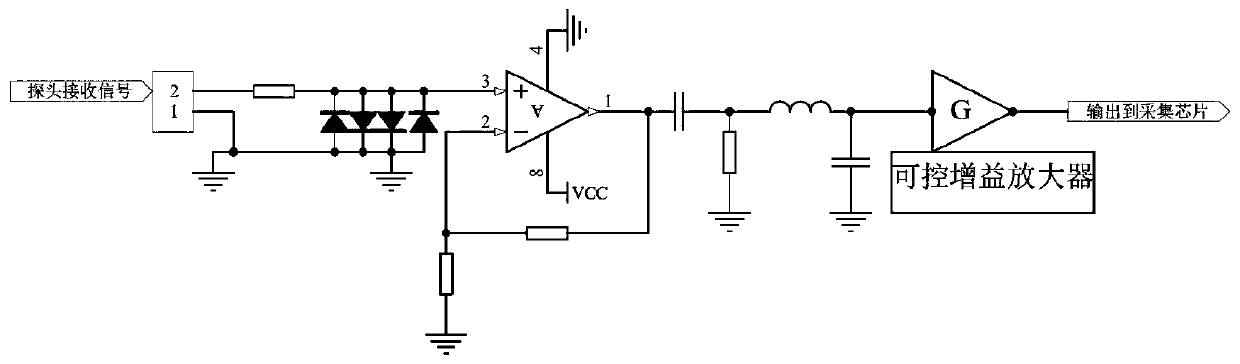

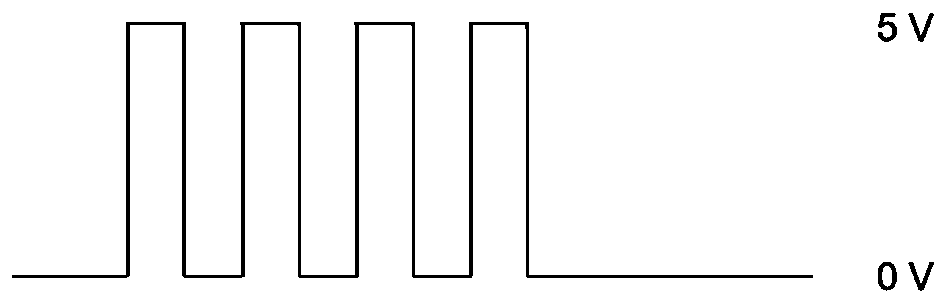

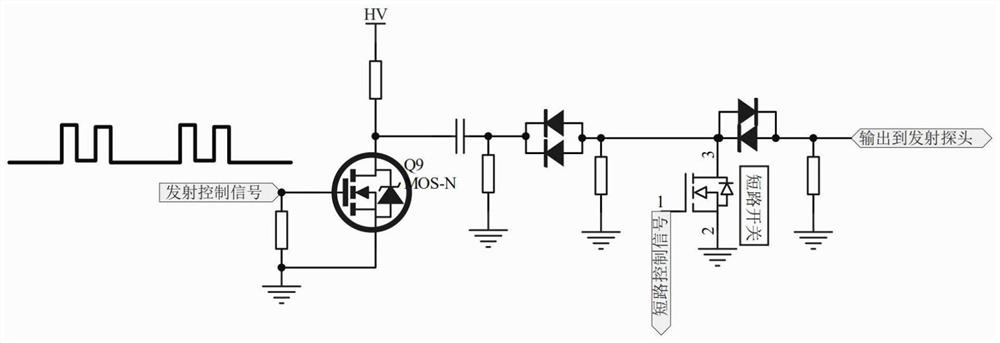

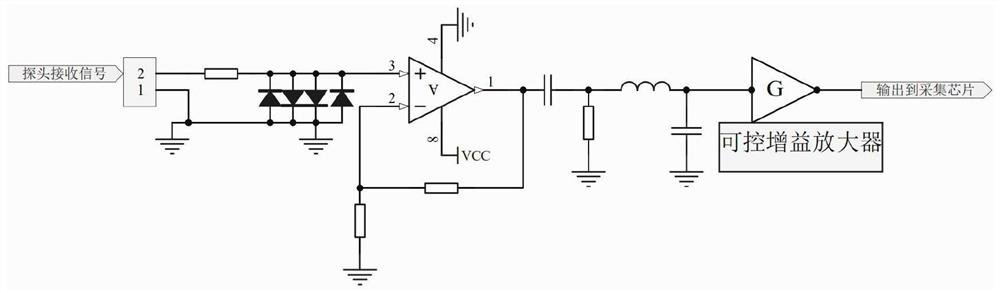

Ultrasonic thickness gauge for metal composite material

ActiveCN110006997AImprove noise reductionHigh sensitivityAnalysing solids using sonic/ultrasonic/infrasonic wavesUsing subsonic/sonic/ultrasonic vibration meansData processing systemCoupling

The invention aims to solve the problems that the thickness of single-layer metal of a metal composite material and the overall thickness of the metal composite material cannot be measured in the prior art. The invention provides a metal composite material ultrasonic thickness gauge capable of measuring the thickness of each layer of material of a metal composite material. The gauge comprises a voltage-adjustable power supply and an ultrasonic transmitting module, an ultrasonic receiving module, a data acquisition module and a data processing system, according to the metal composite material ultrasonic thickness gauge, the power supply supplies power to the ultrasonic transmitting module, the ultrasonic receiving module, the data acquisition module and the data processing system, the precision and the reliability can be ensured, and the thickness can still be accurately measured even under some poor coupling conditions.

Owner:葫芦岛探克科技有限公司

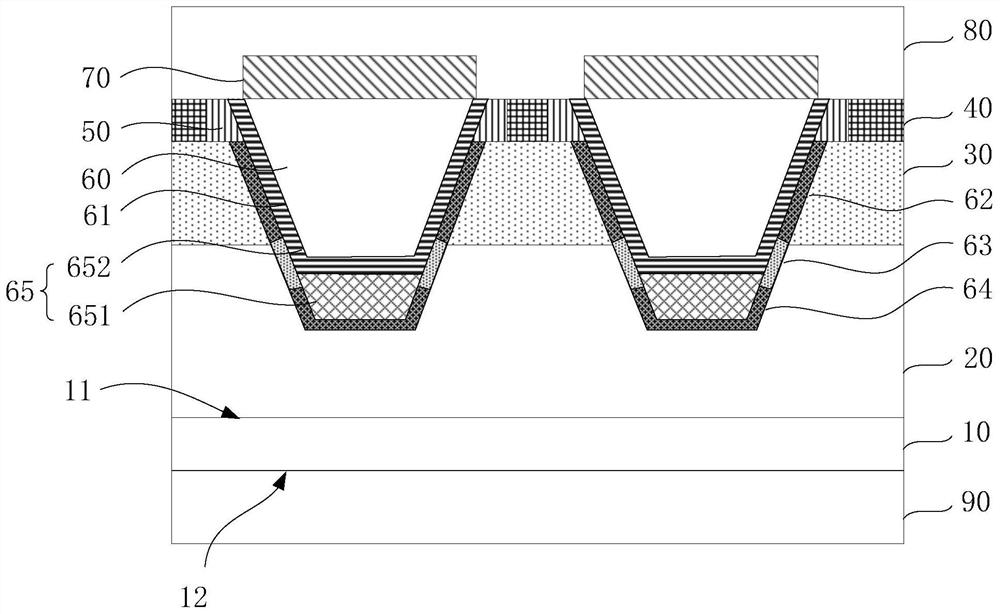

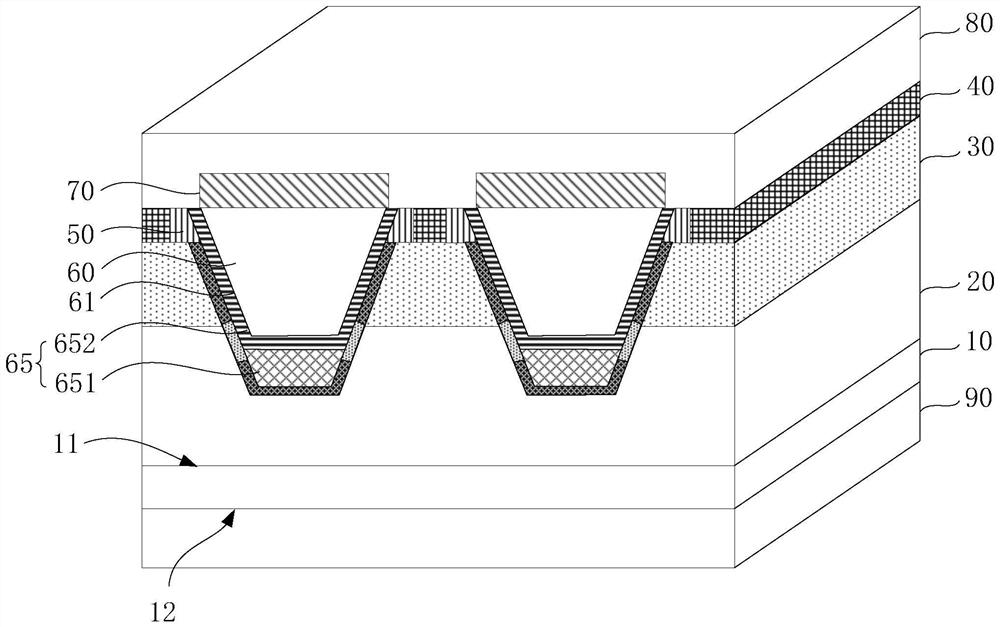

Organic photodiode, X-ray detector and preparation method thereof

PendingCN111244287AImprove external quantum efficiencyHigh sensitivitySolid-state devicesSemiconductor/solid-state device manufacturingOrganic filmCharge carrier mobility

The invention provides an organic photodiode, an X-ray detector and a preparation method of the X-ray detector. The organic photodiode and an organic thin film transistor are prepared by adopting a solution method, so that low-cost equipment can be adopted for production, the preparation process is simplified, and the cost is saved. The organic photodiode and the organic thin film transistor are combined, which is suitable for preparing the flexible X-ray detector. In the organic photodiode, the band gap of an organic active layer is adjustable, so that the external quantum efficiency of the organic photodiode can be improved, and the sensitivity of the X-ray detector is further improved. In the organic thin film transistor, the carrier mobility of an organic channel layer is relatively high, so that the switching rate of the organic thin film transistor can be improved.

Owner:SHANGHAI IRAY TECH

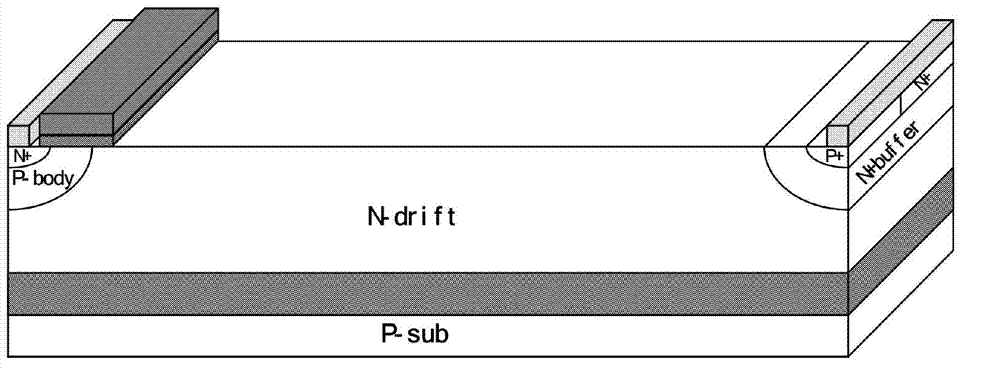

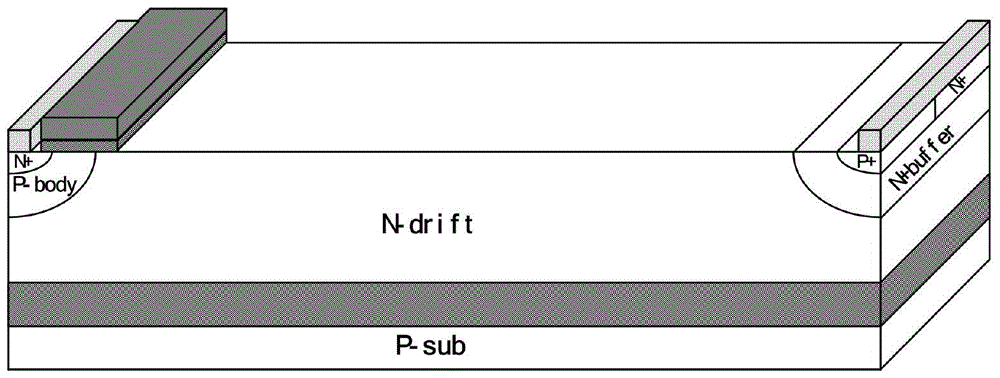

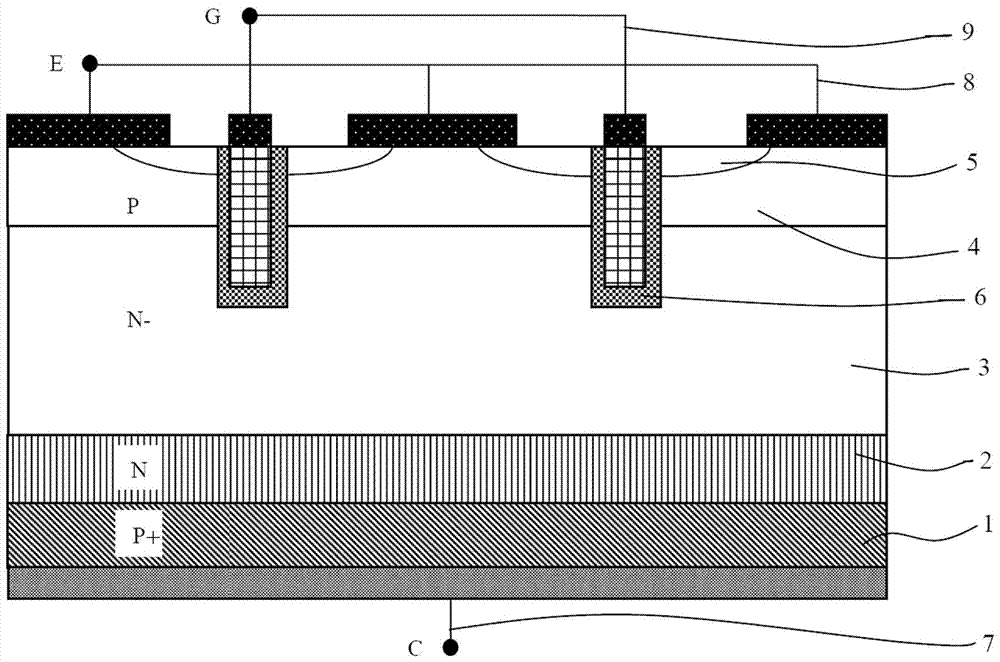

Reverse-conducting double-insulated-gate bipolar transistor

ActiveCN103928507AReduce forward voltage dropIncreased current capabilitySemiconductor devicesParasitic bipolar transistorGate oxide

The invention provides a semiconductor capable of improving the current rebounding phenomenon of a reverse-conducting double-insulated-gate bipolar transistor, improving the turn-off speed and improving voltage resistance. The semiconductor is structurally characterized in that a buried oxide is arranged on a P-type substrate and provided with a drift region, the drift region comprises a first N-type drift region, a first P-type drift region, a second N-type drift region and a second P-type drift region, the first N-type drift region and the first P-type drift region are arranged in an opposite-angle mode, and the second N-type drift region and the second P-type drift region are arranged in an opposite-angle mode; a P-type region is arranged in the first N-type drift region and the second P-type drift region, an N-type emitter region, a P-type collector region and cathode metal connecting the N-type emitter region with the P-type collector region are arranged in the P-type region, and a cathode gate oxide and a cathode polycrystalline silicon layer are arranged on the upper surface of the P-type region; an N-type region is arranged in the first P-type drift region and the second N-type drift region, an N-type collector region, a P-type emitter region and anode metal connecting the N-type collector region with the P-type emitter region are arranged in the N-type region, and an anode gate oxide and an anode polycrystalline silicon layer are arranged on the upper surface of the N-type region.

Owner:SOUTHEAST UNIV

Transistor and forming method thereof

InactiveCN106548943AHigh positioning accuracyAvoid short channel effectsSemiconductor/solid-state device manufacturingSemiconductor devicesParasitic capacitanceIon implantation

The invention relates to a transistor and a forming method thereof. The forming method of the transistor includes the following steps that: a semiconductor substrate including a first region, a second region, and a third region which are adjacent to one another is provided; well region ion implantation is performed, and a well region is formed in the semiconductor substrate; threshold voltage adjustment ion implantation is performed, so that g a first doped region can be formed at the surface of the well region in the second region; a gate structure is formed on the semiconductor substrate in the first region; shallow doping ion implantation is performed, so that a shallowly doped source region is formed in the semiconductor substrate at the second region at one side of the gate structure, and a shallowly doped drain region is formed in the semiconductor substrate at the third region at the other side of the gate structure; and a raised source region is formed on the shallowly doped source region, and a raised drain region is formed on the shallowly doped drain region. With the method of the present invention adopted, parasitic capacitance between the source region and a channel region, between the drain region and the channel region, between the source region and the substrate, as well as between the drain region and the substrate can be decreased.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

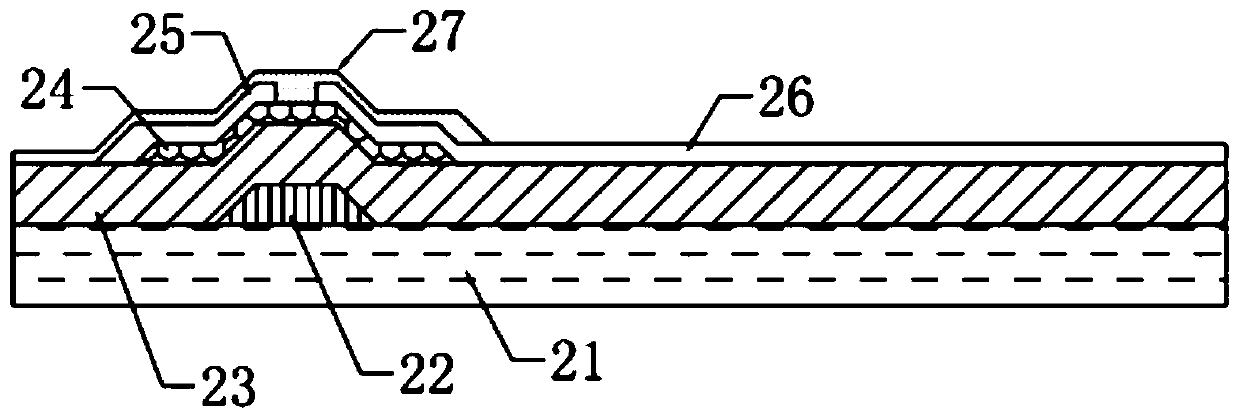

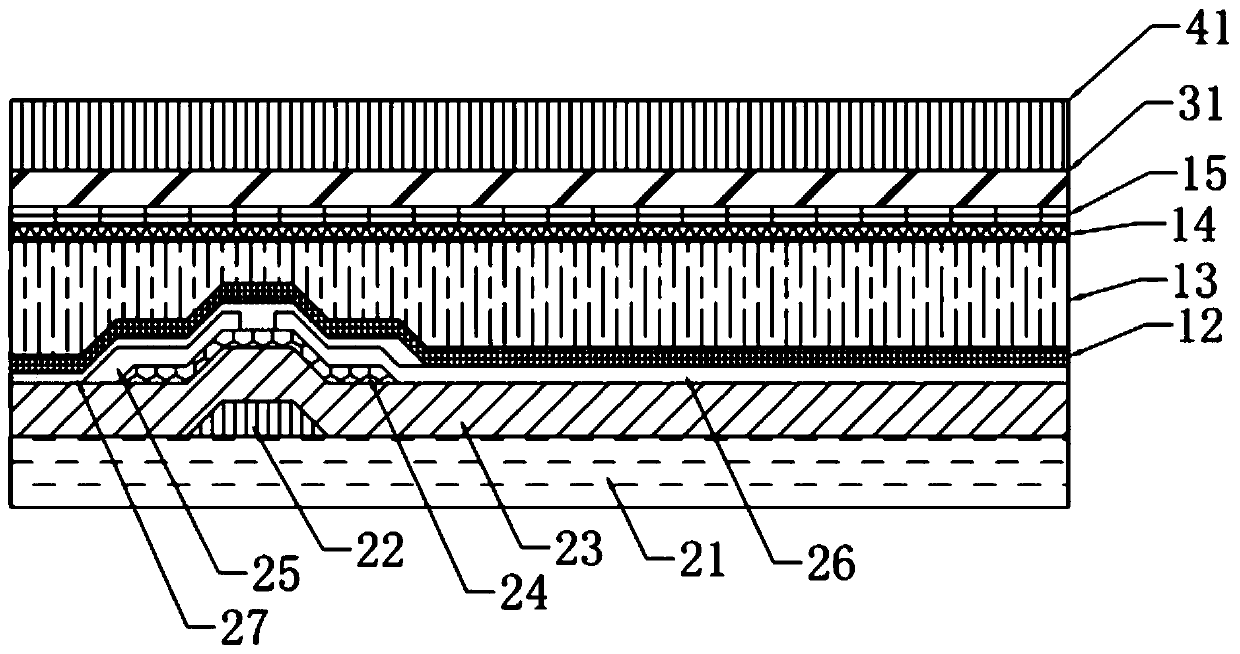

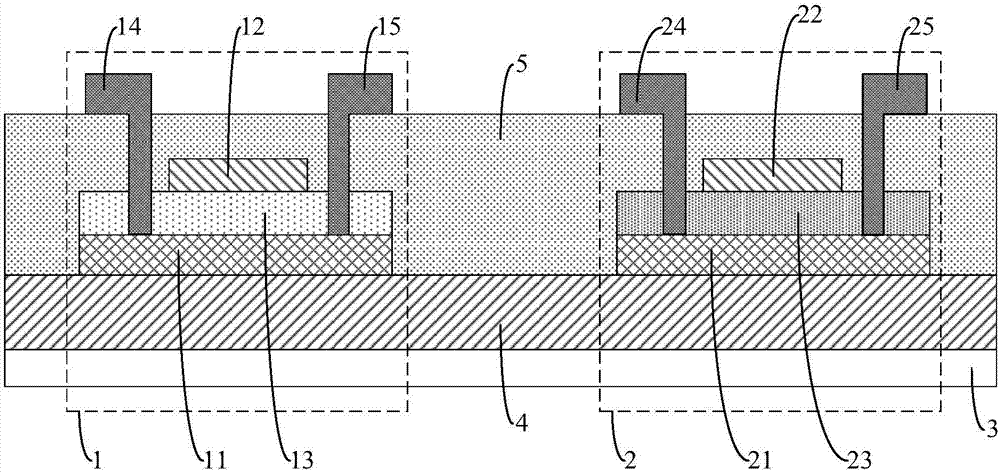

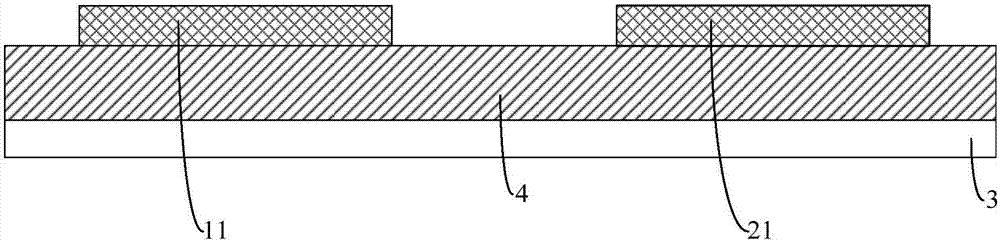

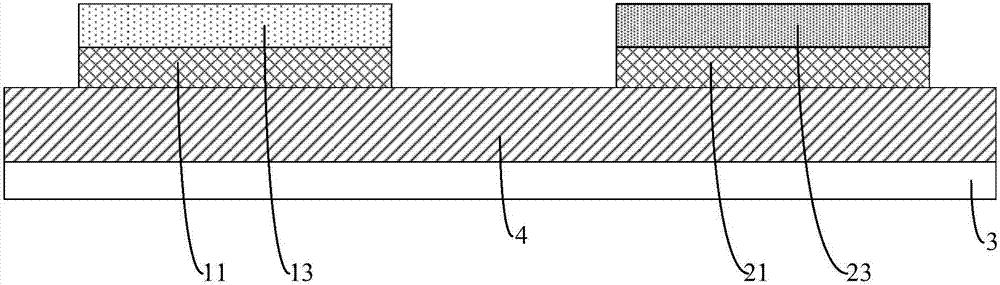

OLED array substrate and preparation method therefor and OLED display apparatus

InactiveCN107170784AIncrease switching speedDelay voltage changeSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceVoltage

The invention provides an OLED array substrate and a preparation method therefor and an OLED display apparatus. The OLED array substrate comprises a switching tube used for controlling pixel display, and a driving tube used for driving pixel display; the switching tube comprises a first insulating layer arranged between an active layer and a gate thereof; the driving tube comprises a second insulating layer arranged between an active layer and a gate thereof; and the dielectric constant of the first insulating layer is higher than that of the second insulating layer. By virtue of the OLED array substrate, the capacitance between the gate and the active layer of the switching tube can be improved relative to that of the driving tube, so that the sub threshold value swing of the switching tube is lowered relative to that of the driving tube, and the switching rate of the switching tube is further improved; and meanwhile, the capacitance between the gate and the active layer of the driving tube can be lowered relative to that of the switching tube, so that the voltage change of the driving tube is delayed, the sub threshold value swing of the driving tube is improved relative to that of the switching tube, and the gray scale display effect of the OLED display device is further reinforced.

Owner:BOE TECH GRP CO LTD

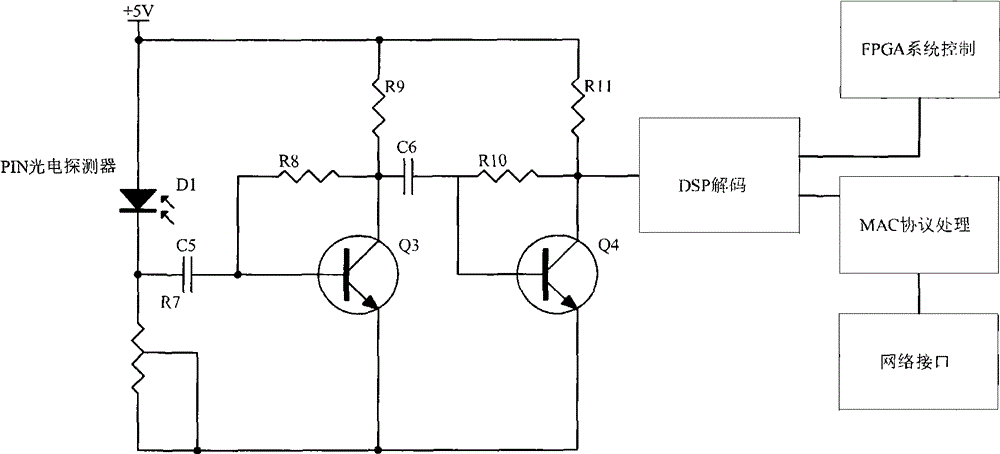

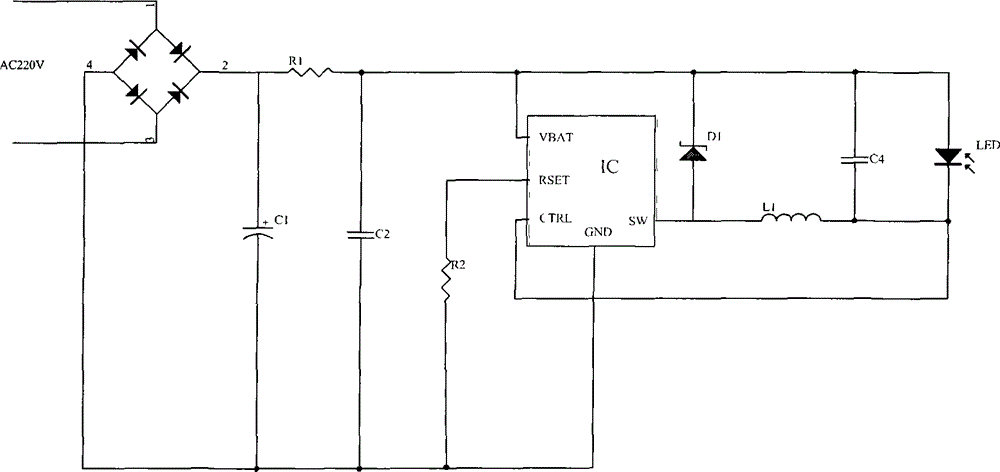

Optical communication device based on white light LED illumination

ActiveCN103561525ASignal transmission is stableHigh bandwidthElectric light circuit arrangementClose-range type systemsCapacitanceFull wave

The invention provides an optical communication device based on white light LED illumination. A communication function is achieved through an LED illuminating lamp array, cost is low, energy is saved, and the environment is protected. The optical communication device based on the white light LED illumination comprises a transmitting end and a receiving end, wherein the transmitting end comprises an LED modulation driving circuit connected with the LED illuminating lamp array, and the receiving end comprises an LED optical communication receiving circuit. The LED modulation driving circuit comprises a full-wave rectification bridge composed of four diodes capable of being connected into an alternating current power supply, the direct current voltage output end of the full-wave rectification bridge is connected with an energy-storage capacitor in parallel, the two ends of the energy-storage capacitor are connected with a filter circuit, the output end of the filter circuit is connected with a light modulation driving chip, a switch control pin of the chip is connected with the negative electrode of the LED illuminating lamp array, a switch pin of the chip is connected with the negative electrode of a voltage stabilizing diode and one end of an inductor, and the other end of the inductor is connected with the negative electrode of the LED illuminating lamp array and one end of a protective capacitor. The LED optical communication receiving circuit comprises a PIN photoelectric detector, an amplifying circuit and a signal processing unit.

Owner:北京格林曼光电科技有限公司

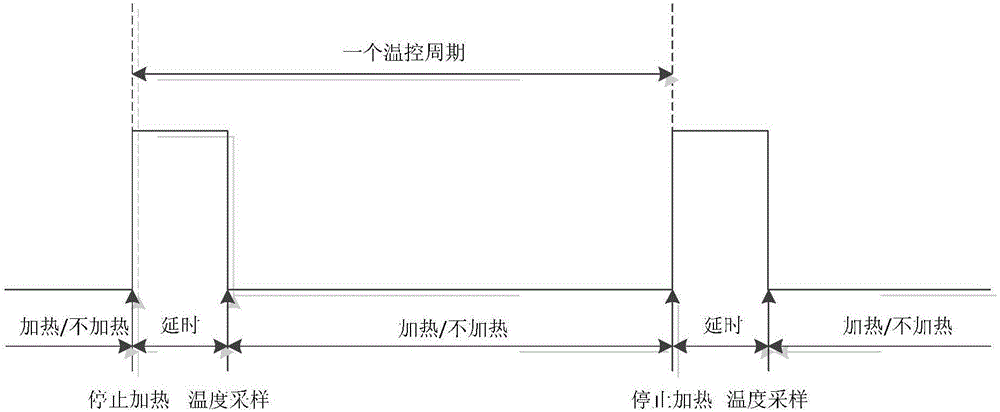

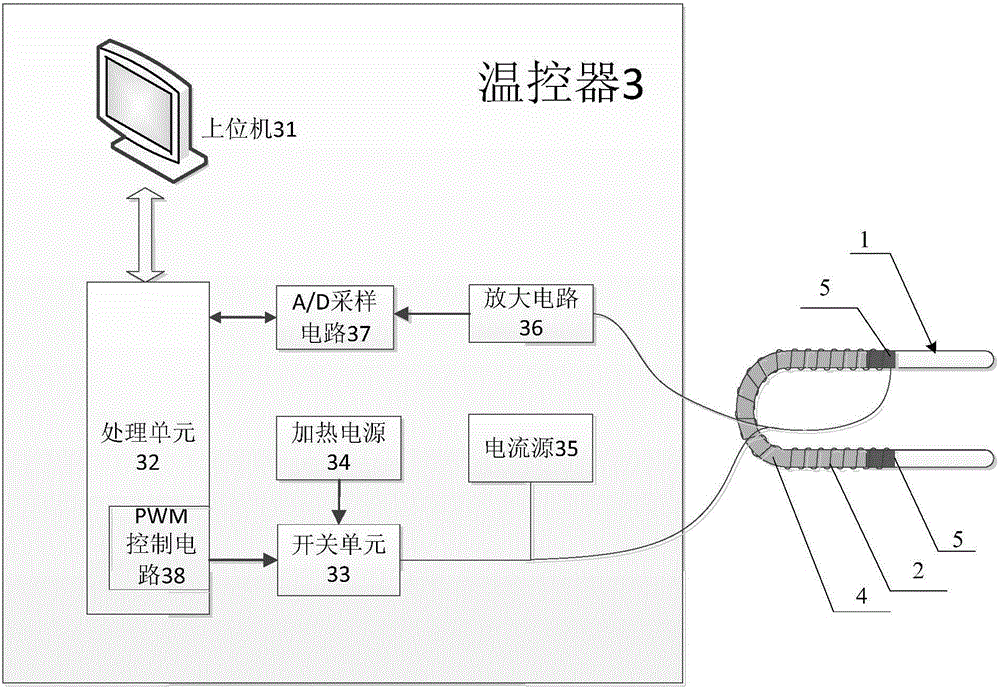

Temperature control method and device for enrichment pipe

InactiveCN106155134AHigh measurement accuracyEvenly heatedTemperatue controlTemperature controlPlatinum

The invention discloses a temperature control method and a temperature control device for an enrichment tube. In the method, when the temperature of the enrichment tube needs to be obtained, firstly, the platinum wire used as a heating element does not generate heat; The temperature value on the platinum wire serving as the temperature measuring element; then use the proportional integral differential algorithm to calculate the obtained temperature value on the platinum wire serving as the temperature measuring element and the temperature required by the enrichment tube to obtain the output control amount, when the output control When the output control value is less than or equal to 0, the platinum wire serving as the heating element will not generate heat until the next temperature control cycle begins; when the output control value is greater than 0, determine the heating power that needs to be loaded on the platinum wire as the heating element so The platinum wire that acts as a heating element heats the enrichment tube at this heating power until the next temperature control cycle begins; the advantage is that the platinum wire acts as both a temperature measuring element and a heating element, so there will be no Changing the temperature field near the temperature measurement point effectively improves the measurement accuracy.

Owner:NINGBO UNIV

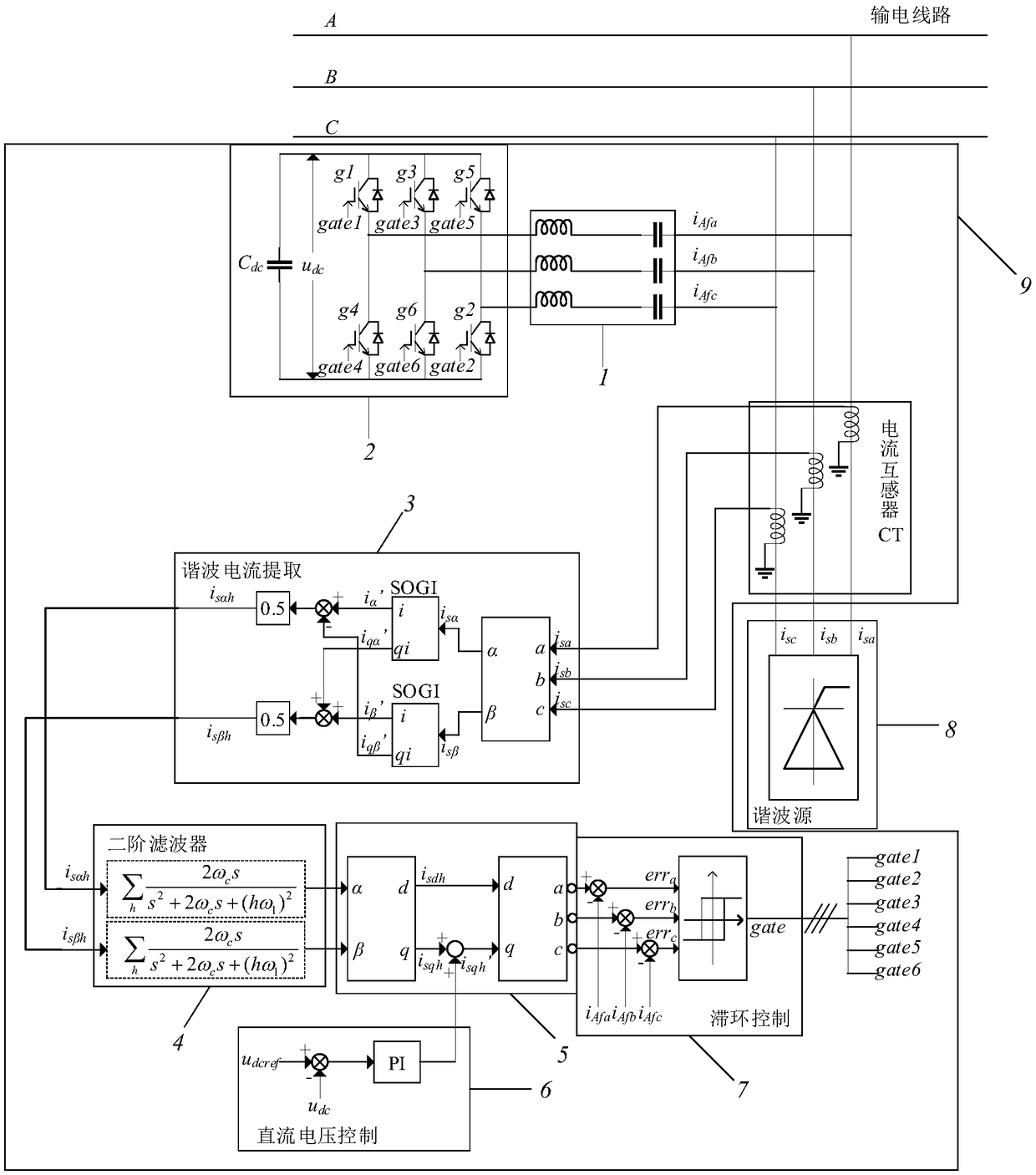

High-frequency harmonic parallel compensation device based on silicon carbide

ActiveCN109473987AHigh impedanceReduce the voltage levelHarmonic reduction arrangementAc network to reduce harmonics/ripplesLoad generationSwitching frequency

The invention discloses a high-frequency harmonic parallel compensation device based on silicon carbide, and relates to the technical field of high-frequency harmonic parallel compensation. Accordingto the high-frequency harmonic parallel compensation device based on silicon carbide provided by the invention, a nonlinear load is simulated by a harmonic source to generate harmonic waves; a capacitor is arranged inside an active filter, the capacitor is serially connected between the active filter and a three-phase alternating current power grid, the voltage level on the output side of the active filter can be reduced effectively, and the active filter can be applied to a high-voltage network; simultaneously, the device is high in impedance for fundamental current and low in impedance for harmonic current; harmonic compensation current which can cancel out harmonic current component in load current in the harmonic waves generated by the harmonic source is generated by the active filter,so that the device solves the disadvantages that an existing active filter mainly uses an IGBT switch device, the compensation ability of the active filter for high-frequency harmonic waves is subjected to the switching frequency of IGBT and the high-frequency harmonic waves cannot be compensated effectively.

Owner:ELECTRIC POWER RES INST OF GUANGXI POWER GRID CO LTD

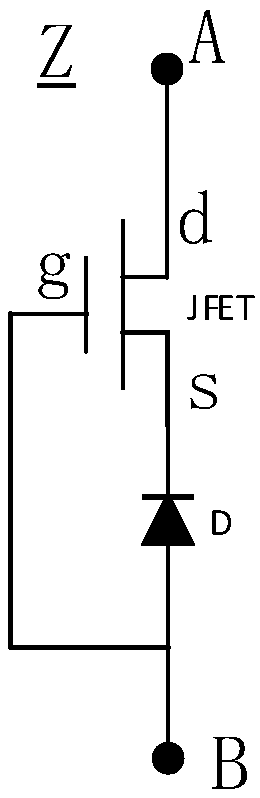

Combined switch

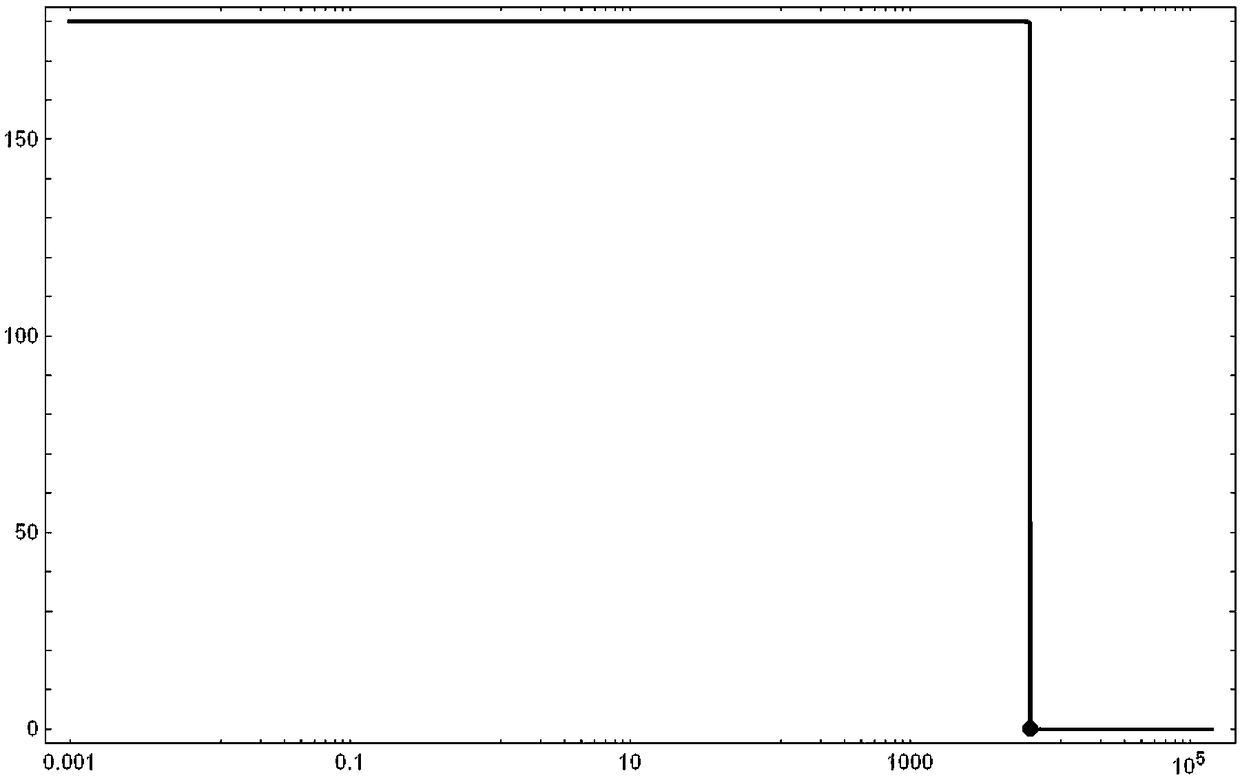

InactiveCN107707235AImprove reverse withstand voltageLower forward voltageDiodeReverse recoveryTunneling field effect transistor

The invention discloses a combined switch. The combined switch comprises a junction field effect transistor and a diode. The junction field effect transistor comprises a gate electrode, a source electrode and a drain electrode; the diode comprises an anode and a cathode; the drain electrode of the junction field effect transistor is a first terminal of the combined switch; the source electrode ofthe junction field effect transistor is connected with the cathode of the diode; the gate electrode of the junction field effect transistor is connected with the anode of the diode; and the anode of the diode is a second terminal of the combined switch. Compared to a single diode, the combined switch disclosed by the invention has a higher reverse withstand voltage, and has zero reverse recovery characteristic and a lower forward turn-on voltage.

Owner:FSP POWERLAND TECH

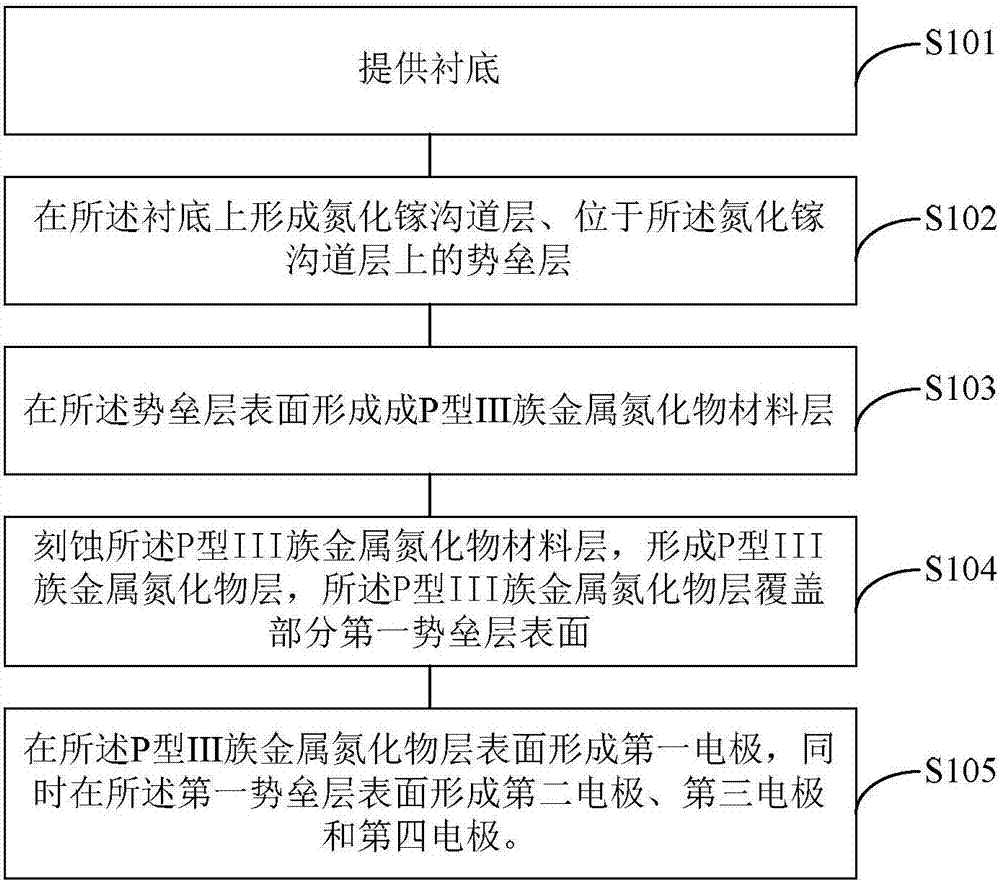

Gallium-nitride-based inverter chip and forming method therefor

ActiveCN106910770ALower on-resistanceIncrease powerSemiconductor/solid-state device manufacturingSemiconductor devicesGallium nitrideNitride

The invention discloses a gallium-nitride-based inverter chip and a forming method therefor, and the chip comprises a substrate; a gallium nitride channel layer located on the substrate; a barrier layer located on the gallium nitride channel layer; a P-type III-family metal nitride layer located on the surface of the barrier layer; a first electrode located on the surface of the P-type III-family metal nitride layer; a second electrode, a third electrode and a fourth electrode, which are all located on the surface of the barrier layer. The chip is good in transmission performance, and is strong in loading capability.

Owner:SHANGHAI SIMGUI TECH

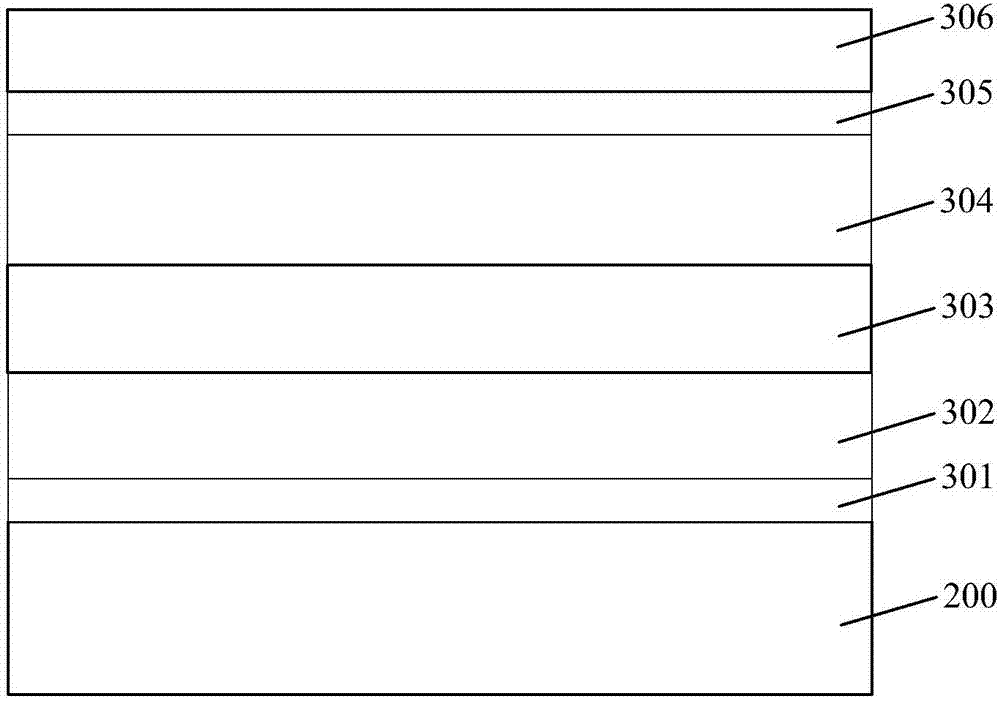

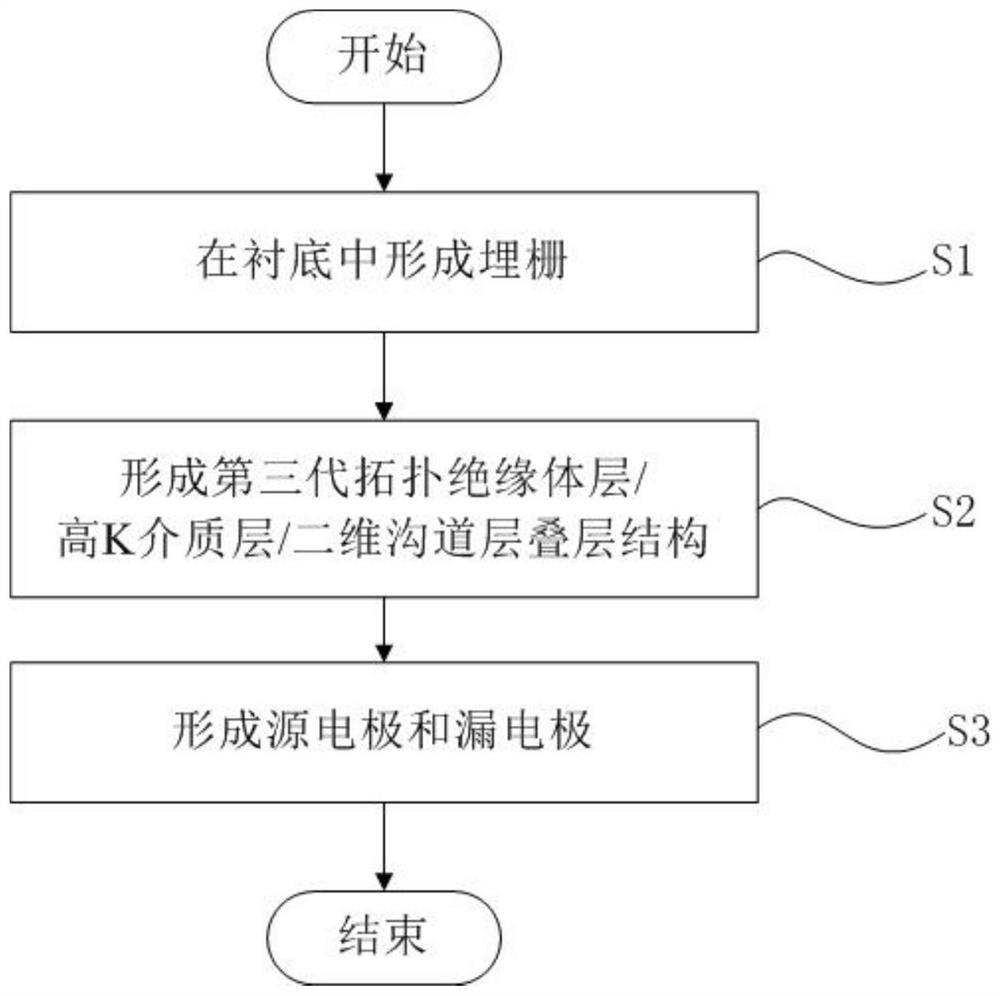

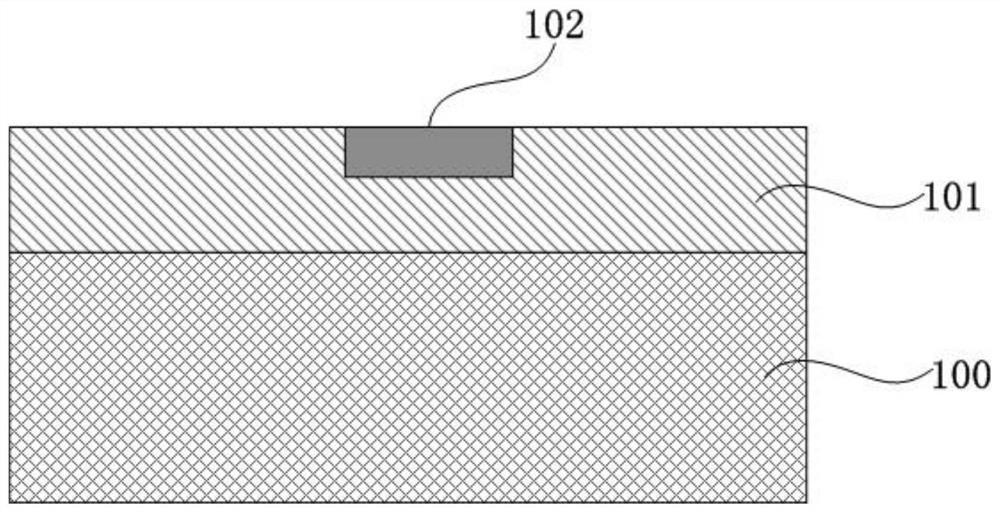

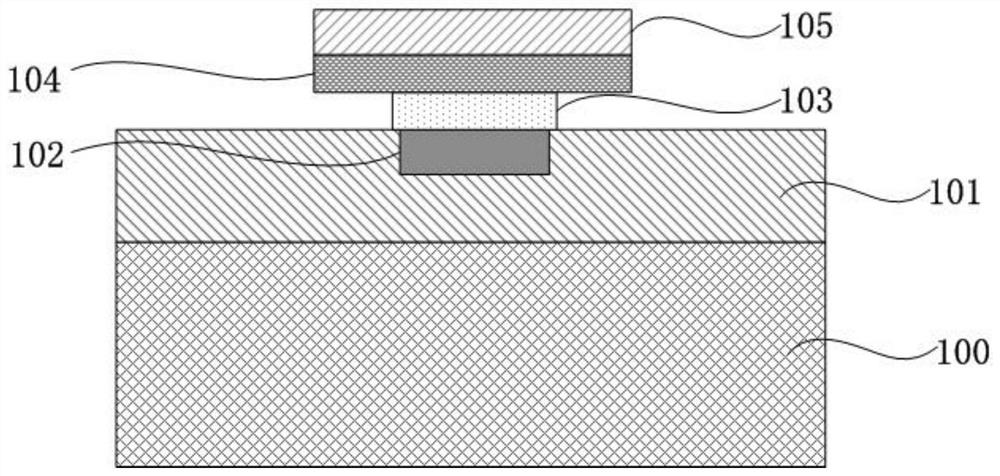

Two-dimensional negative quantum capacitance transistor device and preparation method thereof

ActiveCN113363316AReduce power consumptionIncrease switching speedSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceEngineering

The invention discloses a two-dimensional negative quantum capacitance transistor device and a preparation method thereof. The two-dimensional negative quantum capacitance transistor device comprises a substrate; a buried gate which is formed in the substrate, wherein the upper surface of the buried gate is flush with the upper surface of the substrate; a third-generation topological insulator layer which is formed on the buried gate, wherein the length of the third-generation topological insulator layer is equal to that of the buried gate; a high-K dielectric layer which covers the third-generation topological insulator layer; a two-dimensional channel layer which is formed on the high-K dielectric layer, wherein the two-dimensional channel layer and the third-generation topological insulator layer have a common area; a source electrode and a drain electrode which are formed on the substrate and the two sides of the two-dimensional channel layer respectively, partially cover the two-dimensional channel layer and are not overlapped with the buried gate, wherein the topological insulator layer provides negative quantum capacitance, so the total capacitance of the gate is increased, and the sub-threshold swing is reduced.

Owner:FUDAN UNIV

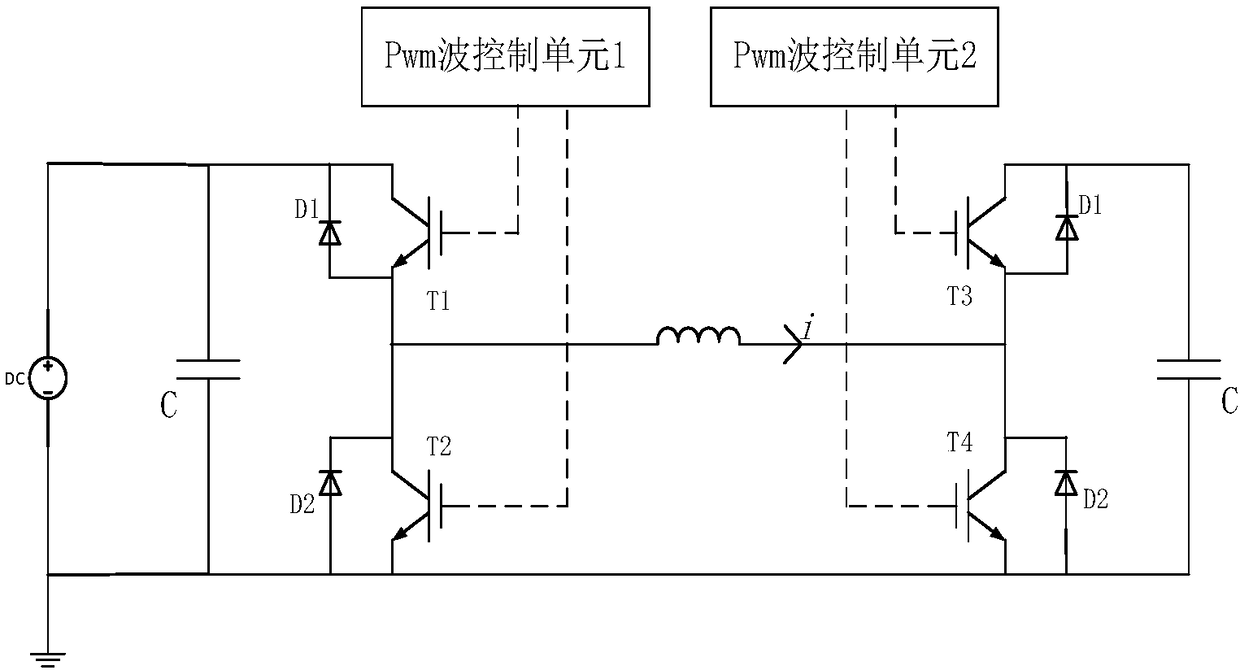

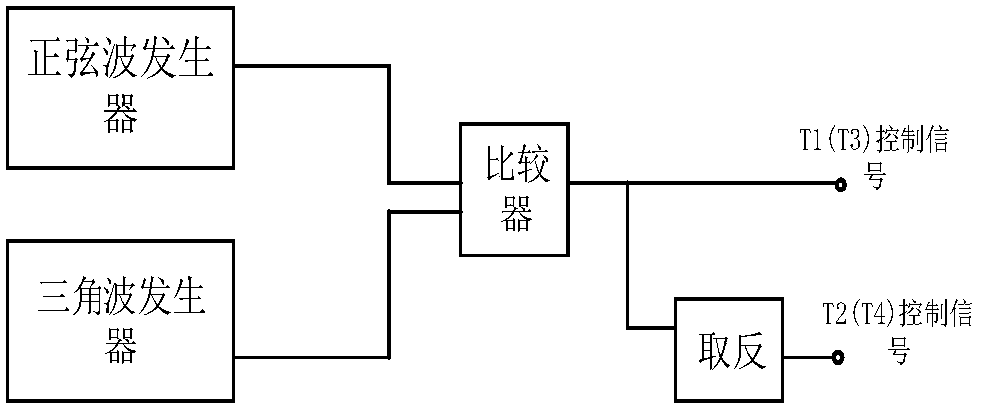

MMC sub-module accelerated life test circuit and method

PendingCN108627709AImprove test efficiencyShorten the timeEnvironmental/reliability testsTest efficiencyTime efficient

The invention provides an MMC sub-module accelerated life test circuit and method. The test circuit is in an H-bridge structure, and comprises an inductor arranged at an H-bridge joint; a PWM wave control unit and a capacitor, which are connected with the two ends of a bridge arm respectively; and a DC power supply, which is connected in parallel with the two ends at one side of the bridge arm. The test method fully utilizes the accelerated life principle, improves test efficiency and saves time.

Owner:CHINA EPRI ELECTRIC POWER ENG CO LTD

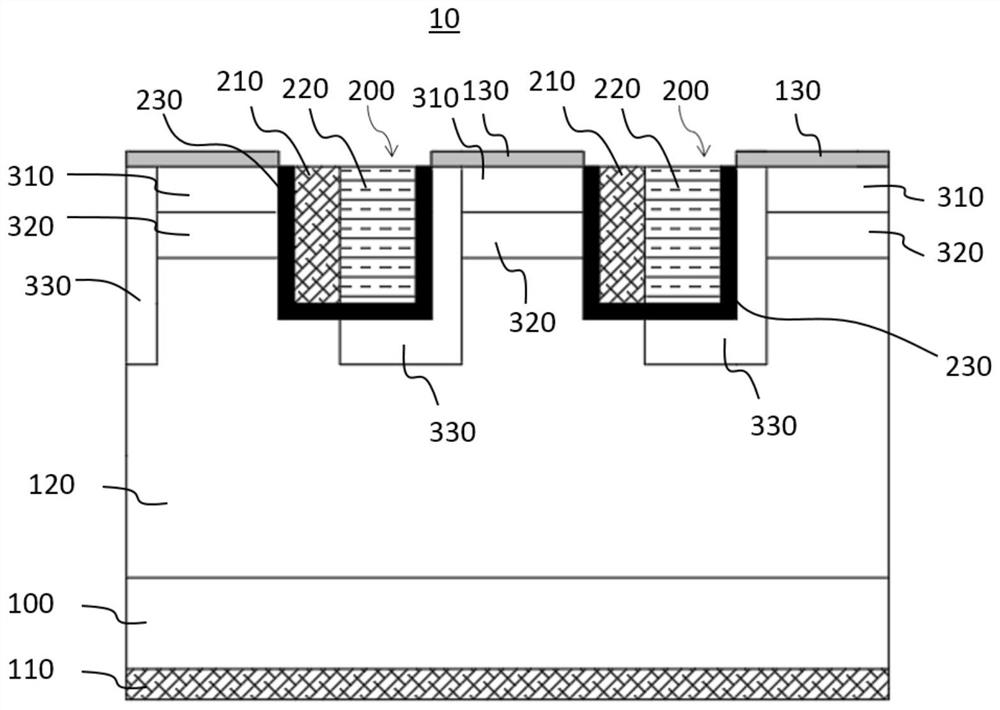

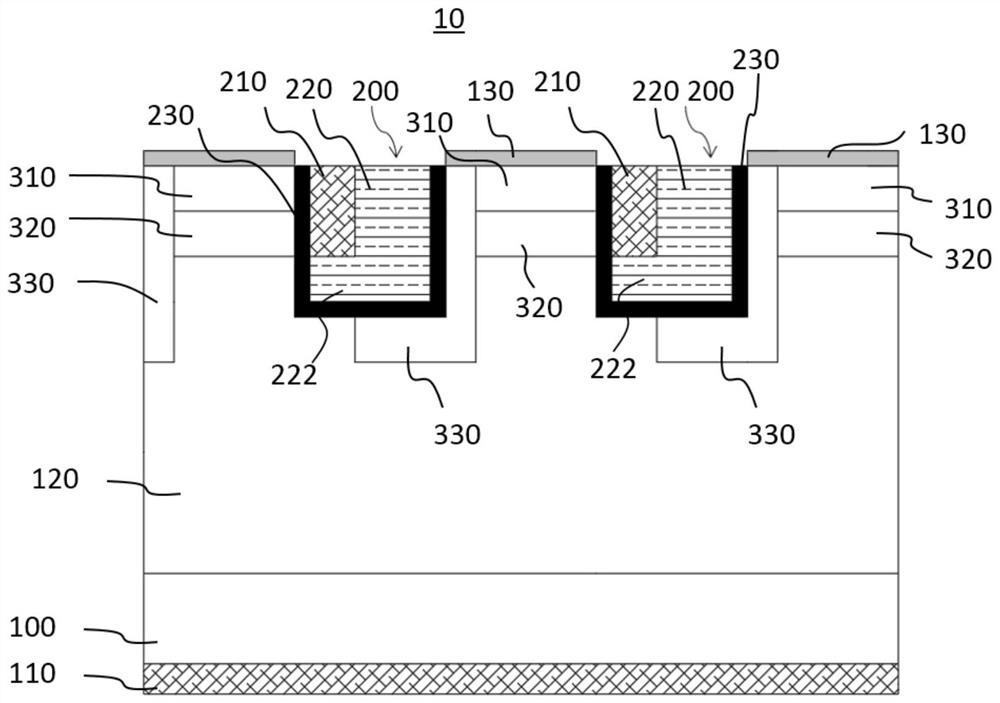

Silicon carbide power semiconductor device and field effect transistor

ActiveCN113571575AIncreasing the thicknessReduce capacitanceSemiconductor devicesCapacitancePower semiconductor device

The invention relates to a silicon carbide power semiconductor device and a field effect transistor. The silicon carbide power semiconductor device comprises a substrate and a plurality of grid electrode grooves arranged at intervals, the plurality of spaced grid electrode grooves are formed at one side of the substrate, and a first grid electrode and a second grid electrode are arranged in each grid electrode groove. The first grid electrode and the second grid electrode are arranged along the extending direction of the substrate, the first grid electrode is of a first conductivity type. and the second grid electrode is of a second conductive type. A grid electrode oxide layer is formed on the inner wall of each grid electrode groove, and is located between the inner wall of the grid electrode groove and the first grid electrode and the second grid electrode. After the first grid electrode and the second grid electrode form a PN junction, the second grid electrode is completely exhausted by the first grid electrode, and a space charge region is formed. The space charge region can bear voltage, equivalently, the thickness of the grid electrode oxide layer is increased, and with the increase of the thickness of the grid electrode oxide layer, the capacitance between the grid electrode and a shielding region is reduced, so that the grid charge is further reduced, the switching rate can be improved, and the switching loss is reduced.

Owner:SONGSHAN LAKE MATERIALS LAB +1

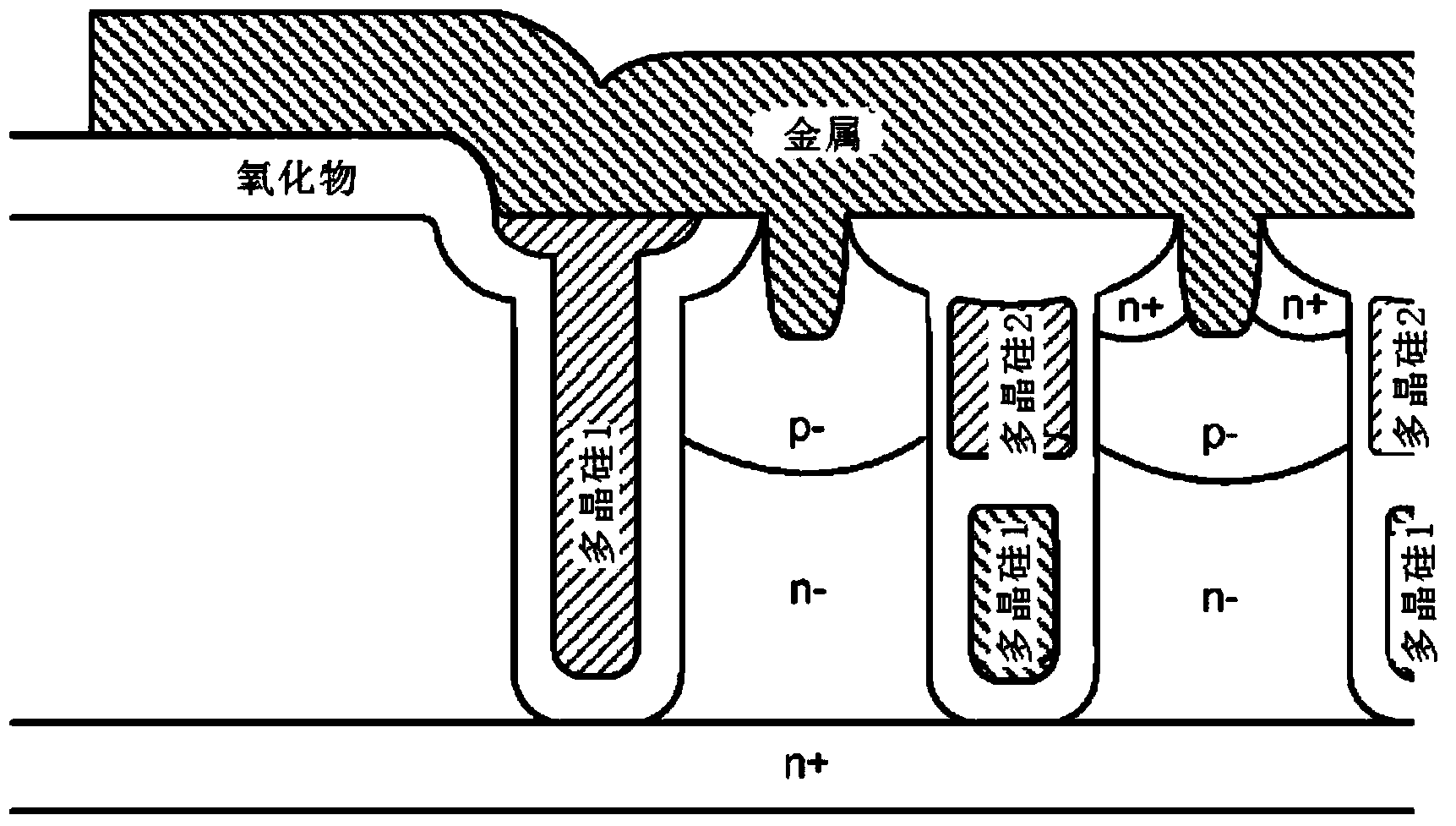

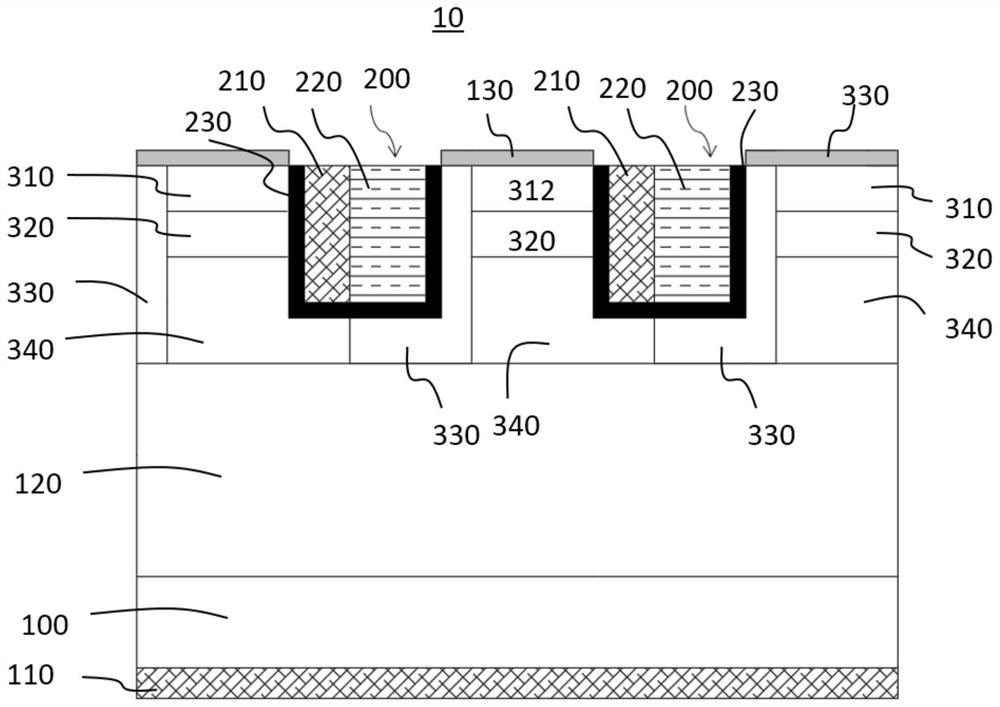

SiC MOSFET device and preparation method thereof

PendingCN113764514ALower on-resistanceReduced conduction power consumptionSemiconductor/solid-state device manufacturingSemiconductor devicesCarbide siliconMOSFET

The invention relates to the field of silicon carbide power devices, and discloses a SiC MOSFET device and a preparation method thereof, and the SiC MOSFET device comprises a substrate, an epitaxial bottom layer, a base layer, a source electrode layer, a grid electrode, a grid dielectric layer, a channel section, a channel length reduction section, a floating section, an isolation layer, a source electrode and a drain electrode. The SiC MOSFET device is prepared based on the following method: forming an epitaxial bottom layer and a base layer on a first surface of a substrate, forming a source layer and a base junction on the base layer, forming a gate, a gate dielectric layer, a channel section, a channel length reduction section and a floating section in a trench, forming an isolation layer on the gate layer, and forming a source on the isolation layer and the source layer, and forming a drain electrode on the second surface of the substrate. The gate dielectric layer is low in defect density, high in breakdown voltage and high in reliability.

Owner:深圳真茂佳半导体有限公司

High reliability and low cost multi-channel rs-422 communication circuit

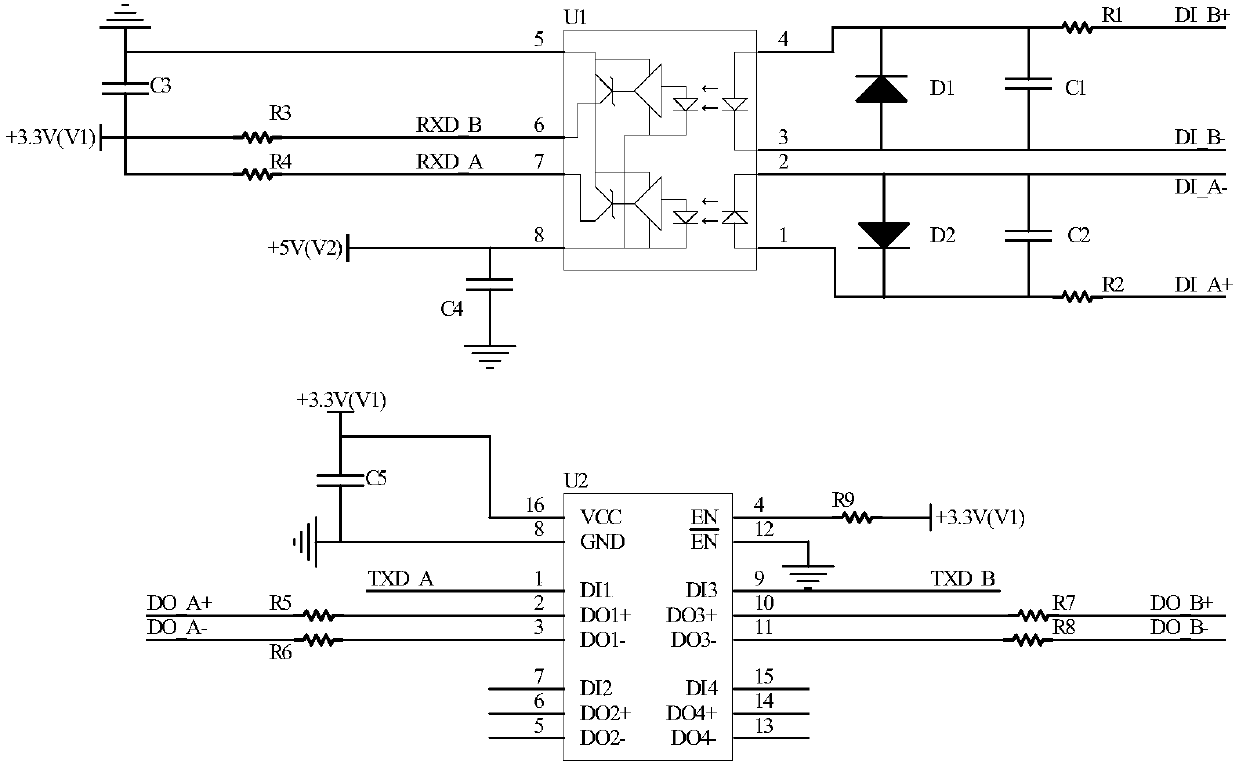

ActiveCN107783921BAnti-jammingIncrease switching speedSelf-propelled projectilesElectric digital data processingTransistor–transistor logicElectrical resistance and conductance

The invention discloses a high-reliability low-cost multichannel RS-422 communication circuit which comprises a signal receiving unit and a signal transmitting unit. The signal receiving unit comprises a photoelectric coupler U1, current limiting resistors, filter capacitors and level clamp diodes, and the signal transmitting unit comprises a transmitting chip U2 and current limiting resistors; RS-422 communication transmitted signals can be transmitted to the transmitting chip U2 from an MCU (microprogrammed logic control unit) in TTL (transistor-transistor logic) level forms and can be converted into differential signals, then the differential signals can be outputted via the second current limiting resistor, currents of RS-422 communication received signals are limited by the first current limiting resistor, voltages of the RS-422 communication received signals are limited by the level clamp diodes, the RS-422 communication received signals are filtered by the filter capacitors andthen are transmitted into the photoelectric coupler U1, light emitting diodes of the photoelectric coupler can be turned on and off under the control, accordingly, the differential signals and TTL level can be converted, and signals can be isolated. According to the scheme, the high-reliability low-cost multichannel RS-422 communication circuit has the advantages that the high-reliability low-costmultichannel RS-422 communication circuit can be applied to RS-422 communication mode circuits on missiles, is high in switching rate and reliability and low in cost and is small and anti-interference, and the like.

Owner:JIANGSU JINLING INST OF INTELLIGENT MFG CO LTD +1

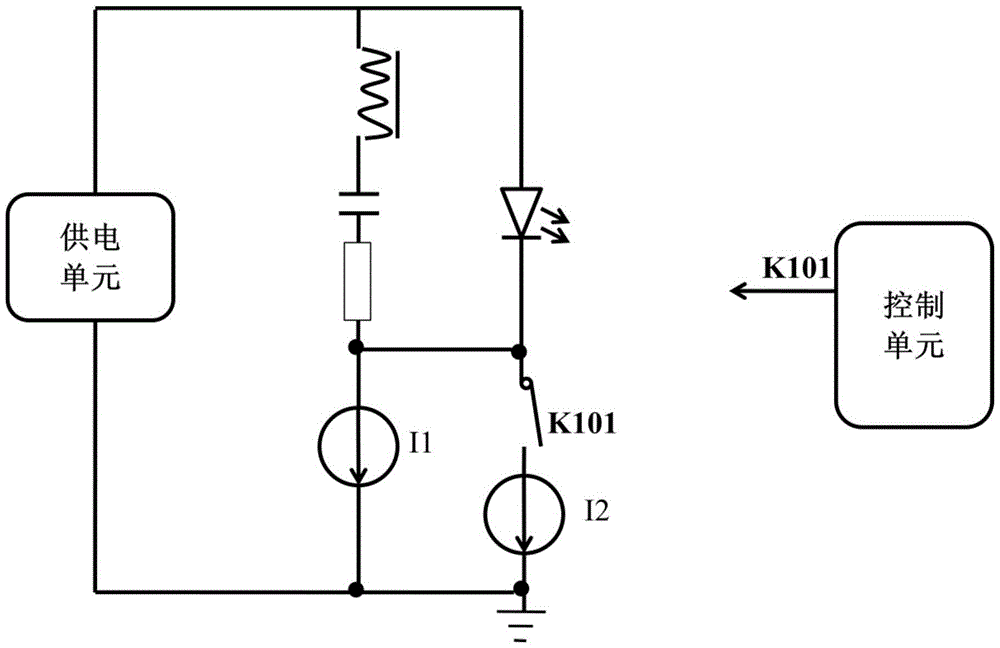

High-speed led optical communication resonant quasi-switching modulator

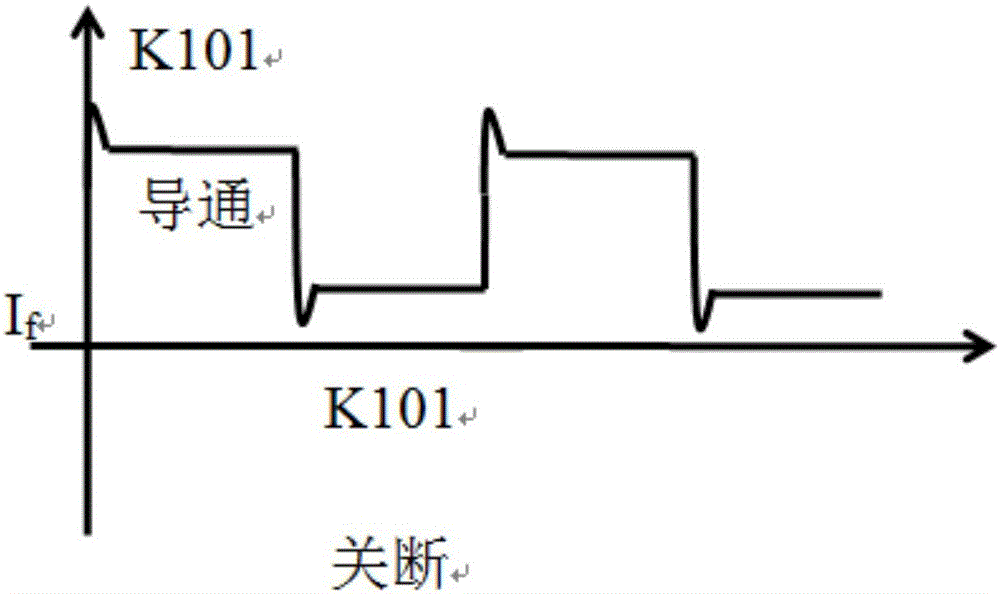

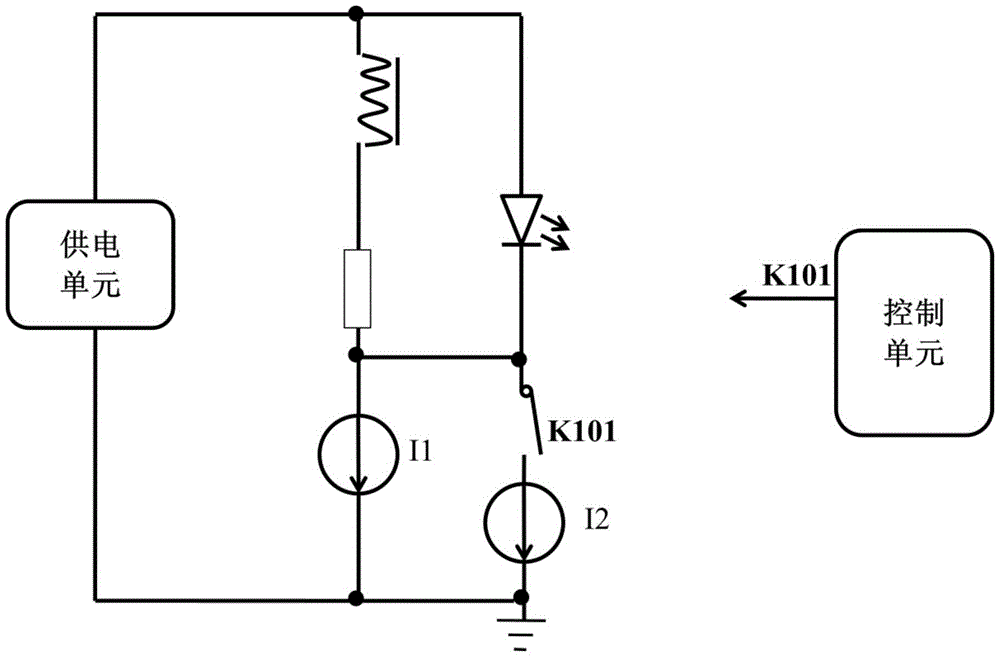

ActiveCN104917571BIncrease compound rateEnhance radiative recombinationElectromagnetic transmissionControl signalCurrent source

The invention discloses a high-speed LED optical communication resonant quasi-switching modulator. The power supply unit is a voltage-limiting constant-current control unit, and the control unit is used to generate and output control signals to realize timing control; the power supply unit, inductance, resistance and current The source I1 is connected in series in sequence to form a loop; the anode of the LED is connected to the positive pole of the power supply unit, and the cathode is connected to the positive pole of the current source I2 through the switch K101; the cathode of the LED is connected to the positive pole of the current source I1; when the control unit sends a control signal to make the switch K101 turn on, the limit The voltage and constant current control unit supplies positive power to the LED to turn on the LED quickly; at the same time, the inductor stores energy; when the control unit sends a control signal and the switch K101 is turned off, the constant current drops, and the inductor generates a negative voltage. Reverse power supply to the LED during the falling time, so that the LED light intensity drops rapidly. The invention has fast switch and good optical communication effect.

Owner:NJU OPTOELECTRONICS ENG RES INST CO LTD

Reactive compensation device and method for partially regulating voltages and capacitance of three-phase four-wire power grid

ActiveCN103490432BReduce capacityReduce lossReactive power adjustment/elimination/compensationReactive power compensationCapacitanceAutotransformer

The invention discloses a reactive compensation device and method for partially regulating voltages and capacitance of a three-phase four-wire power grid. The reactive compensation device comprises a U-phase voltage and capacitance regulating reactive compensation unit, a V-phase voltage and capacitance regulating reactive compensation unit, a W-phase voltage and capacitance regulating reactive compensation unit and a control unit. Each phase of voltage and capacitance regulating reactive compensation unit is mainly composed of a current detection element, a voltage detection element, a full-voltage compensation capacitor bank, an auto-transformer and a voltage-regulating capacitor bank. The control mode of independent reactive compensation in each phase is used in the three-phase four-wire power grid, total capacitance in each phase is uniform, the capacitance in each phase is evenly divided into n sets, wherein one set of the capacitance is subjected to voltage and capacitance regulation through the auto-transformer which totally has m levels of output voltages, each phase has n*m grades of compensation, and multi-level fine compensation for the power grid is achieved.

Owner:GUILIN UNIV OF ELECTRONIC TECH

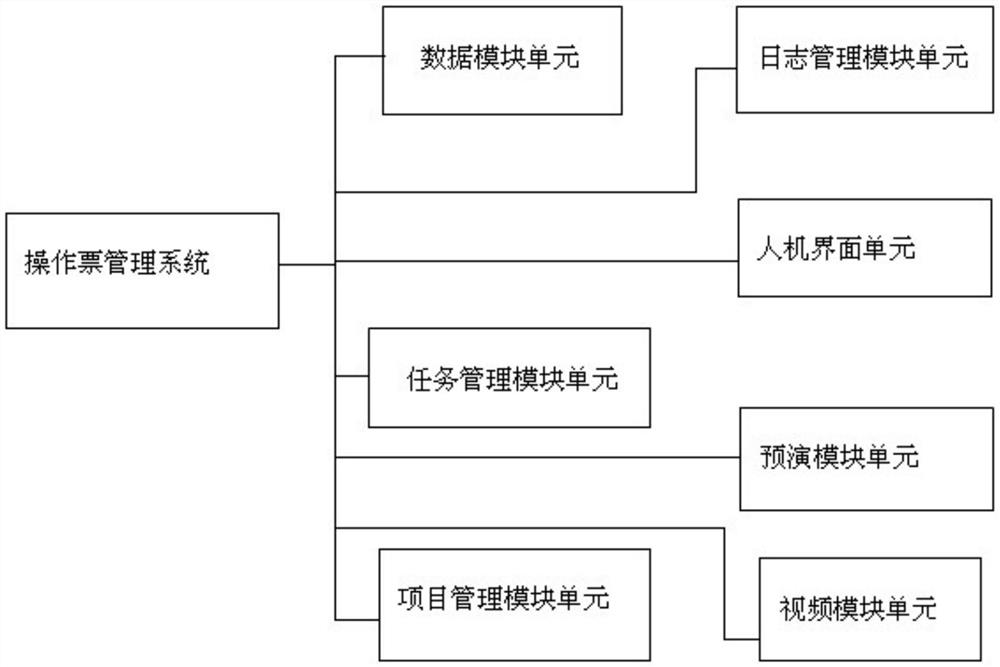

Operation order management system

PendingCN111898993ARealize editingRealize operational workOffice automationResourcesHuman–machine interfaceAutomatic control

The invention relates to an operation order management system comprising a data module unit, a project management module unit, a task management module unit, a rehearsal module unit, a video module unit, a log management module unit and a human-computer interface unit. The data module unit, the project management module unit, the task management module unit, the rehearsal module unit, the video module unit, the log management module unit and the human-computer interface unit are application units installed in a switch cabinet switching control system of an electric power management department.According to the invention, the whole process of writing, approving and executing the operation order is intelligently controlled, and the work of related personnel is standardized. Error caused by personnel negligence is avoided, and the order making accuracy and efficiency of the operation order are improved. Compared with manual switching, the switching speed is improved, and the task accuracyand safety are improved. In actual operation, intelligent monitoring can be carried out on the electric operating mechanisms of multiple switch cabinets, and switching of the electric operating mechanisms is automatically controlled on the basis of operation order specifications.

Owner:艾美肯(厦门)电力科技有限公司

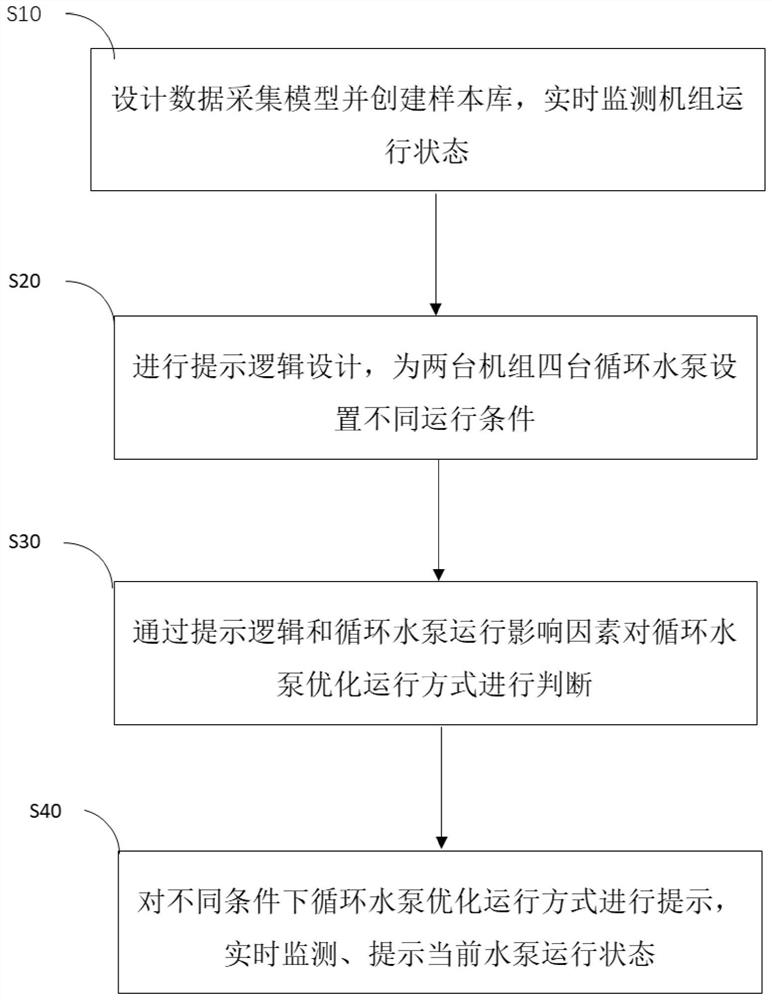

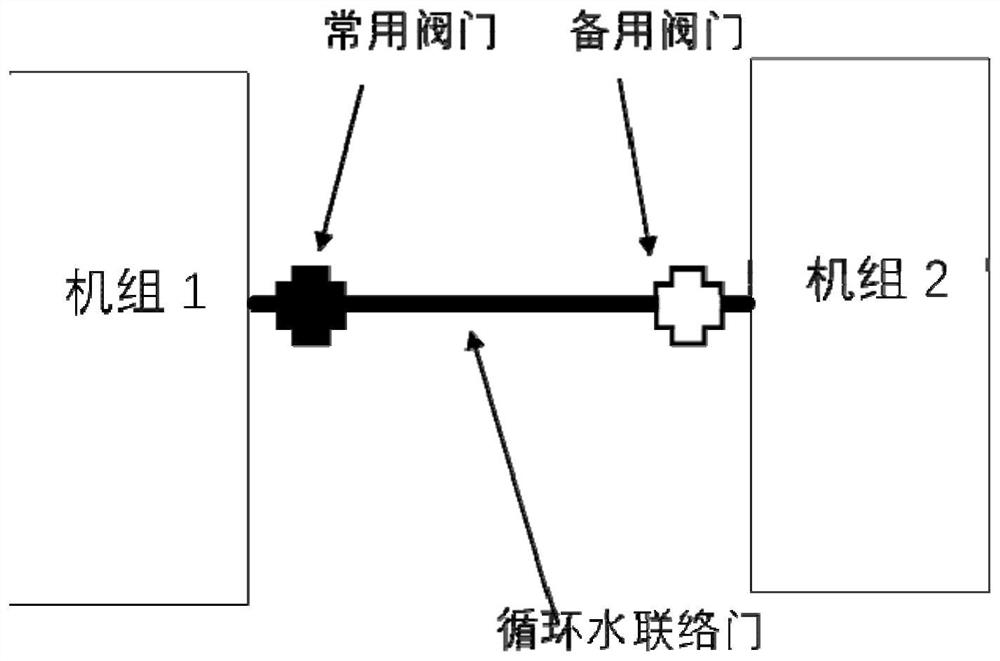

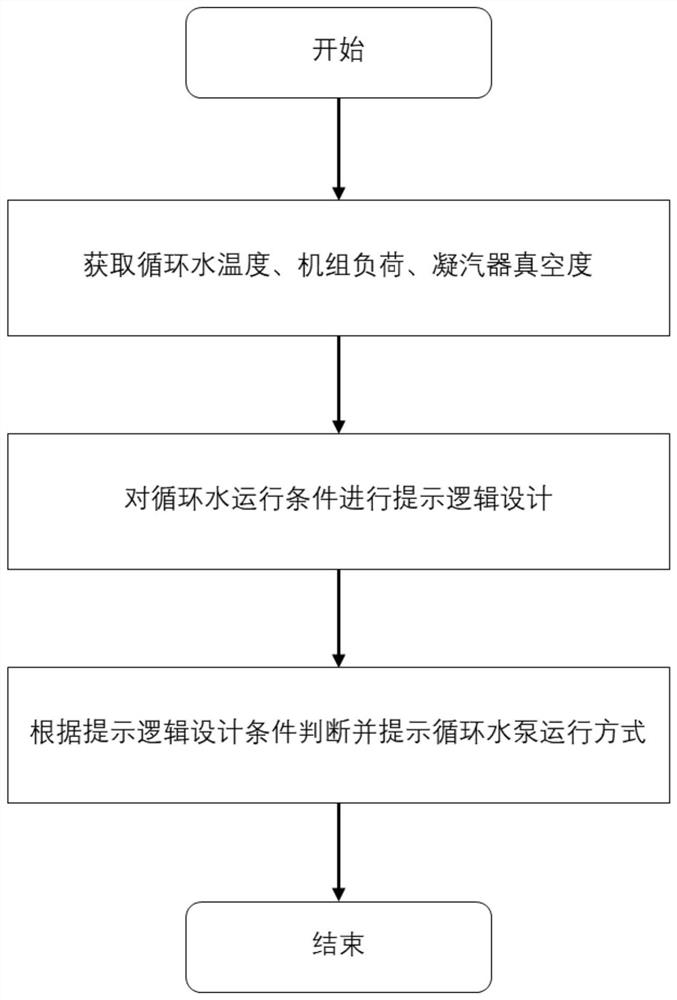

600MW unit circulating water energy-saving optimization operation prompting method

InactiveCN111894828AImprove accuracyIncrease switching speedPump testingPump controlData acquisitionProcess engineering

The invention discloses a 600MW unit circulating water energy-saving optimization operation prompting method. According to the method, through designing a data acquisition model, data acquisition is carried out on circulating water temperature, unit load and condenser vacuum degree, a data sample library is established, and collected data are uploaded to the data sample library; the contents in the data sample library are screened, sorted and stored, and the running state of the unit is monitored in real time; circulating water optimization operation technical measures are judged through the prompt logic, the circulating water optimization operation mode is given in combination with the operation working condition, the state and the performance of a circulating water pump are monitored, operation personnel can be prompted to adjust in time, and the problems that the energy consumption of the unit is increased as existing circulating pump operation optimization measures are not timely executed and the energy waste is caused as circulating switching is not timely are solved.

Owner:贵州华电桐梓发电有限公司

A reverse conduction double gate insulated gate bipolar transistor

ActiveCN103928507BIncreased current capabilityStrong conductance modulation effectSemiconductor devicesPower flowGate oxide

Owner:SOUTHEAST UNIV

Semiconductor element

The invention provides a semiconductor element. The semiconductor element comprises at least one grate structure with the corner being a parabolic shape, and the center of the corner is at the vertexof the parabola so as to realize noninterference among signals by the optical focusing property of the parabola and to cause the driven current to be smooth and orderly, thus increasing the switchingrate of a transistor switch, lowering temperature of the semiconductor element temperature during operation, and enhancing the overall reliability of the semiconductor element.

Owner:泓广科技有限公司

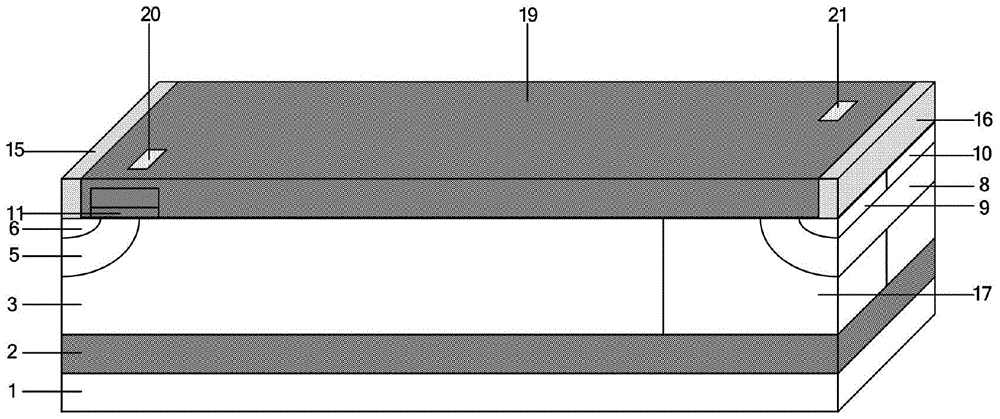

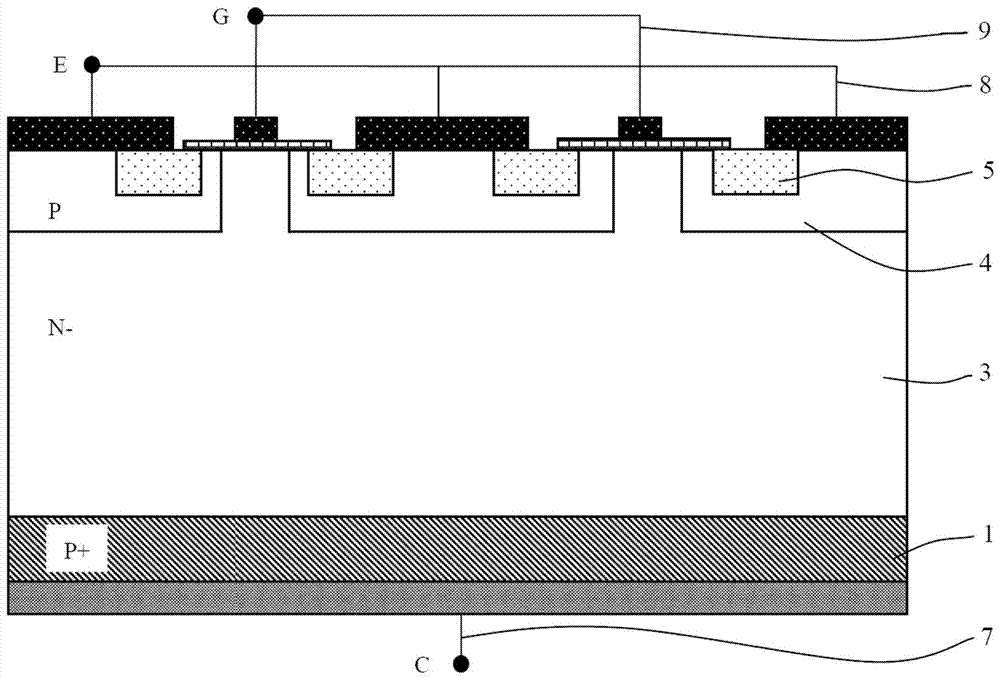

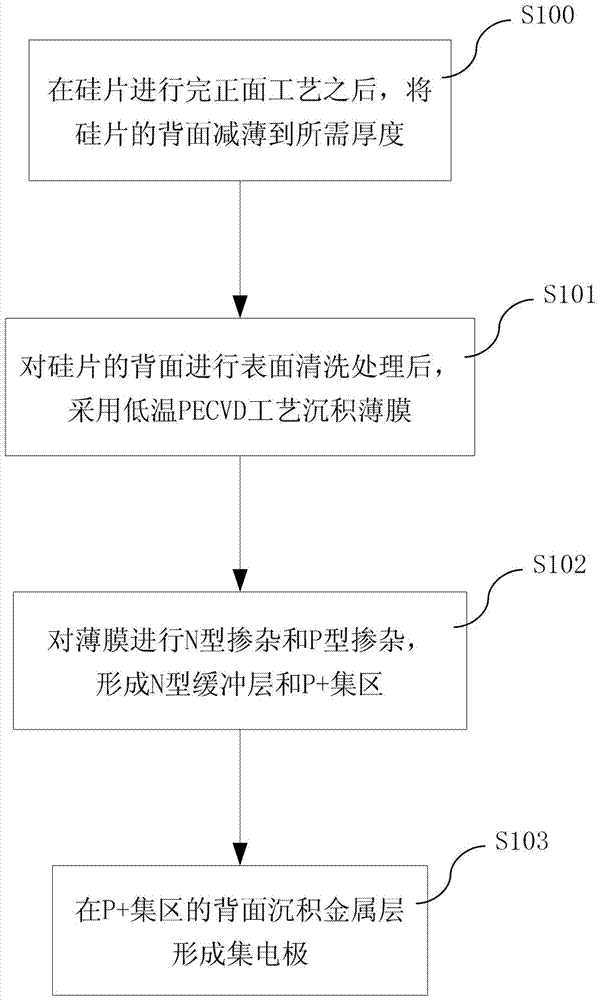

Semiconductor device with buffer layer and manufacturing method thereof

ActiveCN104992969BLow costLower thermal budgetTransistorSemiconductor/solid-state device manufacturingCharge carrierMicrocrystalline silicon

The invention discloses a semiconductor device having a buffer layer and a manufacturing method thereof. The semiconductor device comprises a front surface structure arranged on the front surface of the semiconductor device and a back surface structure arranged on the back surface of the semiconductor device. The back surface structure comprises a P<+> collector region and the N-type buffer layer arranged on the P<+> collector region. The P<+> collector region and the N-type buffer layer each adopt a thin film structure which is formed directly on the back surface of the semiconductor device by utilizing the low-temperature PECVD technology. The P<+> collector region and the N-type buffer layer further adopt the deposited thin film structure formed through the low temperature PECVD technology. The thin film is one or more of amorphous silicon, microcrystalline silicon, carbon-doped amorphous silicon or silicon germanium. According to the semiconductor device having the buffer layer and the manufacturing method thereof, cost of the semiconductor device and thermal budget of the silicon wafer back surface technology can be reduced effectively on the basis of not using an ion implantation device and an annealing process, and injection and extraction rate of carriers on the back surface of a silicon wafer can be adjusted according to the difference of the types of thin-film materials.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

Ultrasonic Thickness Gauge for Metal Composite Materials

ActiveCN110006997BImprove noise reductionHigh sensitivityAnalysing solids using sonic/ultrasonic/infrasonic wavesUsing subsonic/sonic/ultrasonic vibration meansData processing systemUltrasonic pachymeter

The present invention aims at the problem that the thickness of a single layer of metal of a metal composite material cannot be measured and the overall thickness of the metal composite material cannot be measured in the prior art, and provides a metal composite material ultrasonic thickness measurement capable of measuring the thickness of each layer of the metal composite material Instrument, which includes a voltage adjustable power supply, an ultrasonic transmitting module, an ultrasonic receiving module, a data acquisition module, and a data processing system. The power supply provides power for the ultrasonic transmitting module, the ultrasonic receiving module, the data acquisition module, and the data processing system. A kind of ultrasonic thickness gauge for metal composite materials, the accuracy and reliability can be guaranteed, and the thickness can be accurately measured even in some cases of poor coupling.

Owner:葫芦岛探克科技有限公司