Manufacturing method of integrated Schottky split-gate type power MOS device

A technology of MOS devices and split gates, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as complex manufacturing processes, and achieve the effects of process simplification, low on-resistance, and increased switching speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

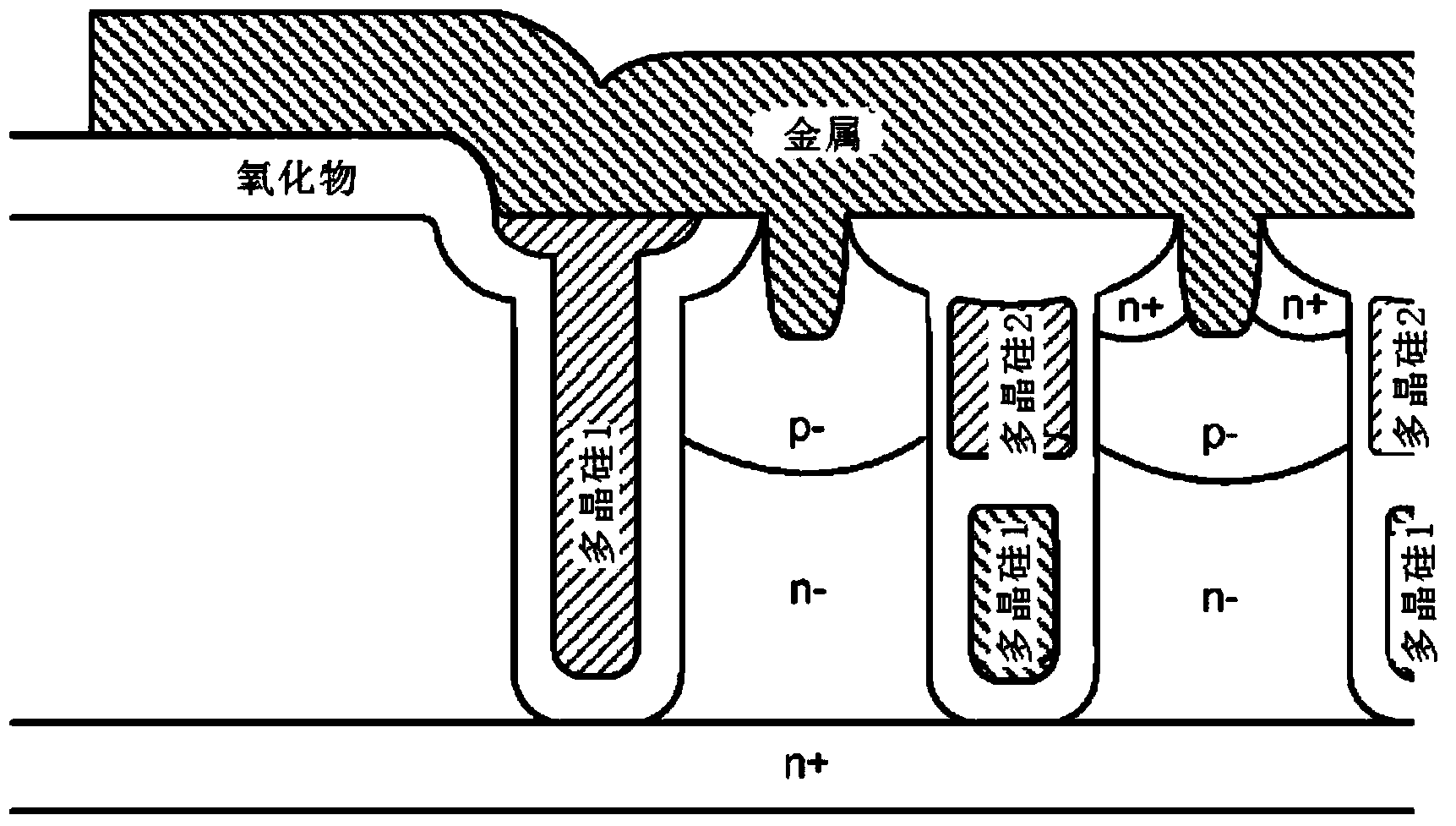

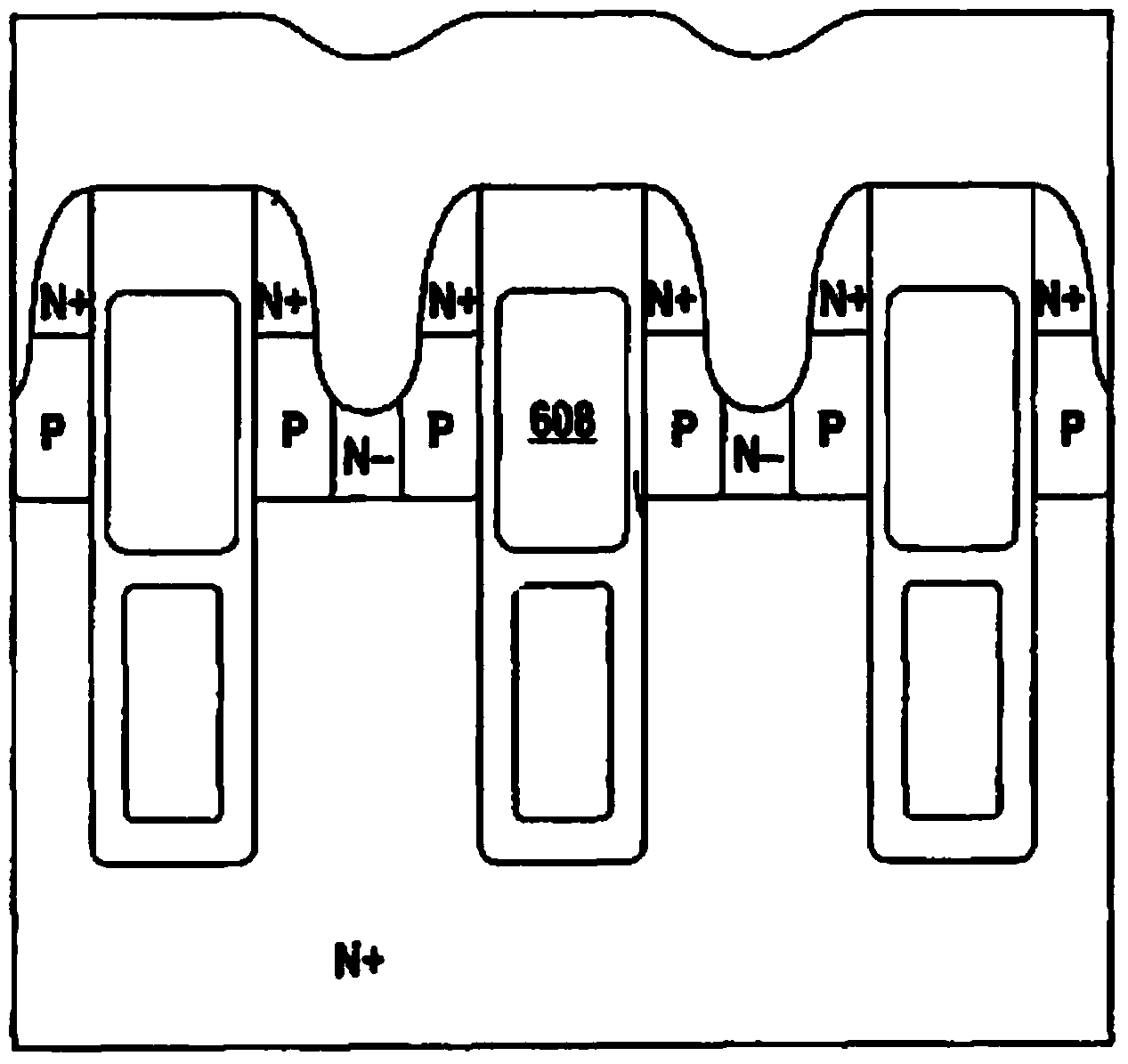

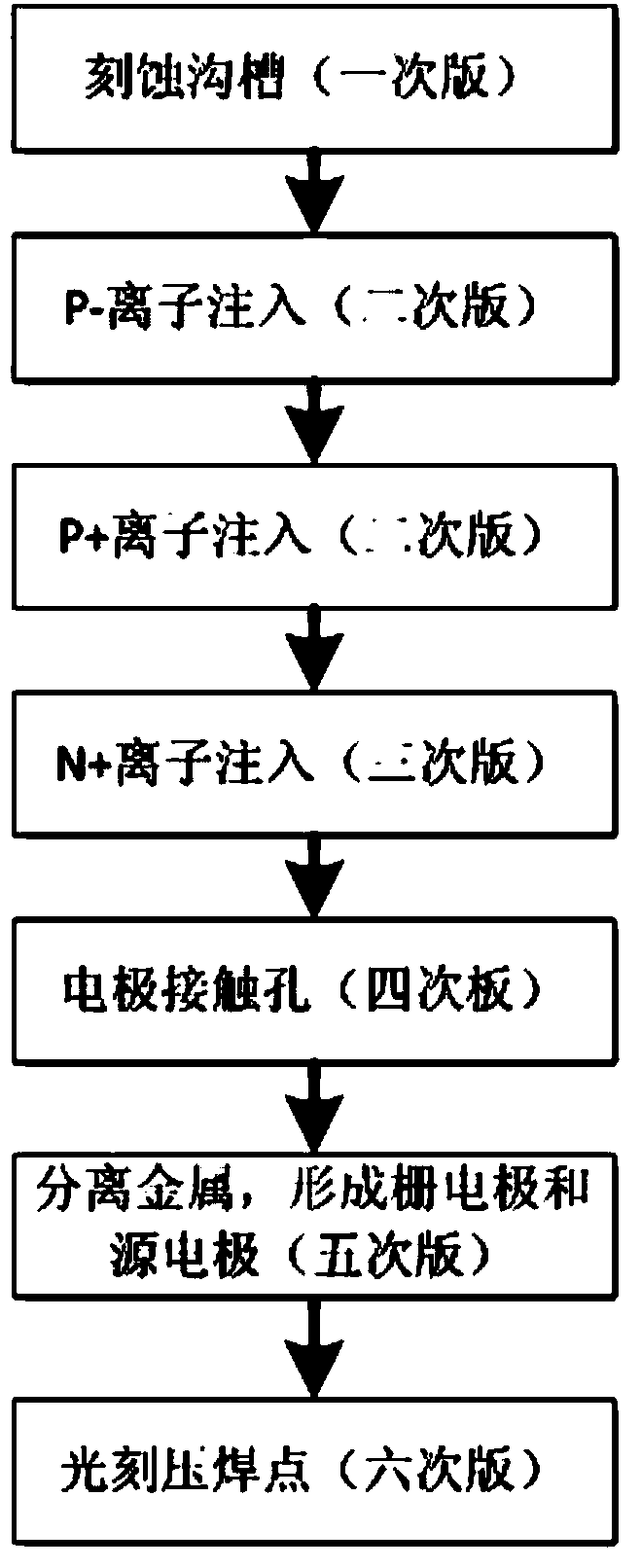

[0027] The implementation of the present invention will be described below in conjunction with the accompanying drawings.

[0028] In the embodiment of the present invention, six photolithography plates are used to realize the layout and process design of an integrated Schottky split gate power MOS device, and the N+ region, the P+ region and the Schottky contact region in the source electrode of the device are respectively drawn out and Shorting, the proportion of Schottky contact in the source electrode is not affected by the trench spacing, which can optimize the performance of the designed device. The whole process requires six plates, and the process is simplified accordingly. While ensuring the ultra-low on-resistance of the device, it does not affect the breakdown voltage of the device. Schottky is integrated in the device cell, and the switching rate of the device is increased, and the utilization rate of the silicon chip is also improved.

[0029] An embodiment of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More