Patents

Literature

193results about How to "Lower thermal budget" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

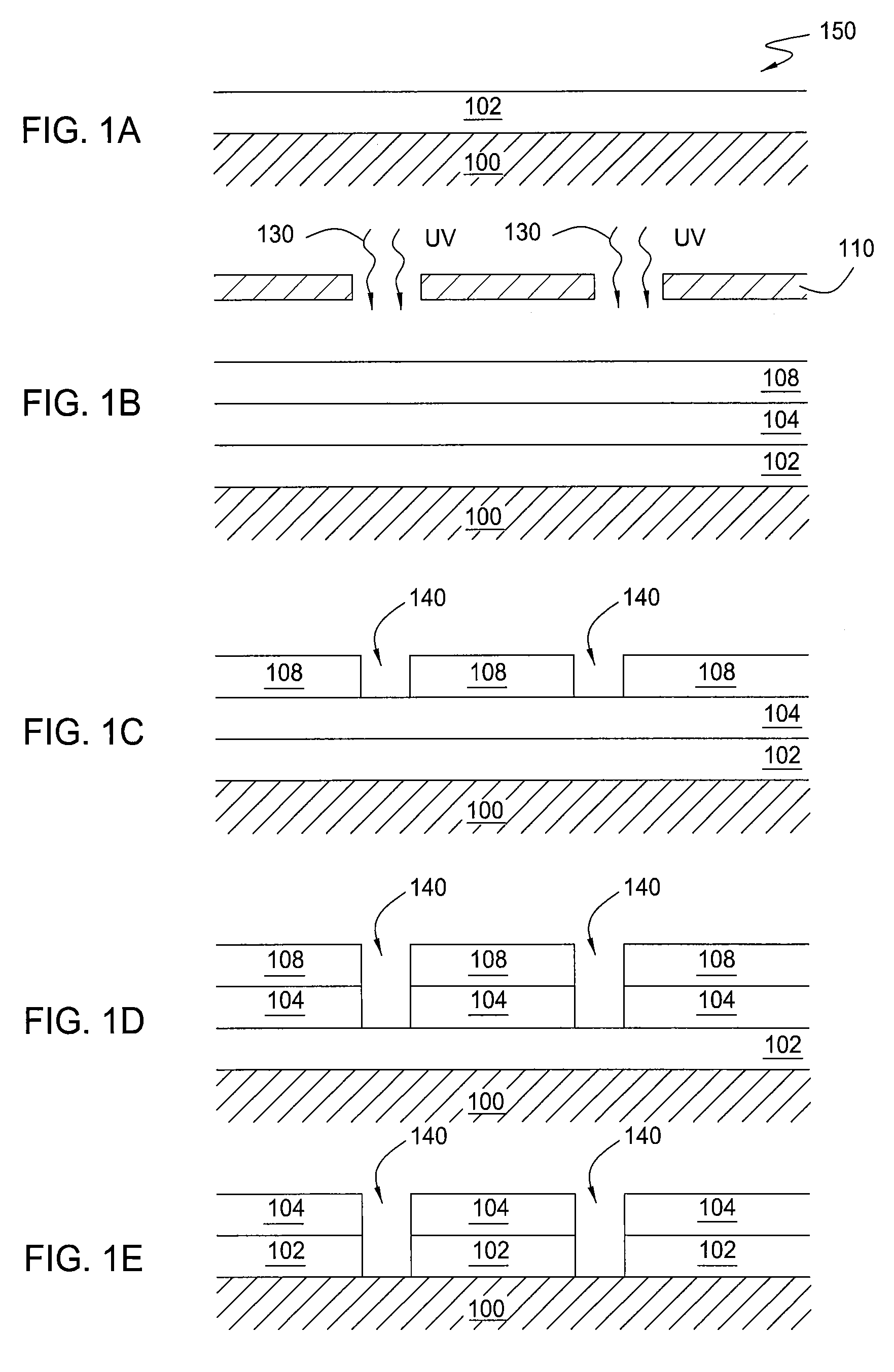

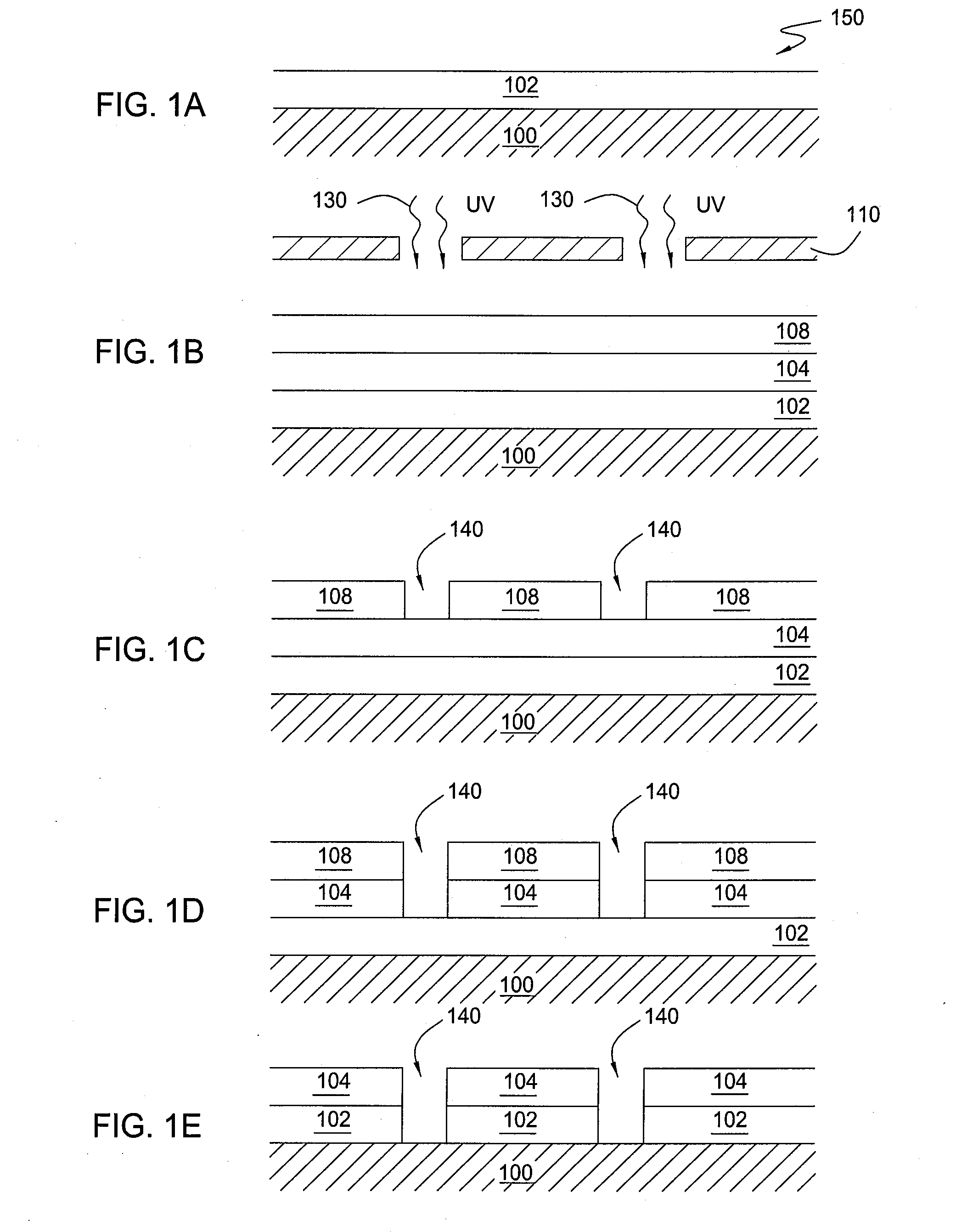

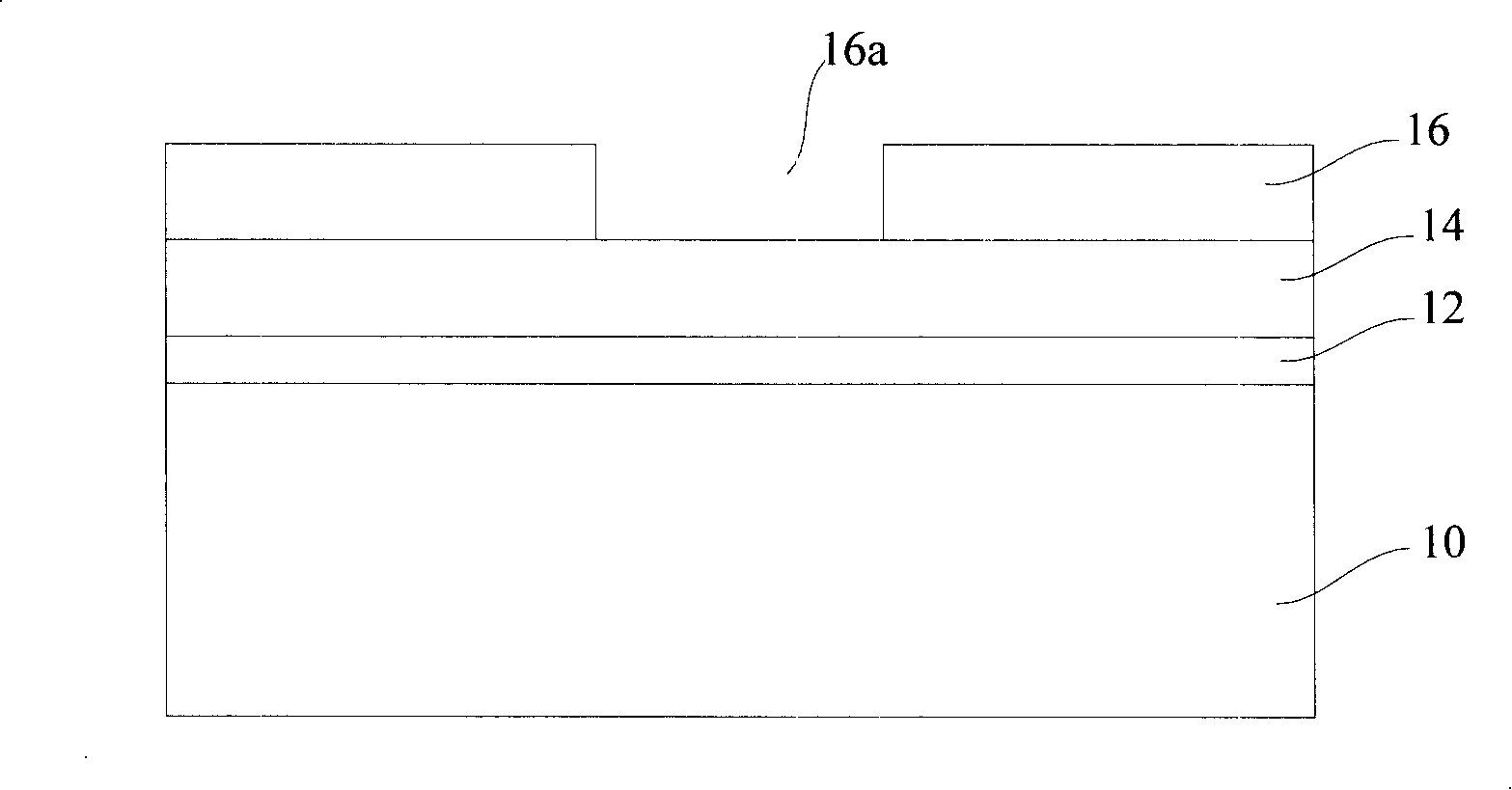

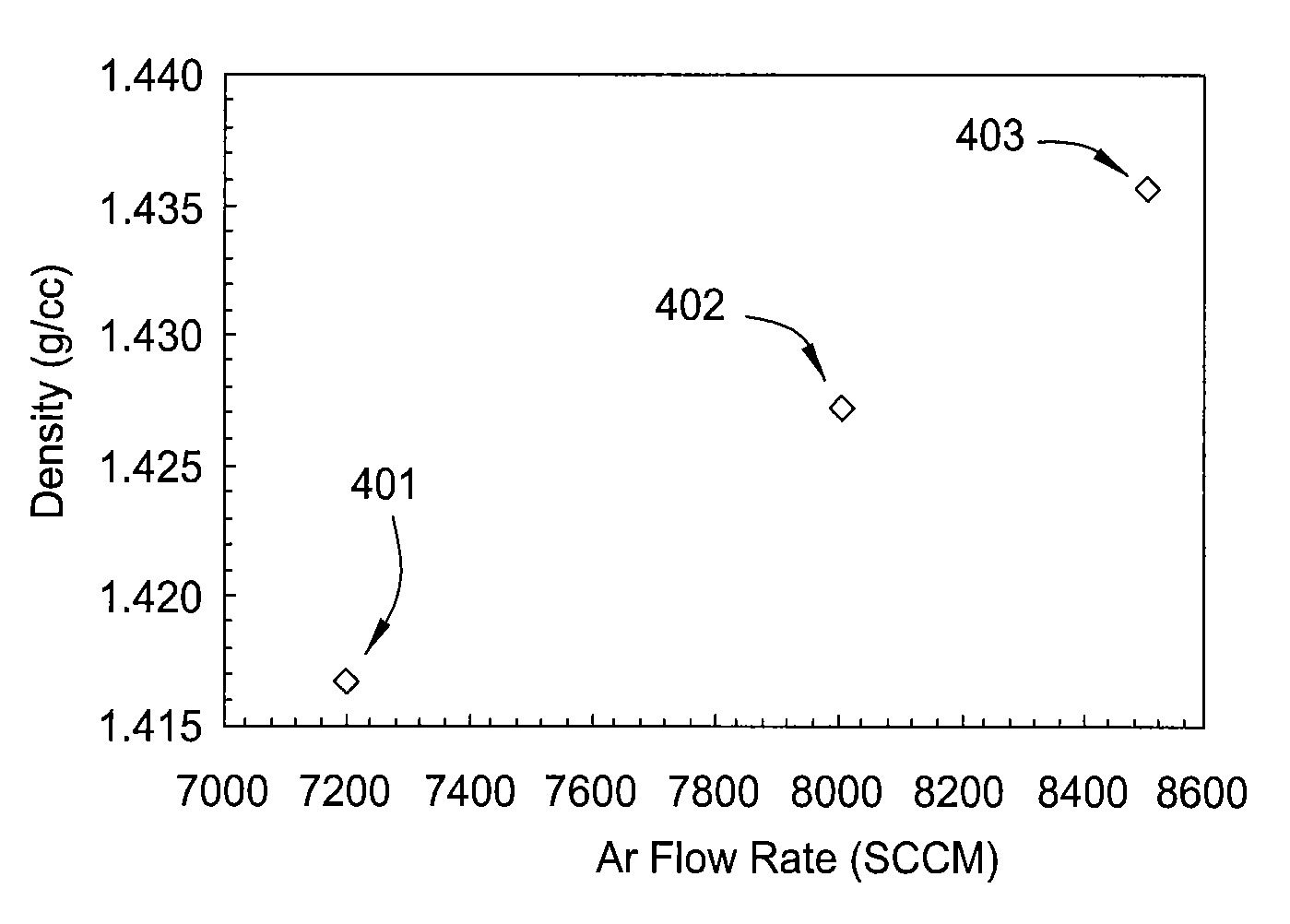

Method For Depositing an Amorphous Carbon Film with Improved Density and Step Coverage

ActiveUS20080003824A1High densityLower thermal budgetPretreated surfacesSemiconductor/solid-state device manufacturingCarbon layerKrypton

A method for depositing an amorphous carbon layer on a substrate includes the steps of positioning a substrate in a chamber, introducing a hydrocarbon source into the processing chamber, introducing a heavy noble gas into the processing chamber, and generating a plasma in the processing chamber. The heavy noble gas is selected from the group consisting of argon, krypton, xenon, and combinations thereof and the molar flow rate of the noble gas is greater than the molar flow rate of the hydrocarbon source. A post-deposition termination step may be included, wherein the flow of the hydrocarbon source and the noble gas is stopped and a plasma is maintained in the chamber for a period of time to remove particles therefrom.

Owner:APPLIED MATERIALS INC

Method for depositing an amorphous carbon film with improved density and step coverage

InactiveUS20080153311A1High densityLower thermal budgetSemiconductor/solid-state device manufacturingChemical vapor deposition coatingProduct gasMolecular physics

A method for depositing an amorphous carbon layer on a substrate includes the steps of positioning a substrate in a chamber, introducing a hydrocarbon source into the processing chamber, introducing a heavy noble gas into the processing chamber, and generating a plasma in the processing chamber. The heavy noble gas is selected from the group consisting of argon, krypton, xenon, and combinations thereof and the molar flow rate of the noble gas is greater than the molar flow rate of the hydrocarbon source. A post-deposition termination step may be included, wherein the flow of the hydrocarbon source and the noble gas is stopped and a plasma is maintained in the chamber for a period of time to remove particles therefrom.

Owner:APPLIED MATERIALS INC

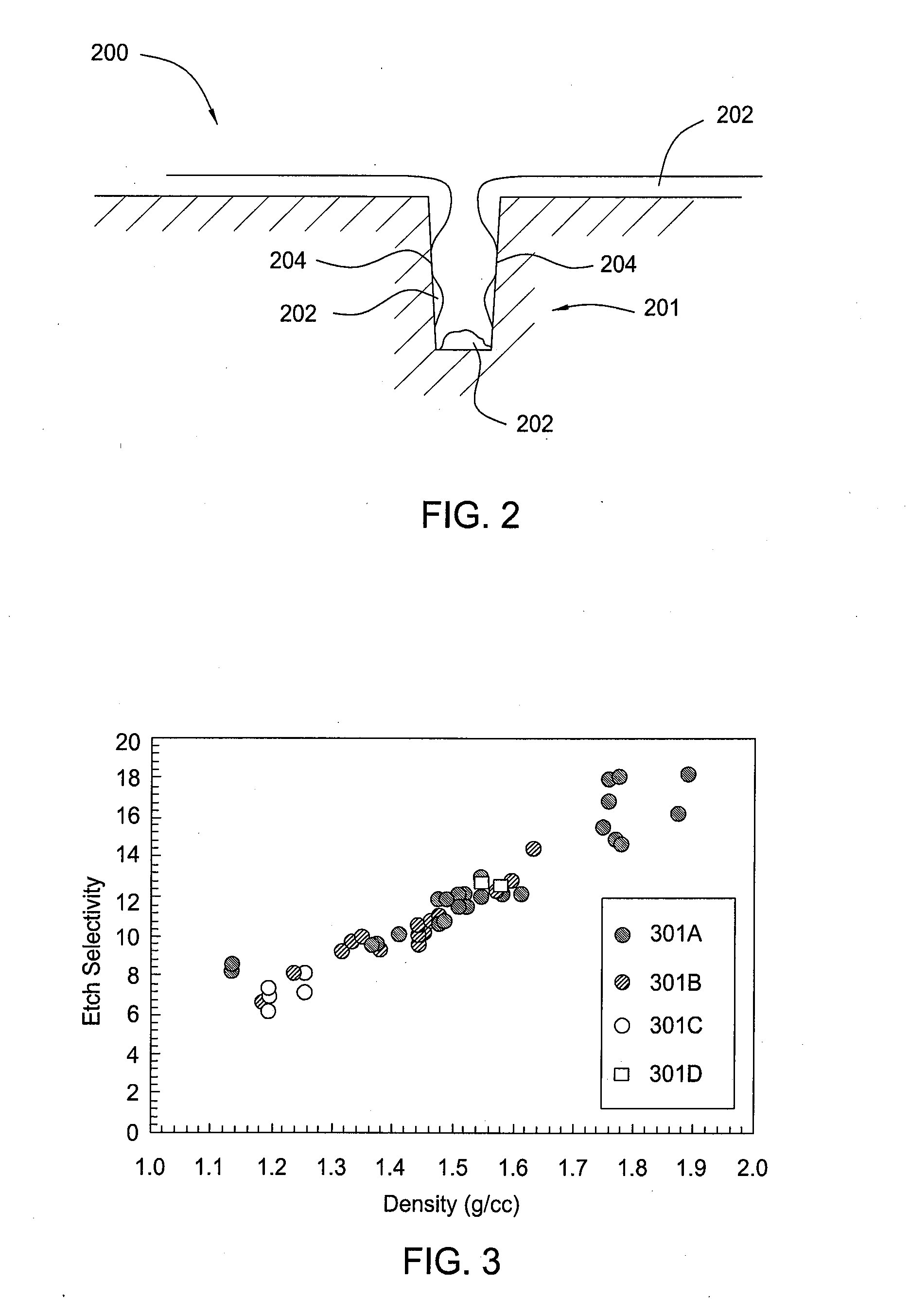

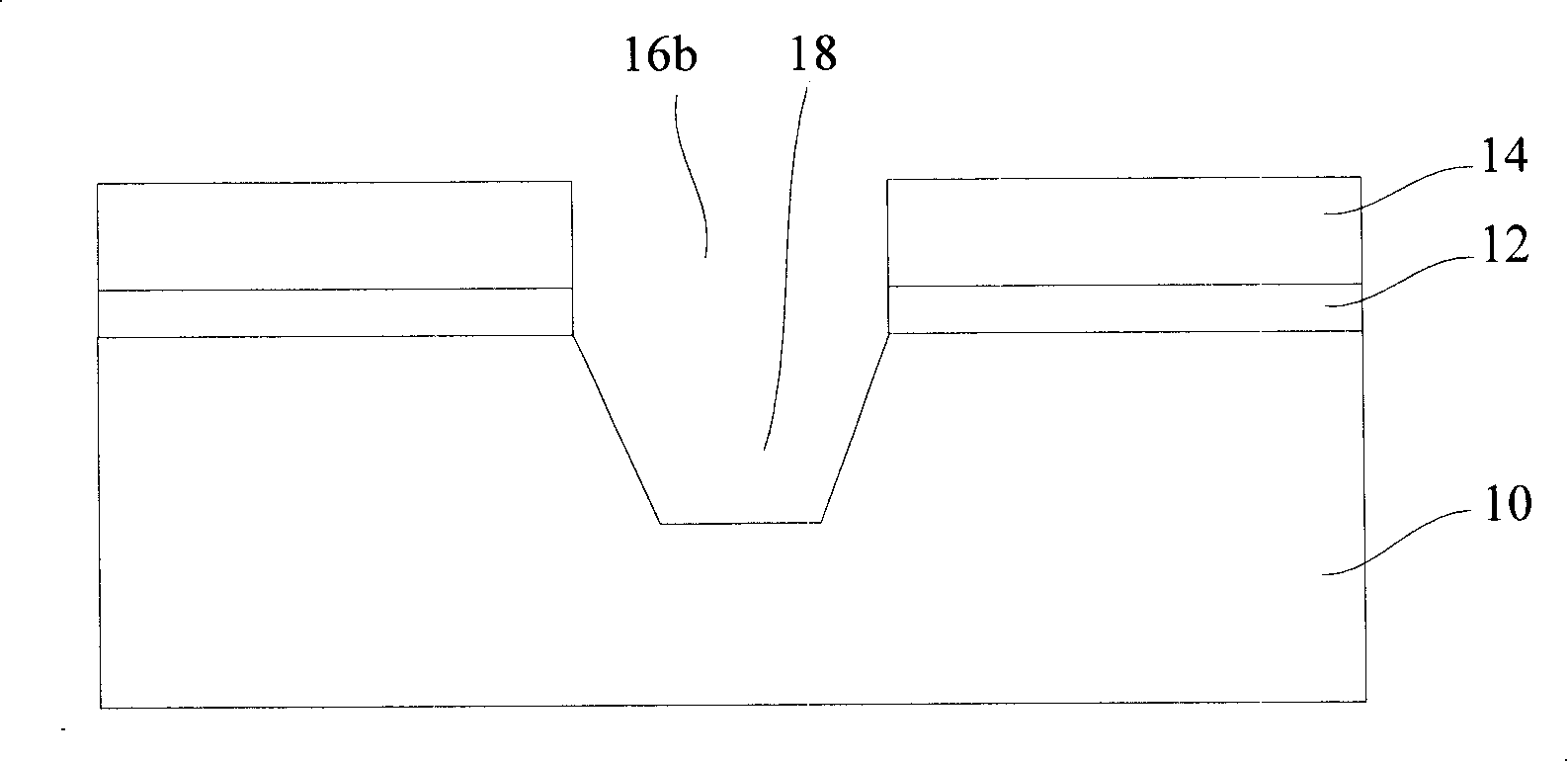

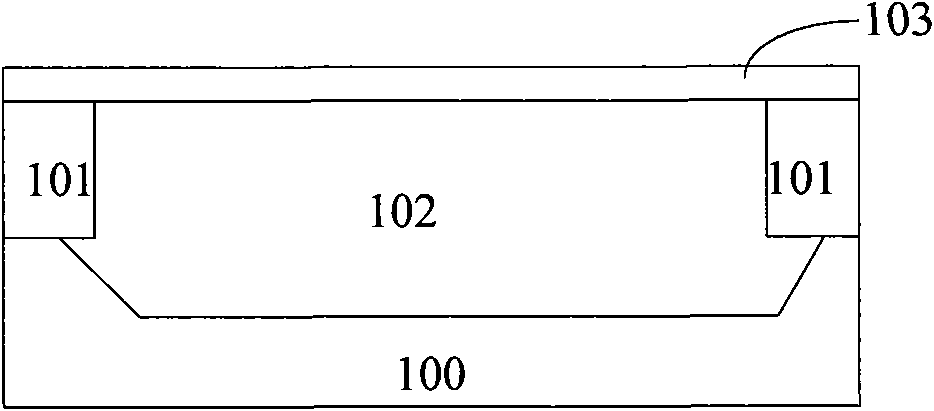

Method for forming shallow trench isolation

InactiveCN101207063AReduce the number of transmissionsReduce pollutionSemiconductor/solid-state device manufacturingEngineeringSemiconductor

The invention relates to a shallow groove isolation formation method. The method comprises the following steps: a semiconductor substrate with a groove is provided; pad oxide layers are formed on the bottom part and the side wall of the groove, and in situ annealing is performed; insulation substance is filled into the groove. The shallow groove isolation formation method of the invention can reduce the transmission frequency of the substrate, reduce the pollution, ensures the process to be simplified, and reduces the cost.

Owner:SEMICON MFG INT (SHANGHAI) CORP

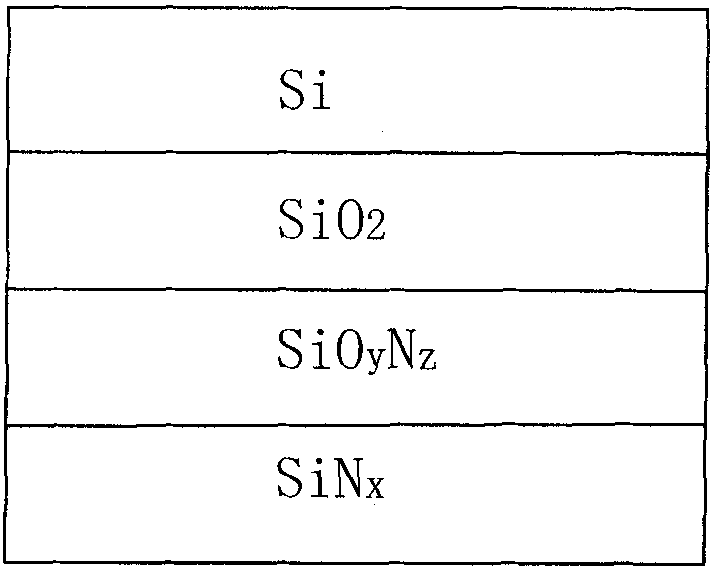

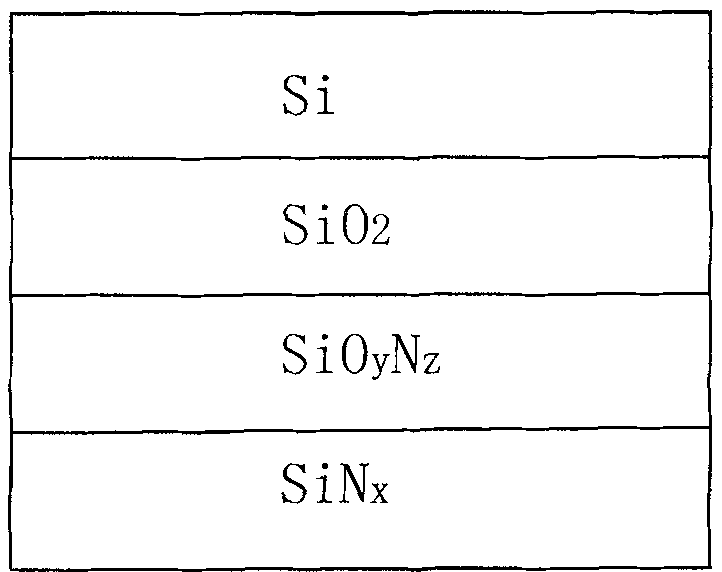

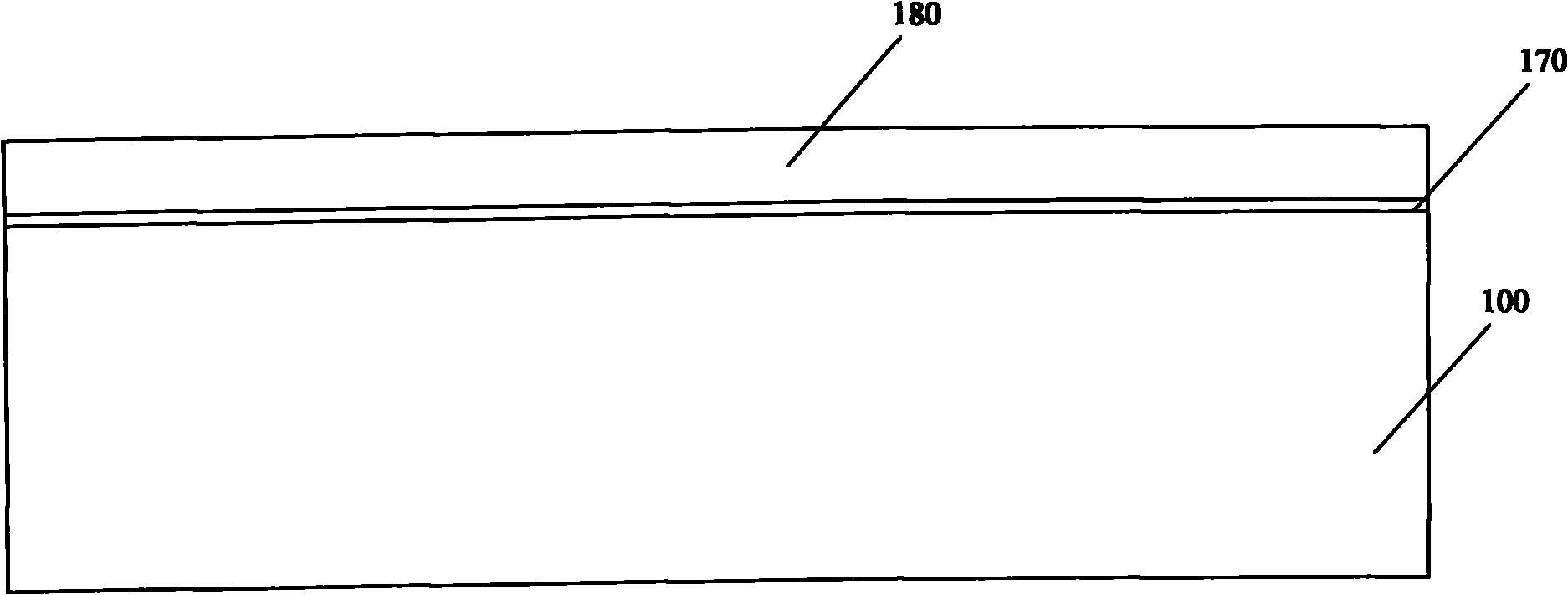

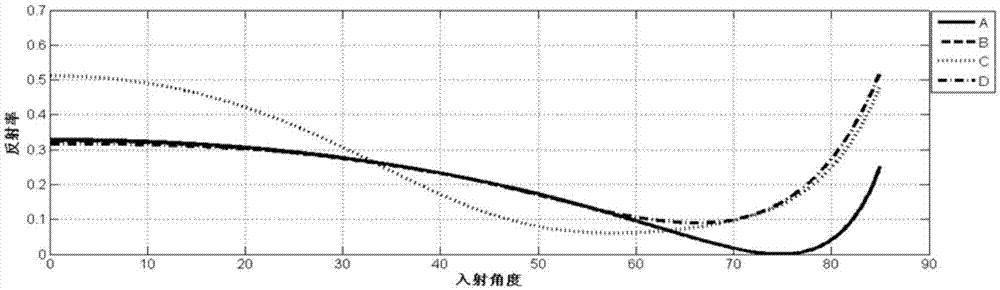

Method for realizing graded laminated passivation film on back surface of solar cell

InactiveCN101964378ALower thermal budgetSave energyChemical vapor deposition coatingPhotovoltaic energy generationNitrogen oxideSolar cell

The invention relates to the field of solar cell production method, especially to a method for realizing a laminated passivation film on the back surface of a solar cell. A film is deposited on the backlight surface of a processed solar cell silicon chip according to chemical vapor deposition technology, the mixed gas of SiH4 and N2O is adopted as the gas at the beginning of the deposition, NH3 is gradually added in the process of deposition so that the component of the film is changed from silicon dioxide on the surface of the silicon chip to nitrogen oxide of silicon in the outward direction and then to silicon nitride in the outward direction, and the thickness of the film ranges from 50nm to 300nm. The method has the characteristics of fast deposition speed, high output, being capable of achieving the deposition of a plurality of films at a time, and high tightness of the deposited film. High temperature process is not needed in the technology, the heat budget required is less, and high temperature influence resulted from thermal oxidization is avoided, in addition, such a graded laminated film can effectively reduce interface state caused by the combination of different films, improve thermal stability compared with silicon nitride only, and lessen film stress.

Owner:TRINA SOLAR CO LTD

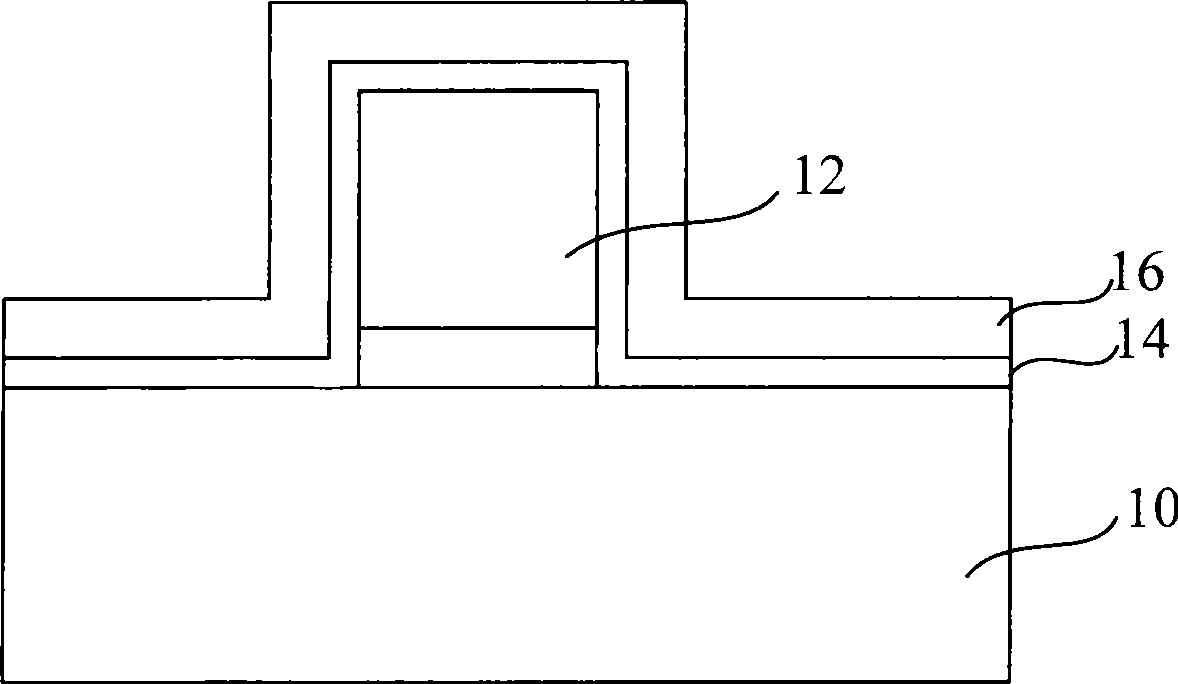

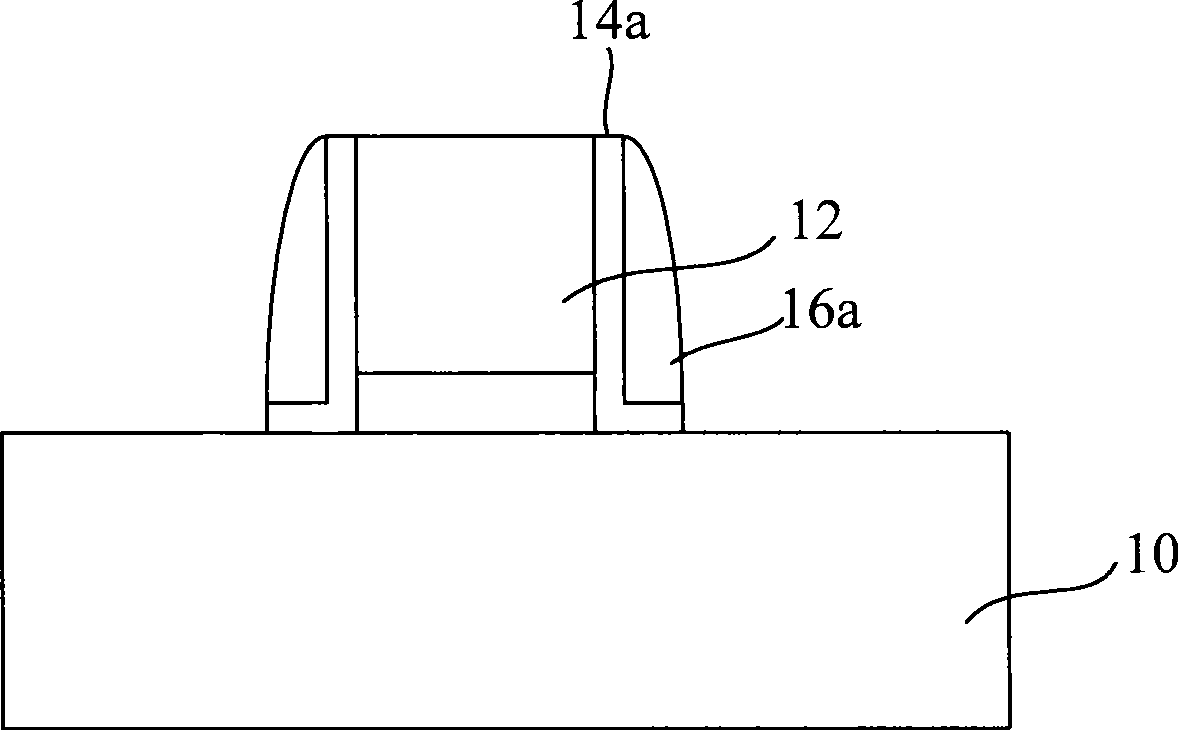

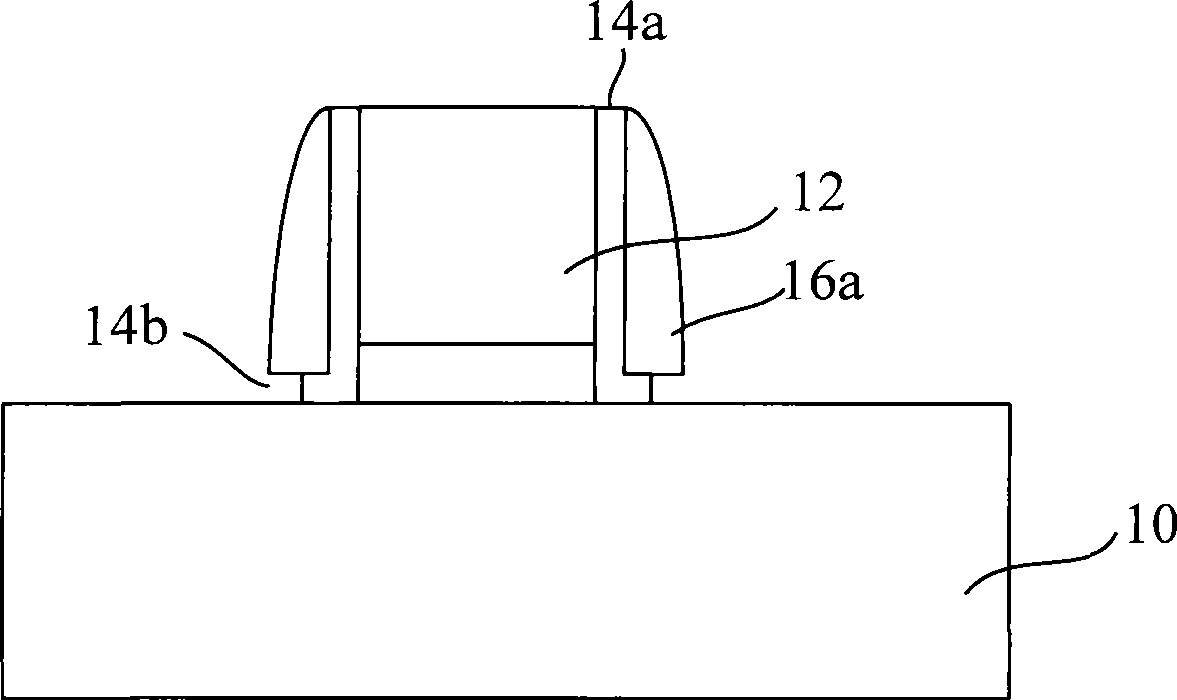

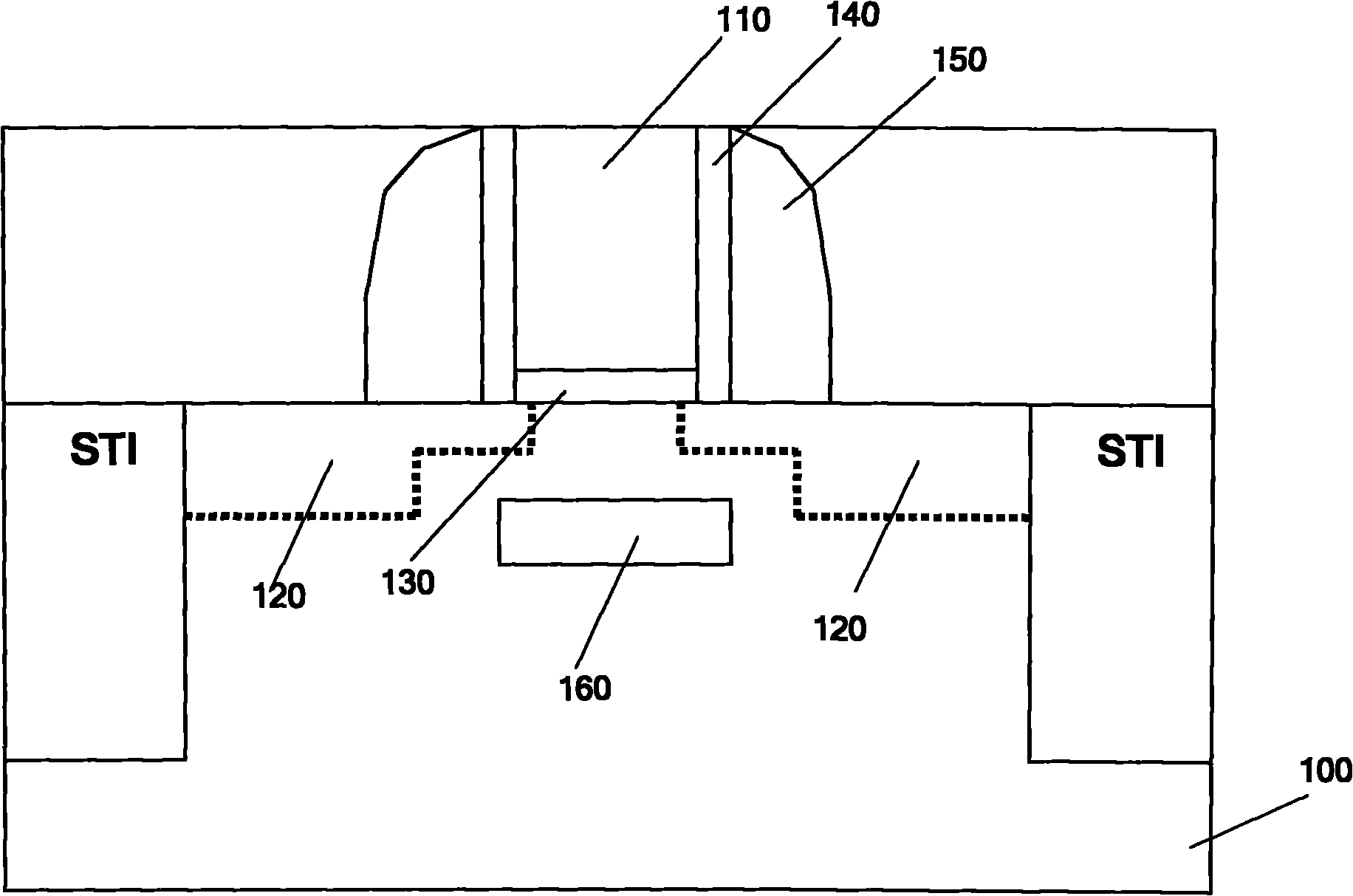

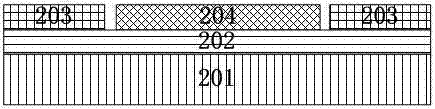

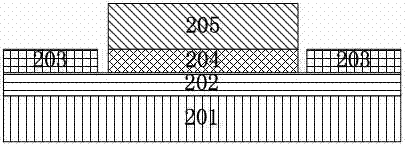

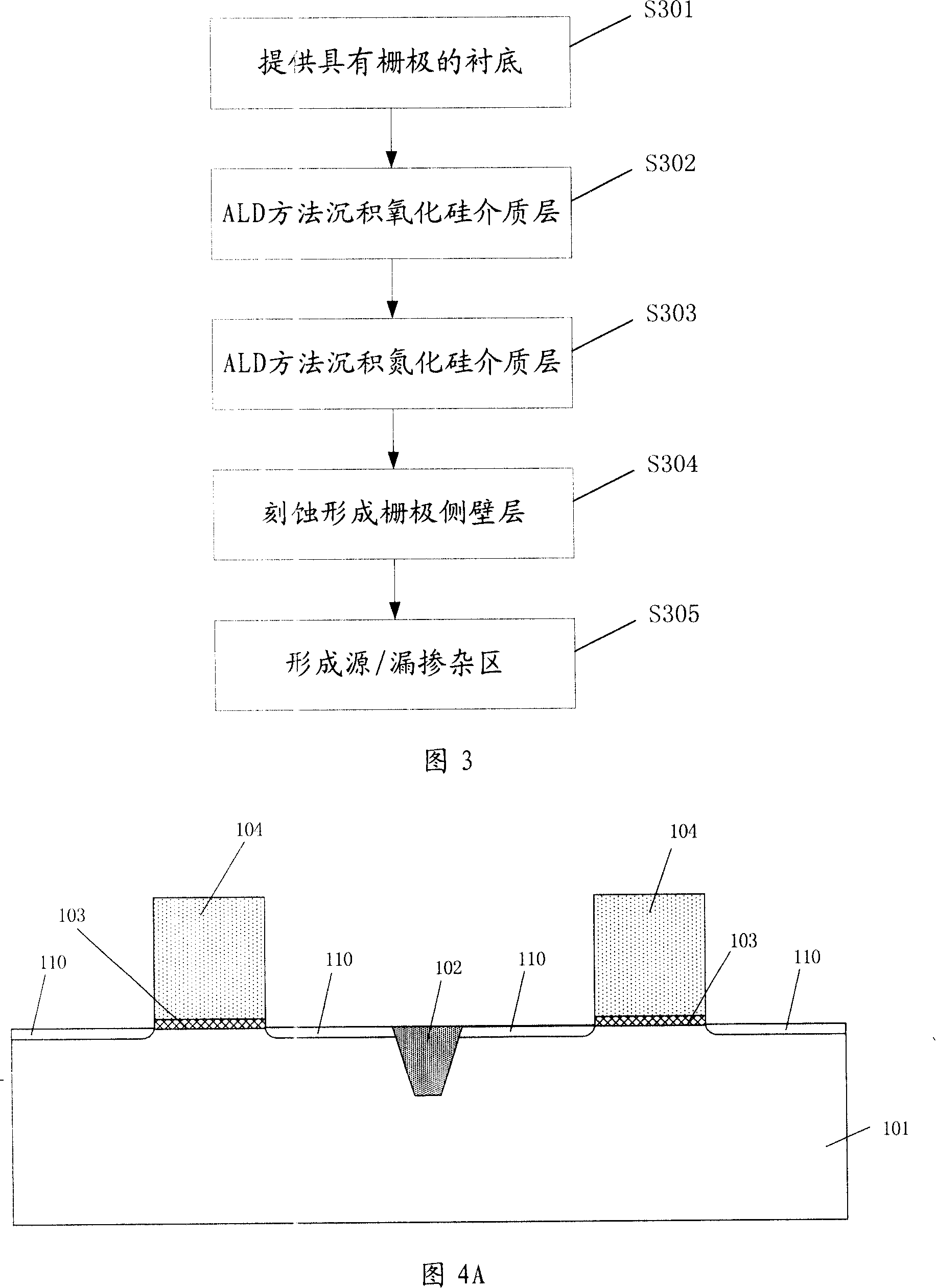

Manufacturing method for gate lateral wall layer and semi-conductor device

InactiveCN101393862AReduce the number of handlingThe process steps are simpleSemiconductor/solid-state device manufacturingSemiconductor devicesSilanesSemiconductor

A method for forming a side wall layer on a grid electrode comprises the following steps: a semi-conductor substrate provided with the grid electrode is provided; a first silica layer is formed on the surfaces of the semi-conductor substrate and the grid electrode; with hexa-chloro silane as a precursor, a first silicon nitride layer is formed on top of the first silica layer; and parts of the first silica layer and the first silicon nitride layer are removed in a selective manner so as to preserve the first silica layer and the first silicon nitride layer already formed on the side wall of the grid electrode. The invention further provides a method for manufacturing a semiconductor device. The invention can solve the problem that the bottom part of the side wall layer on the grid electrode is susceptible to depression.

Owner:SEMICON MFG INT (SHANGHAI) CORP

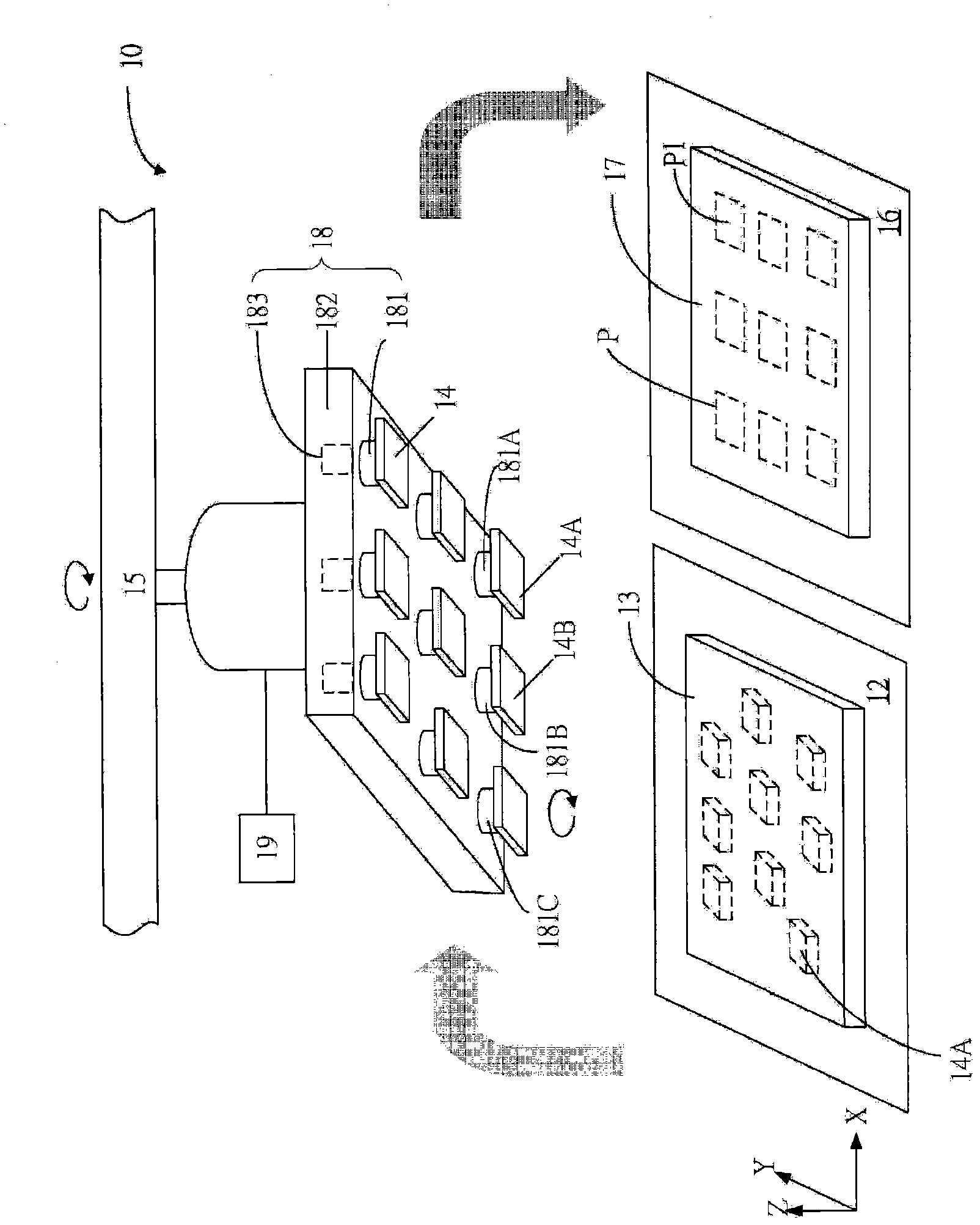

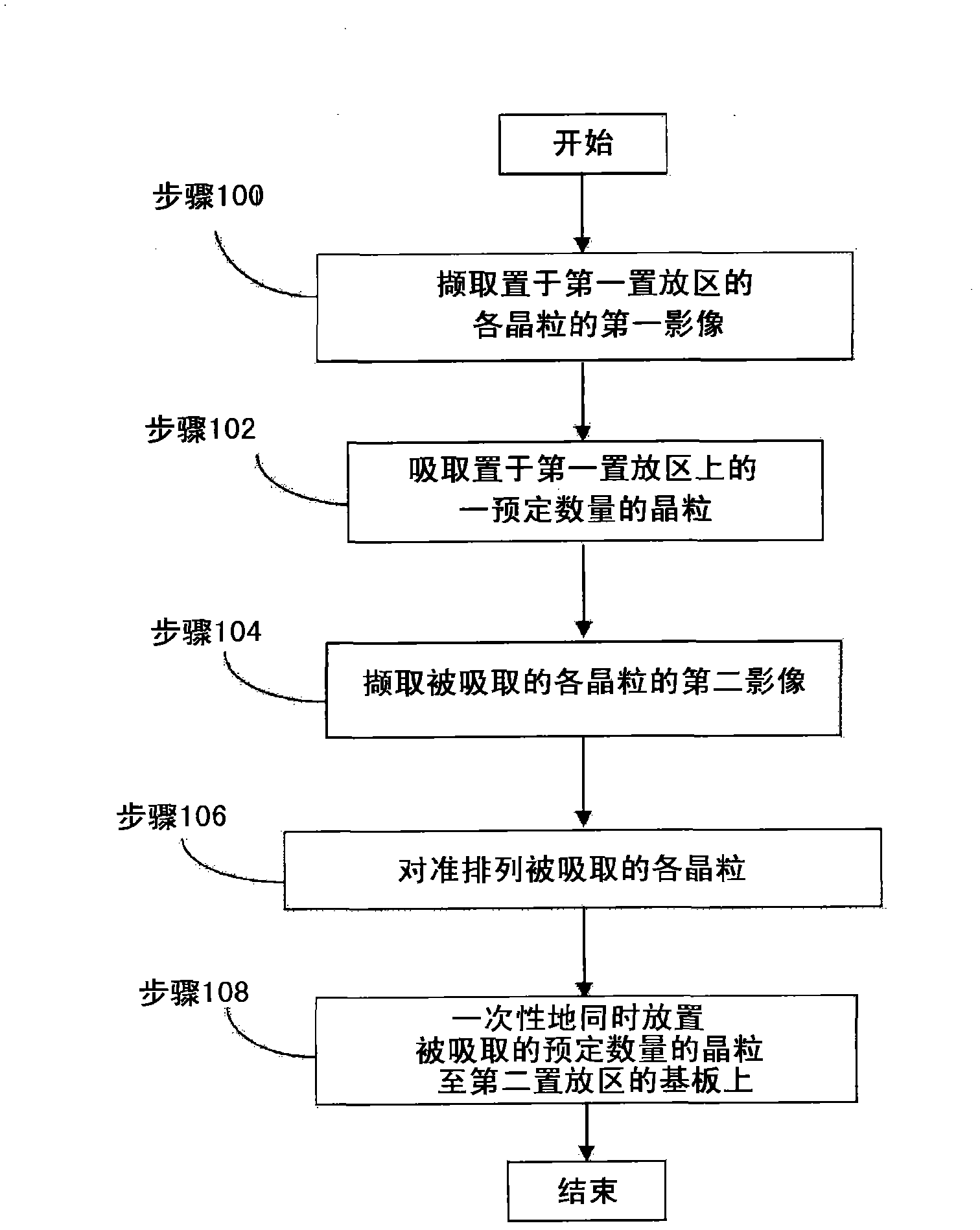

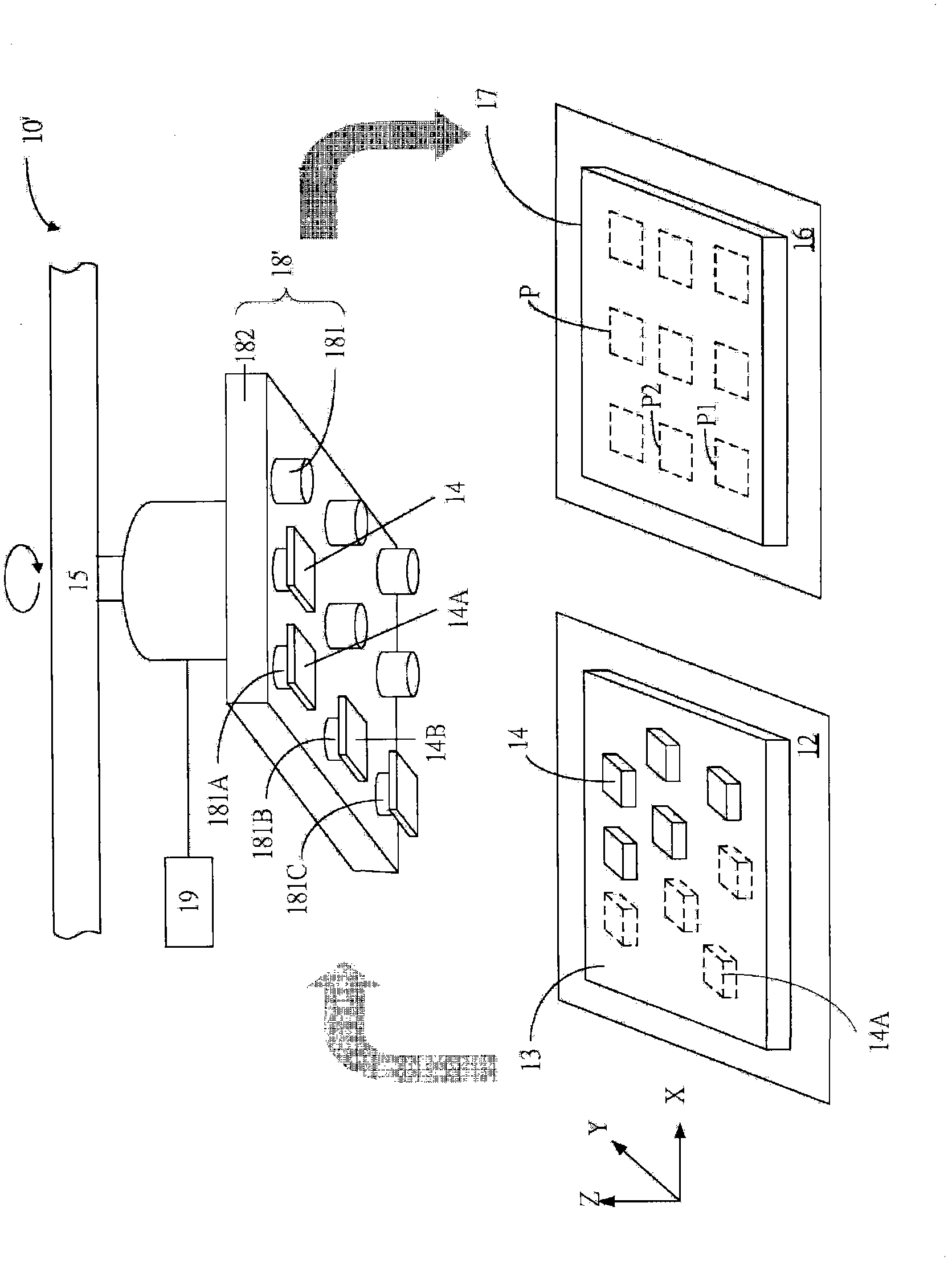

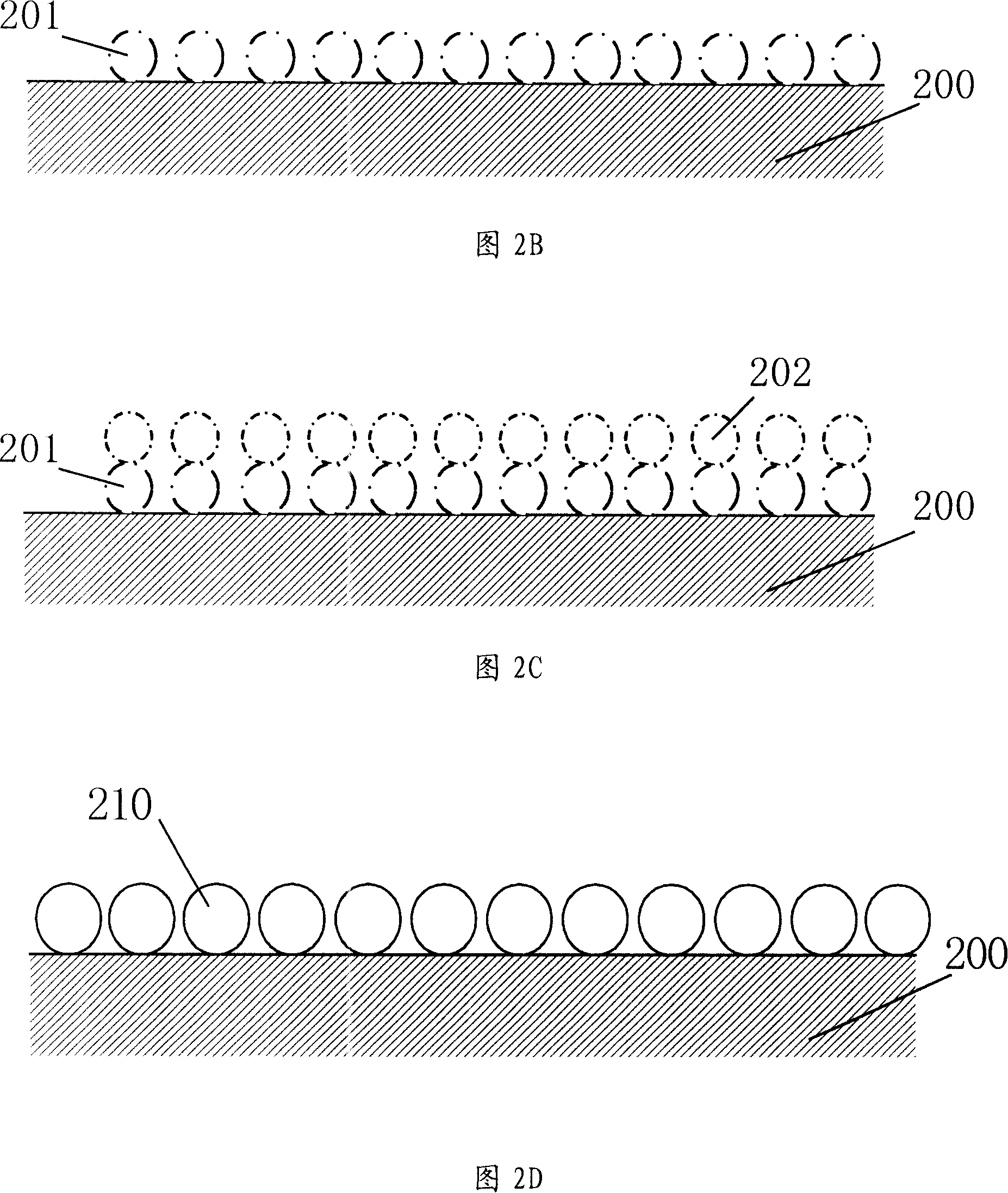

Apparatus and method for die bonding

InactiveCN103107248AAvoid inaccurate alignment and other defectsLower thermal budgetSolid-state devicesSemiconductor/solid-state device manufacturingDie bondingNozzle

Owner:WALSIN LIHWA

Flexible resistive random access memory based on oxidized graphene and preparation method thereof

InactiveCN103490009AIncrease success rateEfficient volatilizationElectrical apparatusEngineeringFlexible electronics

The invention belongs to the technical field of semiconductor devices, and particularly relates to a flexible resistive random access memory based on oxidized graphene and a preparation method thereof. The flexible resistive random access memory comprises a transparent flexible substrate and a three-layer structure device unit on the substrate, the bottom layer of the device unit is a flexible transparent electrode, the top layer electrode can be metal or other electrodes, and the middle functional layer is an oxidized graphene thin film. As the experiment proves, the oxidized graphene has the good resistance change characteristics, rotating coating can be carried out at the indoor temperature to form the functional layer of the resistive random access memory, the high-temperature process required for growing other materials of the functional layer is avoided, and the obtained flexible resistive random access memory can be applied to flexible electronic devices.

Owner:FUDAN UNIV

Silicon wafer rapid heat treatment phosphorus diffusion gettering technology for manufacture of solar cell

InactiveCN101834224AShort processing timeImprove productivityFinal product manufactureSemiconductor devicesSilicon chipAtmosphere

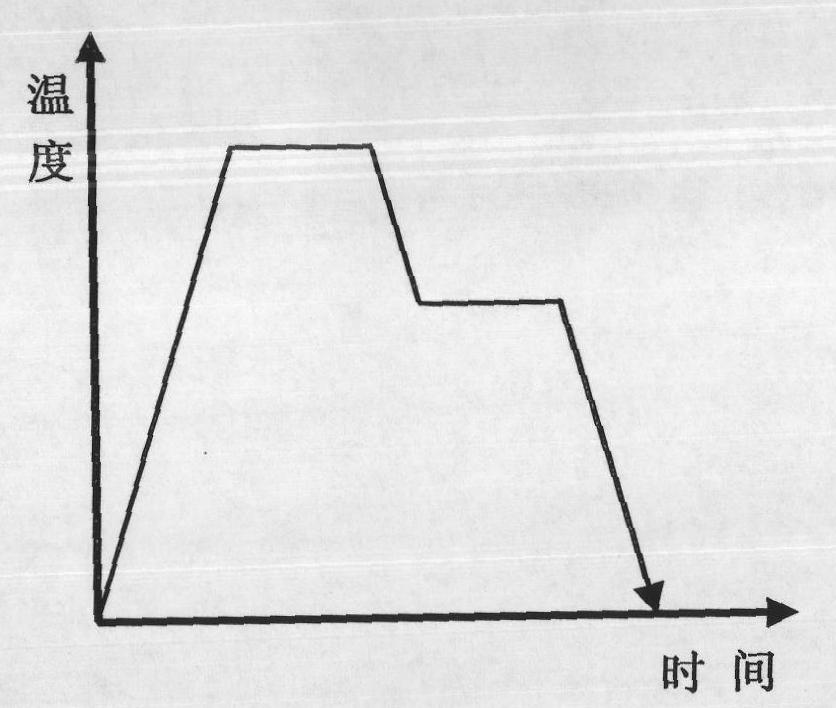

The invention discloses a silicon wafer phosphorus diffusion gettering technology for manufacture of a solar cell, which comprises the following steps of: coating a phosphorus source on the surface of a silicon wafer; heating the silicon wafer to 800-1,100 DEG C at the rate of 50-200 DEG C / s in the presence of a protective gas atmosphere; preserving the temperature for 1-10 minutes; then cooling to 500-800 DEG C and preserving the temperature for 1-10 minutes; and cooling and then removing a phosphorosilicate glass layer. The invention has short process time, low cost and good gettering effect.

Owner:ZHEJIANG UNIV

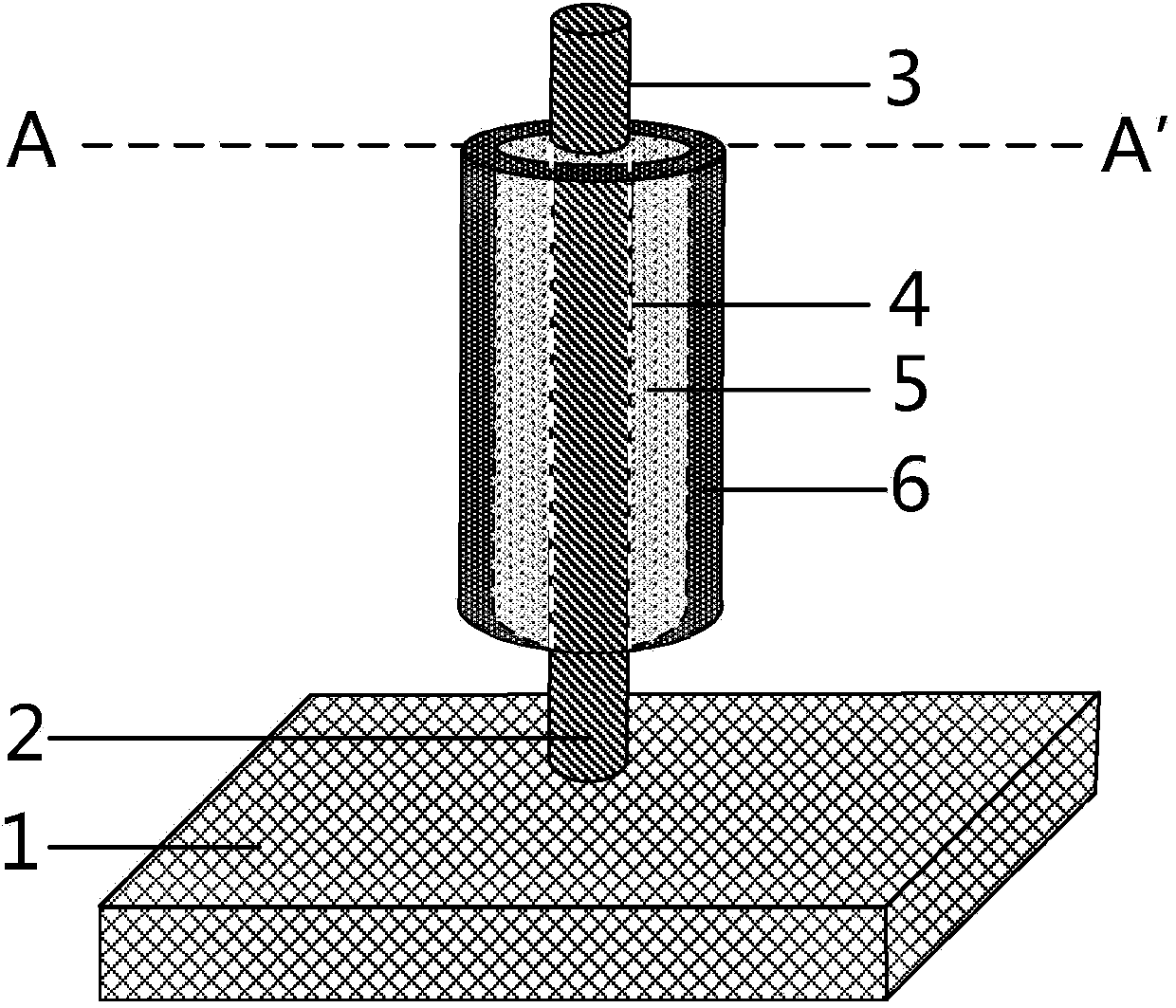

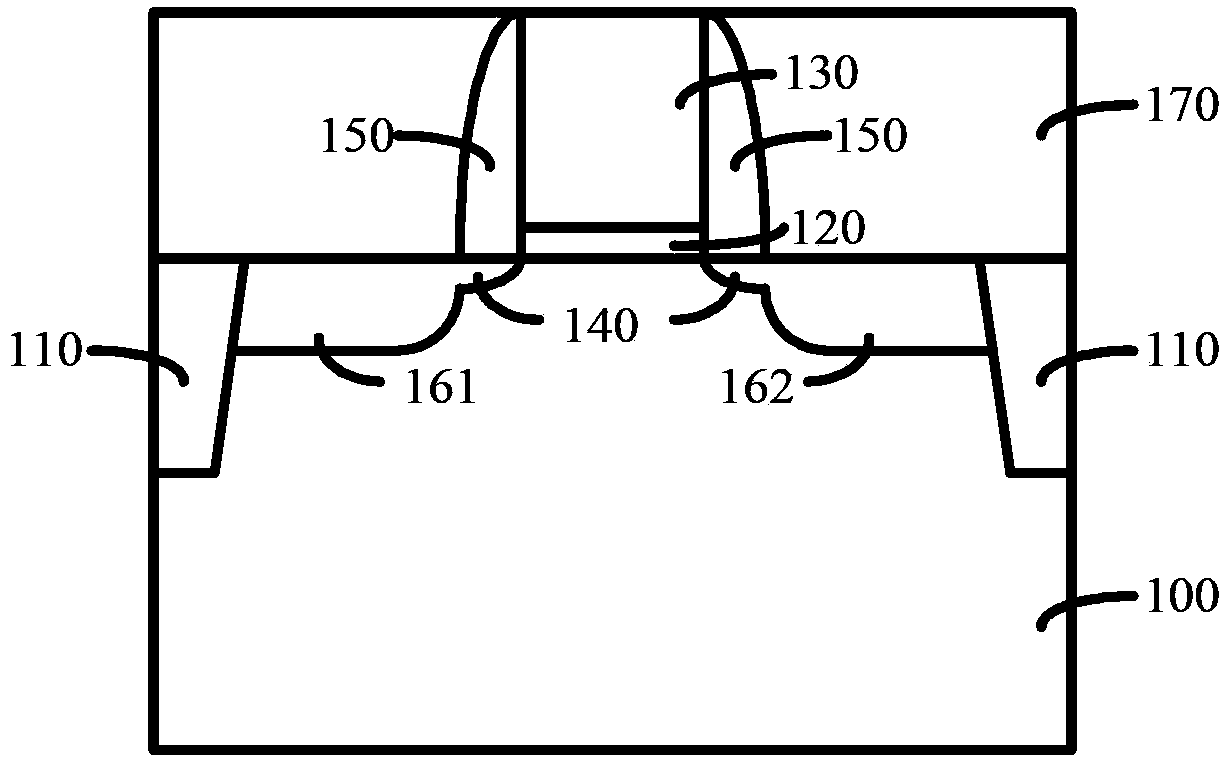

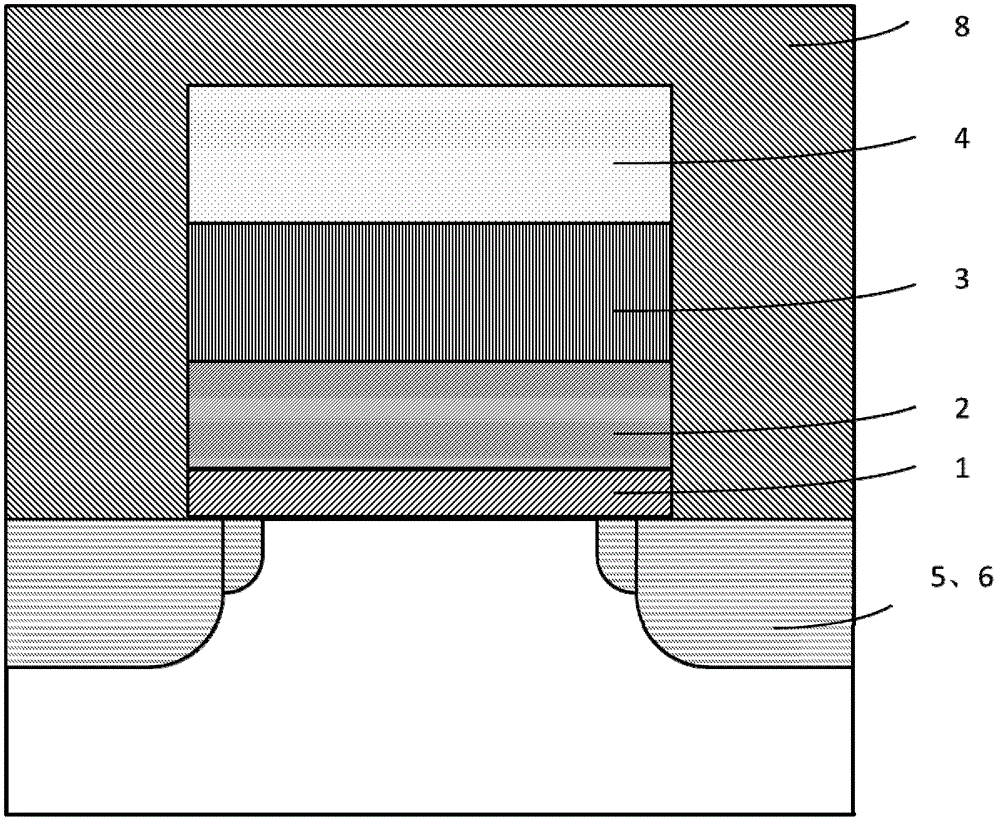

Junction-free field-effect transistor and preparation method thereof

ActiveCN104201195AHighly integratedGood gating abilitySemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricImpurity diffusion

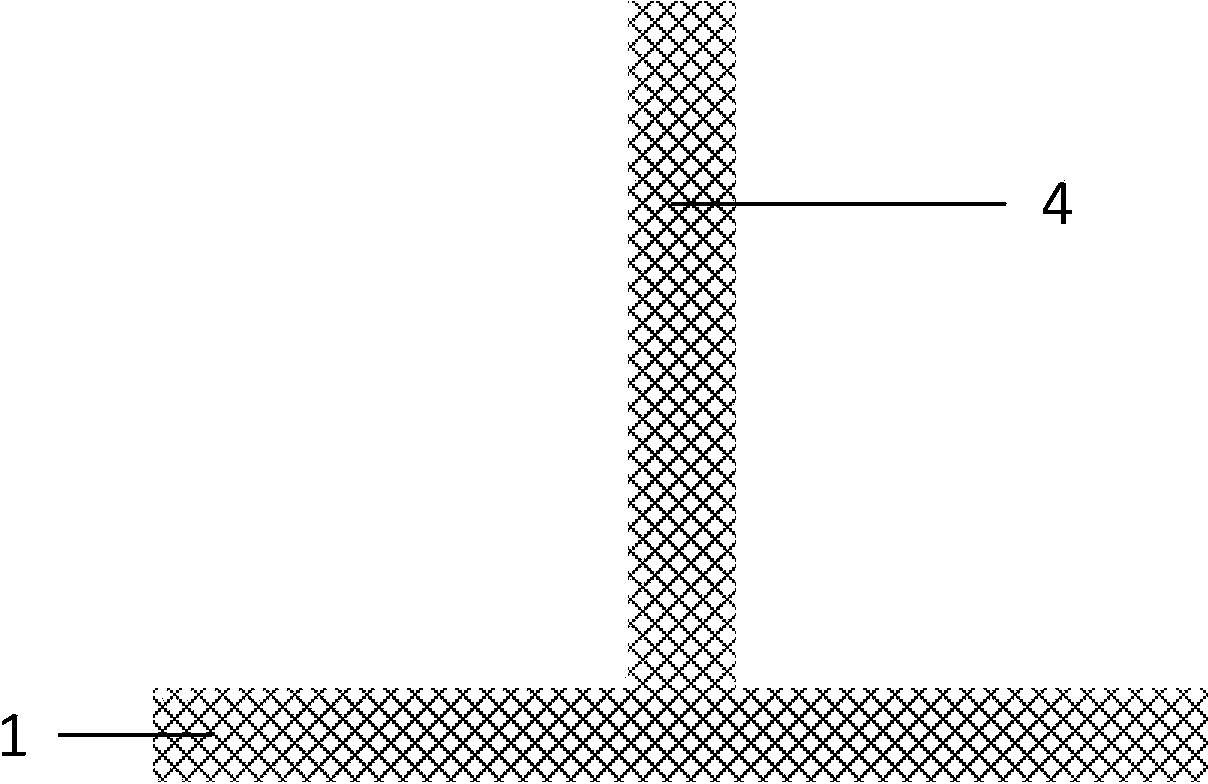

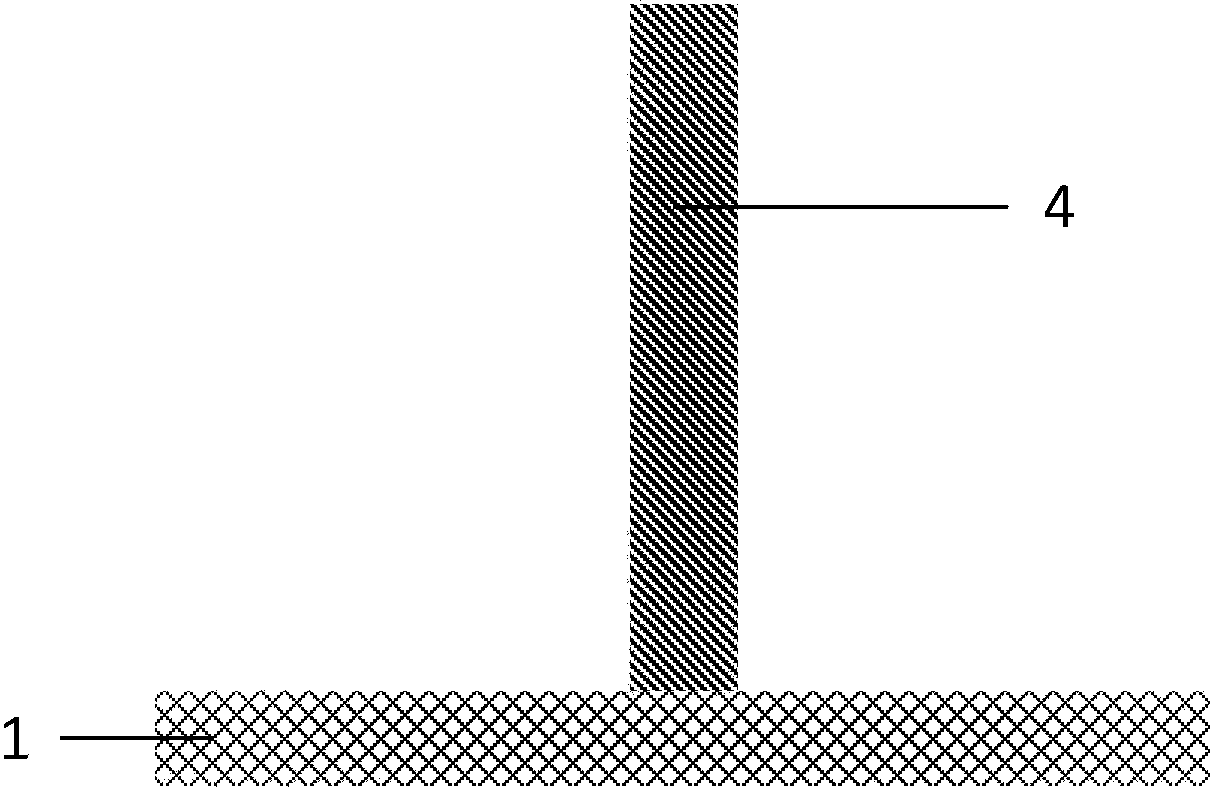

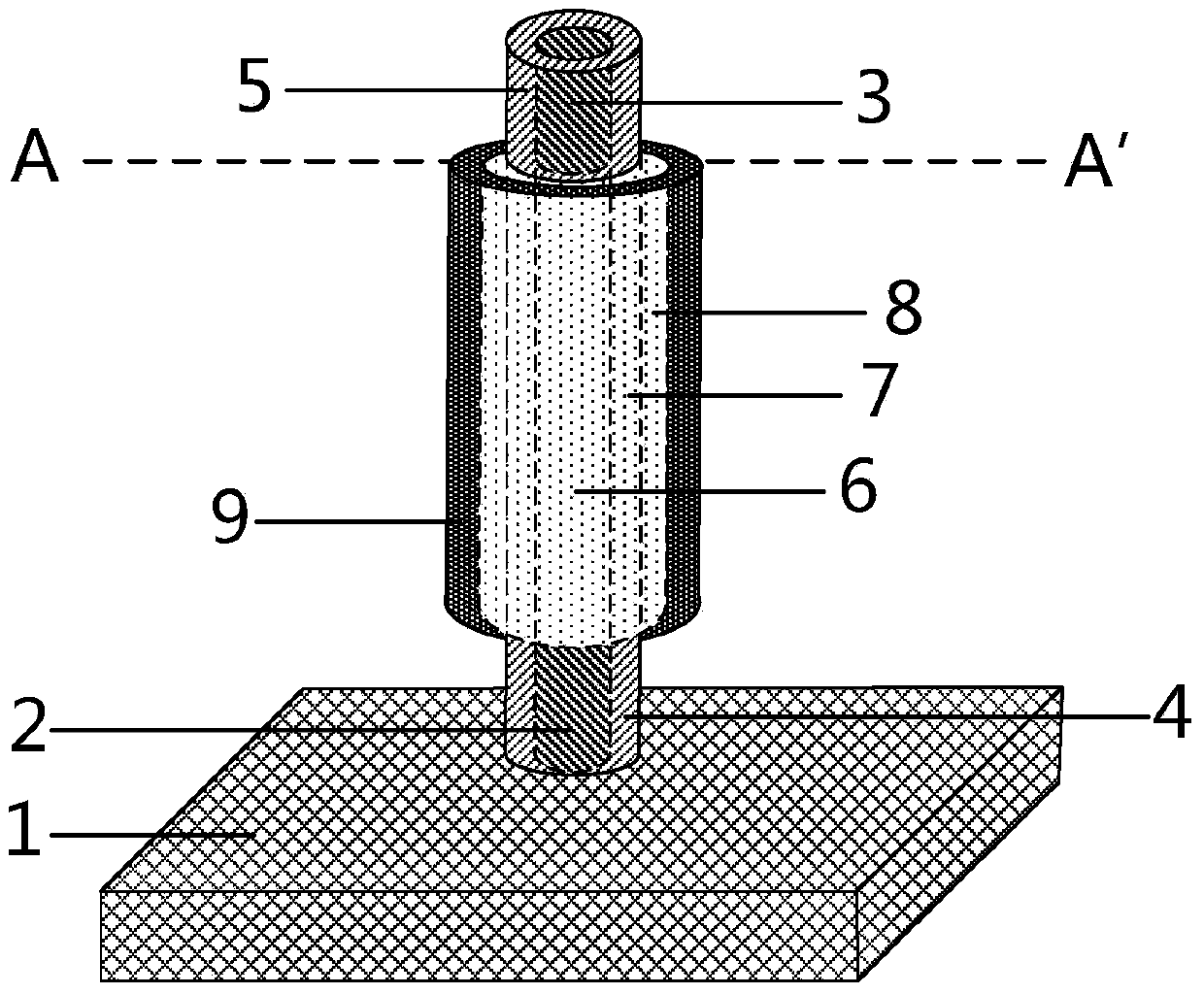

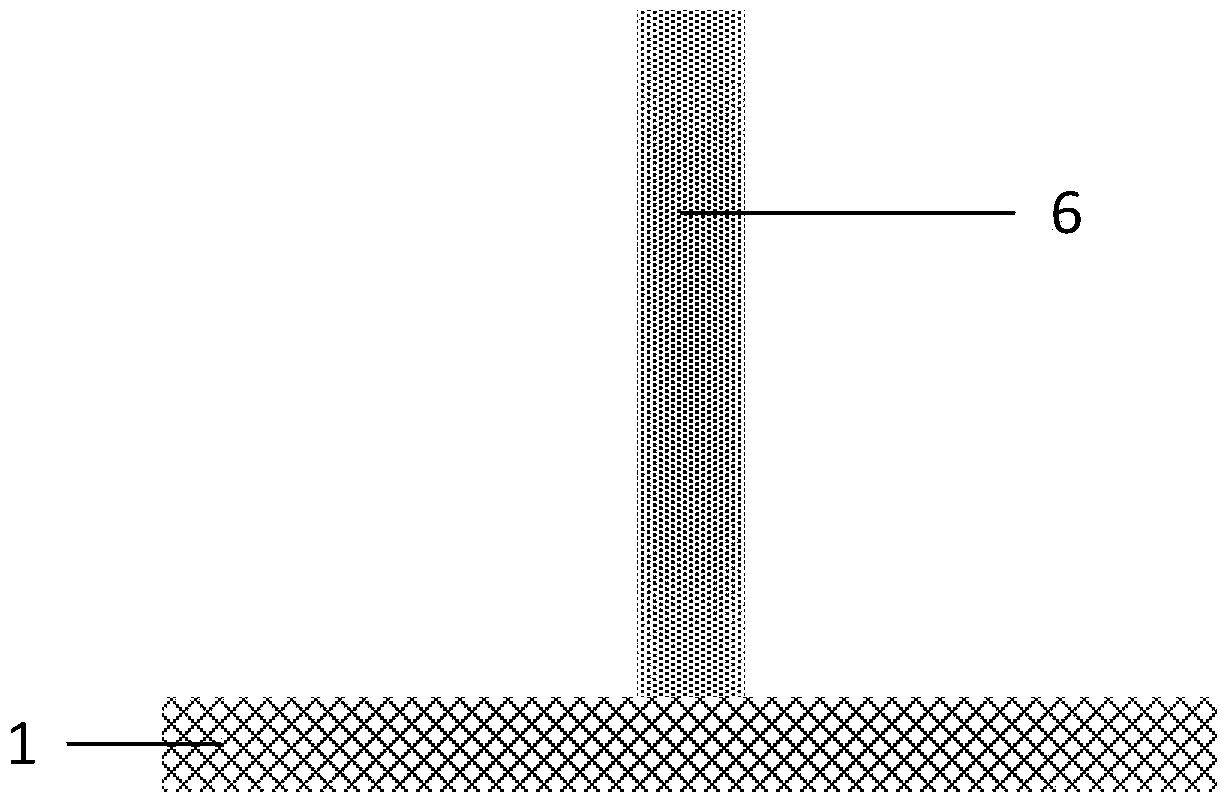

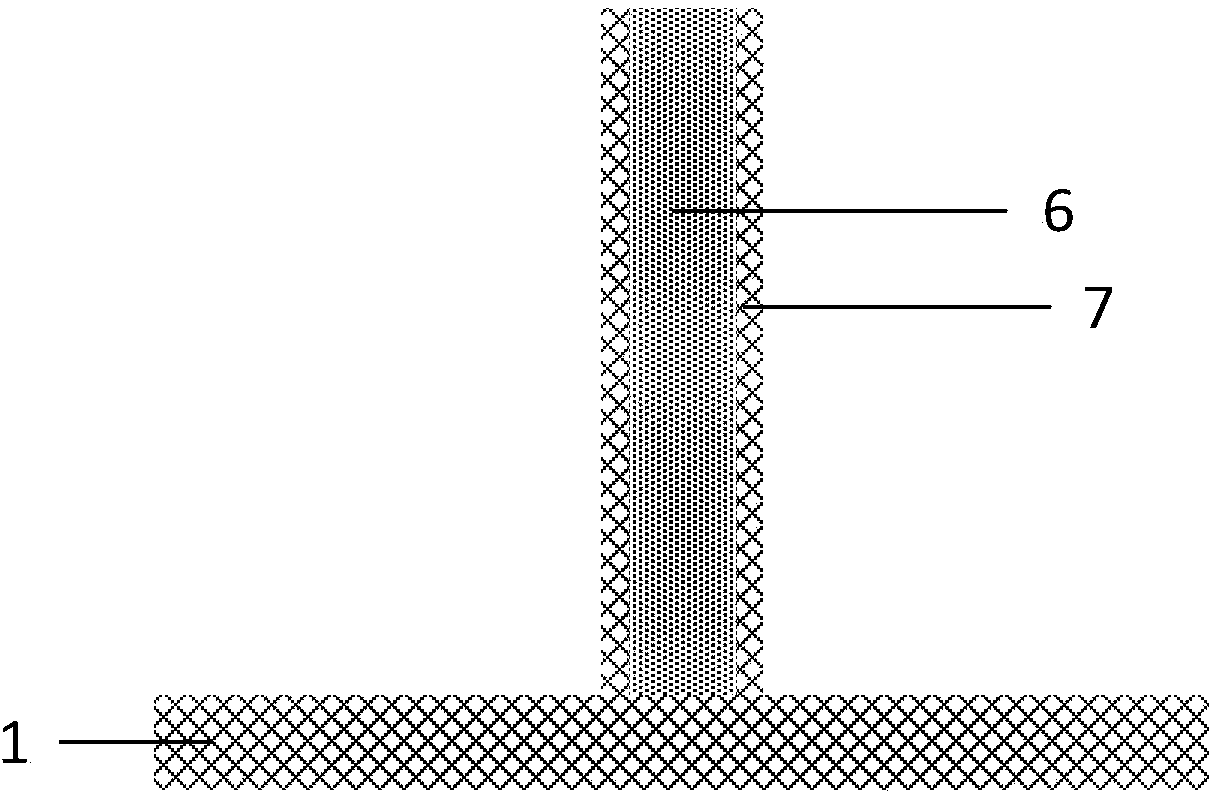

A surrounding gate field-effect transistor combined with a vertical channel (4) and a junction-free structure comprises a surrounding semiconductor channel in the vertical direction, a surrounding gate electrode (6), a surrounding gate dielectric layer (5), a source region (2), a drain region (3) and a semiconductor substrate (1), wherein the source region (2) is located at the bottom of the vertical channel (4) and connected with the substrate (1), the drain region (3) is located at the top of the vertical channel (4), and the gate dielectric layer (5) and the gate electrode (6) surround the vertical channel (4) circularly. The impurities of the same type and concentration are doped into the source region (2), the drain region (3) and the vertical channel (4). The same impurities are doped into source and drain channels of the transistor, so that heat budget is greatly reduced, the impurity diffusion and abrupt junction forming problems are eliminated, process requirements are simplified, integration machining photo-etching ultimate limit is broken through by utilizing the vertical channel and a surrounding gate structure, and the integration degree is improved.

Owner:PEKING UNIV

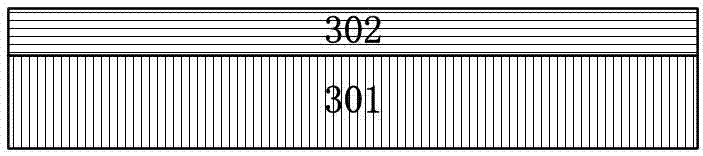

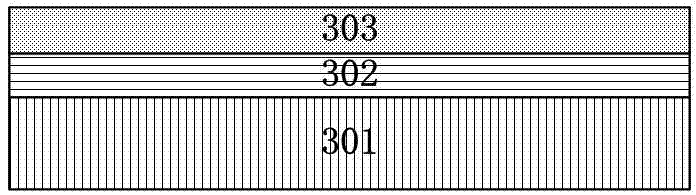

Internal gettering process of Czochralski silicon wafer

ActiveCN102168314ALower thermal budgetReduce the temperaturePolycrystalline material growthAfter-treatment detailsArgon atmosphereNitrogen atmosphere

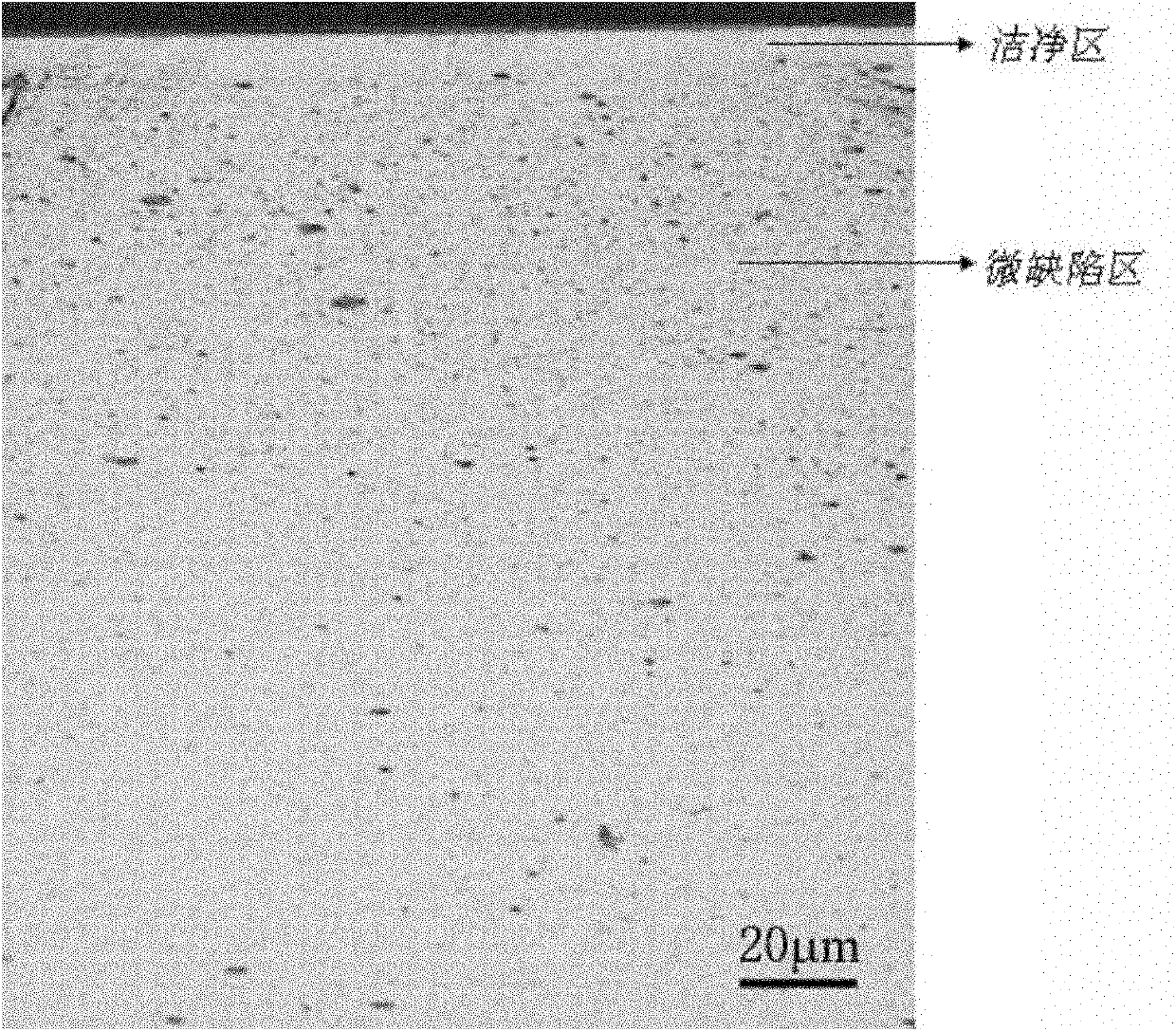

The invention discloses an internal gettering process of a Czochralski silicon wafer, which comprises the following steps of: (1) in nitrogen atmosphere, heating the Czochralski silicon wafer at a speed of 50-100 DEG C / sec to 1200-1250 DEG C, holding for 30-150 seconds, and then cooling the Czochralski silicon wafer at a speed of 5-50 DEG C / sec to 800-1000 DEG C, and naturally cooling; and (2) annealing the Czochralski silicon wafer after being treated in the step (1) in argon atmosphere at a temperature of 800-900 DEG C for 8 to 16 hours. The invention only comprises a two-step heat treatment process, the required temperature and time are lower than those of the traditional process, and the heat budget is obviously reduced; and in addition, the concentration of bulk micro-defect and the width of a clean zone can be conveniently controlled by the temperature, time and cooling speed of rapid heat treatment of the first step.

Owner:ZHEJIANG UNIV

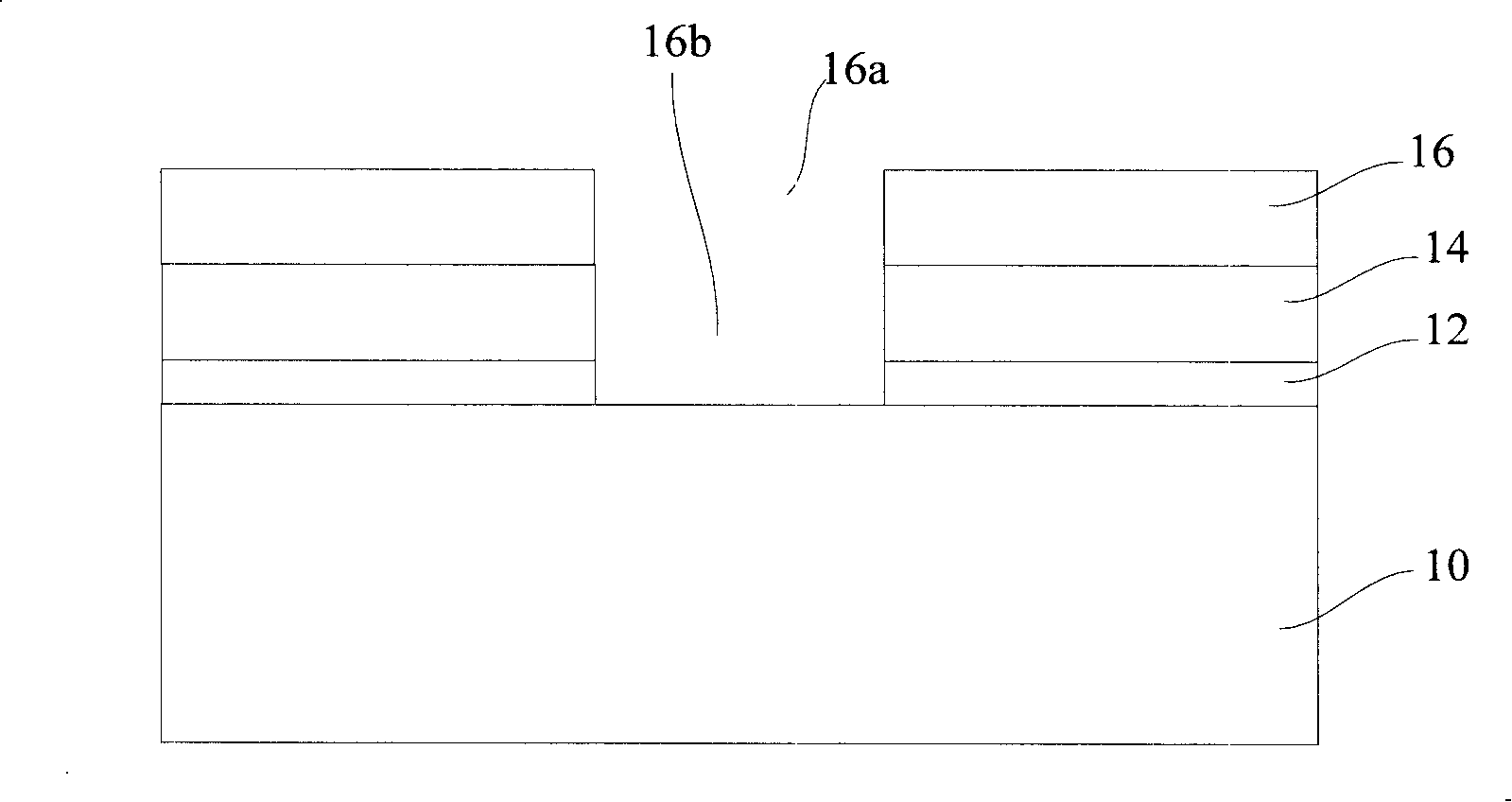

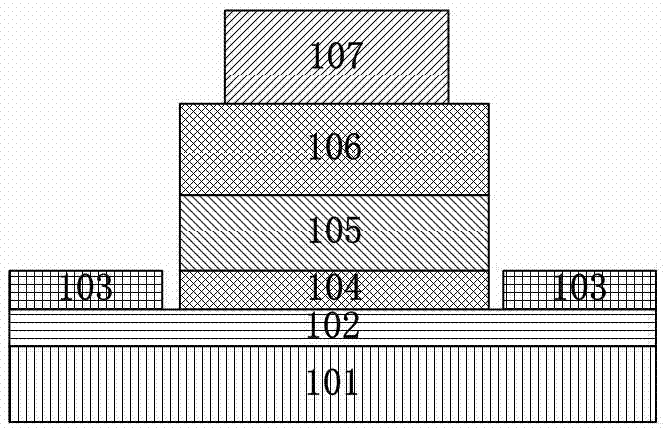

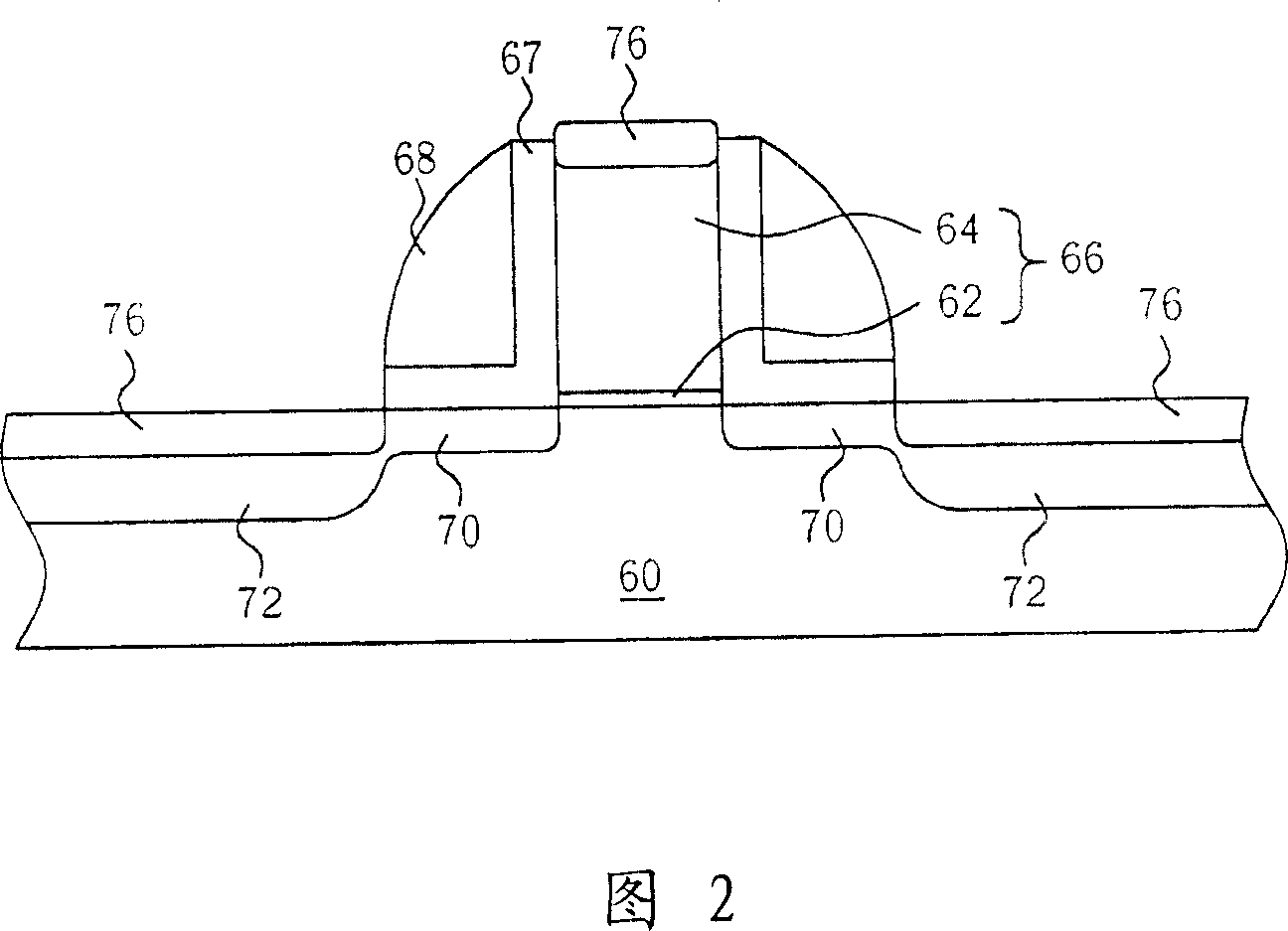

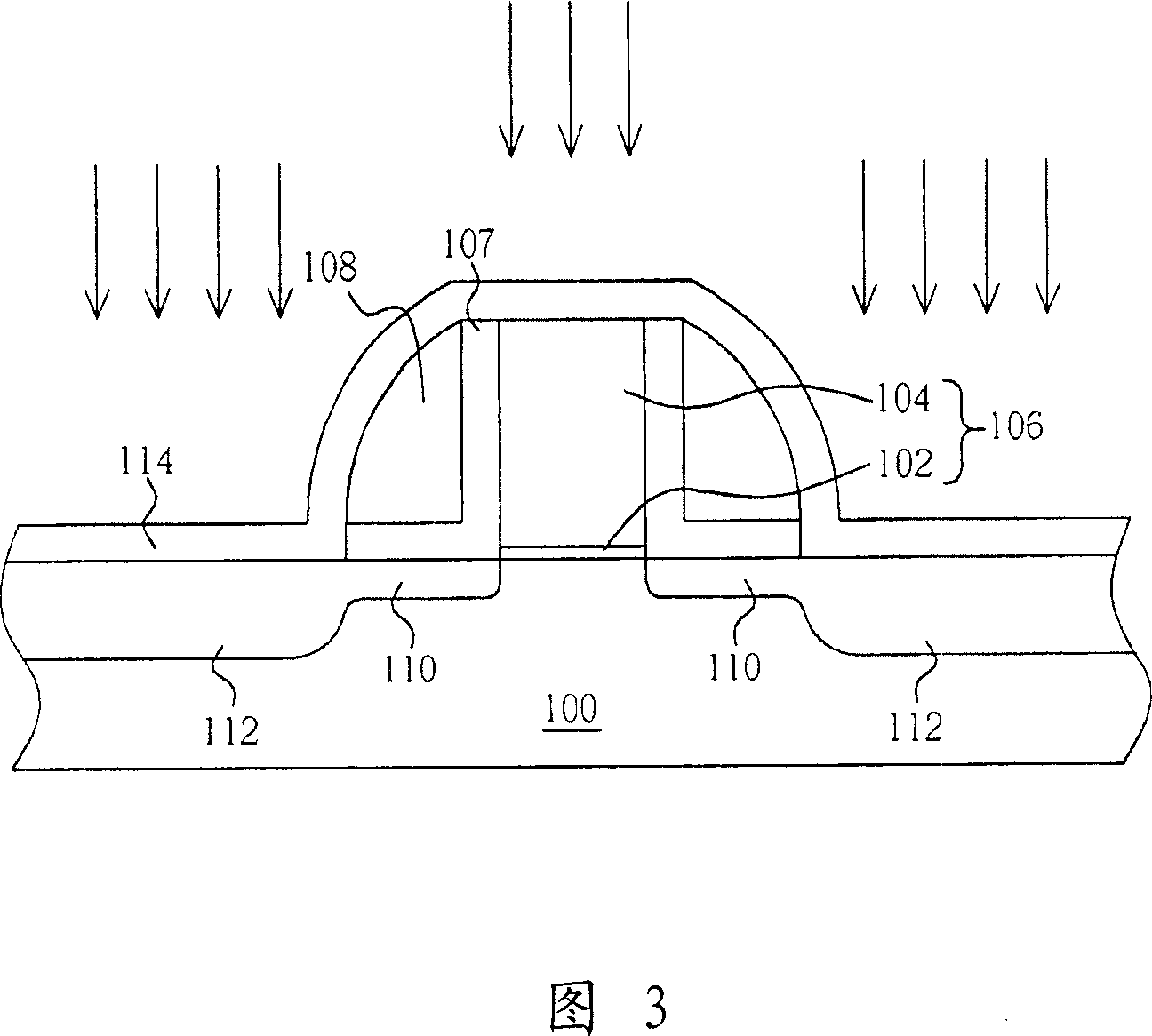

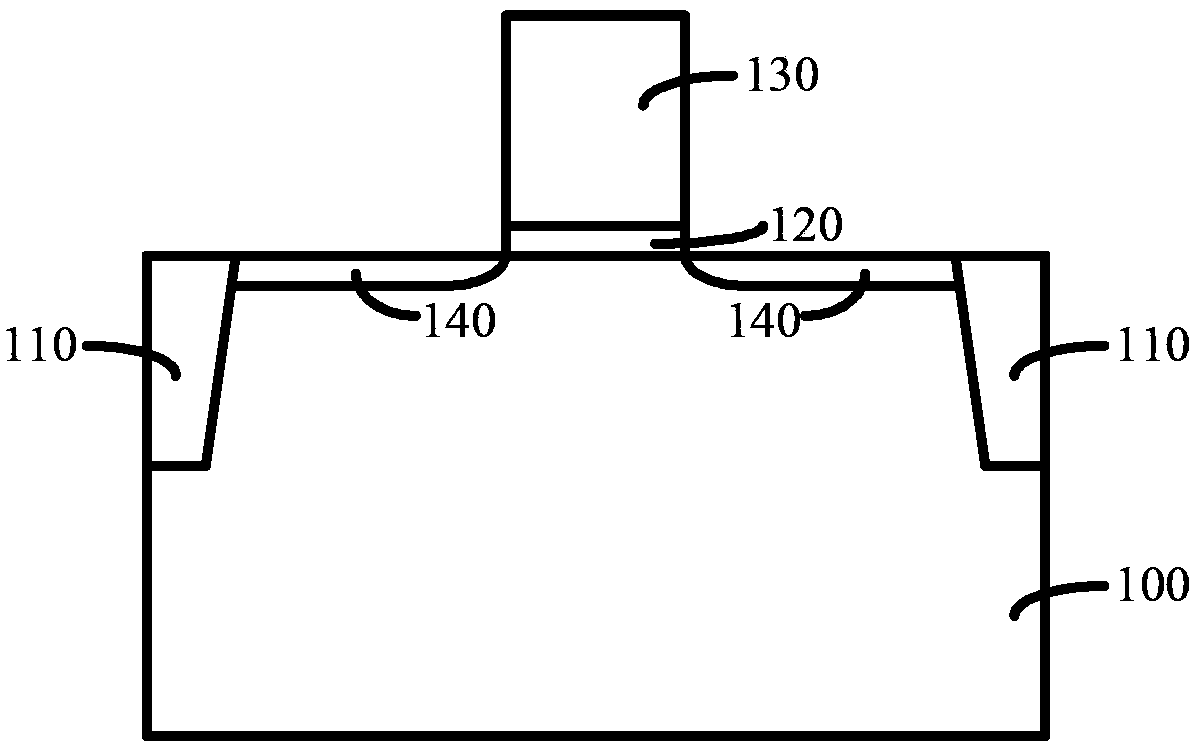

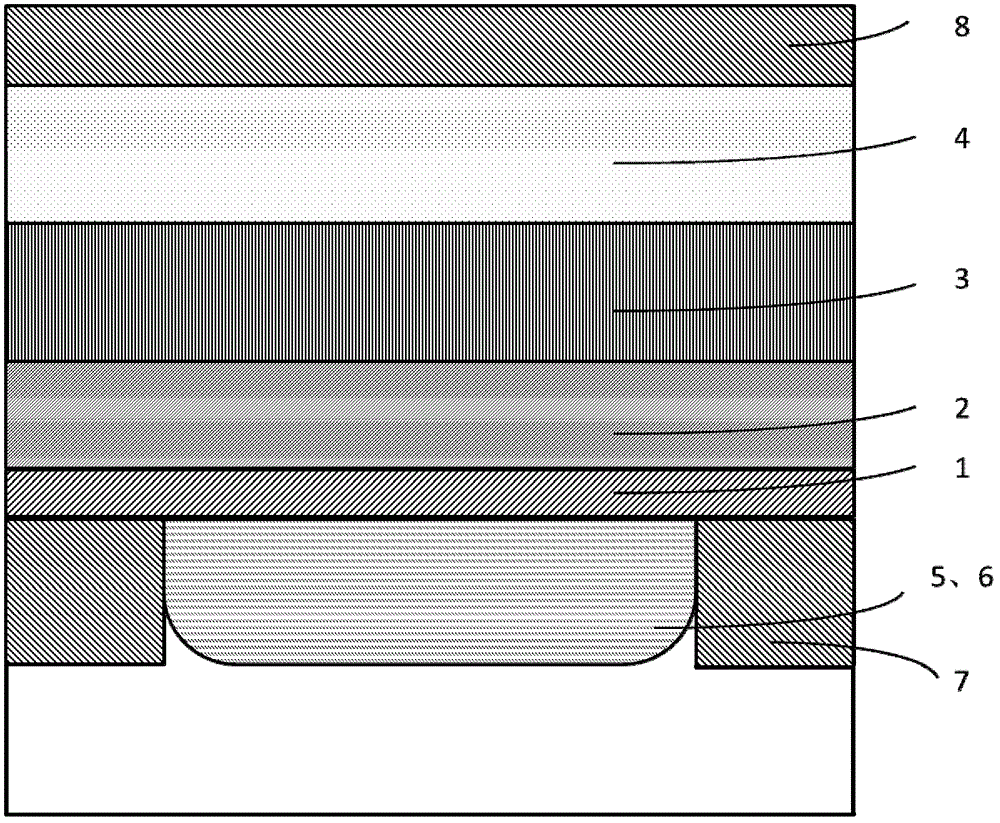

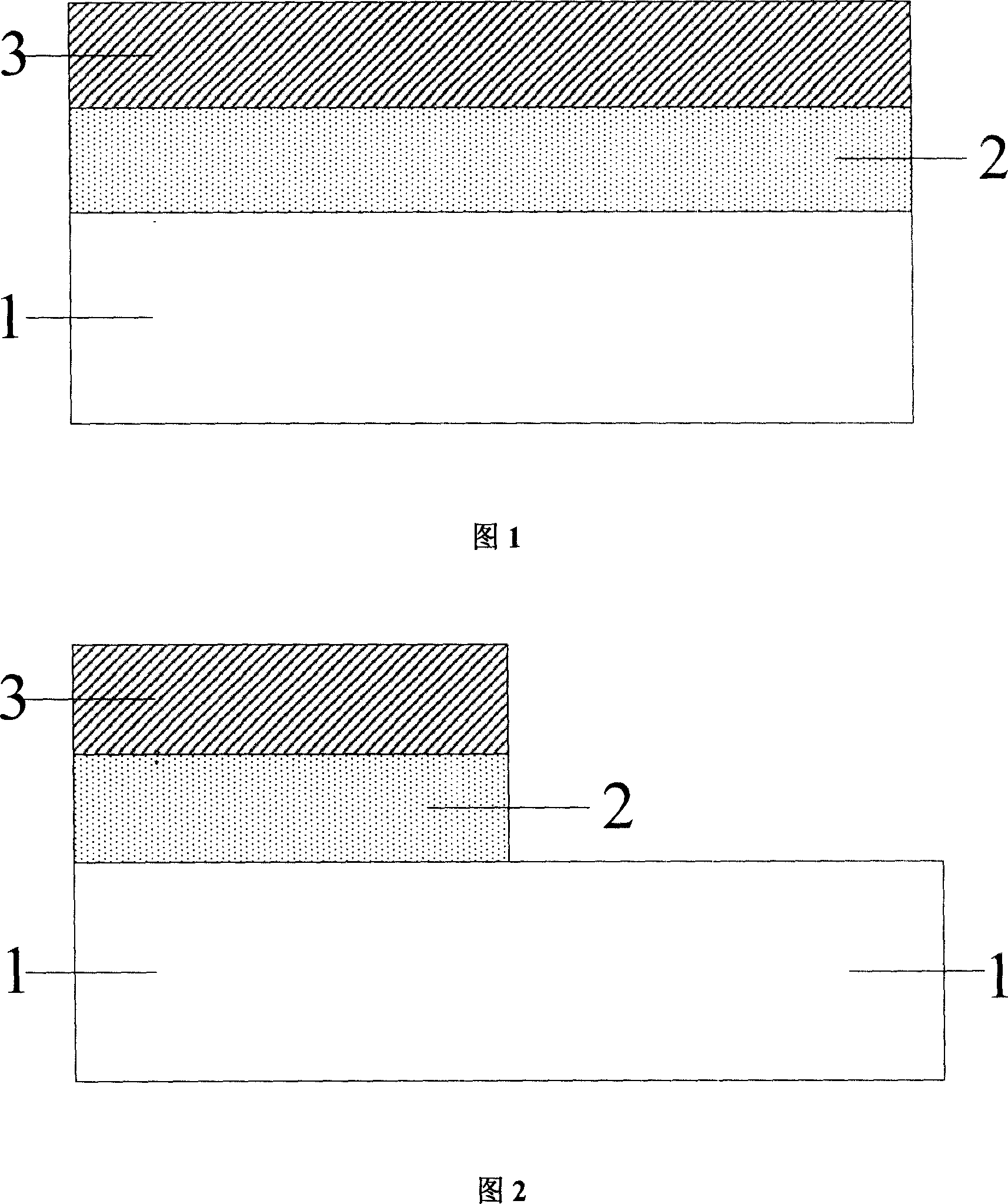

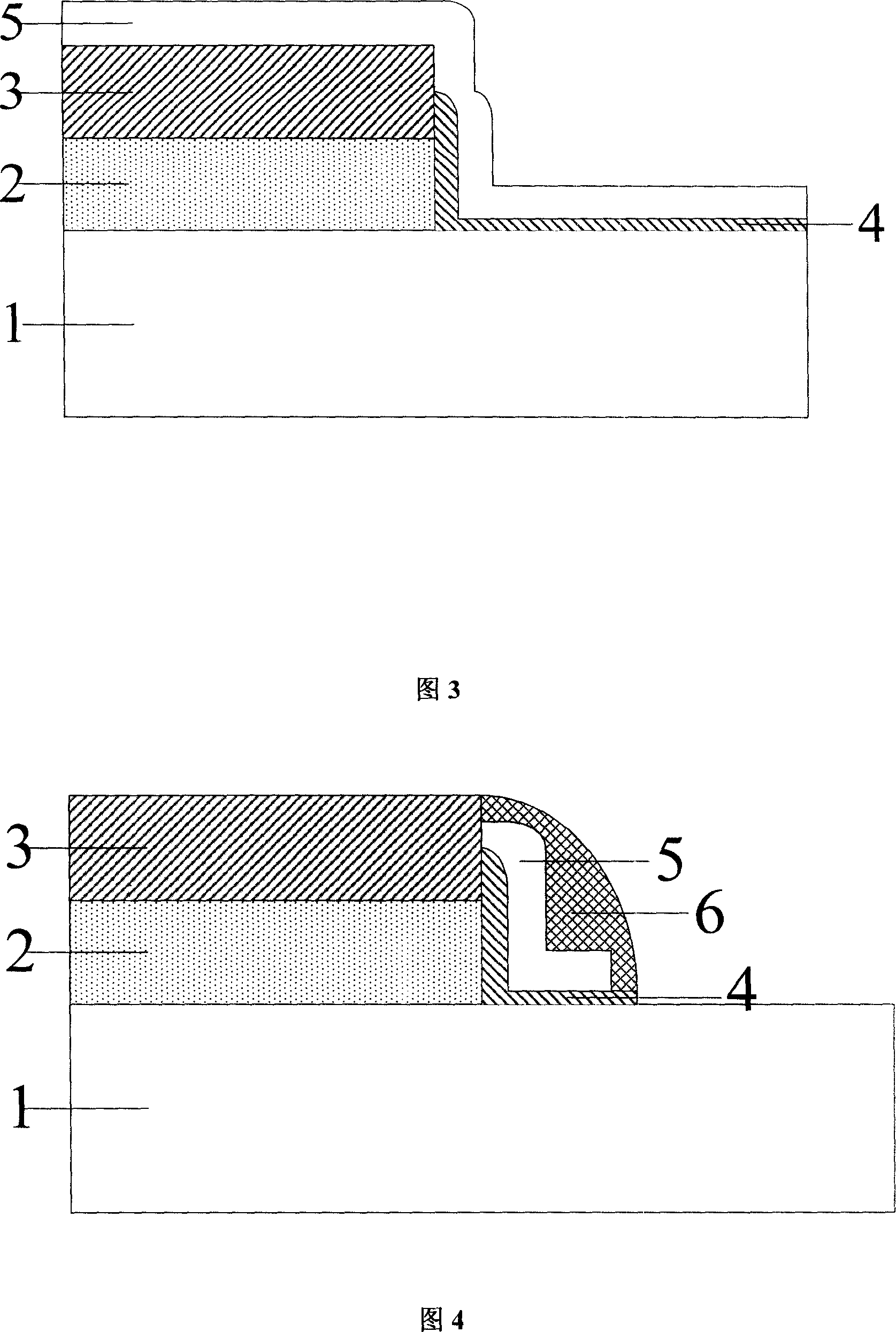

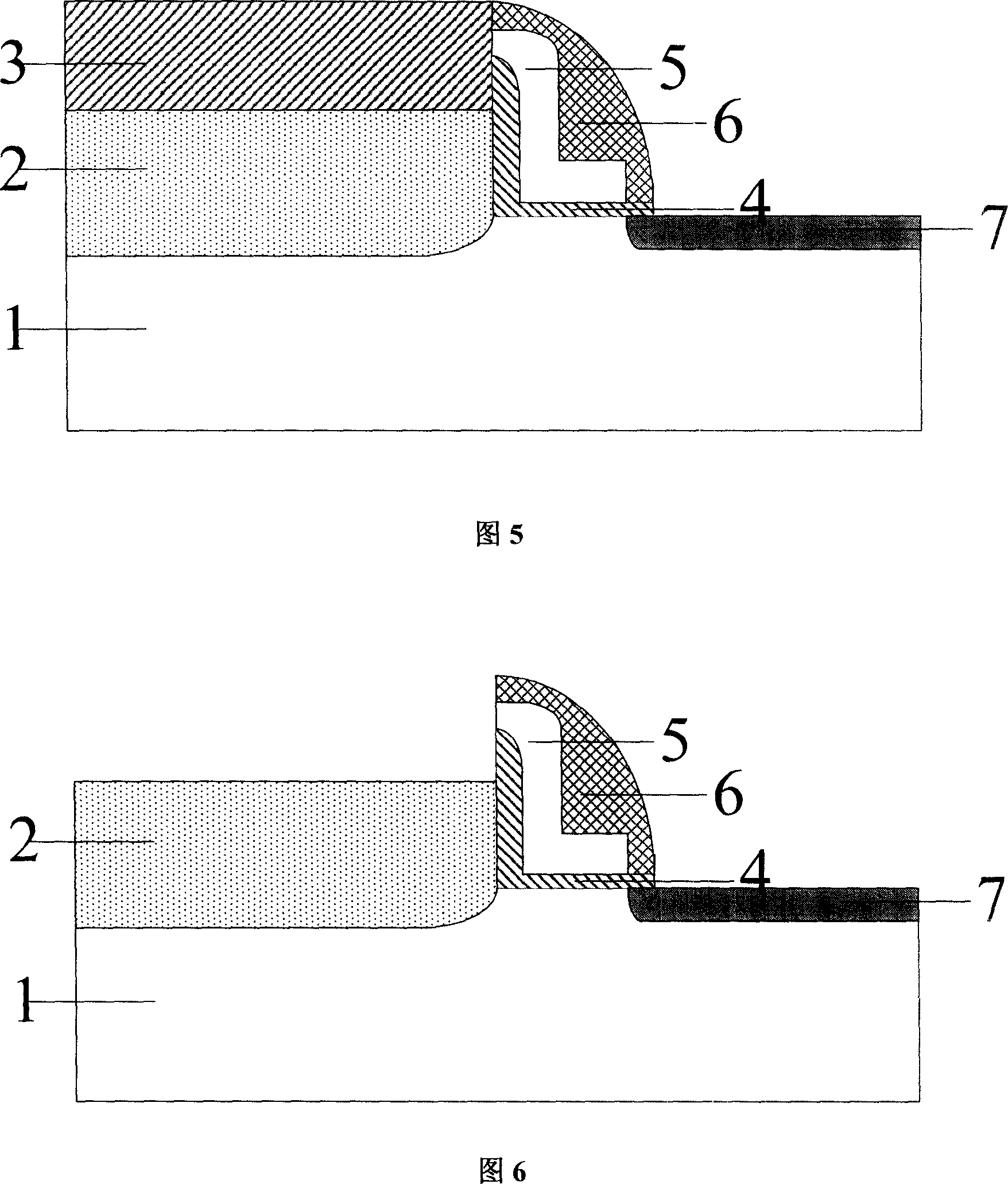

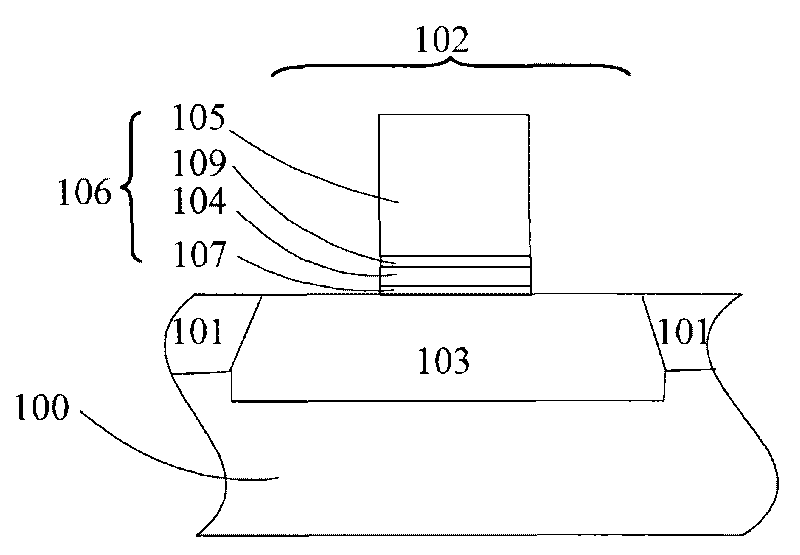

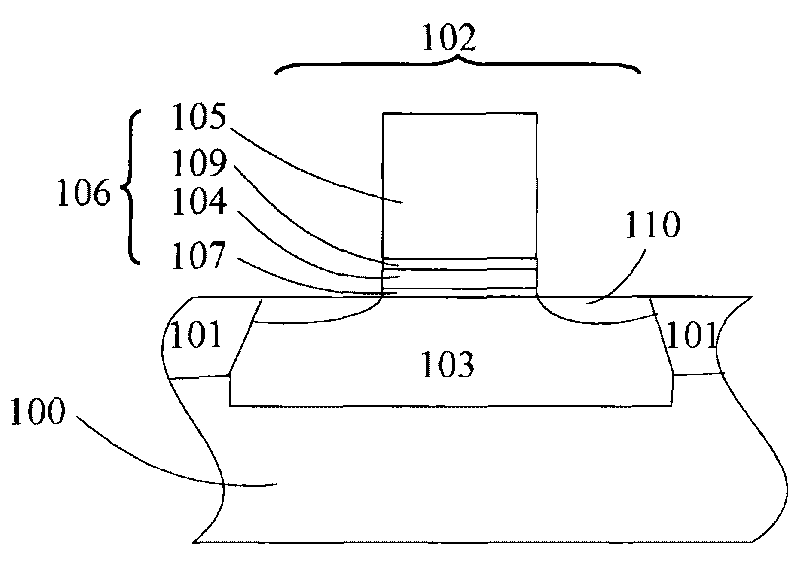

Semiconductor structure with channel stress layer and forming method thereof

InactiveCN102110710AImprove mobilityImprove drive currentTransistorSemiconductor/solid-state device manufacturingDriving currentPower flow

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Method for depositing an amorphous carbon film with improved density and step coverage

ActiveUS7867578B2High densityLower thermal budgetPretreated surfacesSemiconductor/solid-state device manufacturingKryptonCarbon layer

Owner:APPLIED MATERIALS INC

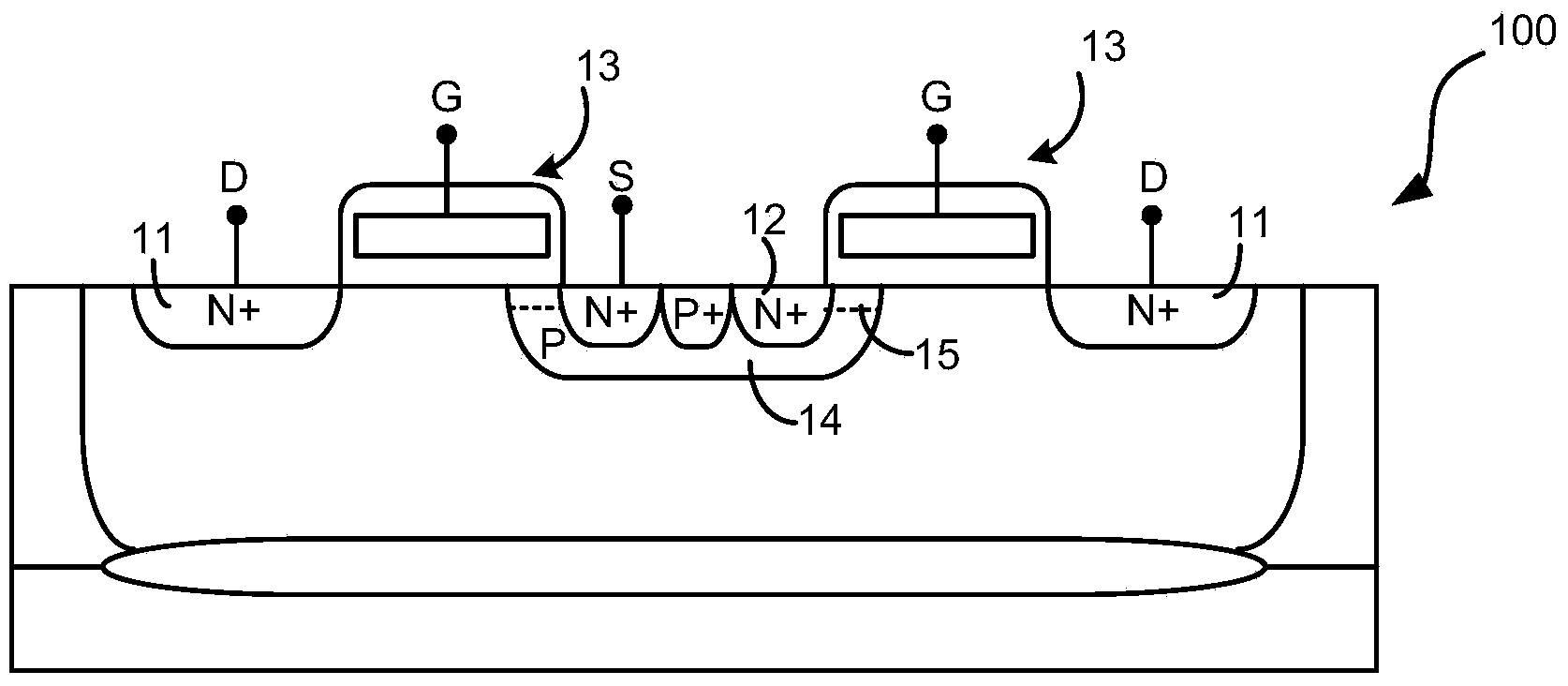

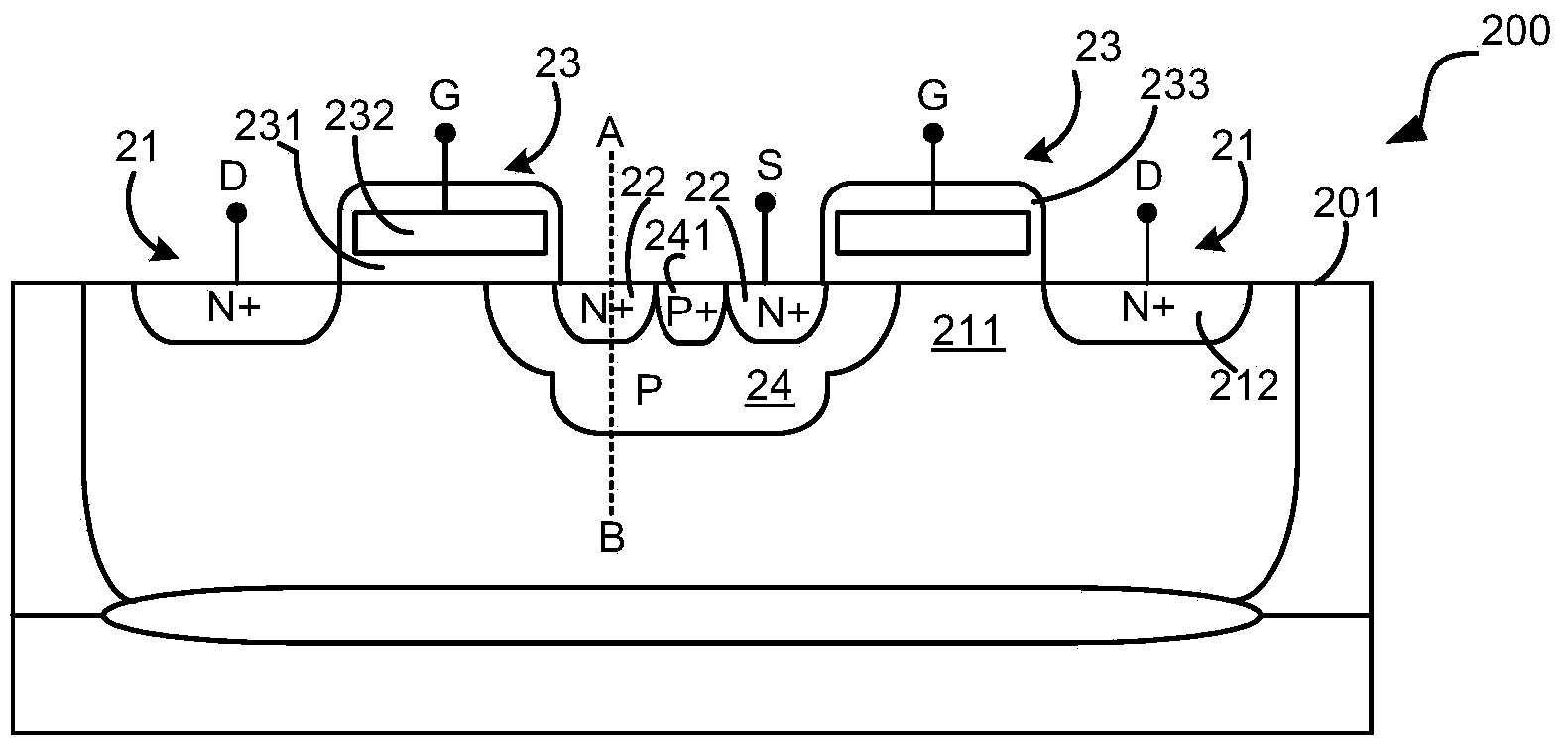

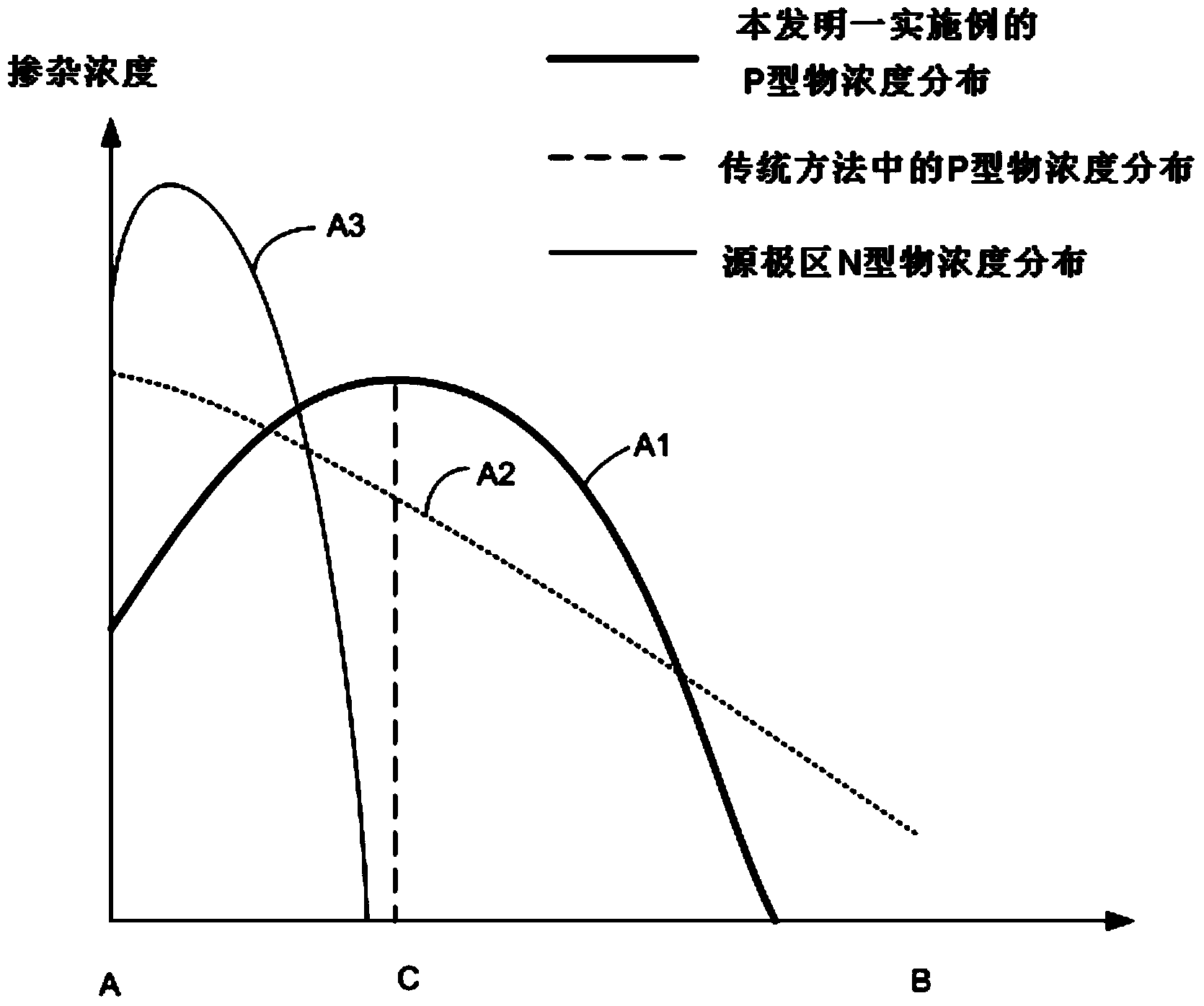

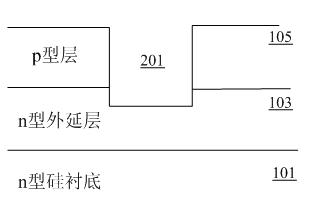

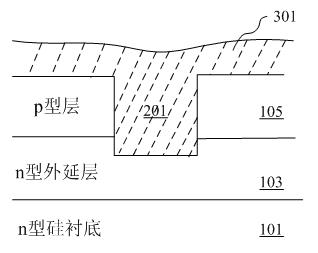

LDMOS device and manufacture method thereof

InactiveCN104299998ALower thermal budgetLower on-resistanceTransistorSemiconductor/solid-state device manufacturingLDMOSElectrode Contact

The invention discloses an LDMOS device and a manufacture method thereof. The manufacture method of the LDMOS device comprises the steps of fabricating a gate region of the LDMOS device on a semiconductor substrate, employing a mask to inject a first doping matter into the semiconductor substrate obliquely at a certain angle and employing the same masking to inject the first doping matter into the semiconductor substrate vertically, wherein the region formed by inclined injection and the region formed by vertical injection are jointly used for forming a body region of the LDMOS device; and fabricating a source electrode region and a drainage electrode contact region of the LDMOS device, wherein the source electrode region and the drainage electrode contact region adopt second doping different from first doping. The method and device are advantaged by low thermal budget, low on-resistance, and high breakdown voltage.

Owner:CHENGDU MONOLITHIC POWER SYST

Flexible charge trap storage based on oxidized graphene

InactiveCN103489870AGood film uniformityReduce pinholesSolid-state devicesSemiconductor devicesGate dielectricEngineering

The invention belongs to the technical field of semiconductor devices and particularly relates to a flexible charge trap storage based on oxidized graphene and a preparation method thereof. According to the flexible charge trap storage and the preparation method, the storage relies on the three-layer structure of an existing charge trap storage, namely, the tunneling layer / charge trap layer / control gate dielectric layer structure, a flexible substrate is utilized as a substrate, and the oxidized graphene is adopted to replace the traditional charge trap layer. The method comprises the specific preparation steps of using a low-temperature atomic layer deposition method, firstly, depositing the dielectric tunneling layer on the flexible substrate, coating the flexible substrate with the oxidized graphene in a rotating mode under the indoor temperature situation, and then, similarly adopting the low-temperature atomic layer deposition technology to grow and control the gate dielectrics. The flexible charge trap storage and the preparation method have the advantages that the low-temperature atomic layer deposition technology and the process of coating the flexible substrate with the oxidized graphene at the indoor temperature in the rotating mode are used, the characteristics of the oxidized graphene is utilized, window erasing is ensured, meanwhile, the process thermal budget is greatly reduced, and practical and reliable schemes are provided for flexible electronic devices in future.

Owner:FUDAN UNIV

Self-aligning metal silicide technology

InactiveCN1937177ALower thermal budgetImprove stabilitySemiconductor/solid-state device manufacturingSalicideMetal silicide

The technique of self-aligned metal silicides (salicide) includes following steps: first providing a surface of containing at least a substrate of a silicon conductive layer; next, carrying out a degas step for the said substrate, and a cooling step for the substrate; then, depositing a metal layer on surface of the substrate, and the metal layer is contacted to the surface of the silicon conductive layer; carrying out a heat treatment in order to form a silicate metal layer on surface of the silicon conductive layer of contacting with the metal layer; finally, removing unreacted the metal layer.

Owner:UNITED MICROELECTRONICS CORP

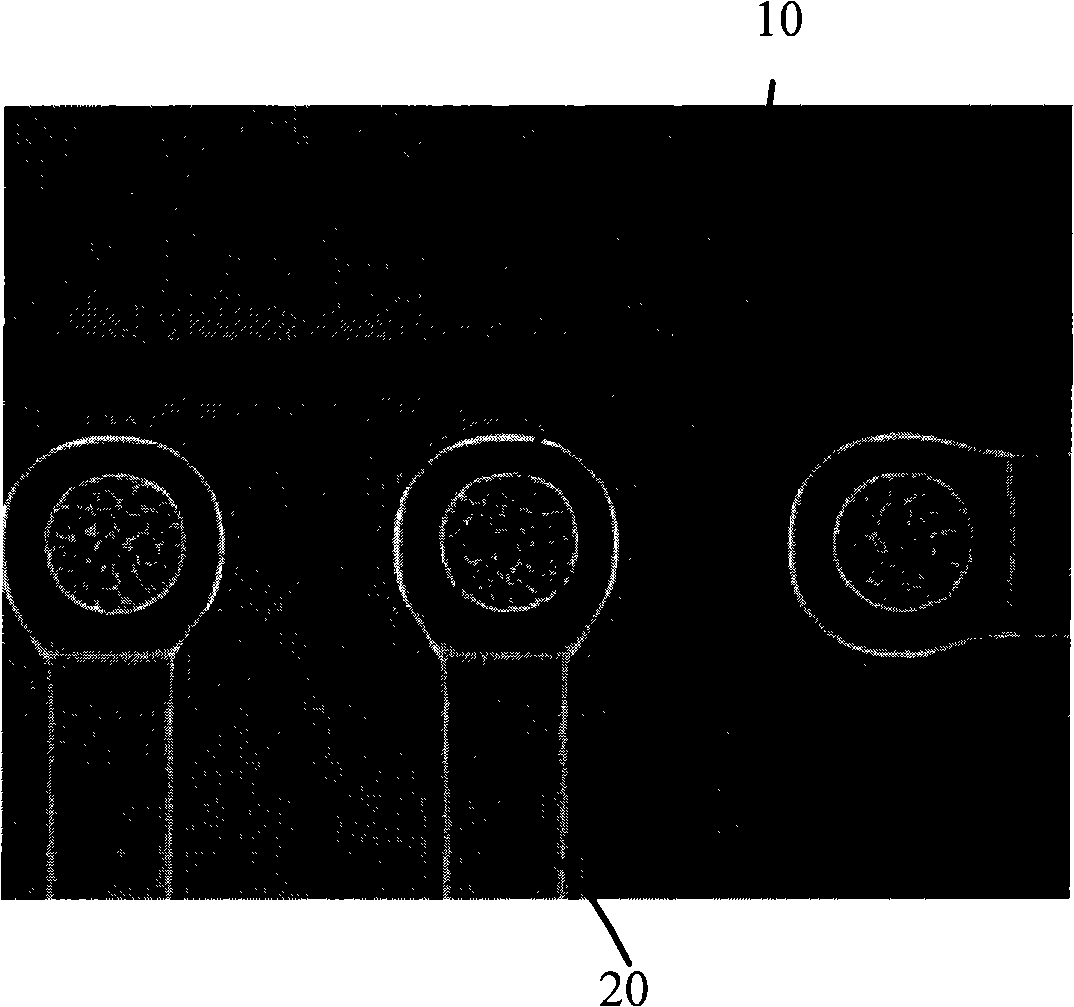

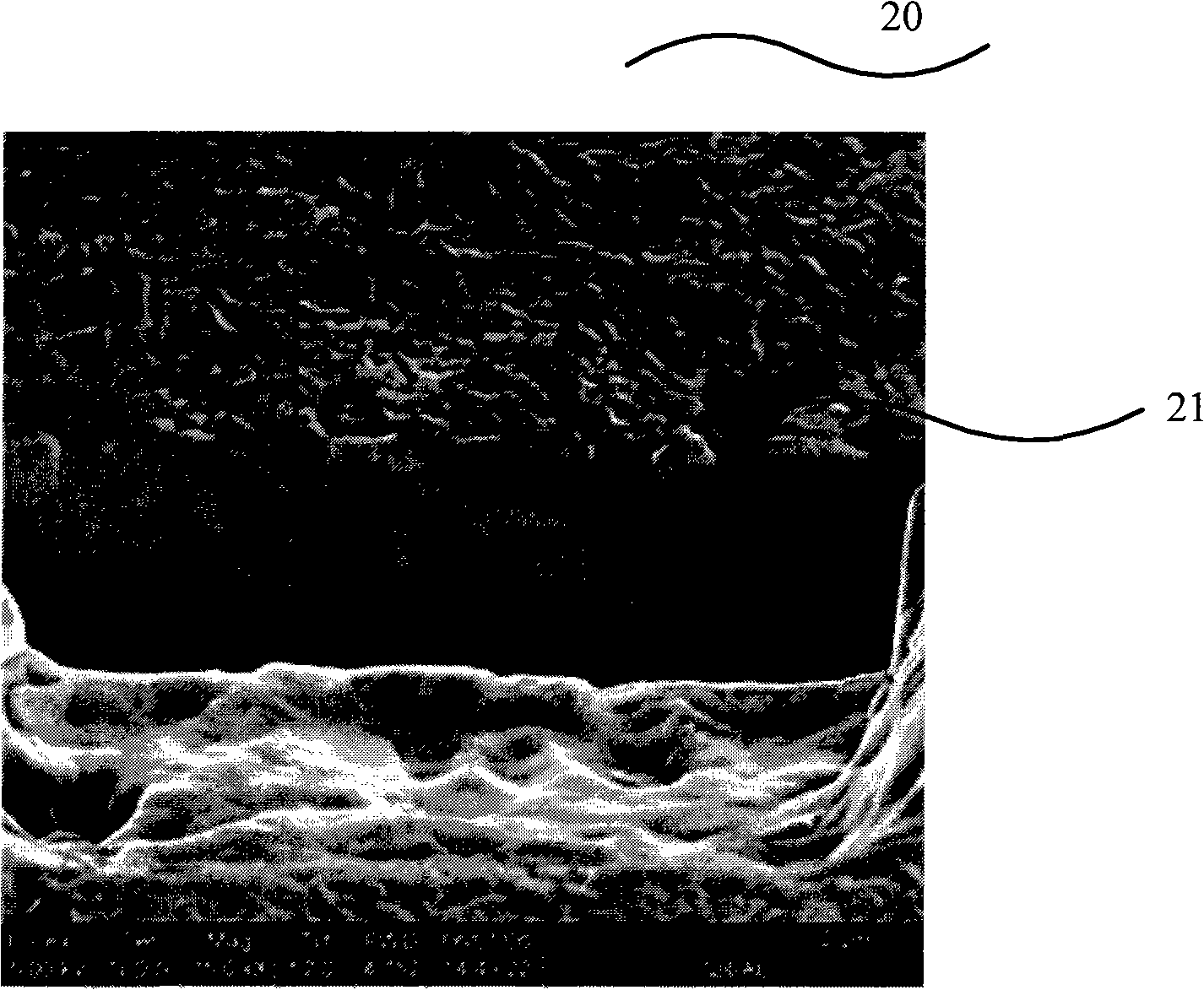

Method for forming grid side wall layer

ActiveCN101154571AProtectImprove thickness uniformitySemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsMedia layer

The invention discloses a method of forming a grid wall layer, including the following steps that: a substrate with at least a grid is provided; the method of atomic layer deposit is utilized to form a complex medium layer in the substrate; a side wall layer is formed in the grid by etching the complex dielectric layer. The invention is not only favorable to improve the performance of the parts with lower heat budgeting, but also improves the uniformity of the performance of the parts with better uniformity of the formed grid side wall layer.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Aluminum cushion layer etching method and bump formation method

InactiveCN101312130AAvoid rough surfacesSimple processSolid-state devicesSemiconductor/solid-state device manufacturingRough surfaceDielectric layer

A method for etching an aluminum pad layer comprises providing a semiconductor substrate, forming an aluminum pad layer, a passivating layer and a dielectric layer on the semiconductor substrate, wherein the aluminum layer is inlaid in the passivating layer and exposes through the passivating layer and a first opening of the dielectric layer, and further utilizing argon plasma to etch the aluminum pad layer, wherein the production power (MF) for generating the argon plasma is arranged between 600W and 800W, the accelerating power (RF) for accelerating the argon plasma is arranged between 100W and 600W, and the etching time is arranged between 55s and 100s. The invention further provides a method for forming bumps. Compared with the prior art, the method for etching an aluminum pad layer reduces the generation power (MF) for generating the argon plasma, the accelerating power (RF) for accelerating the argon plasma and the time to etch the aluminum pad layer, thereby avoiding the problem of rough surface of the aluminum pad layer caused by over-etching to the aluminum pad layer in the prior art.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Formation method of interfacial layer and formation method of metal gate transistor

InactiveCN104103509ALower thermal budgetQuality improvementTransistorSemiconductor/solid-state device manufacturingOxygen atomHigh energy

The invention discloses a formation method of an interfacial layer and a formation method of a metal gate transistor. The formation method of the interfacial layer is different from a conventional formation method of an interfacial layer. The formation method of the interfacial layer involves forming a high-K dielectric layer first and then forming the interfacial layer and specifically comprises performing annealing processing in a gas atmosphere containing an oxidation gas, wherein during an annealing process, the oxidation gas with quite high energy in a high temperature environment can penetrate the high-K dielectric layer and is diffused to an interface between the high-K dielectric layer and a substrate so as to be contacted with the substrate, such that the surface, which is contacted with the high-K dielectric layer, of the substrate can be oxidized and the interfacial layer is grown. Since the interfacial layer is formed after the high-K dielectric layer, some defects of the high-K dielectric layer can be restored during the process of forming the interfacial layer, for instance, in the annealing process when the interfacial layer is formed, the oxidation gas can supplement oxygen atoms to the high-K dielectric layer to enable the actual components of the high-K dielectric layer to be more similar to corresponding components in an ideal chemical molecular formula.

Owner:SEMICON MFG INT (SHANGHAI) CORP

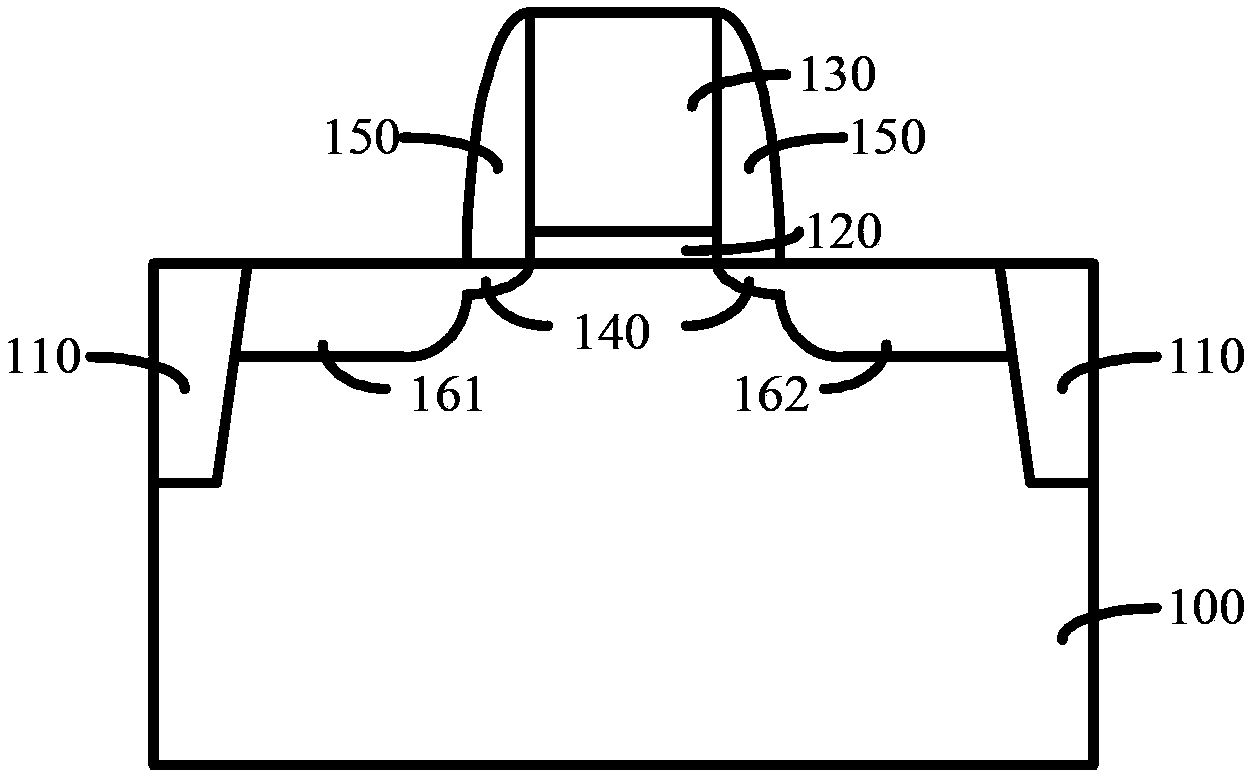

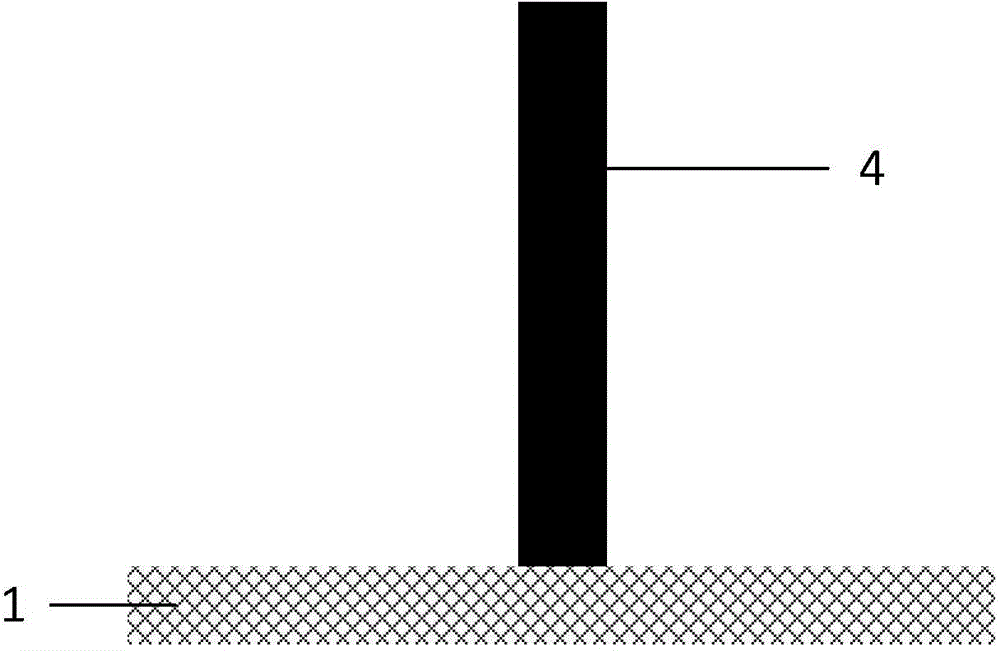

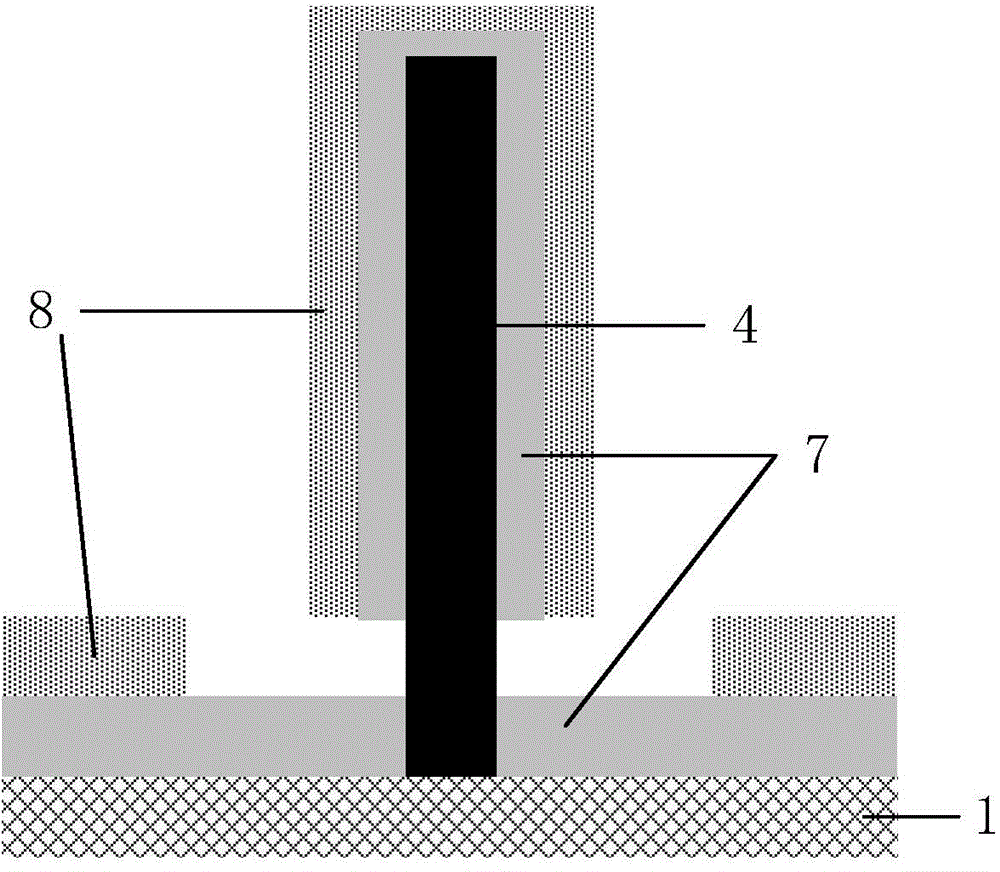

Surrounding-gate field effect transistor and fabrication method thereof

ActiveCN104157686AHighly integratedGood gating abilitySemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSchottky barrier

The invention discloses a surrounding-gate field effect transistor, which combines a vertical channel and a Schottky barrier source / drain structure. The surrounding-gate field effect transistor comprises a surrounding semiconductor channel (4) in the vertical direction, a surrounding gate electrode (6), a surrounding gate dielectric layer (5), a source region (2), a drain region (3) and a semiconductor substrate (1), wherein the source region (2) is located at the bottom part of the vertical channel (4) and is connected with the substrate (1); the drain region (3) is located at the top part of the vertical channel (4); the gate dielectric layer (5) and the gate electrode (6) surround the vertical channel (4); Schottky contact with the same barrier height is respectively formed between the source region (2) and the drain region (3) and the channel (4); and the source region and the drain region use the same metal material. The structure uses the Schottky barrier source / drain structure so as to reduce thermal budget, reduce serial resistance and parasitic capacitance and simplify technology requirements, and uses the vertical channel and the surrounding gate structure so as to break through limitation of integrated processing lithography limit and improve the degree of integration.

Owner:PEKING UNIV

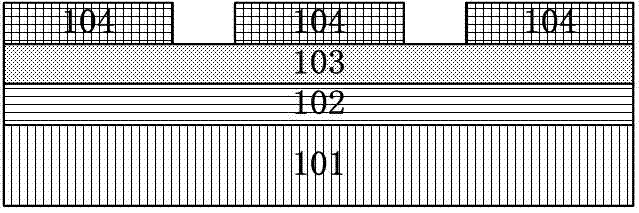

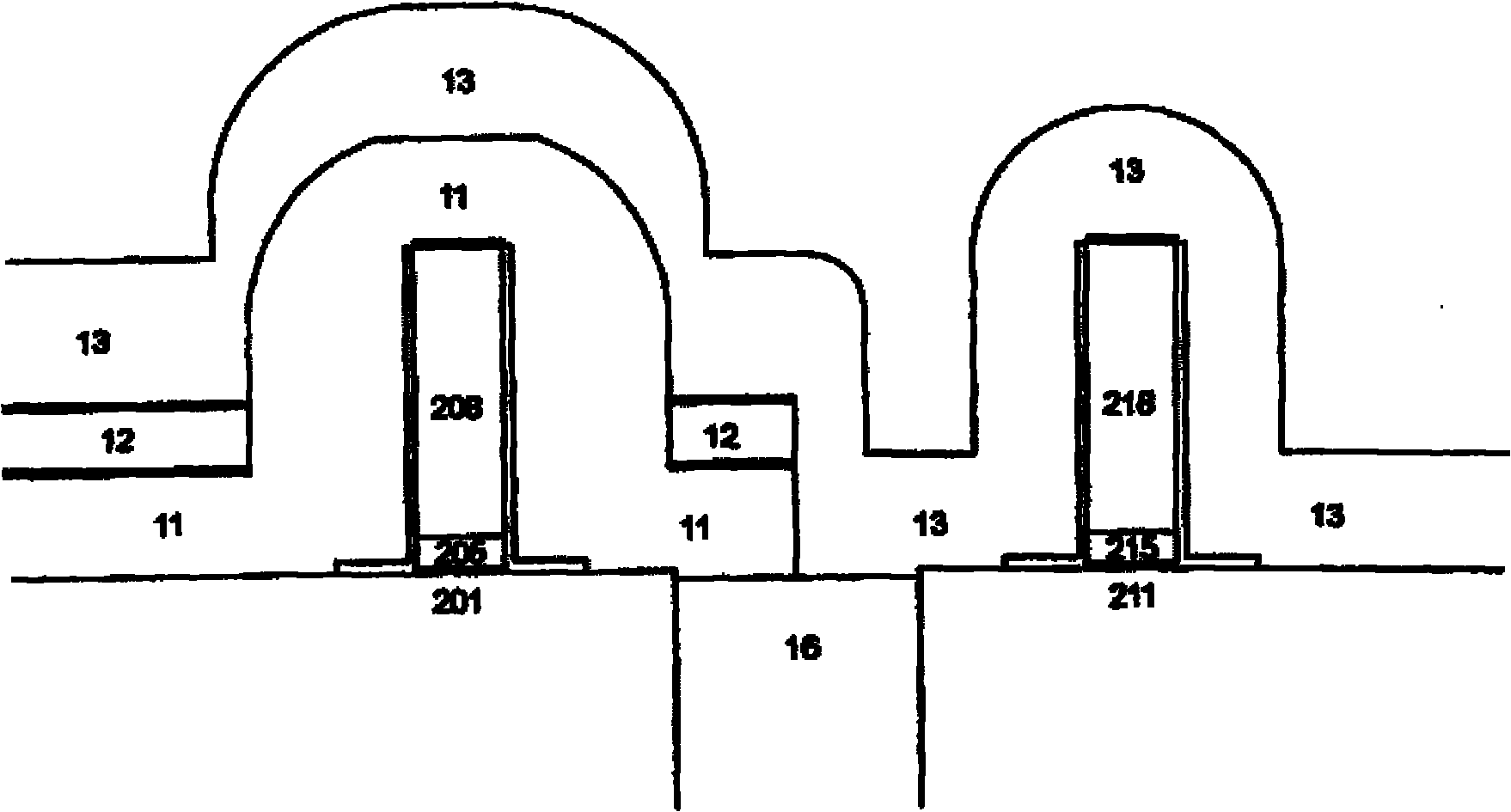

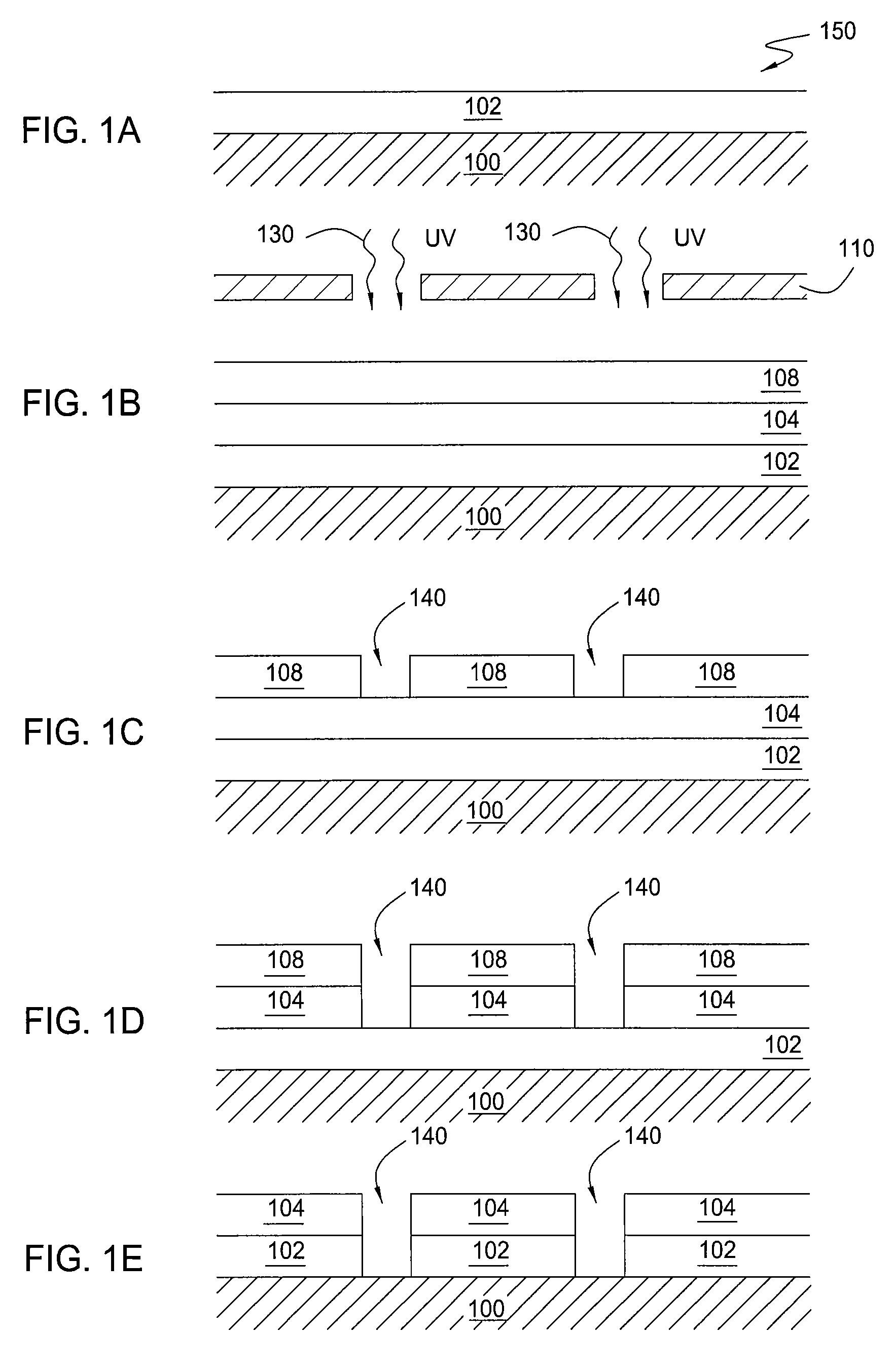

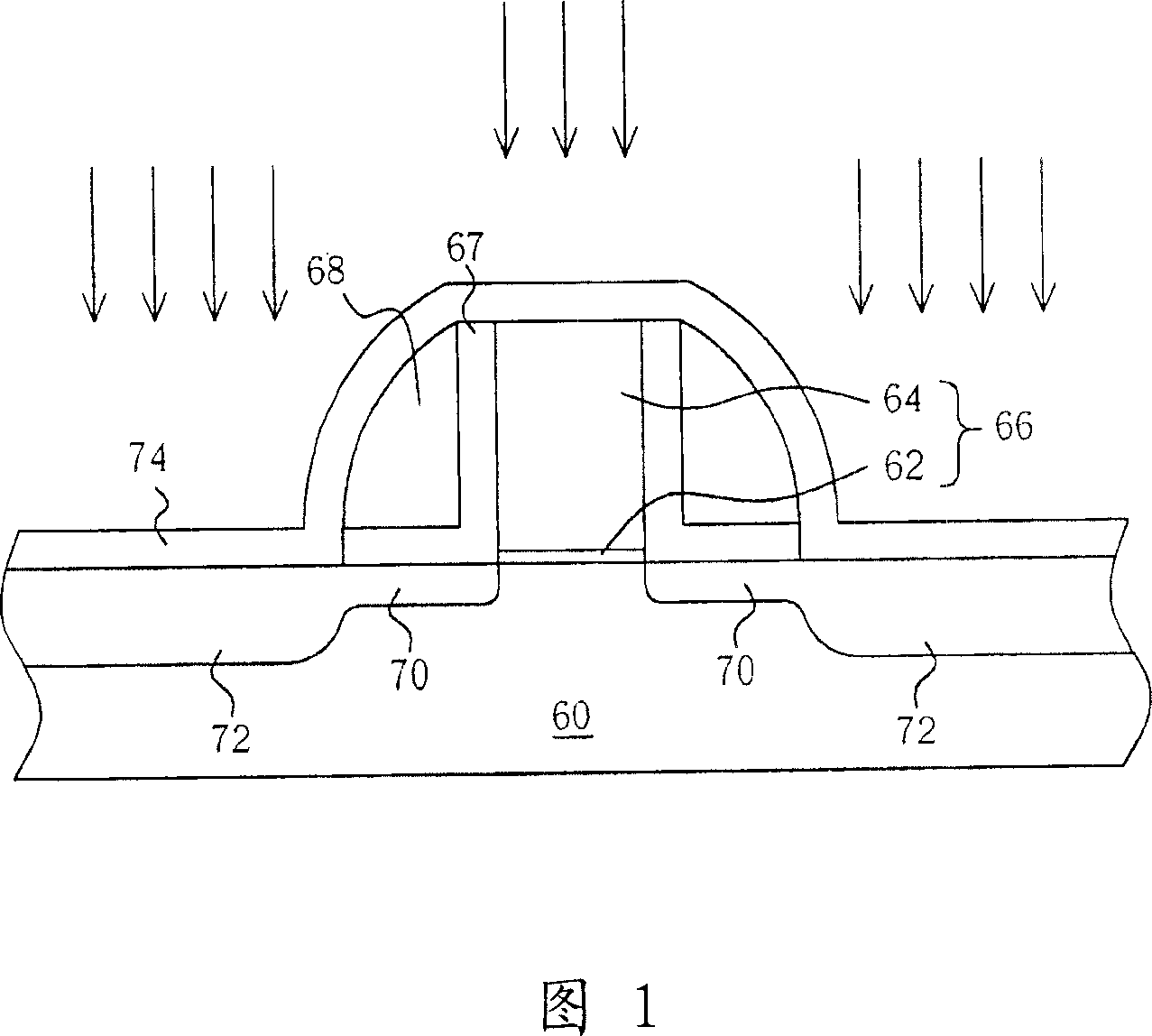

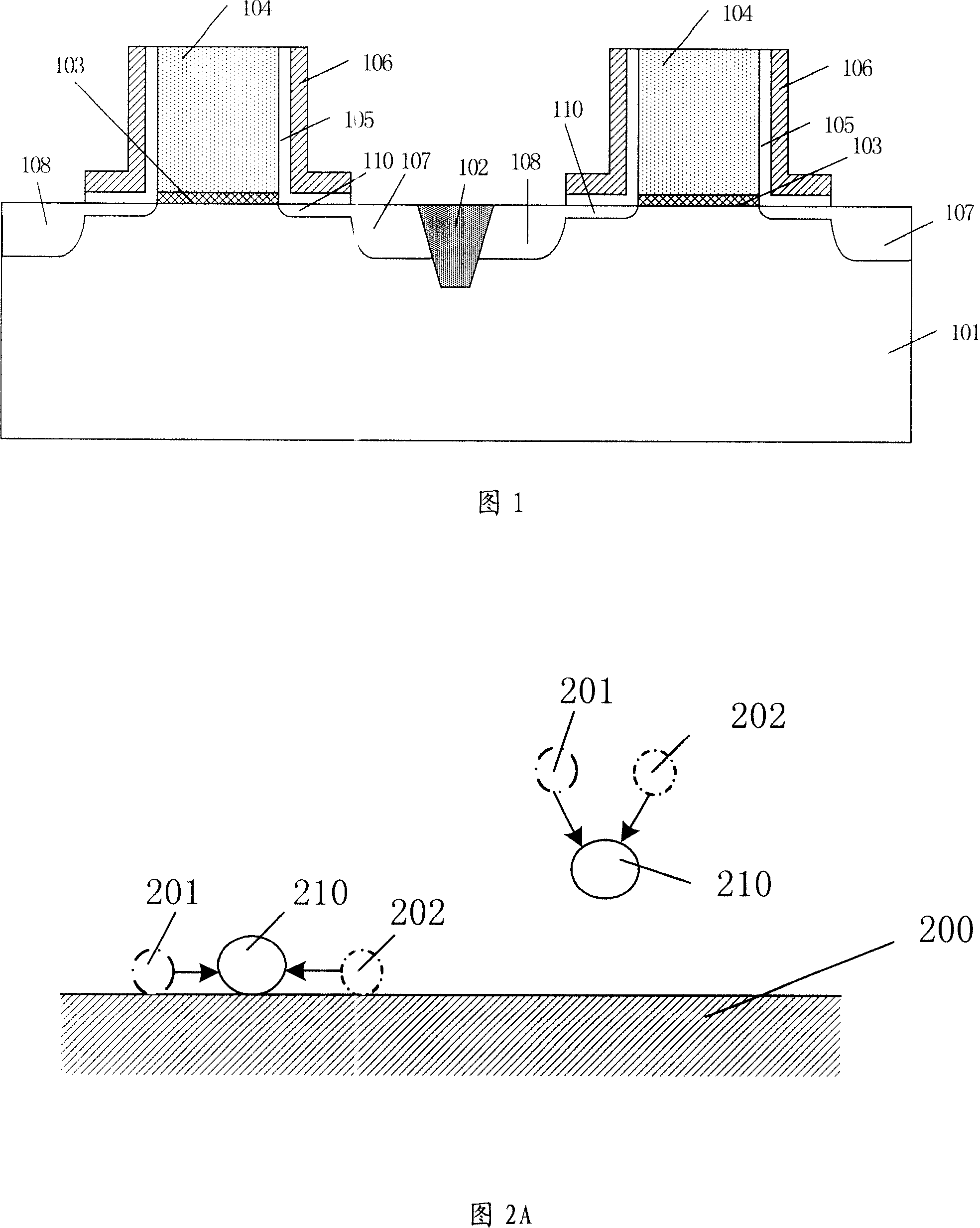

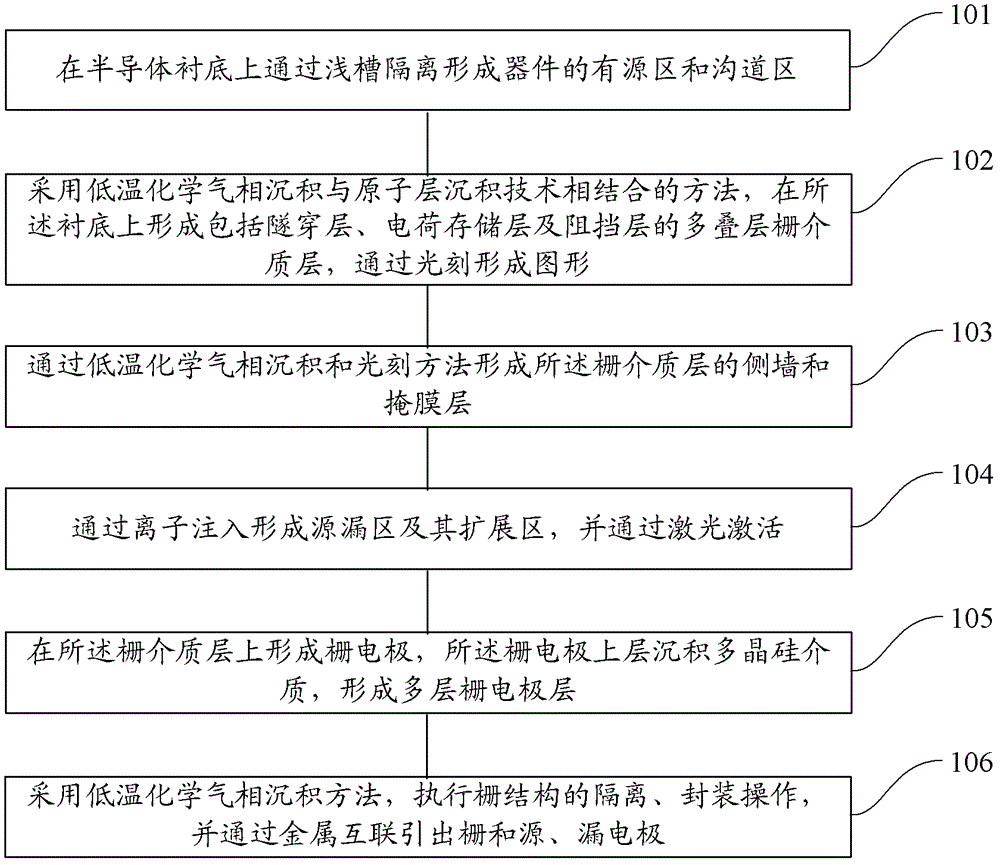

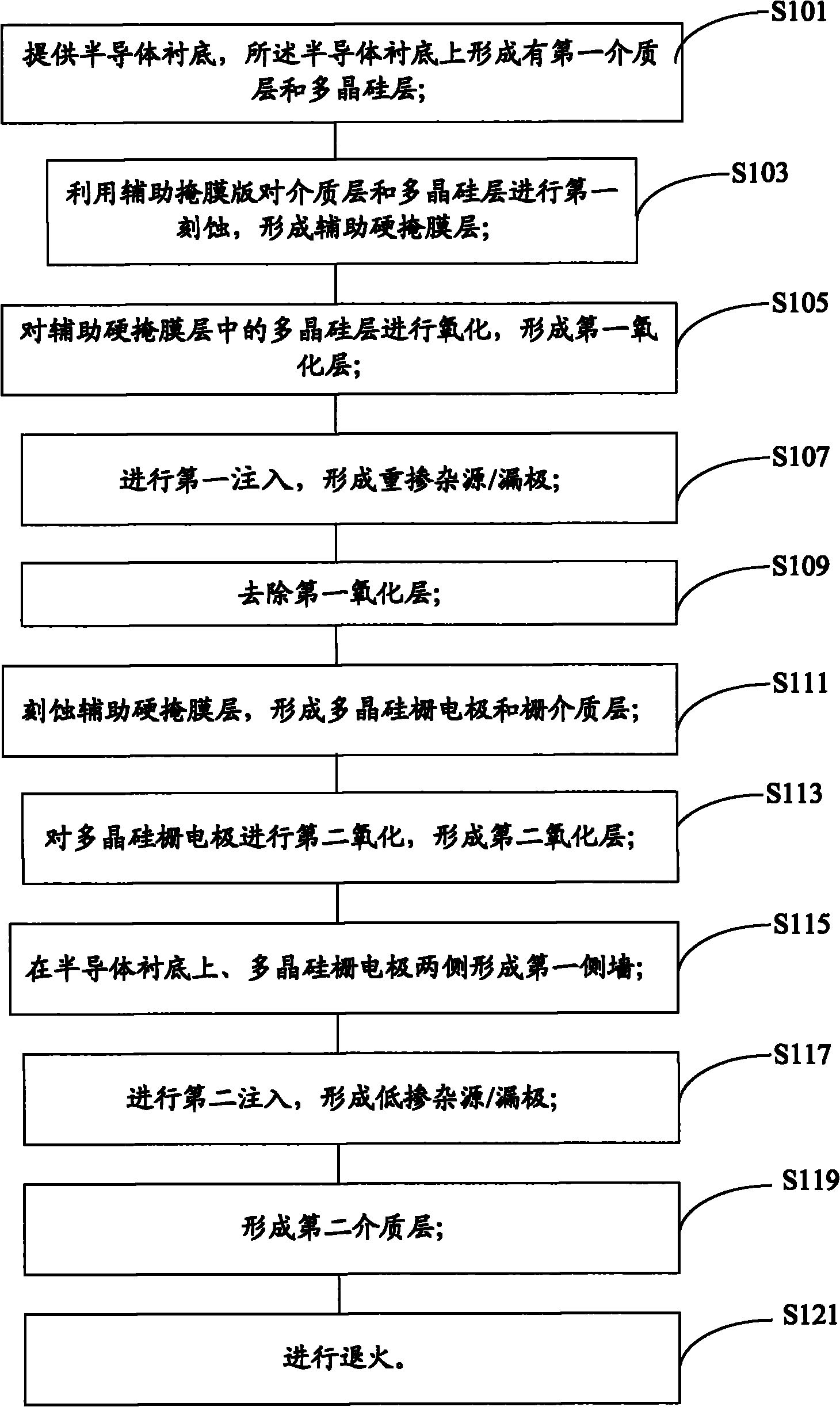

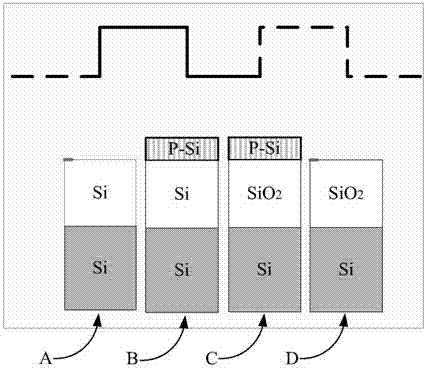

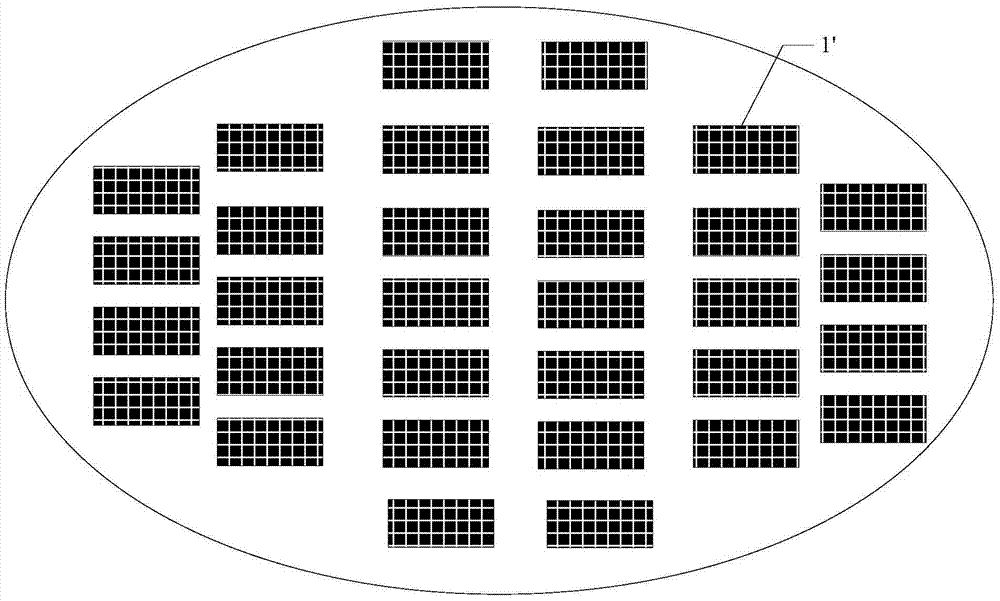

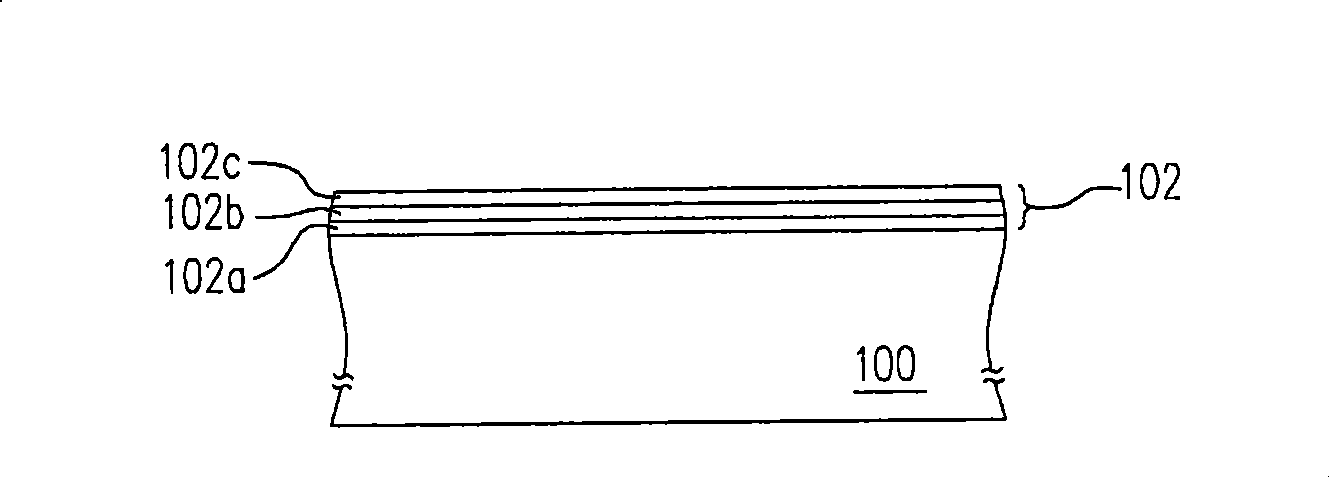

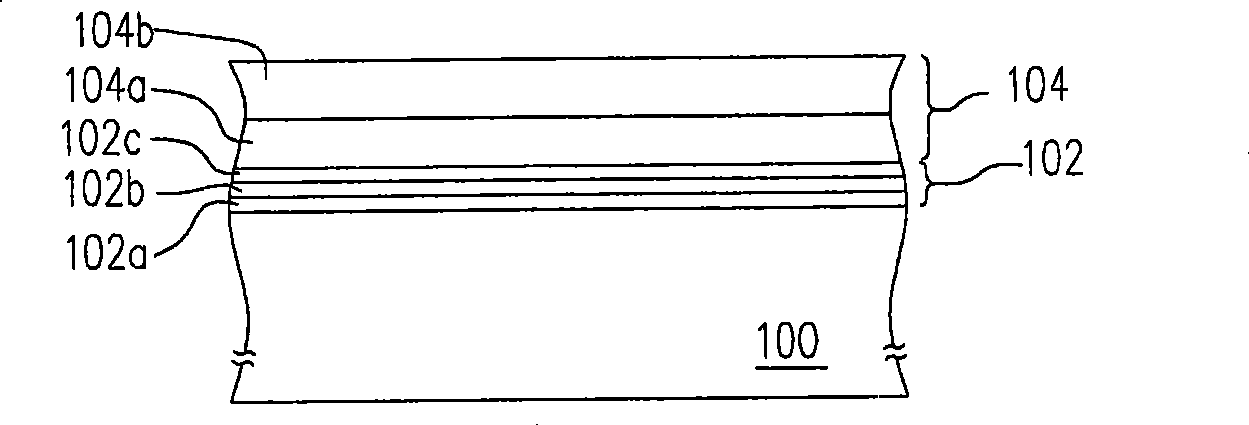

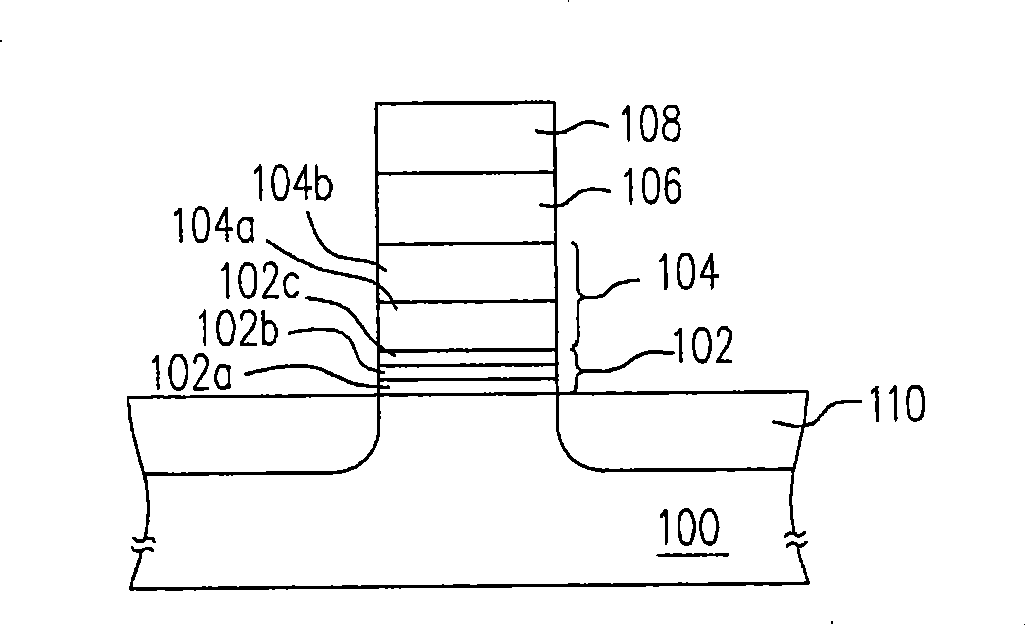

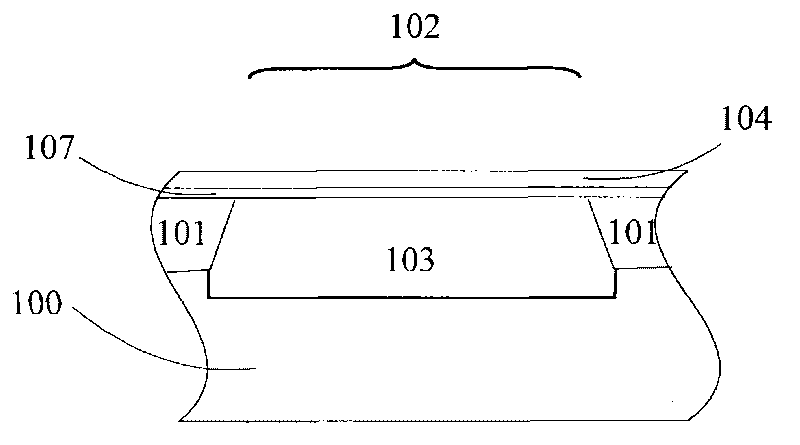

Manufacturing method of charge trapping non-volatile memory

ActiveCN102800632ALower thermal budgetAvoid crystallization problemsSemiconductor/solid-state device manufacturingPhotolithographyPolycrystalline silicon

The invention discloses a manufacturing method of a charge trapping non-volatile memory. The method comprises the following steps of: forming an active region and a channel region of a device on a semiconductor substrate through shallow-trench isolation; forming a multi-stack gate medium layer comprising a tunneling layer, a charge storage layer and a barrier layer on the substrate by combining the low-temperature chemical vapor deposition and atomic layer deposition technology, and forming a pattern through photoetching; forming a side wall and a mask layer of the gate medium layer by a low-temperature chemical vapor deposition and photoetching method; forming a source / drain region and an expansion region thereof through ion implantation, and activating by laser; forming a gate electrode on the gate medium layer, and depositing a polycrystalline silicon medium at the upper layer of the gate electrode to form a multi-gate electrode layer; executing the isolation and encapsulation operations of the gate structure by a low-temperature chemical vapor deposition method; and leading out the gate, source and drain electrodes through metal interconnection. Through the invention, the heat budget in the memory manufacturing process can be reduced, and the crystallization problem of the thin-film medium layer of a high-dielectric constant material is inhibited.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

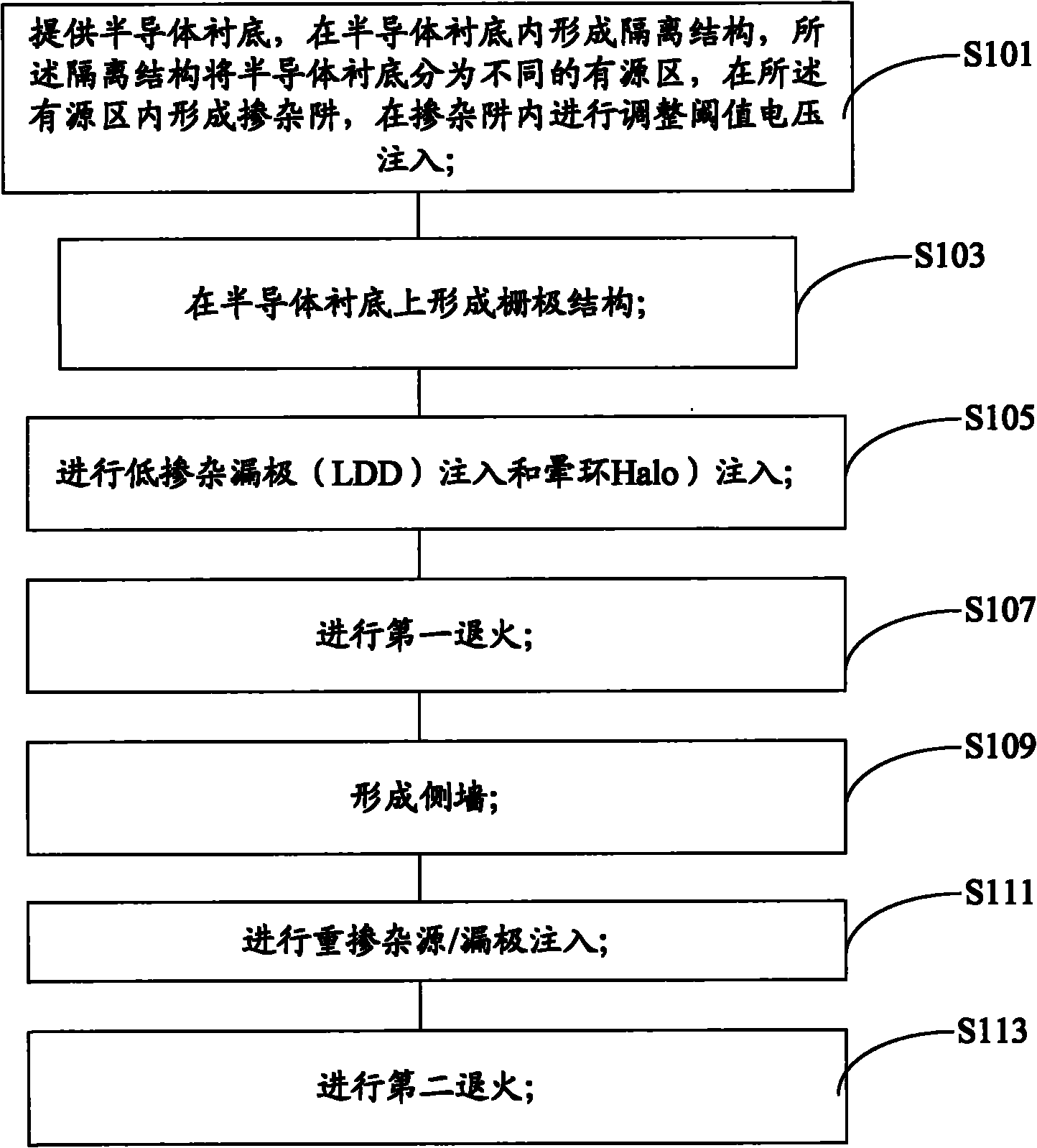

Production method of MOS (Metal Oxide Semiconductor) transistor

ActiveCN101930922ASuper shallow junctionLower thermal budgetSemiconductor/solid-state device manufacturingSemiconductor devicesOxide semiconductorPhysics

The invention relates to a production method of an MOS (Metal Oxide Semiconductor) transistor, which comprises the following steps of: carrying out etching on a first medium layer and a polysilicon layer for the first time to form an auxiliary hard mask layer; oxidizing the polysilicon layer in the auxiliary hard mask layer to form a first oxide layer; injecting for the first time to form high doping source / drain electrodes; removing the first oxide layer; etching the auxiliary hard mask layer to form a polysilicon gate electrode and a gate medium layer; oxidizing the polysilicon gate electrode for the second time to form a second oxide layer; forming first side walls on a semiconductor substrate and two sides of the polysilicon grate electrode; injecting for the second time to form low doping source / drain electrodes and then forming a second medium layer; and annealing. By adjusting the process of the MOS transistor, the high doping source / drain electrodes are formed before the low doping source / drain electrodes are formed, and the high doping source / drain electrodes and the low doping source / drain electrodes are only annealed once, and over-large diffusion area can not be caused by long-time annealing, thereby facilitating the form of ultra shallow junctions.

Owner:SEMICON MFG INT (SHANGHAI) CORP

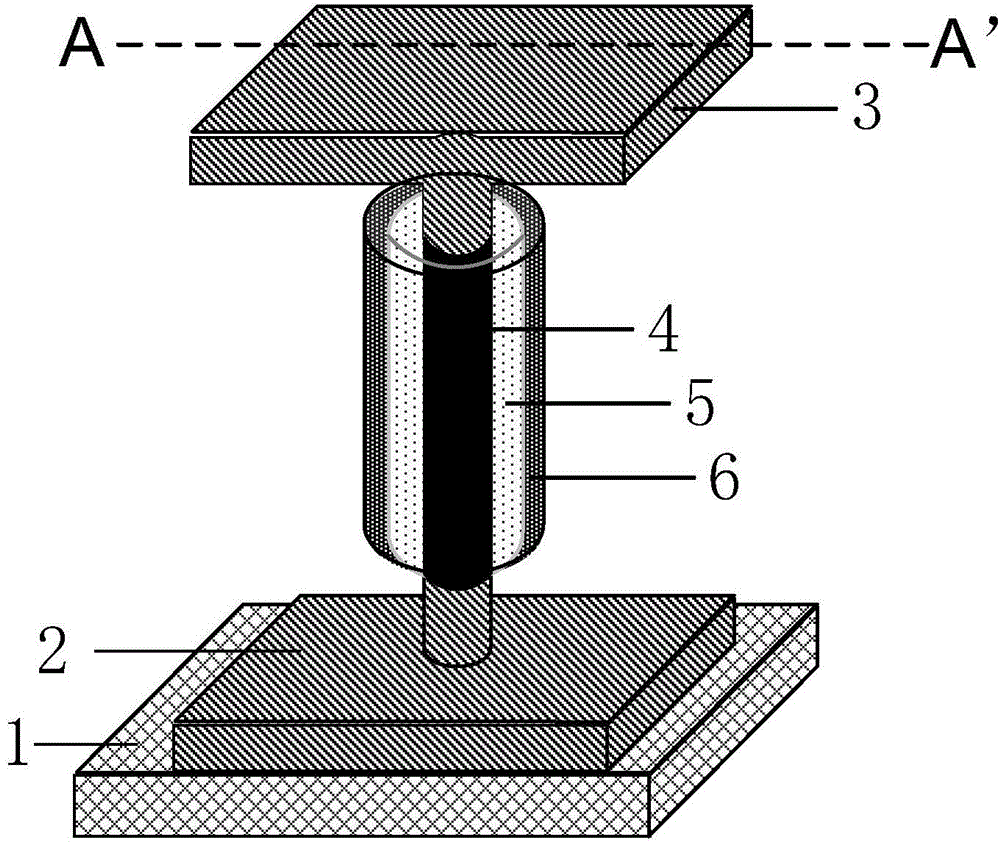

Core-shell field effect transistor and preparation method thereof

ActiveCN104201205AHighly integratedGood gating abilitySemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentGate dielectric

A surrounding gate field-effect transistor combined with a vertical channel, a core-casing structure and a junction-free structure comprises a surrounding semiconductor core in the vertical direction, a surrounding semiconductor casing in the vertical direction, a surrounding gate electrode, a surrounding gate dielectric layer, a core source region, a core drain region, a casing source region, a casing drain region and a semiconductor substrate, wherein the core source region is located at the bottom of a vertical core channel and connected with the substrate, and the core drain region is located at the top of the vertical core channel. The casing source region is located at the bottom of a vertical casing channel and connected with the substrate, and the casing drain region is located at the top of the vertical casing channel. The casing channel surrounds the core channel circularly. The gate dielectric layer surrounds the casing channel. The gate electrode surrounds the gate dielectric layer. The same impurities are doped into source and drain channels of the transistor, so that heat budget is greatly reduced, the impurity diffusion and abrupt junction forming problems are eliminated, process requirements are simplified, drive current is increased by utilizing a germanium core, integration machining photo-etching ultimate limit is broken through by utilizing the vertical channels and a surrounding gate structure, and the integration degree is improved.

Owner:PEKING UNIV

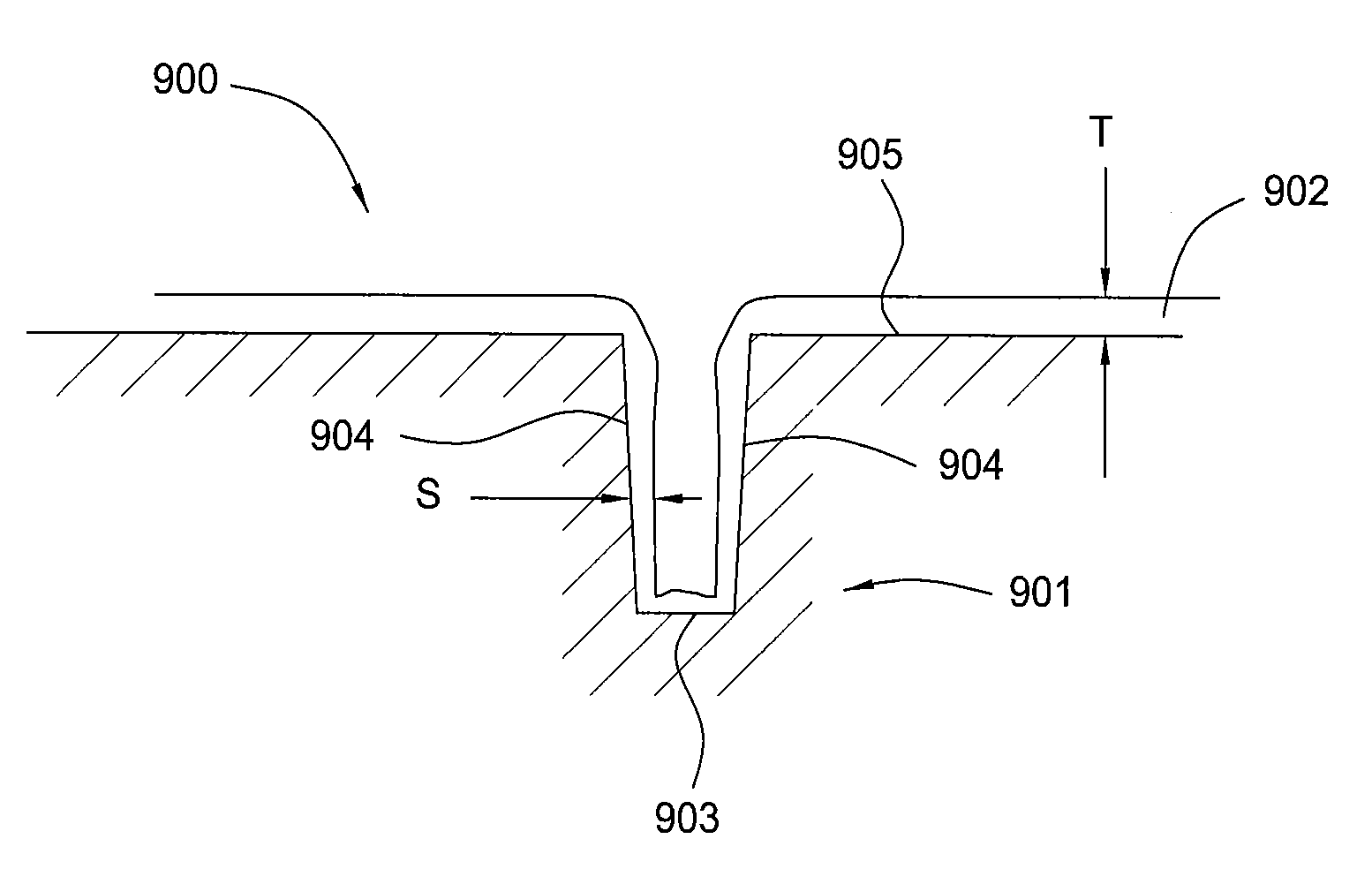

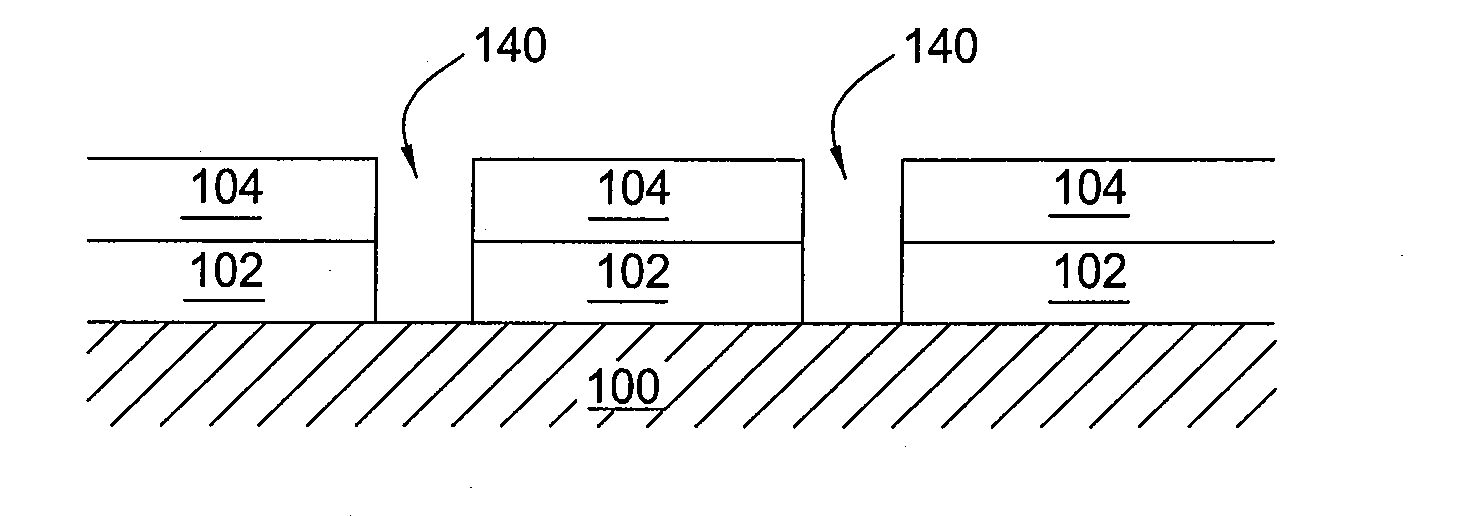

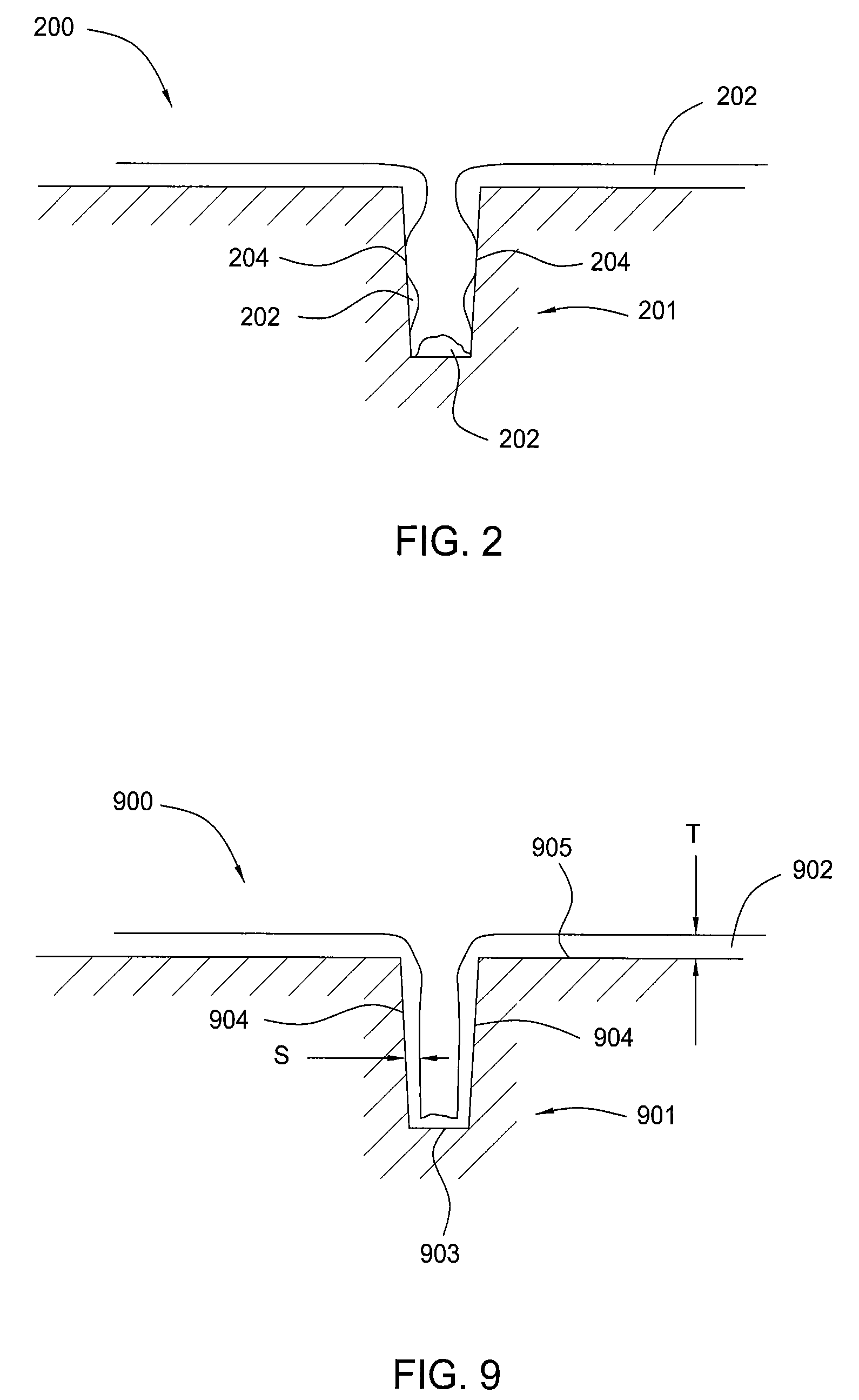

Method for forming a thick bottom oxide (tbo) in a trench mosfet

InactiveCN102013394ALower thermal budgetSemiconductor/solid-state device manufacturingSemiconductor devicesDopantHigh density

Owner:CHENGDU MONOLITHIC POWER SYST

Laser annealing device and annealing method thereof

ActiveCN106935491AStrong process adaptabilitySuppress image effectsSemiconductor/solid-state device manufacturingLaser arrangementsControl systemLaser light

Owner:SHANGHAI MICRO ELECTRONICS EQUIP (GRP) CO LTD

Nonvolatile memory and forming method for the same

ActiveCN101364615ABest programmaticLower thermal budgetSolid-state devicesSemiconductor/solid-state device manufacturingNon-volatile memoryElectric charge

The invention provides a nonvolatile memory, which is positioned on a substrate and comprises a tunneling layer, a charge capture composite layer, a grid and a source electrode / drain electrode area, wherein, the tunneling layer is positioned on the substrate; the charge capture composite layer is positioned on the tunneling layer; the grid is positioned above the charge capture composite layer; and the source electrode / drain electrode area is positioned in the substrate on both sides of the tunneling layer. The nonvolatile memory provided with the charge capture composite layer has good programming and erasing performance and data retaining capability. In addition, the high thermal budget technology is not needed for the formation of the charge capture composite layer, thereby reducing the thermal budget during the technological process.

Owner:MACRONIX INT CO LTD

A MOS resistor and its manufacture method

InactiveCN1964073ALow resistivityReduce source-drain parasitic resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETElectrical resistance and conductance

The provided MOS transistor comprises asymmetric source and drain structures. Wherein, the source uses metal or metal-semiconductor compound and channel to form Schottky barrier contact, while the drain is boost high doped. Compared with traditional MOSFET device, this invention increases on-off current rate greatly, compatible to traditional manufacture technology, and has much room for high-K grid medium and metal grid material since low thermal budget.

Owner:PEKING UNIV

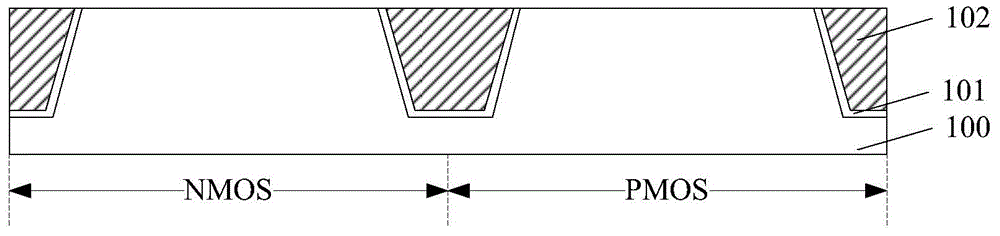

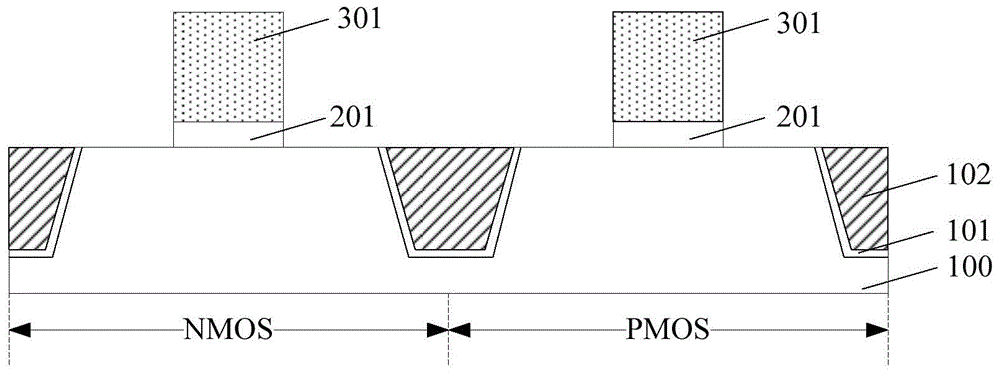

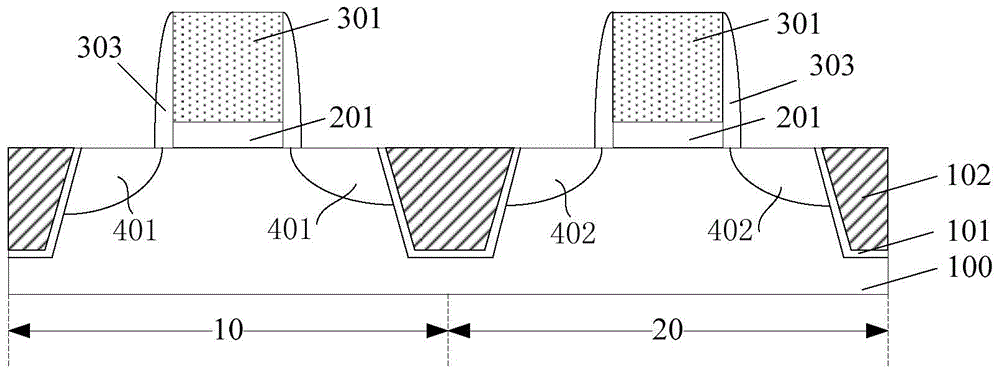

Forming method of CMOS (complementary metal-oxide-semiconductor) transistor

InactiveCN104681490AImprove performancePerformance impactSemiconductor/solid-state device manufacturingCMOSEngineering

The invention provides a forming method of a CMOS (complementary metal-oxide-semiconductor) transistor. The forming method comprises the following steps that a semiconductor substrate is provided, the semiconductor substrate comprises an NMOS (N-channel metal oxide semiconductor) region and a PMOS (P-channel metal oxide semiconductor) region, and a shallow groove isolation structure is also formed in the semiconductor substrate; a pseudo grid structure is respectively formed on the surfaces of the NMOS region and the PMOS region; a dielectric layer is respectively formed on the semiconductor substrate and the surface of the shallow groove isolation region; the pseudo grid structure is removed, a first groove is formed in the surface of the NMOS region, and a second groove is formed in the surface of the PMOS region; a high-K grid dielectric material layer is formed, and displacement ions are doped in the high-K grid dielectric material layer, and can overcome defects in the high-K grid dielectric material layer; the high-K grid dielectric material layer is subjected to annealing processing, and the defects in the high-K grid dielectric material layer are further eliminated; a first grid electrode and a second grid electrode are formed. The forming method of the CMOS transistor has the advantage that the quality of the high-K grid dielectric material layer can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

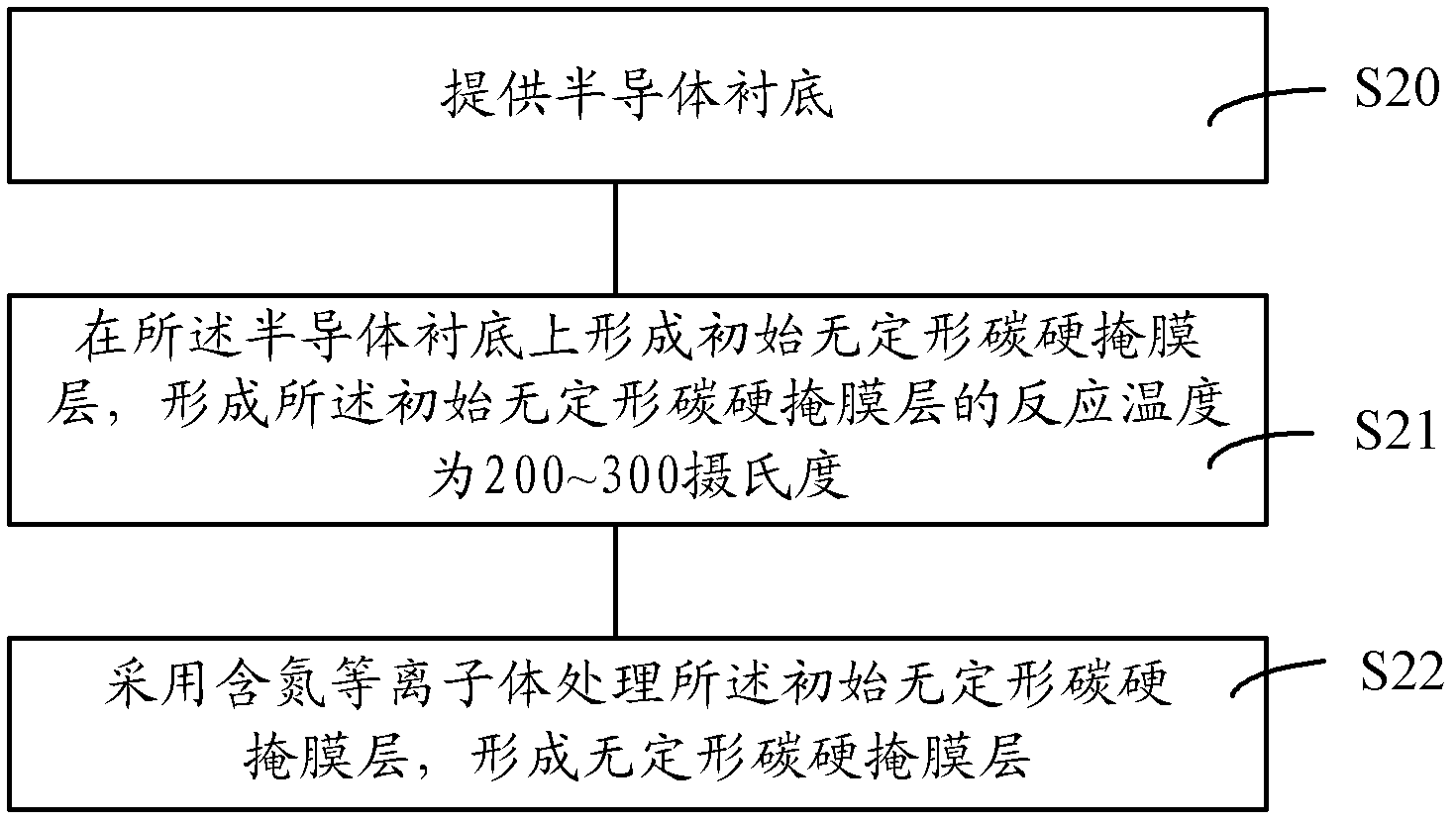

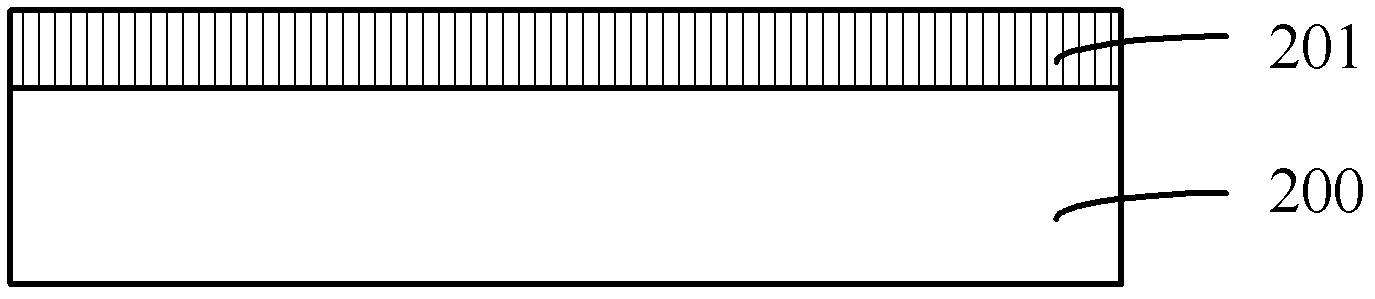

Formation method and etching method for amorphous carbon hard mask layer

ActiveCN103137443ALower the altitudeEnsure consistencySemiconductor/solid-state device manufacturingNitrogen plasmaReaction temperature

Provided is a formation method for an amorphous carbon hard mask layer. The formation method includes that a semiconductor substrate is provided; the initial amorphous carbon hard mask layer is formed on the semiconductor substrate and a reaction temperature for the formation of the initial amorphous carbon hard mask layer is 200 DEG C-300 DEG C; nitrogenous plasma is used for processing the initial amorphous carbon hard mask layer. The formation method of the amorphous carbon hard mask layer forms the amorphous carbon hard mask layer by adopting a low temperature technology, the amorphous carbon hard mask layer with high compactness is formed by the method that the nitrogenous plasma is used for processing the initial amorphous carbon hard mask layer, the heating budget is reduced and stability of a device is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

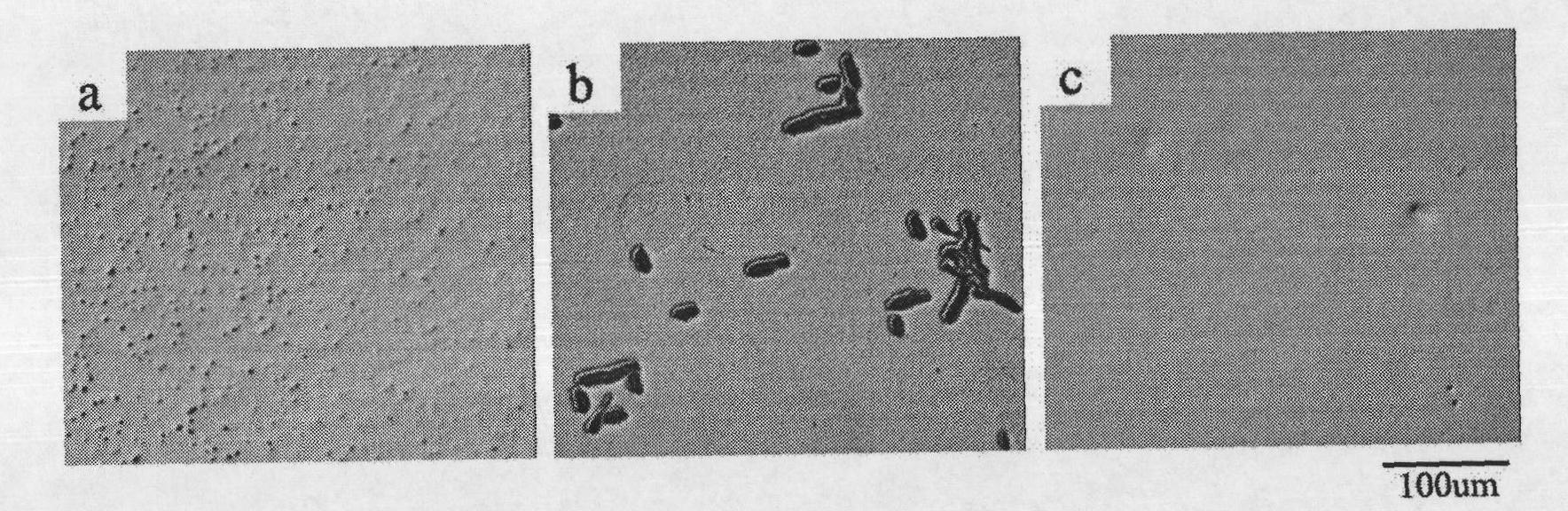

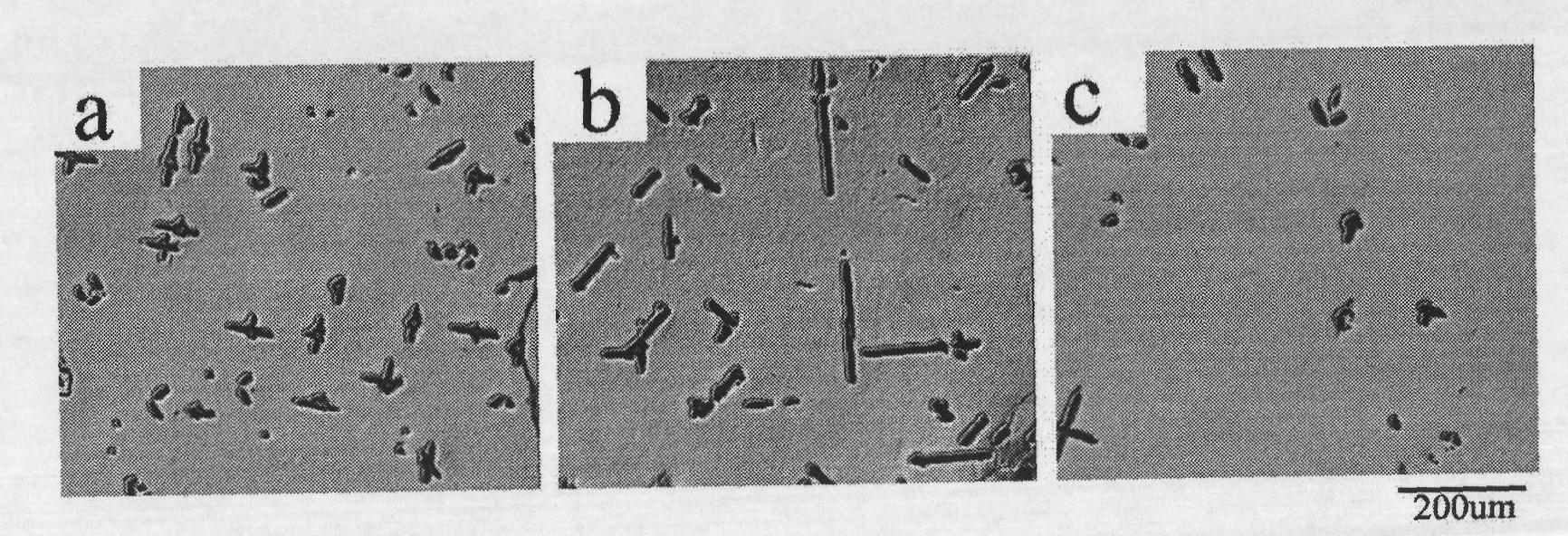

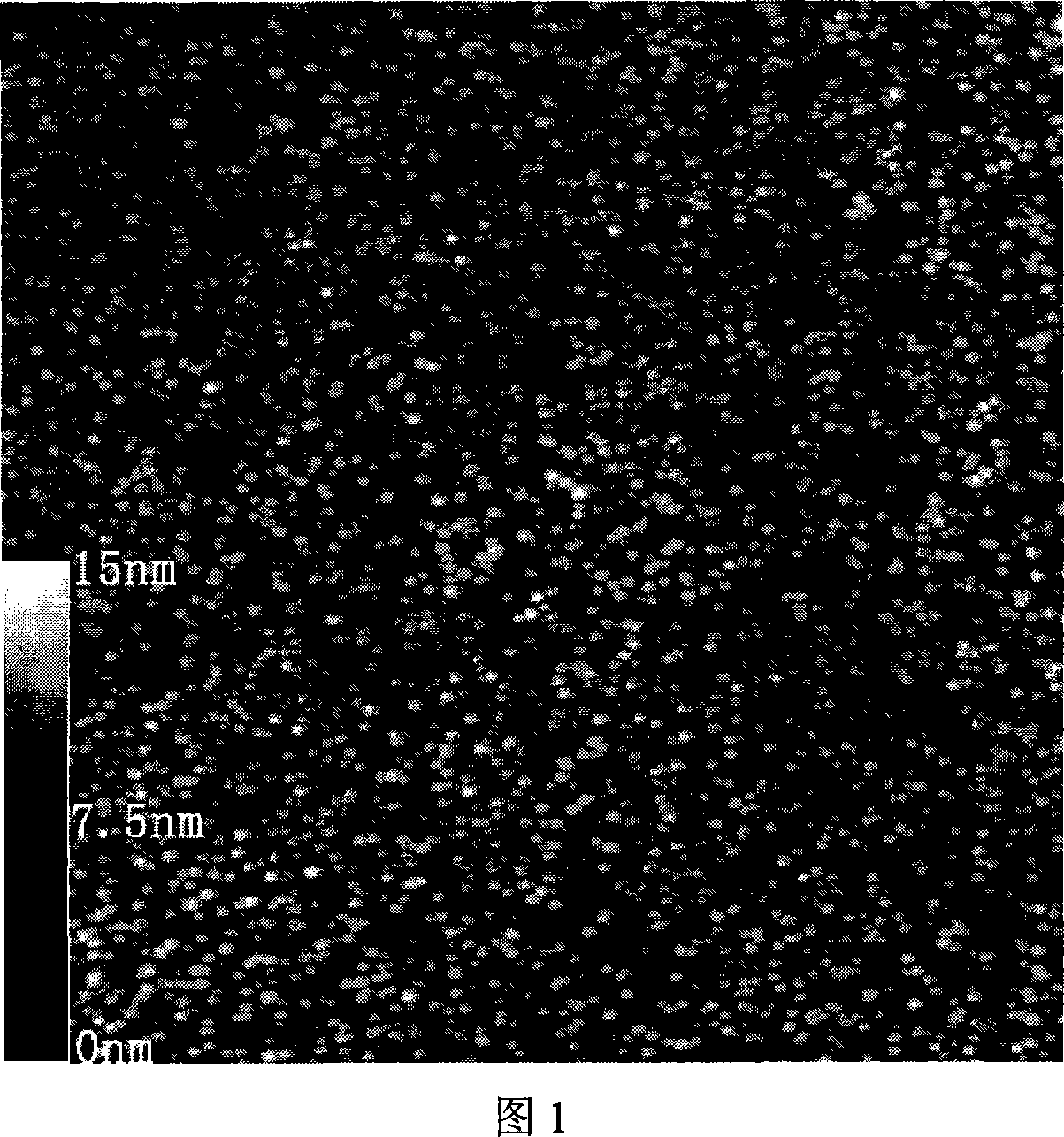

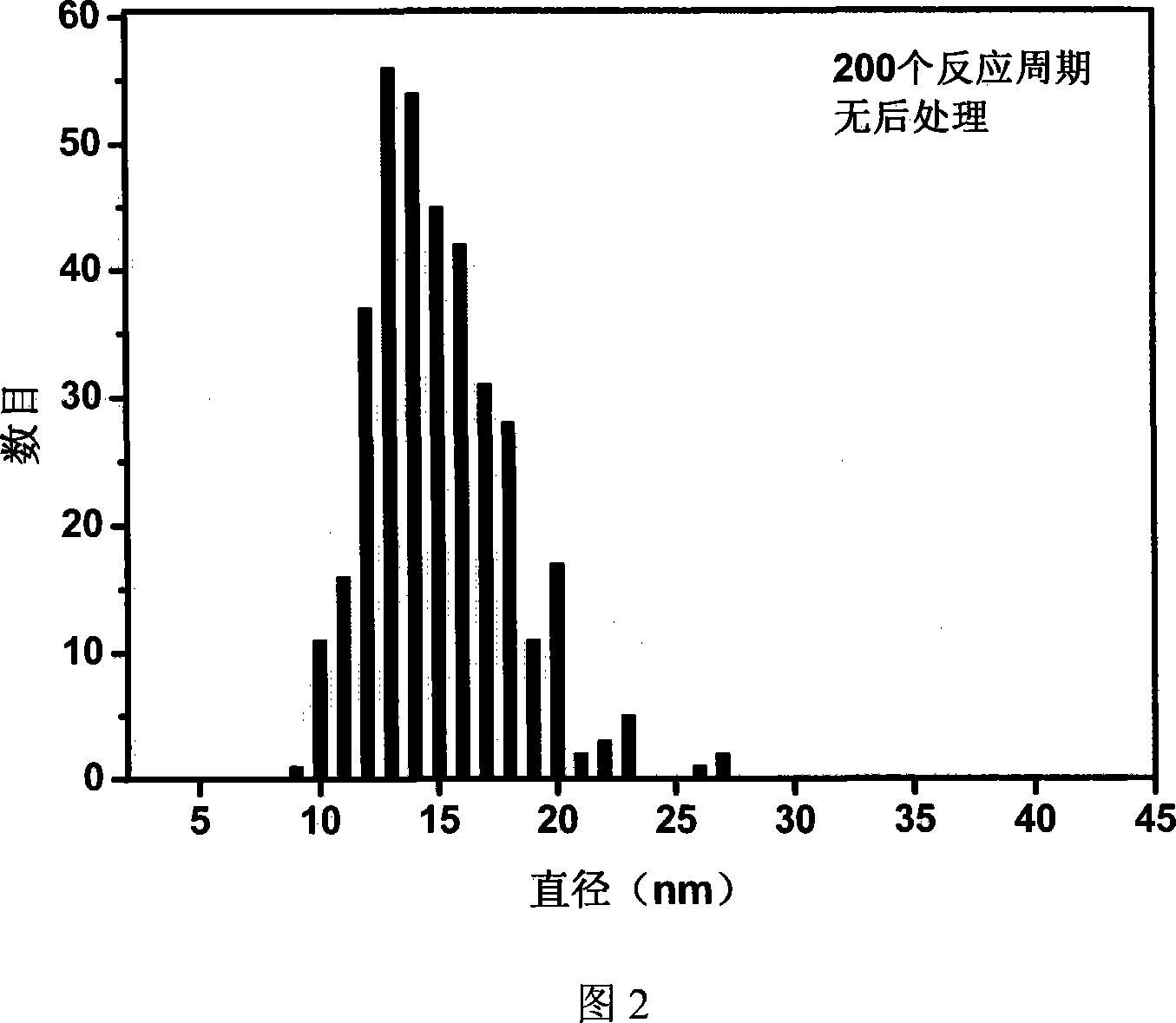

Manufacture method of HD Ru nanocrystalline atomic layer deposition for flash memory

InactiveCN101060077AReduce the formation temperatureLower thermal budgetSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricHigh density

The atomic-layer pulse deposition preparation method for high-density nano-Ru crystal comprises: heat growing SiO2 layer or film with high dielectric constant on the Si surface, depositing 2-5nm Ru film with atomic-layer pulse deposition, and fast annealing at high temperature. This invention is compatible to CMOS technique, and operates simply.

Owner:FUDAN UNIV

Method for forming and processing high-K gate dielectric layer and method for forming transistor

InactiveCN101752235AQuality improvementImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricNitrogen

The invention discloses a method for forming and processing a high-K gate dielectric layer and a method for forming a transistor, wherein the method for forming the high-K gate dielectric layer comprises the following steps: providing a semiconductor substrate; carrying out laser hot treatment on the semiconductor substrate and introducing oxygen or mixed gas of oxygen and nitrogen for forming a buffer layer; and forming the high-K gate dielectric layer on the buffer layer. The invention improves the quality of the subsequent buffer layer and the gate dielectric layer, improves the performance of semiconductor devices, simultaneously reduces the heat budget of the semiconductor devices, improves the local crystallization condition in the high-K gate dielectric layer, and further reduces the generation of the leakage current.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com