Production method of MOS (Metal Oxide Semiconductor) transistor

A technology of a MOS transistor and a manufacturing method, which is applied to the manufacturing field of MOS transistors and can solve the problems of difficulty in forming an ultra-shallow junction, difficulty in lateral diffusion, and the like

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

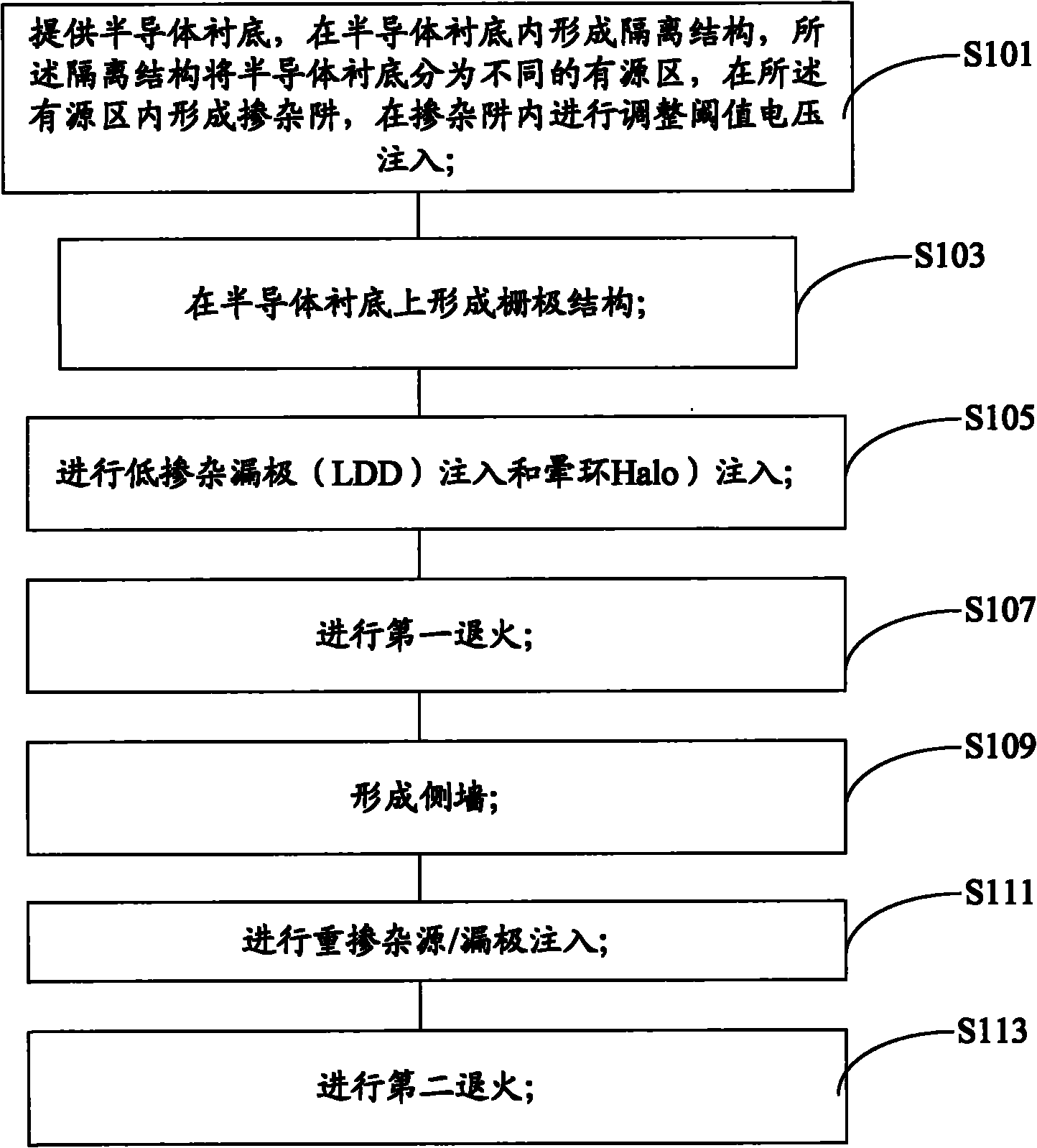

[0028] As mentioned above, based on the above experimental research and theoretical derivation, the inventors of the present invention found that the LDD implanted region in the prior art needs to undergo at least two anneals, making it difficult to form an ultra-shallow junction and to control lateral diffusion. Based on the above findings, the inventors of the present invention annealed the LDD implanted region only once by changing the process, and improved the annealing process to reduce the diffusion of the LDD implanted ions in the depth direction. The technology reduces the dose or energy of LDD implantation to form a shallow junction, so it can prevent the ion diffusion area of the LDD implantation region from being too large, which is conducive to the formation of an ultra-shallow junction; at the same time, because the implantation energy and dose are not reduced, the relatively small area of the LDD implantation region can be maintained. Low resistance, high drai...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com