Method for forming and processing high-K gate dielectric layer and method for forming transistor

A gate dielectric layer and transistor technology, applied in the fields of forming, forming transistors, and processing high-K gate dielectric layers, can solve the problems of increased thermal budget of semiconductor devices, long time, local crystallization of high-K gate dielectric layers, etc., and achieves compactness And the effect of improved uniformity, shorter irradiation time, and improved performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

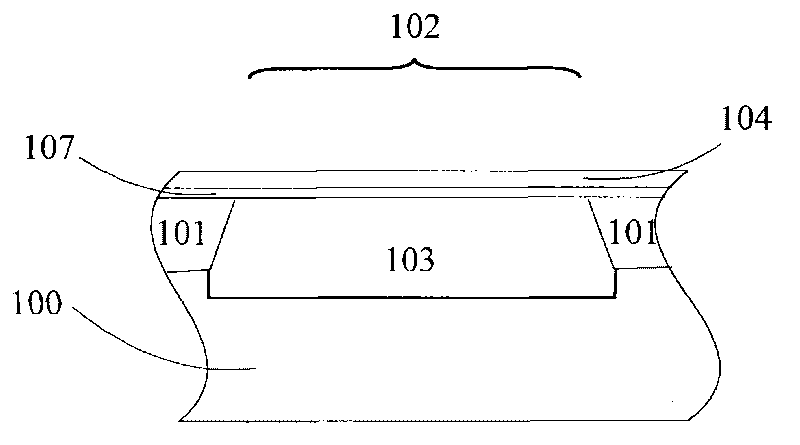

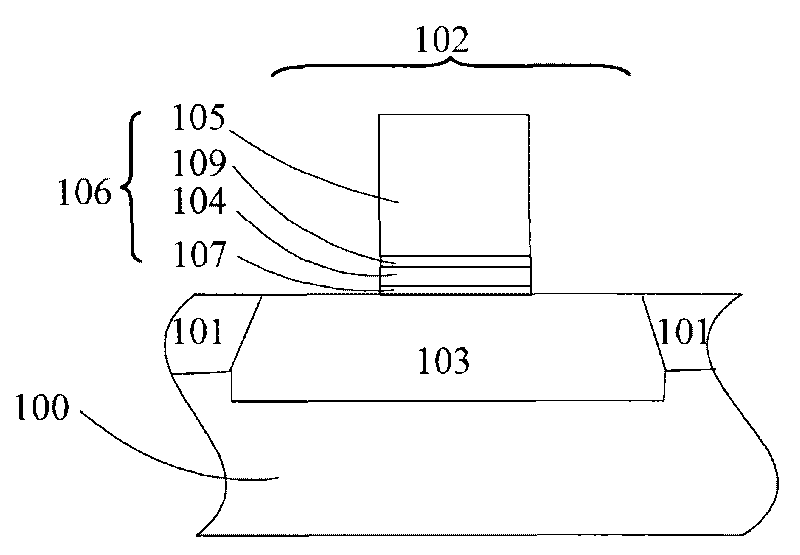

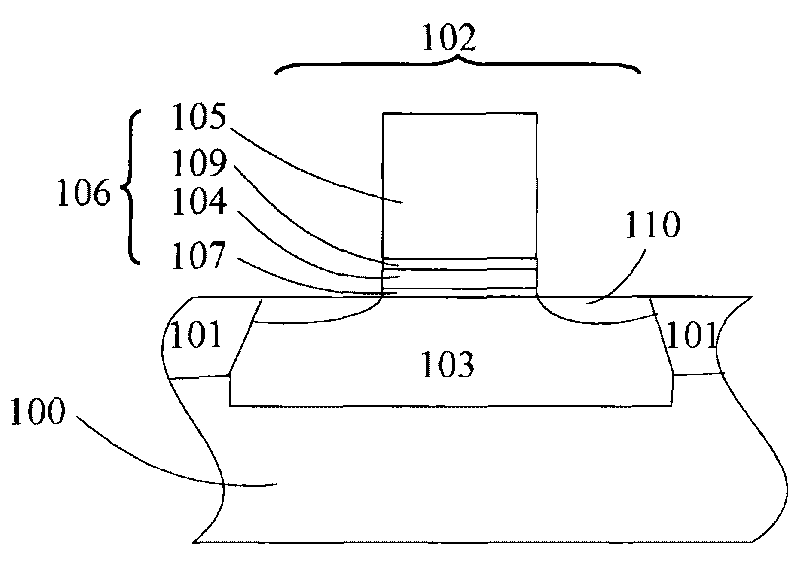

[0037]The present invention uses laser to heat-treat the semiconductor substrate. Due to the characteristics of short laser irradiation time and high intensity, the lattice structure of the native oxide layer naturally oxidized on the semiconductor substrate can be adjusted, and the compactness and uniformity are improved, thereby improving the follow-up process. The quality of the buffer layer and the gate dielectric layer improves the performance of the semiconductor device. In addition, laser heat treatment of the high-K gate dielectric layer can not only repair the defects of the high-K gate dielectric layer, but also reduce the thermal budget of the semiconductor device due to the short time required for laser heat treatment, and improve the local crystallization of the high-K gate dielectric layer. , thereby reducing the generation of leakage current.

[0038] In order to make the above objects, features and advantages of the present invention more comprehensible, specif...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More