A MOS resistor and its manufacture method

A technology of MOS transistors and manufacturing methods, which is applied in the field of MOS transistors with new structures and their manufacturing, can solve the problems of reducing the on-state current of devices, high thermal budget, and difficulty in application, and achieve the reduction of off-state leakage current and switch-state current The effect of improving and lowering the thermal budget

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] The following specific examples help to understand the characteristics and advantages of the present invention, but the implementation of the present invention is by no means limited to the described examples.

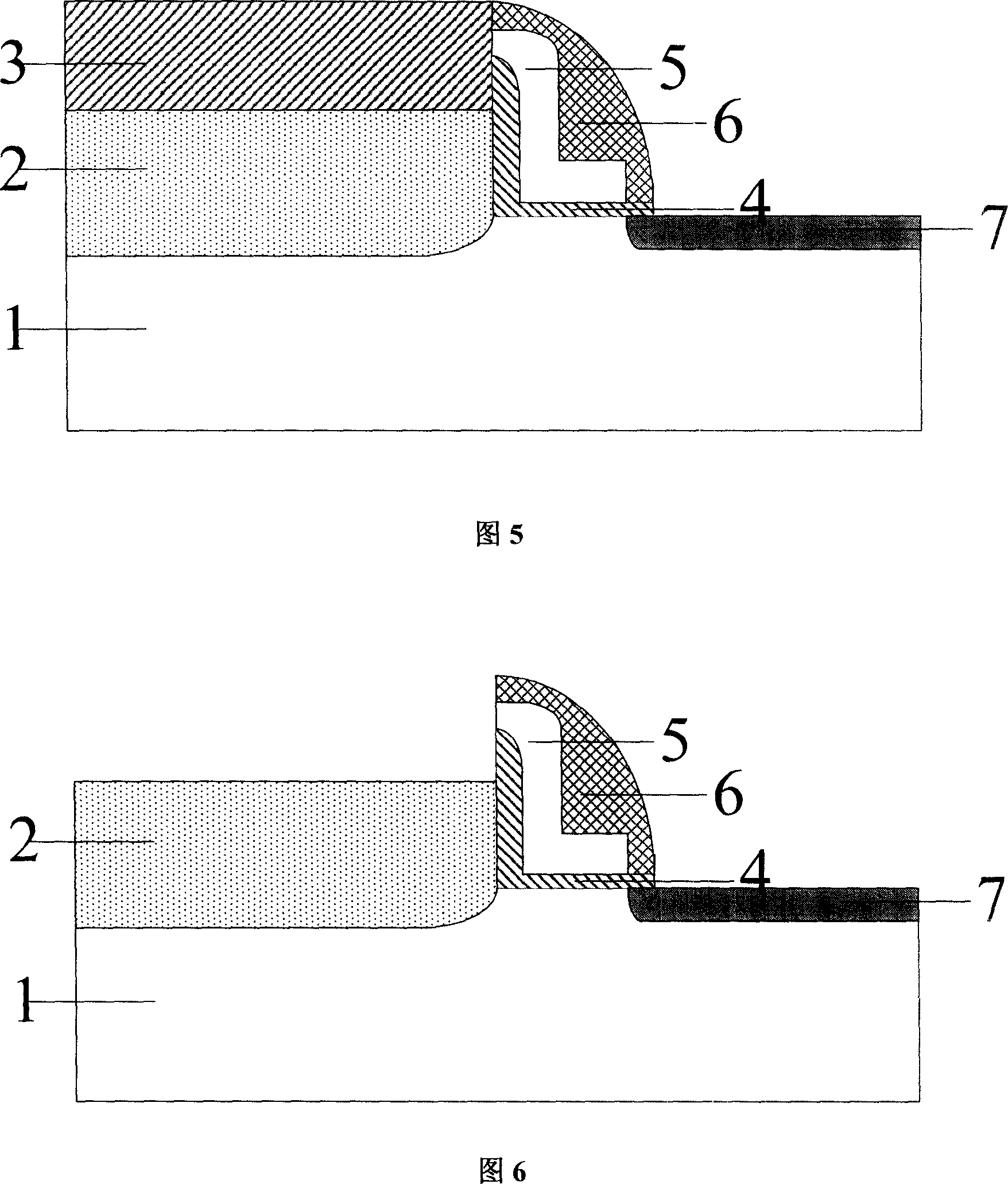

[0040] A specific embodiment of the manufacturing method of the present invention comprises the process steps shown in Fig. 1 to Fig. 6:

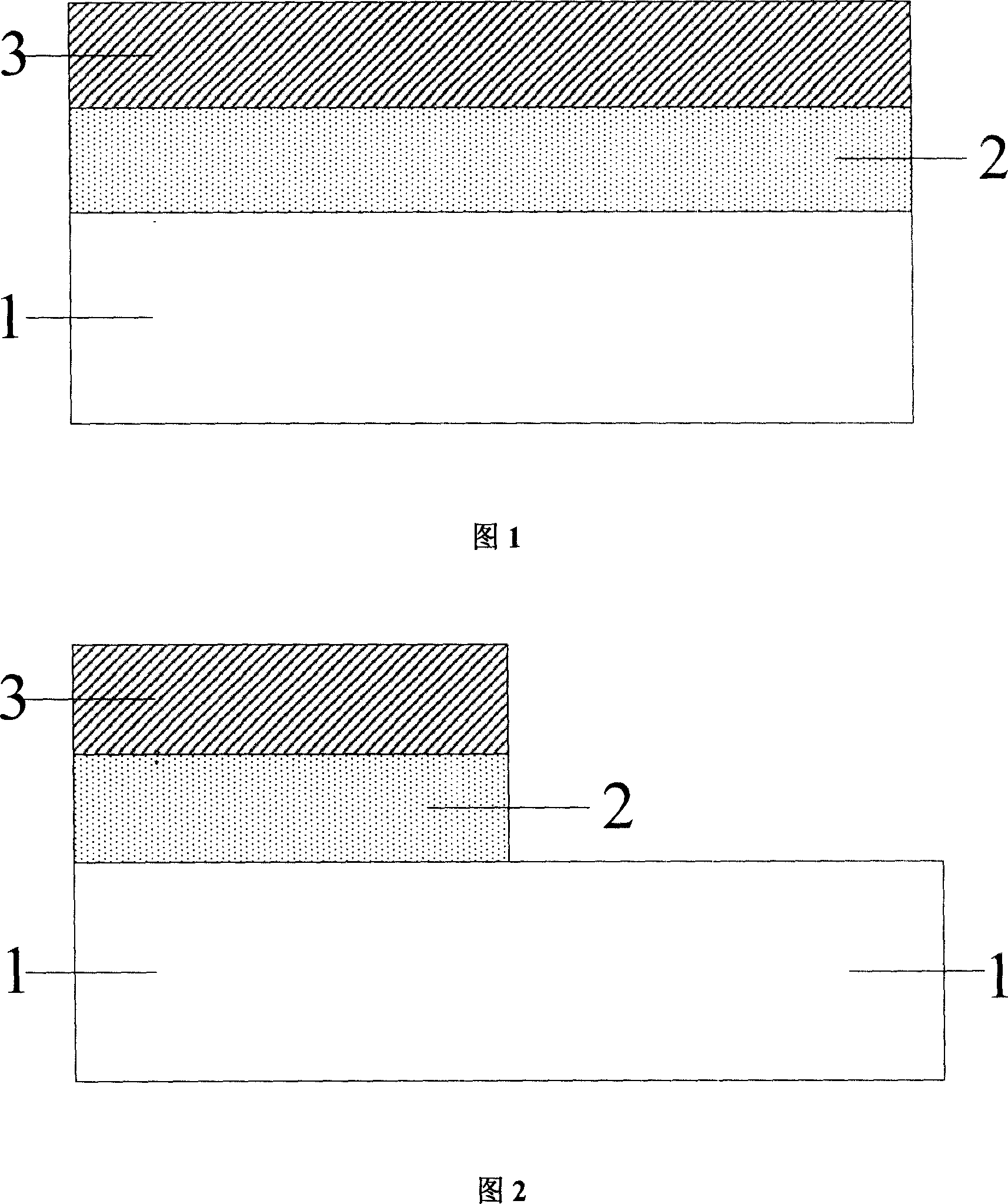

[0041] 1. As shown in Figure 1, the crystal orientation of the bulk silicon substrate (1) used is (100), the body region is initially lightly doped, and the active region is fabricated on the substrate using conventional CMOS shallow trench isolation technology Isolation layer; then perform ion implantation, the ion implantation energy is 30KeV, and the implanted impurity is As; then deposit a layer of TEOS dielectric protection layer (2) with a thickness of 50-100nm.

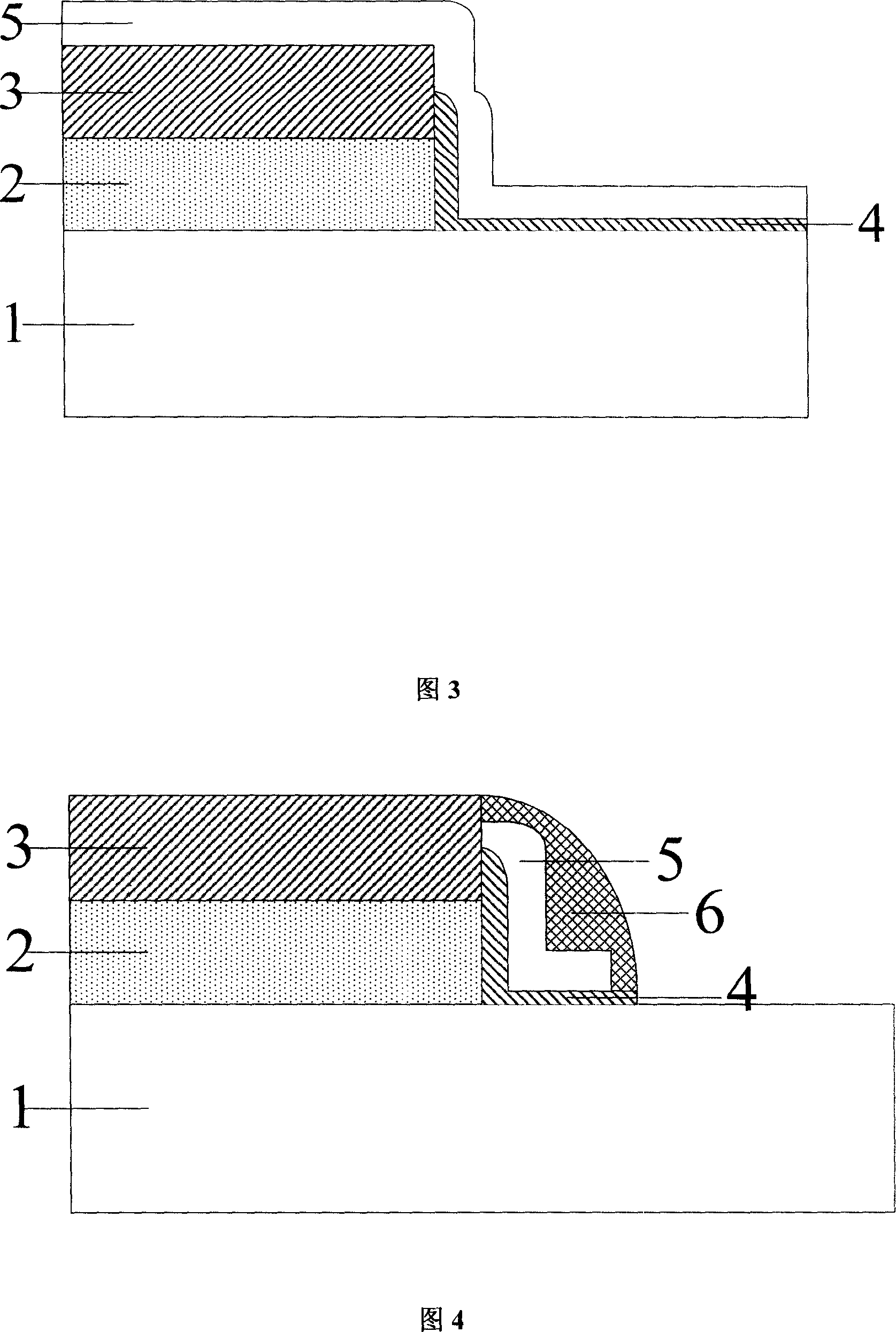

[0042] 2. As shown in FIG. 2, perform photolithography once, etch the TEOS dielectric protection layer (3), and then etch the doped silicon layer (2) until th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More