Patents

Literature

65results about How to "Reduces off-state leakage current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

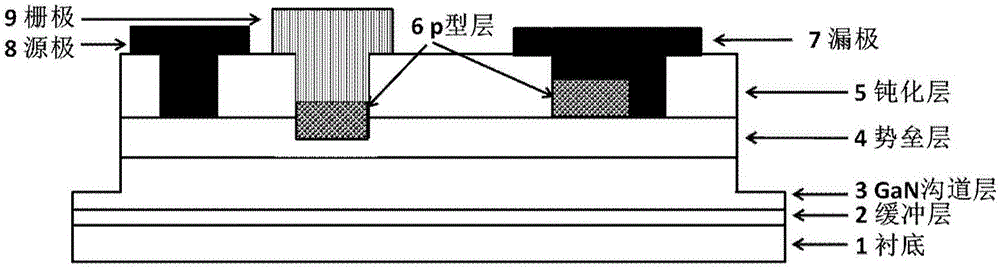

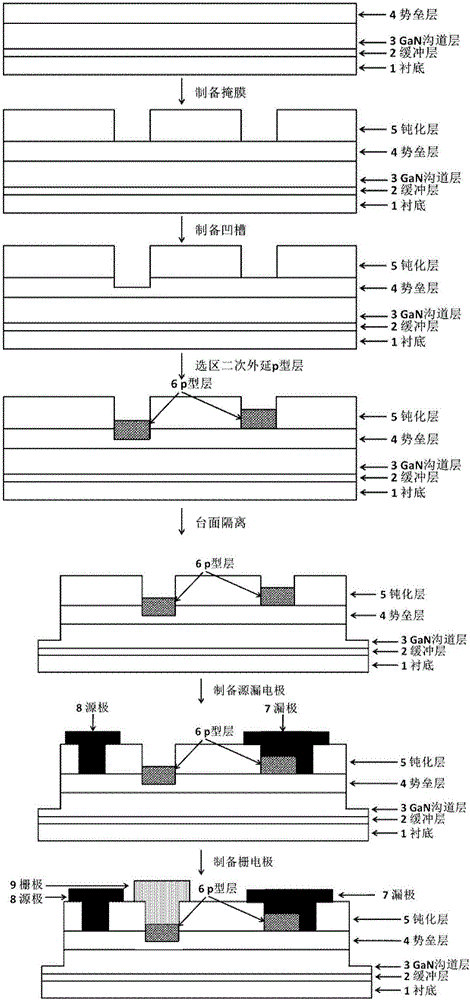

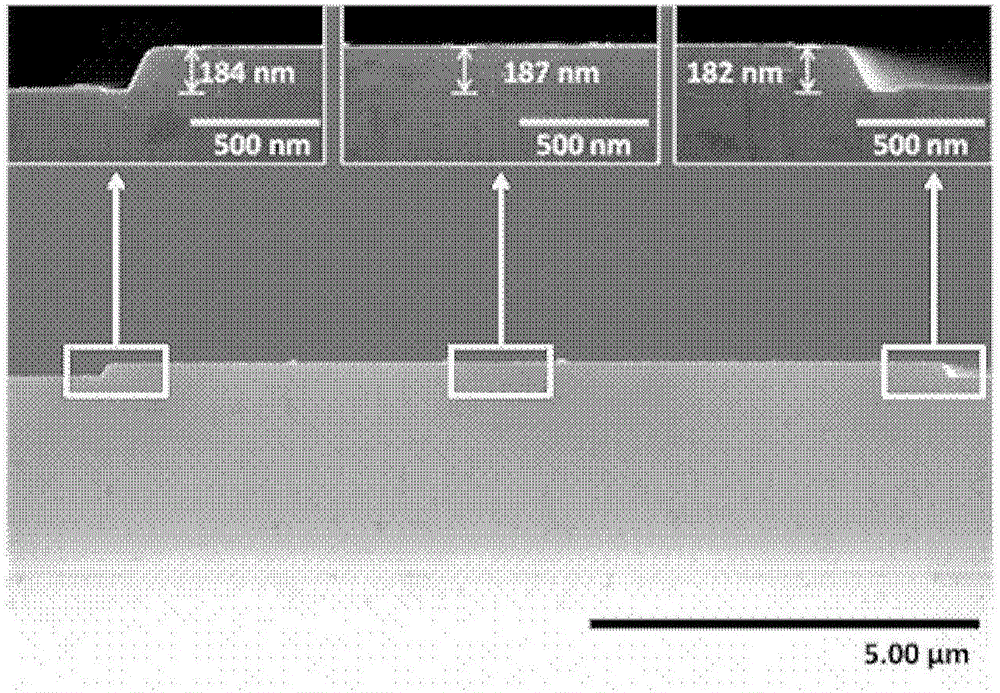

Enhanced-mode high electron mobility transistor, preparation method thereof, and semiconductor device

InactiveCN105720097ARaise the threshold voltageImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowSemiconductor

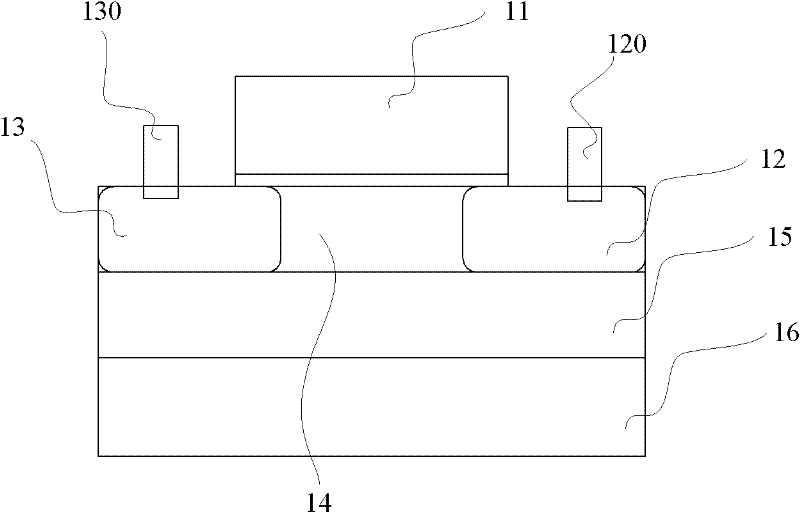

The present invention provides an enhanced-mode high electron mobility transistor. The transistor includes a grid electrode, a source electrode, a drain electrode, a p type layer, a barrier layer, and a passivation layer arranged on the barrier layer. A part region on the passivation layer is provided with a secondary epitaxy figure formed by etching to the upper surface of the barrier layer. The barrier layer also includes a trench formed by further etching to the inner side of the barrier layer in a local region of the figure. The p type layer that is grown through secondary epitaxy is in the figure and the trench. The p type layer in the trench is contacted with a grid electrode metal on the p type layer in the trench. The p type layer that is not in the trench is contacted with a drain electrode metal on the p type layer that is not in the trench. The present invention also provides a preparation method of the transistor and a semiconductor device including the transistor. According to the transistor, due to a trench grid and the p type layer grown through secondary epitaxy in a selected region, a threshold voltage of the device is increased; and a part of the barrier layer is etched, so that a saturated current of the device is greater than the current of the trench grid type high electron mobility transistor (HEMT). In addition, the p type layer is also grown in a selected region of the drain electrode metal, so that the turn-off effect of the device is improved.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Three-dimensional semiconductor device and manufacturing method thereof

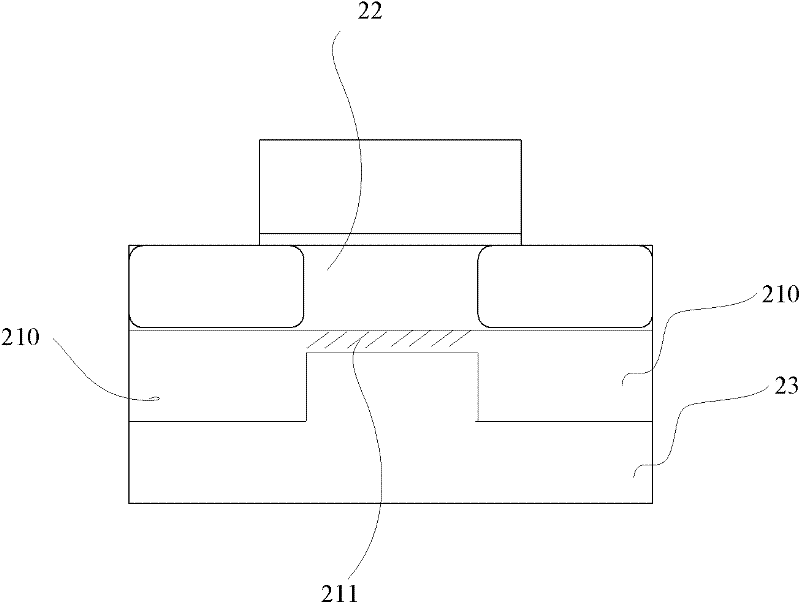

ActiveCN104022121AImprove reliabilityImprove control characteristicsSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETVertical channel

The invention discloses a three-dimensional semiconductor device comprising a plurality of memory unit transistors and a plurality of selection transistors, wherein the plurality of memory unit transistors are at least partially overlapped in the vertical direction; each selection transistor comprises a first drain electrode distributed along the vertical direction, an active region, a common source electrode formed in a substrate and a metal grid electrode distributed around the active region; each memory unit transistor comprises a channel layer distributed vertical to the surface of the substrate, wherein a plurality of interlayer insulating layers and a plurality of grid electrode stacking structures are alternately stacked along the side wall of the channel layer, and a second drain electrode is located at the top of the channel layer; the channel layer is electrically connected with the first drain electrode. According to the three-dimensional semiconductor device and a manufacturing method thereof disclosed by the invention, multi-grid MOSFETs (Metal-Oxide-Semiconductor Field Effect Transistors) are formed below memory unit string stacks comprising vertical channels so as to be used as the selection transistors, thus the threshold voltage control characteristic of the grid electrode is improved, the off-state leakage current is reduced, the over-etching for the substrate is avoided, and the reliability of the device is effectively improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

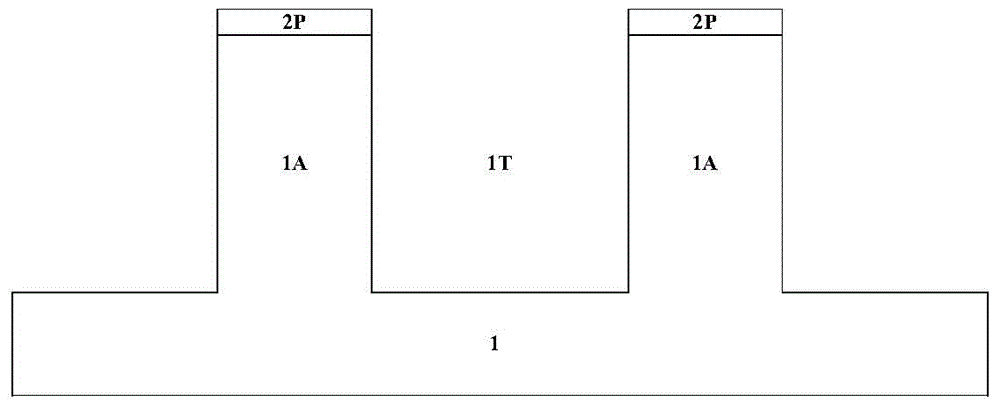

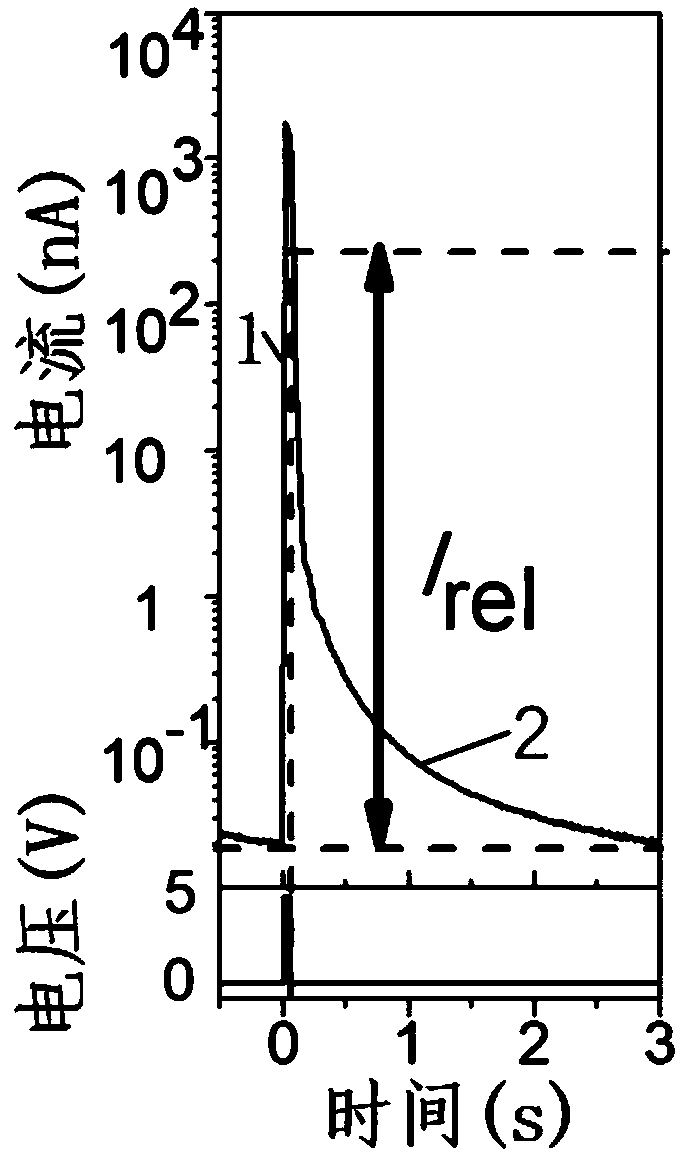

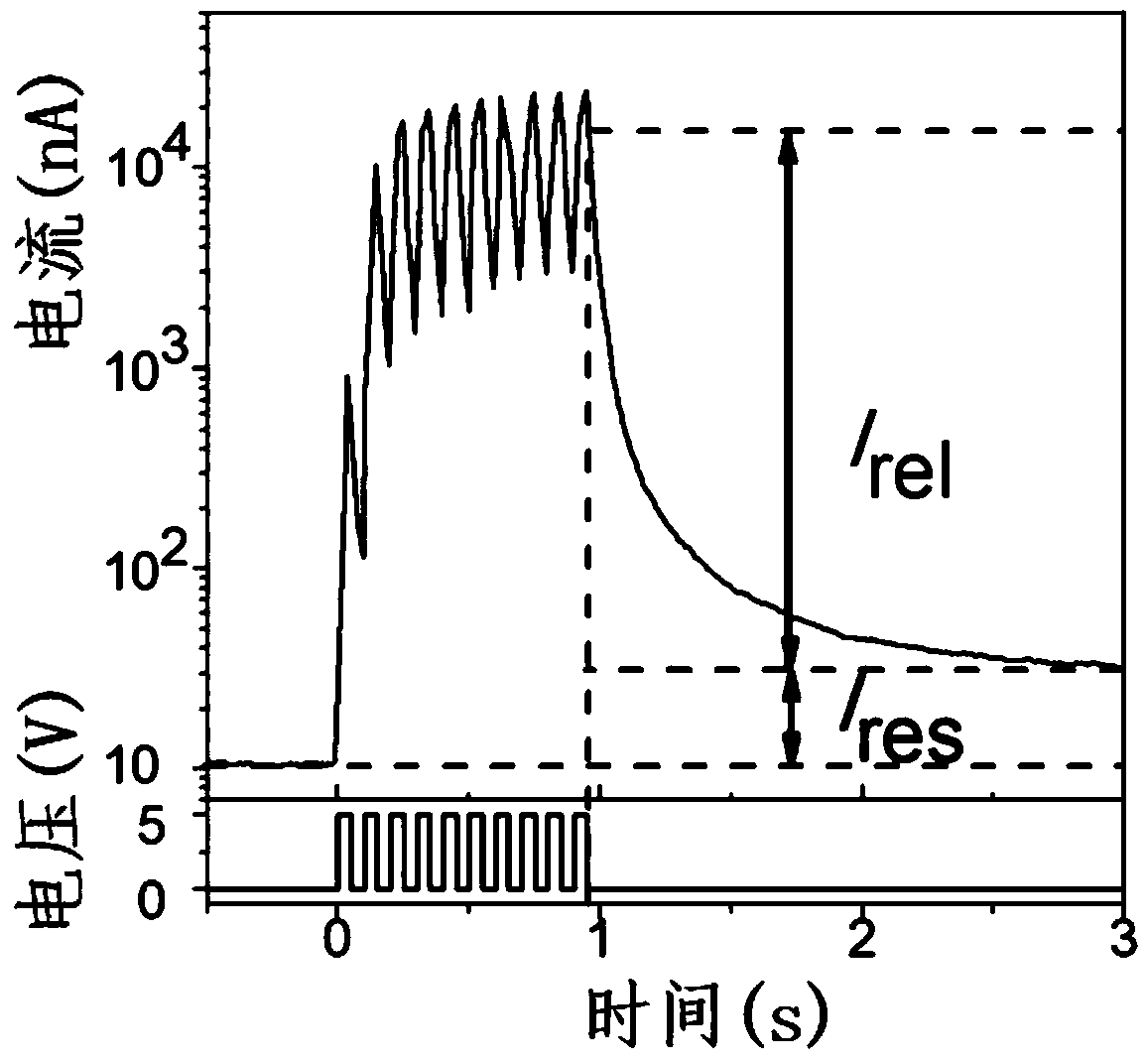

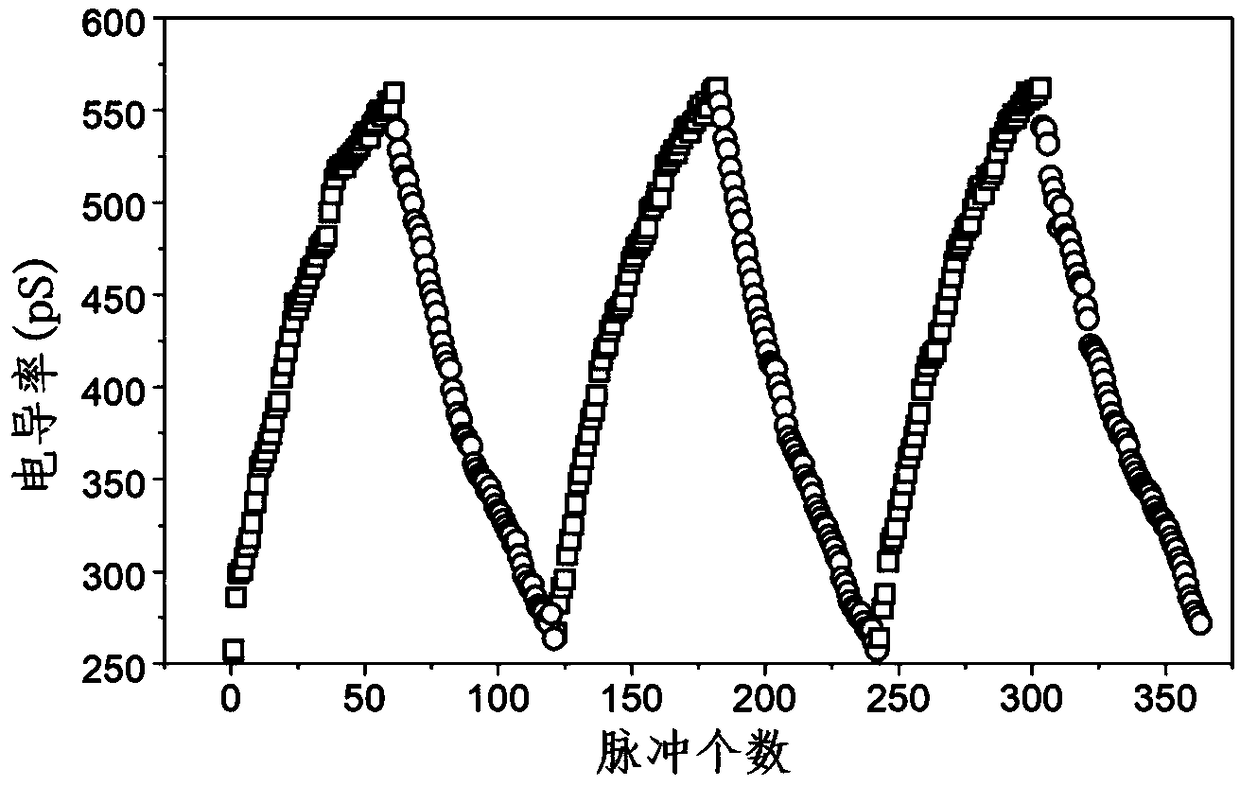

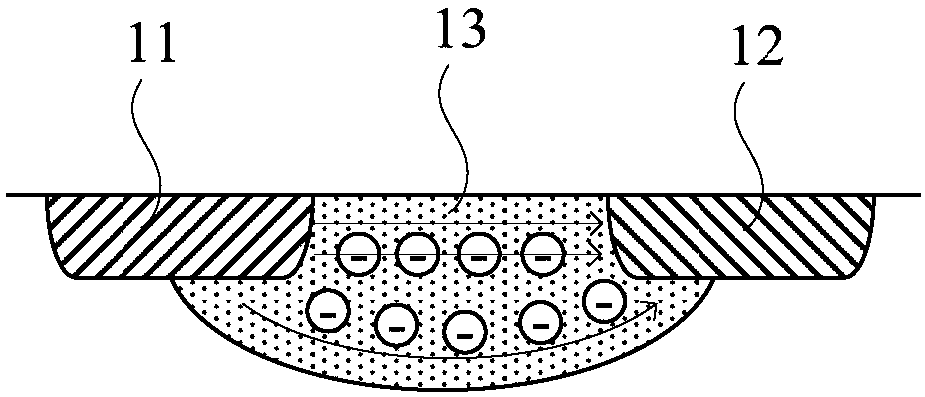

Synaptic transistor based on two-dimensional semiconductor material and preparation method of synaptic transistor

InactiveCN109473549AIncrease surface areaImprove linearitySolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsOhmic contact

The invention discloses a synaptic transistor based on a two-dimensional semiconductor material and a preparation method of the synaptic transistor. The synaptic transistor comprises an insulating substrate, and a channel, a source electrode, a drain electrode and a gate electrode which are arranged on the substrate, wherein the channel is a two-dimensional semiconductor material; the source electrode and the drain electrode are arranged at the two ends of the channel respectively and form an ohmic contact with the channel material; the gate electrode and an electrical interconnection system formed by the channel, the source electrode and the drain electrode are kept in electronic insulation; an organic electrolyte covers a channel region and most of the gate electrode and comprises an organic carrier capable of being electrically insulated and ions capable of being migrated, and effective ion control of the gate to the channel material is formed. According to the synaptic transistor based on the two-dimensional semiconductor material and the preparation method of the synaptic transistor, an ion attachment-intercalation mechanism is utilized, and the characteristics of large surface area and adjustable resistance value of the two-dimensional material are combined, so that the device shows long-term and short-term synaptic plasticity, and the two characteristics can change witheach other along with the change of a gate signal. Meanwhile, the device has good linearity and ultralow operational power consumption, and the implementation and large-scale integration application of a high-precision neuromorphic device are facilitated.

Owner:PEKING UNIV

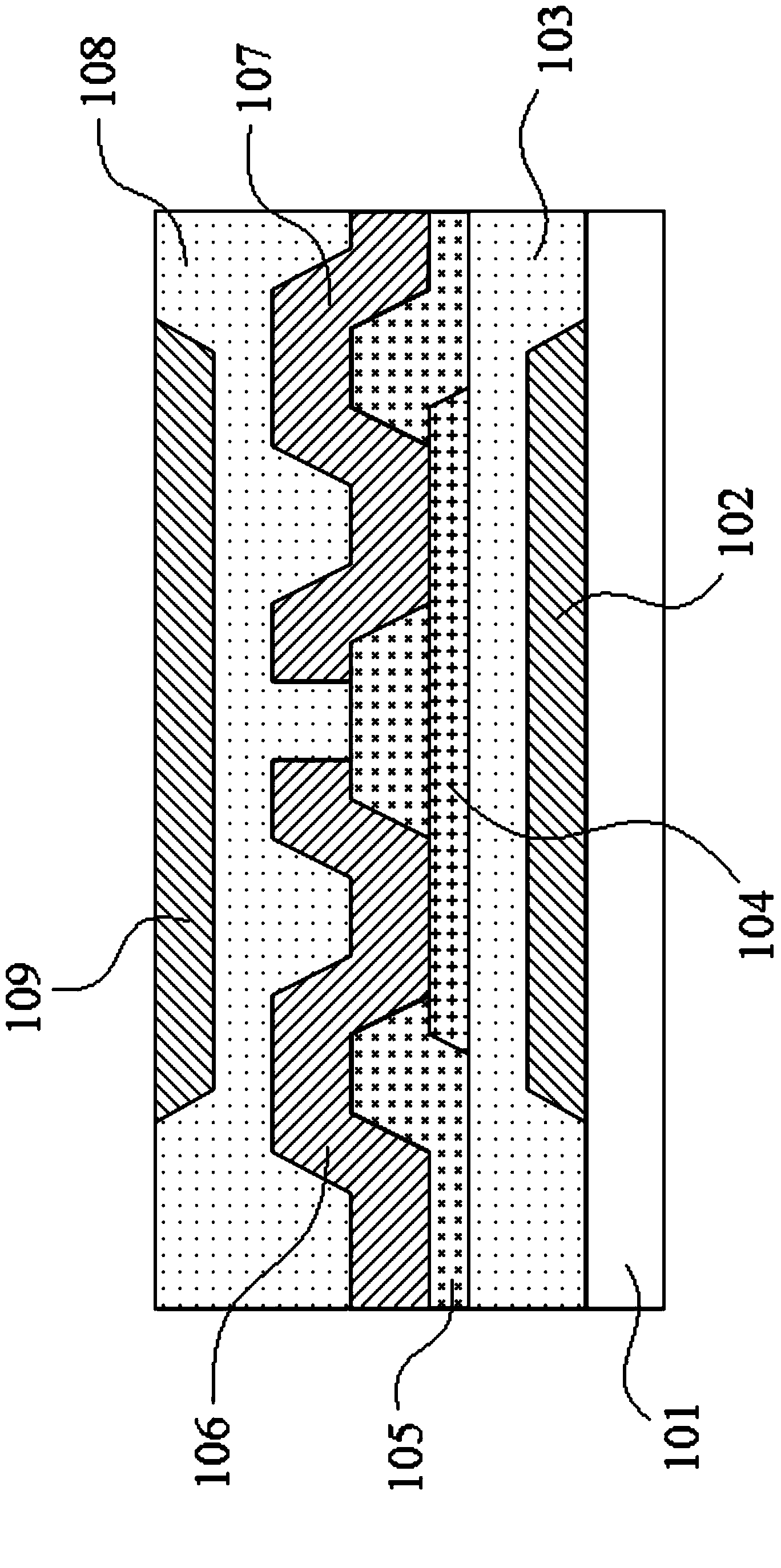

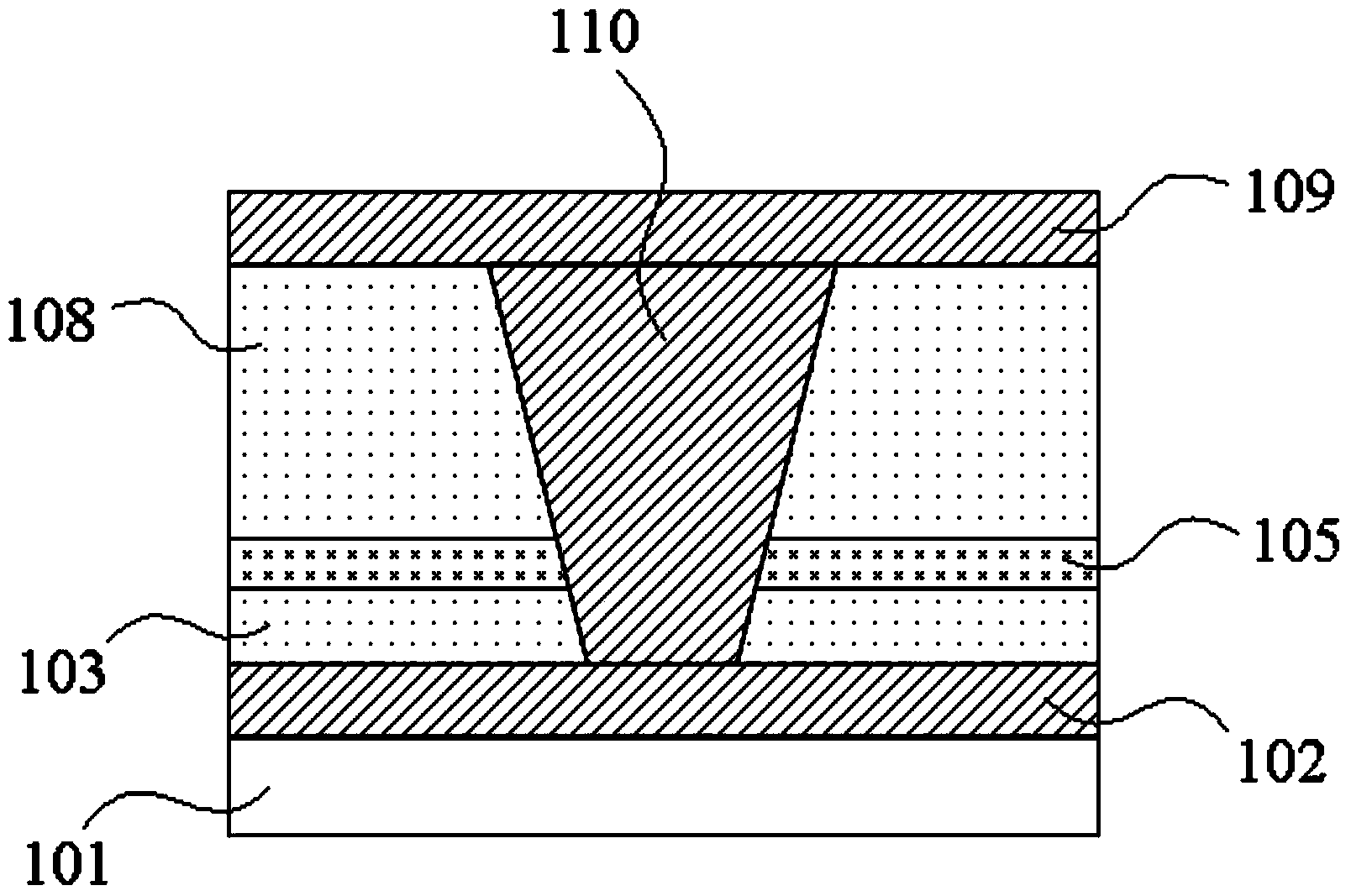

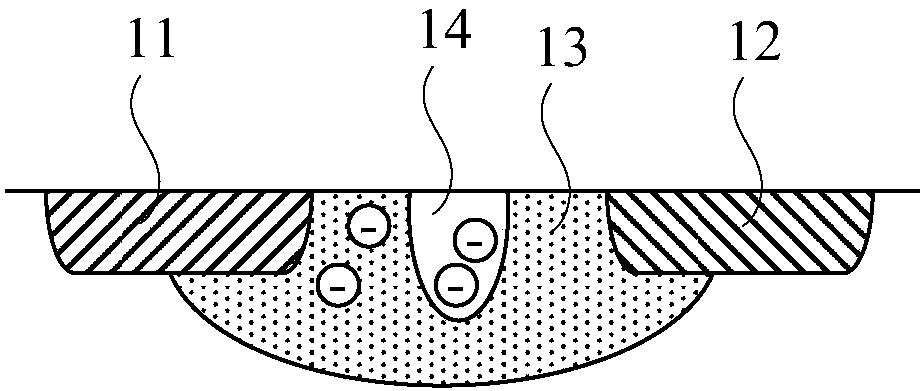

Display device, array substrate, thin film transistor and fabricating method thereof

InactiveCN104538458AReduces off-state leakage currentThe effect of increasing the on-state currentTransistorSolid-state devicesInsulation layerBottom gate

The invention relates to the technical field of display processes, and particularly relates to a display device, an array substrate, a thin film transistor (TFT) and a fabricating method thereof. The thin film transistor sequentially comprises a first gate electrode, a first gate insulation layer, an active layer, a second gate insulation layer, a second gate electrode, a third gate insulation layer, a source electrode and a drain electrode, wherein source and drain light-doped regions and source and drain heavy-doped regions are respectively arranged outside regions corresponding to the active layer and the second gate electrode, the source electrode and the drain electrode are electrically connected with the source heavy-doped region and the drain heavy-doped region; the first gate electrode is arranged below the drain light-doped region of the region corresponding to the drain electrode or the first gate electrode is divided into two parts which are respectively arranged below the light-doped regions of the regions corresponding to the source electrode and the drain electrode. The invention provides the display device, the array substrate, the thin film transistor and a fabricating method thereof. The OFF leakage current of the TFT is reduced by virtue of an LDD structure; meanwhile, the effect of the ON current of the TFT is improved by virtue of a bottom gate structure, and the yield of a product is increased.

Owner:BOE TECH GRP CO LTD

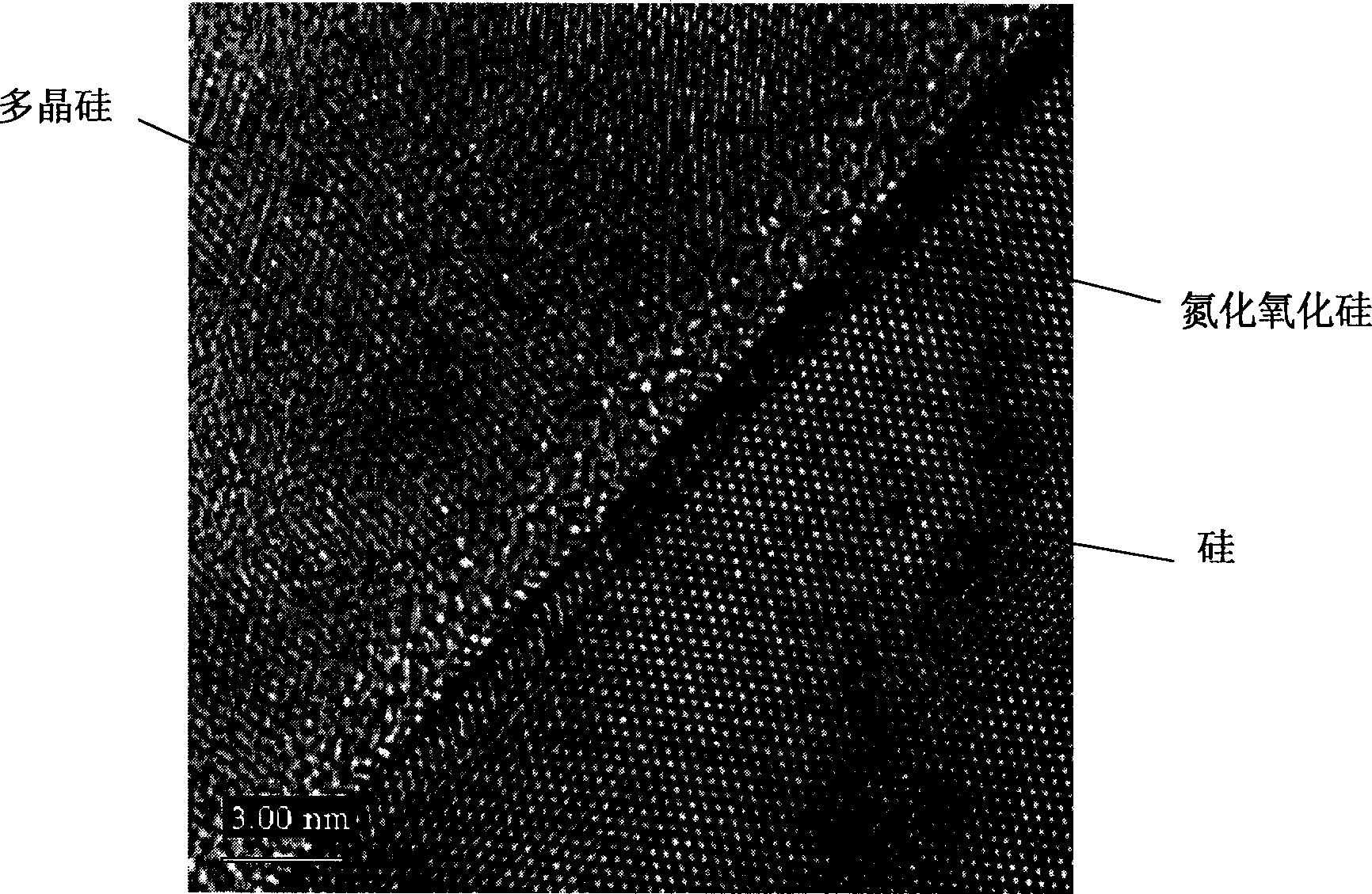

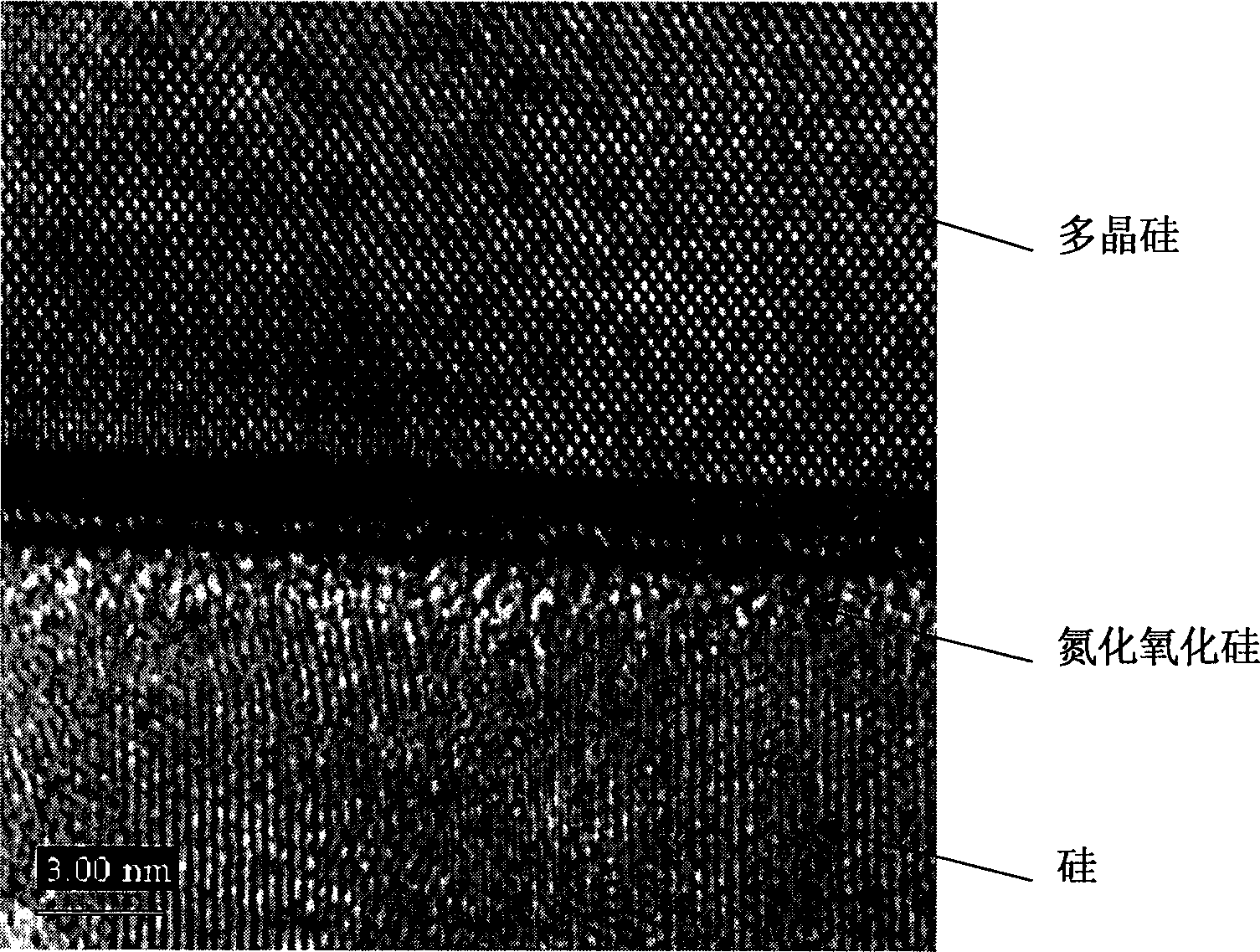

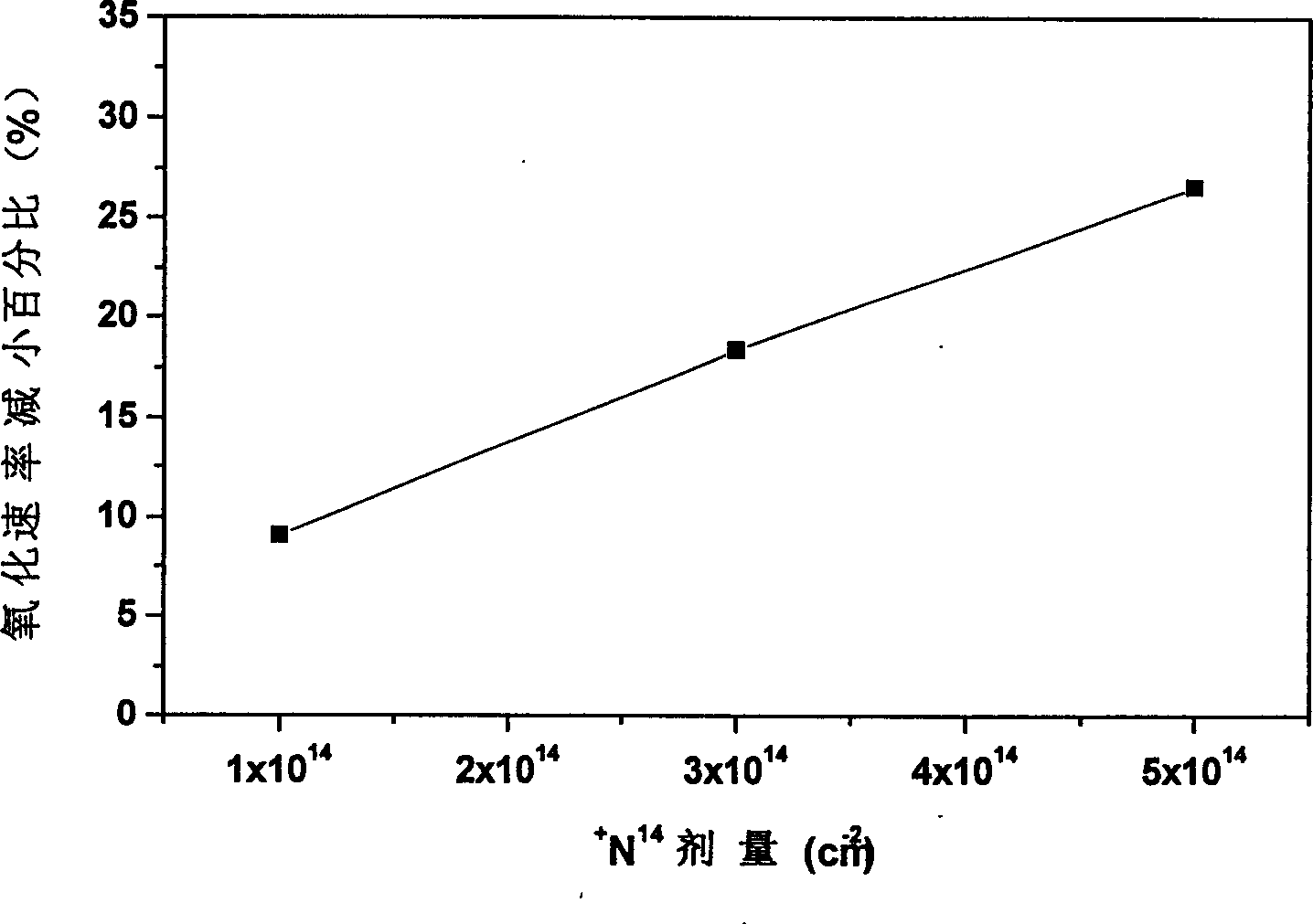

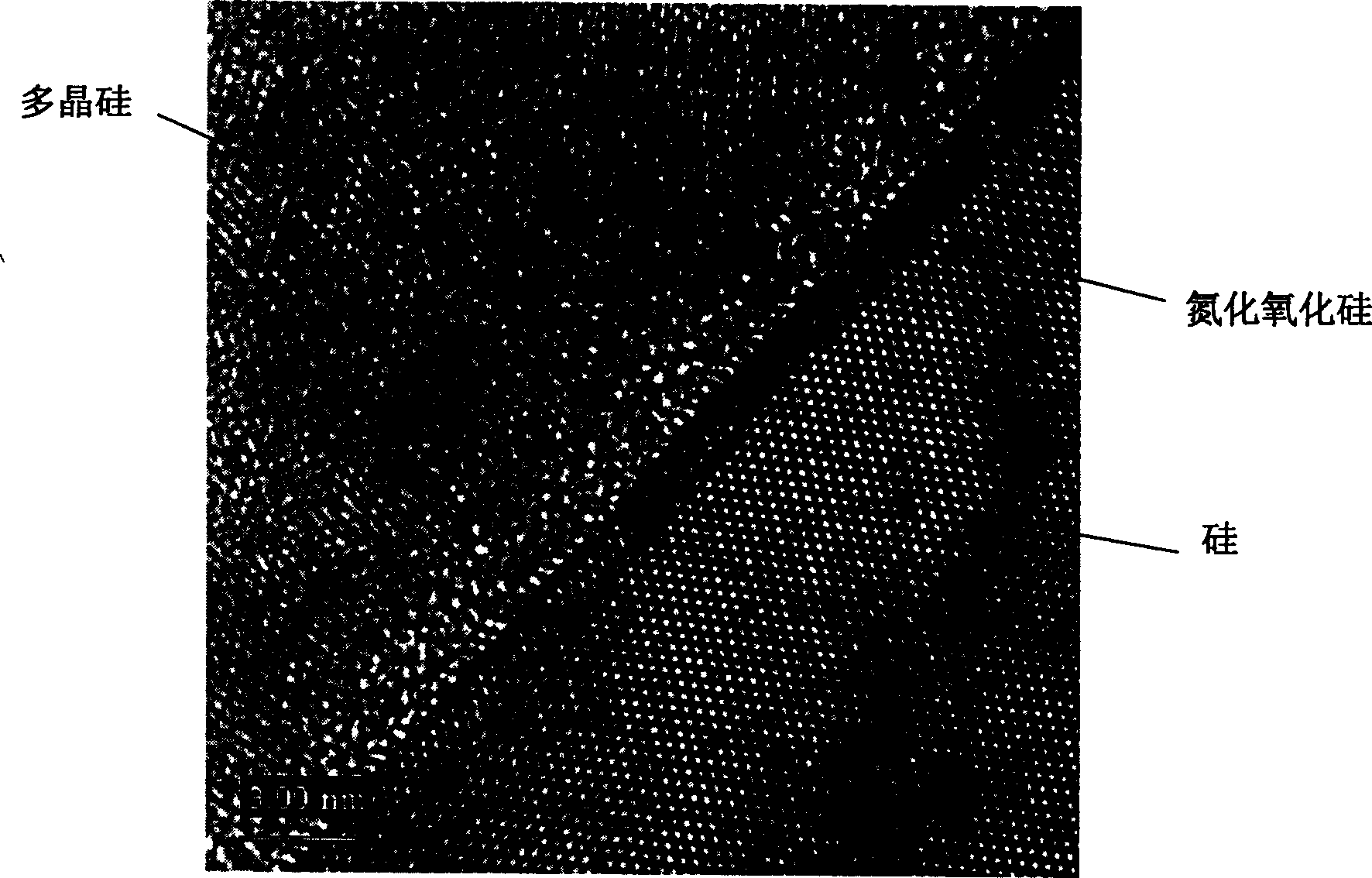

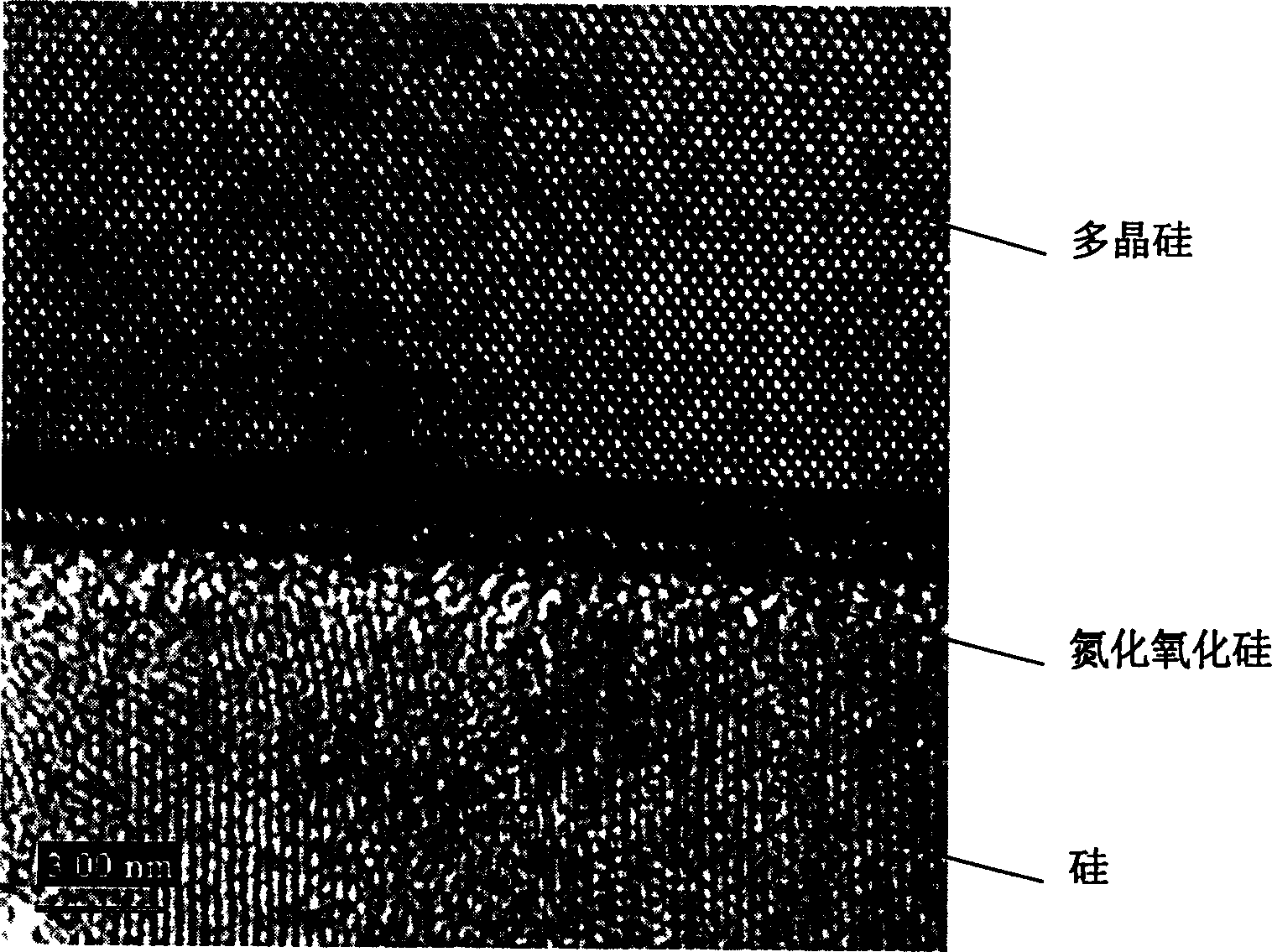

Prepn of nitride-oxide film

InactiveCN1404113AImprove densification performanceImprove uniformitySemiconductor/solid-state device manufacturingRoom temperatureNitrogen

The preparation of nitroxide film is to implant nitrogen ion into silicon substrate before oxidation. The steps includes: growing oxide film on isolated and cleaned silicon chip and implanting nitrogen ion to the active area; rinsing the oxide film; soaking with HF / IPA / H2O at room temperature and rinsing with deionized water before drying and feeding into furnace; feeding the boat slowly under protection of great flow rate of N2; heating to 700-900 deg.c and oxidation in N2 / O2 ratio of 5 for 1-120 min; annealing in N2 atmosphere at 700-900 deg.c for 15-60 min; lowing the temperature to 550 deg.c in N2 atmosphere and withdrawing the boat slowly under protecting of great flow rate of N2; forming polysilicon via LPCVD at 620 deg.c, 0.2 torr, SiH4 200 sccm and Ar 800 sccm.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

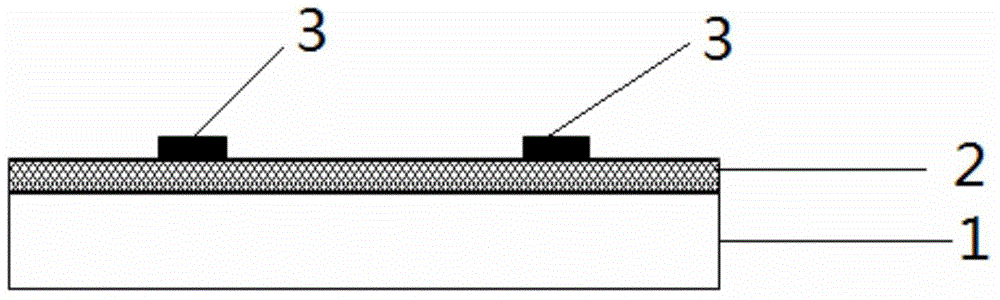

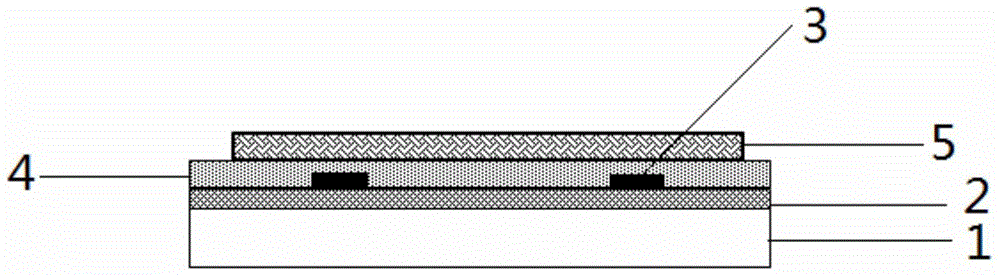

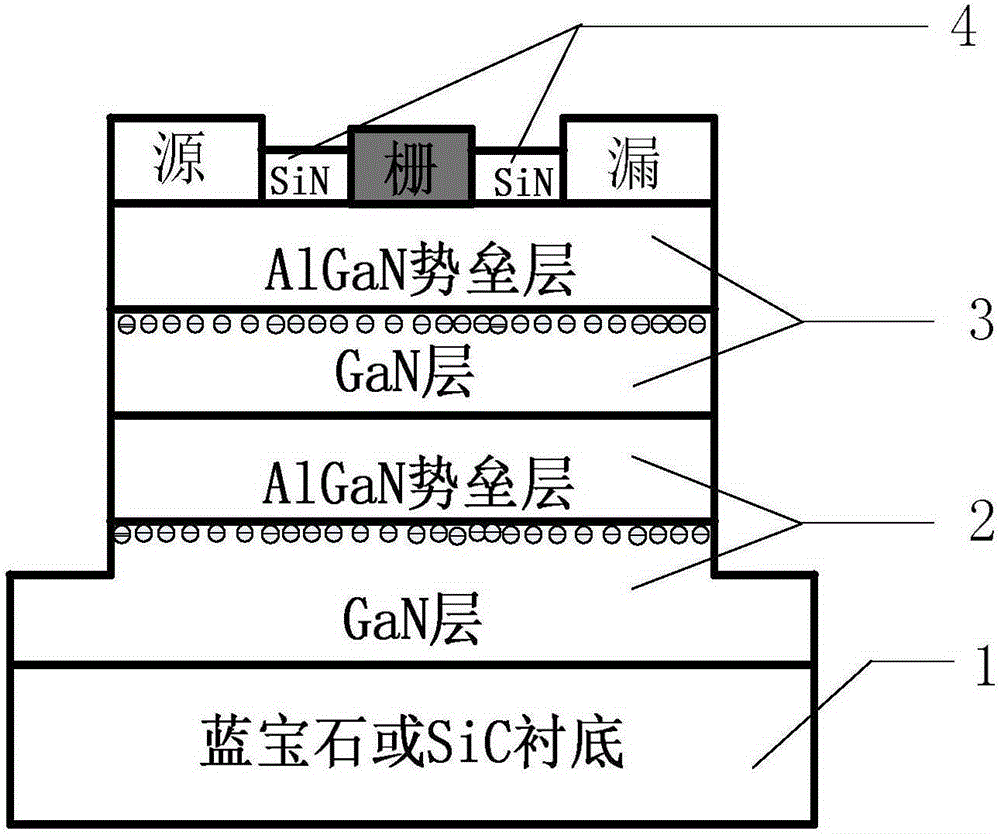

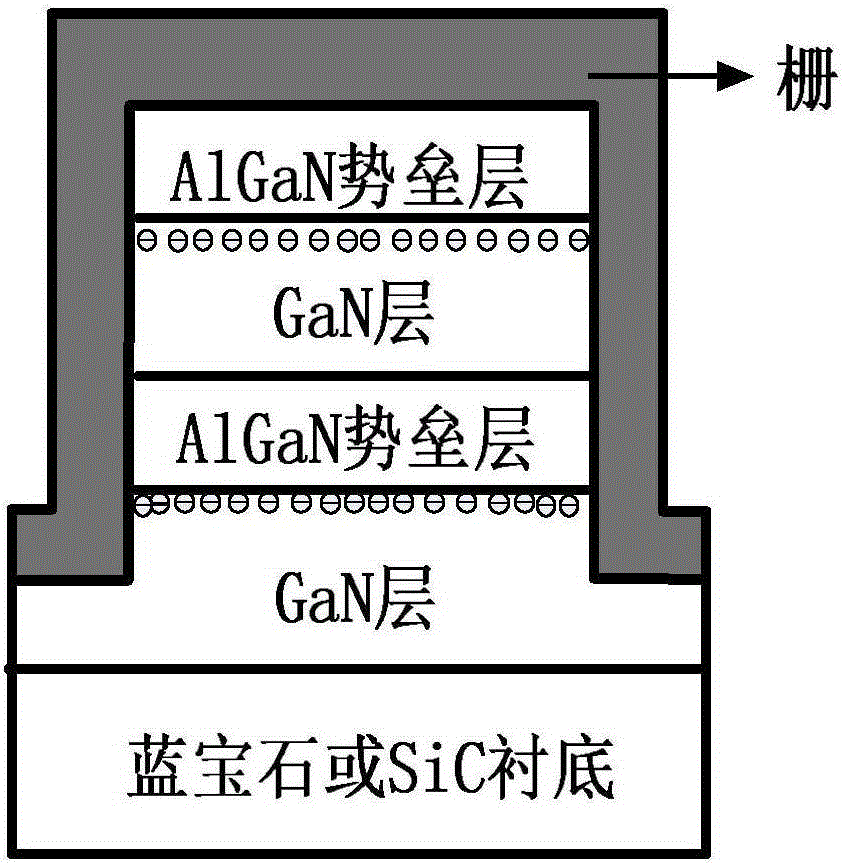

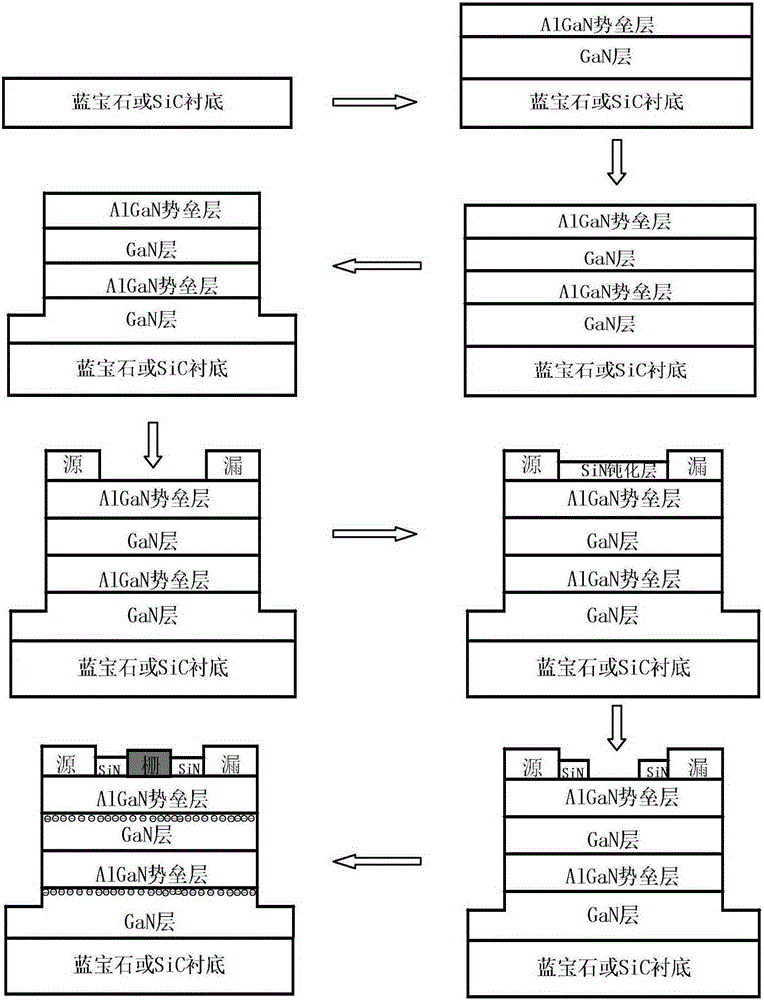

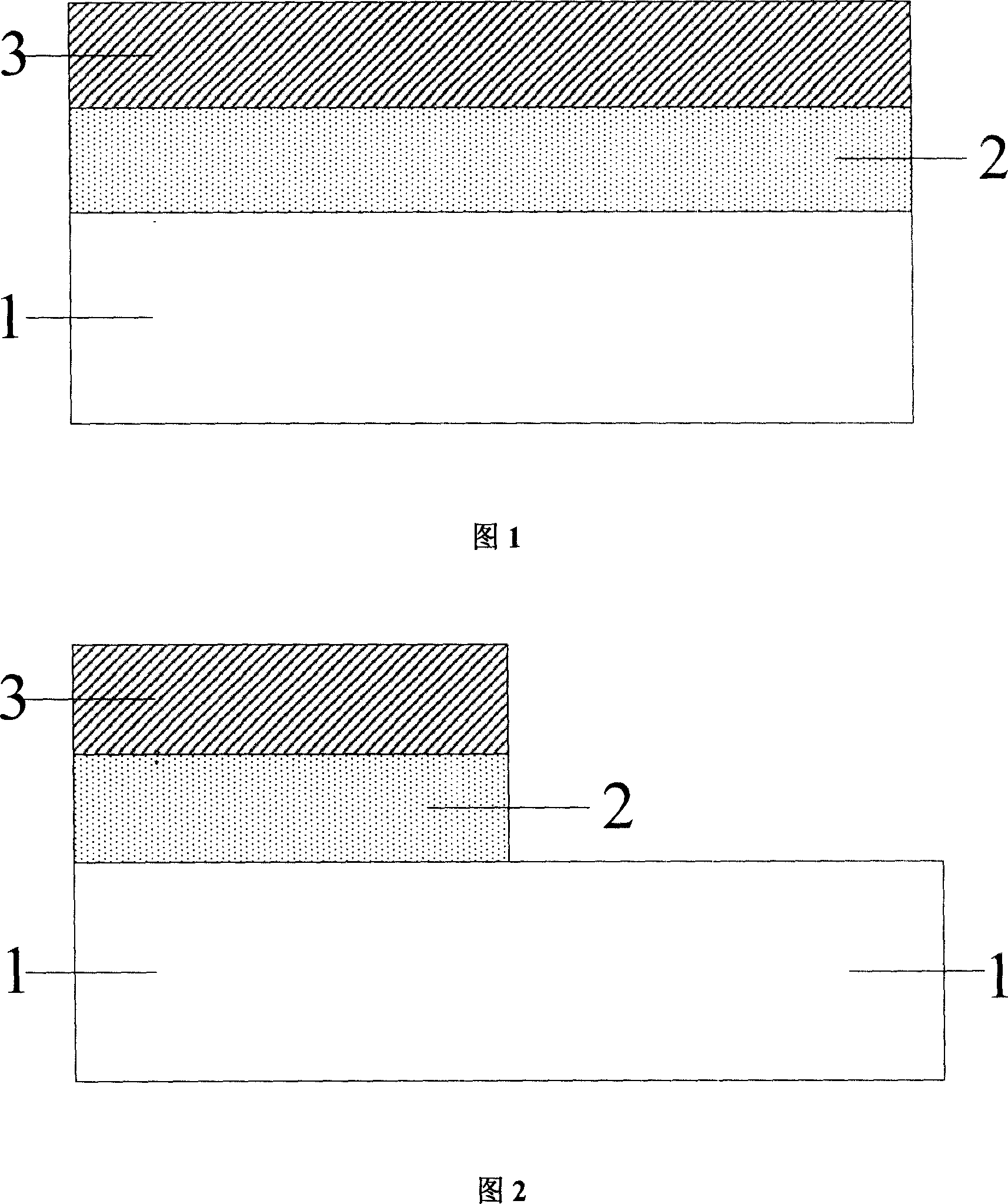

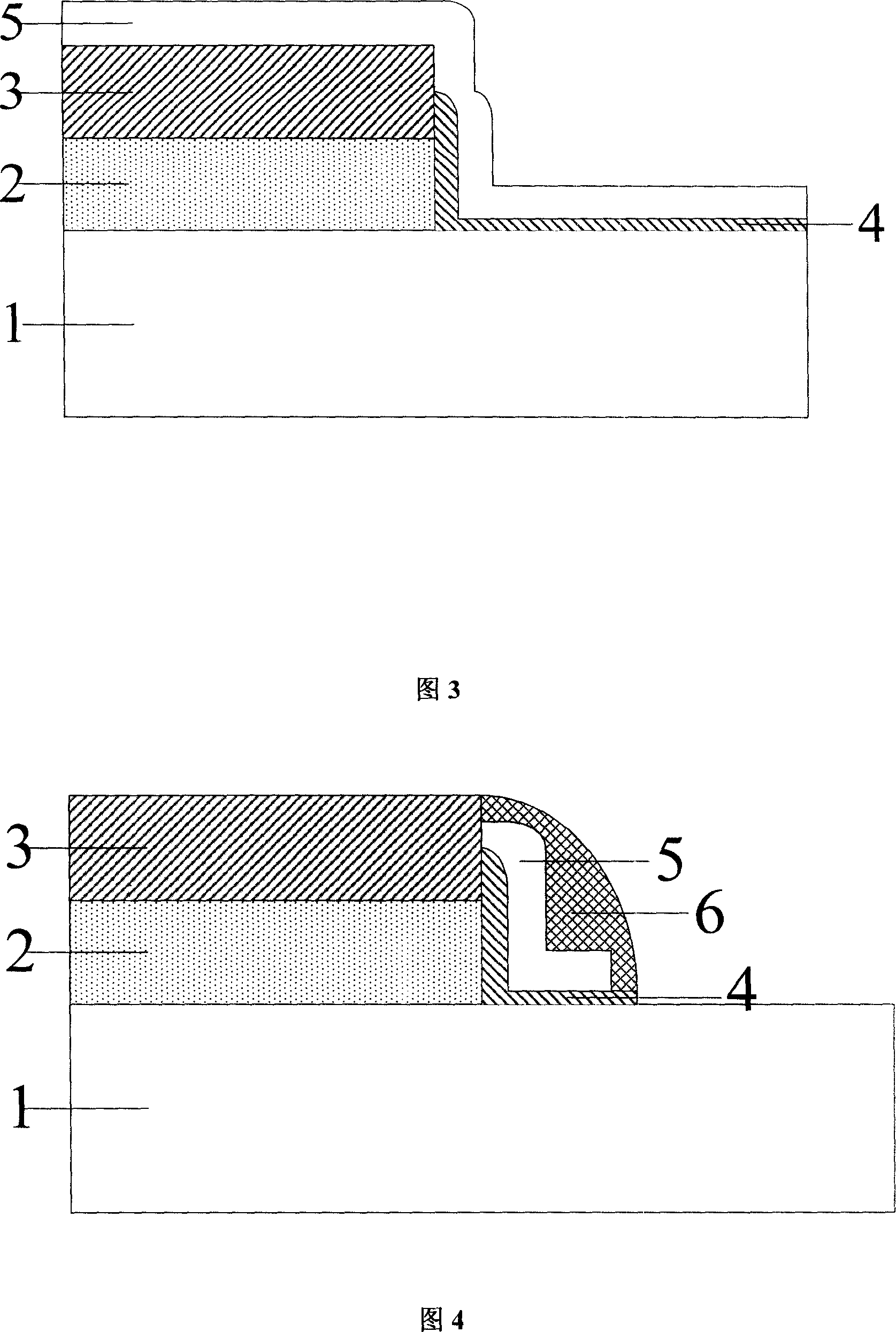

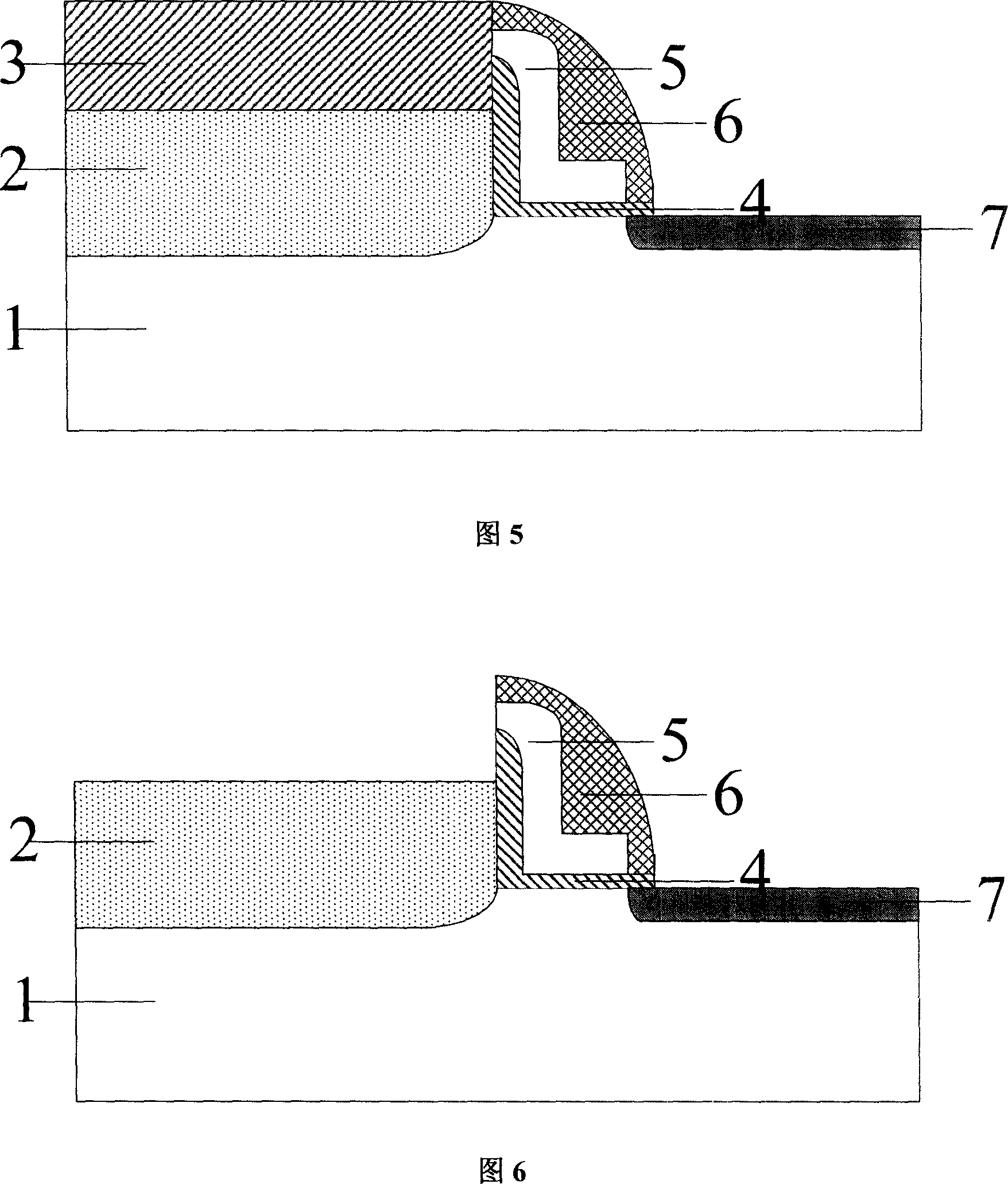

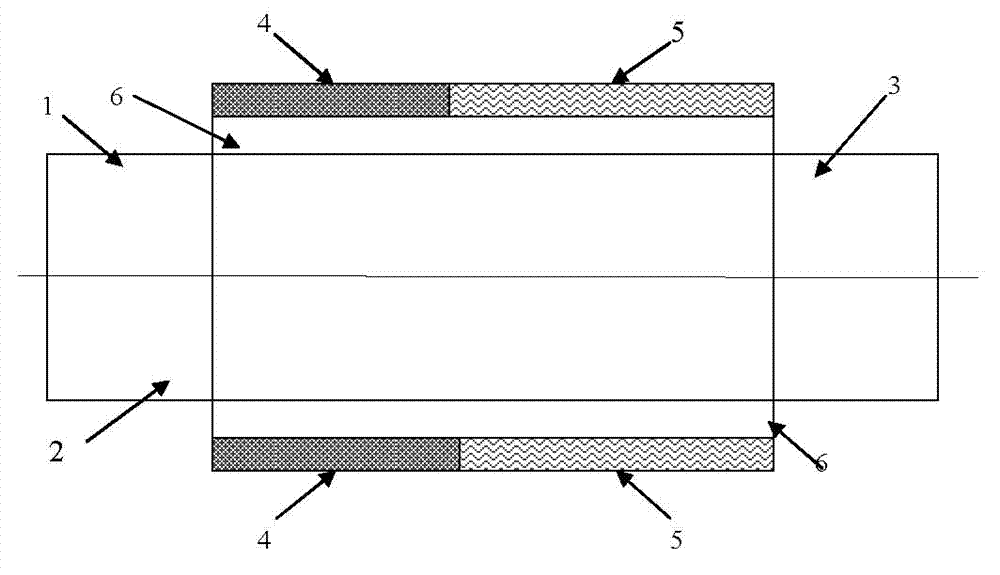

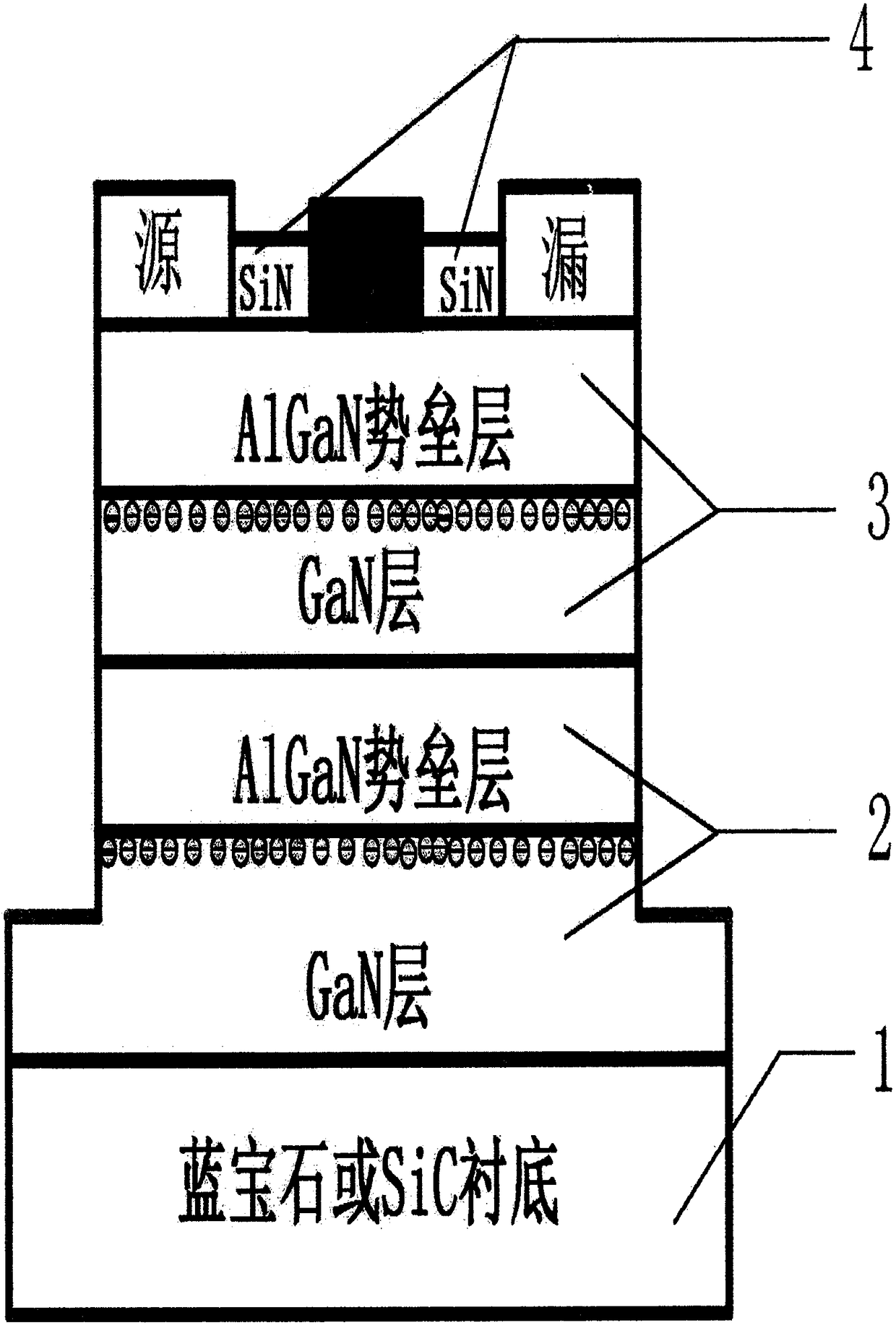

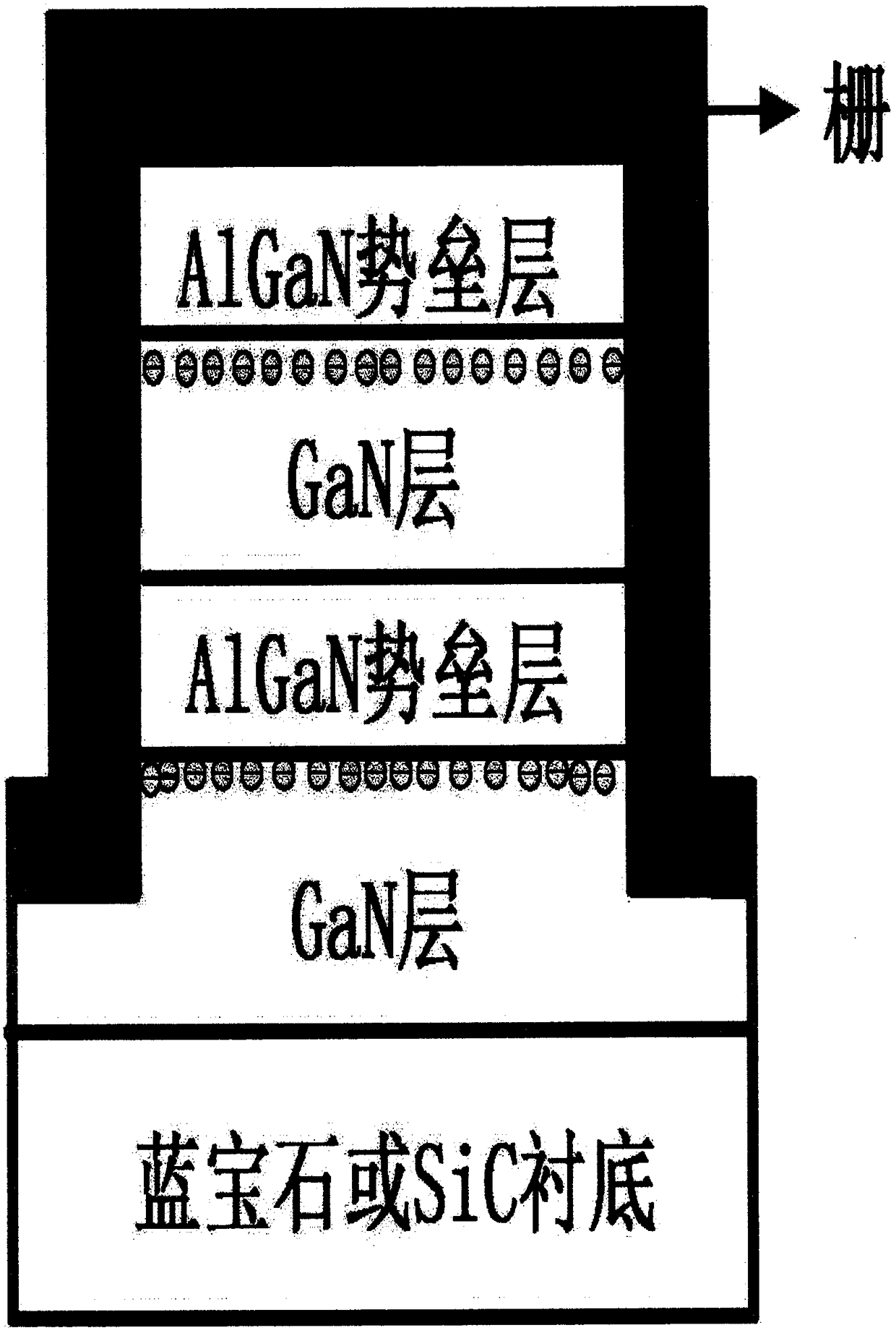

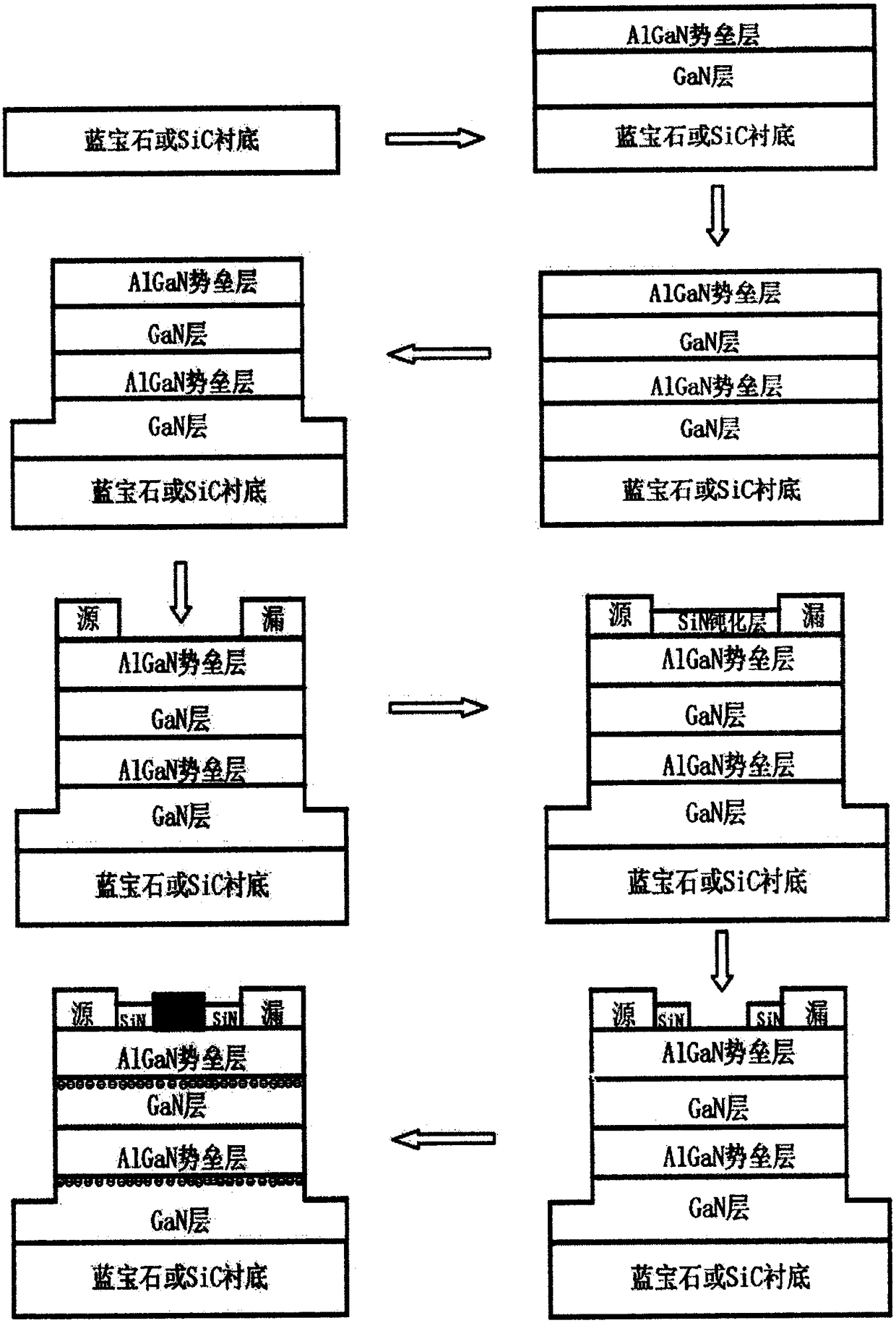

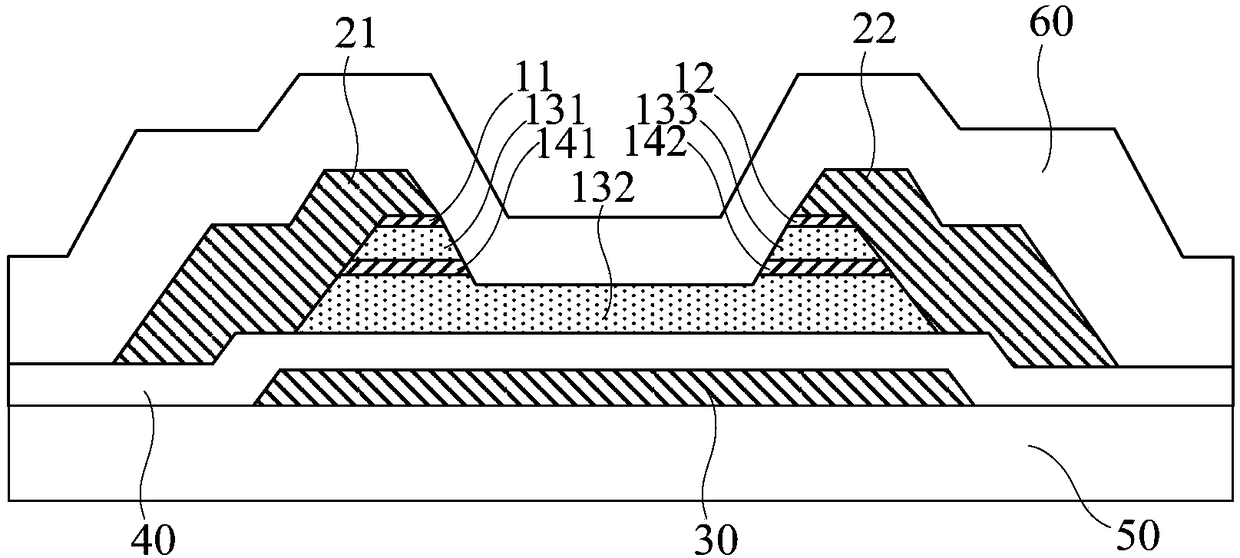

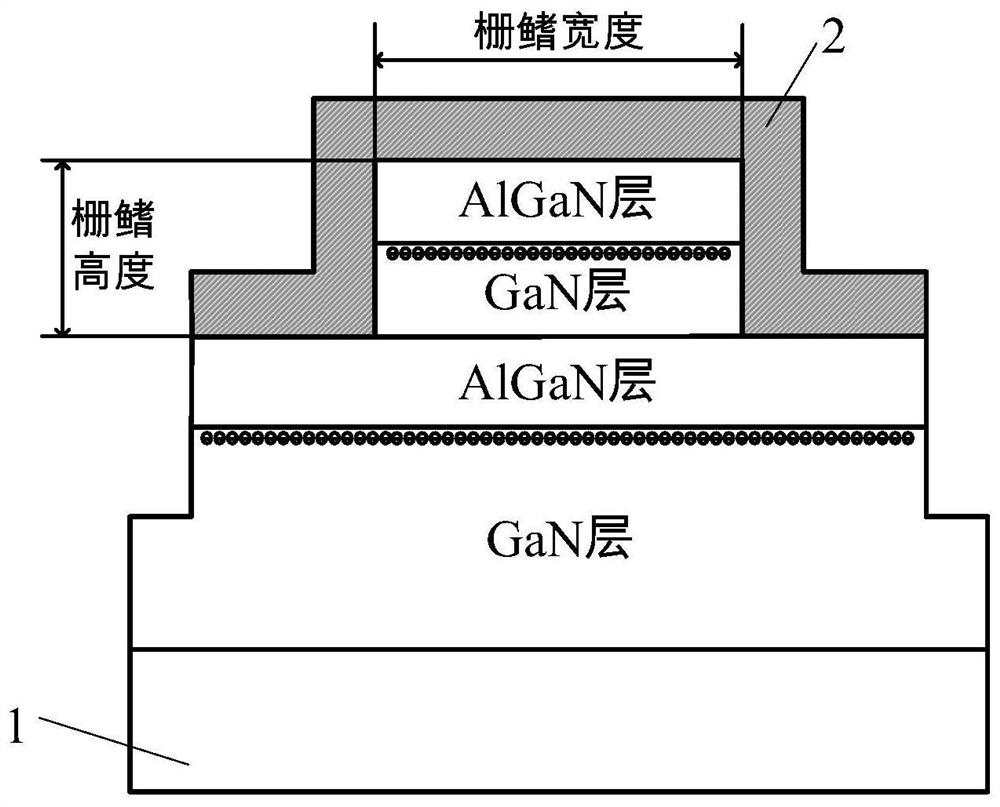

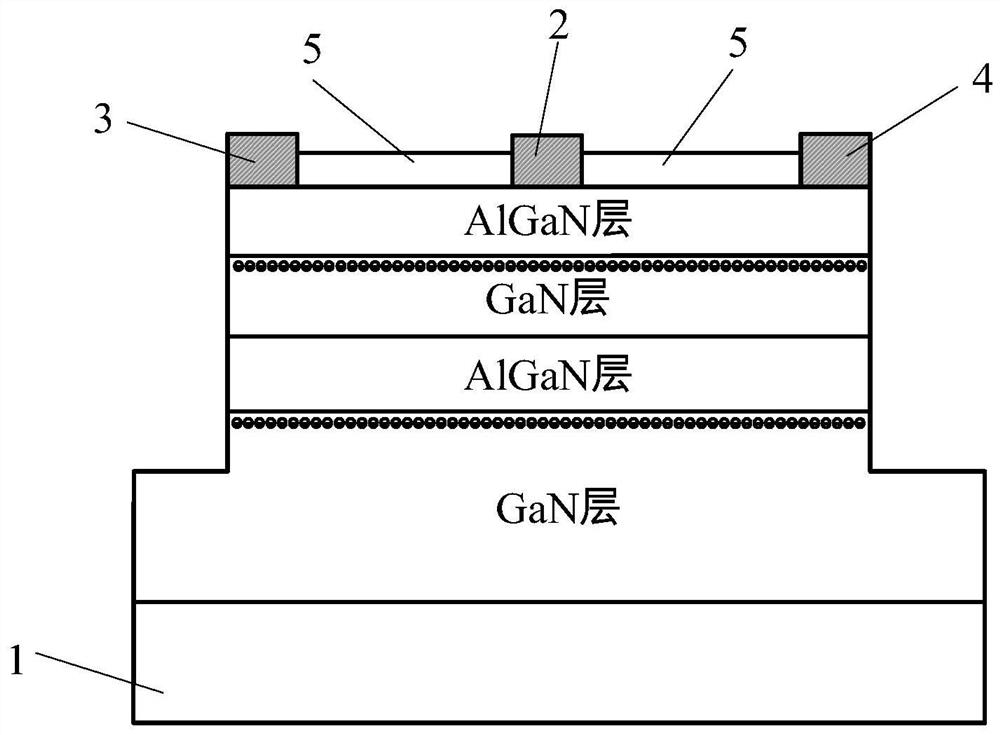

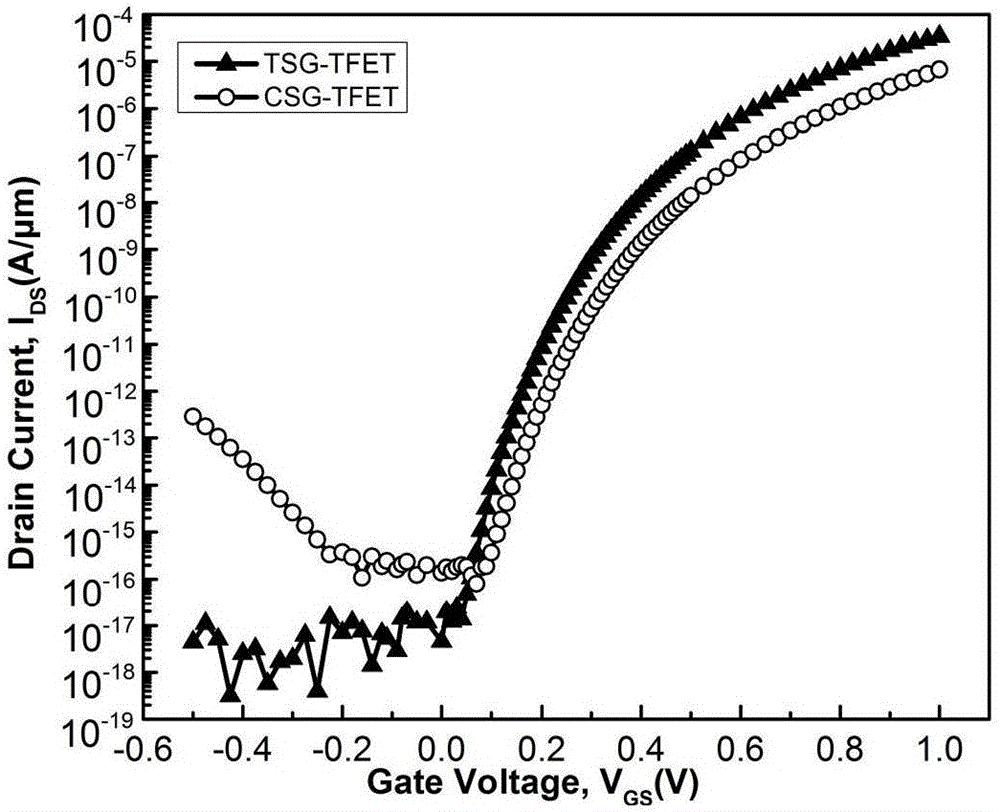

AlGaN/GaN high electron mobility transistor with multi-channel fin-type structure

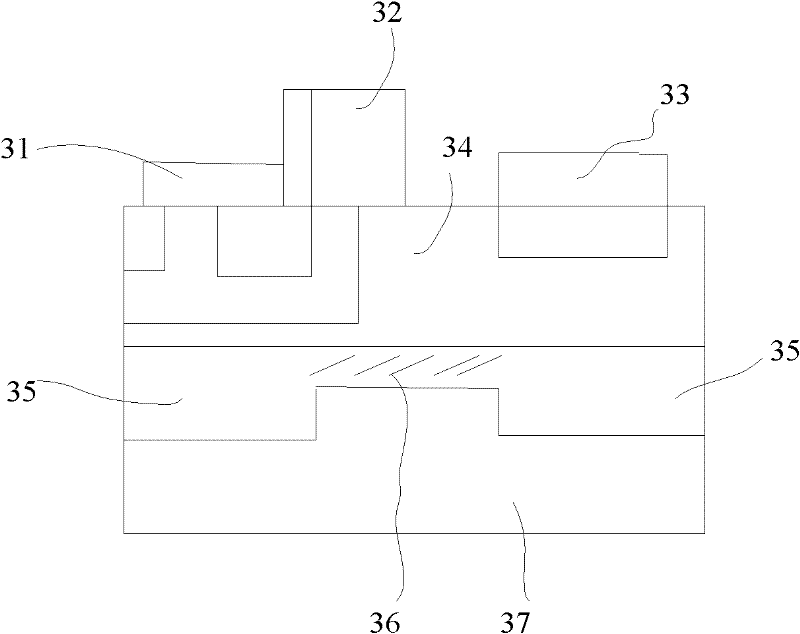

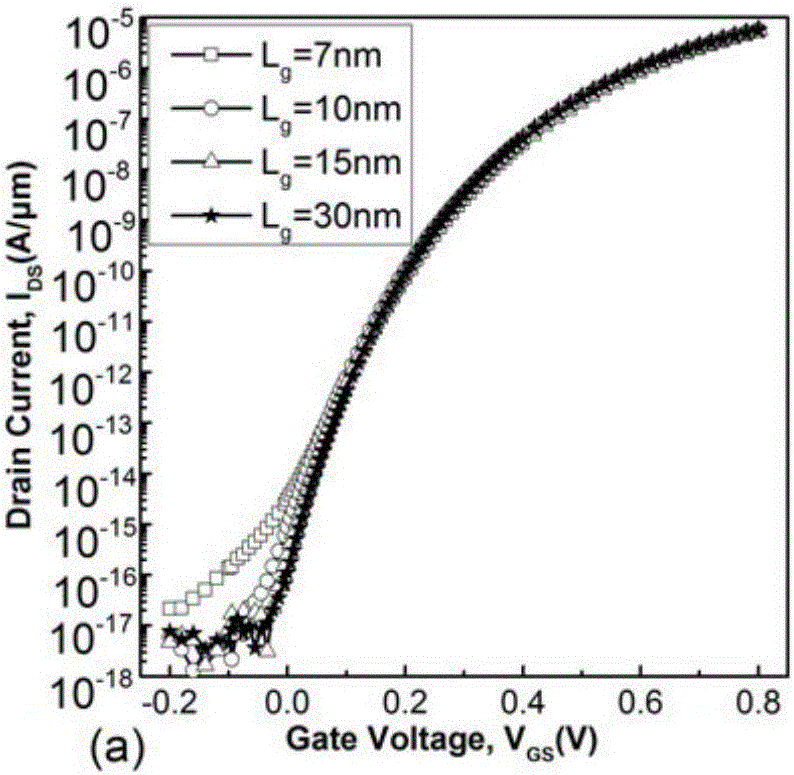

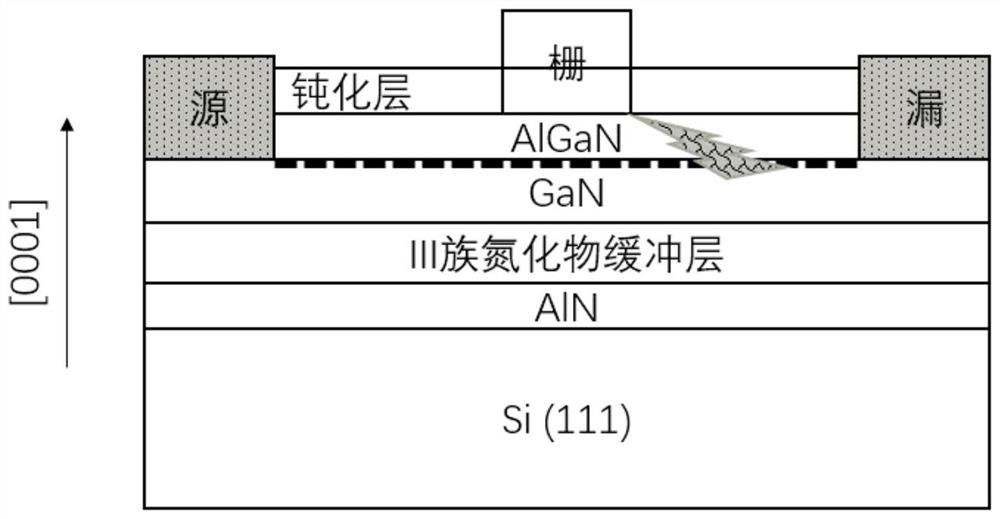

InactiveCN105280696AReduce widthLower resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionLow noise

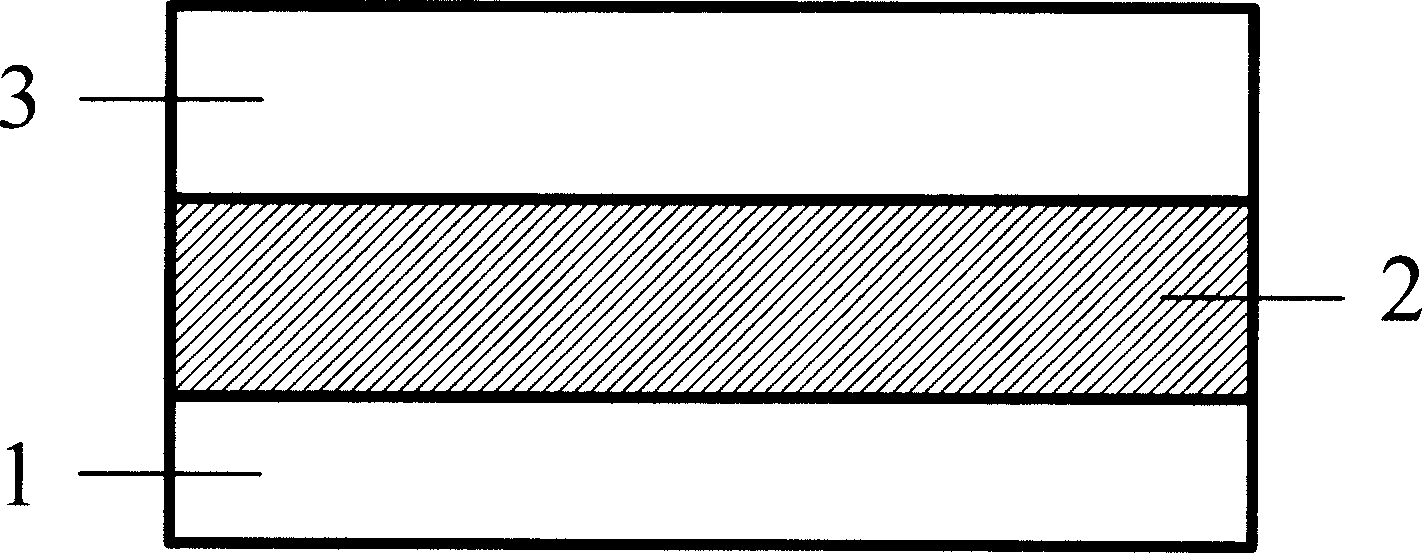

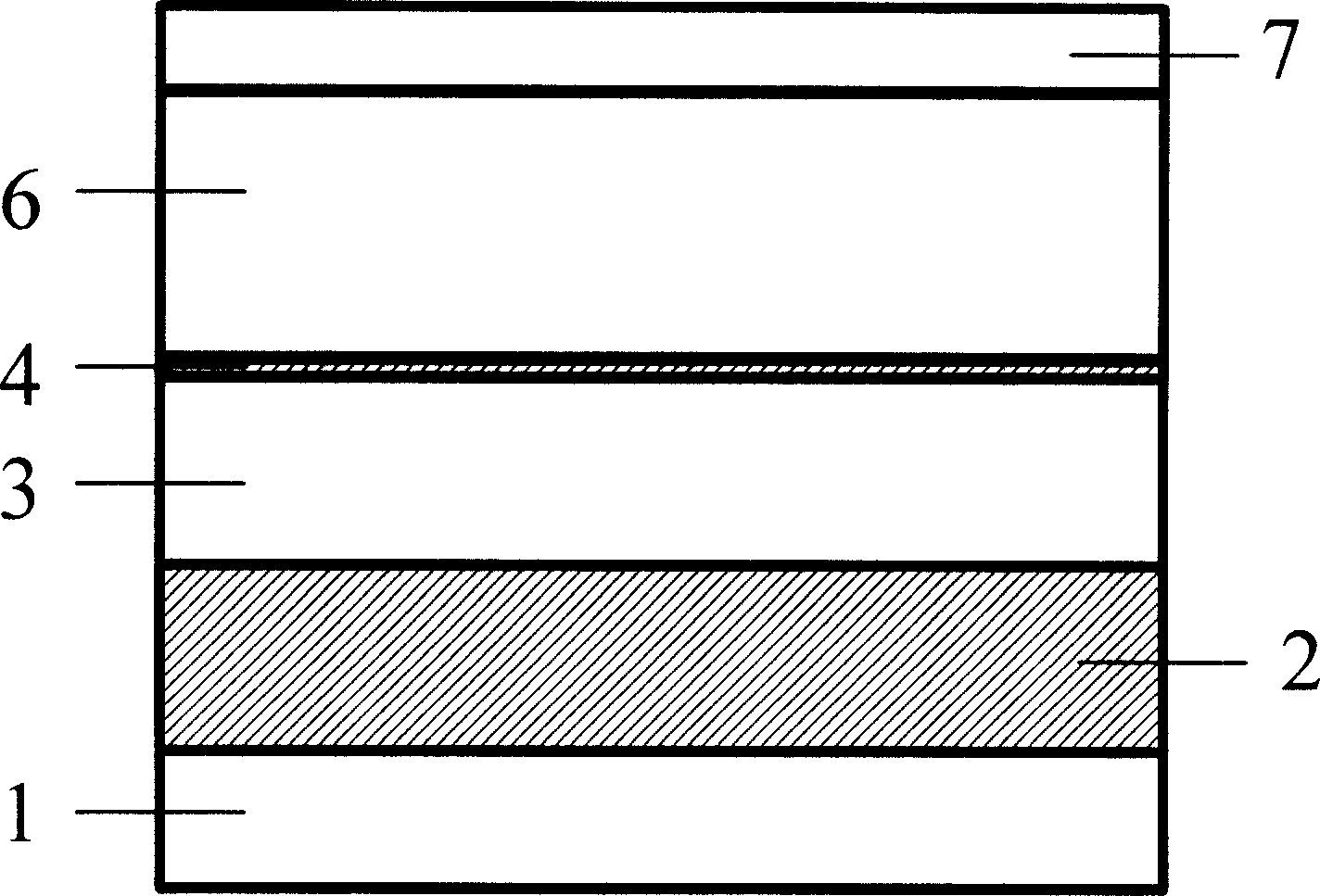

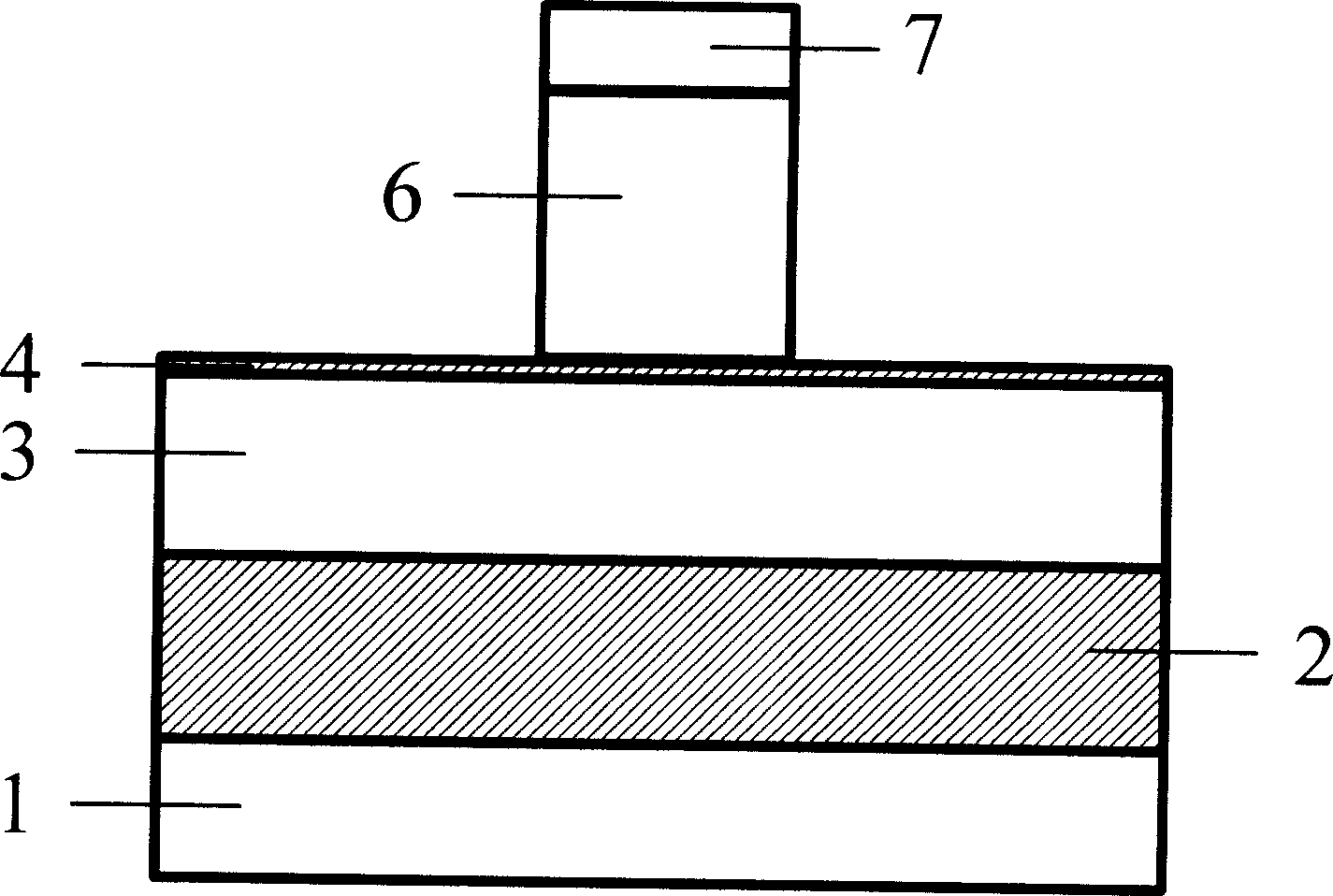

The invention discloses a AlGaN / GaN high electron mobility transistor structure with a multi-channel fin-type structure and a manufacturing method, wherein the AlGaN / GaN high electron mobility transistor is designed mainly to solve the problems of the poor gate control ability of a multi-channel apparatus and low electric current of a FinFET apparatus; the AlGaN / GaN high electron mobility transistor comprises a substrate (1), a first layer AlGaN / GaN heterojunction (2), a SiN passivation layer (4) and a source electrode, a drain electroce, and a gate electrode successively from bottom to top; the source electrode and the drain electrode are located on AlGaN potential barrier layers on top layers at two sides of the SiN passivation layer respectively; the AlGaN / GaN high electron mobility transistor is characterized in that a GaN layer and the AlGaN potential barrier layer are set between the first layer AlGaN / GaN heterojunction and the SiN passivation layer so as to form a second layer AlGaN / GaN heterojuntion (3); and the gate electrode covers the top portion of a second layer heterojuntion and the two side walls of the first and the second heterojunctions. According to the invention, the gate control ability is strong; the saturation current is large; the subthreshold property is good; and the AlGaN / GaN high electron mobility transistor can be used for microwave power apparatus with a shrot gate length, low power consumption and low noise.

Owner:XIDIAN UNIV

Field effect transistor adapted for extra-dup submicrometer field and preparation process thereof

InactiveCN1450653ASuppresses band-to-band tunneling currentReduce source-drain parasitic capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesShort-channel effectEngineering

A fieldistor includes a source-drain, grating medium, grating electrode, channel and a substrate in which, a first medium isolation layer is vortical to the channel direction between the source-drainand the substrate, a connection part of the source-drain and the channel is between top of the first medium isolation layer and the channel surface, a second medium isolation layer parallel to the channel and between the source-drain bottom and substrate is formed to a L shape with the first. Optional extending technology is applied to prepare the first medium layer then to inject combined HHe toprepare the second medium isolation layer, controlling short channel effect.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Array substrate and preparation method and display panel

InactiveCN103811503AIncrease the off-state resistanceReduces off-state leakage currentTransistorSolid-state devicesOxideEngineering

The invention discloses an array substrate and a preparation method thereof and a display panel. The array substrate can reduce the leakage current of a thin film transistor and is used for improving the phenomena of flicker, crosstalk, residual images and the like of the display panel and improving display performance. The array substrate comprises a substratum substrate and grid lines, data lines and a plurality of pixel units which are arranged on the substratum substrate, wherein each pixel unit comprises a first oxide thin film transistor and pixel electrodes. The array substrate is characterized in that each pixel unit also comprises at least one second oxide thin film transistor which is connected in series with the first oxide thin film transistor; the pixel electrodes are connected with a drain electrode of the second oxide thin film transistor; a source electrode of the second oxide thin film transistor is connected with a drain electrode of the first oxide thin film transistor; a source electrode of the first oxide thin film transistor is connected with the data lines; and the second oxide thin film transistor is connected in series with the first oxide thin film transistor to increase off resistance between the pixel electrodes and the data lines. The embodiment of the invention is applied to the technical field of display.

Owner:HEFEI XINSHENG OPTOELECTRONICS TECH CO LTD +1

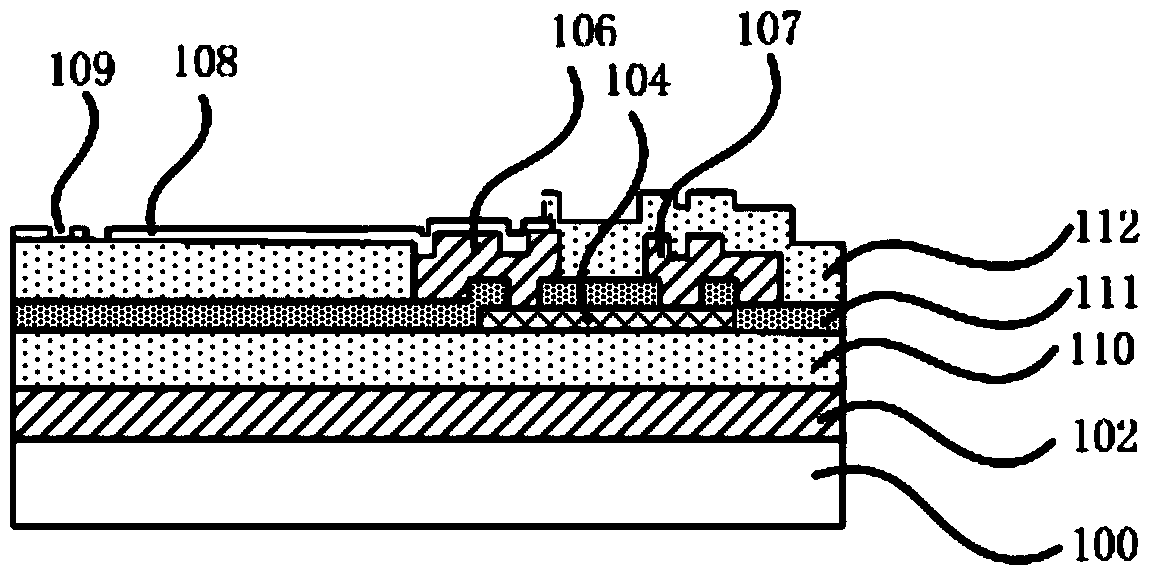

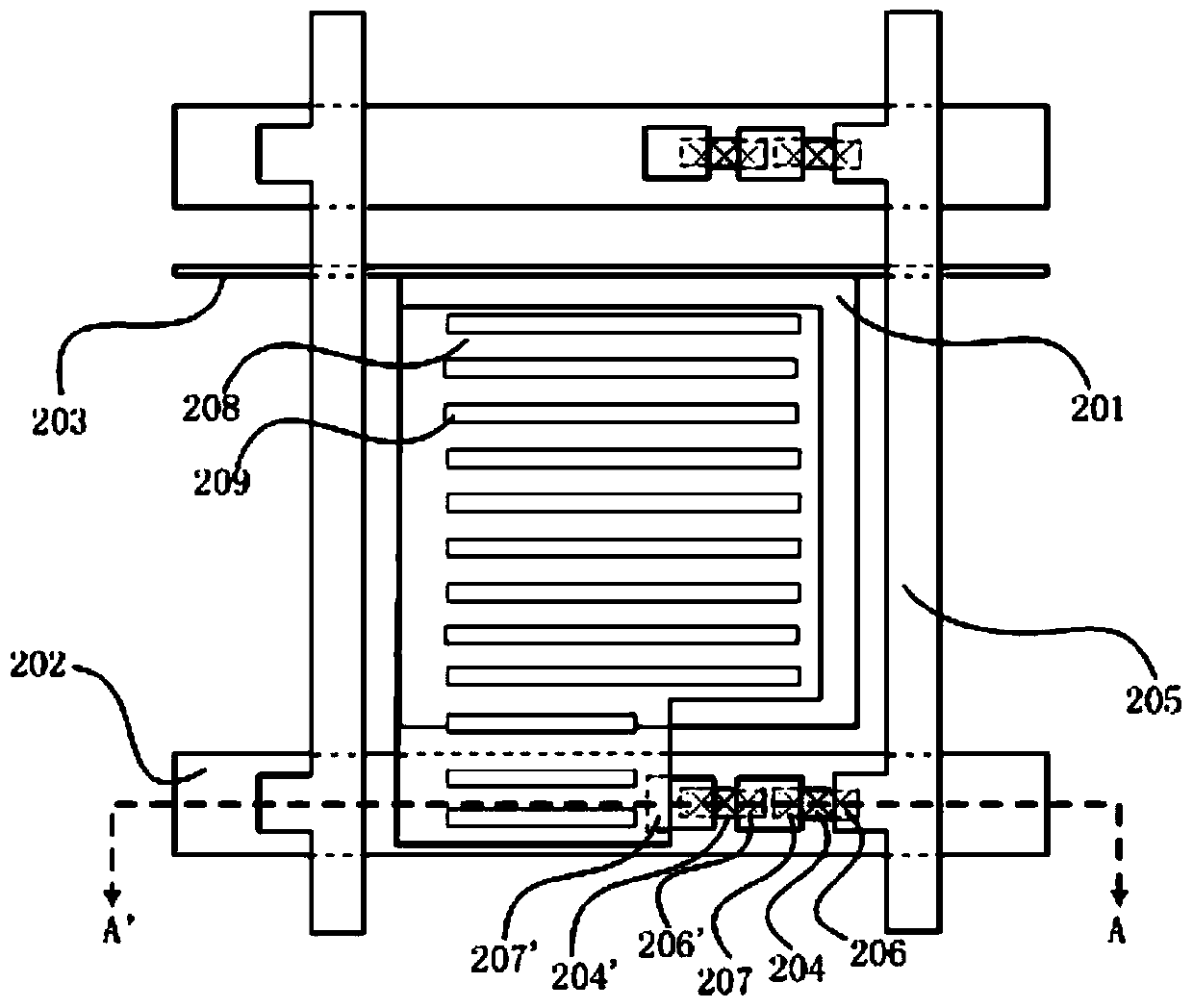

Array substrate, manufacturing method of array substrate and display device

ActiveCN104319279AReduces off-state leakage currentIncrease the on-state currentSolid-state devicesSemiconductor/solid-state device manufacturingLine resistanceDisplay device

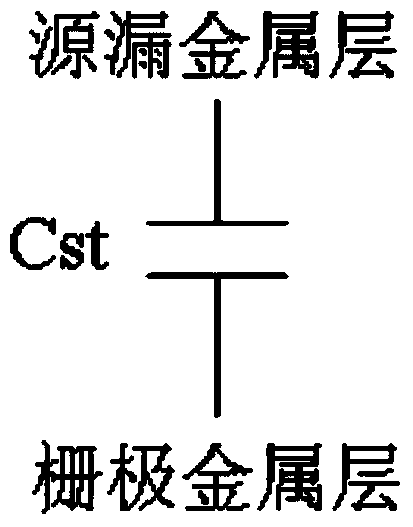

The invention relates to the technical field of display, in particular to an array substrate, a manufacturing method of the array substrate and a display device. The array substrate comprises a first gate metal layer, a first gate insulating layer on the first gate metal layer, an active layer which is arranged on the first gate insulating layer and corresponds to the first gate metal layer, an etching barrier layer on the active layer, a source and drain metal layer comprising a source and a drain, a second gate insulating layer on the source and drain metal layer and a second gate metal layer on the second gate insulating layer, wherein the source and the drain are in contact with the two sides of the active layer respectively and are separated on the etching barrier layer. By means of the array substrate, the manufacturing method of the array substrate and the display device, the TFT characteristic can be optimized, the gate line resistance can be reduced, light irradiating the active layer can be shielded, IR Drop and TFT threshold voltage excursion and generation of the light leakage current of the active layer can be easily restrained, and the performance of the display device can be promoted.

Owner:BOE TECH GRP CO LTD

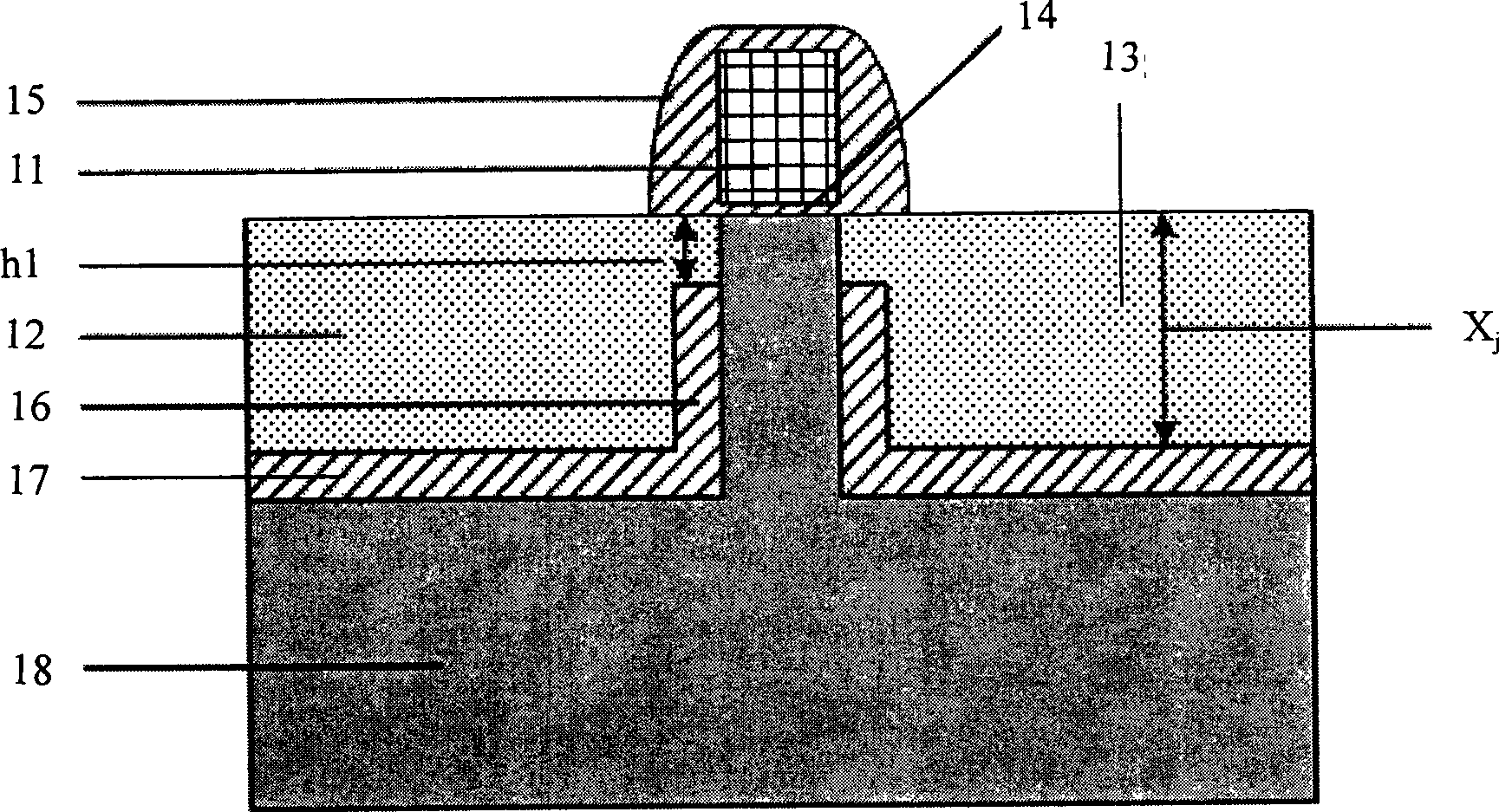

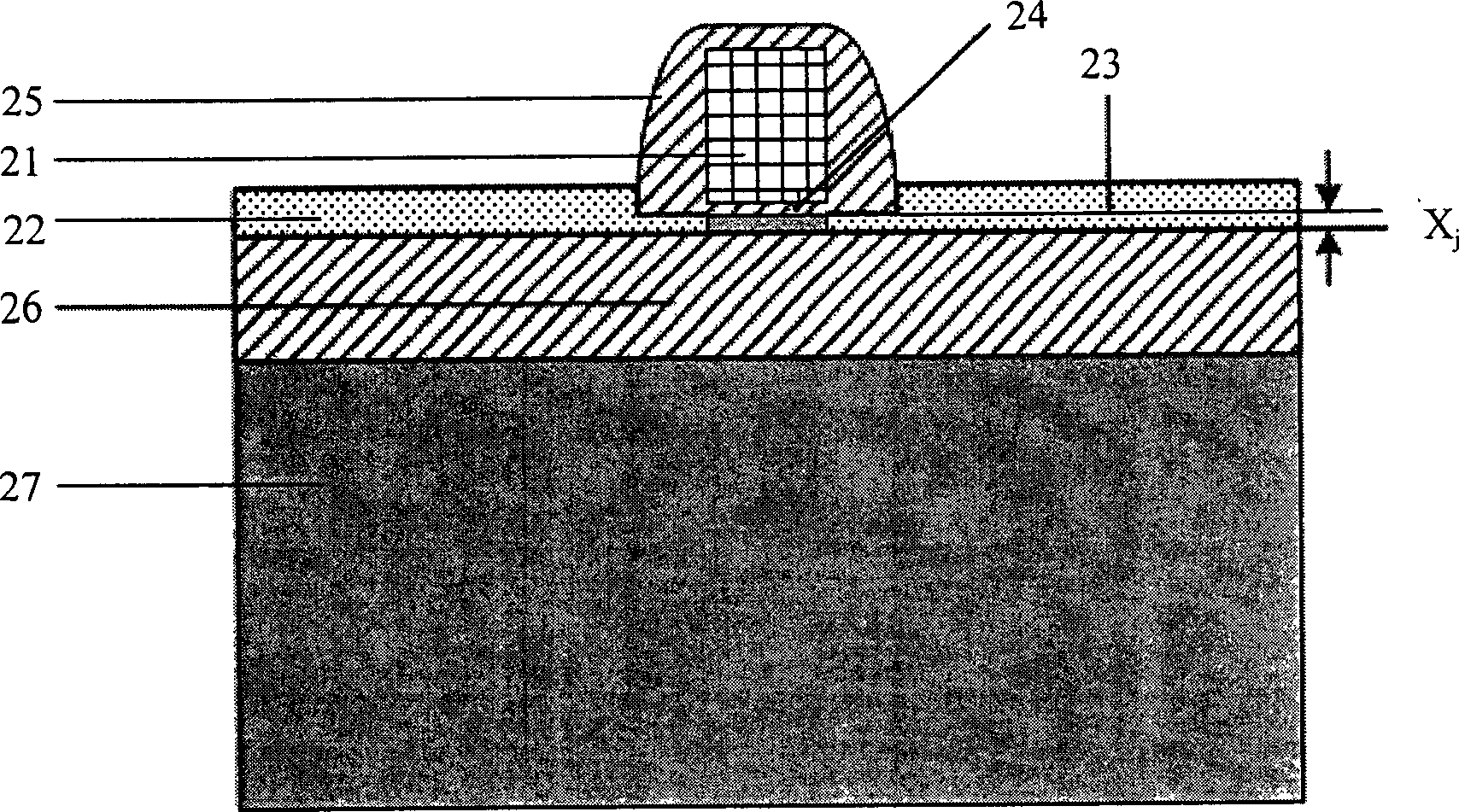

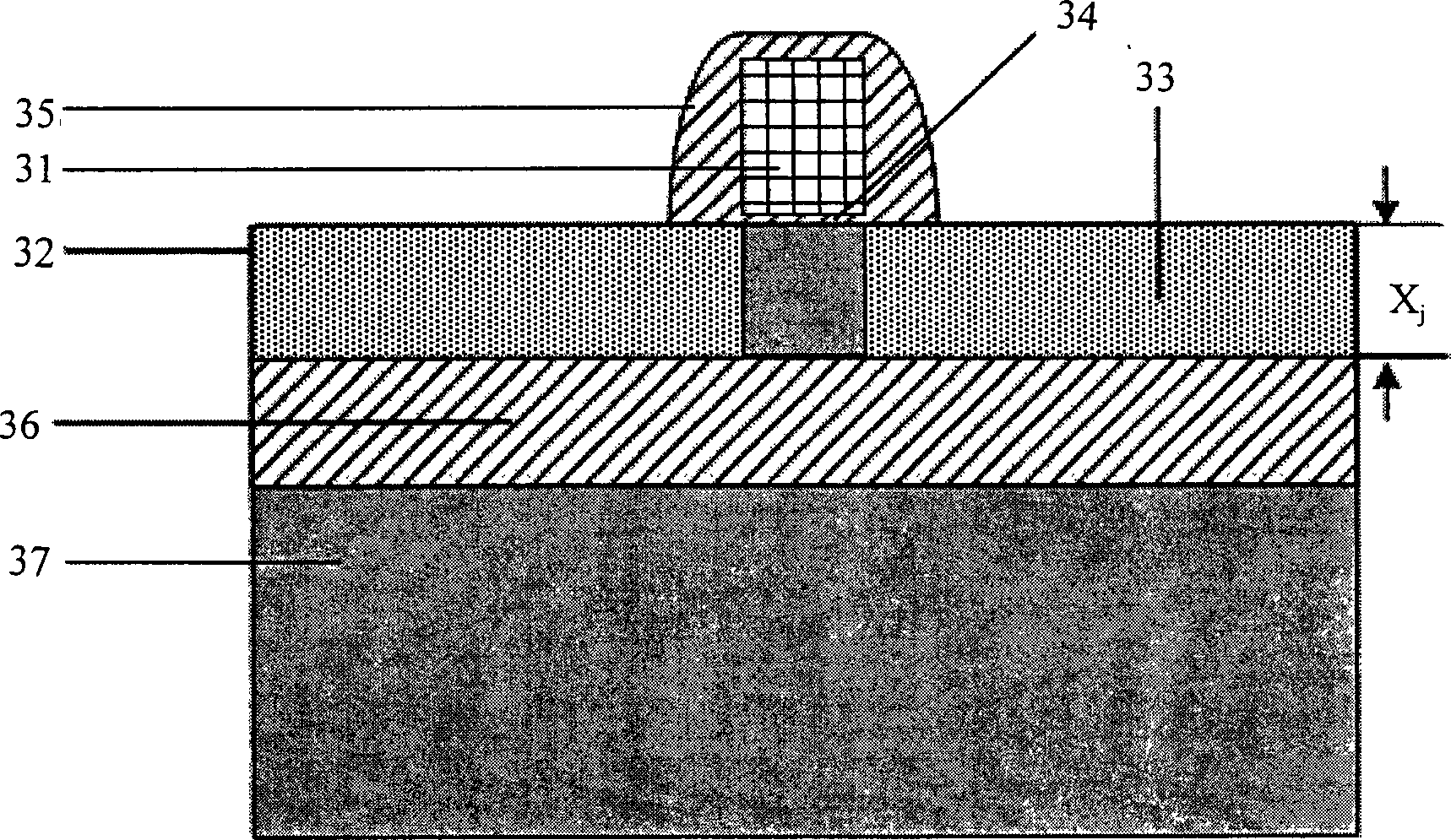

MOS transistor with partial depletion SOI structure and producing method thereof

InactiveCN1889273AEliminate channelEliminate harsh requirementsSemiconductor/solid-state device manufacturingSemiconductor devicesIntegrated circuit manufacturingEngineering

The present invention provides part depletion SOI constructional MOS transistor used in nano integrated circuit manufacturing technology and making method. The upper part of said transistor source drain expansion zone is thin semiconductor layer, the lower part being cavity unit, said structure having advantages of ultrathin unit all depletion SOI MOS transistor and partial depleted SOI MOS transistor and overcoming their shortage. Said invented preparation method is compatible with traditional MOS transistor making technology, with simple technological process and use value.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL +1

A MOS resistor and its manufacture method

InactiveCN1964073ALow resistivityReduce source-drain parasitic resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETElectrical resistance and conductance

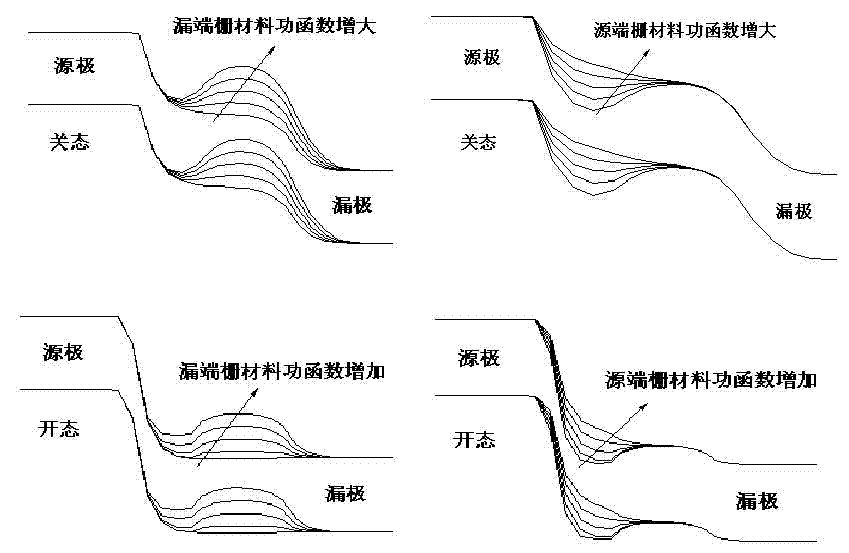

The provided MOS transistor comprises asymmetric source and drain structures. Wherein, the source uses metal or metal-semiconductor compound and channel to form Schottky barrier contact, while the drain is boost high doped. Compared with traditional MOSFET device, this invention increases on-off current rate greatly, compatible to traditional manufacture technology, and has much room for high-K grid medium and metal grid material since low thermal budget.

Owner:PEKING UNIV

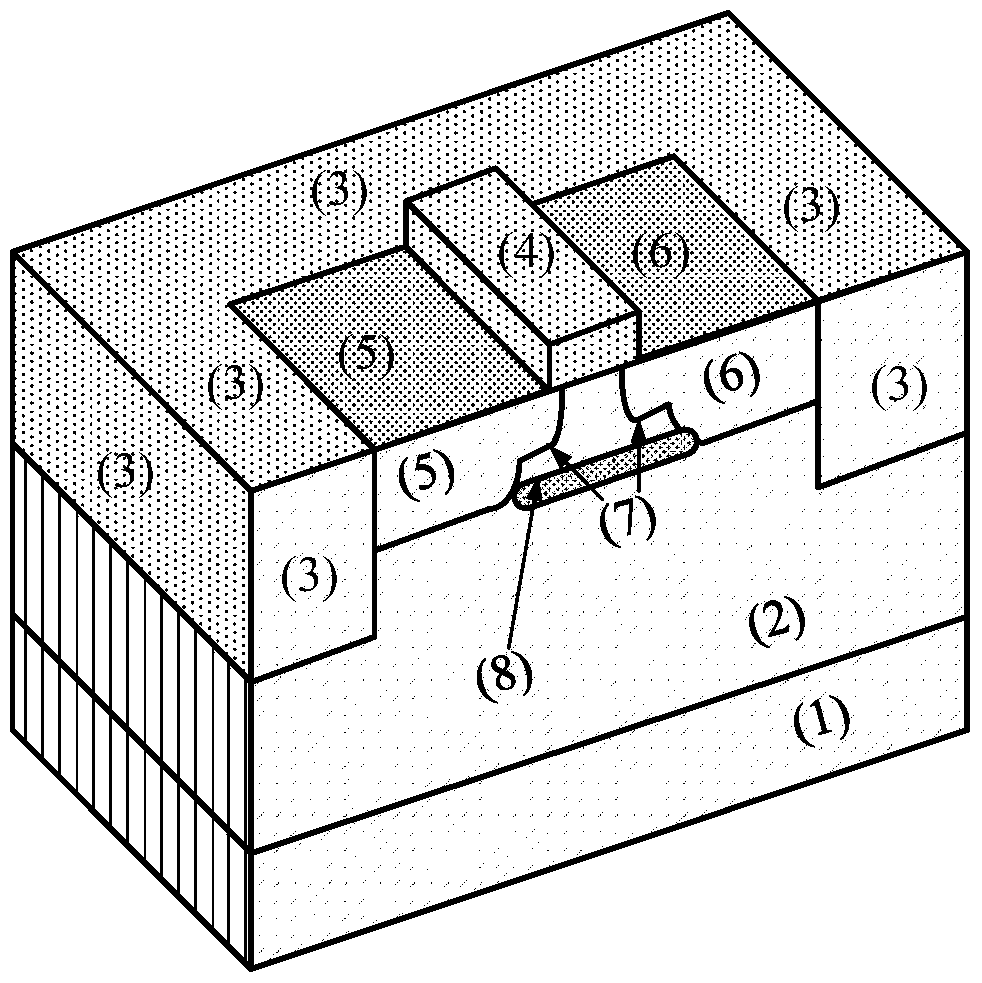

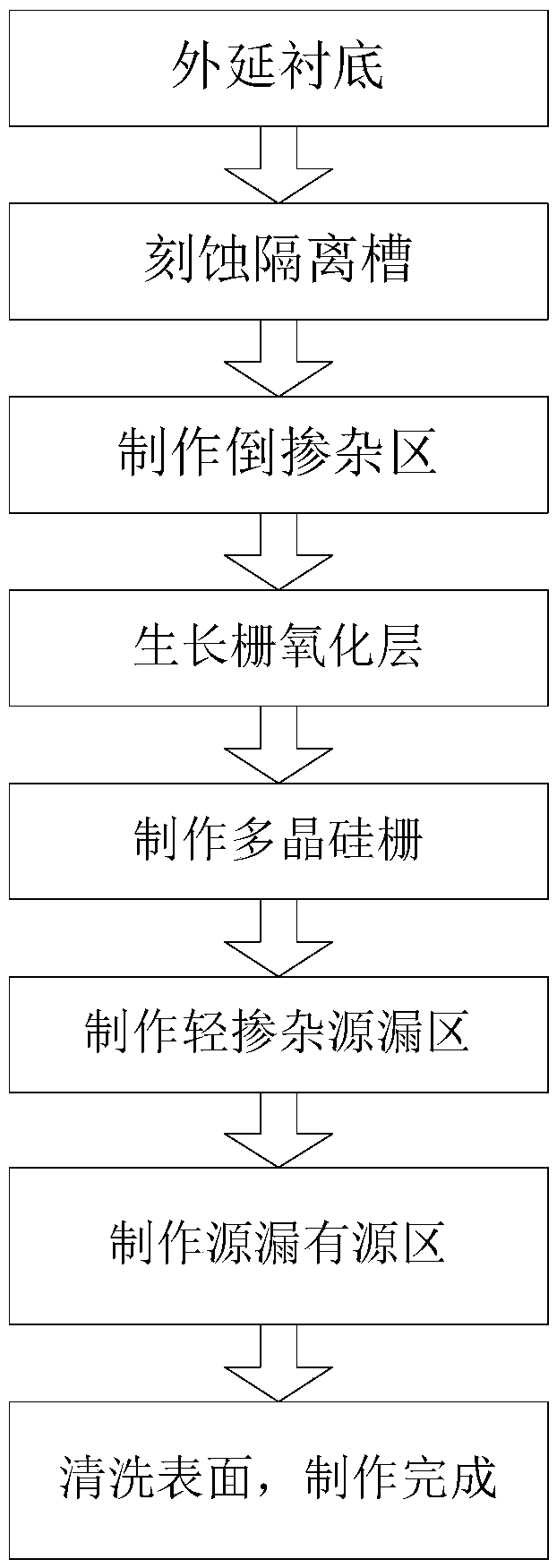

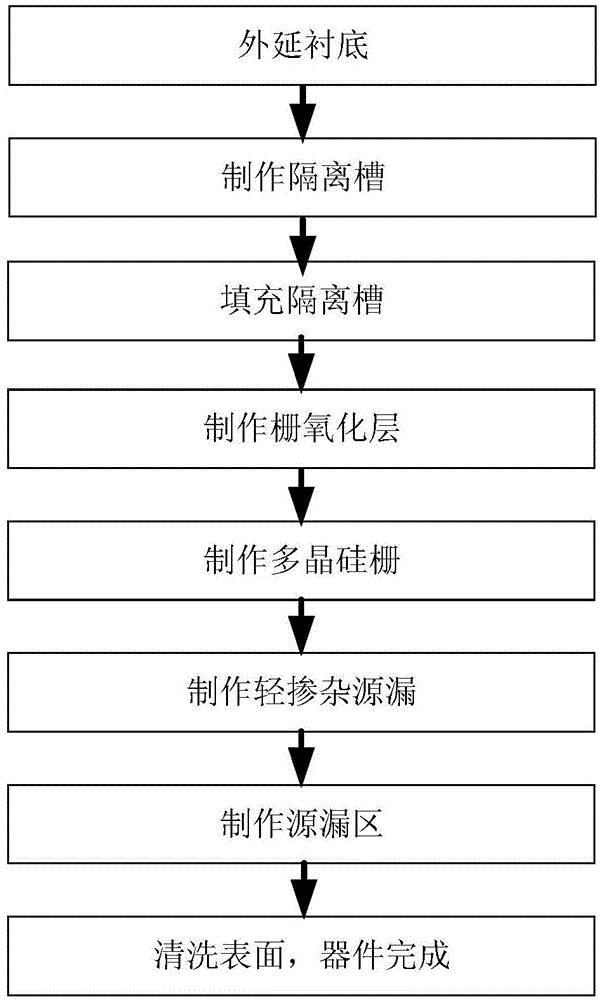

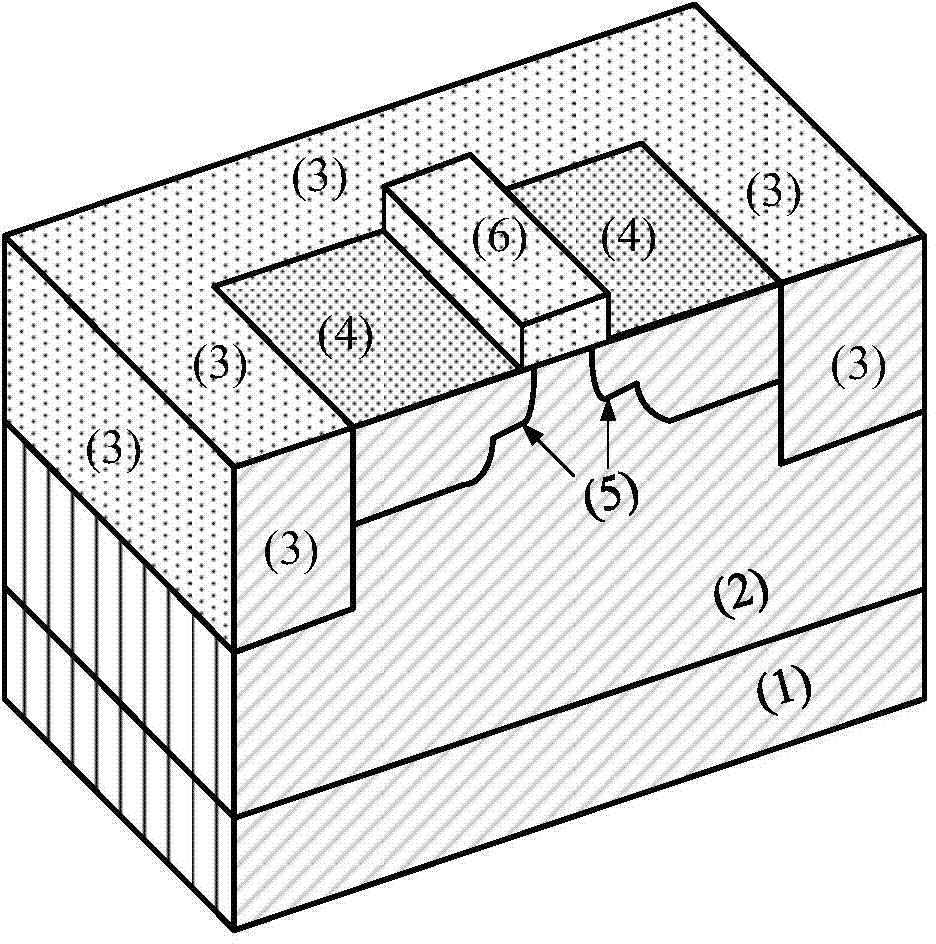

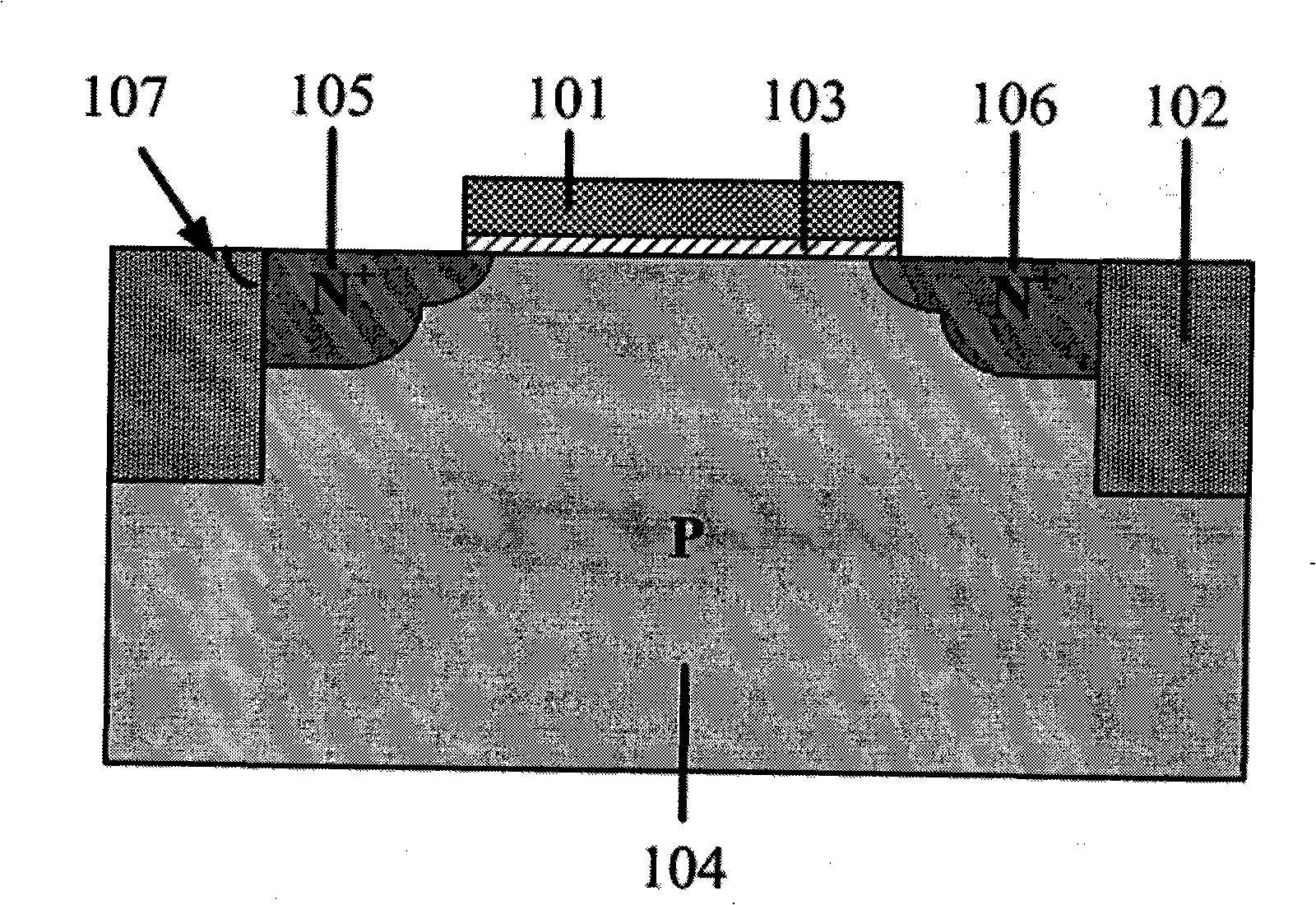

65nm technology-based super-steep reverse-doping radiation-proof MOS field-effect tube

ActiveCN105514169AImprove radiation resistanceDoes not affect integrationSemiconductor/solid-state device detailsSolid-state devicesSubthreshold oscillationsThreshold voltage

The invention discloses a 65nm technology-based super-steep reverse-doping radiation-proof MOS field-effect tube, mainly solving the problems of increased OFF leakage current, threshold voltage drift and subthreshold oscillation amplitude degradation of a conventional 65nm MOS field-effect tube under a total dose radiation environment. The MOS field-effect tube comprises a P-type substrate (1) and an epitaxial layer (2) located on the substrate, wherein an isolation groove (3) is formed around a place above the epitaxial layer, a grid electrode (4) is arranged at the middle above the epitaxial layer, a source region (5) and a drain region (6) are arranged in the epitaxial layer between two side boundaries of the grid electrode and the inner boundary of the isolation groove, light-doping source-drain regions (7) are arranged in the epitaxial layer below the two side boundaries of the grid electrode, a channel is formed in an area between the two light-doping source-drain regions and right below the grid electrode, and a heavy-doping super-steep reverse-doping region (8) is arranged below the channel between the two light-doping source-drain regions. The 65nm technology-based super-steep reverse-doping radiation-proof MOS field-effect tube improves the total dose irradiation resistance of a device, and can be used for the preparation of large scale integrated circuits.

Owner:XIDIAN UNIV

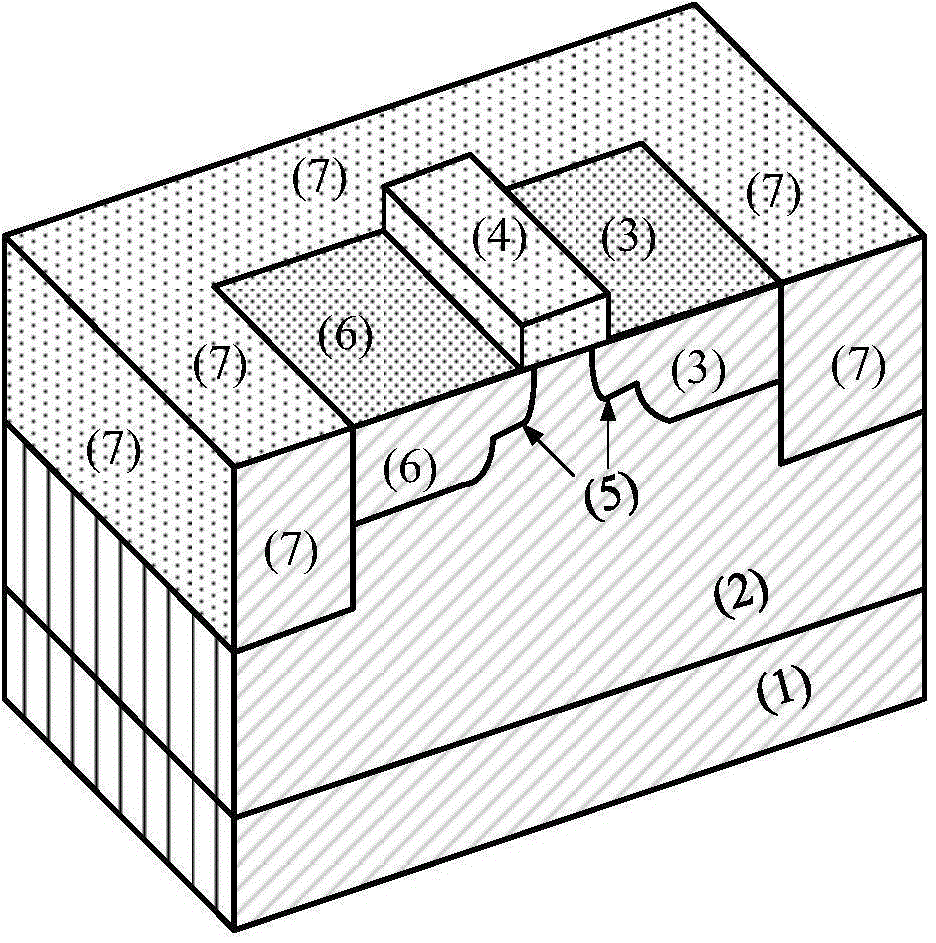

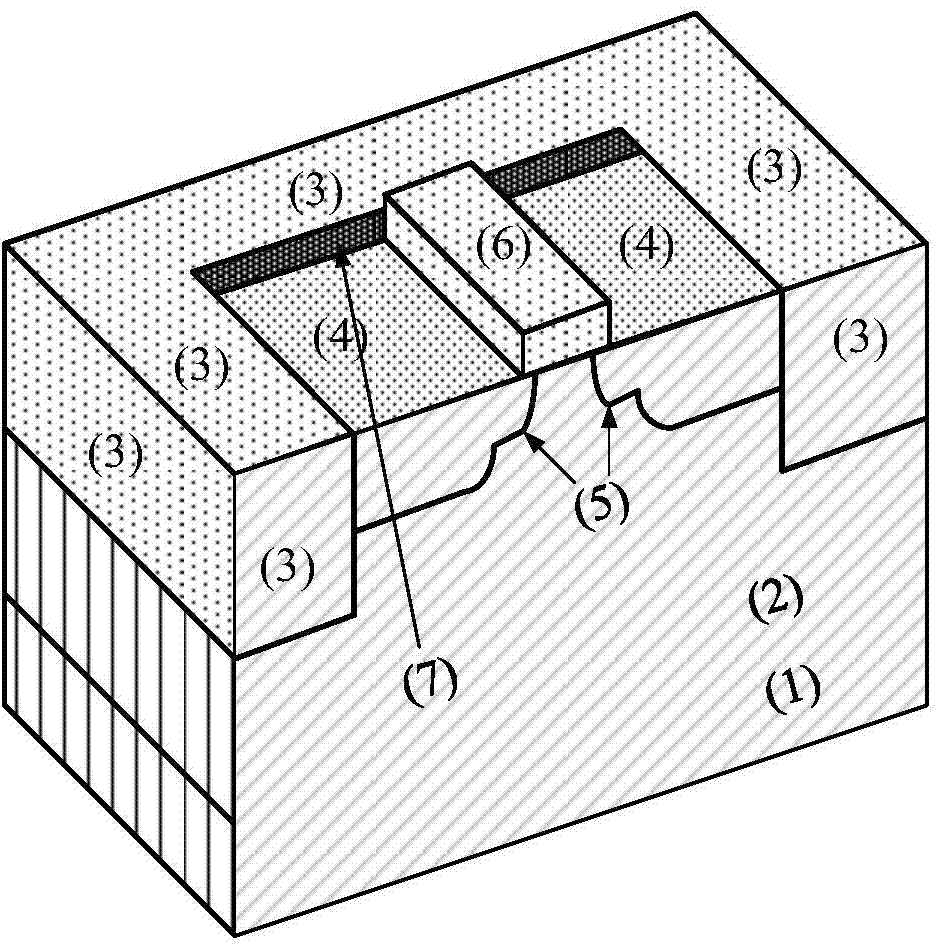

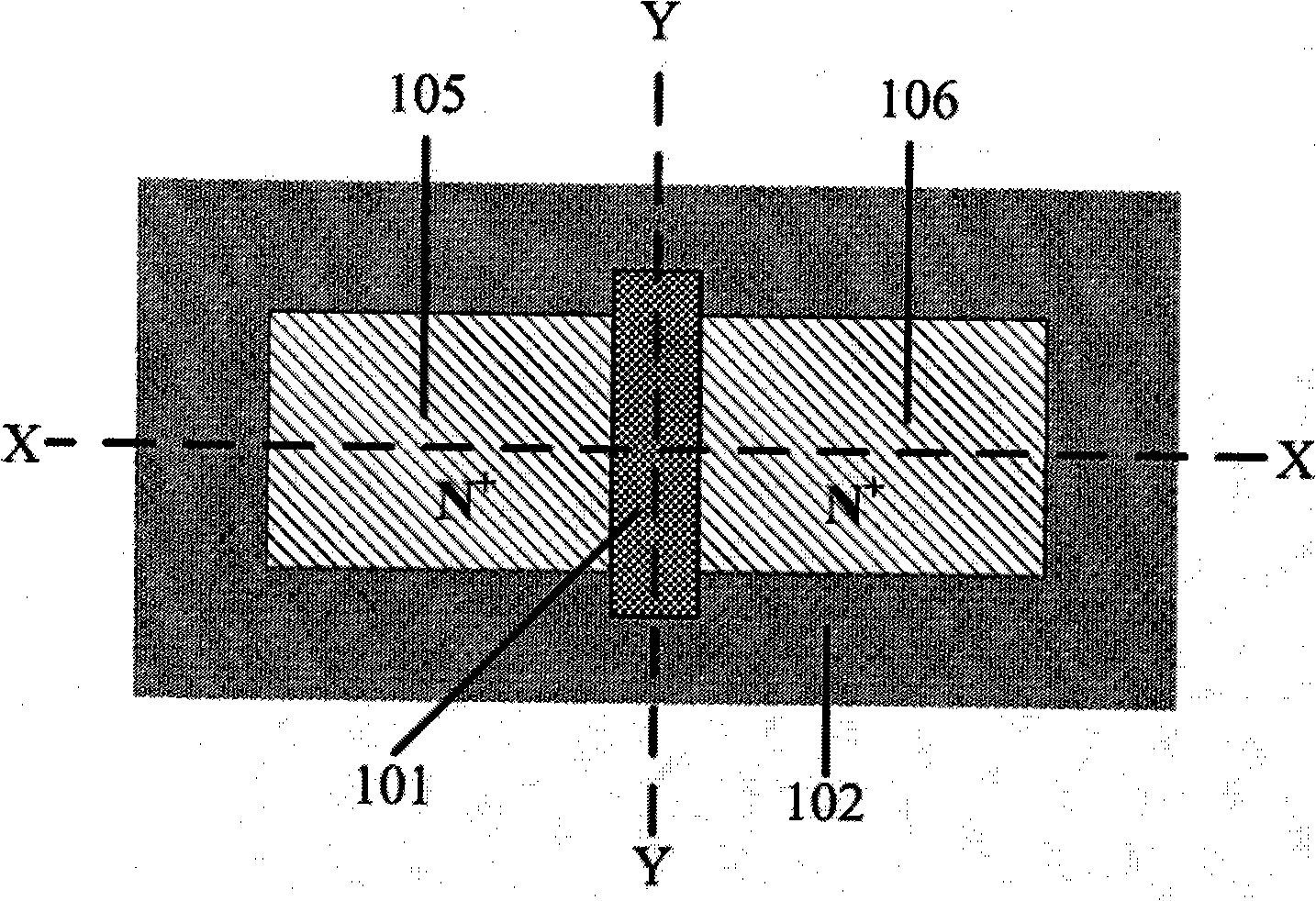

Gate-all-around anti-irradiation MOS field effect transistor based on 65 nm technology

InactiveCN104934475AReduce leakage currentHigh working reliabilityTransistorSemiconductor/solid-state device manufacturingGratingSubthreshold swing

The present invention discloses a gate-all-around anti-irradiation MOS field effect transistor based on a 65 nm technology for mainly solving the problems of threshold voltage drift, subthreshold swing degeneration and off-state leakage current degeneration of a conventional 65 nm MOS field effect transistor under a total dose radiation environment. The gate-all-around anti-irradiation MOS field effect transistor based on the 65 nm technology comprises a P-type substrate (1) and an epitaxial layer (2) located on the substrate, a drain region (3) is arranged in the middle of the epitaxial layer, and a grid (4) is arranged above the epitaxial layer adjacent to the periphery of the drain region (3). Light doping source drain regions (5) are arranged in the epitaxial layer below the boundaries at the inner and outer sides of the grid, an area between the light doping source drain regions forms a channel, and a source region (6) is arranged in the epitaxial layer adjacent to the periphery of the grid. An isolating groove (7) is arranged in the epitaxial layer adjacent to the periphery of source region, and a grating ring, a source ring and an isolating groove ring sleeve structure surrounding the exterior of an active region orderly are formed. The gate-all-around anti-irradiation MOS field effect transistor based on the 65 nm technology of the present invention enables the device anti-total dose radiation capability to be improved, and can be used to manufacture a large-scale integrated circuit.

Owner:XIDIAN UNIV

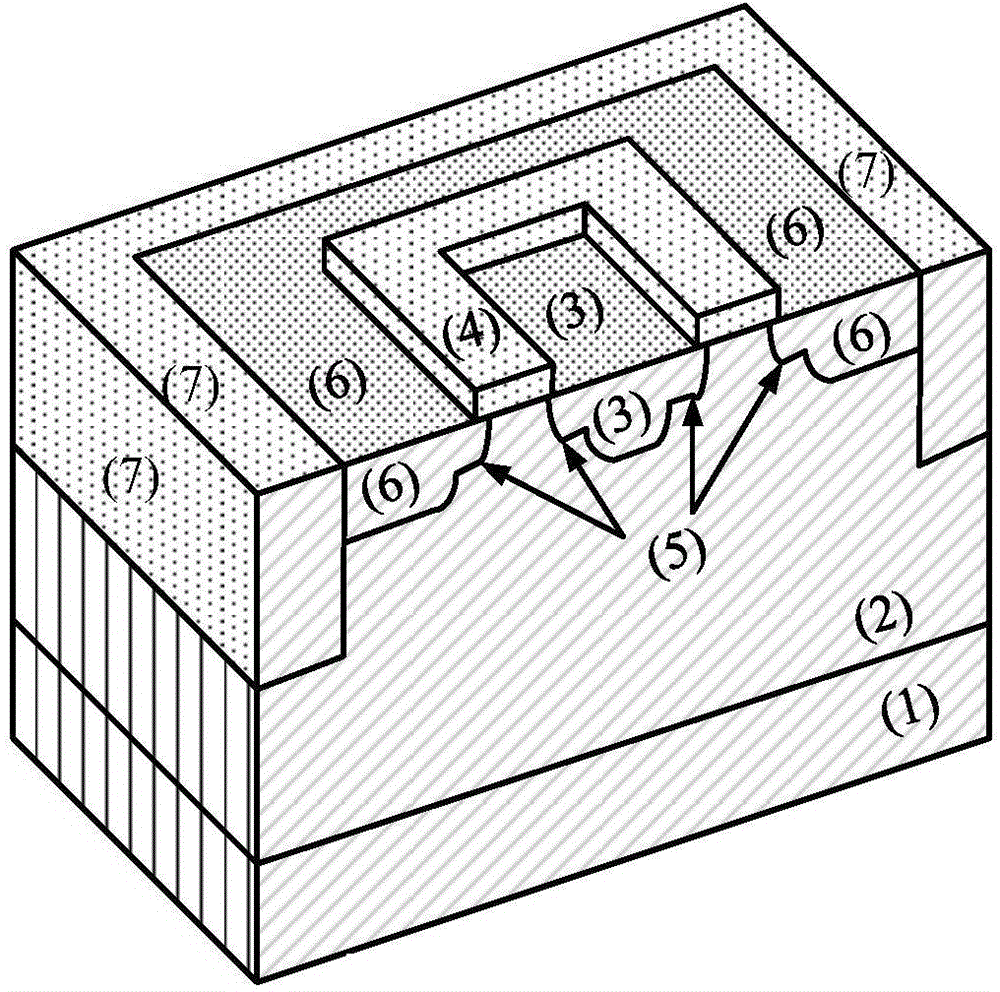

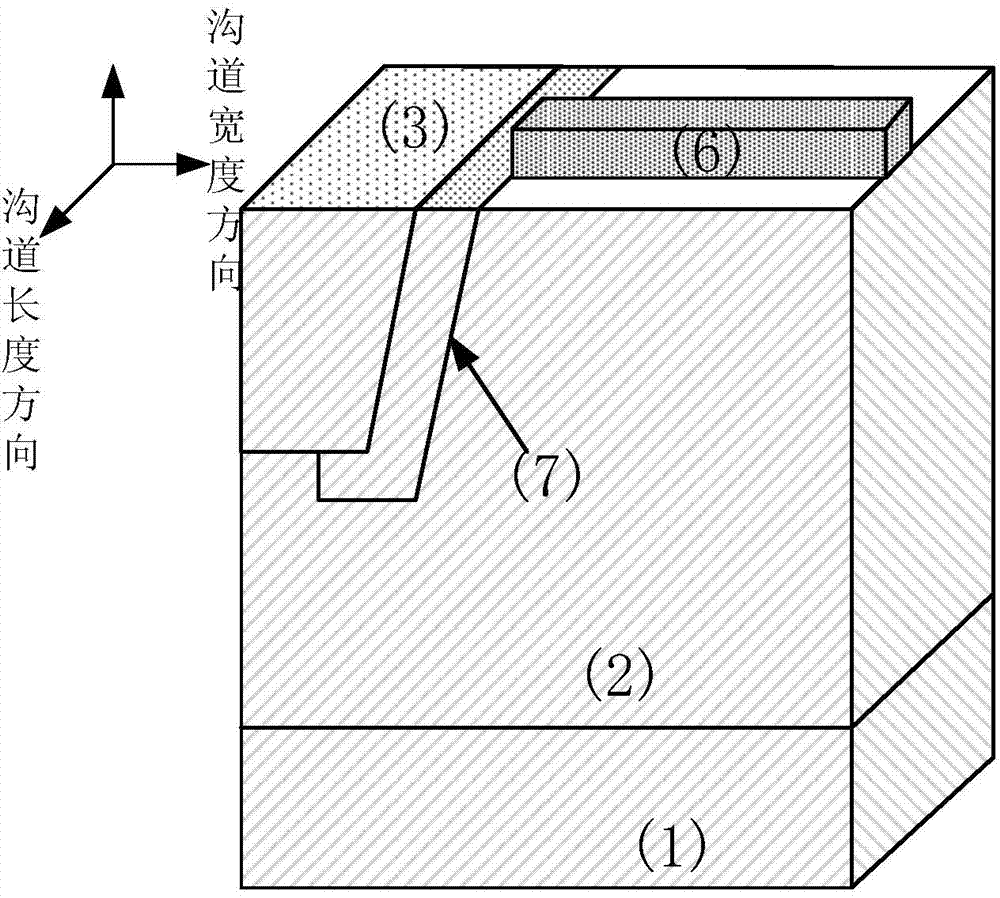

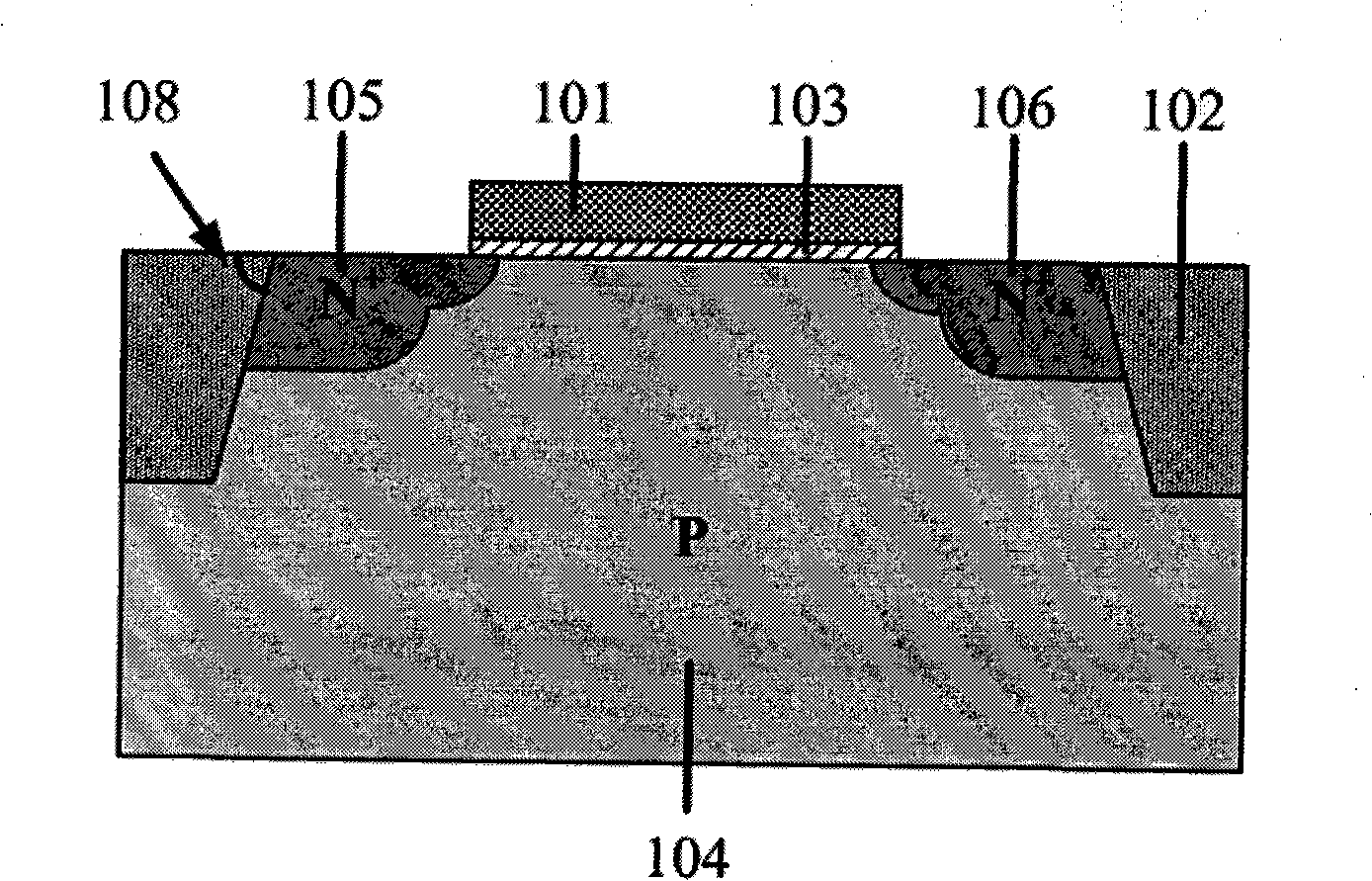

Redundant doping radiation-proof MOS (Metal Oxide Semiconductor) field-effect tube based on 65nm process

ActiveCN104752513AAvoid conductionReduce sensitivitySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringField-effect transistor

The invention discloses a redundant doping radiation-proof MOS (Metal Oxide Semiconductor) field-effect tube based on a 65nm process, and mainly solves that a traditional 65nm MOS field-effect tube has the problems of threshold voltage drifting, sub-threshold swing degeneration and the degeneration of OFF leakage current under a total dose irradiation environment. The field-effect tube comprises a P-type substrate (1) and epitaxial layers (2) located on a substrate, wherein isolation grooves (3) and grids (6) are respectively arranged all around the upper parts and middle parts of the epitaxial layers, the epitaxial layers between the two side boundaries of a grid and the boundaries in the isolation grooves are internally provided with source and drain active areas (4), and the epitaxial layers below the two side boundaries of the grid are internally provided with light dope source and drain areas (5); a channel is formed in an area between the two light dope source and drain areas (5) is located just below the grid, and a redundant doping areas (7) are inserted in the interfaces of the epitaxial layers at the bottom of the two side isolating grooves which are parallel to the length direction of the channel. According to the MOS field-effect tube provided by the invention, the total dose resistant radiation capacity of devices can be improved, and the field-effect tube can be used for preparing massive integrated circuits.

Owner:XIDIAN UNIV

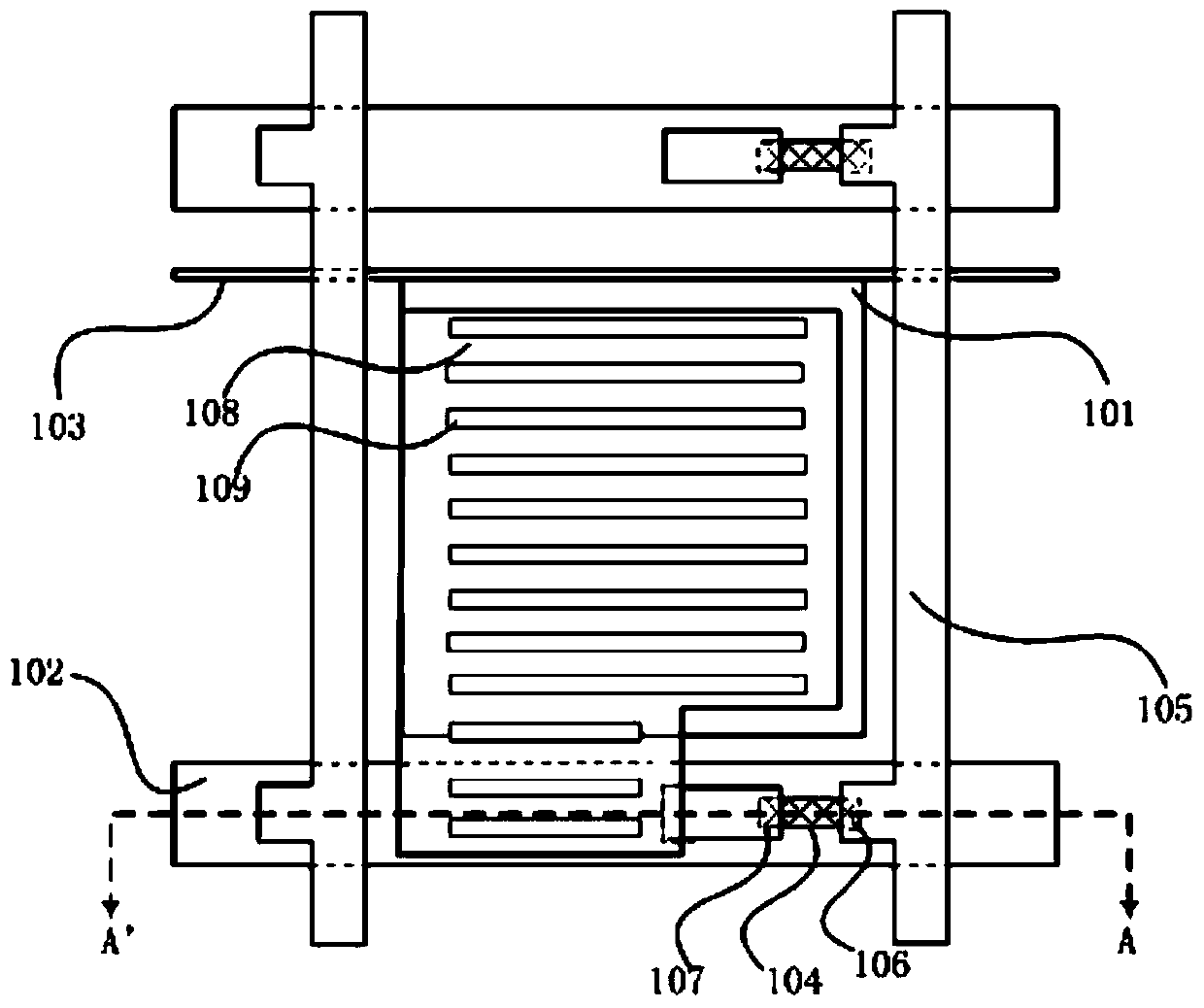

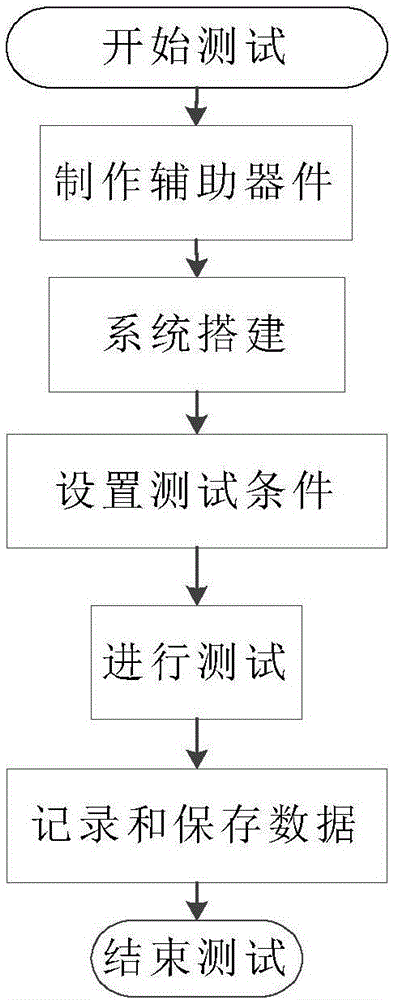

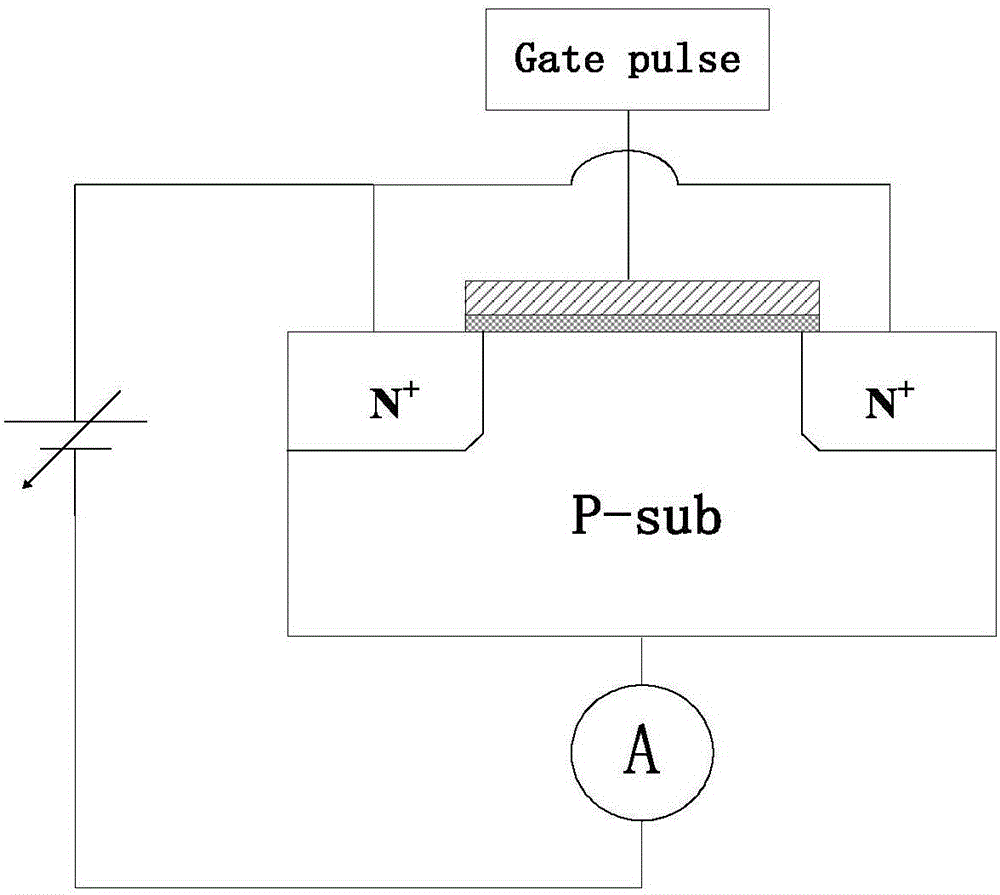

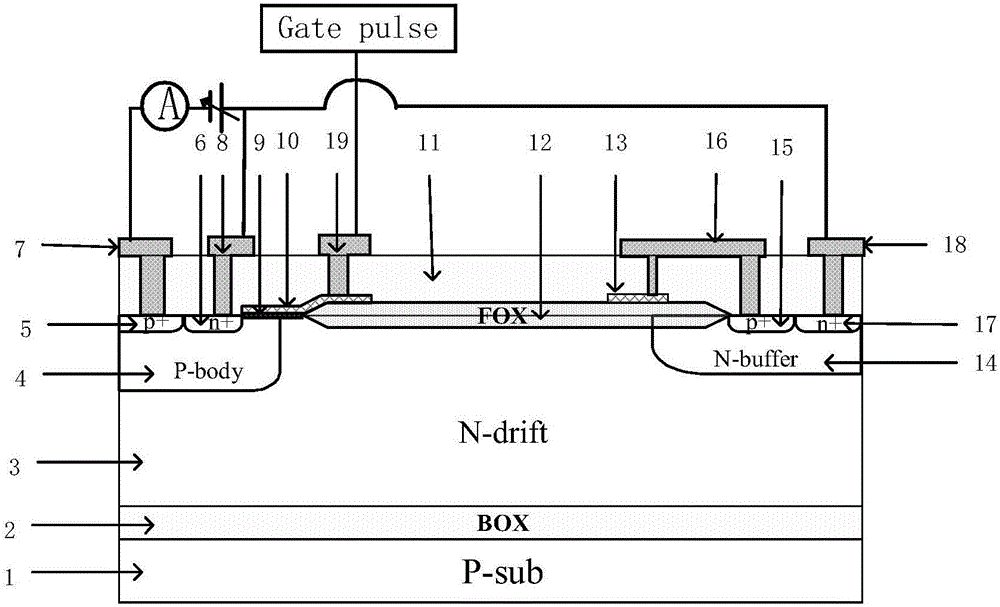

Test method for lateral insulated gate bipolar transistor interface state and five-port device

ActiveCN106356313AThe breakdown voltage does not changeInvariant output characteristicsBipolar transistor testingSemiconductor/solid-state device testing/measurementEngineeringSystem building

The invention relates to a test method for a lateral insulated gate bipolar transistor interface state and a five-port device. The test method for the lateral insulated gate bipolar transistor interface state is characterized by comprising the following steps: testing charge pump current of a channel region, a beak region, a polysilicon gate field plate region and a field plate terminal region, when test is carried out, the five-port device is manufactured beside a target device on the same wafer, system building is carried out on an auxiliary five-port device, test conditions are set, and finally current test operation is carried out on the charge pump. The five-port device used for the test method for the lateral insulated gate bipolar transistor interface state is characterized by comprising one charge pump electron providing region and one test electrode specially used for the charge pump, and the charge pump electron providing region and an anode P+ region are arranged at the upper part of an N type buffer zone side by side and are connected with the test electrode specially used for the charge pump individually. The test method provided by the invention can solve the problem that the traditional method cannot test interface damage of the polysilicon gate field plate region and the field plate terminal region of the lateral insulated gate bipolar transistor.

Owner:SOUTHEAST UNIV

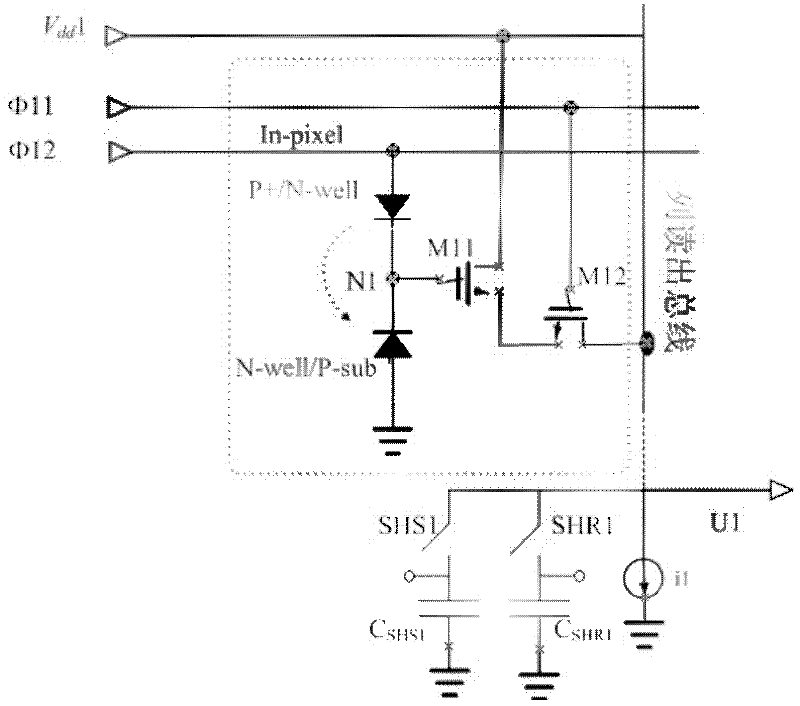

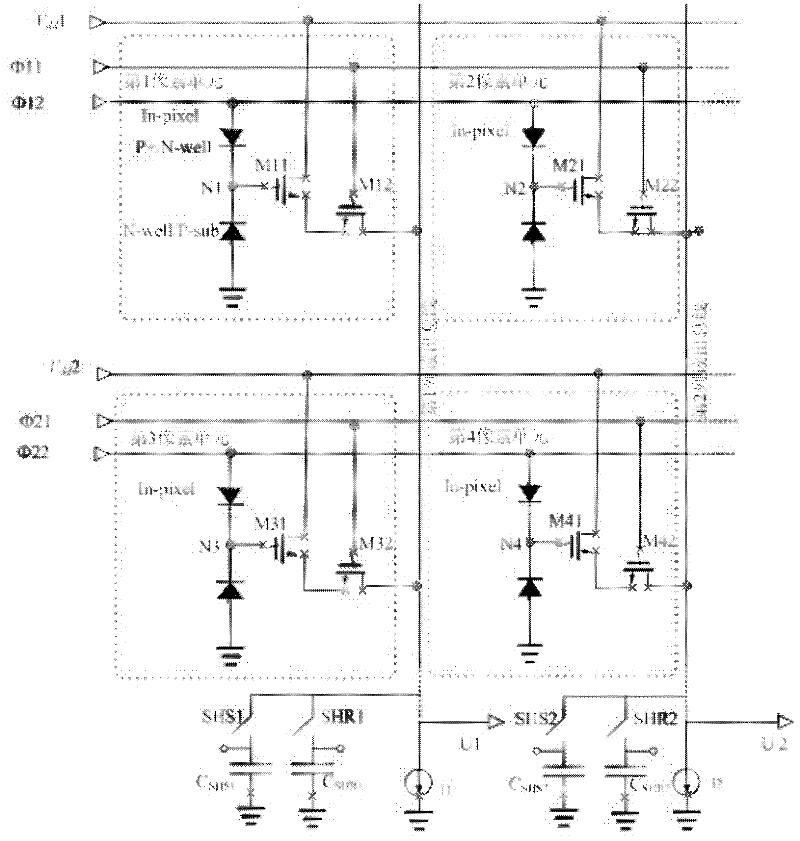

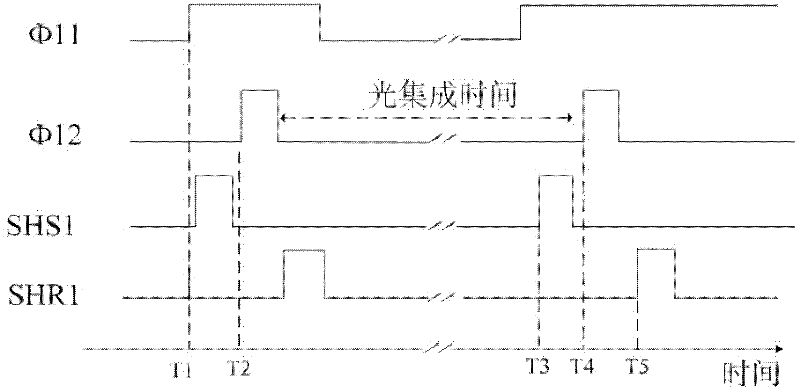

Dual complementary metal oxide semiconductor (CMOS) image sensor pixel unit with high filling factor, and working method

ActiveCN102447851AMeet the needs of ever-shrinking sizeImprove fill factorTelevision system detailsColor television detailsCMOSLight sensing

The invention relates to a dual complementary metal oxide semiconductor (CMOS) image sensor pixel unit with a high filling factor, and a working method. The pixel unit only comprises a diode (N1) with a P+ / N-Well / P-sub structure, a source following transistor (M11) and a selecting transistor (M12). The corresponding pixel array working method comprises the following steps of: resetting, namely applying a selecting control signal (phi12) with high positive voltage and a resetting control signal (phi11) with high positive voltage to activate the diode (N1) with the P+ / N-Well / P-sub structure to charge a node; optically-integrating, namely setting the phi12 and the phi11 to be low positive voltage within a fixed illumination integration time period, wherein a current carrier is produced by partial accumulated light of the N-Well / P-sub structure in the diode, and the node is discharged; and reading out, namely after light integration, changing the phi12 to be the high positive voltage, and reading a light sensing signal corresponding to the current carrier out by column buses through the M11 and the M12.

Owner:PKU HKUST SHENZHEN HONGKONG INSTITUTION

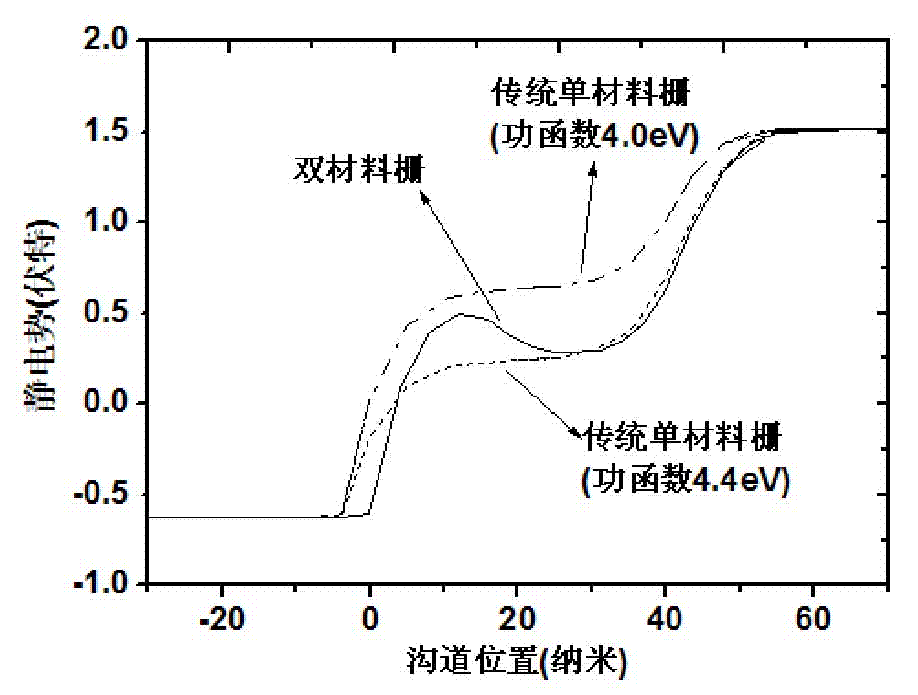

Bi-material railing nanowire tunneling field effect device and manufacturing method thereof

ActiveCN102956709AReduces off-state leakage currentHigh switching current ratioSemiconductor/solid-state device manufacturingSemiconductor devicesOxide semiconductorPhysics

The invention relates to a bi-material railing nanowire tunneling field effect device and a manufacturing method thereof. According to the bi-material railing nanowire tunneling field effect device, a channel is arranged at the center, and a source region and a drain region are respectively arranged at two ends, and an oxide and a gate electrode are covered at the periphery of the channel in sequence. The manufacturing method comprises the steps: SF6 etching a silicon column on a silicon wafer by using a round silicon nitride hard mask; conducting high-temperature oxidation, corroding and reducing the size of the silicon column to be a set diameter value of 6nm-30nm with HF aqueous solution, and conducting high-temperature oxidation to form a silicon column coated by an oxidation layer with set thickness; completing the preparation of a bi-material railing structure by adopting deposition and photoetching technology; and injecting boron and phosphorus of 1*10<20>cm<-2> / 10keV and 5*10<18>cm<-2> / 10keV at 120-150 DEG C respectively, and annealing at 900 DEG C / 10s-1100 DEG C / 10s to prepare the source region and the drain region; completing preparation of a metal electrode by CMOS (Complementary Metal-Oxide-Semiconductor) process; and manufacturing the bi-material railing nanowire tunneling field effect device.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

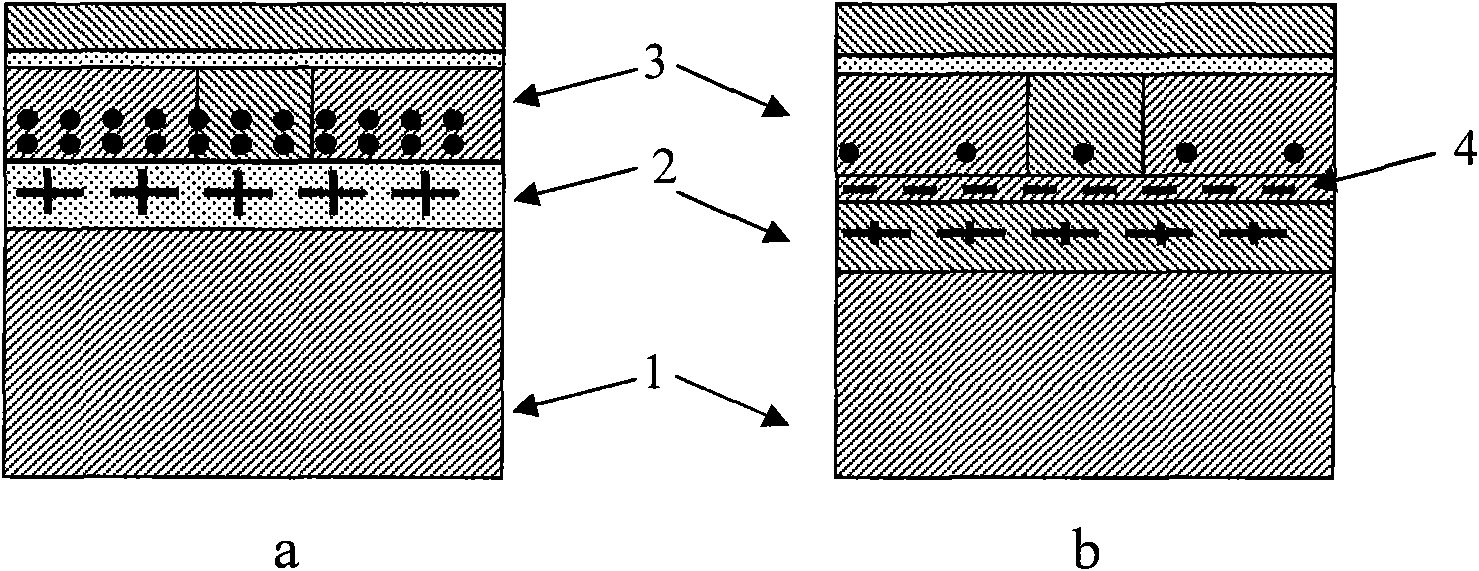

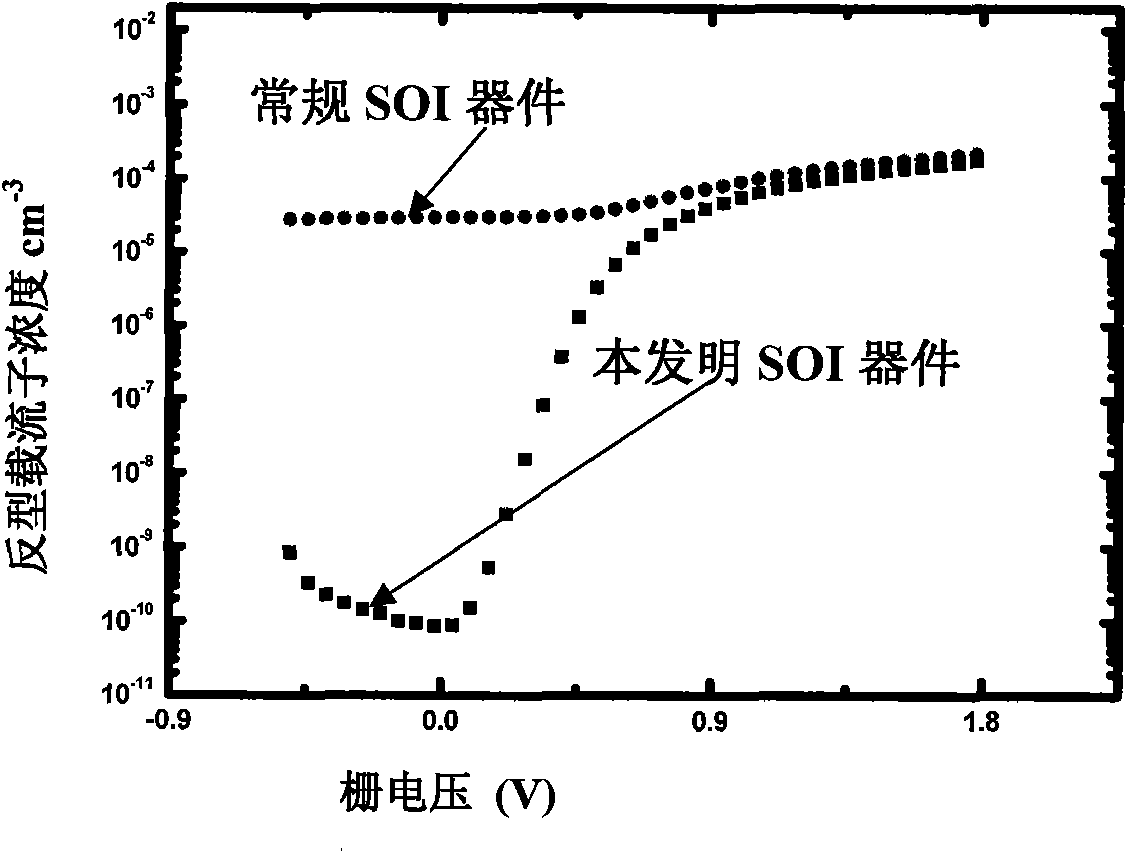

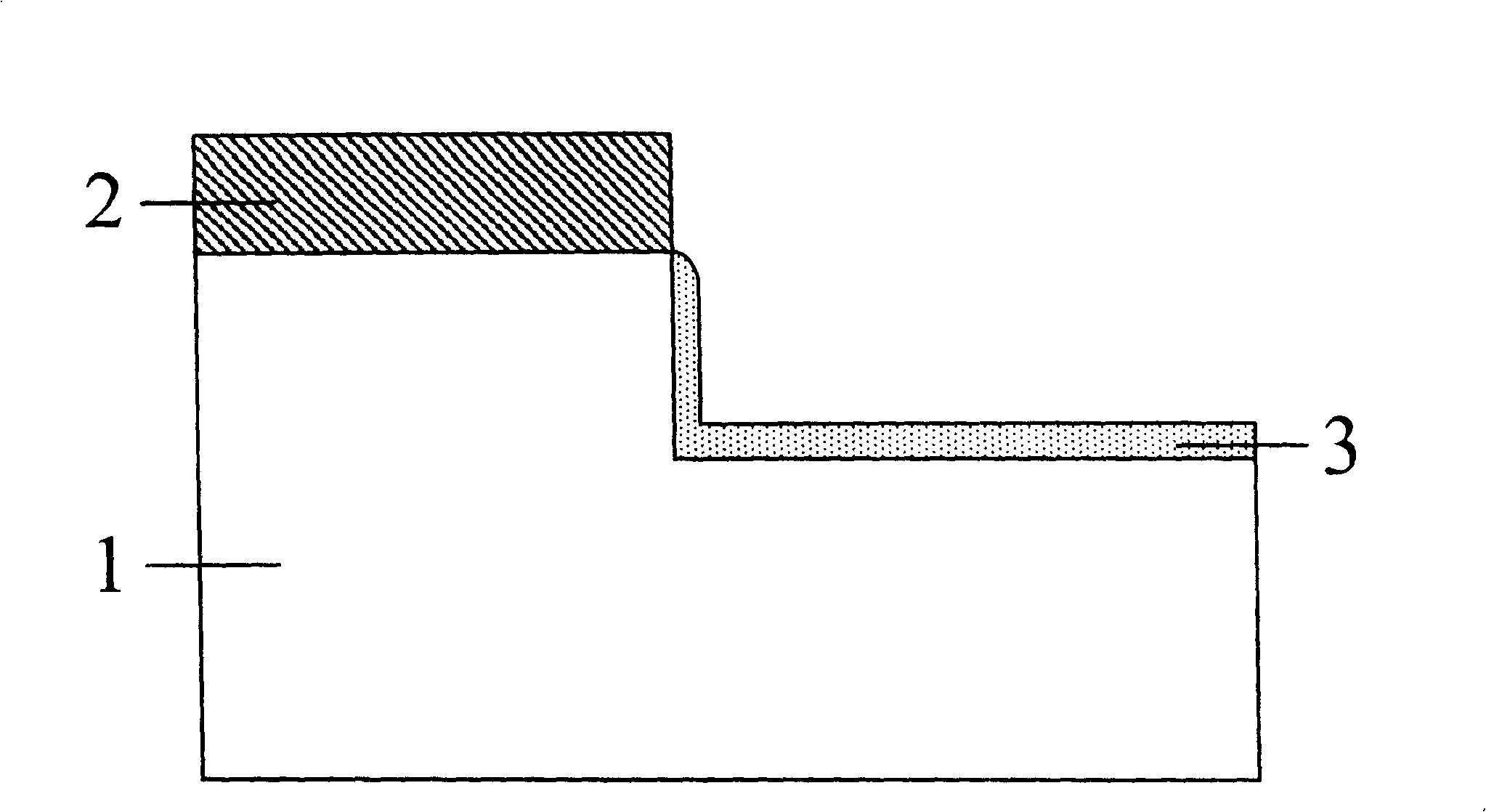

Silicon-on-insulator (SOI) substrate structure and device

InactiveCN102244080AReduce self-heating effectReduces off-state leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingPower flowSoi substrate

The invention provides a silicon-on-insulator (SOI) substrate structure and an SOI device using the SOI substrate structure, for further reducing the self-heating effect of the SOI device and avoiding the problems of substantially reduced SOI device performance, many process modifications and high cost and the like in the existing scheme of reducing the self-heating effect; meanwhile, by the adoption of the invention, current at a drain terminal can be increased, the off-state leakage current of the device can be reduced and the ratio of on-state current to off-state current can be obviously improved. The SOI substrate structure provided by the invention comprises an insulating layer and a bottom substrate below the insulating layer, wherein the insulating layer is divided into a first insulating layer below a channel region and a second insulating layer beyond the first insulating layer, and the thickness of the first insulating layer or a part of the first insulating layer is smaller than that of the second insulating layer.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

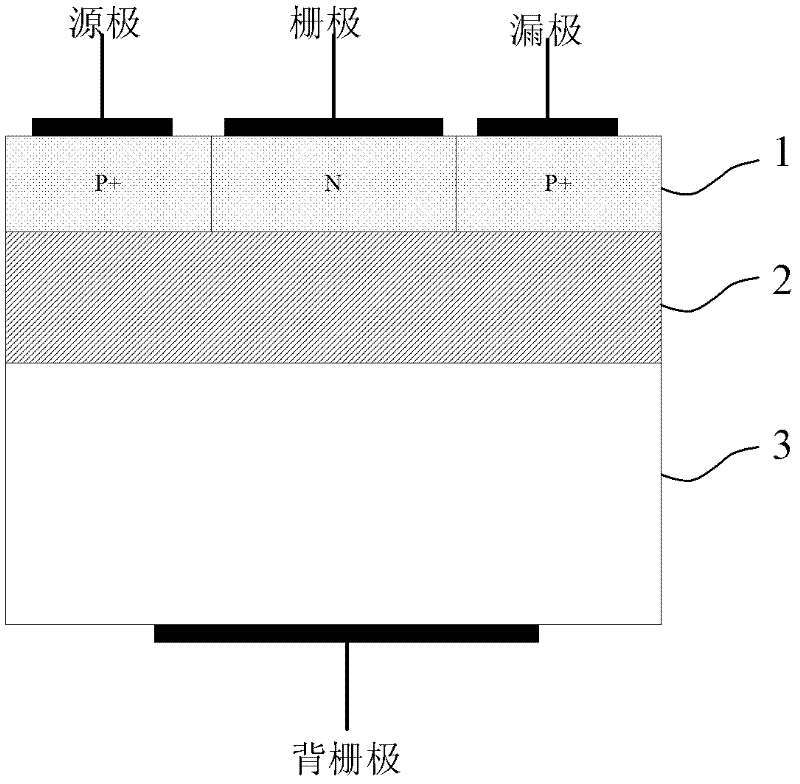

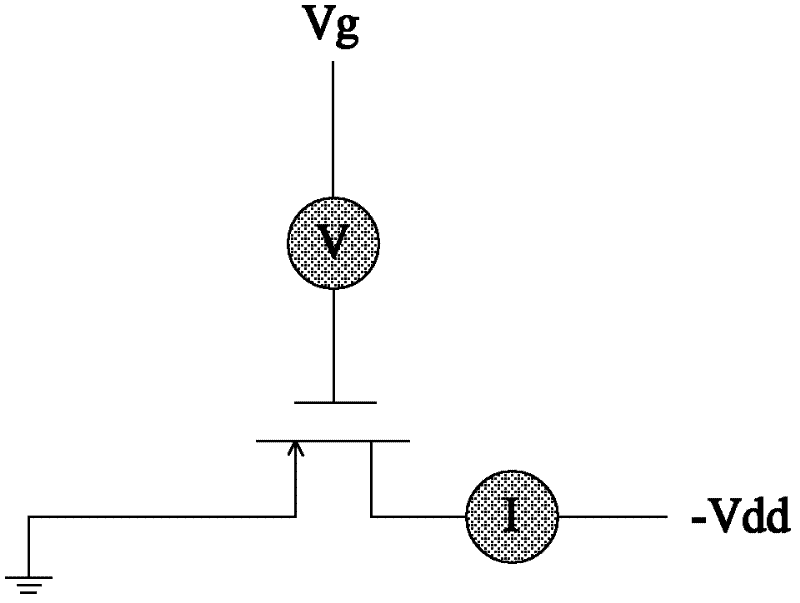

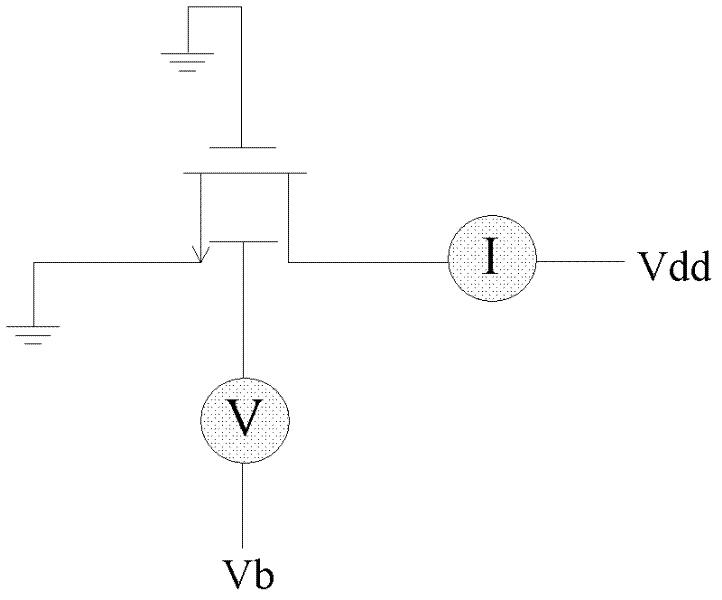

A method for increasing back gate threshold voltage of soi-pmos device

InactiveCN102270582ARaise the threshold voltageAchieving back gate threshold voltageSemiconductor/solid-state device manufacturingSemiconductor devicesIntegrated circuitSemiconductor

The invention relates to the technical field of SOICMOS semiconductor integrated circuits, in particular to a method for increasing the back gate threshold voltage of an SOI-PMOS device. The method specifically includes the following steps: connect the source, drain, and gate of the SOI-PMOS device to the ground potential, connect the back gate of the SOI-PMOS device to a negative DC voltage with an absolute value greater than 80V, and continue for more than 10 seconds time. The invention tests the back gate threshold voltage of the SOI-PMOS device, improves the threshold voltage of the back gate channel opening of the SOI-PMOS device, and can realize the increase of the back gate threshold voltage of the SOI-PMOS device and the reduction of the off-state leakage current .

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

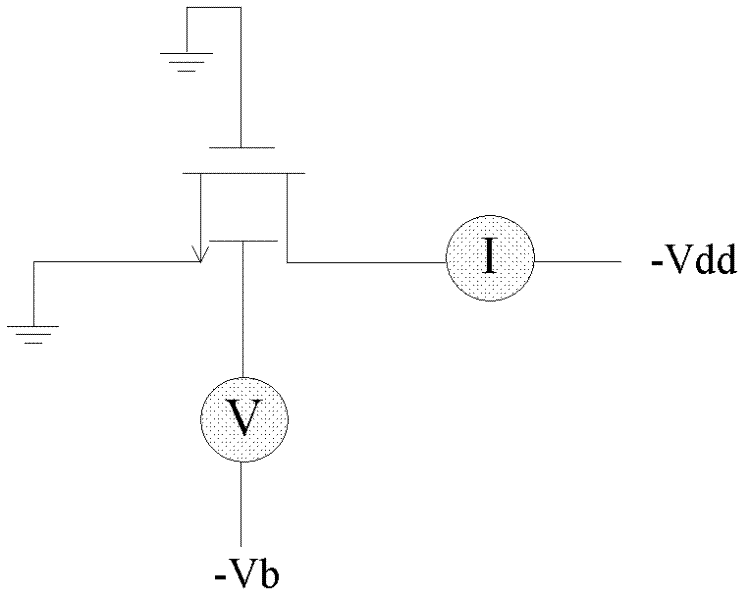

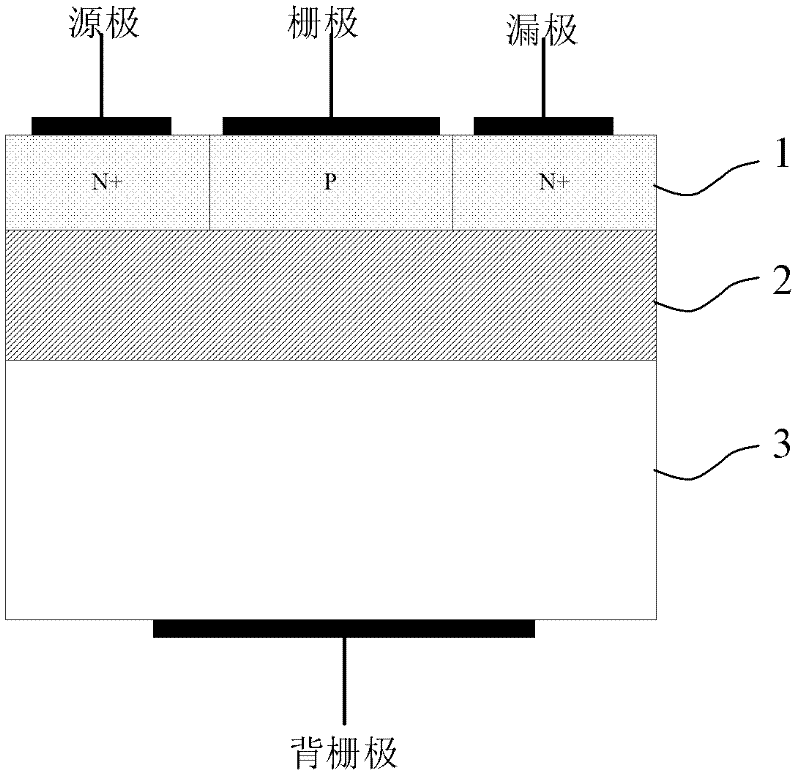

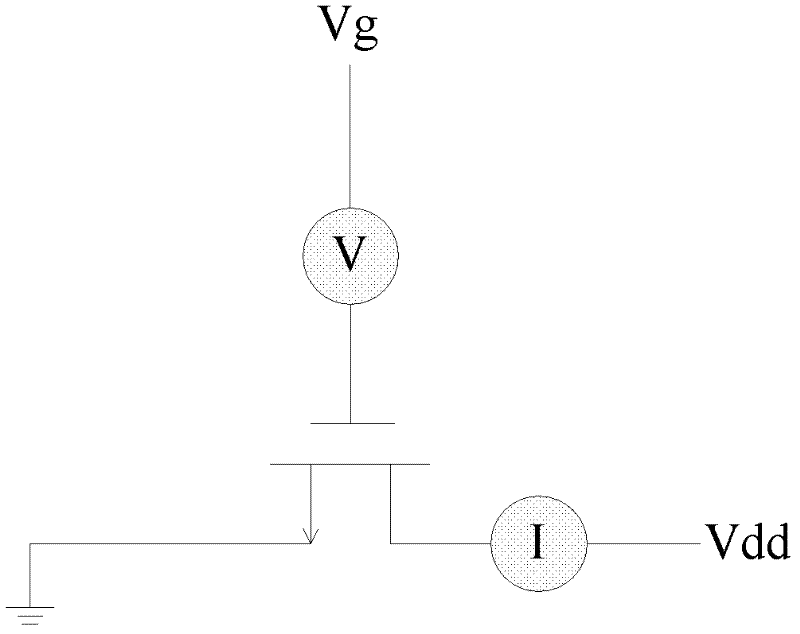

Method for regulating back gate threshold voltage of SOI-NMOS (silicon on insulator-N-channel metal oxide semiconductor) device

InactiveCN102244008AThe back gate threshold voltage increasesReduces off-state leakage currentSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingSilicon on insulatorThreshold voltage

The invention relates to a method for regulating back gate threshold voltage of an SOI-NMOS (silicon on insulator-N-channel metal oxide semiconductor) device. The method comprises the following steps: improving the back gate threshold voltage and lowering the back gate threshold voltage, wherein the method for improving the back gate threshold voltage comprises: grounding potential for a grid electrode, a drain electrode and a source electrode of the SOI-NMOS device; and connecting the positive direct current voltage with the absolute value greater than 80V to a back grid electrode of the SOI-NMOS device for more than 10 seconds; and the method for lowering the back gate threshold voltage comprises: grounding potential for the grid electrode, the drain electrode and the source electrode of the SOI-NMOS device; and connecting the negative direct current voltage with the absolute value greater than 80V to a back grid electrode of the SOI-NMOS device for more than 10 seconds. The threshold voltage of back grid channel start of the SOI-NMOS device is regulated, and the increase of the back gate threshold voltage and the decrease of off leakage current of the SOI-NMOS device can be realized.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

SOI device resistant to total dose radiation and manufacturing method thereof

InactiveCN101859781AAnti-type effect is weakenedIncrease distanceSolid-state devicesSemiconductor/solid-state device manufacturingHigh energyP type silicon

The invention discloses an SOI device resistant to total dose radiation and a manufacturing method thereof, belonging to the field of electric technology. The SOI device comprises a substrate layer, a buried oxide layer and a top layer, wherein a sacrificial layer is arranged between the buried oxide layer and the substrate layer and generates negative charges after the SOI device is subjected to total dose radiation; the sacrificial layer is made of silicon nitride; the substrate layer is made of P-type silicon; and the buried oxide layer is made of silicon dioxide. The manufacturing method comprises the following steps: a) forming the SiO2 buried oxide layer on the silicon wafer; b) forming the silicon nitride sacrificial layer on the SiO2 buried oxide layer; and c) forming the P-type silicon substrate layer on the silicon nitride sacrificial layer. The invention can be applied to such industries related to total dose radiation as aerospace, military, nuclear power, high-energy physics and the like.

Owner:PEKING UNIV

Prepn of nitride-oxide film

InactiveCN1178282CImprove featuresReduces off-state leakage currentSemiconductor/solid-state device manufacturingPhysical chemistrySilicon chip

The preparation of nitroxide film is to implant nitrogen ion into silicon substrate before oxidation. The steps includes: growing oxide film on isolated and cleaned silicon chip and implanting nitrogen ion to the active area; rinsing the oxide film; soaking with HF / IPA / H2O at room temperature and rinsing with deionized water before drying and feeding into furnace; feeding the boat slowly under protection of great flow rate of N2; heating to 700-900 deg.c and oxidation in N2 / O2 ratio of 5 for 1-120 min; annealing in N2 atmosphere at 700-900 deg.c for 15-60 min; lowing the temperature to 550 deg.c in N2 atmosphere and withdrawing the boat slowly under protecting of great flow rate of N2; forming polysilicon via LPCVD at 620 deg.c, 0.2 torr, SiH4 200 sccm and Ar 800 sccm.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

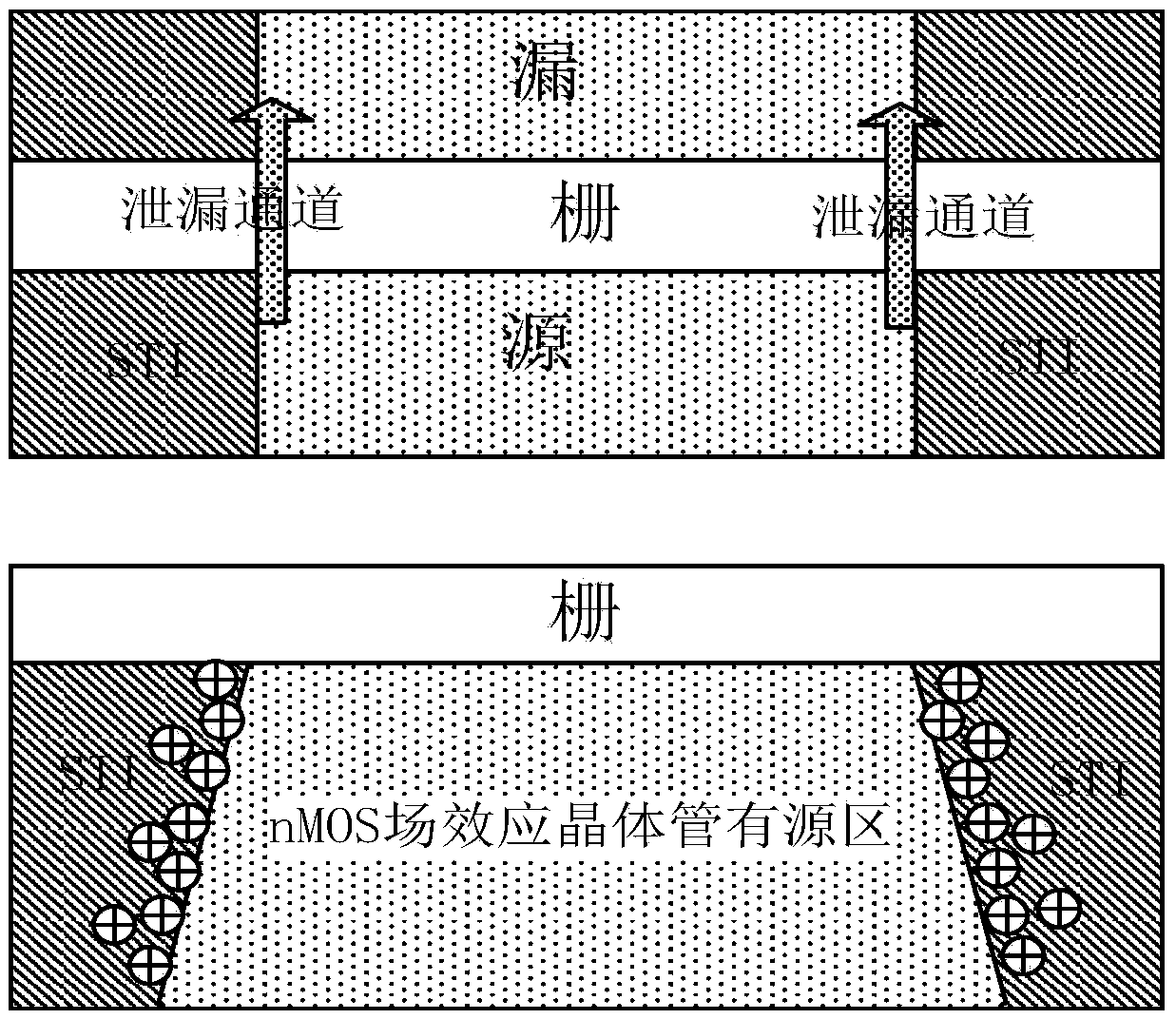

Method for improving MOSFET anti-single particle radiation and MOSFET component

InactiveCN101266972AReduces off-state leakage currentImproving the ability to resist single event radiation effectsSolid-state devicesSemiconductor/solid-state device manufacturingManufacturing cost reductionMOSFET

The invention discloses a method for enhancing anti-single particle radiation ability of MOSFET and a MOSFET element, belonging to field effect transistor technology field. In the MOSFET element according to the invention, an acute angle between the side wall of channel in STI region and the active region of the element is defined as the angle of micro-dosage effect caused by the anti-single particle radiation of the element, with value ranged between 78 degrees to 86 degrees. By using the MOSFET element structure according to the invention, the off-state leakage current of the element caused by the single-particle radiation is lower than that the traditional structure by one magnitude. The structure according to the invention has simple process, completely compatible with traditional CMOS process, capable of enhancing the anti-single particle radiation ability of the element and effectively reducing the manufacturing costs simultaneously.

Owner:PEKING UNIV

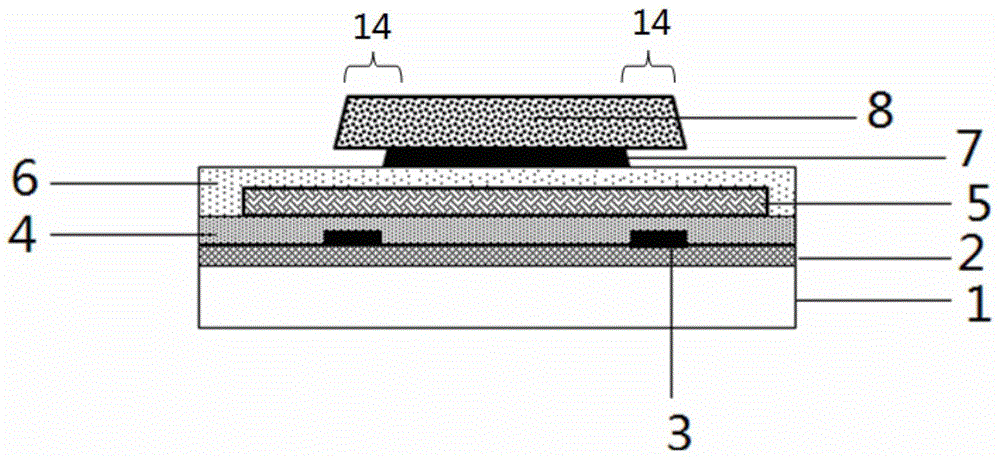

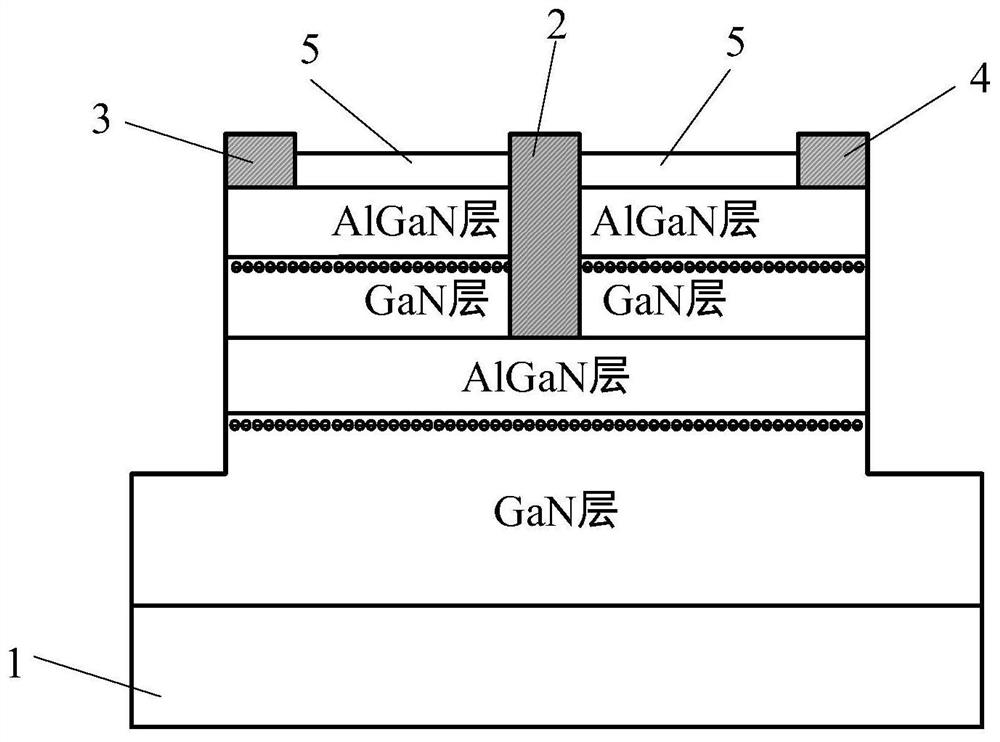

AlGaN/GaN high electron mobility transistor with multi-channel fin-type structure

InactiveCN109285885ALower resistanceImprove current drive capabilitySemiconductor/solid-state device manufacturingSemiconductor devicesLow noiseHeterojunction

The invention discloses an AlGaN / GaN high electron mobility transistor structure with a multi-channel fin-type structure and a manufacturing method, which mainly solves the problems of poor gate control ability of a multi-channel apparatus and low current of a FinFET device. The AlGaN / GaN high electron mobility transistor comprises a substrate (1), a first layer AlGaN / GaN heterojunction (2), a SiNpassivation layer (4), a source electrode, a drain electrode and a grid electrode in sequence from bottom to top, wherein the source electrode and the drain electrode are on a top AlGaN barrier layerat two sides of the SiN passivation layer. The AlGaN / GaN high electron mobility transistor is characterized in that the first layer AlGaN / GaN heterojunction and the SiN passivation layer are providedwith a GaN layer and an AlGaN barrier layer therebetween so as to form a second layer AlGaN / GaN heterojunction (3); and the grid electrode covers the top of the second layer heterojunction and two side walls of the first layer heterojunction and the second layer heterojunction. The AlGaN / GaN high electron mobility transistor is strong in gate control ability, high in saturation current and good in subthreshold characteristic and can be applied to microwave power devices with short gate length, low power consumption and low noise.

Owner:吴绍飞

An asymmetric Schottky barrier MOS transistor and its manufacture method

InactiveCN100448027CReduces off-state leakage currentLarge switch-state current ratioSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierMetallic materials

The provided manufacture method for Schottky barrier source / drain MOS transistor comprises: selecting two types of metal material to prepare asymmetric source and drain; using two metal silicatization reactions, controlling reaction time to obtain the source and drain with different height of Schottky barrier. Compared with prior art, this invention can obtain large on-off current rate or on-state current, while reduces technique complexity, and will fit to sub-50nm scale IC production.

Owner:PEKING UNIV

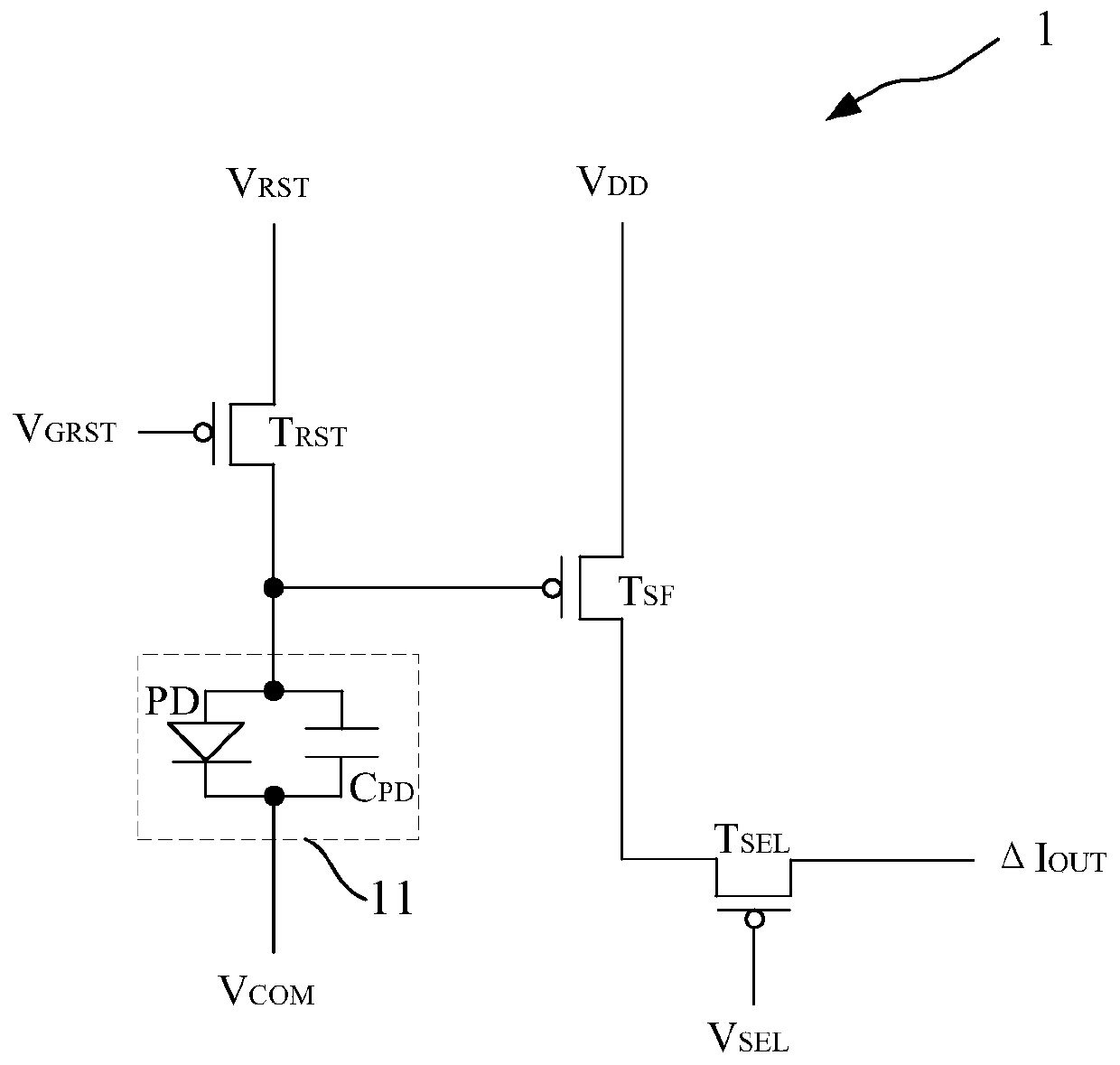

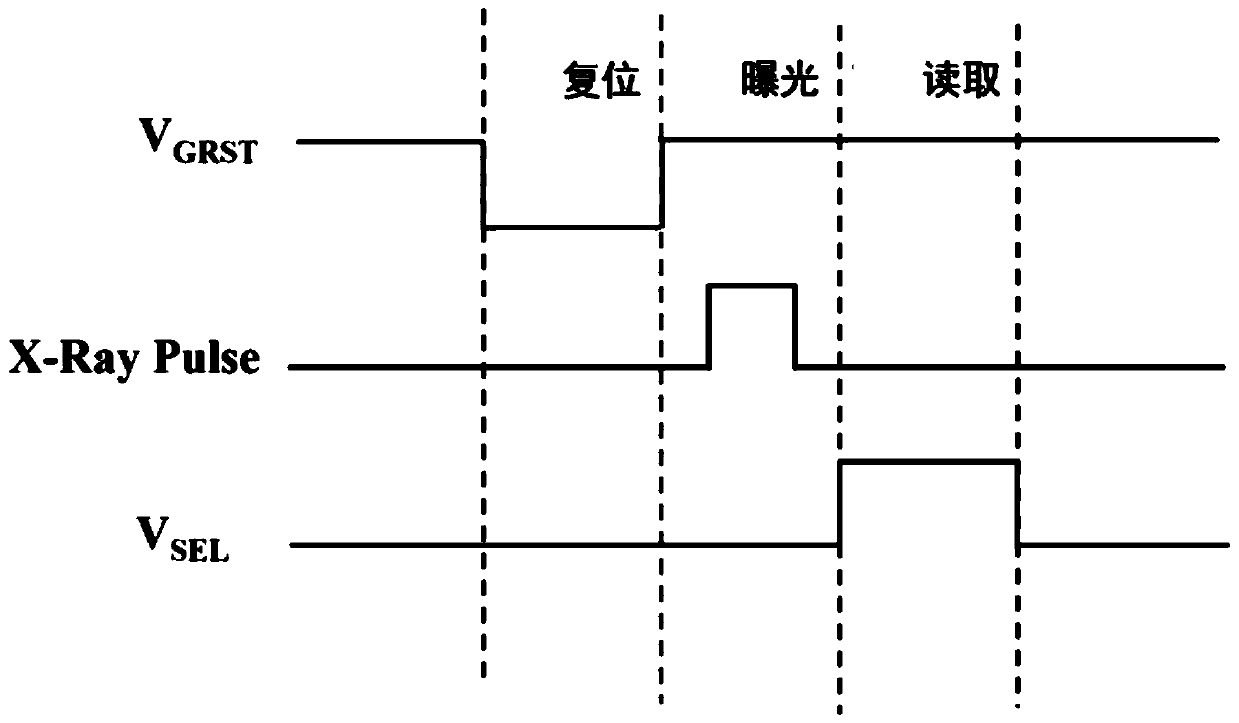

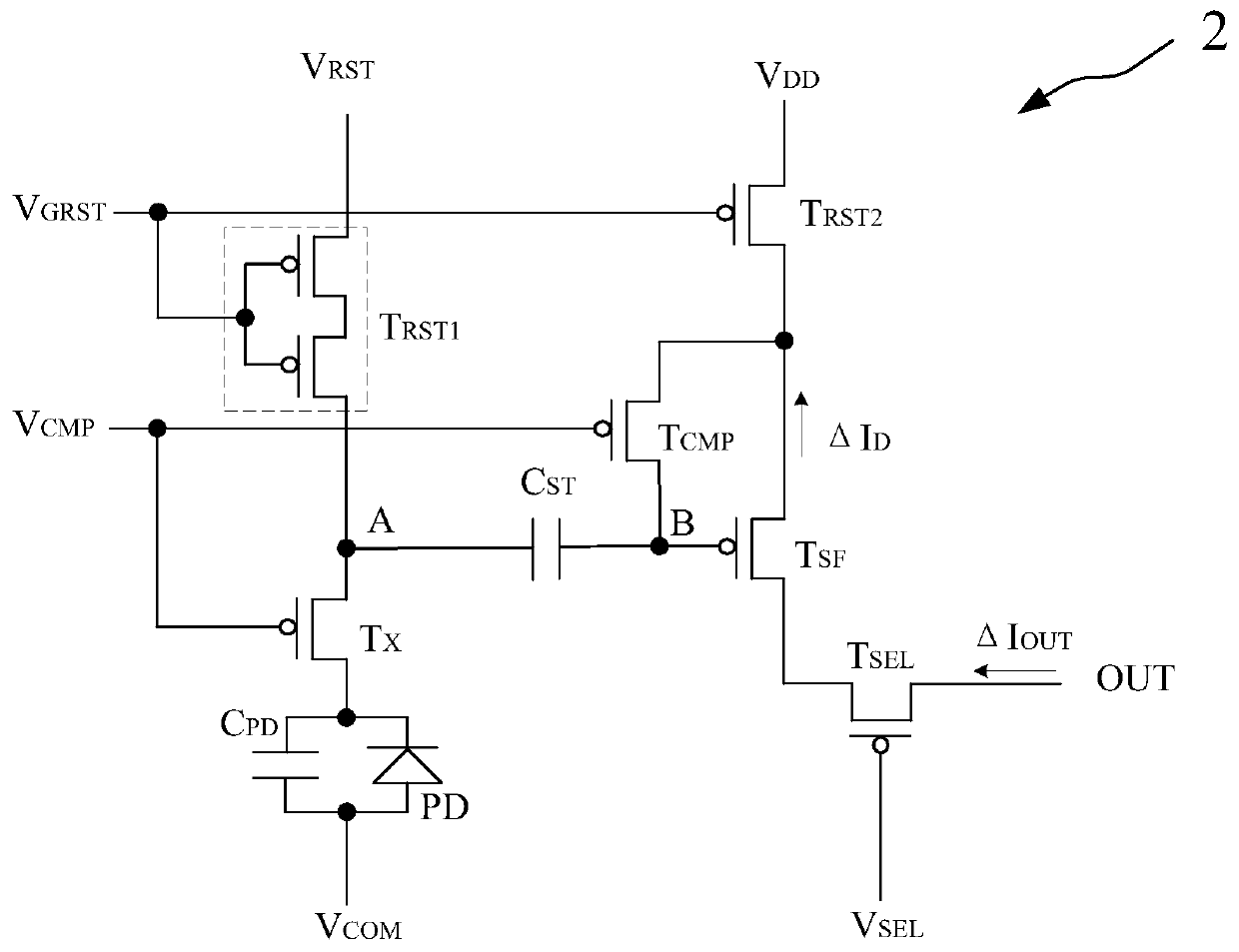

Low-temperature polycrystalline silicon flat panel detector pixel circuit and flat panel detection method

ActiveCN110956923ASuppress interferenceReduces off-state leakage currentStatic indicating devicesRadiation intensity measurementPhysicsTransmission gate

The invention provides a low-temperature polycrystalline silicon flat panel detector pixel circuit and a flat panel detection method. The low-temperature polycrystalline silicon flat panel detector pixel circuit comprises a first reset switch and a transmission gate which are sequentially connected between a reset signal and a cathode of a photosensitive diode in series, and an anode of the photosensitive diode being connected with bias voltage; a second reset switch, a source follower and a selection switch which are sequentially connected between the power supply signal output ends in series; a compensation switch connected between the source electrode and the grid electrode of the source electrode follower; and a storage capacitor connected between the drain electrode of the first resetswitch and the grid electrode of the source follower. The first reset switch and the control end of the first reset switch are connected with a first control signal, and the transmission gate and thecontrol end of the compensation switch are connected with a second control signal. The control end of the selection switch is connected with a third control signal. Internal compensation is carried out on threshold voltage drift of a source follower in the circuit, off-state leakage current of the first reset switch is reduced, and high-frame-rate, high-sensitivity and low-dose dynamic flat paneldetection can be realized.

Owner:SHANGHAI IRAY TECH

Transistor, display substrate, display device and manufacturing method thereof

ActiveCN108231869AReduces off-state leakage currentImprove performanceTransistorSemiconductor/solid-state device manufacturingSemiconductor structureCharge carrier

The invention provides a transistor, a display substrate, a display device and a manufacturing method thereof, and belongs to the field of semiconductors. The transistor comprises a semiconductor structure; the semiconductor structure comprises: a source region, a drain region, a channel region and a capture region, wherein the channel region is located between the source region and the drain region and is constructed as a carrier migration passage between the source region and the drain region in the on-state of the transistor; and the capture region is at least partially embedded in the channel region and is constructed to capture carriers migrating between the source region and the drain region in the off-state of the transistor. Based on the design of embedding the capture region intothe channel region, in the invention, the migration carrier of the off-state leakage current can be restrained by using the capture region, thus the off-state leakage current of the transistor can bereduced, and the performance of relevant devices and products is enhanced.

Owner:BOE TECH GRP CO LTD +1

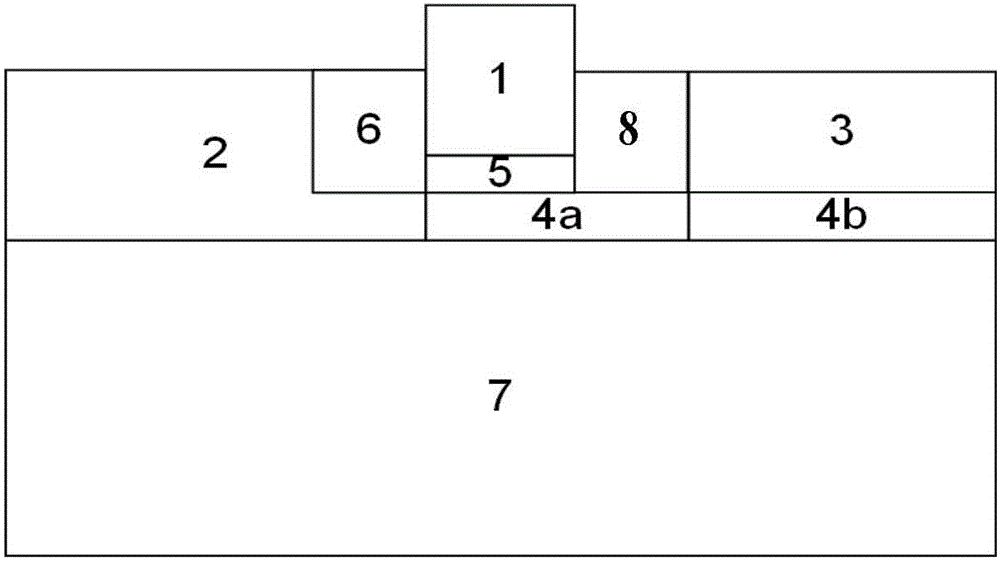

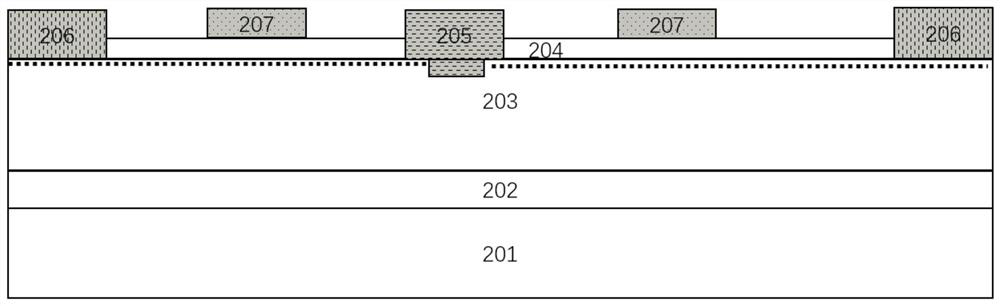

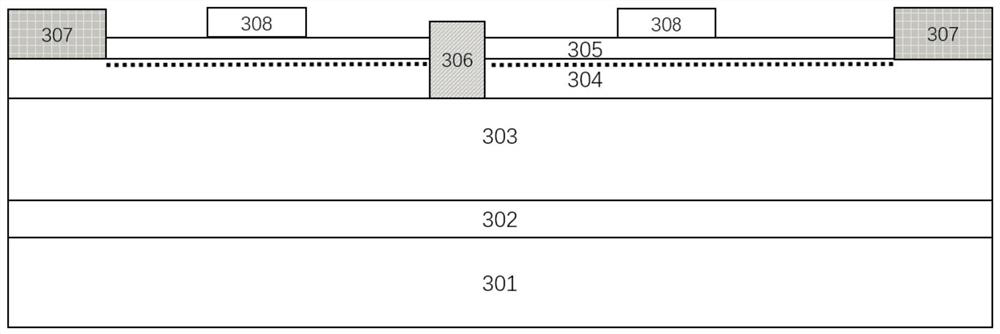

GaN transistor device with high-linearity composite gate structure and preparation method thereof

ActiveCN112825330ASmall resistanceImprove current drive capabilitySemiconductor/solid-state device manufacturingSemiconductor devicesMaterials scienceAtomic physics

The invention relates to a GaN transistor device with a high-linearity composite gate structure and a preparation method of the GaN transistor device. The GaN transistor device comprises a substrate layer; a plurality of channel layers, wherein the plurality of channel layers are stacked on the substrate layer in sequence; grid electrodes arranged on the two sides and the tops of the channel layers and located in the middle of the GaN transistor device, wherein the grid electrodes are not arranged at the two sides of at least the channel layer on the bottommost layer; source electrodes arranged on the plurality of channel layers and positioned at a position close to one side of the GaN transistor device; and drain electrodes arranged on the plurality of channel layers and positioned at a position, close to the other side, of the GaN transistor device. The GaN transistor device provided by the invention has relatively high current driving capability, high linearity and low static power consumption.

Owner:XIDIAN UNIV

Ultrathin channel groove tunneling field effect transistor

The invention discloses an ultrathin channel groove tunneling field effect transistor which is composed of a grid electrode, a source region, a drain region, a first channel region, a second channel region, a grid dielectric layer, a first isolating layer, a second isolating layer and buried oxide layer, wherein the grid electrode and the grid dielectric layer arranged on the position of the channel regions, and the isolation layers are arranged at the two sides of the grid electrode. The new structure has an ultrathin channel so that coupling of the grid electrode and the channel can be enhanced, and thus control capability of the grid electrode can be enhanced and tunneling current of a device can be increased. Another characteristic of the structure is that the intrinsic region (low-doped region) of the channel extends to the drain region. In a word, compared with conventional tunneling transistors, the device of the structure is obviously improved in the aspects of the electrical characteristics of subthreshold swing and switching current ratio and stability.

Owner:HANGZHOU DIANZI UNIV

A high electron mobility transistor having high withstand voltage capability

PendingCN112447836AAvoid uneven distributionImprove pressure resistanceTransistorSemiconductor/solid-state device manufacturingPhysical chemistryEngineering

The invention relates to a semiconductor power device, in particular to a high-voltage-withstanding high-electron-mobility transistor (HEMT). The high-voltage-withstanding high-electron-mobility transistor comprises a gate electrode, a source electrode, a drain electrode, a barrier layer, a P-type nitride semiconductor layer and a substrate, the P-type nitride semiconductor layer is located between the barrier layer and the substrate, which is insufficient to significantly deplete the two-dimensional electron gas in the channel other than the gate stack, and the source electrode is in electrical contact with the P-type nitride semiconductor layer, and both the source electrode and the drain electrode are in electrical contact with the two-dimensional electron gas.

Owner:GUANGDONG ZHINENG TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com