SOI device resistant to total dose radiation and manufacturing method thereof

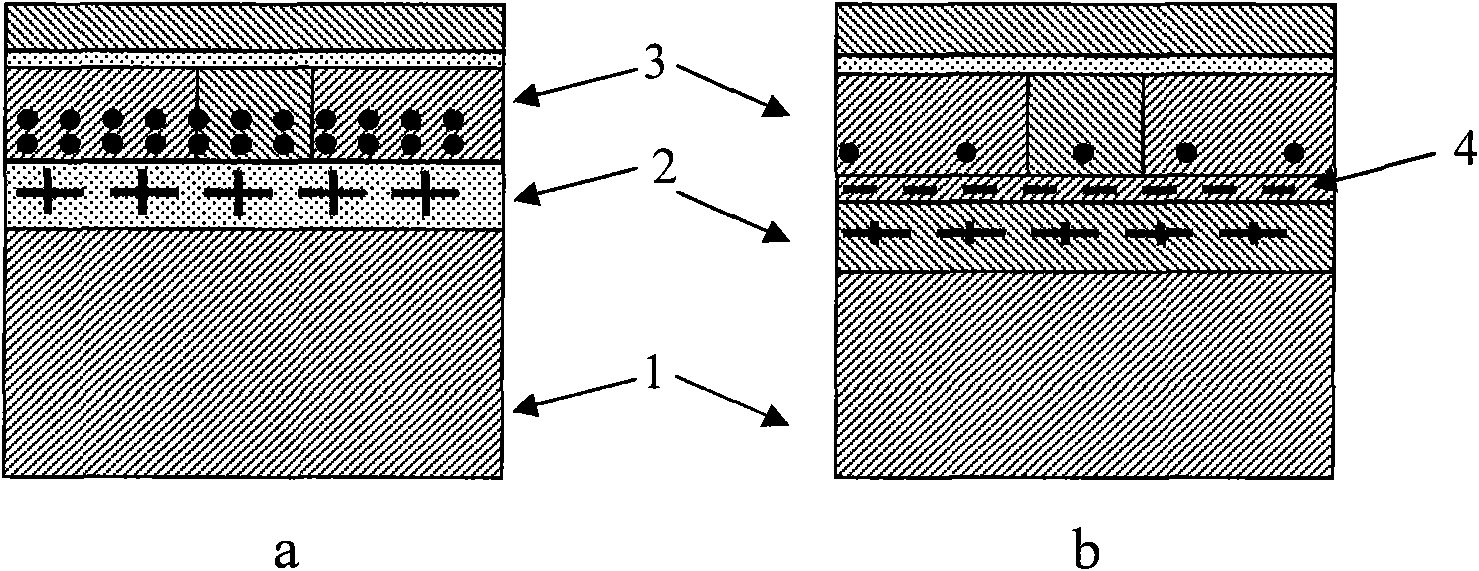

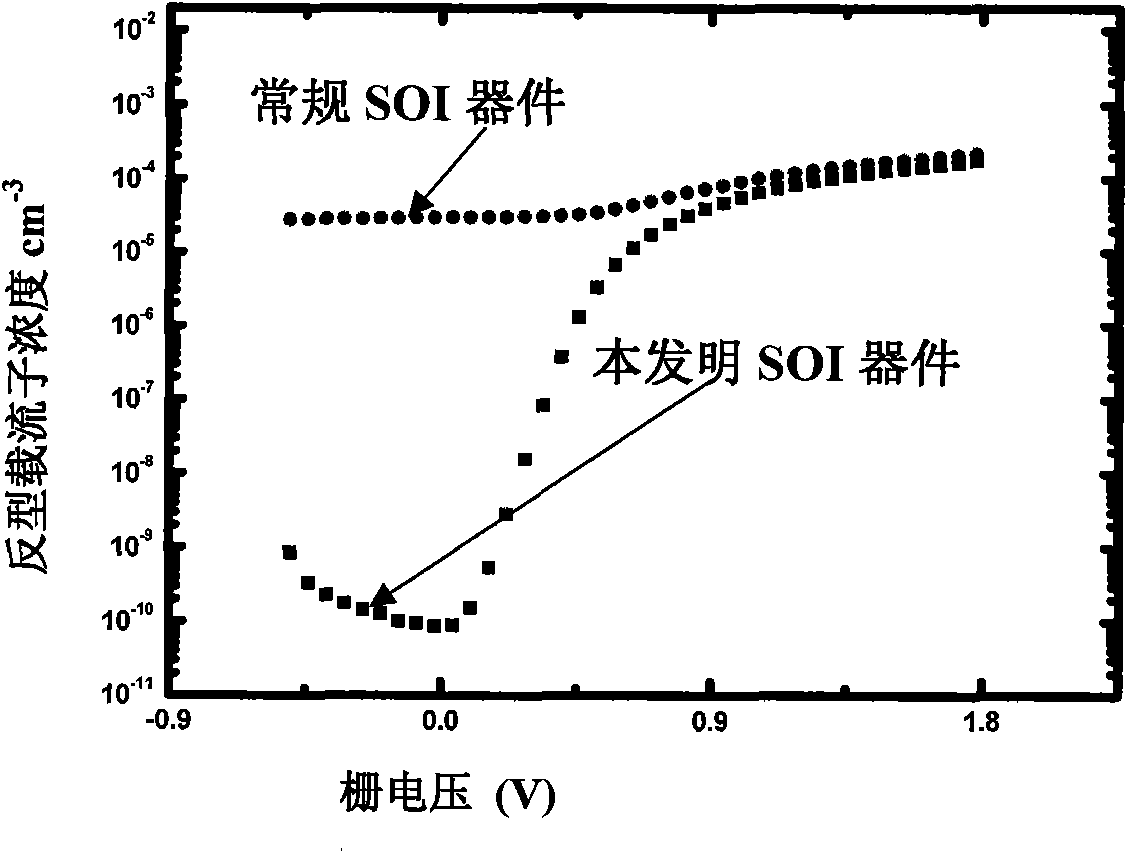

A technology of anti-total dose and manufacturing method, which is applied in the electronic field, can solve the problems of increasing power consumption of CMOS integrated circuits, deterioration of sub-threshold slope, and deterioration of device reliability, so as to reduce off-state leakage current and suppress inversion , the effect of increasing the distance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be further described below through a specific preparation example in conjunction with the accompanying drawings.

[0024] This embodiment prepares the SOI device according to the present invention, and the preparation method mainly includes the following steps:

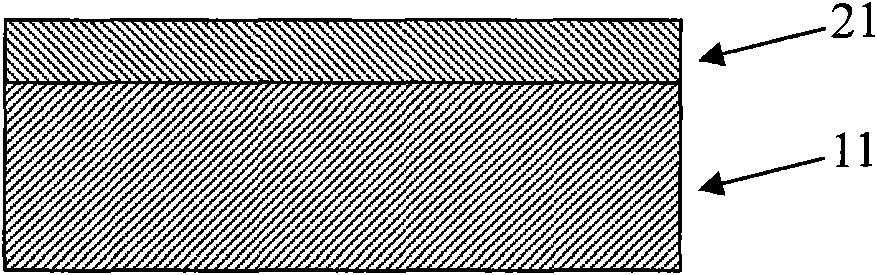

[0025] 1) if image 3 As shown, a silicon dioxide layer 21 is grown on the silicon wafer 11 by a thermal oxidation growth method, that is, a buried oxide layer in the traditional sense, the thermal oxidation temperature is about 1050°C, and the thickness is about 70-80nm; Polishing and other methods planarize the surface of the silicon dioxide layer 21 , making the surface as favorable as possible for the uniform deposition of the next deposition layer.

[0026] 2) if Figure 4 As shown, a silicon nitride layer 41 of 10nm to 20nm is deposited on the surface of silicon dioxide 21 by low pressure chemical vapor deposition (LPCVD).

[0027] 3) if Figure 5 As shown, the surface is al...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com