Silicon-on-insulator (SOI) substrate structure and device

An insulator and silicon substrate technology, applied in the field of silicon substrate structures and devices, can solve problems such as increased power consumption, loss of BOX15, increased capacitance, etc., and achieve the effects of increased operating speed, reduced procedures, and reduced power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

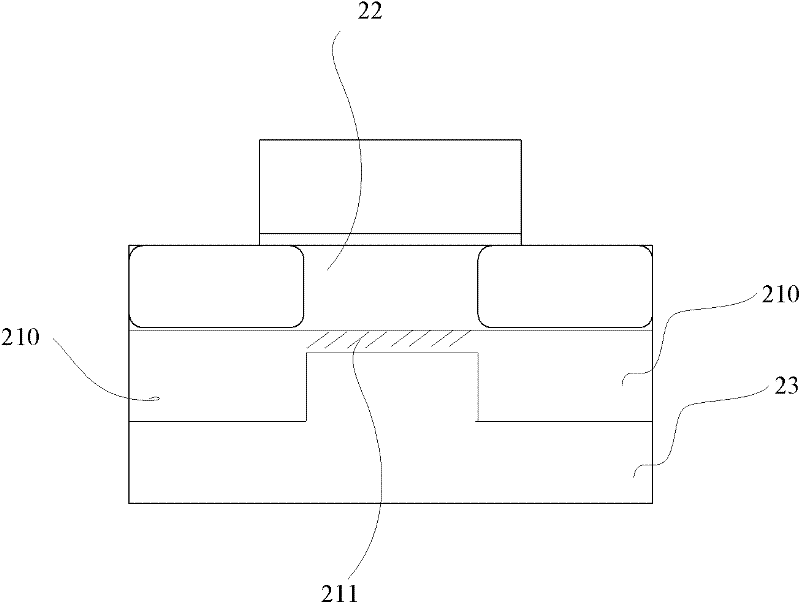

[0021] The first embodiment, FD SOI CMOS.

[0022] Reference figure 2 The insulating layer of the FD SOI CMOS is divided into a first insulating layer 211 under the channel region 22 and an uncovered second insulating layer 210. The thickness H1 of the first insulating layer 211 is smaller than the thickness H2 of the second insulating layer 210. Preferably, H1 is 1 / 10 to 1 / 2 of H2. For ordinary thin film FD SOI CMOS, H2 is above 100 nanometers, and for ultra-thin FD SOI CMOS, H2 is between 20 nanometers and 100 nanometers. The SOI substrate composed of the first insulating layer 211, the second insulating layer 210 and the underlying substrate 23 is an embodiment of the SOI substrate provided by the present invention. In the above embodiment, the underlying substrate 23 may be a silicon substrate, and the insulating layer may be silicon dioxide.

[0023] Through device simulation, when the drain voltage is 1V and H1 is the value within the range of the above-mentioned embodimen...

Embodiment 2

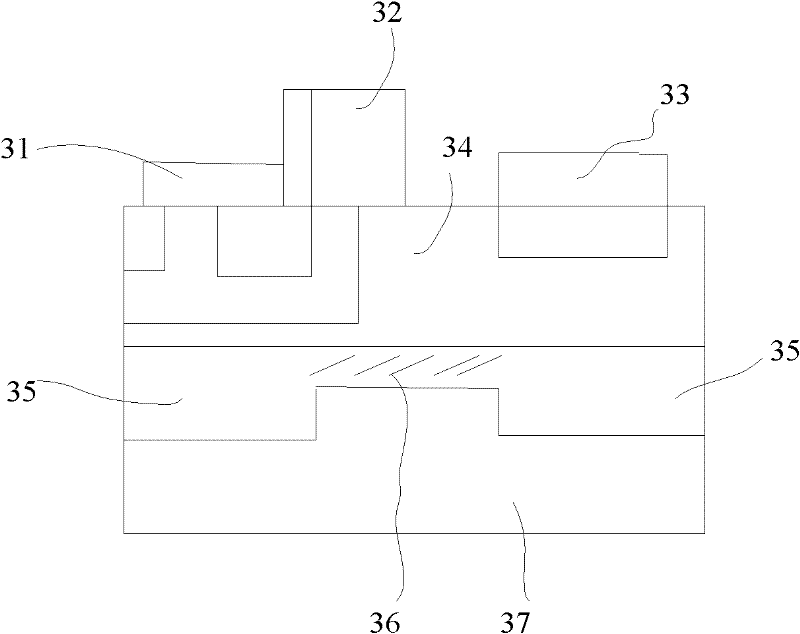

[0027] The second embodiment, SOI LDMOS.

[0028] Reference image 3 , Is a schematic diagram of the structure of an SOI LDMOS device provided by an embodiment of the present invention. The device includes a source 31, a gate 32, a drain 33, a diffusion region 34, an insulating layer, and an underlying substrate 37. The insulating layer includes a third insulating layer 35 and a fourth insulating layer 36. The thickness h3 of the third insulating layer 35 is greater than the thickness h4 of the fourth insulating layer. Compared with existing SOI LDMOS devices, image 3 In the SOI LDMOS device shown, due to the small thickness h4 of the fourth insulating layer, the heat dissipation of the diffusion region 34 is enhanced, and the lattice temperature is significantly reduced. Since the lattice temperature is significantly reduced, the self-heating effect is greatly suppressed, thereby Reduce the degradation of carrier mobility at high temperatures, increase the leakage current of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More