Patents

Literature

94results about How to "Reduce self-heating effect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

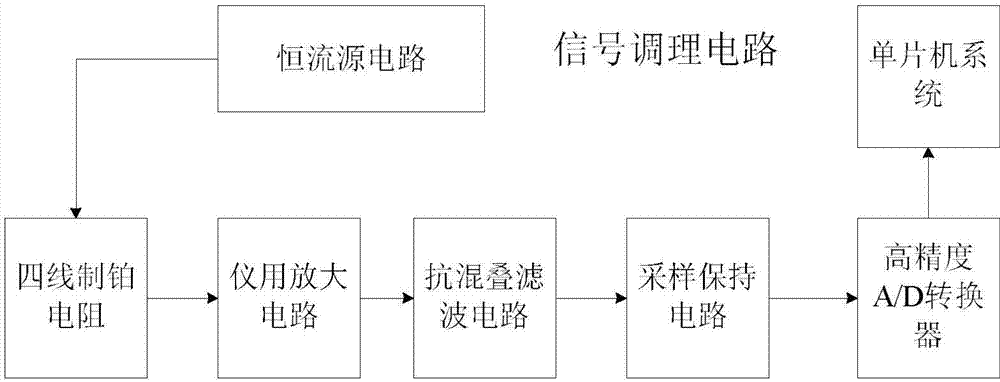

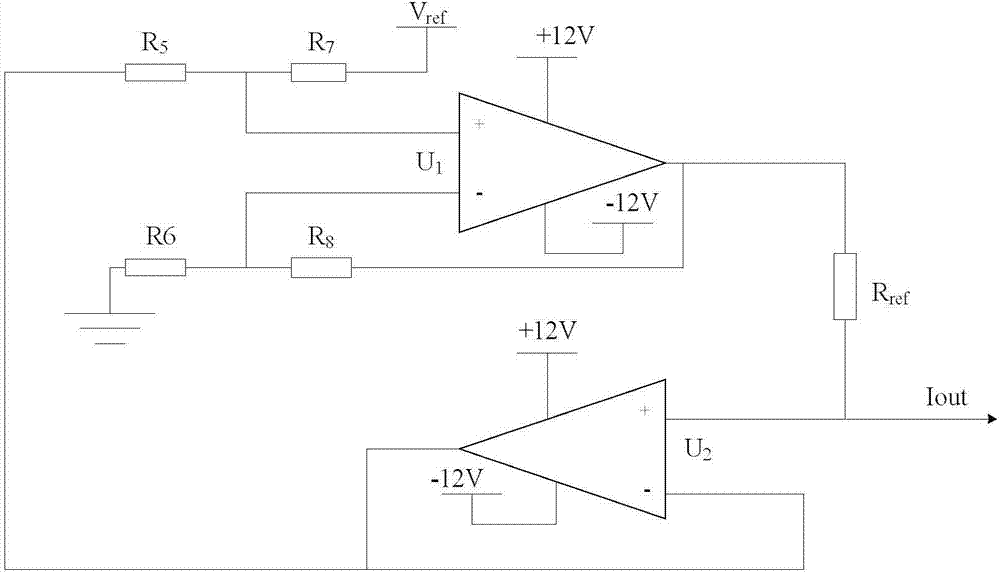

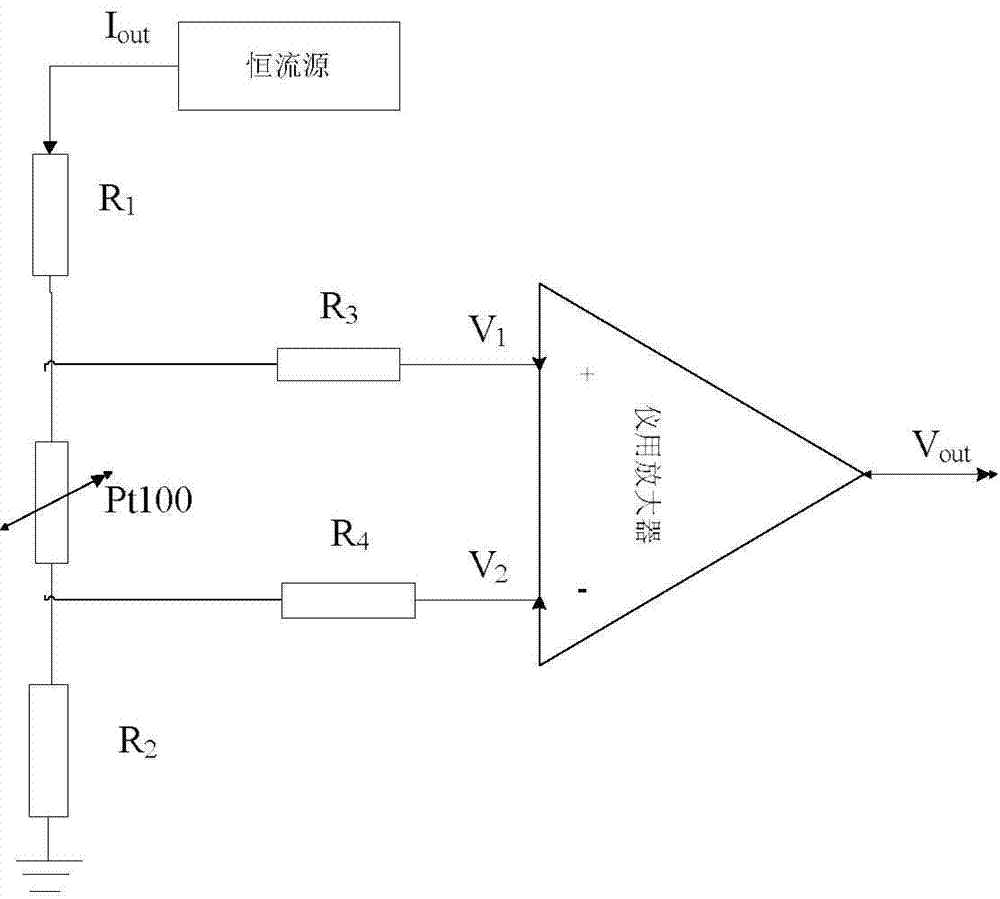

Method and device for precisely measuring temperatures of platinum resistors

InactiveCN104236742AReduce mistakesReduce self-heating effectThermometers using electric/magnetic elementsUsing electrical meansMicrocomputer systemLow-pass filter

The invention discloses a method and a device for precisely measuring temperatures of platinum resistors. The scheme for measuring the temperatures of the micro-current-drive four-wired Pt100 platinum resistors includes that the device for precisely measuring the temperatures of the platinum resistors comprises a constant-current source drive circuit, a four-wired platinum resistor interface circuit, an instrument amplifier circuit, an anti-aliasing filter circuit, a sampling hold circuit, an A / D (analog / digital) sampling circuit and a single chip microcomputer system. A constant-current source comprises two low-noise and low-offset bipolar operational amplifiers OP07CD with high open-loop gain; the four-wired platinum resistor interface circuit is divided into a constant-current source power lead and a voltage drive lead; the instrument amplifier circuit comprises a double-stage differential amplifier circuit; the anti-aliasing filter circuit is an RC low-pass filter circuit; an A / D converter is a 24-bit high-resolution A / D converter CS5550. The method and the device have the advantage that the measurement precision is high, calibrated temperature measurement errors are smaller than + / -0.03 DEG C, and requirements of industrial production procedures on high temperature measurement precision can be met.

Owner:JIANGNAN UNIV

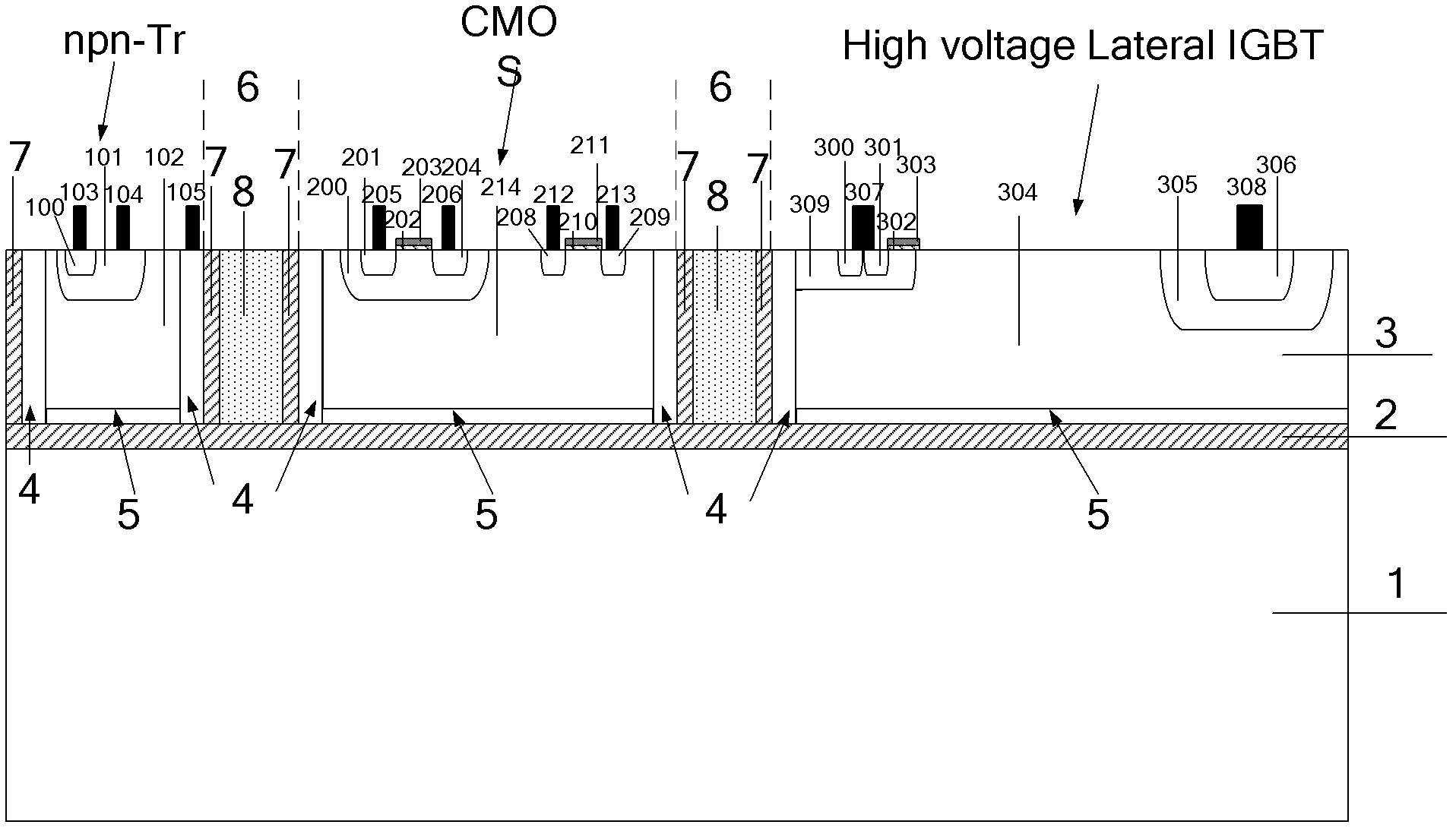

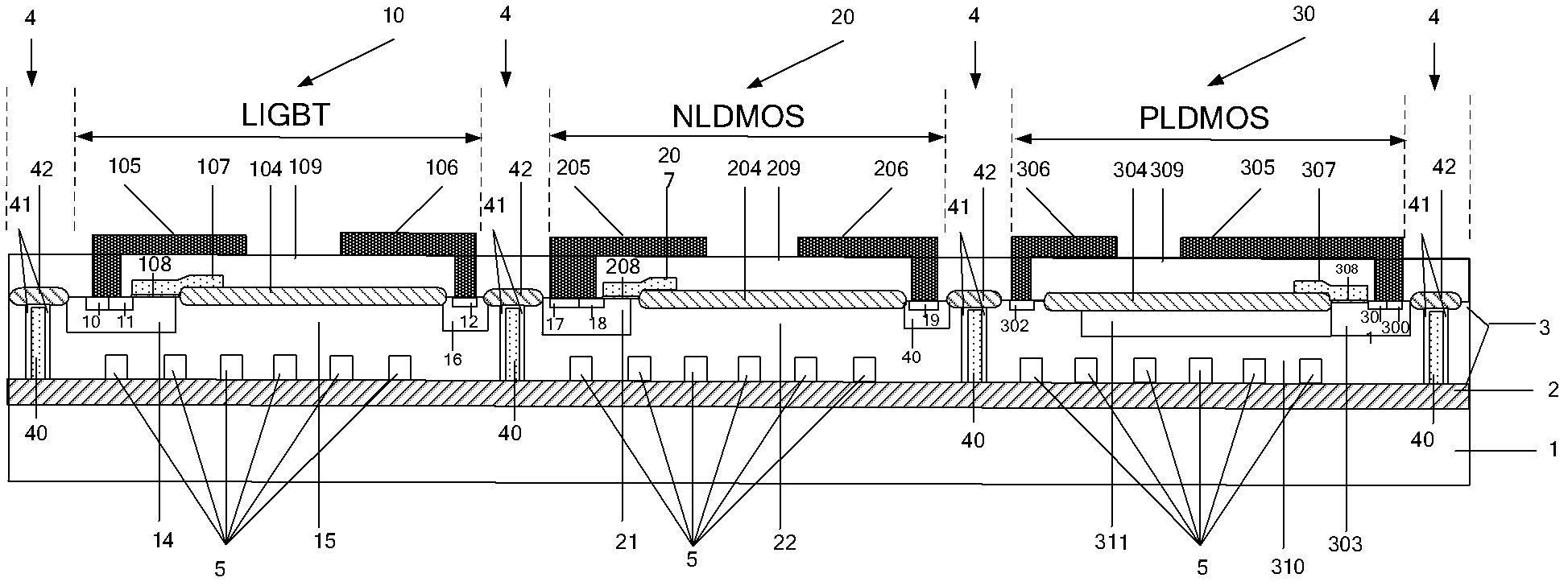

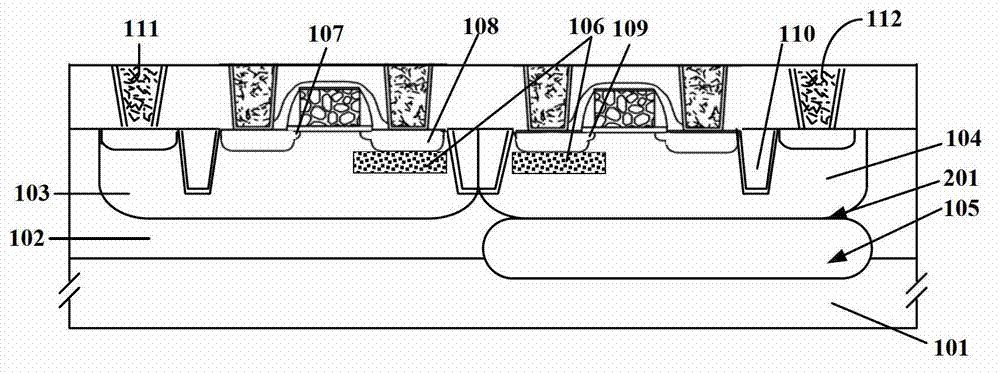

Semiconductor device used for SOI (silicon-on-insulator) high-voltage integrated circuit

InactiveCN102361031AIncrease concentrationControl concentrationSolid-state devicesSemiconductor devicesHigh concentrationLow voltage

The invention relates to a semiconductor device used for an SOI (silicon-on-insulator) high-voltage integrated circuit, belonging to the field of power semiconductor devices. The semiconductor device comprises a semiconductor substrate layer, a dielectric buried layer and a silicon top layer, wherein at least high-voltage LIGBT (lateral insulated gate bipolar transistor), NLDMOS (N-type lateral double-diffused metal-oxide semiconductor) and PLDMOS (P-type lateral double-diffused metal-oxide semiconductor) devices are integrated in the silicon top layer; the thickness of the dielectric buried layer is not more than 5 mum; the thickness of the silicon top layer is not more than 20 mum; multiple incontinuous high-concentration N<+> regions (doping concentration is not lower than 1e16e cm<-3>) are formed at the bottoms of the high-voltage devices and the silicon top layer above the surface of the dielectric buried layer; the high-voltage devices are isolated by dielectric isolation regions; low-voltage MOS (metal oxide semiconductor) devices can also be integrated in the device; the high-voltage devices and low-voltage devices are isolated by the dielectric isolation regions; and different low-voltage devices are isolated by field oxidation layers. The semiconductor device has the advantages that: because of the introduction of the multiple incontinuous high-concentration N<+> regions, the electric field of the silicon top layer is weakened and the electric field of the dielectric buried layer is enhanced at the same time, the breakdown voltage of the device is greatly improved, and the device can be applied in high-voltage integrated circuits in the automobile electronics, consumption electronics, green lighting, industrial control, power supply management, display driving and other fields.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

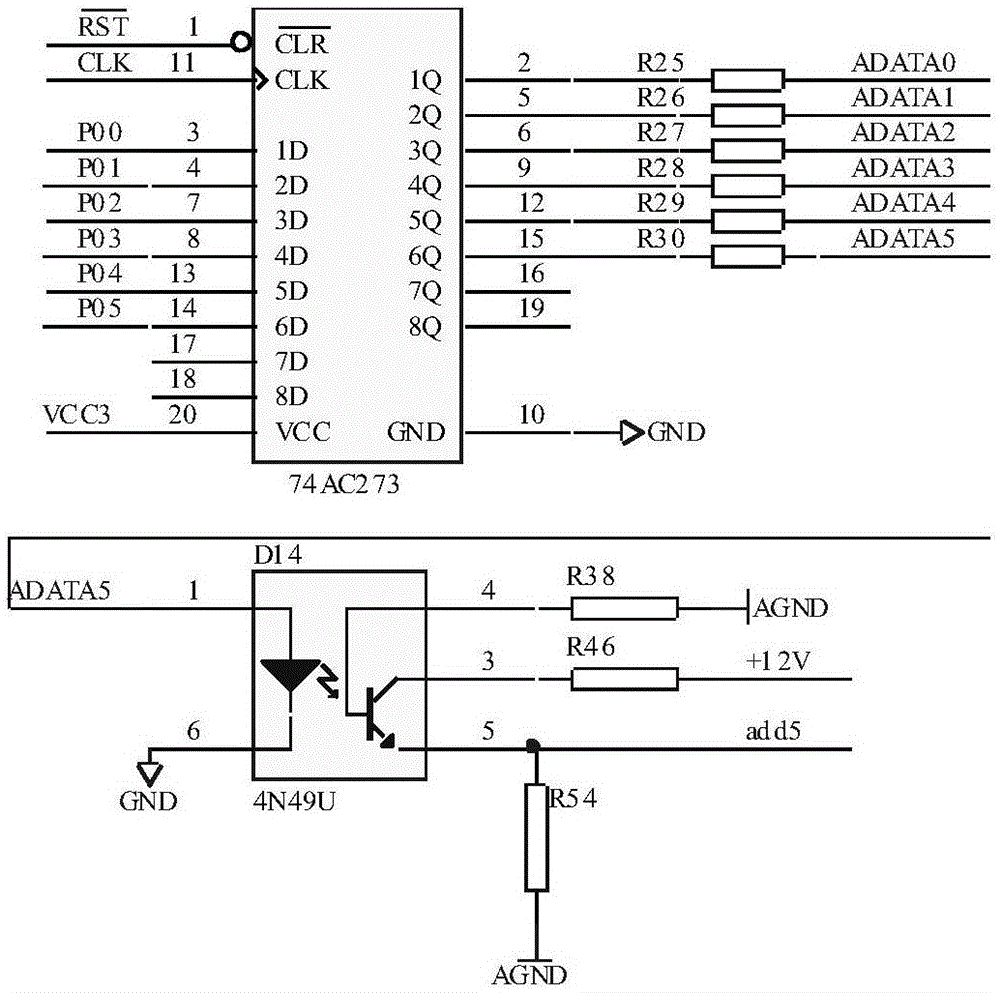

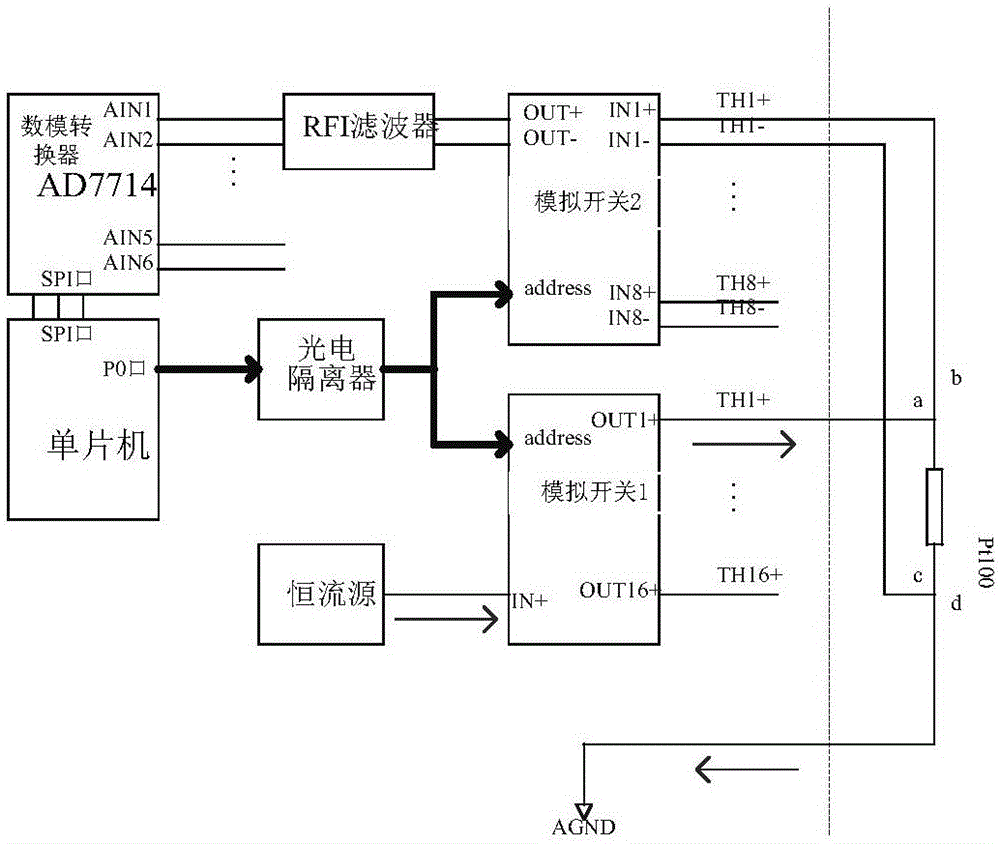

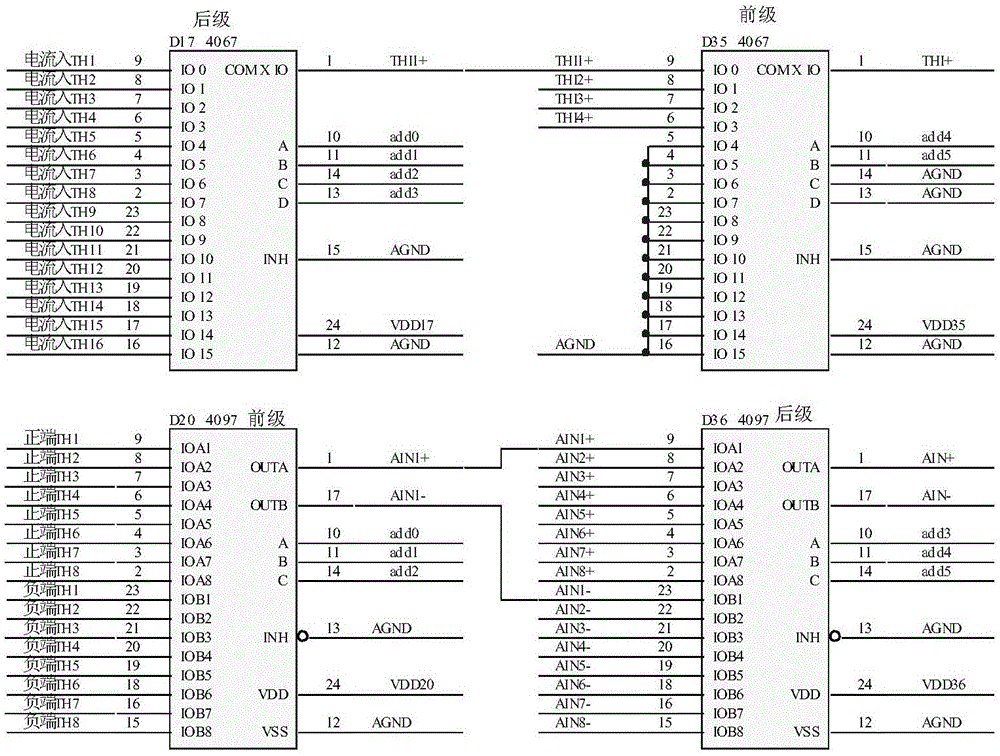

High accuracy multi-channel temperature signal acquisition device

InactiveCN105092075ARealize four-wire connectionEliminate lead resistanceThermometers using electric/magnetic elementsUsing electrical meansAlloyEngineering

The invention discloses a high accuracy multi-channel temperature signal acquisition device. When temperature measurement platinum resistors are used to measure temperature, the constant current of a constant current source is transmitted to each temperature measurement platinum resistor through a first group of analogue switches; the other end of each resistor is grounded; at the same time, a second group of analogue switches are employed to acquire the voltage at two ends of each temperature measurement platinum resistor so that four-wire system connection for each temperature measurement platinum resistor is realized; as no current exists between each pair of input ends of the second group of analogue switches and each resistor, that is, no resistance is generated, the lead resistance can be effectively eliminated and the temperature measurement accuracy can be improved; an analogue circuit part and a digital circuit part employ a photoisolator to perform fine isolation so as to guarantee achievement of higher measurement accuracy; the temperature measurement accuracy for a temperature measurement circuit reaches 0.004DEG C within the -100DEG C to 50DEG C temperature measurement scope, and the linearity for the temperature measurement circuit reaches 0.0135%; and the constant current source current is set as 9.8mA through an RJ711 precise alloy foil resistor so as to eliminate the self-heating effect of each temperature measurement resistor and guarantee that the voltage of the temperature measurement platinum resistor Pt100 is not too low.

Owner:SHANDONG INST OF AEROSPACE ELECTRONICS TECH

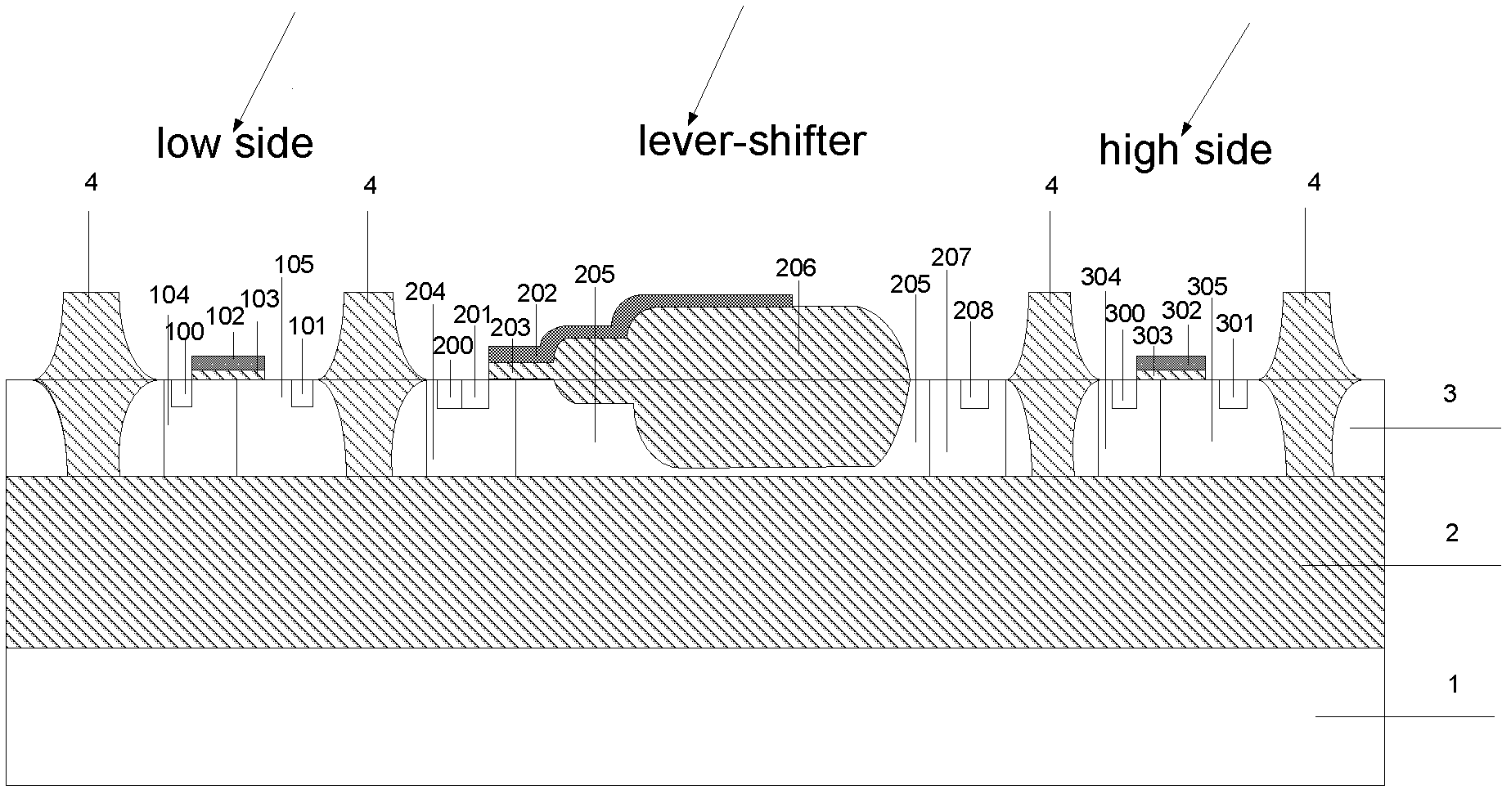

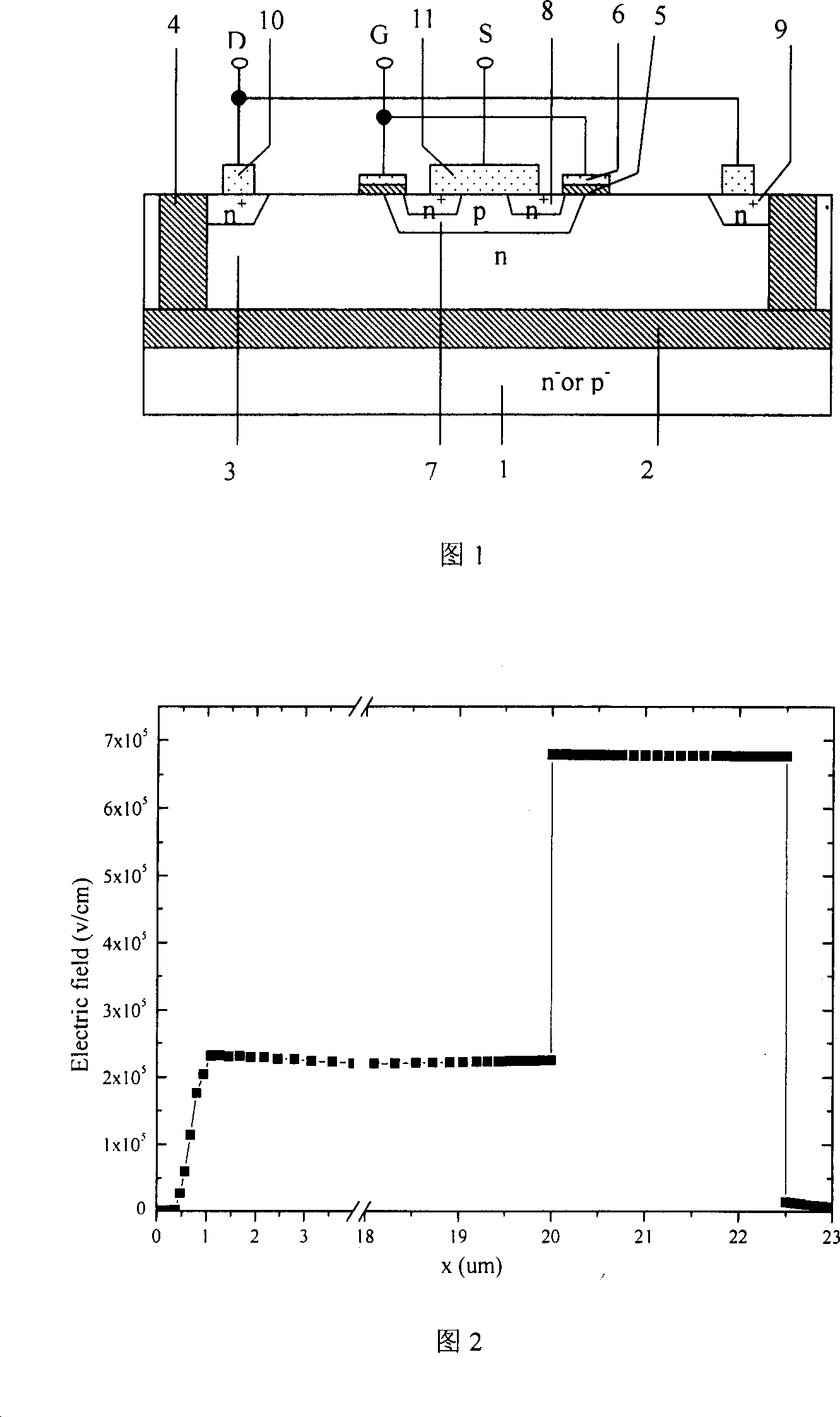

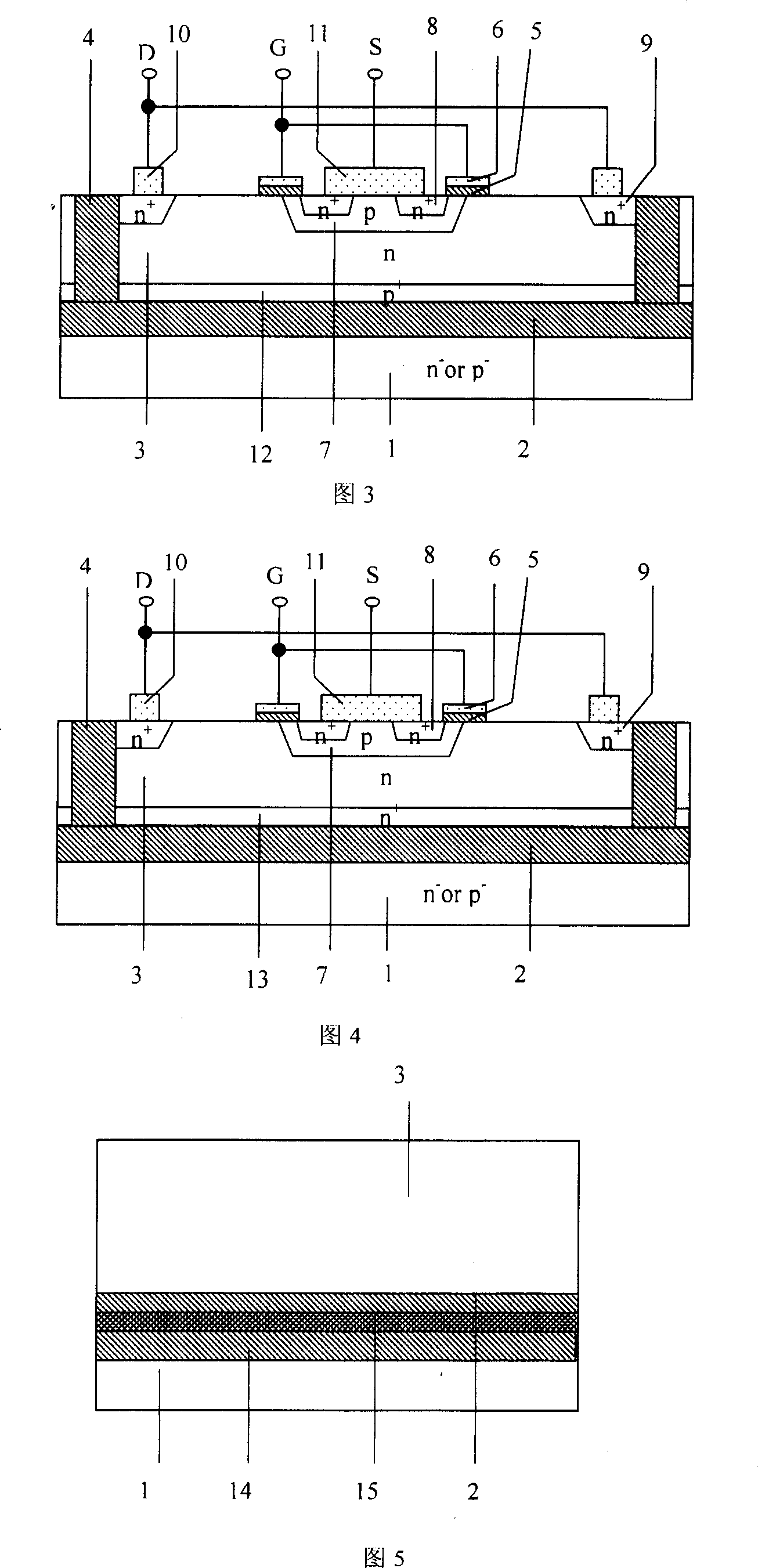

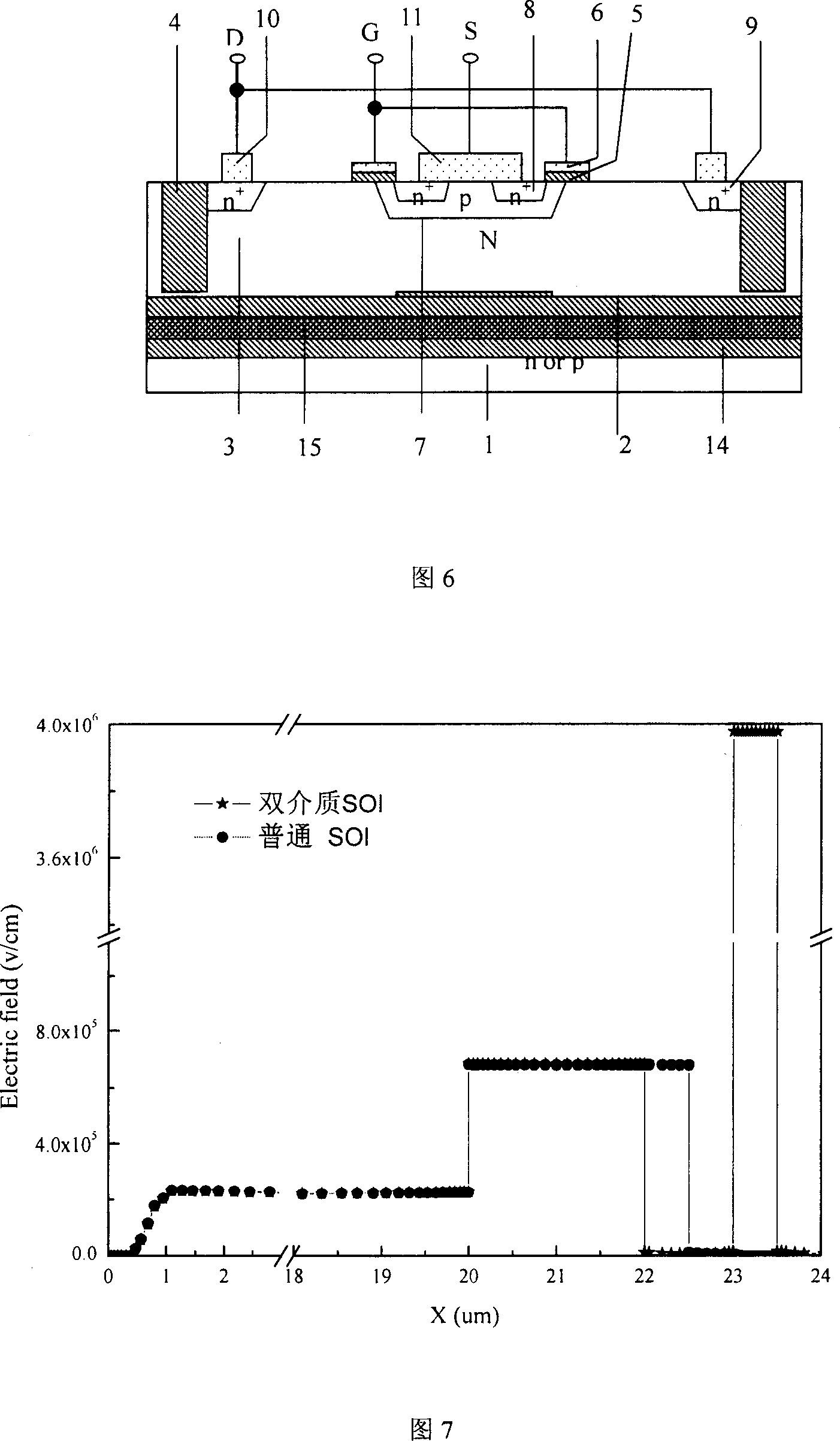

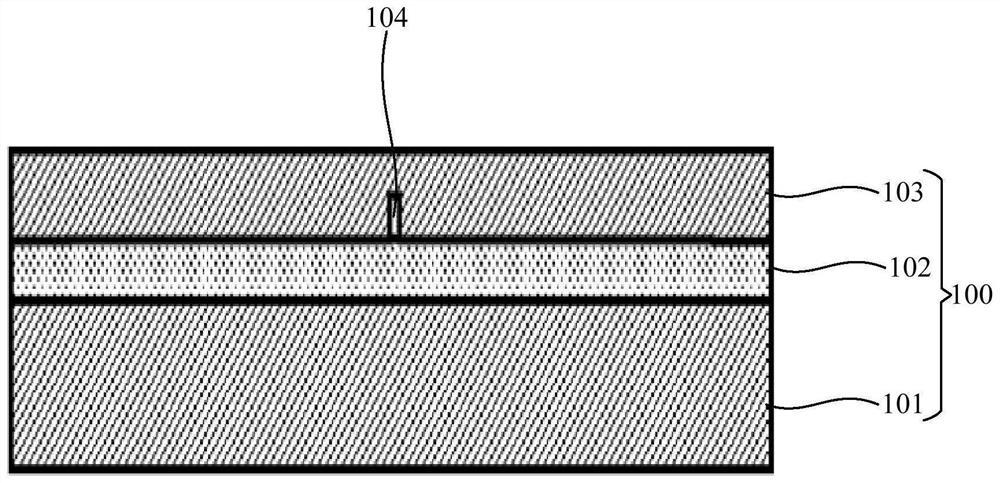

Pressure resistant layer structure having dual-medium buried layer and SOI power device using the same

InactiveCN101083278AImprove pressure resistanceReduce self-heating effectTransistorThyristorInter layerEngineering

The invention provides a voltage resistance layer structure with double medium buried layers for SOI power device, and the SOI power device adopting the voltage resistance layer structure, belonging to the field of voltage resistance technique of SOI power devices. And the voltage resistance layer has double medium buried layers, where an intermediate layer is arranged between them. And the invention can improve voltage resistance on the condition of same thickness of medium buried layer, and largely reduce self-heating effect on the condition of same voltage, thus able to make a high voltage-resistance SOI power device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

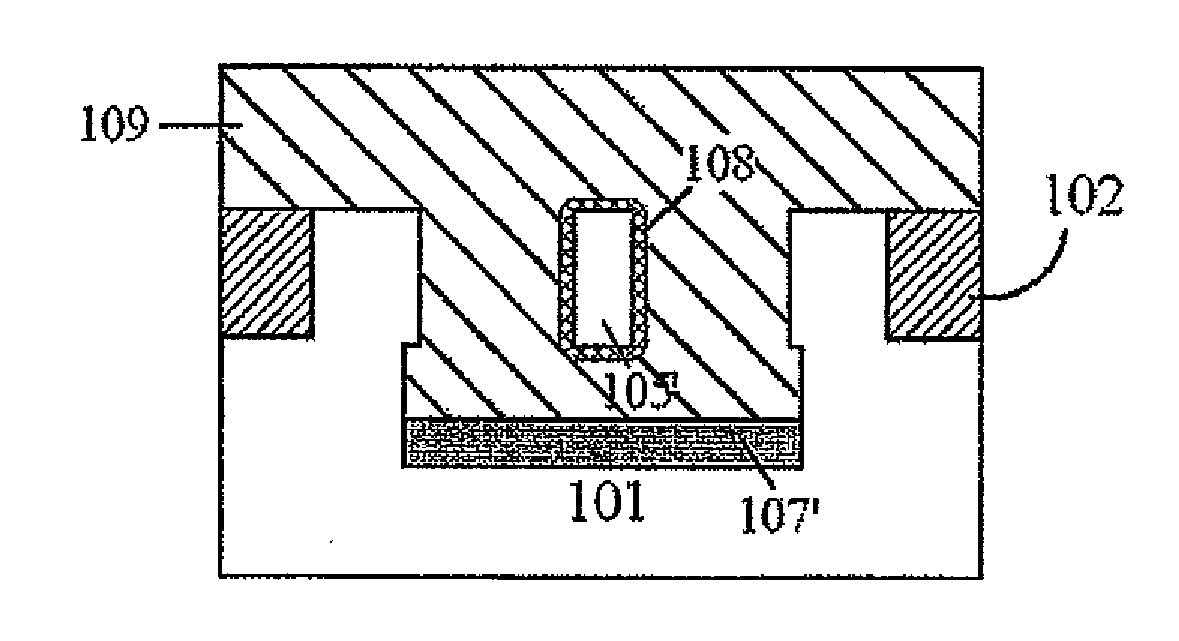

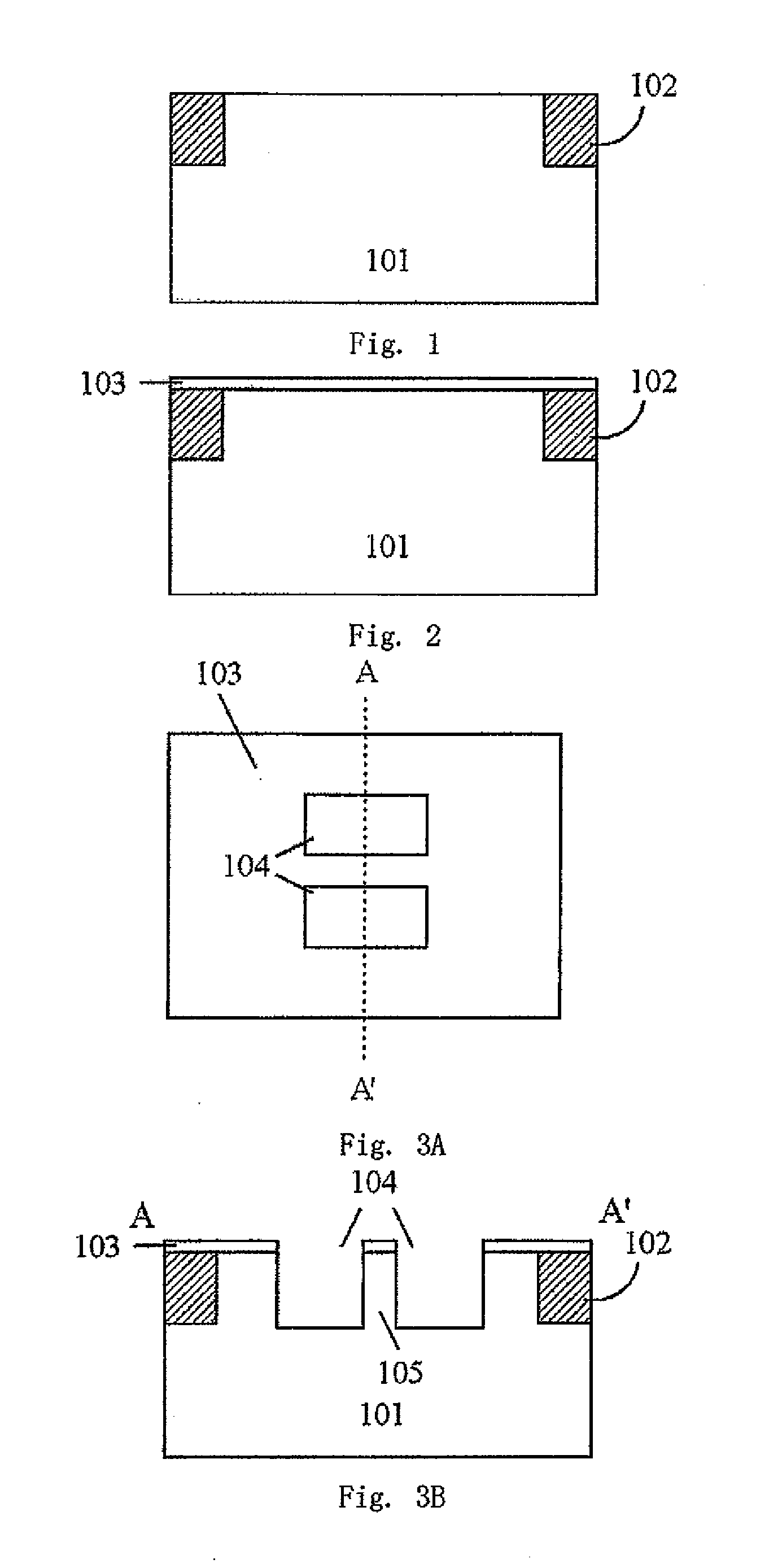

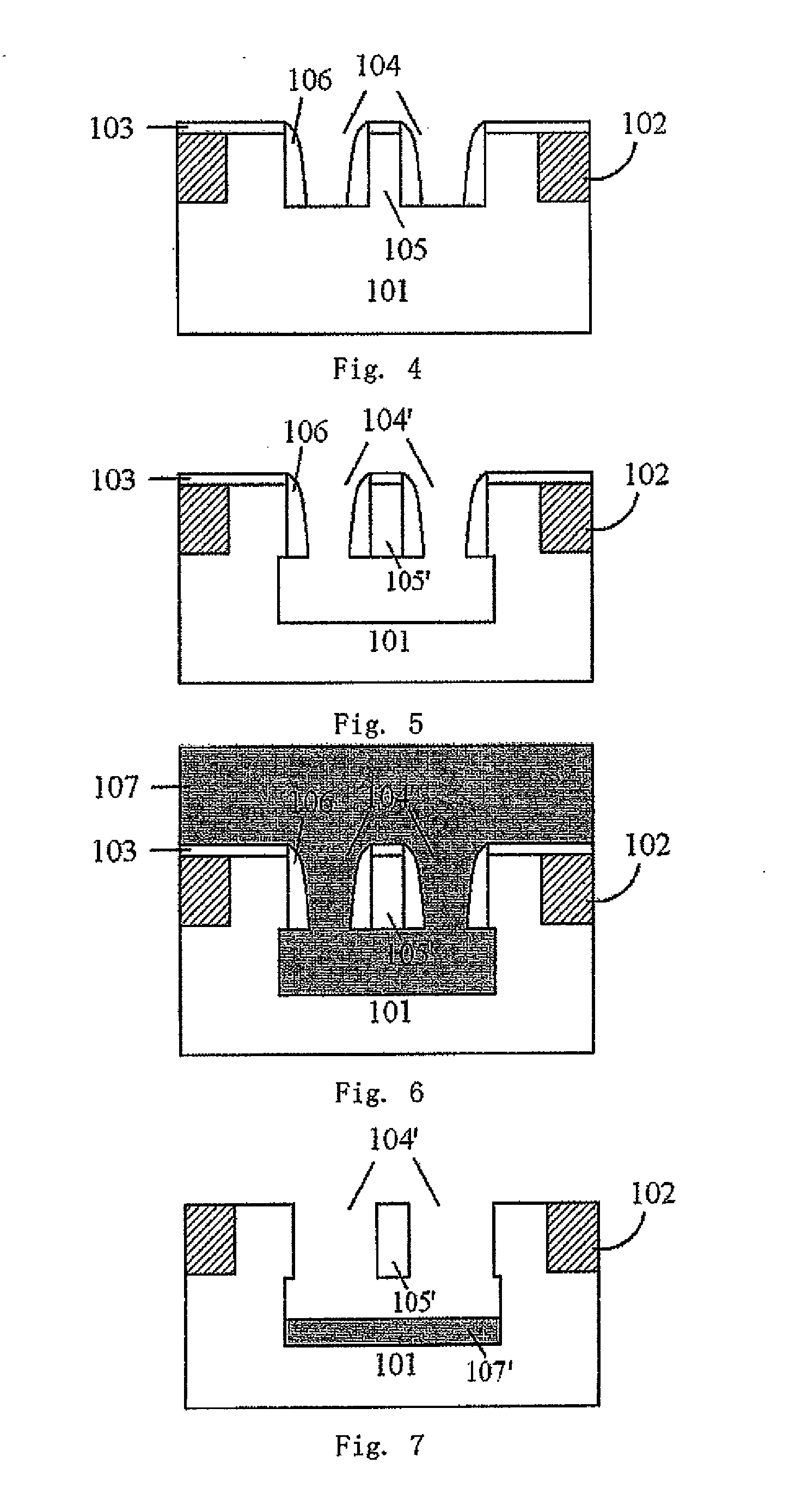

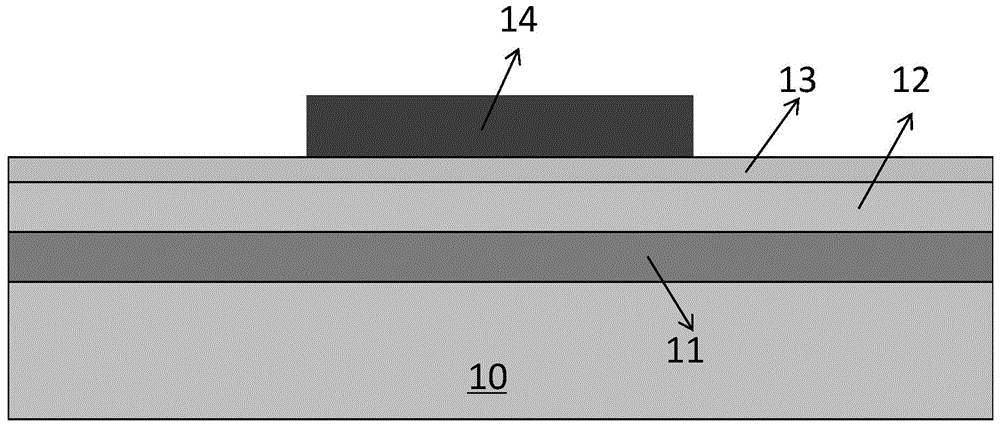

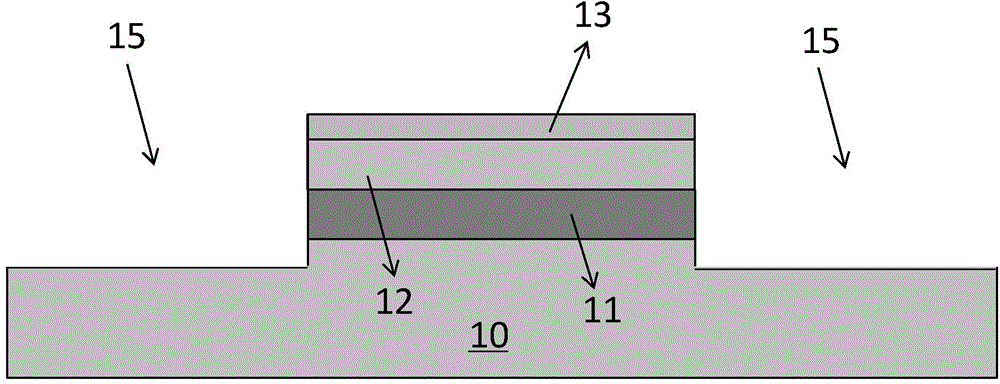

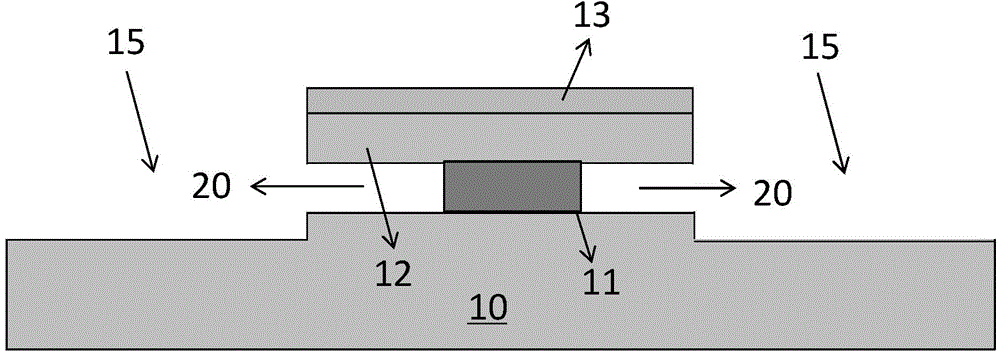

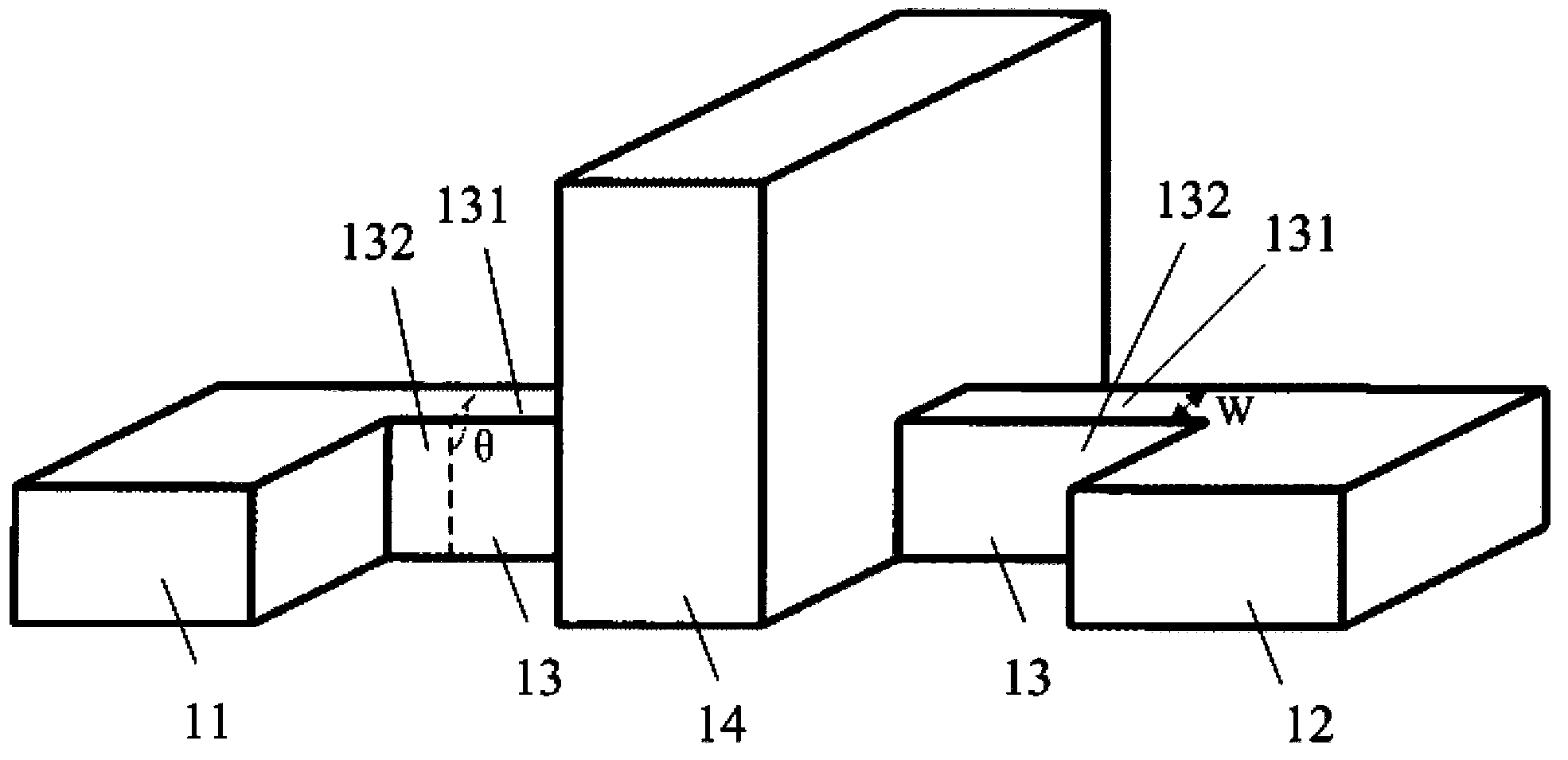

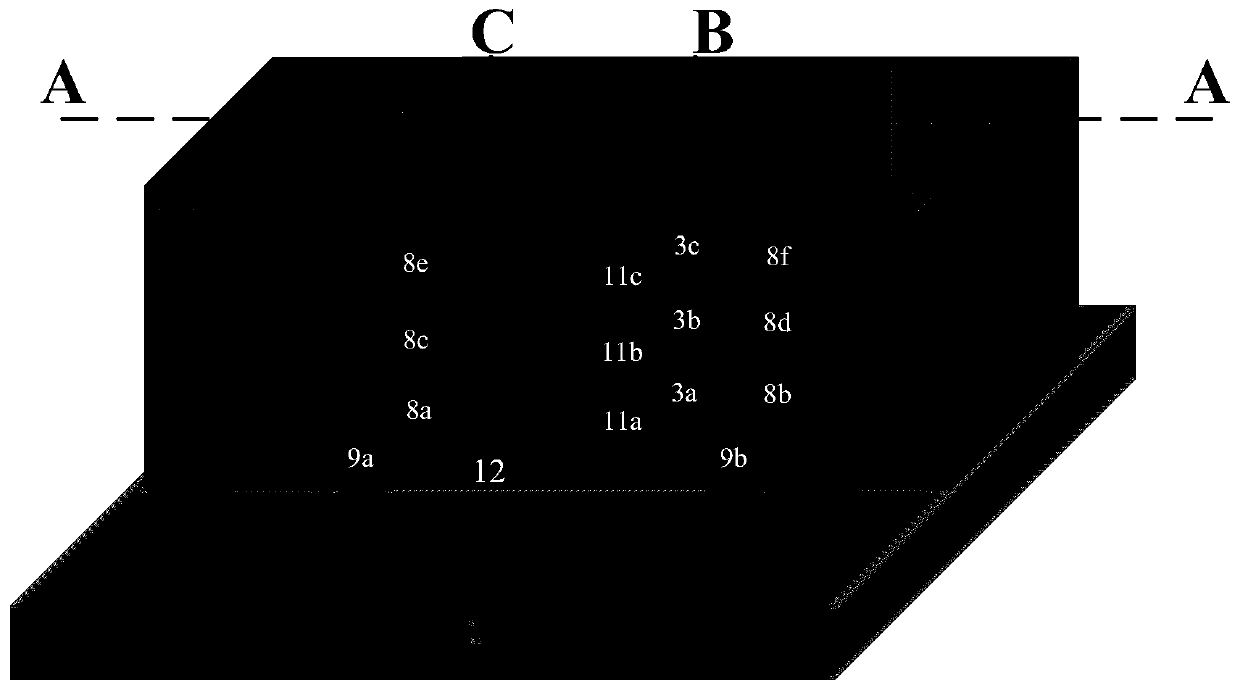

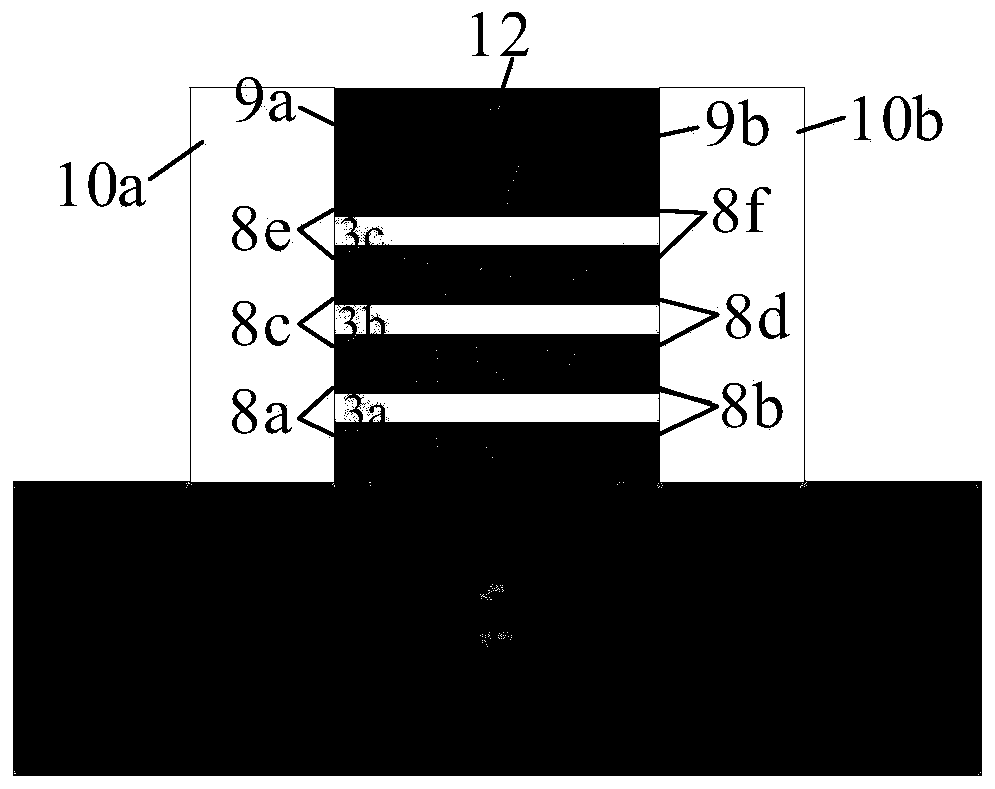

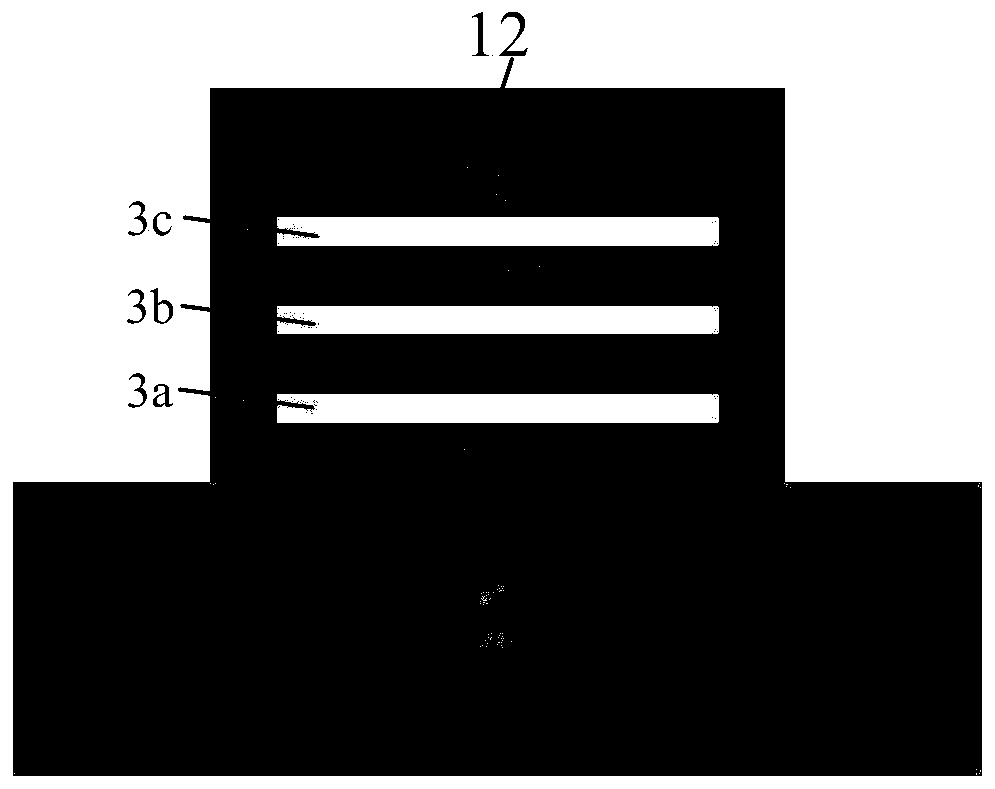

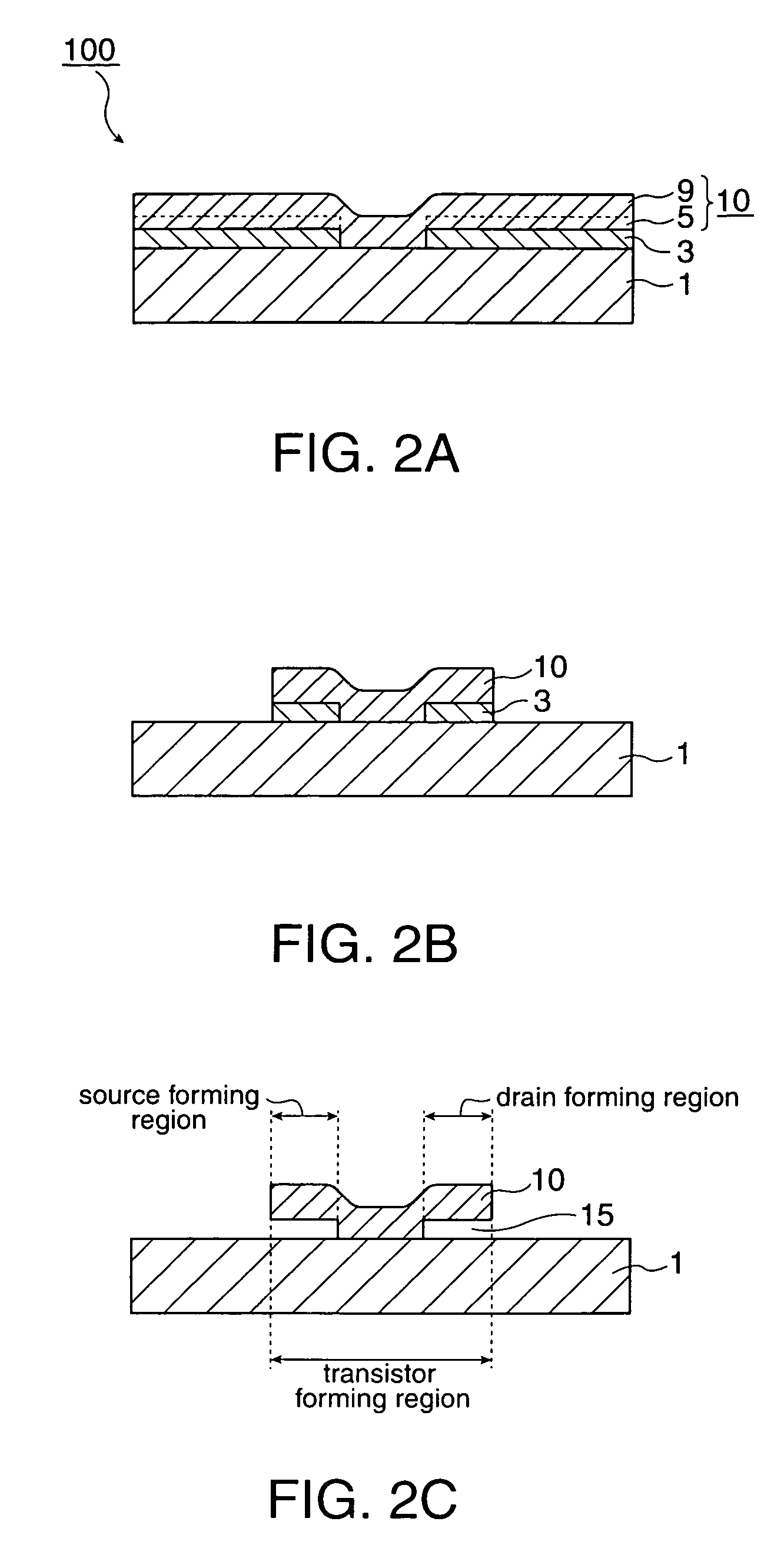

Method for manufacturing suspended fin and gate-all-around field effect transistor

ActiveUS20120149162A1Simple manufacturing processEasy to integrateTransistorSolid-state devicesManufacturing cost reductionFloating body effect

The present application discloses a method for manufacturing a gate-all-around field effect transistor, comprising the steps of forming a suspended fin in a semiconductor substrate; forming a gate stack around the fin; and forming source / drain regions in the fin on both sides of the gate stack, wherein an isolation dielectric layer is formed in a portion of the semiconductor substrate which is adjacent to bottom of both the fin and the gate stack. The present invention relates to a method for manufacturing a gate-all-around device on a bulk silicon substrate, which suppress a self-heating effect and a floating-body effect of the SOI substrate, and lower a manufacture cost. The inventive method is a conventional top-down process with respect to a reference plane, which can be implemented as a simple manufacture process, and is easy to be integrated into and compatible with a planar CMOS process. The inventive method suppresses a short channel effect and promotes miniaturization of MOSFETs.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Silicon on insulator (SOI) transverse high voltage power device with ultralow specific on resistance

ActiveCN103022134AEasy to integrateReduce layout areaSemiconductor devicesPower semiconductor deviceEngineering

A silicon on insulator (SOI) transverse high voltage power device with ultralow specific on resistance belongs to the technical field of power semiconductor devices and comprises a vertical super junction cellular structure and a terminal structure. The terminal structure is located on the outside or the periphery of an integral cellular structure. The device is manufactured on an SOI layer of an SOI material. The vertical super junction cellular structure improves breakdown voltage, reduces specific on resistance simultaneously and reduces domain area. The device is integrated by a single cellular or a plurality of cellulars, the plurality of cellulars connected in parallel can share one terminal, and a drain leading out structure is utilized to lead out a drain transversely to enable the drain, a grid and a source to be located on the surface. The device can be easily integrated with a common circuit, greatly reduces domain area and further reduces process cost. In addition, the device is capable of increasing a device vertical electric field by adopting a thin oxygen burying layer and simultaneously can effectively relieve self-heating effect.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

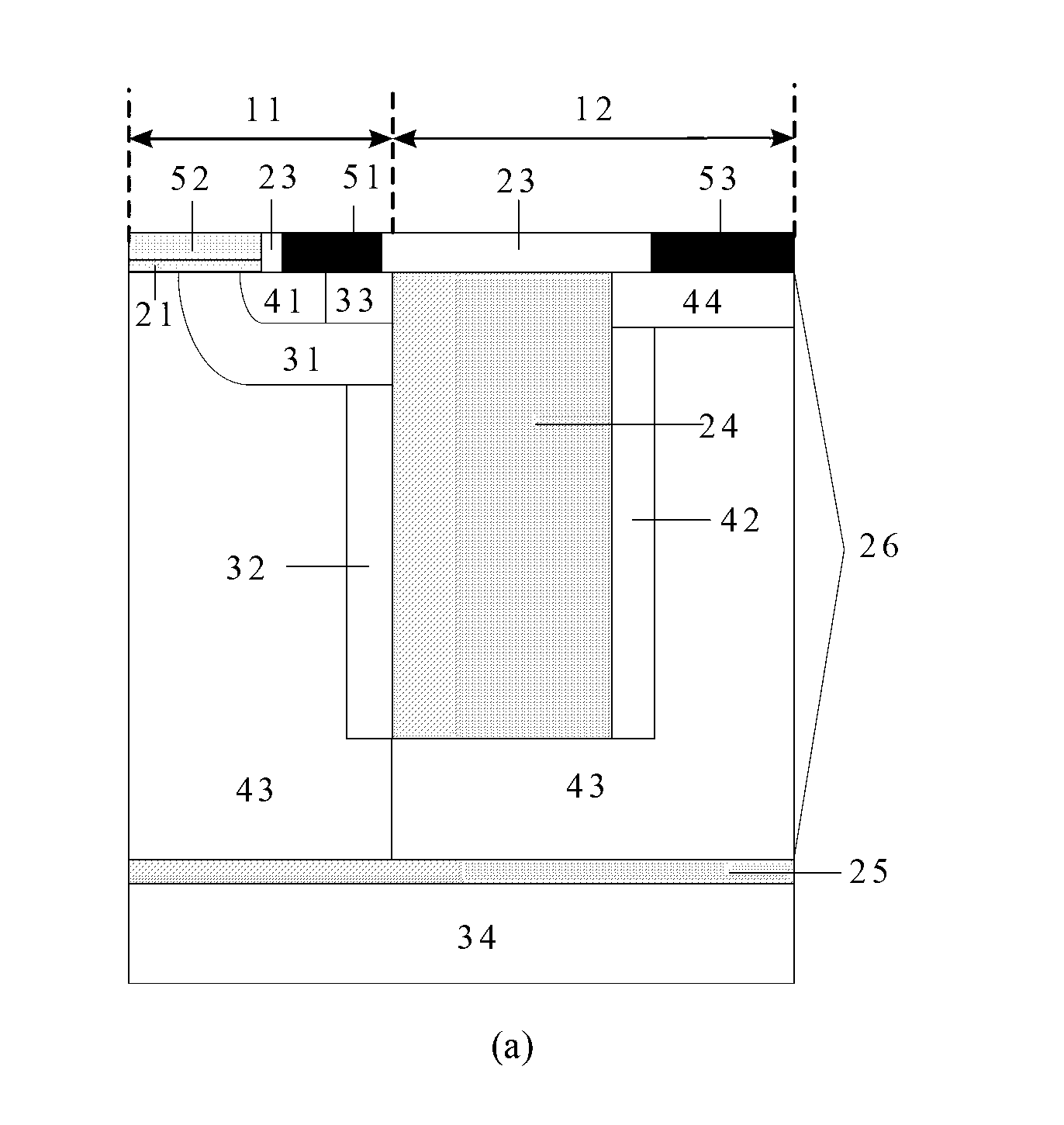

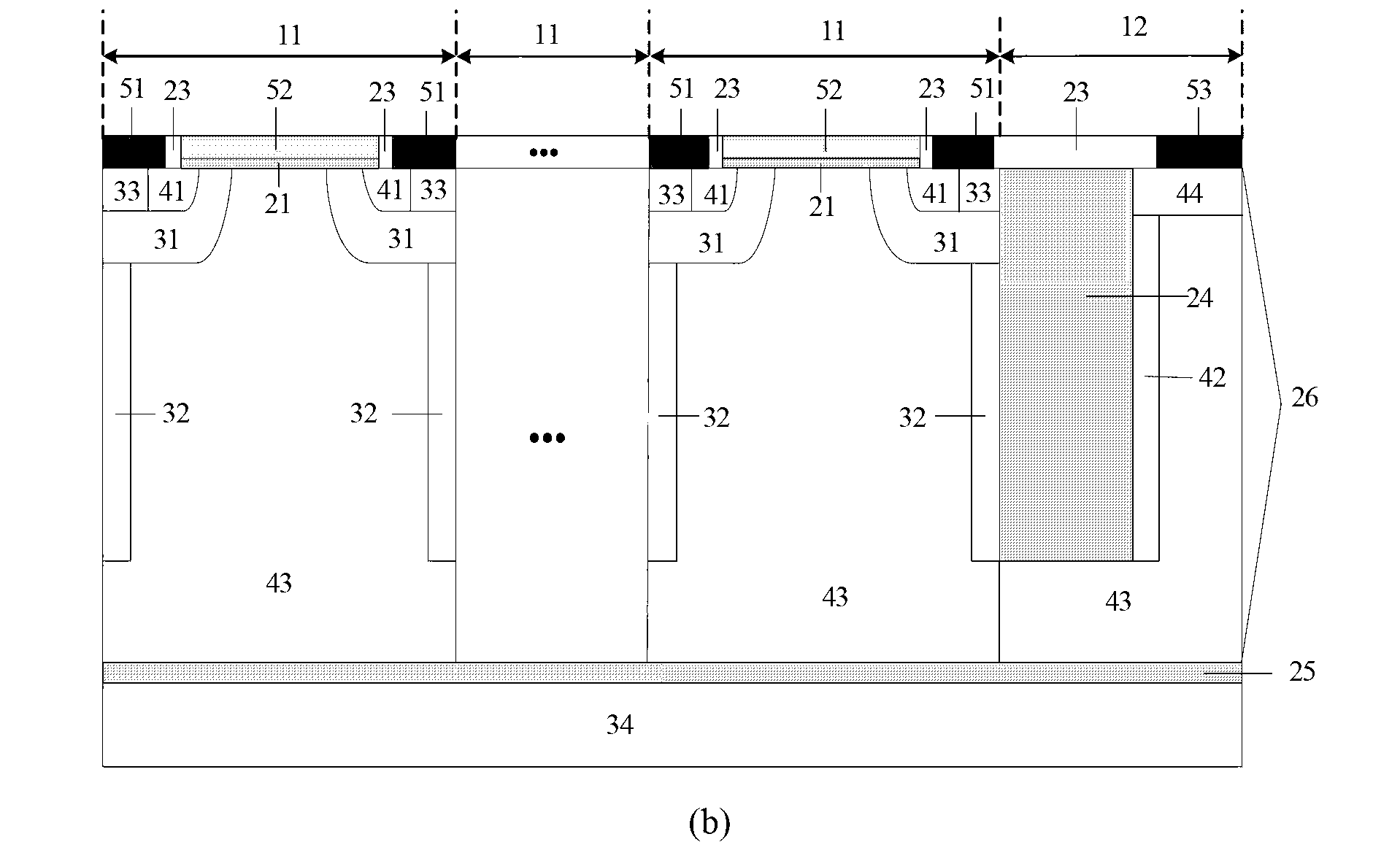

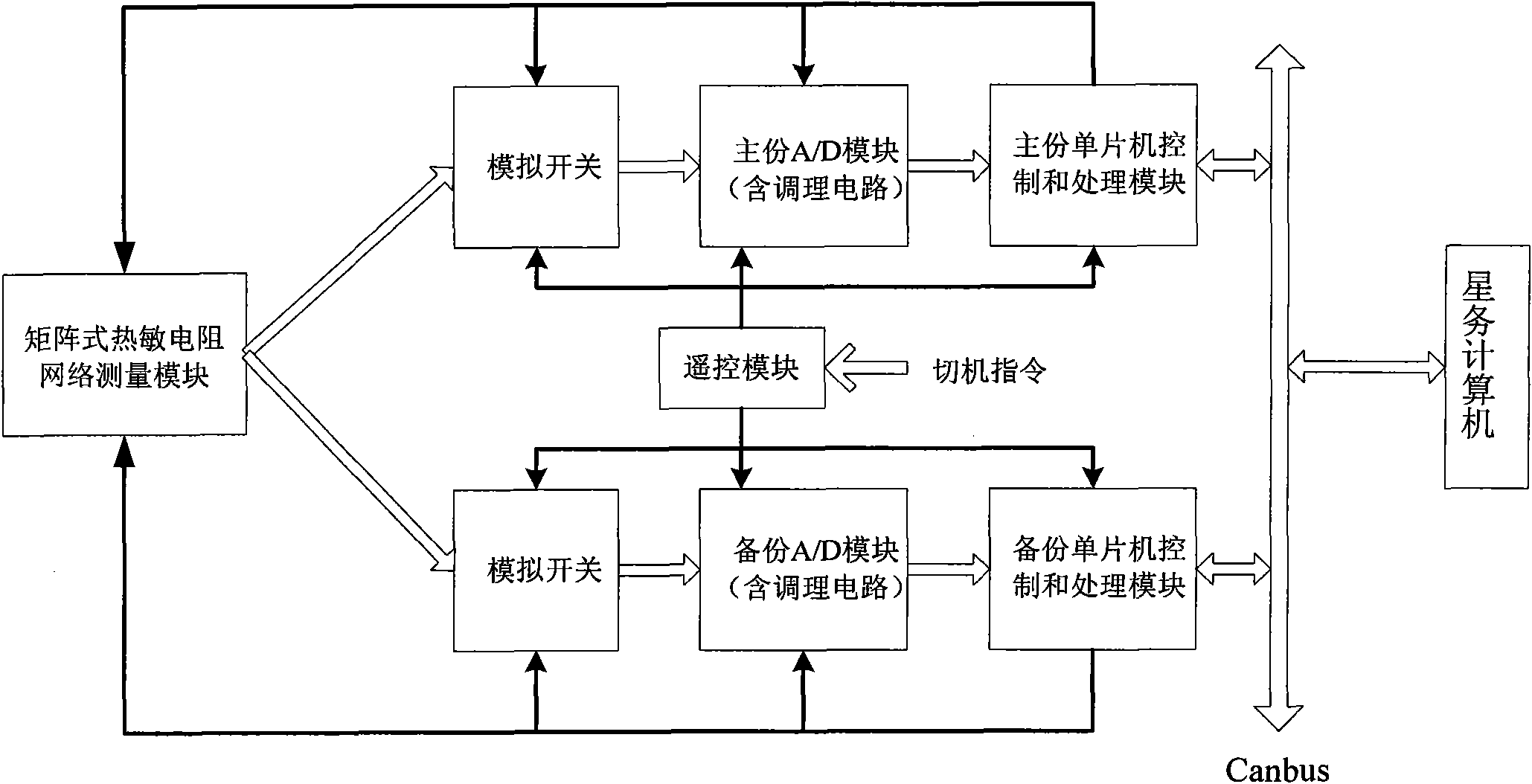

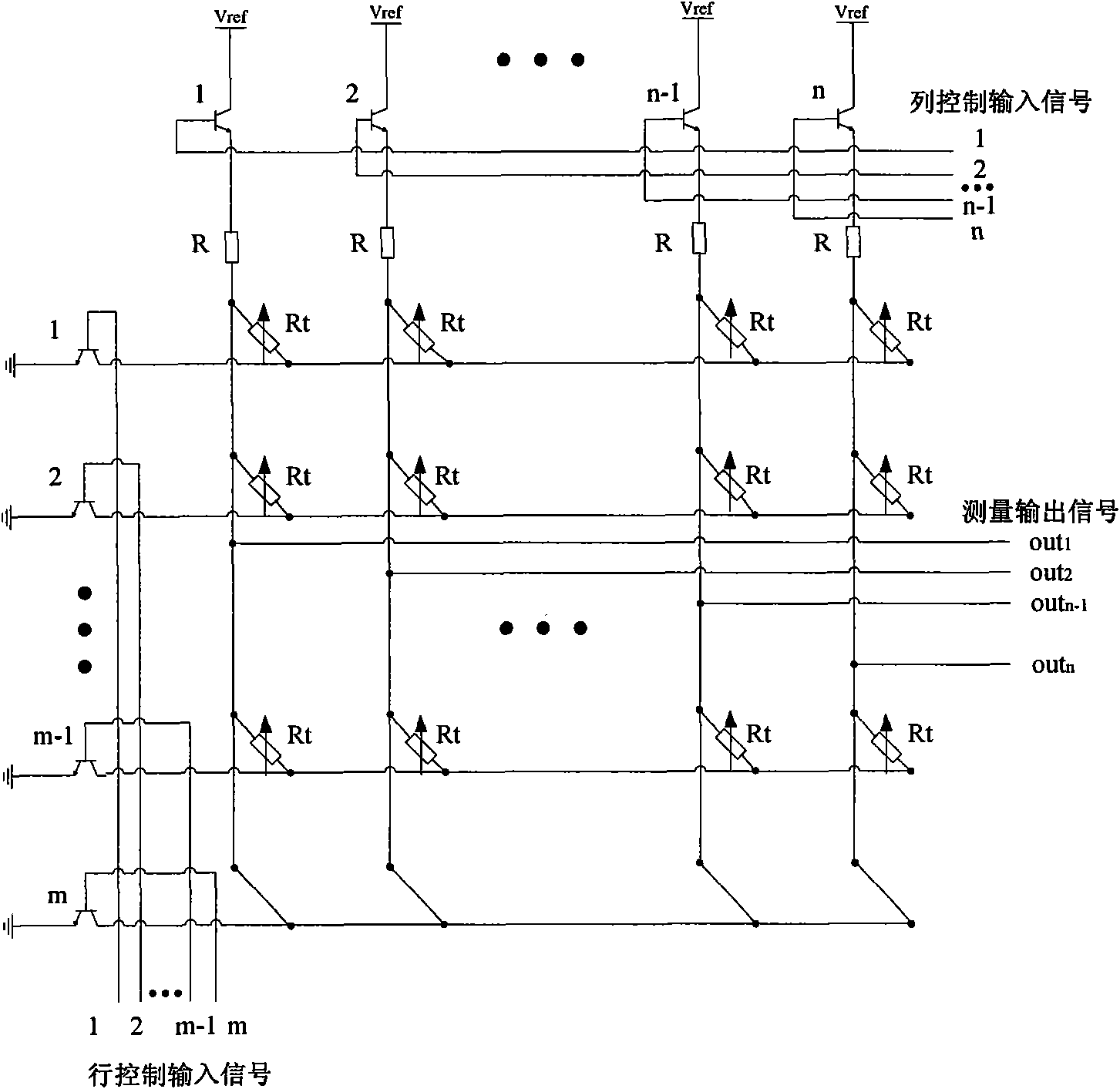

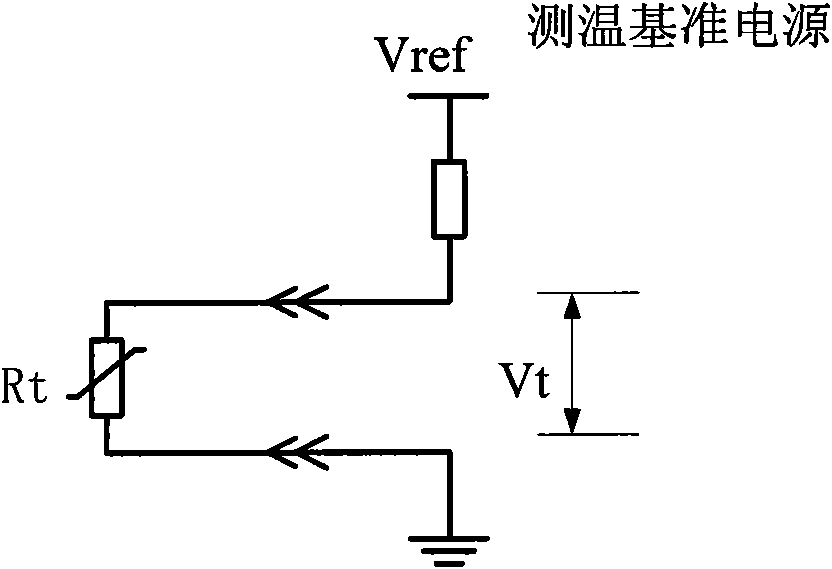

Matrix multi-path temperature detection circuit for small satellite platform

InactiveCN102062645AReduce self-heating effectHigh measurement accuracyThermometers using electric/magnetic elementsUsing electrical meansSatelliteThermistor

The invention provides a matrix multi-path temperature detection circuit for a small satellite platform, comprising a matrix thermistor measurement network, an analog switch, a main backup analog / digital (A / D) conversion module and a main backup singlechip controlling and processing module, wherein the matrix thermistor measurement network completes voltage value collection of the terhmistor of each temperature monitor point in a satellite system; the analog switch is matched with the matrix thermistor measurement network to select the voltage of a particular temperature monitor point transmitted to the A / D conversion module; the A / D conversion module is used for carrying out the filtration, amplification and A / D conversion on a collected temperature voltage; and the singlechip controlling and processing module is used for setting and outputting an inspection control signal of the matrix thermistor network and the analog switch, converting the voltage output by the A / D conversion module into a temperature value, and managing communication with a controller area network (CAN) bus. By utilizing the temperature detection circuit, elements and devices required for temperature measurement of the satellite platform are reduced, the self-heating effect of the thermistor is reduced, the backup design is added simultaneously, and the reliability is improved.

Owner:AEROSPACE DONGFANGHONG SATELLITE

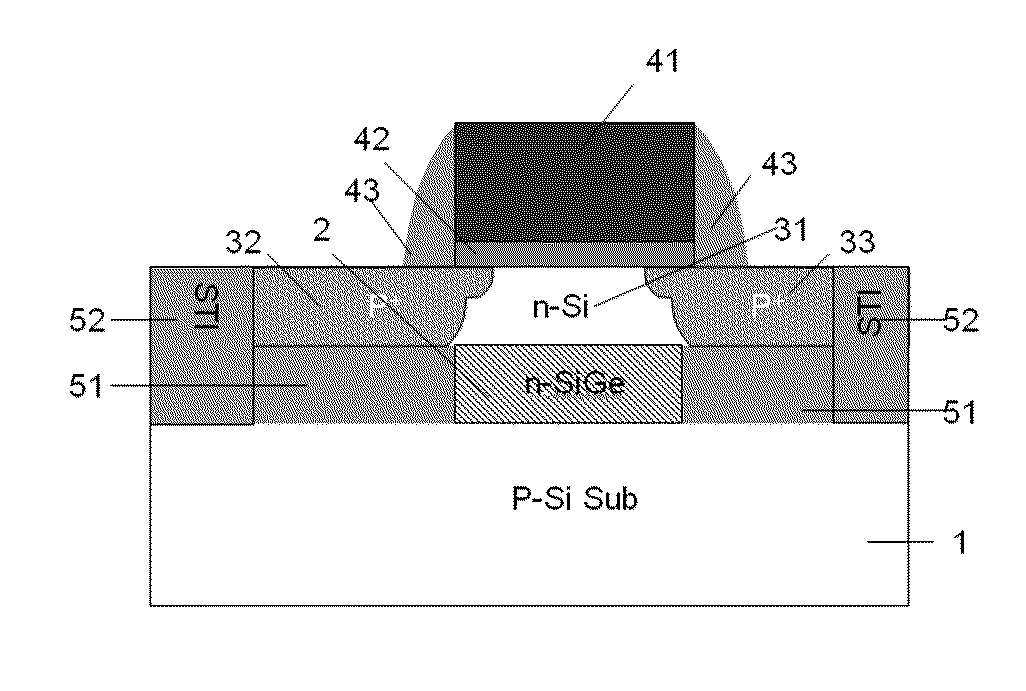

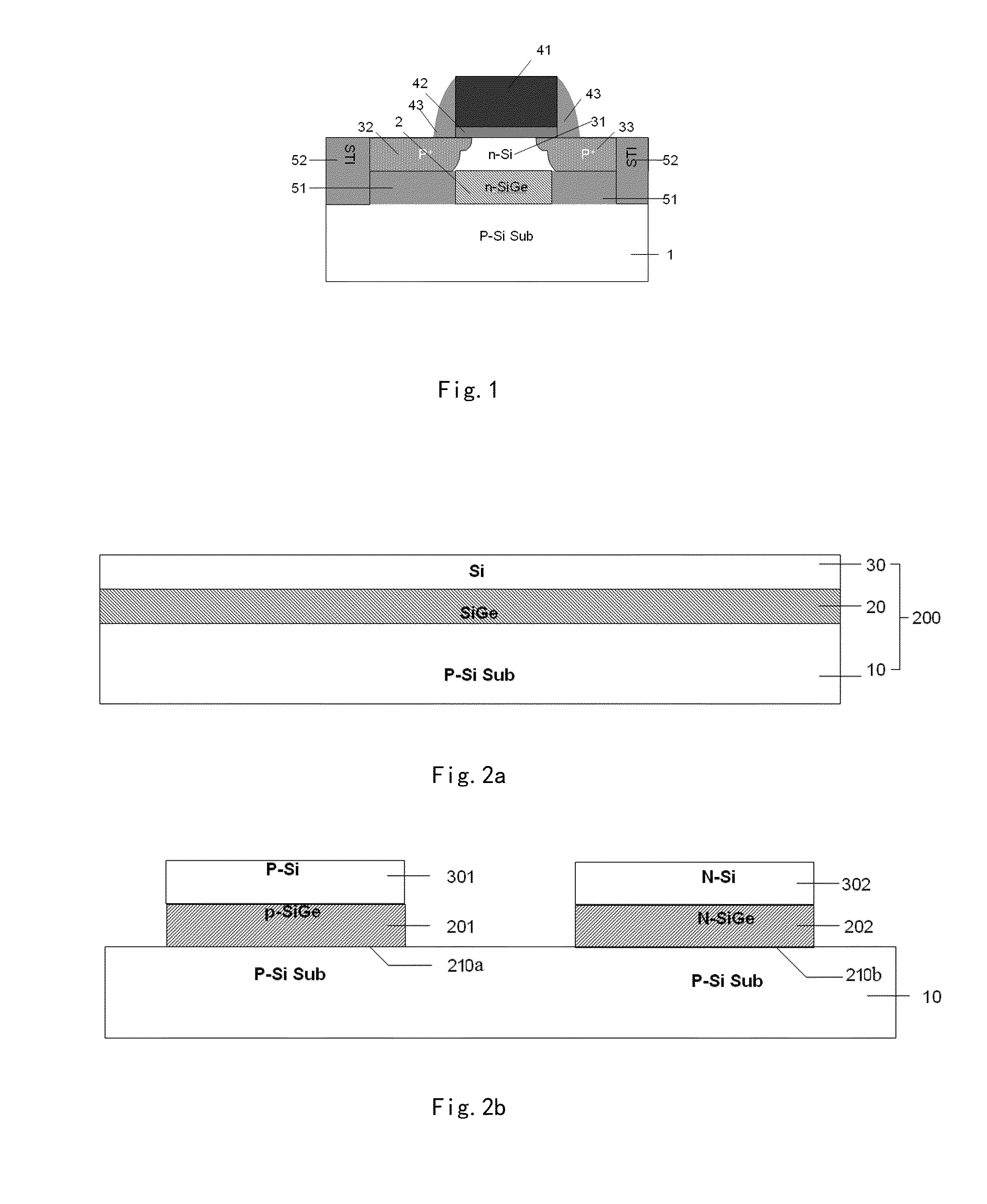

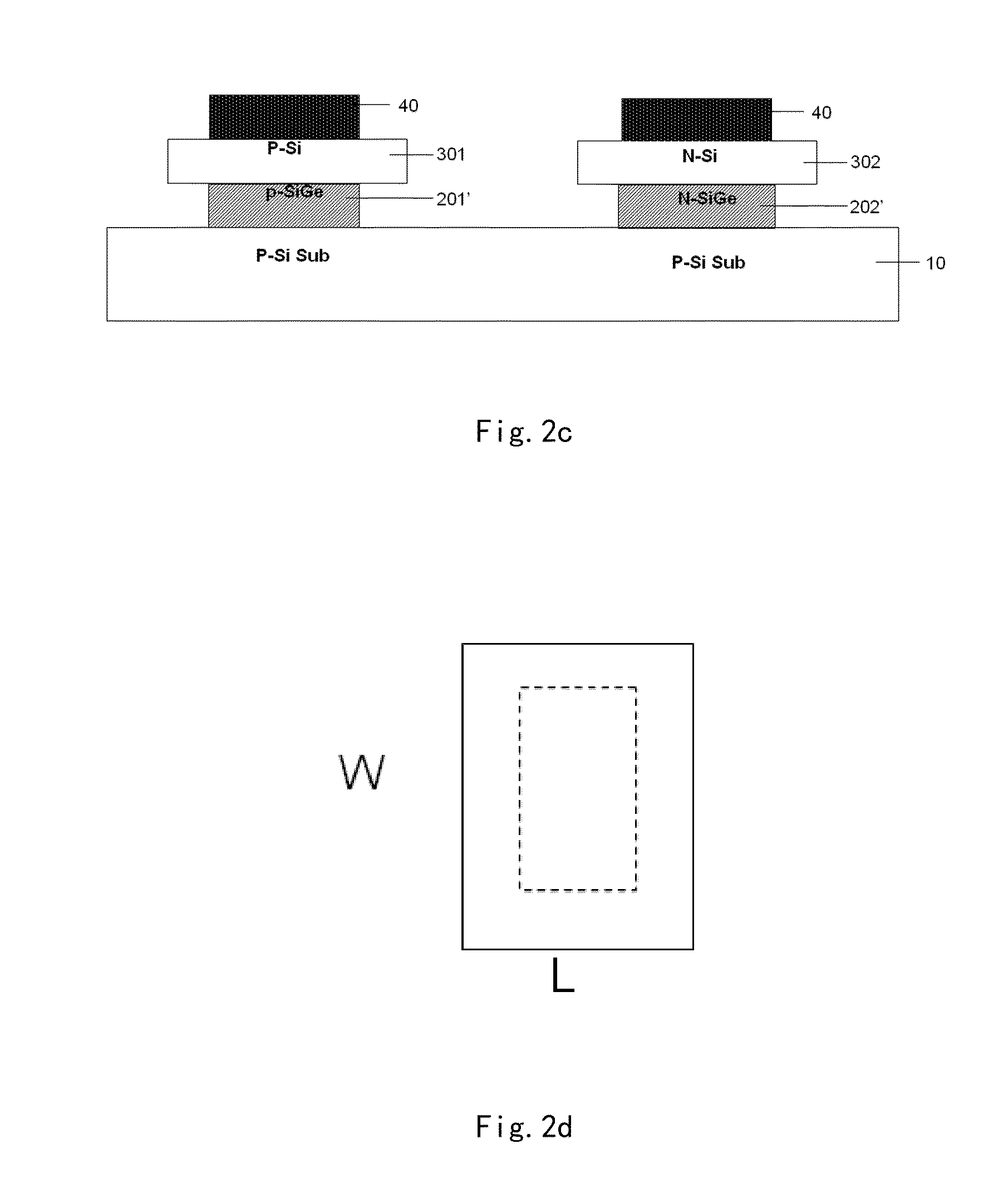

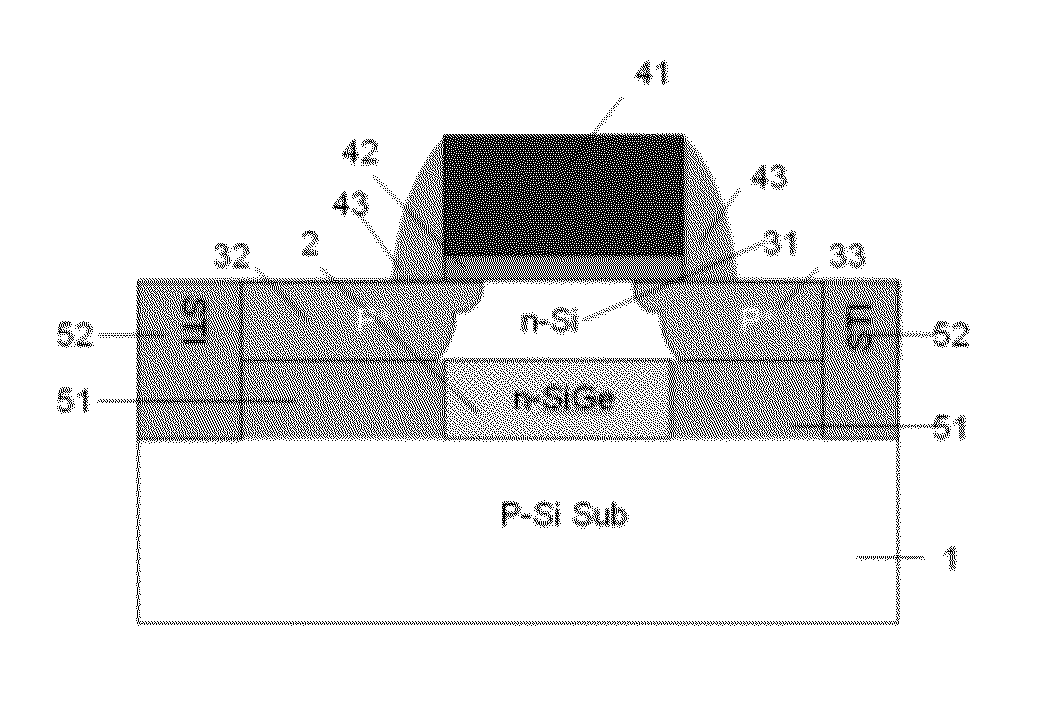

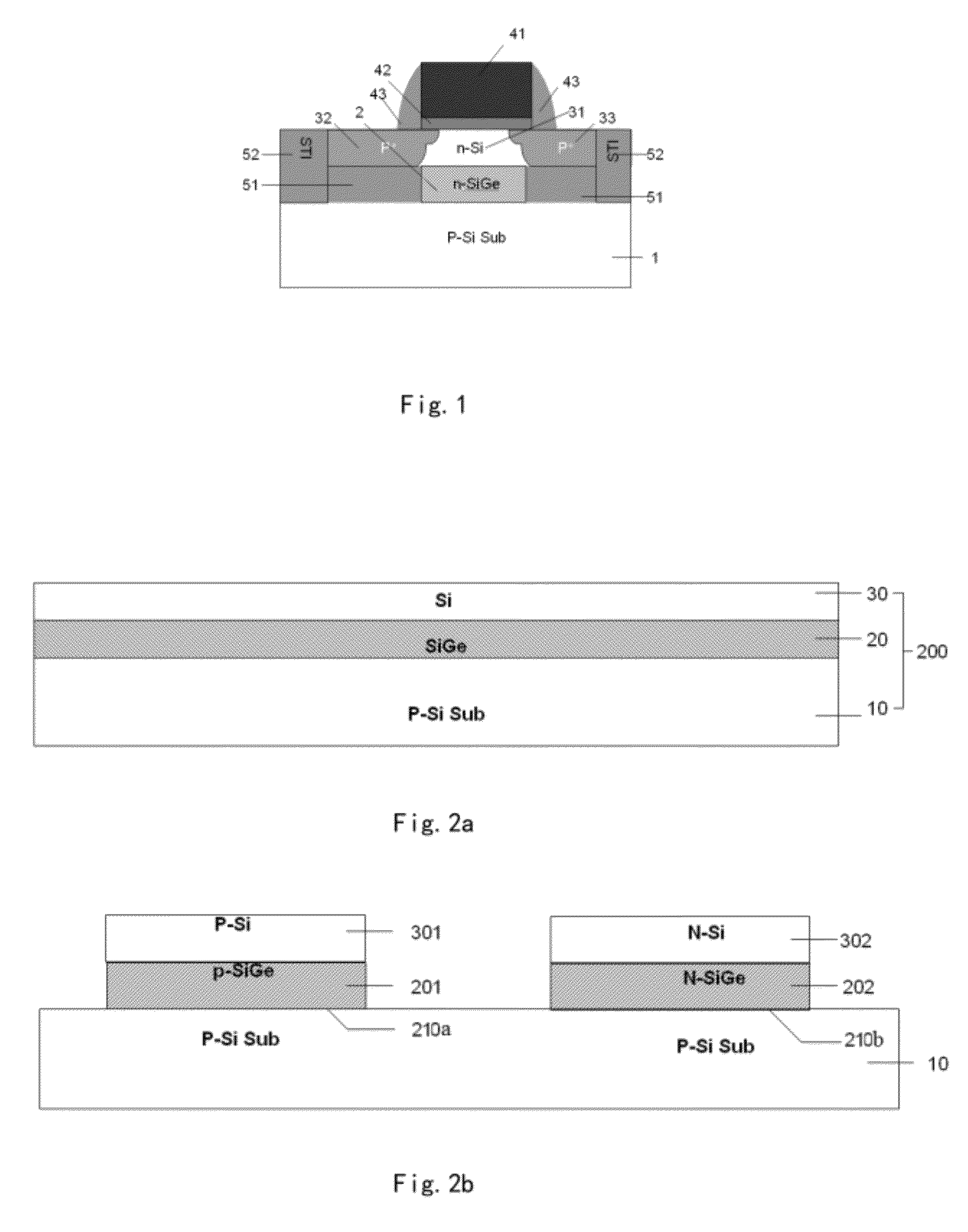

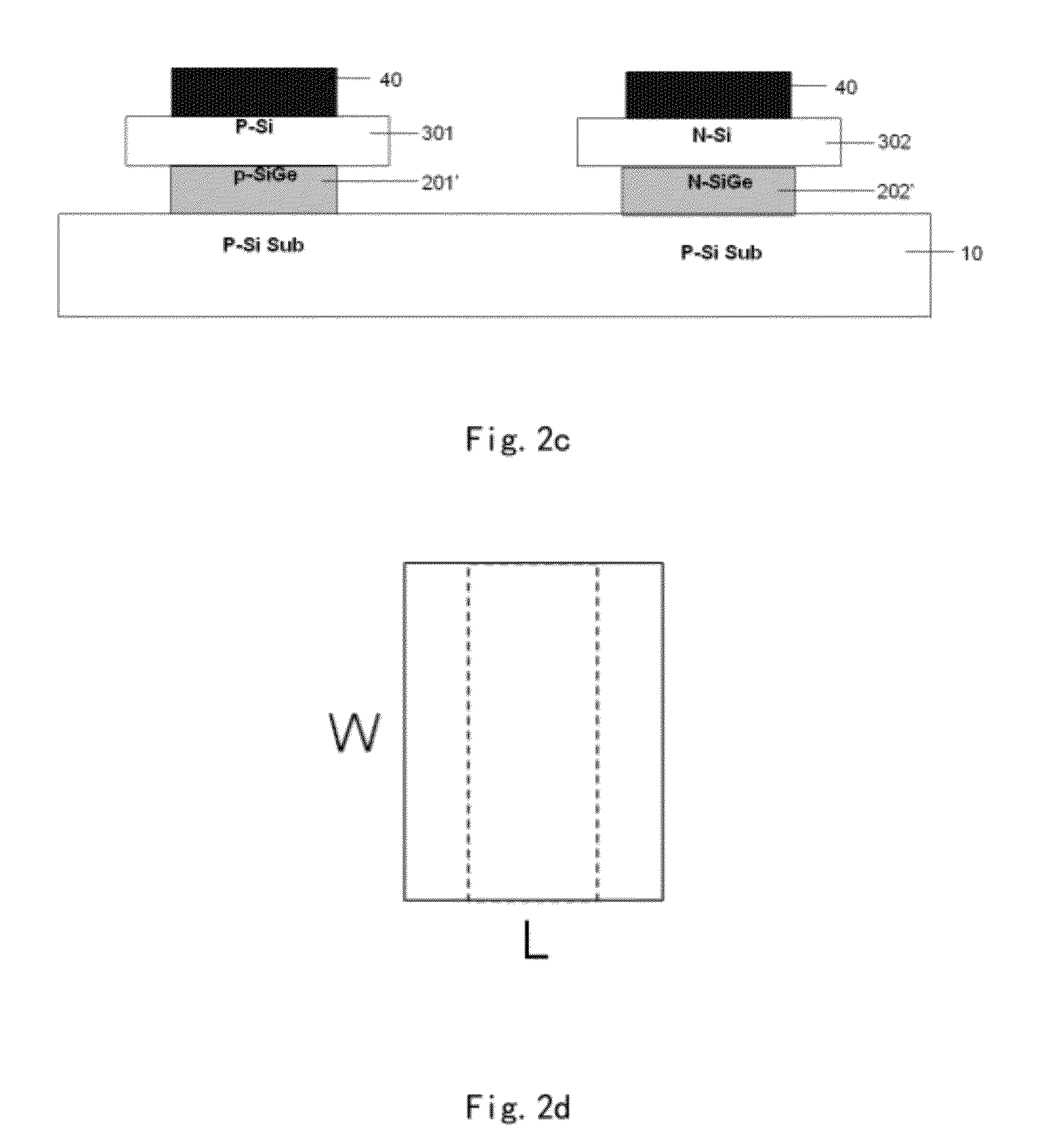

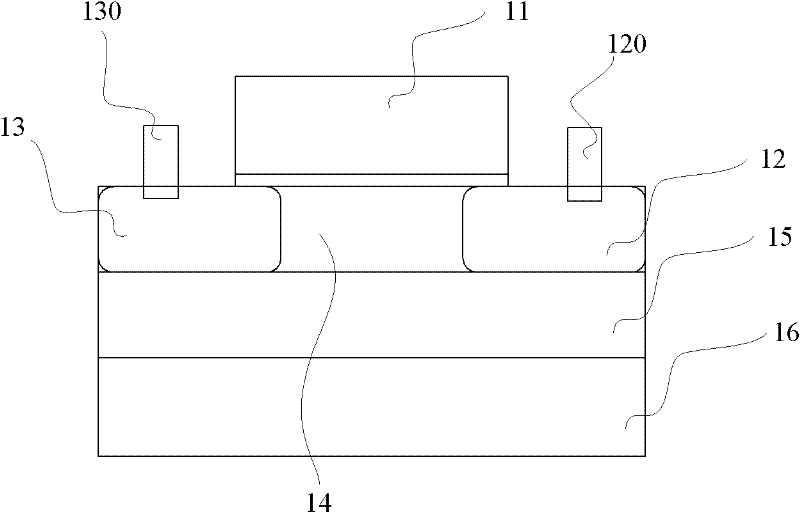

Mos device for eliminating floating body effects and self-heating effects

InactiveUS20120018809A1Suppression of floating body effectReduce self-heating effectSolid-state devicesSemiconductor/solid-state device manufacturingFloating chargeFloating body effect

A MOS device having low floating charge and low self-heating effects are disclosed. The device includes a connective layer coupling the active gate channel to the Si substrate. The connective layer provides electrical and thermal passages during device operation, which could eliminate floating effects and self-heating effects. An example of a MOS device having a SiGe connector between a Si active channel and a Si substrate is disclosed in detail and a manufacturing process is provided.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

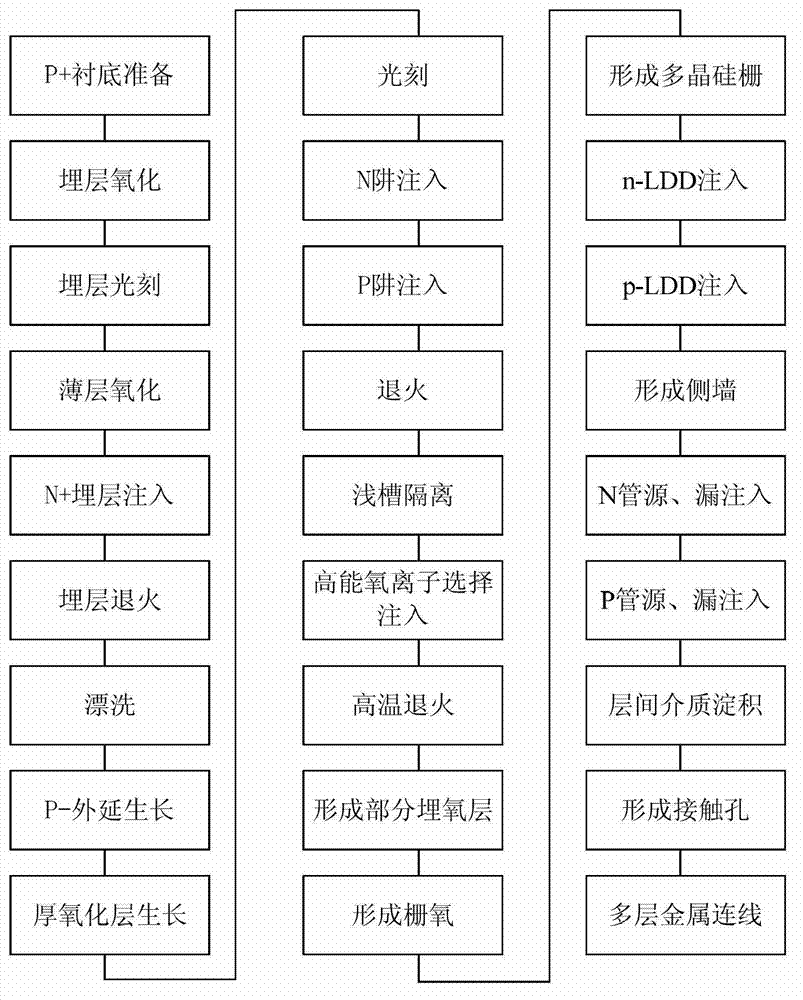

Anti-single-particle-radiation MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) apparatus and preparation method

InactiveCN102969316APulse time width narrowedReduce self-heating effectTransistorSemiconductor/solid-state device manufacturingHigh concentrationMOSFET

The invention relates to an anti-single-particle-radiation MOSFET (Metal-Oxide -Semiconductor Field Effect Transistor) apparatus and a preparation method, and relates to an integrated circuit technology. The anti-single-particle-radiation MOSFET apparatus comprises a high concentration substrate, source and drain regions, an epitaxial layer, an epitaxial layer abnormal well and an epitaxial layer isotypical well, wherein the wells are reversed doped wells; a part of oxygen burying layer is arranged below the drain region vertically; and a buried layer opposite to the epitaxial layer in type is arranged below the well in the same type of the epitaxial layer to form a PN node absorbing layer with a well boundary. The apparatus has the beneficial effects that the transient current impulse time width generated by the single particle is halved, and the impulse height is reduced to 40% of that of the original one. Compared with an SOI (Silicon on Insulator) apparatus, the self-heating effect and floating effect and the like can be effectively weakened.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

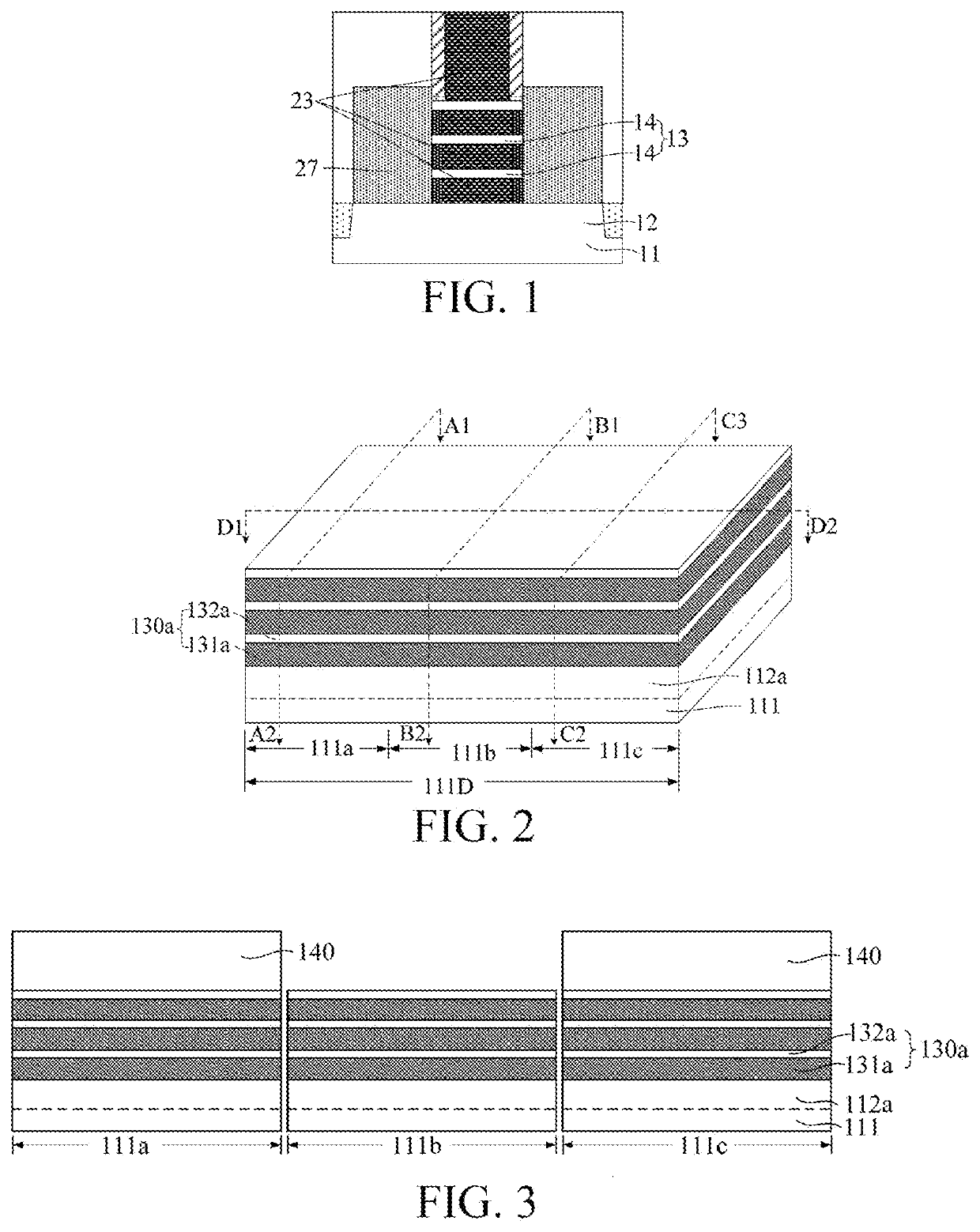

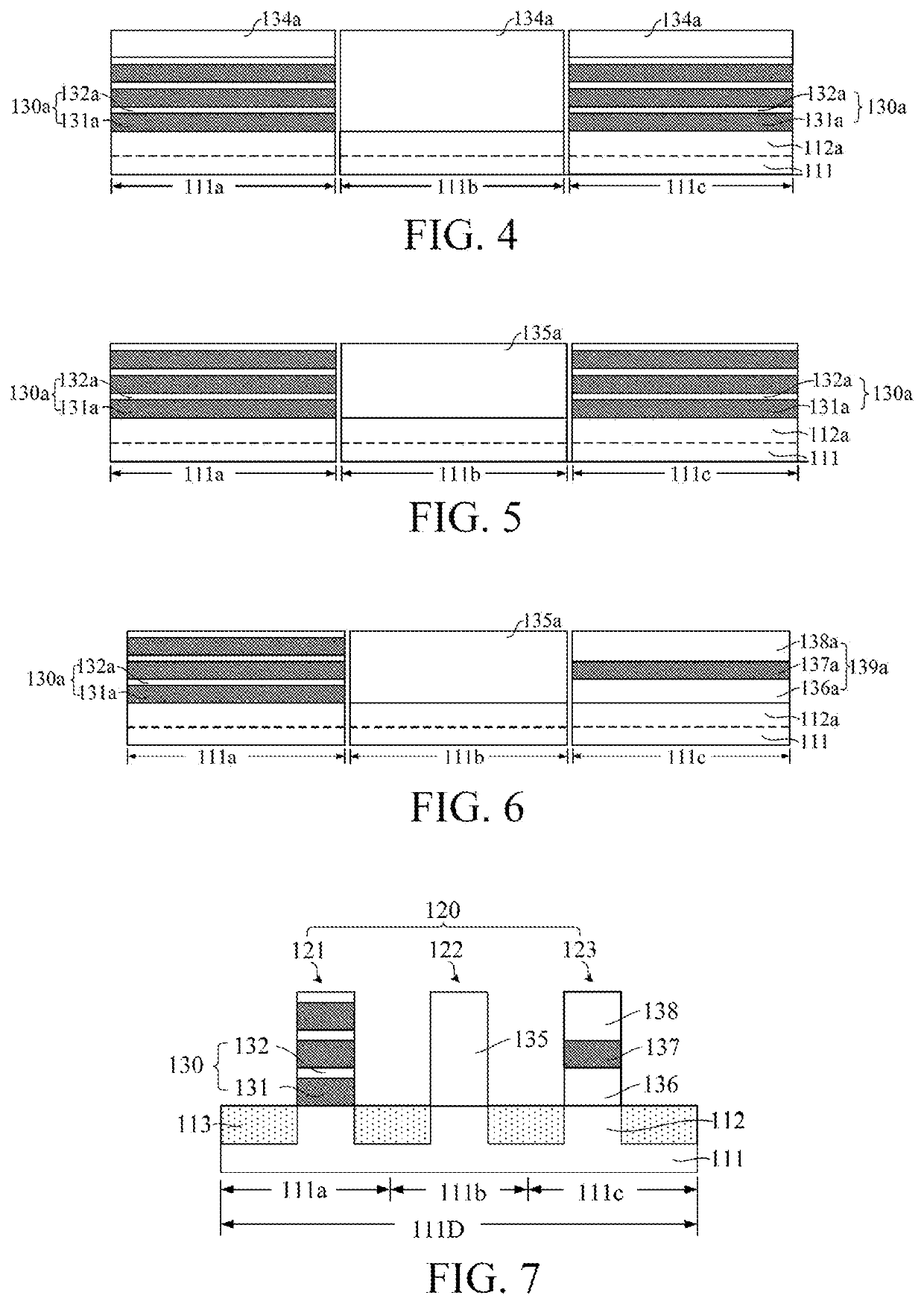

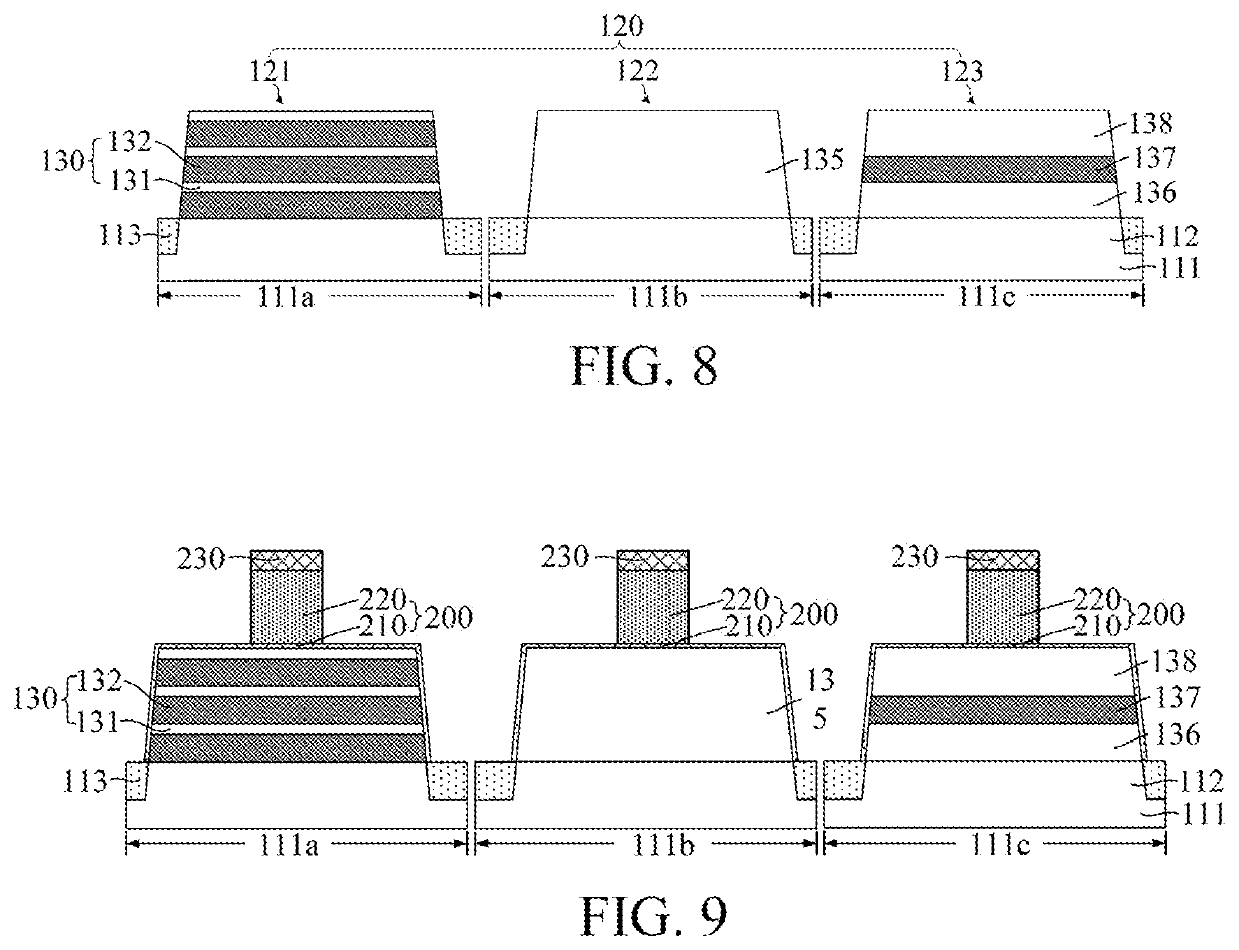

Semiconductor structure and method for forming same

ActiveUS20200058800A1Improving channel controlling capabilityImprove channel controlTransistorSolid-state devicesSemiconductor structureDielectric layer

A semiconductor structure and a method for forming same are provided. One form of the method includes: providing a substrate including a device unit area, where at least two fins are formed on the substrate of the device unit area, a channel structure layer is formed on the fins, the channel structure layer includes a first channel structure layer located on at least one fin and a second channel structure layer located on at least one fin, the first channel structure layer includes multiple channel laminates, each channel laminate includes a first sacrificial layer and a first channel layer located on the first sacrificial layer, and the second channel structure layer is a second channel layer of a single-layer structure; forming a dummy gate structure across the channel structure layer of the device unit area; forming a source-drain doping layer in the channel structure layer on two sides of the dummy gate structure; forming an interlayer dielectric layer on the substrate exposed by the dummy gate structure; and after forming the interlayer dielectric layer, forming a gate structure at positions of the dummy gate structure and the first sacrificial layer. The present disclosure can improve overall performance of a device.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

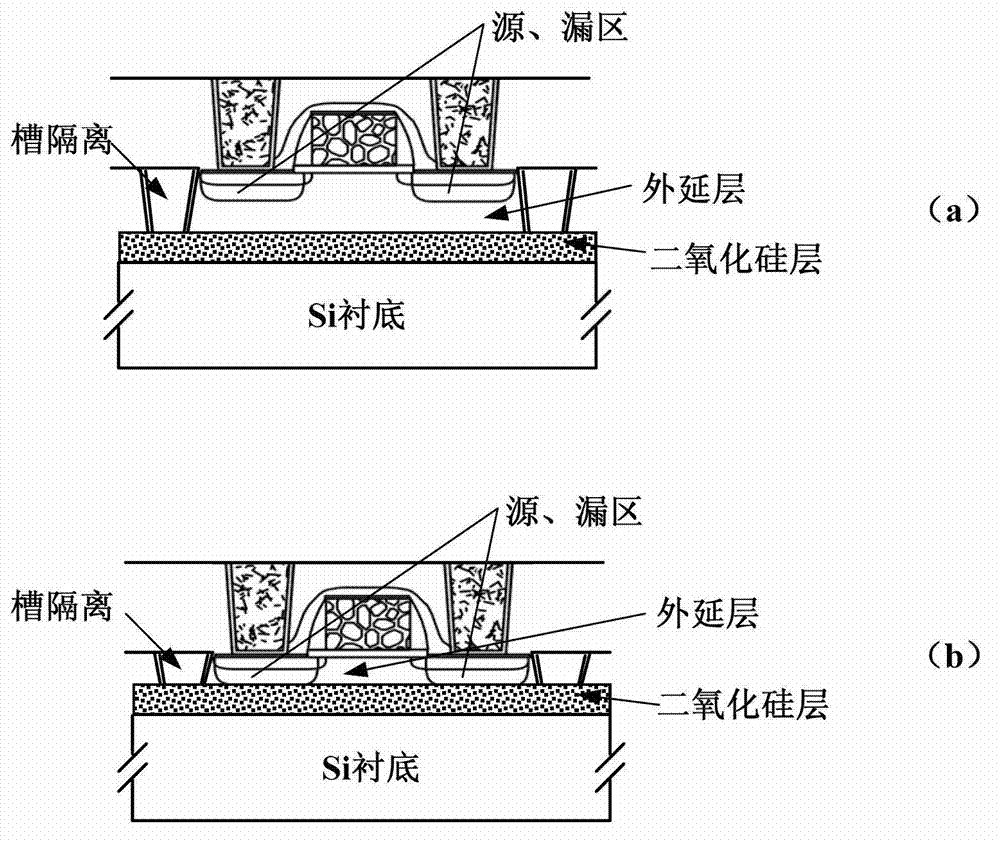

Partial SOI (silicon on insulator) traverse double-diffused device

ActiveCN102082169AEfficient deliveryReduce doping concentrationSemiconductor devicesNitrogenHeating effect

The invention relates to the SOI (silicon on insulator) technology. The invention solves the problem that the heating effect of the existing conventional SOI device is obvious, and provides a partial SOI traverse double-diffused device. The technical scheme of the invention is summarized as follows: one end of an oxide buried layer of the partial SOI traverse double-diffused device is arranged below a source electrode and is contacted with the edge of the device, the horizontal distance between the other end of the oxide buried layer and a drain type II impurity ohm contact area is not less than zero, a PN (phosphorus-nitrogen) junction is formed by the way that a type I impurity substrate is contacted with the silicon layer of the type II impurity top layer between the other end of the oxide buried layer and the edge of the device below the drain. The partial SOI traverse double-diffused device has the beneficial effects that the oxide buried layer is provided with an opening below the drain, the heat produced by an SOI device can be effectively transferred, and the partial SOI traverse double-diffused device is applicable to SOI devices.

Owner:SICHUAN CHANGHONG ELECTRIC CO LTD

Semiconductor device with height-controllable fin and preparation method

ActiveCN103681275AGood static performanceEliminate parasitic capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceIsotropic etching

The invention relates to a semiconductor device with a height-controllable fin and a preparation method. The preparation method comprises the following steps: providing a semiconductor substrate; forming a first semiconductor material layer, a second semiconductor material layer and a hard mask layer on the substrate; etching the hard mask layer, a second semiconductor material layer and a first semiconductor material layer to form a trench and a fin pattern; performing isotropic etching to remove a part of the first semiconductor material layer in the fin pattern to form a virtual fin with reduced critical size; depositing dielectric layers to fill the trench and cover the fin pattern; etching the dielectric layers till the second semiconductor material layer below, in order to expose the second semiconductor material layer to form the fin. The preparation process of the fin is easy to control, and the obtained device is more stable.

Owner:SEMICON MFG INT (SHANGHAI) CORP

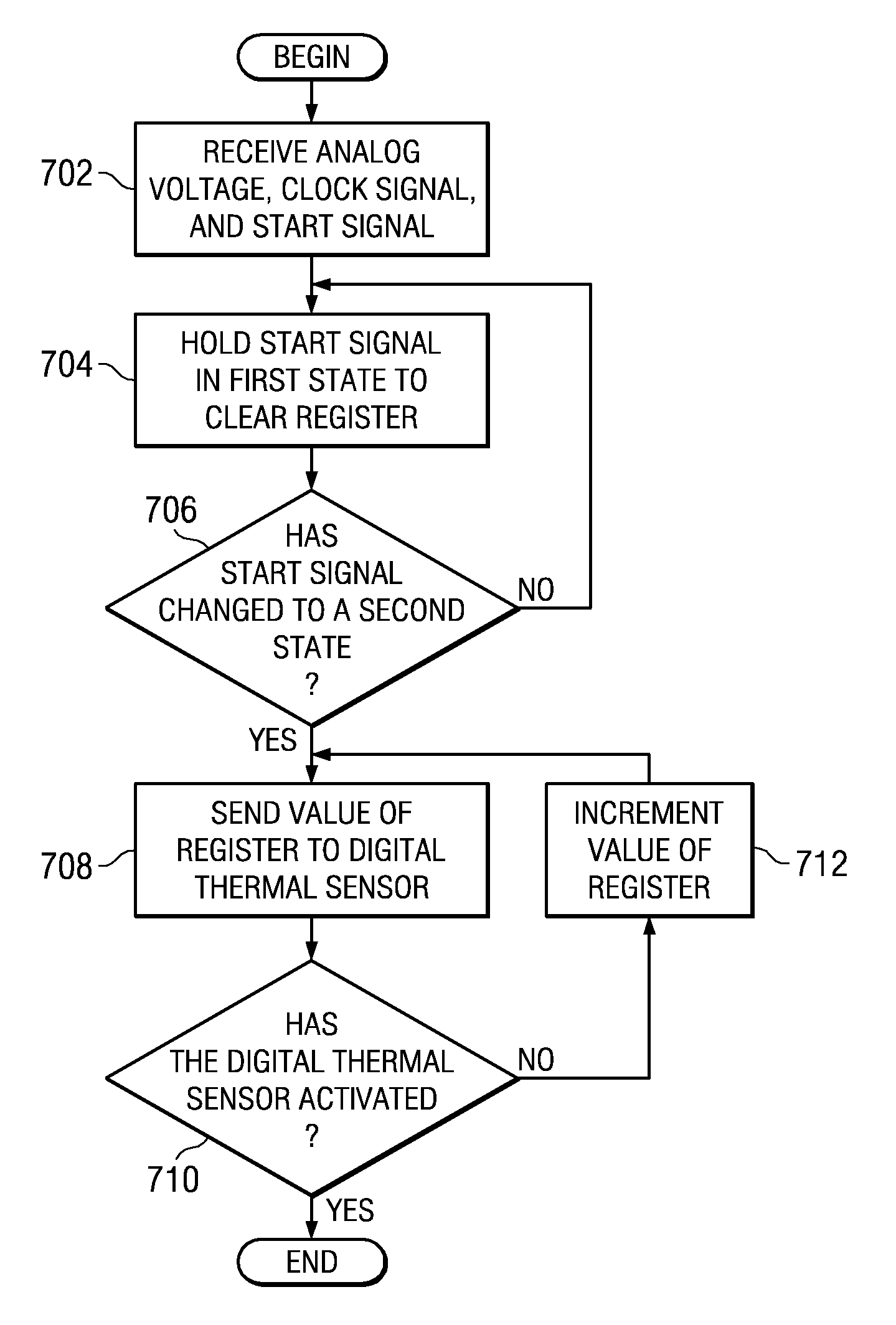

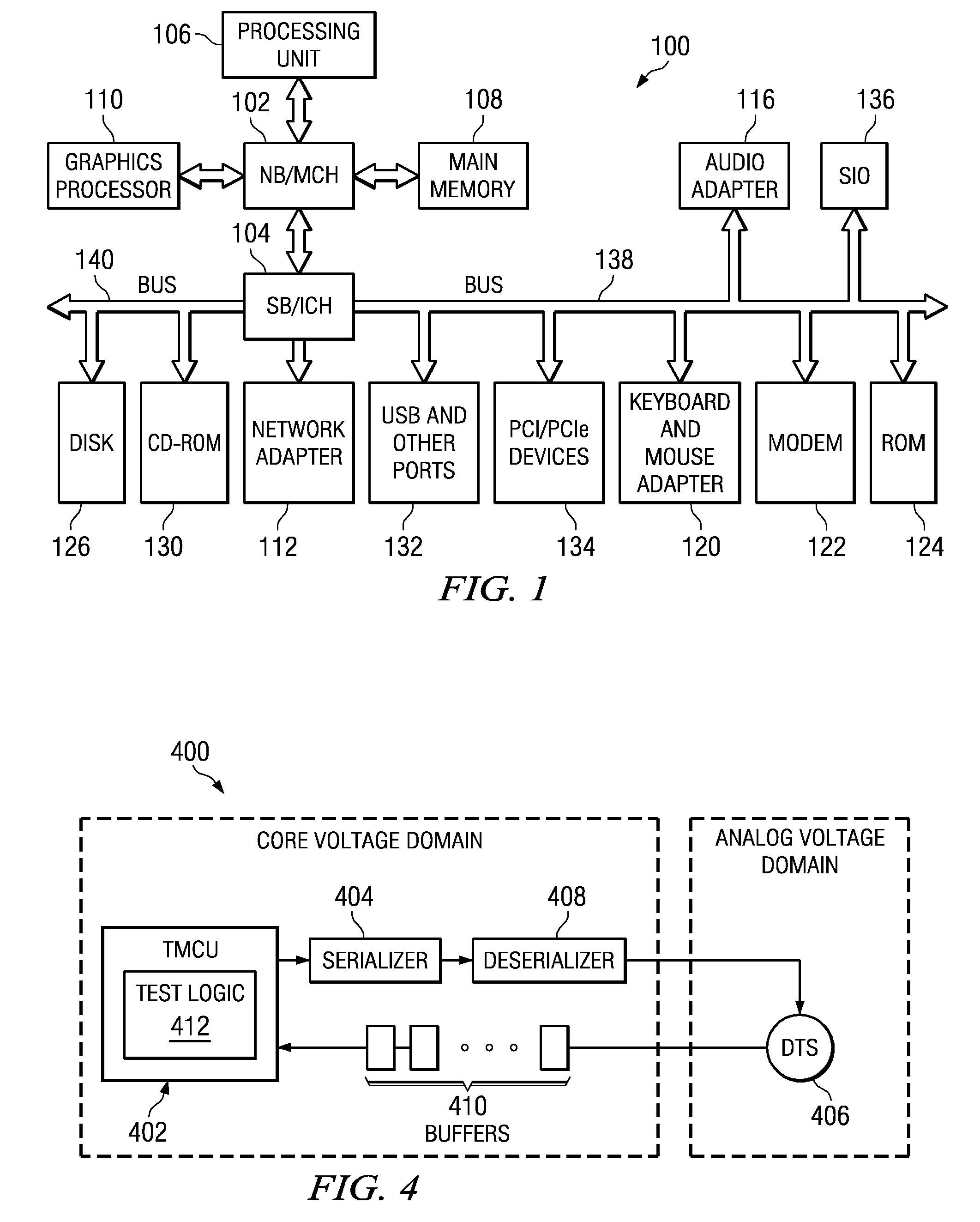

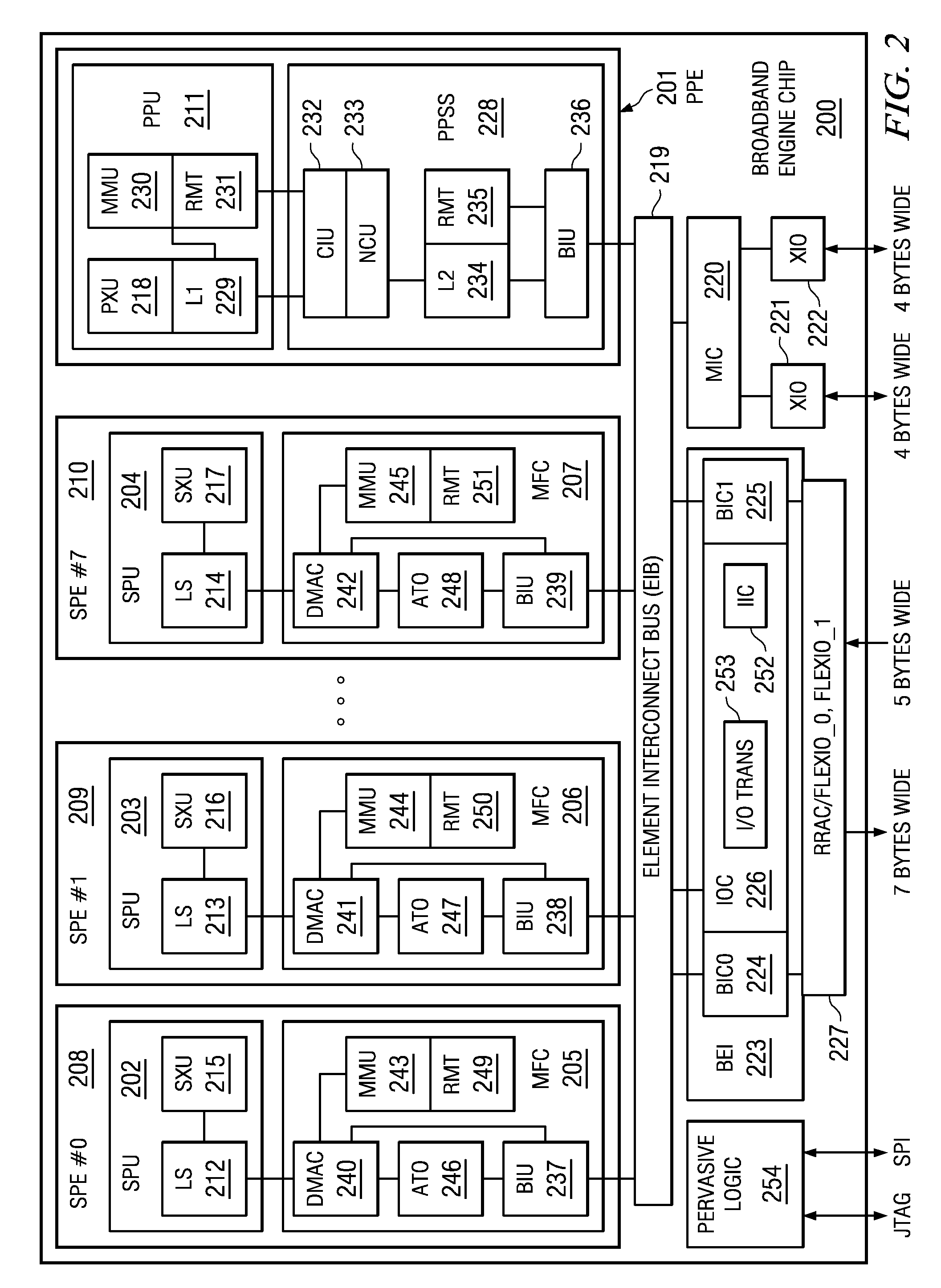

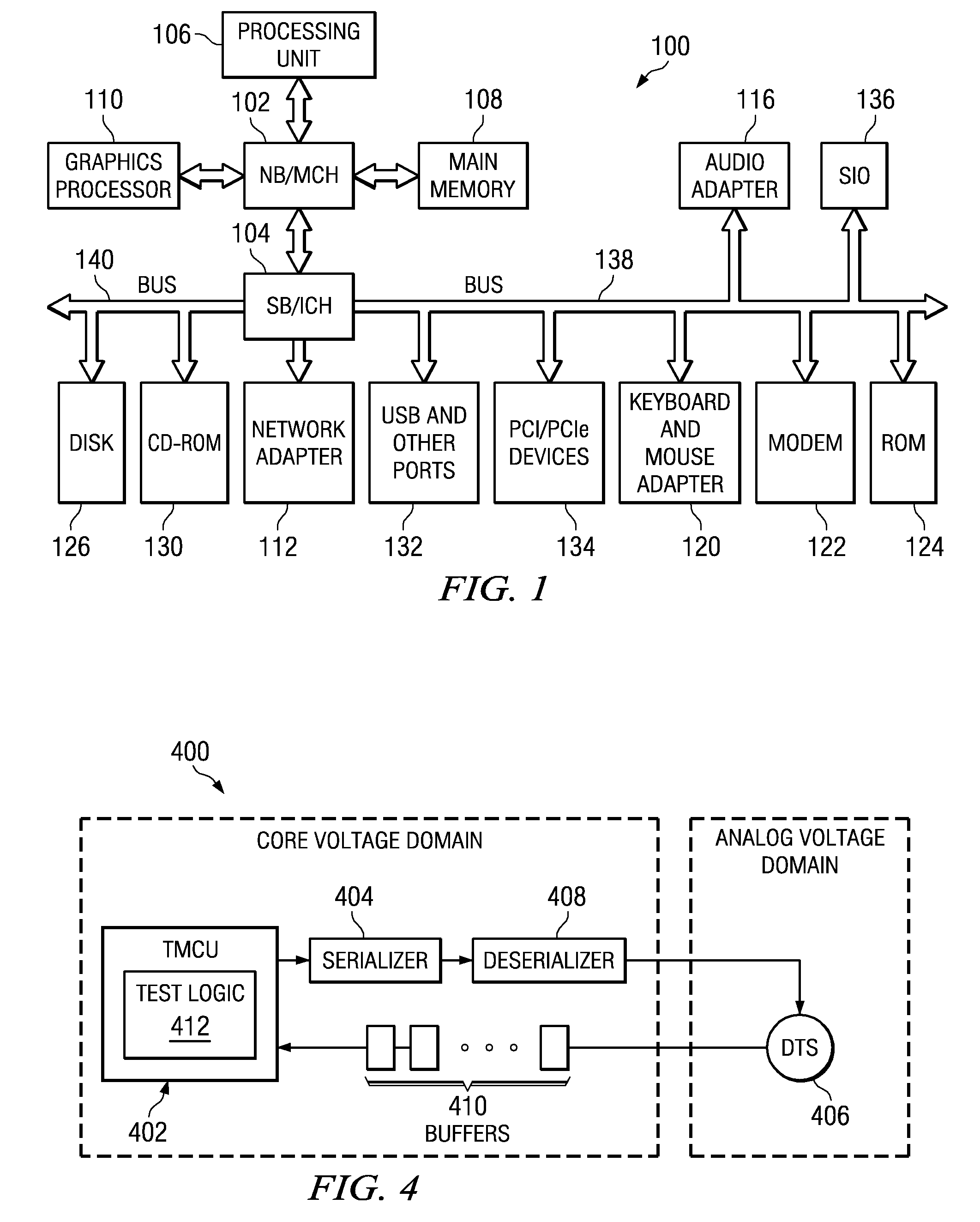

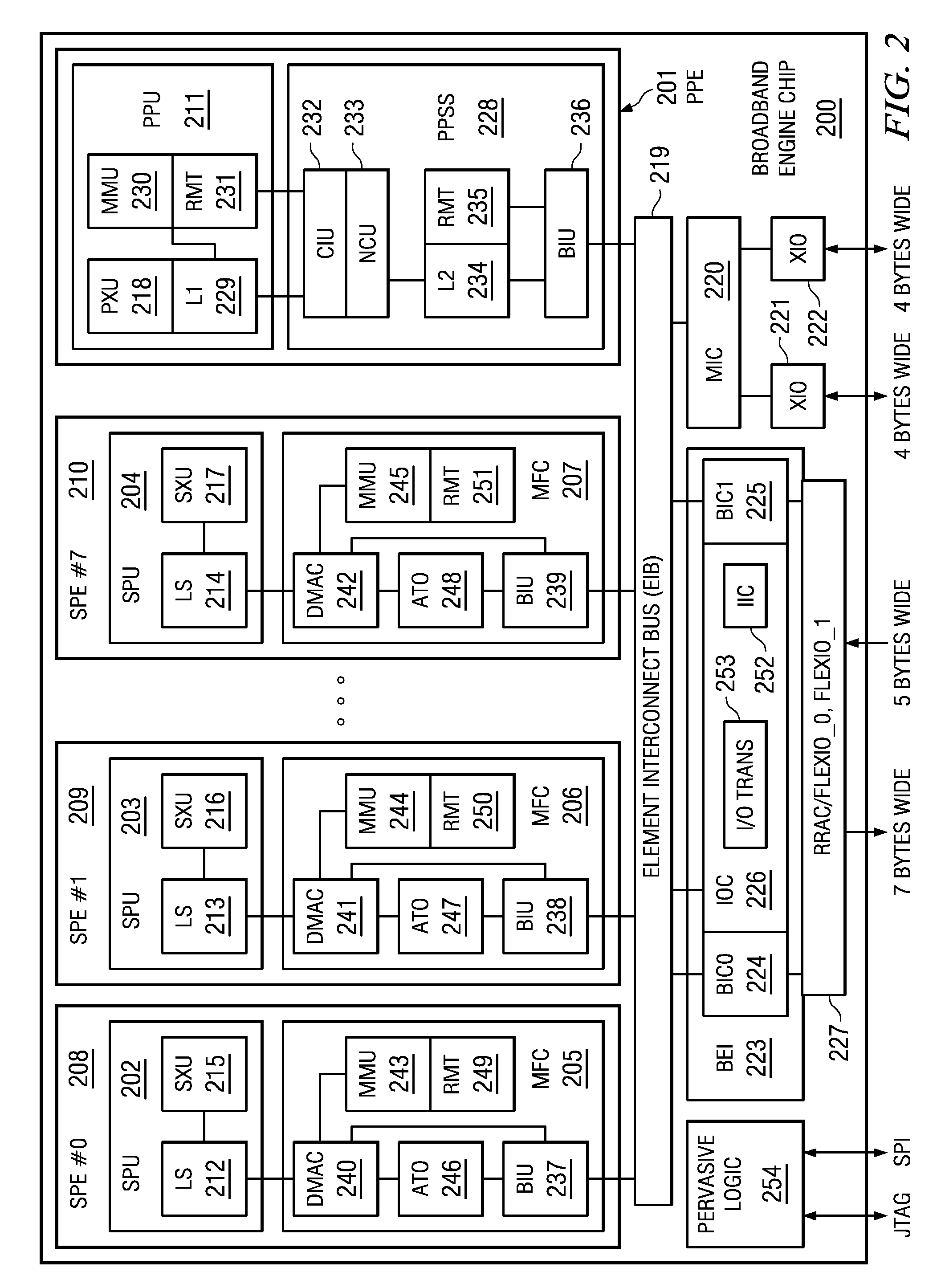

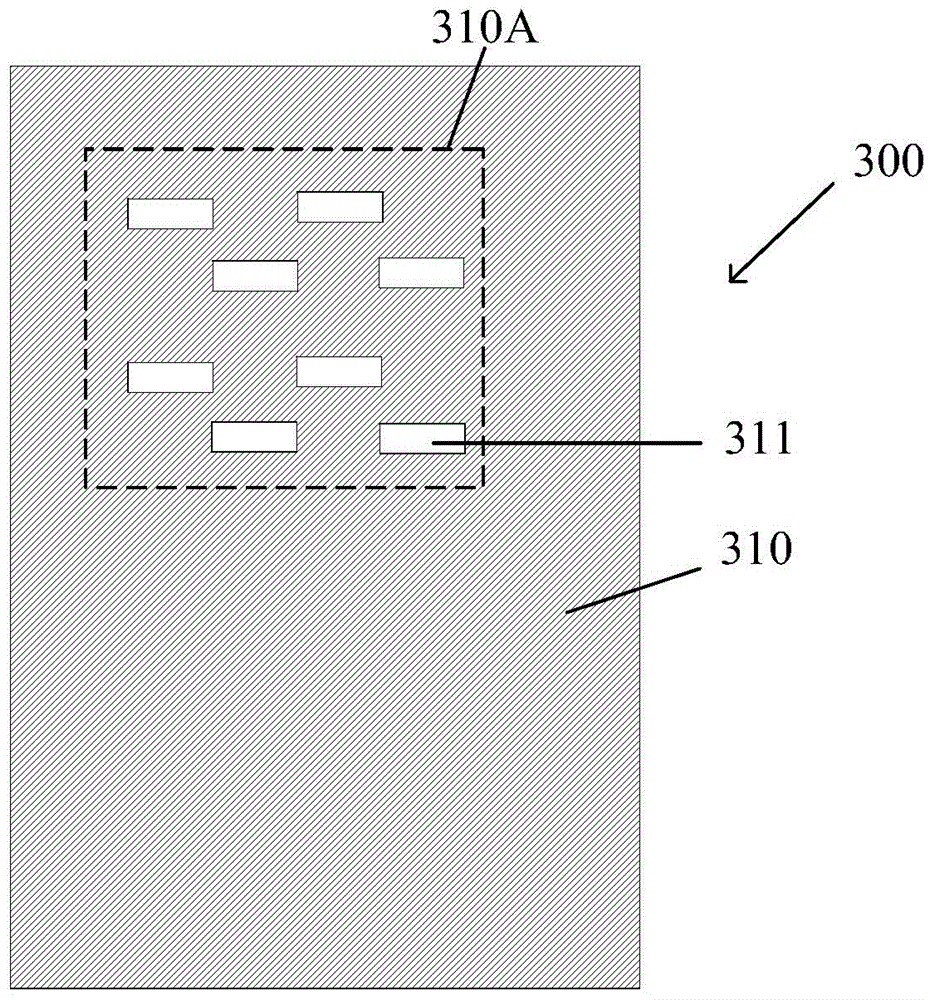

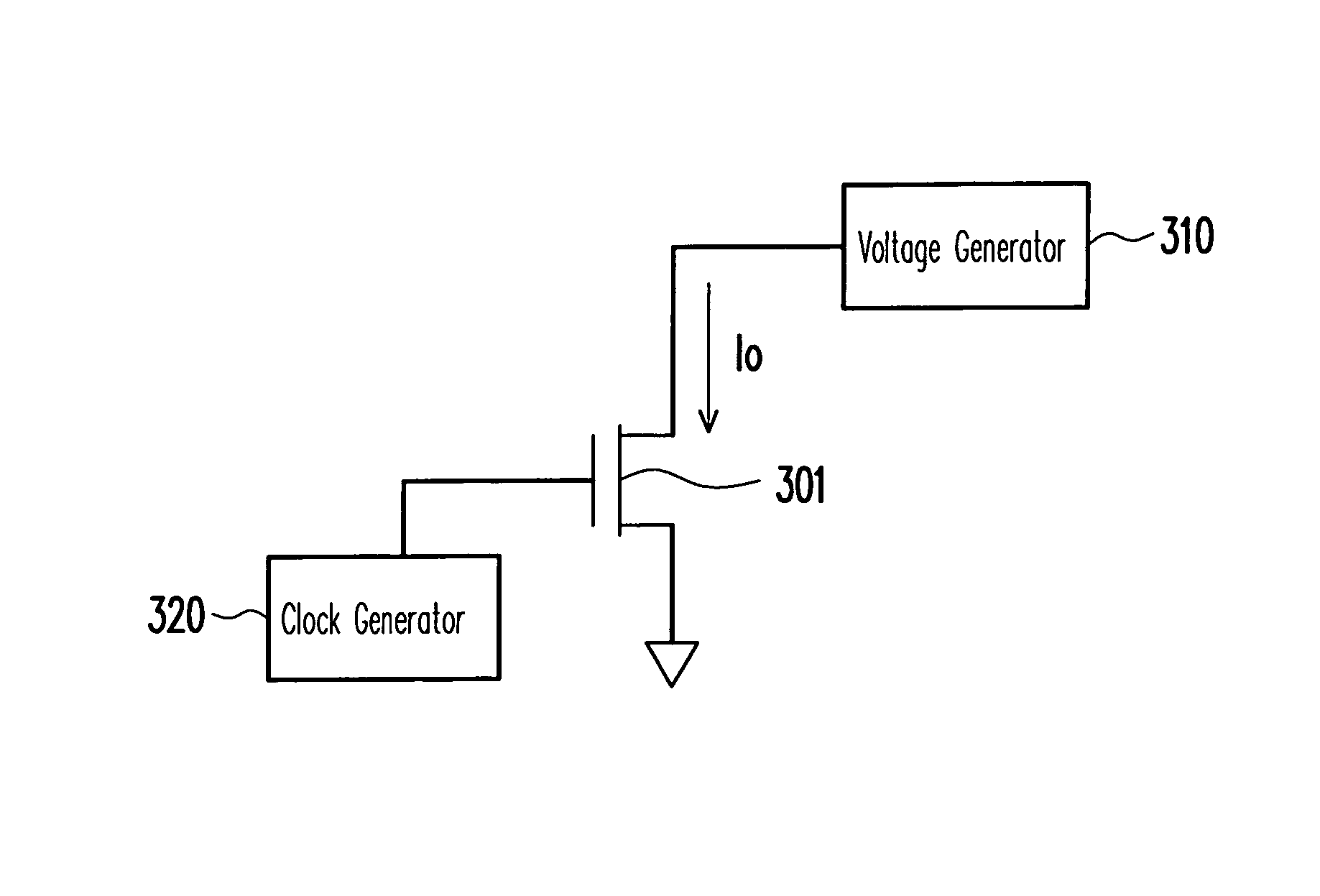

Digital thermal sensor test implementation without using main core voltage supply

InactiveUS8027798B2Reduce self-heating effectSimplify sequenceTesting/calibration apparatusSpeed measurement using gyroscopic effectsProcessor registerThermal threshold

A method and apparatus are provided for calibrating digital thermal sensors. A processor chip with a plurality of digital thermal sensors receives an analog voltage. A test circuit coupled to the processor chip receives a clock signal and a register coupled to the test circuit outputs a value on each clock cycle to a digital thermal sensor in the plurality of digital thermal sensors. The digital thermal sensor transitions an output state in response to the value of the register received in the digital thermal sensor equaling a temperature threshold of the digital thermal sensor. The value of the register at the point of transition is used to calibrate the digital thermal sensor. An incrementer increments the value of the register on each clock cycle in response to the value of the register received in the digital thermal sensor failing to equal the temperature threshold of the digital thermal sensor.

Owner:IBM CORP

Mos device for eliminating floating body effects and self-heating effects

InactiveUS20120025267A1Suppression of floating body effectReduce self-heating effectTransistorSolid-state devicesFloating body effectEngineering

A SOI MOS device for eliminating floating body effects and self-heating effects are disclosed. The device includes a connective layer coupling the active gate channel to the Si substrate. The connective layer provides electrical and thermal passages during device operation, which could eliminate floating body effects and self-heating effects. An example of a MOS device having a SiGe connector between a Si active channel and a Si substrate is disclosed in detail and a manufacturing process is provided.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

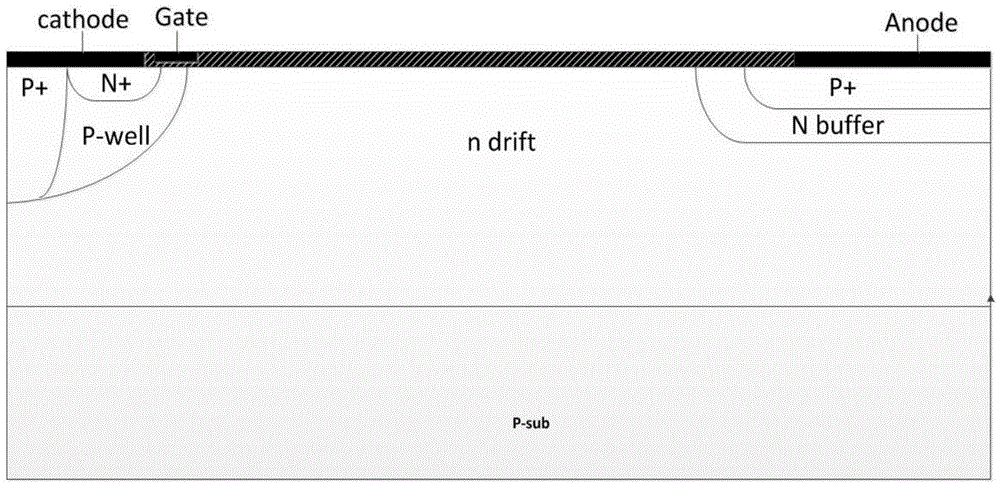

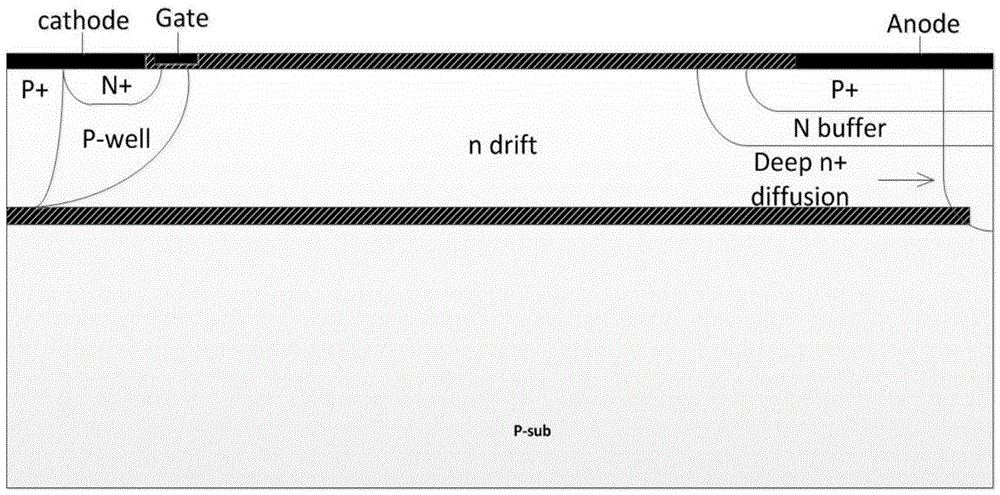

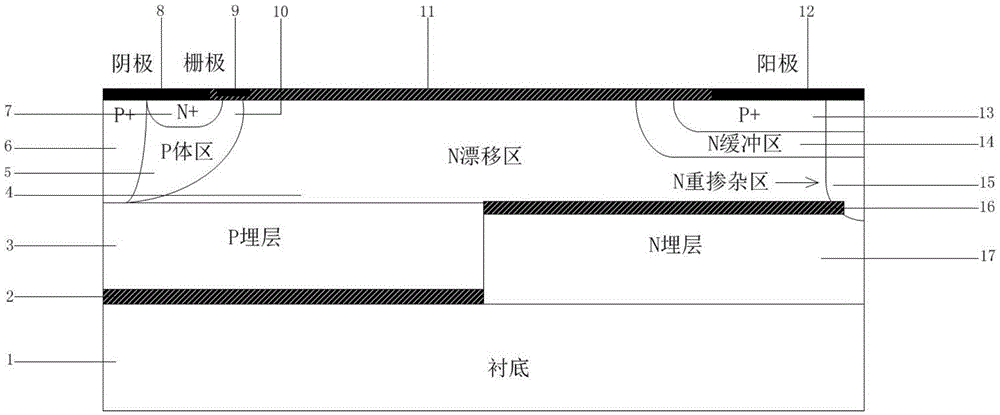

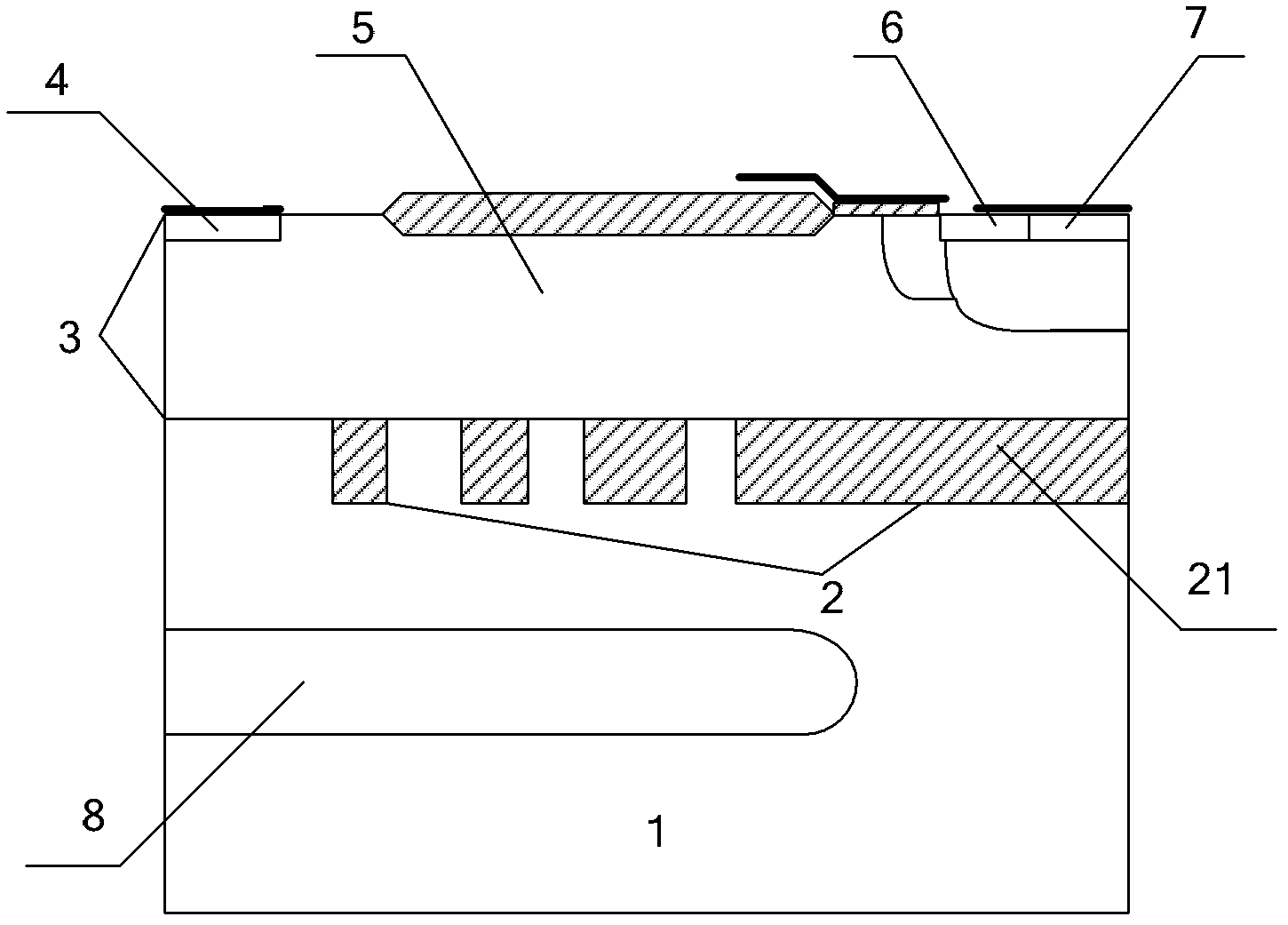

Double-layer sectioned SOI LIGBT device and manufacturing method thereof

ActiveCN105633140AFacilitate conductionReduce self-heating effectSemiconductor/solid-state device detailsSolid-state devicesOperating temperatureSilicon

The invention discloses a double-layer sectioned SOI LIGBT device. The double-layer sectioned SOI LIGBT device comprises a silicon substrate; a first buried oxide layer and an N buried layer are sequentially arranged on the silicon substrate from left to right; the upper surface of the N buried layer is higher than the upper surface of the first buried oxide layer; a P buried layer is arranged on the first buried oxide layer; a second buried oxide layer is arranged on the N buried layer; the upper surface of the P buried layer and the upper surface of the second buried oxide layer are at the same height; and an N type drift region is arranged on the P buried layer and the second buried oxide layer. The invention also discloses a manufacturing method of the double-layer sectioned SOI LIGBT device. According to the manufacturing method, the oxide layer of a conventional SOI LIGBT is divided into two layers, and layers are separated from each other through reverse PN junctions; and with a novel sectionally-isolated structure adopted, excellent substrate leakage current isolation of the device can be ensured, heat dissipation performance can be improved, operating temperature can be decreased, and breakdown voltage can be improved.

Owner:NANJING UNIV OF POSTS & TELECOMM

Semiconductor device and manufacturing method thereof

InactiveCN105261587ALow costReduce power consumptionSemiconductor/solid-state device manufacturingSemiconductor devicesElectricityElectrical conductor

The invention provides a semiconductor device, which comprises a substrate, a second conductor layer, a third conductor layer, isolating structures, hollow cavities, oxide layers, oxidation barrier layers on the oxide layers, and a device structure, wherein the substrate comprises a first semiconductor material; the second conductor layer is located on the substrate; the third conductor layer is located on the second conductor layer; the isolating structure is located at two sides of the third semiconductor layer above the substrate; and the hollow cavities are located at the end parts of the second semiconductor layer and between the third semiconductor layer and the substrate; the oxide layers and the oxidation barrier layers thereon are located on the inner surfaces of the hollow cavities and on the side walls of the isolating structures; the device structure is located on the third semiconductor layer; and source-drain regions of the device structure are located above the hollow cavities. The device structure provided by the invention simultaneously has the advantages of a bulk-silicon device and an SOI device, and has the characteristics of low cost, small electricity leakage, low power consumption, high speed, relatively simple process and high integration level.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Digital Thermal Sensor Test Implementation Without Using Main Core Voltage Supply

InactiveUS20090125267A1Eliminate self-heating effectsSimpler test/calibration sequenceTesting/calibration apparatusSpeed measurement using gyroscopic effectsEngineeringElectrical and Electronics engineering

A method and apparatus are provided for calibrating digital thermal sensors. A processor chip with a plurality of digital thermal sensors receives an analog voltage. A test circuit coupled to the processor chip receives a clock signal and a register coupled to the test circuit outputs a value on each clock cycle to a digital thermal sensor in the plurality of digital thermal sensors. The digital thermal sensor transitions an output state in response to the value of the register received in the digital thermal sensor equaling a temperature threshold of the digital thermal sensor. The value of the register at the point of transition is used to calibrate the digital thermal sensor. An incrementer increments the value of the register on each clock cycle in response to the value of the register received in the digital thermal sensor failing to equal the temperature threshold of the digital thermal sensor.

Owner:IBM CORP

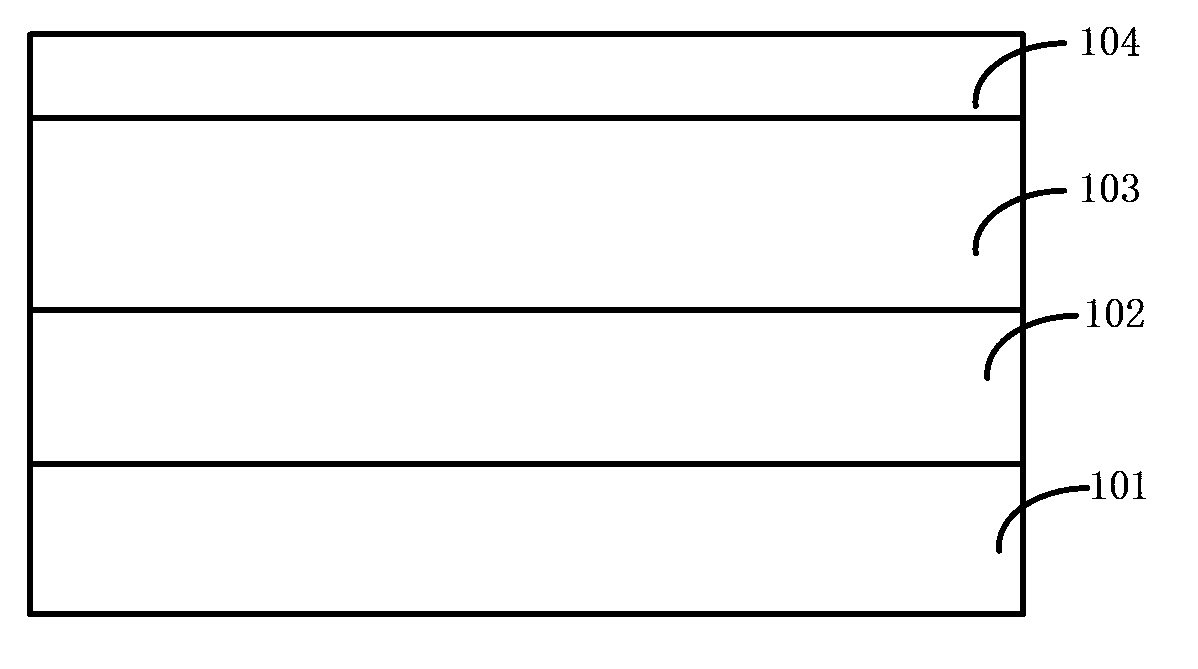

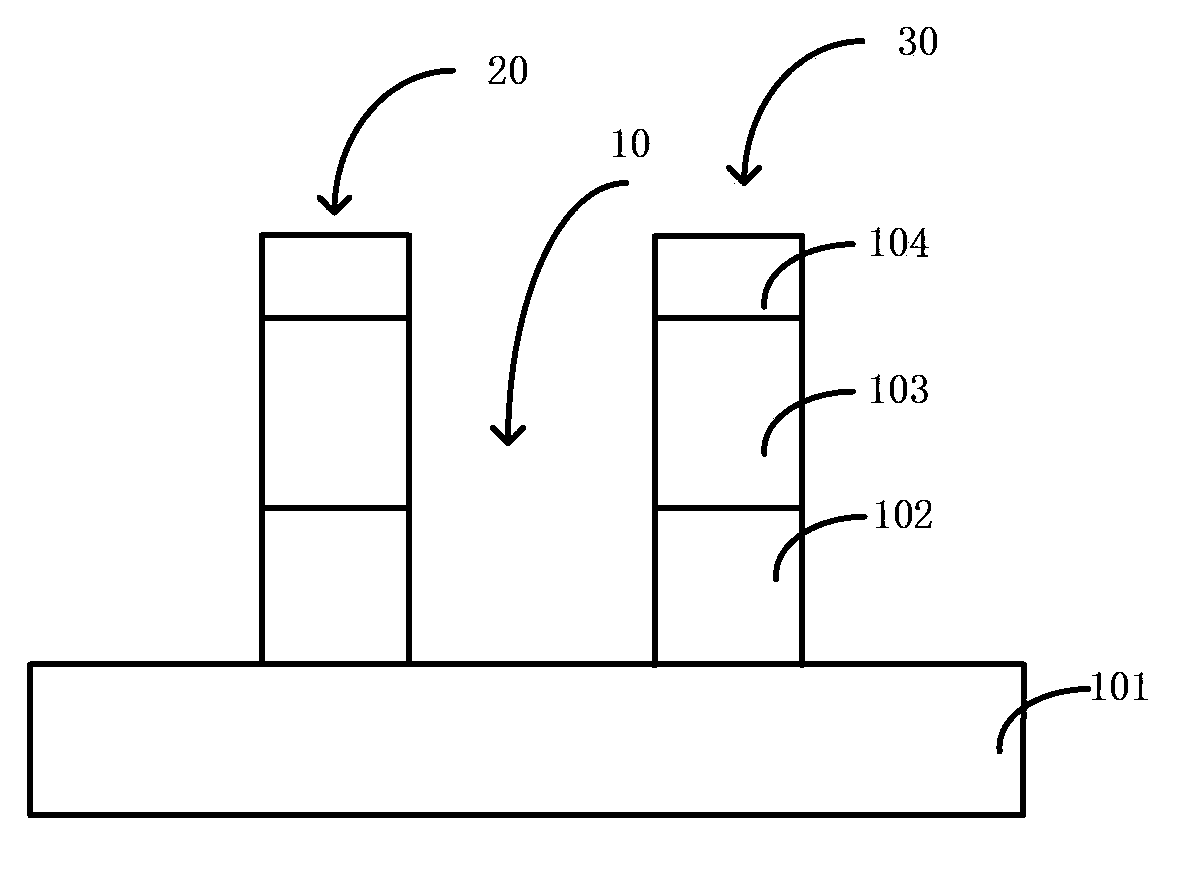

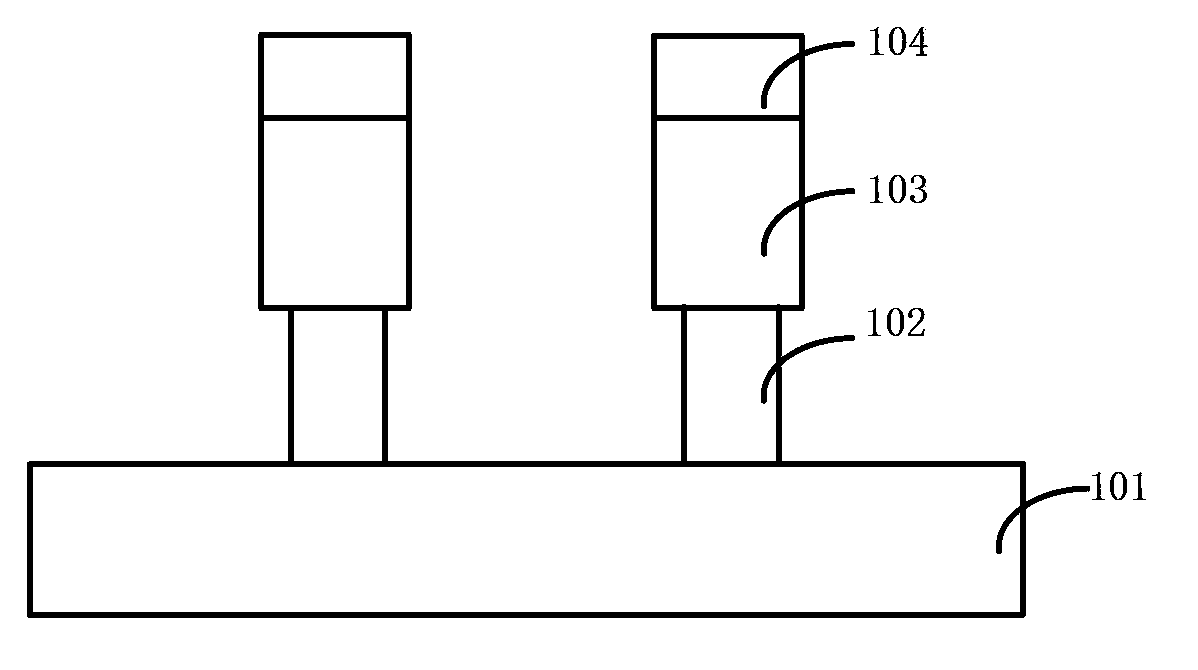

Finned field-effect transistor (FET) and forming method thereof

ActiveCN104347415AReduces serious problems with self-heating effectsSolve the problem of serious self-heating effectSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringField-effect transistor

The invention provides a finned field-effect transistor (FET) and a forming method thereof. The forming method of the finned FET comprises the steps: providing an on-insulator semiconductor substrate, wherein the on-insulator semiconductor substrate comprises a semiconductor layer; patterning the semiconductor layer until fin part structures, of which the upper surfaces are level, are formed; forming mask layers at the middle parts of the upper surfaces of the fin part structures; carrying out first-time anisotropic etching on the fin part structures in a manner of taking the mask layers as masks until the exposed upper surfaces of the fin part structures are etched into curved surfaces; removing the mask layers. The forming method is simple in process and low in process cost, and the formed finned FET is free from the problem of serious self-heating effect.

Owner:SEMICON MFG INT (SHANGHAI) CORP

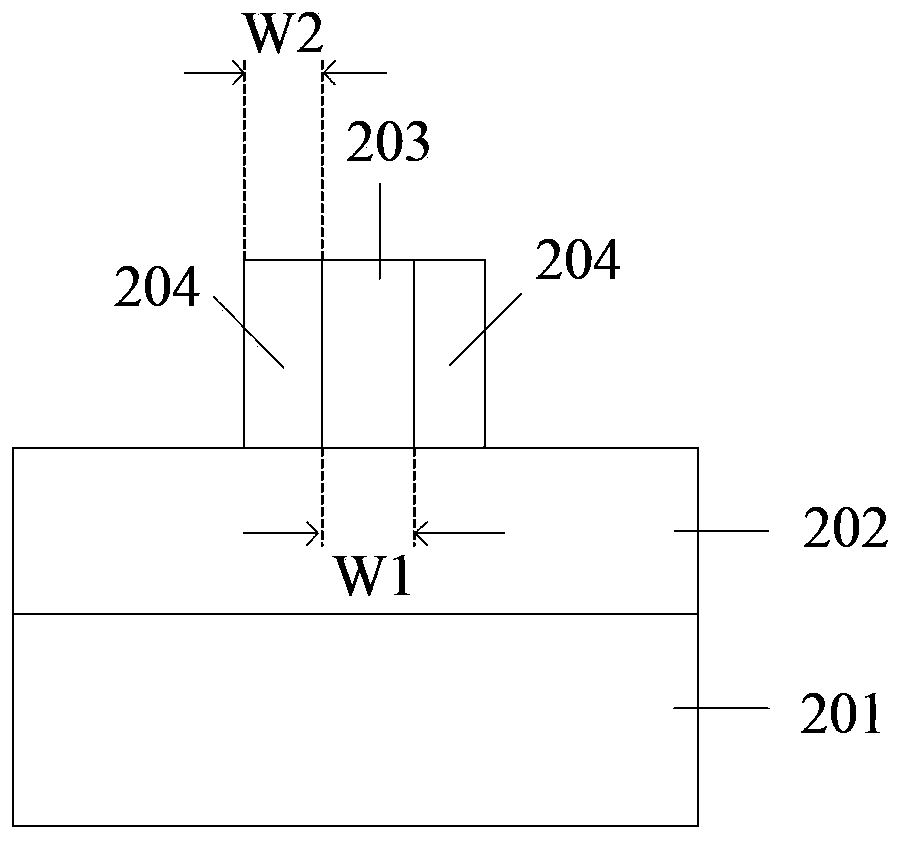

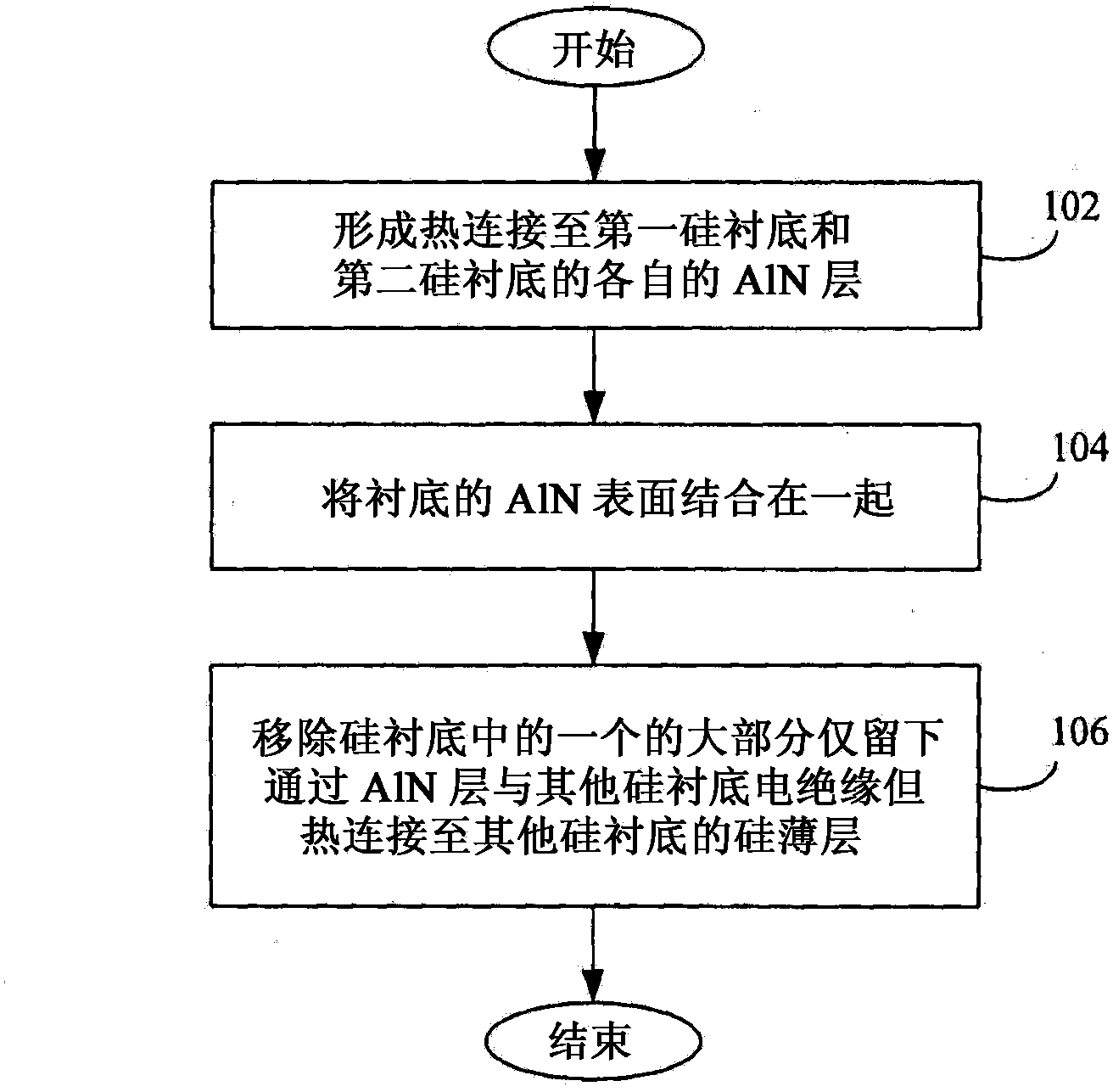

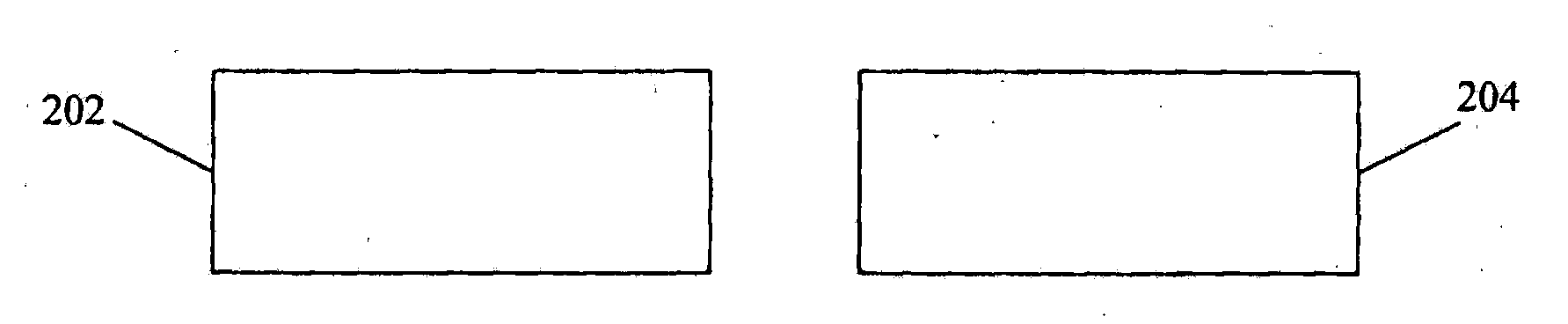

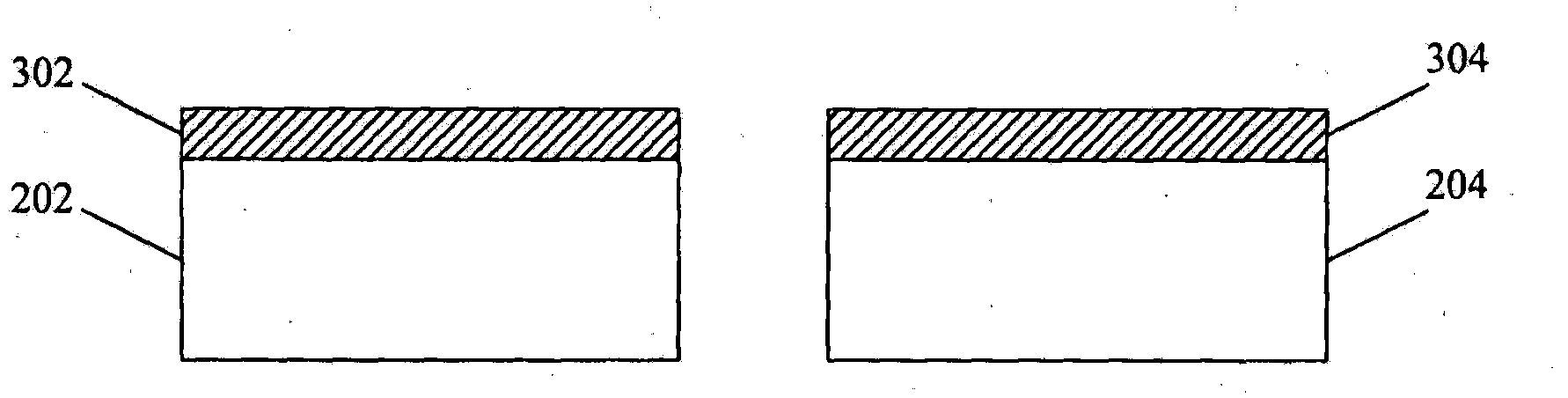

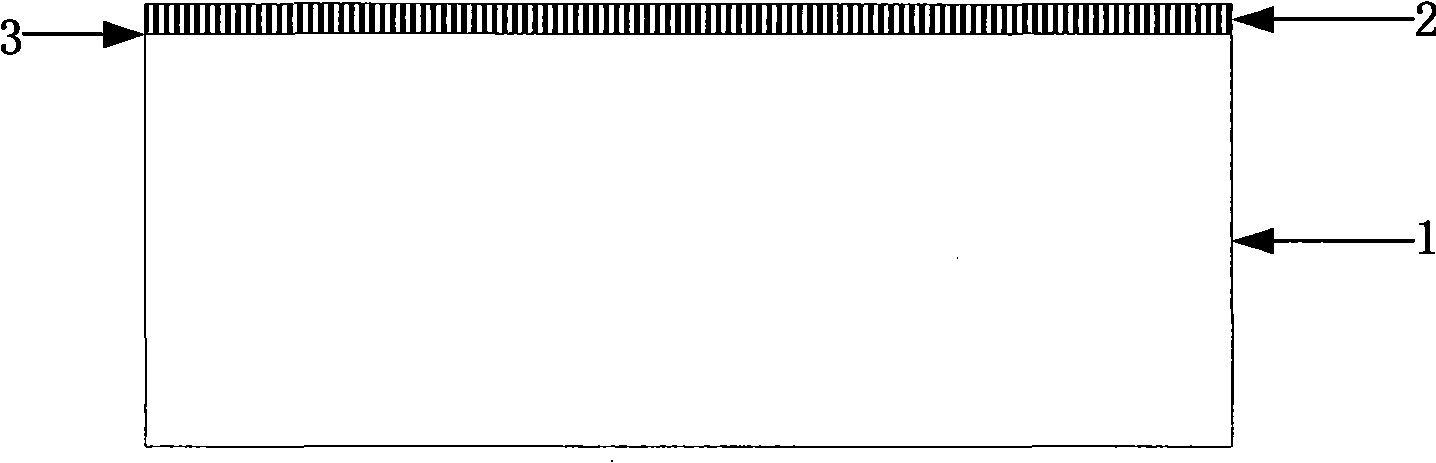

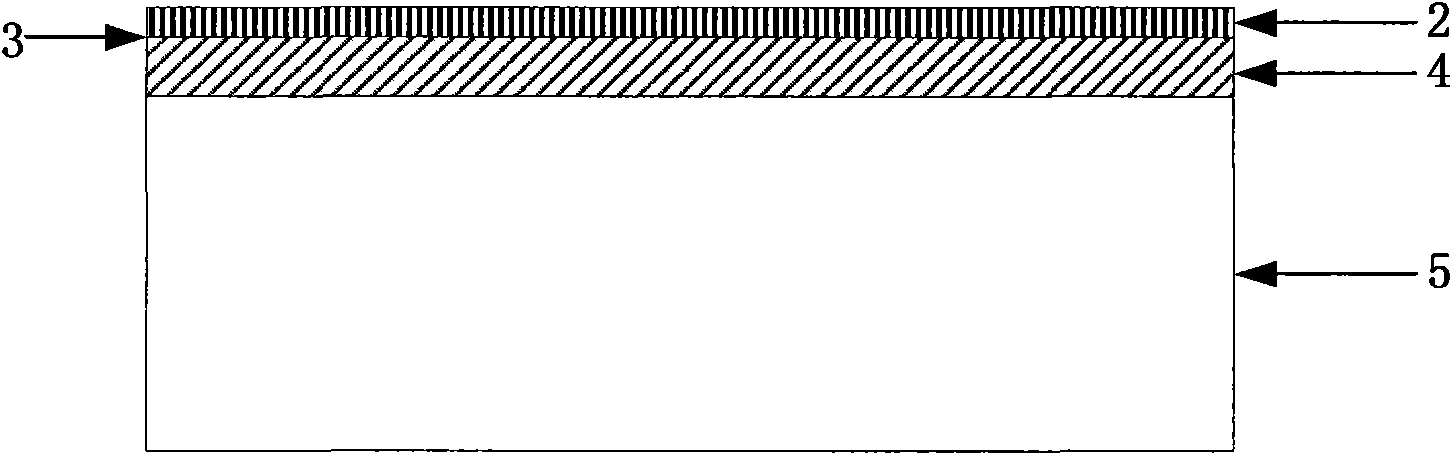

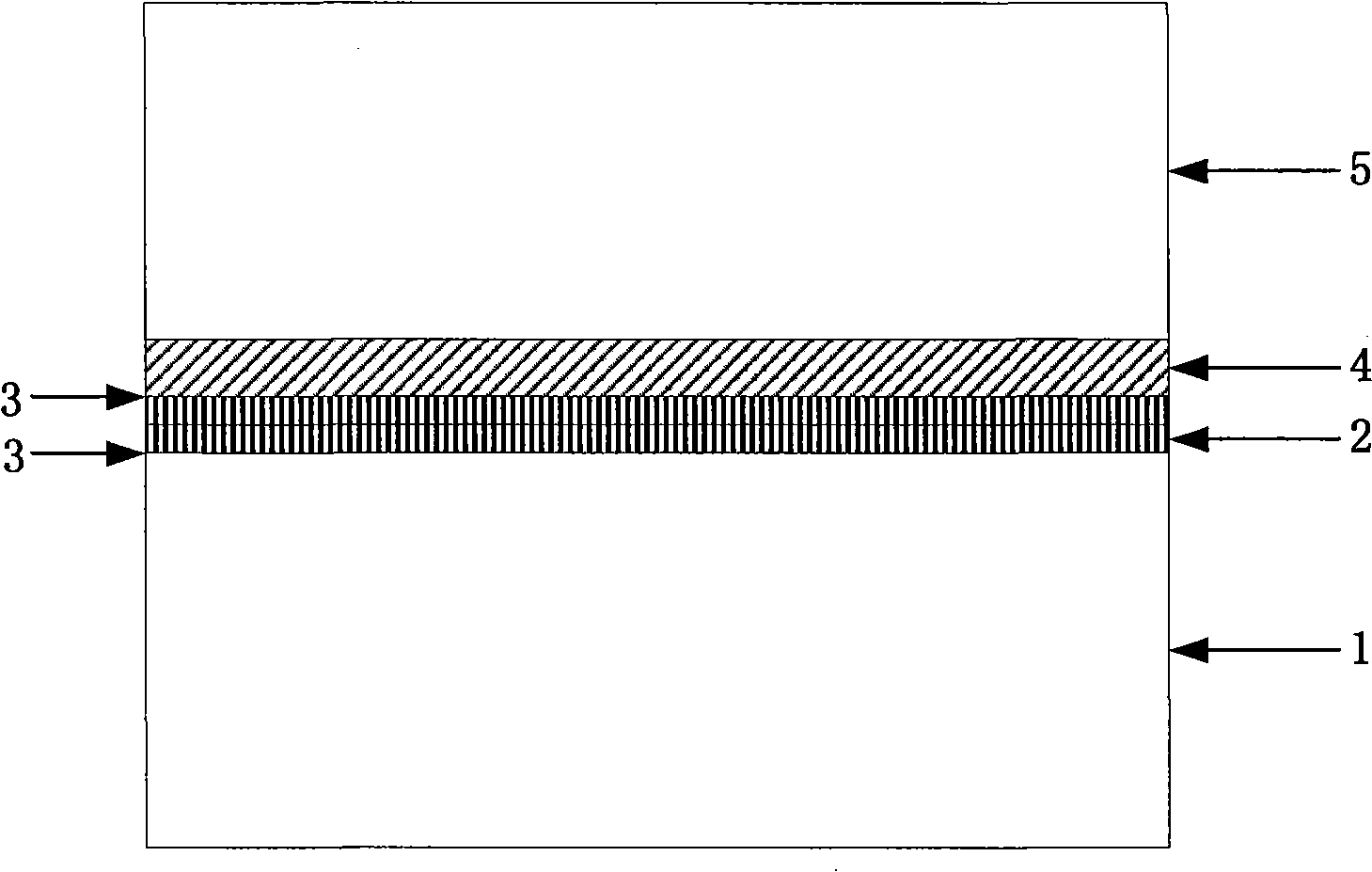

Method of producing silicon-on-insulator article

InactiveCN104094399AImprove thermal conductivityImprove qualitySolid-state devicesSemiconductor/solid-state device manufacturingSurface layerSilicon on insulator

A method of producing a silicon-on-insulator article is provided. The method includes: forming a first aluminium nitride layer thermally coupled to a first silicon substrate; forming a second aluminium nitride layer thermally coupled to a second substrate, the second substrate including at least a surface layer of silicon; bonding the first and second aluminium nitride layers of the first and second substrates together so that the first and second aluminium nitride layers are disposed between the first and second substrates; and removing most of the second substrate to leave a layer of silicon that is electrically insulated from but thermally coupled to the first silicon substrate by the first and second aluminium nitride layers.

Owner:SILANNA GRP

Nano-sheet ring-gate field effect transistor with double-layer side wall structure

ActiveCN110246899AImprove the coupling effectImprove gate control abilitySemiconductor/solid-state device manufacturingSemiconductor devicesCouplingEngineering

The invention discloses a nano-sheet ring-gate field effect transistor with a double-layer side wall structure. The device has two layers of side walls, a side wall close to a nano-sheet channel is made of a material with a low dielectric constant (low-k for short) and high thermal conductivity, and a side wall away from the nano-sheet channel is made of a material with a high dielectric constant (high-k for short). The side wall formed by the low-k material facilitates the heat radiation of the device, the side wall formed by the high-k material facilitates the reinforcement of the coupling between a device gate and the channel, and therefore, the device still has good heat dissipation effect under a large on-state current condition. In addition, the heat dissipation capability and DC performance of the device can be flexibly regulated by changing the thickness ratio of the low-k material to the high-k material.

Owner:EAST CHINA NORMAL UNIV +1

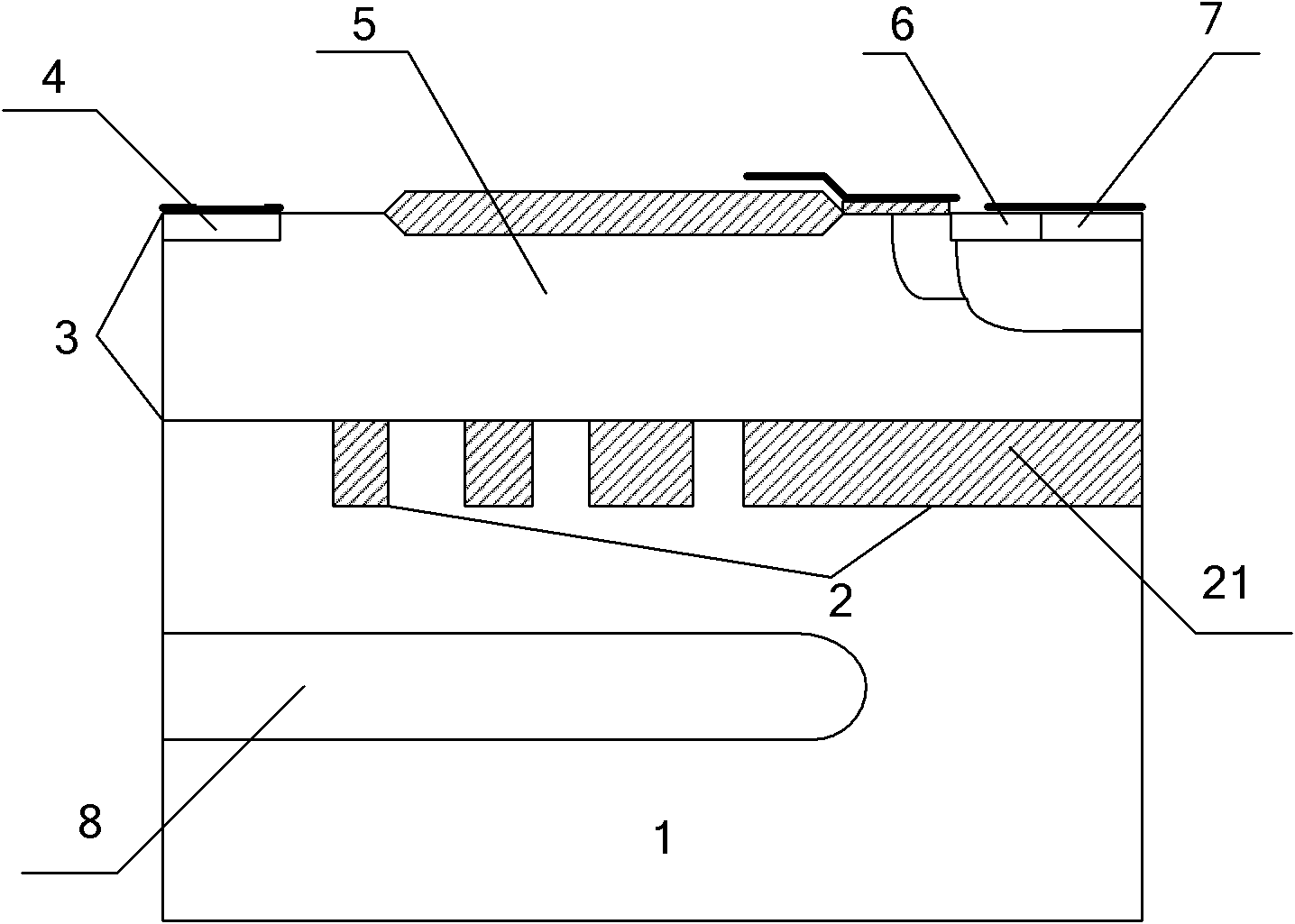

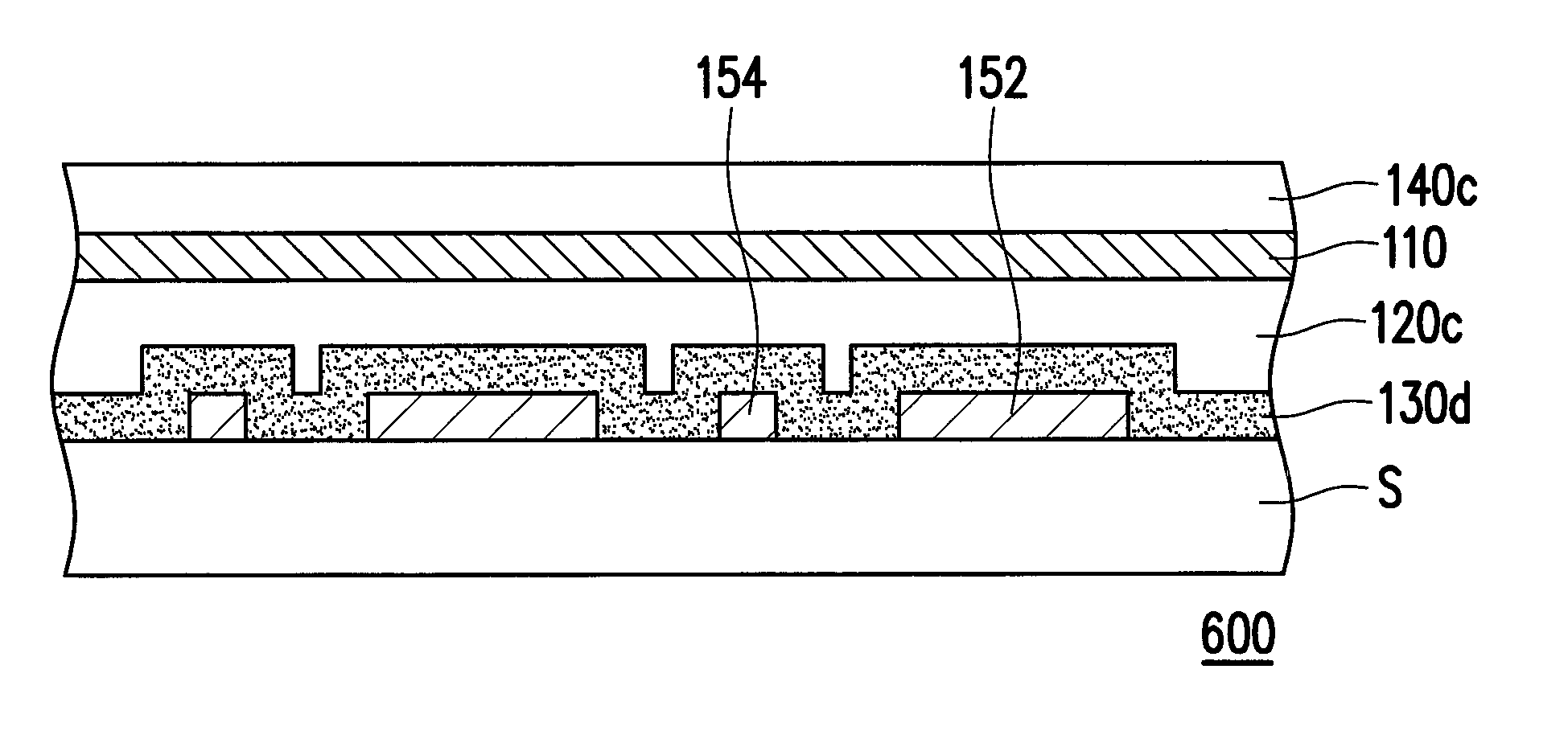

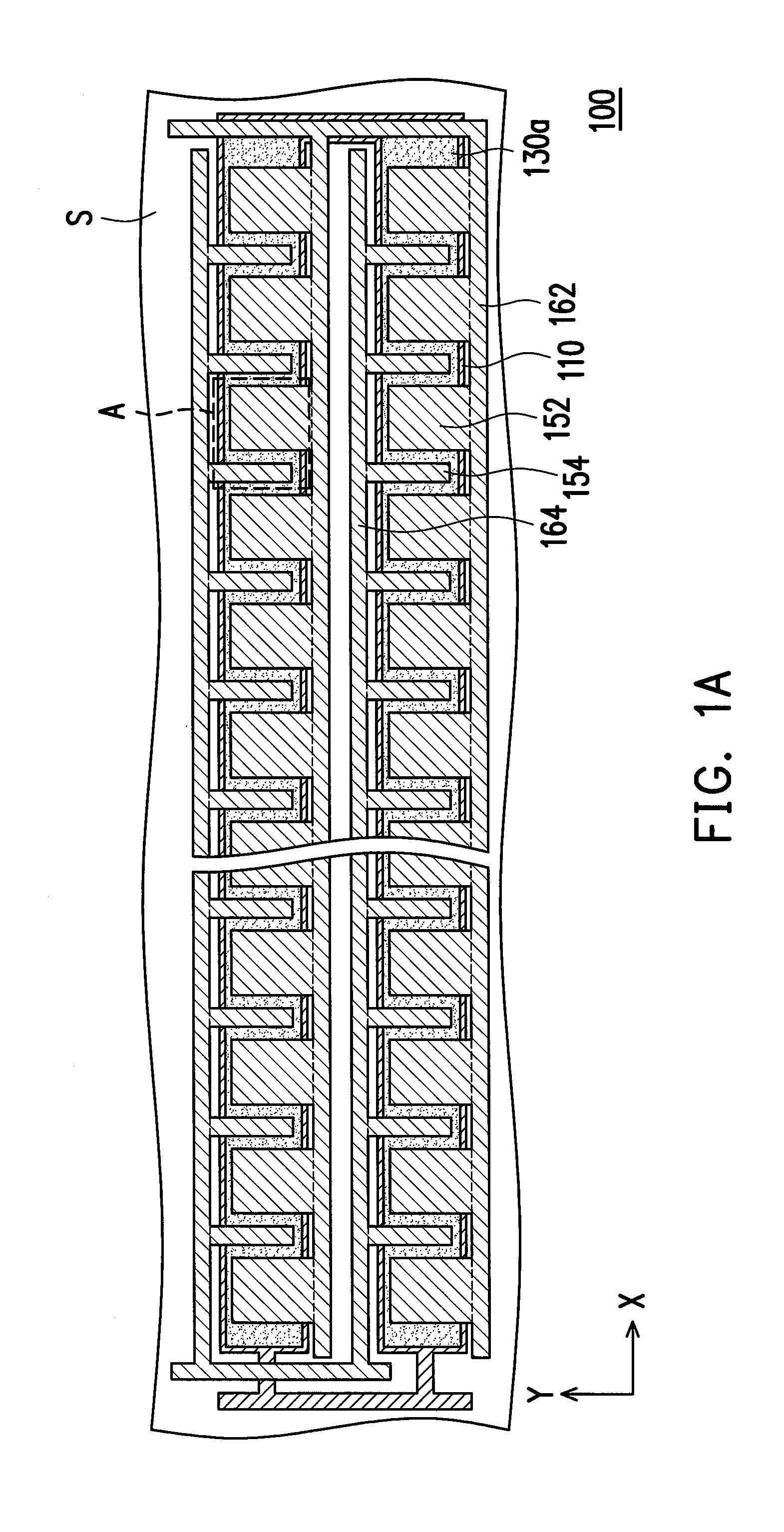

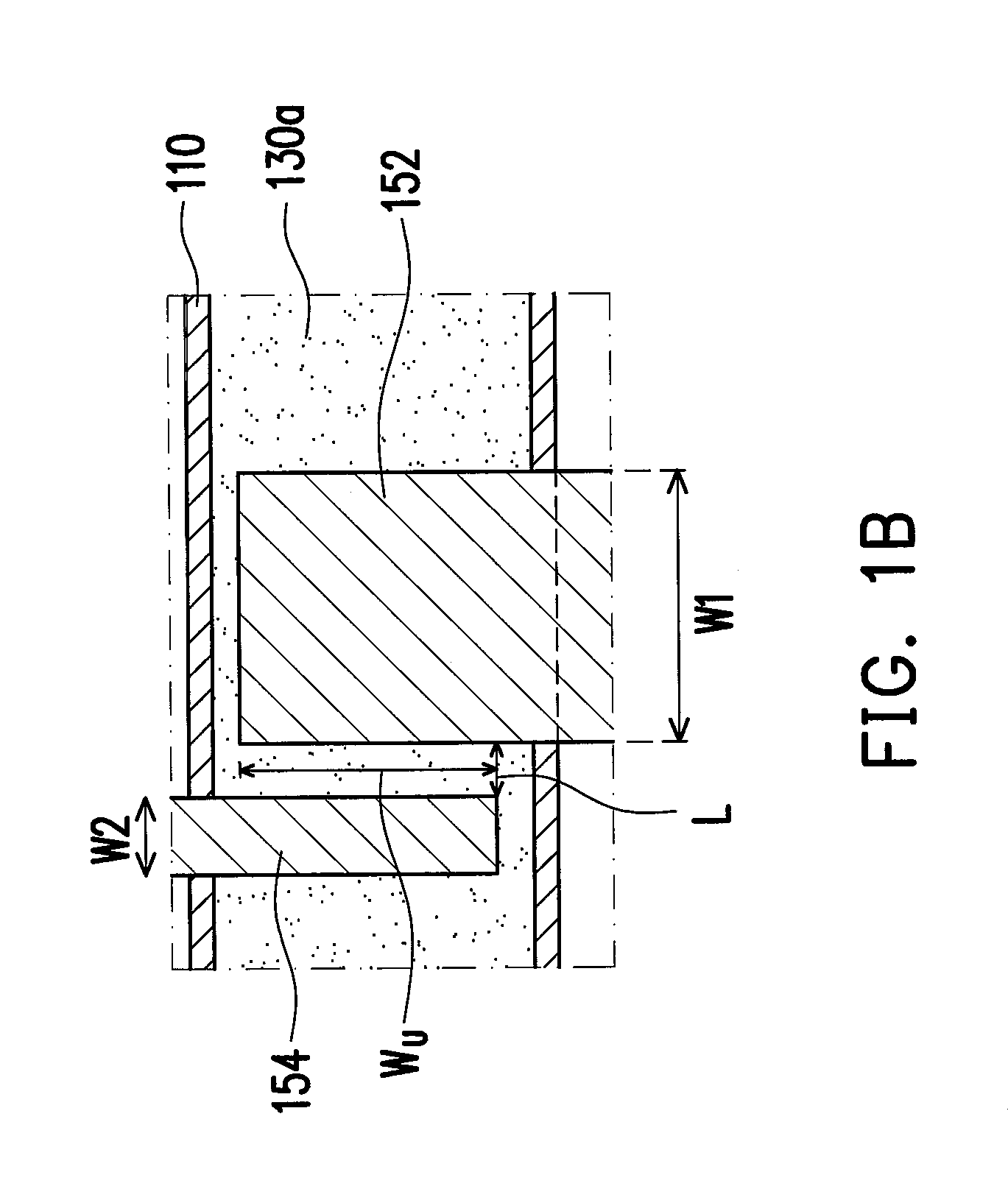

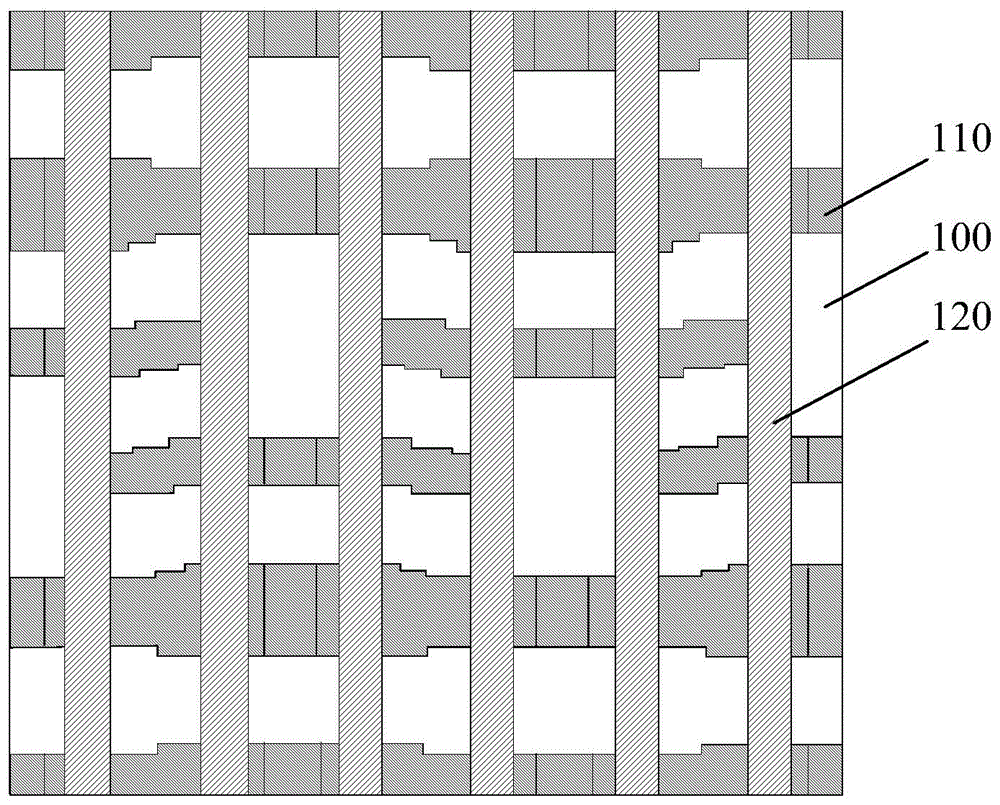

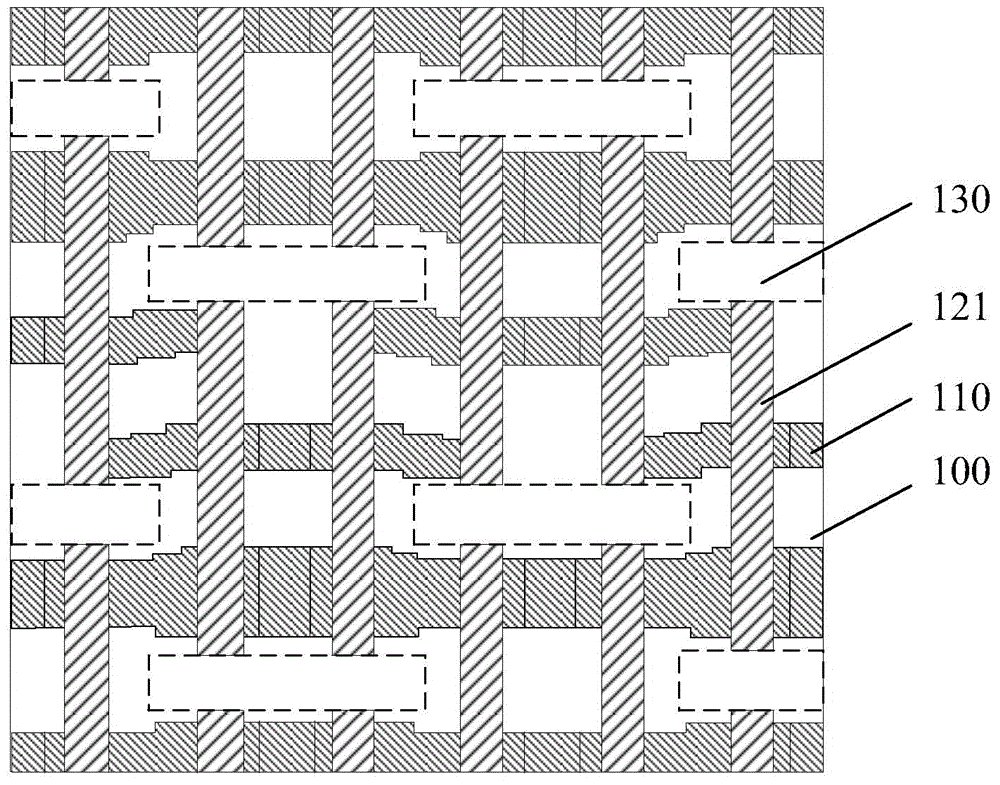

Transistor structure and driving circuit structure

ActiveUS20130306968A1Improve stabilityImprove reliabilityTransistorStatic indicating devicesEngineeringTransistor

A transistor structure disposed on a substrate includes a gate electrode, a gate insulating layer overlapping the gate electrode, a channel layer overlapping the gate electrode, and a plurality of first electrodes and a plurality of second electrodes overlapping the gate electrode. The gate insulating layer is disposed between the channel layer and the gate electrode. Besides, the gate insulating layer is located among the first electrodes, the second electrodes, and the gate electrode. The first electrodes and the second electrodes are alternately arranged along a first direction. Each of the first electrodes has a first width along the first direction. Each of the second electrodes has a second width along the first direction. A ratio of the first width to the second width ranges from 2 to 20. A driving circuit structure having the transistor structure is also provided.

Owner:AU OPTRONICS CORP

Partial SOI (Silicon On Insulator) transverse double-diffused device

ActiveCN102569359AEfficient deliveryReduce doping concentrationSemiconductor devicesOhmic contactComputer science

The invention relates to SOI technology. The invention provides a partial SOI (Silicon On Insulator) transverse double-diffused device, which solves the problem of obvious self-heating effect in the traditional SOI device. The technical scheme can be summarized as follows: in the partial SOI transverse double-diffused device, one end of a buried oxide layer is positioned below a source and contacts with the edge of the device; the horizontal distance between the other end of the buried oxide layer and a type II impurity ohmic contact region of a drain is not less than zero; and between the other end of the buried oxide layer and the device edge below the drain, a type I impurity substrate and a type II impurity top silicon layer are in contact with each other to form a PN junction. The partial SOI transverse double-diffused device provided by the invention has the following advantages that the thermal generated by the SOI device can be effectively transmitted because the buried oxide layer is open below the drain and is suitable for SOI devices.

Owner:SICHUAN CHANGHONG ELECTRIC CO LTD

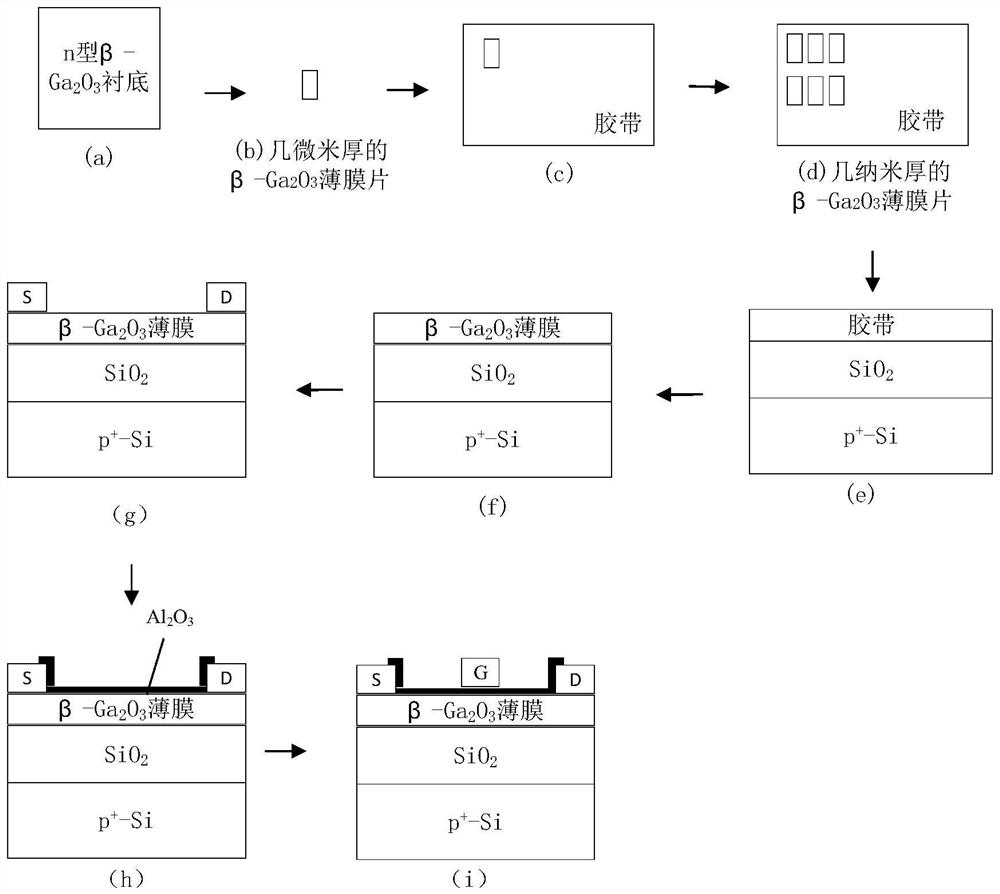

Preparation method of high-performance gallium oxide field effect transistor with insulating substrate

InactiveCN112133755AImprove integritySimple and fast operationSemiconductor/solid-state device manufacturingSemiconductor devicesLattice mismatchEngineering

The invention discloses a preparation method of a high-performance gallium oxide field effect transistor with an insulating substrate, and mainly solves the problems that the cost of growing a Ga2O3 thin film by an existing epitaxial method is high, and lattice mismatch and thermal mismatch between the substrate and the thin film are difficult to eliminate. The method comprises the steps of selecting an n-type beta-Ga2O3 single crystal substrate, cleaning the n-type beta-Ga2O3 single crystal substrate, and obtaining a nano-scale beta-Ga2O3 thin film through multiple times of mechanical stripping; soaking the insulating substrate in acetone to remove organic pollutants and the like, transferring the nano-scale beta-Ga2O3 thin film to the insulating substrate, and sequentially performing photoetching and metal layer deposition on the thin film to form a source end electrode and a drain end electrode; and depositing Al2O3 on the surface of a sample piece with the manufactured source and drain electrodes, sequentially carrying out photoetching and metal layer deposition on the surface of Al2O3 to form a gate electrode, and completing manufacturing of the gallium oxide-based device. Thepreparation method is simple in preparation process and low in cost, and the prepared Ga2O3 film is high in quality and can be used for preparing a high-performance gallium oxide-based device.

Owner:XIDIAN UNIV

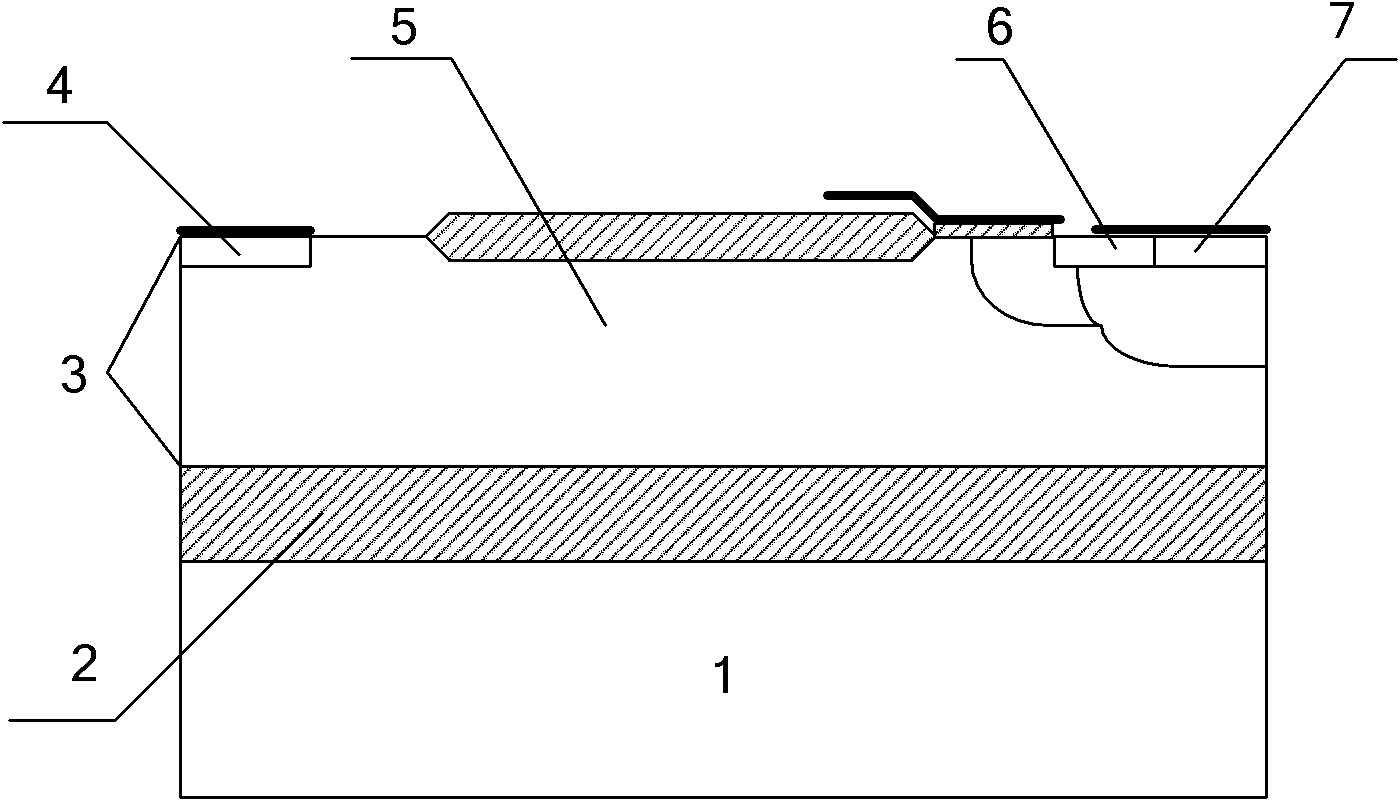

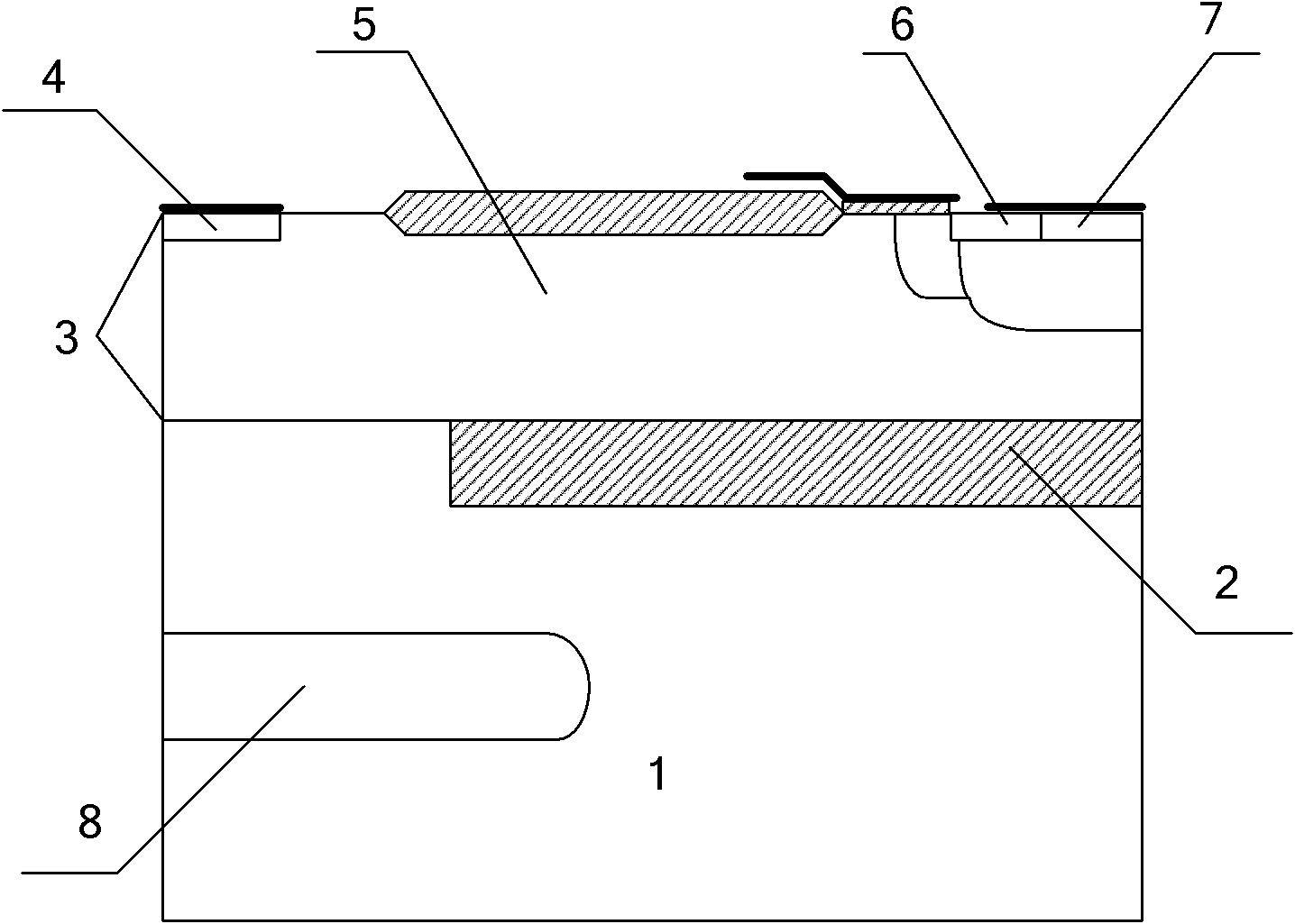

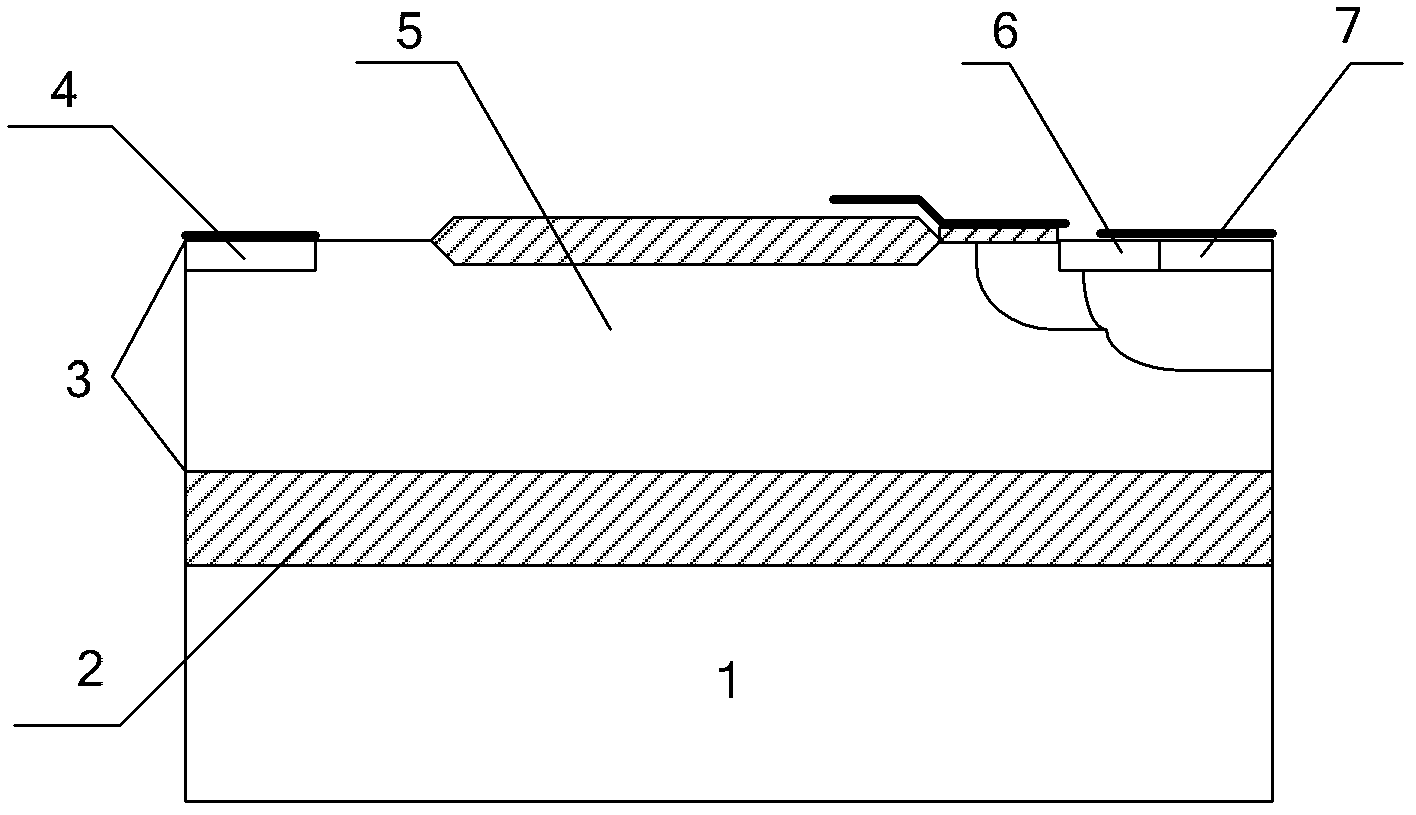

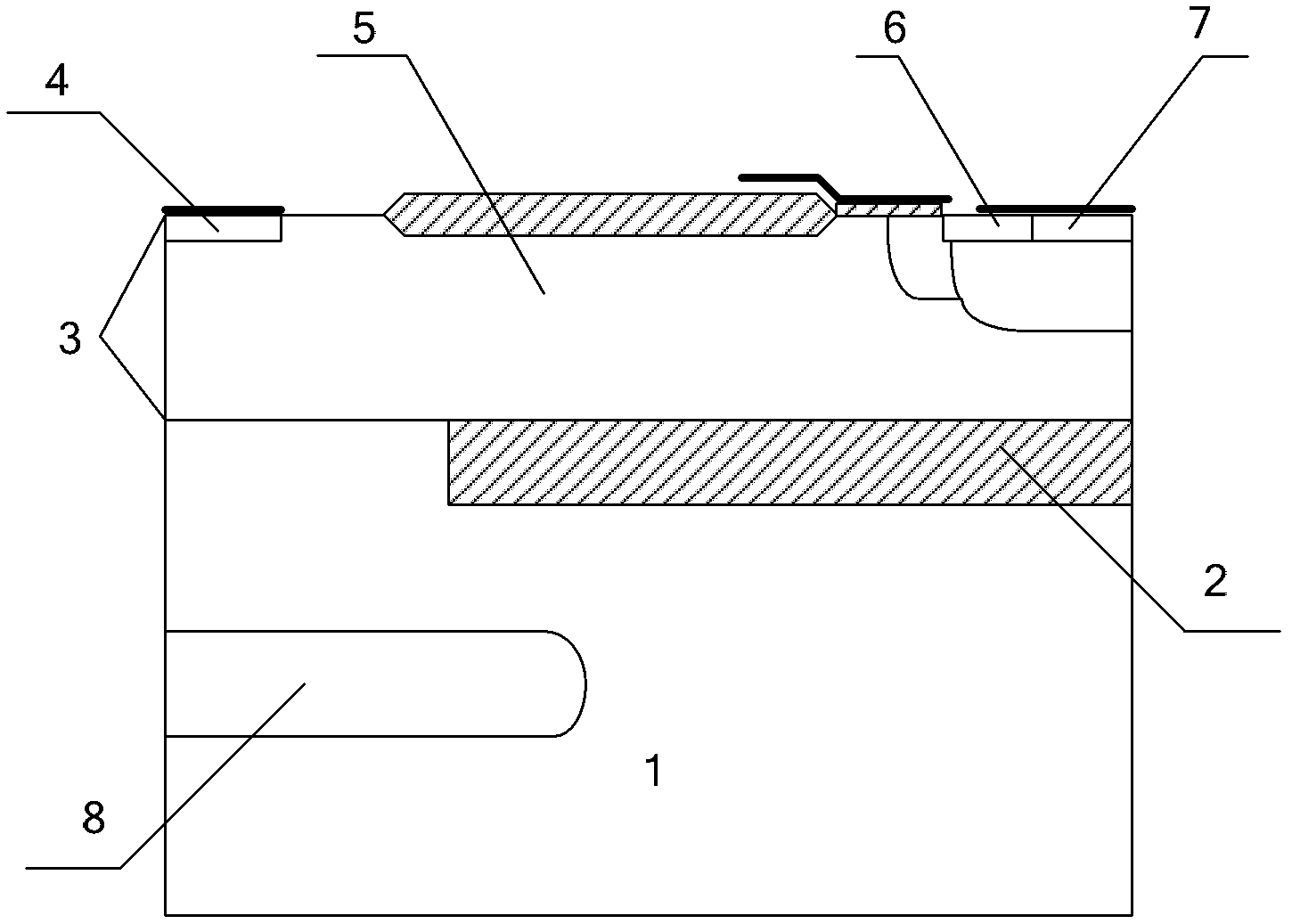

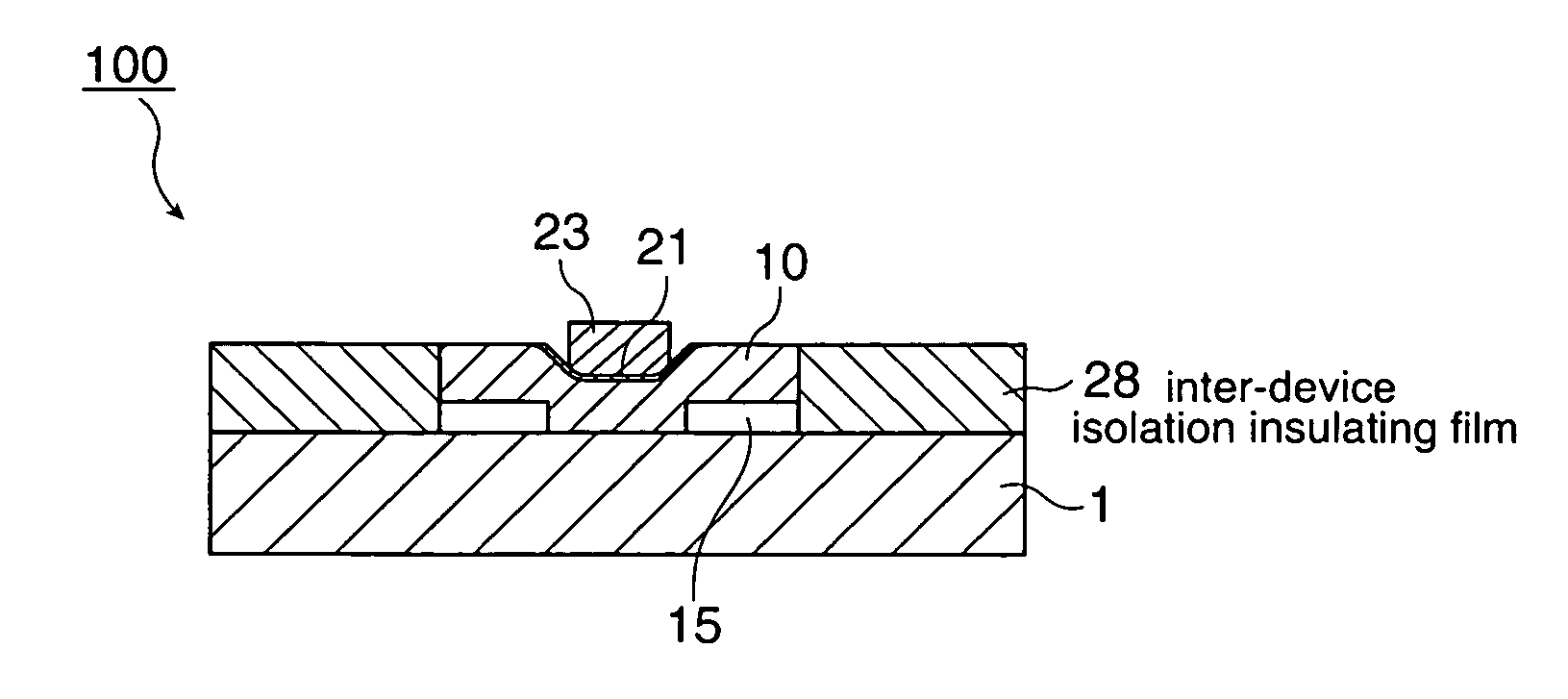

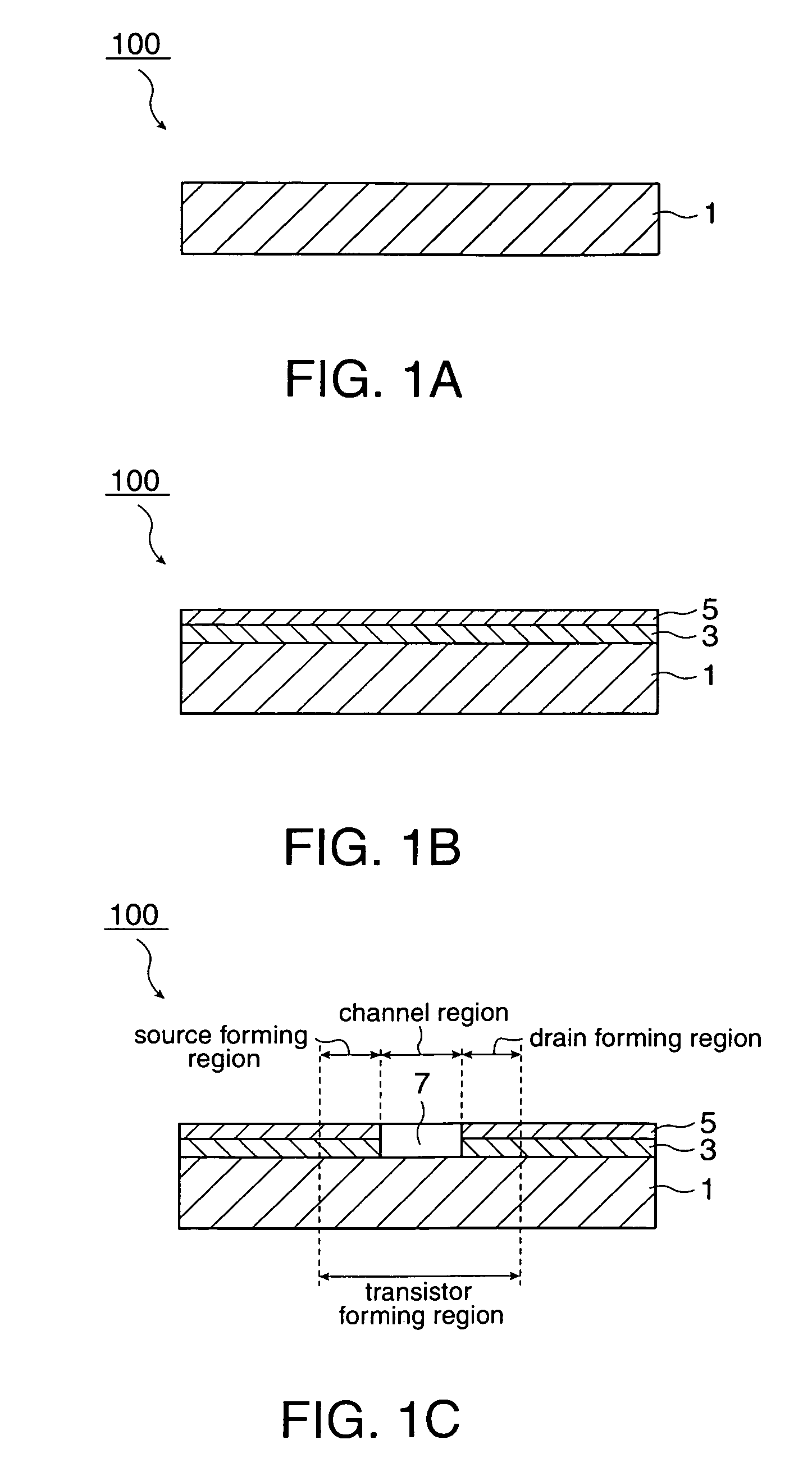

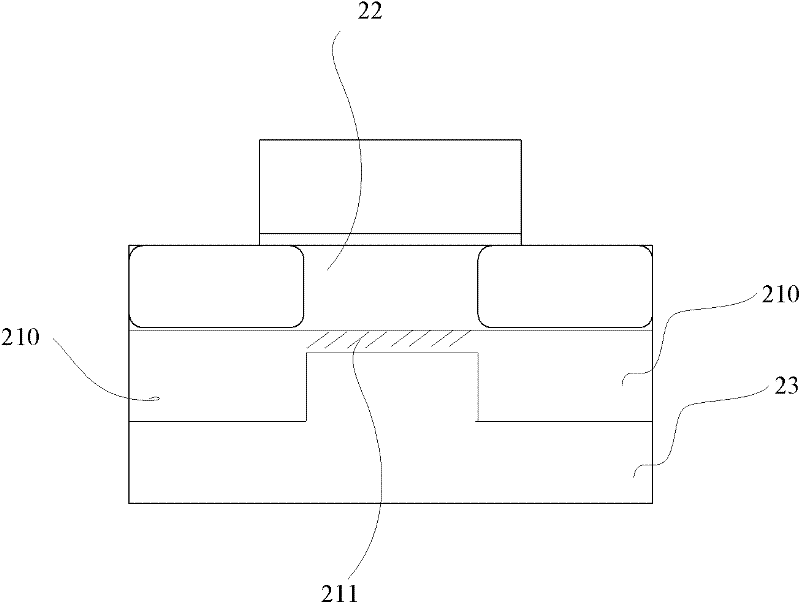

Semiconductor device and method for manufacturing the same

InactiveUS7534687B2Reduce self-heating effectEliminate the effects ofSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorSemiconductor device

A semiconductor device, comprises: a transistor having structured to include a gate electrode formed on a semiconductor layer on a semiconductor substrate via a gate insulating film, and a source layer and a drain layer formed on the semiconductor layer sandwiching the gate electrode; a hollow portion existing between the source layer and the semiconductor substrate, and between the drain layer and the semiconductor substrate, respectively; and the hollow portion in absence between the semiconductor layer under the gate electrode and the semiconductor substrate.

Owner:SEIKO EPSON CORP

Silicon-on-insulator (SOI) substrate structure and device

InactiveCN102244080AReduce self-heating effectReduces off-state leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingPower flowSoi substrate

The invention provides a silicon-on-insulator (SOI) substrate structure and an SOI device using the SOI substrate structure, for further reducing the self-heating effect of the SOI device and avoiding the problems of substantially reduced SOI device performance, many process modifications and high cost and the like in the existing scheme of reducing the self-heating effect; meanwhile, by the adoption of the invention, current at a drain terminal can be increased, the off-state leakage current of the device can be reduced and the ratio of on-state current to off-state current can be obviously improved. The SOI substrate structure provided by the invention comprises an insulating layer and a bottom substrate below the insulating layer, wherein the insulating layer is divided into a first insulating layer below a channel region and a second insulating layer beyond the first insulating layer, and the thickness of the first insulating layer or a part of the first insulating layer is smaller than that of the second insulating layer.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Reticle and forming method of semiconductor device

ActiveCN105629658AHigh light transmittanceReduce self-heating effectOriginals for photomechanical treatmentEngineeringOptical transmittance

The invention provides a reticle and a forming method of a semiconductor device. The reticle comprises a substrate, a shade layer placed on the substrate and a main pattern placed in the shade layer and further comprises an auxiliary pattern placed in the shade layer, wherein the auxiliary pattern is placed inside the main pattern or at the periphery of the main pattern and is used for increasing the light transmittance of the reticle. The reticle has the advantages that the light transmittance of the reticle is increased due to arrangement of the auxiliary pattern; since the area of the reticle, receiving irradiation of exposure light, is reduced, absorbed light is reduced, the self-heating effect of the reticle is decreased, the self deformation of the reticle is reduced, further the deflection of a device pattern formed by using the reticle can be prevented, and the pattern accuracy of a semiconductor device formed by using the reticle can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

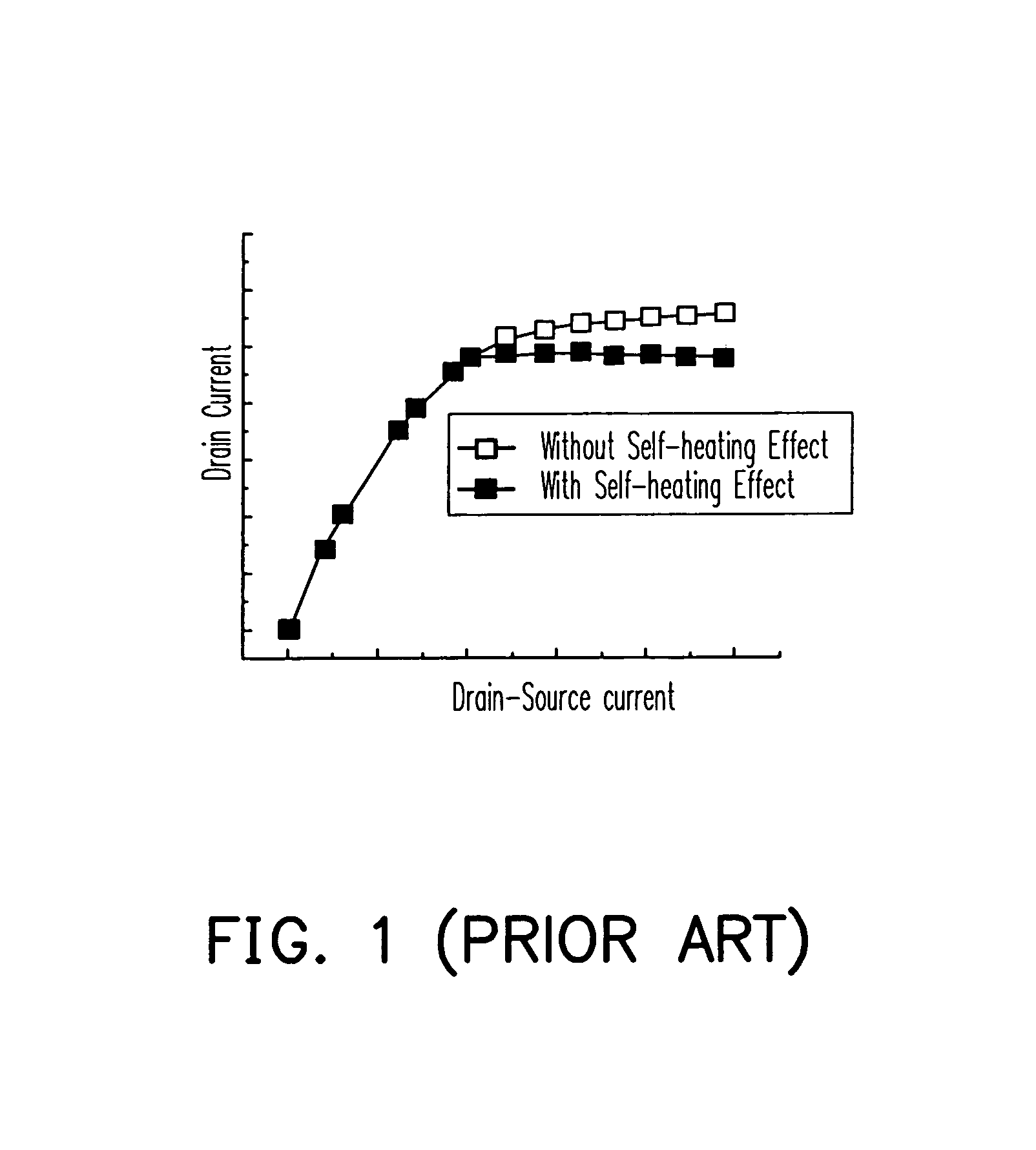

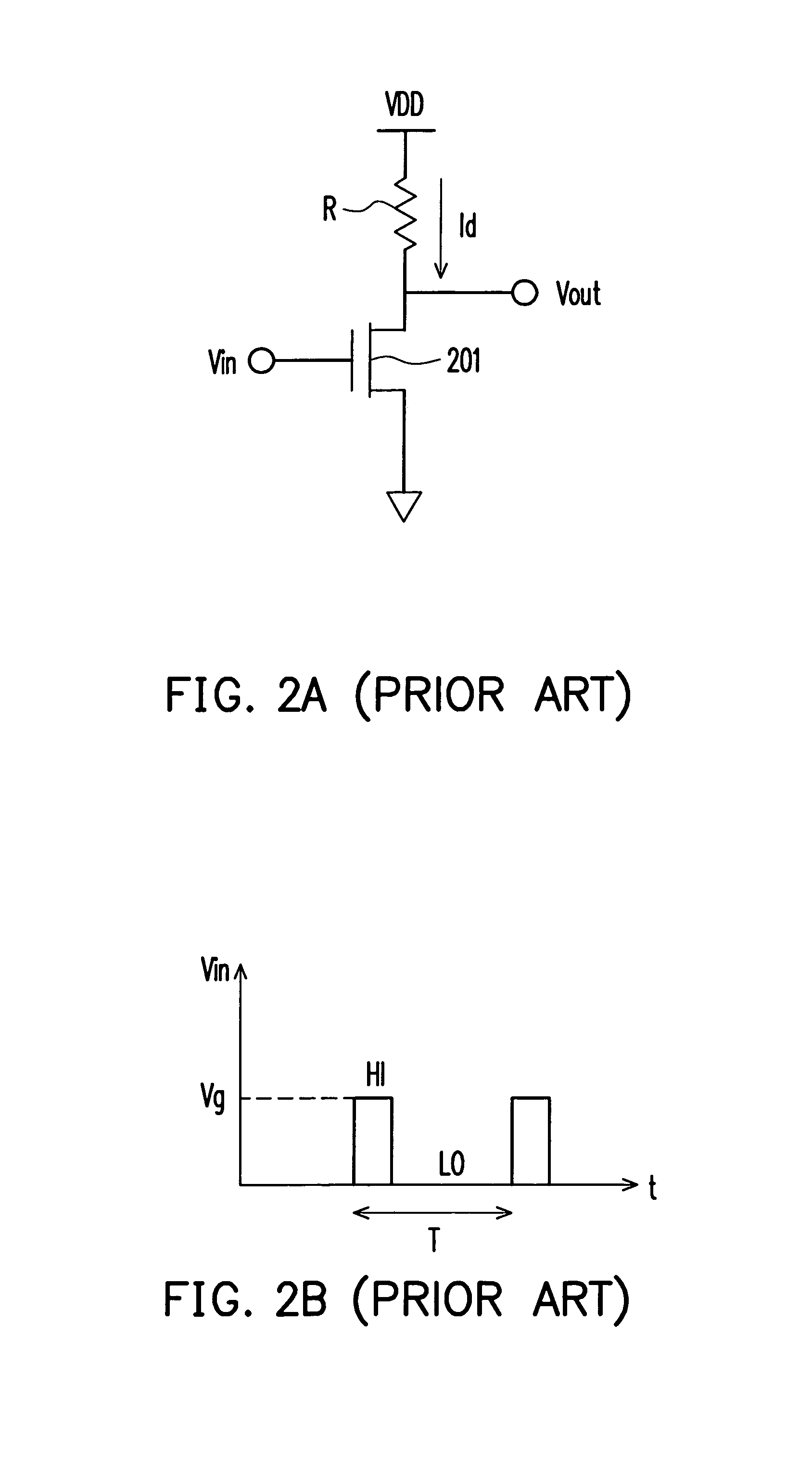

Method and circuit for extracting current-voltage characteristics of device

InactiveUS7362122B2Reduce self-heating effectIncrease the measurable rangeTemperature compensation modificationElectronic switchingCurrent voltageEngineering

Owner:MACRONIX INT CO LTD

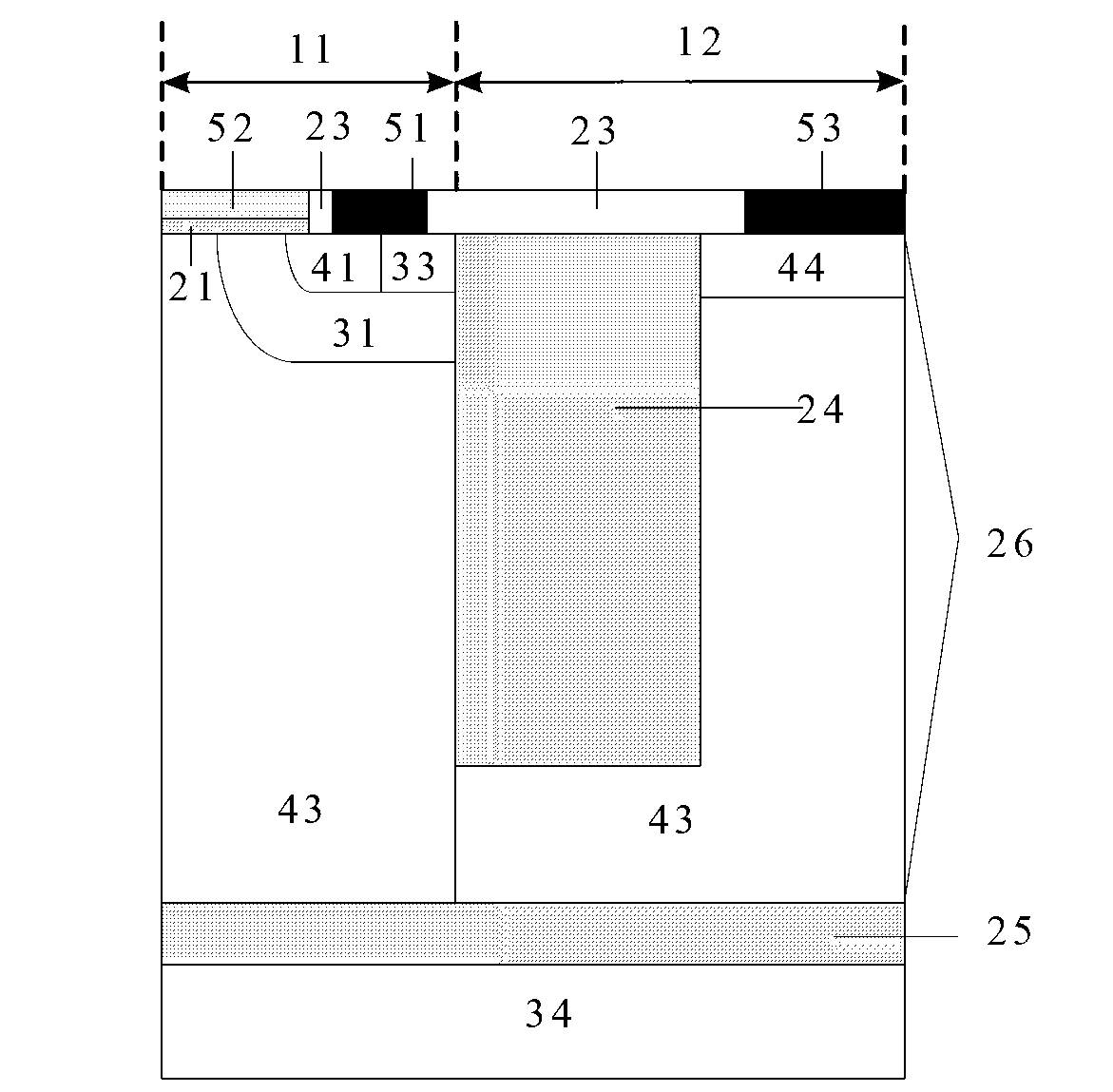

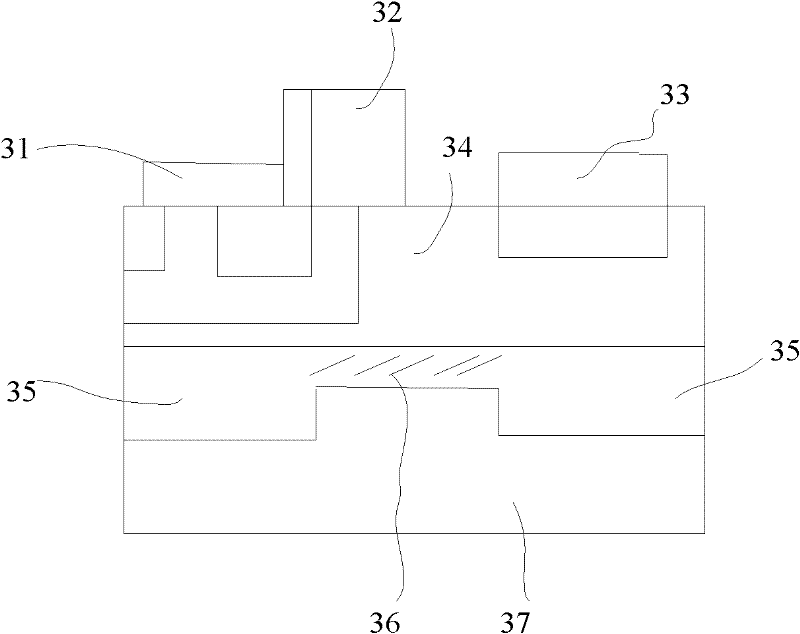

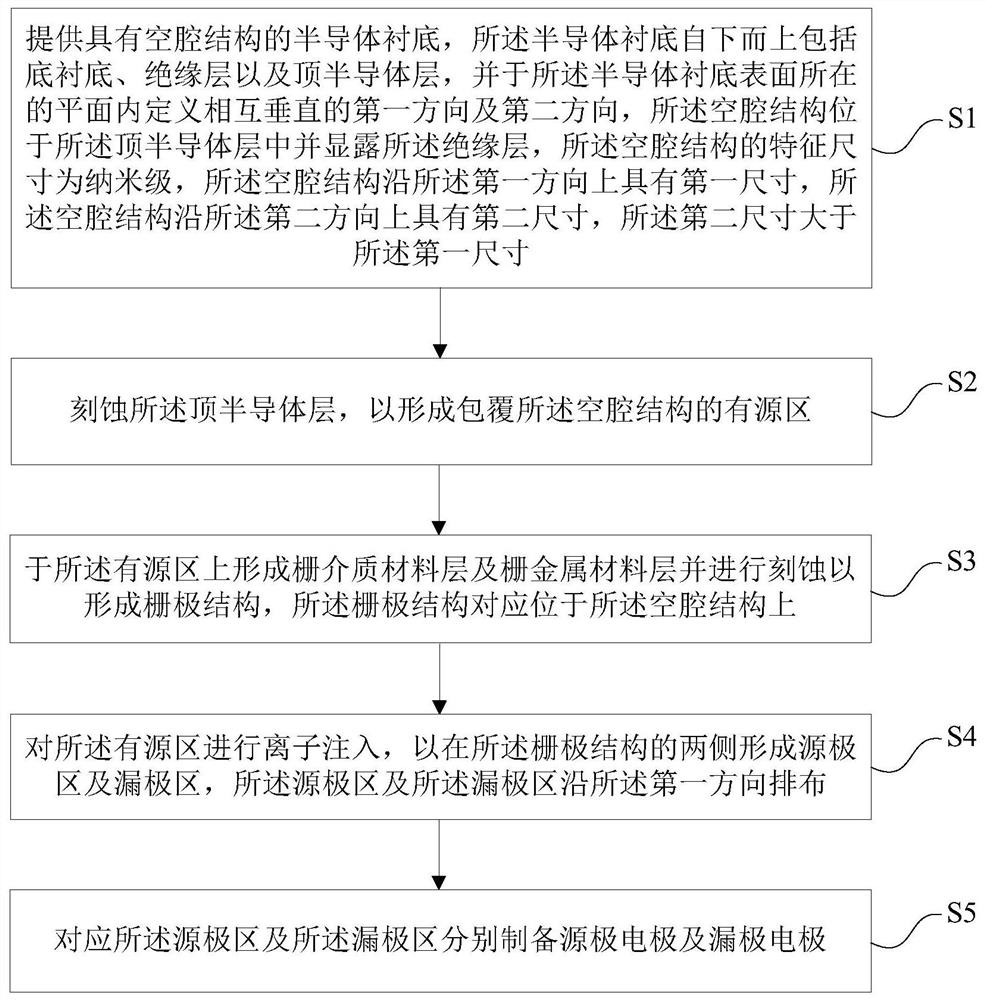

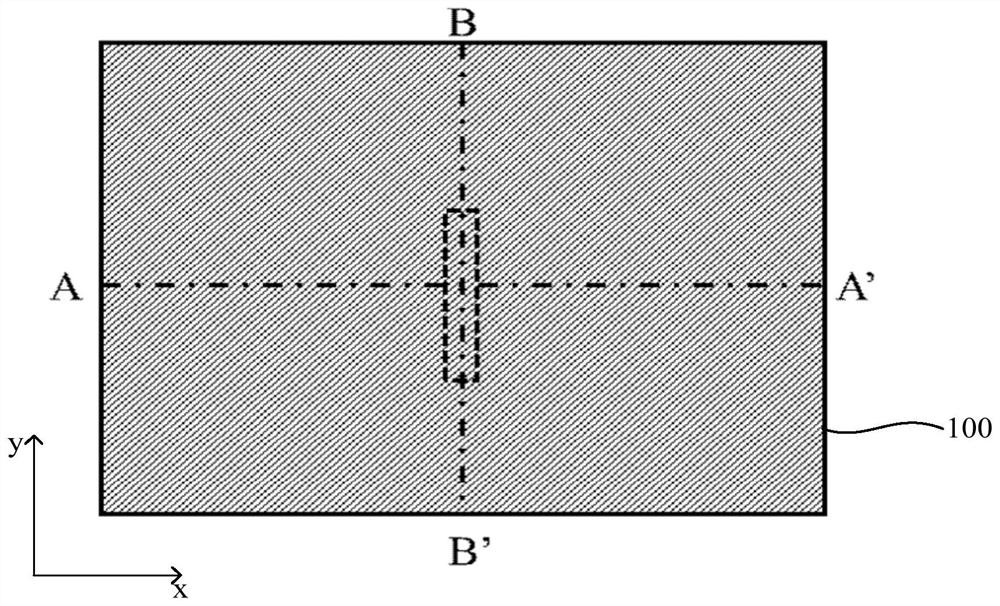

SOI device capable of improving self-heating effect and preparation method thereof

ActiveCN111986996AGuaranteed breakageReduce self-heating effectTransistorSemiconductor/solid-state device manufacturingFloating body effectEngineering

The invention provides an SOI device capable of improving a self-heating effect and a preparation method thereof. The preparation comprises the steps: providing a semiconductor substrate with a cavitystructure, enabling the cavity structure to be located in a top semiconductor layer and exposing an insulating layer, preparing an active region coating the cavity structure, and preparing a gate electrode structure, a source-drain region and a source-drain electrode. The SOI substrate with the nanoscale cavity is adopted, the cavity structure is located in the top semiconductor layer, the size of the cavity is effectively reduced, the cavity is in the nanoscale size in the channel length direction, the heat dissipation path of the device cannot be obviously blocked, and compared with a device with a large-size cavity, the self-heating effect is relieved. Theoretically, the thickness of the top semiconductor layer above the cavity can reach 2 nm, it is guaranteed that top silicon is not damaged, a channel can be completely exhausted by a gate electrode, and the floating body effect is effectively restrained. The cavity is located in the top semiconductor layer and makes contact with the insulating layer, parasitic charges in the insulating layer cannot be introduced into a parasitic channel at the bottom of the top semiconductor layer, and the total dose radiation effect is effectively restrained.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Conductive layer under SOI oxygen buried layer and manufacturing process thereof

InactiveCN101916761AReduce self-heating effectMitigate the effects of charge distributionSolid-state devicesSemiconductor/solid-state device manufacturingSilicon membraneOxygen

The invention discloses a conductive layer under an SOI oxygen buried layer and a manufacturing process thereof. The SOI comprises a bottom silicon film, an oxygen buried layer and a top silicon film, from bottom to upper, wherein the conductive layer is grown between the bottom silicon film and the oxygen buried layer; the conductive layer comprises a charge conductive layer and a barrier layer; the barrier layer is grown on the upper and lower surfaces of the charge conductive layer. The invention can discharge the heat generated in a device to the exterior through the conductive layer, so as to efficiently decrease the SOI self-heating effect. The effect of non-insulate substrate is as same as the effect of the insulate substrate. Besides, the accumulated surplus charges can be released so as to decrease the influence of the longitudinal electric field on the charge distribution inside the device.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI +1