Nano-sheet ring-gate field effect transistor with double-layer side wall structure

A field-effect transistor and sidewall structure technology, which is applied in the field of field-effect transistor logic devices, can solve problems such as serious self-heating effects, achieve the effects of alleviating self-heating effects, enhancing coupling effects, and reducing thermal resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

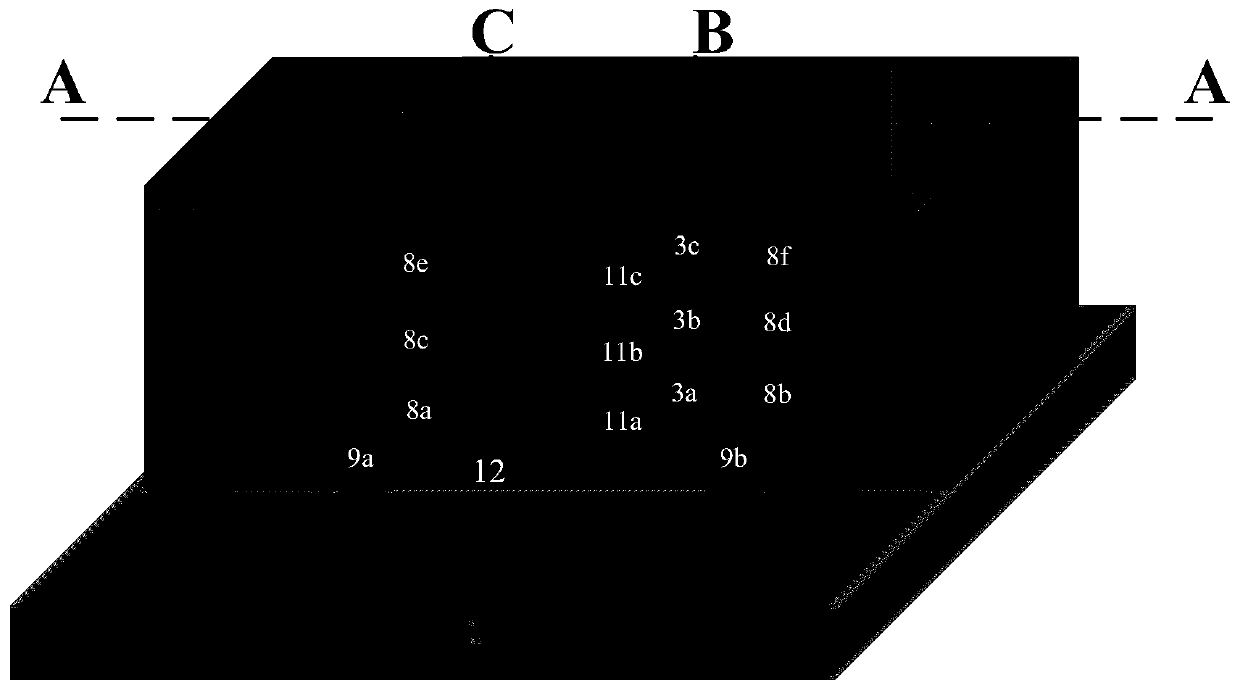

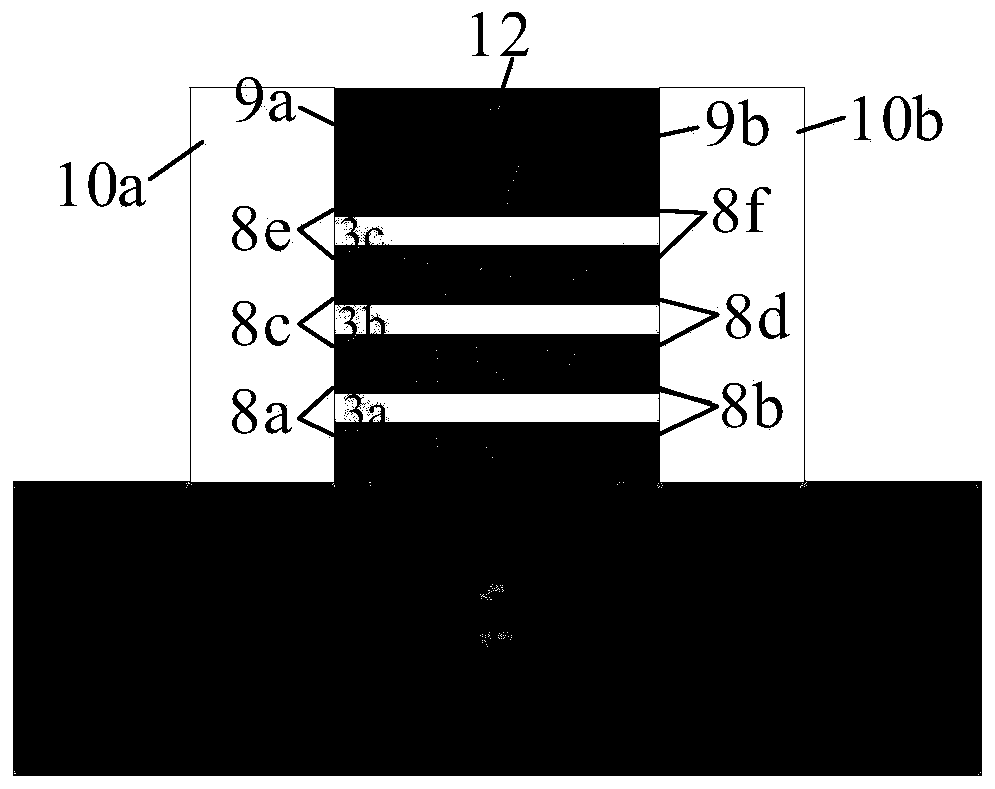

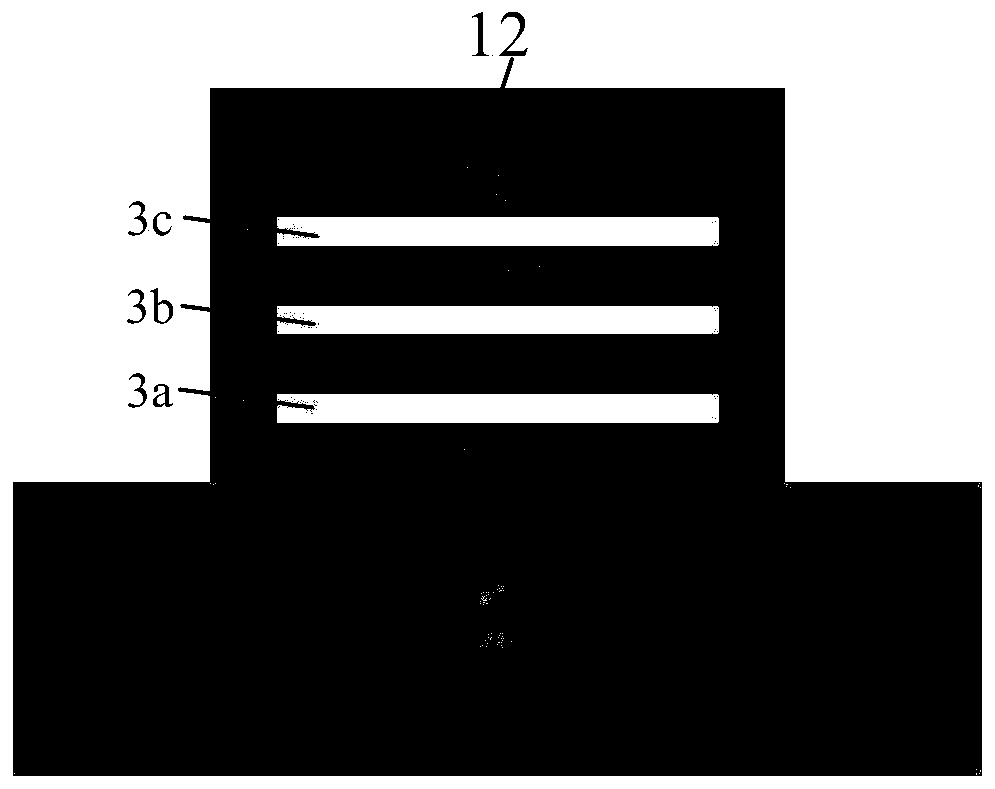

[0031] In this embodiment, the channel region is vertically stacked with three layers as an example.

[0032] refer to Figure 1 to Figure 4 The nanosheet gate-all-around field effect transistor with a double-layer sidewall structure proposed by the present invention includes the following structures: nanosheet channel regions 3a, 3b, 3c, gate dielectric layers 11a, 11b, 11c, gate metal layer 12, Substrate 1, raised source 10a, raised drain 10b, source low-k sidewalls 8a, 8c, 8e, source high-k sidewalls 9a, drain low-k sidewalls 8b, 8d, 8f and drain end high-k sidewall 9b, the nanosheet channel regions 3a, 3b, 3c are composed of three vertically stacked channels, and the periphery of each vertically stacked channel is sequentially provided with source end low-k sidewalls 8a along the horizontal direction . The low-k sidewalls 8a, 8c, and 8e at the source end have three layers, and each layer does not touch; the low-k sidewalls 8b, 8d, and 8f at the drain end have three layer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More