Patents

Literature

294results about How to "Process compatible" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

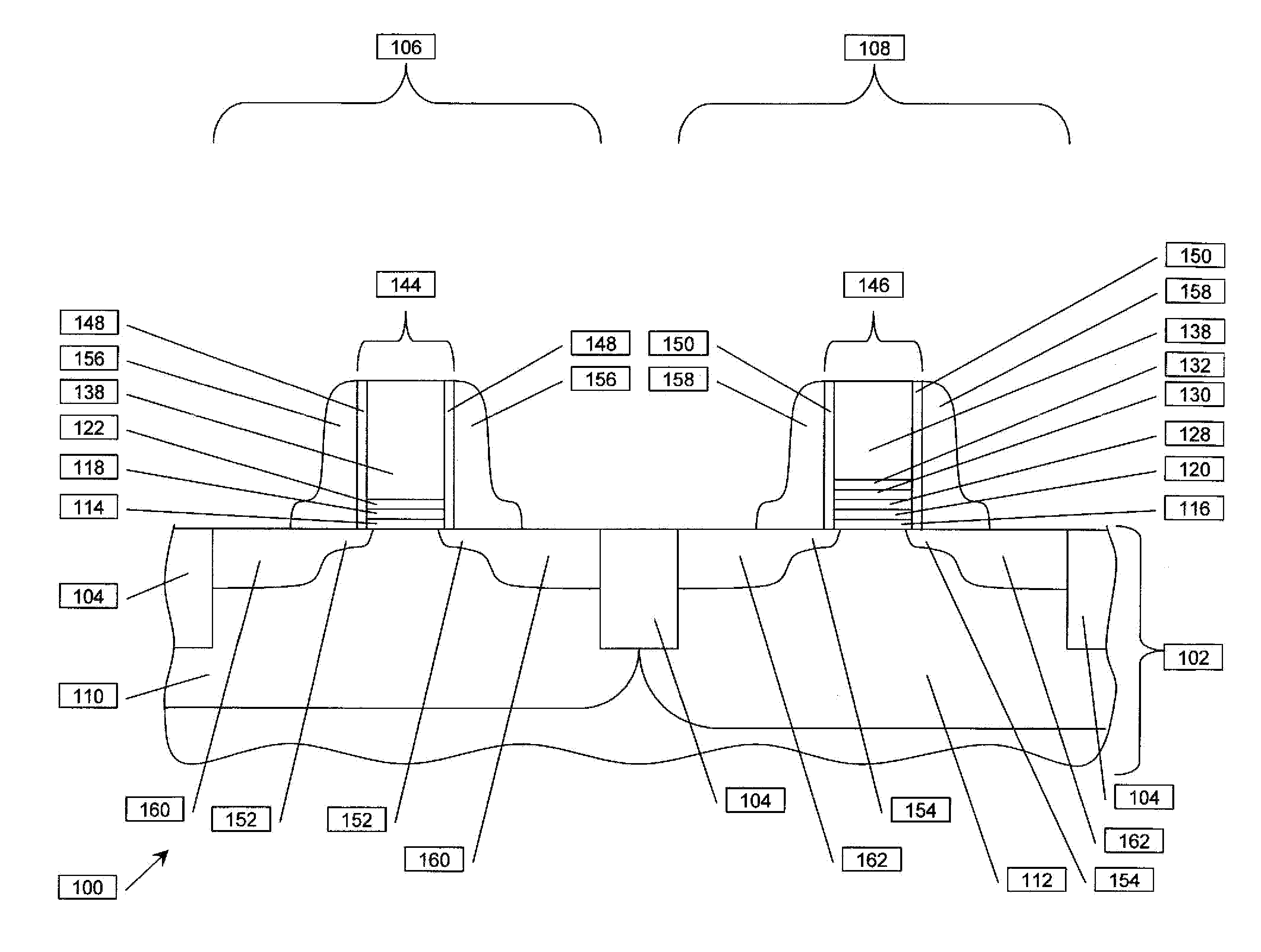

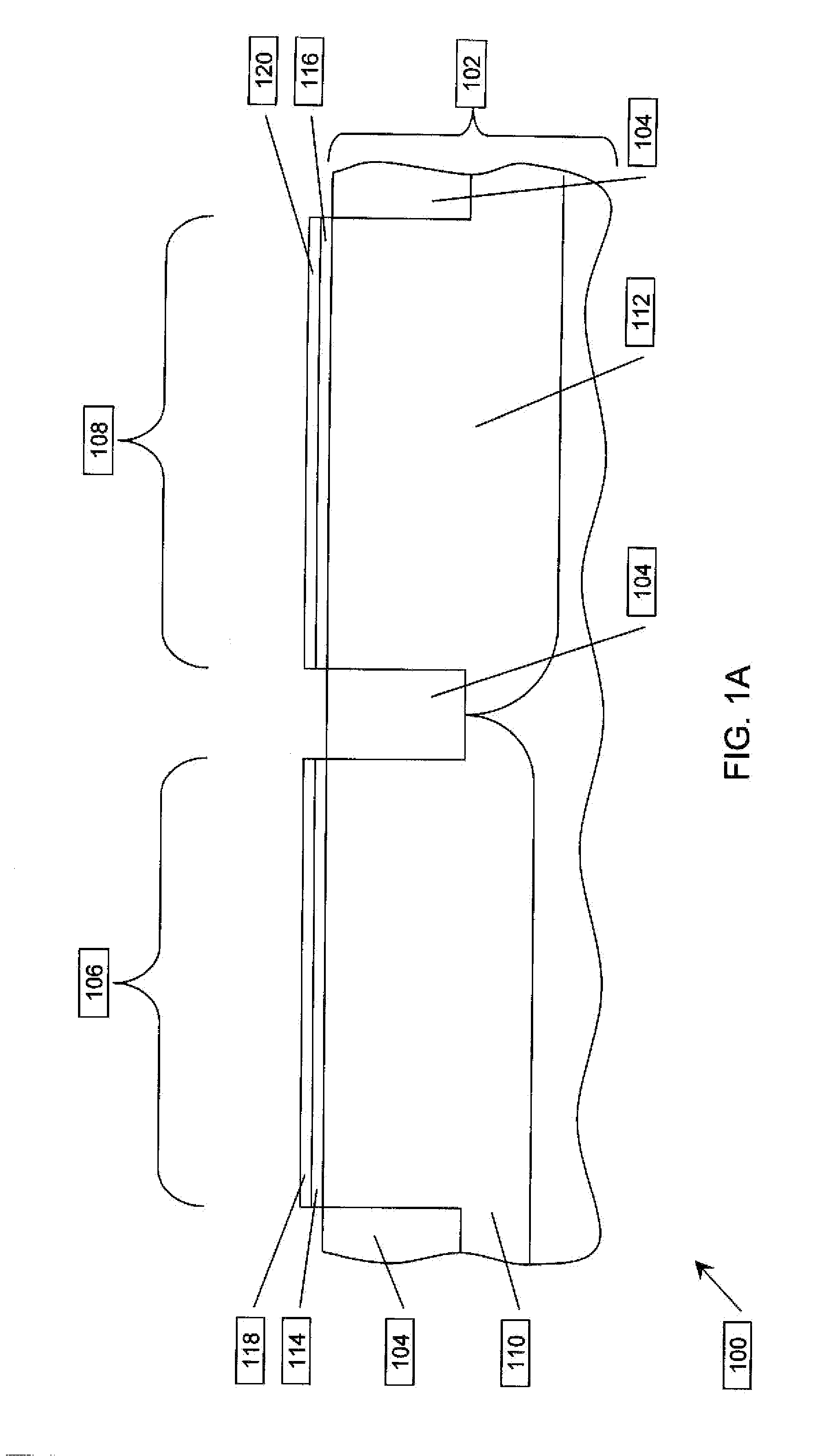

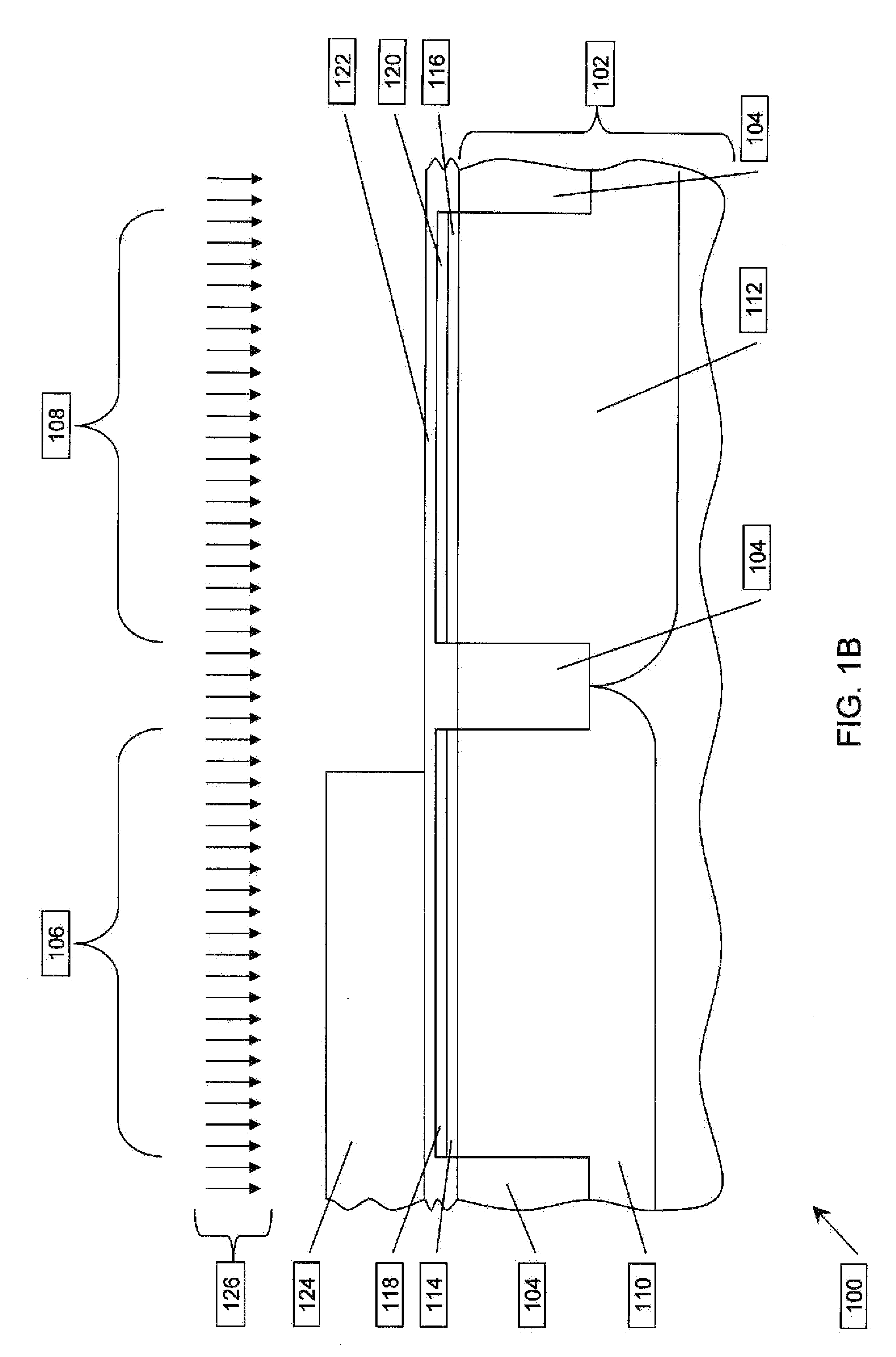

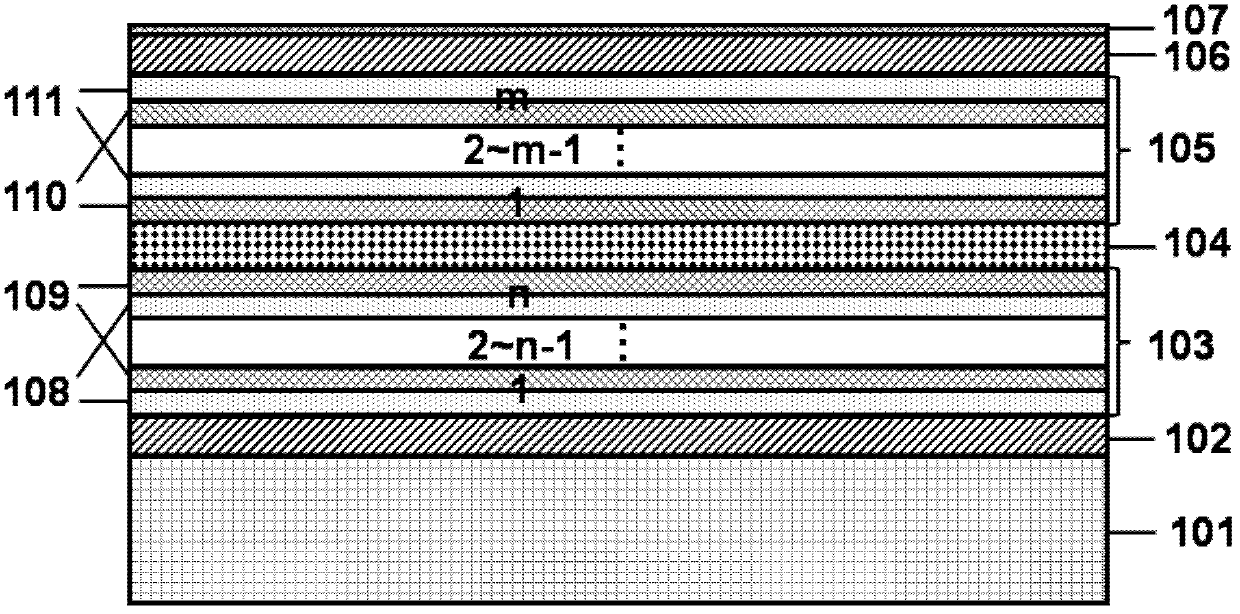

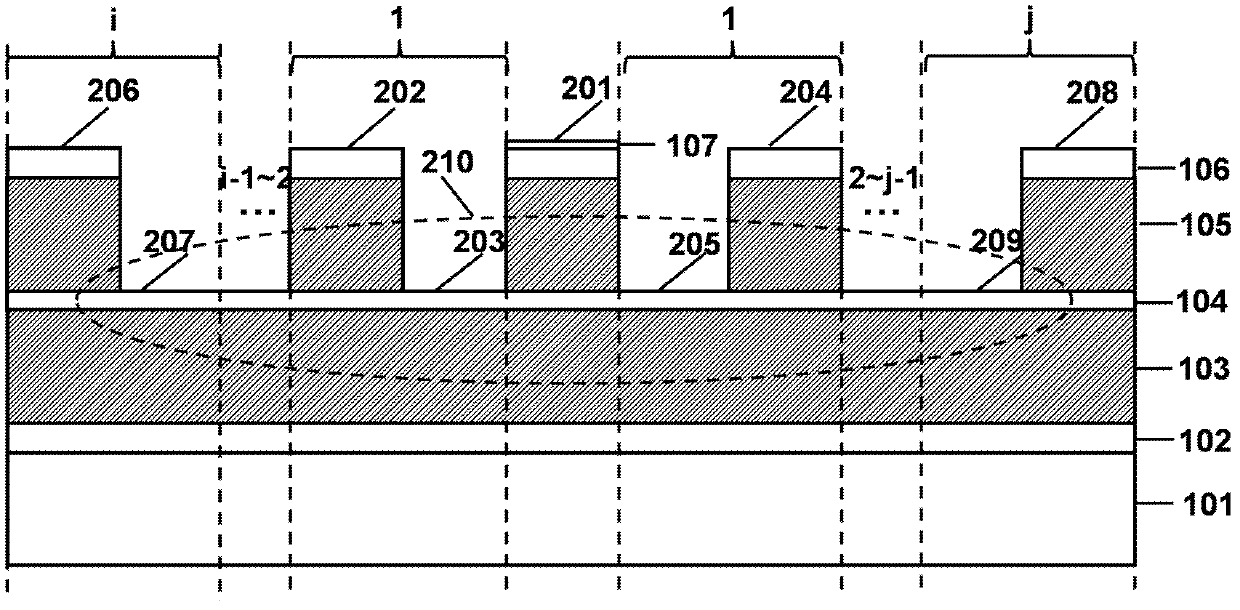

Semiconductor devices with reduced active region defects and unique contacting schemes

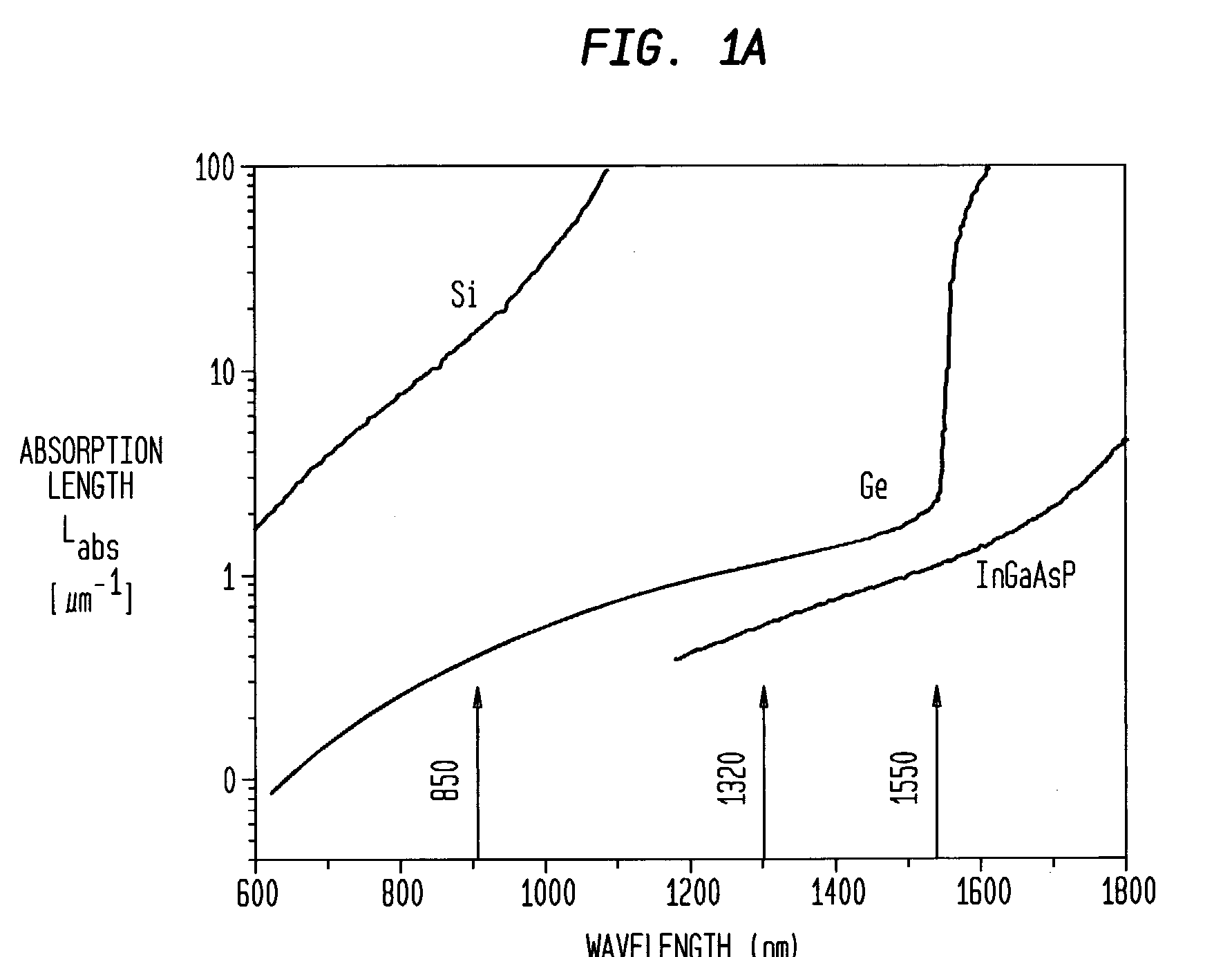

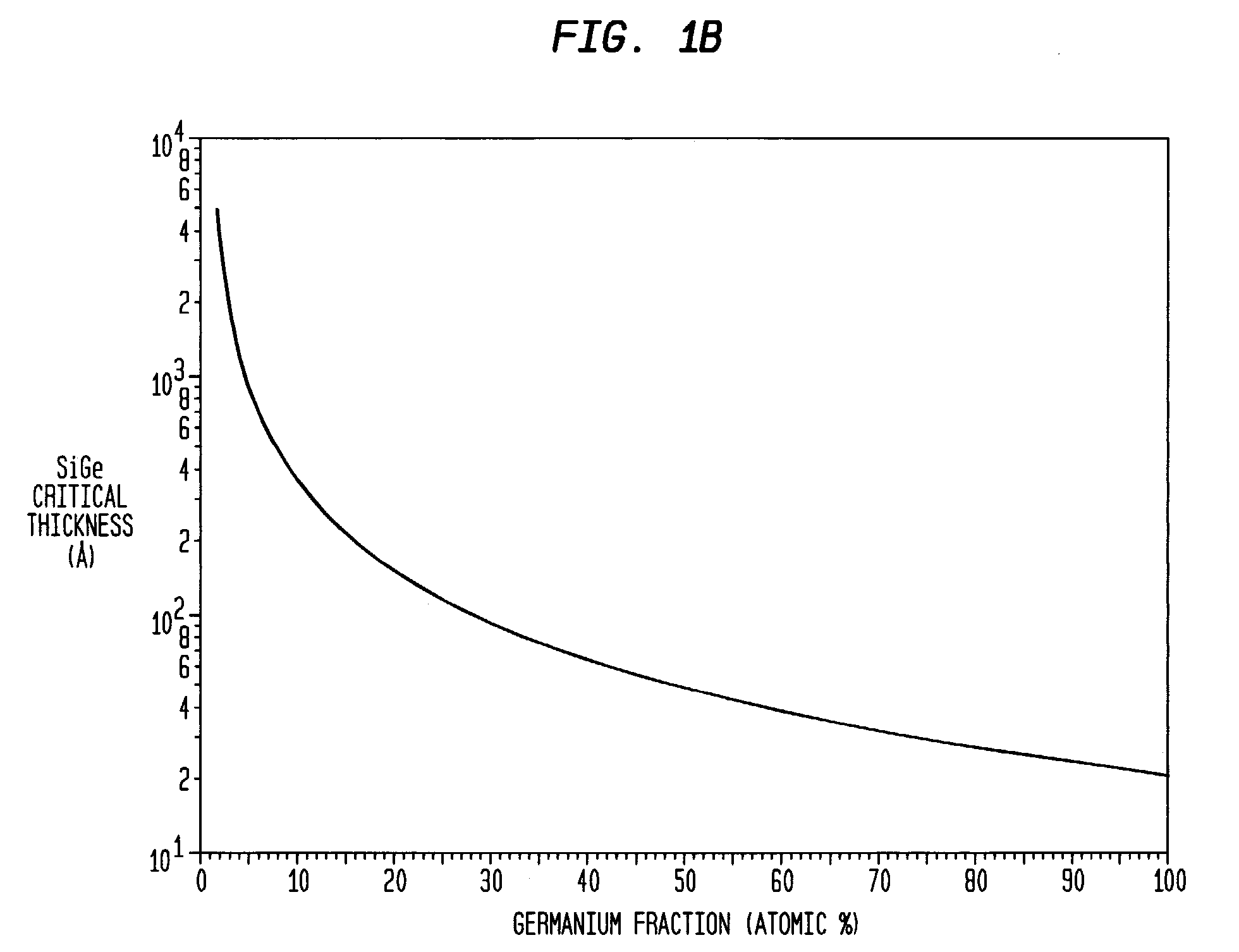

InactiveUS20060057825A1Increase speedHigh QYSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETSemiconductor materials

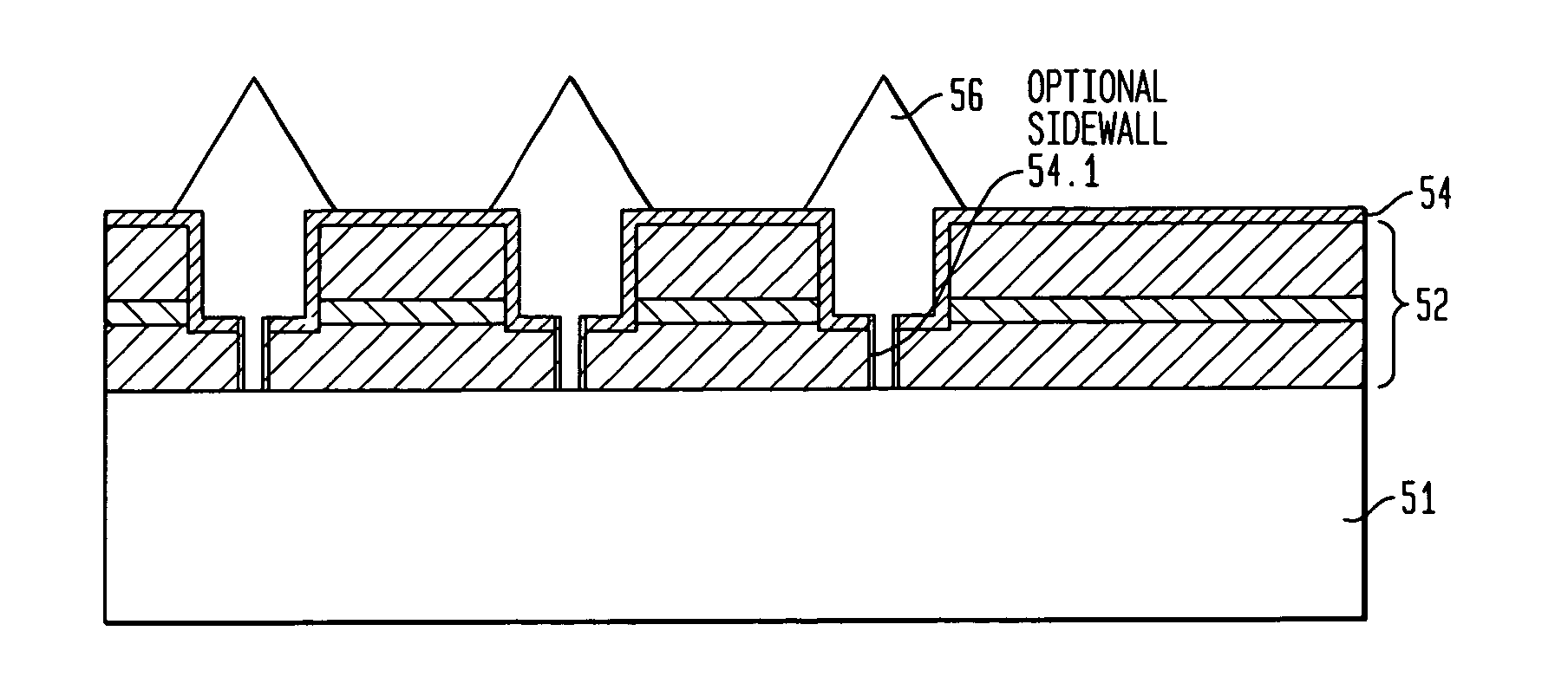

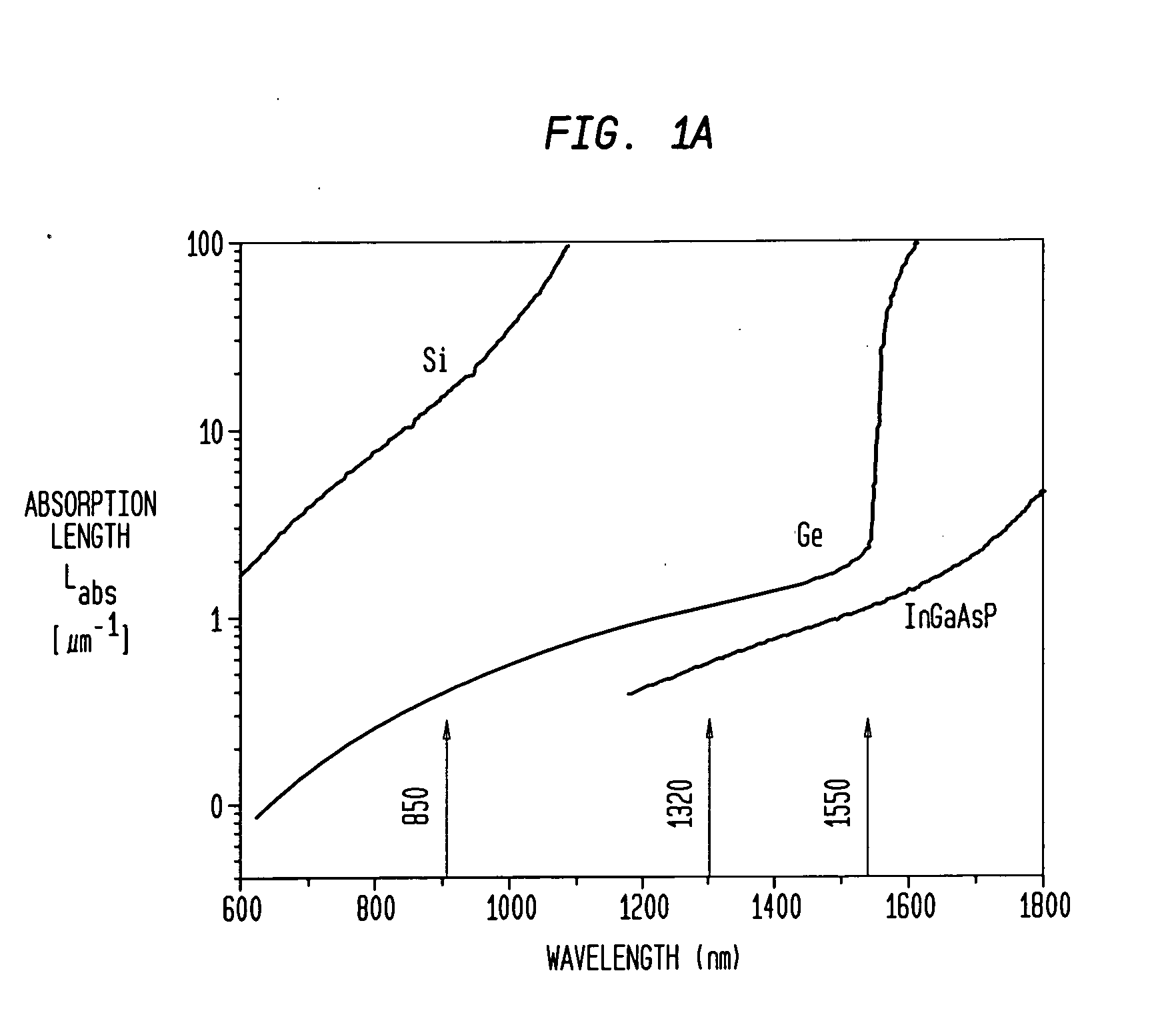

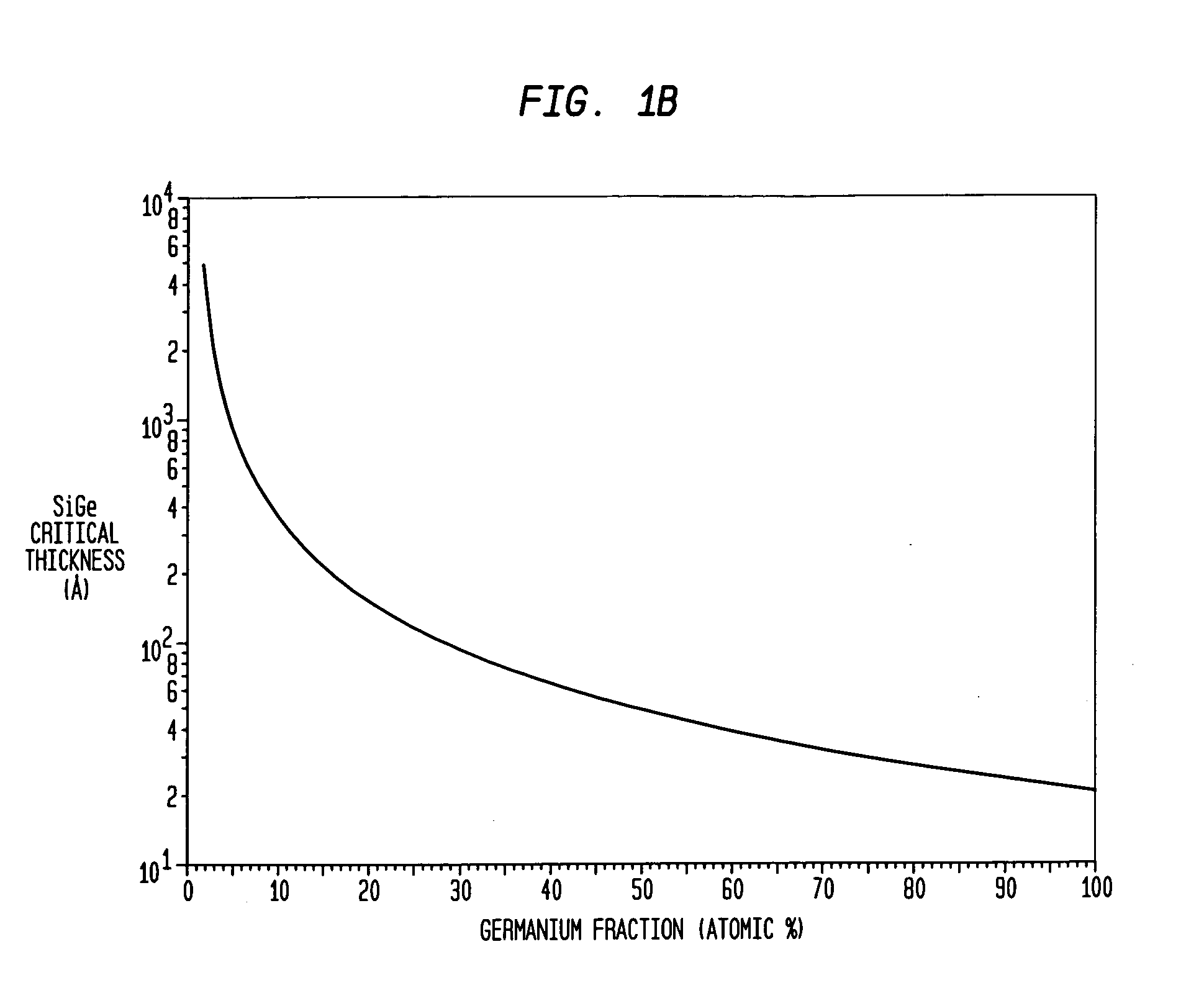

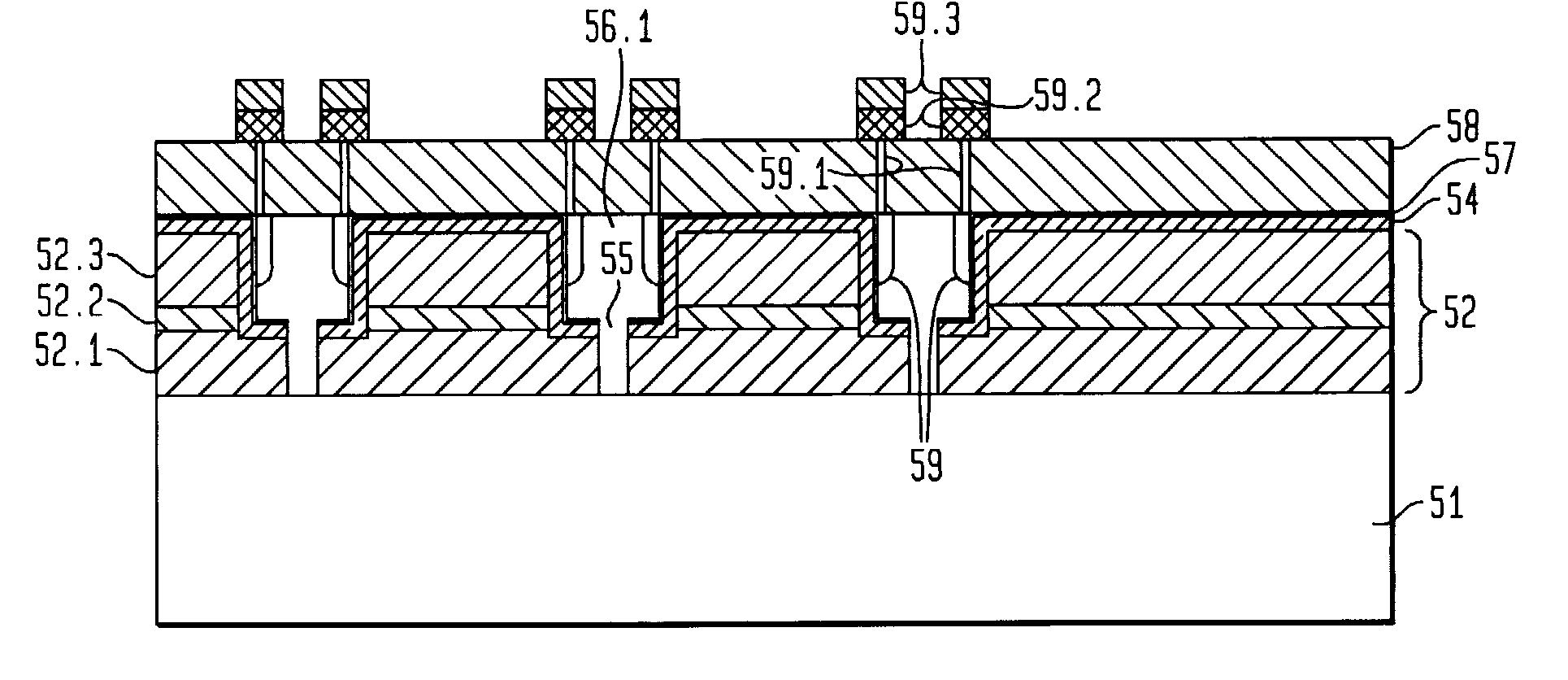

A method of making a semiconductor device having a predetermined epitaxial region, such as an active region, with reduced defect density includes the steps of: (a) forming a dielectric cladding region on a major surface of a single crystal body of a first material; (b) forming a first opening that extends to a first depth into the cladding region; (c) forming a smaller second opening, within the first opening, that extends to a second depth greater than the first depth and that exposes an underlying portion of the major surface of the single crystal body; (d) epitaxially growing regions of a second semiconductor material in each of the openings and on the top of the cladding region; (e) controlling the dimensions of the second opening so that defects are confined to the epitaxial regions grown within the second opening and on top of the cladding region, a first predetermined region being located within the first opening and being essentially free of defects; (f) planarizing the top of the device to remove all epitaxial regions that extend above the top of the cladding layer, thereby making the top of the first predetermined region grown in the second opening essentially flush with the top of the cladding region; and (g) performing additional steps to complete the fabrication of the device. Also described are unique devices, such as photodetectors and MOSFETs, fabricated by this method, as well as unique contacting configurations that enhance their performance.

Owner:NOBLE DEVICE TECH CORP +2

Semiconductor devices with reduced active region defects and unique contacting schemes

InactiveUS7012314B2Increase speedHigh QYSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETSemiconductor materials

A method of making a semiconductor device having a predetermined epitaxial region, such as an active region, with reduced defect density includes the steps of: (a) forming a dielectric cladding region on a major surface of a single crystal body of a first material; (b) forming a first opening that extends to a first depth into the cladding region; (c) forming a smaller second opening, within the first opening, that extends to a second depth greater than the first depth and that exposes an underlying portion of the major surface of the single crystal body; (d) epitaxially growing regions of a second semiconductor material in each of the openings and on the top of the cladding region; (e) controlling the dimensions of the second opening so that defects are confined to the epitaxial regions grown within the second opening and on top of the cladding region, a first predetermined region being located within the first opening and being essentially free of defects; (D planarizing the top of the device to remove all epitaxial regions that extend above the top of the cladding layer, thereby making the top of the first predetermined region grown in the second opening essentially flush with the top of the cladding region; and (g) performing additional steps to complete the fabrication of the device. Also described are unique devices, such as photodetectors and MOSFETs, fabricated by this method, as well as unique contacting configurations that enhance their performance.

Owner:NOBLE DEVICE TECH CORP +1

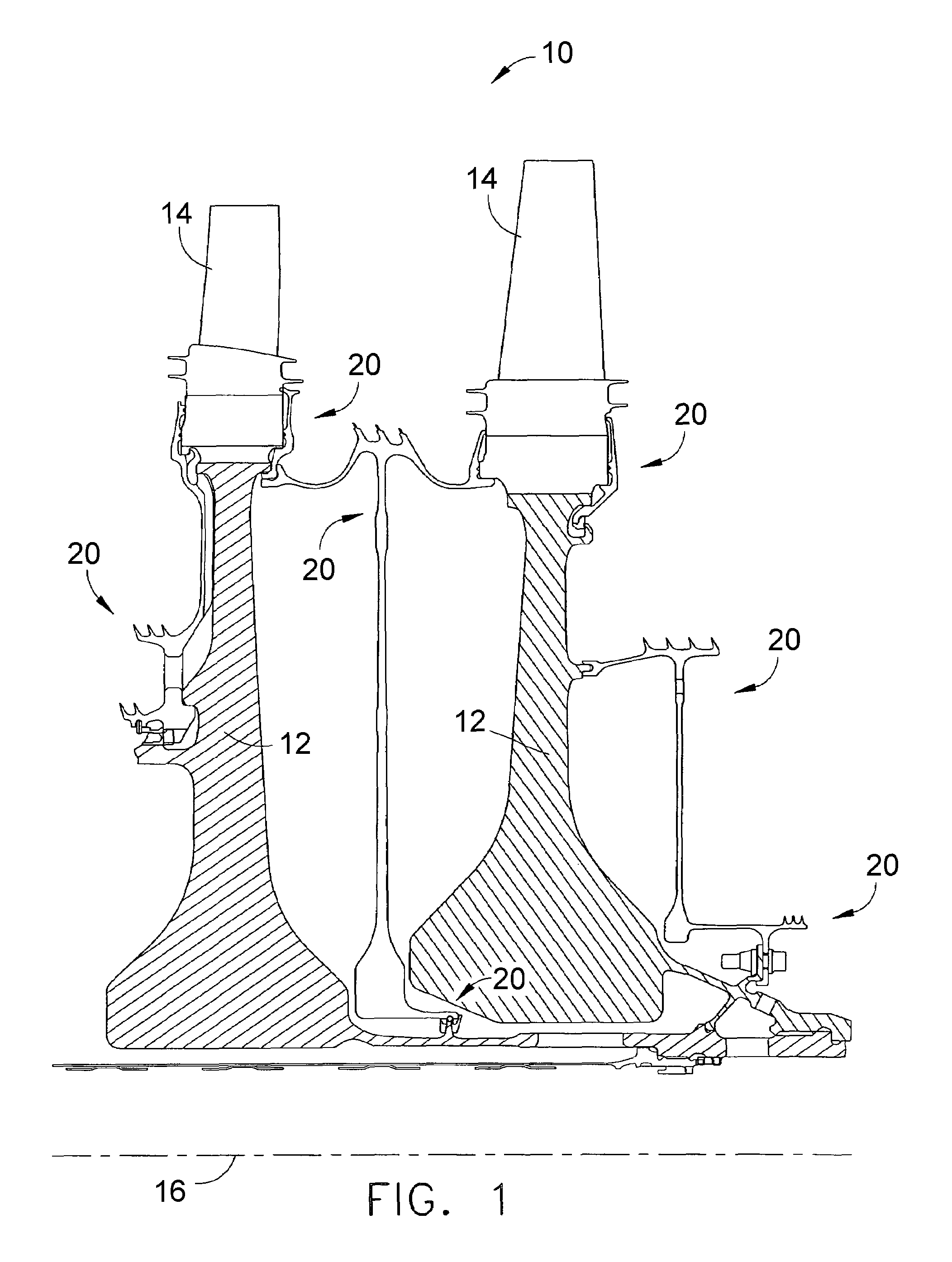

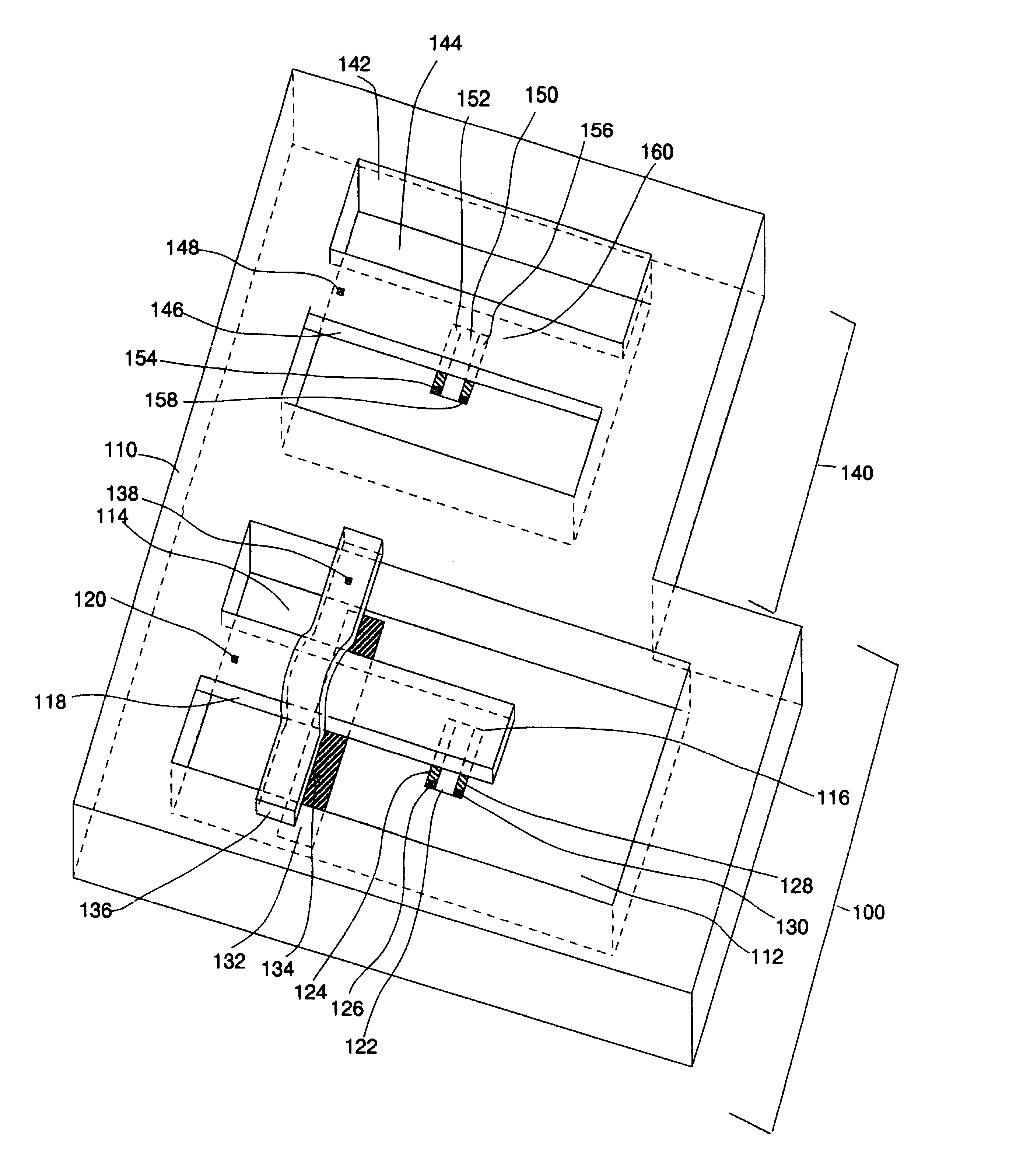

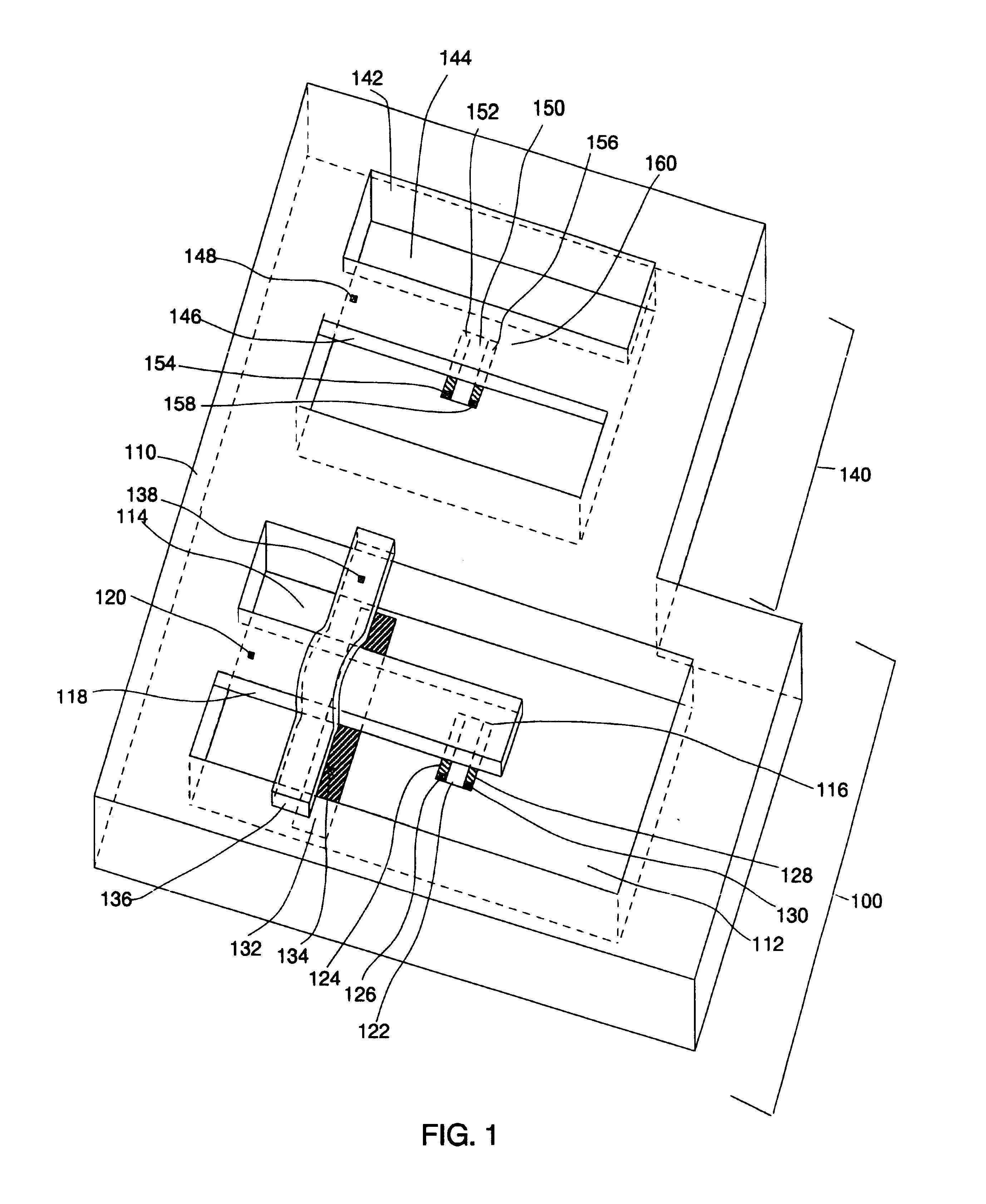

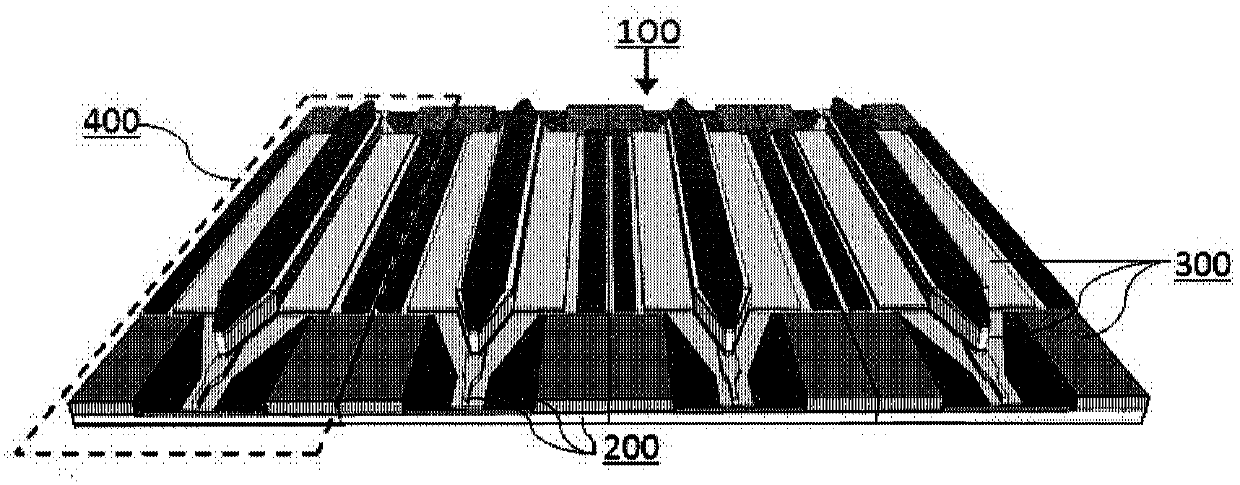

Energy Harvester with Adjustable Resonant Frequency

ActiveUS20080129147A1Facilitates great functionalityLess limitationPiezoelectric/electrostriction/magnetostriction machinesTyre measurementsCapacitanceElectricity

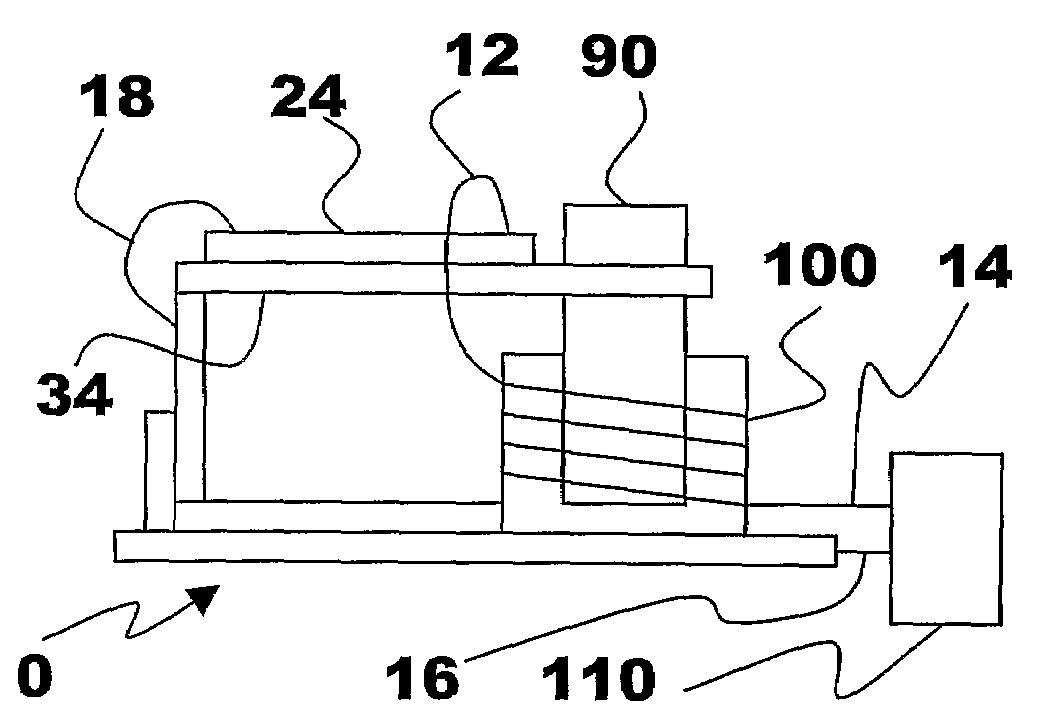

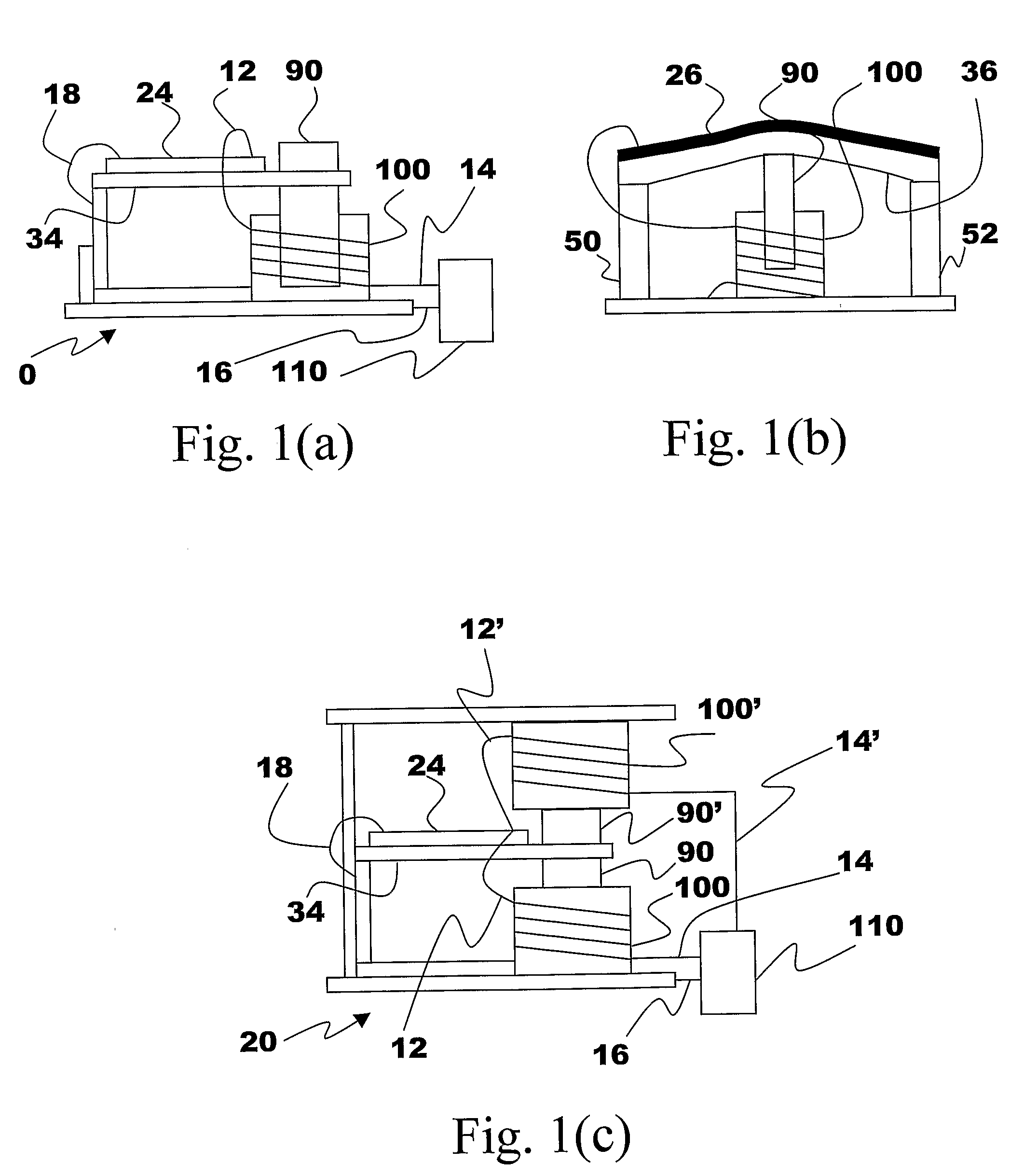

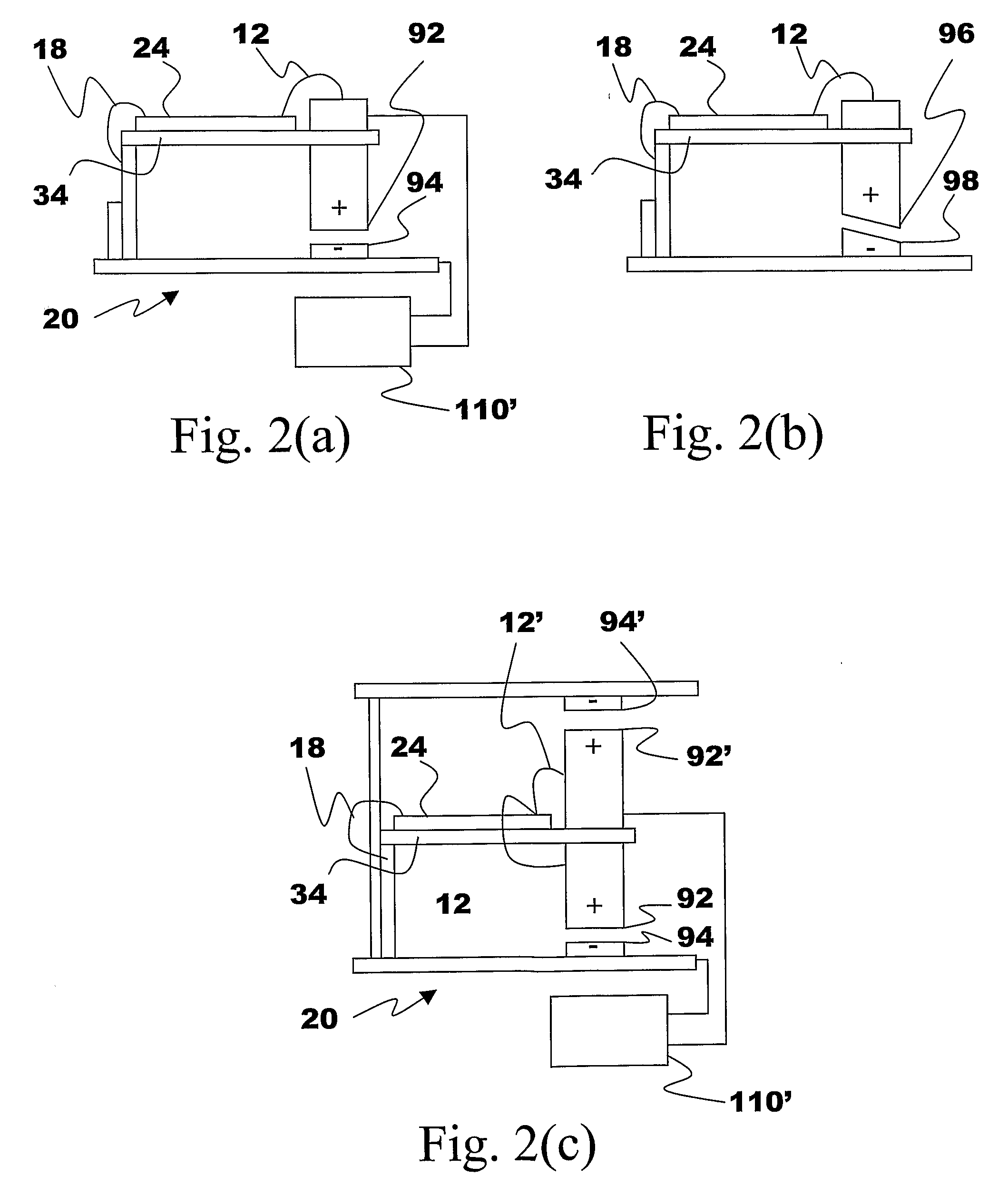

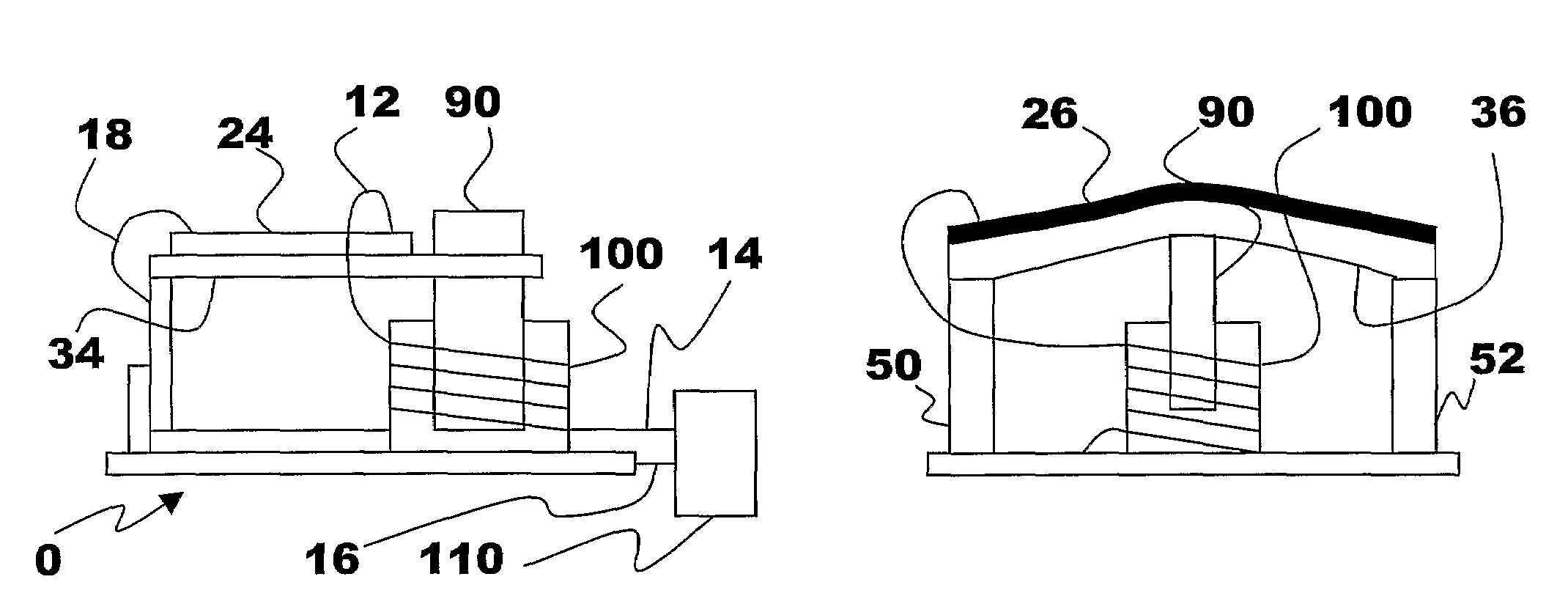

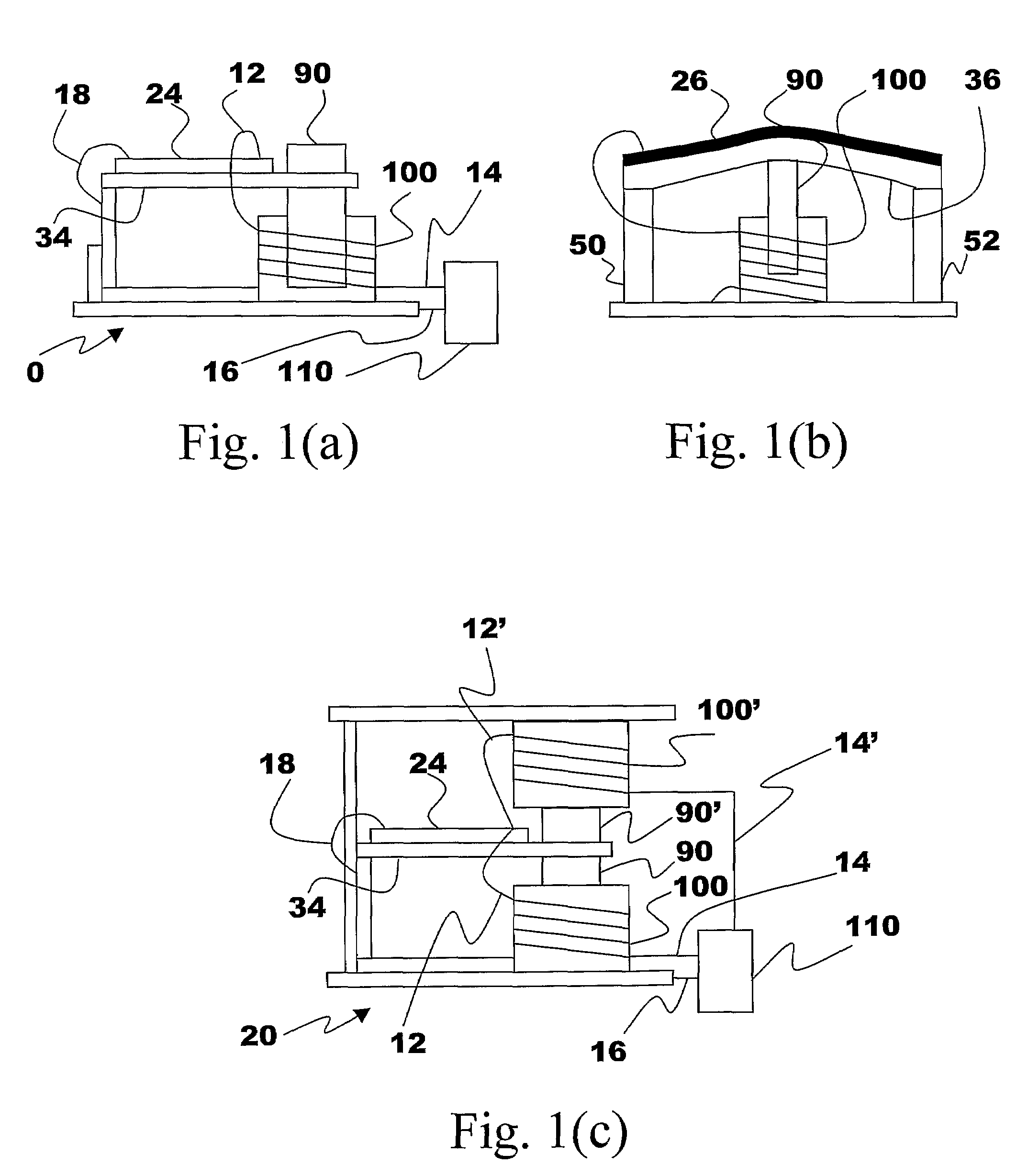

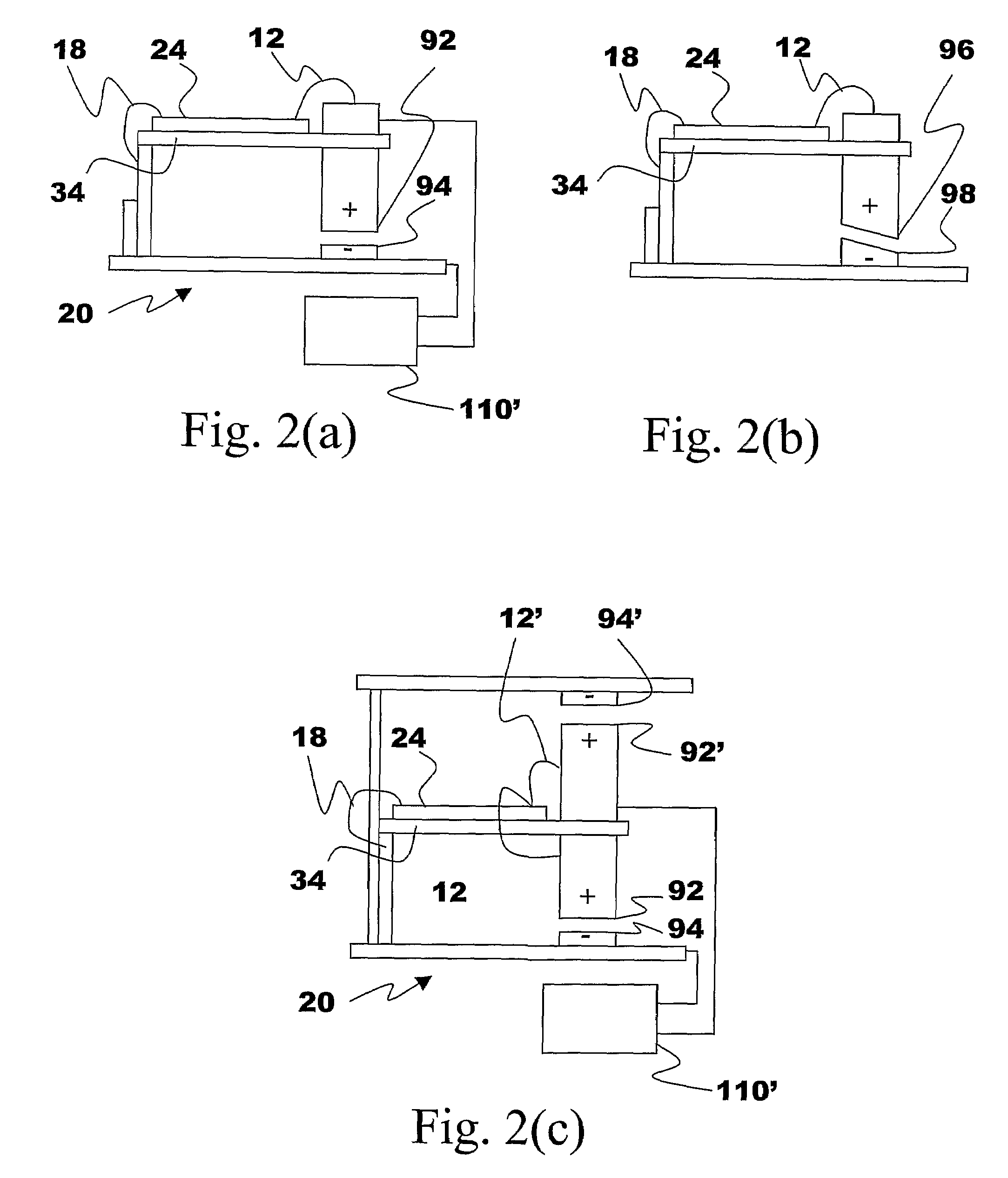

The present subject matter discloses devices, systems, and methodologies for harvesting power from environmentally induced vibrations. Piezoelectric devices (24) and structures are disclosed that may be employed in combination with electro-magnetic (100) or capacitive (92, 94) elements to enhance the power harvesting capabilities of the piezoelectric devices (24). The electromagnetic (100) and capacitive (92, 94) elements may be used to assist in maintaining system mechanical resonance in order to maximize energy harvesting capabilities. Power harvesting devices and systems in accordance with the subject technology may concurrently operate as sensors in motion sensitive applications thus providing self-powered monitoring capabilities.

Owner:MICHELIN RECH & TECH SA

Energy harvester with adjustable resonant frequency

ActiveUS7471033B2Compact manufacturingProcess compatiblePiezoelectric/electrostriction/magnetostriction machinesTyre measurementsCapacitanceElectricity

The present subject matter discloses devices, systems, and methodologies for harvesting power from environmentally induced vibrations. Piezoelectric devices (24) and structures are disclosed that may be employed in combination with electro-magnetic (100) or capacitive (92, 94) elements to enhance the power harvesting capabilities of the piezoelectric devices (24). The electromagnetic (100) and capacitive (92, 94) elements may be used to assist in maintaining system mechanical resonance in order to maximize energy harvesting capabilities. Power harvesting devices and systems in accordance with the subject technology may concurrently operate as sensors in motion sensitive applications thus providing self-powered monitoring capabilities.

Owner:MICHELIN & CO CIE GEN DES ESTAB MICHELIN

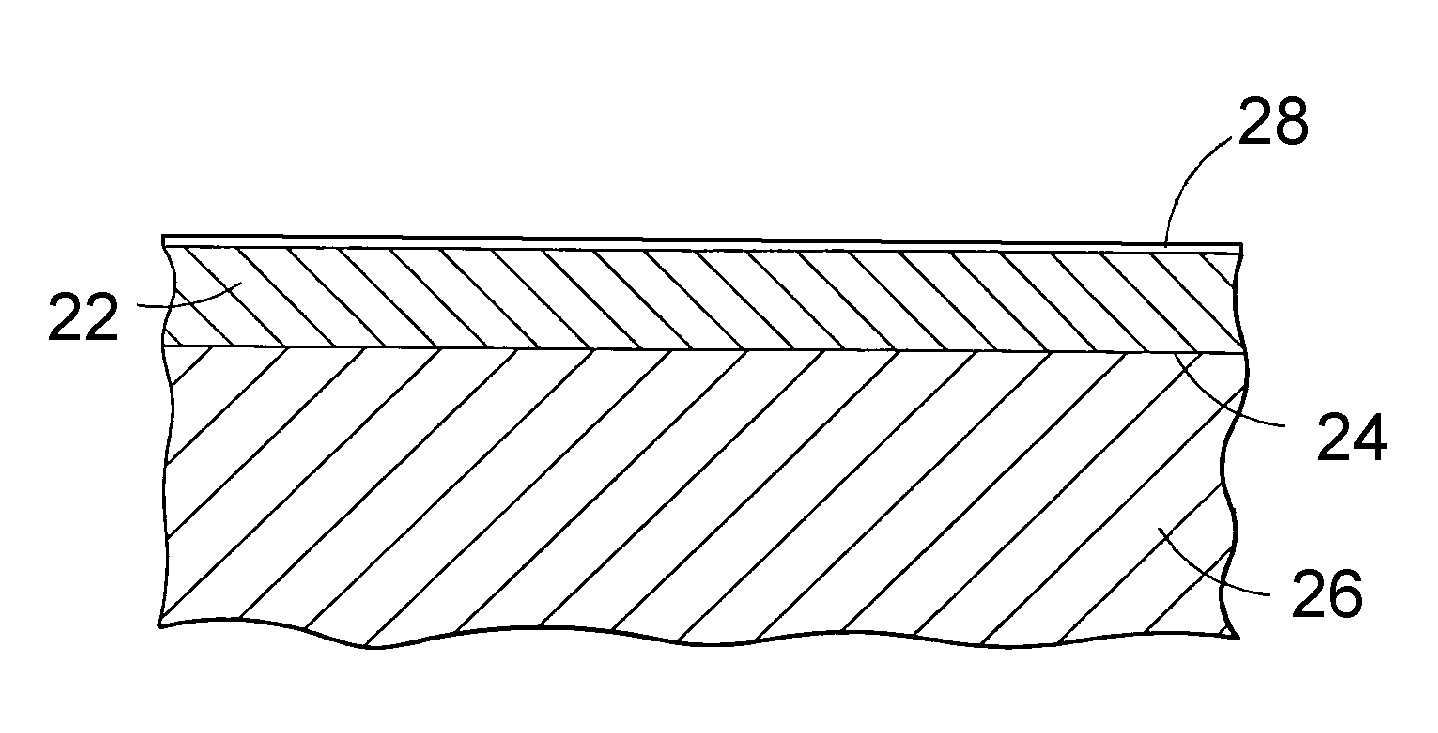

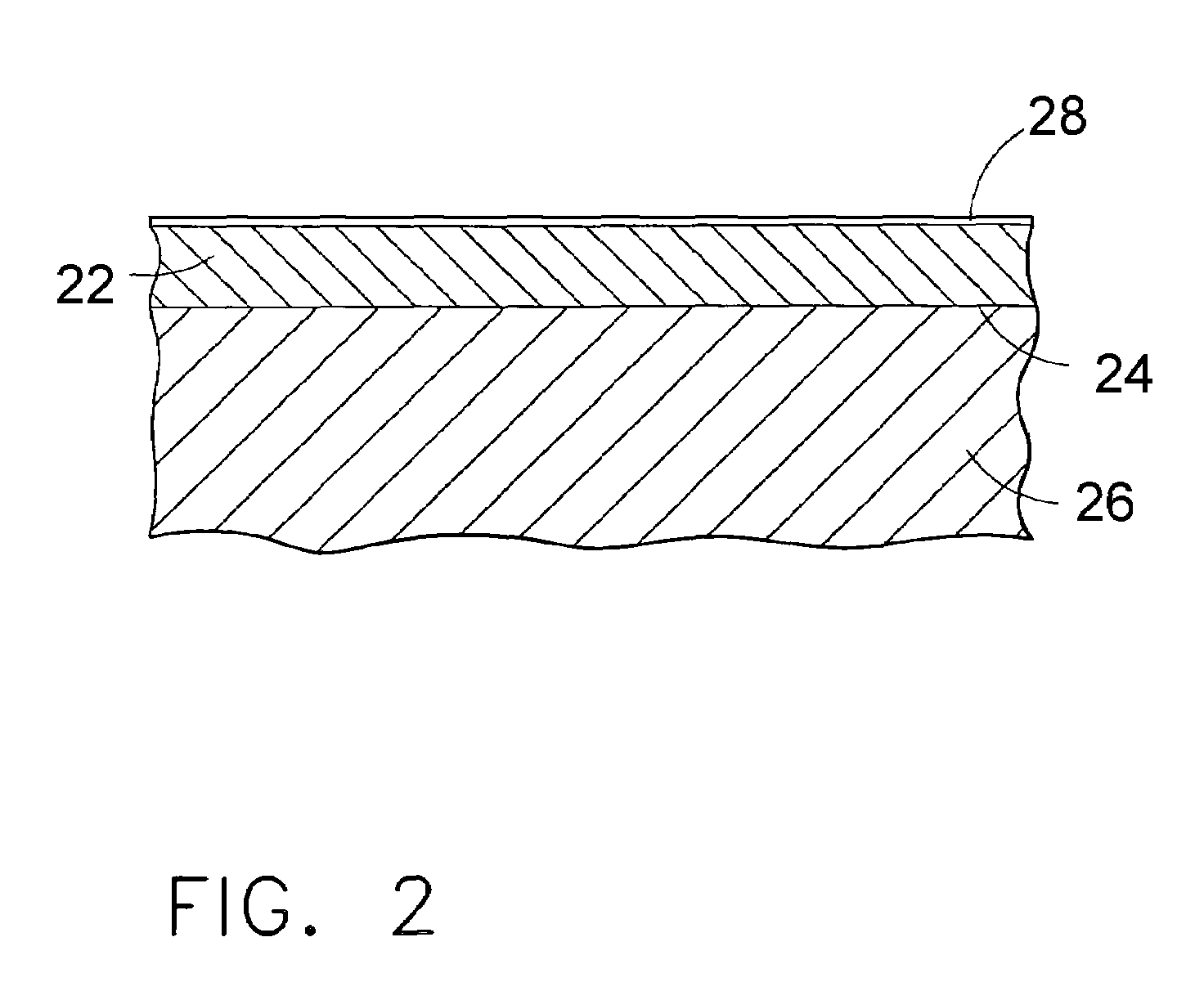

Turbine component protected with environmental coating

ActiveUS7364801B1Suitable for useReliable long-term protection from oxidation and hot corrosionMolten spray coatingPropellersSolid solutionCobalt

An environmental coating suitable for use on turbine components, such as turbine disks and turbine seal elements, formed of alloys susceptible to oxidation and hot corrosion. The environmental coating is predominantly a solid solution phase of nickel, iron, and / or cobalt. The coating contains about 18 weight percent to about 60 weight percent chromium, which ensures the formation of a protective chromia (Cr2O3) scale while also exhibiting high ductility. The coating may further contain up to about 8 weight percent aluminum, as well as other optional additives. The environmental coating is preferably sufficiently thin and ductile to enable compressive stresses to be induced in the underlying substrate through shot peening without cracking the coating.

Owner:GENERAL ELECTRIC CO

Engineered oxygen profile in metal gate electrode and nitrided high-k gate dielectrics structure for high performance pmos devices

ActiveUS20100052071A1Reduce diffuseImprove work functionTransistorSemiconductor/solid-state device manufacturingNitrogenLow oxygen

A PMOS transistor is disclosed which includes a nitrogen containing barrier to oxygen diffusion between a gate dielectric layer and a metal gate in the PMOS transistor, in combination with a low oxygen region of the metal gate in direct contact with the nitrogen containing barrier and an oxygen rich region of the metal gate above the low oxygen content metal region. The nitrogen containing barrier may be formed by depositing nitrogen containing barrier material on the gate dielectric layer or by nitridating a top region of the gate dielectric layer. The oxygen rich region of the metal gate may be formed by depositing oxidized metal on the low oxygen region of the metal gate or by oxidizing a top region of the low oxygen region of the metal gate.

Owner:TEXAS INSTR INC

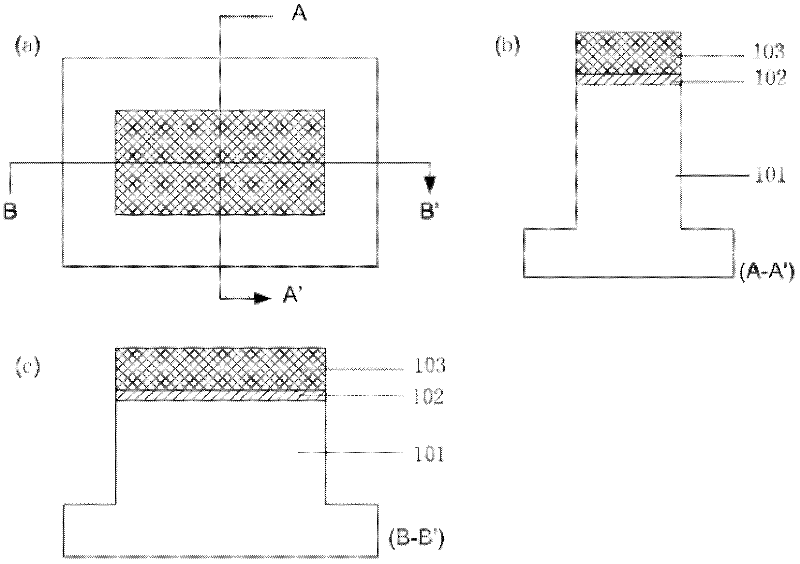

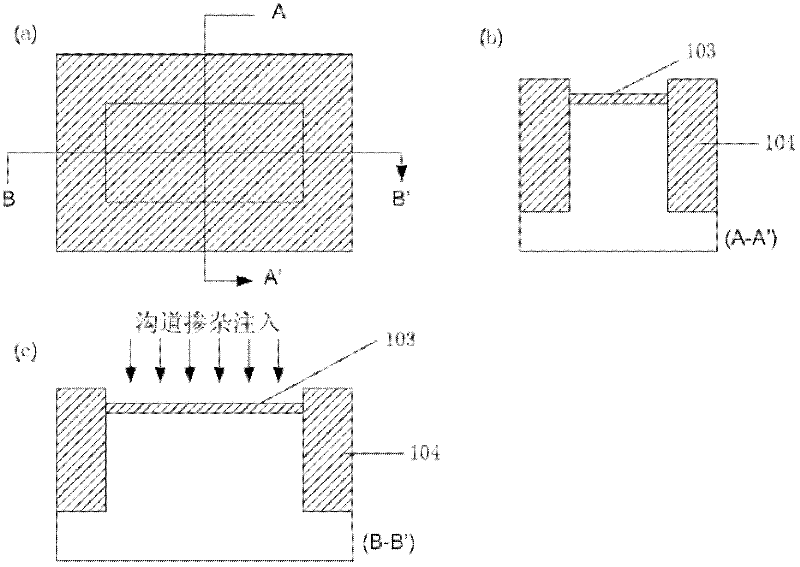

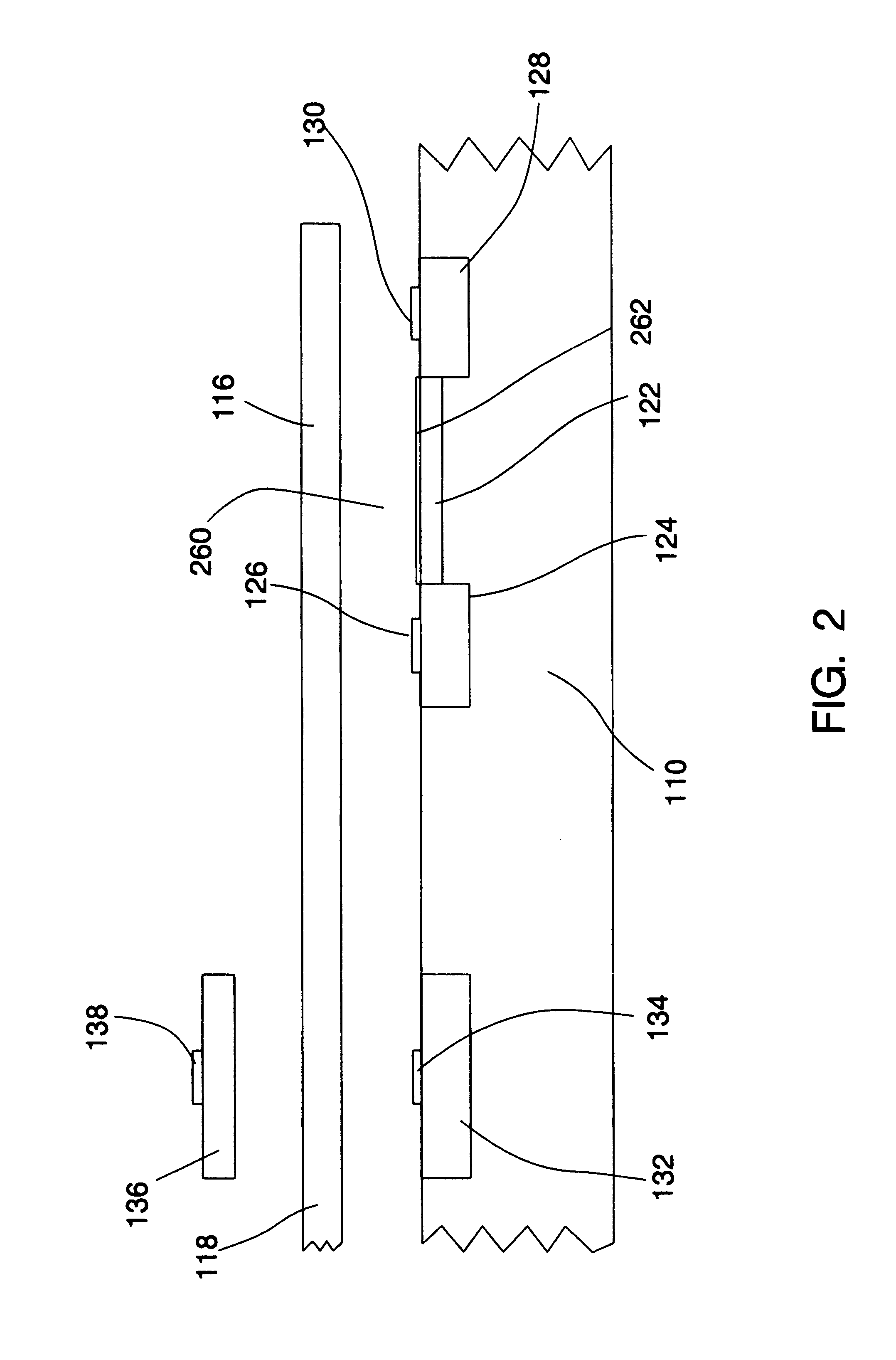

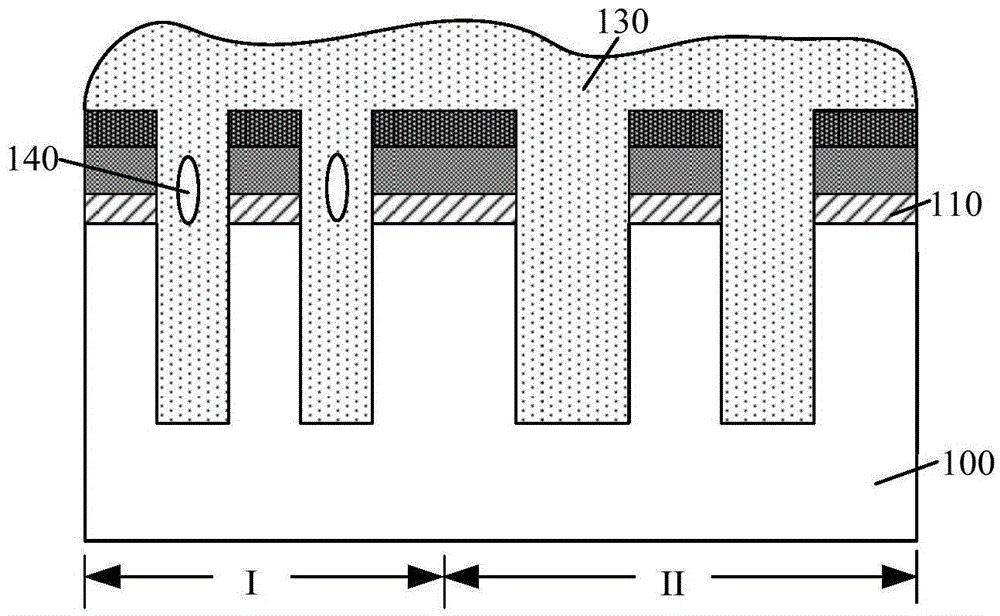

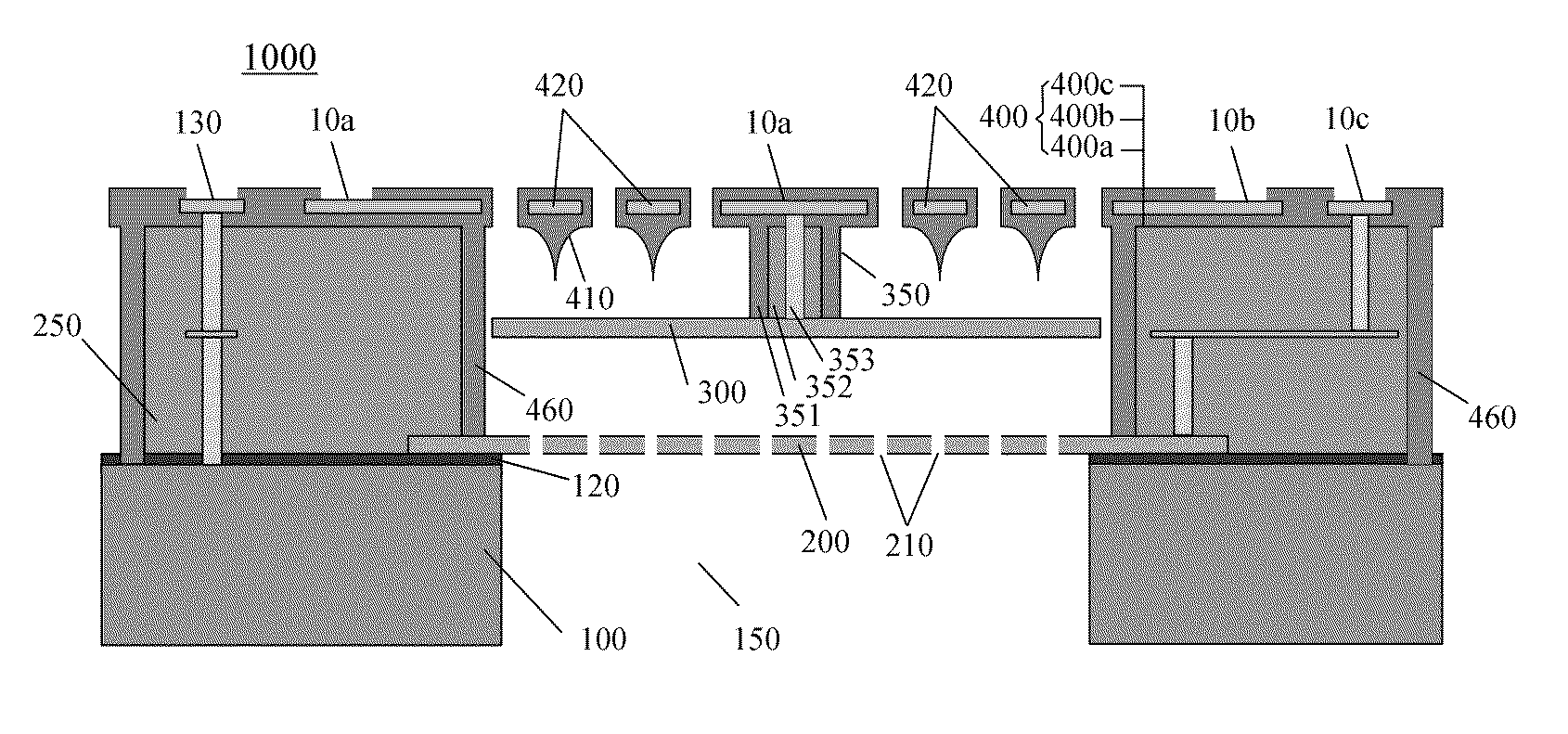

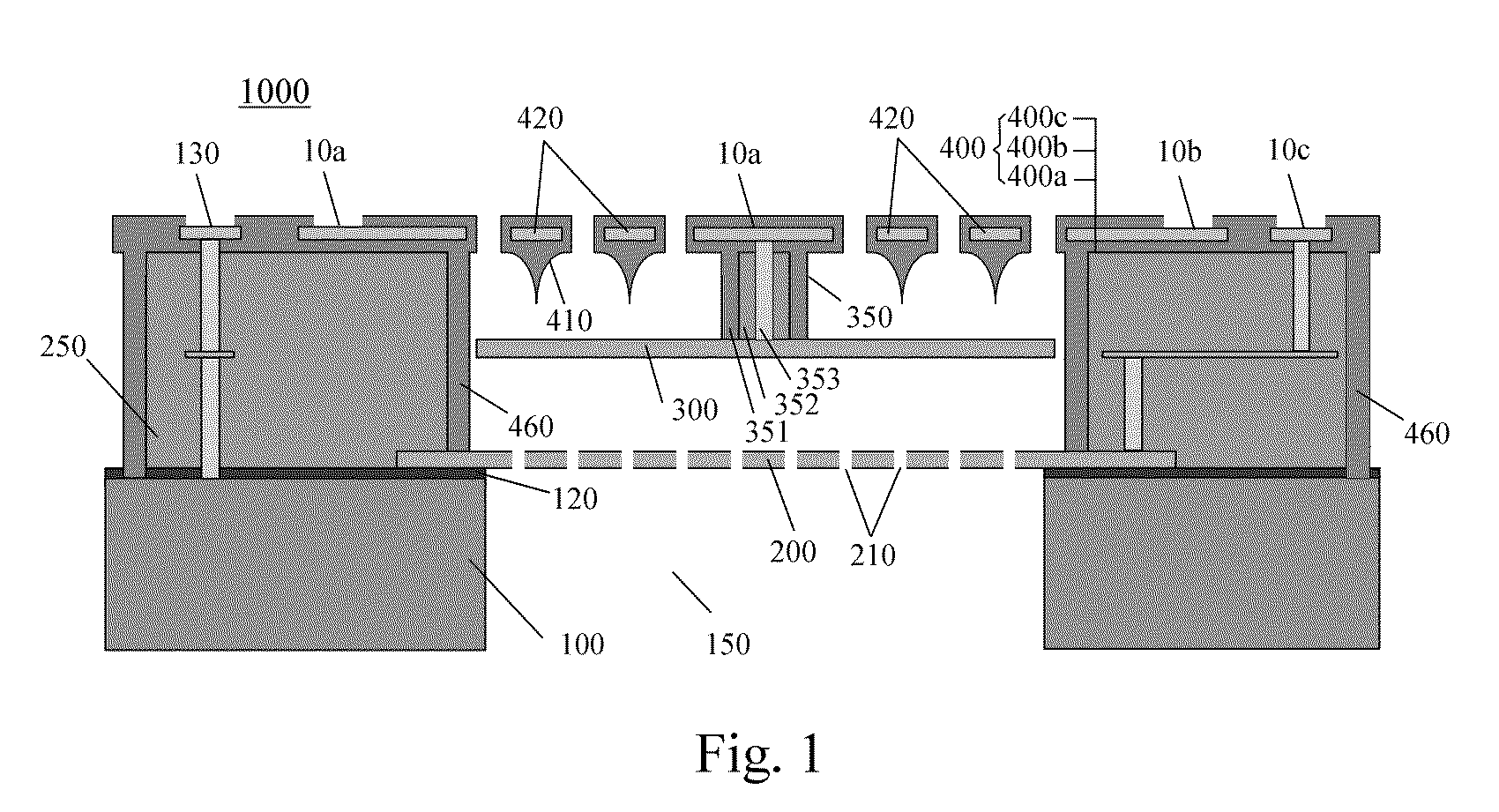

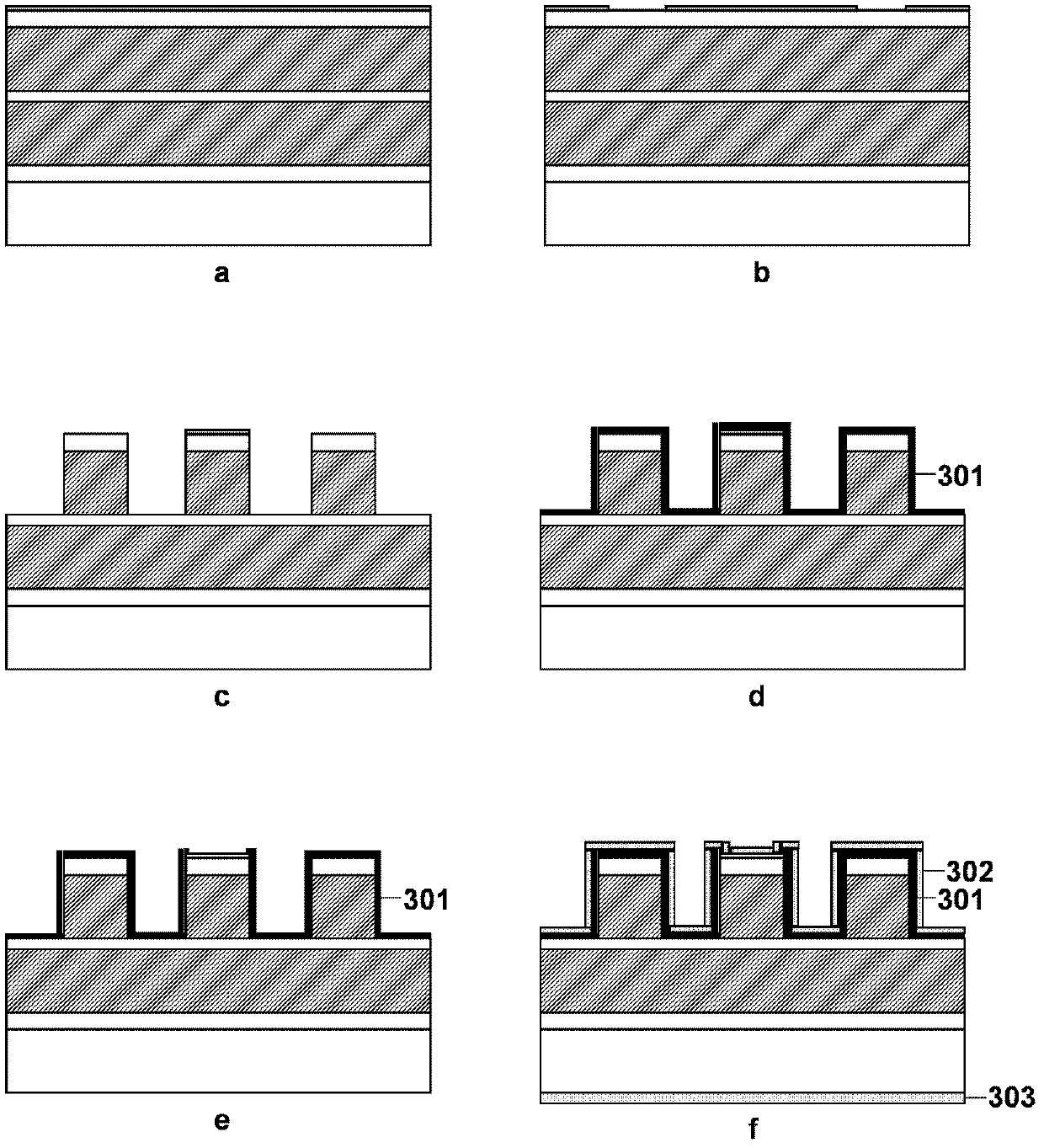

Preparation method of FinFET (Fin Field Effect Transistor) in large-scale integration circuit

ActiveCN102646599APhotolithographic planarizationSmall amount of etchingSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringDry etching

The invention discloses a preparation method of a FinFET (Fin Field Effect Transistor) in a large-scale integration circuit. The method disclosed by the invention is a rear gate process and comprises the following steps of: carrying out primary pseudo gate photoetching and etching on a plane by utilizing STI (Shallow Trench Isolation) chemical-mechanical polishing; forming a source drain; depositing an intermediate medium layer; grinding the intermediate medium layer to reach the top of the primary pseudo gate by utilizing chemical-mechanical polishing again; removing the pseudo gate by utilizing a dry etching and wet etching combination method; re-etching an STI medium by utilizing a hard mask formed by the intermediate medium layer, thereby forming a Fin structure only on the area of a gate electrode; and finally carrying out real gate medium and gate electrode material deposition, thereby obtaining a final device structure. The method disclosed by the invention can be used for obtaining a flat gate line photoetching plane, and simultaneously avoiding the problem of gate material residues on a Fin sidewall, and in addition, the method disclosed by the invention can be used for effectively integrating a high-K metal gate process, avoiding increase in electric equivalent thickness and shift of a work function, thereby obtaining excellent device characteristics.

Owner:PEKING UNIV

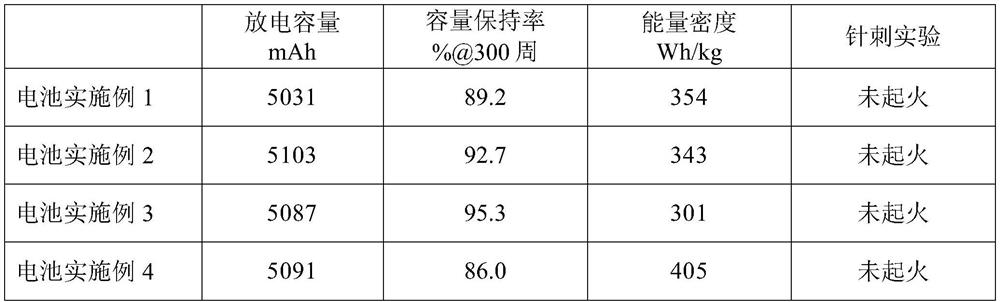

In-situ composite solid electrolyte, application thereof, all-solid-state battery and preparation method thereof

ActiveCN108550907AGood compatibilityEasy to prepareFinal product manufactureElectrolyte accumulators manufactureSolid state electrolyteAll solid state

The invention provides a preparation method for an all-solid-state battery. The method comprises the steps of S1, mixing lithium salt, additive and initiator to obtain mixed solution, wherein the additive is micromolecule monomer comprising unsaturated bond; and S2, carrying out in-situ polymerization and adhesion by the solution in a cathode layer, a solid electrolyte layer and an anode layer andamong the layers, thereby obtaining composite solid electrolyte, wherein a solid electrolyte layer comprises inorganic solid electrolyte and adhesive. Compared with the prior art, the method has theadvantages that through utilization of flowability of the micromolecule monomer additive comprising the unsaturated bond, solid particles are wetted sufficiently, ion transport channels are constructed through in-situ polymerization and solidification, electrode layers are adhered once, and a battery is moulded; the compatibility of the solid-solid interface in the all-solid-state battery can be effectively improved; and the preparation method is simple and fast, is compatible with the existing battery technology and is beneficial for large-scale preparation.

Owner:BEIJING WELION NEW ENERGY TECH CO LTD +1

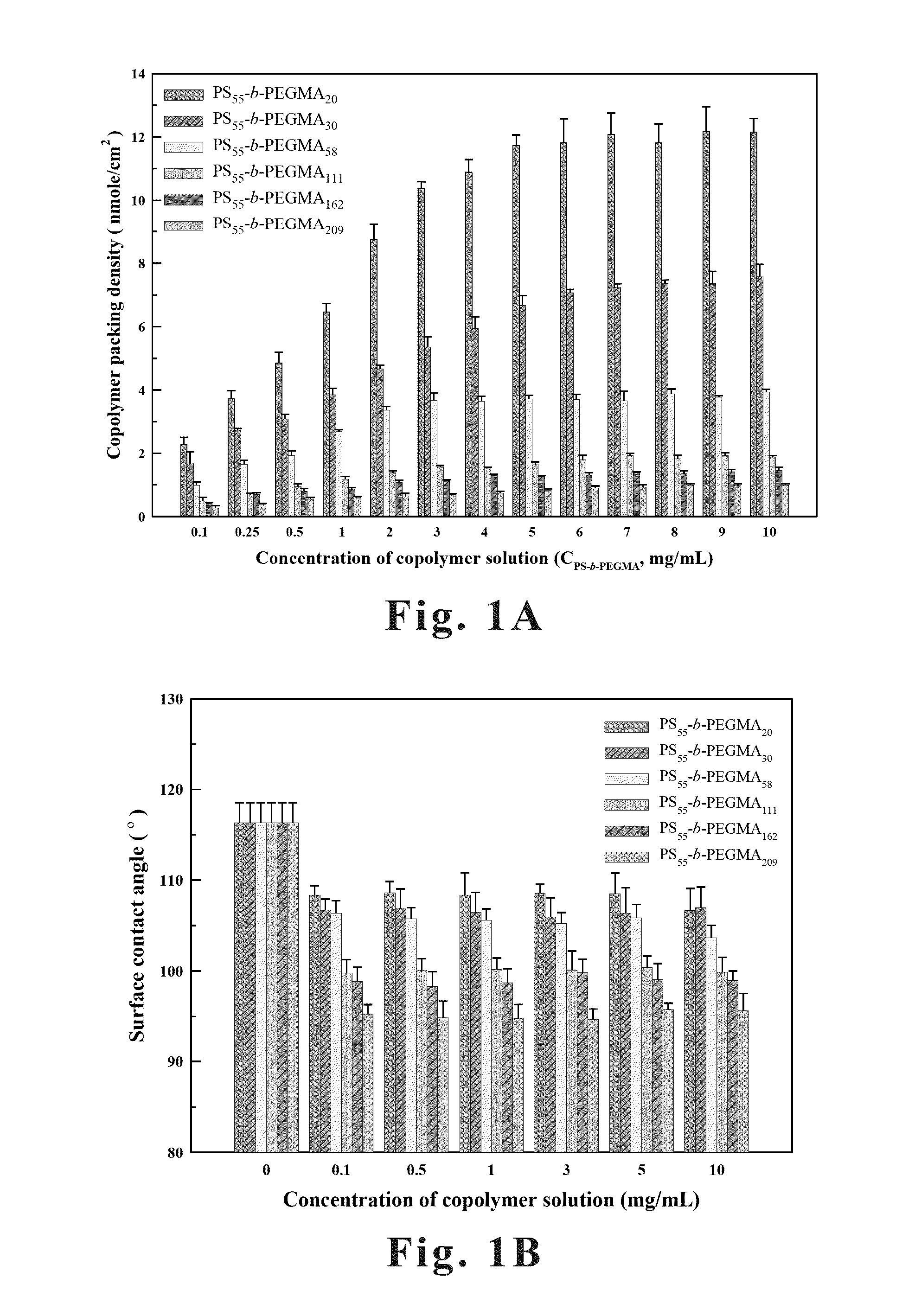

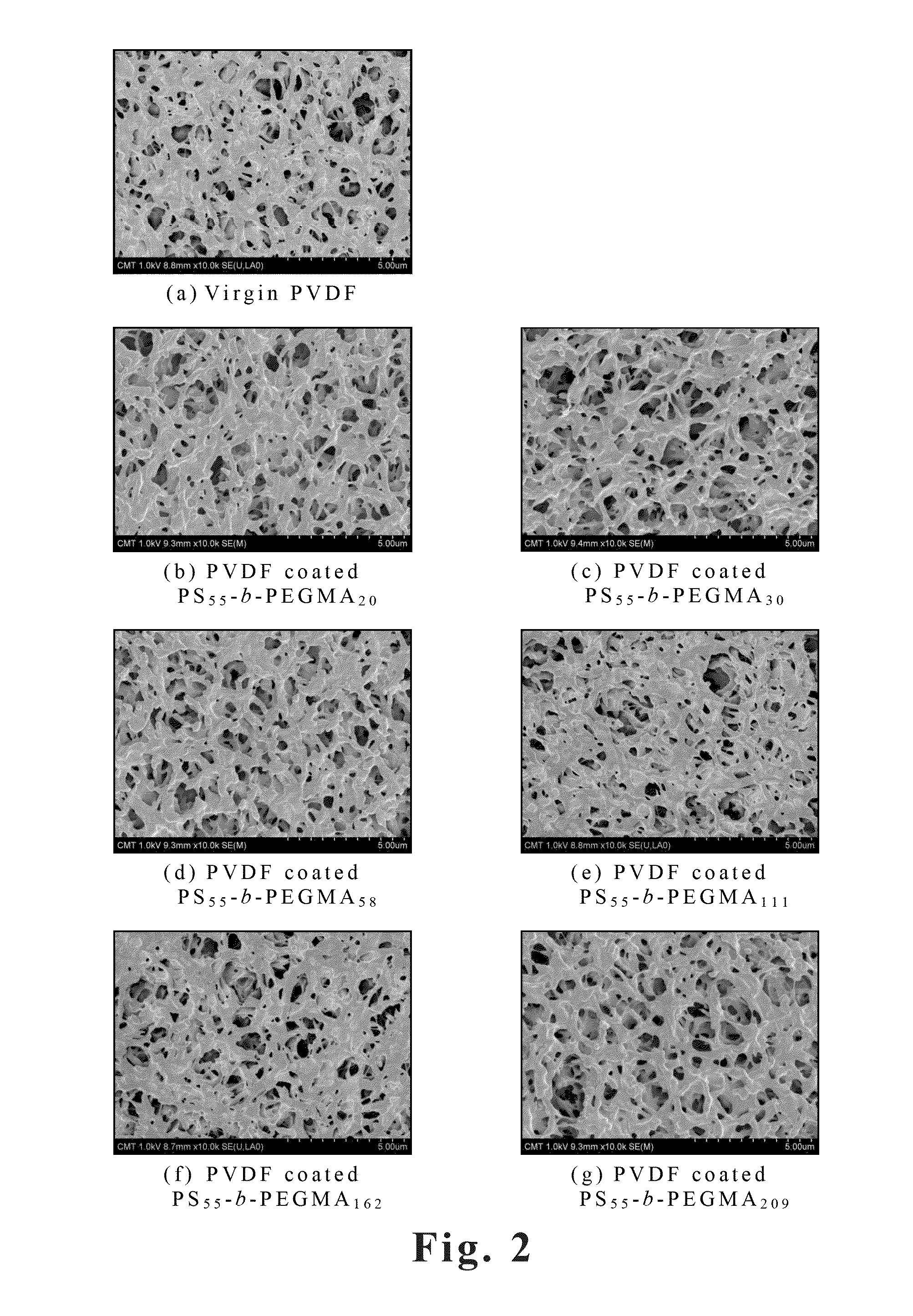

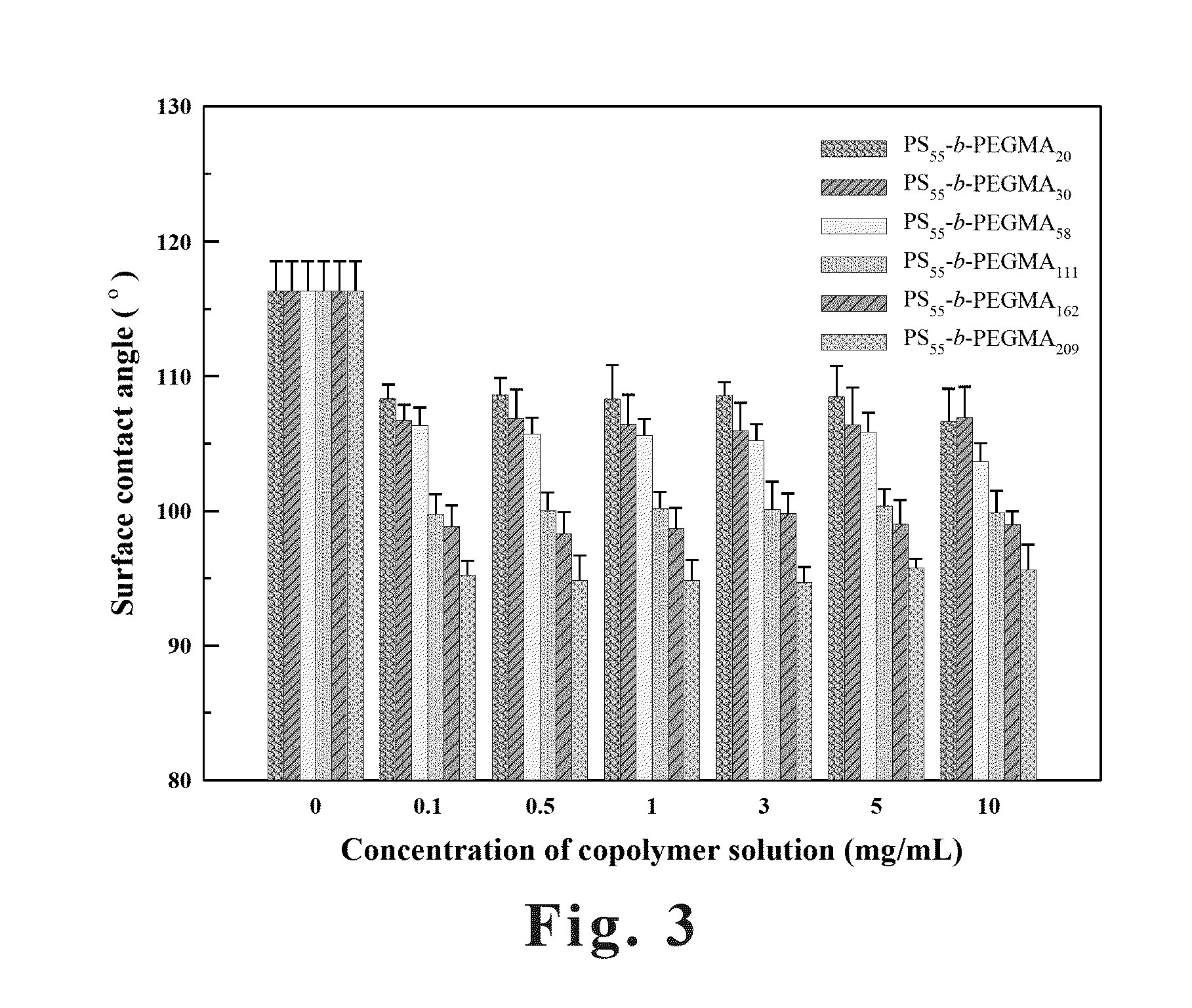

Anti-biofouling Membrane for Water-Treatment

InactiveUS20140083931A1Easy to makeReduce manufacturing costSemi-permeable membranesMembranesBiofoulingOrganic chemistry

This invention discloses an anti-biofouling membrane for water-treatment. The anti-biofouling membrane for water-treatment comprises a substrate, and an anti-biofouling copolymer on the substrate. The anti-biofouling copolymer comprises a plurality of hydrophobic groups and a plurality of hydrophilic groups. The anti-biofouling copolymer can be stably coated on the surface of the substrate by the hydrophobic groups. And the hydrophilic groups can help the anti-biofouling membrane to present excellent anti-biofouling capability. Preferably, the anti-biofouling copolymer coated on the substrate will not decrease the permeability of the substrate. More preferably, the presented capability of the mentioned anti-biofouling membrane for water-treatment can achieve the commercial level filtering membrane.

Owner:CHUNG YUAN CHRISTIAN UNIVERSITY

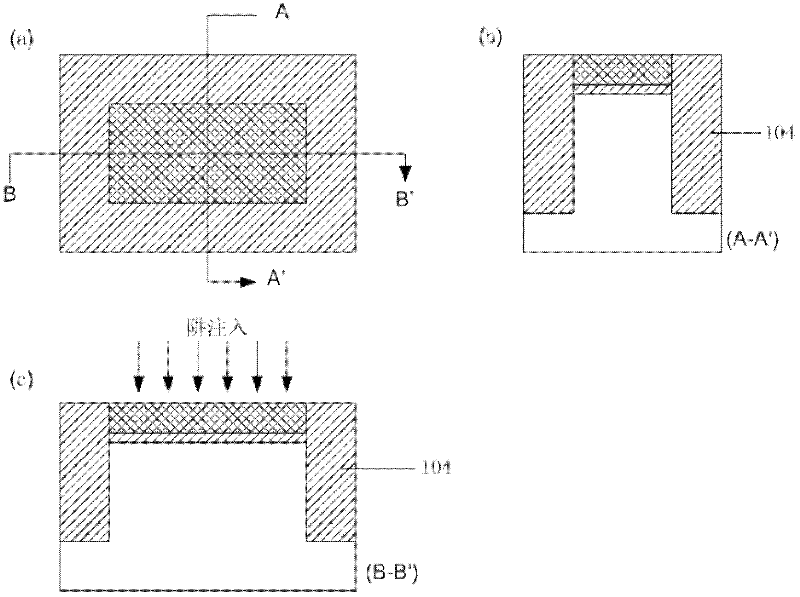

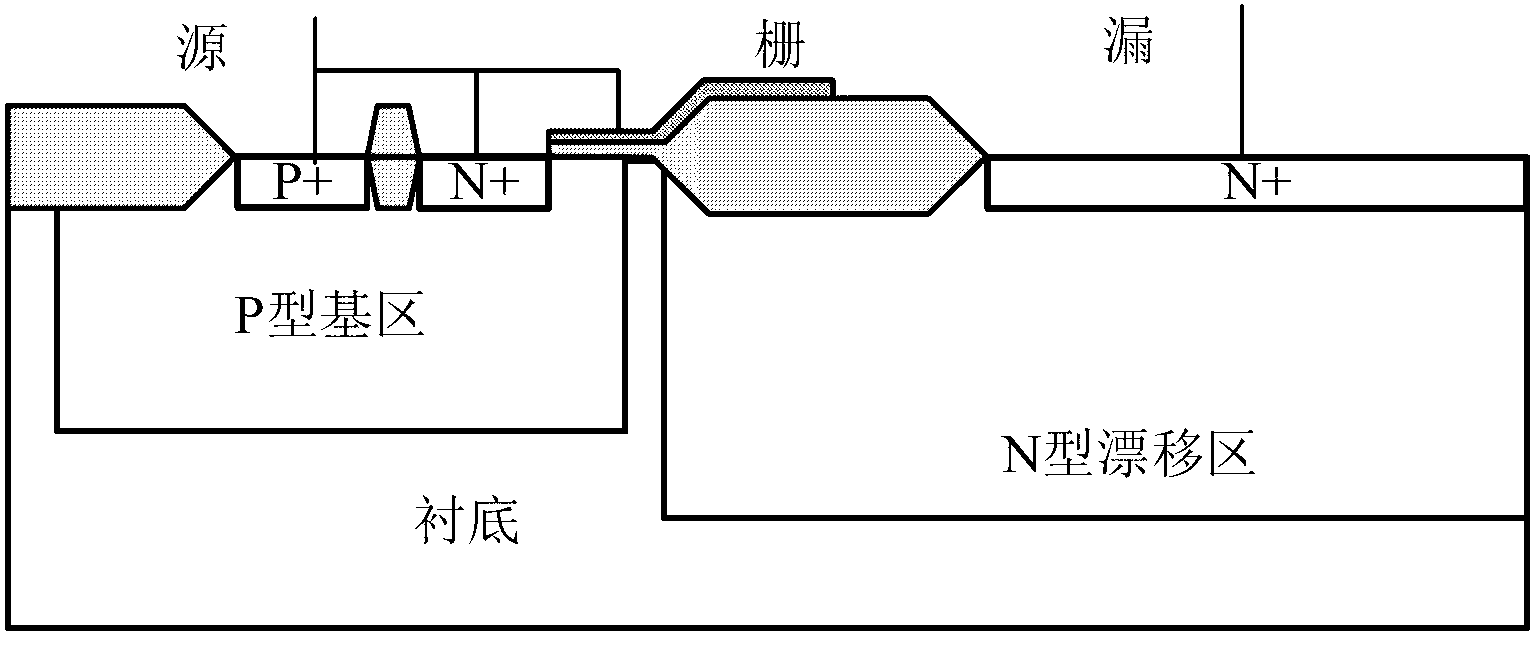

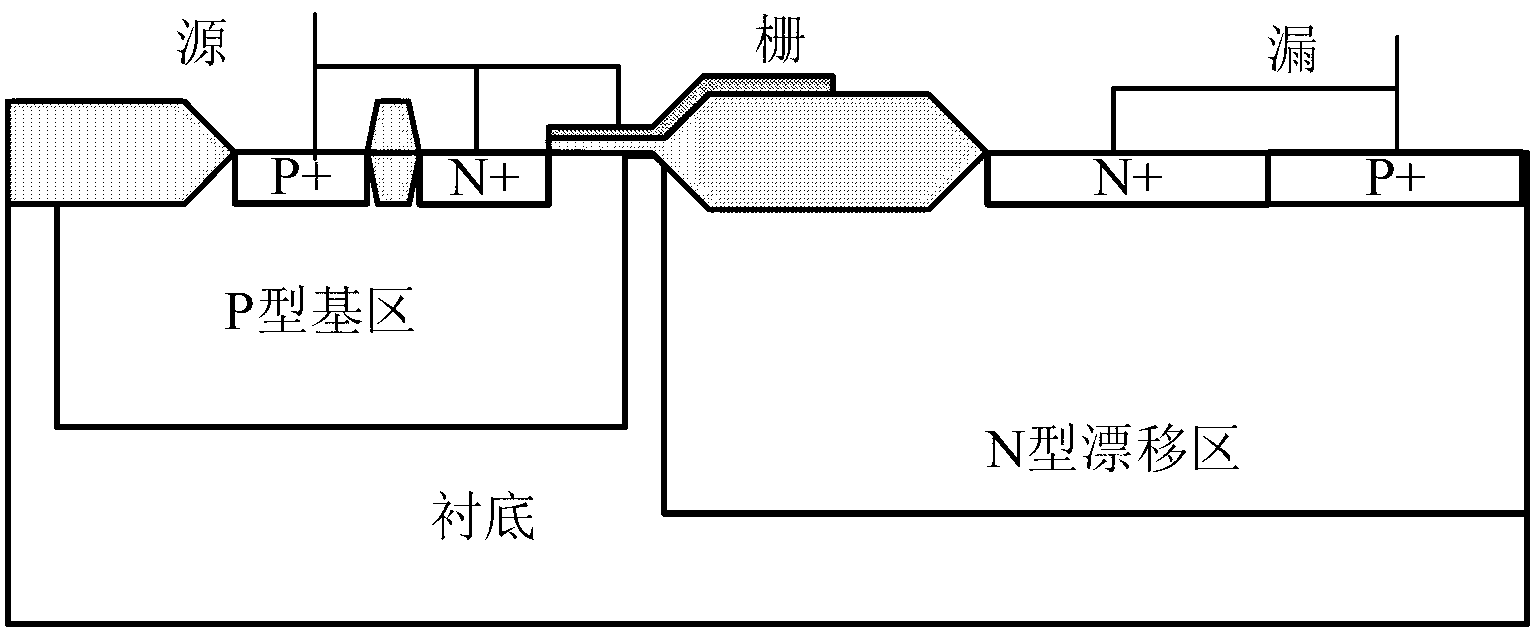

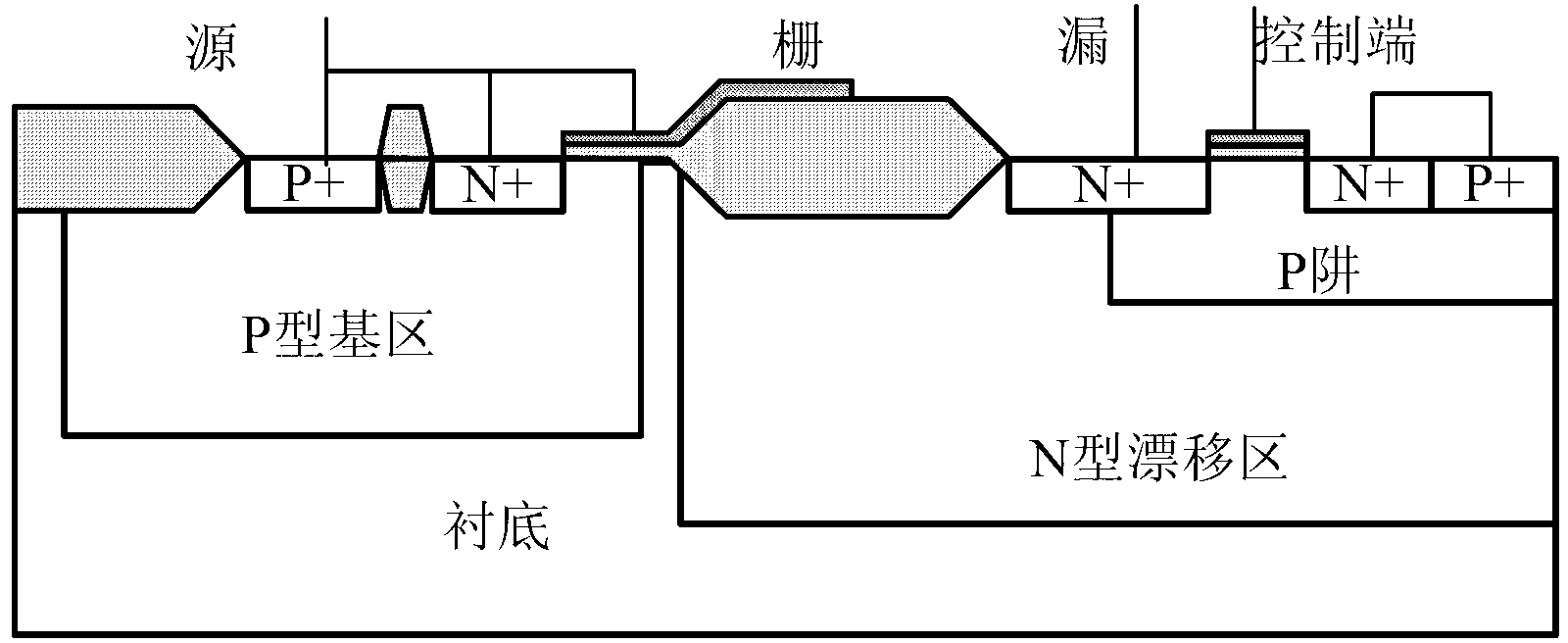

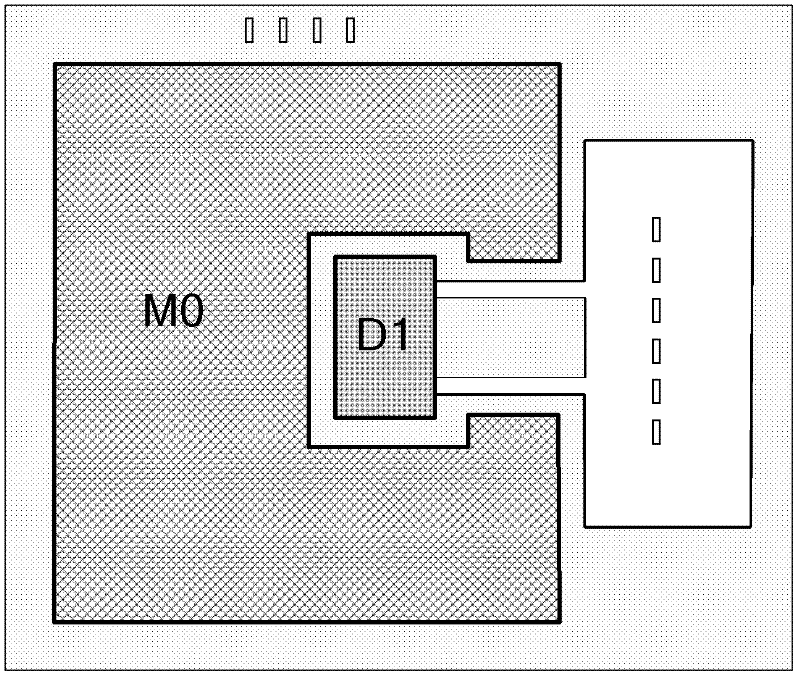

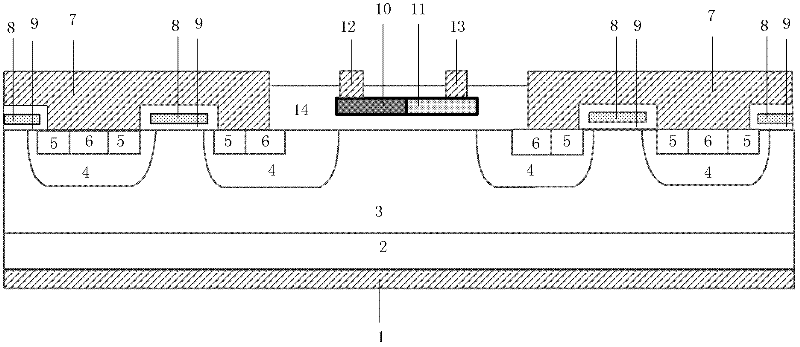

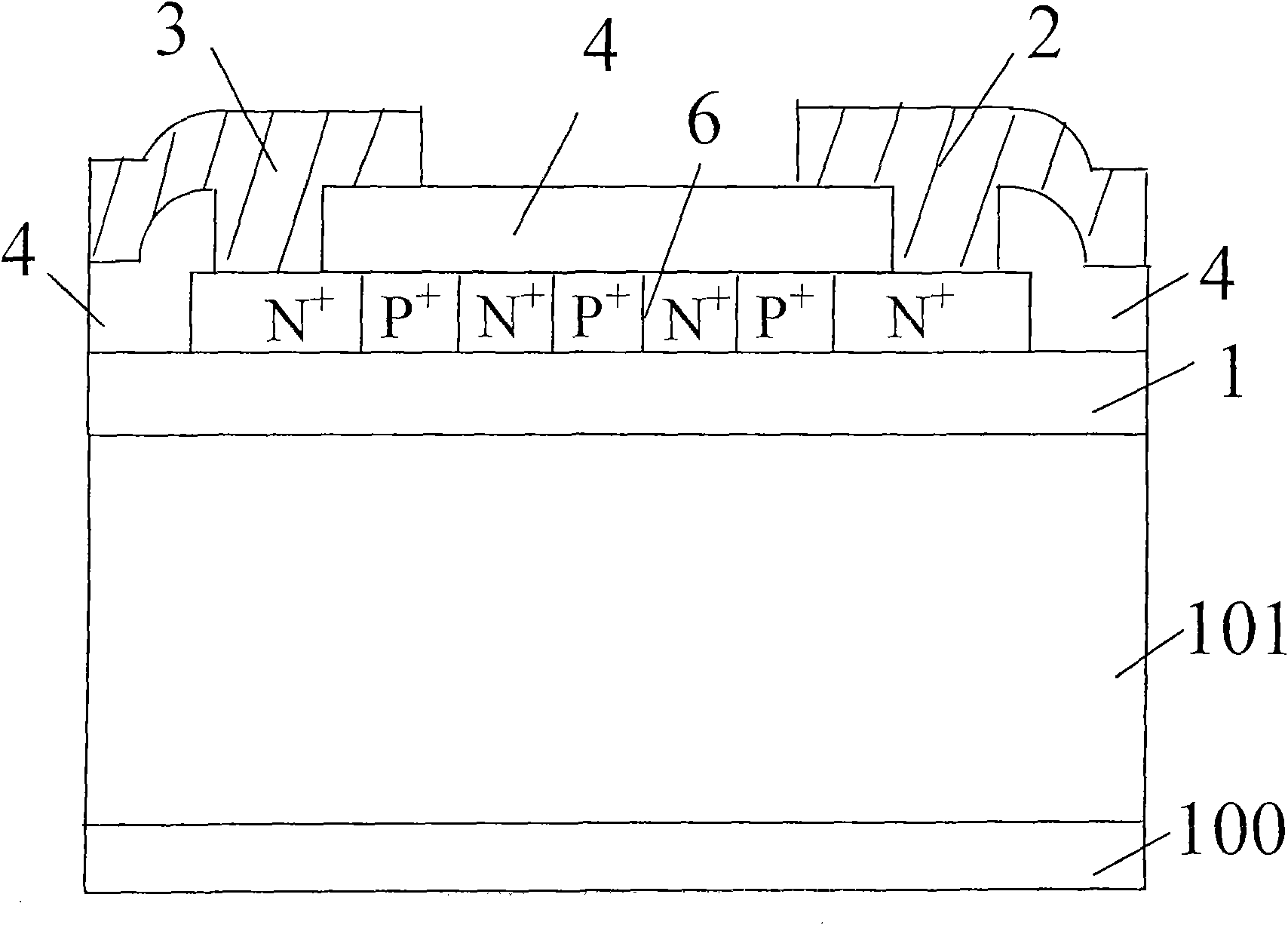

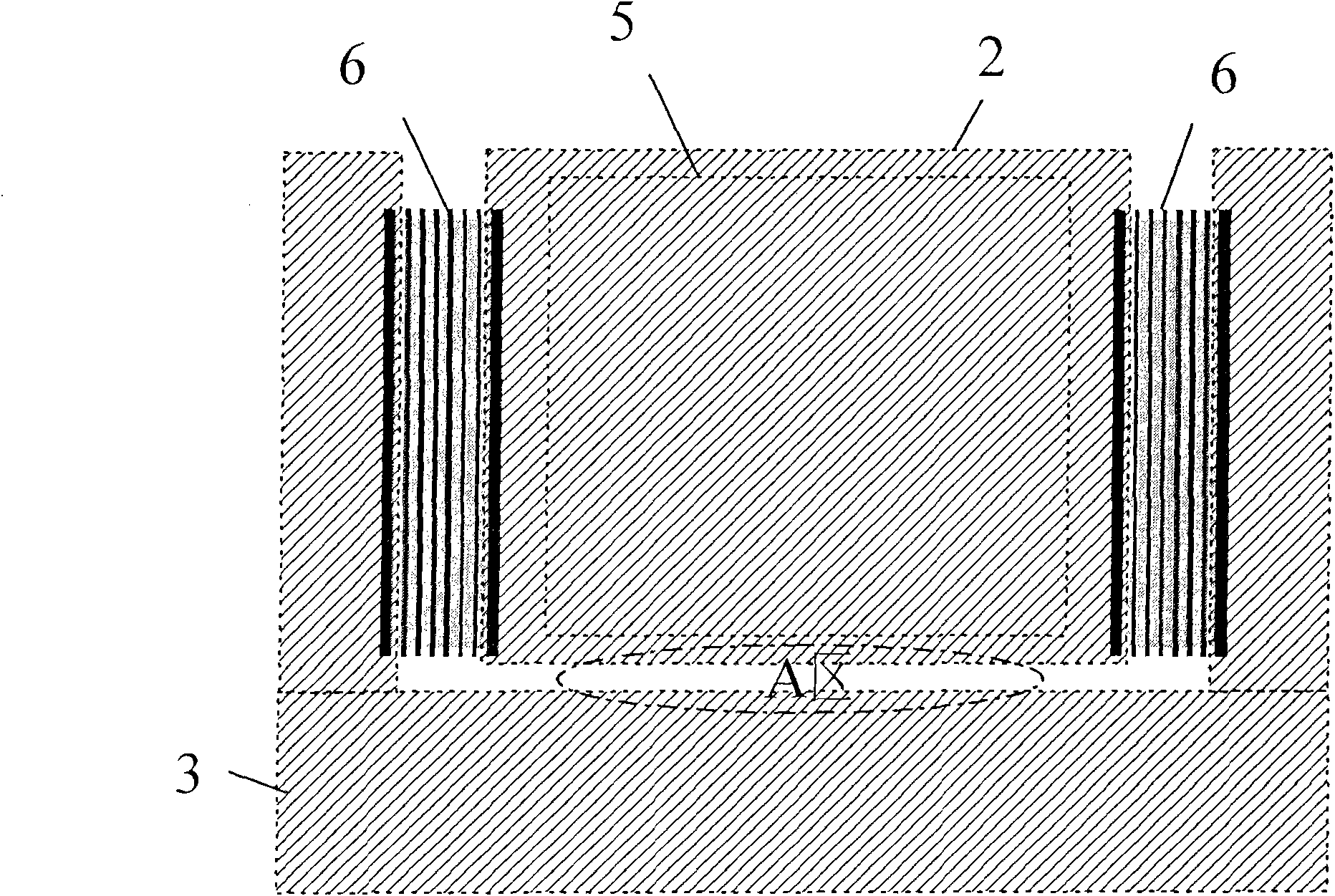

LDMOS SCR for protection against integrated circuit chip ESD

InactiveCN103258814AIncrease the Vhold valueImproves latch-up immunitySemiconductor/solid-state device detailsSolid-state devicesLow voltageHigh voltage

The invention discloses an LDMOS SCR for protection against integrated circuit chip ESD protection and belongs to the technical field of electrons. According to the LDMOS SCR for the protection against the integrated circuit chip ESD, a low-voltage MOS is integrated on the basis of a traditional structure of the LDMOS SCR for the protection against the integrated circuit chip ESD and the low-voltage MOS is used for limiting a hole current injected from the positive electrode of the nested SCR, so that value of the holding voltage Vhold is improved and latch-up immune ability of the LDMOS SCR in high-voltage application is improved. In addition, compared with an ordinary LDMOS, the LDMOS SCR for the protection against the integrated circuit chip ESD is stronger in ability of the protection against the ESD due to the integrated SCR. Besides, the LDMOS SCR for the protection against the integrated circuit chip ESD and the Bipolar CMOS DMOS technology are compatible.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

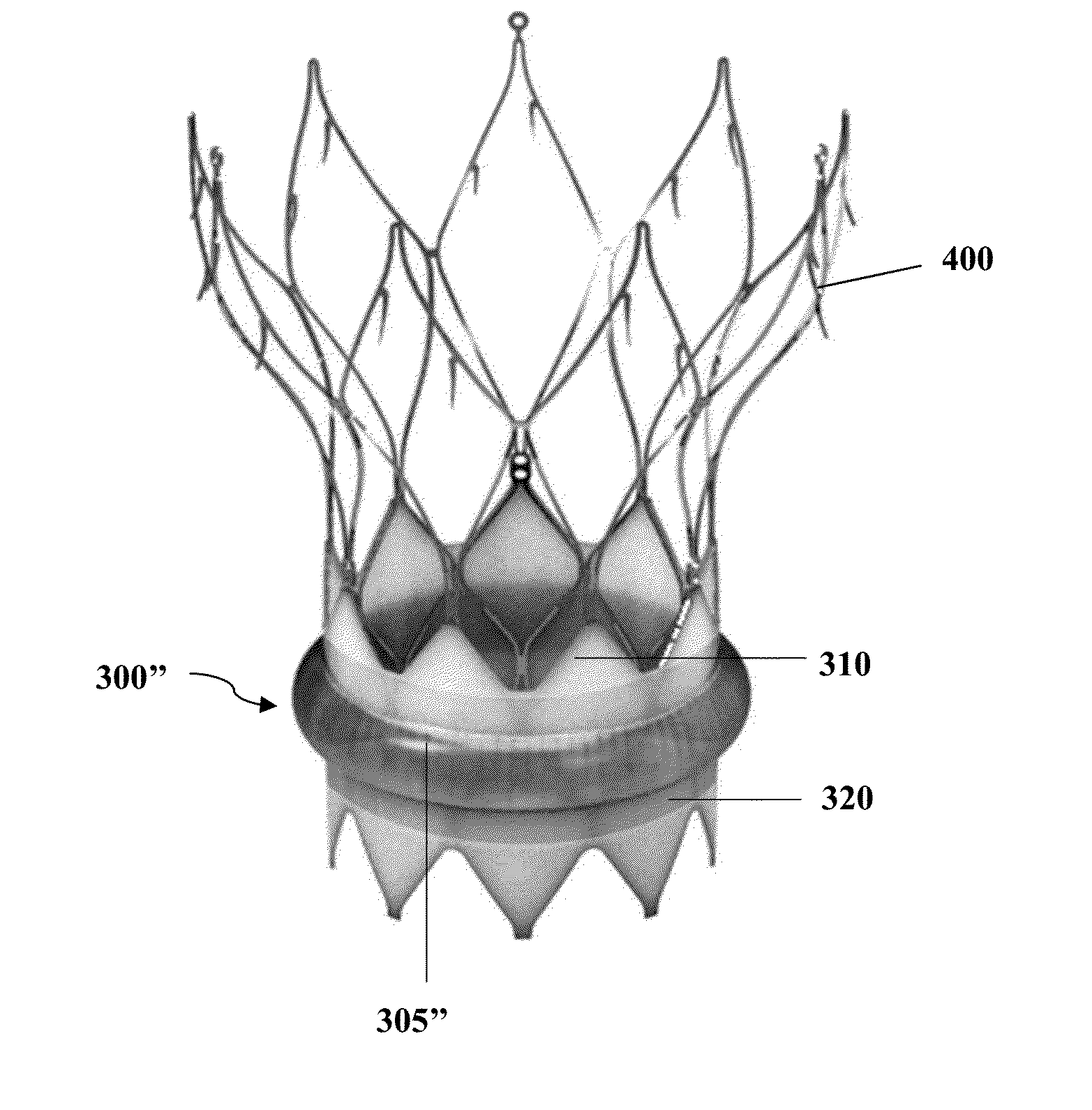

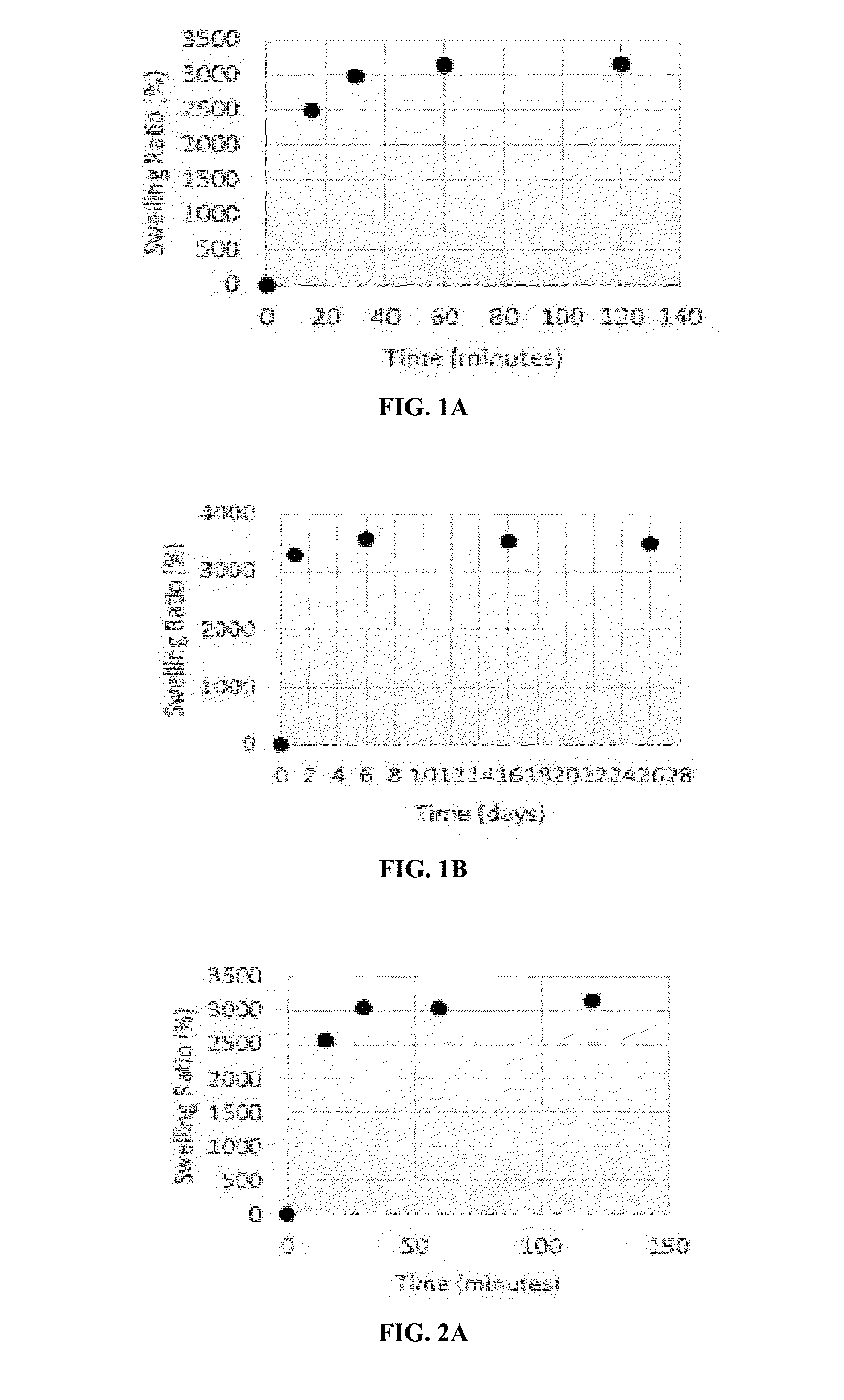

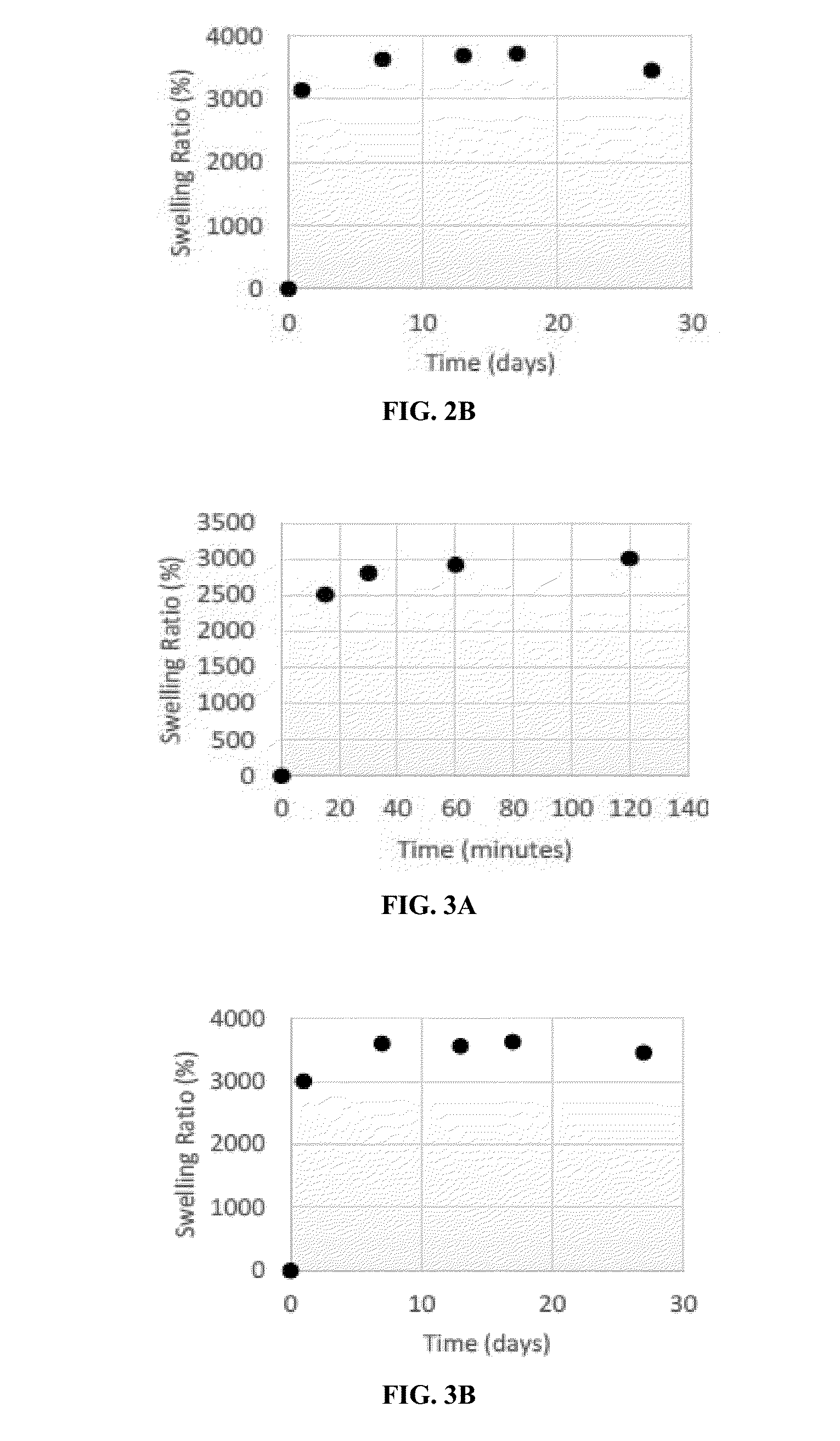

Highly expandable hydrogels in medical device sealing technology

Highly expandable materials have been developed for filling an aneurysm sac and for sealing of endoluminal devices vessel walls. The expandable materials have appropriate chemical and physical properties to withstand radiation, sterilization, or storage in sterilizing solution, without loss of expandable characteristics. The expandable materials may contain protectants, prophylactic, diagnostic, therapeutic, or imaging agents. The expandable materials form a seal that actively conforms to vascular anatomy sealing any leaks that may occur after device implantation. In one embodiment, the technology is used to prevent leaks associated with abdominal aortic aneurysm (AAA) repair, especially for complex AAA repair.

Owner:ENDOLUMINAL SCI

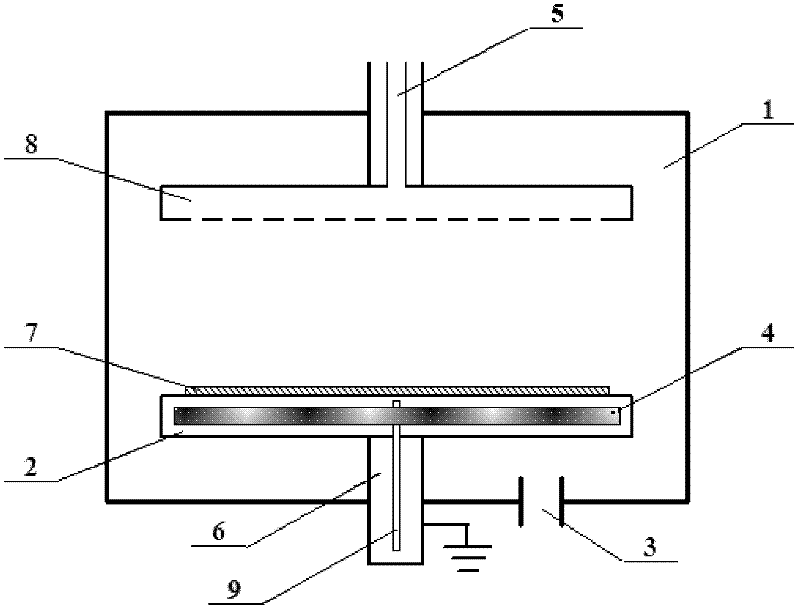

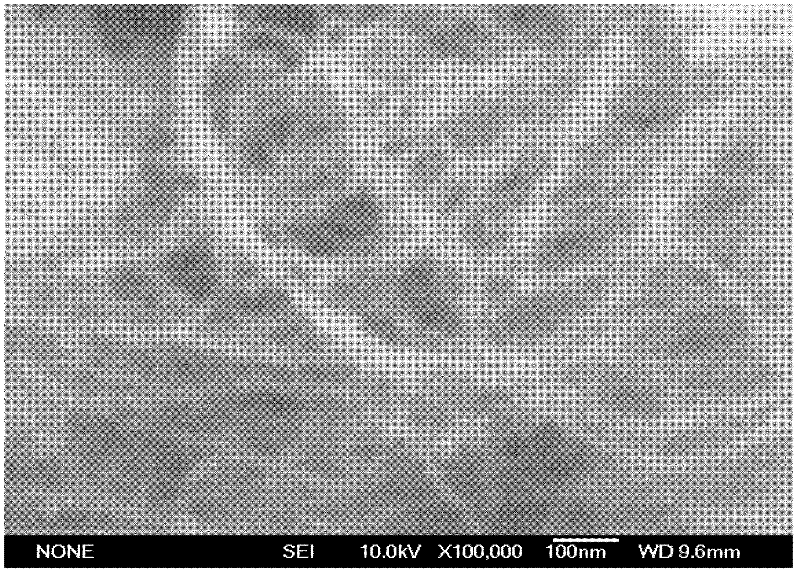

A low-temperature preparation method of carbon nanotubes

A low-temperature preparation method of carbon nanotubes by a chemical vapor deposition method with Ni / MgO as a catalyst comprises the following steps: dissolving nicdel nitrate hexahydrate and magnesium nitrate hexahydrate in ethanol according to different ratios and concentrations to obtain a mixed solution of nicdel nitrate and magnesium nitrate which is used as a catalyst precursor for carbonnanotube growth; spraying the catalyst precursor solution on a substrate such as silicon, glass, and the like, placing the substrate on a sample stage of a chemical vapor deposition system, heating and decomposing to generate nickel oxide and magnesium oxide, introducing hydrogen, performing reduction in hydrogen plasma of the plasma chemical vapor deposition system to generate nickel nanometer metal particles and to obtain a Ni / MgO catalyst system; introducing hydrocarbons, preparing carbon nanotubes for various demands under different process conditions. The advantages of the invention are that the carbon nanotube preparation process is simple, high in yield, and low in synthetic temperature, and the obtained carbon nanotubes have good quality, high purity, uniform tube diameter distribution, and microelectronic process compatibility.

Owner:TIANJIN UNIVERSITY OF TECHNOLOGY

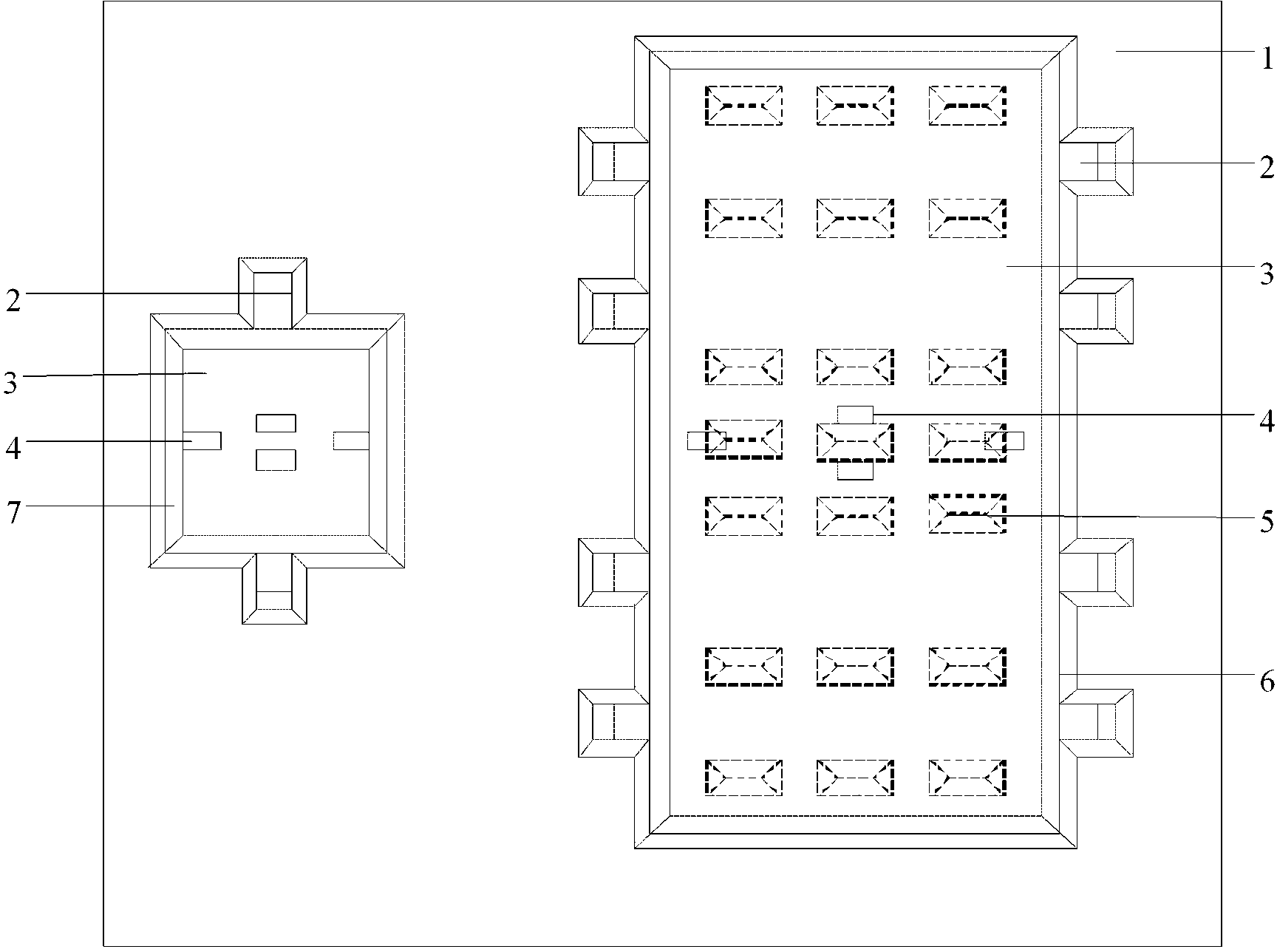

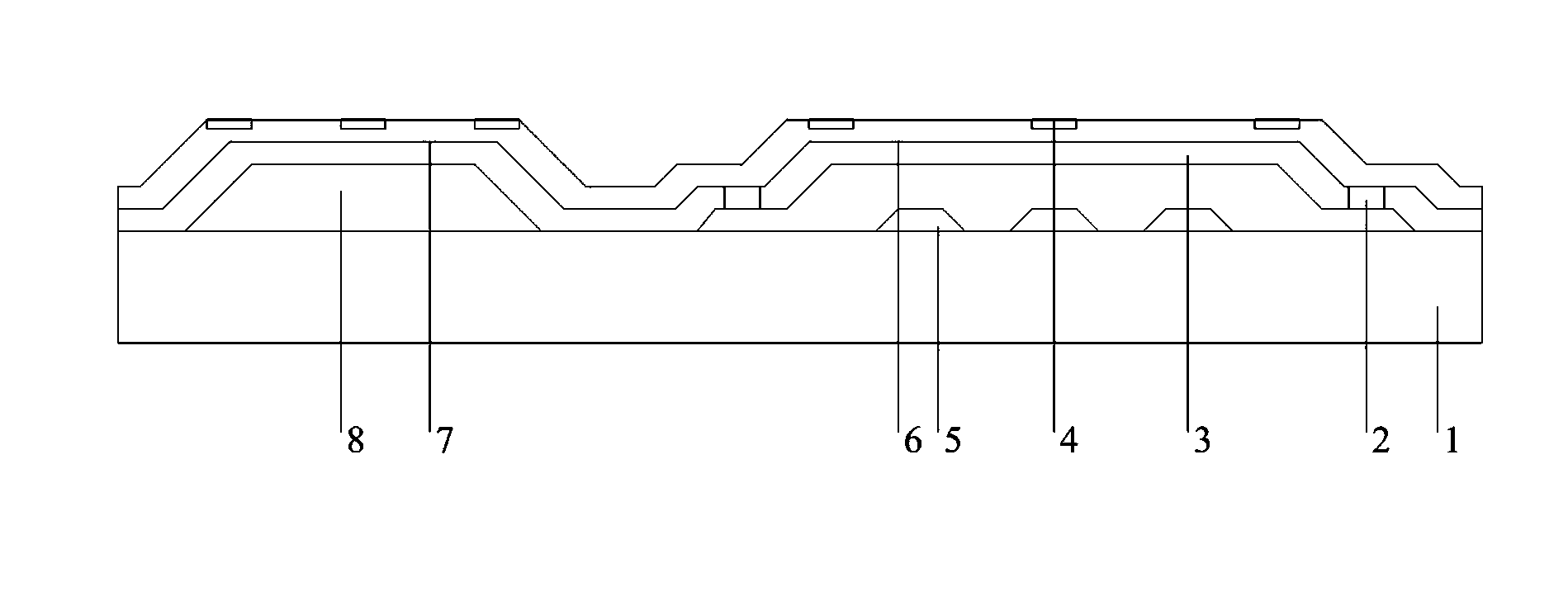

Multi-range integrated pressure sensor chip

InactiveCN102798498AHigh sensitivityImprove temperature stabilityFluid pressure measurement using ohmic-resistance variationForce measurementAviationLow voltage

The invention discloses a multi-range integrated pressure sensor chip which comprises a silicon substrate, wherein two or more pressure sensors with different ranges are arranged on the silicon substrate; each pressure sensor consists of a corrosion hole, a membrane and strain resistors; the four symmetric strain resistors are respectively arranged on the upper surface of each membrane and connected with one another through conductors to form a Wheatstone bridge; the membranes are connected with the silicon substrate to form a cavity; and the corrosion holes are formed on the supporting edges of the membranes. The multi-range integrated pressure sensor chip has the characteristics of being small in size, wide in range, high in low-voltage sensitivity, small in temperature drift coefficient and compatible in manufacturing process and integrated circuit process, can be used for multipath pressure measurement in automobiles, pressure measurement of environment control and pressure measurement in the fields of aviation systems, petrochemical industries and the like, and is suitable for popularization and application.

Owner:SHENYANG POLYTECHNIC UNIV

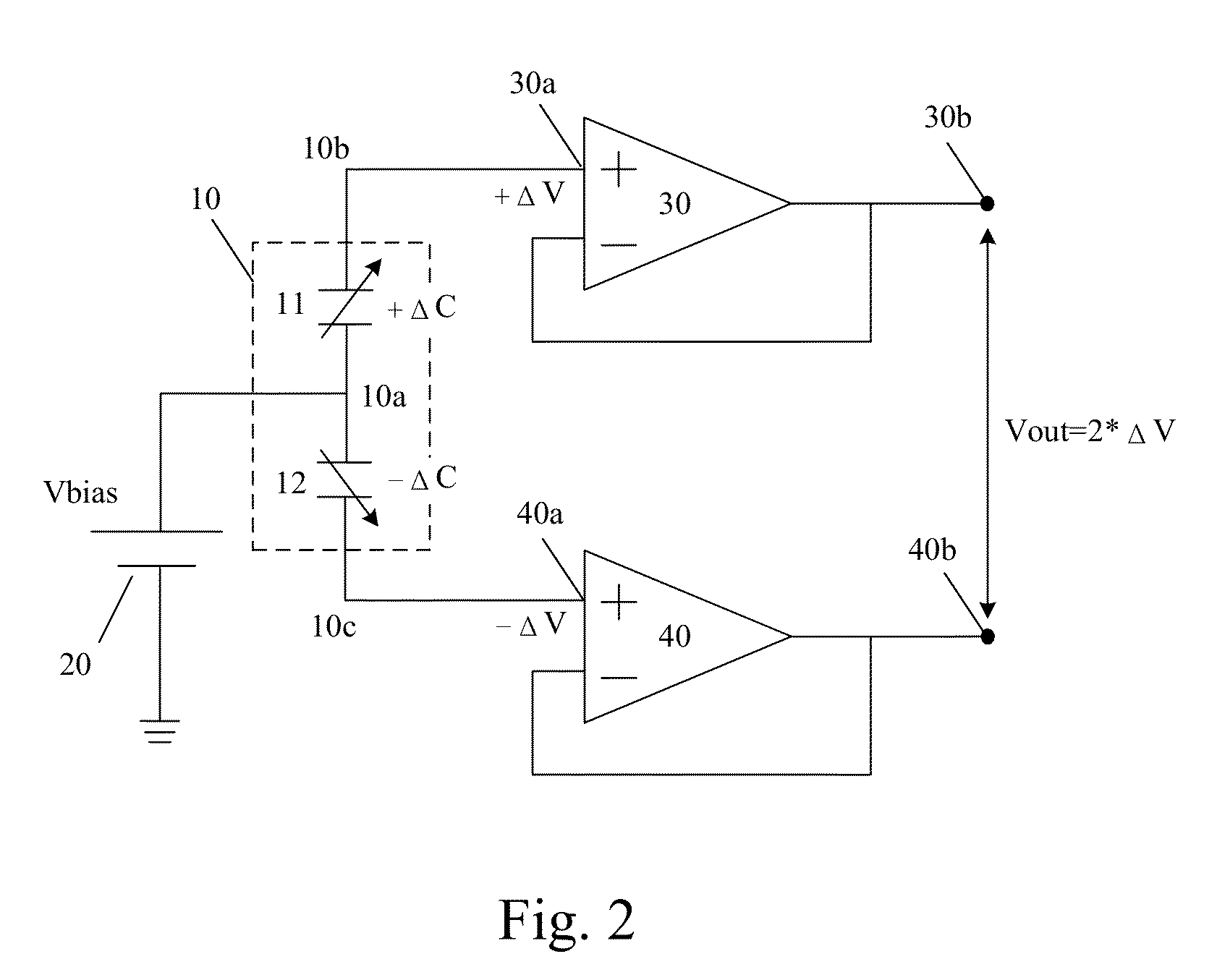

Differential wideband vibration sensor

InactiveUS6220096B1Eliminates costly precision tuningIncrease capacitanceVibration measurement in solidsMaterial analysis using sonic/ultrasonic/infrasonic wavesEngineeringField-effect transistor

This invention relates to an apparatus for making highly sensitive differential measurements of acceleration. The vibration sensor includes the use of moveable gate field effect transistors to sense the motion of a cantilever beam relative to the motion sensed by a reference structure, it also includes an actuator element formed by a pair of electrodes actuating electrostatically on the beam. A feedback control loop is also included for force balance operation resulting in a very wide dynamic range for the sensor.

Owner:INTERSCI

Forming method of semiconductor structure

InactiveCN105655286AReduce aspect ratioImprove formation qualitySemiconductor/solid-state device manufacturingSemiconductor structureElectric properties

The invention discloses a forming method of a semiconductor structure. The method comprises the following steps: providing a substrate which comprises a first region for forming a core storage circuit; orderly forming a gate electrode film and an initial hard mask film on the substrate; etching the initial hard mask film by using the first etching process, forming a first opening penetrating through the initial hard mask film in the first region; filling a sacrifice layer in the first opening; etching the sacrifice layer and the substrate at the bottom of the first opening by using the second etching process, and forming a first groove in the first region substrate; and forming a first isolation structure in the first groove. The method comprises: firstly forming the first opening penetrating through the initial hard mask film in the first region, and then filling the sacrifice layer in the first opening to form the first groove, wherien the sacrifice layer is firstly etched along the first opening and then the substrate is etched, thereby acquiring the first groove with small depth so as to reduce the depth-to-width ratio of the first groove; and the condition of forming a gap in the first isolation structure is avoided, thereby improving the forming quality of the first isolation structure, and then improving the electric property of a semiconductor device.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

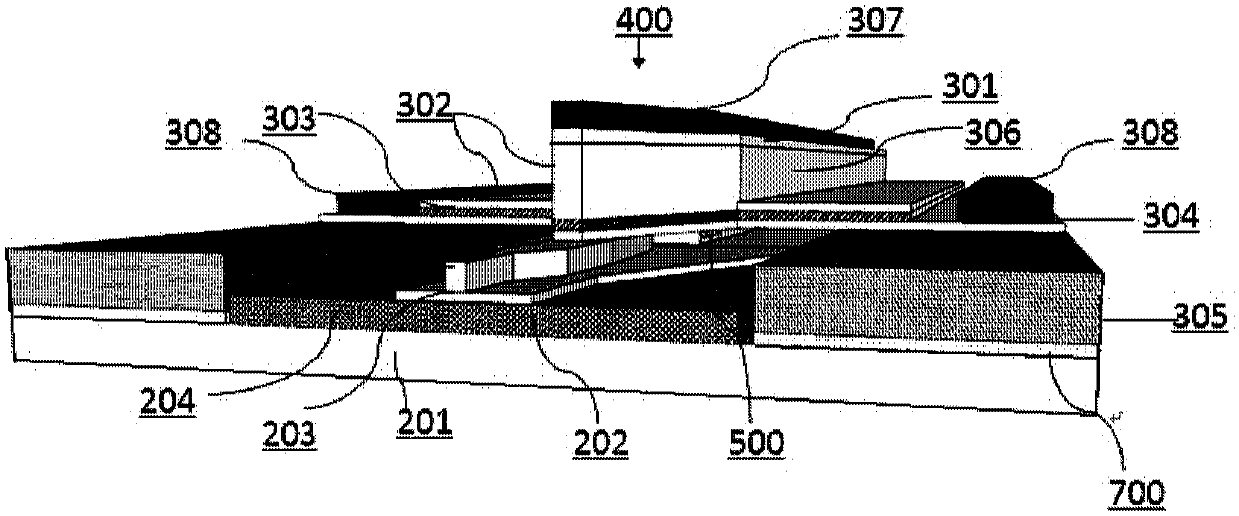

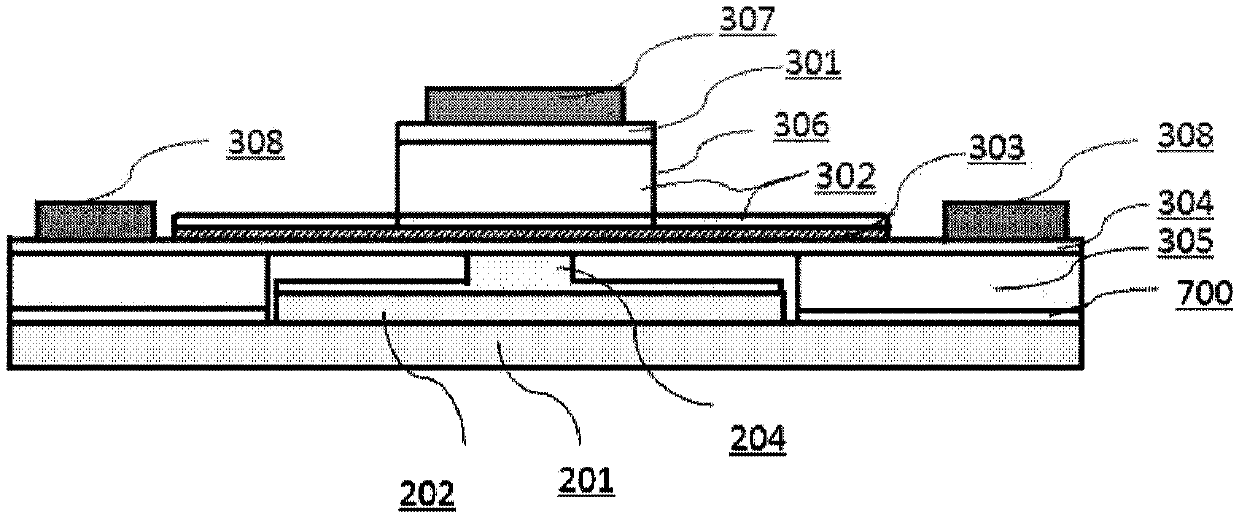

CMOS compatible silicon differential condenser microphone and method for manufacturing the same

ActiveUS8860154B2Improve signal-to-noise ratioProcess compatibleAcceleration measurement using interia forcesTransducer detailsCMOSEngineering

The present invention provides a CMOS compatible silicon differential condenser microphone and a method of manufacturing the same. Said microphone comprises a silicon substrate, wherein a CMOS circuitry is accommodated thereon; a first rigid conductive perforated backplate supported on the silicon substrate with an insulating layer inserted therebetween; a second rigid perforated backplate formed above the first backplate, including CMOS passivation layers and a metal layer sandwiched between the CMOS passivation layers as an electrode plate of the second plate, wherein an air gap, with a spacer forming its boundary, is provided between the opposite perforated areas of the first backplate and the second backplate; a compliant diaphragm provided between the first backplate and the second backplate, wherein a back hole is formed to be open in the silicon substrate underneath the first backplate so as to allow sound pass through, and the diaphragm and the first backplate form a first variable condenser, the diaphragm and the second backplate form a second variable condenser, and the first variable condenser and the second variable condenser form differential condensers.

Owner:GOERTEK MICROELECTRONICS CO LTD

Novel method for separation of human sperm from biological samples for application in human identification

InactiveUS20060141512A1High throughputProcess compatibleMicrobiological testing/measurementDisease diagnosisCELL DEBRISN-Acetylglucosamine

The development of an isolation methodology for separation of human sperm cells from biological samples containing human epithelial cells is provided. Using sperm binding proteins, glycopeptides, lectins, derivatives of N-acetylglucosamine, triazine dyes or inhibitors of glycosyltransferase linked to an insoluble support, our invention enables binding of human sperm cells from biological samples. Bound sperms can be dissociated and used for in vitro analyses or subsequently lysed on the insoluble support for isolation of male specific DNA. Other cell types such as epithelial cells, white blood cells and cell debris present in the biological samples are not bound to the derivatized insoluble support. The sperm cells, thus isolated, can be processed for isolation of nuclear DNA for human identification and forensic DNA analysis.

Owner:RELIAGENE TECH +1

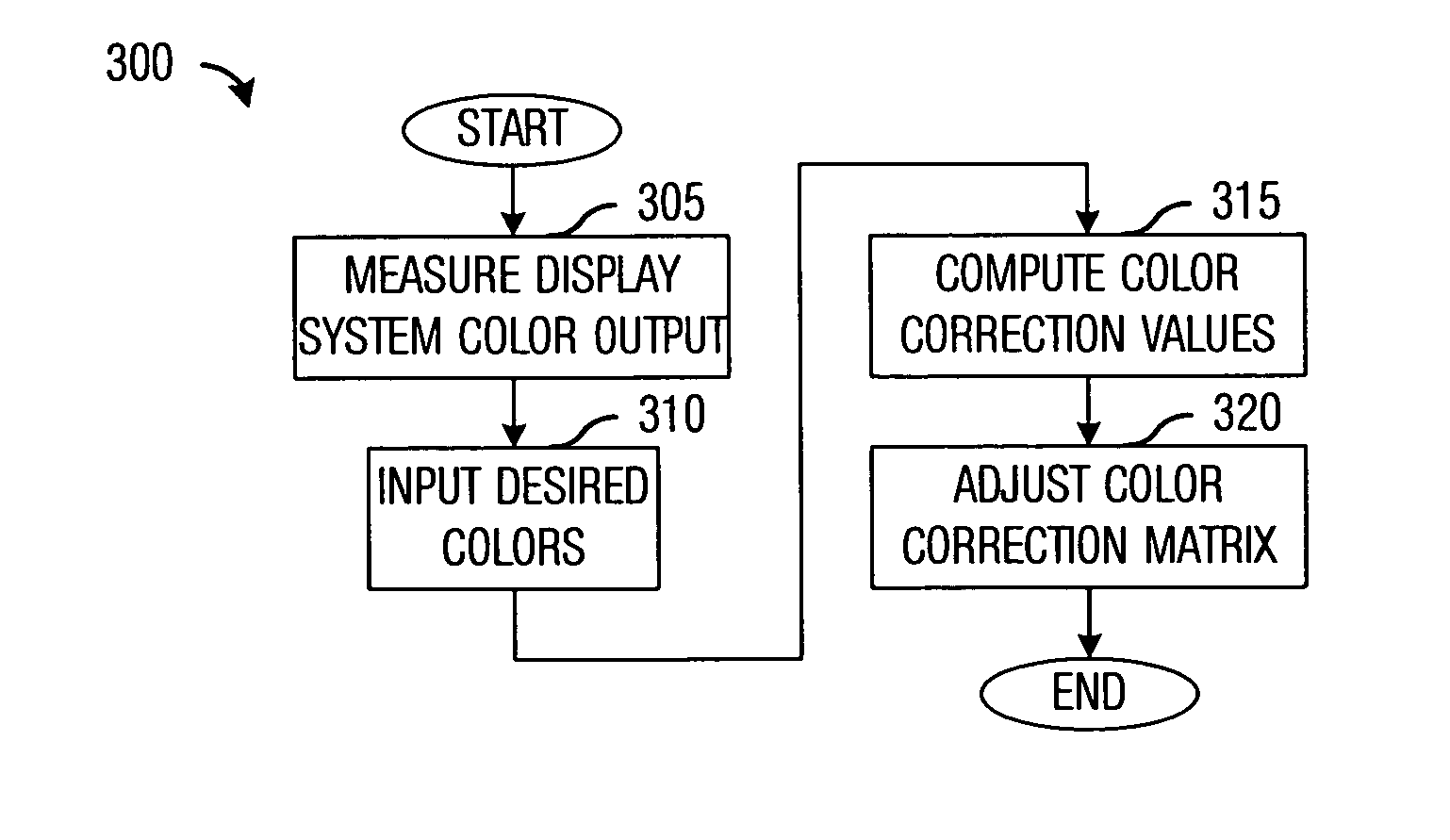

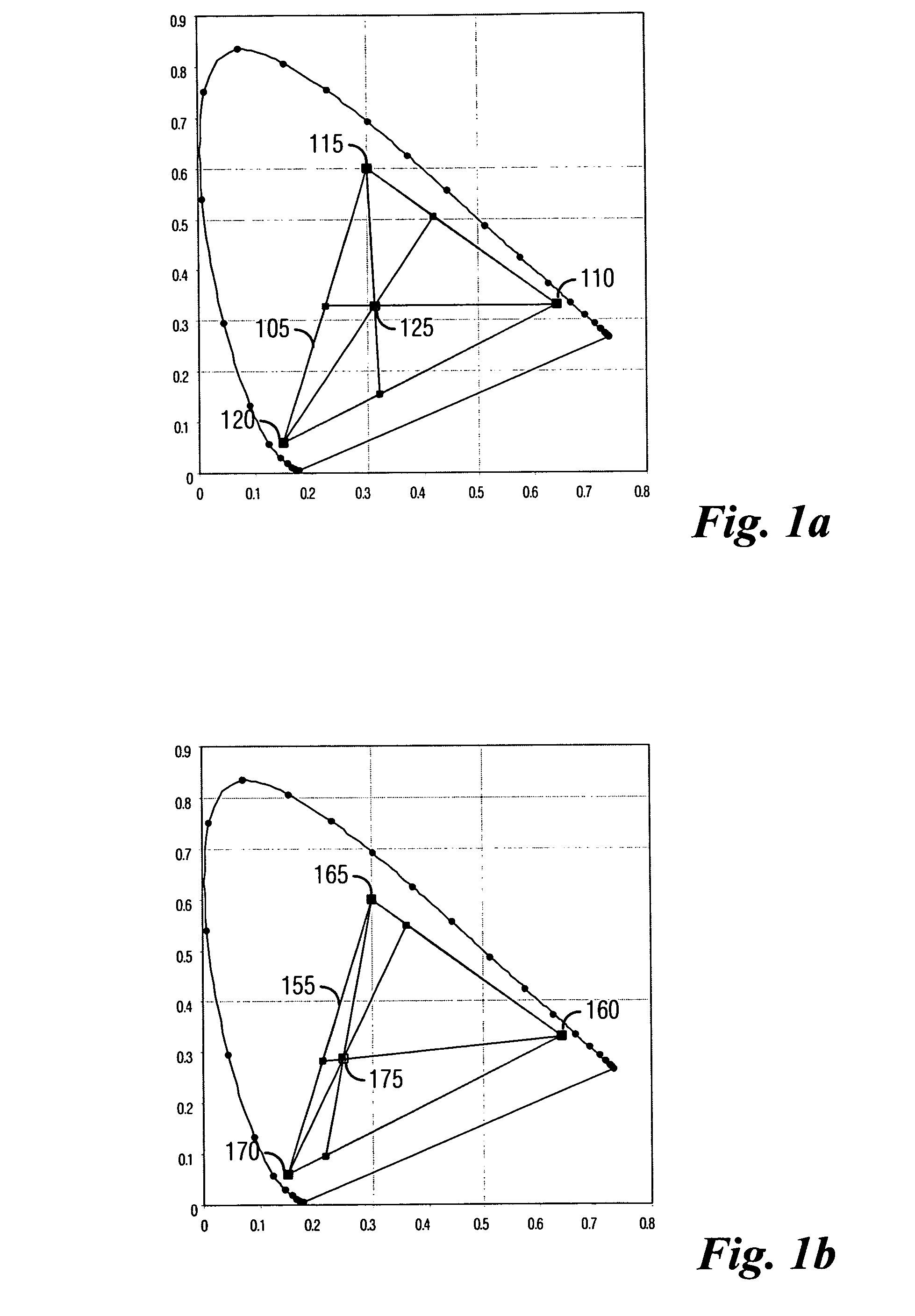

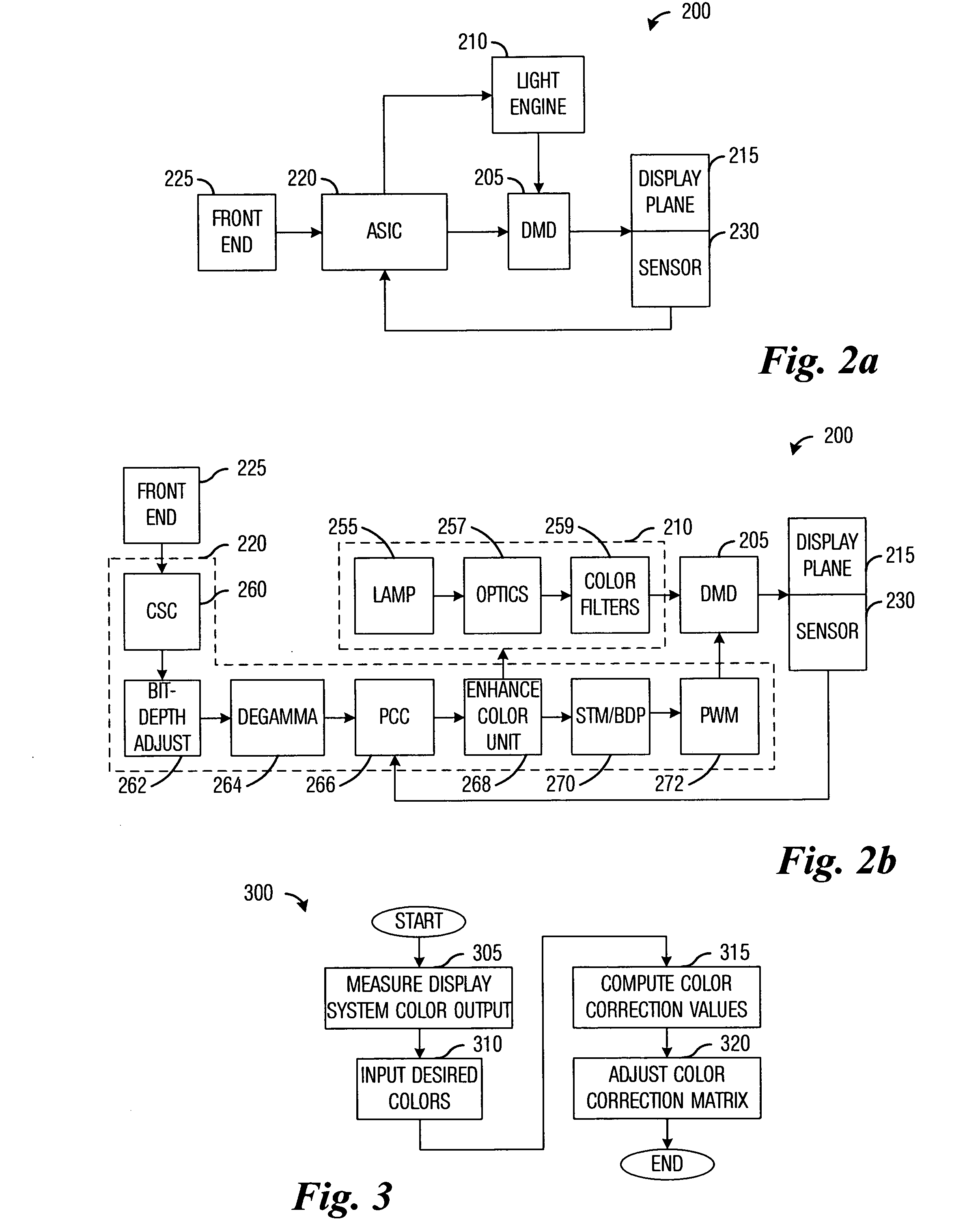

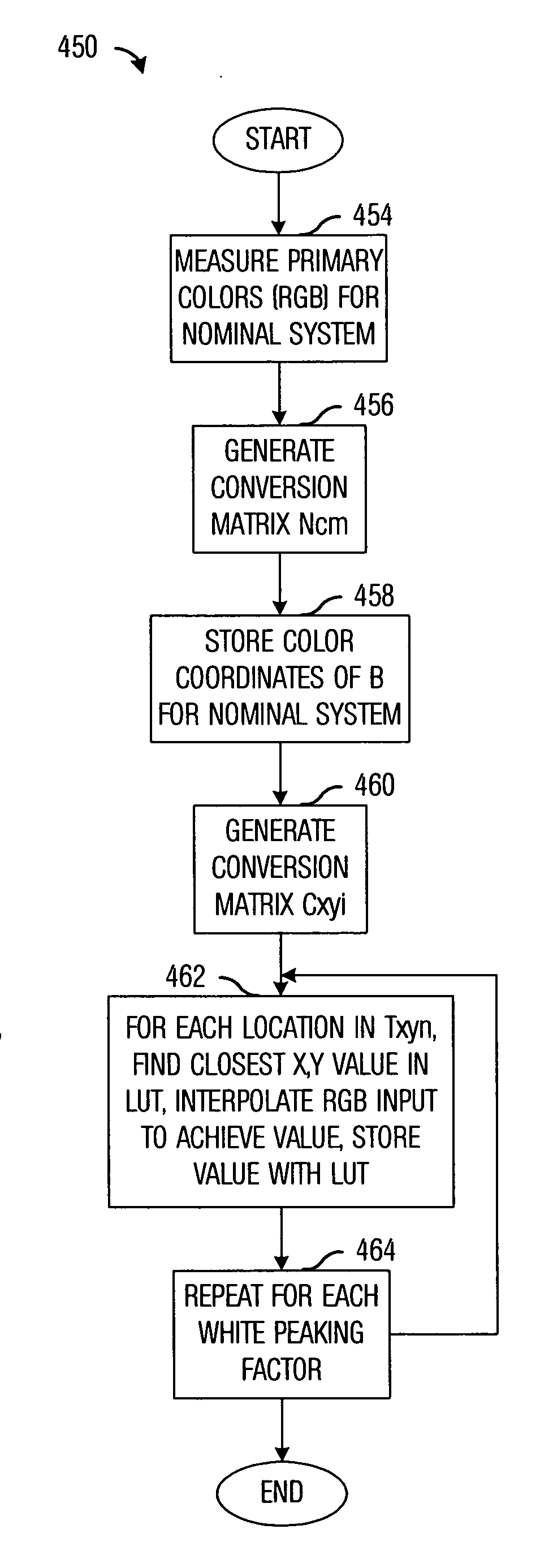

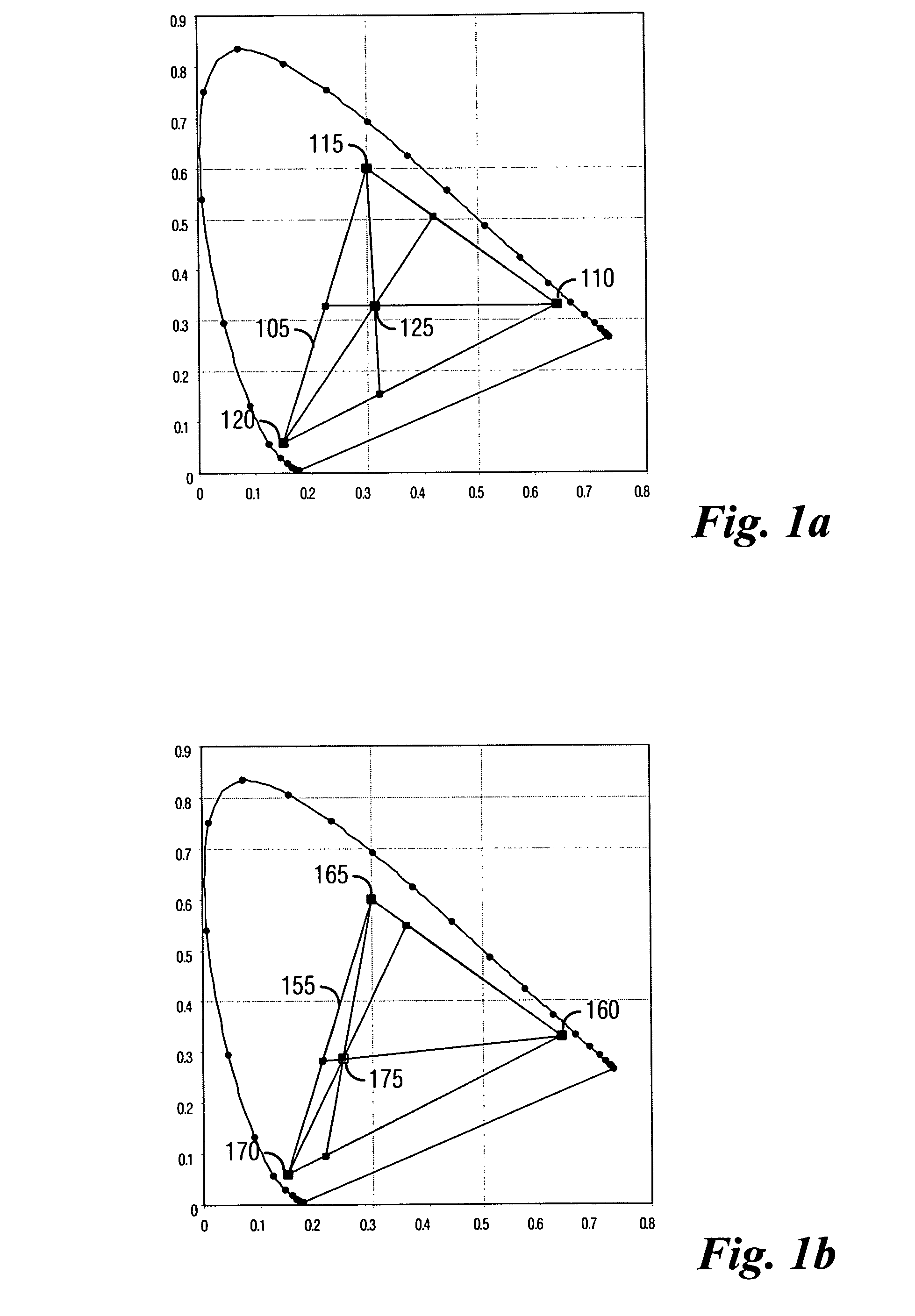

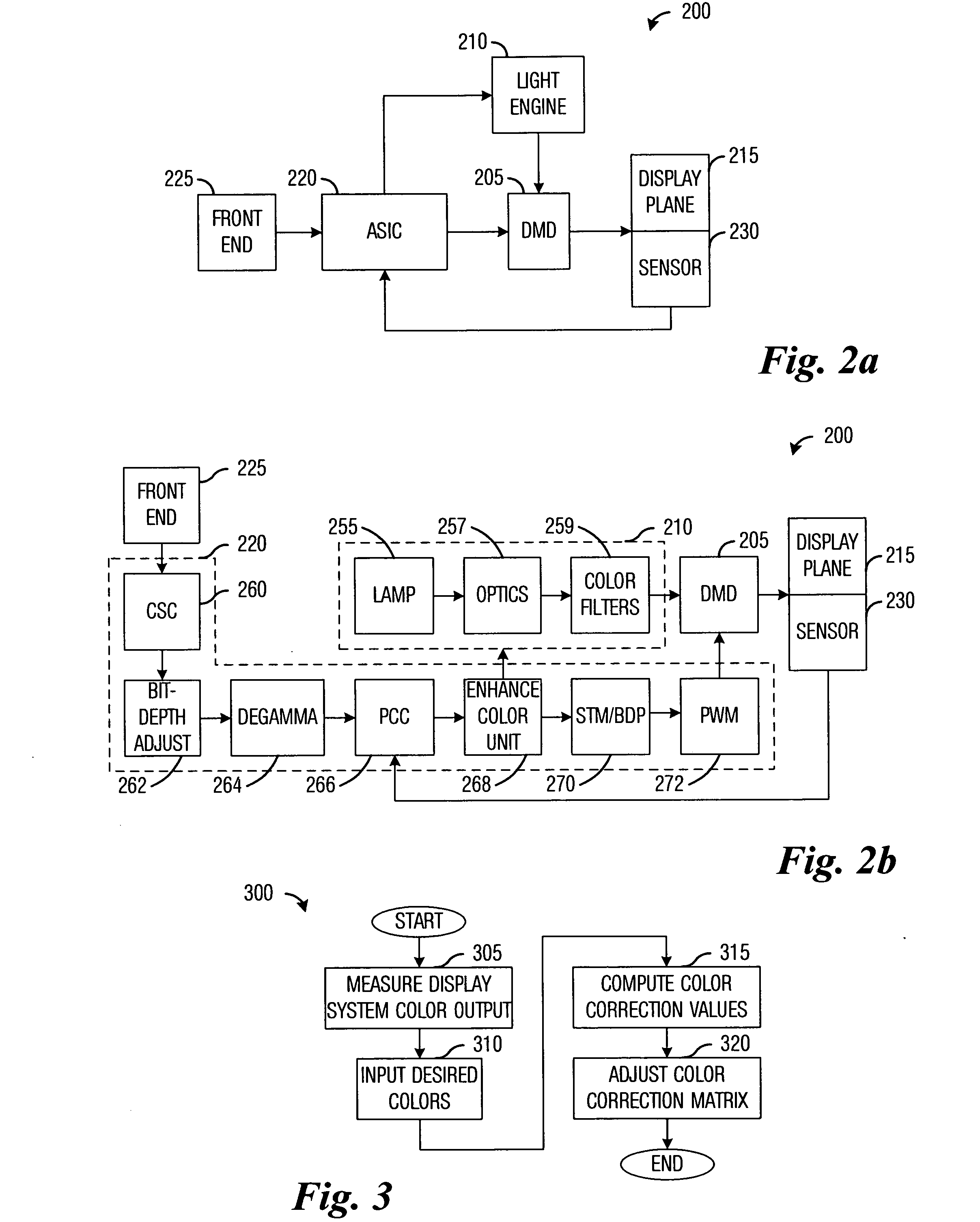

System and method for computing color correction coefficients

ActiveUS7737989B2Process compatibleWide applicabilityTelevision system detailsPicture reproducers using cathode ray tubesSystems designColor correction

System and method for computing coefficients for color correcting rendered colors used in displaying images. A preferred embodiment comprises measuring color values of light output for a display system, receiving color values of desired colors, and computing a color correction matrix based on the measured color values and the input color values. The color correction matrix may be used to modify color commands to a light engine of the display system. The modifications to the color commands permit the storage and use of a set of color commands designed for a reference display system, simplifying display system design and manufacture.

Owner:TEXAS INSTR INC

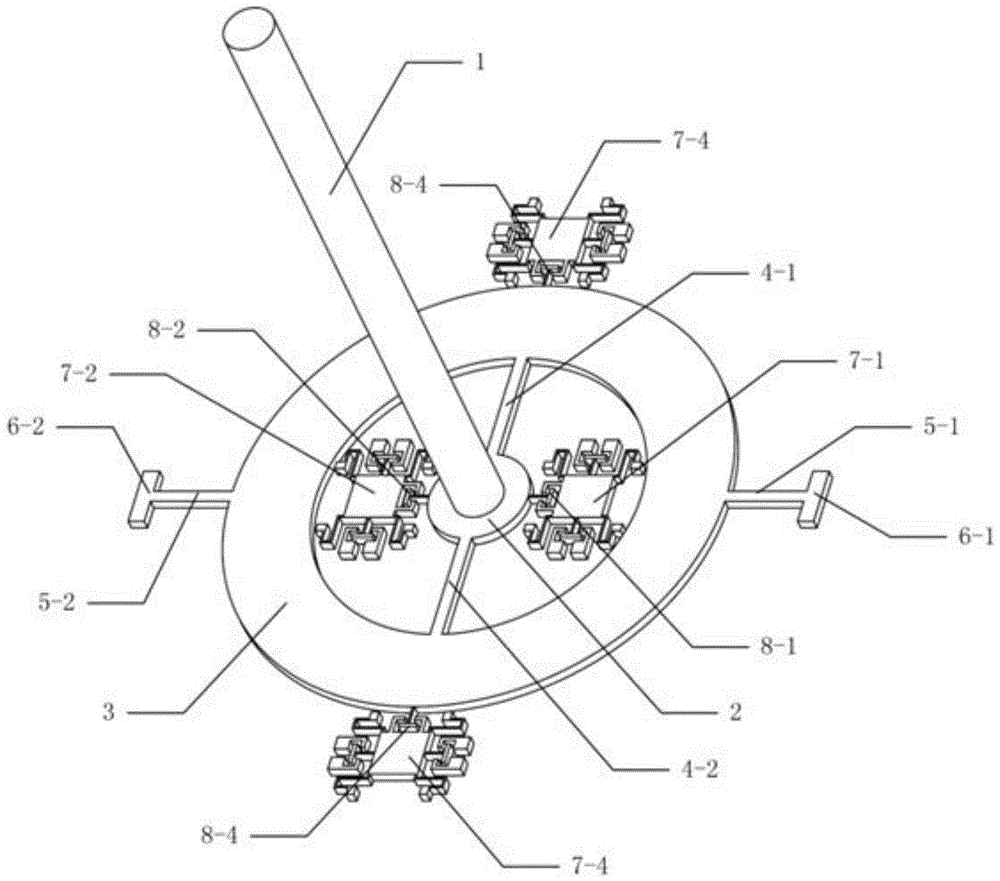

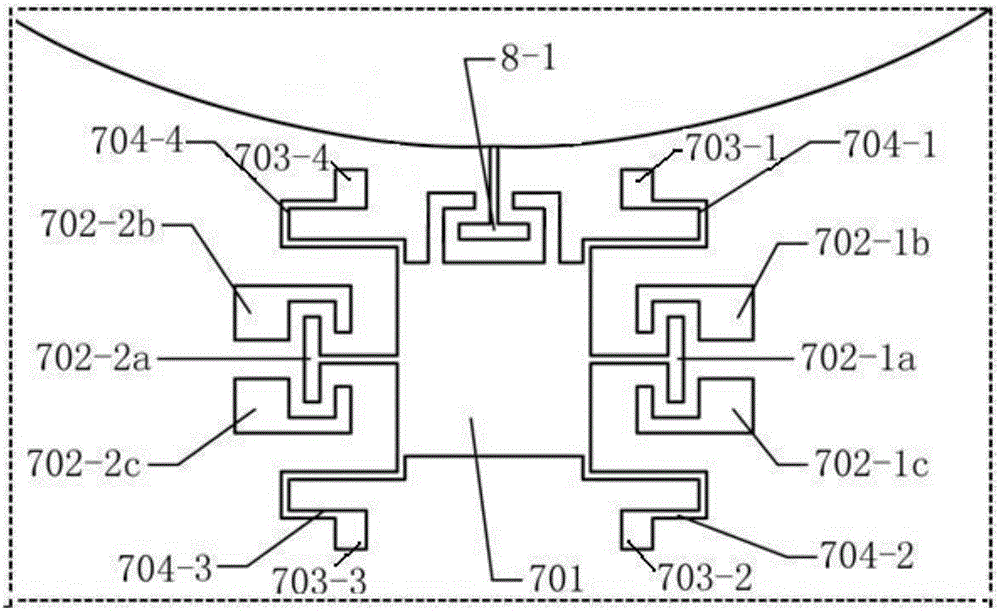

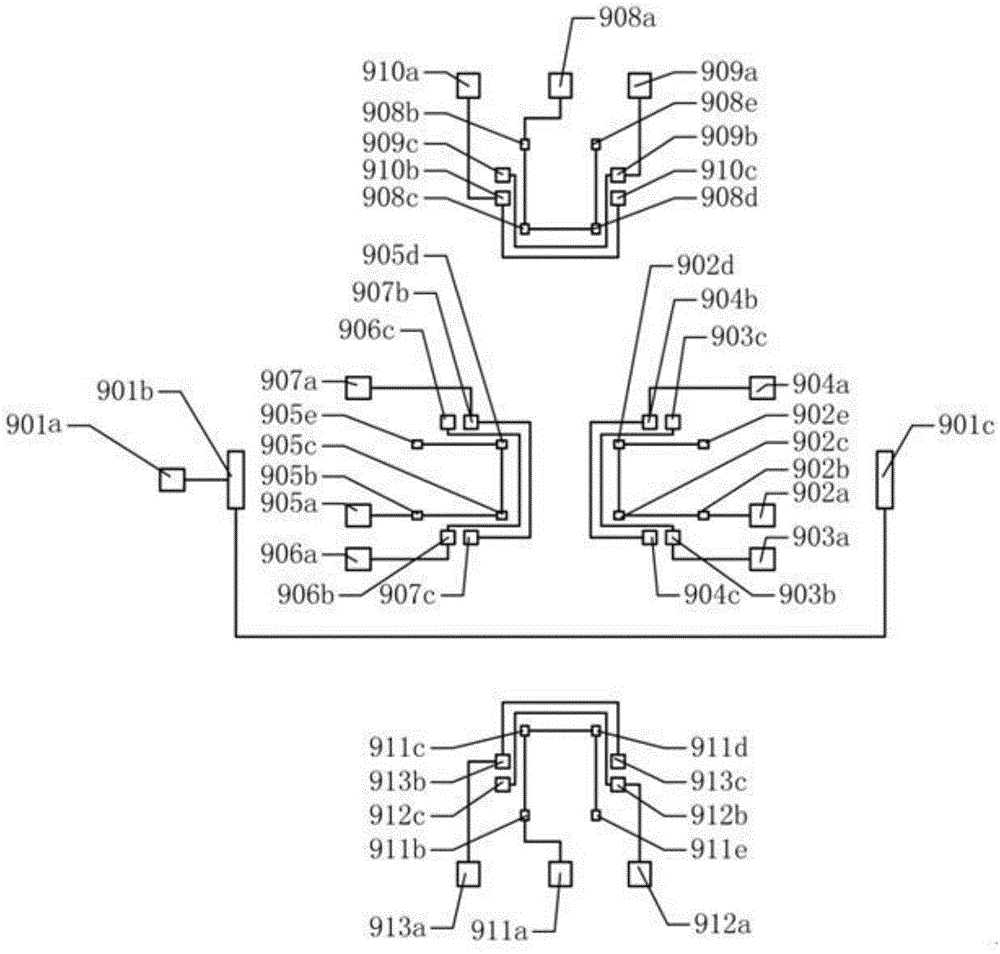

Bionic hair sensor for being sensitive to flow velocity and accelerated velocity vectors and detection method thereof

ActiveCN104833350ALarge volume ratioHigh sensitivitySpeed measurement using gyroscopic effectsGyroscopes/turn-sensitive devicesCouplingNegative stiffness

The invention discloses a bionic hair sensor for being sensitive to flow velocity and accelerated velocity vectors and a detection method thereof; the bionic hair sensor includes a top polymer hair, a middle annular silicon micro-sensor structure, and a bottom signal wire prepared on a glass substrate. When acted by an external accelerated velocity or fluid, the top hair drives a round mass block and an annular mass block in the annular silicon micro-sensor structure to swing; with use of a negative stiffness effect principle of an electrostatic force, and through swinging of the round mass block and the annular mass block in the annular silicon micro-sensor structure, resonant frequencies of resonators arranged around the round mass block and the annular mass block are caused to be changed, and values of the flow velocity and the accelerated velocity are detected; with use of a coupling structure of the mass block and the annular mass block, the swinging direction of the top hair is subjected to vector decomposition, and the vector direction of the accelerated velocity or the fluid velocity is detected.

Owner:SOUTHEAST UNIV

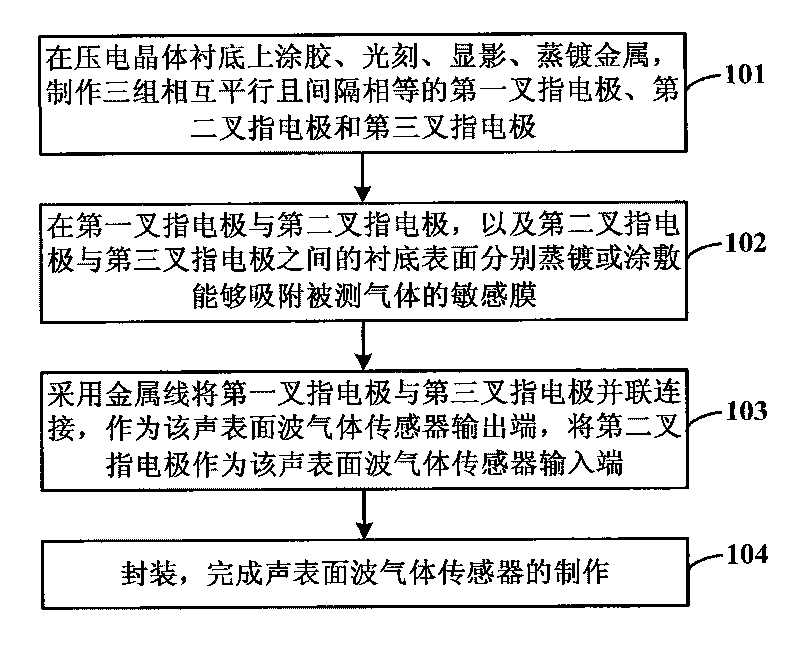

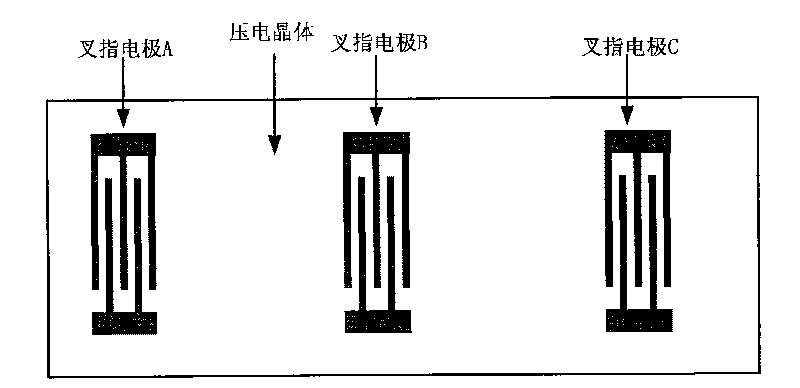

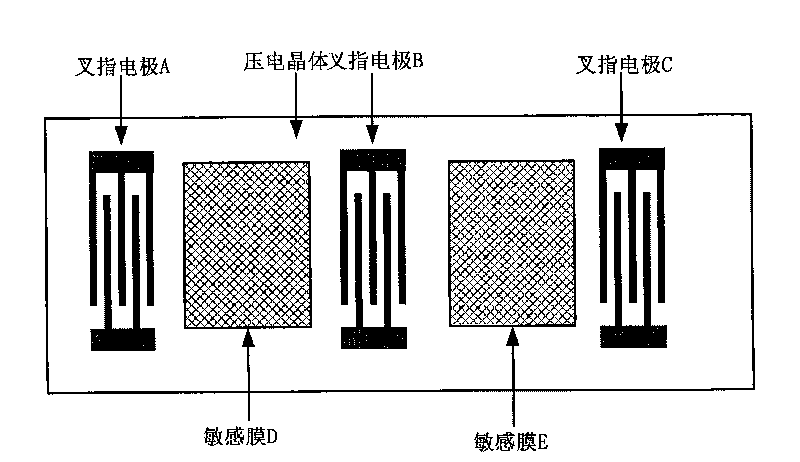

Acoustic surface wave gas sensor and manufacturing method thereof

InactiveCN101726538AResolve interferenceSimple structureAnalysing fluids using sonic/ultrasonic/infrasonic wavesAcousticsSignal processing

The invention discloses an acoustic surface wave gas sensor which comprises a piezoelectric crystal substrate, a first interdigital electrode, a second interdigital electrode, a third interdigital electrode and sensitive films, wherein the first interdigital electrode, the second interdigital electrode and the third interdigital electrode are arranged on the surface of the piezoelectric crystal substrate in parallel and at intervals; and the sensitive films capable of absorbing gas to be measured are separately evaporated or coated on the substrate surfaces between the first interdigital electrode and the second interdigital electrode, and between the second interdigital electrode and the third interdigital electrode. The invention also discloses a method for manufacturing the acoustic surface wave gas sensor. The acoustic surface sensor can be used for measuring different gases after matched with different sensitive films, and has the advantages of high sensitivity, simple structure, convenient manufacture, easy signal processing, and compatibility with semiconductor process.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

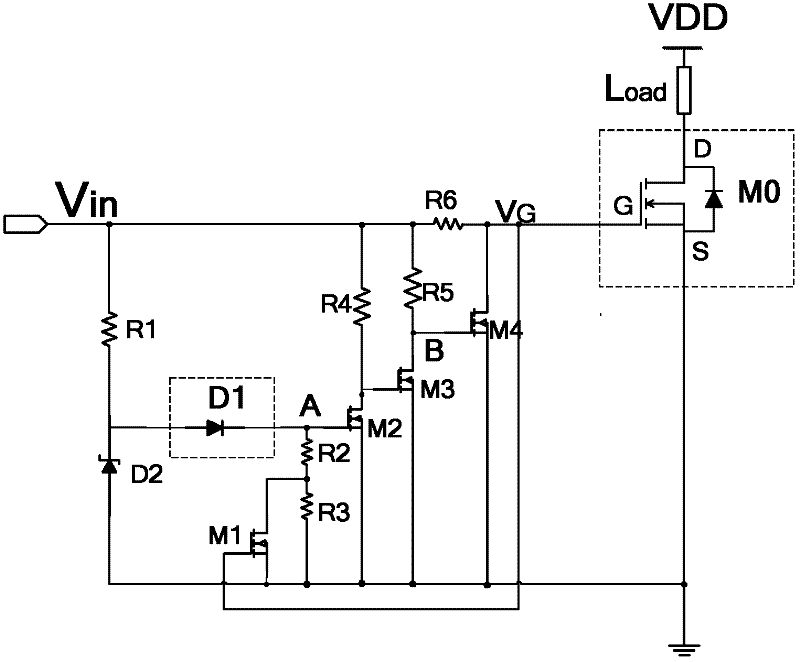

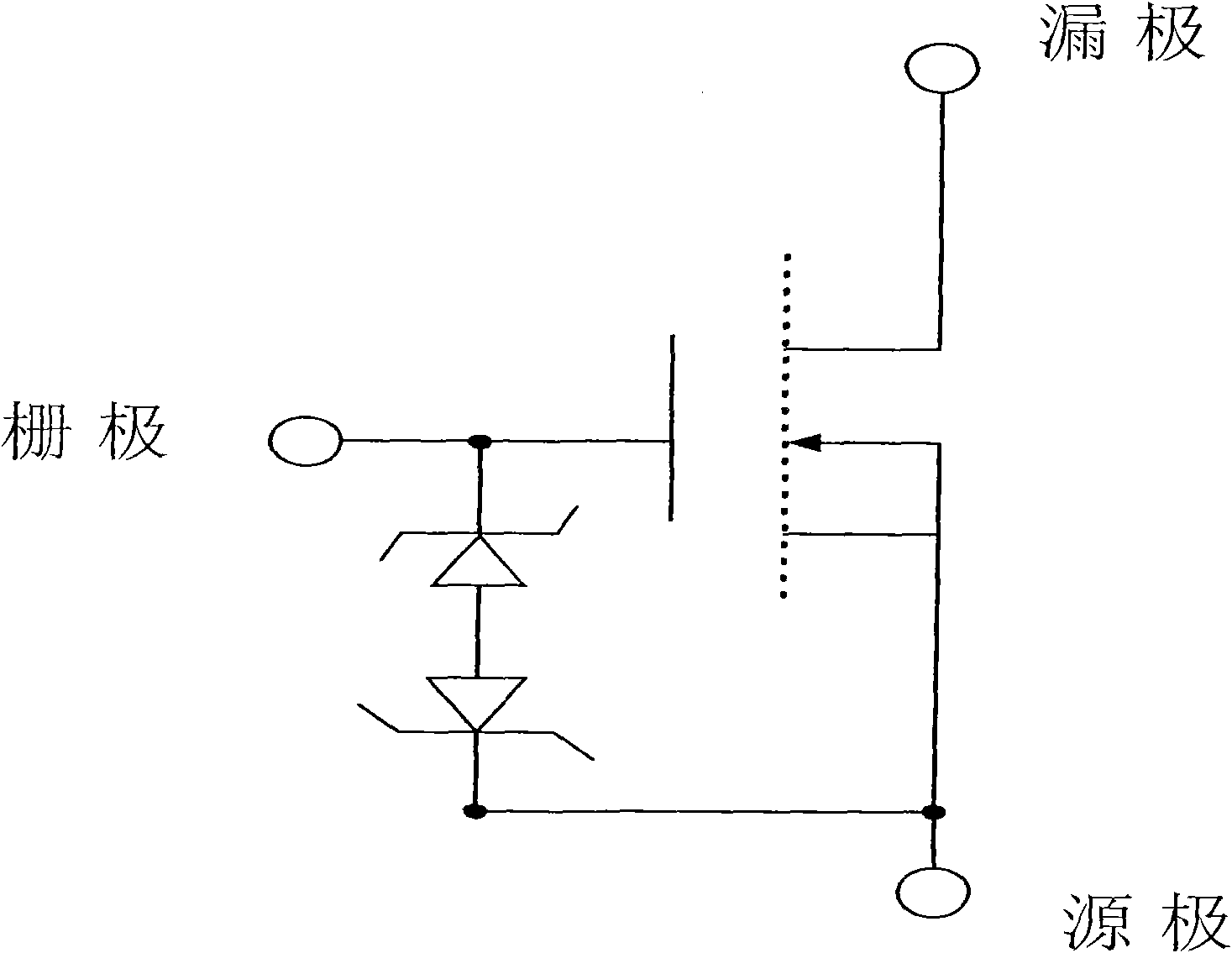

Composite VDMOS device possessing temperature sampling and over-temperature protection function

InactiveCN102394237AReduce failure rateAccurate samplingSolid-state devicesDiodePower semiconductor deviceNegative temperature

A composite VDMOS device possessing a temperature sampling and over-temperature protection function belongs to the power semiconductor device field. In the invention, a VDMOS device, a polysilicon thermal diode and an over-temperature protection circuit are integrated. Through using a negative temperature characteristic of forward voltage drop of the polysilicon thermal diode, the polysilicon thermal diode is made on an insulating layer of a VDMOS device surface so as to realize sampling of a VDMOS device operating temperature. Based on a temperature sampling signal of the polysilicon thermal diode, the over-temperature protection circuit carries out partial pressure to a gate input voltage Vin of the whole composite VDMOS device so as to obtain a gate control voltage VG of the VDMOS device. Therefore, the over-temperature protection can be performed to the VDMOS device, which is characterized by: when the operating temperature of the VDMOS device reaches TH, turning off the VDMOS device; when the internal temperature drops to TL after the VDMOS device is turned off, starting the VDMOS device, wherein temperature return difference can be represented as a following formula: Delta T=TH-TL. By using the composite VDMOS device of the invention, the accurate sampling and the over-temperature protection can be performed to the VDMOS device so that thermal failure of the device can be avoided and a service life of the device can be prolonged. A structure is simple and sampling accuracy is high. The device is compatible with a VDMOS device technology. The device is monolithic and has many other advantages.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Silicon-based hybrid integrated laser array and preparation method thereof

ActiveCN109560462ASolve the problem of poor heat dissipation characteristicsImprove heat dissipation characteristicsOptical wave guidanceSemiconductor laser arrangementsLaser arrayOhmic contact

The invention discloses a silicon-based hybrid integrated laser array and a preparation method thereof. The silicon-based hybrid integrated laser array comprises a plurality of distributed silicon-based hybrid integrated lasers in parallel integrated on an SOI substrate and an III-V semiconductor epitaxial layer. Each silicon-based hybrid integrated laser comprises: a silicon ridge waveguide; heatconducting layers located in special areas at two sides of the silicon ridge waveguide, wherein the special area is an area obtained after the SOI substrate removes a top silicon and a buried oxide layer; an intrinsic layer in a shape of a saddle and comprising a protrusion portion and a connection portion at two ends, wherein the protrusion portion at one end covers the upper portion of the heatconducting layers, the connection portion of the intrinsic layer is provided with an N-type waveguide layer, an active region and a P-type cover layer in order; an III-V waveguide formed by patterning the III-V semiconductor epitaxial layer and connected with the silicon ridge waveguide; a P-type ohmic contact layer; a P electrode; and an N electrode. The silicon-based hybrid integrated laser array is good in heat dissipation, simple and stable in preparation process, good in repeatability and low in manufacturing cost.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

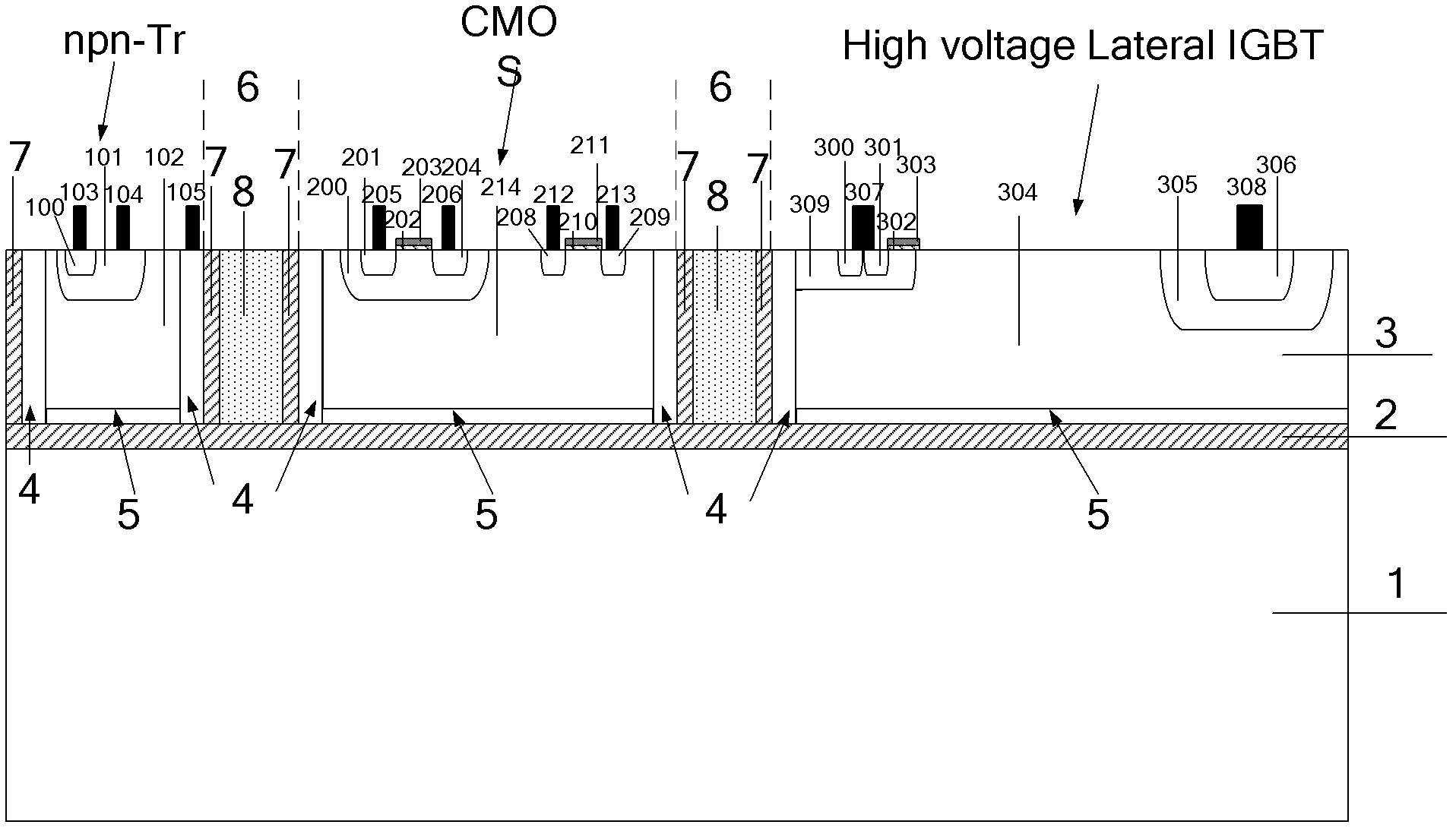

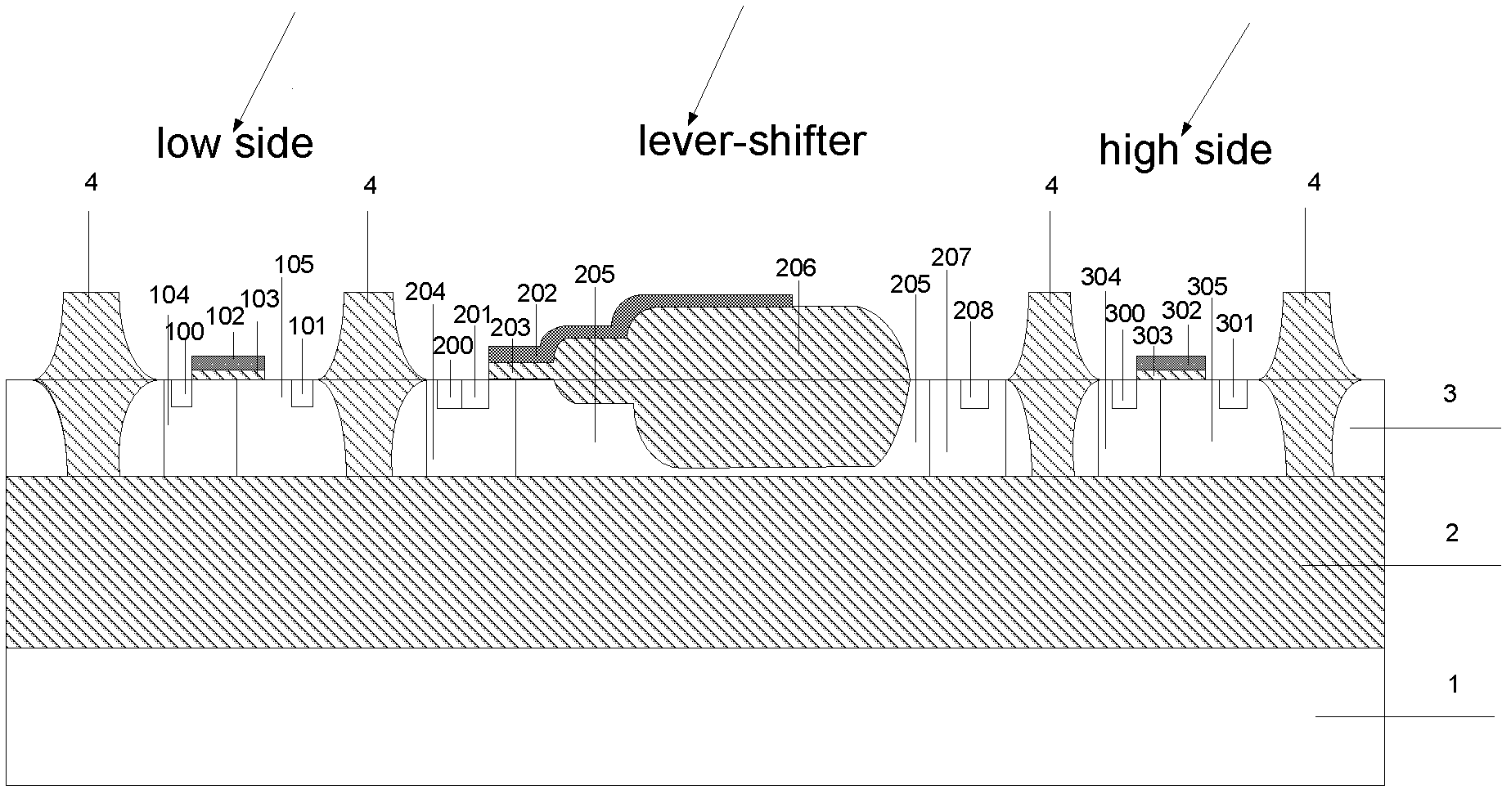

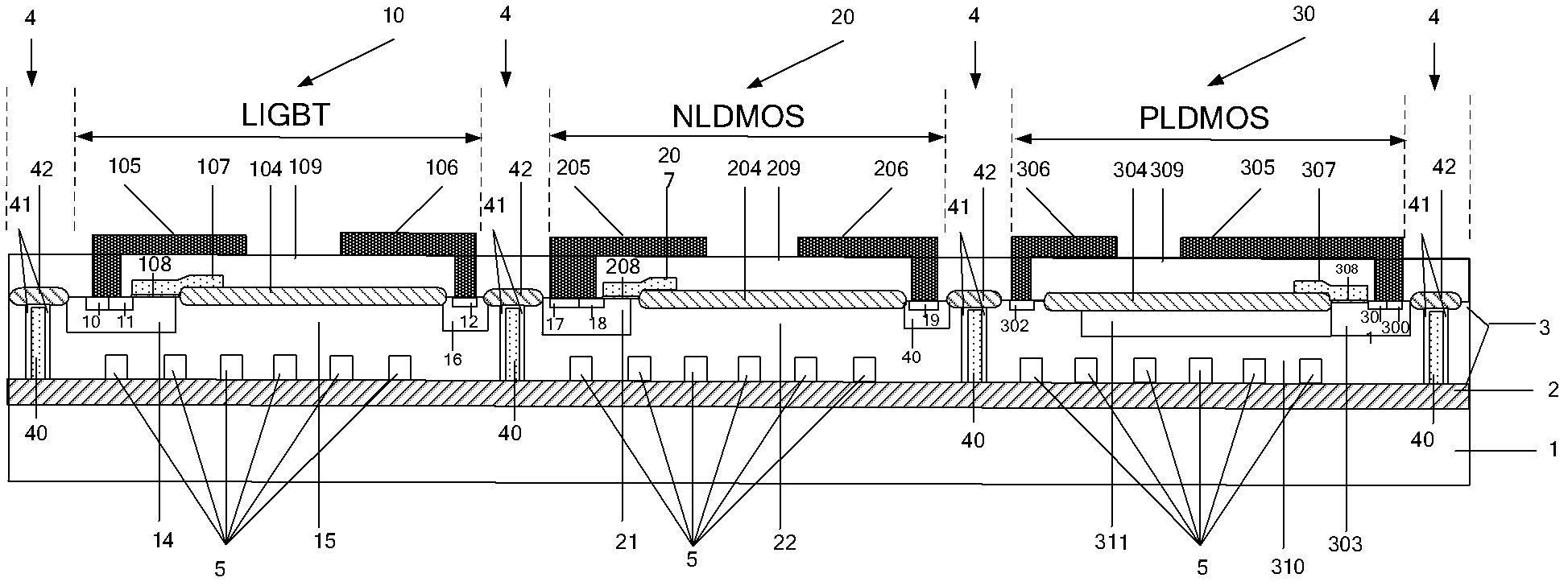

Semiconductor device used for SOI (silicon-on-insulator) high-voltage integrated circuit

InactiveCN102361031AIncrease concentrationControl concentrationSolid-state devicesSemiconductor devicesHigh concentrationLow voltage

The invention relates to a semiconductor device used for an SOI (silicon-on-insulator) high-voltage integrated circuit, belonging to the field of power semiconductor devices. The semiconductor device comprises a semiconductor substrate layer, a dielectric buried layer and a silicon top layer, wherein at least high-voltage LIGBT (lateral insulated gate bipolar transistor), NLDMOS (N-type lateral double-diffused metal-oxide semiconductor) and PLDMOS (P-type lateral double-diffused metal-oxide semiconductor) devices are integrated in the silicon top layer; the thickness of the dielectric buried layer is not more than 5 mum; the thickness of the silicon top layer is not more than 20 mum; multiple incontinuous high-concentration N<+> regions (doping concentration is not lower than 1e16e cm<-3>) are formed at the bottoms of the high-voltage devices and the silicon top layer above the surface of the dielectric buried layer; the high-voltage devices are isolated by dielectric isolation regions; low-voltage MOS (metal oxide semiconductor) devices can also be integrated in the device; the high-voltage devices and low-voltage devices are isolated by the dielectric isolation regions; and different low-voltage devices are isolated by field oxidation layers. The semiconductor device has the advantages that: because of the introduction of the multiple incontinuous high-concentration N<+> regions, the electric field of the silicon top layer is weakened and the electric field of the dielectric buried layer is enhanced at the same time, the breakdown voltage of the device is greatly improved, and the device can be applied in high-voltage integrated circuits in the automobile electronics, consumption electronics, green lighting, industrial control, power supply management, display driving and other fields.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

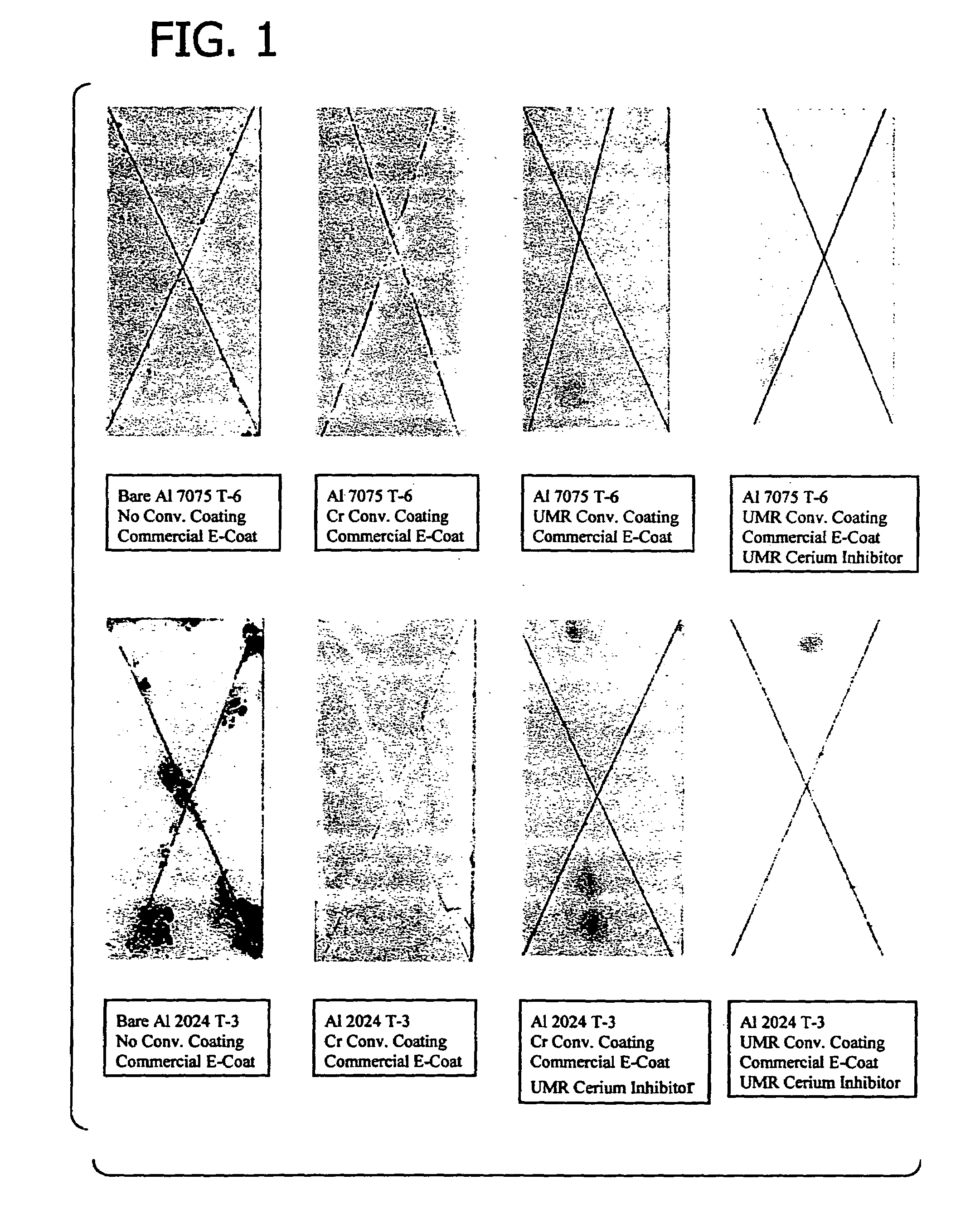

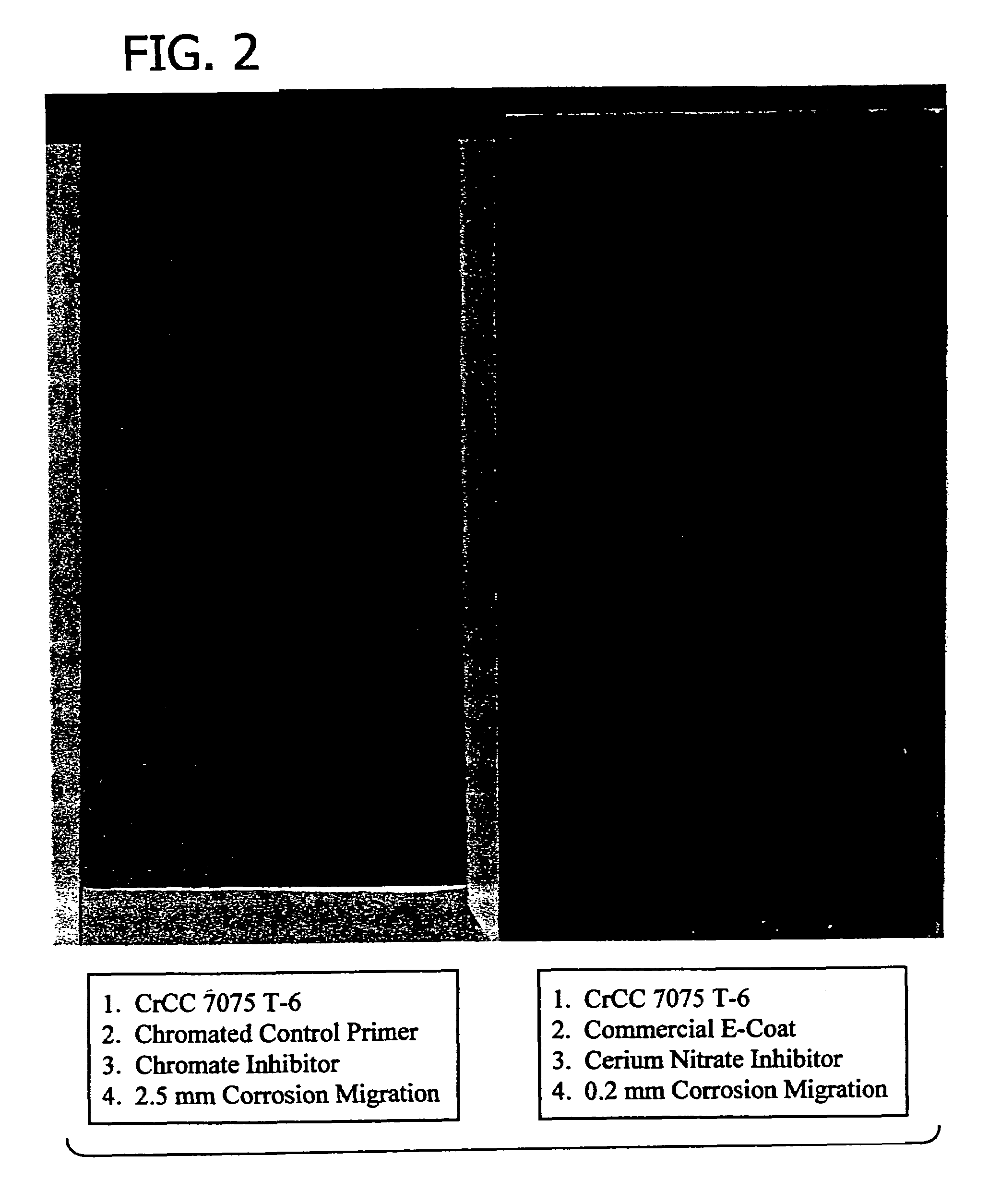

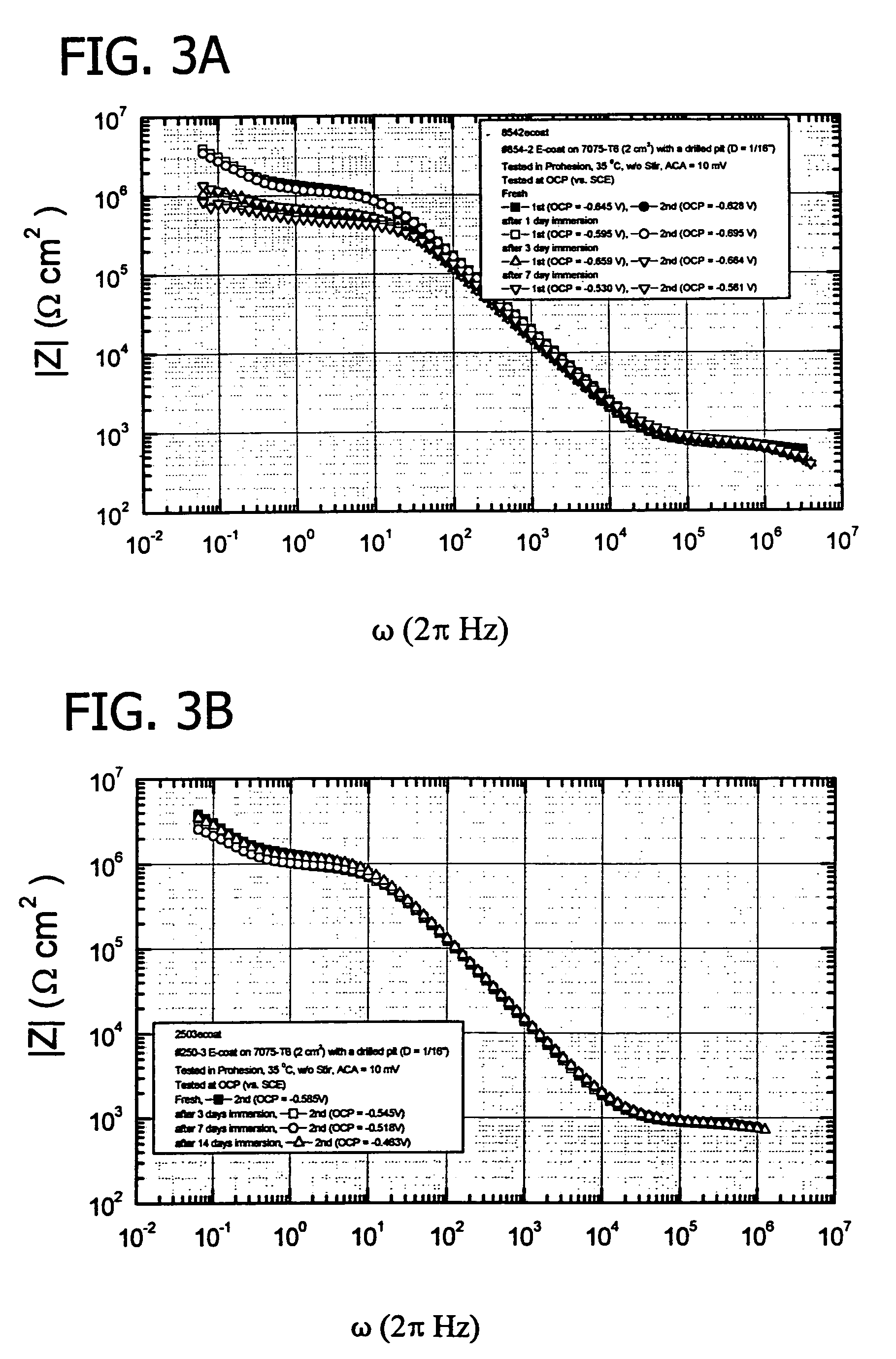

Additive-assisted, cerium-based, corrosion-resistant e-coating

InactiveUS7241371B2Improve corrosion resistanceImprove performanceElectrolysis componentsVolume/mass flow measurementIonCorrosion resistant

Corrosion resistance of metallic components such as stainless steel components of vehicles, and especially aluminum-based components of aircraft, is enhanced by application of an e-coat paint or primer which is enhanced by incorporation of cerium ions into the e-coat electrolytic bath. The resulting overall coating includes a cerium-based layer under a cerium-enhanced e-coat paint or primer layer.

Owner:CURATORS OF UNIV OF MISSOURI THE +1

In-situ polymerized organic-inorganic composite solid-state battery

ActiveCN111933894AIncrease elasticityGood compatibilityFinal product manufactureSecondary cellsElectrical conductorIn situ polymerization

The invention discloses an in-situ polymerized organic-inorganic composite solid-state battery, which is characterized in that a polymer solid-state electrolyte monomer or oligomer small molecule is compactly connected with an electrode active material, an inorganic fast ion conductor and a lithium salt in an in-situ polymerization manner, wherein the polymer solid electrolyte monomer or oligomersmall molecule at least comprises one compound containing an unsaturated carbon-carbon bond and carbonyl or sulfonyl or sulfinyl; the polymer solid electrolyte monomer or oligomer small molecule at least comprises one compound containing two or more unsaturated carbon-carbon bonds. The battery is small in interface resistance, high in conductivity and resistant to high voltage, the problem that asolid-state battery is poor in room-temperature and low-temperature performance is solved, and the production technological process is simple and reliable.

Owner:安普瑞斯(无锡)有限公司

System and method for computing color correction coefficients

ActiveUS20080100639A1Wide applicabilityProcess compatibleTelevision system detailsPicture reproducers using cathode ray tubesSystems designColor correction

System and method for computing coefficients for color correcting rendered colors used in displaying images. A preferred embodiment comprises measuring color values of light output for a display system, receiving color values of desired colors, and computing a color correction matrix based on the measured color values and the input color values. The color correction matrix may be used to modify color commands to a light engine of the display system. The modifications to the color commands permit the storage and use of a set of color commands designed for a reference display system, simplifying display system design and manufacture.

Owner:TEXAS INSTR INC

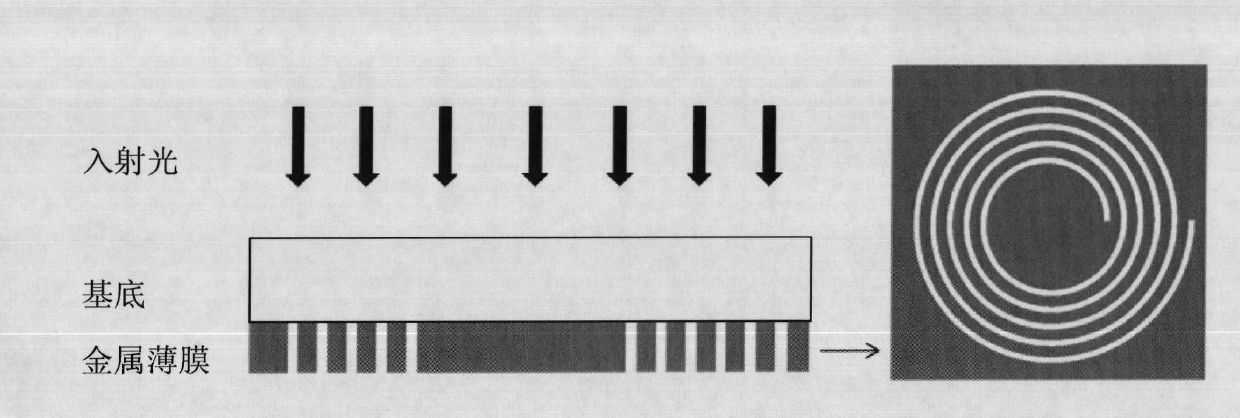

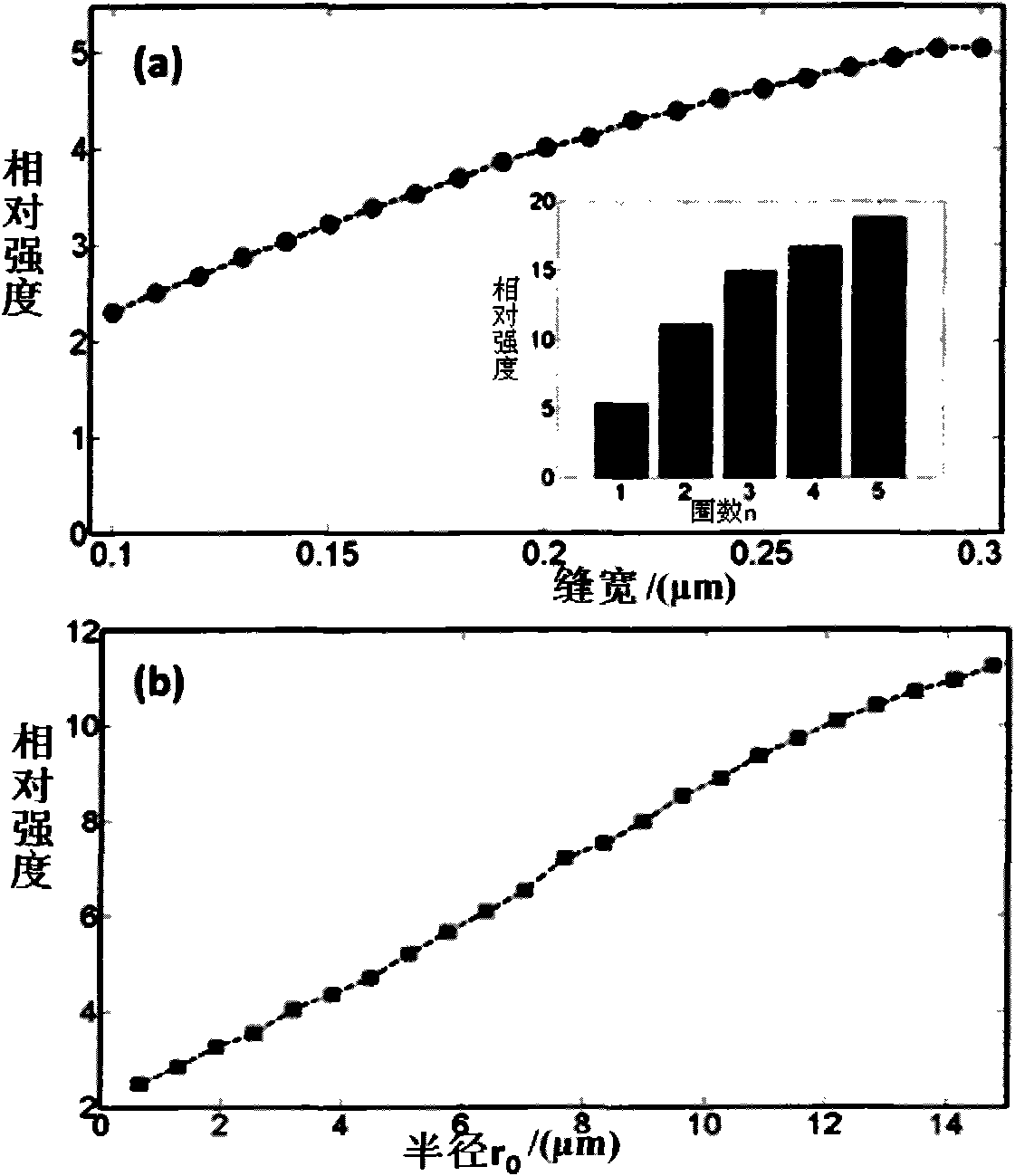

Plasma slab lens and near-field focusing method thereof

The invention provides a plasma slab lens which comprises a light-permeable substrate and a metal film made on the light-permeable substrate, wherein the metal film is provided with a levorotatory or dextrorotatory helical structure; the helical structure meets the condition that Phi is greater than or equal to 0 but is less than or equal to 2pi, wherein n is equal to 1, 2, 3...; k is equal to 1,2, 3...; rn (Phi) is a distance from a phase Phi of the No. n circle of the helical structure to the center in a polar coordinate; rn0 is the shortest distance from each circle of the helical structure to the center; and lambda sp is a wavelength of the surface plasma of the metal film. A preparing process of the plasma slab lens is compatible with an existing process, is easy to integrate and islow in cost. The center of a light source needs not be aligned with the center of the lens structure and the plasma slab lens can be more conveniently and simply used and can be easily made into a lens array; the plasma slab lens can break through a diffraction limit and has a huge focus depth; and the field intensity at a focal point can be controlled by adjusting the shape and size of the helical structure.

Owner:THE NAT CENT FOR NANOSCI & TECH NCNST OF CHINA

ESD protection integrated power MOSFET or IGBT and preparation method thereof

ActiveCN101982881AImprove the protective effectReduce leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingPower MOSFETBreakdown voltage

The invention improves the ESD protection integrated power MOSFET or IGBT. The invention is characterized in that the concentration of all P type areas in a poly-crystal diode set in an ESD protection unit is as same as the P type concentration of the power MOSFET or IGBT; the concentration of the N type area is as same as the N+ source of the power MOSFET or IGBT; the poly-crystal diode set is semi-circled around a grid bonding area between the grid bonding area and a structure cell area. If being a grid inserting structure, the middle of the semi-circled poly-crystal diode set is separated by the grid inserting structure so as to form left and right L-shaped parts which are disconnected, wherein all the P type areas and the N type areas in the poly-crystal diode are respectively formed by injecting and spreading the P well and N+ source of the power MOSFET or IGBT. The leakage between the grid and source electrodes of the acquired ESD protection integrated power MOSFET or IGBT is small. When preparing, a breakdown voltage between the grid and source electrodes is adjustable, the ESD discharging capability is high, the reliability is high and the manufacture is simple.

Owner:江苏东晨电子科技有限公司 +1

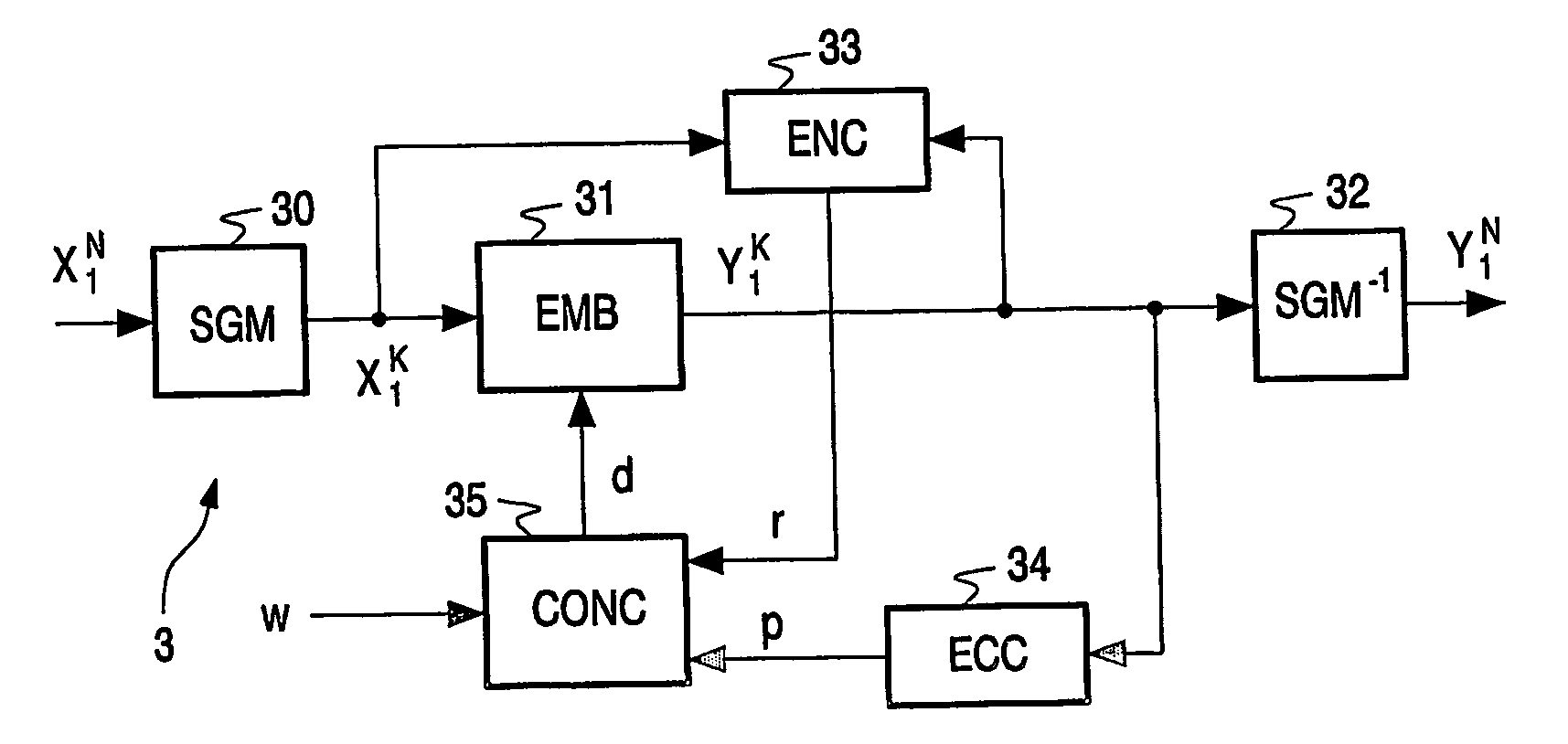

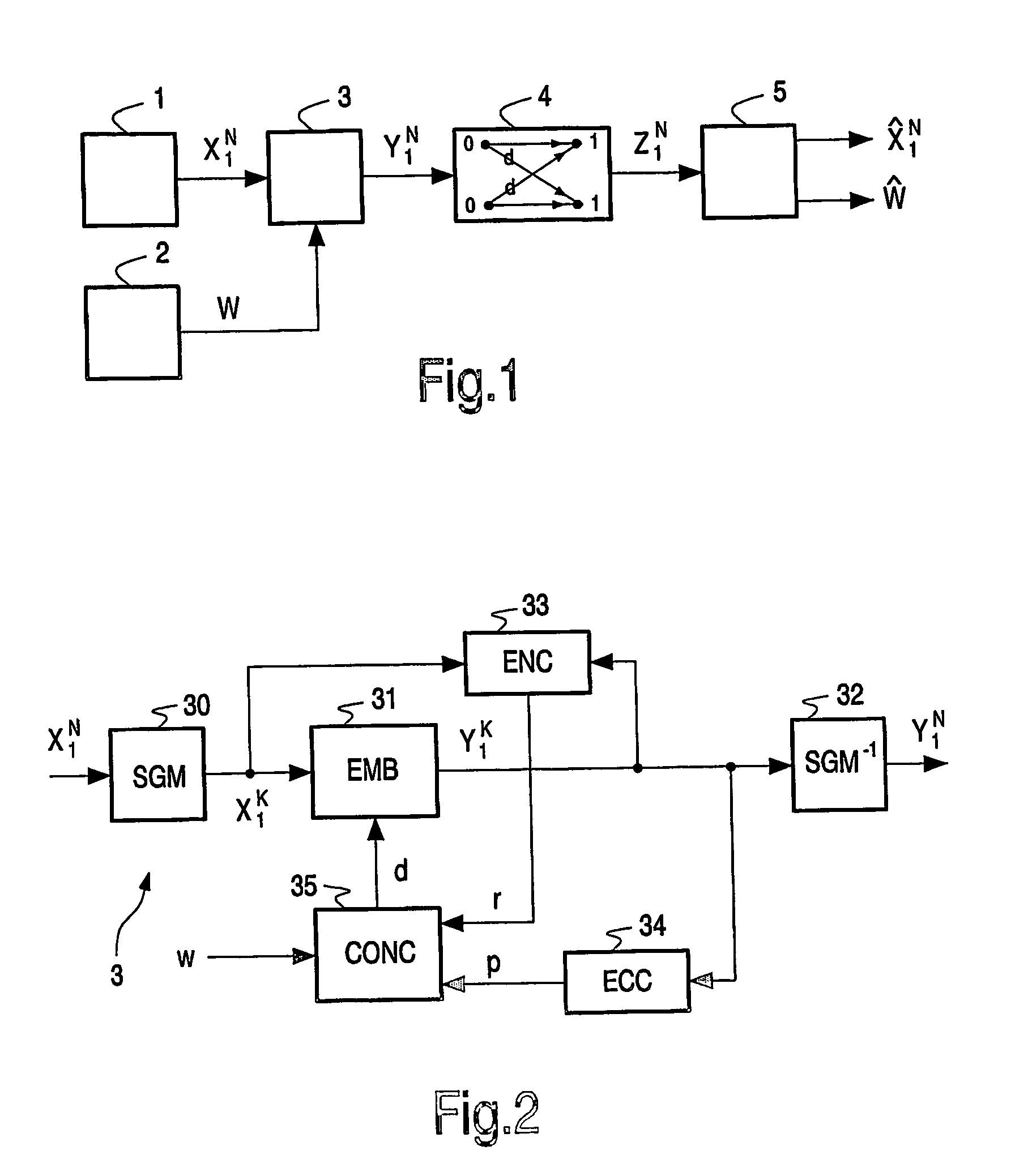

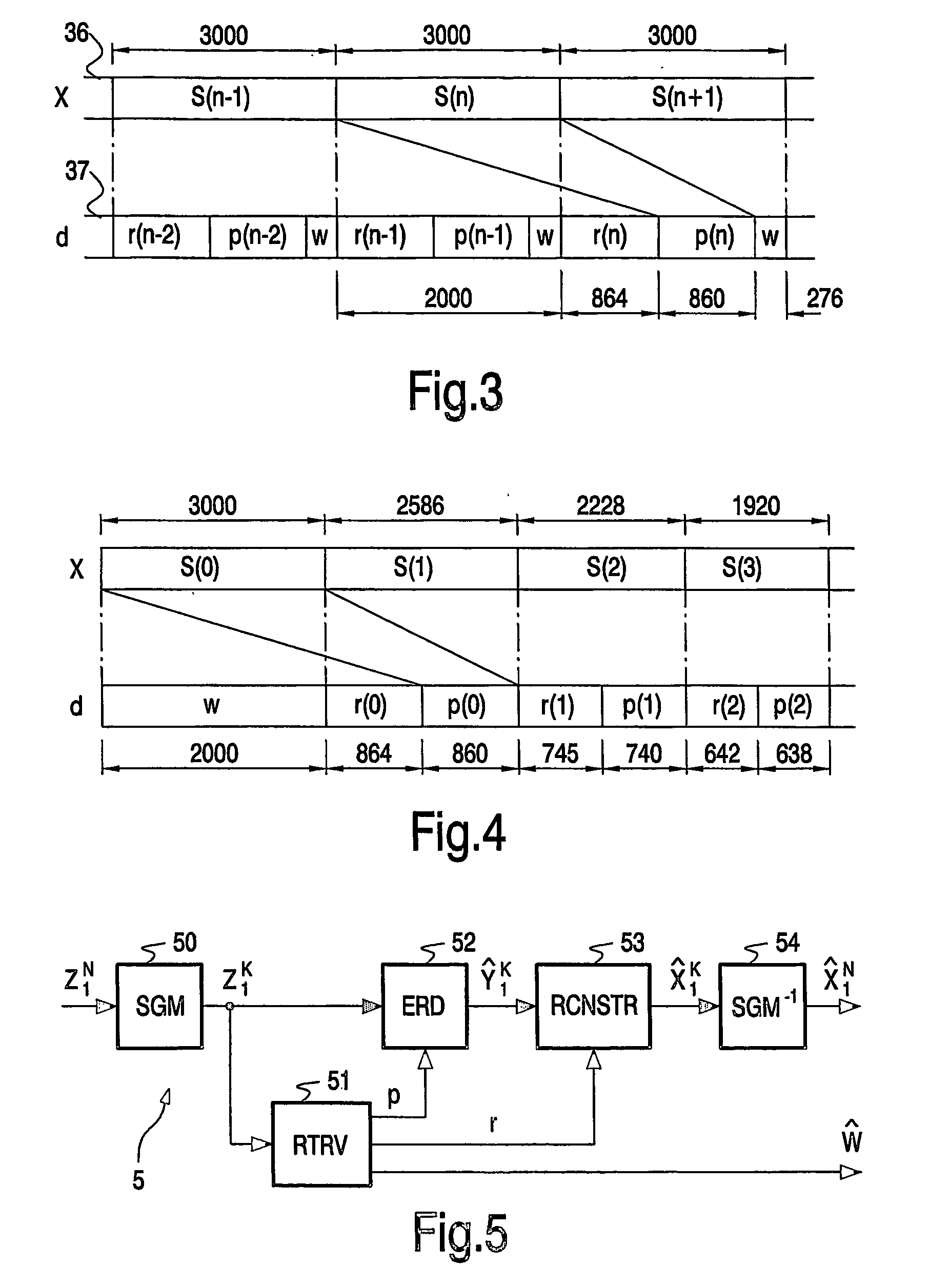

Lossless data embedding

InactiveUS20060075240A1High embedding rateProcess compatibleUser identity/authority verificationCode conversionComputer scienceAncillary data

Many methods for reversible watermarking (embedding schemes that allow perfect reconstruction of the original host signal) are highly fragile in the sense that the slightest modification of watermarked content prohibits the recovery of both the original signal as well as the embedded auxiliary data. In order to obtain robustness against transmission or channel errors, the embedding method according to the invention accommodates error correction data in a portion of the data embedding capacity. In an advantageous embodiment, the host signal (36) is segmented in segments, and error correction data (p(n)) for a segment (S(n)) is accommodated in data (37) being embedded in a subsequent segment (S(n+1)) along with restoration data (r(n)) for reconstructing the host signal. The remaining portion of the embedding capacity is used for payload (w).

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

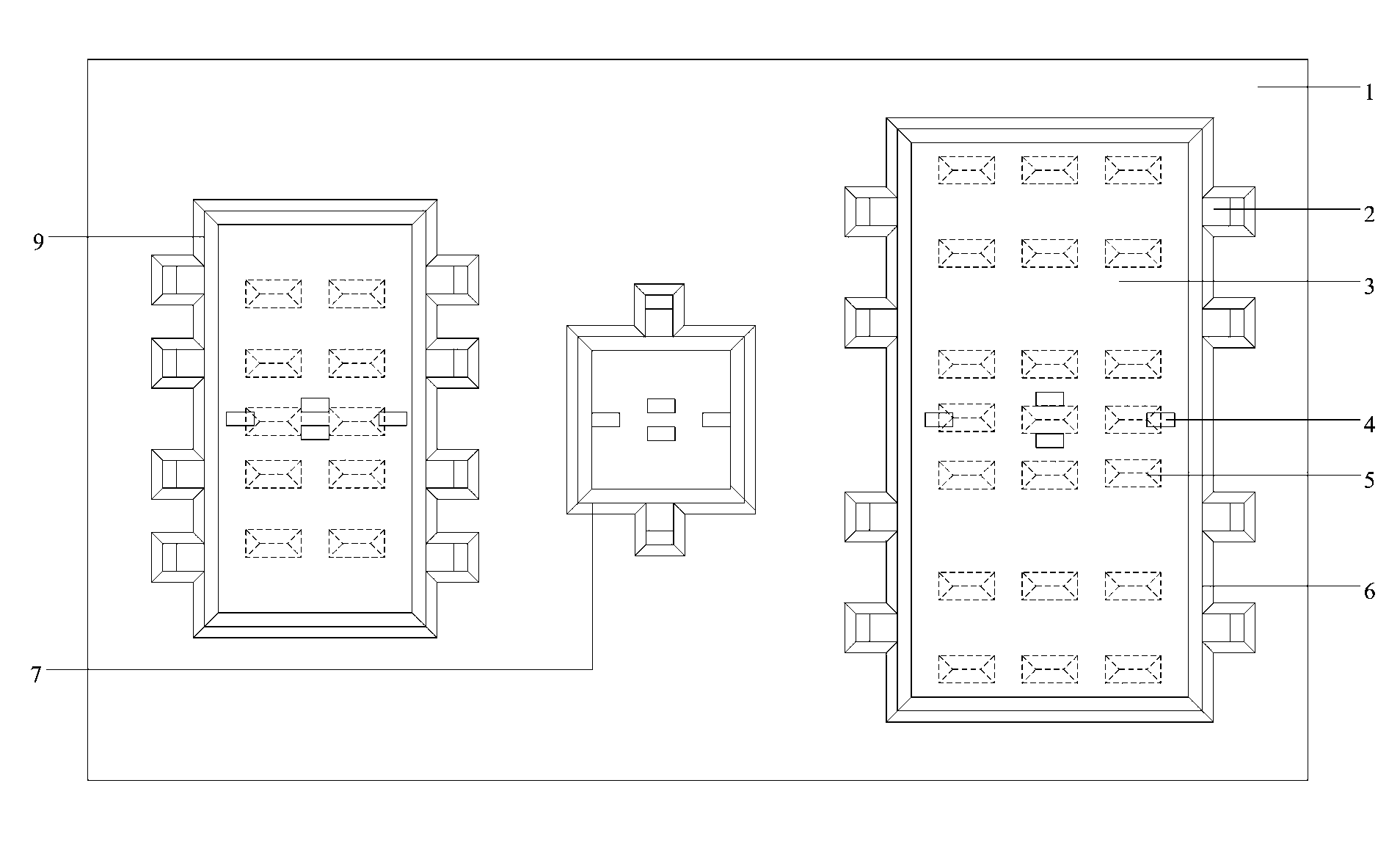

Low divergence angle full Bragg reflector waveguide semiconductor laser array

ActiveCN102611002AHigh beam qualityHigh brightness laser outputOptical wave guidancePower flowLaser array

The invention relates to a low divergence angle full Bragg reflector waveguide semiconductor laser array, belonging to the field of the semiconductor laser. For lowering the longitudinal and transverse divergence angle, improving the beam quality of the laser and obtaining the high luminance laser output, the invention designs the low divergence angle full Bragg reflector waveguide semiconductor laser array. The array longitudinal structure comprises an N-type substrate, an N-type limiting layer, an N-type Bragg reflector waveguide, an active area, a P-type Bragg reflector waveguide, a P-type limiting layer and a P-type cap layer in turn from bottom to top. The N-type Bragg reflector waveguide and P-type Bragg reflector waveguide in the longitudinal structure are formed by respectively arranging at least one pair of high and low refractive index materials periodically. The array transverse structure comprises a current injection area and a transverse Bragg reflector waveguide set at two sides thereof. The transverse Bragg reflector waveguide set at two sides are respectively formed by arranging at least one pair of high and low ridge structures periodically. The lower ridge part is close to the current injection area. The low divergence angle full Bragg reflector waveguide semiconductor laser array realizes the high luminance laser output.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI