Forming method of semiconductor structure

A semiconductor and isolation structure technology, applied in the field of semiconductor structure formation, can solve the problems of semiconductor device electrical performance degradation, etc., achieve the effect of improving formation quality, improving electrical performance, and avoiding voids

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] It can be seen from the background art that the shallow trench isolation structure in the prior art tends to degrade the electrical performance of the semiconductor device. Analyze the reasons for this:

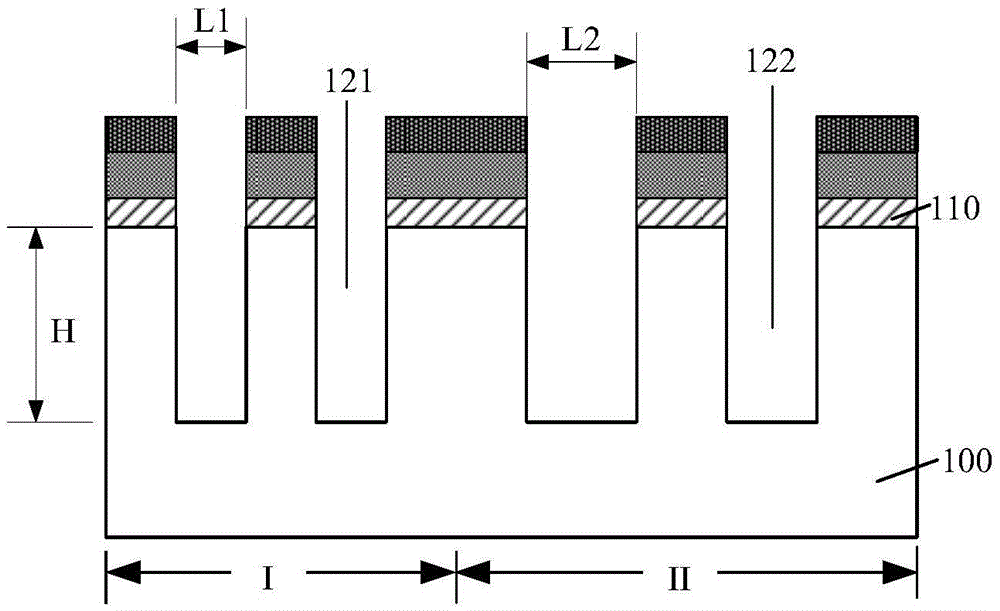

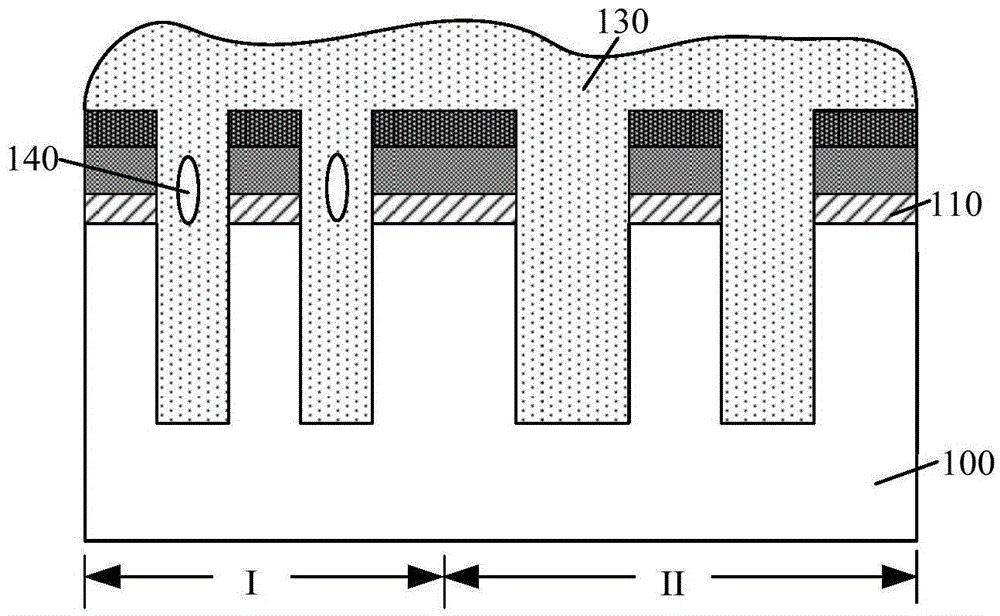

[0022] Such as figure 1 As shown, the substrate 100 of the conventional flash memory includes a core area I and a peripheral area II, the core area I is used to form devices with smaller feature sizes, and the peripheral area II is used to form devices with larger feature sizes. Among them, the distance between the gate electrode layers 110 of adjacent devices in the core region I is small, while the distance between the gate electrode layers 110 of adjacent devices in the peripheral region II is relatively large, that is to say, the two adjacent gate electrodes in the core region I The line width L1 of the shallow trench 121 between the electrode layers 110 is smaller than the line width L2 of the shallow trench 122 between two adjacent gate electrode layers 110 in t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More